Patents

Literature

142results about How to "Avoid latch-up" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

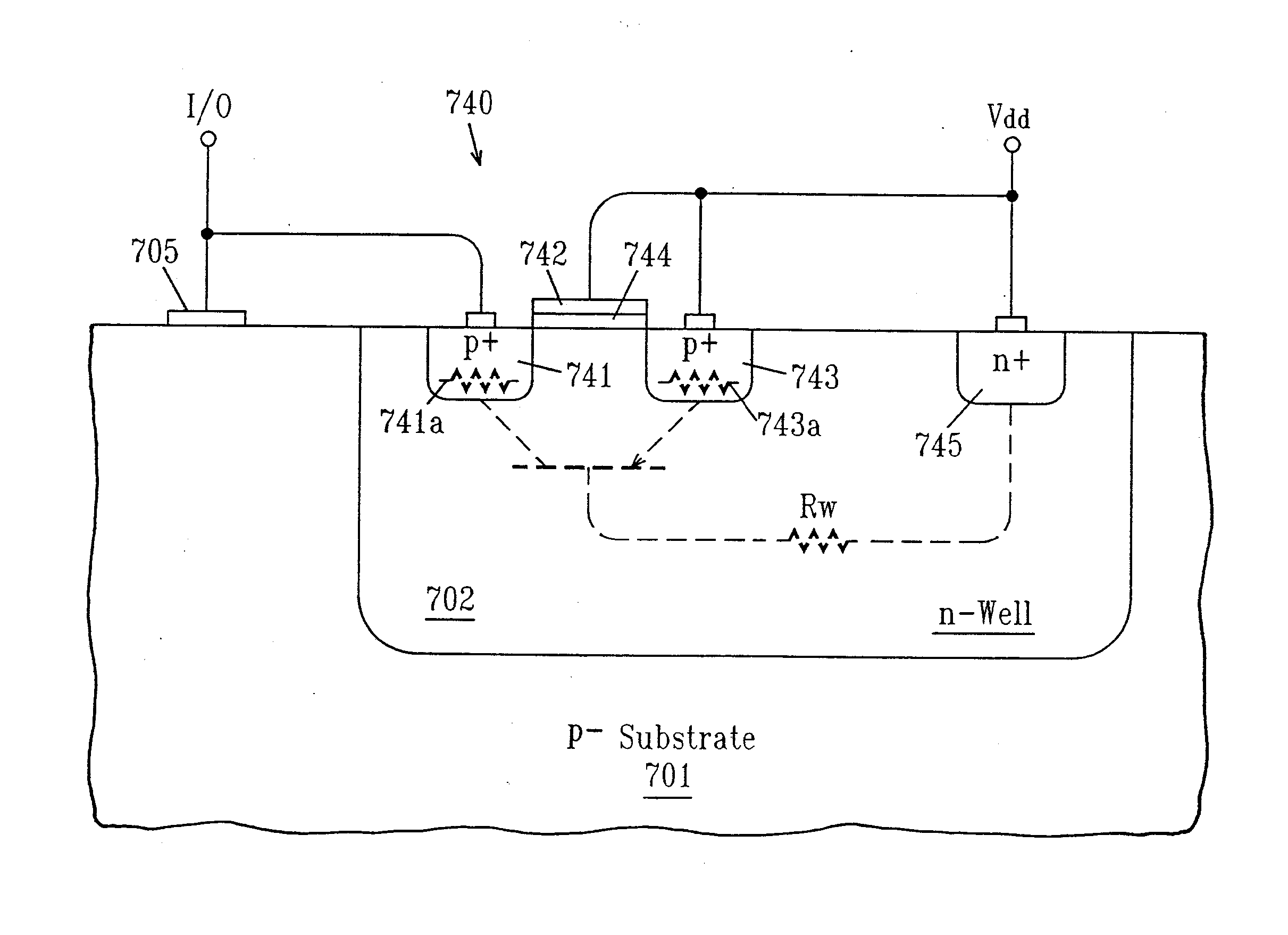

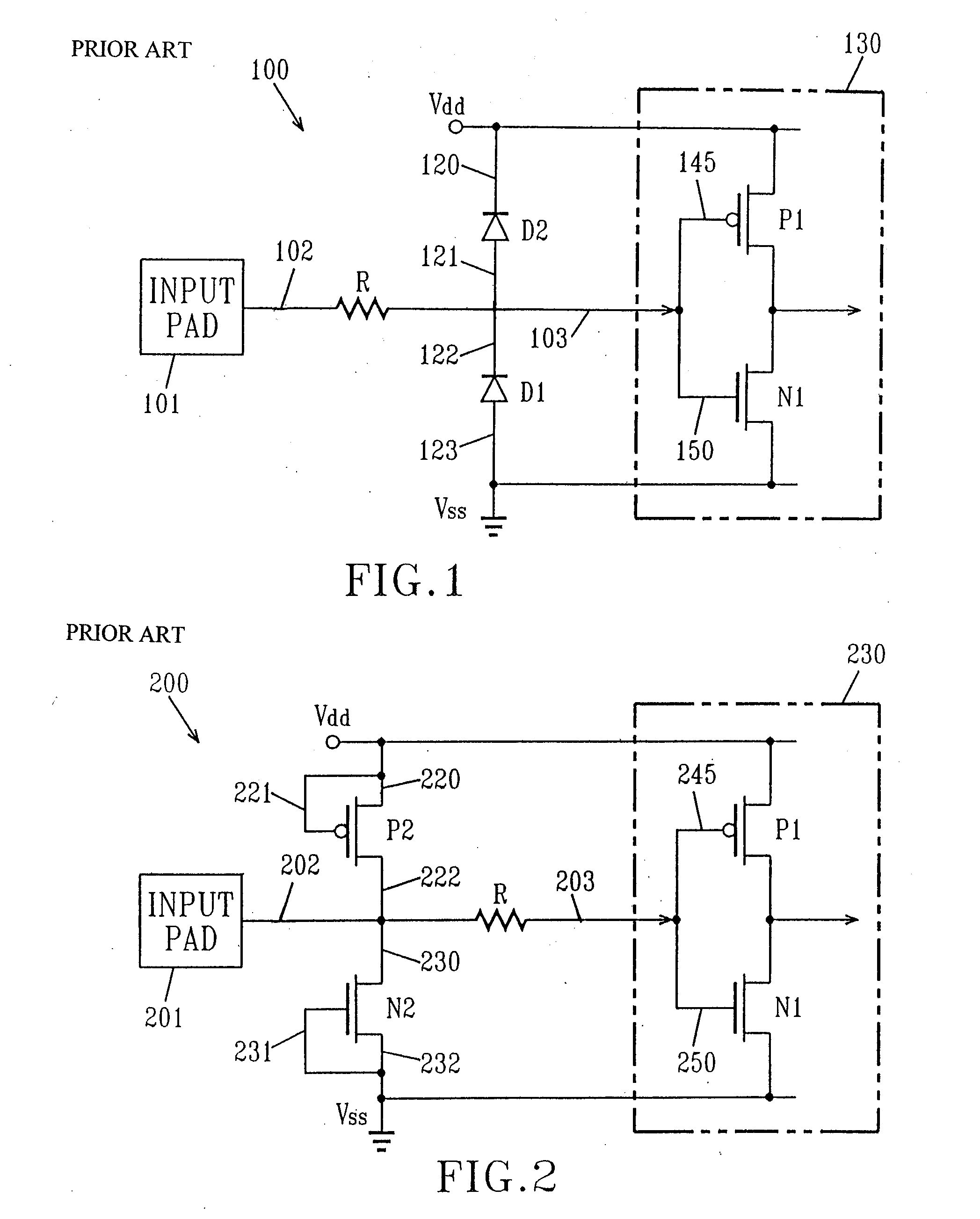

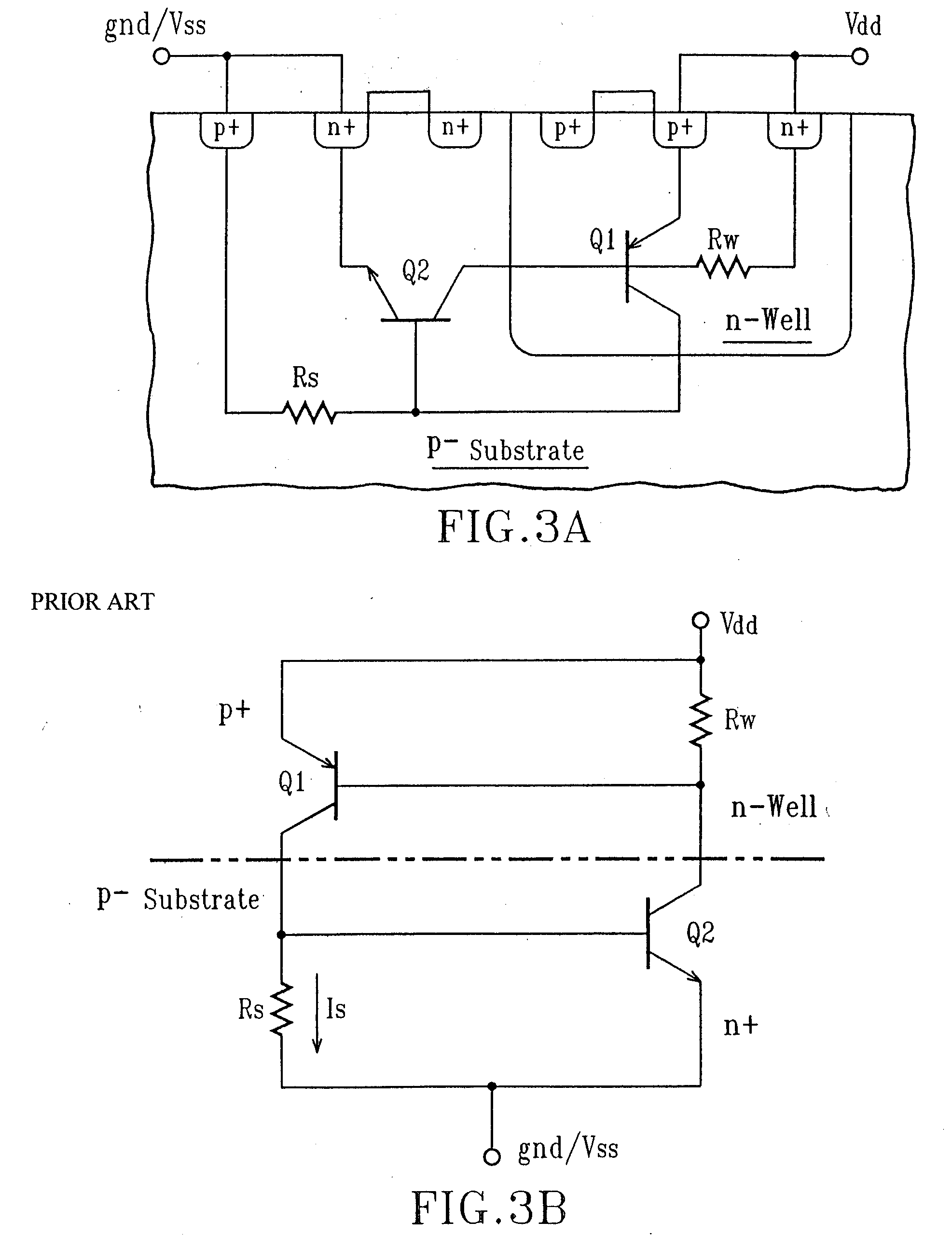

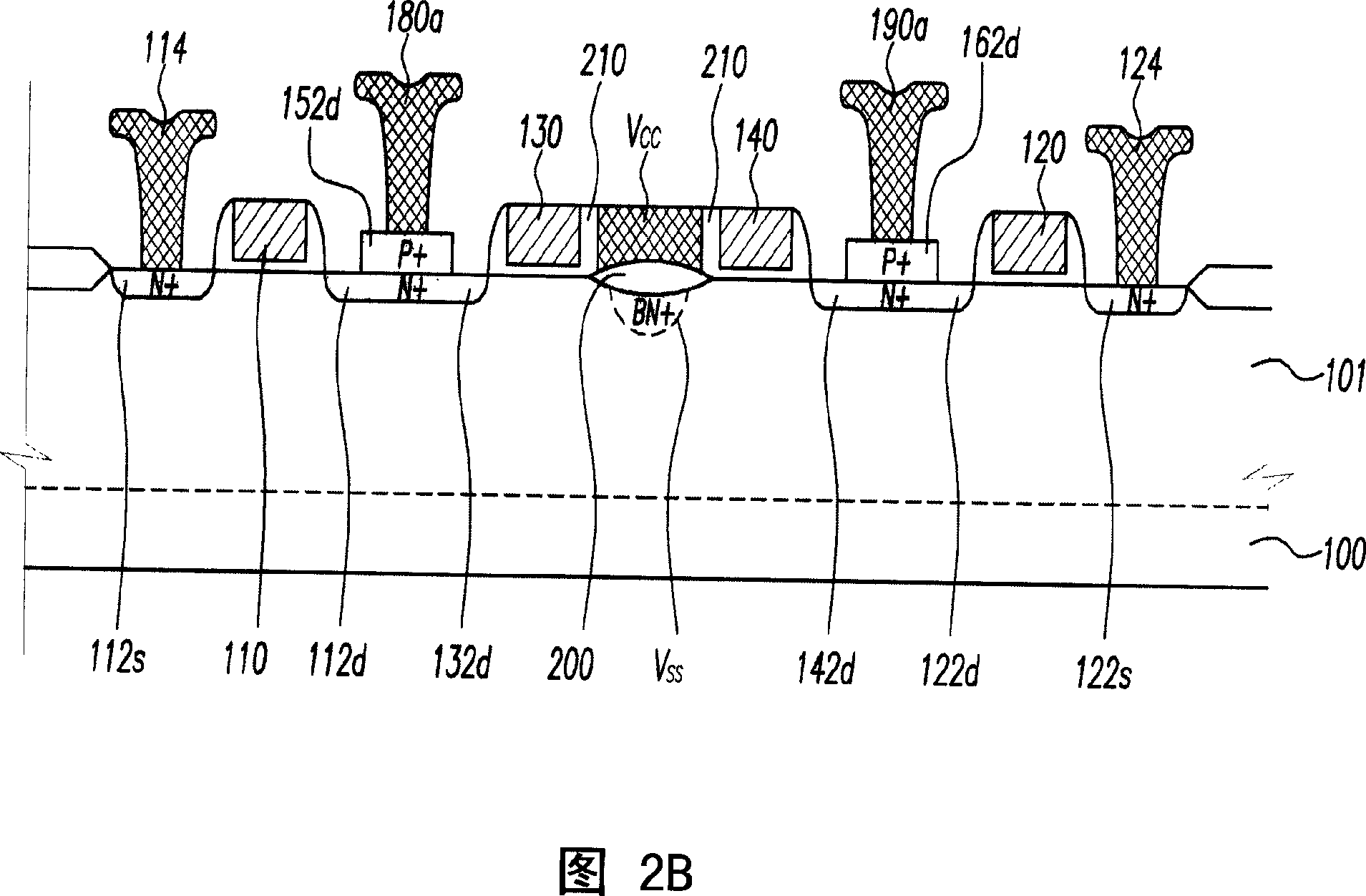

Pfet-based ESD protection strategy for improved external latch-up robustness

InactiveUS20050045952A1Avoid latch-upLatch-up robustness be improveTransistorSemiconductor/solid-state device detailsElectrostatic dischargeIntegrated circuit

A method and apparatus for protection against electrostatic discharge (ESD) with improved latch-up robustness featuring a silicide blocked p-type field effect transistor is disclosed. The transistor has a snapback voltage that is less than the breakdown voltage of its gate oxide. The transistor is part of an integrated circuit and coupled to an I / O pad having no n-diffusions connected directly to it. A given integrated circuit may employ one or more the transistors configured in accordance with the invention that are associated with one or more I / O pads within the integrated circuit.

Owner:IBM CORP

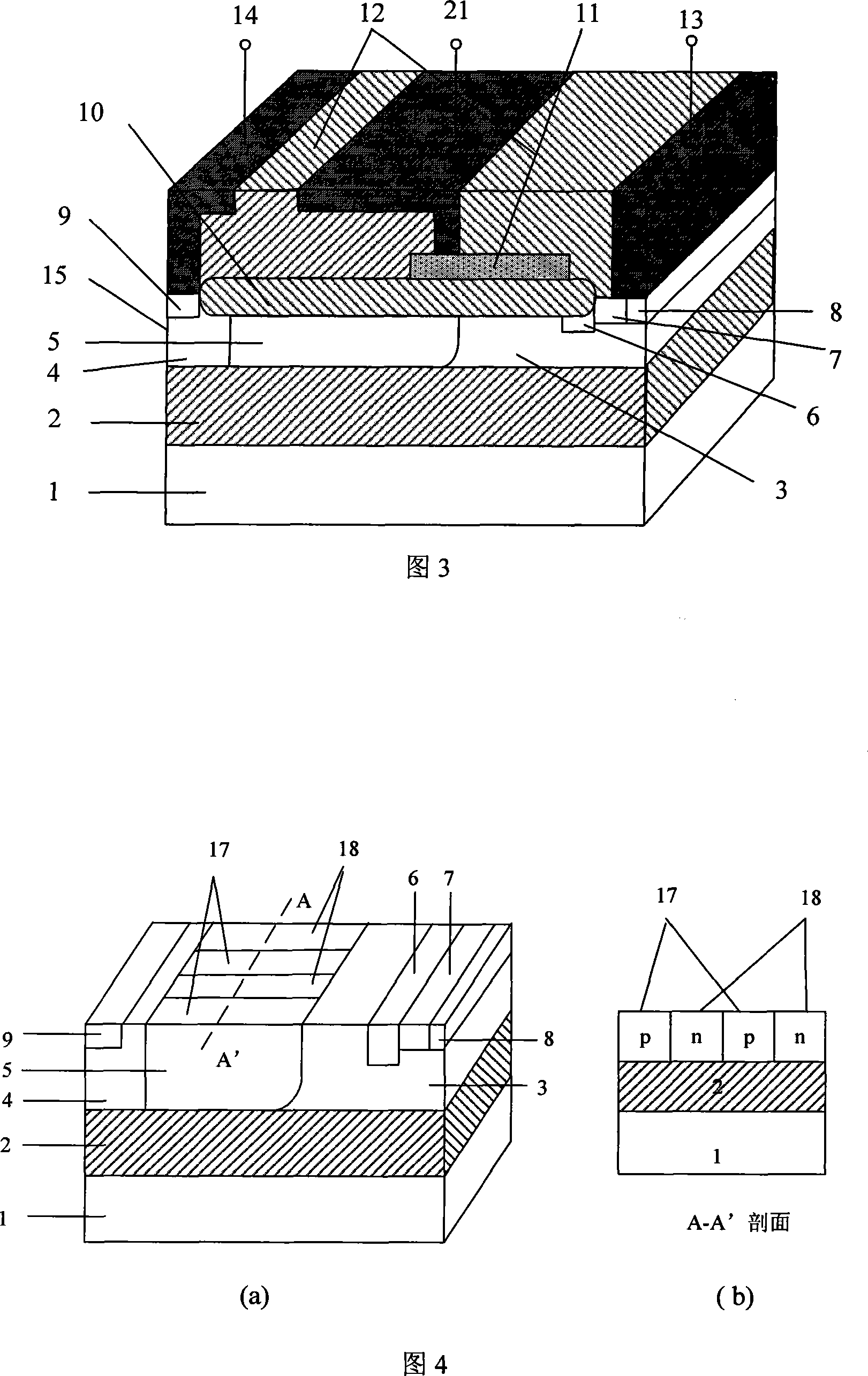

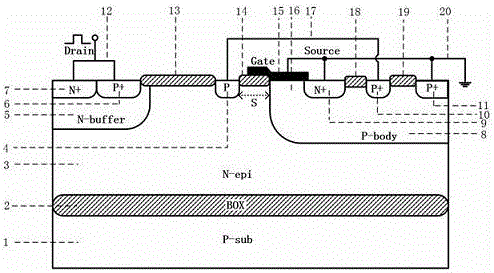

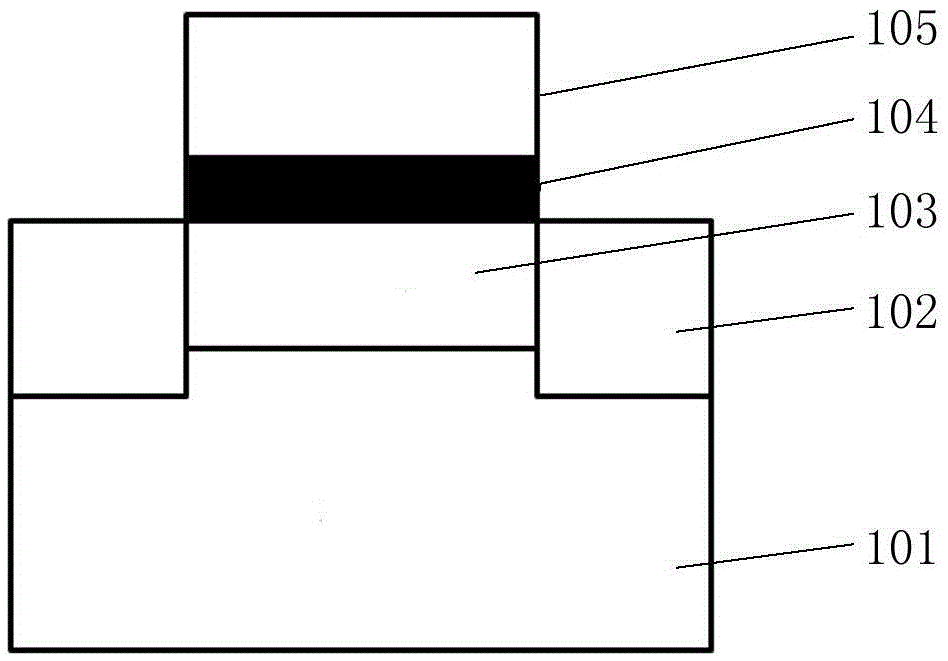

Thin film SOI thick grid oxygen power device with grid field plate

InactiveCN101221986AFast switching speedImprove breakdown characteristicsSemiconductor devicesPeak valueOxygen

The invention belongs to the semi-conductor power device technical field. A SOI layer of the device is thinner (1to 2um); a grid oxide layer is thick (100 to 800nm); a grid field plate gets across a grid and extends above a drift region. An active expansion region positioned below the thick grid oxide layer and connected with a source region can be also arranged in the body of the device to assure the more effective formation of the whole device. The grid oxide layer of the invention is thicker, can bear high grid-source voltage and meet the need of a level displacement circuit; the SIO layer is thinner, can decrease the parasitic effect of the device and reduce consumption; through adding the grid field plate striding over the grid on the surface of the power device, the depletion of the drift region can be increased, the electric field peak value on the silicon surface at the tail end of the grid is decreased, the breakdown characteristic of the device is improved, further more the concentration of the drift region is helped to improve, and the on-state resistance of the device is decreased. The invention has the advantages of low parasitic effect, fast speed, low power consumption, strong radiation-resistant ability and so on, and is compatible with the standard process. By adopting the invention, various high-voltage, high-speed and low conducting loss devices of excellent performance can be produced.

Owner:UNIV OF ELECTRONICS SCI & TECH OF CHINA

Clamp ESD protection circuit for latch-up prevention type power supply

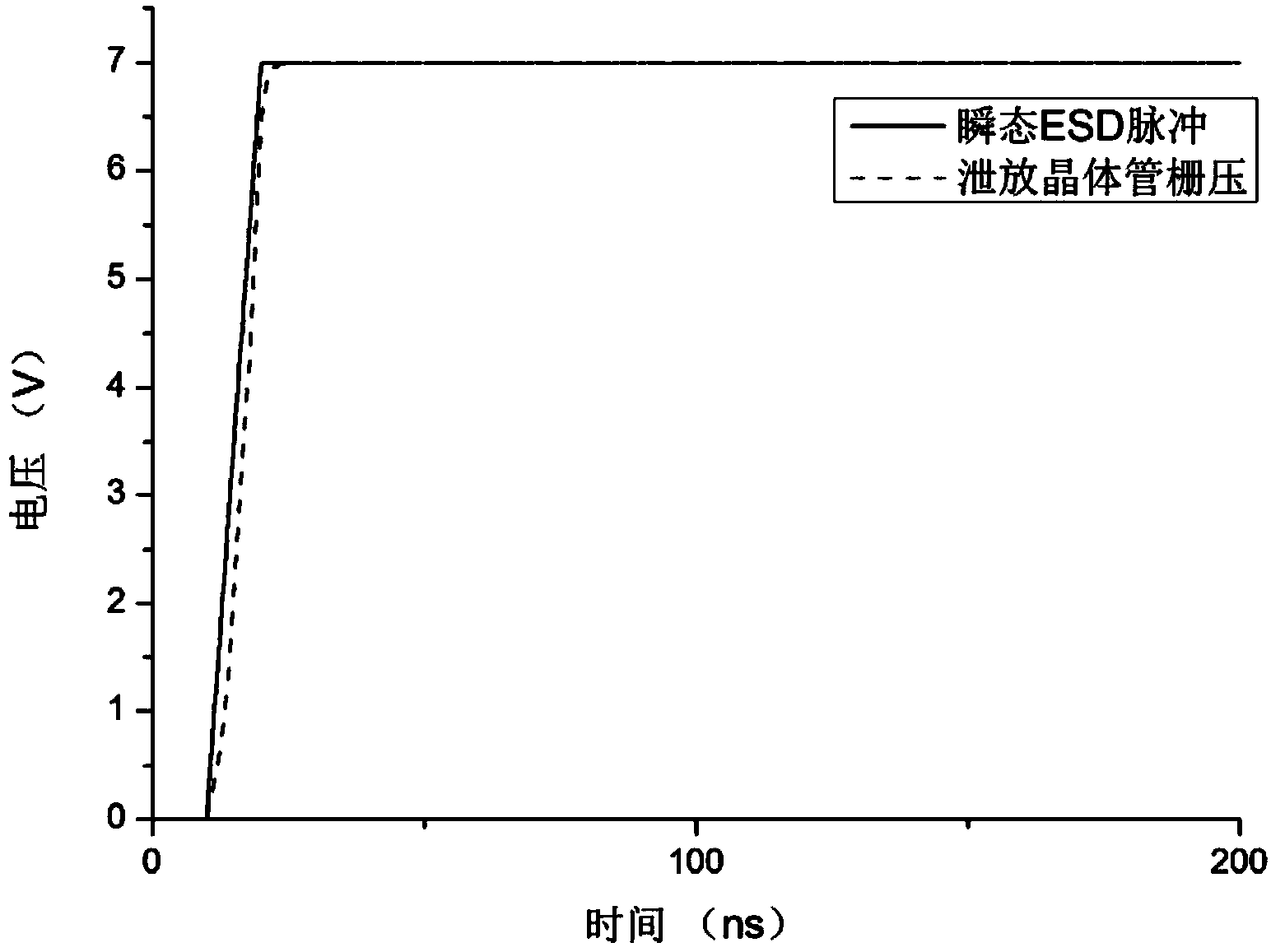

InactiveCN104242285AQuick transferAvoid latch-upEmergency protective arrangements for limiting excess voltage/currentEngineeringPrevention types

The invention relates to a clamp ESD protection circuit for a latch-up prevention type power supply, and relates to the technical field of electronic static discharge protection design of integrated circuit chips. The clamp ESD protection circuit for the latch-up prevention type power supply comprises a transient trigger module, a direct-current voltage detection module and a discharge transistor. Triggering of the discharge transistor of the clamp ESD protection circuit for the latch-up prevention type power supply is achieved through the transient trigger module, and maintenance of the start state of the discharge transistor is achieved through the direct-current voltage detection module. If the clamp ESD protection circuit for the latch-up prevention type power supply is mistakenly triggered by high-frequency noise, the circuit is automatically out of the mistaken trigger state in a short time, and the latch-up phenomenon is effectively prevented.

Owner:PEKING UNIV

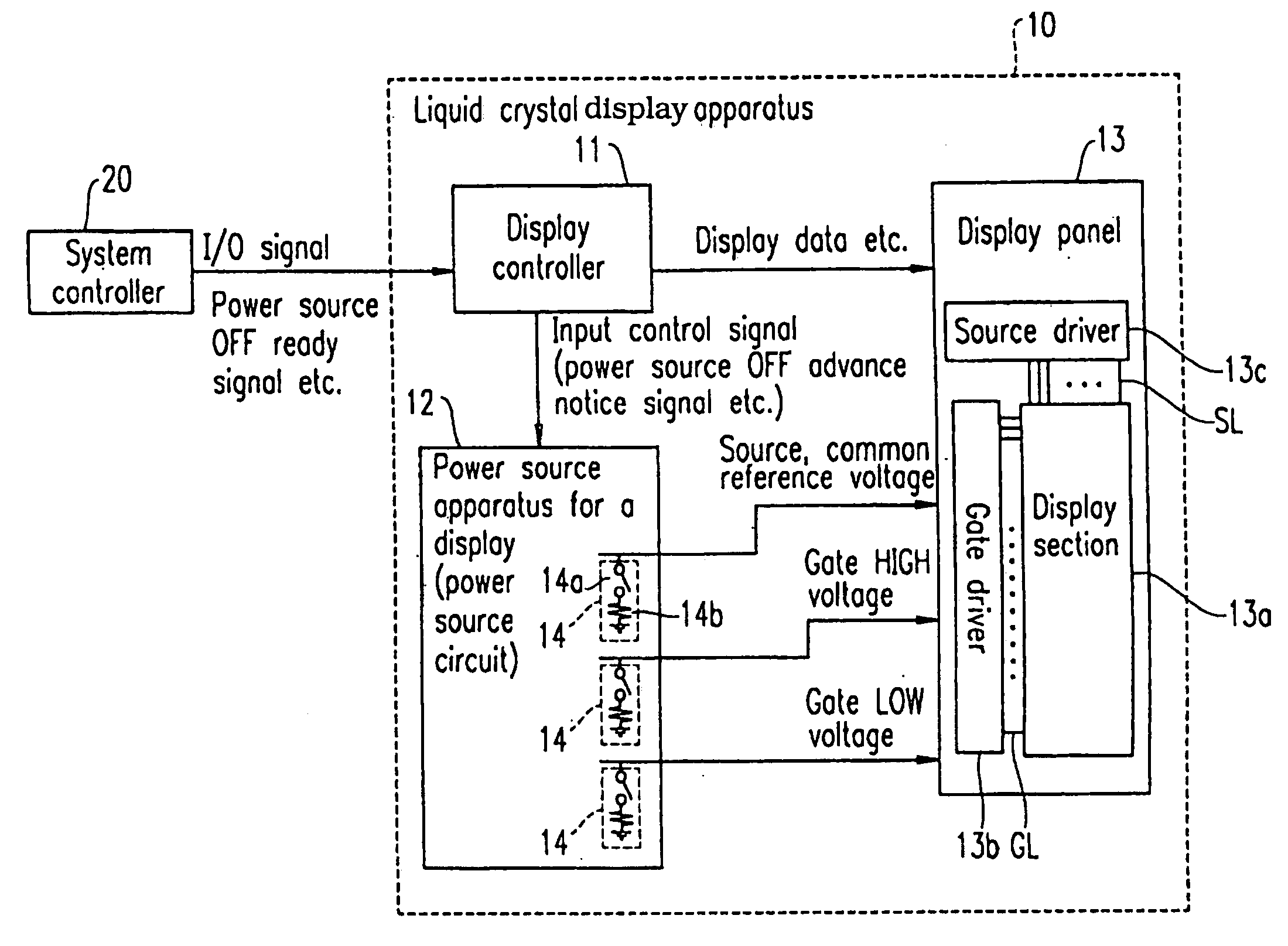

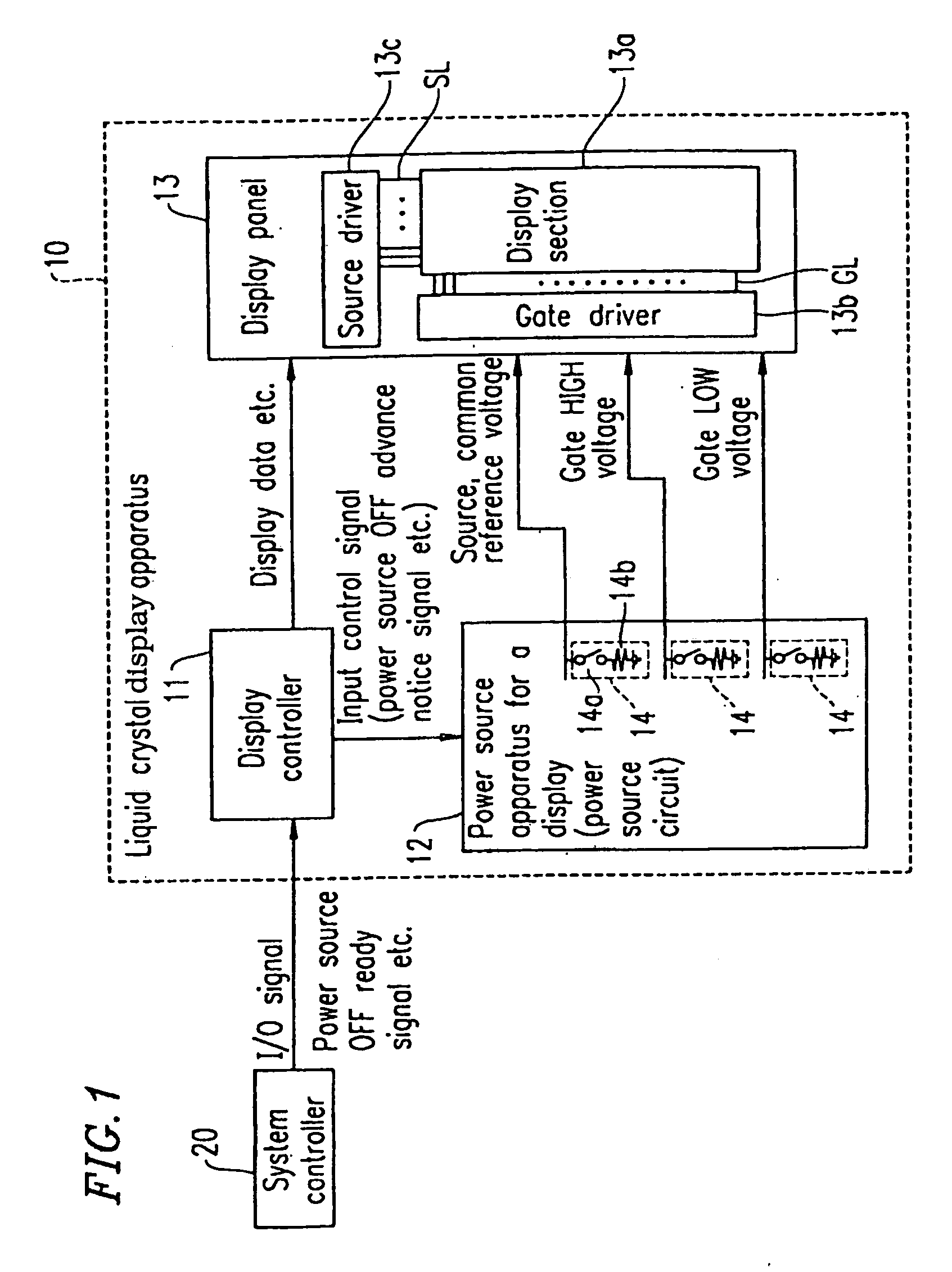

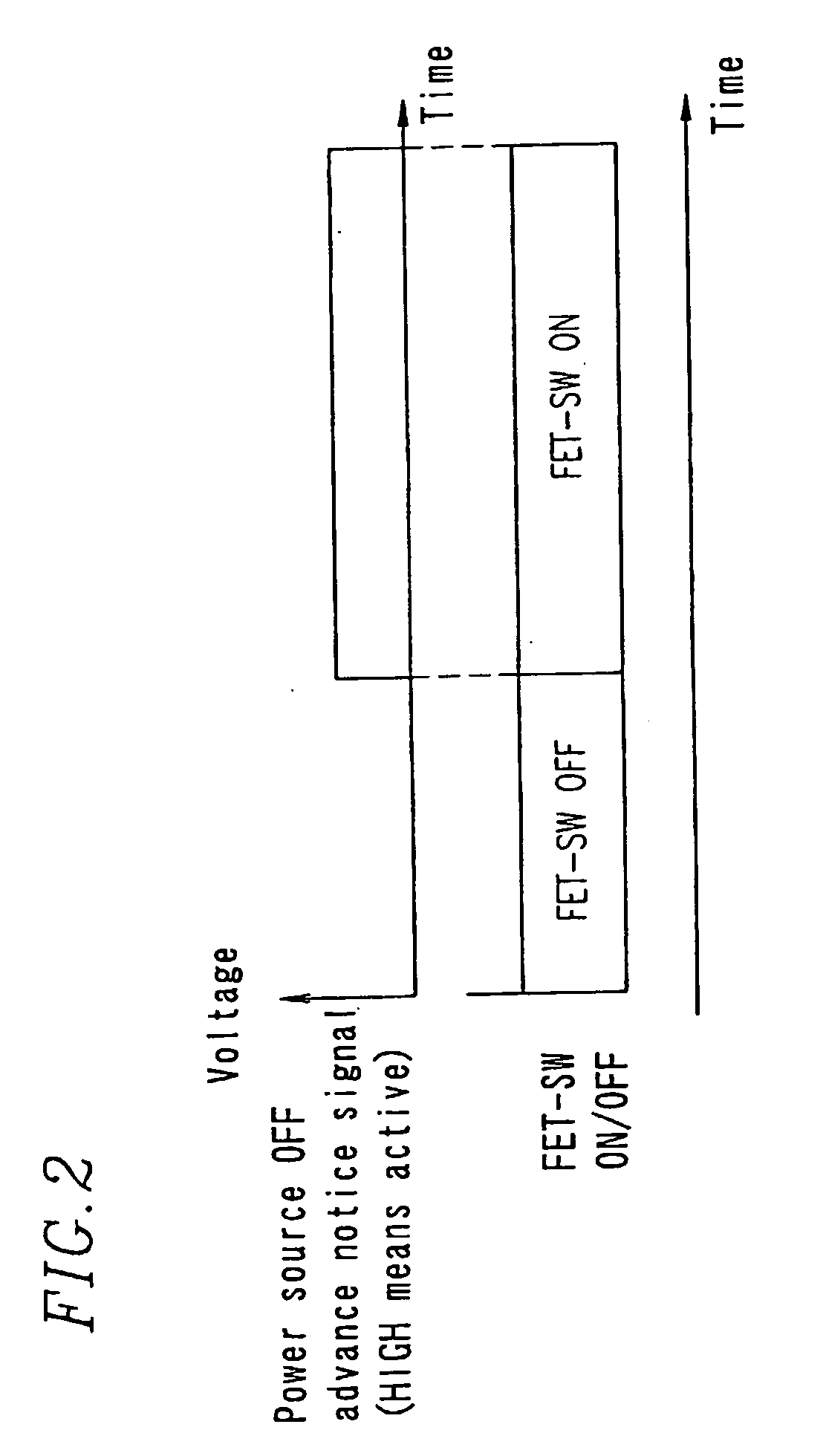

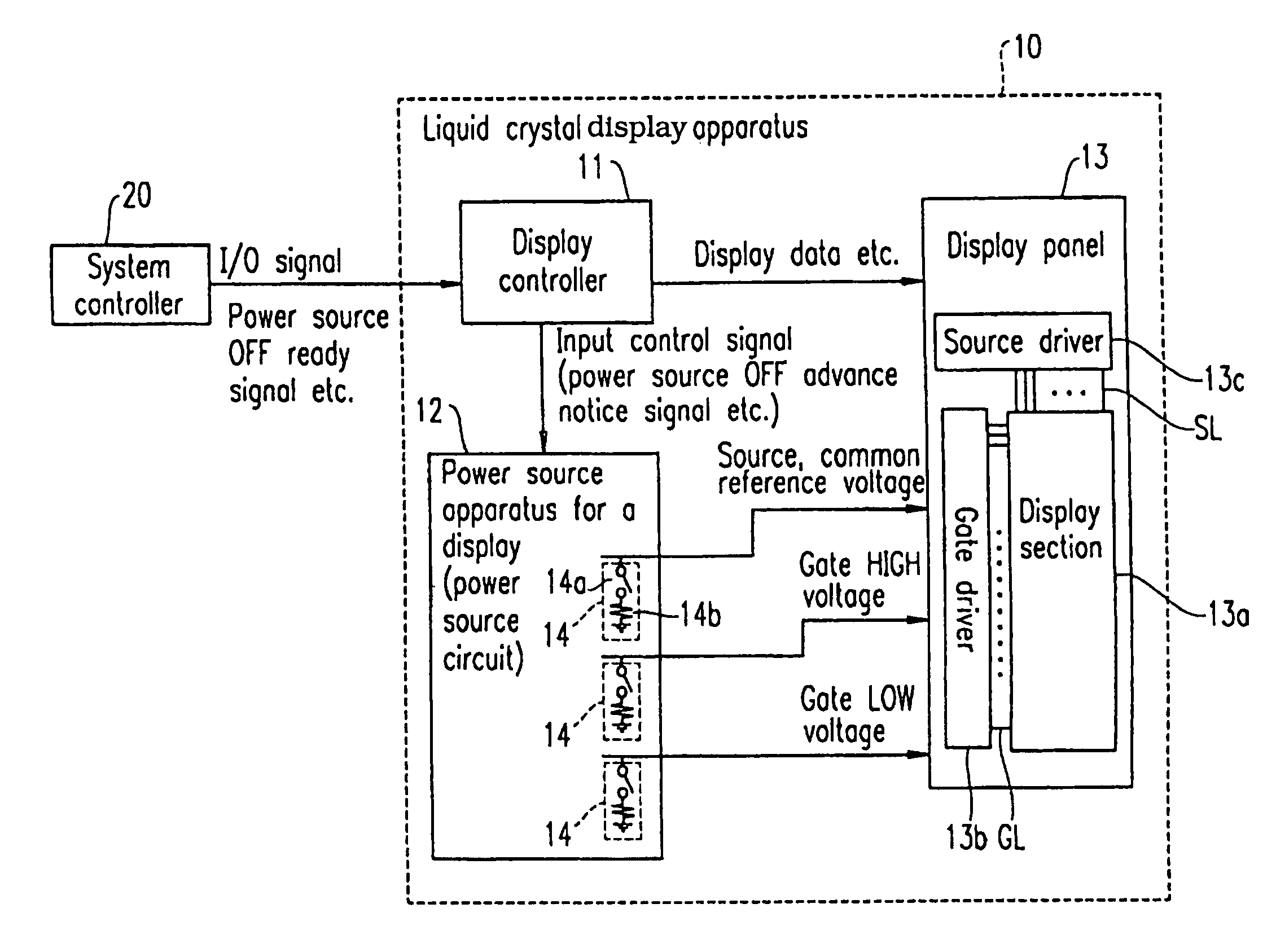

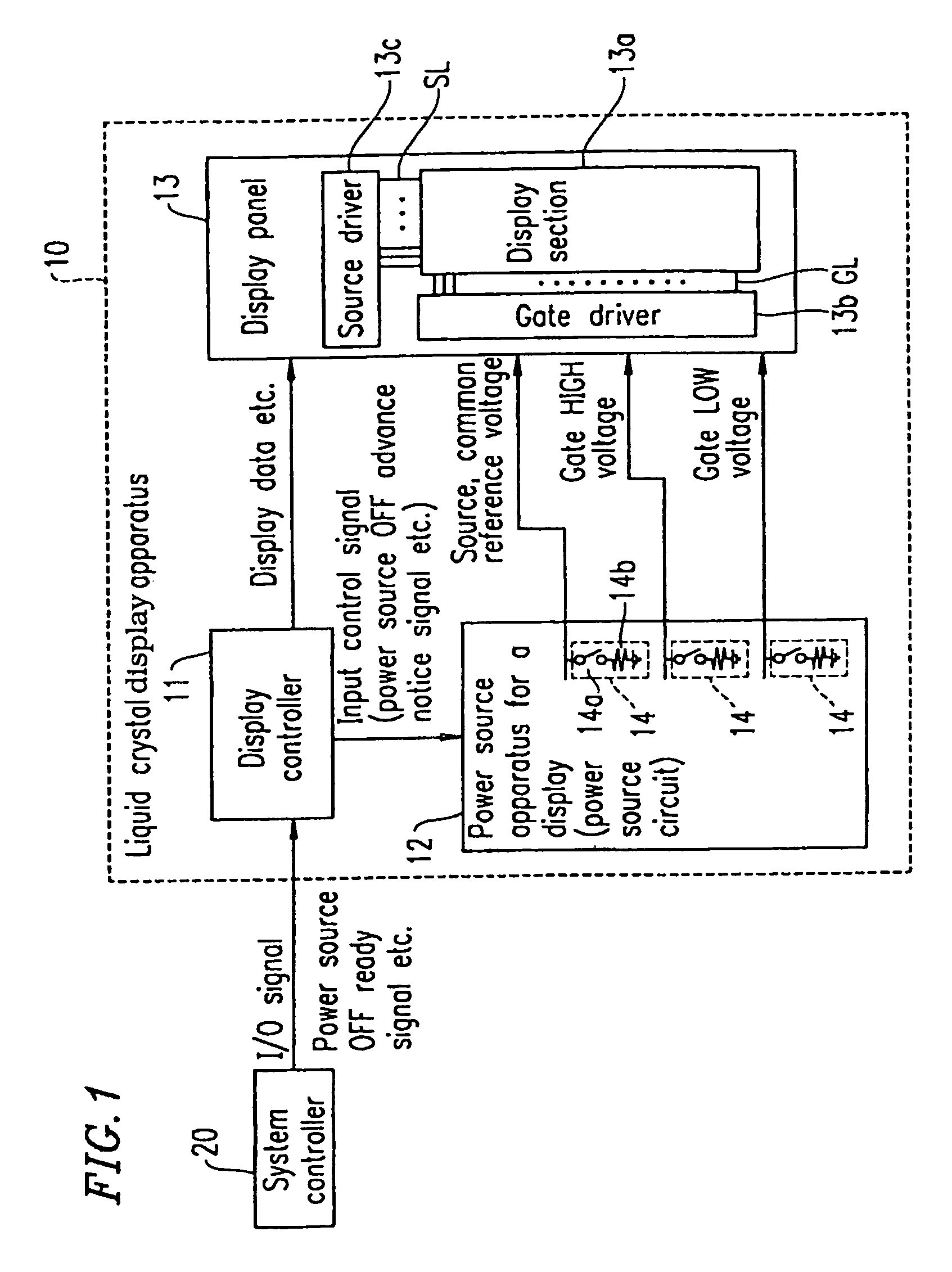

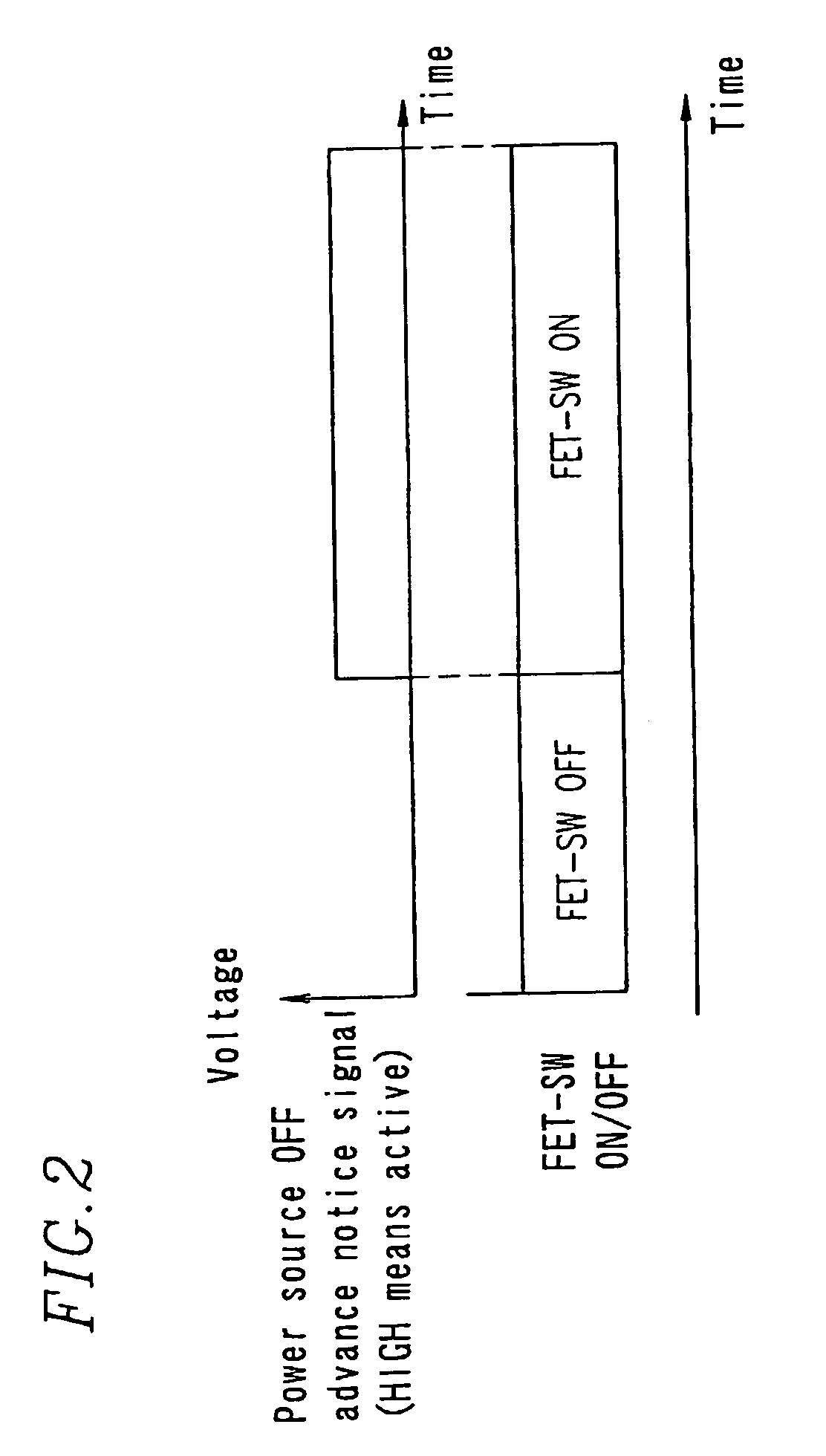

Power source apparatus for display and image display apparatus

InactiveUS20100156883A1Reduce power consumptionAvoid it happening againVolume/mass flow measurementElectrode and associated part arrangementsDisplay deviceVoltage

A power source apparatus for a display is provided, which comprises a voltage generating section capable of controlling outputting or output termination of one or more predetermined output voltages, and a switching section provided between an output terminal of the predetermined output voltage and a predetermined reference potential terminal. The switch section is turned from OFF to ON when the voltage generating section performs the output termination control.

Owner:SHARP KK

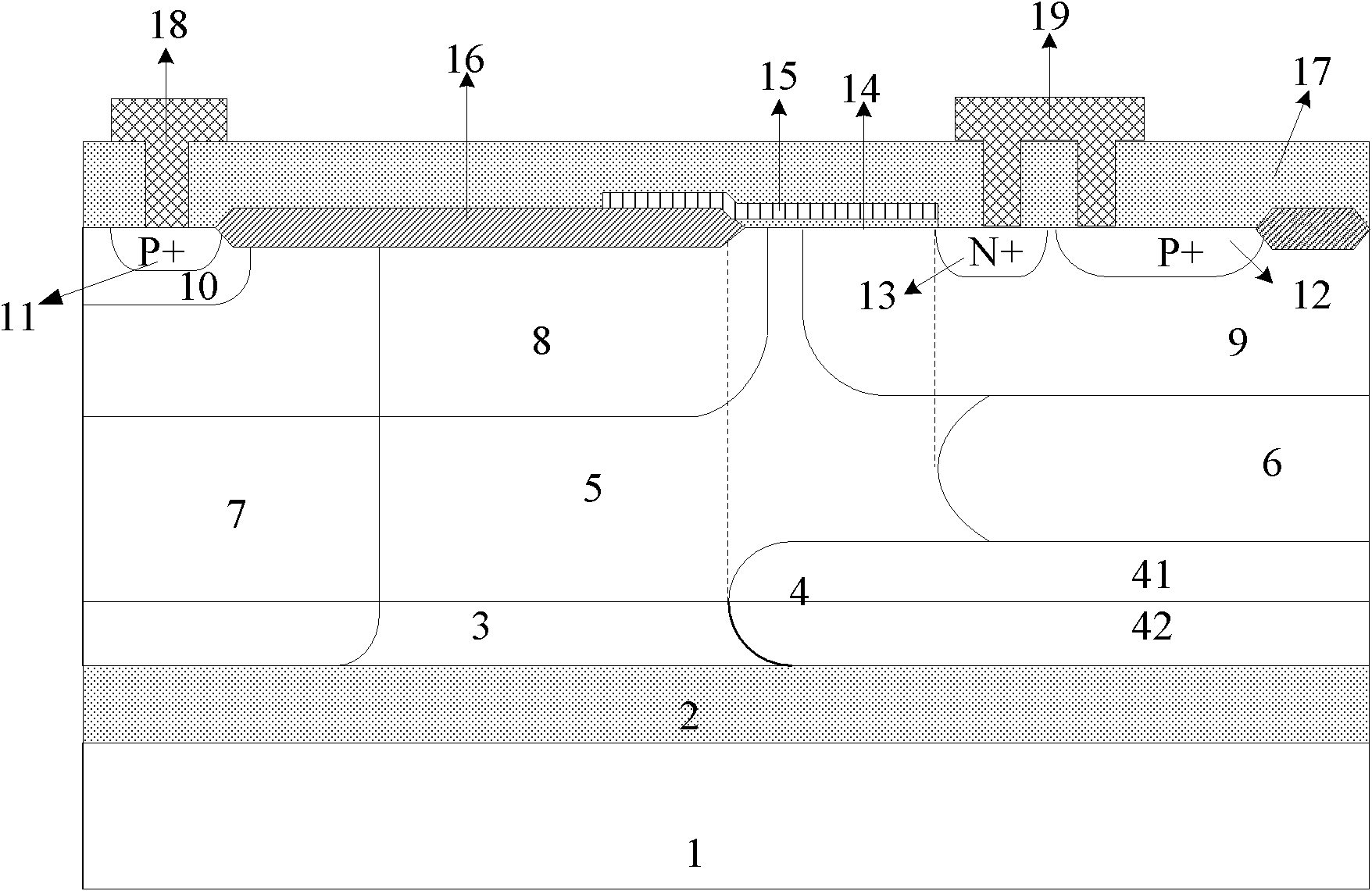

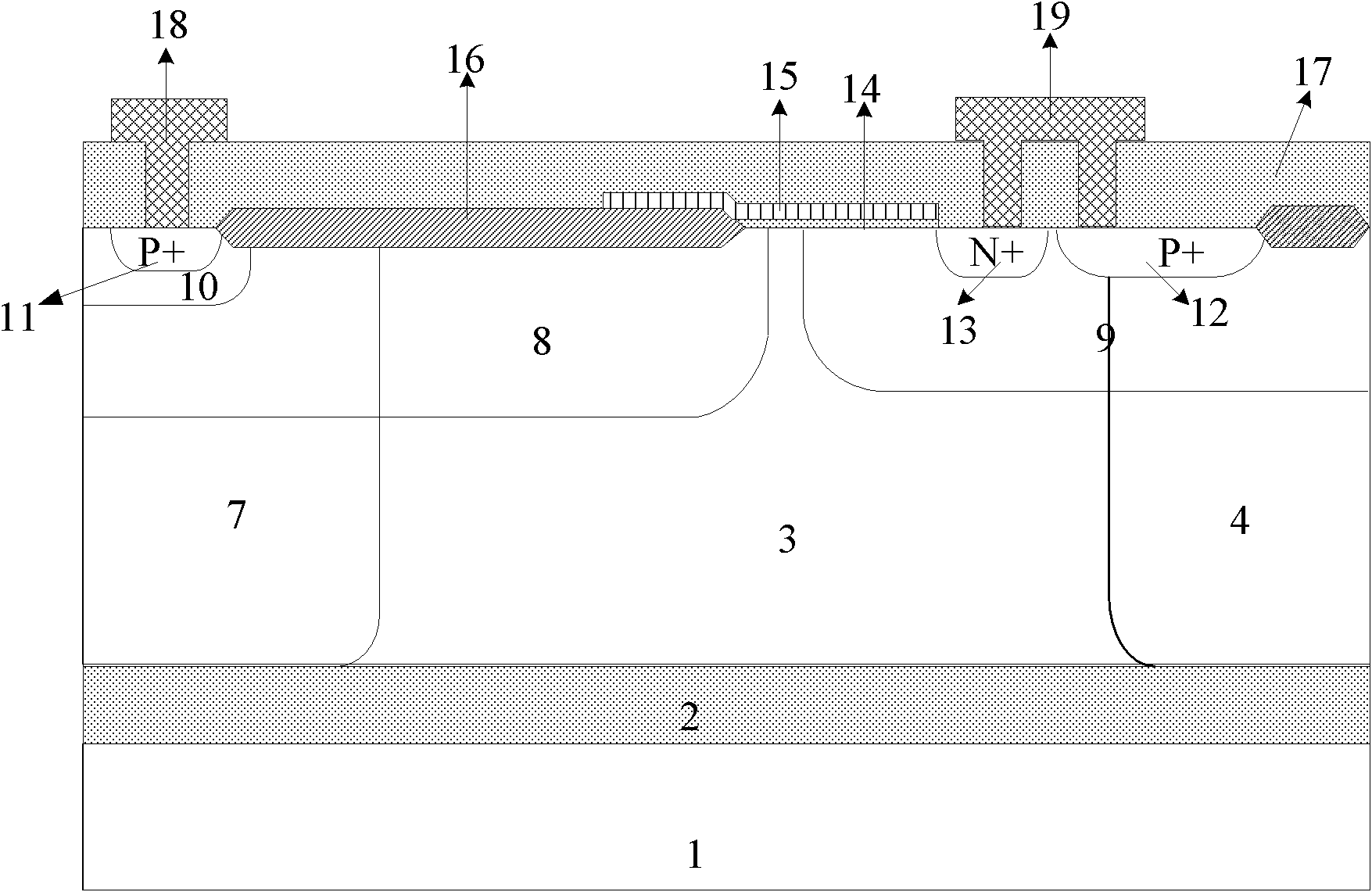

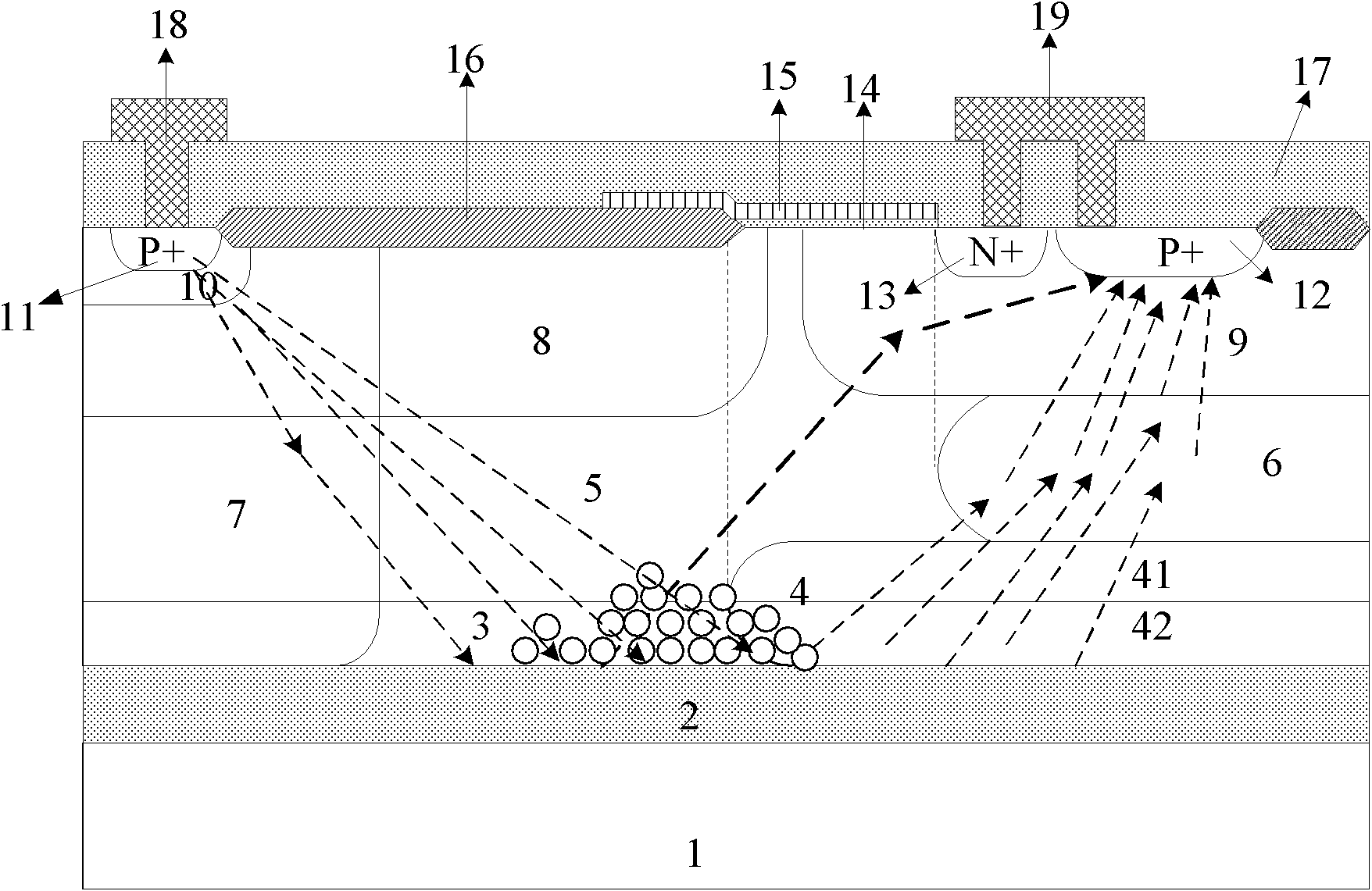

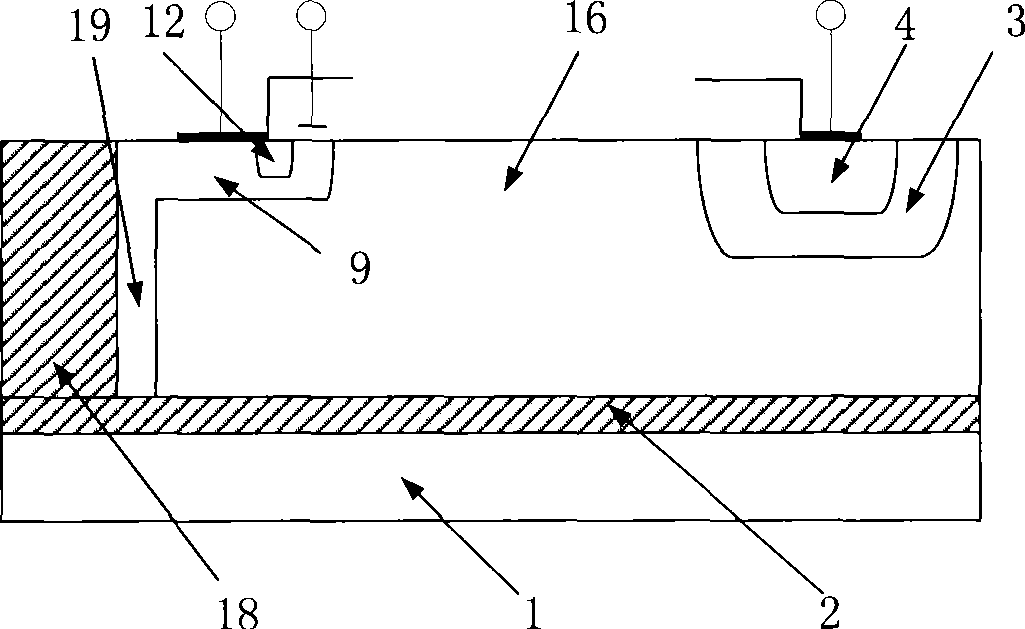

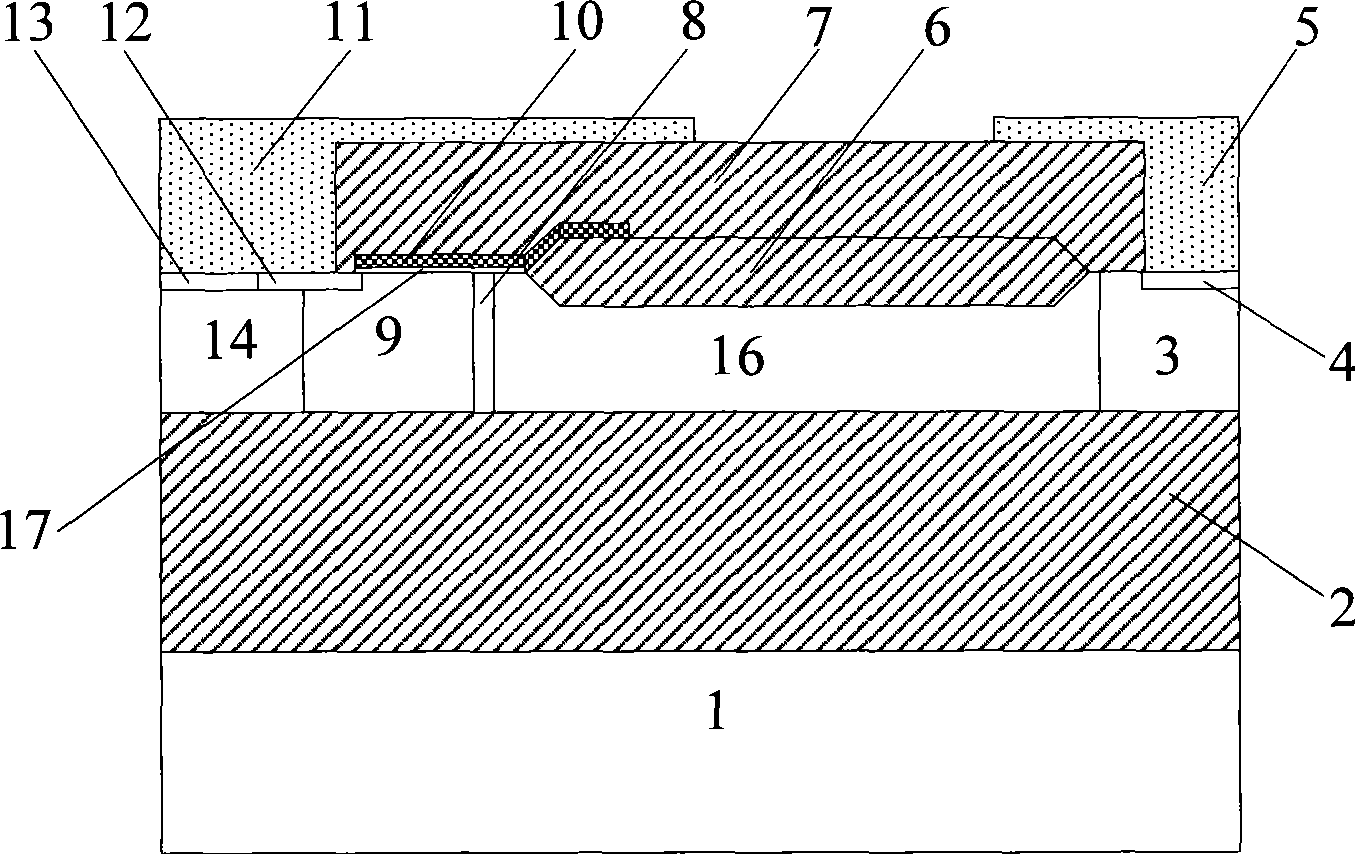

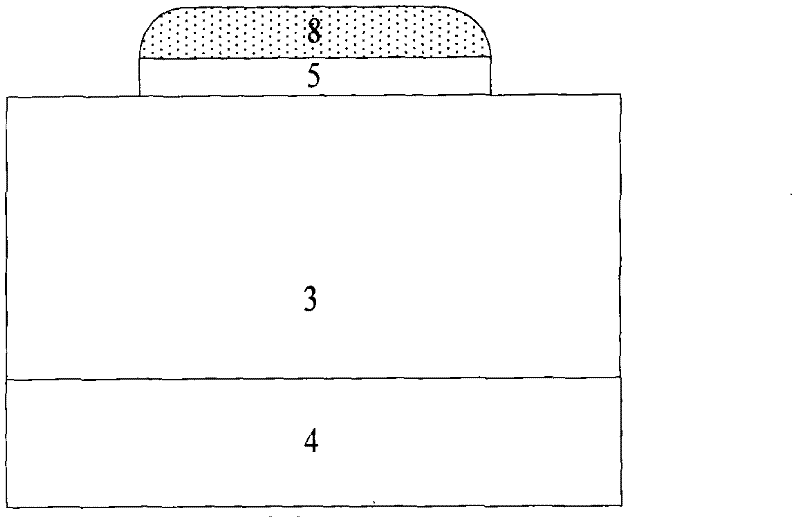

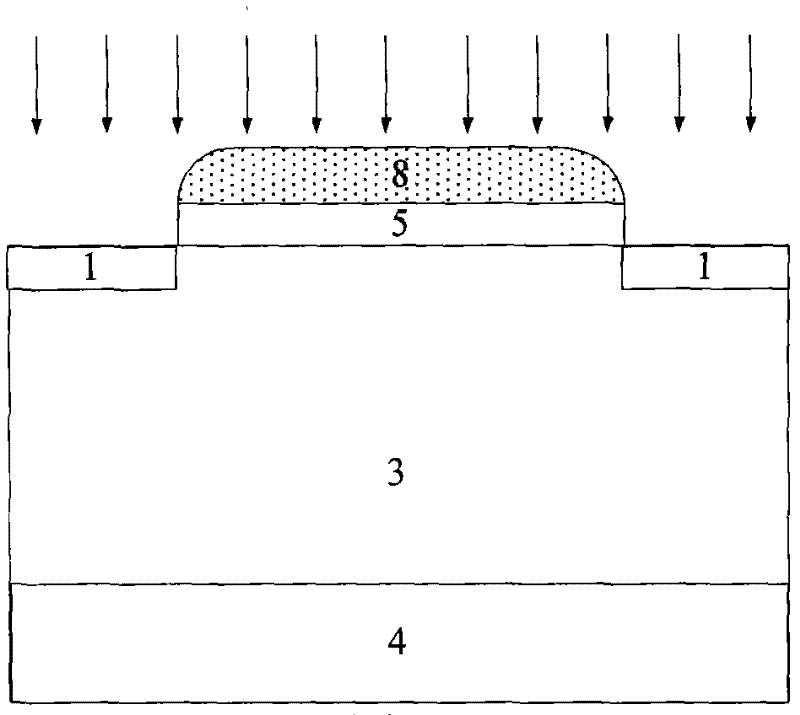

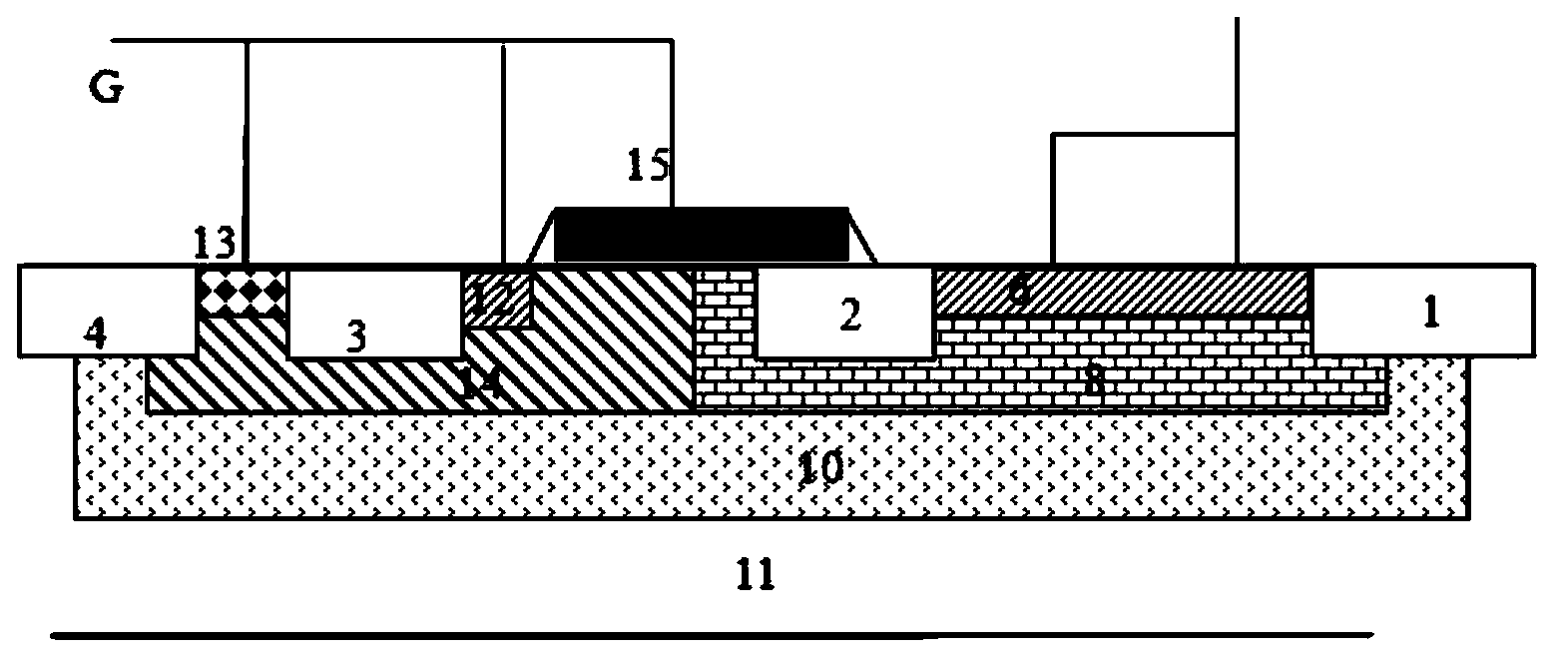

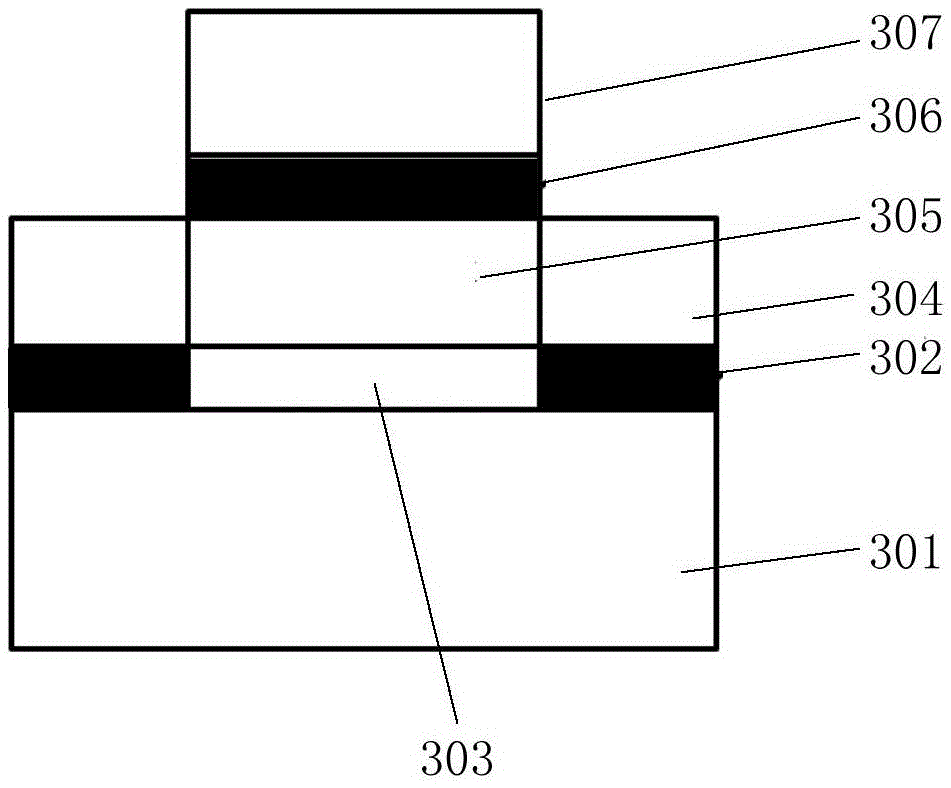

Silicon-on-insulator N-type transverse insulated gate bipolar transistor and preparation method thereof

InactiveCN102130153ARaise the trigger threshold conditionRaise the threshold voltageSemiconductor/solid-state device manufacturingSemiconductor devicesPhysicsPolycrystalline silicon

The invention relates to a silicon-on-insulator N-type transverse insulated gate bipolar transistor and a preparation method thereof. The silicon-on-insulator N-type transverse insulated gate bipolar transistor comprises a P-type silicon-on-insulator silicon wafer, wherein the right region of a first P-type epitaxial layer is provided with a P-type buried layer; a second P-type epitaxial layer is arranged above the first P-type epitaxial layer; a P-type high-energy ion-implantation layer and a P-type channel region are arranged in the second P-type epitaxial layer; the left side is provided with an N-type deep well and an N-type drift region; an N-type buffer layer and a P-type anode contact region are arranged in the N-type drift region; an N-type cathode contact region and a P-type body contact region are arranged in the P-type channel region; a first field oxide layer and a gate oxide layer are arranged above the N-type drift region; the gate oxide layer extends rightwards to above the P-type channel region; and polycrystalline silicon is arranged above the gate oxide layer and used as a gate. The preparation method comprises the following steps: carrying out implantation onto the right region of the first P-type epitaxial layer to form the P-type buried layer, and carrying out implantation onto the right region of the second P-type epitaxial layer to form the P-type high-energy ion-implantation layer which is communicated with the P-type buried layer, so that the concentration gradually increases from bottom to top so as to form an electrically conductive path which can effectively inhibit the latch effect.

Owner:SOUTHEAST UNIV

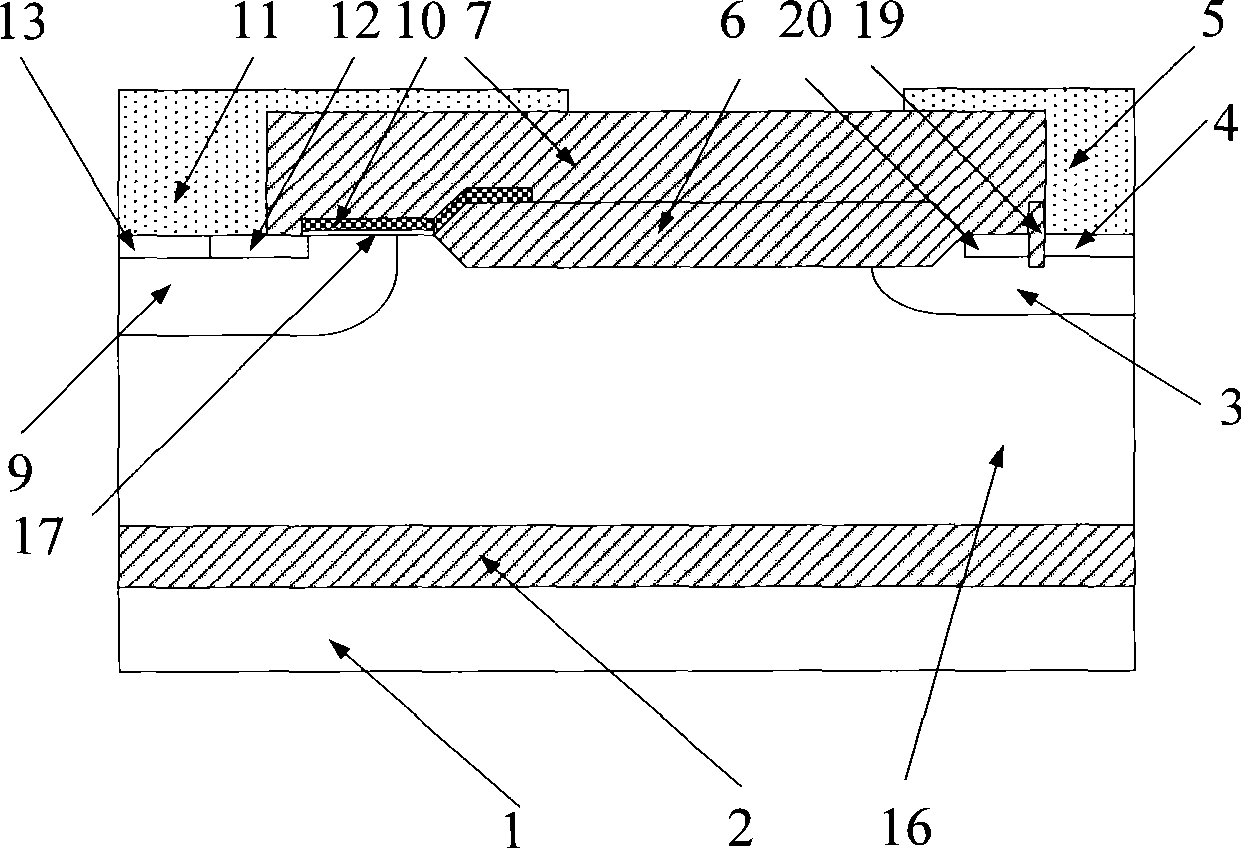

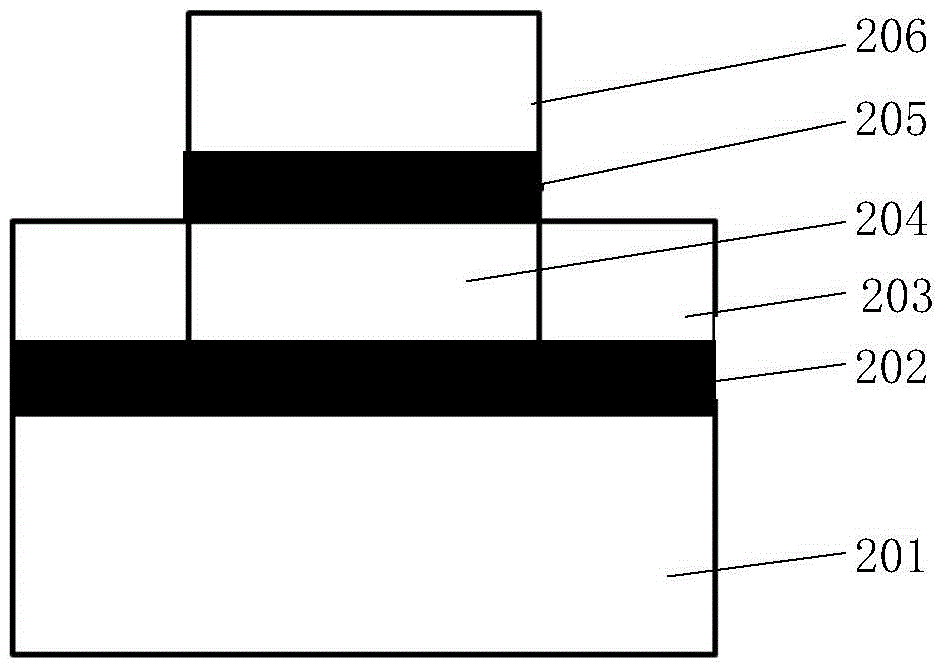

Thin layer SOILIGBT device

InactiveCN101431097AReduce power consumptionStrong radiation resistanceSemiconductor devicesThin layerConduction loss

The invention relates to a folium SOILIGBT device which belongs to the technical field of semiconductor power device. The thickness of SOI layer of the device is 1 mu m to 2 mu m; a cavity barrier layer is arranged between a body zone and a drift zone; the cavity is blocked in the drift zone to the utmost extent; and then the cavity consistence near the side of a cathode in the drift zone is increased; and conduction losses of the device are reduced. A P type depletion zone can also be added near the cavity barrier layer to assist to deplete the N type cavity barrier layer, and so drift zone depletion is strengthened when the device bears a high pressure, and breakdown characteristics of the device are improved. The folium SOILIGBT device has the advantages of small parasitics, fast speed, low power consumption, strong anti-radiation performance, and is compatible with the standard process. An LIGBT device having good performance, high pressure, high speed and low conduction losses can be made when the folium SOILIGBT device is adopted.

Owner:UNIV OF ELECTRONICS SCI & TECH OF CHINA

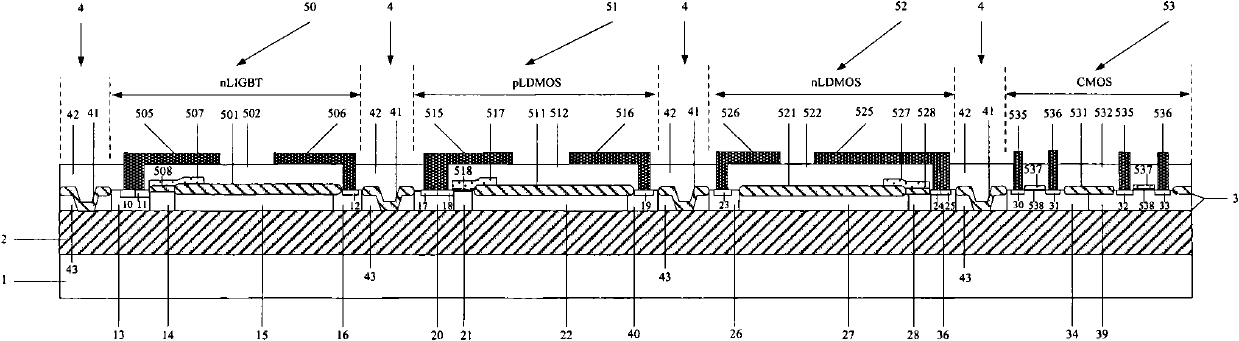

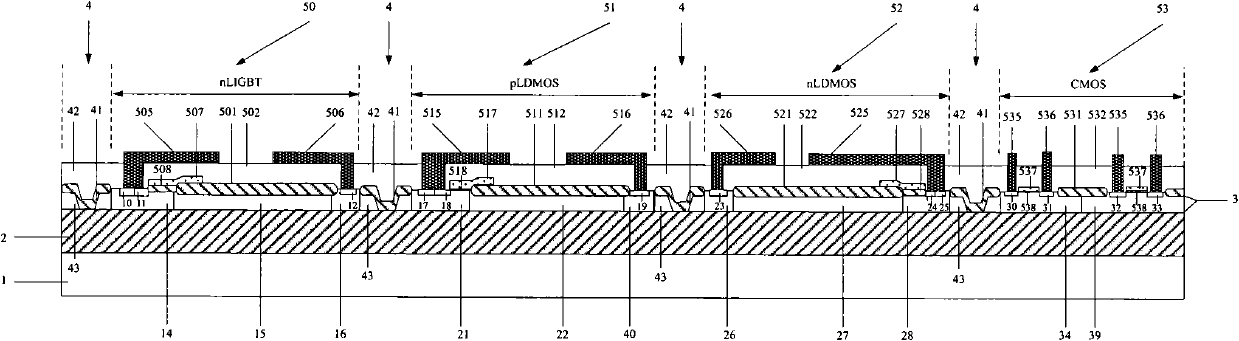

Integrated power device on silicon on insulator (SOI) layer for negative supply voltage

InactiveCN102024825AImprove compatibilityReduce processing difficultySolid-state devicesSemiconductor devicesDielectricLow voltage

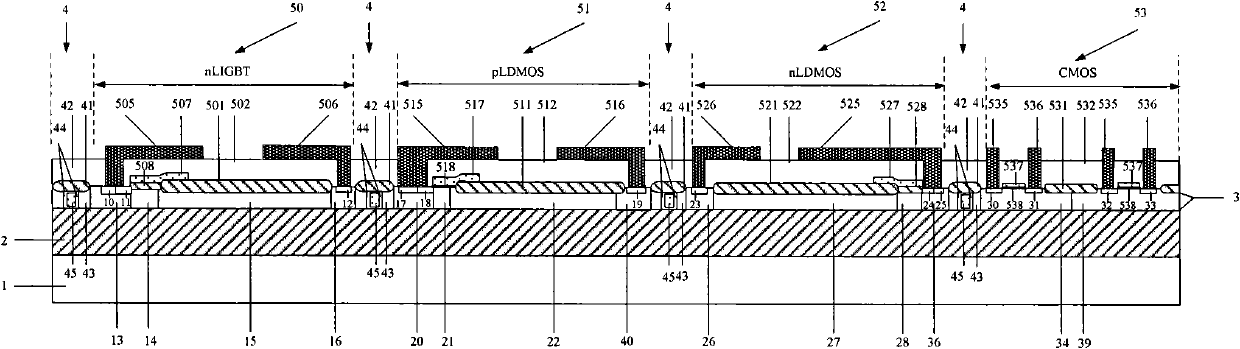

The invention provides an integrated power device on a silicon on insulator (SOI) layer for negative supply voltage, belonging to the field of semiconductor power devices. The integrated power device on the SOI layer for the negative supply voltage is characterized in that the SOI layer is integrated with at least two or three high-voltage devices of an n-type lateral insulated gate bipolar transistor (nLIGBT), a p-type laterally diffused metal oxide semiconductor (pLDMOS) and an n-type laterally diffused metal oxide semiconductor (nLDMOS), and also can be integrated with a low-voltage metal oxide semiconductor (MOS) device; buried oxide layers and dielectrically isolated areas connected with the buried oxide layer are used to realize the complete isolation among the different devices; a conventional local oxidation of silicon (LOCOS) technology or a shallow trench isolation technology is adopted for realizing the dielectrically isolated area; the SOI layer is 0.5-3mu m in thickness; and the dielectric electric-field strength of the thick gate oxide layer of the high-voltage nLIGBT and nLDMOS devices is less than 5*106V / cm so as to meet the requirements of the high-voltage integrated circuit of the negative supply voltage for high voltage resistance between the grid electrodes and source electrodes of the devices. The integrated power device on a SOI layer for the negative supply voltage has the advantages of small parasitic effect, fast speed, low power consumption, strong irradiation resistance and the like, realizes compatibility of the high-voltage devices with the low-voltage devices, and meets the requirements of the working environment of the negative supply voltage. The integrated power device on a SOI layer for the negative supply voltage is used to manufacture a plurality of high-voltage, high-speed and low conducting-loss power devices with good performances, and is used for the high-voltage application of the negative supply voltage.

Owner:UNIV OF ELECTRONICS SCI & TECH OF CHINA

Multichannel SRAM single-event test method and device

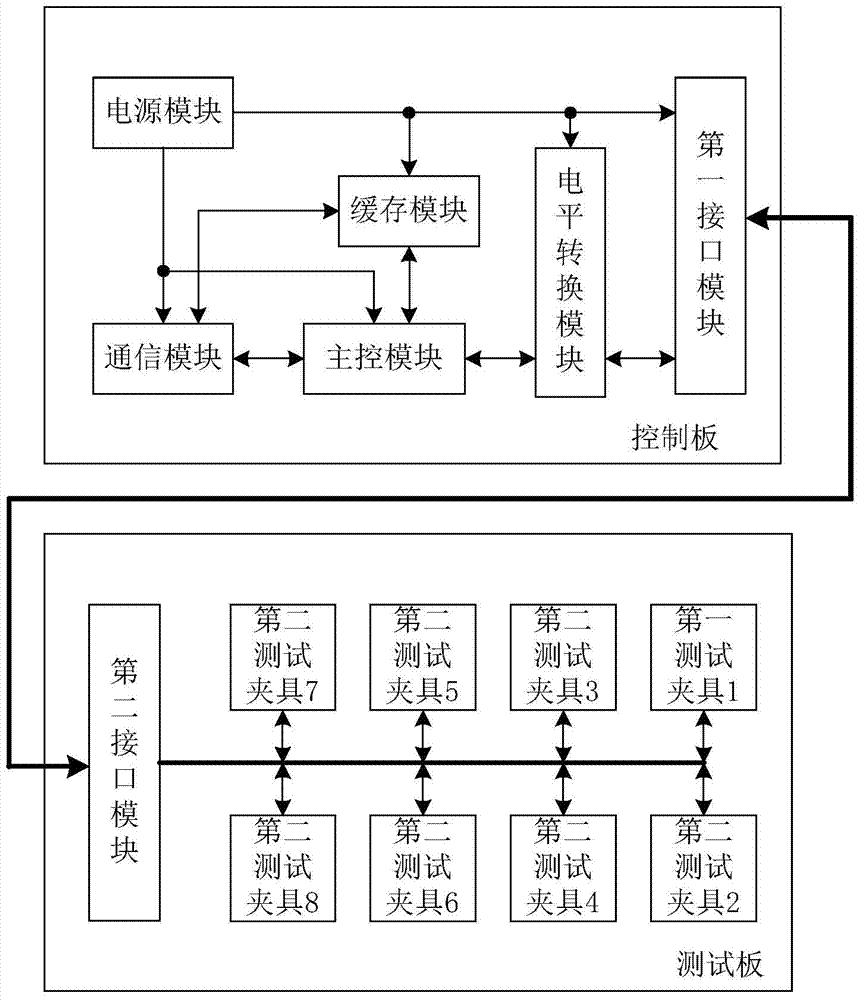

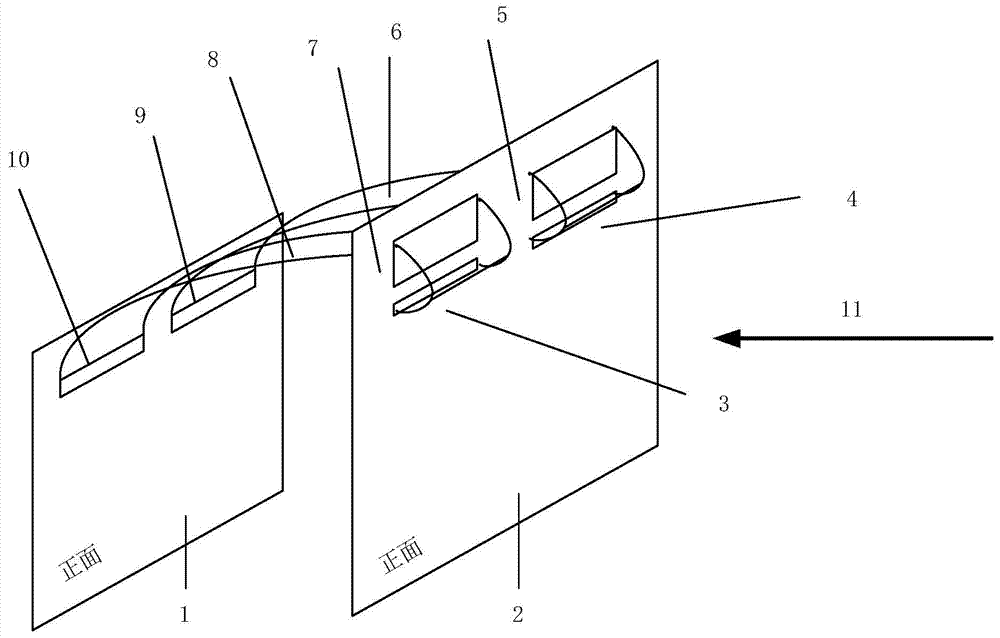

ActiveCN104505125AImprove accuracyReal-time detection of working currentStatic storageEngineeringIrradiation

The invention provides a multichannel SRAM single-event test device which comprises a test board and a main control board, wherein the test board is used for fixing and connecting a to-be-tested chip, and the main control board is used for controlling an irradiation testing system and reading and recording data in the to-be-tested chip. The device can test single event effects of multiple SRAM devices at the same time, obtains characteristic parameters of the single event effects, improves the accuracy of estimating the single event effect resistance of a to-be-tested device, and further can detect the working current of the to-be-tested device in real time, so as to avoid the generation of latch-up.

Owner:INST OF MICROELECTRONICS CHINESE ACAD OF SCI

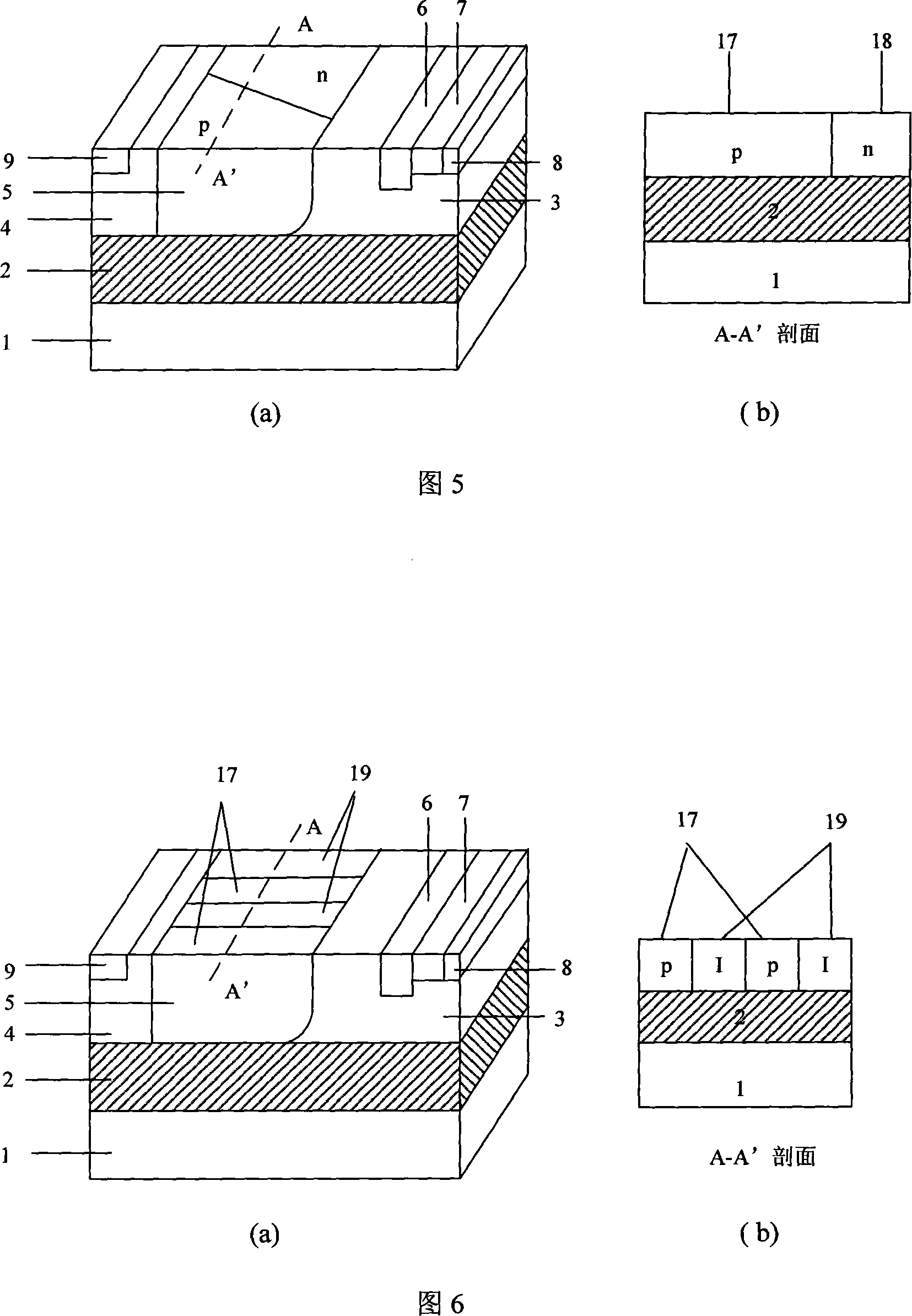

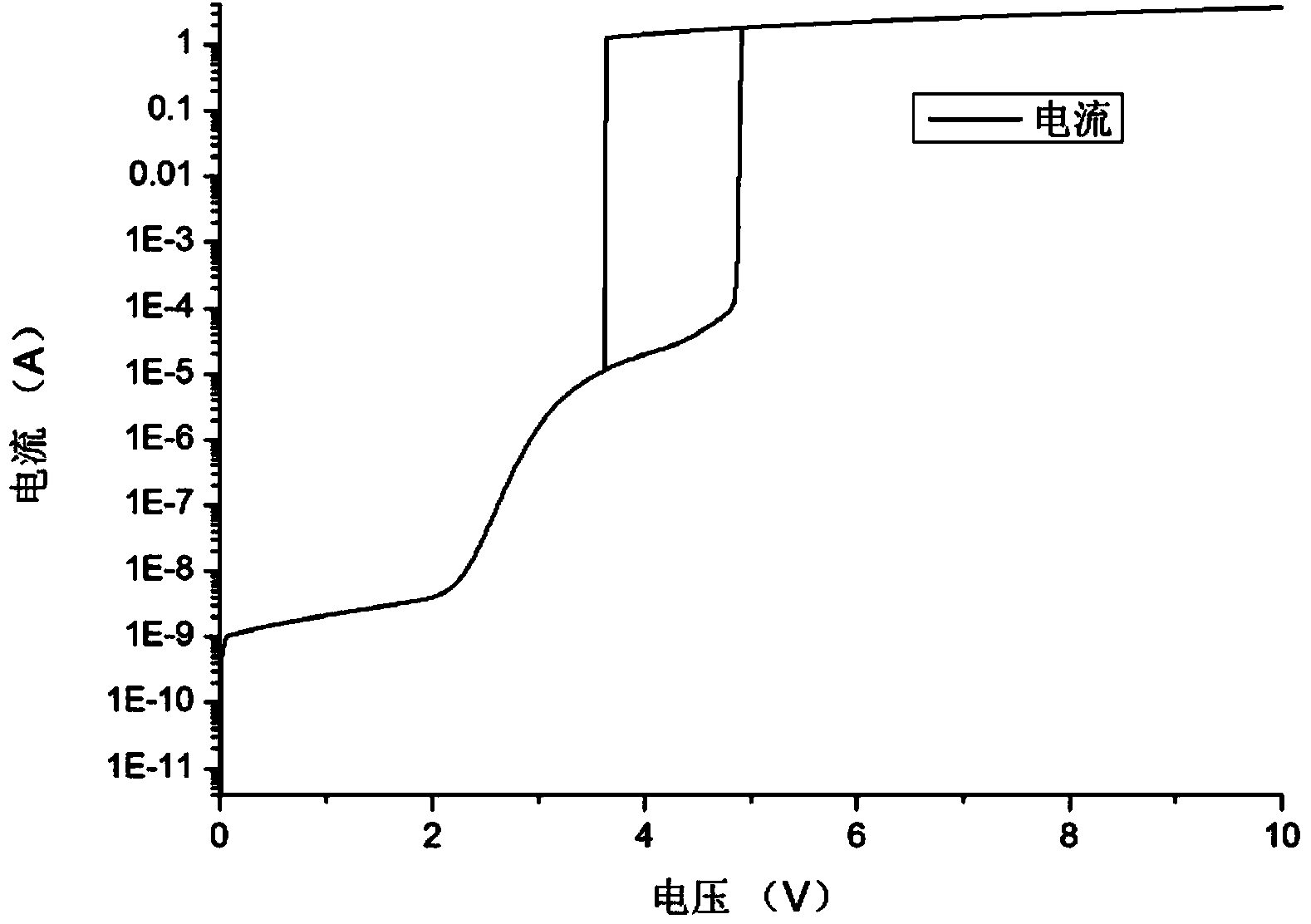

High-voltage electronic static discharge (ESD) protection device with positive-negative (PN) junction auxiliary trigger silicon controlled rectifier-laterally diffused metal oxide semiconductor (SCR-LDMOS) structure

ActiveCN105742281AImprove ESD protection capabilityEnhanced ESD robustnessSolid-state devicesDiodeNegative feedbackLDMOS

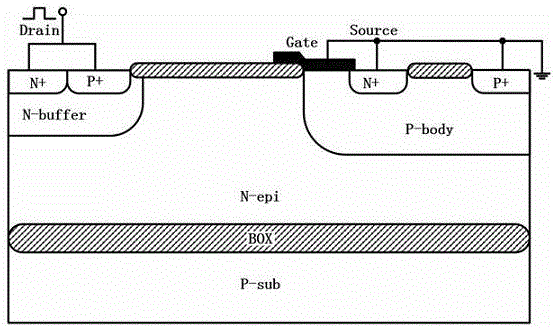

The invention discloses a high-voltage electronic static discharge (ESD) protection device with a positive-negative (PN) junction auxiliary trigger silicon controlled rectifier-laterally diffused metal oxide semiconductor (SCR-LDMOS) structure. The high-voltage ESD protection device comprises a P-type substrate, wherein a buried oxygen layer is arranged on the P-type substrate, a shift region is arranged on the buried oxygen layer, an N-buffer region, a P region and a P-body region are sequentially arranged on the shift region from left to right, a first drain heavily-doping N+ region and a first drain heavily-doping P+ region are sequentially arranged in the N-buffer region from left to right, a second source heavily-doping N+ region, a second source heavily-doping P+ region and a third source heavily-doping P+ region are sequentially arranged in the P-body region from left to right, and the P region and the second source heavily-doping P+ region are connected through a wire. When a drain of the ESD protection device encounters a positive ESD pulse, a reverse bias PN junction is used for helping improving the hole carrier concentration before trigger starting, and a trigger voltage V<t1> is reduced; and moreover, with the introduction of the reverse bias PN junction into the device, the positive and negative feedback effect of a parasitic SCR can be effectively prevented, thus, the maintaining voltage V<h> of the device can be effectively increased, and the latch-up effect of the device is prevented.

Owner:ANHUI LONGXINWEI TECH CO LTD

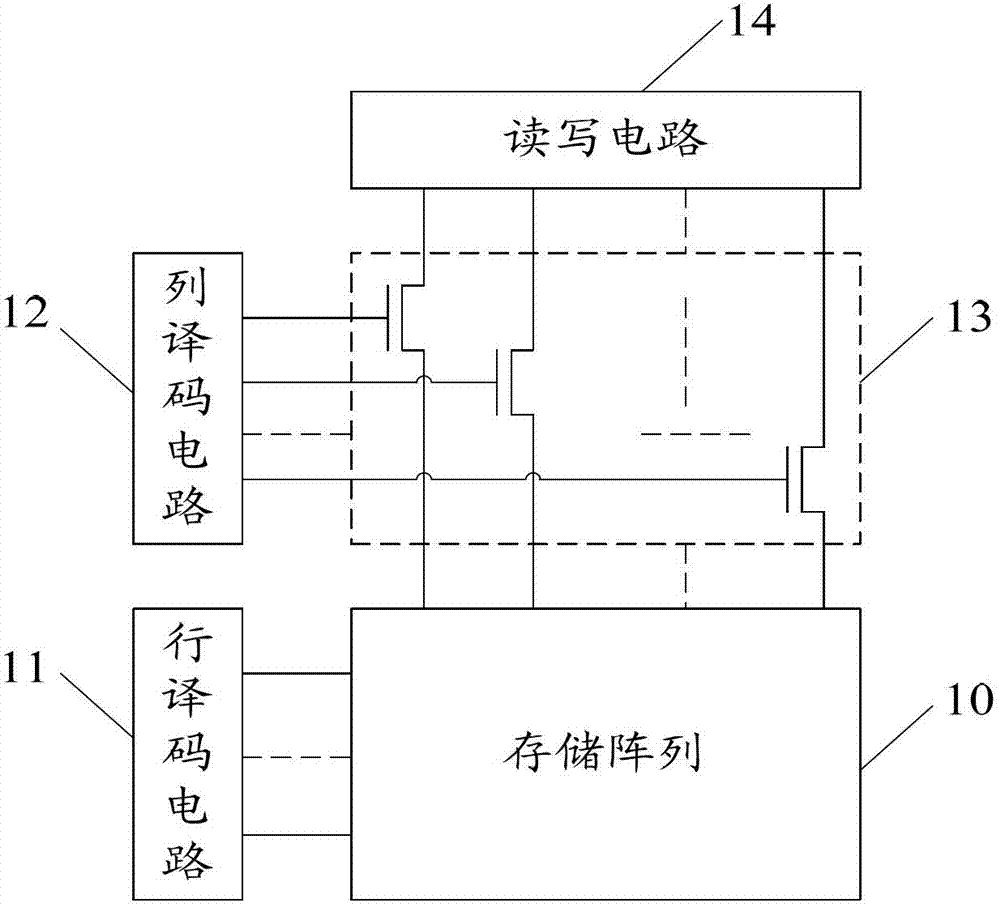

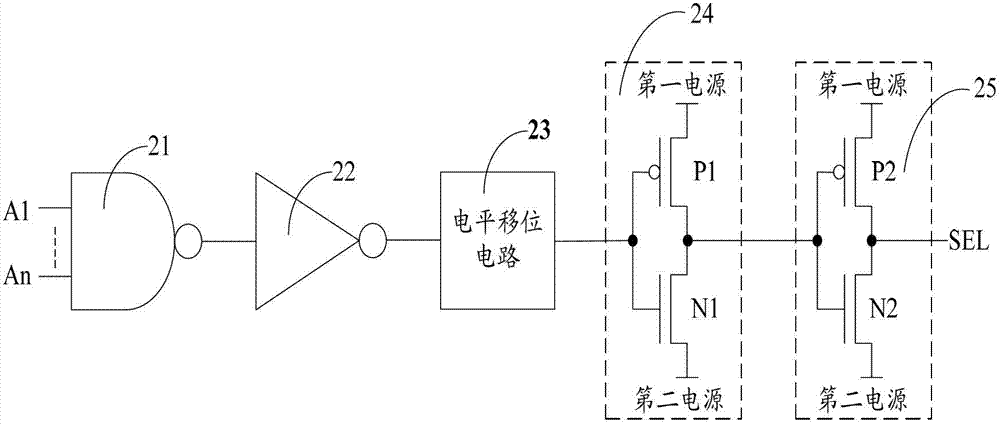

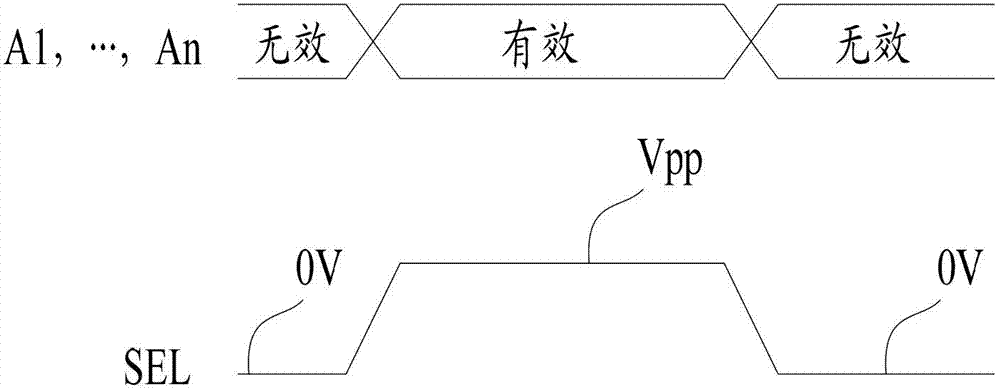

Storage and column decoding circuit thereof

The invention discloses a storage and a column decoding circuit thereof. The column decoding circuit of the storage comprises a NAND gate circuit, a NOT gate circuit, a level shift circuit and a first driving circuit, which are connected in sequence, as well as a second driving circuit and a precharging circuit, wherein the second driving circuit comprises a first PMOS (P-channel Metal Oxide Semiconductor) tube, a first NMOS (N-channel metal oxide semiconductor) tube and a second NMOS tube; the precharging circuit comprises a second PMOS tube and a third NMOS tube; a source electrode of the second PMOS tube is suitable for being connected with a precharging power supply; and when the storage performs read operation, a voltage provided by the precharging power supply is a supply voltage of the storage. According to the storage and the column decoding circuit thereof provided by the technical scheme of the invention, the power consumption of the storage in reading operation can be reduced.

Owner:SHANGHAI HUAHONG GRACE SEMICON MFG CORP

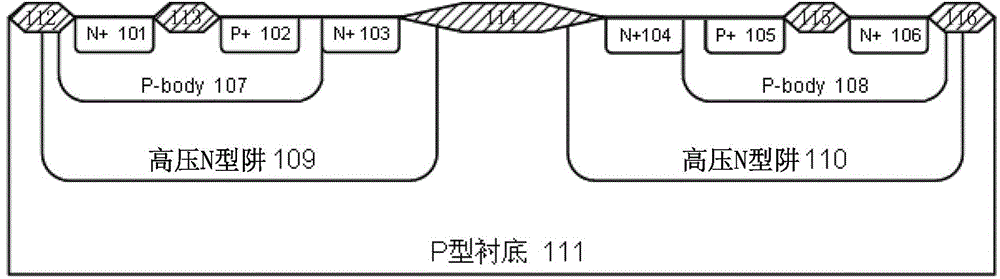

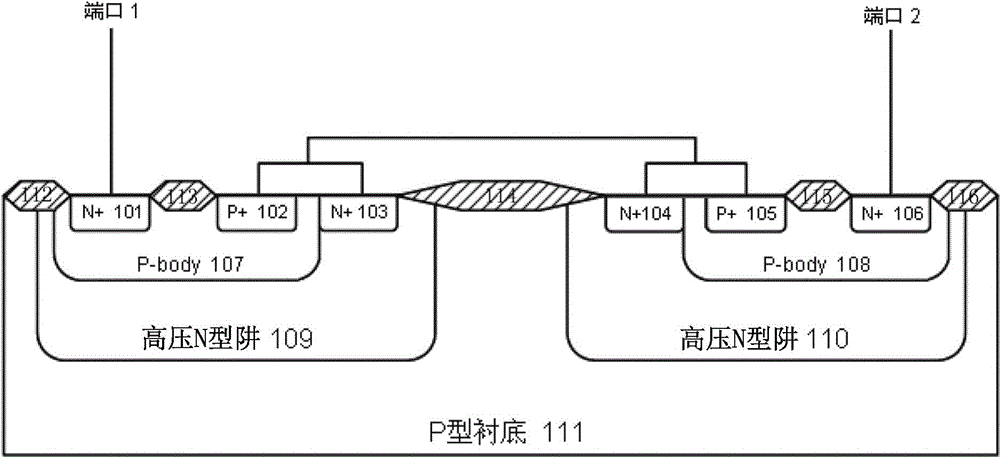

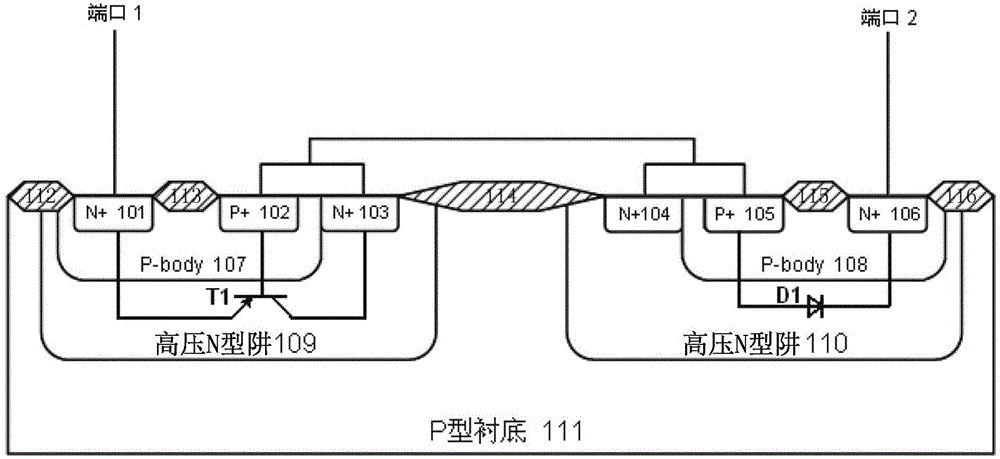

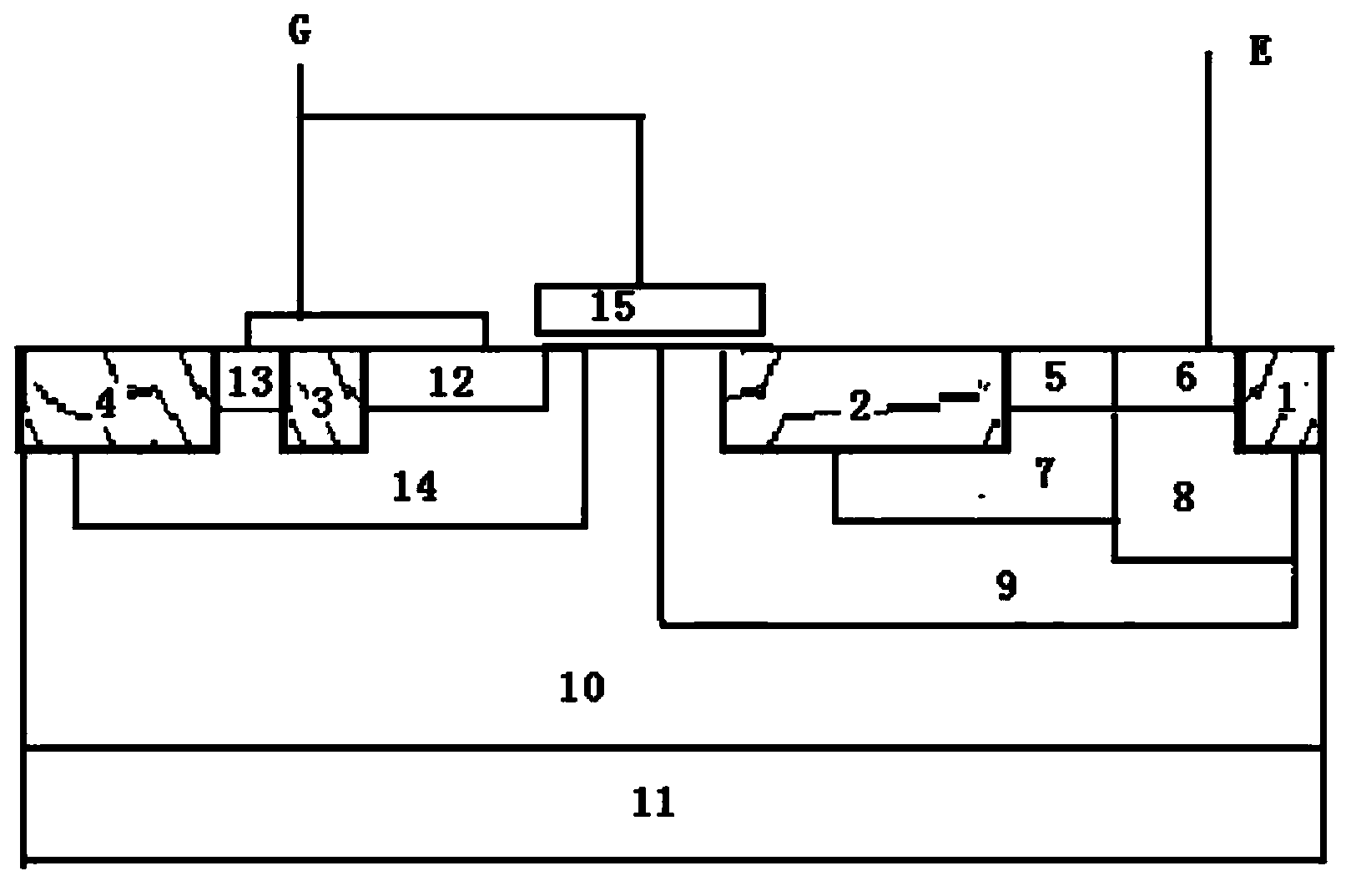

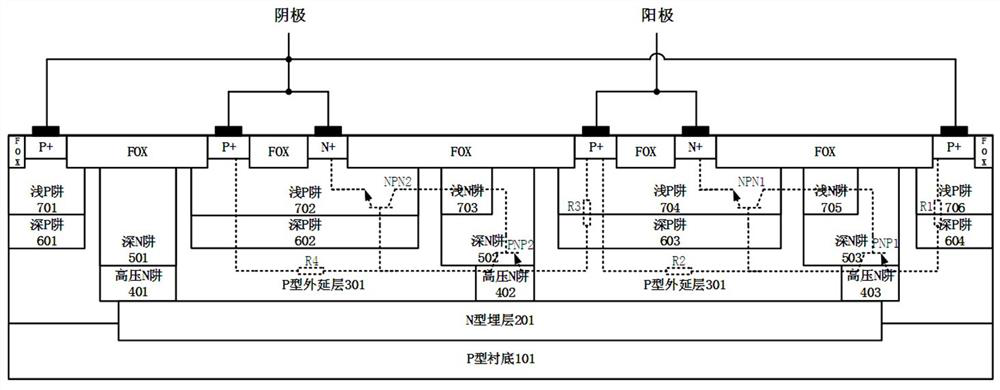

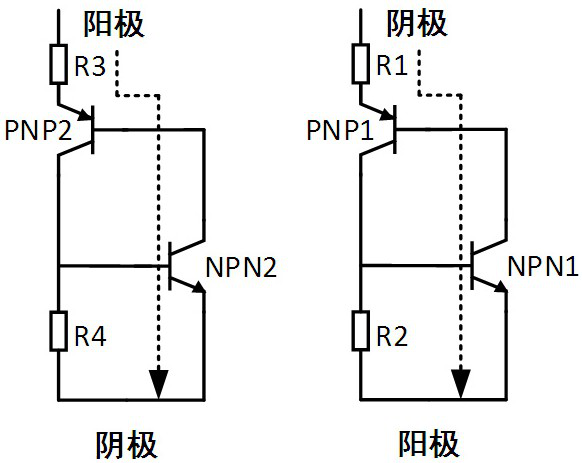

High-voltage bidirectional ESD protective device based on longitudinal NPN structure

ActiveCN104600068ASymmetrical ProtectionIncrease flexibilitySolid-state devicesSemiconductor devicesIsolation layerHigh pressure

The invention relates to a high-voltage bidirectional ESD protective device based on a longitudinal NPN structure. The high-voltage bidirectional ESD protective device based on the longitudinal NPN structure comprises a P type substrate, a first high-voltage N type trap, a second high-voltage N type trap, a first P-body injection region, a second P-body injection region, a first N+ injection region, a first P+ injection region, a second N+ injection region, a third N+ injection region, a second P+ injection region, a fourth N+ injection region and a plurality of oxide isolation layers. Compared with the prior art, the reverse PN junction of the inside longitudinal NPN structure is triggered to conduct under the forward or negative ESD pulse effect, and meanwhile, the positive PN junction in the other N trap is conducted, an ESD current discharge route composed of a longitudinal NPN transistor and a forward diode in a series mode would be generated, the voltage of the device can be kept temporarily through respectively stretching the emitting zone width of each of two NPNS and separately changing the forward or reverse ESD pulse, and the device use environment flexibility is improved.

Owner:武汉芯光虹创科技有限公司

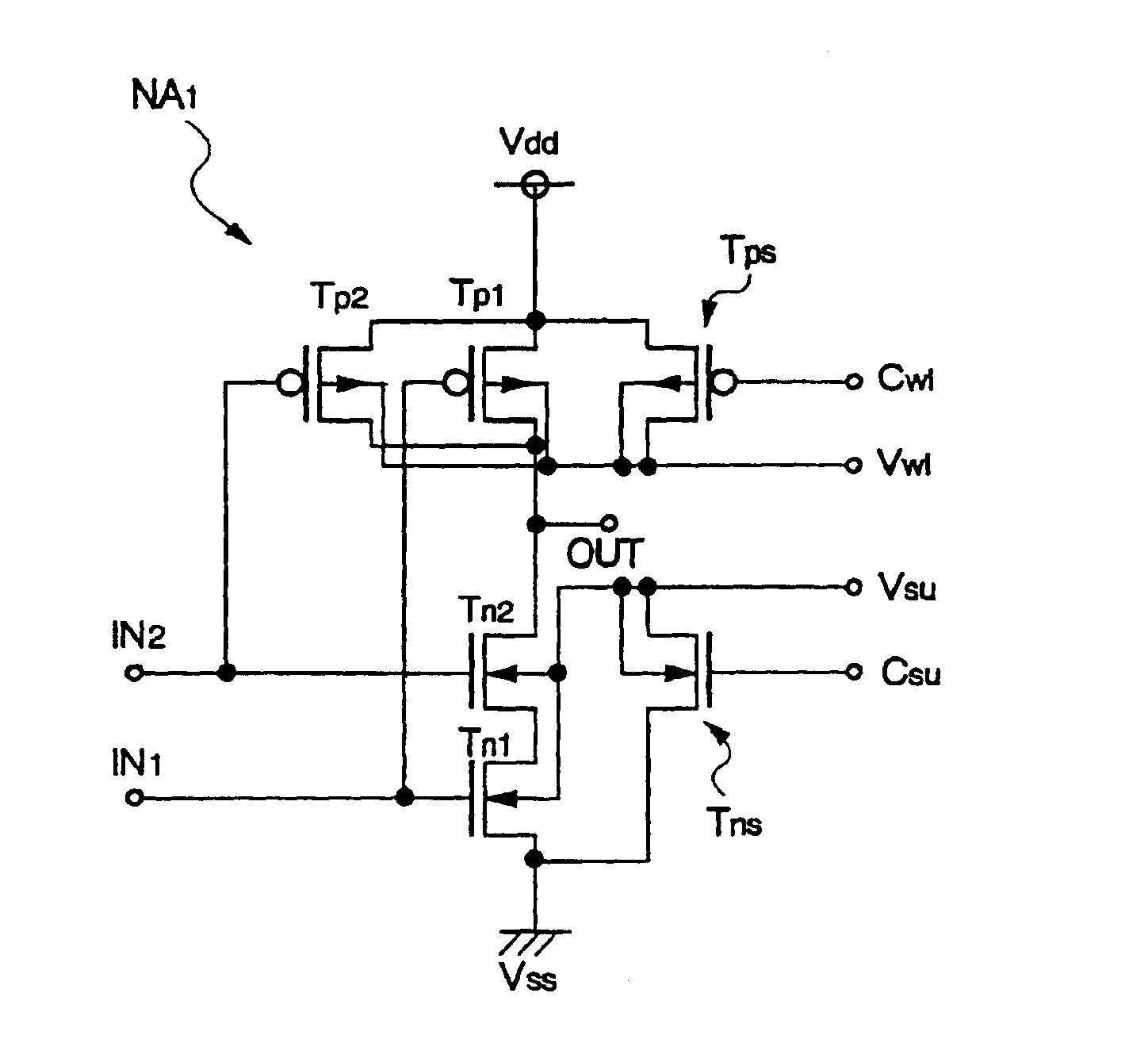

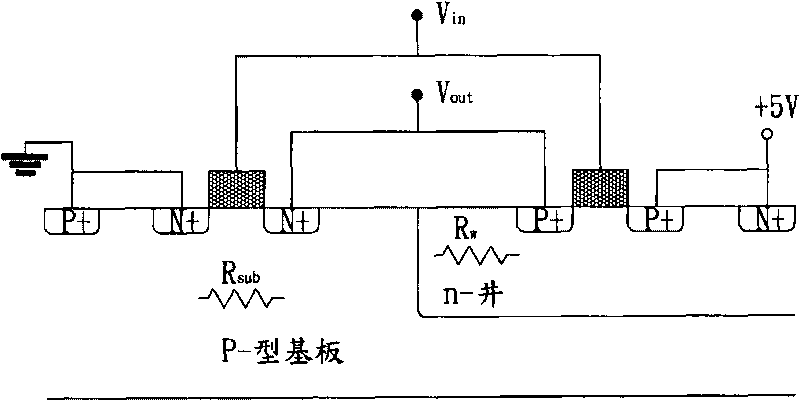

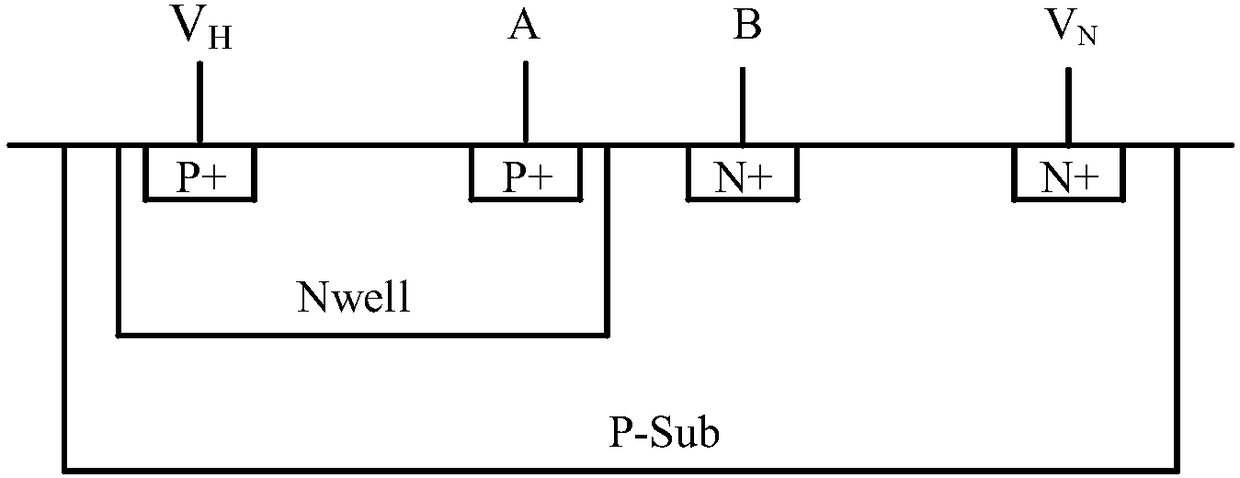

Semiconductor integrated circuit

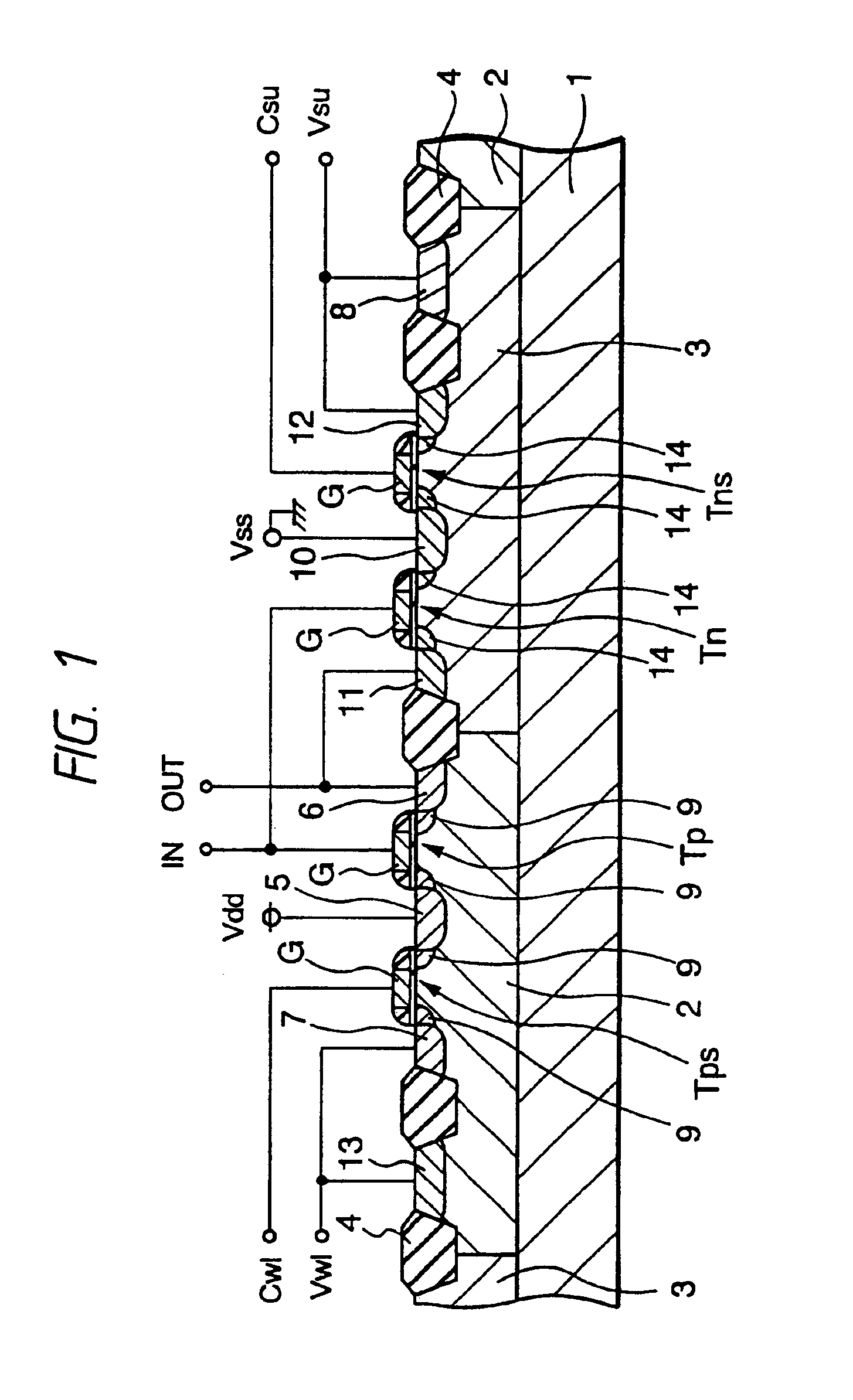

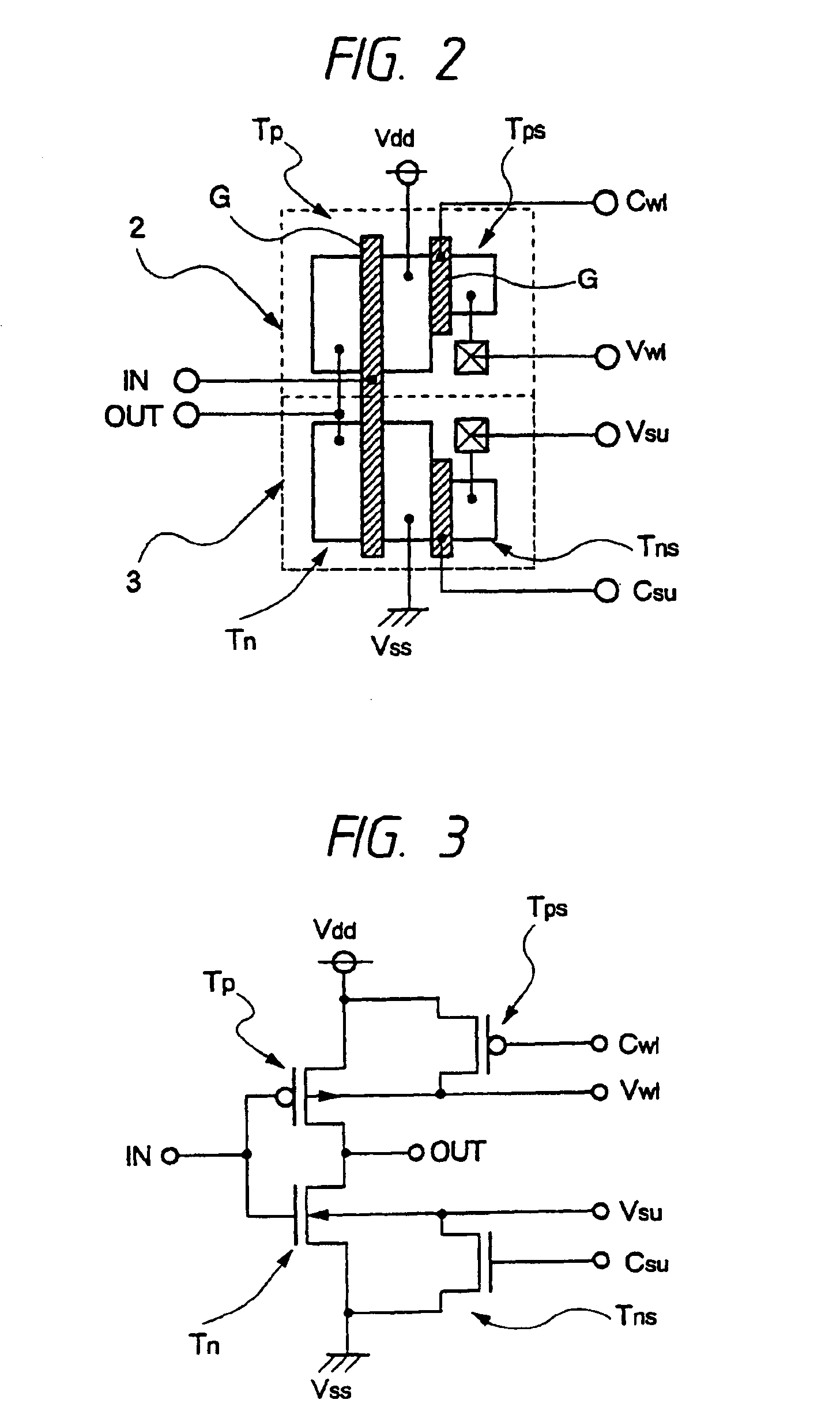

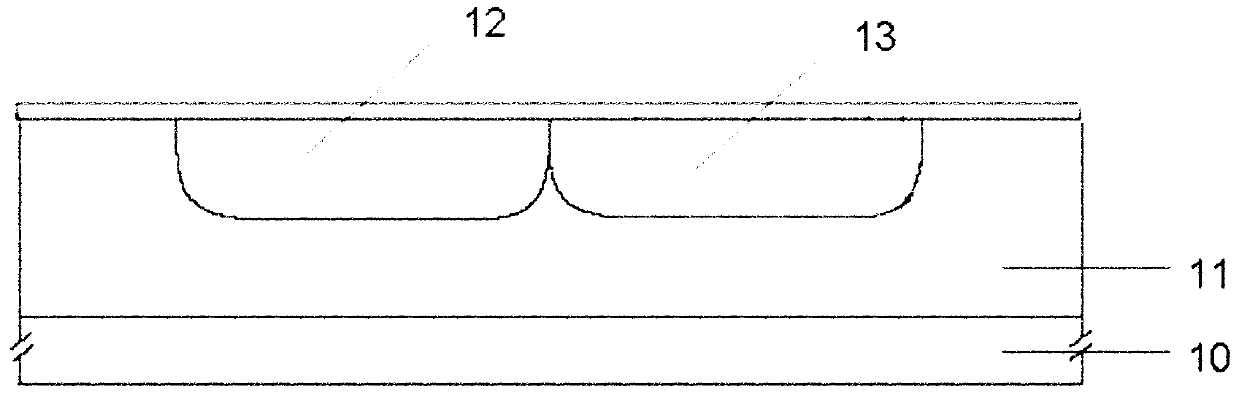

InactiveUS6937068B2Avoid latch-upAvoid leakage currentTransistorReliability increasing modificationsCMOSEngineering

An integrated circuit having a CMOS circuit constituted by electrically connecting an n-type well 2, in which p-channel transistor Tp of the CMOS circuit is set, with a supply line Vdd through switching transistor Tps, and electrically connecting a p-type well 3, in which n-channel transistor Tn of the CMOS circuit is set, with supply line Vss through switching transistor Tns. Thermal runaway due to leakage current can be controlled by turning off switching transistors Tps and Tns and supplying potentials suitable for a test to the n-type well 2 and the p-type well 3 from an external unit when the integrated circuit is being tested. Fluctuations of the latch-up phenomenon and operation speed can be prevented by turning on switching transistors Tps and Tns and setting the n-type well 2 and the p-type well 3 to the voltages Vdd and Vss, respectively.

Owner:RENESAS ELECTRONICS CORP

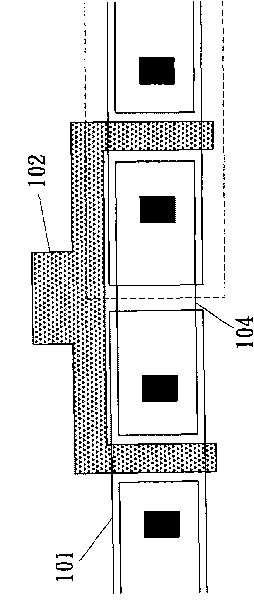

CMOS (Complementary Metal Oxide Semiconductors) semiconductor integrated circuit with high irradiation resistance and preparation method thereof

InactiveCN101950747AIncrease widthPromote recombinationTransistorSemiconductor/solid-state device manufacturingCMOSParasitic bipolar transistor

The invention relates to a CMOS (Complementary Metal Oxide Semiconductors) semiconductor integrated circuit with high irradiation resistance and a preparation method thereof, relating to the technical field of integrated circuits. The CMOS semiconductor integrated circuit comprises a substrate (10), an epitaxial layer (11), a p well and an n well, wherein at least one isolation groove (31) is arranged between the p well and the n well and penetrates through the epitaxial layer (11); the bottom end of each isolation groove (31) is arranged on the substrate (10); and insulating mediums are filled in the isolation grooves (31). The invention enhances the combination of base regions of a parasitic bipolar transistor, thereby reducing the gain and also greatly reducing the gain of a loop and then effectively preventing latch-up effect.

Owner:UNIV OF ELECTRONICS SCI & TECH OF CHINA

OTP memory

The invention provides an OTP memory which includes a memory unit array, which is composed of a plurality of memory units, and a peripheral circuit structure. Each memory unit includes a selectron and a memotron. The peripheral circuit structure includes a bit line, a word line and a voltage bus used for accessing a programming voltage. Grid electrodes of the selectron and the memotron are connected to the word line. A source electrode or a drain electrode of the selectron is connected to the bit line. Current-limiting resistors are disposed on the word line, and the bit line and / or the voltage bus used for accessing the programming voltage. The OTP memory also comprises substrate protective rings, each of which encircling at least two adjacent memory units. The current-limiting resistors can inhibit generation of hot carrier and prevent latch-up effect. In addition, each protective ring can at least enclose two adjacent memory units, so that the OTP memory is reduced in area when compared with the prior art.

Owner:ZHUHAI CHUANGFEIXIN TECH CO LTD

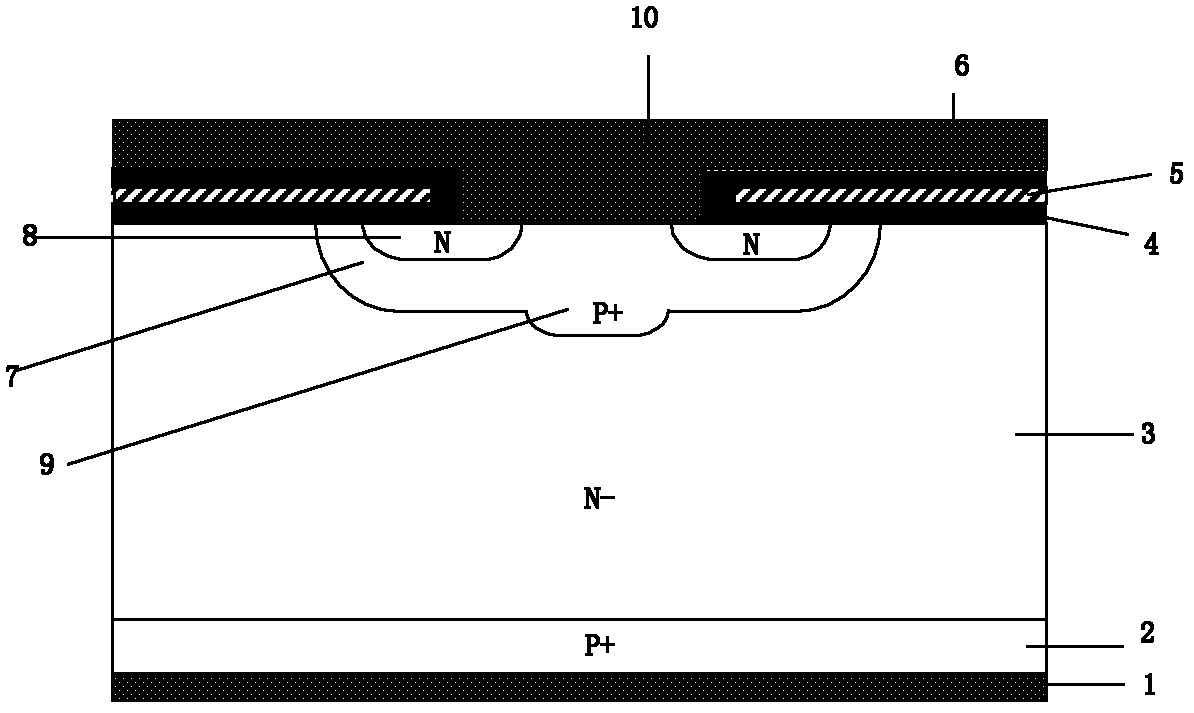

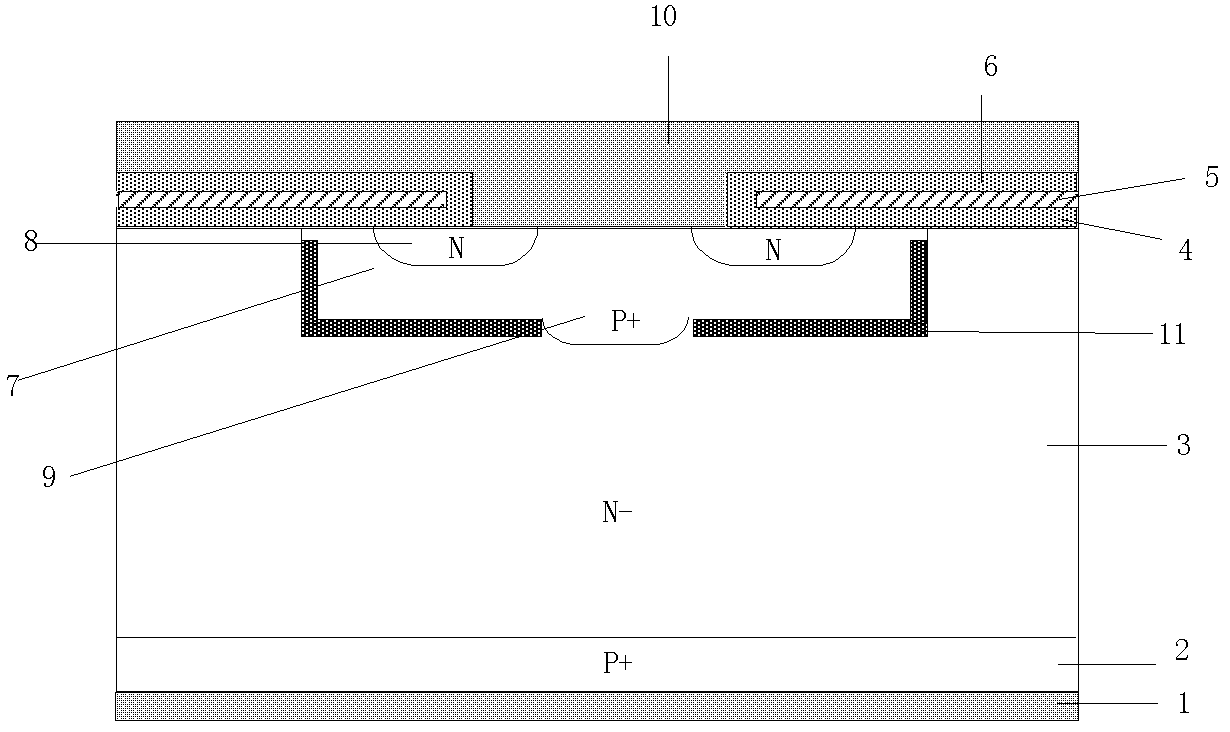

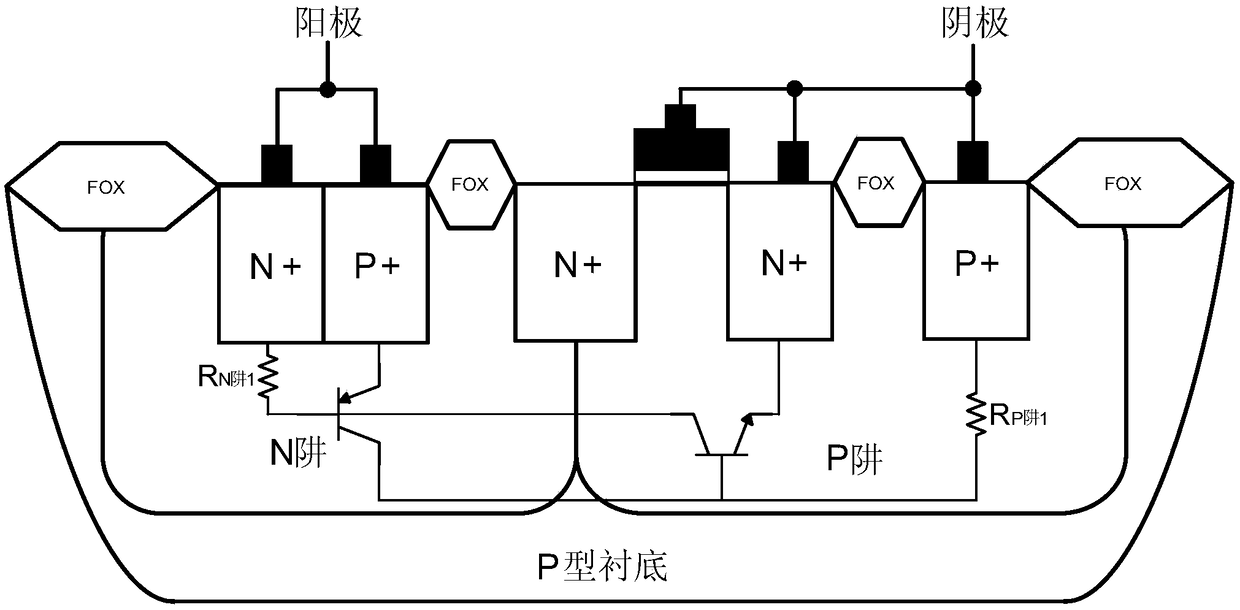

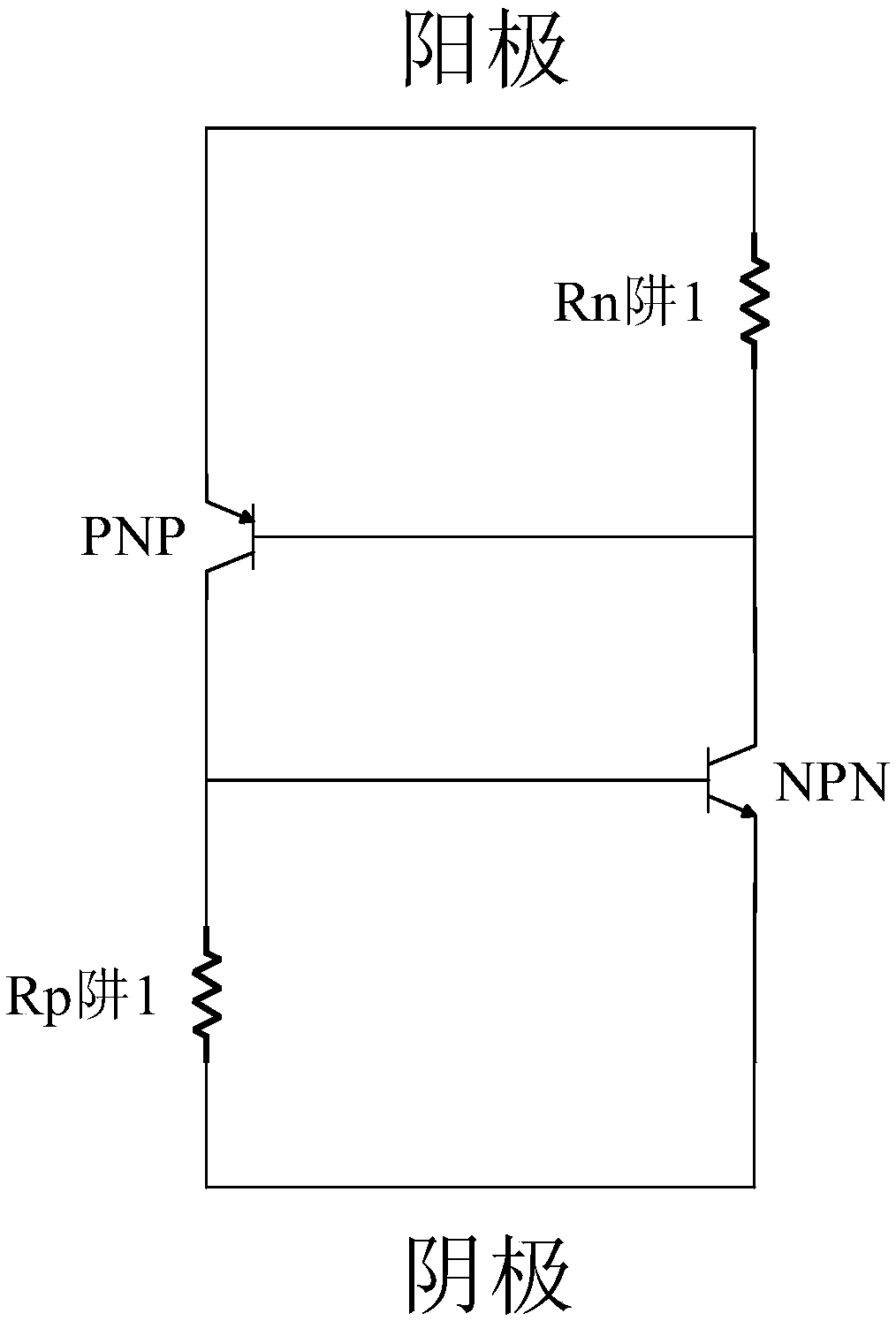

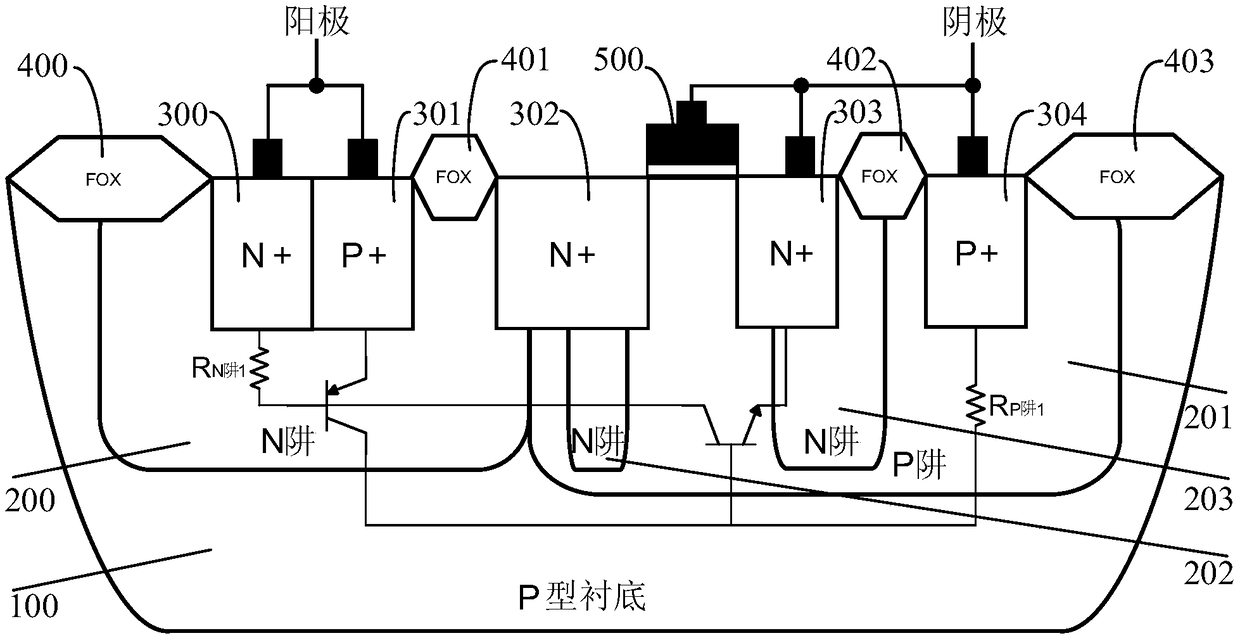

Insulated gate bipolar transistor (IGBT) with anti-latchup effect

InactiveCN102354707AAvoid latch-upImprove current carrying capacitySemiconductor devicesPhysicsSafe operating area

The invention discloses an insulated gate bipolar transistor (IGBT) with an anti-latchup effect, belonging to the technical field of power semiconductor devices. In the invention, partial SOI silicon wafer is used through an ion implantation, deposition or thermal growth method or directly; an isolation medium layer is arranged on the interface between the P-type base region and an N-drift region; a current channel for the hole current in the N-drift region to flow into an N-type source region through the P-type base region is blocked; and therefore, the opening of a parasitic NPN transistor in the IGBT structure can be effectively prevented, and the latchup effect caused by the NPNP structure in the IGBT is avoided so as to improve the current bearing capability of the device and providing a larger safe working region. The IGBT provided by the invention can be applied to the field of low-power and high-power semiconductor power devices as well as power integration circuits.

Owner:UNIV OF ELECTRONIC SCI & TECH OF CHINA +1

Electrostatic releasing device of low-voltage triggering and high-maintenance voltage silicon-controlled rectifier

ActiveCN108807372AThe current drain path growsOpen quicklyTransistorSolid-state devicesSilicon-controlled rectifierLow voltage

The invention discloses an electrostatic releasing device of a low-voltage triggering and high-maintenance voltage silicon-controlled rectifier. The electrostatic releasing device comprises a P-type substrate, wherein a first N well and a P well are arranged in the P-type substrate, a first N+ injection region and a first P+ injection region are arranged in the first N well, a second N well, a third N+ injection region, a third N well and a second P+ injection region are arranged in the P well, a second N+ injection region bridges between the first N well and the P well, a poly-silicon gate isarranged between the second N+ injection region and the third N+ injection region, and the second N+ injection region, the poly-silicon gate and the third N+ injection region form a parasitic MOSFETfield-effect transistor structure. By adding the two N wells into the P well, the area of a parasitic NPN emitter is expanded to increase a failure current; and moreover, the current relief path can be extended after breakdown conduction of the device, the passing well resistance is increased, the device is more rapidly started, so that the maintenance voltage and the failure current of the deviceare increased, and the latch-up effect can be effectively prevented.

Owner:XIANGTAN UNIV

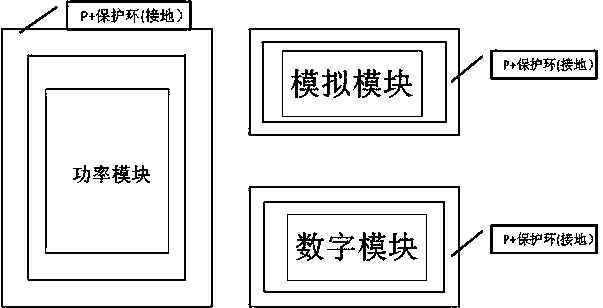

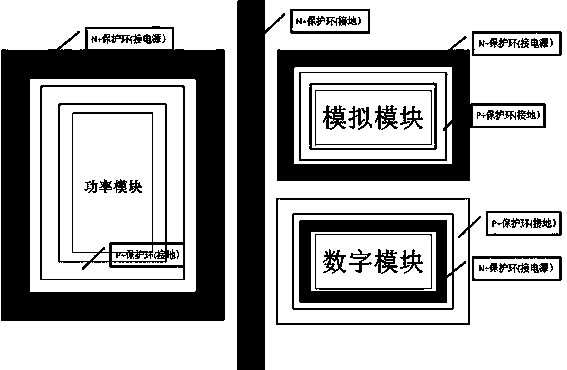

Chip layout structure and method for preventing latch up effects and noise interference

InactiveCN105552073AImprove work performanceReduce concentrationSolid-state devicesSemiconductor/solid-state device manufacturingWork performanceComputer module

The invention discloses a chip layout structure and a method for preventing latch up effects and noise interference. Dual-ring protection is adopted, an analog module of the chip is wrapped by firstly using a P+ring (is grounded) and then using an N+ring (is connected with a power supply); a power module is protected by using the dual-ring structure which is the same as the analog module; and a digital module is wrapped by firstly using the N+ring (is connected with the power supply) and then using the P+ring (is grounded). A certain distance is kept between the analog module and the digital module for preventing the analog module from being disturbed by digital noise. An N+ (minority carrier) protection ring is added between the power module and other modules, the N+ring is connected with a ground potential, the concentration of a substrate close to the minority carrier ring is reduced, substrate resistance is added, the latch up effects can be prevented from happening to the chip, and noise of the digital module can be prevented from disturbing the power module. Effects of good anti-latch up effects and noise isolation can be generated, and the working performance of the chip is improved.

Owner:WUHAN XINCHANG TECH CO LTD

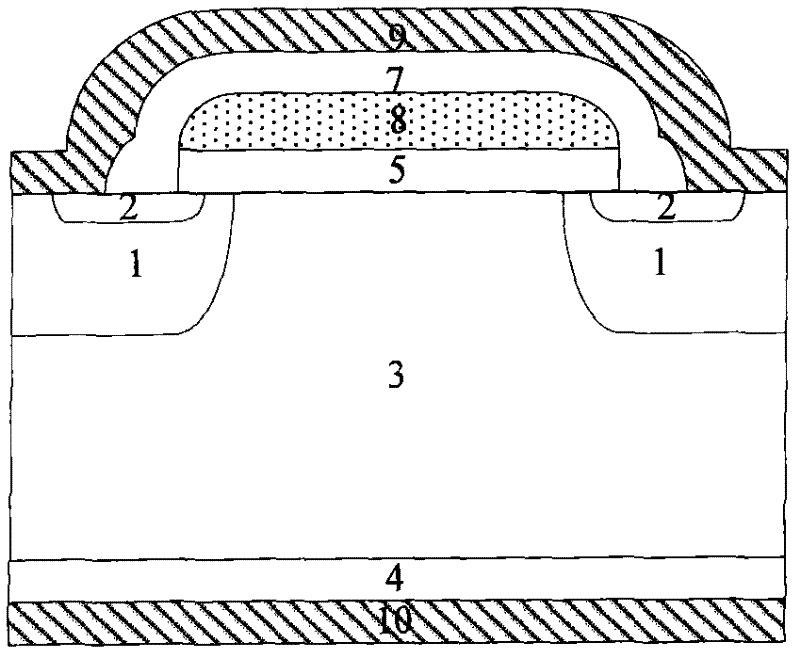

MOS (metal oxide semiconductor) power device and manufacturing method thereof

ActiveCN102544083AAvoid latch-upSemiconductor/solid-state device manufacturingSemiconductor devicesElectrical conductorSource area

The invention provides a manufacturing method of an MOS (metal oxide semiconductor) power device, which includes the following steps of (1) forming a first oxidation layer on a semiconductor substrate; (2) forming a polycrystalline layer on the first oxidation layer; (3) forming stopping layers on two sides of the polycrystalline layer; (4) forming a first conductive trap area; (5) removing the stopping layers and forming a second conductive source area in the first conductive trap area; (6) forming a second oxidation layer on the polycrystalline; (7) forming a first metal layer on the source area and the surface of the trap area; and (8) forming a back electrode on the back of the semiconductor substrate. By the method, the stopping layers are formed on two sides of the polycrystalline layer firstly, so that the MOS power device with larger trap depth can be obtained on the premise of keeping the identical channel length by the aid of transverse stopping of the stopping layers during injection of ions in the process of forming the first conductive trap area, and latch-up effect can be prevented effectively.

Owner:BYD SEMICON CO LTD

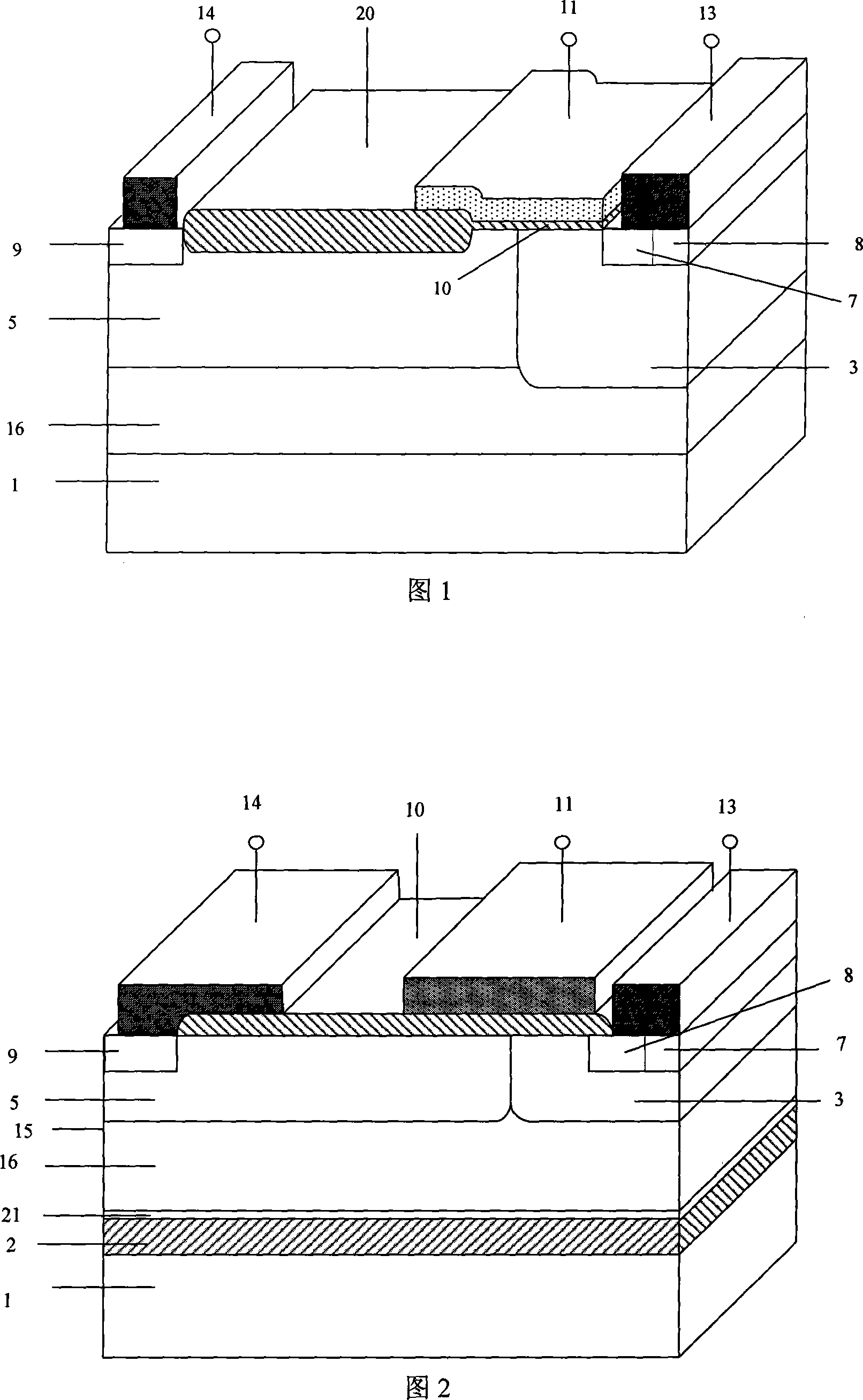

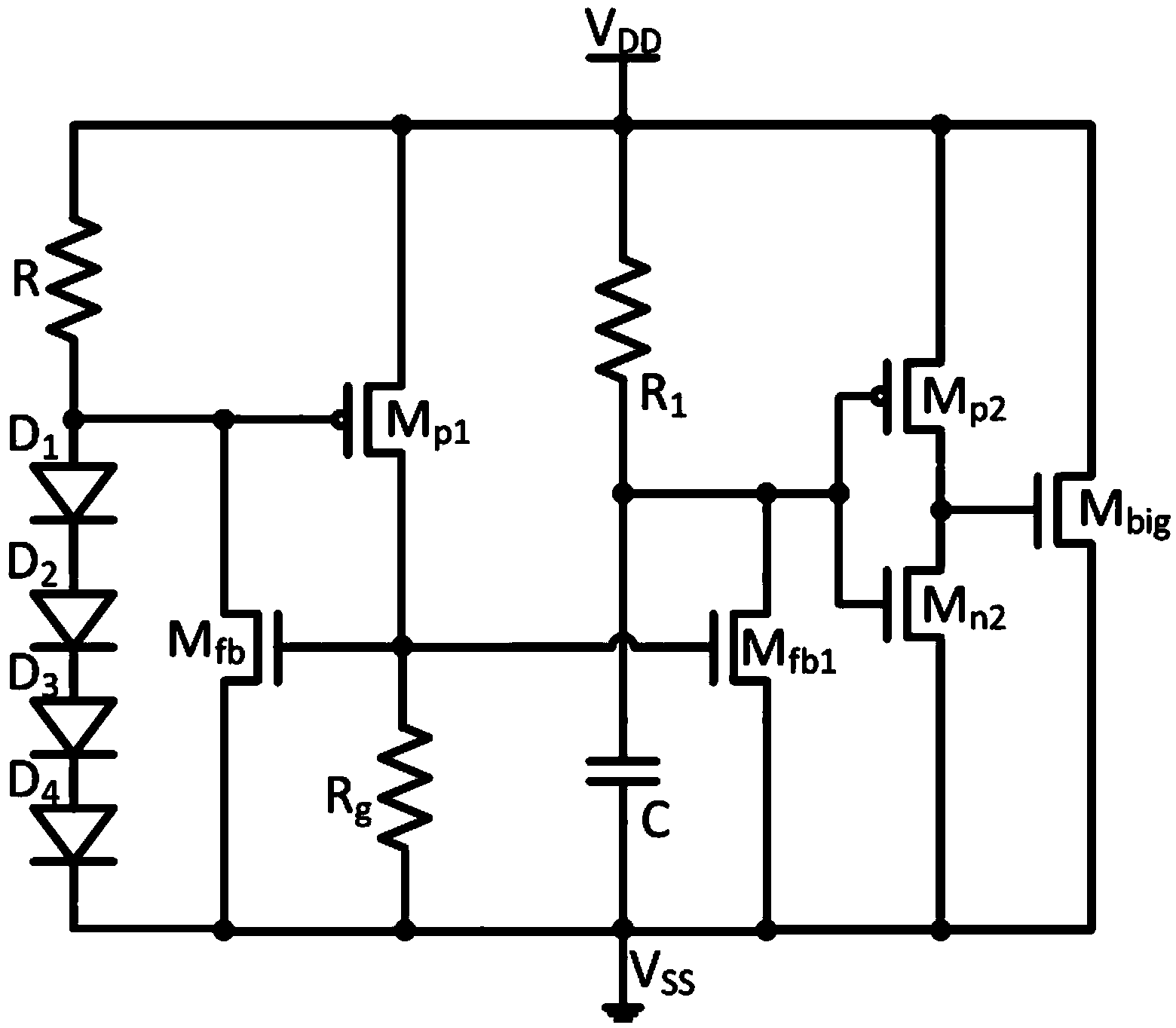

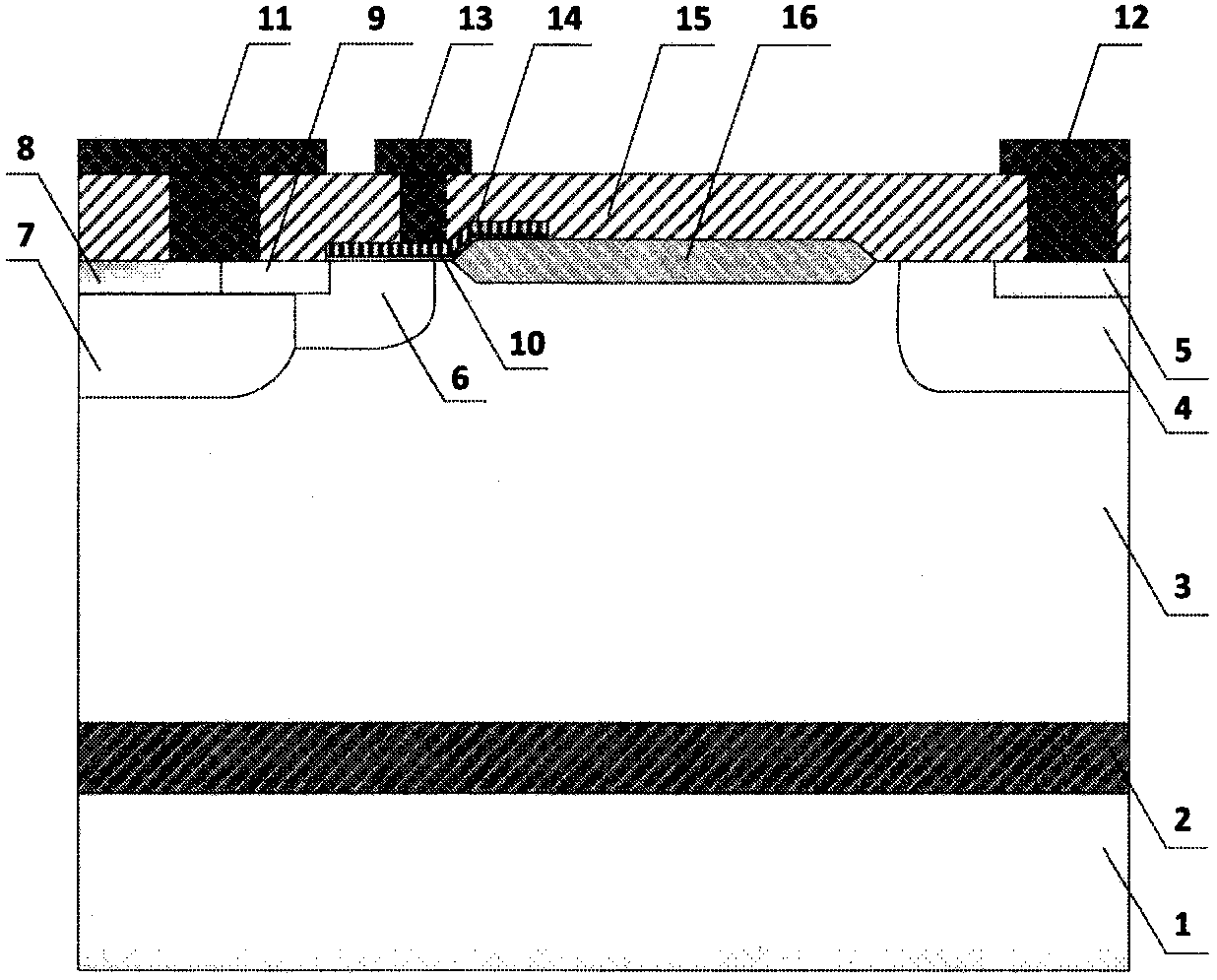

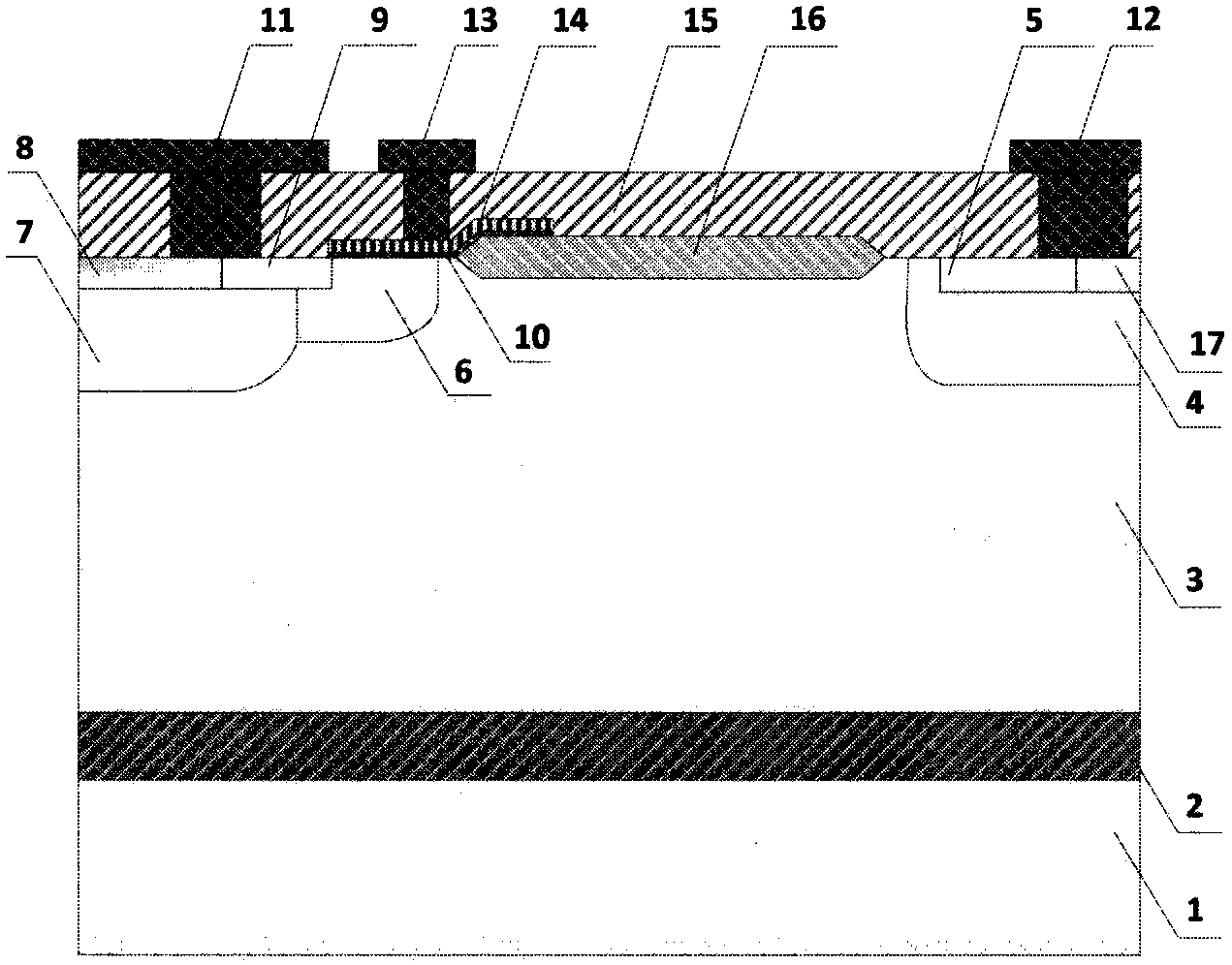

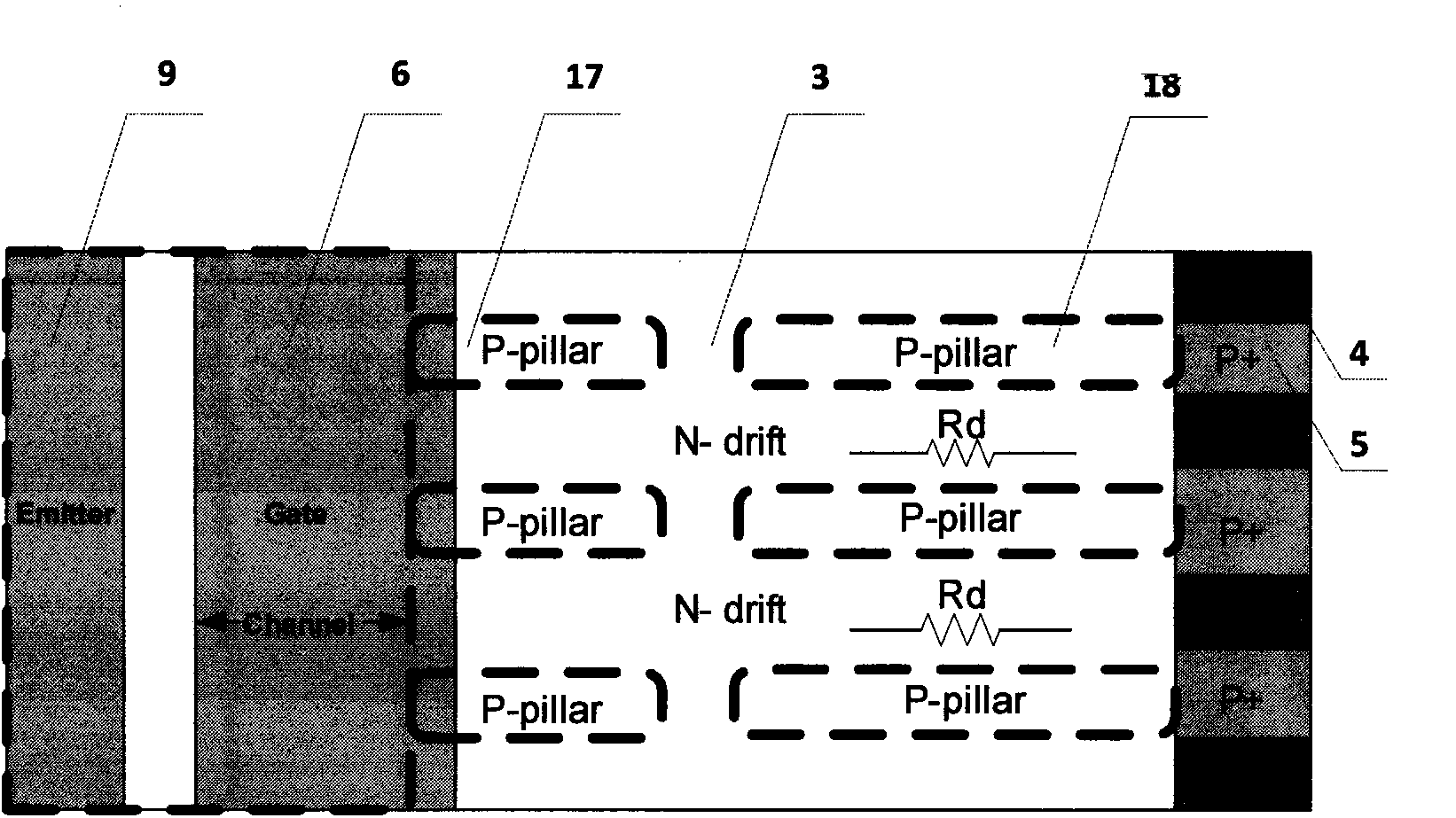

Novel power semiconductor device

InactiveCN103887332ANo conductance modulationReduce on-state voltage dropSemiconductor devicesPower semiconductor deviceBody region

The invention relates to a semiconductor device, and discloses a novel power semiconductor device comprising a substrate (1), an anode P+ region (5), an anode N+ region (4), anode metal (12), an N-type drift region (3), a field oxide layer (16), a cathode P+ region (8), a cathode P-type body region (7), a P-type channel region (6), an emitting electrode N+ region (9), cathode metal (11), a poly-silicon gate (14), a gate oxide layer (10), poly-silicon gate metal (13) and P-type cylinder regions (17,18). The two P-type cylinder regions (17, 18) are additionally arranged in the P-type channel region (6) and the anode P+ region (5), and the structure that the anode P+ region (5) and the anode N+ region (4) are arranged in an alternating way is adopted so that the inverse resistance effect of the device is inhibited, the latch-up effect of the device in the high-current working state is overcome, turn-off speed and voltage resistance of the device are enhanced and power consumption of the device is reduced.

Owner:HANGZHOU ENNENG TECH

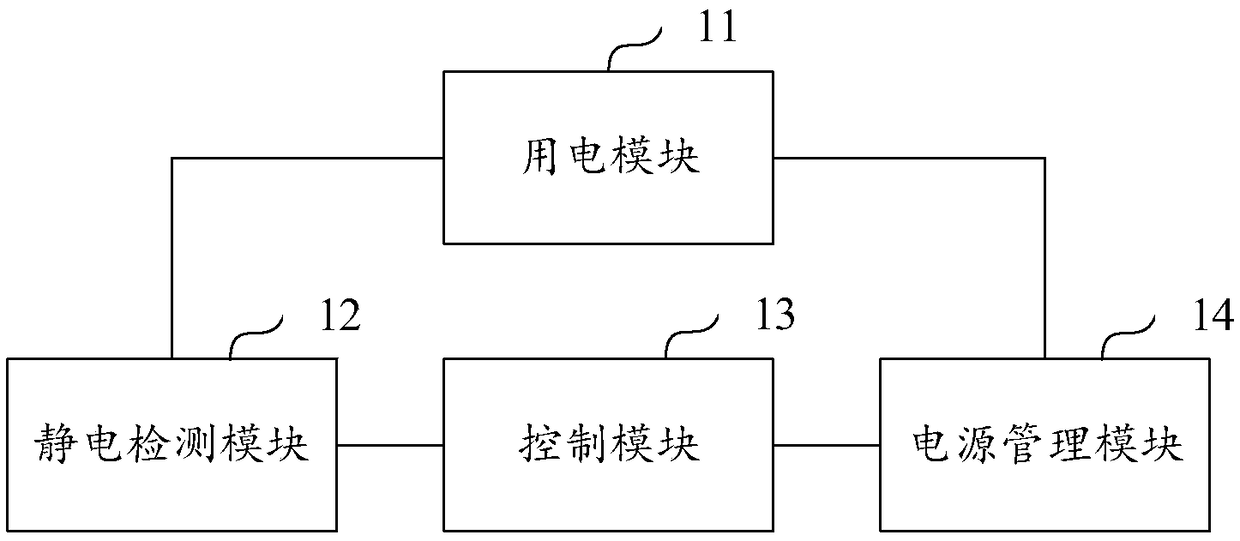

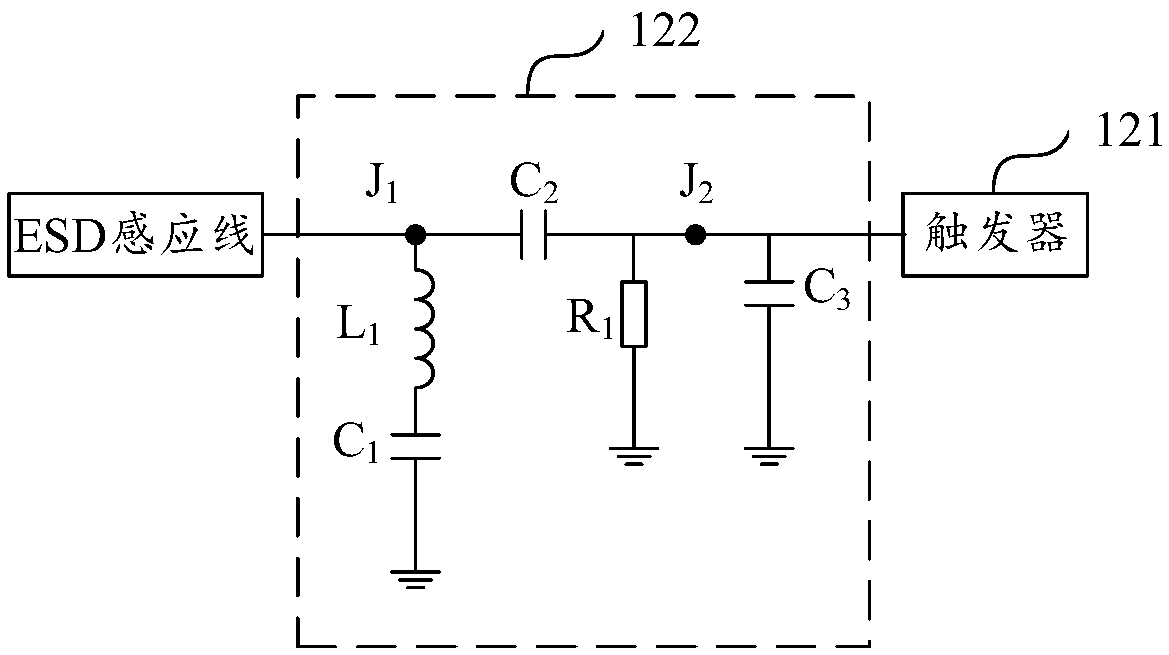

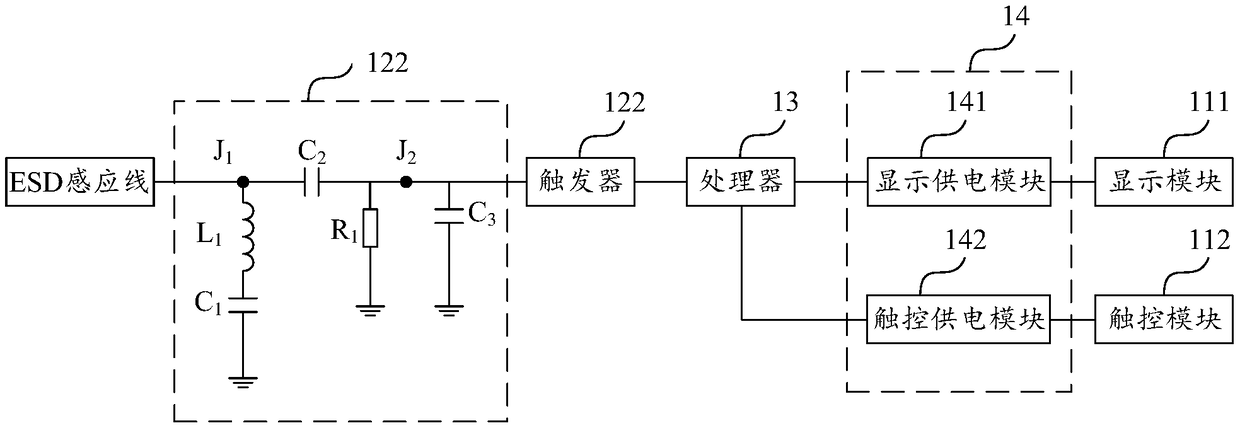

An electrostatic protection device and method

InactiveCN109038482AAvoid heat damageImprove protectionArrangements responsive to excess voltagePower managementHigh pressure

The present application relate to the field of termination technology, and more particularly relates to an electrostatic protection device and method for alleviate the problem of irreversible damage caused by electrostatic breakdown of field effect transistors in the prior art. The device comprises an electrostatic detection module which generates a trigger signal and sends the trigger signal to the control module when detecting that the electrostatic voltage meets the protection condition; The control module generates a power-off signal according to the triggering signal and sends the power-off signal to the power management module. The power management module stops supplying power to the power module corresponding to the power-off signal. The application cuts off the power supply to turnoff the field effect transistor in the electronic equipment, so that the conduction between the source electrode and the drain electrode is not conducted, and static electricity is prevented from passing through the source electrode and the drain electrode. Thus, the latch-up effect caused by the high-voltage static electricity passing through the source electrode and the drain electrode of the field effect transistor is avoided, the damage to field effect transistor due to high-temperature caused by the latch-up effect is avoided, the static electricity protection capability of the electronic equipment is improved, and the static electricity damage to the electronic equipment is reduced.

Owner:VIVO MOBILE COMM CO LTD

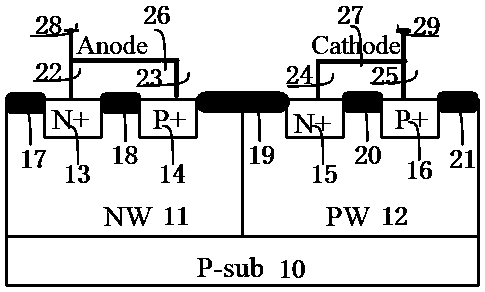

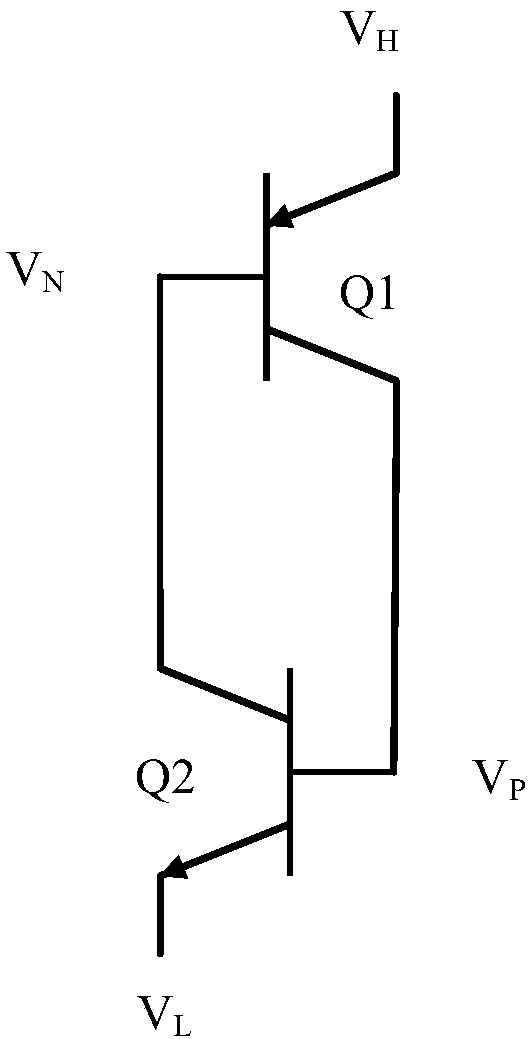

SCR type ESD protection device for PMOS triggering and internal voltage clamping

ActiveCN108493186ALower the trigger voltageEasy to openTransistorSolid-state devicesP–n junctionPositive feedback

The invention relates to an SCR type ESD protection device for PMOS triggering and internal voltage clamping. For the SCR structure, a PMOS structure is added in an N well, and a PMOS drain terminal is connected with a P well. Under the forward ESD pulse, a PMOS is broken down earlier than a reverse PN junction, and the current is transmitted to the P well through a drain terminal P+, the P-well potential is raised, a parasitic NPN transistor turns on faster, and the device trigger voltage is reduced; in addition, the new parasitic transistor for clamping the internal voltage is added into thedevice, the positive feedback mechanism is suppressed, and the sustain voltage of the device is increased.

Owner:NANJING UNIV OF POSTS & TELECOMM

High-voltage static protection structure

ActiveCN104282665AUniform conduction capabilityImprove the protective effectSemiconductor/solid-state device detailsSolid-state devicesLDMOSOxidation zone

The invention discloses a high-voltage static protection structure. The high-voltage static protection structure comprises an N-type LDMOS which is arranged in an N-type buried layer on a silicon substrate; an active region on the right side of a polycrystalline silicon gate is a drain region of the LDMOS, and is composed of a high-voltage N trap, a P-type injection region, an N-type injection region, a first P+ type diffusion zone and a first N+ type diffusion zone; the P-type injection region is arranged below the first P+ type diffusion zone and part of a field oxidation region, the N-type injection region is arranged below the first N+ type diffusion zone, and the P-type injection region and the N-type injection region are surrounded by the high-voltage N trap; an active region on the left side of the polycrystalline silicon gate is a source region of the N-type LDMOS and is composed of a second N+ type diffusion zone; a second P+ type diffusion zone is arranged between the second N+ type diffusion zone and a third field oxidation zone; the first N+ type diffusion zone of the drain region is connected with an ESD inlet end, and the second N+ type diffusion zone, the second P+ type diffusion zone and the polycrystalline silicon gate of the source region are jointly connected with the ground. By means of the high-voltage static protection structure, the even conduction capacity can be improved, and the snapback voltage can be improved for preventing the latch-up effect.

Owner:SHANGHAI HUAHONG GRACE SEMICON MFG CORP

Finned-type field effect transistor and fabrication method thereof

InactiveCN105552126ACost controlReduce leakage currentSemiconductor/solid-state device manufacturingSemiconductor devicesFine structureSemiconductor materials

The invention provides a finned-type field effect transistor structure and a fabrication method thereof. The finned-type field effect transistor structure comprises a silicon substrate, a finned structure, a gate insulation layer and a gate electrode, wherein the fined structure is arranged on the silicon structure, the gate insulation layer and the gate electrode are arranged on the finned structure, a dual-layer structure is arranged at the middle part of the finned structure below the gate electrode and forms a dual-layer channel structure, an upper channel is arranged at the upper layer of the dual-layer structure, a low channel is arranged at the lower layer of the dual-layer structure, single-layer structures are arranged at the two ends of the finned structure, insulation mediums are arranged between the single-layer structures and the silicon substrate, and the single-layer structures form source-drain extension regions. By isolating the source-drain extension regions from the silicon substrate through the insulation mediums, leakage passages between a source and a drain of the device and between devices are effectively blocked, the leakage current is reduced, and the latch-up effect is effectively avoided; on the other hand, the upper channel and the substrate are connected by a semiconductor material of the lower channel, the cooling performance is high, and the self heating effect is prevented; and moreover, the method provided by the invention is low in cost, and the process is simple and controllable.

Owner:SHANGHAI INTEGRATED CIRCUIT RES & DEV CENT +1

Power source apparatus for display and image display apparatus

InactiveUS8484490B2Reduce power consumptionAvoid it happening againVolume/mass flow measurementElectrode and associated part arrangementsDisplay deviceVoltage

A power source apparatus for a display is provided, which comprises a voltage generating section capable of controlling outputting or output termination of one or more predetermined output voltages, and a switching section provided between an output terminal of the predetermined output voltage and a predetermined reference potential terminal. The switch section is turned from OFF to ON when the voltage generating section performs the output termination control.

Owner:SHARP KK

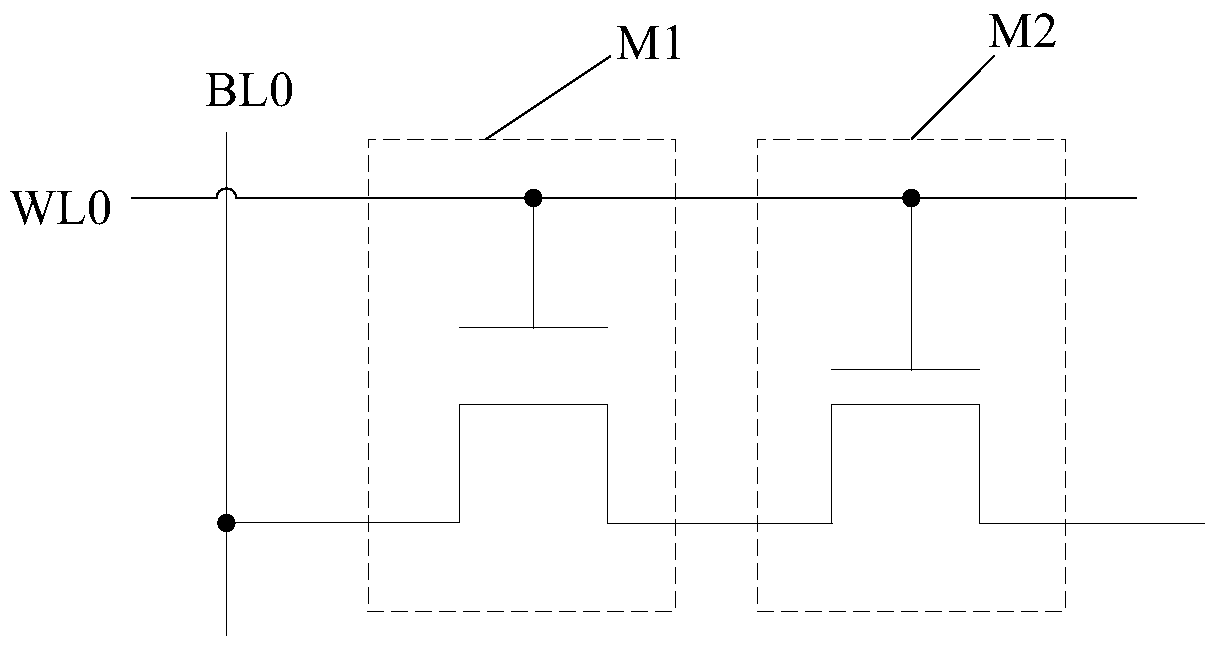

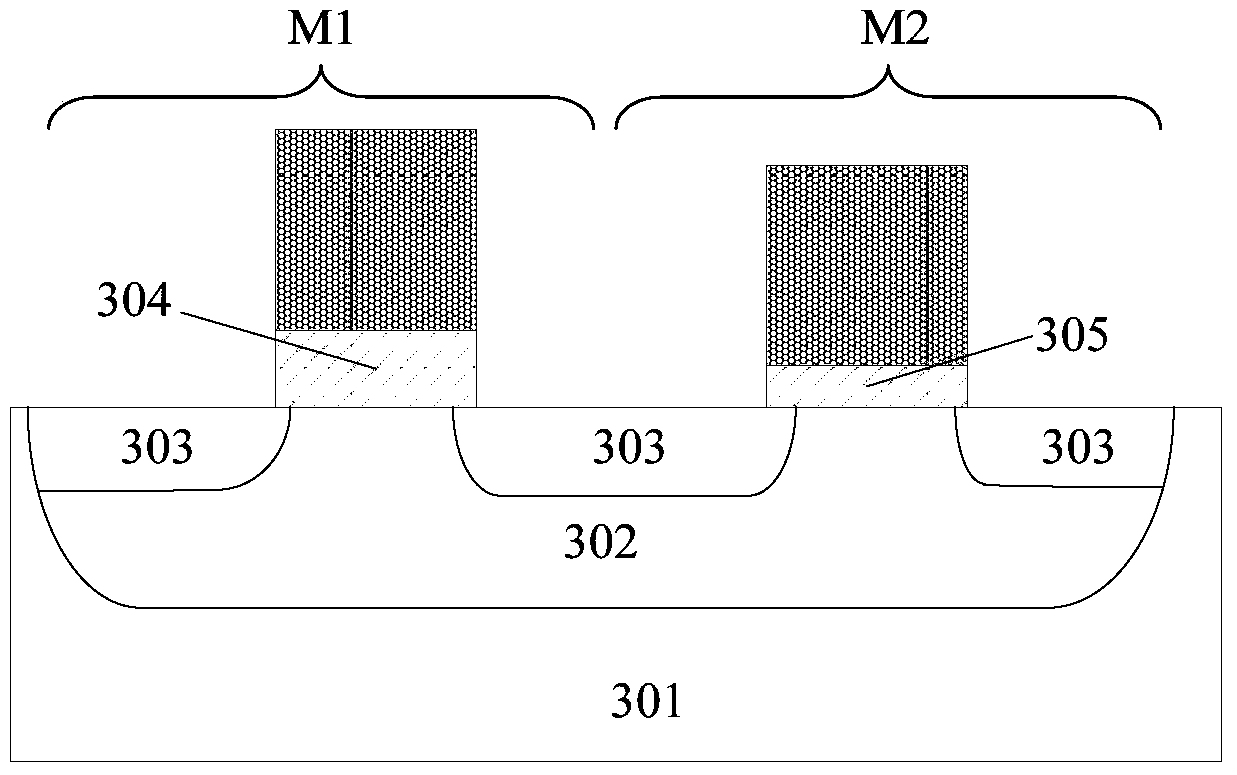

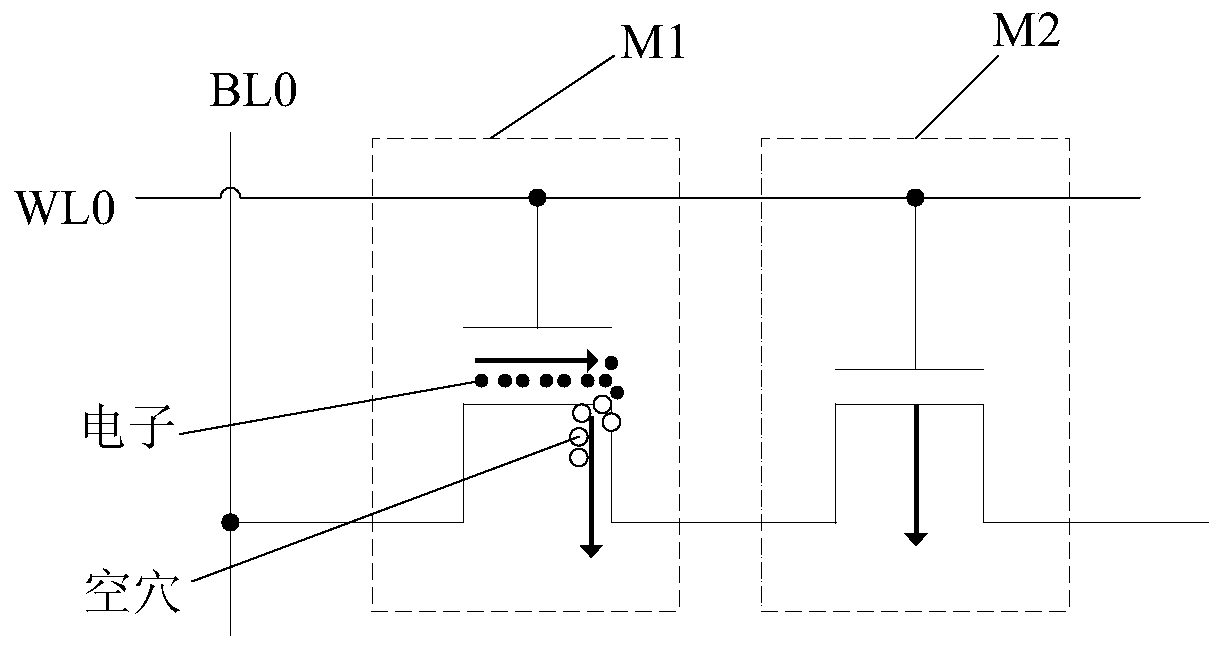

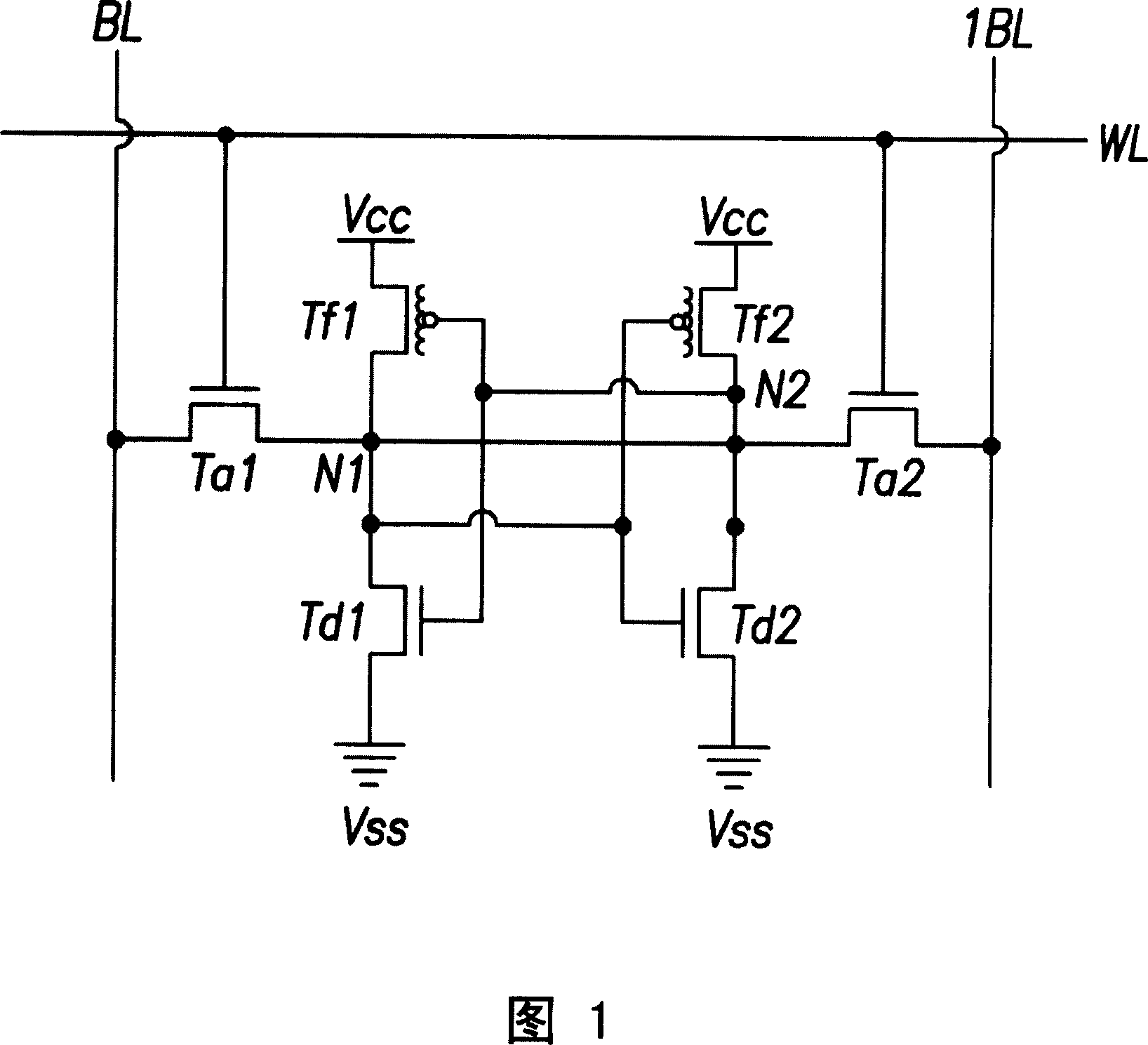

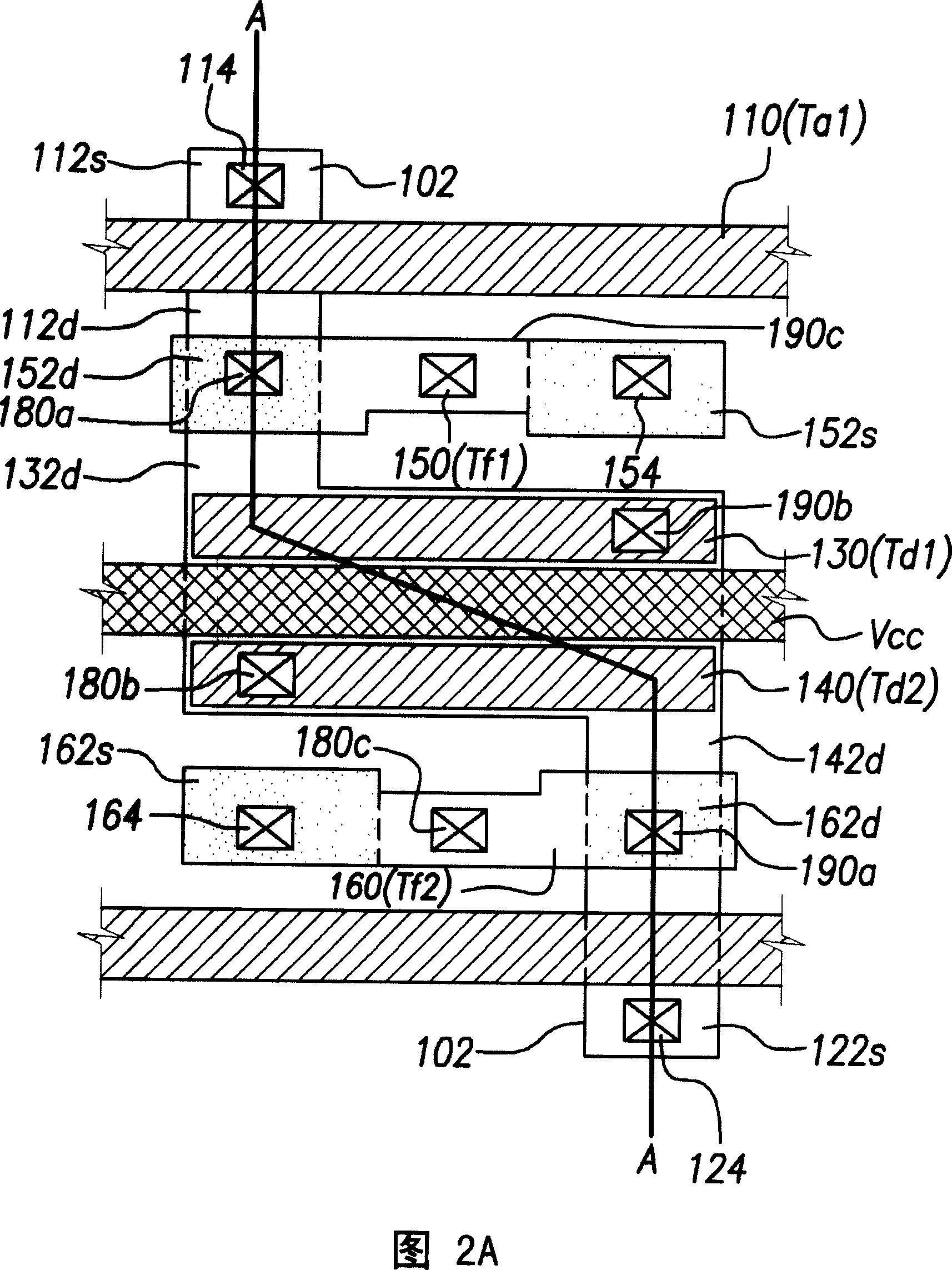

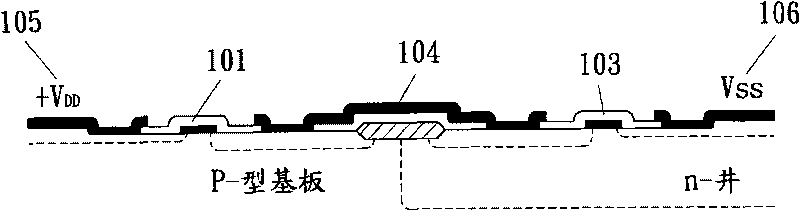

Static random access memory and method for manufacturing the same

InactiveCN1992281ARun fastAvoid latch-upTransistorSolid-state devicesDopantStatic random-access memory

Disclosed is a static random access memory (SRAM), which includes first and second access transistors composed of metal oxide semiconductor (MOS) transistors, first and second drive transistors composed of MOS transistors, and first and second p-channel thin film transistors (TFTs) used as pull-up devices. The SRAM includes a ground potential layer disposed as a common source of the first and second drive transistors, and formed by implanting a dopant into a semiconductor substrate, a power supply potential layer connected with sources of the first and second p-channel TFTs, and an insulating layer formed on the substrate and interposed between the ground potential layer and the power supply potential layer.

Owner:DONGBU ELECTRONICS CO LTD

Coaxial transistor structure

ActiveCN101728431AAvoid latch-upImprove concentrationTransistorLogic circuits characterised by logic functionWafer bondingField-effect transistor

The invention relates to a coaxial transistor structure and discloses a coaxial transistor on a basal plate, in particular to a metal-oxide-semiconductor field-effect transistor with a coaxial structure, and stack chips or basal plates (Wafer Bonding) and axes through holes can be permeated and connected to be manufactured into a coaxial full-symmetry complementary metal-oxide-semiconductor field-effect transistor integrated circuit with higher integration but without latch-up effect. The invention can thoroughly avoid the latch-up effect and can increase the integration and response speed by adopting methods that the conventional PMOS is manufactured into a CPMOS with the coaxial structure, the conventional NMOS is manufactured into a CNMOS with the coaxial structure and then the CPMOS and the CNMOS are turned upside down to be jointed and manufactured into the full-symmetry complementary coaxial metal-oxide-semiconductor field-effect transistor CCMOS structure.

Owner:杨春足

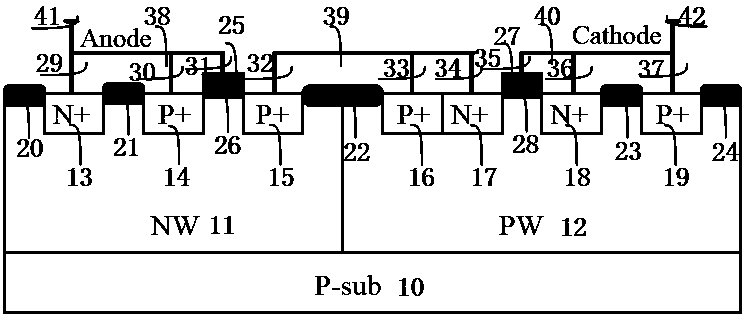

A segmented type asymmetric silicon controlled rectifier electrostatic discharge device embedded with P+ injection regions

ActiveCN110828453AIncrease parasitic resistanceIncrease widthSolid-state devicesSemiconductor devicesSilicon-controlled rectifierOhmic contact

The invention discloses a segmented type asymmetric silicon controlled rectifier electrostatic discharge device embedded with P+ injection regions. The device is characterized in that, to begin with,a floating P+ injection region is added into a shallow P well, so that the width and concentration of a base electrode of a transverse parasitic NPN transistor are increased, the amplification times of the transverse parasitic NPN transistor is reduced, static electricity tends to be discharged from a longitudinal parasitic NPN transistor, a current path becomes deeper and longer, and the maintaining voltage of the device can be effectively improved; then, the P+ injection region used for ohmic contact of the shallow P well adopts a segmented structure, so that the parasitic resistance of theshallow P well is increased; and meanwhile, an N+injection region adopts a comb-shaped structure, so that the emitter area of a parasitic triode can be increased, the emission efficiency can be improved, and the failure current of the device can be effectively improved. The silicon controlled rectifier electrostatic discharge device has the characteristics of high maintaining voltage and high failure current, and can realize a high protection level while effectively avoiding a latch-up effect.

Owner:XIANGTAN UNIV

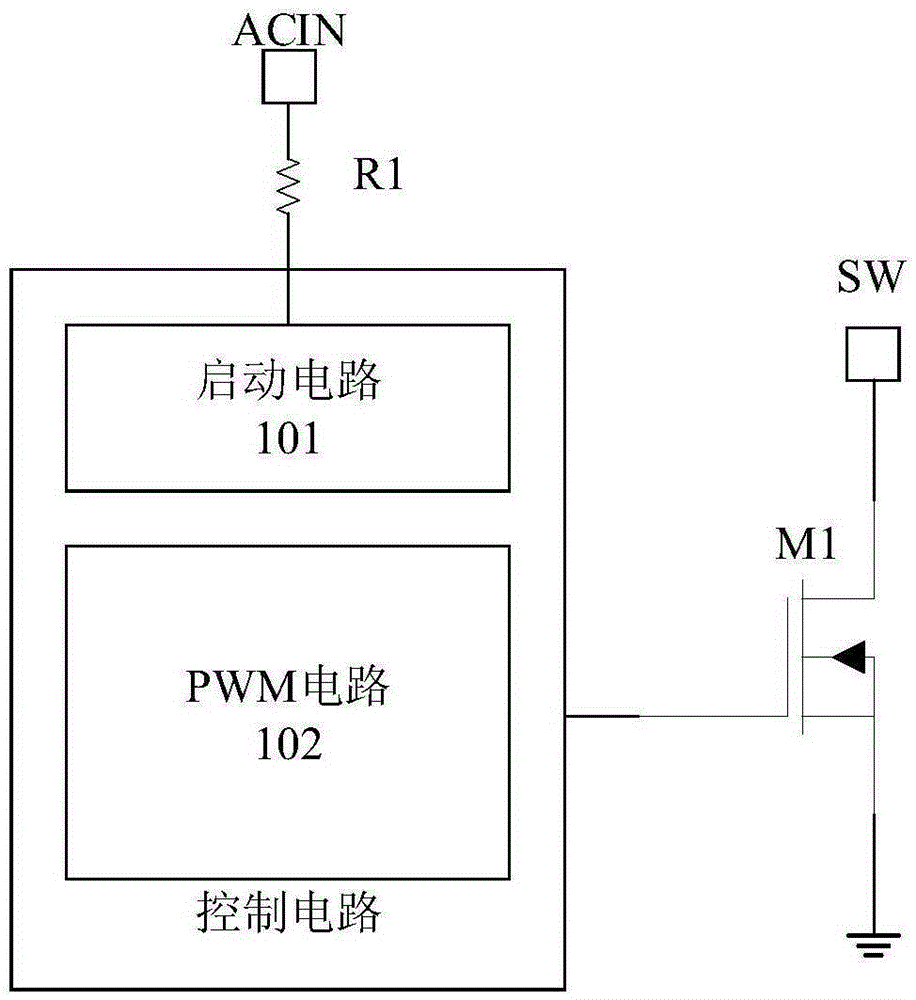

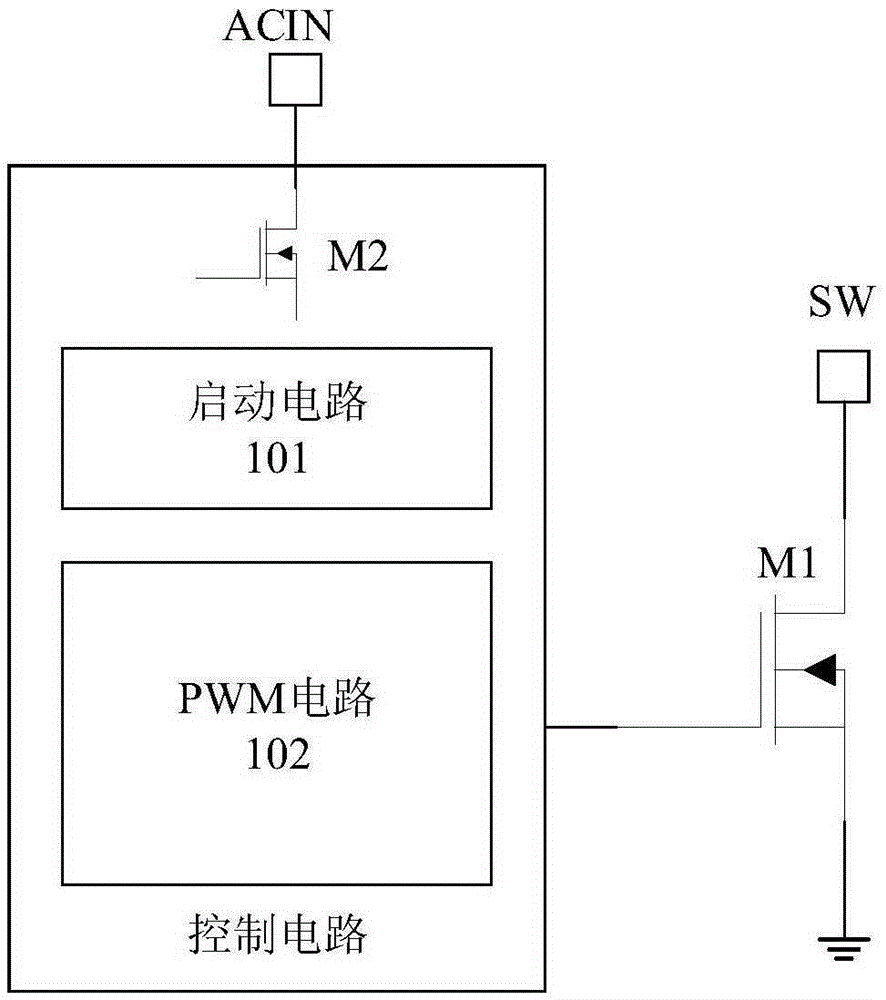

Power MOS field effect transistor integrated with depletion startup device

ActiveCN105304627AAvoid latch-upImprove stabilitySolid-state devicesSemiconductor devicesCommon drainEngineering

The invention relates to a power MOS field effect transistor integrated with a depletion startup device. The power MOS field effect transistor comprises an enhanced MOS field effect transistor, a depletion MOS field effect transistor and a POLY resistor, wherein the enhanced MOS field effect transistor and the depletion MOS field effect transistor are connected in a common drain; the POLY resistor is connected between a grid and a source of the depletion MOS field effect transistor in series; the common drain of the enhanced MOS field effect transistor and the depletion MOS field effect transistor is led out as a drain electrode of the power MOS field effect transistor; the grid of the enhanced MOS field effect transistor is led out as a first gate electrode of the power MOS field effect transistor; the source of the enhanced MOS field effect transistor is led out as a first source electrode of the power MOS field effect transistor; a connection end of the source of the depletion MOS field effect transistor and the POLY resistor is led out as a second source electrode of the power MOS field effect transistor; and the connection end of the grid of the depletion MOS field effect transistor and the POLY resistor is led out as a second gate electrode of the power MOS field effect transistor. The overall power MOS field effect transistor is low in power consumption; the design complexity is simplified; and the cost is reduced.

Owner:SUZHOU KAIWEITE SEMICON

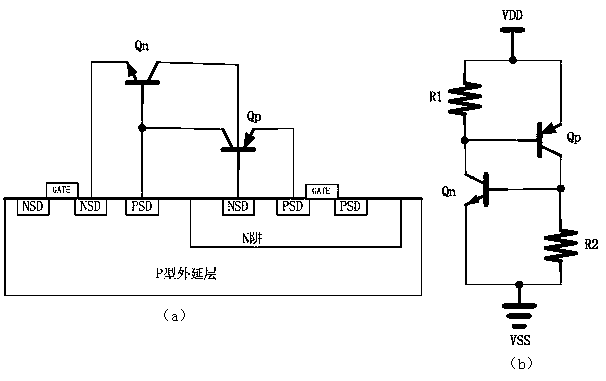

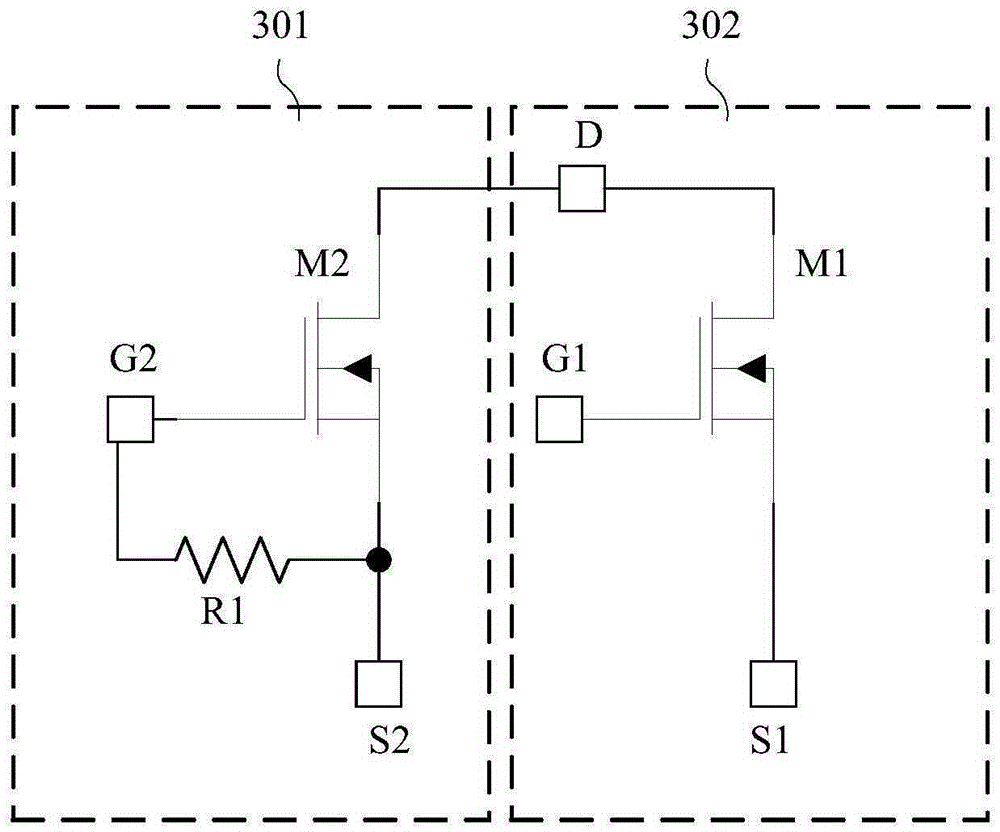

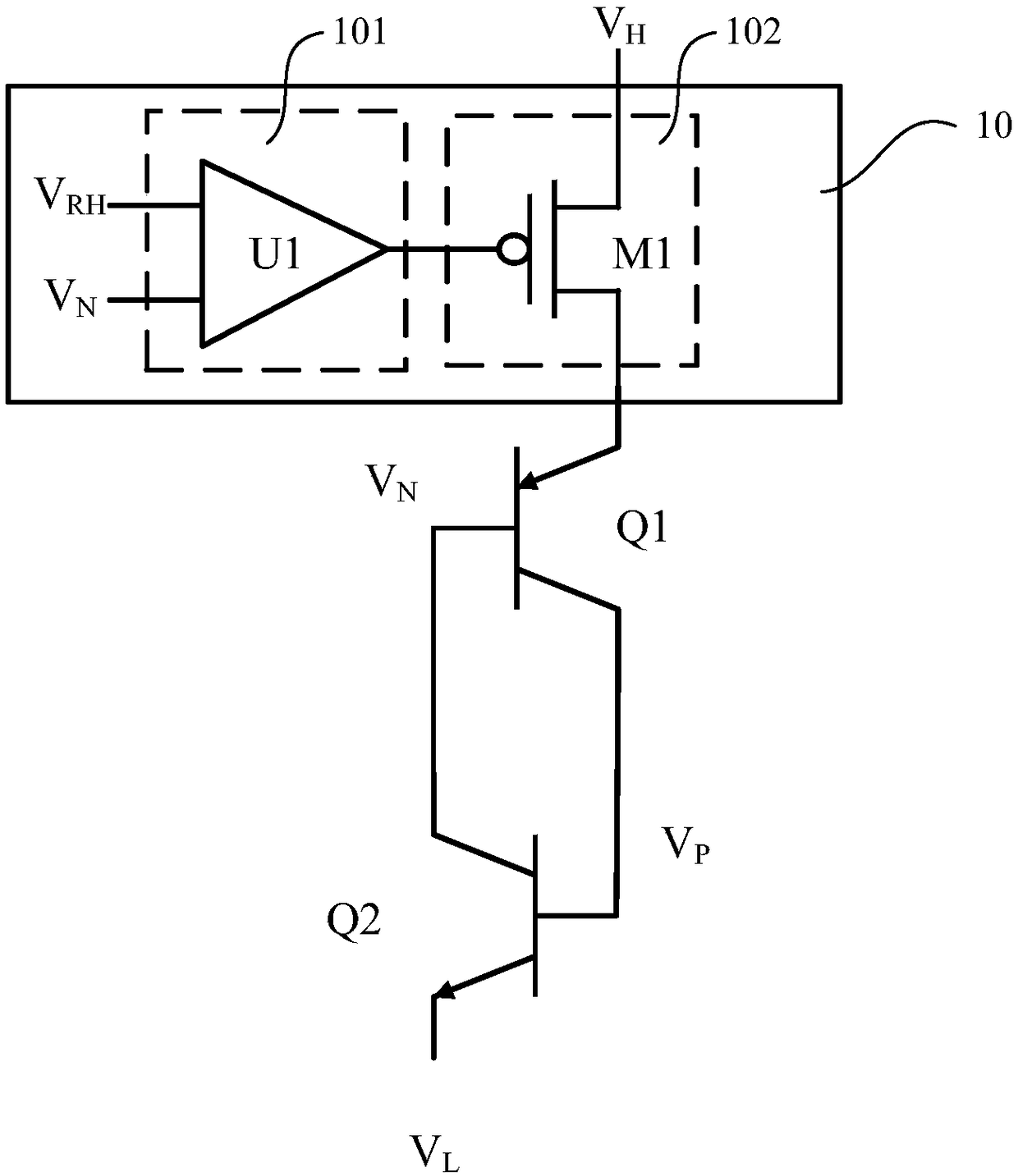

Anti-latch circuit and integrated circuit

PendingCN108270422AAvoid latch-upTransistorElectronic switchingIntegrated circuit layoutControl circuit

The invention discloses an anti-latch circuit, comprising a first transistor, a second transistor and a control circuit, wherein the control end of the first transistor receives a first control voltage, and a first end of the first transistor receives a first power supply voltage; the second transistor has an opposite type of the first transistor, the control end of the second transistor receivesa second control voltage and is connected with a second end of the first transistor, a first end of the second transistor is connected with the control end of the first transistor, and a second end ofthe second transistor receives a second power supply voltage; and the control circuit is arranged on a path formed by the first transistor and the second transistor between the first power supply voltage and the second power supply voltage and is used to cut off the path when the first control voltage and / or the second control voltage exceed / exceeds a preset range. According to the anti-latch circuit provided by the invention, the control circuit is arranged on the path formed by the first transistor and the second transistor between the first power supply voltage and the second power supplyvoltage, the control circuit cuts off the path when the first control voltage and / or the second control voltage exceed / exceeds the preset range, and thus the occurrence of a latch-up effect in a power-on state can be prevented.

Owner:CHIPONE TECH BEIJINGCO LTD

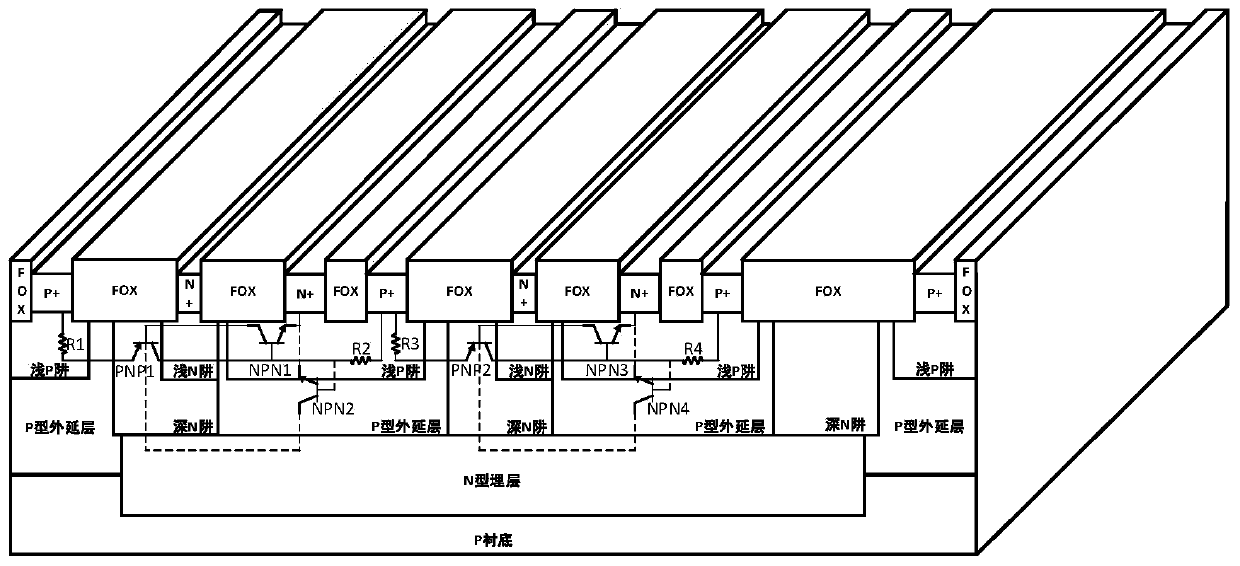

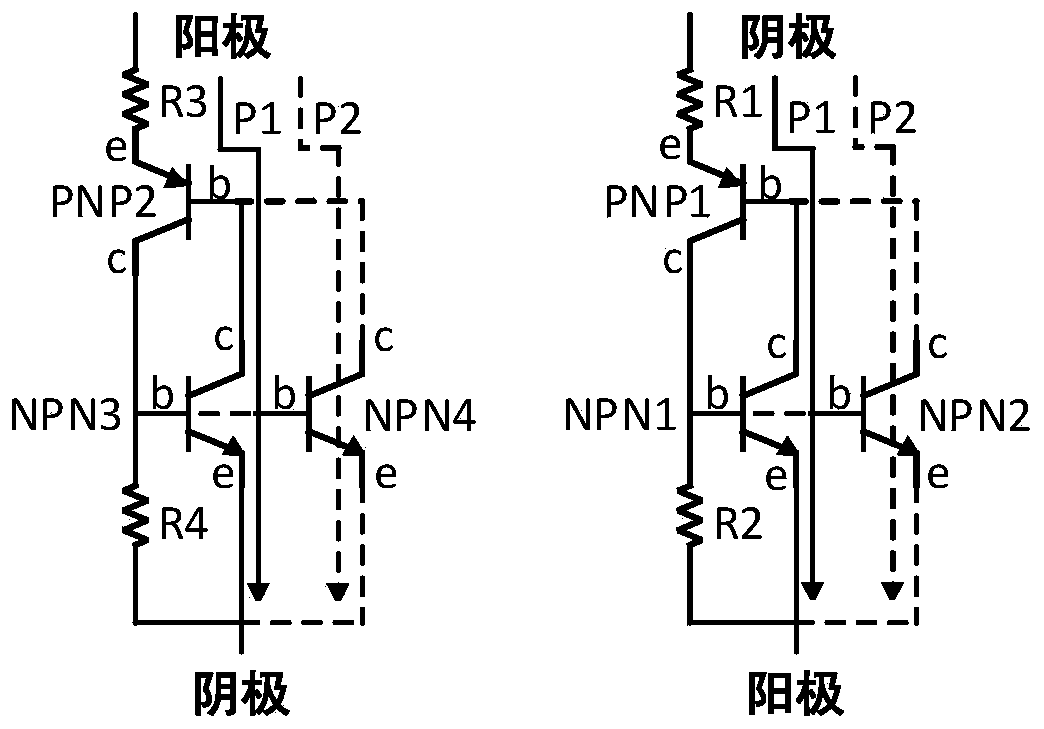

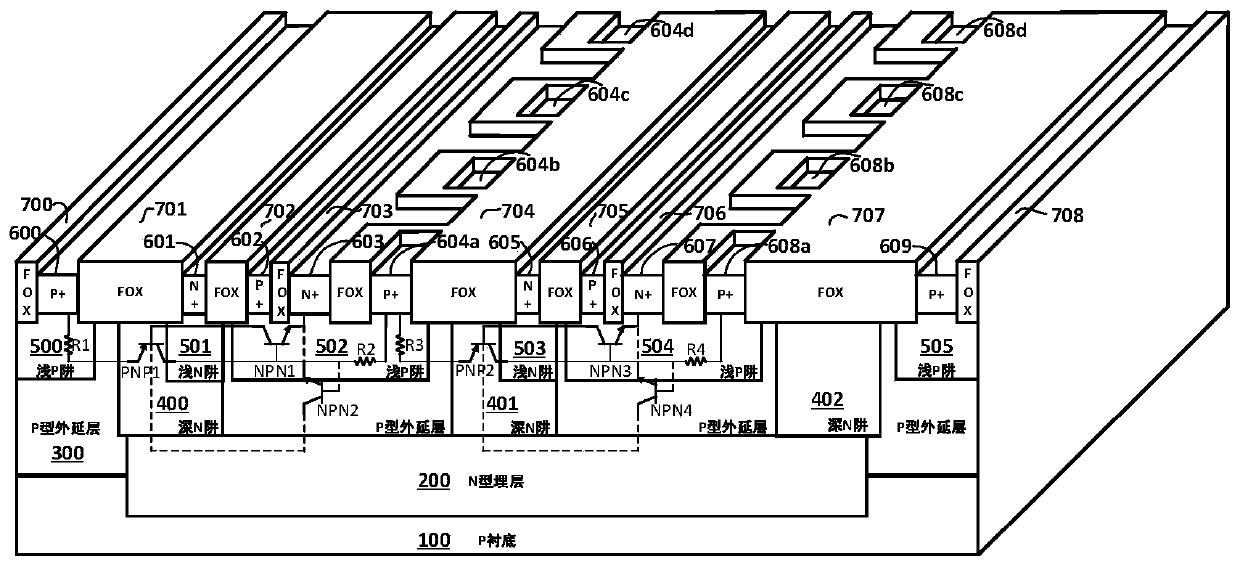

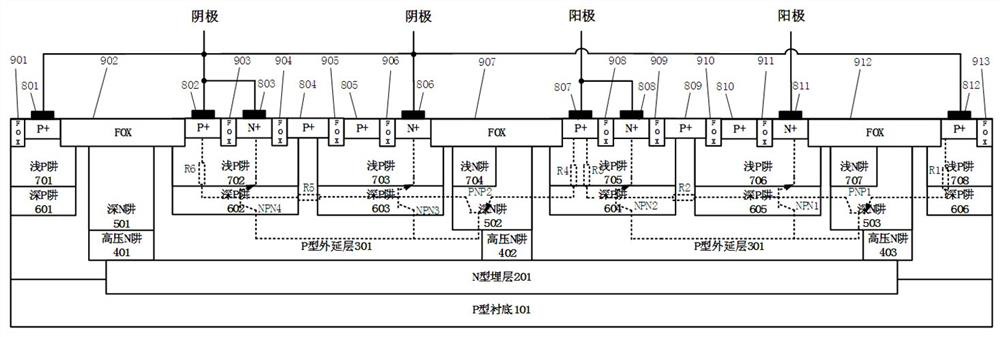

Asymmetric bidirectional silicon controlled rectifier electrostatic discharge device in an interdigital mode and manufacturing method thereof

ActiveCN111799258AAvoid guard ring parasitic path problemsFast conduction speedTransistorSolid-state devicesSilicon-controlled rectifierCurrent distribution

The invention discloses an asymmetric bidirectional silicon controlled rectifier electrostatic discharge device in an interdigital mode. An asymmetric silicon controlled rectifier structure is selected, a path of a protection ring is used as a temporary discharge path for negative pulses, and a problem that a traditional device has a parasitic path of the protection ring can be solved; and the protection grade of the device can be controlled by increasing or decreasing the number of cathodes in a novel interdigital mode. If the device protection grade is high, the number of cathodes is increased; and if the device protection grade is low, the number of cathodes is reduced, and the layout area is saved. The P + of the inner side interdigital is floated, so that the parasitic NPN base resistance of the inner side interdigital is increased; meanwhile, the outer side interdigital is helped be started, so that the conduction speed of the device is increased, and the current distribution ismore uniform; and finally, the maintaining voltage of the whole device is generally determined by the innermost interdigital, so that the problem that the maintaining voltage of the device in the traditional interdigital mode is reduced along with the increase of the interdigital index is solved.

Owner:XIANGTAN UNIV