Static random access memory and method for manufacturing the same

A static random access and memory technology, which is applied in semiconductor/solid-state device manufacturing, electric solid-state devices, semiconductor devices, etc., and can solve the problems of increasing the integration of memory cells and low running speed of all CMOS SRAMs

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0012] Hereinafter, a static random access memory (SRAM) and a method of manufacturing the memory according to an embodiment of the present invention will be described with reference to the accompanying drawings.

[0013] In the following description of the embodiments of the present invention, when one layer is formed on another layer, it may be directly formed on the other layer, or one or more intervening layers may appear.

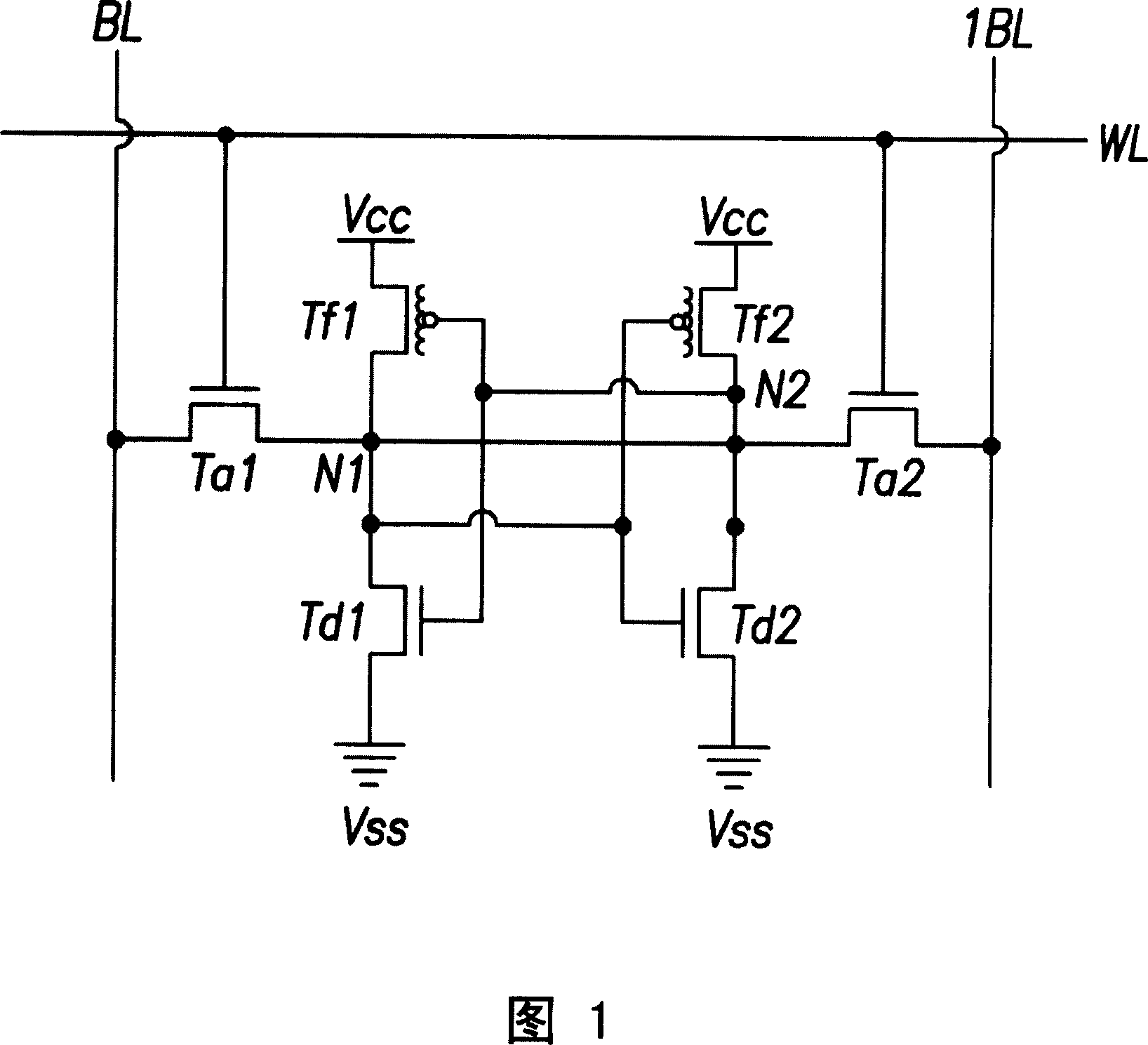

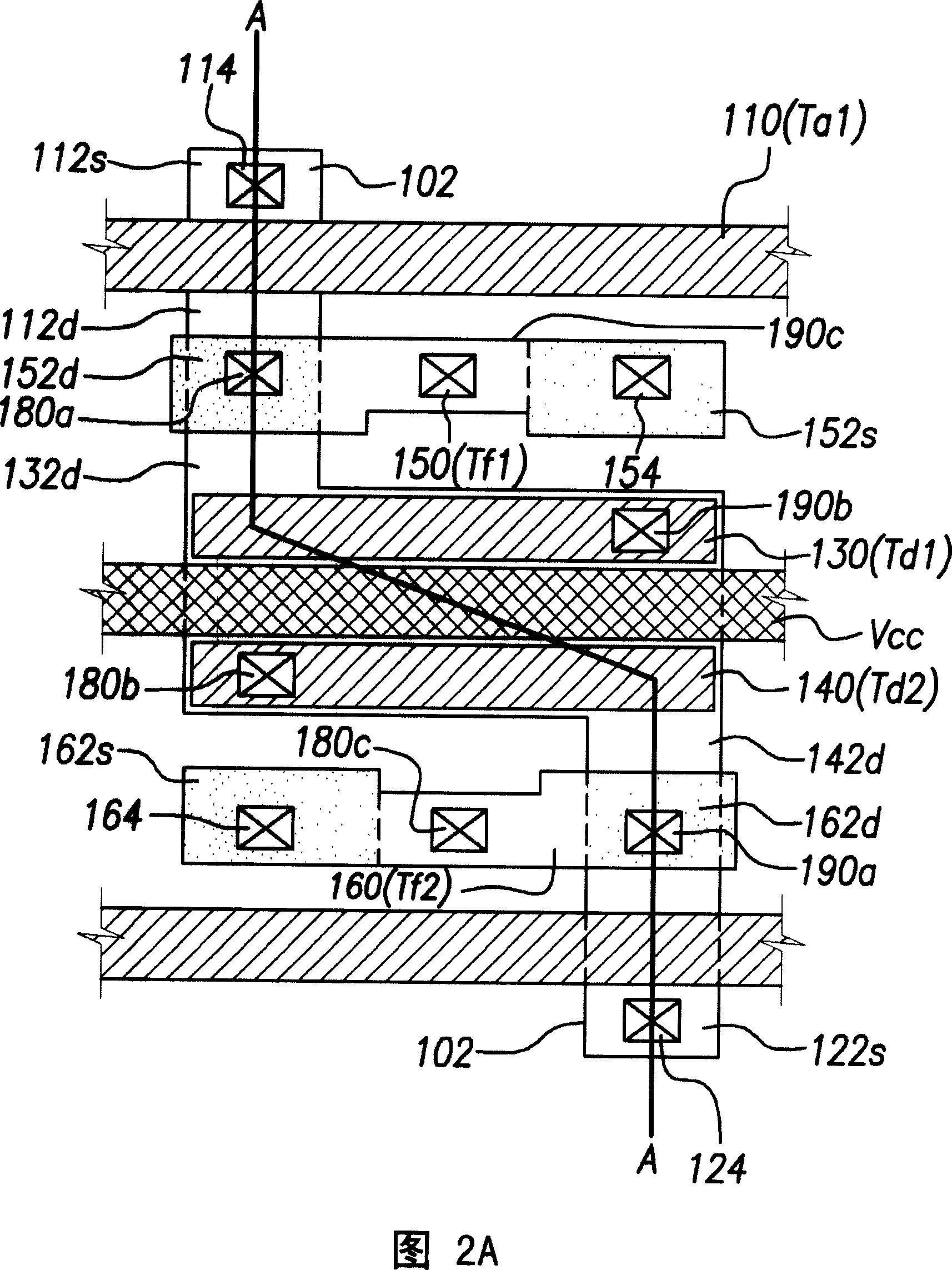

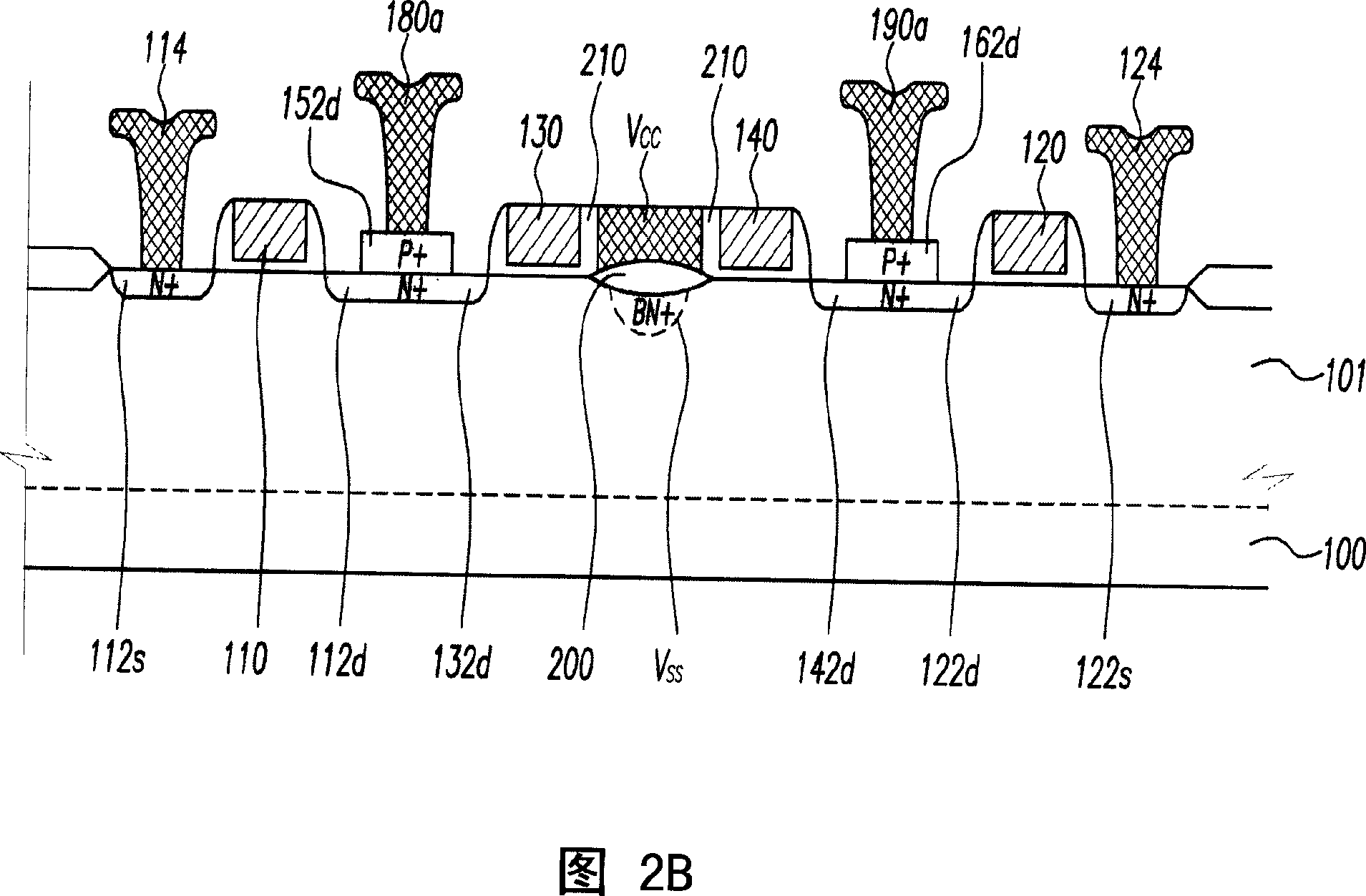

[0014] FIG. 1 is a circuit diagram showing a static random access memory (SRAM) according to an embodiment of the present invention. Here, the PMOS transistor is used as an example of a resistance device. And FIG. 2A is a layout diagram showing an SRAM according to an embodiment of the present invention, and FIG. 2B is a cross-sectional view taken along the line A-A of FIG. 2A.

[0015] 1, the SRAM cell includes: a first access NMOS transistor (TFT) Ta1 and a second access NMOS transistor (TFT) Ta2, the transistors are connected to the bit line through the...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More