Patents

Literature

901 results about "Circuit diagram" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

A circuit diagram (electrical diagram, elementary diagram, electronic schematic) is a graphical representation of an electrical circuit. A pictorial circuit diagram uses simple images of components, while a schematic diagram shows the components and interconnections of the circuit using standardized symbolic representations. The presentation of the interconnections between circuit components in the schematic diagram does not necessarily correspond to the physical arrangements in the finished device.

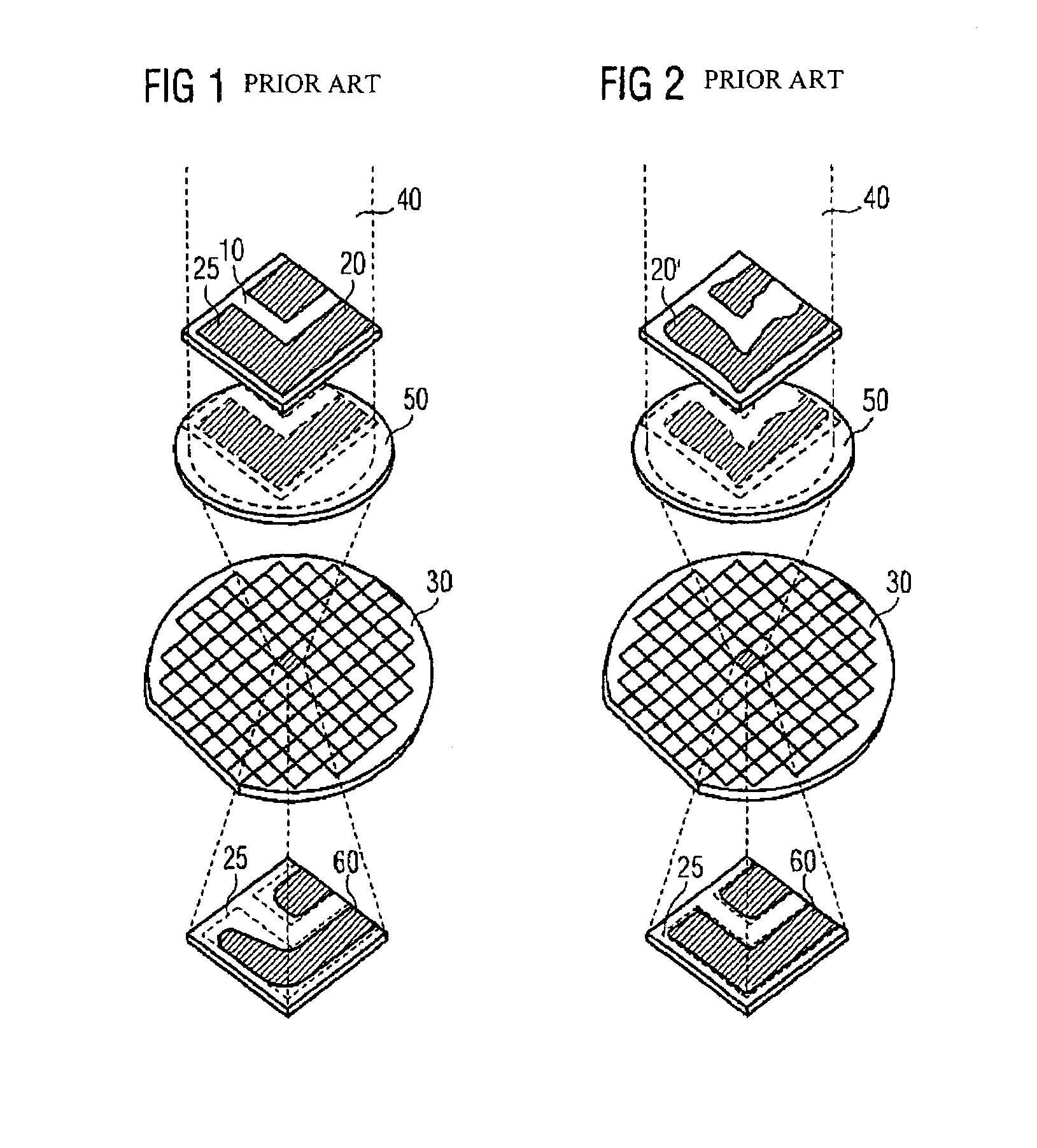

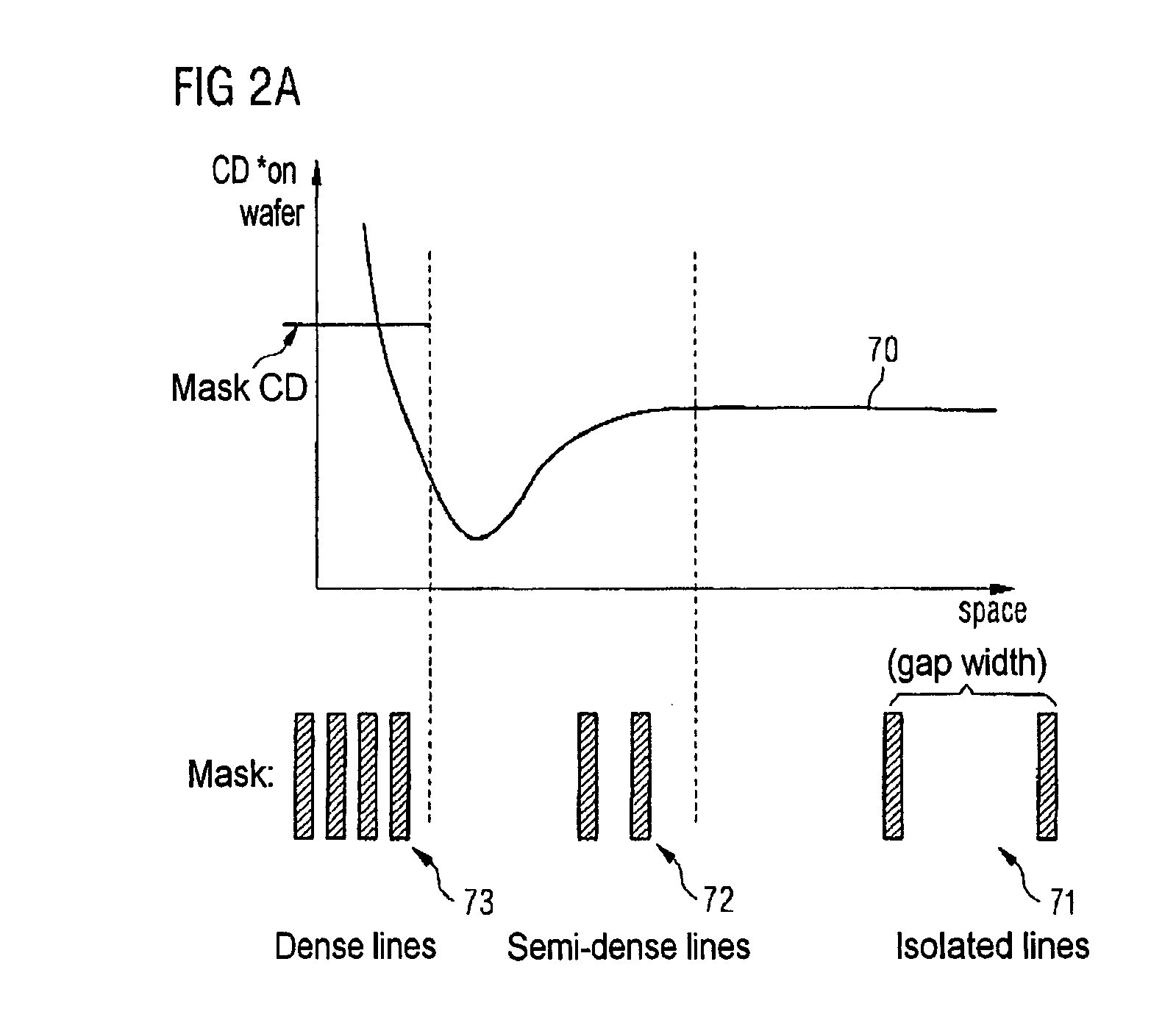

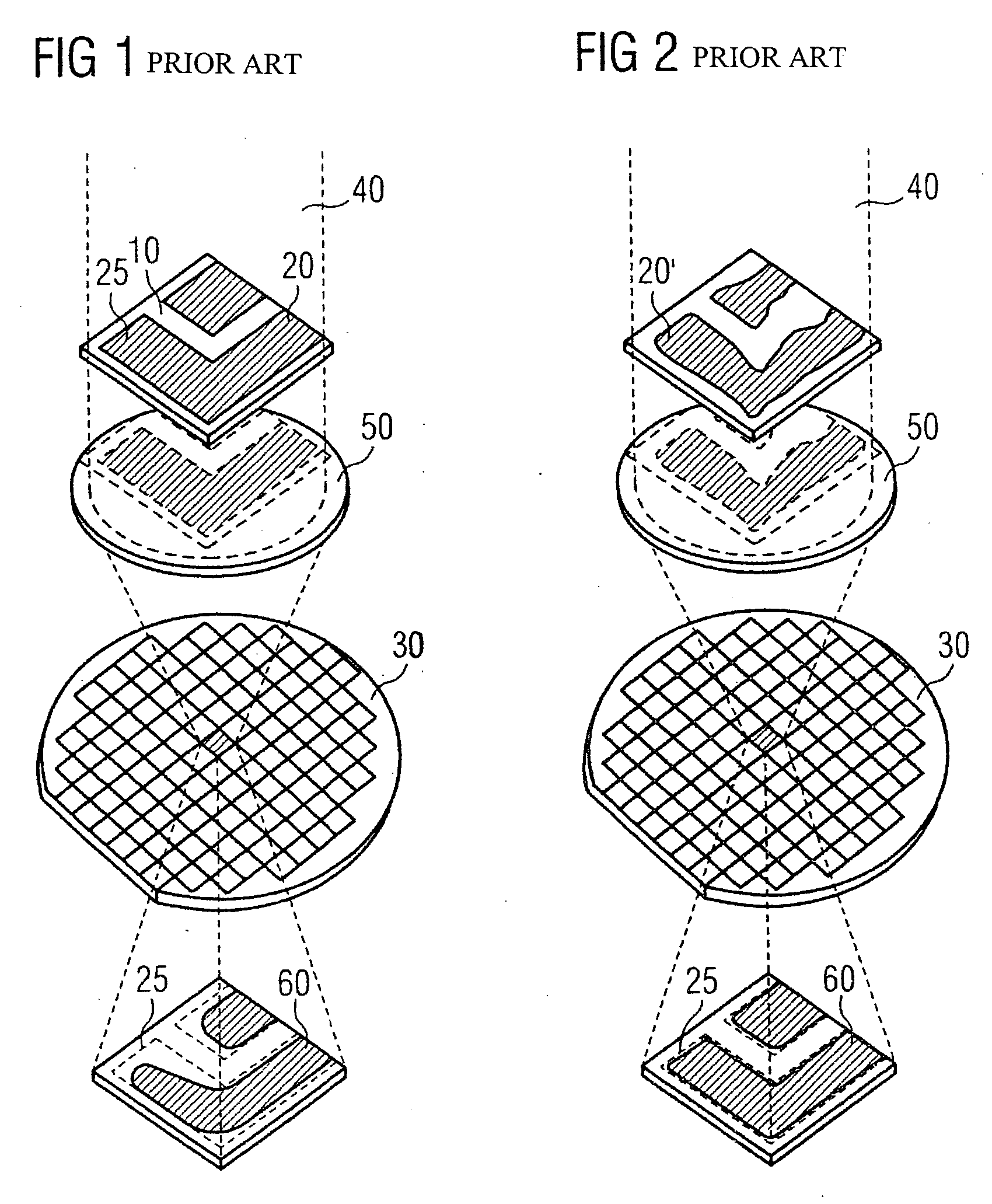

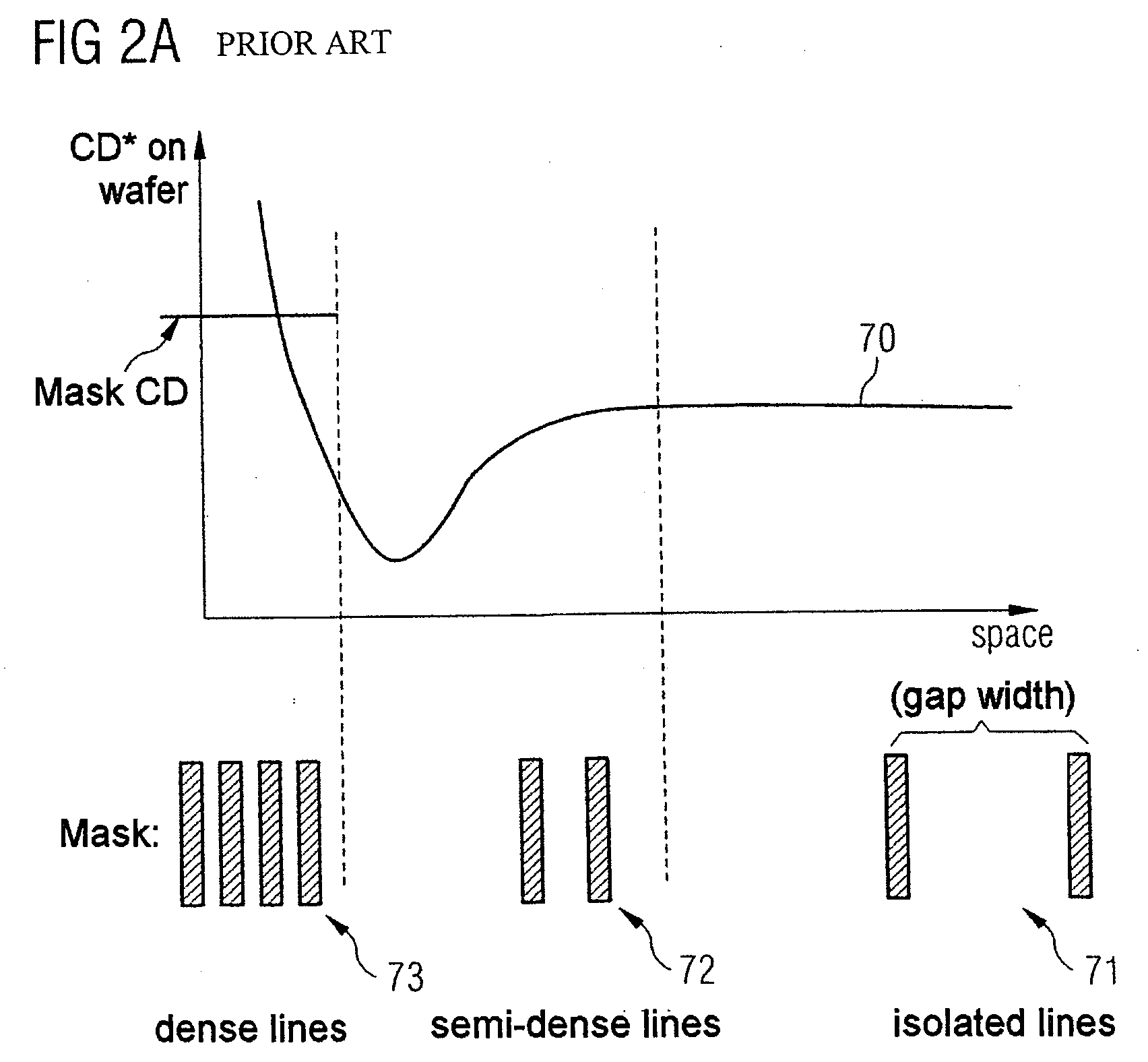

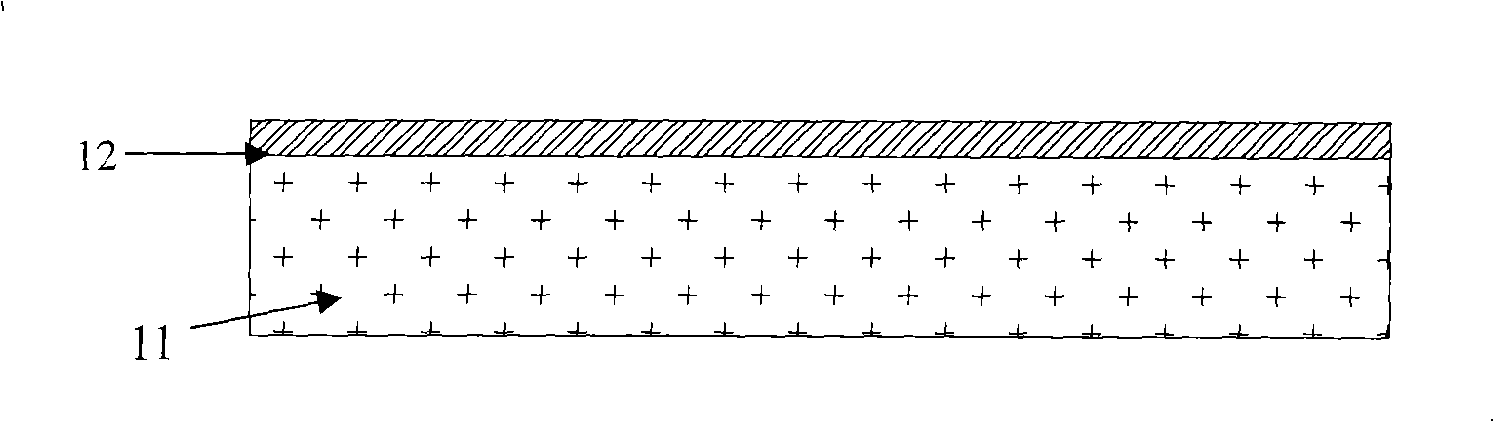

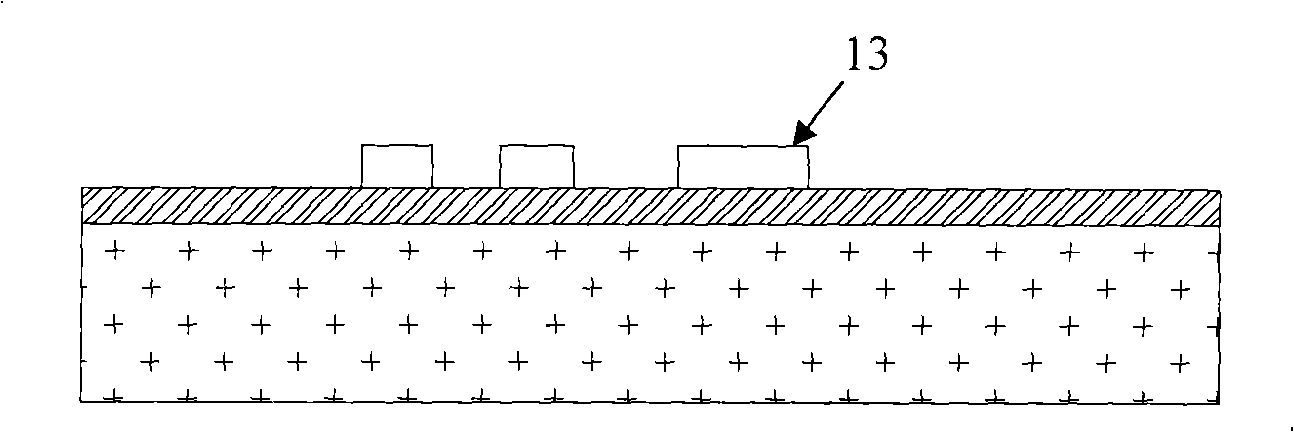

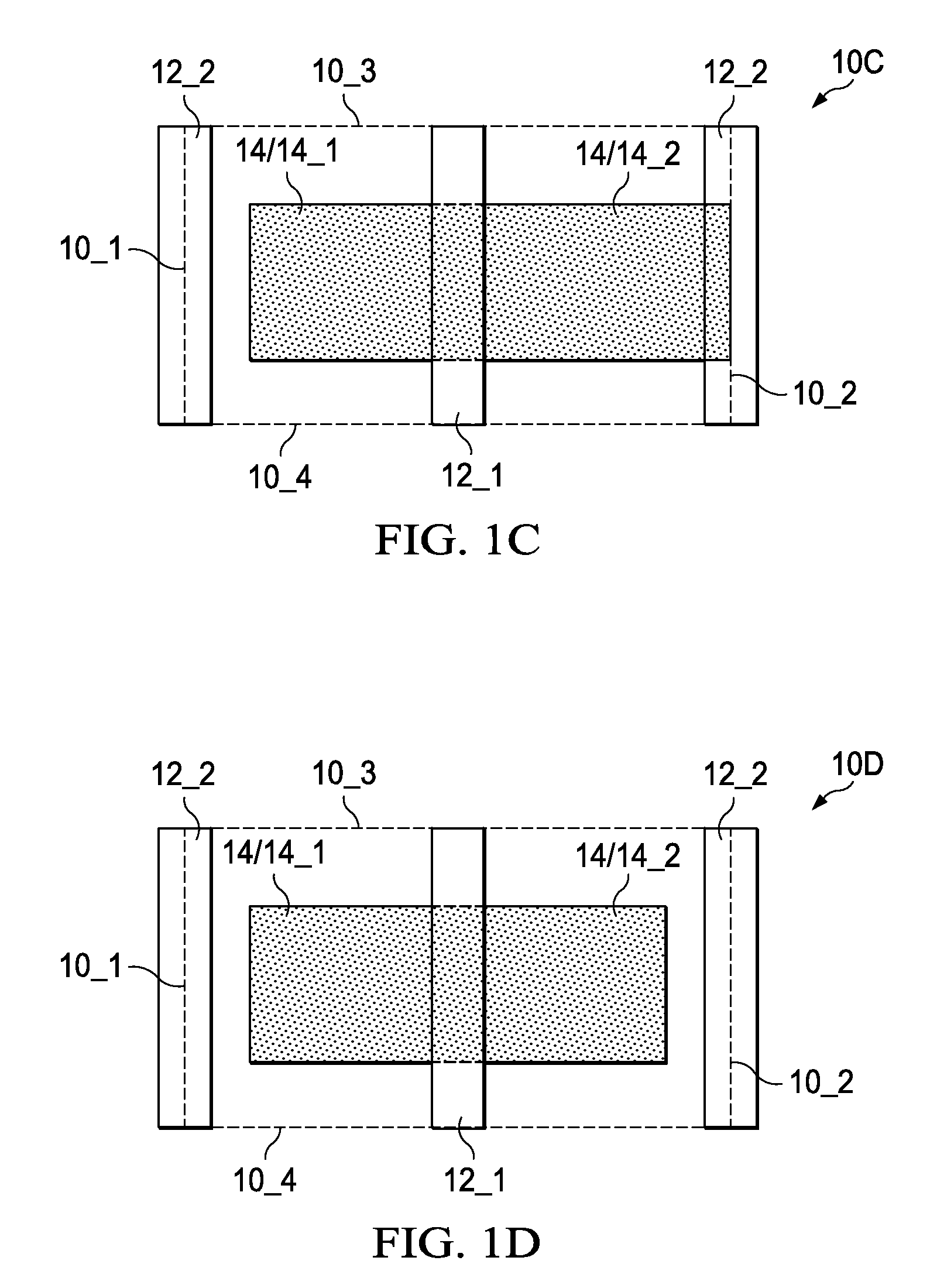

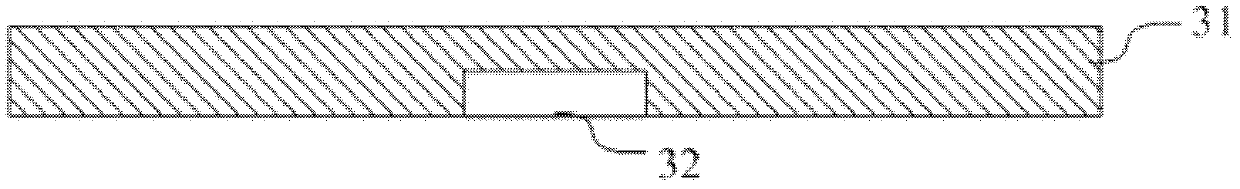

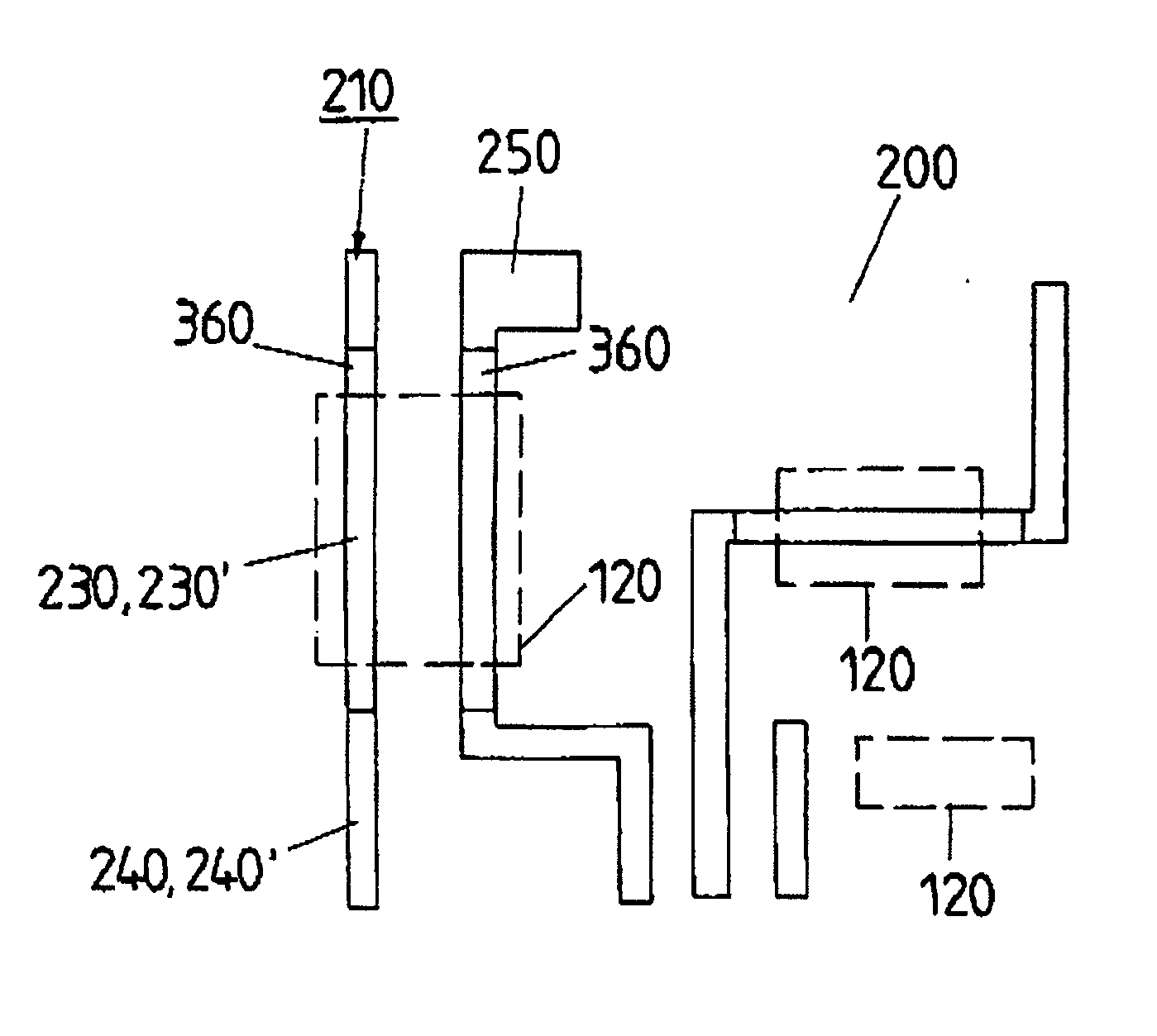

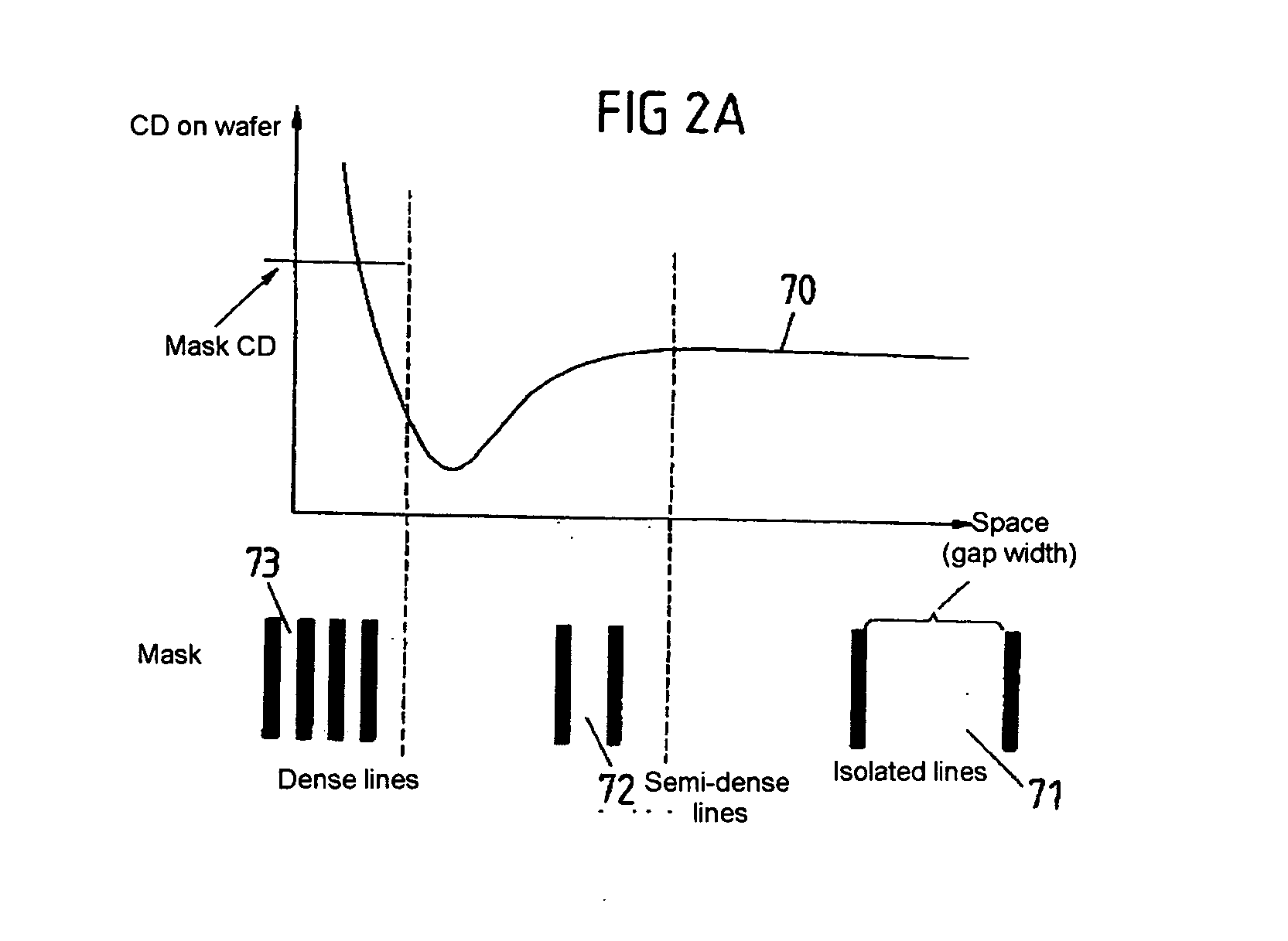

Method for producing a mask layout avoiding imaging errors for a mask

InactiveUS20060070018A1Originals for photomechanical treatmentSpecial data processing applicationsCircuit diagram

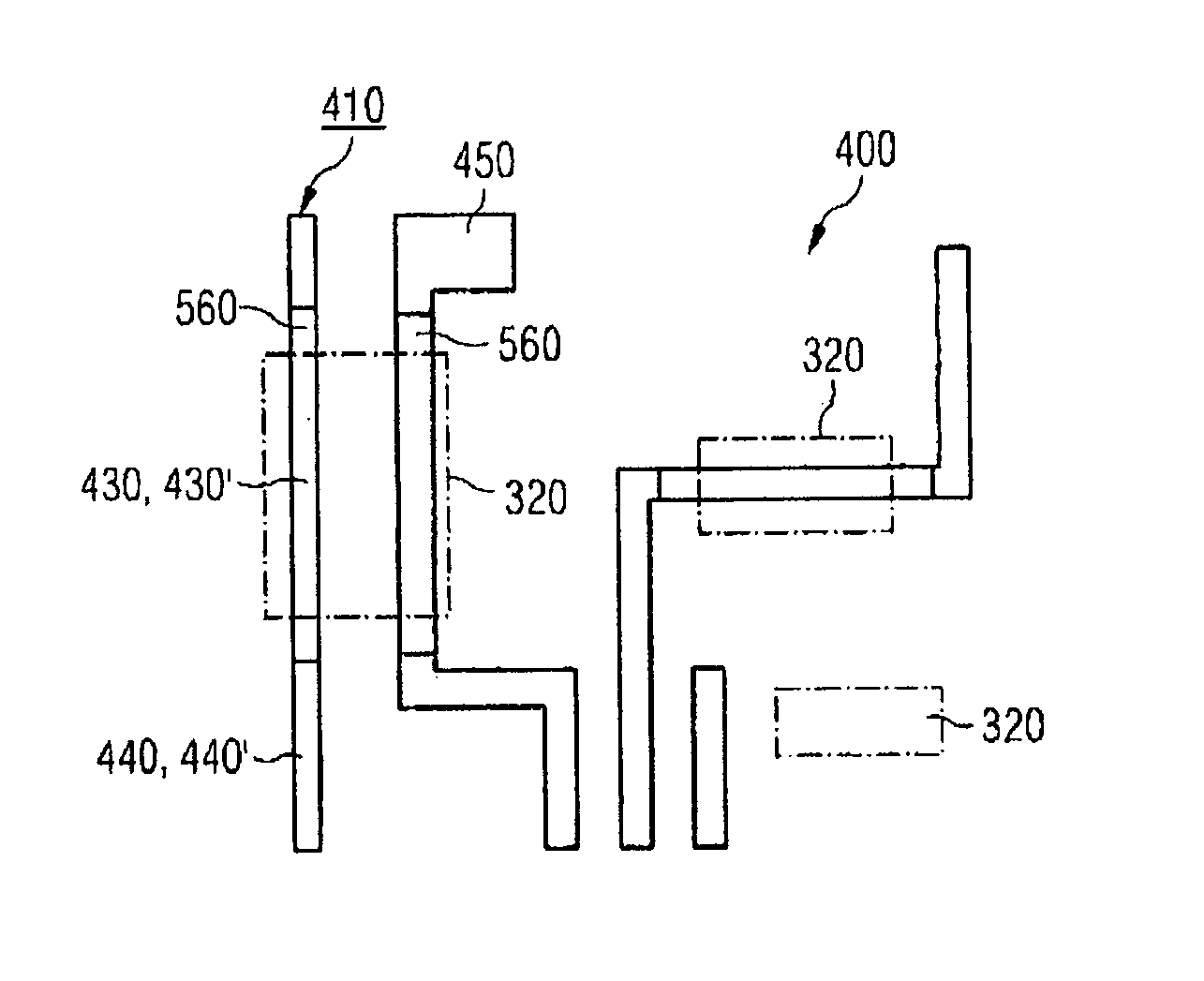

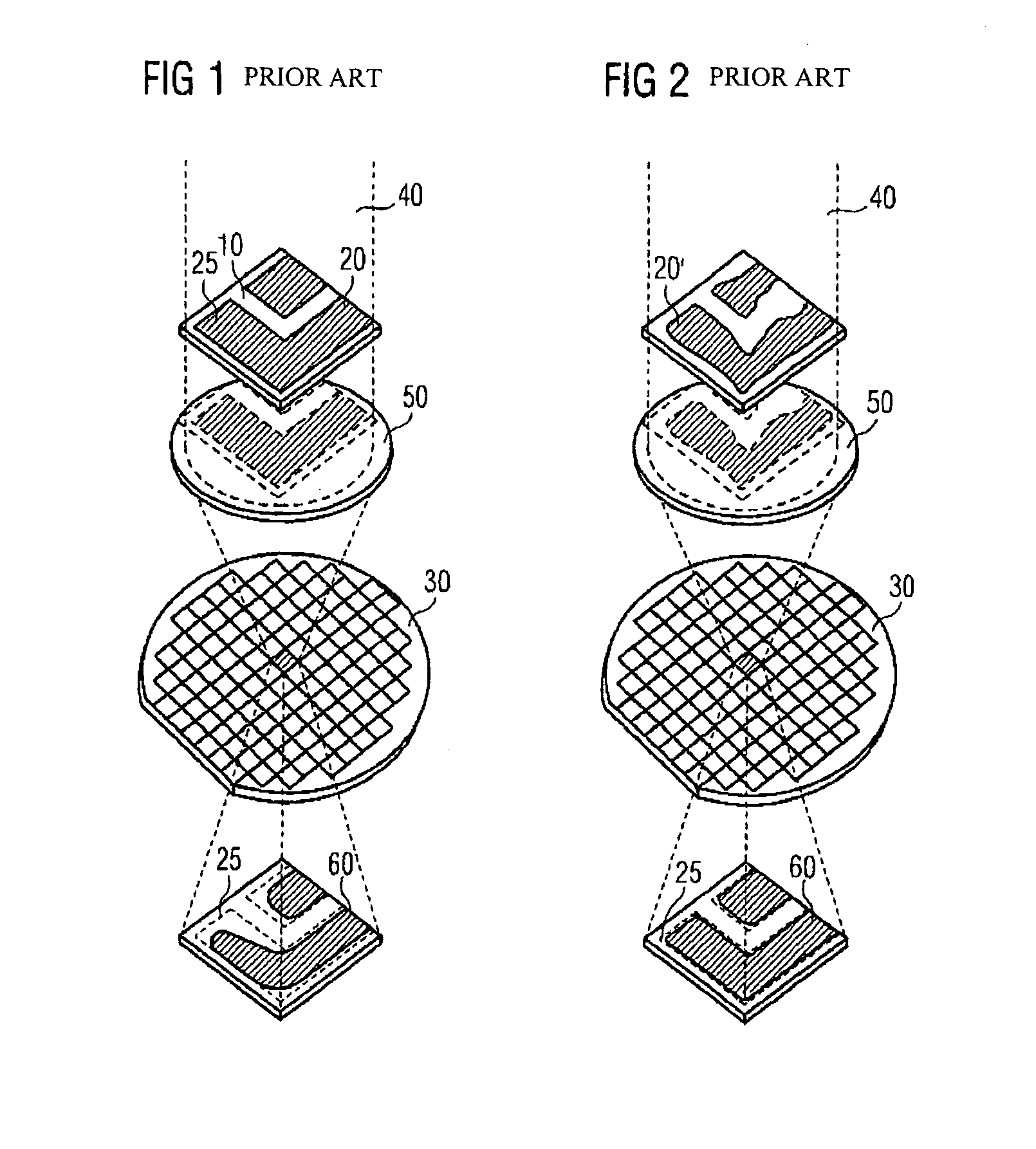

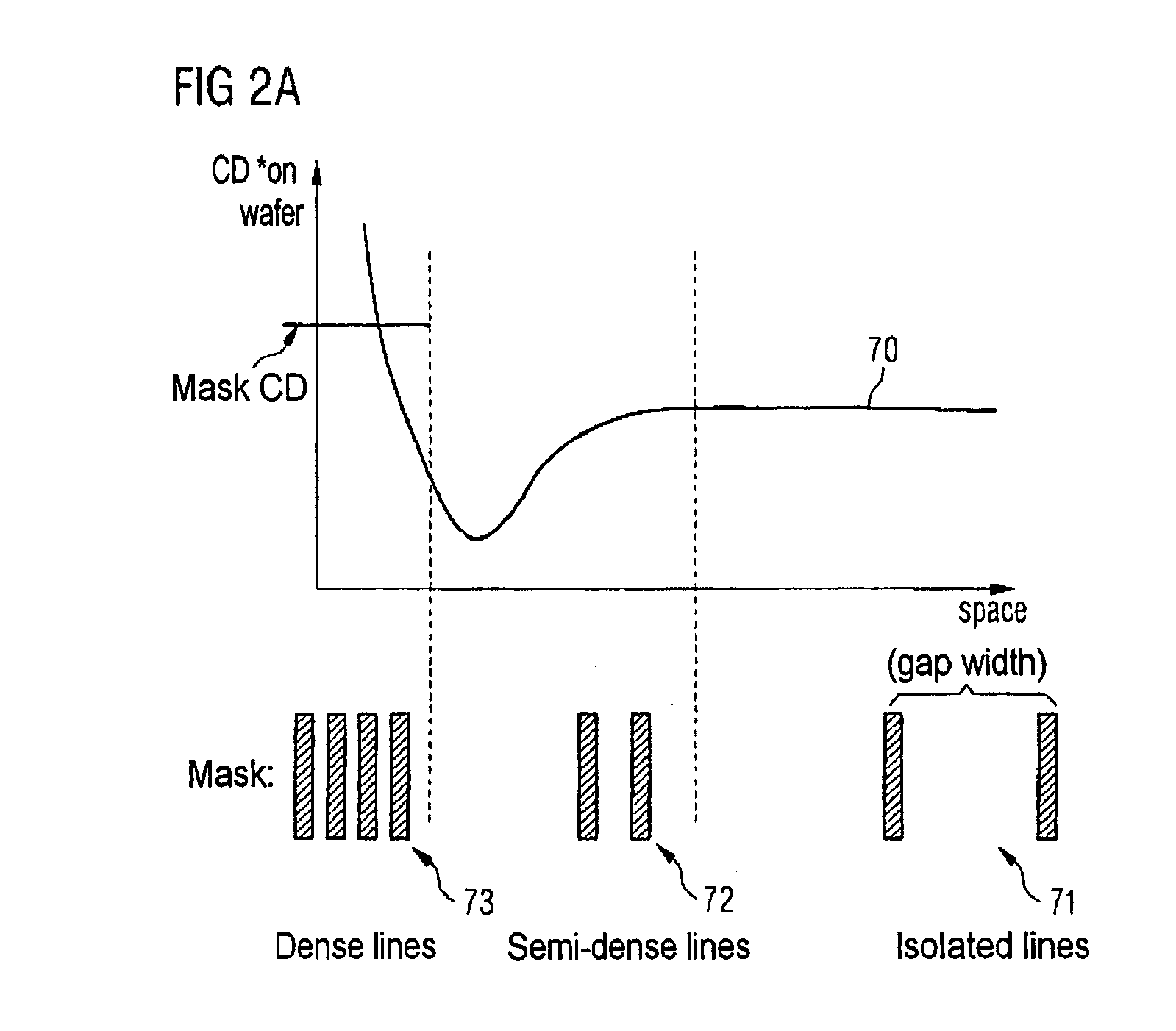

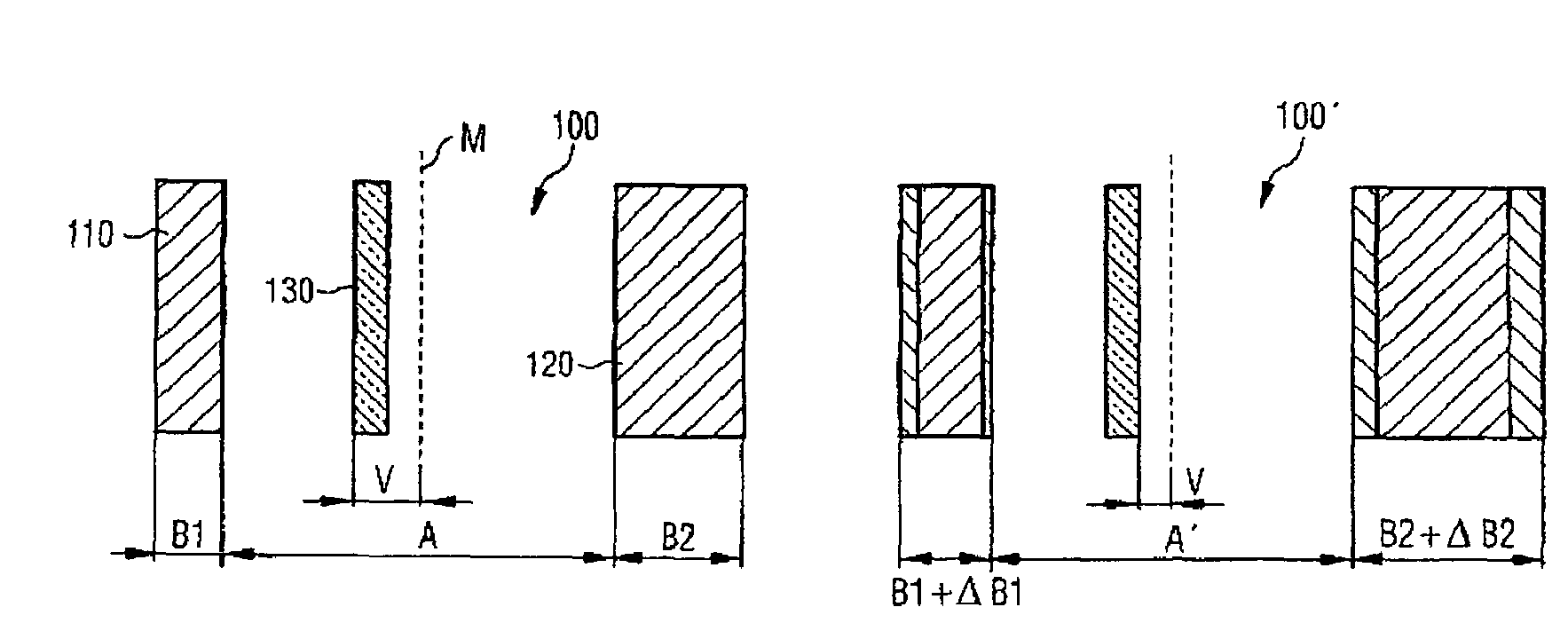

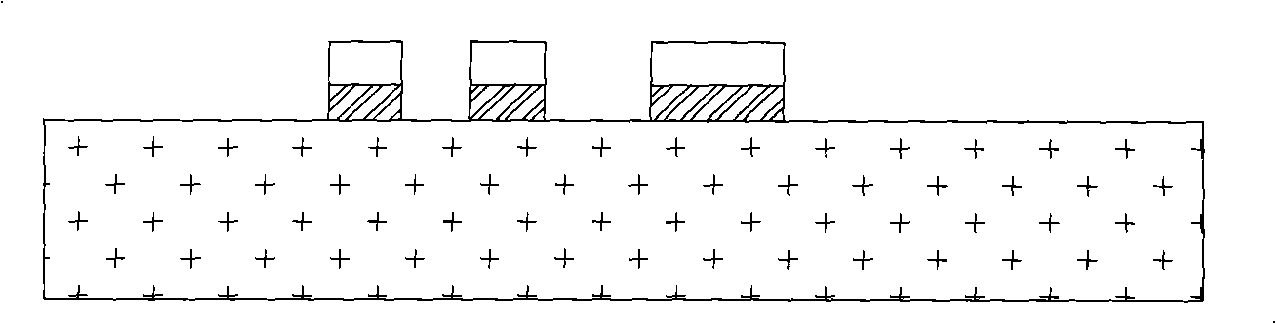

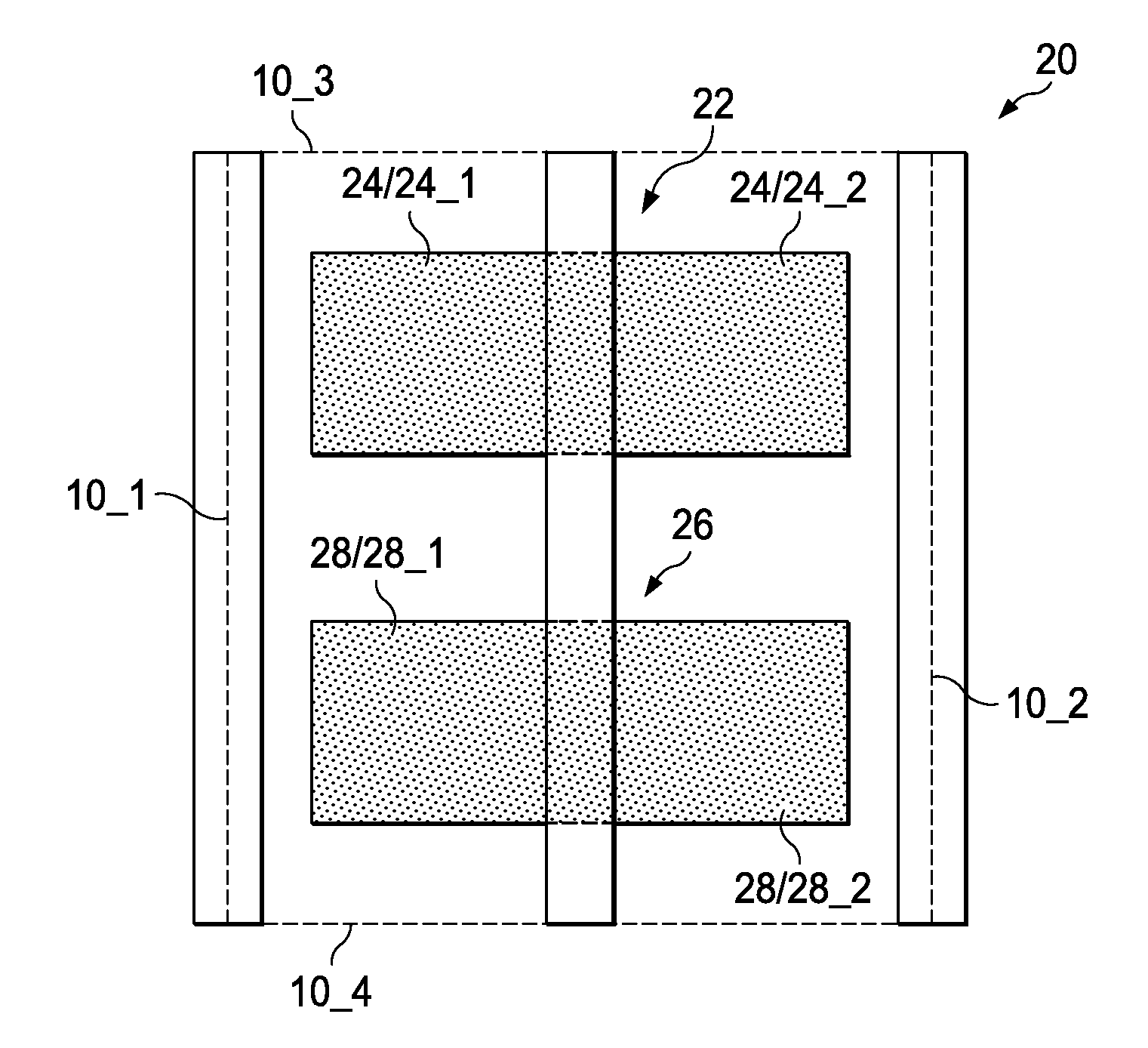

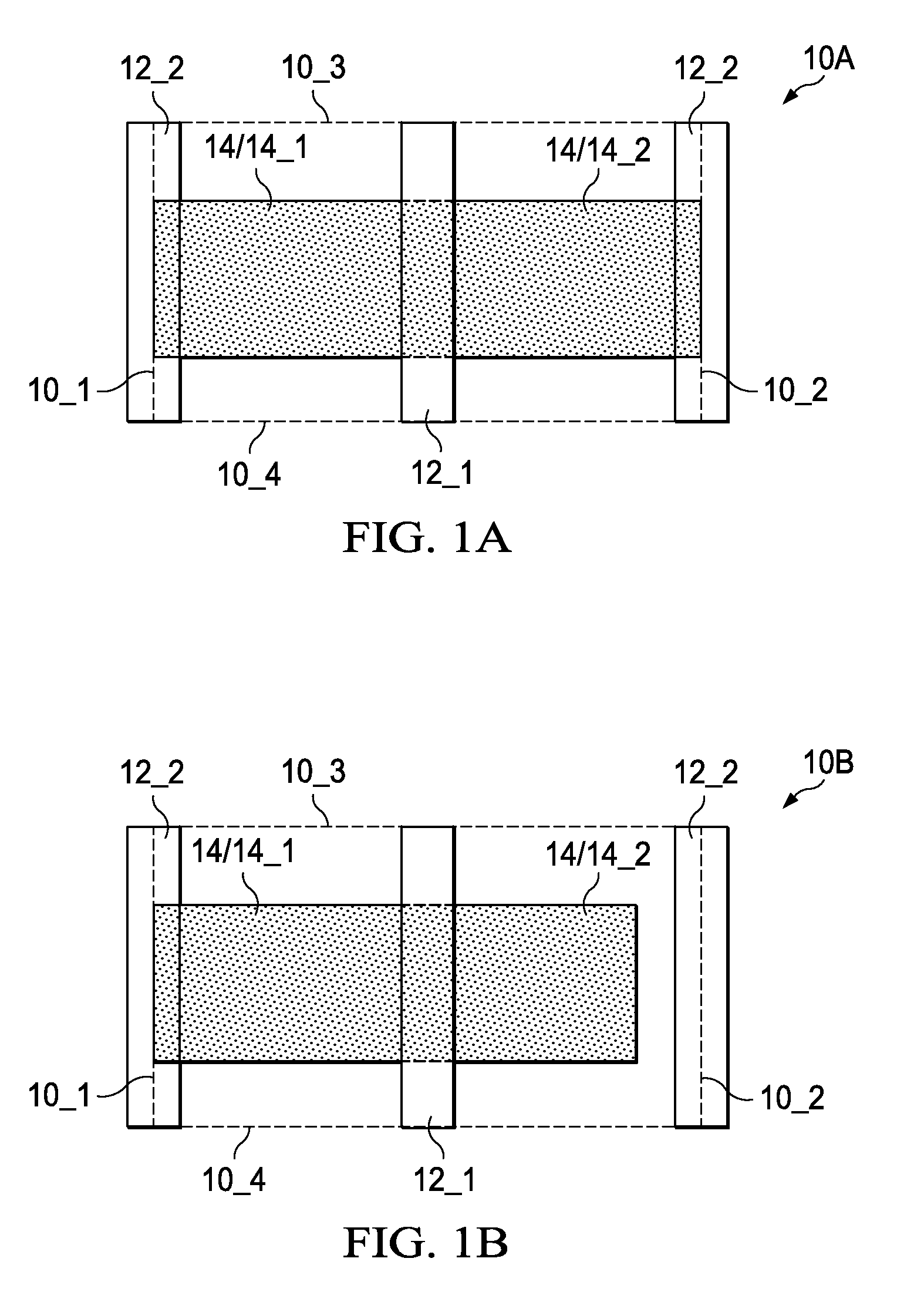

A final mask layout (20′) is produced by producing a provisional auxiliary mask layout in accordance with a predefined electrical circuit diagram and converting it into the final mask layout (20′) with the aid of an OPC method. Before carrying out the OPC method, with the provisional auxiliary mask layout (100), firstly a modified auxiliary mask layout (100′) is formed by arranging at least one optically non-resolvable auxiliary structure (130) between two mask structures (110, 120) of the provisional auxiliary mask layout (100). The optically non-resolvable auxiliary structure (130) is positioned between the two mask structures (110, 120) in a manner dependent on the structure size (B1, B2) of the two mask structures, (110, 120). An eccentric offset (V) of the optically non-resolvable auxiliary structure (130) between the two mask structures is effected in the case of differing structure sizes (ΔB) of the two mask structures.

Owner:POLARIS INNOVATIONS LTD

Method for producing a mask layout avoiding imaging errors for a mask

InactiveUS7346885B2Originals for photomechanical treatmentSpecial data processing applicationsCircuit diagramEngineering

Owner:POLARIS INNOVATIONS LTD

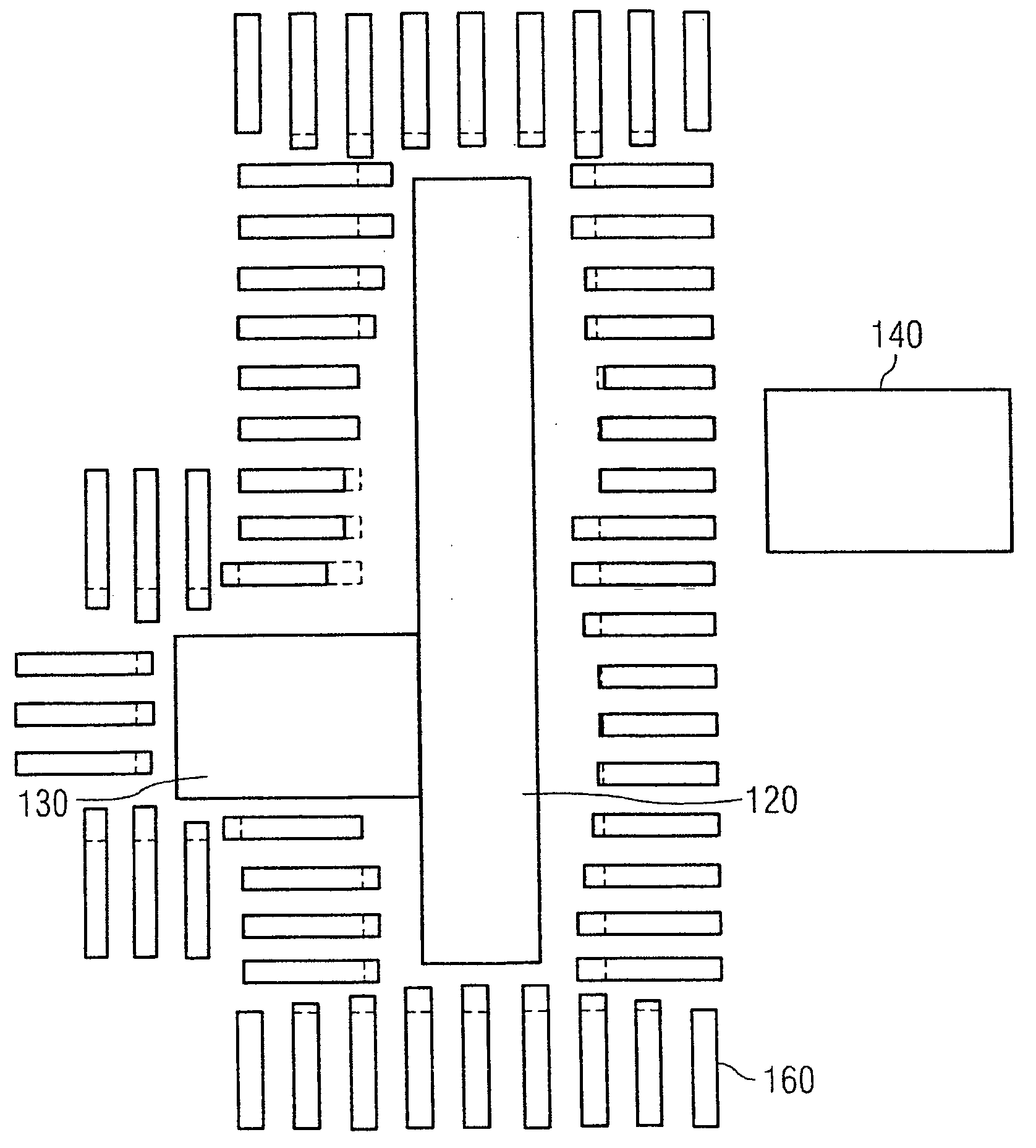

Method for producing a mask layout avoiding imaging errors for a mask

InactiveUS20060177744A1Avoid imaging errorsSimple rulesPhotomechanical apparatusSemiconductor/solid-state device manufacturingBiomedical engineeringCircuit diagram

A method for producing a final mask layout (20′) avoids imaging errors. A provisional auxiliary mask layout (110) is produced, in particular in accordance with a predefined electrical circuit diagram, and is converted into the final mask layout (20′) with the aid of an OPC method. A main structure (120, 130) of the provisional auxiliary mask layout (110) is assigned optically non-resolvable auxiliary structures (160, 320). Exclusively the optically non-resolvable auxiliary structures (160, 320) are altered in the context of the OPC method, and the main structure (120, 130) itself remains unaltered.

Owner:INFINEON TECH AG

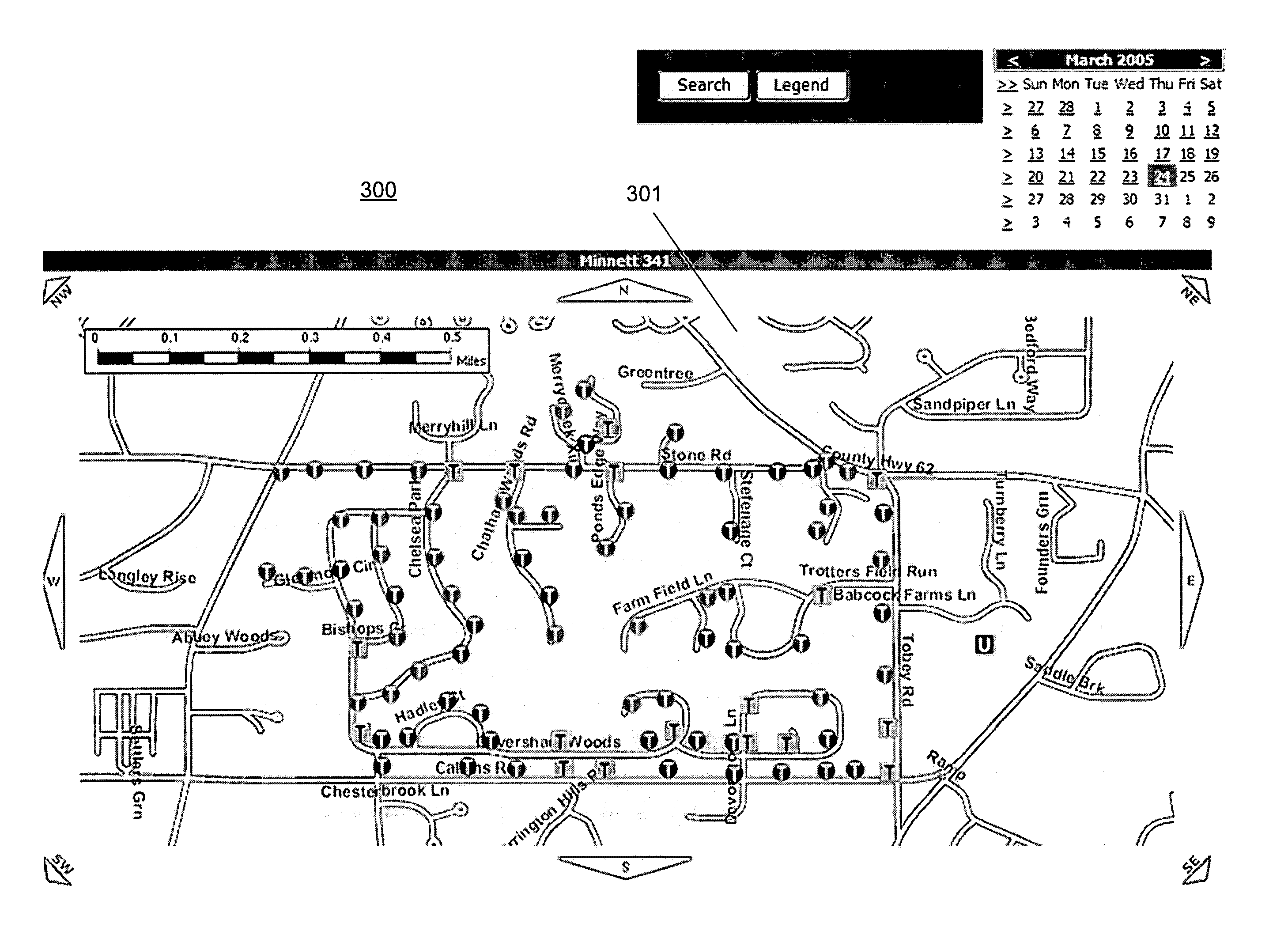

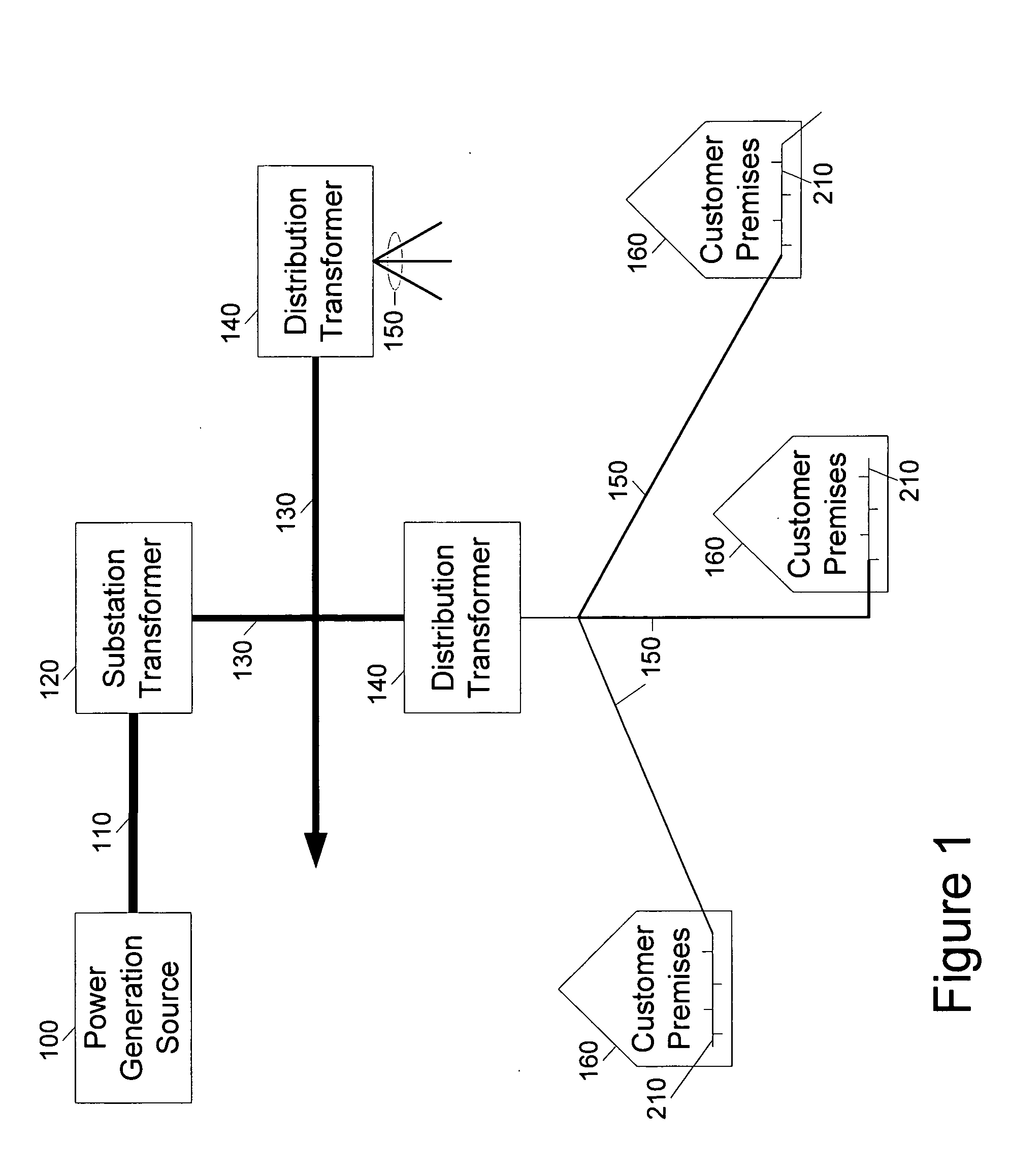

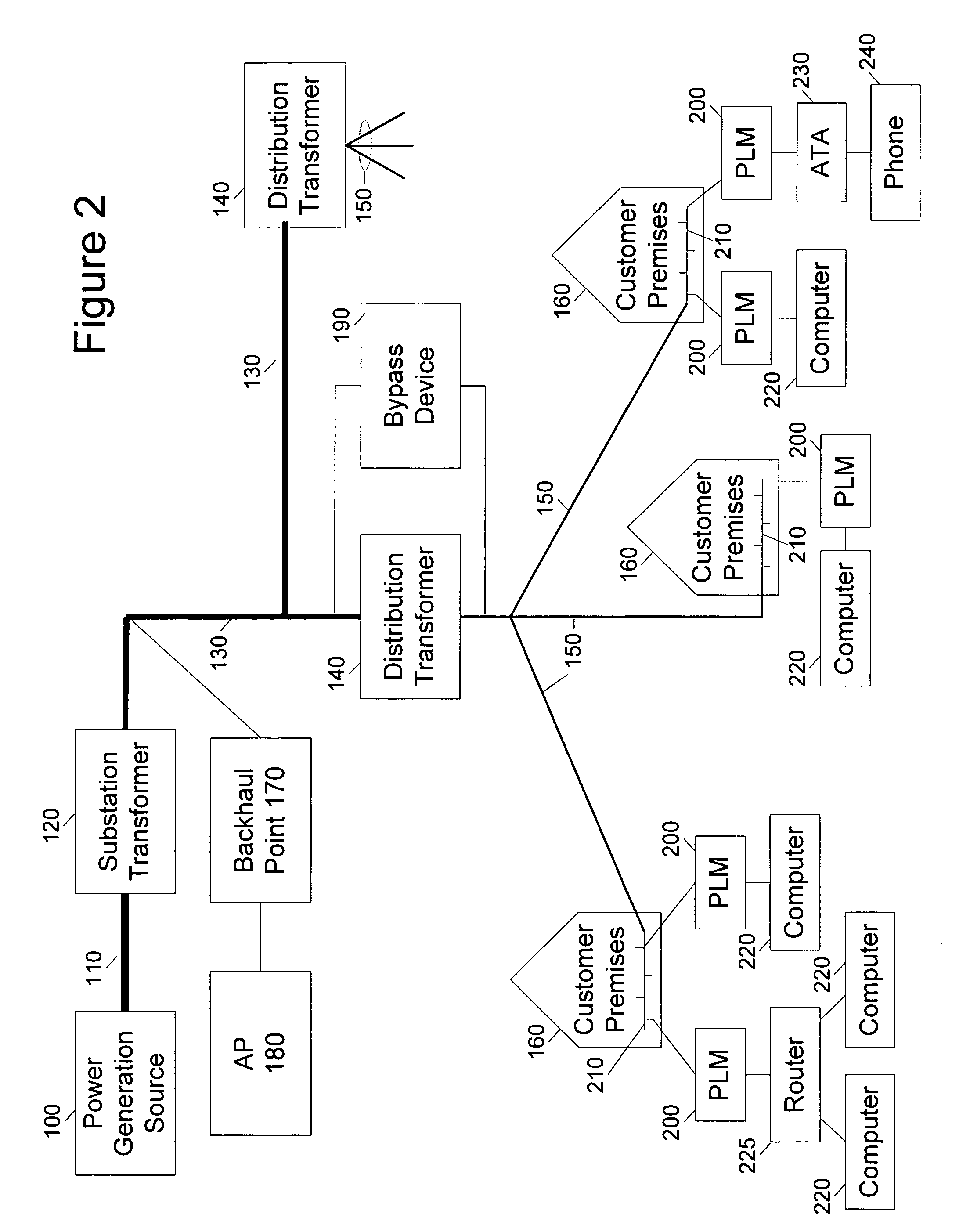

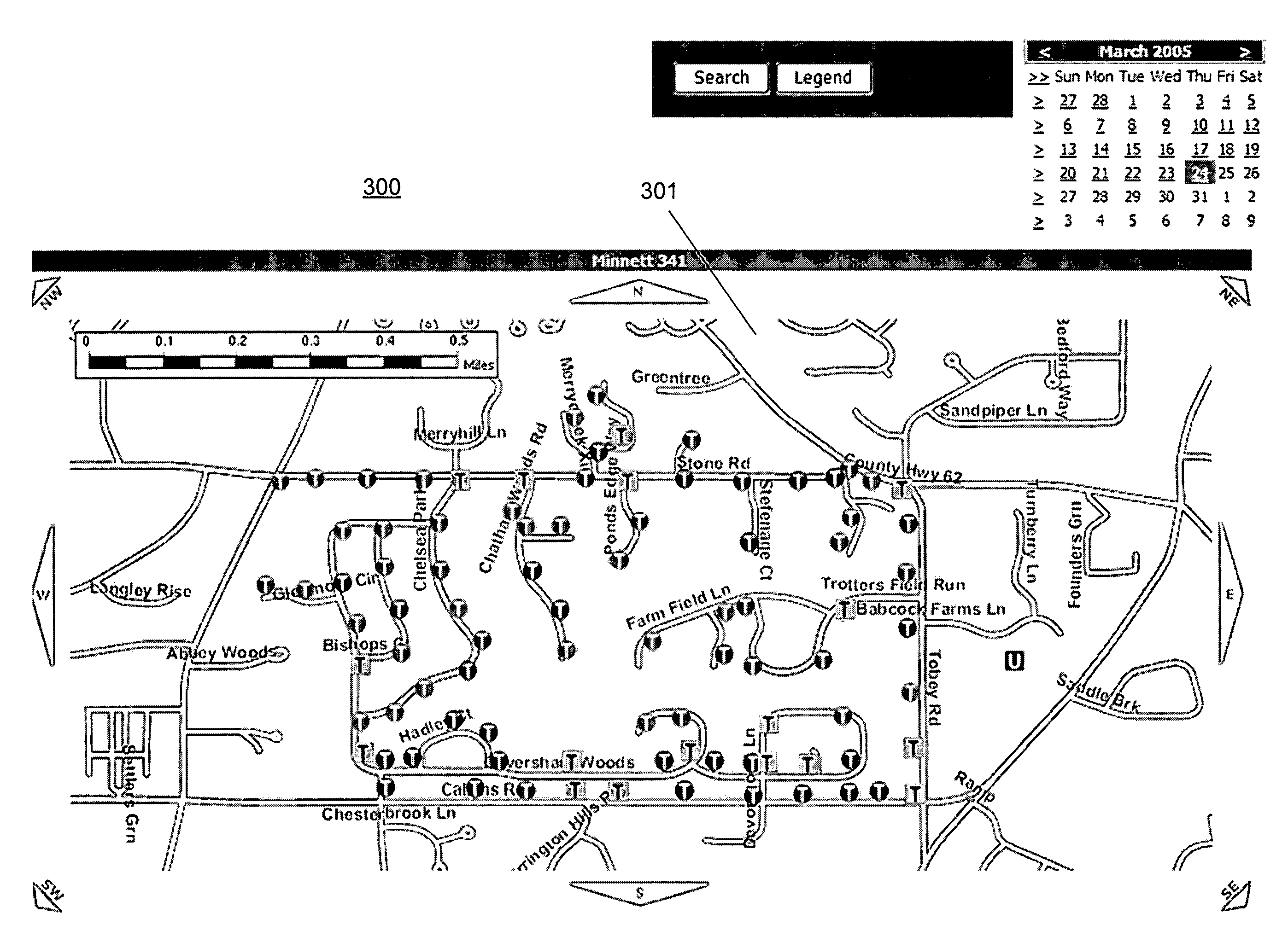

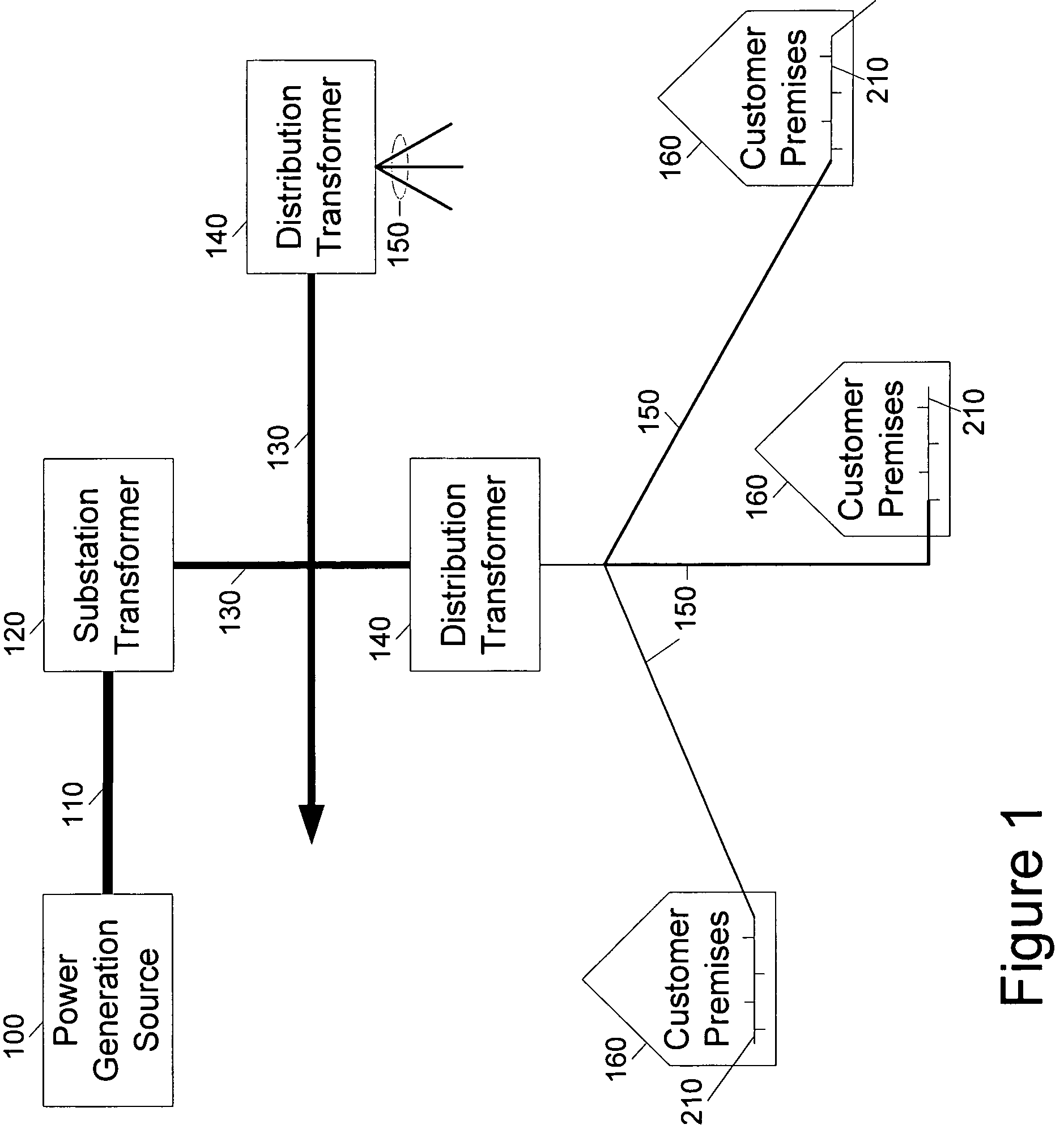

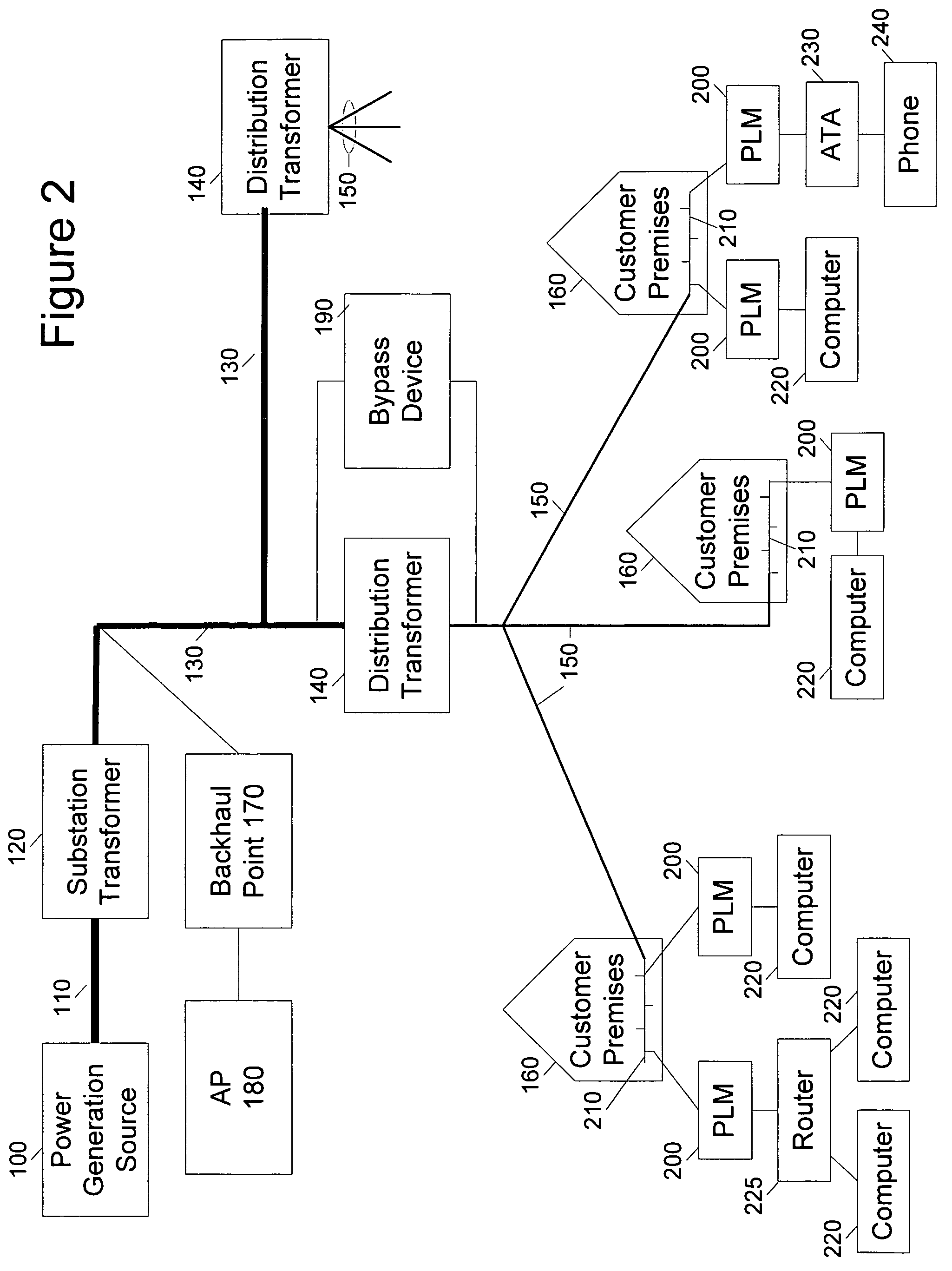

Power distribution network performance data presentation system and method

A visualization system for monitoring performance data of an electrical power distribution network is provided. In one embodiment, a user may select a network circuit and view a network circuit diagram that includes indicia representing transformers and other electrical power distribution network elements positioned on a map. The relative positions of the indicia on the network circuit diagram may correspond to the relative physical locations of the transformers in the geographical area represented by the map. The indicia may be color coded to convey performance data to the user.

Owner:CURRENT COMM SERVICES

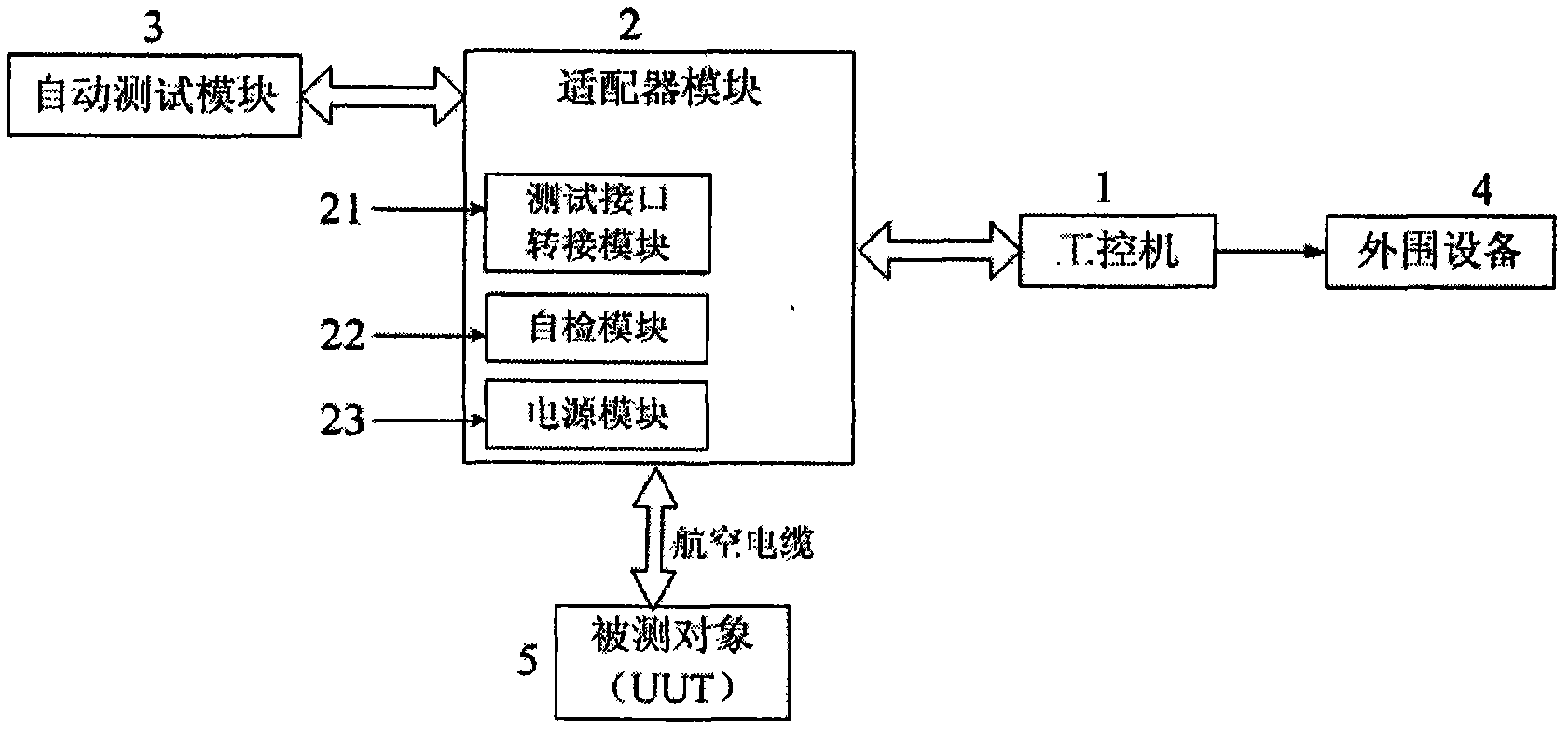

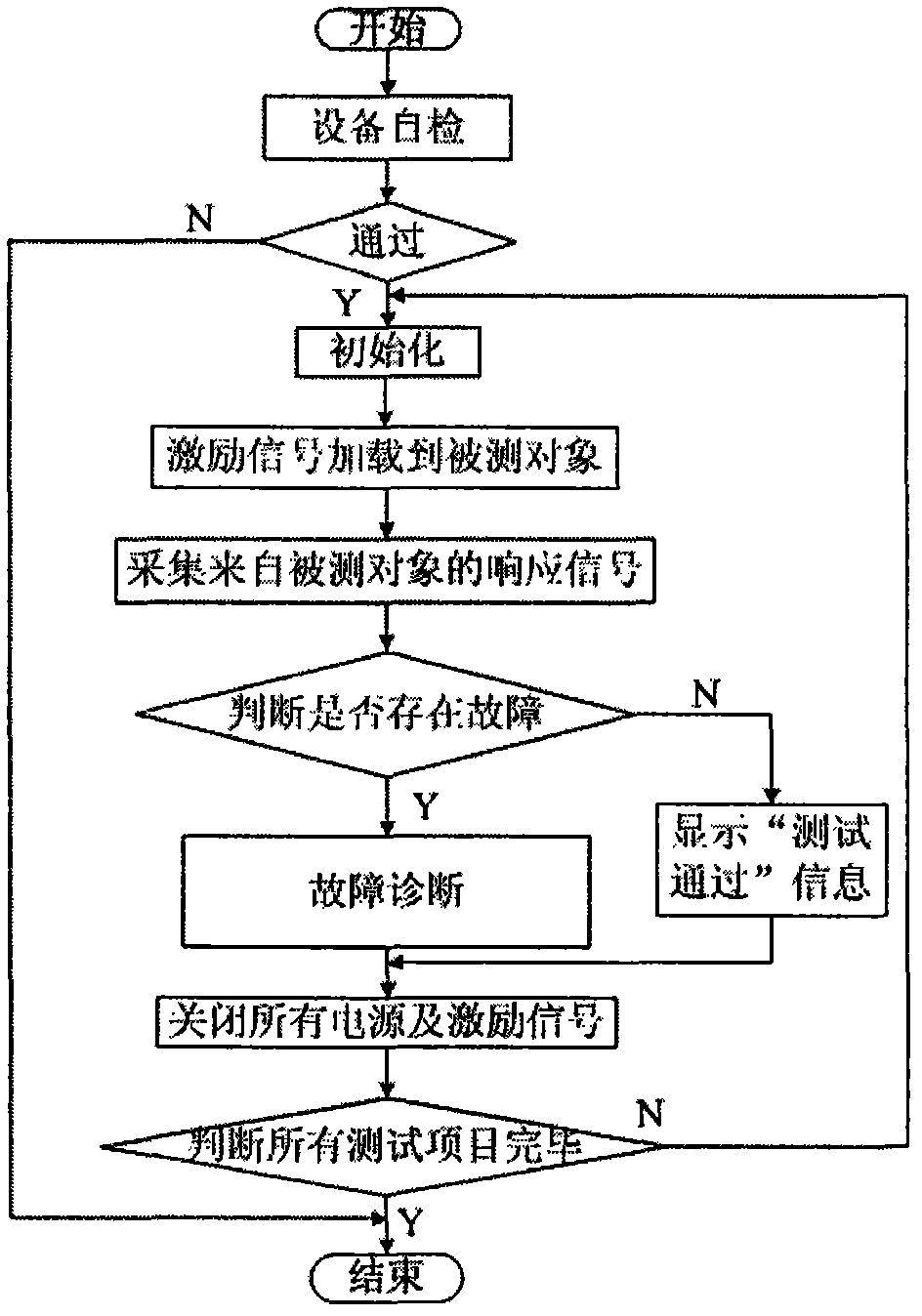

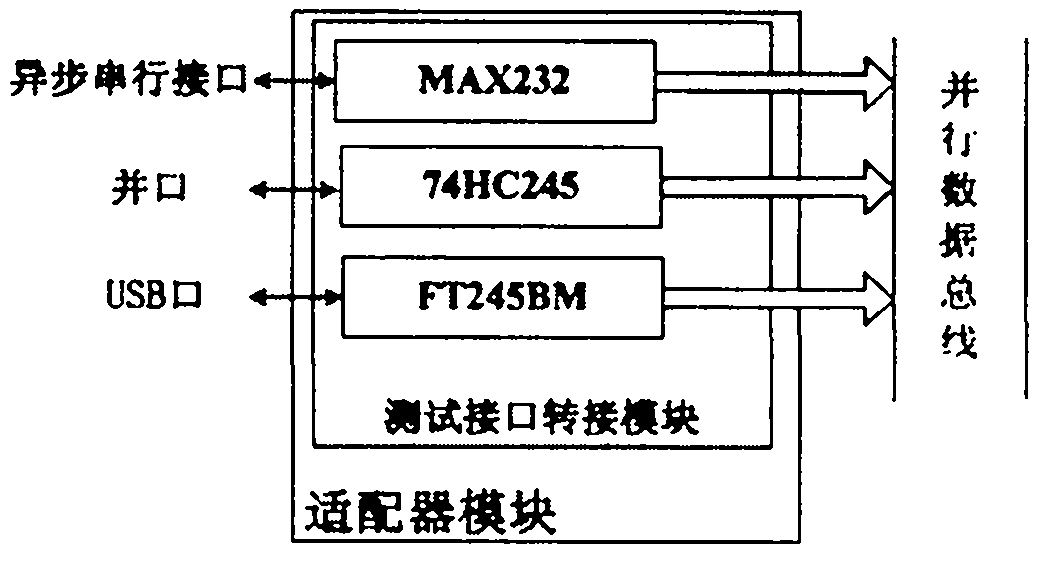

Device and method for automatic test and fault diagnosis of plane audio integrated system

ActiveCN102092477AWith fault diagnosis functionReduce labor intensityStructural/machines measurementAircraft maintainanceData informationCapability Maturity Model

The invention relates to a device and method for automatic test and fault diagnosis of a plane audio integrated system, which are used for maintaining the plane audio integrated system of Airbus series and Boeing series. The method comprises the steps of: operating test software by an industrial personal computer to provide a man-machine interaction environment, and carrying out analysis, computation and statistic treatment on acquired data so as to further complete fault diagnosis; compiling a fault diagnosis program according to all circuit diagrams and test point information of the audio integrated system, provided by a CMM (Capability Maturity Model for Software) manual, and clearing up injected data information on faults, excitation, response and the like to form a fault record in a fault dictionary; in the fault diagnosis program, providing the positions of testing points in need of manual measurement and corresponding test information; testing the testing points in need of manual measurement by detection personnel to confirm a fault area, and displaying corresponding diagnosis results. The device and method provided by the invention can commonly meet the requirement of the automatic test for two types of audio integrated systems including the AMU (Audio Management Unit) of Airbus series planes and the REU (Remote Electronic unit) of the Boeing series planes, and are favorable for reducing the labor intensity of maintenance personnel and improving maintenance efficiency.

Owner:CIVIL AVIATION UNIV OF CHINA

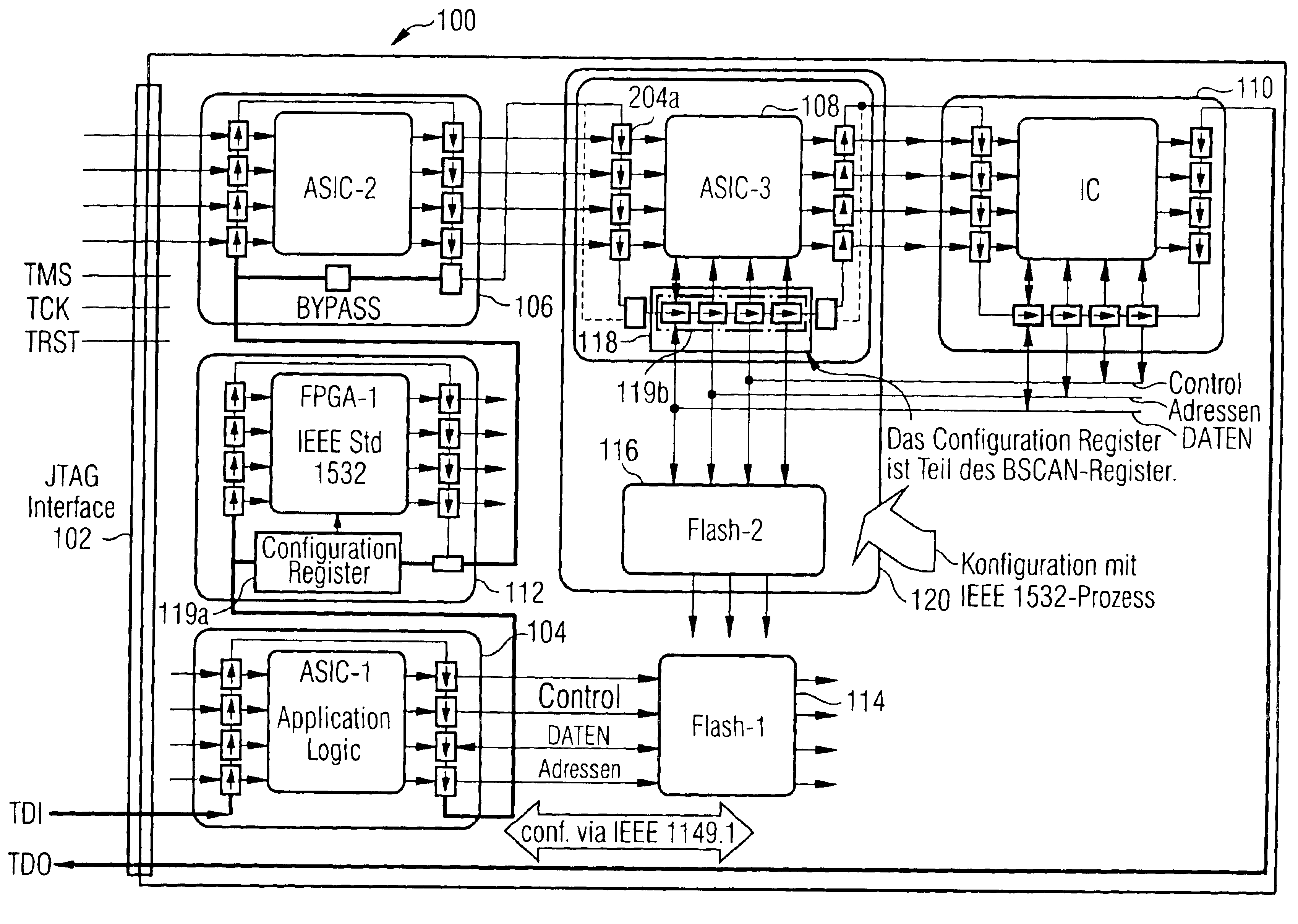

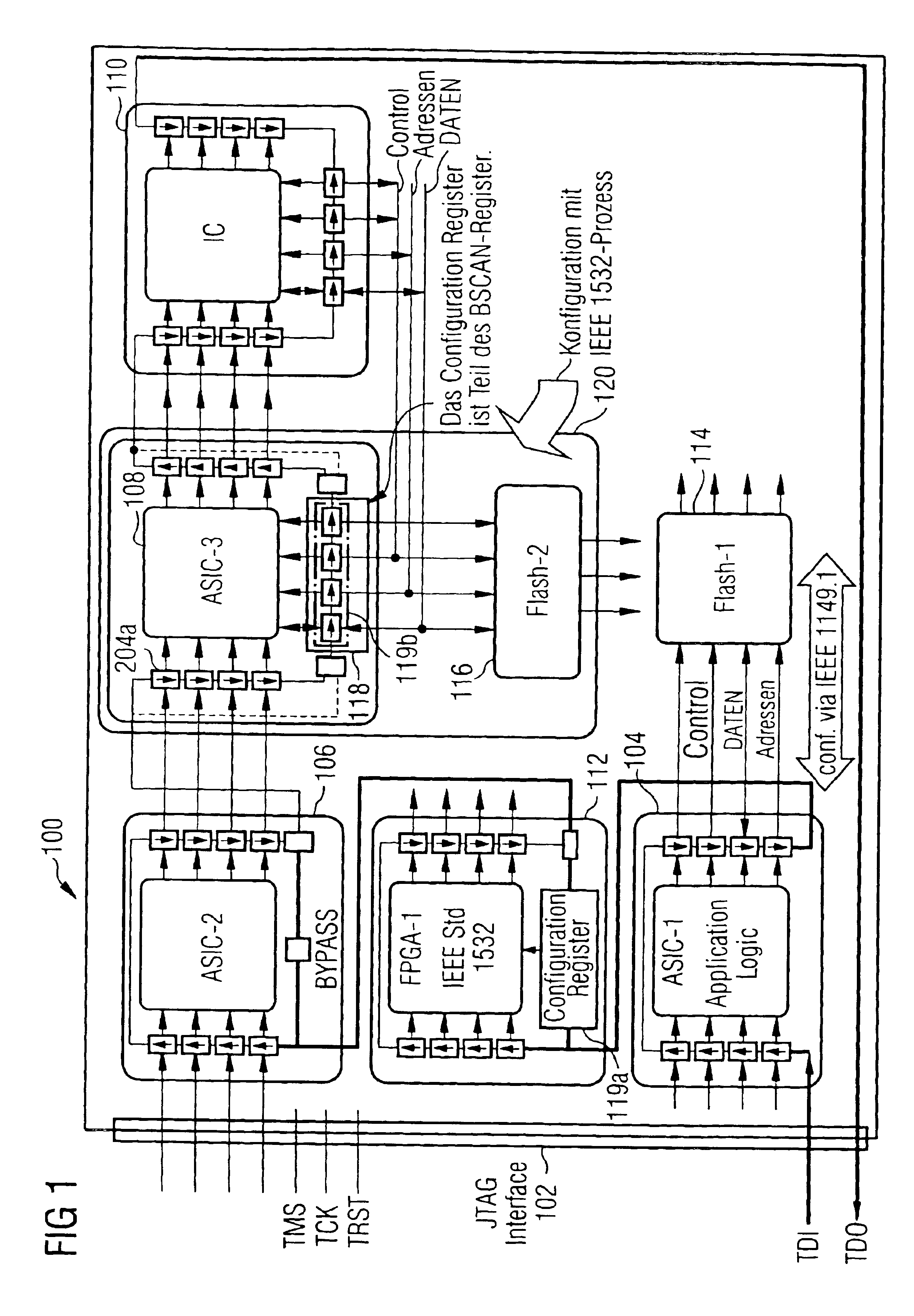

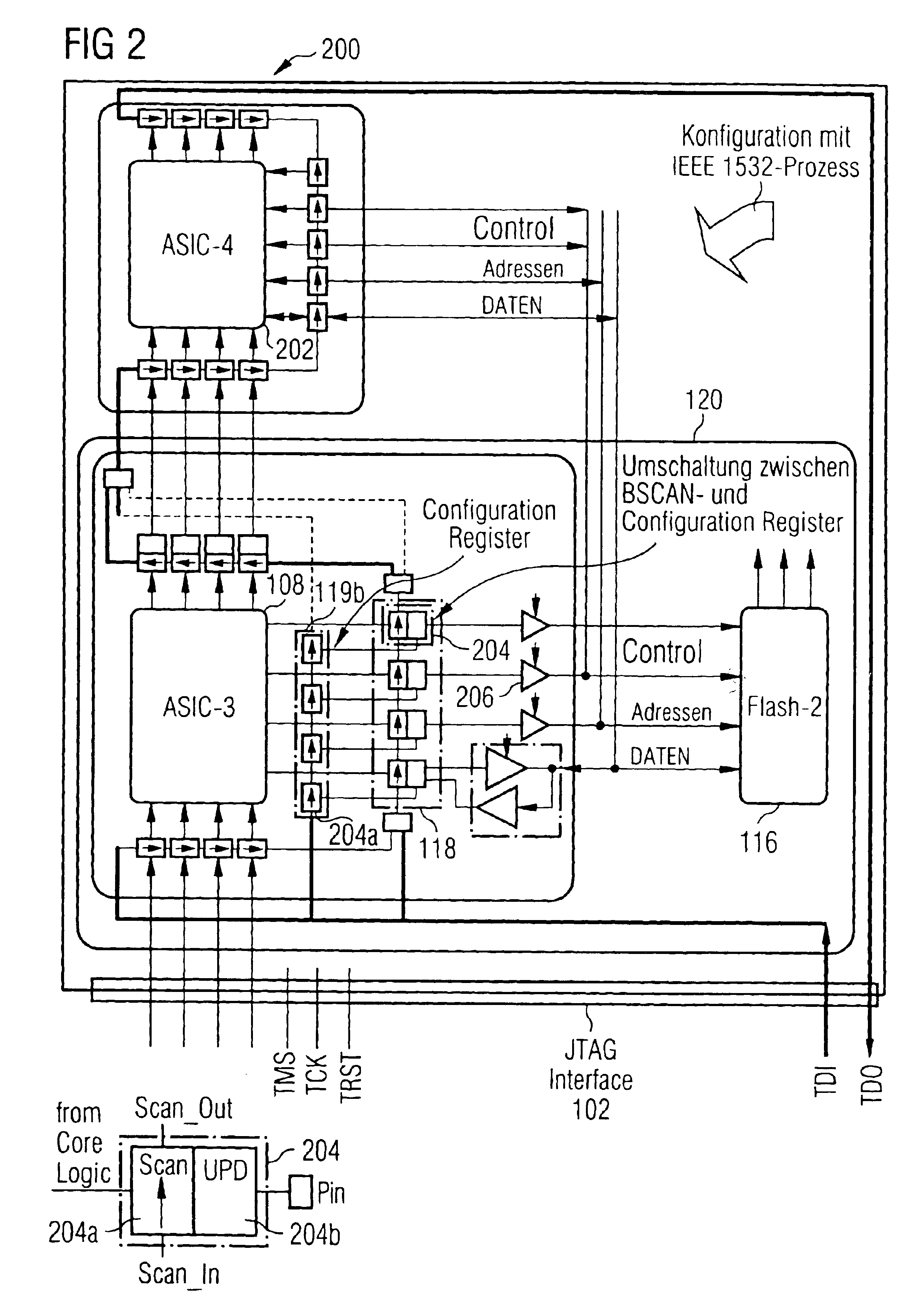

Programming flash memory via a boundary scan register

ActiveUS6937493B2Reduce effortElectronic circuit testingRead-only memoriesFunctional testingOn board

A method and parallel interface for on-board programming and / or In-System Configuration of a flash memory mounted on a printed circuit board by controlling its inputs with the aid of an ASIC mounted on the same circuit board via a Boundary Scan register of which the output signals are provided for activating or deactivating a write operation. The architecture description of the ASIC, flash memory, and the data format of the program and configuration data are stored in a Boundary-Scan Description Language file. The circuit board can be controlled via a JTAG interface suitable for performing function testing of the flash memory for input or output of standard bus signals and for input of the control signals of the ASIC. To reduce the programming effort, the data of the circuit diagram or of the network list derived from it is stored in the BSDL file.

Owner:NOKIA SIEMENS NETWORKS GMBH & CO KG +1

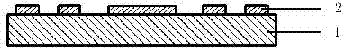

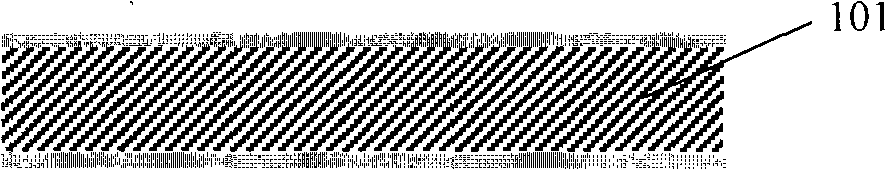

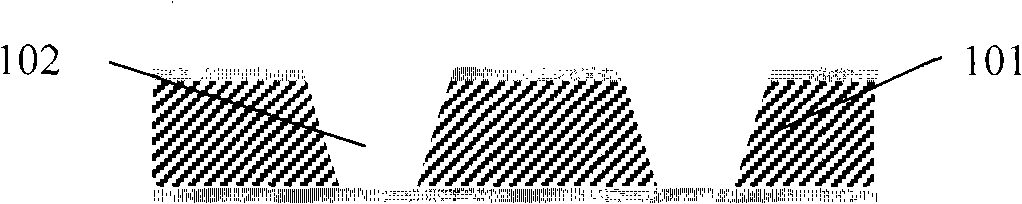

Printed circuit board and producing method of encapsulation base of integrated circuit

ActiveCN101286454AFinely craftedAvoid production capacity constraintsPrinted circuit aspectsSemiconductor/solid-state device manufacturingEngineeringInterconnection

The invention relates to a manufacturing method of a printed circuit board and an integrated circuit packaging substrate; based on the interconnection of electroplating pore filling and a semi-additive forming layer and a fine circuit, the method comprises the following steps: (1) a dielectric layer is manufactured on the substrate; (2) blind hole structure is manufactured on the dielectric layer; (3) after the blind hole structure is completed, a first conductive seed layer is manufactured; (4) a solid conductive via hole is manufactured by adopting the method of electroplating pore filling, and a copper layer grows and covers on the first seed layer in the process of electroplating pore filling; (5) the copper layer and the first seed layer are removed, and a solid copper cylinder in the solid conductive via hole is retained; (6) a second seed layer of semi-additive manufacturing circuit is manufactured; (7) a photosensitive thin film is glued, an anti-plating layer is formed by transferring diagram and the circuit diagram is exposed: (8) the circuit in the circuit diagram is thickened; (9) the photosensitive thin film and the exposed second seed layer are removed, the thickened circuit is retained, and a needed conductive diagram is formed; (10) all the steps from (1) to (9) are repeated on the new circuit surface, and the manufacture of fine circuits of following circuit layers and the connection of the solid conductive via holes in the layers are completed.

Owner:SHANGHAI MEADVILLE SCI & TECH

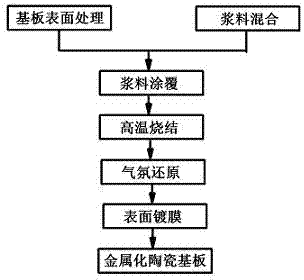

Preparation method of ceramic substrate for high-power LED packaging

The invention provides a preparation method of a ceramic substrate for high-power LED packaging, comprising the following steps of: preparing for the surface-processed ceramic substrate, covering the ceramic substrate with prepared cuprous oxide slurry, forming a circuit diagram, drying, sintering, reducing and plating a film to prepare ceramic substrate with a smooth and compact metal surface. With the combination of a thick film technology and a bonded copper principle on the surface of the ceramic substrate, metallization is realized without coating equipment and a complex technology required by a thin preparation technology and a special technology for direct bonded copper. In addition, with the combination of a direct bonded copper principle, the bonding strength of the metal layer and ceramic is raised and the spalling problem caused by thermal shock is minimized. According to the invention, the technology is simple; large-scale equipment is not required; raw materials are low-priced; the yield is high; metal patterning is convenient; surface fineness is high; and the copper layer thickness on the surface of the substrate is especially controllable so as to make the operation of a power electronic device more stable.

Owner:江苏景邦照明科技有限公司

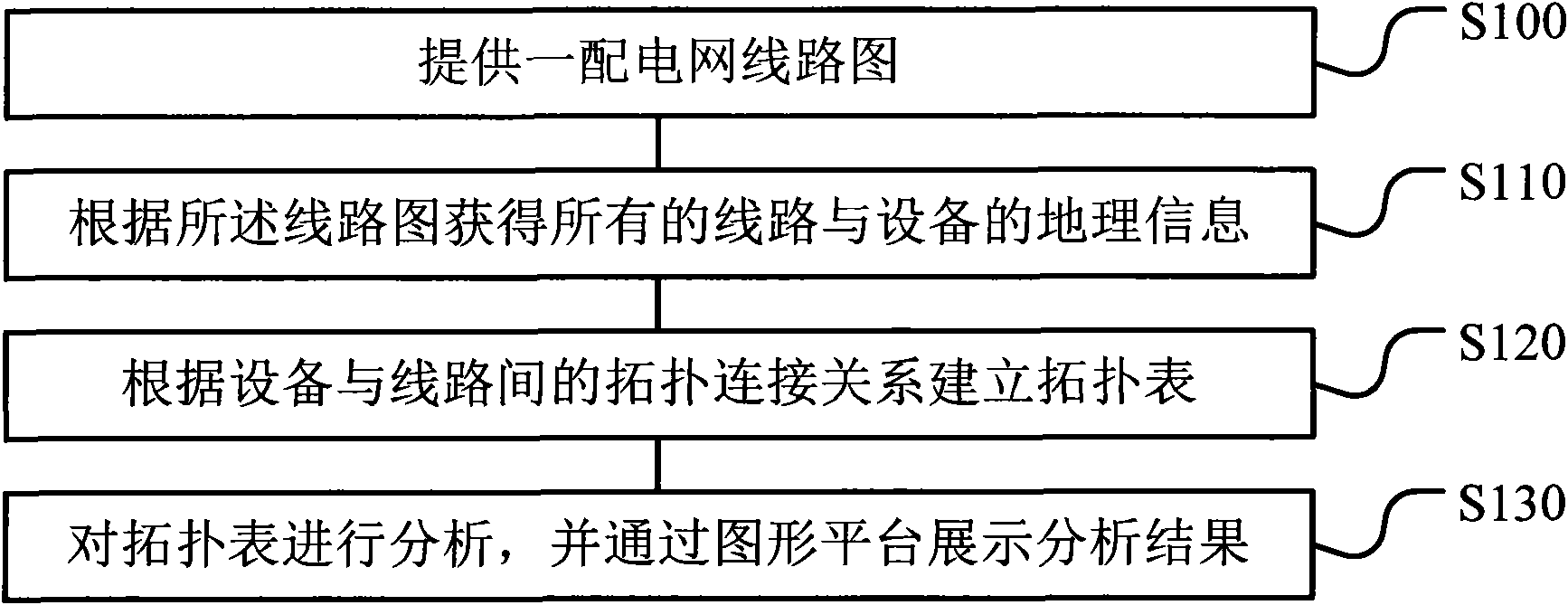

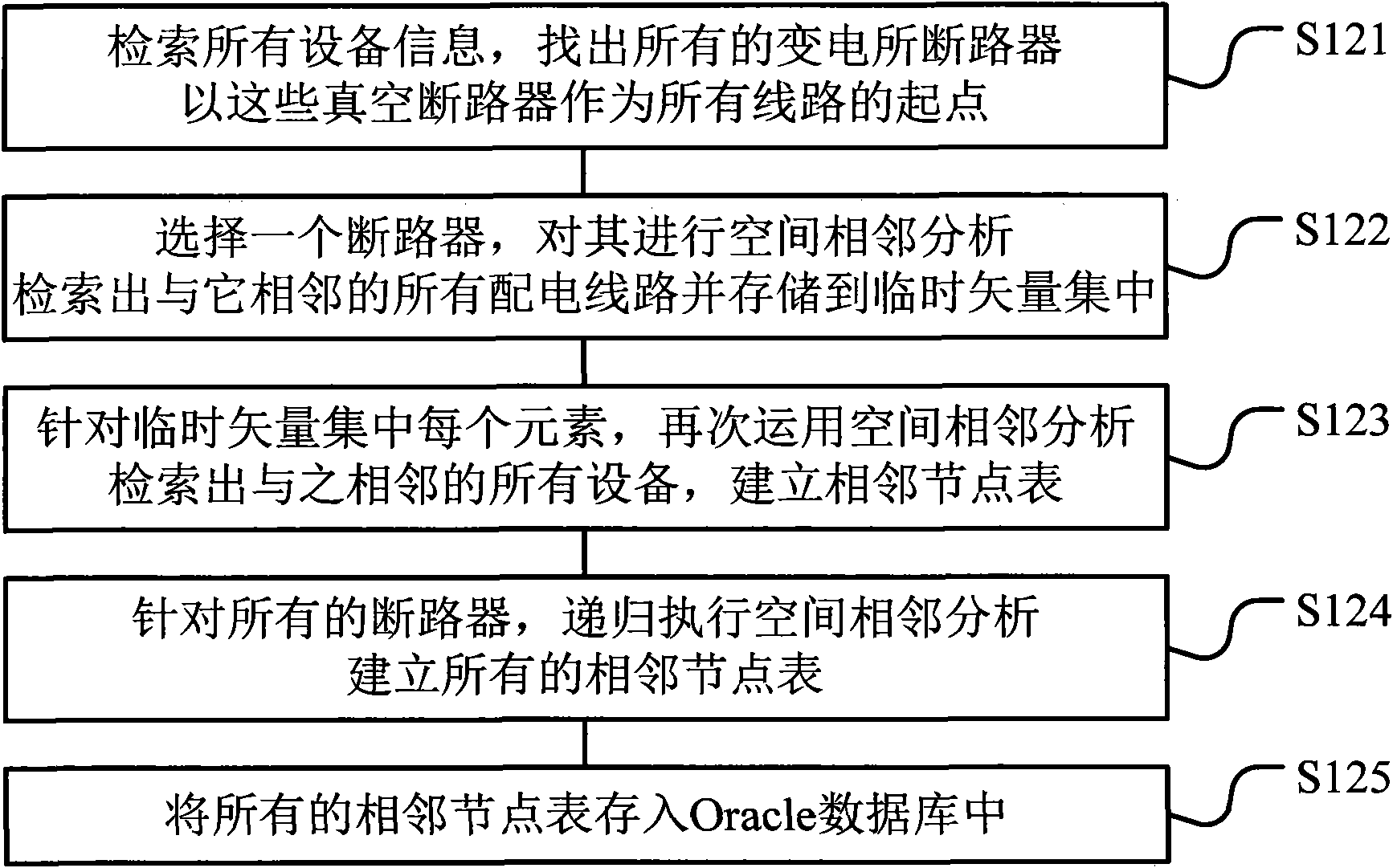

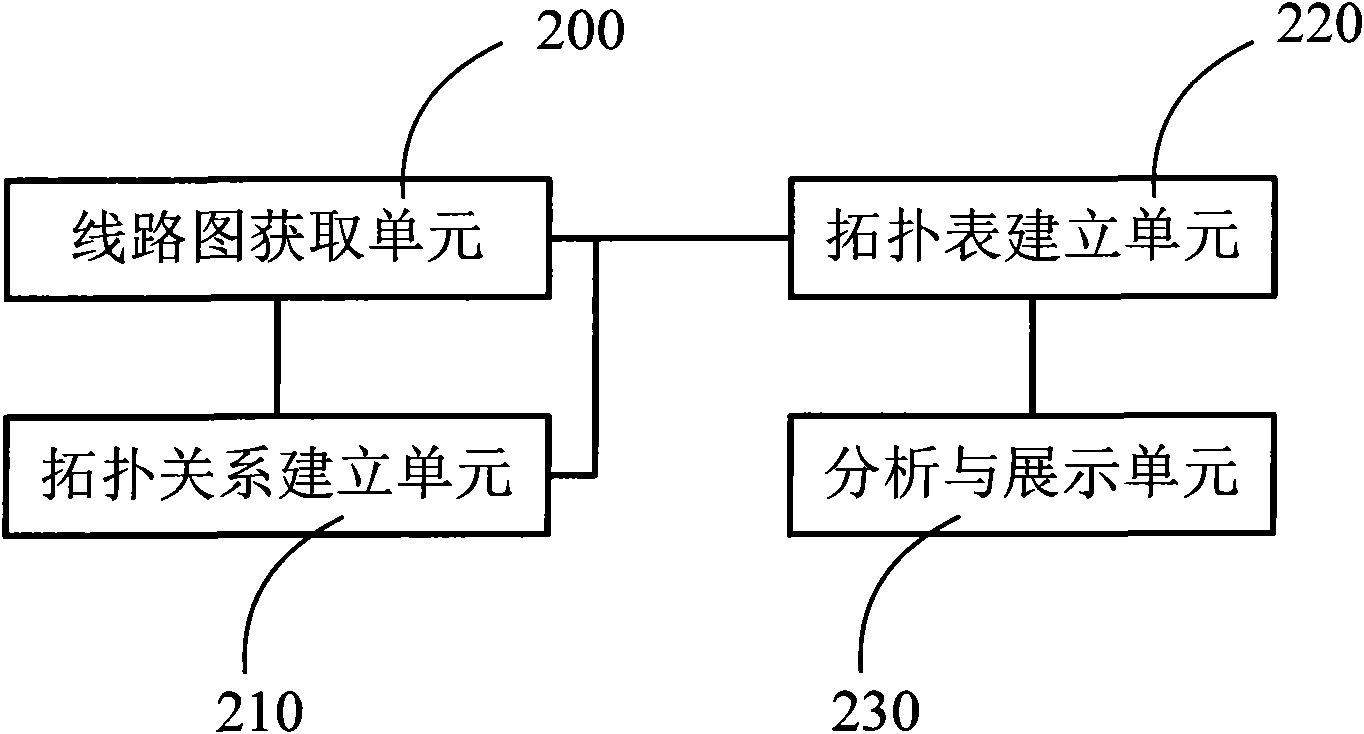

Special topology analysis method and device for distribution network

InactiveCN102044869ARealize topology analysis functionTopological operation is convenient and clearSpecial data processing applicationsAc network circuit arrangementsGraphicsSimulation

The invention relates to a special topology analysis method for a distribution network. The method comprises the following steps of: providing distribution network circuit diagrams; obtaining all the geographic information of circuits and equipment according to the circuit diagrams so as to establish a topology connection relation between the equipment and the circuits; establishing a topology table according to the topology connection relation between the equipment and the circuits; and analyzing the topology table. The invention has the advantages that different objects in the same layer can be represented by setting special graphic symbols according to the requirement of a user, then a topology layer is added on all diagram layers to ensure that the user cannot feel the existence of the topology, thus the method can realize the functions of real-time topology connection and disconnection, and the states of affected equipment can be changed in real time according to the topology states of the equipment. The method and the device disclosed by the invention can be used for accurately and reliably realizing the topology analysis function of the distribution network in real time andalso for conveniently realizing the applications of power cut simulation, power supply range, power supply tracking, and the like.

Owner:SHANGHAI DIANJI UNIV

Power distribution network performance data presentation system and method

A visualization system for monitoring performance data of an electrical power distribution network is provided. In one embodiment, a user may select a network circuit and view a network circuit diagram that includes indicia representing transformers and other electrical power distribution network elements positioned on a map. The relative positions of the indicia on the network circuit diagram may correspond to the relative physical locations of the transformers in the geographical area represented by the map. The indicia may be color coded to convey performance data to the user.

Owner:CURRENT COMM SERVICES

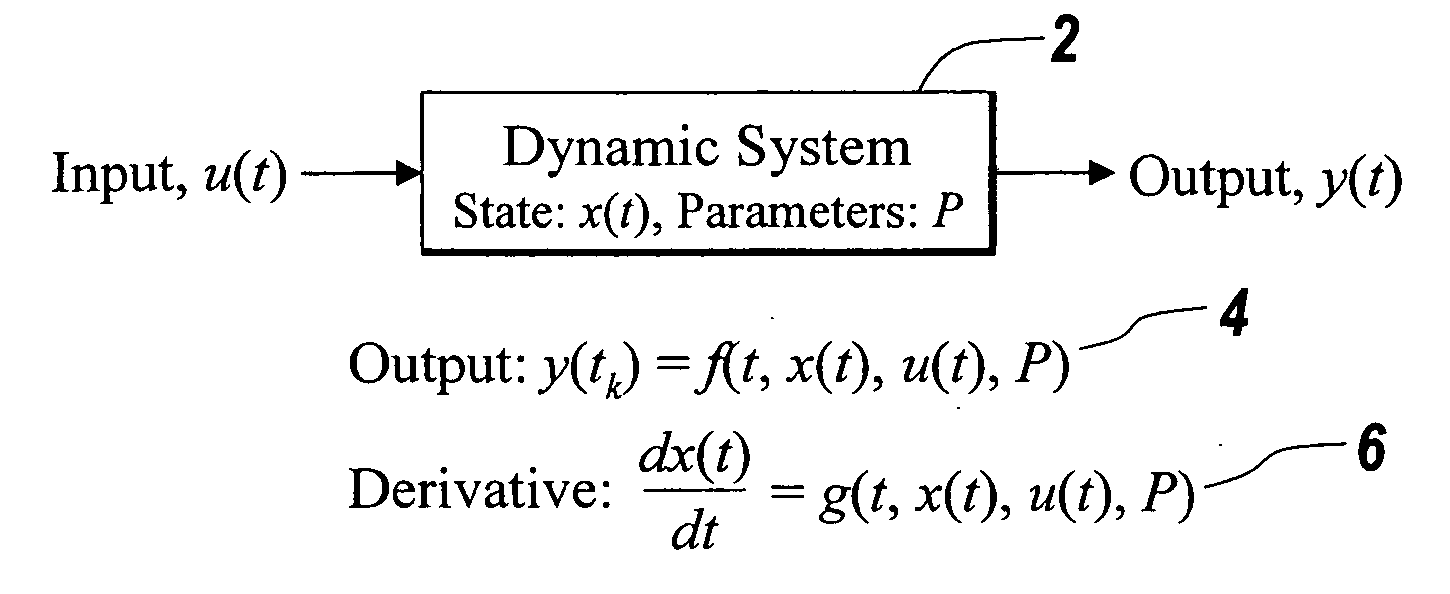

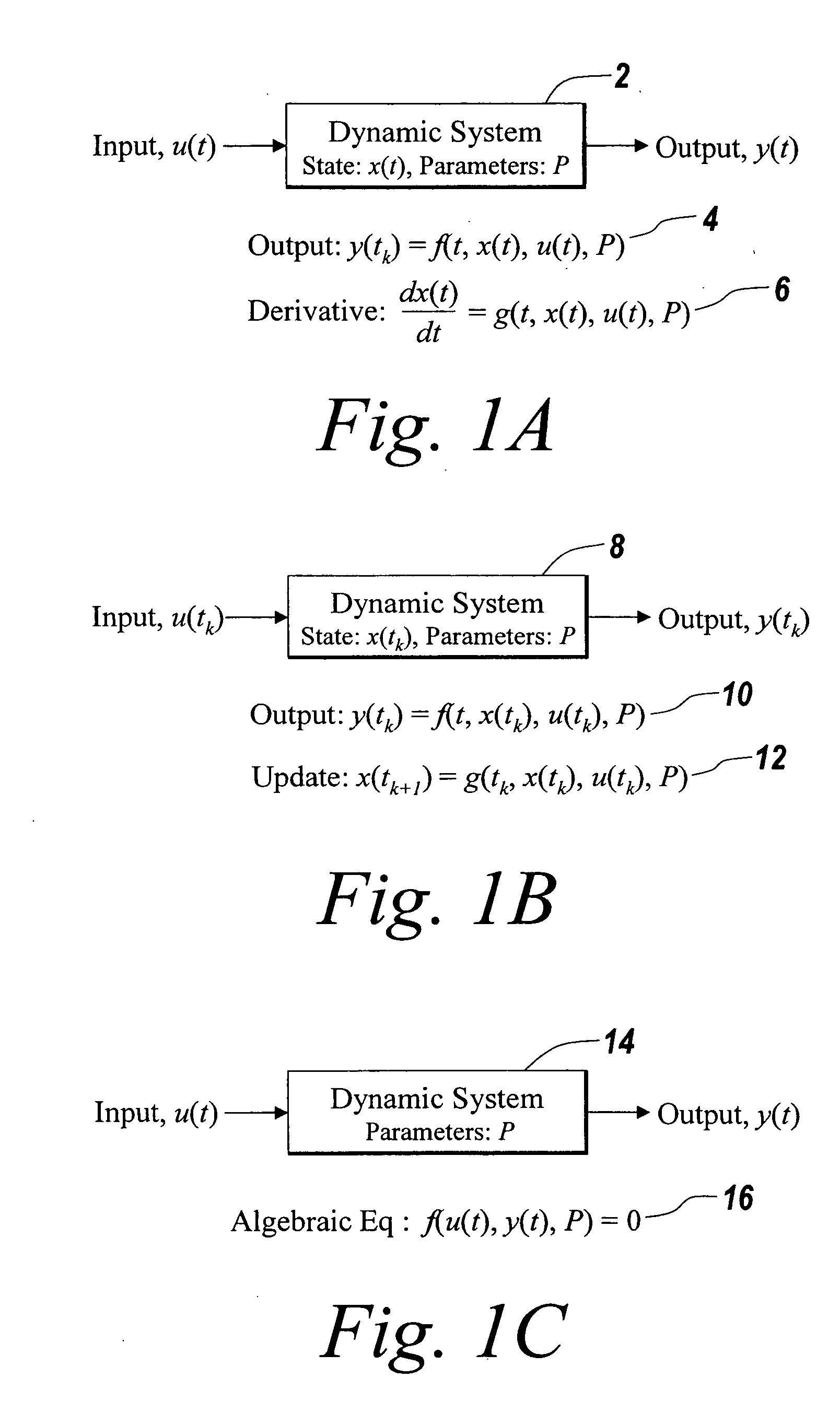

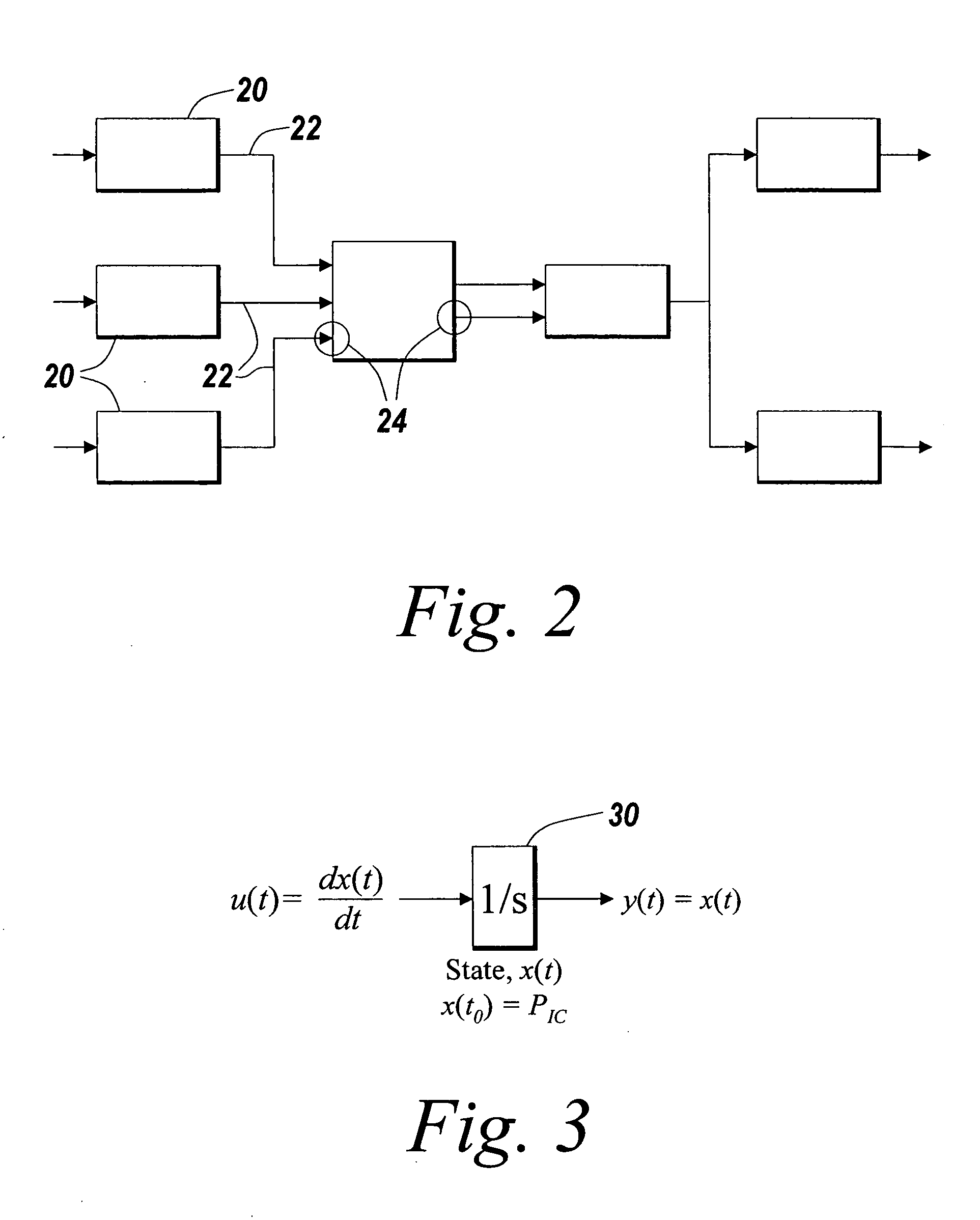

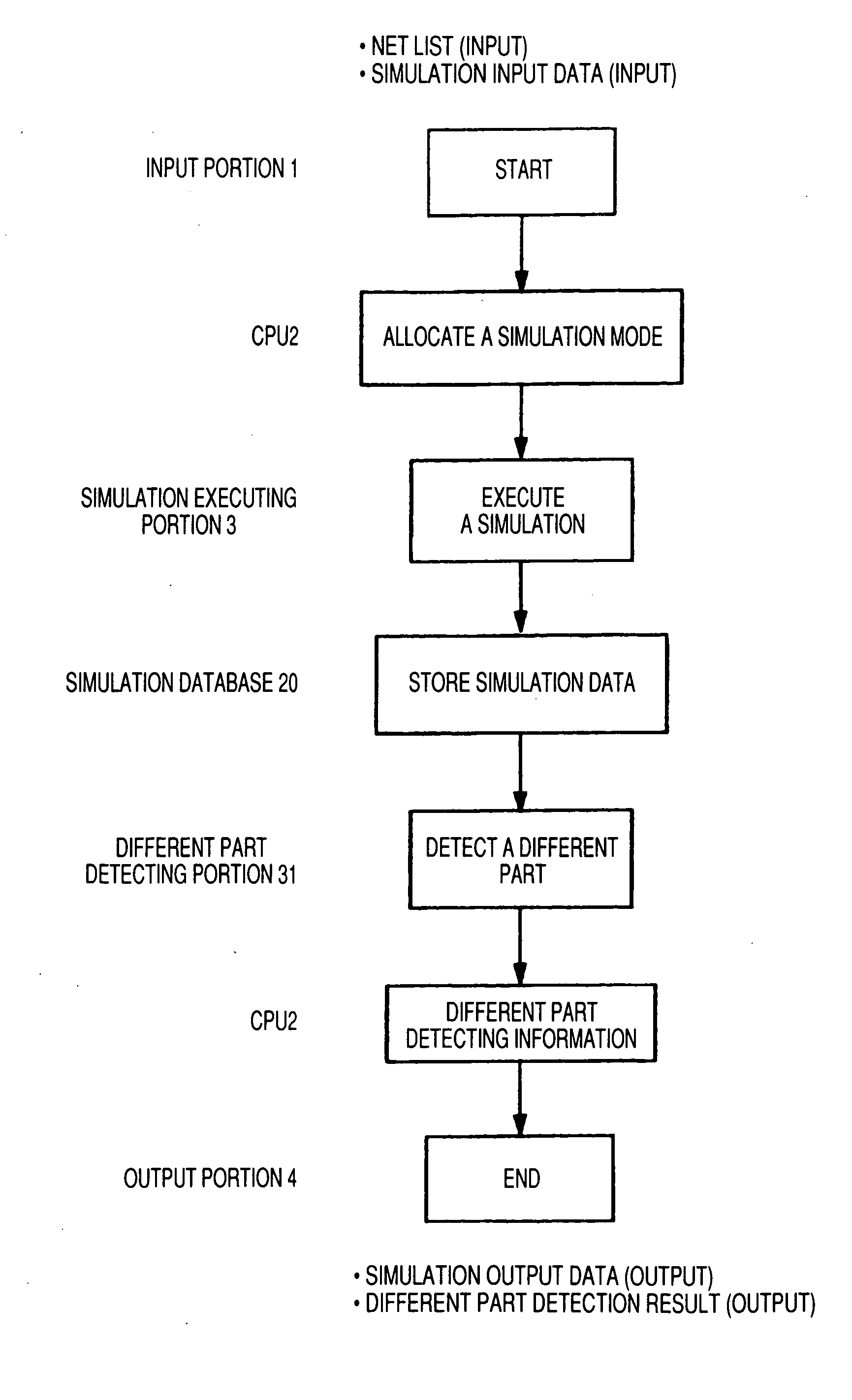

Propagation of characteristics in a graphical model environment

ActiveUS20050107998A1Visual/graphical programmingSpecific program execution arrangementsGraphicsSoftware

An electronic device and method are provided to enable a user to control characteristics of graphical objects of a graphical model environment without requiring manual entry of characteristics into each object. Propagation of characteristics from one or more objects to one or more objects may be specified and performed without requiring manual entry of characteristics into each objects. Examples of graphical model environments can include block diagrams, data-flow diagrams, state-based diagrams, circuit diagrams, mechanical diagrams, biological diagrams, network diagrams and software diagrams.

Owner:THE MATHWORKS INC

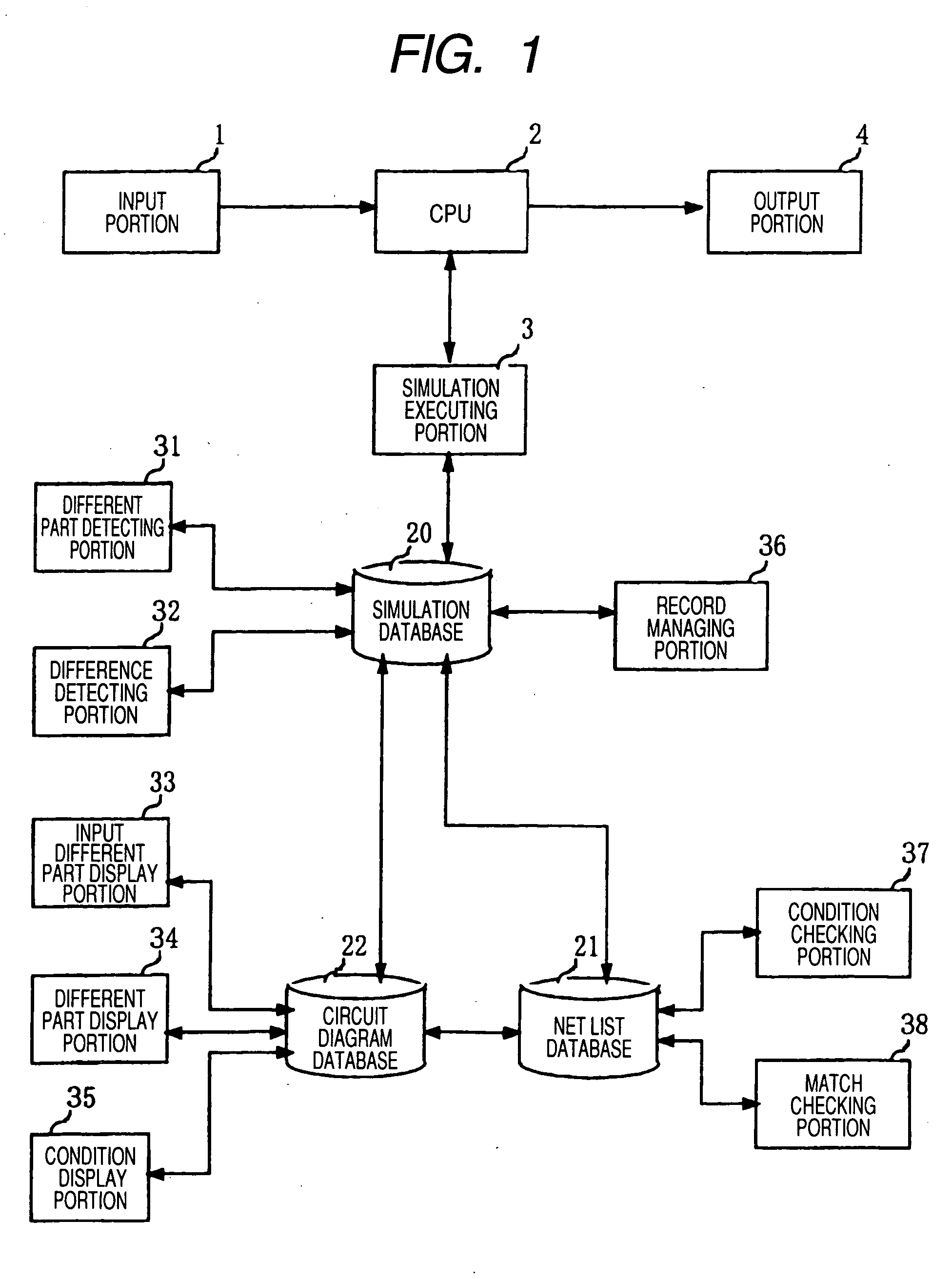

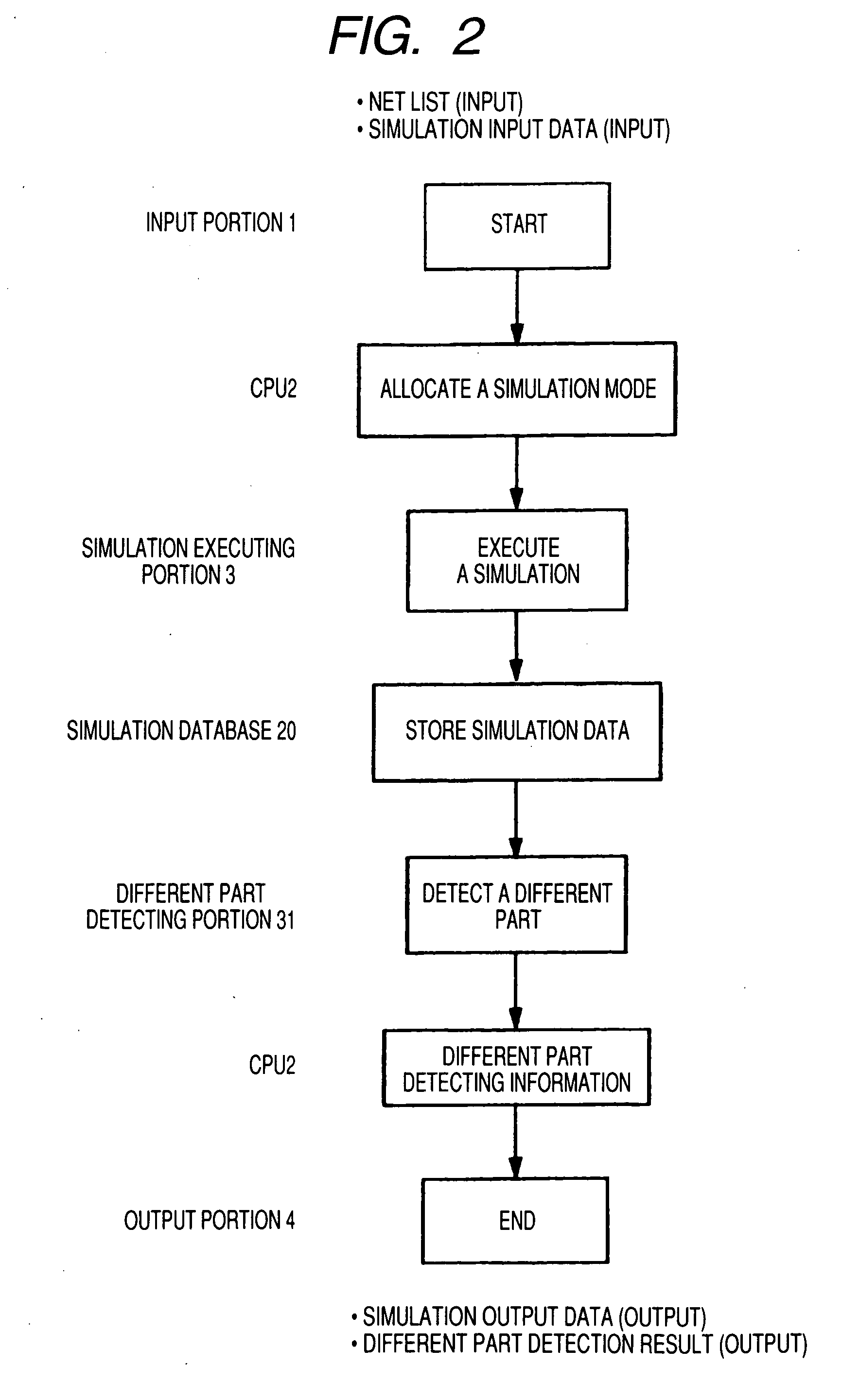

Semiconductor designing apparatus

InactiveUS20060206297A1Preventing executionReduce time spentCAD circuit designSpecial data processing applicationsComputer architectureRecords management

There are provided a different part detecting portion for detecting the different part of the result of a simulation, a difference detecting portion for detecting a difference in the result of a simulation, an input different part display portion for displaying any of circuits having different simulation modes which has a difference, a different part display portion for displaying a circuit having a difference in the result of a simulation, a condition display portion for displaying, on a circuit diagram, an option to be used in a simulation, a record managing portion for managing the execution history of the result of a simulation, a condition checking portion for ascertaining whether or not a condition is accurately set in each circuit in the execution of a simulation, and a match checking portion for confirming the non-coincidence of the names and numbers of pins between the simulation modes.

Owner:PANASONIC CORP

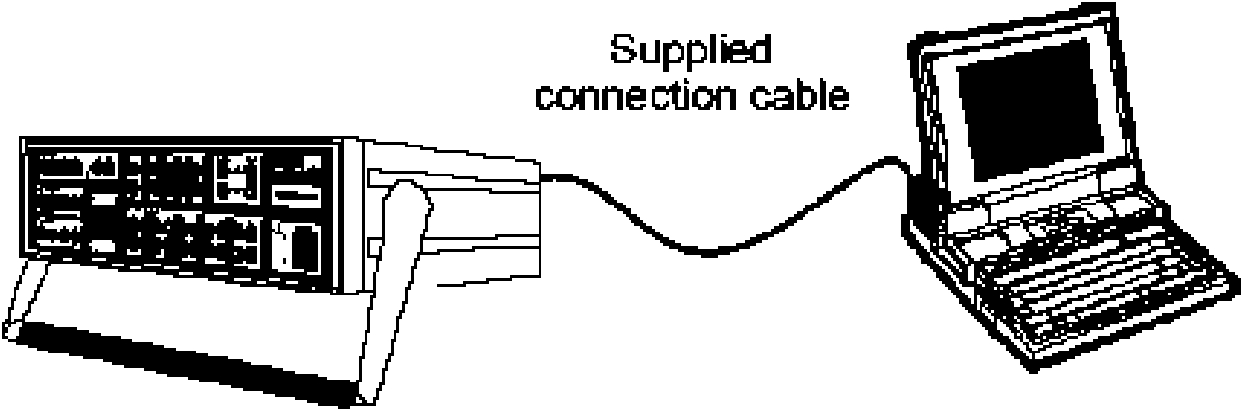

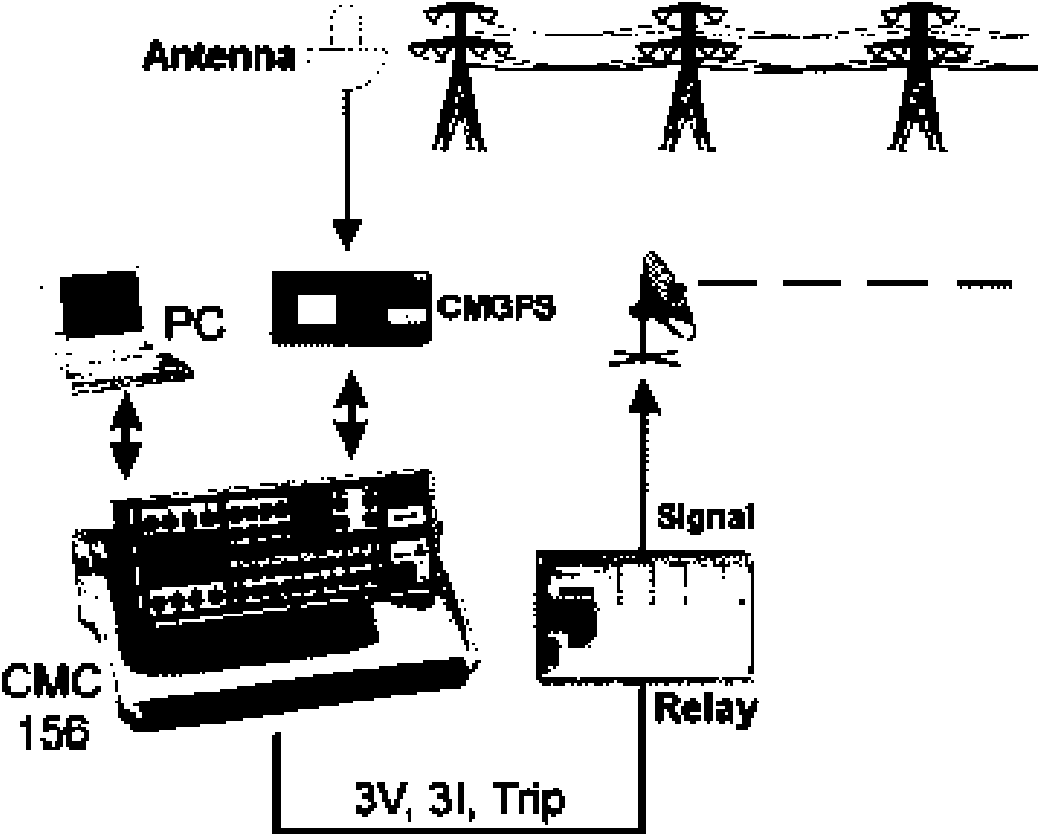

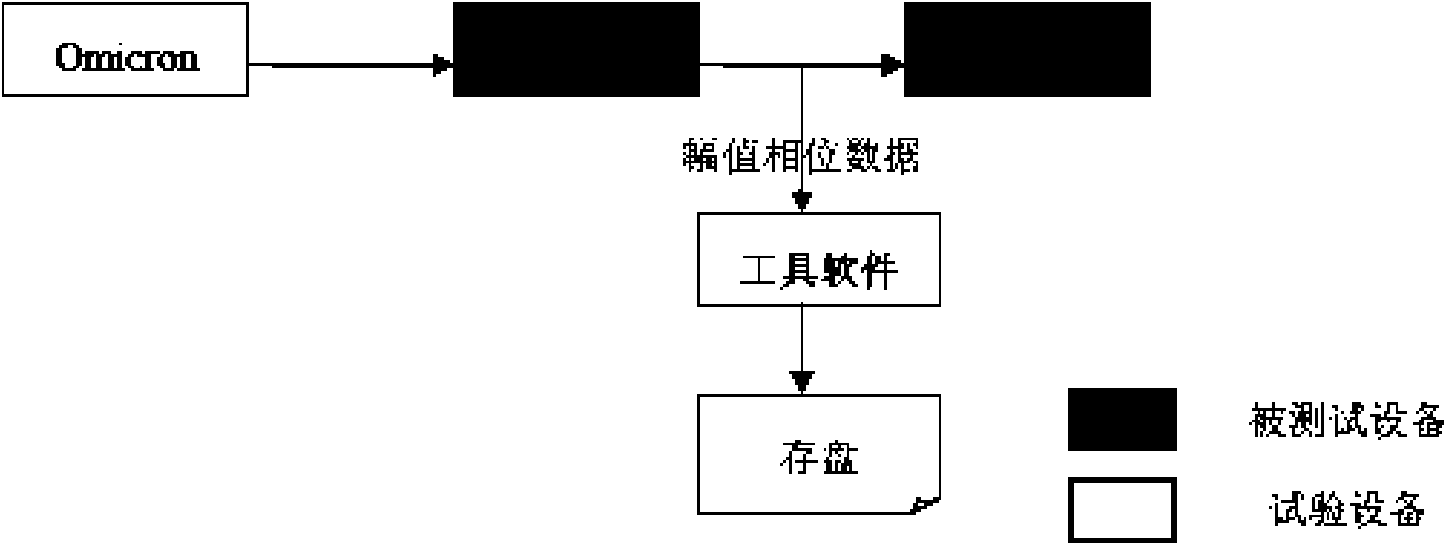

Detection method of phasor measurement unit PMU

InactiveCN101629995AResolve uncertaintySolve the problem of untraceabilityElectrical measurementsComputer hardwareData acquisition

The invention relates to a detection method of a phasor measurement unit (PMU), which comprises the following steps: firstly, establishing various needed waveform library based on the test items, then establishing a circuit diagram with a PSCAD tool and adjusting each parameter according to the test demands to form various waveforms; when in test, selecting a corresponding .seq file or a waveform file of a COMTRADE format according to the test items; playing back the .seq file or COMTRADE file by using an Omicron relay protection testing device; when in playback of the .seq file, setting a waveform playback time in the 'GPS Set' to play back the waveform in a prescribed moment; executing data acquisition by using a PMU, and then delivering messages to main station simulation tool software through a communication protocol; reading the protocol message in virtue of the PMU synchronized phasor data analysis software, and converting and storing the message into the amplitude and phase data; performing frequency analysis for a static measurement precision test; and finding the optimal range of device measurement precision.

Owner:CENT CHINA GRID +1

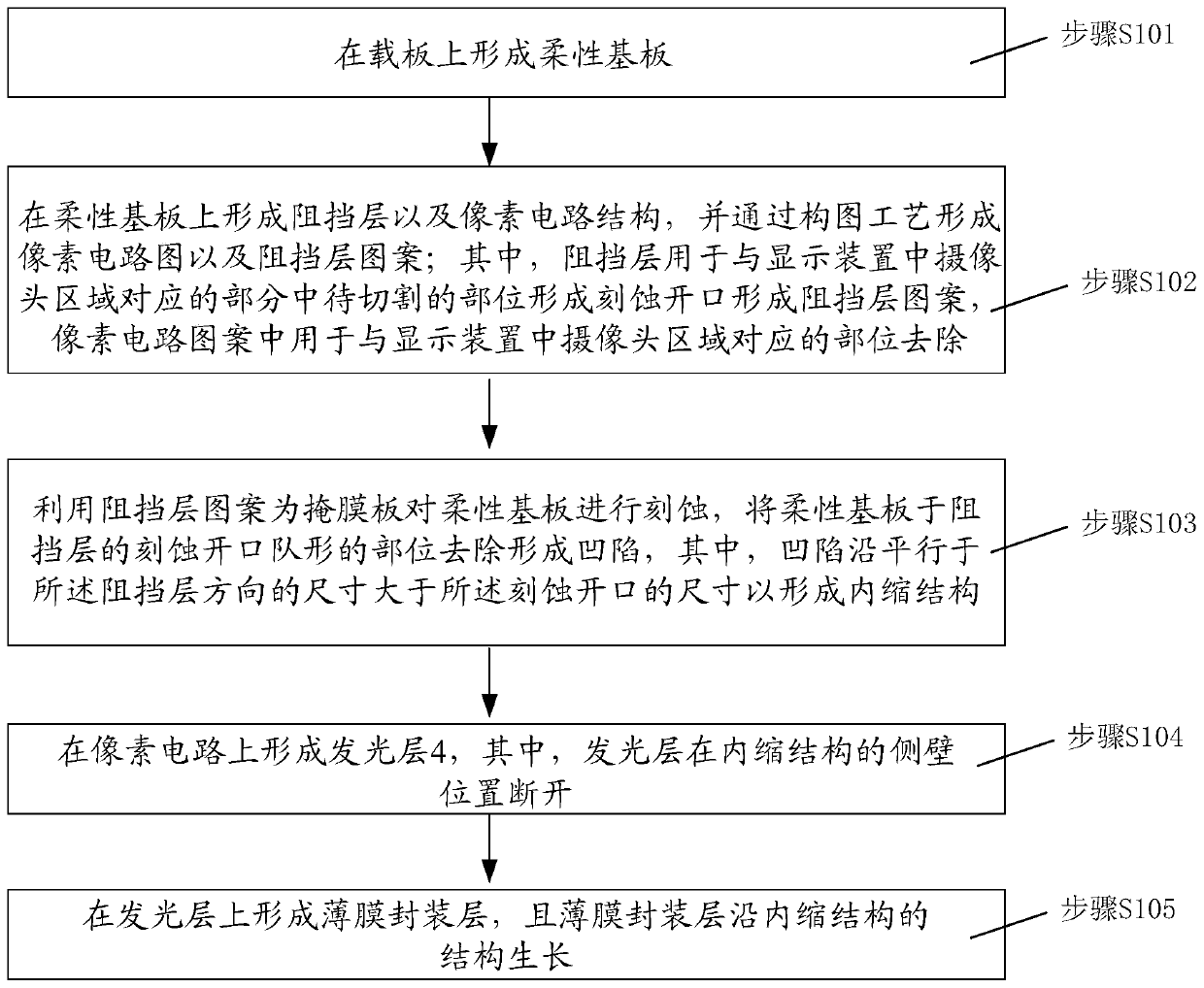

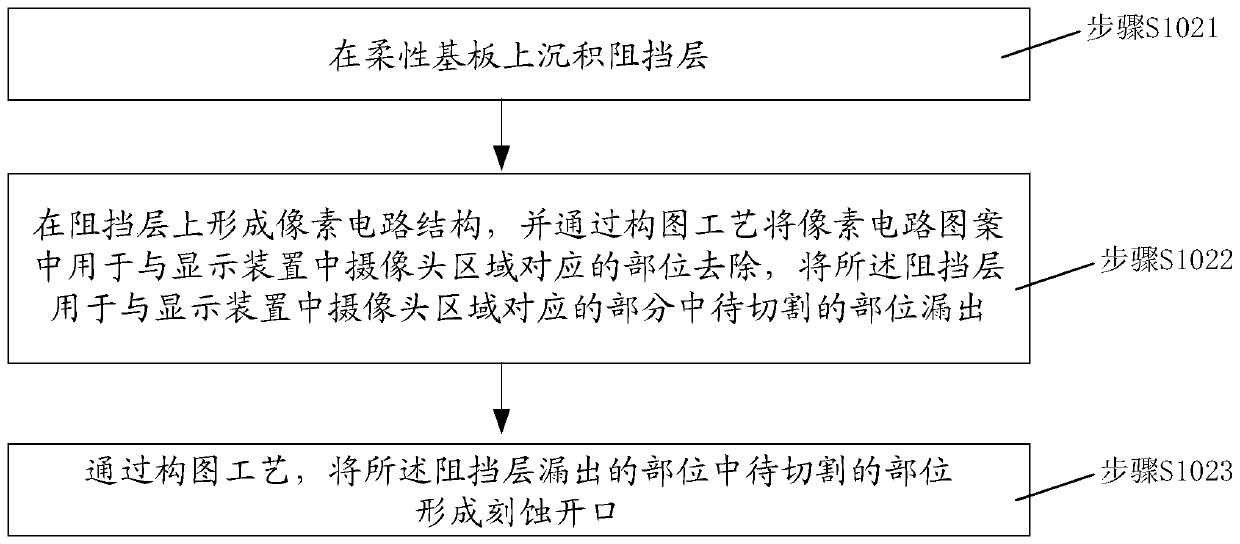

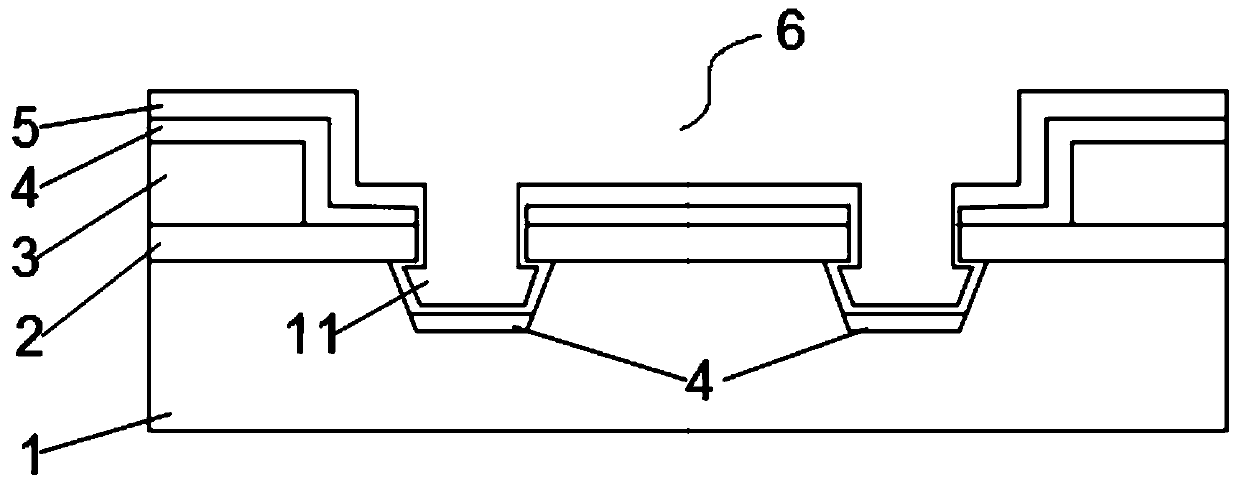

Preparation method for organic light emitting diode display device and display device

InactiveCN109786427ASolid-state devicesSemiconductor/solid-state device manufacturingDisplay deviceLight-emitting diode

The invention provides a preparation method for organic light emitting diode display device and the display device. The preparation method comprises the steps of forming a flexible substrate on a support plate; forming a blocking layer and a pixel circuit structure on the flexible substrate, and forming a pixel circuit diagram and a blocking layer pattern through utilization of a composition technology; etching the flexible substrate through utilization of the blocking layer pattern as a mask plate, and removing parts of the flexible substrate corresponding to etching openings of the blockinglayer to form sunken parts, wherein sizes of the sunken parts along a direction of the blocking layer are greater than those of the etching openings, thereby forming inward retraction structures; forming a light emitting layer on a pixel circuit, wherein the light emitting layer is disconnected at positions of side walls of the inward retraction structures; and forming a thin film packaging layeron the light emitting layer, wherein the thin film packaging layer grows along the structures of the inward retraction structures. According to the preparation method provided by the invention, aftera hole is set on the display device, a packaging effect of a hole area can be ensured, packaging reliability of the device is ensured.

Owner:BOE TECH GRP CO LTD

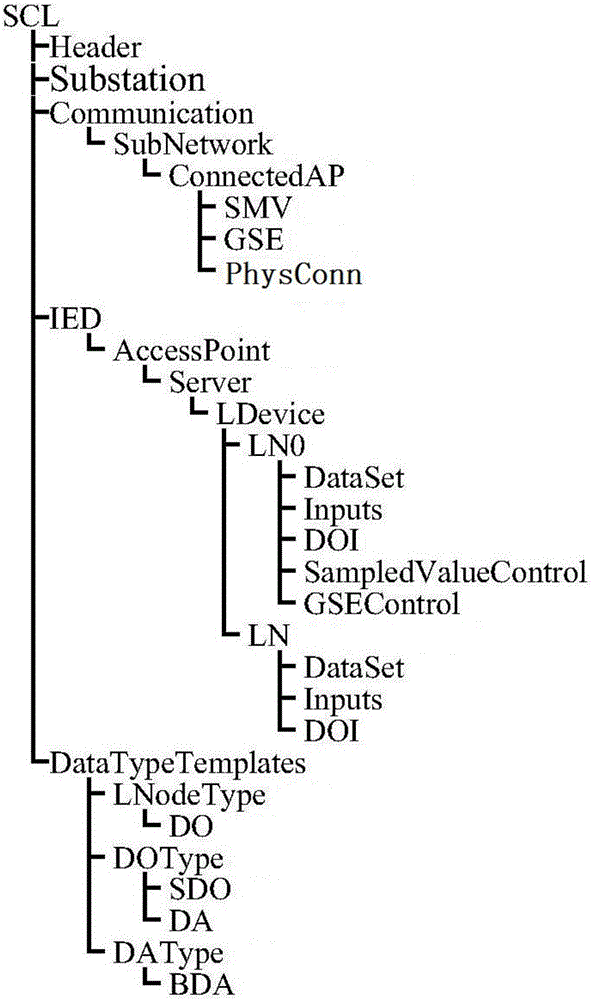

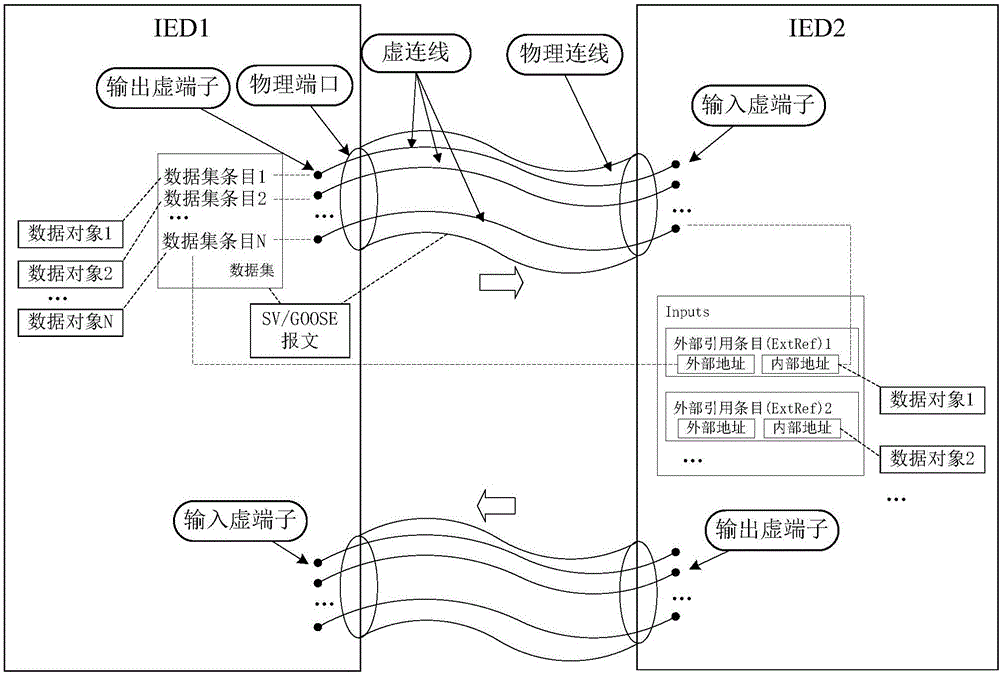

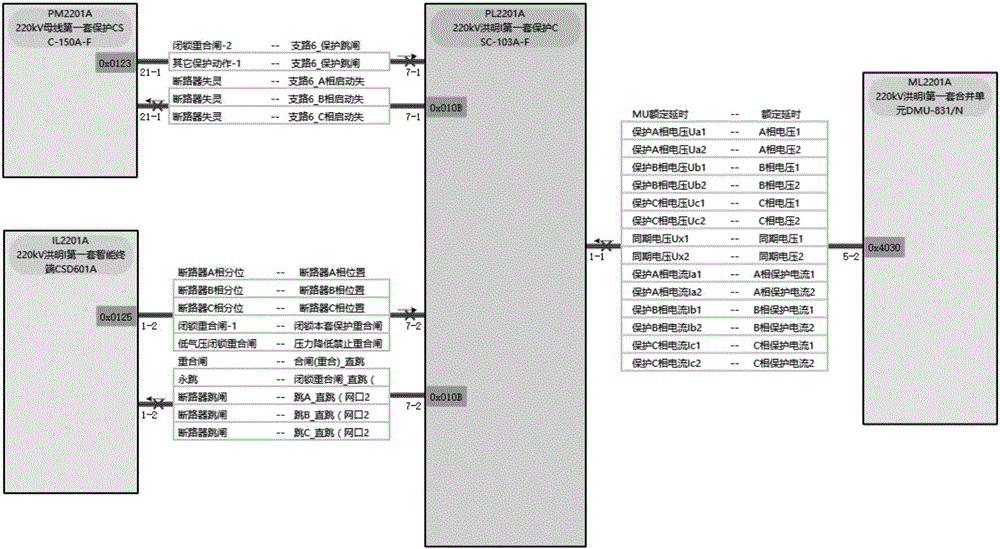

Visualized display method for relay protection secondary virtual or true circuit of intelligent transformer substation

ActiveCN106294989AIntuitively display associations to usersDisplay associationDesign optimisation/simulationSpecial data processing applicationsVirtual terminalSmart substation

The invention relates to a visualized display method for a relay protection secondary virtual or true circuit of an intelligent transformer substation. The method comprises the following steps: resolving an SCD (Security Coding Device) file of the intelligent transformer substation, extracting SV / GOOSE message configuration information of each IED, external data reference information and physical port configuration information; analyzing external reference entries of each IED, and constructing a virtual connection line; analyzing physical port configuration information of each IED, and constructing a physical connection line between ports; finding out physical ports, relevant to each output virtual terminal and each input virtual terminal, of each IED; and drawing a secondary virtual or true circuit diagram. The method can be used for displaying a secondary virtual or true circuit diagram, greatly facilitating checking of a relay protection secondary circuit of the intelligent transformer substation, and obviously improving the secondary virtual or true circuit inspection efficiency.

Owner:WUHAN KEMOV ELECTRIC

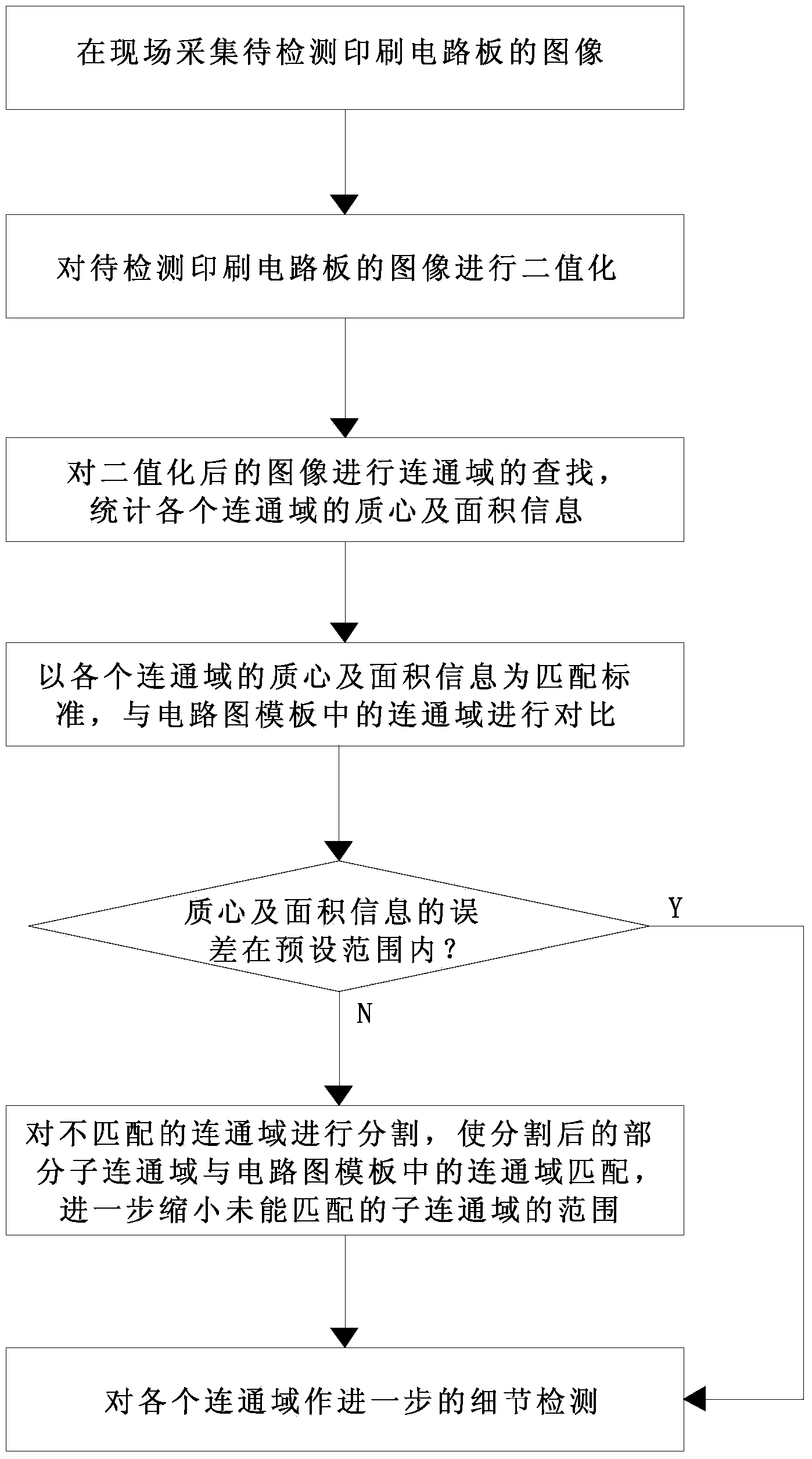

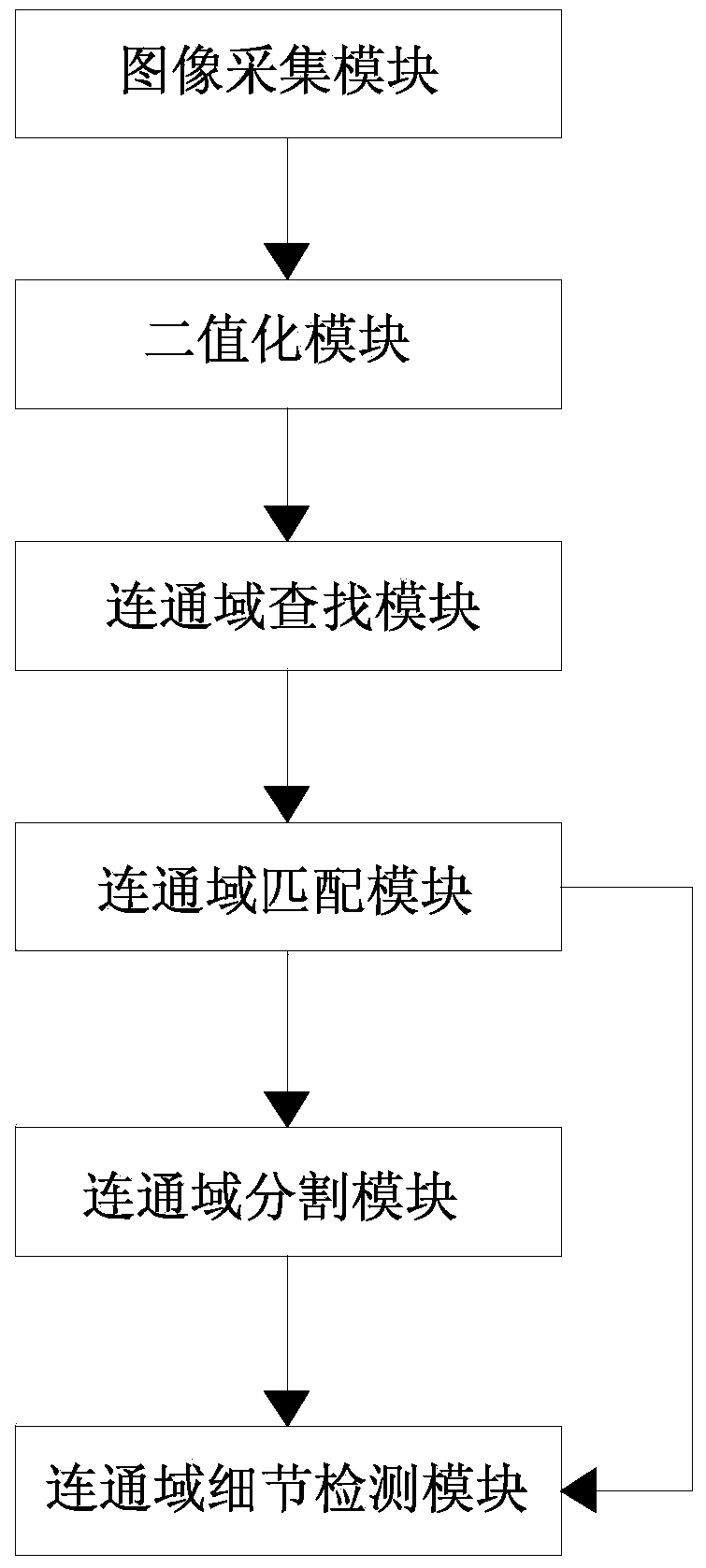

Mixing-method-based method and system applied to defect detection of printed circuit board

ActiveCN104297254AMeet defect detection needsGood distinctionOptically investigating flaws/contaminationMisinformationPrinted circuit board

The invention discloses a mixing-method-based method and a mixing-method-based system applied to defect detection of a printed circuit board. The method comprises the following steps: collecting an image of a to-be-detected printed circuit board in the field; carrying out binaryzation on the image of the to-be-detected printed circuit board; searching communication domains of the binaryzated image and counting information of mass center and area of each communication area; comparing each communication area with communication domains in a circuit diagram template by taking the information of mass center and area of each communication area as a matching standard, determining that the communication domains are matched with one another if the error of the information of mass center and area is in a predetermined range, or determining that the communication domains are unmatched with one another; cutting the unmatched communication domains, enabling part of secondary communication domains after cutting to be matched with the communication domains in the circuit diagram template, and further diminishing the range of the unmatched secondary communication domains; and further detecting each communication domain in detail. By virtue of the method and the system, the defect misinformation caused by rotating, horizontally moving, extending and retracting, inclining and the like can be well avoided; the reasonable deformation and defects can be well distinguished.

Owner:SOUTH CHINA UNIV OF TECH

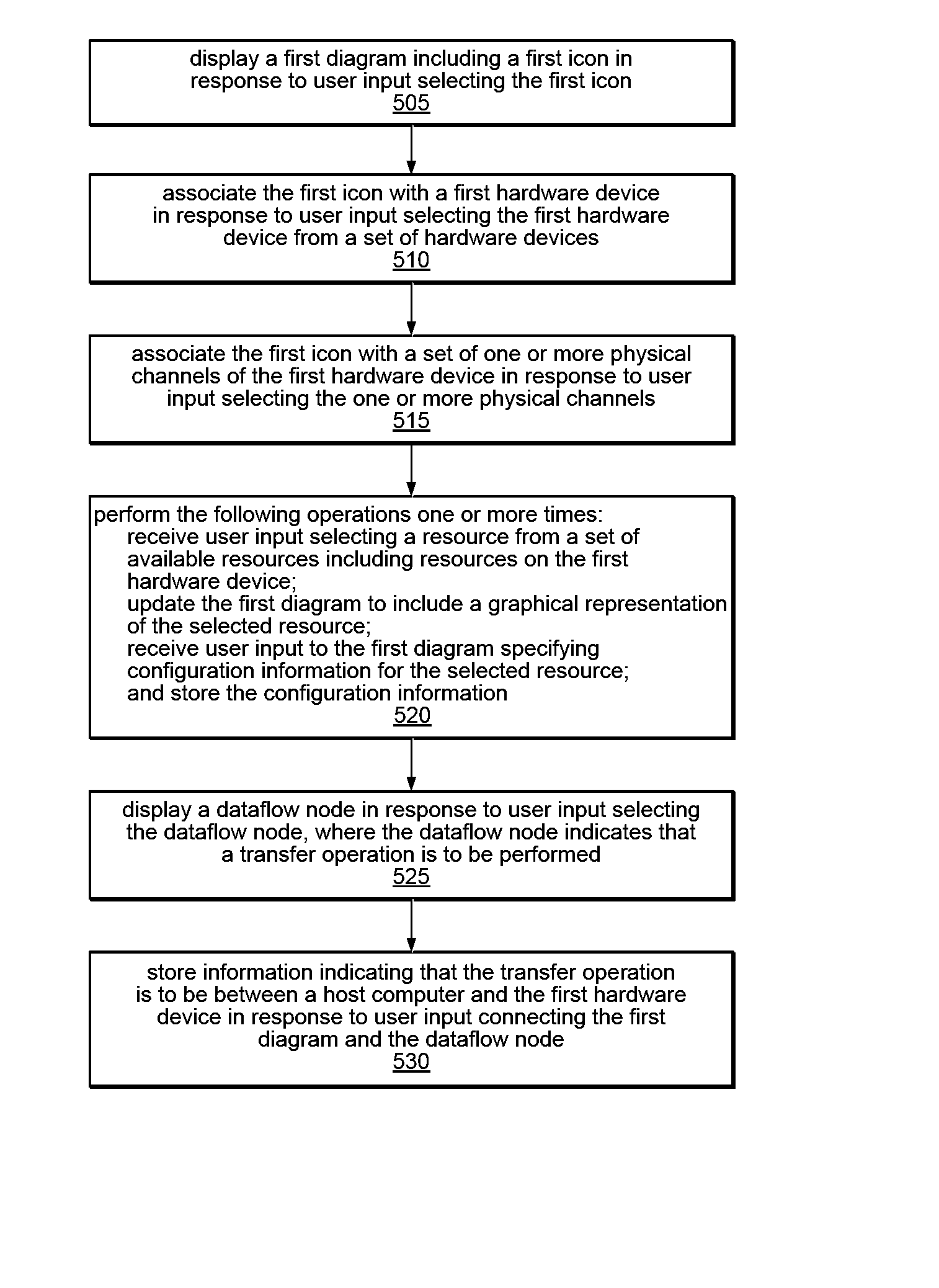

Automatically Generating a Graphical Data Flow Program Based on a Circuit Diagram

A method and system configured to: (a) display a first diagram including a first icon in response to input selecting the first icon; (b) associate the first icon with a first hardware device in response to input selecting the first hardware device from a set of hardware devices; (c) associate the first icon with a set of physical channels of the first hardware device in response to user input selecting the physical channels; and (d) perform the following operations one or more times: receive user input selecting a resource from a set of available resources including resources on the first hardware device; update the first diagram to include a graphical representation of the selected resource; receive user input to the first diagram specifying configuration information for the selected resource; and store the configuration information; (e) display a dataflow node indicating a transfer operation to be performed.

Owner:NATIONAL INSTRUMENTS

Integrated Circuit Design using DFM-Enhanced Architecture

InactiveUS20100281446A1Improve performanceReduce power consumptionCAD circuit designTotal factory controlDiffusionEngineering

Integrated circuit libraries include a first standard cell having a first left boundary and a first right boundary, and a second standard cell having a second left boundary and a second right boundary. The first standard cell and the second standard cell are of a same cell variant. A first active region in the first standard cell has a different length of diffusion than a second active region in the second standard cell. The first active region and the second active region are corresponding active regions represented by a same component of a same circuit diagram representing both the first standard cell and the second standard cell.

Owner:TAIWAN SEMICON MFG CO LTD

Making method of electric nickel and golden circuit board for saving nickel and gold dosage

InactiveCN101267713AOvercoming major deficienciesReduce dosageConductive material chemical/electrolytical removalCopper platingSecondary circuit

A manufacturing method of an electrolytic nickel and gold wiring board capable of saving dosage of nickel and gold, comprises broaching, copper precipitation, and copperizing on a copper-coated plate. The method is characterized by further comprising: a, adhering a dry film or printing a wet film on the wiring board, then adhering a positive sheet, exposing and developing to form a primary circuit; b, electroplating nickel and gold on all positions to be welded and copper surfaces of metal holes, then stripping; c, printing a wet film or adhering a dry film, then adhering a negative sheet, exposing and developing to form a secondary circuit; d, etching a circuit diagram, removing non-circuit portions, holding circuit portions, then performing stripping and etching detection; e, performing deoxidation treatment to the wiring board to remove oxides on the copper surfaces; f, after deoxidation treatment, resistance welding, exposing, developing, printing element symbols and machining shapes so as to manufacture the electrolytic nickel and gold wiring board only at the positions to be welded and the metal hole positions. With the method, the area of the nickel and gold can be reduced by 40-60%, thereby saving the noble metal nickel and gold and effectively reducing enterprise production cost.

Owner:陈国富

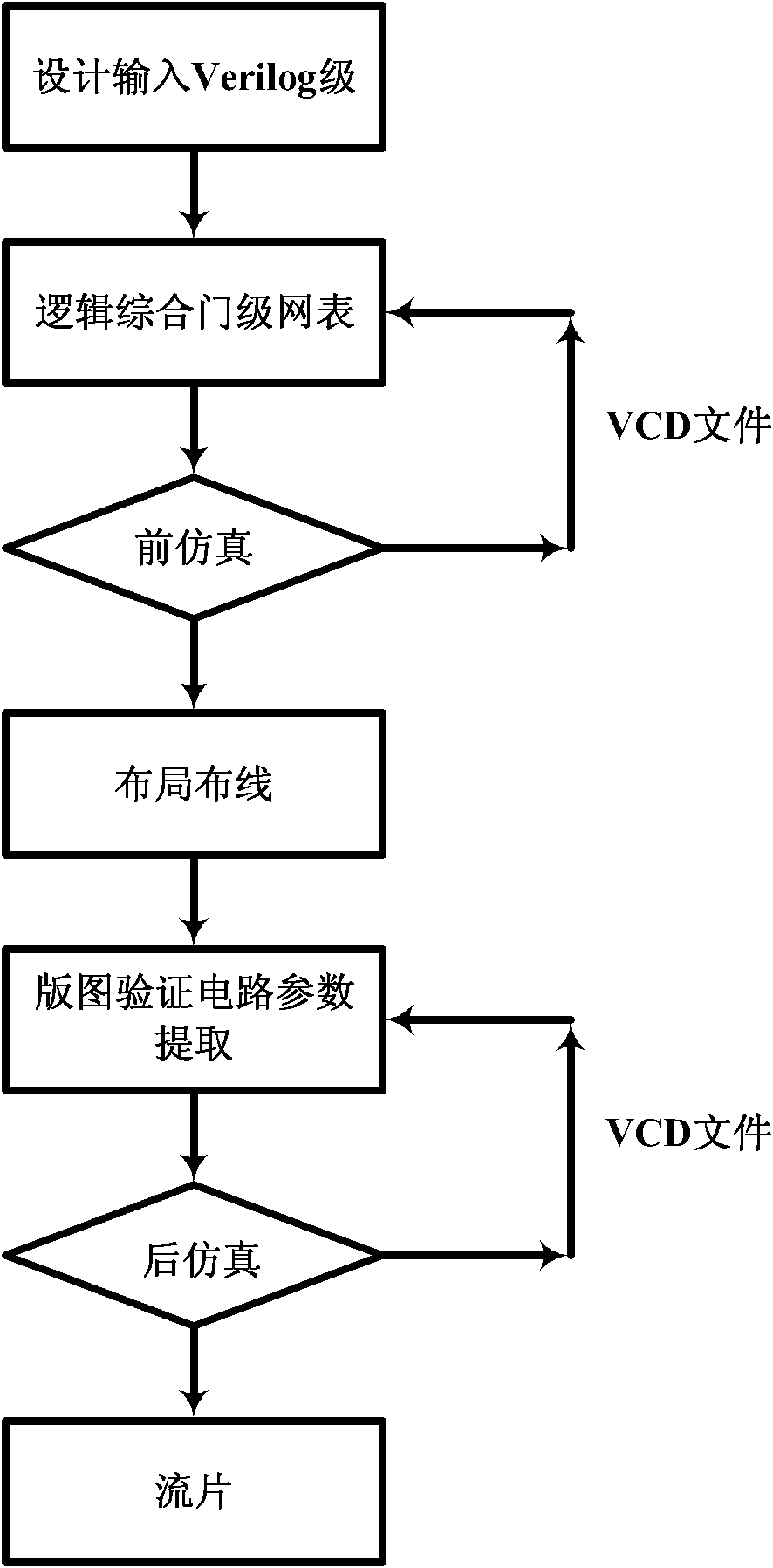

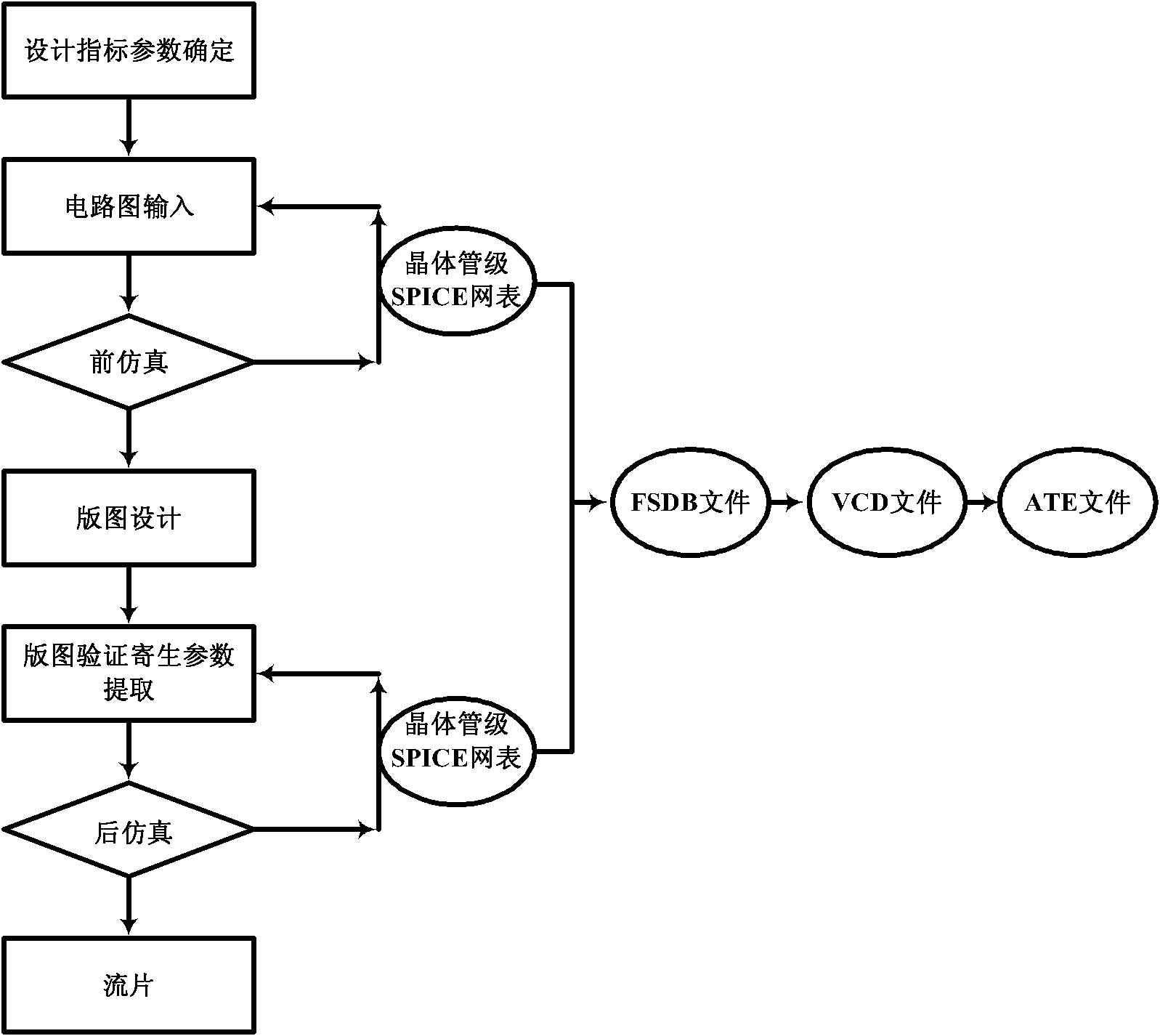

Integrated circuit testing method

ActiveCN102866349ASpeed up testingAvoid misinterpretationElectrical testingTest platformAutomatic testing

The invention provides an integrated circuit testing method, which comprises the steps of design index parameter determination, circuit diagram input, pre-simulation, layout design, layout verification and parasitic parameter extraction, post-simulation and tape-out. The integrated circuit testing method is characterized in that both the pre-simulation and the post-simulation use a transistor-level SPICE netlist, which can be converted to documents required for an automatic testing platform. The testing method provided by the invention can be used to greatly shorten the original test vector writing time for chip testing personnel, speed up the progress of the test, avoid understanding deviation between designers and testers and achieve seamless butting.

Owner:INST OF MICROELECTRONICS CHINESE ACAD OF SCI

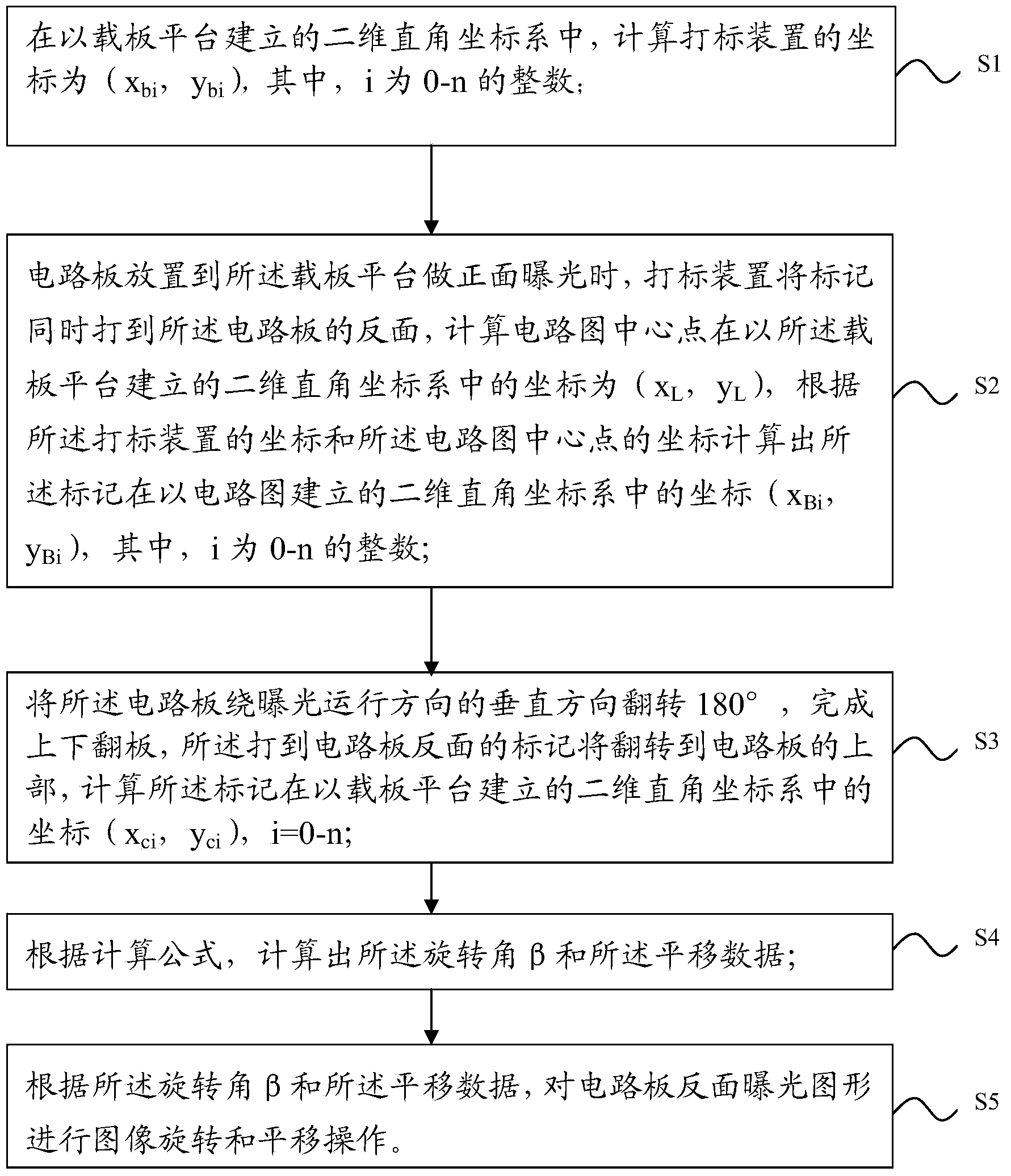

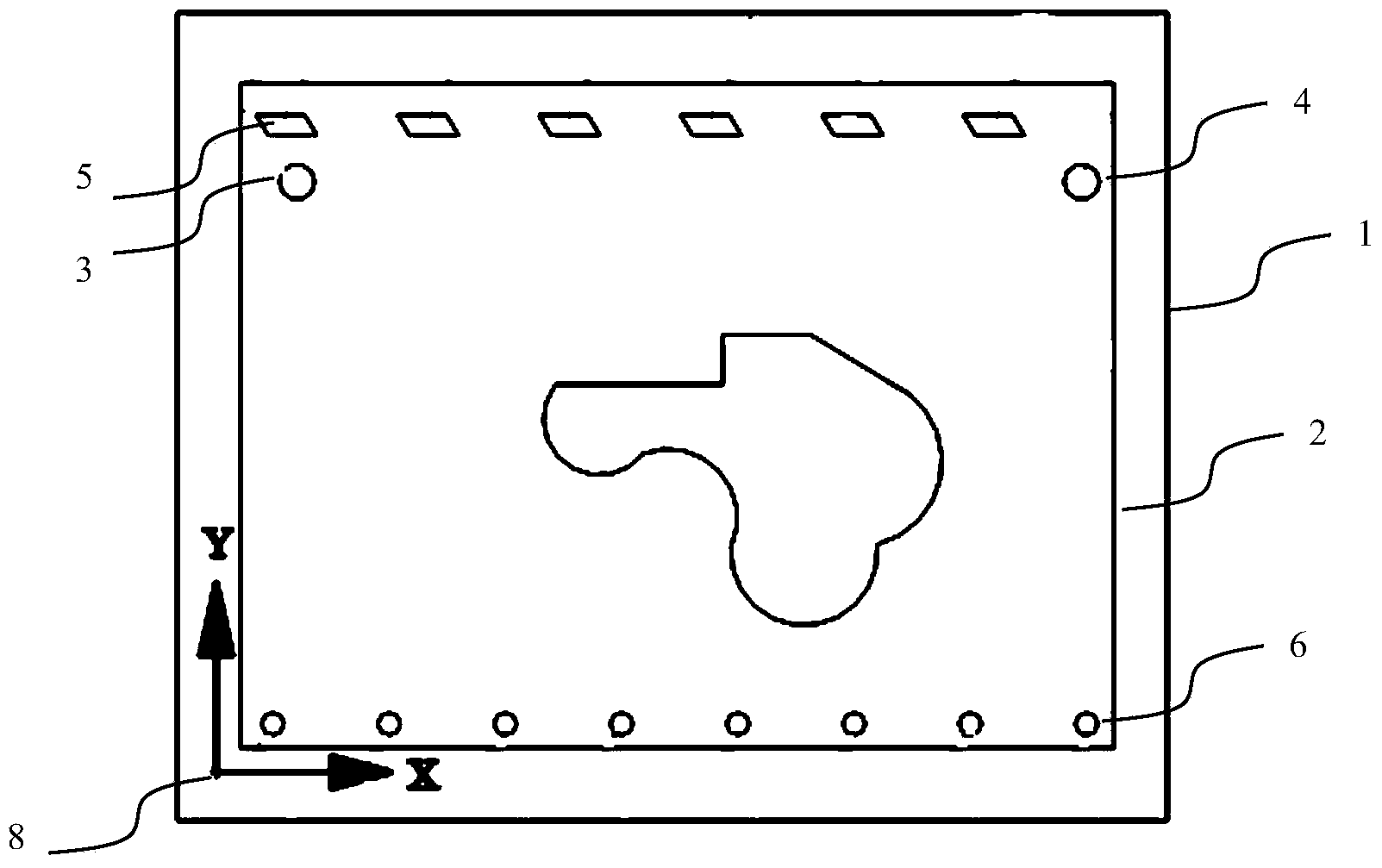

Alignment method for internal layers in direct writing type photoetching system

InactiveCN103529654AGuaranteed Alignment AccuracyEasy and fast measurementPhotomechanical exposure apparatusMicrolithography exposure apparatusDirect writingAngle of rotation

The invention discloses an alignment method for internal layers in a direct writing type photoetching system. According to the method, during exposure of a front circuit diagram of a circuit board, a marking apparatus leaves marks on the back surface of the circuit board at same time, the marks are left at blank positions on the lower frame of the circuit board, and the position data (x[bi], y[bi]) of the marks relative to the coordinate system of a carrier platform are transformed into the coordinate system of the circuit board to obtain the coordinate (x[Bi], y[Bi]), wherein i is in range of 0 to n and n may be 7 in the position data (x[bi], y[bi]), i is in range of 0 to n in the coordinate (x[Bi], y[Bi]), the center of the circuit board has to be the datum of the coordinate system of the circuit board, and the circuit diagram overturns around a direction perpendicular to an exposure operation direction during exposure of the back surface, i.e., up-and-down overturning; the position data (x[bi], y[bi]) of the marks relative to the coordinate system of the carrier platform are measured, recorded and stored in advance by area array CCD in the system; after up-and-down overturning, exposure of the back surface of the circuit board is carried out, the area array CCD in the system is also used for measuring the position coordinate (x[ci], y[ci]) of the marks, wherein i is in range of 0 to n, the position coordinate (x[ci], y[ci]) and the transformed coordinate (x[Bi], y[Bi]) of the marks in the circuit diagram are analyzed, and rotation and translation data of the circuit diagram are calculated, wherein the angle of rotation is calculated before calculation of the translation data during calculation.

Owner:TIANJIN JINXIN MICROELECTRONICS TECH CO LTD

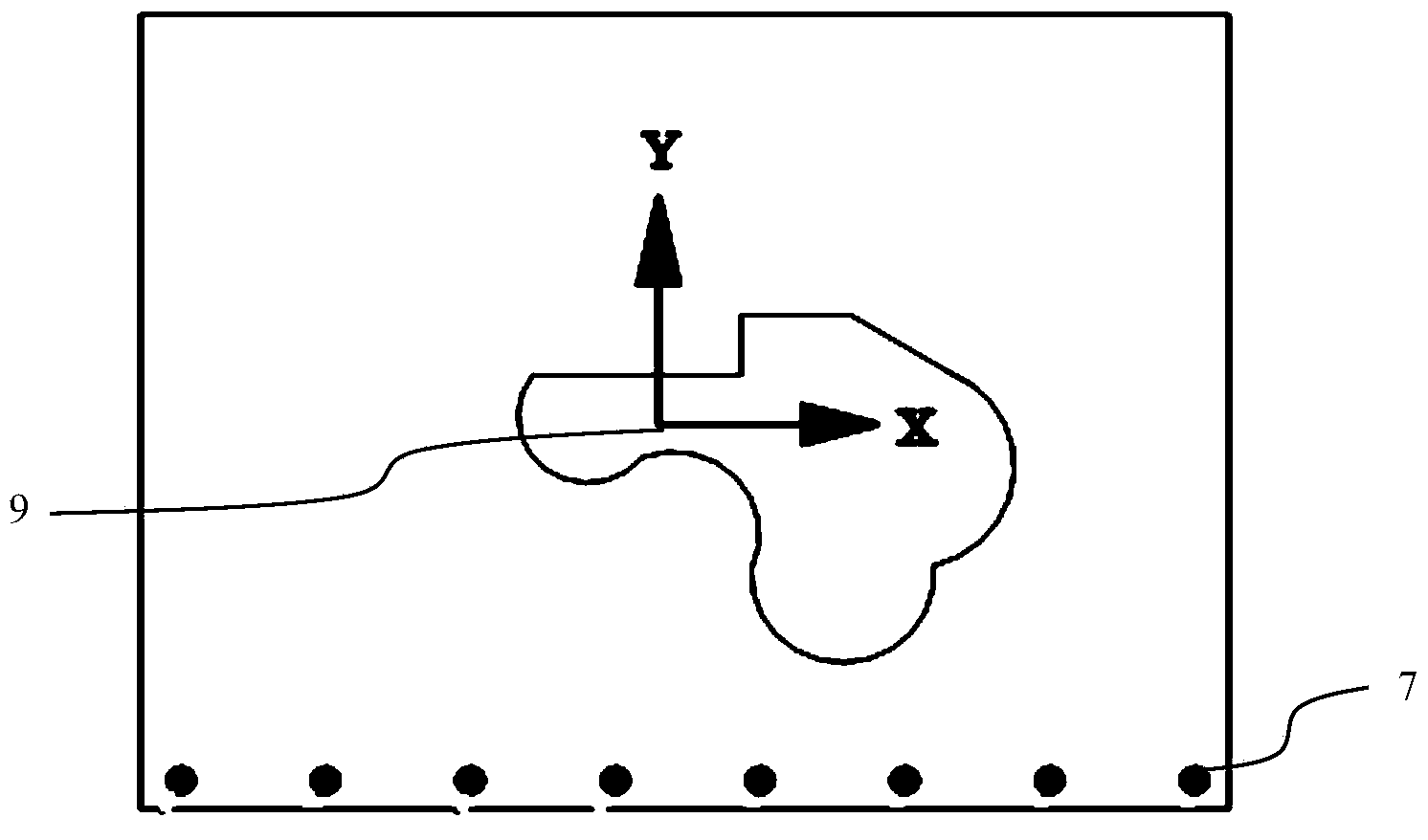

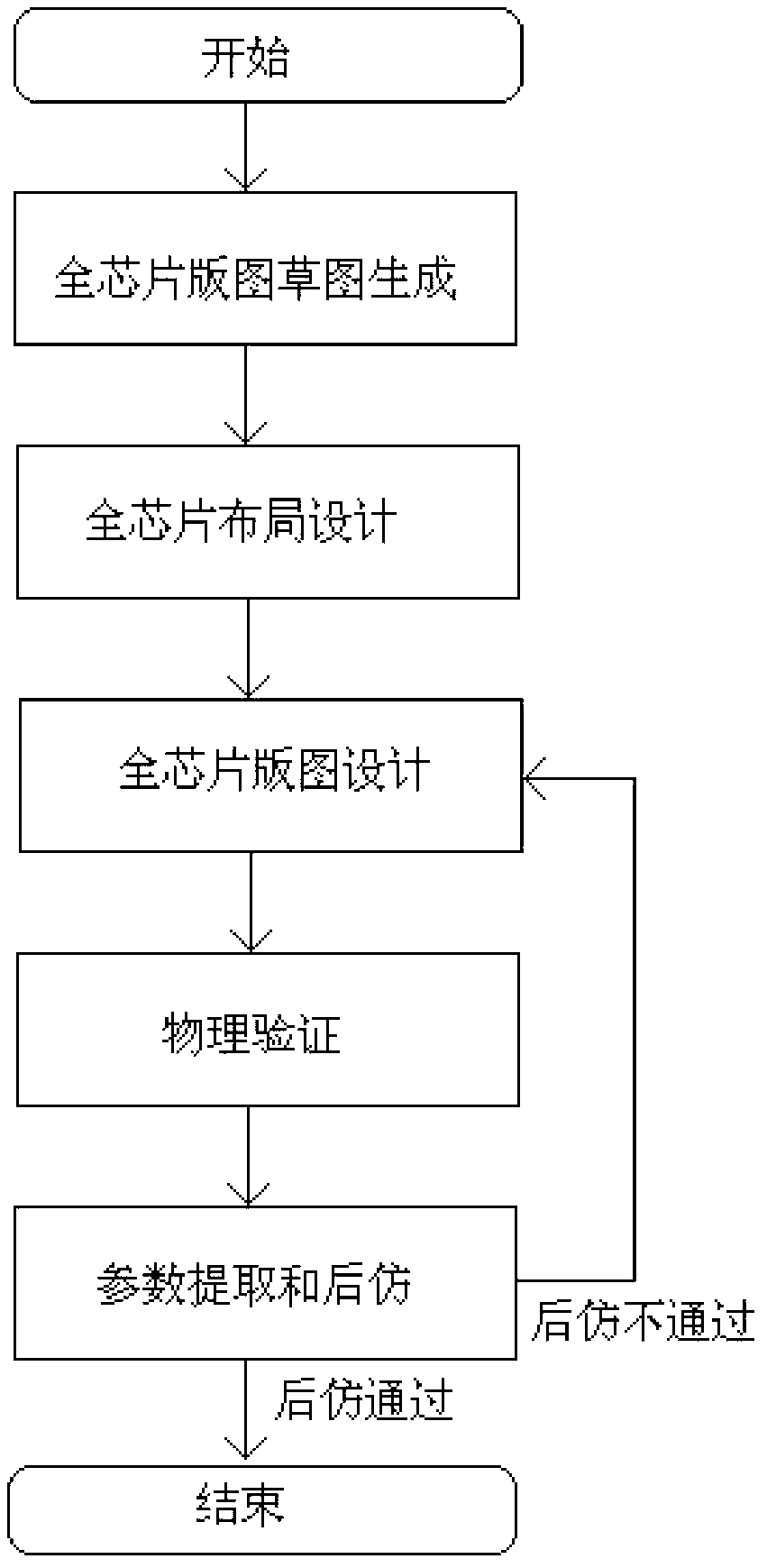

Analogue integrated circuit layout designing method capable of improving layout efficiency

ActiveCN103268380AImprove performanceReduce rationalitySpecial data processing applicationsIntegrated circuit layoutCircuit performance

The invention relates to an analogue integrated circuit layout designing method capable of improving layout efficiency. The method includes the following steps: (1) generation of a full-chip physical layout draft: automatic generation of a layout of various modules in a schematic circuit diagram and automatic generation of the hierarchical full-chip physical layout draft by using of process database devices of circuit design according to the circuit top-level principle, (2) full-chip layout design: optimization and adjustment on the position of the layout of the various modules in the full-chip physical layout draft, determination of routes of data lines and routes of signal lines, and optimization and adjustment on positions of key devices in the layout of the various modules, and (3) design of the full-chip physical layout: completion of the final layout design of the various modules, completion of connection of the signal lines among the various modules, then completion of connection of the full-chip signal lines among the various modules, and acquisition of the full-chip physical layout. The analogue integrated circuit layout designing method can improve the layout efficiency and guarantee consistency of parasitic parameters of the devices in technology, circuit and layout design processes, simplifies design procedures, and achieves the purpose of improving circuit performance.

Owner:EAST CHINA INST OF OPTOELECTRONICS INTEGRATEDDEVICE

Two-board-in-one processing method for substrate manufacture of printed circuit board or integrated circuit package

InactiveCN101359601ALow costIncrease productivitySemiconductor/solid-state device manufacturingMultilayer circuit manufactureElectrical conductorProcess patterns

Disclosed is a method for combining two plates in the fabrication process of an enclosure baseplate of a printed circuit or an integrated circuit. The method includes the following steps: splicing two chip plates through a bonding sheet so as to make a machining plate which is big in thickness, higher in rigidity and can satisfy common equipment machining requirements; processing pattern transfer to the spliced machining plate and developing a necessary circuit diagram of a conductor on the surface of the machining plate; developing an insulating medium layer and a conducting copper layer on the surface of the newly developed circuit diagram of the conductor through the method of lamination; repeating above processes so as to form a multilayer machining plate; separating the machining plate at two sides of the splicing sheet from the splicing sheet after the machining plate reaches certain thickness and rigidity, thus forming two machining plates; and respectively processing the two machining plates through regular lamination, boring, electroplating and pattern transfer techniques until the necessary circuit board and the enclosure baseplate are finished. The method requires no special equipment or machining tools and can reduce cost by a large margin and improve production efficiency and yield.

Owner:SHANGHAI MEADVILLE SCI & TECH +2

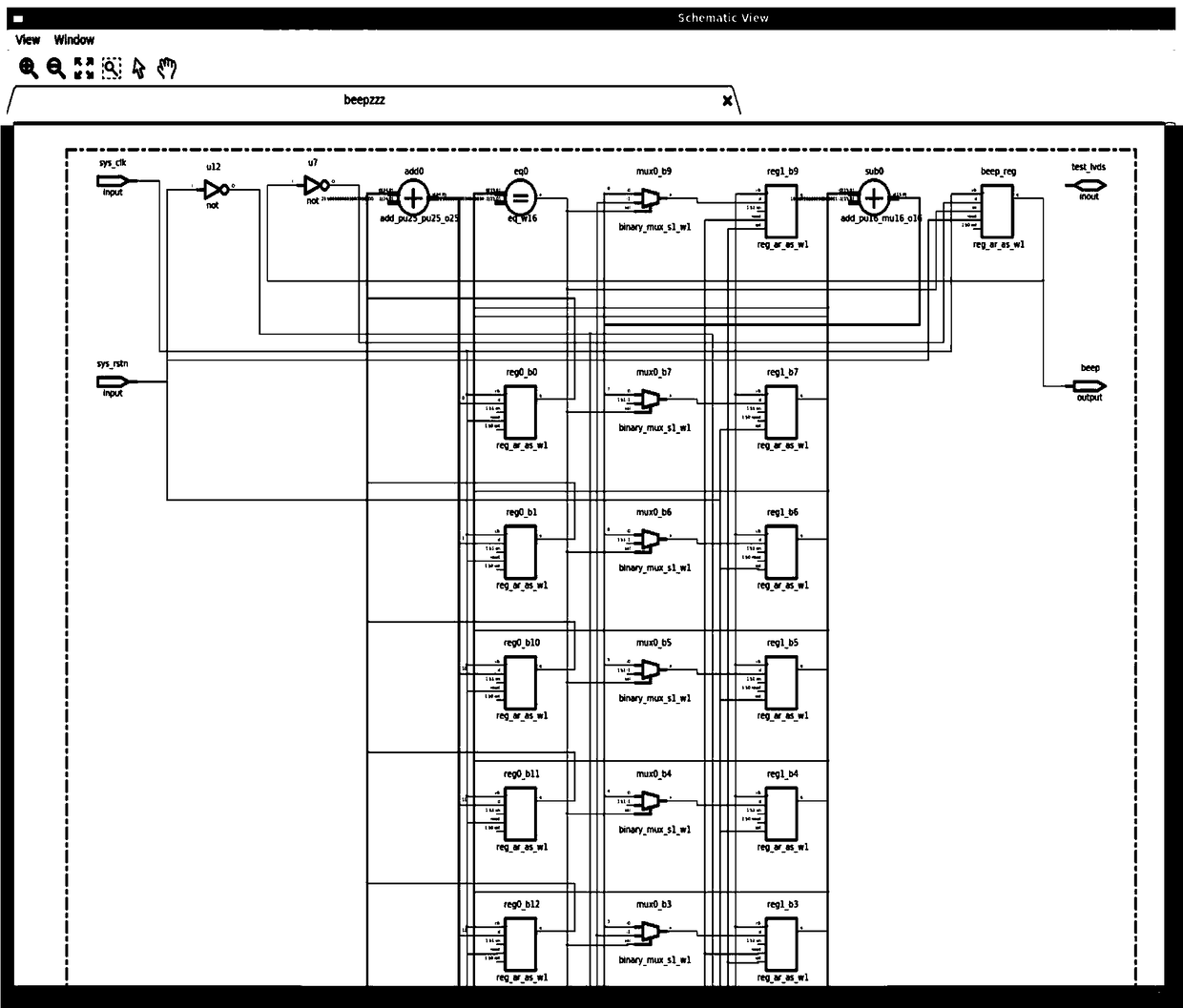

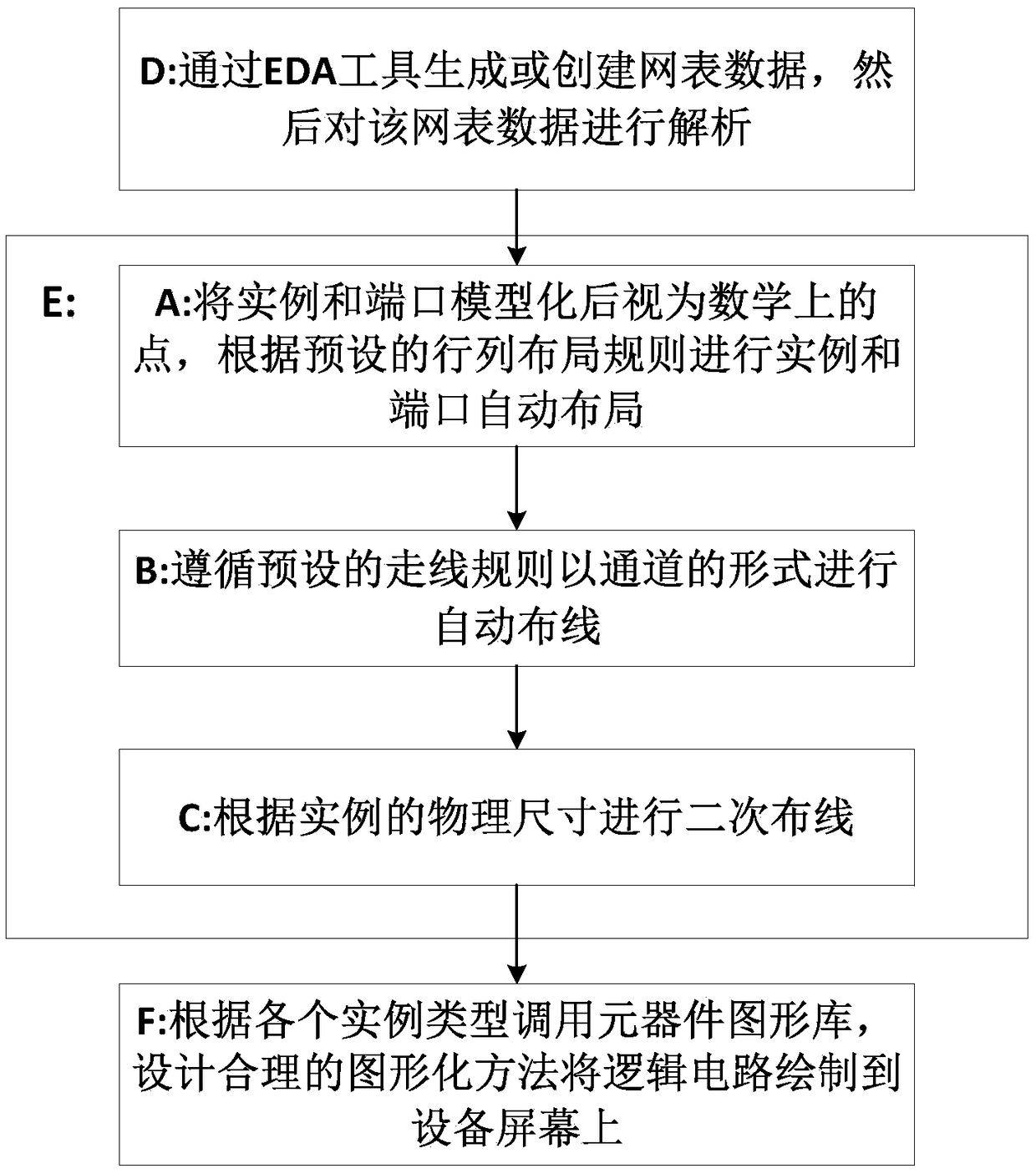

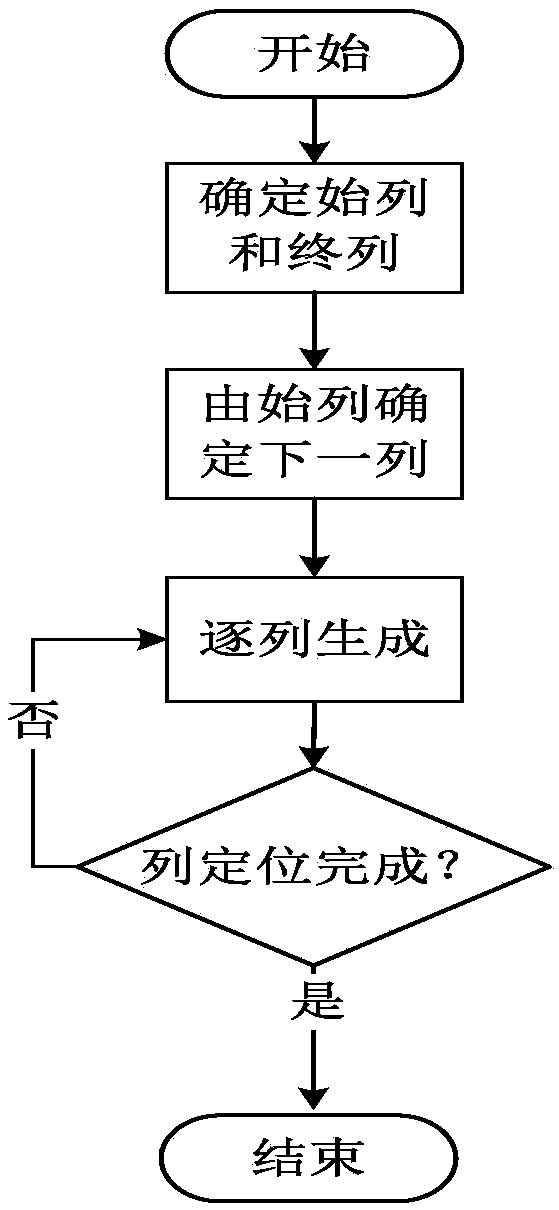

Circuit layout method, graphic display method and system thereof

ActiveCN109284578AOptimizing place and route methodsIn line with the habitSpecial data processing applicationsIntersection of a polyhedron with a lineHabit

The present application relates to a programmable logic array, and discloses a logic circuit layout and routing method, a graphical display method and a system thereof. The present invention is directed to graphical display of logic circuits, directed acyclic graph generation algorithm and preset column distribution rules are used to allocate logical columns, and heuristic algorithm is used to allocate logical rows based on median sorting, so as to optimize the number of intersection points. At the same time, the physical coordinates of components are allocated according to their physical dimensions in the process of automatic layout, so that the components are centralized and arranged compactly. The method of cache and windowing is also used to realize the fast response when the logic circuit of large layout is dragged to view. Finally, the generated logic circuit diagram is uniformly distributed, the input and output conform to the circuit habits, the number of intersection points isless, and the plotting is fast.

Owner:SHANGHAI ANLOGIC INFOTECH CO LTD

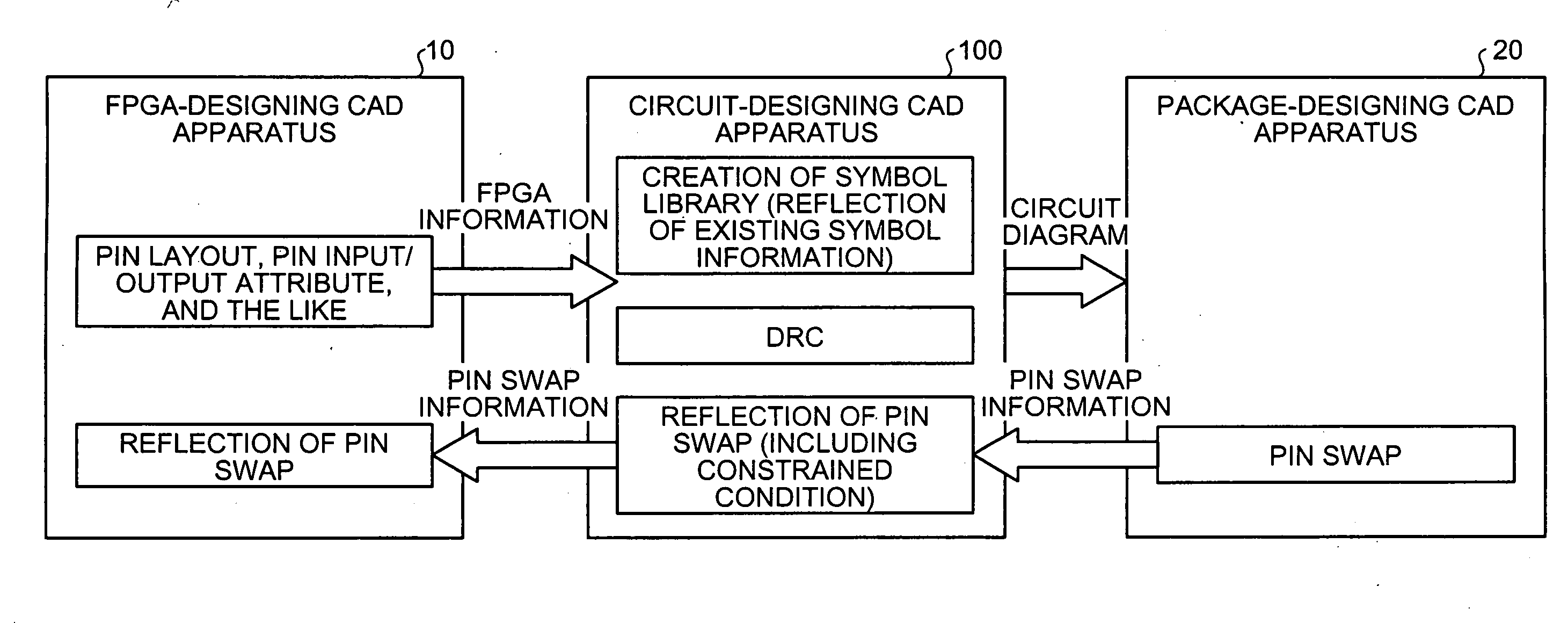

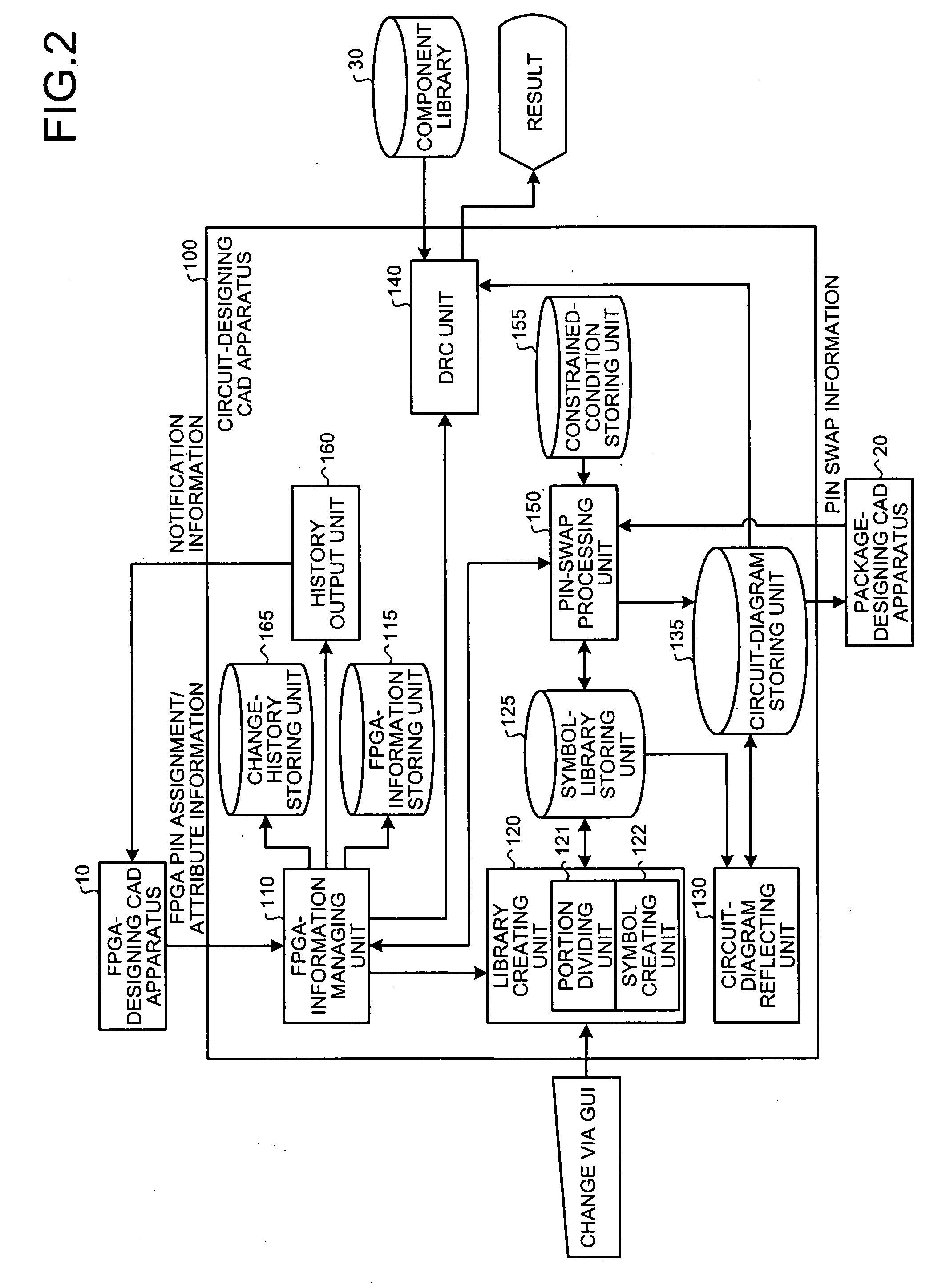

Circuit-design supporting apparatus, circuit-design supporting method, computer product, and printed-circuit-board manufacturing method

ActiveUS20080263500A1Solve problemsCAD circuit designSpecial data processing applicationsManagement unitPackage design

An FPGA-information managing unit included in a circuit-designing CAD apparatus retrieves FPGA information, such as pin-assignment information and attribute information, that is created by an FPGA-designing CAD apparatus. A library creating unit creates a symbol library by using the FPGA information. A pin-swap processing unit retrieves pin swap information from a package-designing CAD apparatus, and reflect the pin swap in the symbol library, the FPGA information, a circuit diagram, and a constrained condition.

Owner:FUJITSU LTD

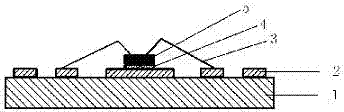

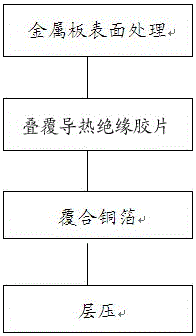

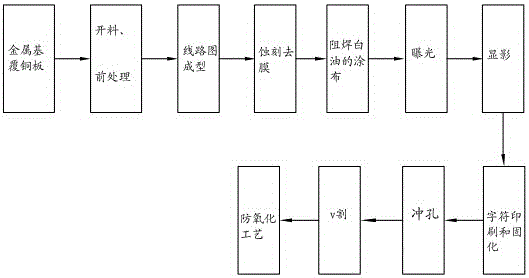

Manufacturing method of metal-based circuit board of LED

ActiveCN106132098AChange the traditional formStrong adhesionConductive material chemical/electrolytical removalCircuit precursor manufacturePunchingHigh volume manufacturing

The invention relates to a manufacturing method of a metal-based circuit board of an LED. A finished product is obtained through a metal plate surface treatment step, a heat-conducting insulating film superimposing step, a combined copper foil laminating step, a cutting step, a location hole drilling step, a pretreatment step, a circuit diagram forming step, an etching and stripping step, a solder resist white oil coating step, an exposure step, a developing step, a character printing and solidifying step, a punching step, a v cutting step and an anti-oxidation process. PP glue is combined on a metal-based base plate; and a printing technology or an exposure technology is adopted for circuit diagram forming. Through the technical scheme provided by the invention, the metal-based circuit board integrating a drive power supply and a light source can be massively produced; and the manufactured LED and power supply have good heat dissipation performance.

Owner:ZHEJIANG LEUCHTEK ELECTRONICS

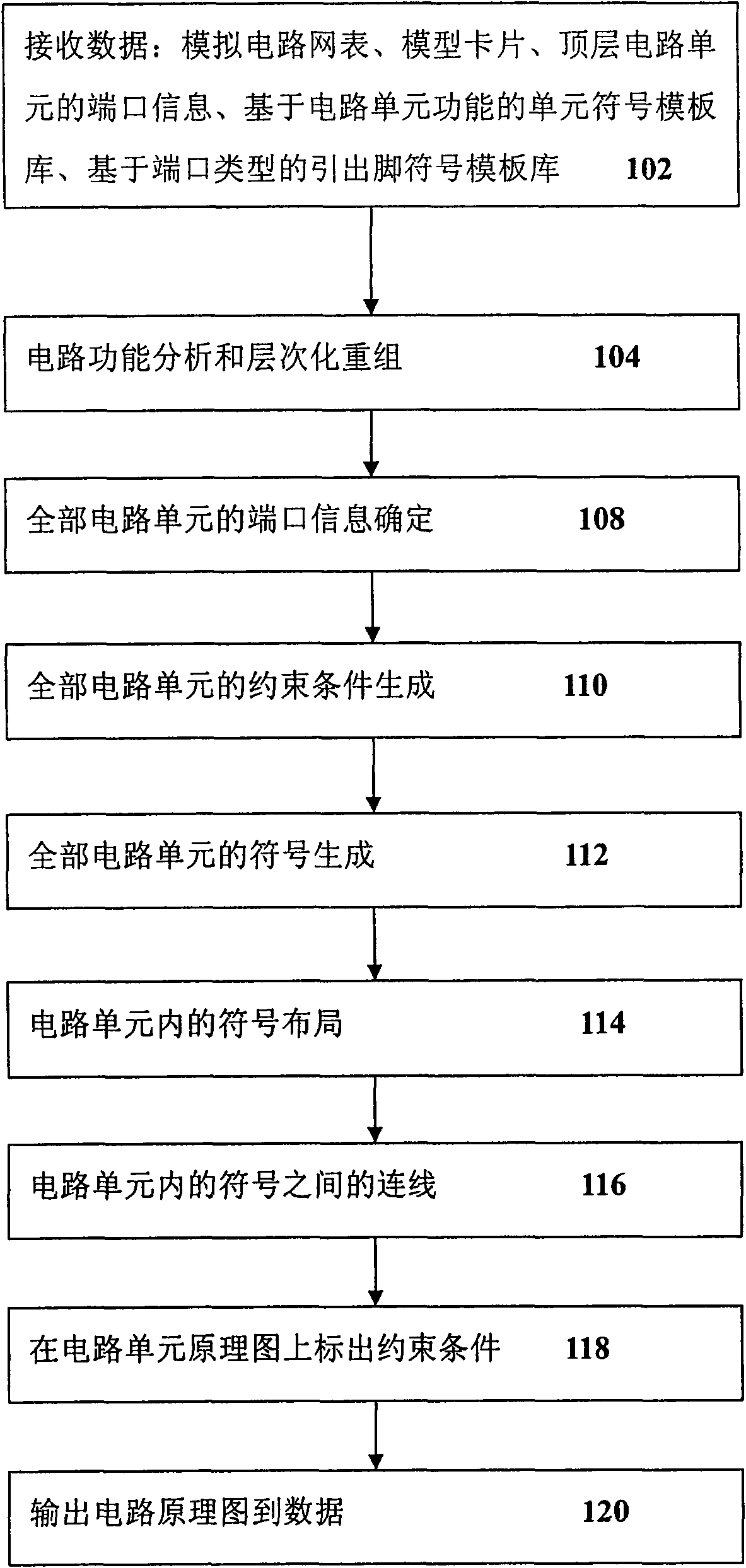

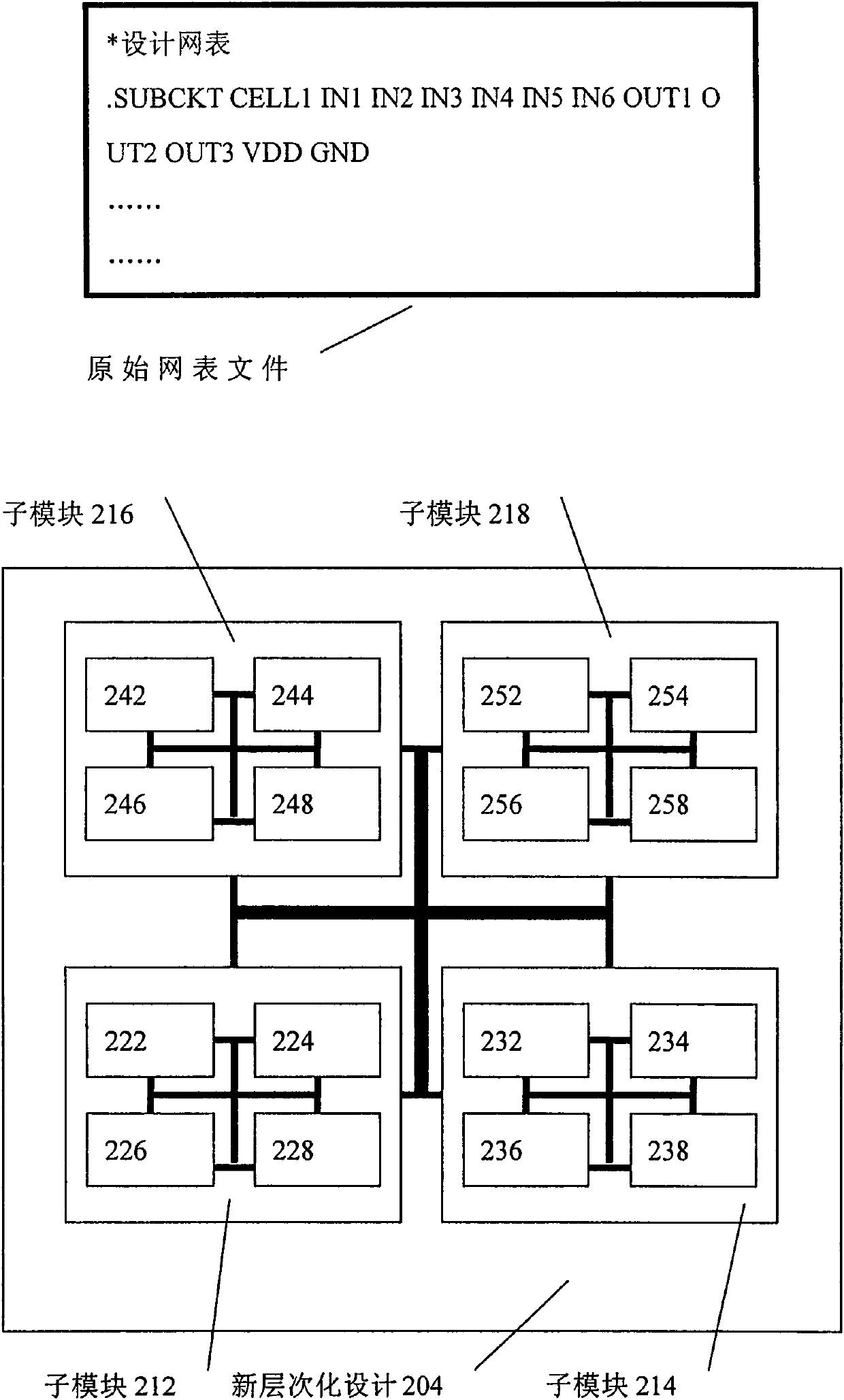

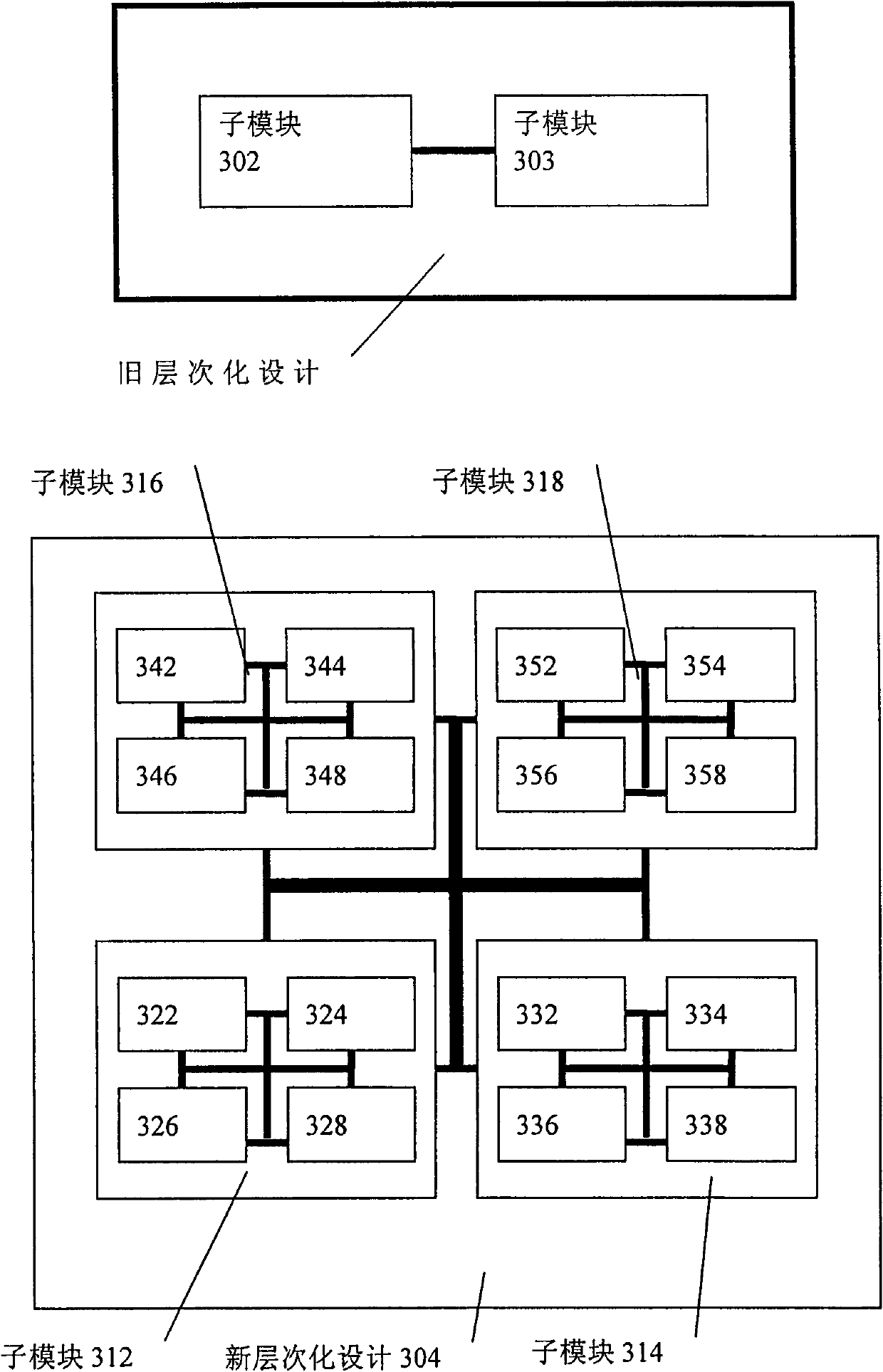

Automatic generation method of analog circuit schematic through analog circuit netlist

ActiveCN102024066AClearly reflect the characteristicsClearly reflect the functionSpecial data processing applicationsDisplay deviceComputer science

The invention discloses an automatic generation method of analog circuit schematic through analog circuit netlist, which comprises the steps of receiving the data which is assigned by users in the form of graphical interface or command line; analyzing the circuit functions based on an analog circuit function structure characteristic template database and stratifying based on the circuit functions; determining the port types of all circuit units; automatically generating constraint conditions of all the circuit units; automatically generating symbols of all the circuit units; performing automatic layout of the symbols in the circuit units; automatically wiring the net among the symbols in the circuit units; automatically marking the constraint conditions on a circuit diagram of the circuitunits; and outputting the circuit diagram to a database of a circuit diagram editor / displayer. According the invention, a circuit diagram which can accurately reflect the analog circuit functions, the structural characteristics, and the functional hierarchy, and clearly indicate direct current paths, signal flow paths and the constrained conditions required by the subsequent circuit optimization and layout optimization can be automatically generated.

Owner:INST OF MICROELECTRONICS CHINESE ACAD OF SCI

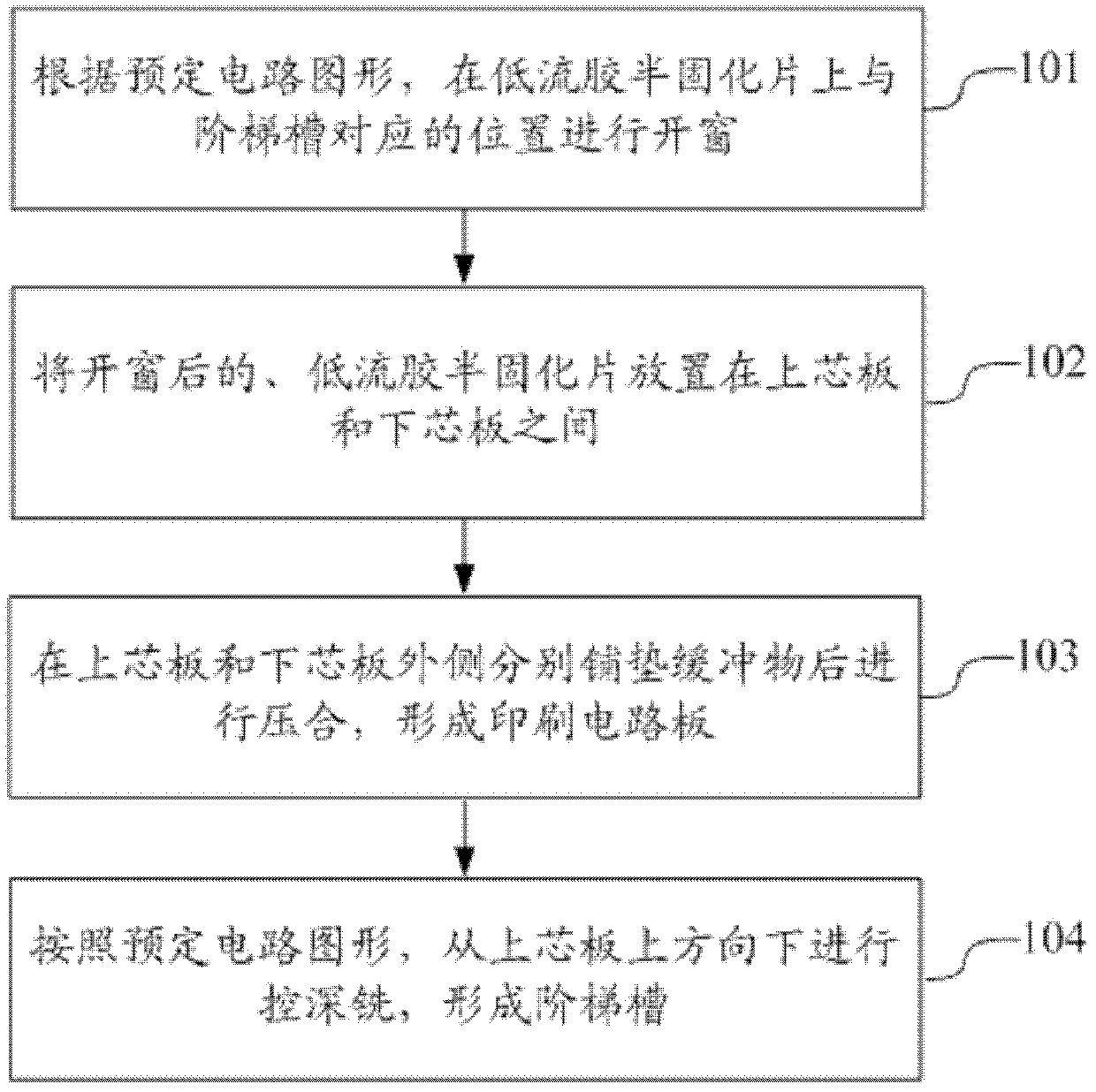

Manufacturing method of printed circuit board stepped slot and printed circuit board comprising stepped slot

ActiveCN103313515ALow costEasy to take outPrinted circuit detailsPrinted circuit manufactureEngineeringPrinted circuit board

The invention relates to the technical field of a printed circuit board, in particular to a manufacturing method of a printed circuit board stepped slot and a printed circuit board comprising the stepped slot. The method comprises the steps of: windowing on a low flow glue prepreg at a position corresponding to a stepped slot according to a predetermined circuit diagram; placing the windowed low flow glue prepreg between an upper core plate and a lower core plate; paving a buffer on the outer sides of the upper core plate and the lower core plate respectively and then laminating to form the printed circuit board; performing controlled deep milling from the up direction of the upper core plate according to the predetermined circuit diagram to form the stepped slot. By using the manufacturing method of the printed circuit board stepped slot and the printed circuit board comprising the stepped slot provided by the embodiment of the invention, the manufacturing flow of the printed circuit board stepped slot can be simplified, the manufacturing efficiency can be improved and the cost can be saved.

Owner:NEW FOUNDER HLDG DEV LLC +1

Method for producing for a mask a mask layout which avoids aberrations

InactiveUS20050120326A1Simple methodImprove stabilityOriginals for photomechanical treatmentSpecial data processing applicationsEngineeringCircuit diagram

A method for producing for a mask a mask layout which avoids aberrations in which a provisional auxiliary mask layout produced, in particular in accordance with a prescribed electrical circuit diagram is converted into the mask layout with the aid of an OPC method. At least two different OPC variants are used in the course of the OPC method by subdividing the original auxiliary mask layout into at least two layout areas and processing each of the layout areas in accordance with one of the at least two OPC variants.

Owner:INFINEON TECH AG

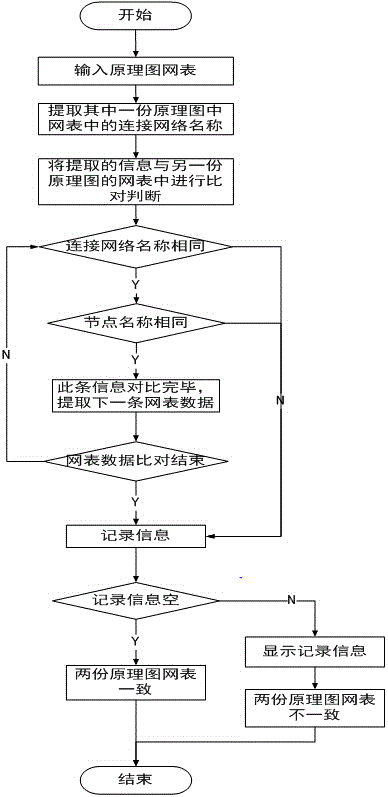

Schematic circuit diagram netlist comparison method

InactiveCN104091161AGuaranteed accuracyImprove design qualityCharacter and pattern recognitionNetlistBit numbering

The invention relates to a schematic circuit diagram comparison method, in particular to a schematic circuit diagram netlist comparison method. According to the schematic circuit diagram netlist comparison method, by extracting network node names, the names of connected networks, component bit numbers, packaging information and other aspects in schematic diagram netlist, calculation is conducted, the consistency of connection of each network node, the consistency of connection of pins of each component, the consistency of the component bit numbers and the consistency of packaging in the netlists can be compared rapidly and directly, the difference between the components and the inconsistency of connection are represented, inconsistent results are classified into different classes and are output and displayed, and therefore the accuracy of a result is guaranteed. The schematic circuit diagram comparison method can be executed through software, use is convenient, and the quality and the efficiency of design of a schematic diagram of a circuit board are improved.

Owner:SHANDONG CHAOYUE DATA CONTROL ELECTRONICS CO LTD