Analogue integrated circuit layout designing method capable of improving layout efficiency

A design method and integrated circuit technology, applied in computing, electrical digital data processing, special data processing applications, etc., can solve problems such as unreasonable design, restricting the time to market of integrated circuit products, and reducing layout efficiency, so as to improve circuit performance , improve layout efficiency, and simplify the design process

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

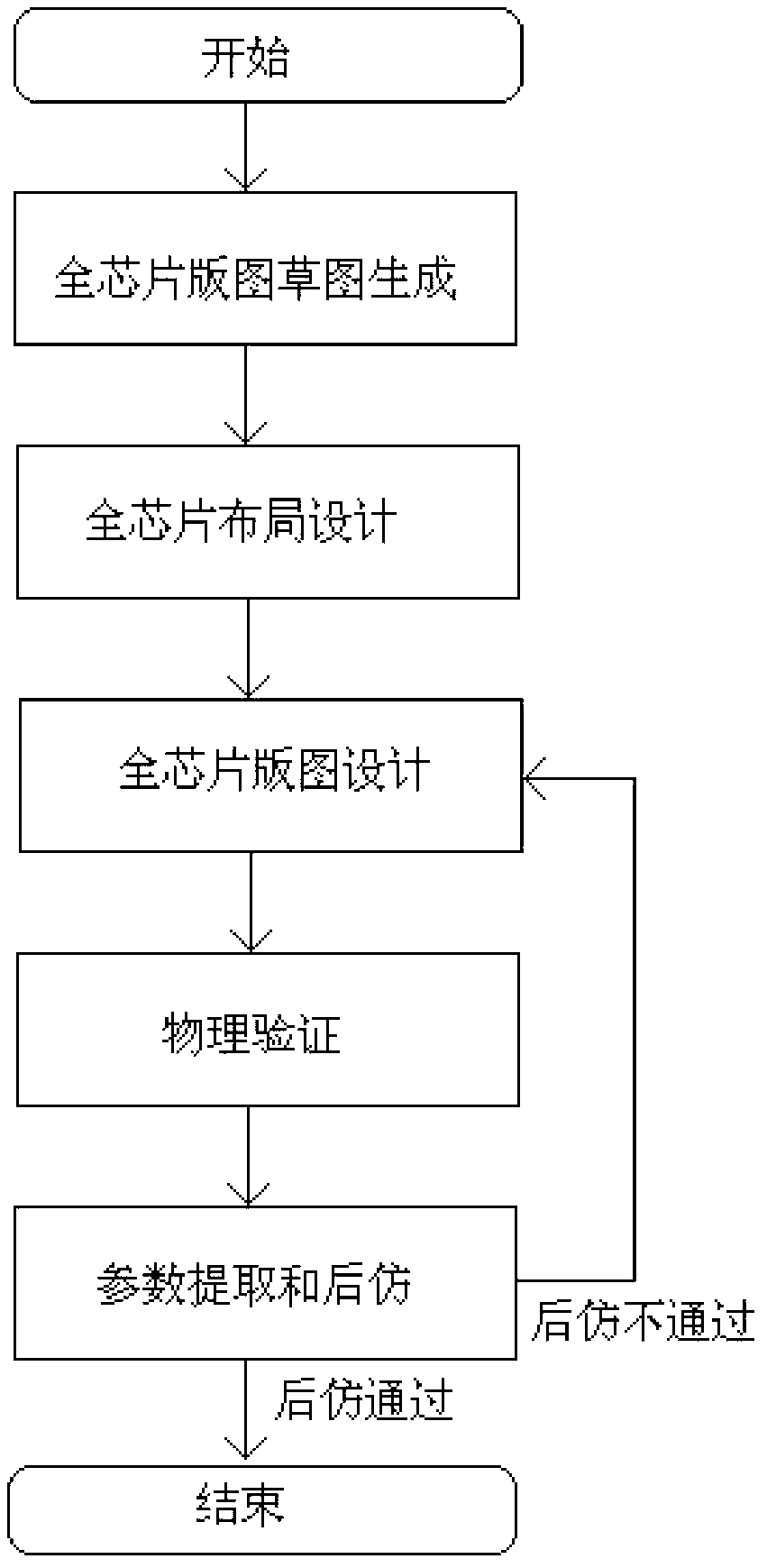

[0018] Embodiment one: see attached figure 1 shown. A method for designing an analog integrated circuit layout that improves layout efficiency, and is used to convert a schematic circuit diagram composed of several modules into a specific physical layout of a full chip. The design method includes the following steps:

[0019] (1) Generation of the physical layout sketch of the full chip:

[0020] Citing the process library devices used in circuit design and using the top-level principle of the circuit to automatically generate the layout of each module in the circuit schematic diagram, and generate a hierarchical full-chip physical layout sketch, the layout of any module includes the layout of all devices in the module , the physical layout sketch of the full chip includes the layout and location of each module;

[0021] (2) Full chip layout design:

[0022] Optimize and adjust the position of the layout of each module in the physical layout sketch of the full chip, and d...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More