Printed circuit board and producing method of encapsulation base of integrated circuit

一种印制电路板、集成电路的技术,应用在印刷电路制造、印刷电路、印刷电路等方向,能够解决不利精细线路、线路铜厚厚、限制半加成法应用等问题,达到降低的困难、增加布线密度、避免成本较高的效果

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0033] The manufacturing method of the present invention will be further described below in conjunction with the accompanying drawings.

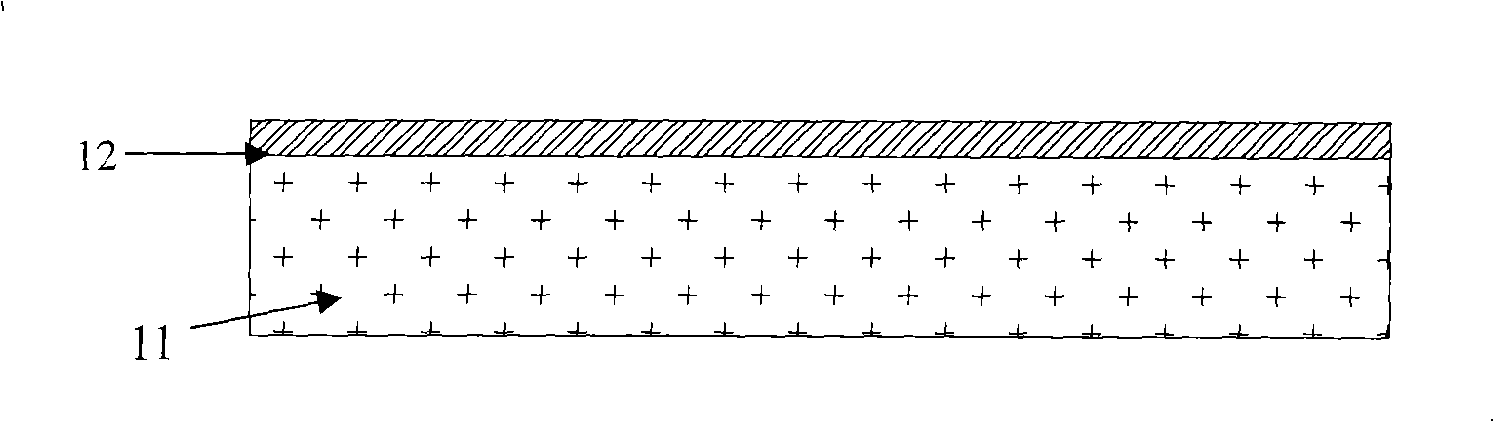

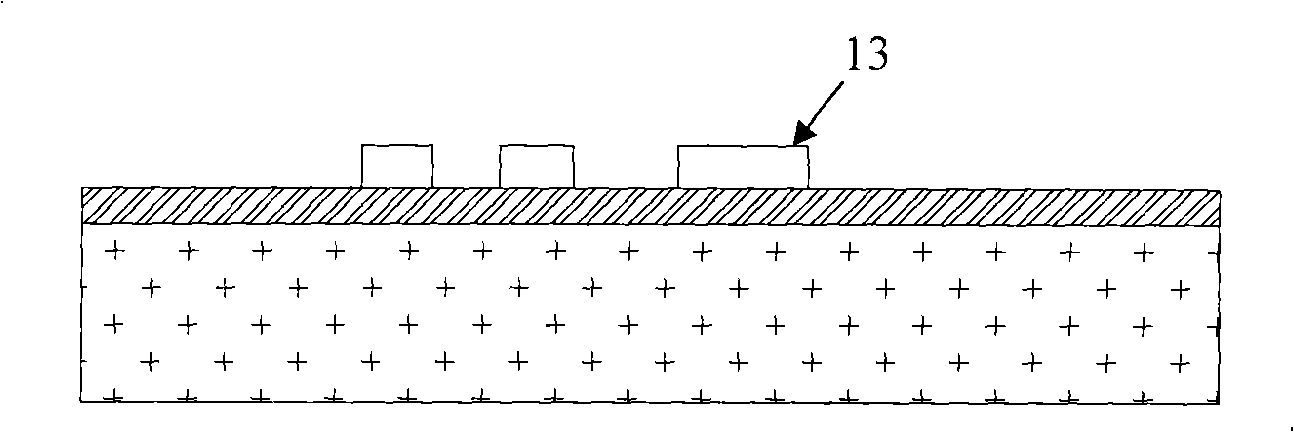

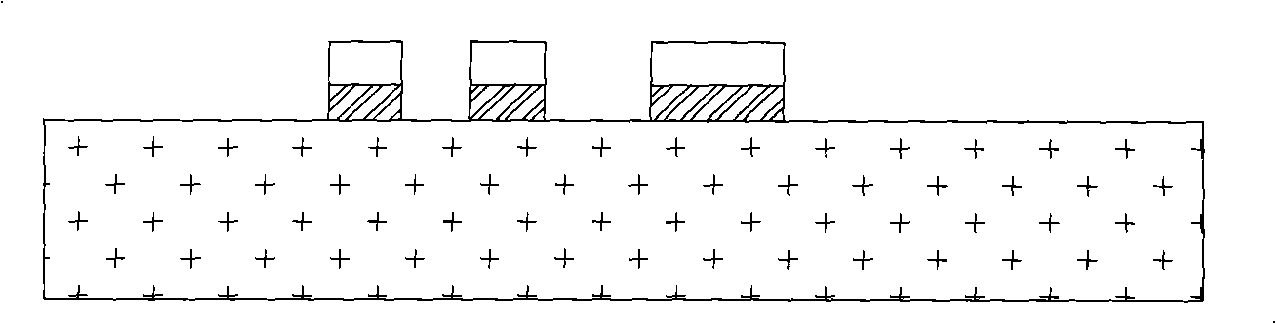

[0034] Such as Figure 6a , Figure 6b , Figure 6c , Figure 6d , Figure 6e , Figure 6f , Figure 6g , Figure 6h , Figure 6i , Figure 6j As shown (in the figure, 61 is the bottom dielectric layer, 62 is the copper foil, 63 is the dielectric layer, 64 is the first seed layer, 65 is the copper layer, 66 is the second seed layer, and 67 is the anti-plating layer), the concrete made by the present invention The steps are:

[0035] step 1( Figure 6a ), first fabricate a dielectric layer 63 on the substrate: in this embodiment, the substrate is a composite material of a bottom dielectric layer 61 and a layer of copper foil 62 . The dielectric layer can be fabricated on the substrate by resin coating, film sticking, or lamination of the dielectric layer. If lamination is used, the laminate dielectric layer may or may not be cover...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More