Patents

Literature

Hiro is an intelligent assistant for R&D personnel, combined with Patent DNA, to facilitate innovative research.

5038results about "Conductive material chemical/electrolytical removal" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

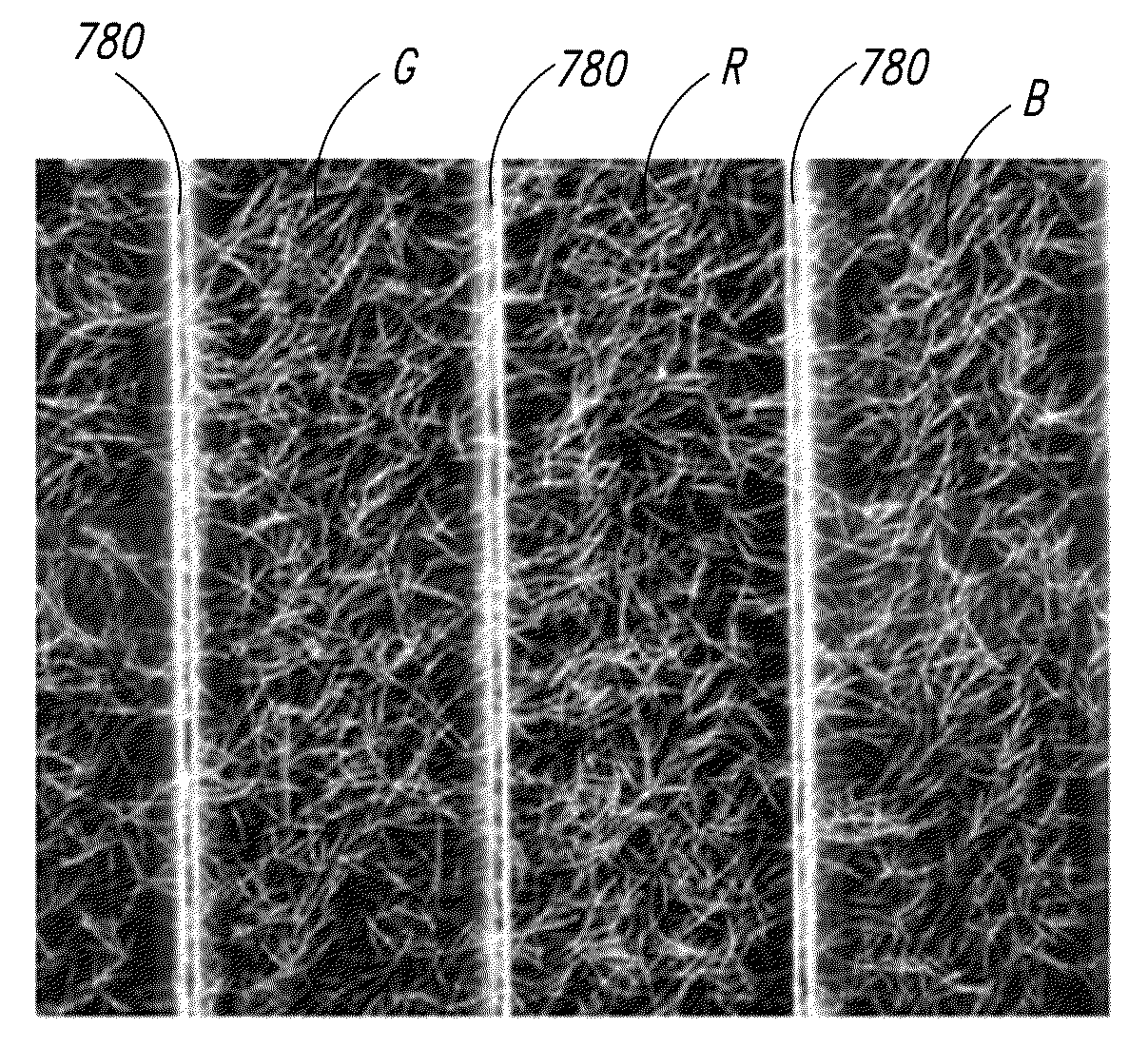

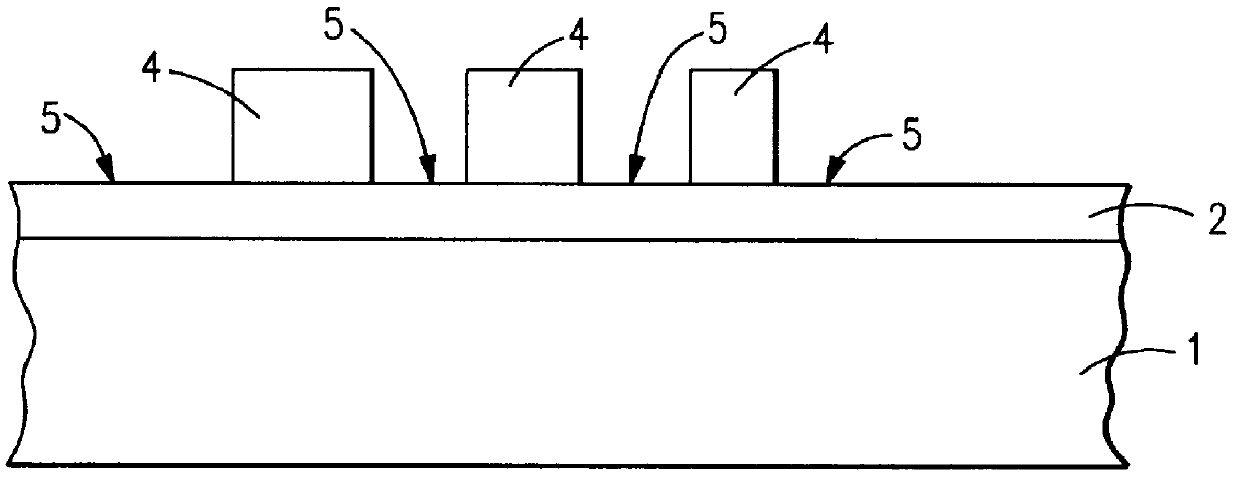

Nanowire-based transparent conductors and applications thereof

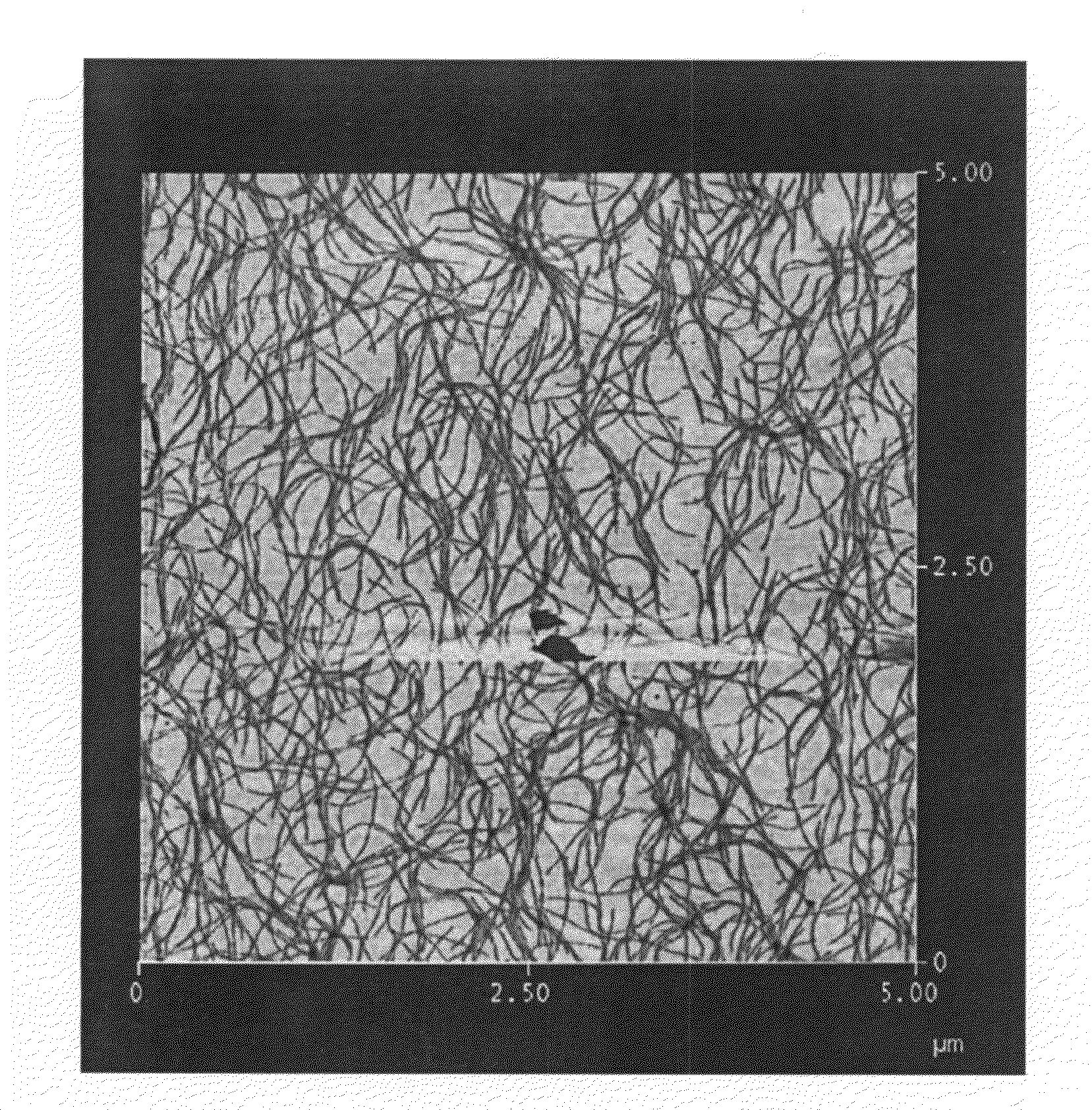

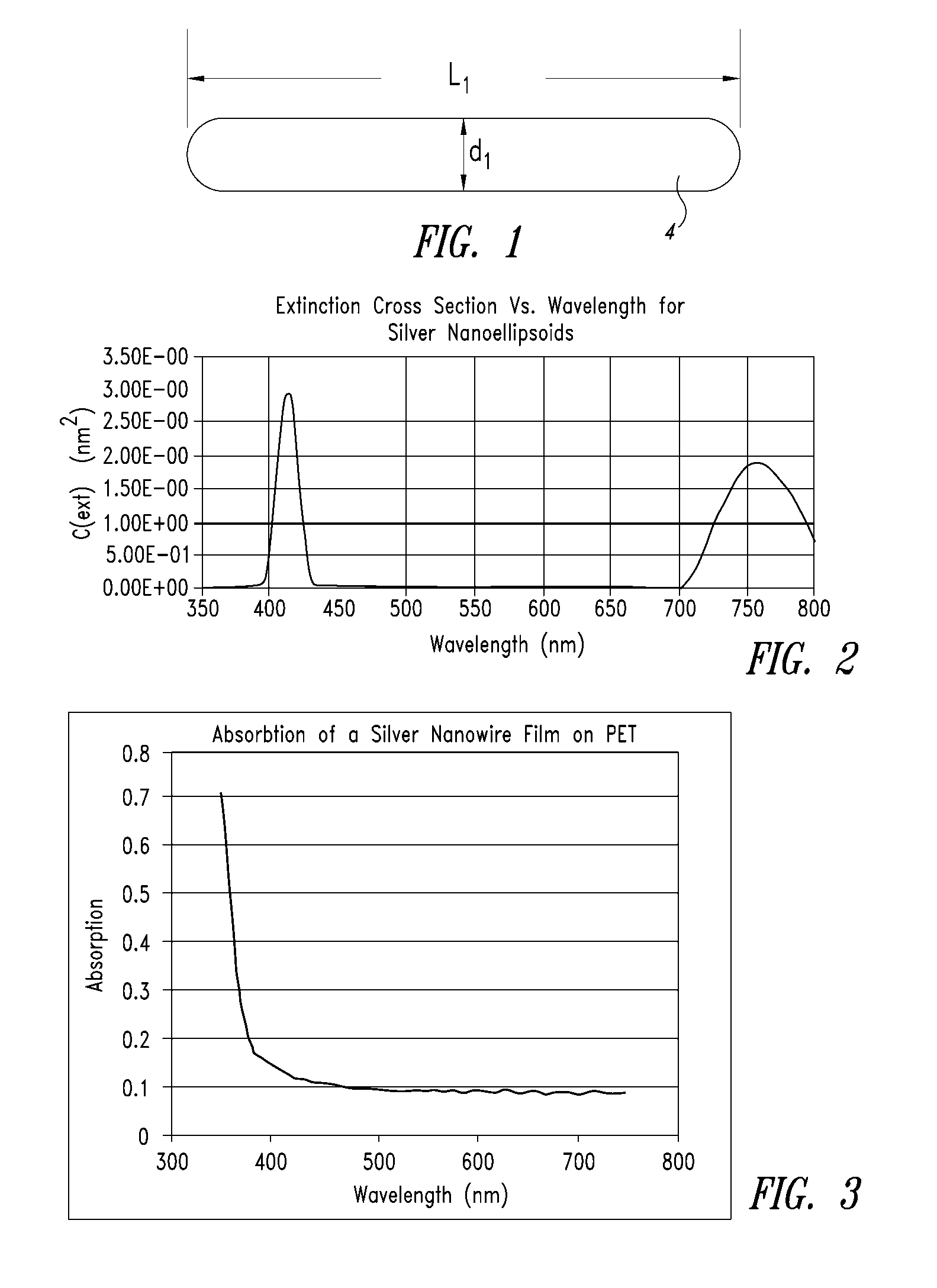

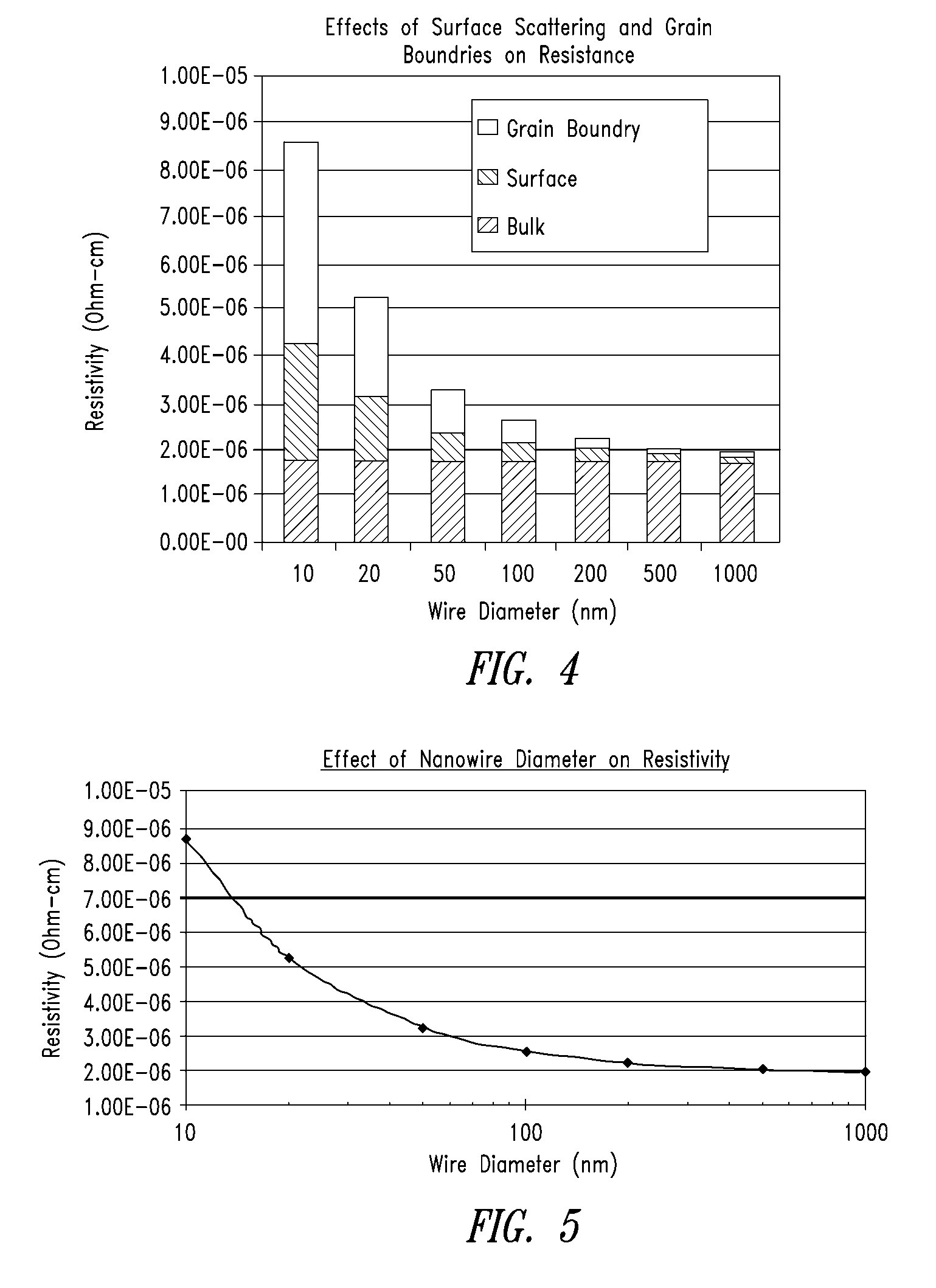

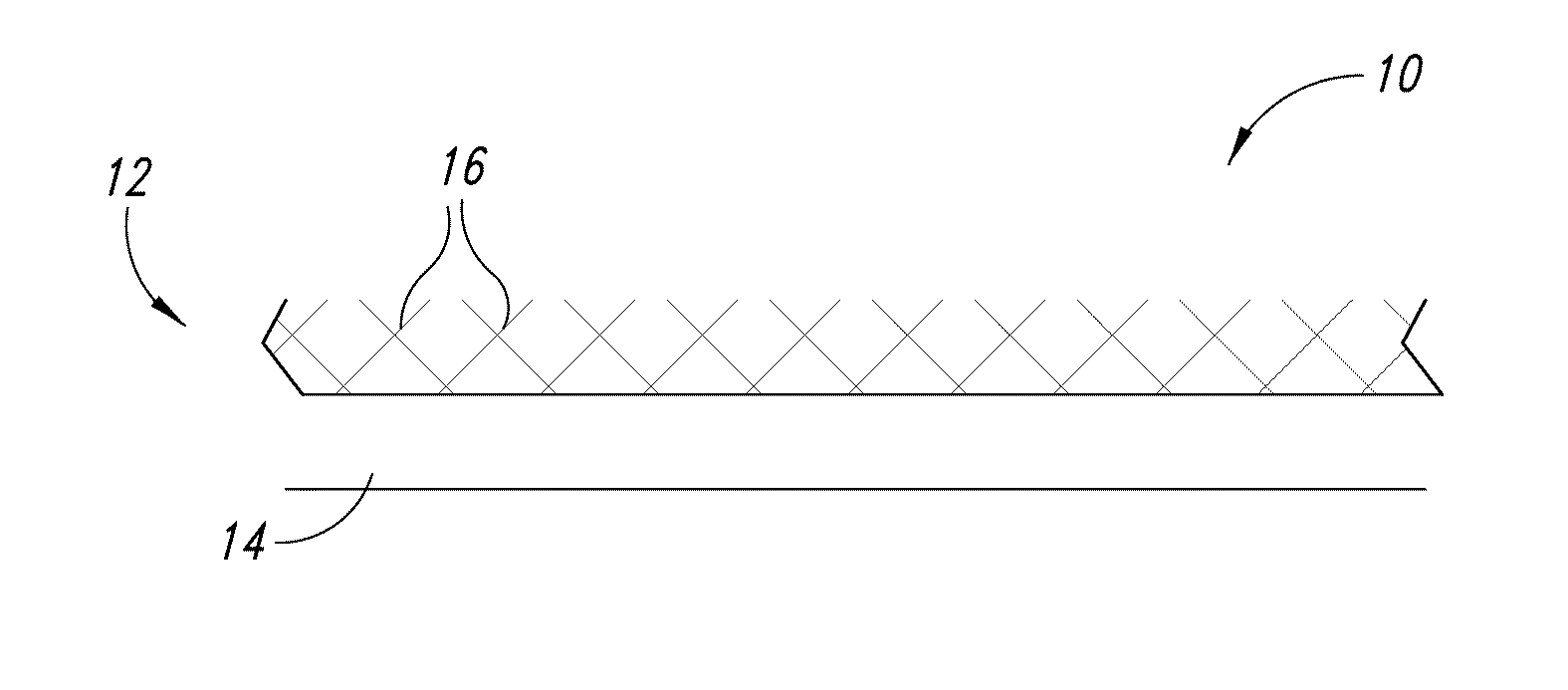

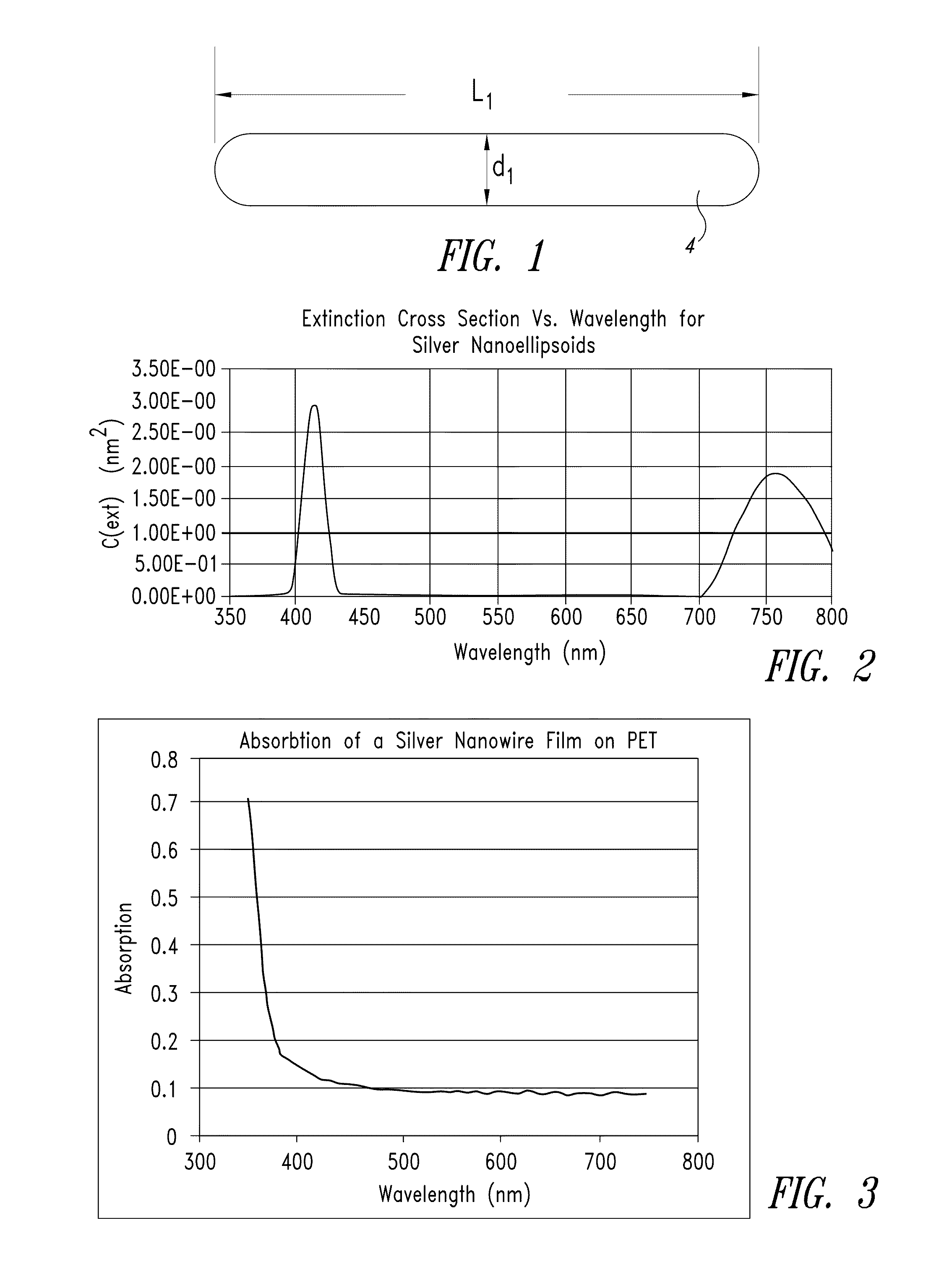

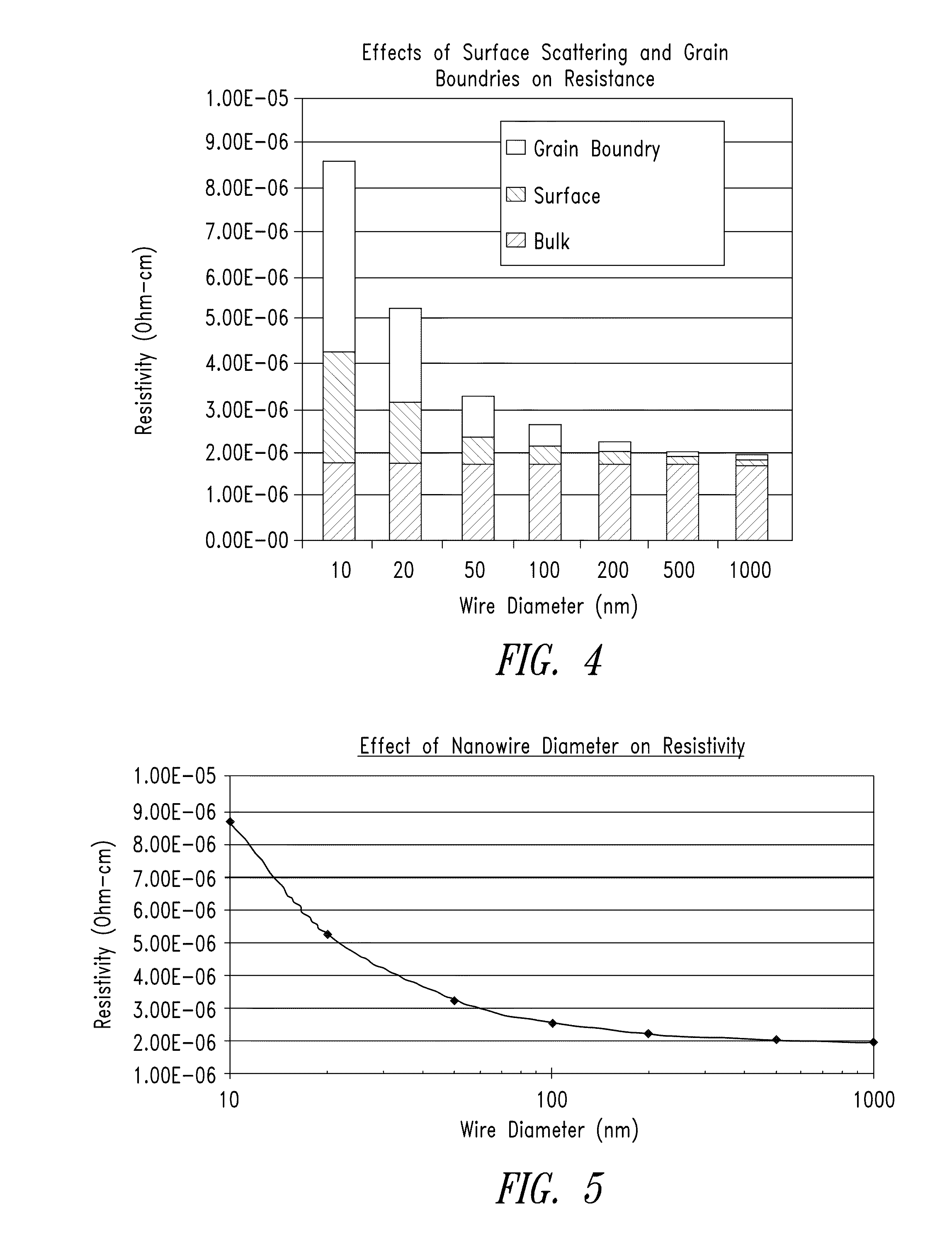

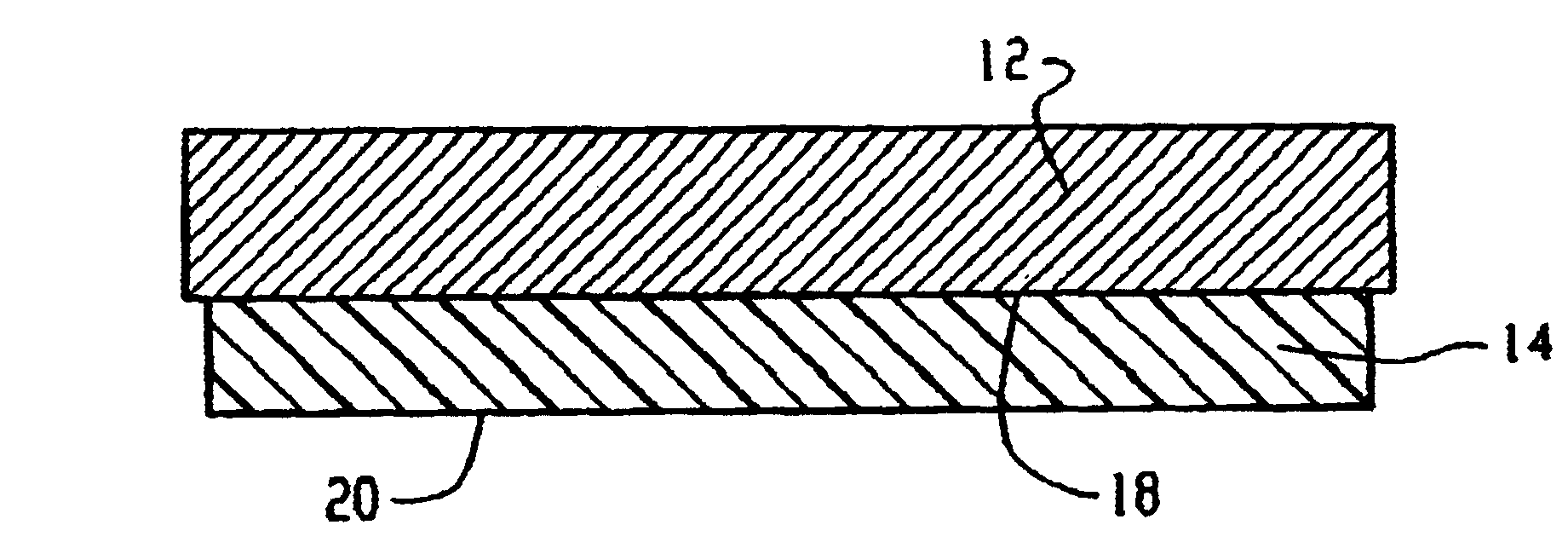

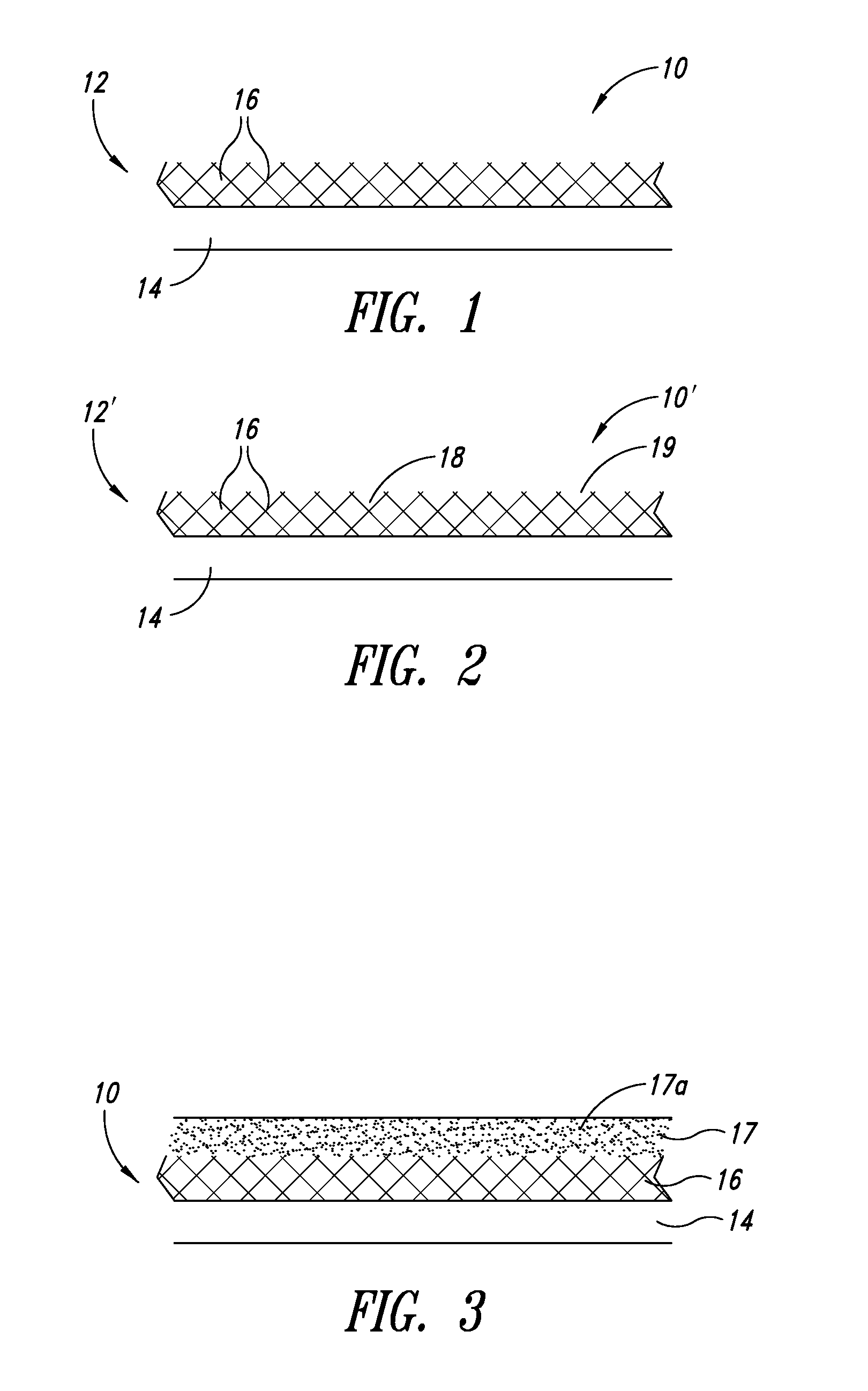

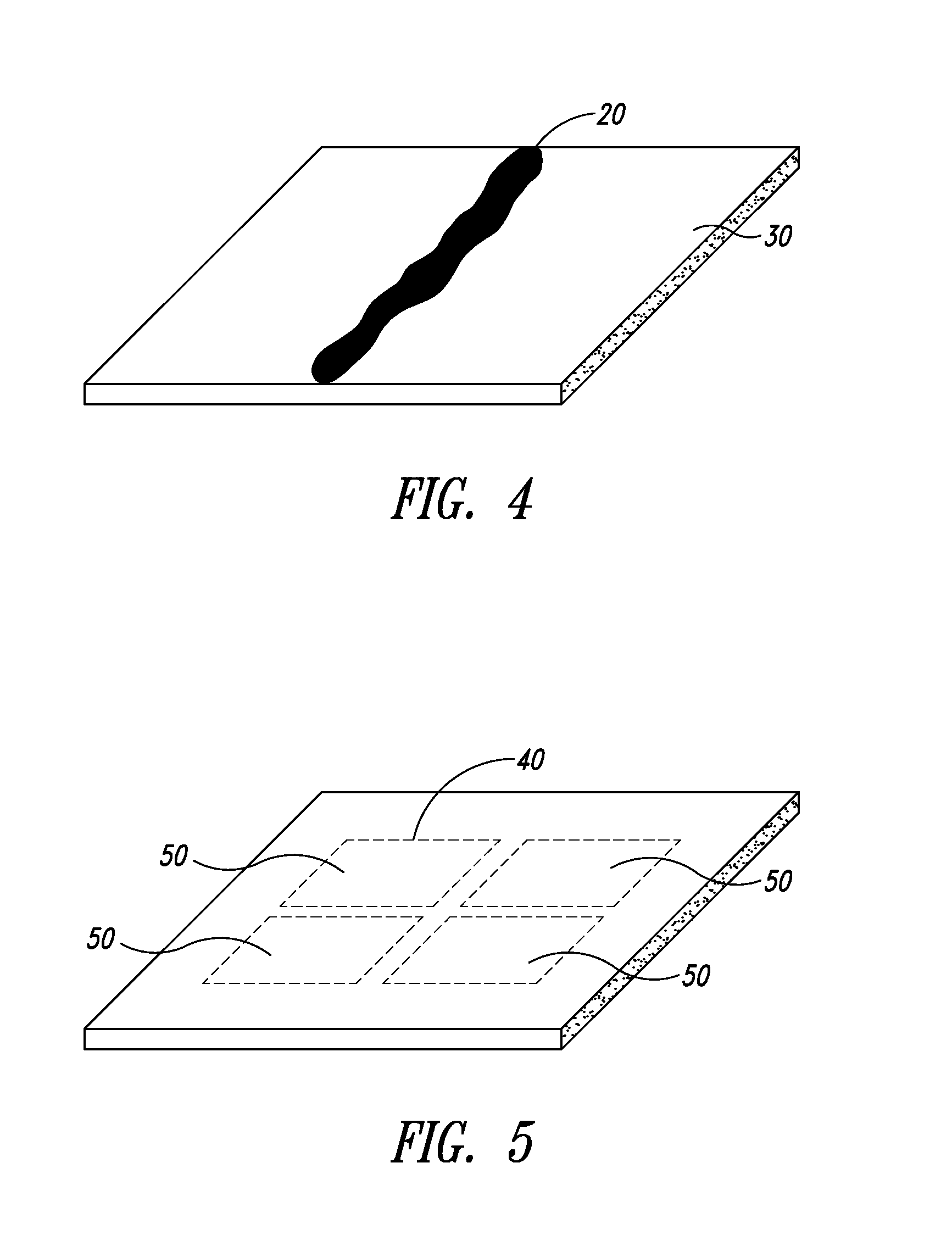

A transparent conductor including a conductive layer coated on a substrate is described. More specifically, the conductive layer comprises a network of nanowires that may be embedded in a matrix. The conductive layer is optically clear, patternable and is suitable as a transparent electrode in visual display devices such as touch screens, liquid crystal displays, plasma display panels and the like.

Owner:CHAMP GREAT INTL

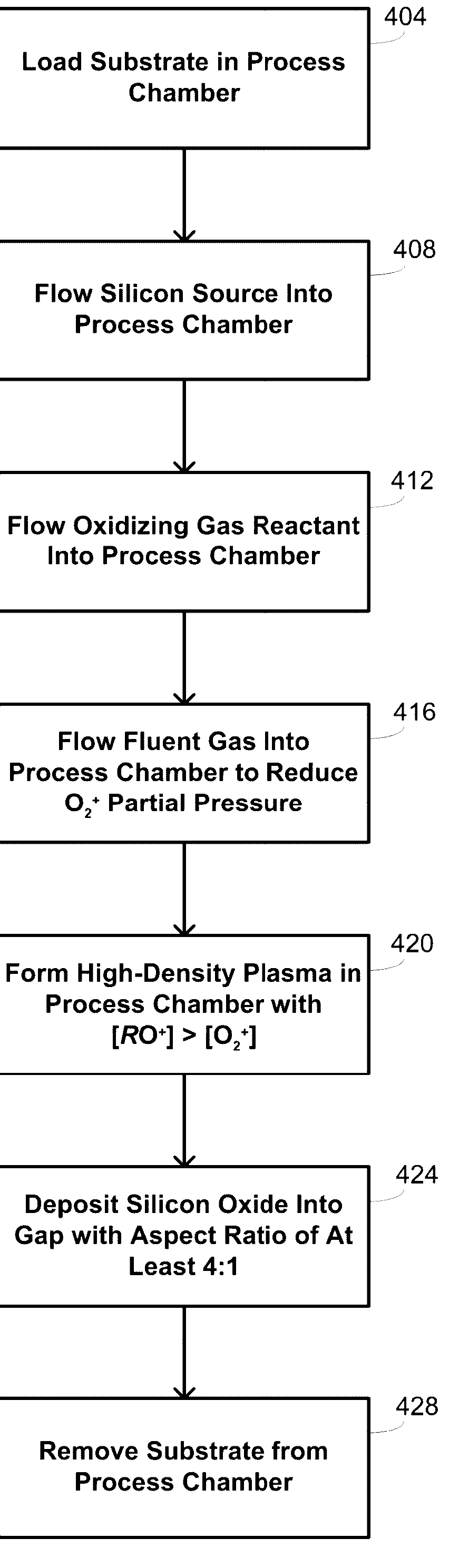

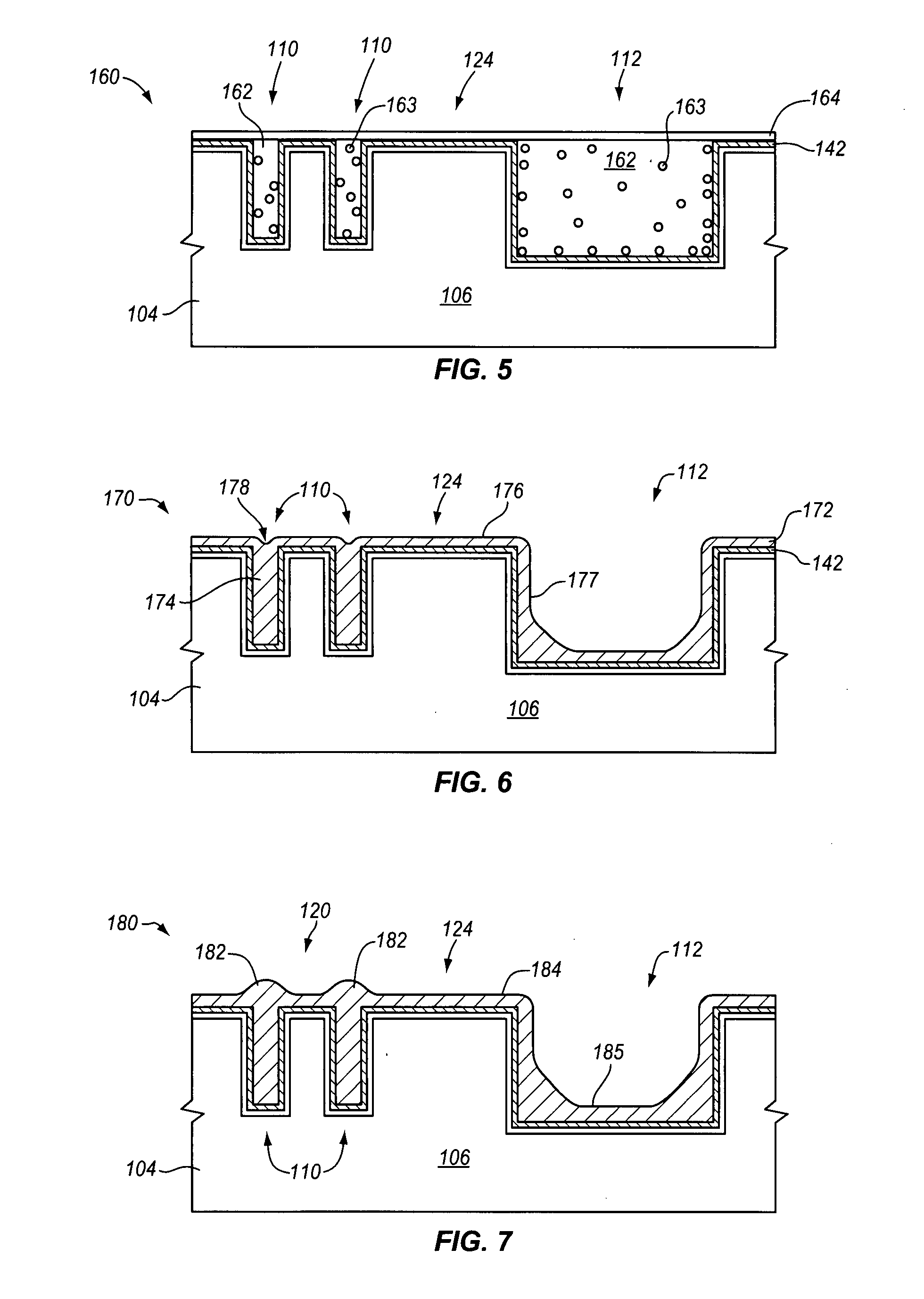

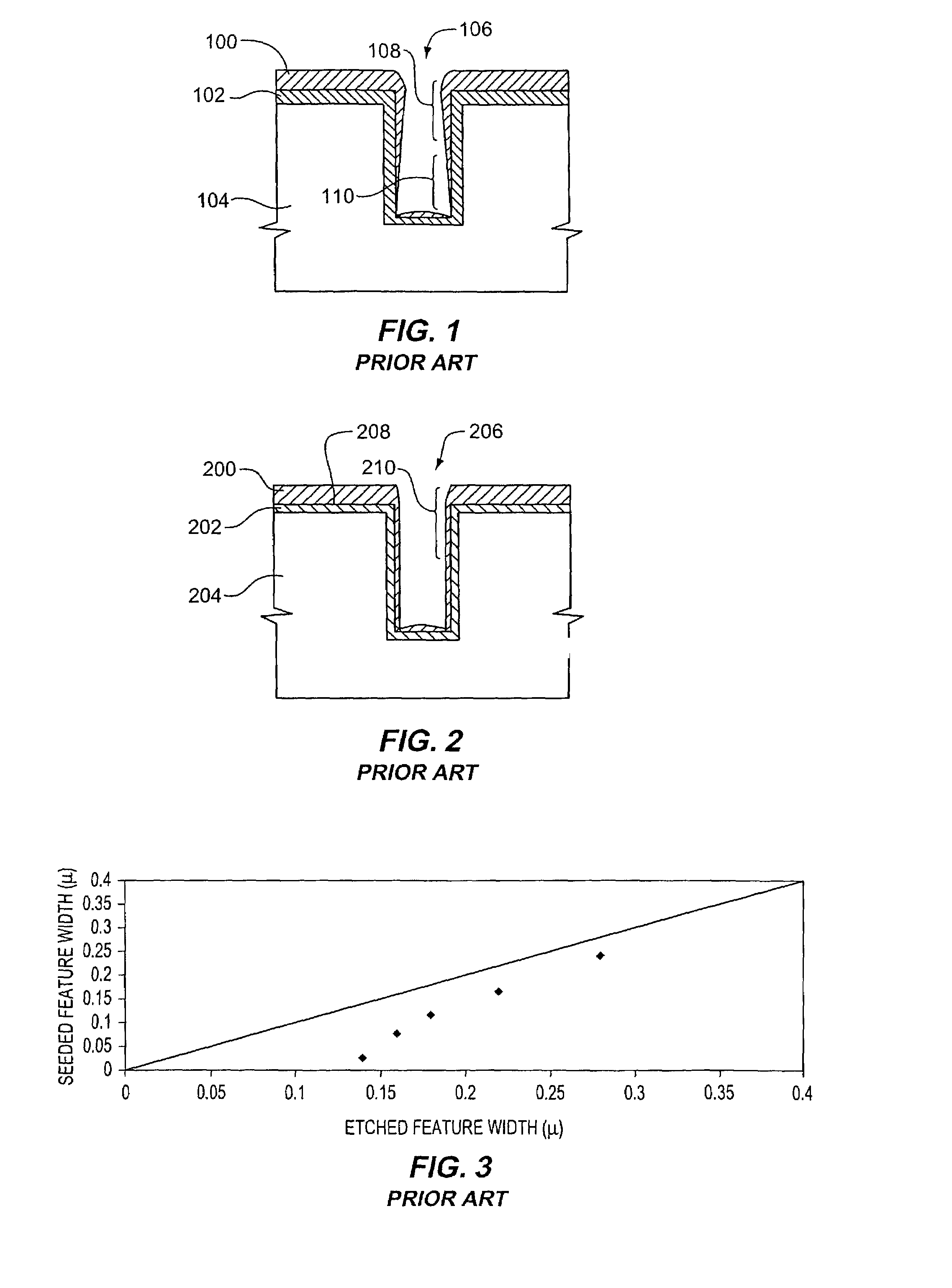

Hdp-cvd multistep gapfill process

InactiveUS20040245091A1Reduce molecular weightReduced sputtering characteristicVacuum evaporation coatingSputtering coatingProduct gasChemistry

Abstract of the Disclosure A gapfill process is provided using cycling of HDP-CVD deposition, etching, and deposition step. The fluent gas during the first deposition step includes an inert gas such as He, but includes H2 during the remainder deposition step. The higher average molecular weight of the fluent gas during the first deposition step provides some cusping over structures that define the gap to protect them during the etching step. The lower average molecular weight of the fluent gas during the remainder deposition step has reduced sputtering characteristics and is effective at filling the remainder of the gap.

Owner:APPLIED MATERIALS INC

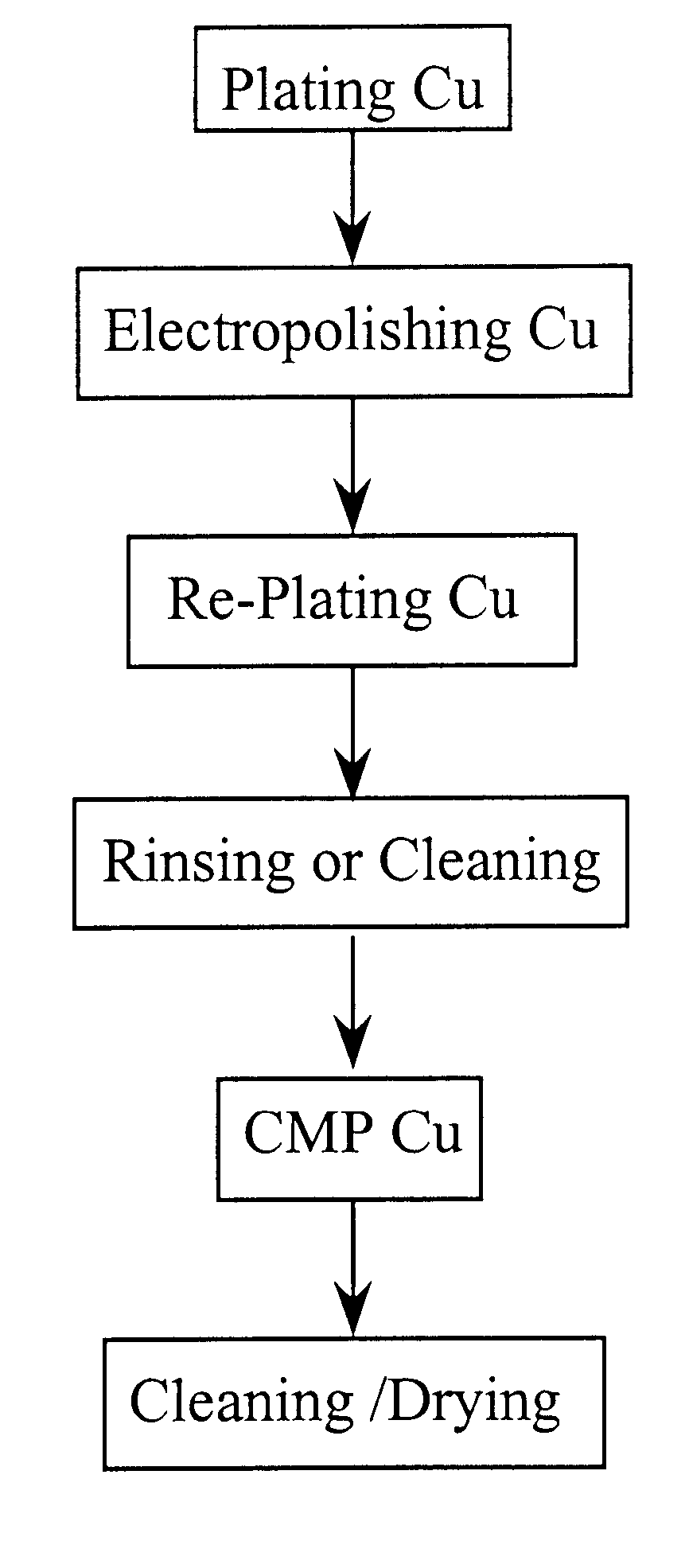

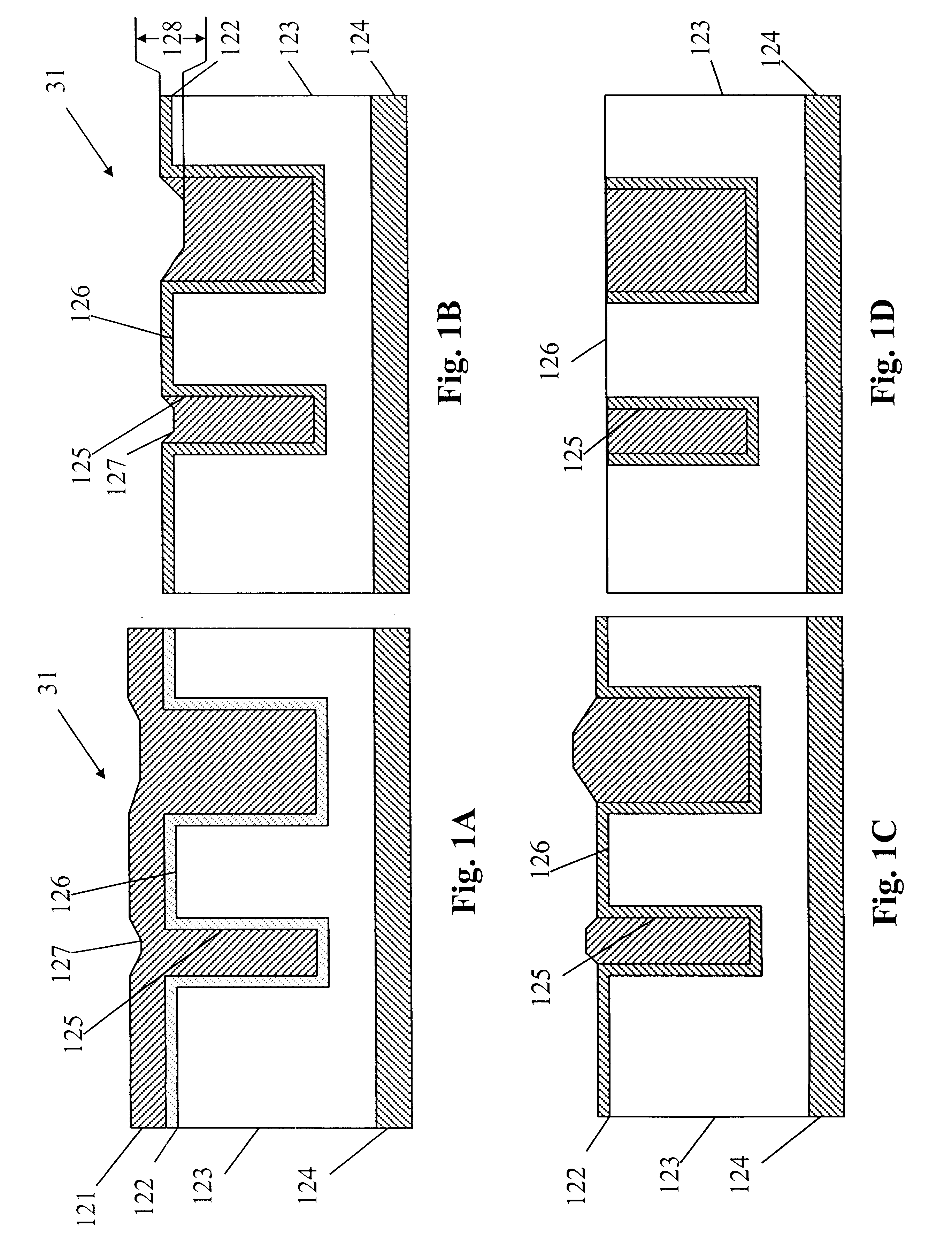

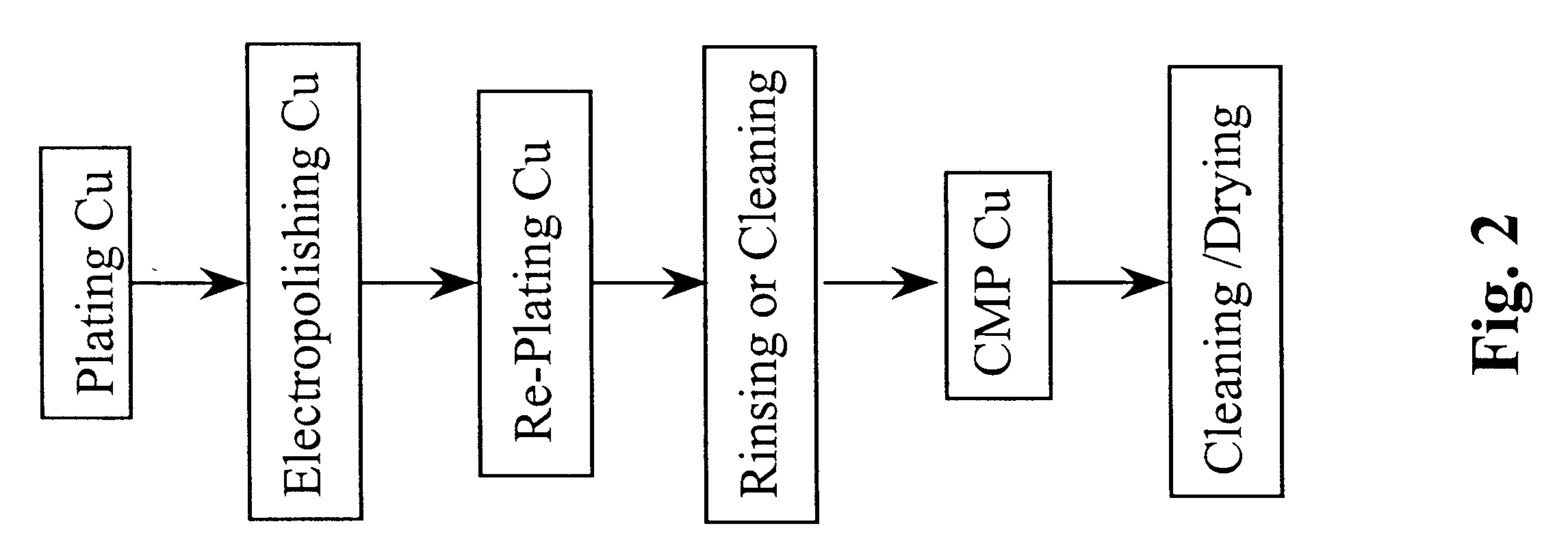

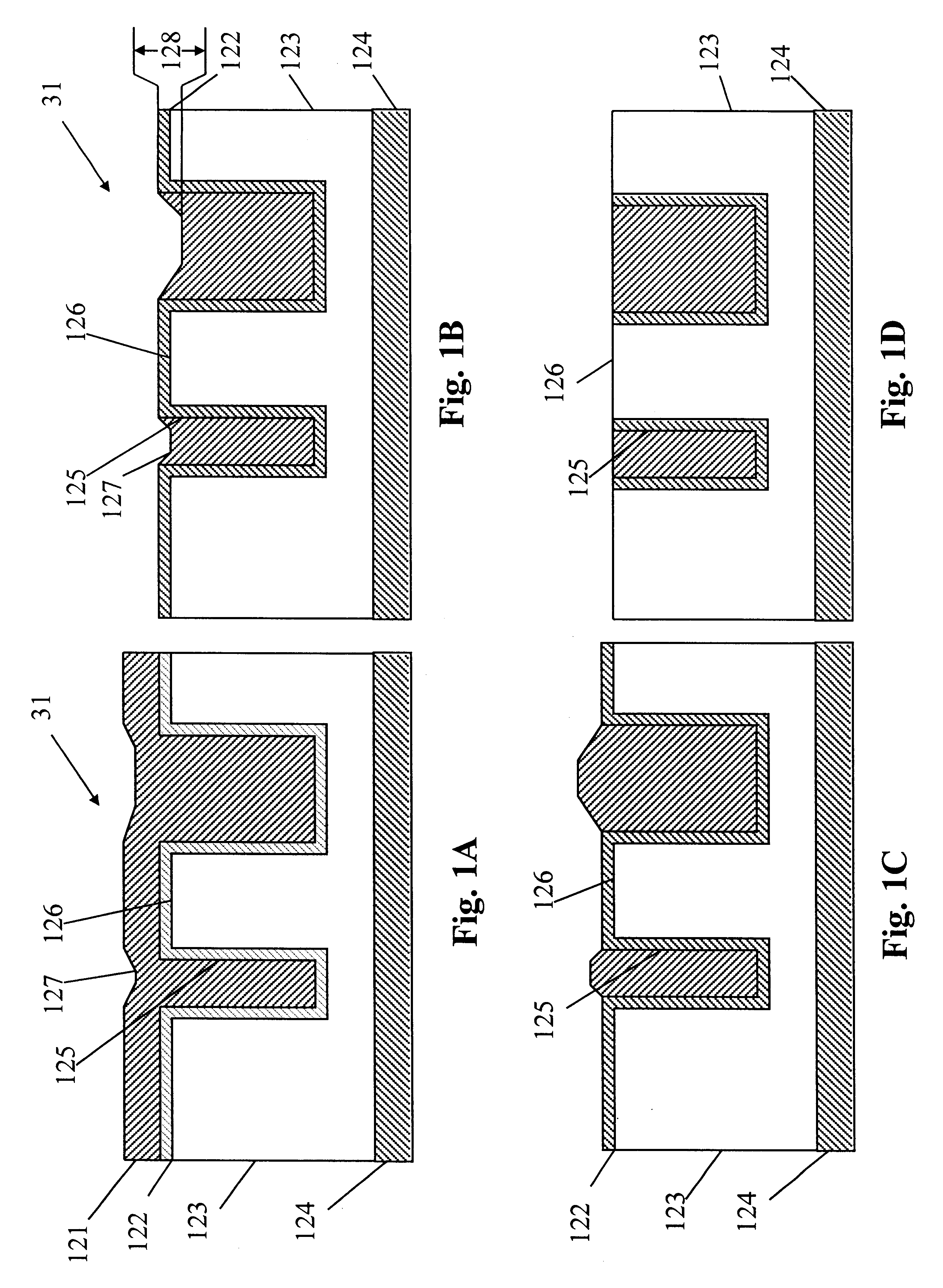

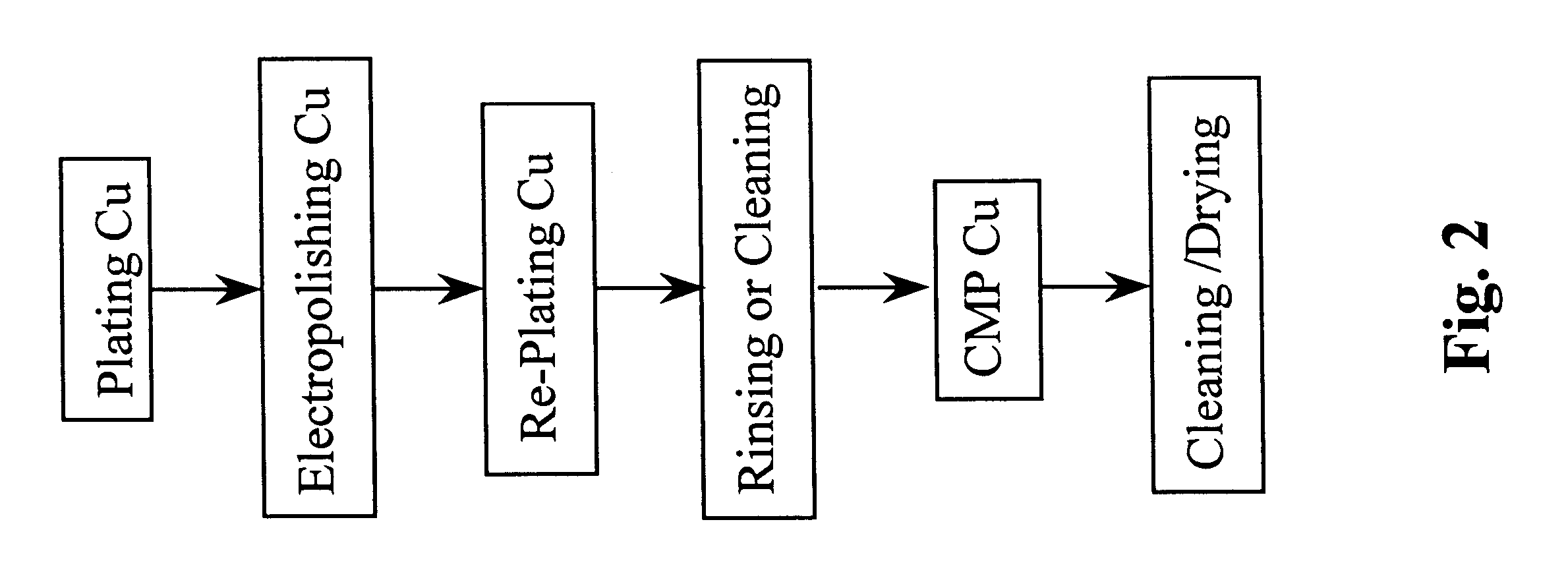

Method for electropolishing metal on semiconductor devices

An electropolishing apparatus for polishing a metal layer formed on a wafer (31) includes an electrolyte (34), a polishing receptacle (100), a wafer chuck (29), a fluid inlet (5, 7, 9), and at least one cathode (1, 2, 3). The wafer chuck (29) holds and positions the wafer (31) within the polishing receptacle (100). The electrolyte (34) is delivered through the fluid inlet (5, 7, 9) into the polishing receptacle (100). The cathode (1, 2, 3) then applies an electropolishing current to the electrolyte to electropolish the wafer (31). In accordance with one aspect of the present invention, discrete portions of the wafer (31) can be electropolished to enhance the uniformity of the electropolished wafer.

Owner:ACM RES

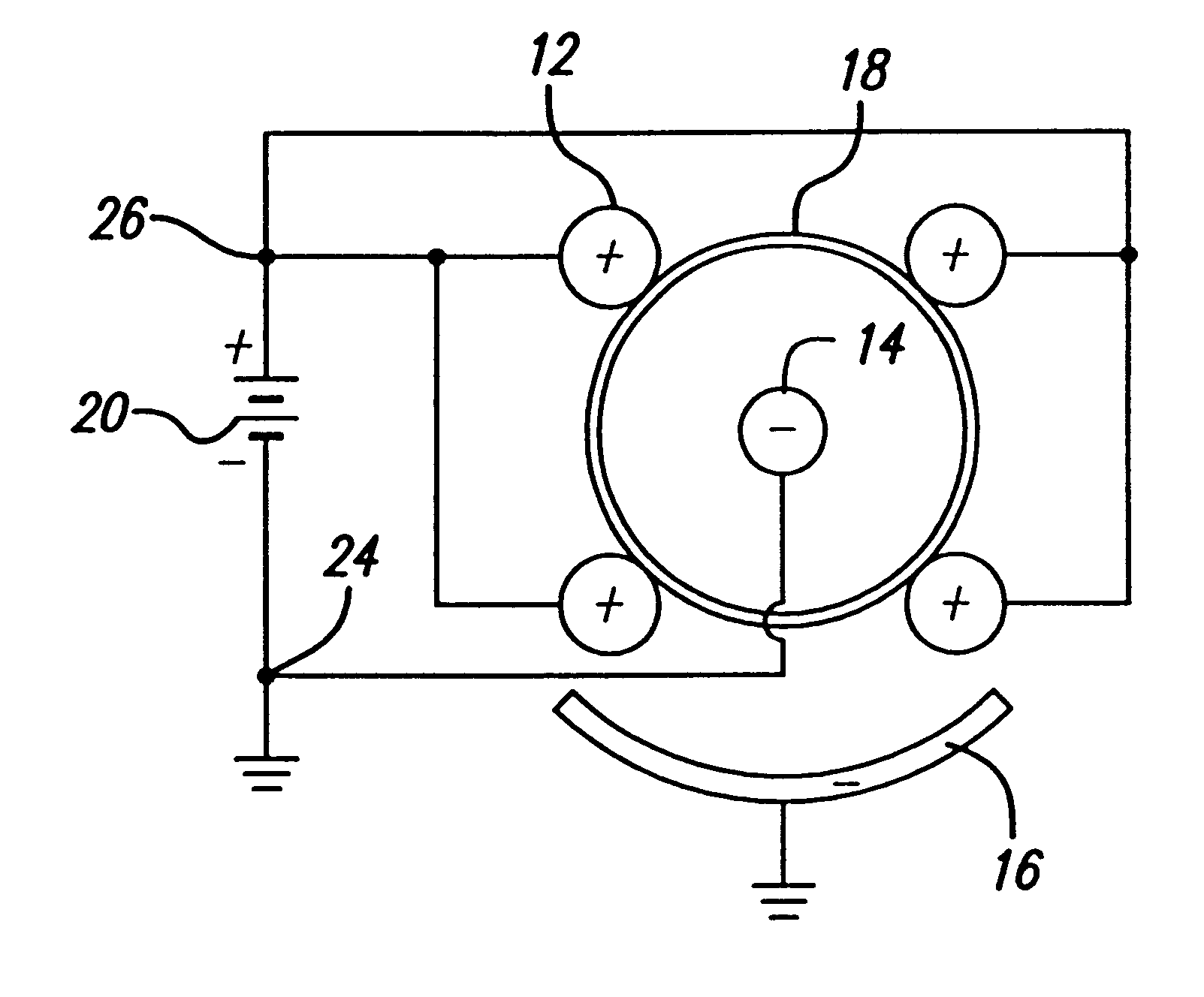

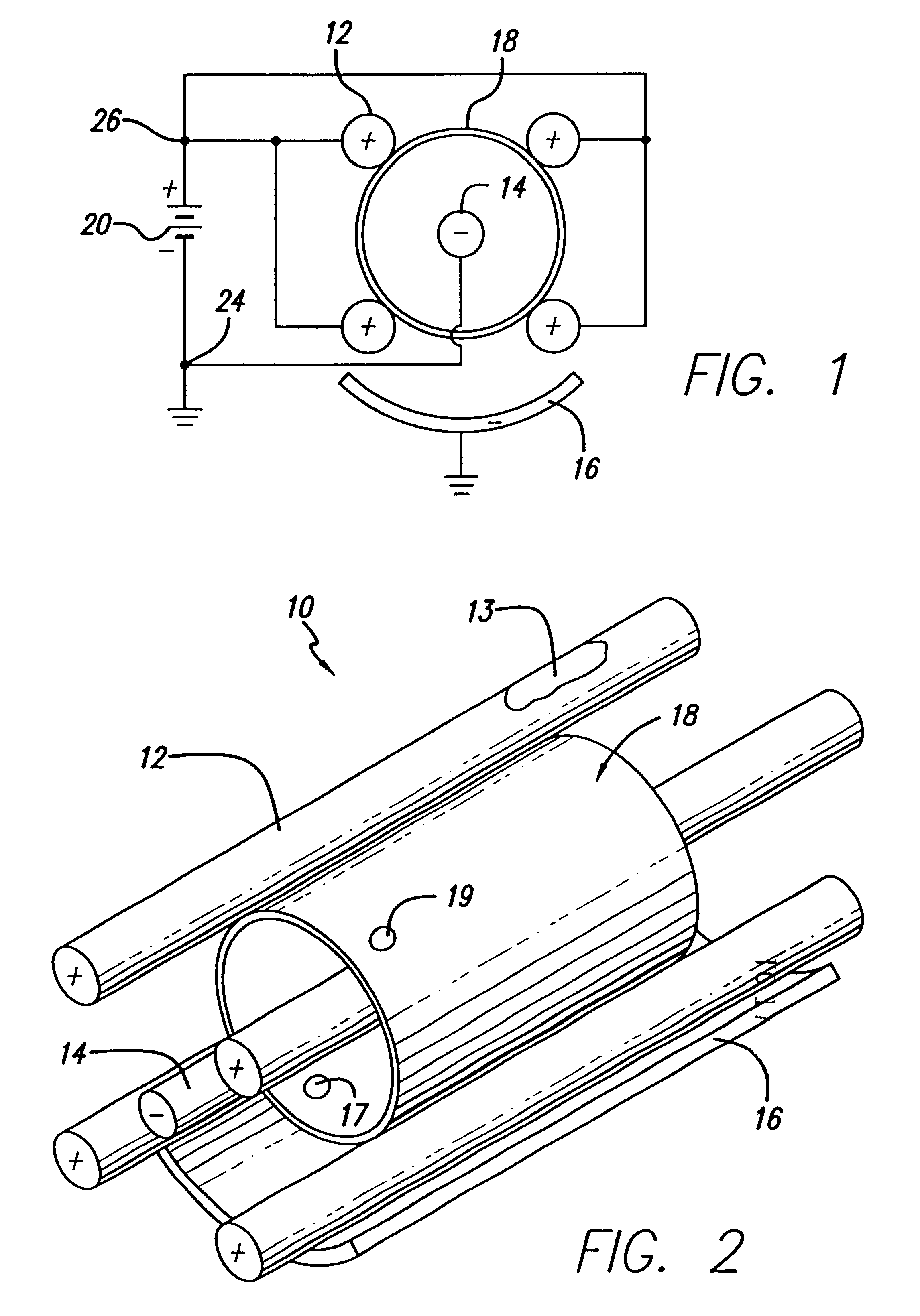

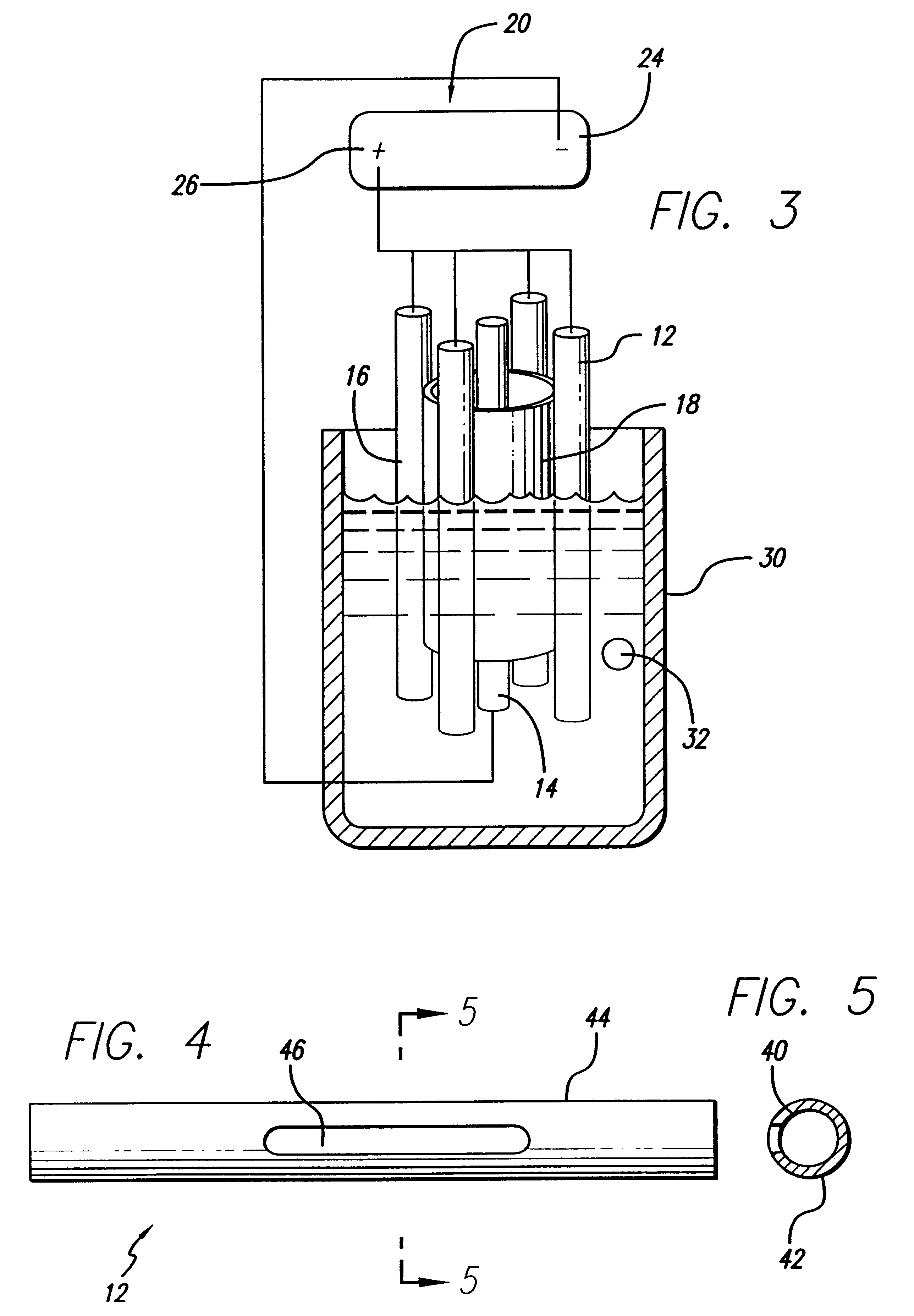

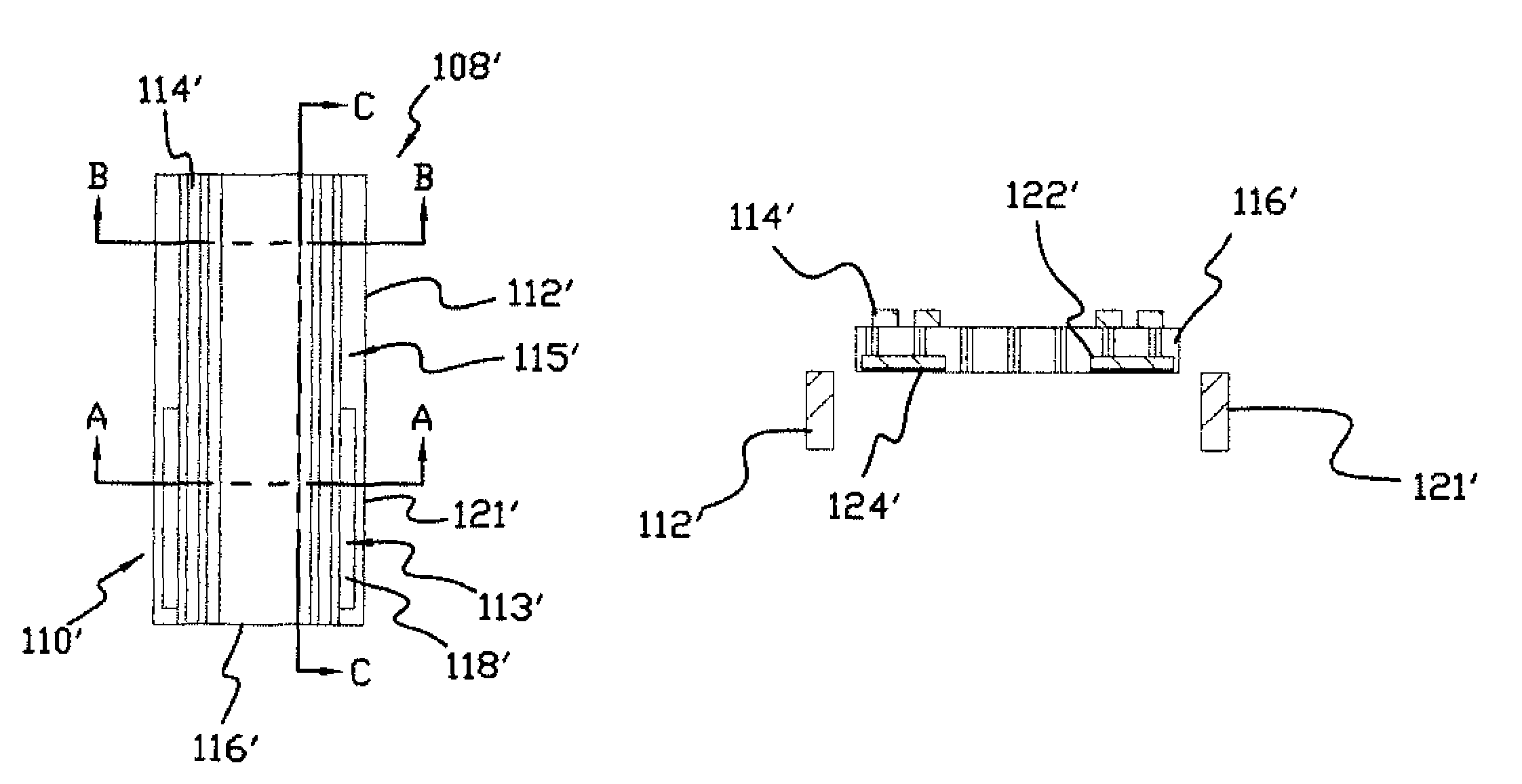

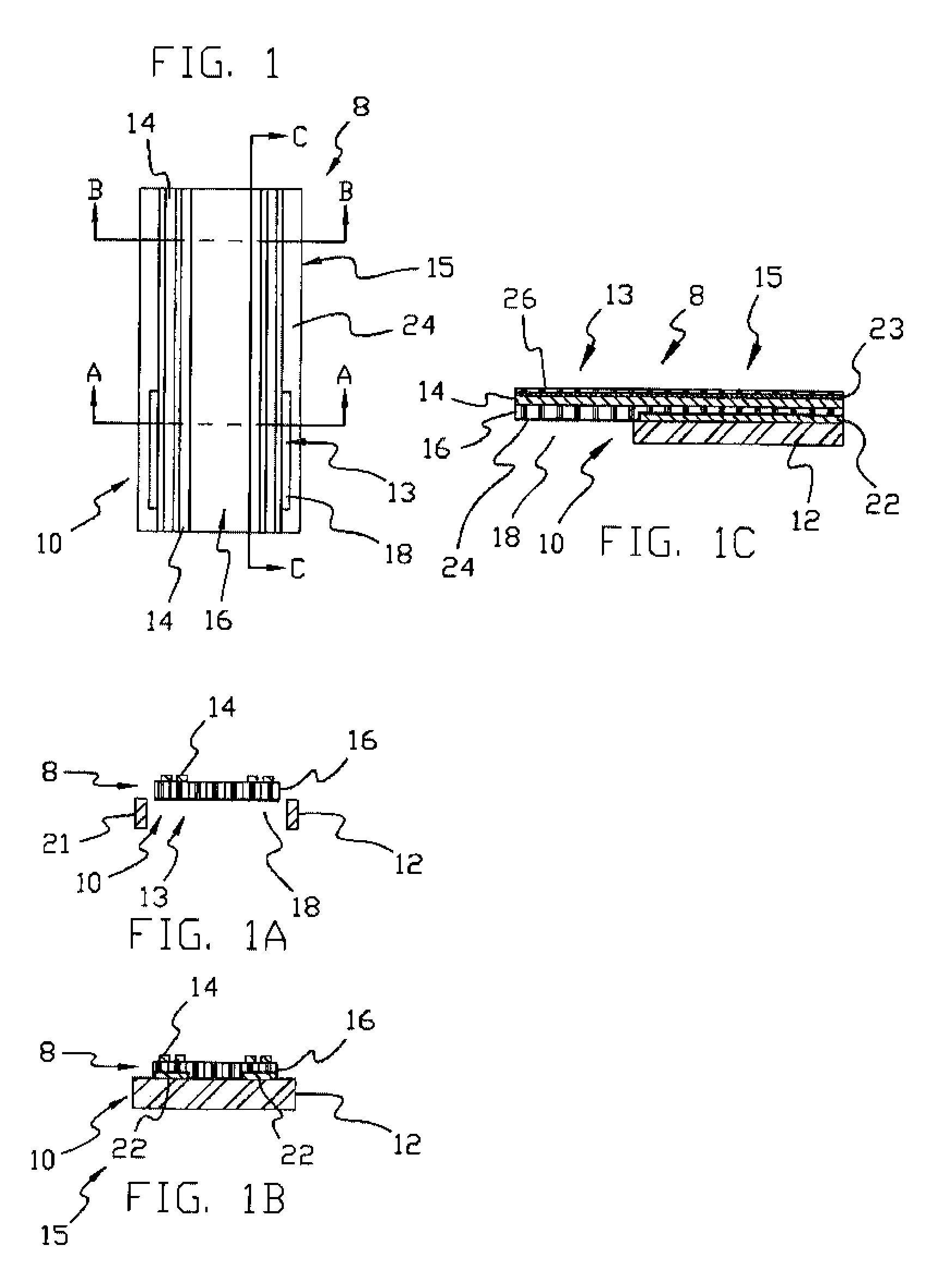

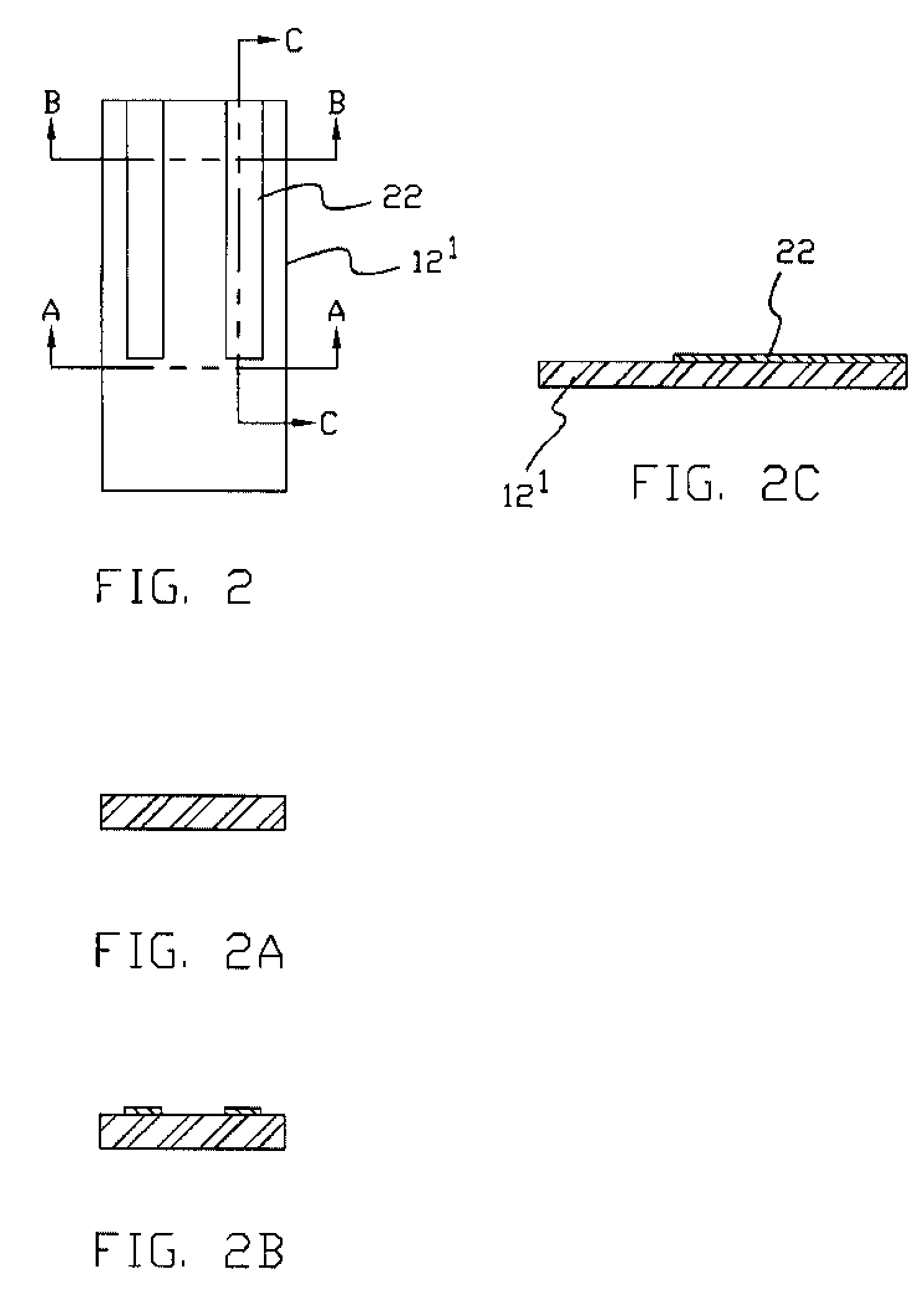

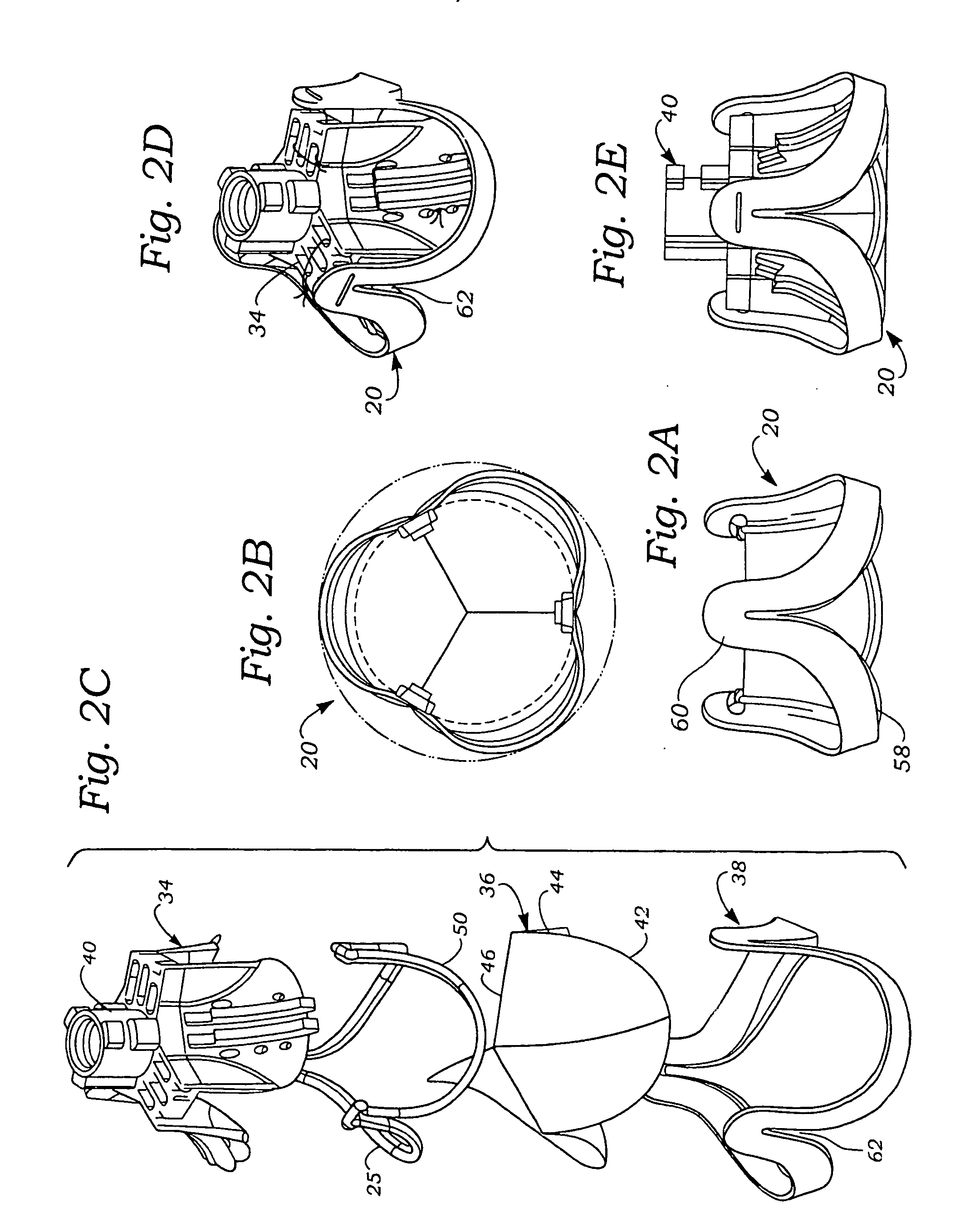

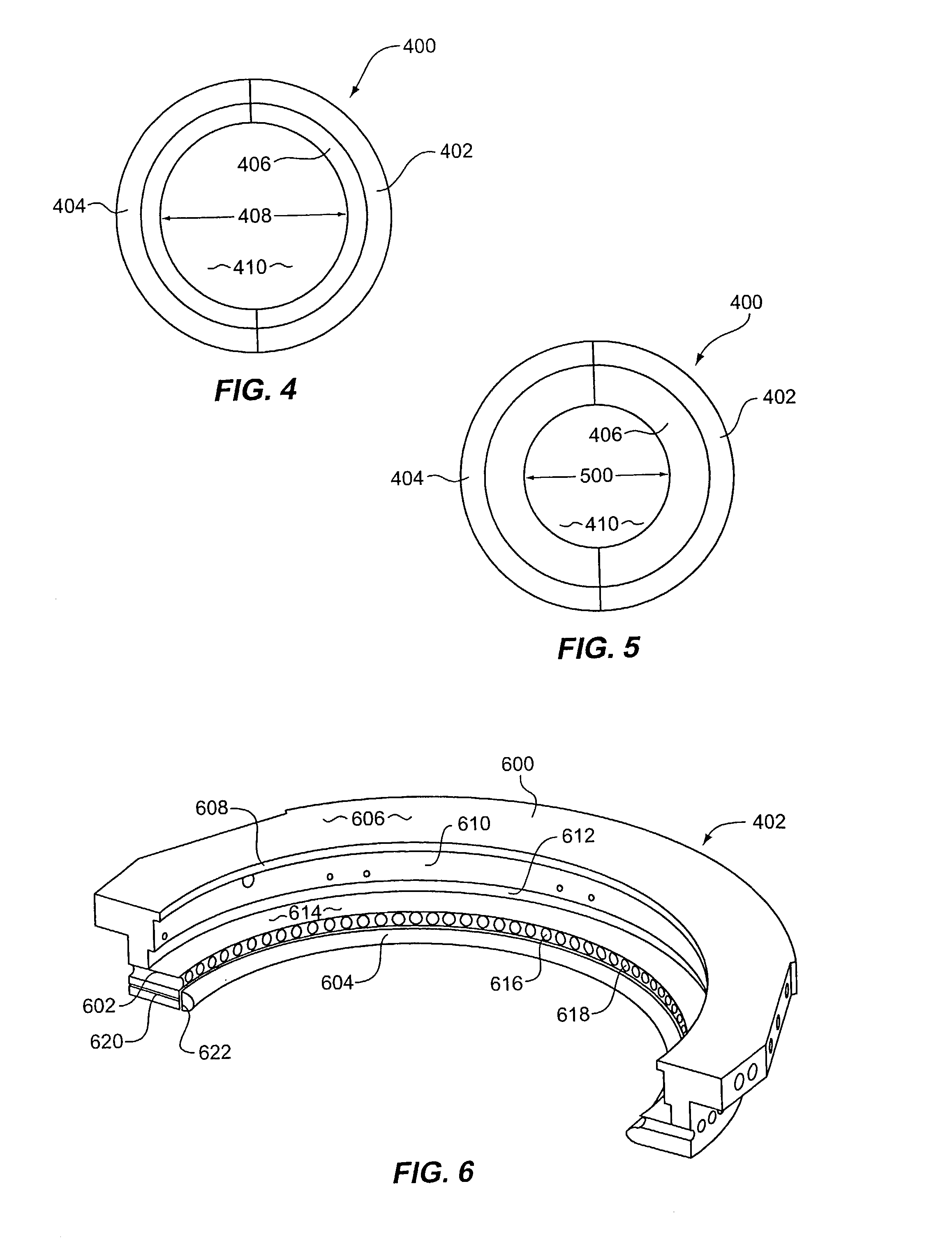

Electro-polishing fixture and electrolyte solution for polishing stents and method

An electro-polishing fixture for polishing stents which incorporates multiple anodes in contact with the stent and a center cathode disposed coaxially within the interior of the stent and a curved exterior cathode disposed about the perimeter of the stent. The invention further includes an electrolyte solution adapted for polishing stents composed of nickel-titanium alloy and a method of using the electrolyte in combination with the electro-polishing fixture.

Owner:ABBOTT CARDIOVASCULAR

Nanowire-based transparent conductors and applications thereof

A transparent conductor including a conductive layer coated on a substrate is described. More specifically, the conductive layer comprises a network of nanowires that may be embedded in a matrix. The conductive layer is optically clear, patternable and is suitable as a transparent electrode in visual display devices such as touch screens, liquid crystal displays, plasma display panels and the like.

Owner:CHAMP GREAT INTL

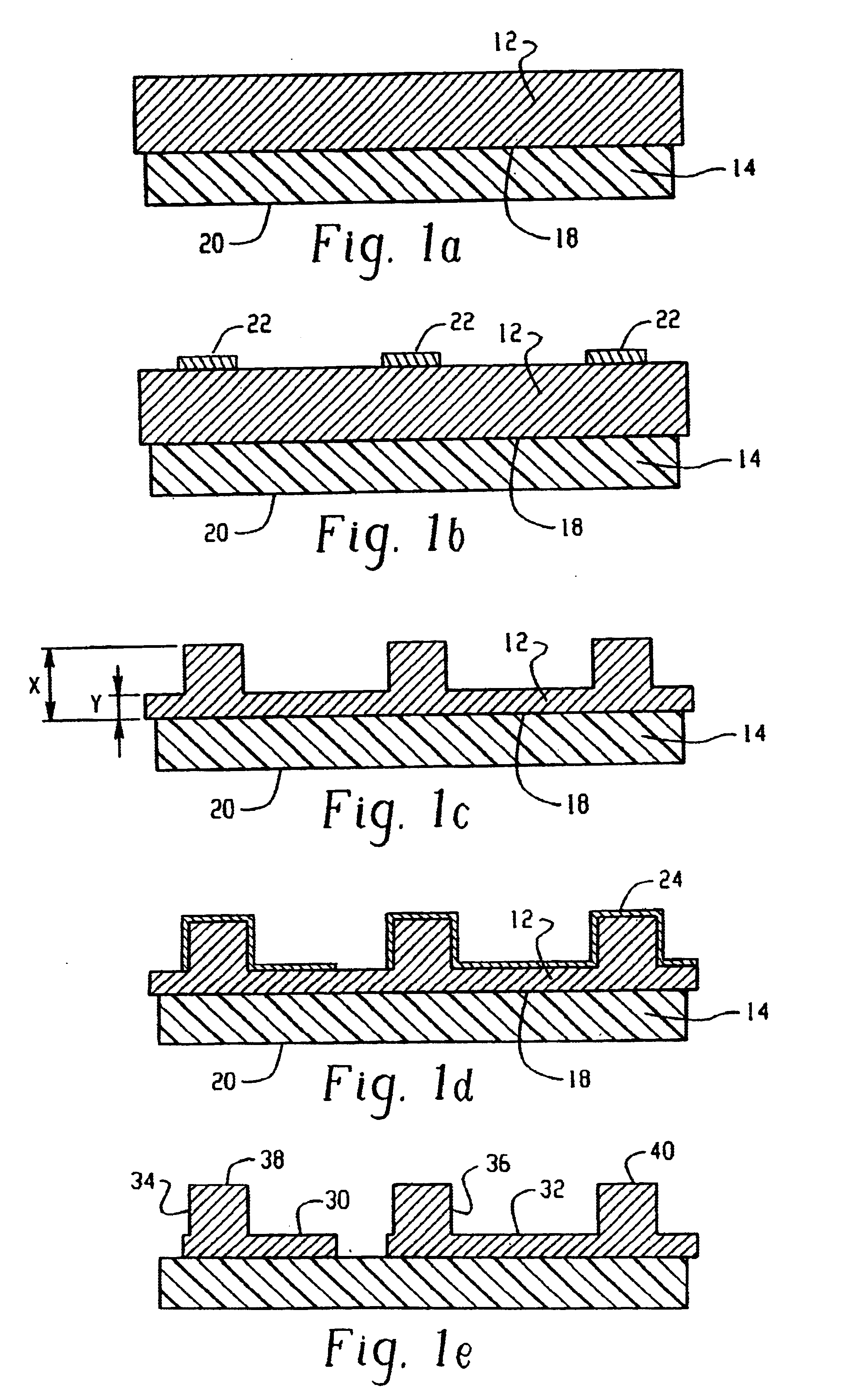

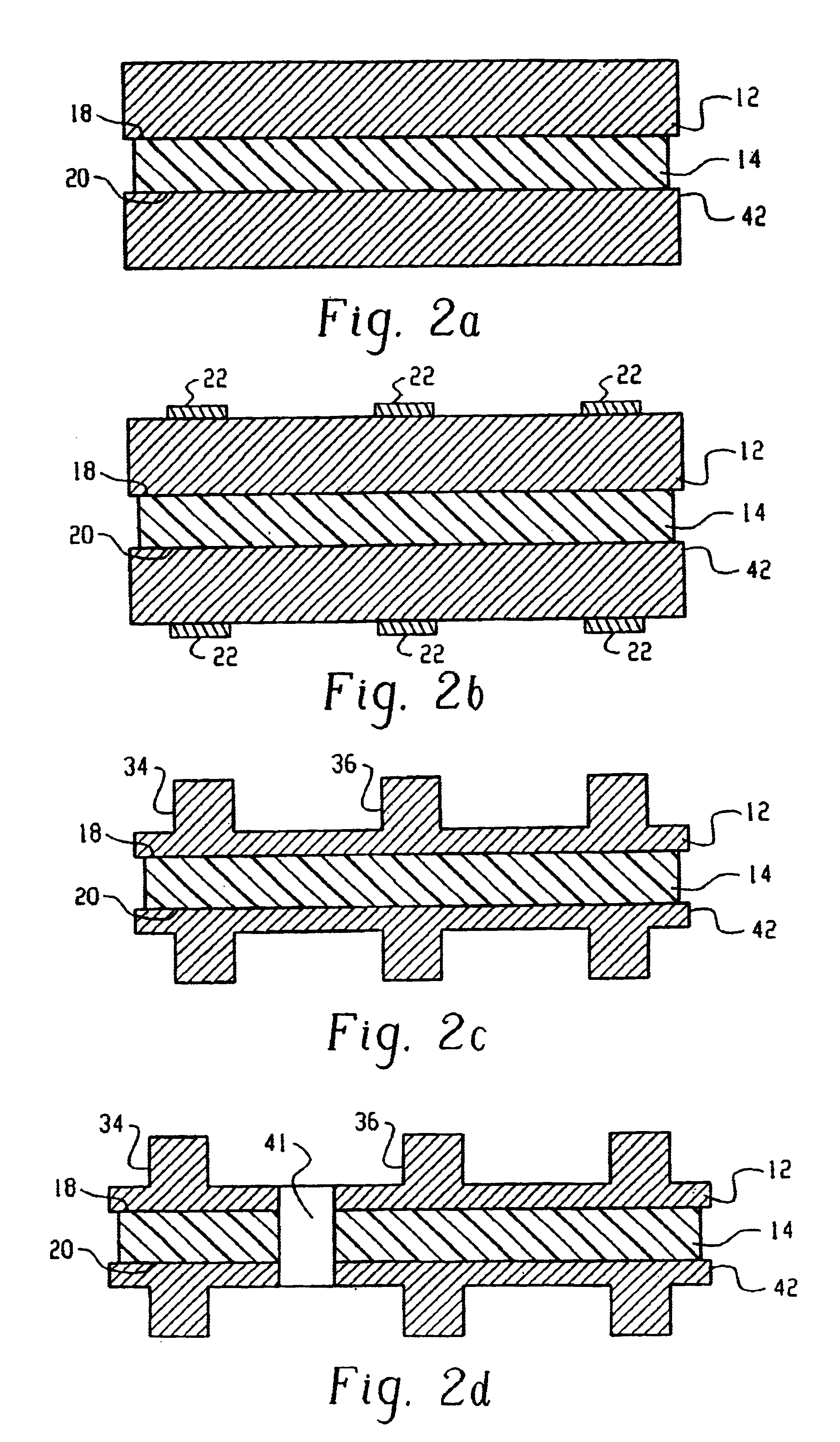

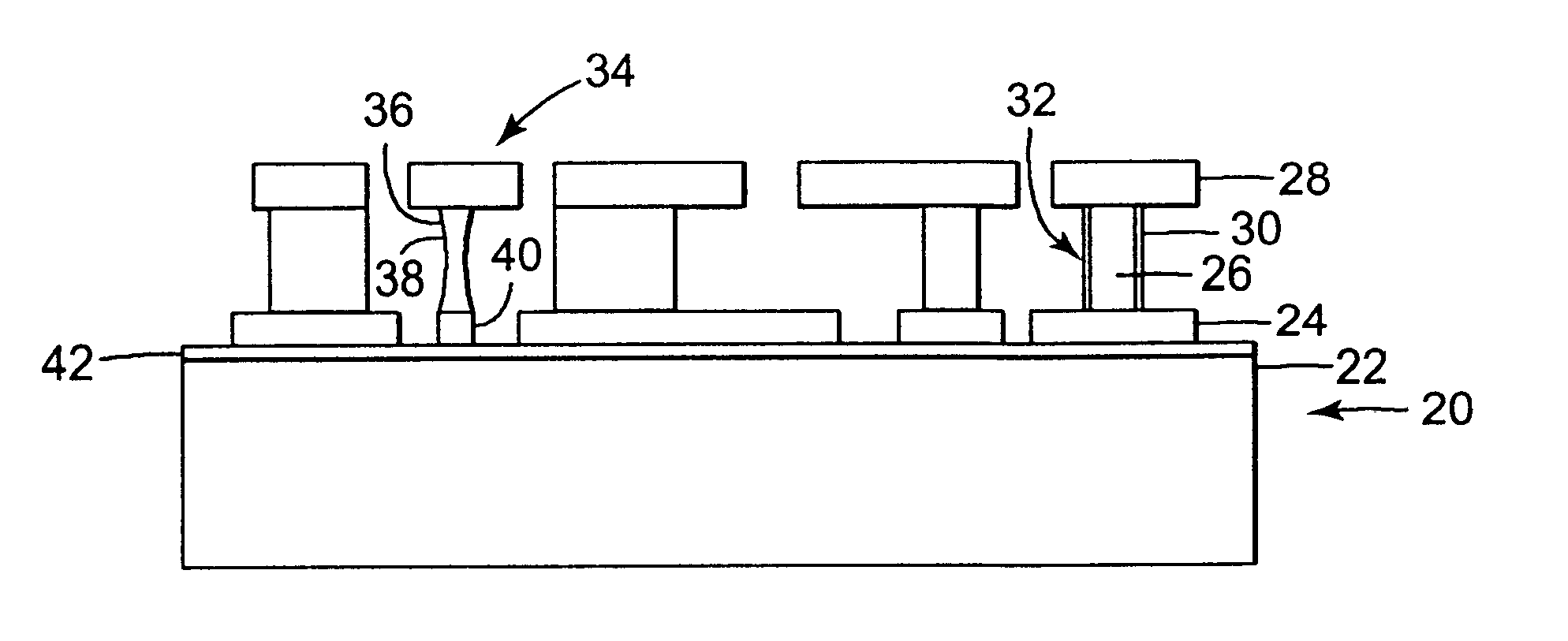

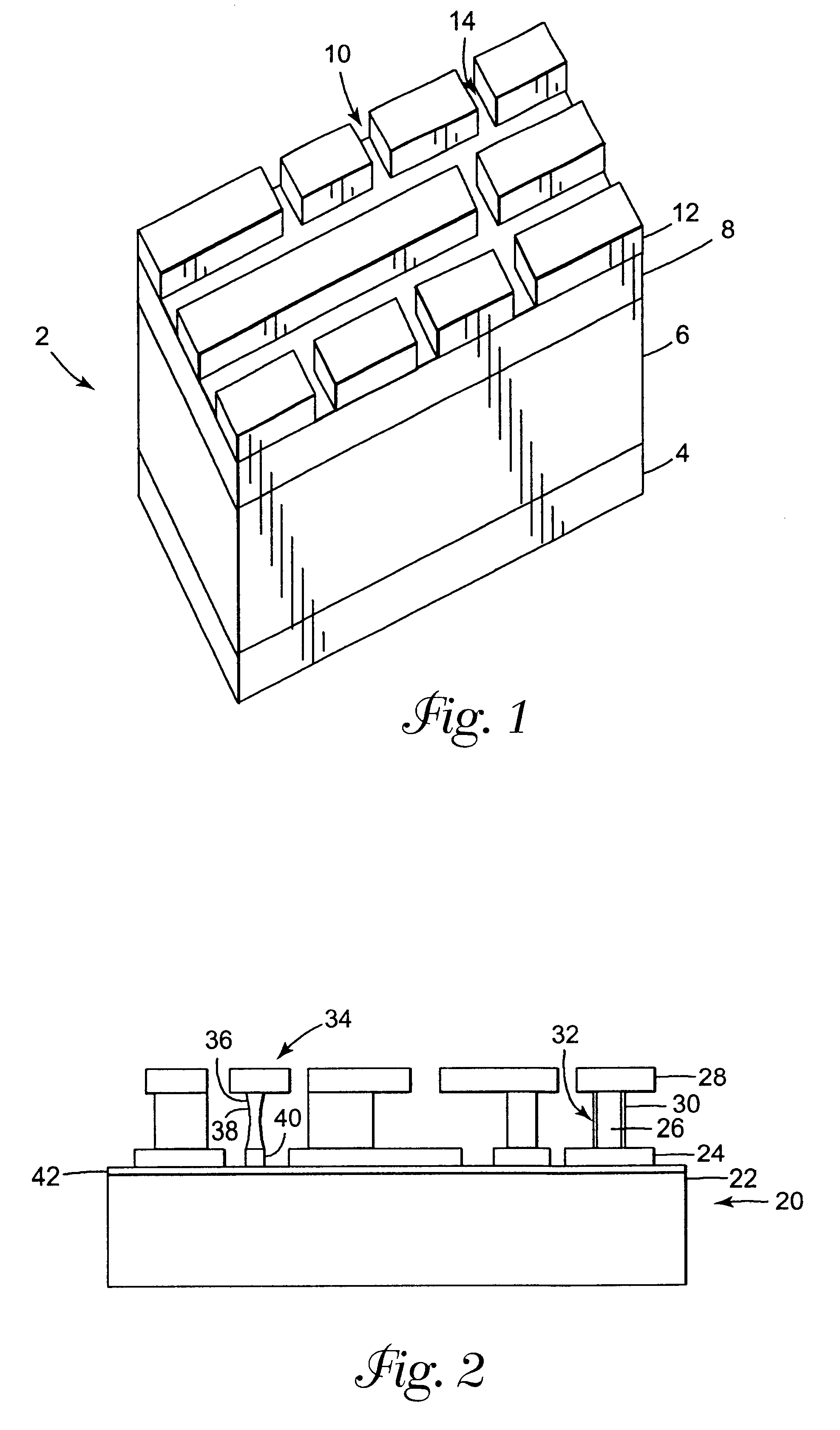

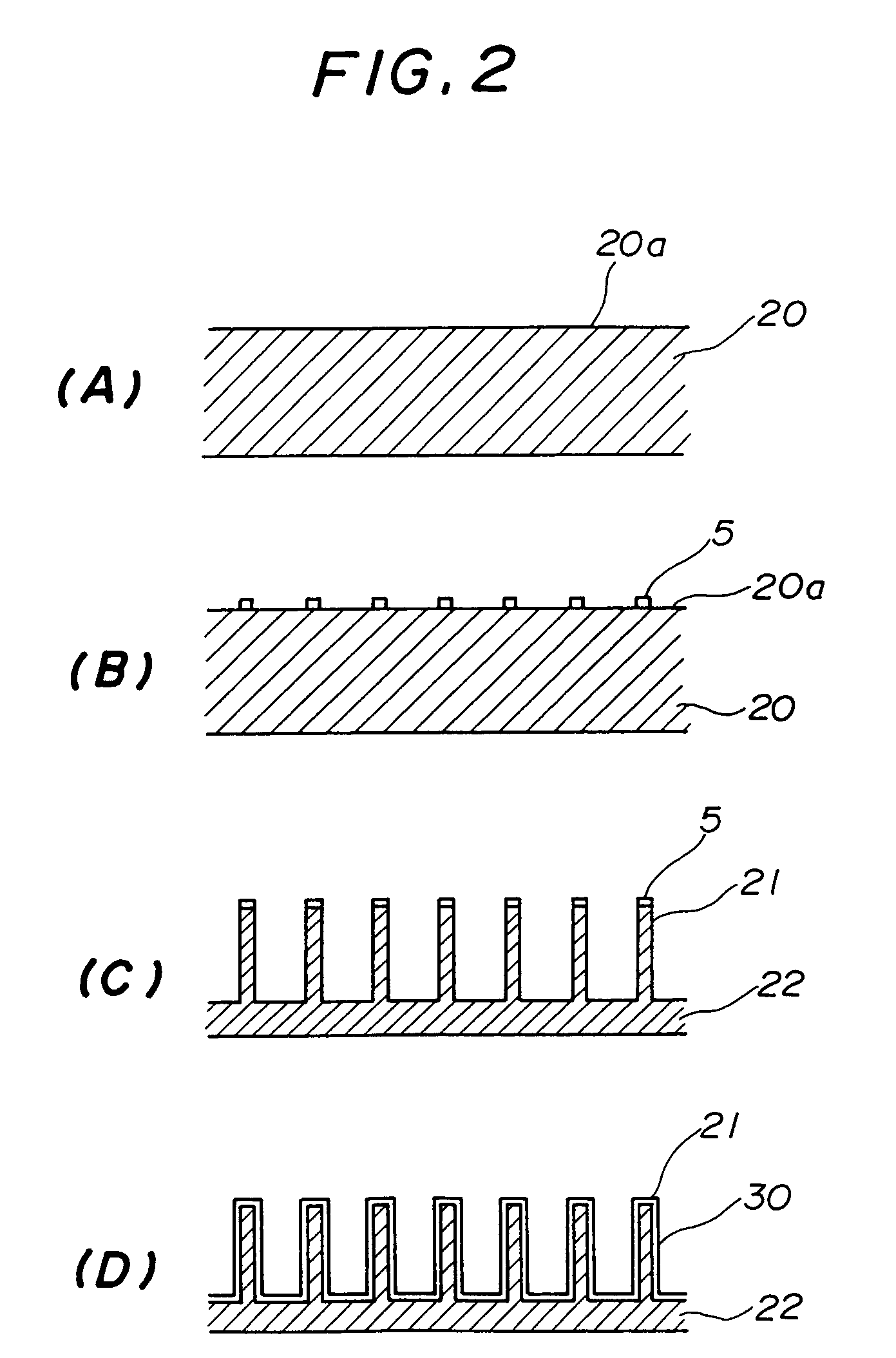

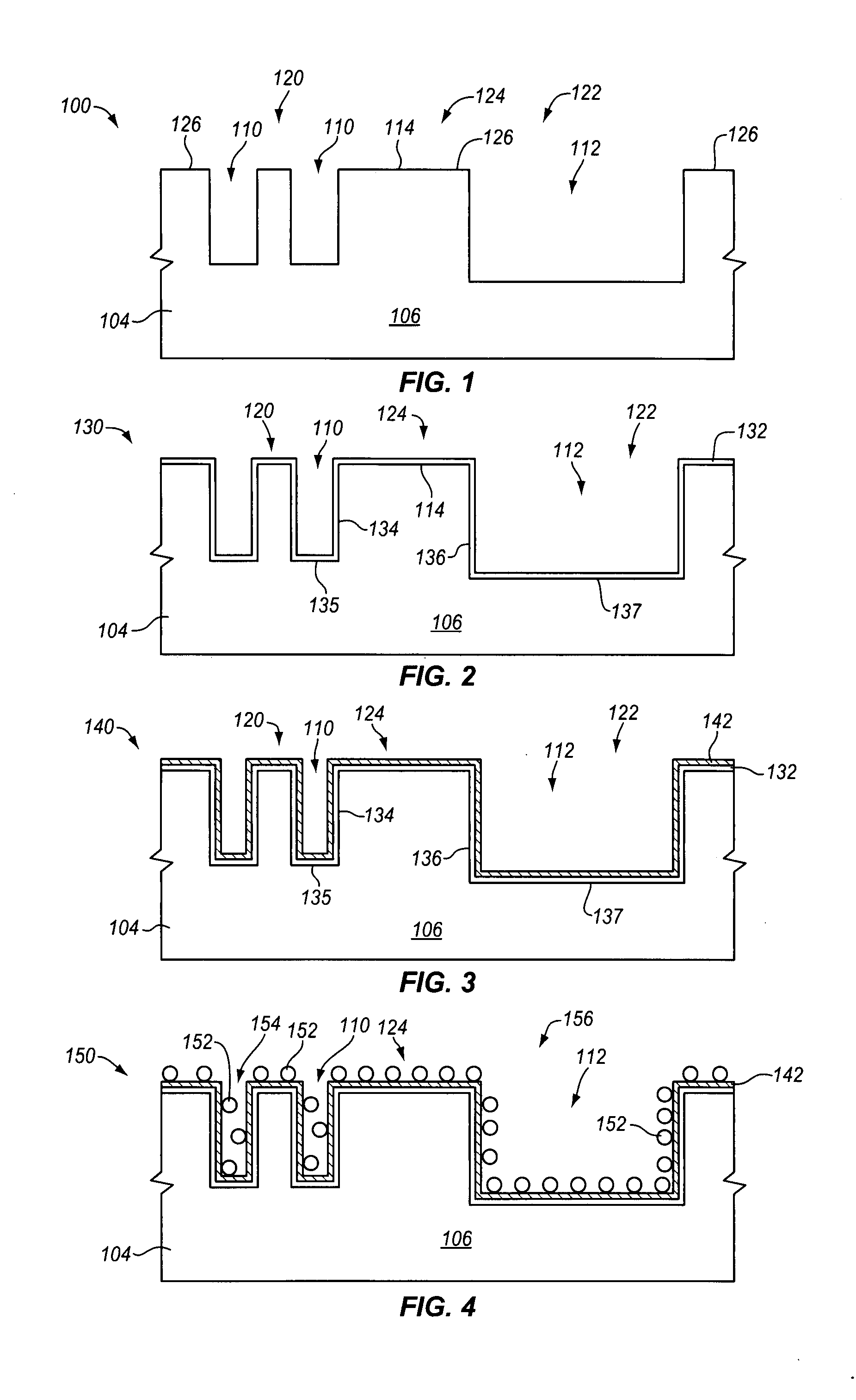

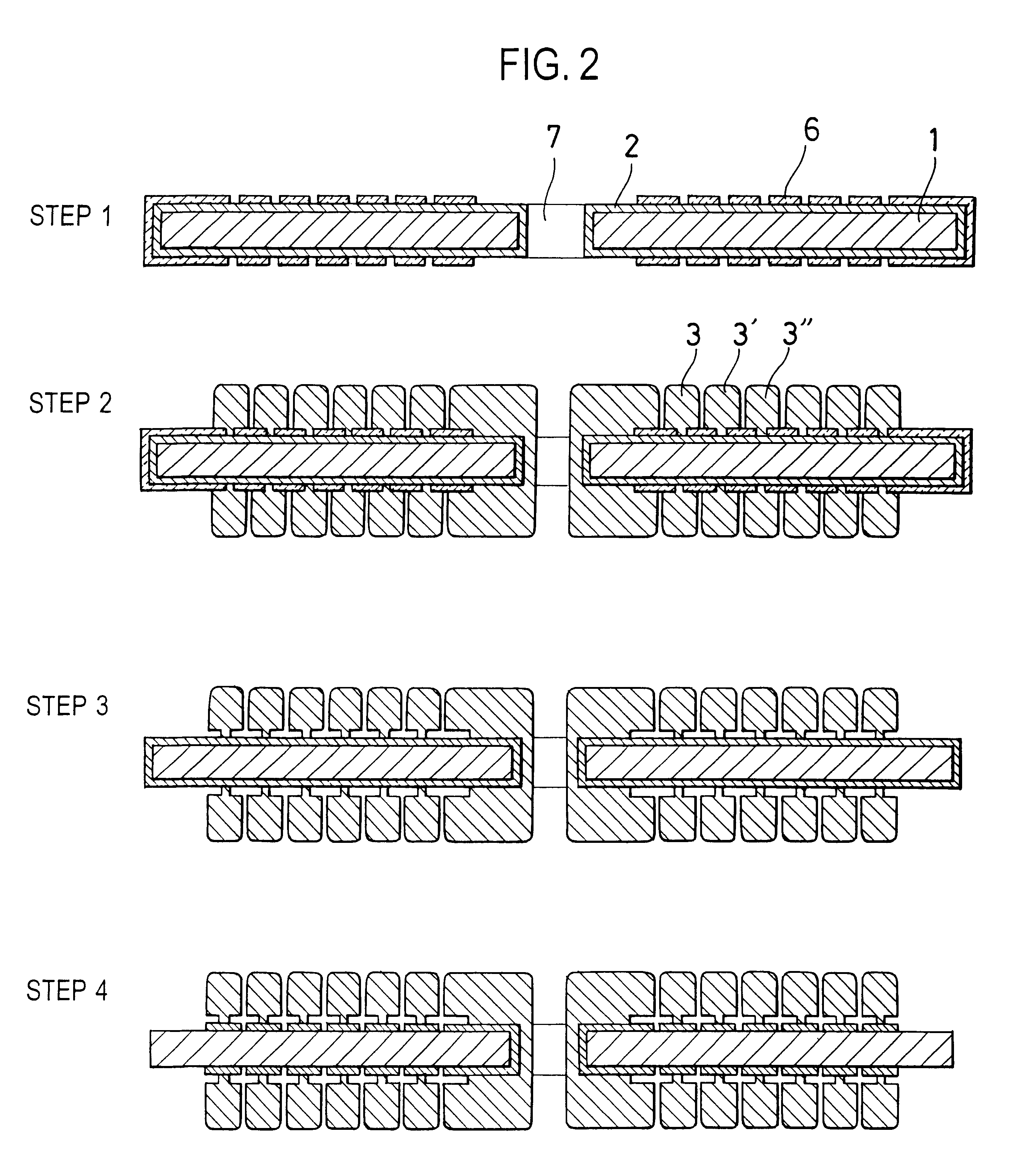

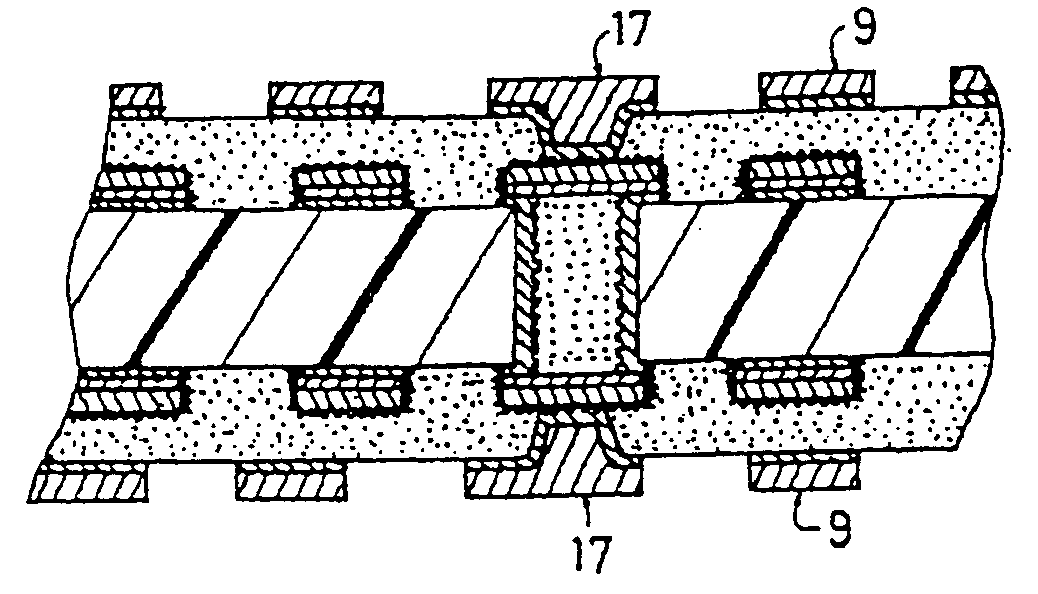

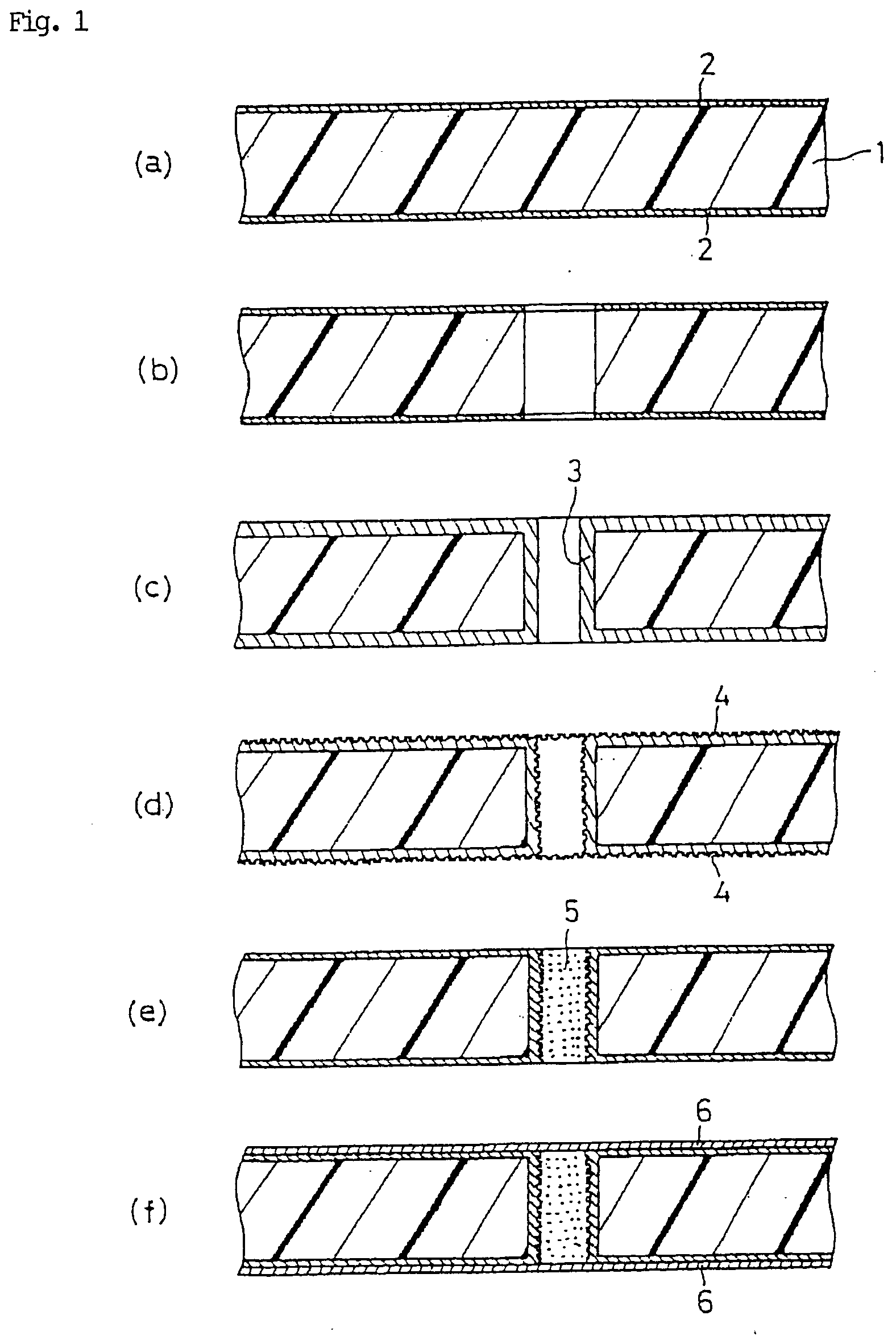

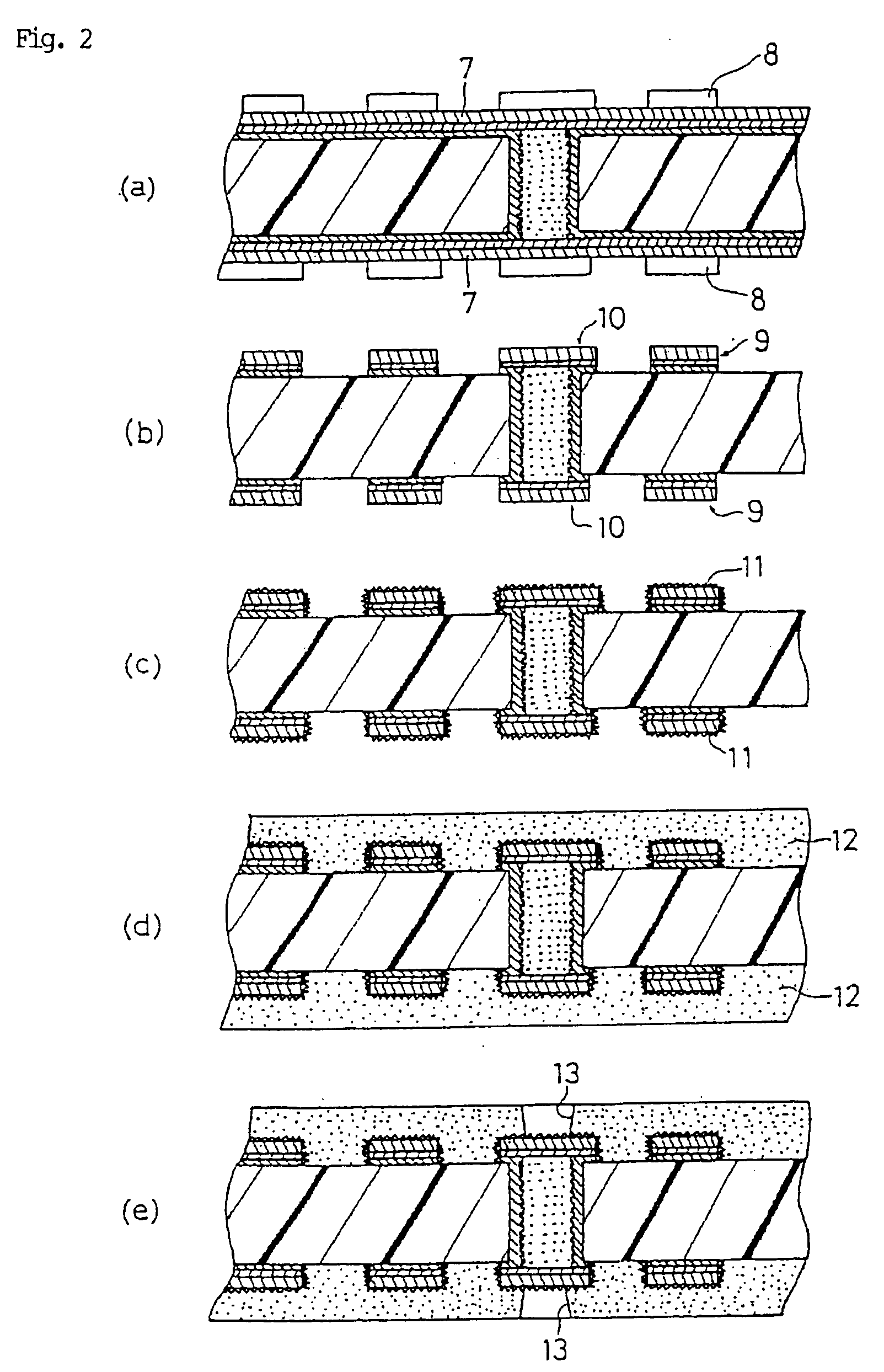

Manufacturing methods for printed circuit boards

InactiveUS6902869B2Improve rigidityEasy to handleLine/current collector detailsWave amplification devicesDielectric substratePhotoresist

A method of forming a plurality of solid conductive bumps for interconnecting two conductive layers of a circuit board with substantially coplanar upper surfaces. The method comprises the steps of applying a continuous homogenous metal layer onto a dielectric substrate, applying a first photoresist and exposing and developing said first photoresist to define a pattern of conductive bumps; etching the metal layer exposed by said development to form said plurality of conductive bumps; removing said first photoresist; applying a second photoresist onto the metal layer; exposing and developing said second photoresist to define a pattern of conductive bumps and circuit lines; etching the metal layer exposed by said development to form a pattern of circuit lines in said metal layer; and removing said second photoresist. The methods of the present invention also provides for fabricating a multilayer circuit board and a metallic border for providing rigidity to a panel.

Owner:GLOBALFOUNDRIES INC

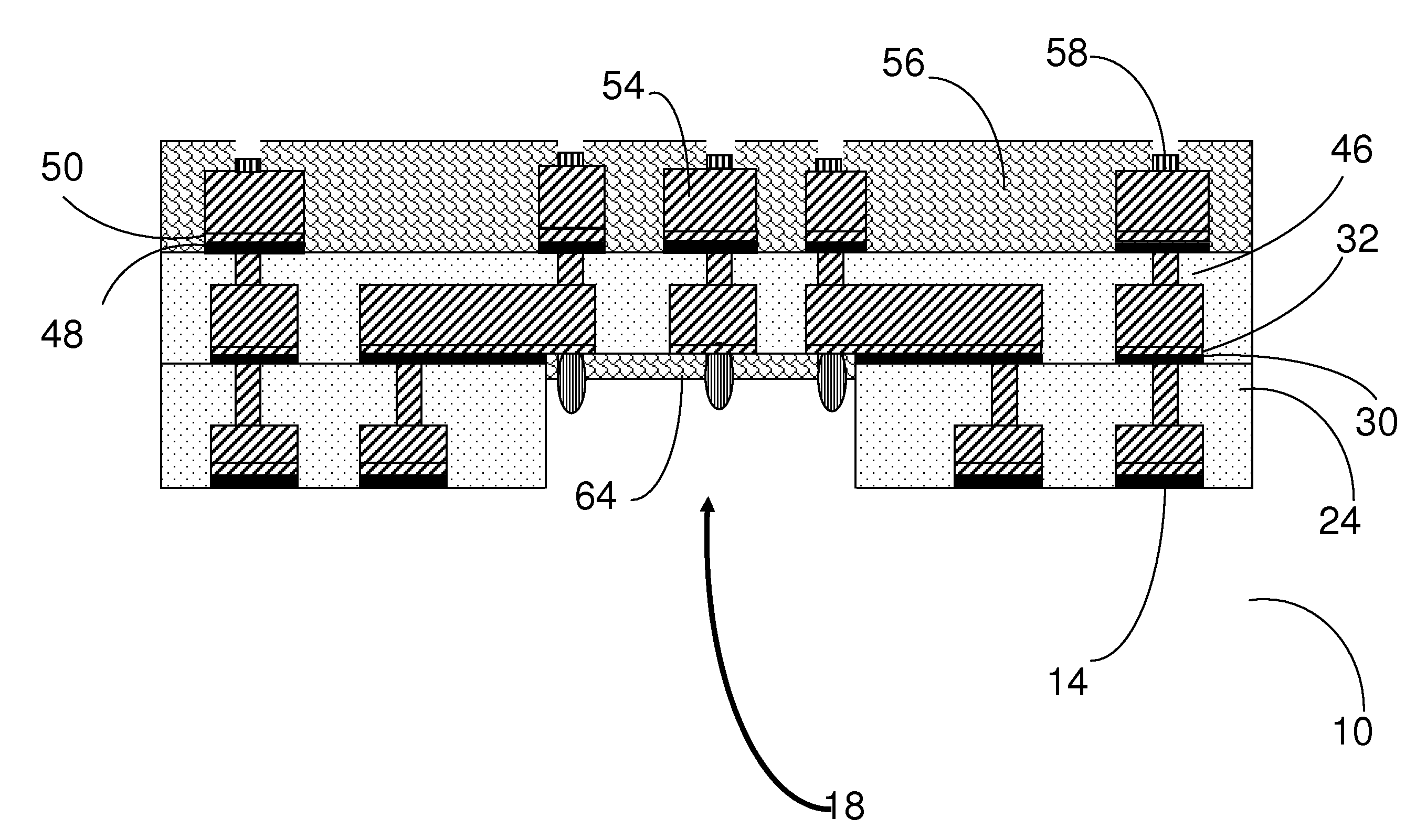

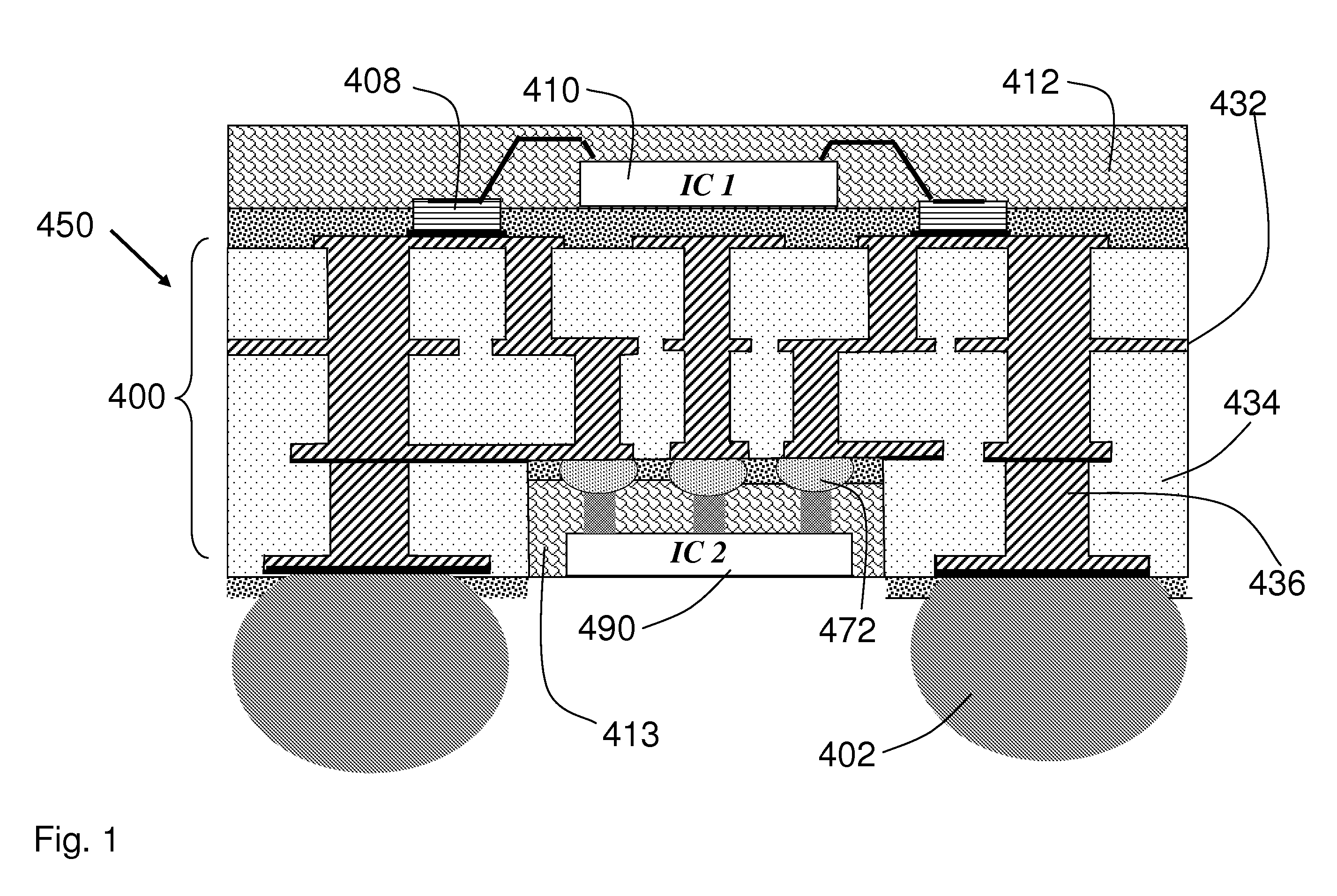

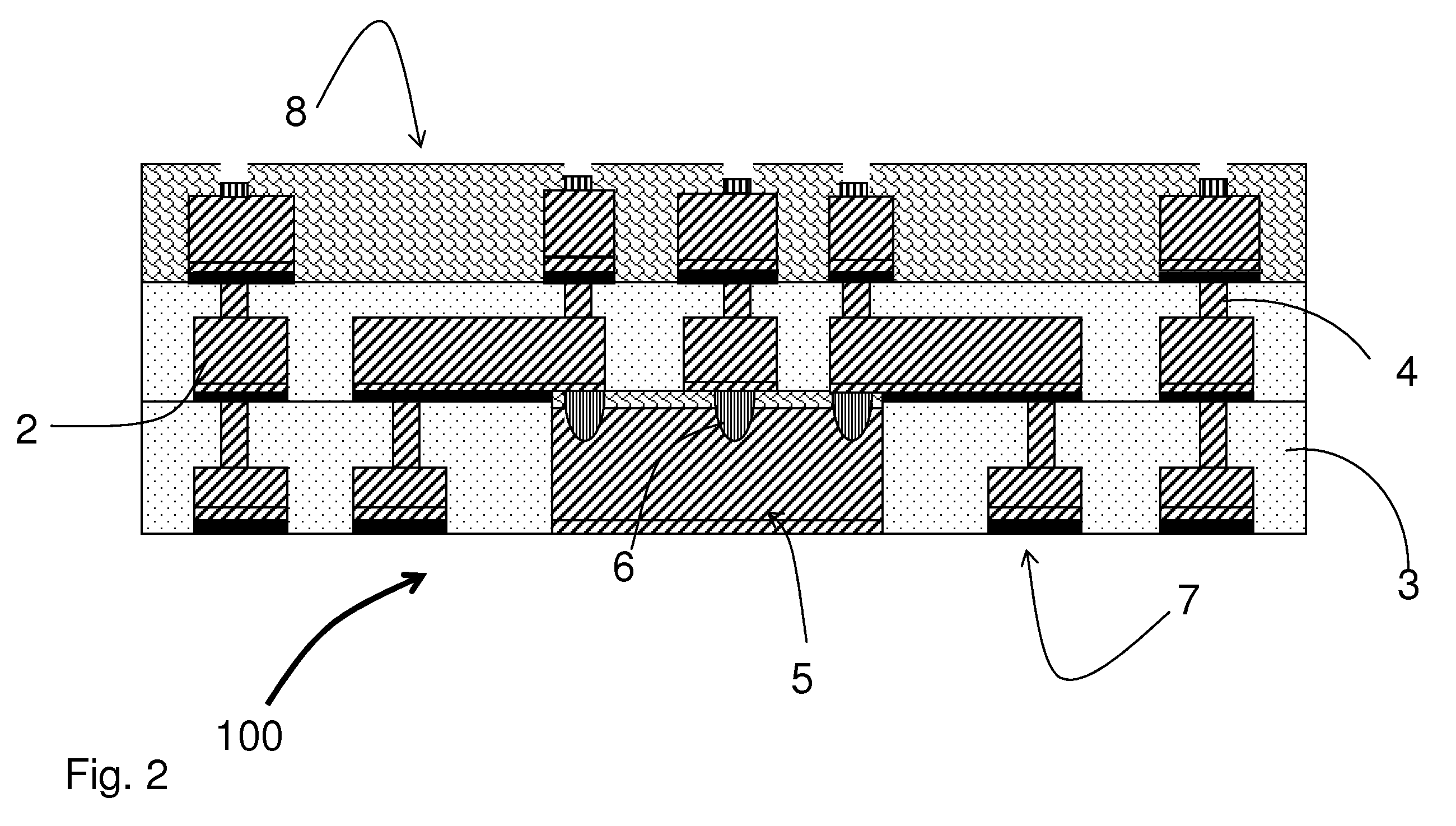

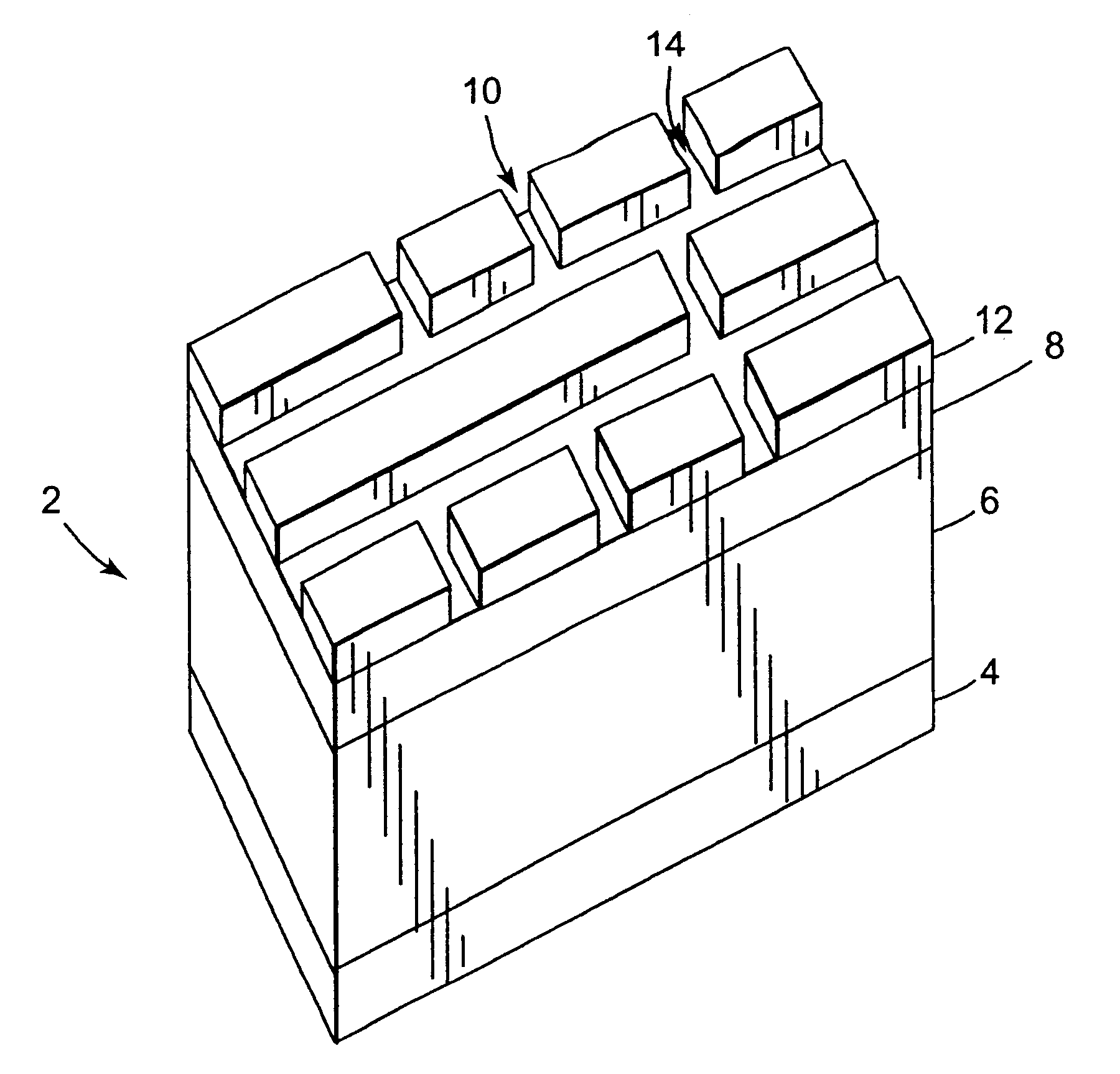

Coreless cavity substrates for chip packaging and their fabrication

ActiveUS7669320B2High yieldSuitable for mass productionDecorative surface effectsSemiconductor/solid-state device detailsCopperElectrical and Electronics engineering

A method for fabricating an IC support for supporting a first IC die connected in series with a second IC die; the IC support comprising a stack of alternating layers of copper features and vias in insulating surround, the first IC die being bondable onto the IC support, and the second IC die being bondable within a cavity inside the IC support, wherein the cavity is formed by etching away a copper base and selectively etching away built up copper.

Owner:ZHUHAI ADVANCED CHIP CARRIERS & ELECTRONICS SUBSTRATE SOLUTIONS TECH

Etching of metallic composite articles

A process for the etching of multiple layers of at least two different metals comprisies:forming a resist pattern over a first layer of metal, said resist pattern having a pattern of openings therein, applying a first etch solution onto said resist pattern so that at least some etch solution contacts exposed areas of the first layer of metal, etching away the majority of the depth of the first metal in exposed areas of metal in the first layer of metal, applying a second etch solution onto the resist pattern the second etch solution having a rate of etch towards the first metal as compared to the first etch solution that is at least 20% less than the millimeter / minute rate of etch of the first etch solution at the same etch solution temperature, removing the second etch solution from said resist pattern after at least the first metal layer has been etched sufficiently to expose areas of a second metal layer underlying the first metal layer by forming an etched first metal layer, and applying a third etch solution to said etched first metal layer, the third etch solution having a faster rate of etch towards the second metal than towards the first metal to etch into said second metal layer without destroying the etched first metal layer.

Owner:BMC INDS

Methods and apparatus for end-point detection

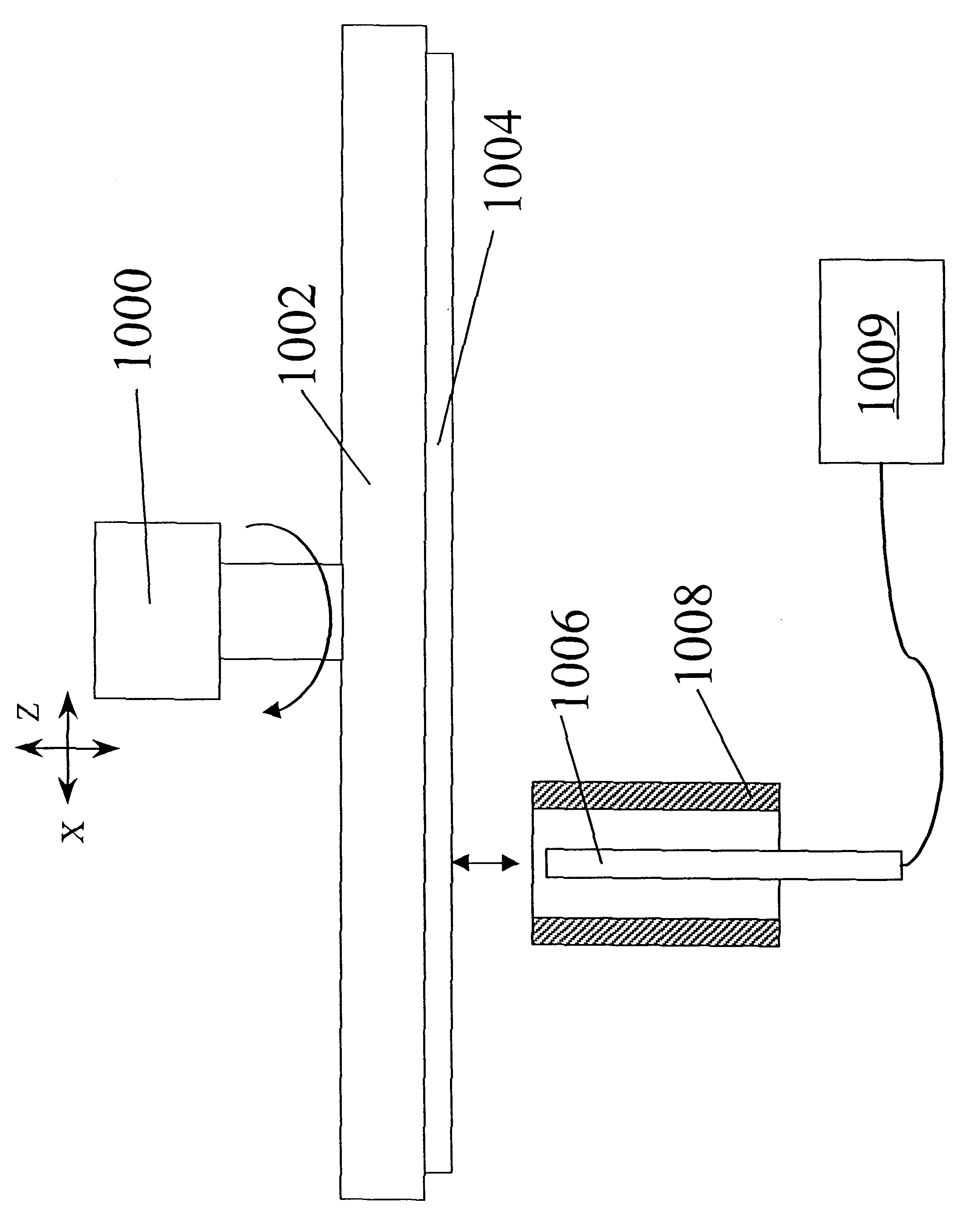

An apparatus for detecting the end-point of an electropolishing process of a metal layer formed on a wafer includes an end-point detector. The end-point detector is disposed adjacent the nozzle used to electropolish the wafer. In one embodiment, the end-point detector is configured to measure the optical reflectivity of the portion of the wafer being electropolished.

Owner:ACM RES

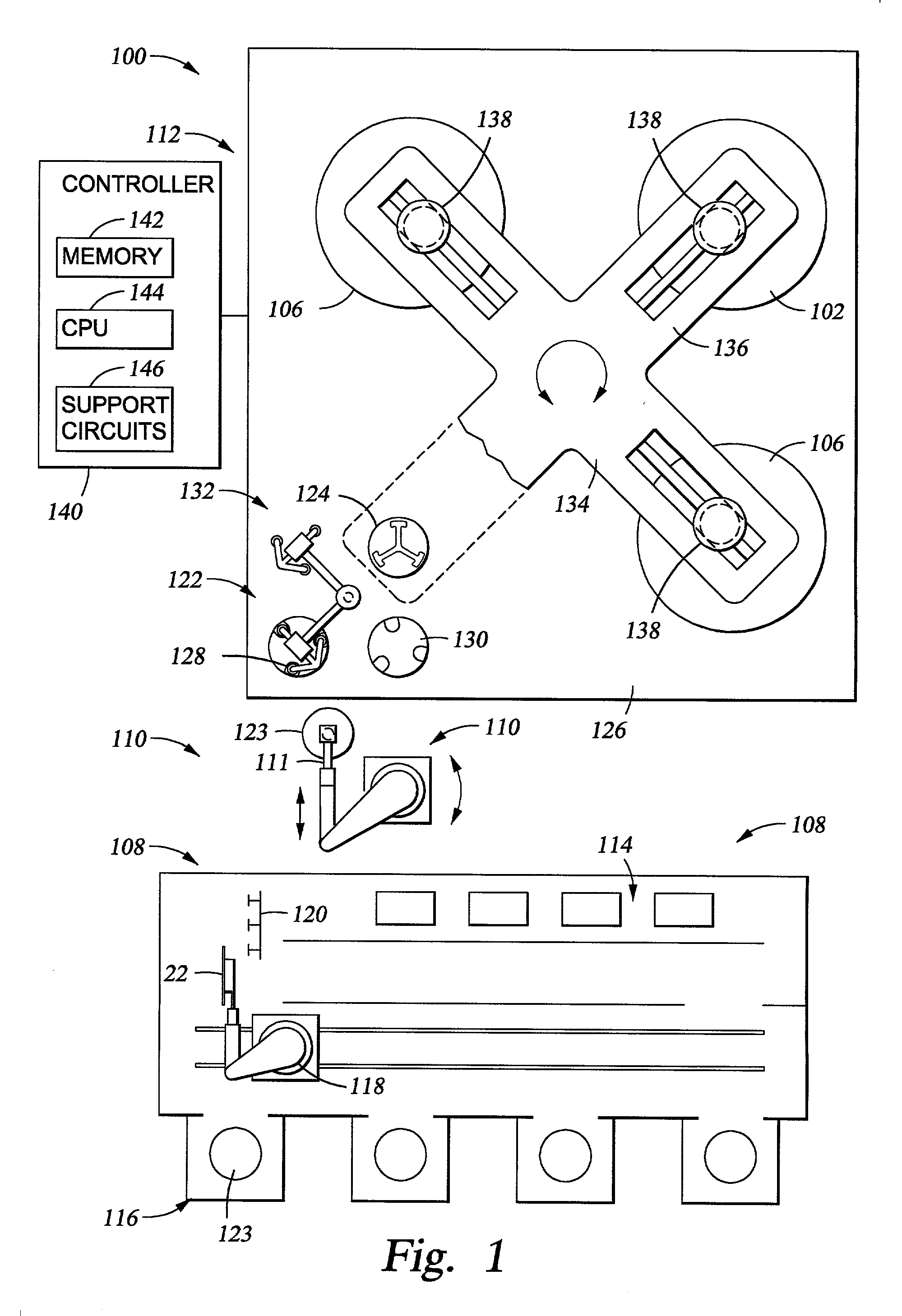

Planarization of substrates using electrochemical mechanical polishing

InactiveUS20020130049A1Electrolysis componentsSemiconductor/solid-state device manufacturingEngineeringSubstrate surface

A method and apparatus are provided for planarizing a material layer on a substrate. In one aspect, a method is provided for processing a substrate including forming a passivation layer on a substrate surface, polishing the substrate in an electrolyte solution, applying an anodic bias to the substrate surface, and removing material from at least a portion of the substrate surface. In another aspect, an apparatus is provided which includes a partial enclosure, polishing article, a cathode, a power source, a substrate carrier movably disposed above the polishing article, and a computer based controller to position a substrate in an electrolyte solution to form a passivation layer on a substrate surface, to polish the substrate in the electrolyte solution with the polishing article, and to apply an anodic bias to the substrate surface or polishing article to remove material from at least a portion of the substrate surface.

Owner:APPLIED MATERIALS INC

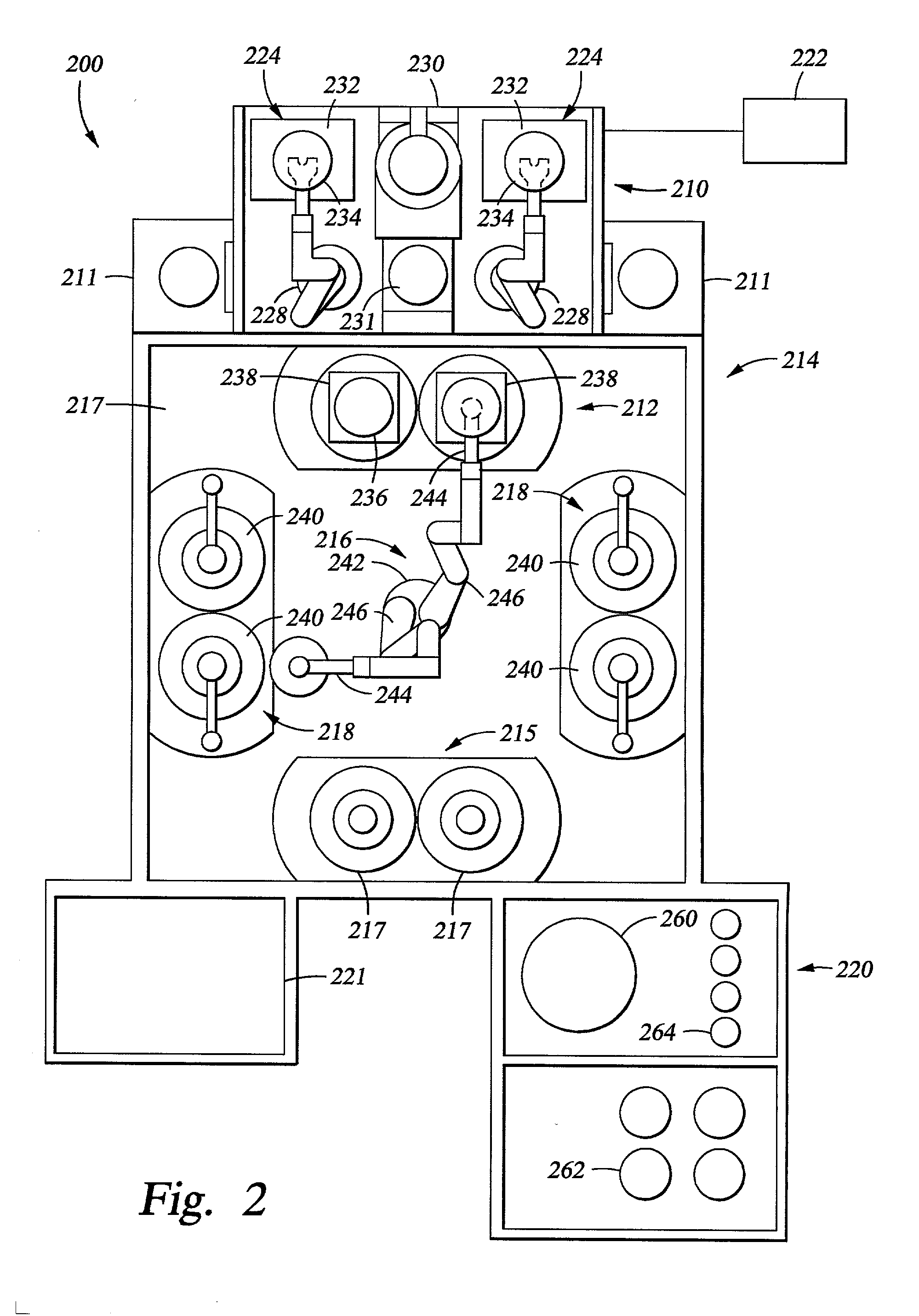

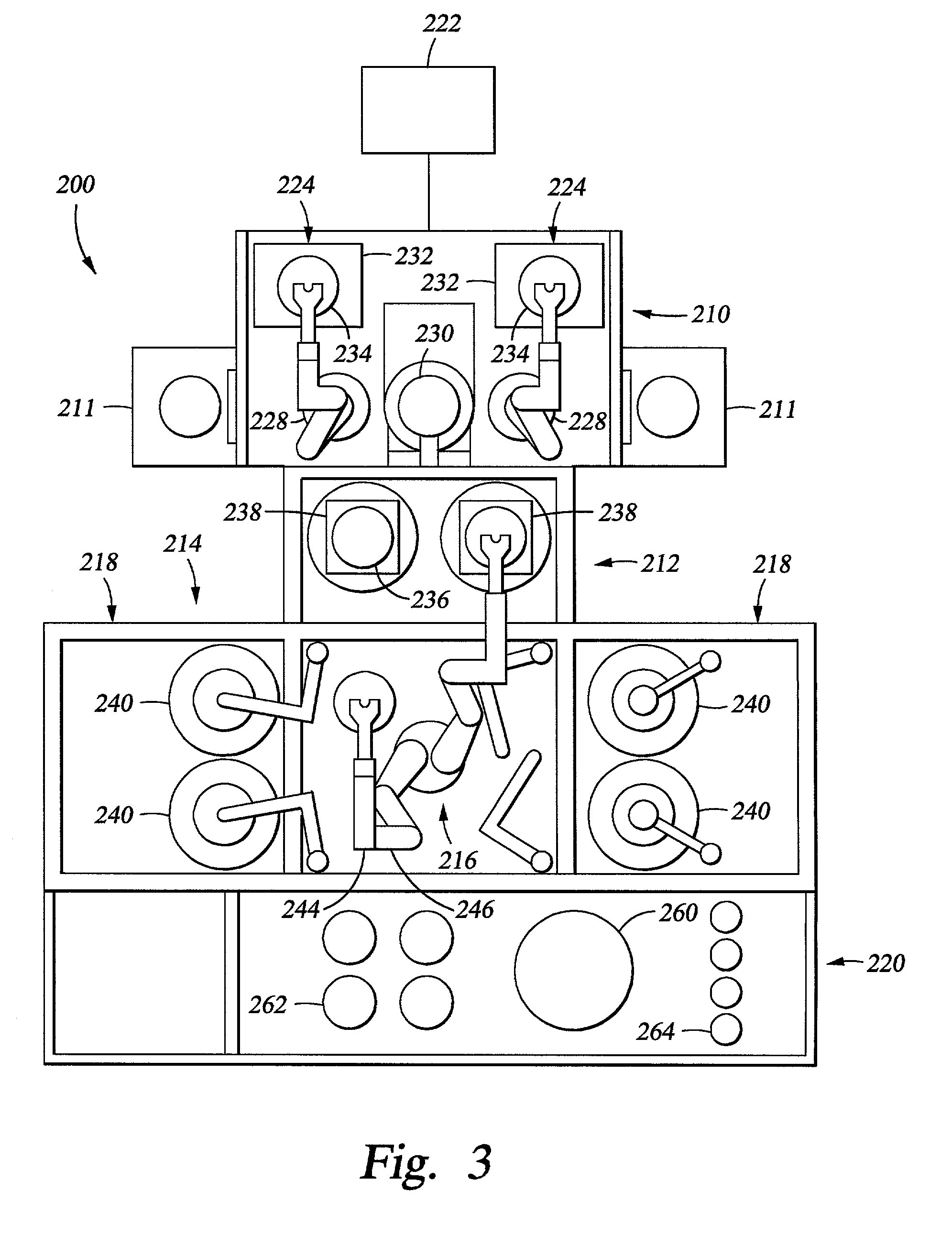

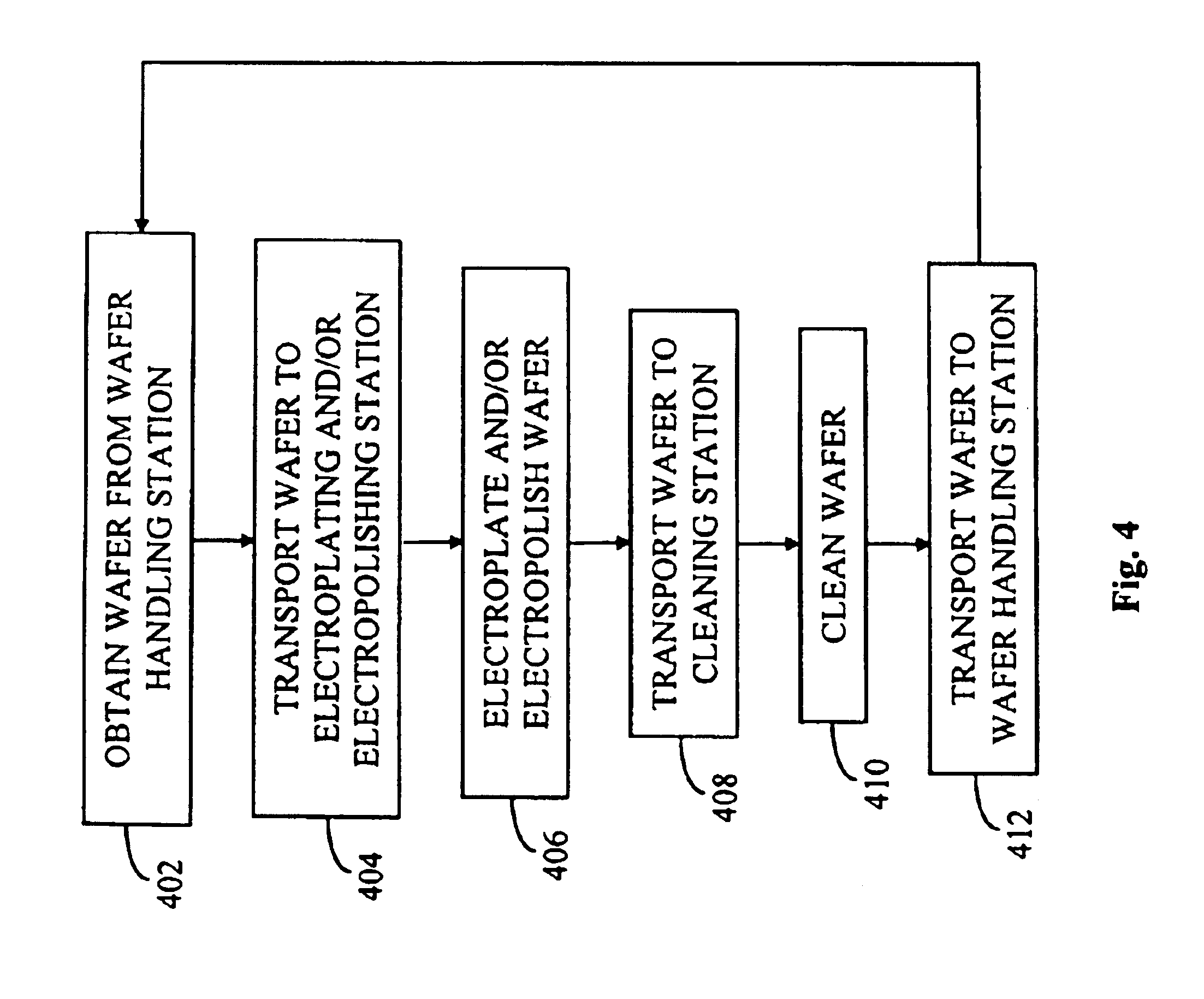

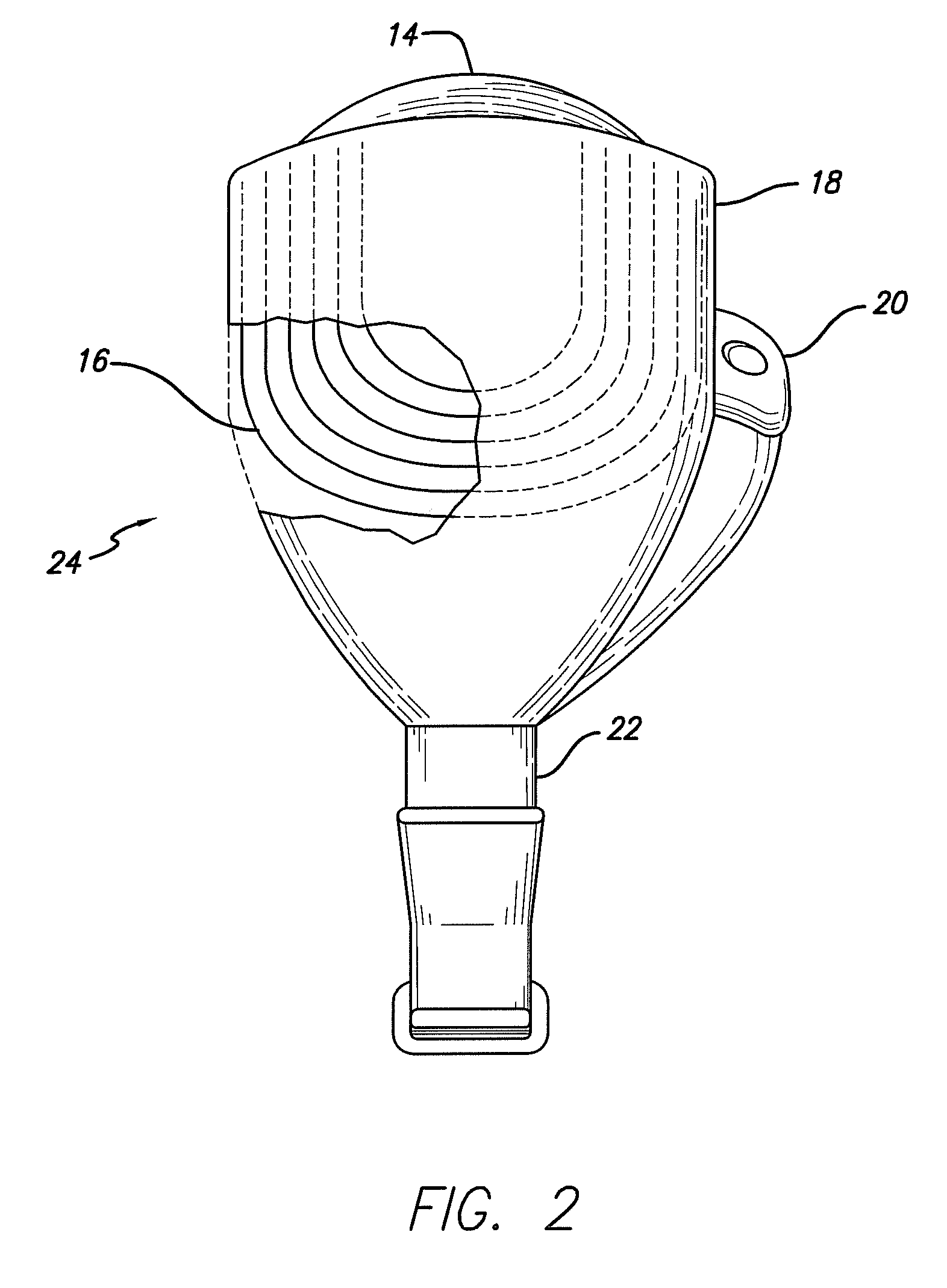

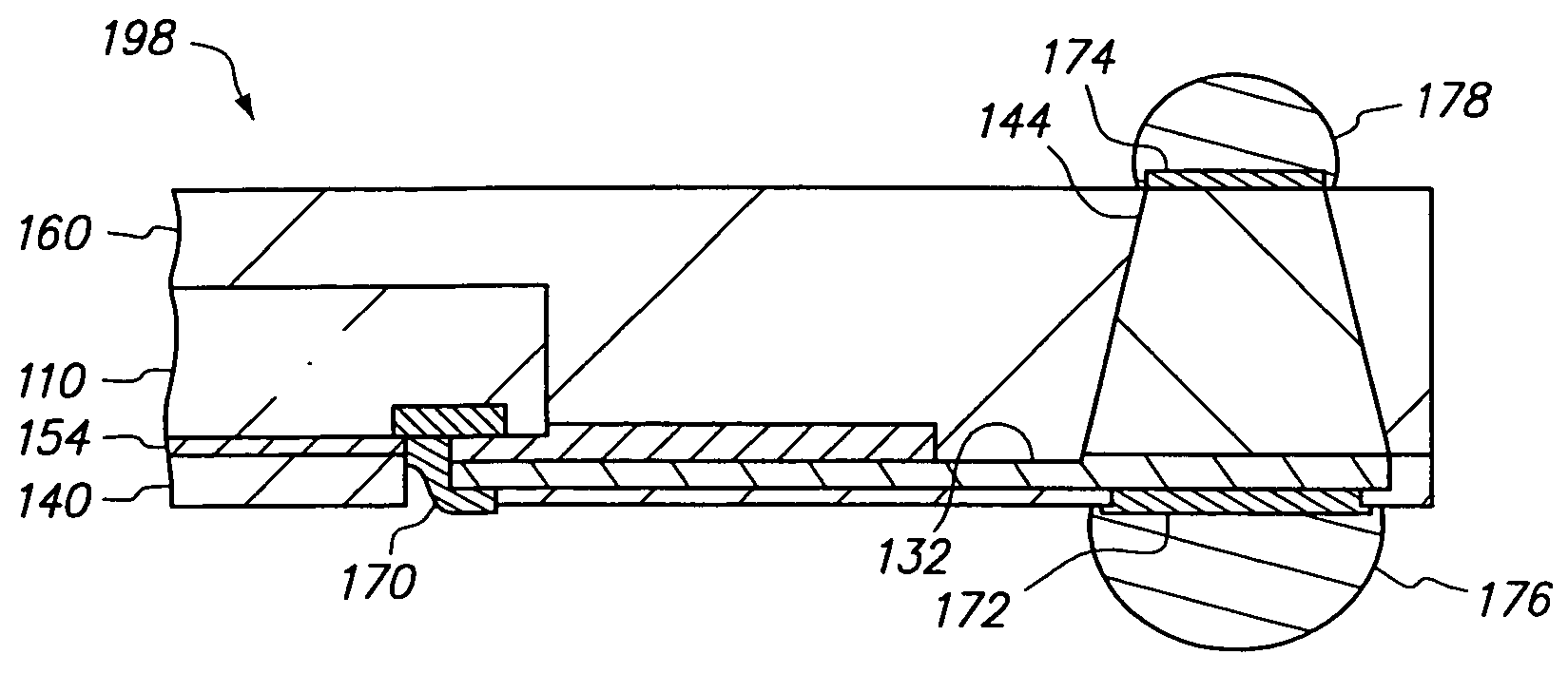

Methods and apparatus for holding and positioning semiconductor workpieces during electropolishing and/or electroplating of the workpieces

A wafer chuck assembly for holding a wafer during electroplating and / or electropolishing of the wafer includes a wafer chuck for receiving the wafer. The wafer chuck assembly also includes an actuator assembly for moving the wafer chuck between a first and a second position. When in the first position, the wafer chuck is opened. When in the second position, the wafer chuck is closed.

Owner:ACM RES

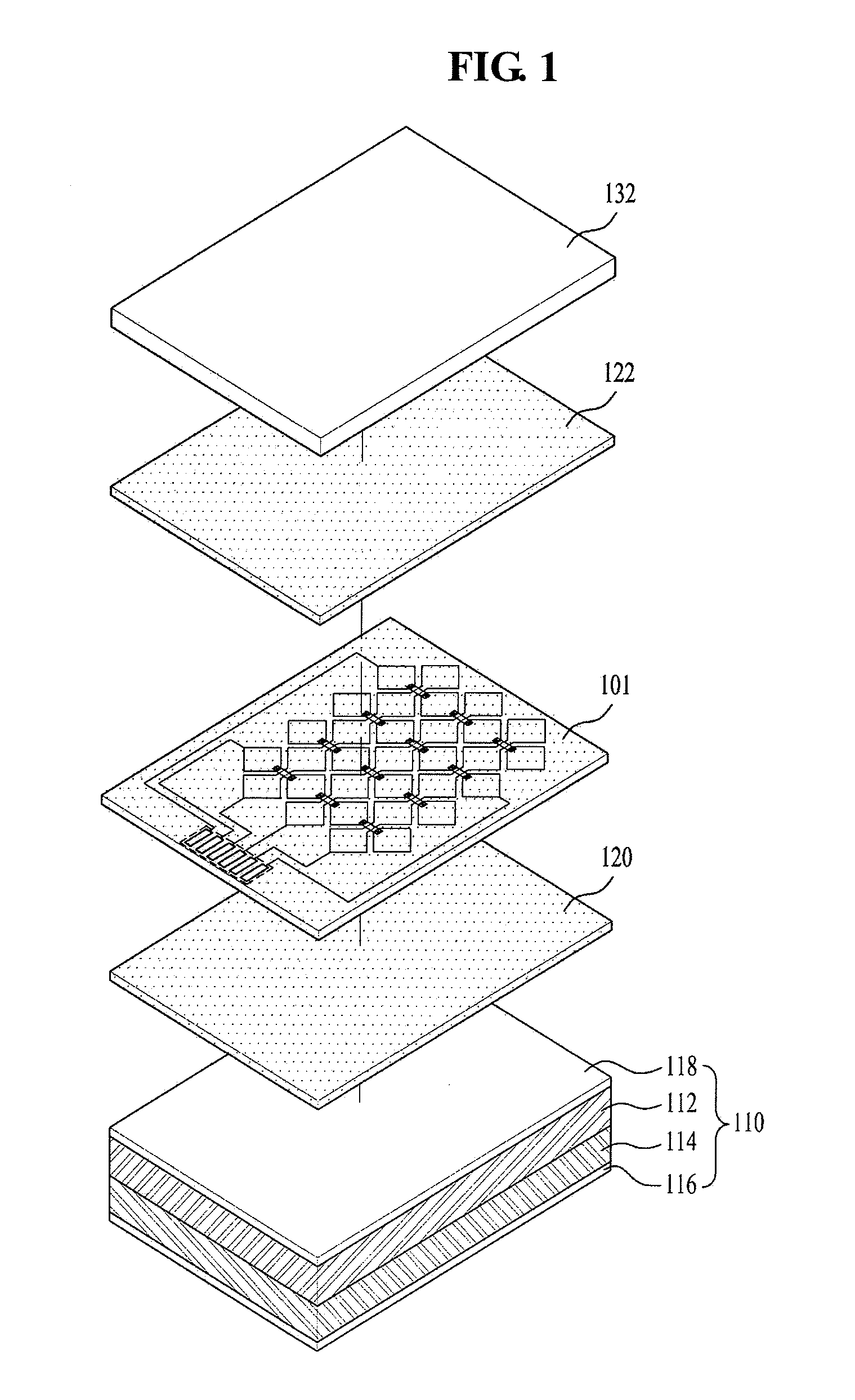

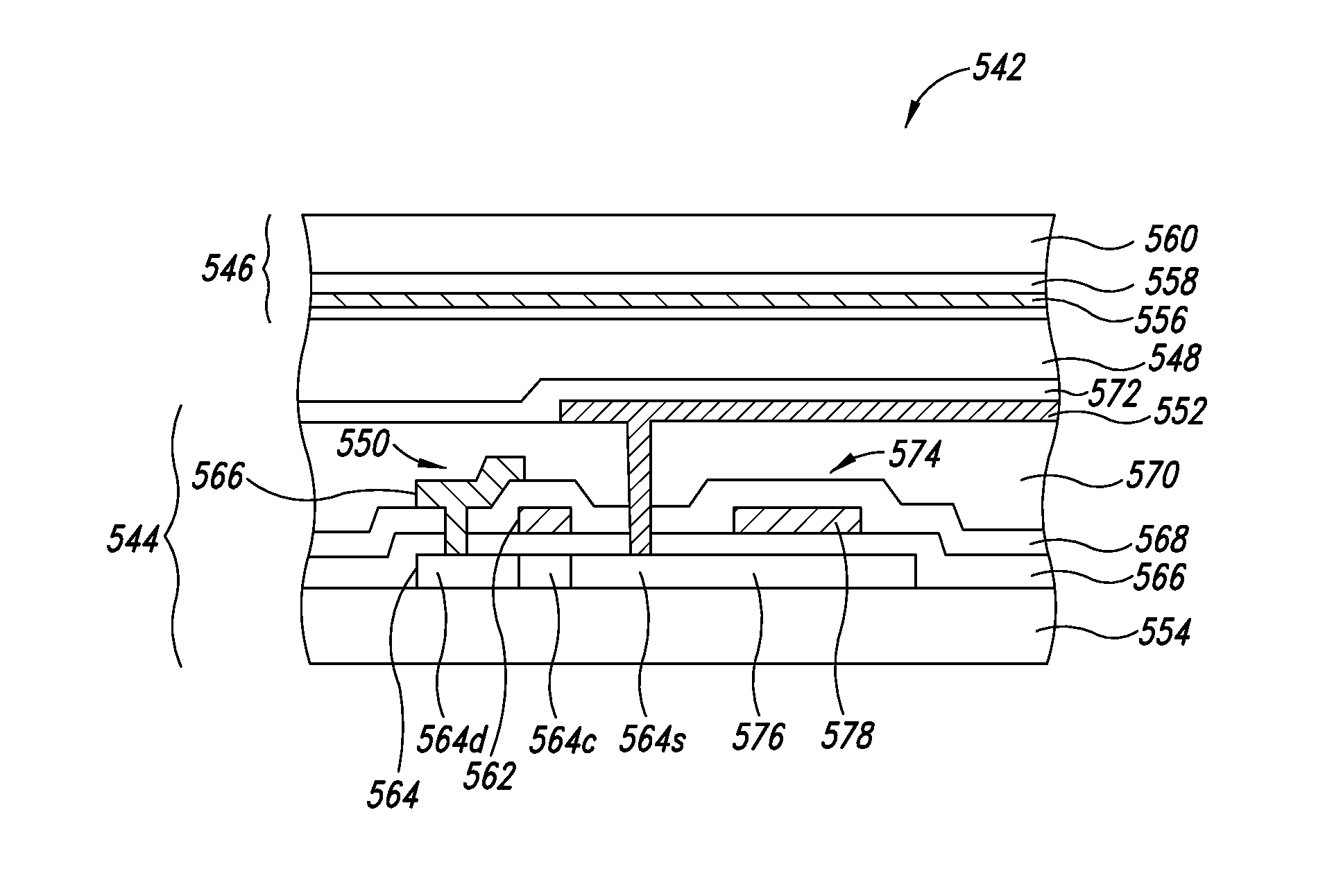

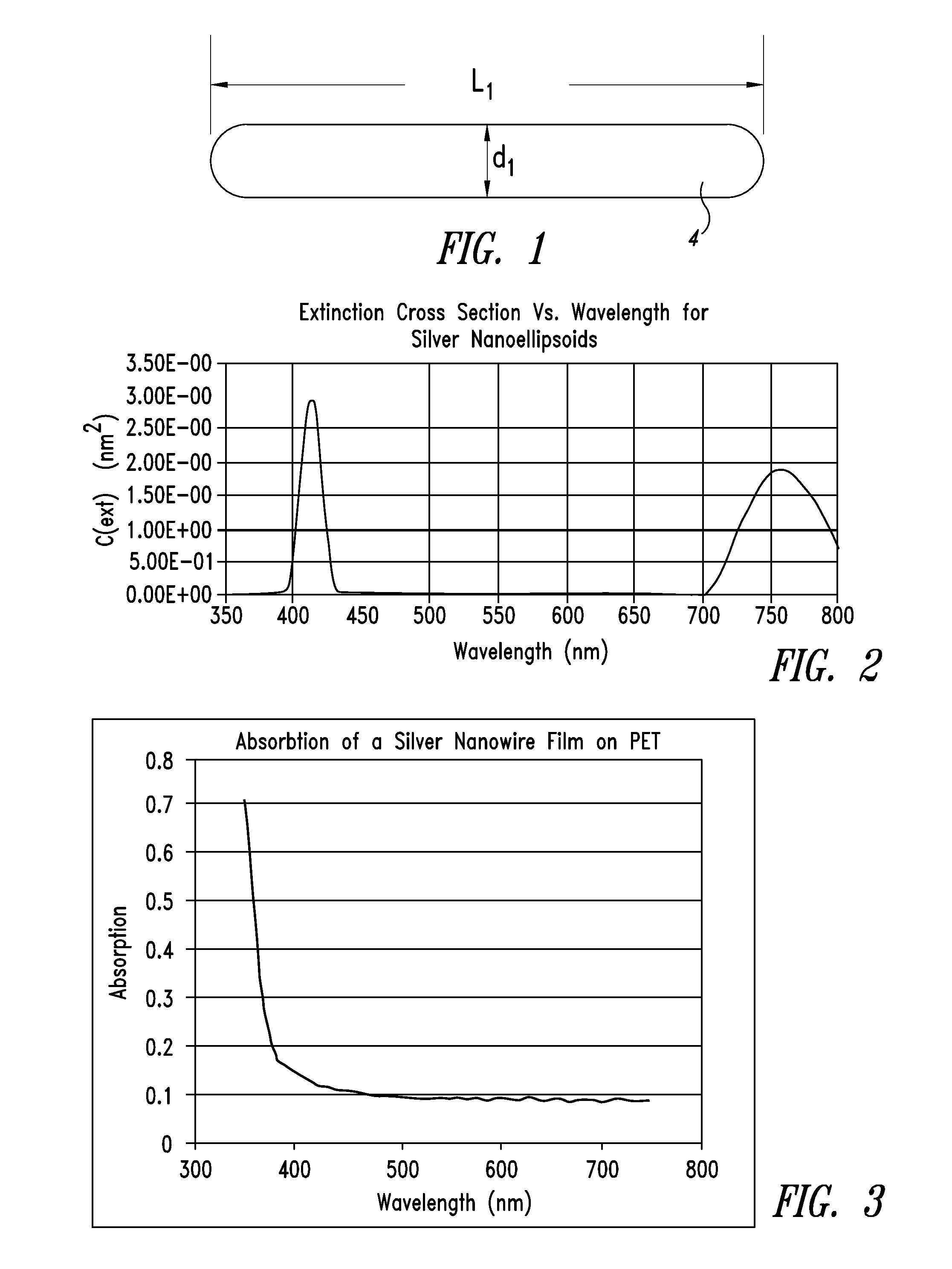

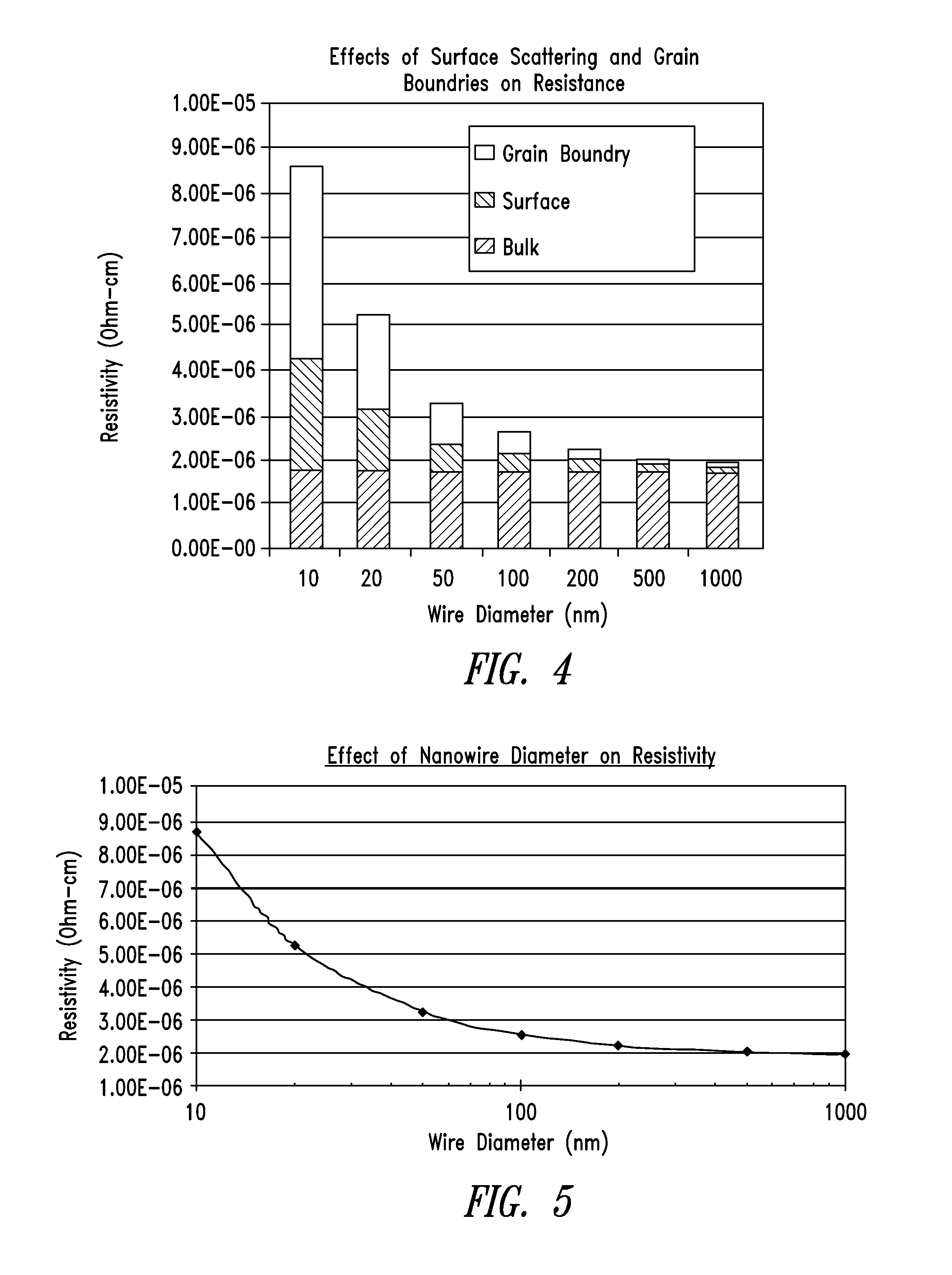

Nanowire-based transparent conductors and applications thereof

A transparent conductor including a conductive layer coated on a substrate is described. More specifically, the conductive layer comprises a network of nanowires that may be embedded in a matrix. The conductive layer is optically clear, patternable and is suitable as a transparent electrode in visual display devices such as touch screens, liquid crystal displays, plasma display panels and the like.

Owner:CHAMP GREAT INTL

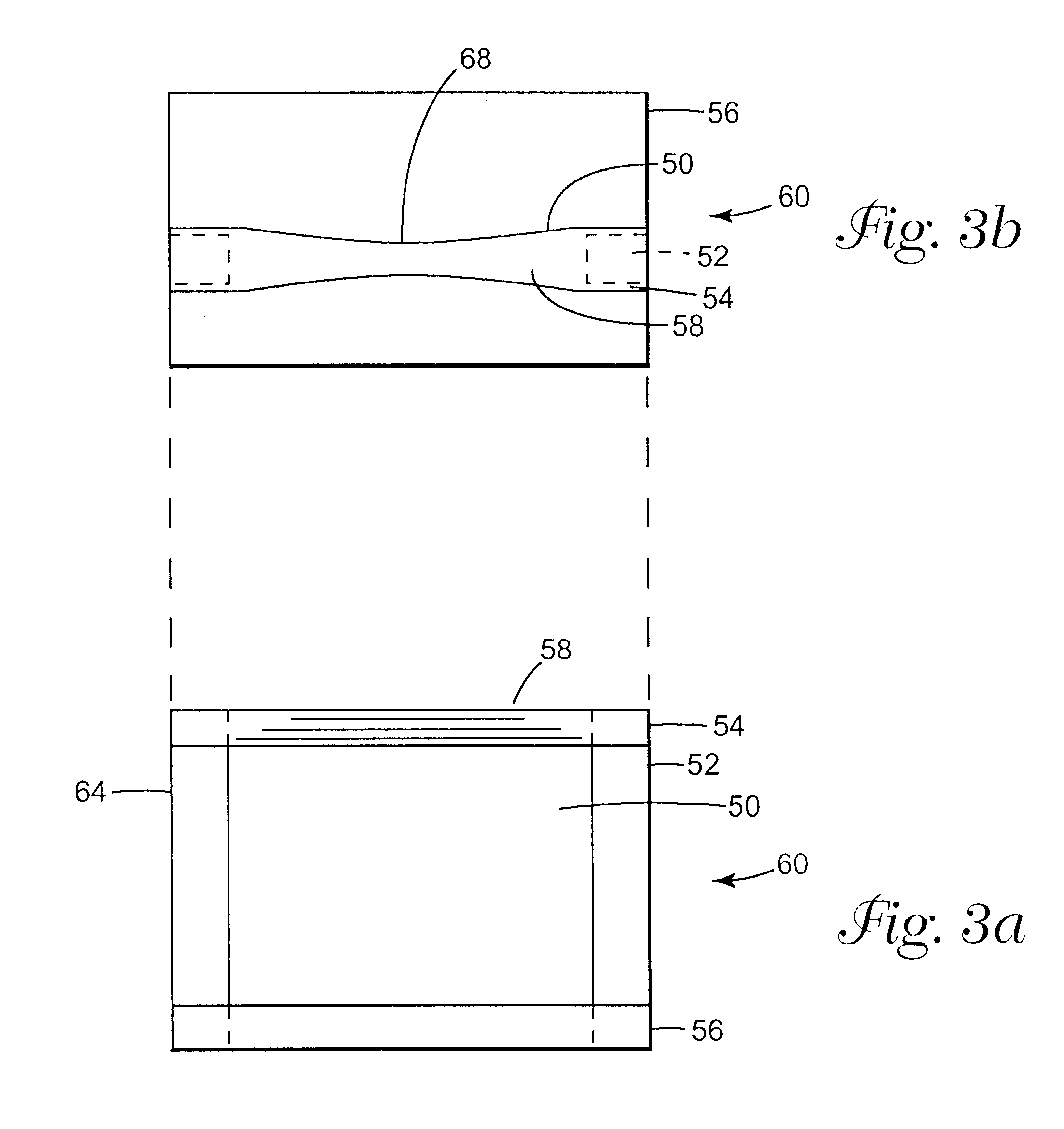

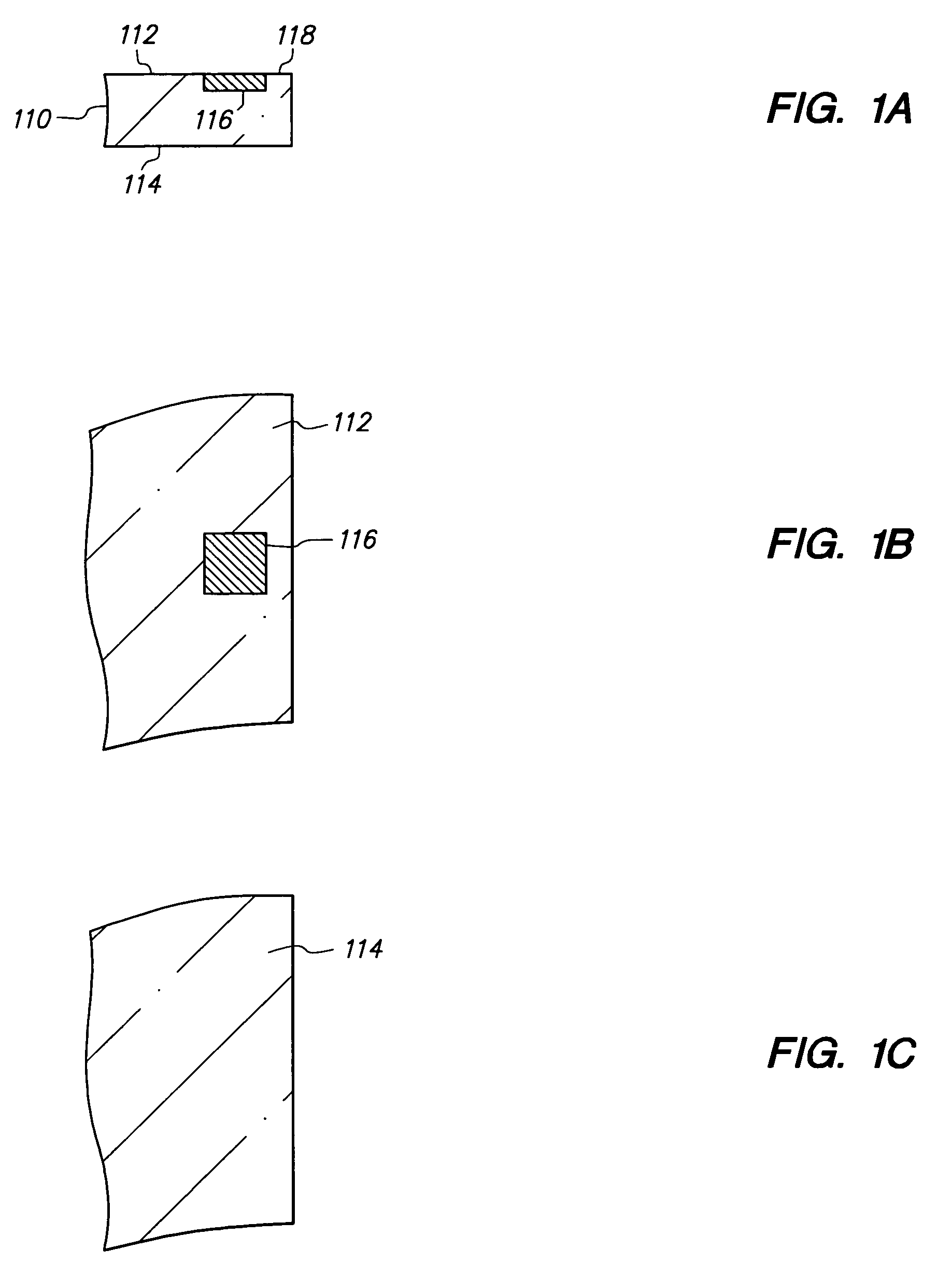

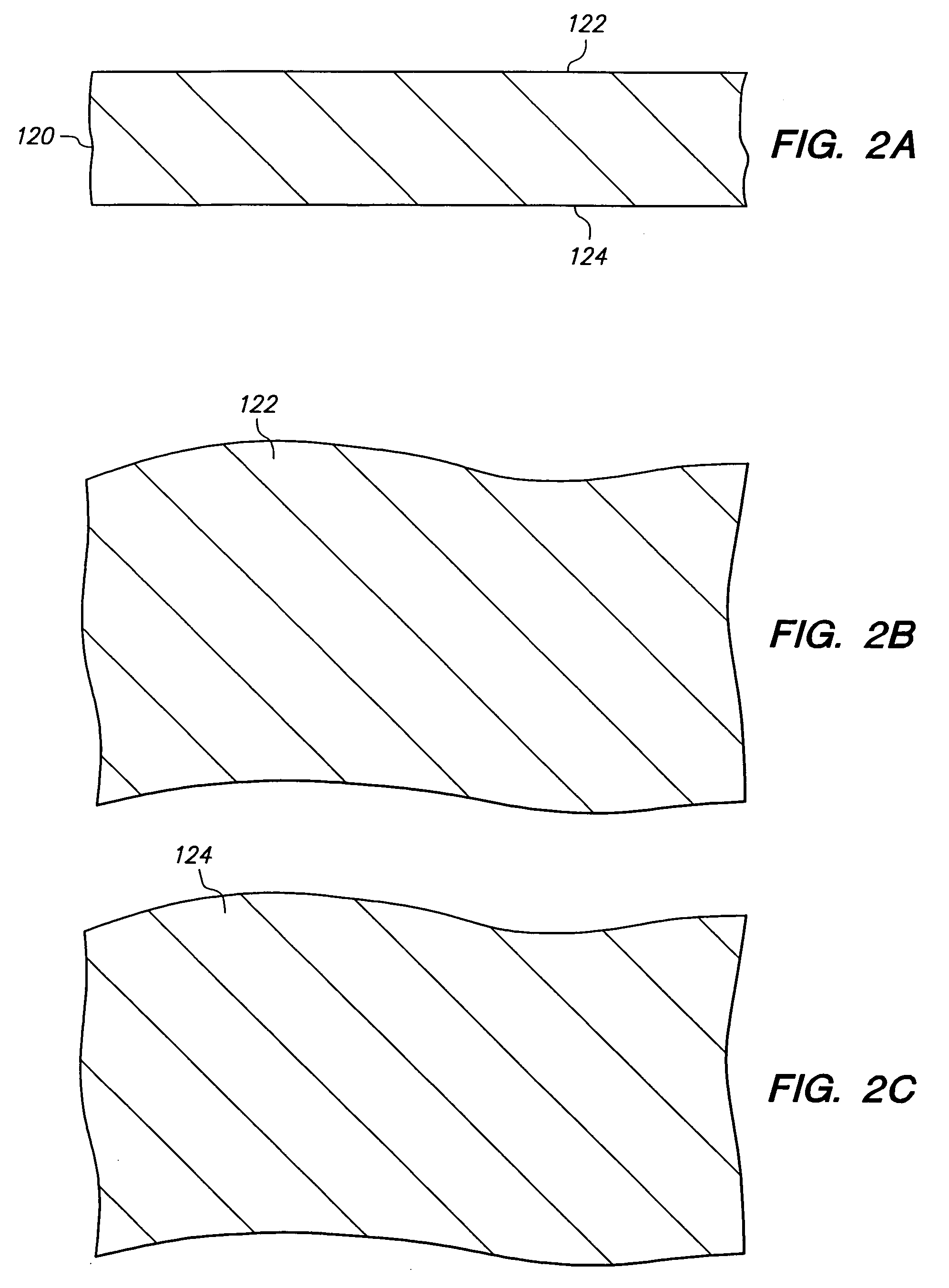

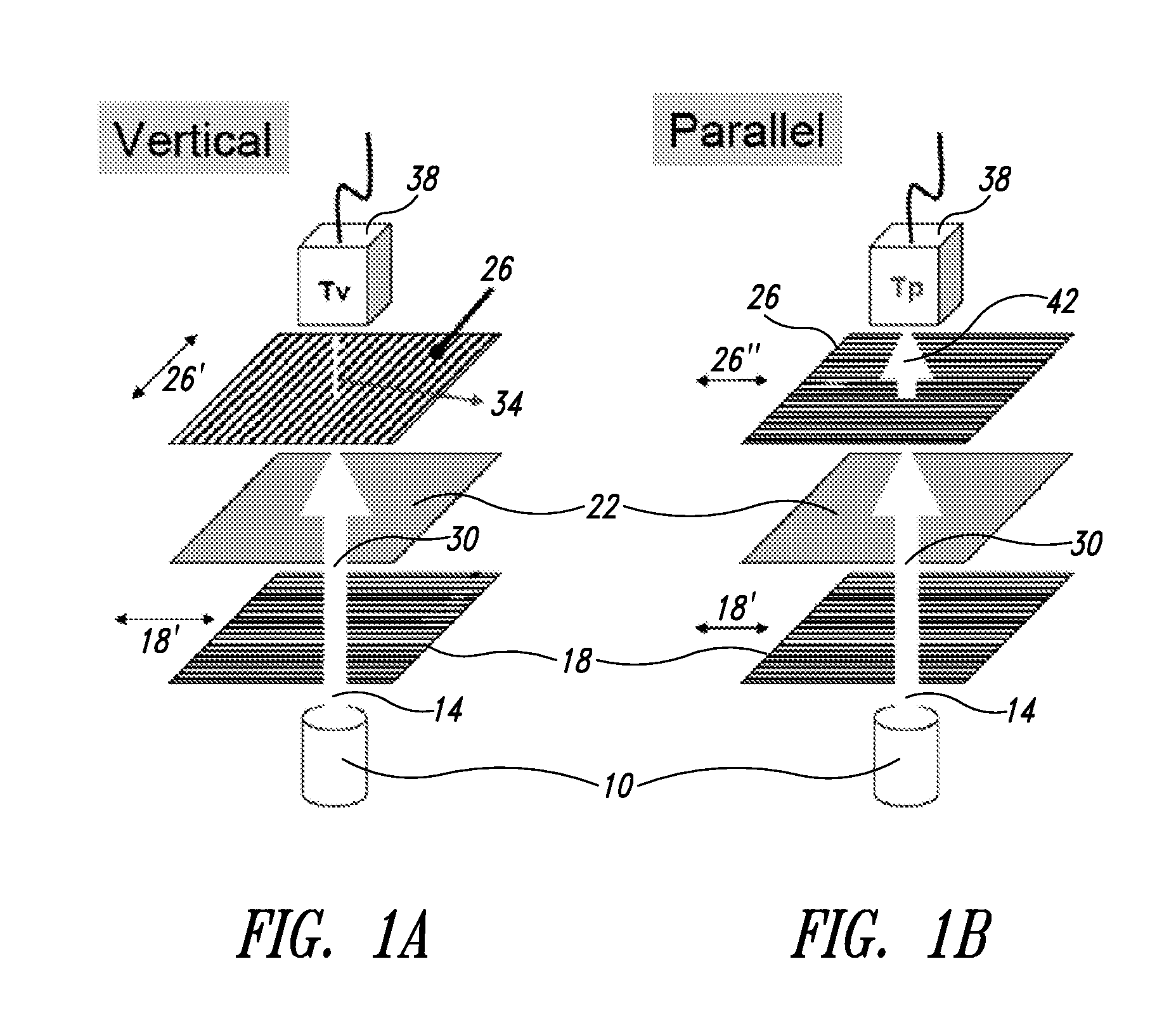

Multi-layer ground plane structures for integrated lead suspensions

ActiveUS7929252B1Additive manufacturing apparatusHigh frequency circuit adaptationsStructure of the EarthGround plane

Multi-layer ground plane structures and methods of manufacture for integrated lead suspension flexures. A flexure in accordance with one embodiment of the invention includes an insulating layer, a plurality of traces on the insulating layer and a stainless steel base layer on the side of the insulating layer opposite the traces. The stainless steel base layer includes one or more void portions with voids in the base layer opposite the insulating layer from the traces and one or more backed portions with the base layer backing the traces. A plurality of patterned and transversely-spaced first conductive ground planes are located opposite the insulating layer from the traces at the void portions and backed portions of the stainless steel base layer. A continuous gold second conductive ground plane is located opposite the insulating layer and the first ground planes from the side of the insulating layer adjacent to the traces at the void portions and backed portions of the stainless steel base layer. The gold ground plane can be used as an etch stop during formation of the voids in the base layer.

Owner:HUTCHINSON TECH

Process for integrated circuit wiring

Metal wiring is provided in an integrated circuit by sputter coating onto a semiconductor substrate a copper seed layer; depositing and patterning a photoresist; electroplating or electrolessly plating a metal within the openings of the photoresist; stripping the remaining photoresist; and etching the copper seed layer with an etchant that preferentially etches the copper seed layer at a rate higher than that for the electroplated or electrolessly plated metal.

Owner:IBM CORP

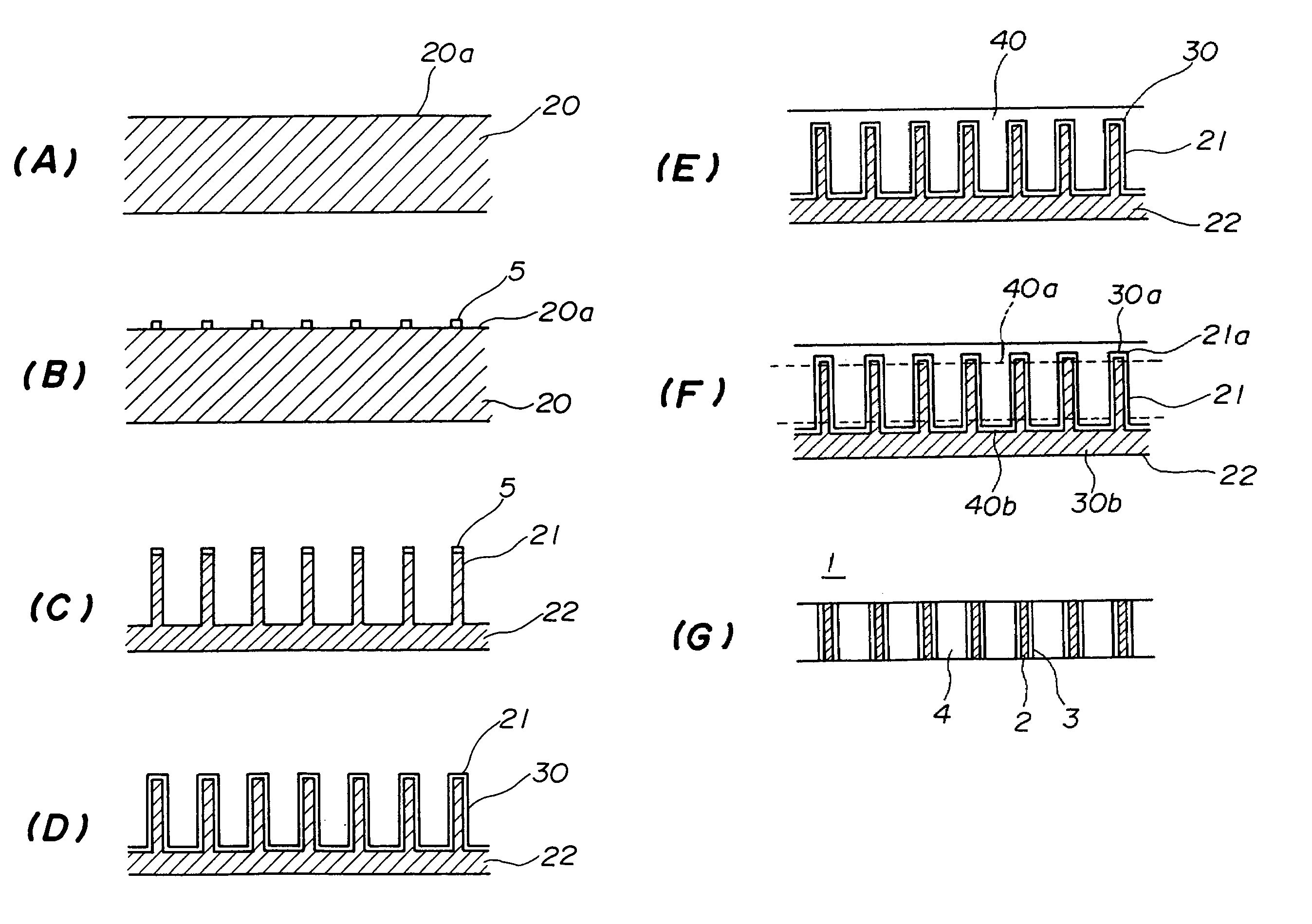

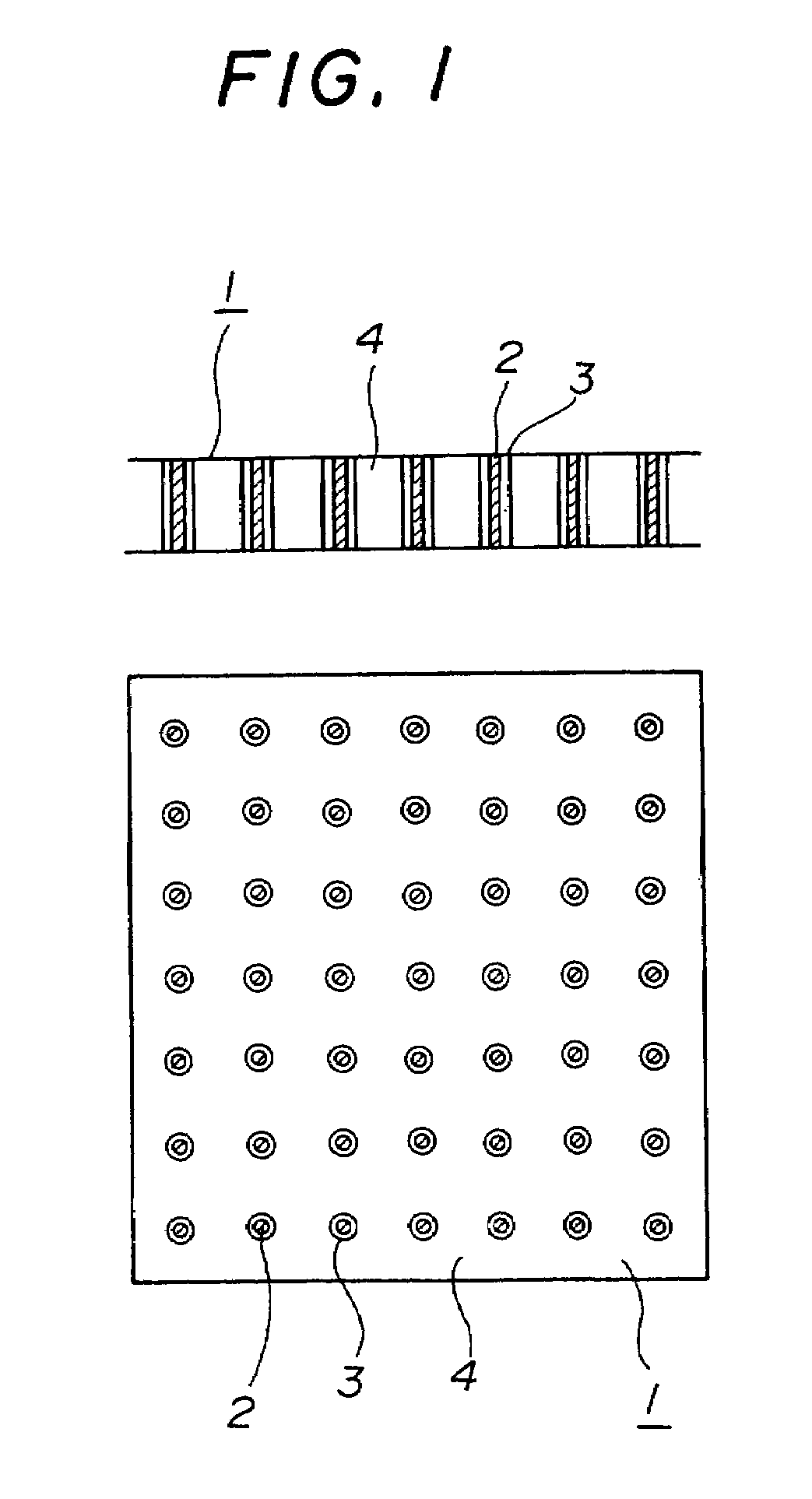

Method for making a front and back conductive substrate

InactiveUS7222420B2Improve integration densityPrinted circuit assemblingContact member manufacturingEngineeringElectrically conductive

A front-and-back electrically conductive substrate includes a plurality of posts composed of a material that can be anisotropically etched and having an electrically conductive portion that has at least a first surface and a second surface that communicate with each other, and an insulative substrate that supports the plurality of posts.

Owner:FUJITSU LTD

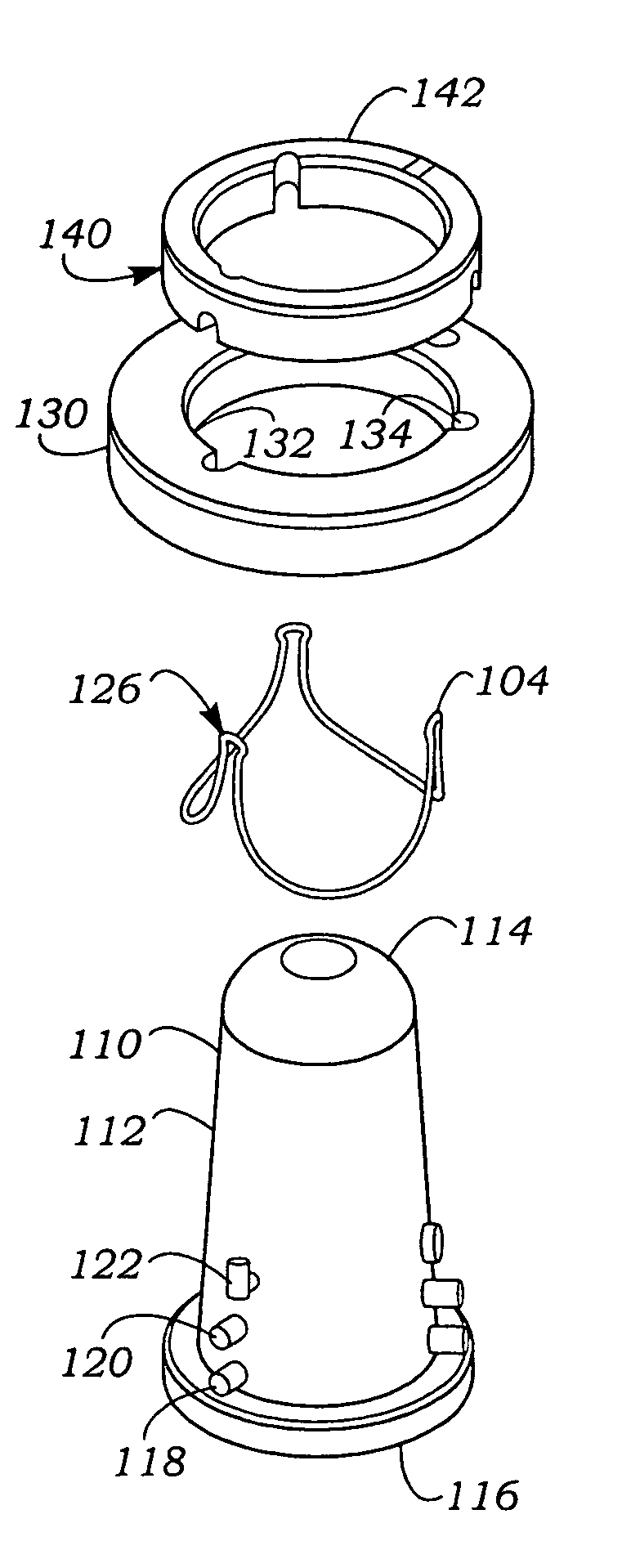

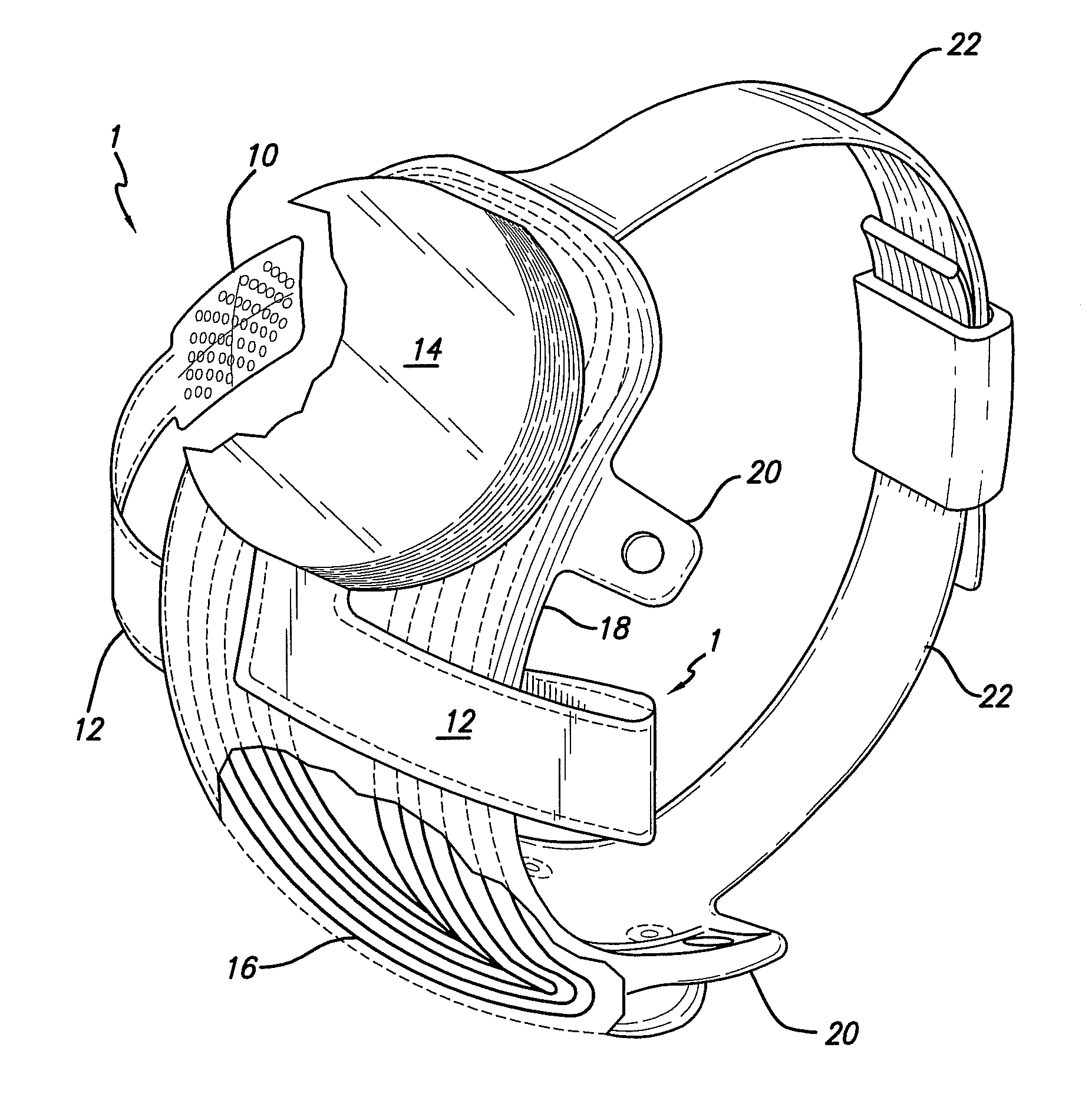

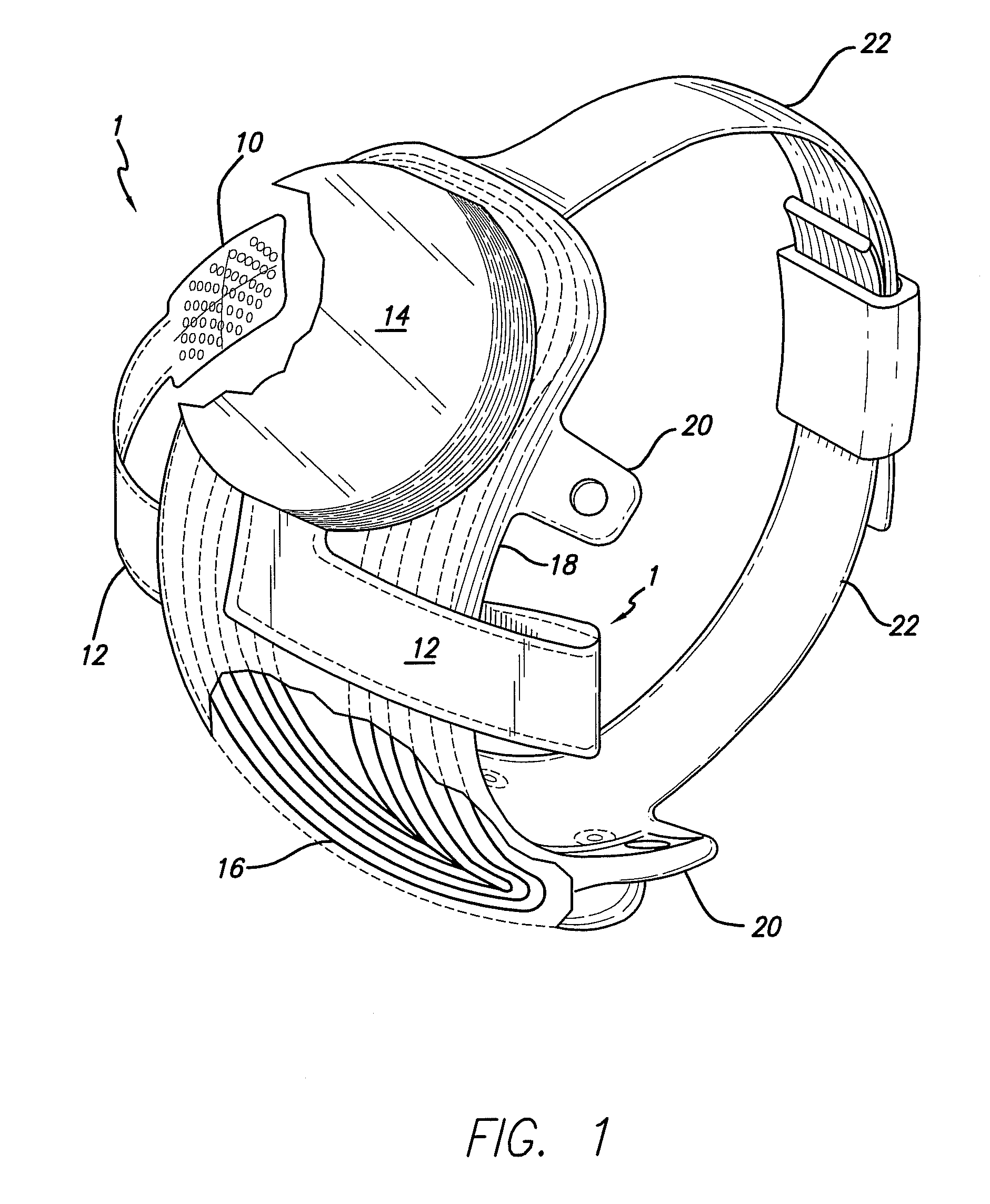

Method of manufacture of a heart valve support frame

InactiveUS20050150775A1Eliminate unevennessIncrease flexibilityElectrolysis componentsFrom normal temperature solutionsEngineeringReady to use

Methods for forming a support frame for flexible leaflet heart valves from a starting blank include converting a two-dimensional starting blank into the three-dimensional support frame. The material may be superelastic, such as NITINOL, and the method may include bending the 2-D blank into the 3-D form and shape setting it. A merely elastic material such as ELGILOY may be used and plastically deformed in stages, possibly accompanied by annealing, to obtain the 3-D shape. Alternatively, a tubular blank could be formed to define a non-tubular shape, typically conical. A method for calculating the precise 2-D blank shape is also disclosed. A mandrel assembly includes a mandrel and ring elements for pressing the blank against the external surface of the mandrel prior to shape setting.

Owner:EDWARDS LIFESCIENCES CORP

Etch patterning of nanostructure transparent conductors

Owner:CHAMP GREAT INTL

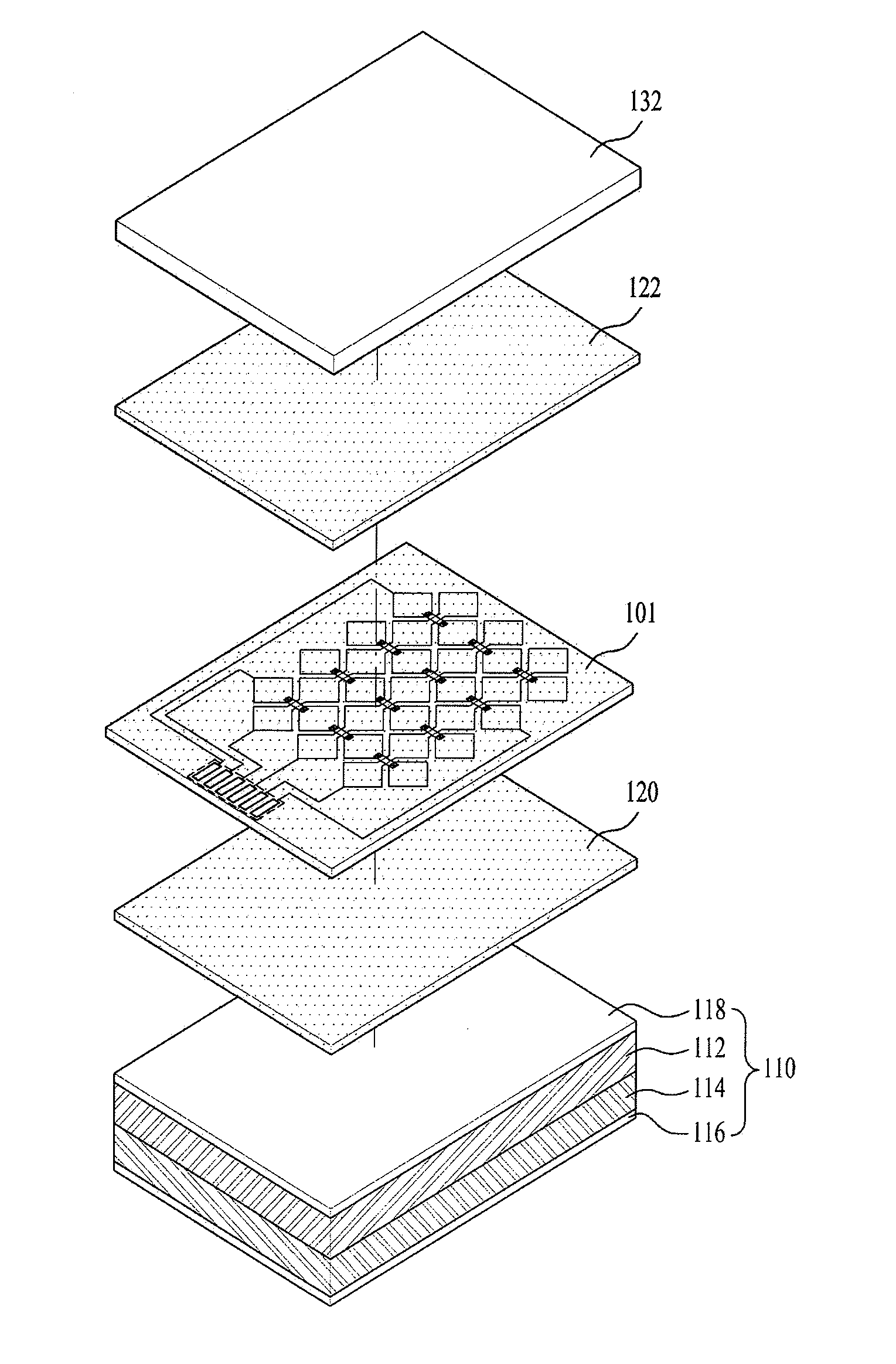

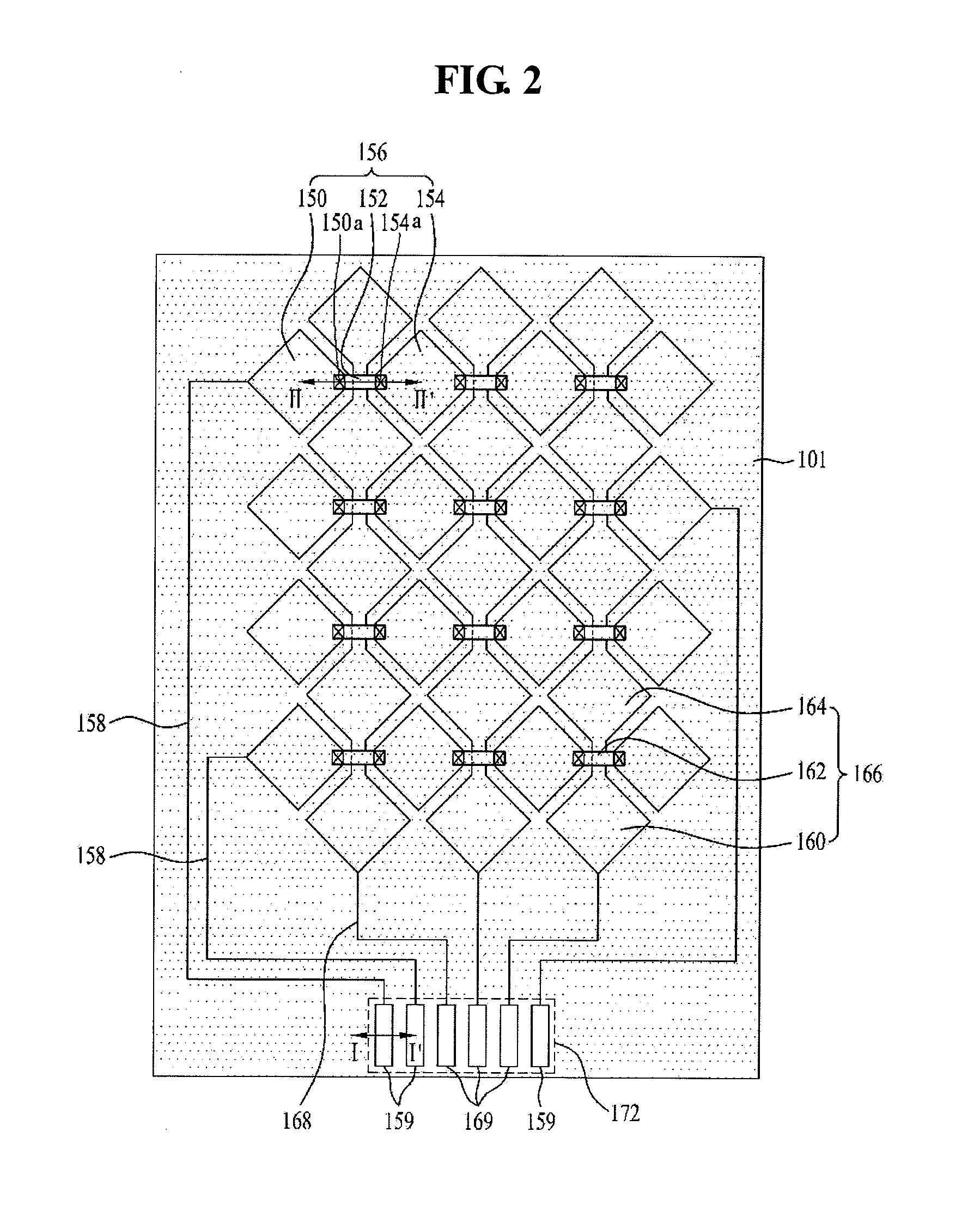

Touch panel and method for fabricating the same

ActiveUS20120262385A1Reduce in quantityLiquid/solution decomposition chemical coatingSolid/suspension decomposition chemical coatingEngineeringTouch panel

A touch panel is made by forming a routing and pad pattern group on a substrate to include first and second routing lines, first pad electrodes connected to the first routing line, and second pad electrodes connected to the second routing line, by using a first mask; forming a sensor electrode pattern group on the substrate having the routing and pad pattern group formed thereon to include first sensor electrodes formed in a first direction, second sensor electrodes formed in a second direction, and connection portions that each connects adjacent first sensor electrodes, by using a second mask; forming a first insulating layer to include contact holes to expose portions of the second sensor electrodes, respectively, by using a third mask; and forming bridges that each connects adjacent second sensor electrodes through the contact holes and a second insulating layer on the bridges, by using a fourth mask.

Owner:LG DISPLAY CO LTD

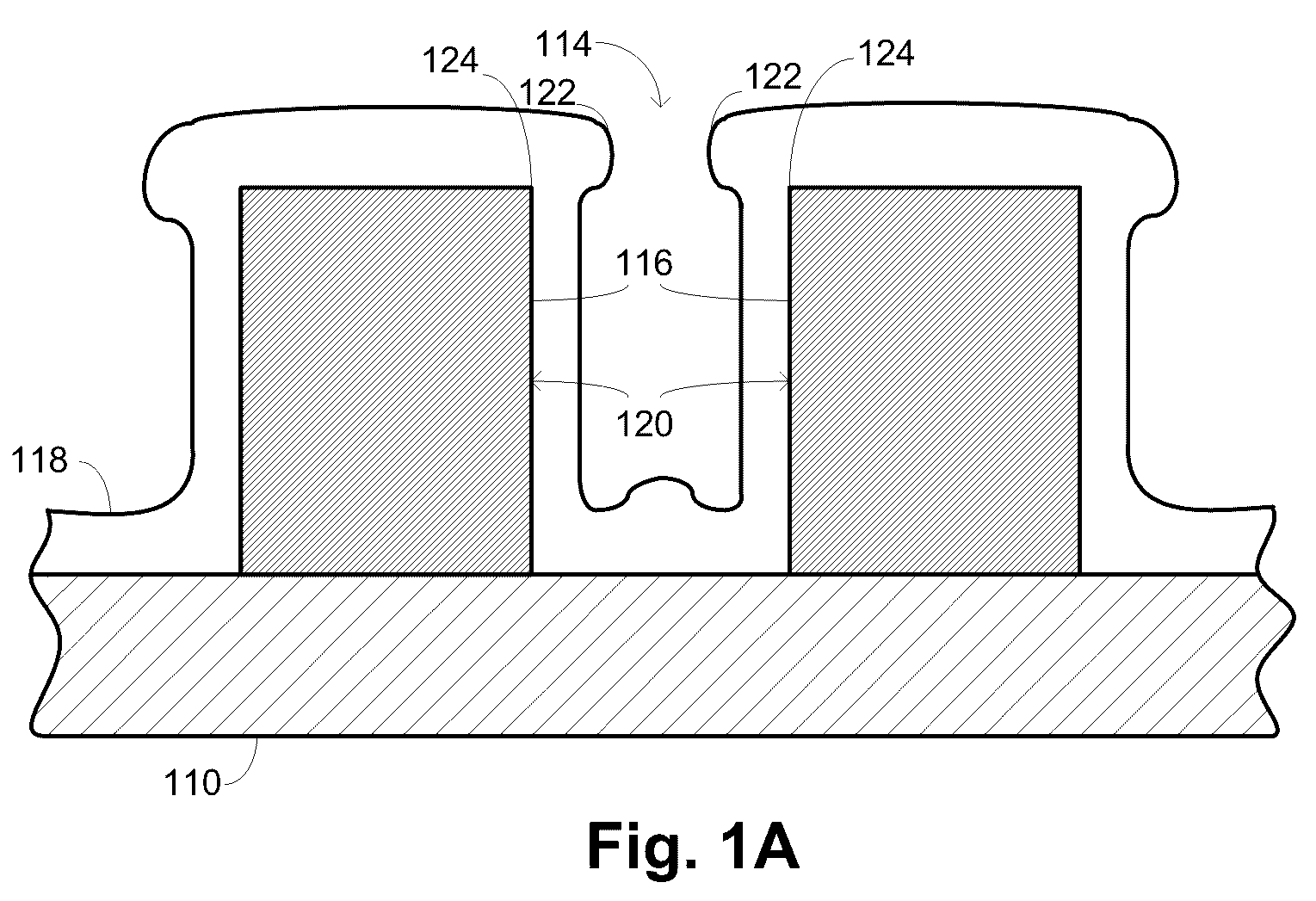

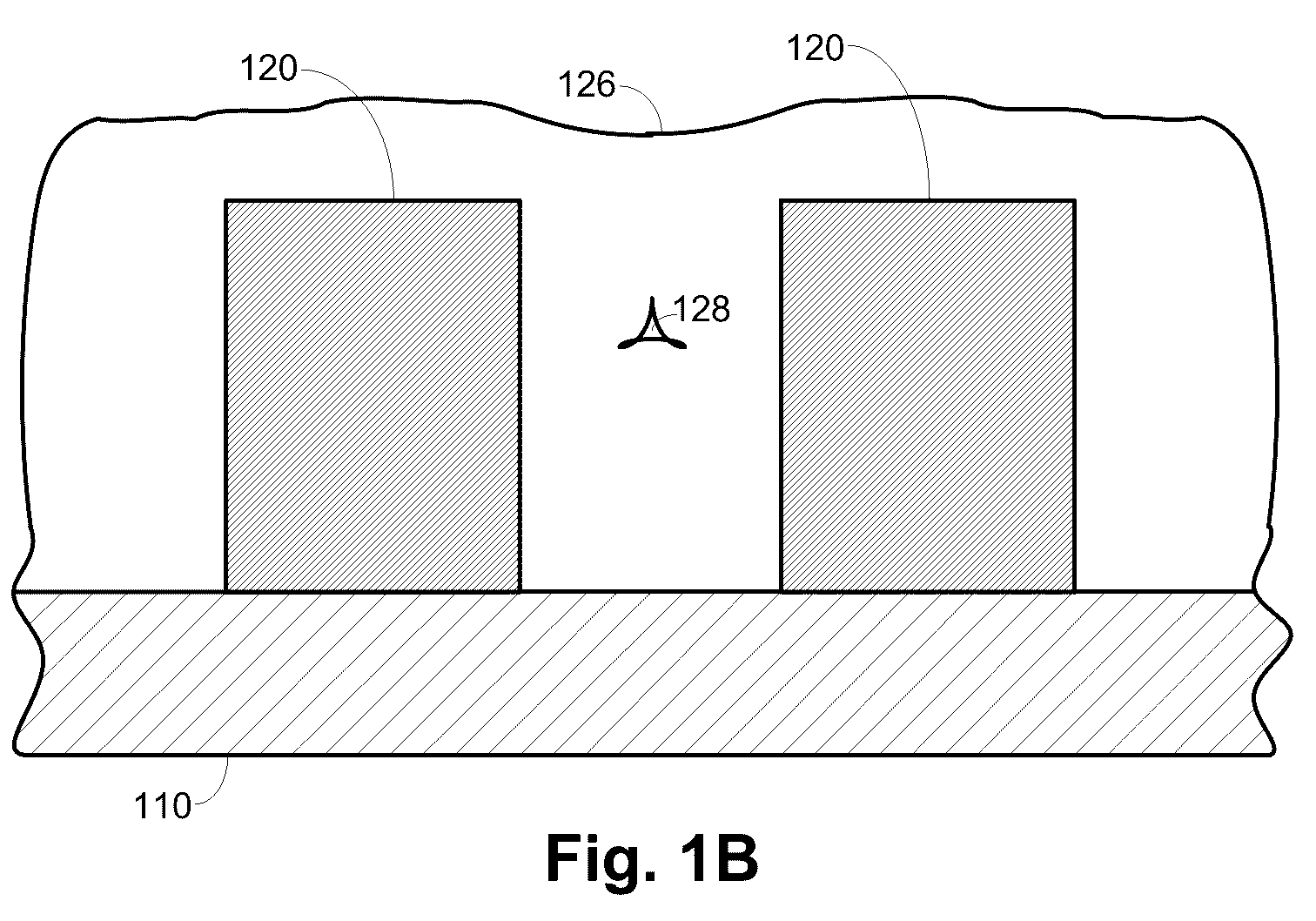

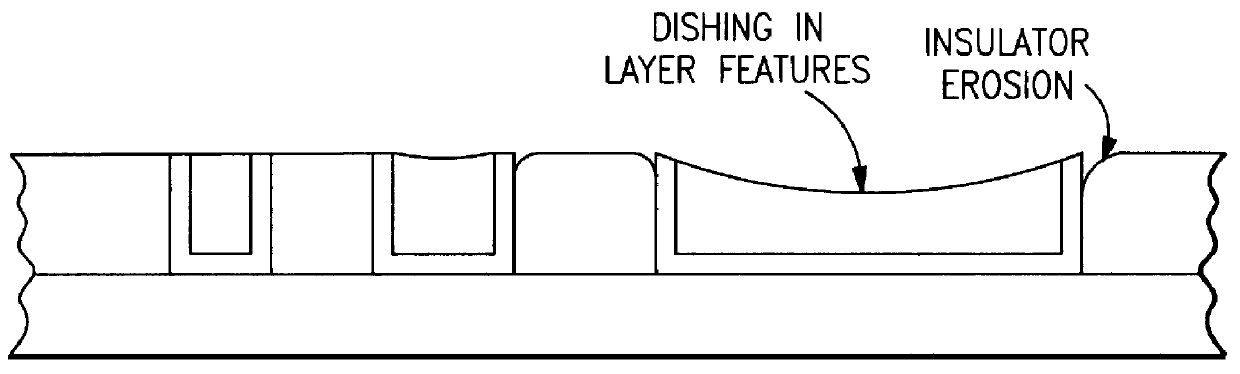

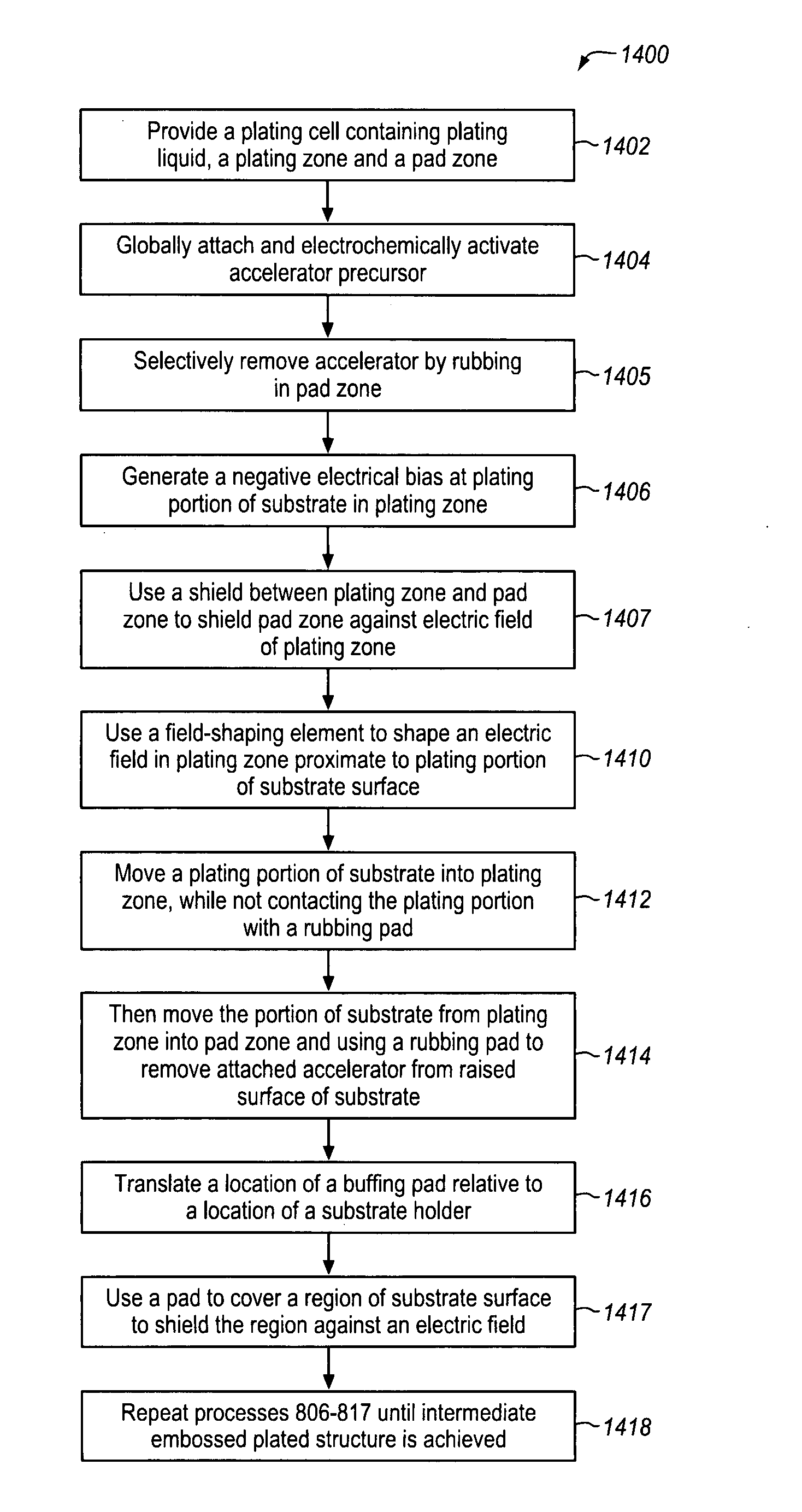

Topography reduction and control by selective accelerator removal

ActiveUS20090280649A1Improve throughputLow costCellsDecorative surface effectsMetal interconnectEtching

Plating accelerator is applied selectively to a substantially-unfilled wide (e.g., low-aspect-ratio feature cavity. Then, plating of metal is conducted to fill the wide feature cavity and to form an embossed structure in which the height of a wide-feature metal protrusion over the metal-filled wide-feature cavity is higher than the height of metal over field regions. Most of the overburden metal is removed using non-contact techniques, such as chemical wet etching. Metal above the wide feature cavity protects the metal-filled wide-feature interconnect against dishing, and improved planarization techniques avoid erosion of the metal interconnect and dielectric insulating layer. In some embodiments, plating of metal onto a substrate is conducted to fill narrow (e.g., high-aspect-ratio feature cavities) in the dielectric layer before selective application of plating accelerator and filling of the wide feature cavity.

Owner:NOVELLUS SYSTEMS

Nanowire-based transparent conductors and applications thereof

A transparent conductor including a conductive layer coated on a substrate is described. More specifically, the conductive layer comprises a network of nanowires that may be embedded in a matrix. The conductive layer is optically clear, patternable and is suitable as a transparent electrode in visual display devices such as touch screens, liquid crystal displays, plasma display panels and the like.

Owner:CHAMP GREAT INTL

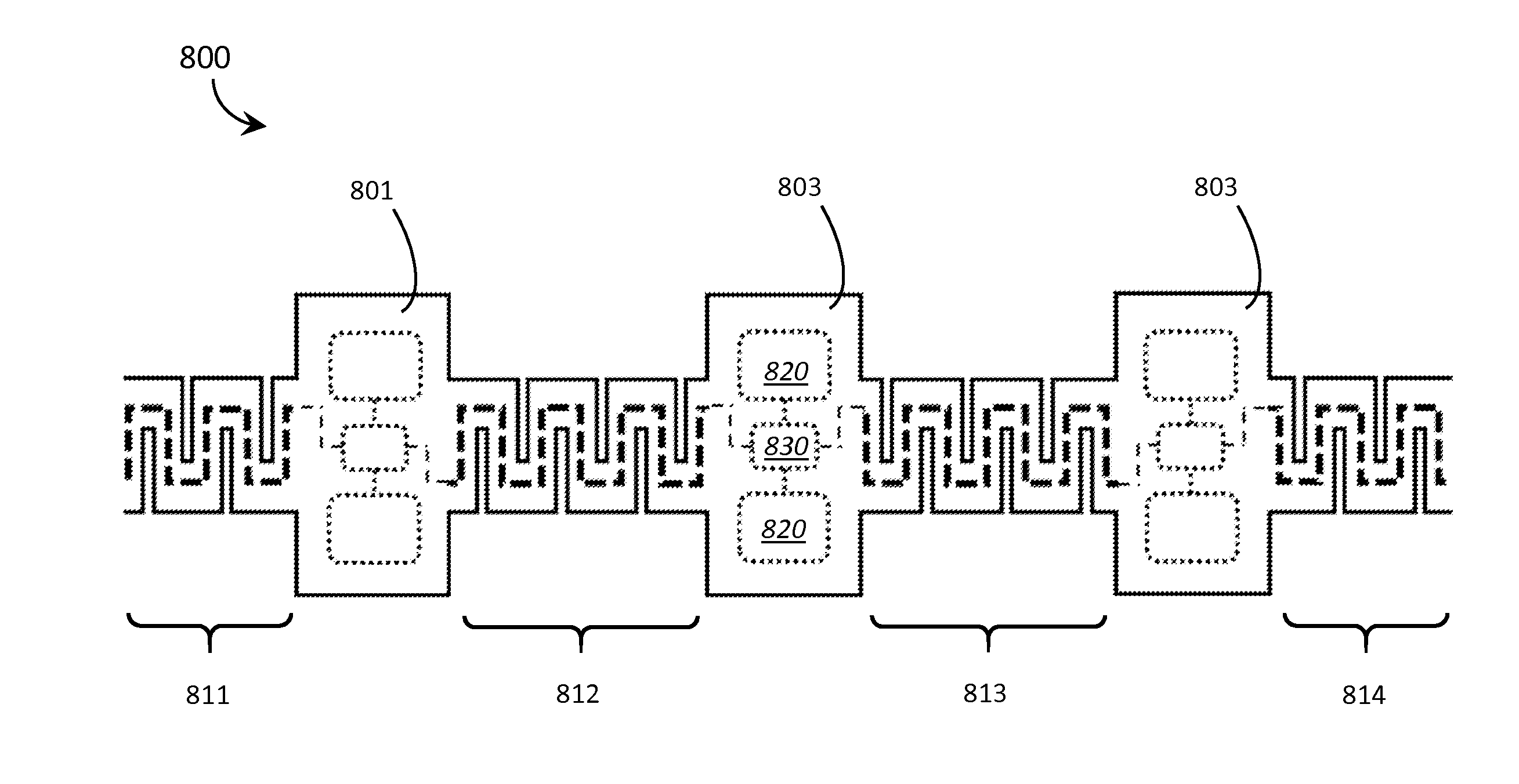

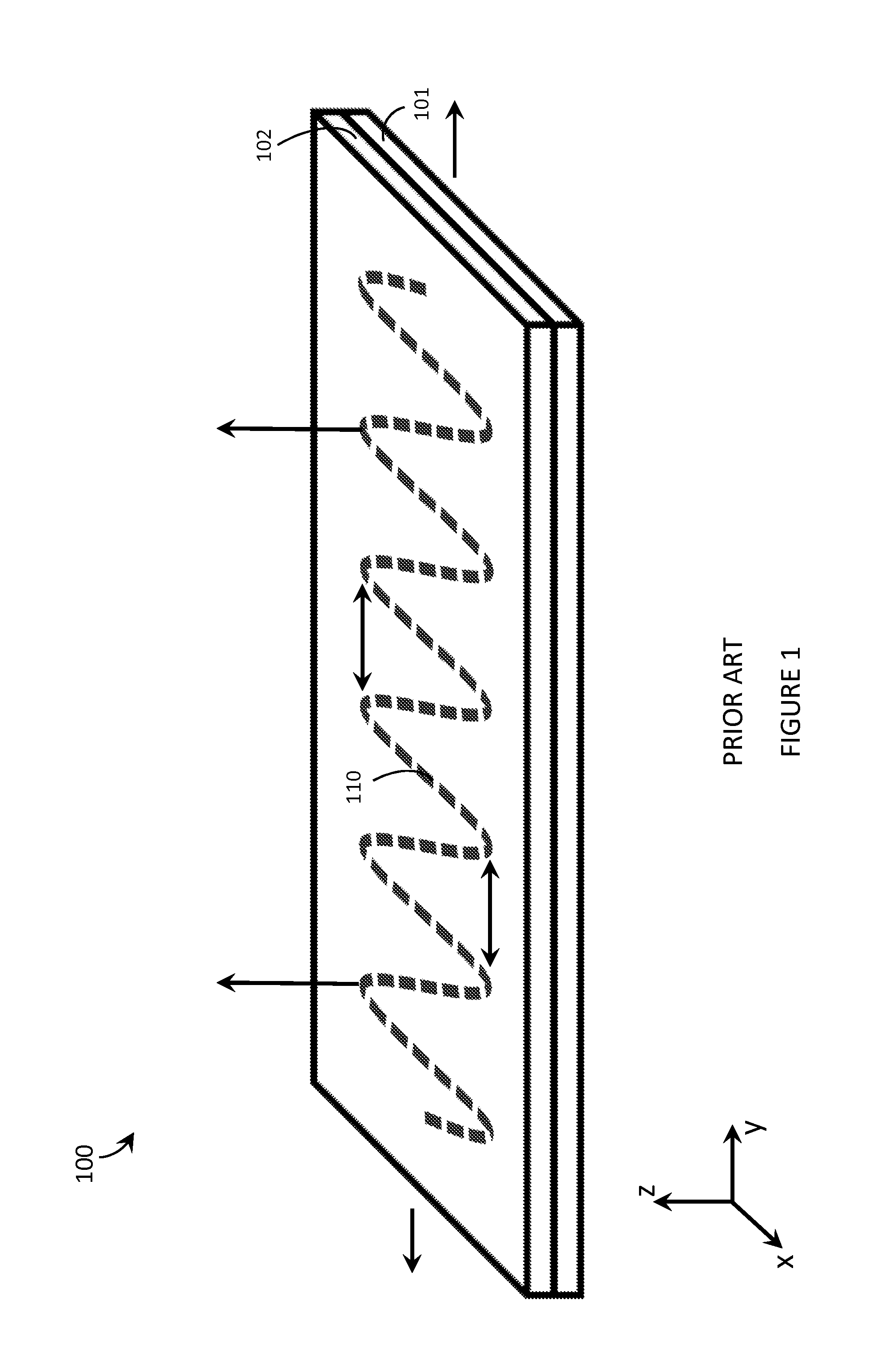

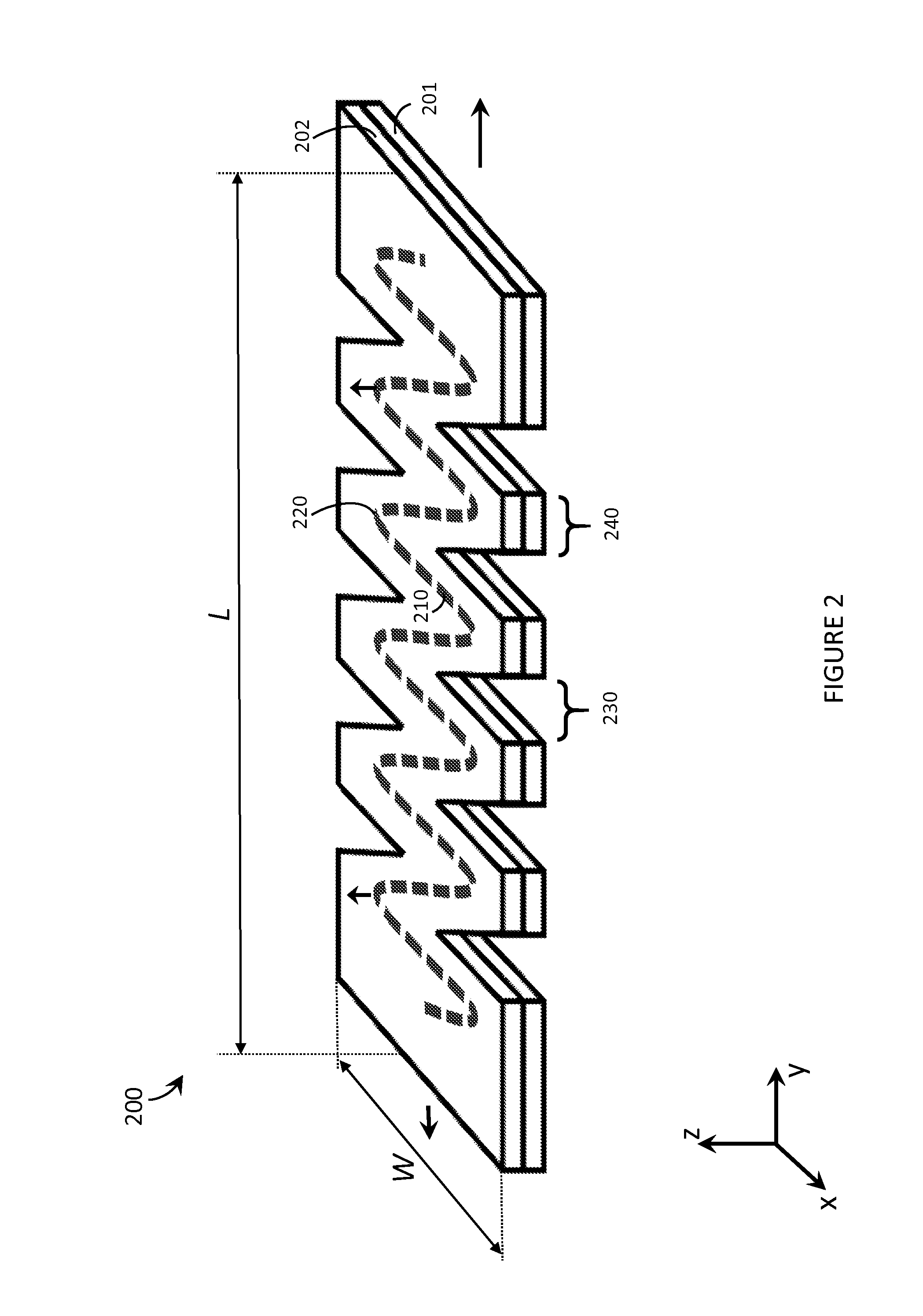

Systems, articles, and methods for stretchable printed circuit boards

ActiveUS20150065840A1Insulating layers/substrates workingSurface layering apparatusElectrical and Electronics engineering

Improved stretchable printed circuit boards, and fabrication methods thereof, are described. The improved stretchable printed circuit boards include a serpentine conductive trace enclosed by stretchable dielectric material. The stretchable dielectric material has a serpentine shape itself, realized by crenulated edges. The crenulated edges reduce torsional strain on the conductive trace and are formed, for example, by cutting away sections of the stretchable dielectric material proximate segments of the serpentine conductive trace where the serpentine conductive trace changes direction.

Owner:GOOGLE LLC

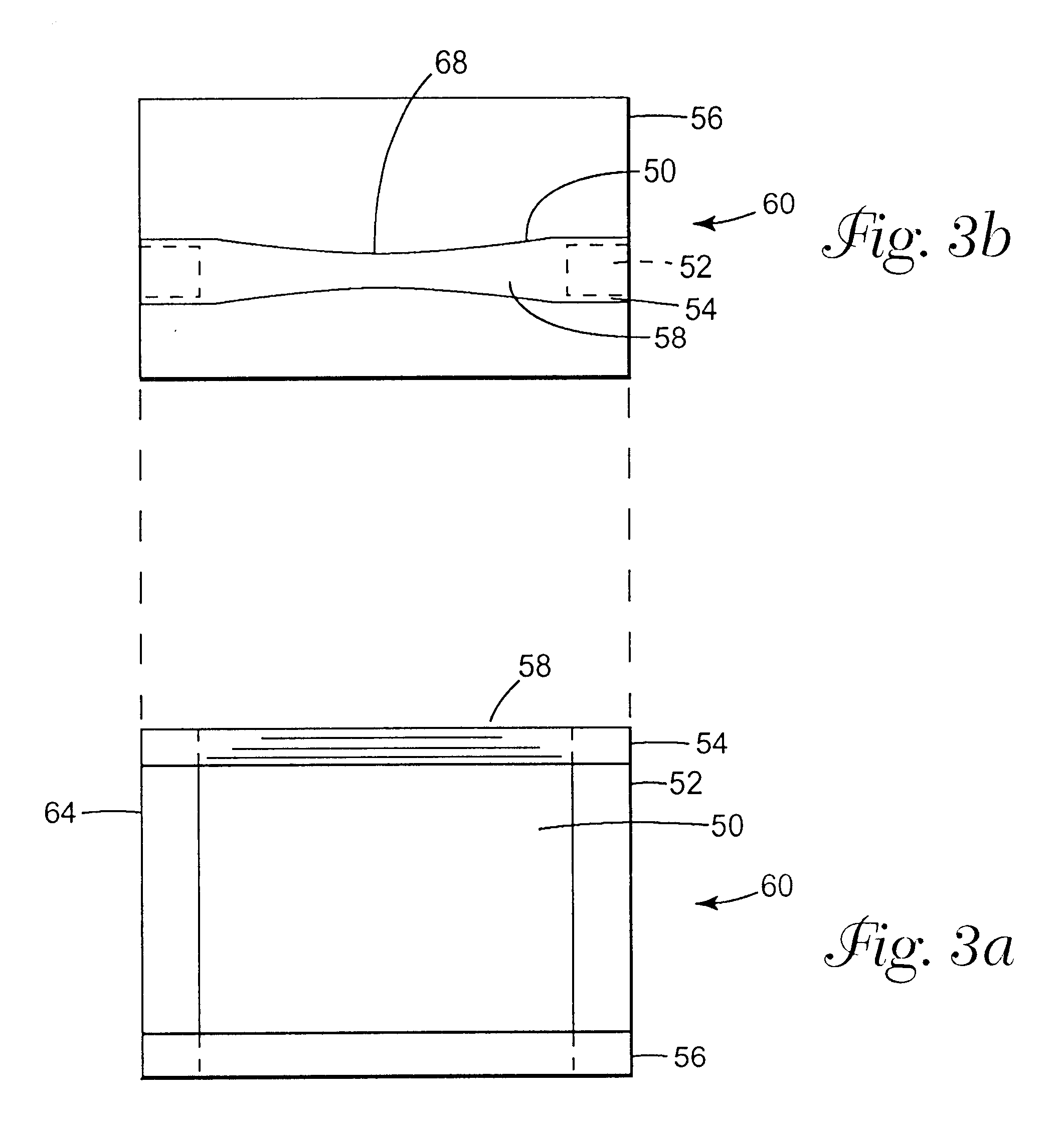

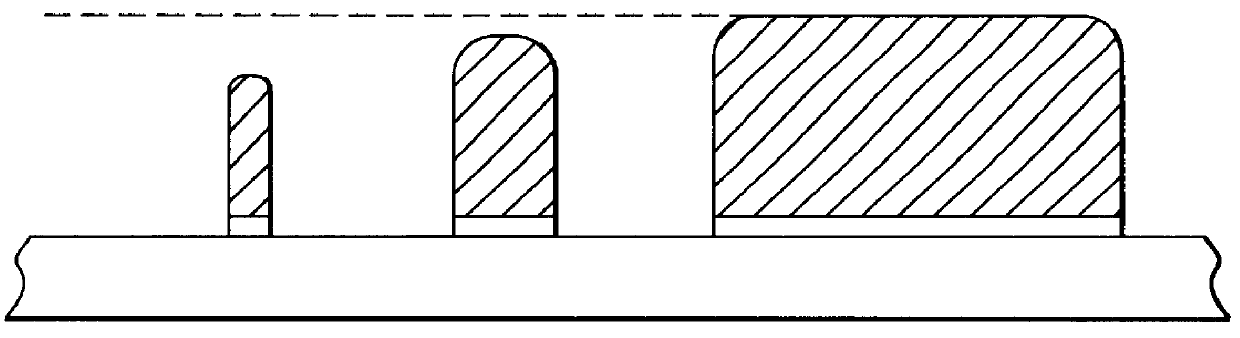

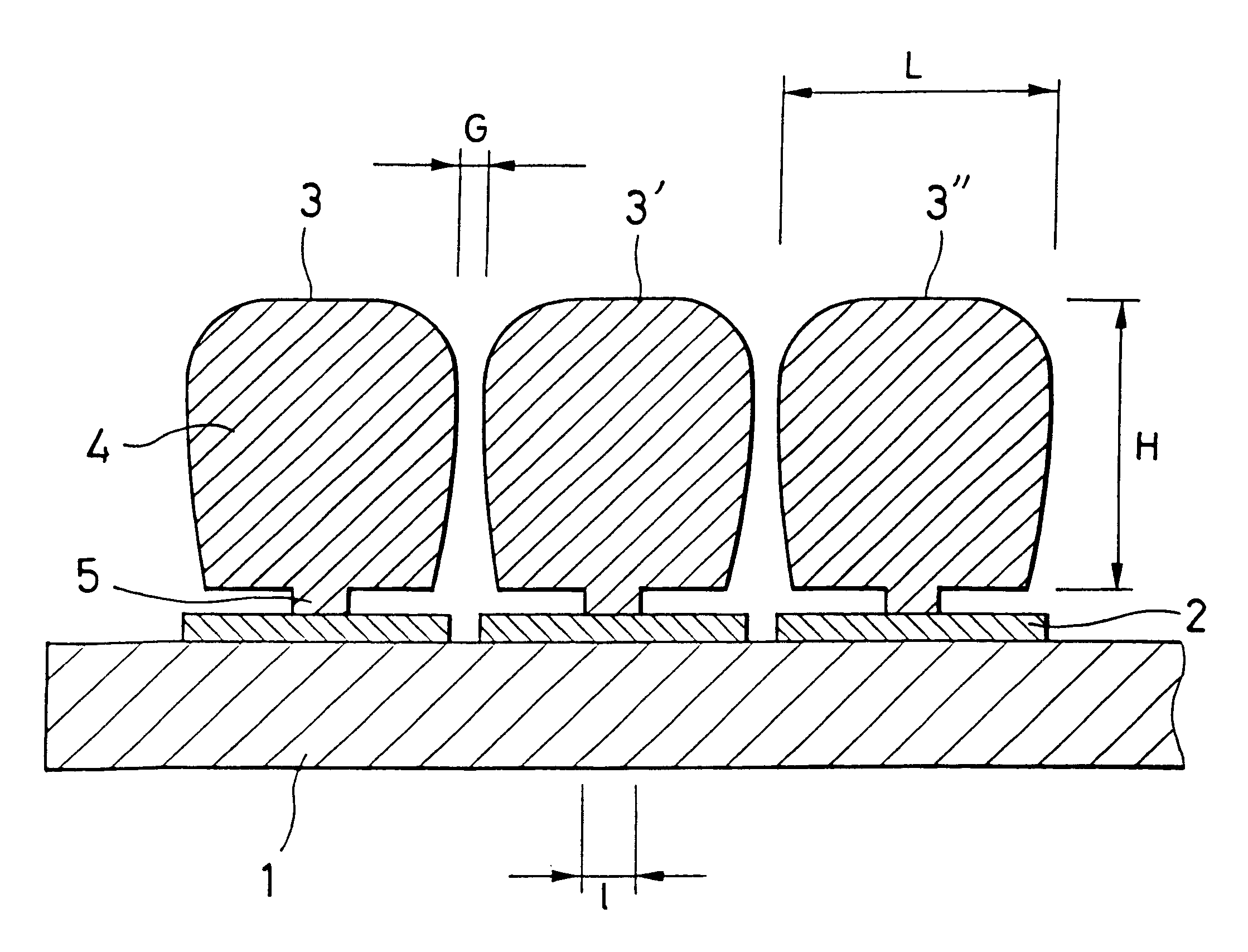

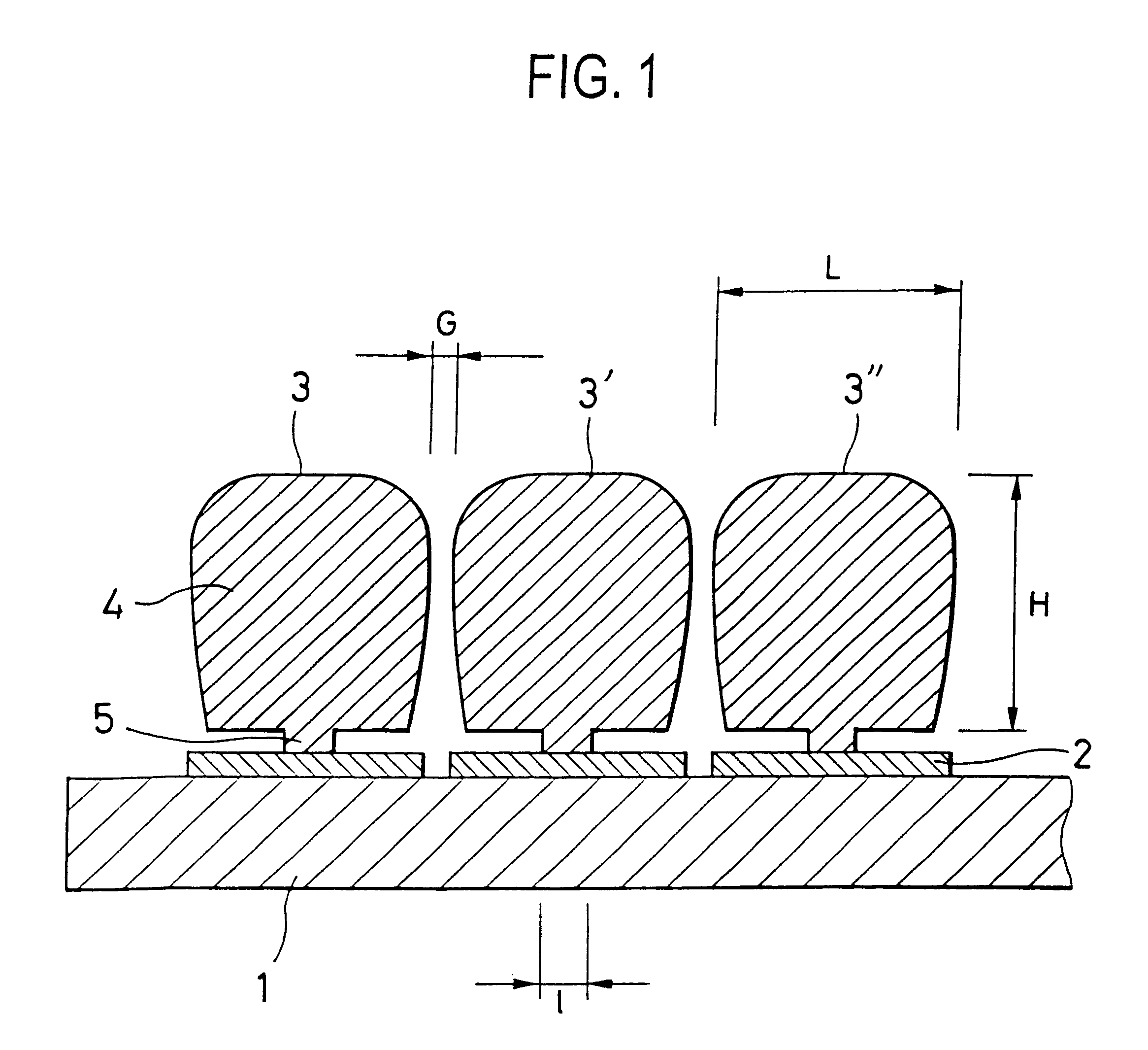

Planar coil and planar transformer, and process of fabricating a high-aspect conductive device

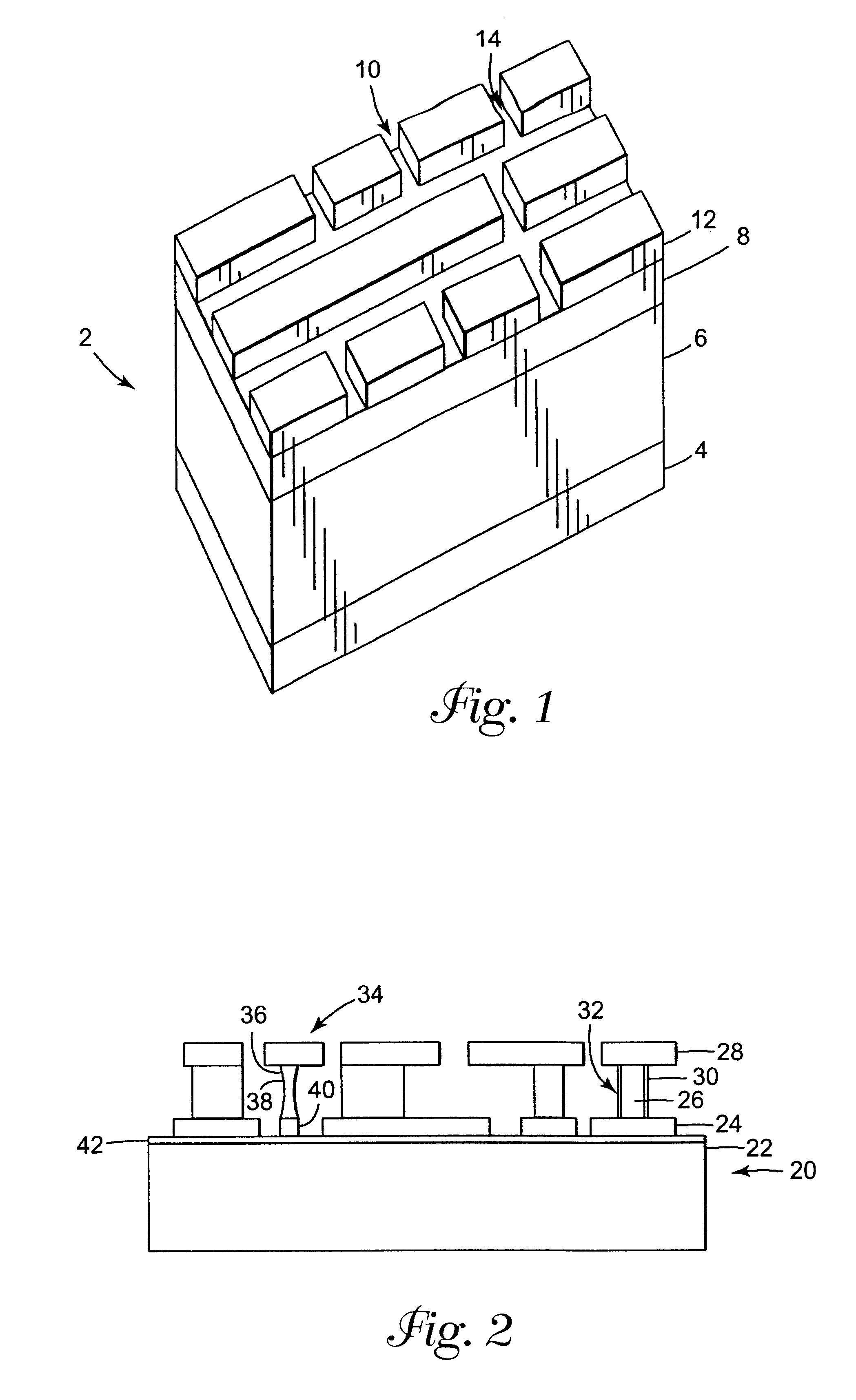

InactiveUS6600404B1Improve electrical performanceIncreases conductor thicknessTransformers/inductances coils/windings/connectionsPrinted circuit aspectsPlanar transformersPhysics

A planar coil including and insulating substrate, and a coil conductive filament having a thickness of 20 to 400 mum and formed on at least one surface of the insulating substrate, the coil conductive filament having a gap whose aspect ratio (H / G) is at least 1. The coil conductive filament has a cross-section in a substantially mushroom shape having a head and a neck, the head has a width (L) which is a least twice as large as a width (l) of the neck thereof, at most 1.5 times as large as a height of the head, and at least twice as large as a minimum spacing (G) between adjacent coil conductive filaments.

Owner:TDK CORPARATION

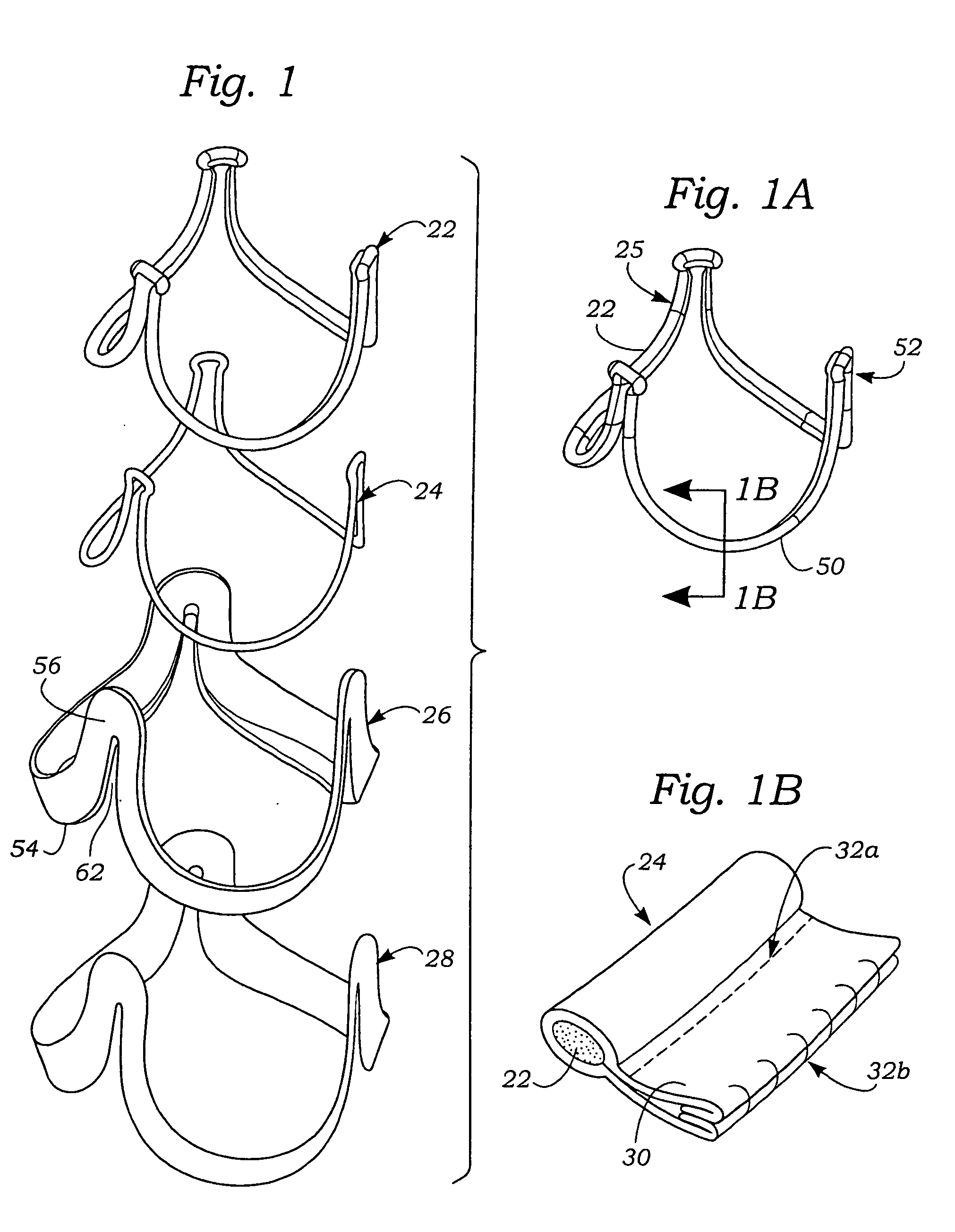

Flexible Circuit Electrode Array

ActiveUS20080288037A1Head electrodesPrinted circuit secondary treatmentFlexible circuitsElectrode array

A flexible circuit electrode array with more than one layer of metal traces comprising: a polymer base layer; more than one layer of metal traces, separated by polymer layers, deposited on said polymer base layer, including electrodes suitable to stimulate neural tissue; and a polymer top layer deposited on said polymer base layer and said metal traces. Polymer materials are useful as electrode array bodies for neural stimulation. They are particularly useful for retinal stimulation to create artificial vision, cochlear stimulation to create artificial hearing, or cortical stimulation many purposes. The pressure applied against the retina, or other neural tissue, by an electrode array is critical. Too little pressure causes increased electrical resistance, along with electric field dispersion. Too much pressure may block blood flow.

Owner:CORTIGENT INC

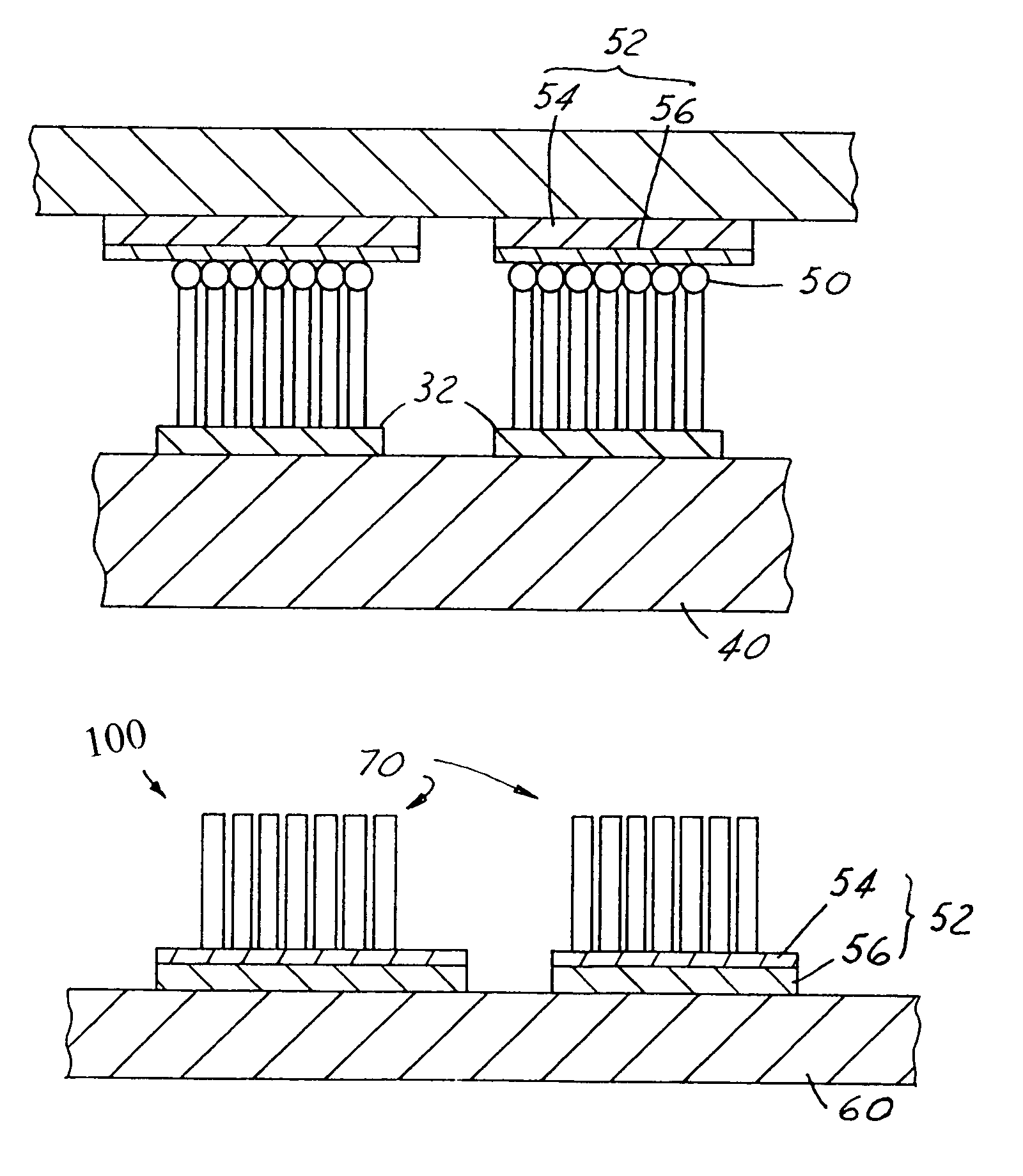

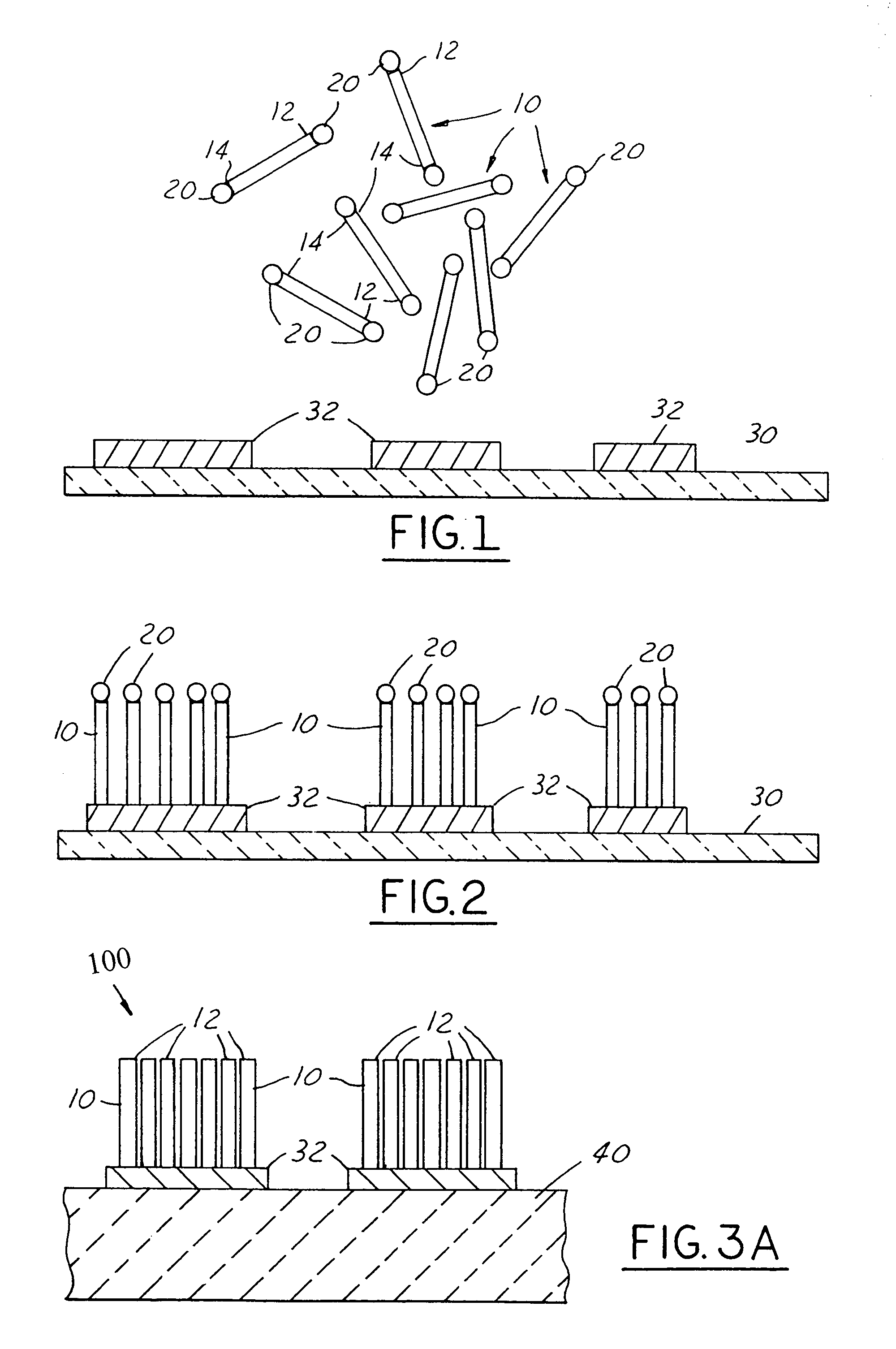

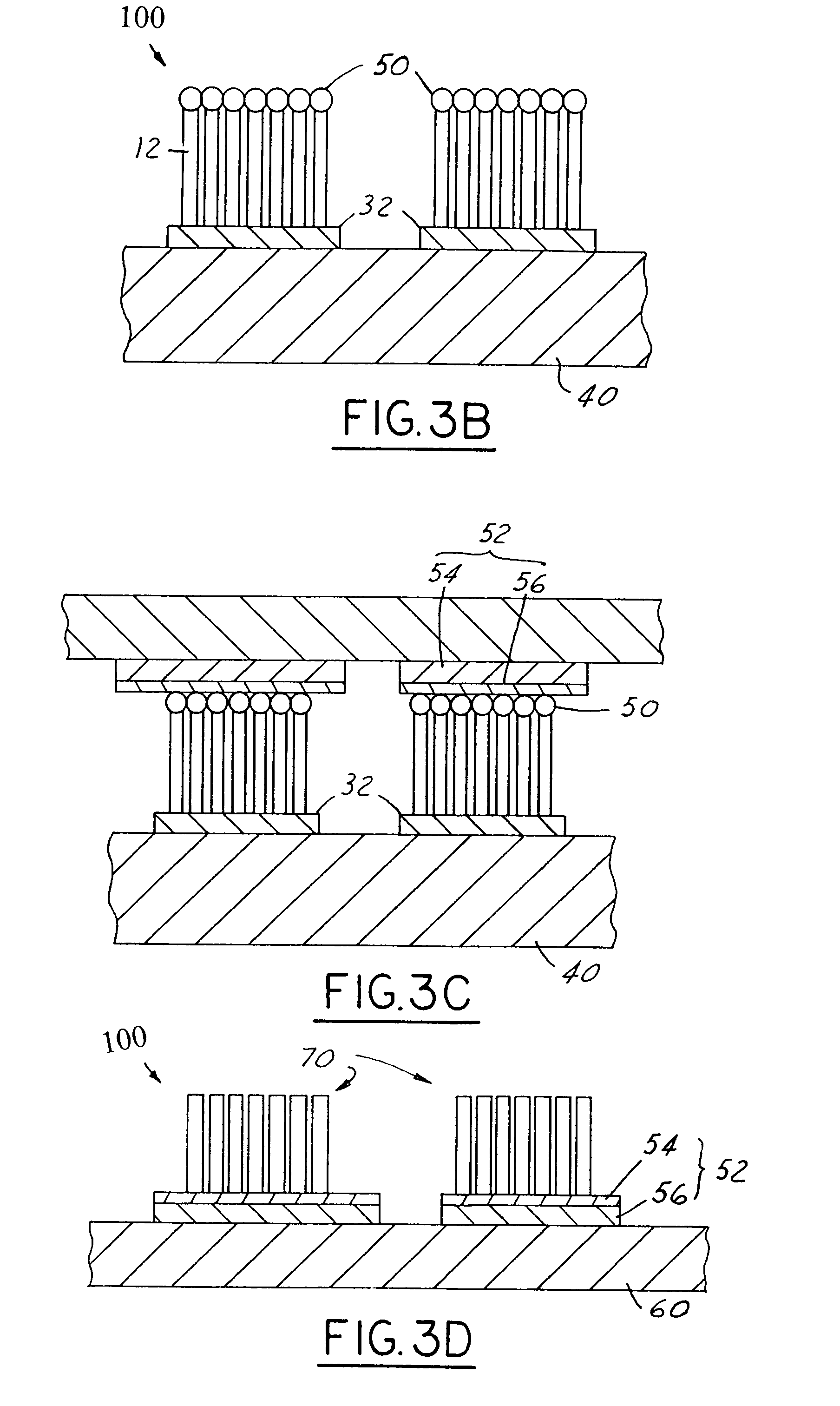

Self-assembled nanometer conductive bumps and method for fabricating

Owner:IND TECH RES INST

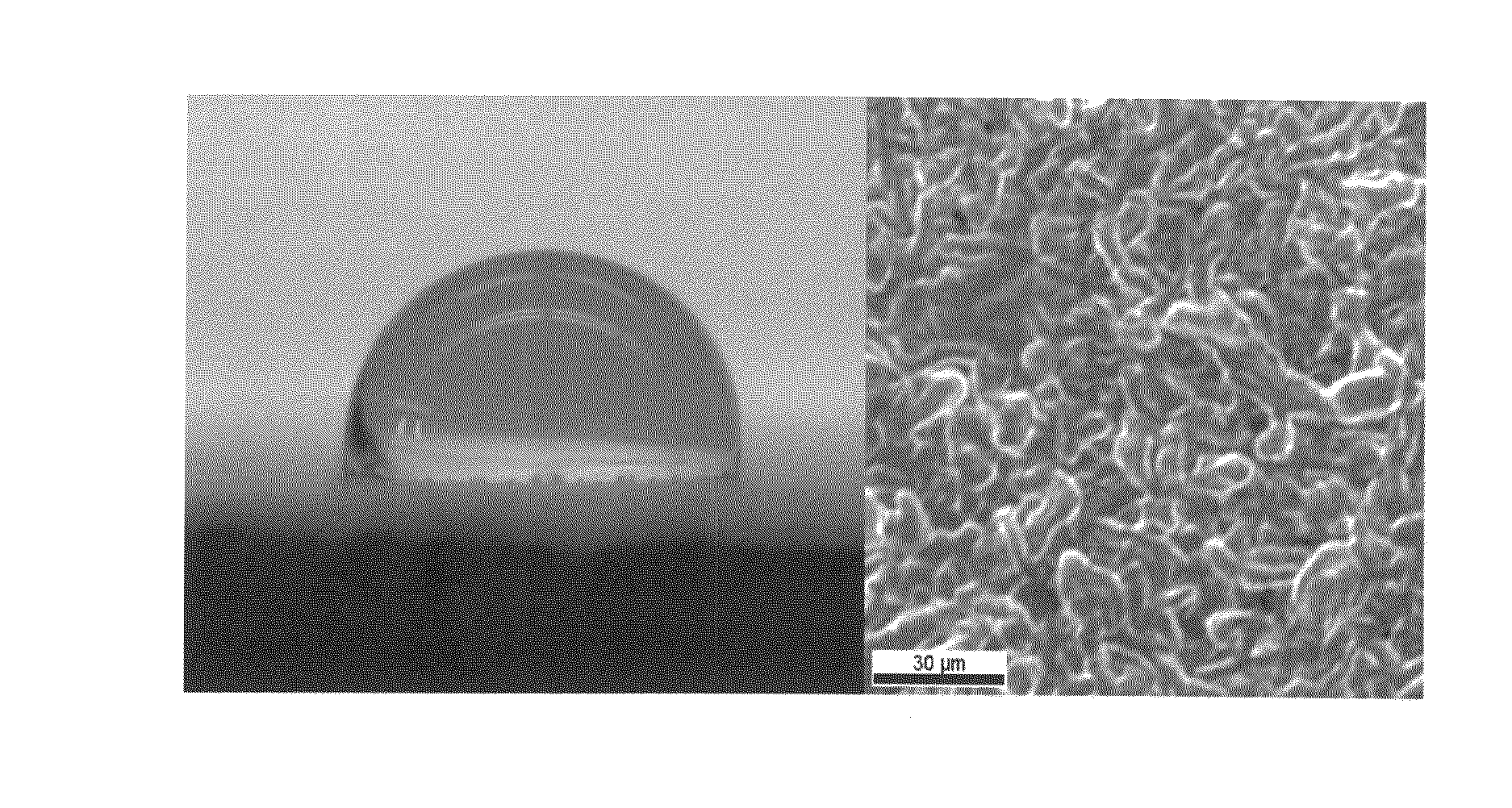

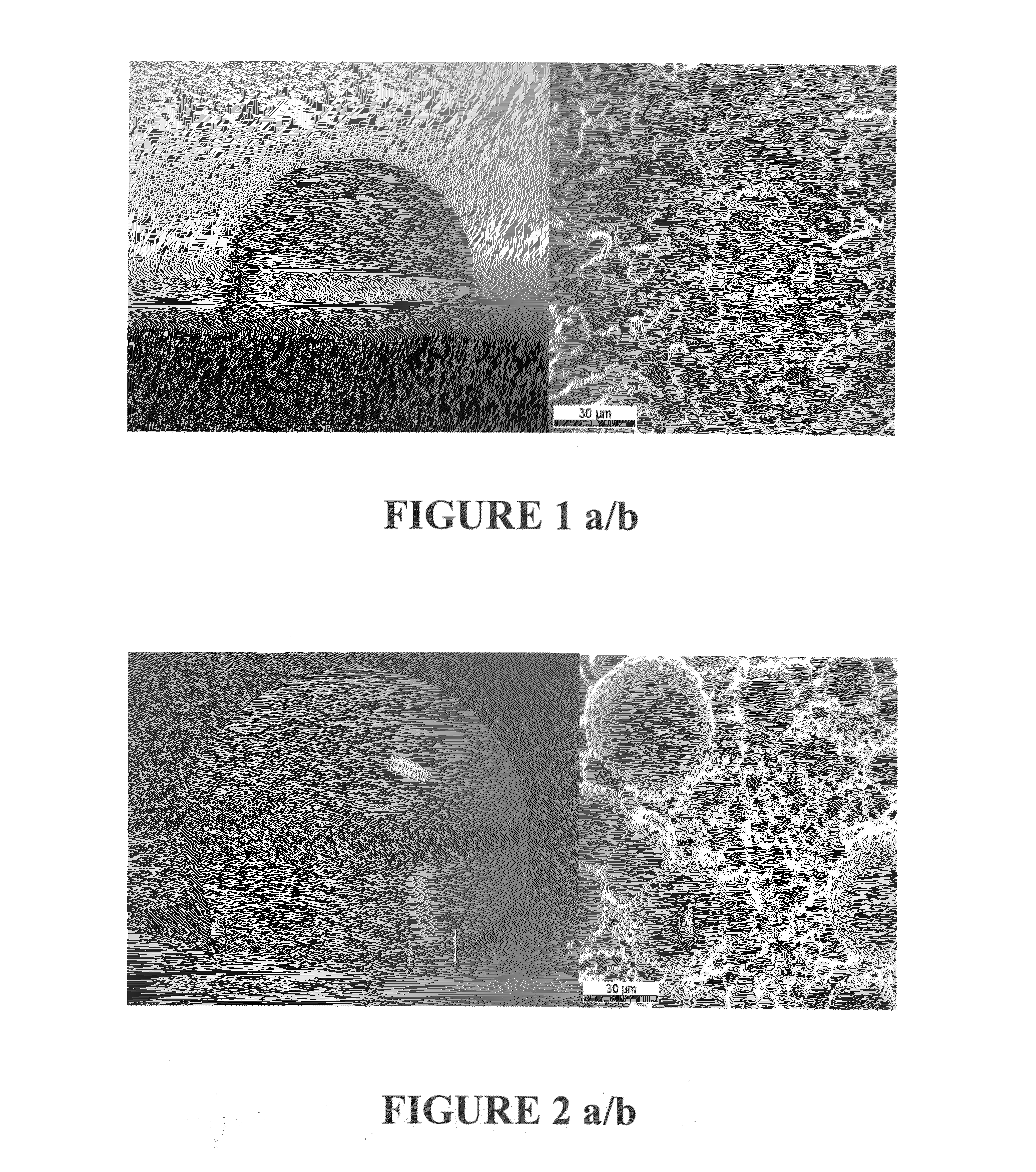

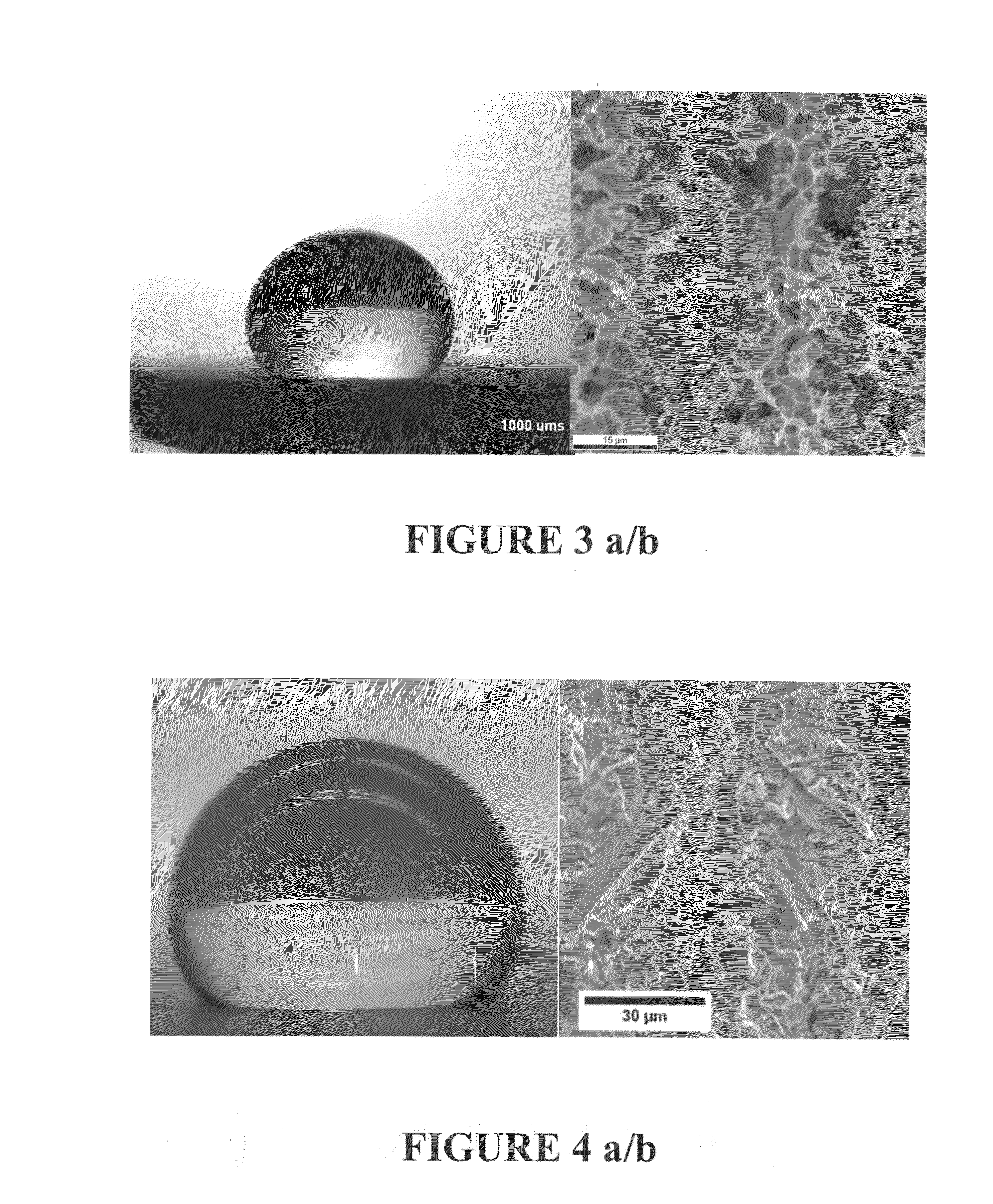

Metallic articles with hydrophobic surfaces

ActiveUS20110287223A1Lower contact angleLarge scaleElectrolysis componentsPretreated surfacesMetal coatingMetallic materials

Articles containing fine-grained and / or amorphous metallic coatings / layers on at least part of their exposed surfaces are imprinted with surface structures to raise the contact angle for water in the imprinted areas at room temperature by equal to or greater than 10°, when compared to the flat and smooth metallic material surface of the same composition.

Owner:INTEGRAN TECH

Circuit manufacturing using etched tri-metal media

InactiveUS6365057B1Printed circuit aspectsSemiconductor/solid-state device manufacturingElectrical connectionCopper

A process for the formation of an article having multiple electrical circuits comprises:providing a first sub-element comprising in sequence a first metal layer of copper in electrical contact with a second metal layer of aluminum in electrical contact with a third metal layer of copper;etching an electrical circuit design in the first metal layer and in a separate etch step, etching away at least 10%, but less than 100% of the second metal layer to provide electrical connections between the first metal layer and the third metal layer;etching an electrical circuit design into the third metal layer;adhering an etched surface comprising the circuit design of the first or third metal layer to a first surface of a support layer to form a circuit board.The process may etch the first and third metal layers simultaneously or sequentially. After adhering an etched surface comprising the circuit design of the first or third metal layer to a support layer to form a circuit board, an additional step may be performed, which additional step is selected from the group consisting of;a) adhering an etched surface of a second tri-metal subelement to a second surface of the support layer andb) adhering a second support layer to said third or first metal layer, respectively, and adhering an etched surface of a second tri-metal subelement to the second support layer.

Owner:BMC INDS

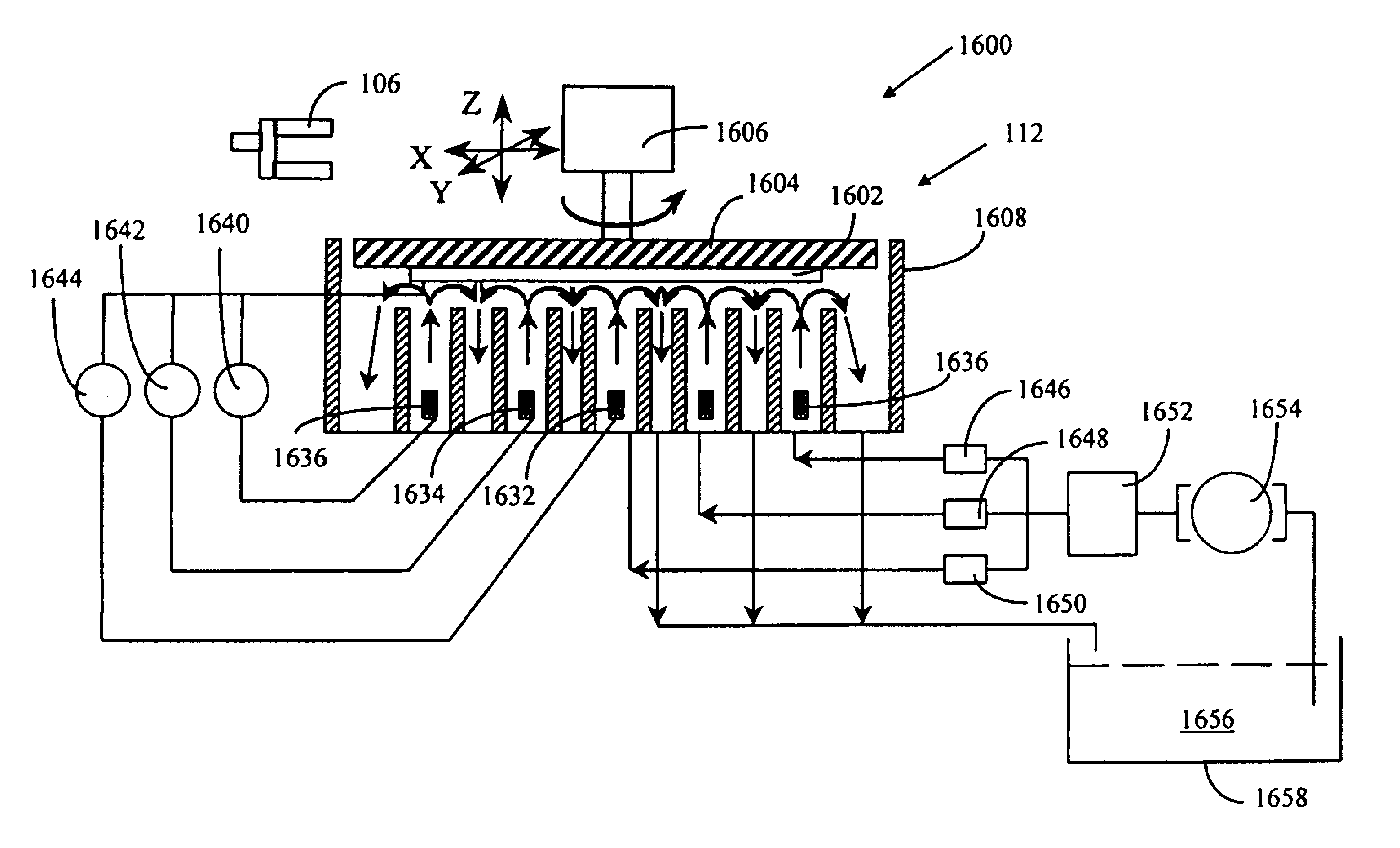

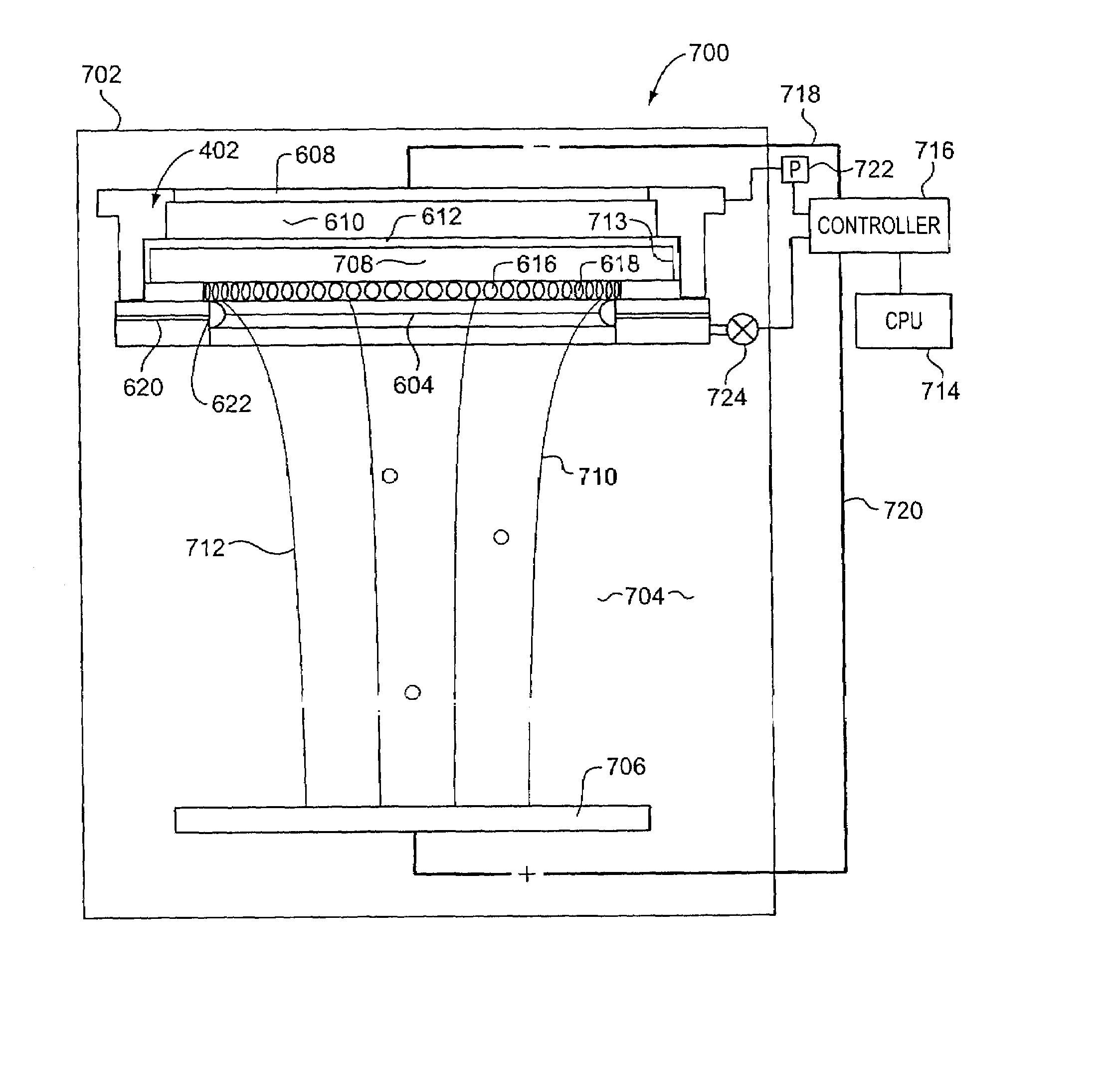

Dynamically variable field shaping element

InactiveUS7070686B2Uniform current distributionUniform currentAnodisationMachining electric circuitsElectrical resistance and conductanceElectrochemical response

In an electrochemical reactor used for electrochemical treatment of a substrate, for example, for electroplating or electropolishing the substrate, one or more of the surface area of a field-shaping shield, the shield's distance between the anode and cathode, and the shield's angular orientation is varied during electrochemical treatment to screen the applied field and to compensate for potential drop along the radius of a wafer. The shield establishes an inverse potential drop in the electrolytic fluid to overcome the resistance of a thin film of conductive metal on the wafer.

Owner:NOVELLUS SYSTEMS

Semiconductor chip assembly with embedded metal pillar

InactiveUS7190080B1Enhancing mechanical supportImprove protectionSemiconductor/solid-state device detailsSolid-state devicesSemiconductor chipMetal

A semiconductor chip assembly includes a semiconductor chip that includes a conductive pad, a conductive trace that includes a routing line and a pillar, a connection joint that electrically connects the routing line and the pad, and an encapsulant. The routing line extends laterally from the pillar towards the chip, the pillar includes tapered sidewalls, and the chip and the pillar are embedded in the encapsulant and extend vertically beyond the routing line in the same direction.

Owner:BRIDGE SEMICON

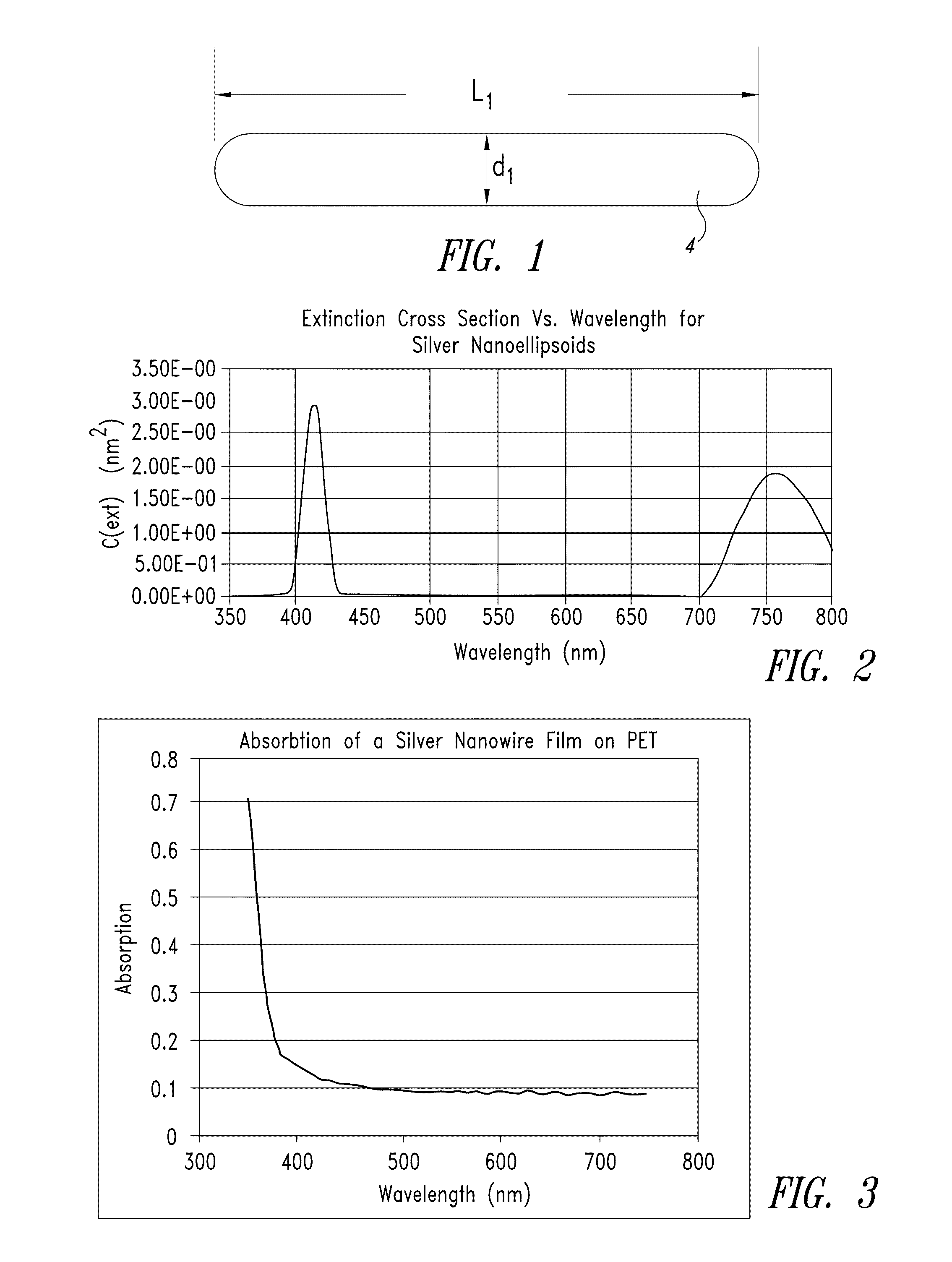

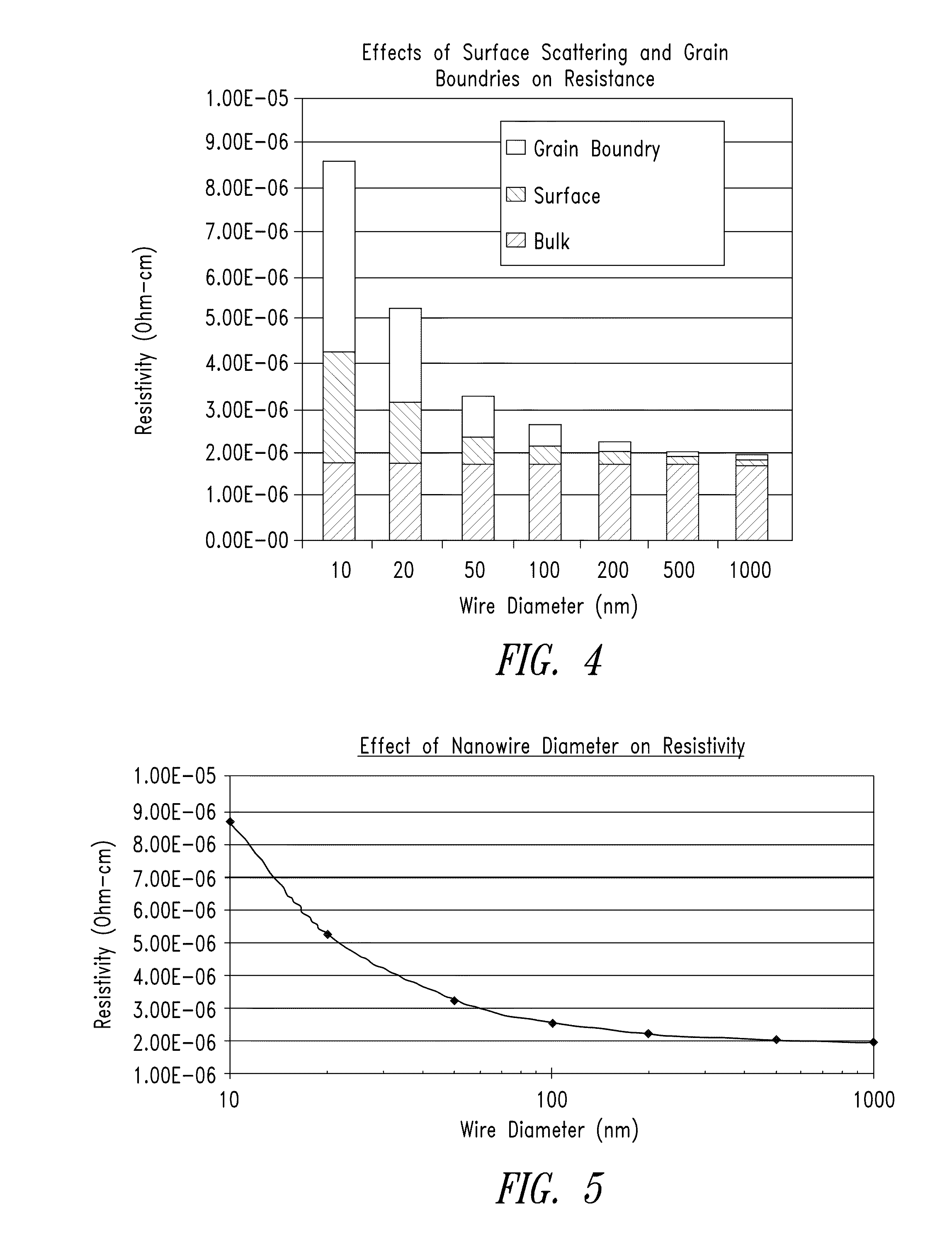

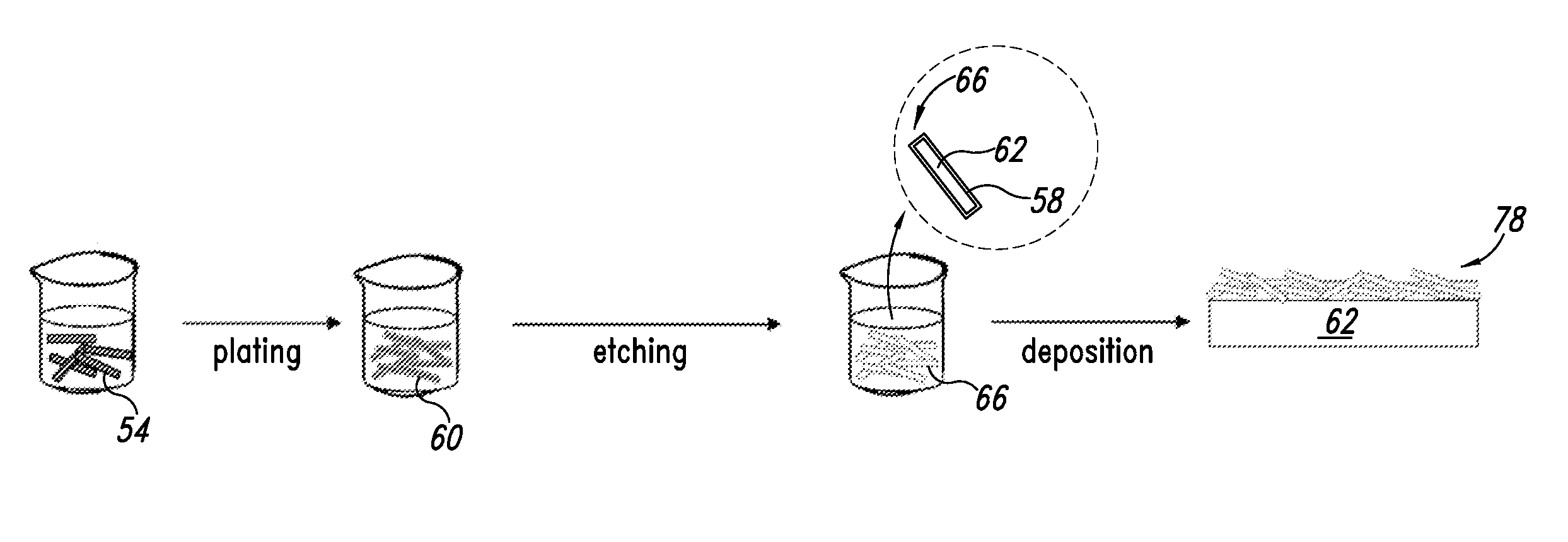

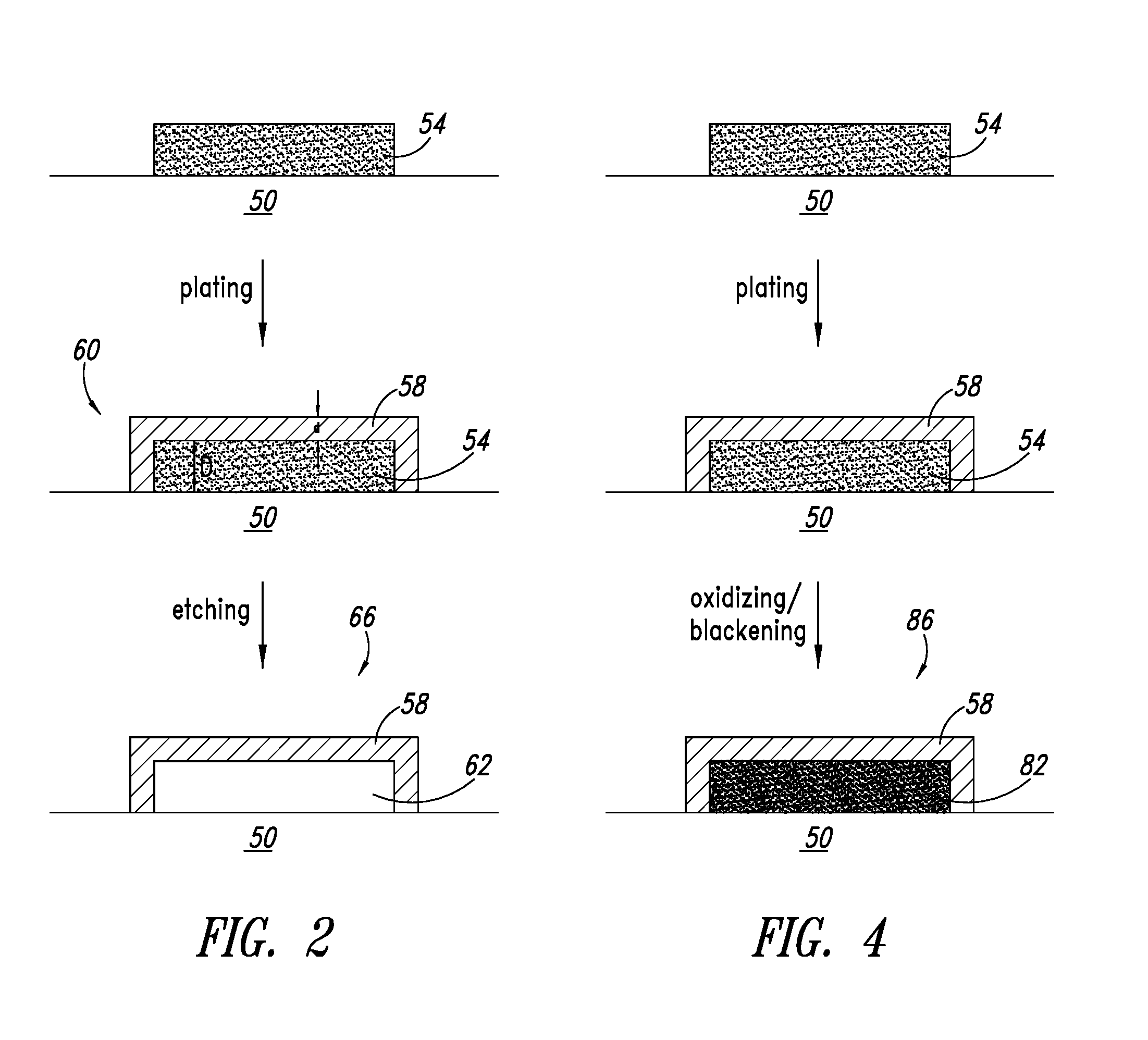

High contrast transparent conductors and methods of forming the same

InactiveUS20090321113A1Material nanotechnologyElectrolysis componentsElectrical conductorNanostructure

Methods of enhancing contrast ratio of conductive nanostructure-based transparent conductors are described. Contrast ratio is significantly improved by reduction of light scattering and reflectivity of the nanostructures through steps of plating the conductive nanostructures followed by etching or oxidizing the underlying conductive nanostructures.

Owner:CAM HLDG CORP +1

Printed wiring board and method for producing the same

InactiveUS20050258522A1Satisfactory in adhesionSatisfactory in dielectric constantInsulating substrate metal adhesion improvementSemiconductor/solid-state device detailsElectrical conductorPolyolefin

The present invention has for its object to provide a multilayer printed circuit board which is very satisfactory in facture toughness, dielectric constant, adhesion and processability, among other characteristics. The present invention is directed to a multilayer printed circuit board comprising a substrate board, a resin insulating layer formed on said board and a conductor circuit constructed on said resin insulating layer, wherein said resin insulating layer comprises a polyolefin resin.

Owner:IBIDEN CO LTD

Features

- R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

Why Patsnap Eureka

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Social media

Patsnap Eureka Blog

Learn More Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com