Patents

Literature

260 results about "Programmable logic array" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

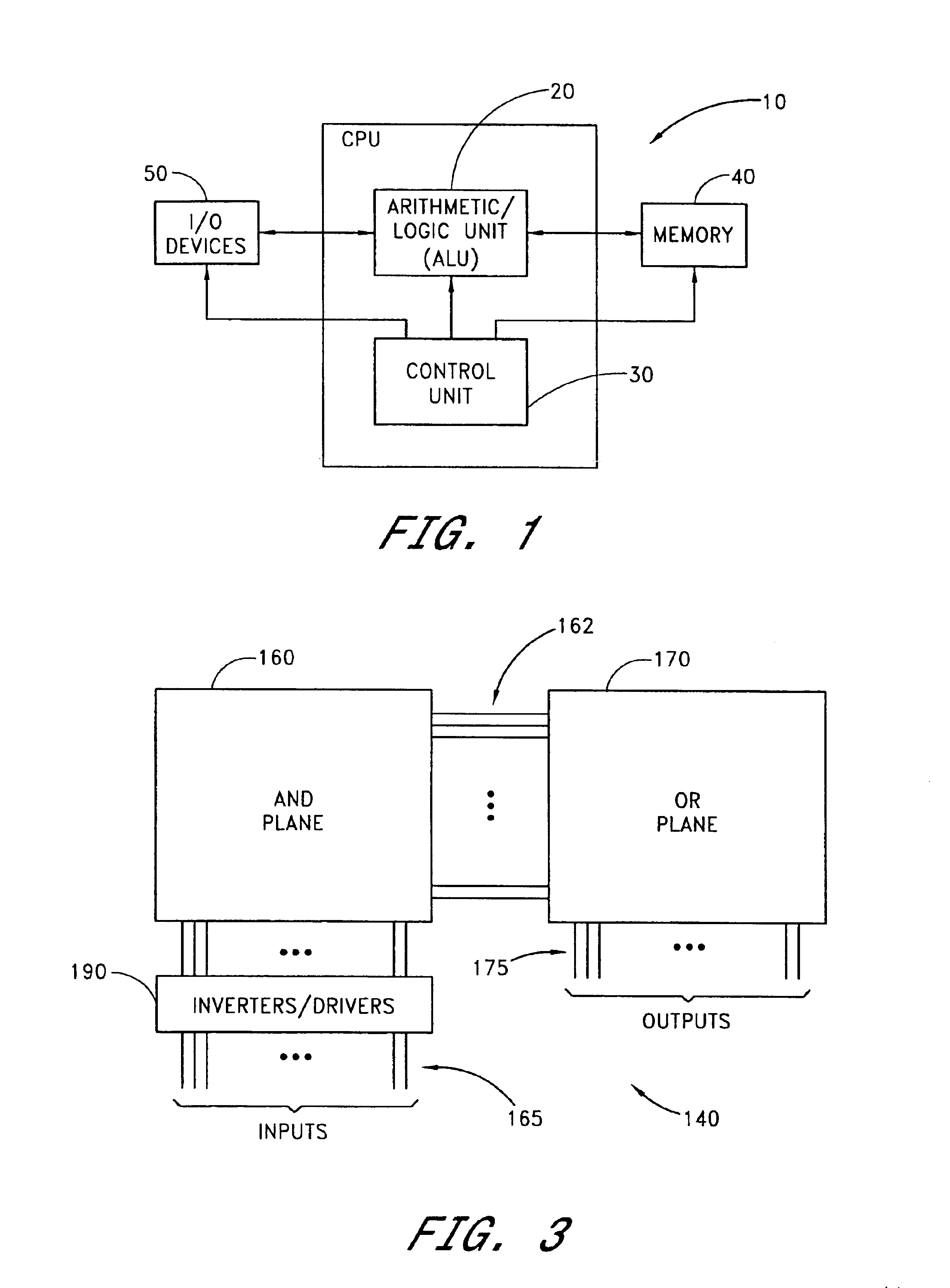

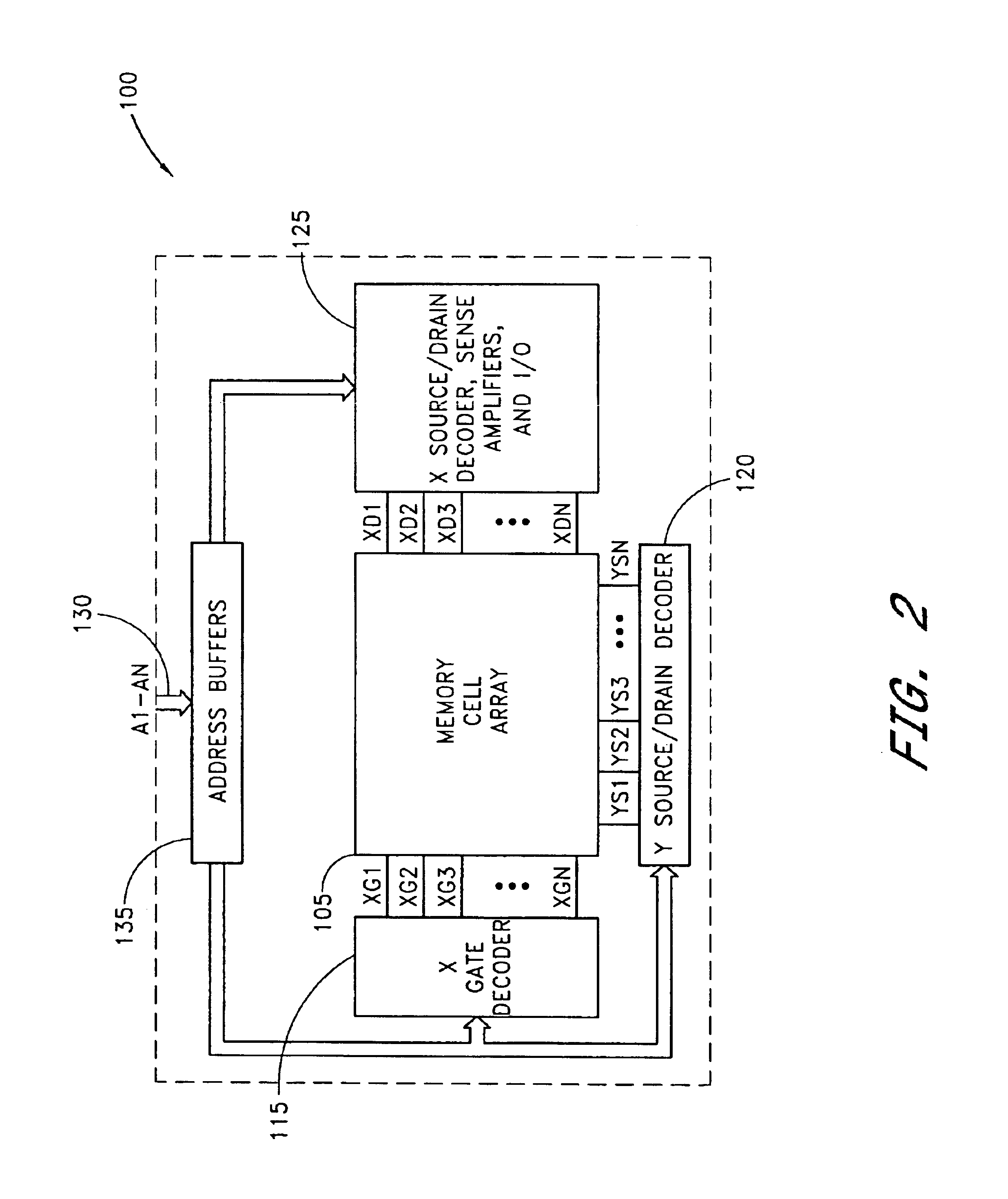

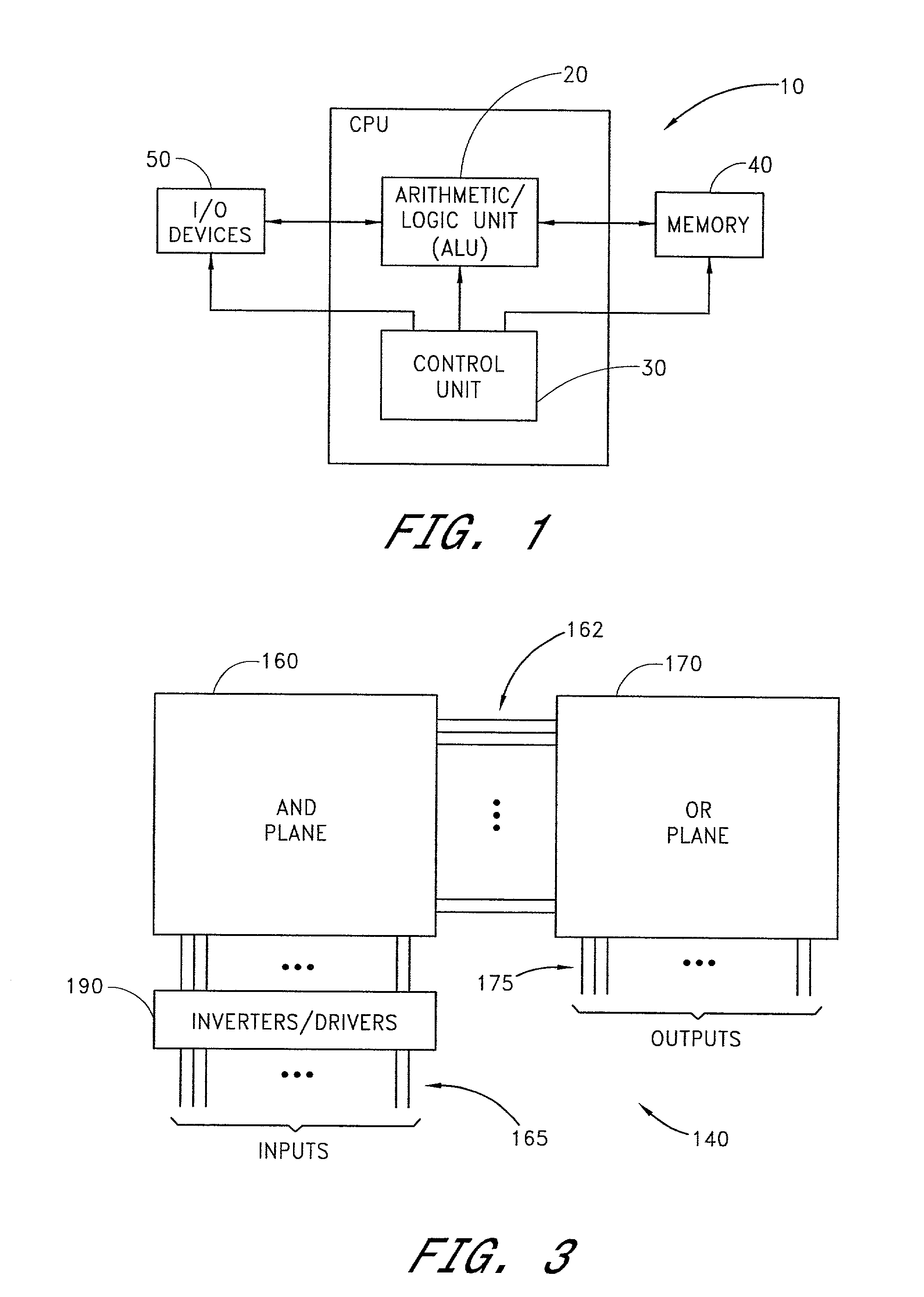

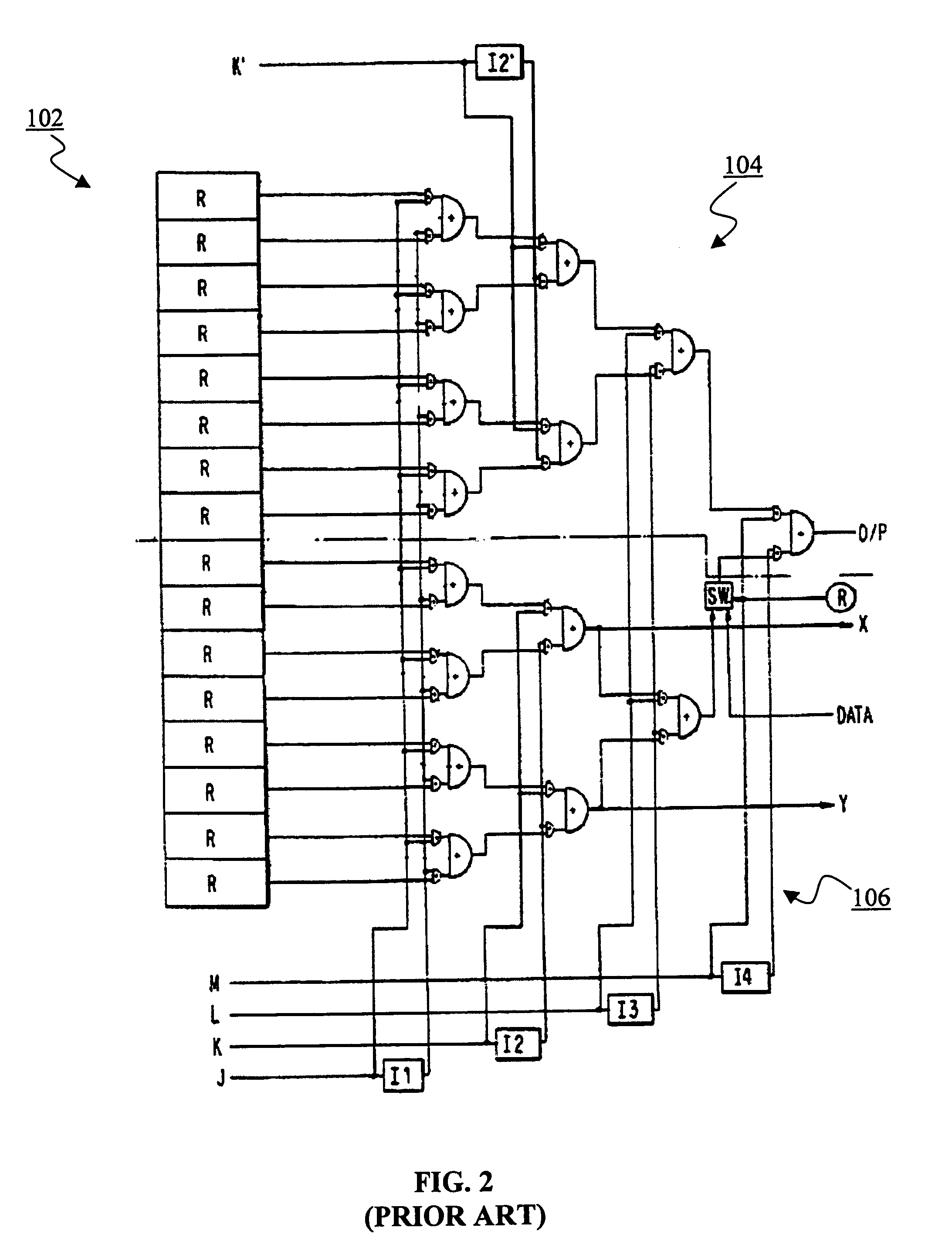

A programmable logic array (PLA) is a kind of programmable logic device used to implement combinational logic circuits. The PLA has a set of programmable AND gate planes, which link to a set of programmable OR gate planes, which can then be conditionally complemented to produce an output. It has 2ᴺ AND Gates for N input variables, and for M outputs from PLA, there should be M OR Gates, each with programmable inputs from all of the AND gates. This layout allows for many logic functions to be synthesized in the sum of products canonical forms.

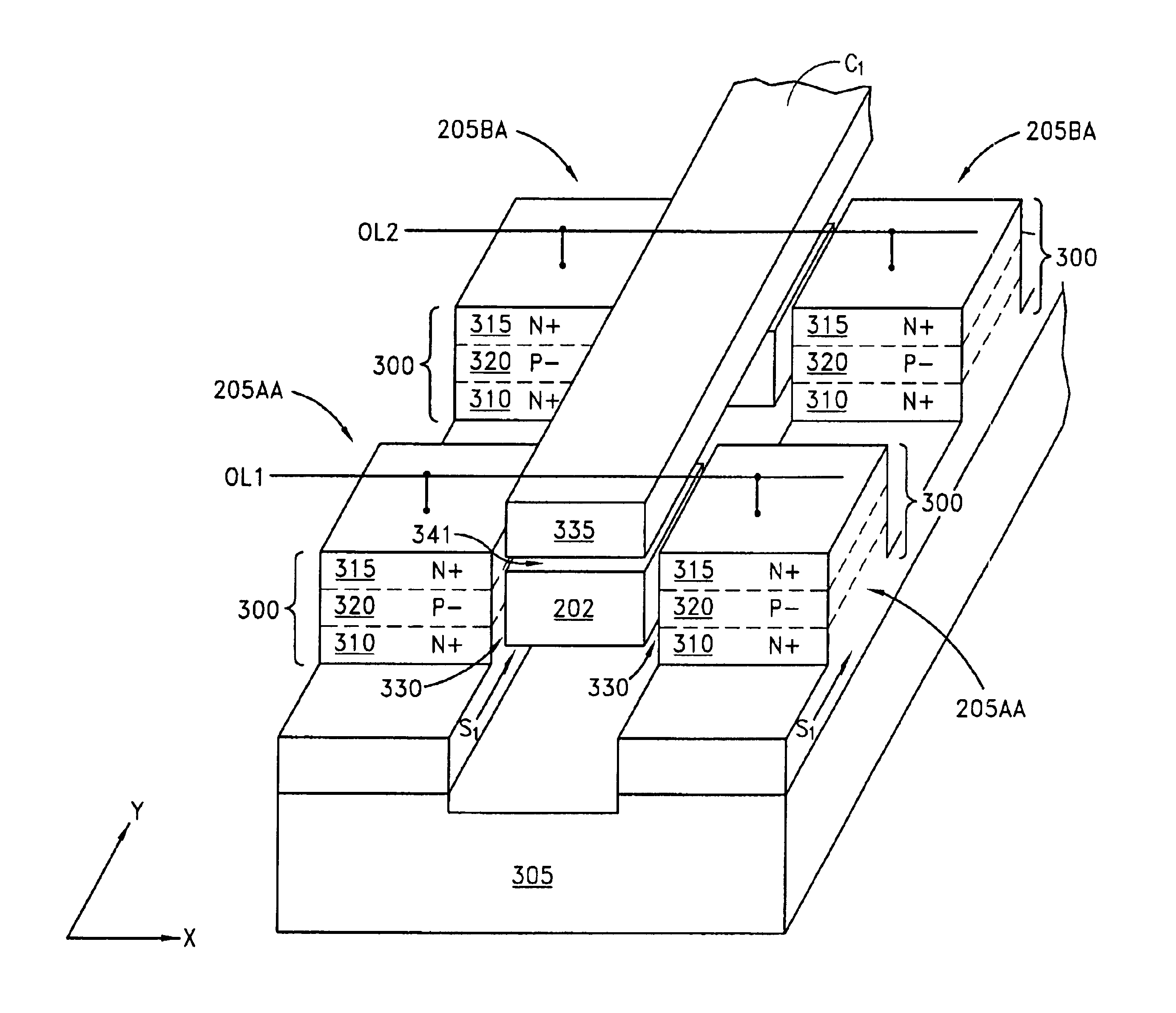

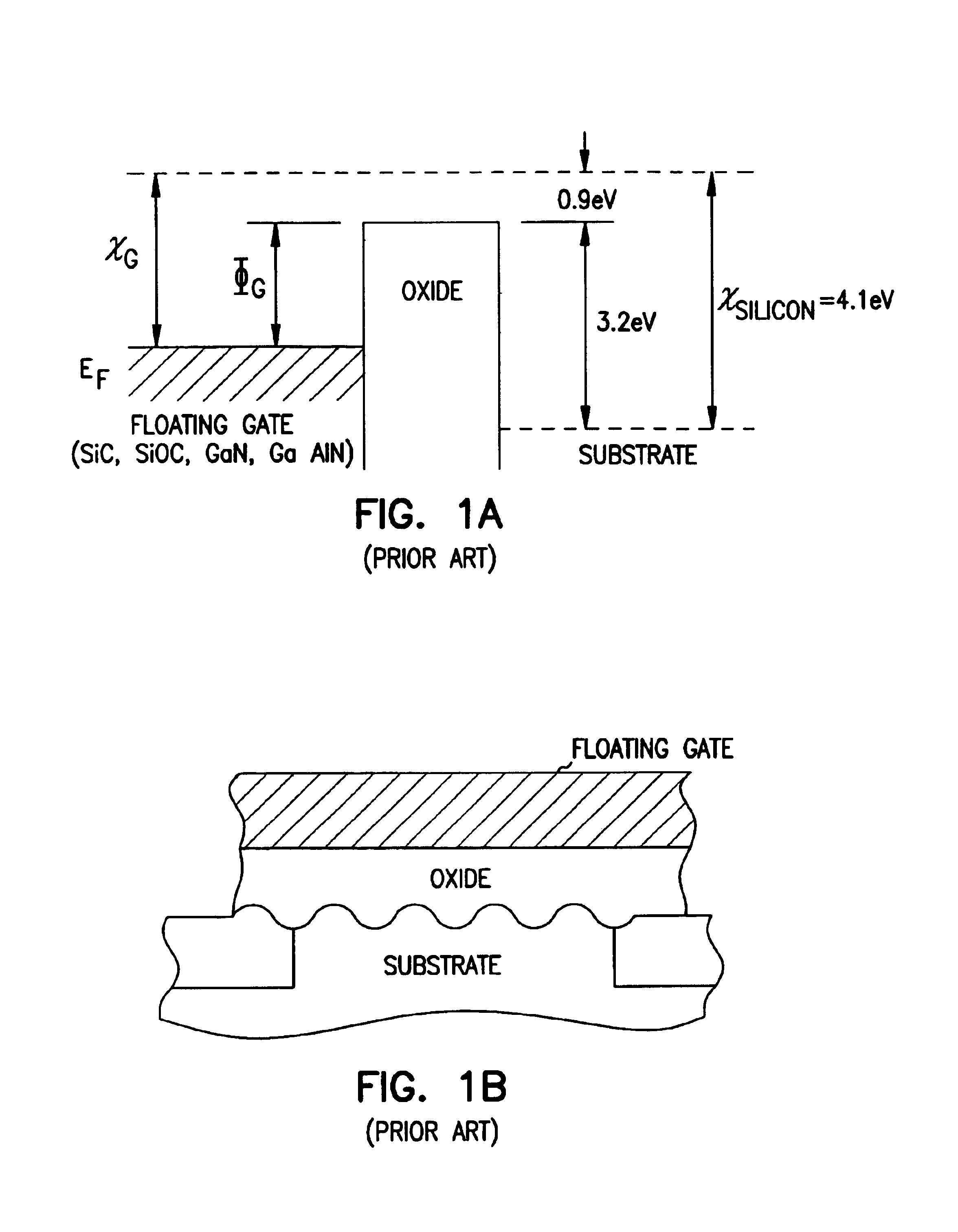

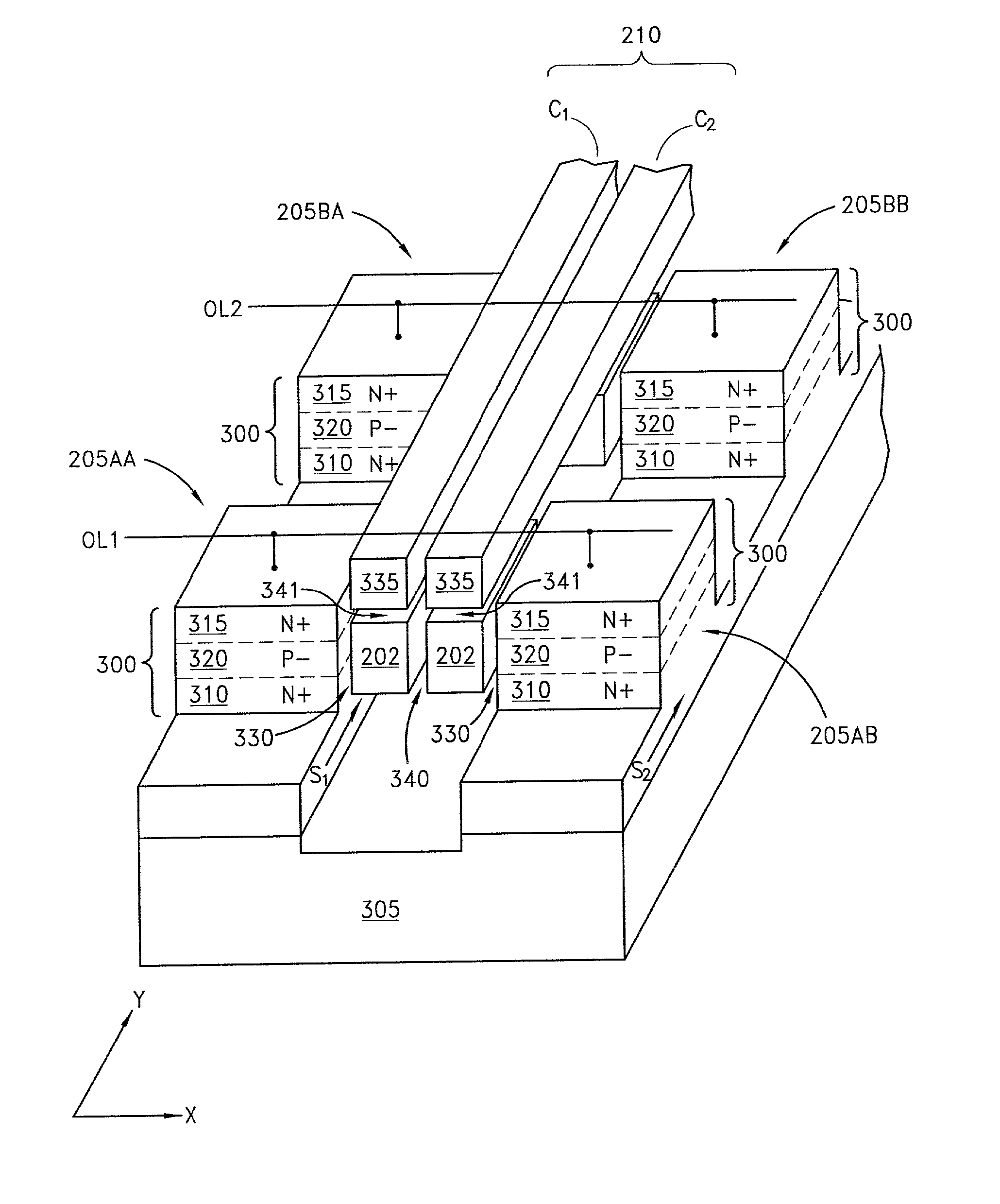

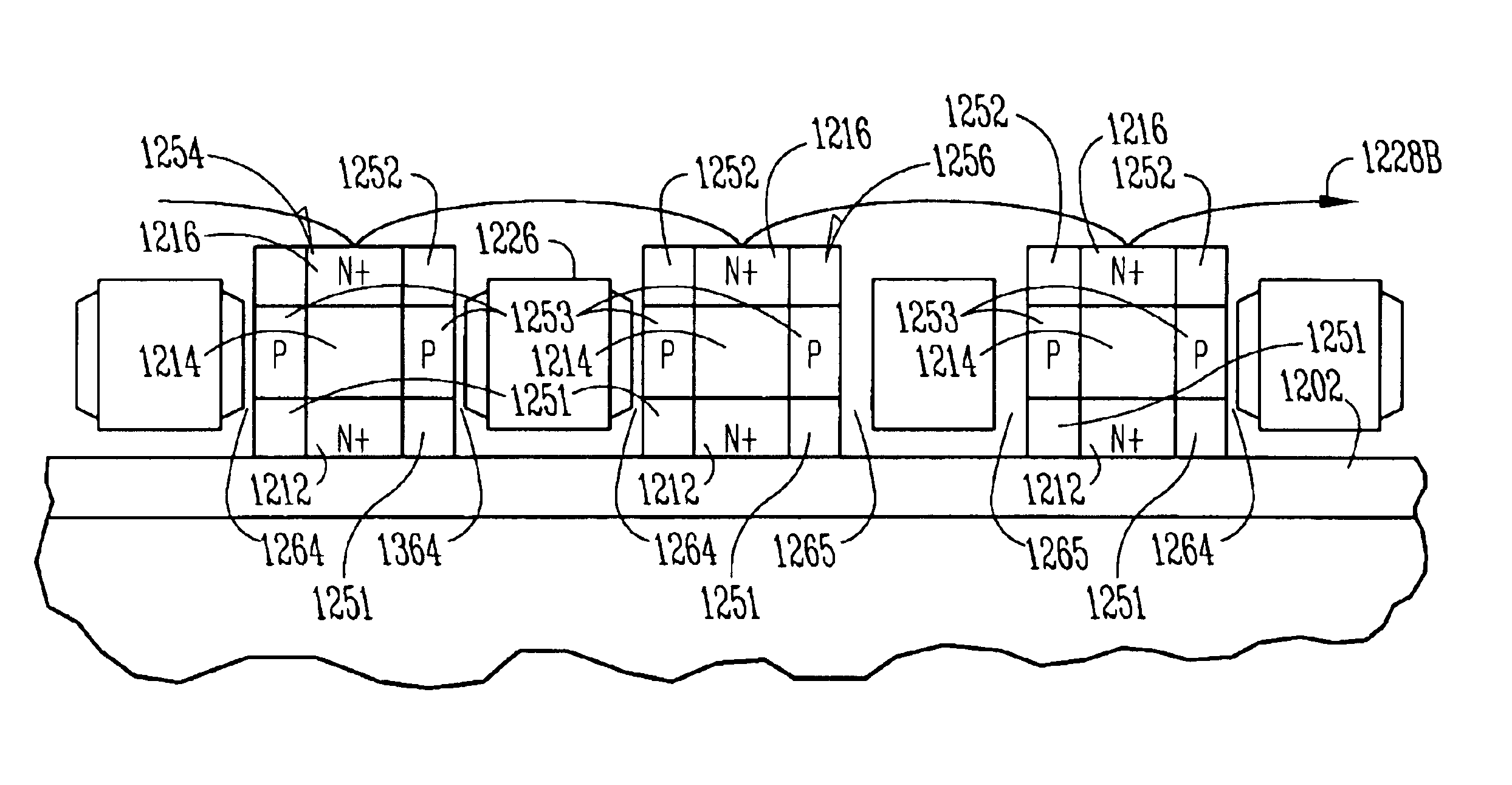

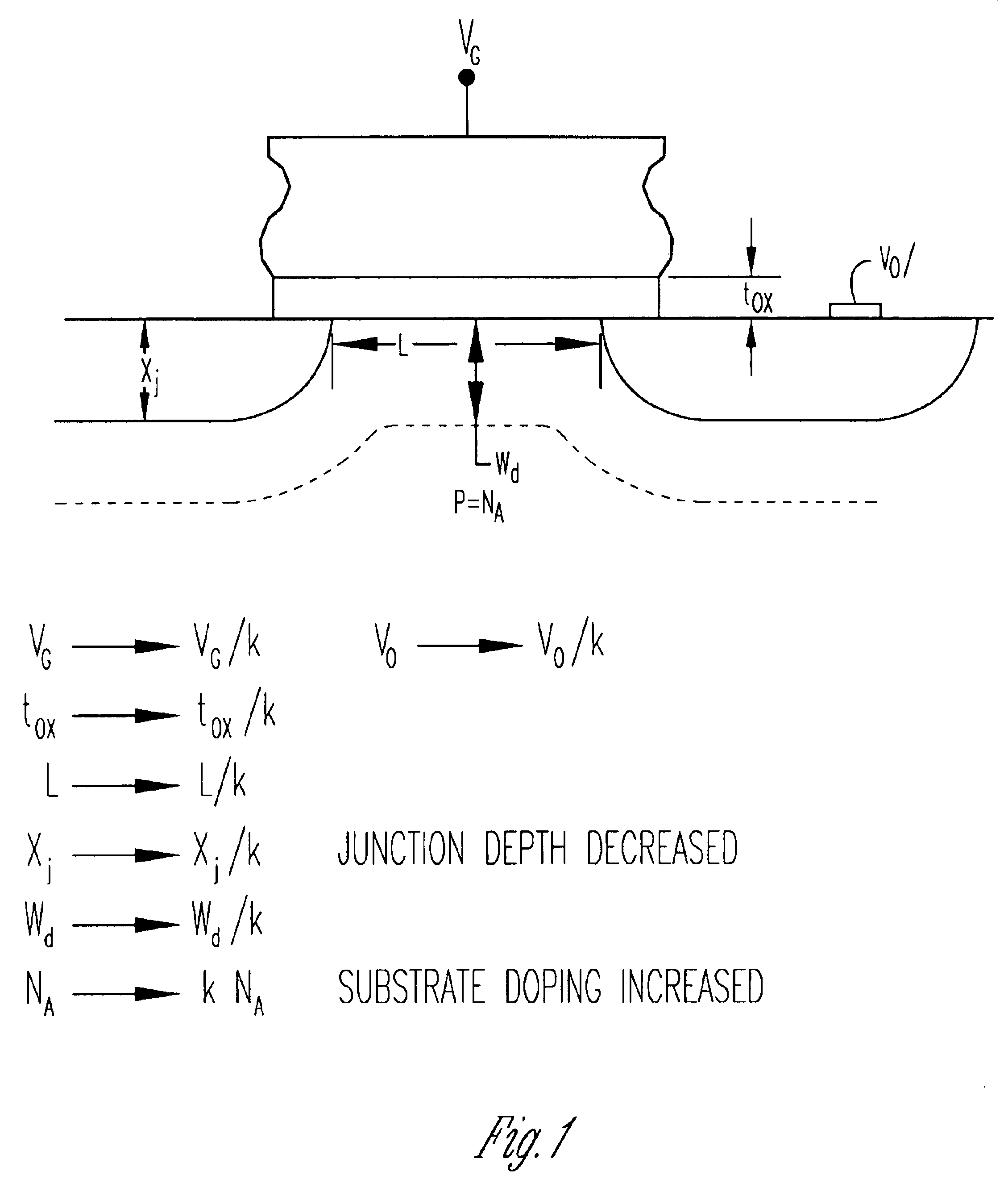

Floating gate transistor with horizontal gate layers stacked next to vertical body

Vertical body transistors with adjacent horizontal gate layers are used to form a memory array in a high density flash electrically erasable and programmable read only memory (EEPROM) or a logic array in a high density field programmable logic array (FPLA). The transistor is a field-effect transistor (FET) having an electrically isolated (floating) gate that controls electrical conduction between source regions and drain regions. If a particular floating gate is charged with stored electrons, then the transistor will not turn on and will provide an indication of the stored data at this location in the memory array within the EEPROM or will act as the absence of a transistor at this location in the logic array within the FPLA. The memory array or the logic array includes densely packed cells, each cell having a semiconductor pillar providing shared source and drain regions for two vertical body transistors that have control gates overlaying floating gates distributed on opposing sides of the semiconductor pillar. Both bulk semiconductor and silicon-on-insulator embodiments are provided. If a floating gate transistor is used to store a single bit of data or to represent a logic function, an area of only 2F<2 >is needed per respective bit of data or bit of logic, where F is the minimum lithographic feature size.

Owner:MICRON TECH INC

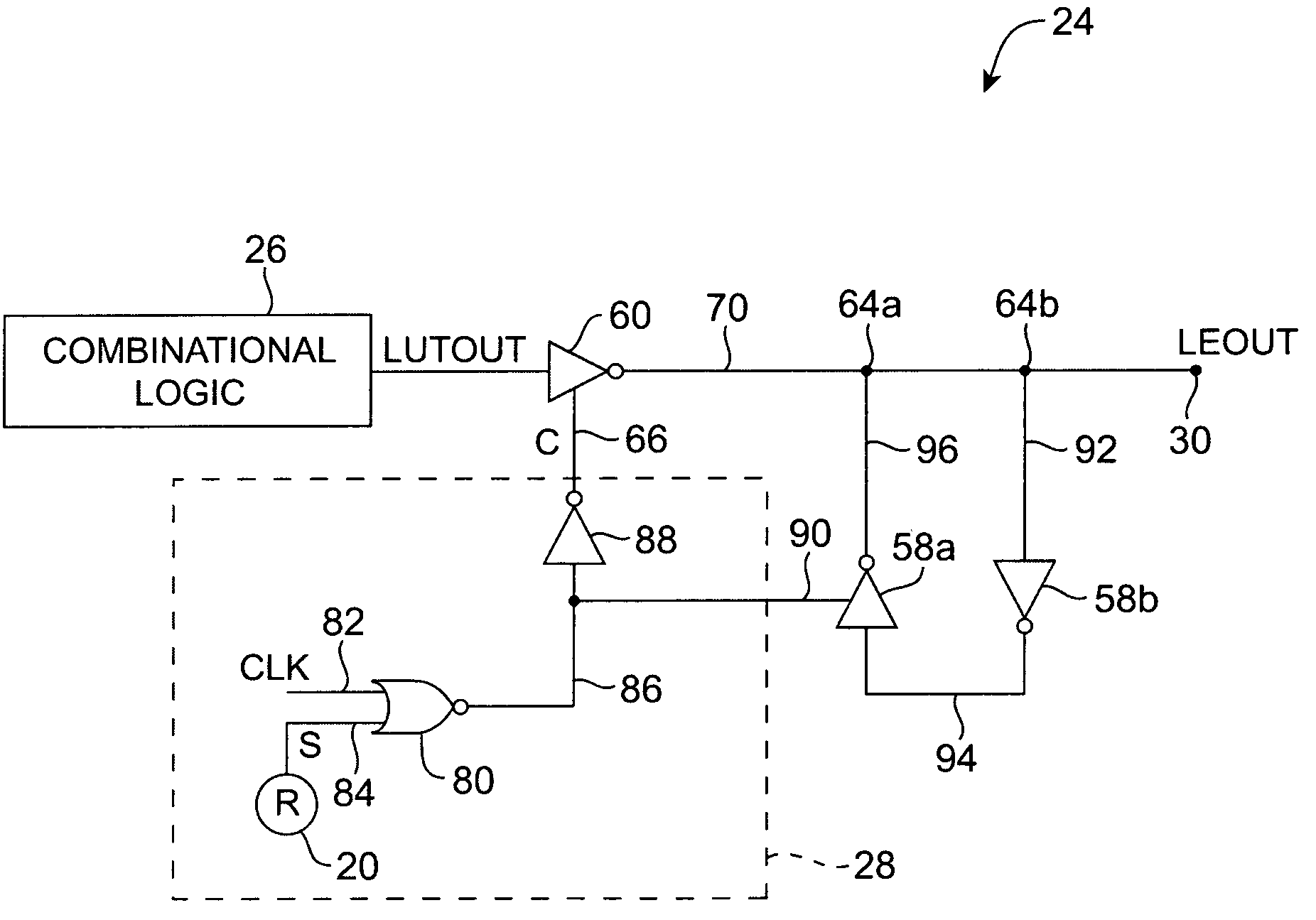

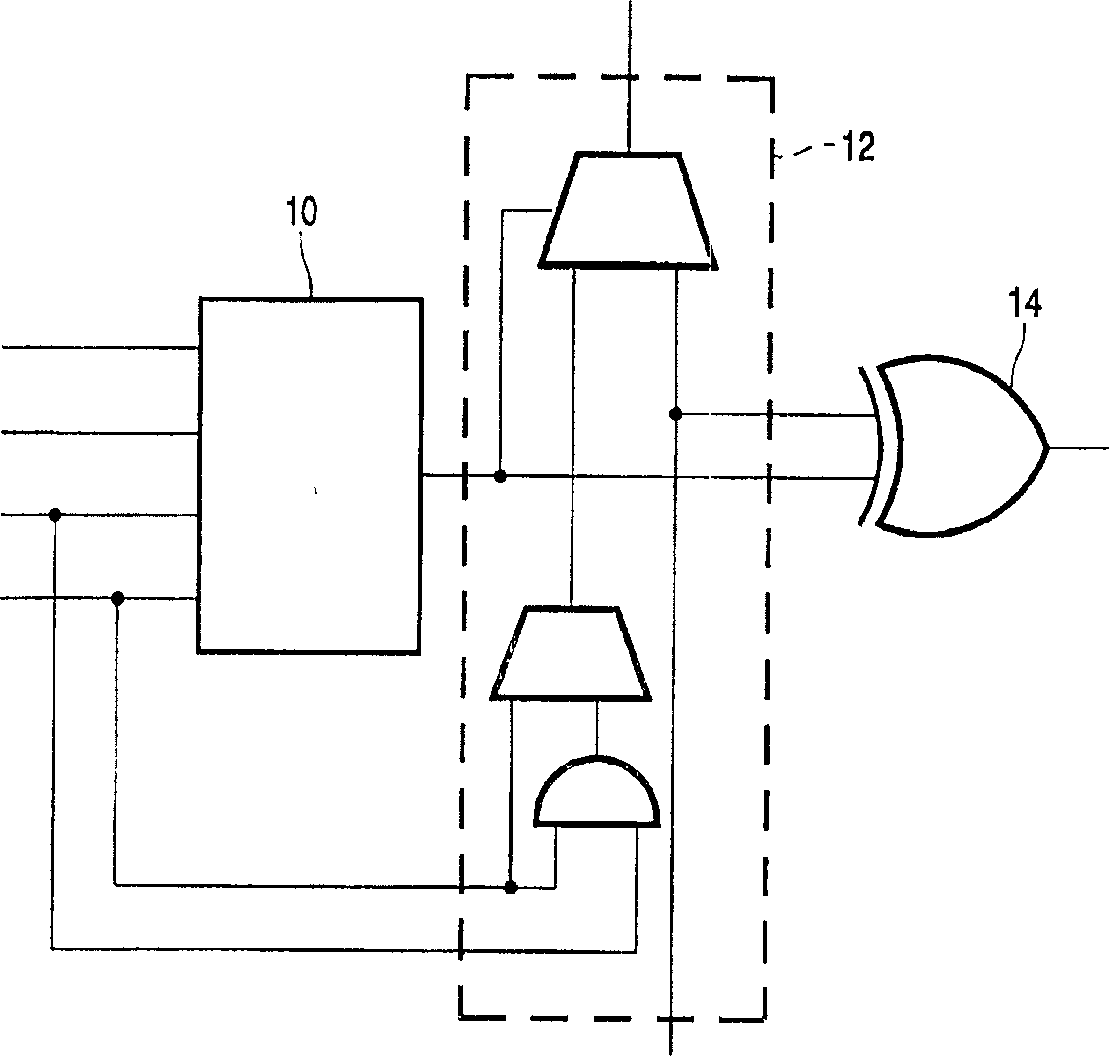

Programmable logic device latch circuits

InactiveUS7088136B1Logic circuits using elementary logic circuit componentsComputation using denominational number representationEngineeringProgrammable logic array

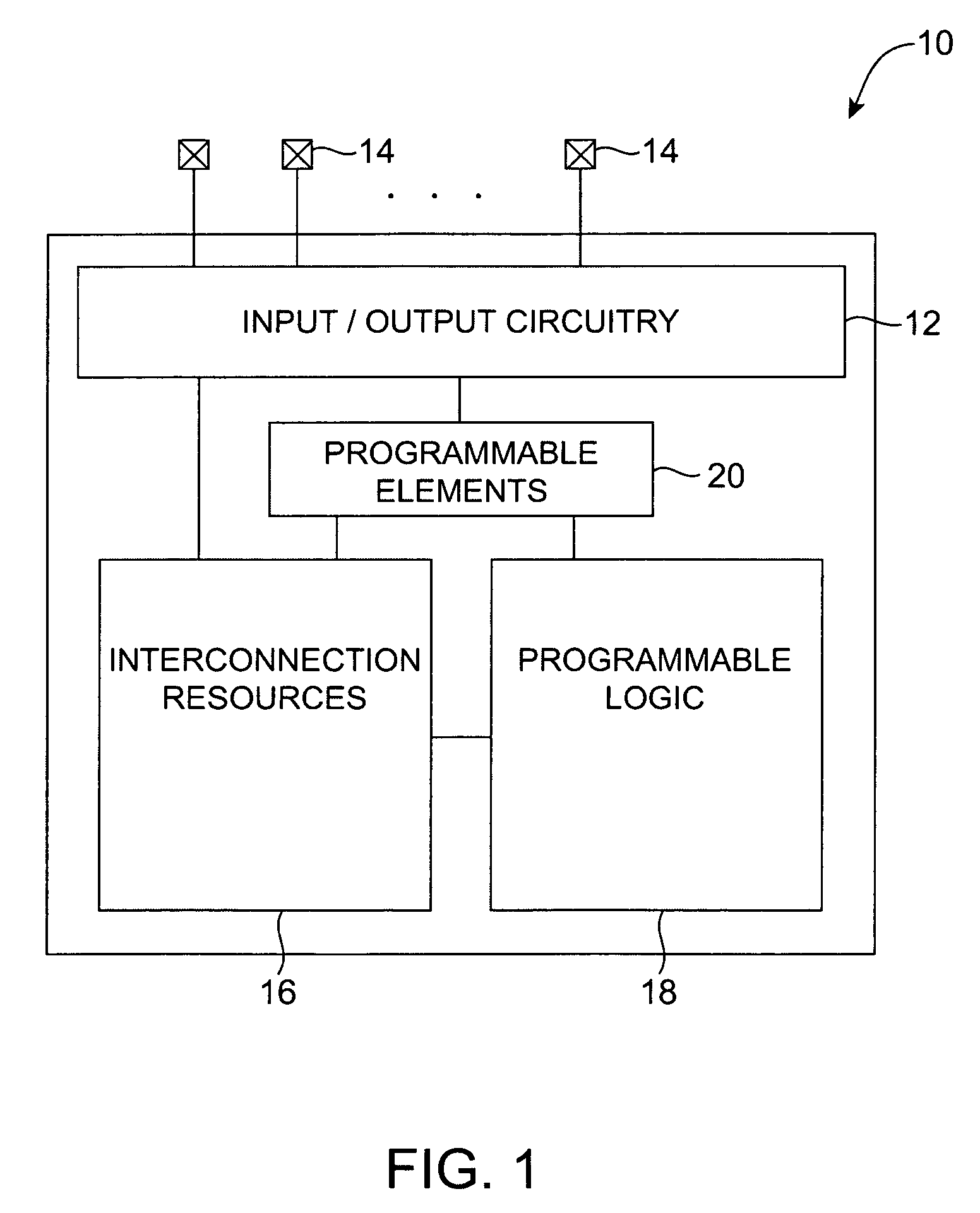

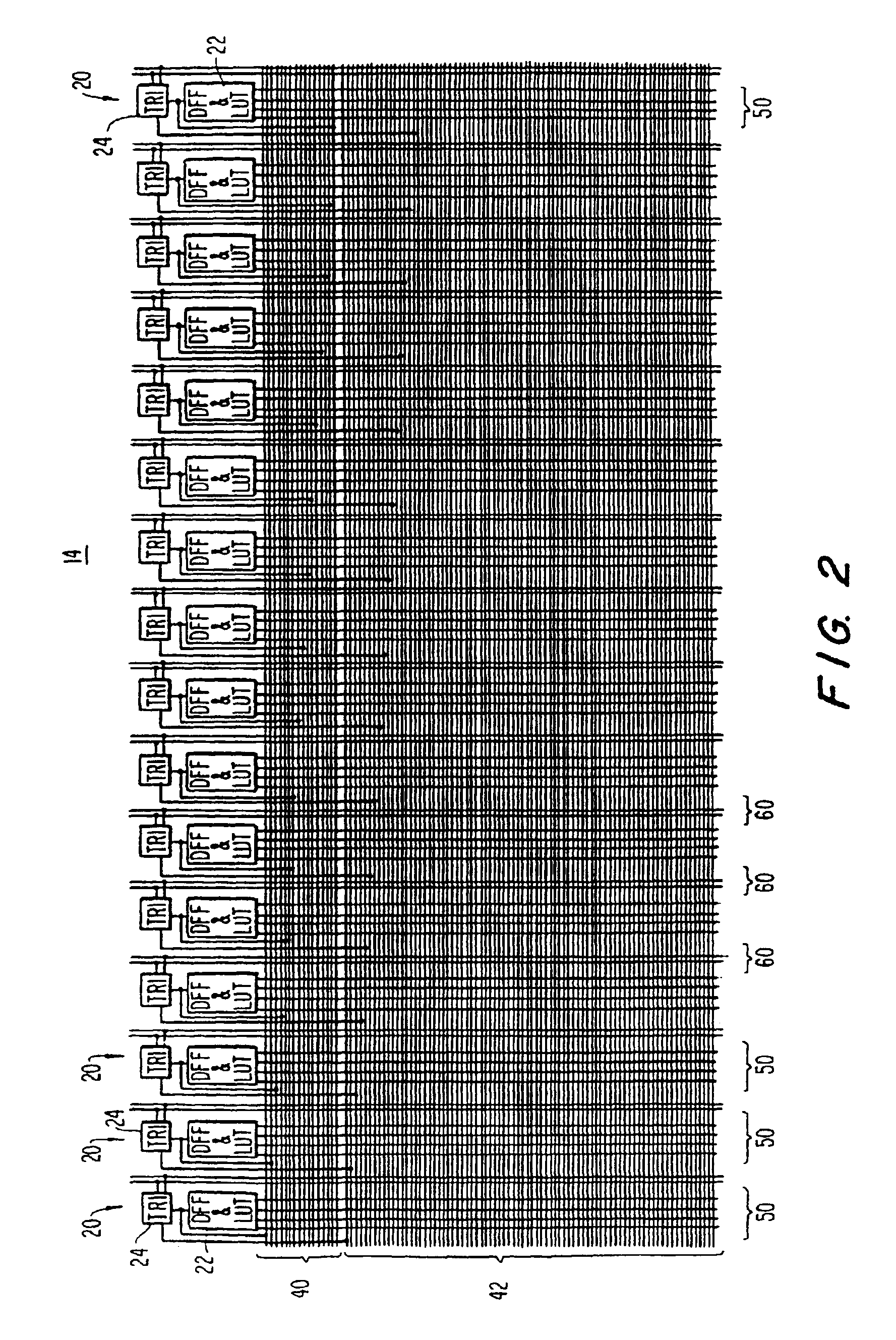

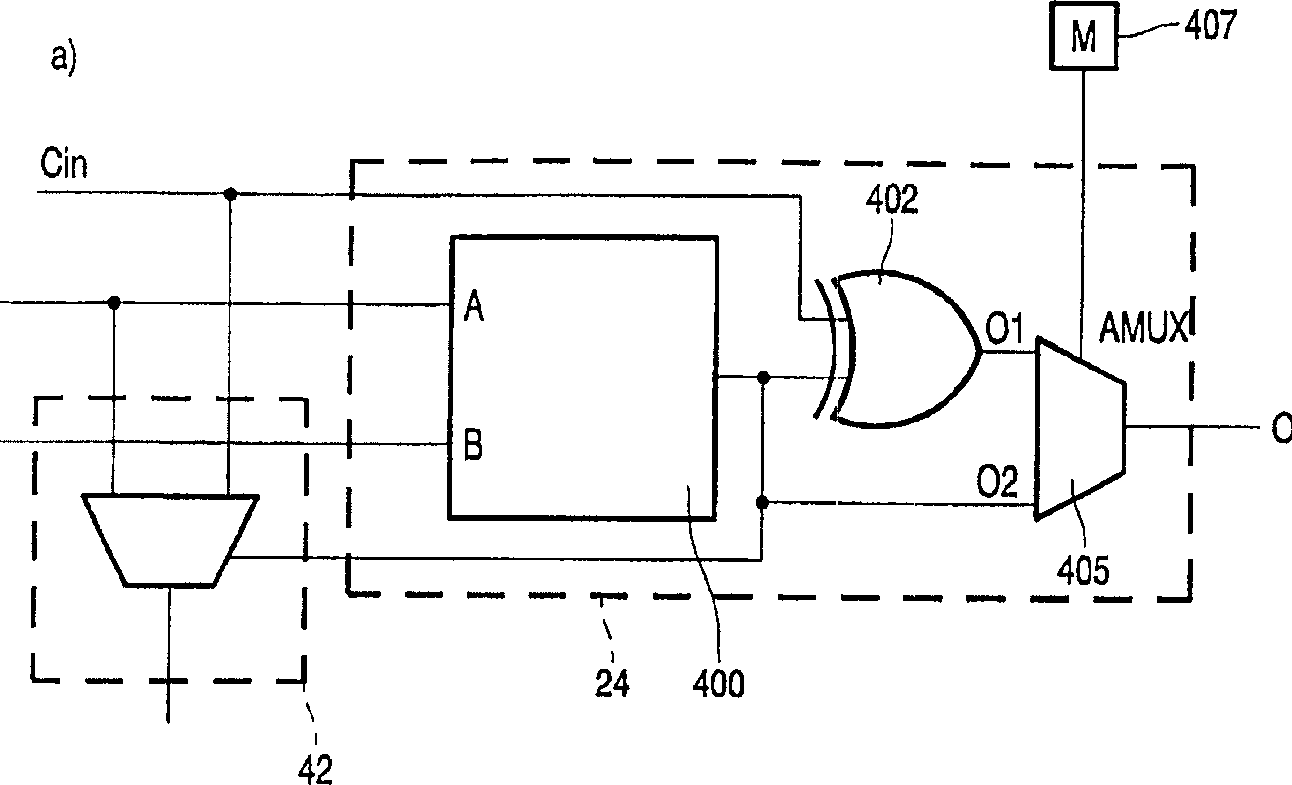

Latch circuitry is provided for programmable logic regions on integrated circuits such as programmable logic device integrated circuits. A programmable logic device may have programmable logic regions based on programmable combinational logic circuits. Latch circuitry in a logic region may be provided between an output of a programmable combinational logic circuit in the logic region and an output of the logic region. When the latch circuitry is enabled, the latch circuitry performs the functions of a level-sensitive latch. When the latch circuitry is disabled, the latch circuitry acts as a passive data path. The passive data path may include only a single driver so that the latch circuitry adds essentially zero additional delay to the data produced by the combinational logic.

Owner:ALTERA CORP

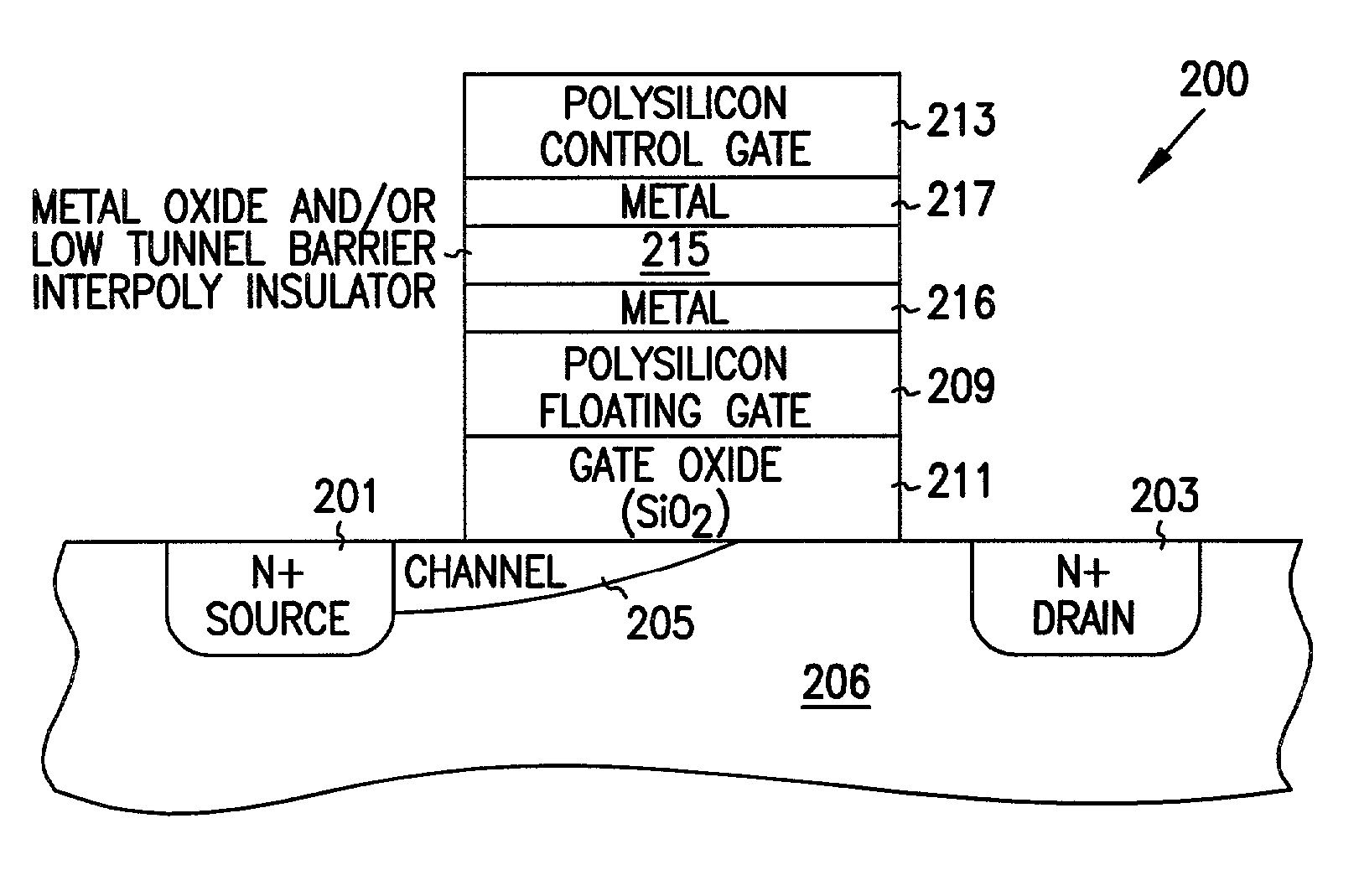

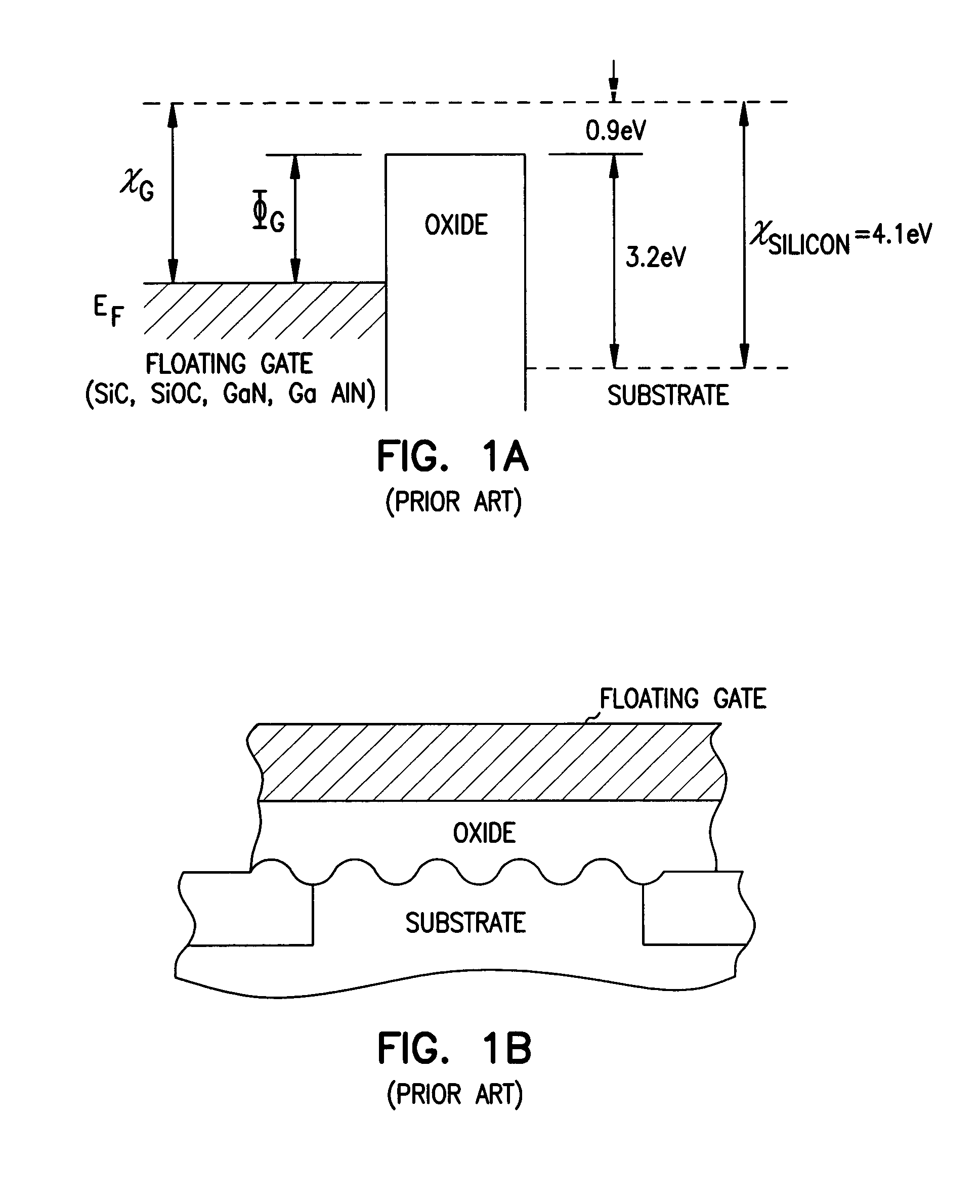

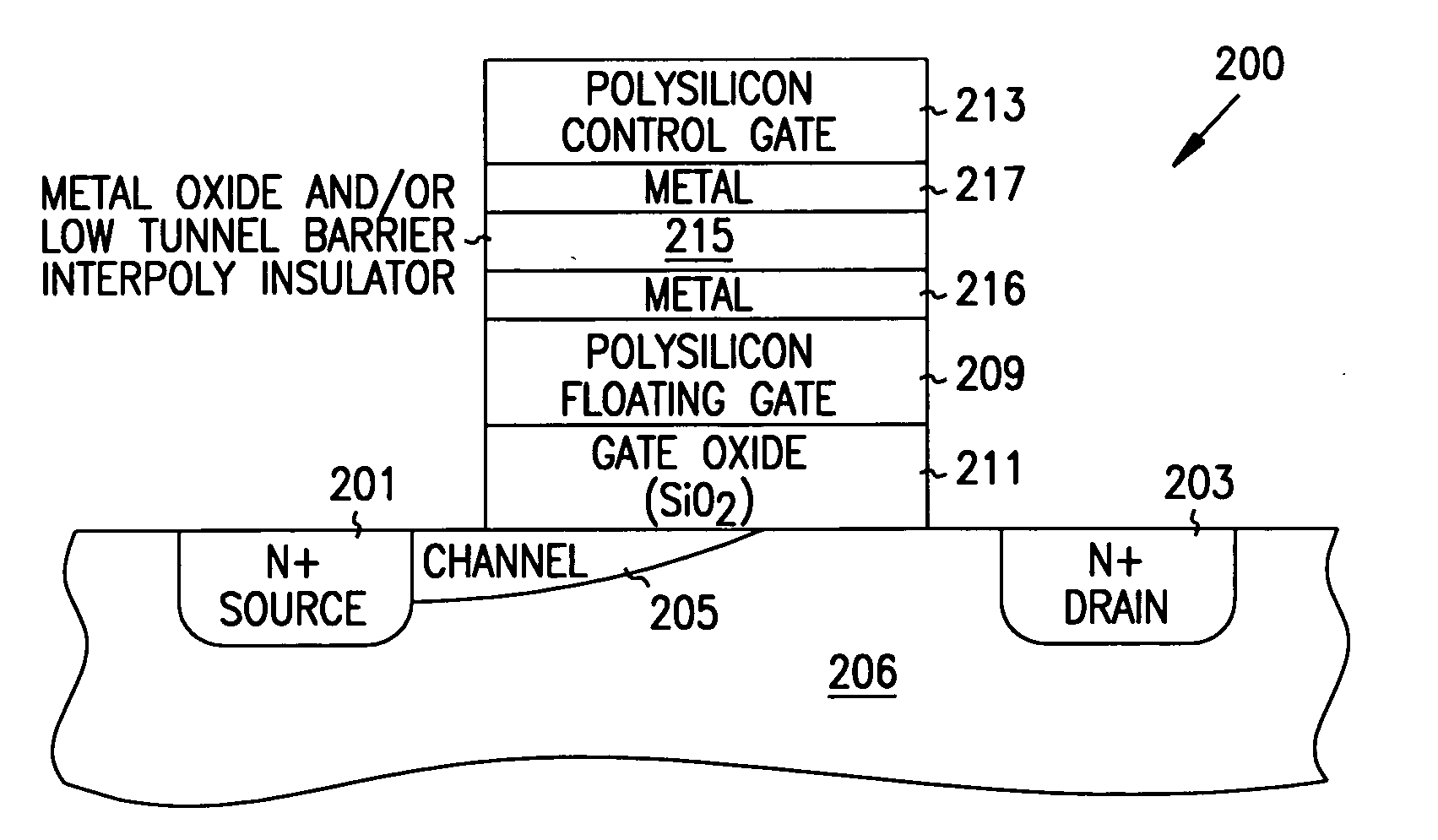

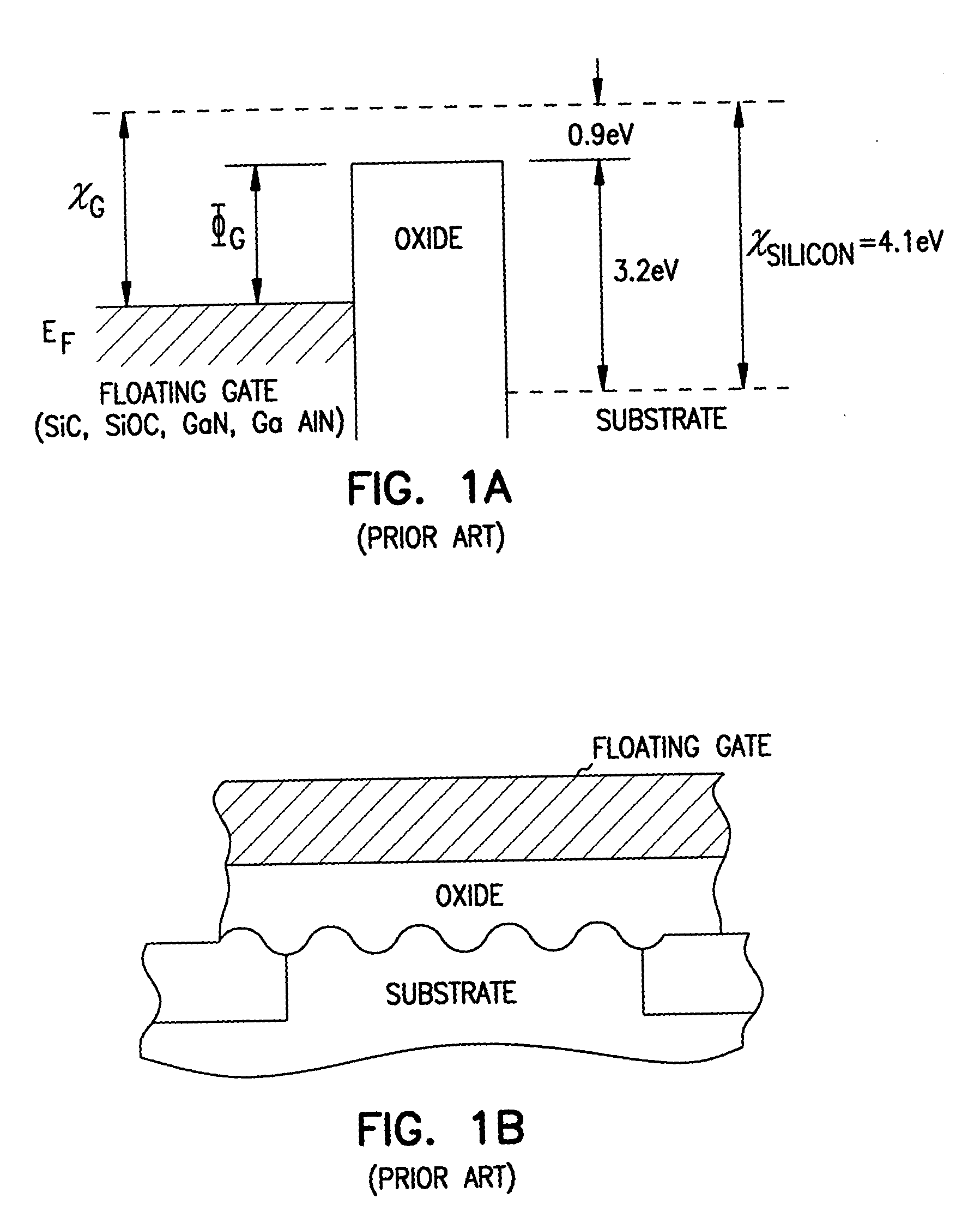

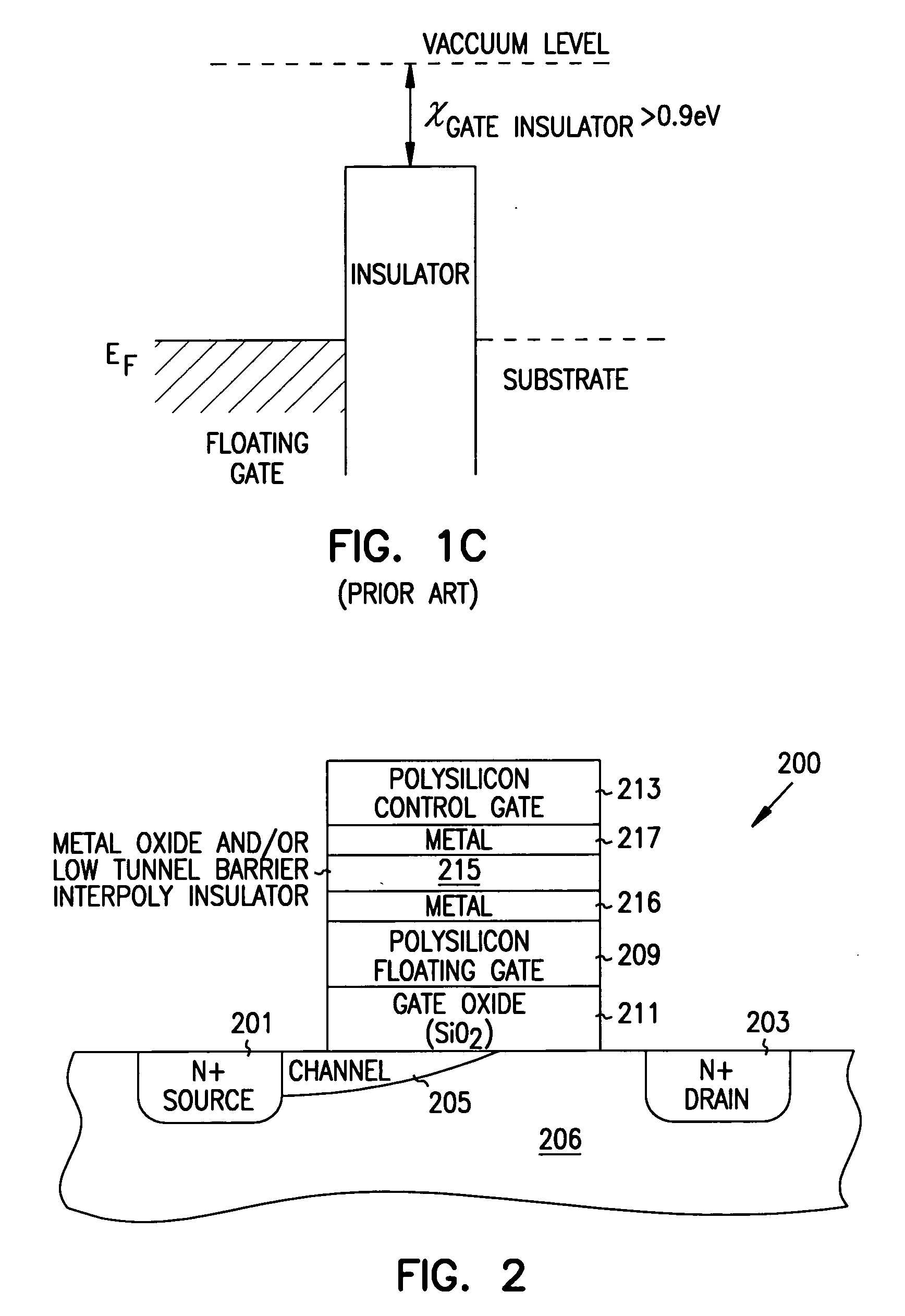

In service programmable logic arrays with low tunnel barrier interpoly insulators

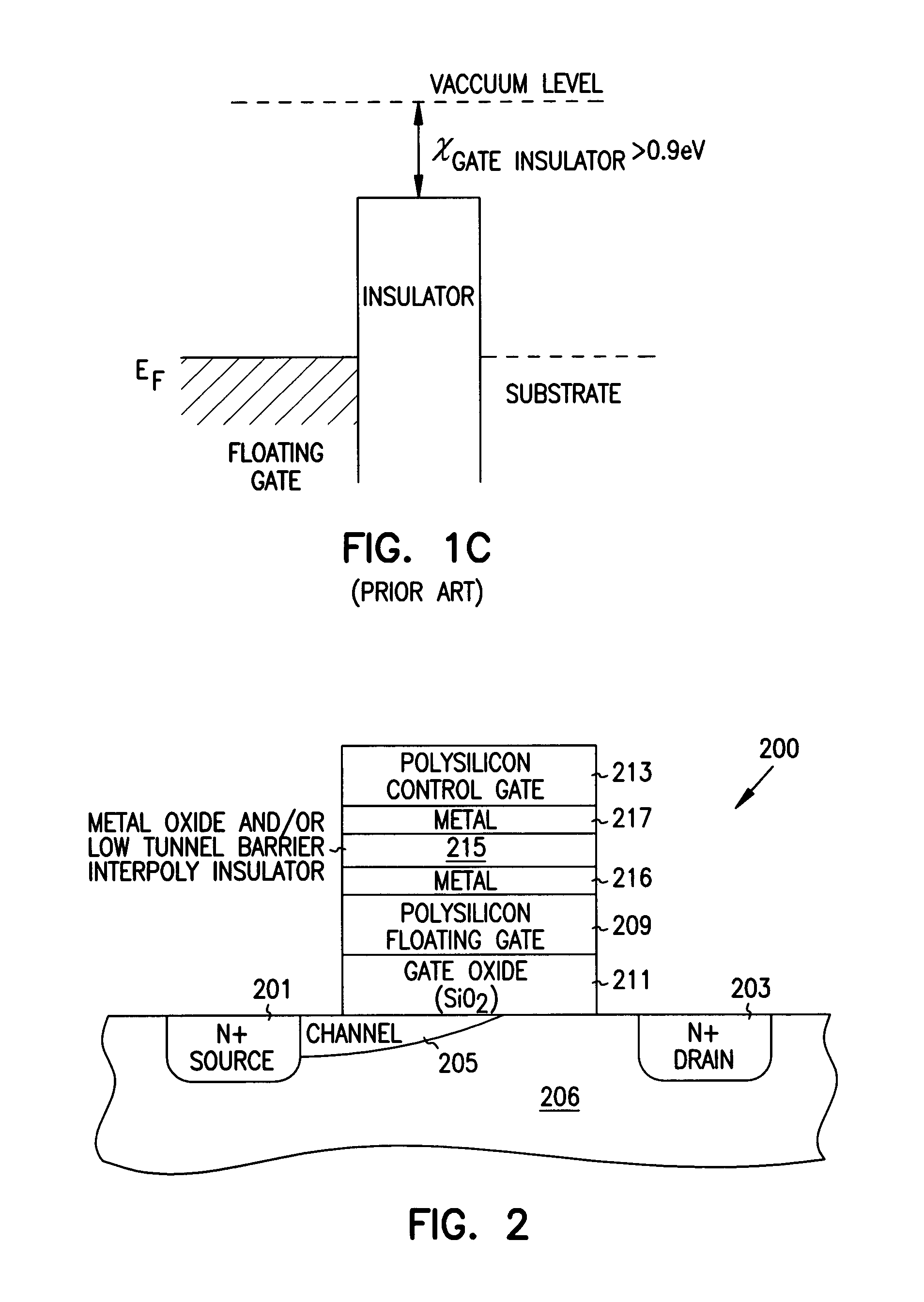

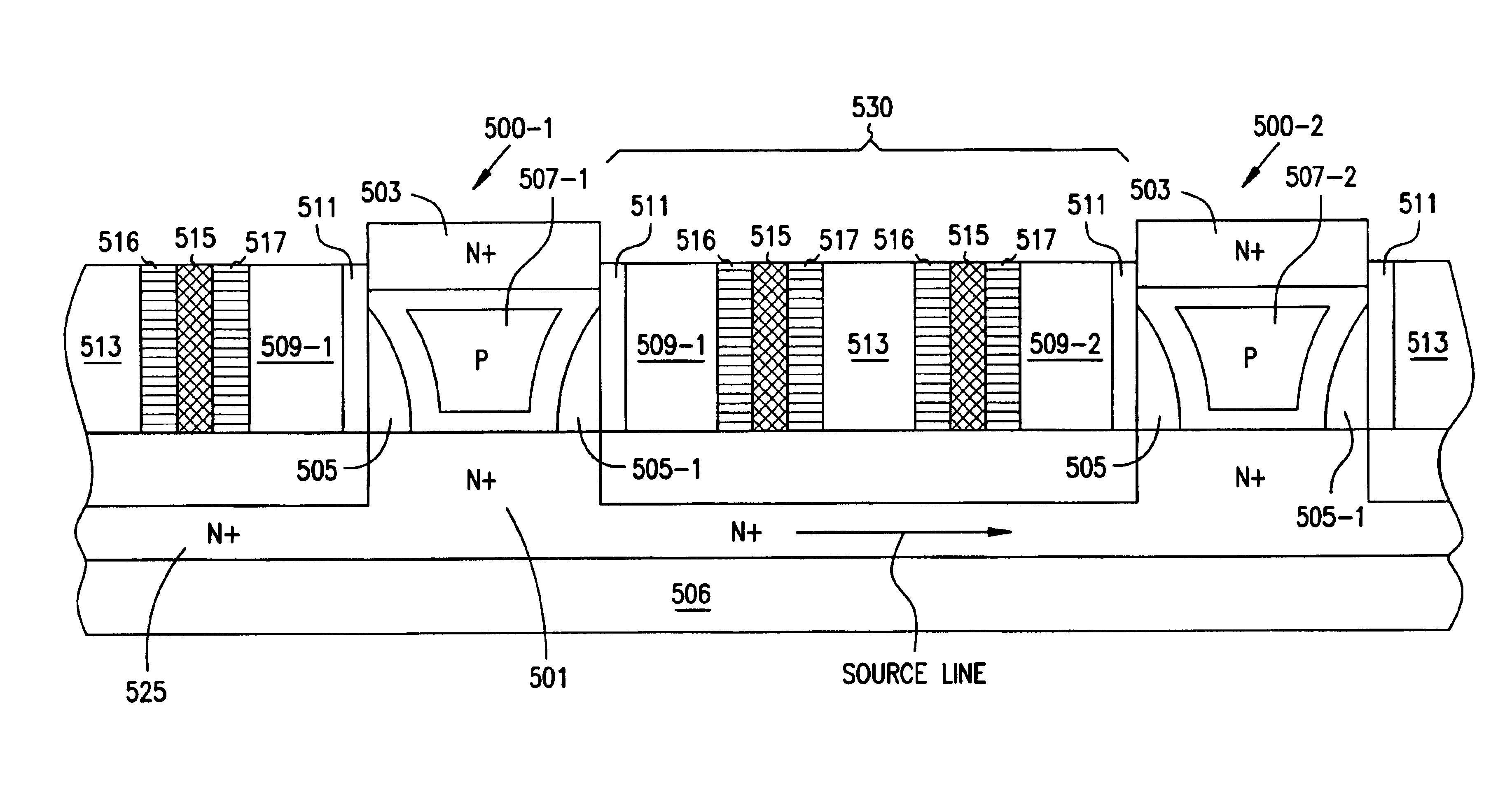

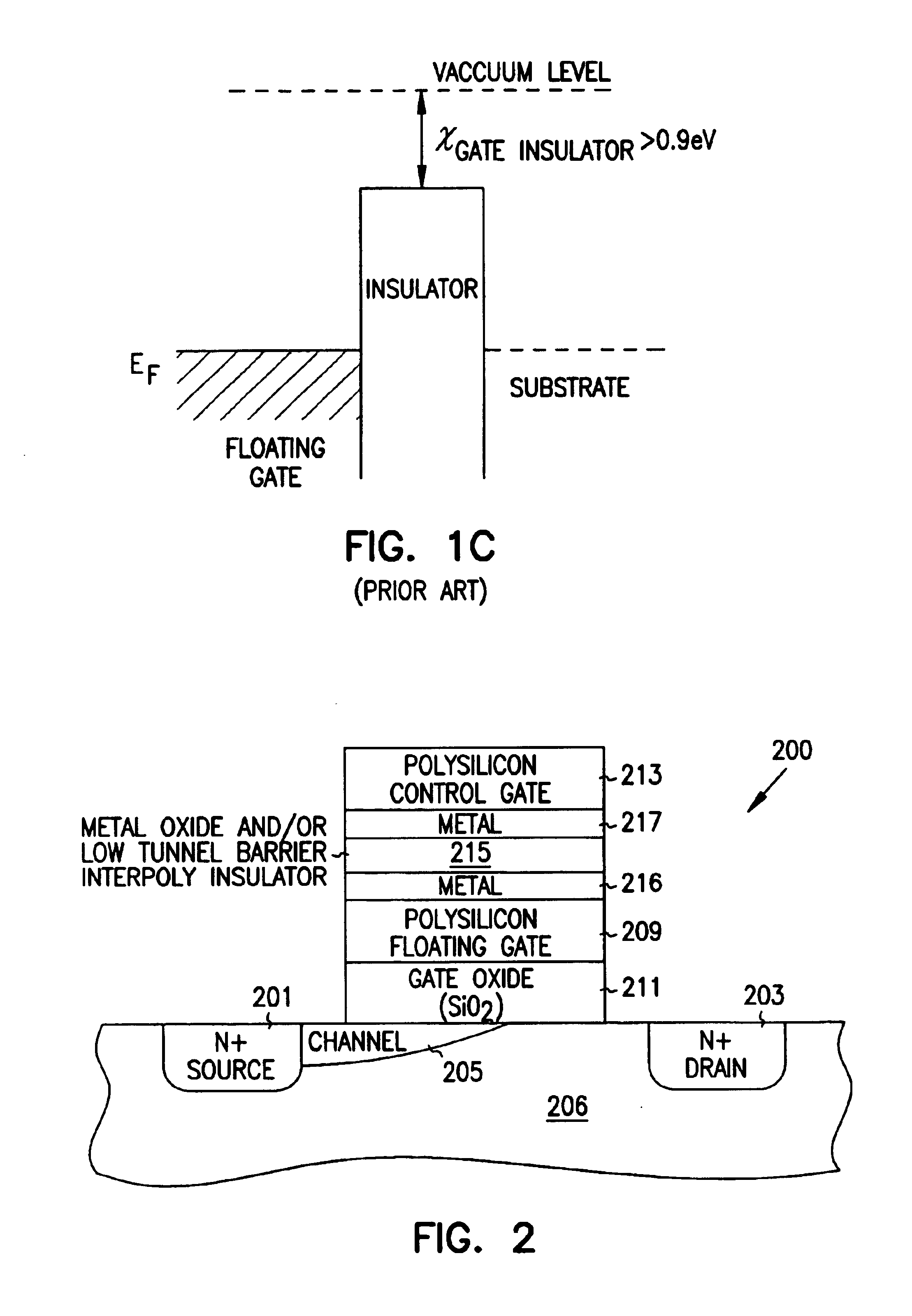

Structures and methods for in service programmable logic arrays with low tunnel barrier interpoly insulators are provided. The in-service programmable logic array includes a first logic and a second logic plan having a number of logic cells arranged in rows and columns that are interconnected to produce a number of logical outputs such that the in service programmable logic array implements a logical function. The logic cell includes a first source / drain region and a second source / drain region separated by a channel region in a substrate. A floating gate opposing the channel region and is separated therefrom by a gate oxide. A control gate opposes the floating gate. The control gate is separated from the floating gate by a low tunnel barrier intergate insulator. The low tunnel barrier intergate insulator includes a metal oxide insulator selected from the group consisting of PbO, Al2O3, Ta2O5, TiO2, ZrO2, Nb2O5 and / or a Perovskite oxide tunnel barrier.

Owner:MICRON TECH INC

Service programmable logic arrays with low tunnel barrier interpoly insulators

Structures and methods for in service programmable logic arrays with low tunnel barrier interpoly insulators are provided. The in-service programmable logic array includes a first logic and a second logic plan having a number of logic cells arranged in rows and columns that are interconnected to produce a number of logical outputs such that the in service programmable logic array implements a logical function. The logic cell includes a first source / drain region and a second source / drain region separated by a channel region in a substrate. A floating gate opposing the channel region and is separated therefrom by a gate oxide. A control gate opposes the floating gate. The control gate is separated from the floating gate by a low tunnel barrier intergate insulator. The low tunnel barrier intergate insulator includes a metal oxide insulator selected from the group consisting of PbO, Al2O3, Ta2O5, TiO2, ZrO2, Nb2O5 and / or a Perovskite oxide tunnel barrier.

Owner:MICRON TECH INC

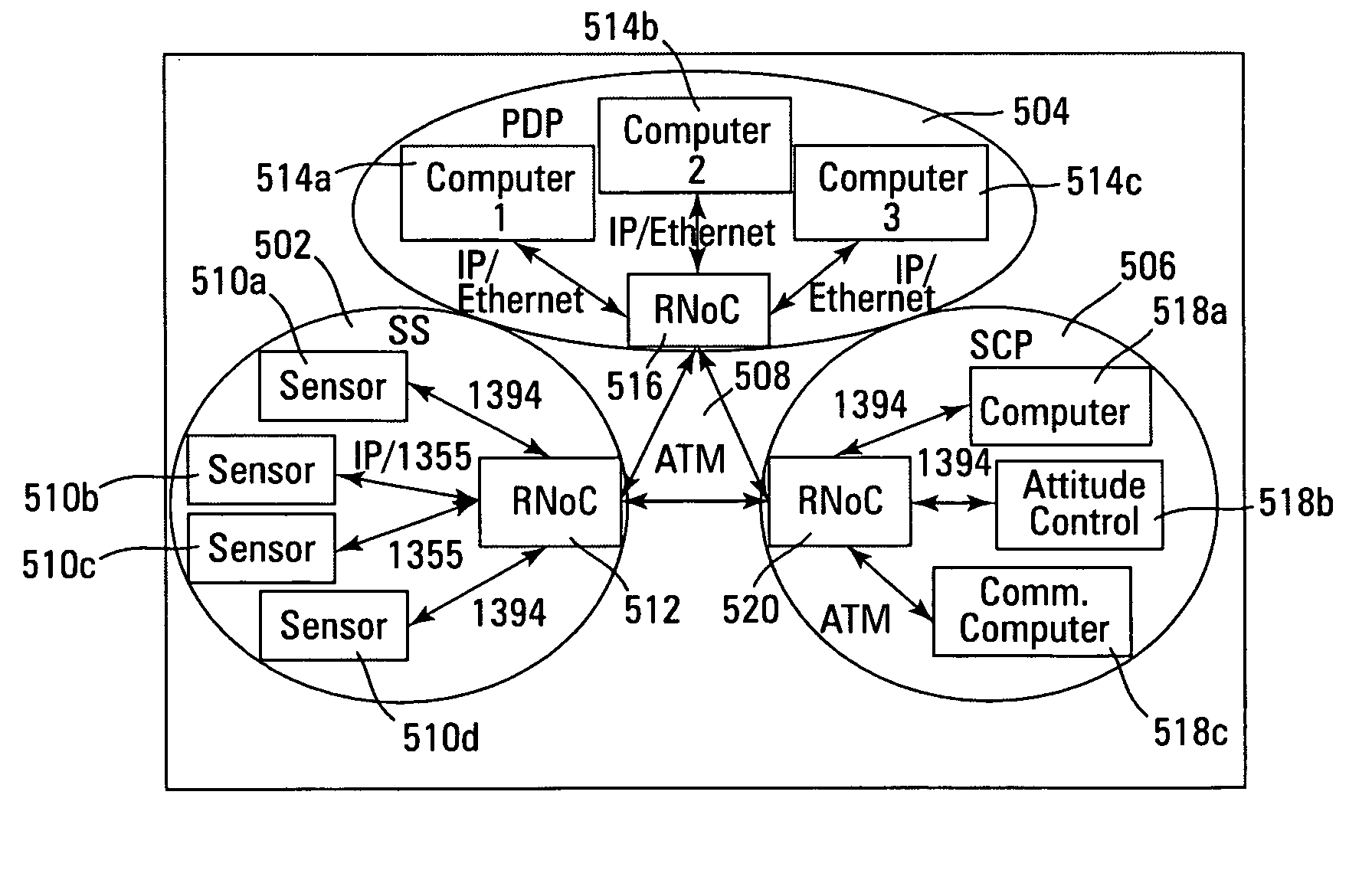

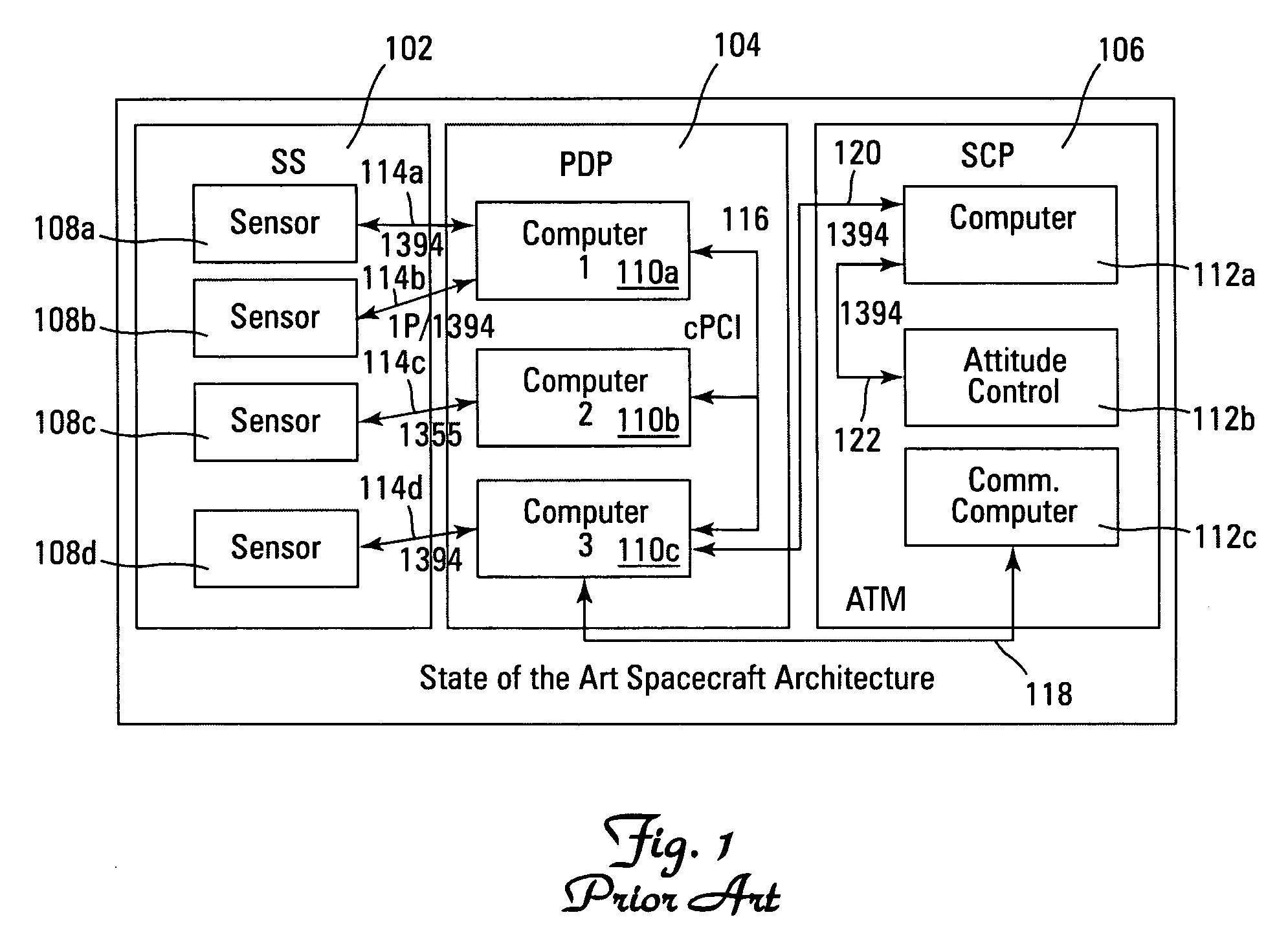

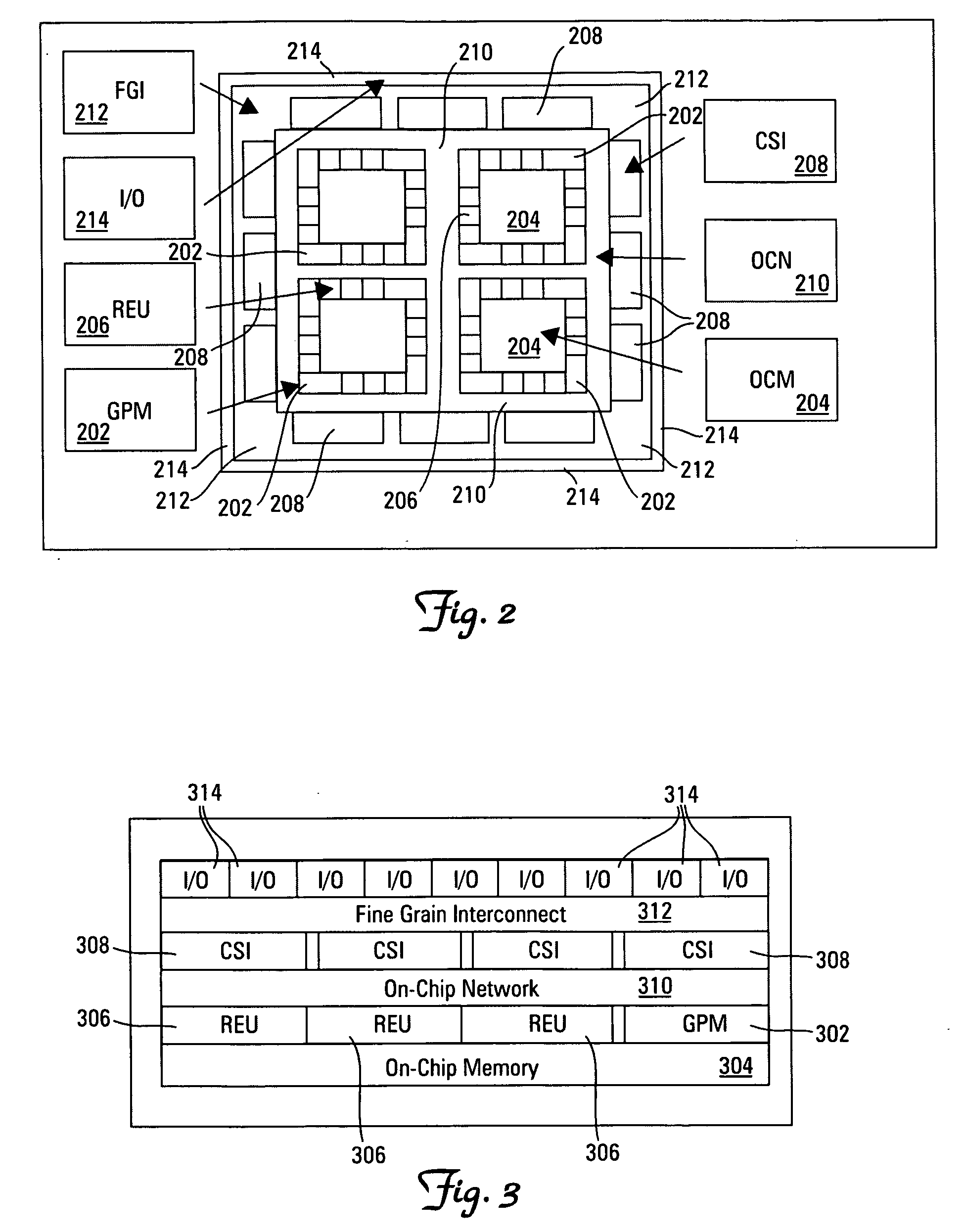

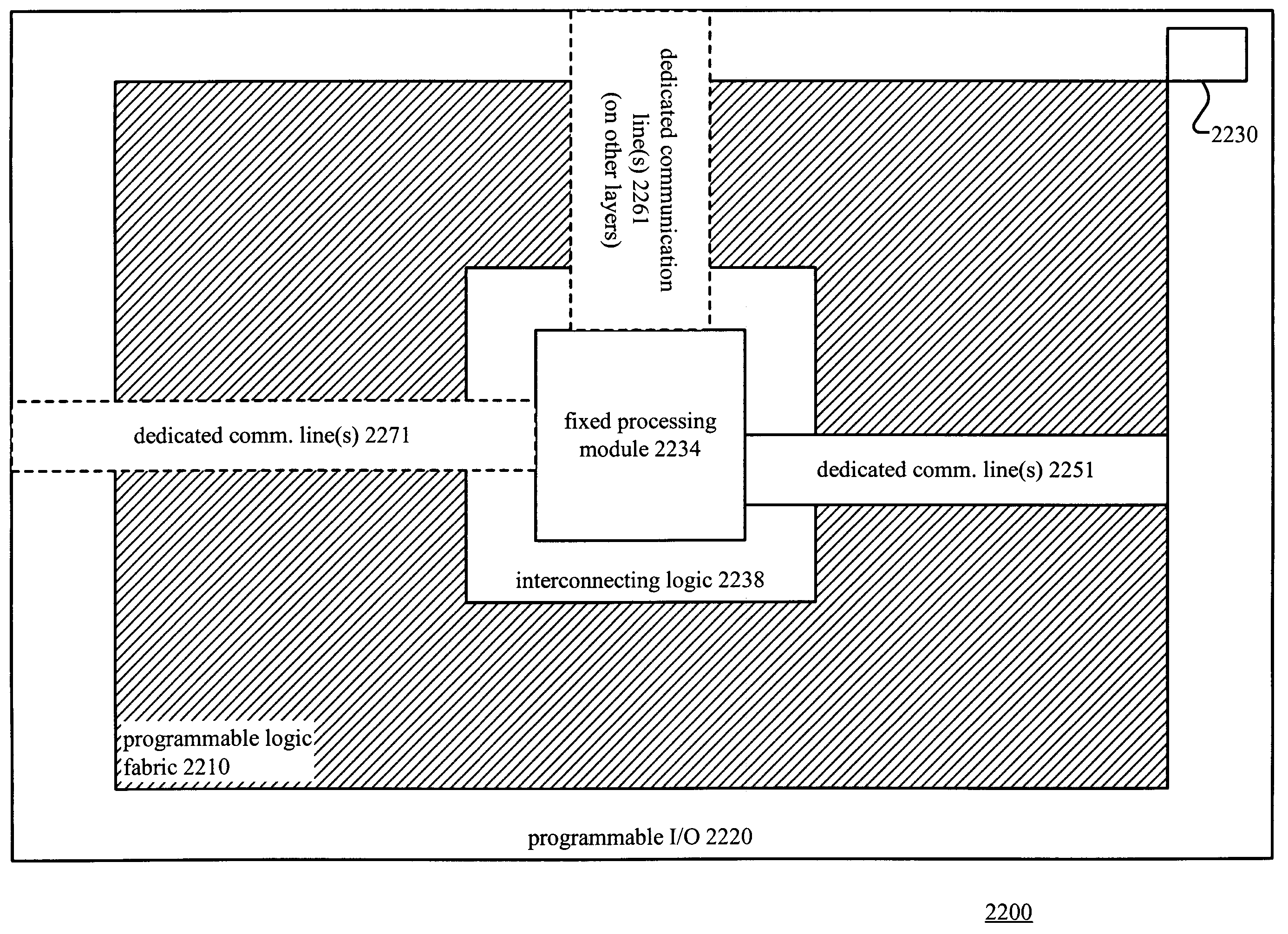

Reconfigurable network on a chip

ActiveUS7382154B2Easy programmingIncrease flexibilitySolid-state devicesDigital computer detailsSemiconductor chipProgrammable logic array

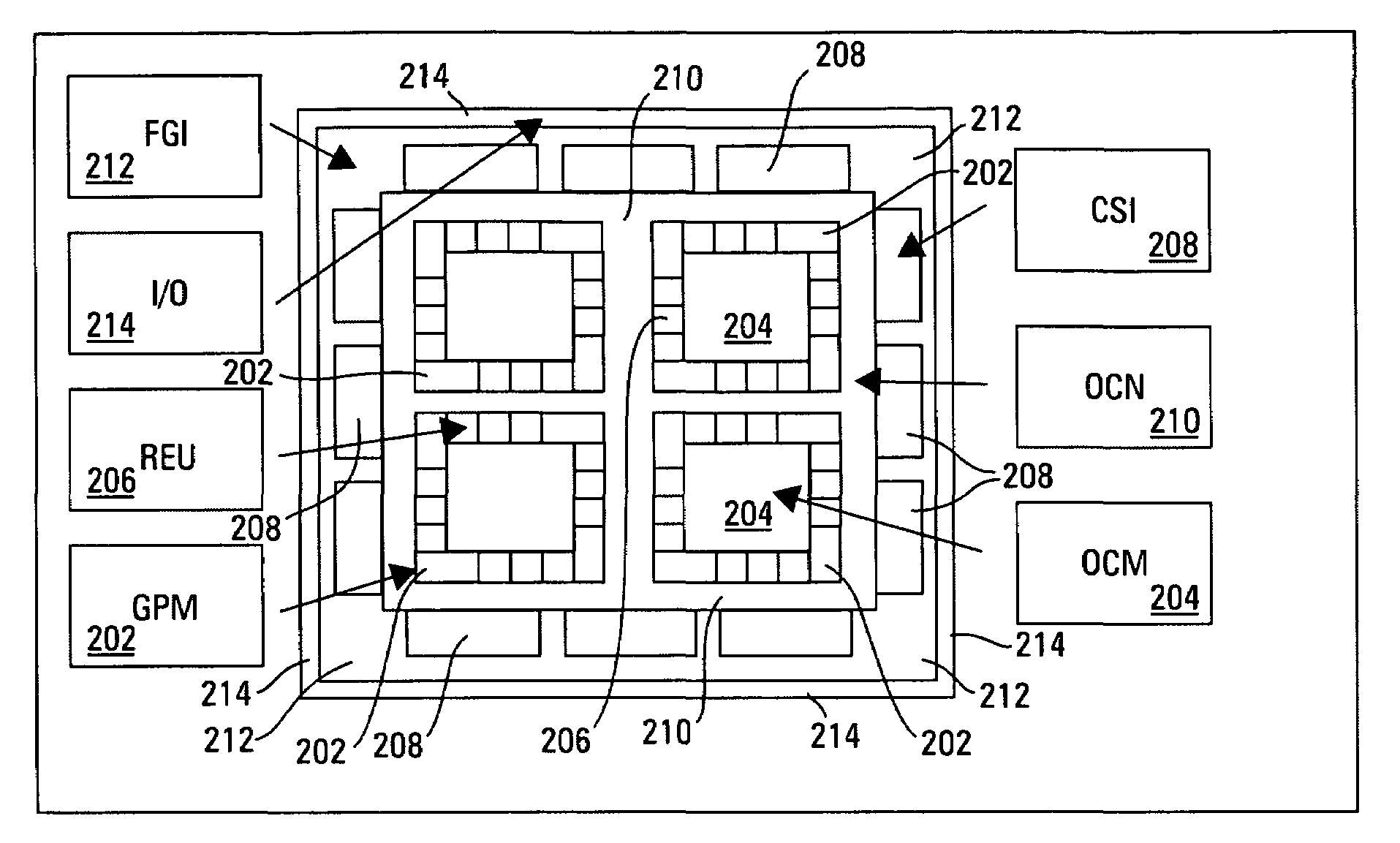

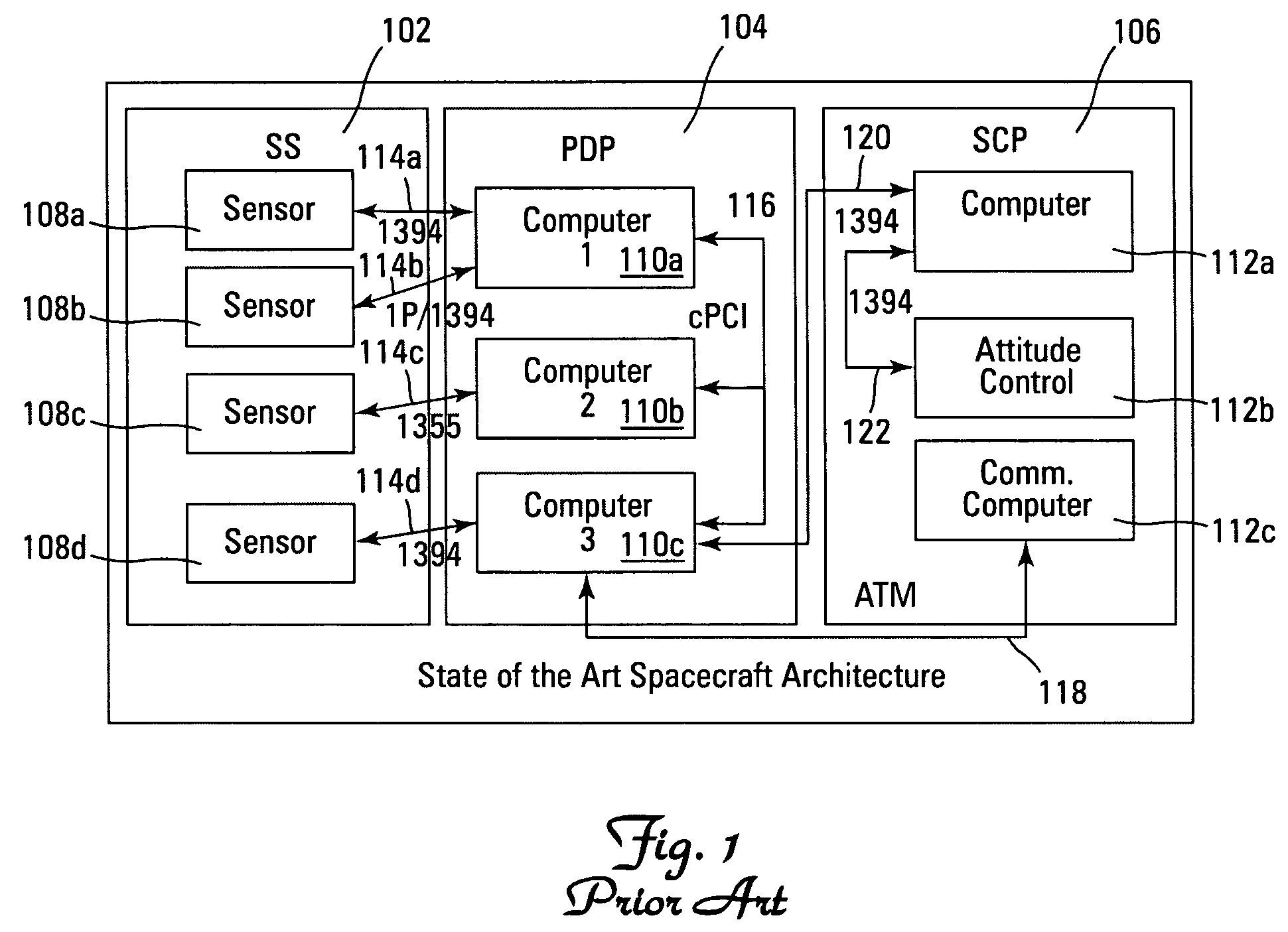

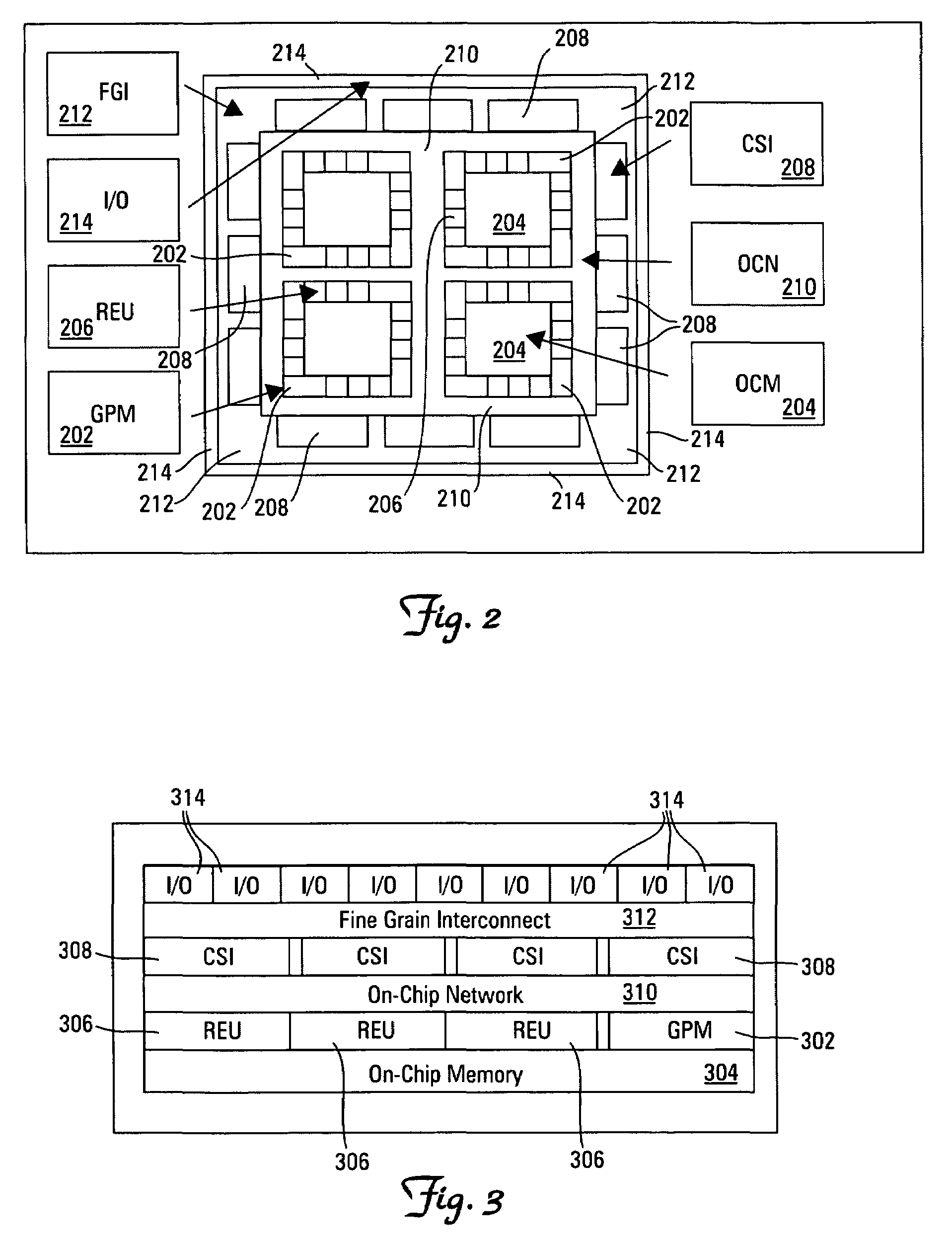

An architecture for a reconfigurable network that can be implemented on a semiconductor chip is disclosed, which includes a hierarchical organization of network components and functions that are readily programmable and highly flexible. Essentially, a reconfigurable network on a chip is disclosed, which includes aspects of reconfigurable computing, system on a chip, and network on a chip designs. More precisely, a reconfigurable network on a chip includes a general purpose microprocessor for implementing software tasks, a plurality of on-chip memories for facilitating the processing of large data structures as well as processor collaboration, a plurality of reconfigurable execution units including self-contained, individually reconfigurable programmable logic arrays, a plurality of configurable system interface units that provide interconnections between on-chip memories, networks or buses, an on-chip network including a network interconnection interface that enables communication between all reconfigurable execution units, configurable system interface units and general purpose microprocessors, a fine grain interconnect unit that gathers associated input / output signals for a particular interface and attaches them to a designated system interface resource, and a plurality of input / output blocks that supply the link between an on-chip interface resource and a particular external network or device interface. Advantageously, the network minimizes the configuration latency of the reconfigurable execution units and also enables reconfiguration on-the-fly.

Owner:HONEYWELL INT INC

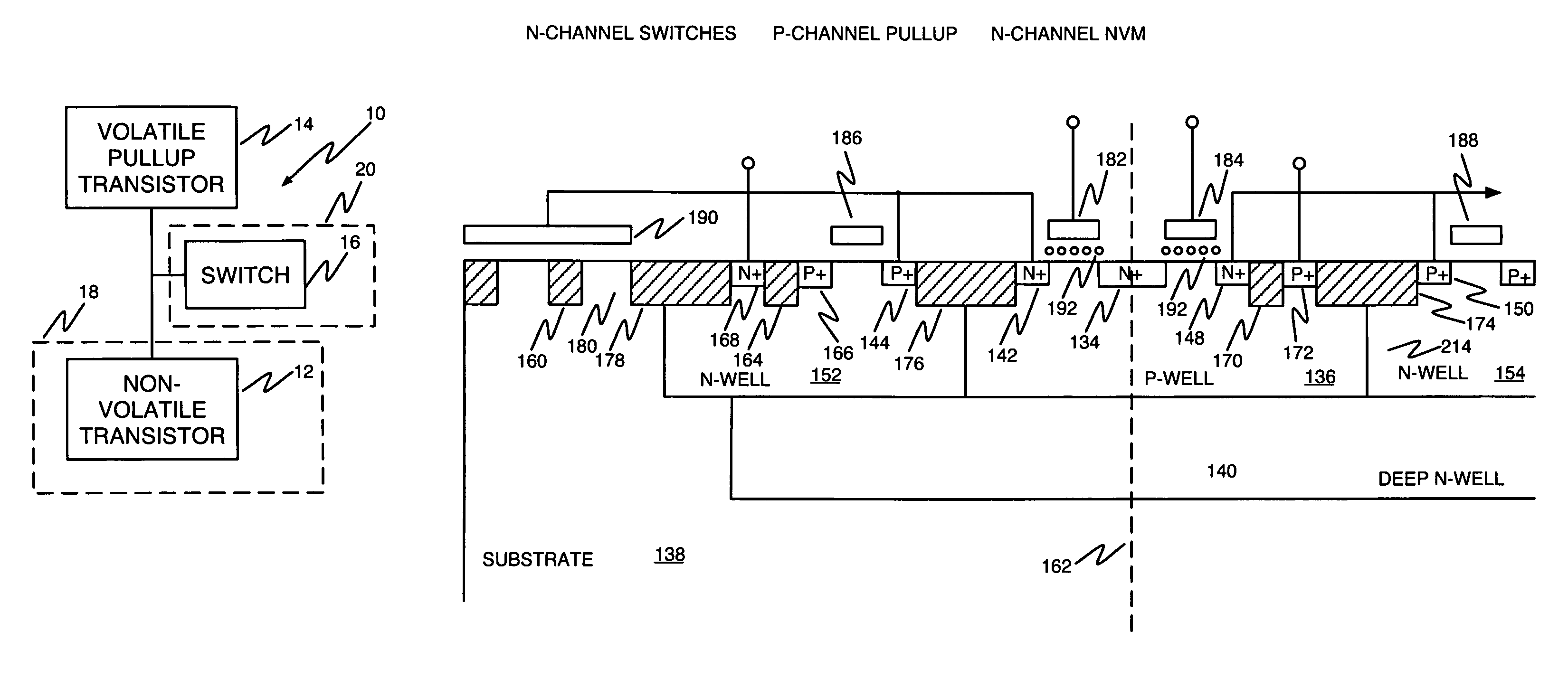

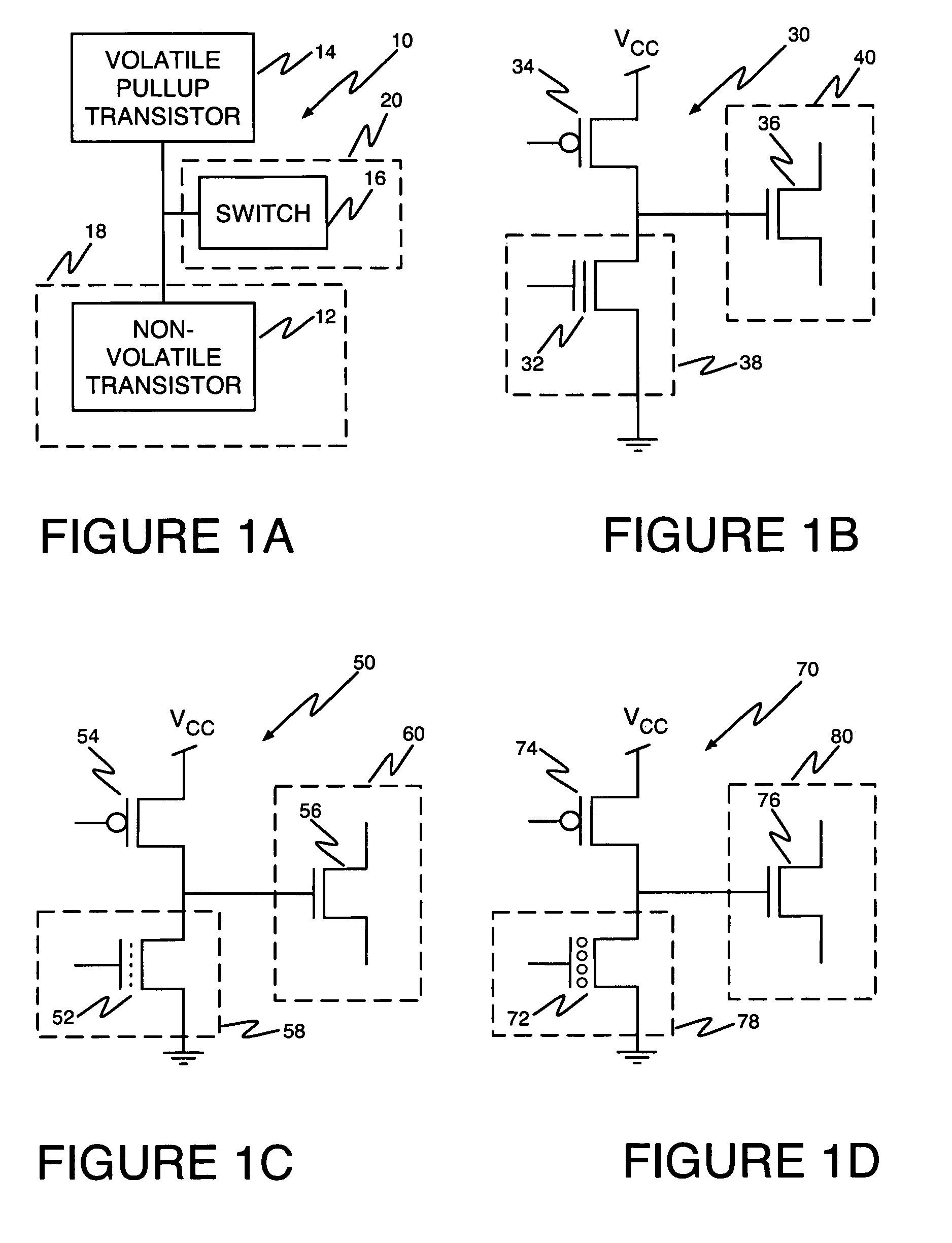

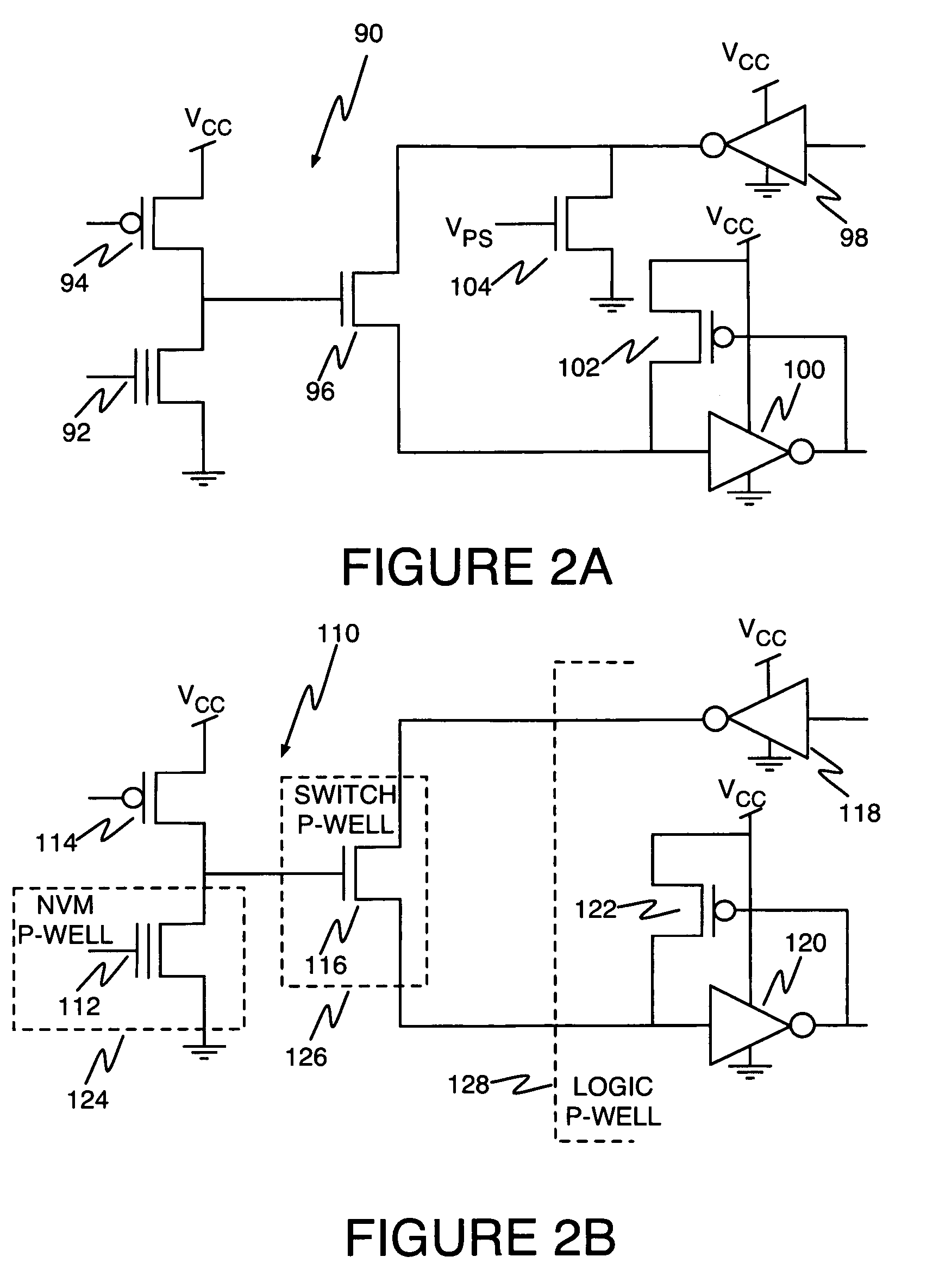

Non-volatile programmable memory cell and array for programmable logic array

A non-volatile programmable memory cell suitable for use in a programmable logic array includes a non-volatile MOS transistor of a first conductivity type in series with a volatile MOS transistor of a second conductivity type. The non-volatile MOS transistor may be a floating gate transistor, such as a flash transistor, or may be another type of non-volatile transistor such as a floating charge-trapping SONOS, MONOS transistor, or a nano-crystal transistor. A volatile MOS transistor, an inverter, or a buffer may be driven by coupling its gate or input to the common connection between the non-volatile MOS transistor and the volatile MOS transistor.

Owner:MICROSEMI SOC

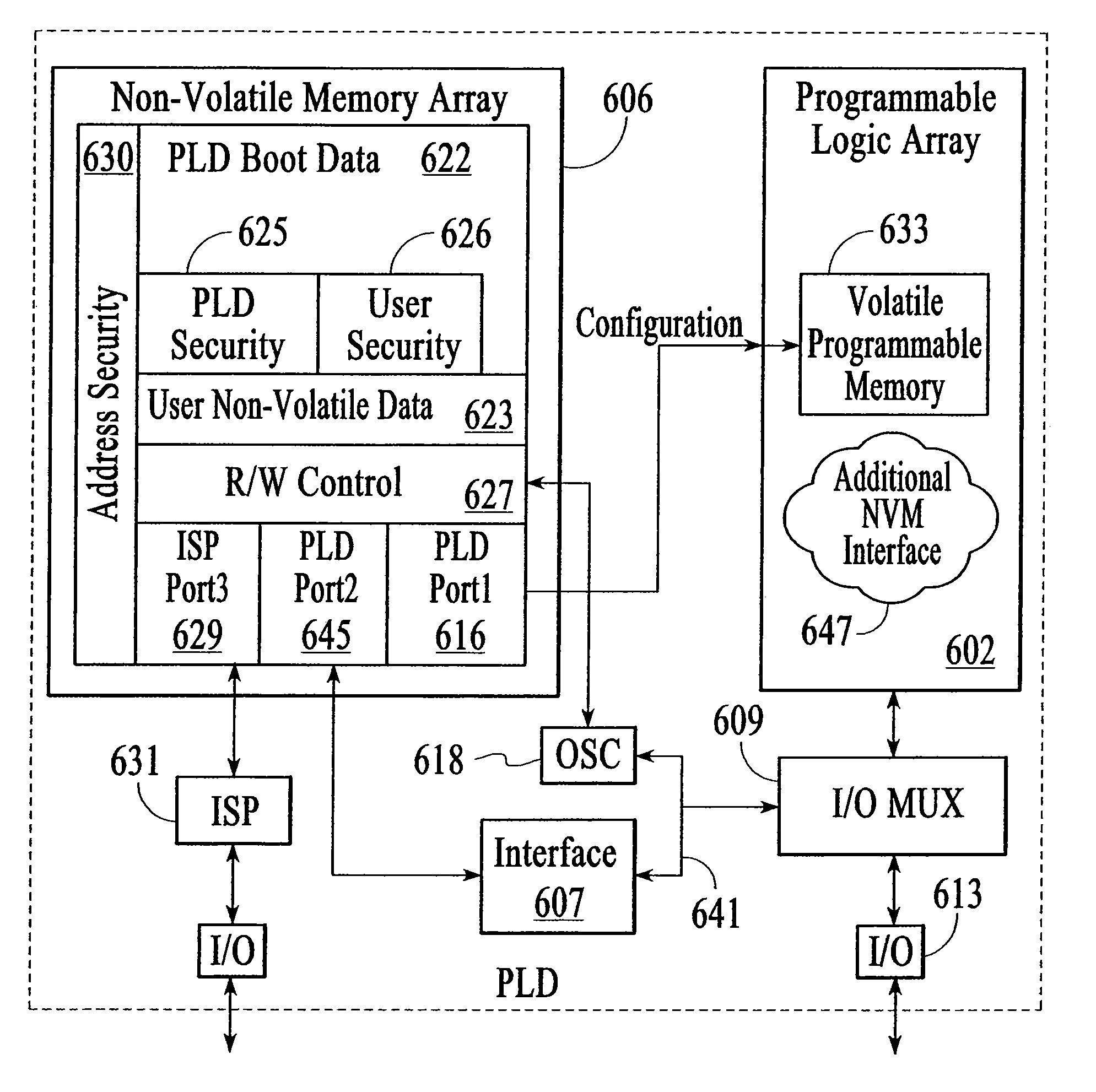

Programmable logic device with on-chip nonvolatile user memory

ActiveUS7550994B1Reduce complexitySave resourcesSolid-state devicesDigital storageProgrammable logic arrayNon-volatile memory

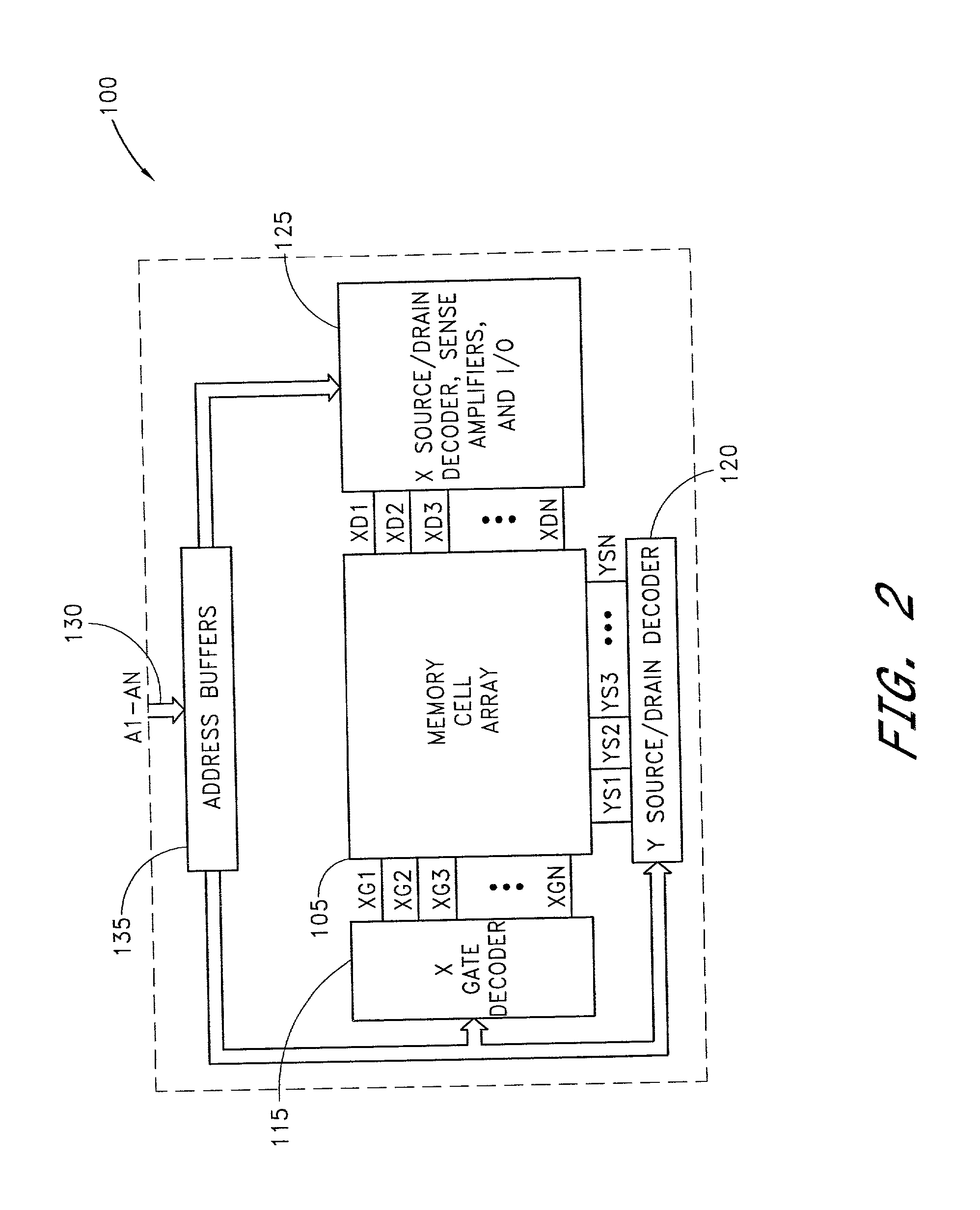

A programmable logic integrated circuit has user-accessible nonvolatile memory for use by the programmable logic. In a specific embodiment, the programmable logic integrated circuit has a programmable logic array portion and a nonvolatile memory array portion. The nonvolatile memory array portion is segregated into a boot data part and a user data partition. The boot data partition holds data for configuring the programmable logic portion on power up, and the user data partition is for use by the programmable logic. A user can store and retrieve data from the user data partition. A built-in oscillator can be programmably connected from the nonvolatile memory portion to the PLD portion.

Owner:TAHOE RES LTD

Hardware/software design tool and language specification mechanism enabling efficient technology retargeting and optimization

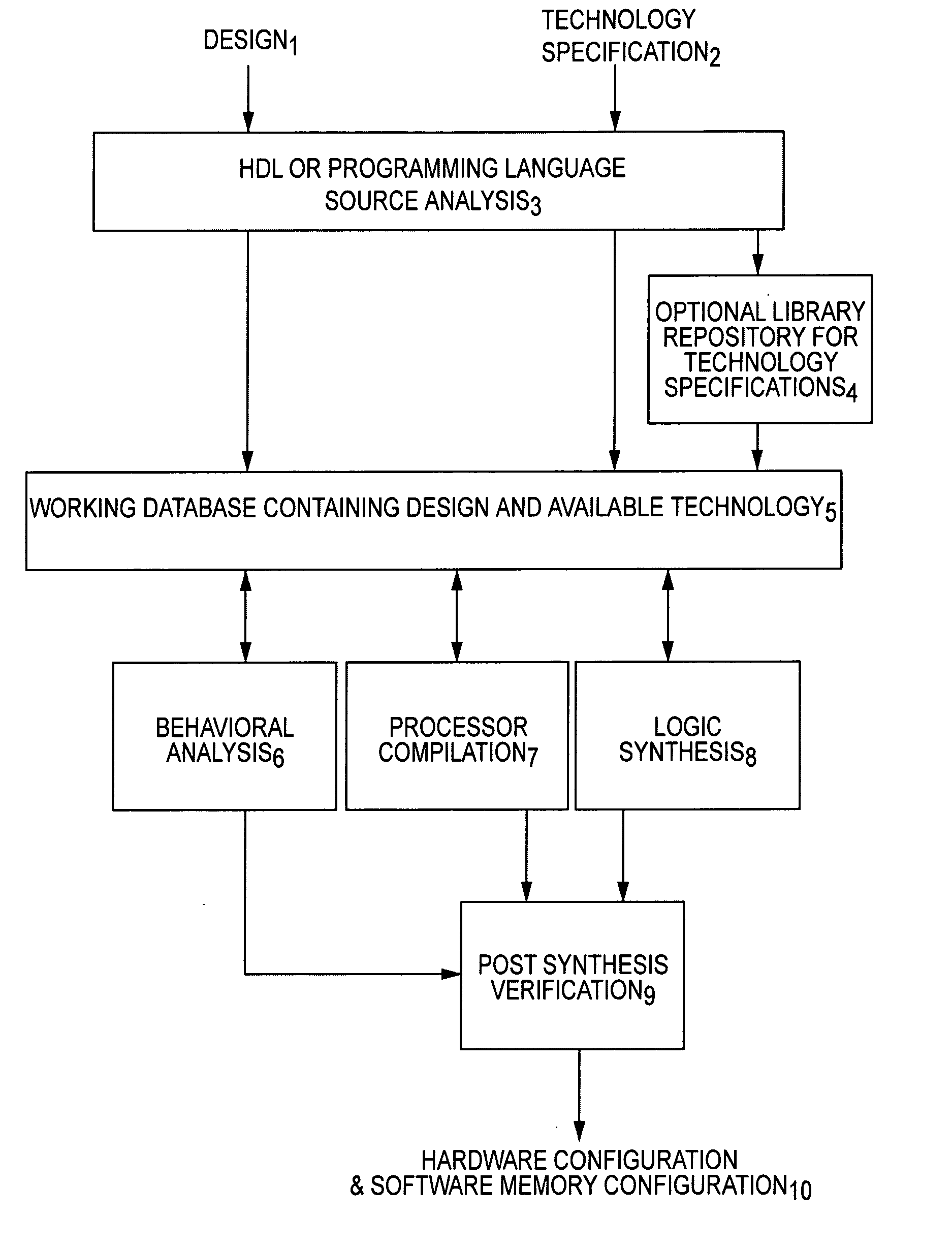

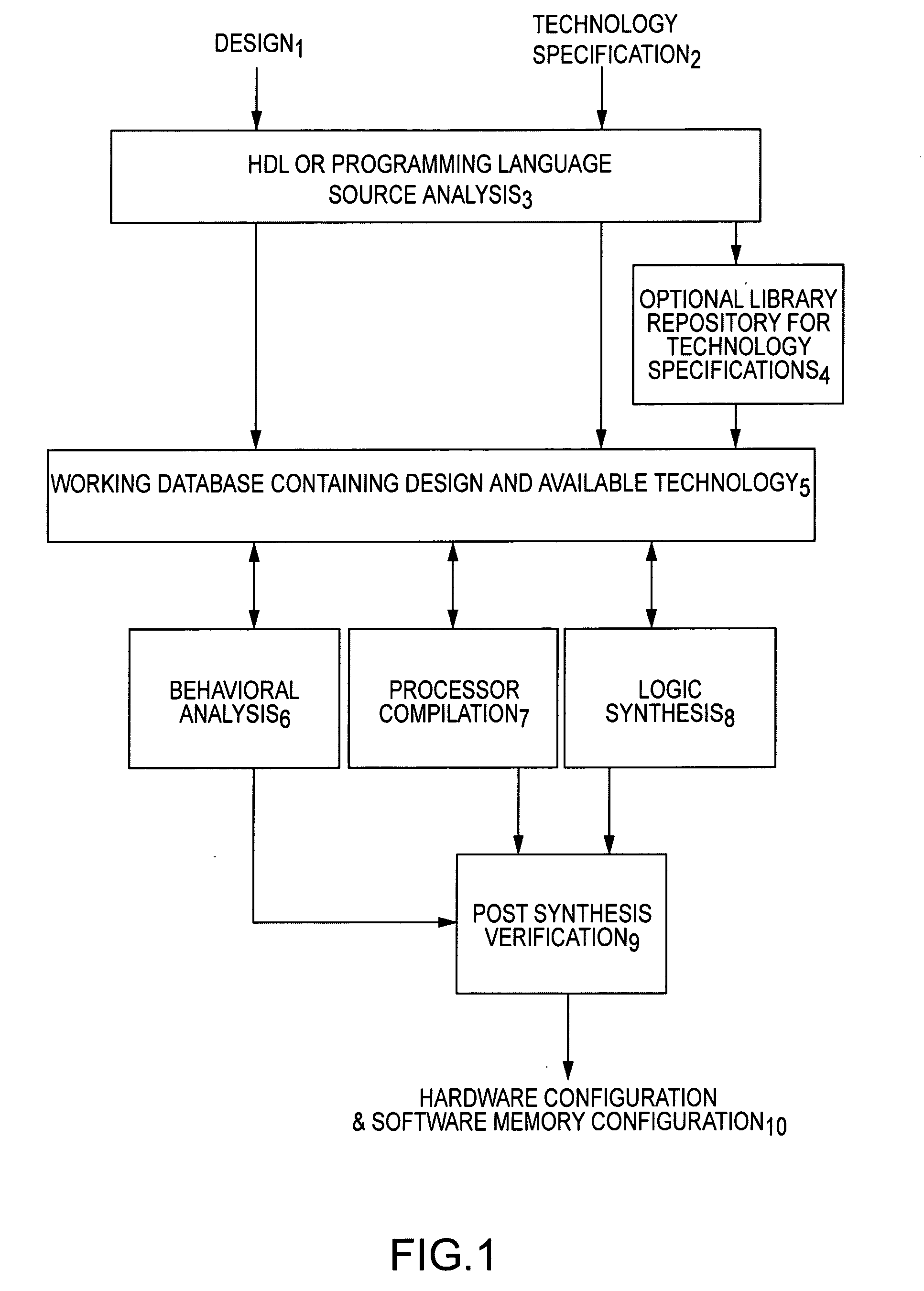

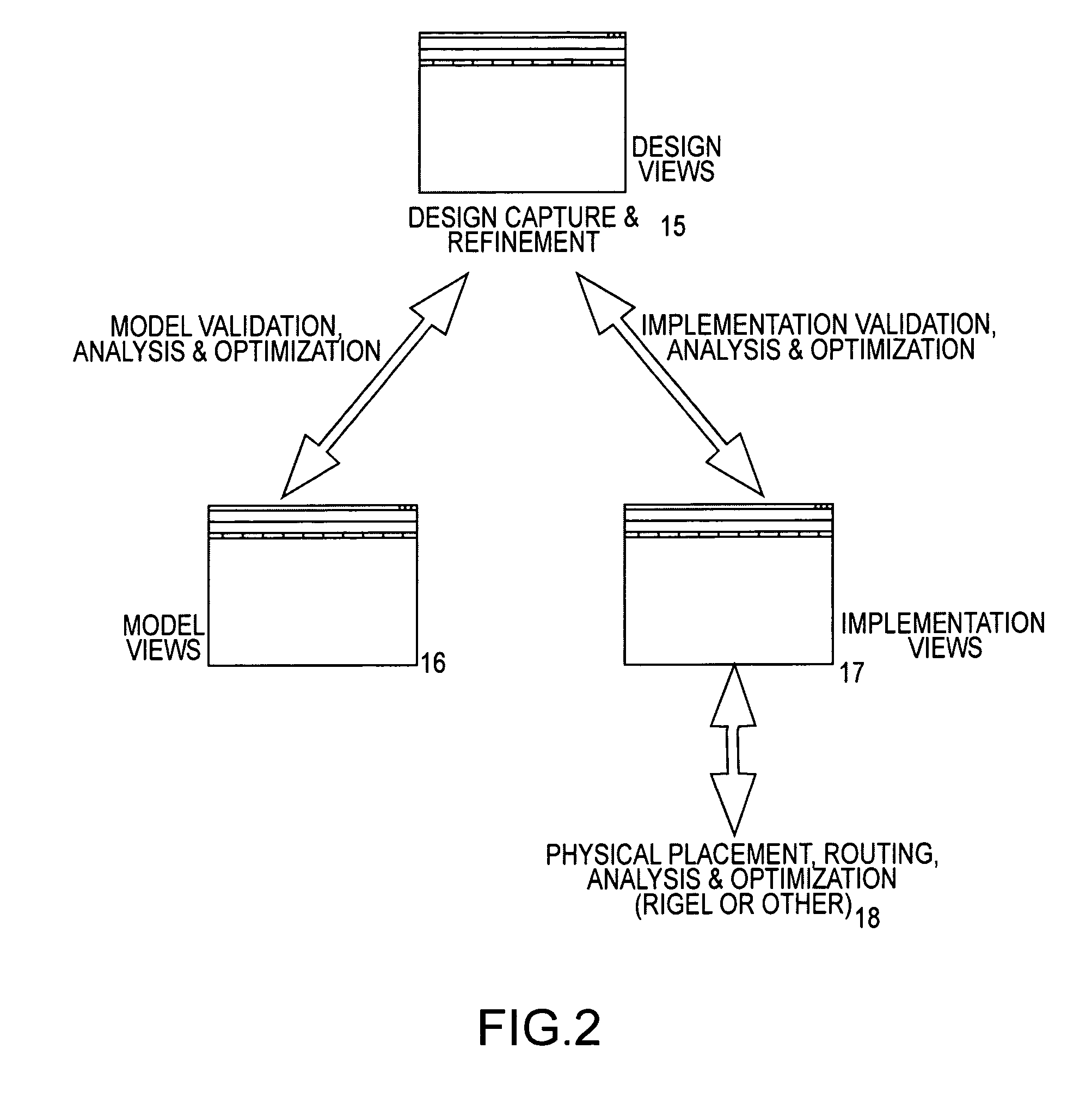

InactiveUS20050289485A1More compactEfficient designElectrical testingDigital computer detailsComputer architectureSoftware system

An innovative hardware / software design tool provides four modes of operation for converting an electronic design specification and zero or more technology specifications into realization of the electronic design in computer hardware, software and firmware. The first mode of operation compiles design and logic technology specifications into a model which can be utilized for behavioral analysis (such as simulation or formal verification) of logical characteristics (the model). The second mode of operation translates (compiles) partitions of the design and one or more logic technologies into one or more processor intermediates or binaries (embedded binary) suitable for execution on multi-purpose processing units (embedded or general purpose processors). The third mode of operation translates (synthesizes) partitions of the design and logic technology into a collection of cells and interconnects (net-list implementation) suitable for input to physical design processes such as is required to target a field-programmable logic array (FPGA), application specific integrated circuit (ASIC), system-on-a-chip (SOC) or custom logic). The fourth mode of operation analyzes (verifies) behavior of the embedded binaries running on processing units and implementations augmented by additional physical technology and parameters, yielding a more detailed (accurate) prediction of the resulting hardware / software system behavior when realized through manufacturing. Critically, the design specification, logic specifications, physical specifications and definition of each multi-purpose processing unit may be defined external to the hardware / software design tool using an innovative augmentation of standard hardware description or programming languages taught in this patent application. In the prior art, specification of the logic technology, physical technology and embedded or general purpose processor architecture are either incorporated directly into the design tool by the tool developer or are maintained entirely external to the design tool (such as an encapsulated component model or intermediate code interpreter). The present invention is an innovative and valuable improvement over prior art in that design specifications are combined by the tool from distinct specification(s) of generalized logic, physical and processor technology, leading to more efficient behavioral design, opportunities for third parties to add functionality by incorporating generalized logic and physical technology modules into the analysis and synthesis process and opportunities for semi-automatic, goal-directed optimization through application of various logic, physical and processor technologies by the design tool.

Owner:FTL SYST

Service programmable logic arrays with low tunnel barrier interpoly insulators

Structures and methods for in service programmable logic arrays with low tunnel barrier interpoly insulators are provided. The in-service programmable logic array includes a first logic and a second logic plan having a number of logic cells arranged in rows and columns that are interconnected to produce a number of logical outputs such that the in service programmable logic array implements a logical function. The logic cell includes a first source / drain region and a second source / drain region separated by a channel region in a substrate. A floating gate opposing the channel region and is separated therefrom by a gate oxide. A control gate opposes the floating gate. The control gate is separated from the floating gate by a low tunnel barrier intergate insulator. The low tunnel barrier intergate insulator includes a metal oxide insulator selected from the group consisting of PbO, Al2O3, Ta2O5, TiO2, ZrO2, Nb2O5 and / or a Perovskite oxide tunnel barrier.

Owner:MICRON TECH INC

Reconfigurable network on a chip

ActiveUS20070075734A1Easy programmingIncrease flexibilitySolid-state devicesDigital computer detailsSemiconductor chipProgrammable logic array

An architecture for a reconfigurable network that can be implemented on a semiconductor chip is disclosed, which includes a hierarchical organization of network components and functions that are readily programmable and highly flexible. Essentially, a reconfigurable network on a chip is disclosed, which includes aspects of reconfigurable computing, system on a chip, and network on a chip designs. More precisely, a reconfigurable network on a chip includes a general purpose microprocessor for implementing software tasks, a plurality of on-chip memories for facilitating the processing of large data structures as well as processor collaboration, a plurality of reconfigurable execution units including self-contained, individually reconfigurable programmable logic arrays, a plurality of configurable system interface units that provide interconnections between on-chip memories, networks or buses, an on-chip network including a network interconnection interface that enables communication between all reconfigurable execution units, configurable system interface units and general purpose microprocessors, a fine grain interconnect unit that gathers associated input / output signals for a particular interface and attaches them to a designated system interface resource, and a plurality of input / output blocks that supply the link between an on-chip interface resource and a particular external network or device interface. Advantageously, the network minimizes the configuration latency of the reconfigurable execution units and also enables reconfiguration on-the-fly.

Owner:HONEYWELL INT INC

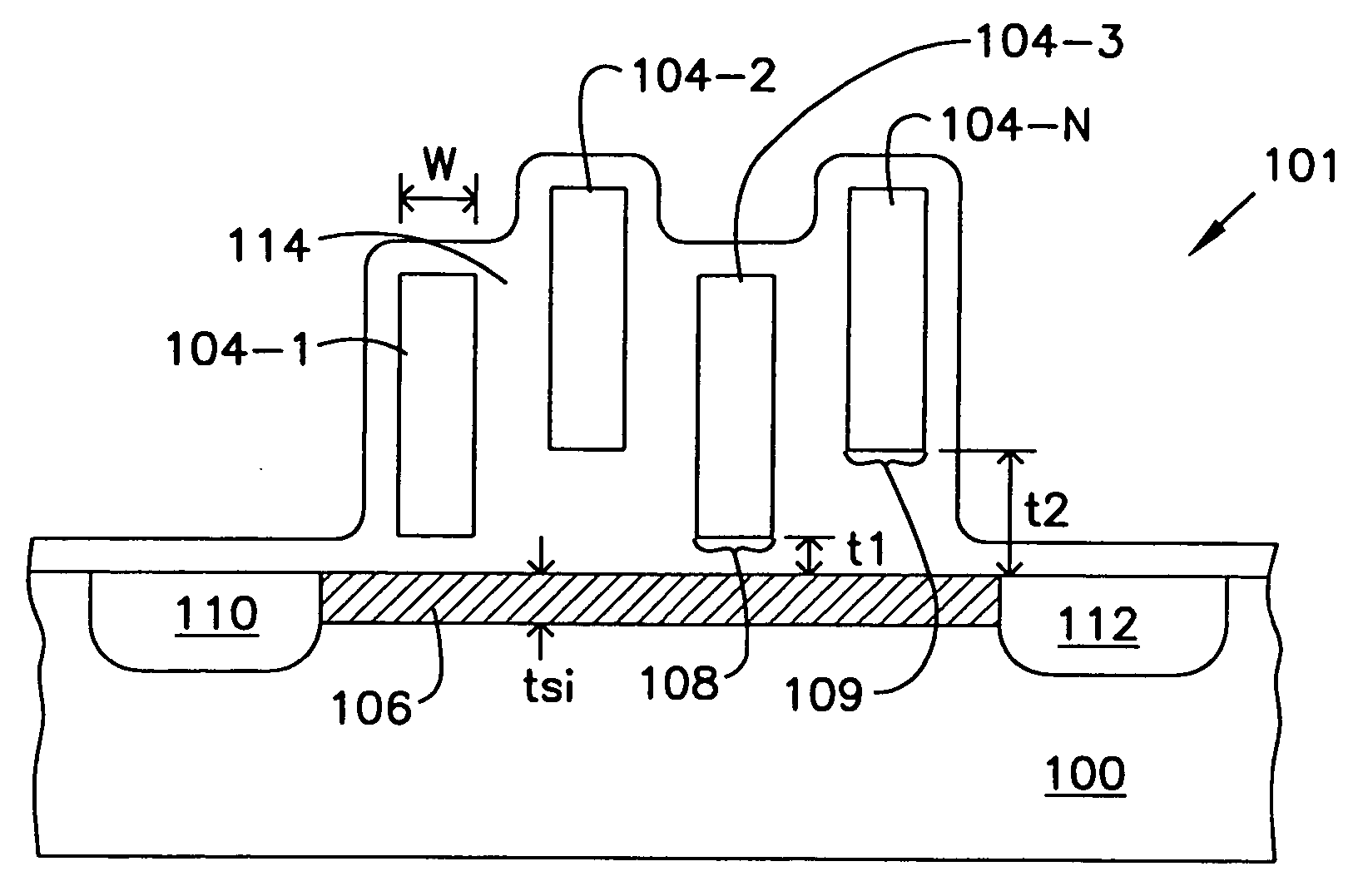

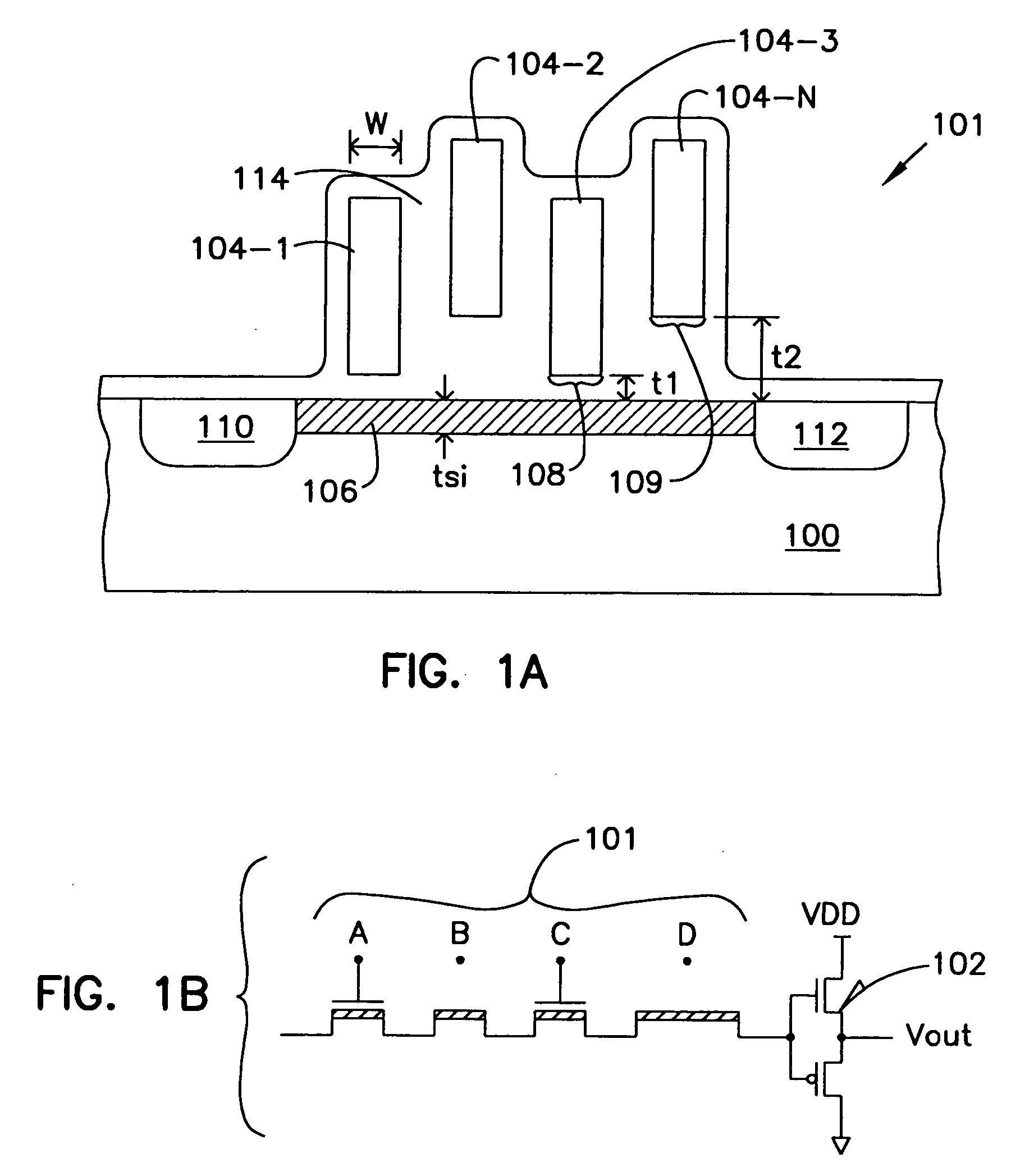

Vertical transistor with horizontal gate layers

InactiveUS20030038318A1TransistorSolid-state devicesProgrammable read-only memoryArray data structure

Vertical body transistors with adjacent horizontal gate layers are used to form a memory array in a high density flash electrically erasable and programmable read only memory (EEPROM) or a logic array in a high density field programmable logic array (FPLA). The transistor is a field-effect transistor (FET) having an electrically isolated (floating) gate that controls electrical conduction between source regions and drain regions. If a particular floating gate is charged with stored electrons, then the transistor will not turn on and will provide an indication of the stored data at this location in the memory array within the EEPROM or will act as the absence of a transistor at this location in the logic array within the FPLA. The memory array or the logic array includes densely packed cells, each cell having a semiconductor pillar providing shared source and drain regions for two vertical body transistors that have control gates overlaying floating gates distributed on opposing sides of the semiconductor pillar. Both bulk semiconductor and silicon-on-insulator embodiments are provided. If a floating gate transistor is used to store a single bit of data or to represent a logic function, an area of only 2F2 is needed per respective bit of data or bit of logic, where F is the minimum lithographic feature size.

Owner:MICRON TECH INC

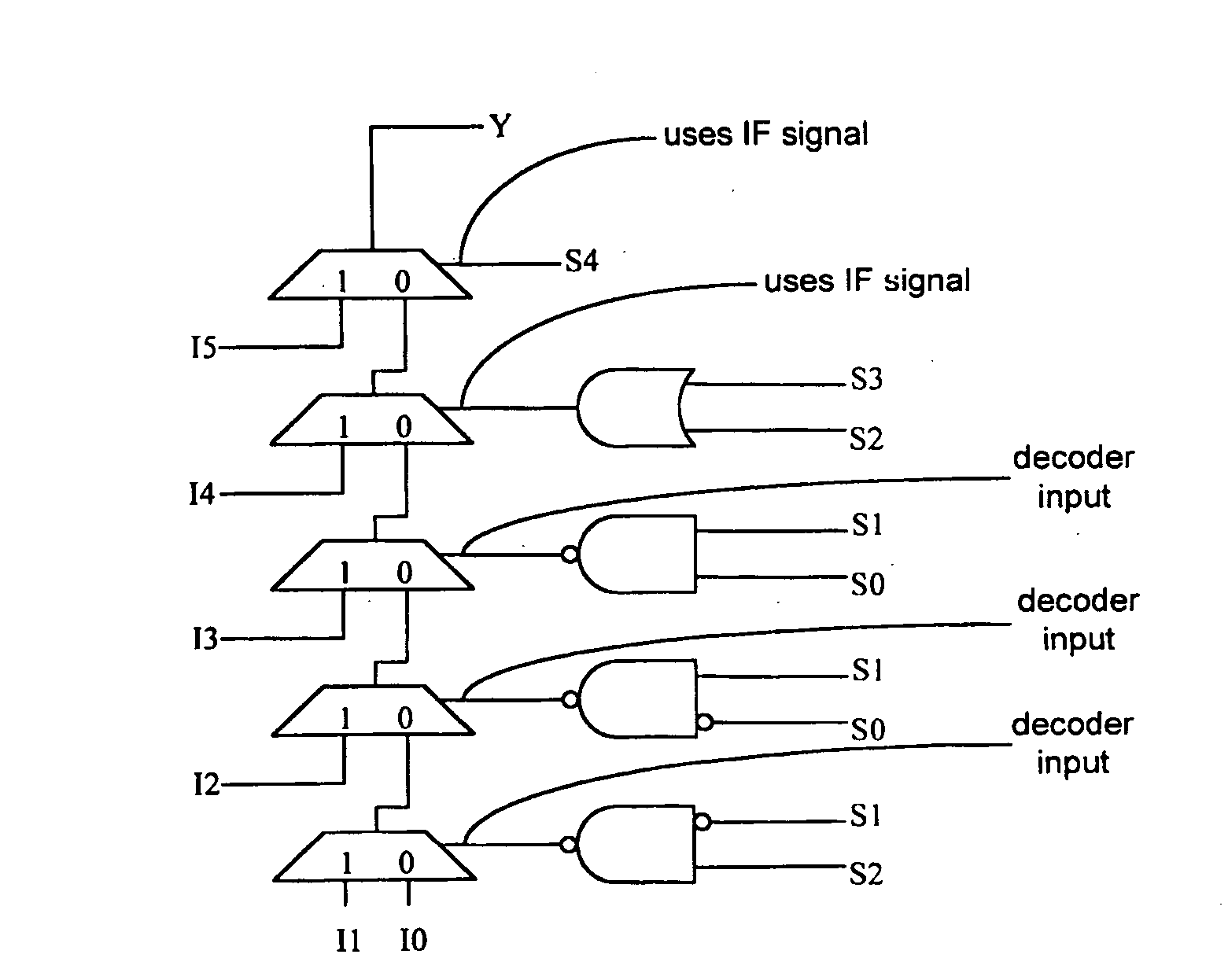

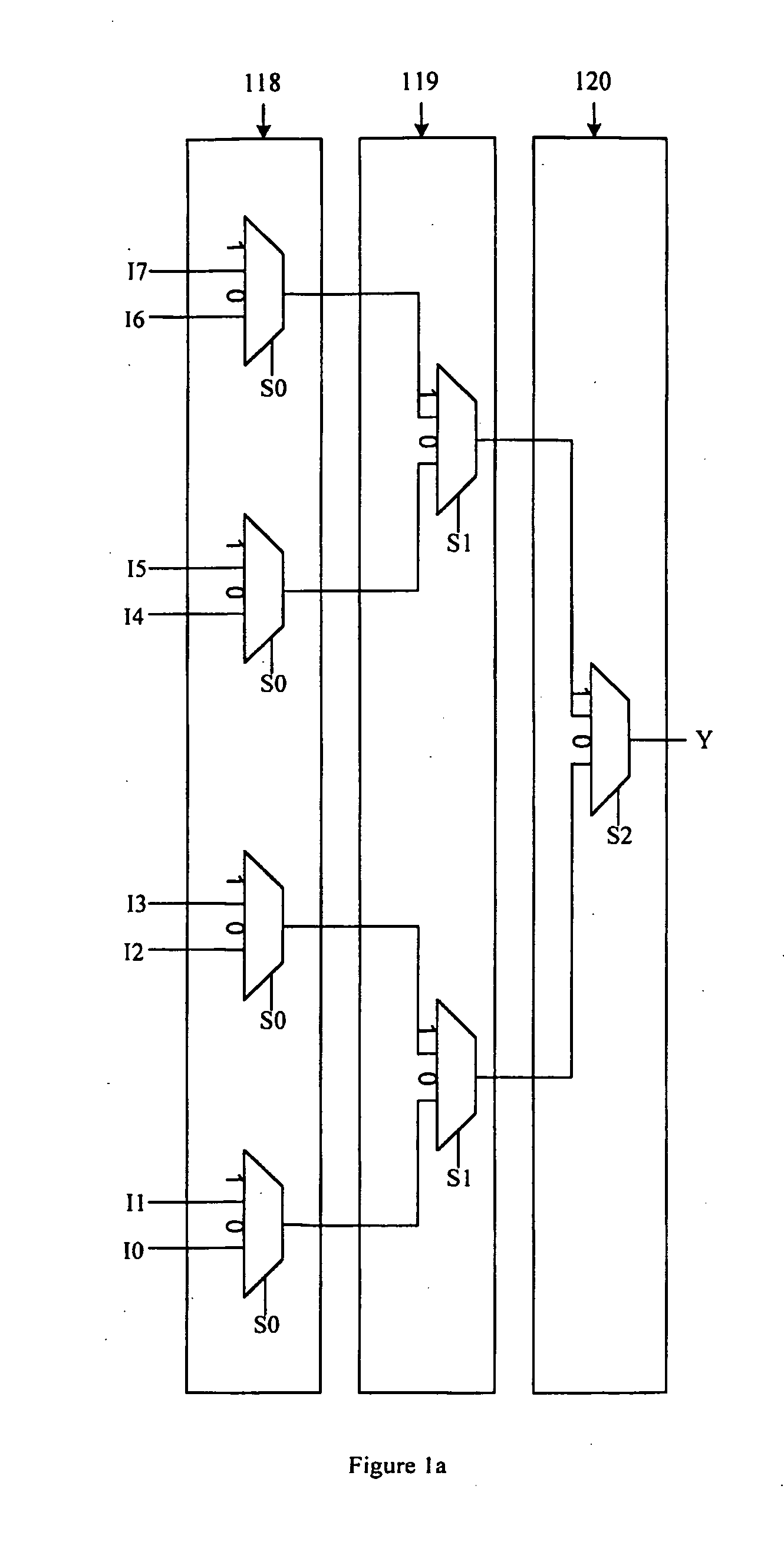

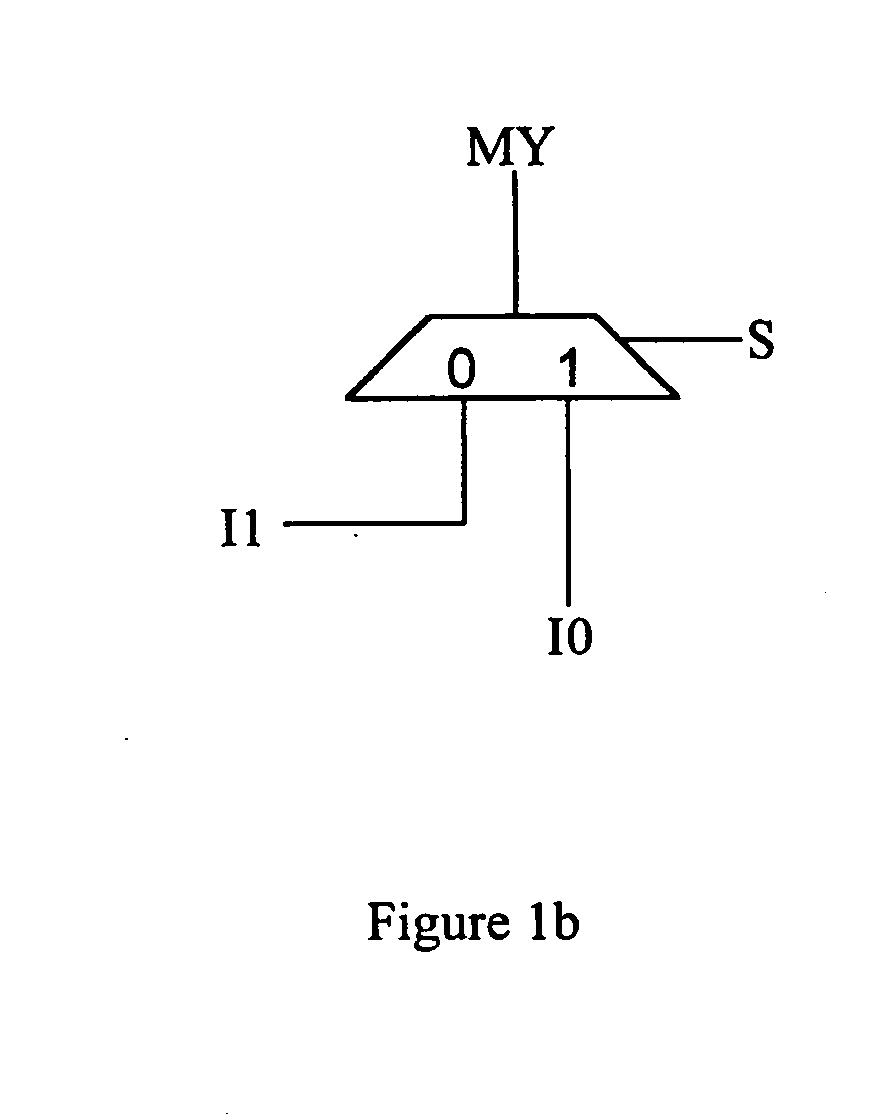

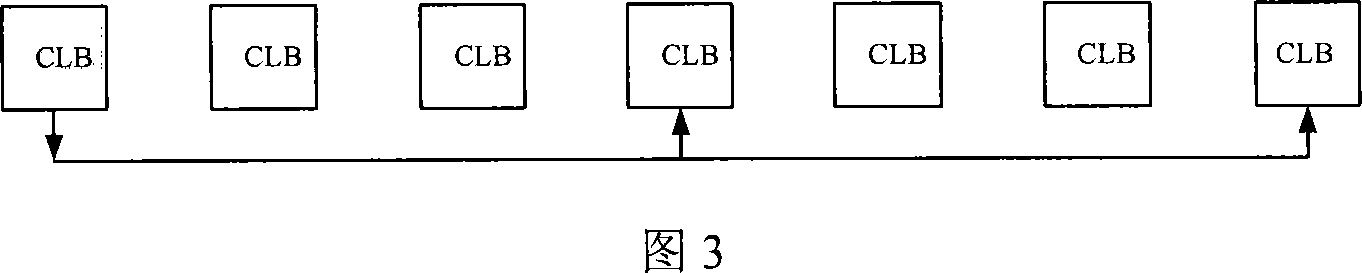

Versatile multiplexer-structures in programmable logic using serial chaining and novel selection schemes

Owner:AGATE LOGIC BEIJING

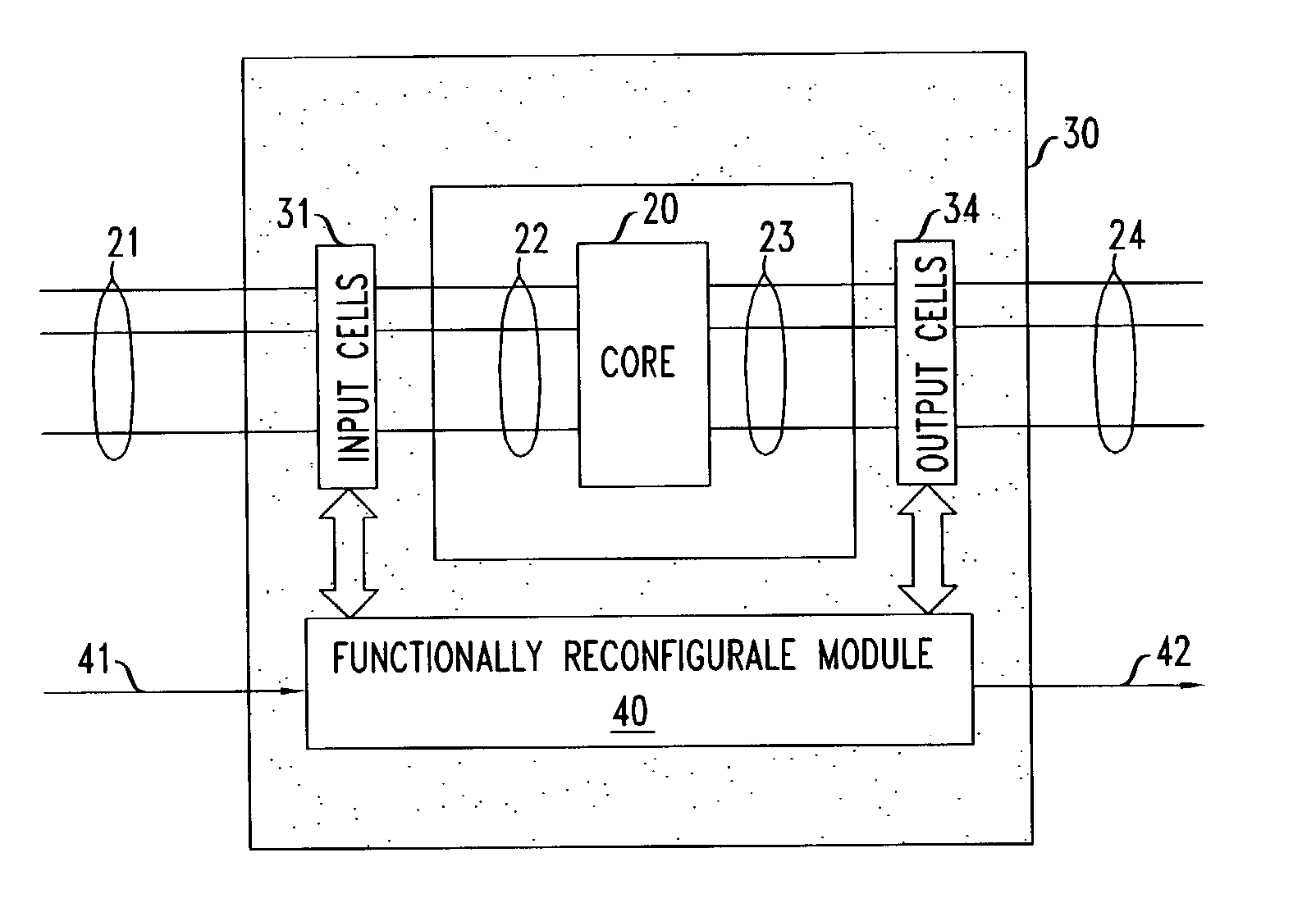

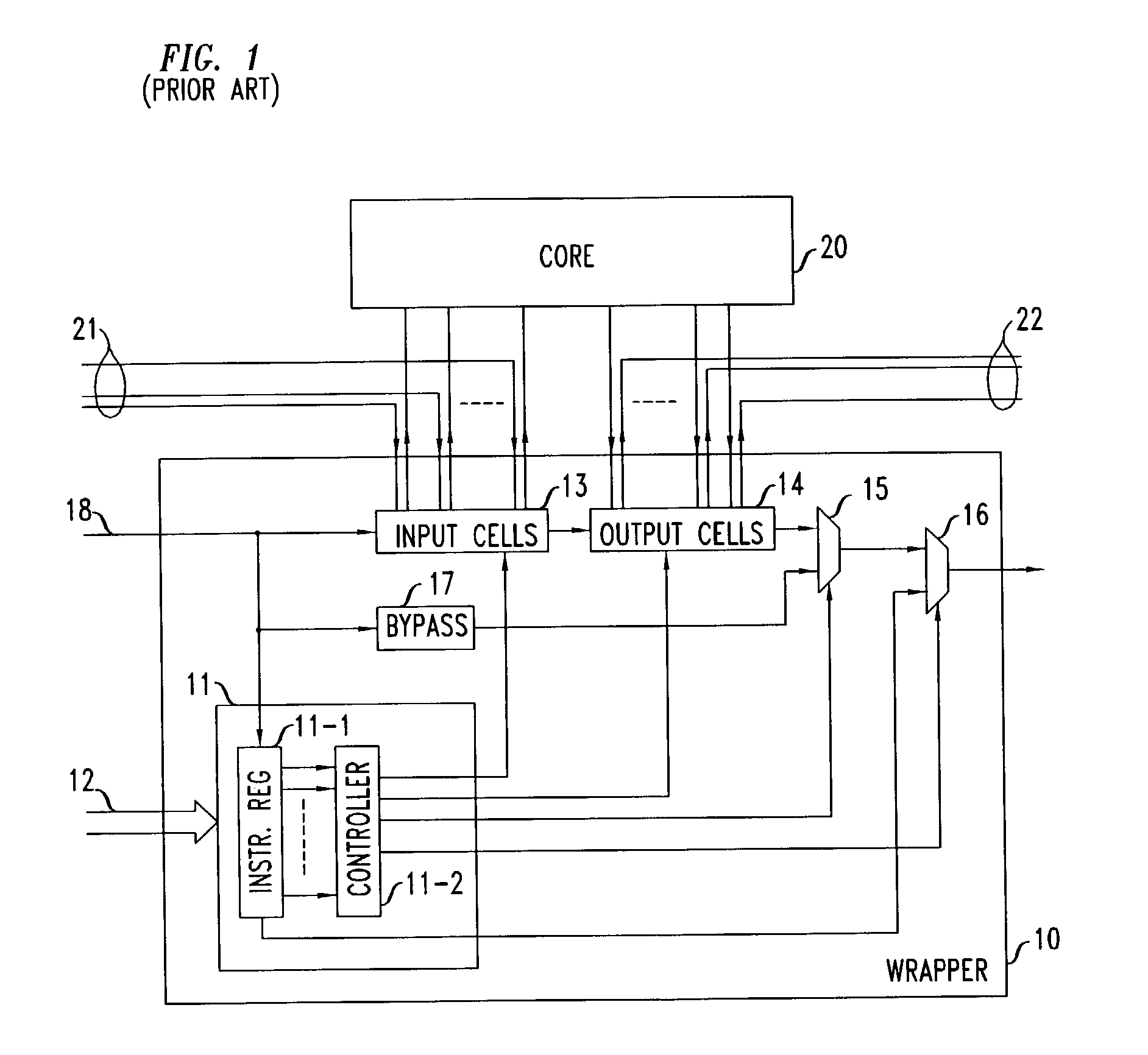

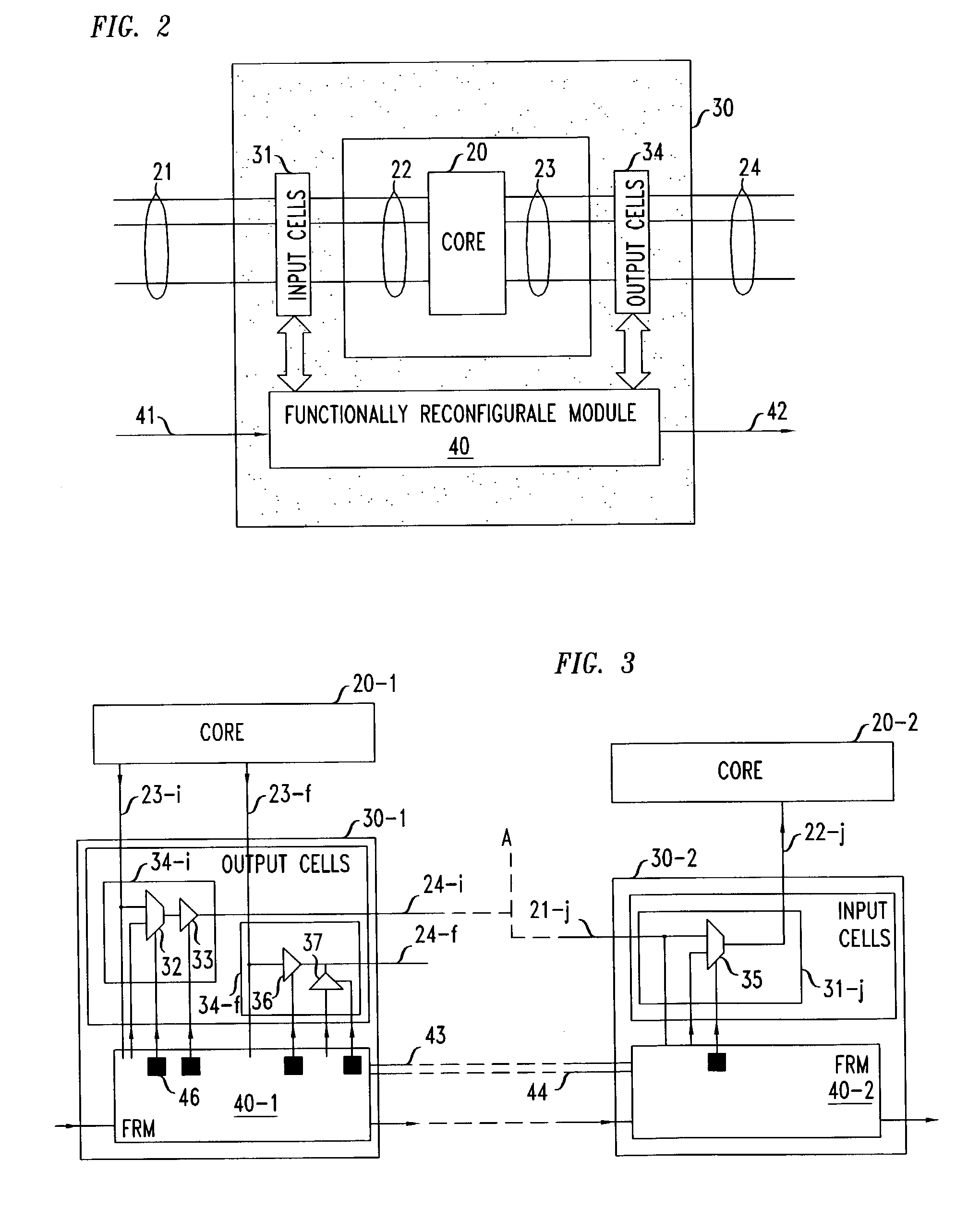

Reconfigurable fabric for SoCs using functional I/O leads

ActiveUS7058918B2Increase flexibilityIncrease the number ofElectrical testingSpecial data processing applicationsPath networkComputer module

An exceptionally effective SoC design is achieved by the user of wrappers that comprise a functionally reconfigurable module (FRM) that is capable of affecting the operational functionality of the wrapper and that, consequently, is capable of affecting the operational functionality of a designed SoC. One embodiment of a core+wrapper combination comprises distinct input and output cells within the wrapper, and a separate FRM. Another embodiment may embed the input and output cells within the FRM. The FRM may be implemented with, for example, a field programmable logic array (FPLA). An additional advance is realized by providing a number of spare leads in the signal paths network that interconnects the various SoC elements.

Owner:DAFCA

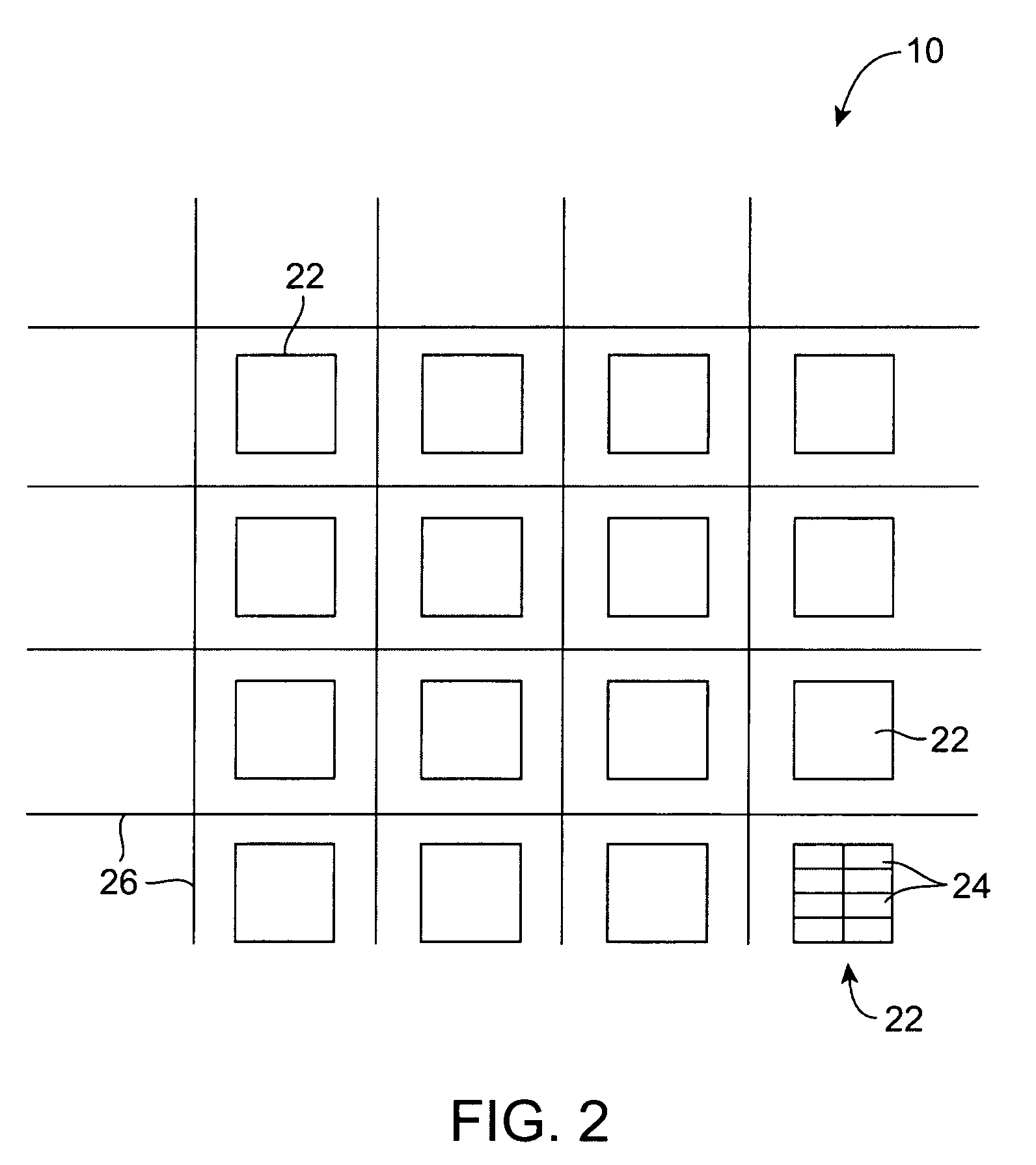

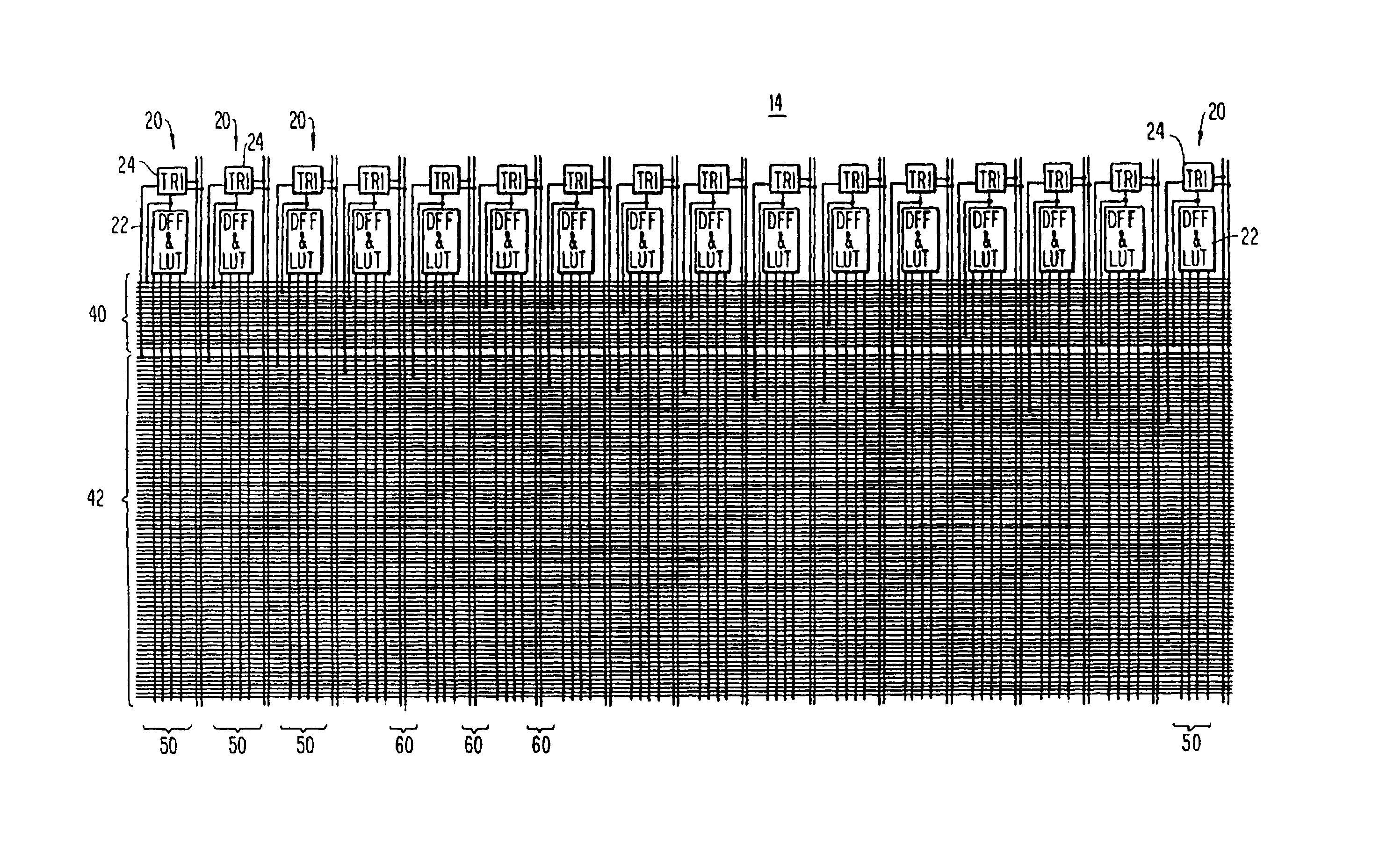

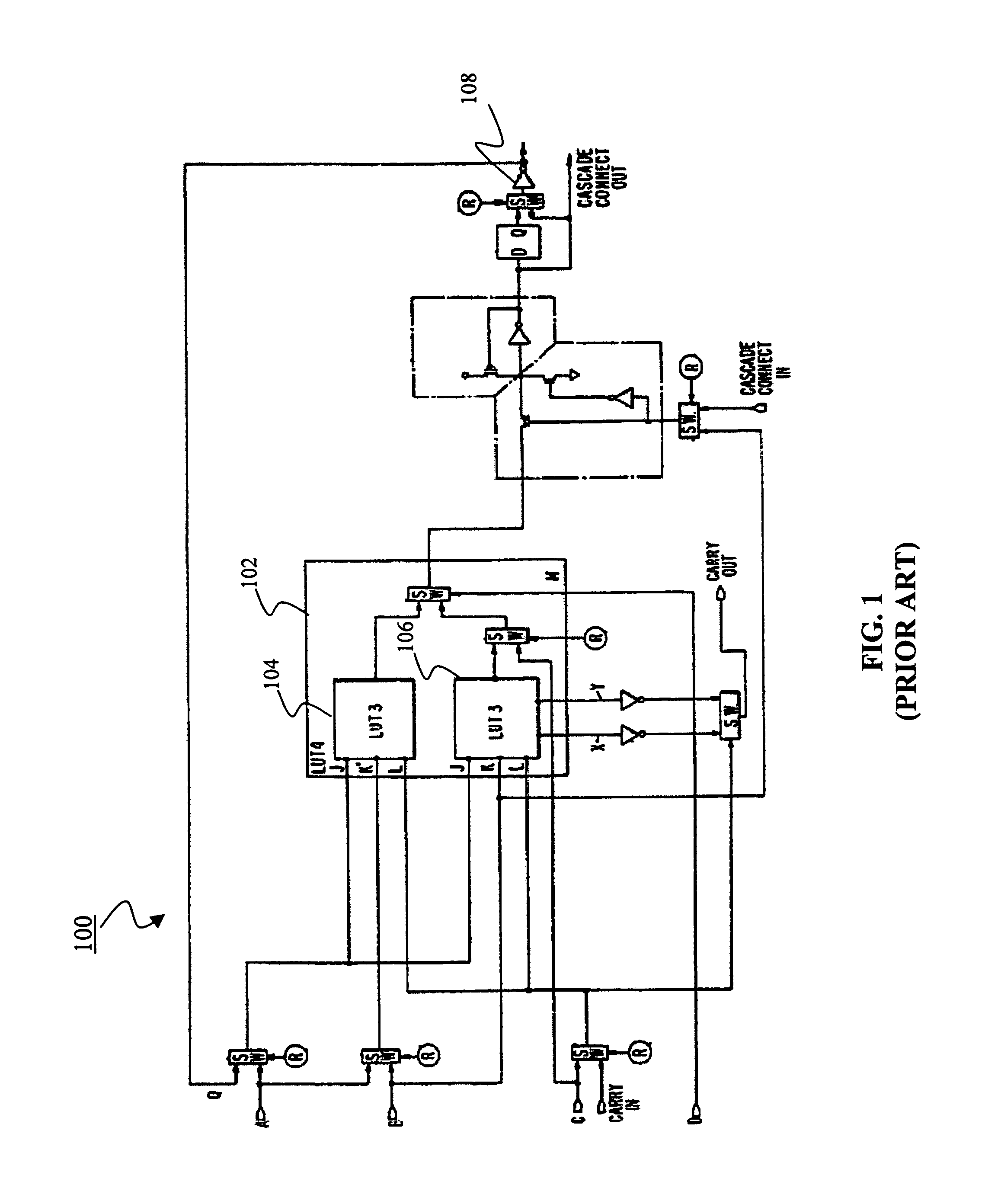

Programmable logic array integrated circuits

InactiveUS6897679B2Simple taskReduce in quantityElectronic circuit testingSolid-state devicesElectrical conductorMultiplexer

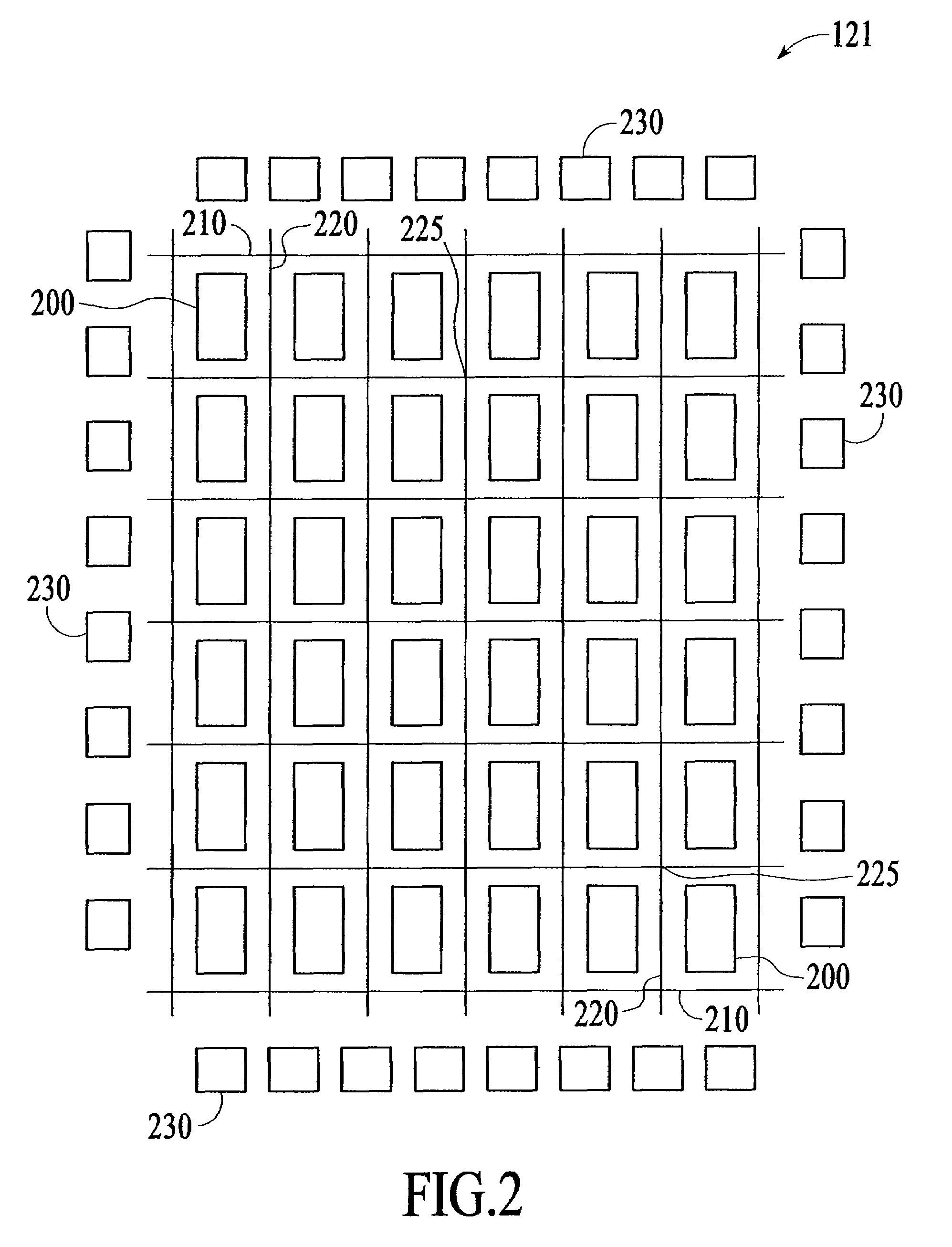

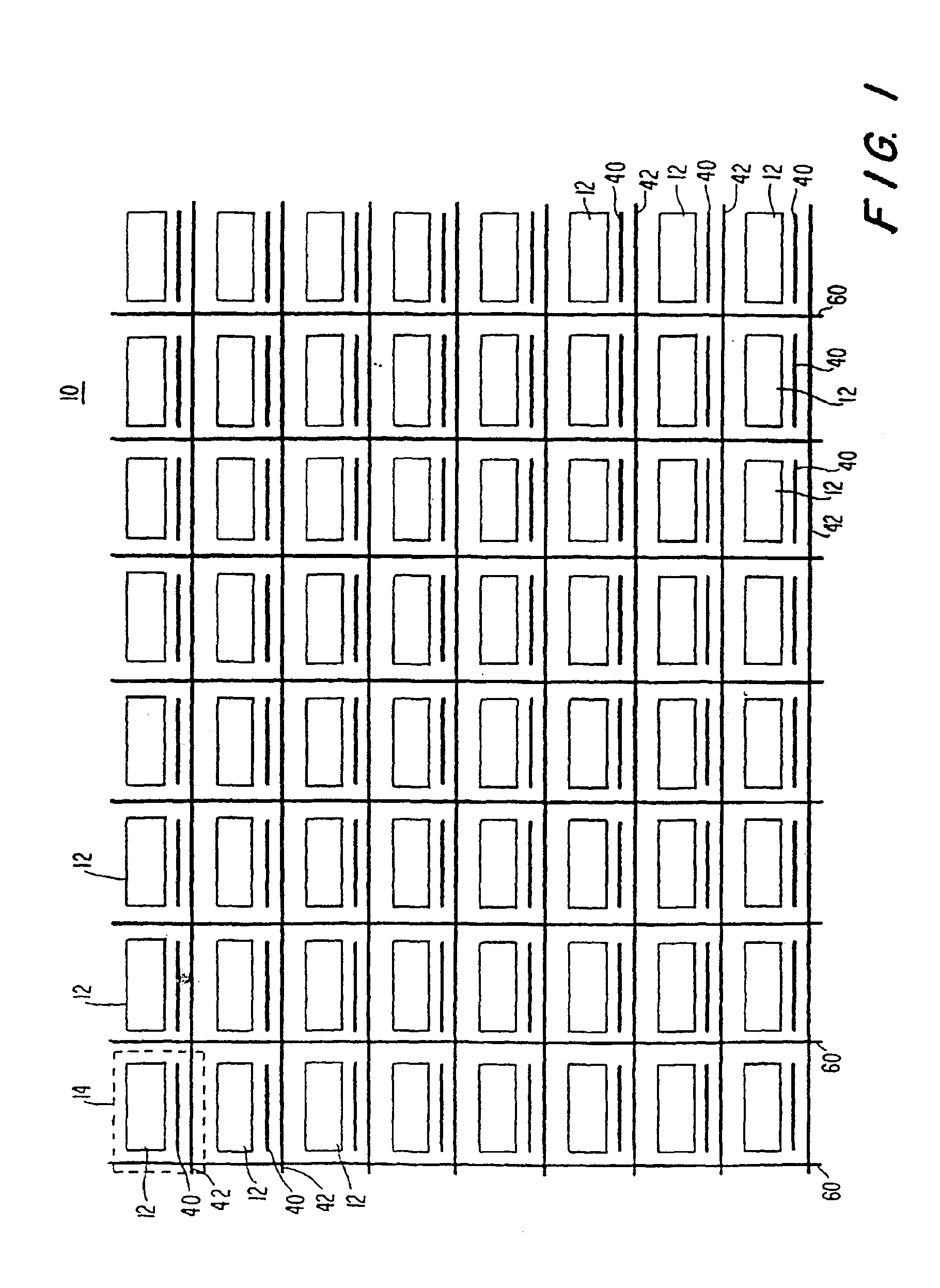

A programmable logic array integrated circuit has a number of programmable logic modules which are grouped together in a plurality of logic array blocks (“LABs”). The LABs are arranged on the circuit in a two dimensional array. A conductor network is provided for interconnecting any logic module with any other logic module. In addition, adjacent or nearby logic modules are connectable to one another for such special purposes as providing a carry chain between logic modules and / or for connecting two or more modules together to provide more complex logic functions without having to make use of the general interconnection network. Another network of so-called fast or universal conductors is provided for distributing widely used logic signals such as clock and clear signals throughout the circuit. Multiplexers can be used in various ways to reduce the number of programmable interconnections required between signal conductors.

Owner:ALTERA CORP

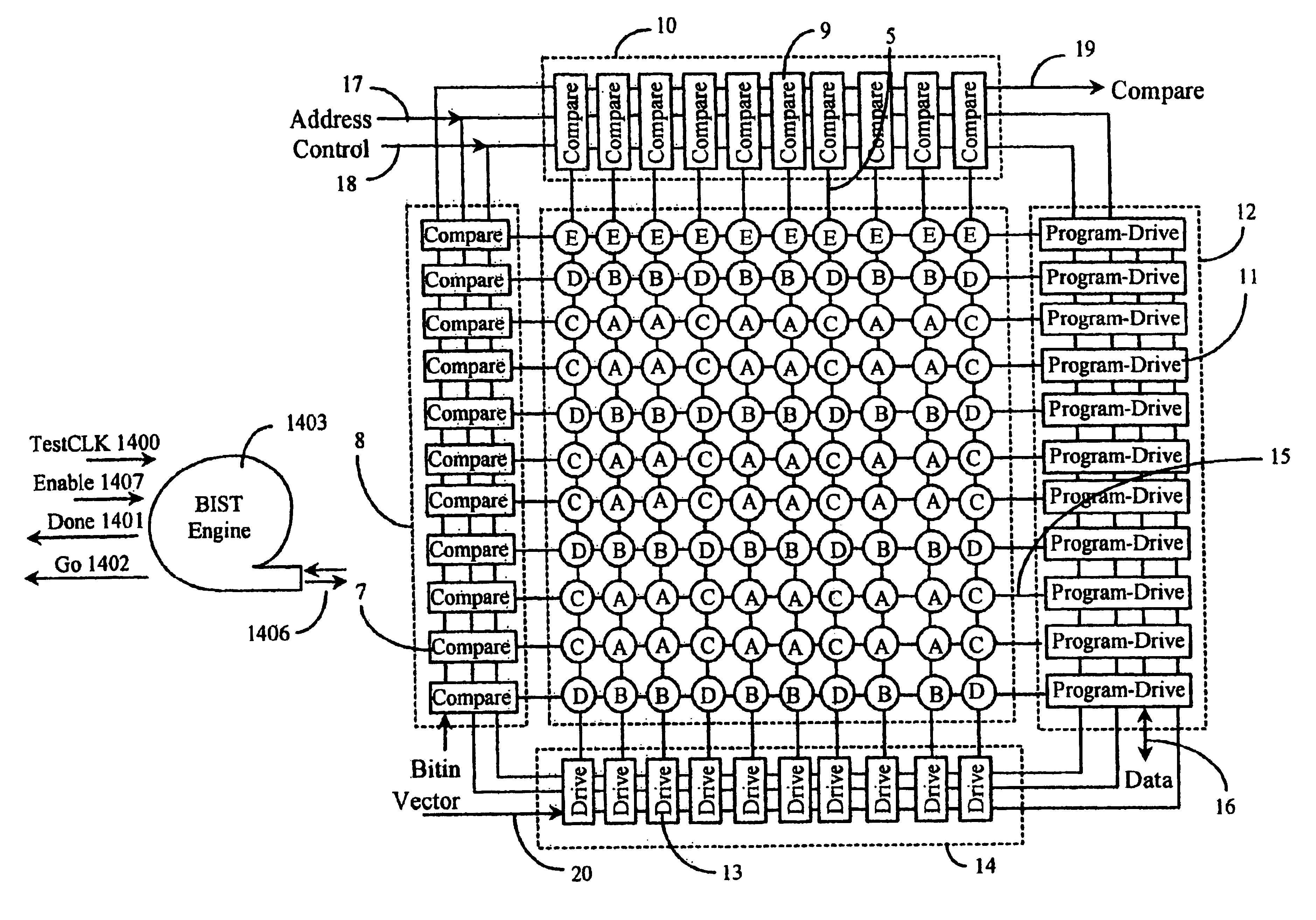

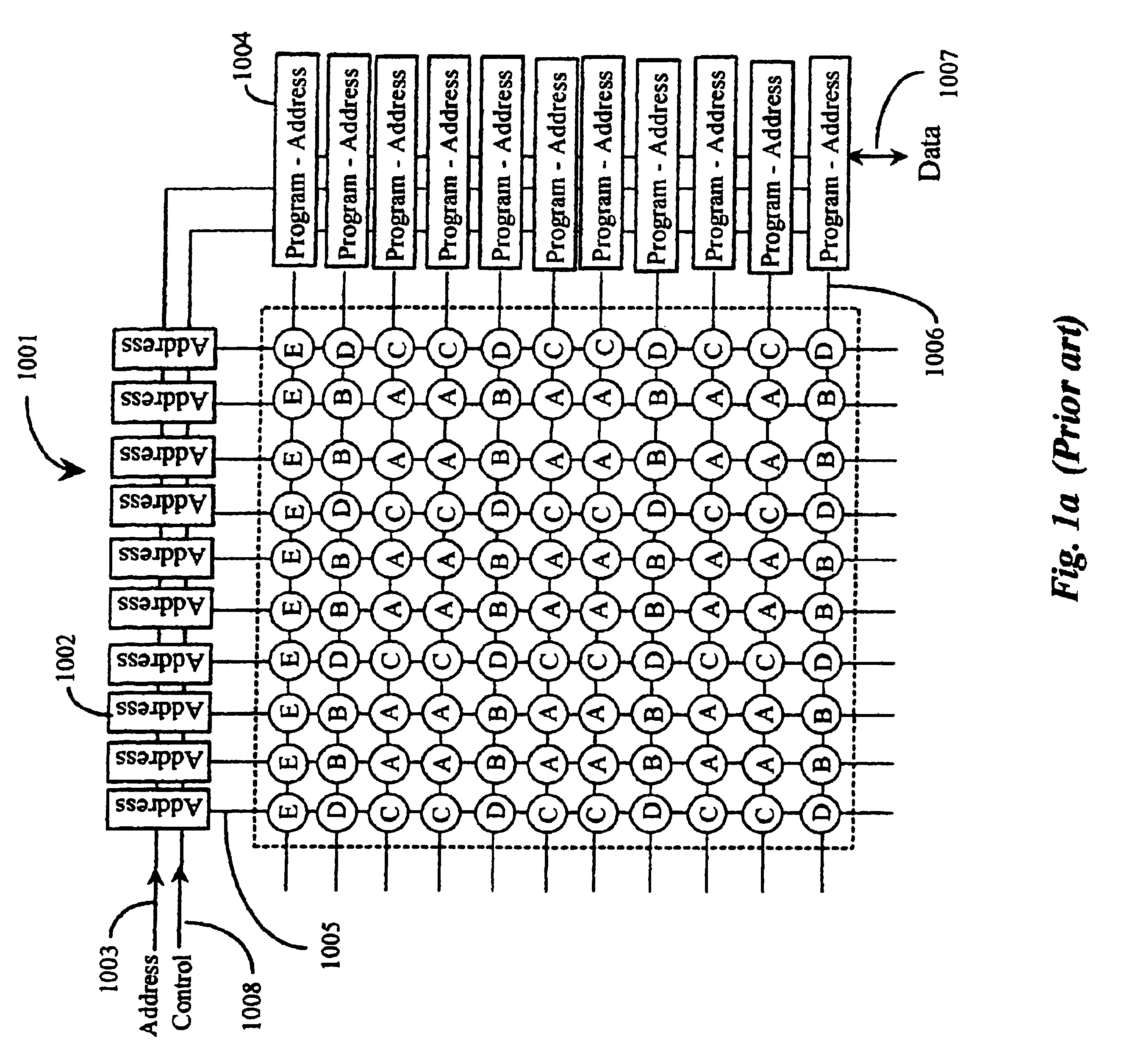

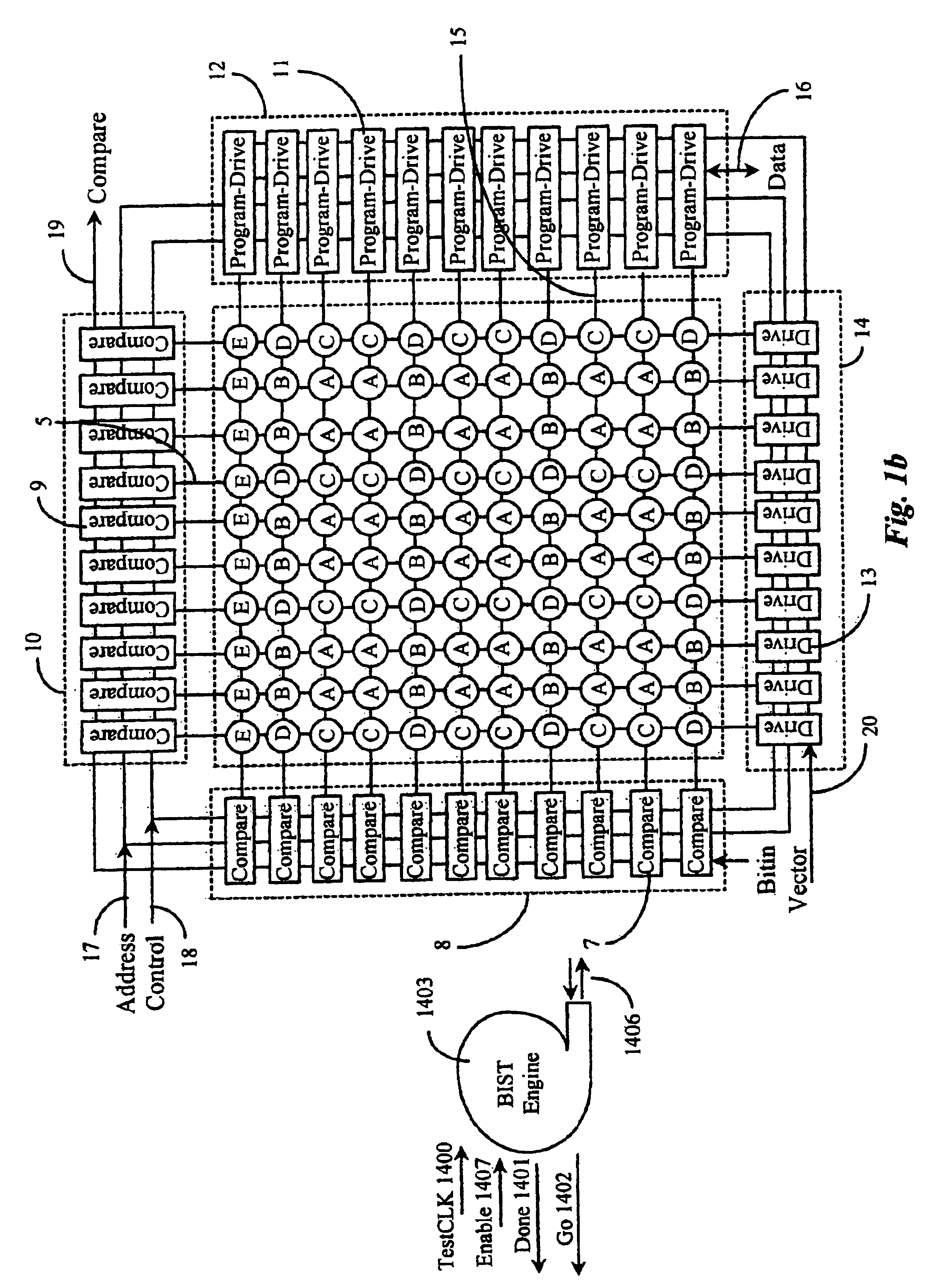

Apparatus and method for self testing programmable logic arrays

Owner:XILINX INC

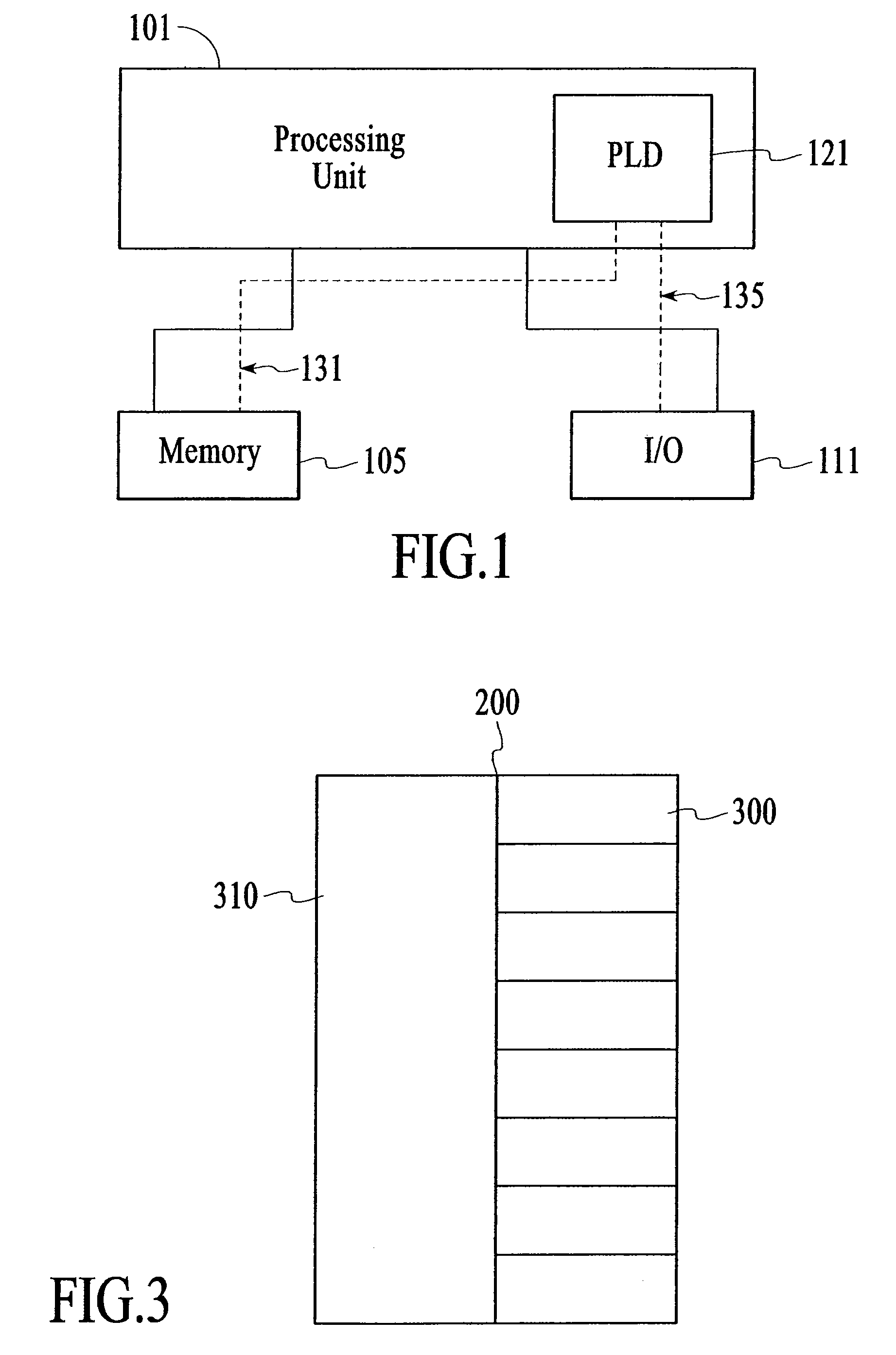

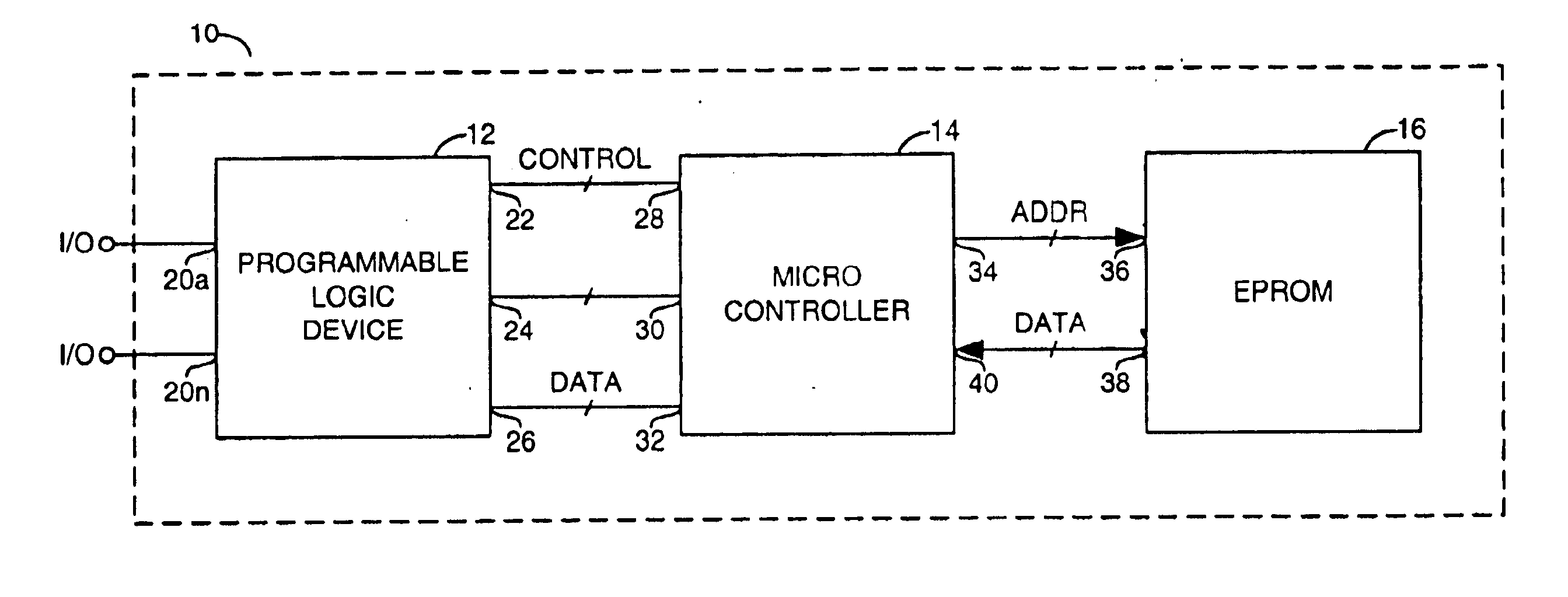

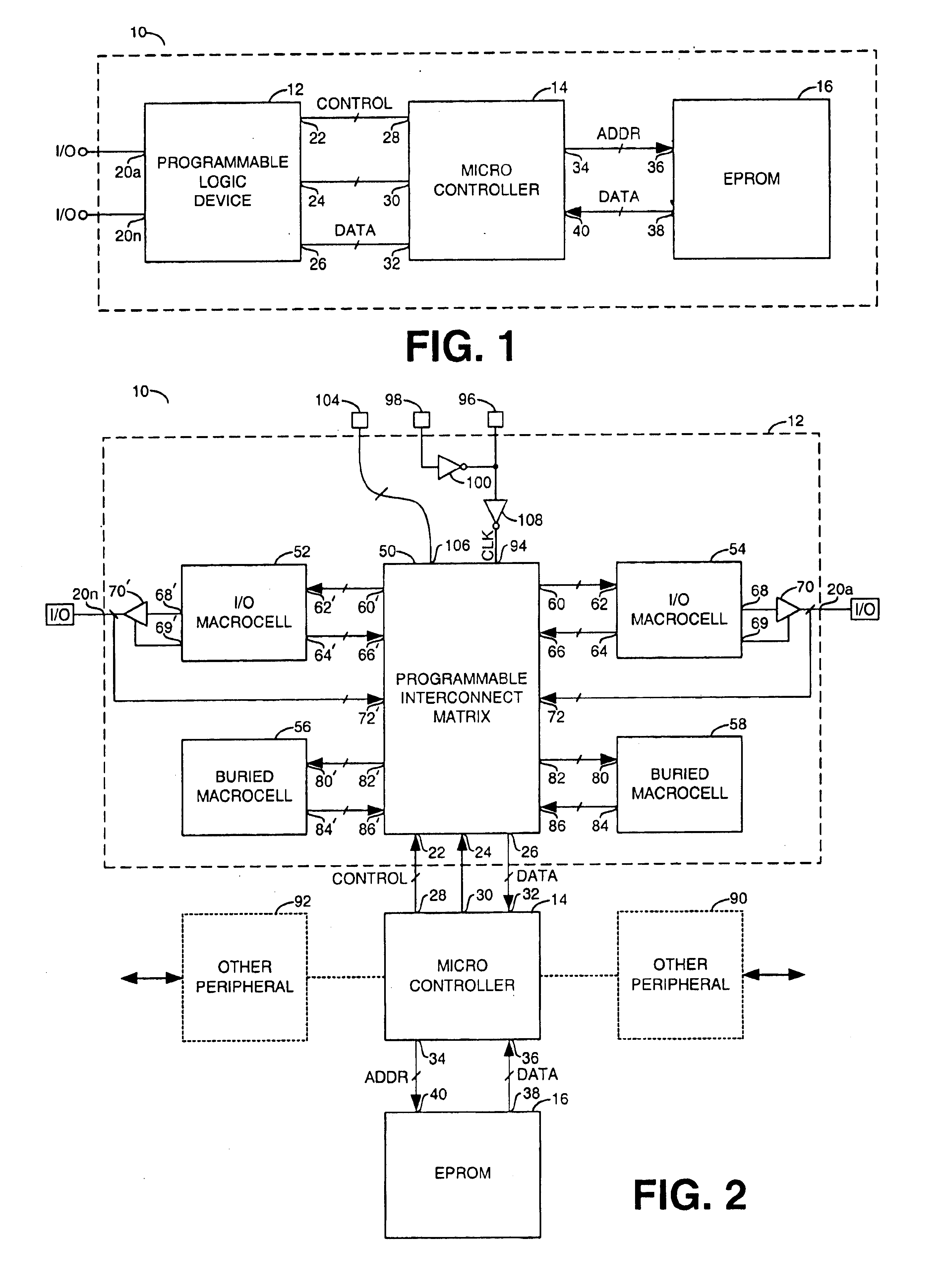

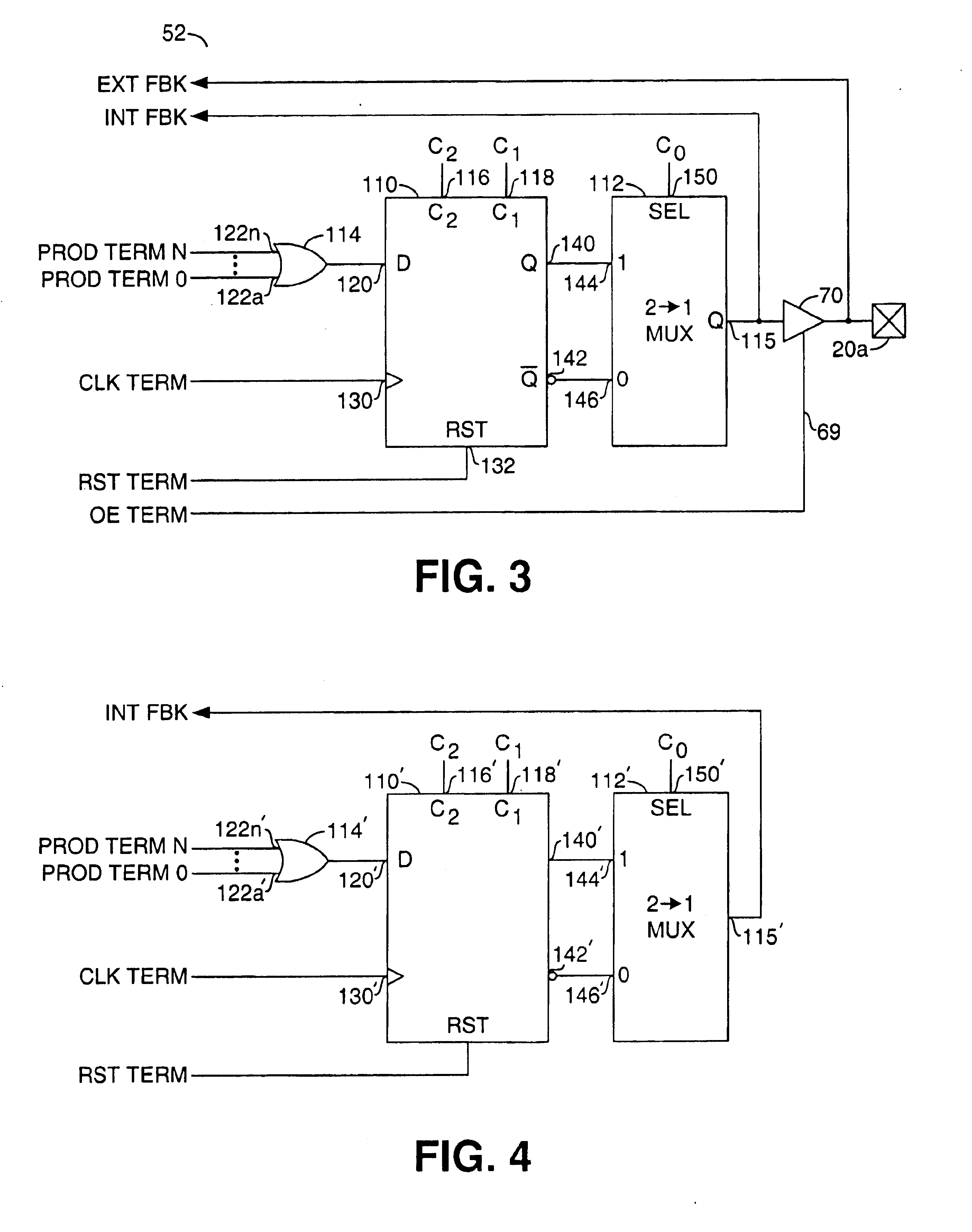

Microcontroller with programmable logic on a single chip

InactiveUS6898101B1Static storageArchitecture with single central processing unitMicrocontrollerErasable programmable logic device

A programmable logic device, a memory device and a microcontroller manufactured on a single integrated circuit chip. In one example, the programmable logic device may comprise one or more macrocells each comprising an input / output macrocell or a buried macrocell. In another example, the programmable logic device may be a complex programmable logic device (CPLD) or a programmable logic array (PLA).

Owner:MONTEREY RES LLC

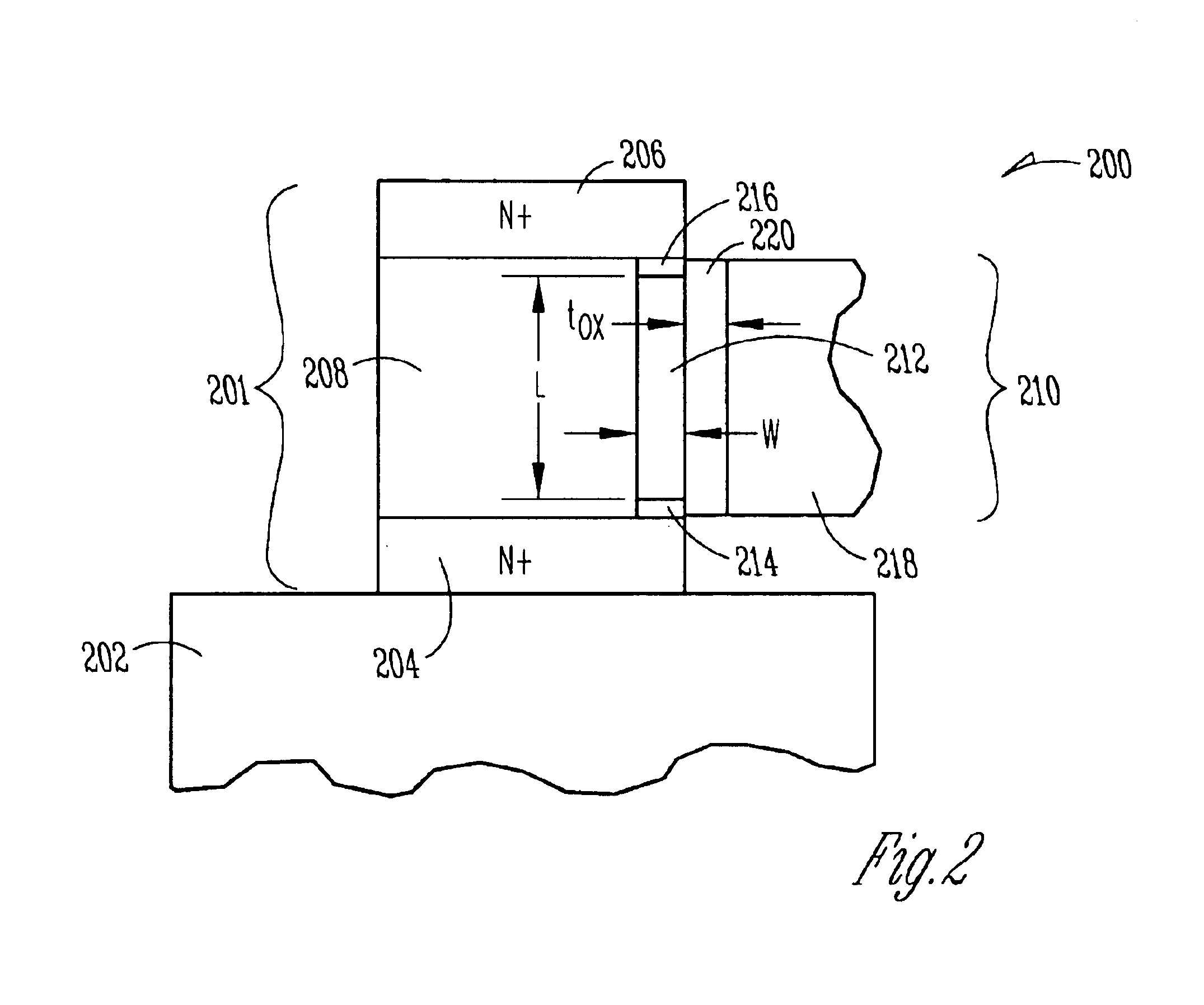

Programmable logic arrays with ultra thin body transistors

Structures and methods for programmable logic arrays are provided. In one embodiment, the programmable logic array includes a first logic plane and a second logic plane. The first logic plane receives a number of input signals. The first logic plane has a plurality of logic cells arranged in rows and columns that are interconnected to provide a number of logical outputs. The second logic plane has a number of logic cells arranged in rows and columns that receive the outputs of the first logic plane and that are interconnected to produce a number of logical outputs such that the programmable logic array implements a logical function. Each of the logic cells includes a vertical pillar extending outwardly from a semiconductor substrate. Each pillar includes a single crystalline first contact layer and a second contact layer separated by an oxide layer. Each logic cell further includes at least one single crystalline ultra thin vertical transistor that is selectively disposed adjacent the vertical pillar. The single crystalline vertical transistors have an ultra thin single crystalline vertical first source / drain region coupled to the first contact layer, an ultra thin single crystalline vertical second source / drain region coupled to the second contact layer; and an ultra thin single crystalline vertical body region which opposes the oxide layer and couples the first and the second source / drain regions.

Owner:MICRON TECH INC

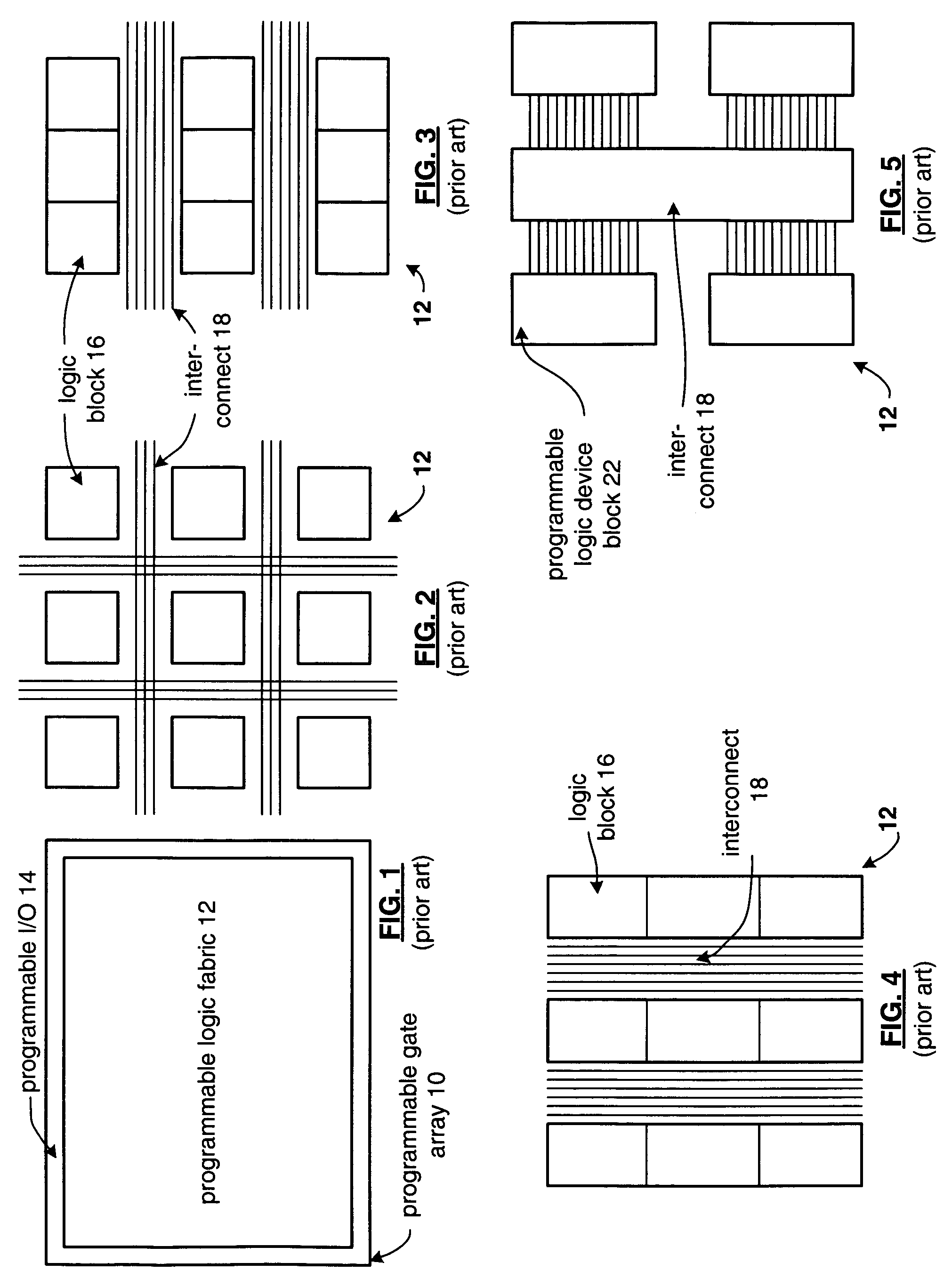

Programmable gate array and embedded circuitry initialization and processing

InactiveUS7420392B2Power reduction by control/clock signalSolid-state devicesGate arrayData transmission

Interconnecting logic provides connectivity of an embedded fixed logic circuit, or circuits, with programmable logic fabric of a programmable gate array such that the fixed logic circuit functions as an extension of the programmable logic fabric. The interconnecting logic includes interconnecting tiles and may further include interfacing logic. The interconnecting tiles provide selective connectivity between inputs and / or outputs of the fixed logic circuit and interconnect of the programmable logic fabric. The interfacing logic, when included, provides logic circuitry that conditions data transfers between the fixed logic circuit and the programmable logic fabric. In one operation, the programmable logic fabric is configured prior to the startup / boot sequence of the fixed logic circuit. In another operation, the fixed logic circuit is started up and is employed to configure the programmable logic fabric.

Owner:XILINX INC

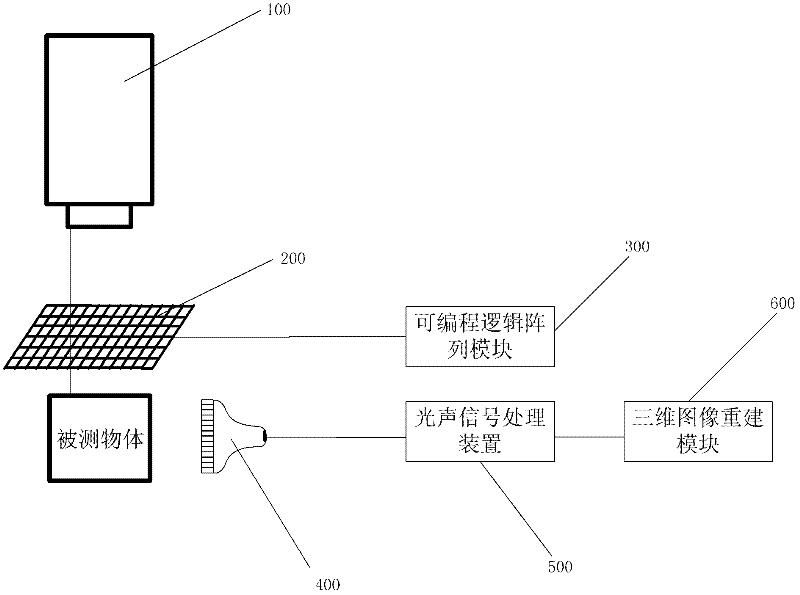

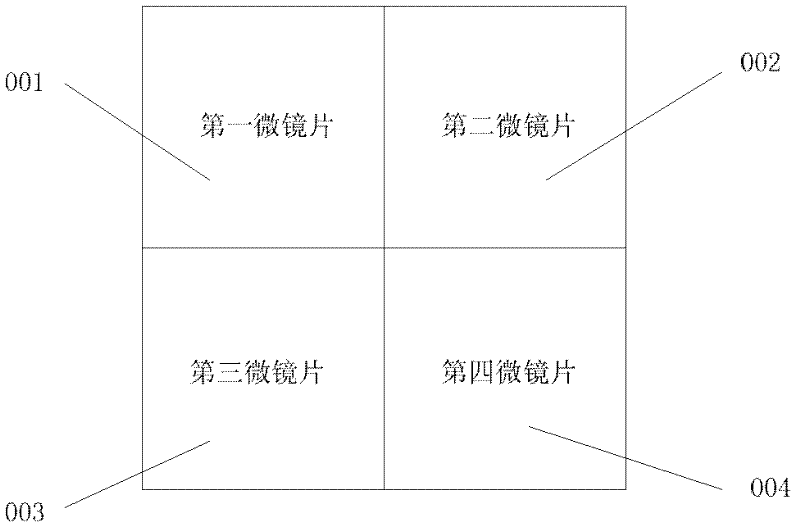

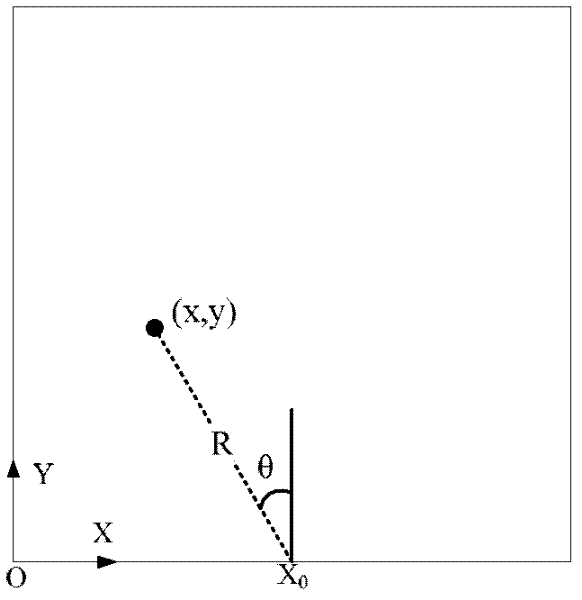

Fast opto-acoustic three-dimensional imaging device

ActiveCN102389321ASolve the problem of slow imaging speedOn-off changes rapidlyUltrasonic/sonic/infrasonic diagnosticsInfrasonic diagnosticsTest objectLaser beams

The invention discloses a fast opto-acoustic three-dimensional imaging device which comprises a laser generating device, an optical mask, a programmable logic array module, an optical signal receiving device, an opto-acoustic signal processing device and a three-dimensional image reconstruction module. According to the fast opto-acoustic three-dimensional imaging device, the connection and disconnection of all micro lenses in the optical mask can be controlled by the programmable logic array module, and further laser beams are controlled to irradiate areas on a tested object through the optical mask, so that opto-acoustic signals are generated and are reconstructed into a three-dimensional image. According to the fast opto-acoustic three-dimensional imaging device, since the change of theconnection and disconnection of all the micro lenses in the optical mask is extremely rapid, the areas irradiated by the laser beams on the tested object can be changed rapidly, further enough opto-acoustic signals can be received in extremely-short time and can be reconstructed into the three-dimensional image, and the problem that the imaging speed of the existing opto-acoustic three-dimensional imaging device is low is solved.

Owner:SONOSCAPE MEDICAL CORP +1

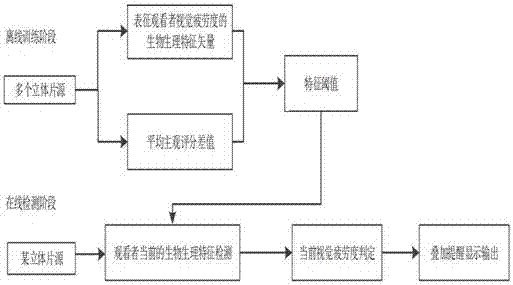

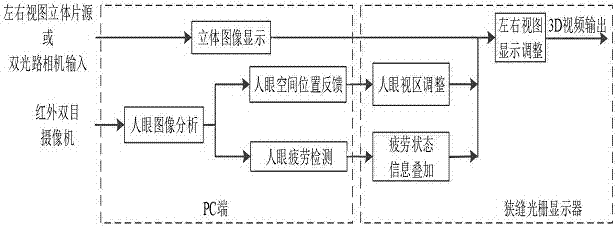

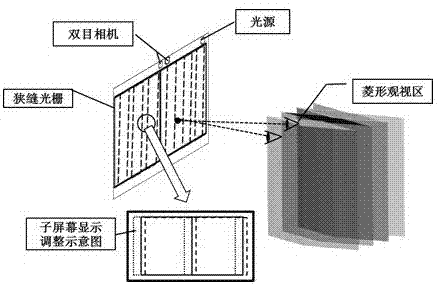

Naked eye three-dimensional display device and method through combination of visual fatigue detection

The invention relates to a naked eye three-dimensional display device and method through combination of visual fatigue detection. The device mainly is composed of an infrared binocular camera, an eye image analysis unit, an eye space position feedback unit, an eye visual area adjustment unit, a left and right view display and adjustment unit, an eye fatigue detection unit and a video output unit. According to the method, space coordinates of eyes are positioned in real time through adoption of an eyeball tracking technology; eye position movement is tracked in real time and subpixels of corresponding liquid crystal raster image are rearranged through adoption of a programmable logic array technology, thereby changing an optimum viewpoint area, the image crosstalk in an eye watching process is effectively reduced, and the viewing experience of a user is improved. Through application of the technologies, an eye fatigue state of the user in the viewing process is detected, measured and evaluated in real time, and the bad physiological reaction degree of the user is judged, thereby prompting the user to take measures to prevent or mitigate visual fatigue timely.

Owner:SHANGHAI UNIV

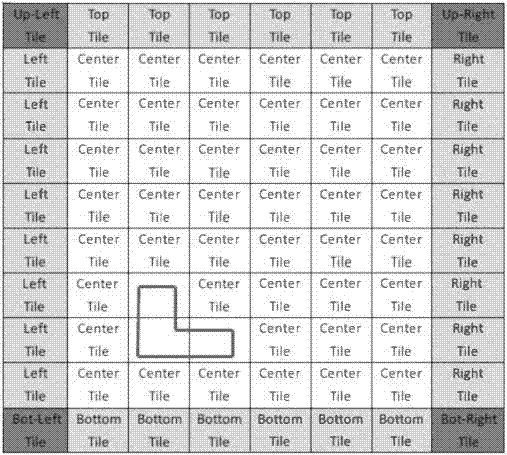

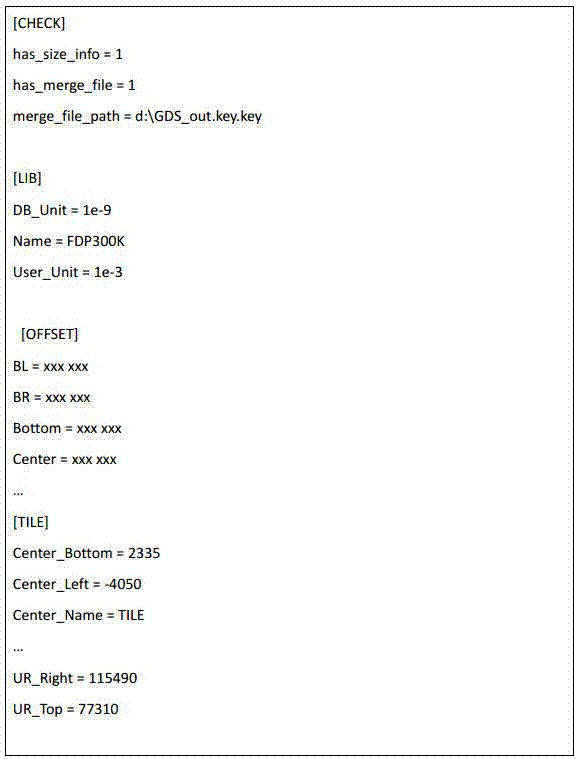

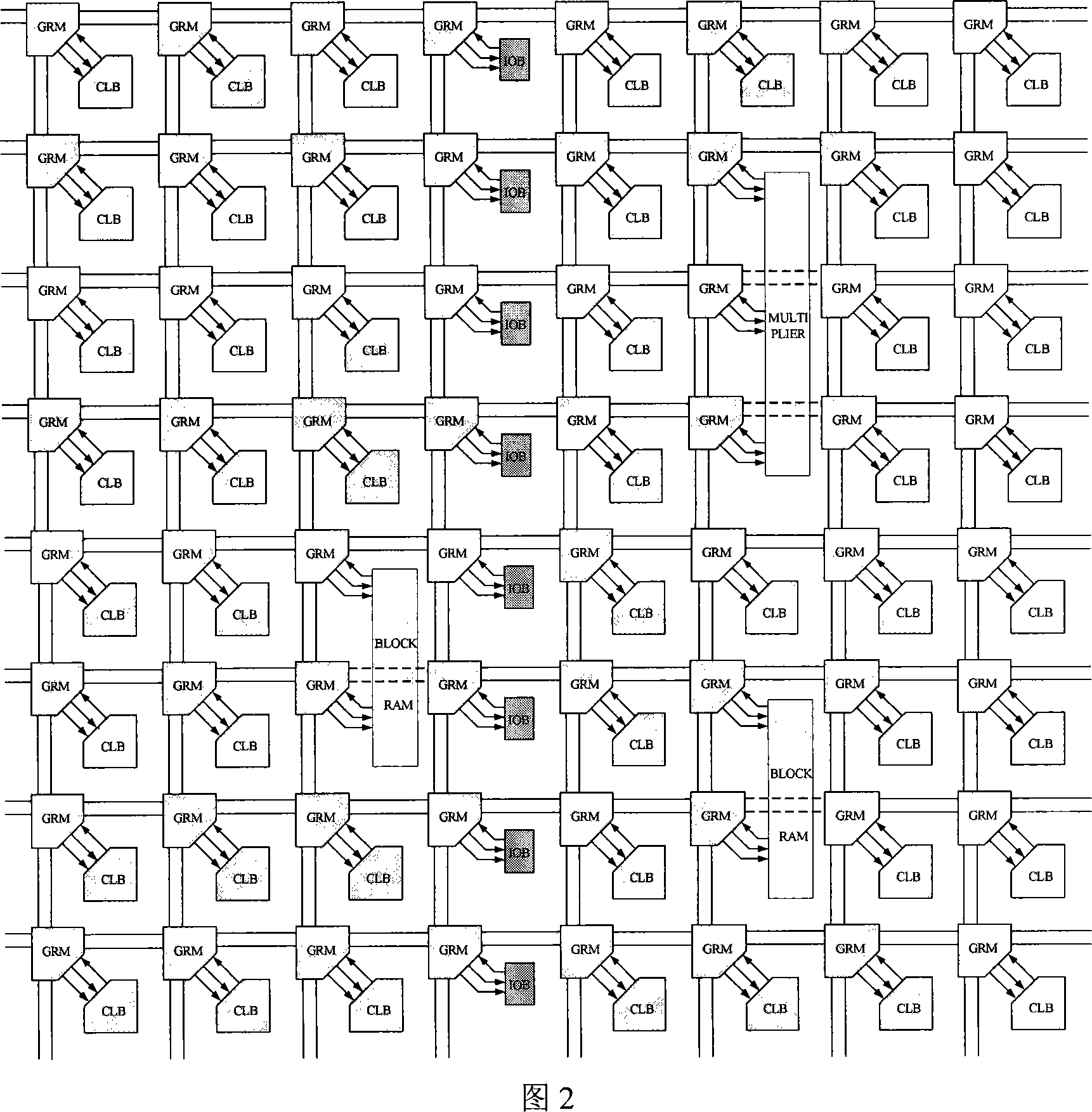

Fast generating method of user-customizable PLD (programmable logic device) layouts

The invention belongs to the technical field of electronic design automation and particularly relates to a fast generating method of a user-customizable PLD (programmable logic device) layouts. The fast generating method includes: preparing unit layouts and building a configuration file for each unit layout; calculating scale of each unit layout; splicing the unit layouts; and reserving customized layout shapes. On the basis of the existing unit layout library, layout files of optionally designed scales can be generated fast and performance of the layouts generated is similar to that of manually customized layouts. The layouts generated by the method has the advantages that scales of the generated programmable logic array layouts are customizable, namely a user can assign the scales of layout arrays, areas can be reserved automatically on the layouts according to the layout shape requirements set by a user, and other IP (intellectual property) cores can be embedded in the programmable logic array layouts conveniently.

Owner:FUDAN UNIV

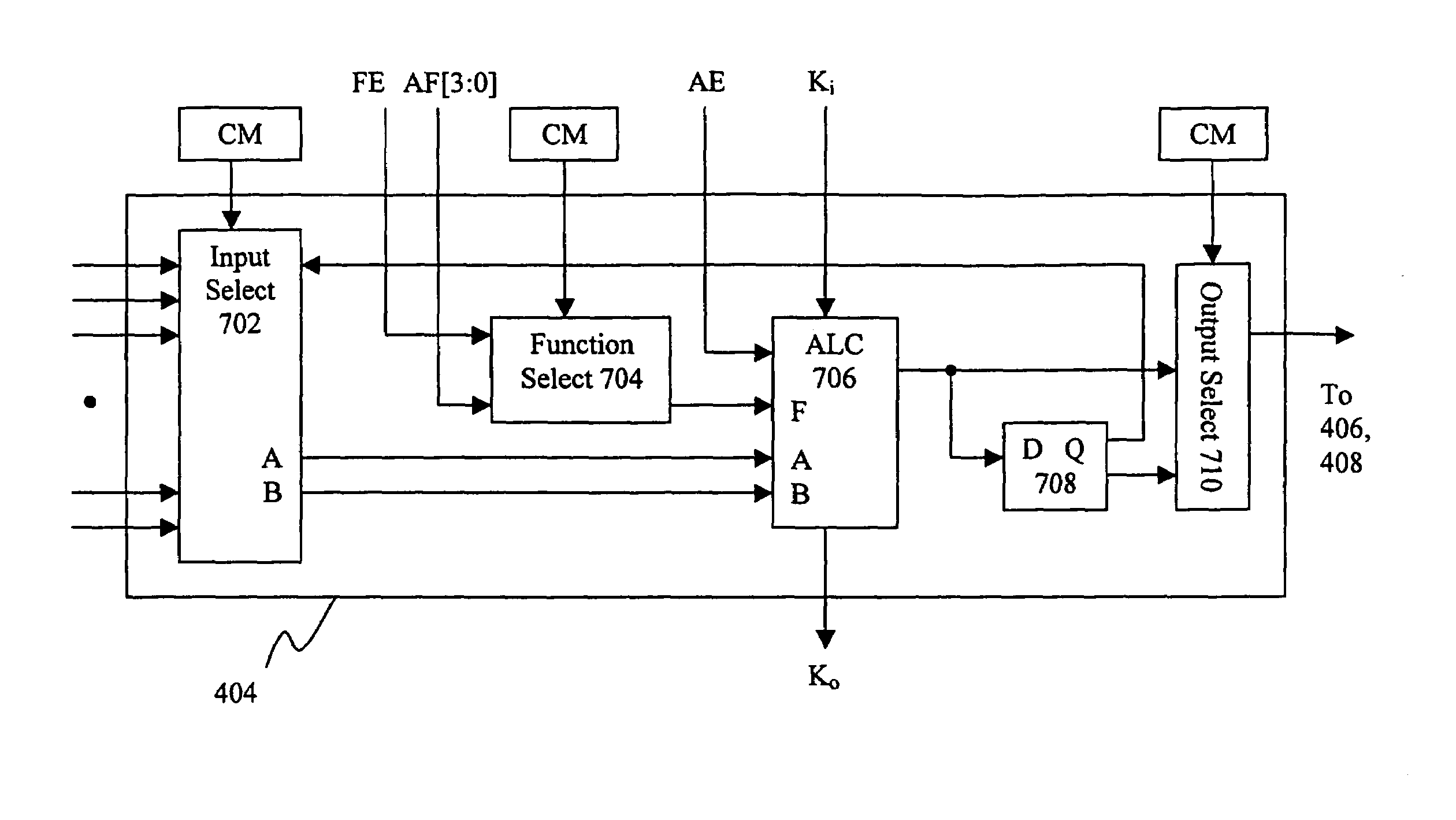

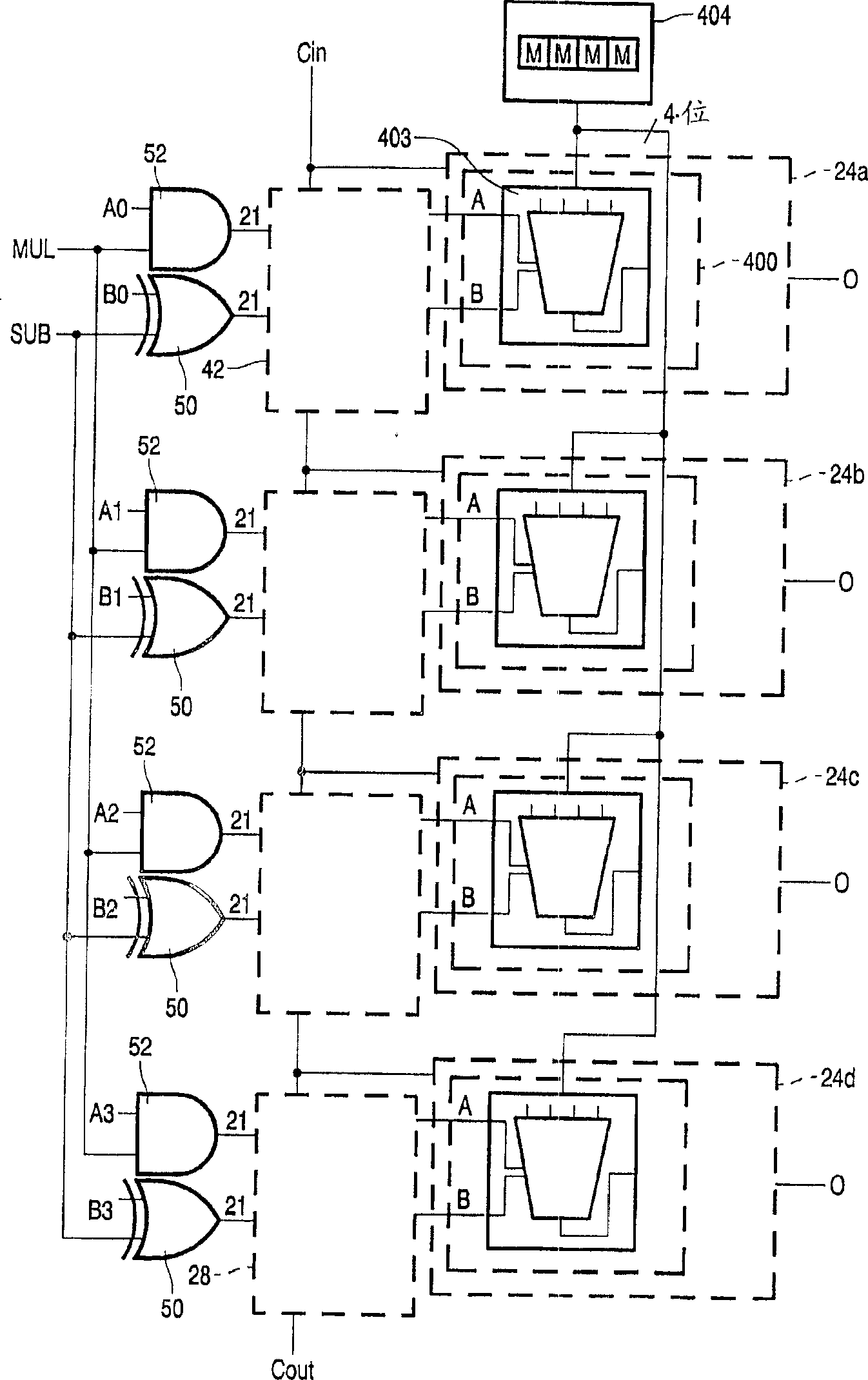

Multi-scale programmable array

InactiveUS7062520B2Lower performance requirementsIncrease costLogic circuits using elementary logic circuit componentsComputation using denominational number representationArithmetic logic unitCall gate

A novel architecture for a multi-scale programmable logic array (MSA) to be used in the design of complex digital systems allows digital logic to be programmed using both small-scale blocks (also called gate level blocks) as well as medium scale blocks (also called Register Transfer Level or RTL blocks). The MSA concept is based on a bit sliceable Arithmetic Logic Unit (ALU). Each bit-slice may be programmed to perform a basic Boolean logic operation or may be programmed to contribute to higher-level functions that are further programmed by an ALU controller circuit. The ALU controller level in this new approach also allows the primitive logic operations computed at the bit-slice level to be combined to perform complex random logic operations. The data shifting capability of this new programmable logic architecture reduces the complexity of the programmable routing needed to implement shift operations including multiplier arrays. The new array also allows logic variables under program control to dynamically modify the micro-program of each ALU. This technique is called configuration overlay and simplifies the programming of complex arithmetic and random logic functions.

Owner:XILINX INC

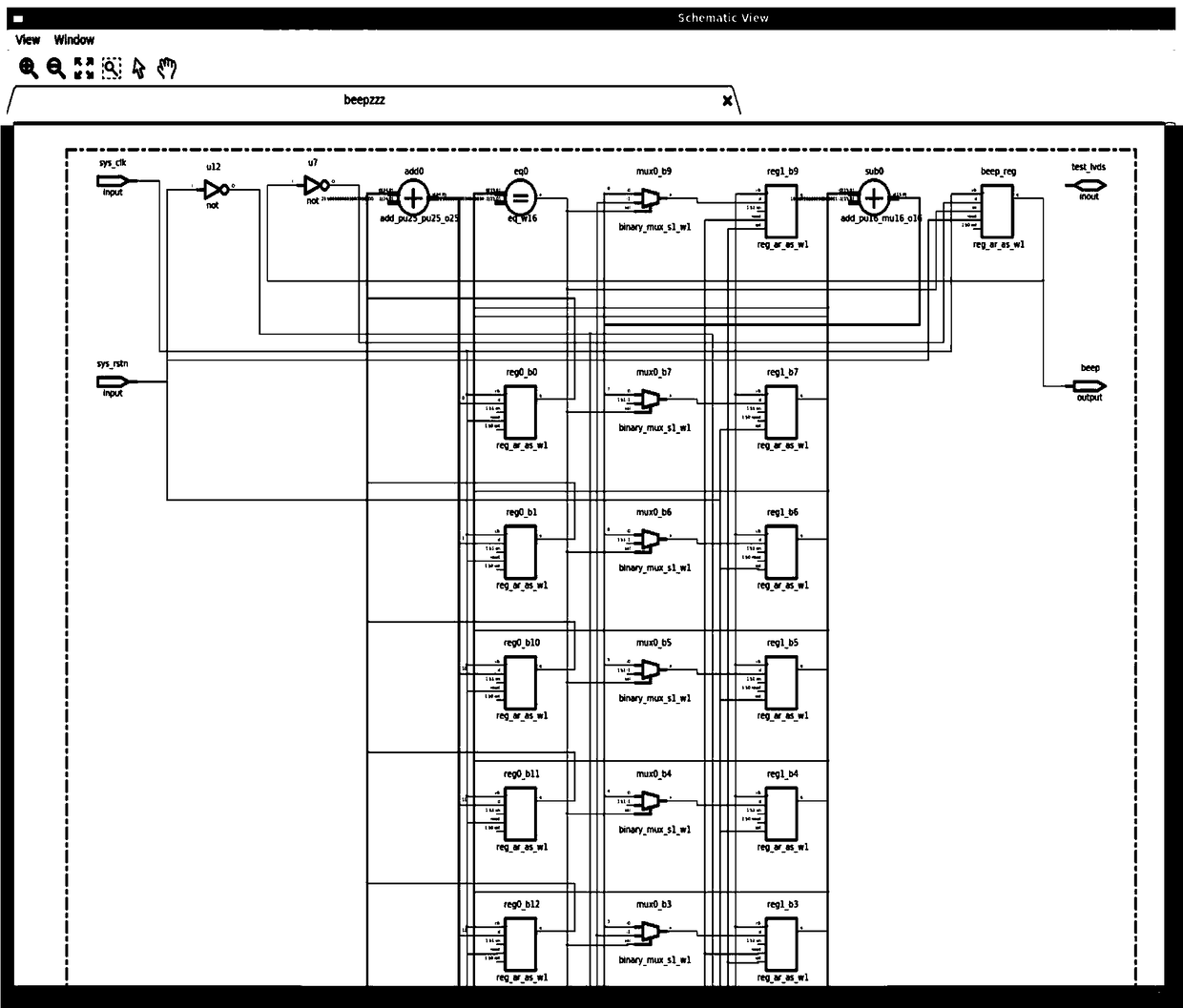

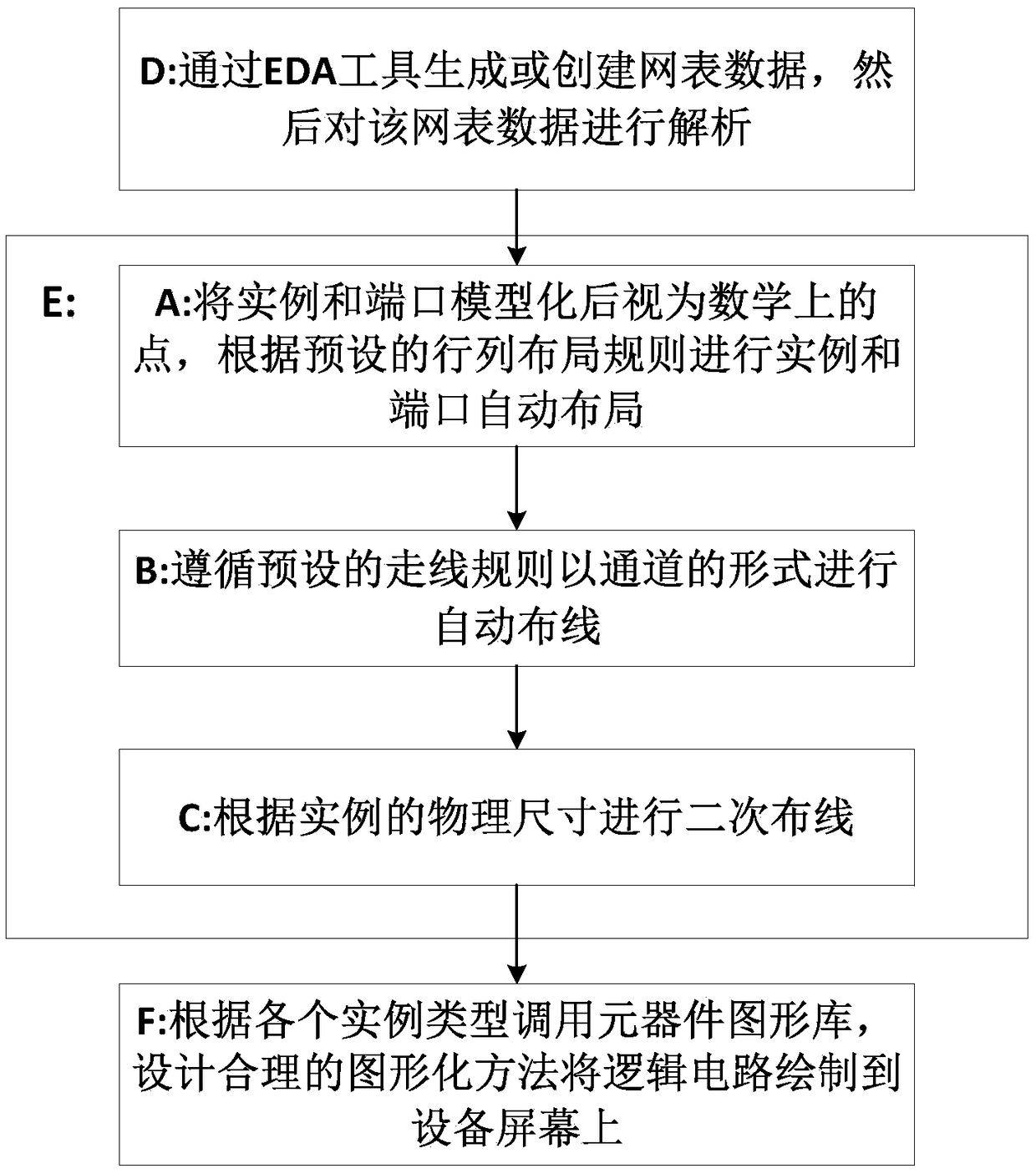

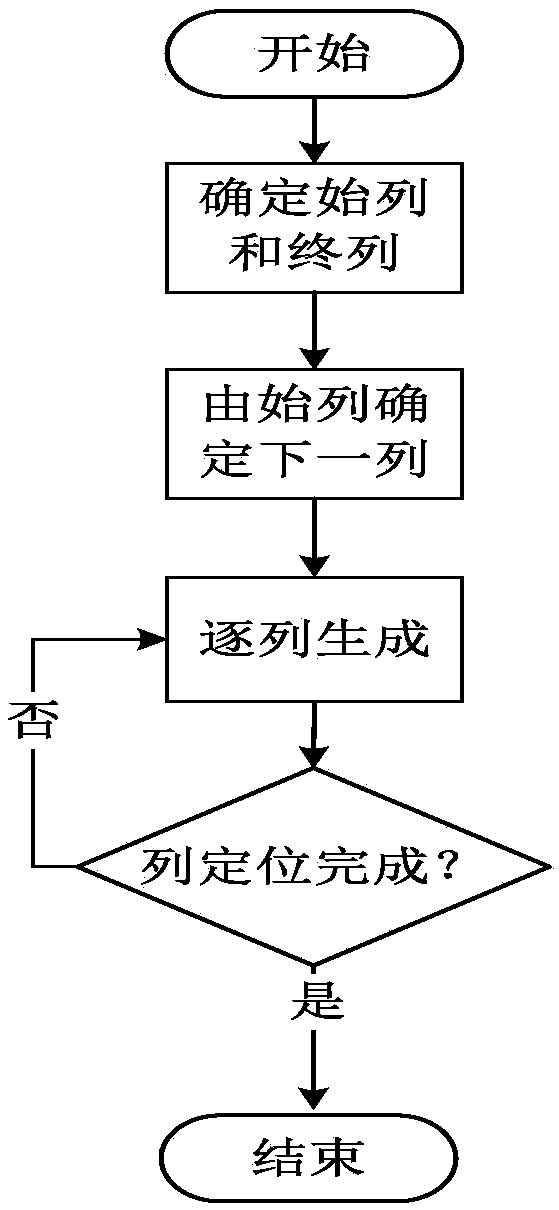

Circuit layout method, graphic display method and system thereof

ActiveCN109284578AOptimizing place and route methodsIn line with the habitSpecial data processing applicationsIntersection of a polyhedron with a lineHabit

The present application relates to a programmable logic array, and discloses a logic circuit layout and routing method, a graphical display method and a system thereof. The present invention is directed to graphical display of logic circuits, directed acyclic graph generation algorithm and preset column distribution rules are used to allocate logical columns, and heuristic algorithm is used to allocate logical rows based on median sorting, so as to optimize the number of intersection points. At the same time, the physical coordinates of components are allocated according to their physical dimensions in the process of automatic layout, so that the components are centralized and arranged compactly. The method of cache and windowing is also used to realize the fast response when the logic circuit of large layout is dragged to view. Finally, the generated logic circuit diagram is uniformly distributed, the input and output conform to the circuit habits, the number of intersection points isless, and the plotting is fast.

Owner:SHANGHAI ANLOGIC INFOTECH CO LTD

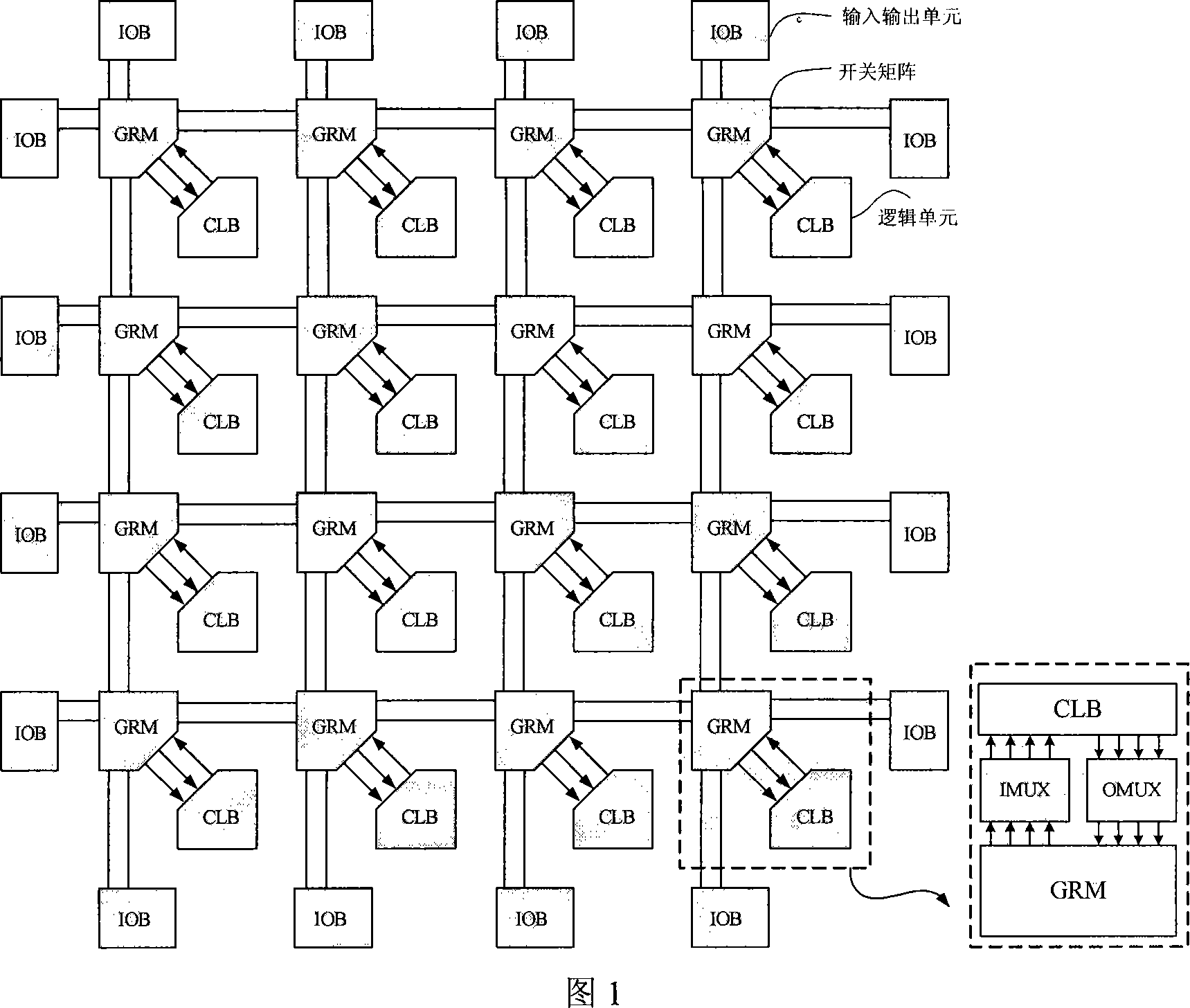

Field programmable logical array wiring resource structure and its modeling approach thereof

ActiveCN101043213AReduce duplicationFlexible descriptionLogic circuits using elementary logic circuit componentsAnd logic unitMulti path

The invention belongs to programmable component structure technology field, specially a local programmable logic array wiring resource structure and modeling method which supports the crutch line. The wiring resource structure of the invention includes: programmable interconnected line, uniform switch matrix, input and output multi path selector array and logic unit. It breaks the limit of level and uprightness interlinkage resource, introduces the concept of crutch line, makes the wiring path not pass the programmable switch, it gives attention to speed and agility. The description of wiring line resource, the interconnected line is distributed to the repeated unit then integral interconnected resource is described by describing an interconnected line resource in a repeated unit. This describing method is very flexible, the kind, amount, proportion of interconnected resource can be changed conveniently, and any switch array can be generated.

Owner:FUDAN UNIV

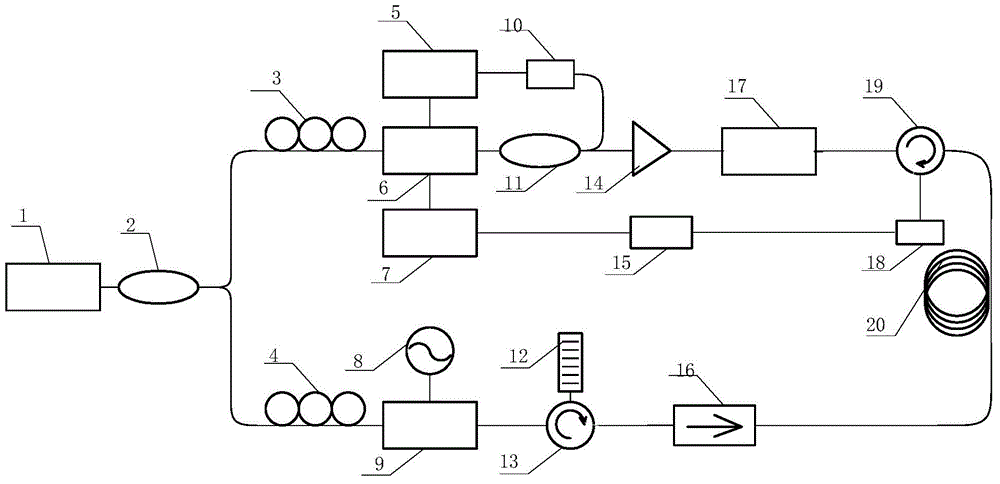

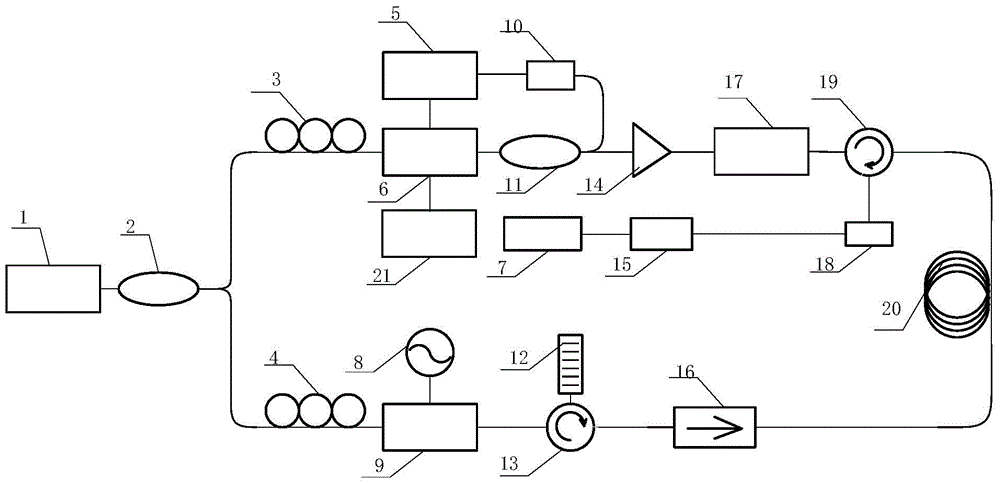

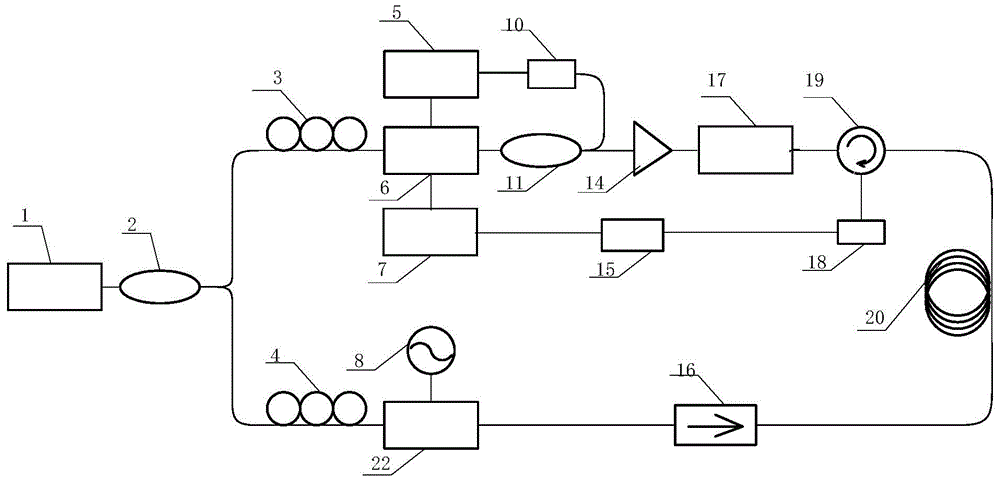

Brillouin optical-time-domain analyzer based on coherence dual-pulse pair sequence technology and method for restraining common-mode noise by utilizing same

ActiveCN104019836AReduced conversion timeAchieve inhibitionConverting sensor output opticallySpecial purpose recording/indication apparatusOptical fiber couplerSignal-to-quantization-noise ratio

The invention relates to a Brillouin optical-time-domain analyzer based on a coherence dual-pulse pair sequence technology and a method for restraining common-mode noise by utilizing the same, belongs to the field of optics, and solves the problems that a traditional Brillouin optical-time-domain analyzer is low in spatial resolution, long in measuring signal time and low in signal-to-noise ratio. A laser is adopted, an upper branch of light divided by an optical-fiber coupler I is used as pump light, pulse pairs with different pulse widths can be periodically generated by a field-programmable logic array in a programming manner, and the pulse pairs are continuously and optically modulated to form a coherence pulse pair sequence through a photoelectric modulator; a lower branch provides detection light, the detection light enters a photoelectric modulator after a polarization state is adjusted, upper marginal frequency light and lower marginal frequency light which having the frequency difference of Brillouin frequency shifting gamma B are generated on the basis of carrier light, the pump light consisting of the coherence pulse pair sequence and the modulated detection light has a Brillouin scattering phenomenon in a sensing optical fiber, and two Brillouin signals are detected by a photoelectric detector. The Brillouin optical-time-domain analyzer and the method are suitable for restraining the common-mode noise.

Owner:HARBIN INST OF TECH

Electronic circuit with array of programmable logic cells

ActiveCN1751361AComputation using non-contact making devicesRead-only memoriesMultiplexingLogic cell

An electronic circuit has a programmable logic cell with a plurality of programmable logic units that are capable of being configured to operate in a multi-bit operand mode and a multiplexing mode. The programmable logic units are coupled in parallel between an input circuit and an output circuit. In a multi-bit operand processing mode the input circuit is configured to supply logic input signals from different ones of the logic inputs to the programmable logic units. The programmable logic units are coupled to successive positions along a carry chain at least in the multi-bit operand mode, so as to process carry signals from the carry chain. An output circuit passes outputs from the programmable logic units in parallel in the multi-bit operand mode. The programmable logic units have look-up tables which share the same configuration bits. The programmable logic units can also have multiplexers for passing one of the received input signals when configured to operate in a multiplexing mode of operation.

Owner:网络系统技术有限责任公司

Method for forming programmable logic arrays using vertical gate transistors

InactiveUS20050029545A1Solid-state devicesSemiconductor/solid-state device manufacturingLogic cellEngineering

One aspect disclosed herein relates to a method for forming a programmable logic array. Various embodiments of the method include forming a first logic plane and a second logic plane, each including a plurality of logic cells interconnected to implement a logical function. Forming the logic cells includes forming a horizontal substrate with a source region, a drain region, and a depletion mode channel region separating the source and the drain regions, and further includes forming a number of vertical gates located above different portions of the depletion mode channel region. At least one vertical gate is separated from the depletion mode channel region by a first oxide thickness, and at least one of the vertical gates is separated from the depletion mode channel region by a second oxide thickness. Other aspects and embodiments are provided herein.

Owner:MICRON TECH INC

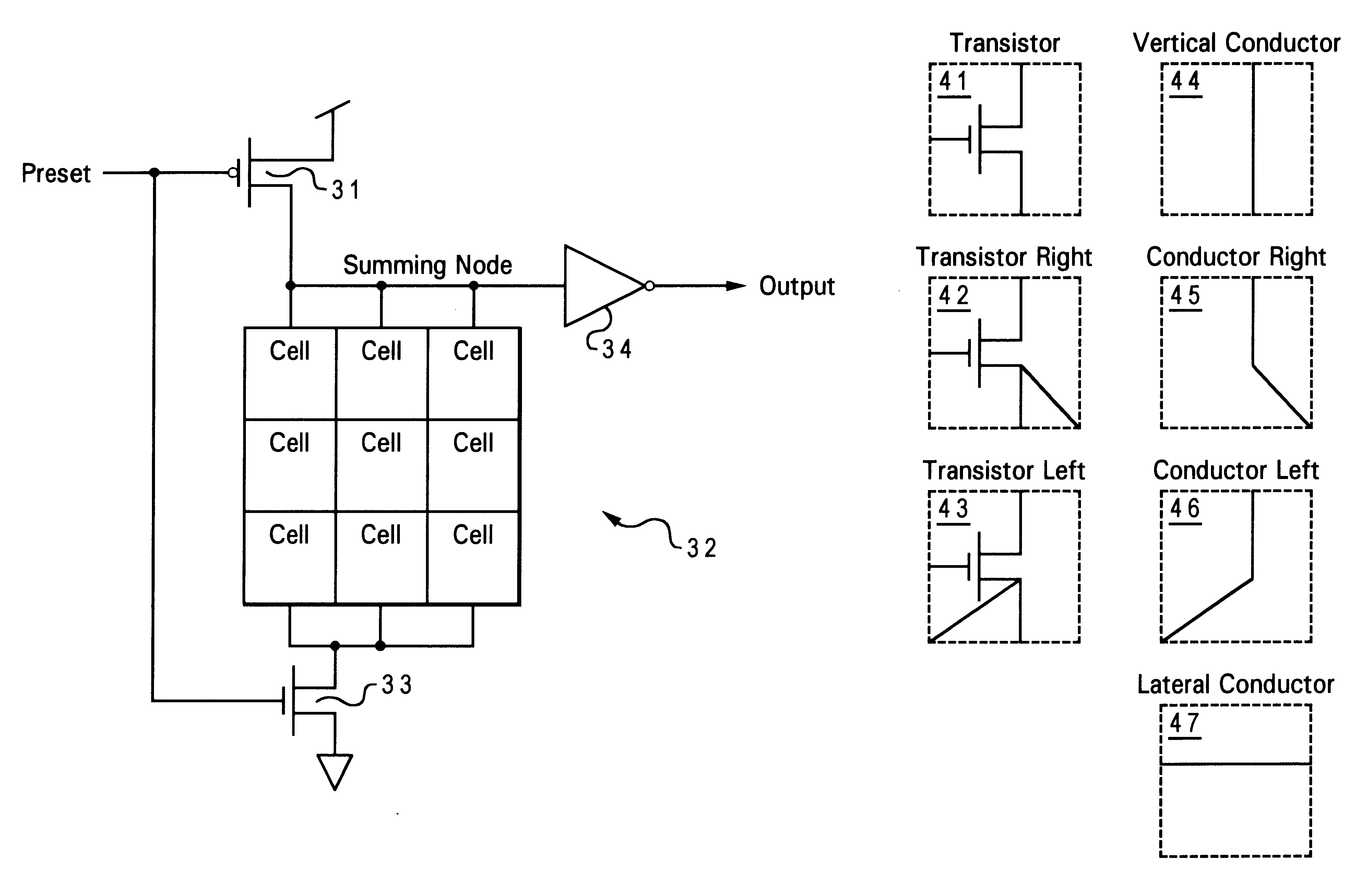

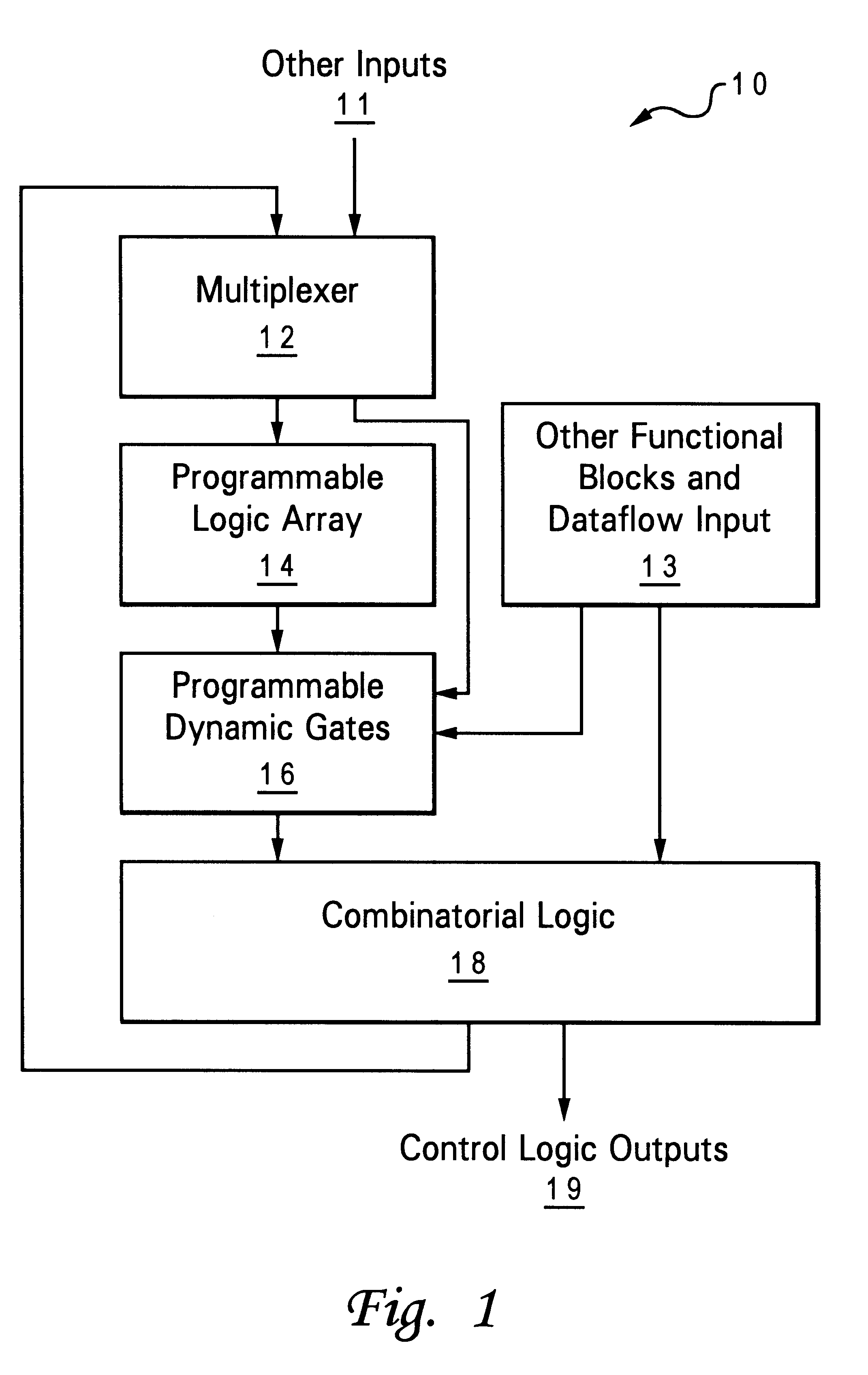

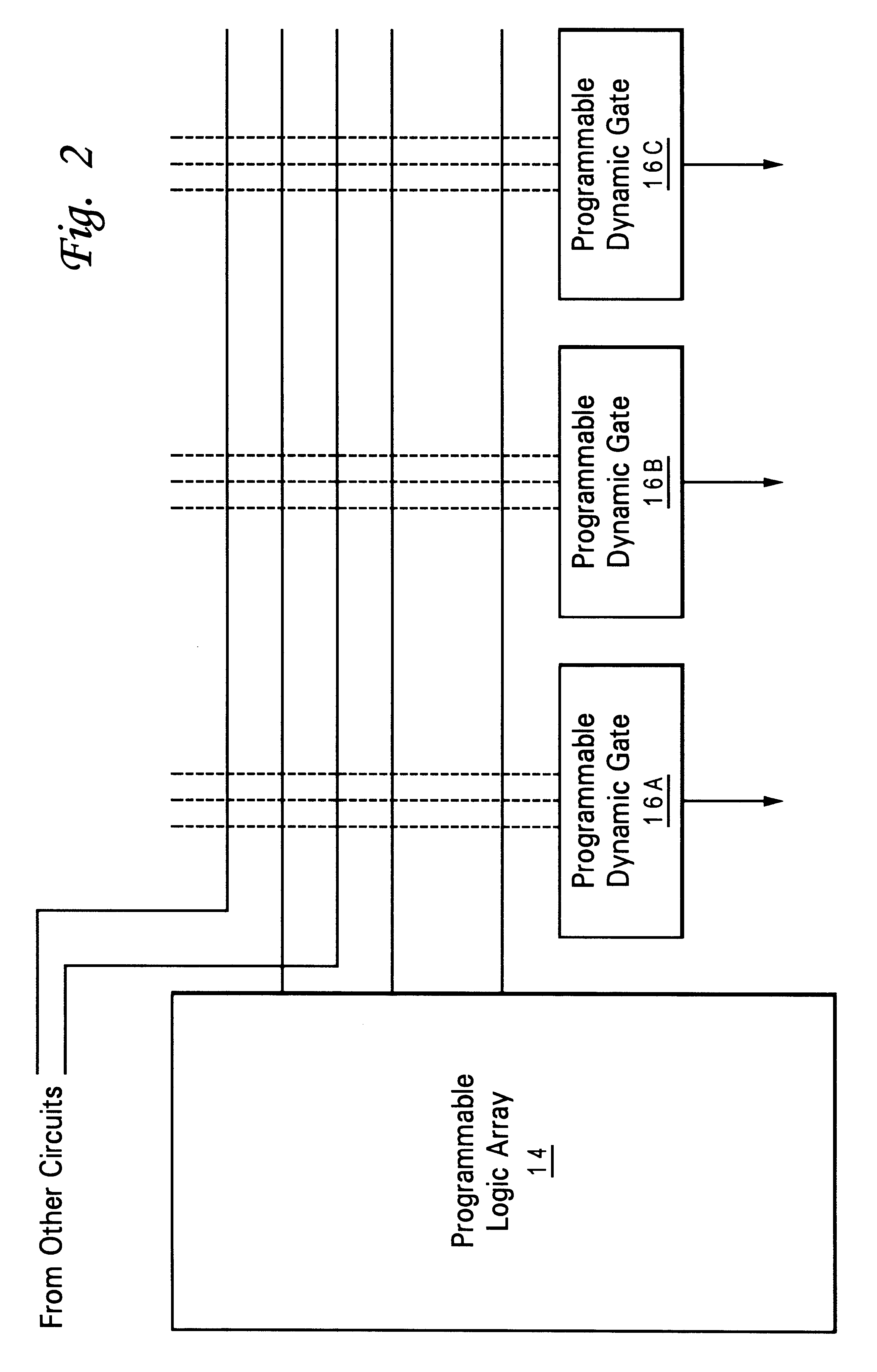

Method and apparatus for implementing logic using mask-programmable dynamic logic gates

InactiveUS6285218B1Logic circuits characterised by logic functionSemiconductor/solid-state device manufacturingProcessor designProgrammable logic array

A method and apparatus for implementing dynamic logic with programmable dynamic logic gates acts as a complement to programmable logic arrays (PLAs) used in high-speed microprocessor designs. A matrix of selectable cells provides powerful logic functions such as AND-OR gate capability with a minimum of inputs and transistors. By using programmable logic arrays and programmable dynamic gates, the efficiency of a logic block can be dramatically improved with little added circuit area.

Owner:IBM CORP

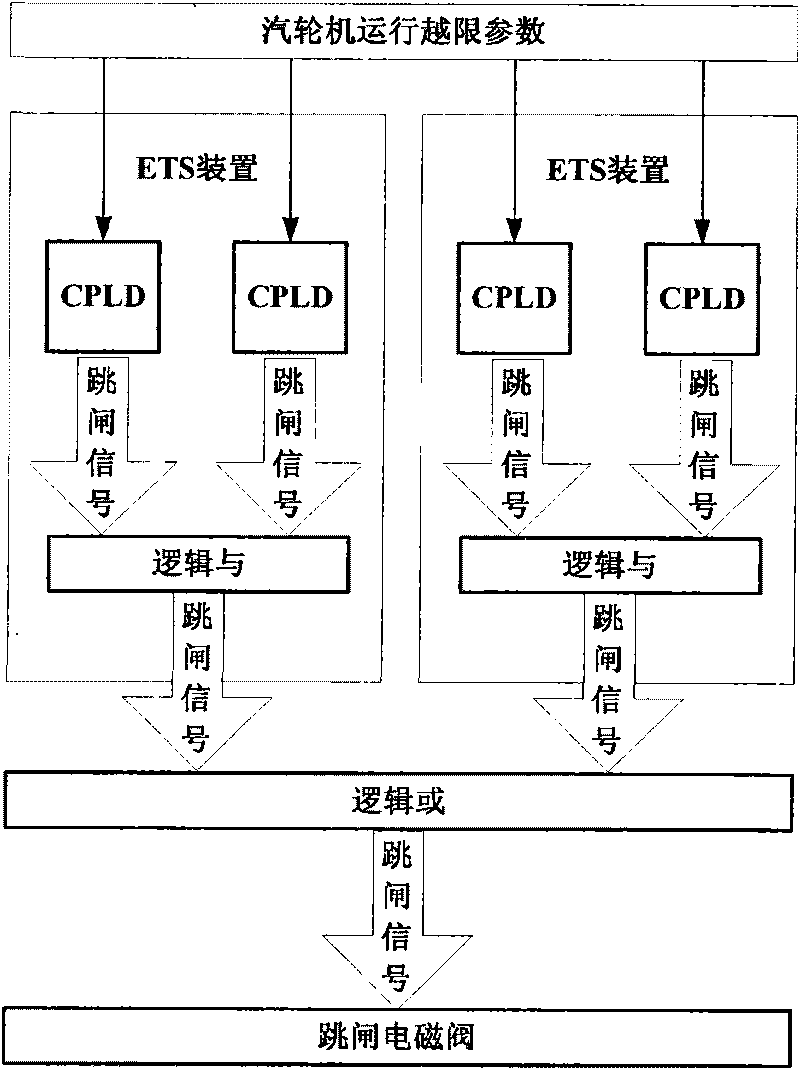

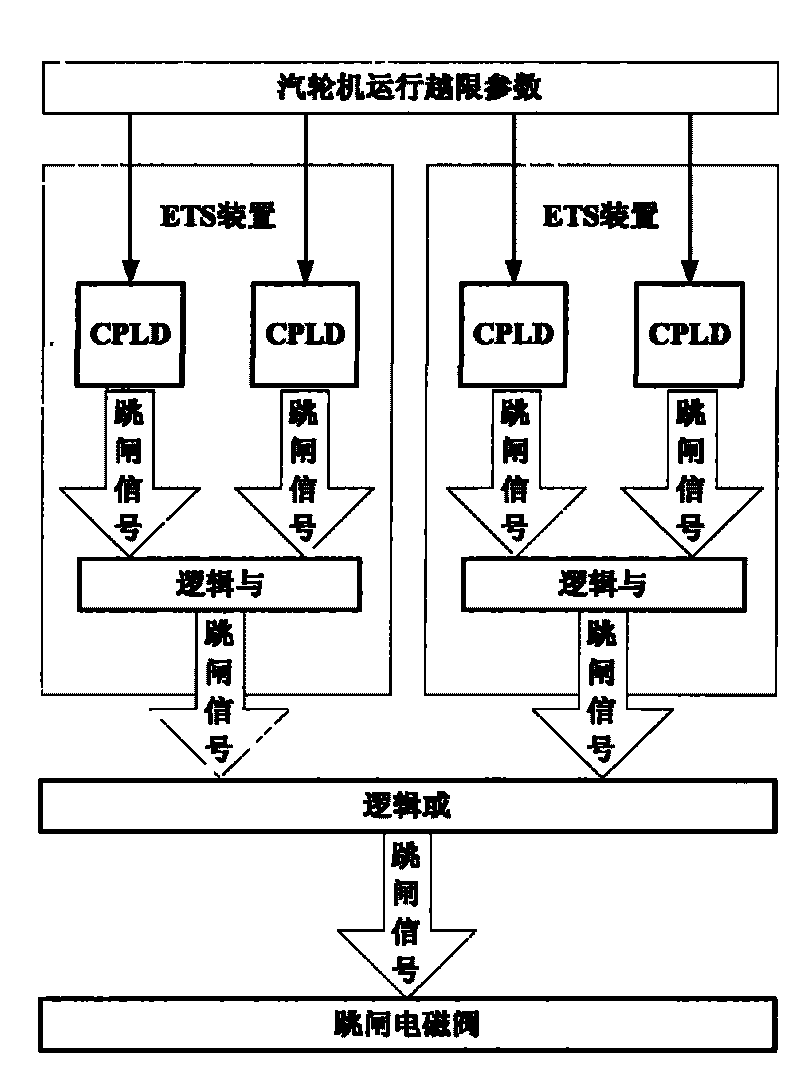

Turbine emergency protective system capable of preventing misoperation

ActiveCN101737100AImprove securityImprove reliabilityMachines/enginesSafety/regulatory devicesComplex programmable logic deviceProtection system

The invention provides a turbine emergency protective system capable of preventing misoperation, which comprises two sets of electronic traction support (ETS) devices. The turbine emergency protective system is characterized in that each ETS device is internally provided with two complex programmable logic arrays, the input end of each complex programmable lock array is connected with a turbine operation out-of-limit parameter switching value input signal, the output ends of the two complex programmable logic arrays in each set of ETS device are subjected to And logic through hardware and then output, the output ends of the two sets of ETS device are subjected to Or logic through the hardware and then output, the total output end trip signal is connected with a trip electromagnetic valve, and the complex programmable logic array comprises a complex programmable logic element and a field programmable gate array. The ETS systems greatly improve the safety of the whole system, achieve actual no misaction and no misoperation, and have low cost.

Owner:GUODIAN NANJING AUTOMATION

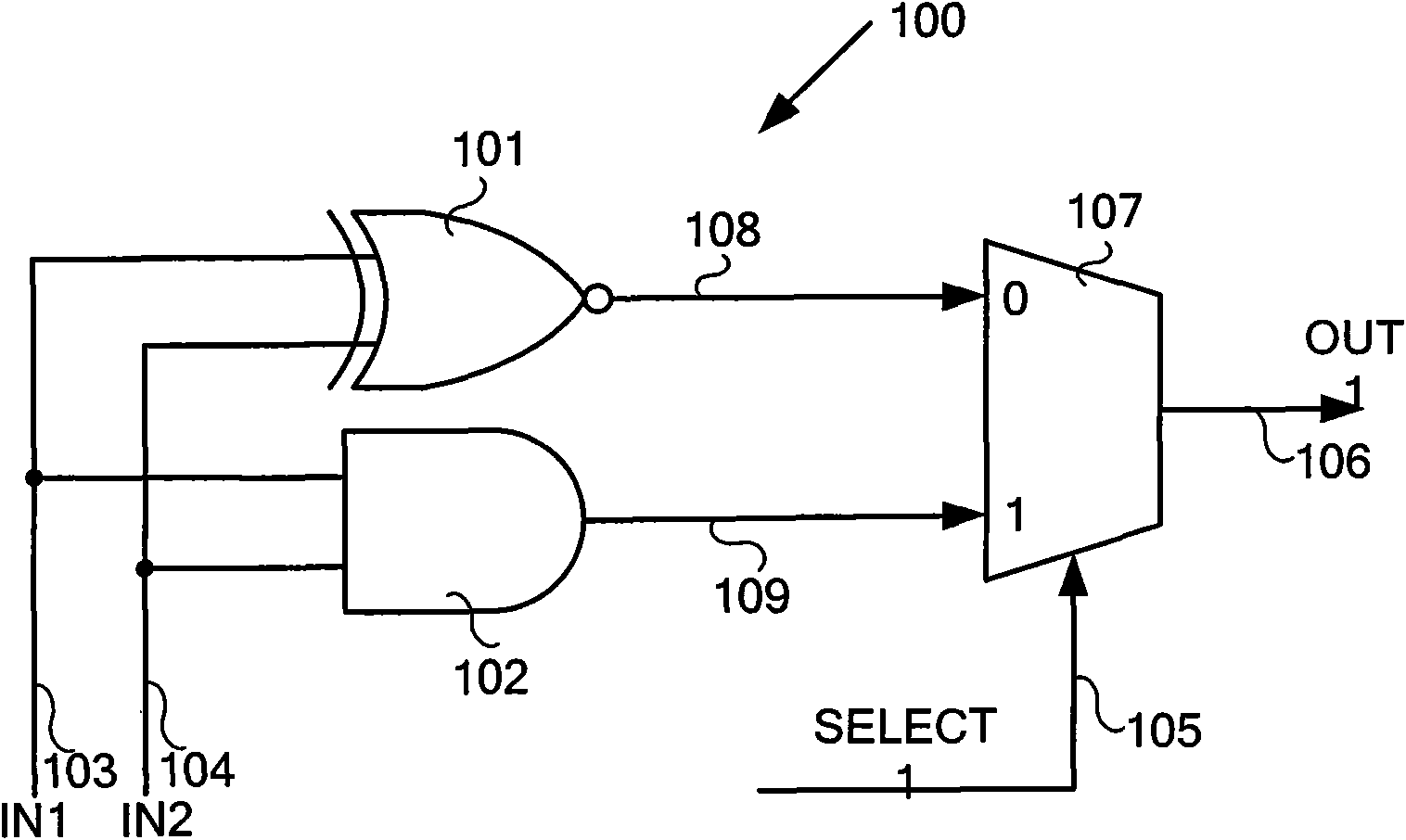

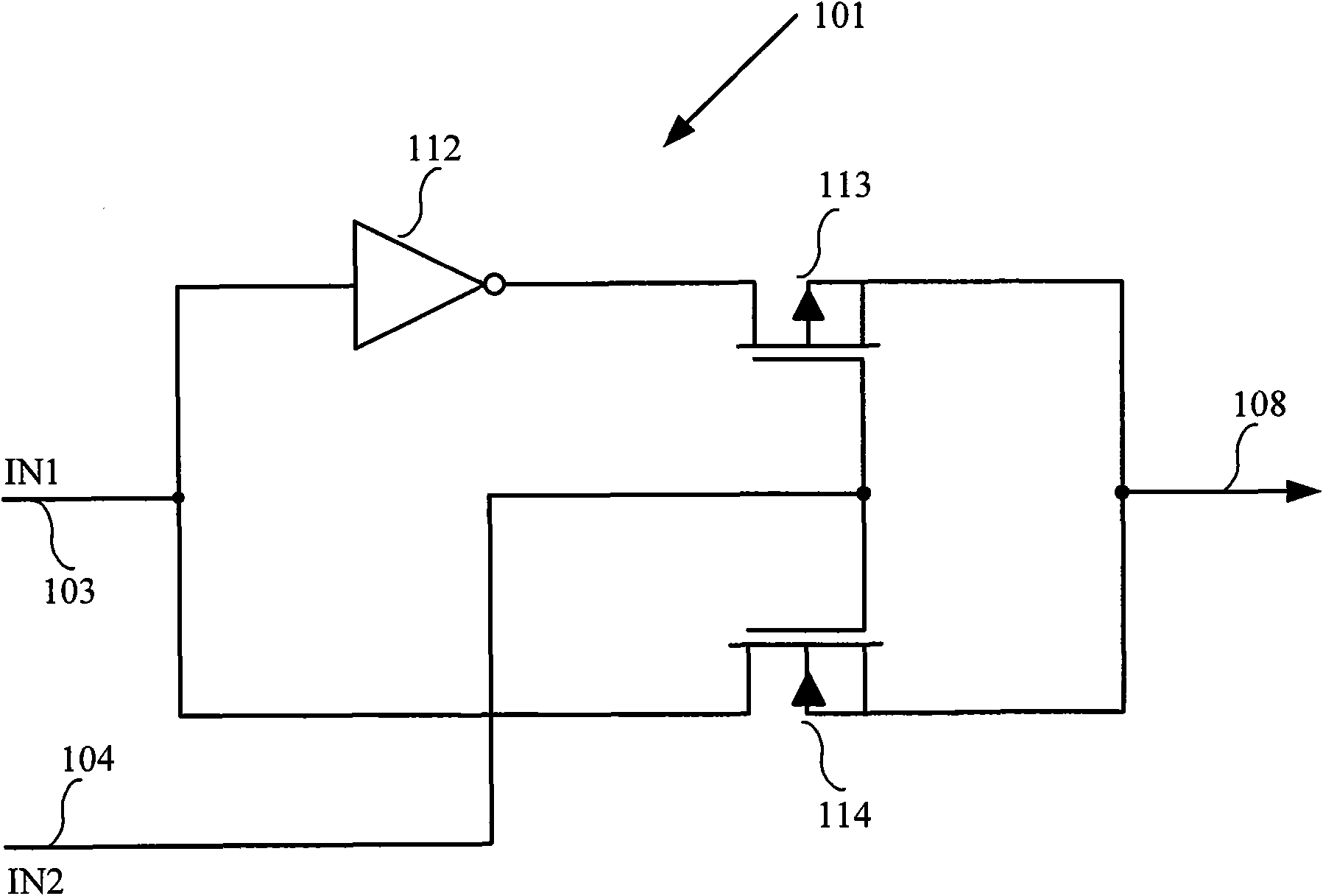

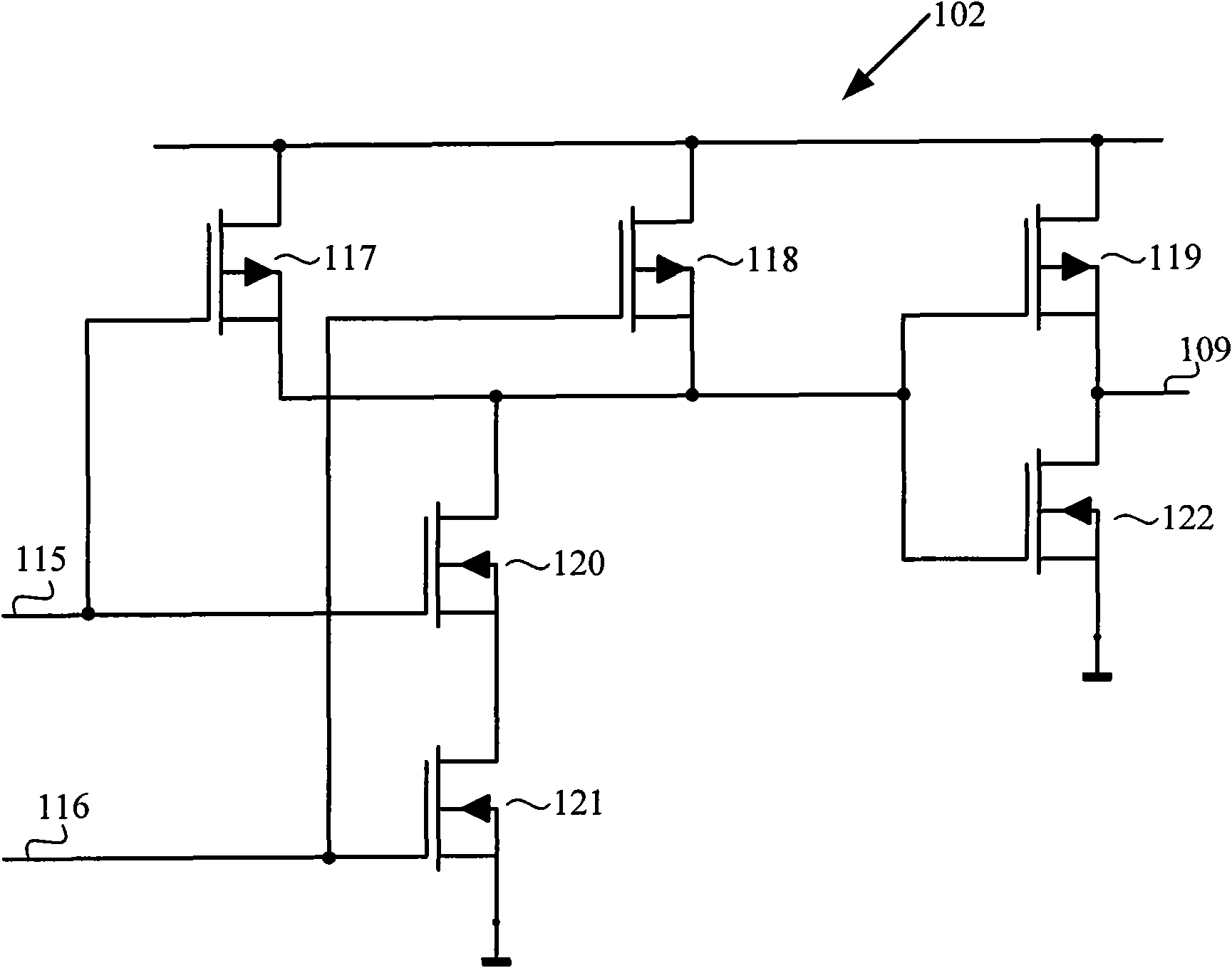

Programmable logic circuit

ActiveCN101997539AReduce the numberIncrease power consumptionLogic circuits characterised by logic functionMultiplexerP channel

The invention discloses a programmable logic circuit. The programmable logic circuit comprises 4 P-channel metal oxide semiconductor (PMOS) transistors and 6 N-channel metal oxide semiconductor (NMOS) transistors. Four logical functions, namely AND, OR, XOR and XNOR logics of two input signals, are realized by only using ten transistors and are four basic circuits which are commonly used for establishing systems. The ten transistors are divided into three groups, wherein the first group consists of two NMOS transistors and two PMOS transistors for realizing the logical functions such as AND and XNOR; the second group consists of two NMOS transistors and two PMOS transistors for realizing the logical functions such as OR and XOR; and the third group consists of two NMOS transistors for realizing the logical function of selecting whether to output the first group or the second group finally by using an either-or multiplexer. The circuit structure respectively realizes the circuit structure of the first group and the circuit structure of the second group by ingeniously utilizing the relationships between truth tables of two input AND logics and XNOR logics as well as two input OR logics and XOR logics. The same circuit functions as those of the programmable logic circuit are realized by 26 transistors in a conventional method; however, only 10 transistors are used in the programmable logic circuit.

Owner:BEIJING MXTRONICS CORP +1