Patents

Literature

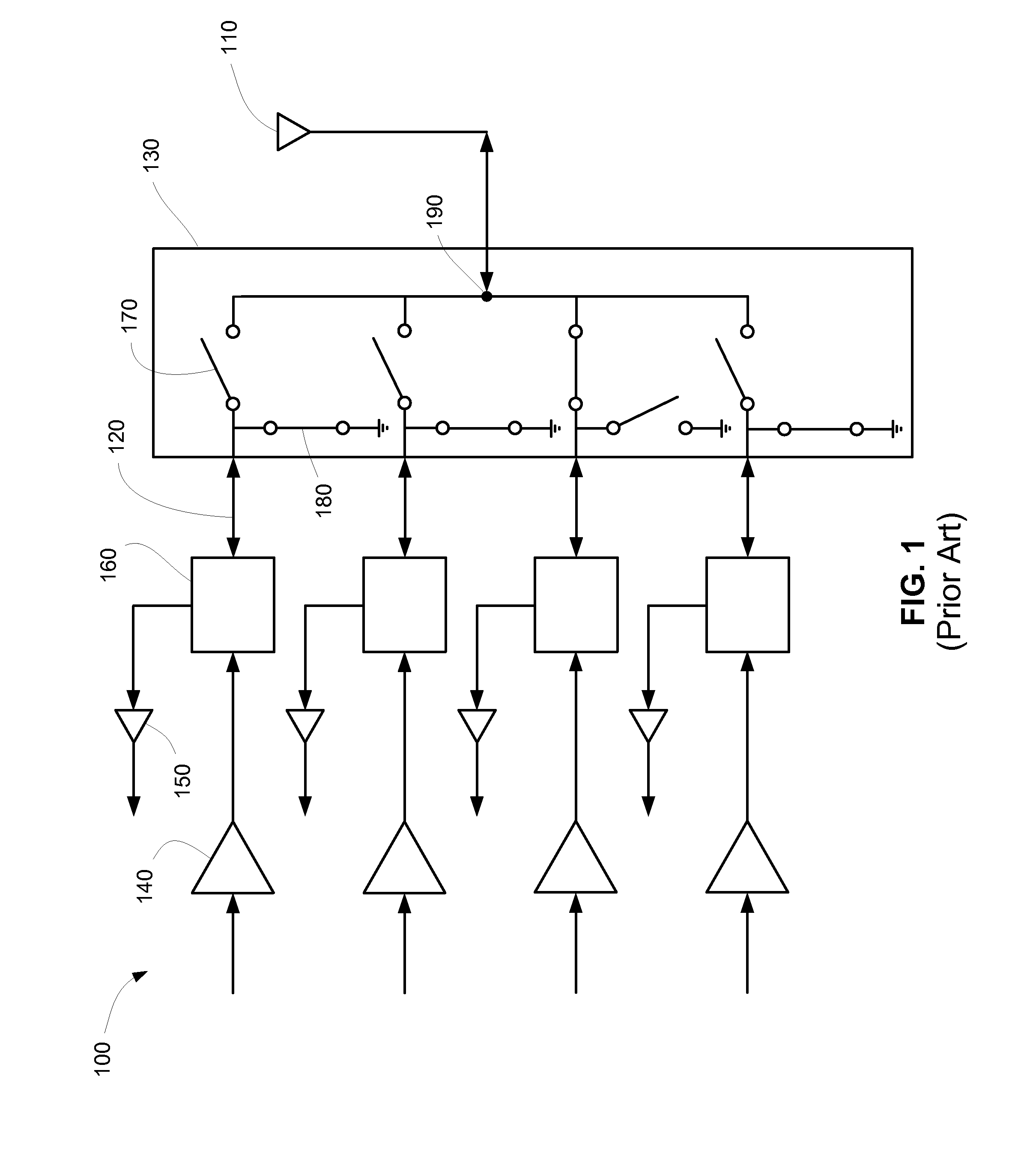

168 results about "Transistor stacking" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

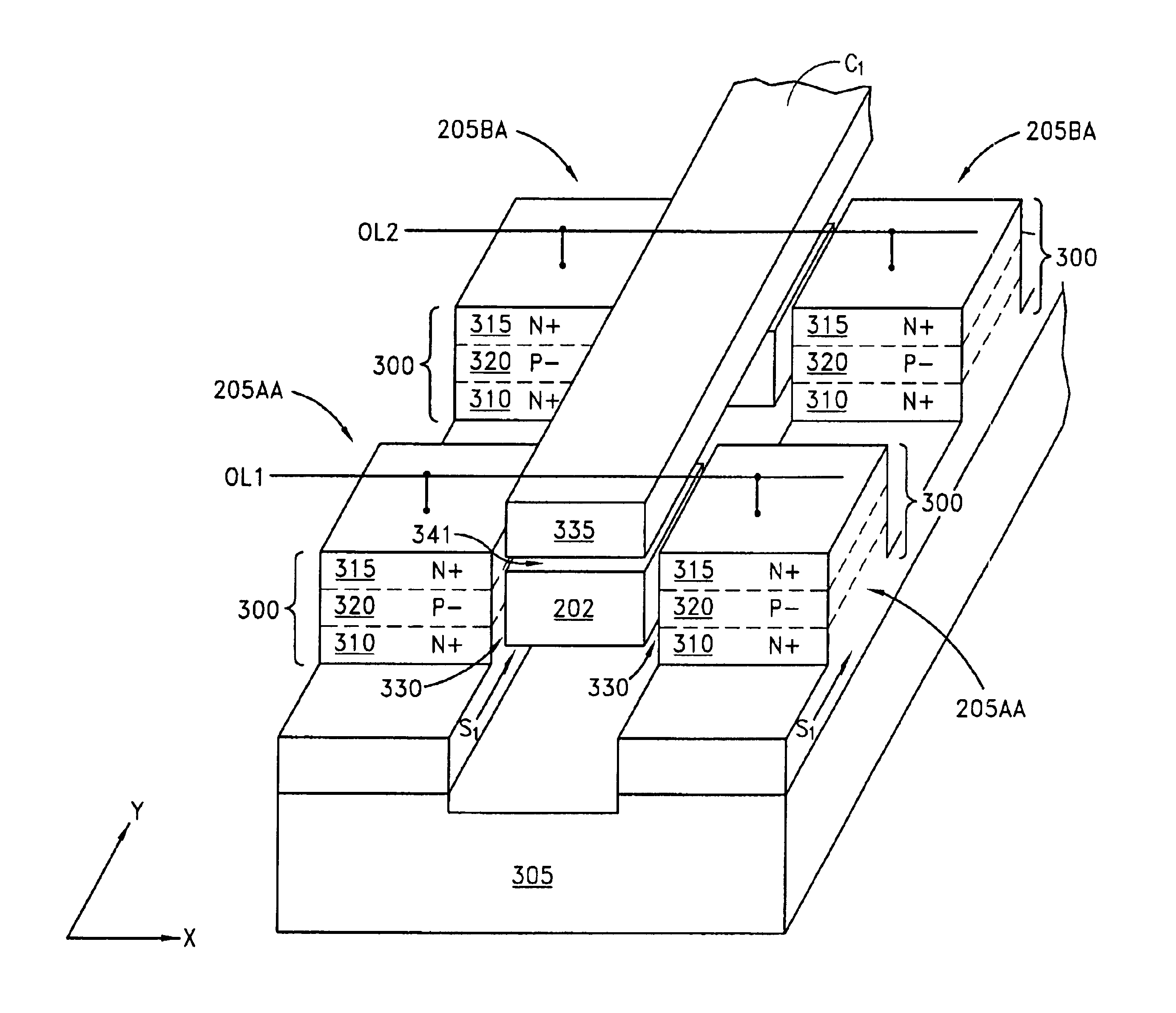

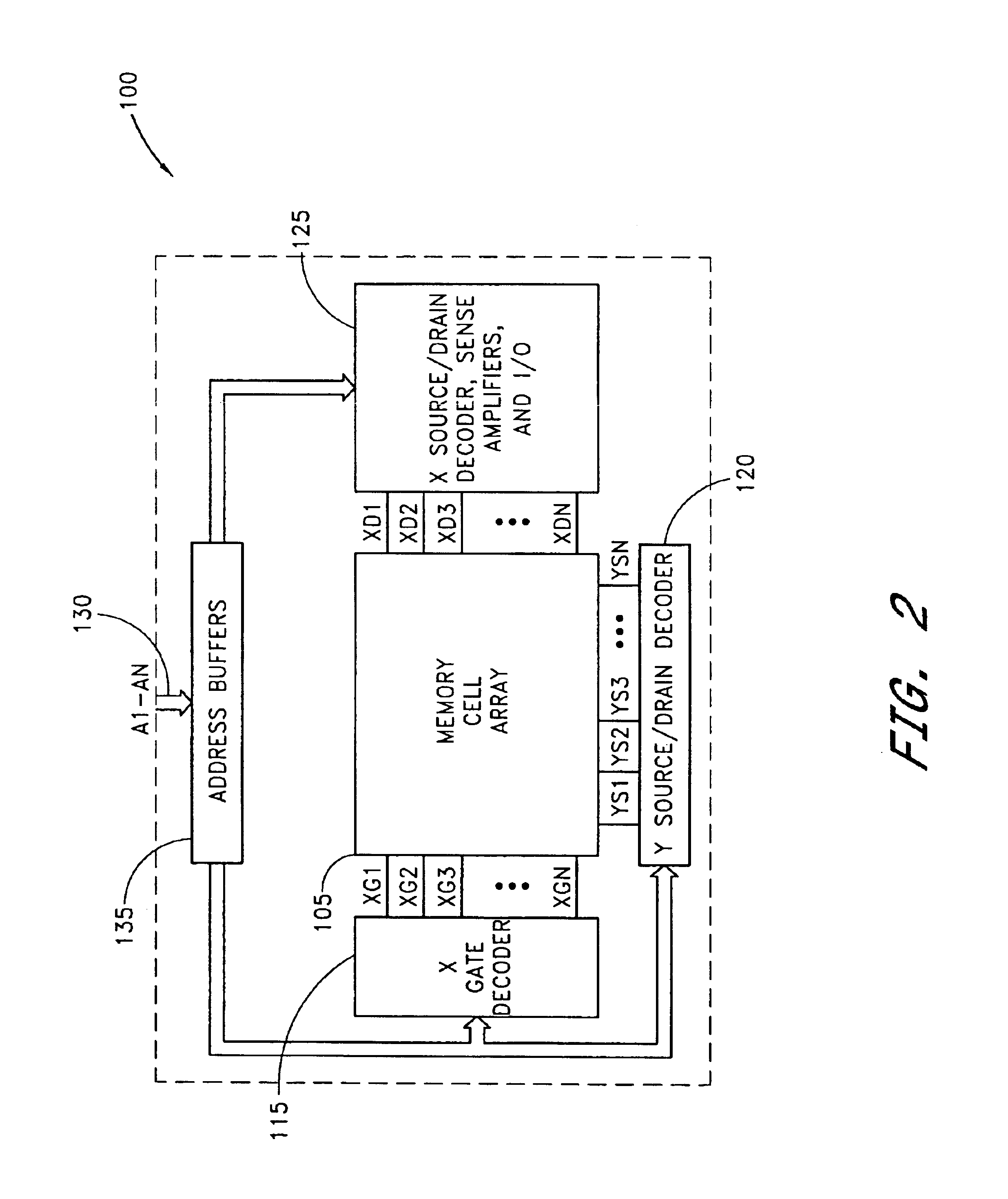

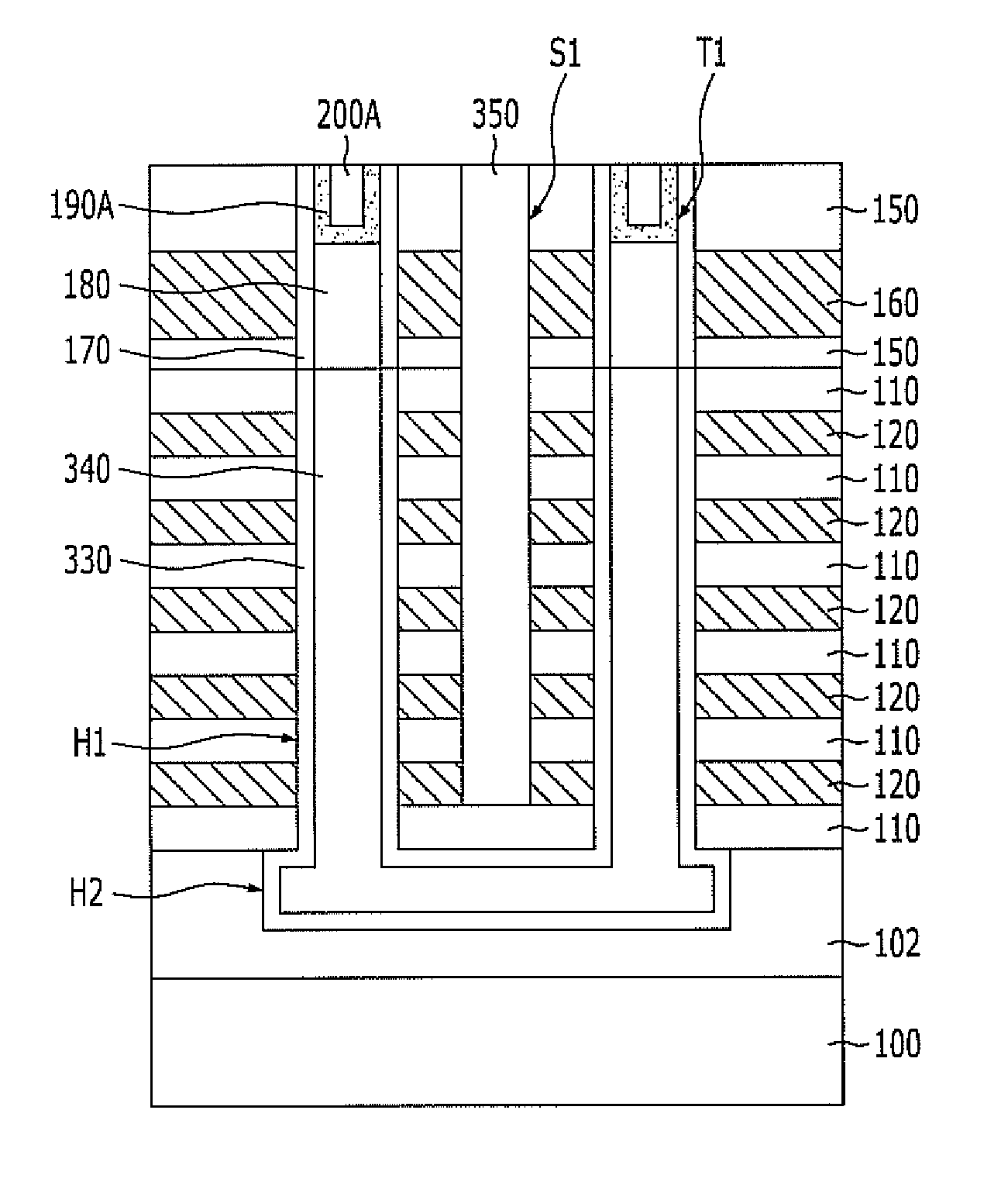

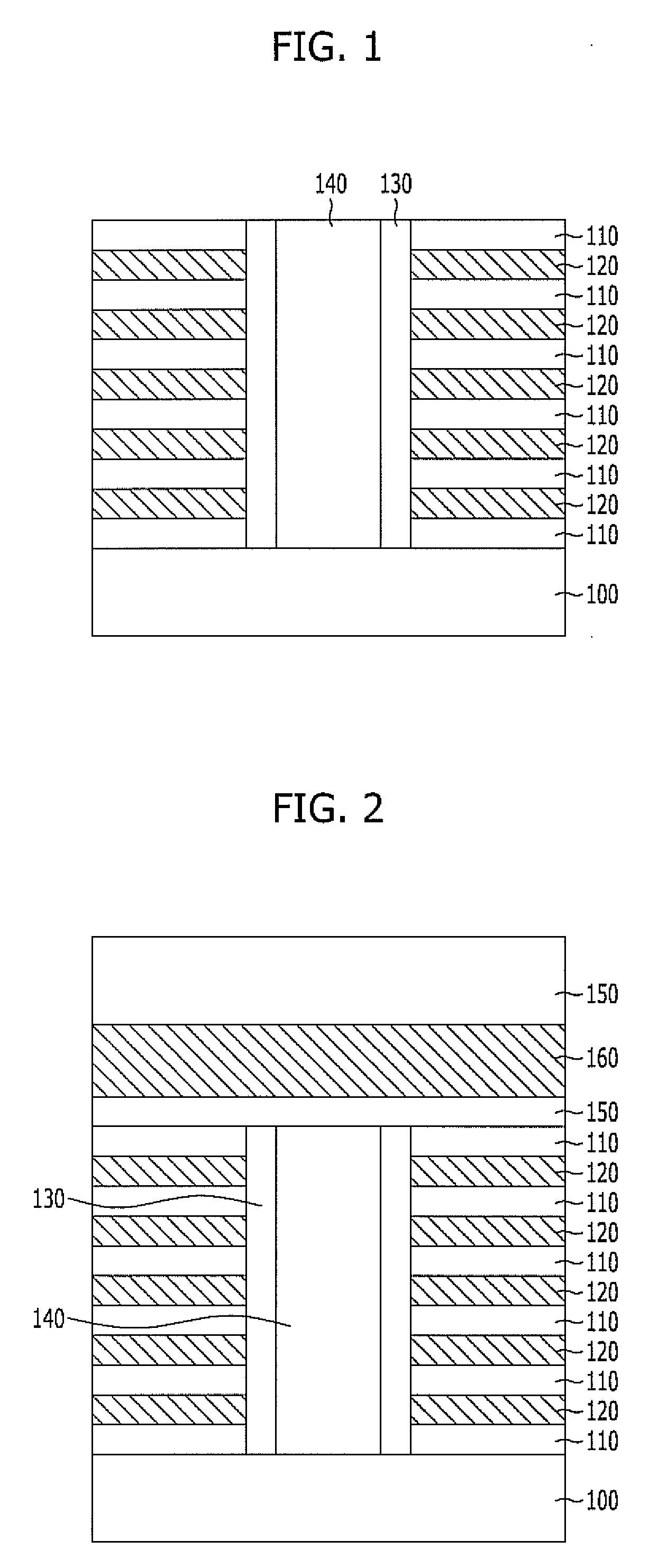

Floating gate transistor with horizontal gate layers stacked next to vertical body

Vertical body transistors with adjacent horizontal gate layers are used to form a memory array in a high density flash electrically erasable and programmable read only memory (EEPROM) or a logic array in a high density field programmable logic array (FPLA). The transistor is a field-effect transistor (FET) having an electrically isolated (floating) gate that controls electrical conduction between source regions and drain regions. If a particular floating gate is charged with stored electrons, then the transistor will not turn on and will provide an indication of the stored data at this location in the memory array within the EEPROM or will act as the absence of a transistor at this location in the logic array within the FPLA. The memory array or the logic array includes densely packed cells, each cell having a semiconductor pillar providing shared source and drain regions for two vertical body transistors that have control gates overlaying floating gates distributed on opposing sides of the semiconductor pillar. Both bulk semiconductor and silicon-on-insulator embodiments are provided. If a floating gate transistor is used to store a single bit of data or to represent a logic function, an area of only 2F<2 >is needed per respective bit of data or bit of logic, where F is the minimum lithographic feature size.

Owner:MICRON TECH INC

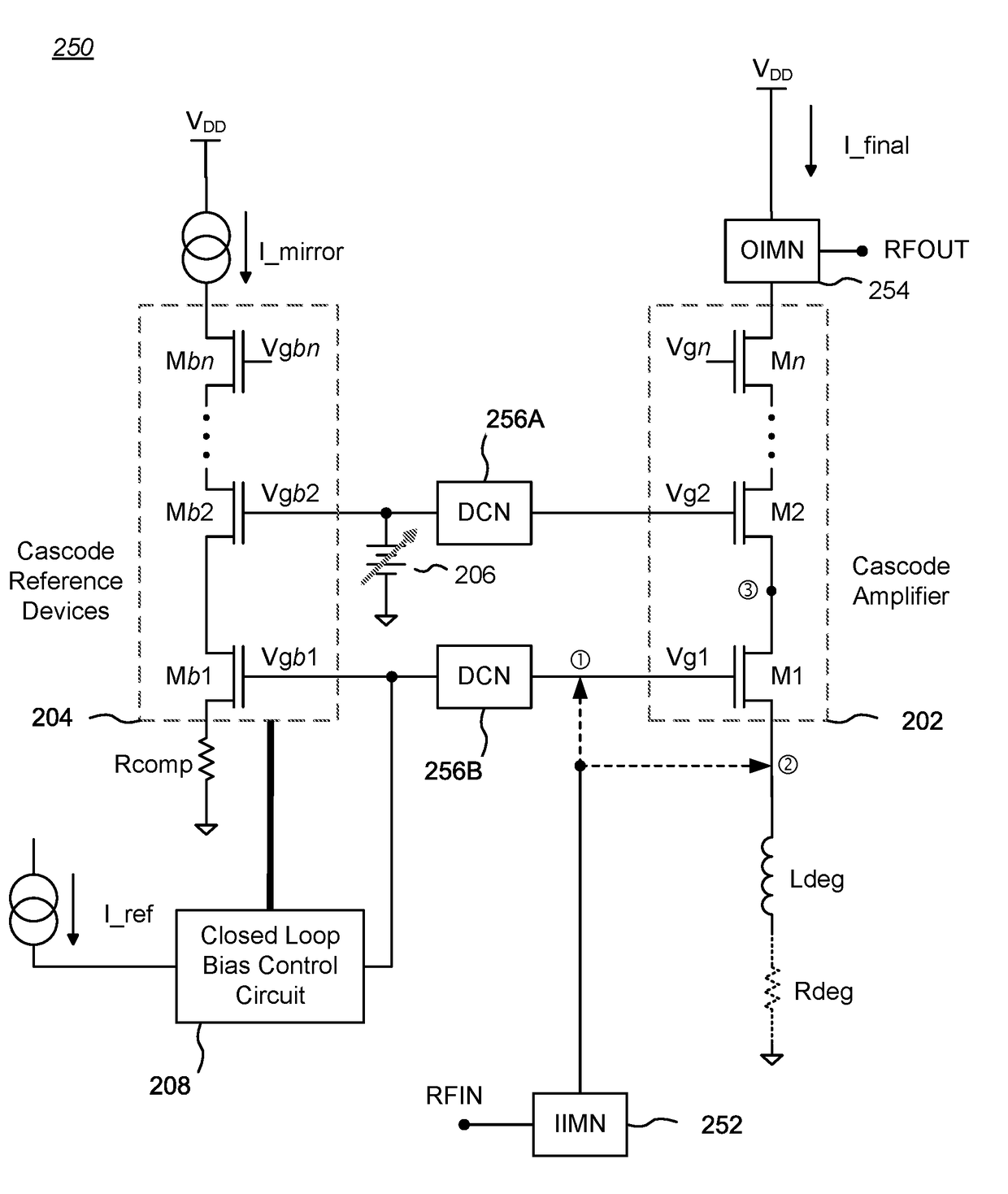

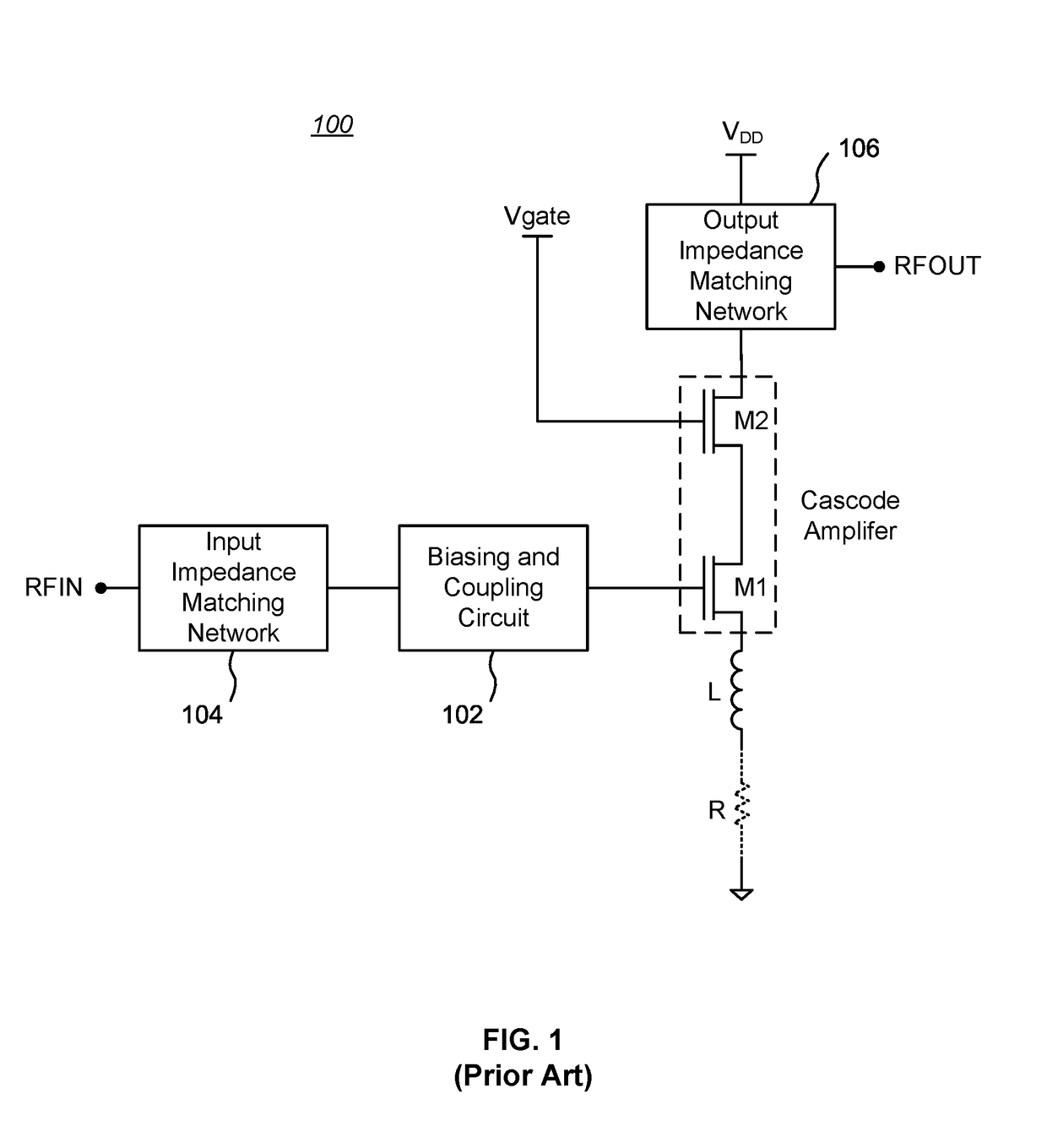

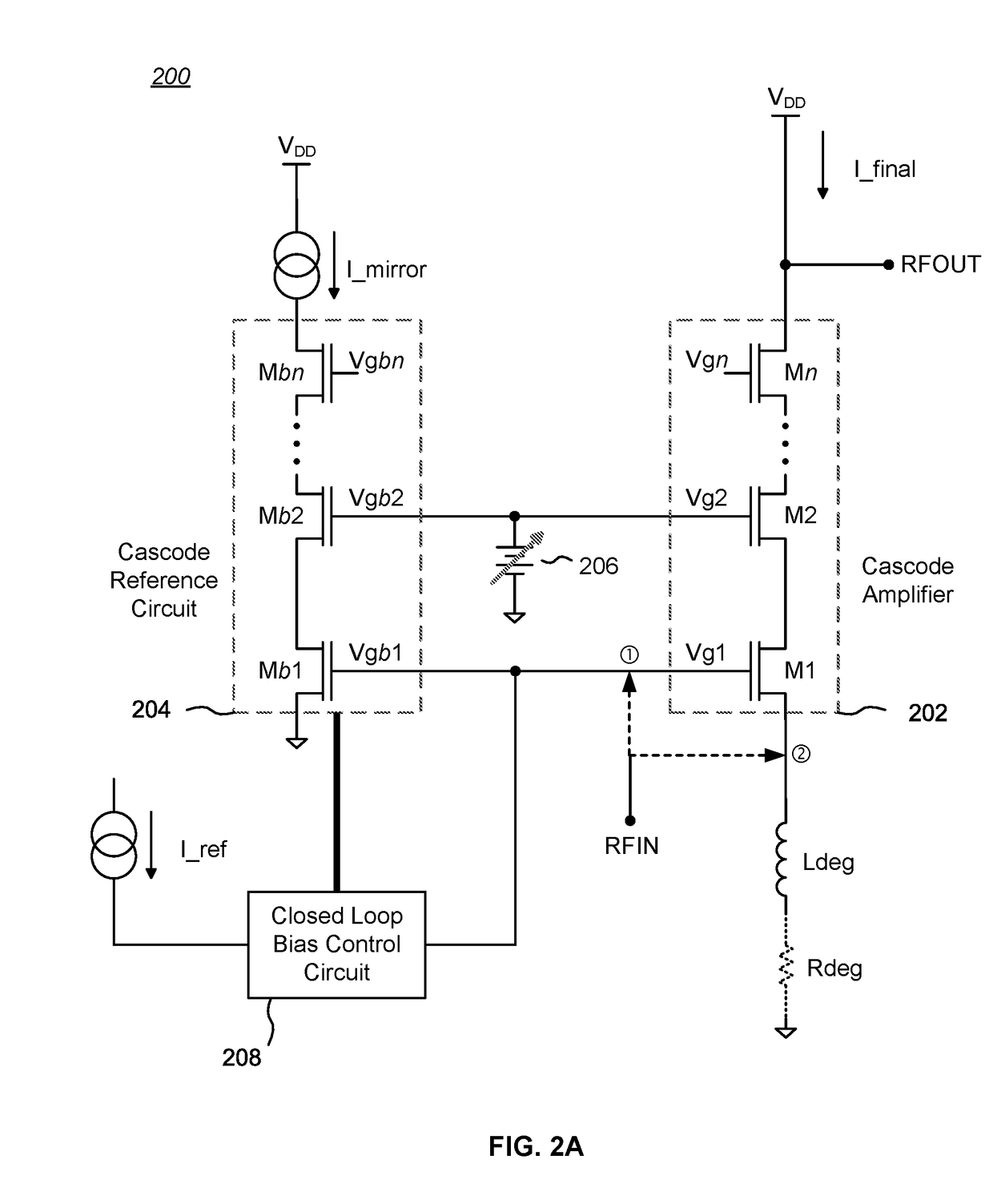

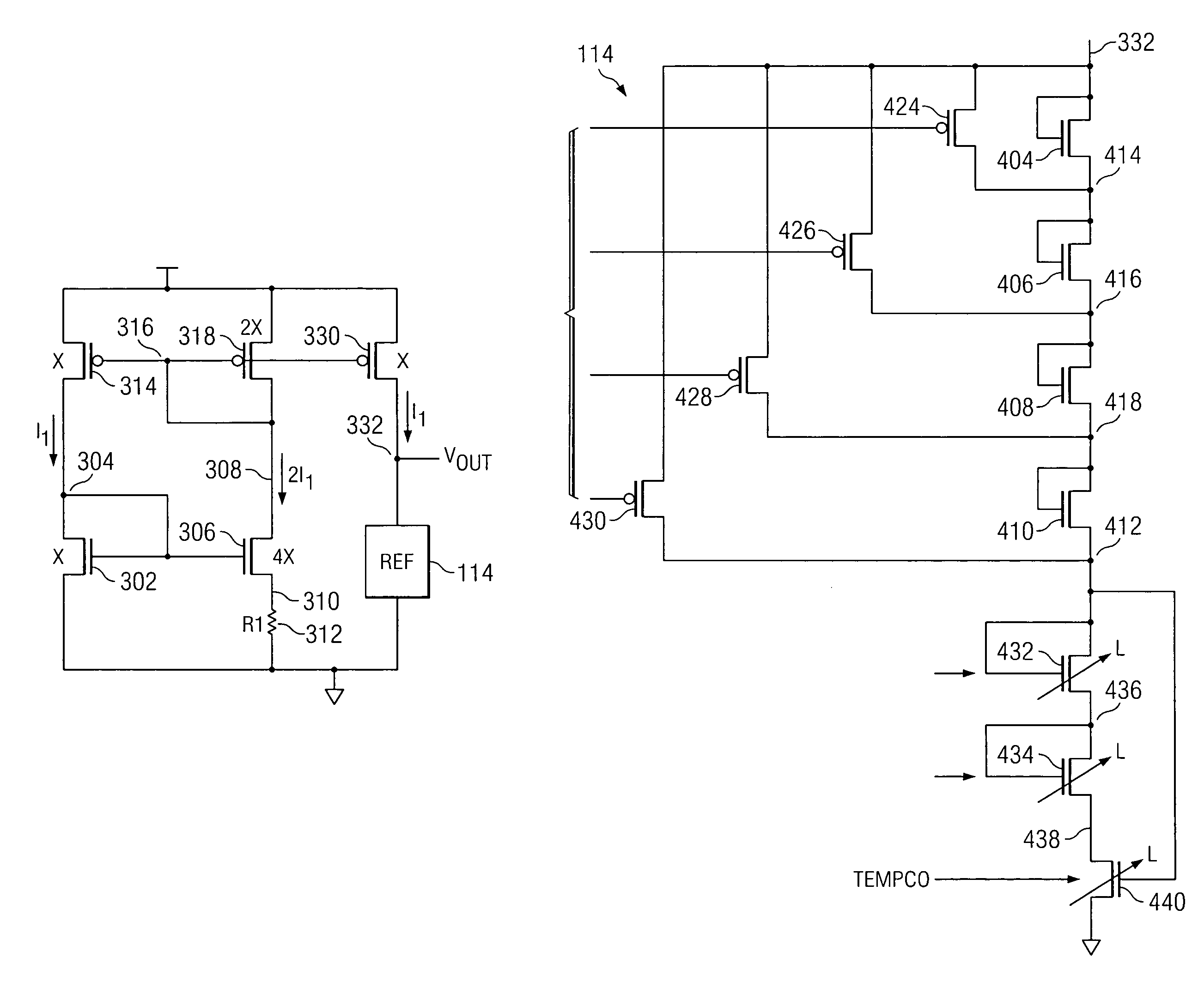

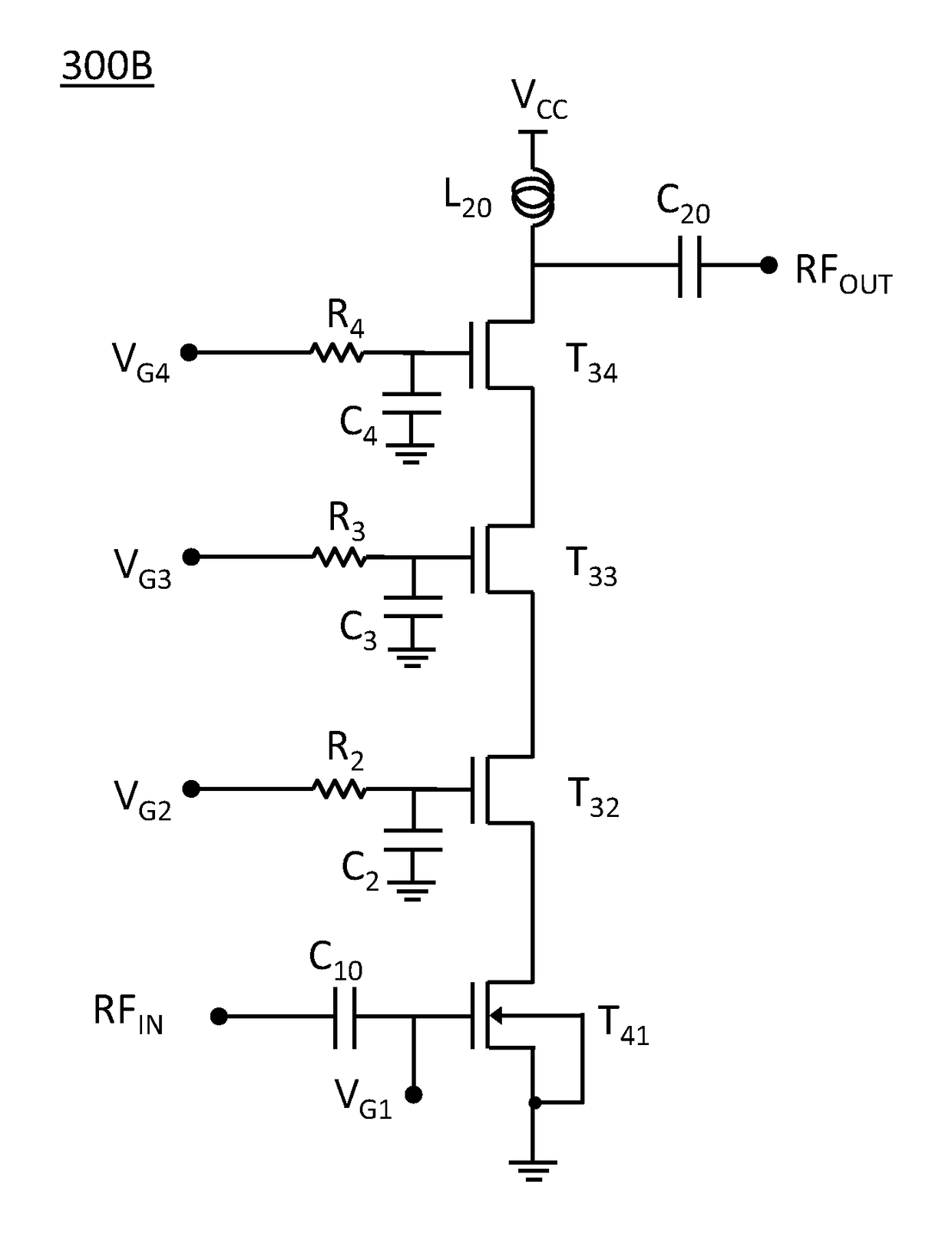

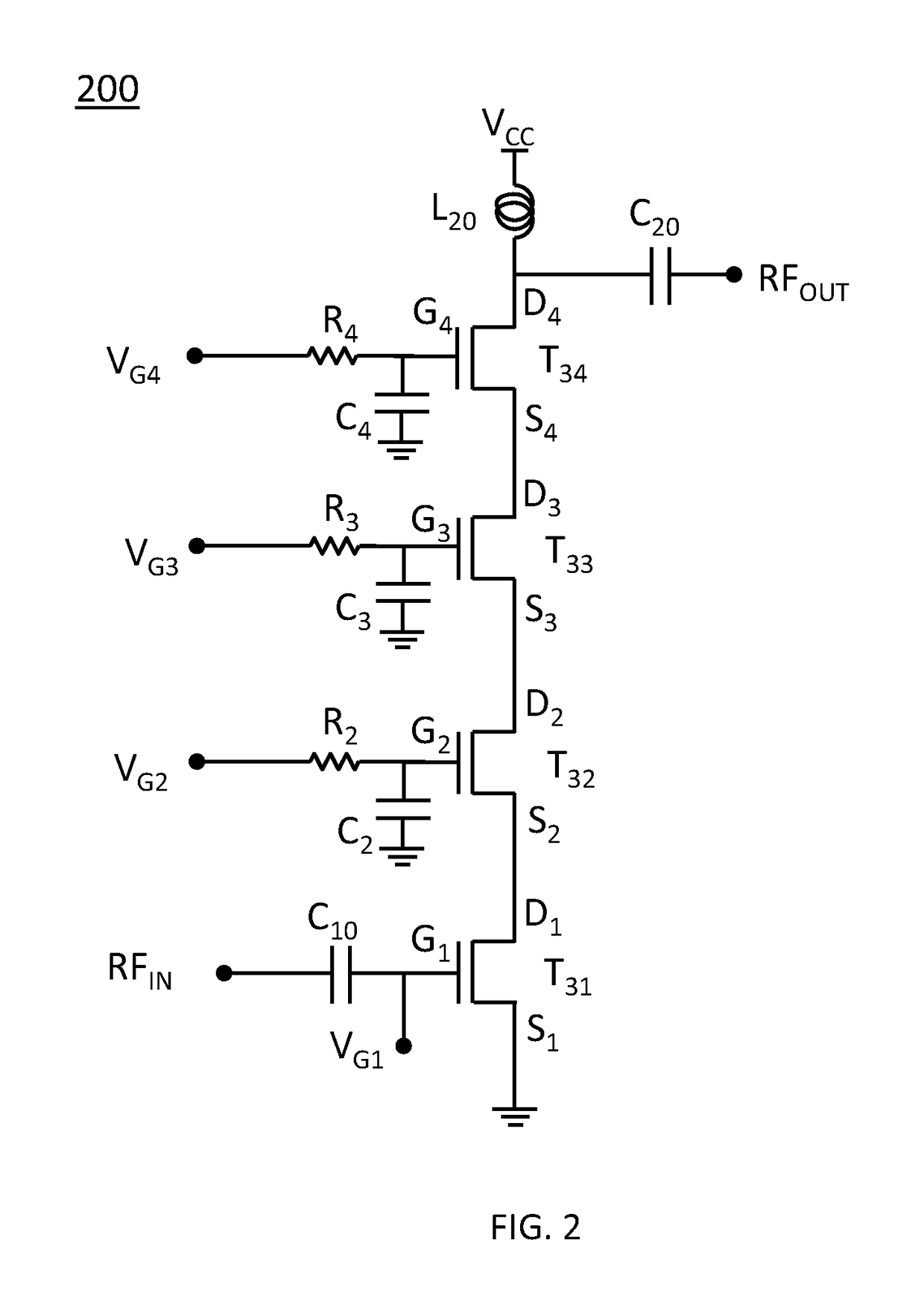

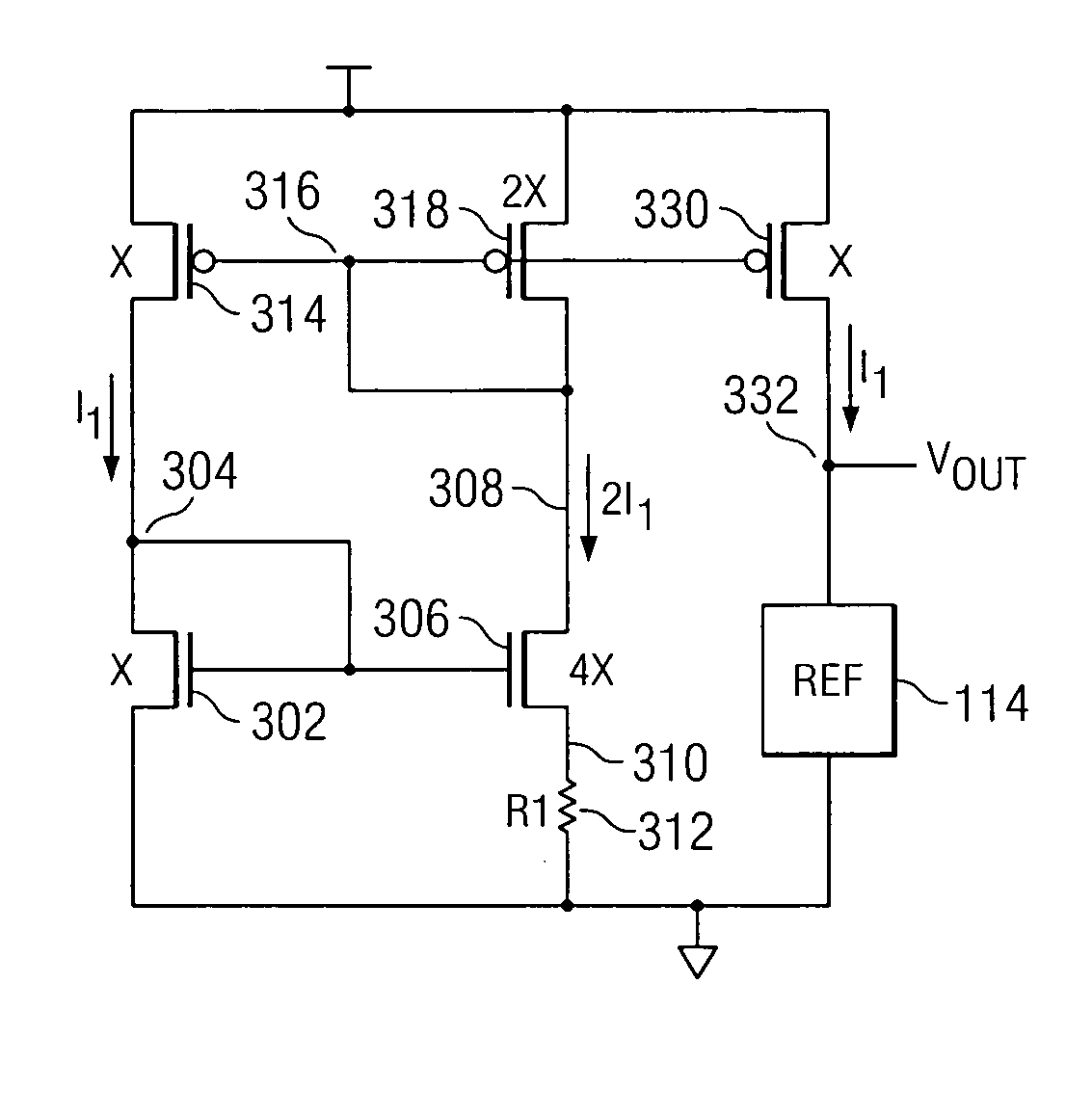

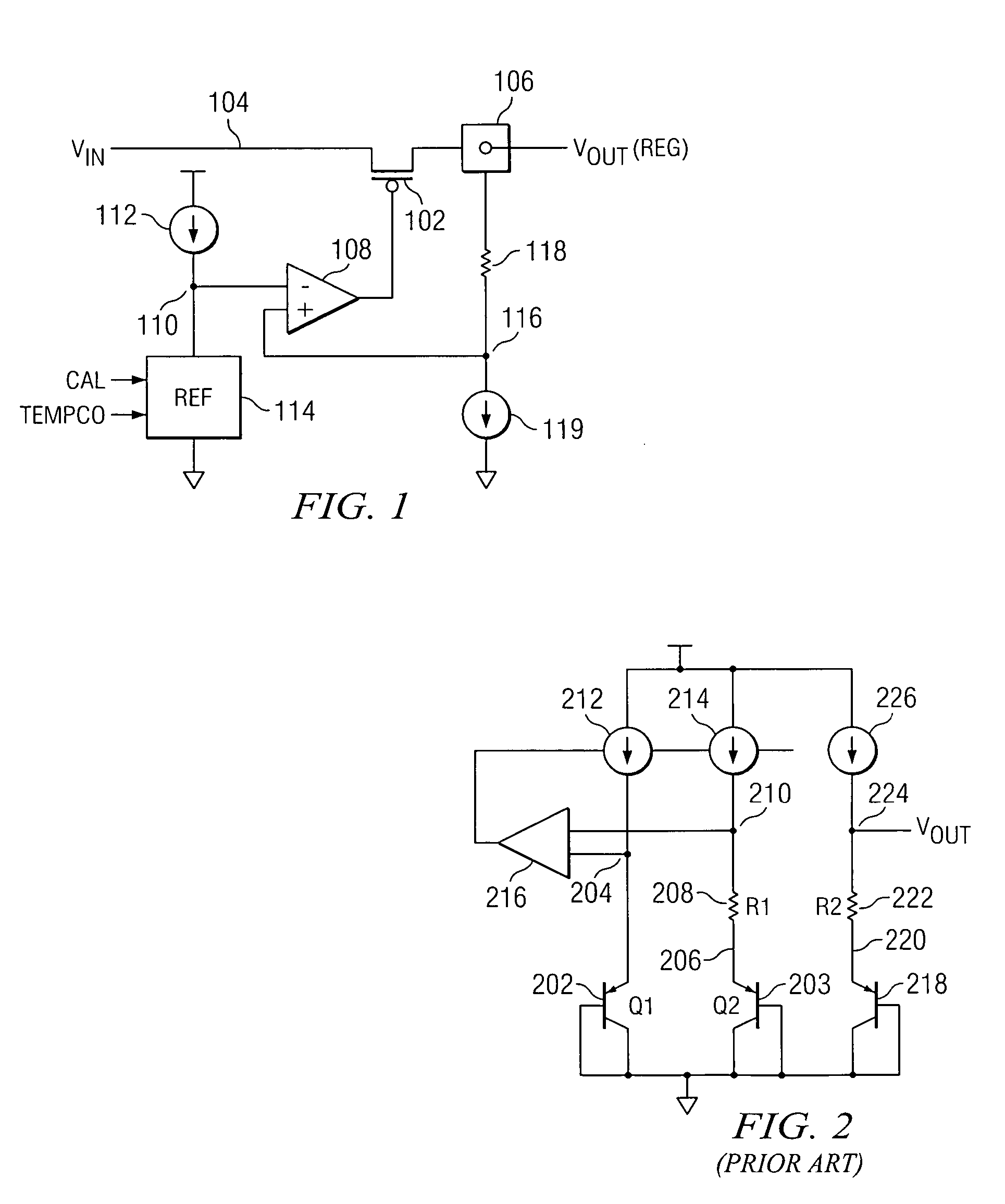

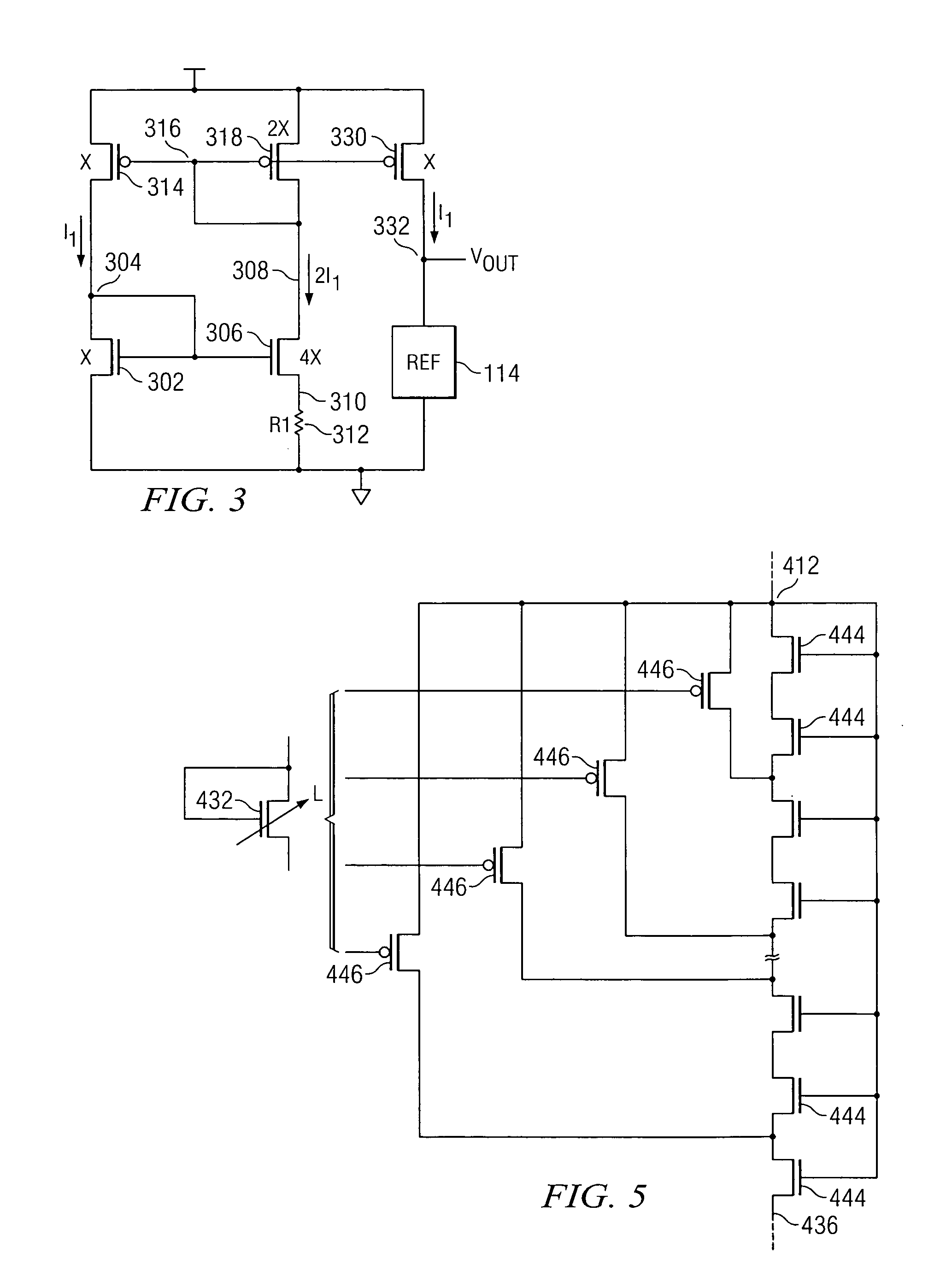

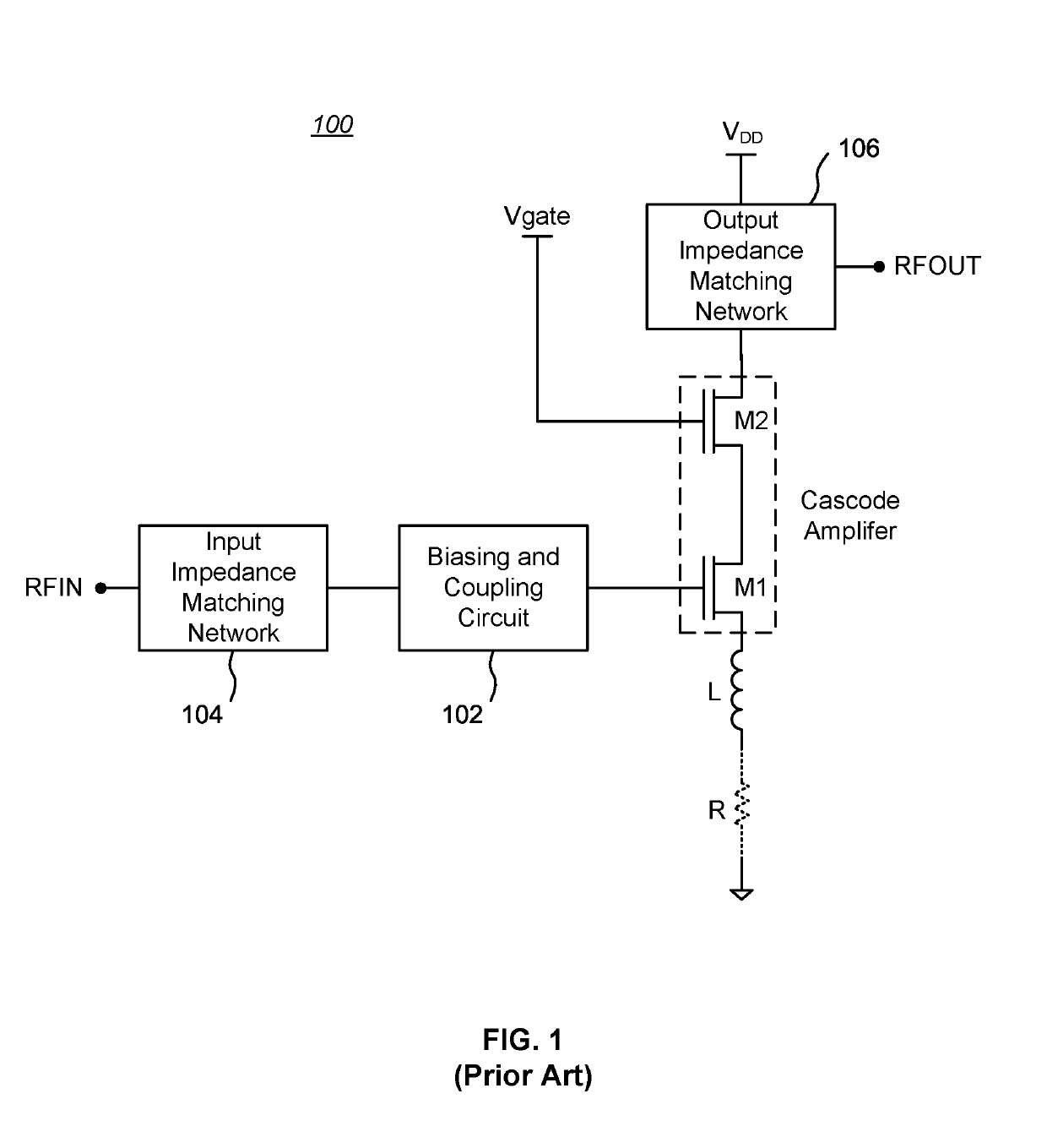

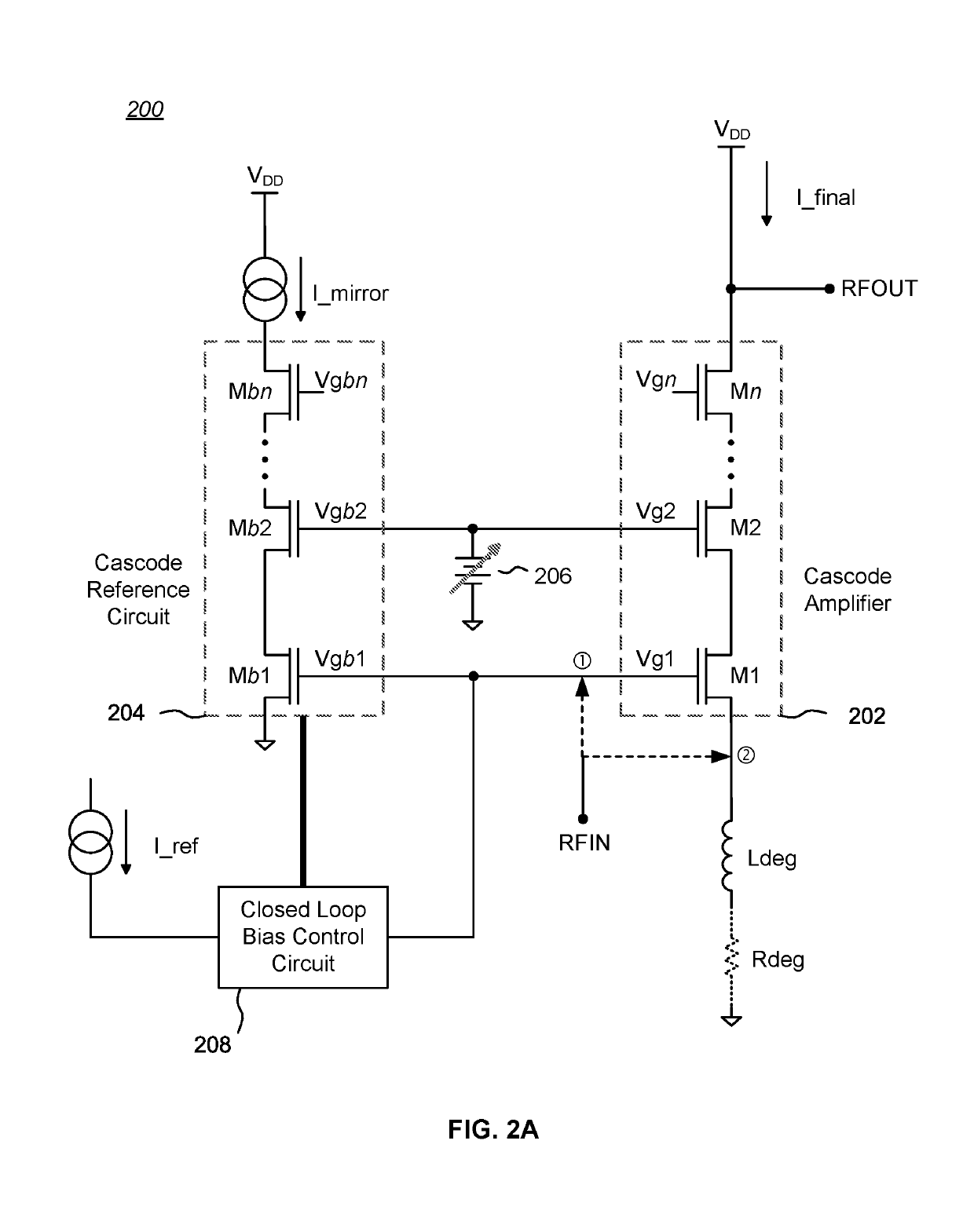

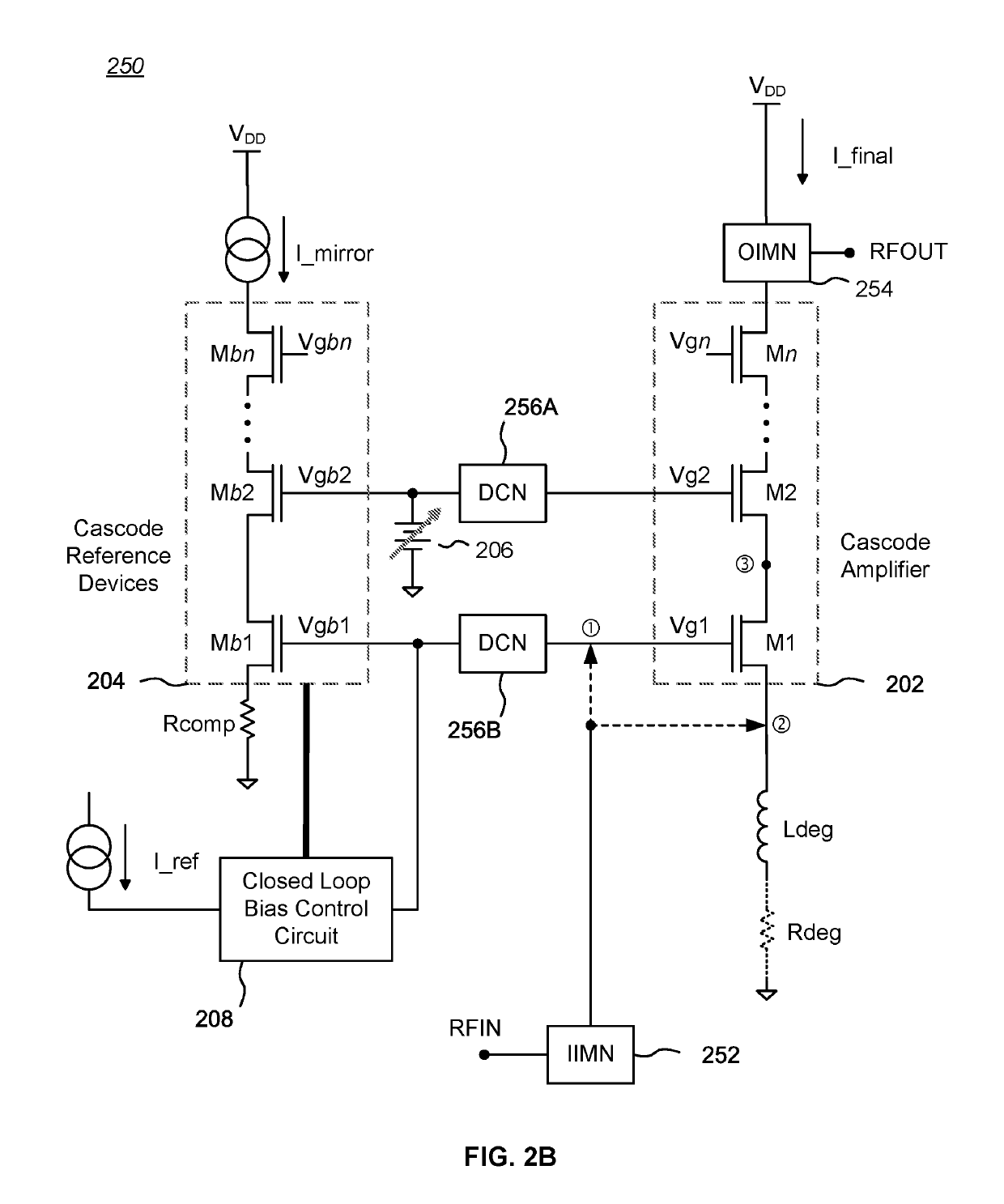

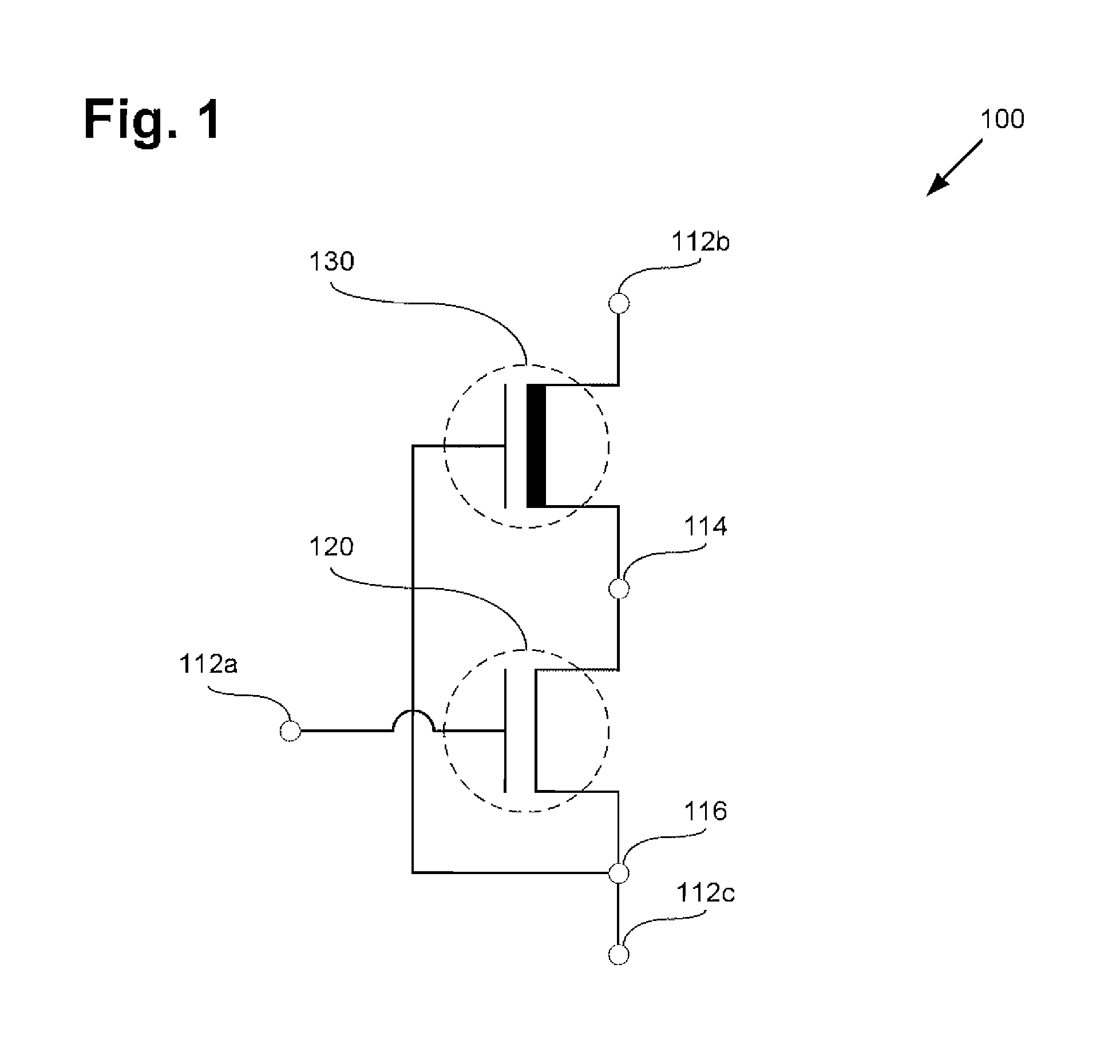

Cascode Amplifier Bias Circuits

ActiveUS20180083578A1Amplifier modifications to reduce temperature/voltage variationAmplifier with semiconductor-devices/discharge-tubesLow noiseAudio power amplifier

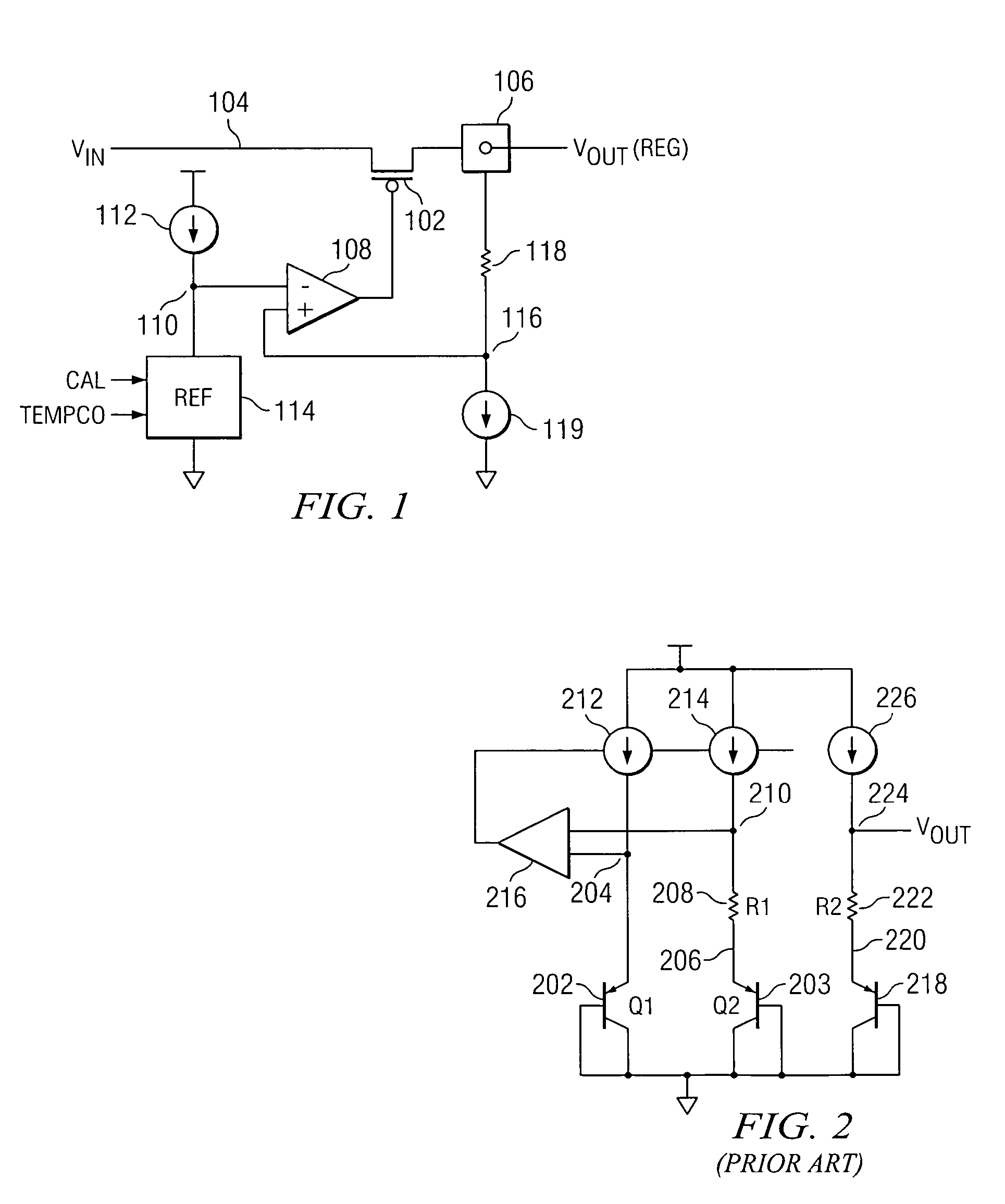

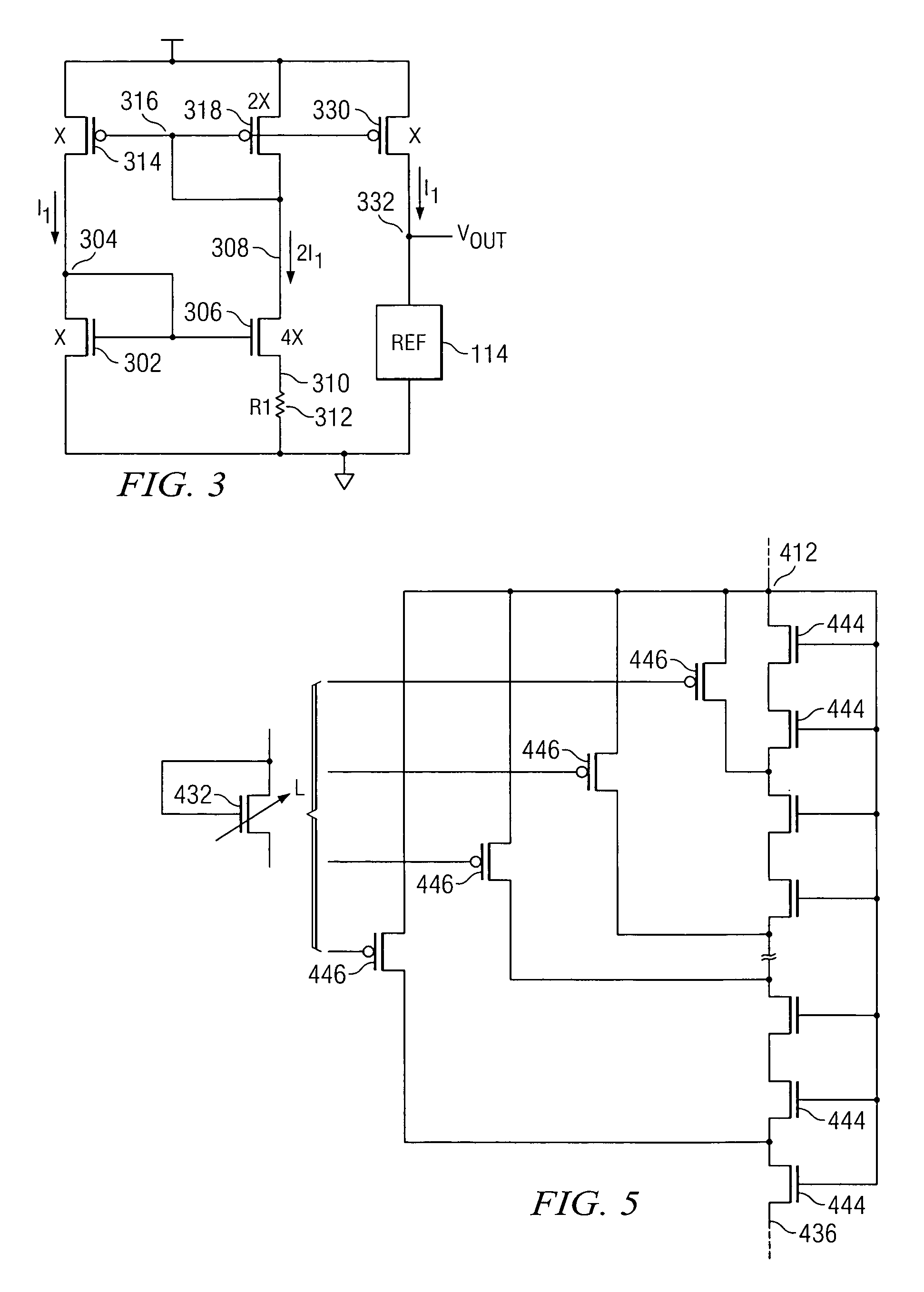

Bias circuits and methods for silicon-based amplifier architectures that are tolerant of supply and bias voltage variations, bias current variations, and transistor stack height, and compensate for poor output resistance characteristics. Embodiments include power amplifiers and low-noise amplifiers that utilize a cascode reference circuit to bias the final stages of a cascode amplifier under the control of a closed loop bias control circuit. The closed loop bias control circuit ensures that the current in the cascode reference circuit is approximately equal to a selected multiple of a known current value by adjusting the gate bias voltage to the final stage of the cascode amplifier. The final current through the cascode amplifier is a multiple of the current in the cascode reference circuit, based on a device scaling factor representing the relative sizes of the transistor devices in the cascode amplifier and in the cascode reference circuit.

Owner:PSEMI CORP

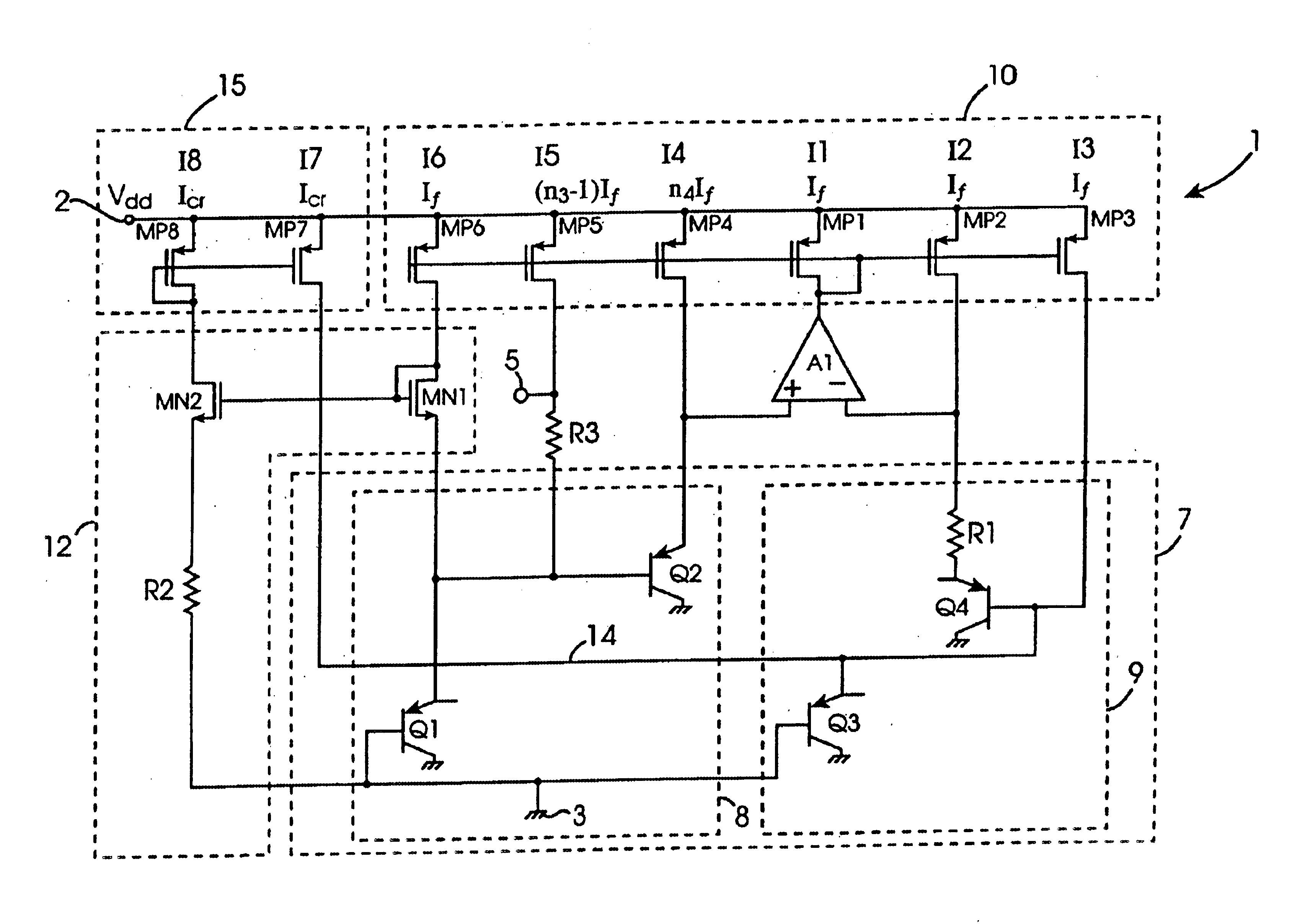

Bandgap voltage reference circuit and method for producing a temperature curvature corrected voltage reference

InactiveUS6828847B1Easy to implementLower requirementElectronic switchingPulse generation by opto-electronic devicesAudio power amplifierEngineering

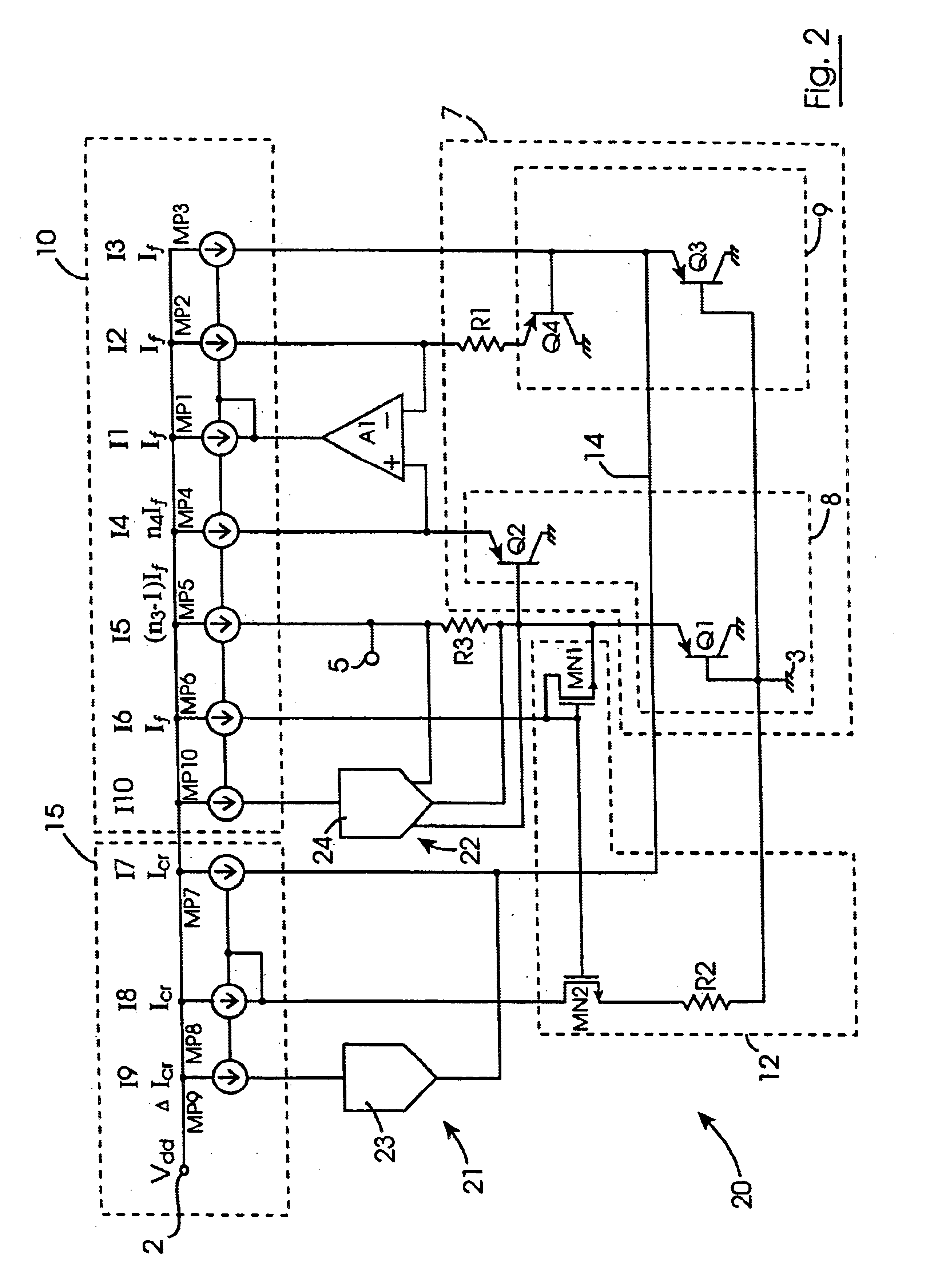

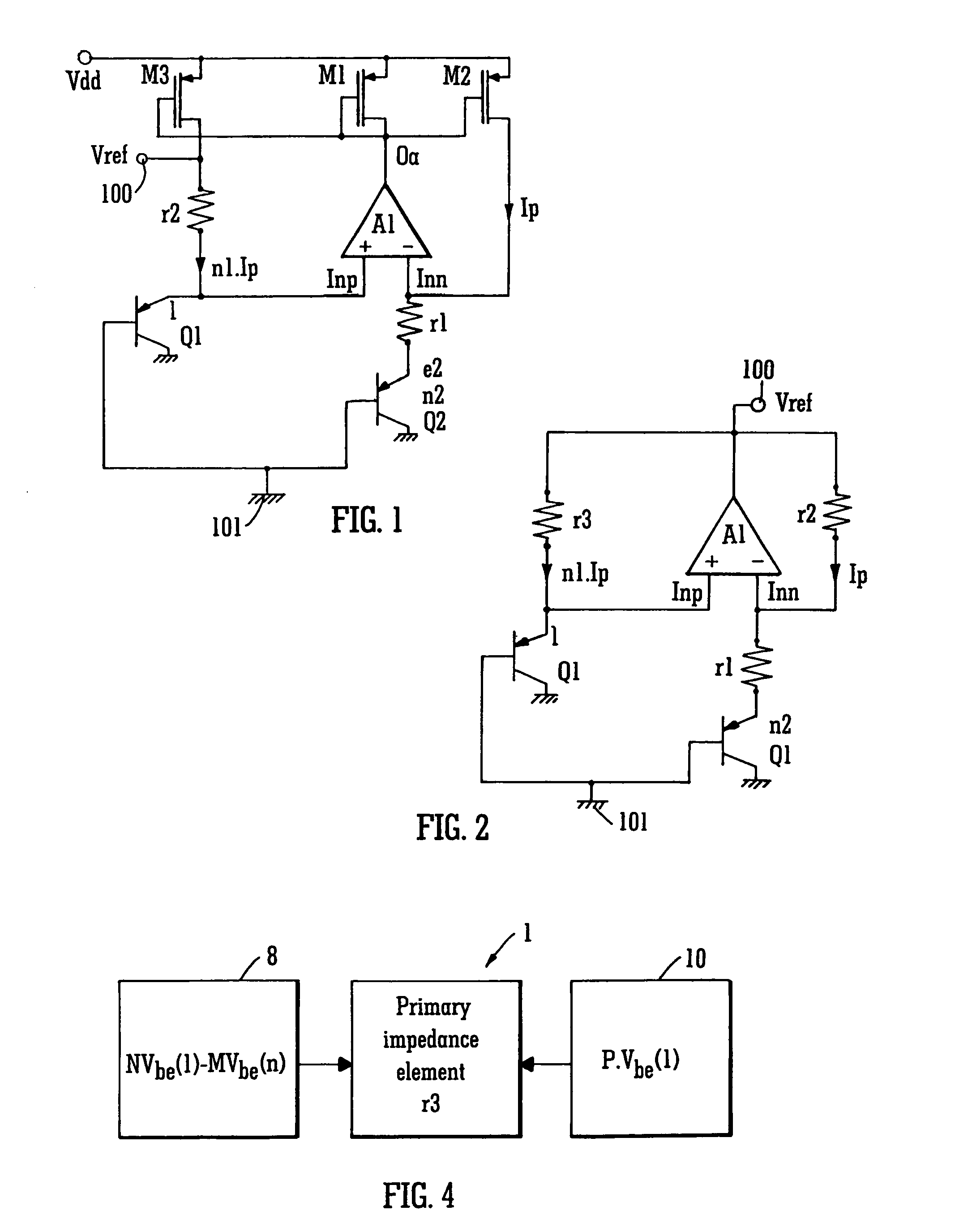

A bandgap voltage reference circuit (1) comprises a bandgap cell (7) comprising first and second transistor stacks (8,9) of first transistors (Q1,Q2) and second transistors (Q3,Q4), respectively, arranged for developing a correcting PTAT voltage (DeltaVbe) across a primary resistor (R1) proportional to the difference in the base-emitter voltages of the first and second transistor stacks (8,9). A first current mirror circuit (10) provides PTAT currents (12 to 15) to the emitters of the first and second transistors (Q1 to Q4), and an operational amplifier (A1) maintains the voltage on the emitter of the first transistor (Q2) of the first transistor stack (8) at the same level as the resistor (R1) and sinks a PTAT current from the first current mirror circuit (10) from which the other PTAT currents are mirrored. The correcting PTAT voltage (DeltaVbe) developed across the primary resistor (R1) is scaled onto a secondary resistor (R3) and summed with the uncorrected base-emitter CTAT voltage of the first transistor (Q1) of the first transistor stack (8) for providing the voltage reference between an output terminal (5) and ground (3). A CTAT correcting current (Icr) is summed with the PTAT current (13) and applied to the emitter of the second transistor (Q3) of the second transistor stack (9) so that the correcting PTAT voltage (DeltaVbe) developed across the primary resistor (R1) has a TlnT curvature complementary to the TlnT temperature curvature of the uncorrected base-emitter CTAT voltage of the first transistor (Q1). Thus the reference voltage developed between the output terminal (5) and the ground (3) is temperature stable and TlnT temperature curvature corrected. The CTAT correcting current is derived from the base-emitter CTAT voltage of the first transistor (Q1) in a CTAT current generating circuit (12) through a second current mirror circuit (15).

Owner:ANALOG DEVICES INC

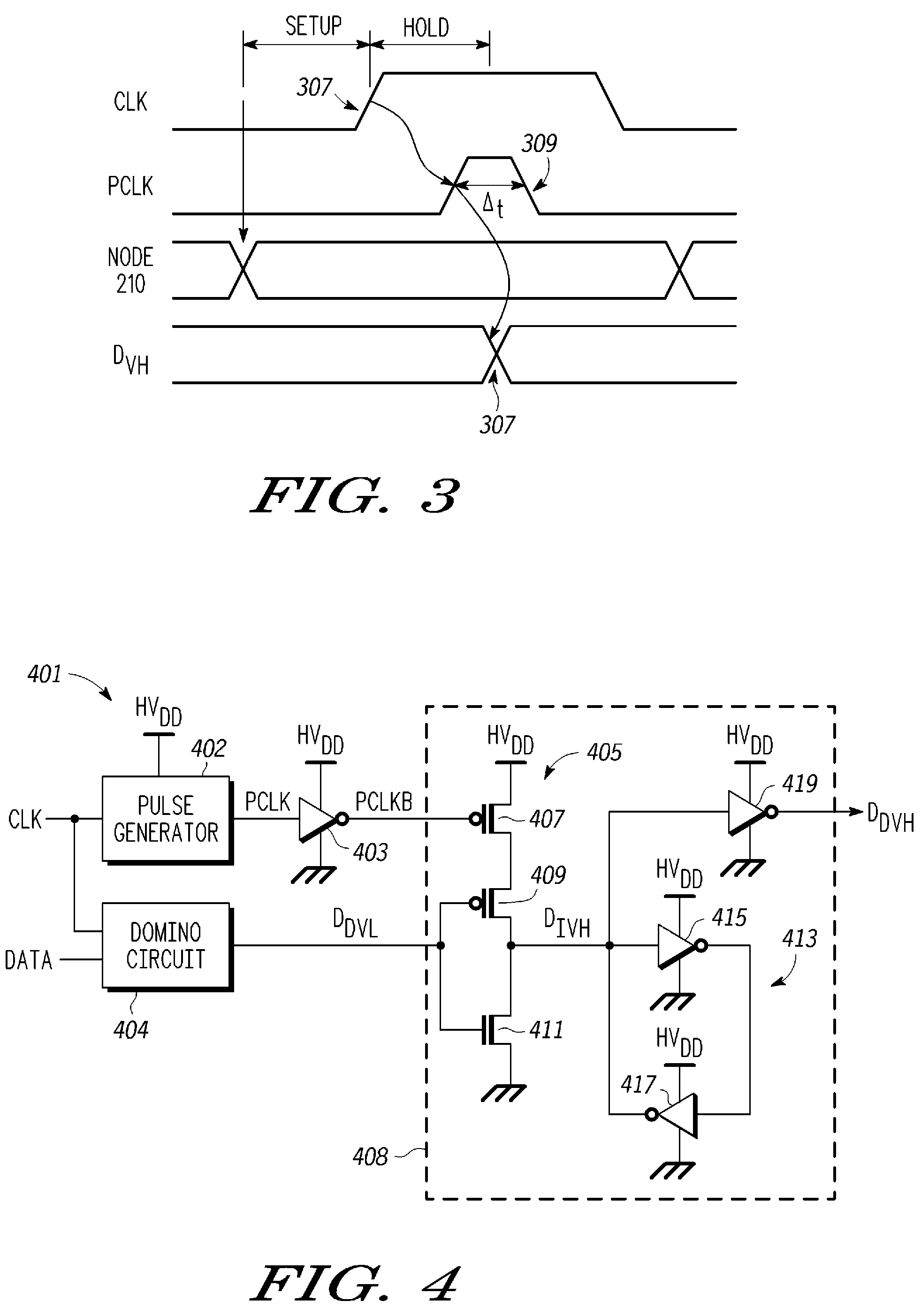

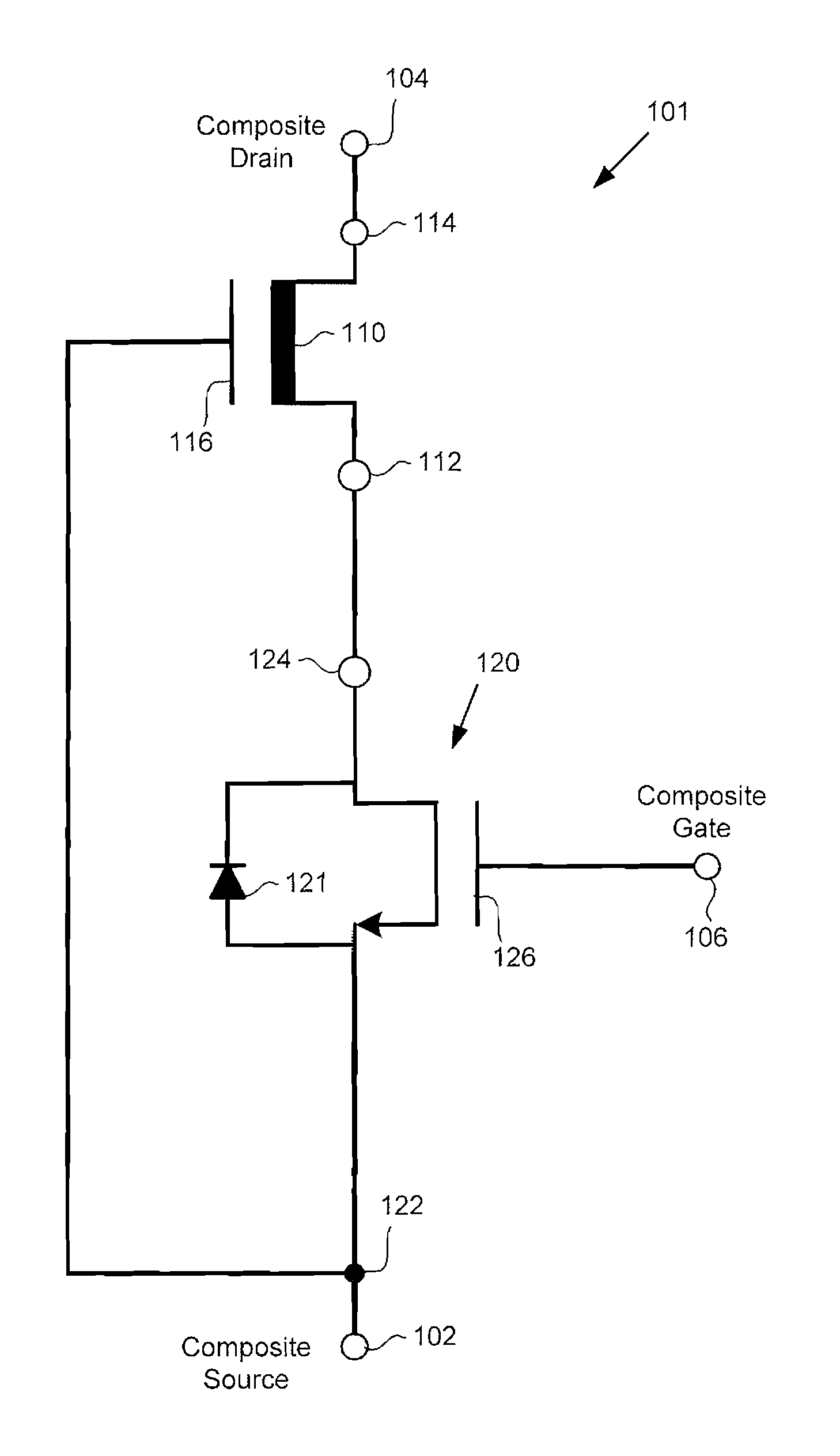

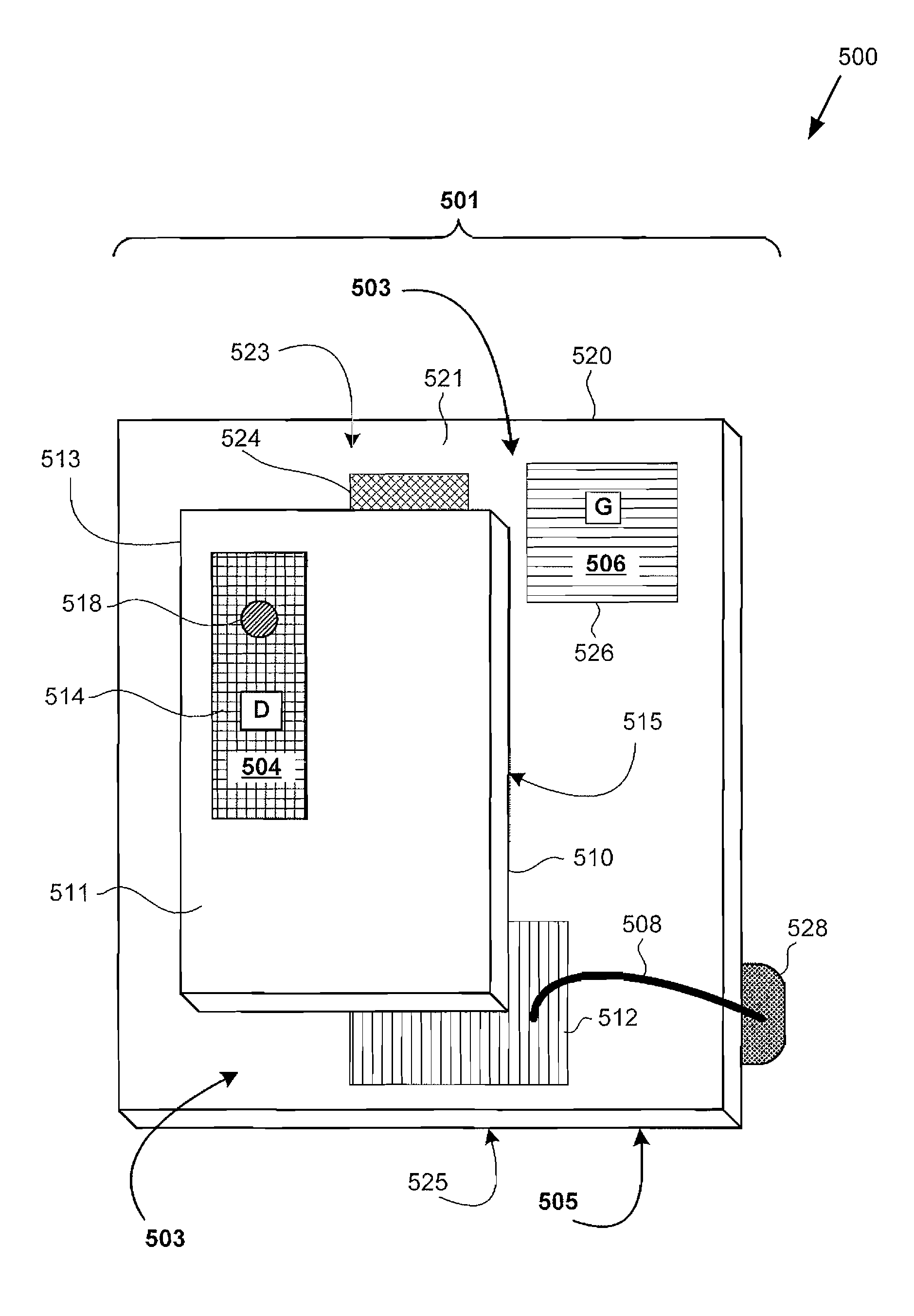

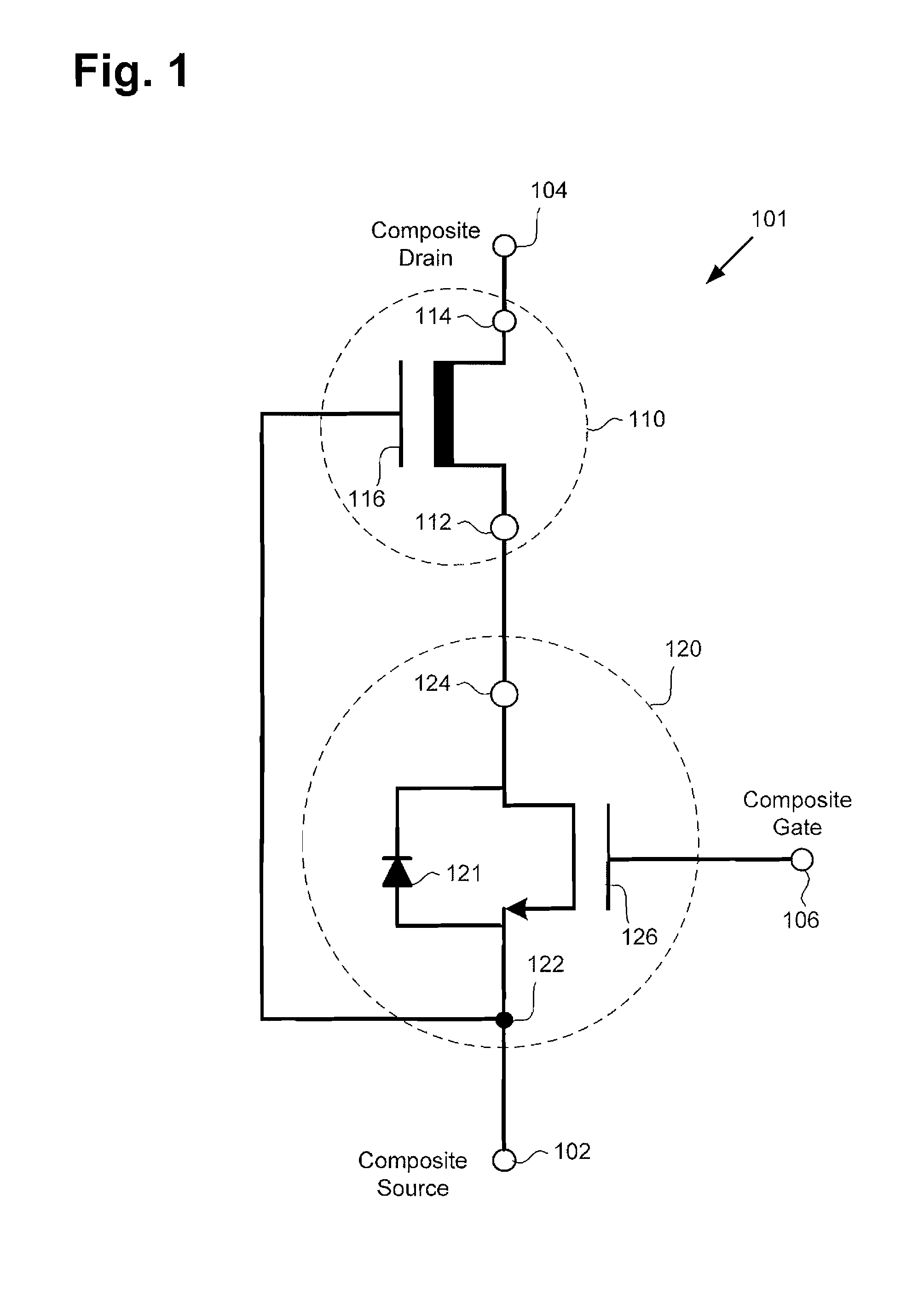

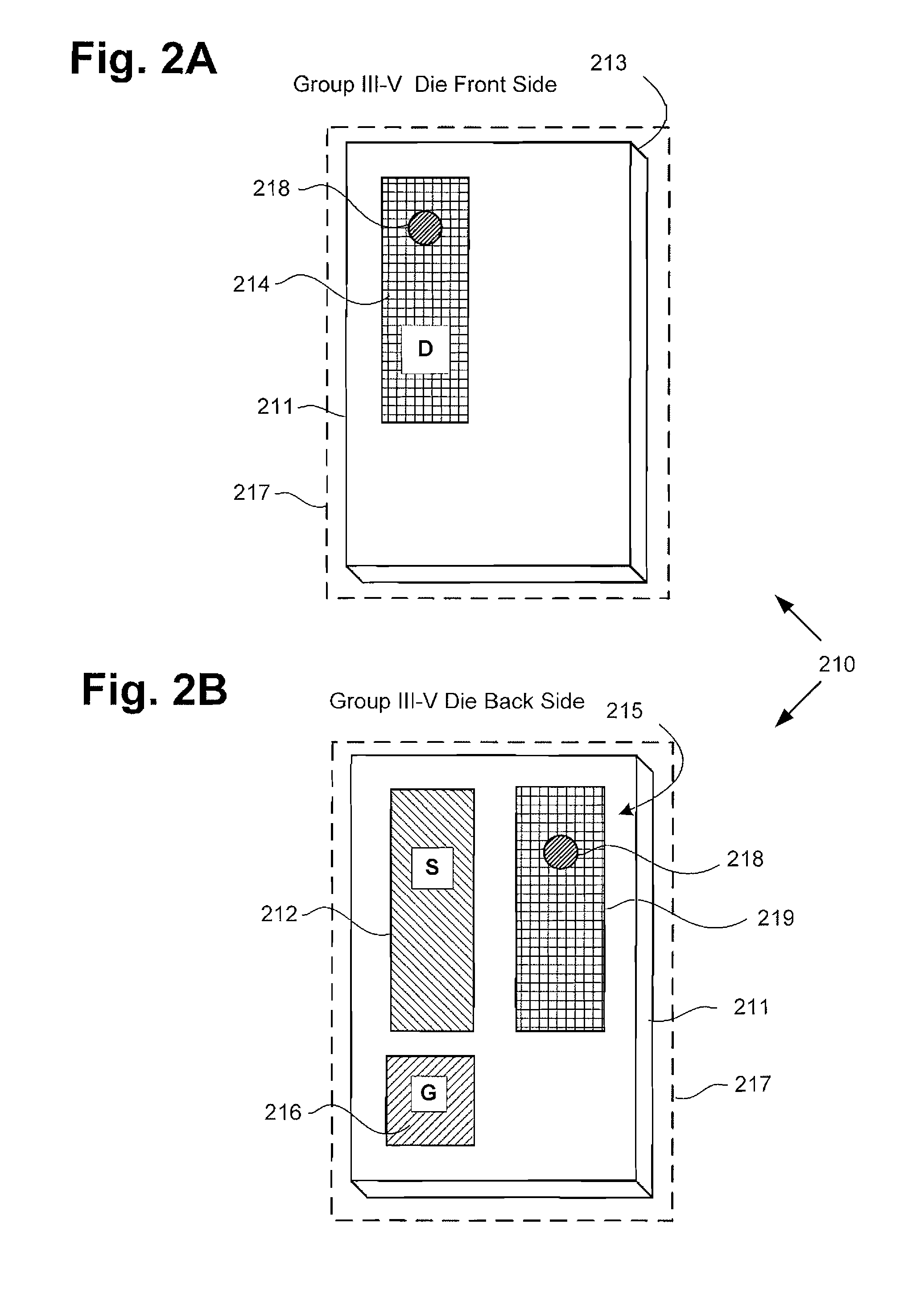

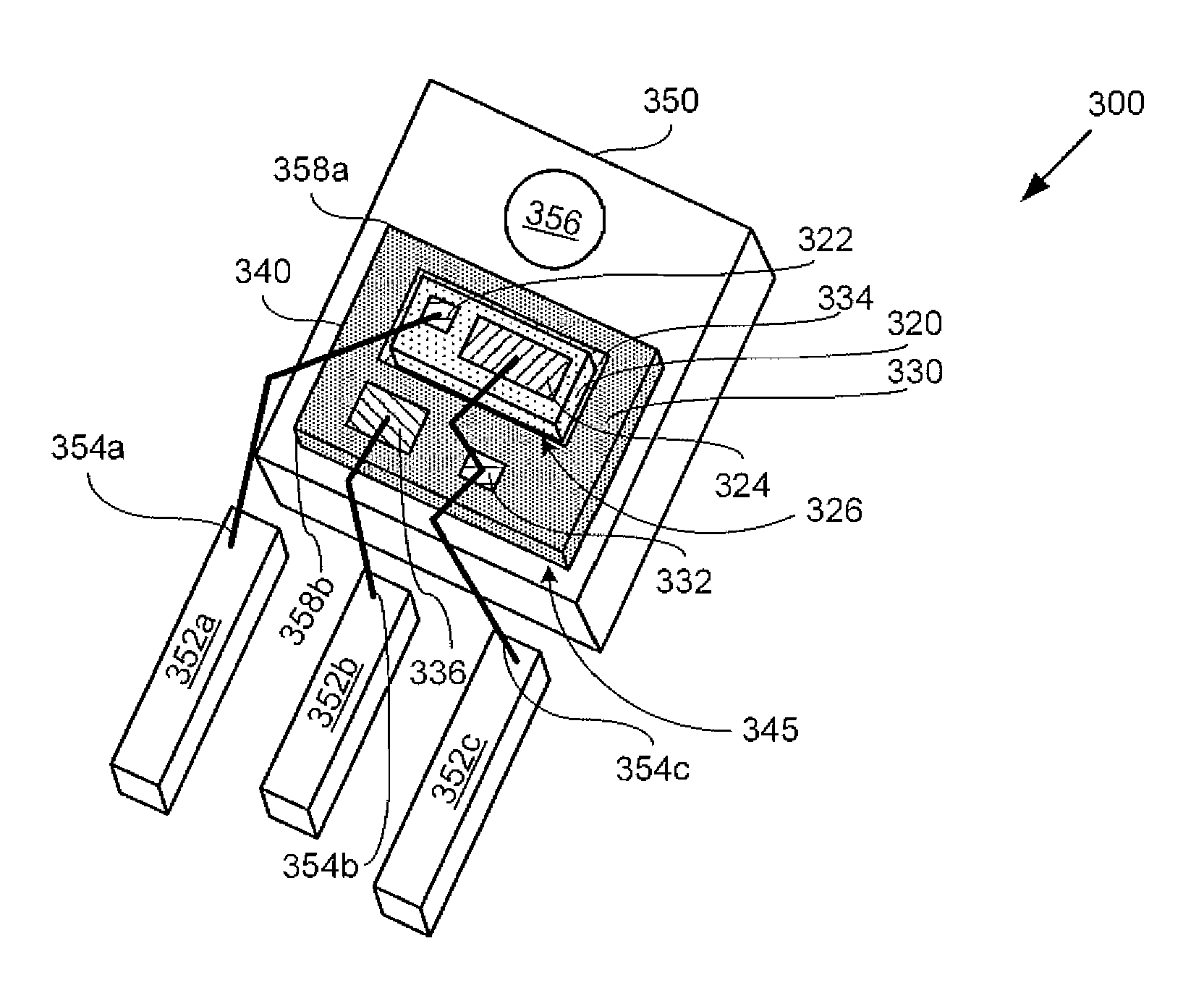

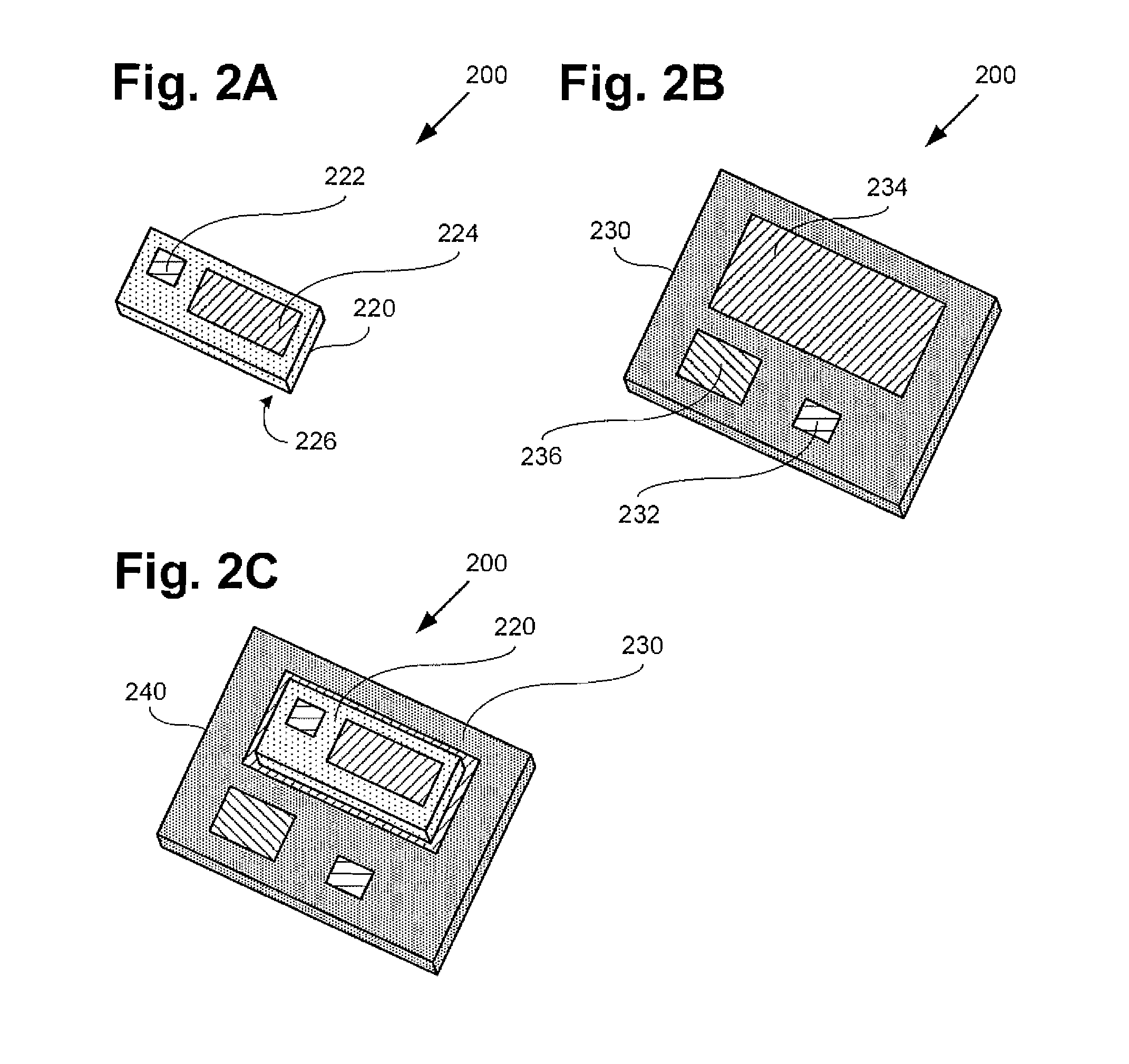

III-Nitride Transistor Stacked with FET in a Package

ActiveUS20120223321A1Semiconductor/solid-state device detailsSolid-state devicesSmall form factorField-effect transistor

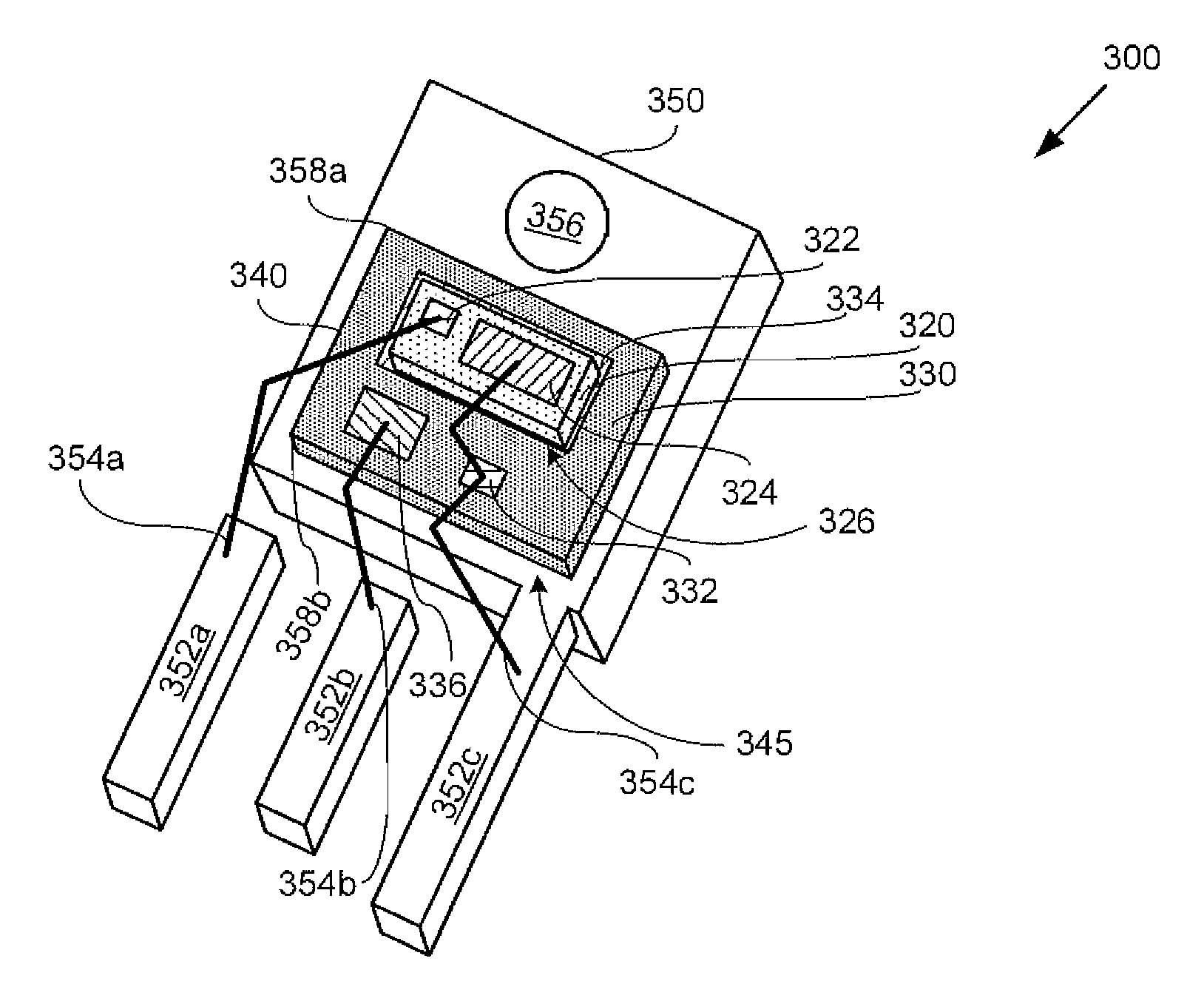

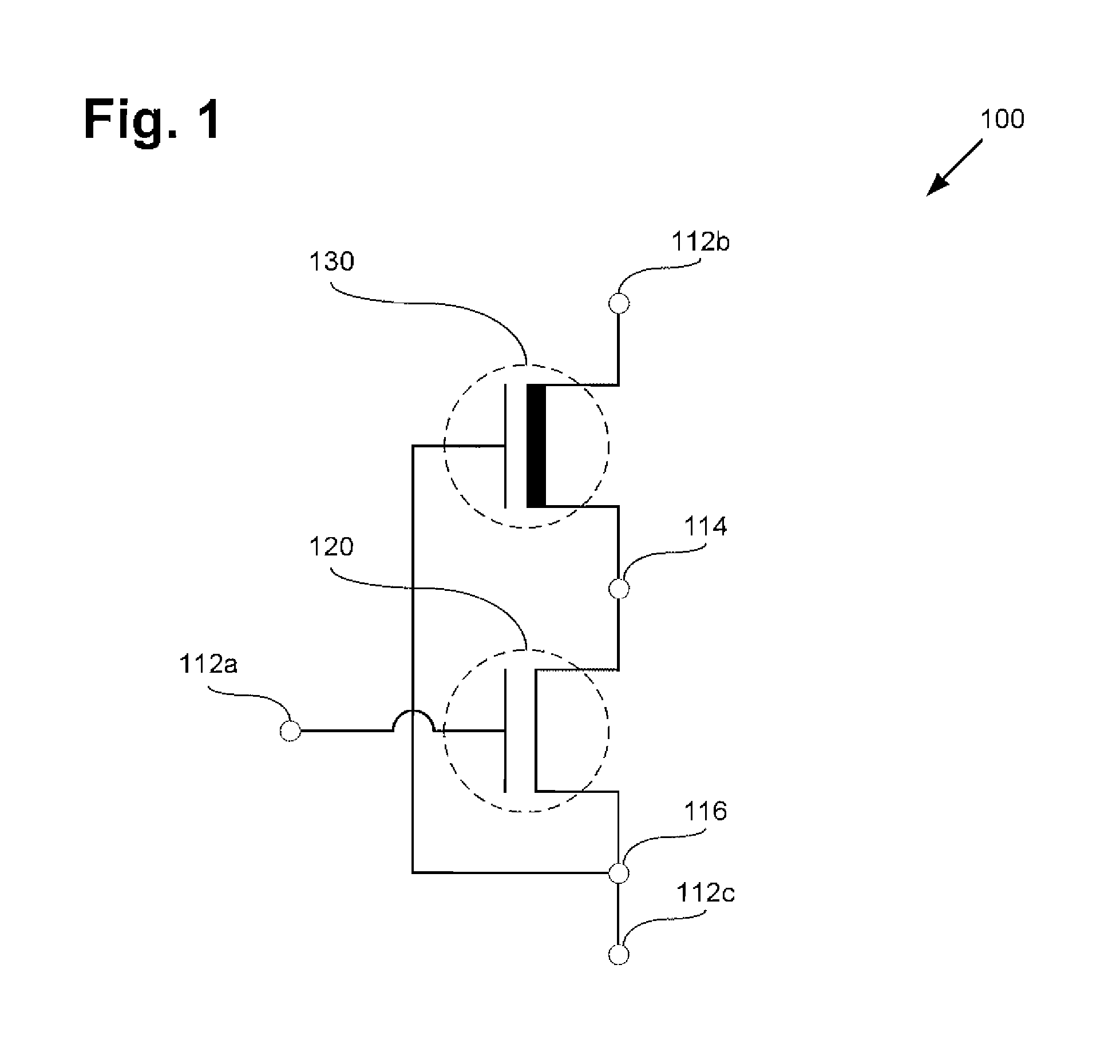

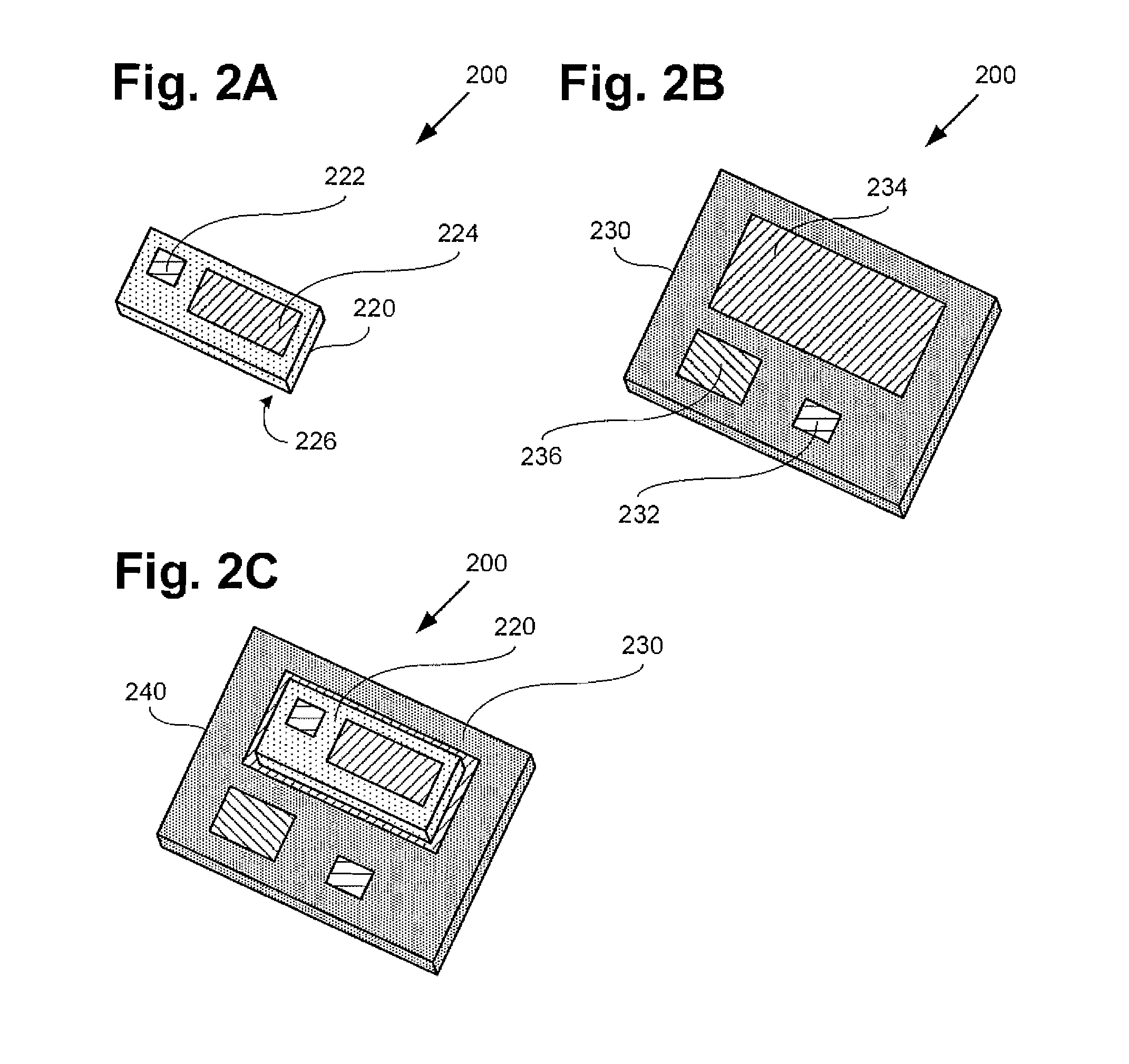

One exemplary disclosed embodiment comprises a three-terminal stacked-die package including a field effect transistor (FET), such as a silicon FET, stacked atop a III-nitride transistor, such that a drain of the FET resides on and is electrically coupled to a source of the III-nitride transistor. A first terminal of the package is coupled to a gate of the FET, a second terminal of the package is coupled to a drain of the III-nitride transistor. A third terminal of the package is coupled to a source of the FET. In this manner, devices such as cascoded switches may be packaged in a stacked-die form, resulting in reduced parasitic inductance and resistance, improved thermal dissipation, smaller form factor, and lower manufacturing cost compared to conventional packages.

Owner:INFINEON TECH AMERICAS CORP

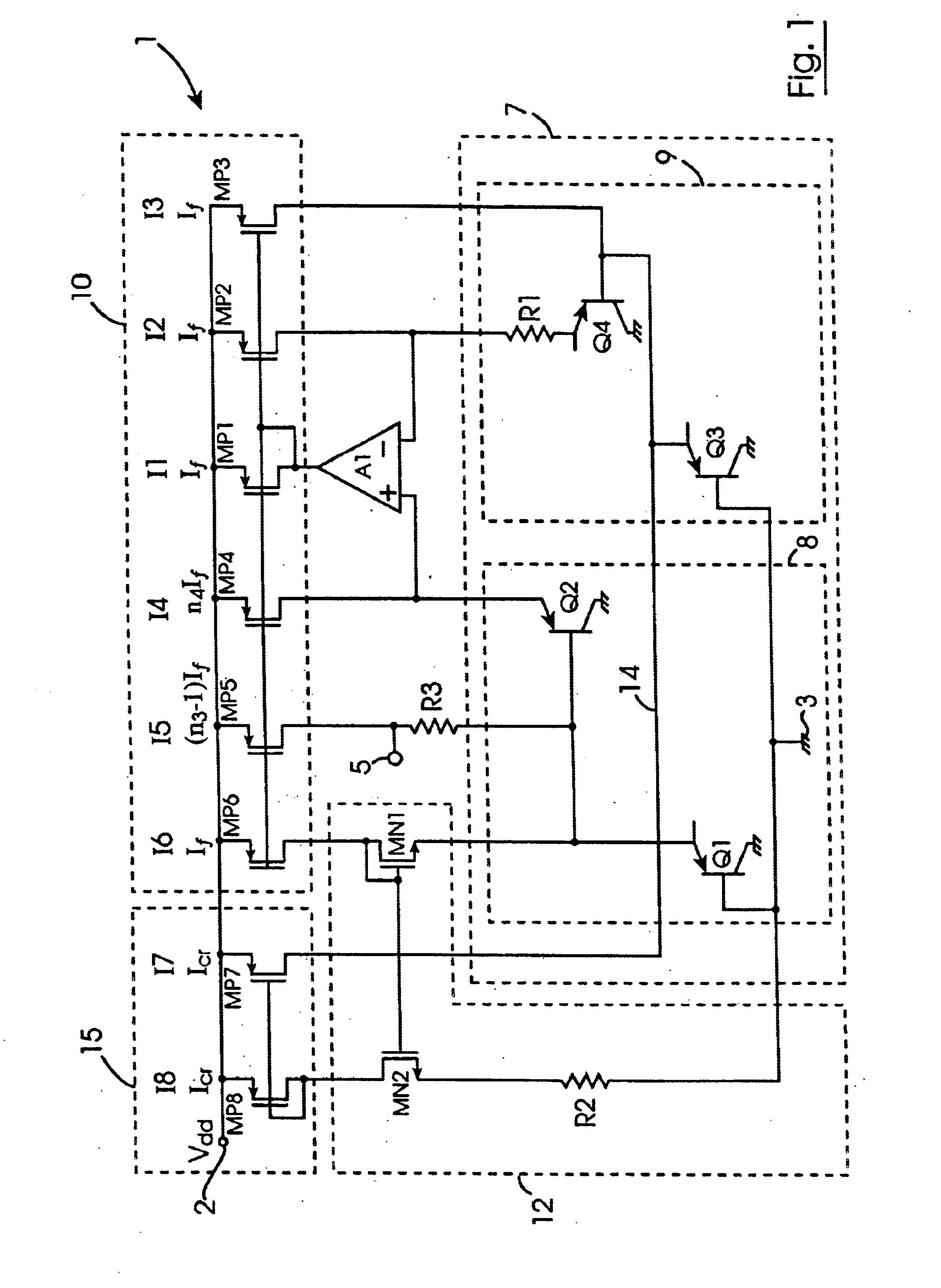

Method and a circuit for producing a PTAT voltage, and a method and a circuit for producing a bandgap voltage reference

ActiveUS7193454B1Great gain factorMinimizing sensitivityGenerating/distributing signalsElectric variable regulationElectrical resistance and conductanceNegative feedback

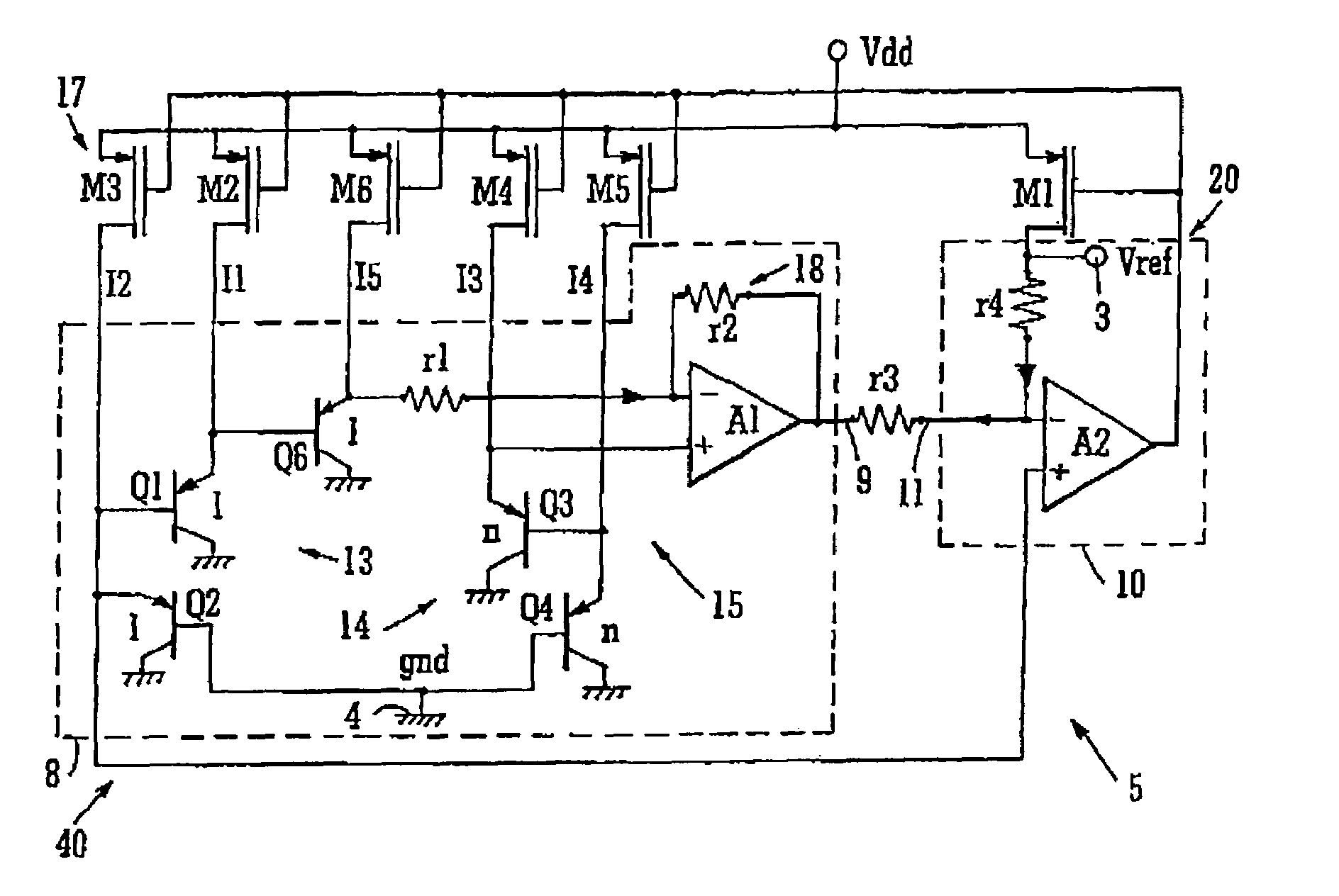

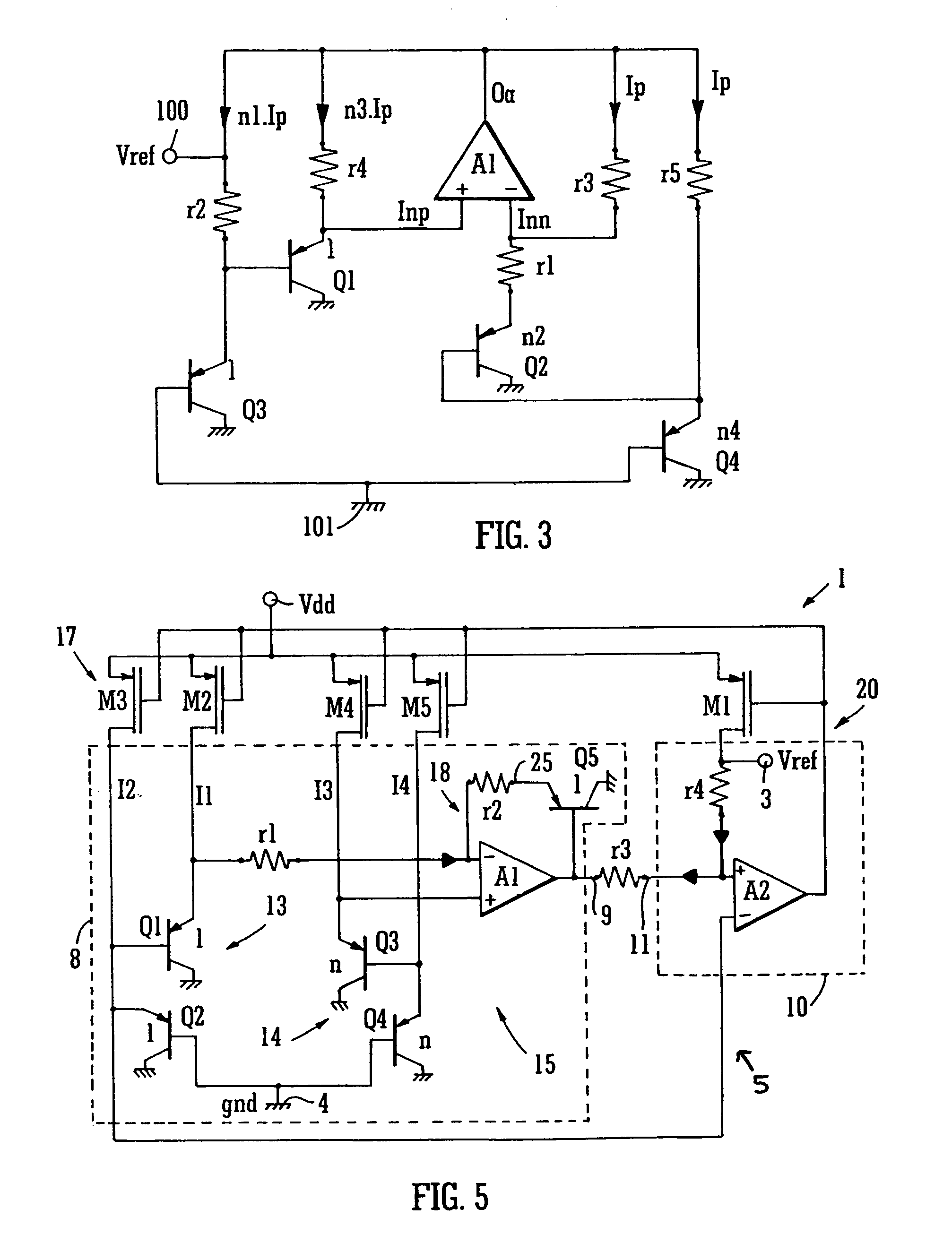

A bandgap voltage reference circuit (1) produces a bandgap voltage reference (Vref) on an output terminal (3) relative to a common ground voltage terminal (4). The circuit (1) develops a PTAT voltage across a primary resistor (r3) which is reflected and gained up across an output resistor (r4) and summed with a CTAT voltage to produce the voltage reference (Vref). A first circuit comprising a PTAT voltage cell (15) having first and second transistor stacks of first and second transistors (Q1,Q2) and (Q3,Q4) operated at different current densities develops a PTAT (2ΔVbe) across a first resistor (r1). The PTAT voltage developed across the first resistor (r1) is applied to an inverting input of a first op-amp (A1), the output of which is coupled to a first end (9) of the primary resistor (r3). A first voltage level relative to the ground terminal (4) is applied to the first end (9) of the primary resistor (r3) through a feedback loop of the first op-amp (A1) having a second resistor (r2) and a third transistor (Q5), similar to the first transistors (Q1,Q2). A second end (11) of the primary resistor (r3) is held at a second voltage level of one first base-emitter voltage relative to the ground terminal (4) by a second op-amp (A2) so that a PTAT voltage is developed across the primary resistor (r3) by the difference of the first voltage level and the second voltage level. The PTAT voltage developed across the primary resistor (r3) is reflected and gained up across the output resistor (r4) in a negative feedback loop (20) of the second op-amp (A2) and is summed with the first base-emitter voltage derived from the first transistor (Q2) to produce the bandgap voltage reference (Vref) on the output terminal 3, which is given by the equation:Vref=Vbe(1)+2ΔVbe(1+r2r1)r4r3FIG. 5 to accompany the abstract.

Owner:ANALOG DEVICES INC

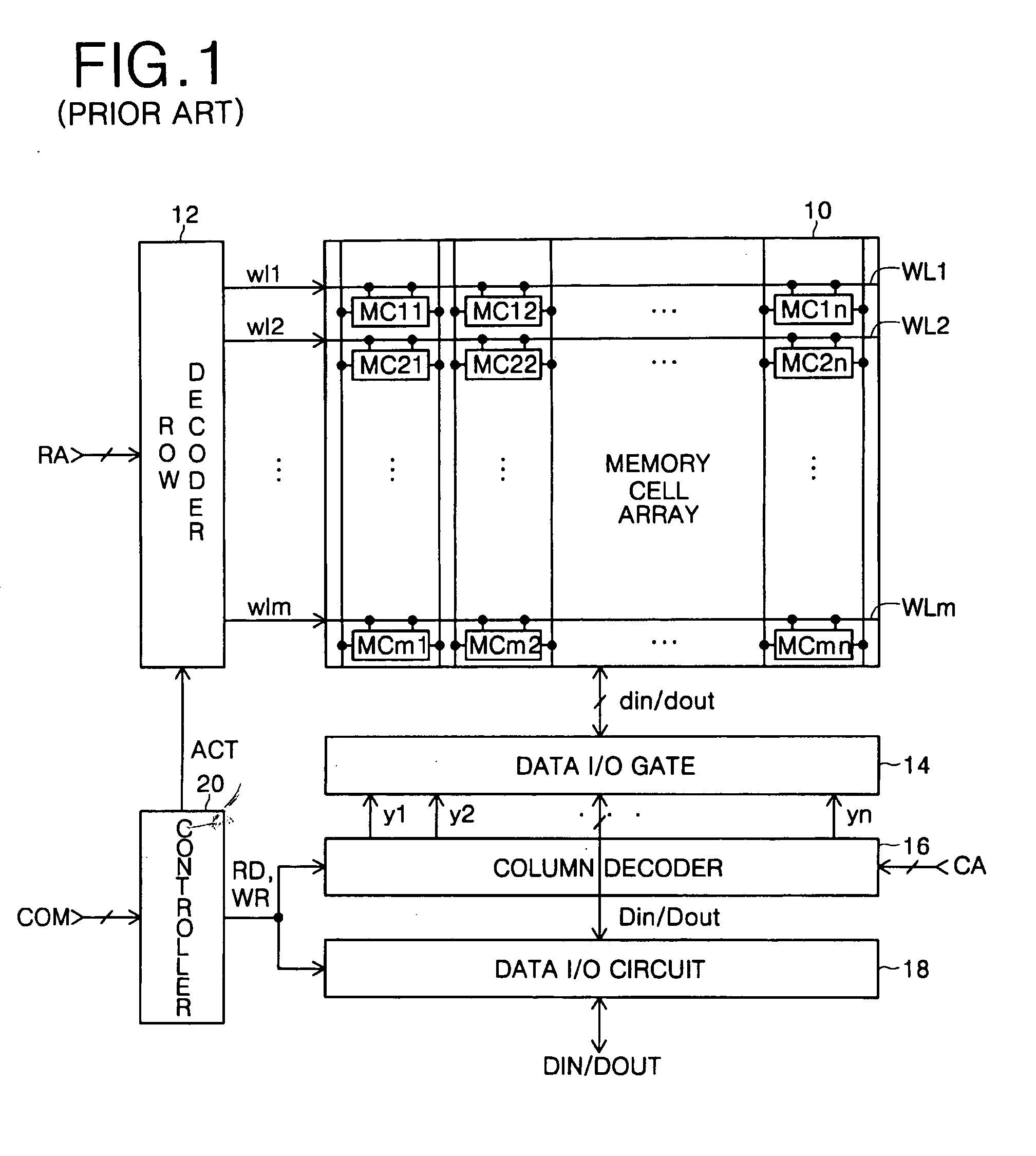

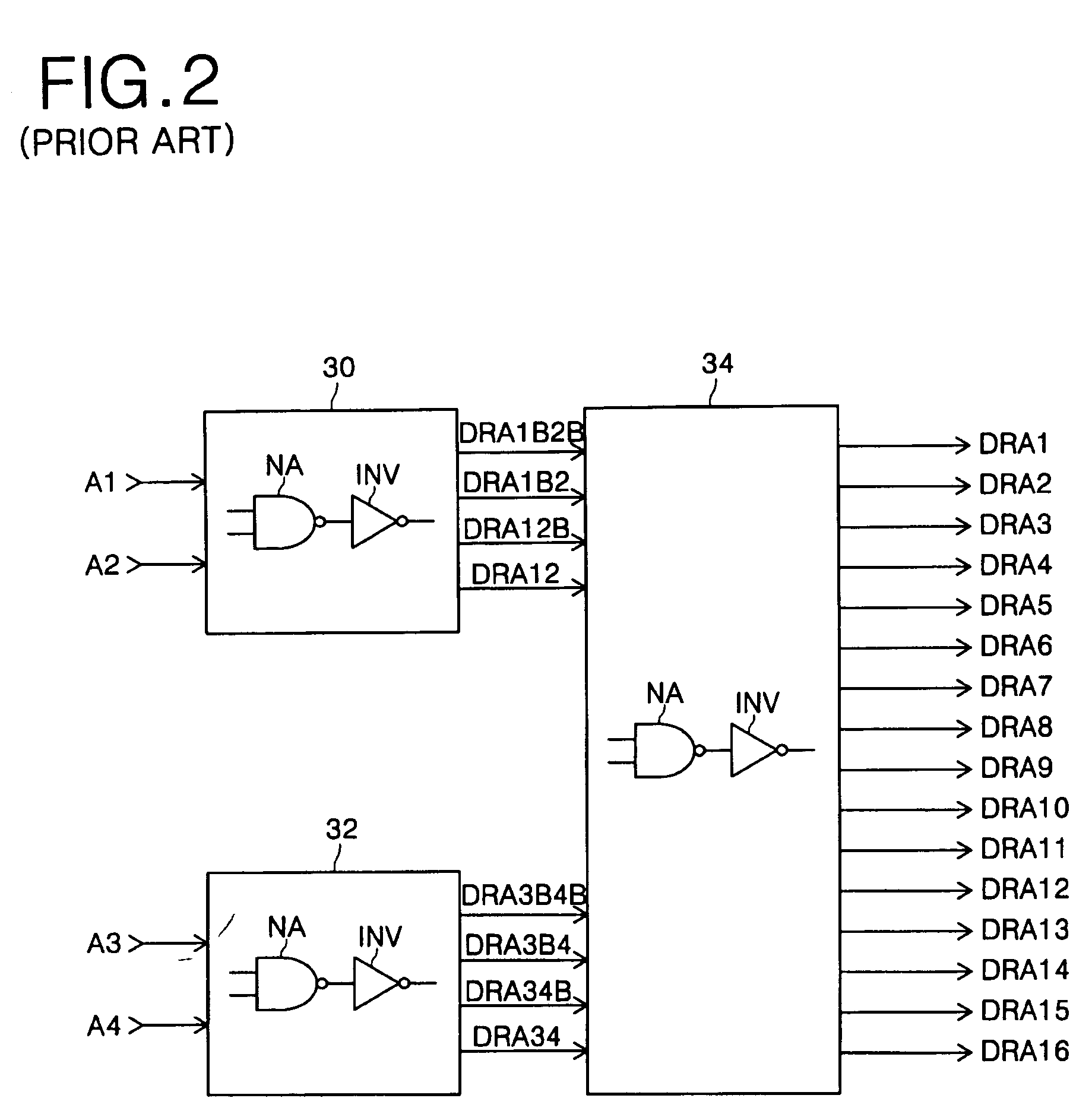

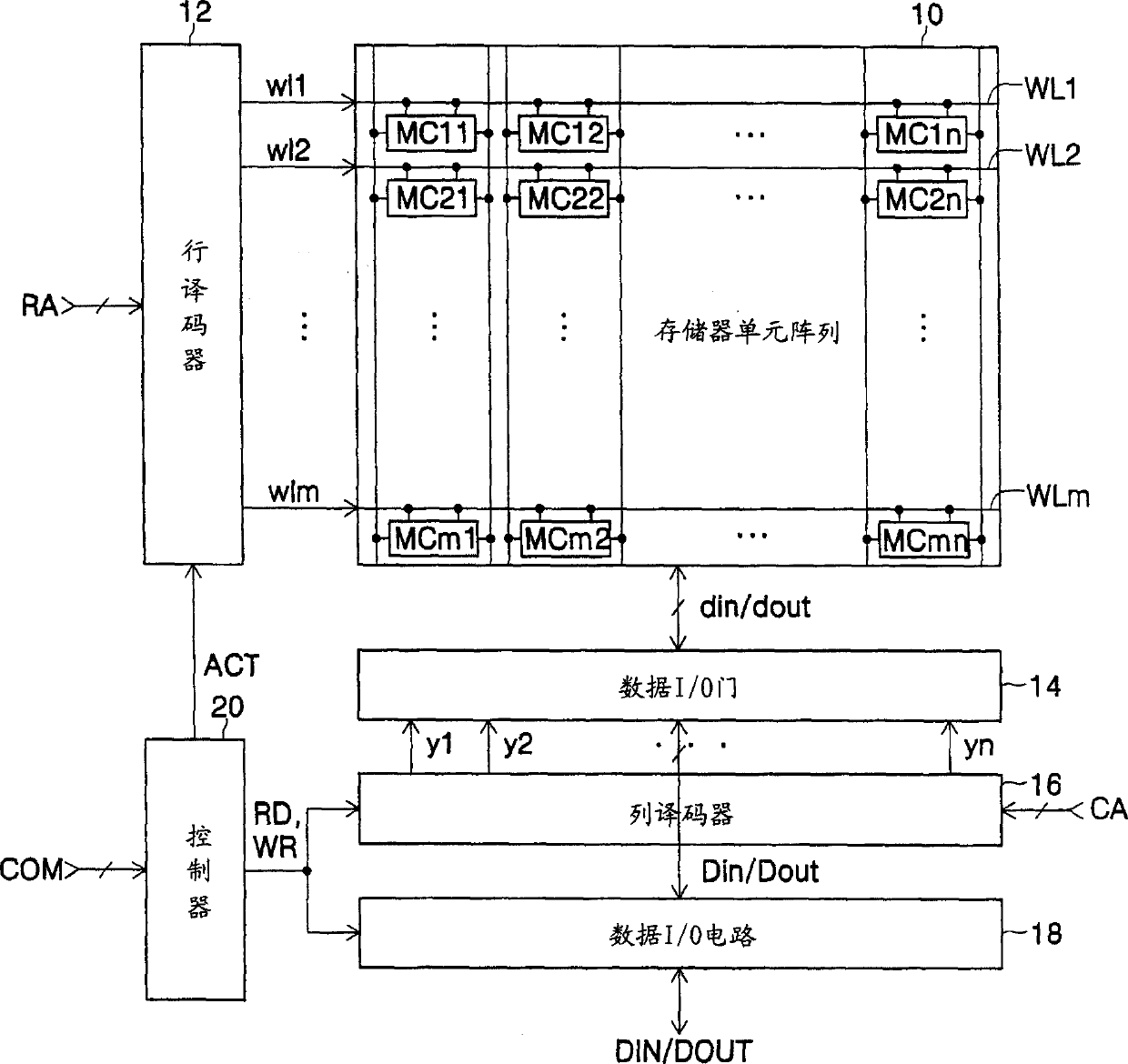

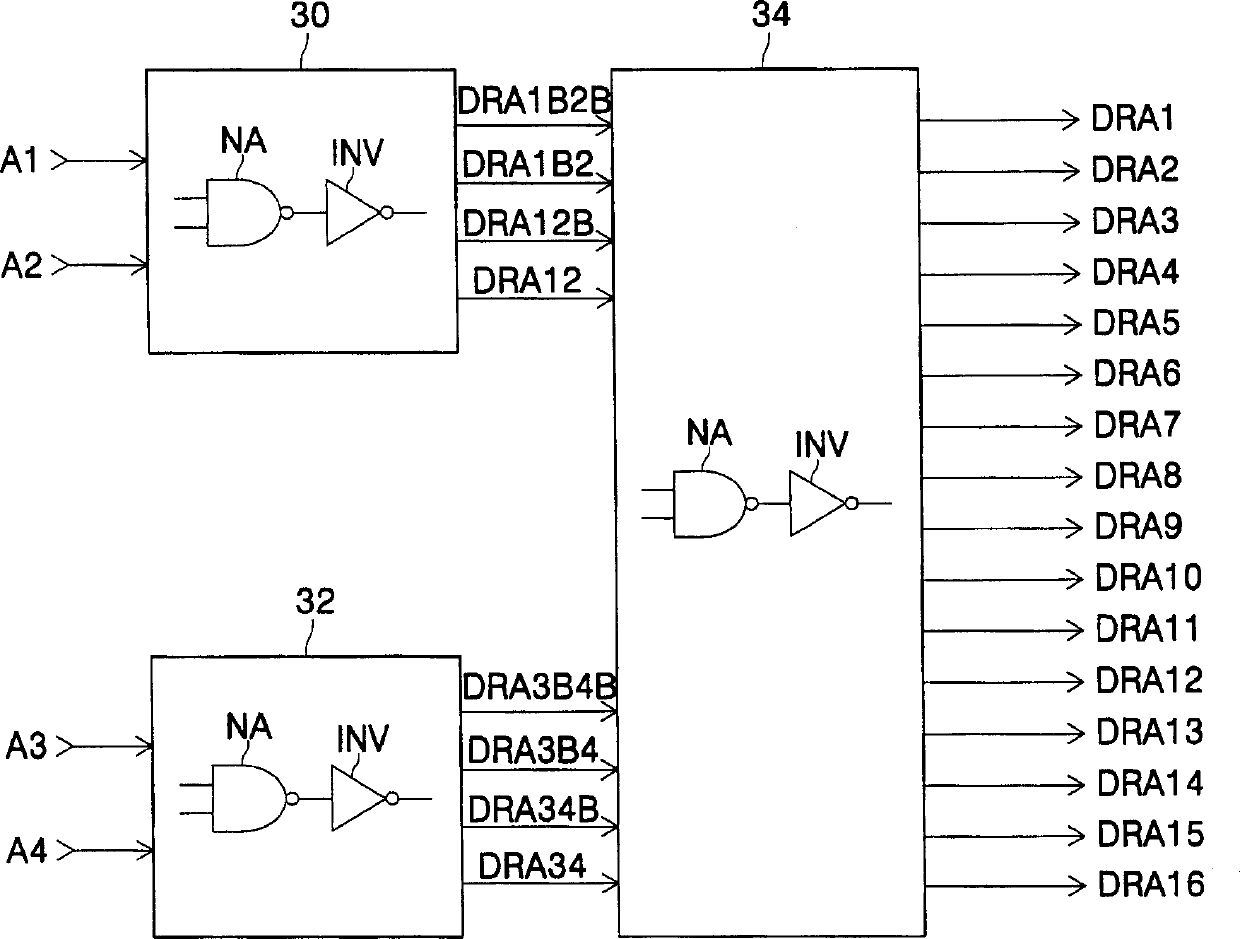

Semiconductor memory device and method for arranging and manufacturing the same

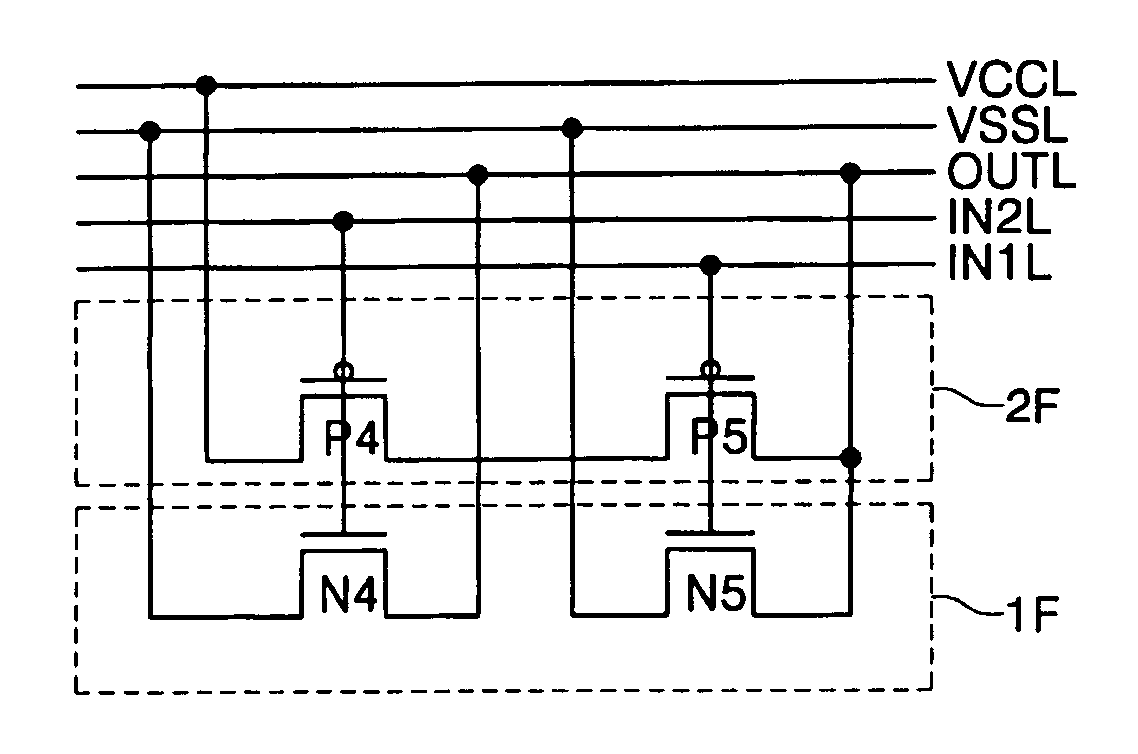

A semiconductor device and method for arranging and manufacturing the same are disclosed. The semiconductor device includes a plurality of inverters including at least one first pull-up transistor and first pull-down transistor and inverting and outputting an input signal, respectively; and a plurality of NAND gates including at least two second pull-up transistor and second pull-down transistor and generating an output signal having a high level if at least one of at least two input signals has a low level, respectively, wherein the at least one first pull-up transistor and first pull-down transistor and the at least two second pull-up transistor and second pull-down transistor are stacked and arranged on at least two layers.

Owner:SAMSUNG ELECTRONICS CO LTD

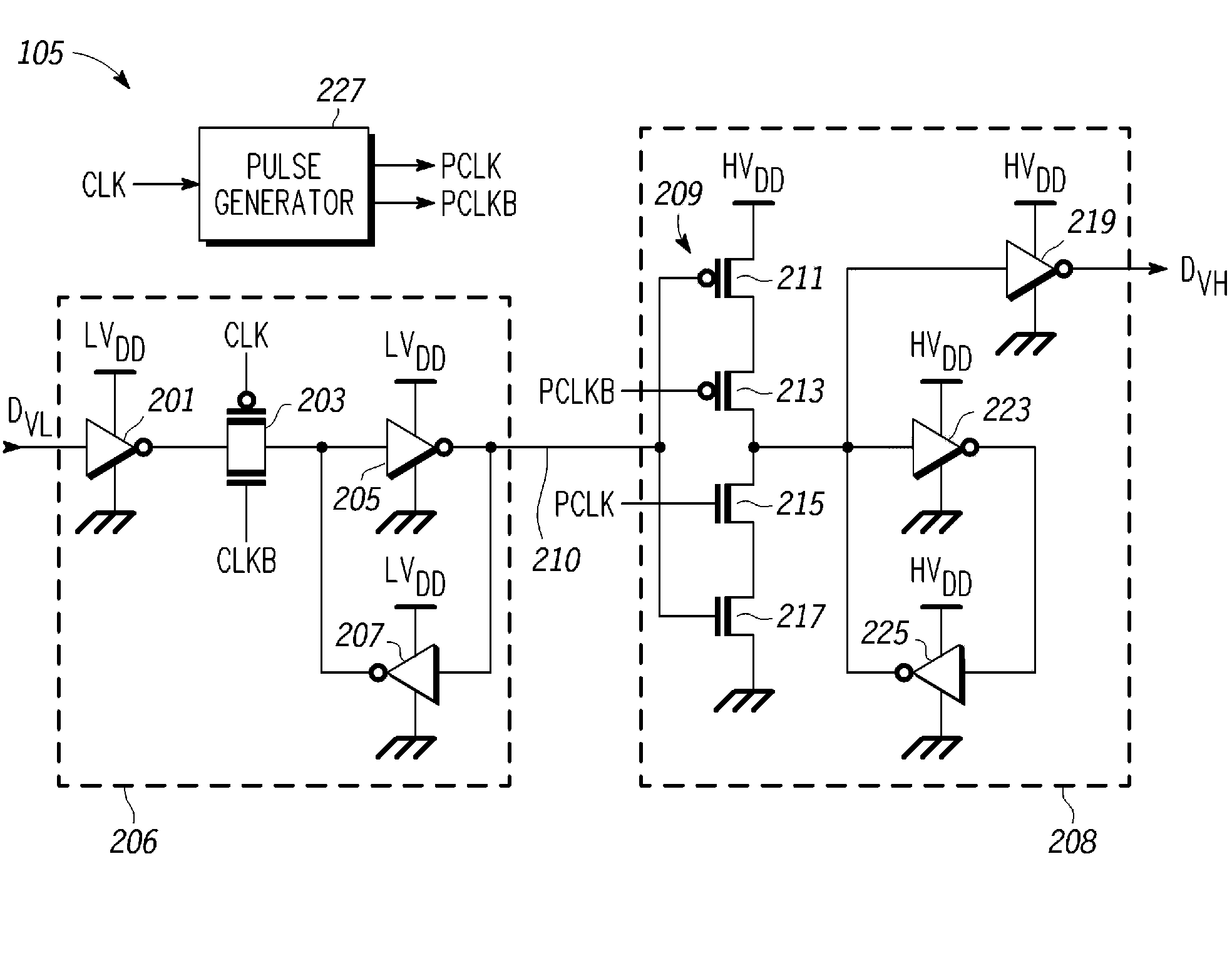

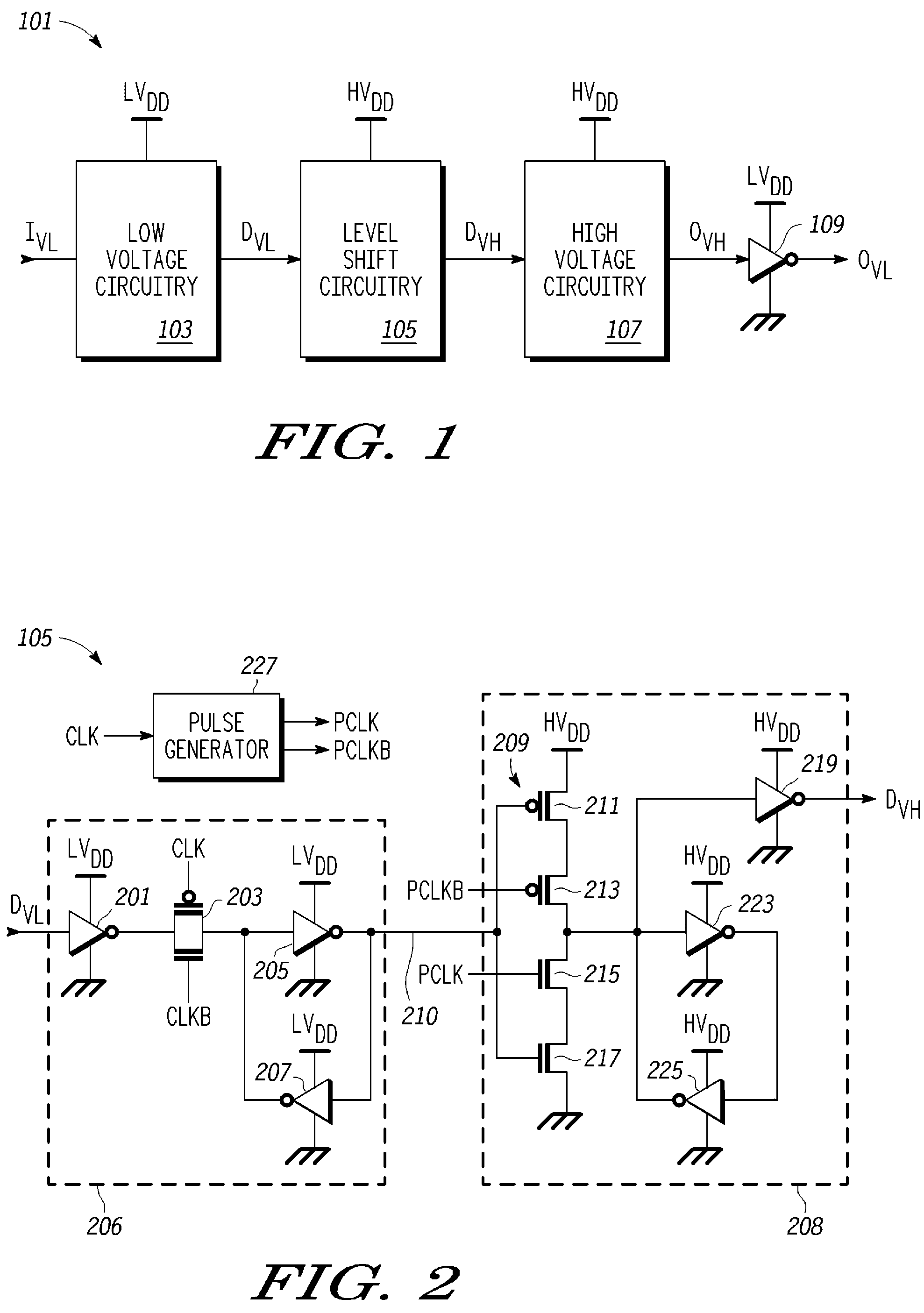

Level shifting circuit

A level shifting circuit having a signal input that operates in a first voltage domain and a signal output that operates in a second voltage domain. In some embodiments, the level shifting circuit includes a clocked level shifter. In some embodiments, the level shifting circuit includes a level shifting latch that latches a translated output signal. In one example, the level shifting latch includes a latch portion and a stack of transistors with a transistor having a control electrode coupled to a clock input.

Owner:NXP USA INC

Stacked Composite Device Including a Group III-V Transistor and a Group IV Lateral Transistor

In one implementation, a stacked composite device comprises a group IV lateral transistor and a group III-V transistor stacked over the group IV lateral transistor. A drain of the group IV lateral transistor is in contact with a source of the group III-V transistor, a source of the group IV lateral transistor is coupled to a gate of the group III-V transistor to provide a composite source on a top side of the stacked composite device, and a drain of the group III-V transistor provides a composite drain on the top side of the stacked composite device. A gate of the group IV lateral transistor provides a composite gate on the top side of the stacked composite device, and a substrate of the group IV lateral transistor is on a bottom side of the stacked composite device.

Owner:INFINEON TECH AMERICAS CORP

Stacked Composite Device Including a Group III-V Transistor and a Group IV Vertical Transistor

In one implementation, a stacked composite device comprises a group IV vertical transistor and a group III-V transistor stacked over the group IV vertical transistor. A drain of the group IV vertical transistor is in contact with a source of the group III-V transistor, a source of the group IV vertical transistor is coupled to a gate of the group III-V transistor to provide a composite source on a bottom side of the stacked composite device, and a drain of the group III-V transistor provides a composite drain on a top side of the stacked composite device. A gate of the group IV vertical transistor provides a composite gate on the top side of the stacked composite device.

Owner:INFINEON TECH AMERICAS CORP

Voltage reference circuit using PTAT voltage

ActiveUS7119527B2Dc source parallel operationElectric variable regulationElectrical resistance and conductanceInternal resistance

A voltage reference generator is disclosed that includes a current generator for generating a current that is proportional to absolute temperature (PTAT), the current generator having an internal resistance. This provides a PTAT current that is proportional to the resistance and wherein the temperature coefficient of the PTAT current is defined by the resistance. An output node is driven by the current generator with the PTAT current. A stack of serial connected MOS devices is connected between the output voltage and a ground reference voltage. The stack of transistors has a transimpedance associated therewith which has a temperature coefficient that is opposite in polarity to the temperature coefficient of the internal resistance and of a magnitude to provide a voltage on the output node that is substantially stable over temperature.

Owner:SILICON LAB INC

Active device and active device array substrate

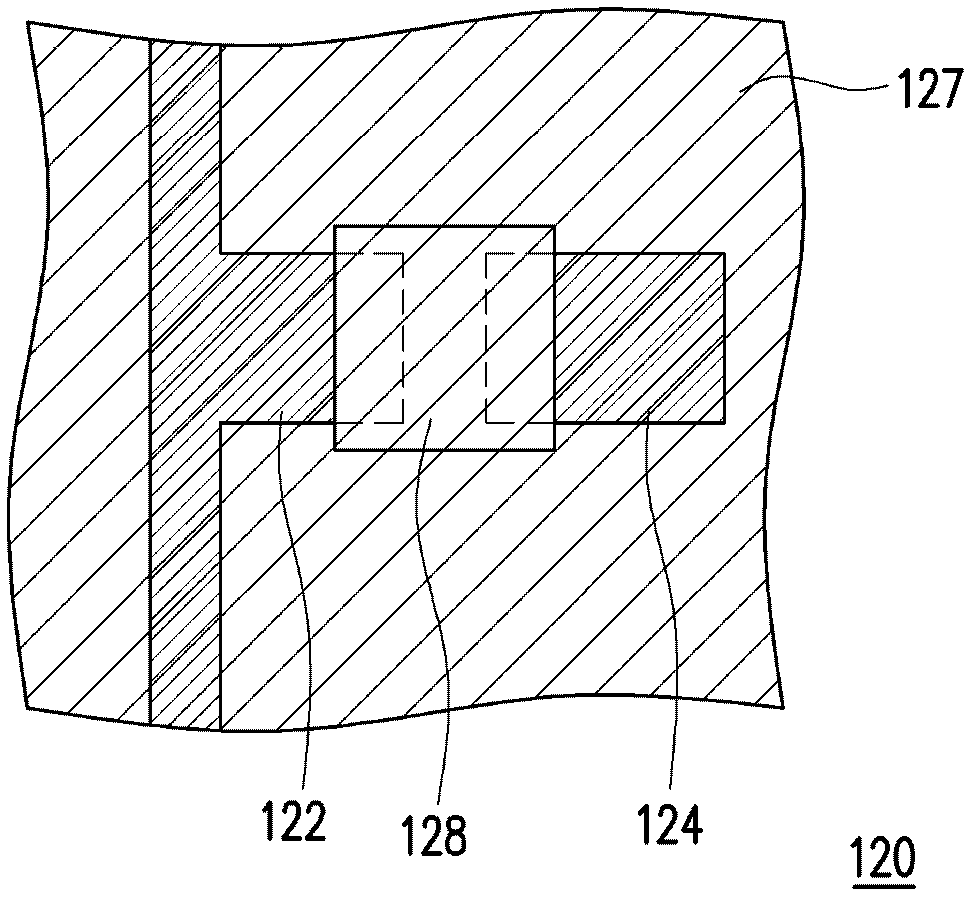

InactiveCN103367353AIncrease effective widthImprove charging effectTransistorSolid-state devicesTransistorTransistor stacking

The invention provides an active device and an active device array substrate. The active device array substrate comprises a substrate and a plurality of active devices located on the substrate. At least one of the active devices comprises a first transistor and a second transistor, wherein the first transistor is located on the substrate and provided with a first channel layer; the second transistor is stacked on the first transistor and provided with a second channel layer; the first transistor and the second transistor share a common grid electrode; and the common grid electrode is located between the first channel layer and the second channel layer.

Owner:DONGGUAN MASSTOP LIQUID CRYSTAL DISPLAY +1

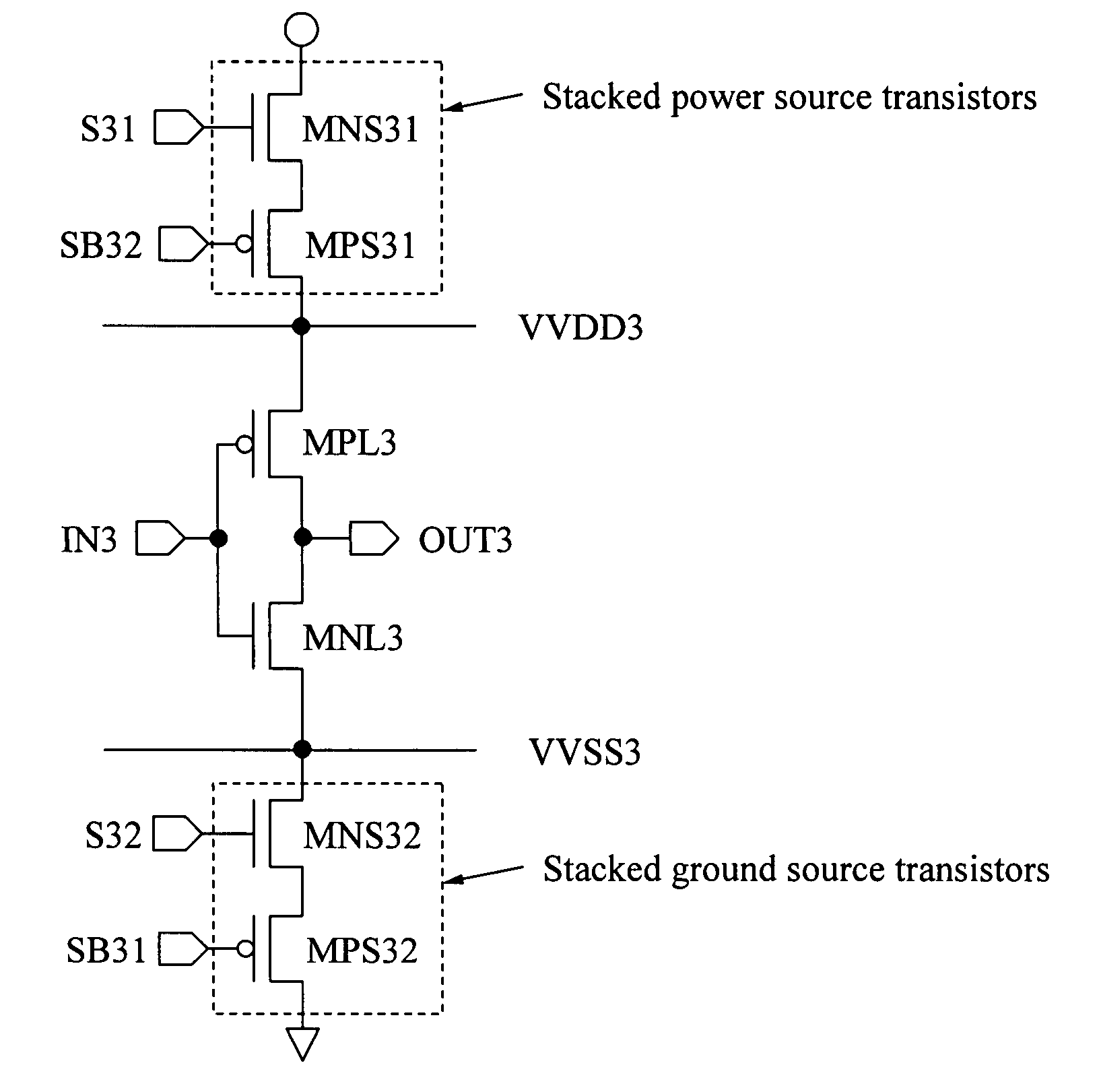

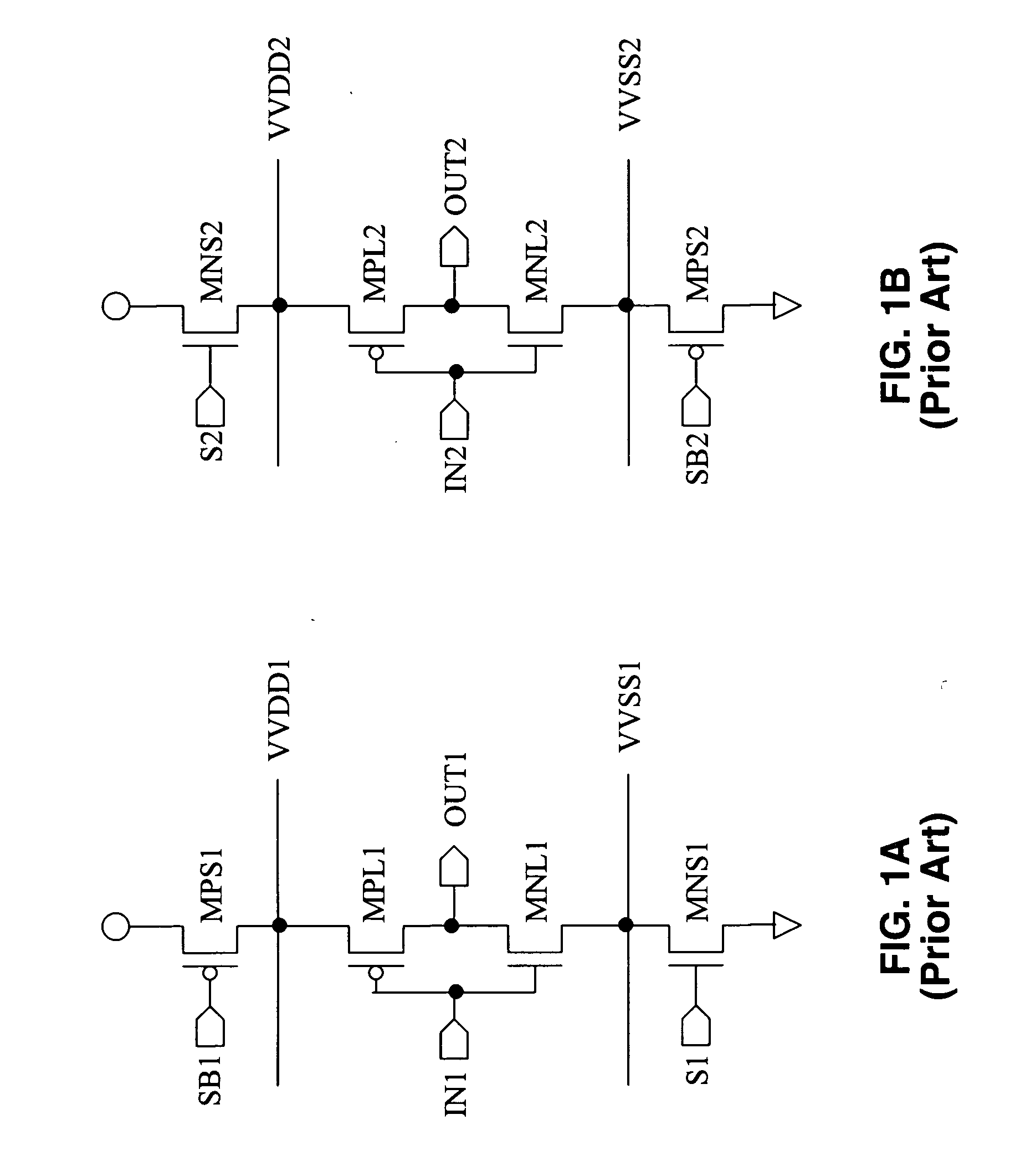

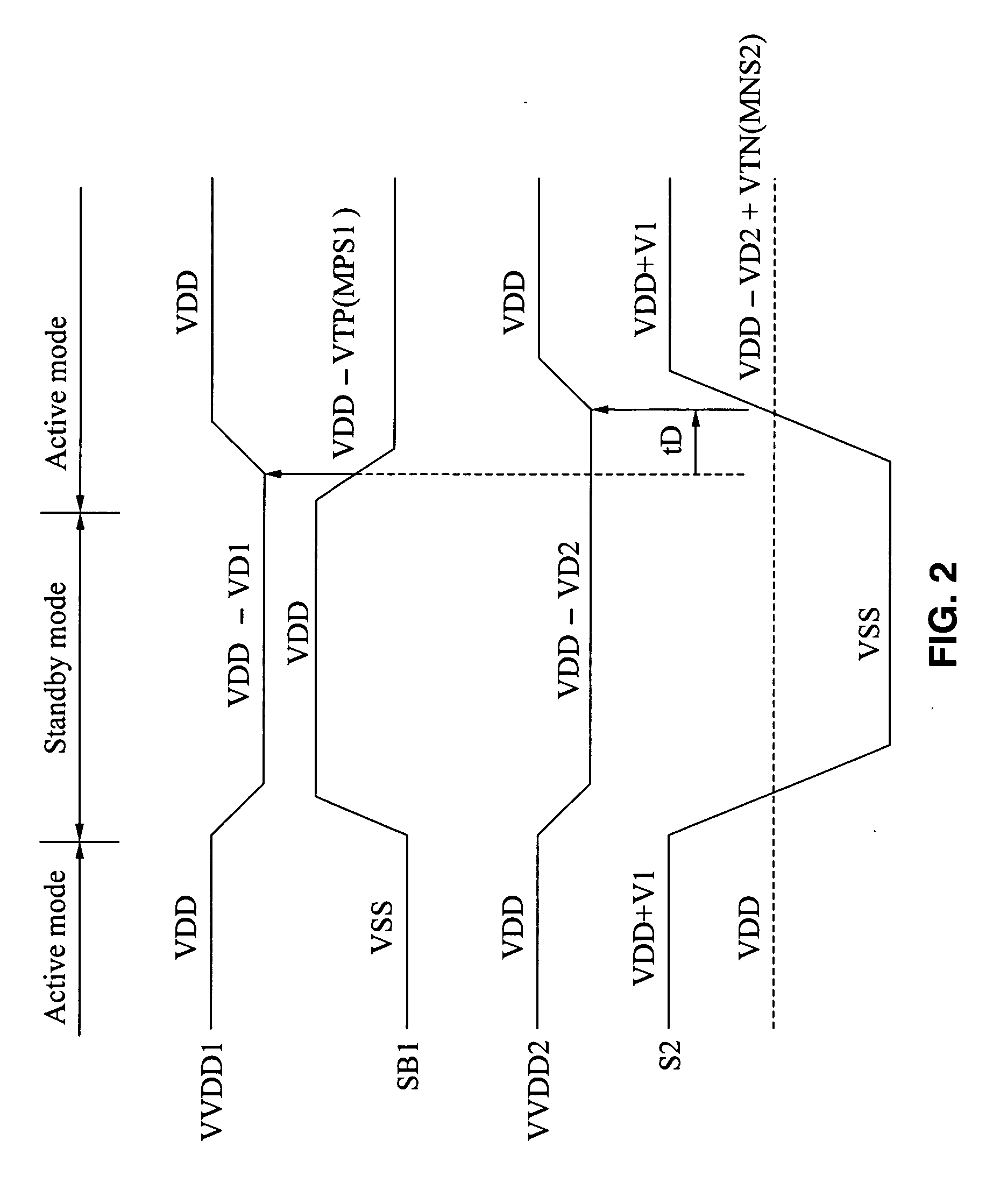

Source transistor configurations and control methods

InactiveUS20070063763A1Reduce leakageIncrease speedReliability increasing modificationsPower reduction by control/clock signalPower modeElectricity

Source transistor configurations are described for reducing leakage and delay within integrated circuits. Virtual power and ground nodes are supported with the use of stacked transistor configurations, such as a two transistor stack between a first virtual supply connection and VSS, and a second virtual supply connection and VDD. Gate drives of these stacked transistors are modulated with different voltage levels in response to the operating power mode of the circuit, for example active mode, active-standby mode, and deep power-down mode. Means for driving these source stacks are described. In one embodiment separate virtual nodes are adapted for different types of circuits, such as buffers, row address strobe, and column address strobe. Other techniques, such as directional placement of the transistors is also described.

Owner:ZMOS TECH

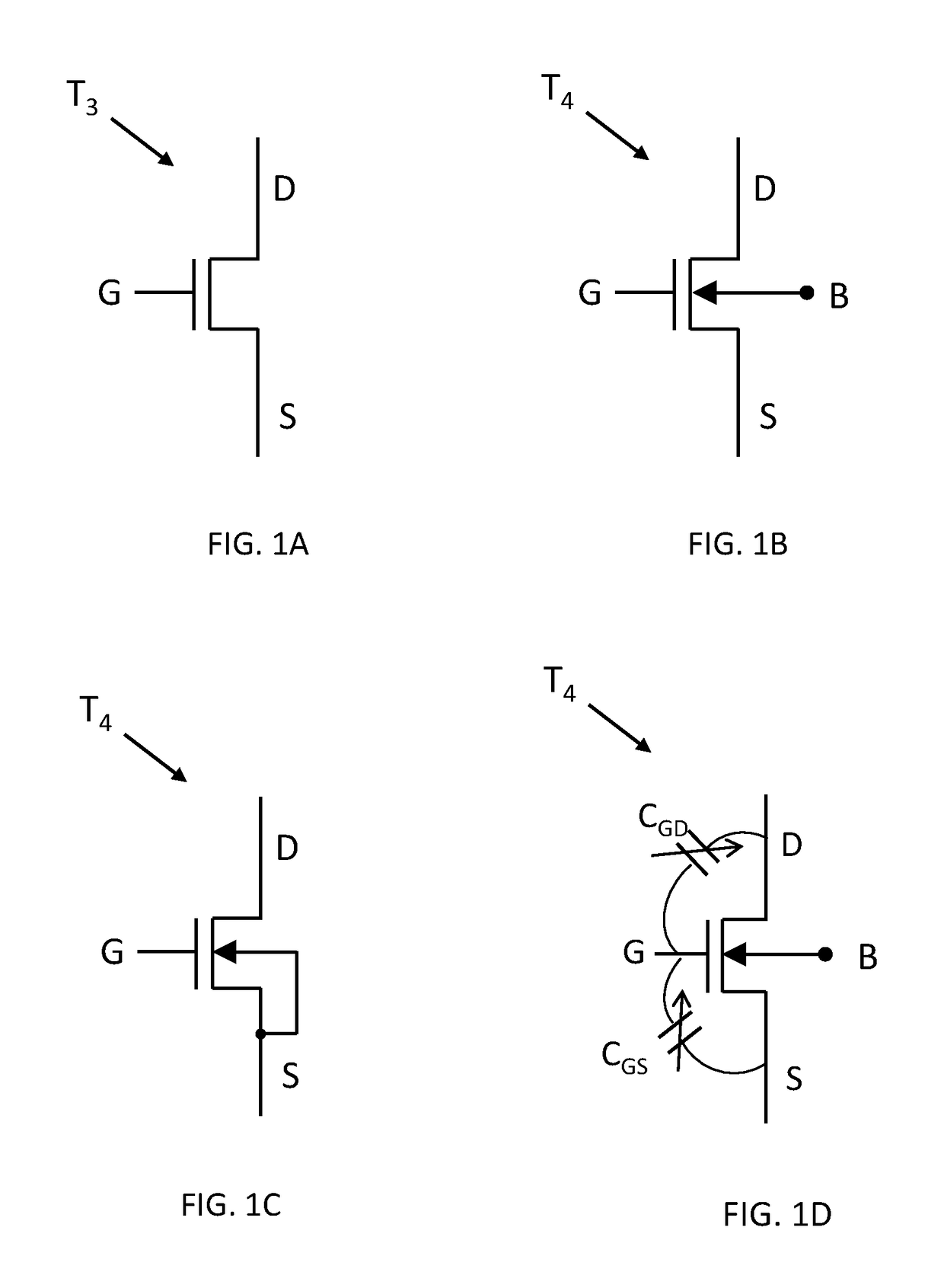

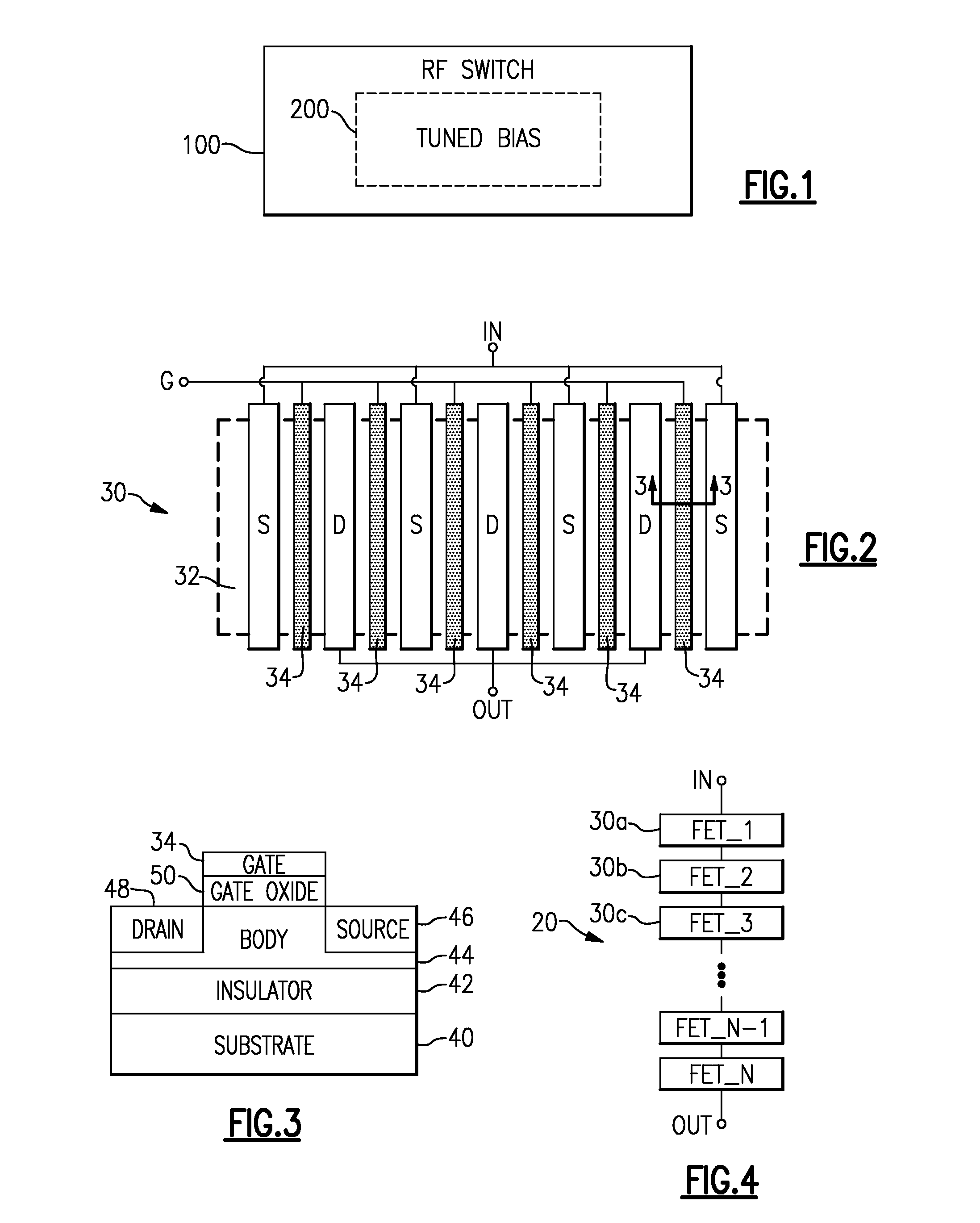

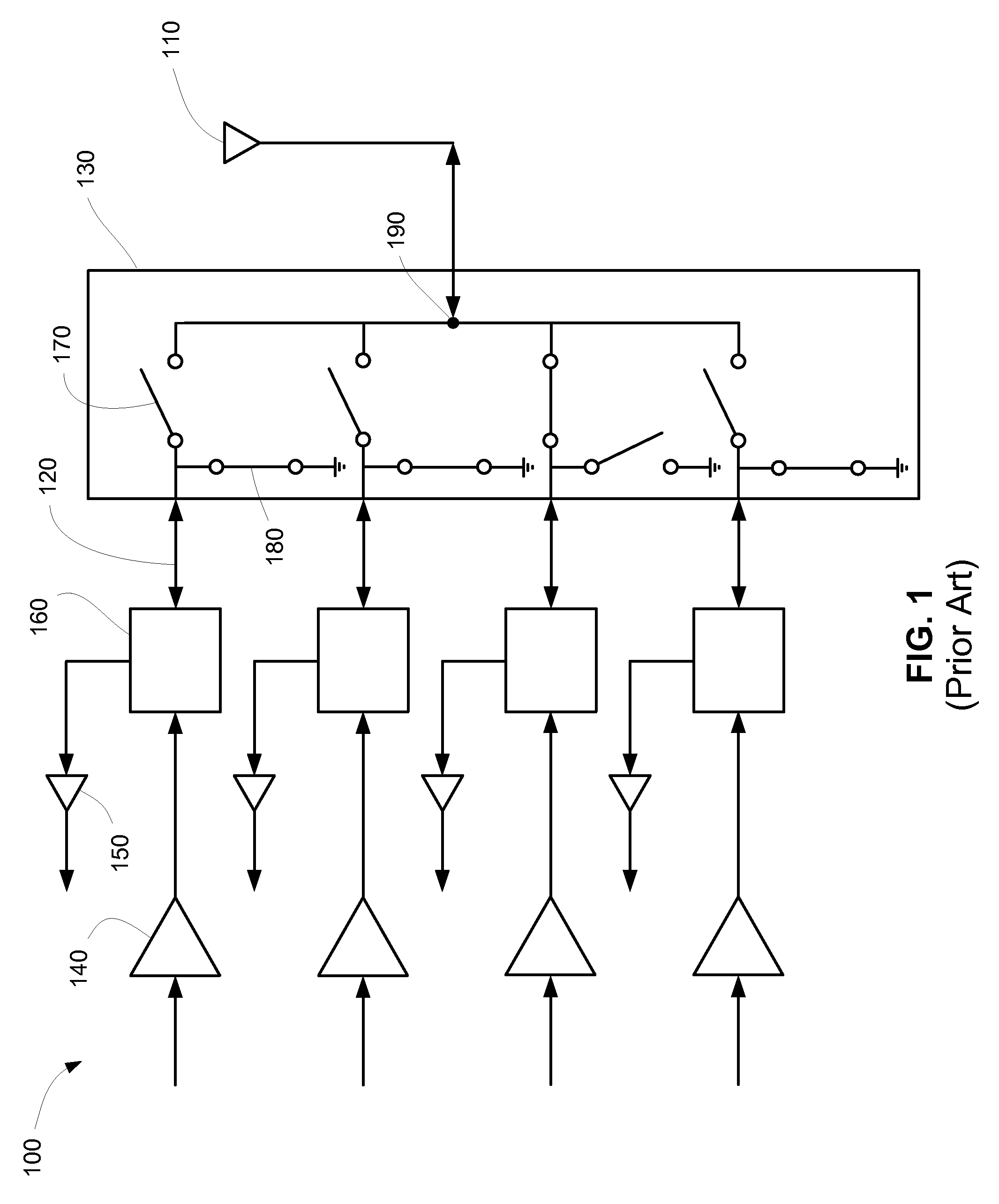

Body tie optimization for stacked transistor amplifier

ActiveUS9882531B1Improve RF performanceImprove performancePower amplifiersAmplifier modifications to raise efficiencyAudio power amplifierTransistor stacking

A transistor stack can include a combination of floating and body tied devices. Improved performance of the RF amplifier can be obtained by using a single body tied device as the input transistor of the stack, or as the output transistor of the stack, while other transistors of the stack are floating transistors. Transient response of the RF amplifier can be improved by using all body tied devices in the stack.

Owner:PSEMI CORP

Nonvolatile memory device and method for fabricating the same

ActiveUS20120299076A1Minimize diffusionSolid-state devicesSemiconductor/solid-state device manufacturingDiffusion barrierImpurity

A nonvolatile memory device includes a channel vertically extending from a substrate and comprising a first region that is doped with first impurities and a second region that is disposed under the first region, a plurality of memory cells and a selection transistor stacked over the substrate along the channel, and a diffusion barrier interposed between the first region and the second region, wherein a density of the first impurities is higher than a density of impurities of the second region.

Owner:SK HYNIX INC

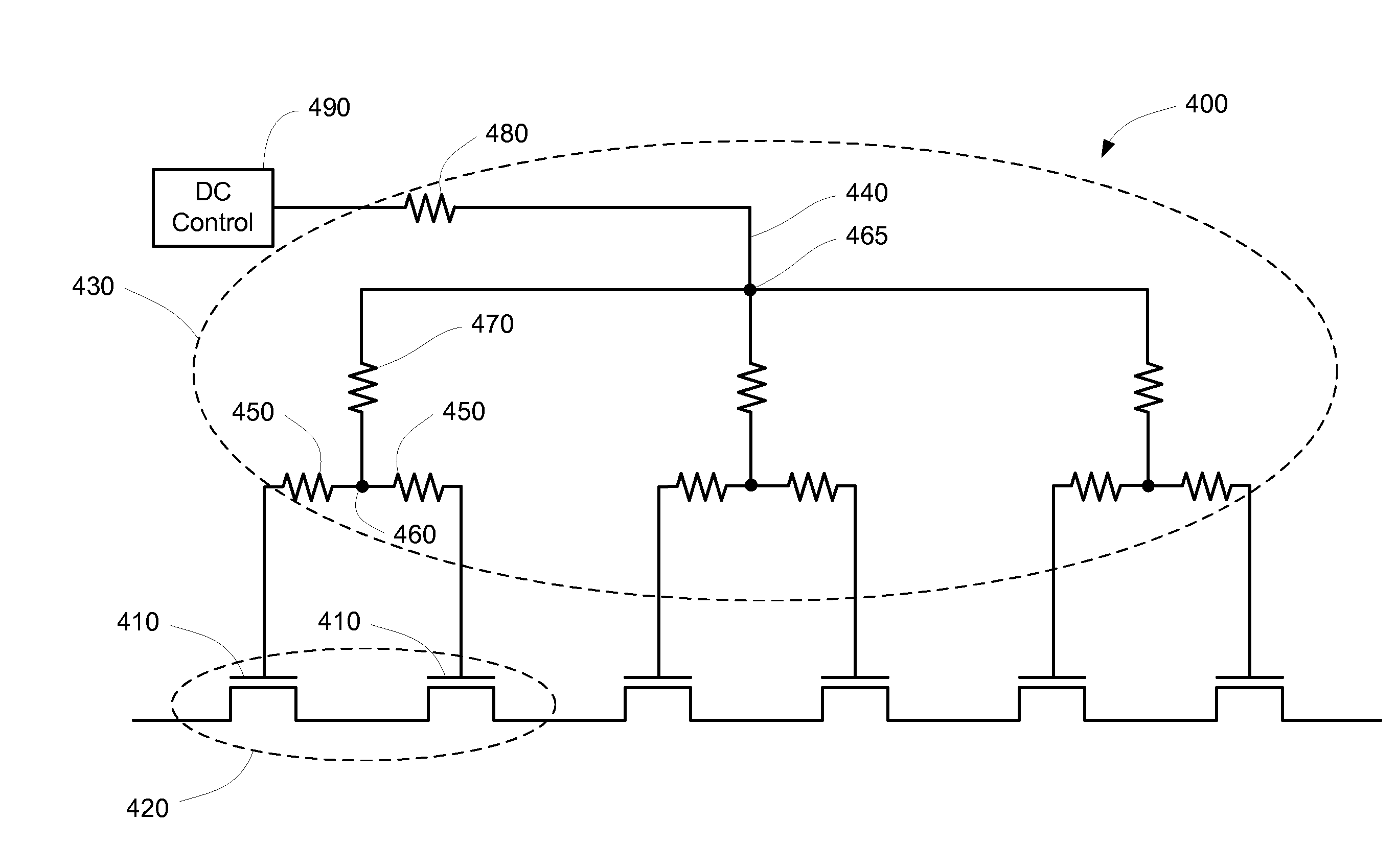

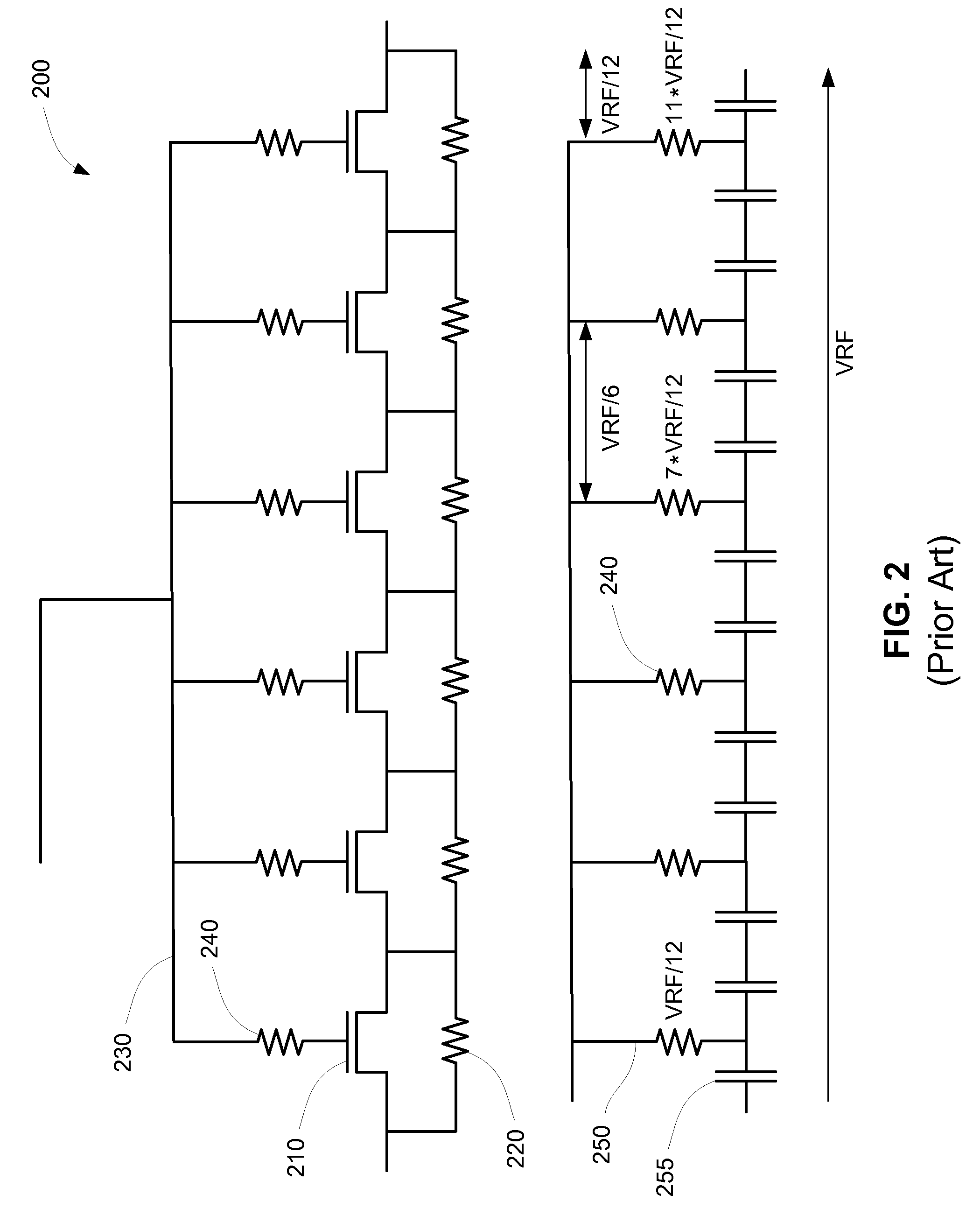

Switch Controls

Switches for use in RF devices are provided that offer a better balance of power losses and switching times than switches of the prior art. Switches of the present invention comprise a stack of transistors controlled a symmetric bias network. The stack of transistors includes an even number of transistors arranged in series, where every two successive transistors defines a pair. The bias network includes a symmetrically branching set of connections, where the gates of every pair of transistors are connected by a first connection having a first node, and two or more first nodes are connected by a second connection to a second node, and so forth. The symmetry of the bias network tends to reject even harmonics, and the rejection of even harmonics can be further enhanced by adding capacitors between the bias network and the stack of transistors at points of symmetry.

Owner:STMICROELECTRONICS INT NV

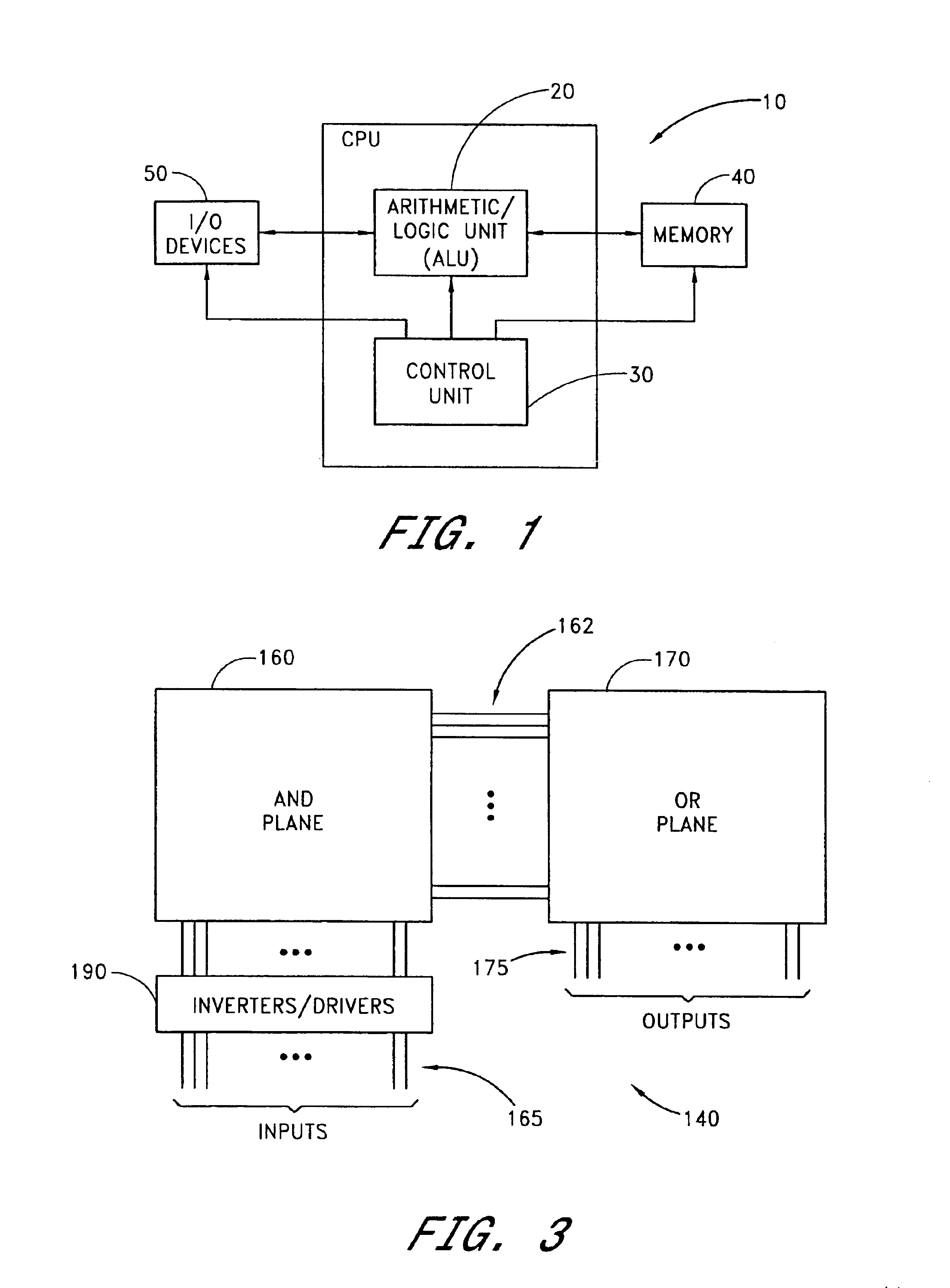

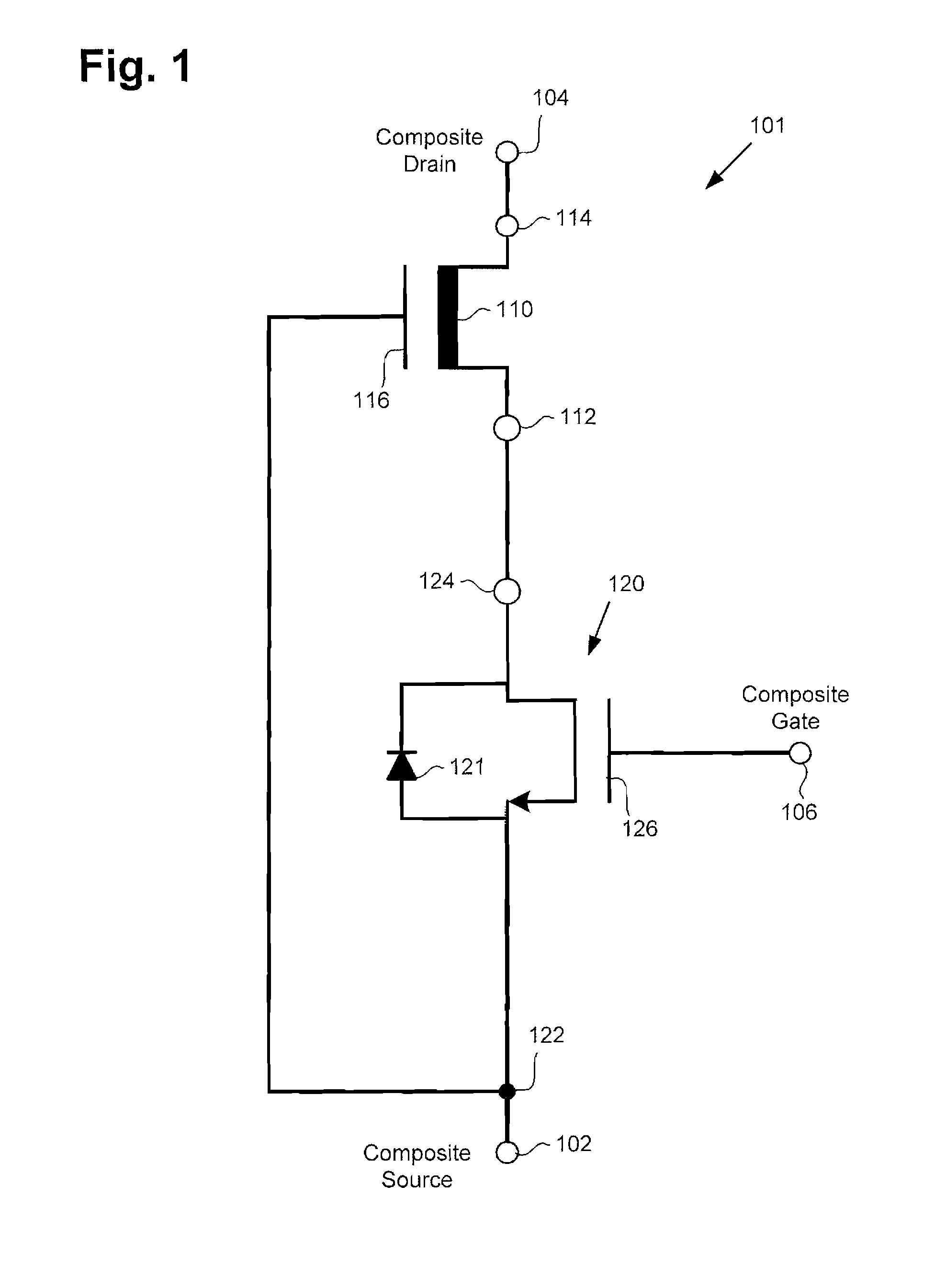

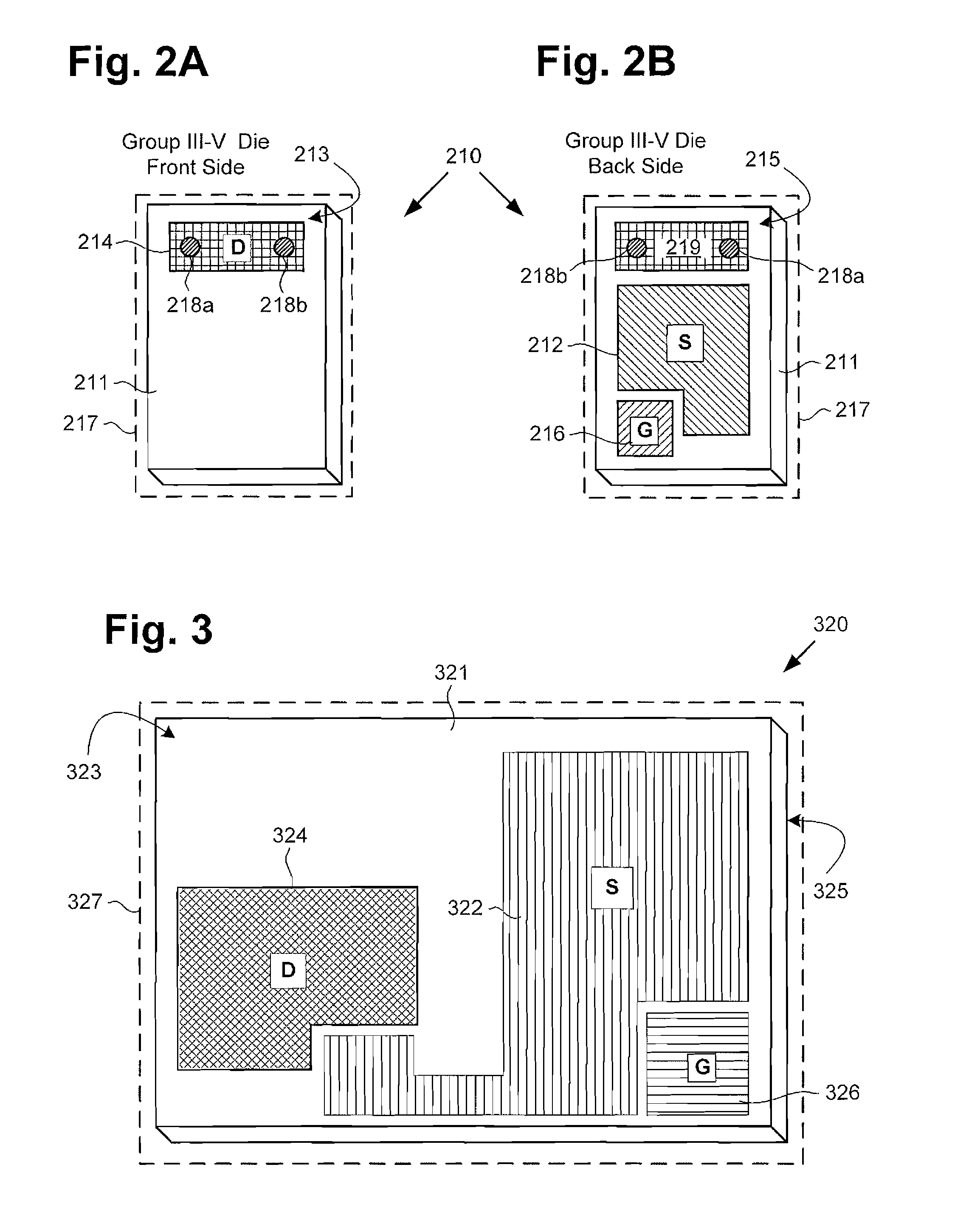

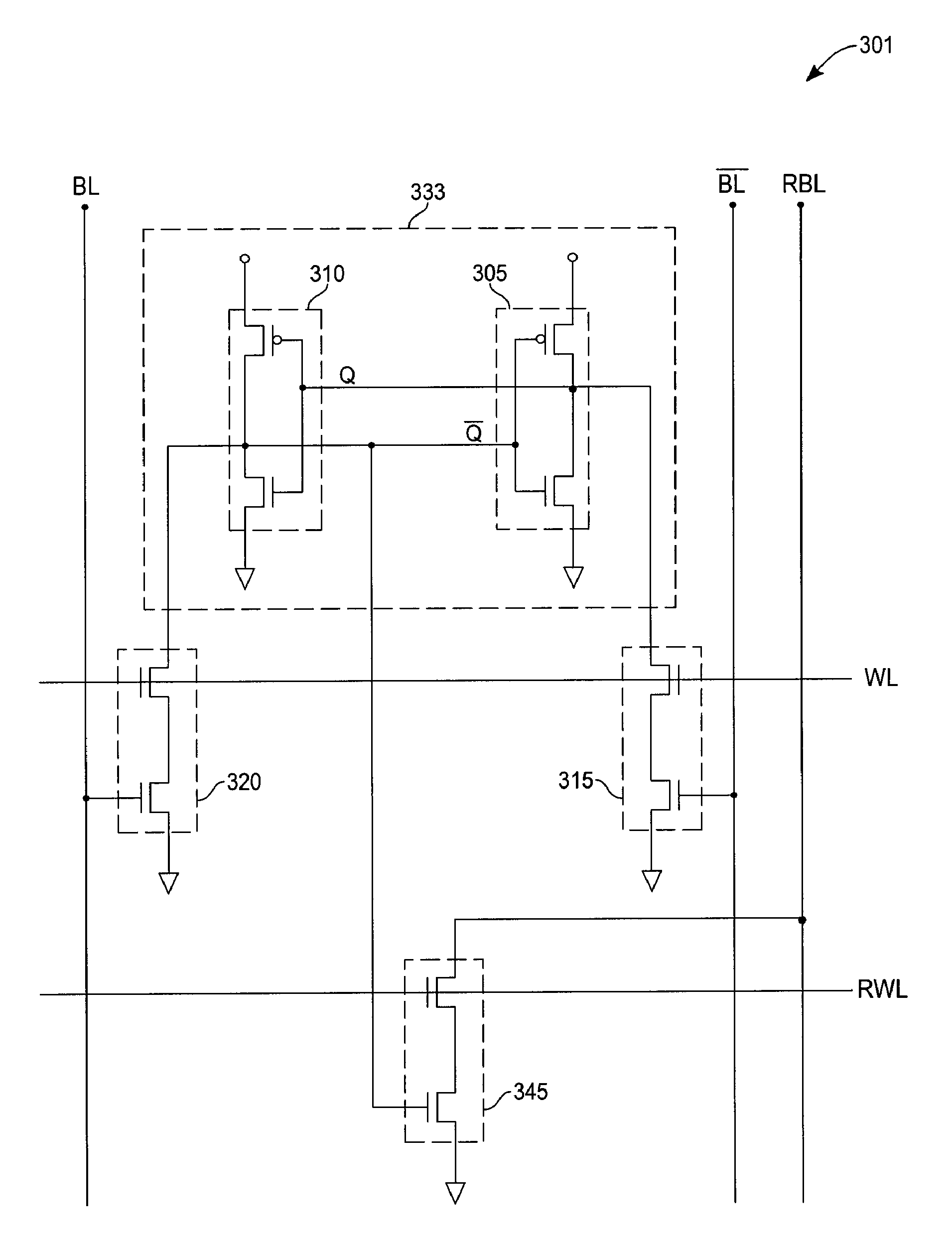

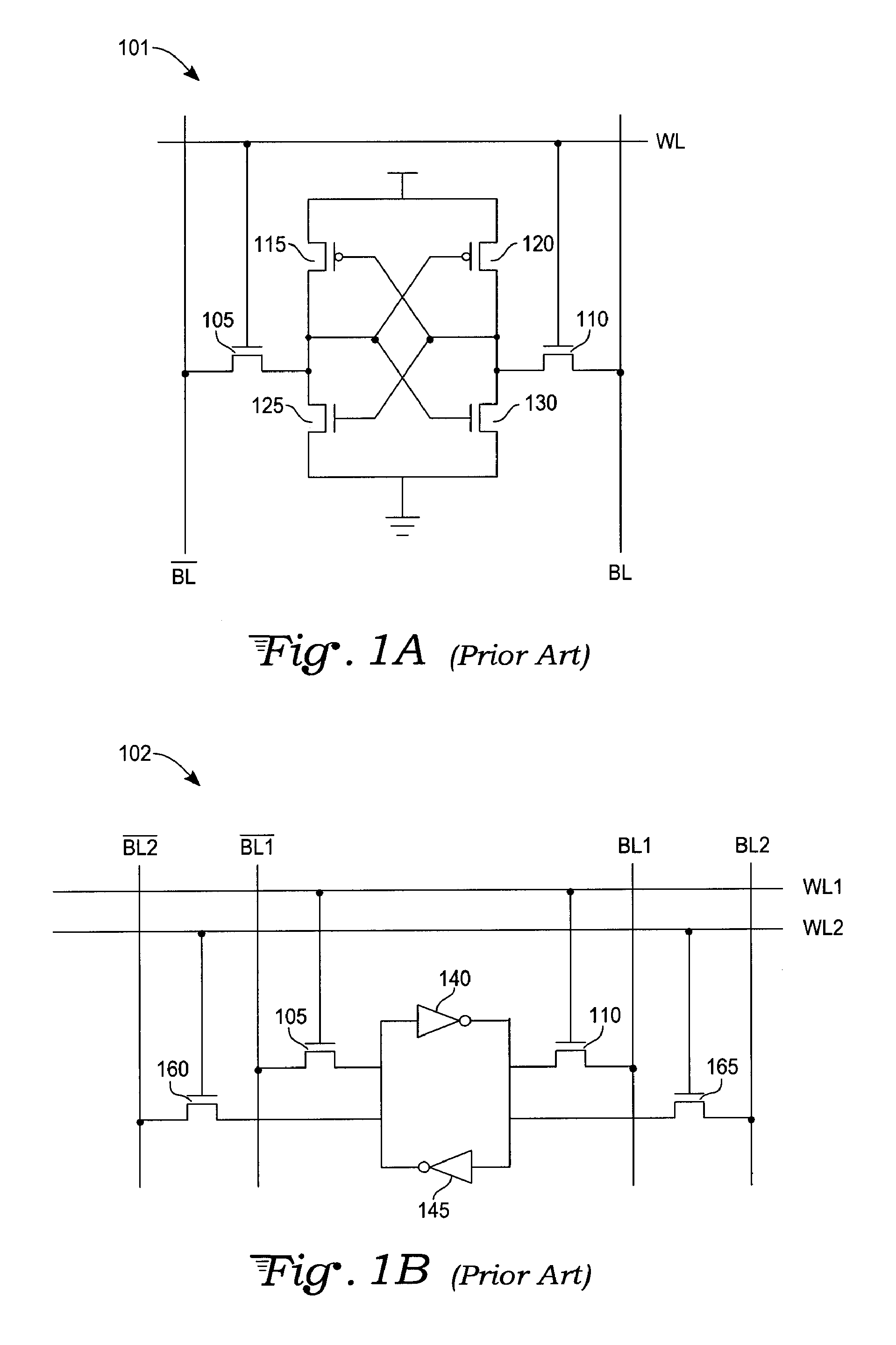

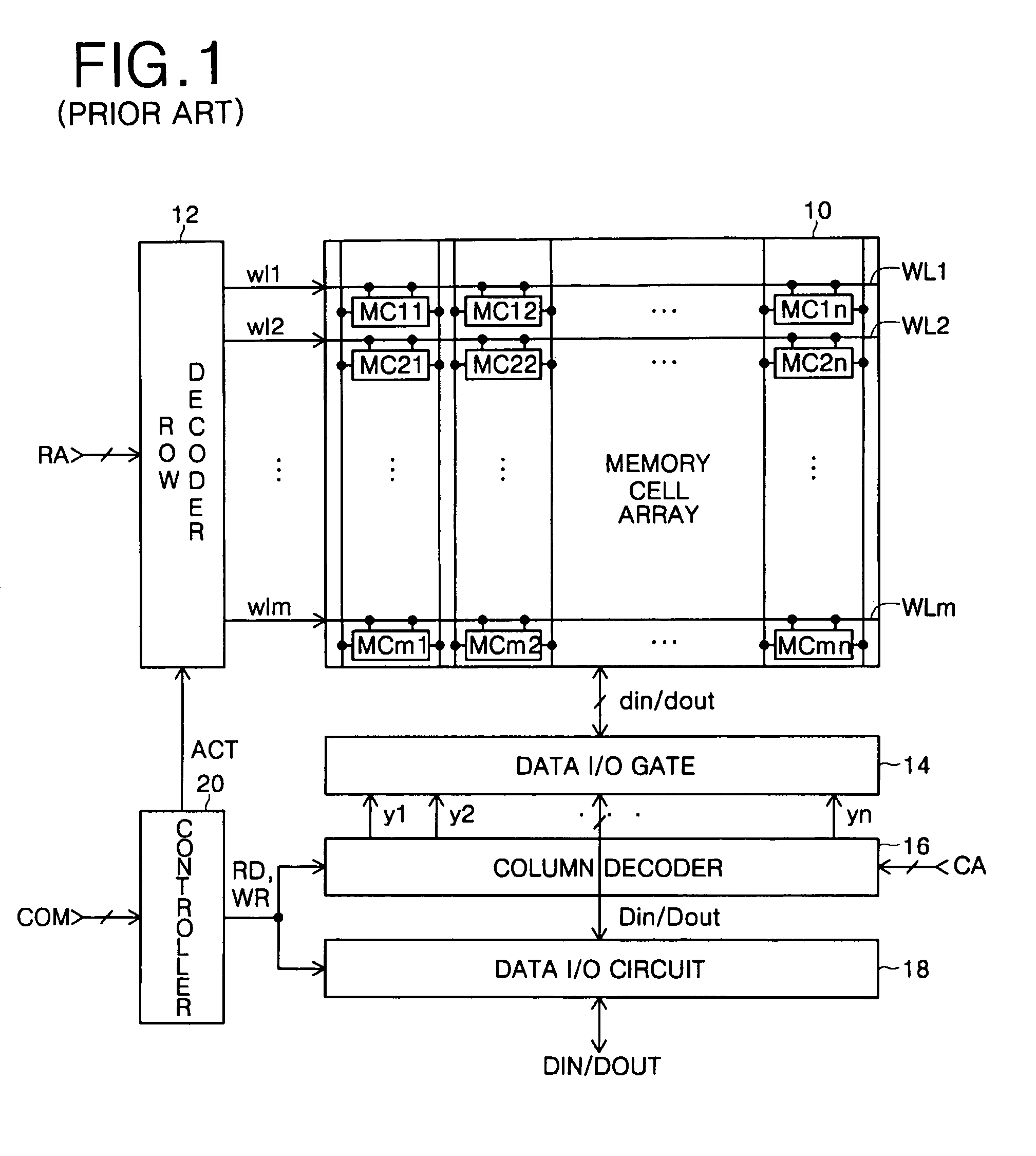

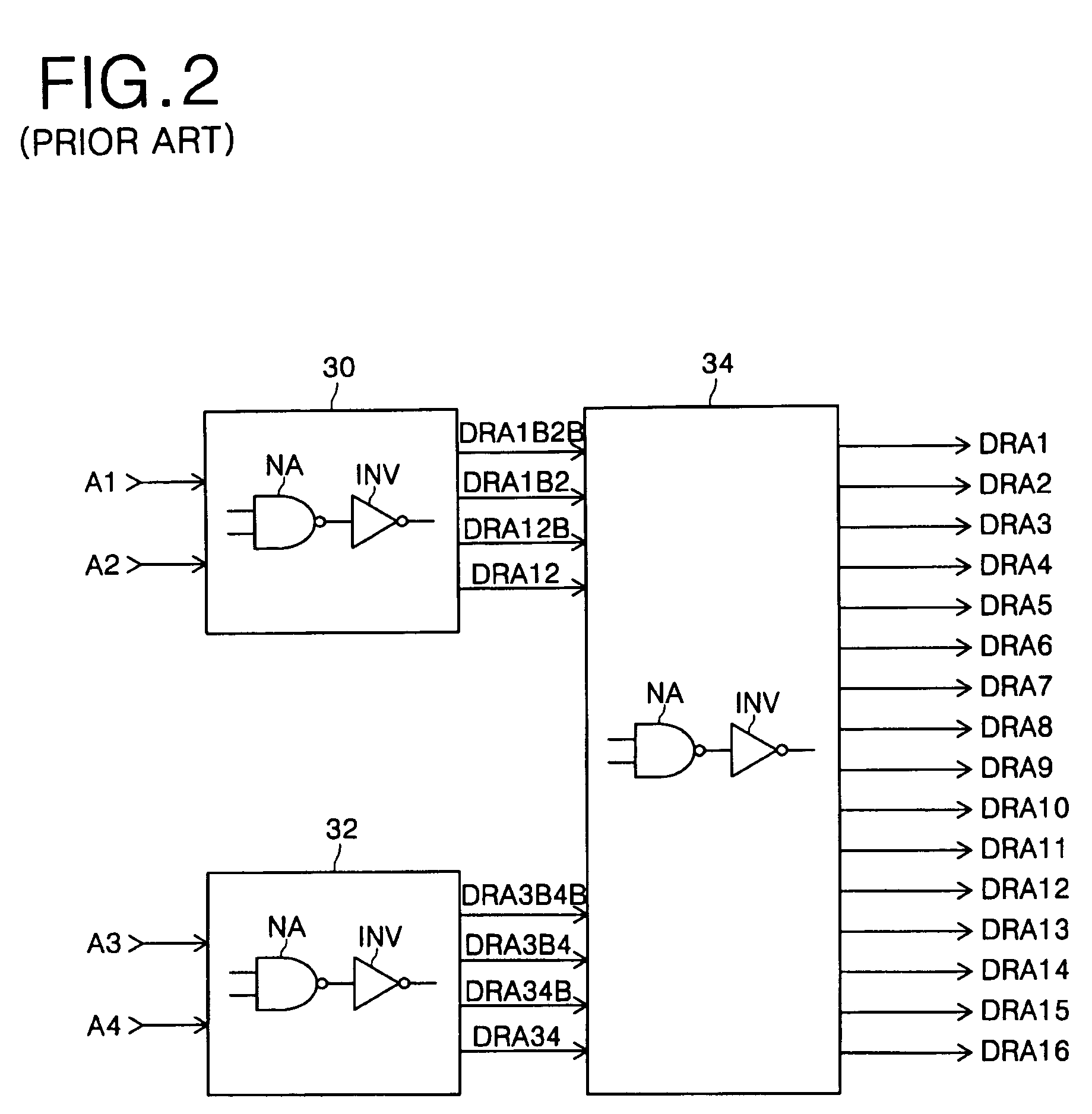

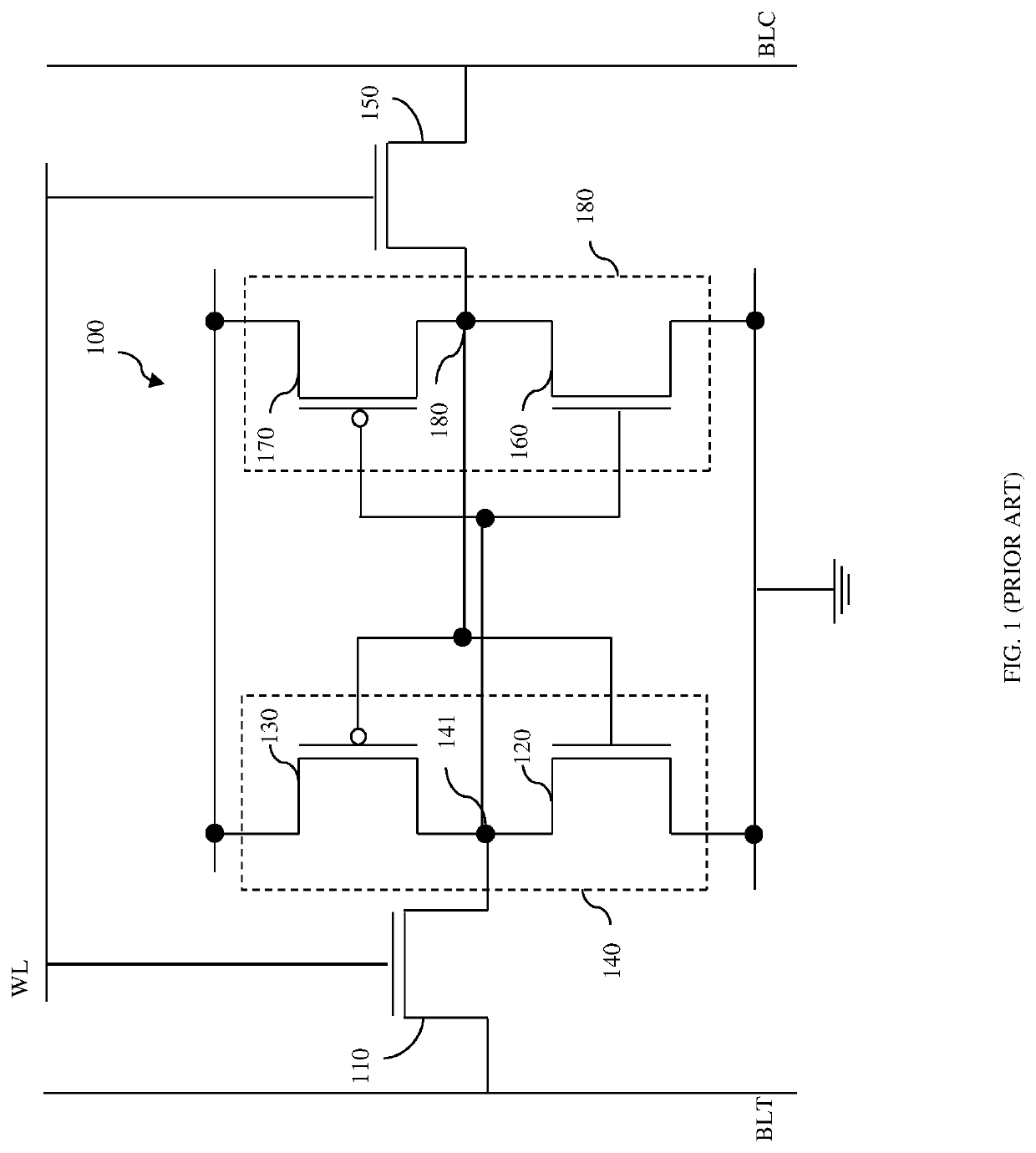

Fast read port for register file

InactiveUS20070189101A1Minimal likelihoodRapid read responseDigital storageAudio power amplifierProcessor register

Separate read and write ports in a memory system allow simultaneous access to a memory cell array by read and write operations. A single cycle operation of a central processing unit coupled to a memory array depends on a memory access capability providing simultaneous reading and writing to different locations. A pair of pull-down transistor stacks connected to memory cell latch loops allows a single selected pull-down stack of the pair to toggle a memory cell latch loop to a desired data content without any requirement for a precharge scheme. A single pull-down stack of transistors connected to a memory cell latch loop provides a read port with low input loading. A sense amplifier provides a mid-supply-level precharging capability provided by a feedback device within a front-end inversion stage. When not in a feedback mode, the front-end inversion stage cascaded with a second inversion stage provides a rapid read response.

Owner:ATMEL CORP

Voltage reference circuit using PTAT voltage

ActiveUS20060001412A1Sufficient magnitudeStable temperatureElectric variable regulationElectrical resistance and conductanceInternal resistance

A voltage reference generator is disclosed that includes a current generator for generating a current that is proportional to absolute temperature (PTAT), the current generator having an internal resistance. This provides a PTAT current that is proportional to the resistance and wherein the temperature coefficient of the PTAT current is defined by the resistance. An output node is driven by the current generator with the PTAT current. A stack of serial connected MOS devices is connected between the output voltage and a ground reference voltage. The stack of transistors has a transimpedance associated therewith which has a temperature coefficient that is opposite in polarity to the temperature coefficient of the internal resistance and of a magnitude to provide a voltage on the output node that is substantially stable over temperature.

Owner:SILICON LAB INC

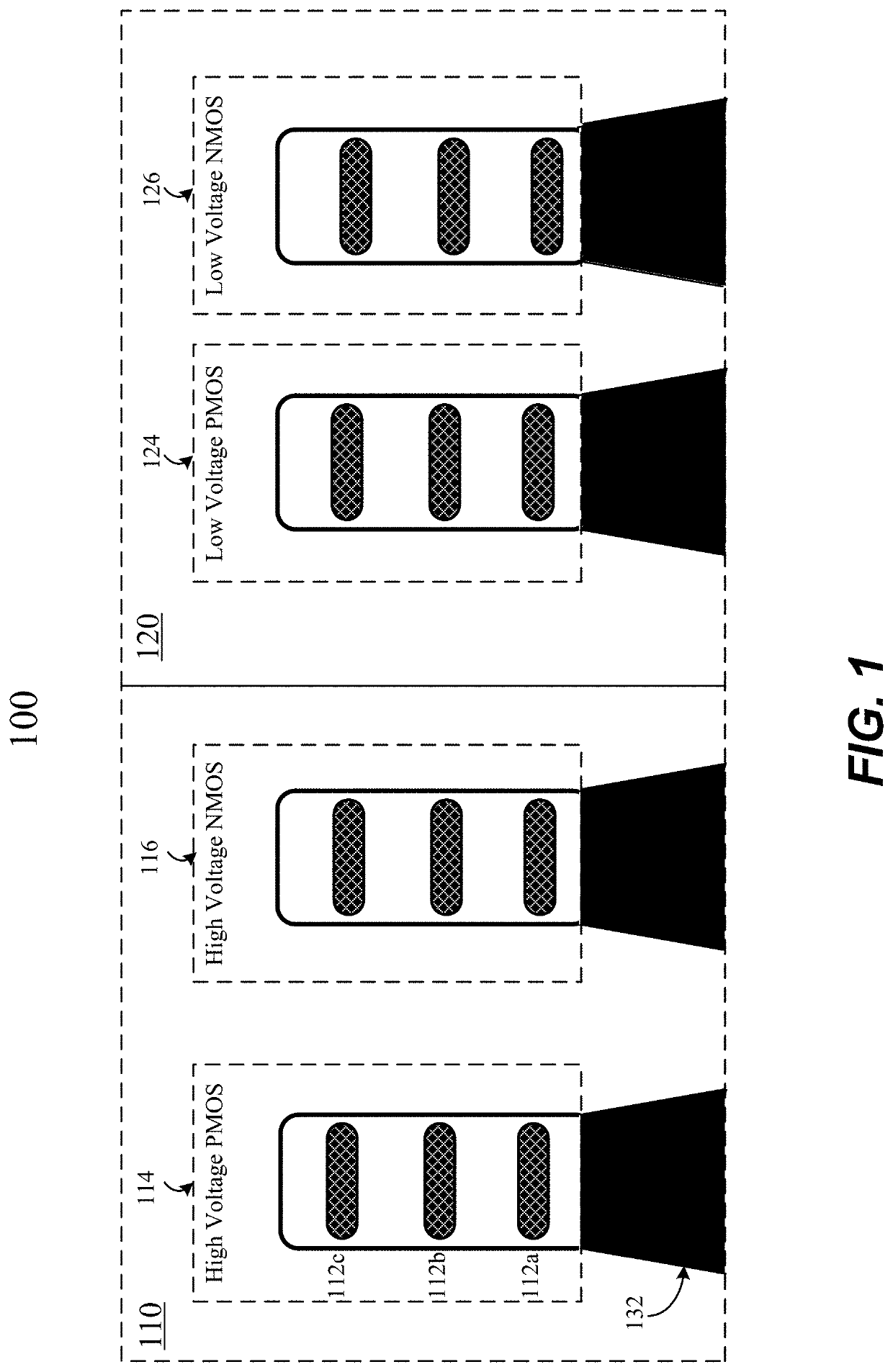

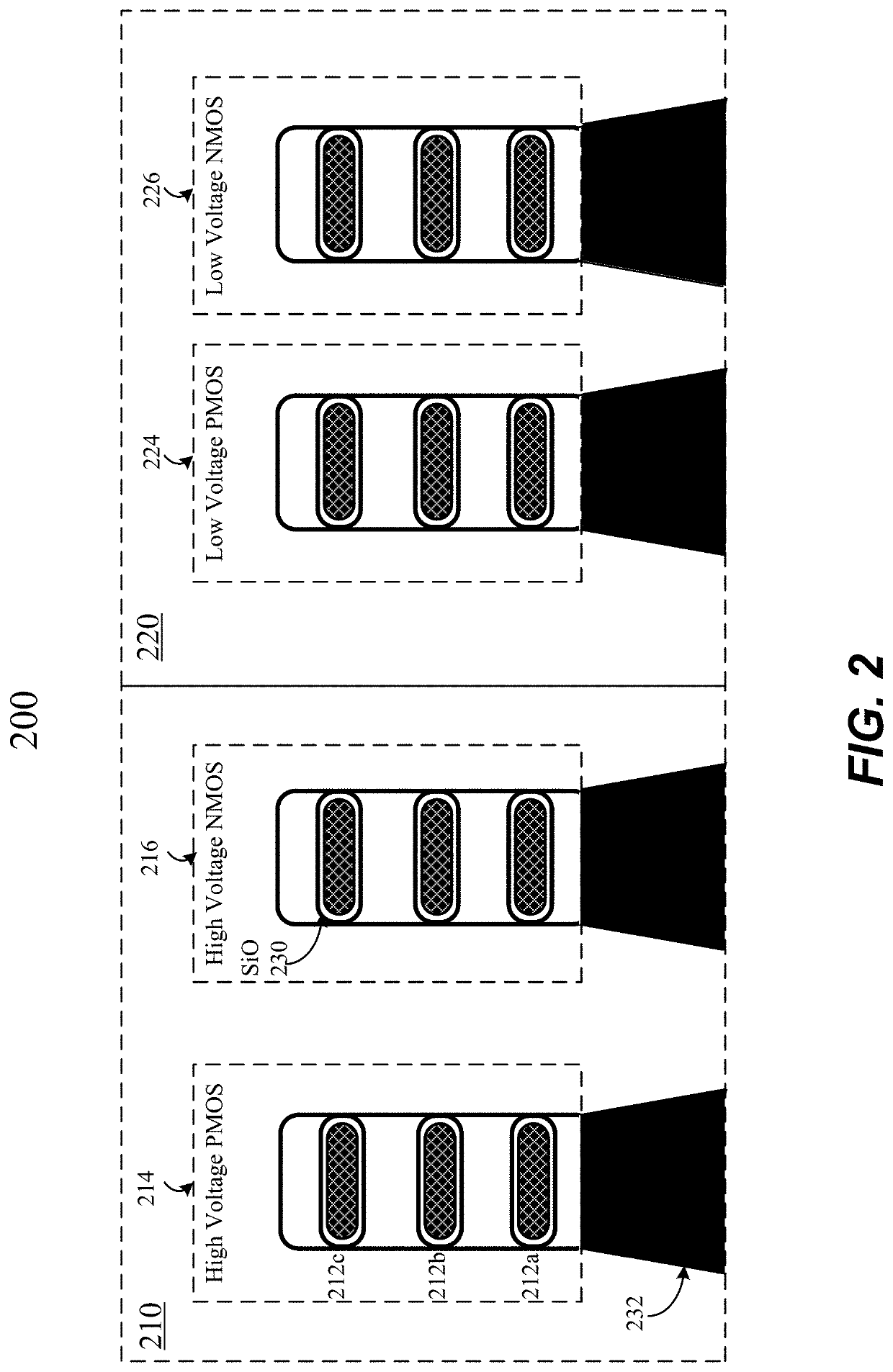

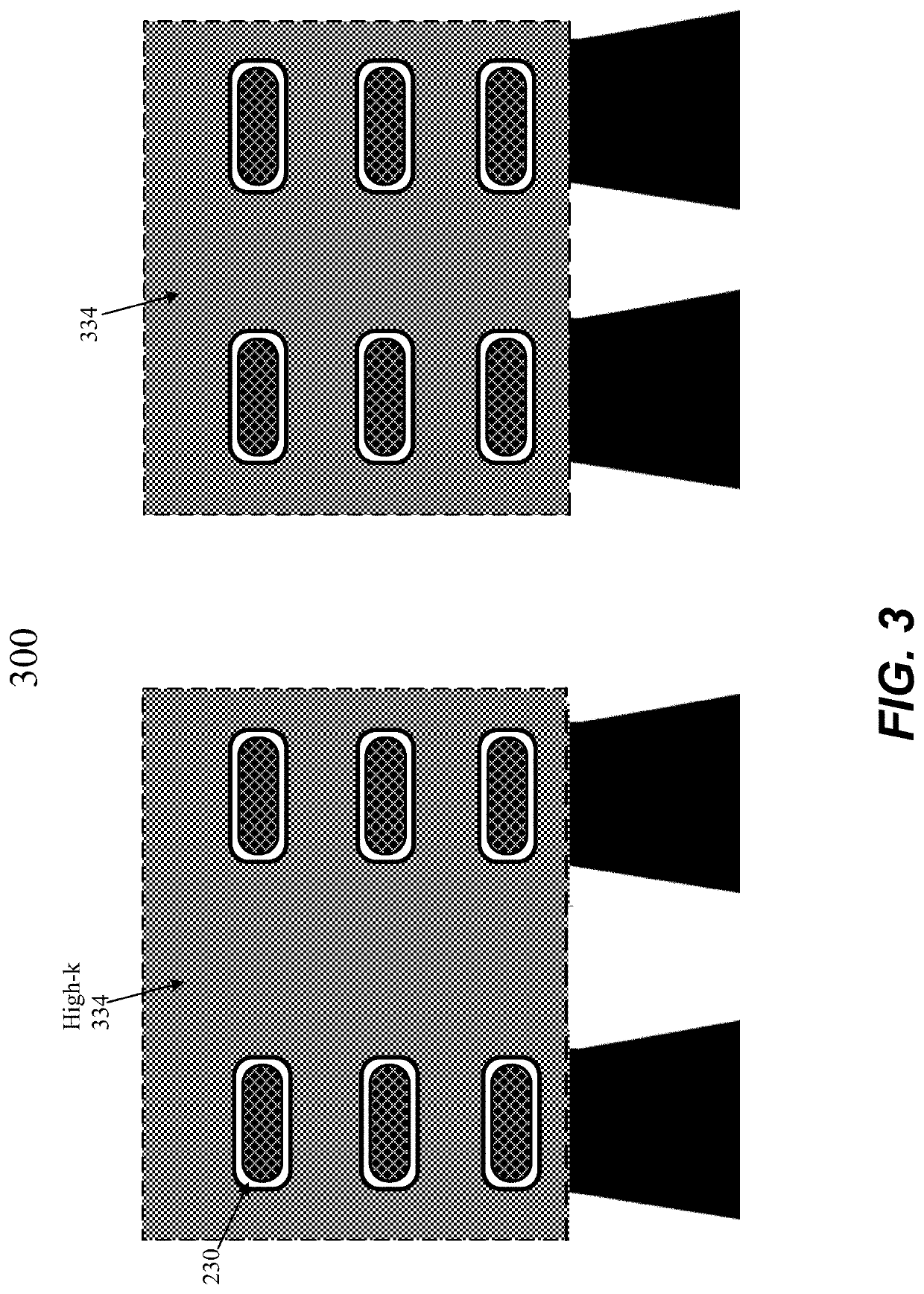

Method for threshold voltage tuning through selective deposition of high-k metal gate (HKMG) film stacks

A method for microfabrication of a three dimensional transistor stack having gate-all-around field-effect transistor devices. The channels hang between source / drain regions. Each channel is selectively deposited with layers of materials designed for adjusting the threshold voltage of the channel. The layers may be oxides, high-k materials, work function materials and metallization. The three dimensional transistor stack forms an array of high threshold voltage devices and low threshold voltage devices in a single package.

Owner:TOKYO ELECTRON LTD

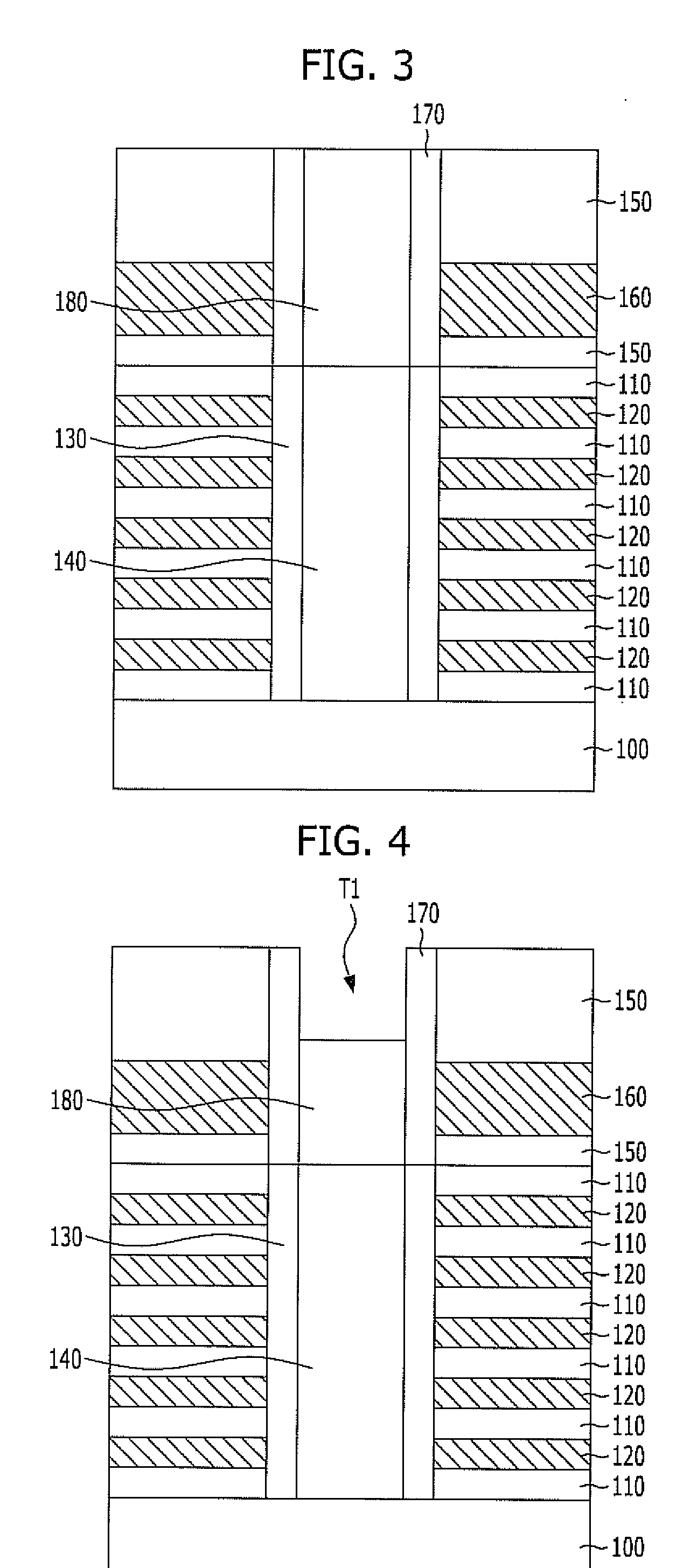

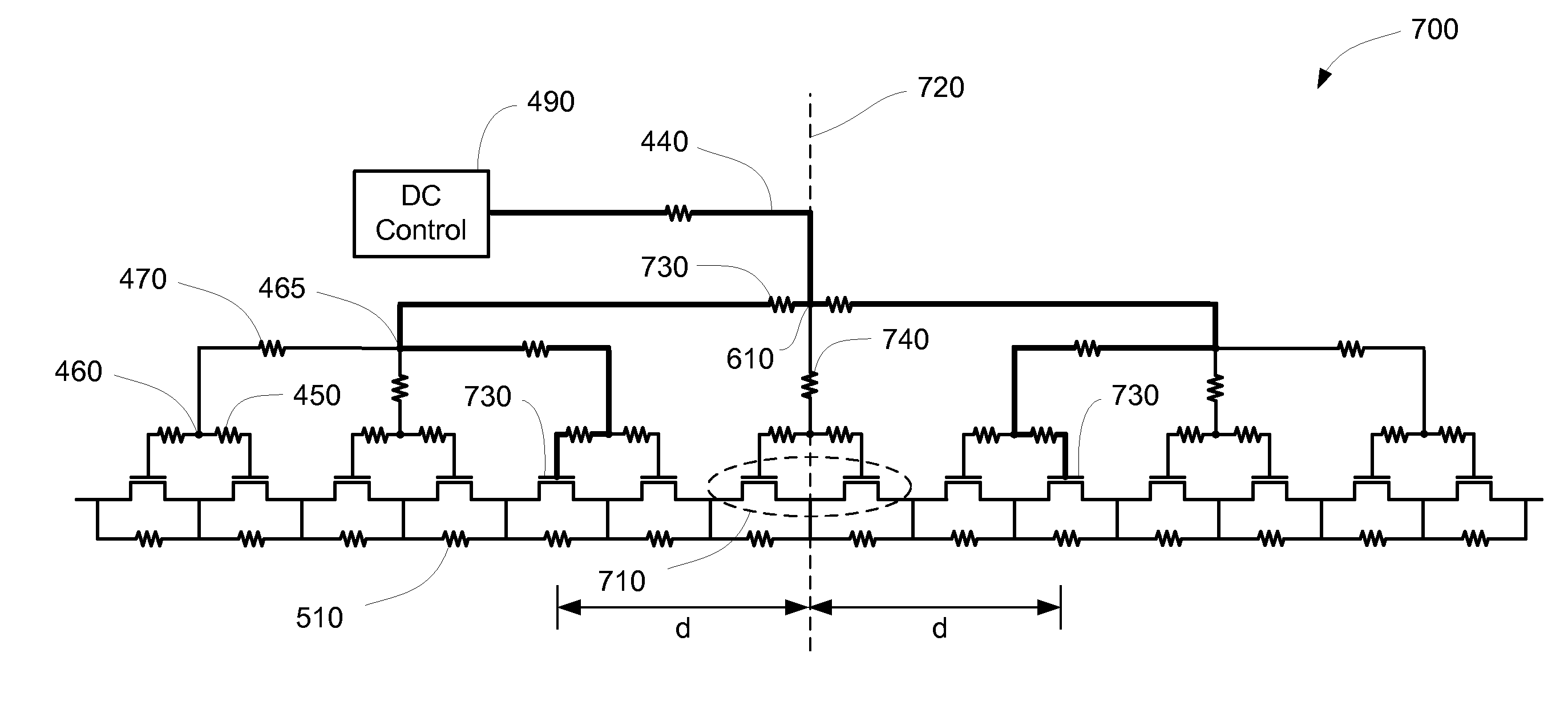

Circuits and methods for improved quality factor in a stack of transistors

InactiveUS20150171860A1Reduce lossesSolid-state devicesSemiconductor/solid-state device manufacturingTransistor circuitsField-effect transistor

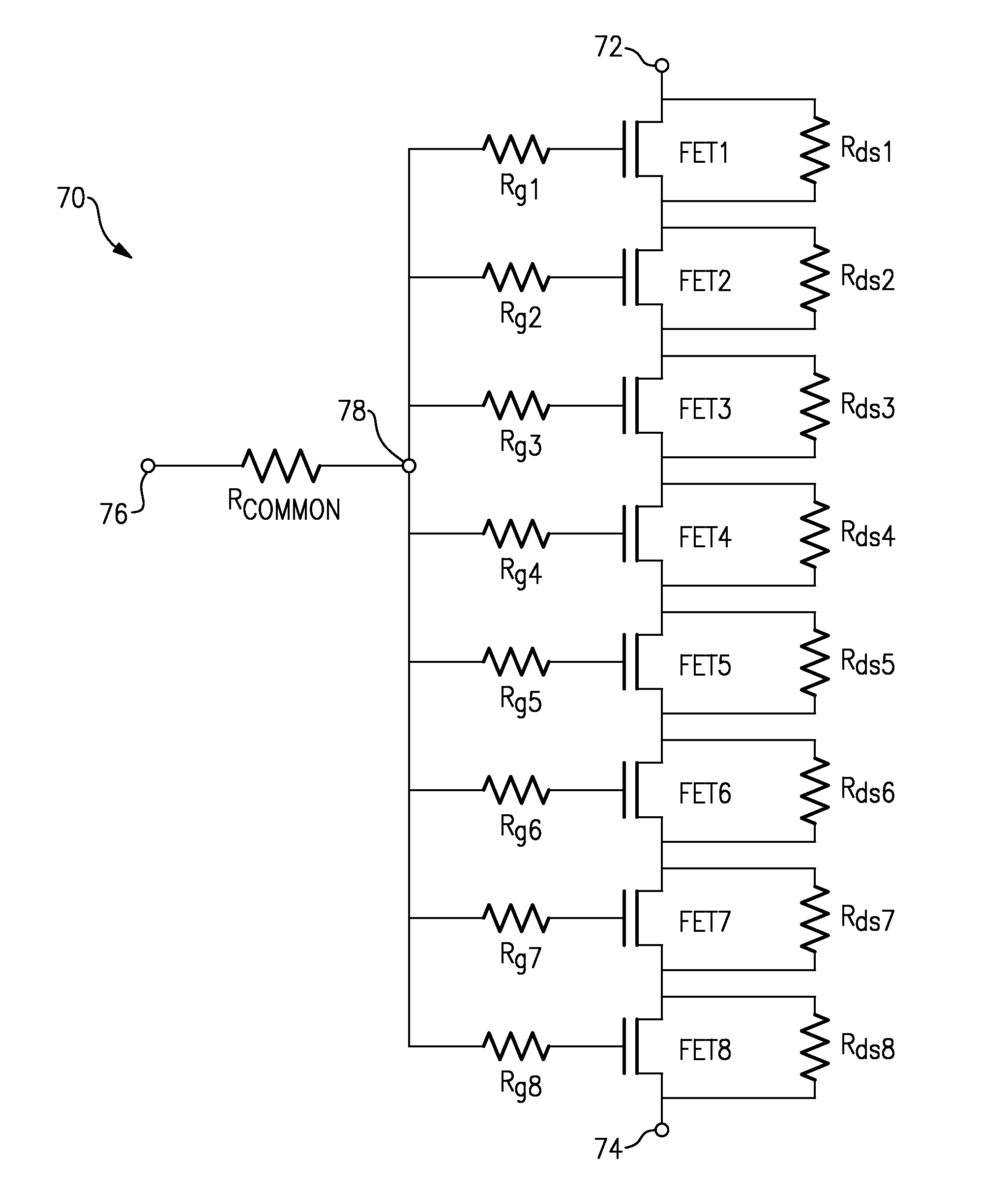

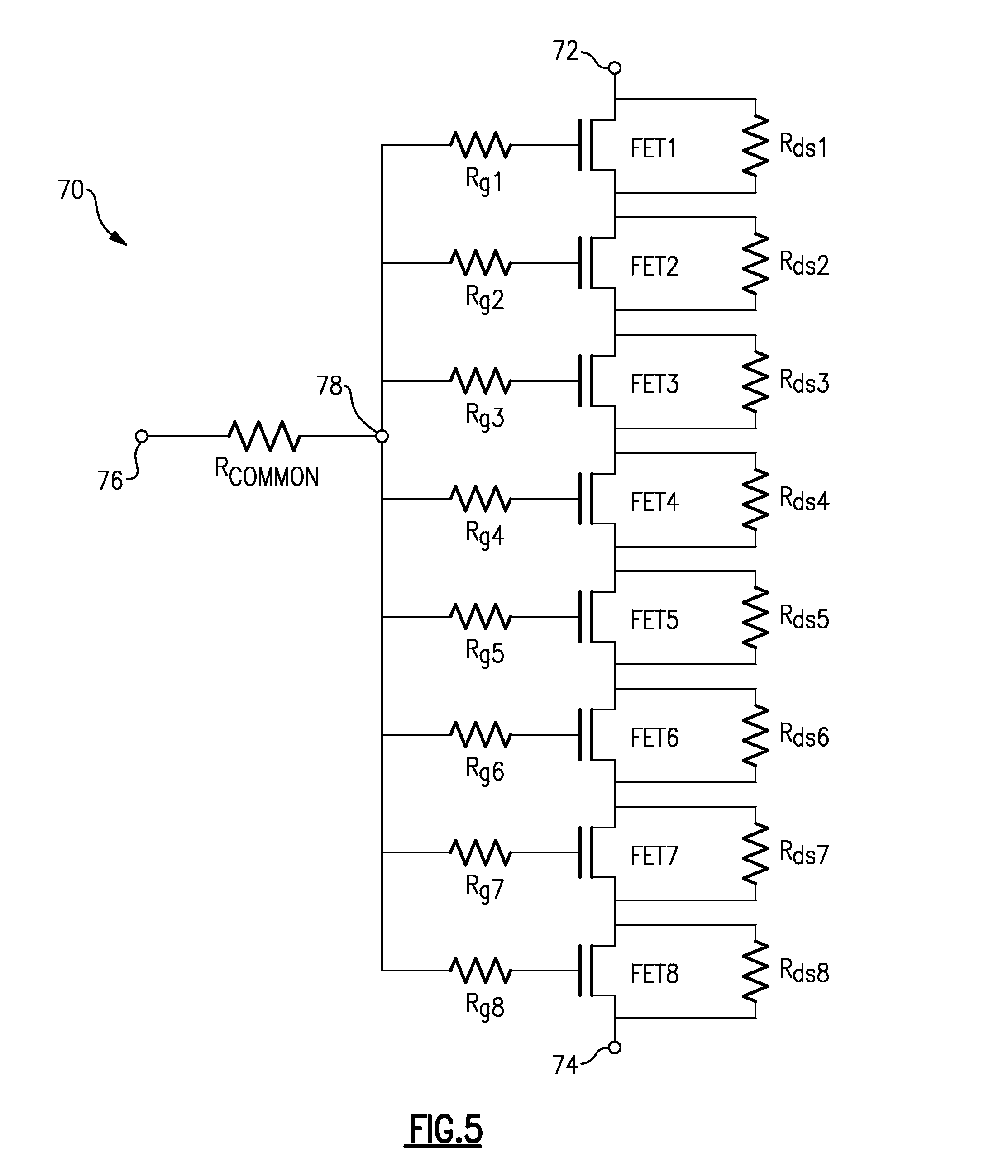

Circuits and method for improved quality factor in a stack of transistors. A switching device can include a plurality of field-effect transistors (FETs) implemented in a stack configuration. The switching device can further include a bias circuit having a distribution network that couples a bias input node to the gate of each FET. The distribution network can include a plurality of first nodes, with each first node connected to one or more of the gates through one or more respective resistive paths. The distribution network can further include one or more second nodes, with each second node connected to one or more of the first nodes through one or more respective resistive paths. At least some of the resistive paths can have resistance values selected to reduce loss of a radio-frequency (RF) signal when the FETs are in an OFF state.

Owner:SKYWORKS SOLUTIONS INC

Semiconductor memory device and method for arranging and manufacturing the same

Owner:SAMSUNG ELECTRONICS CO LTD

Cascode amplifier bias circuits

ActiveUS10250199B2Amplifier modifications to reduce temperature/voltage variationPower amplifiersLow noiseAudio power amplifier

Bias circuits and methods for silicon-based amplifier architectures that are tolerant of supply and bias voltage variations, bias current variations, and transistor stack height, and compensate for poor output resistance characteristics. Embodiments include power amplifiers and low-noise amplifiers that utilize a cascode reference circuit to bias the final stages of a cascode amplifier under the control of a closed loop bias control circuit. The closed loop bias control circuit ensures that the current in the cascode reference circuit is approximately equal to a selected multiple of a known current value by adjusting the gate bias voltage to the final stage of the cascode amplifier. The final current through the cascode amplifier is a multiple of the current in the cascode reference circuit, based on a device scaling factor representing the relative sizes of the transistor devices in the cascode amplifier and in the cascode reference circuit.

Owner:PSEMI CORP

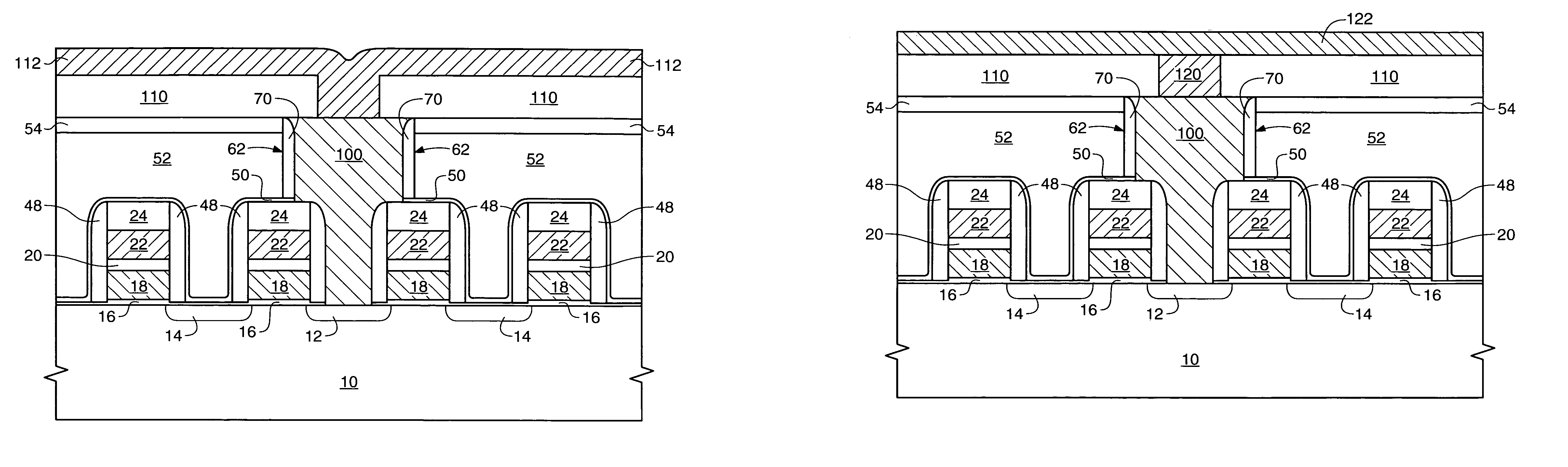

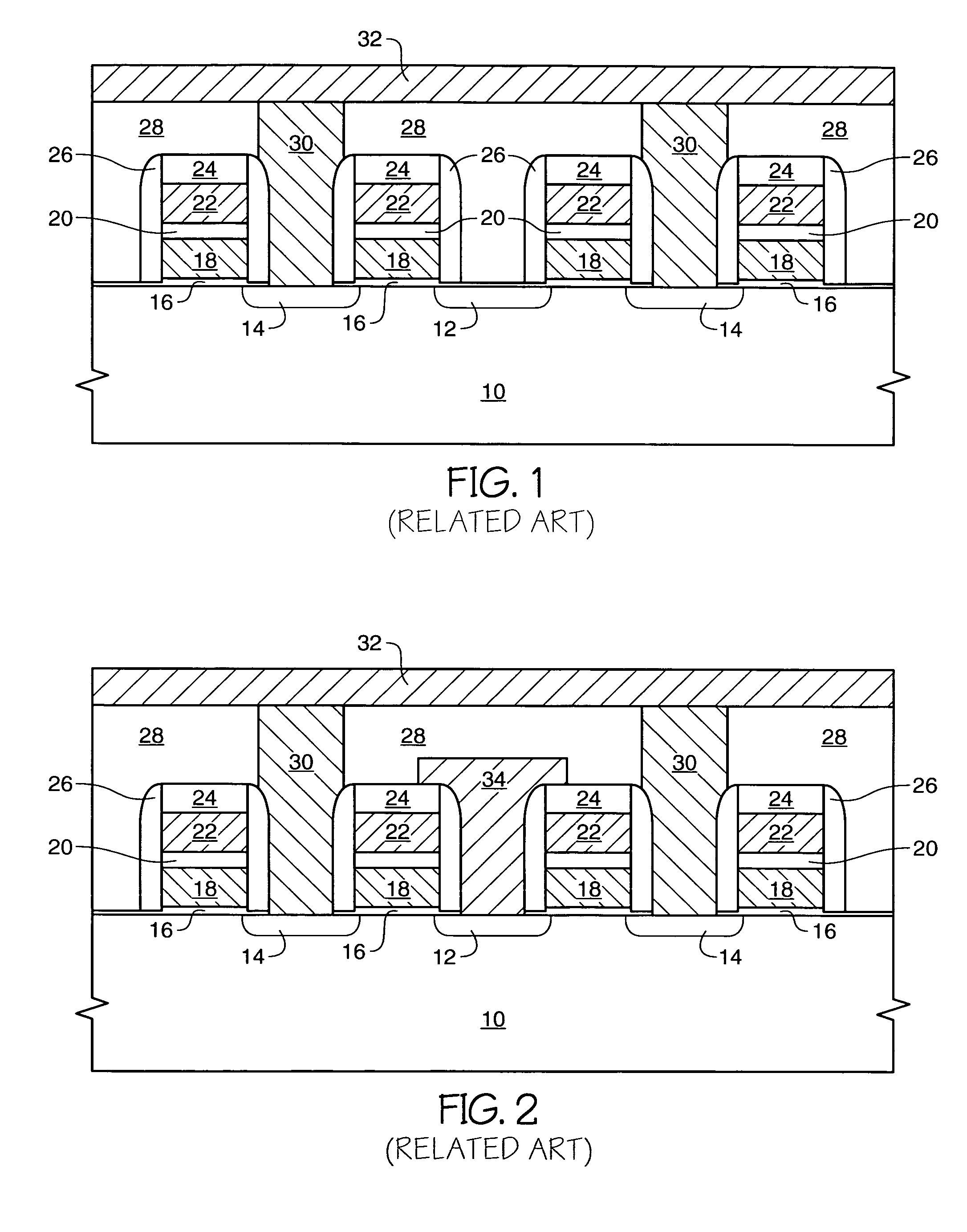

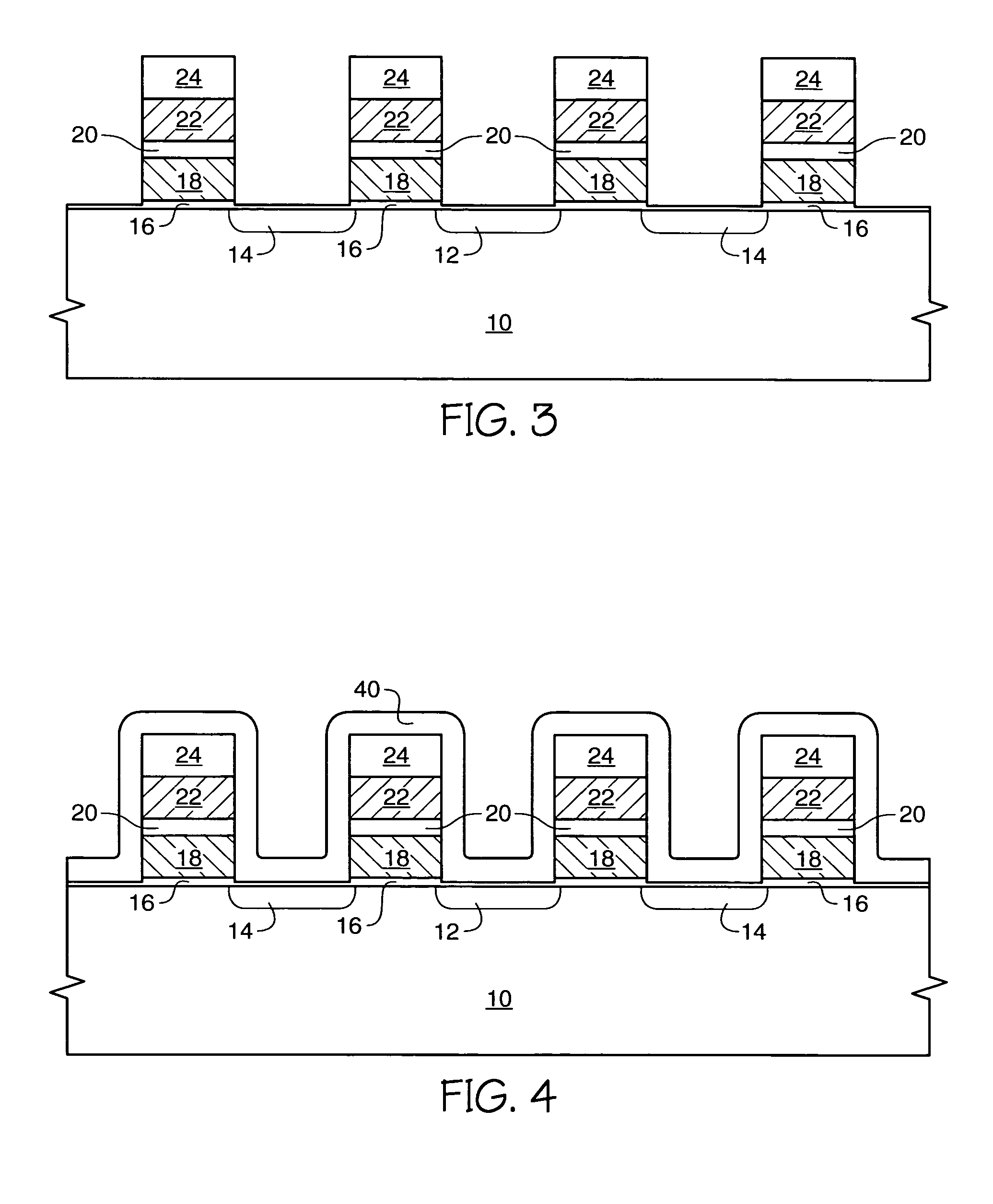

Method and apparatus for a flash memory device comprising a source local interconnect

InactiveUS7053444B2Minimal spaceMore scaleable deviceTransistorSolid-state devicesGate oxideSemiconductor

A method for forming a flash memory device having a local interconnect connecting source regions of a plurality of transistors within a sector allows for a highly selective wet etch of a dielectric region overlying the source region. An embodiment of the method comprises the use of an etch-resistant layer covering various features such as any gate oxide remaining over the source region, spacers along sidewalls of the transistor stacks, and a capping layer of the transistor. An in-process semiconductor device resulting from the inventive method is also disclosed.

Owner:MICRON TECH INC

III-nitride transistor stacked with FET in a package

ActiveUS8847408B2Semiconductor/solid-state device detailsSolid-state devicesSmall form factorEngineering

One exemplary disclosed embodiment comprises a three-terminal stacked-die package including a field effect transistor (FET), such as a silicon FET, stacked atop a III-nitride transistor, such that a drain of the FET resides on and is electrically coupled to a source of the III-nitride transistor. A first terminal of the package is coupled to a gate of the FET, a second terminal of the package is coupled to a drain of the III-nitride transistor. A third terminal of the package is coupled to a source of the FET. In this manner, devices such as cascoded switches may be packaged in a stacked-die form, resulting in reduced parasitic inductance and resistance, improved thermal dissipation, smaller form factor, and lower manufacturing cost compared to conventional packages.

Owner:INFINEON TECH AMERICAS CORP

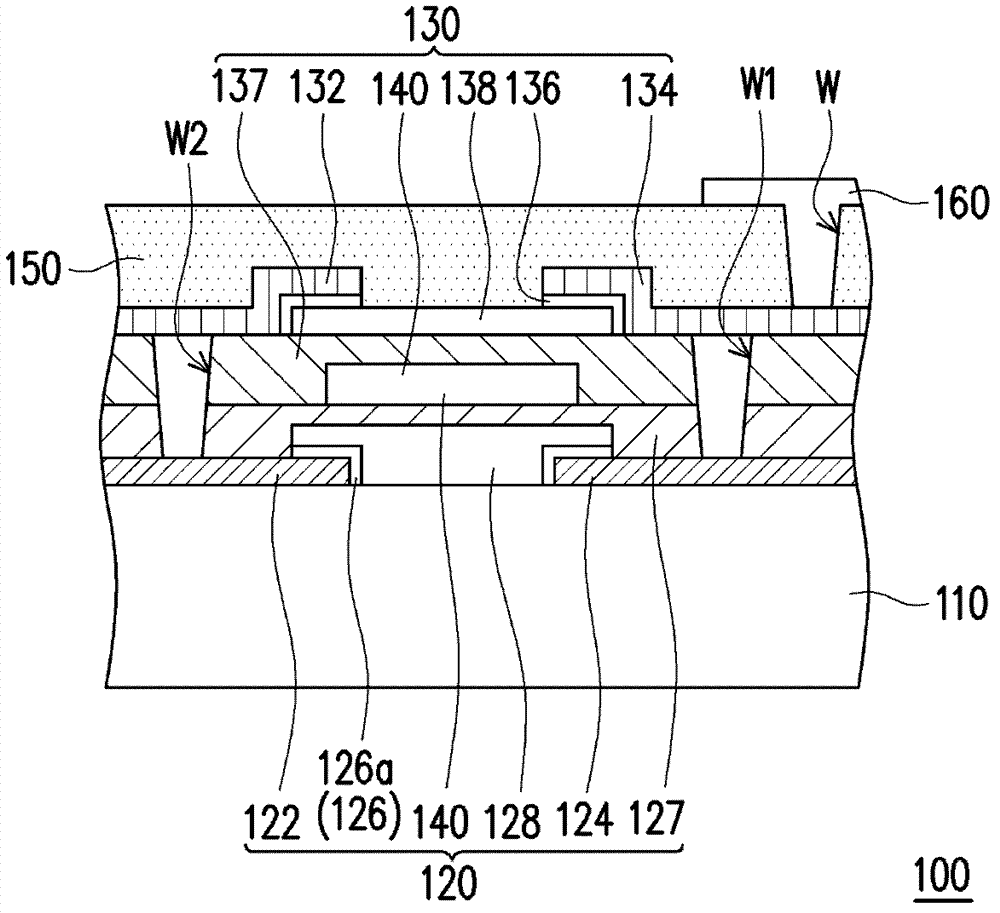

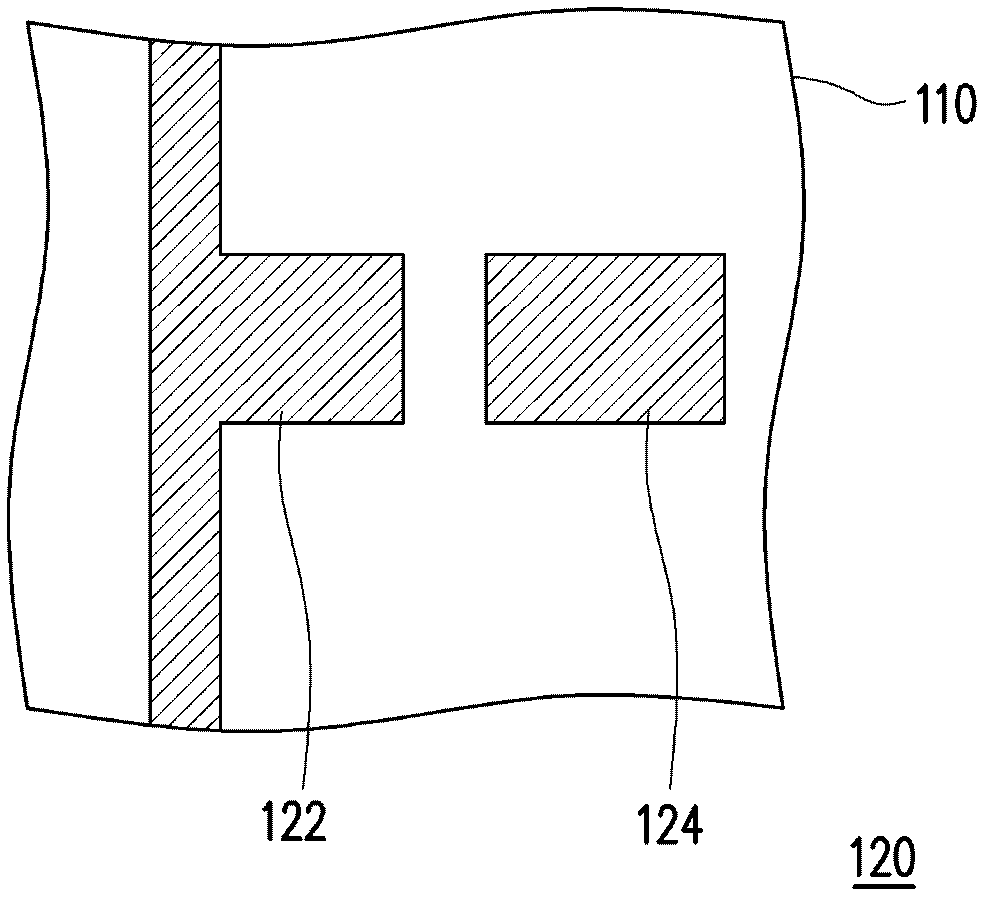

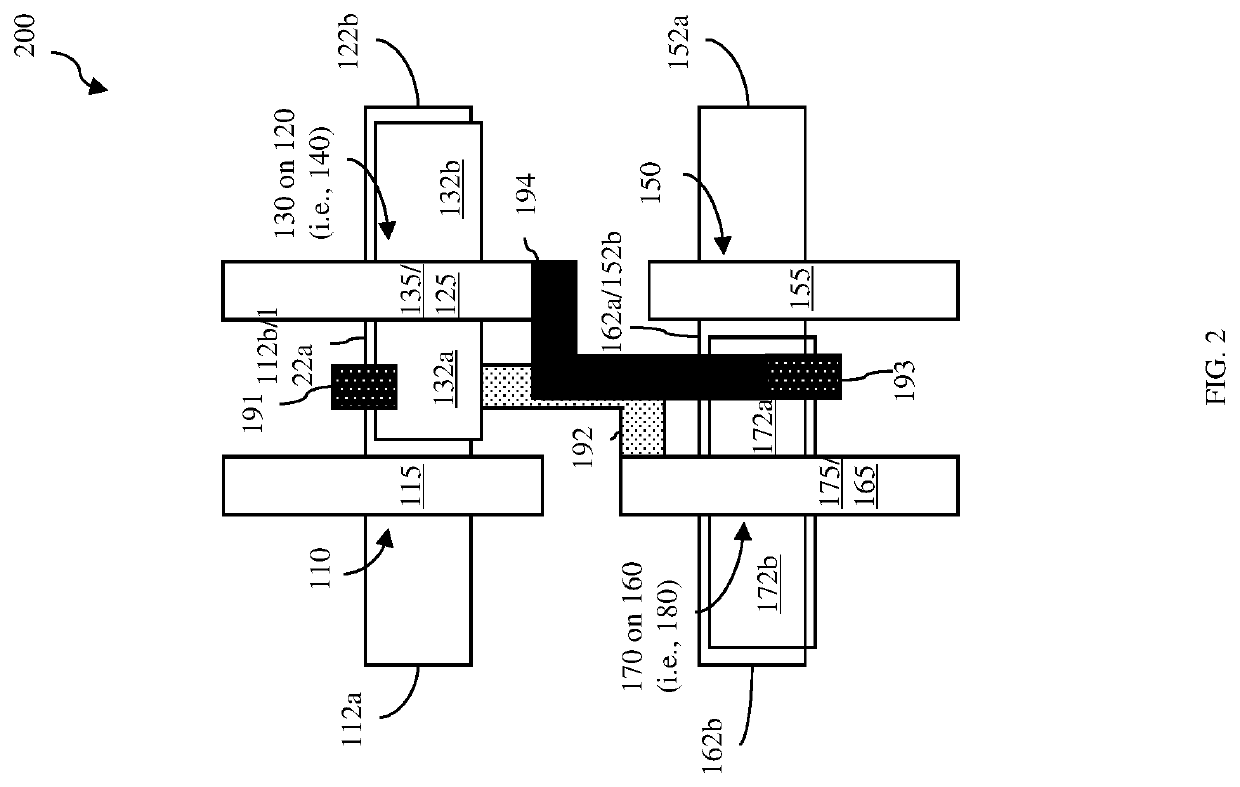

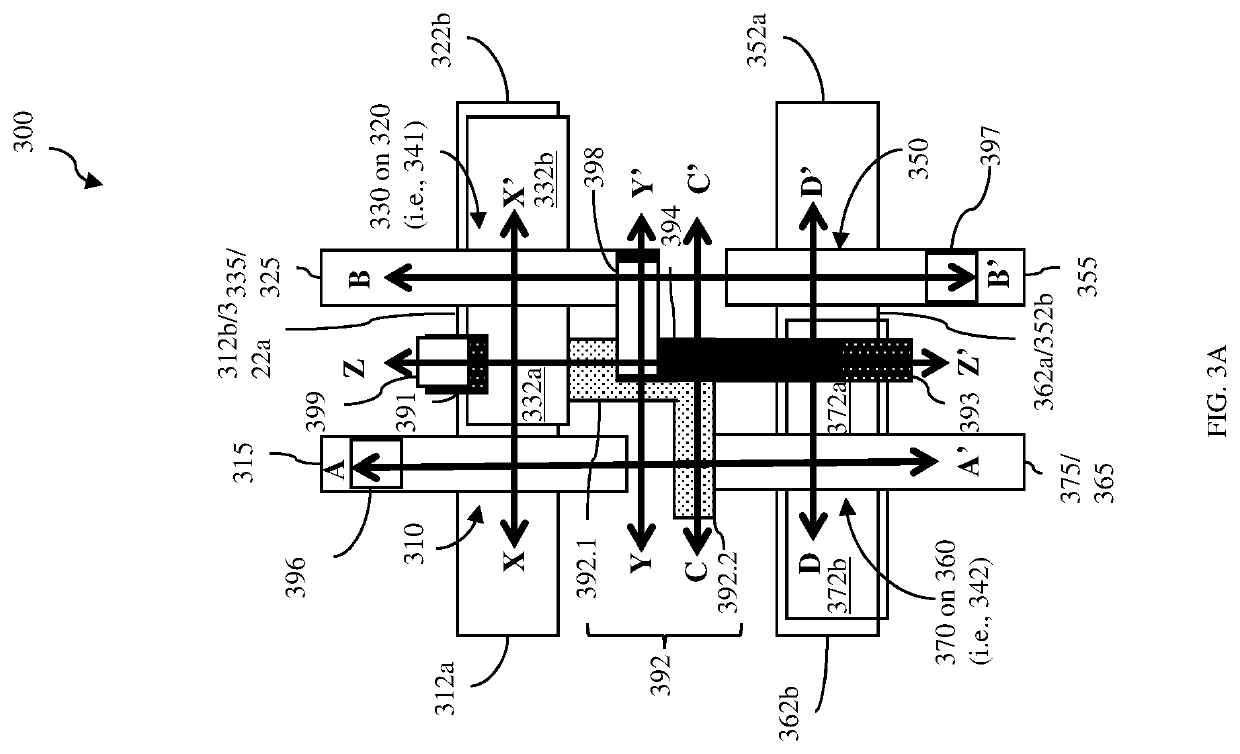

Integrated circuit structure with complementary field effect transistor and buried metal interconnect and method

ActiveUS20200111798A1TransistorSemiconductor/solid-state device detailsMetal interconnectMemory cell

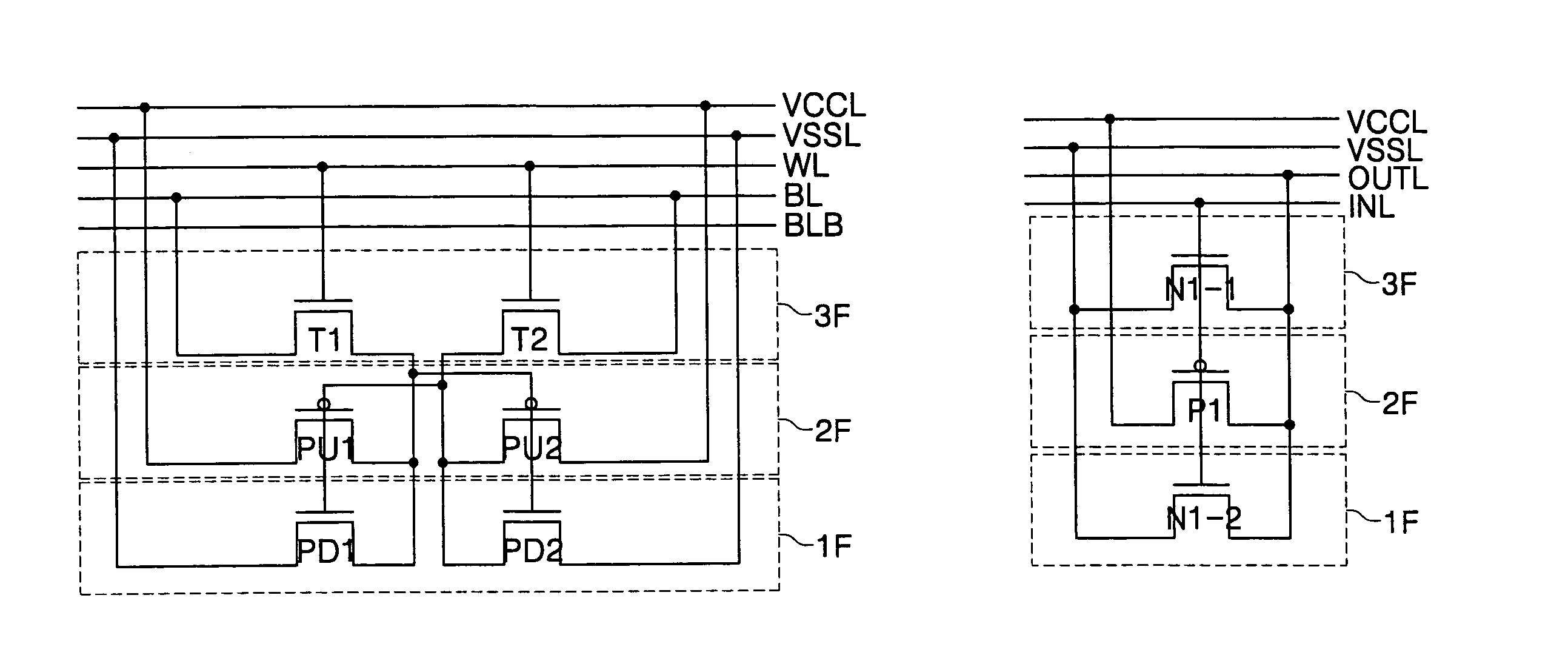

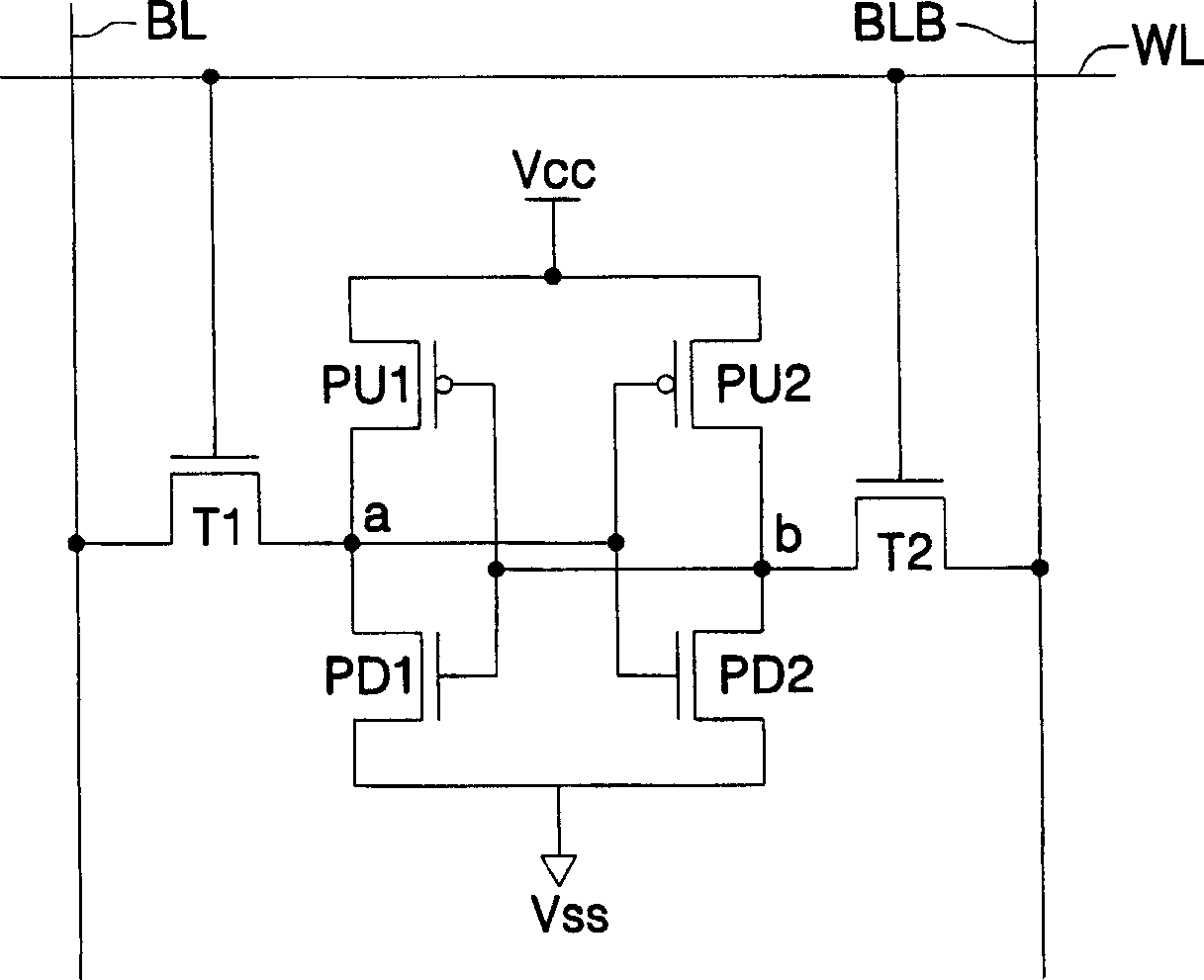

Disclosed are structures with a complementary field effect transistor (CFET) and a buried metal interconnect that electrically connects a source / drain region of a lower-level transistor of the CFET with another device. The structure can include a memory cell with first and second CFETs, where each CFET includes a pull-up transistor stacked on and having a common gate with a pull-down transistor and each pull-down transistor has a common source / drain region with a pass-gate transistor. The metal interconnect connects a lower-level source / drain region of the first CFET (i.e., the common source / drain region of first pass-gate and pull-up transistors) to the common gate of the second CFET (i.e., to the common gate of second pull-down and pull-up transistors). Formation methods include forming an interconnect placeholder during lower-level source / drain region formation. After upper-level source / drain regions and replacement metal gates are formed, the interconnect placeholder is exposed, removed and replaced with a metal interconnect.

Owner:GLOBALFOUNDRIES US INC

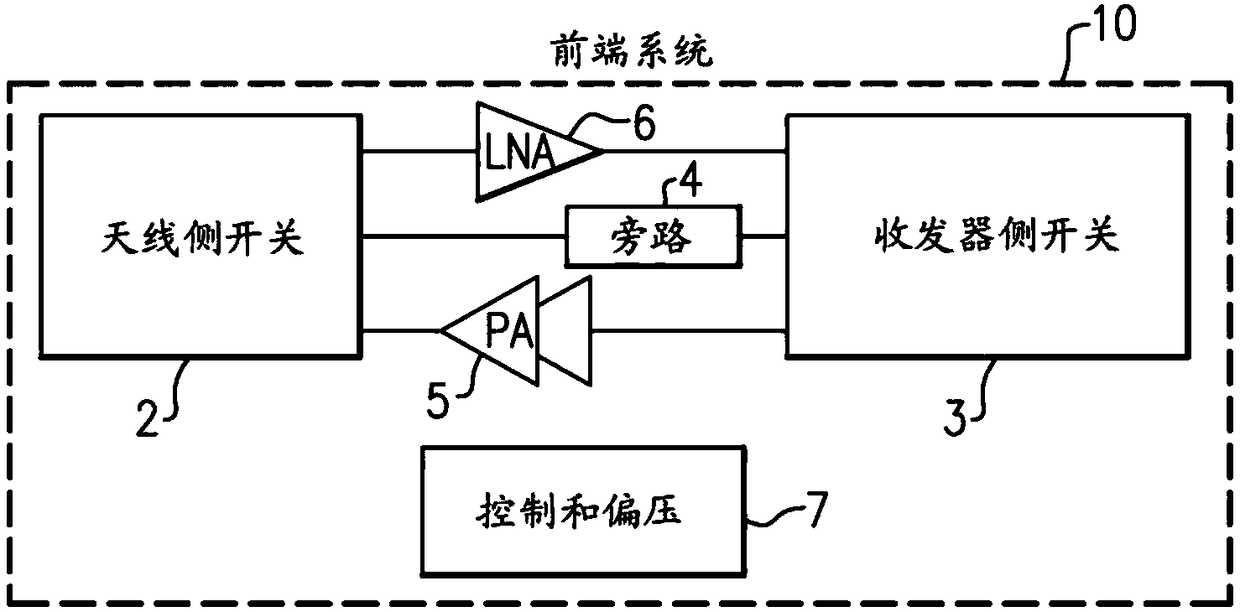

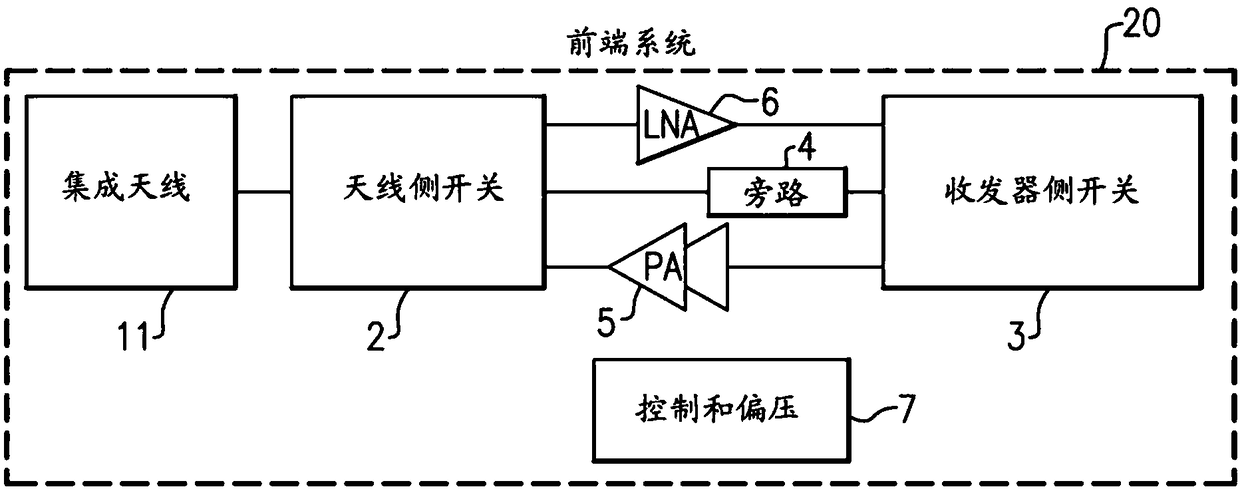

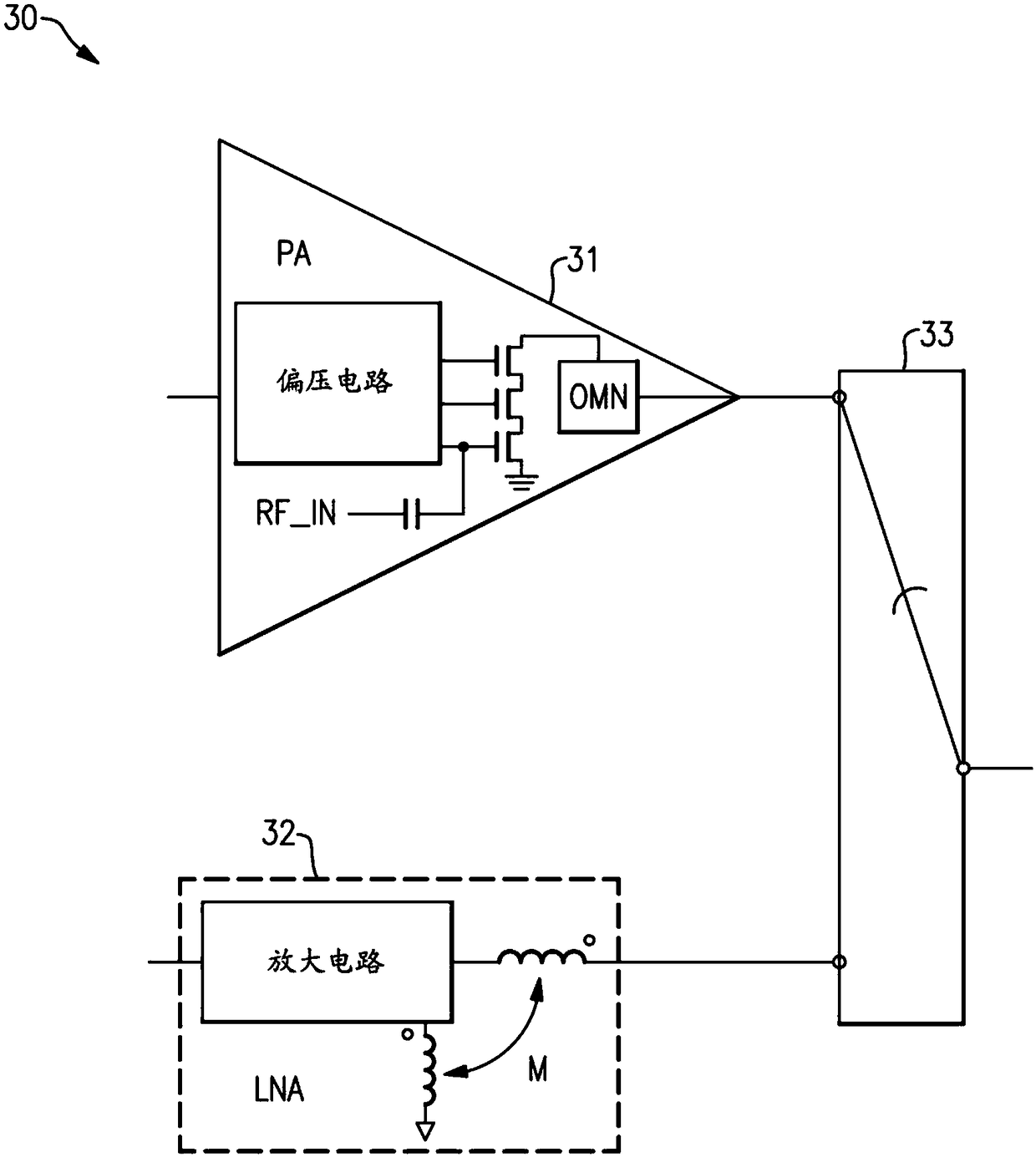

Front end systems and related devices integrated circuits modules and methods

ActiveCN108270464ASemiconductor/solid-state device detailsElectric circuit arrangementsLow noiseNegative feedback

Front end systems and related devices, integrated circuits, modules, and methods are disclosed. One such front end system includes a low noise amplifier in a receive path and a multi-mode power amplifier circuit in a transmit path. The low noise amplifier includes a first inductor, an amplification circuit, and a second inductor magnetically coupled to the first inductor to provide negative feedback to linearize the low noise amplifier. The multi-mode power amplifier circuit includes a stacked output stage including a transistor stack of two or more transistors. The multi-mode power amplifiercircuit also includes a bias circuit configured to control a bias of at least one transistor of the transistor stack based on a mode of the multi-mode power amplifier circuit. Other embodiments of front end systems are disclosed, along with related devices, integrated circuits, modules, methods, and components thereof.

Owner:SKYWORKS SOLUTIONS INC

Switch controls

ActiveUS9143124B2Waveguide hornsModulation transference by semiconductor devices with minimum 2 electrodesHarmonicEngineering

Switches for use in RF devices are provided that offer a better balance of power losses and switching times than switches of the prior art. Switches of the present invention comprise a stack of transistors controlled a symmetric bias network. The stack of transistors includes an even number of transistors arranged in series, where every two successive transistors defines a pair. The bias network includes a symmetrically branching set of connections, where the gates of every pair of transistors are connected by a first connection having a first node, and two or more first nodes are connected by a second connection to a second node, and so forth. The symmetry of the bias network tends to reject even harmonics, and the rejection of even harmonics can be further enhanced by adding capacitors between the bias network and the stack of transistors at points of symmetry.

Owner:STMICROELECTRONICS INT NV

Semiconductor device and methods of arranging and manufacturing same

The present invention discloses a semiconductor device and a method for arranging and manufacturing the same. The semiconductor device includes a plurality of inverters including at least one first pull-up transistor and a first pull-down transistor and respectively converting and outputting an input signal; and a plurality of NAND gates including at least two second pull-up transistors and The second pull-down transistor generates an output signal with a high level if at least one of the at least two input signals has a low level, respectively, wherein at least one first pull-up transistor and a first pull-down transistor and at least two second The pull-up transistor and the second pull-down transistor are stacked and arranged on at least two layers.

Owner:SAMSUNG ELECTRONICS CO LTD

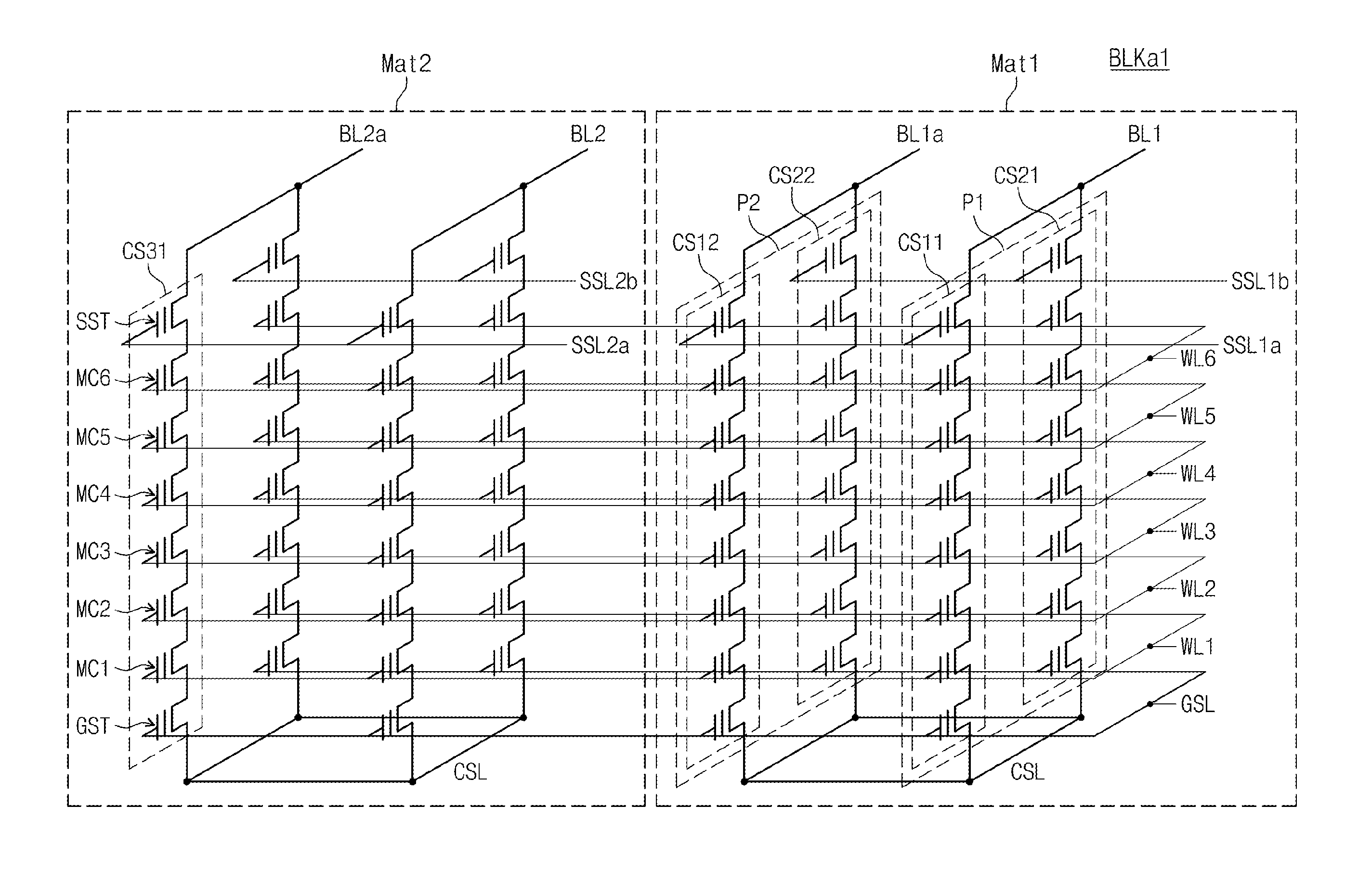

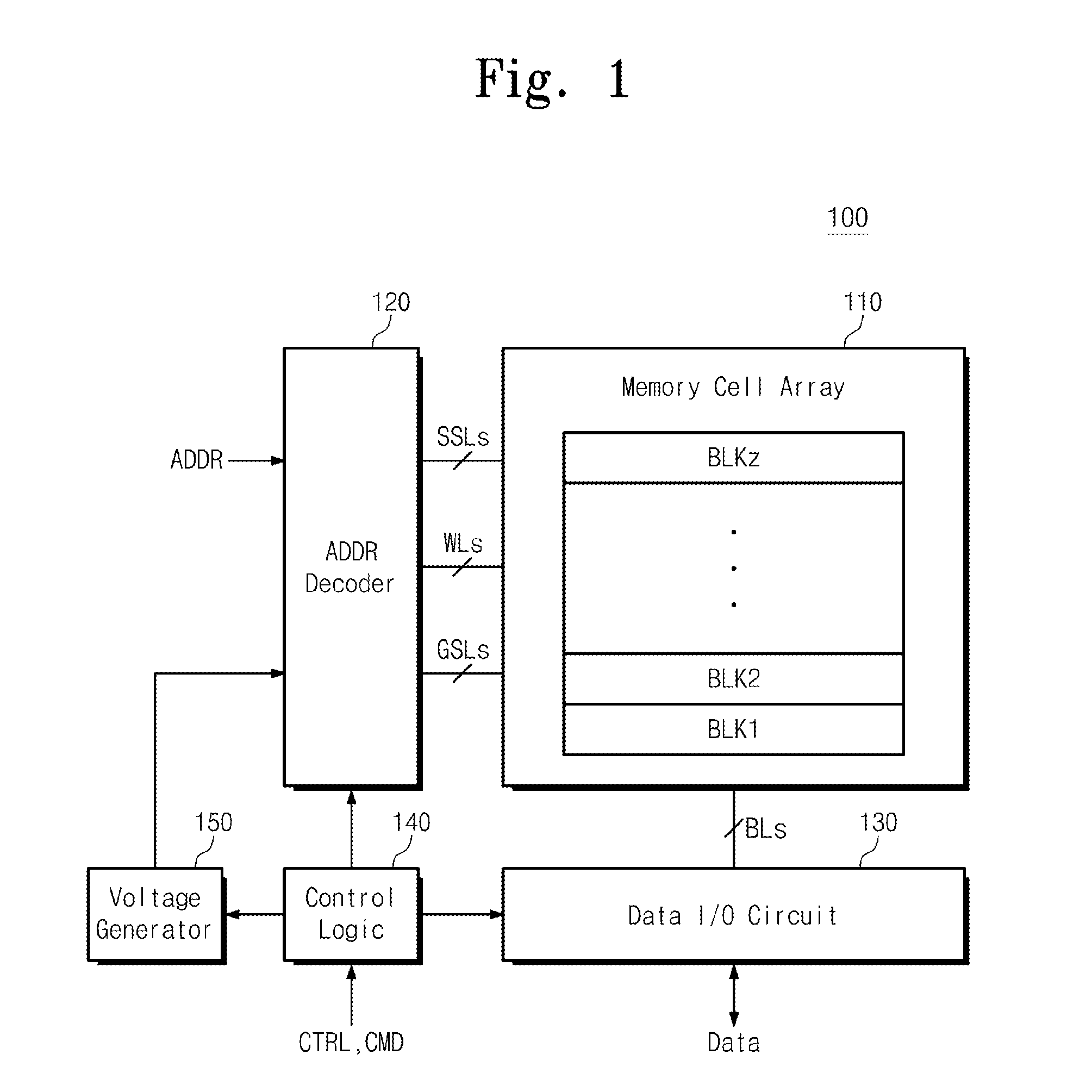

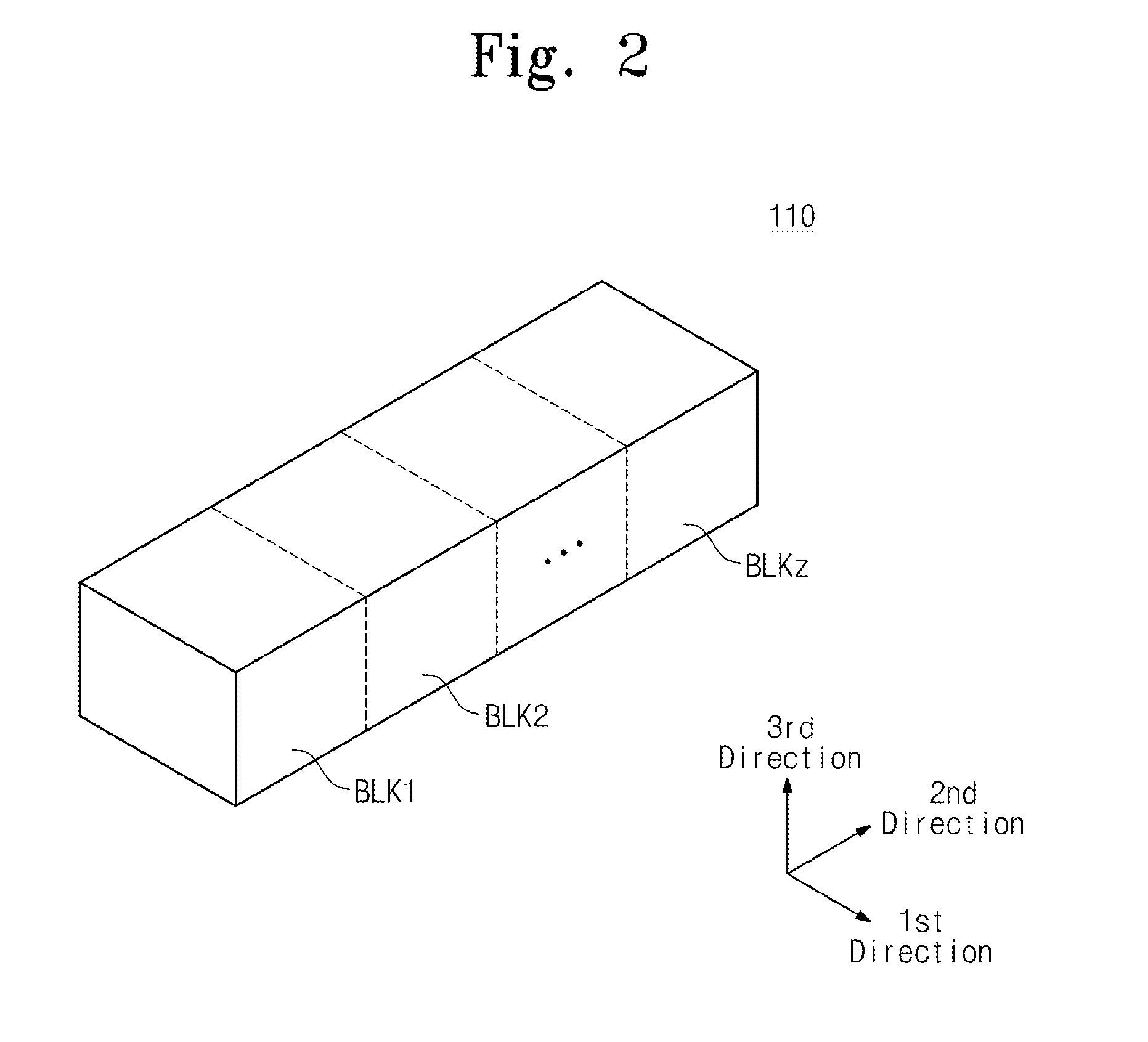

Nonvolatile memory device and memory system comprising same

InactiveUS20140160847A1Improve reliabilityReduce in quantityRead-only memoriesDigital storageBit lineTheoretical computer science

A nonvolatile memory device comprises a 3D memory cell array comprising multiple mats corresponding to different bit lines, each of the mats comprising multiple memory blocks, each of the memory blocks comprising multiple cell strings disposed perpendicular to a substrate and multiple string selection lines configured to select or unselect the cell strings, and each of the cell strings comprising at least one ground selection transistor, multiple memory cells, and at least one string selection transistor stacked in a direction perpendicular to the substrate. The nonvolatile memory device further comprises a string selection controller electrically connected to the mats through the string selection lines and configured to provide multiple string selection signals respectively corresponding to the string selection lines. Each of the string selection lines is connected with only one of the mats and the string selection signals are controlled independent from one another to independently select or unselect cell strings of different mats.

Owner:SAMSUNG ELECTRONICS CO LTD

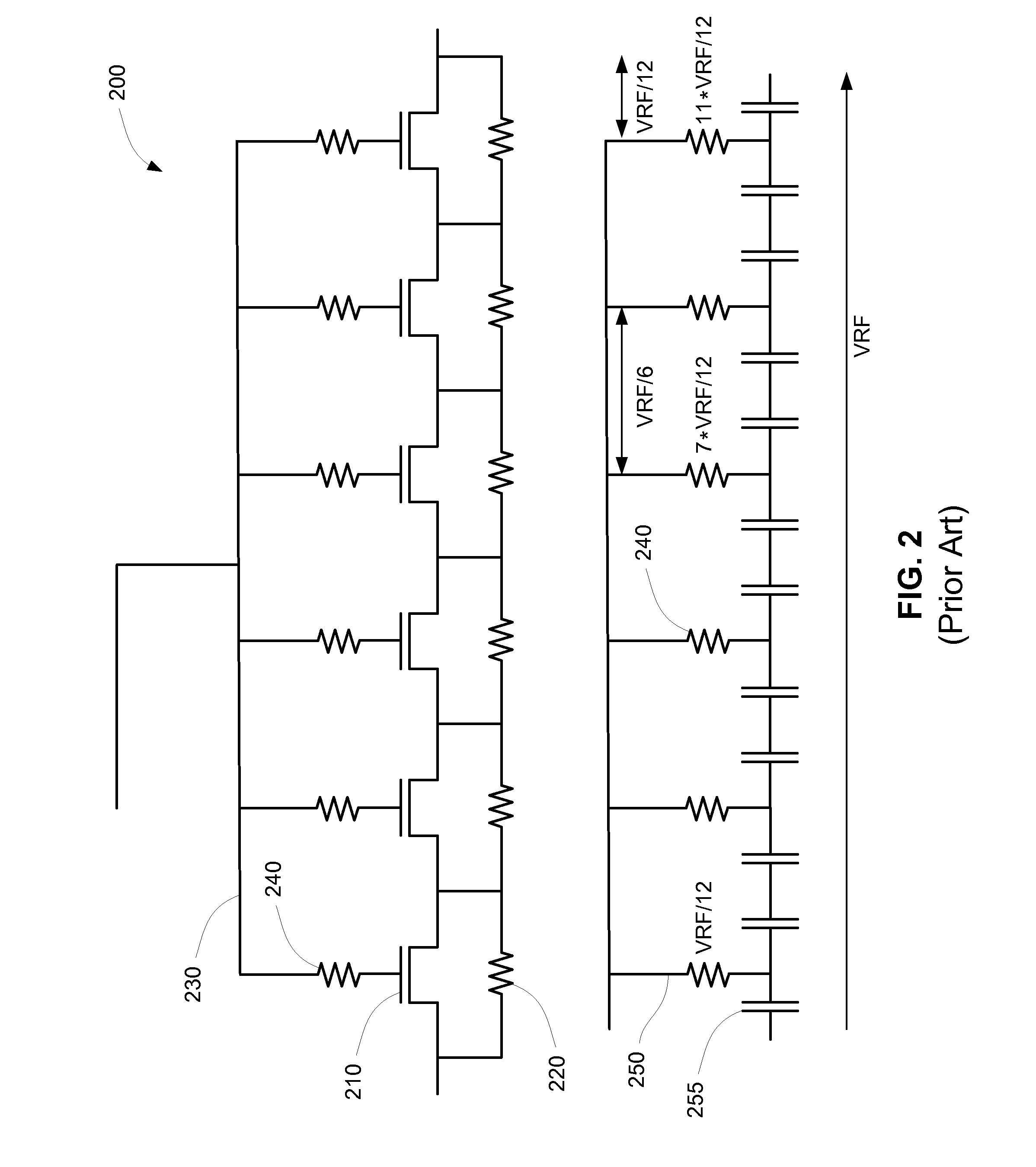

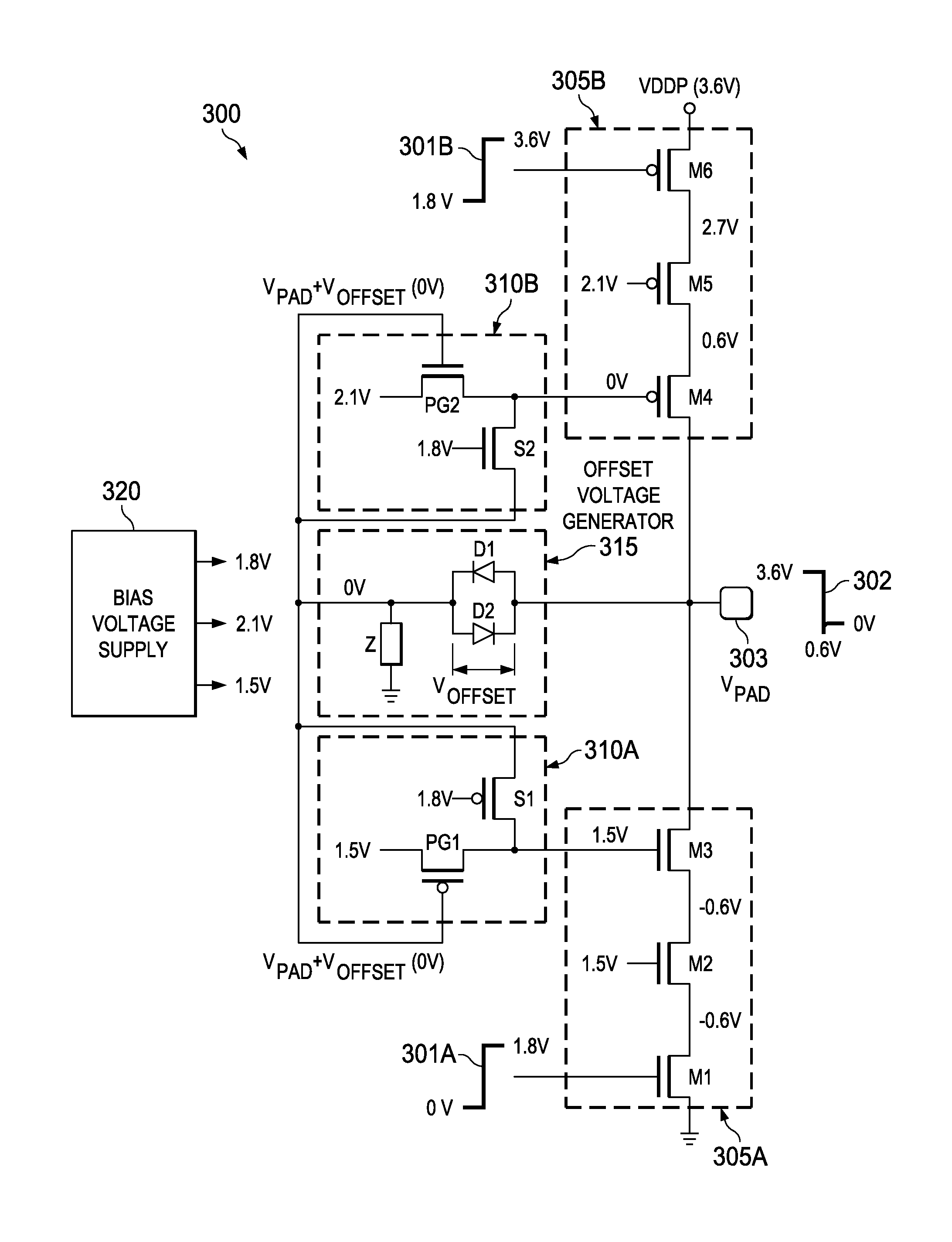

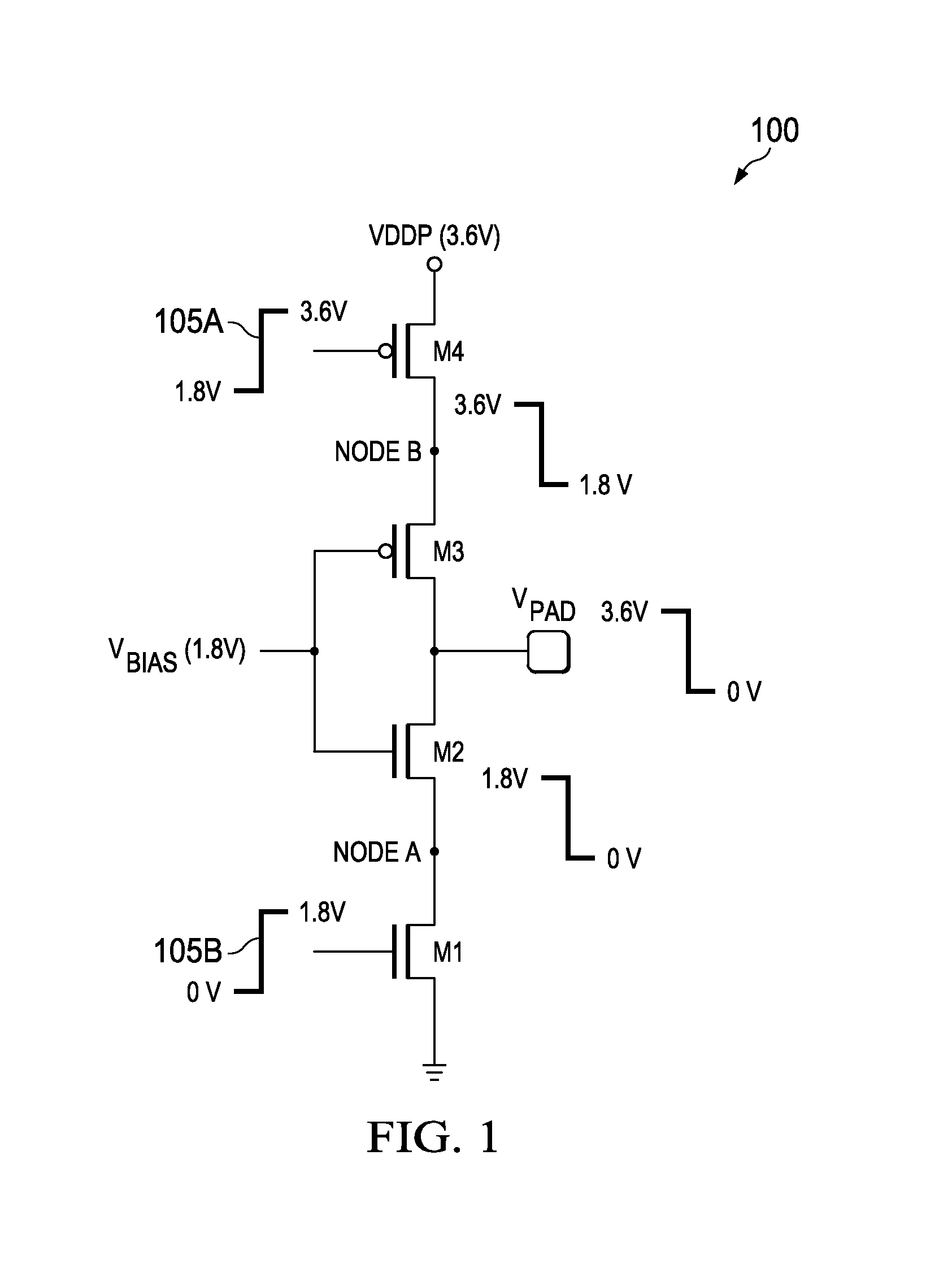

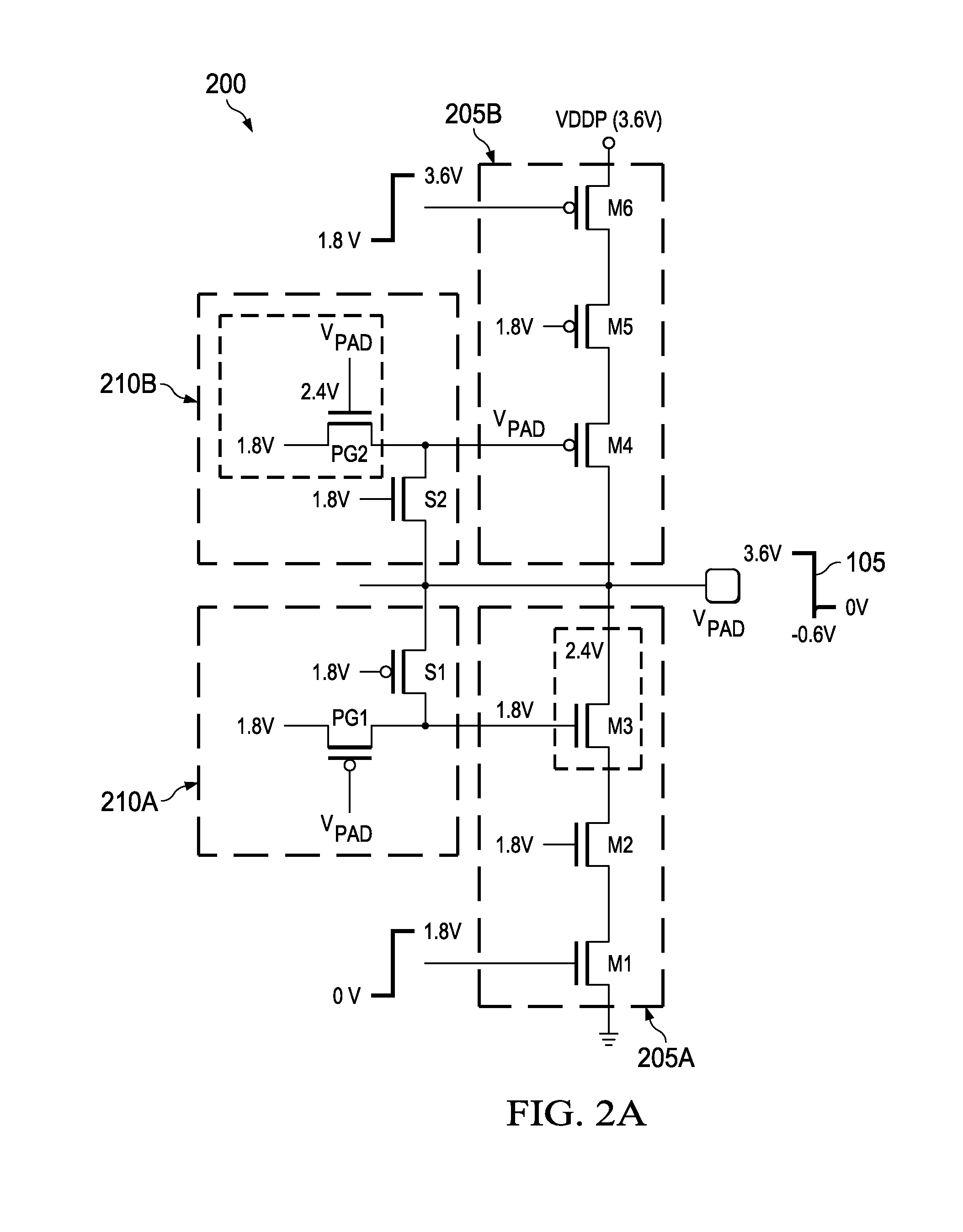

Oxide stress reduction for a cascode stack circuit

ActiveUS8860497B1Reduced oxide stressReduce oxidative stressTransistorApparatus without intermediate ac conversionVoltage generatorCascode

A reduced oxide stress cascode stack circuit includes a cascade transistor stack and dynamic bias circuits that supply an output voltage having a magnitude greater than an oxide reliability voltage of their component transistors. The reduced oxide stress cascode stack circuit also includes an offset voltage generator that provides an offset voltage based on a transient extreme of the output voltage, wherein the offset voltage is applied to the cascade transistor stack and the dynamic bias circuits to reduce component transistor voltages commensurate with the oxide reliability voltage. The reduced oxide stress cascode stack circuit further includes a bias voltage supply that modifies a bias voltage value of the cascade transistor stack and dynamic bias circuits by an amount proportional to the offset voltage. A method of reducing oxide stress in a cascode stack circuit is also provided.

Owner:NVIDIA CORP

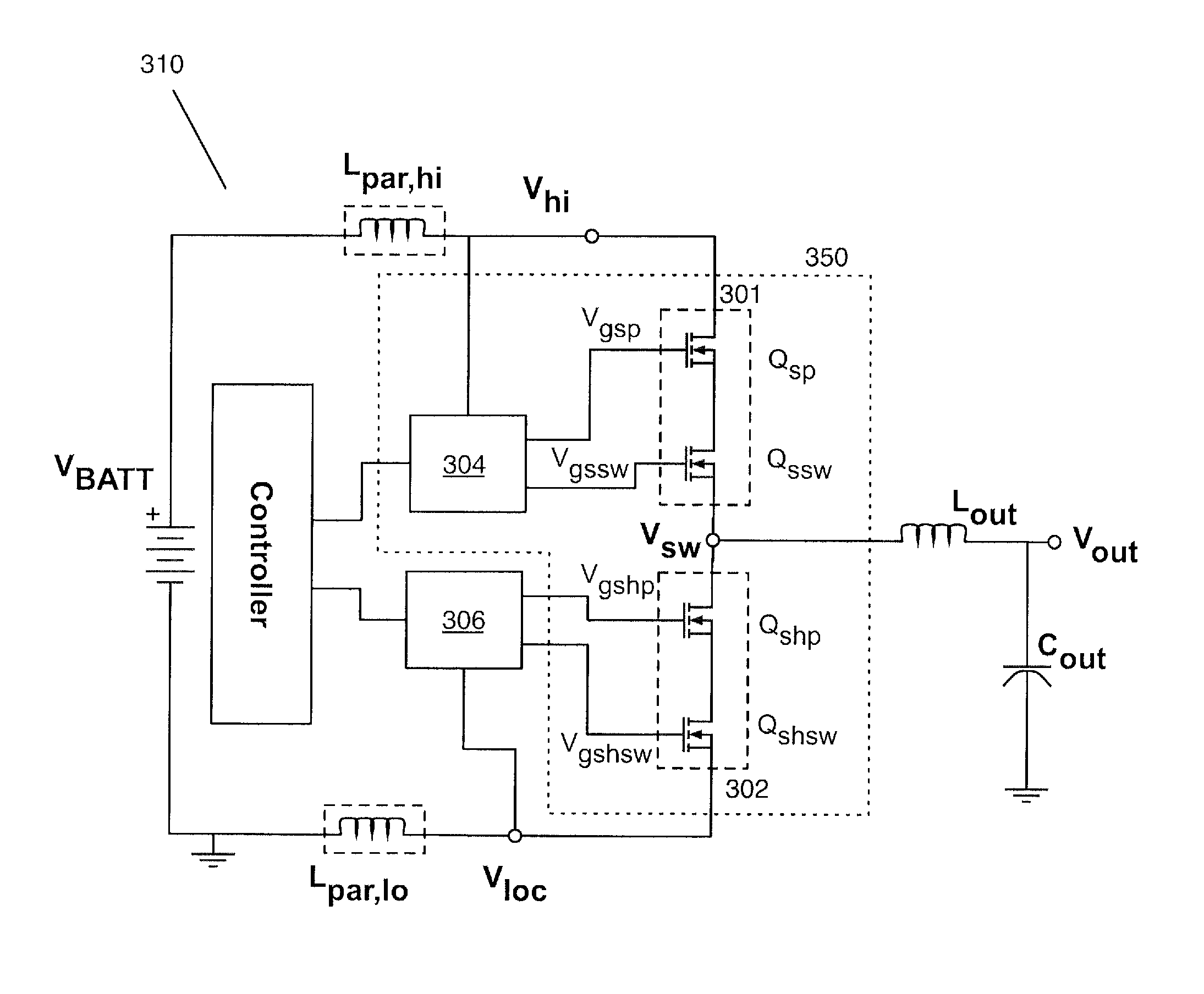

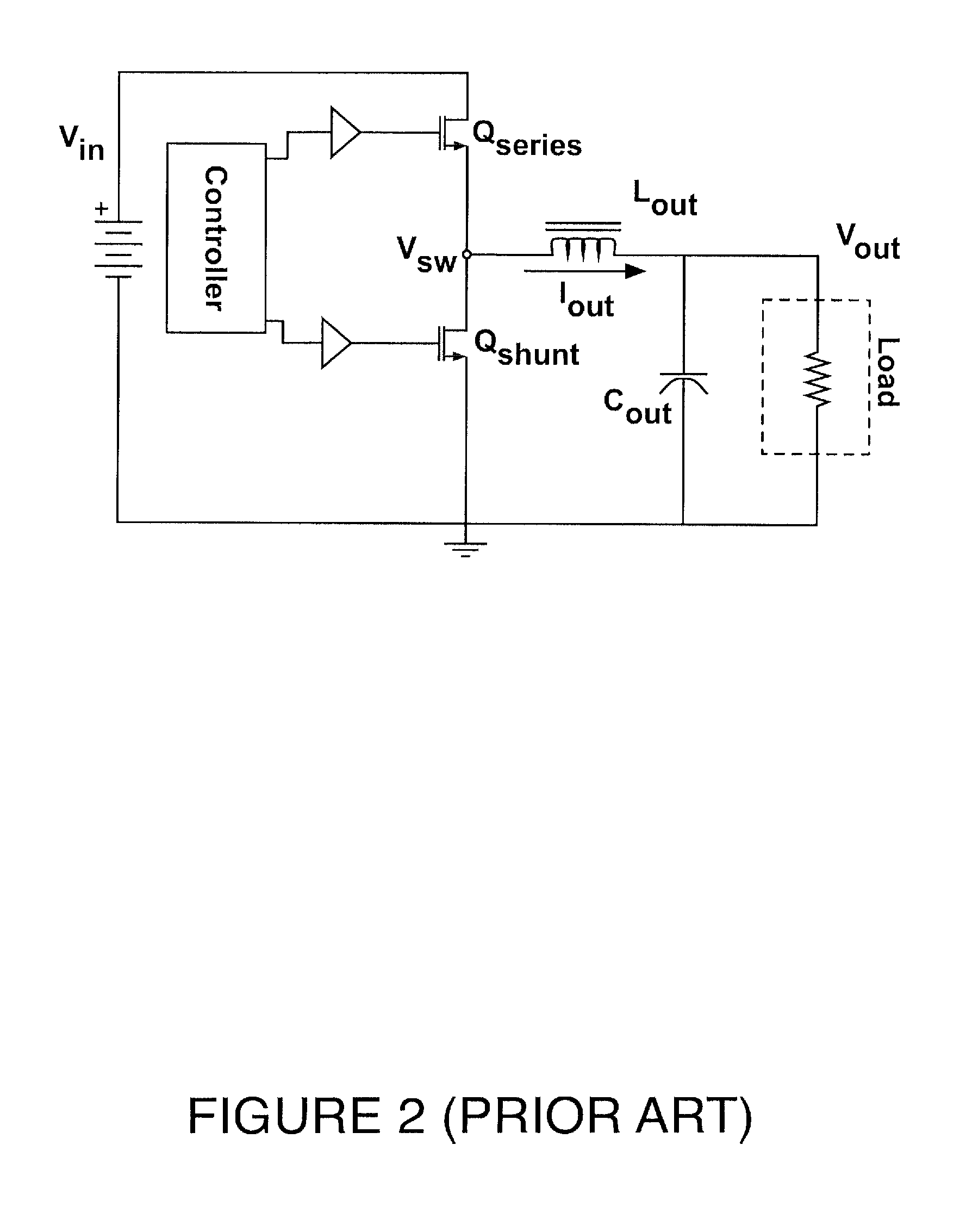

Stacked NMOS DC-to-DC power conversion

Embodiments for at least one method and apparatus of generating a regulated voltage are disclosed. One method includes generating the regulated voltage though controlled closing and opening of a series switch element and shunt switch element, the series switch element being connected between a first voltage supply and a common node, and the shunt switch being connected between the common node and a second supply voltage. The series switch element includes an NMOS series switching transistor stacked with an NMOS series protection transistor, and closing the series switch element during a first period includes applying a switching gate voltage to a gate of the NMOS series switch transistor of the series switch element, wherein the switching gate voltage has a voltage potential of at least a threshold voltage greater than a voltage potential of the common node. The shunt switch element includes an NMOS shunt switching transistor stacked with an NMOS shunt protection transistor, and the shunt switch element is closed during a second period.

Owner:R2 SEMICON