Fast read port for register file

a register file and read port technology, applied in information storage, static storage, digital storage, etc., can solve the problems of increasing the size and complexity of the overall memory array of pullup stack replication, and achieve the effect of low input loading, minimal likelihood of upsetting the data content of memory cells, and rapid read respons

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Benefits of technology

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

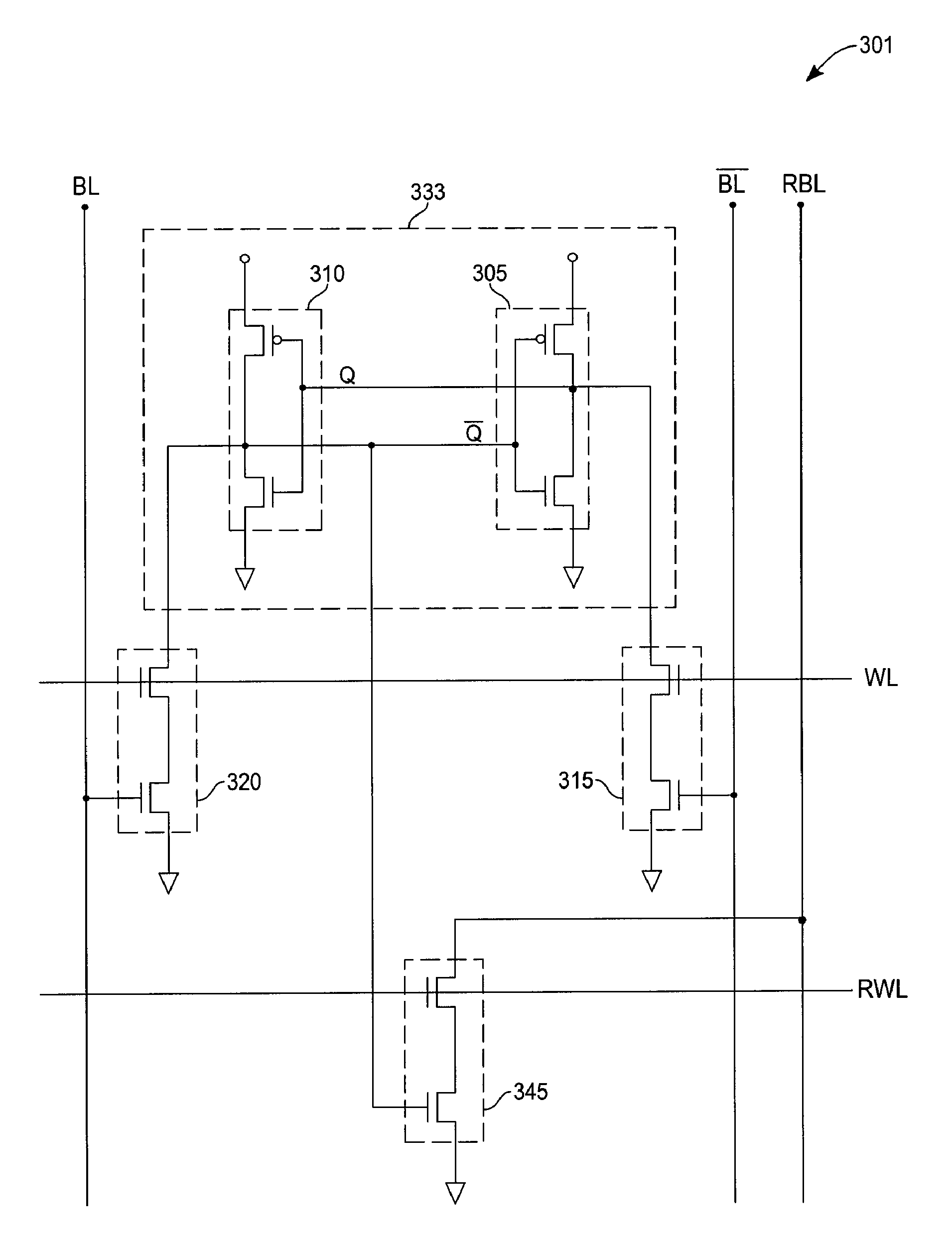

[0024] With reference to FIG. 3A, a first CMOS inverter 305 is cross-coupled with a second CMOS inverter 310 in an exemplary schematic diagram of a static memory cell 301. The first and second CMOS inverters 305, 310 form a memory cell latch loop 333 of a static RAM cell. A first output of the memory cell latch loop Q and a second output of the memory cell latch loop Q are formed by the outputs of the first and second CMOS inverters 305, 310 respectively. The first output of the memory cell latch loop Q connects to an output drain of a first two-transistor stack 315. The second output of the memory cell latch loop Q connects to an output drain of a second two-transistor stack 320. The second output of the memory cell latch loop Q also connects to a data input of a third two-transistor stack 345. The first, second, and third two-transistor stacks 315, 320, 345 are shown, for example, as a series connection of NMOS transistors with common source-drain diffusion and conductive channels...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More