Integrated circuit structure with complementary field effect transistor and buried metal interconnect and method

a technology of integrated circuits and transistors, applied in the field of complementary field effect transistors, can solve the problems of quite complex signal connection to the source/drain region of the lower-level gaafets (e.g., )

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Benefits of technology

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

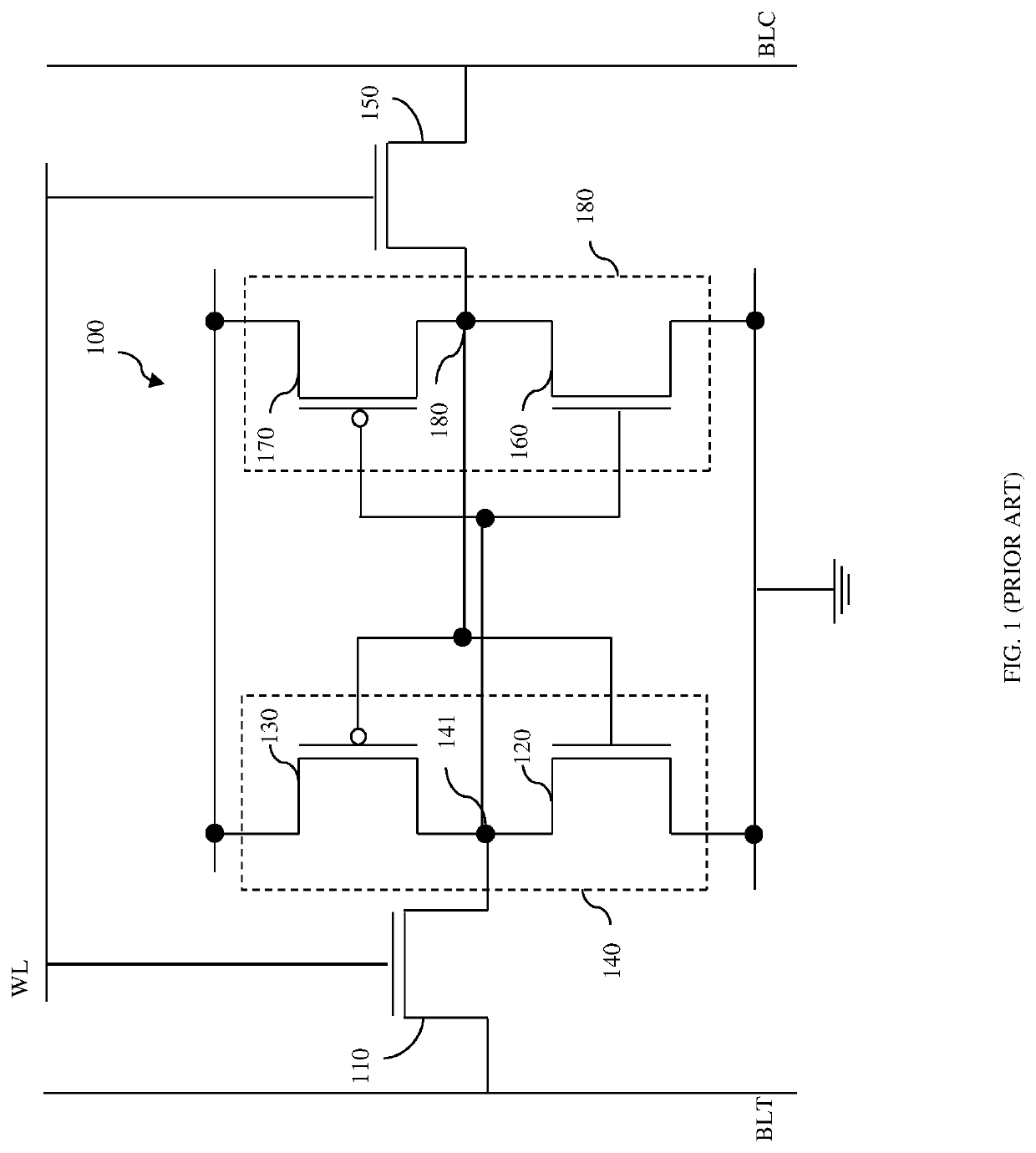

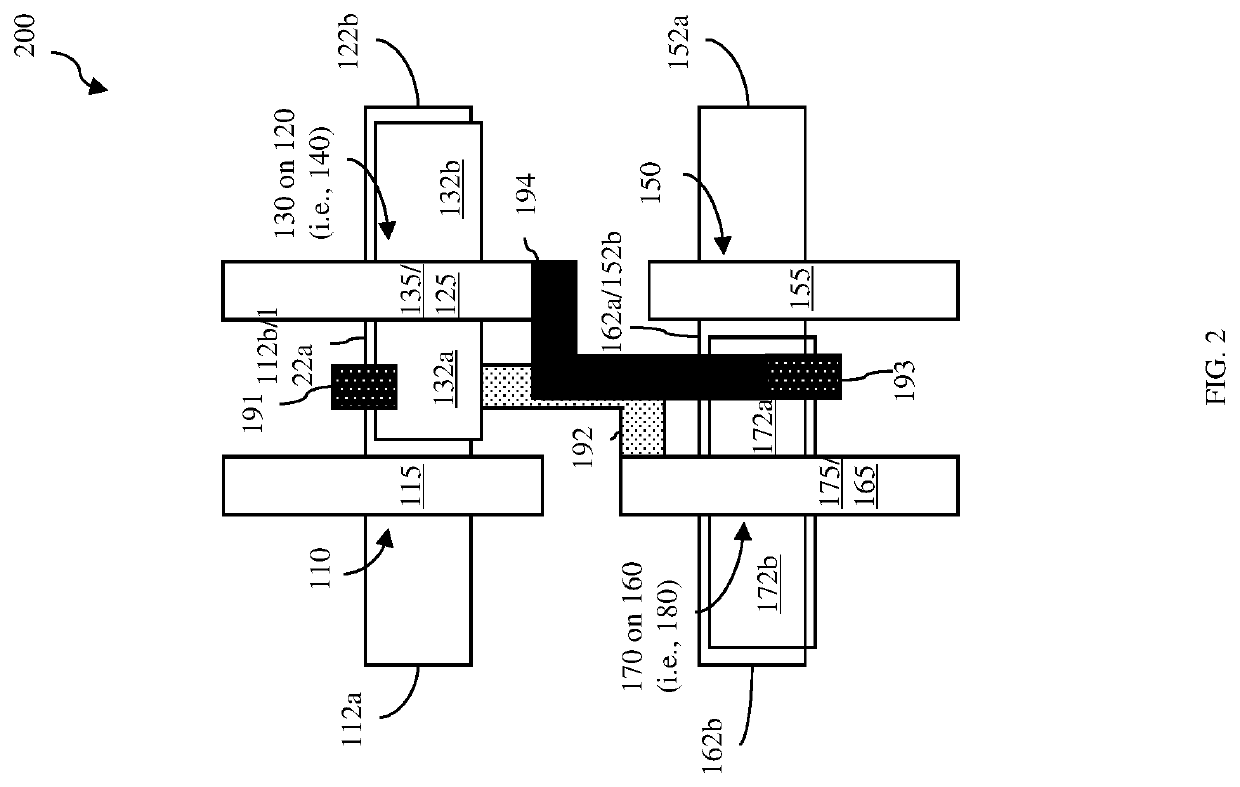

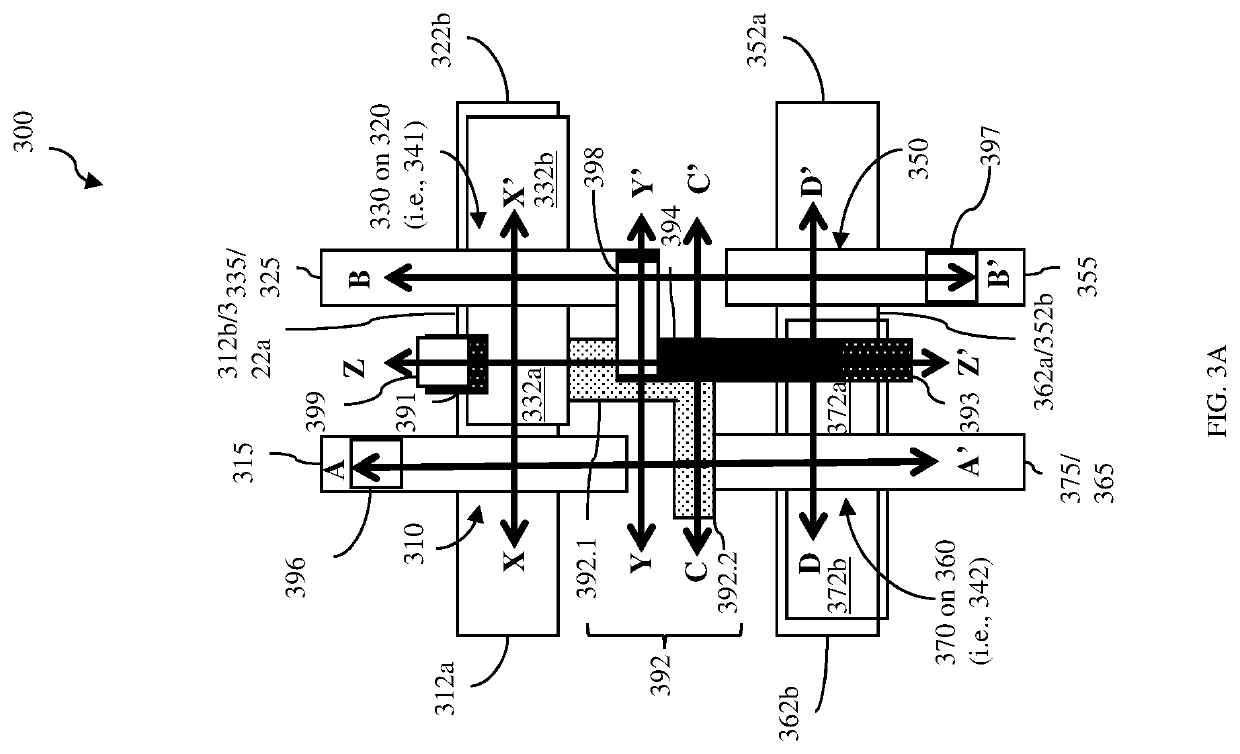

[0036]As mentioned above, a complementary field effect transistor (CFET) typically includes an N-type gate-all-around field effect transistor (GAAFET) on one-level, a P-type GAAFET on an adjacent level (i.e., above or below) and, a common gate that extends vertically across and wraps around the stacked channel regions of the N-type and P-type GAAFETs. Typically, the source / drain regions of the lower-level GAAFET will be electrically isolated from the source / drain regions of the upper-level GAAFET by one or more isolation layers. Such CFETs can, for example, be incorporated into a six-transistor (6T) static random access memory (SRAM) cell, one for each pair of pull-down and pull-up field effect transistors, respectively. While using CFETs can increase on-chip device density and reduce area consumption, providing signal connections to the source / drain regions of the lower-level GAAFETs (e.g., to achieve the cross-couple connection in an SRAM cell) can be quite complex.

[0037]For examp...

PUM

| Property | Measurement | Unit |

|---|---|---|

| work function | aaaaa | aaaaa |

| work function | aaaaa | aaaaa |

| work function | aaaaa | aaaaa |

Abstract

Description

Claims

Application Information

Login to View More

Login to View More