Patents

Literature

122results about How to "Increase effective width" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

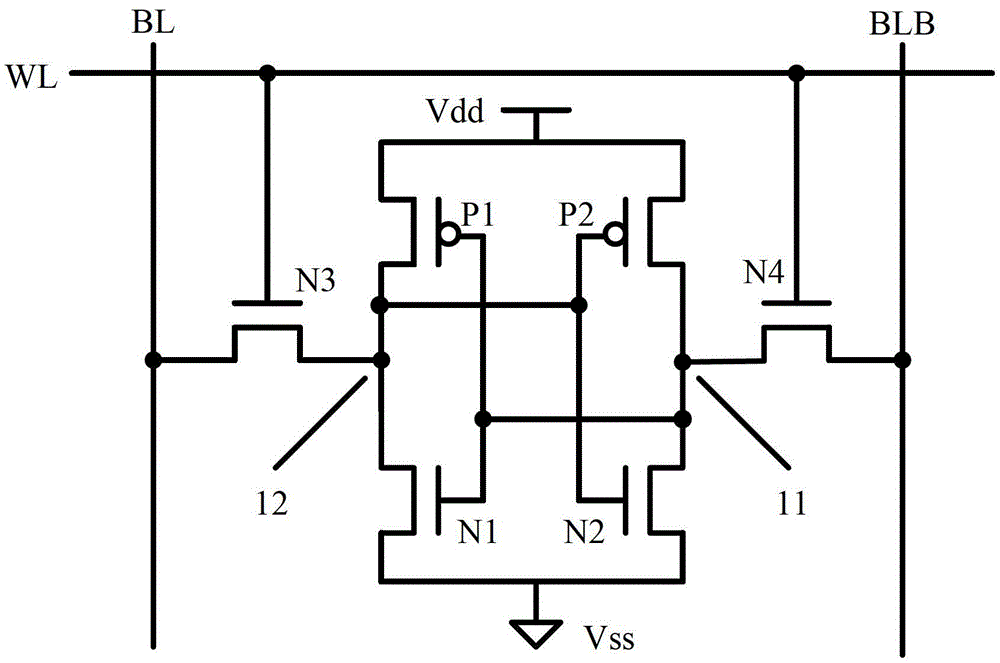

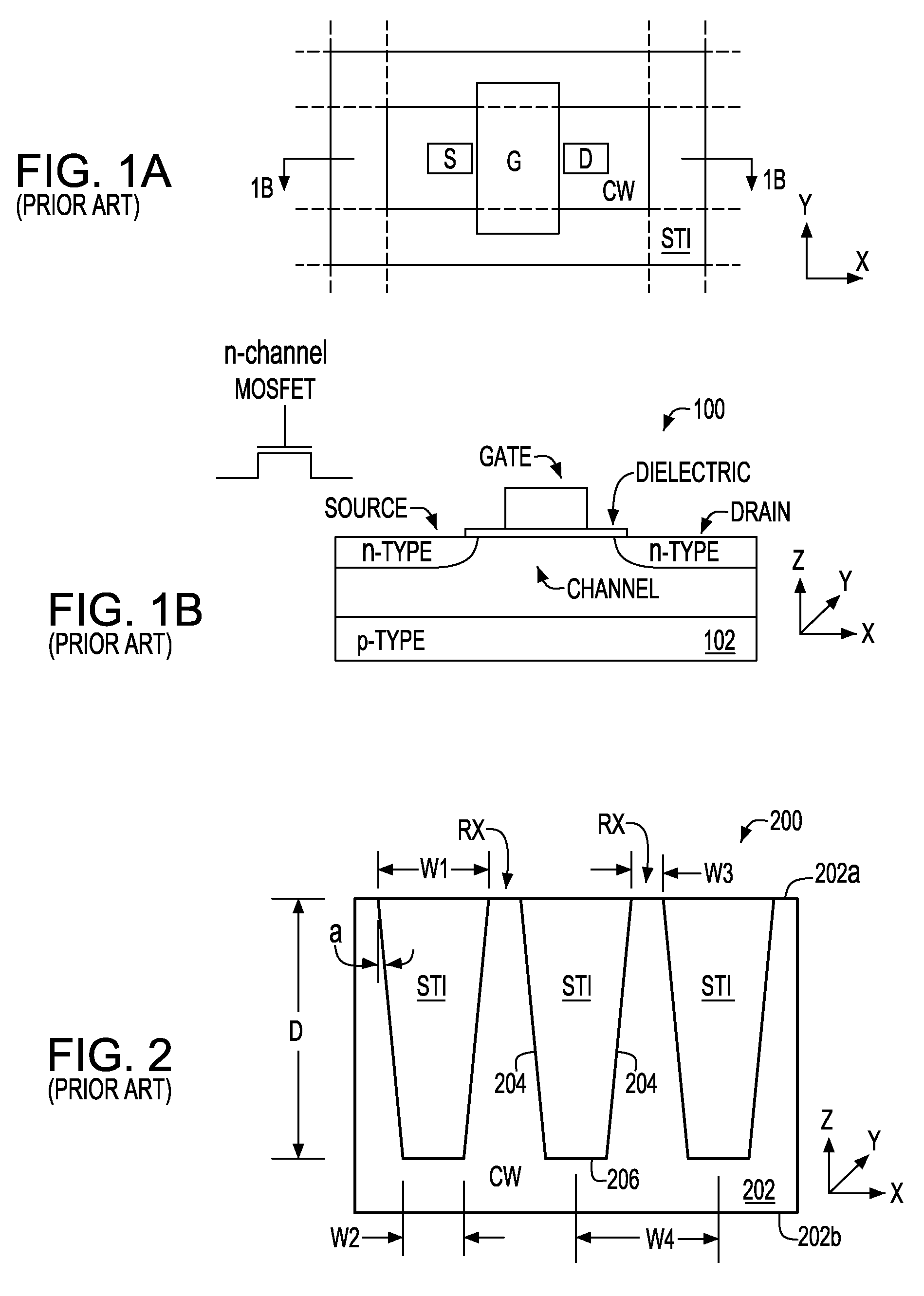

SRAM cell

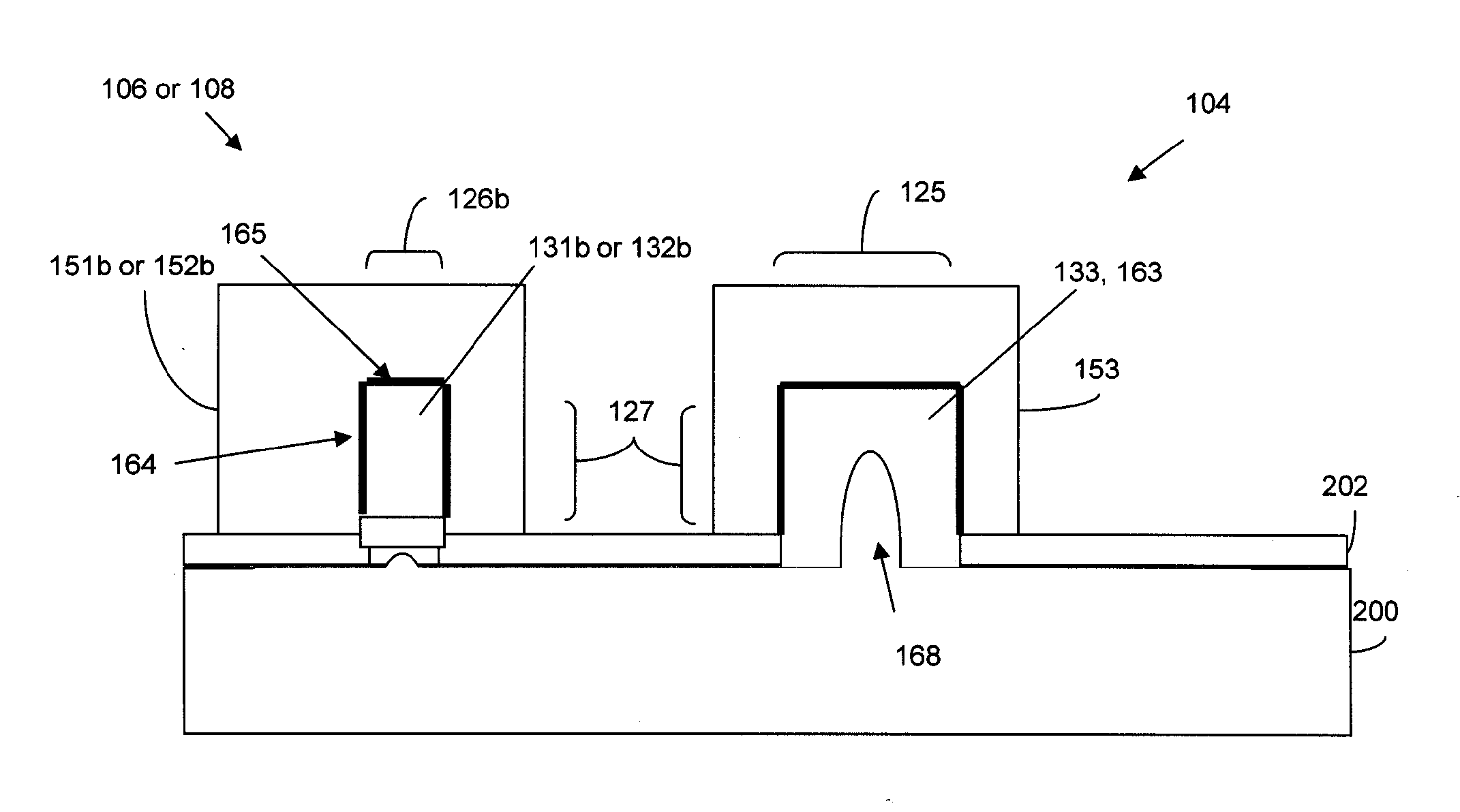

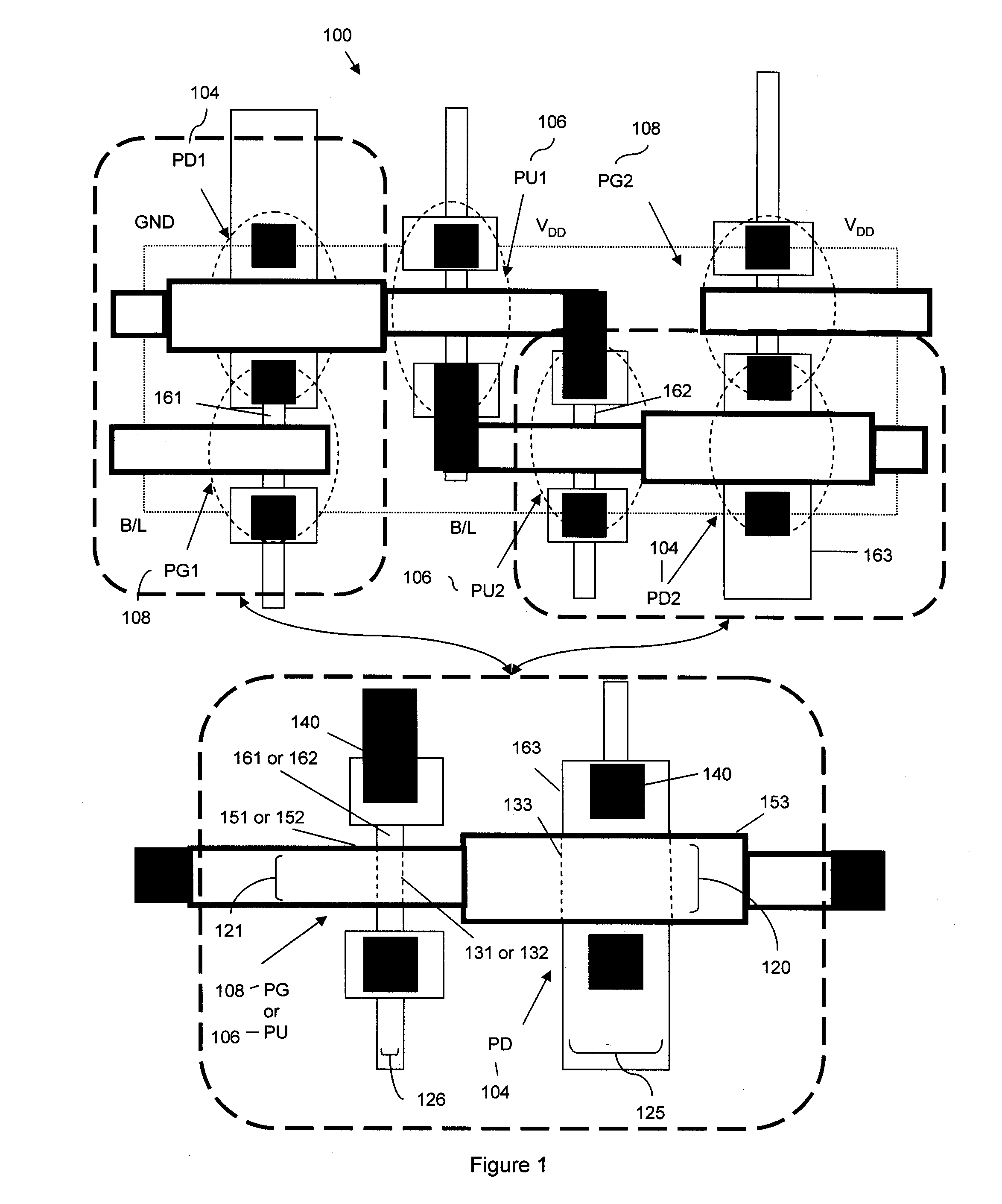

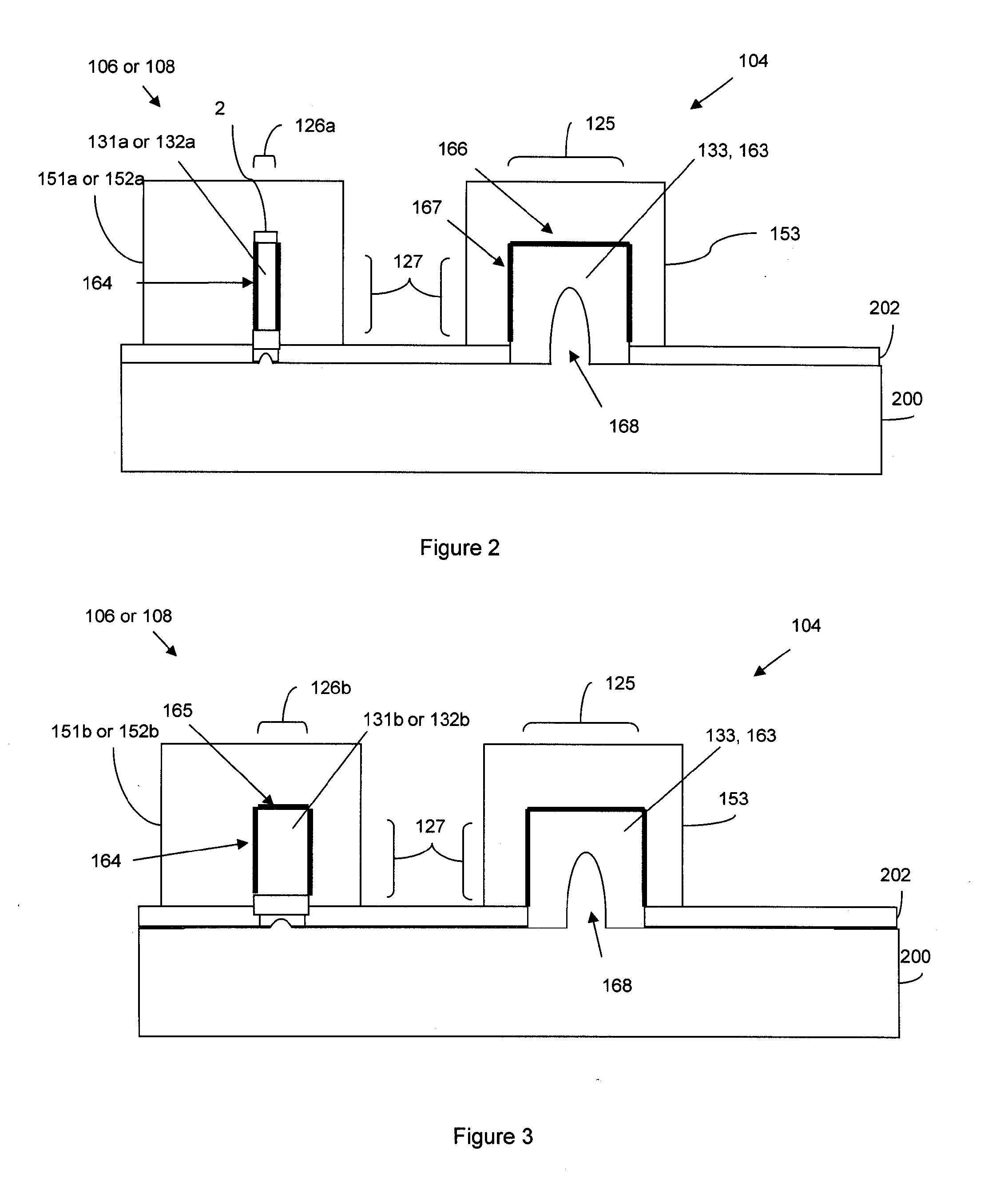

InactiveUS20070108528A1Increase effective widthImprove carrying capacityTransistorSolid-state devicesDriving currentEngineering

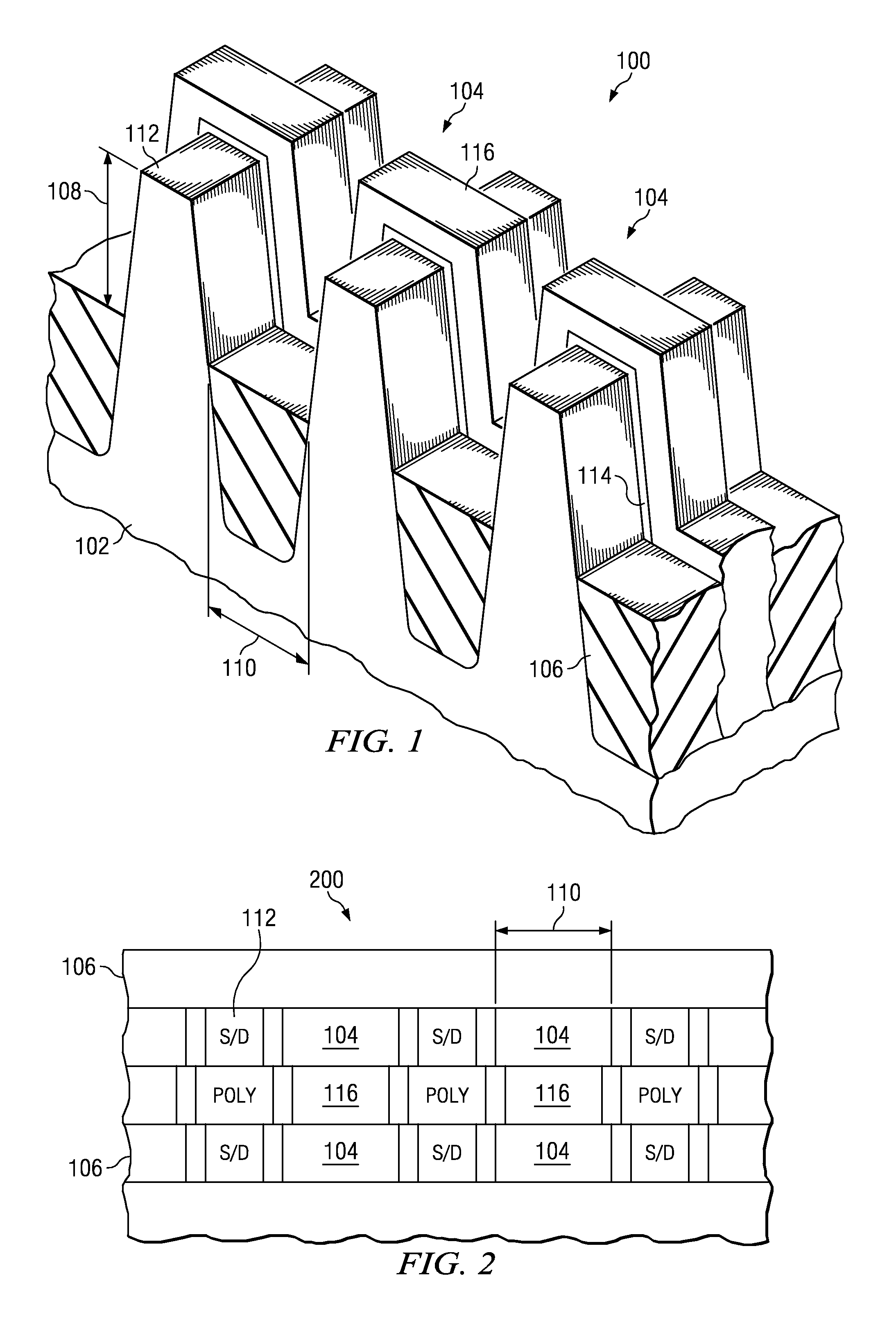

Disclosed is an SRAM cell on an SOI, bulk or HOT wafer with two pass-gate n-FETs, two pull-up p-FETs and two pull-down n-FETs and the associated methods of making the SRAM cell. The pass-gate FETs and pull-down FETs are non-planar fully depleted finFETs or trigate FETs. The pull-down FETs comprise non-planar partially depleted three-gated FETs having a greater channel width and a greater gate length and, thus, a greater drive current relative to the pass-gate and pull-up FETs. Additionally, for optimal electron mobility and hole mobility, respectively, the channels of the n-FETs and p-FETs can comprise semiconductors with different crystalline orientations.

Owner:IBM CORP

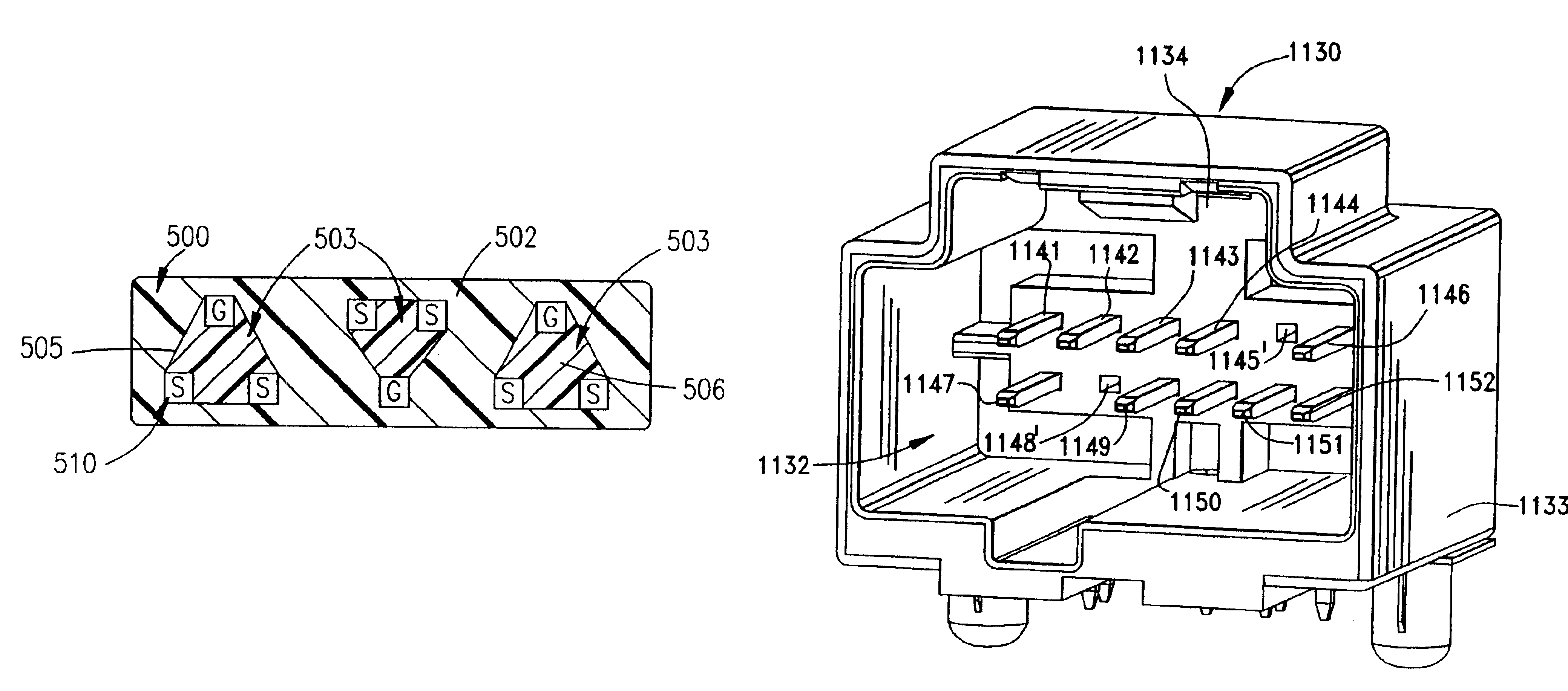

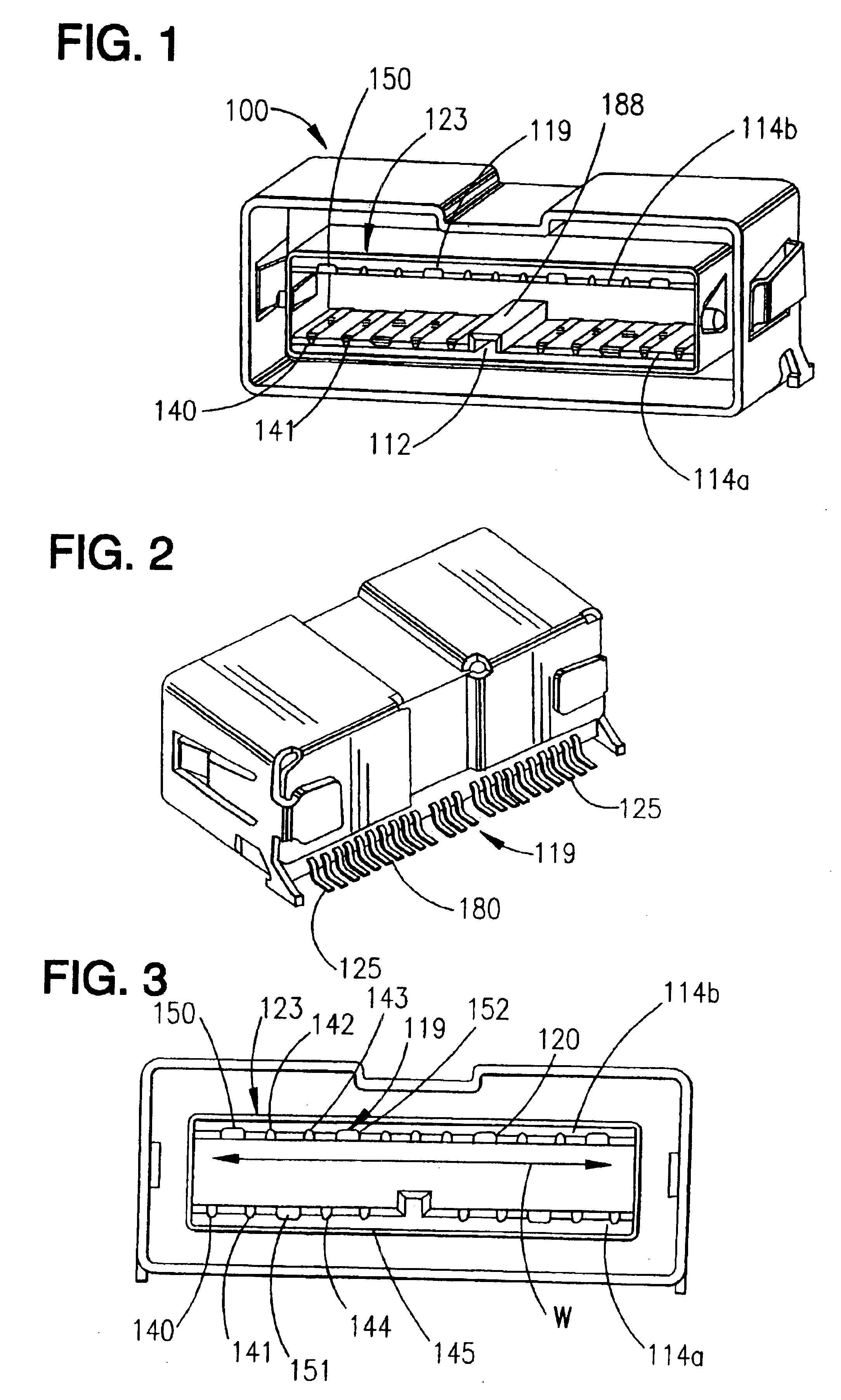

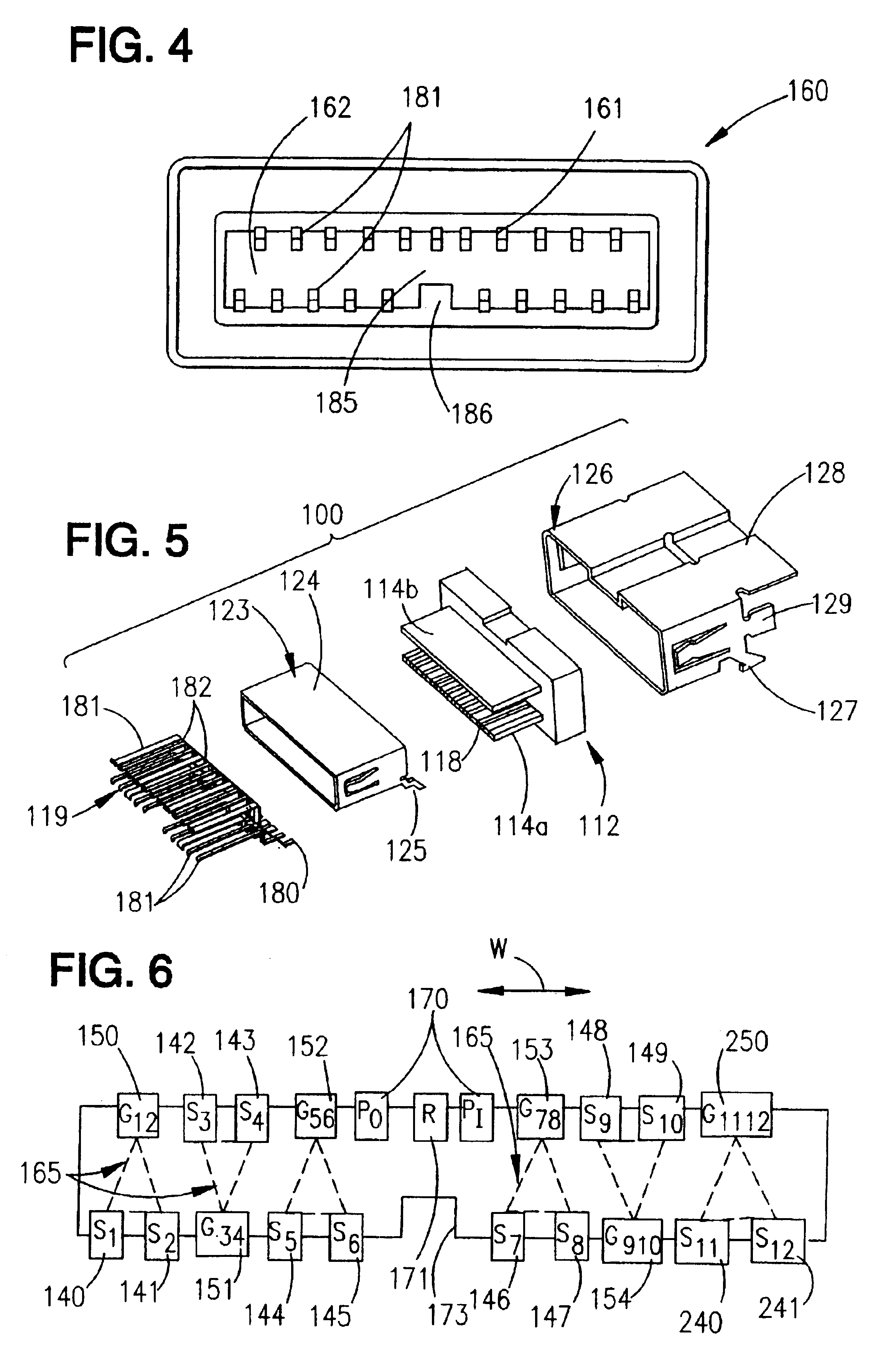

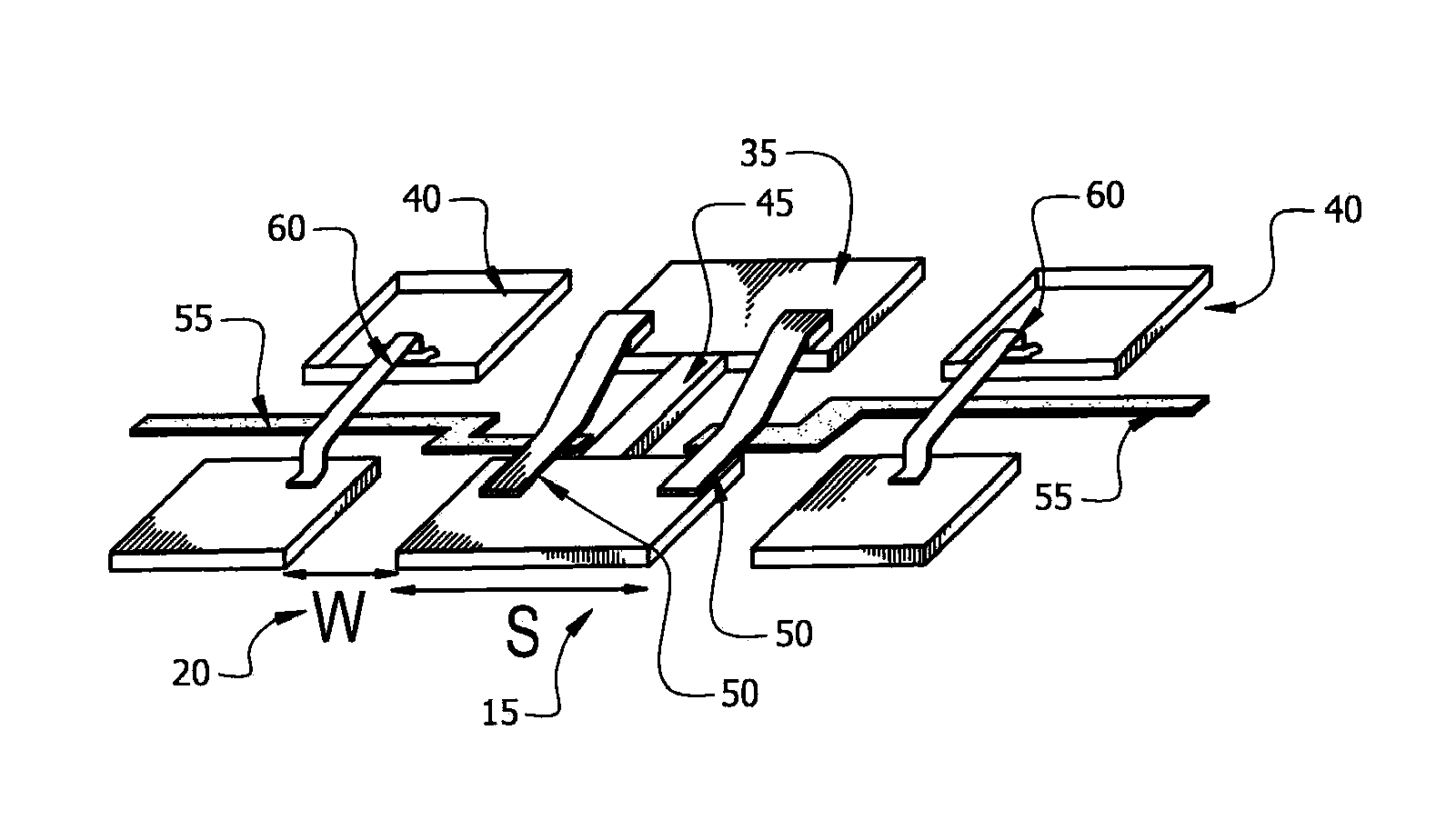

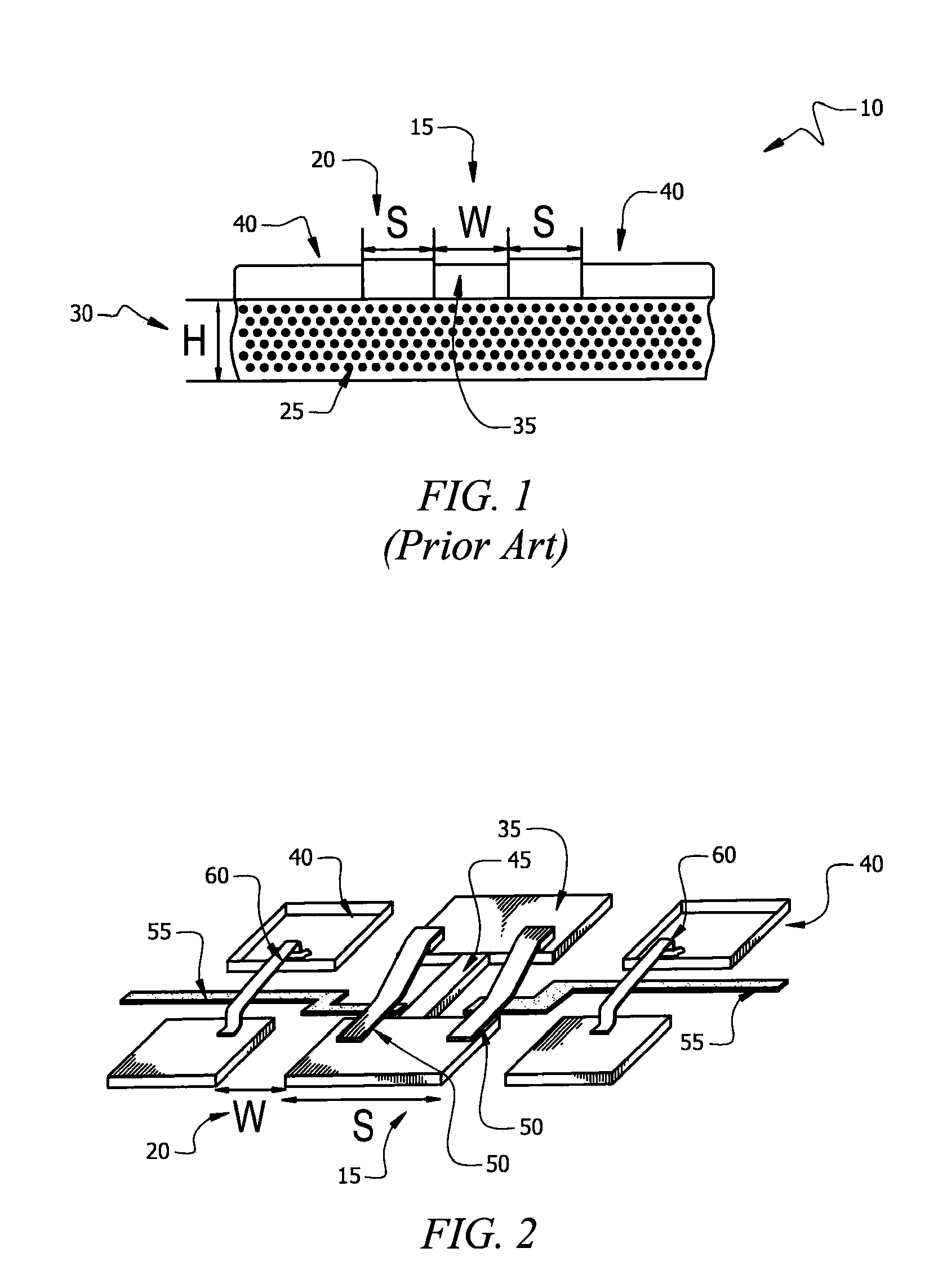

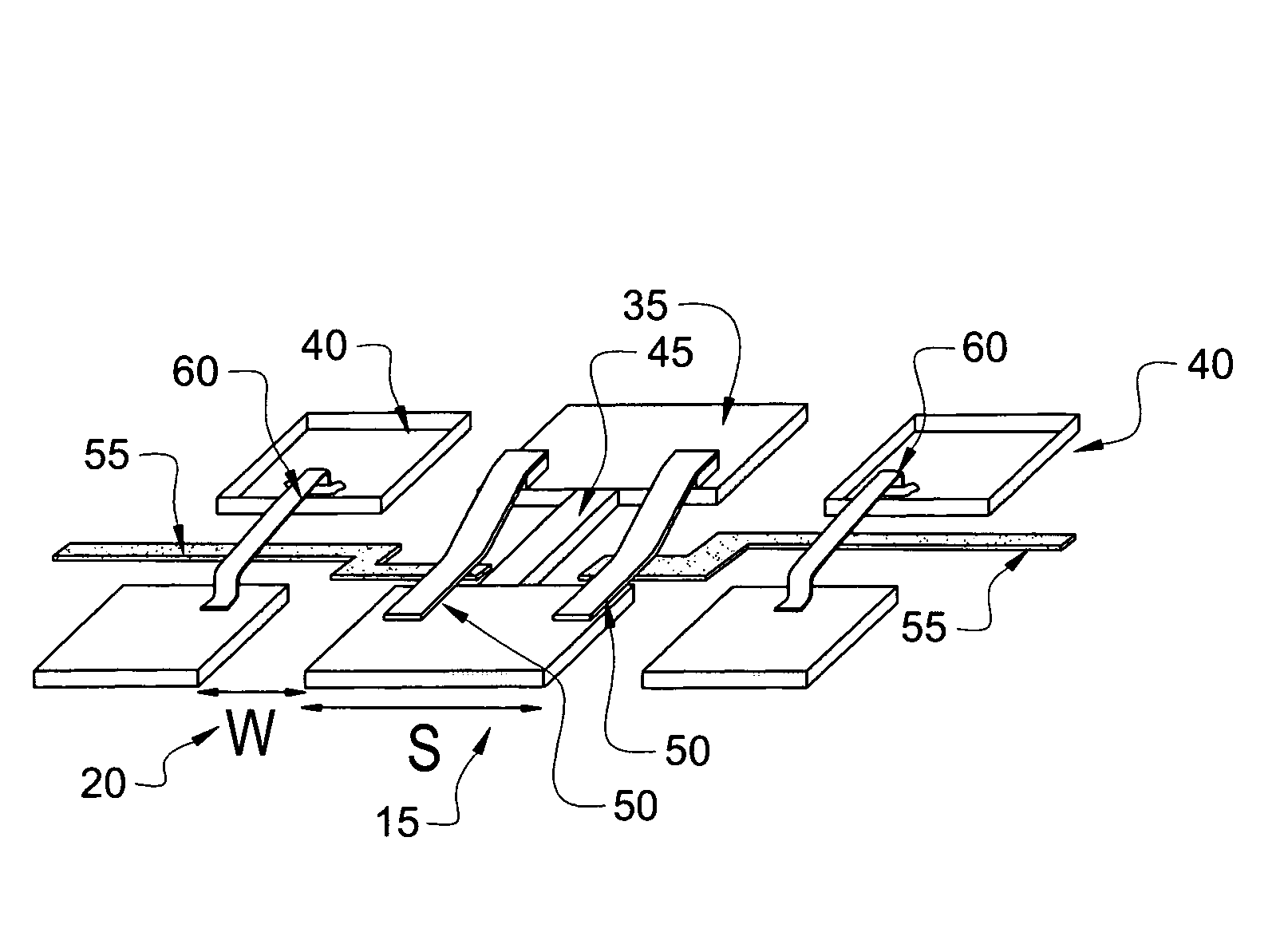

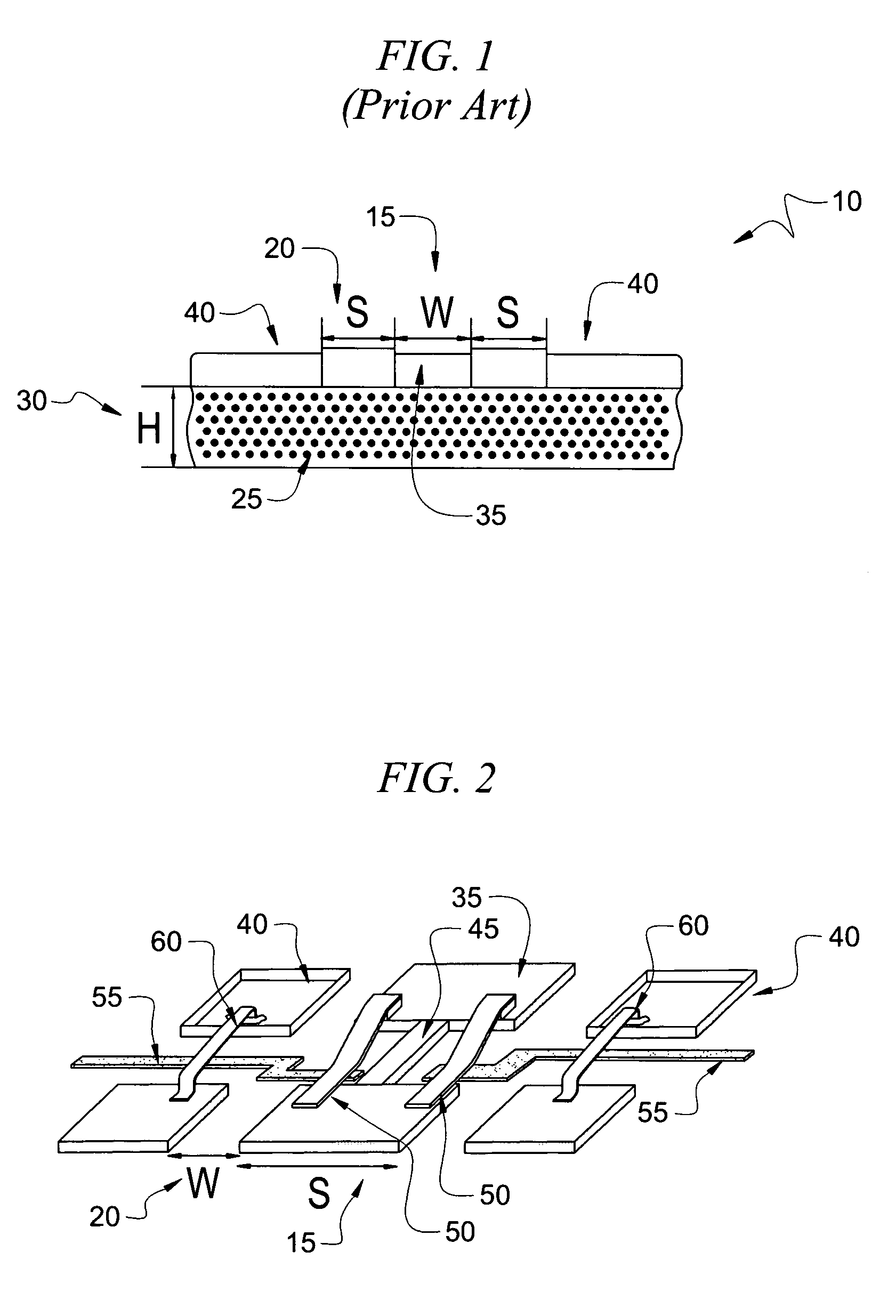

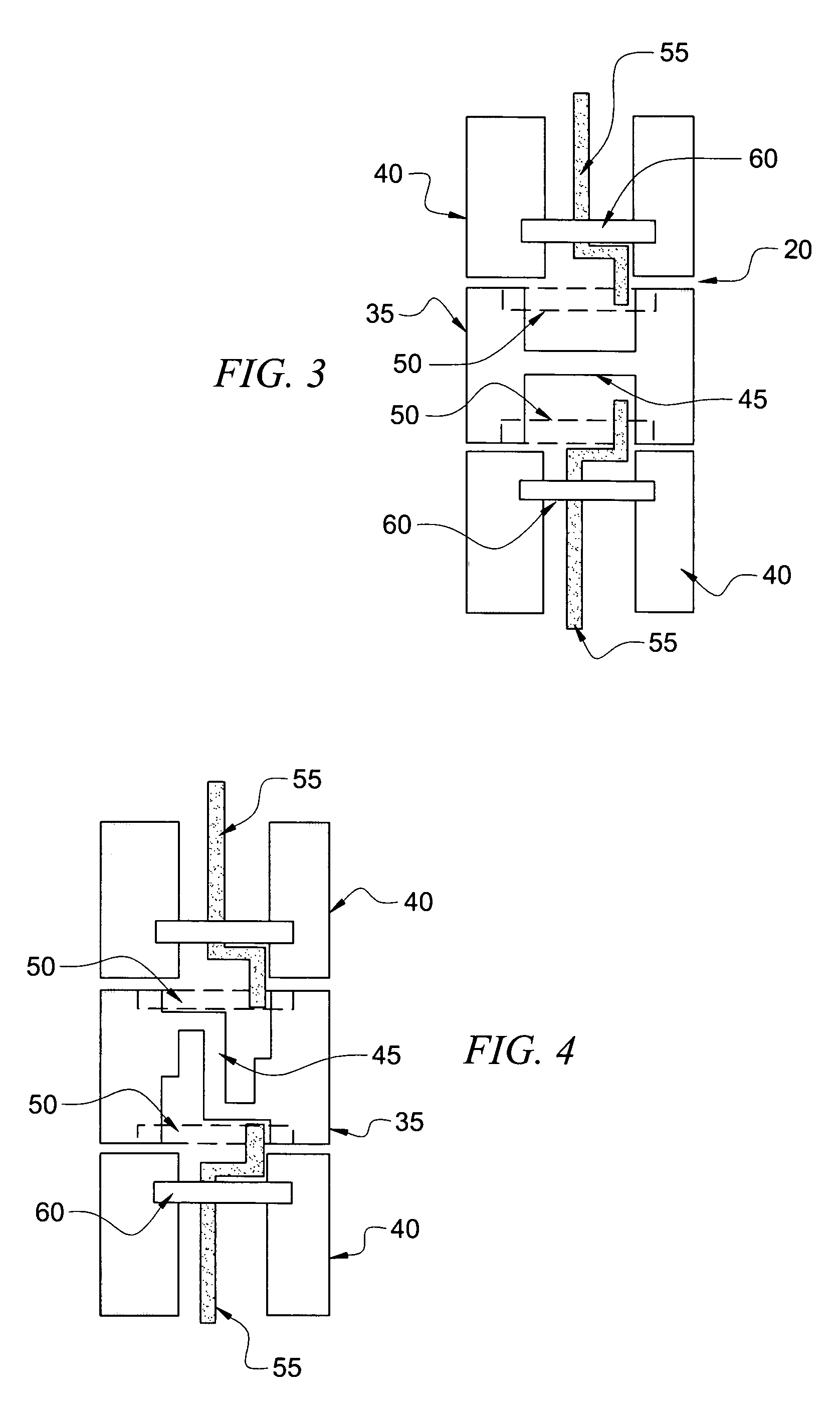

Impedance-tuned terminal contact arrangement and connectors incorporating same

InactiveUS6863549B2Impedance matchingIncrease effective widthPrinted circuitsCoupling protective earth/shielding arrangementsDifferential signalingEngineering

A terminal contact arrangement for a connector promotes reduction in deviation of the impedance of the connector when mated to an opposing connector and energized. The connector has an insulative housing with a plurality of terminal-receiving passages disposed in it. Conductive terminals are supported in some, but not all of the passages. The terminal contain distinct terminal sets that include a pair of differential signal terminals and at least two associated ground reference terminals. The two associated ground reference terminals are interconnected together so that electrically, they act as a single ground terminal having a width equal to the sum of the widths of the two connected ground reference terminals. The ground reference terminals of the sets are disposed in a single row of terminals, while the differential signal terminals of the same terminal set are disposed in another row of terminals spaced apart from the row of ground reference terminals. The differential signal terminals are separated from each other within their terminal row by an empty passage so that the two differential signal terminals of each terminal set are spaced farther apart from each other than they are spaced apart from their associated ground reference terminals.

Owner:MOLEX INC

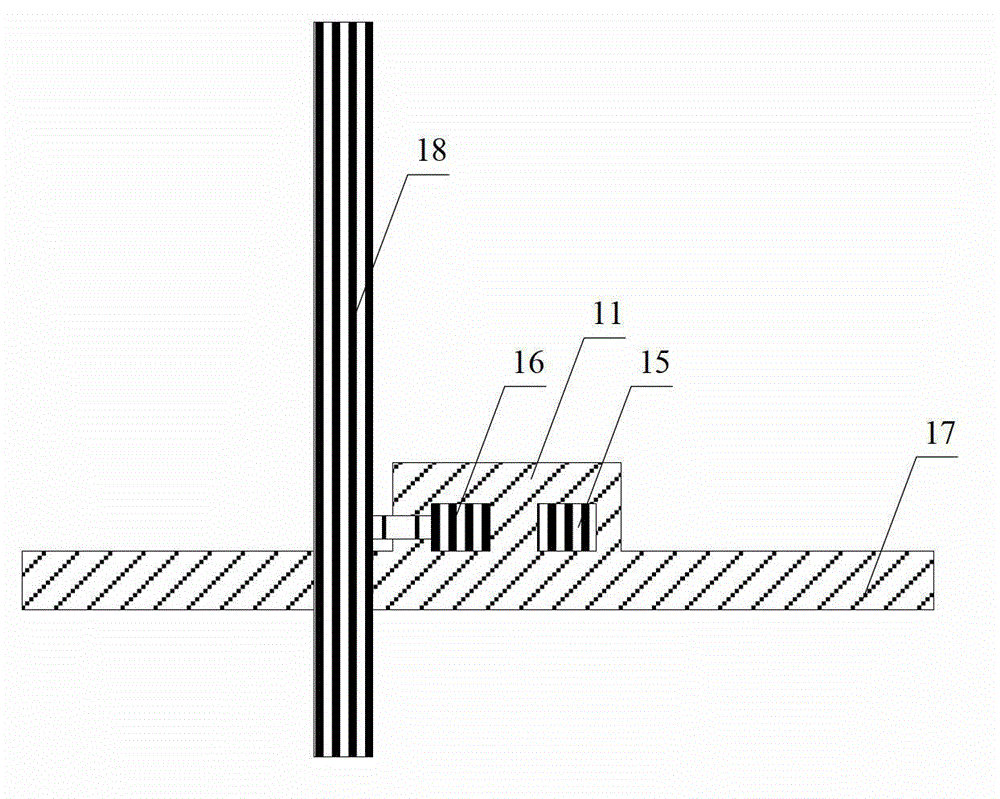

Active device and active device array substrate

InactiveUS20130240886A1Increase the on-currentEffectively improve ON-currentSolid-state devicesSemiconductor devicesEngineeringCommon gate

An active device and an active device array substrate are provided, wherein the active device array substrate includes a substrate and a plurality of active devices being located on the substrate, and at least one of the active devices includes a first thin film transistor and a second thin film transistor. The first thin film transistor is located on the substrate and has a first channel layer. The second thin film transistor stacks on the first thin film transistor, wherein the second thin film transistor has a second channel layer. The first thin film transistor and the second thin film transistor share a common gate electrode and the common gate electrode is located between the first channel layer and the second channel layer.

Owner:DONGGUAN MASSTOP LIQUID CRYSTAL DISPLAY +1

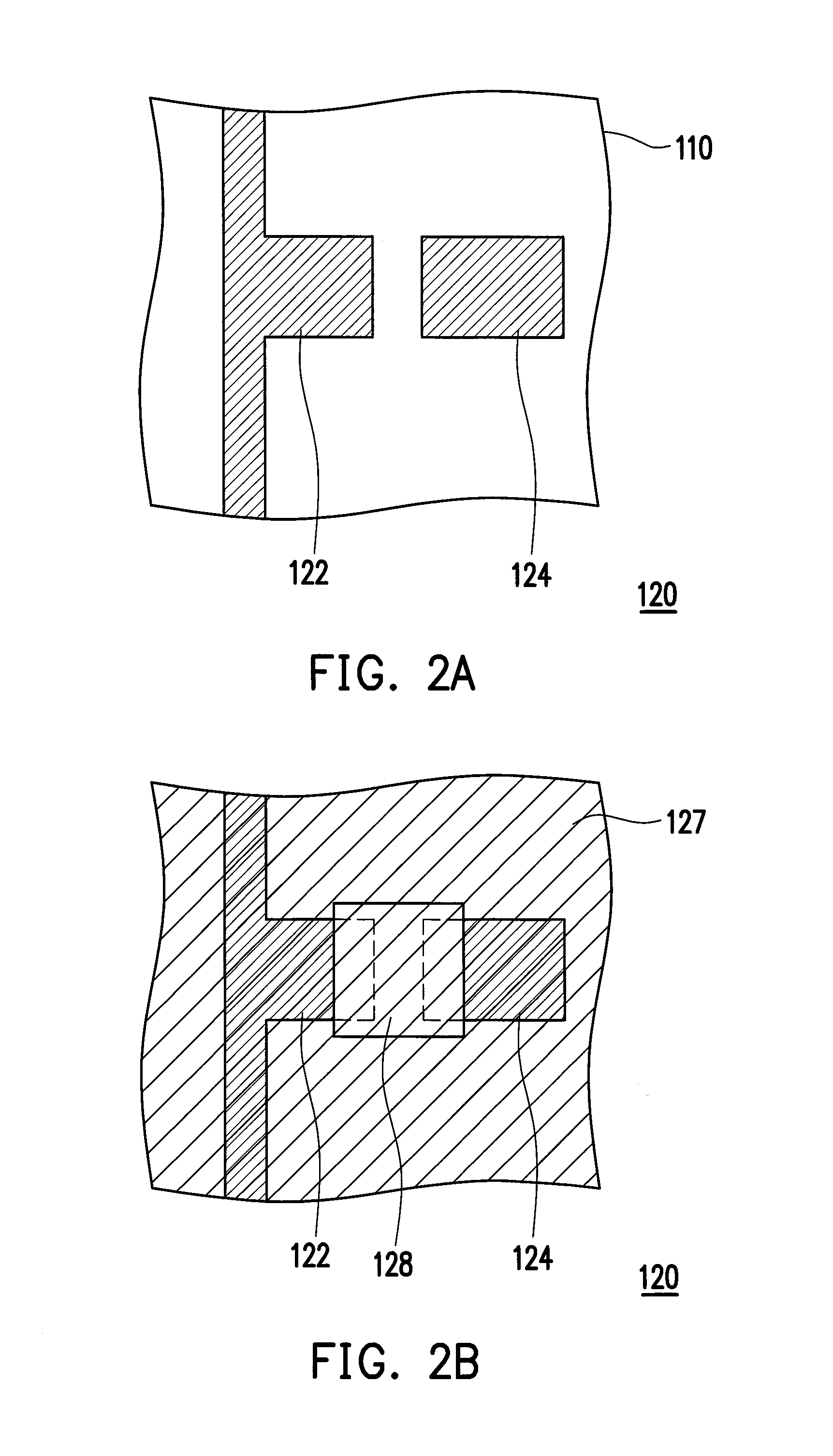

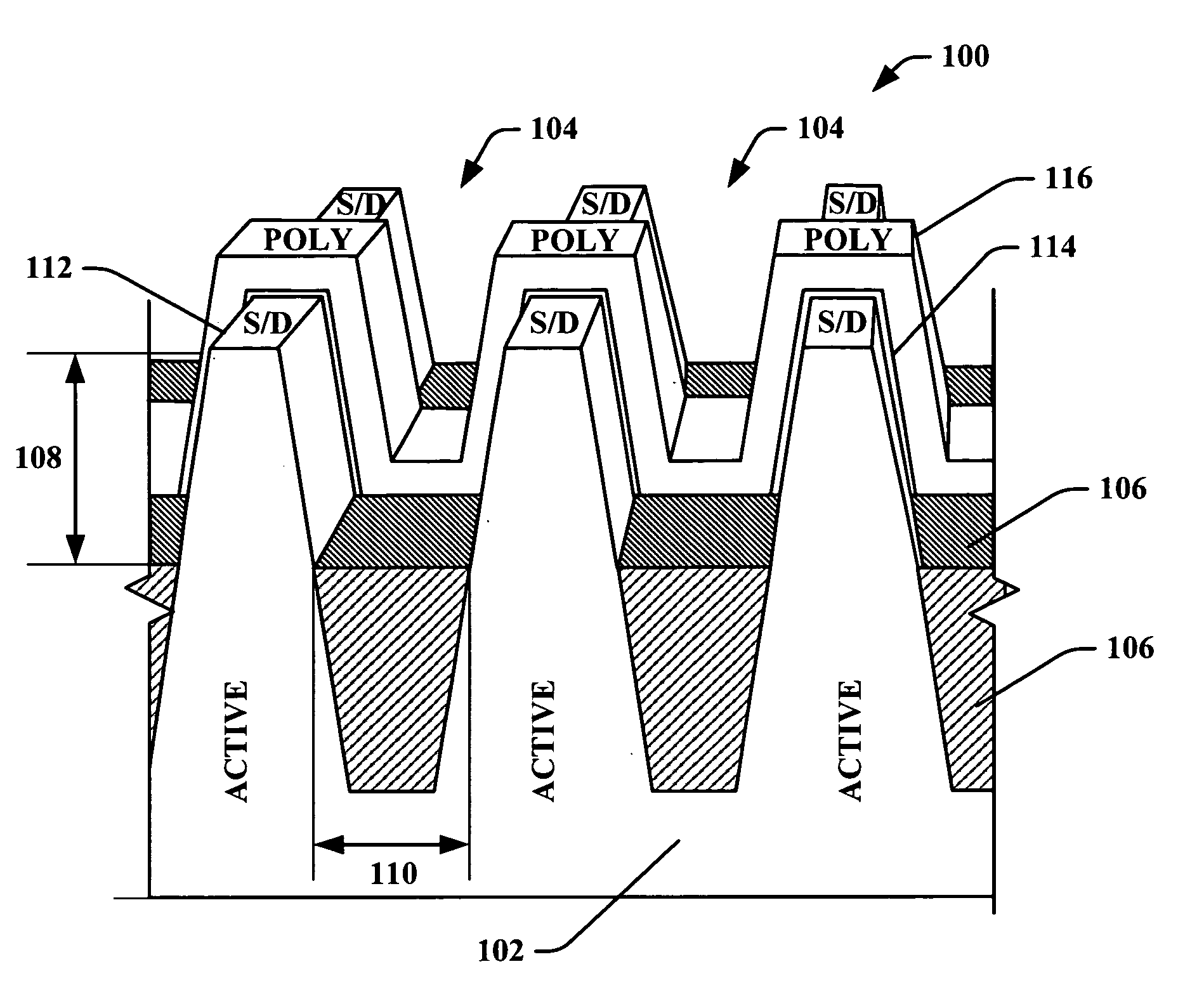

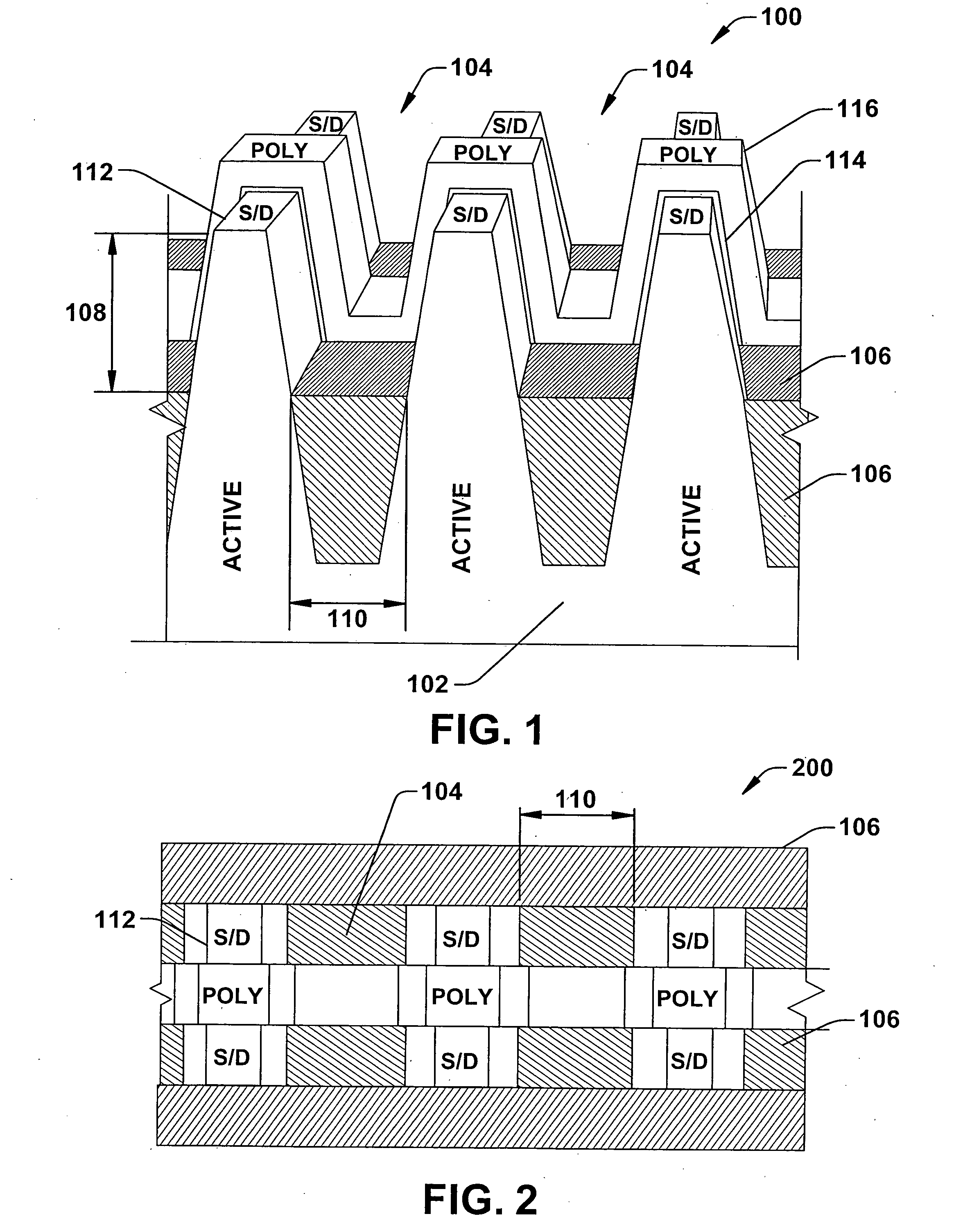

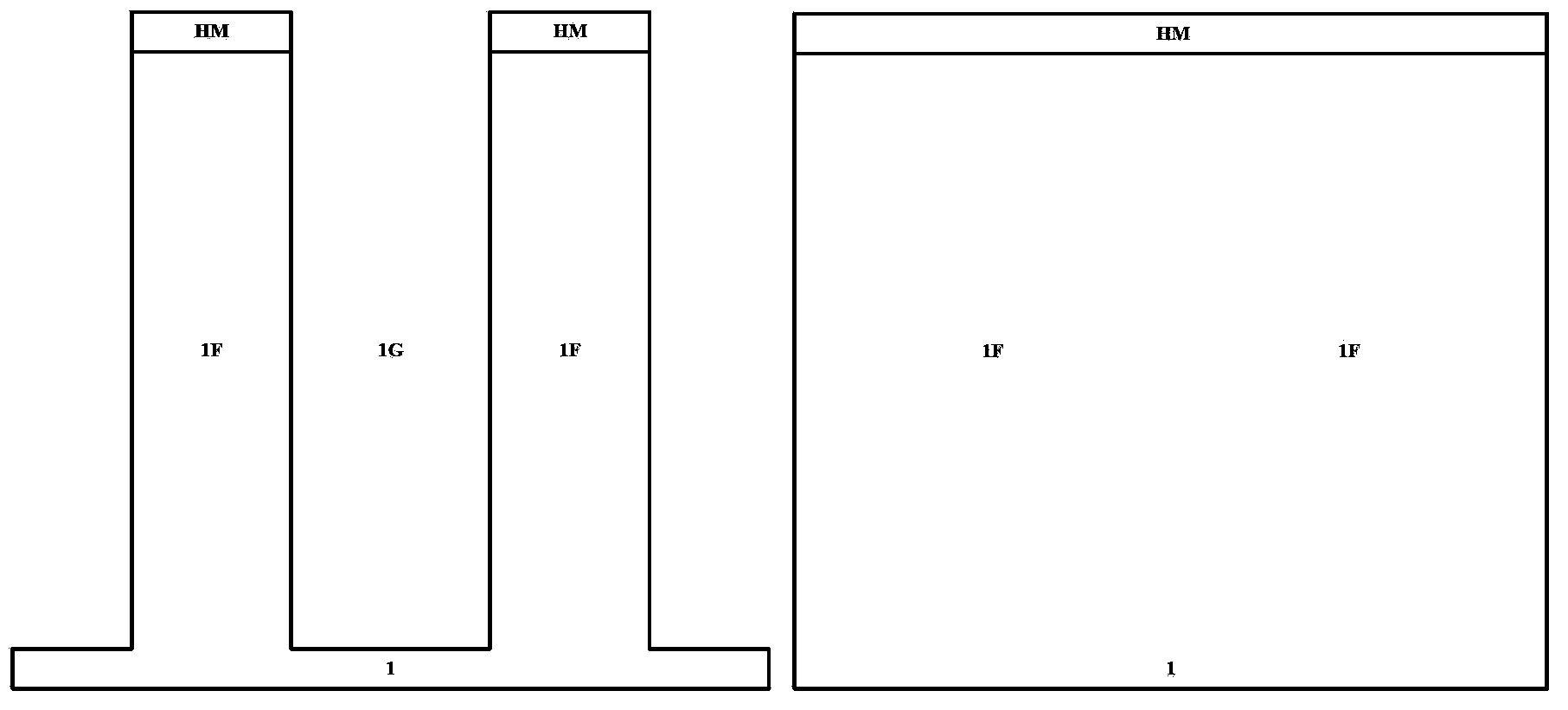

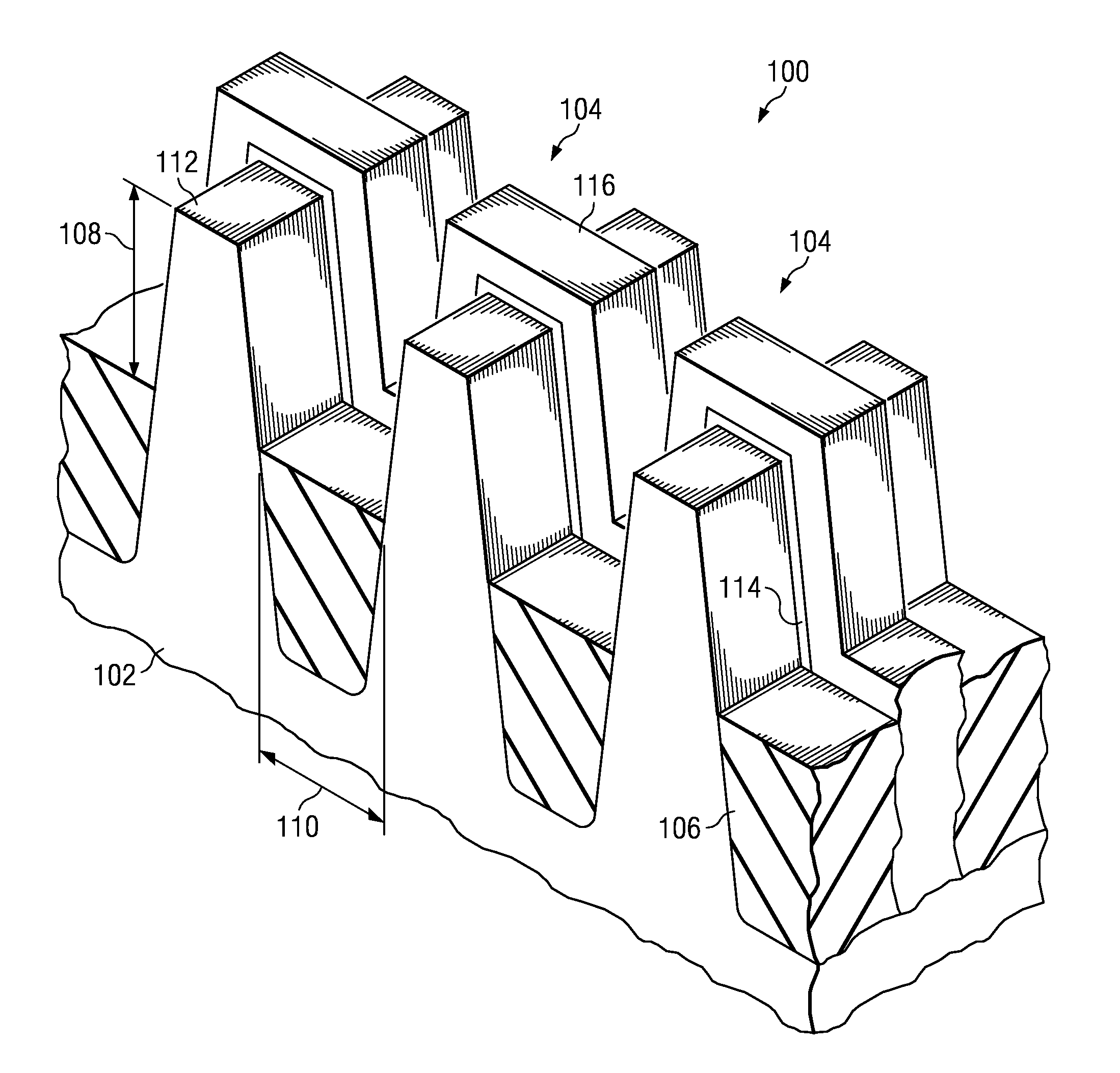

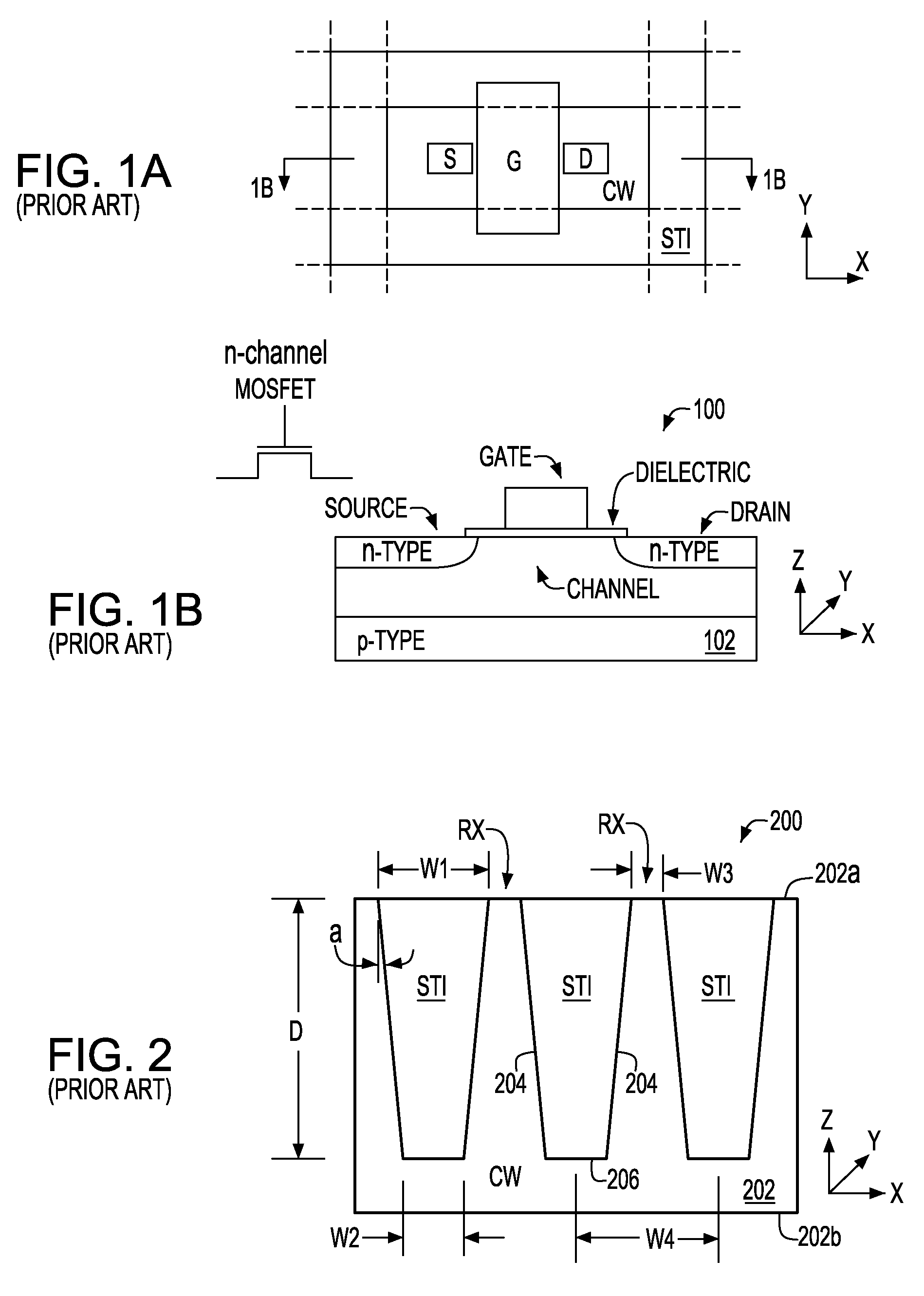

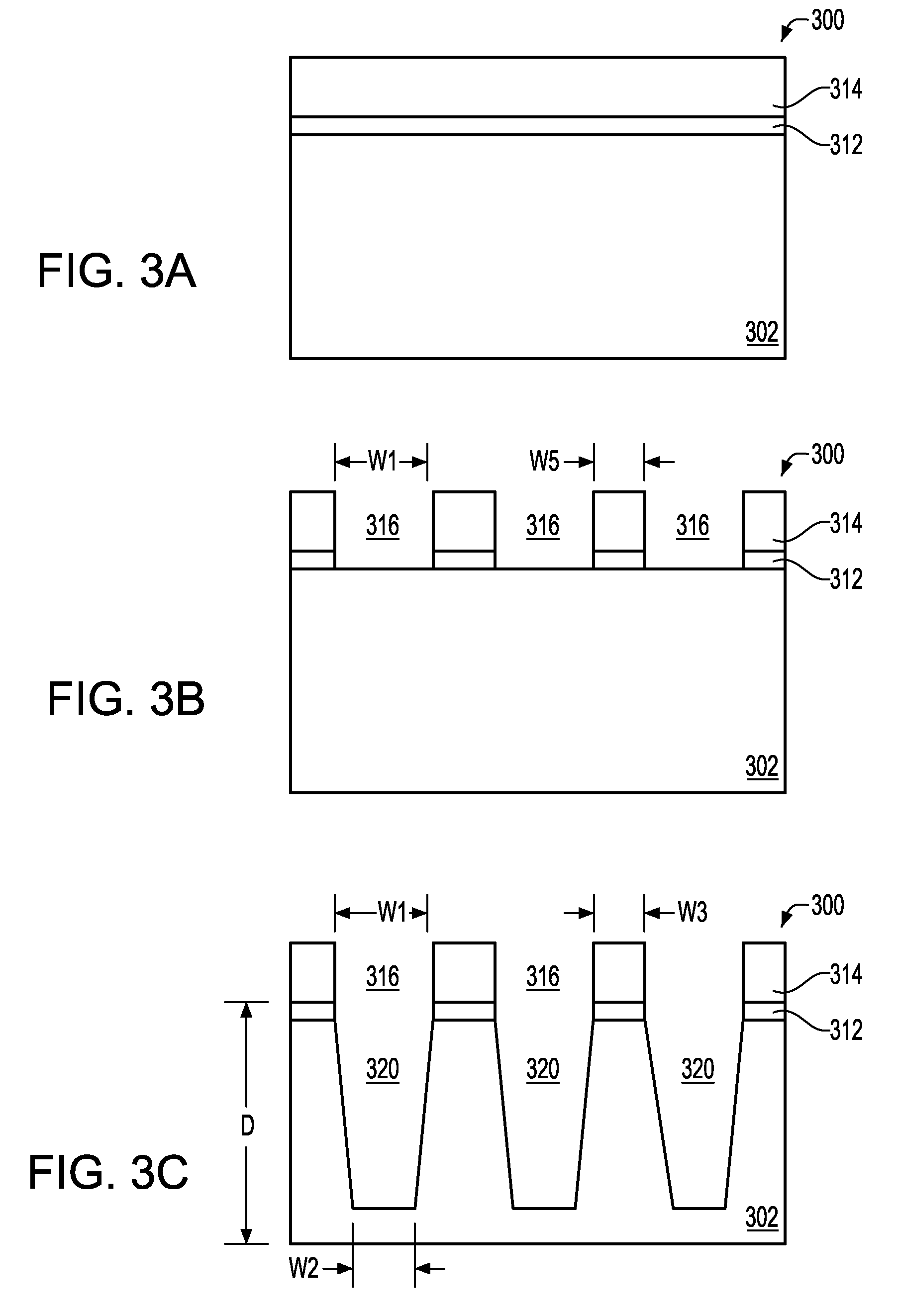

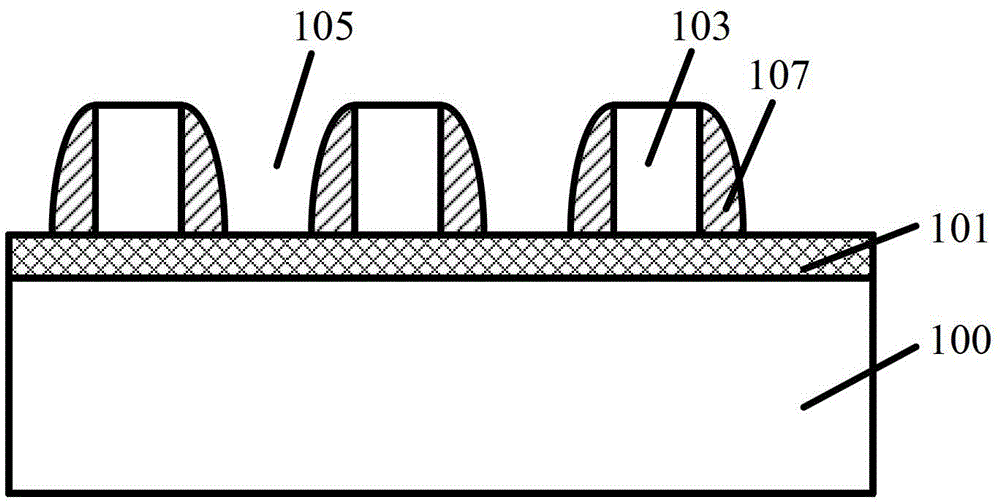

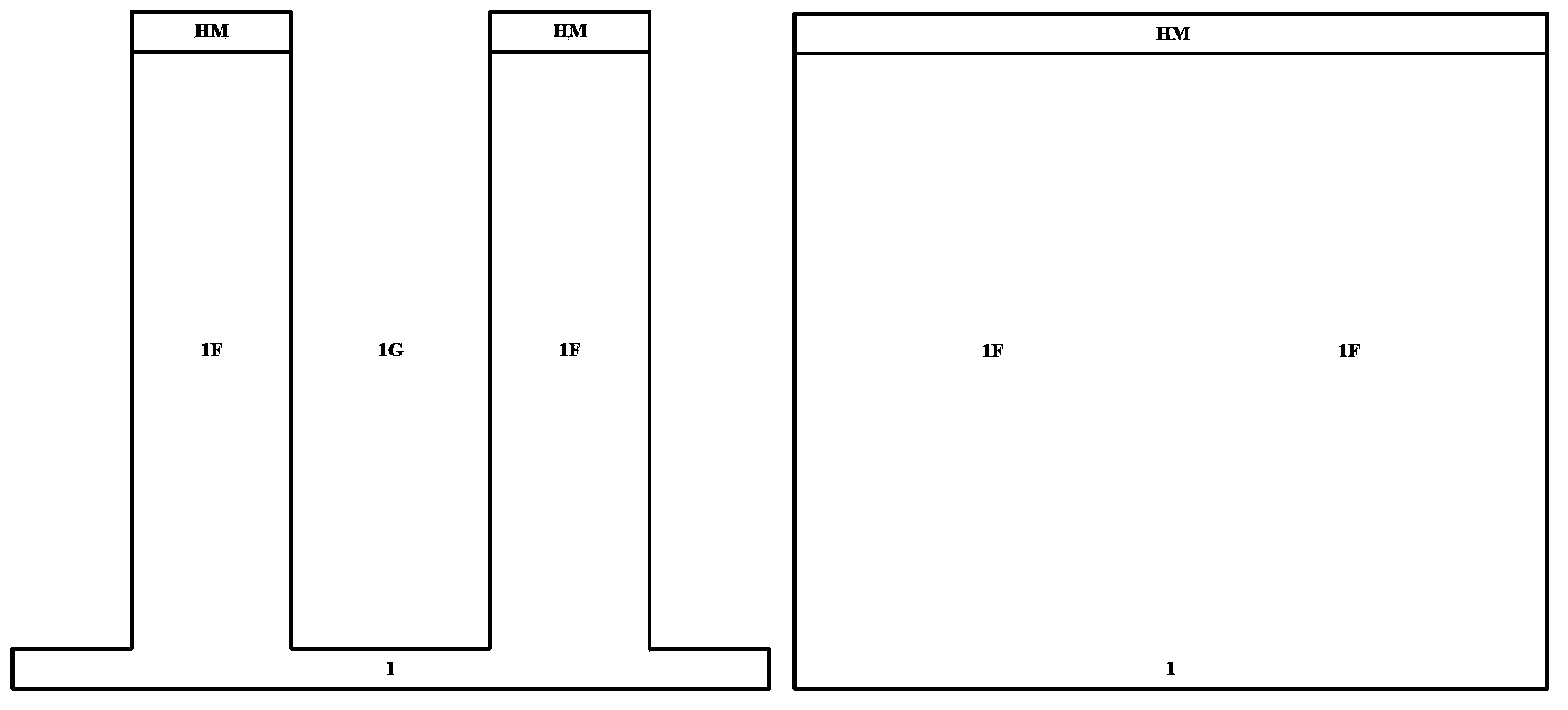

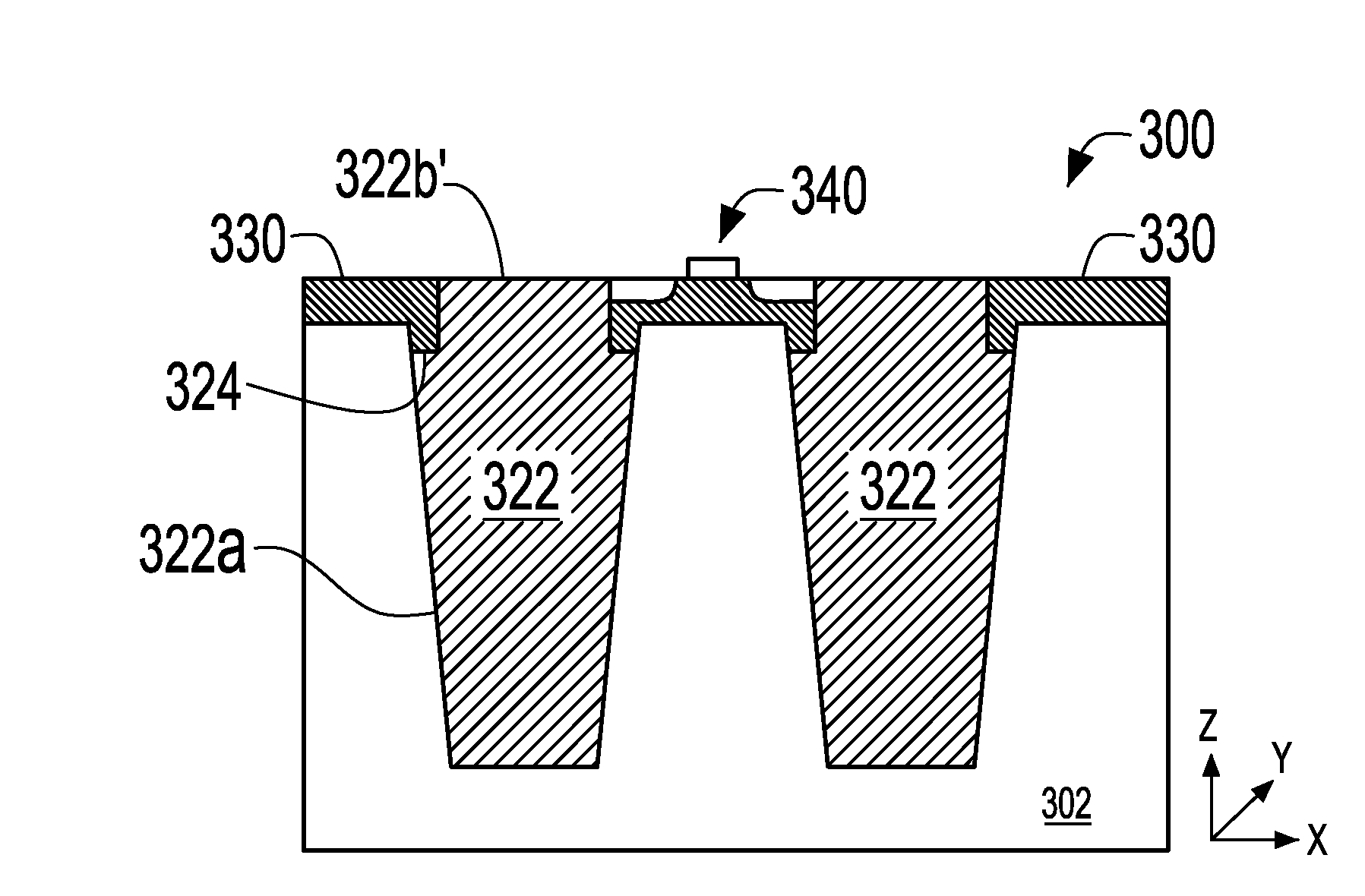

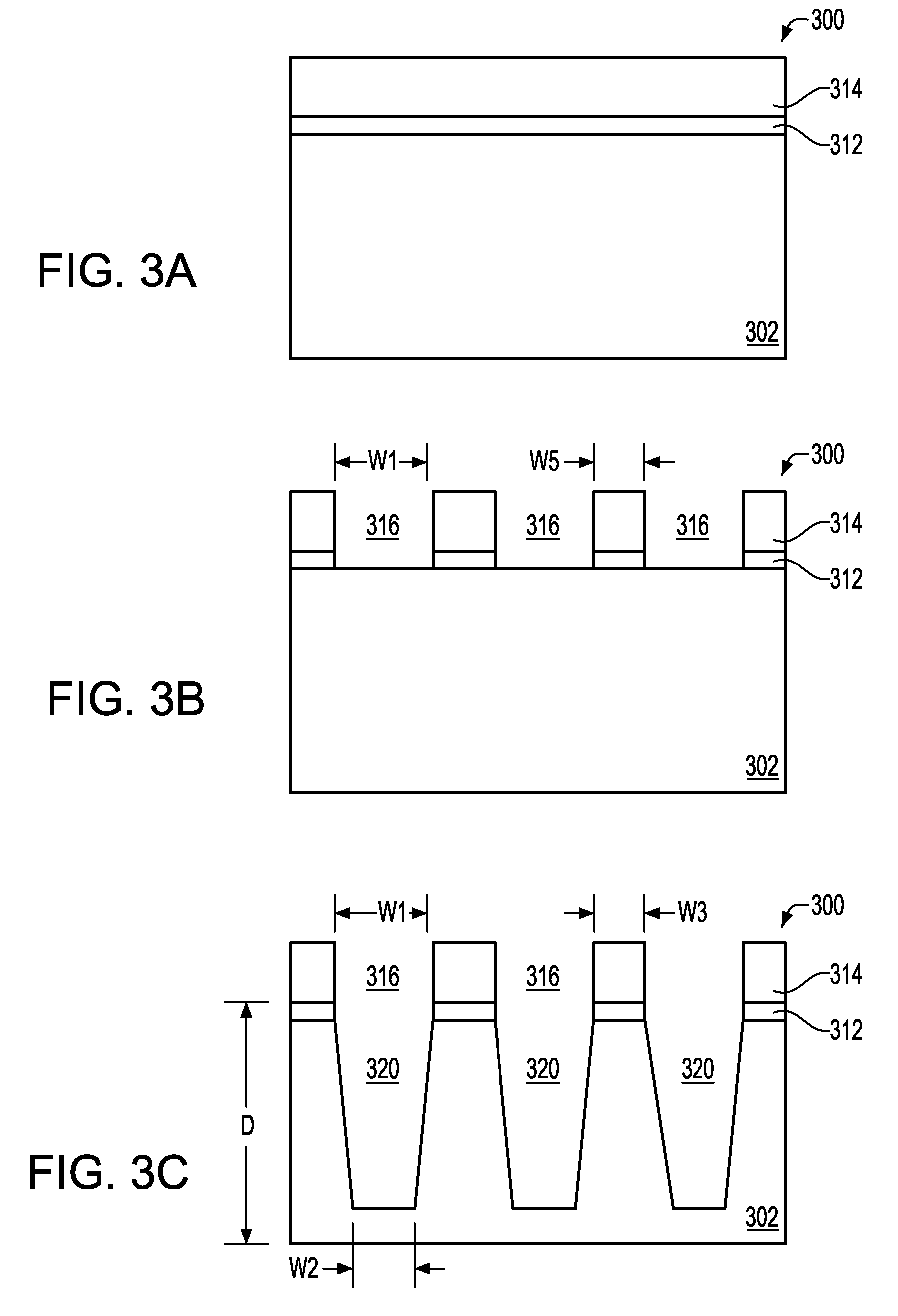

Recessed STI for wide transistors

ActiveUS20080081404A1Increase effective widthIncrease gate widthSemiconductor/solid-state device manufacturingSubstrate surfaceSemiconductor

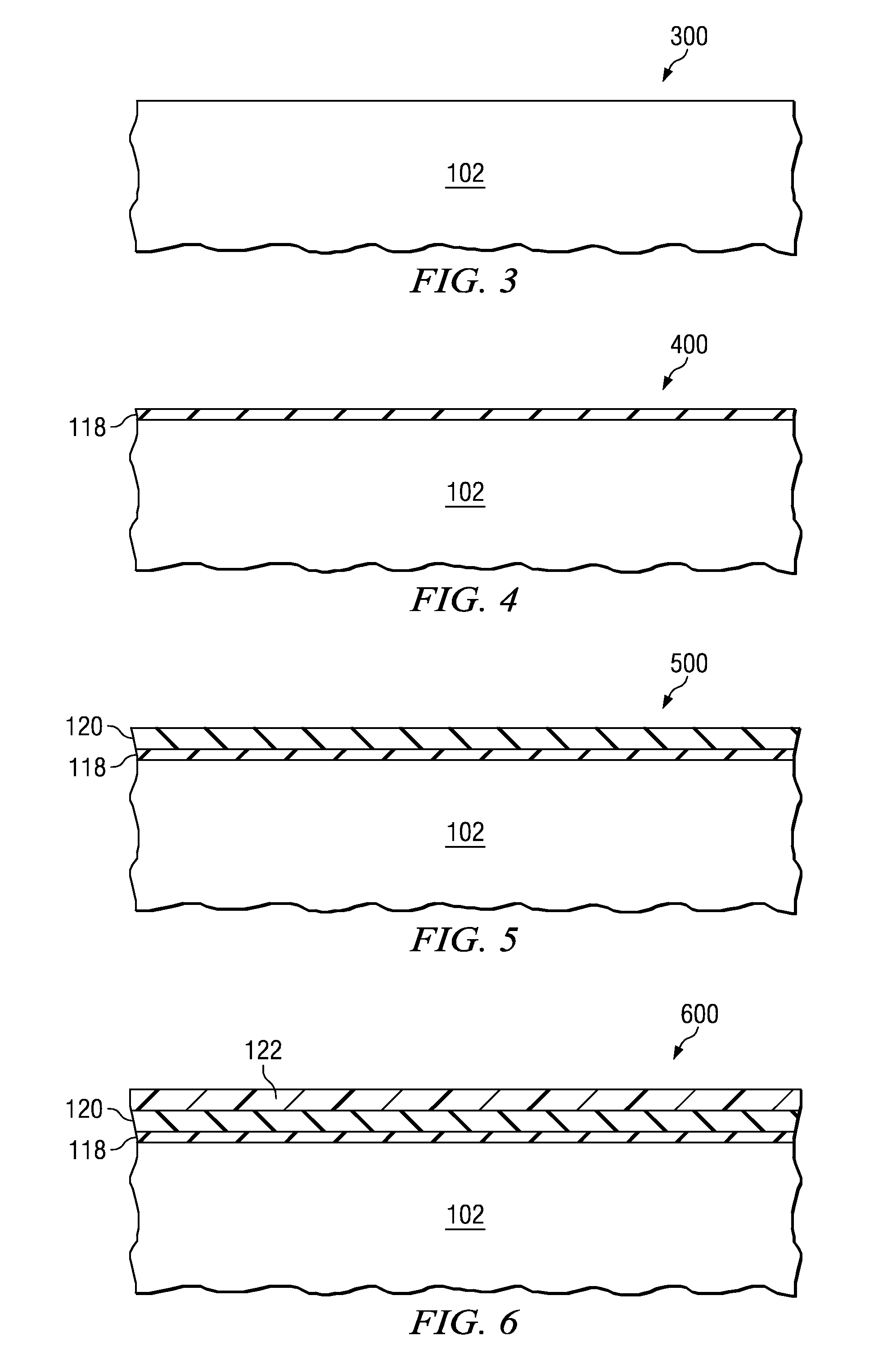

A method of manufacturing a semiconductor device having shallow trench isolation includes steps of forming a hard mask layer on the substrate surface, etching a trench through the hard mask, filling the trench with an isolation material, forming a recessed trench, and forming a serpentine gate structure to connect electronic sources and drains.

Owner:TEXAS INSTR INC

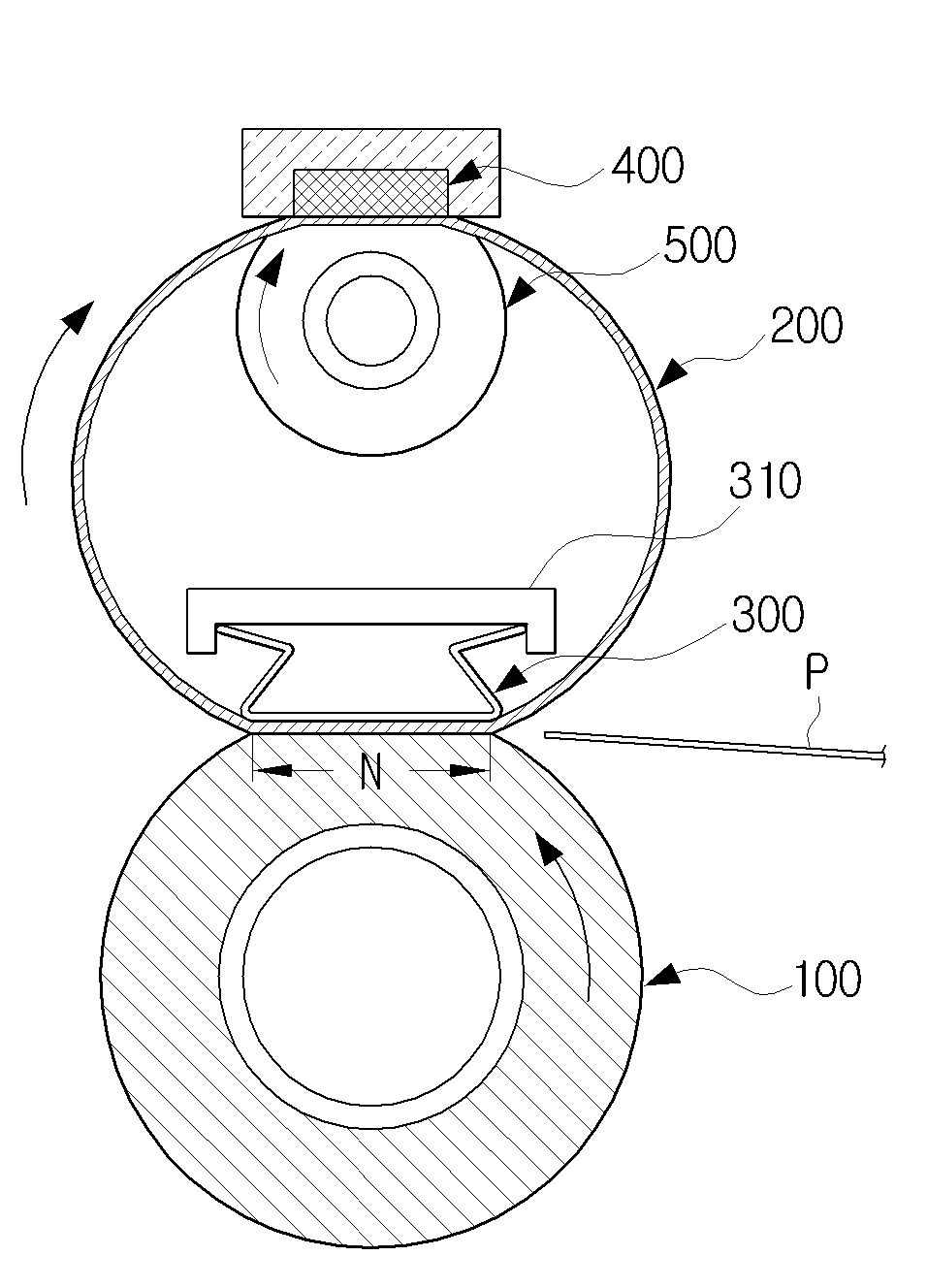

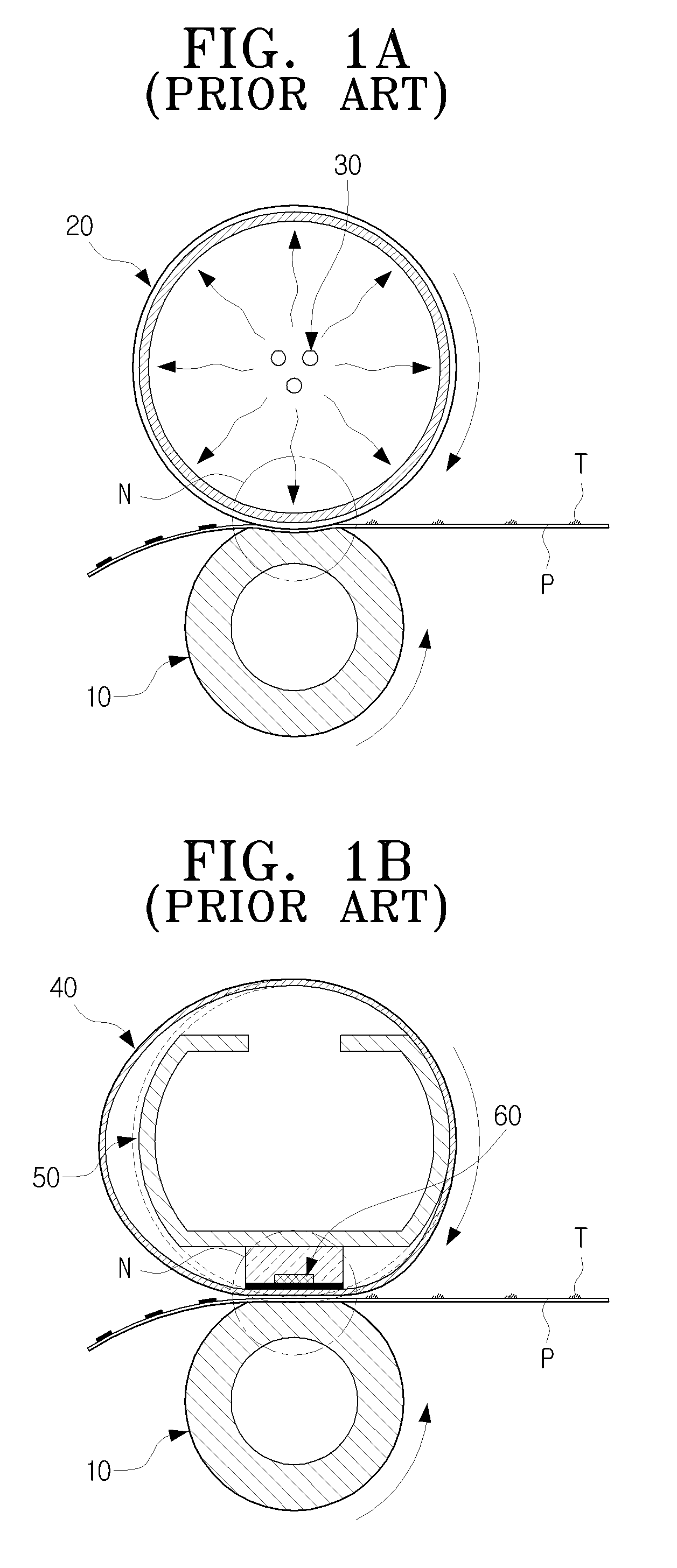

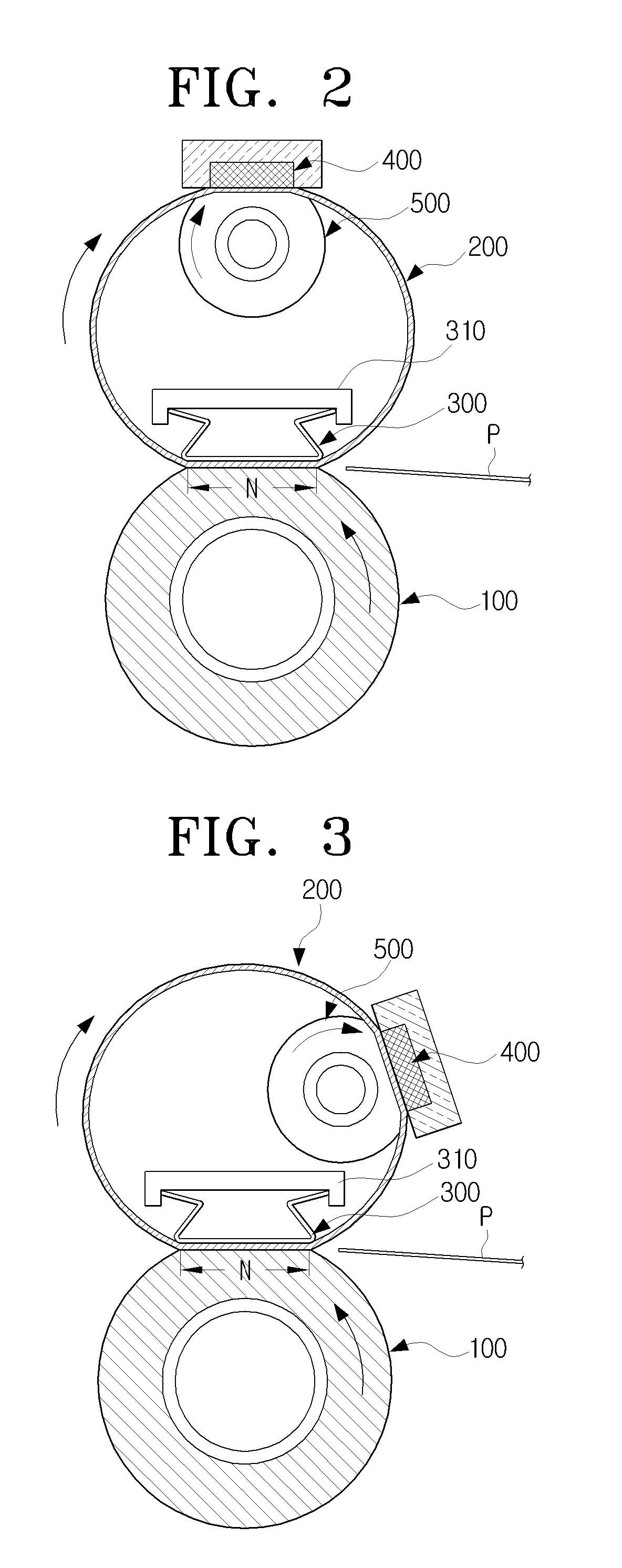

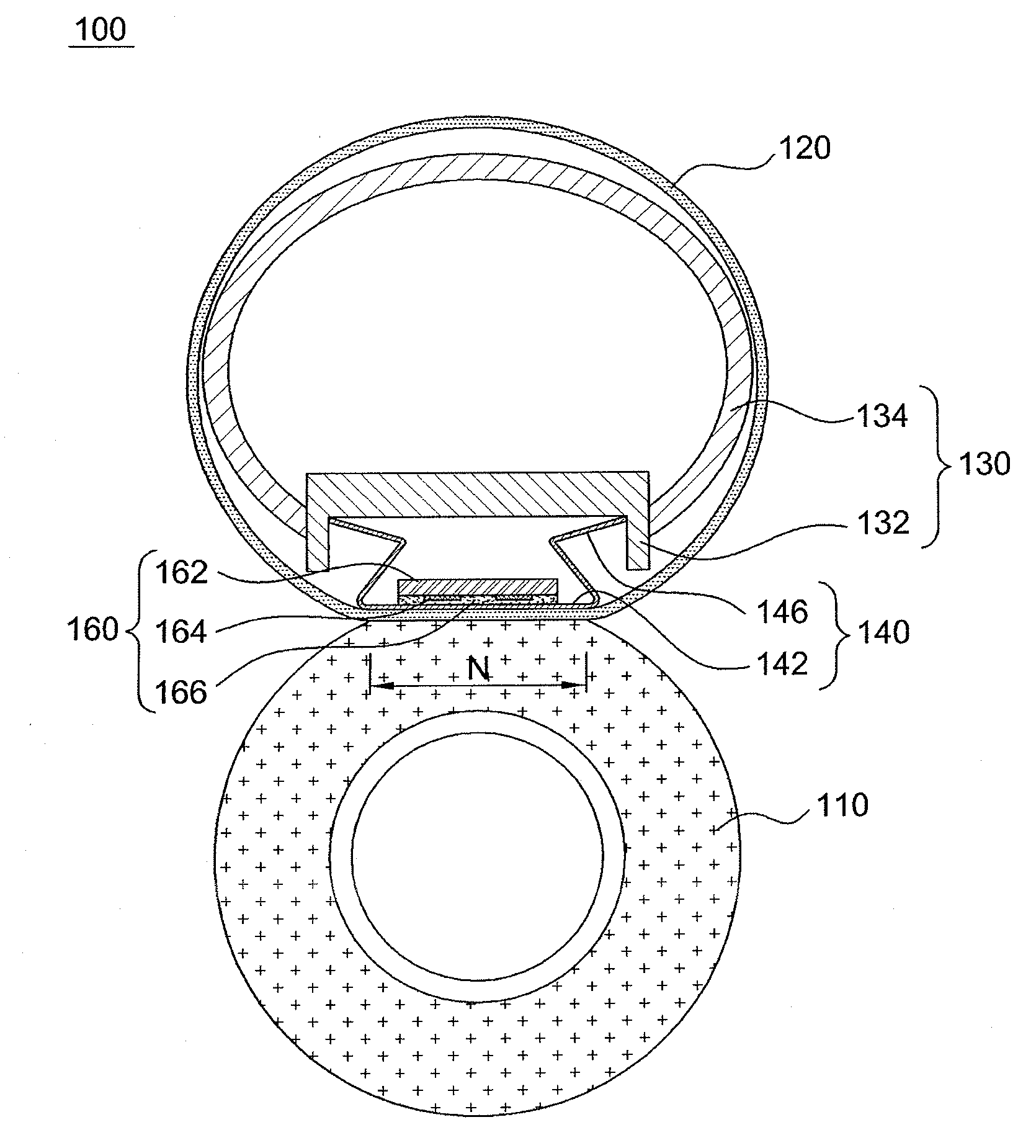

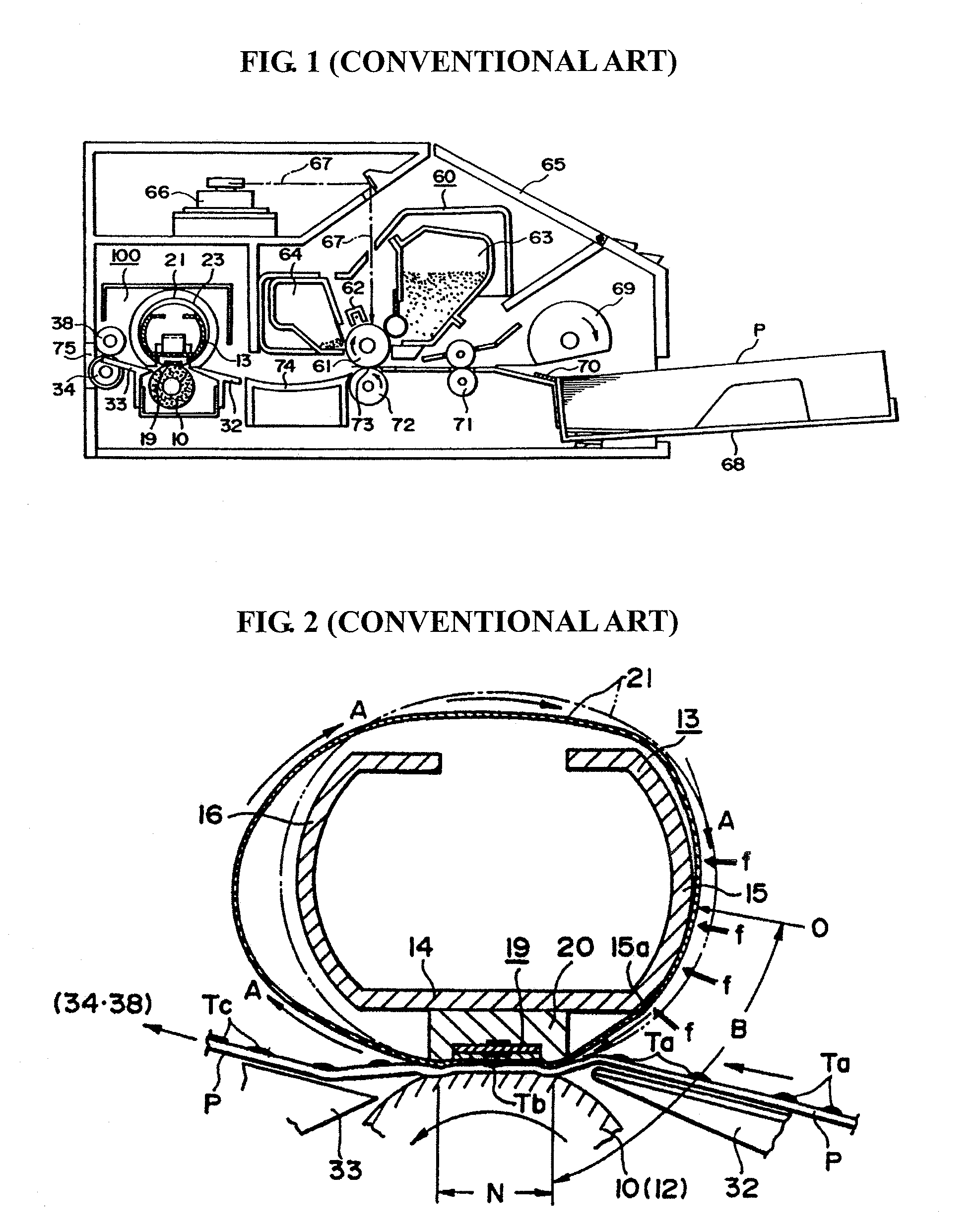

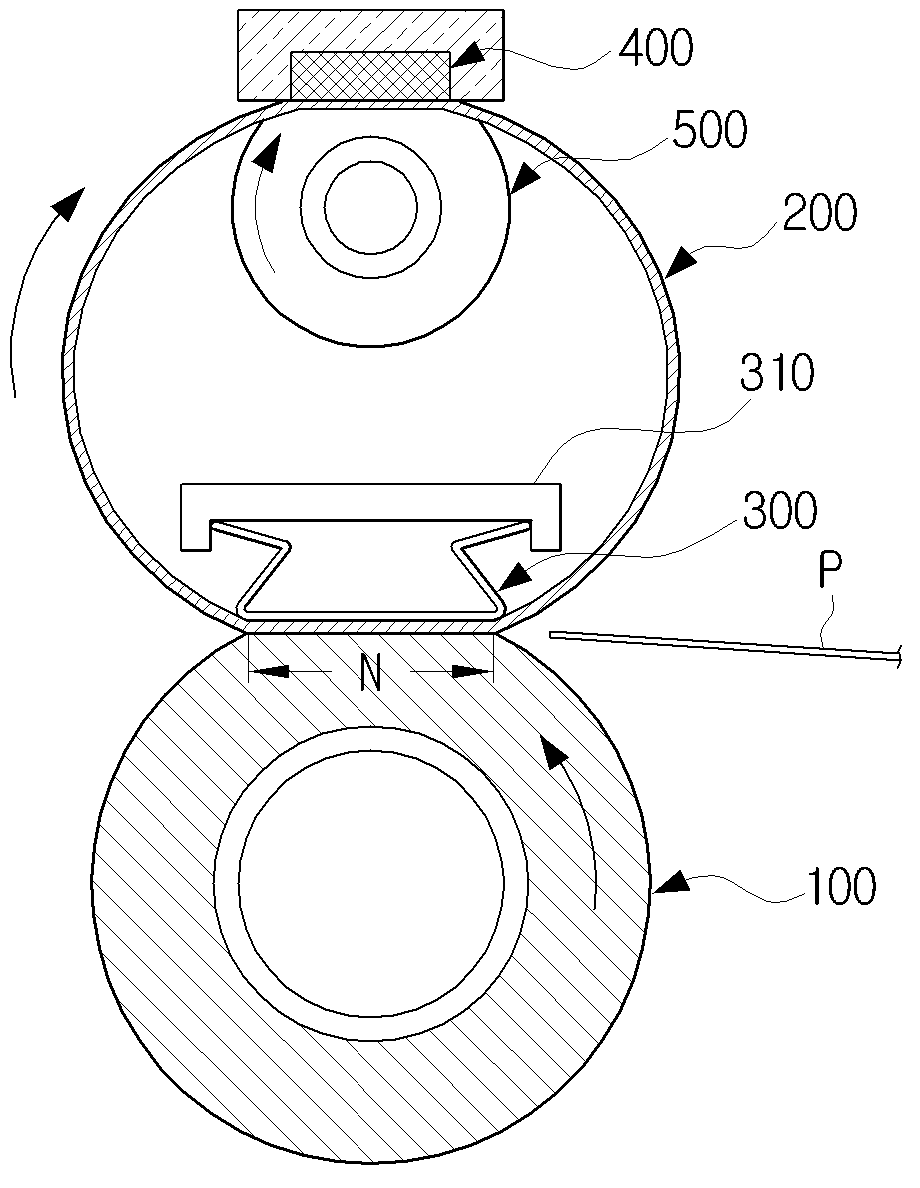

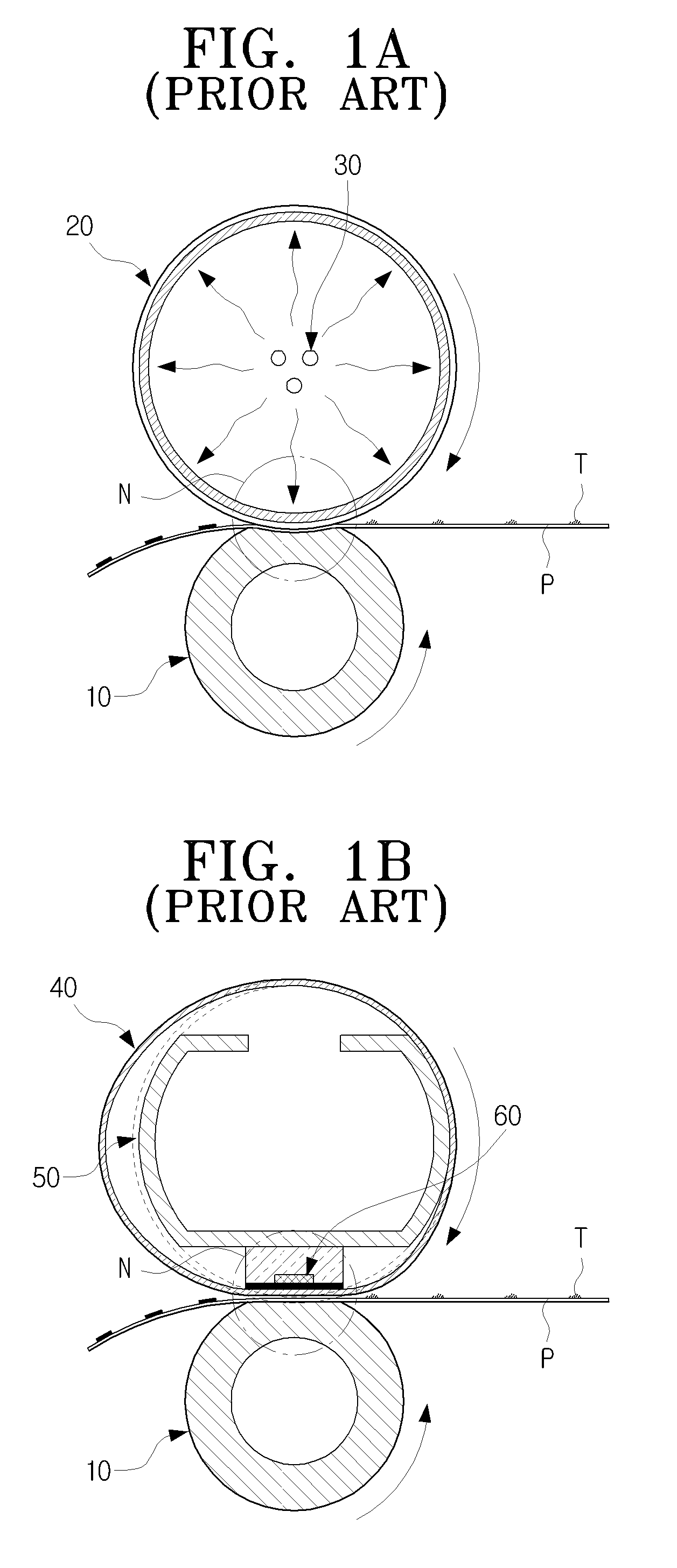

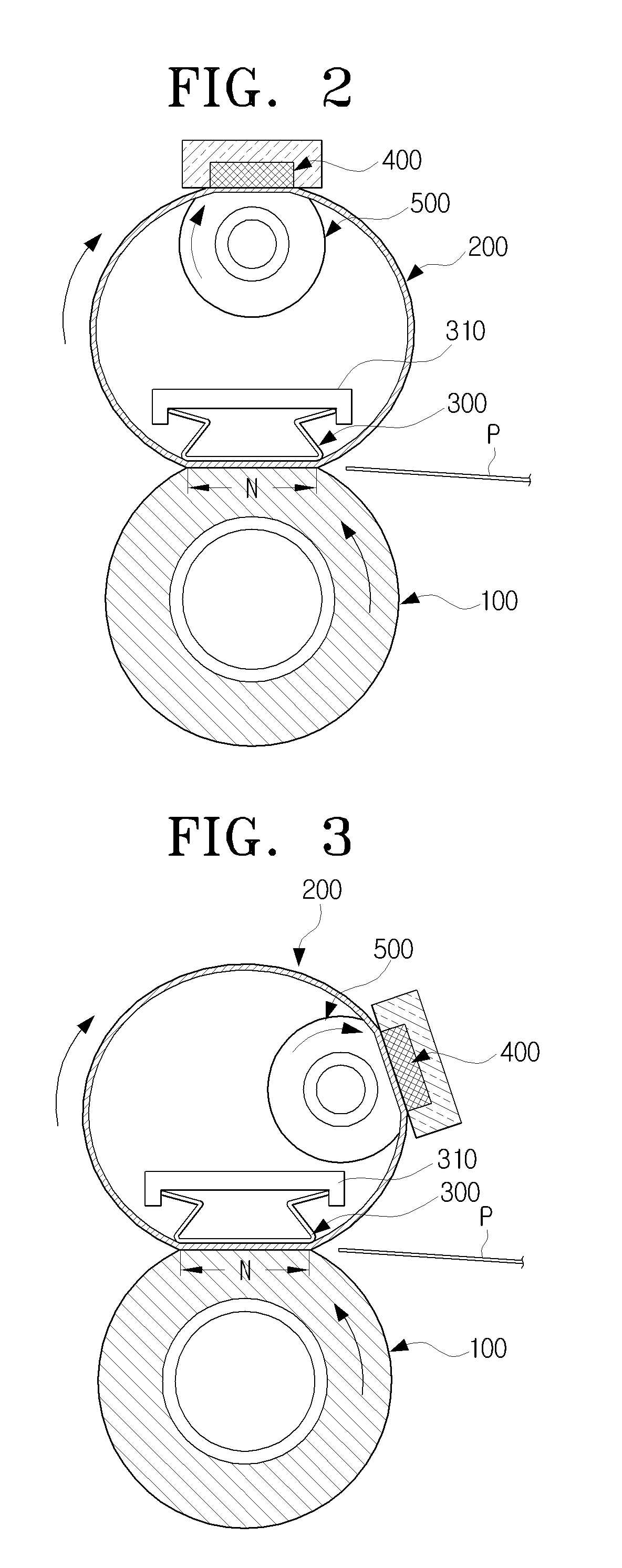

Fixing device and image forming apparatus having the same

ActiveUS20080247789A1Avoid damageEffective width of nipElectrographic process apparatusThermal deformationEngineering

A fixing device includes a fixing roller, a fixing belt which is made to rotate by a rotation force received from the fixing roller, a nip forming unit to form a nip zone at a contact area between the fixing roller and the fixing belt, and a first heating unit, which is separated from the nip zone, to apply heat to the fixing belt. The nip zone and the heating unit are separated, so that the heating unit can be prevented from being broken as a result of the pressurization and thermal deformation.

Owner:HEWLETT PACKARD DEV CO LP

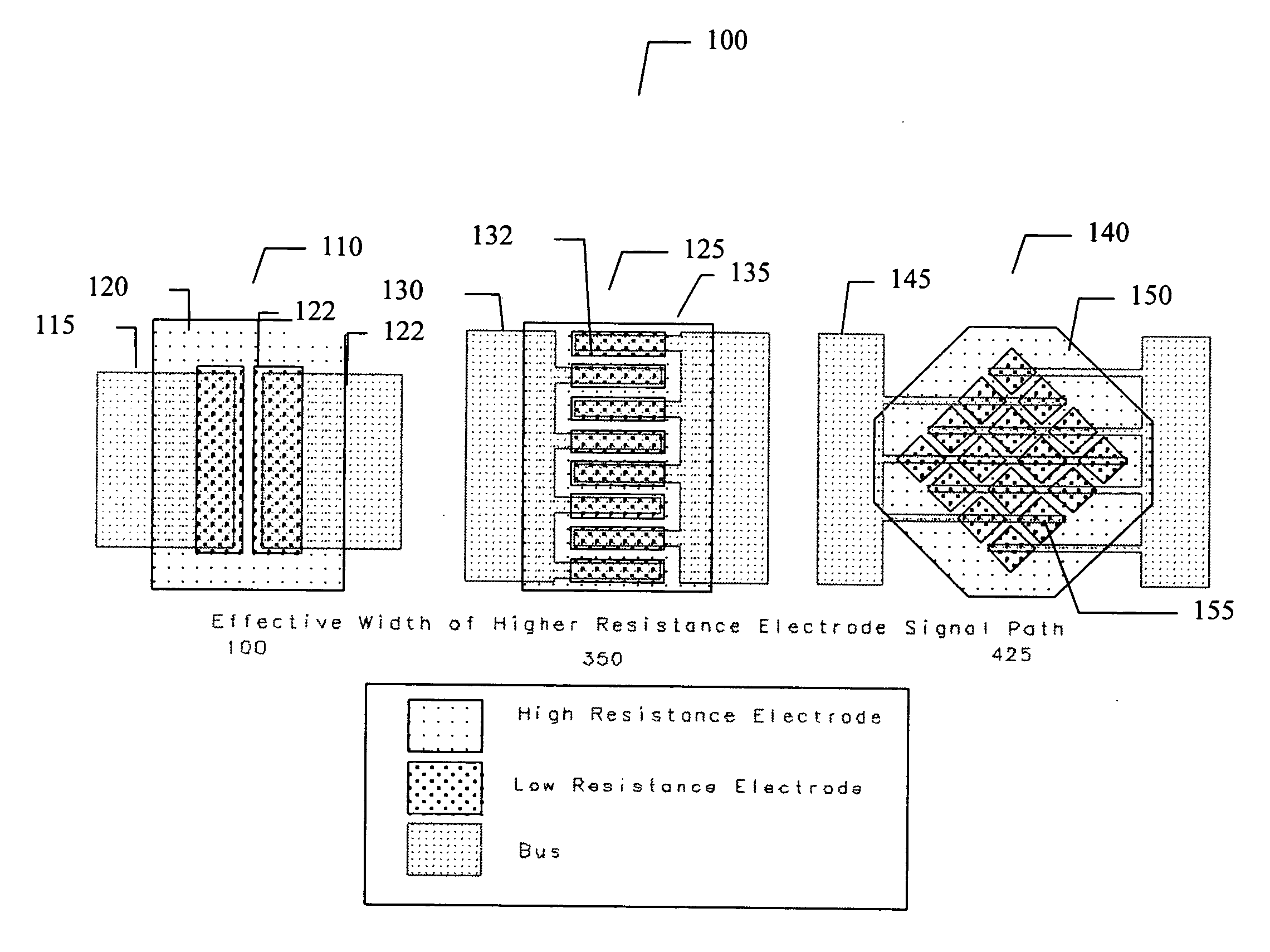

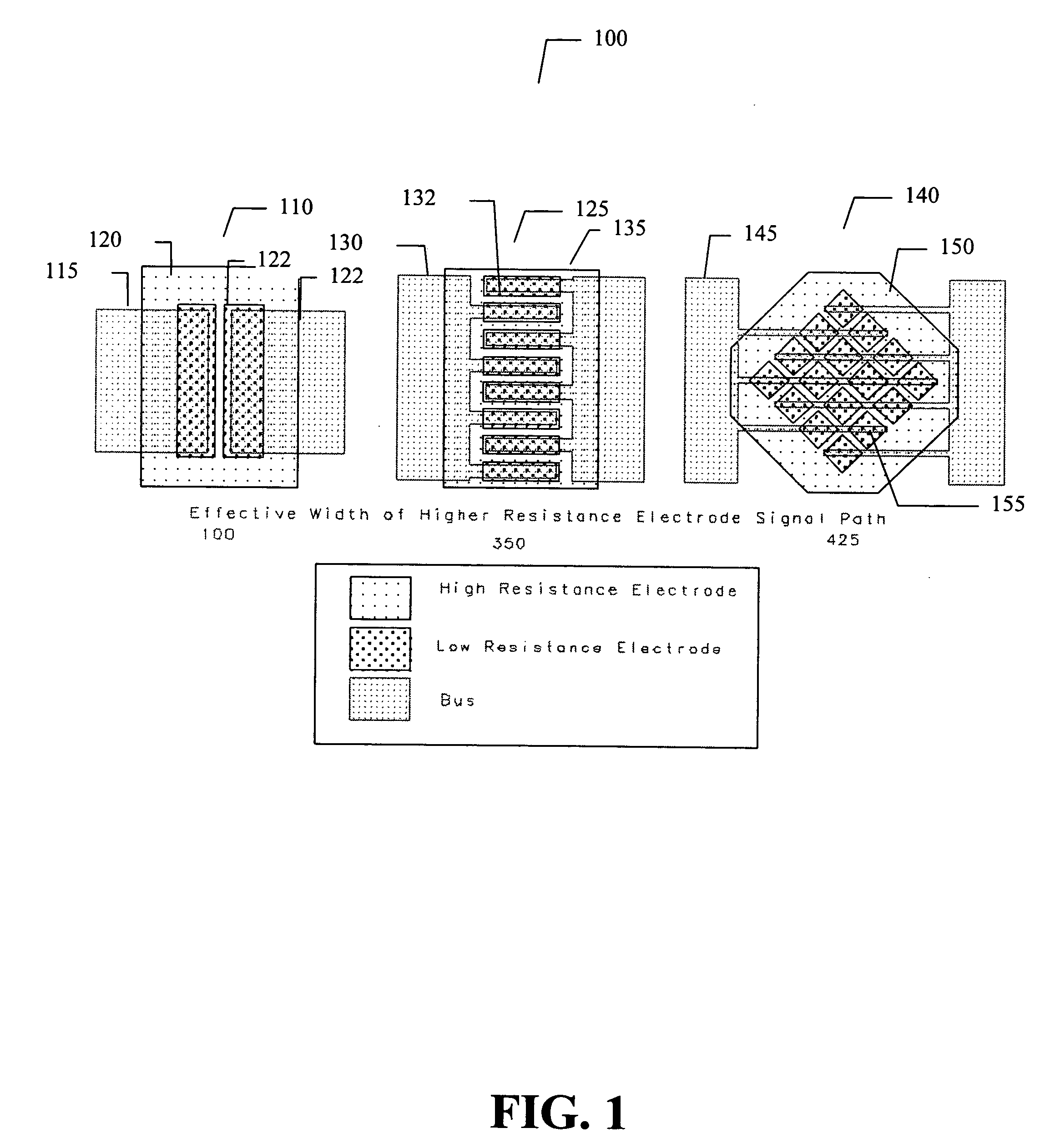

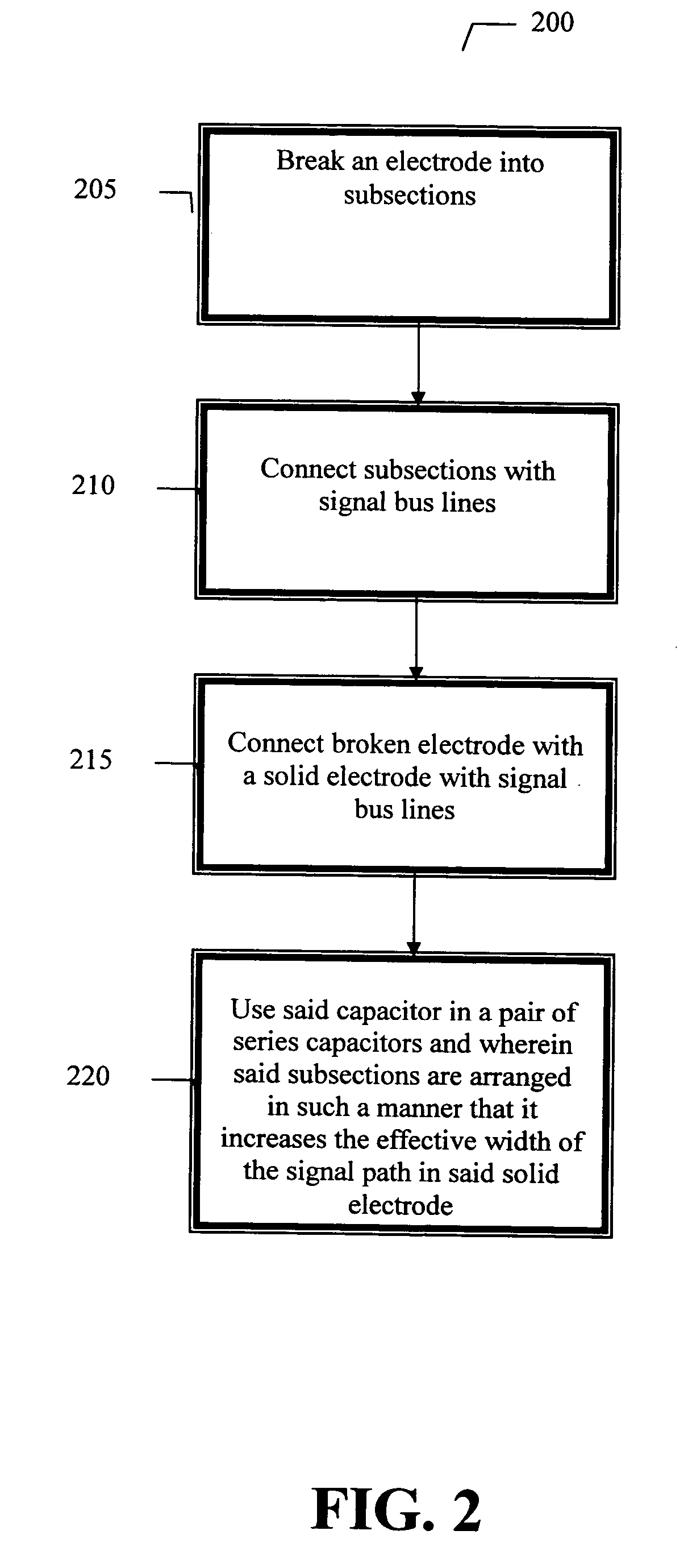

High Q and low stress capacitor electrode array

ActiveUS20070109716A1Increase effective widthMultiple fixed capacitorsFixed capacitor electrodesElectrode arrayEngineering

Owner:NXP USA INC

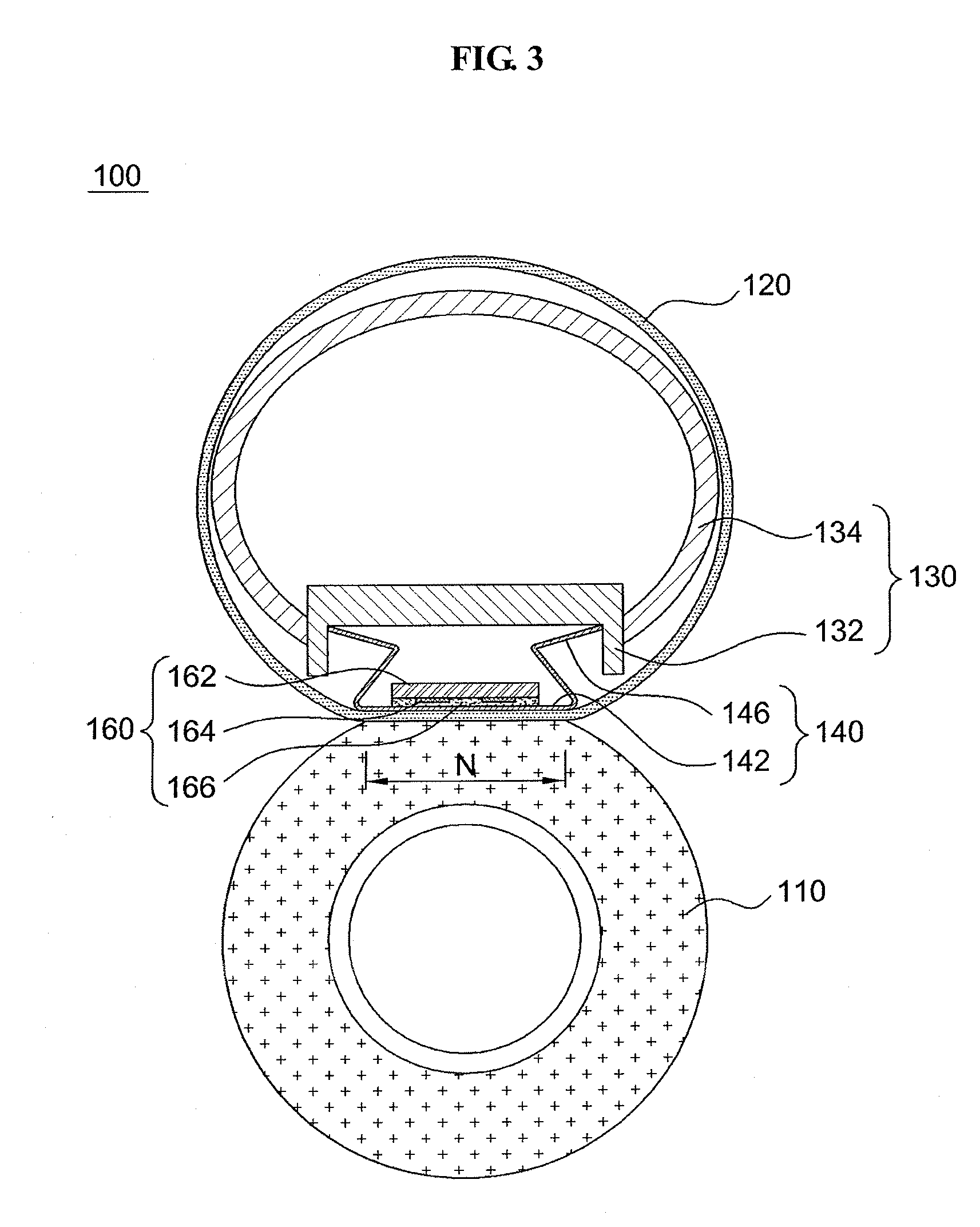

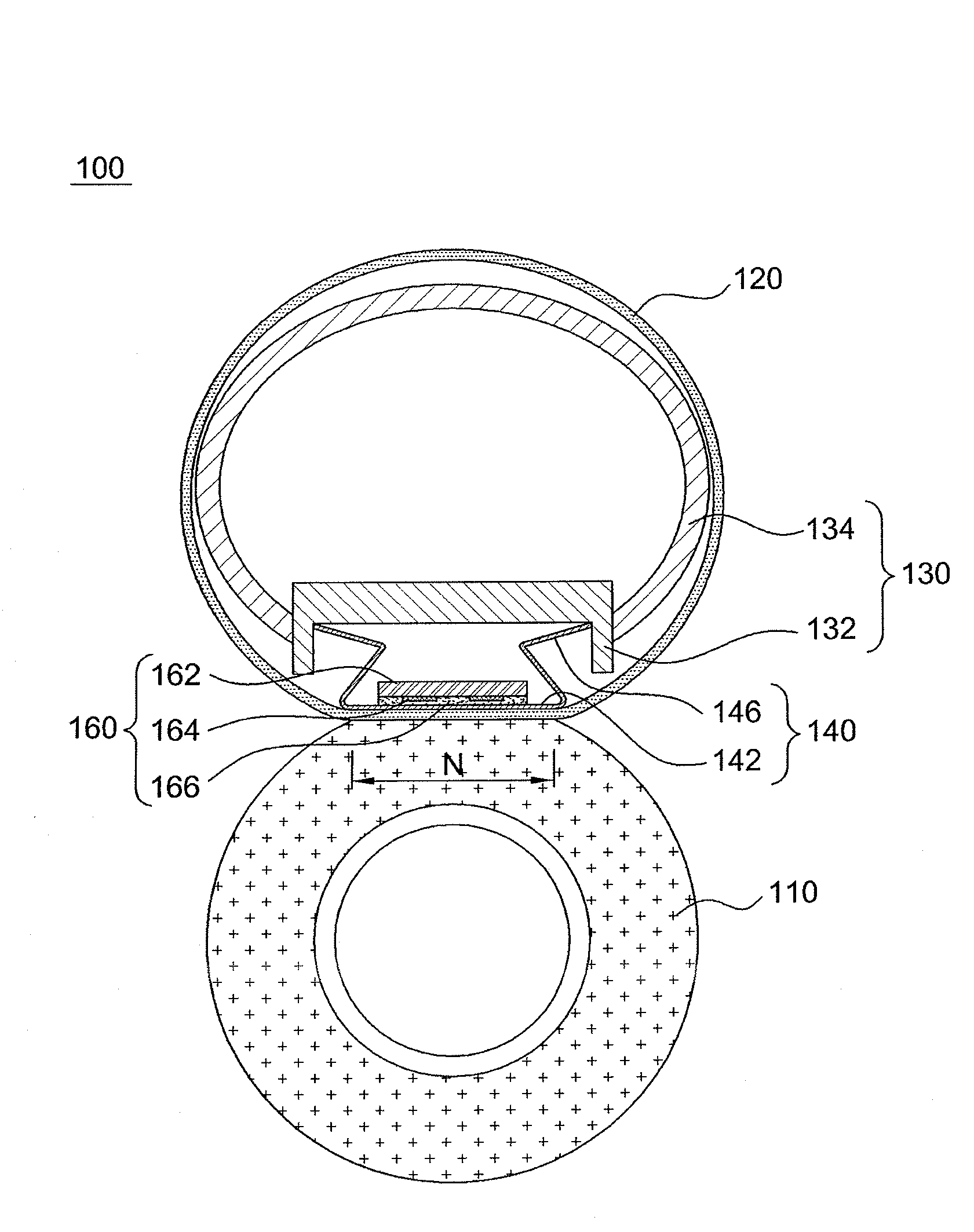

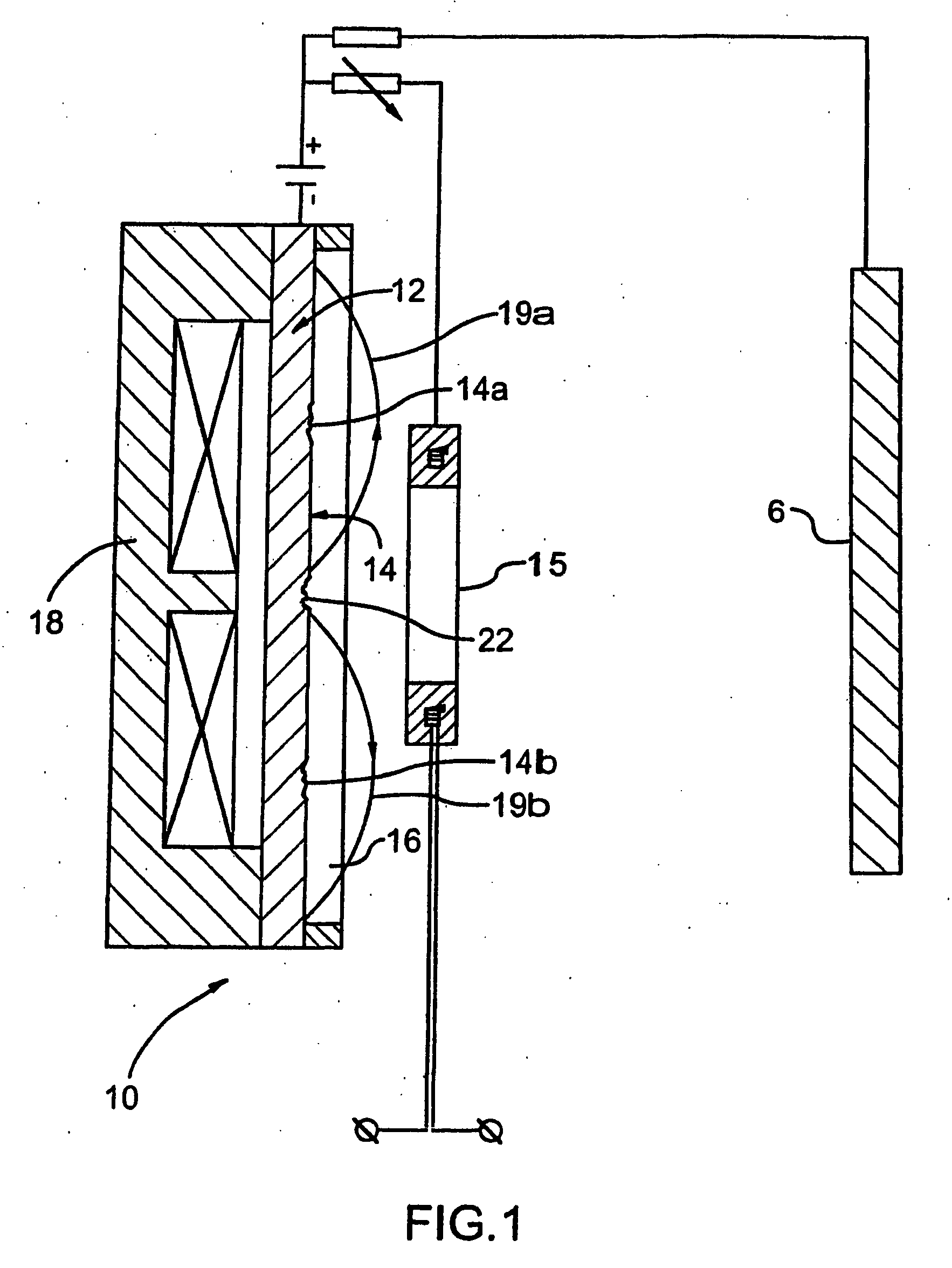

Tunable micro electromechanical inductor

The present invention provides a monolithic inductor developed using radio frequency micro electromechanical (RF MEMS) techniques. In a particular embodiment of the present invention, a tunable radio frequency microelectromechanical inductor includes a coplanar waveguide and a direct current actuatable contact switch positioned to vary the effective width of a narrow inductive section of the center conductor of the CPW line upon actuation the DC contact switch. In a specific embodiment of the present invention, the direct current actuatable contact switch is a diamond air-bridge integrated on an alumina substrate to realize an RF switch in the CPW and microstrip topology.

Owner:UNIV OF SOUTH FLORIDA

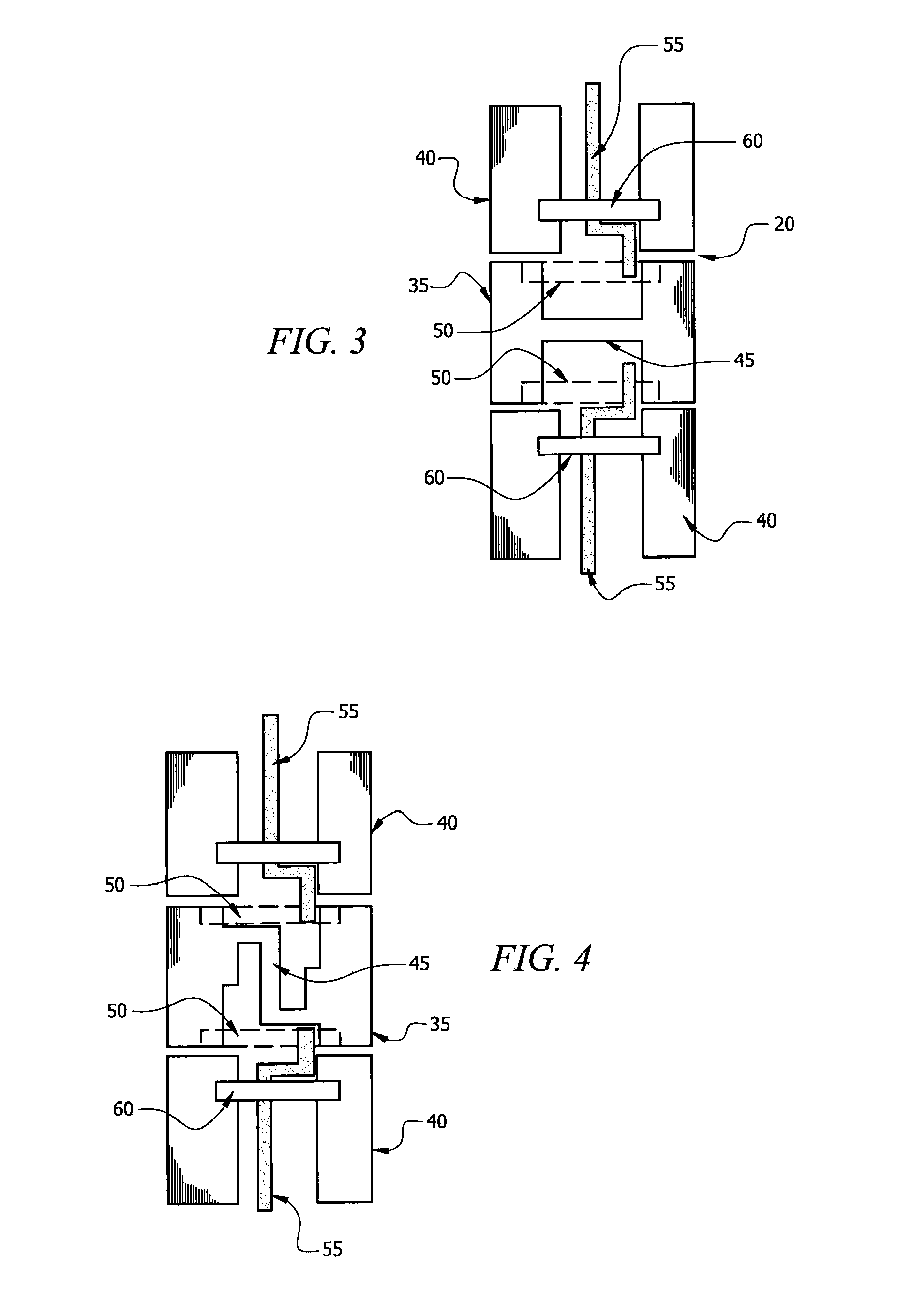

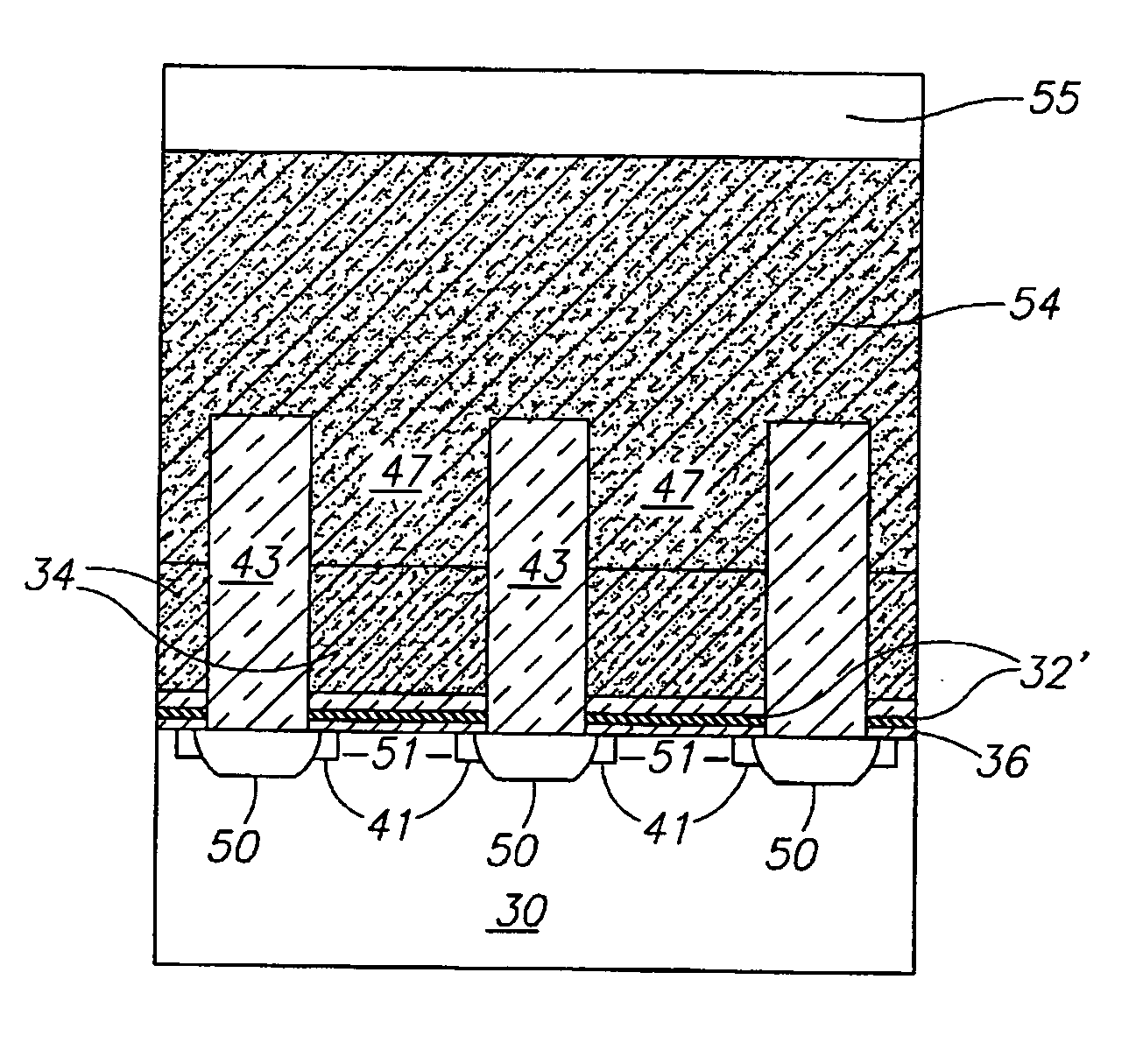

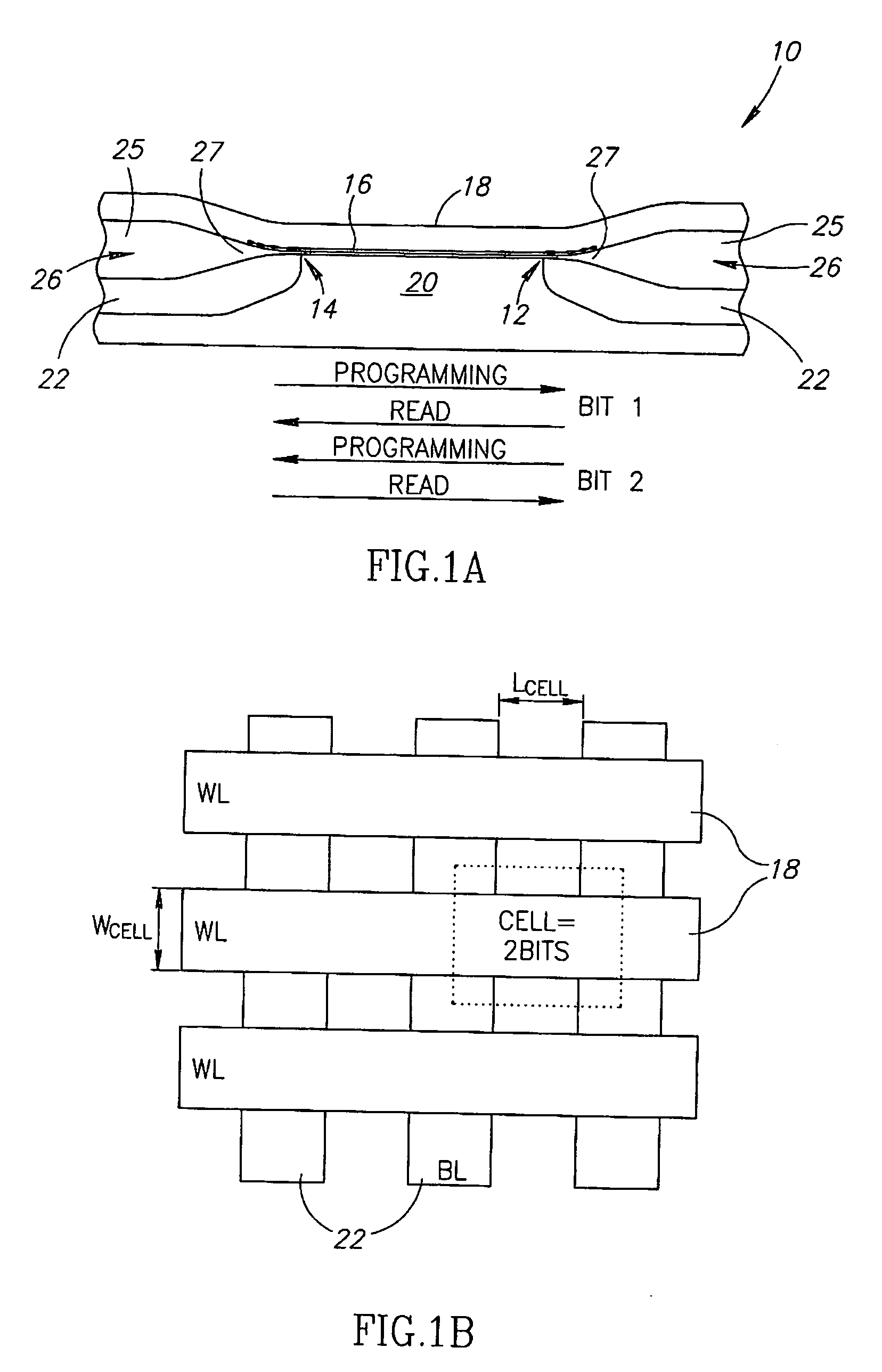

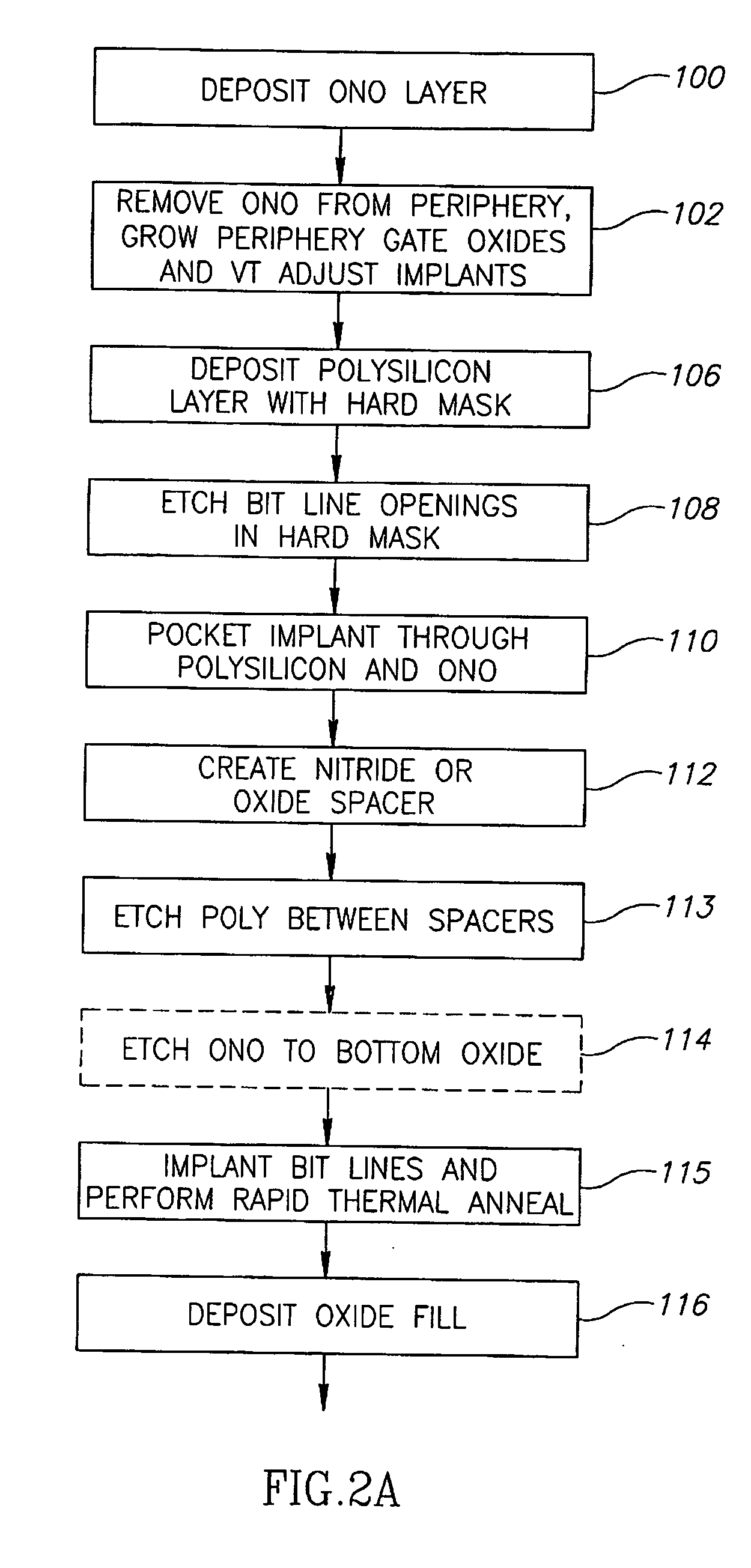

Non-volatile memory structure and method of fabrication

ActiveUS20060211188A1Increase in sizeIncrease effective widthSolid-state devicesSemiconductor/solid-state device manufacturingBit lineEngineering

A method for creating a non-volatile memory array includes implanting pocket implants in a substrate at least between mask columns of a given width and at least through an ONO layer covering the substrate, generating increased-width polysilicon columns from the mask columns, generating bit lines in the substrate at least between the increased-width polysilicon columns and depositing oxide at least between the polysilicon columns.

Owner:SAIFUN SEMICON

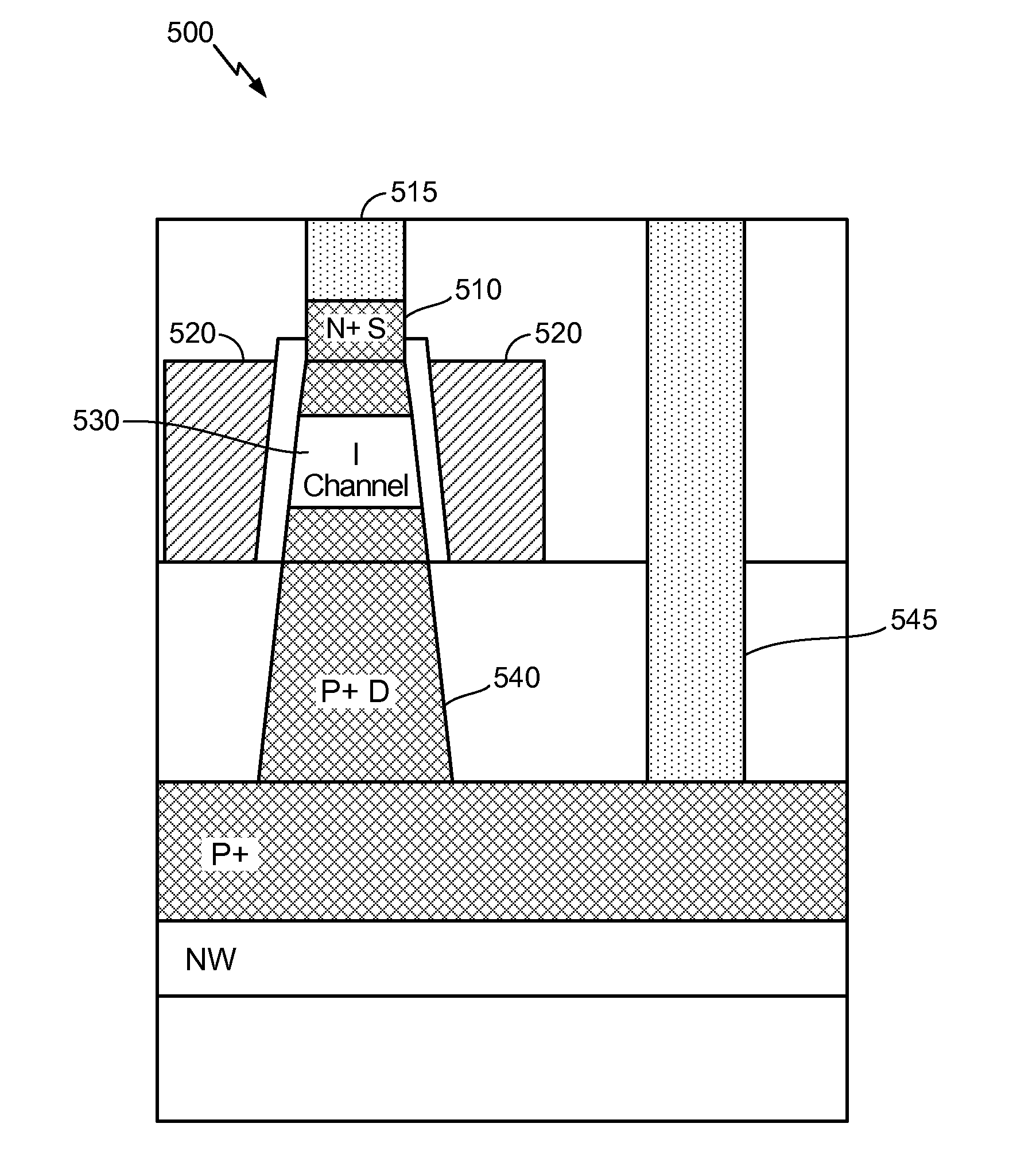

Tunnel field effect transistor and method of making the same

InactiveUS20160336324A1Large horizontal widthImprove drivabilityTransistorSolid-state devicesEngineeringTunnel field-effect transistor

A vertically integrated transistor device increases the effective active area of the device to improve the performance characteristics of the device. The transistor device may include a plurality of gate elements, a plurality of source-drain elements extending parallel to the plurality of gate elements and horizontally spaced therefrom; and a plurality of fin elements extending parallel to the plurality of gate elements and vertically spaced therefrom, wherein each of the plurality of fin elements is horizontally spaced a first distance from each of the other ones of the plurality of fin elements.

Owner:QUALCOMM INC

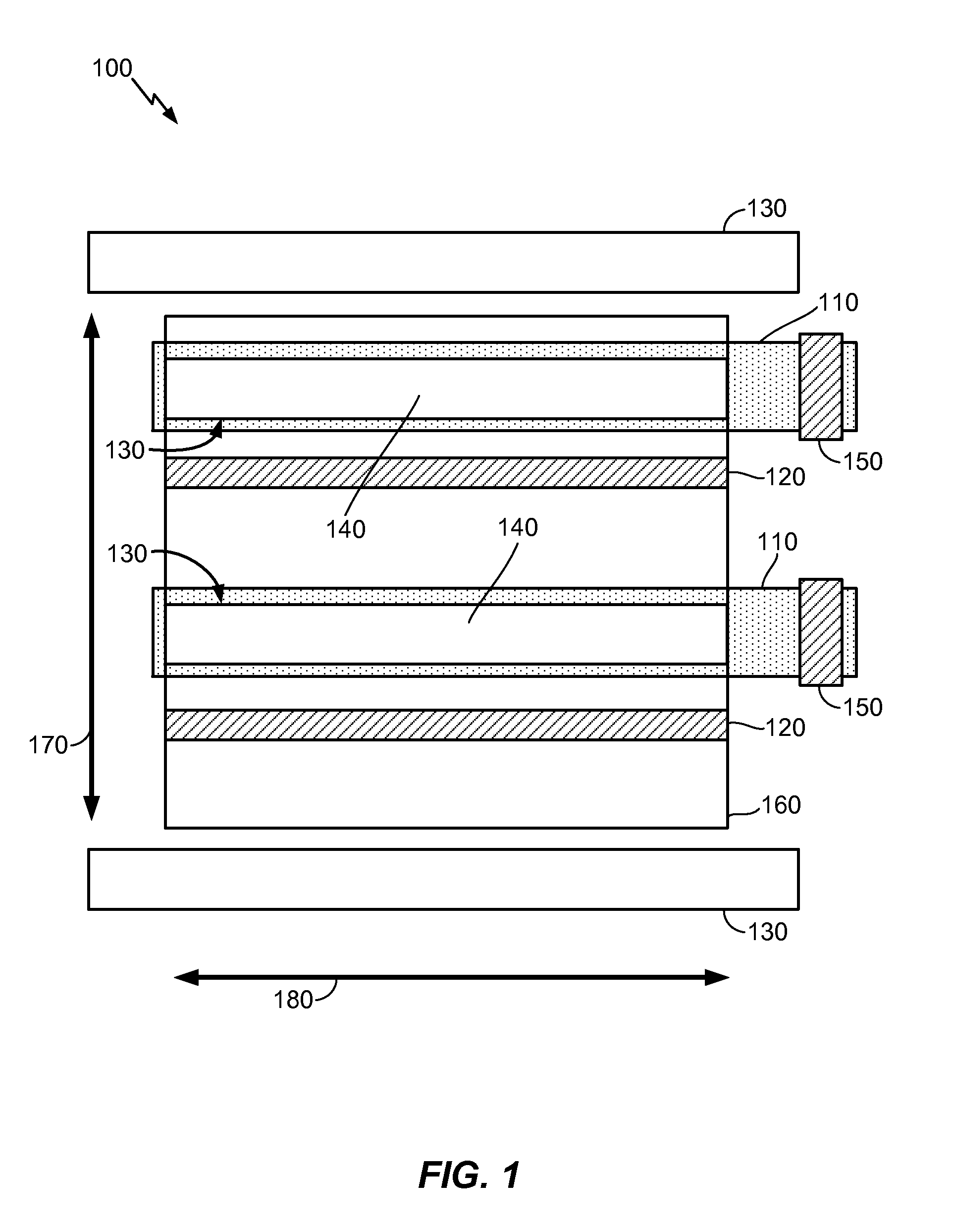

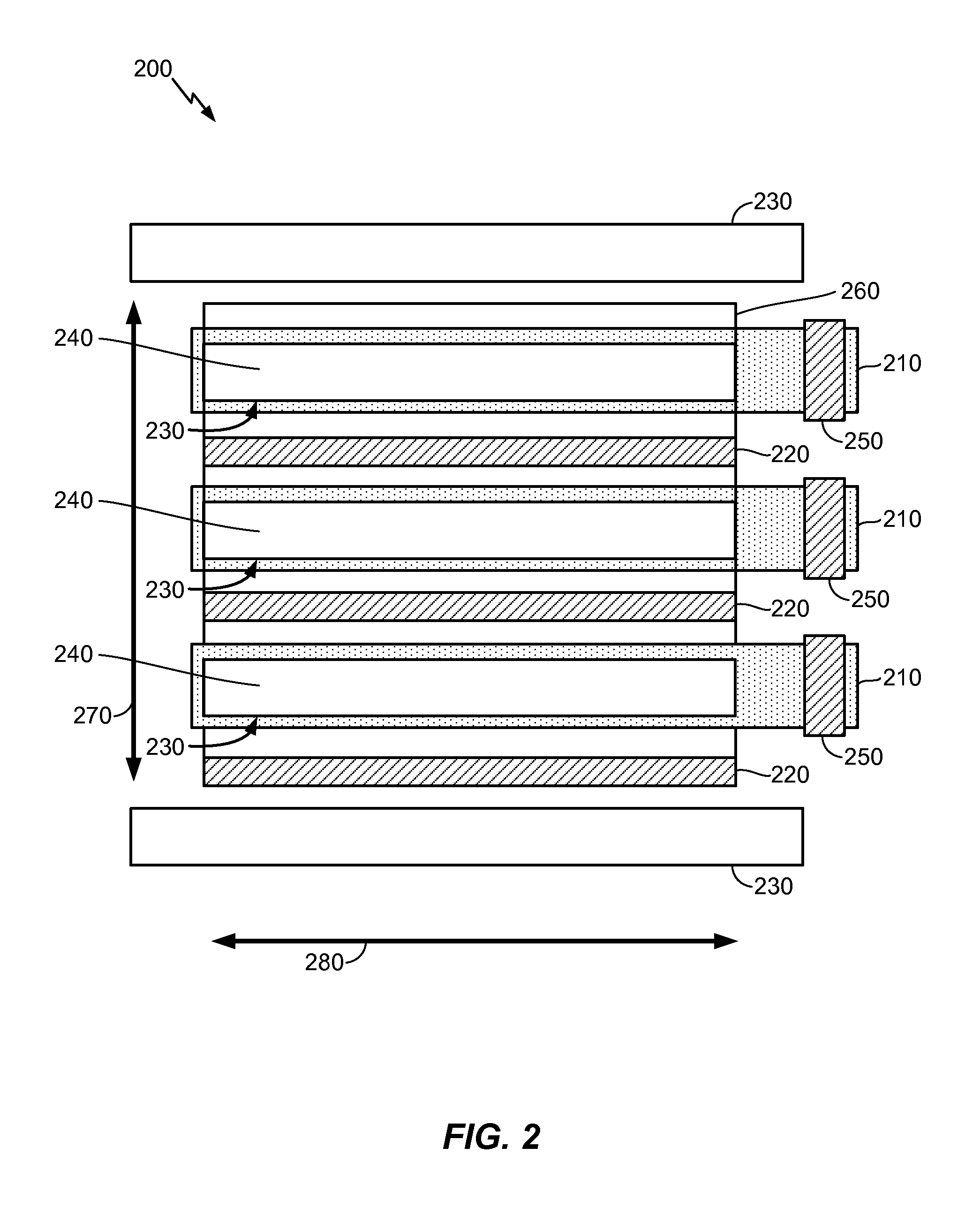

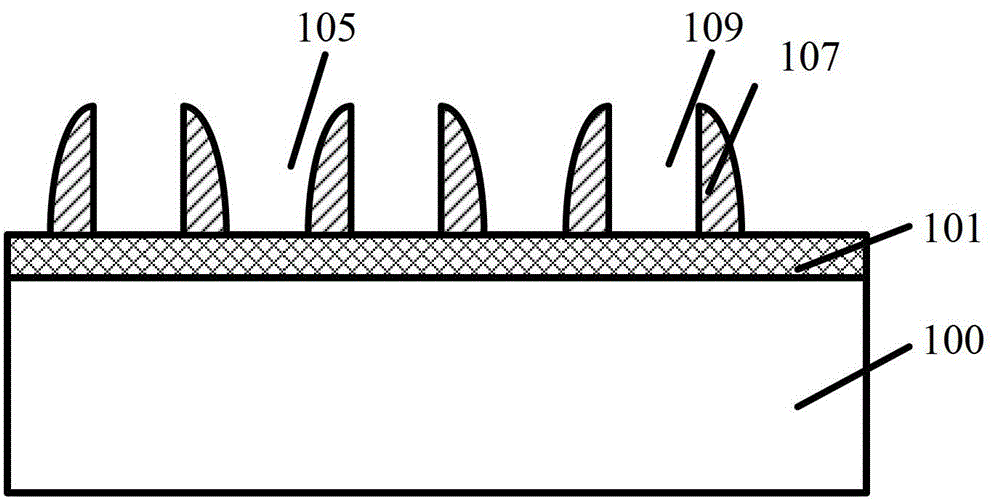

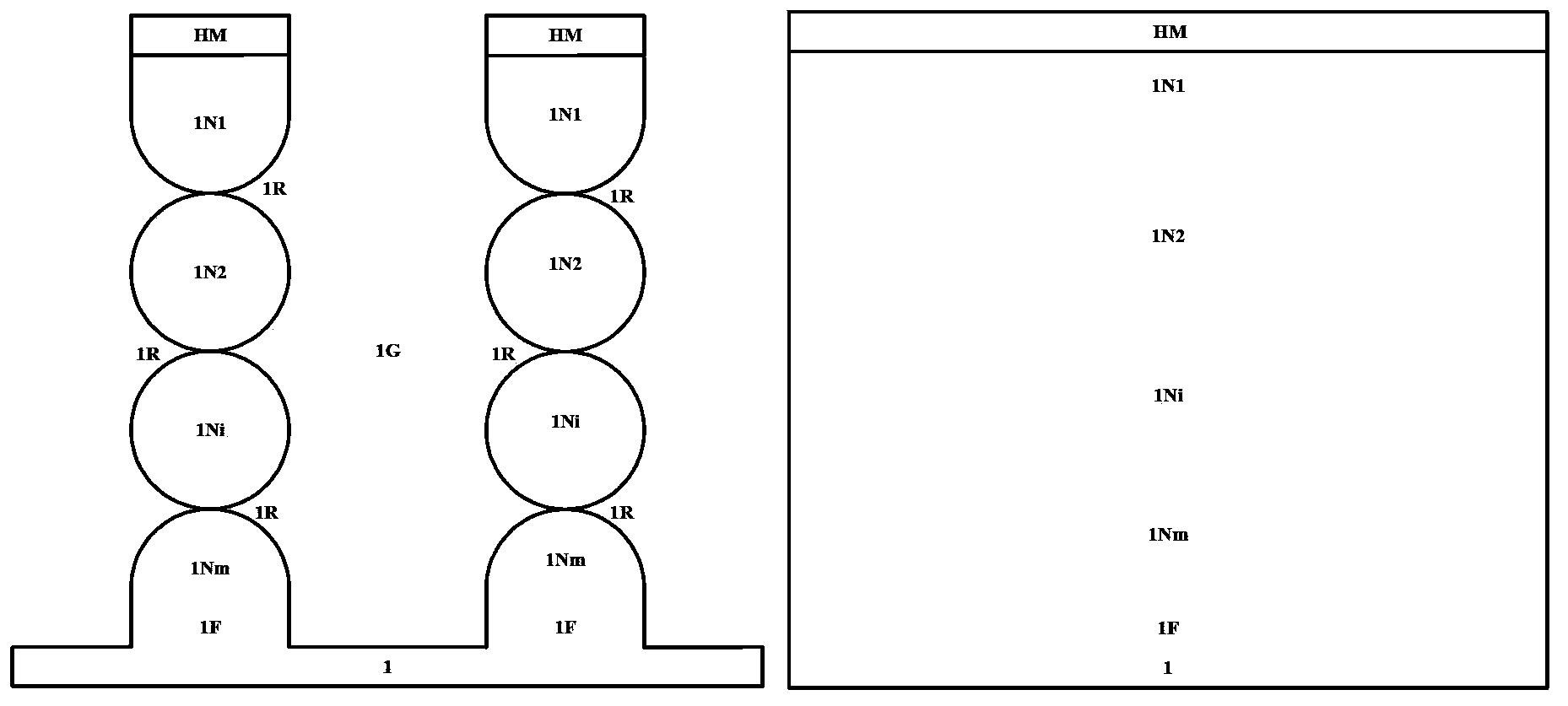

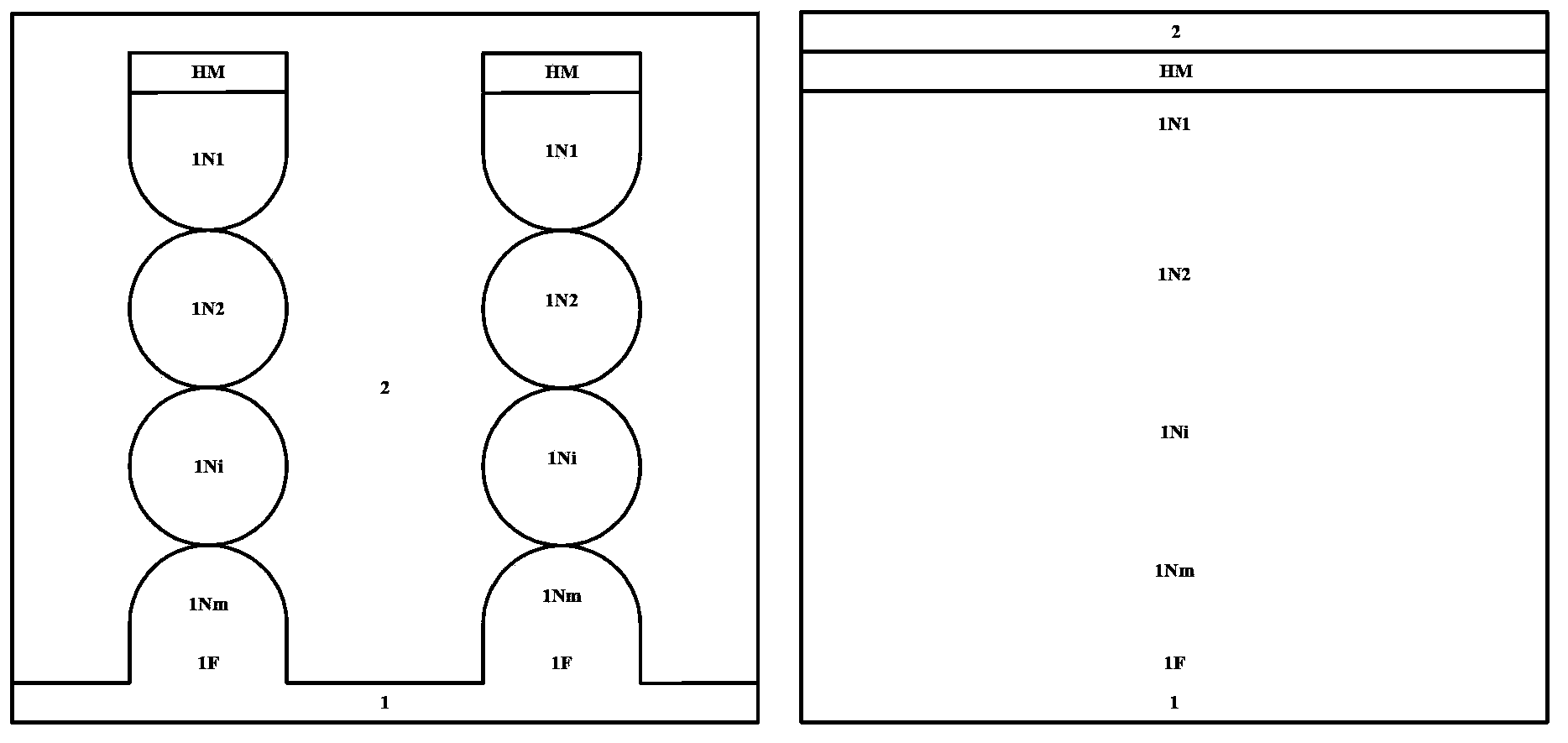

MOS transistor with stacked nanometer lines and manufacturing method of MOS transistor

InactiveCN104282559AIncrease effective widthIncrease the effective conductive total cross-sectional areaNanoinformaticsSemiconductor/solid-state device manufacturingDriving currentPower flow

The invention discloses an MOS transistor with stacked nanometer lines and a manufacturing method of the MOS transistor. The MOS transistor comprises toruliform nanometer line stacks, a plurality of grid stacks, a plurality of source and drain regions and a plurality of channel regions, wherein each nanometer line stack is formed by stacking the nanometer lines in the longitudinal direction and extends on a substrate in the first direction; the grid stacks extend in the second direction and cross over the nanometer stacks; the source and drain regions are located on the two sides of each grid stack in the second direction; the channel regions are formed by the nanometer line stacks between the source and drain regions. According to the MOS transistor with the stacked nanometer lines and the manufacturing method of the MOS transistor, the toruliform nanometer line stacks with good quality are formed by means of etching carried out many times and sideward etching and filling of grooves, effective widths of conducting channels are increased at low cost, the total area of effective conductive sections is increased and drive currents are increased.

Owner:INST OF MICROELECTRONICS CHINESE ACAD OF SCI

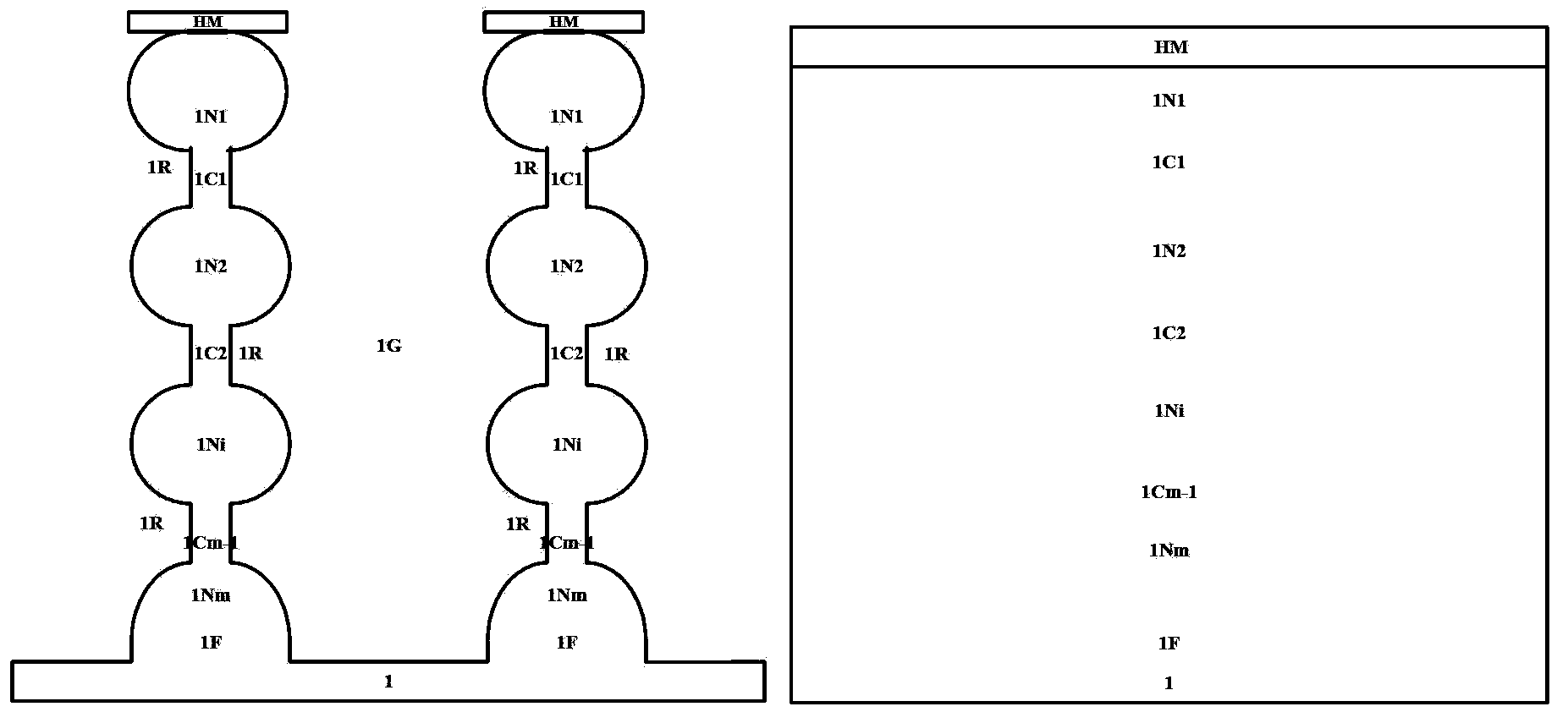

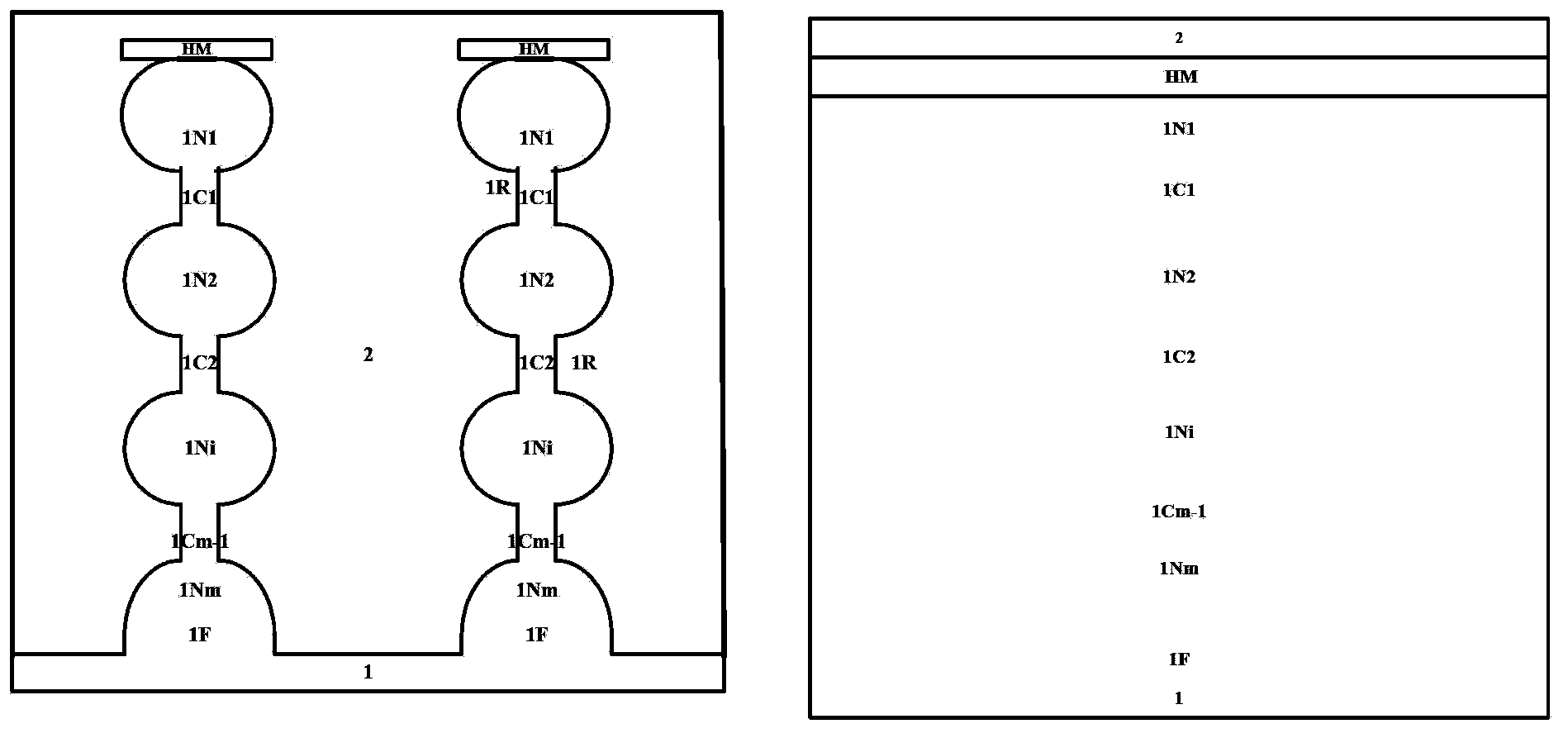

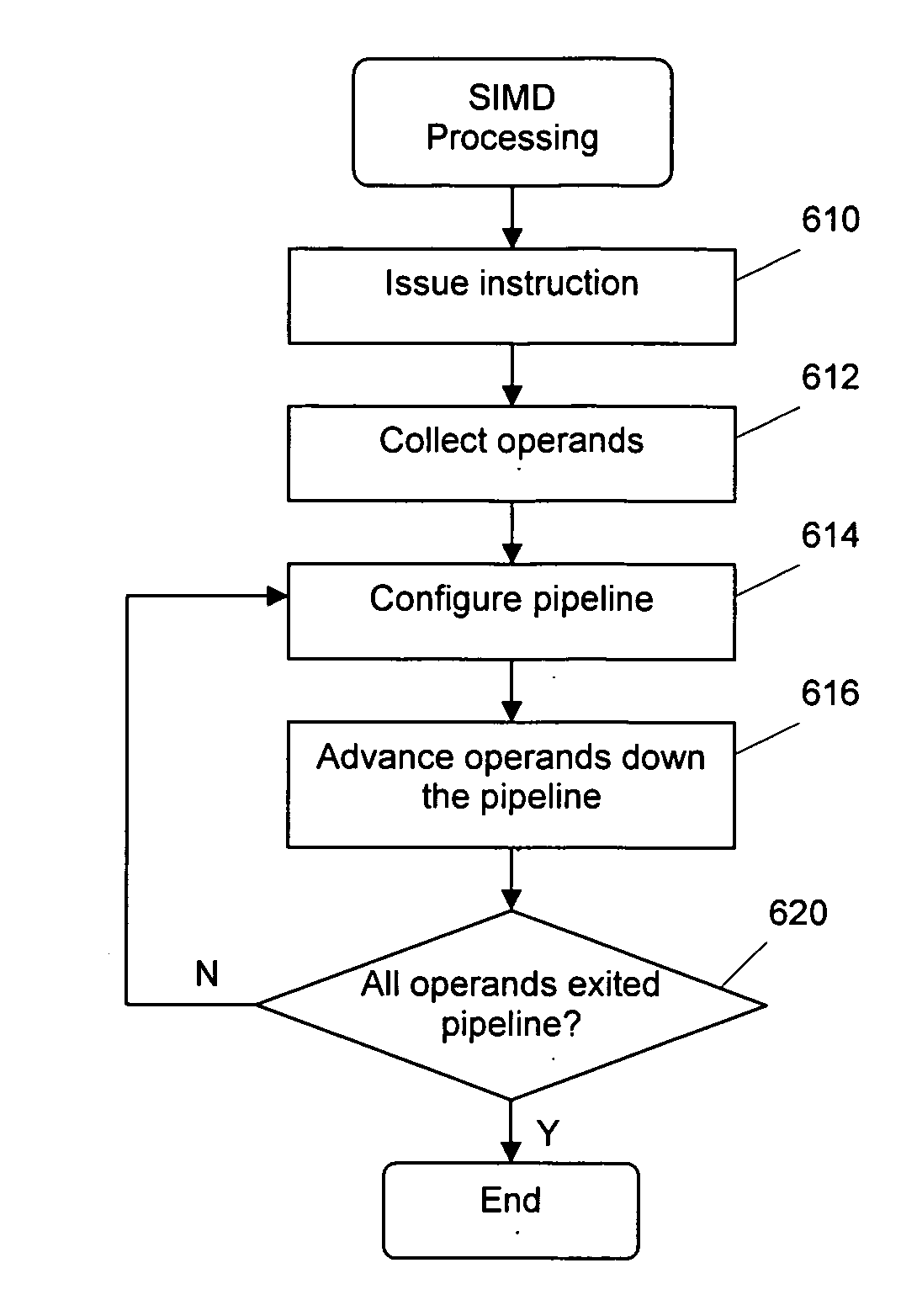

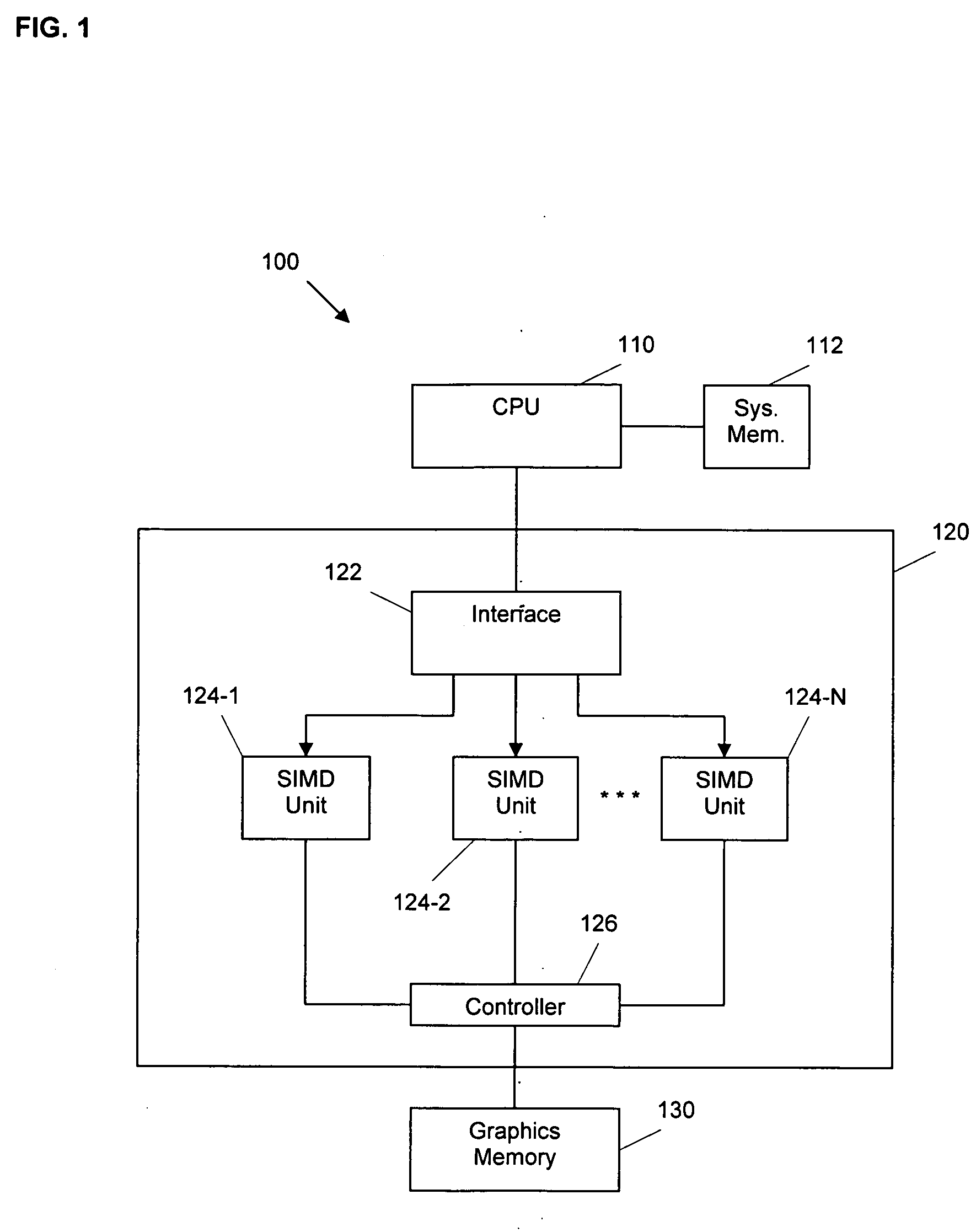

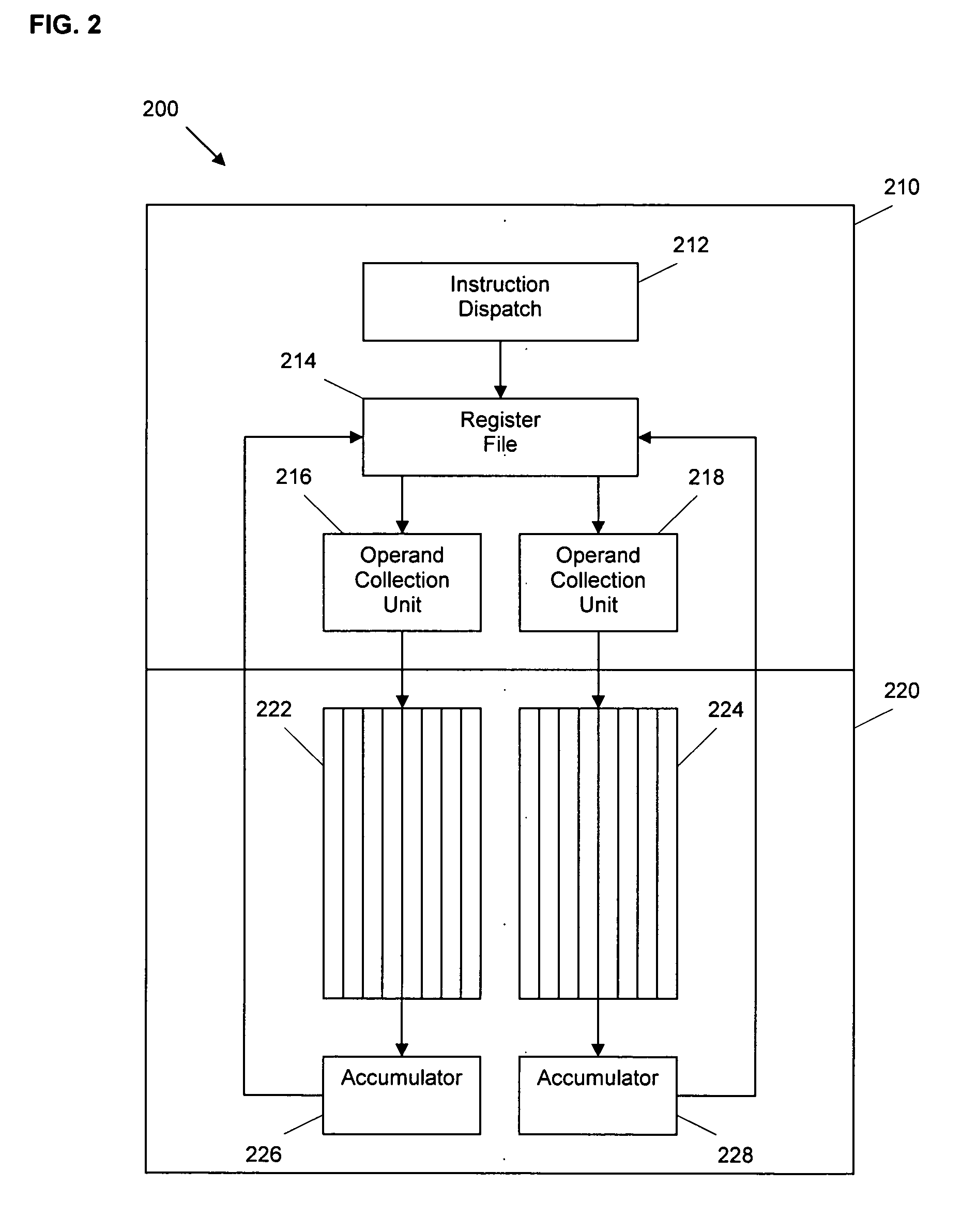

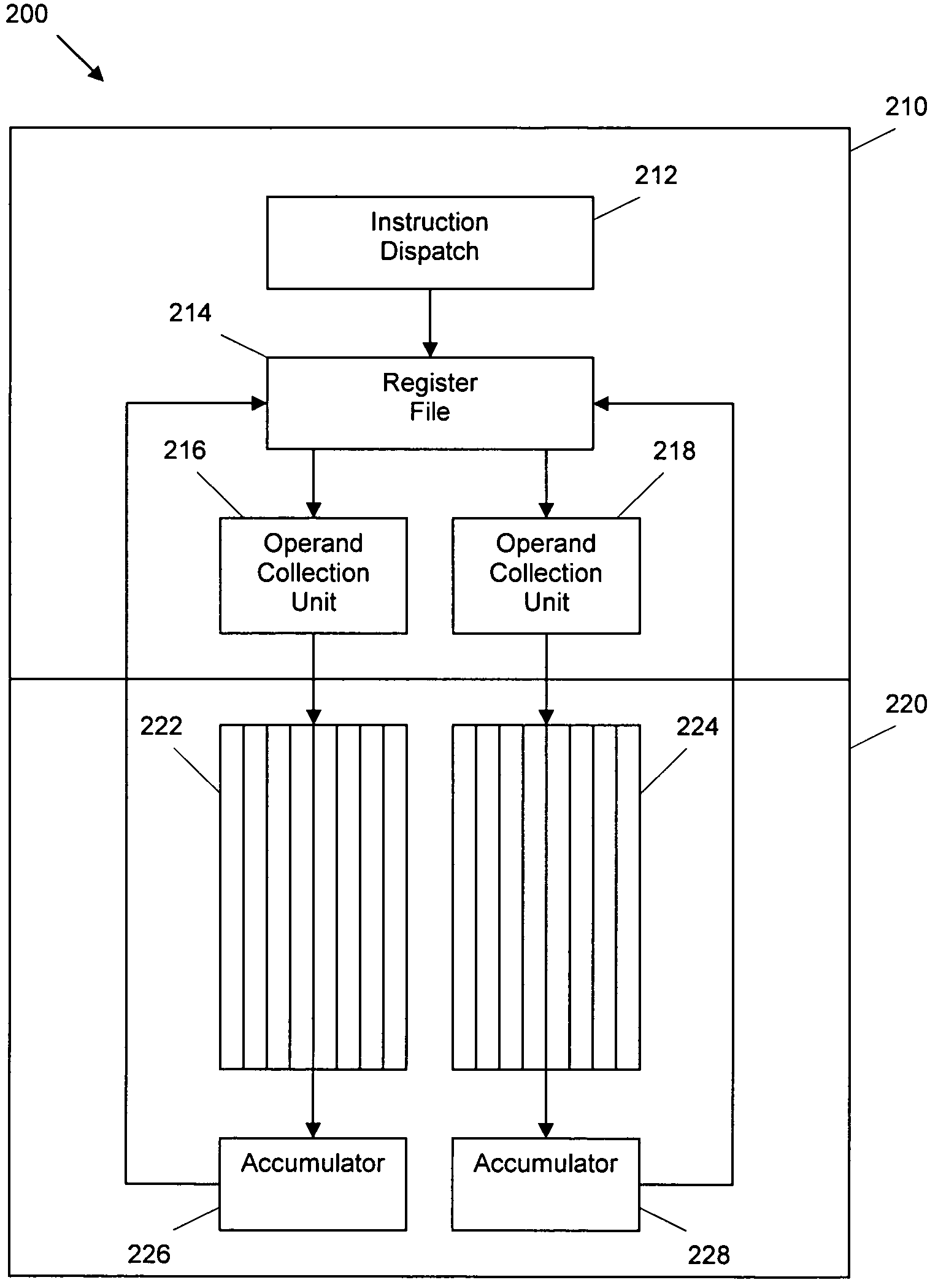

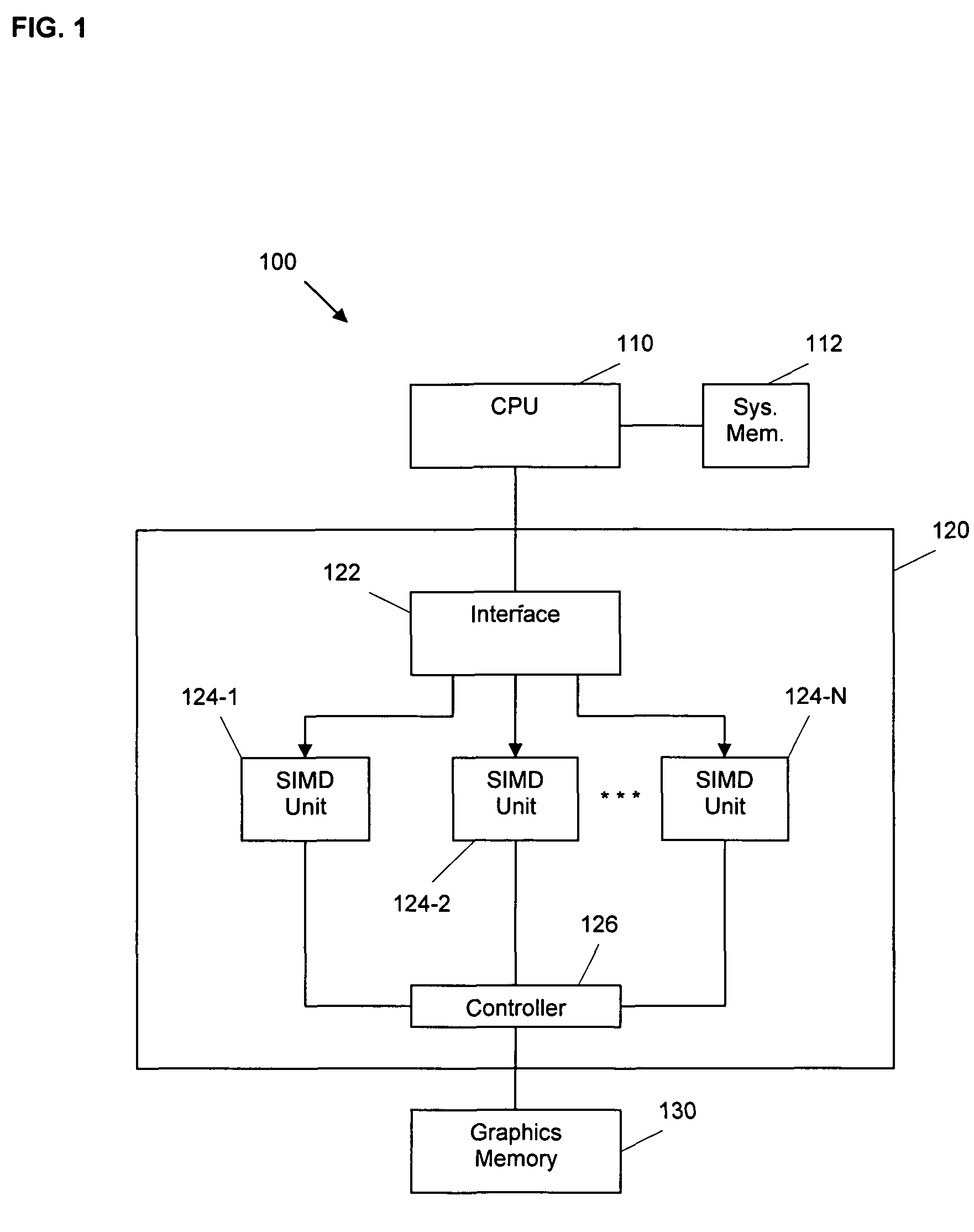

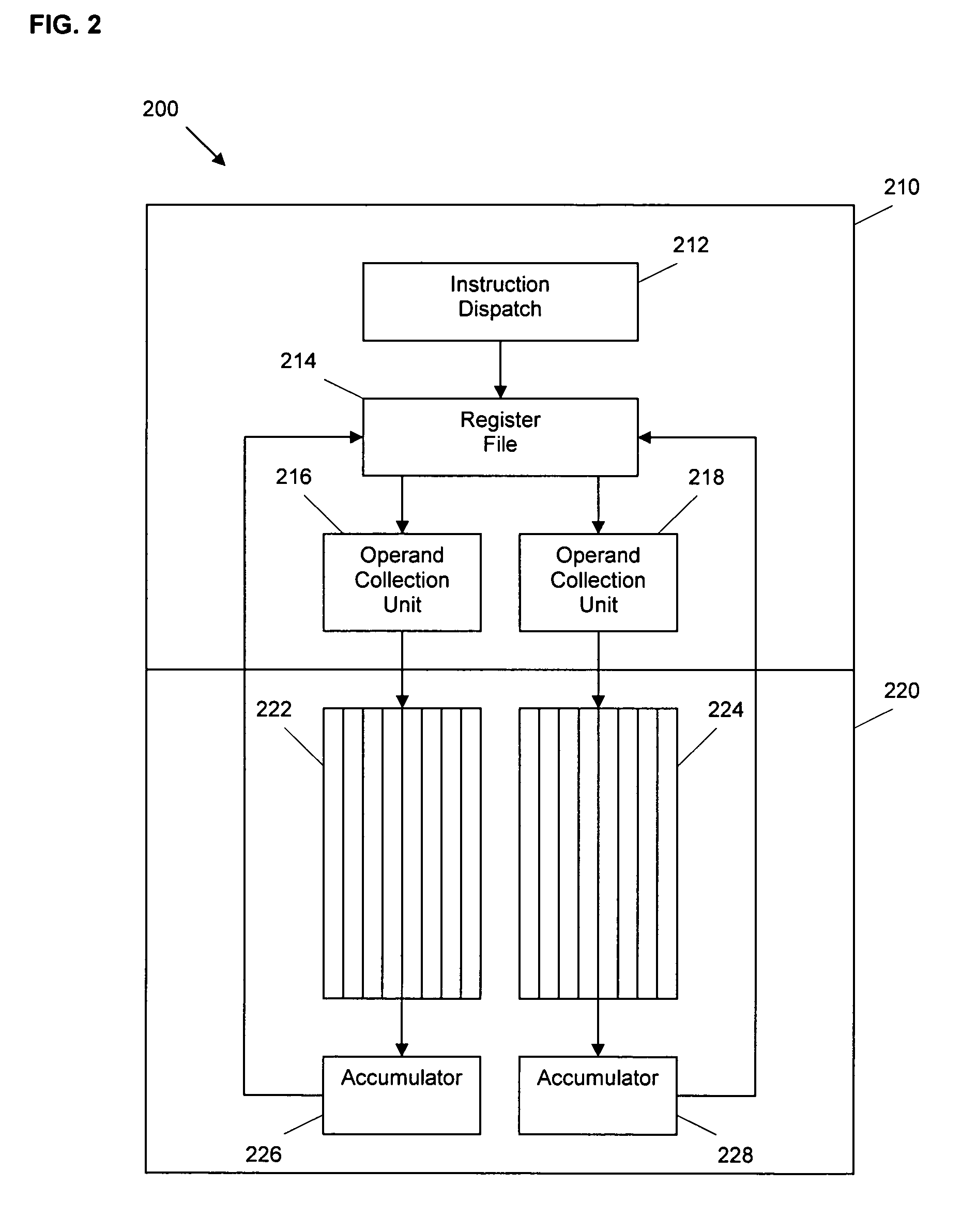

System and method for processing thread groups in a SIMD architecture

ActiveUS20070130447A1Reduce clock frequencyLow hardware requirementsGeneral purpose stored program computerMemory systemsGraphicsDatapath

A SIMD processor efficiently utilizes its hardware resources to achieve higher data processing throughput. The effective width of a SIMD processor is extended by clocking the instruction processing side of the SIMD processor at a fraction of the rate of the data processing side and by providing multiple execution pipelines, each with multiple data paths. As a result, higher data processing throughput is achieved while an instruction is fetched and issued once per clock. This configuration also allows a large group of threads to be clustered and executed together through the SIMD processor so that greater memory efficiency can be achieved for certain types of operations like texture memory accesses performed in connection with graphics processing.

Owner:NVIDIA CORP

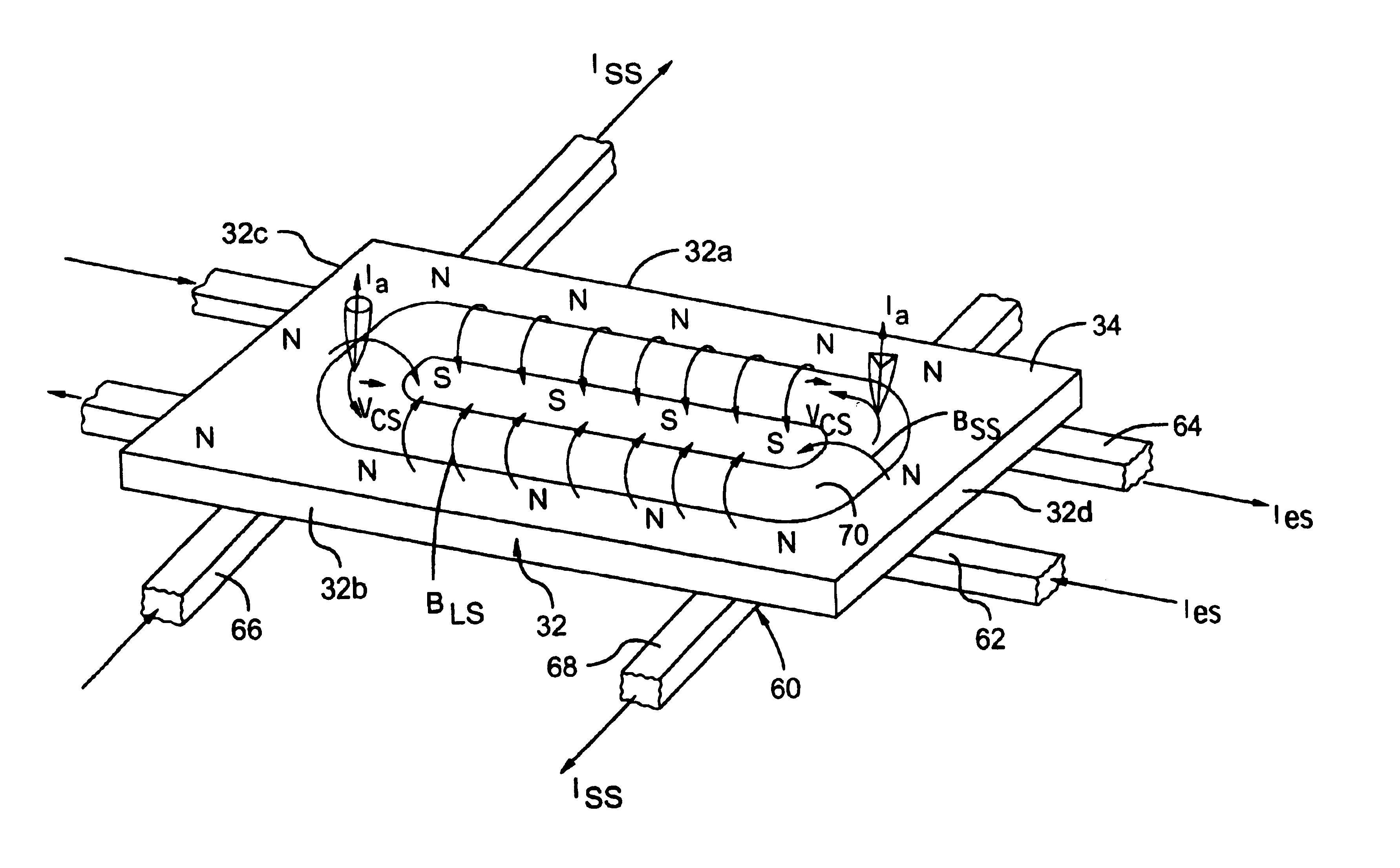

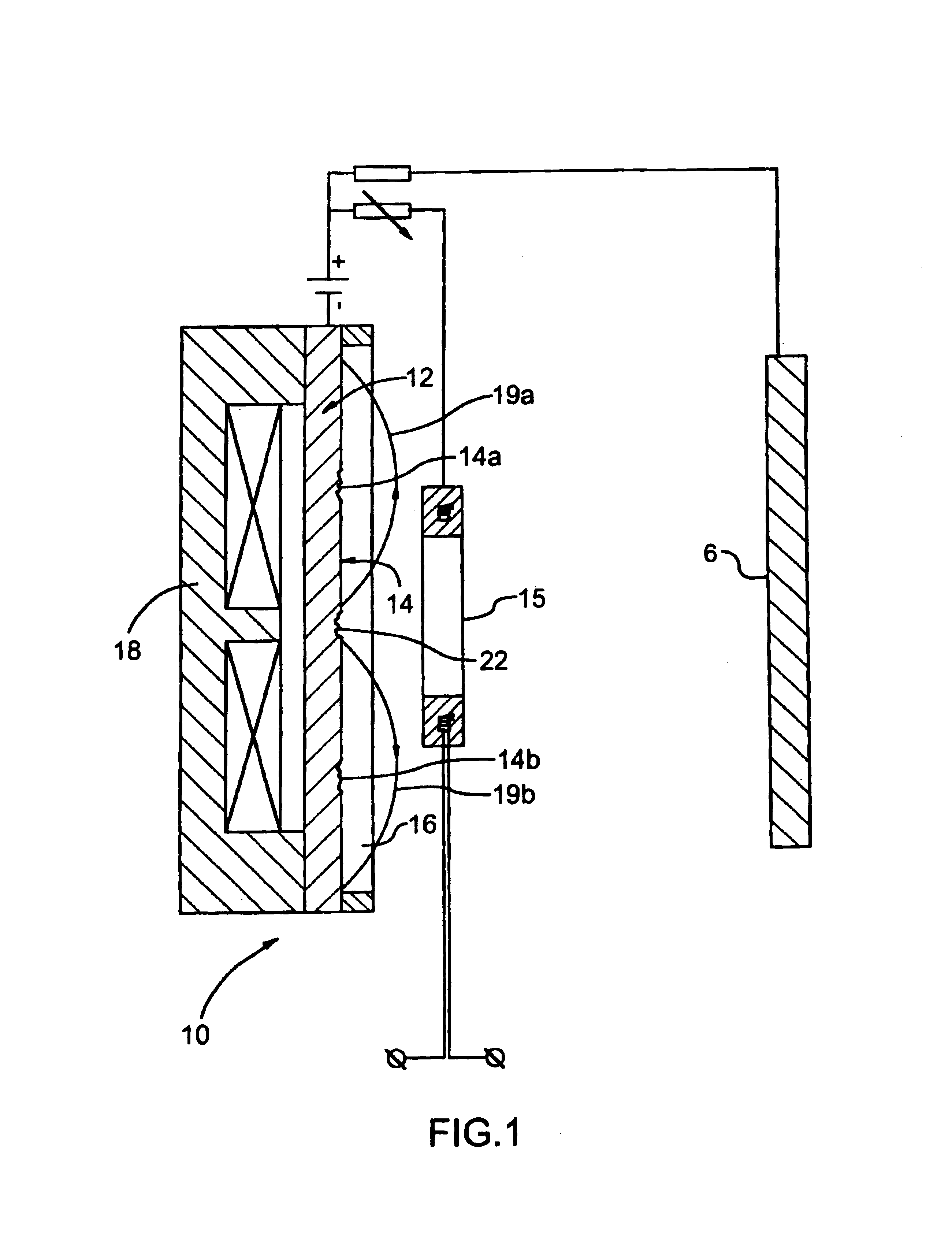

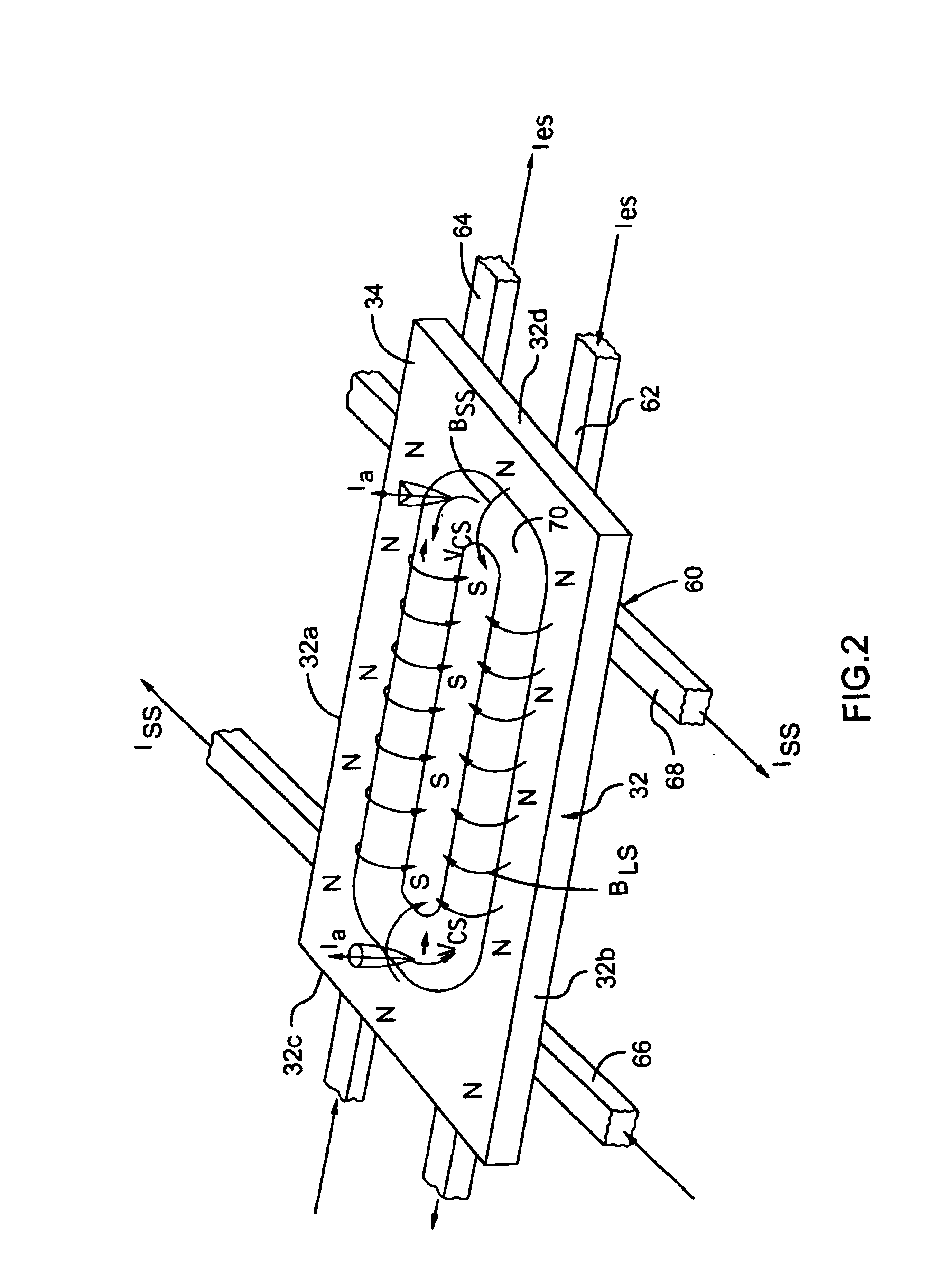

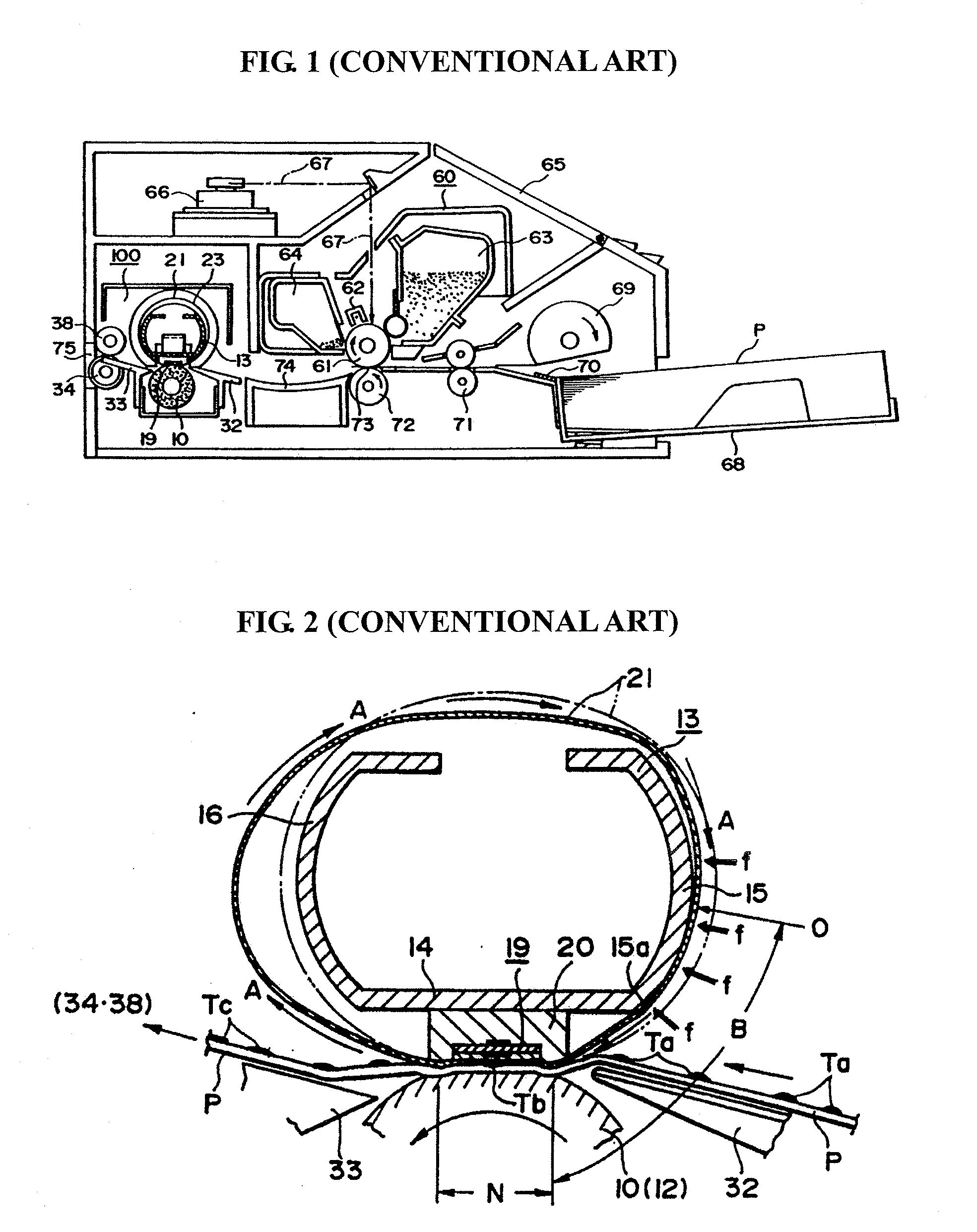

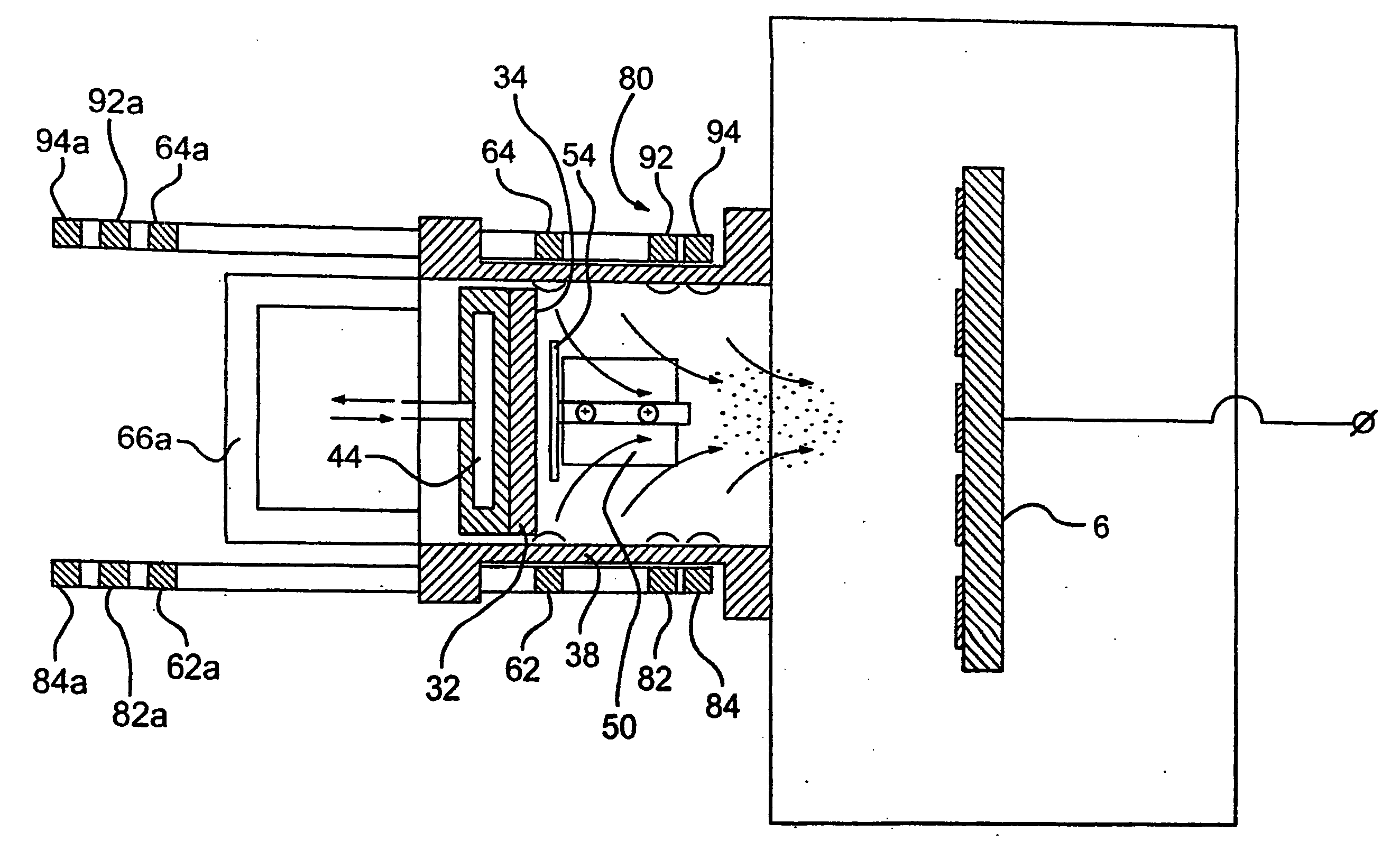

Rectangular cathodic arc source and method of steering an arc spot

InactiveUS6929727B2Improve distributionUniform coatingCellsLiquid surface applicatorsElectrical conductorEvaporation

The invention provides an arc coating apparatus having a steering magnetic field source comprising steering conductors disposed along the short sides of a rectangular target behind the target, and a magnetic focusing system disposed along the long sides of the target in front of the target which confines the flow of plasma between magnetic fields generated on opposite long sides of the target. The plasma focusing system can be used to deflect the plasma flow off of the working axis of the cathode. Each steering conductor can be controlled independently. In a further embodiment, electrically independent steering conductors are disposed along opposite long sides of the cathode plate, and by selectively varying a current through one conductor, the path of the arc spot shifts to widen an erosion corridor. The invention also provides a plurality of internal anodes, and optionally a surrounding anode for deflecting the plasma flow and preserving a high ionization level of the plasma. The invention also provides a shield at floating potential, restricting the cathode spot from migrating into selected regions of the target evaporation surface outside of the desired erosion zone. The shield may be positioned immediately above the region of the target surface in the vicinity of the anode, protecting the anode from deposition of cathodic evaporate and providing better distribution of cathodic evaporate over the substrates to be coated. The invention further provides correcting magnets adjacent to the short sides of the target, to move the arc spot between the long sides.

Owner:G&H TECH LLC

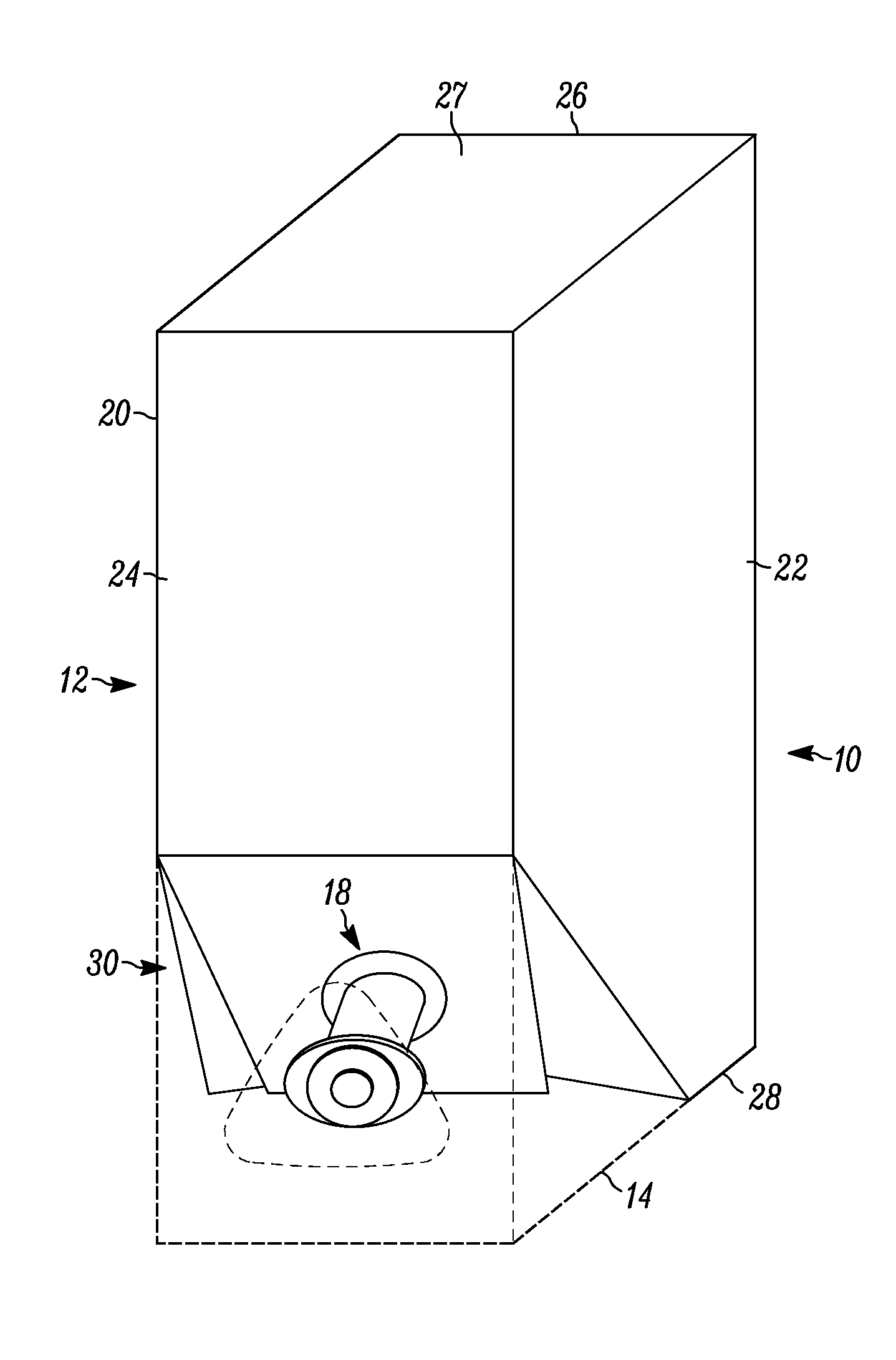

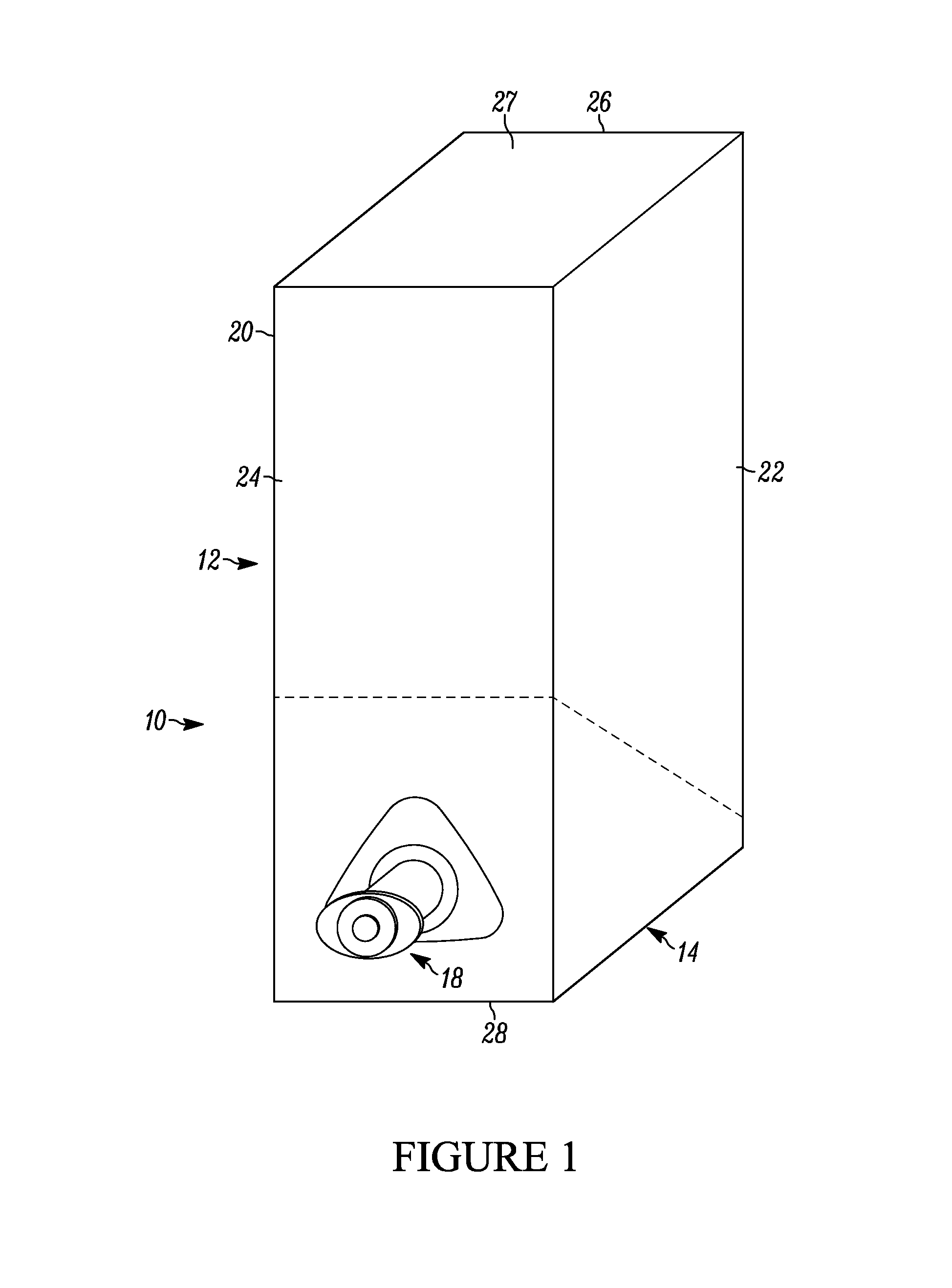

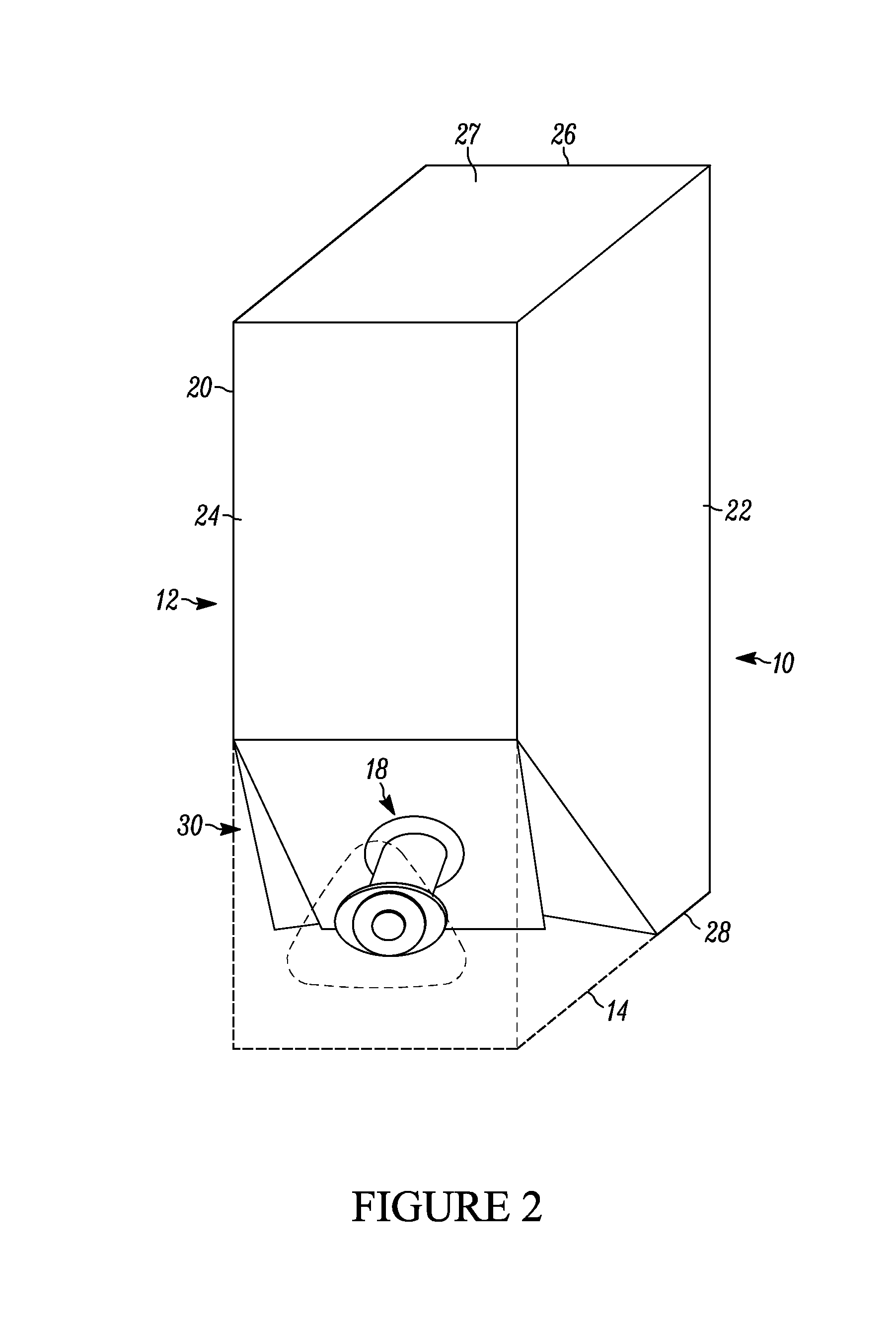

Bag In Box Packaging

ActiveUS20140076927A1Increase effective widthFlexible containersPliable tubular containersWebbingBag-in-box

An outer box for a bag in box packaging includes a plurality of walls and an articulatable portion. The articulatable portion is hingedly coupled to each of the dispensing wall, the first sidewall and the second sidewall. The articulatable portion also includes a front portion, a first side webbing and a second side webbing. Inward rotation of the front portion causes the first and second panels of each of the first and second side webbing to rotate about a respective one of the central folds thereof. An outer surface of each of the first and second panels face each other, with the articulated portion overlying a portion of the first panel of each of the first side webbing and second side webbing.

Owner:SCHOLLE IPN CORP

Recessed STI for wide transistors

ActiveUS8058161B2Increase effective widthIncrease gate widthSemiconductor/solid-state device manufacturingEngineeringSemiconductor

Owner:TEXAS INSTR INC

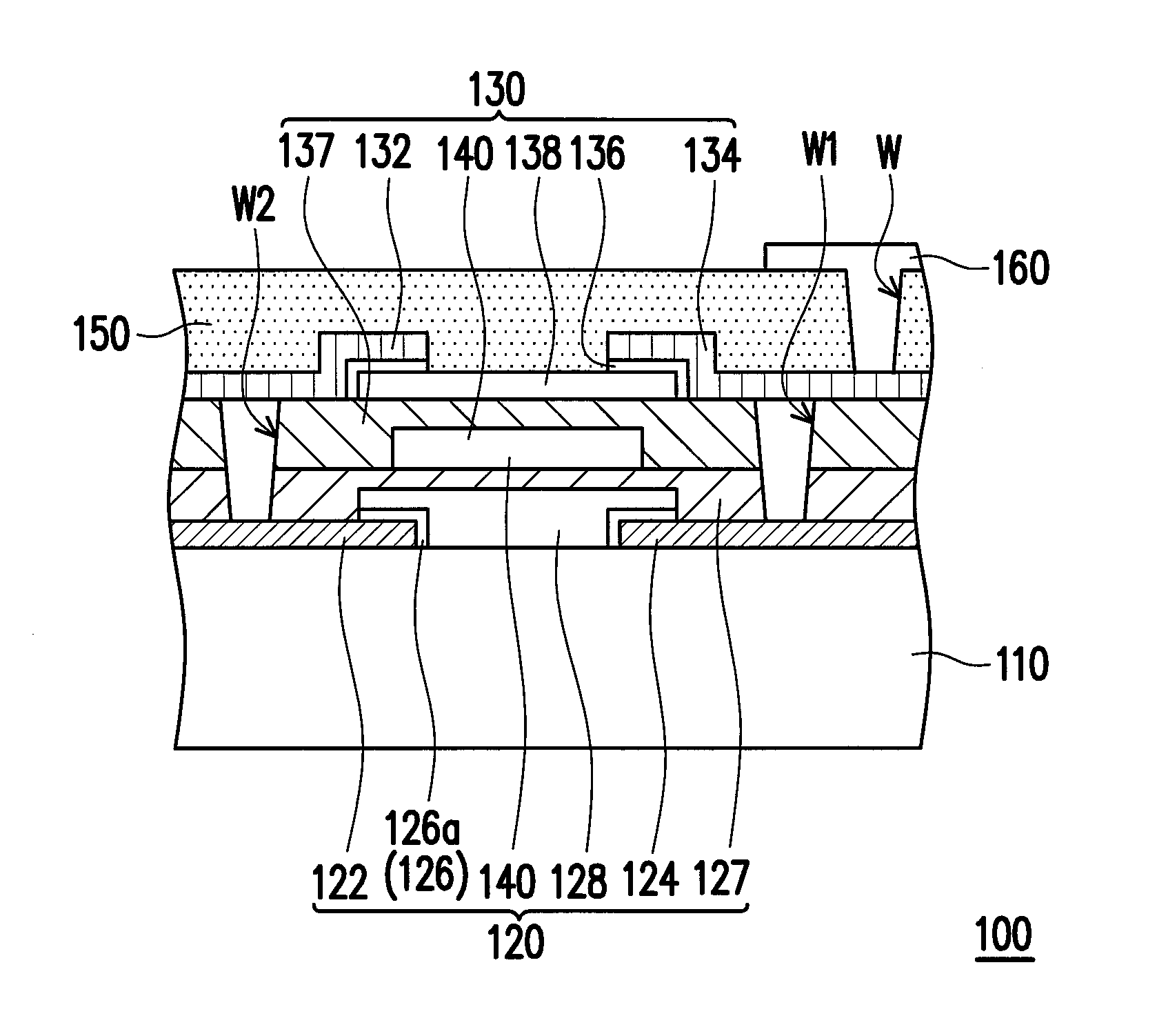

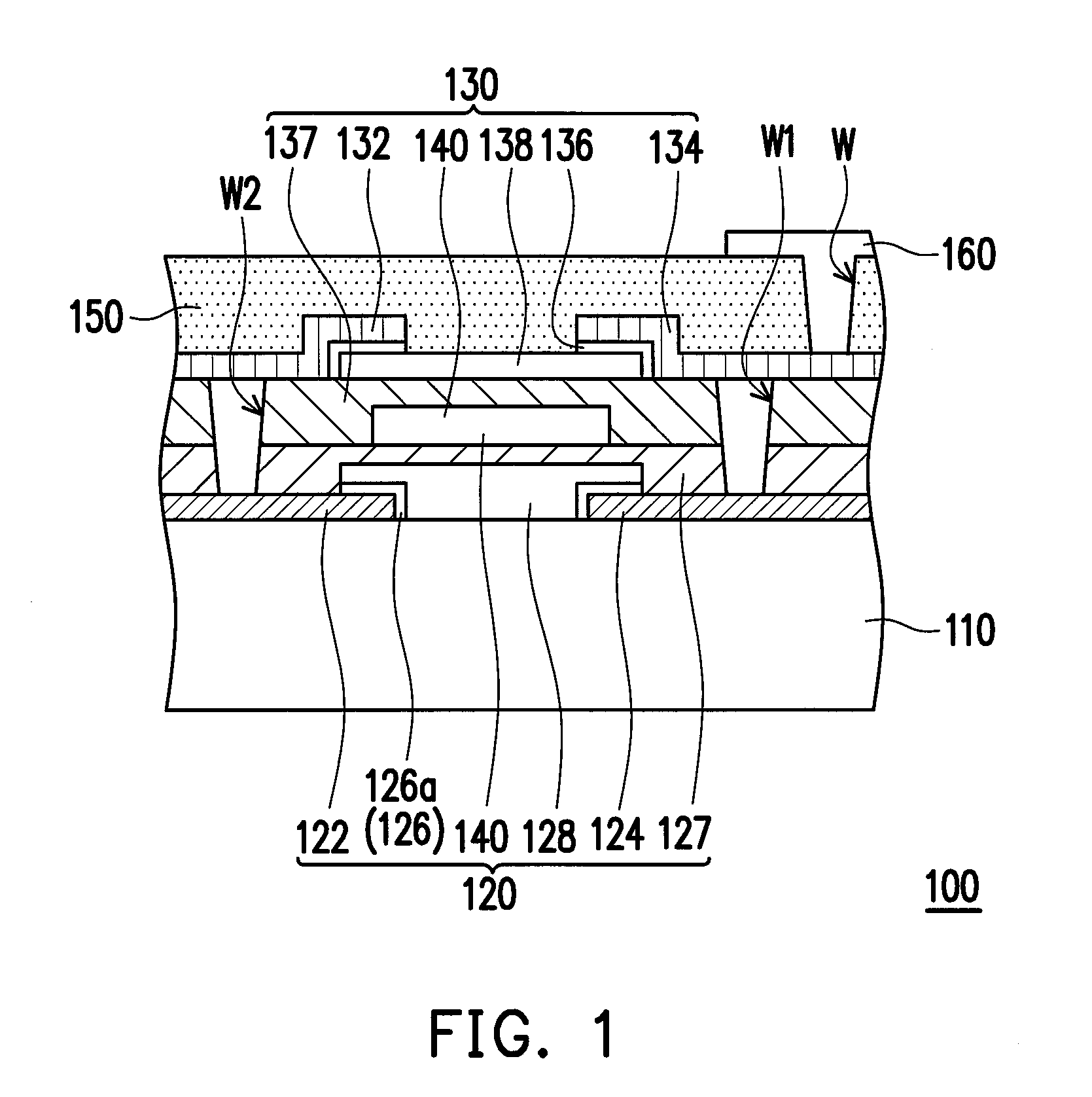

Structure and method to increase effective mosfet width

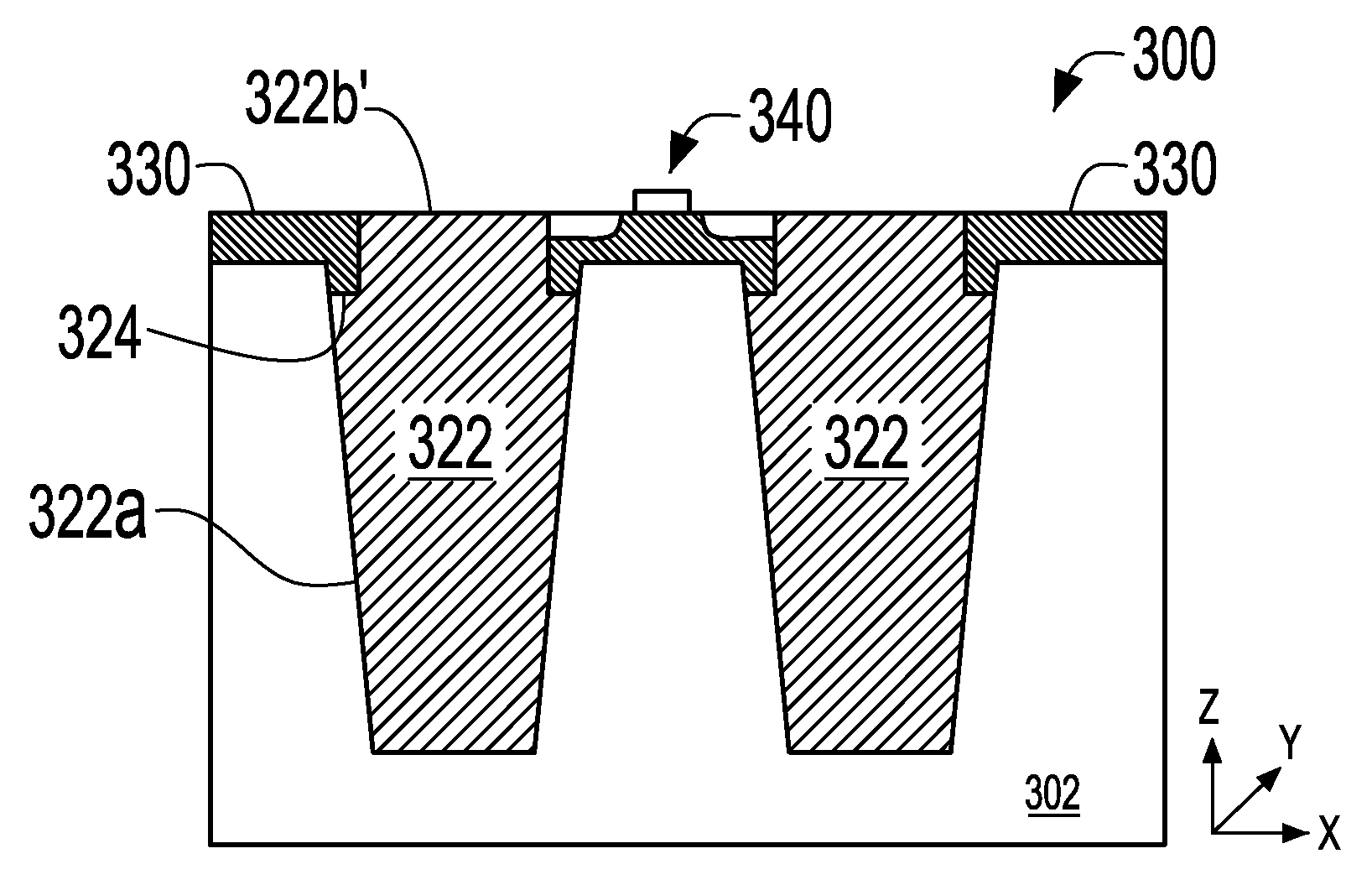

InactiveUS20090146263A1Increase effective widthPromotes lateral growthSemiconductor/solid-state device manufacturingSemiconductor devicesMOSFETCapacitance

An epitaxial layer of silicon (Si) or silicon-germanium (SiGe) extends over the edge of silicon trench isolation (STI), thereby increasing the effective width of an active silicon region (RX) bordered by the STI. The RX region may have a <100> crystal orientation. An effective width of an FET device formed in the RX region may be increased, therefore performance may be improved with same density. Isolation may not be degraded since RX-to-RX distance is same at bottom. Junction capacitance may be reduced since part of the RX is on STI.

Owner:ALSEPHINA INNOVATIONS INC

Tunable micro electromechanical inductor

ActiveUS7274278B2Increasing inductance ratioIncrease effective widthWaveguidesCoupling devicesElectrical conductorCoplanar waveguide

The present invention provides a monolithic inductor developed using radio frequency micro electromechanical (RF MEMS) techniques. In a particular embodiment of the present invention, a tunable radio frequency microelectromechanical inductor includes a coplanar waveguide and at least one direct current actuatable contact switch positioned to vary the effective width of a narrow inductive section of the center conductor of the CPW line upon actuation the DC contact switch.

Owner:UNIV OF SOUTH FLORIDA

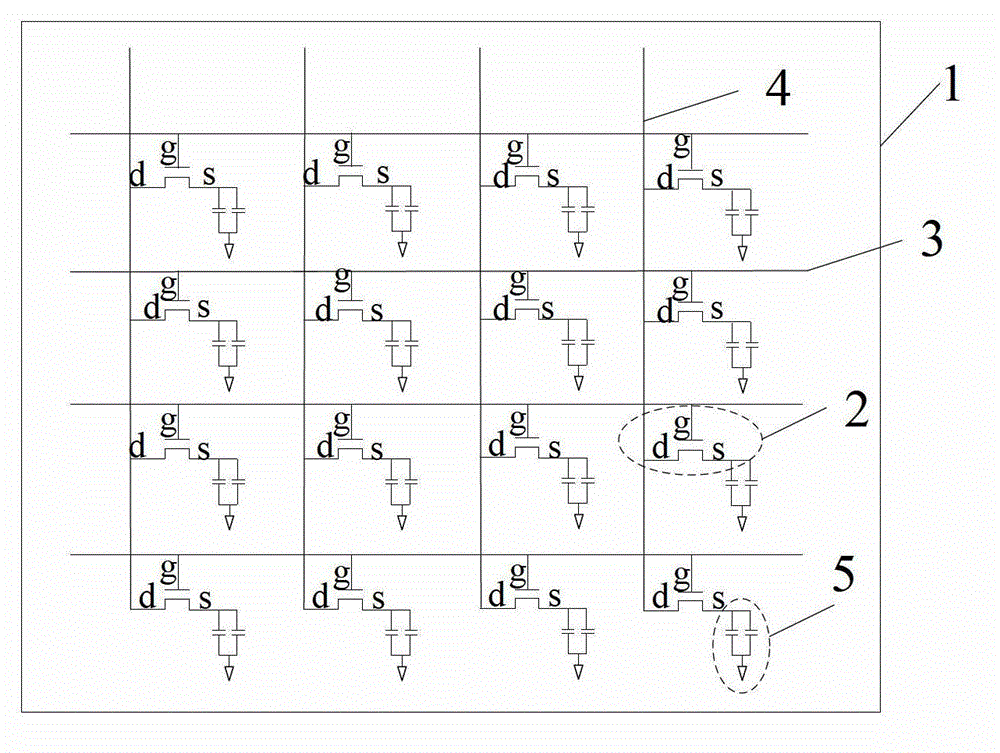

Static memory cell and forming method thereof

ActiveCN104022116AQuality improvementImprove performanceSolid-state devicesSemiconductor/solid-state device manufacturingInsulation layerMedia layer

A static memory cell and a forming method thereof are provided; the static memory cell comprises the following elements: a semiconductor substrate comprising a first zone forming a pull down transistor and a second zone forming a pull up transistor; a first pin portion positioned on a surface of the semiconductor substrate in the first zone and a second fin portion positioned on a surface of the semiconductor in the second zone, wherein a top of the second fin portion is provided with an insulation layer; an interlayer medium layer covering the semiconductor substrate surface besides the first fin portion and the second fin portion, and a surface of the interlayer medium layer is lower than a top surface of the first and second fin portions; a first grid electrode structure positioned on the surface of the interlayer medium layer and capable of crossing the top and a side wall of the single first fin portion, and a second grid electrode structure positioned on the surface of the interlayer medium layer and capable of crossing a top and a side wall of the single second fin portion, and the second grid electrode structure is isolated from the top portion of the second fin portion through an insulation layer. The static memory cell is stable in performance, and a finally formed SRAM memory is excellent in performance.

Owner:SEMICON MFG INT (SHANGHAI) CORP

Method for manufacturing MOS transistor with cascaded and stacked nanowires

ActiveCN104282560AIncrease the effective conductive total cross-sectional areaIncrease drive currentSemiconductor/solid-state device manufacturingSemiconductor devicesEngineeringGate stack

A stacked nanowire MOS transistor and a manufacturing method therefor. The stacked nanowire MOS transistor comprises multiple nanowire stacks, multiple gate stacks, multiple source and drain regions, and multiple channel regions. The nanowire stacks extend along a first direction (Y-Y') on a substrate (1). The gate stacks extend along a second direction (X-X') and cross each nanowire stack. The source and drain regions are located on two sides of each gate stack along the second direction (X-X'). The channel regions are formed by the nanowire stacks among the multiple source and drain regions. The multiple nanowire stacks are stacks formed by multiple cascaded nanowires. By performing etch-backs, performing side etching on the channels and performing filling many times, cascaded nanometer stacks with good quality are formed and the effective width of electric conduction channels are fully increased by using low cost, and the total electric conduction area is improved, thereby improving a driving current.

Owner:INST OF MICROELECTRONICS CHINESE ACAD OF SCI

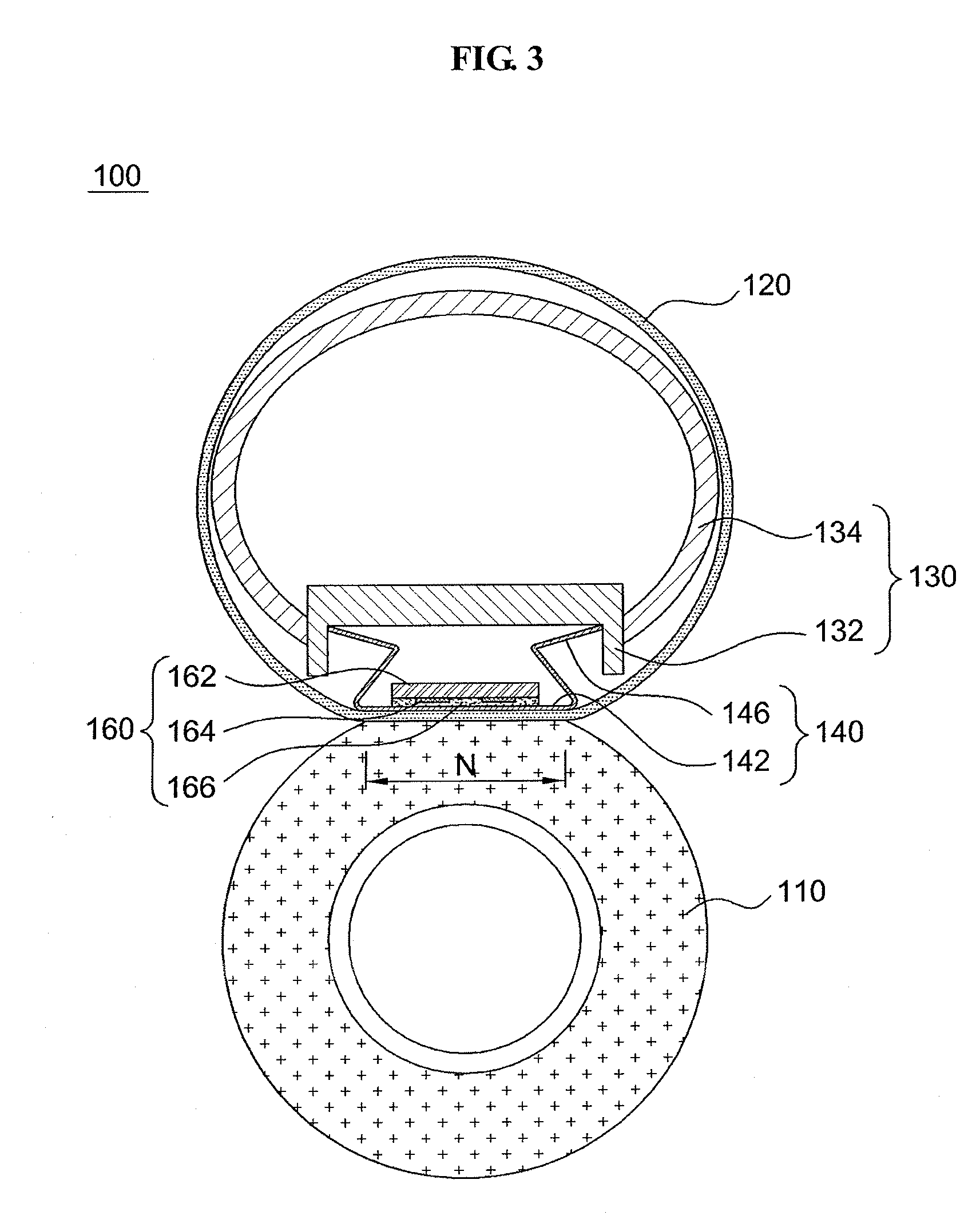

Apparatus and method of heating image on recordable material

ActiveUS20080219723A1Increase effective widthUniform pressure distributionElectrographic process apparatusBand shapeEngineering

Owner:HEWLETT PACKARD DEV CO LP

Method to increase effective MOSFET width

InactiveUS8062951B2Increase effective widthPromotes lateral growthSemiconductor/solid-state device manufacturingSemiconductor devicesCapacitanceMOSFET

An epitaxial layer of silicon (Si) or silicon-germanium (SiGe) extends over the edge of silicon trench isolation (STI), thereby increasing the effective width of an active silicon region (RX) bordered by the STI. The RX region may have a <100> crystal orientation. An effective width of an FET device formed in the RX region may be increased, therefore performance may be improved with same density. Isolation may not be degraded since RX-to-RX distance is same at bottom. Junction capacitance may be reduced since part of the RX is on STI.

Owner:ALSEPHINA INNOVATIONS INC

Formation method for relieving wavy edge of low-voltage formed foil

ActiveCN108183031ALighten the wavy edgesIncrease effective widthSurface reaction electrolytic coatingCapacitor electrodesPrimary repairLow voltage

The invention provides a formation method for relieving a wavy edge of a low-voltage formed foil, which is characterized in that the process route comprises pretreatment, five-stage formation treatment, washing, polarization treatment, washing, primary repair formation treatment, washing, middle treatment, thermal treatment, secondary repair formation treatment and drying treatment. The formationmethod has the advantages that the wavy edge of the low-voltage formed foil is relieved, the effective width of the formed foil is increased, and the edge is good in each index.

Owner:NANTONG HAIXING ELECTRONICS +2

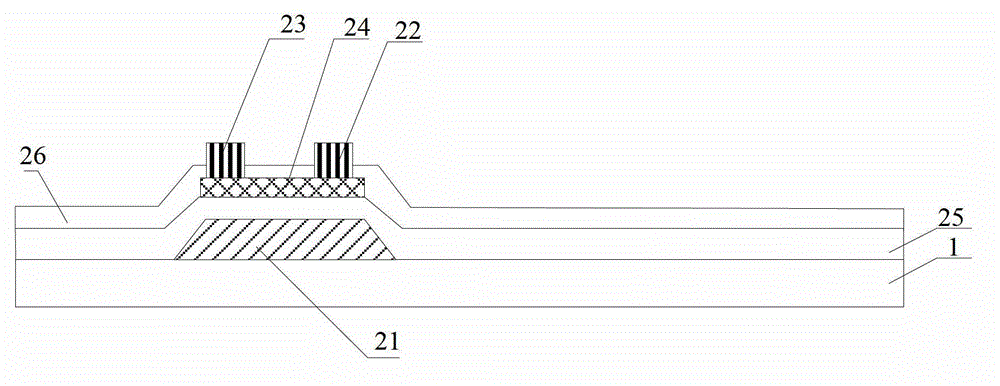

Thin-film transistor, manufacturing method of thin-film transistor, array substrate and display device

ActiveCN102916051AImprove performanceIncrease capacitanceTransistorSolid-state devicesCapacitanceImaging quality

The invention discloses a thin film transistor (TFT), a manufacturing method of the TFT, an array substrate and a display device, and ensures that the width of a conducting channel of the TFT is increased under the premise of not changing the capacitance of a source electrode, the performance of the TFT is improved and the image quality is improved accordingly. The TFT comprises a substrate, as well as a grid electrode, a source electrode, at least two drain electrodes and a semiconductor layer which are formed on the substrate, a grid electrode protective layer formed on the substrate and positioned between the grid electrode and the semiconductor layer, and an etching blocking layer formed on the substrate and positioned between the semiconductor layer and the source electrode, and between the semiconductor layer and the drain electrodes, wherein the source electrode and the drain electrodes are respectively connected with the semiconductor layer through via holes.

Owner:BOE TECH GRP CO LTD +1

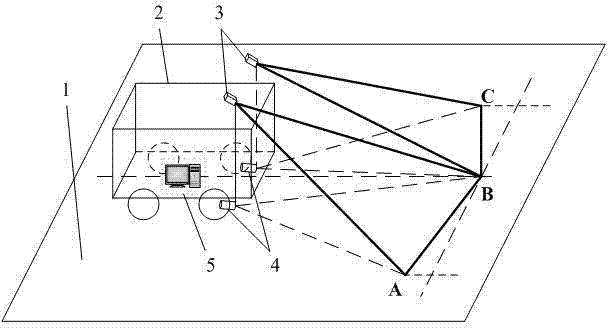

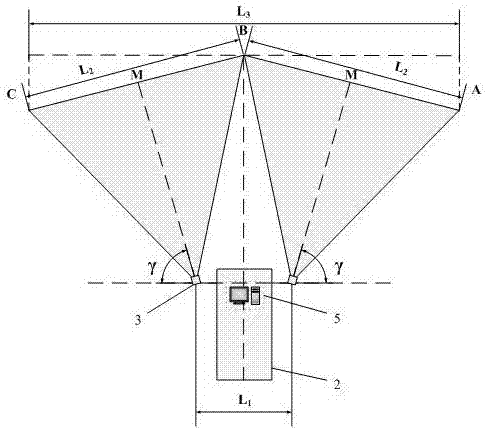

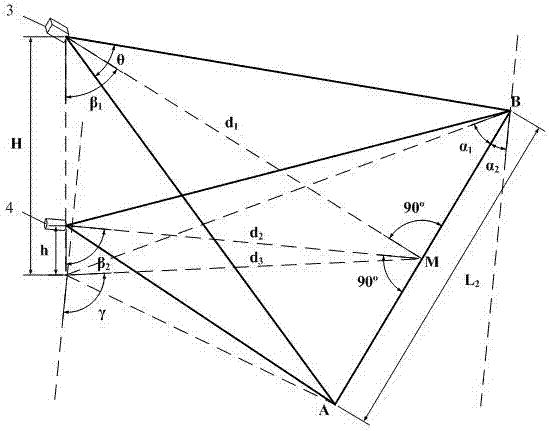

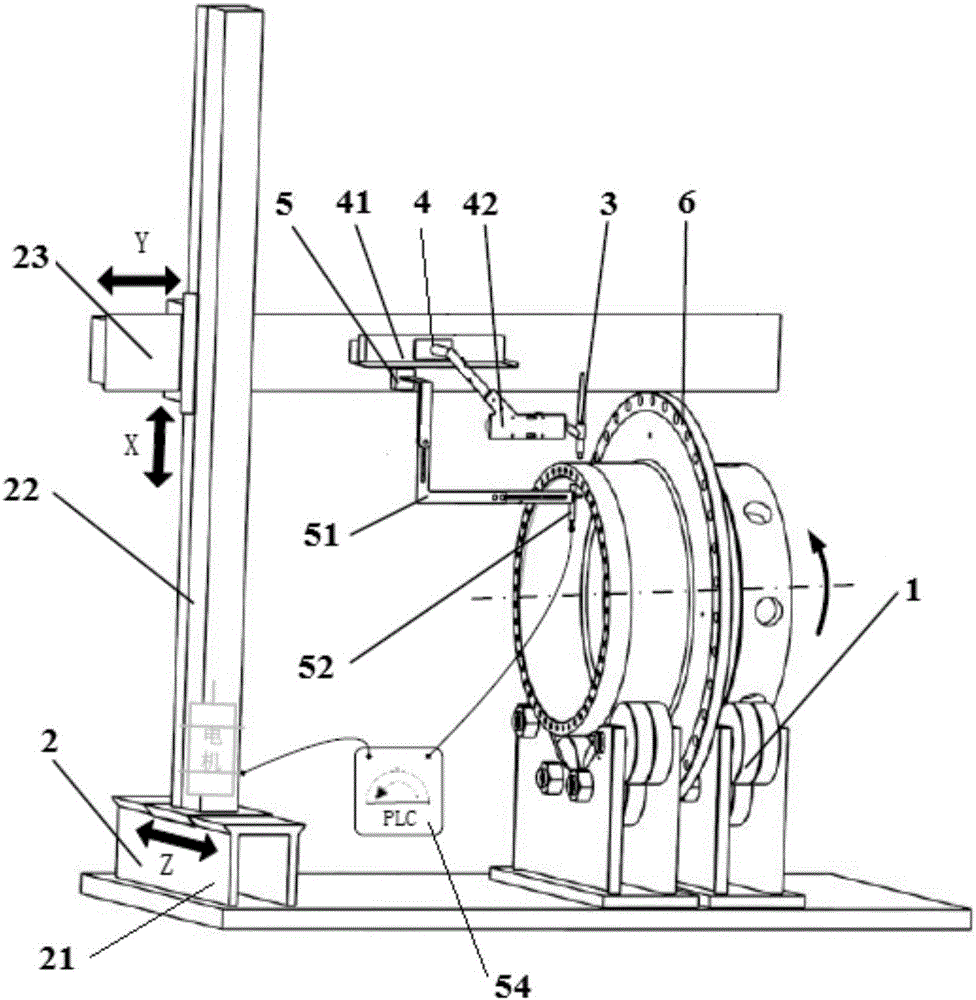

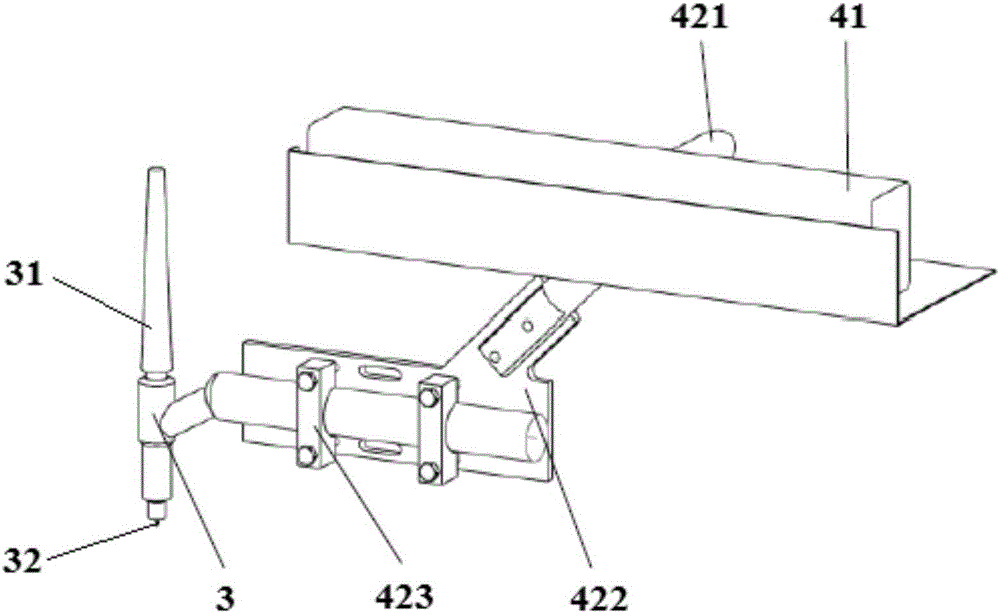

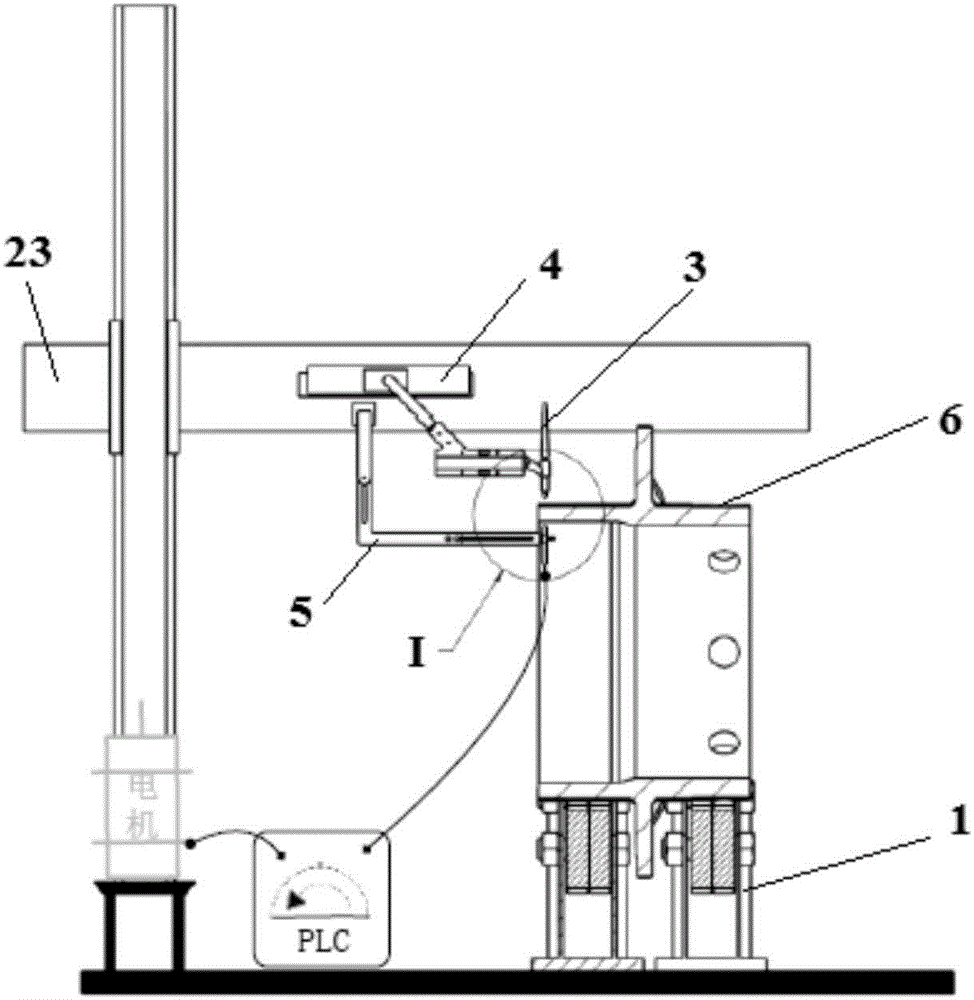

Structural light-based airport runway foreign body detection system

ActiveCN107390285AEfficient detectionDetection system, which uses structured light to detect effectiveOptical detectionEngineeringRoad surface

The present invention discloses a structural light-based airport runway foreign body detection system. The system includes a detection vehicle as well as a line laser module, an image acquisition module and a computer control and processing module which are all mounted on the detection vehicle; the line laser module is mounted at the rear end of the detection vehicle and projects a structural light plane to the surface of a runway with a certain attitude so that the structural light plane can form a structural light strip; the image acquisition module is located at the rear end of the test vehicle and is located at the same plane with the line laser module, wherein the plane is perpendicular to the surface of the runway; the image acquisition module acquires the light strip image of the surface of the runway with a certain attitude and transmits light strip image data to a computer; and the computer control and processing module is located inside the detection vehicle, controls the image acquisition module to acquire the light strip image of the surface of the runway, and processes the light strip image data in real time through related software and judges whether a foreign body exists on the runway.

Owner:NANJING UNIV OF AERONAUTICS & ASTRONAUTICS

Apparatus and method of heating image on recordable material

ActiveUS7664448B2Increase effective widthUniform pressure distributionElectrographic process apparatusBand shapeEngineering

Owner:HEWLETT PACKARD DEV CO LP

Rectangular filtered vapor plasma source and method of controlling vapor plasma flow

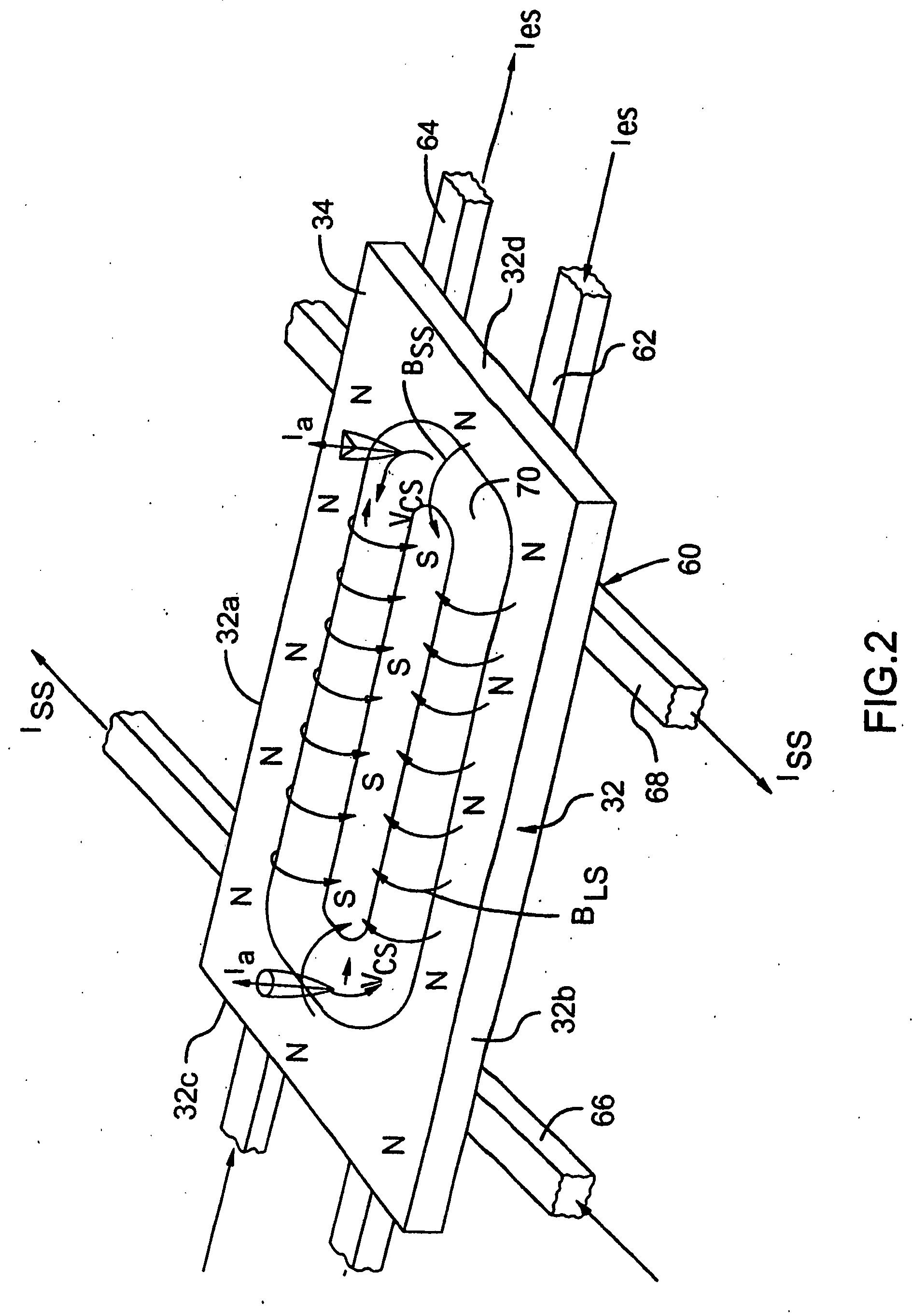

InactiveUS20070029188A1Increase in sizeIncrease the magnetic field strengthCellsLiquid surface applicatorsElectrical conductorPlasma flow

The invention provides an arc coating apparatus having a steering magnetic field source comprising steering conductors (62, 64, 66, 68) disposed along the short sides (32c, 32d) of a rectangular target (32) behind the target, and a magnetic focusing system disposed along the long sides (32a, 32b) of the target (32) in front of the target which confines the flow of plasma between magnetic fields generated on opposite long sides (32a, 32b) of the target (32). The plasma focusing system can be used to deflect the plasma flow off of the working axis of the cathode. Each steering conductor (62, 64, 66, 68) can be controlled independently. In a further embodiment, electrically independent steering conductors (62, 64, 66, 68) are disposed along opposite long sides (32a, 32b) of the cathode plate (32), and by selectively varying a current through one conductor, the path of the arc spot shifts to widen the erosion corridor. The invention also provides a plurality of internal anodes, and optionally a surrounding anode for deflecting the plasma flow.

Owner:G&H TECH LLC

Fixing device and image forming apparatus having the same

ActiveUS7773930B2Avoid damageEffective width of nipElectrographic process apparatusThermal deformationImage formation

A fixing device includes a fixing roller, a fixing belt which is made to rotate by a rotation force received from the fixing roller, a nip forming unit to form a nip zone at a contact area between the fixing roller and the fixing belt, and a first heating unit, which is separated from the nip zone, to apply heat to the fixing belt. The nip zone and the heating unit are separated, so that the heating unit can be prevented from being broken as a result of the pressurization and thermal deformation.

Owner:HEWLETT PACKARD DEV CO LP

System and method for processing thread groups in a SIMD architecture

ActiveUS7836276B2Efficient use ofImprove throughputGeneral purpose stored program computerConcurrent instruction executionGraphicsSimd processor

A SIMD processor efficiently utilizes its hardware resources to achieve higher data processing throughput. The effective width of a SIMD processor is extended by clocking the instruction processing side of the SIMD processor at a fraction of the rate of the data processing side and by providing multiple execution pipelines, each with multiple data paths. As a result, higher data processing throughput is achieved while an instruction is fetched and issued once per clock. This configuration also allows a large group of threads to be clustered and executed together through the SIMD processor so that greater memory efficiency can be achieved for certain types of operations like texture memory accesses performed in connection with graphics processing.

Owner:NVIDIA CORP

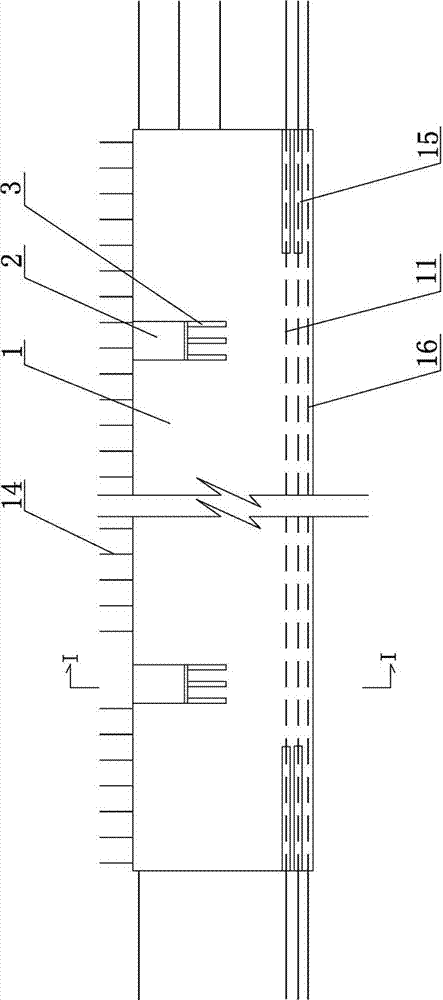

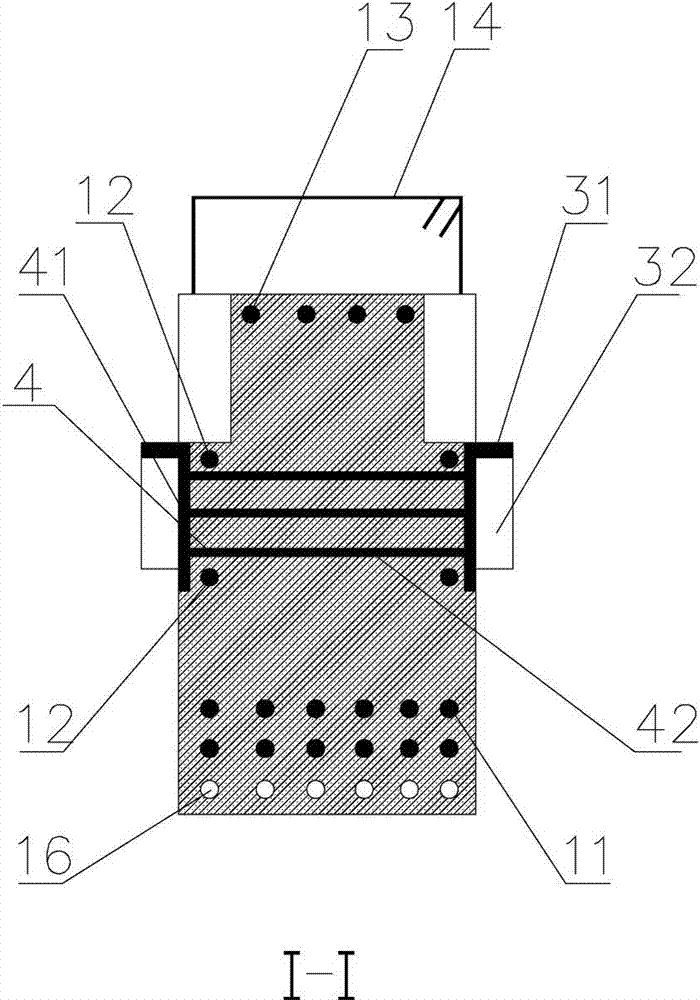

Pretension prestress composite beam prefabricated component having gaps and corbels

ActiveCN102733544AIncrease the effective sectionFully utilizeLoad-supporting elementsPre stressClassical mechanics

Owner:HUA HUI ENGINEERING DESIGN GROUP CO LTD

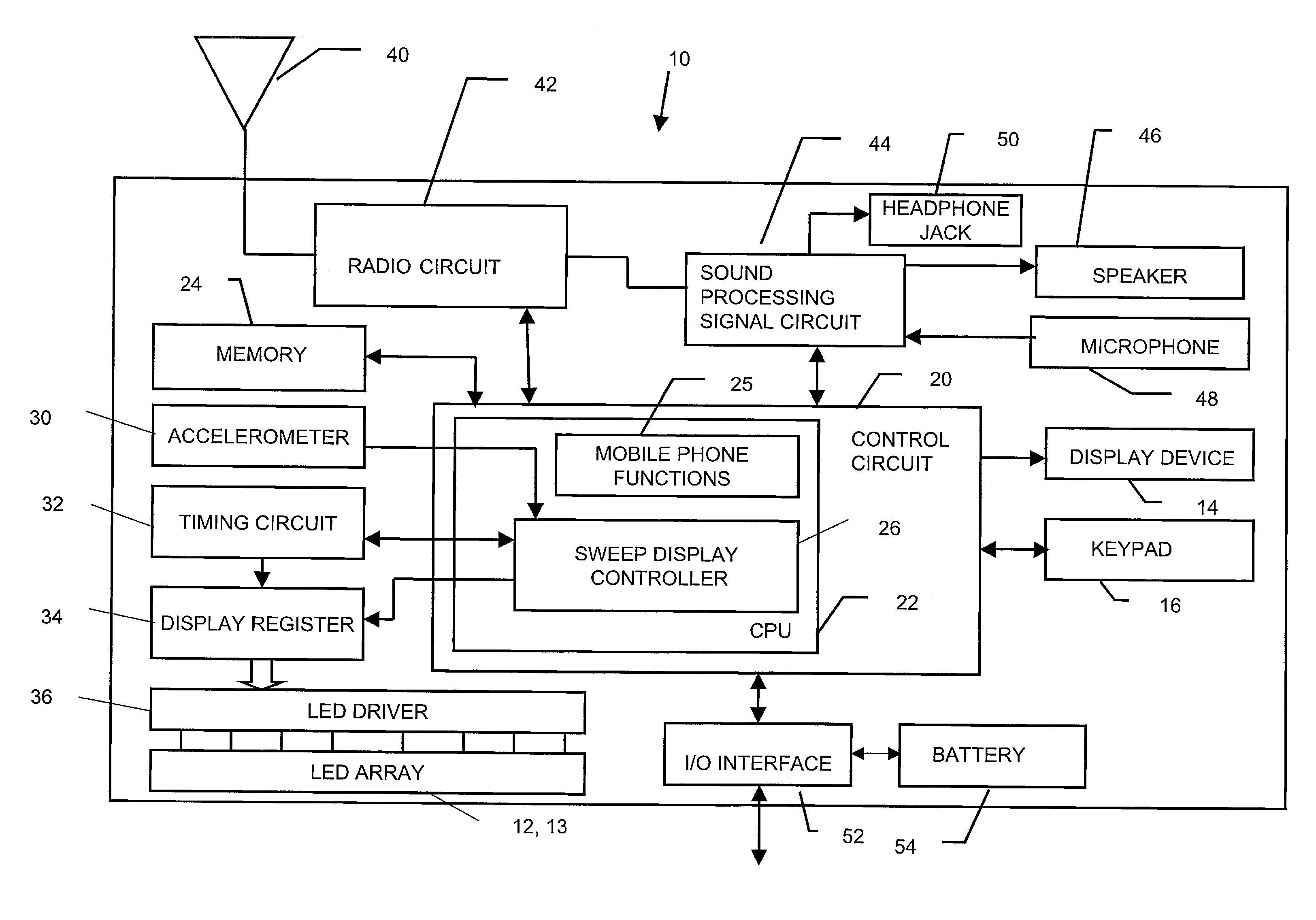

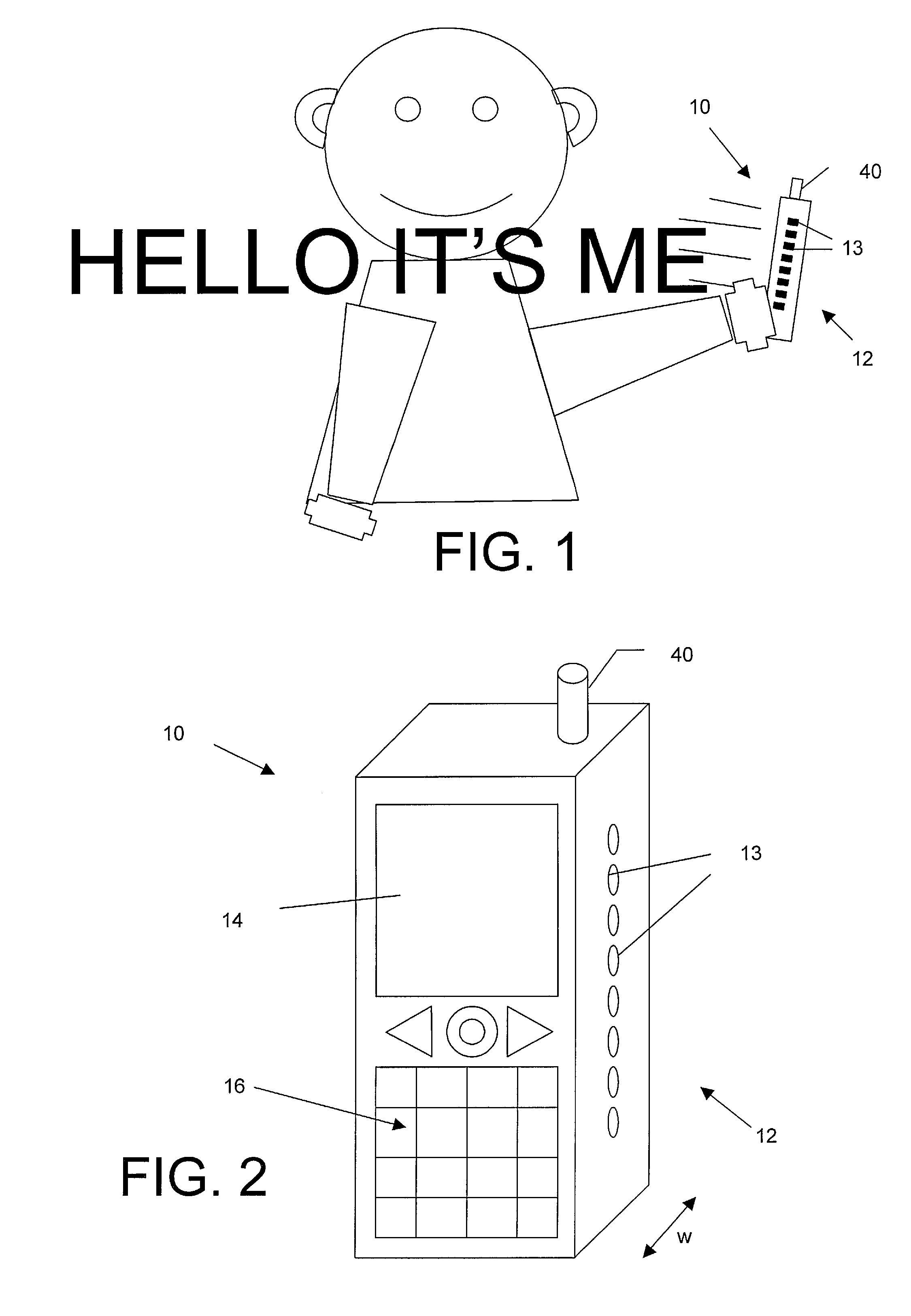

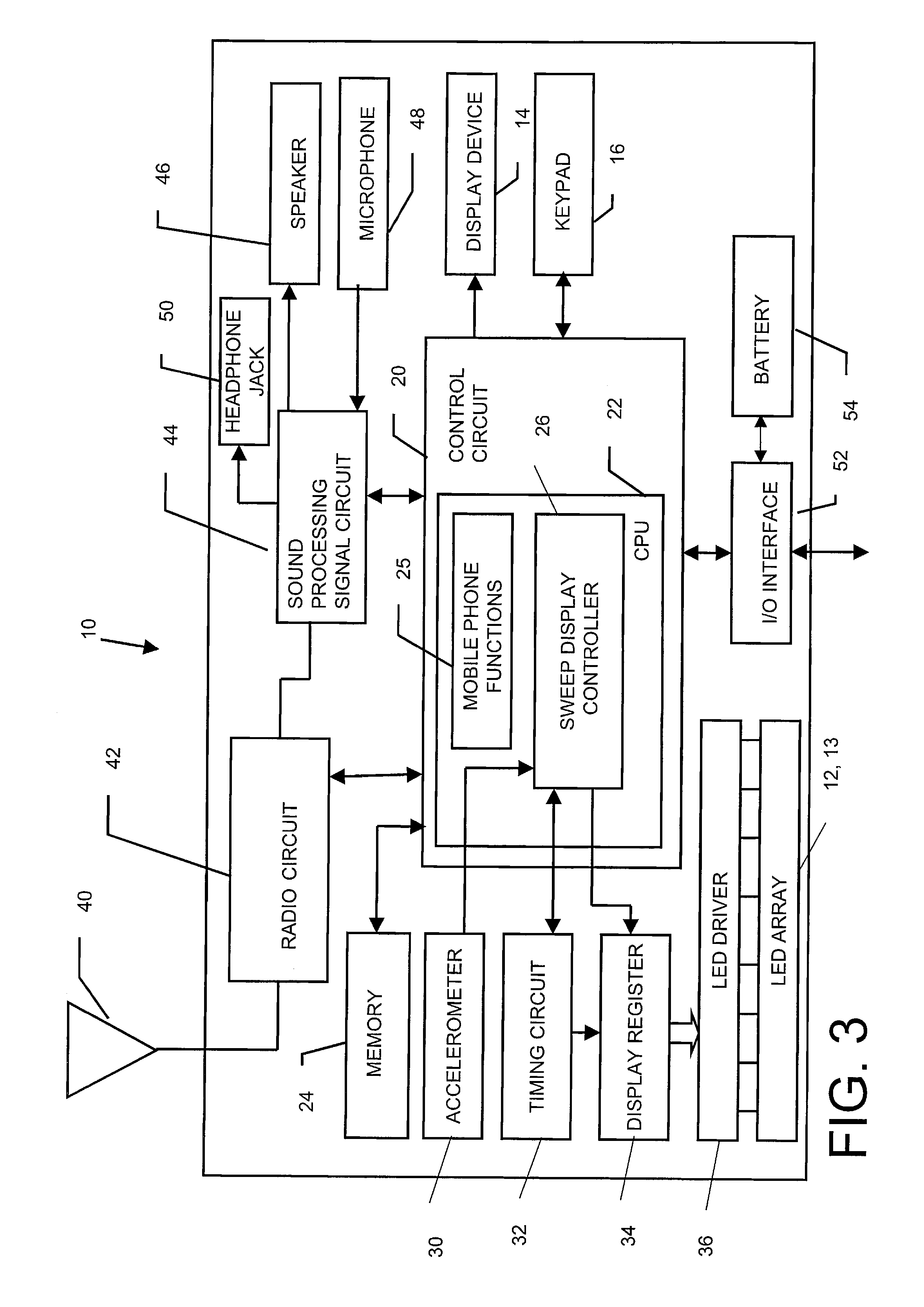

Optical display for portable electronic device

InactiveUS20070291188A1Increase effective widthTelevision system detailsTelevision system scanning detailsAccelerometerDisplay device

A portable electronic device is provided that includes an optical display, a display controller for presenting display data to the optical display in order to display the display data; and an accelerometer operatively coupled to the display controller. The display controller presents the display data to the optical display as a function of motion of the portable electronic device as sensed by the accelerometer.

Owner:SONY ERICSSON MOBILE COMM AB

Remelting device and method

ActiveCN106670628AReduced risk of crackingHigh mechanical strengthIncreasing energy efficiencyWelding accessoriesUltimate tensile strengthMechanical engineering

The invention relates to the technical field of remelting, in particular to a remelting device and method. The remelting device comprises a workpiece bearing device, a remelting structure provided with a remelting piece, and a remelting piece adjustment device provided with a first adjustment device. The remelting piece adjustment device can control and achieve feeding of the remelting piece in the central axis direction of a workpiece and can further adjust the effective widths of remelting layers. The overlap amount is increased and / or the consistency of the overlap amount is improved by increasing the effective widths of all the single-pass remelting layers and / or enabling the effective widths of the different single-pass remelting layers to be kept consistent, all overlap regions are more fully melted, the risks that cracks and / or weak regions appear on the workpiece are reduced, the performance such as the mechanical strength and the fatigue strength of the workpiece can be enhanced, the working reliability of the workpiece is improved, and the service life of the workpiece is prolonged.

Owner:JIANGSU XCMG CONSTR MASCH RES INST LTD