Patents

Literature

62results about How to "Increase gate width" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

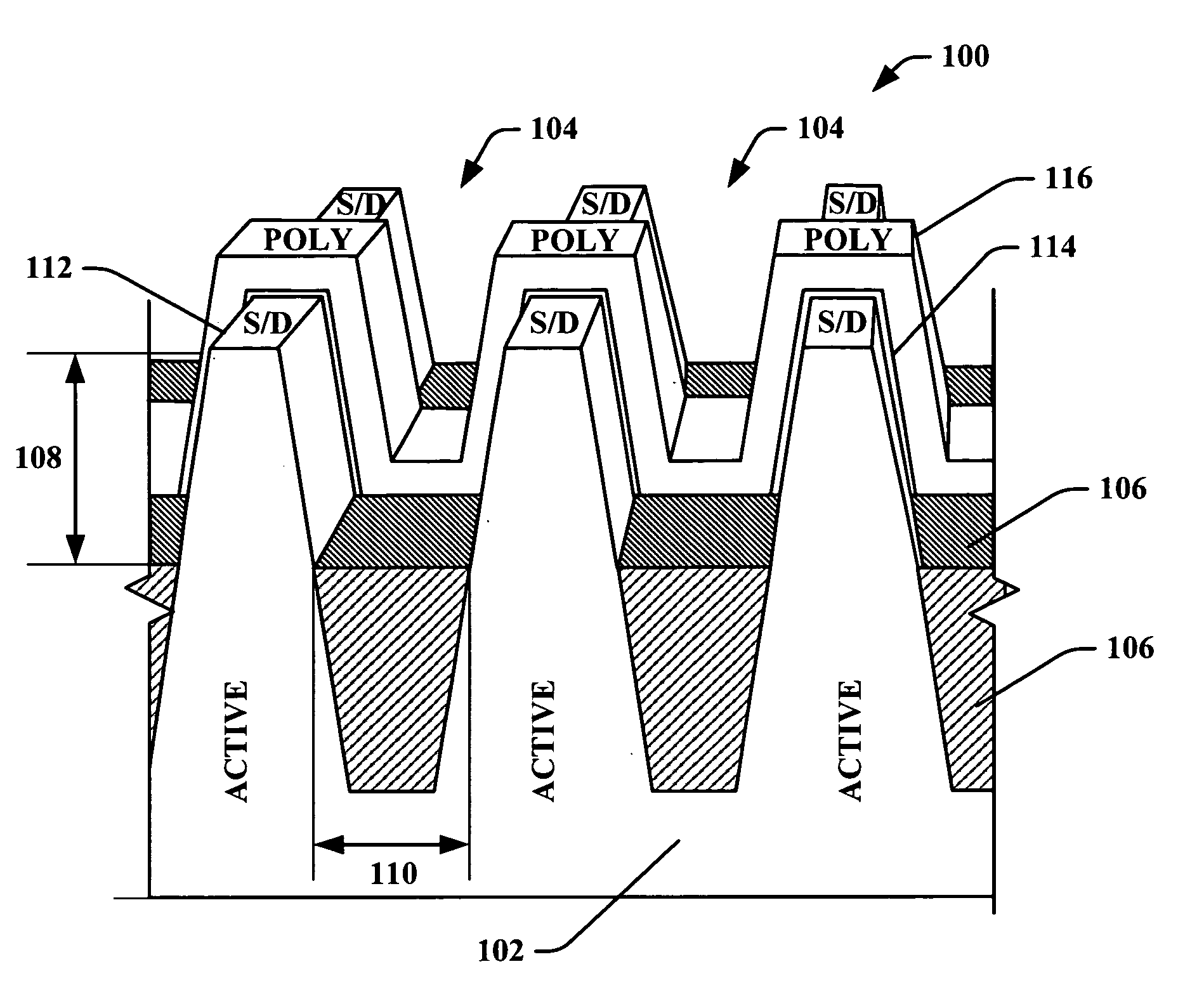

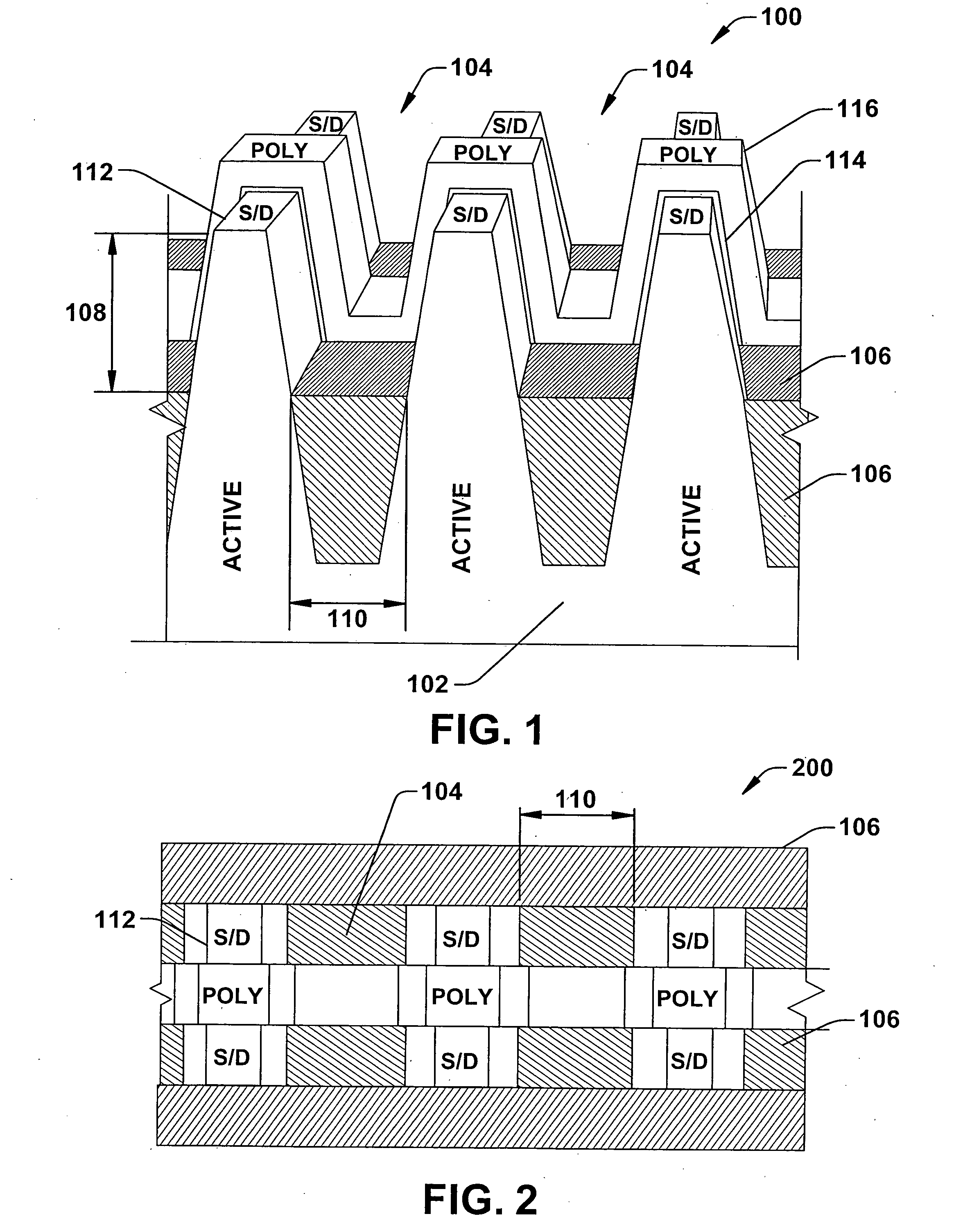

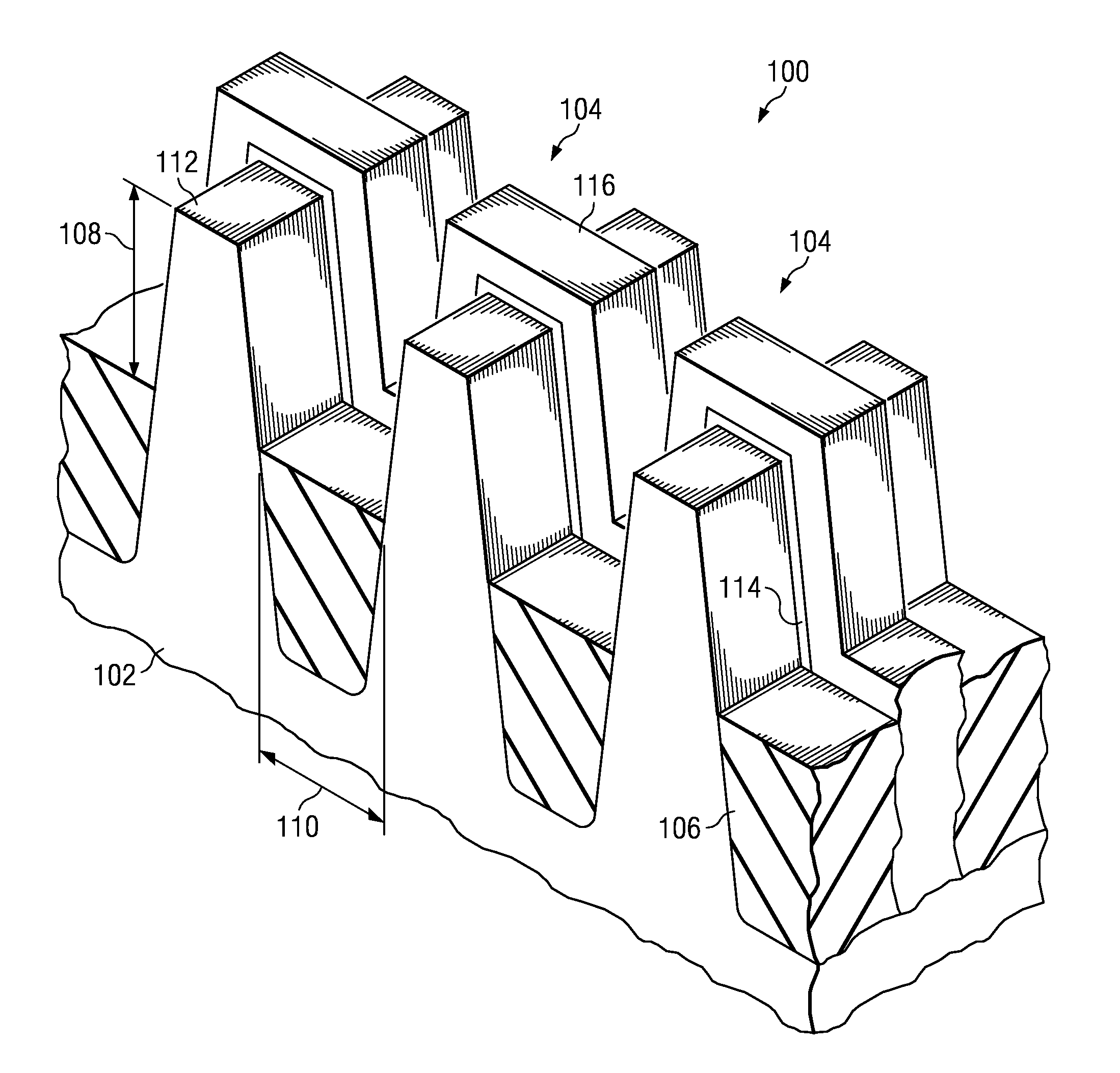

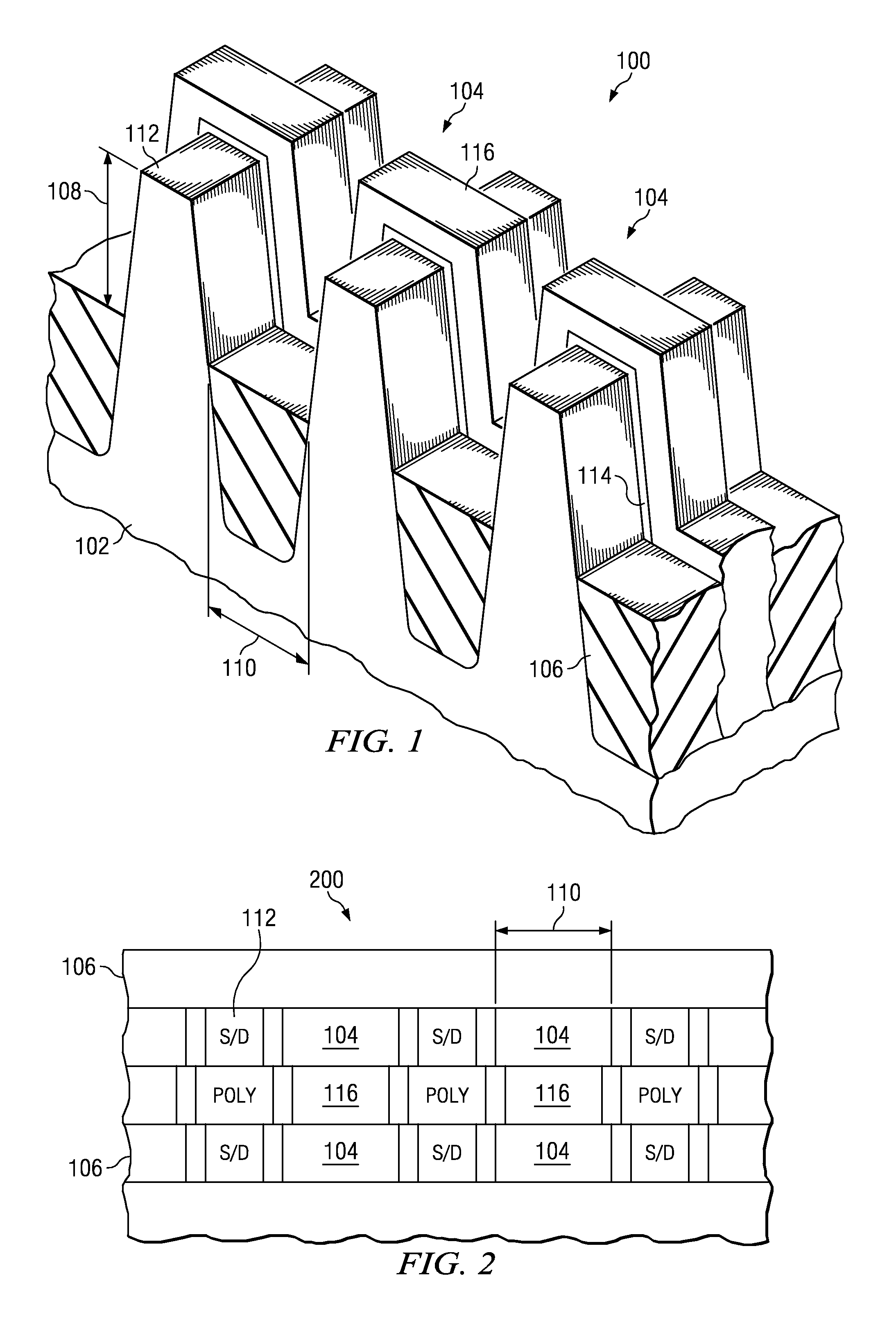

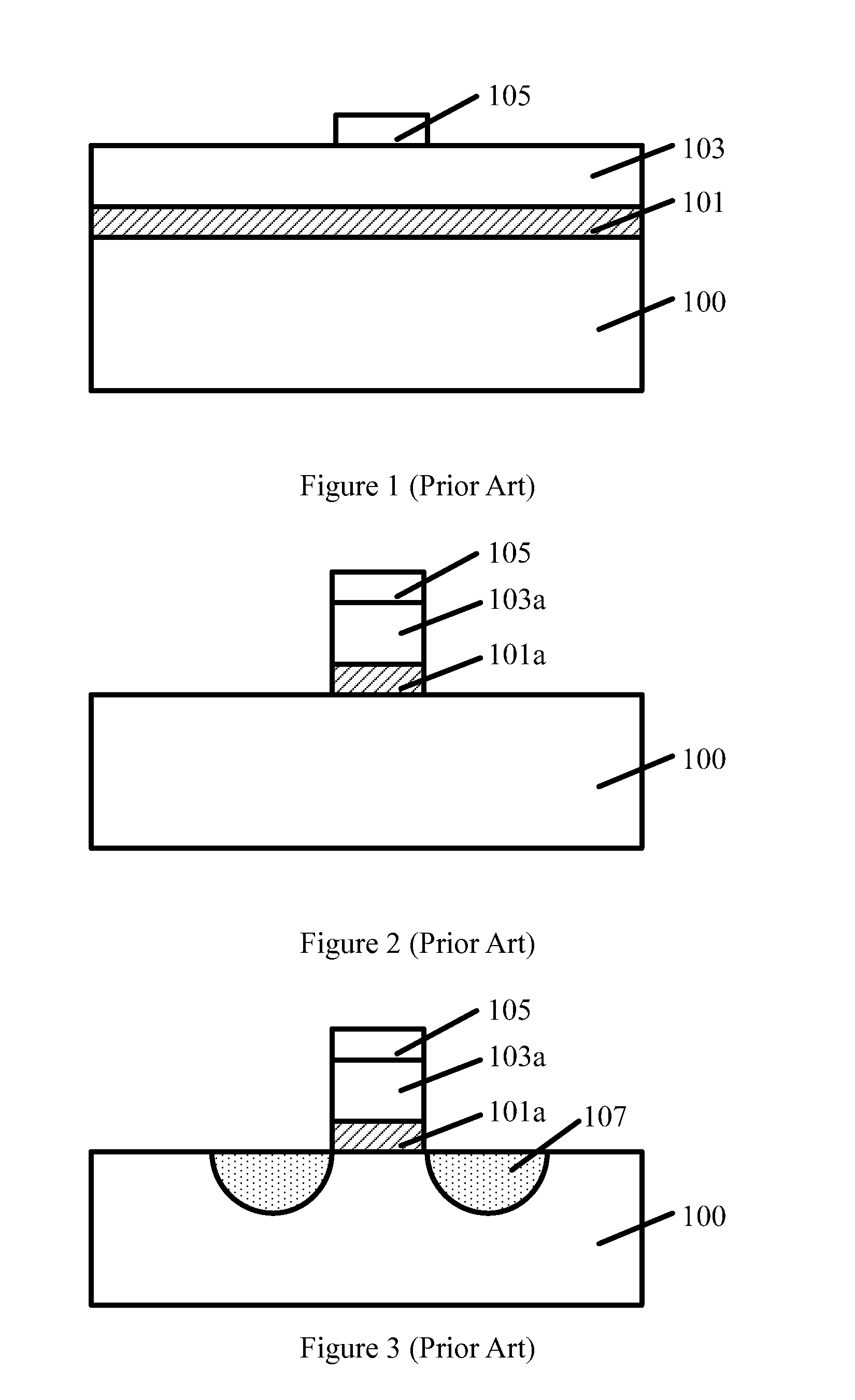

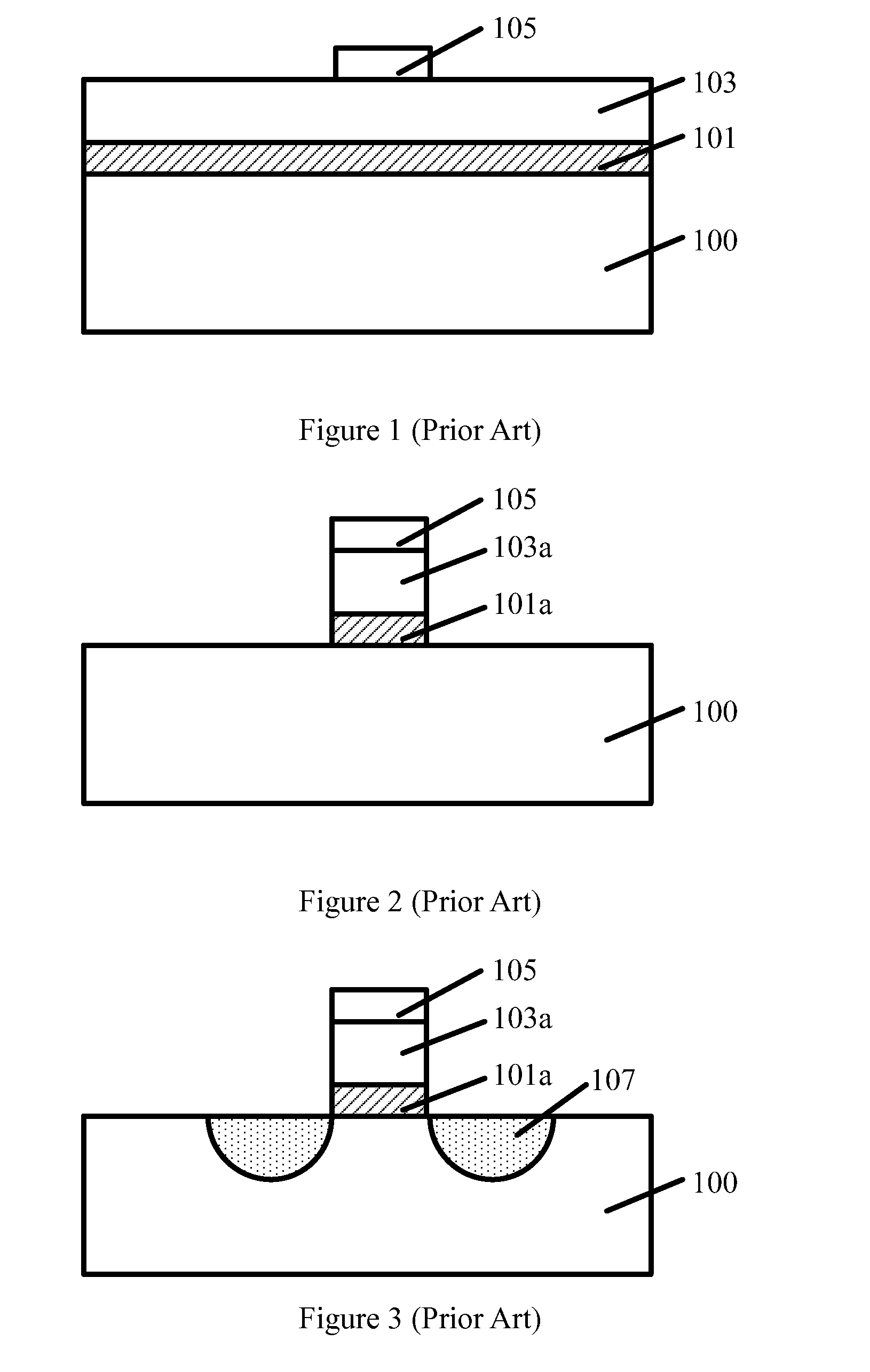

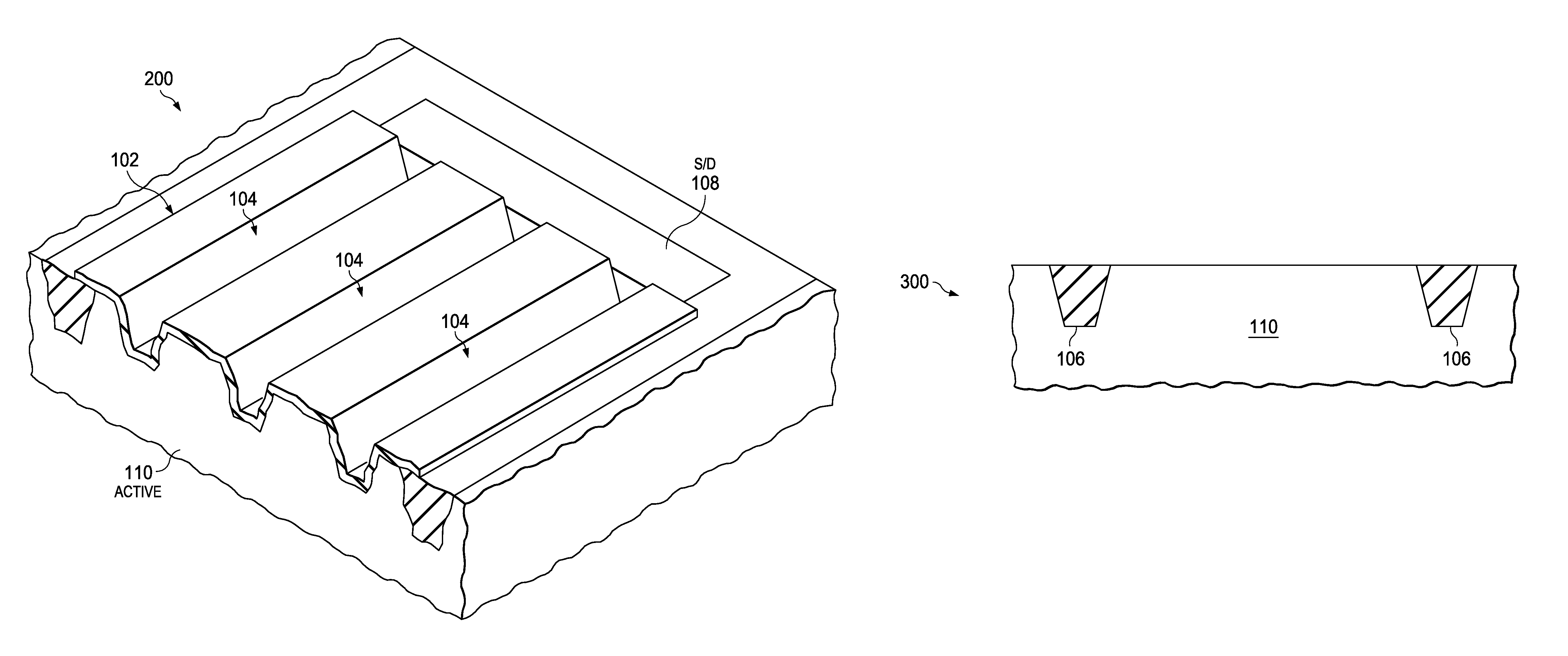

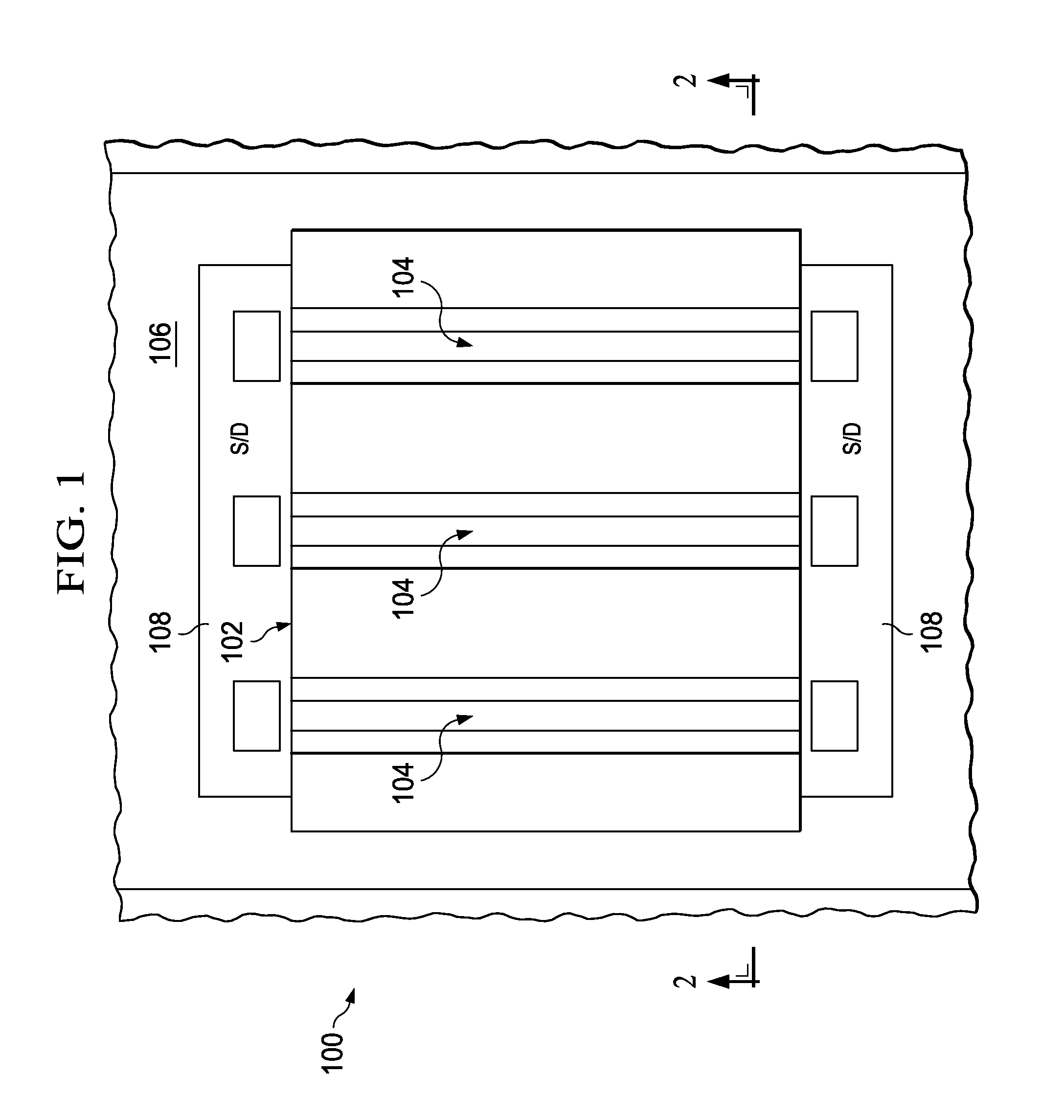

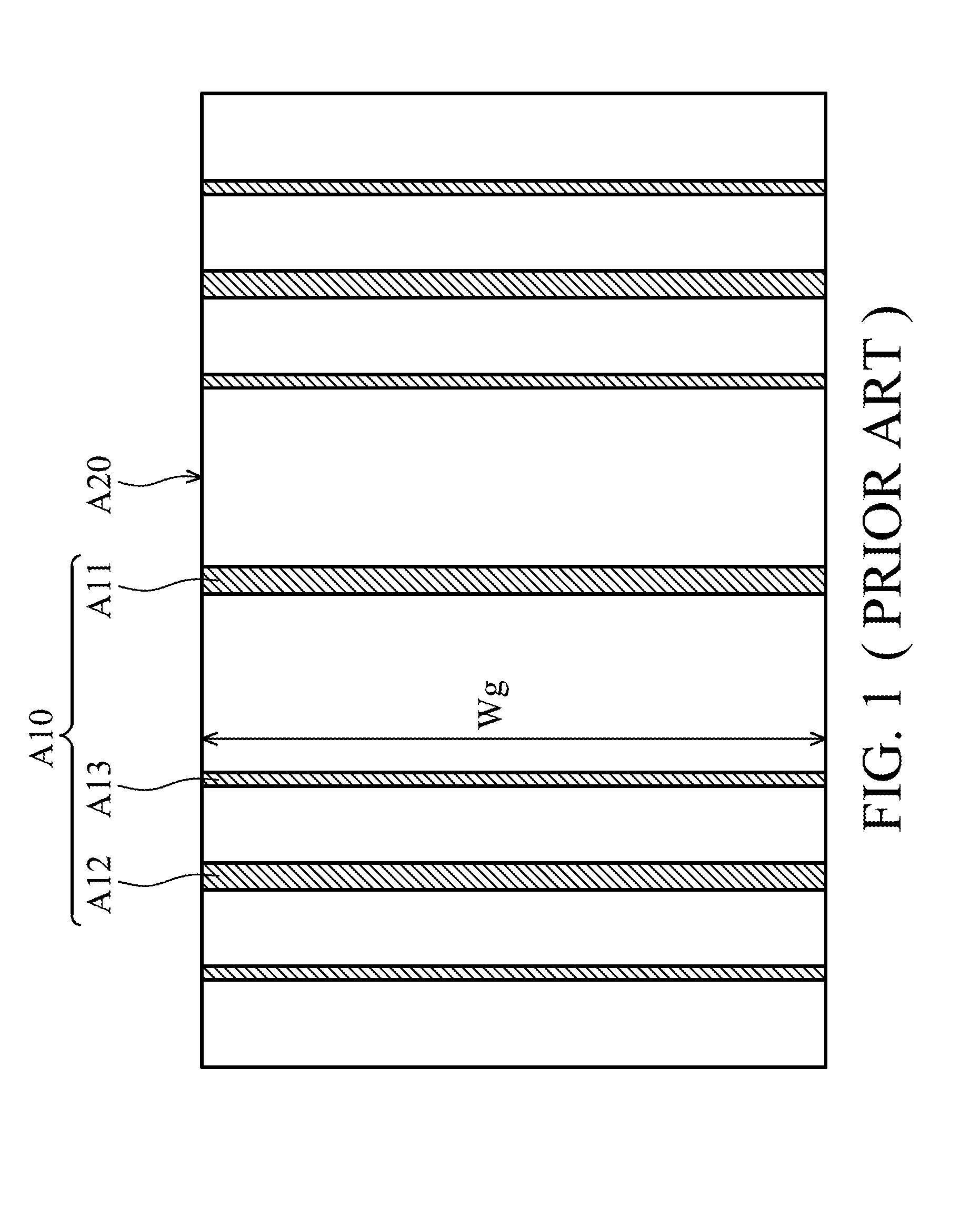

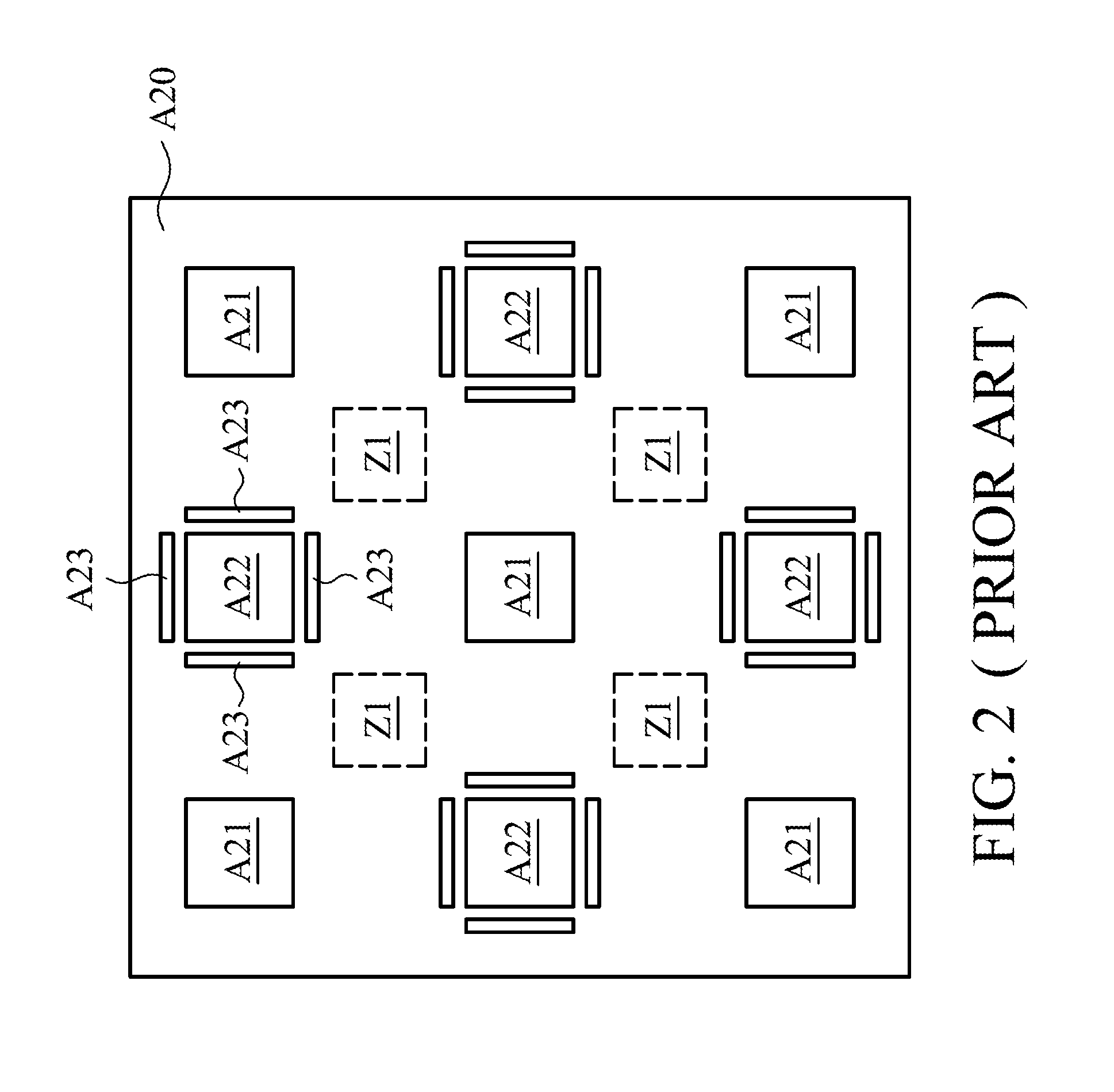

Recessed STI for wide transistors

ActiveUS20080081404A1Increase effective widthIncrease gate widthSemiconductor/solid-state device manufacturingSubstrate surfaceSemiconductor

A method of manufacturing a semiconductor device having shallow trench isolation includes steps of forming a hard mask layer on the substrate surface, etching a trench through the hard mask, filling the trench with an isolation material, forming a recessed trench, and forming a serpentine gate structure to connect electronic sources and drains.

Owner:TEXAS INSTR INC

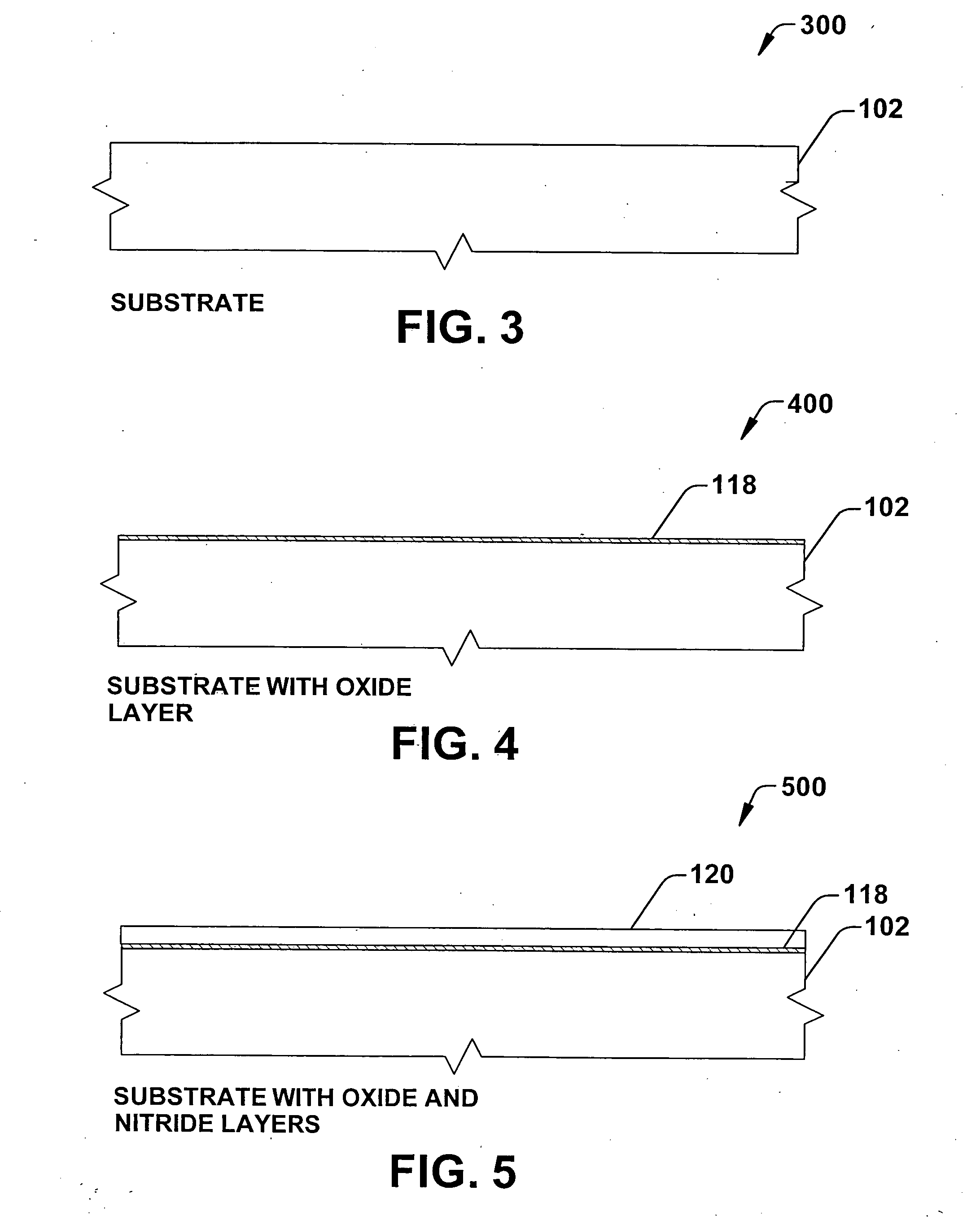

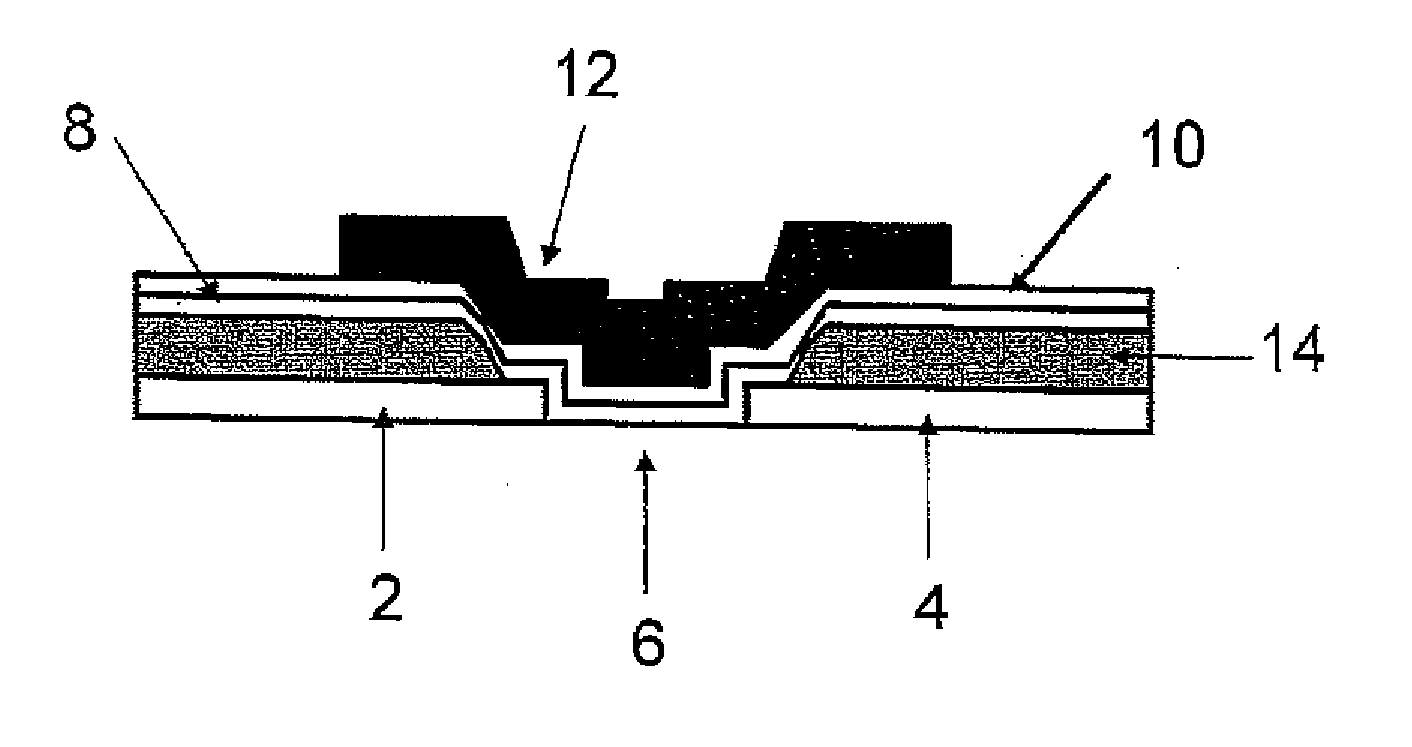

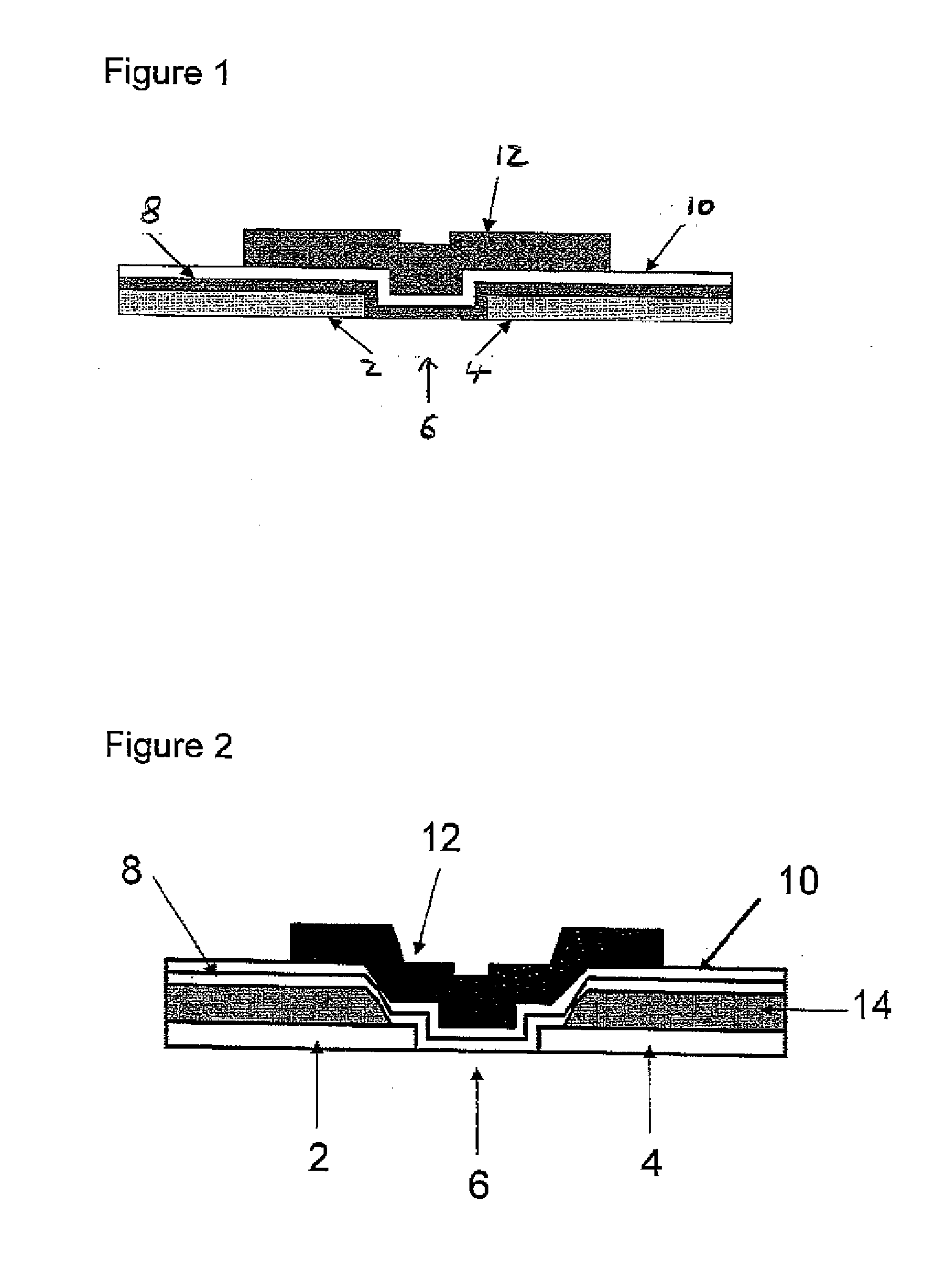

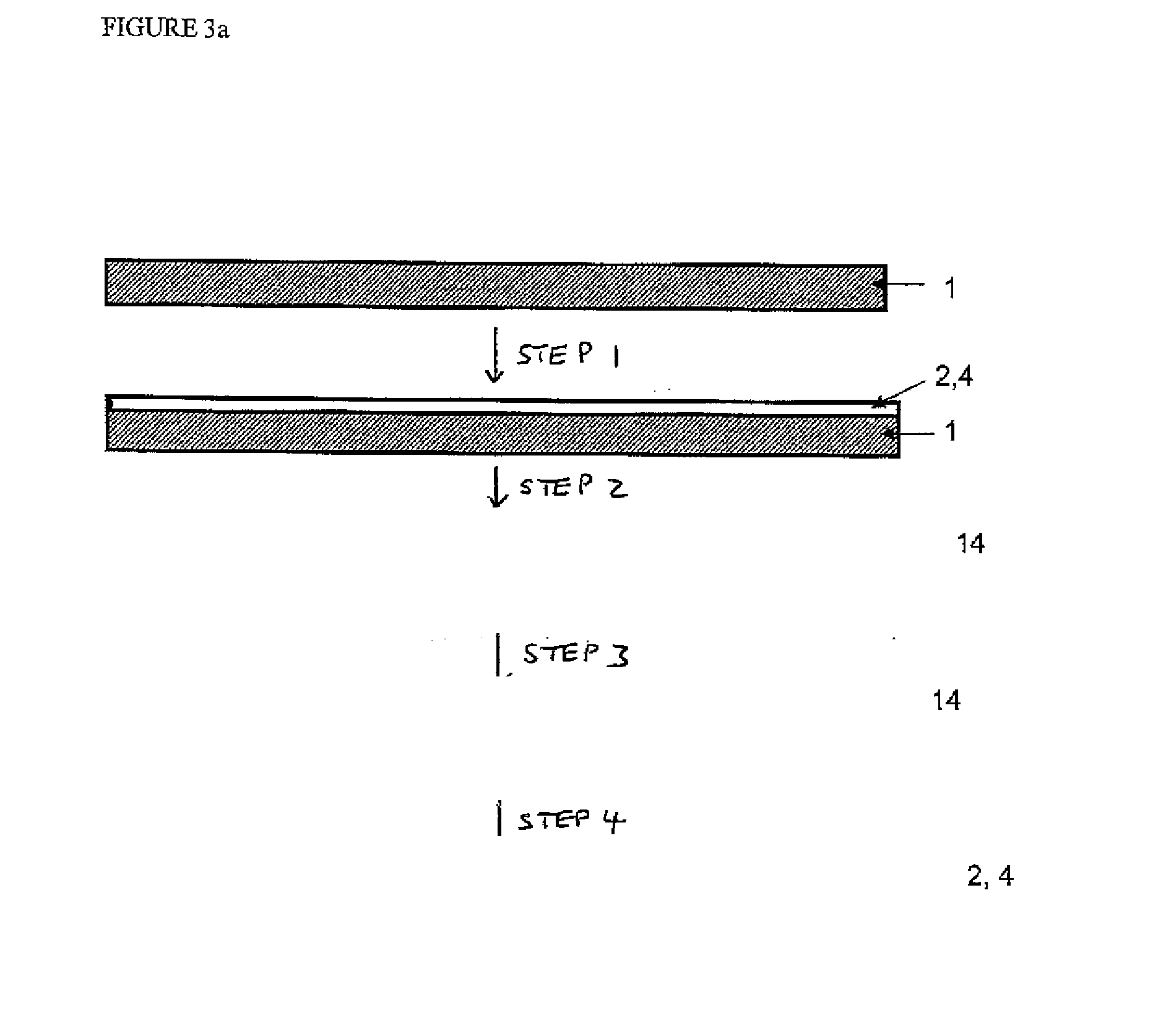

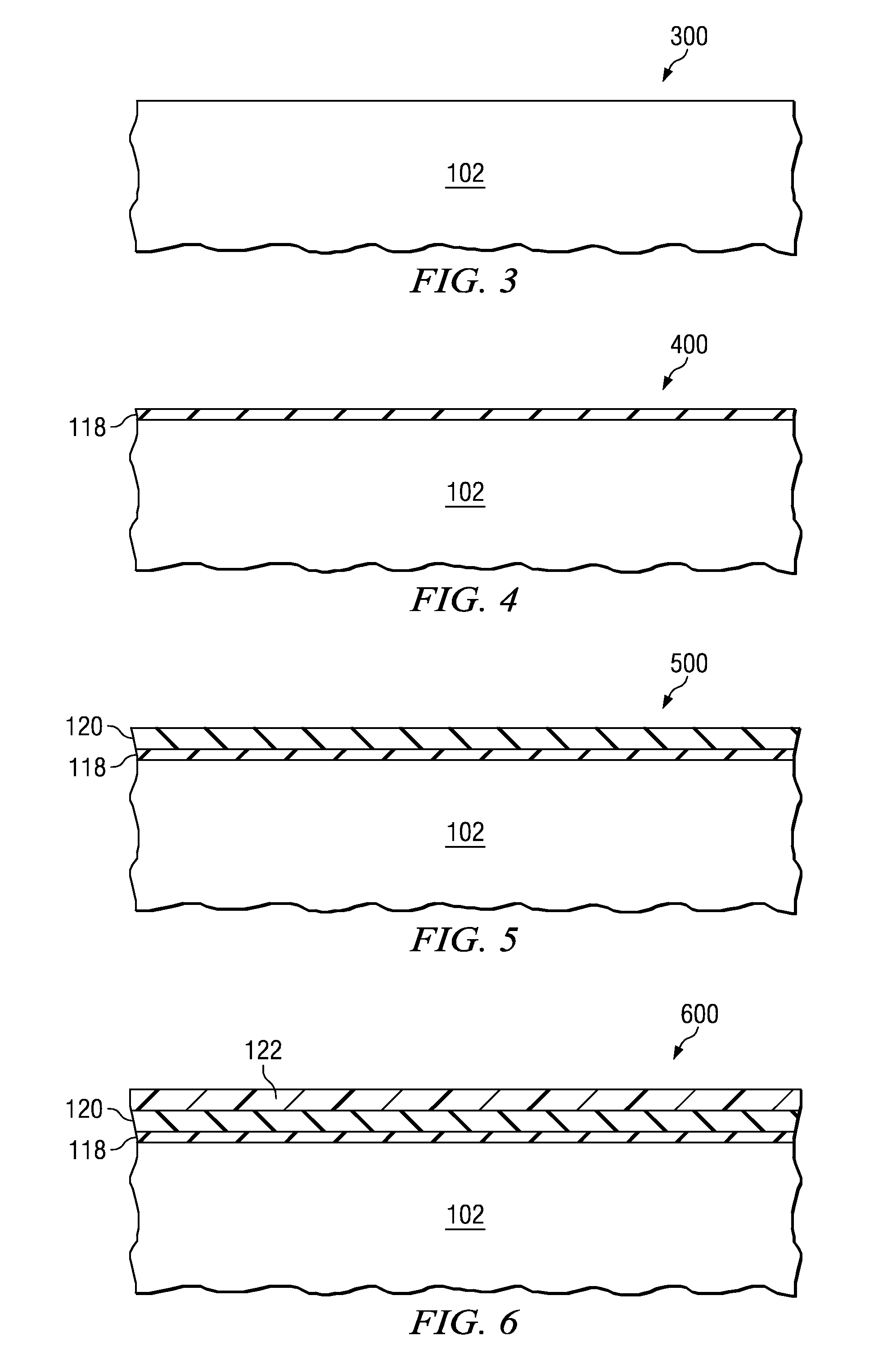

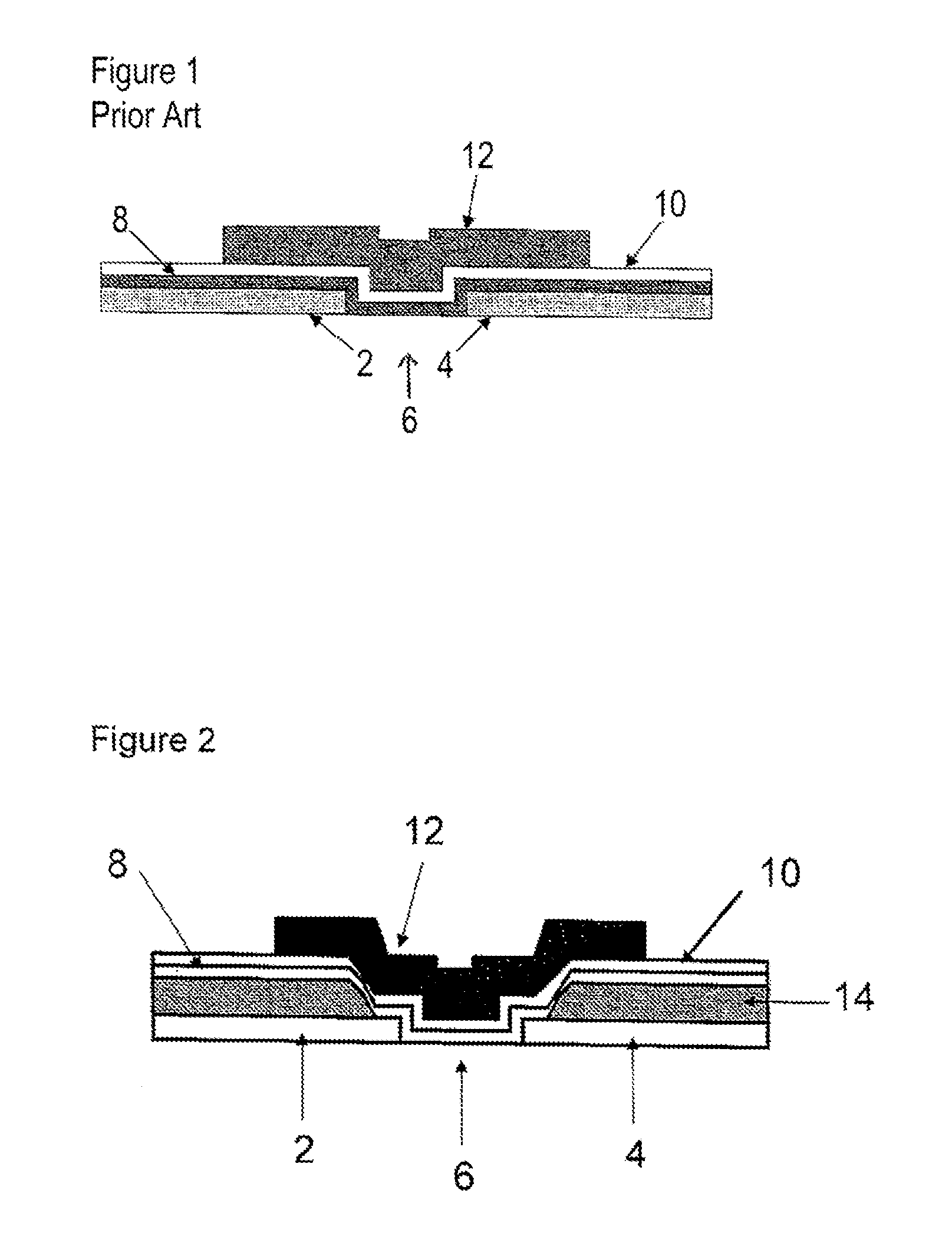

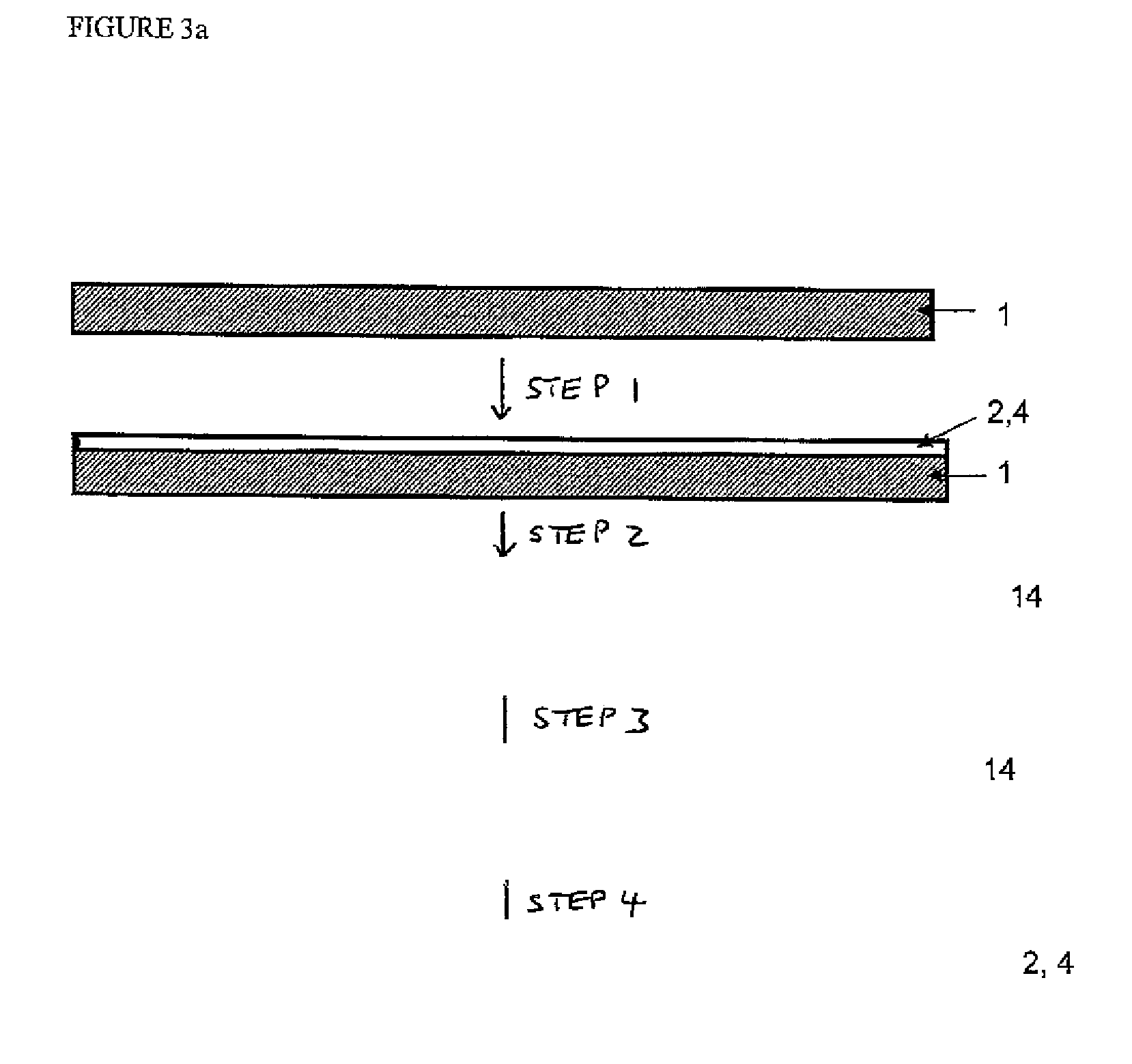

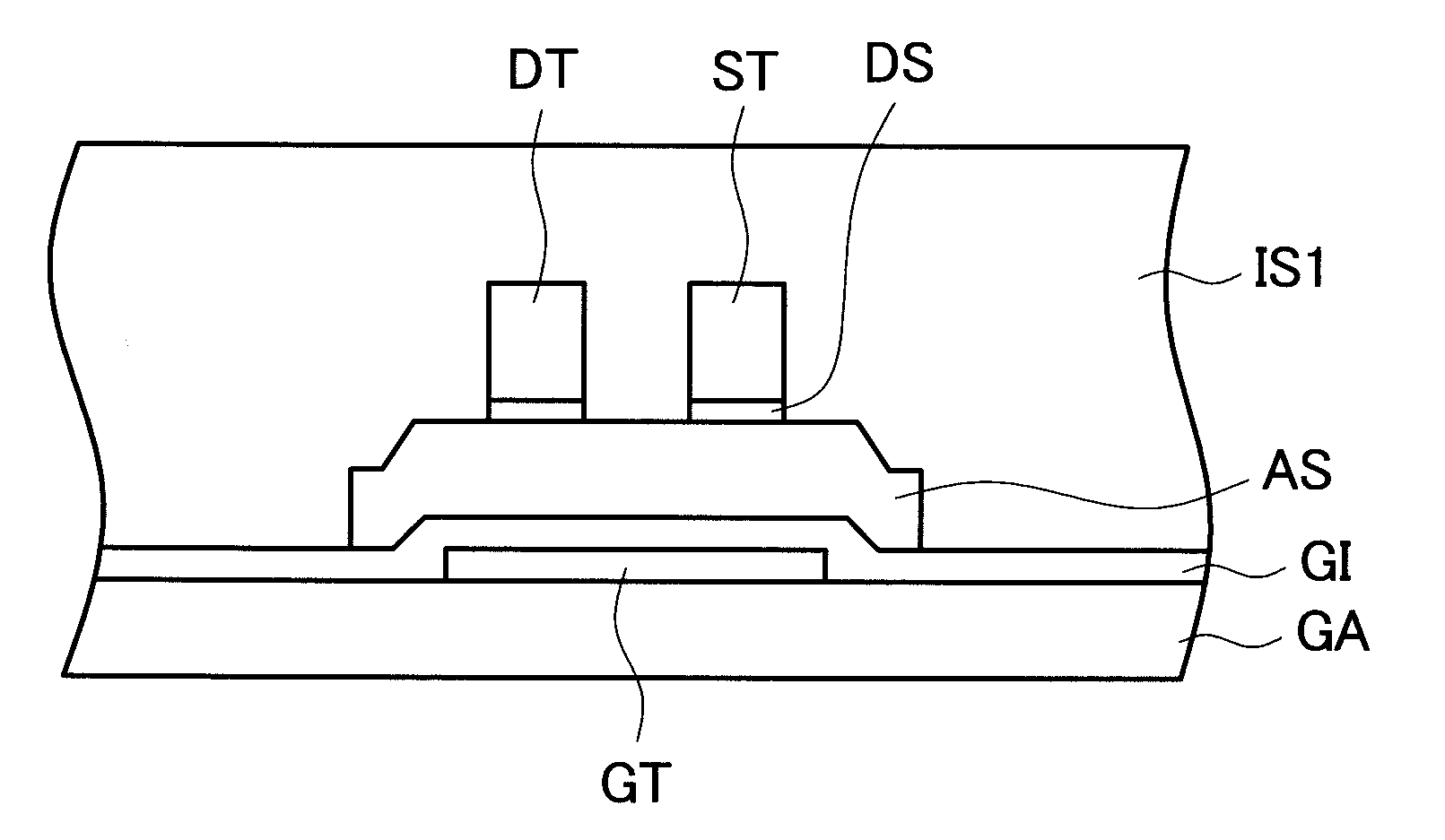

Organic Thin Film Transistors

InactiveUS20100051922A1Minimize parasitic capacitanceMinimise capacitanceTransistorSolid-state devicesConductive materialsOrganic semiconductor

An organic thin film transistor comprising: a substrate; a source electrode and a drain electrode defining a channel; a layer of insulating material disposed over the source and drain electrodes; a layer of organic semi-conductive material extending across the channel; a layer of dielectric material; and a gate electrode disposed over the layer of dielectric material.

Owner:CAMBRIDGE DISPLAY TECH LTD +1

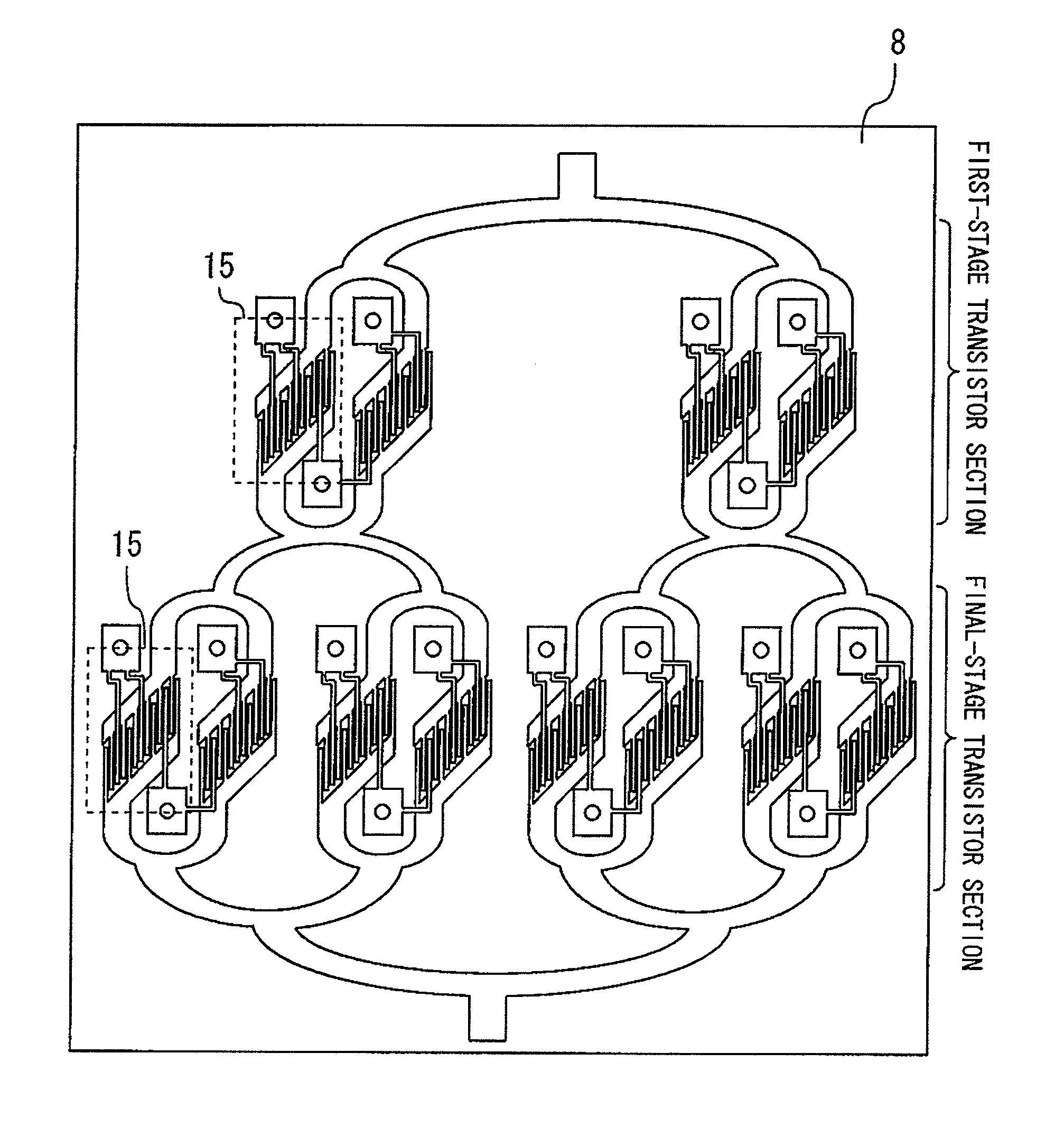

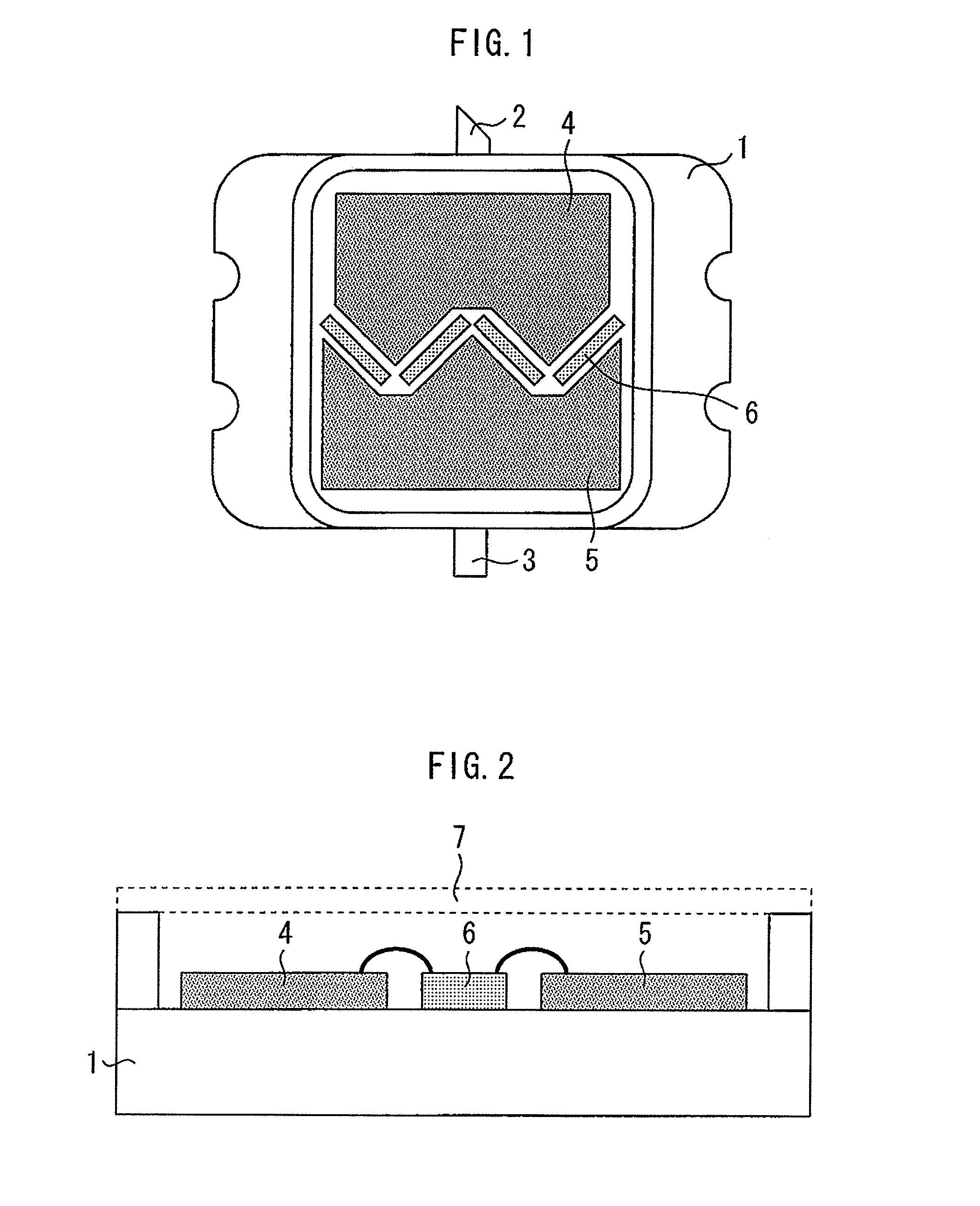

Semiconductor device

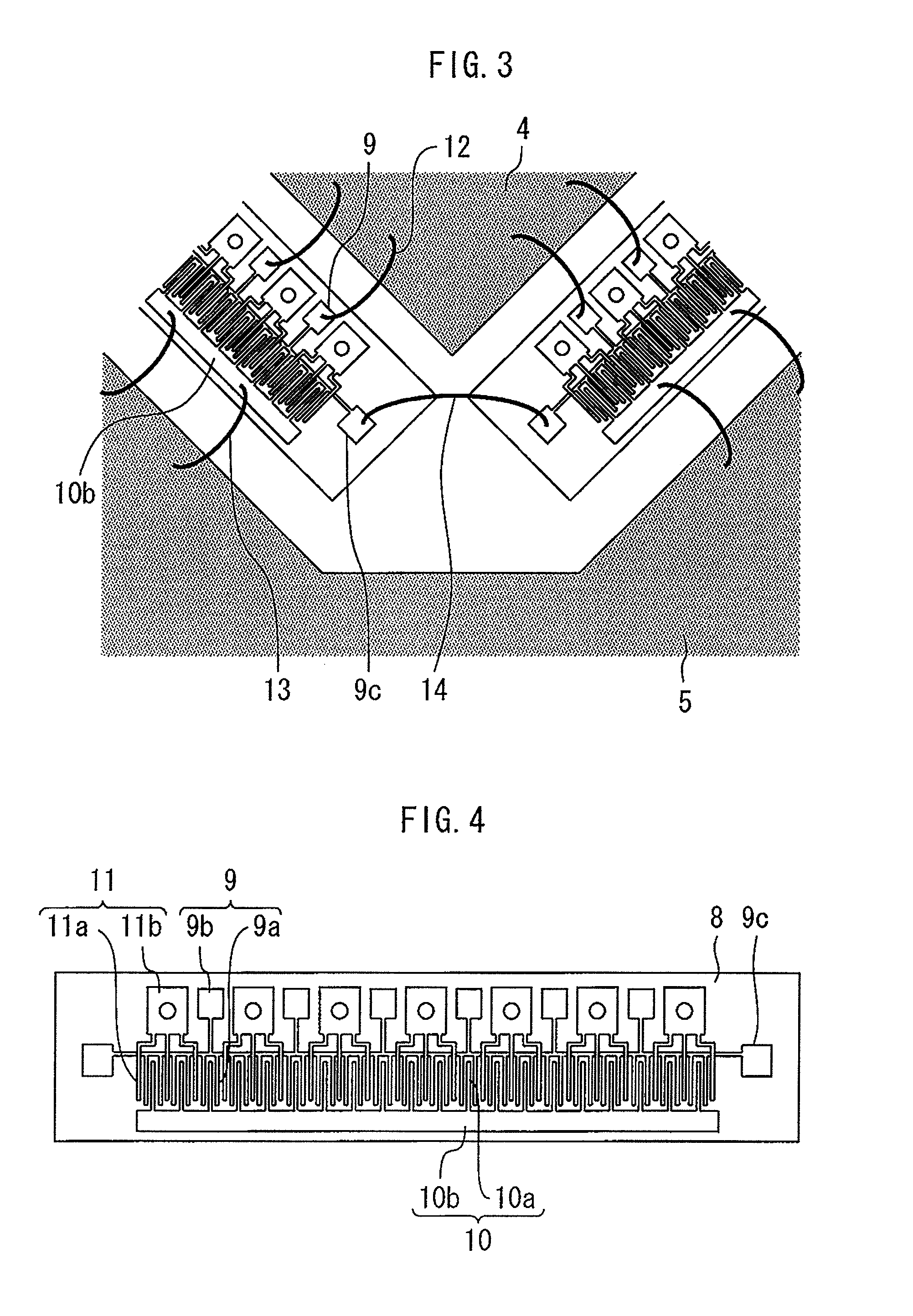

ActiveUS20140014969A1Characteristic deterioratedReliability deterioratedSemiconductor/solid-state device detailsSolid-state devicesPower semiconductor deviceSemiconductor

A semiconductor device includes: a package; an input matching circuit and an output matching circuit in the package; and transistor chips between the input matching circuit and the output matching circuit in the package. Each transistor chip includes a semiconductor substrate having long sides and short sides that are shorter than the long sides, and a gate electrode, a drain electrode and a source electrode on the semiconductor substrate. The gate electrode has gate fingers arranged along the long sides of the semiconductor substrate and a gate pad commonly connected to the gate fingers and connected to the input matching circuit via a first wire. The drain electrode is connected to the output matching circuit via a second wire. The long sides of the semiconductor substrates of the transistor chips are oblique with respect to an input / output direction extending from the input matching circuit to the output matching circuit.

Owner:ROHM CO LTD

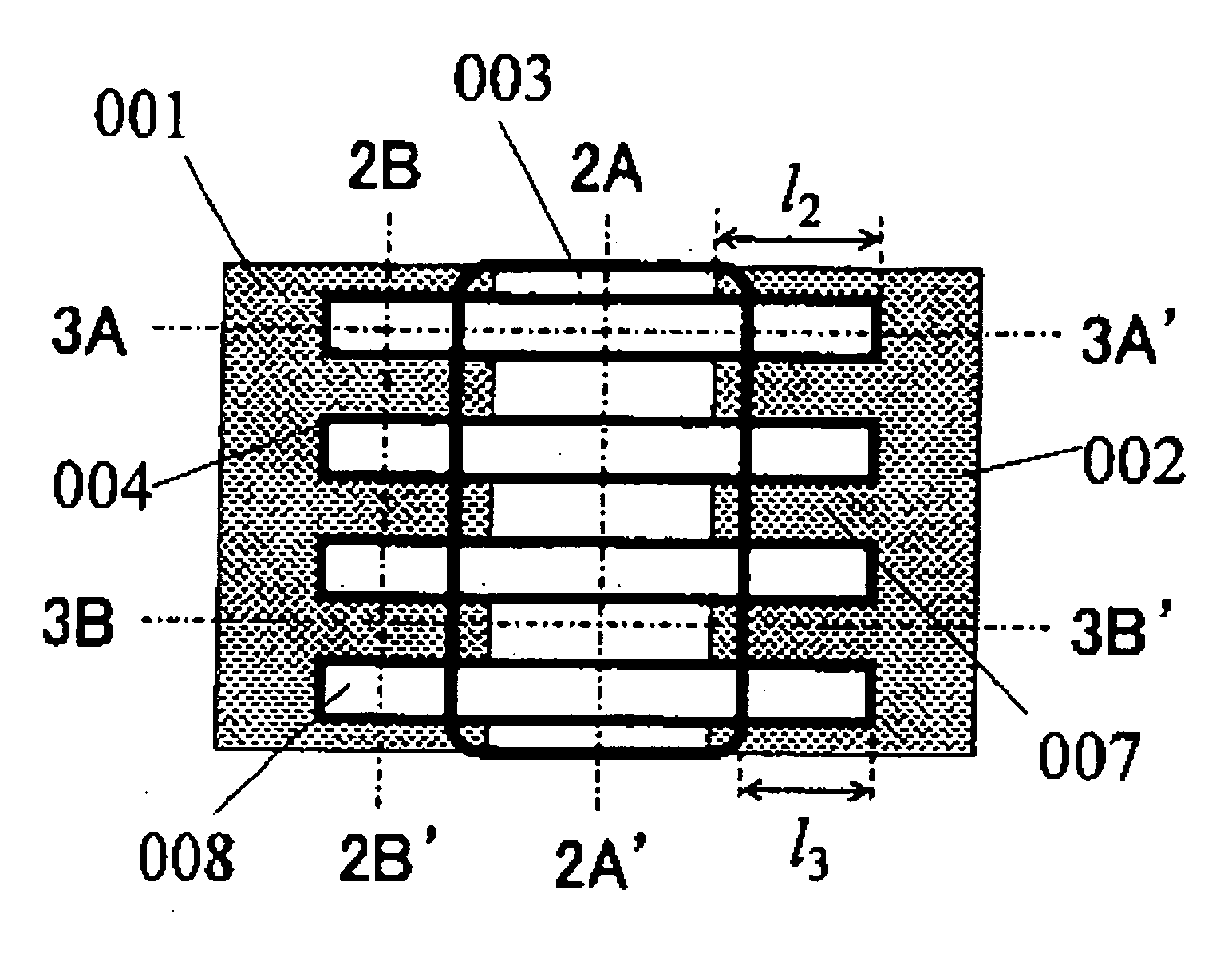

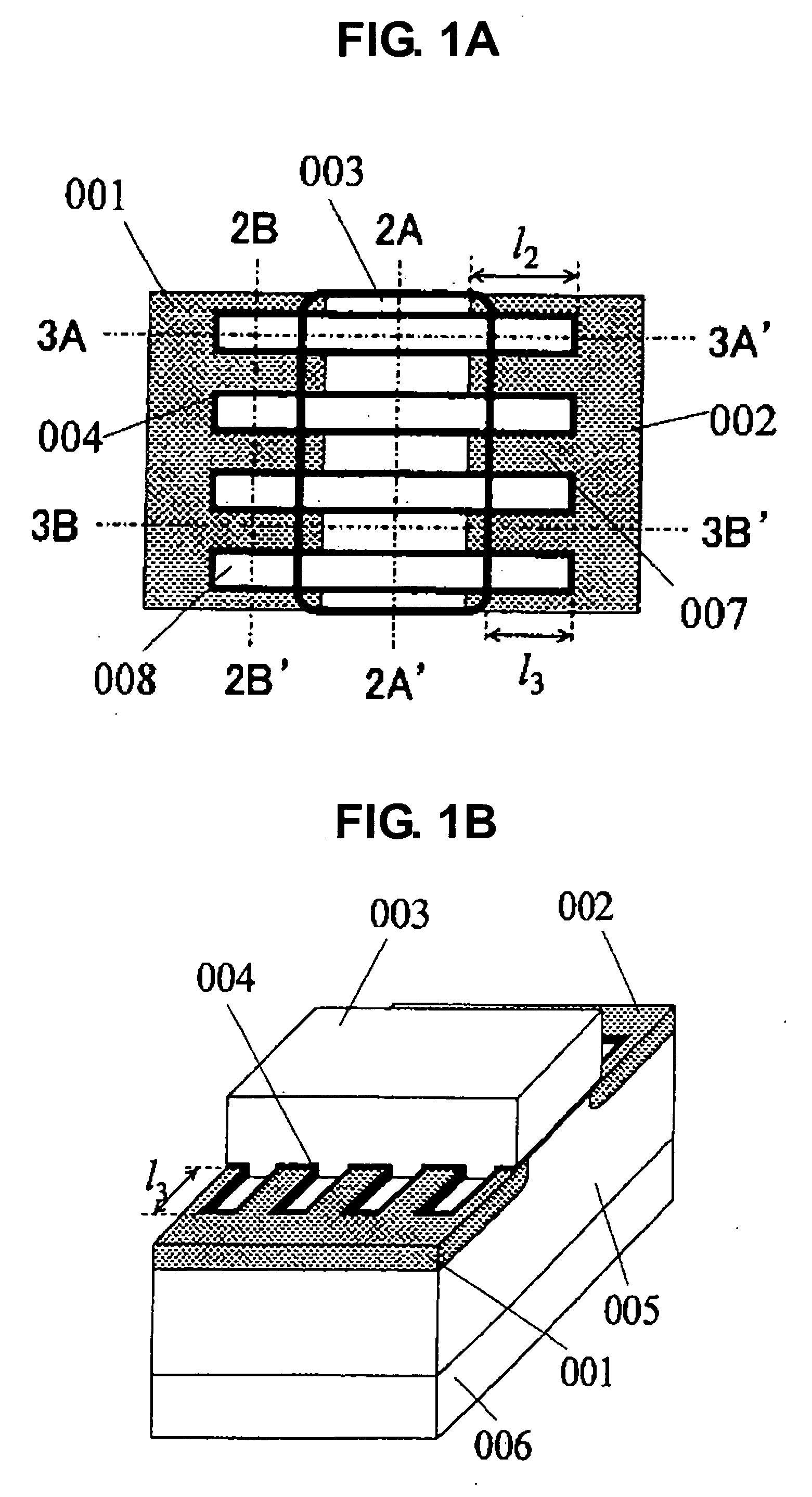

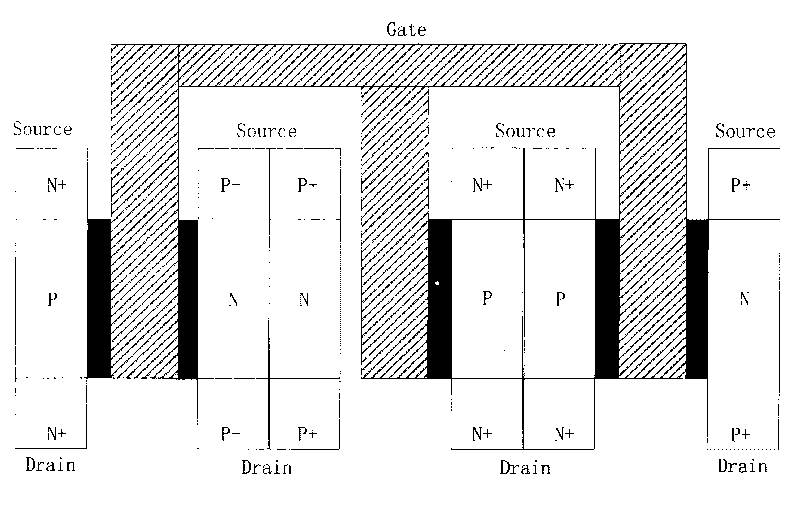

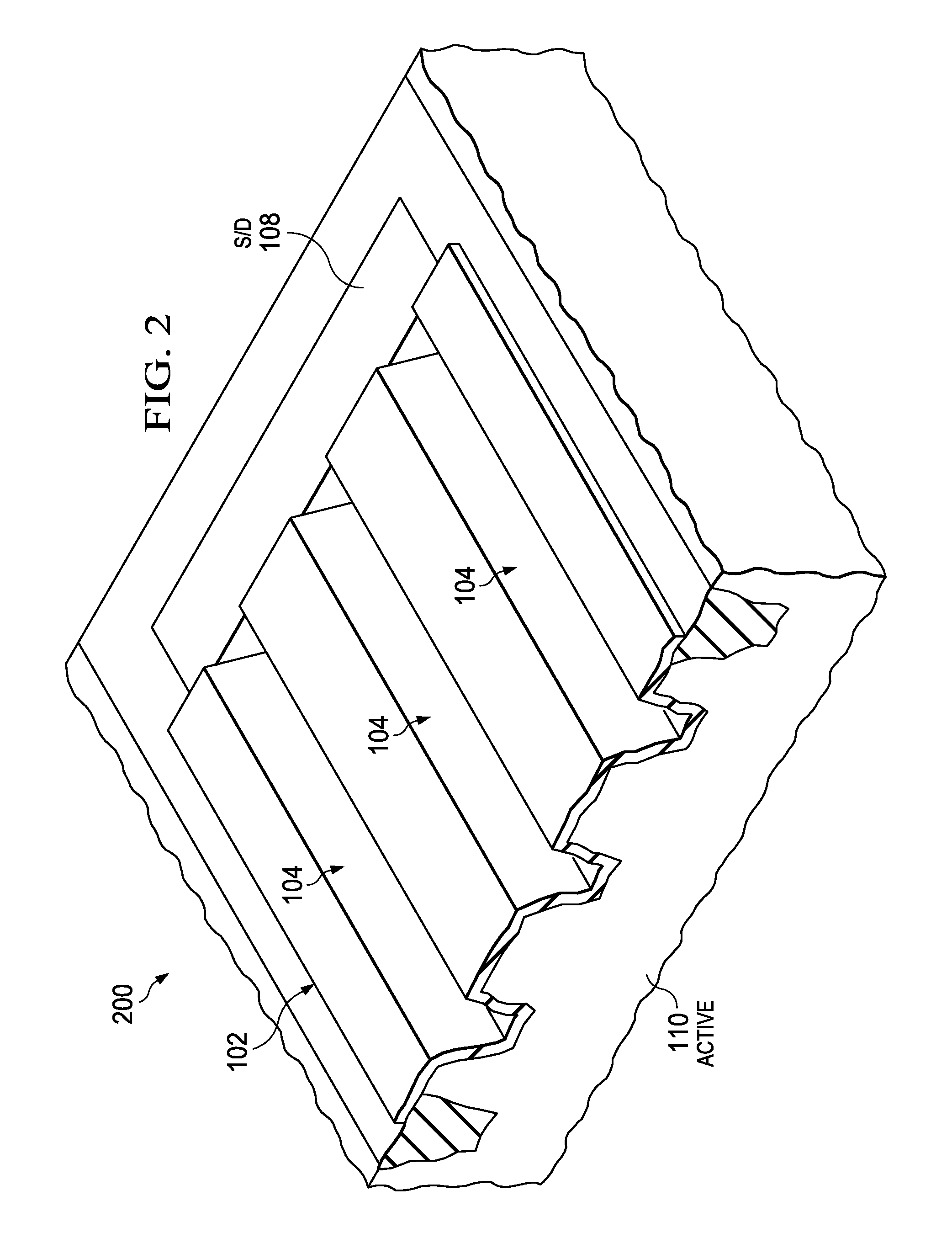

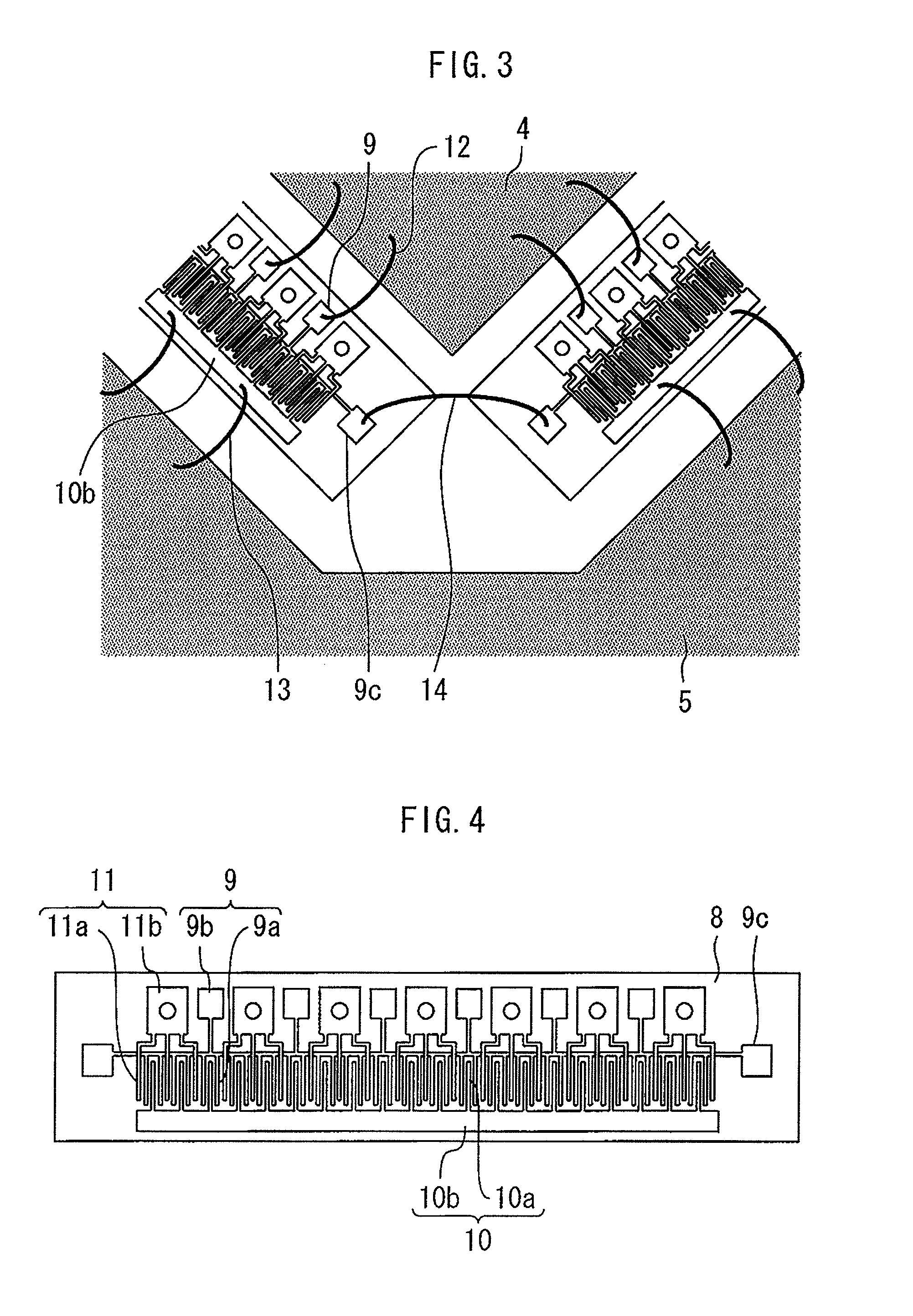

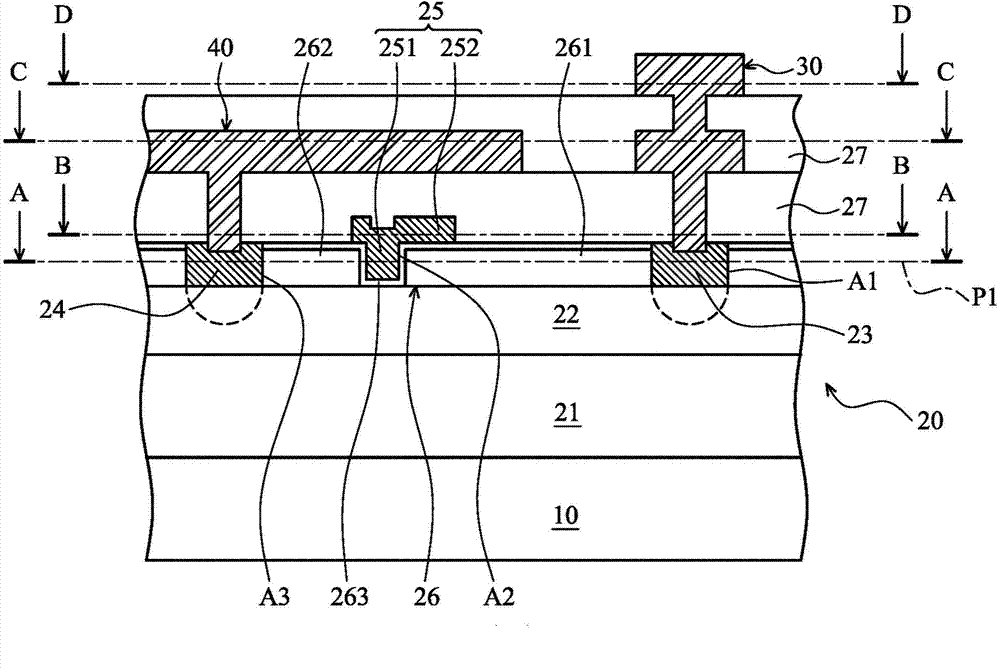

Semiconductor device and method of manufacturing the same

InactiveUS20060223253A1Increase gate widthImprove performanceSemiconductor/solid-state device manufacturingSemiconductor devicesHigh resistanceDevice material

Provided is a semiconductor device having a structure in which: a well region of a high resistance p-type semiconductor is disposed in a given depth from a surface of an n-type or p-type semiconductor substrate; a plurality of trenches extend from the surface of the well region to a certain depth; a gate insulating film is formed on a surface of a convex / concave portion on which the trenches are formed; a gate electrode is embedded into the trenches. The semiconductor device includes: a gate electrode film that is disposed on a substrate surface in contact with the gate electrode embedded into the trenches in the convexo-concave portion region except for a portion in the vicinity of both ends of the trenches; and a source region and a drain region that are two low resistance n-type semiconductor layers which are disposed shallower than the depth of the well region in the well region except for a lower portion of the gate electrode film.

Owner:ABLIC INC

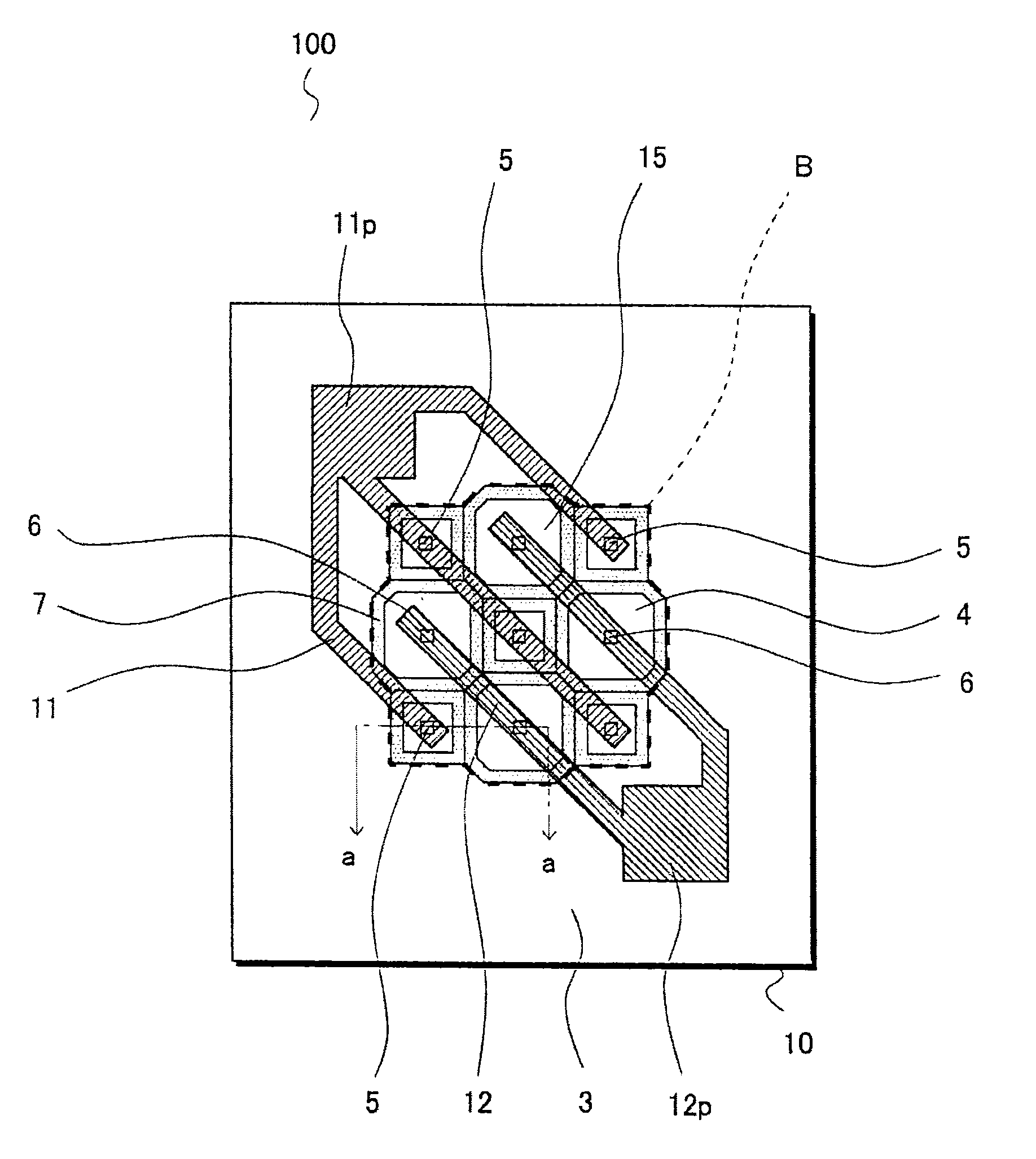

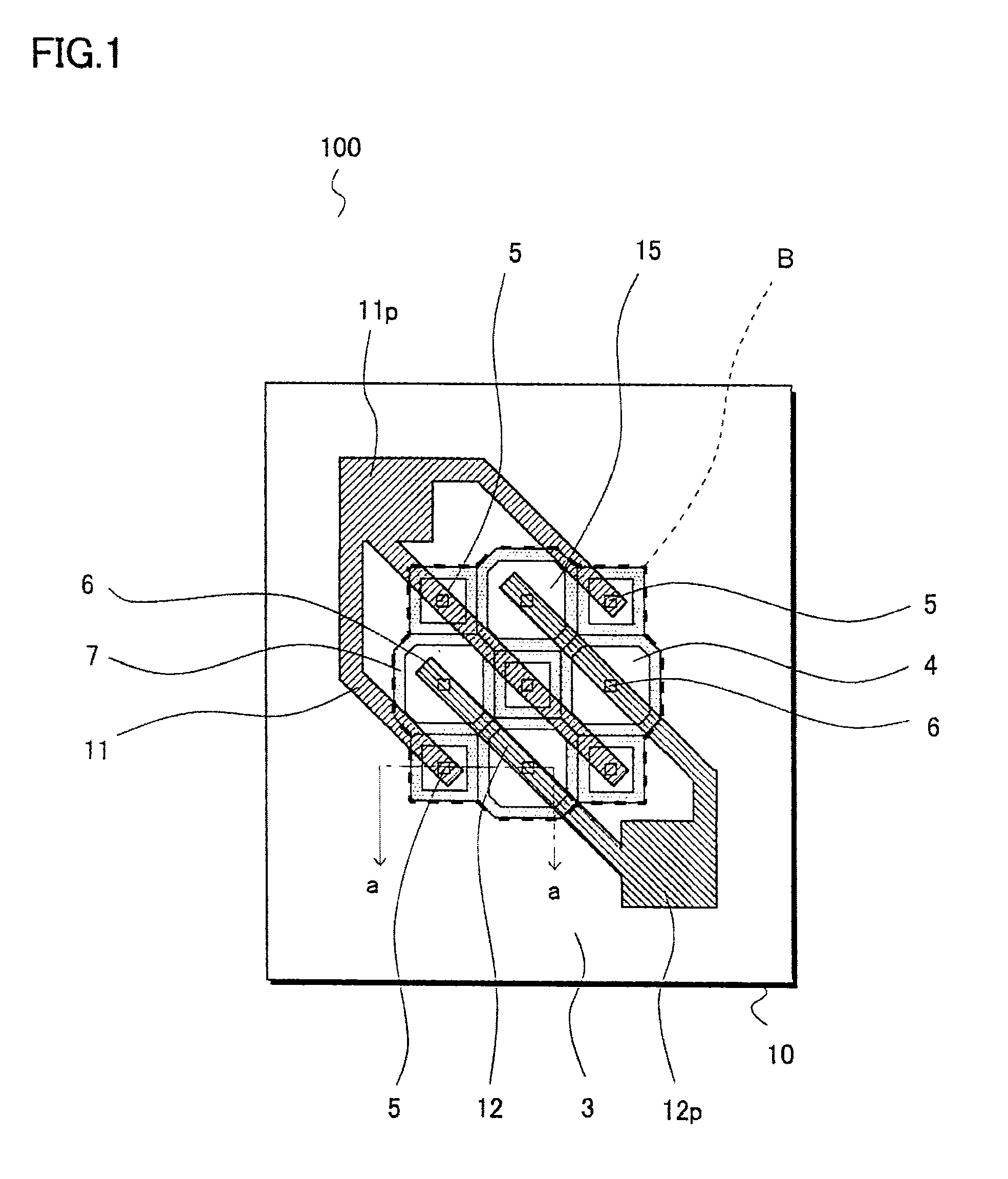

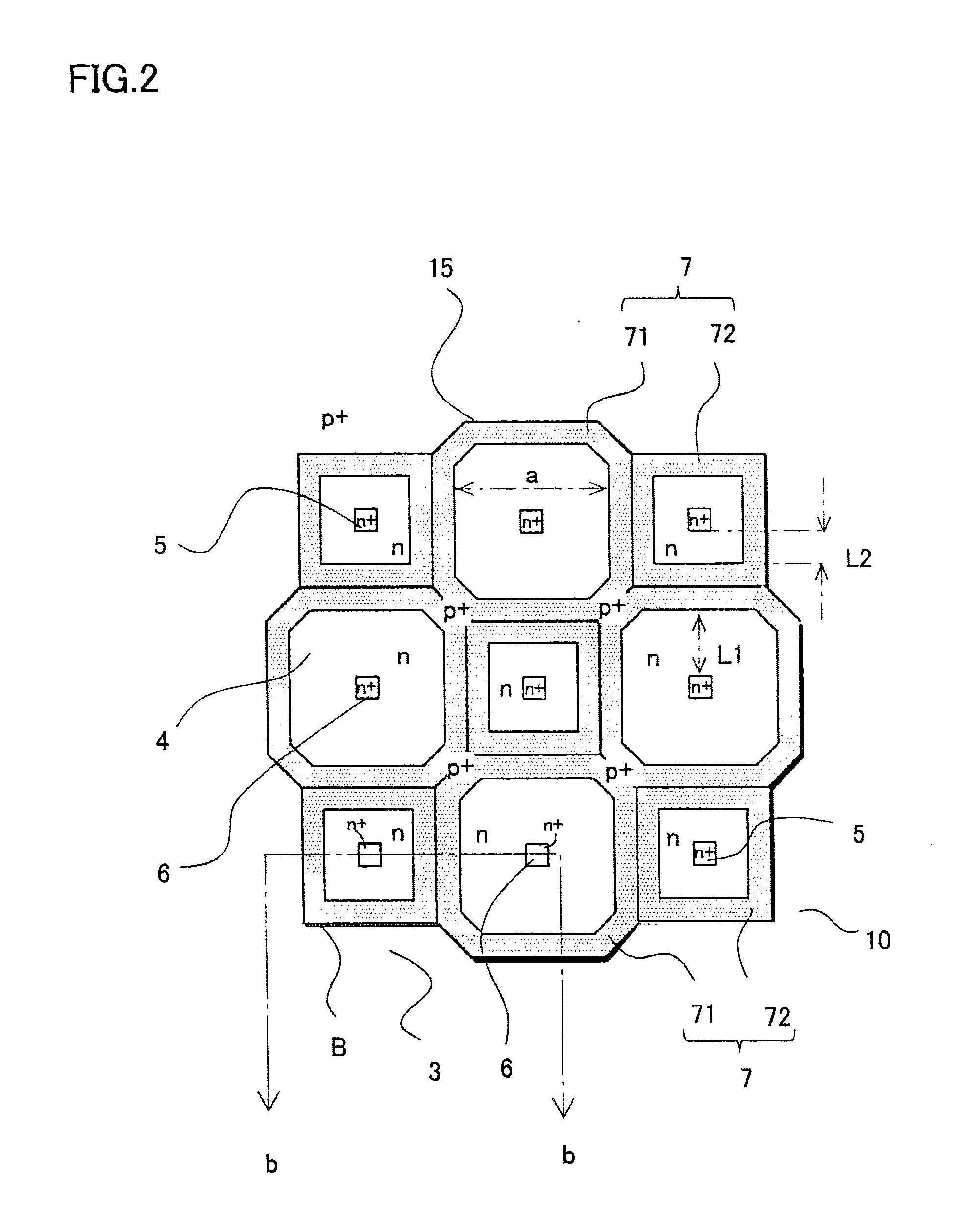

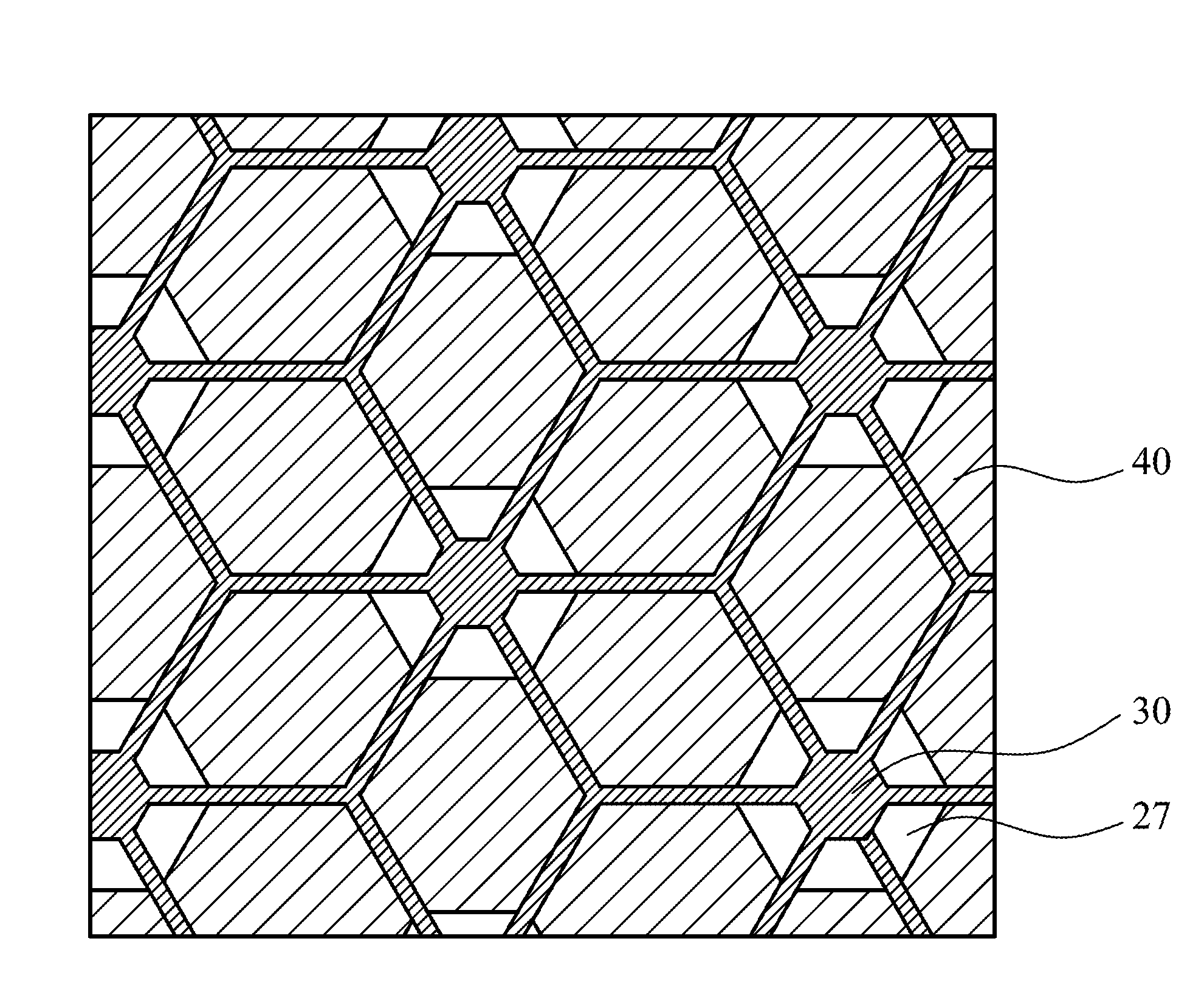

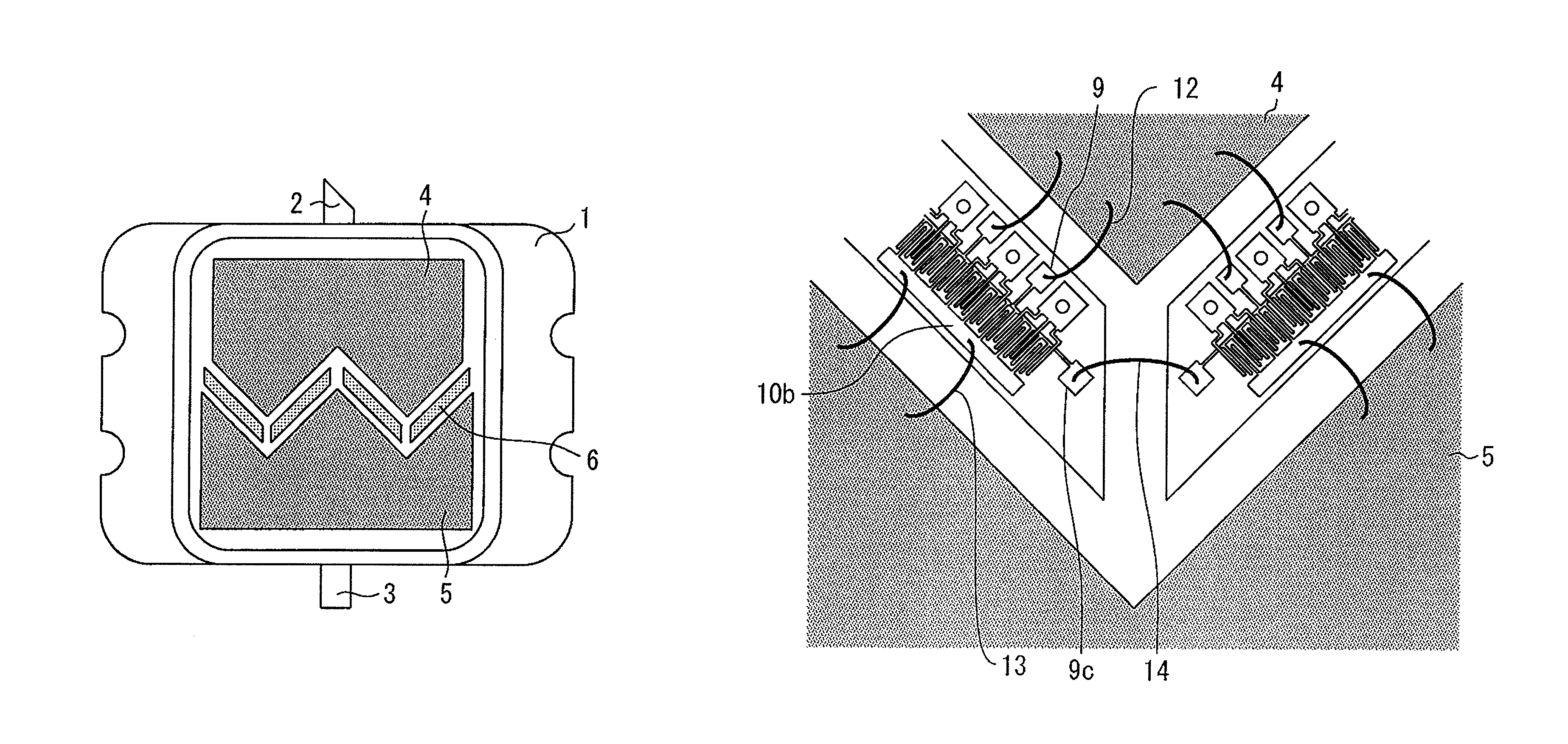

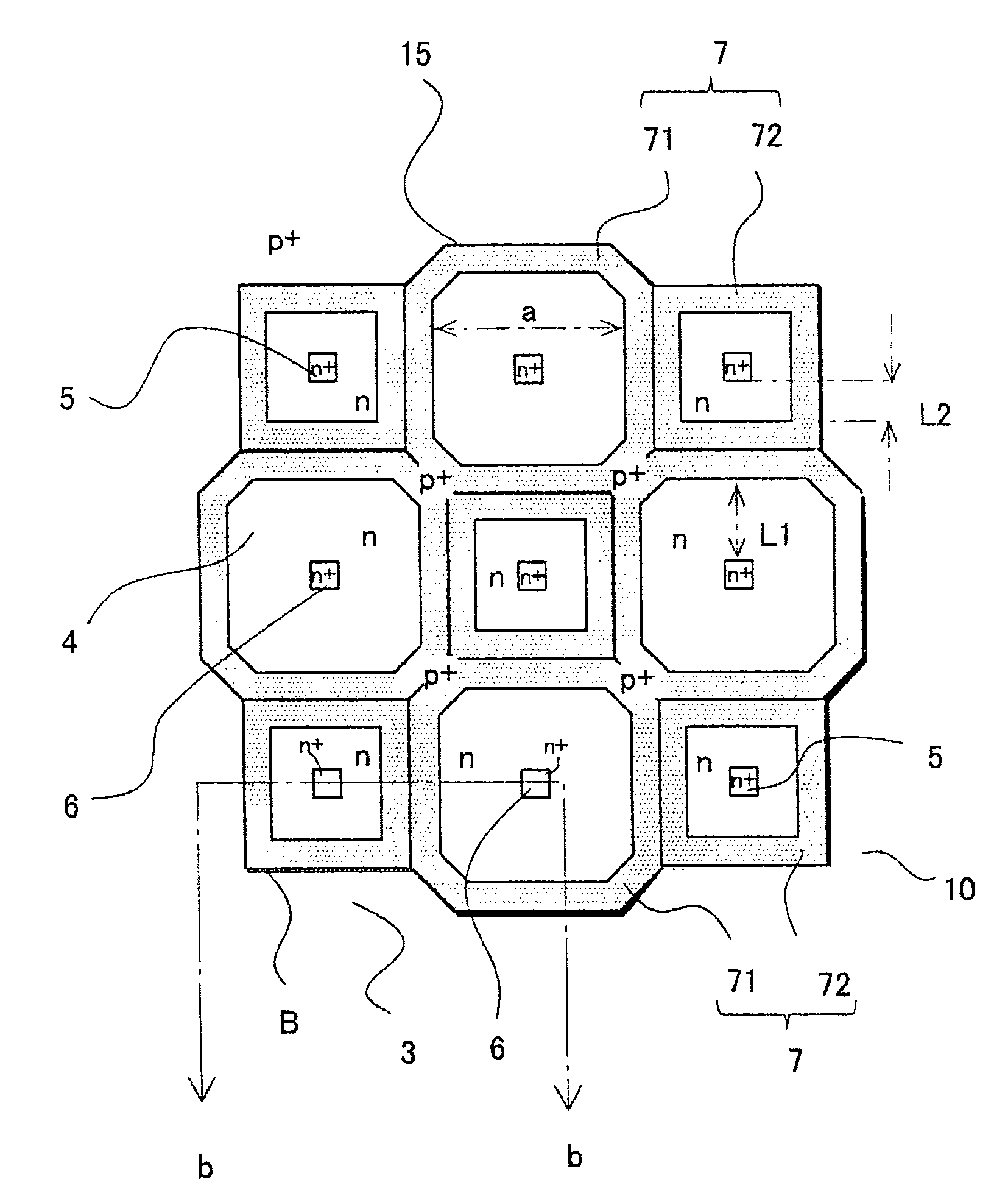

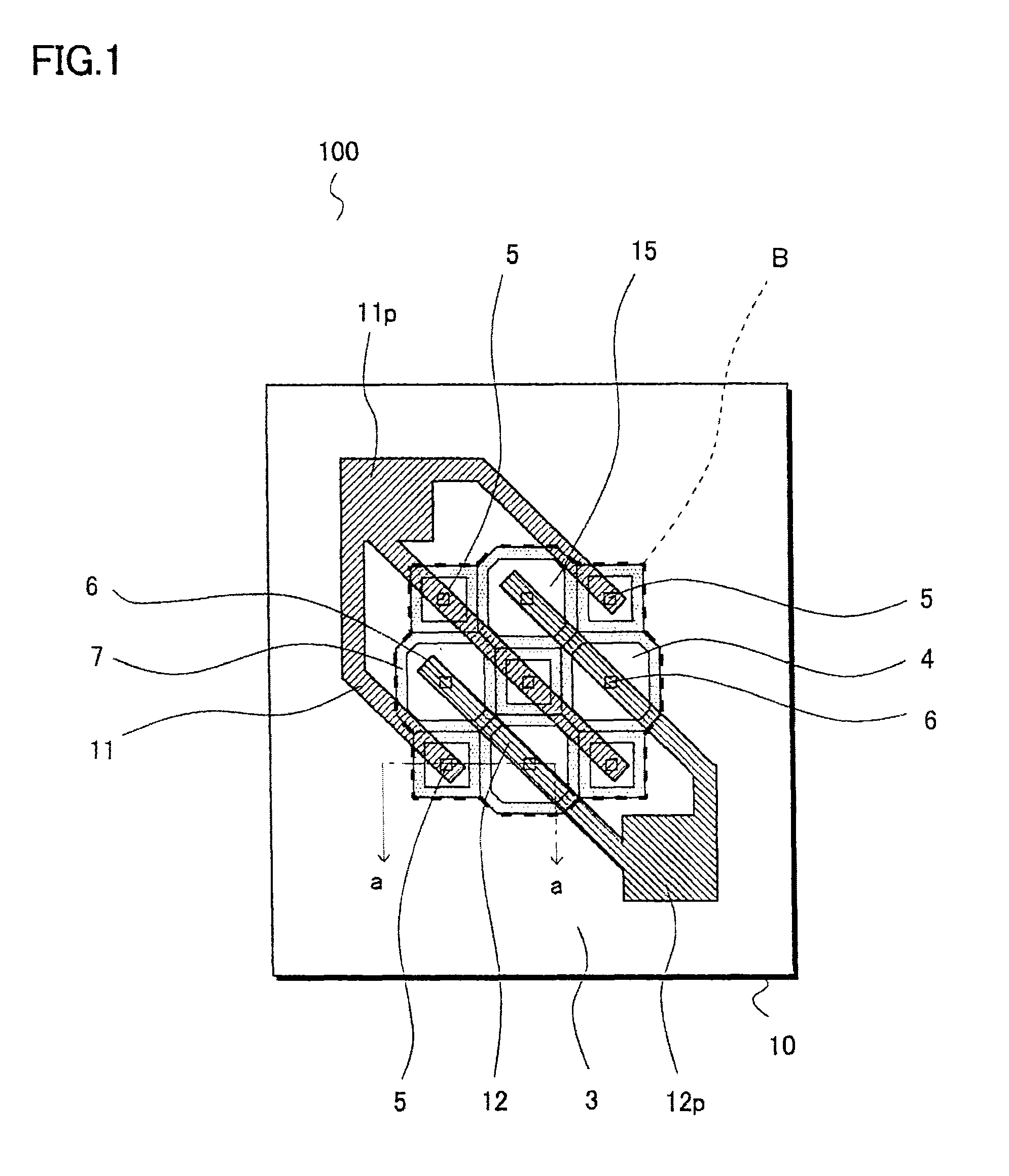

Semiconductor device

ActiveUS20090026506A1Increase gate widthRaise transfer toTransistorTelevision system detailsCapacitanceGrid pattern

In the semiconductor device, a gate region is formed in a mesh pattern having first polygonal shapes and second polygonal shapes the area of which is smaller than that of the first polygonal shapes, and drain regions and source regions are disposed within the first polygonal shapes and the second polygonal shapes, respectively. With this configuration, the forward transfer admittance gm can be increased as compared with a structure in which gate regions are disposed in a stripe pattern. Furthermore, compared with a case in which a gate region is disposed in a grid pattern, deterioration in forward transfer characteristics (amplification characteristics) due to an increase in input capacitance Ciss can be minimized while a predetermined withstand voltage is maintained.

Owner:SEMICON COMPONENTS IND LLC

Recessed STI for wide transistors

ActiveUS8058161B2Increase effective widthIncrease gate widthSemiconductor/solid-state device manufacturingEngineeringSemiconductor

Owner:TEXAS INSTR INC

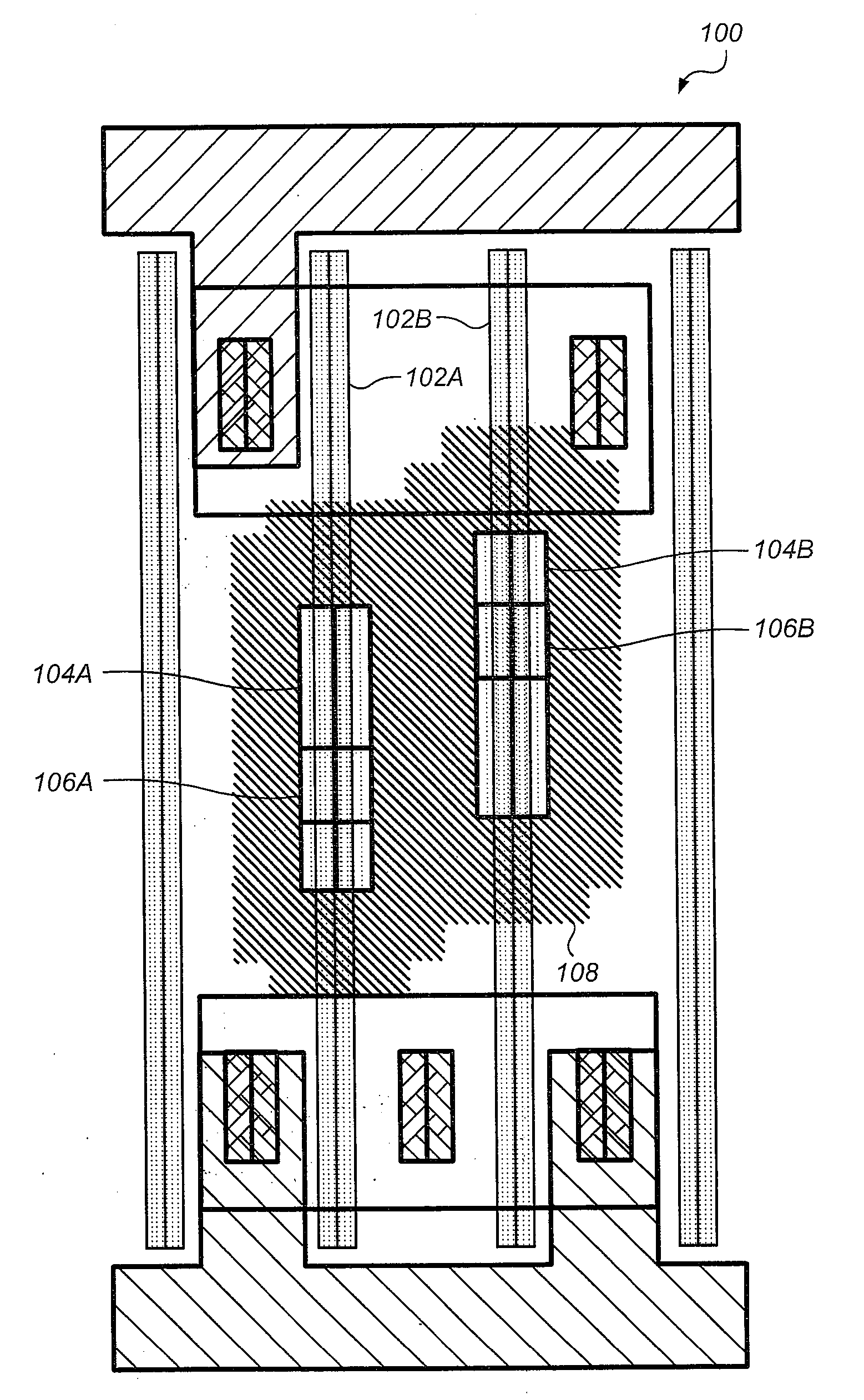

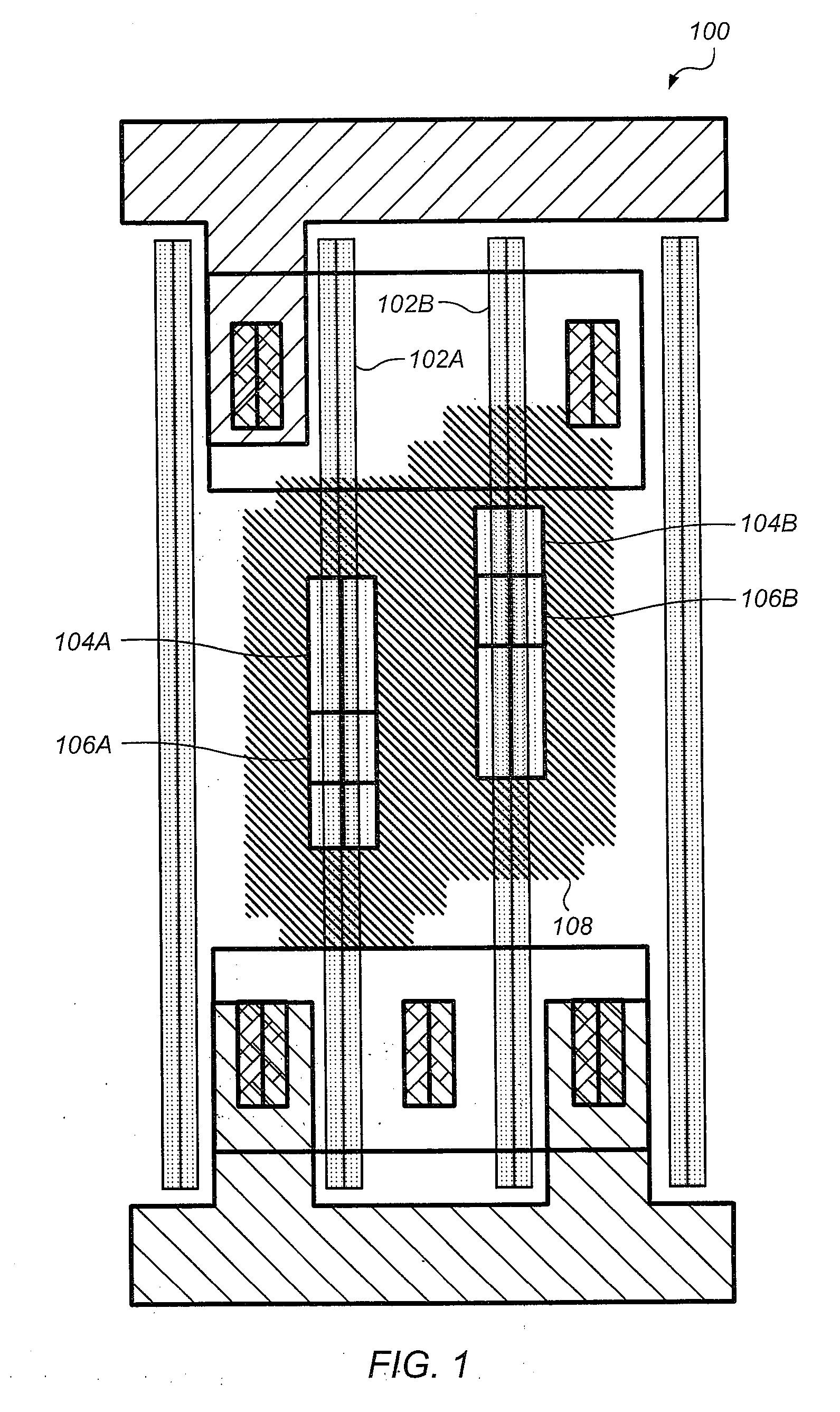

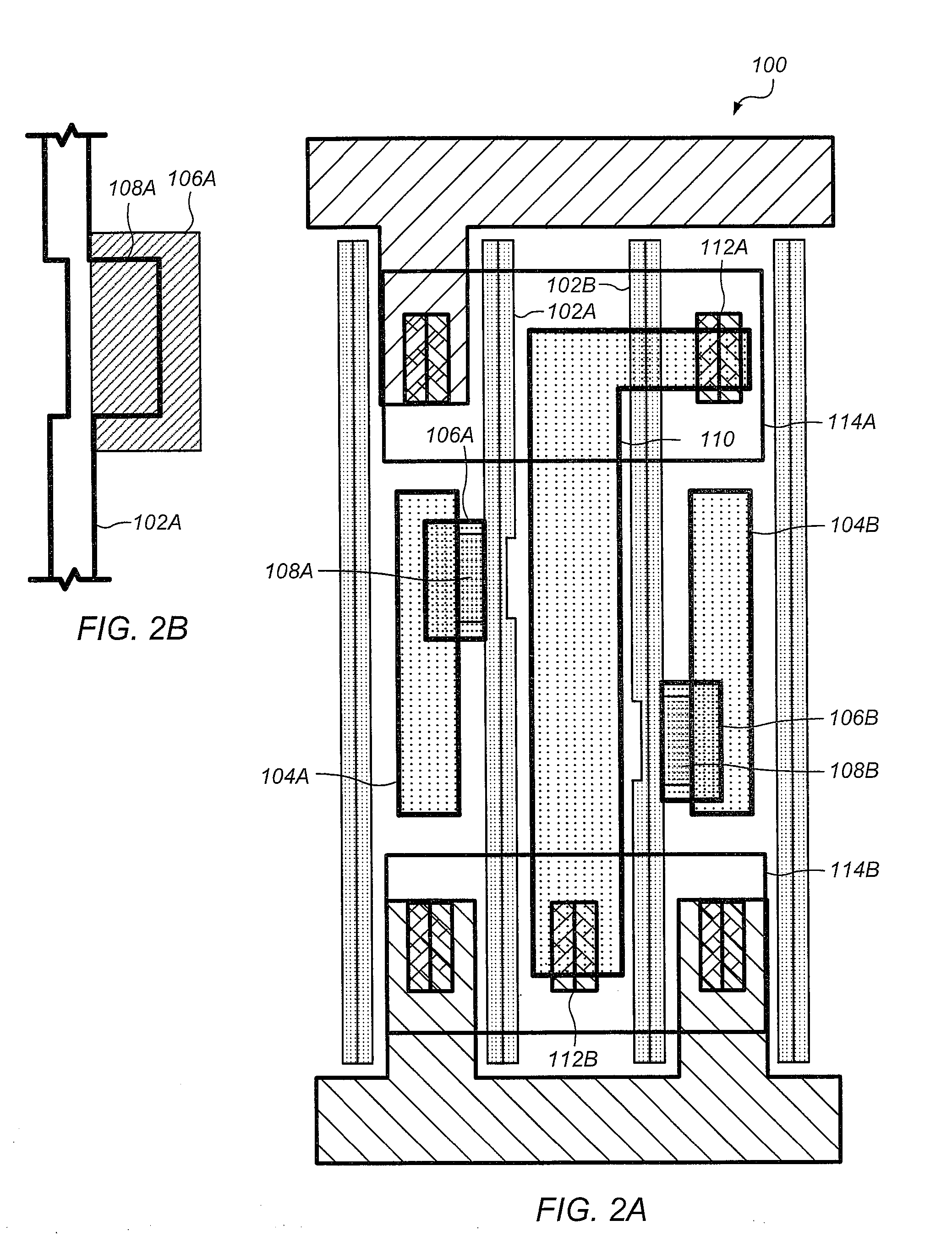

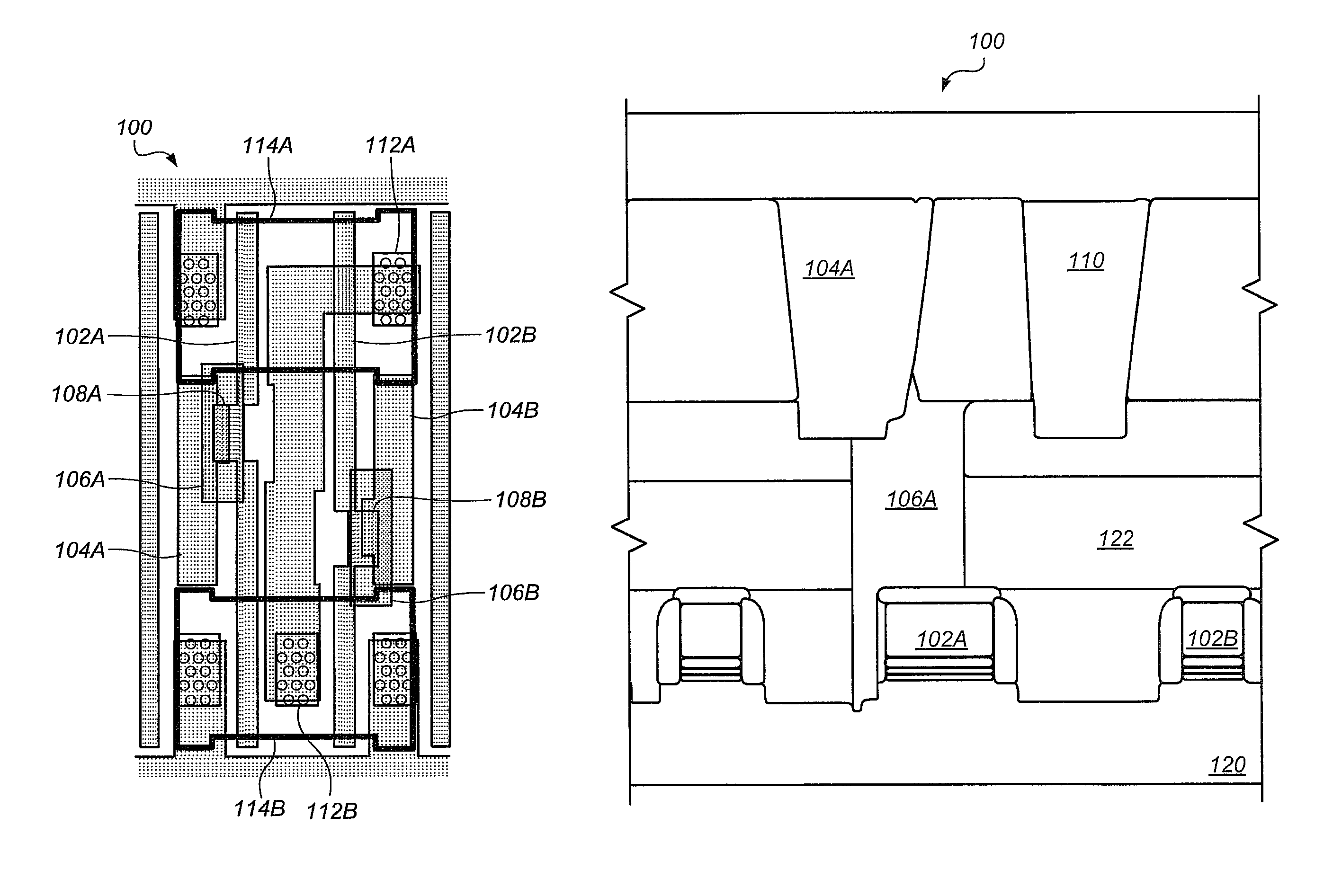

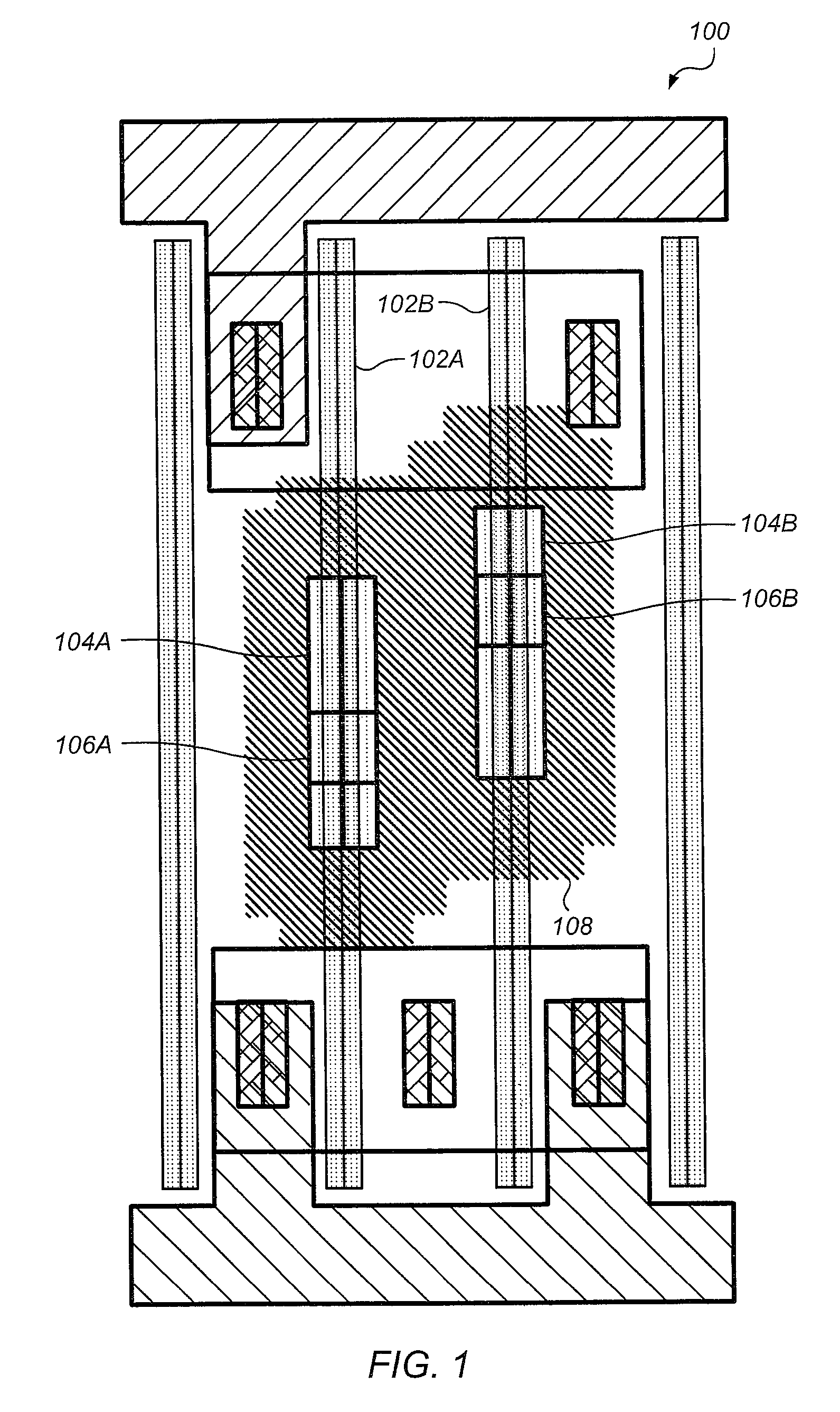

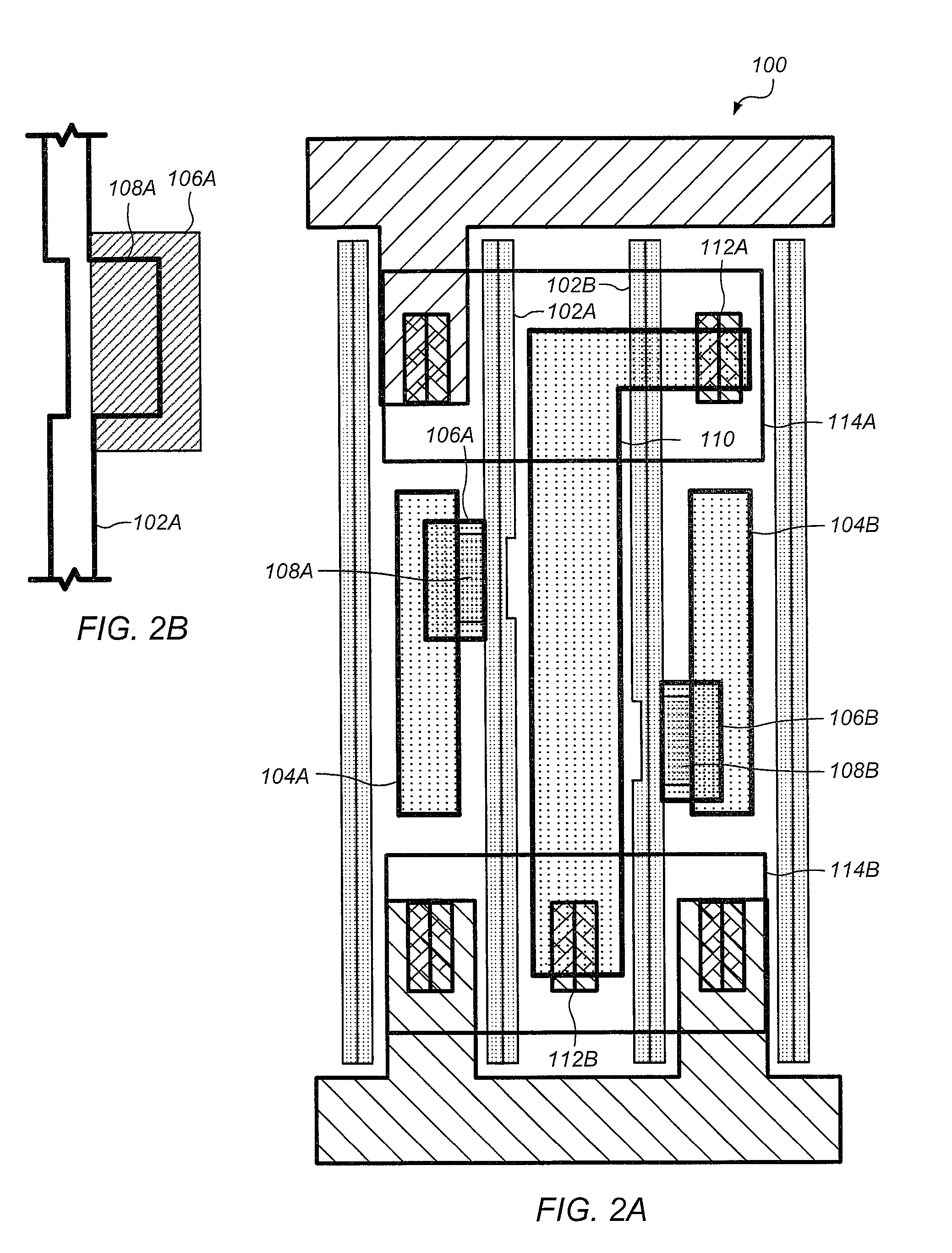

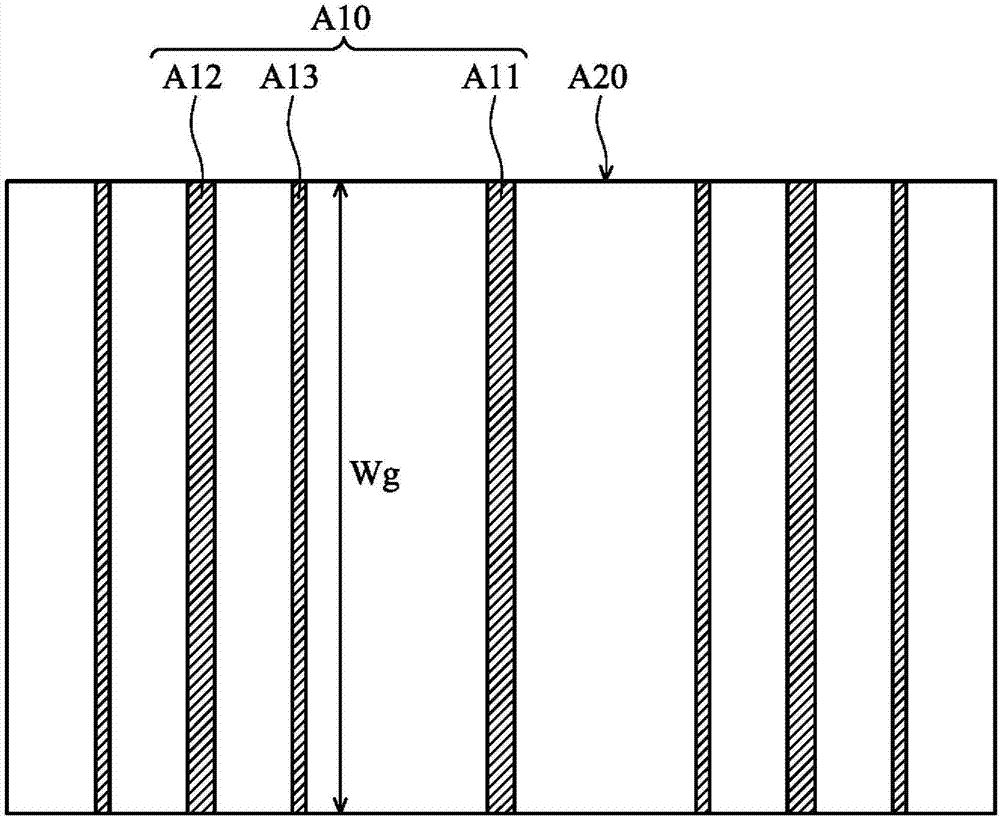

Handshake structure for improving layout density

ActiveUS20110049635A1Improve the layout densityIncrease gate widthTransistorSemiconductor/solid-state device detailsSemiconductorSemiconductor device

A semiconductor device includes a gate on a semiconductor substrate. One side wall of the gate may include at least one protrusion and an opposite side wall of the gate may include at least one depression. A contact is formed through an insulating layer disposed over the gate. The contact at least partially overlaps at least one of the protrusions in the gate. A metal layer is disposed on the insulating layer. The metal layer includes a first structure shifted to a first side of the gate. The first structure at least partially overlaps the contact such that the contact electrically couples the first structure to the gate through the insulating layer.

Owner:ADVANCED MICRO DEVICES INC

Handshake structure for improving layout density

ActiveUS8258578B2Improve the layout densityIncrease gate widthTransistorSemiconductor/solid-state device detailsSemiconductorSemiconductor device

A semiconductor device includes a gate on a semiconductor substrate. One side wall of the gate may include at least one protrusion and an opposite side wall of the gate may include at least one depression. A contact is formed through an insulating layer disposed over the gate. The contact at least partially overlaps at least one of the protrusions in the gate. A metal layer is disposed on the insulating layer. The metal layer includes a first structure shifted to a first side of the gate. The first structure at least partially overlaps the contact such that the contact electrically couples the first structure to the gate through the insulating layer.

Owner:ADVANCED MICRO DEVICES INC

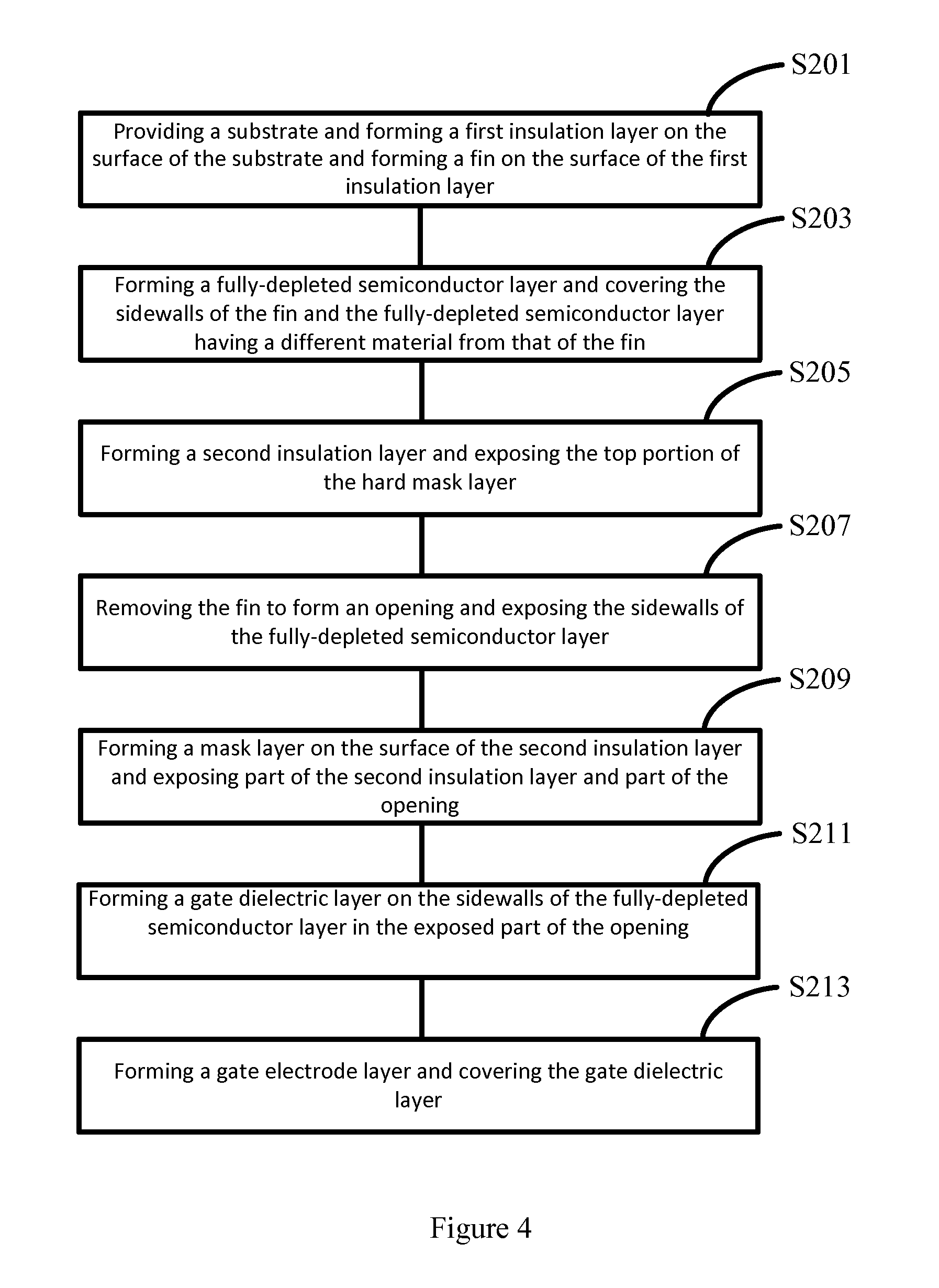

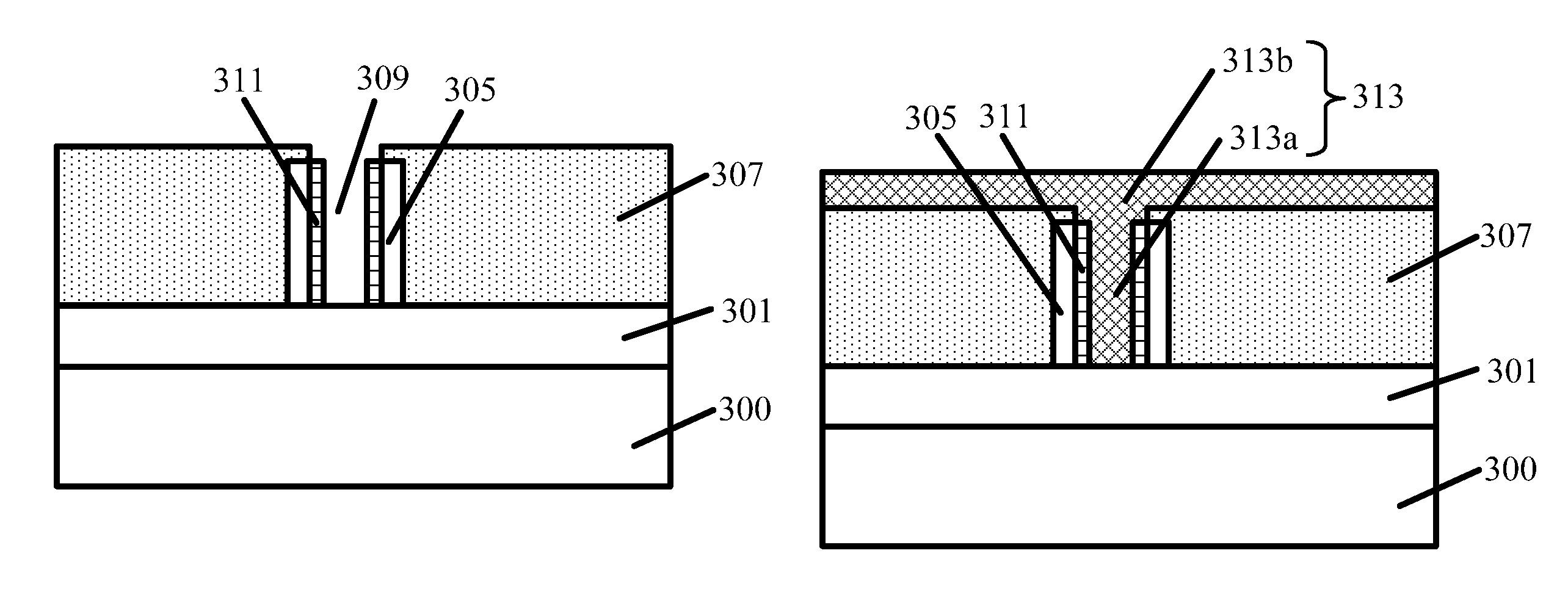

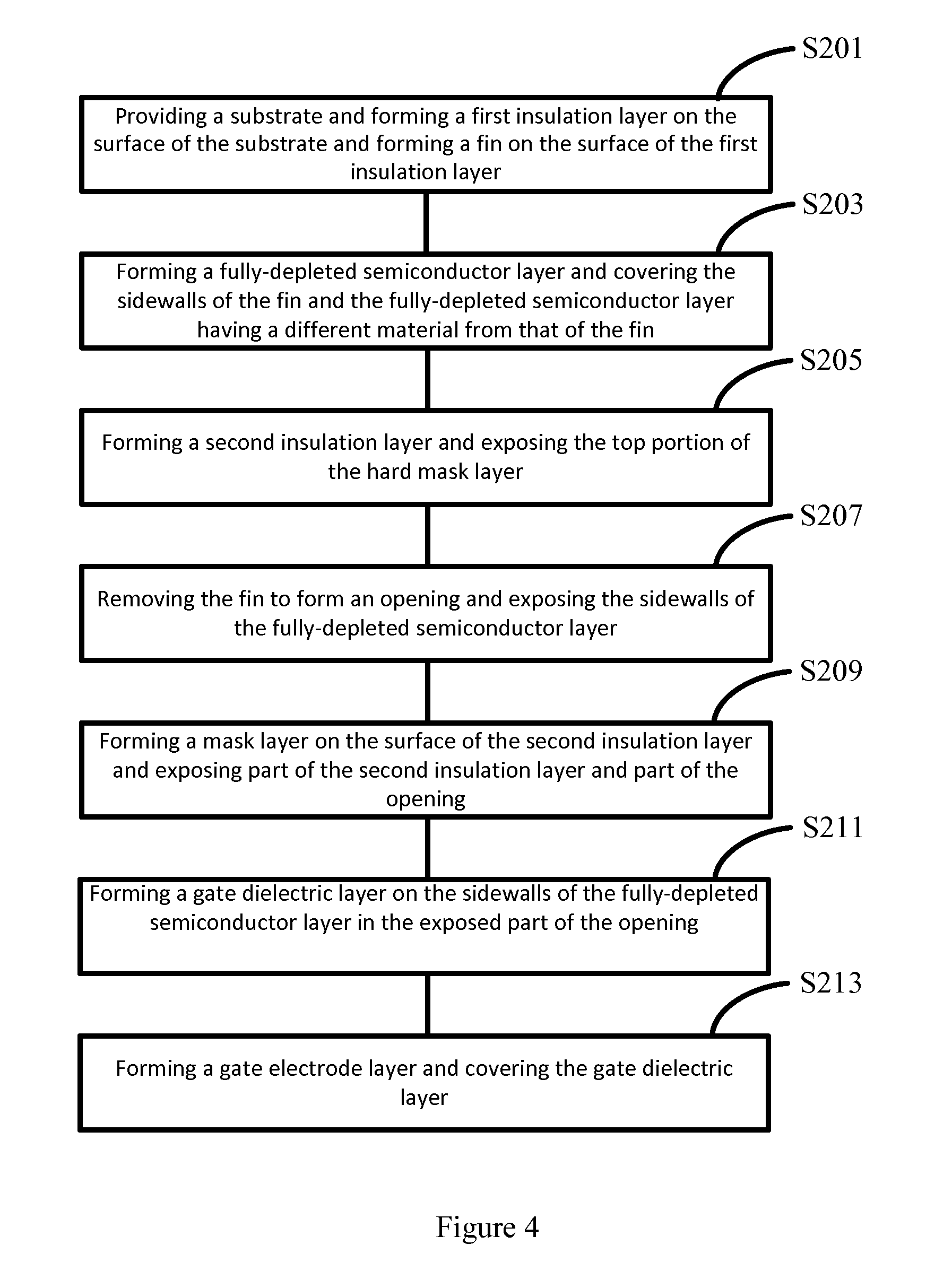

Semiconductor device and manufacturing method

ActiveUS20130299875A1Eliminate interactionElectric fieldSemiconductor/solid-state device manufacturingSemiconductor devicesInsulation layerGate dielectric

A fabrication process of a semiconductor device is disclosed. The method includes providing a semiconductor substrate with a first insulation layer formed on the semiconductor substrate and a fin formed on the surface of the first insulation layer, and forming a fully-depleted semiconductor layer on sidewalls of the fin, and the fully-depleted semiconductor layer having a material different from that of the fin. The method also includes forming a second insulation layer covering the fully-depleted semiconductor layer, and removing the fin to form an opening exposing sidewalls of the fully-depleted semiconductor layer. Further, the method includes forming a gate dielectric layer on part of the sidewalls of the fully-depleted semiconductor layer such that the part of the sidewalls of the fully-depleted semiconductor layer form channel regions of the semiconductor device, and forming a gate electrode layer covering the gate dielectric layer.

Owner:SEMICON MFG INT (SHANGHAI) CORP

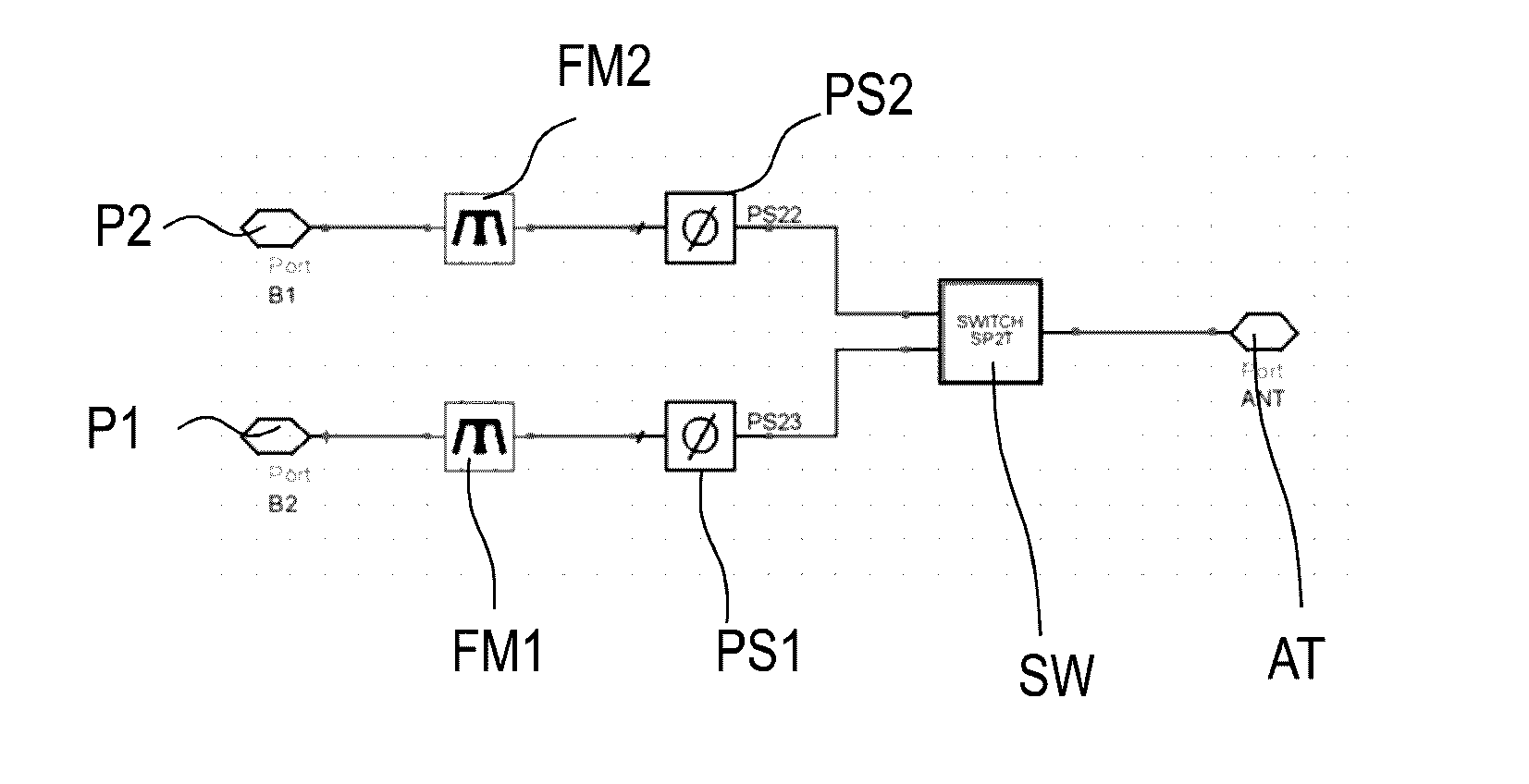

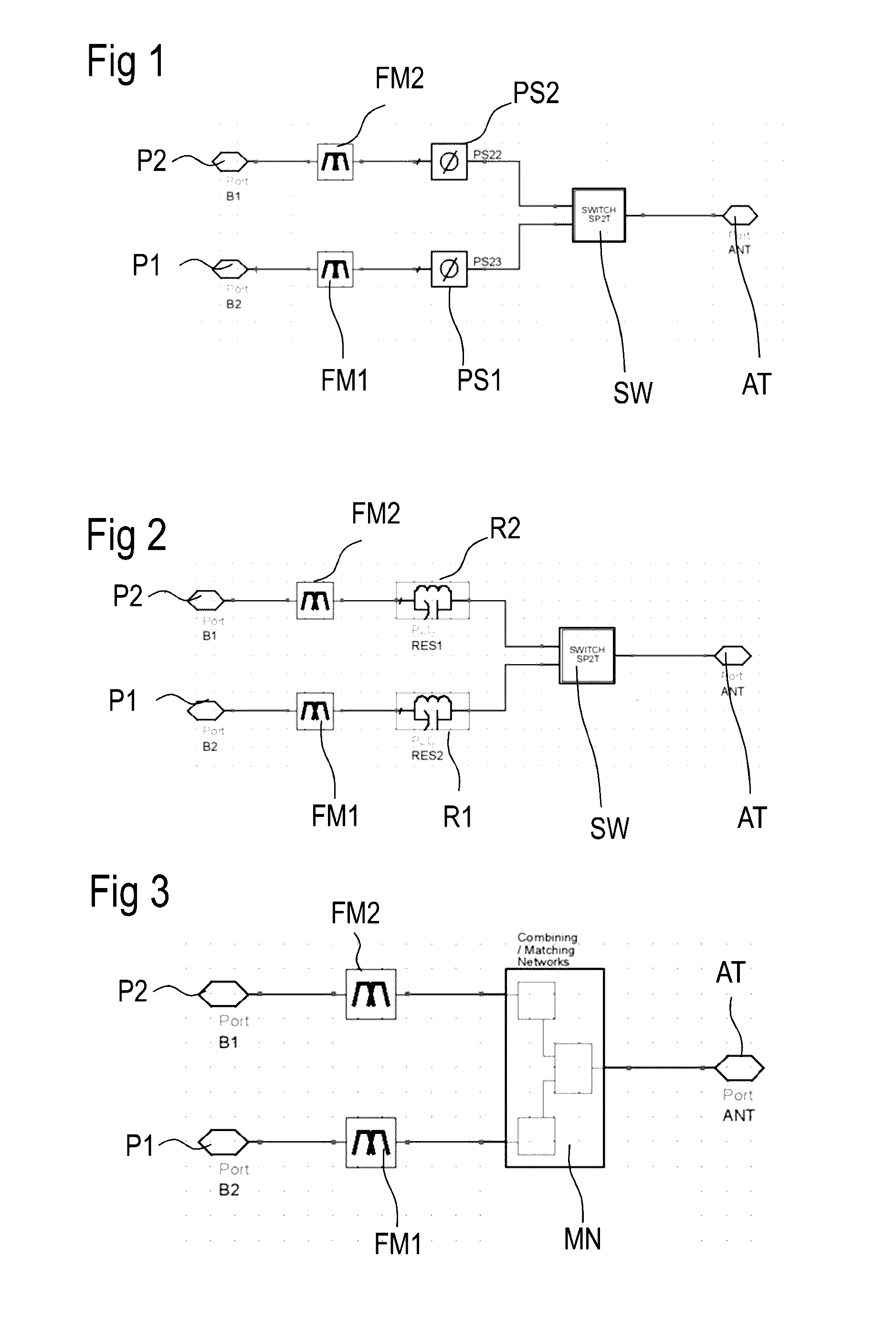

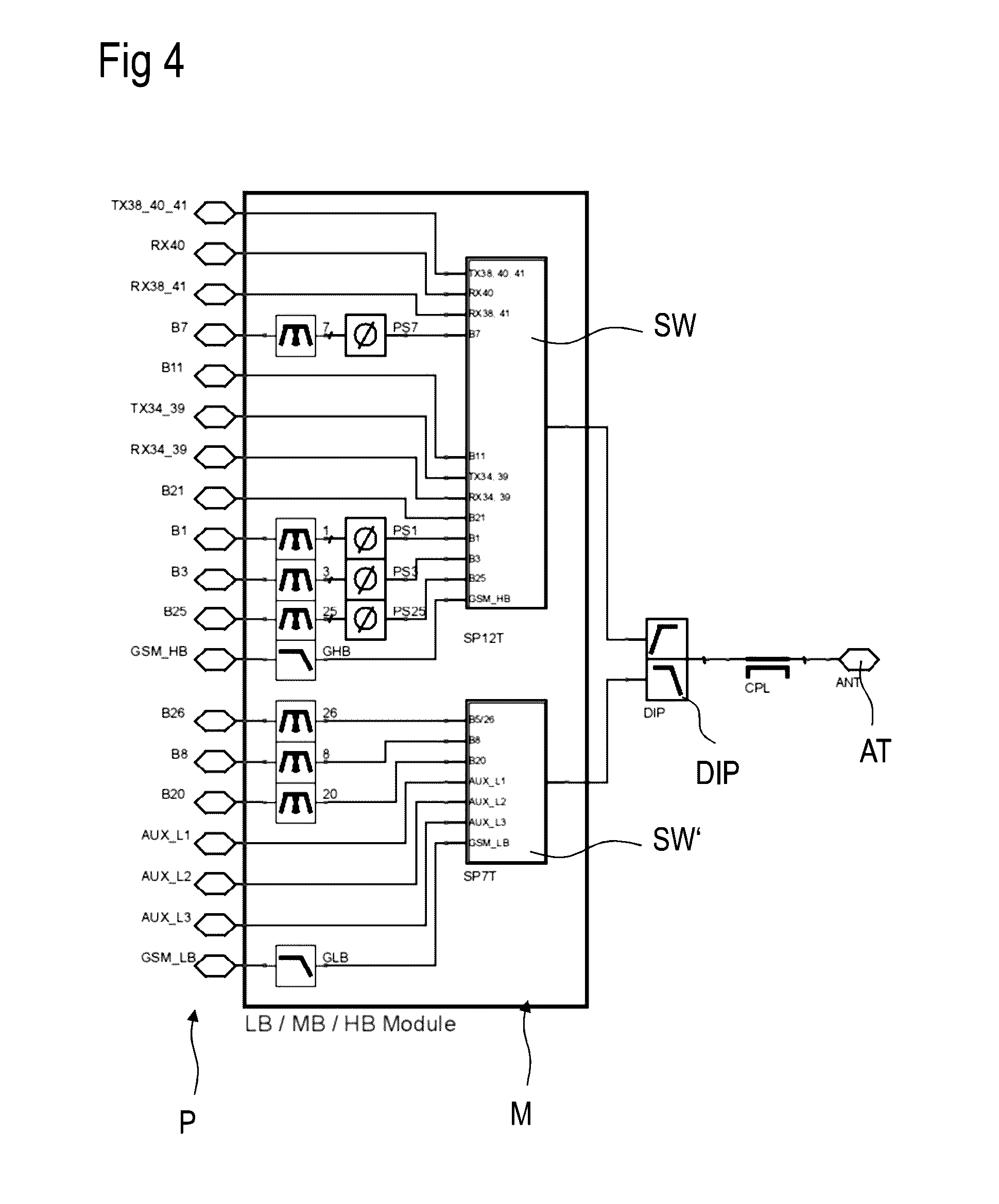

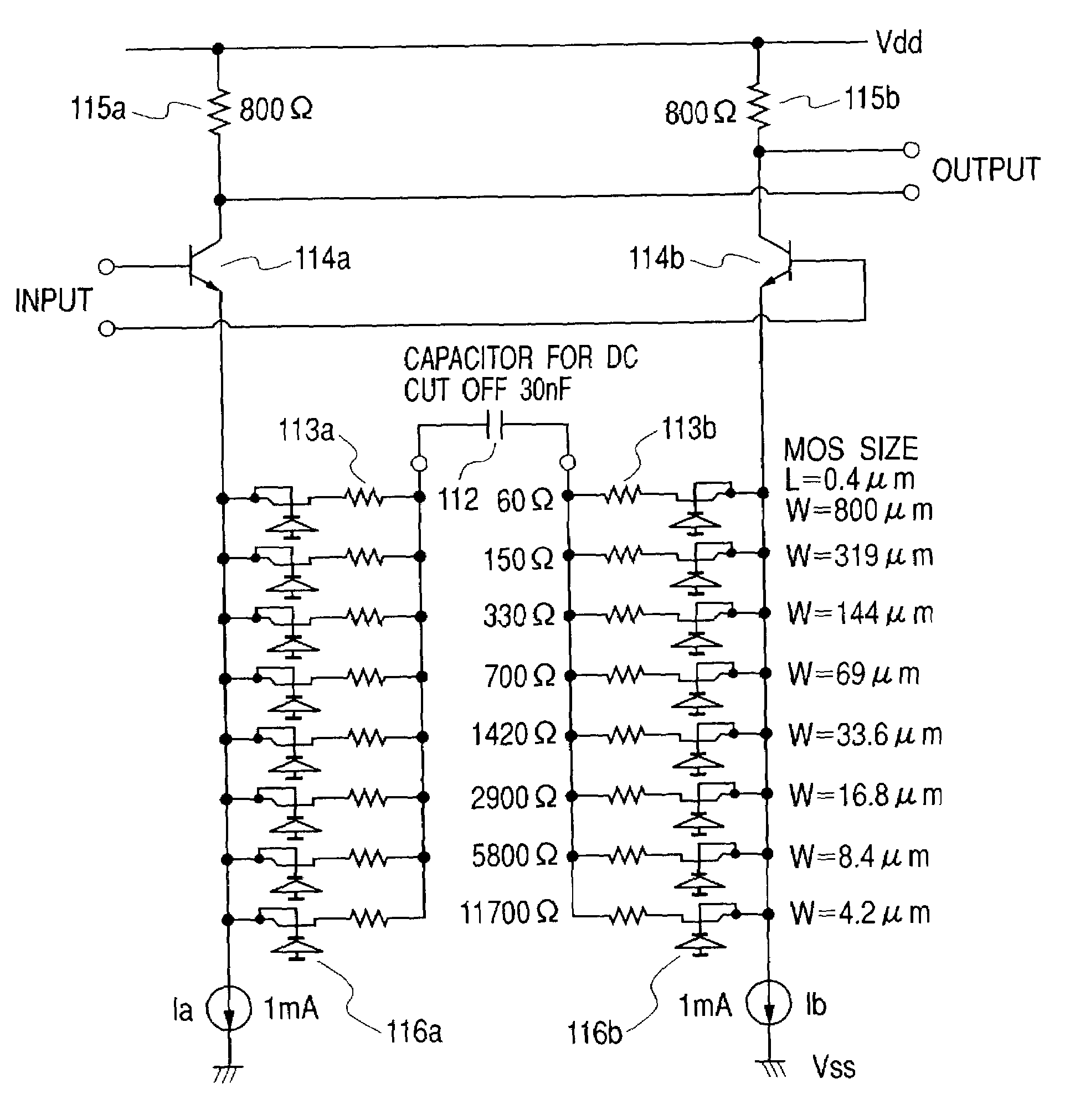

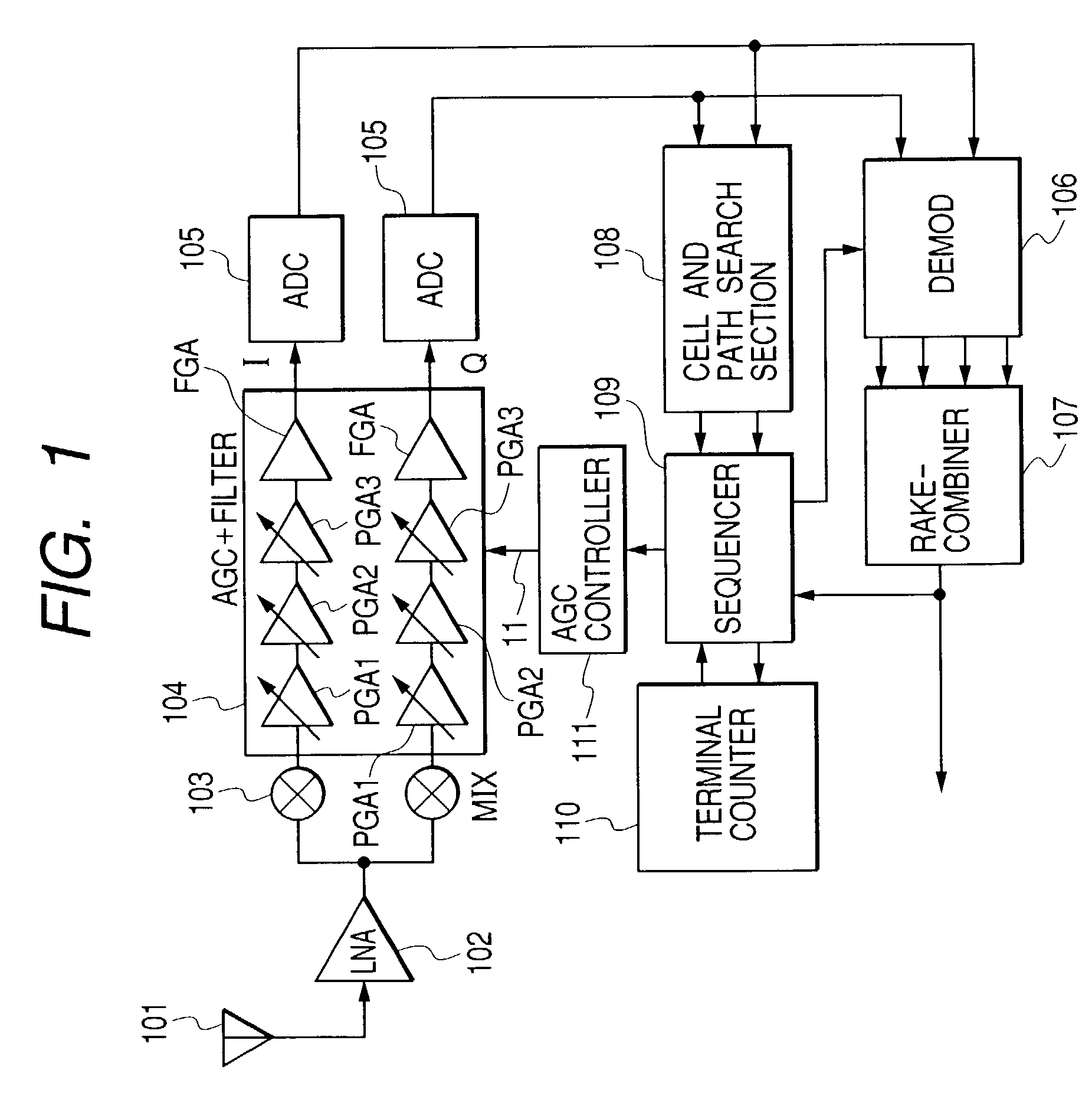

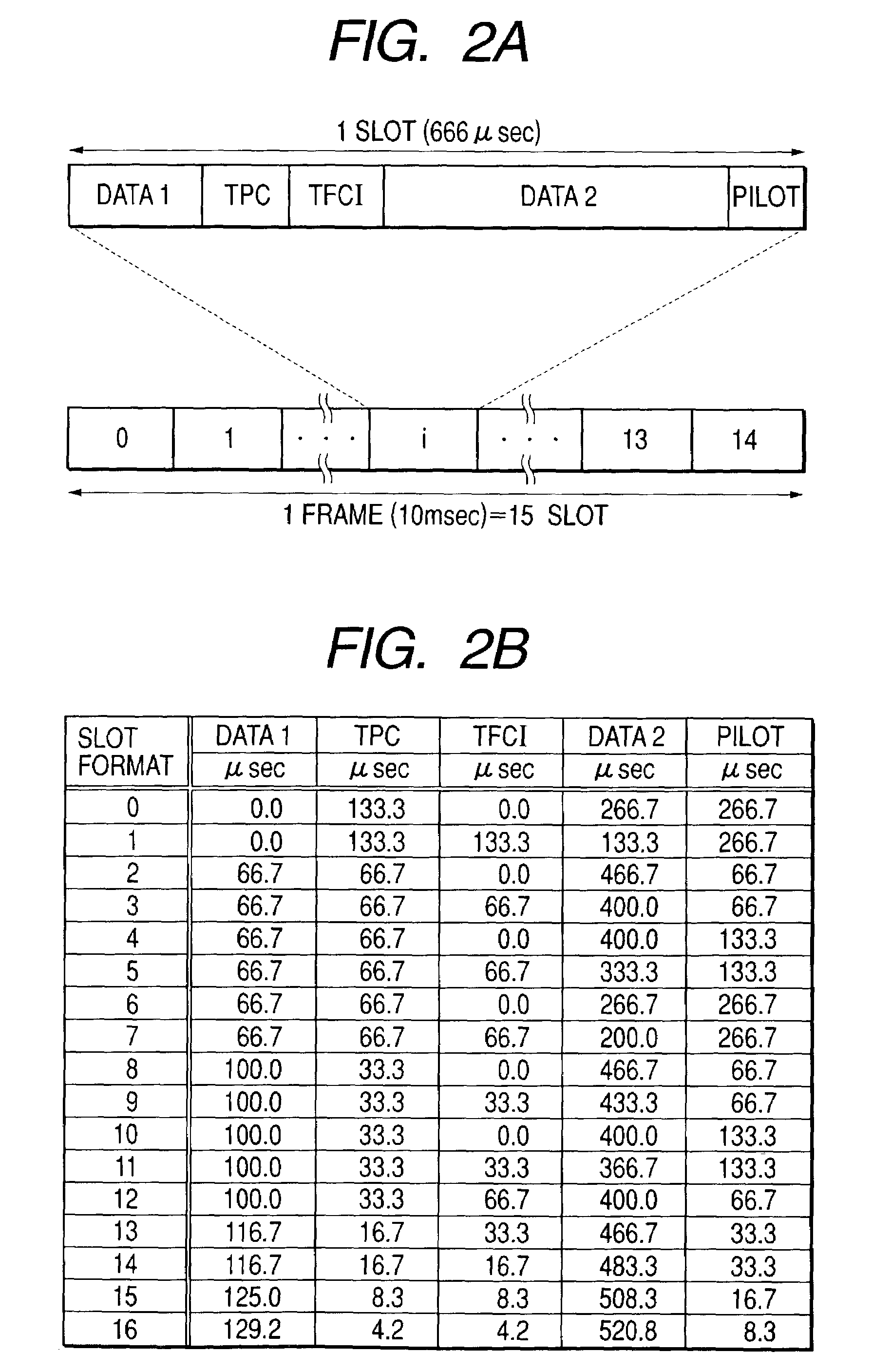

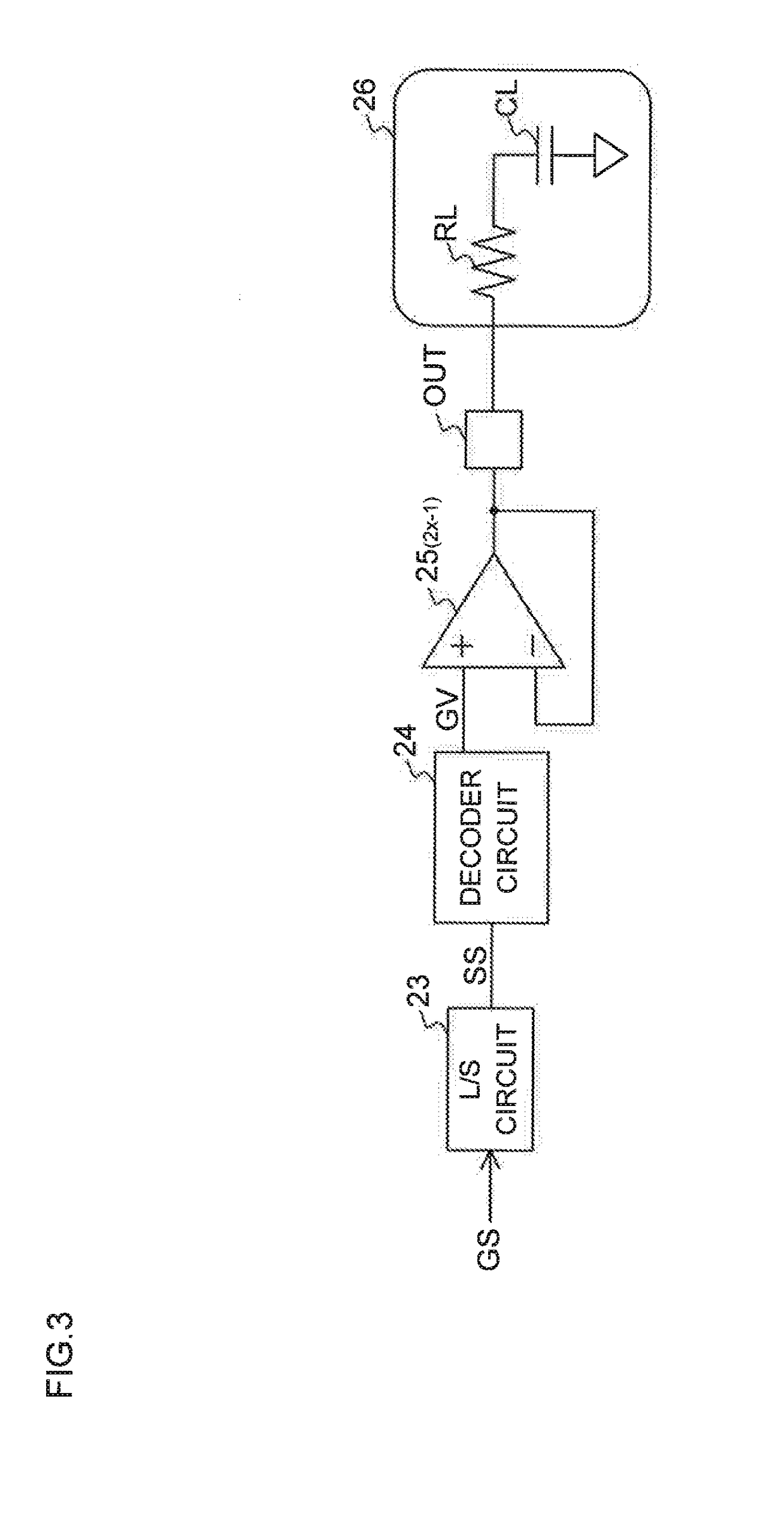

Wireless communication receiver

InactiveUS7194244B2Increase gate widthIncrease riseGain controlAmplitude-modulated carrier systemsProgrammable-gain amplifierControl function

A wireless communication receiver that is able to lessen the effect of noise that accompanies gain change by programmable gain amplifiers. The receiver includes an AGC controller which controls the timing at which the programmable gain amplifiers make gain change, using a terminal counter and a sequencer. The receiver prevents gain change noise signals during the reception of control signals and other signals that are susceptible to noise. By the timing control feature, the programmable gain amplifiers make gain change while reducing noise impact.

Owner:RENESAS ELECTRONICS CORP

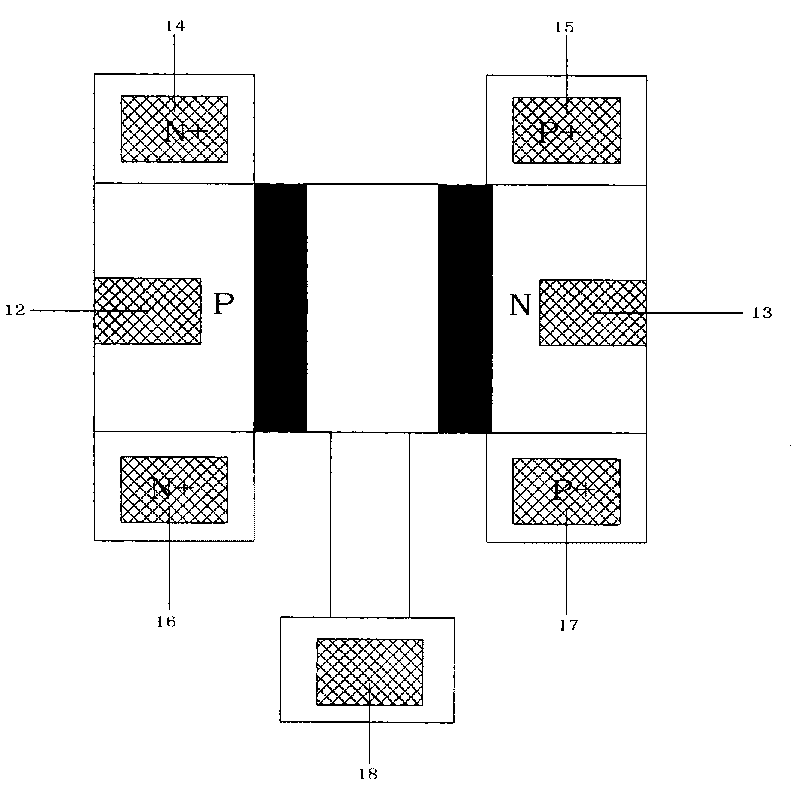

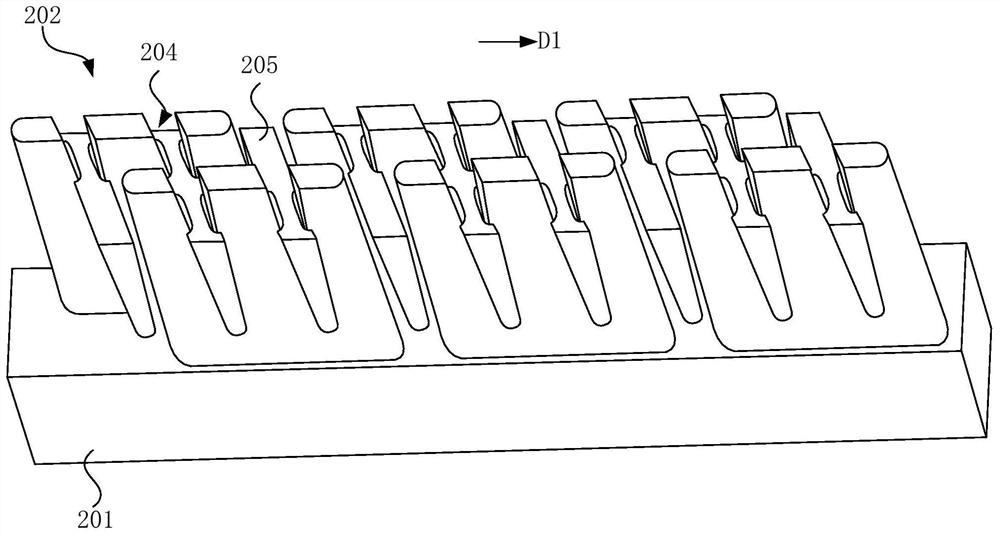

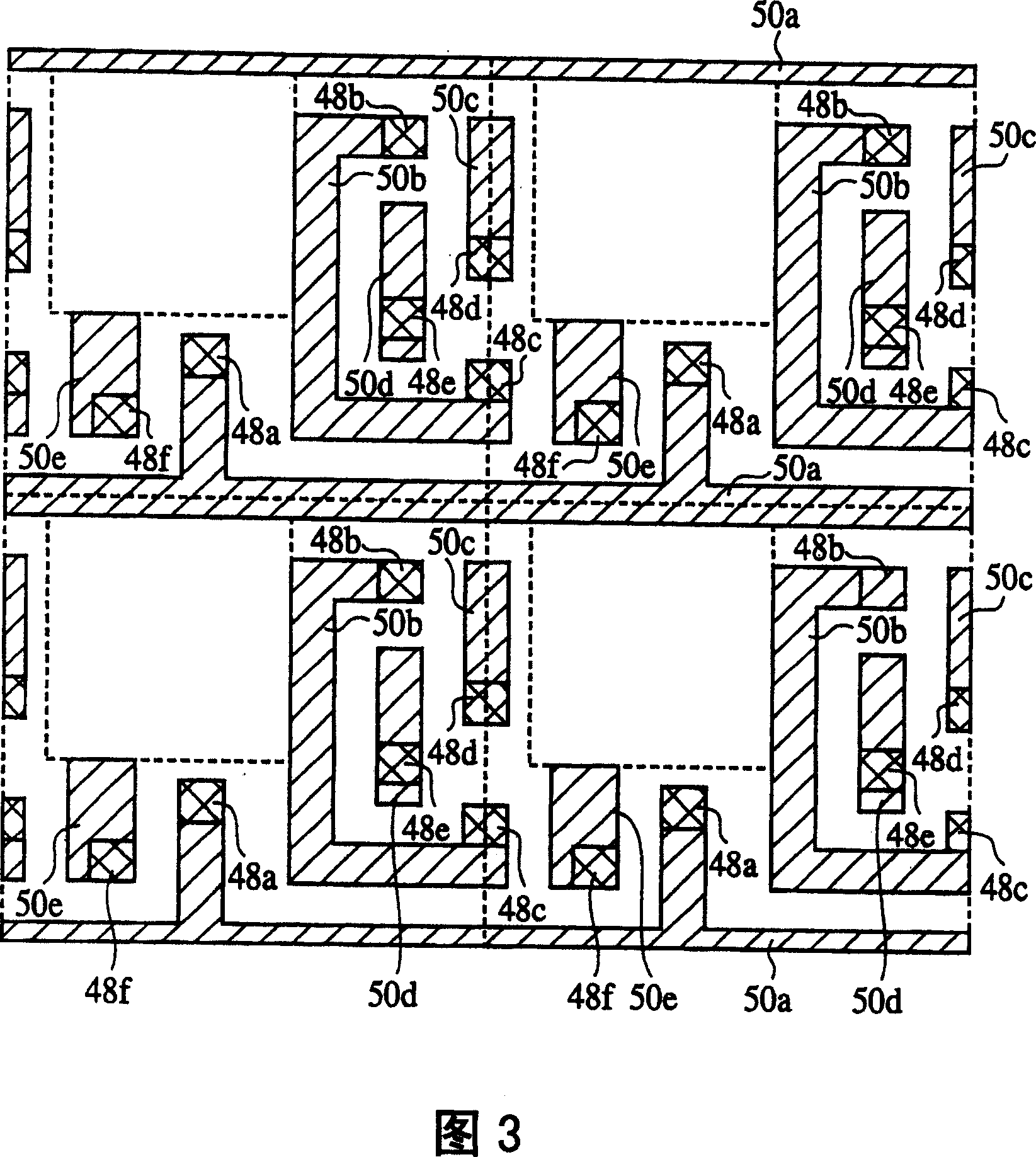

Interdigital structure capable of regulating channel current of vertical gate SOI CMOS devices

InactiveCN101764136AIncrease gate widthSemiconductor/solid-state device detailsSolid-state devicesSoi cmosCMOS

The invention discloses an interdigital structure capable of regulating the channel current of vertical gate SOI CMOS devices, which comprises a plurality of vertical gate SOI CMOS devices which are distributed in parallel, wherein PMOS regions of the adjacent vertical gate SOI CMOS devices are adjacent, and NMOS regions are also adjacent; source regions of all of the vertical gate SOI CMOS devices are positioned on the same side, and drain regions are positioned on the other side; and gate electrodes of all of the vertical gate SOI CMOS devices are led out of the side surface to form interdigital gate electrodes. The adjacent PMOS regions share one body electrode; the adjacent NMOS regions share one body electrode; and all of the body electrodes are connected in parallel to form an interdigital body electrode. All source electrodes led out from the source regions are connected in parallel to form an interdigital source electrode; and all drain electrodes led out from the drain regions are connected in parallel to form an interdigital drain electrode. In the invention, the gate electrodes of the plurality of the CMOS devices are connected in parallel by an interdigital topological structure, which is equivalent to improving the equivalent gate width of the vertical gate SOI CMOS devices so as to fulfill the aim of regulating the channel current of the vertical gate SOI CMOS devices.

Owner:SHANGHAI INST OF MICROSYSTEM & INFORMATION TECH CHINESE ACAD OF SCI +1

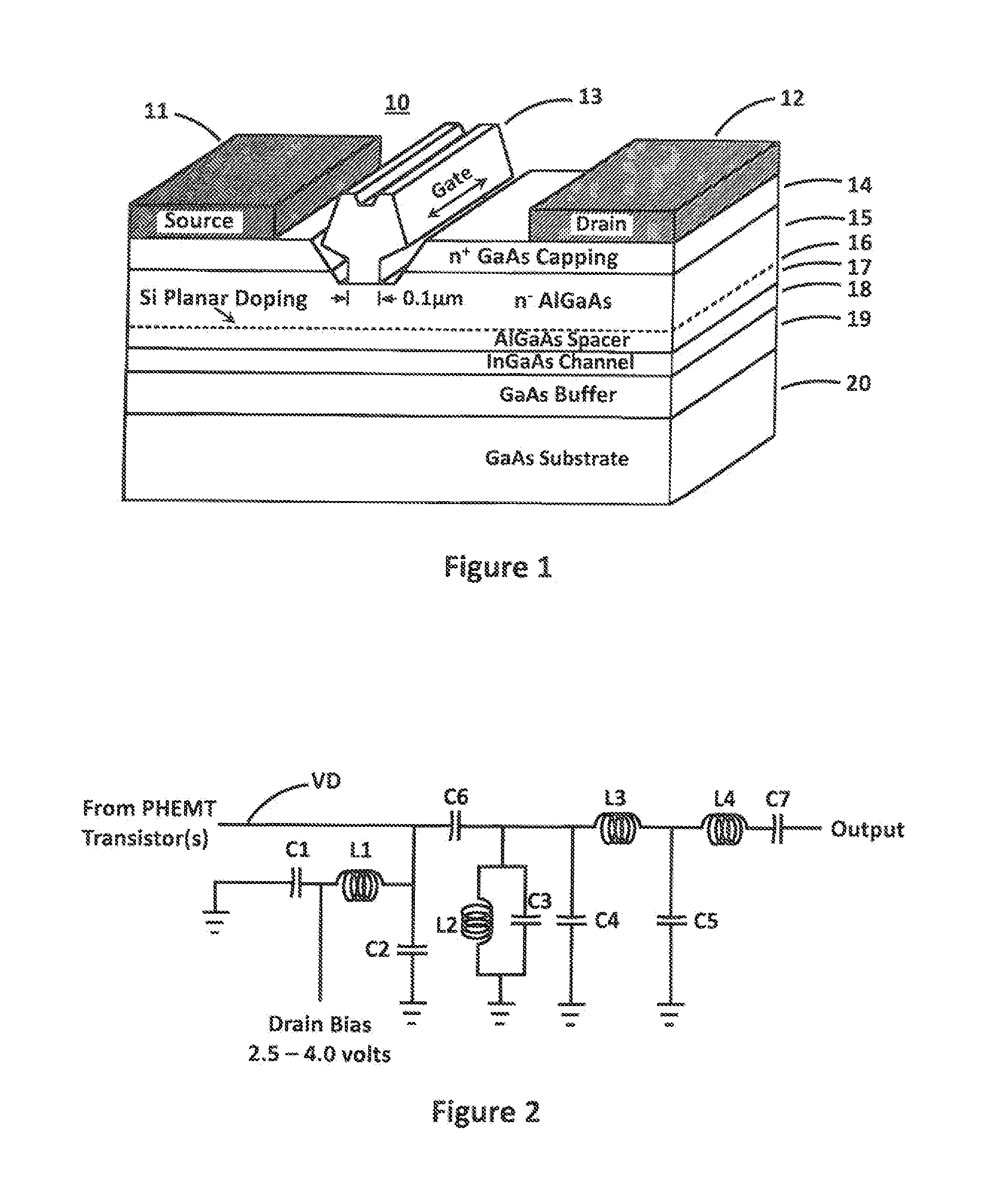

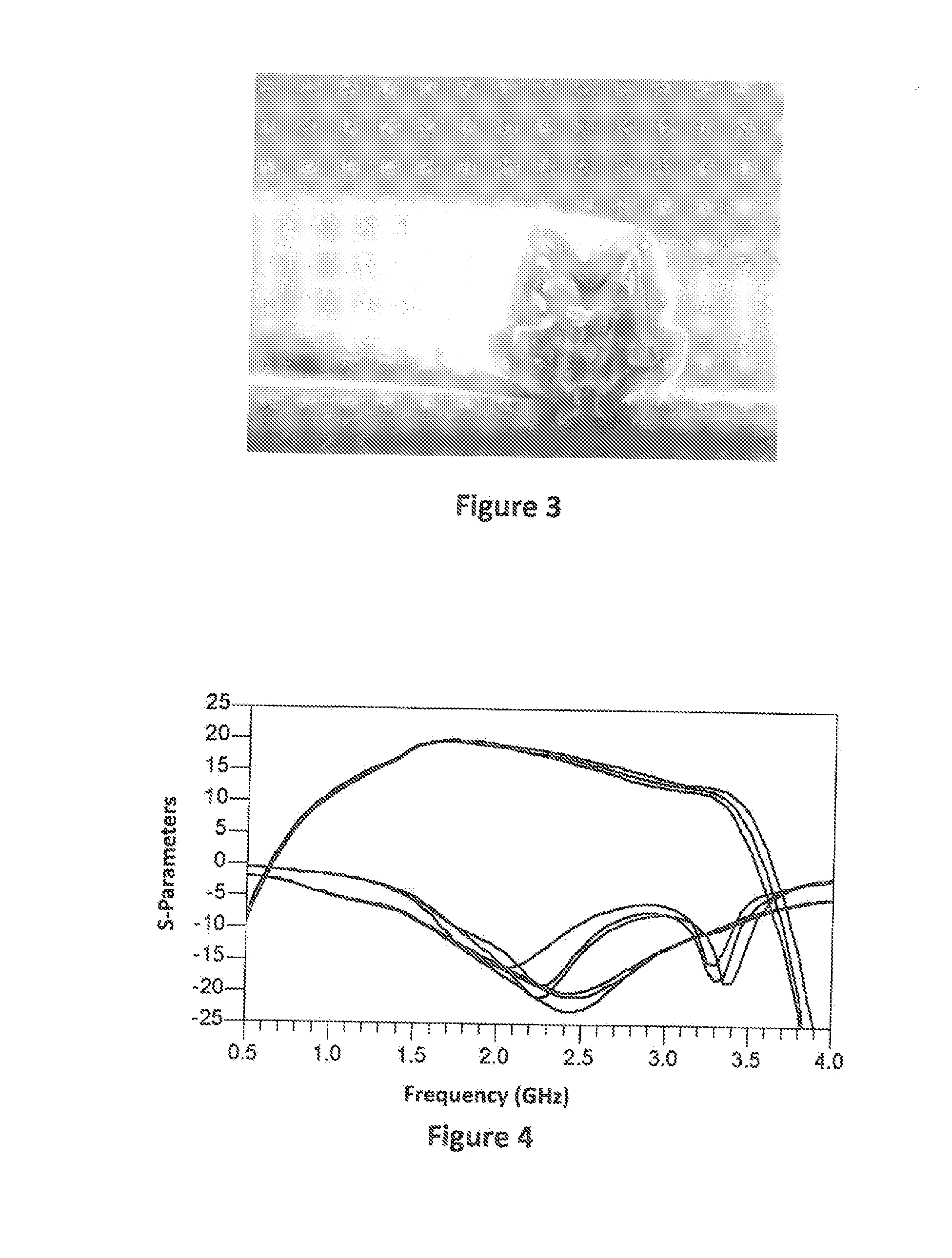

Low voltage high efficiency gallium arsenide power amplifier

InactiveUS20130321087A1Reduce lossOvercome problemsPower amplifiersAmplififers with field-effect devicesAudio power amplifierLow voltage

A low voltage, switch mode PHEMT power amplifier with a 0.1 μm gate length and a low loss, lumped element, output matching circuit is disclosed that provides high performance over a frequency range of 1.4 GHz-2.5 GHz. The amplifier makes use of monolithic circuit technology for the first stage and output transistor, and uses a printed circuit board with surface mount components for the output matching network. The power output of the power amplifier is stable over a range of 60 degrees centigrade, has high power efficiencies of 44-53% with greater than 2 watts output power over the frequency range of 1.4 GHz and 2.5 GHz. In addition, through drain voltage control, the output power can be varied over a wide range between about 0.8 to 2.5 watts while still maintaining a high efficiency in the range of 50±3%.

Owner:BAE SYST INFORMATION & ELECTRONICS SYST INTERGRATION INC

Organic thin film transistors

InactiveUS8450142B2Minimise capacitanceMinimise leakageTransistorSolid-state devicesConductive materialsOrganic semiconductor

An organic thin film transistor comprising: a substrate; a source electrode and a drain electrode defining a channel; a layer of insulating material disposed over the source and drain electrodes; a layer of organic semi-conductive material extending across the channel; a layer of dielectric material; and a gate electrode disposed over the layer of dielectric material.

Owner:CAMBRIDGE DISPLAY TECH LTD +1

Semiconductor device with electrically broken fuse and its manufacture method

InactiveUS20070171691A1Increase gate widthIncrease the areaRead-only memoriesDigital storageElectricitySurface layer

An electric fuse is formed over a semiconductor substrate, the electric fuse being broken when a current flows therethrough. A breaker transistor is formed in a first surface layer of the semiconductor substrate of a first conductivity type, the breaker transistor including a source region, a drain region and a gate electrode. The source and drain regions sandwiches a channel region. The gate electrode controls a conduction state between the source and drain regions. The drain region is connected to one end of the electric fuse. A breaker pad is connected to the end of the electric fuse to supply a fusing current to the electric fuse. A back-bias pad applies a fixed voltage to the first surface layer independently from both a power supply voltage and a ground potential. A fuse information read circuit reads a breakdown / non-breakdown state of the electric fuse.

Owner:SOCIONEXT INC

Semiconductor device with electrically broken fuse and its manufacture method

InactiveUS7292493B1Increase gate widthIncrease the areaRead-only memoriesDigital storageElectricitySurface layer

Owner:SOCIONEXT INC

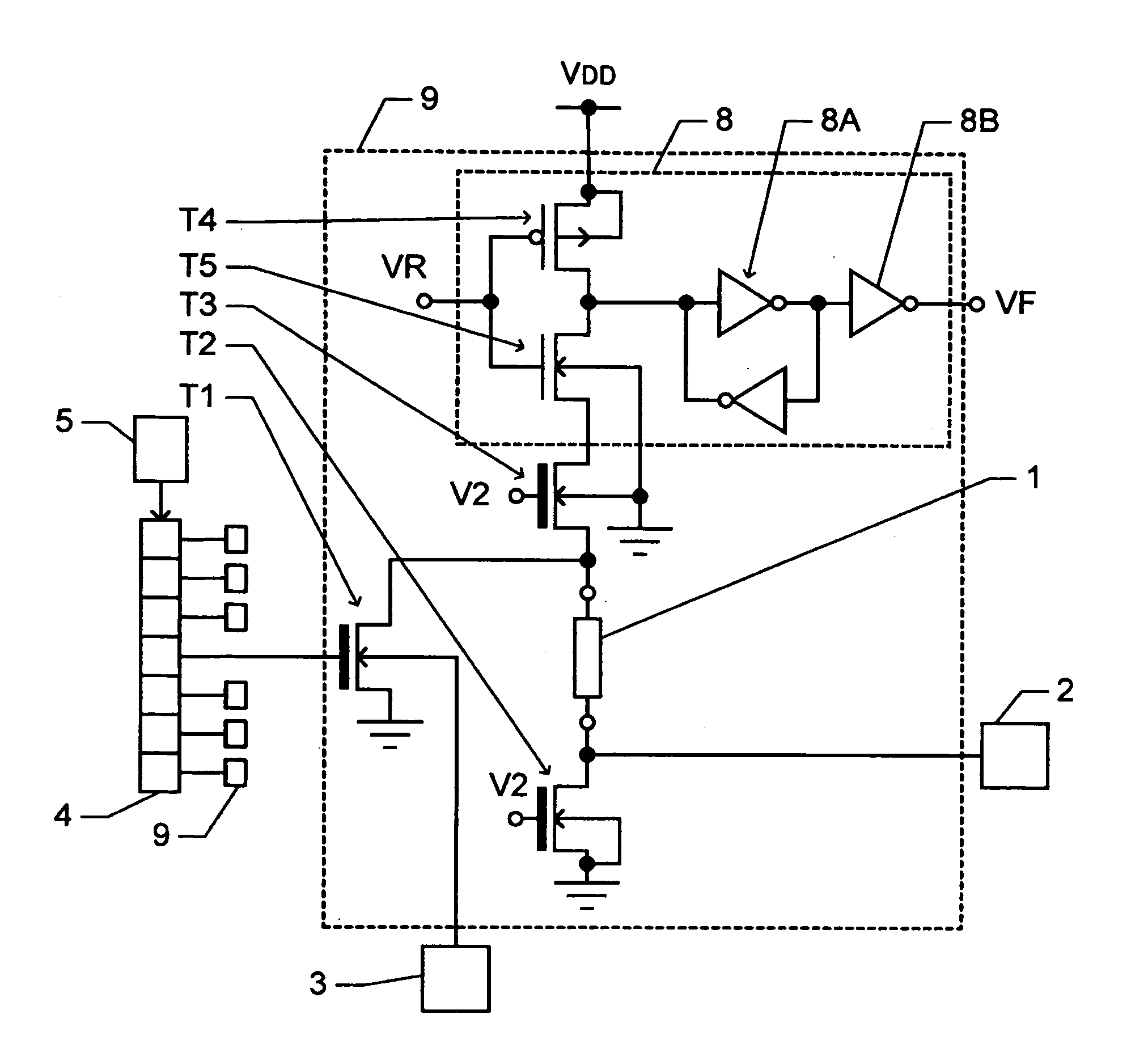

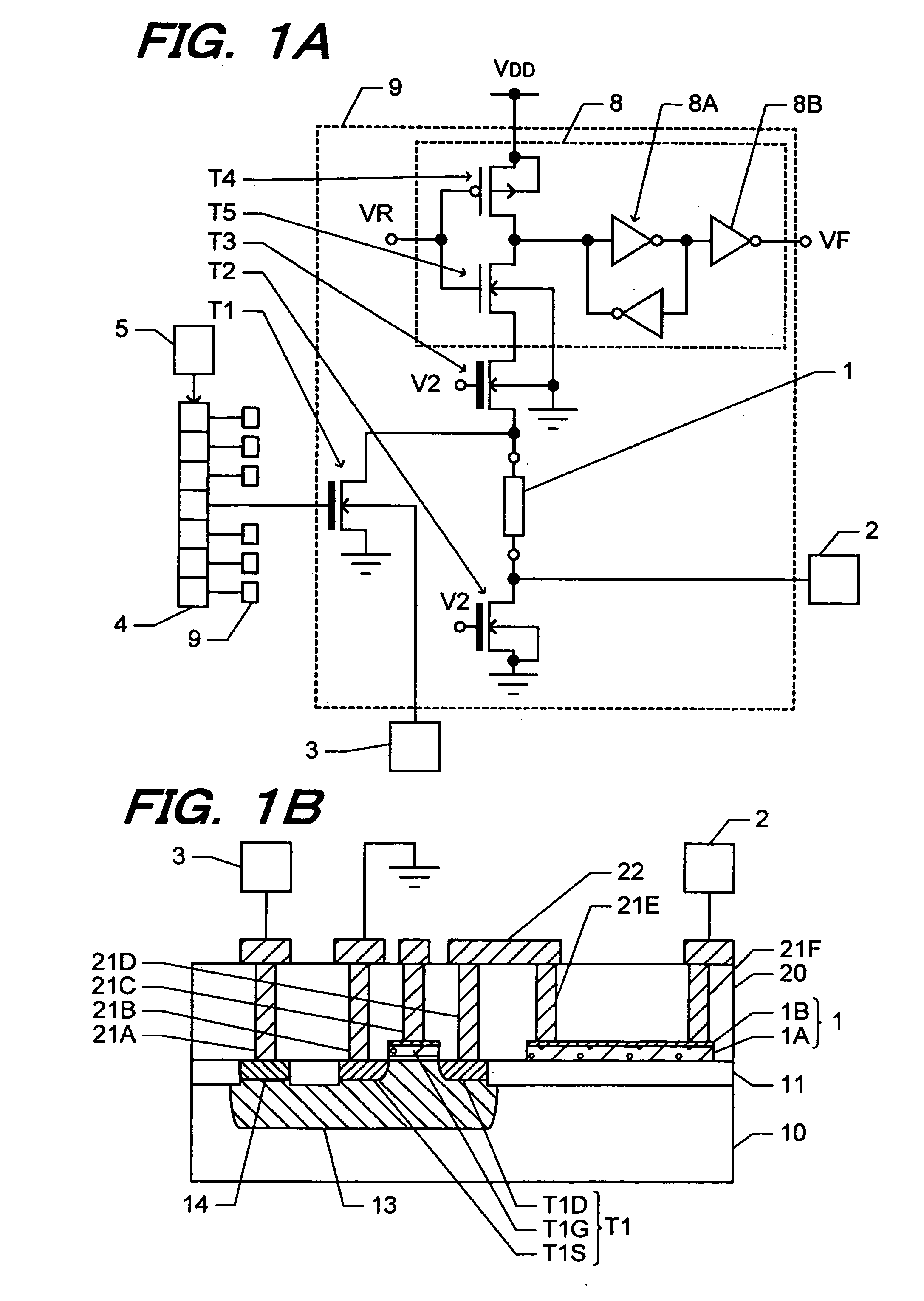

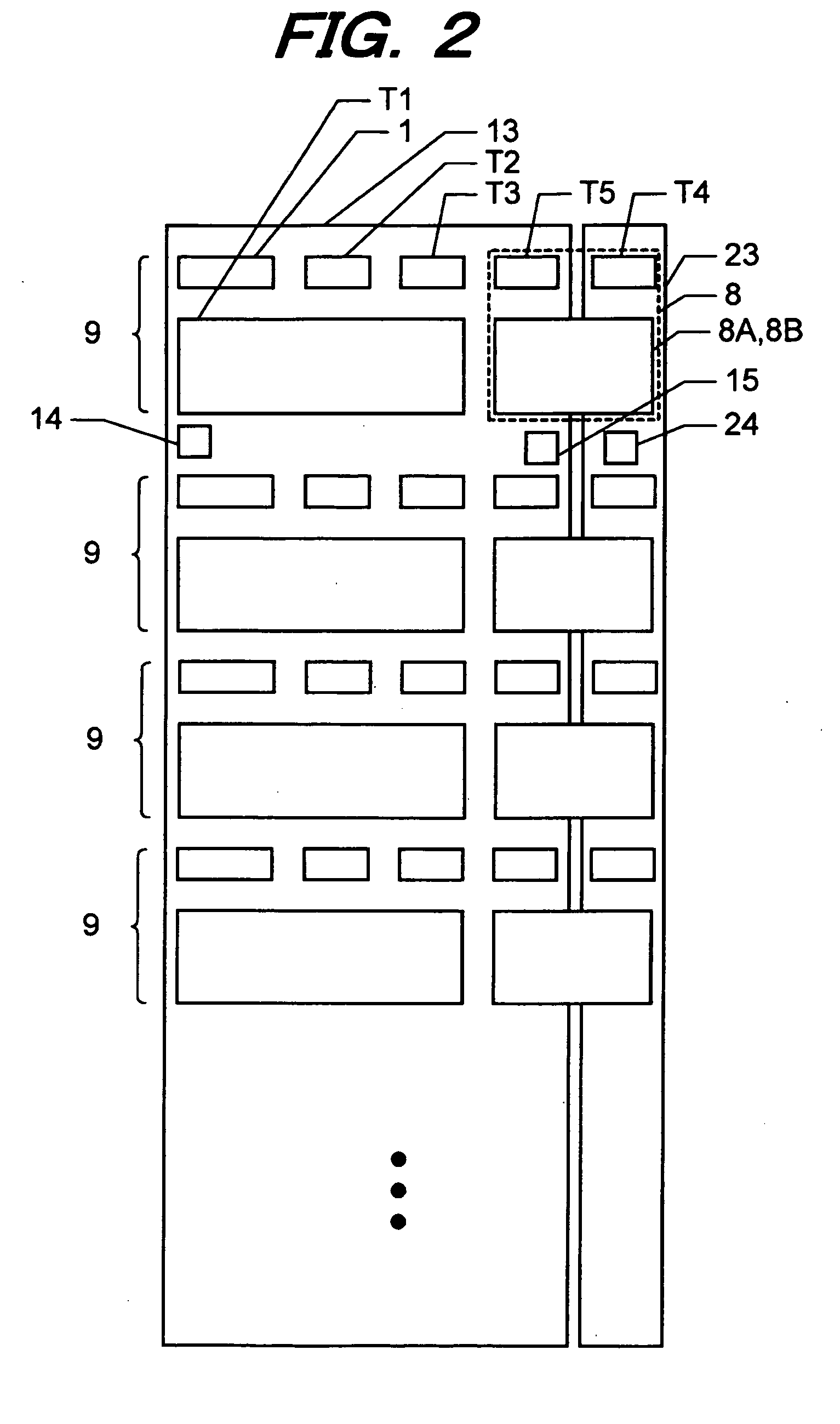

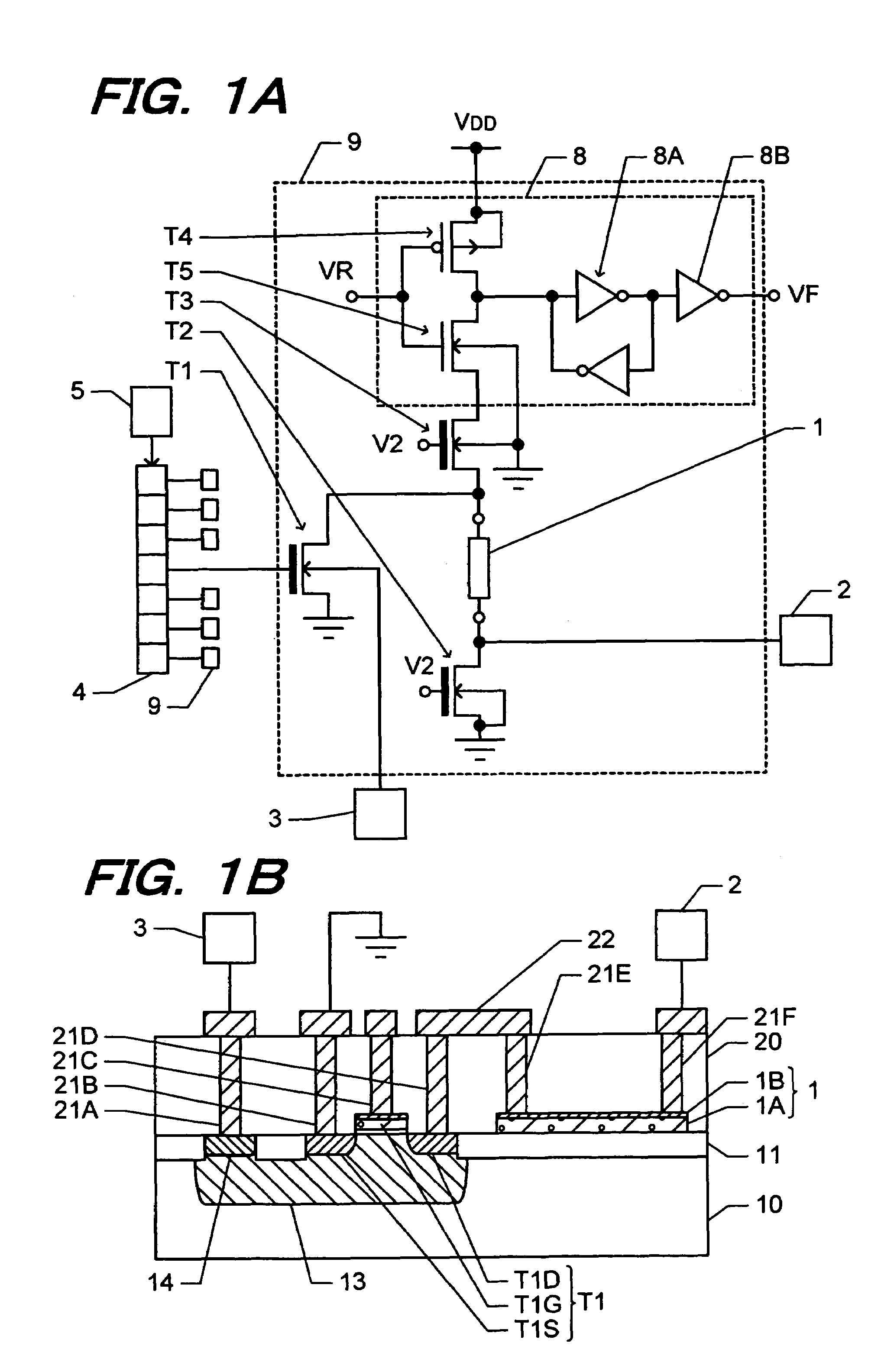

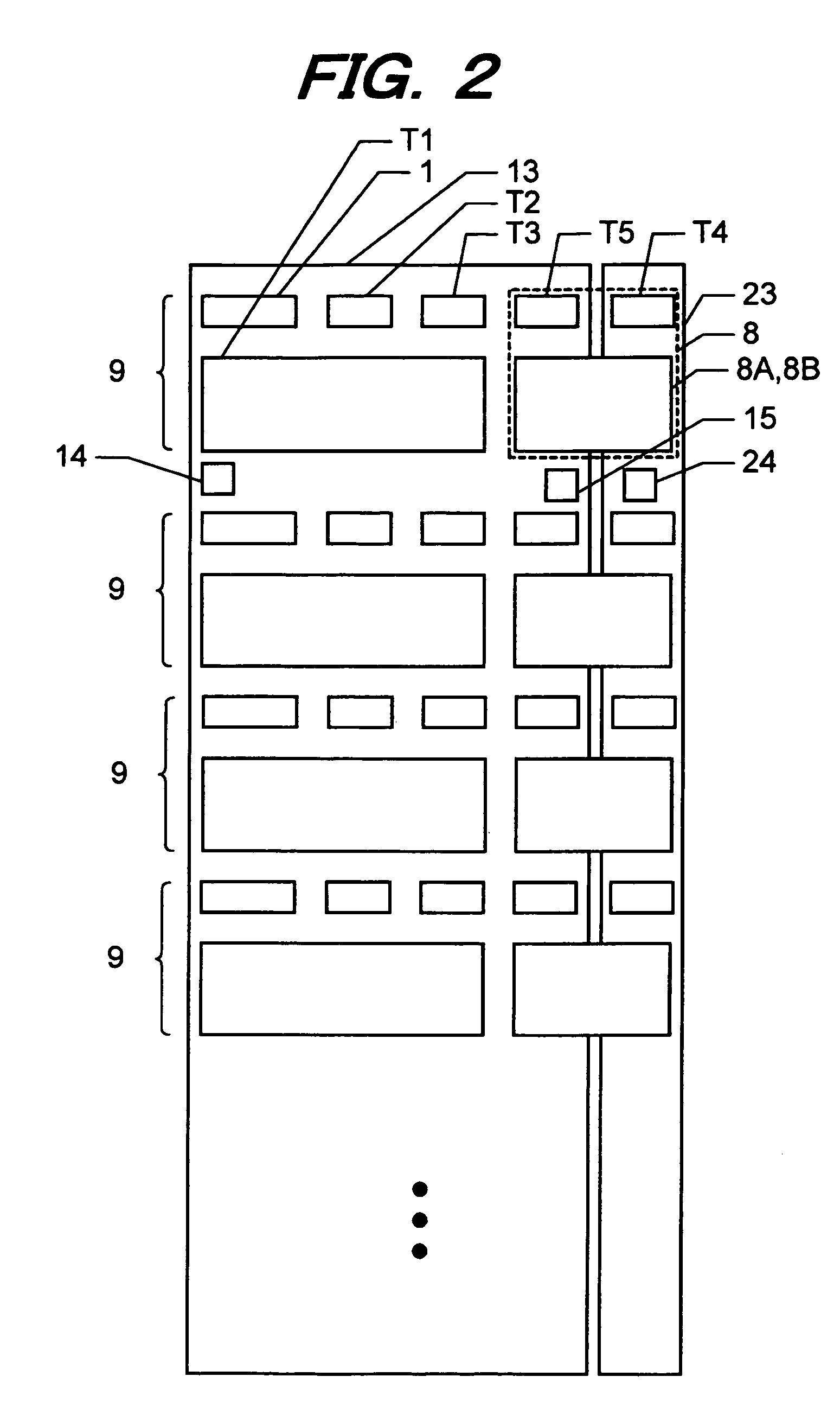

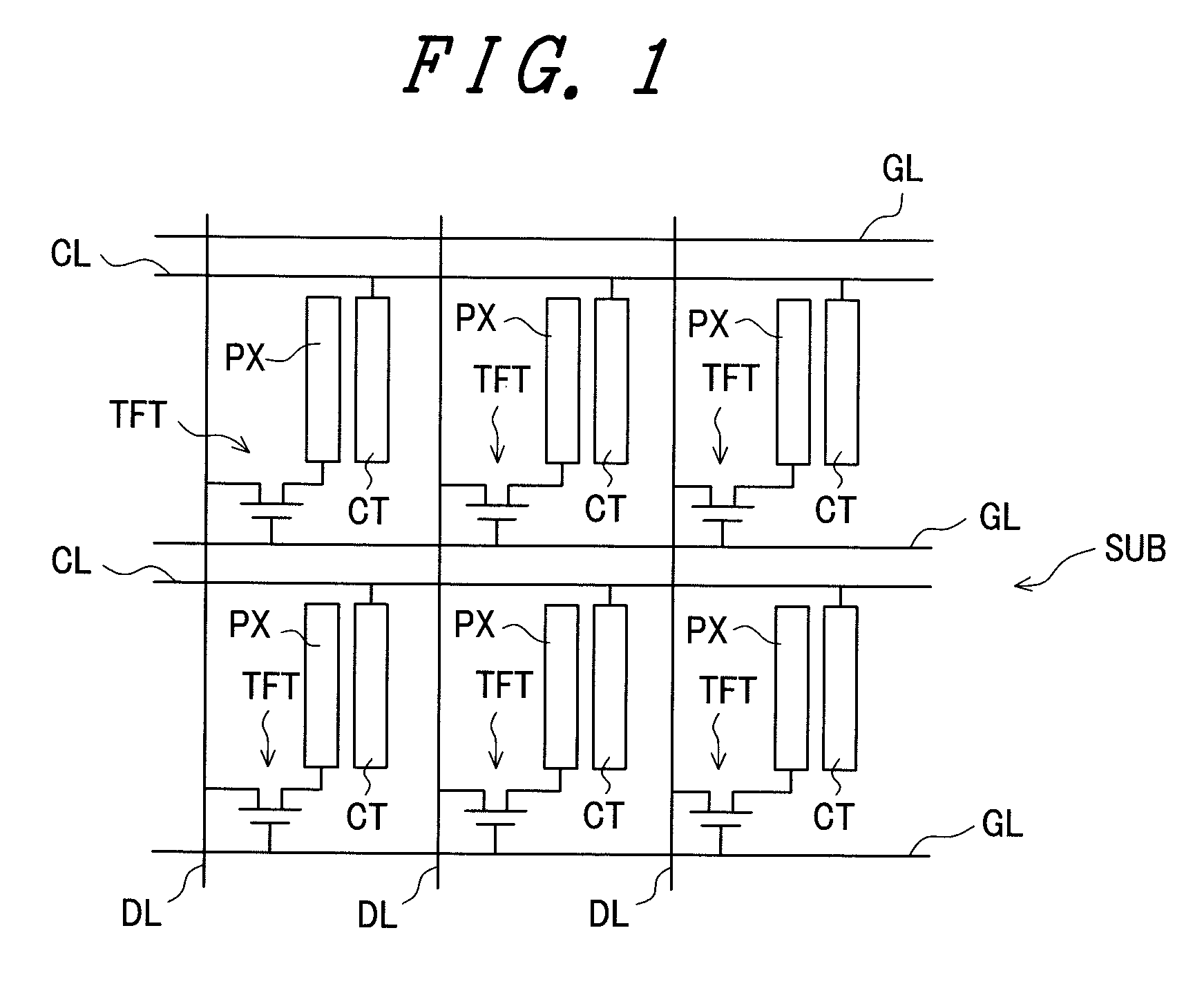

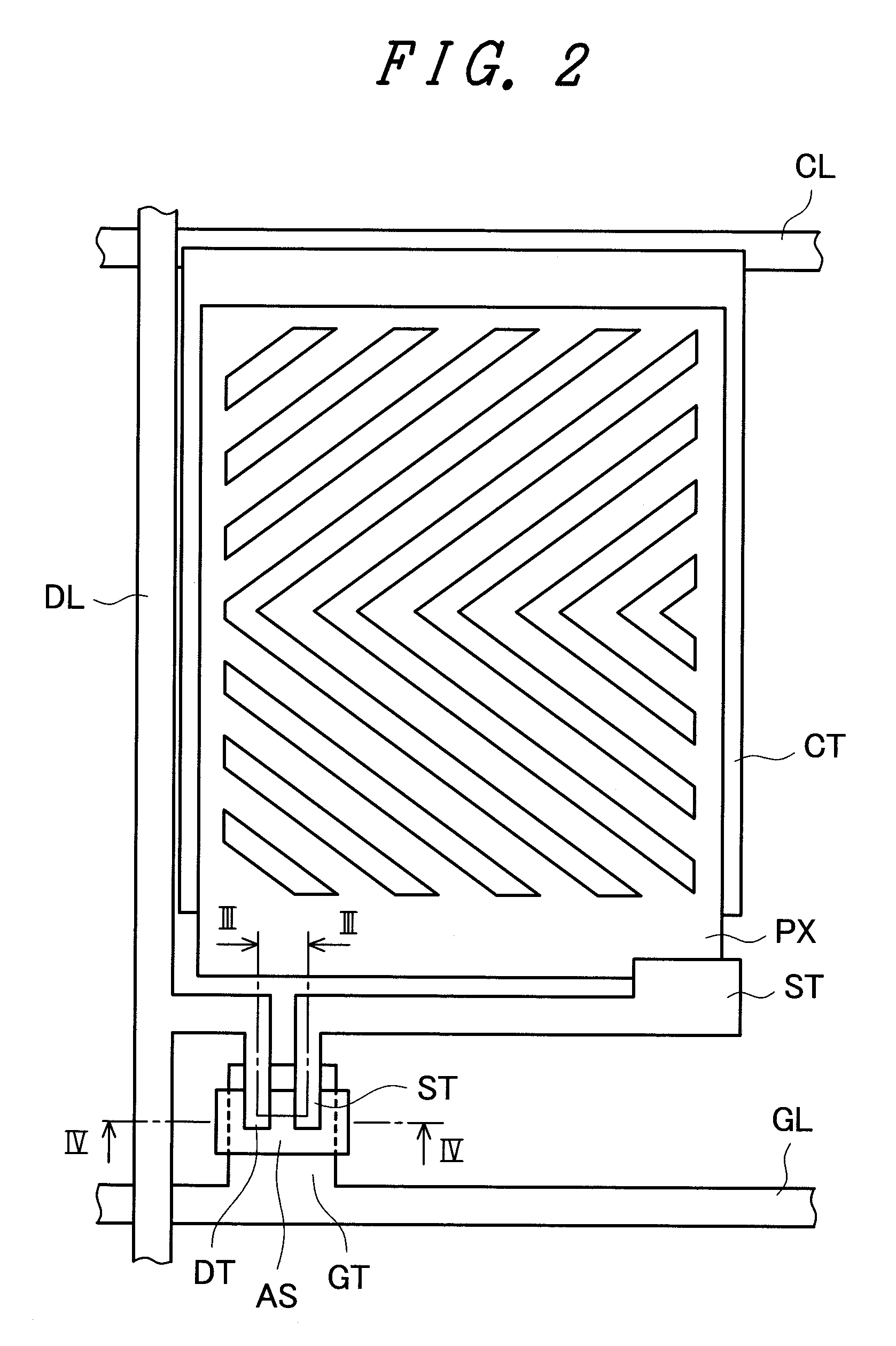

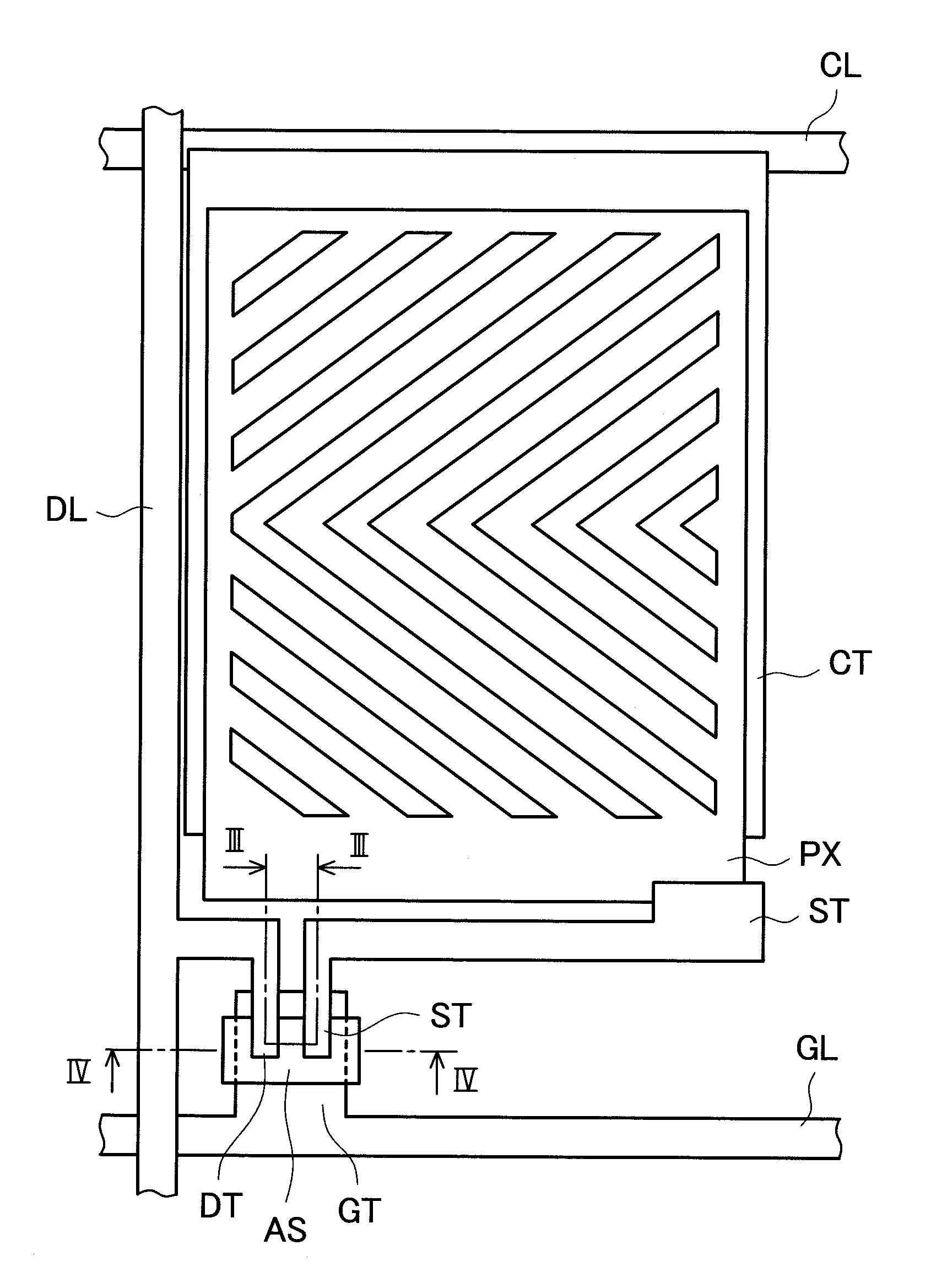

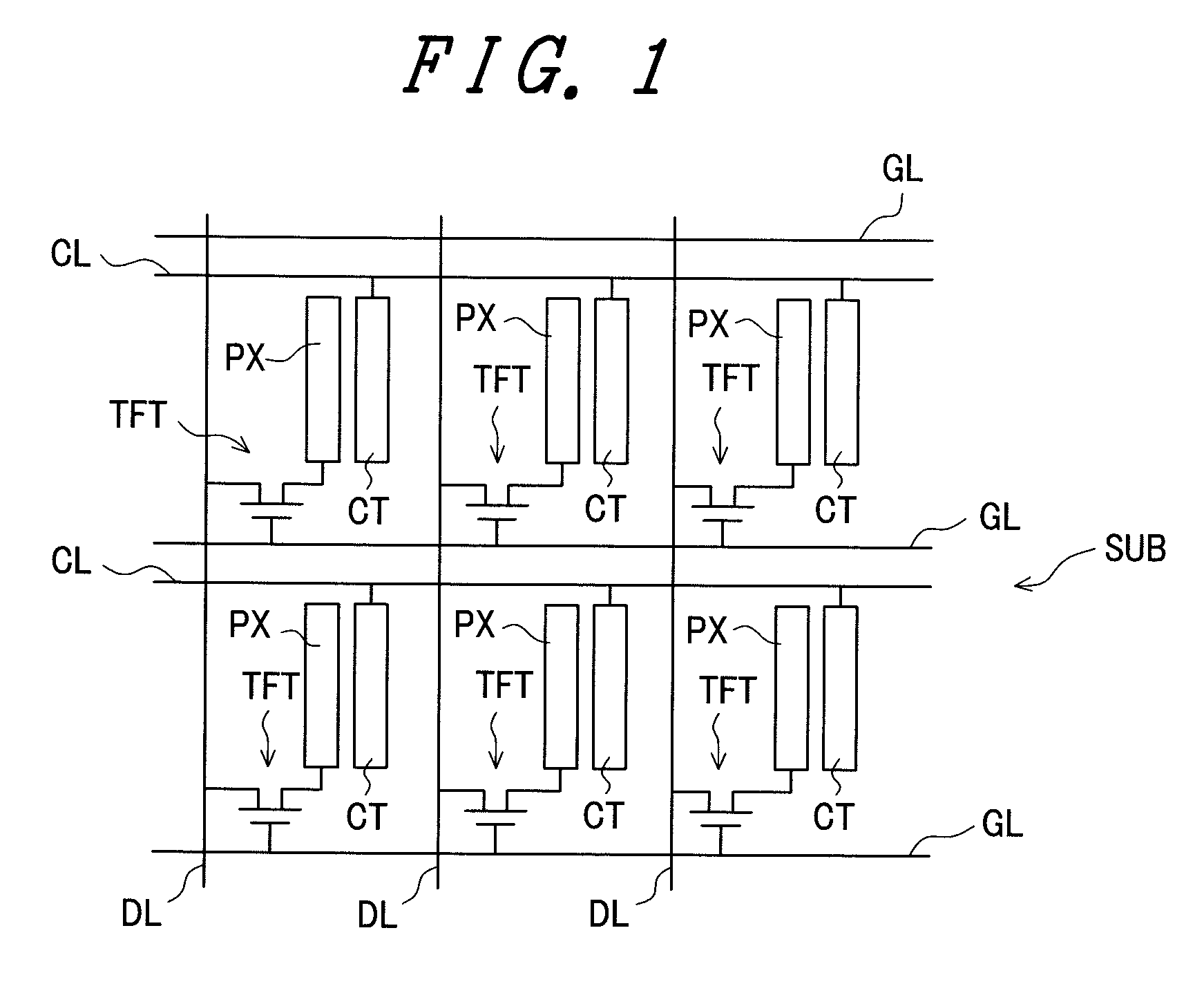

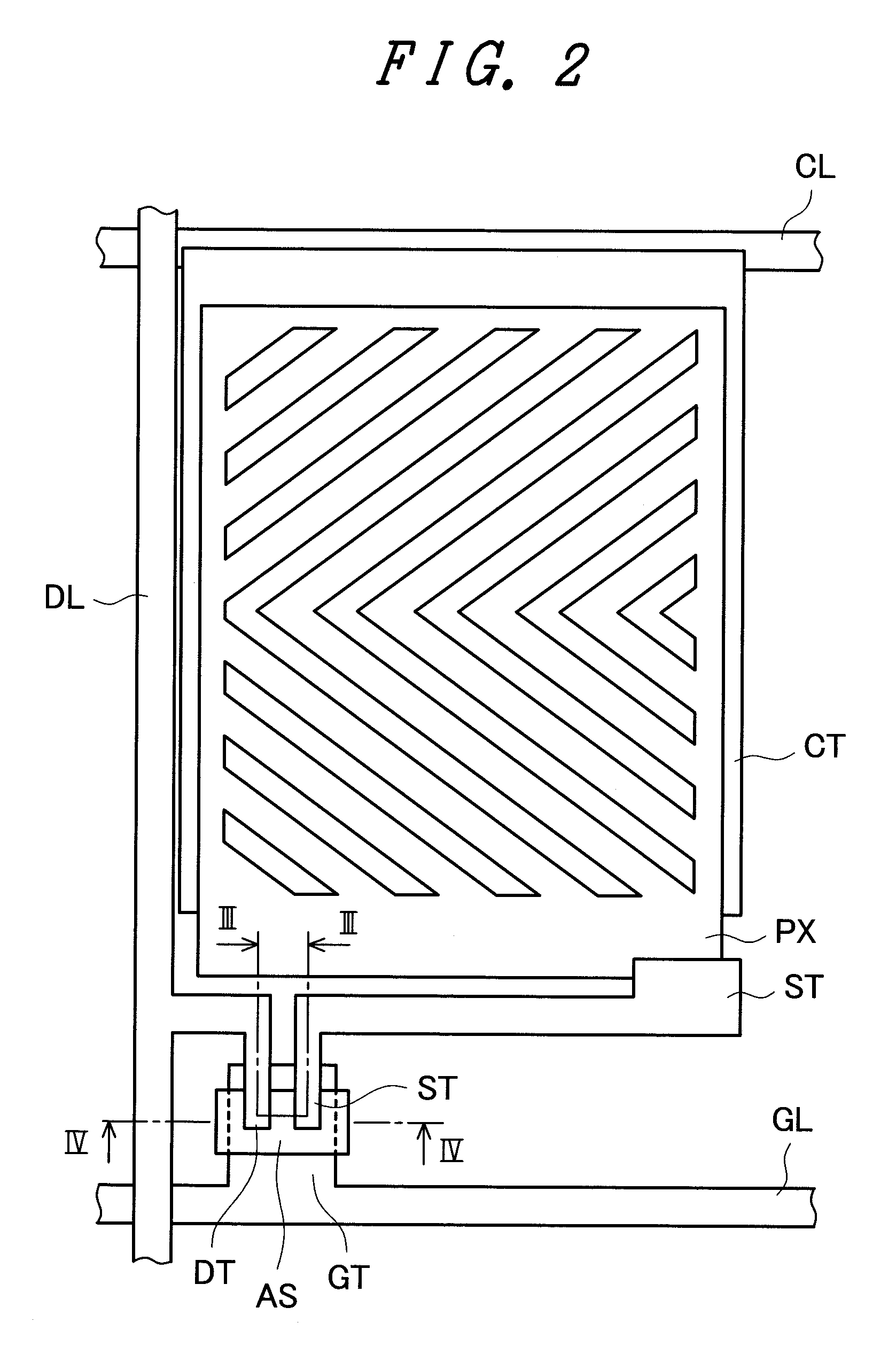

Liquid crystal display device

ActiveUS20110001897A1Current be suppressQuality improvementSolid-state devicesNon-linear opticsElectric fieldLiquid-crystal display

A liquid crystal display device having thin film transistors which can alleviate the required alignment accuracy of a semiconductor film while suppressing the generation of an optical leak current is provided. The liquid crystal display device includes: a transparent substrate; gate electrodes which are stacked above the transparent substrate; source electrodes and drain electrodes which are stacked above the gate electrodes; and semiconductor films each of which is stacked above the gate electrode and controls an electric current between the source electrode and the drain electrode based on an electric field generated by the gate electrode, wherein the semiconductor film is formed into a planar shape, and includes a first region which overlaps with the gate electrode in plane and a second region which does not overlap with the gate electrode in plane, and the source electrode and the drain electrode are not connected to the semiconductor film in the second region, and are connected to the semiconductor film in the first region.

Owner:PANASONIC LIQUID CRYSTAL DISPLAY CO LTD +1

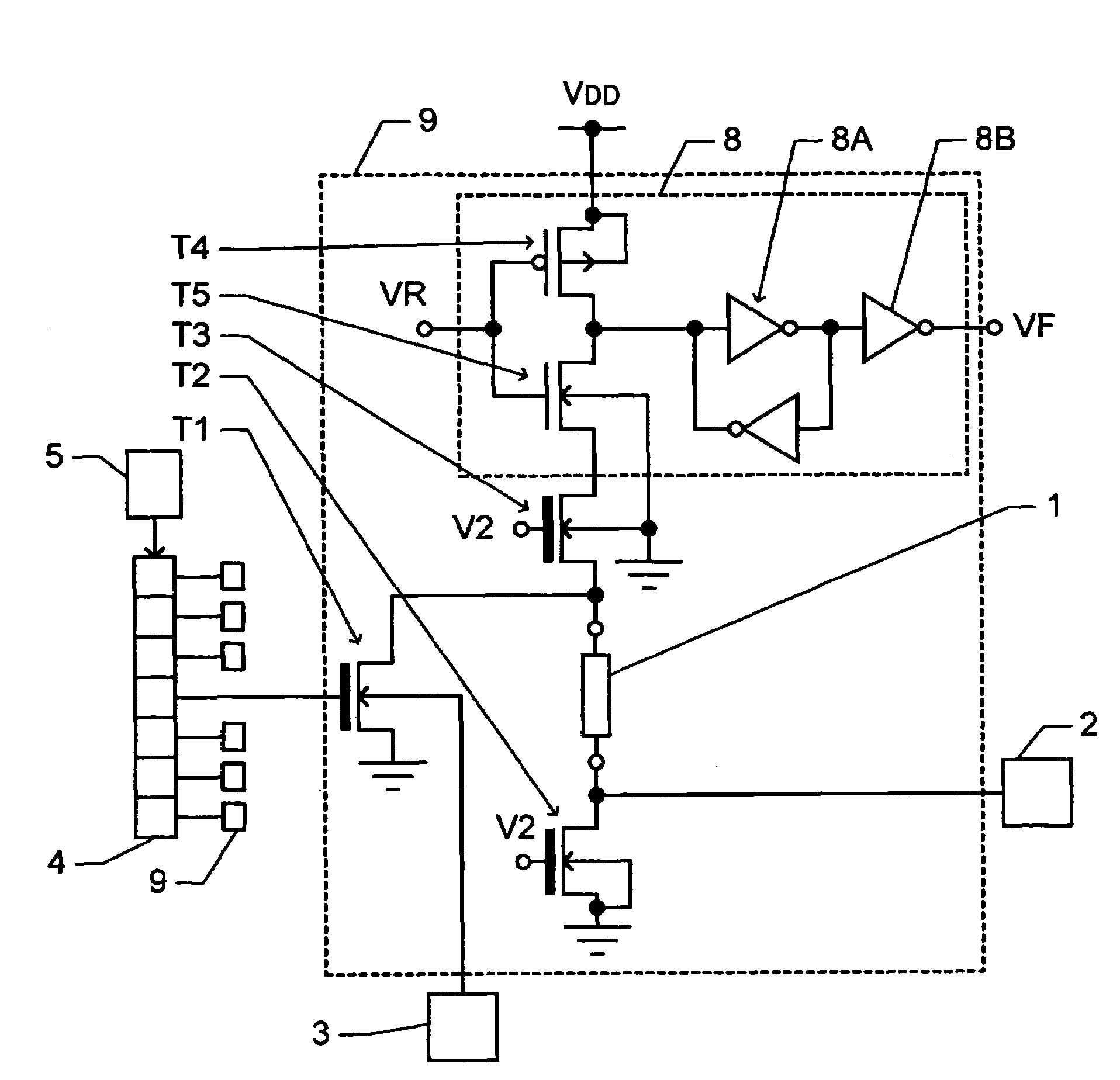

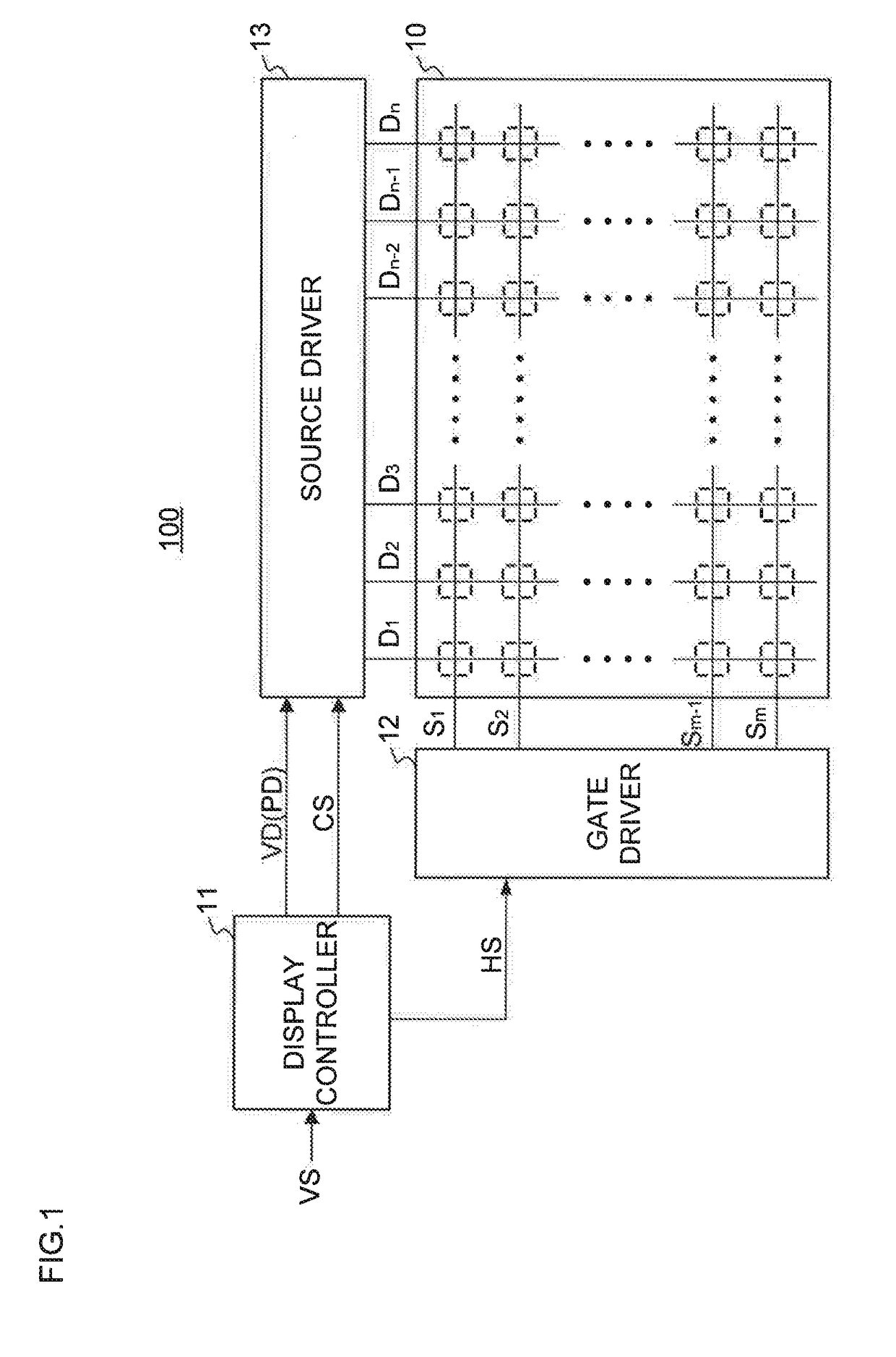

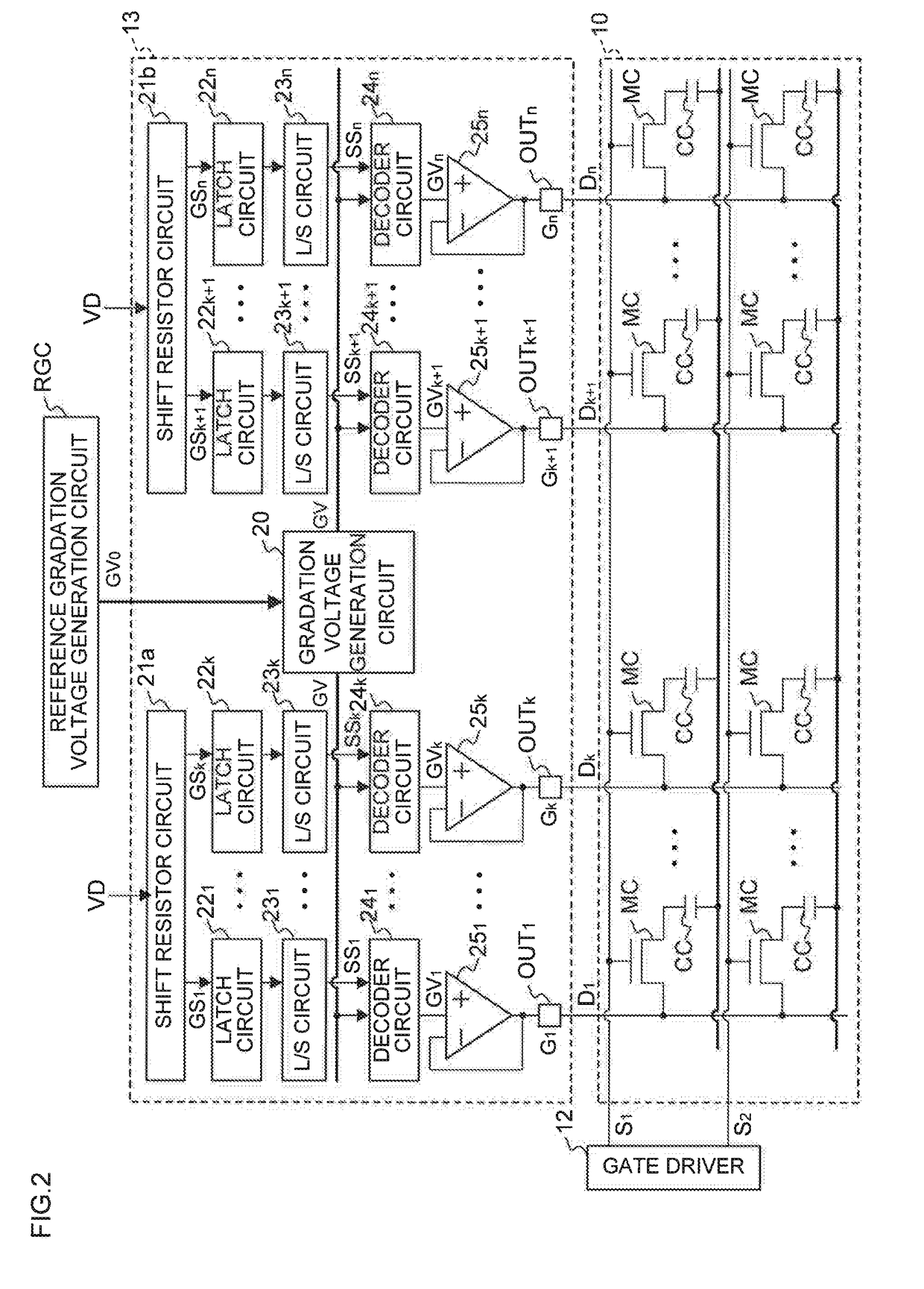

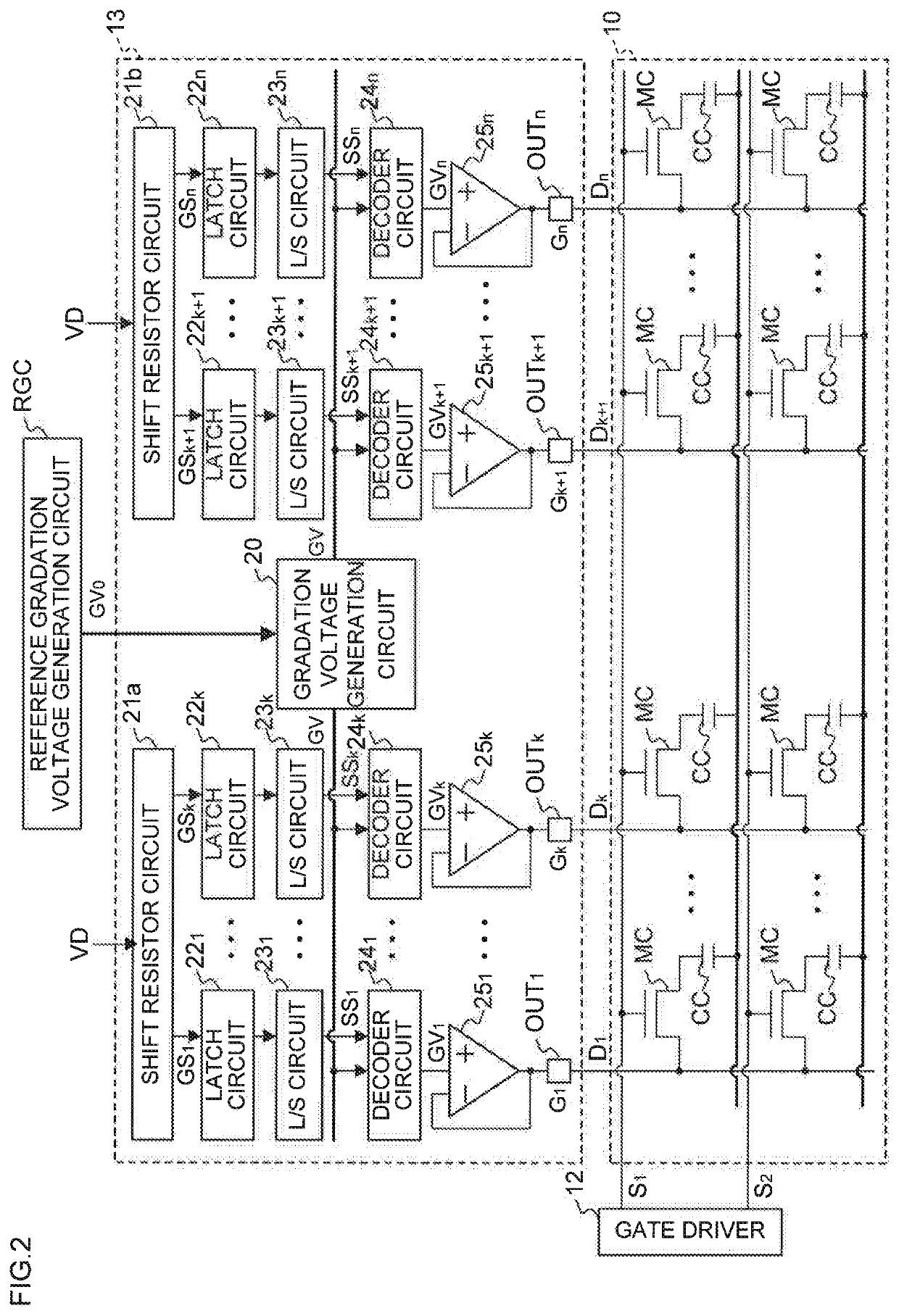

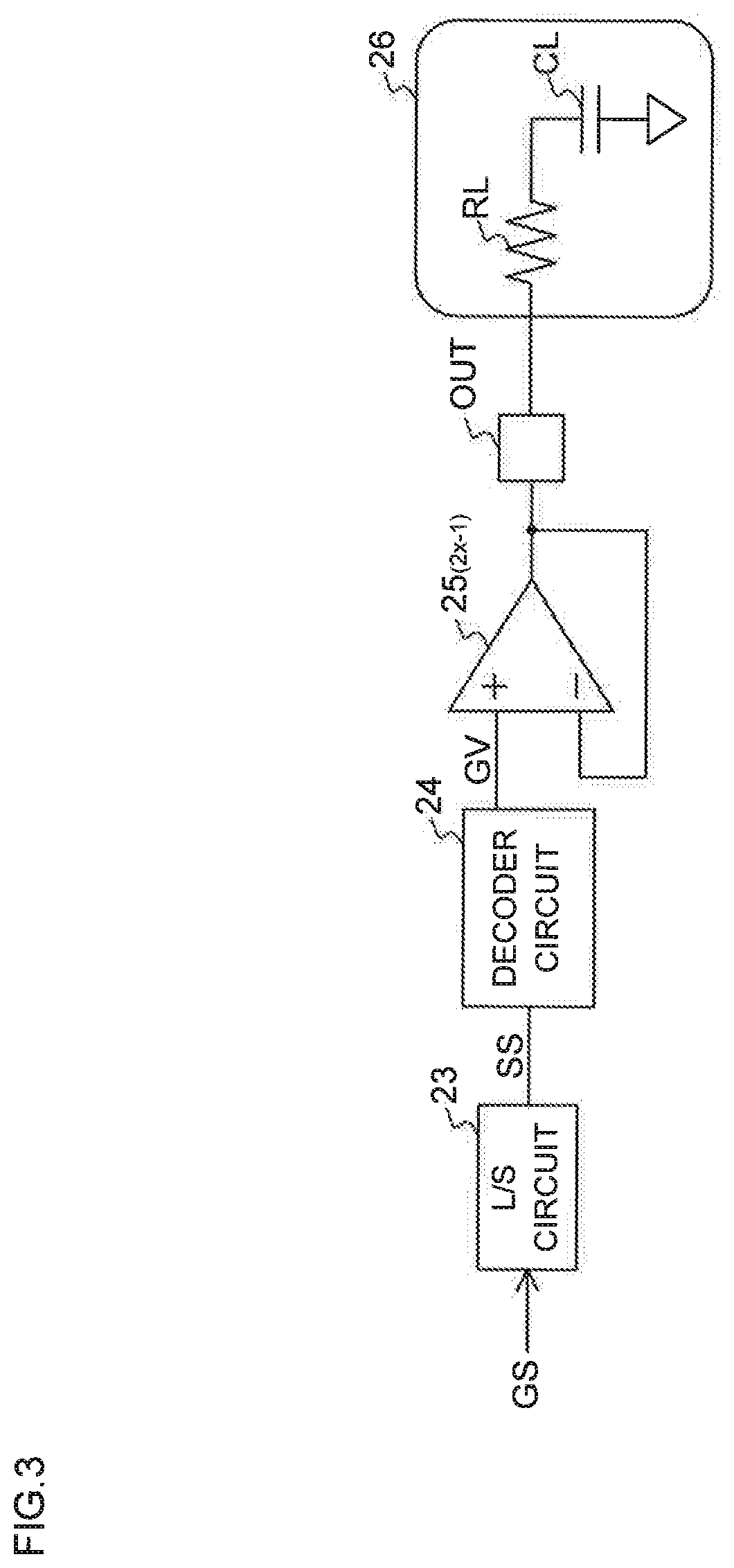

Output amplifier and display driver

ActiveUS20190012980A1Increase gate widthImprove wiringStatic indicating devicesDifferential amplifiersAudio power amplifierVoltage regulation

Provided is an output amplifier including a differential unit which sends a current corresponding to a voltage difference between a gradation voltage and an amplified gradation voltage to a first current line; a current mirror unit which sends an amount of current corresponding to the current flowing through the first current line, to a second current line; and an output unit including a first and a second drive line, an output line through which the amplified gradation voltage is output, a first output transistor which sends a current based on a voltage of the first drive line, and a second output transistor which sends a current based on a voltage of the second drive line. The output unit includes a voltage regulation circuit which controls the voltage of the first drive line being higher than the voltage of the second drive line.

Owner:LAPIS SEMICON CO LTD

Semiconductor device and manufacturing method

ActiveUS8975167B2Eliminate interactionElectric fieldSemiconductor/solid-state device manufacturingSemiconductor devicesInsulation layerGate dielectric

A fabrication process of a semiconductor device is disclosed. The method includes providing a semiconductor substrate with a first insulation layer formed on the semiconductor substrate and a fin formed on the surface of the first insulation layer, and forming a fully-depleted semiconductor layer on sidewalls of the fin, and the fully-depleted semiconductor layer having a material different from that of the fin. The method also includes forming a second insulation layer covering the fully-depleted semiconductor layer, and removing the fin to form an opening exposing sidewalls of the fully-depleted semiconductor layer. Further, the method includes forming a gate dielectric layer on part of the sidewalls of the fully-depleted semiconductor layer such that the part of the sidewalls of the fully-depleted semiconductor layer form channel regions of the semiconductor device, and forming a gate electrode layer covering the gate dielectric layer.

Owner:SEMICON MFG INT (SHANGHAI) CORP

Transistors with recessed active trenches for increased effective gate width

ActiveUS7642144B2Increase effective widthIncrease gate widthSemiconductor/solid-state device manufacturingSemiconductor devicesPlanar substrateNitride

A method of manufacturing a semiconductor device having recessed active trenches by providing a substrate with STI and active regions, forming a first oxide layer on the substrate, forming an nitride layer on the first oxide layer, employing a photolithographic process to create at least one recessed active trench through the first oxide layer and the nitride layer and into the substrate to create an isolation region, wherein the at least one trench is perpendicular to at least one gate structure in an active area of the substrate, layering the trench with a second oxide layer, removing the first oxide layer and second oxide layer, forming a third oxide layer on the planar substrate with recessed active trench, and forming the at least one circuitous gate structure on the third oxide layer connecting at least one electronic source and drain.

Owner:TEXAS INSTR INC

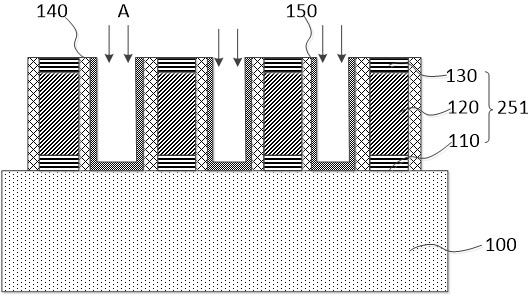

DRAM and forming method thereof

PendingCN112447605ALower resistanceIncrease the cross-sectional areaTransistorSemiconductor/solid-state device manufacturingConduction currentElectrically conductive

The invention discloses a DRAM and a forming method thereof. The method comprises the following steps: after the active region and the isolation layer are etched to form a word line trench, continuously etching the isolation layer along the side wall of the word line trench in the isolation layer, so that the width of the word line trench in the isolation layer is increased, and the width of the part of the word line trench in the isolation layer is greater than that of the part of the word line trench in the active region; and forming a word line structure in the word line trench, wherein thewidth of the part of word line structure in the isolation layer is greater than the width of the part of word line structure in the active region. The formed word line structure is wavy, so that on one hand, the resistance of the word line structure is reduced; and on the other hand, a channel is formed at the boundary of the active region, that is, the width of the conductive channel of a deviceis increased, and the conduction current of the transistor of the DRAM is increased, so that the reading speed of memory is increased, and the integration level of the transistor of the DRAM is increased.

Owner:CHANGXIN MEMORY TECH INC

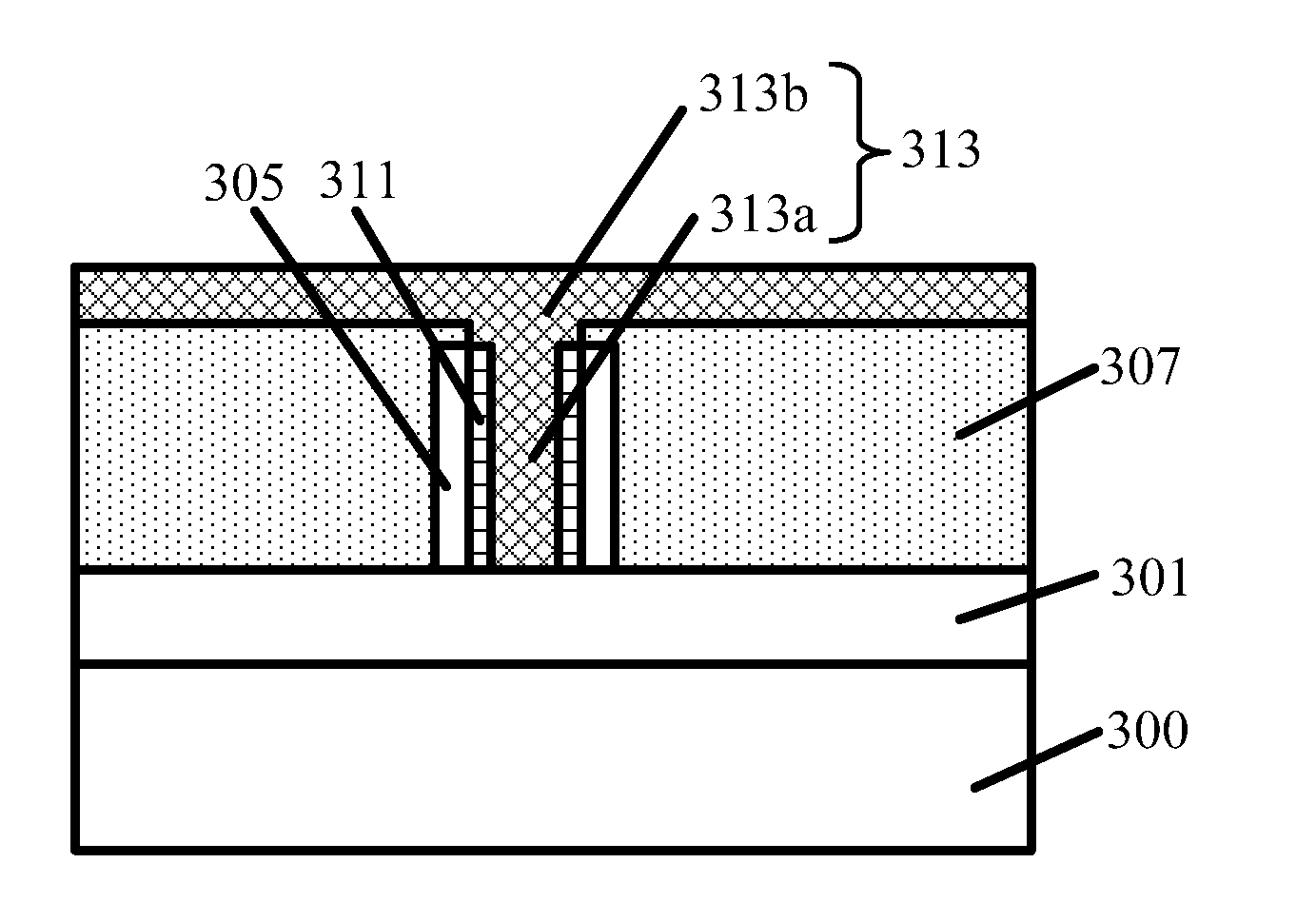

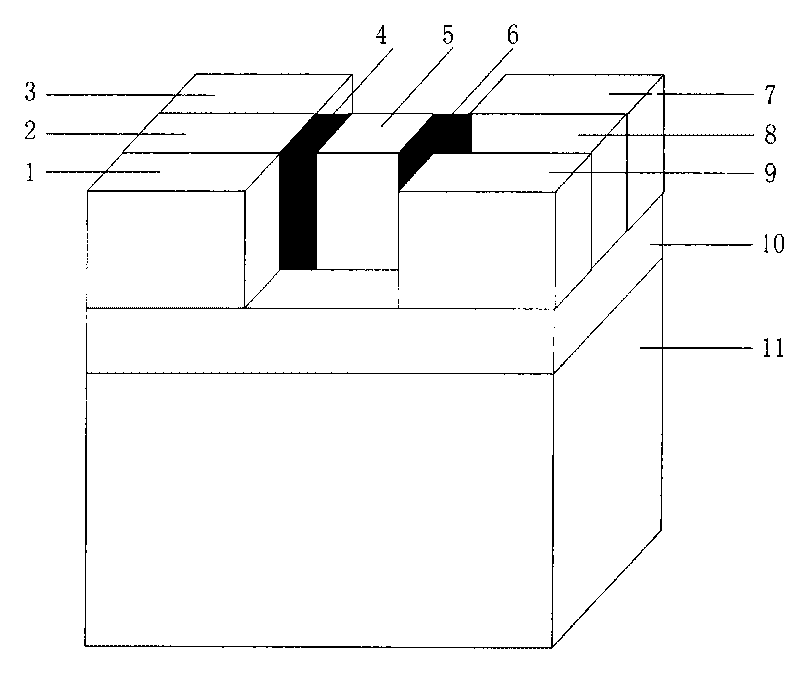

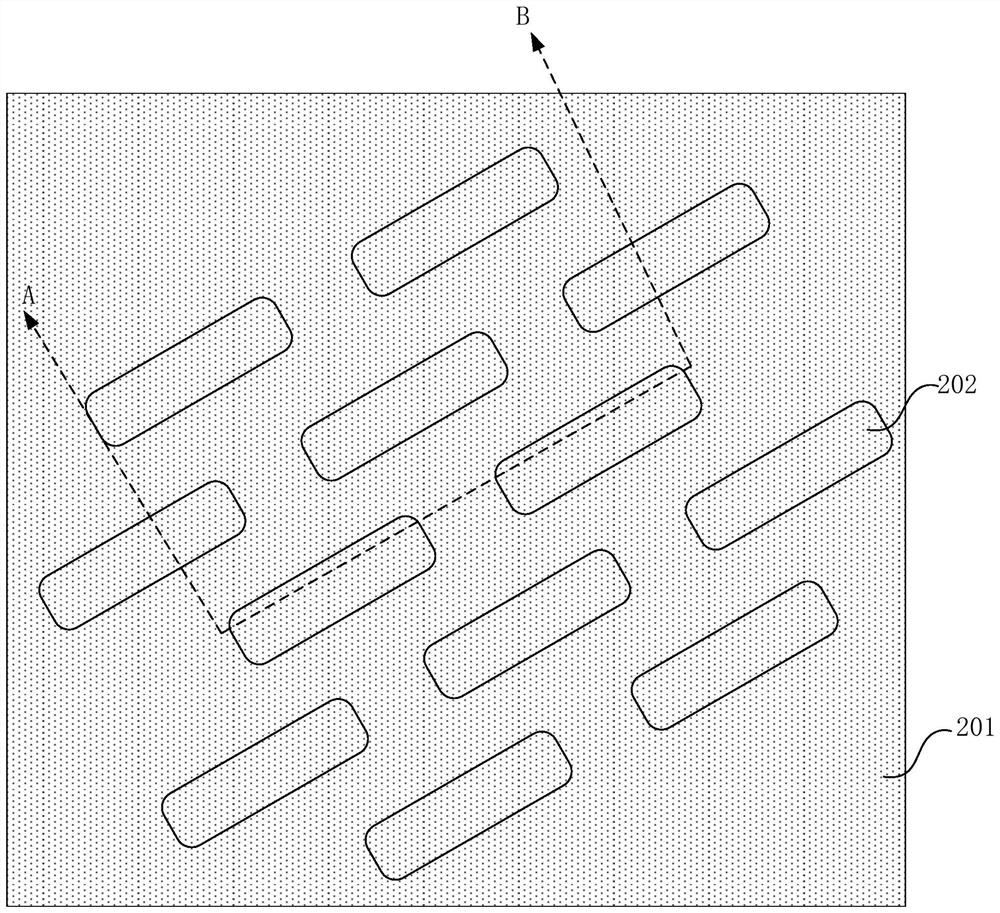

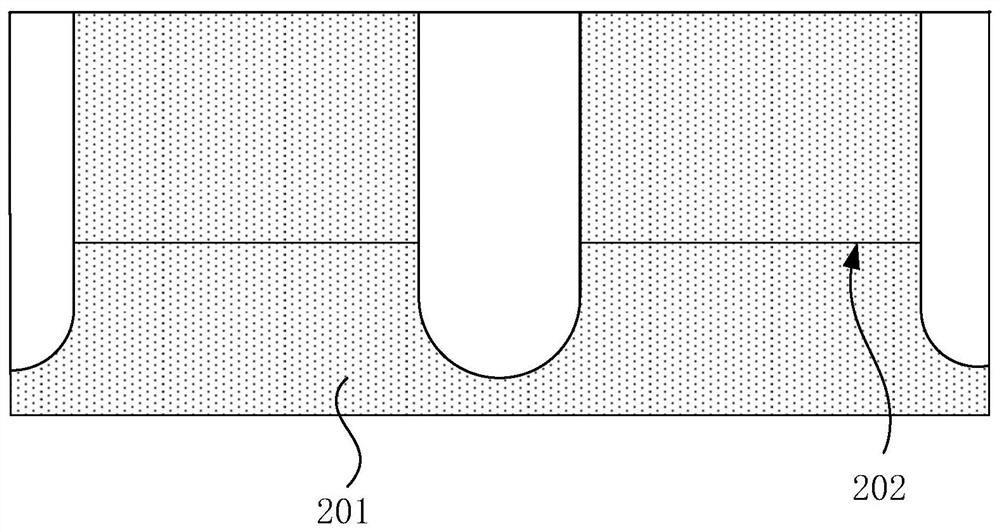

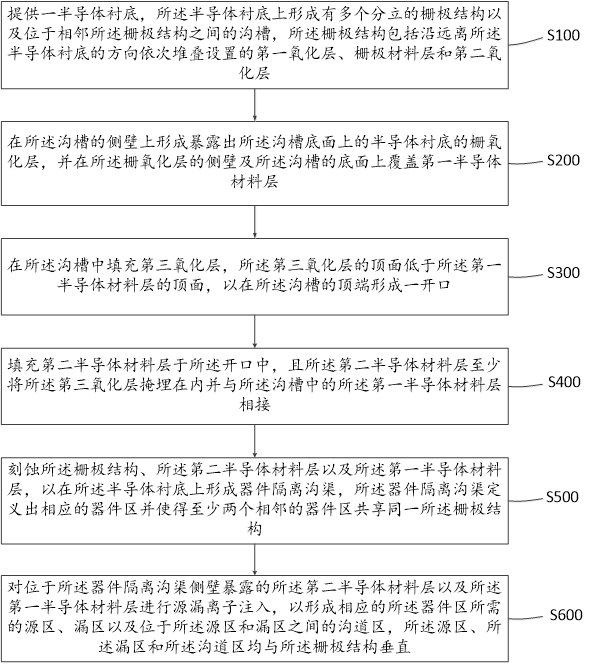

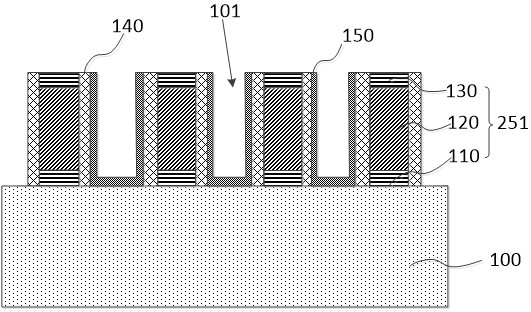

3D semiconductor device and forming method thereof

ActiveCN113013037AIncrease gate widthIncrease channel lengthSemiconductor/solid-state device manufacturingSemiconductor devicesWaferingDevice material

The invention provides a 3D semiconductor device and a forming method thereof, and is applied to the technical field of semiconductors. According to the forming method of the 3D semiconductor device provided by the invention, a grid electrode is shared by two adjacent MOS devices, the grid electrode and the drain electrode / source electrodes of the MOS devices are arranged on the surface of the semiconductor substrate, and the grid electrode and the drain electrode / source electrodes are horizontally connected, so that the width of the grid electrode of the MOS devices can be increased in the vertical direction, the 3D semiconductor device can be formed, and the channel length of the MOS device is increased, and the wafer area can be saved under the condition of reducing the short channel effect of the MOS device.

Owner:晶芯成(北京)科技有限公司

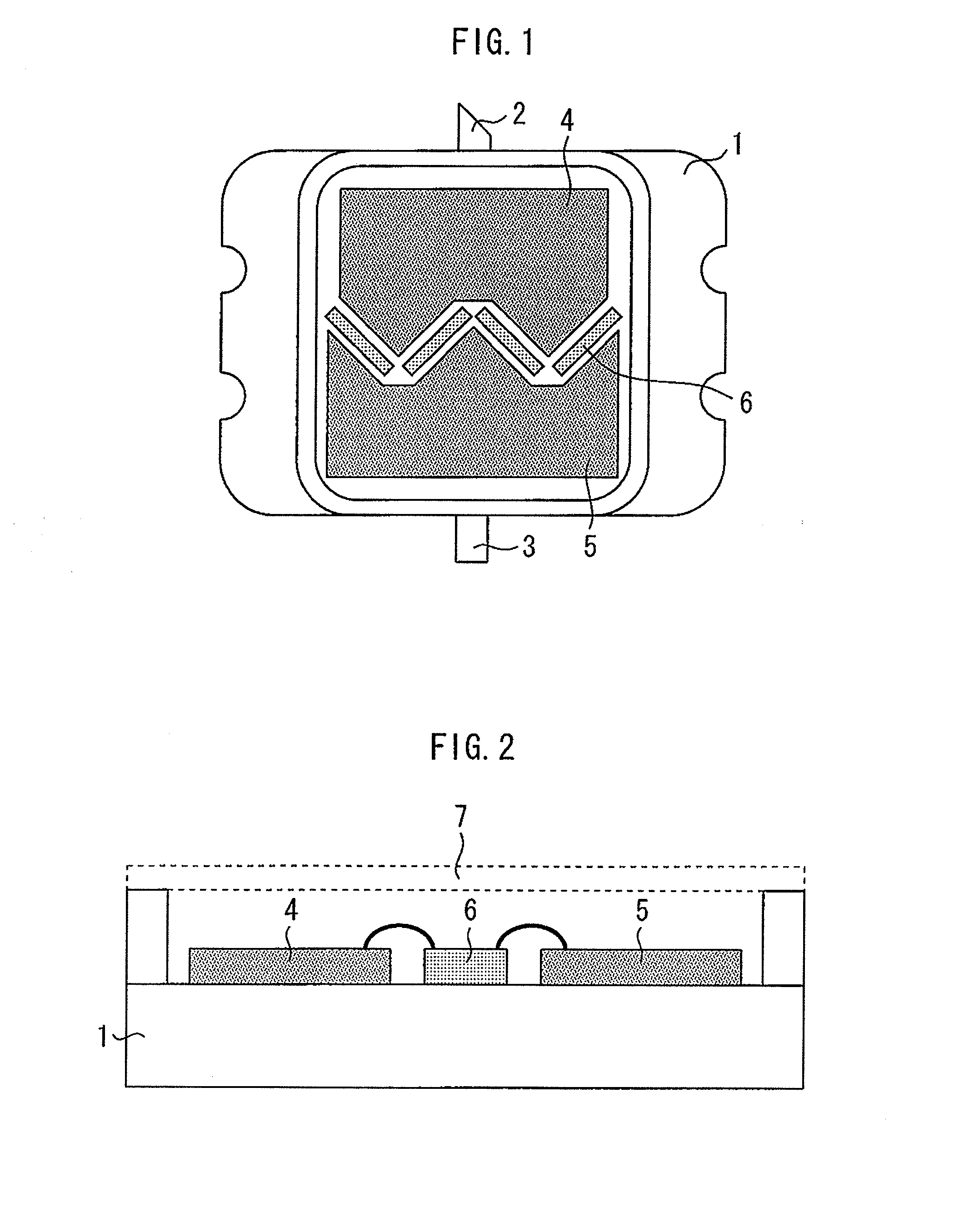

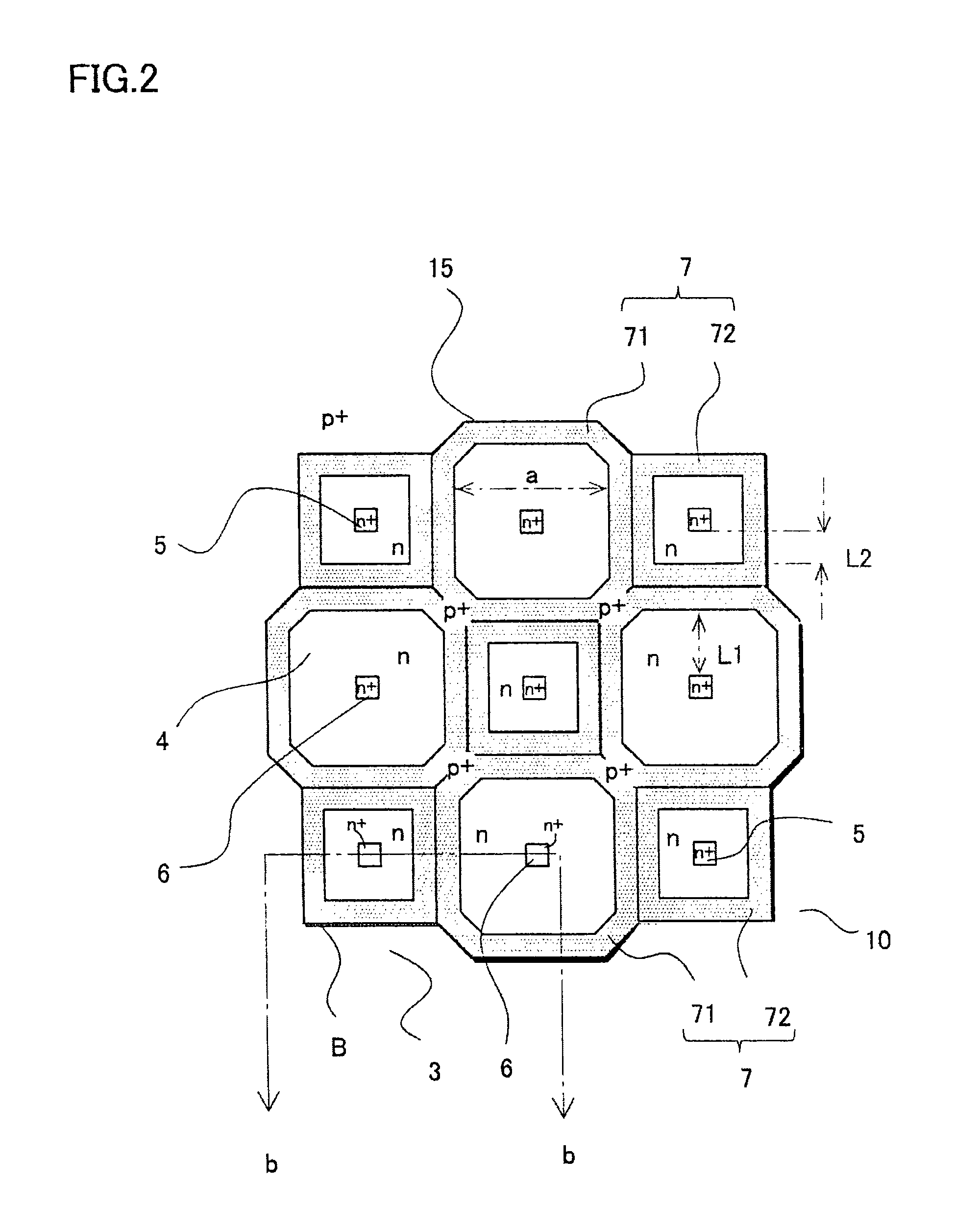

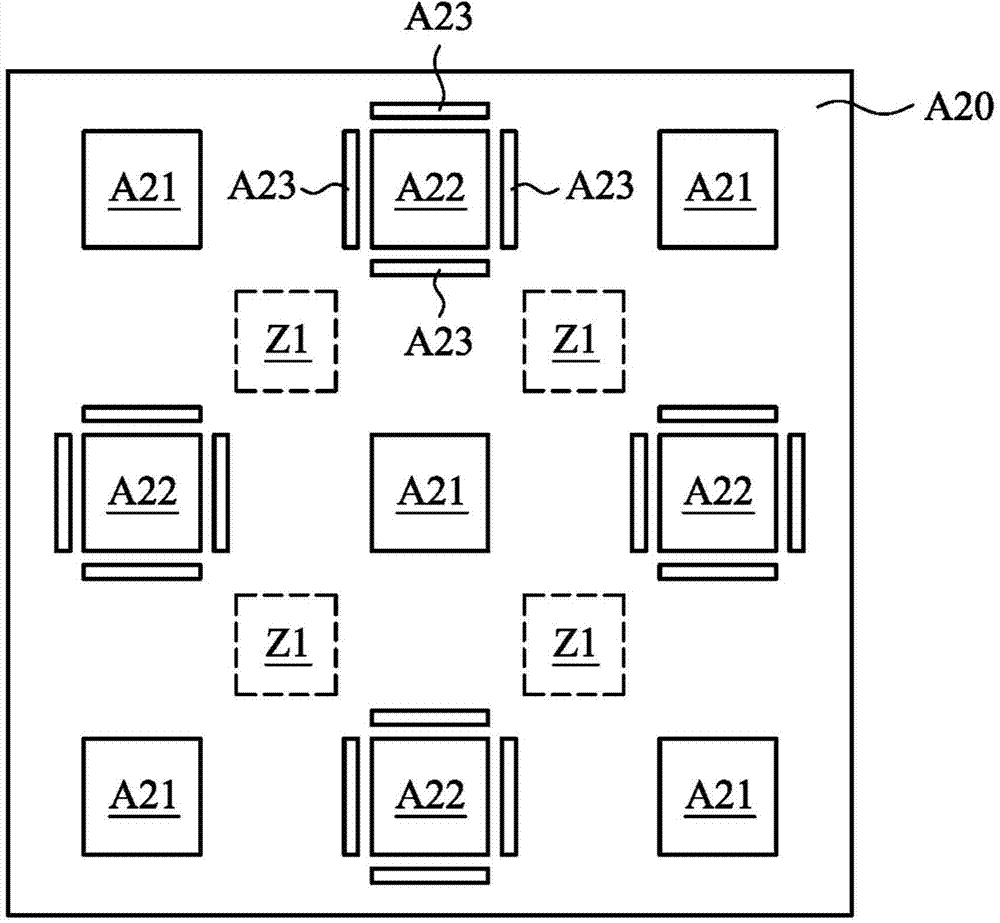

Semiconductor device

ActiveUS20150091095A1Increase in gate widthIncrease currentTransistorSemiconductor/solid-state device manufacturingPhysicsSemiconductor

A semiconductor device includes a substrate and a plurality of transistors arranged on the substrate in an array. The transistor includes a first electrode, a plurality of second electrodes, and a gate electrode. The second electrodes are arranged around the first electrode. The gate electrode is located between the first electrode and the second electrodes. The first electrode is a circle or polygon. The gate electrode is around the first electrode, and an edge of the gate electrode facing the first electrode has a shape corresponding to that of the first electrode.

Owner:ANCORA SEMICON INC

Semiconductor device including transistor chips having oblique gate electrode fingers

ActiveUS8796697B2Increase horizontal widthIncrease productionSemiconductor/solid-state device detailsSolid-state devicesPower semiconductor deviceEngineering

Owner:ROHM CO LTD

Semiconductor device

ActiveUS7812377B2Increase gate widthRaise transfer toTransistorTelevision system detailsCapacitanceGrid pattern

In the semiconductor device, a gate region is formed in a mesh pattern having first polygonal shapes and second polygonal shapes the area of which is smaller than that of the first polygonal shapes, and drain regions and source regions are disposed within the first polygonal shapes and the second polygonal shapes, respectively. With this configuration, the forward transfer admittance gm can be increased as compared with a structure in which gate regions are disposed in a stripe pattern. Furthermore, compared with a case in which a gate region is disposed in a grid pattern, deterioration in forward transfer characteristics (amplification characteristics) due to an increase in input capacitance Ciss can be minimized while a predetermined withstand voltage is maintained.

Owner:SEMICON COMPONENTS IND LLC

Liquid crystal display device

ActiveUS8384836B2Quality improvementGeneration of an optical leak current can be suppressedSolid-state devicesNon-linear opticsLiquid-crystal displayEngineering

Owner:JAPAN DISPLAY INC +1

Output amplifier and display driver

ActiveUS10650771B2Increase gate widthImprove wiringStatic indicating devicesDifferential amplifiersVoltage regulationHemt circuits

Provided is an output amplifier including a differential unit which sends a current corresponding to a voltage difference between a gradation voltage and an amplified gradation voltage to a first current line; a current mirror unit which sends an amount of current corresponding to the current flowing through the first current line, to a second current line; and an output unit including a first and a second drive line, an output line through which the amplified gradation voltage is output, a first output transistor which sends a current based on a voltage of the first drive line, and a second output transistor which sends a current based on a voltage of the second drive line. The output unit includes a voltage regulation circuit which controls the voltage of the first drive line being higher than the voltage of the second drive line.

Owner:LAPIS SEMICON CO LTD

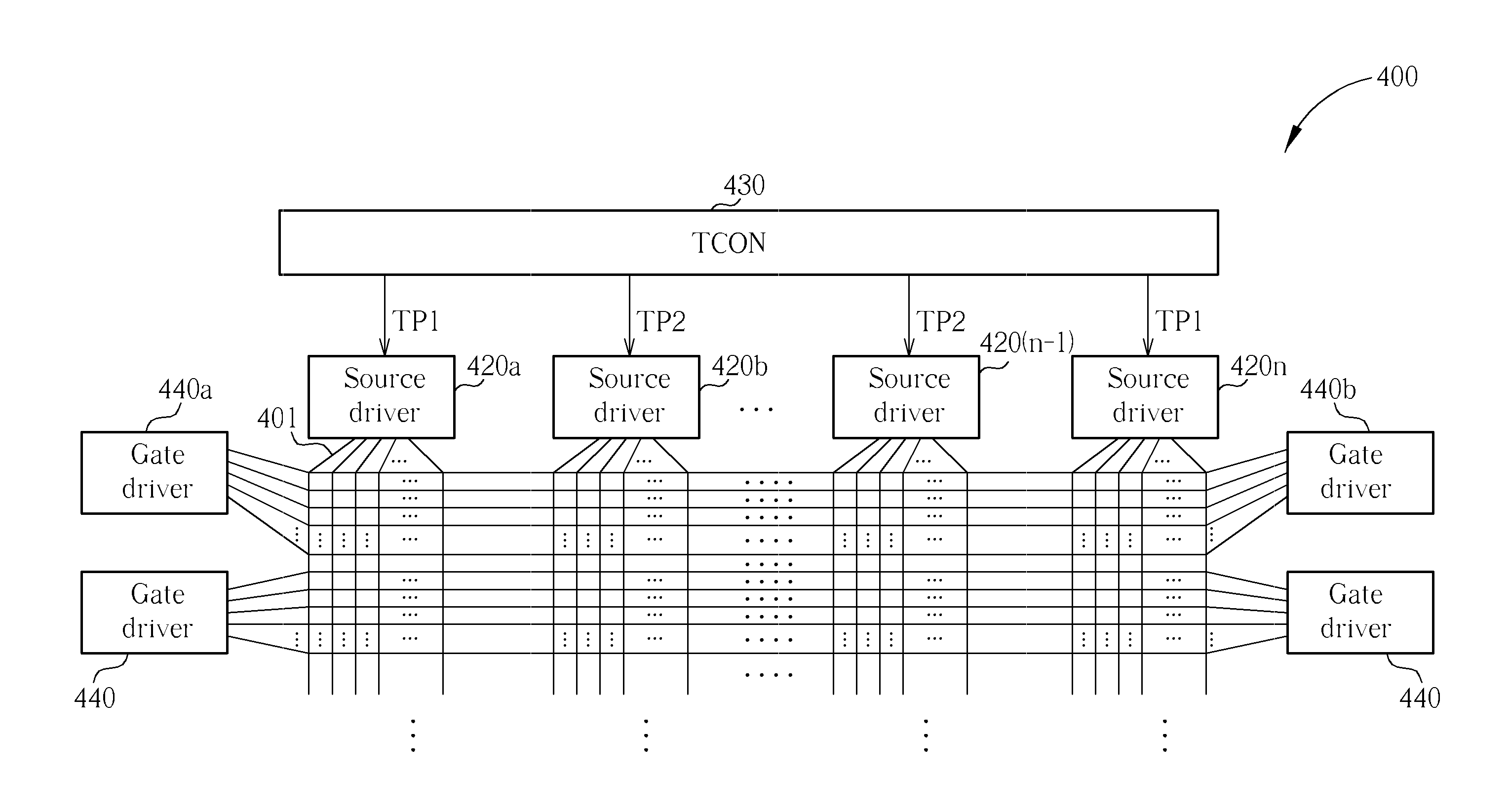

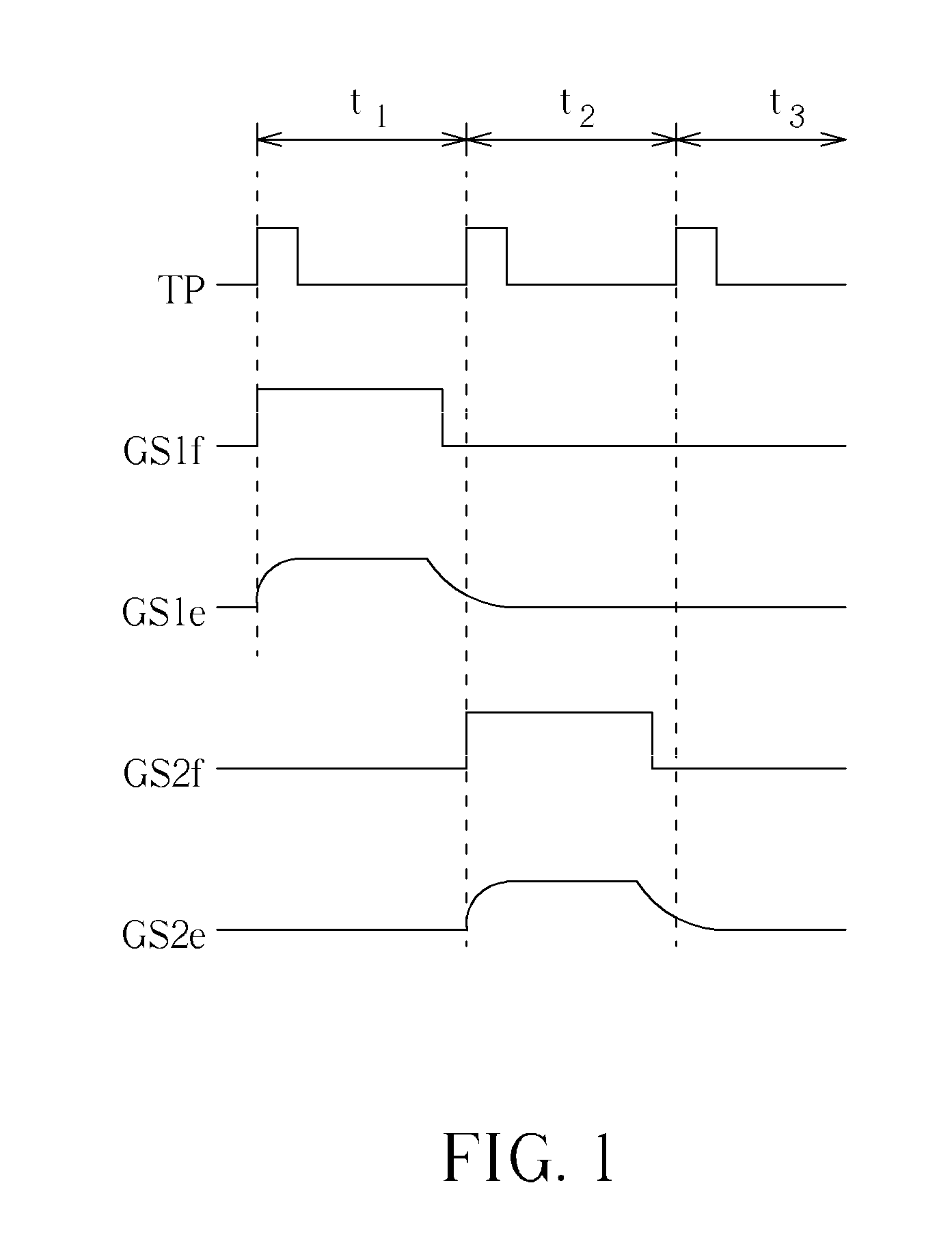

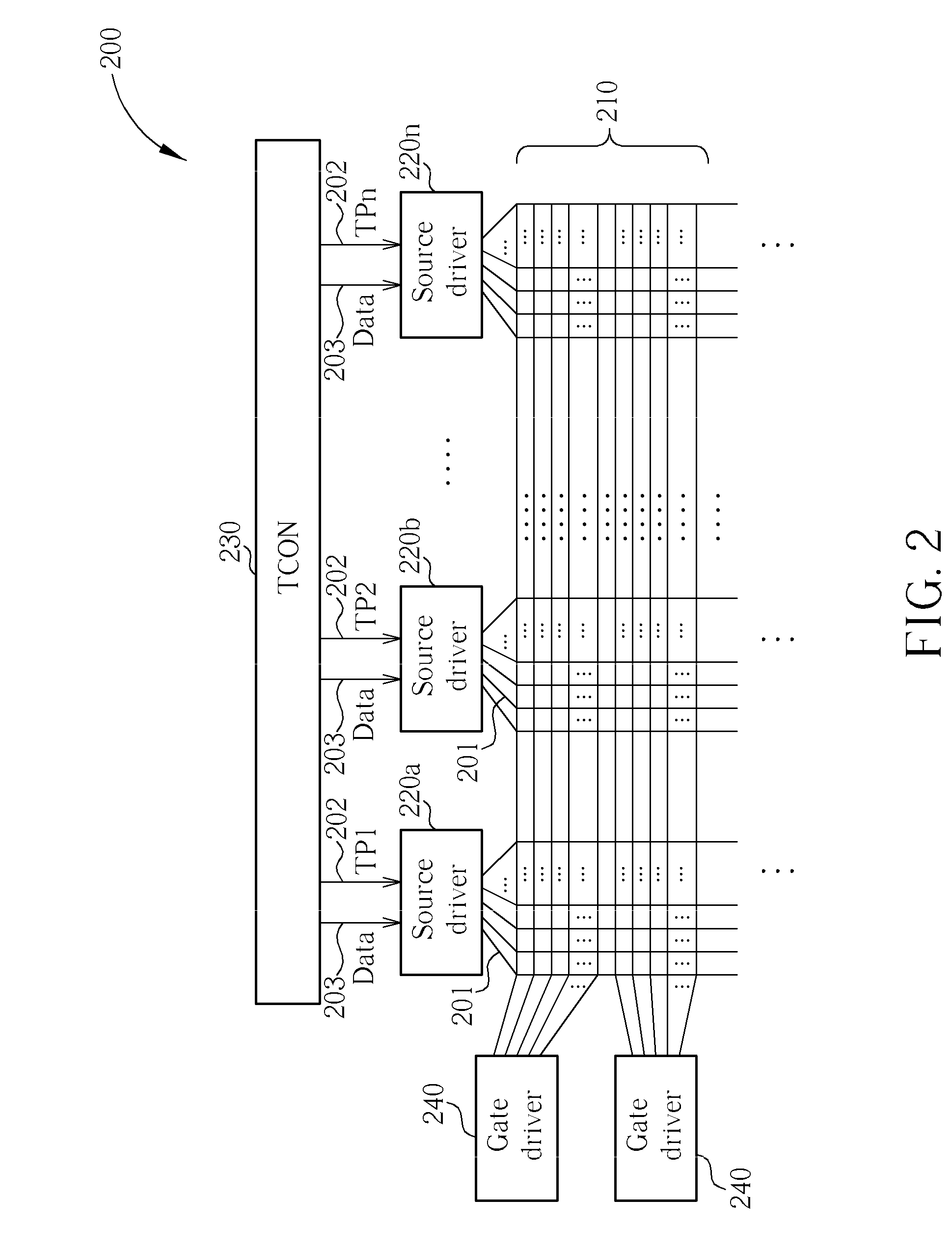

Display controlling system utilizing non-identical transfer pulse signals to control display and controlling method thereof

InactiveUS8456407B2Enhanced signalIncrease gate widthElectrical apparatusElectric lighting sourcesControl systemDisplay device

A display controlling system utilized in a display, such as an LCD, includes a plurality of data lines and a plurality of source drivers. The source drivers receive a plurality of transfer pulse signals, each of which corresponds to one of the source drivers, and drive the corresponding data lines upon receiving the corresponding transfer pulse signal, wherein the transfer pulse signals are not all identical. The transfer pulse signal can be produced by the timing controller of the display, or the transfer pulse information required for generating the transfer pulse signals can be embedded in the source data to be delivered to the source drivers that generate the transfer pulse signals after obtaining the transfer pulse information. The transfer pulse signal lines between the timing controller and the source drivers can therefore be removed.

Owner:HIMAX TECH LTD

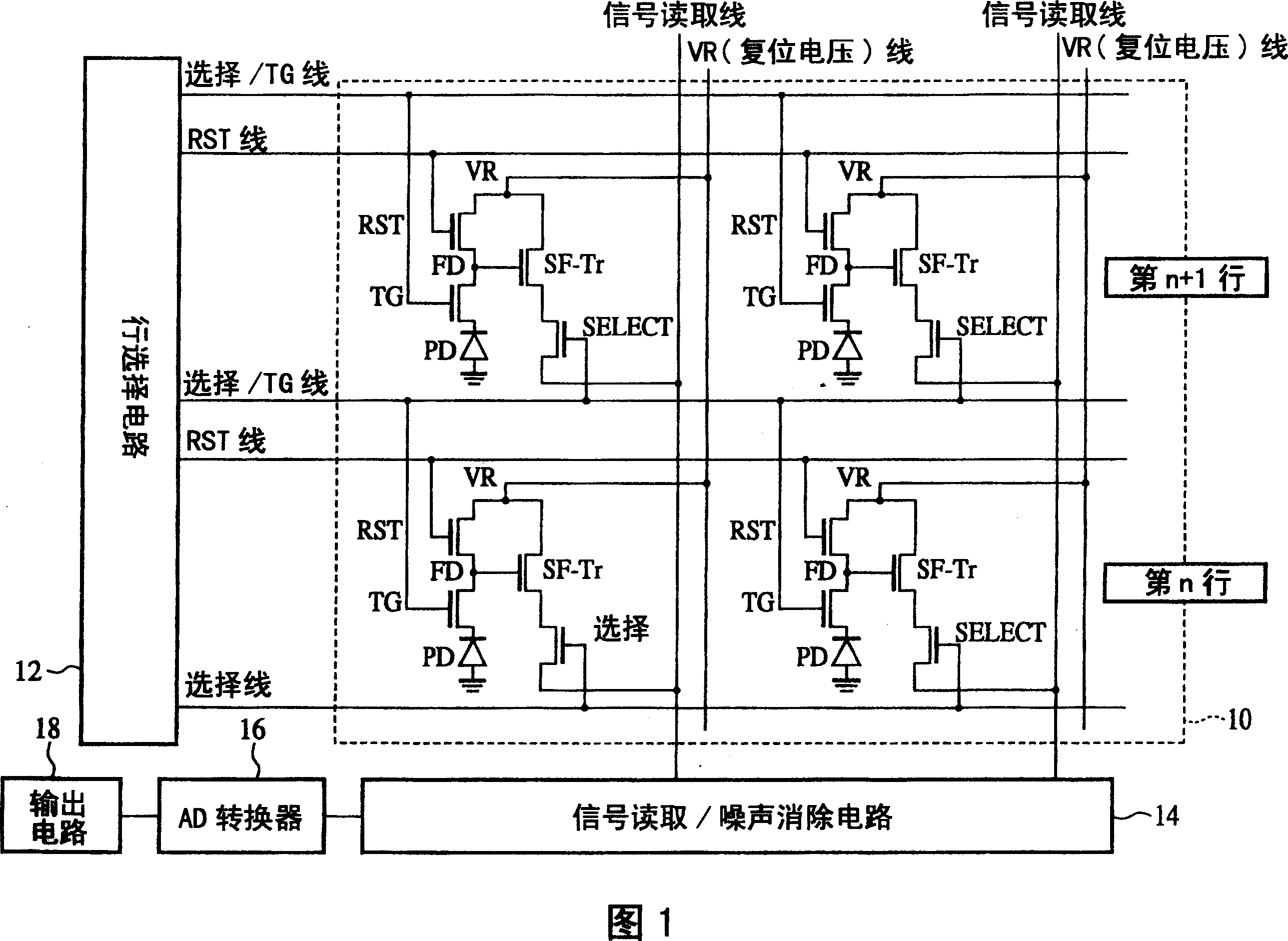

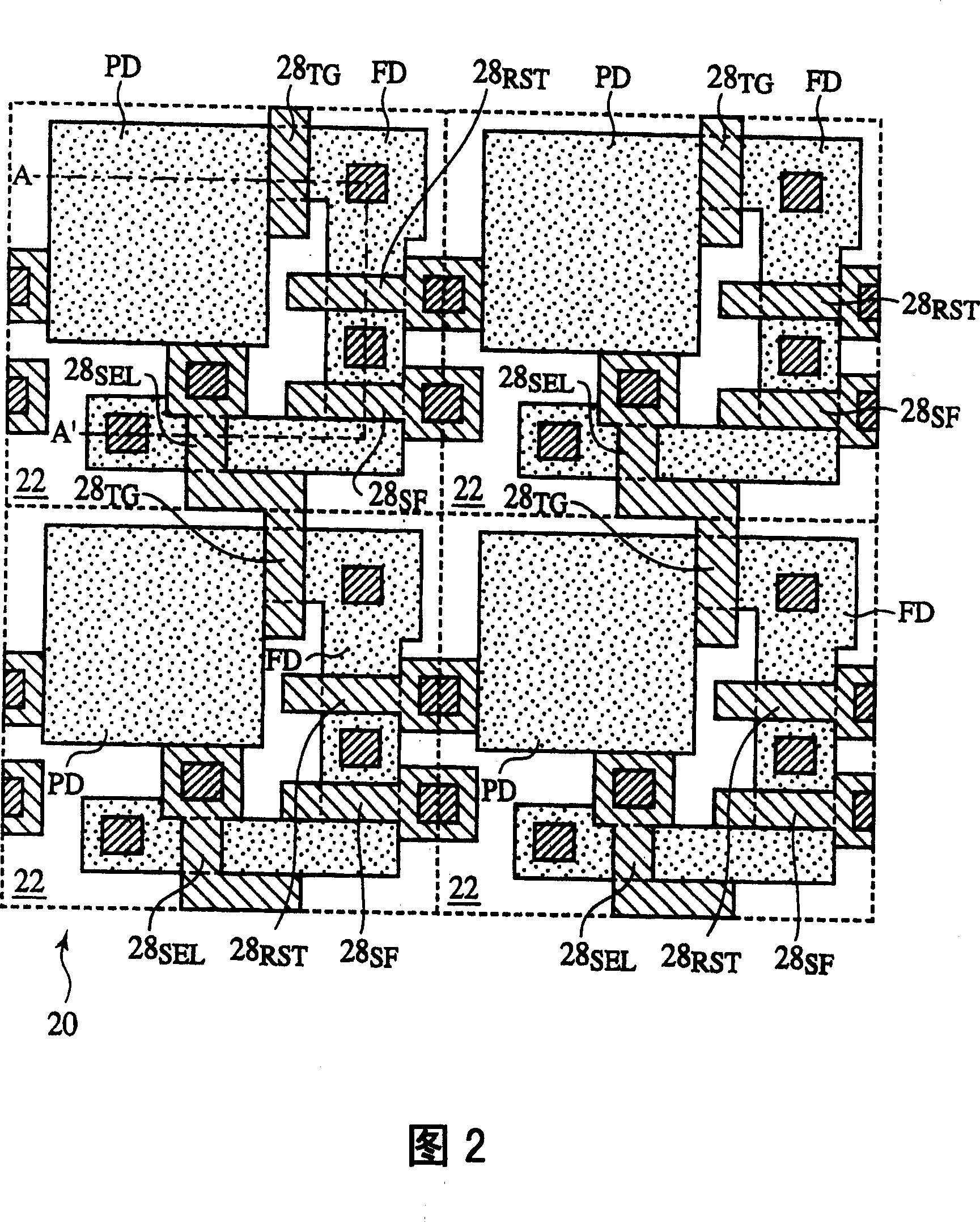

Solid image sensor and image fetching method

InactiveCN100349300CIncrease gate widthIncrease the areaTelevision system detailsTelevision system scanning detailsJunction leakageInterconnection

Owner:FUJITSU MICROELECTRONICS LTD

Semiconductor device

The invention discloses a semiconductor device. The semiconductor device comprises a substrate and a plurality of transistors arrayed on the substrate. Each transistor comprises a first electrode, a plurality of second electrodes and a grid electrode, wherein the second electrodes are arranged around the first electrode, and the grid electrode is of annular structure and arranged between the first electrode and the second electrodes. The first electrodes and the grid electrodes are circular or polygonal, and the sides of the second electrodes correspond to the shape of the grid electrodes. The semiconductor device can increase output current of the transistors, and invalid area of the substrate is decreased and manufacturing cost is reduced.

Owner:ANCORA SEMICON INC