Interdigital structure capable of regulating channel current of vertical gate SOI CMOS devices

A technology of channel current and vertical gate, which is applied in the direction of electric solid-state devices, semiconductor devices, semiconductor/solid-state device components, etc., can solve the problem of inability to design channel width vertical gate SOICMOS devices, etc., to improve the equivalent channel current , Improve the effect of gate width

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

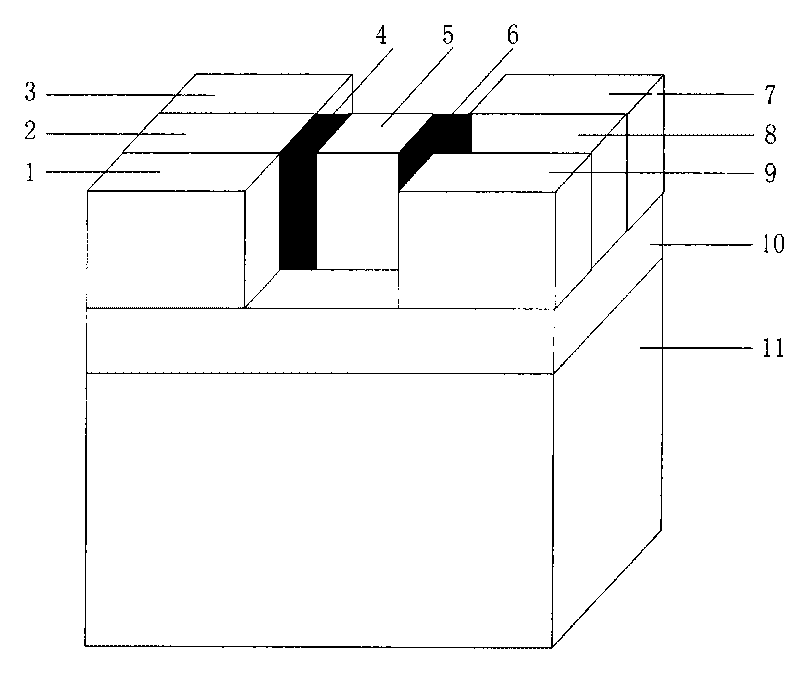

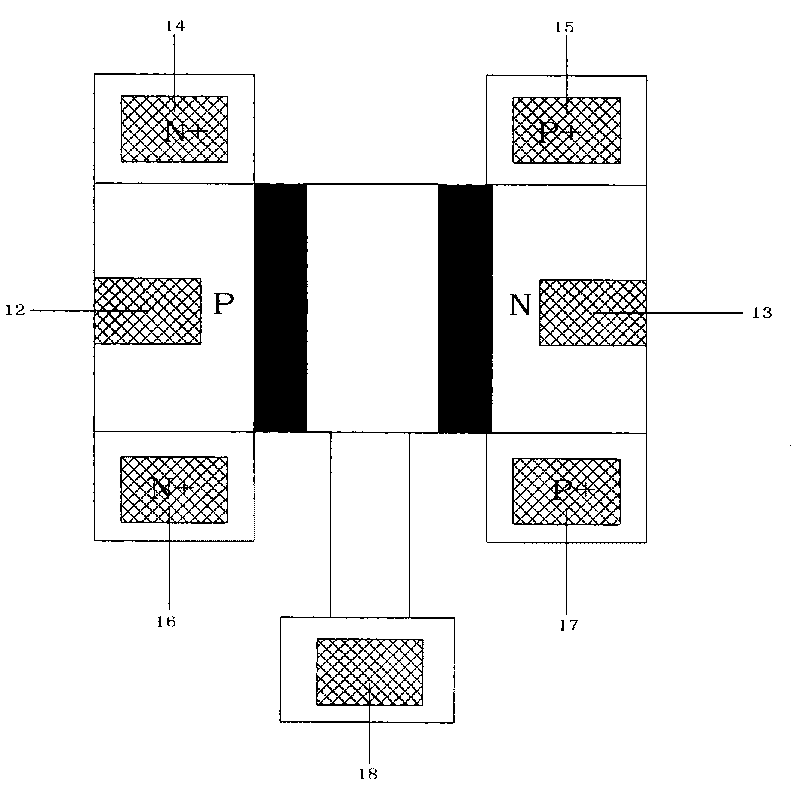

[0031] This embodiment provides an interdigital structure that can adjust the channel current of a vertical-gate SOI CMOS device, which is formed by arranging a plurality of vertical-gate SOI CMOS devices in parallel, wherein the PMOS regions of adjacent vertical-gate SOI CMOS devices are The PMOS area is adjacent, the NMOS area is adjacent to the NMOS area; the source area of all vertical gate SOI CMOS devices is on the same side, and the drain area is on the other side; the gates of all vertical gate SOI CMOS devices are drawn from the side to form an interdigitated gate . Adjacent PMOS regions share one body electrode, and adjacent NMOS regions share one body electrode. All body electrodes are connected in parallel to form interdigital body electrodes. All sources drawn from the source region are connected in parallel to form an interdigitated source; all drains drawn from a drain region are connected in parallel to form an interdigitated drain.

[0032] The interdigitated ...

Embodiment 2

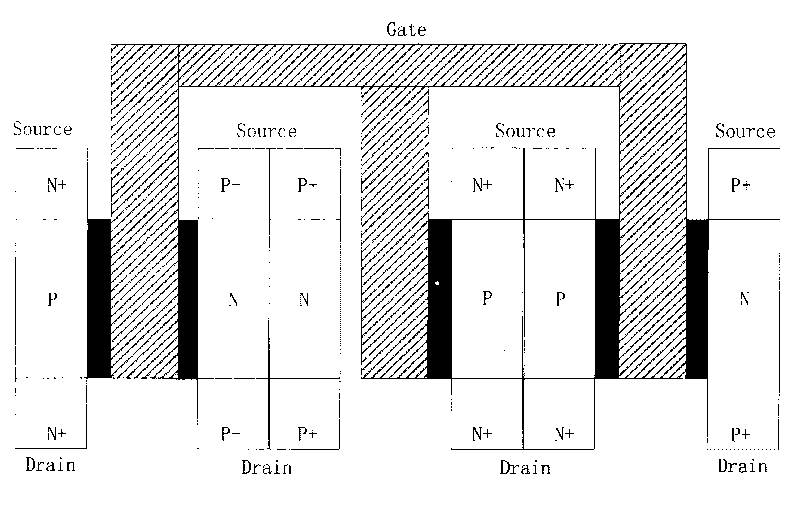

[0034] This embodiment provides an interdigital structure that can adjust the SOI CMOS channel current and increase the equivalent channel width, see image 3 . The structure includes an SOI substrate, multiple PMOS regions with P-channels, multiple NMOS regions with N-channels, and interdigital common gates; among them, PMOS and NMOS in the same CMOS share one gate, and multiple CMOS is distributed side by side and shares an interdigitated gate, and between adjacent CMOSs, NMOS and NMOS are in parallel, and PMOS and PMOS are in parallel. This interdigitated structure can solve the problem that the SOI CMOS vertical gate structure cannot adjust the gate width. It not only reflects the advantage of the SOI CMOS vertical gate structure to eliminate the floating body effect, but also can design different channel widths according to needs, and then design with different Channel current SOI CMOS vertical gate device.

[0035] Such as Figure 4 As shown, the structural features of th...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More