3D semiconductor device and forming method thereof

A semiconductor and device technology, applied in the field of 3D semiconductor devices and their formation, can solve the problems of increasing static power consumption of MOS devices, reducing device reliability, and decreasing gate control capability of MOS devices, reducing short-channel effects, increasing Channel length, wafer area saving effect

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

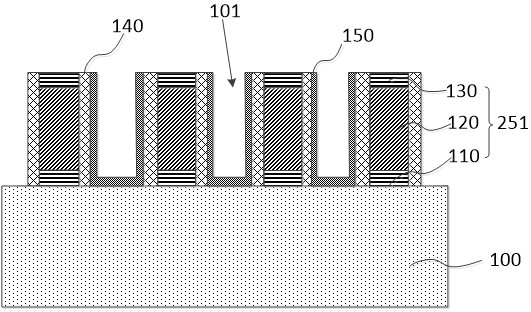

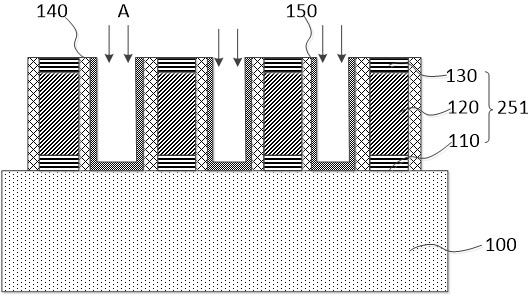

[0050] As mentioned in the background, at present, in the manufacture of integrated circuit devices, in order to pursue high device performance and save the chip area occupied by each device, the size of MOS devices continues to shrink. However, as the MOS device continues to shrink, the channel length of the MOS device shrinks and the thickness of the tunnel oxide layer becomes thinner and thinner. However, when the size of the MOS device is reduced to a certain extent, the short channel effect will be induced. The short channel effect will lead to a decrease in the control ability of the gate of the MOS device, which will cause a threshold voltage drift and a drain-induced barrier lowering effect, resulting in an increase in the static power consumption of the MOS device. At the same time, the shrinking device size will lead to an increase in the electric field inside the device, increasing the generation of hot carriers and reducing the reliability of the device.

[0051] ...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More