Patents

Literature

157results about How to "Increase channel length" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

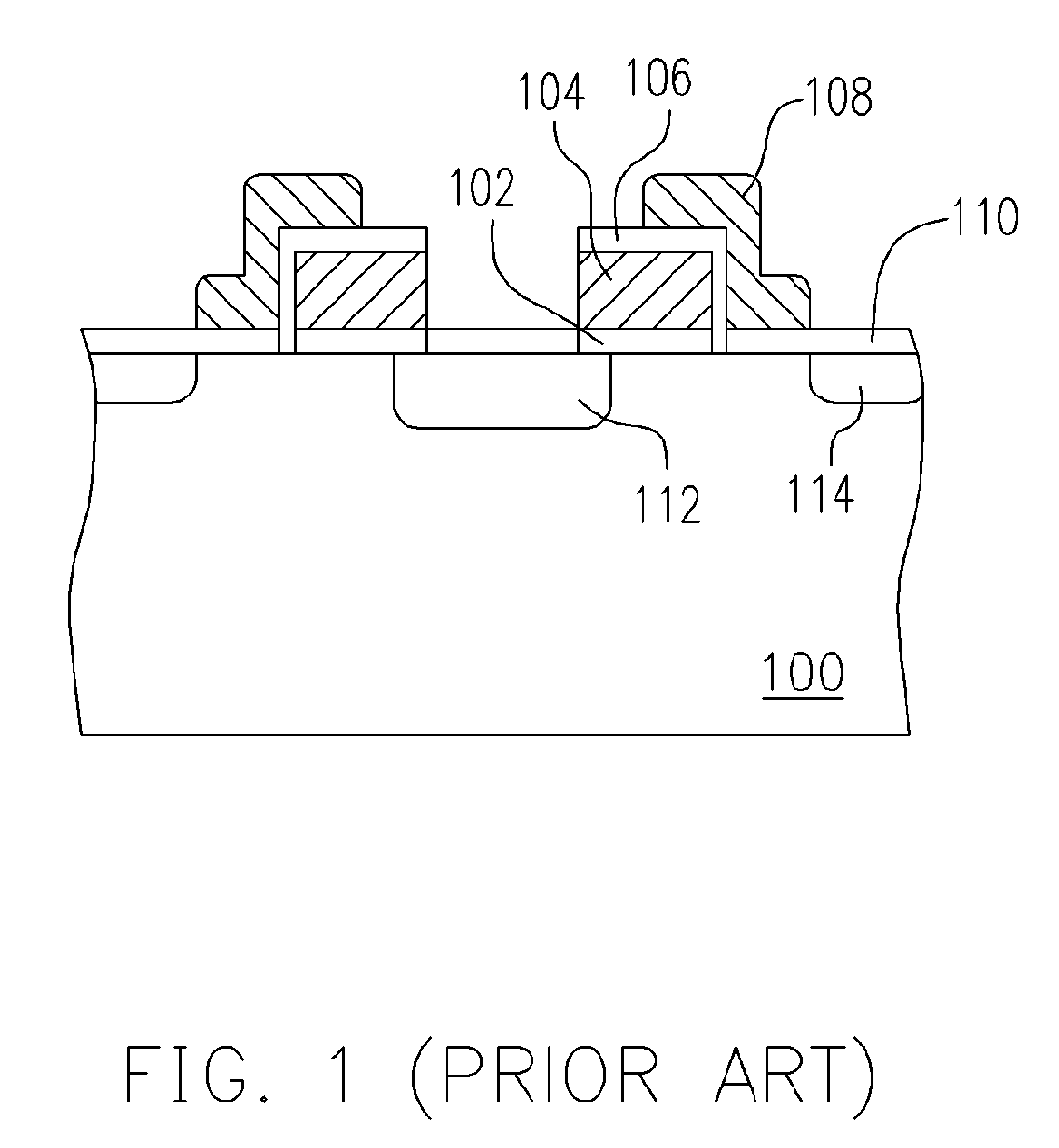

Method for fabricating recess gate in semiconductor device

InactiveUS20090087960A1Suppress generationReduce line widthTransistorSolid-state devicesEtchingOxide

A method for fabricating a recess gate in a semiconductor device includes etching a silicon substrate to form a trench that defines an active region, forming a device isolation layer that gap-fills the trench, forming a hard mask layer over the silicon substrate, the hard mask layer comprising a stack of an oxide layer and an amorphous carbon layer, wherein the hard mask layer exposes a channel target region of the active region, and forming a recess region with a dual profile by first etching and second etching the channel target region using the hard mask layer as an etch barrier, wherein the second etching is performed after removing the amorphous carbon layer.

Owner:SK HYNIX INC

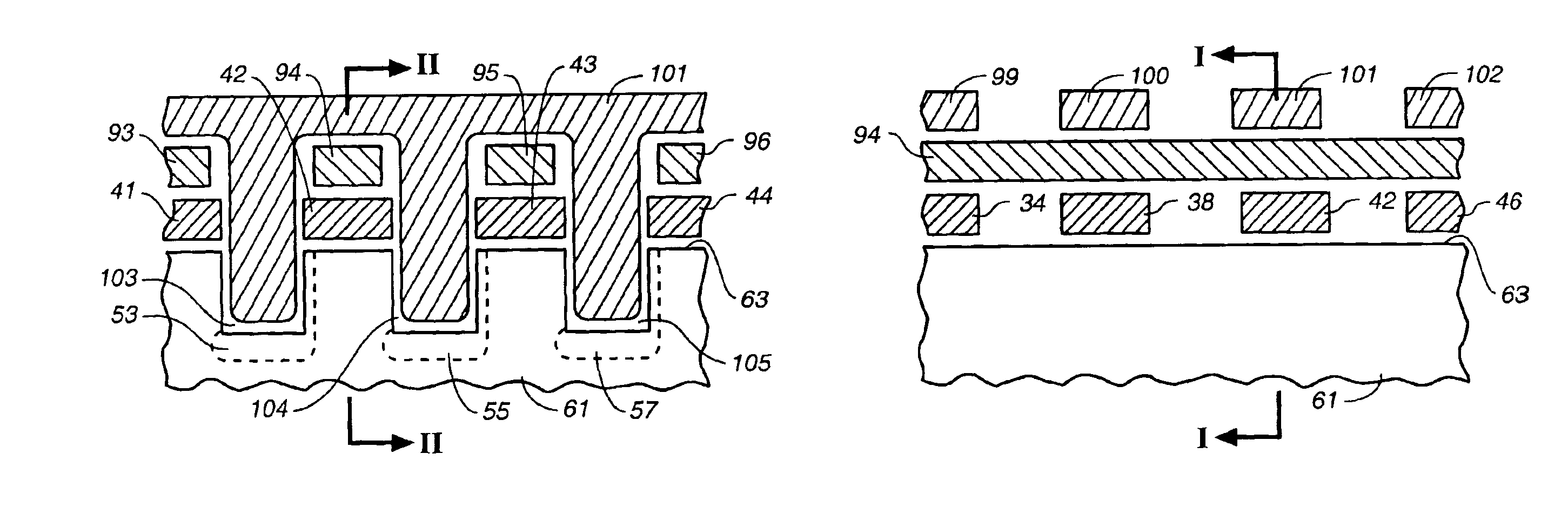

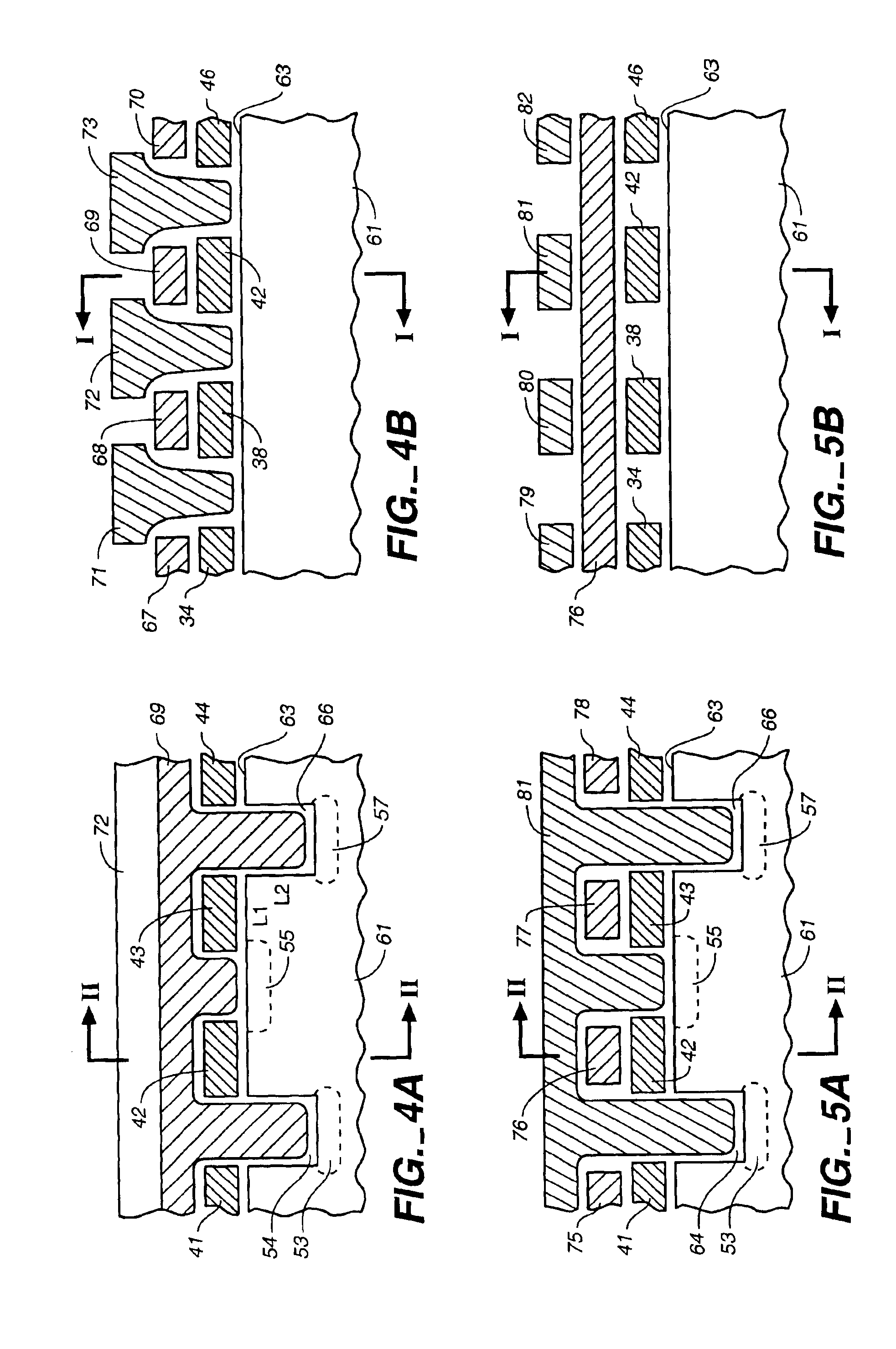

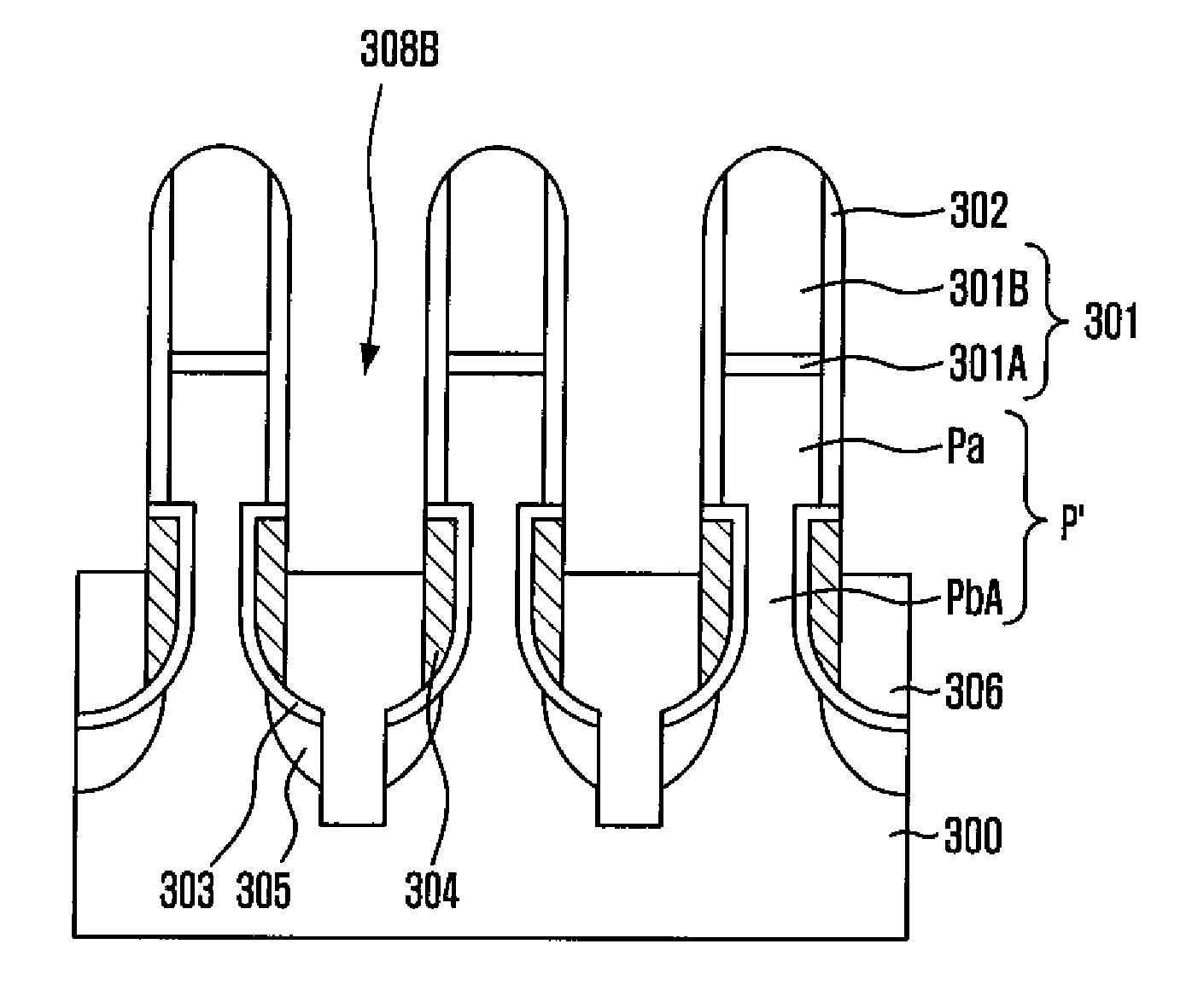

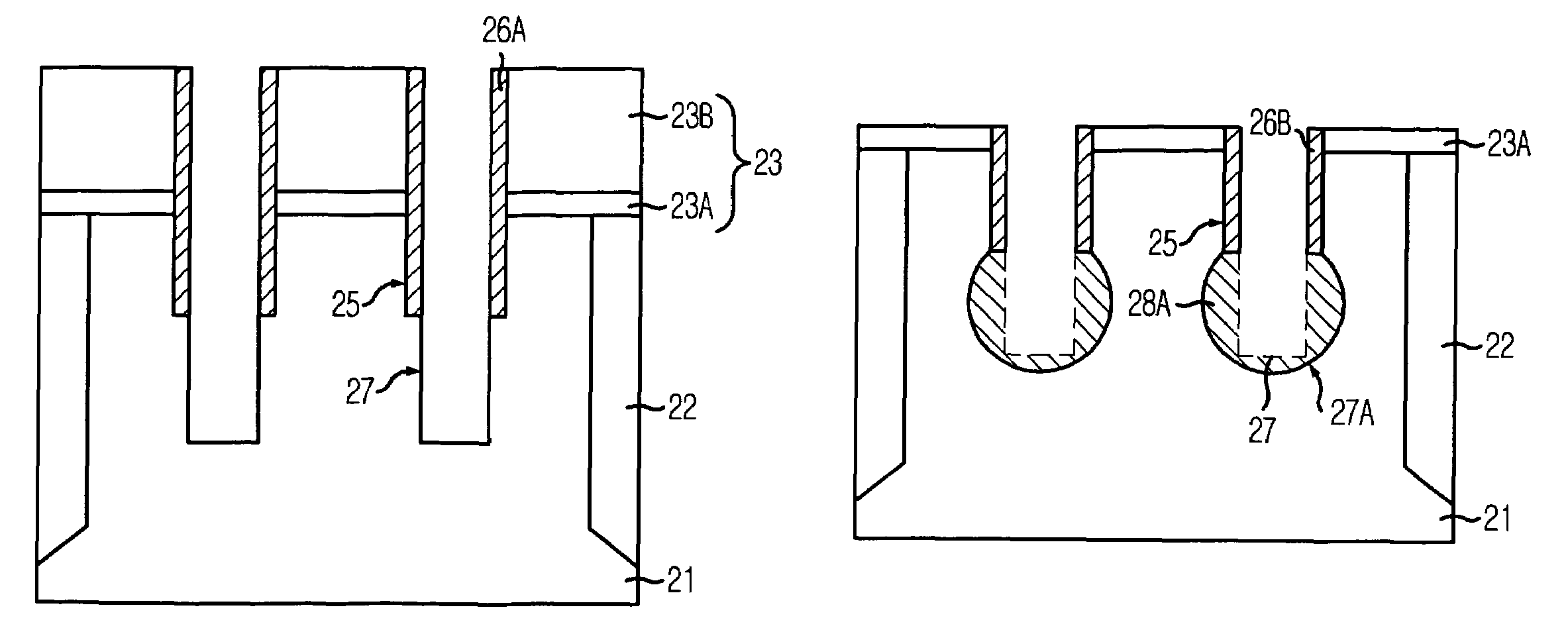

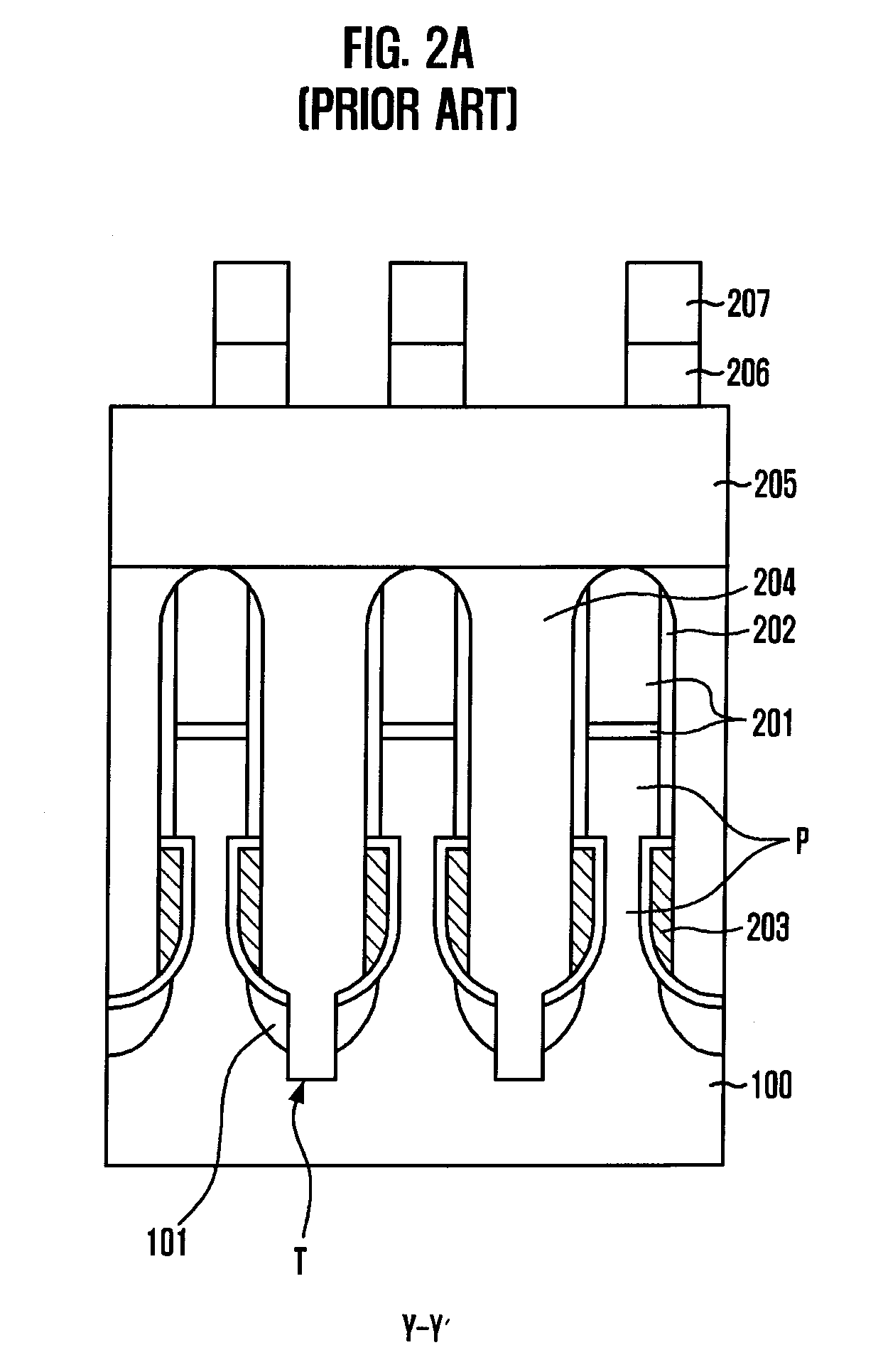

Non-volatile memory cells utilizing substrate trenches

InactiveUS6936887B2Small sizeImprove performanceTransistorSolid-state devicesCapacitanceCapacitive coupling

Several embodiments of flash EEPROM split-channel cell arrays are described that position the channels of cell select transistors along sidewalls of trenches in the substrate, thereby reducing the cell area. Select transistor gates are formed as part of the word lines and extend downward into the trenches with capacitive coupling between the trench sidewall channel portion and the select gate. In one embodiment, trenches are formed between every other floating gate along a row, the two trench sidewalls providing the select transistor channels for adjacent cells, and a common source / drain diffusion is positioned at the bottom of the trench. A third gate provides either erase or steering capabilities. In another embodiment, trenches are formed between every floating gate along a row, a source / drain diffusion extending along the bottom of the trench and upwards along one side with the opposite side of the trench being the select transistor channel for a cell. In another embodiment, select transistor gates of dual floating gate memory cells are extended into trenches or recesses in the substrate in order to lengthen the select transistor channel as the surface dimensions of the cell are being decreased. Techniques for manufacturing such flash EEPROM split-channel cell arrays are also included.

Owner:SANDISK TECH LLC

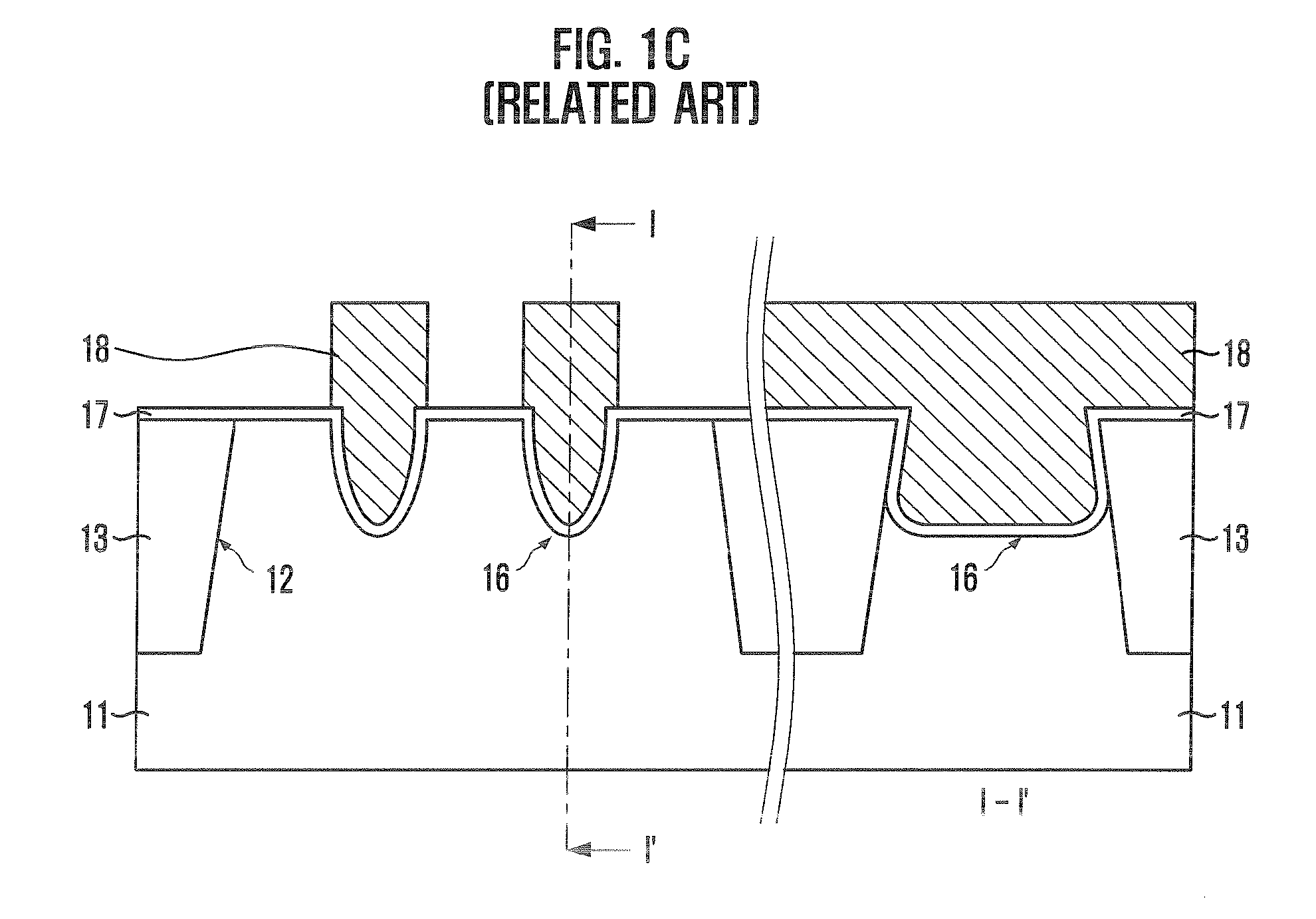

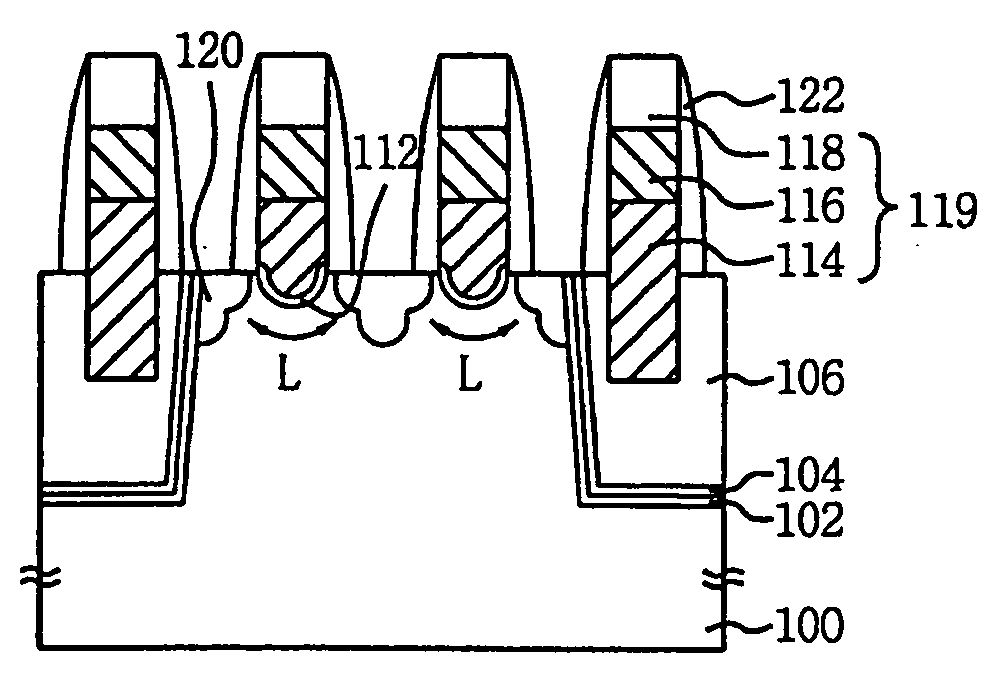

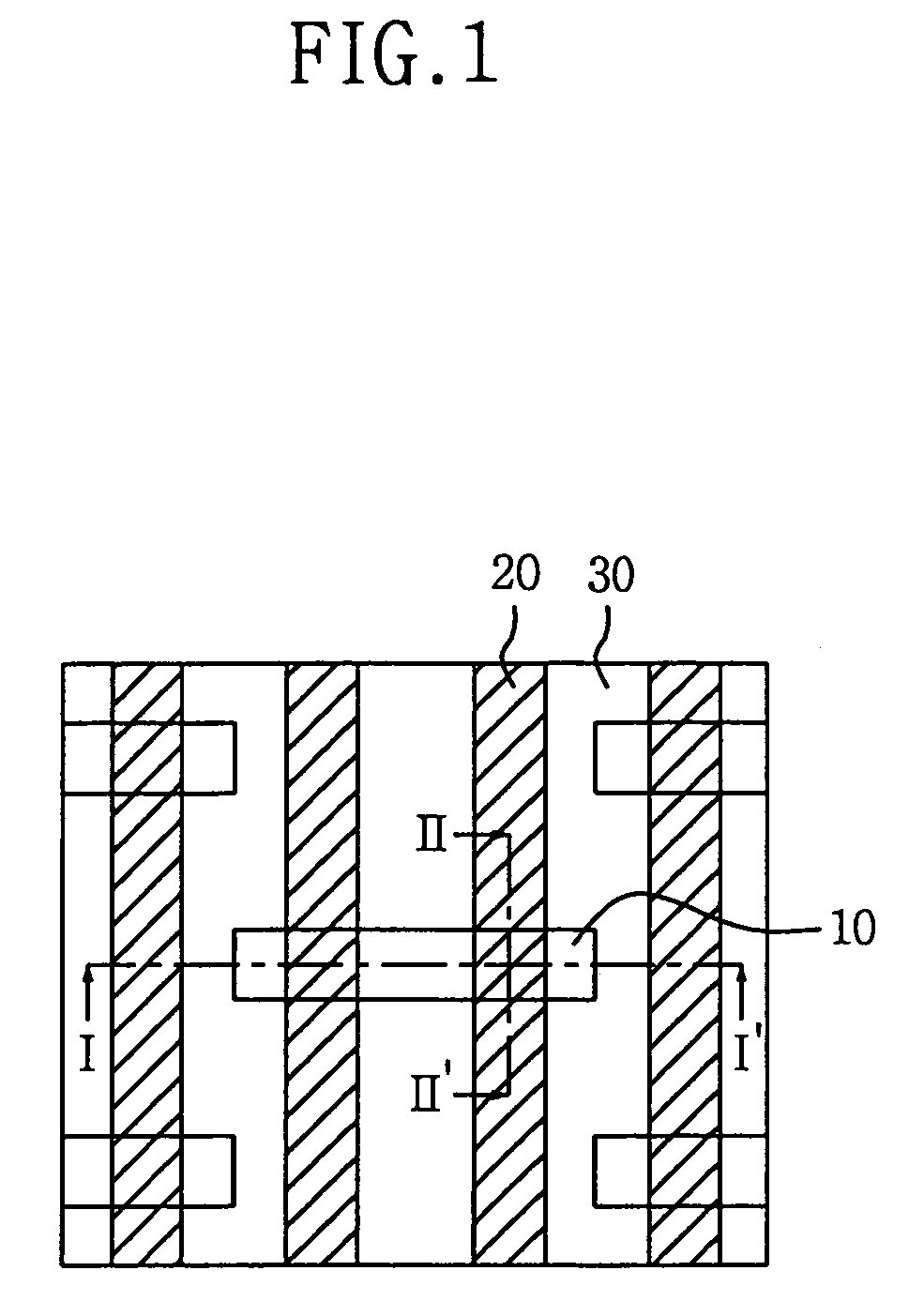

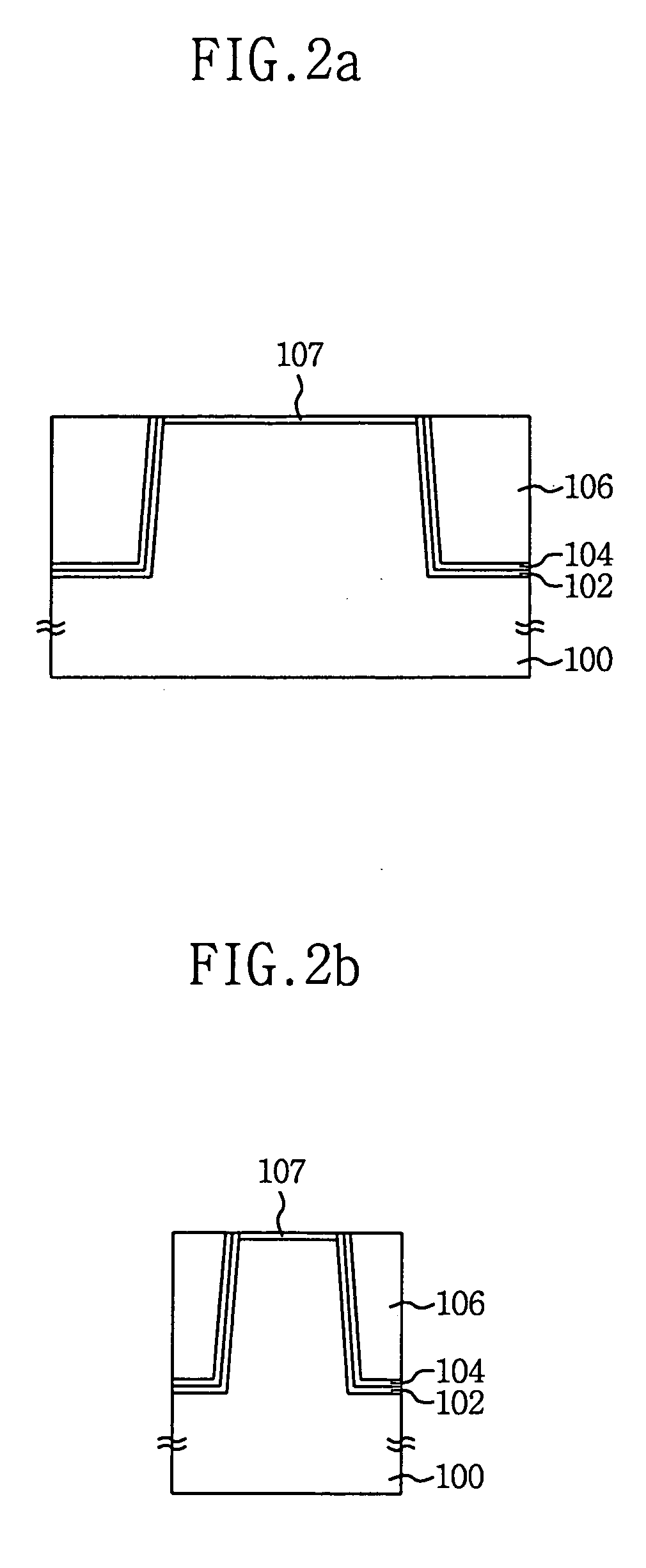

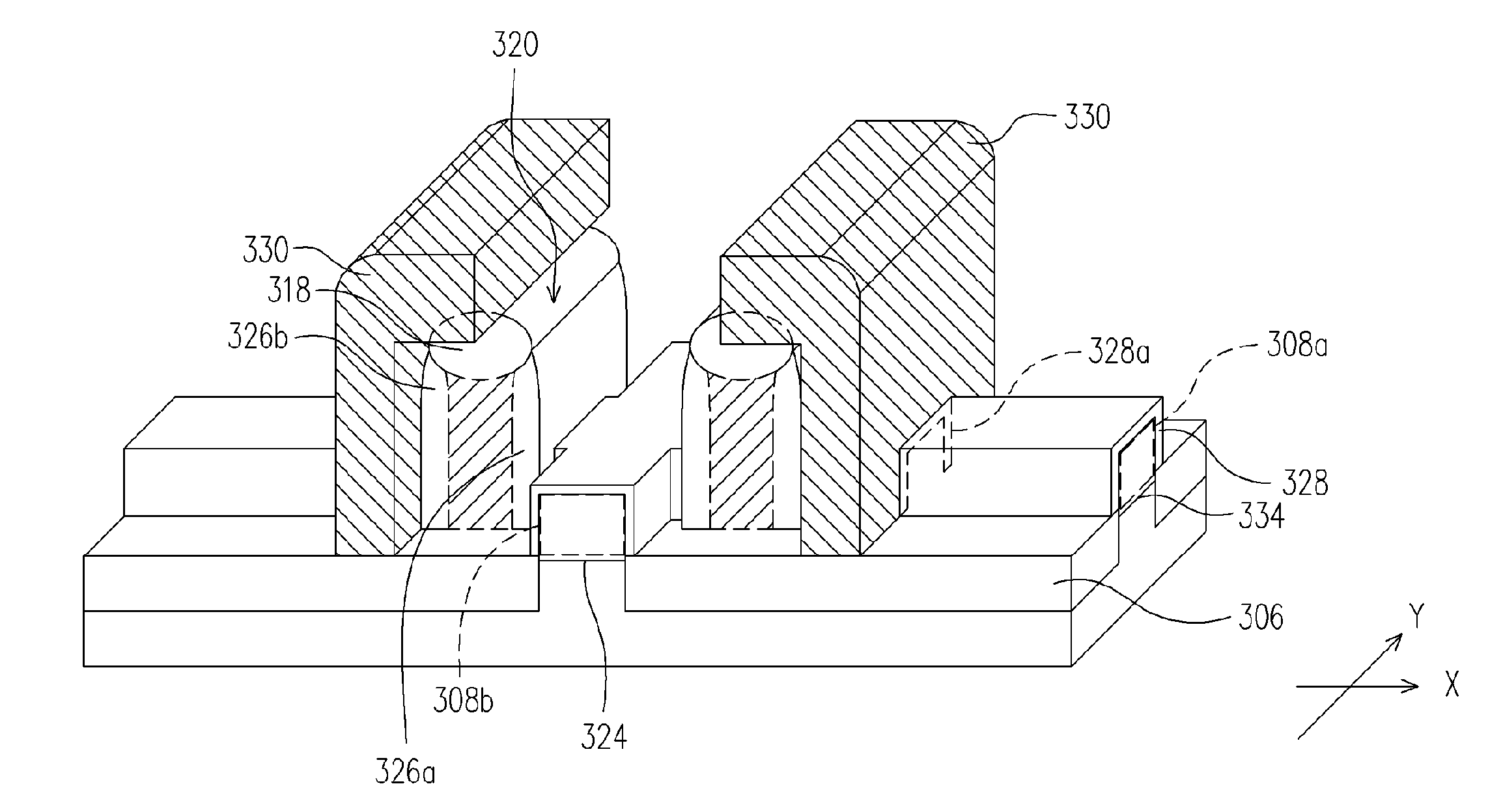

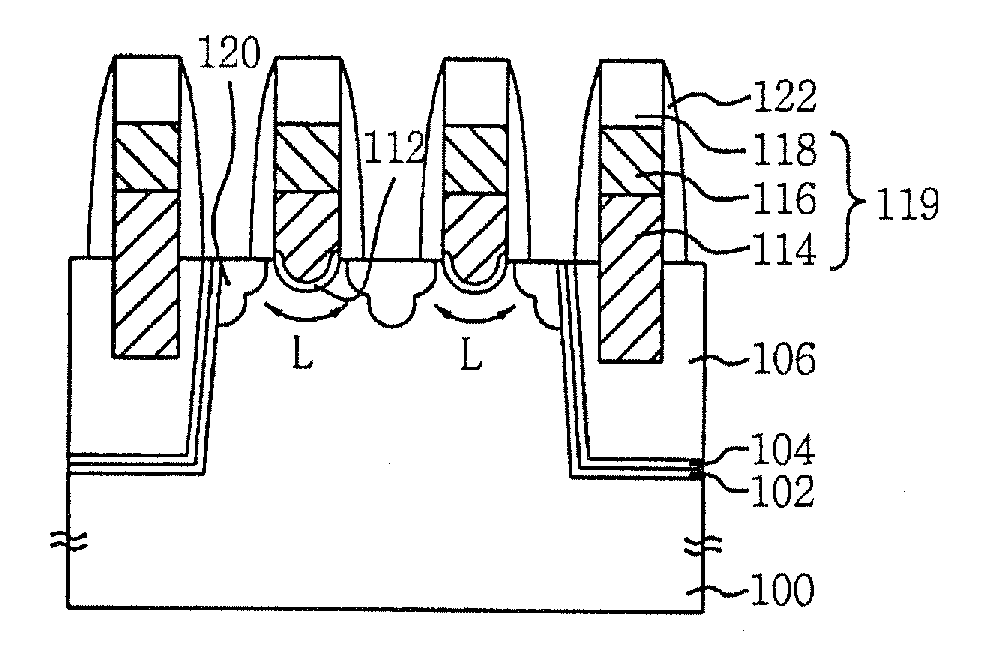

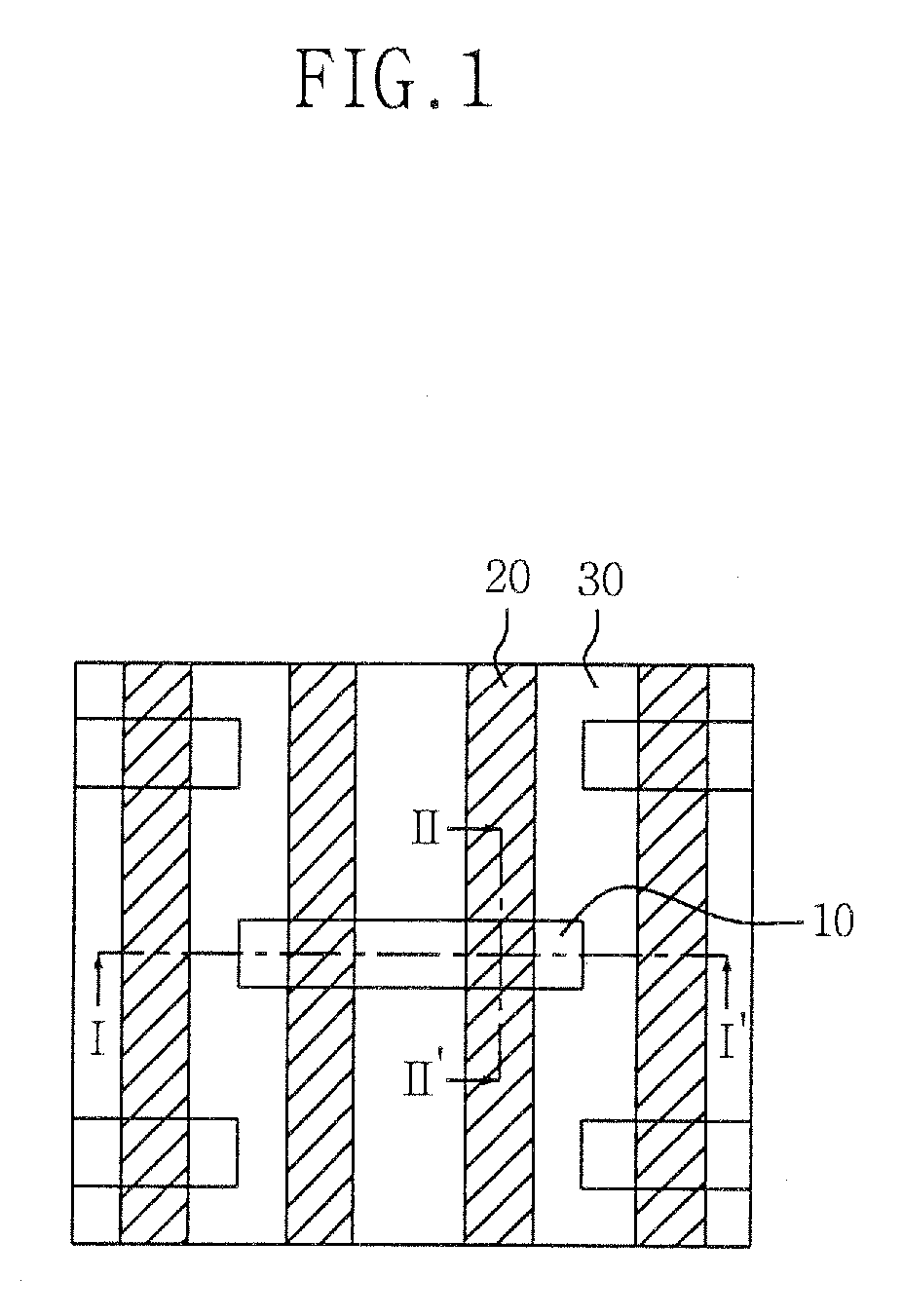

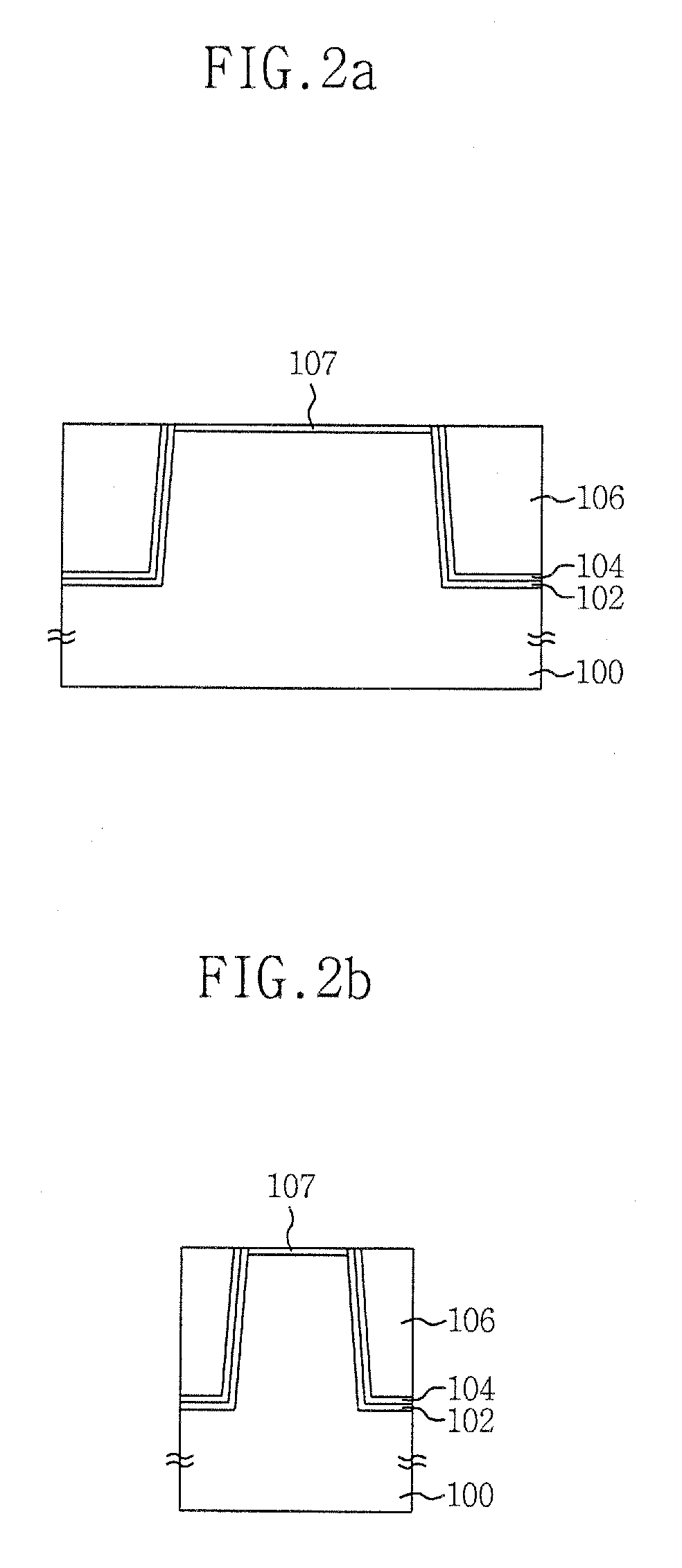

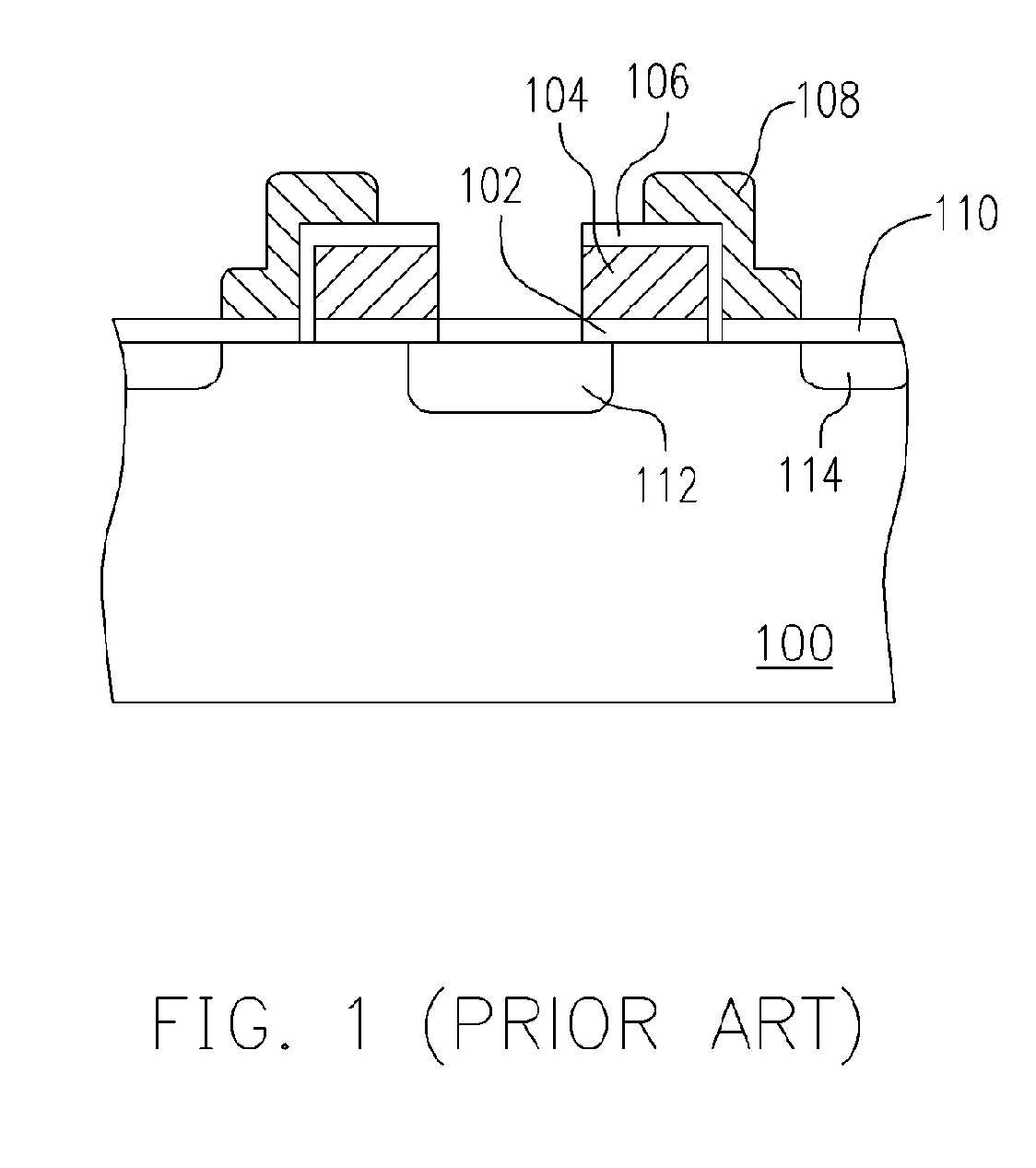

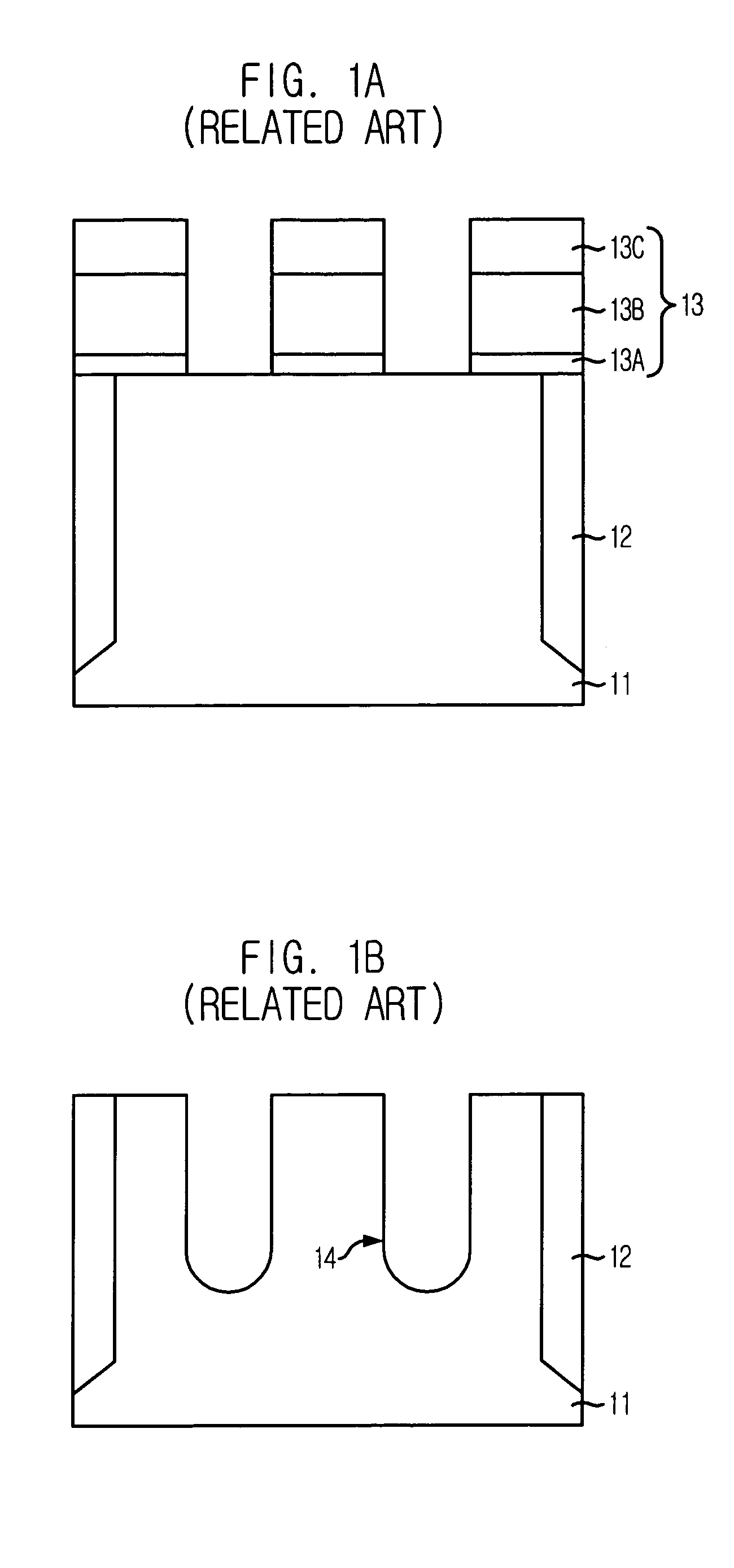

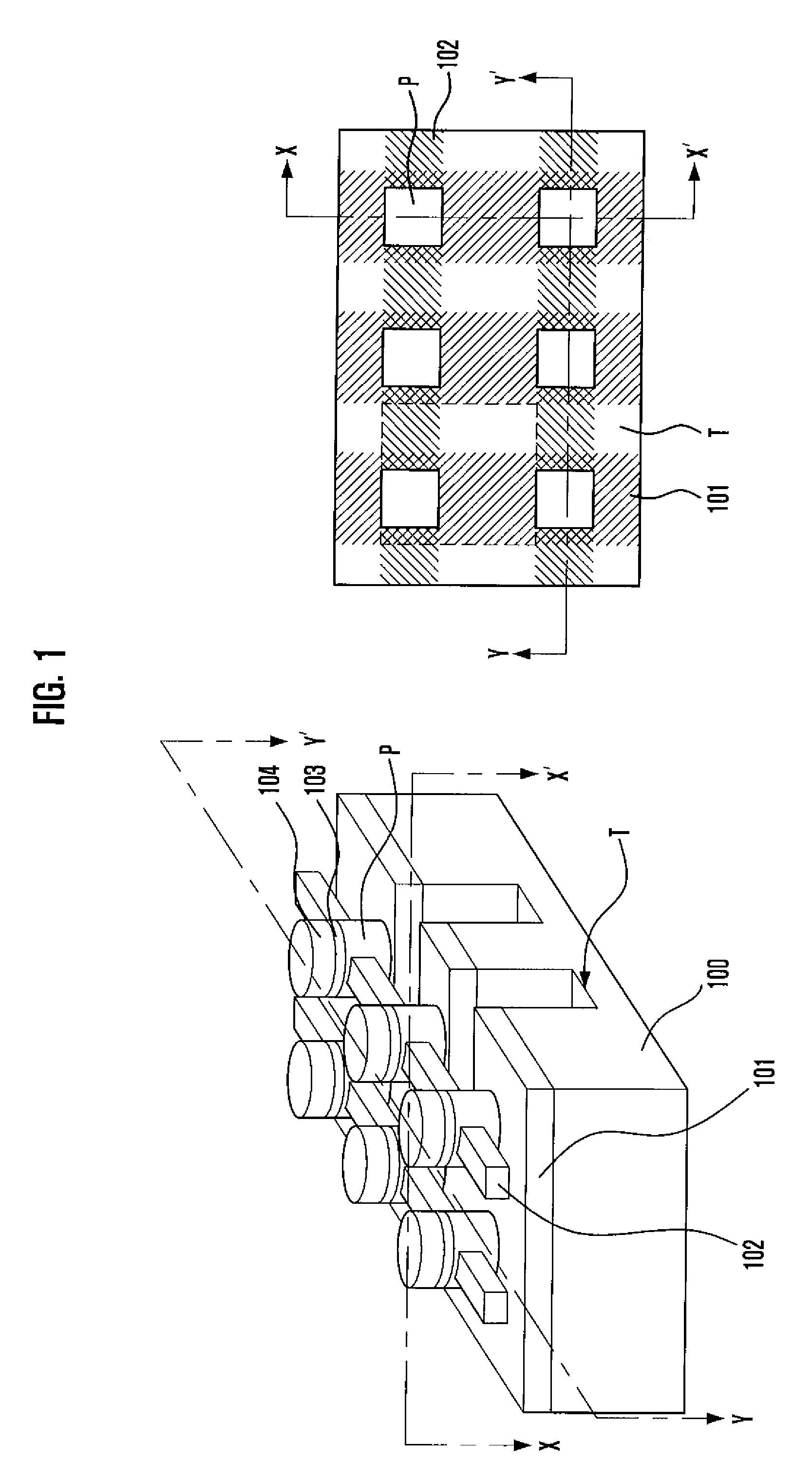

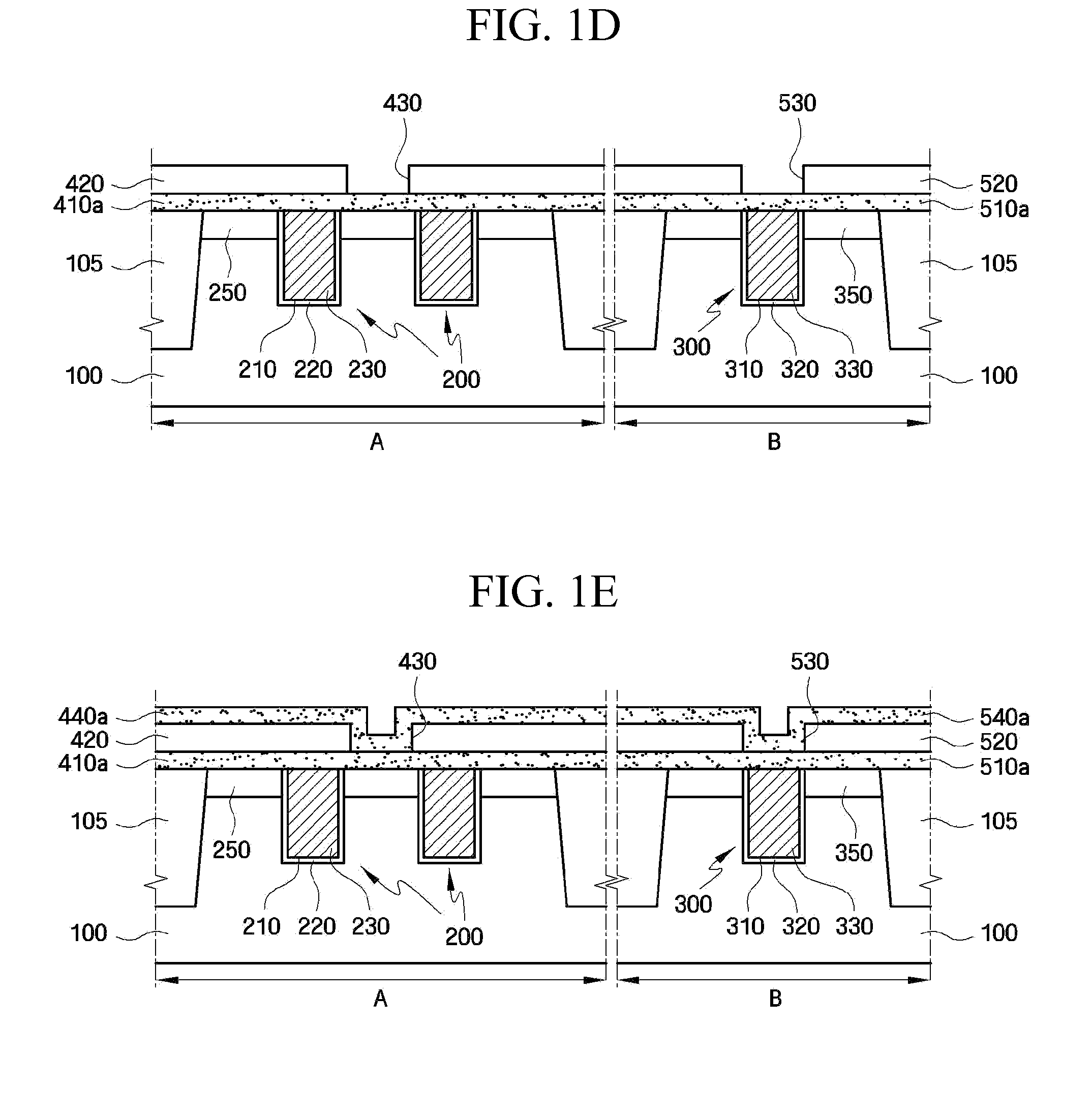

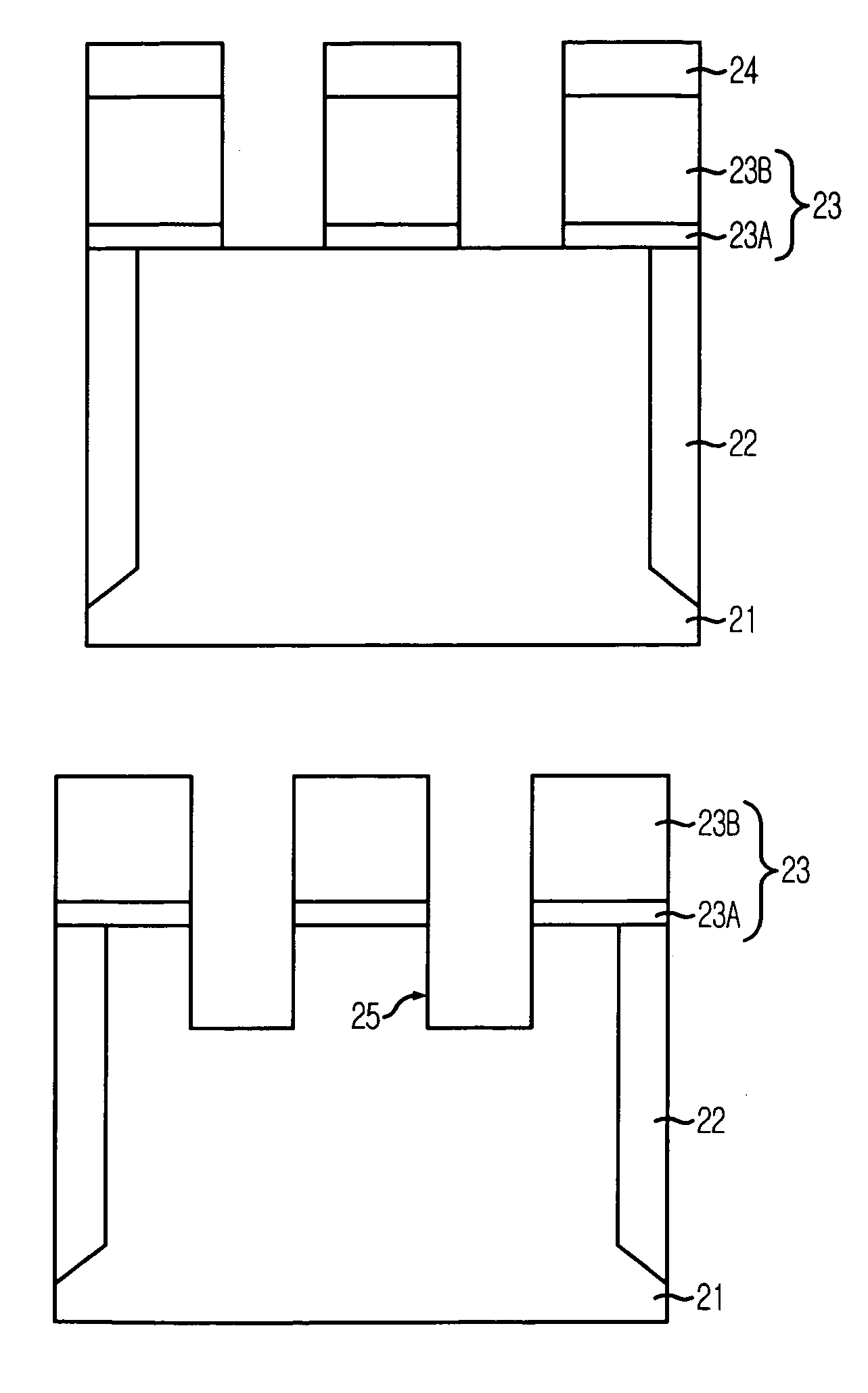

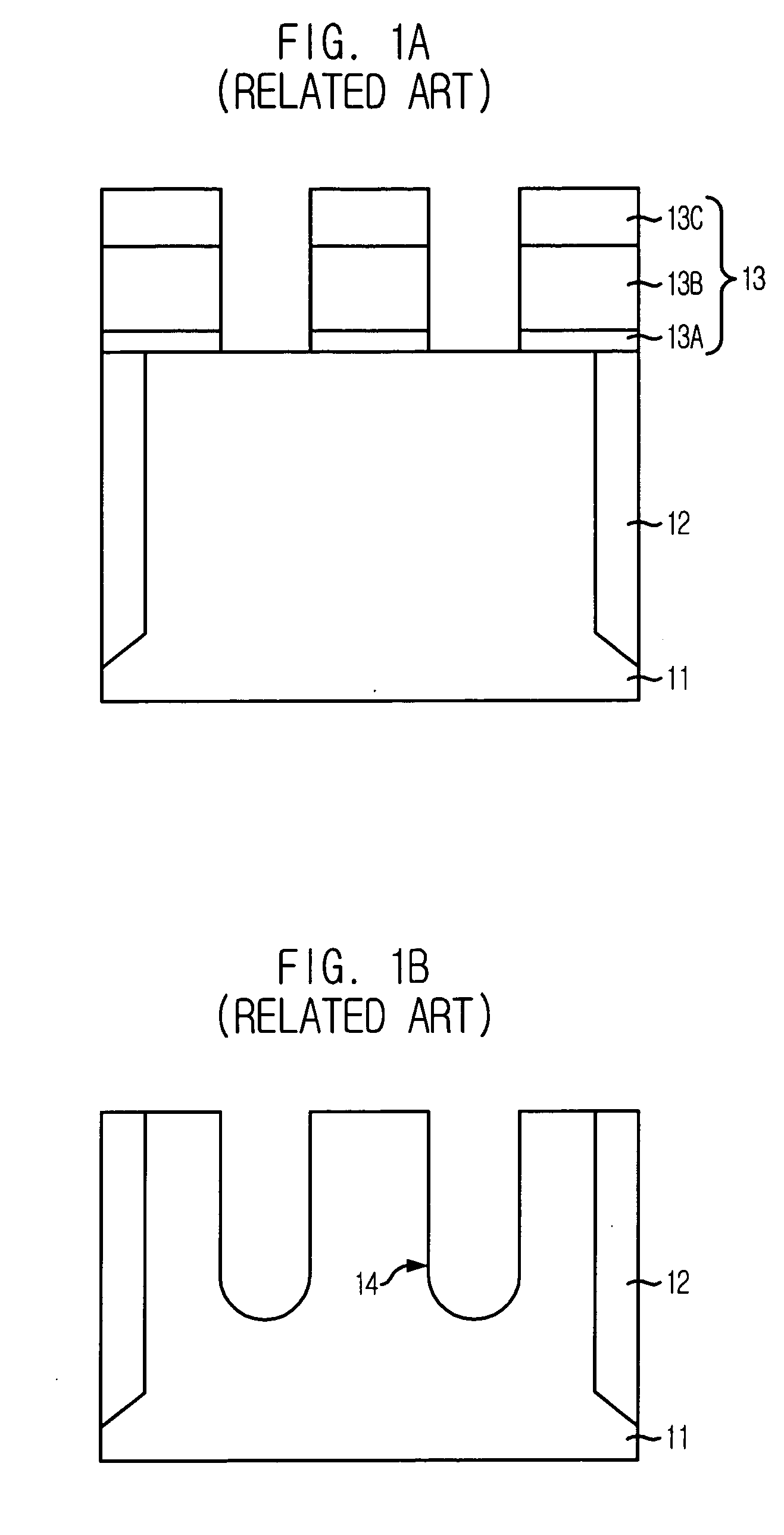

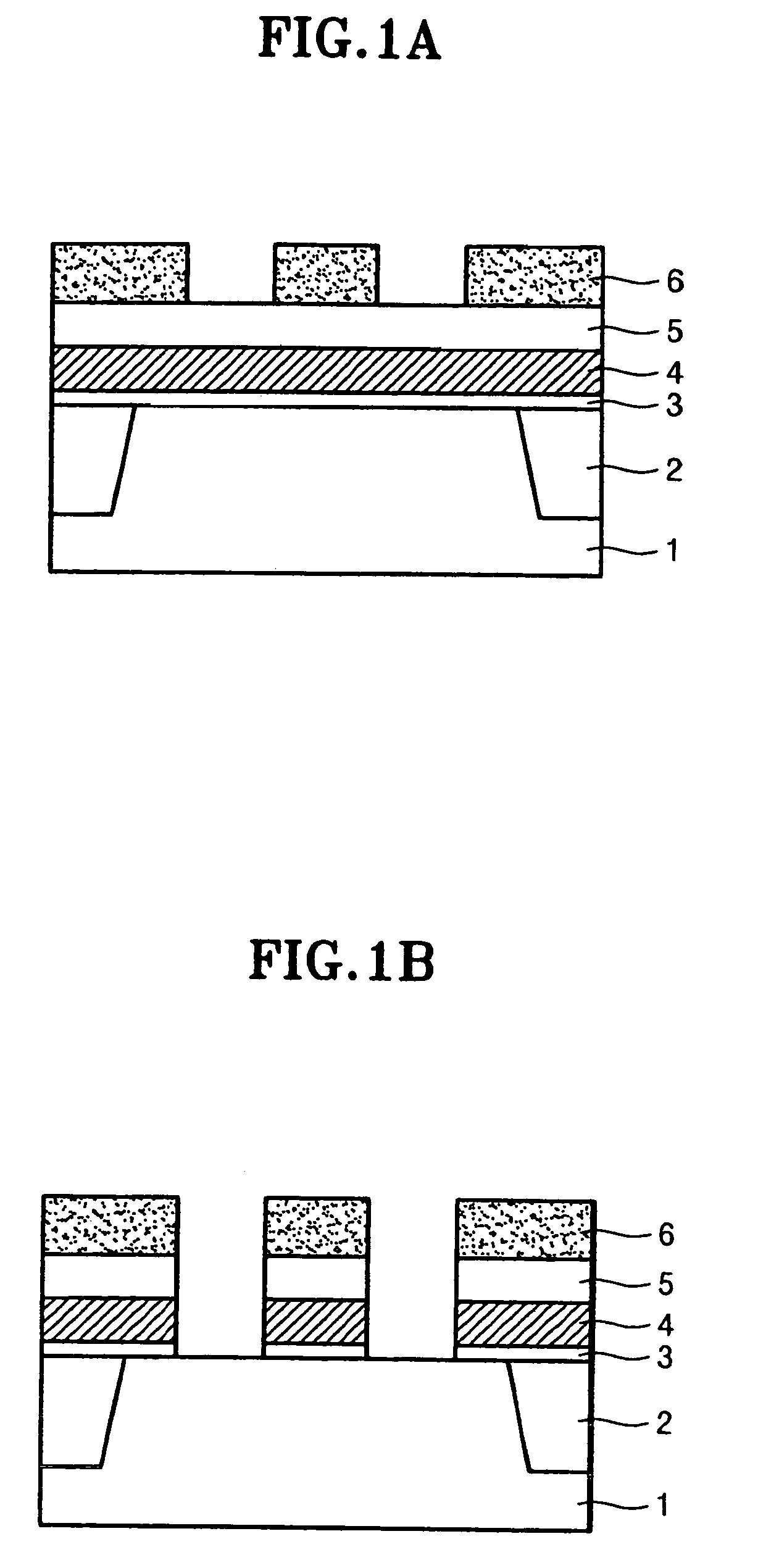

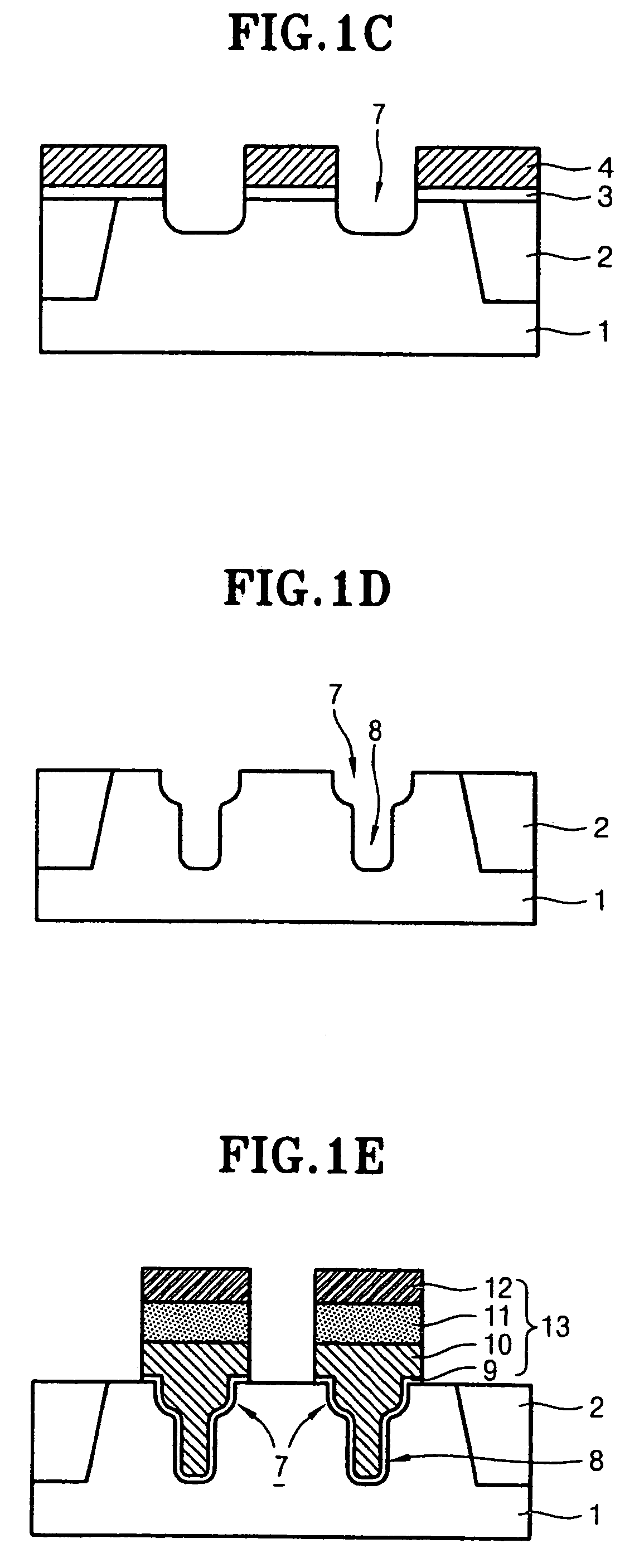

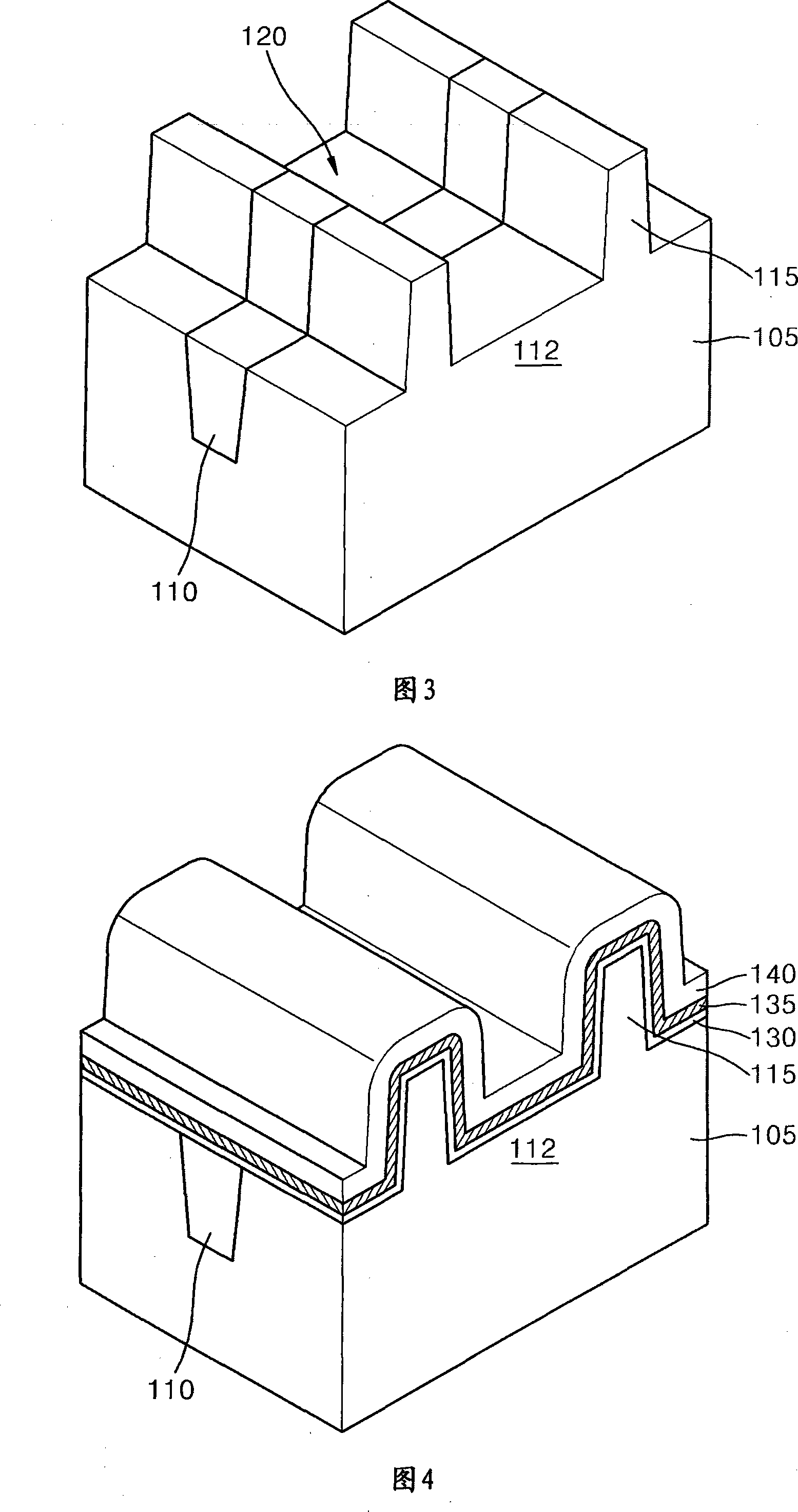

Fin FET and method of fabricating same

ActiveUS20050173759A1Improving swing characteristicReducing electric fieldTransistorSolid-state devicesInsulation layerSilicon

A fin field effect transistor (fin FET) is formed using a bulk silicon substrate and sufficiently guarantees a top channel length formed under a gate, by forming a recess having a predetermined depth in a fin active region and then by forming the gate in an upper part of the recess. A device isolation film is formed to define a non-active region and a fin active region in a predetermined region of the substrate. In a portion of the device isolation film a first recess is formed, and in a portion of the fin active region a second recess having a depth shallower than the first recess is formed. A gate insulation layer is formed within the second recess, and a gate is formed in an upper part of the second recess. A source / drain region is formed in the fin active region of both sides of a gate electrode.

Owner:SAMSUNG ELECTRONICS CO LTD

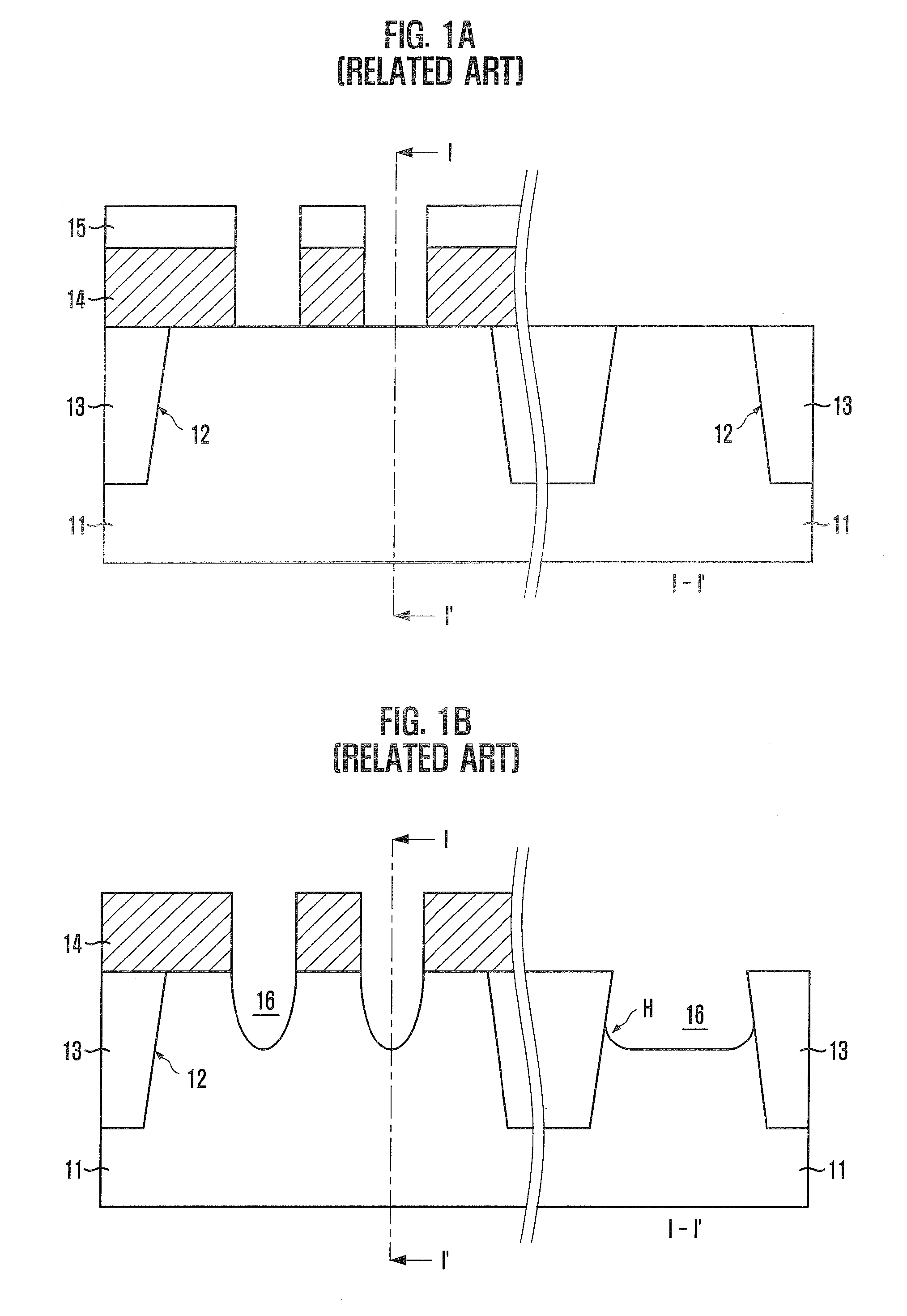

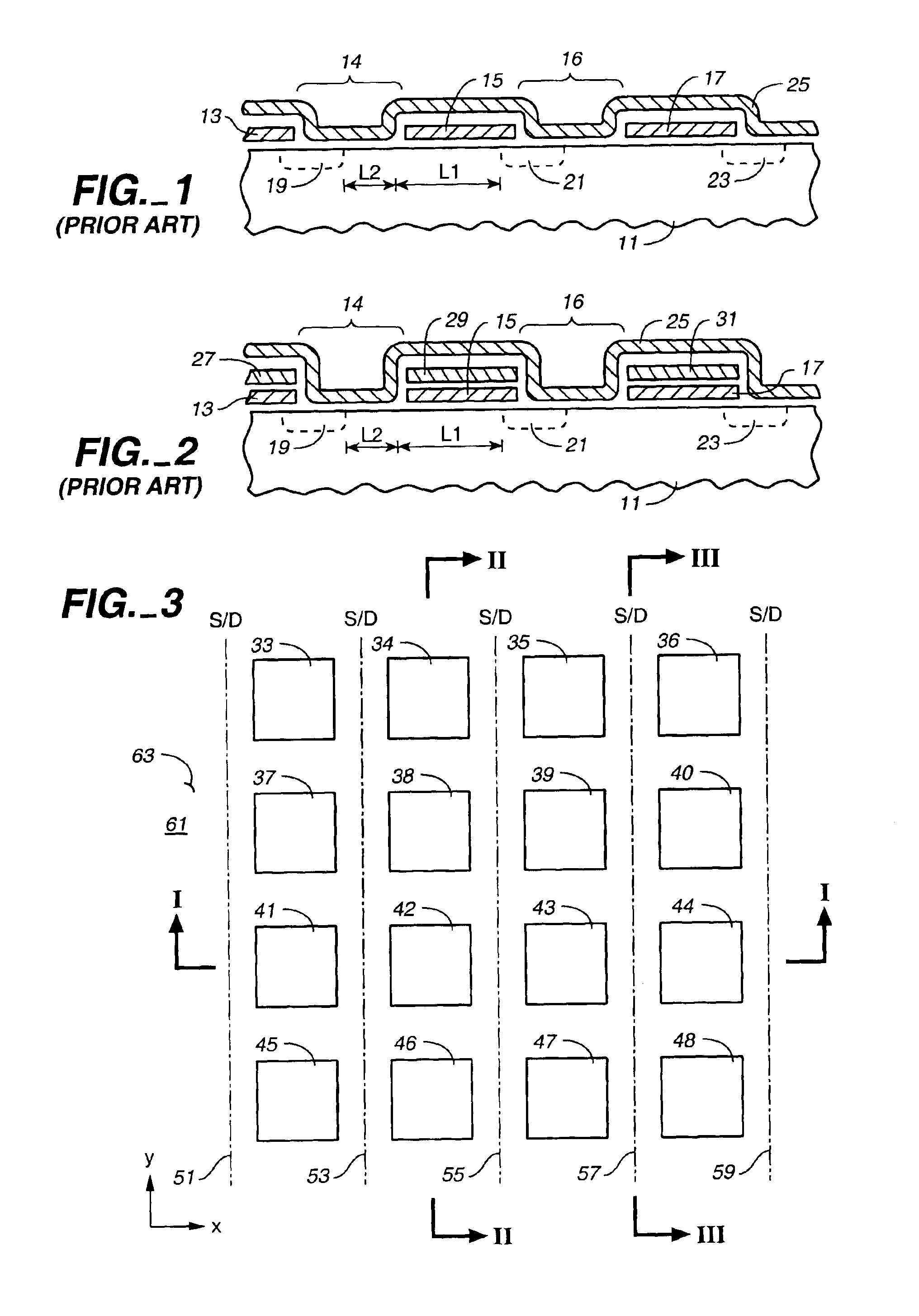

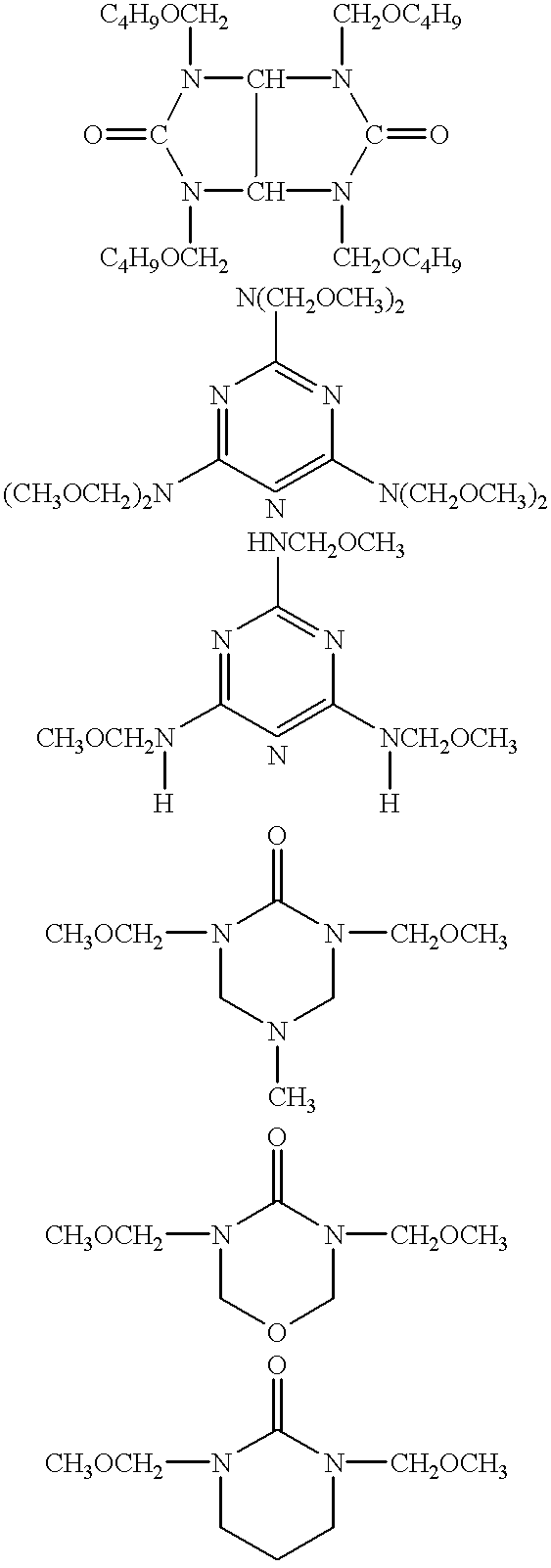

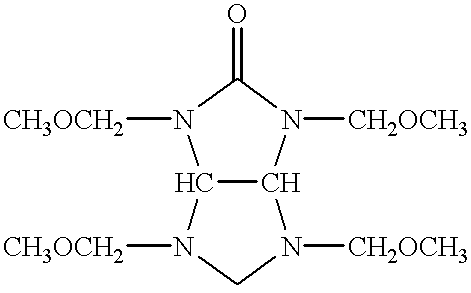

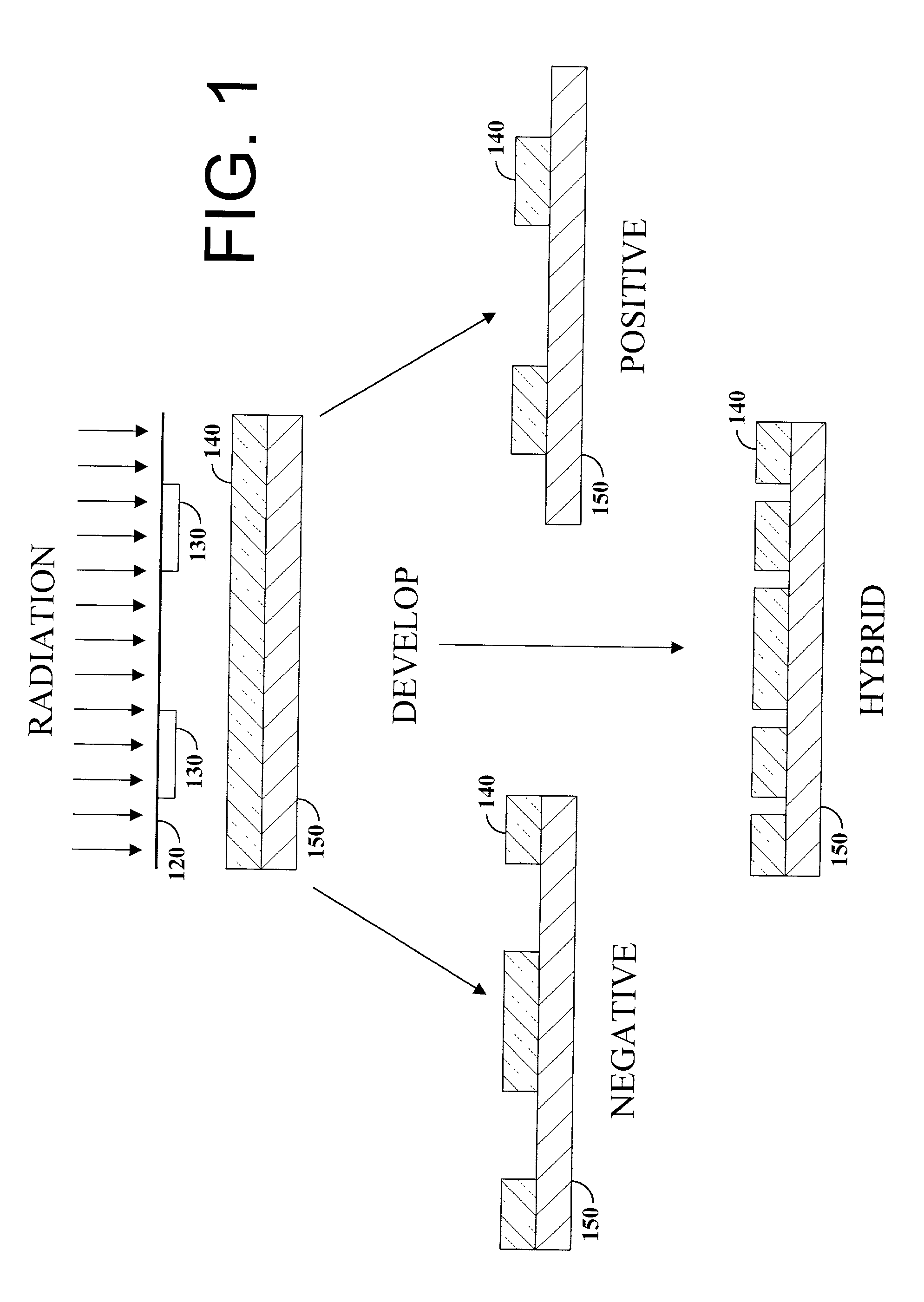

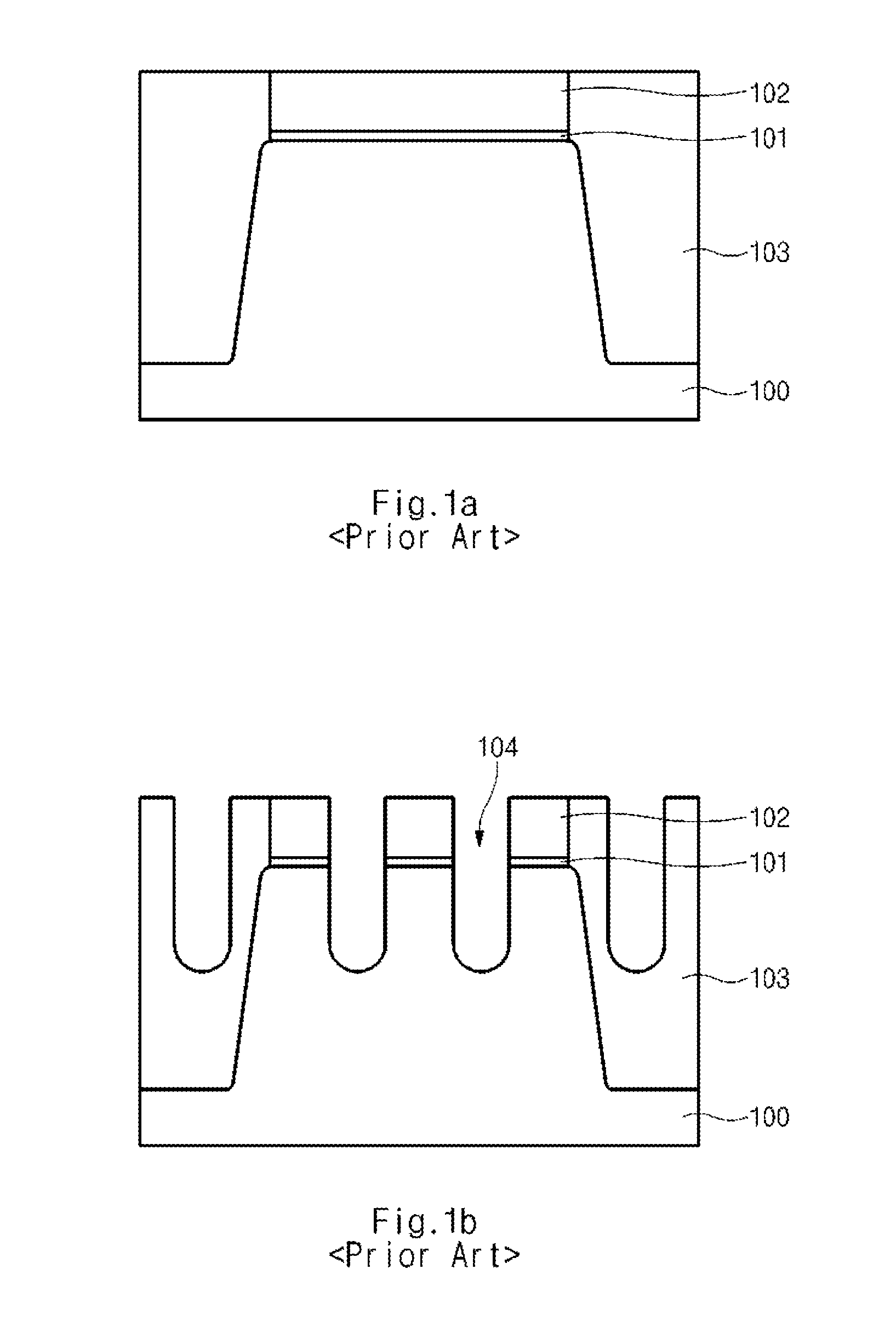

Fabrication of a high density long channel dram gate with or without a grooved gate

InactiveUS20010003034A1Limit leakage currentIncrease channel lengthTransistorSolid-state devicesSize increaseImage enhancement

The present invention lengthens gate conductors used in memory chips to limit leakage current, while still allowing the overall size of cells to remain the same. The channel length for each gate is increased by decreasing the size of spaces between gates. Decreases in space size occurs by using photolithographic image enhancement techniques. These techniques allow the space between gate conductors to be smaller while the gate size increases. In addition, a groove may be added that additionally lengthens the effective channel length and provides an additional electrical shield to limit leakage current. These techniques lead to the same density memory cells for a given process with less leakage. Finally, if grooved gate structures are used, having a longer gate conductor allows a three sigma process to be used, which increases yields.

Owner:IBM CORP

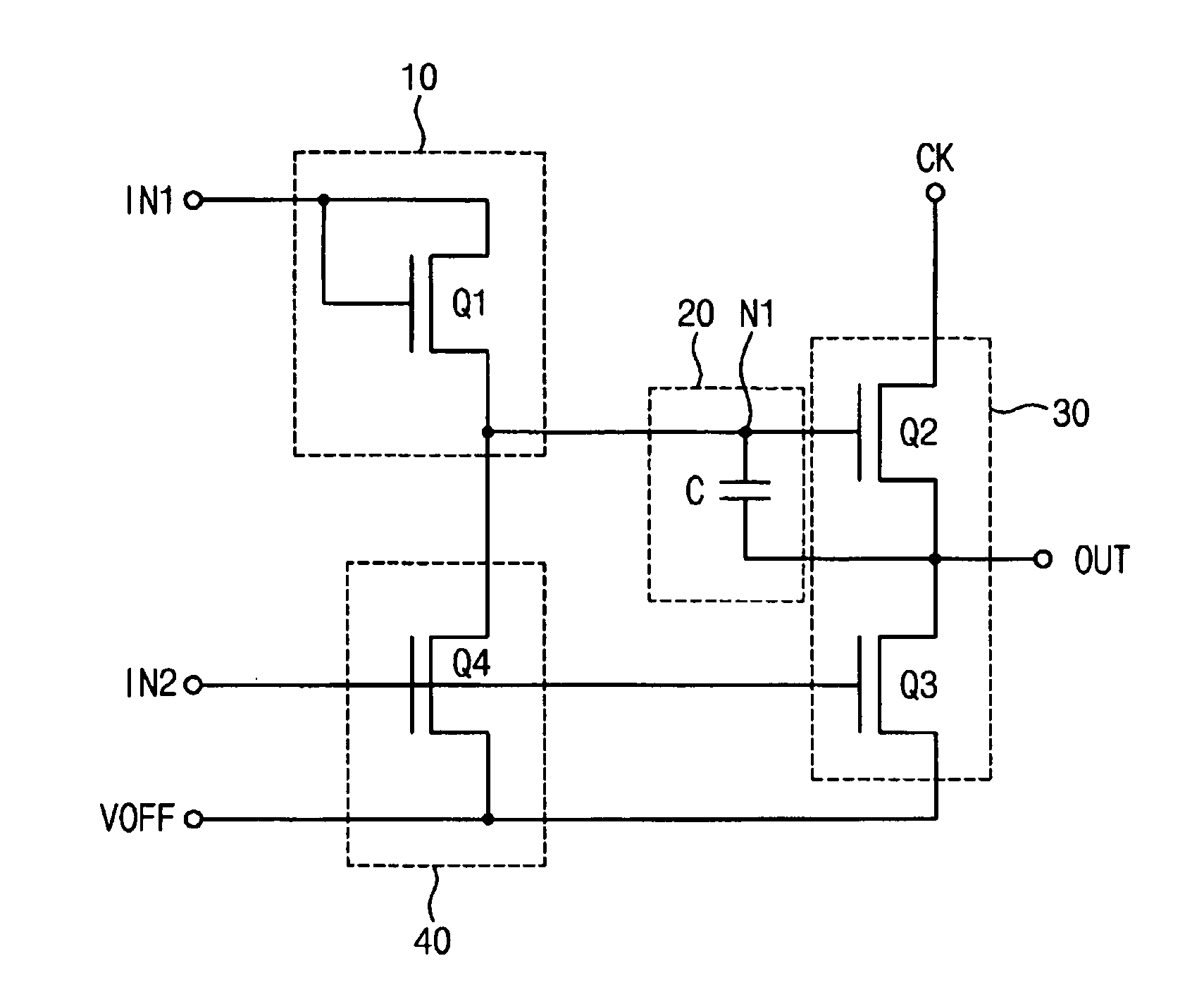

Shift register and display device having the same, and method thereof

InactiveUS20060267912A1Charging rateImprove output waveformStatic indicating devicesDigital data processing detailsShift registerDisplay device

A shift register invention includes a plurality of stages outputting a plurality of output signals, in sequence. Each of the stages includes a driving part and a discharging part. The driving part includes a driving transistor. The driving transistor has a control electrode, a first electrode, a second electrode and a channel layer. The control electrode receives one of a start signal or an output signal of a previous stage. The first electrode receives a clock signal. The second electrode outputs an output signal of a present stage. The channel layer has a different length from a channel layer of a driving transistor of the previous stage. The discharging part discharges the output signal of the present stage based on an output signal of a next stage, therefore improving the electrical characteristics of the shift register.

Owner:SAMSUNG ELECTRONICS CO LTD

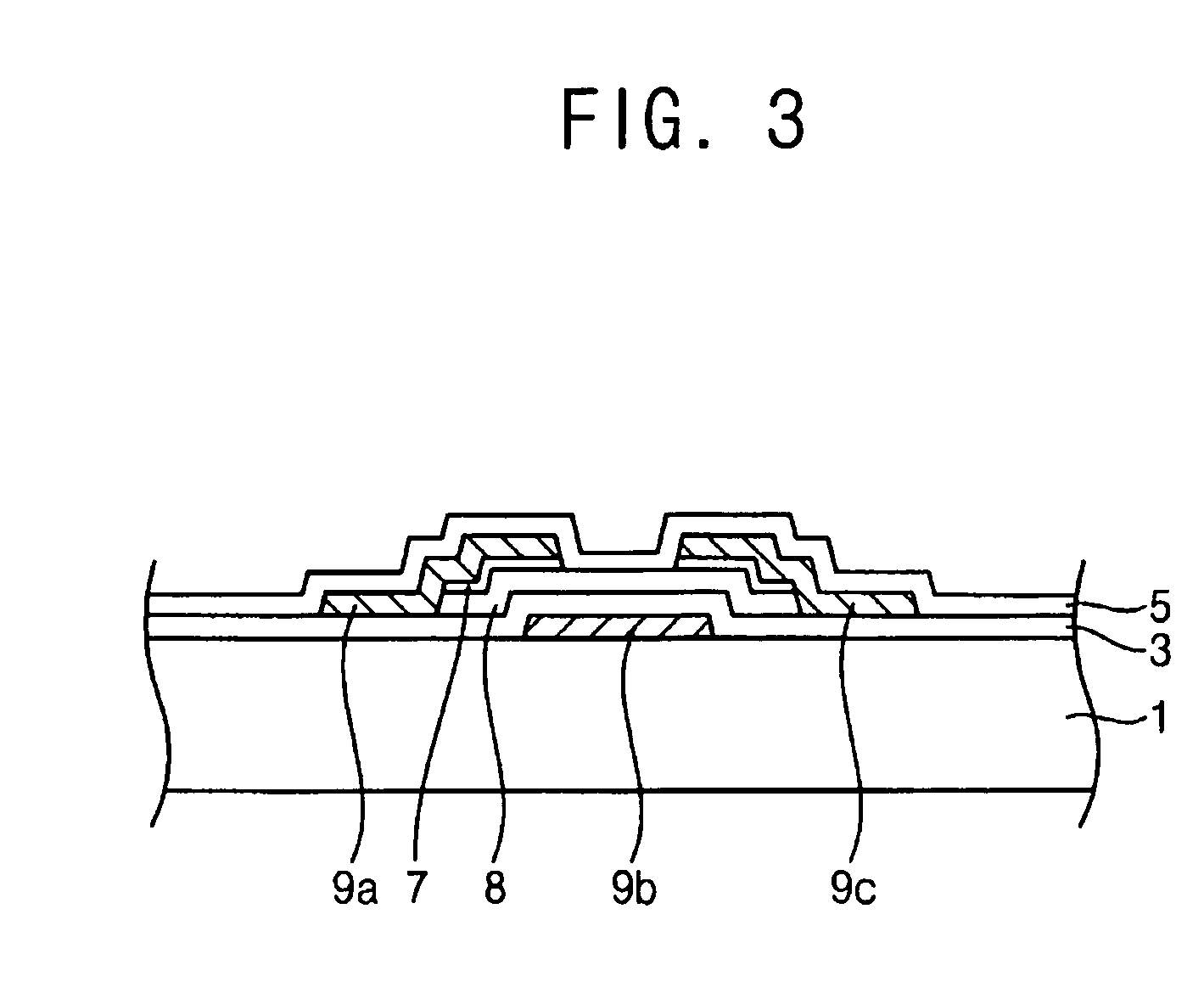

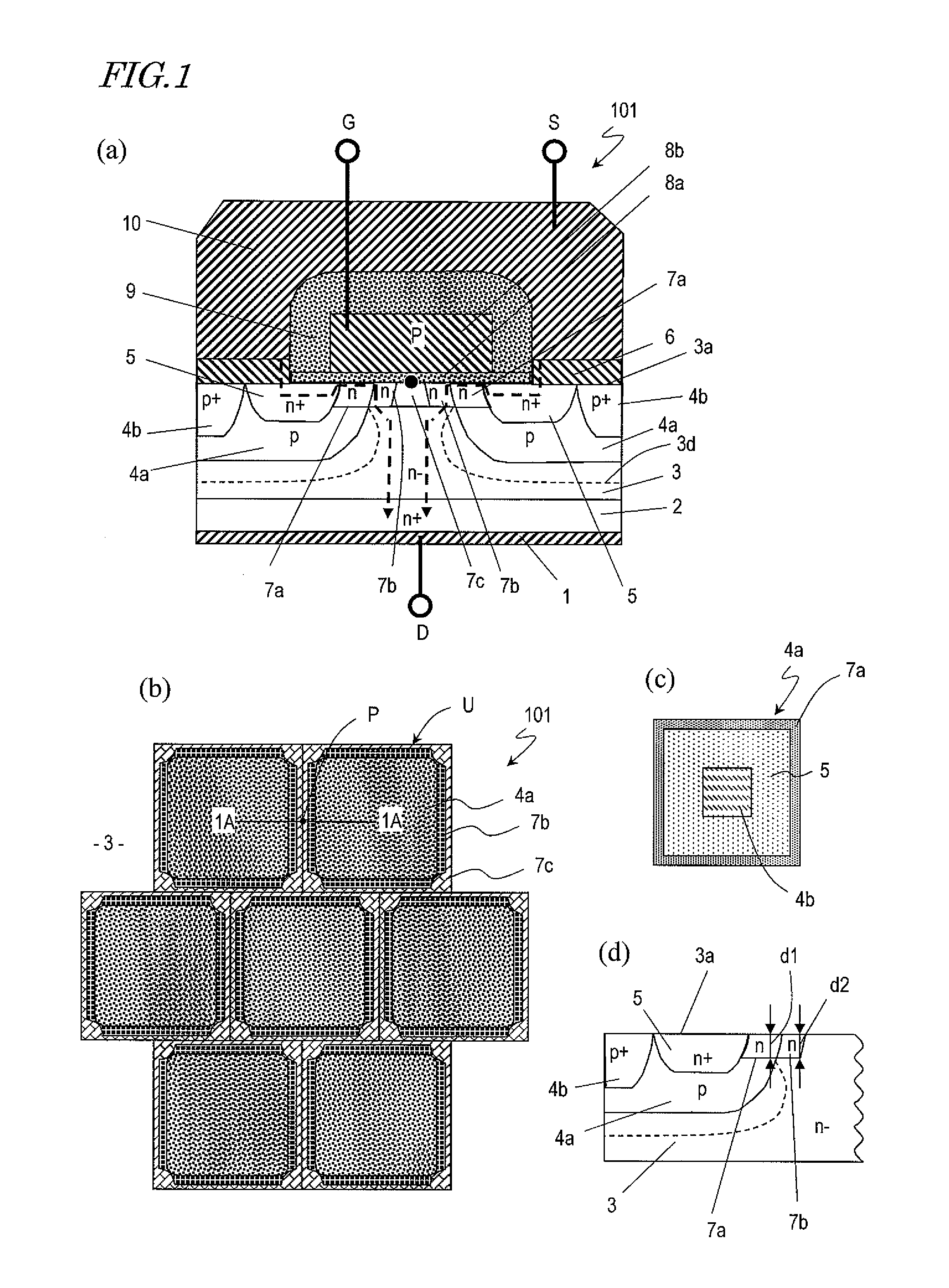

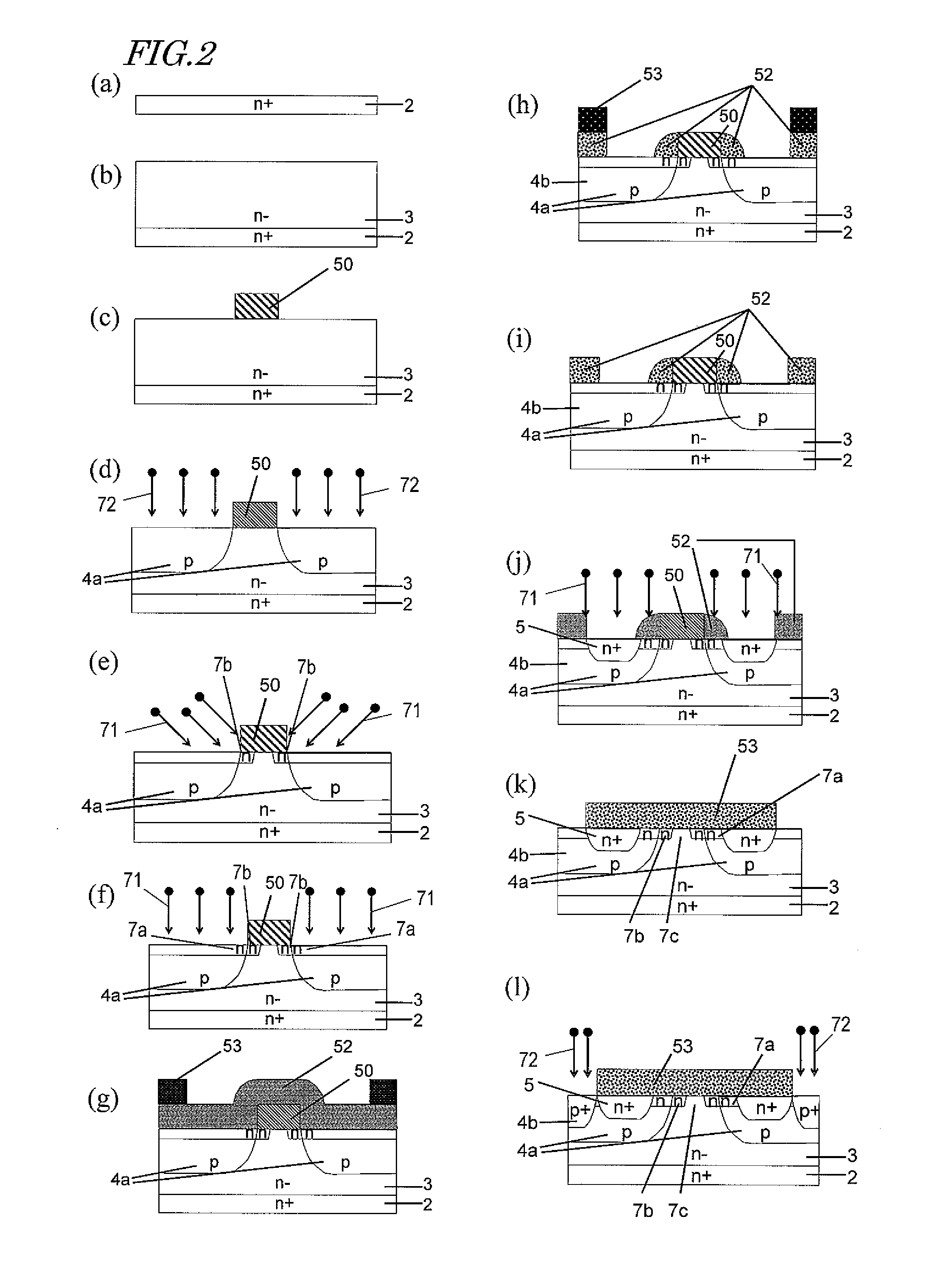

Semiconductor device and process for production thereof

InactiveUS8421151B2Increase channel lengthReduce channel resistanceSemiconductor/solid-state device manufacturingSemiconductor devicesBody regionSemiconductor

Owner:PANASONIC CORP

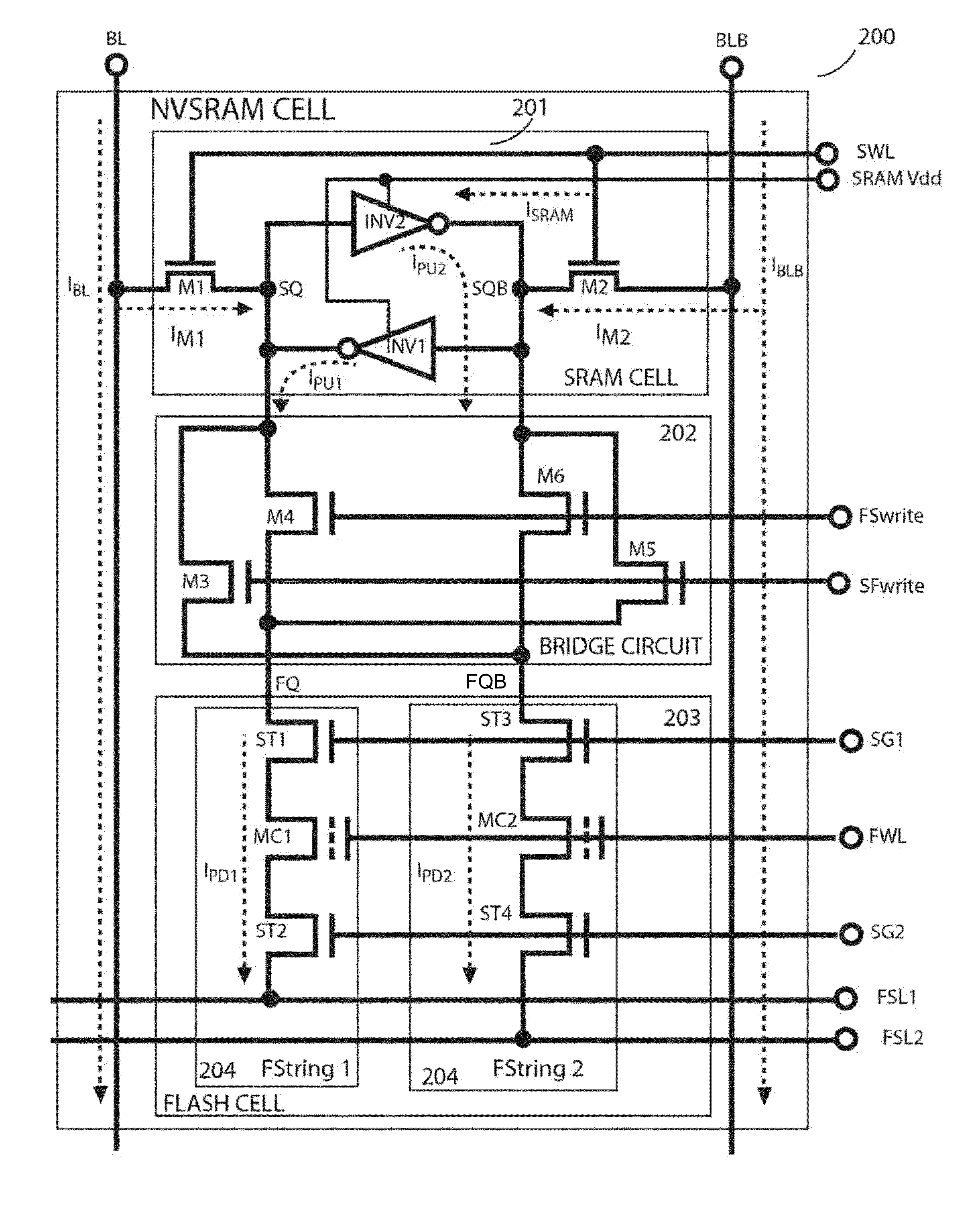

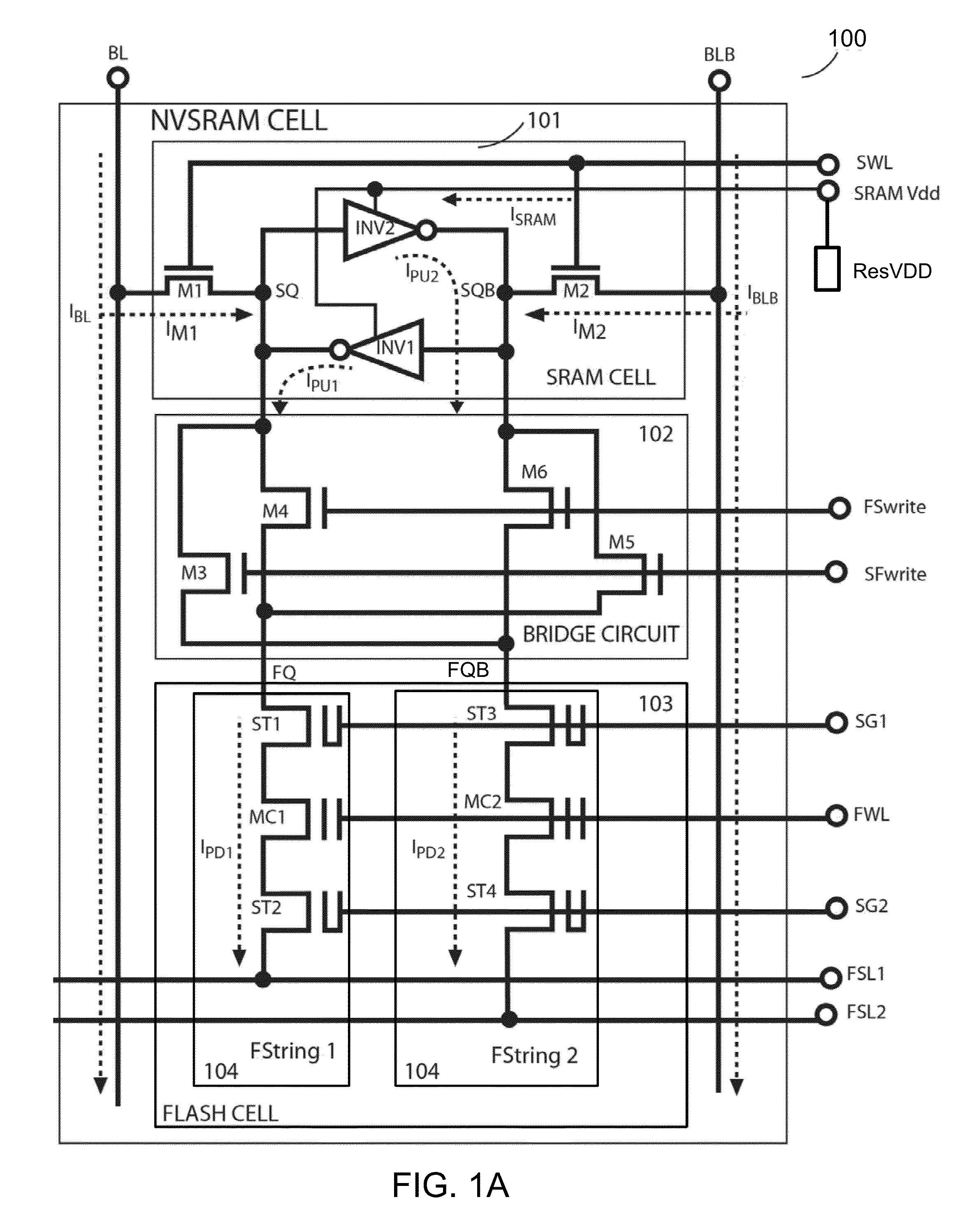

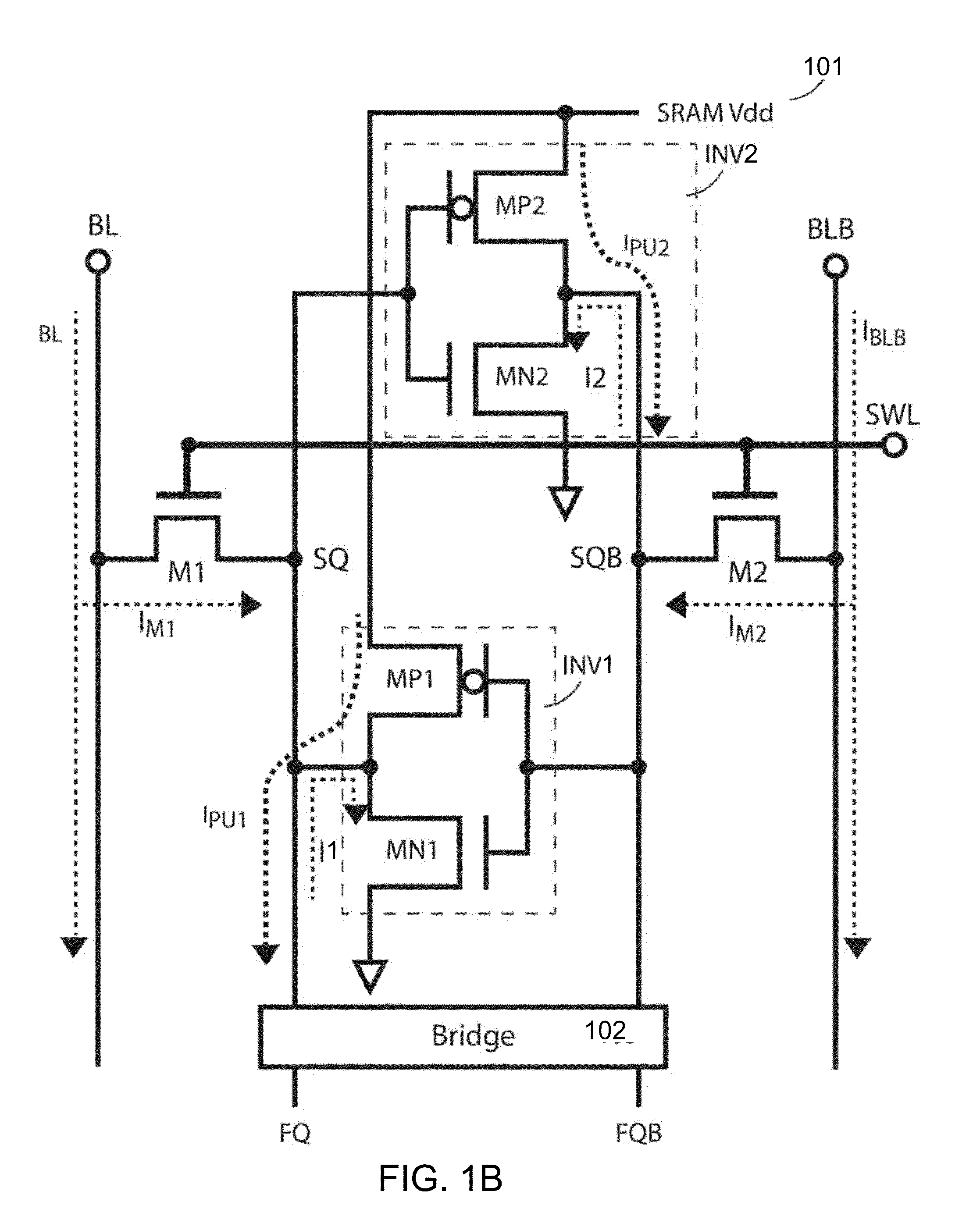

Method and architecture for improving defect detectability, coupling area, and flexibility of nvsram cells and arrays

InactiveUS20140085978A1Increase total coupling areaQuick filterSolid-state devicesRead-only memoriesNvSRAMPolycrystalline silicon

Several preferred embodiments of 1S1F 16T NVSRAM, 1S1F 20T NVSRAM, 1S2F 22T NVSRAM, 1S2F 14T NVSRAM cells are proposed, regardless of 1-poly, 2-poly, PMOS or NOS flash cell structures. Two separate sourcelines for the paired flash Strings are also proposed for easy adding ability for the NVSRAM circuit to detect the marginally erased Vt0 and marginally programmed Vt1 of the paired flash cell. By increasing an resistance added to common SRAM power line, the pull-down current through flash Strings to grounding source line can be made much larger than the pull-up current to improve SFwrite program operation. Simple method by increasing flash cell channel length to effectively enhance coupling area is applied to secure SRAM-to-Flash store operation under self-boost-program-inhibit scheme. 1S2F architecture also provide flexibility for alternate erasing and programming during both a recall and store operation.

Owner:APLUS FLASH TECH

Fin FET and method of fabricating same

ActiveUS7217623B2Improving swing characteristicReducing electric fieldTransistorSolid-state devicesInsulation layerEngineering

A fin field effect transistor (fin FET) is formed using a bulk silicon substrate and sufficiently guarantees a top channel length formed under a gate, by forming a recess having a predetermined depth in a fin active region and then by forming the gate in an upper part of the recess. A device isolation film is formed to define a non-active region and a fin active region in a predetermined region of the substrate. In a portion of the device isolation film a first recess is formed, and in a portion of the fin active region a second recess having a depth shallower than the first recess is formed. A gate insulation layer is formed within the second recess, and a gate is formed in an upper part of the second recess. A source / drain region is formed in the fin active region of both sides of a gate electrode.

Owner:SAMSUNG ELECTRONICS CO LTD

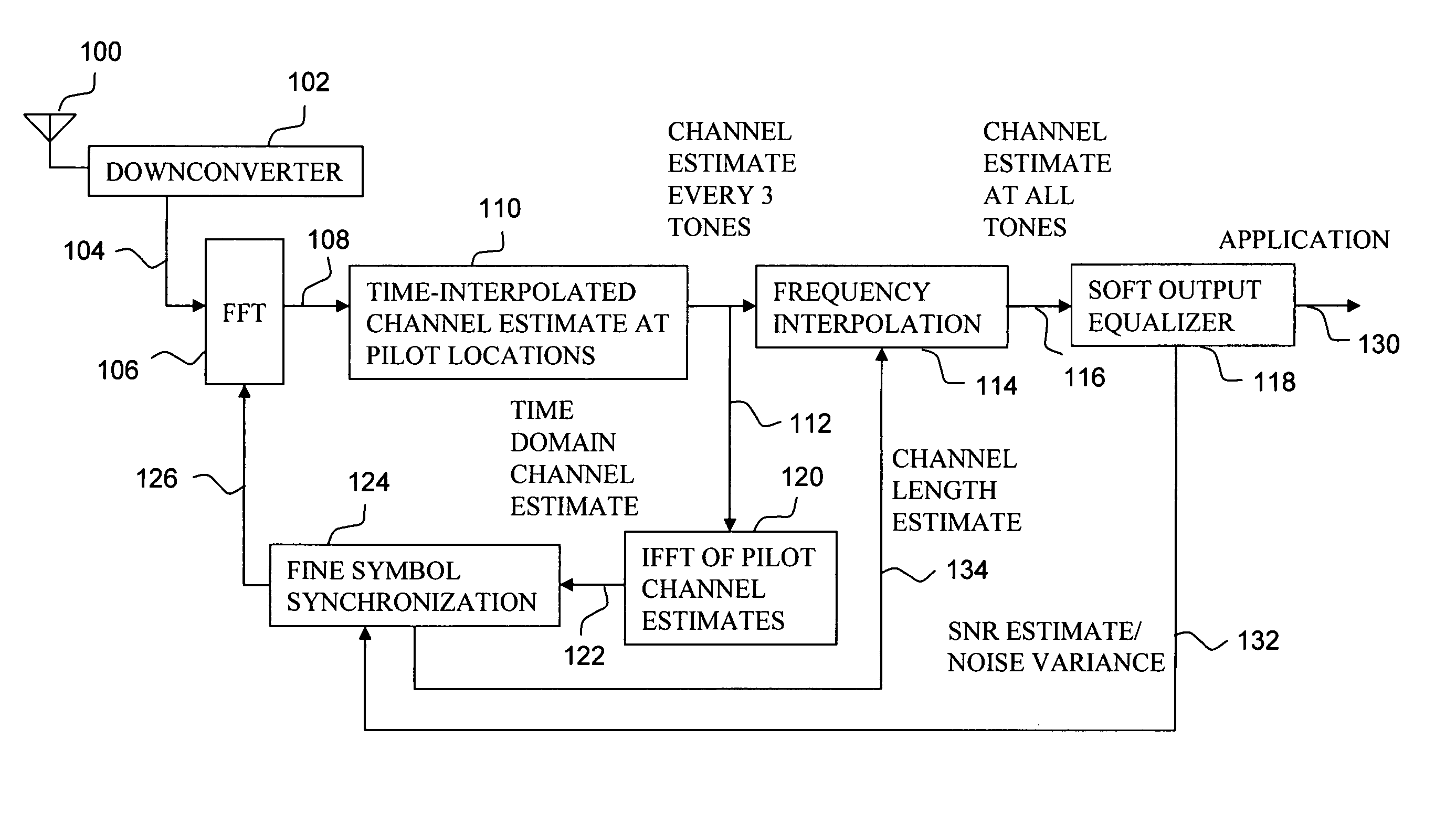

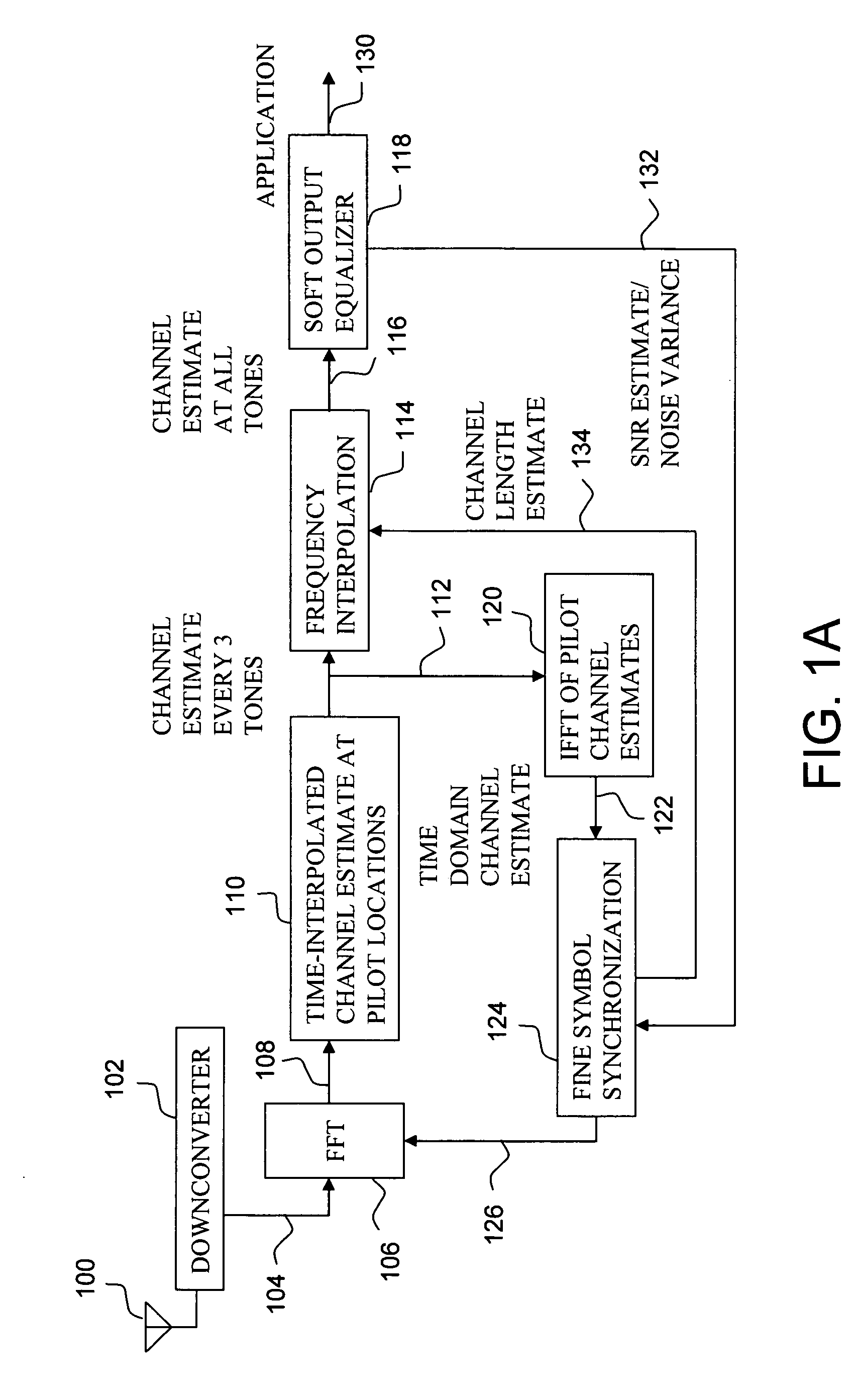

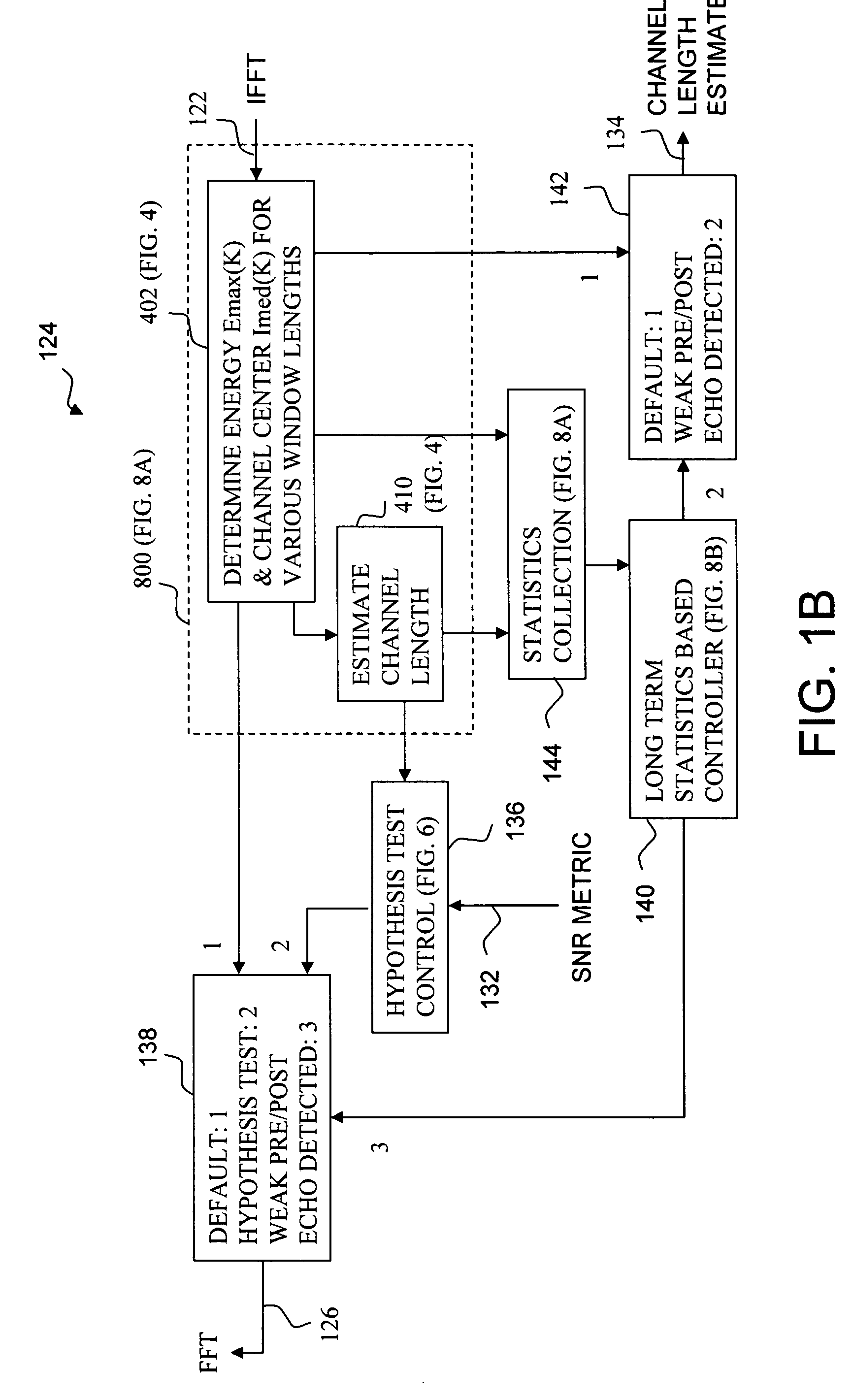

Channel length estimation and accurate FFT window placement for high-mobility OFDM receivers in single frequency networks

ActiveUS20060222099A1Increase channel lengthImproved channel estimationAmplitude-modulated carrier systemsSecret communicationTransmitterSingle-frequency network

A method of estimating a channel length (304) in a wireless receiver is disclosed. The receiver receives a signal (122) from a remote transmitter. The receiver selects a plurality (K) of different candidate channel lengths and determines a respective criterion value (402) of the signal for each of the plurality of different candidate channel lengths. The receiver selects a channel length (410) from the plurality of different candidate channel lengths in response to the respective criterion value (404).

Owner:TEXAS INSTR INC

Split gate flash memory

ActiveUS7208796B2Avoid short lengthHighly integratedTransistorSolid-state devicesGate dielectricIsolation layer

A split gate flash memory is provided. Trenches are formed in the substrate to define active layers. The device isolation layers are formed in the trenches. The surface of the device isolation layers is lower than the surface of the active layers. The stacked gate structures each including a tunneling dielectric layer, a floating gate and a cap layer are formed on the active layers. The inter-gate dielectric layers are formed on the sidewalls of the stacked gate structures. The select gates are formed on one side of the stacked gate structure and across the active layer. The select gate dielectric layers are formed between the select gates and the active layers. The source regions are formed in the active layers on the other side of the stacked gate structures. The drain regions are formed in the active layers on one side of the select gates.

Owner:POWERCHIP SEMICON MFG CORP

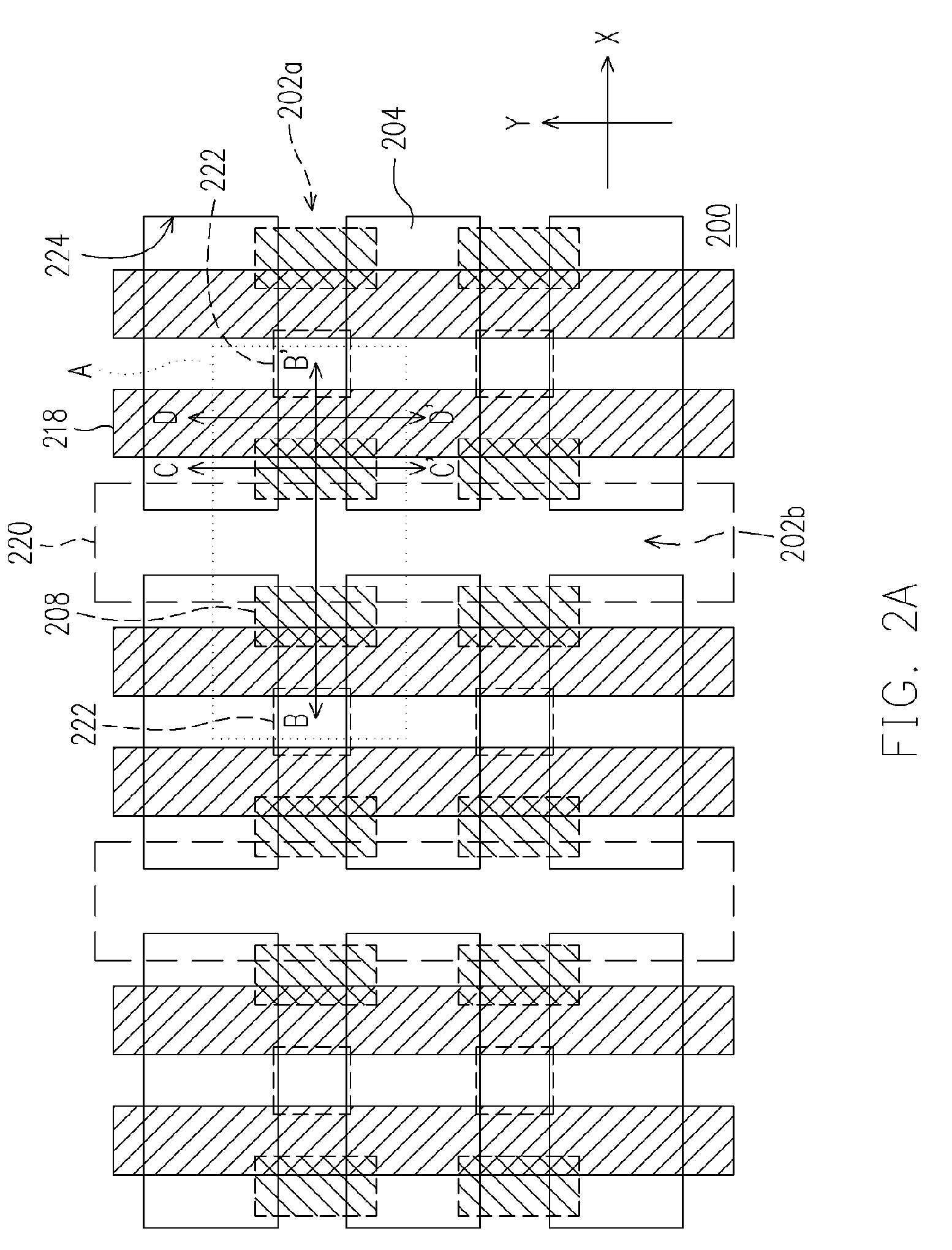

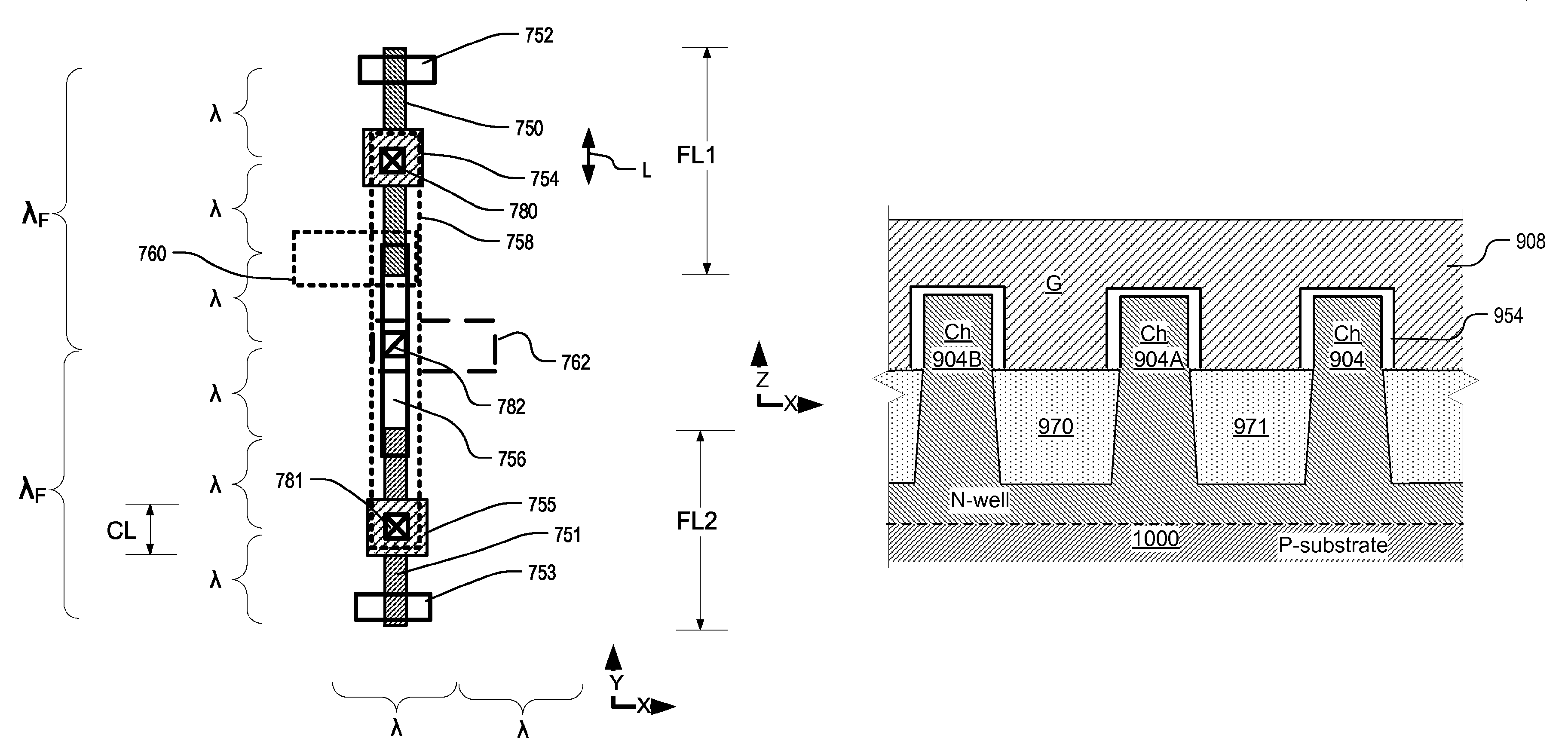

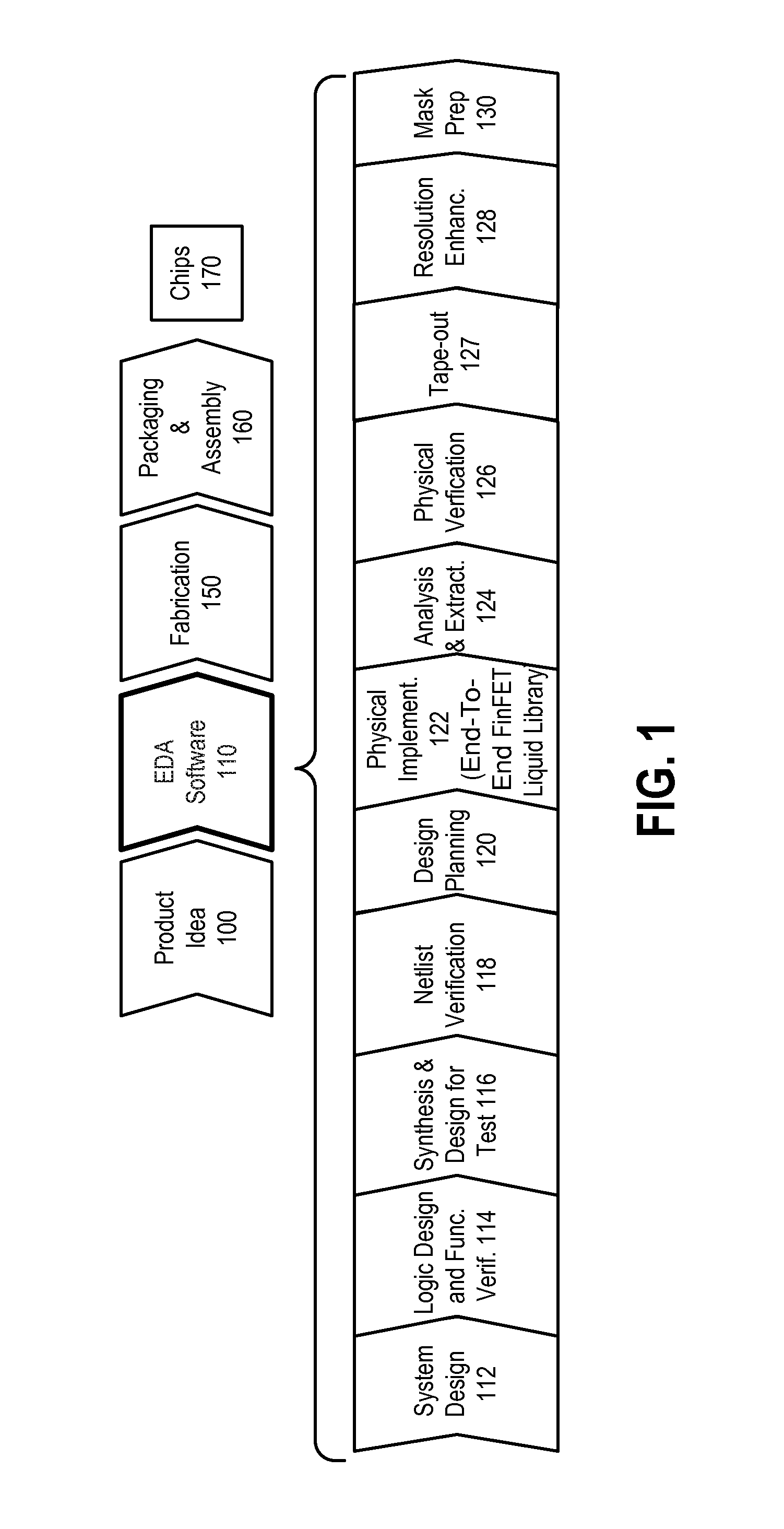

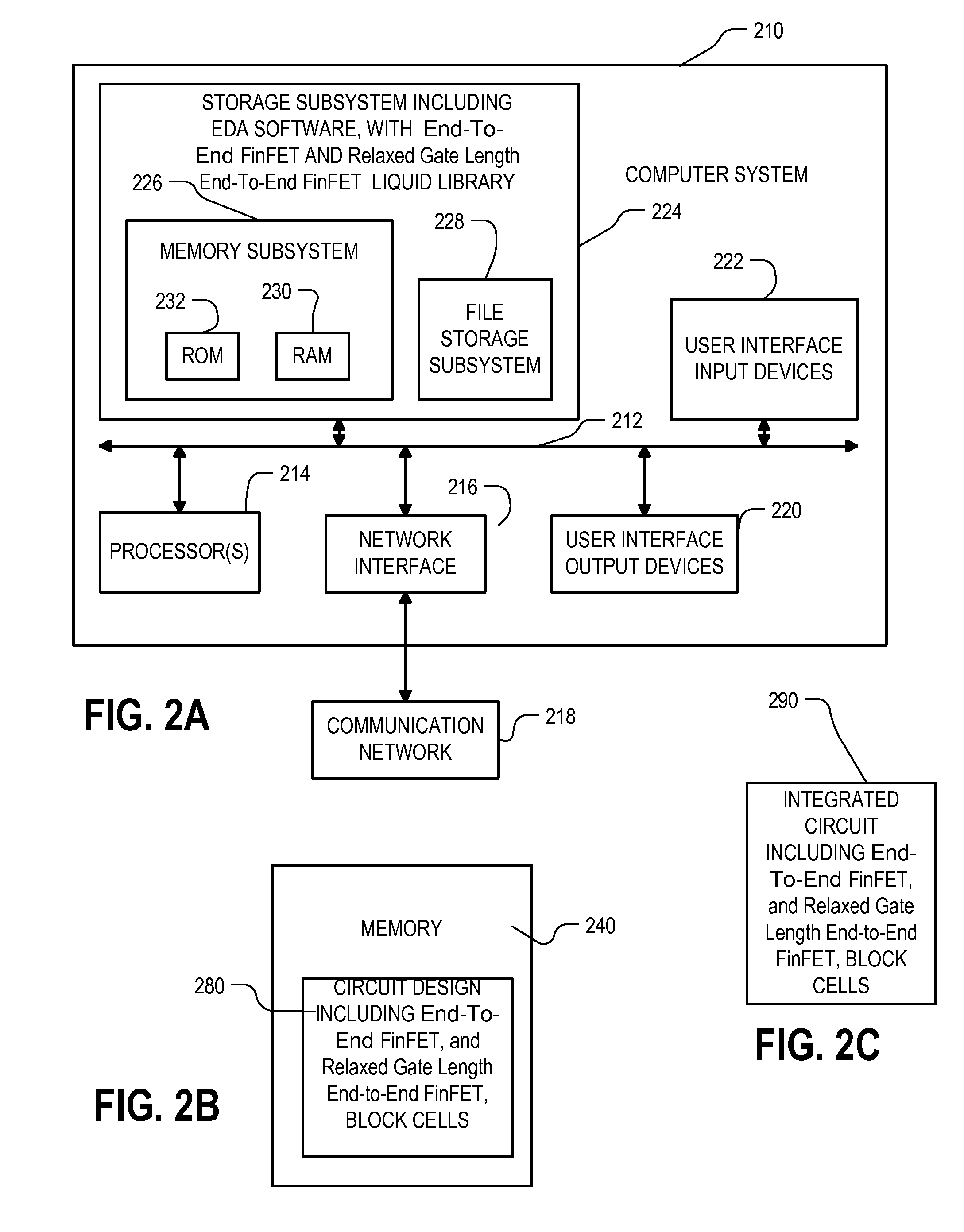

N-channel and P-channel end-to-end finFET cell architecture with relaxed gate pitch

ActiveUS8723268B2Increase channel lengthSuppress leakageSemiconductor/solid-state device detailsSolid-state devicesEngineering physicsSemiconductor

A finFET block architecture uses end-to-end finFET blocks in which the fin lengths are at least twice the contact pitch, whereby there is enough space for interlayer connectors to be placed on the proximal end and the distal end of a given semiconductor fin, and on the gate element on the given semiconductor fin. A first set of semiconductor fins having a first conductivity type and a second set of semiconductor fins having a second conductivity type can be aligned end-to-end. Interlayer connectors can be aligned over corresponding semiconductor fins which connect to gate elements.

Owner:SYNOPSYS INC

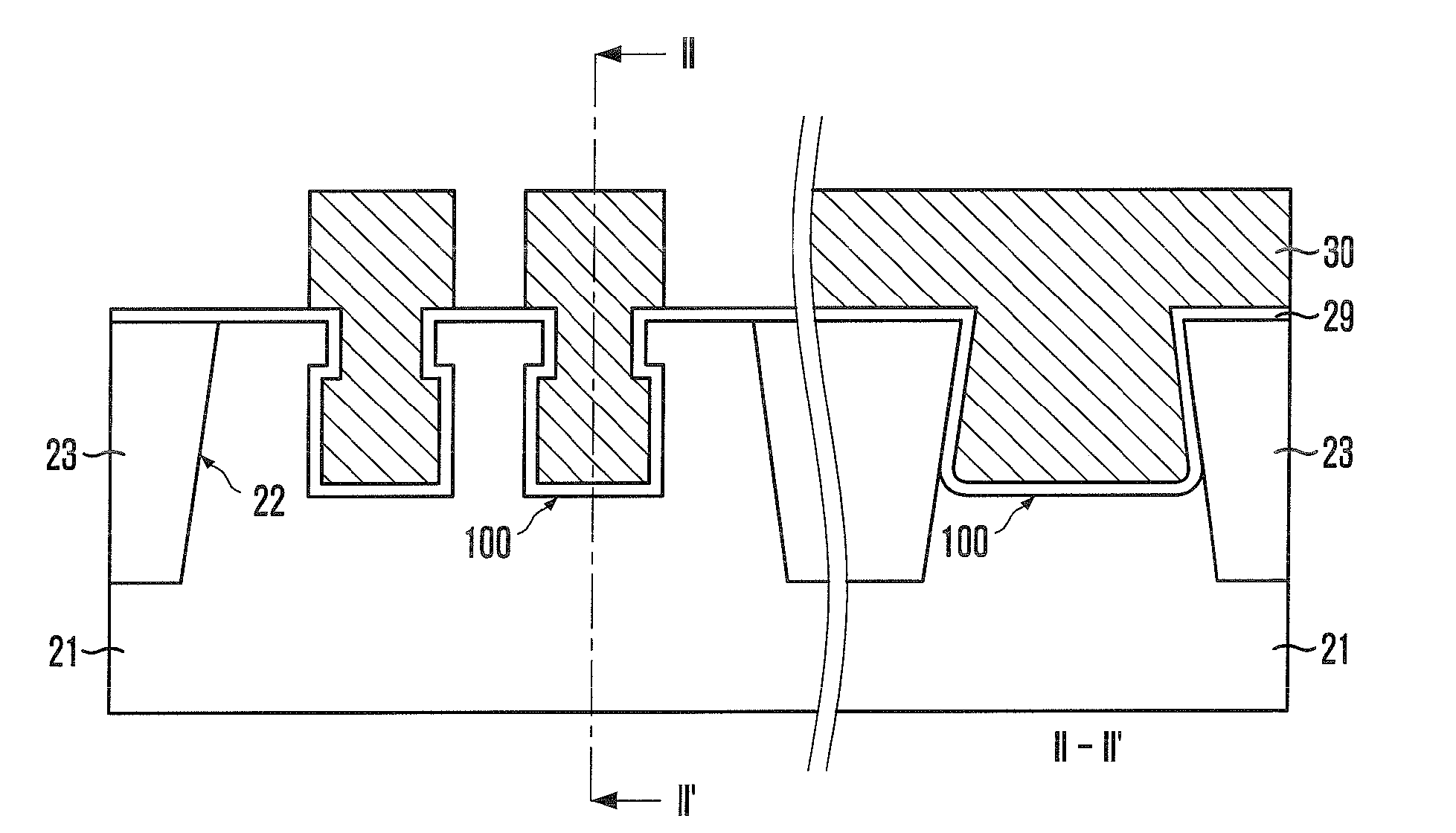

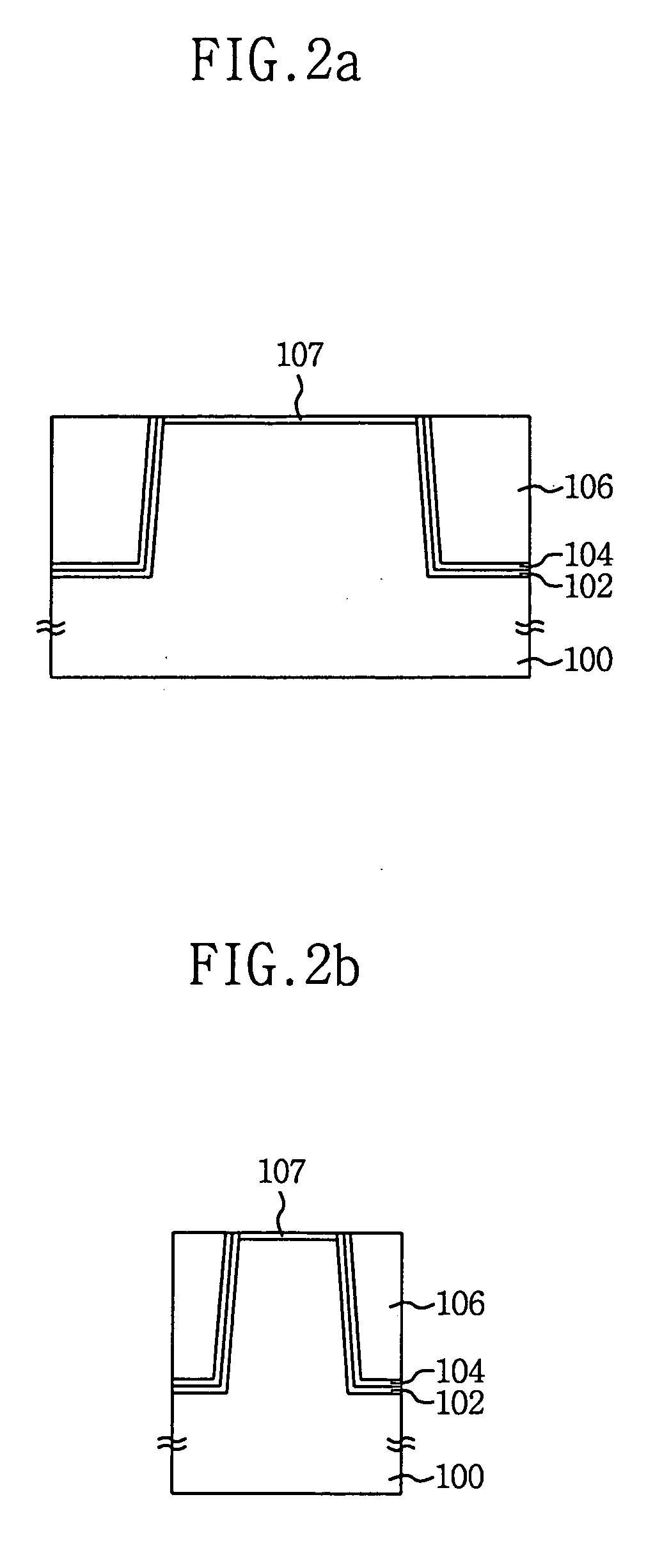

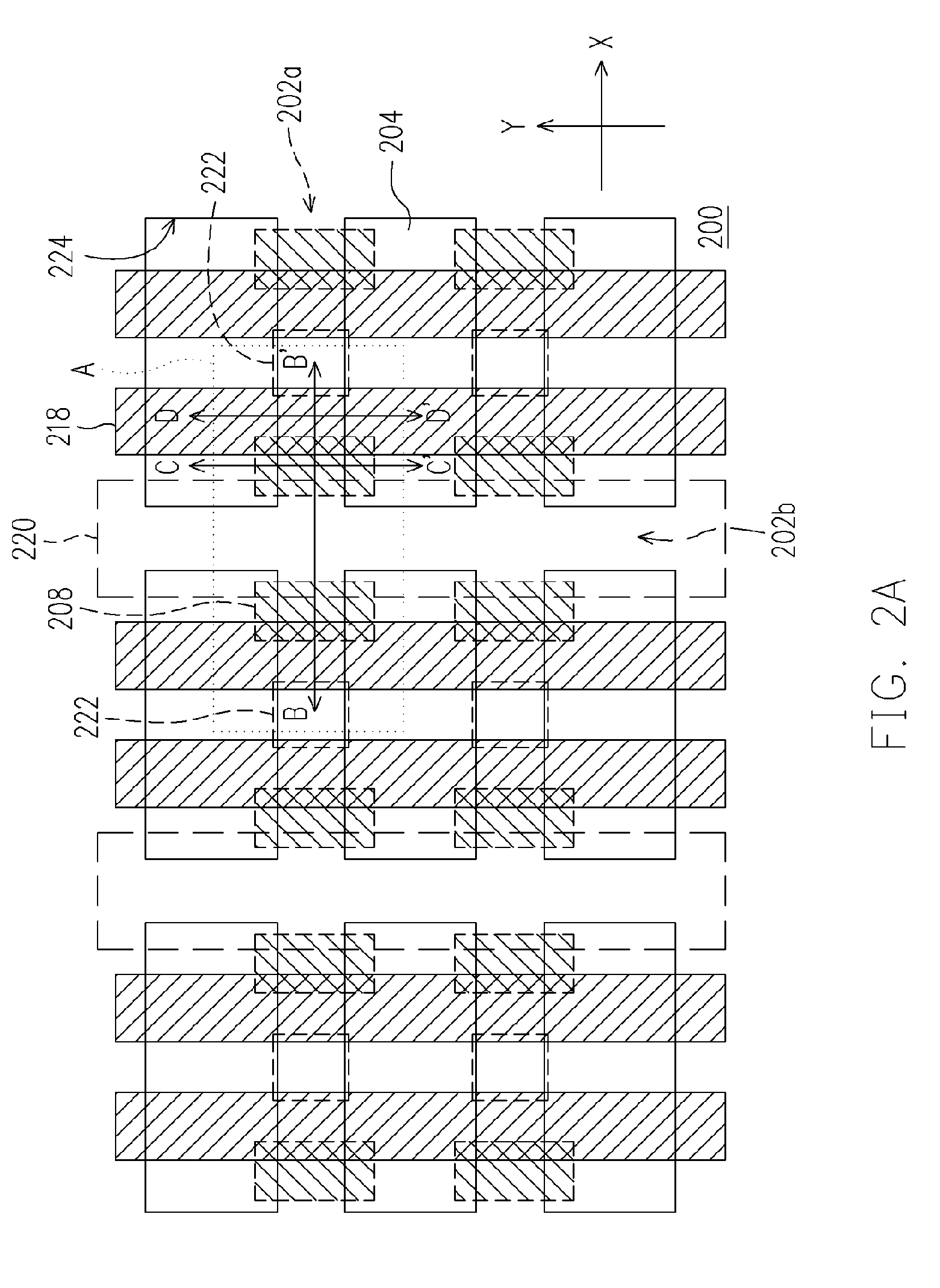

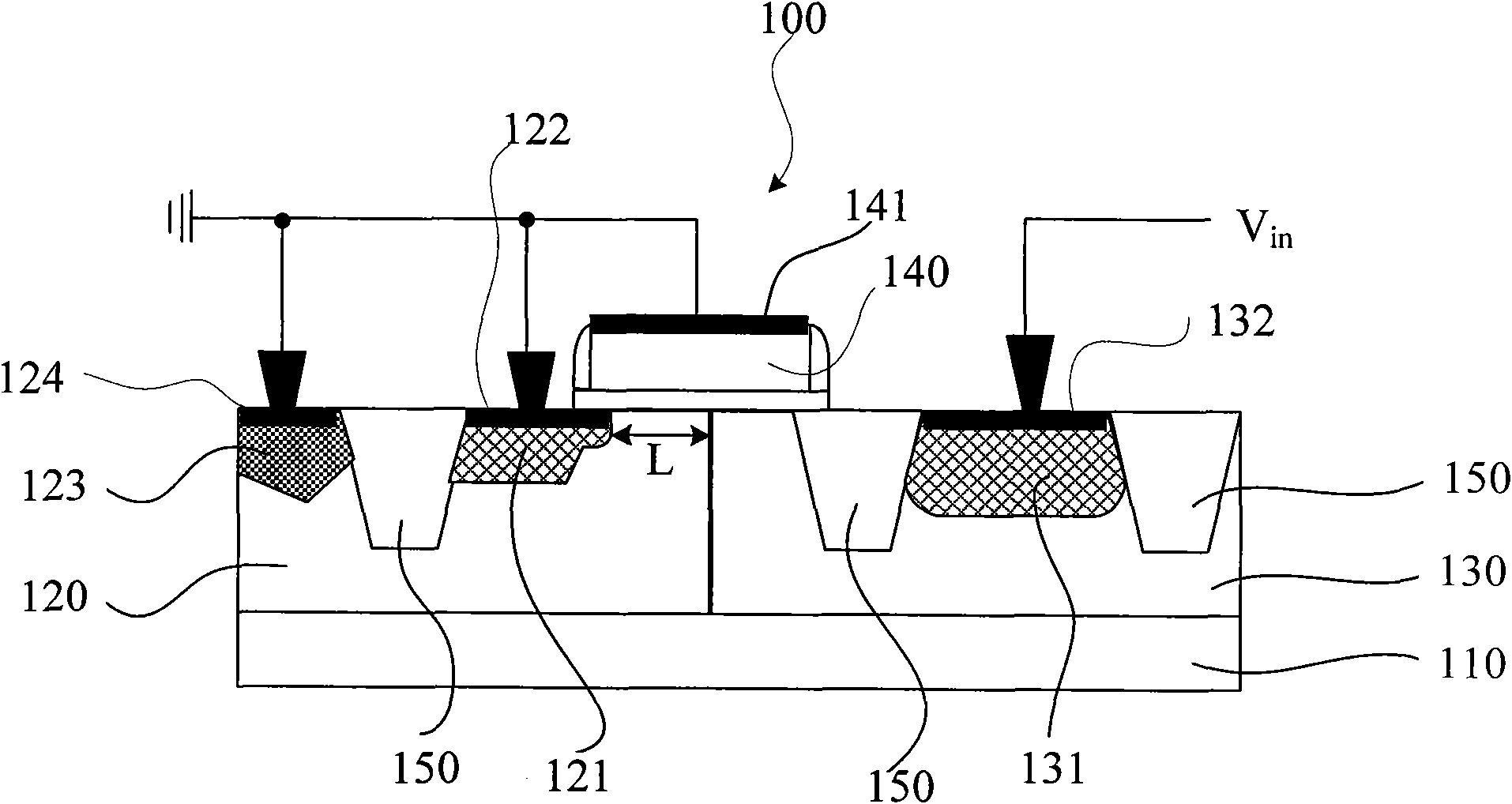

Semiconductor device and method of forming the same

InactiveUS20080073708A1Increase channel lengthIncrease parasitic capacitanceSolid-state devicesSemiconductor/solid-state device manufacturingEngineeringTrench gate

A semiconductor device and a method of forming the semiconductor device are provided. The semiconductor device may include, but is not limited to, a semiconductor substrate and a third array of semiconductor elements. The semiconductor substrate may include a first array of separate grooves, a second array of separate active regions, and at least an isolating region, the isolating region separating the separate active regions from each other. Each separate groove extends in the separate active region and does not extend over the isolating region. The third array of semiconductor elements is provided on the semiconductor substrate. Each of the semiconductor elements has an electrically conductive portion that is provided in the separate groove. The semiconductor element may be a trench gate transistor, and the electrically conductive portion may be a gate electrode.

Owner:ELPIDA MEMORY INC

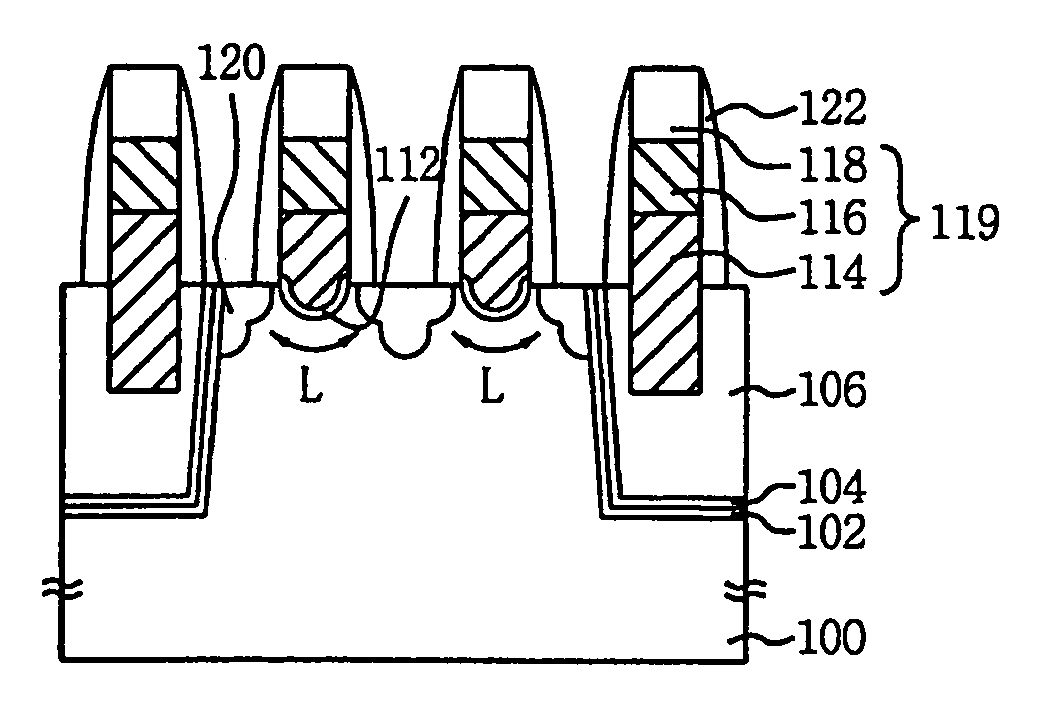

Fin FET and method of fabricating same

ActiveUS20070176245A1Improving swing characteristicReducing electric fieldTransistorSolid-state devicesInsulation layerSilicon

A fin field effect transistor (fin FET) is formed using a bulk silicon substrate and sufficiently guarantees a top channel length formed under a gate, by forming a recess having a predetermined depth in a fin active region and then by forming the gate in an upper part of the recess. A device isolation film is formed to define a non-active region and a fin active region in a predetermined region of the substrate. In a portion of the device isolation film a first recess is formed, and in a portion of the fin active region a second recess having a depth shallower than the first recess is formed. A gate insulation layer is formed within the second recess, and a gate is formed in an upper part of the second recess. A source / drain region is formed in the fin active region of both sides of a gate electrode.

Owner:SAMSUNG ELECTRONICS CO LTD

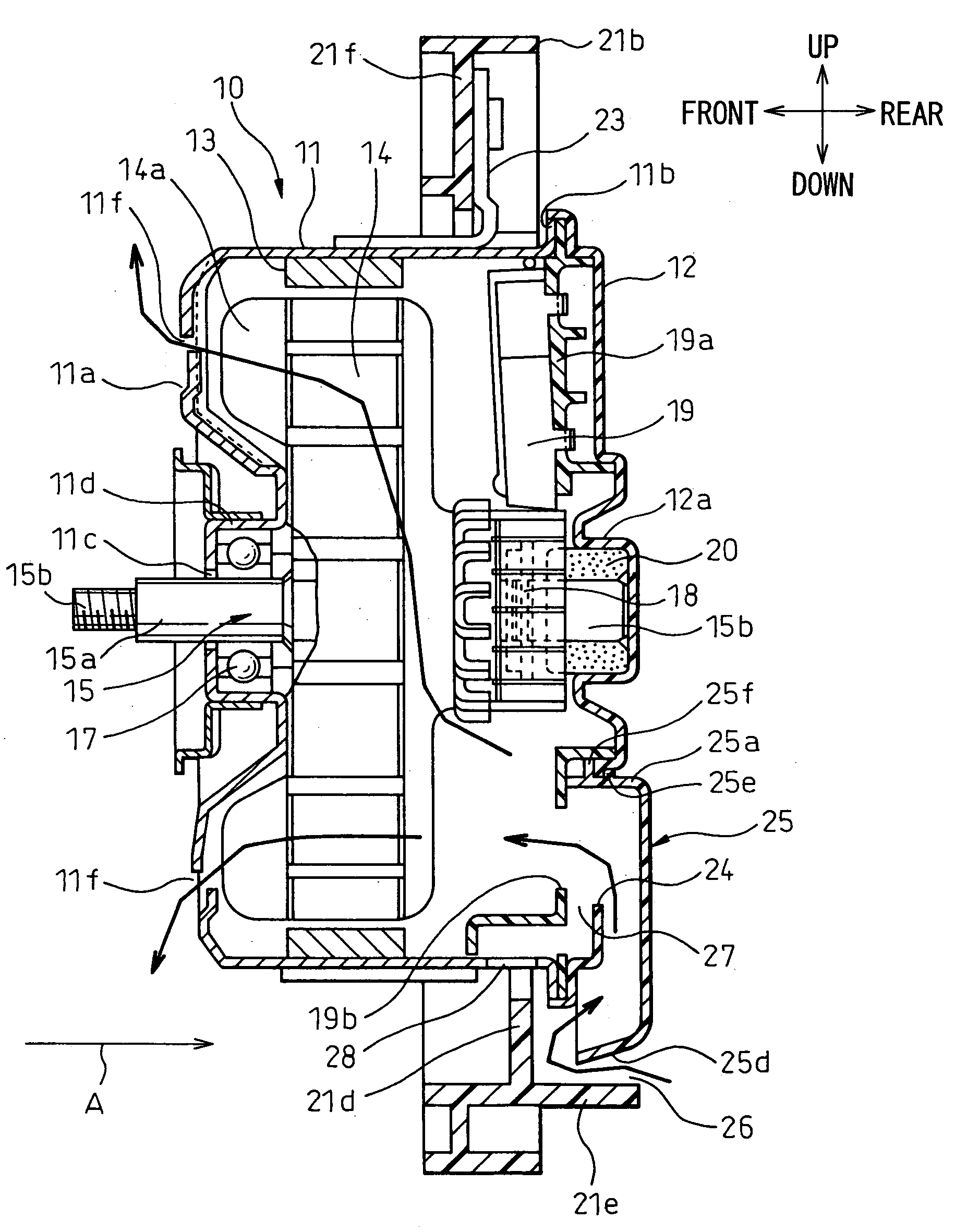

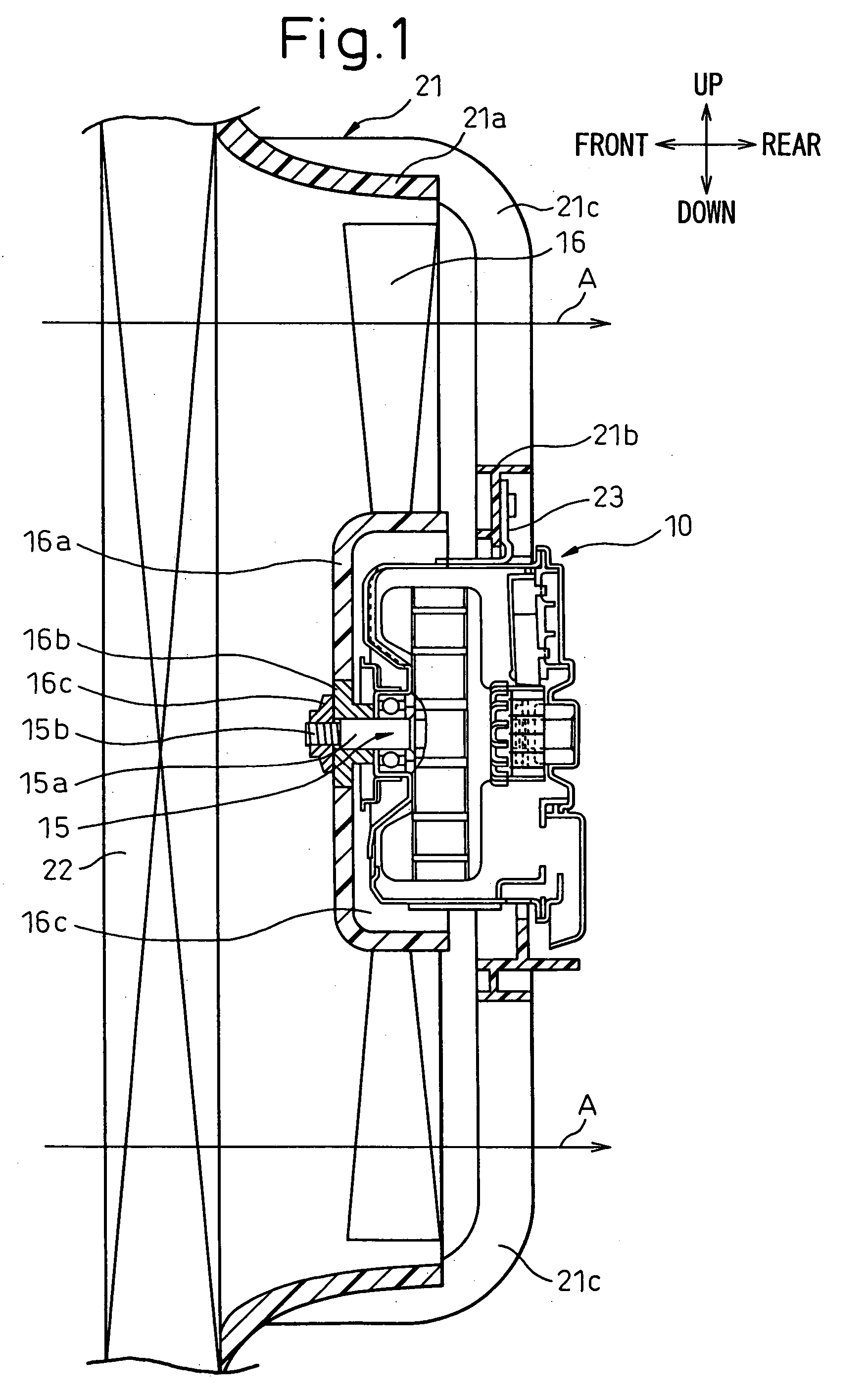

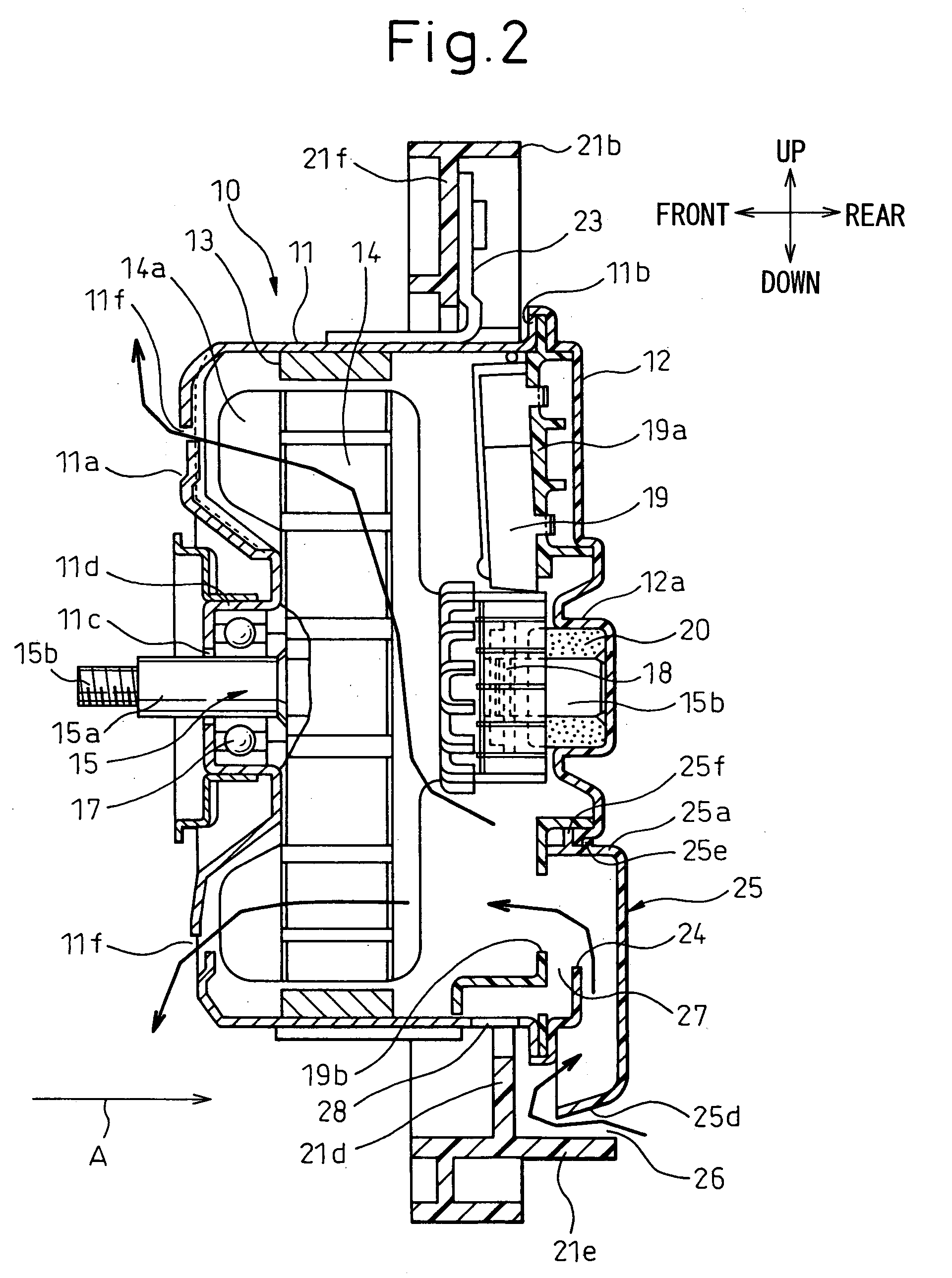

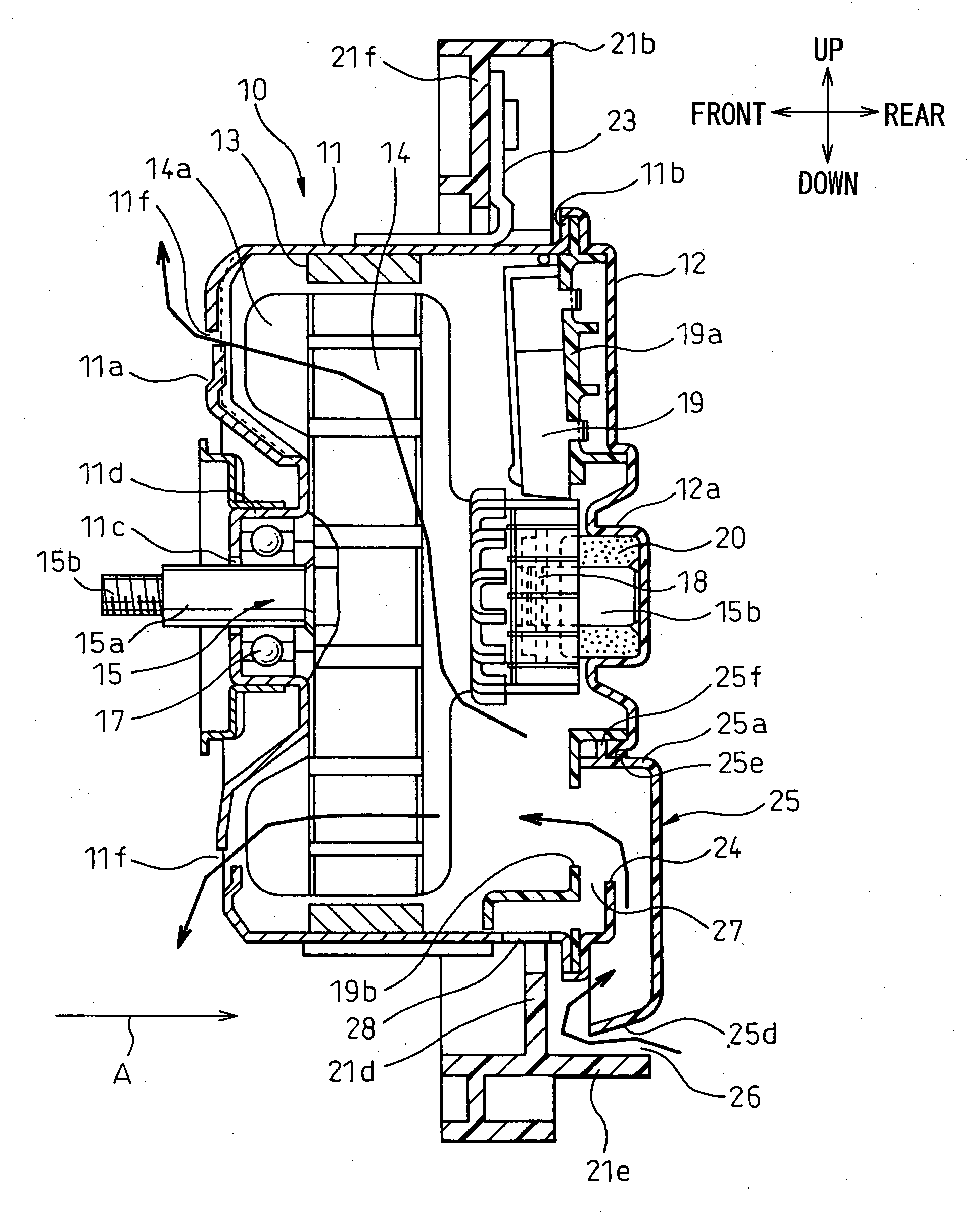

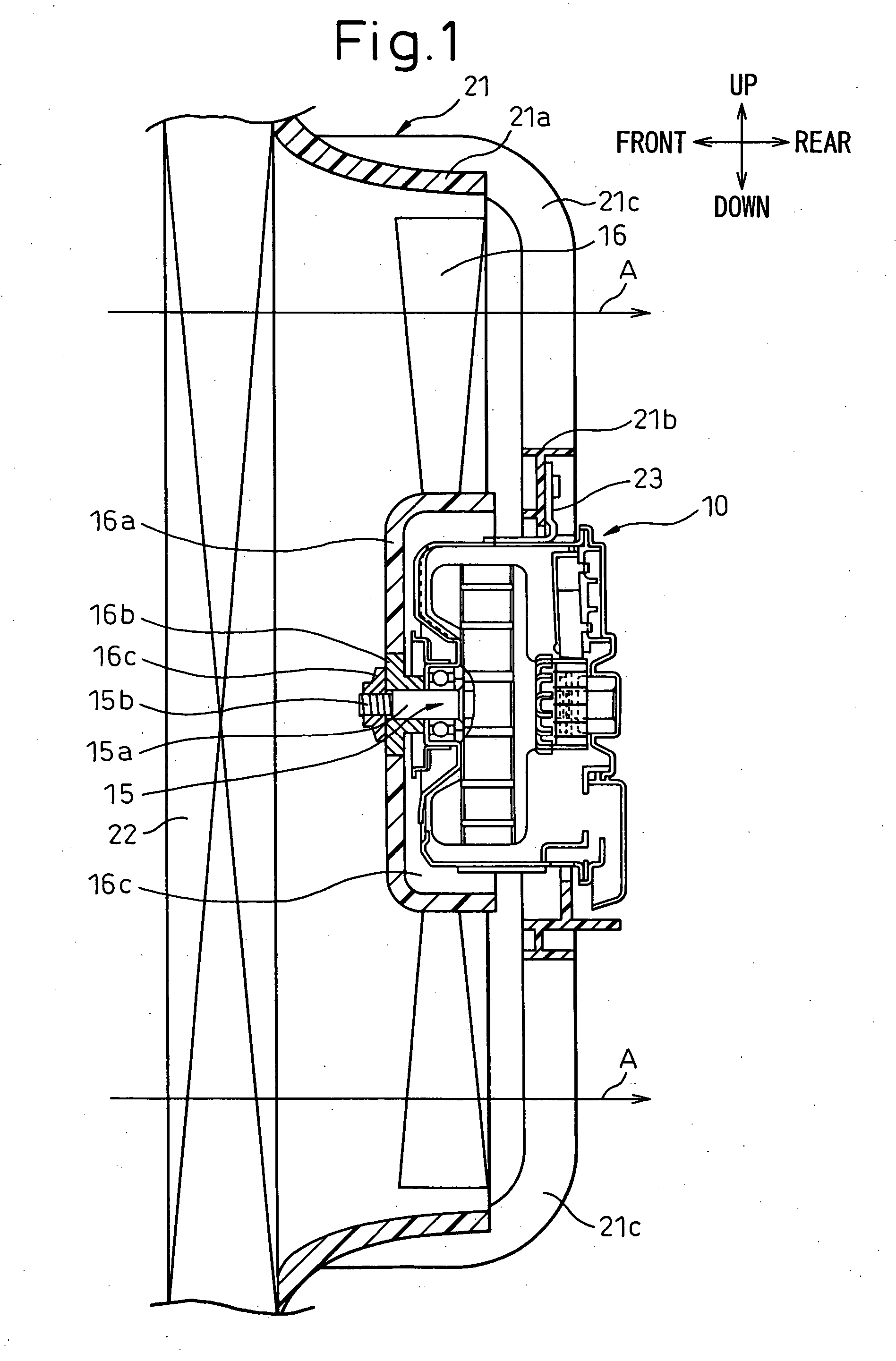

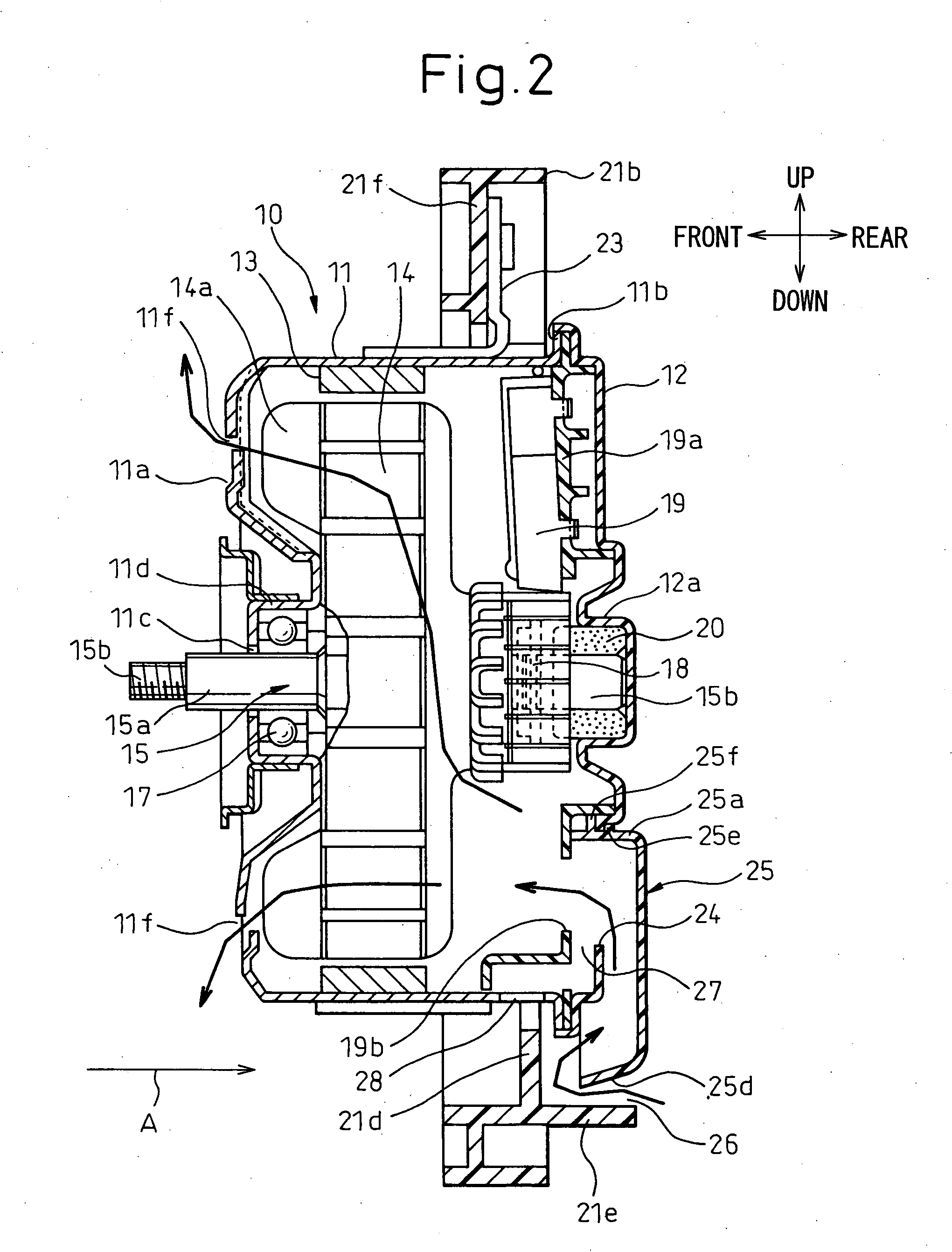

Electric fan for vehicle use

ActiveUS7132772B2Efficient separationBig spacePositive displacement pump componentsPiston pumpsEngineeringLabyrinth structure

The cooling air introducing port 24 is open to a lower portion of an axial direction end portion of the motor housing member 11, 12, the water-proof cover 25 for covering the cooling air introducing port 24 is attached to the outside of the axial direction end portion of the housing member 11, 12, and the air introducing passage 26 having a labyrinth structure is composed of the bent portion 25d provided in a lower end portion of the water-proof cover 25, the first wall face 21d provided in the annular portion 21b of the shroud and the second wall face 21e.

Owner:DENSO CORP +1

Method for fabricating semiconductor device with vertical channel transistor

ActiveUS20090163017A1Avoid attackReduce lossesSolid-state devicesSemiconductor/solid-state device manufacturingInsulation layerEngineering

A method for fabricating a semiconductor memory device with a vertical channel transistor includes forming a plurality of pillars each having a hard mask pattern thereon over a substrate, each of the plurality of pillars comprising an upper pillar and a lower pillar; forming a surround type gate electrode surrounding the lower pillar; forming an insulation layer filling a space between the pillars; forming a preliminary trench by primarily etching the insulation layer using a mask pattern for a word line until a portion of the upper pillar is exposed; forming a buffer layer over a resultant structure including the preliminary trench except on a bottom of the preliminary trench; and forming a trench for a word line by secondarily etching the insulation layer until the surround type gate electrode is exposed.

Owner:SK HYNIX INC

Split gate flash memory and manufacturing method thereof

ActiveUS20060208307A1Longer channel lengthIncrease level of integrationTransistorSolid-state devicesElectrical and Electronics engineeringIsolation layer

A split gate flash memory is provided. Trenches are formed in the substrate to define active layers. The device isolation layers are formed in the trenches. The surface of the device isolation layers is lower than the surface of the active layers. The stacked gate structures each including a tunneling dielectric layer, a floating gate and a cap layer are formed on the active layers. The inter-gate dielectric layers are formed on the sidewalls of the stacked gate structures. The select gates are formed on one side of the stacked gate structure and across the active layer. The select gate dielectric layers are formed between the select gates and the active layers. The source regions are formed in the active layers on the other side of the stacked gate structures. The drain regions are formed in the active layers on one side of the select gates.

Owner:POWERCHIP SEMICON MFG CORP

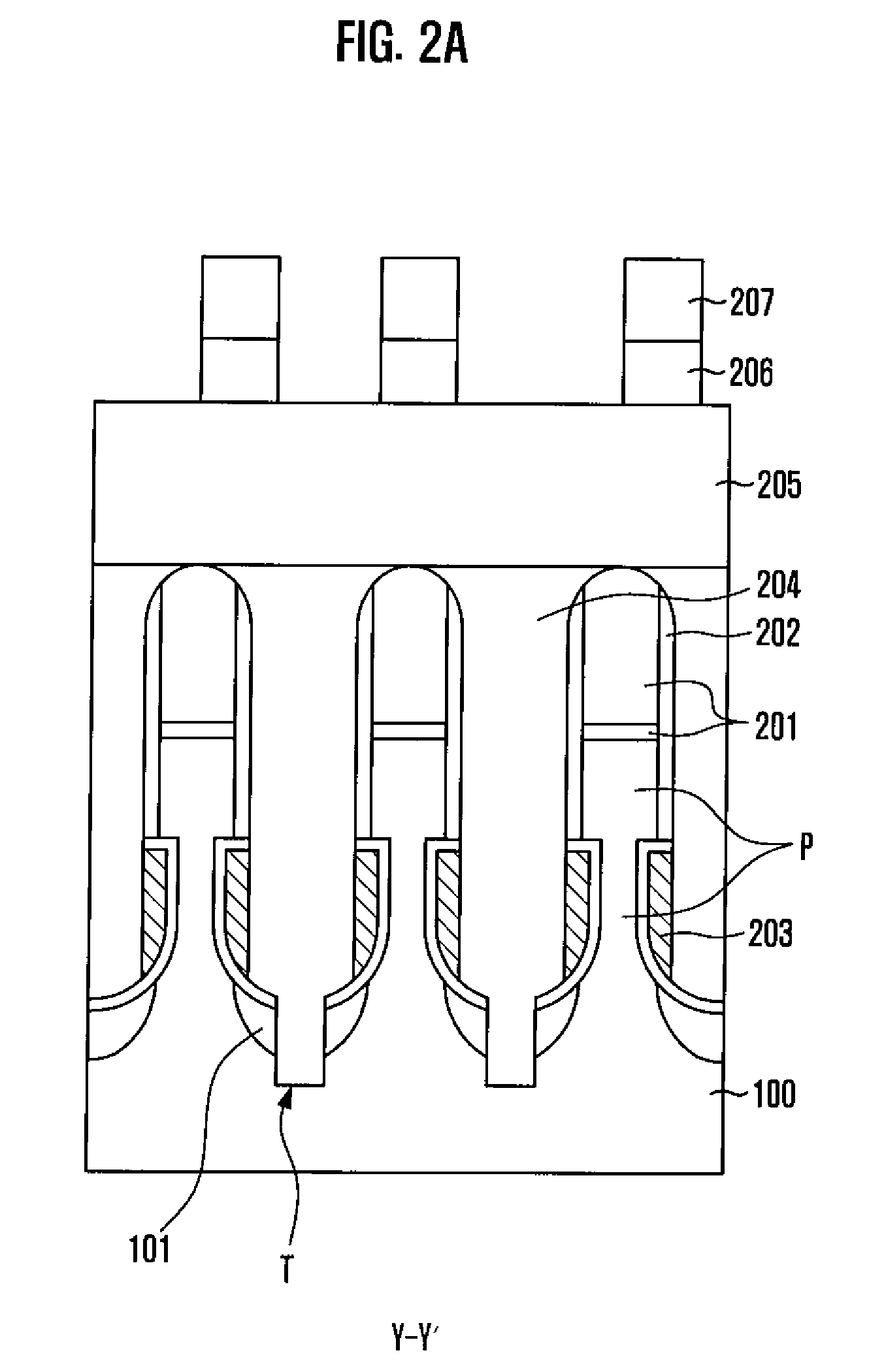

Semiconductor memory device and method for fabricating the same

InactiveUS20100327337A1Reduce generationIncrease channel lengthTransistorSolid-state devicesIsolation layerEngineering

A semiconductor memory device has an asymmetric buried gate structure with a stepped top surface and a method for fabricating the same. The method for fabricating the semiconductor memory device includes: etching a predetermined region of a semiconductor substrate to form an isolation layer defining an active region; forming a recess within the active region; forming a metal layer filling the recess; asymmetrically etching the metal layer to form an asymmetric gate having a stepped top surface at a predetermined portion of the recess; and forming a capping oxide layer filling a remaining portion of the recess where the asymmetric gate is not formed, thereby obtaining an asymmetric buried gate including the asymmetric gate and the capping oxide layer.

Owner:SK HYNIX INC

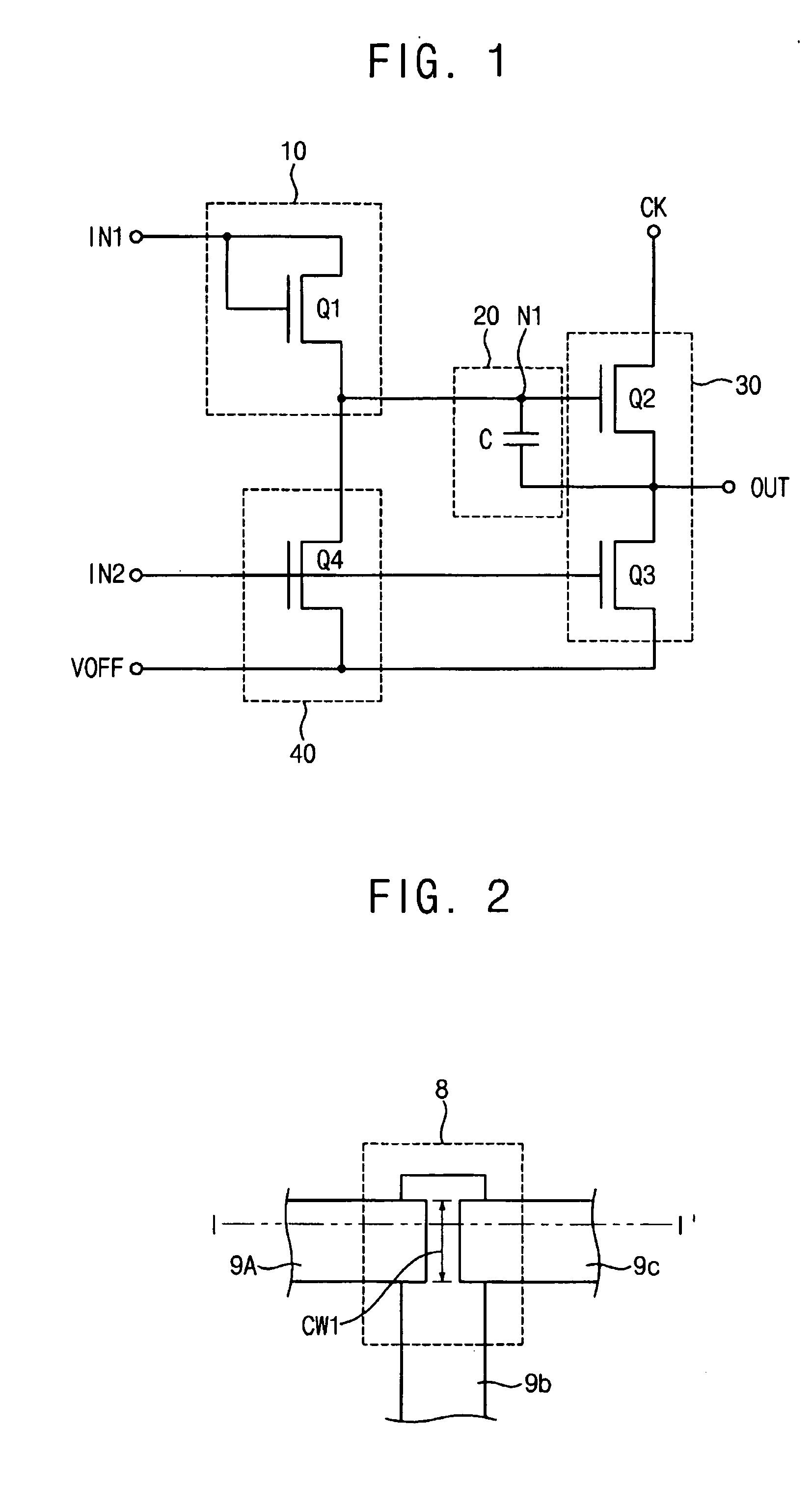

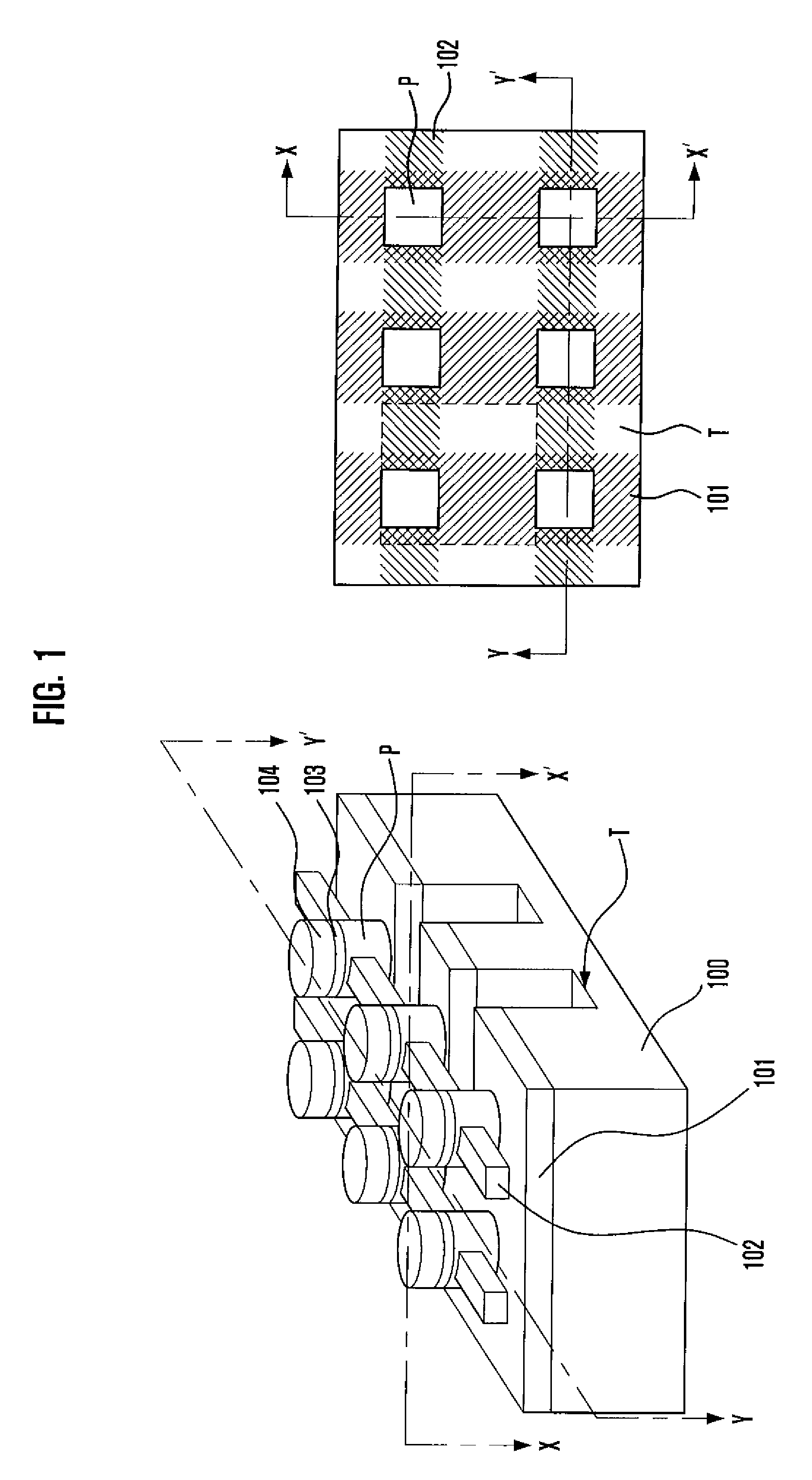

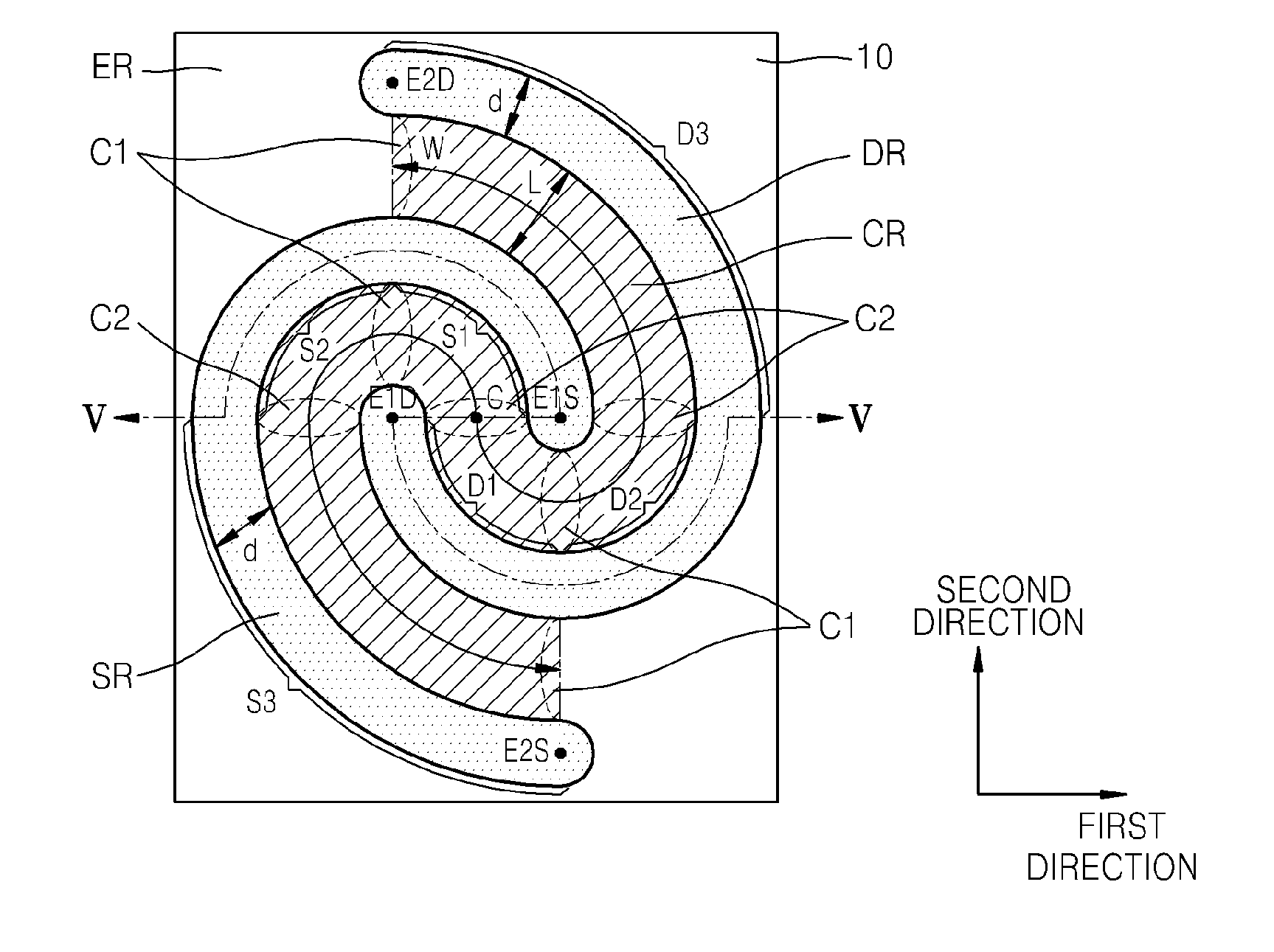

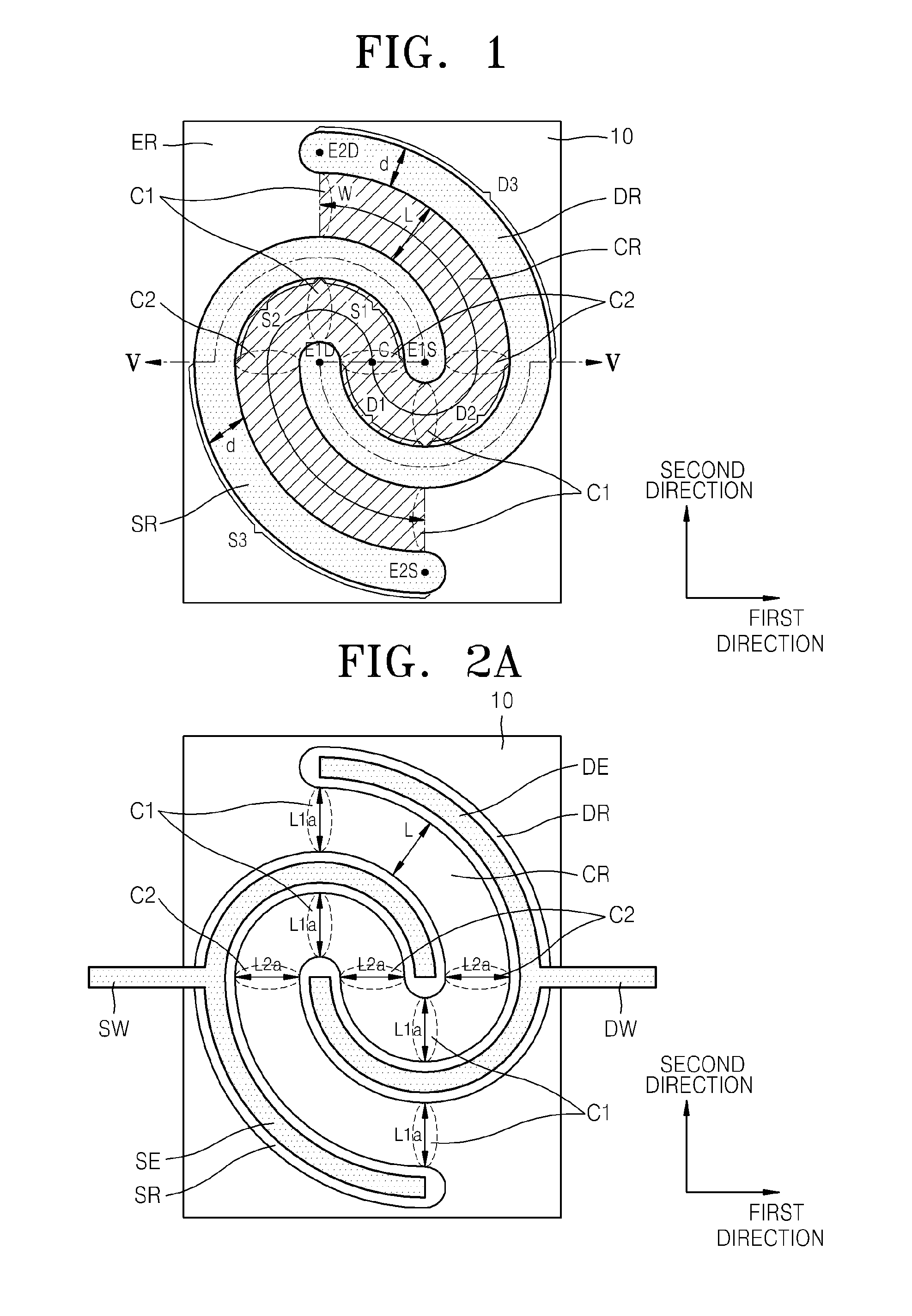

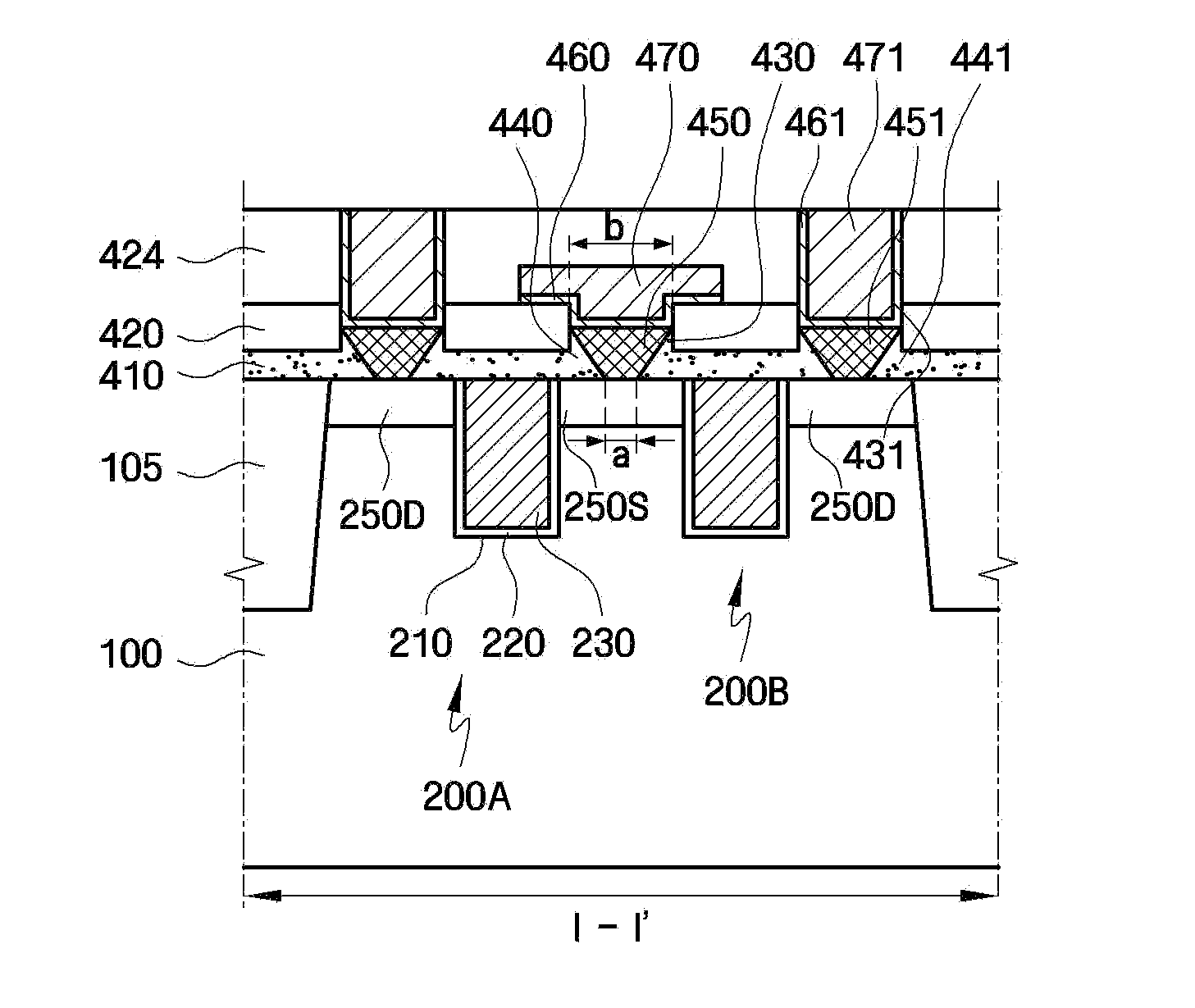

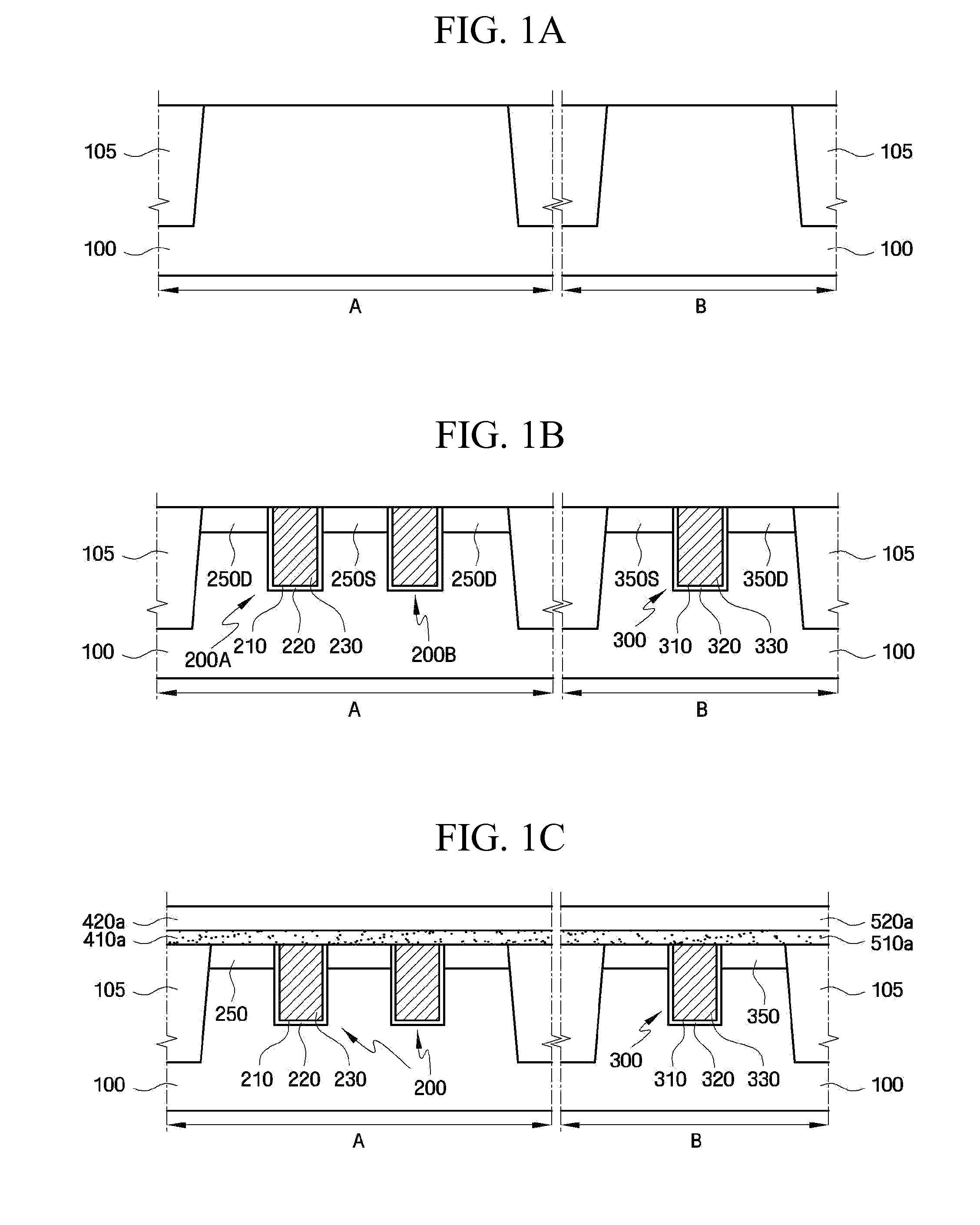

Thin film semiconductor device and organic light-emitting display device

ActiveUS20140306191A1Increase channel lengthDecrease channel lengthTransistorSolid-state devicesPhysicsPower semiconductor device

A thin film semiconductor device including a thin film transistor (TFT) that maintains a constant electrical characteristic and an organic light-emitting display device. The thin film semiconductor device includes: a substrate; and a thin film transistor (TFT) disposed on the substrate and comprising a semiconductor layer comprising a source region and a drain region, wherein a part of the source region is spaced apart from the drain region and partially surrounds the drain region, and wherein a part of the drain region is spaced apart from the source region and partially surrounds the source region.

Owner:SAMSUNG DISPLAY CO LTD

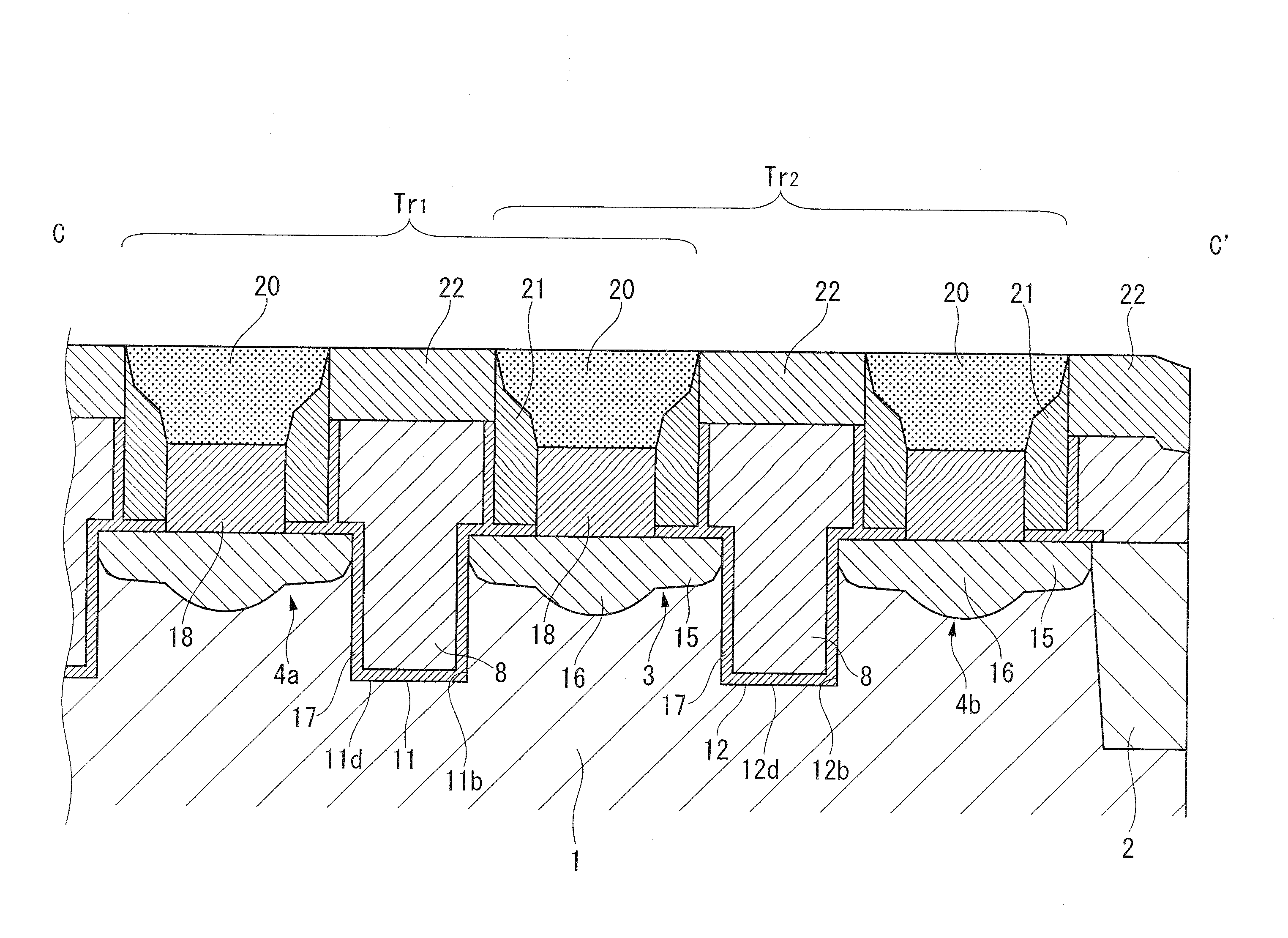

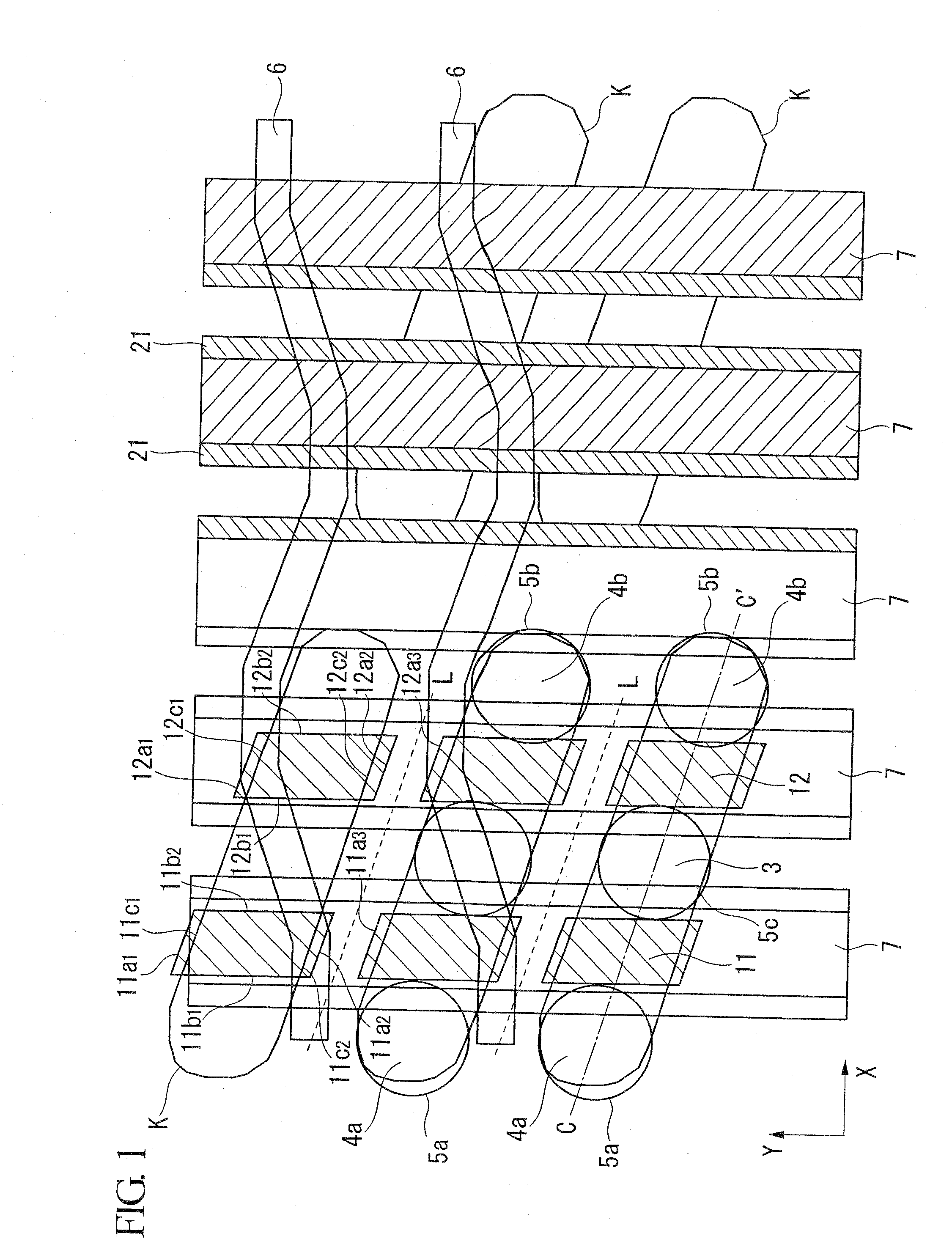

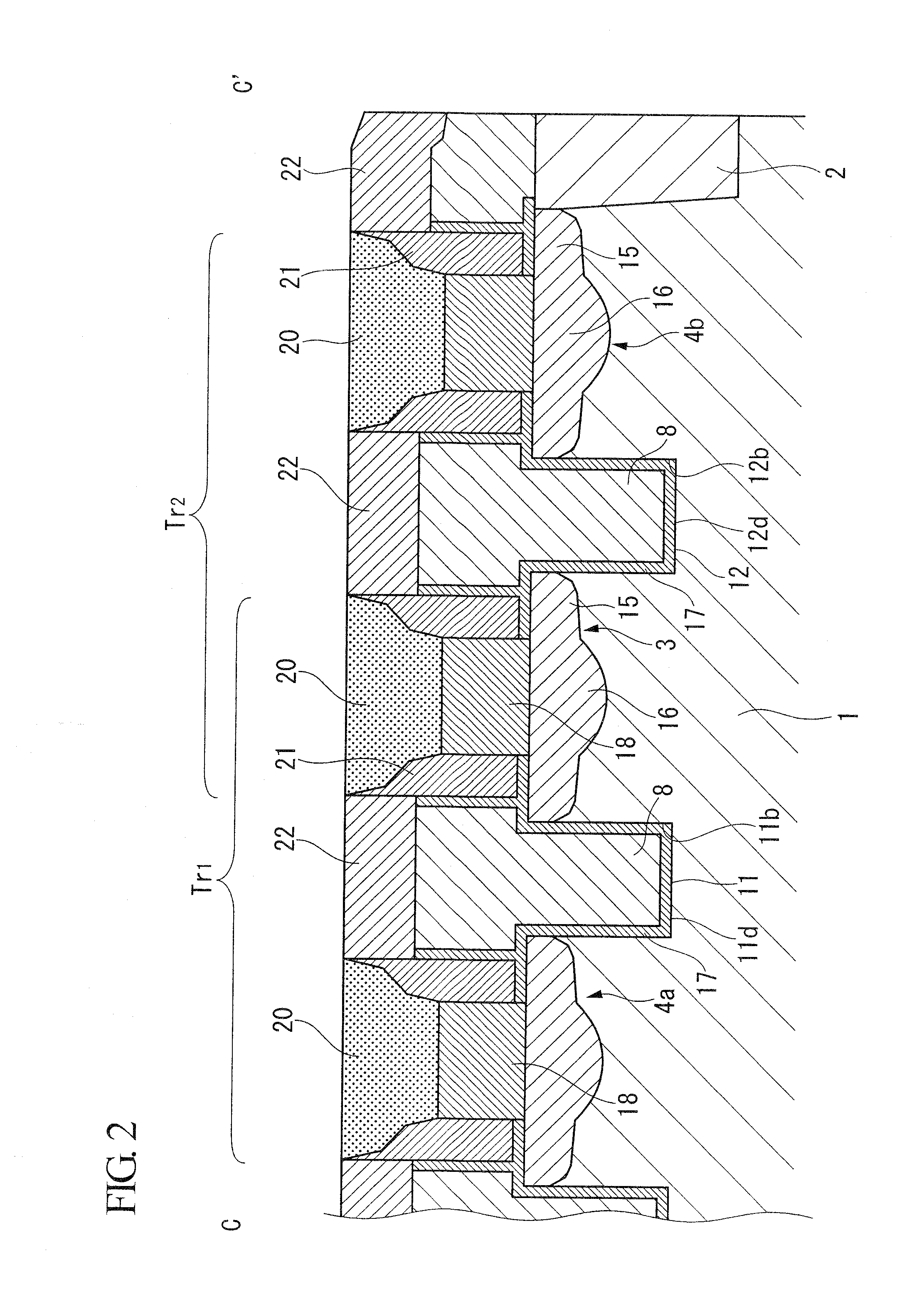

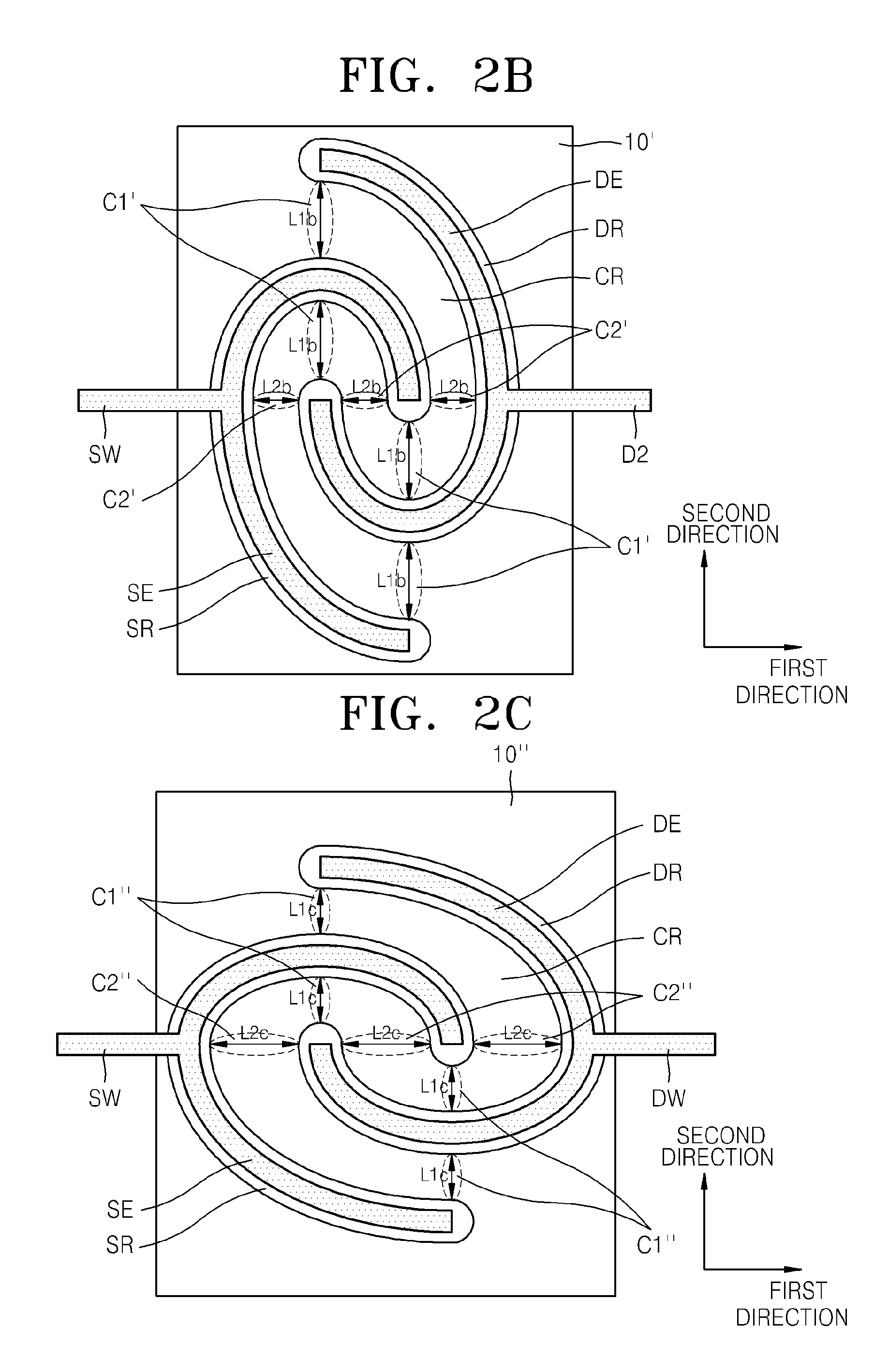

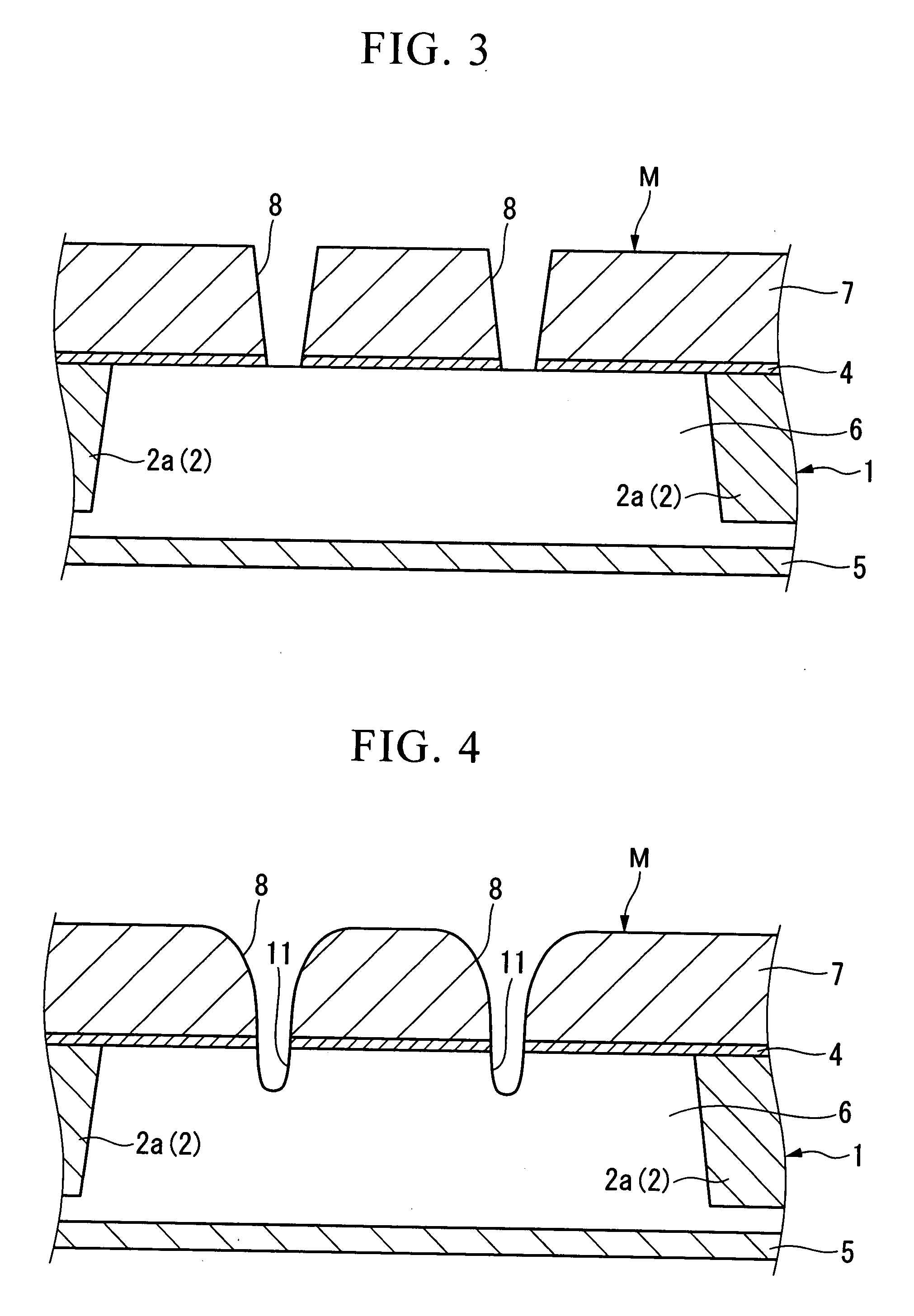

Semiconductor device and method of manufacturing the same

ActiveUS20080073709A1Improve gate reliabilityImprove reliabilityTransistorSolid-state devicesGate dielectricEngineering

A semiconductor device in which the reliability of a gate dielectric film is high and a channel length is sufficiently secured and a method of manufacturing the same are provided. The semiconductor device comprises a trench gate transistor. The trench gate transistor comprises: a trench provided in a semiconductor substrate; a gate electrode formed in the trench through a gate dielectric film; and a diffusion layer formed in the vicinity of the trench. The trench comprises: an opening portion provided in a surface of the semiconductor substrate; a recess curved surface portion whose cross-sectional contour is a substantially circular arc shape; and a connection curved surface portion connecting the recess curved surface portion and the opening portion. The connection curved surface portion and the recess curved surface portion are integrated in a continuous curved surface without interposing a ridge line portion therebetween.

Owner:MICRON TECH INC

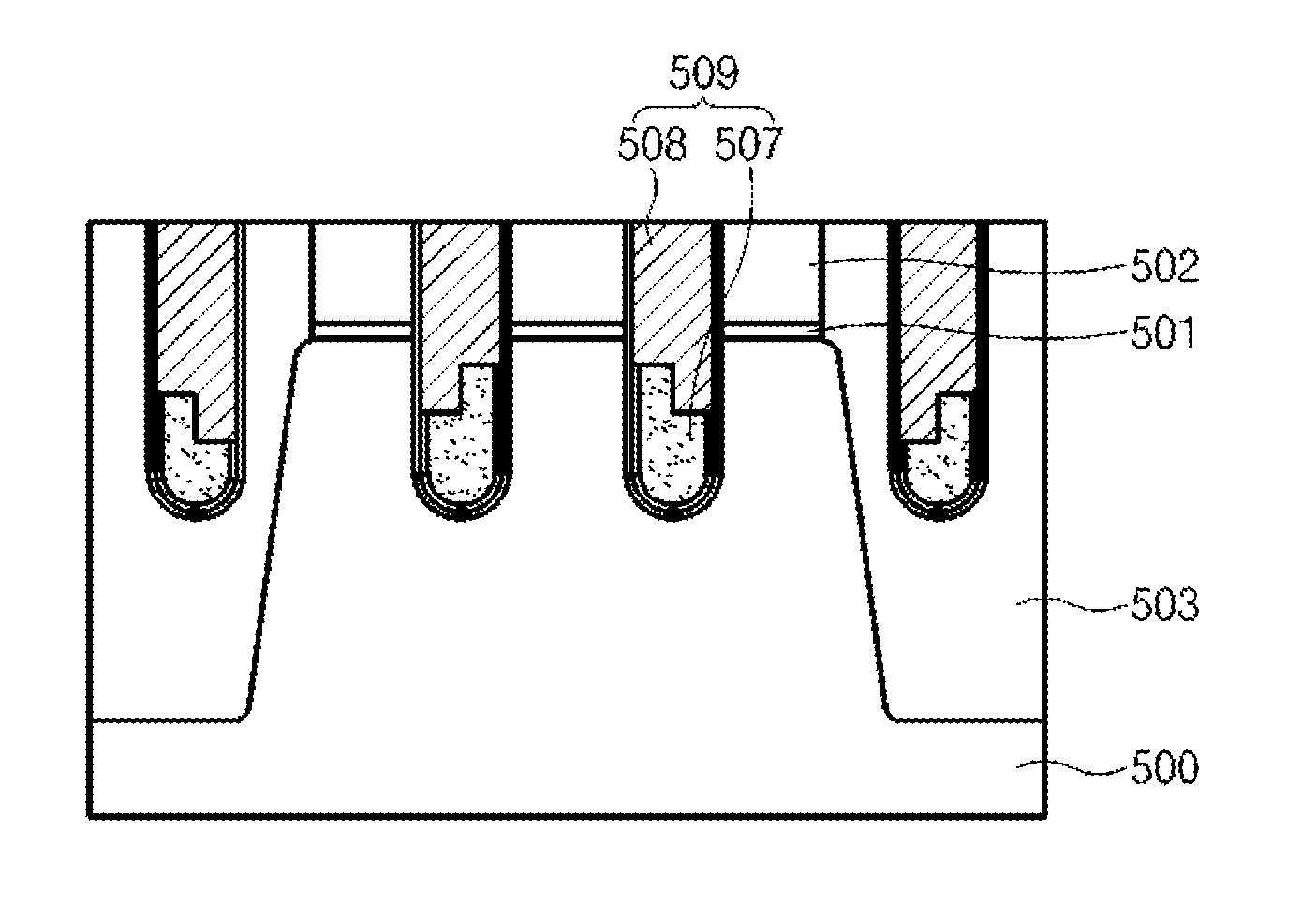

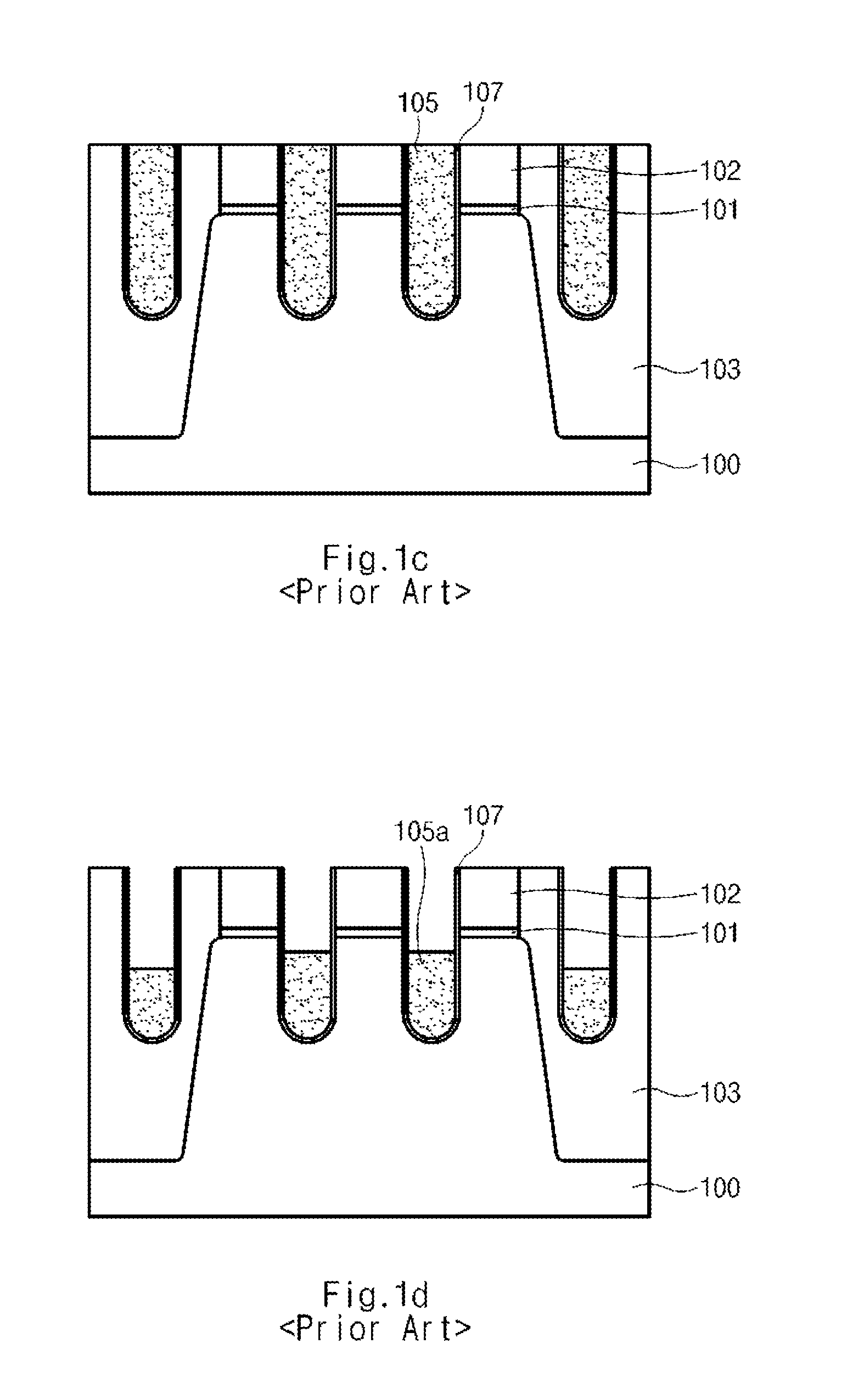

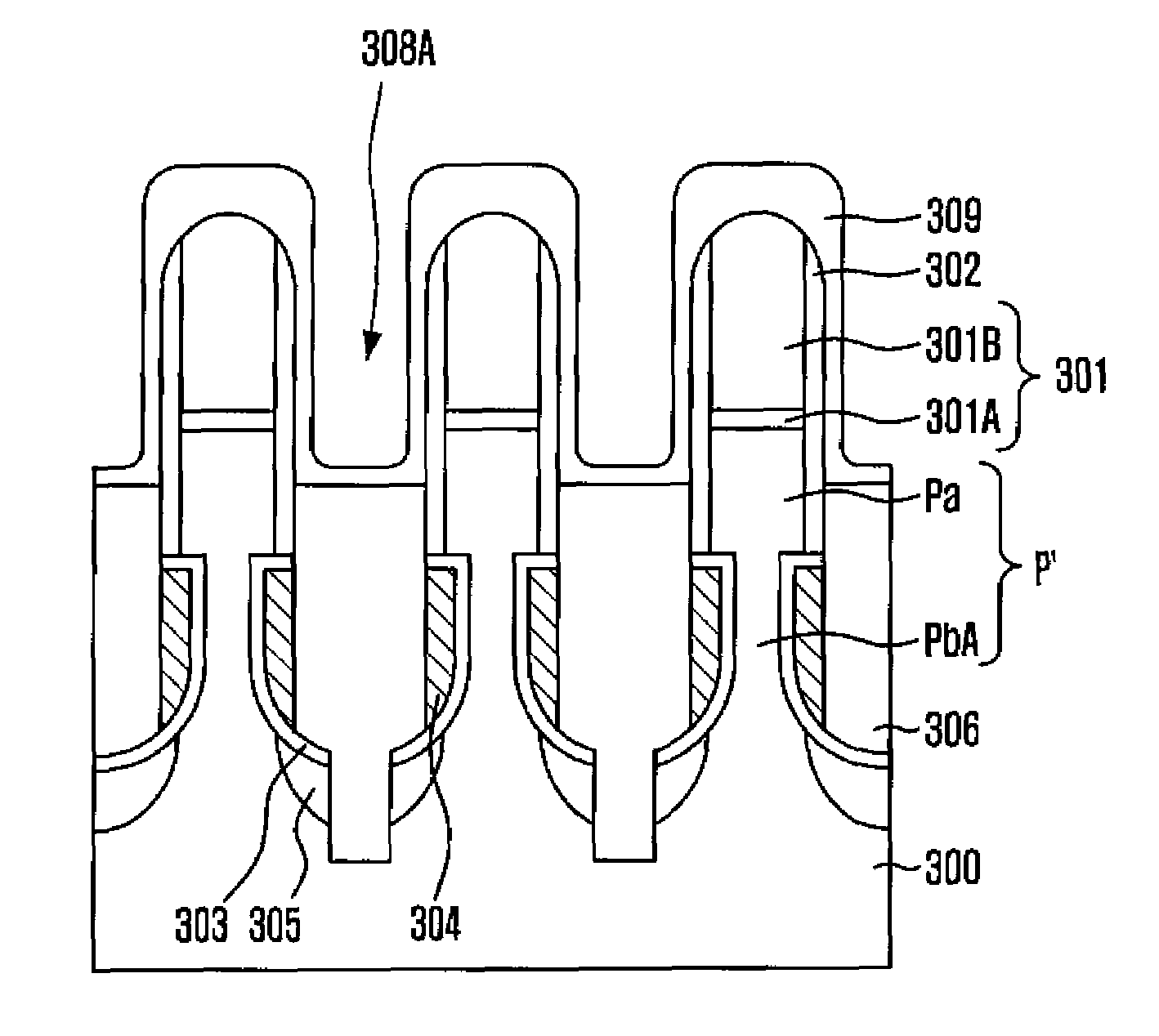

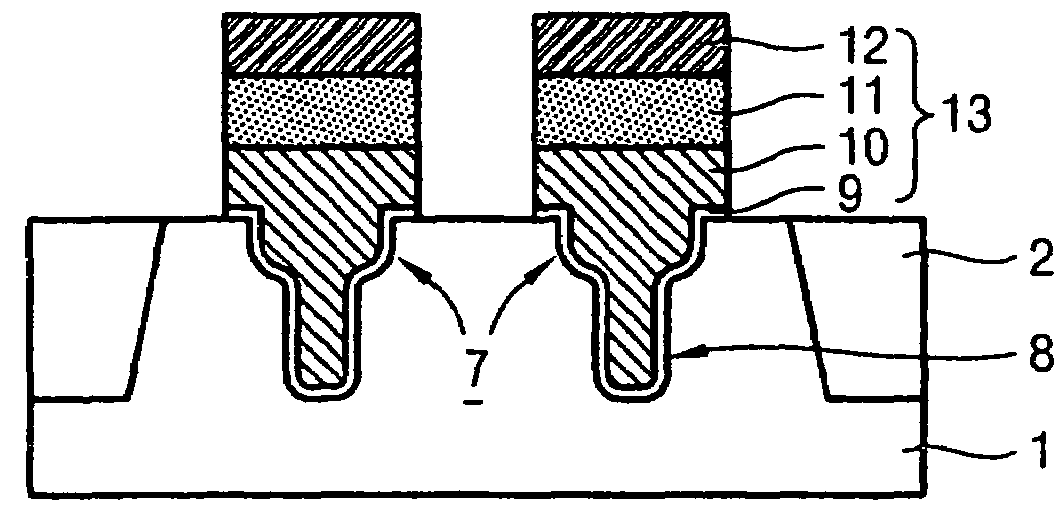

Method for fabricating semiconductor device having flask type recess gate

ActiveUS7485557B2Reduce generationIncrease channel lengthSemiconductor/solid-state device manufacturingSemiconductor devicesEngineeringSilicon oxide

A method for fabricating a semiconductor device having a flask type recess gate includes forming a hard mask pattern on a substrate, etching the substrate to a predetermined depth using the hard mask pattern to form a first recess pattern, forming a passivation layer on sidewalls of the first recess pattern and the hard mask pattern, etching a bottom surface of the first recess pattern exposed by the passivation layer to form a second recess pattern, oxidizing sidewalls of the second recess pattern to form a silicon oxide layer, removing the passivation layer and the silicon oxide layer in sequential order, and forming a gate pattern over an intended recess pattern including the first recess pattern and the second recess pattern.

Owner:SK HYNIX INC

Method for fabricating semiconductor device with vertical channel transistor

ActiveUS7670909B2Avoid short channel effectsIncrease channel lengthSolid-state devicesSemiconductor/solid-state device manufacturingInsulation layerEngineering

A method for fabricating a semiconductor memory device with a vertical channel transistor includes forming a plurality of pillars each having a hard mask pattern thereon over a substrate, each of the plurality of pillars comprising an upper pillar and a lower pillar; forming a surround type gate electrode surrounding the lower pillar; forming an insulation layer filling a space between the pillars; forming a preliminary trench by primarily etching the insulation layer using a mask pattern for a word line until a portion of the upper pillar is exposed; forming a buffer layer over a resultant structure including the preliminary trench except on a bottom of the preliminary trench; and forming a trench for a word line by secondarily etching the insulation layer until the surround type gate electrode is exposed.

Owner:SK HYNIX INC

Electric fan for vehicle use

ActiveUS20060012256A1Big spaceReduce the cross-sectional areaPropellersReaction enginesEngineeringLabyrinth structure

The cooling air introducing port 24 is open to a lower portion of an axial direction end portion of the motor housing member 11, 12, the water-proof cover 25 for covering the cooling air introducing port 24 is attached to the outside of the axial direction end portion of the housing member 11, 12, and the air introducing passage 26 having a labyrinth structure is composed of the bent portion 25d provided in a lower end portion of the water-proof cover 25, the first wall face 21d provided in the annular portion 21b of the shroud and the second wall face 21e.

Owner:DENSO CORP +1

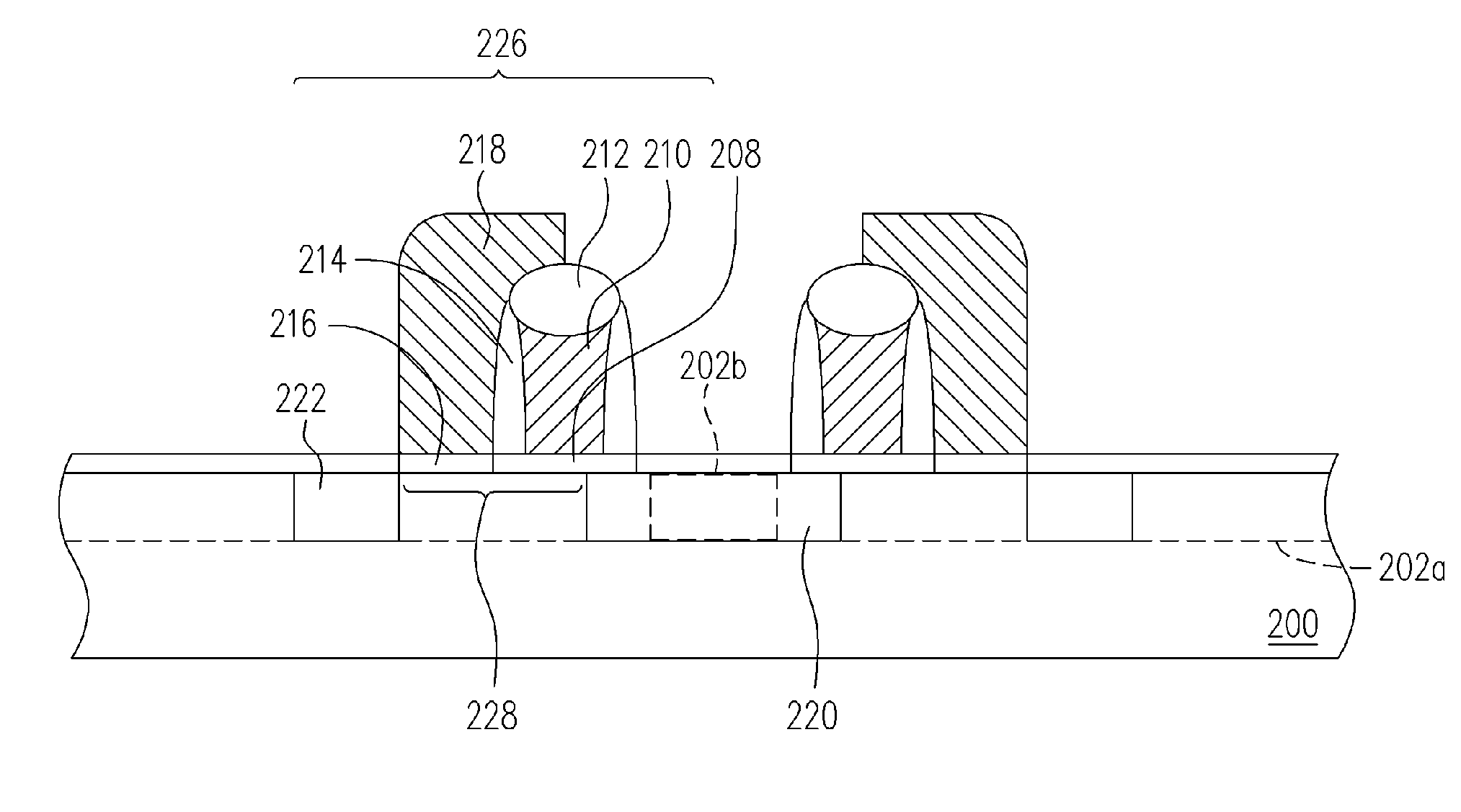

Semiconductor integrated circuit devices and fabrication methods thereof

ActiveUS20090020808A1Easy to separateImprove critical dimensionsTransistorSolid-state devicesInsulation layerEngineering

A memory cell of memory device, comprises an active region of a memory cell defined in a semiconductor substrate, and a conductive gate electrode in a trench of the active region. The gate electrode is isolated from the semiconductor substrate. An insulation layer is on the active region and on the conductive gate electrode. A conductive contact is in the insulation layer on the active region at a side of the gate electrode and isolated from the gate electrode. The contact has a first width at a top portion thereof and a second width at a bottom portion thereof, the first width being greater than the second width. The contact is formed of a single-crystal material.

Owner:IMBERATEK LLC

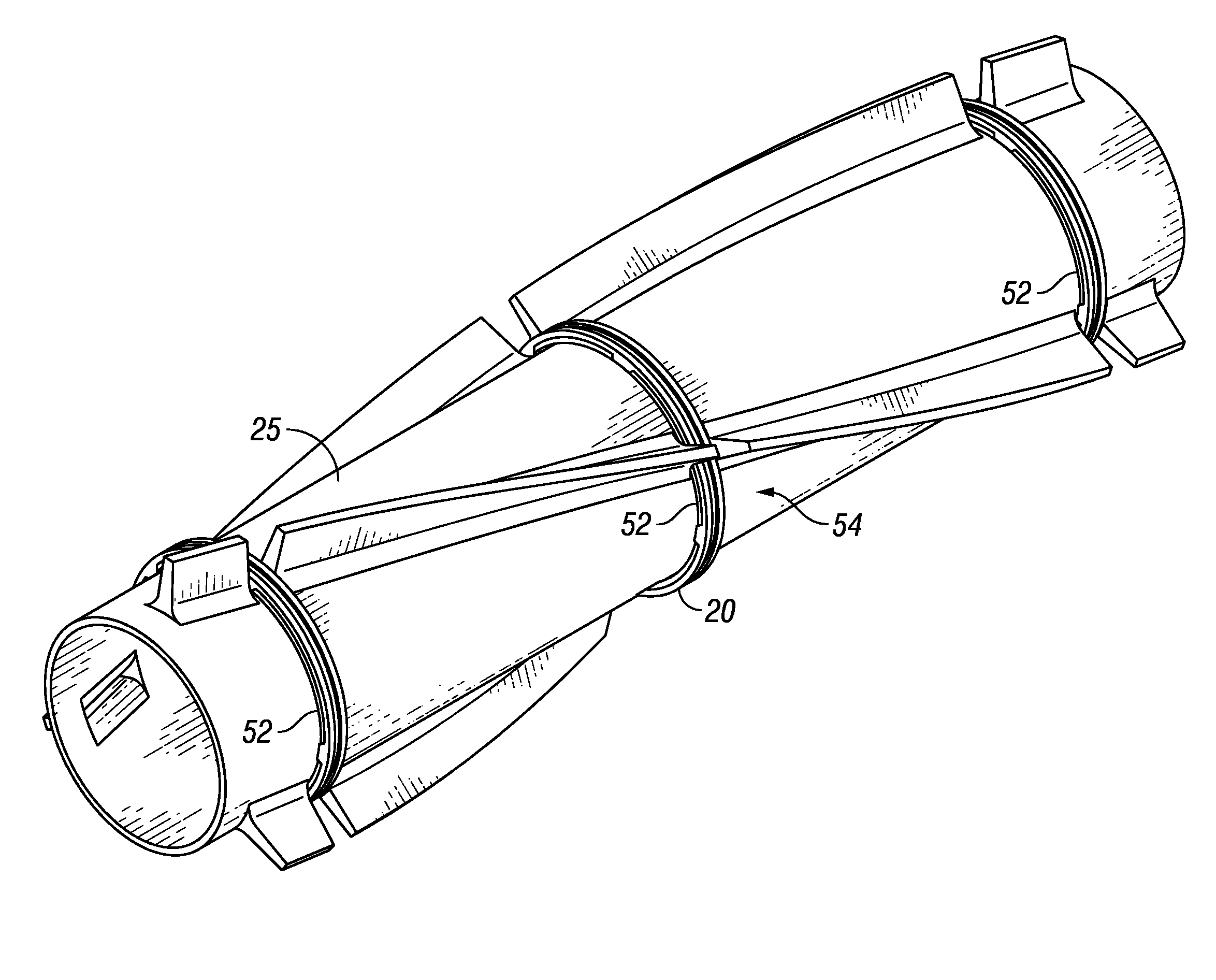

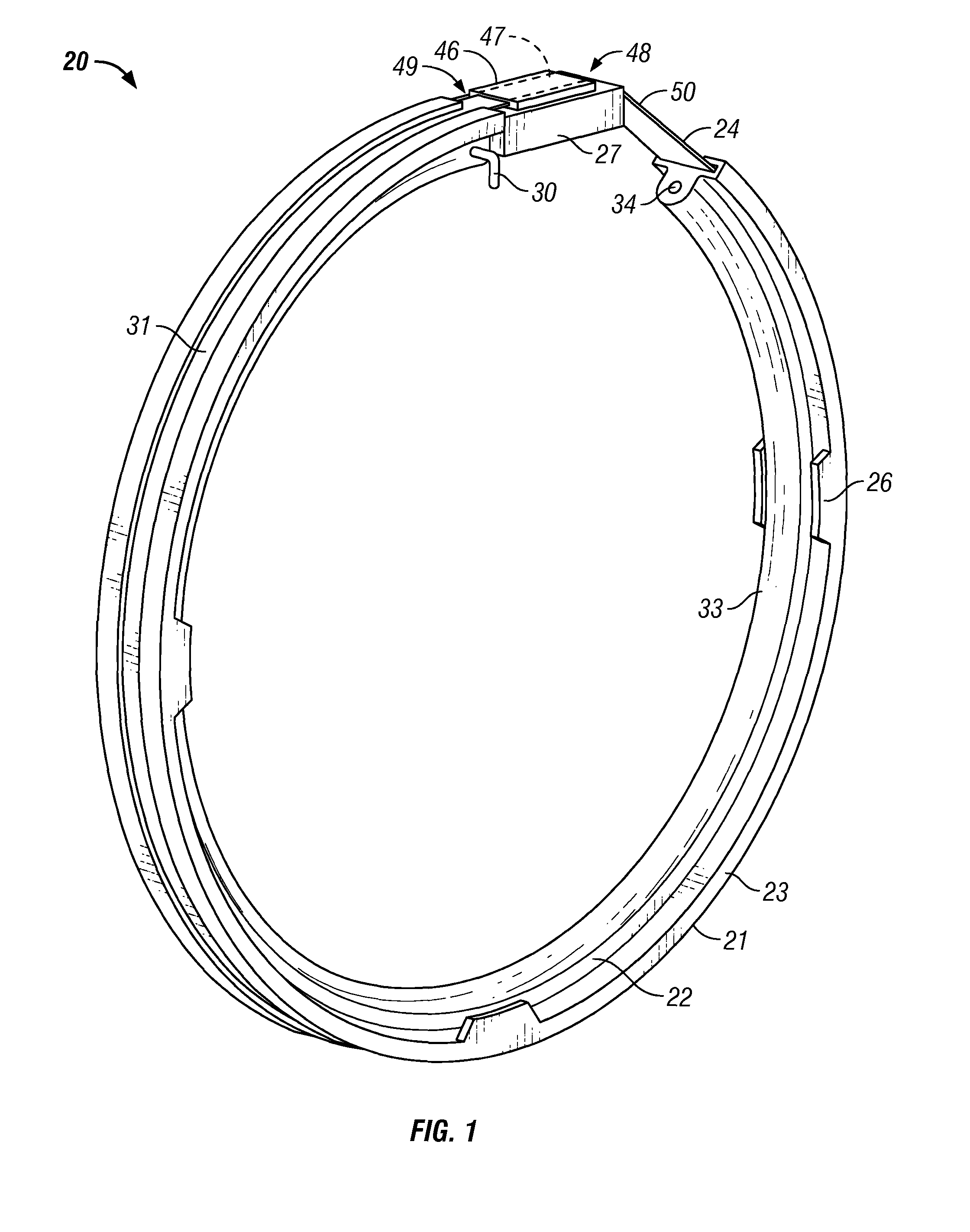

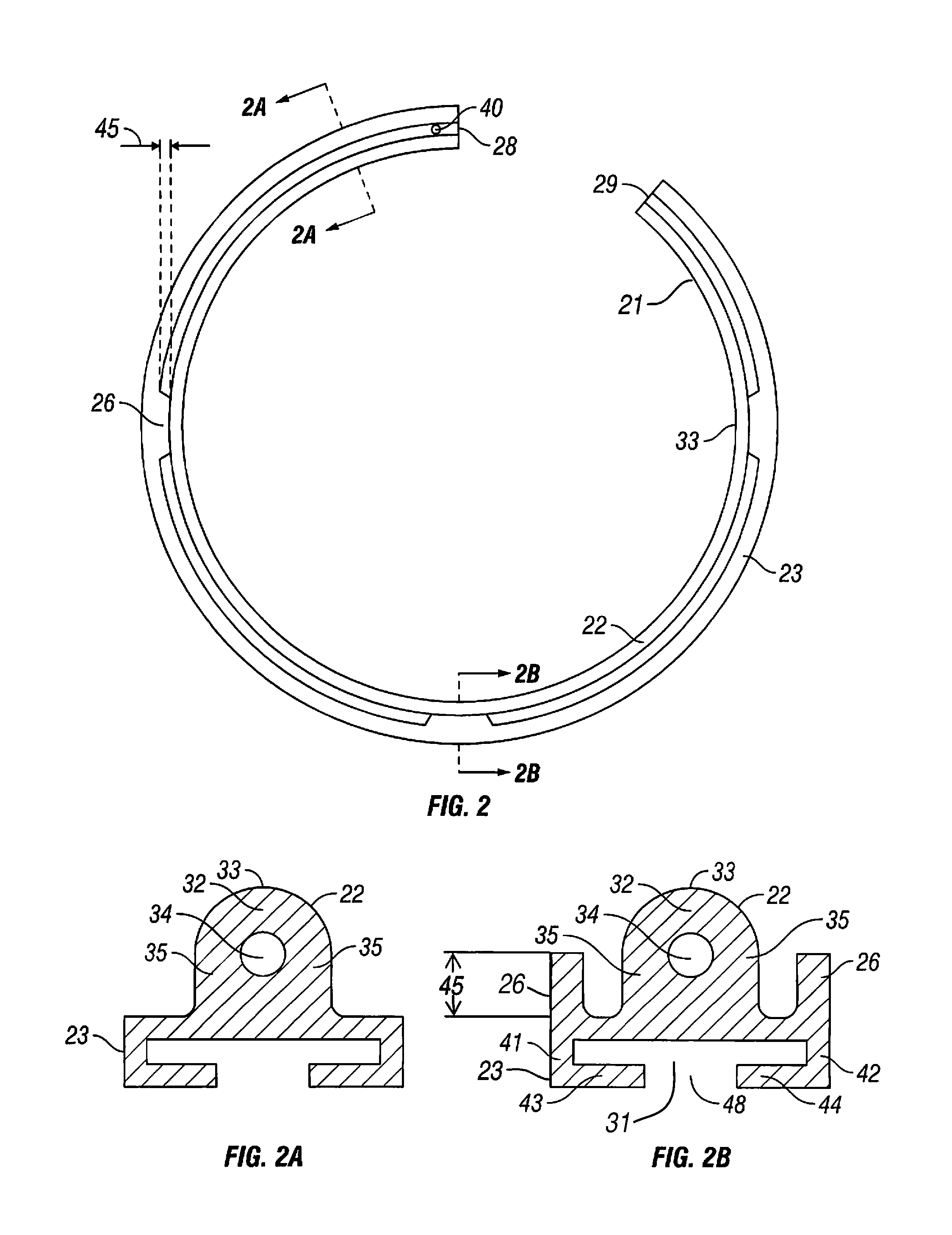

Compliant banding system

InactiveUS7845299B2Avoid displacementIncrease channel lengthPipe laying and repairWaterborne vesselsStrakeAerospace engineering

The present invention discloses a compliant banding system for use in a marine environment comprising a flexible compliant member and an abaxial relatively rigid strap, both constructed to extend circumferentially around an underlying structure such as a strake or fairing collar. The strap maintains a fixed circumference while the compliant member flexes intermediate the strap and an underlying.

Owner:VIV SUPPRESSION

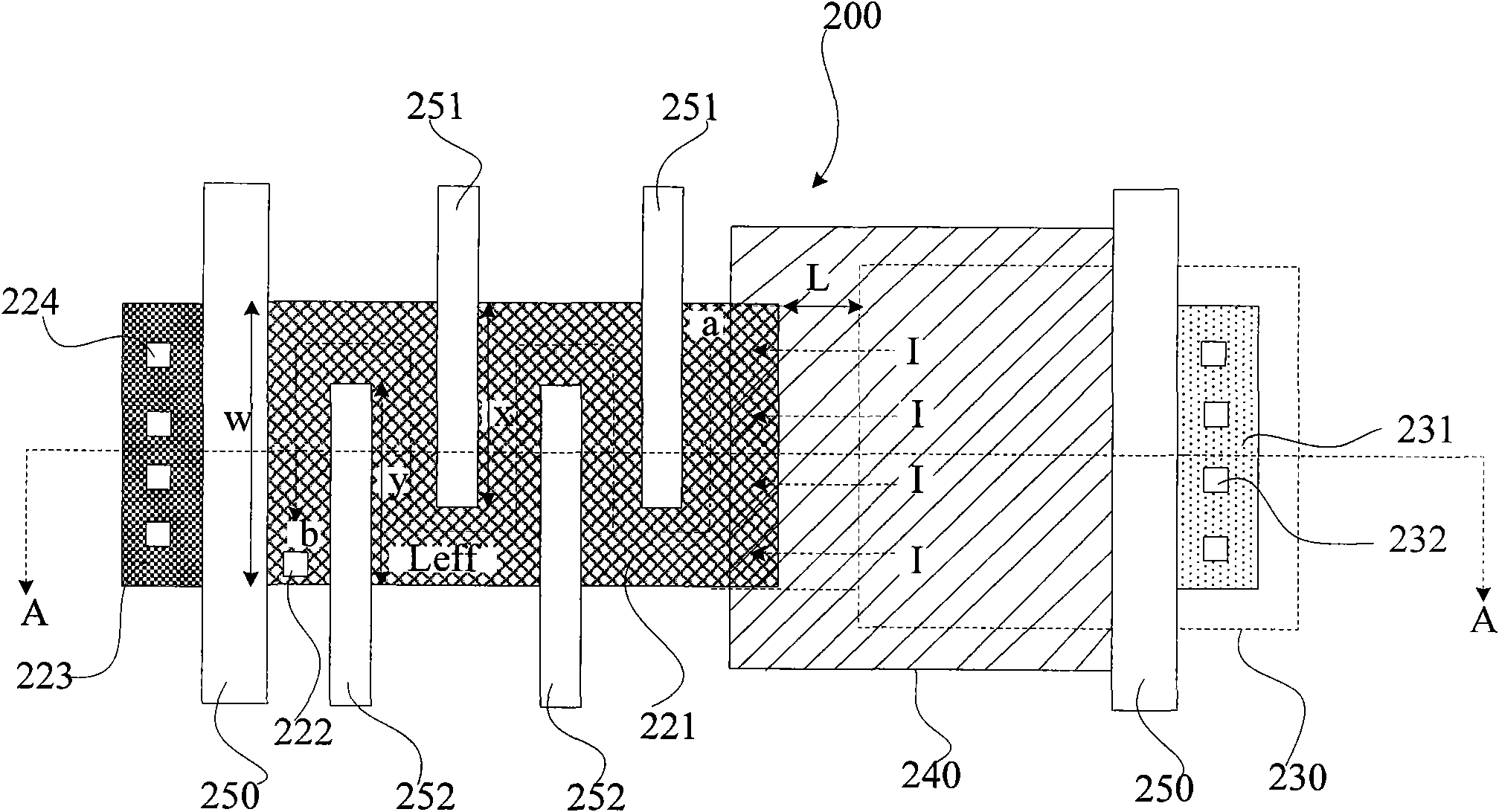

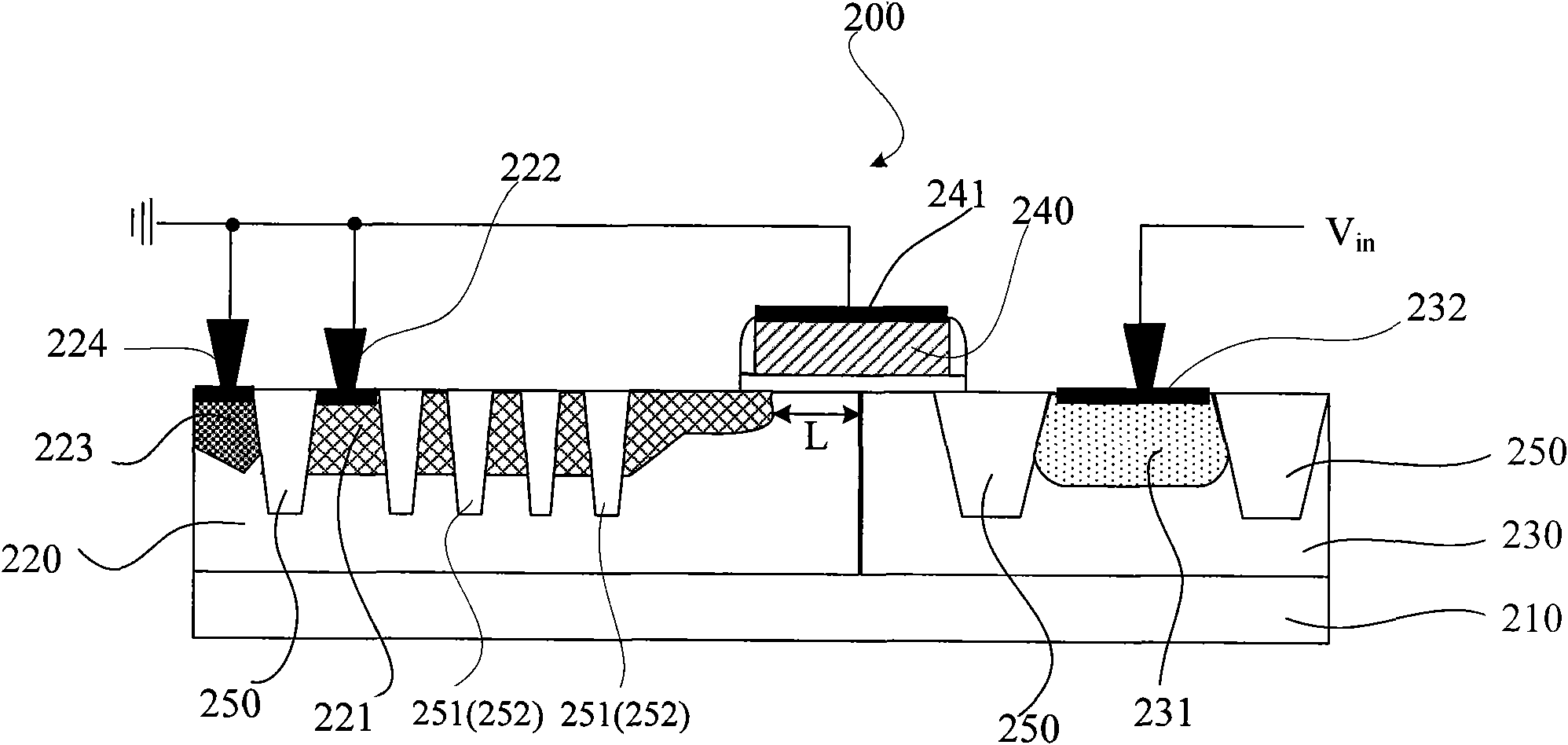

LDMOS ESD(Laterally Diffused Metal Oxide Semiconductor Electro-Static Discharge) structure

ActiveCN102376761AImprove antistatic performanceIncrease the lengthSemiconductor devicesLDMOSSquare waveform

The invention discloses an LDMOS ESD(Laterally Diffused Metal Oxide Semiconductor Electro-Static Discharge) structure comprising a gate region, a drain region and a source region, wherein an interdigitated STI(Shallow-Trench Isolation) structure is arranged in the source region, so that the flow direction of the electrostatic leakage current of the LDMOS ESD is of a square-wave form. Therefore, the effective channel length is increased while the actual channel length is not increased, and the effective channel resistance is increased, thereby further increasing the sustaining voltage and enhancing the antistatic effect of the LDMOS ESD.

Owner:SEMICONDUCTOR MANUFACTURING INTERNATIONAL (BEIJING) CORP +1

Fabrication of a high density long channel DRAM gate with or without a grooved gate

InactiveUS6426175B2Limit leakage currentIncrease channel lengthTransistorSolid-state devicesMemory chipHigh density

The present invention lengthens gate conductors used in memory chips to limit leakage current, while still allowing the overall size of cells to remain the same. The channel length for each gate is increased by decreasing the size of spaces between gates. Decreases in space size occurs by using photolithographic image enhancement techniques. These techniques allow the space between gate conductors to be smaller while the gate size increases. In addition, a groove may be added that additionally lengthens the effective channel length and provides an additional electrical shield to limit leakage current. These techniques lead to the same density memory cells for a given process with less leakage. Finally, if grooved gate structures are used, having a longer gate conductor allows a three sigma process to be used, which increases yields.

Owner:INT BUSINESS MASCH CORP

Method for fabricating semiconductor device having flask type recess gate

ActiveUS20070123014A1Reduce generationIncrease channel lengthSemiconductor/solid-state device manufacturingSemiconductor devicesDevice materialEngineering

A method for fabricating a semiconductor device having a flask type recess gate includes forming a hard mask pattern on a substrate, etching the substrate to a predetermined depth using the hard mask pattern to form a first recess pattern, forming a passivation layer on sidewalls of the first recess pattern and the hard mask pattern, etching a bottom surface of the first recess pattern exposed by the passivation layer to form a second recess pattern, oxidizing sidewalls of the second recess pattern to form a silicon oxide layer, removing the passivation layer and the silicon oxide layer in sequential order, and forming a gate pattern over an intended recess pattern including the first recess pattern and the second recess pattern.

Owner:SK HYNIX INC

Method of manufacturing semiconductor device having recess gate structure with varying recess width for increased channel length

ActiveUS7413969B2Increase channel lengthTotal current dropSemiconductor/solid-state device manufacturingSemiconductor devicesEngineeringSemiconductor

A varying-width recess gate structure having a varying-width recess formed in a semiconductor device can sufficiently increase the channel length of the transistor having a gate formed in the varying-width recess, thereby effectively reducing the current leakage and improving the refresh characteristics. In the method of manufacturing the recess gate structure, etching is performed twice or more, so as to form a gate recess having varying width in the substrate, and a gate is formed in the gate recess.

Owner:SK HYNIX INC

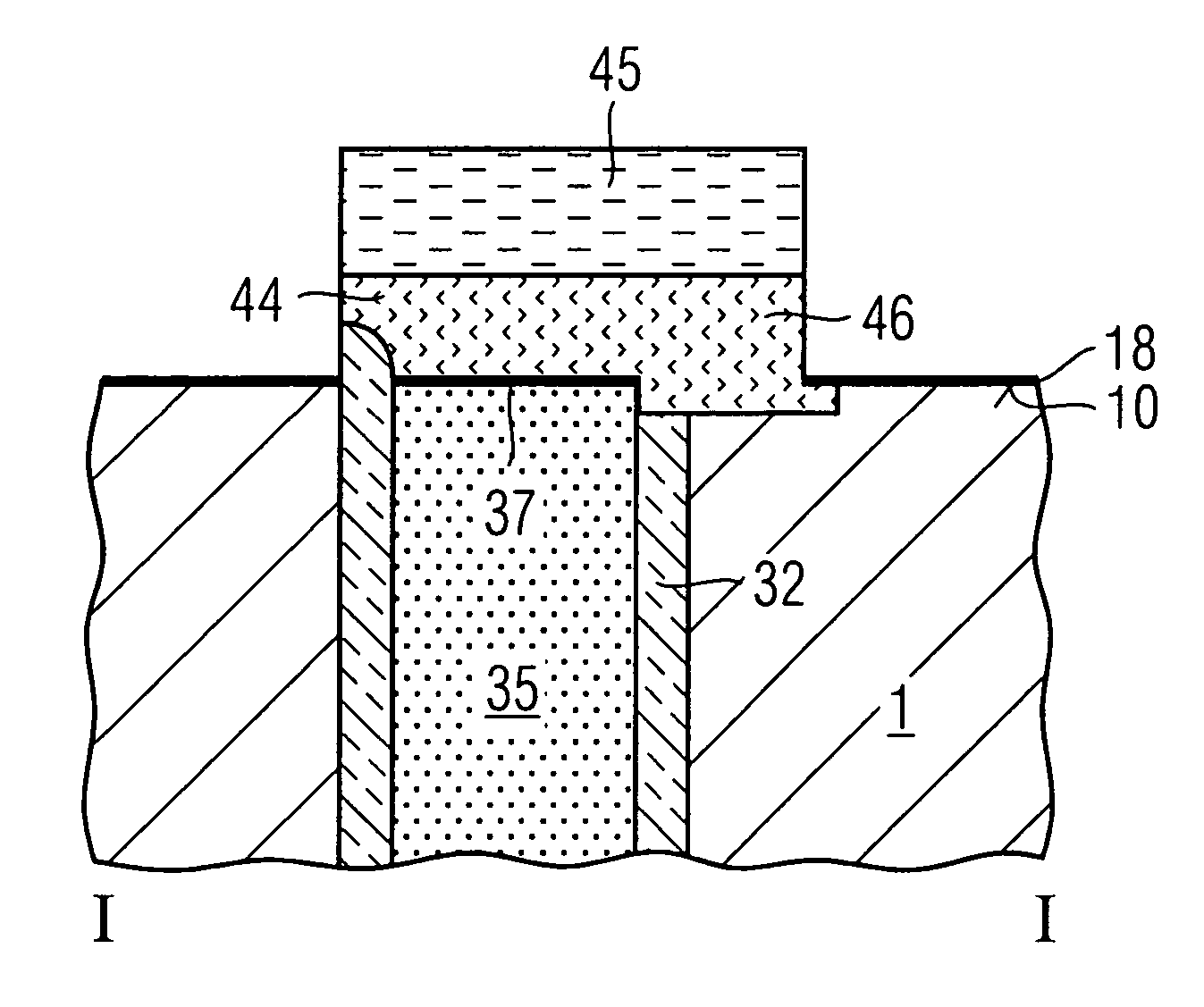

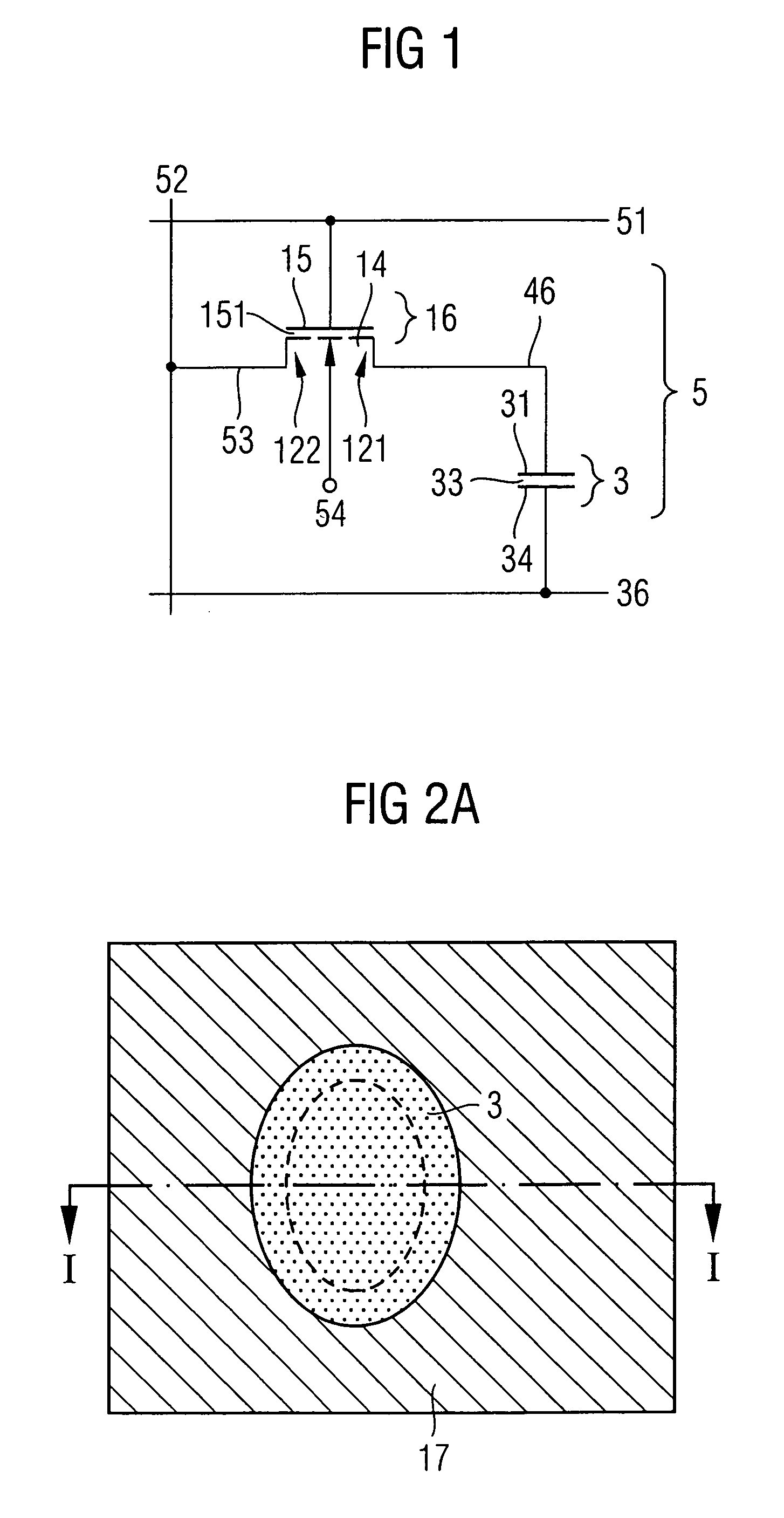

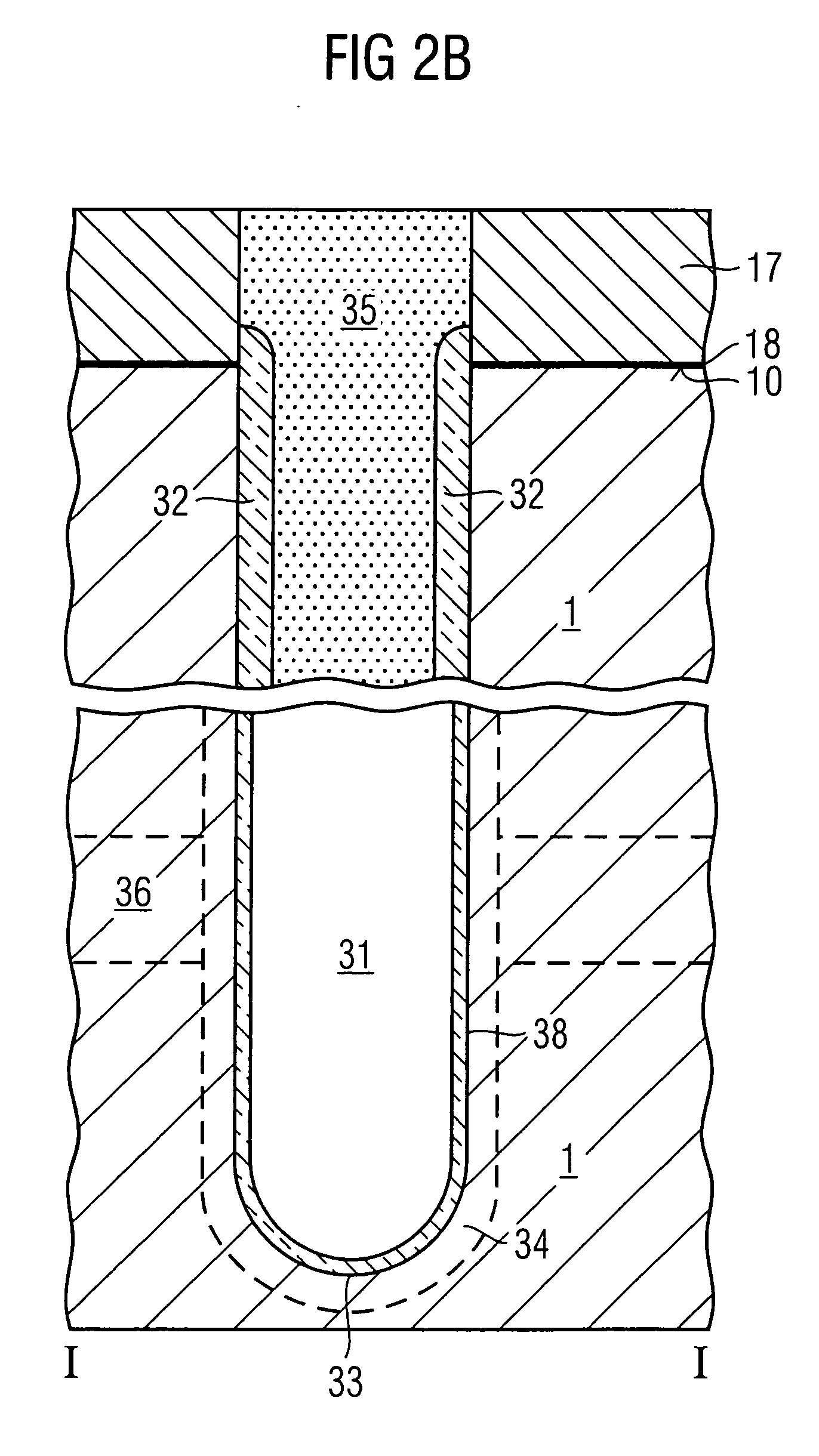

Connecting structure and method for manufacturing the same

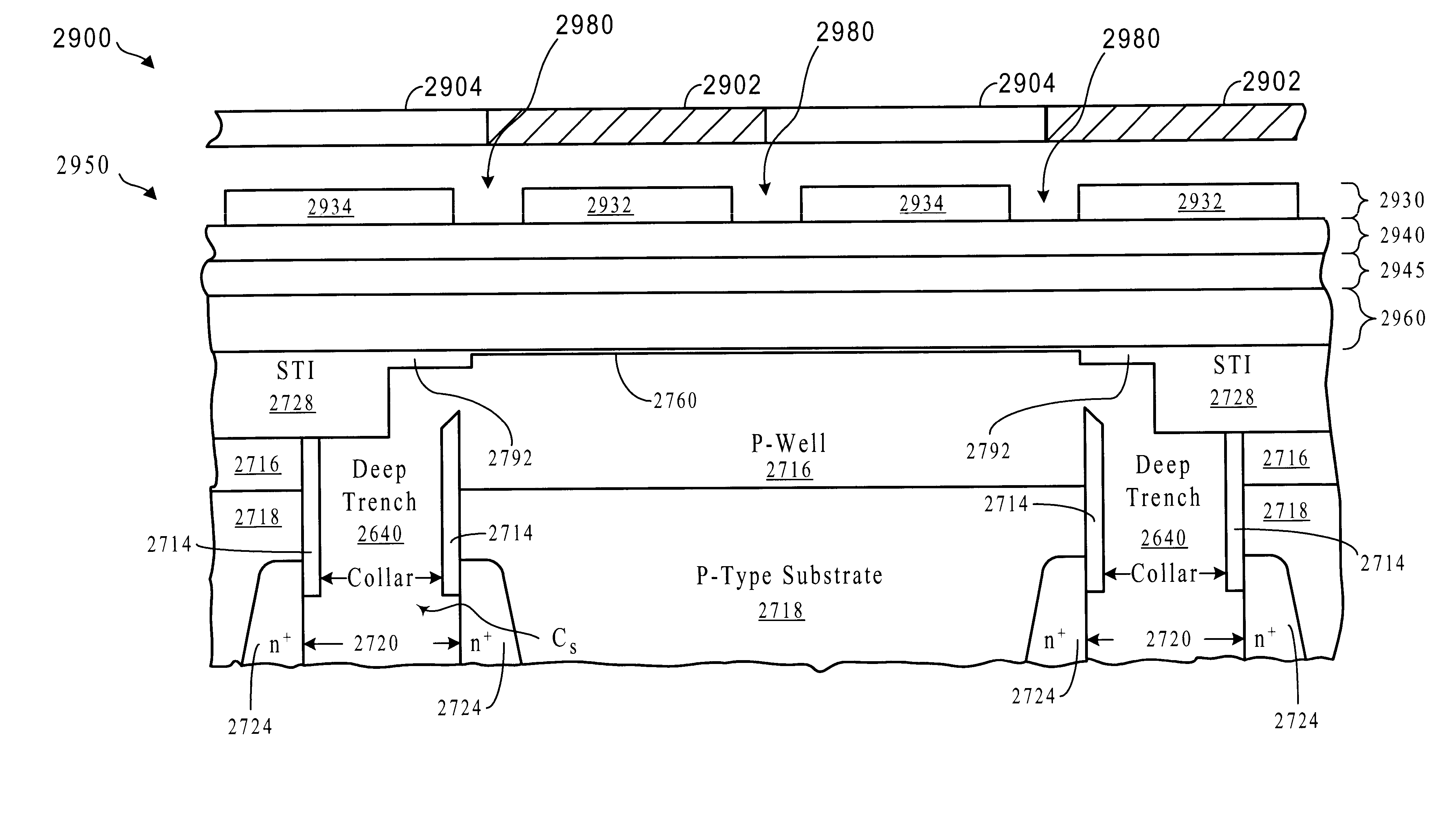

InactiveUS20070032032A1Increase channel lengthLarge thicknessSolid-state devicesSemiconductor/solid-state device manufacturingEngineeringCapacitor

A method for manufacturing a surface strap connection between a trench capacitor and a selection transistor includes providing a masking material on a surface of a semiconductor substrate in areas where no trench capacitors have been formed. An undoped semiconductor layer having vertical and horizontal areas is applied. An oblique ion implantation is performed such that a vertical area of the semiconductor layer on which the connecting structure is to be formed is not doped. After removal of the undoped portion of the semiconductor layer, the exposed portion of the masking material is laterally etched, one part of the substrate surface is exposed, and the doped part of the semiconductor layer is removed. An electrically conducting connection material is applied so that an electrical contact exists between the exposed portion of the substrate surface and the storage electrode.

Owner:INFINEON TECH AG

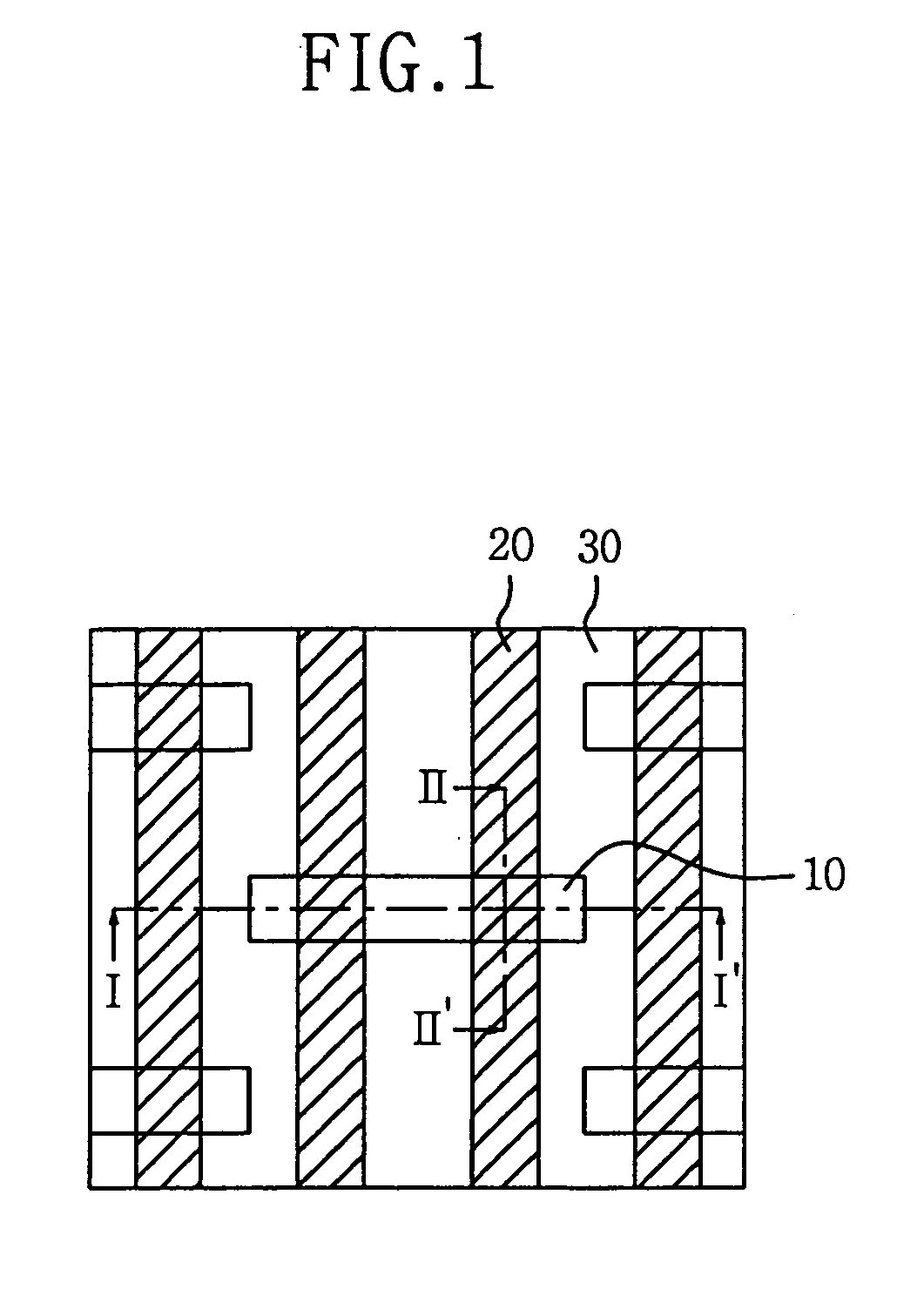

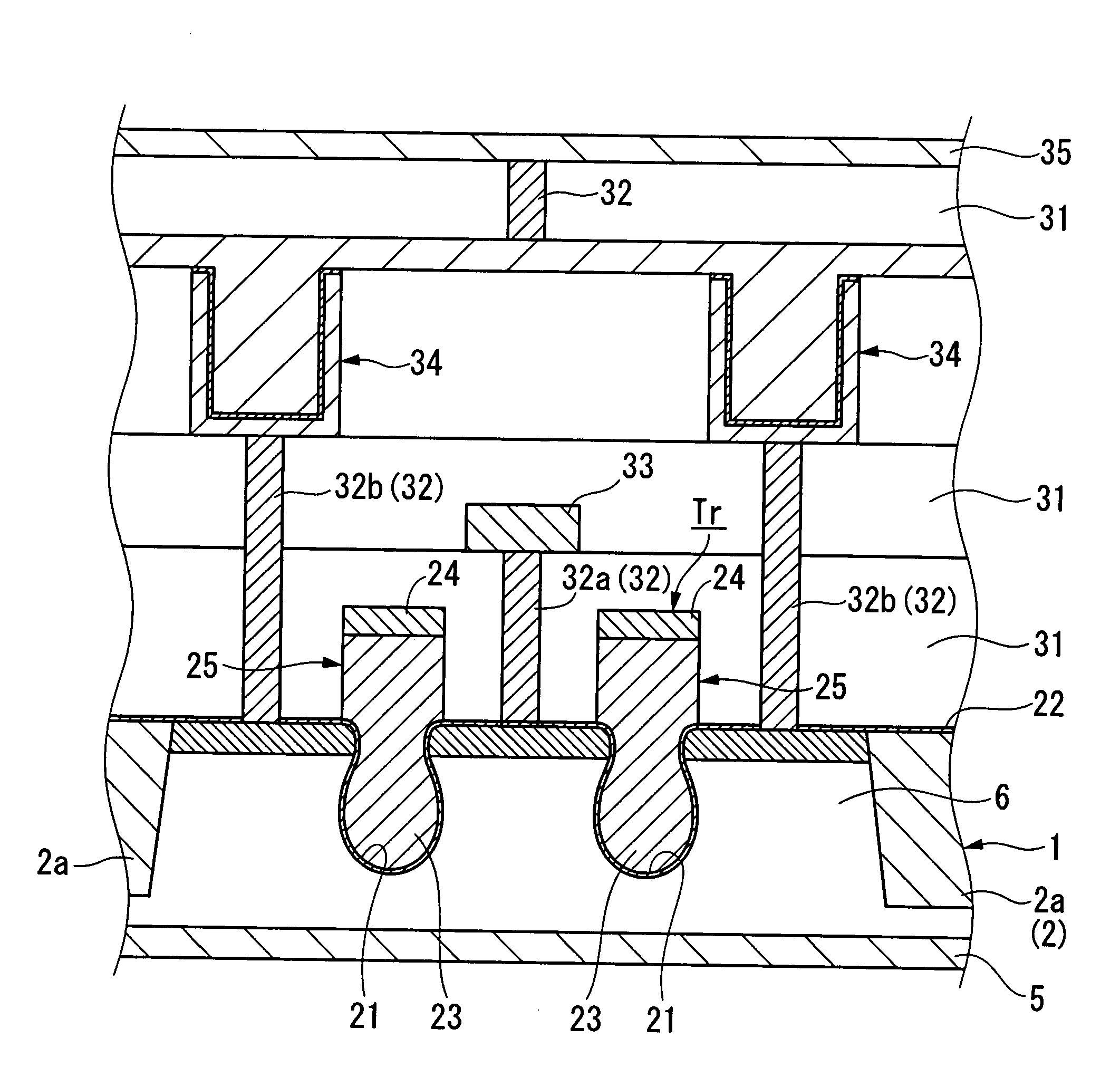

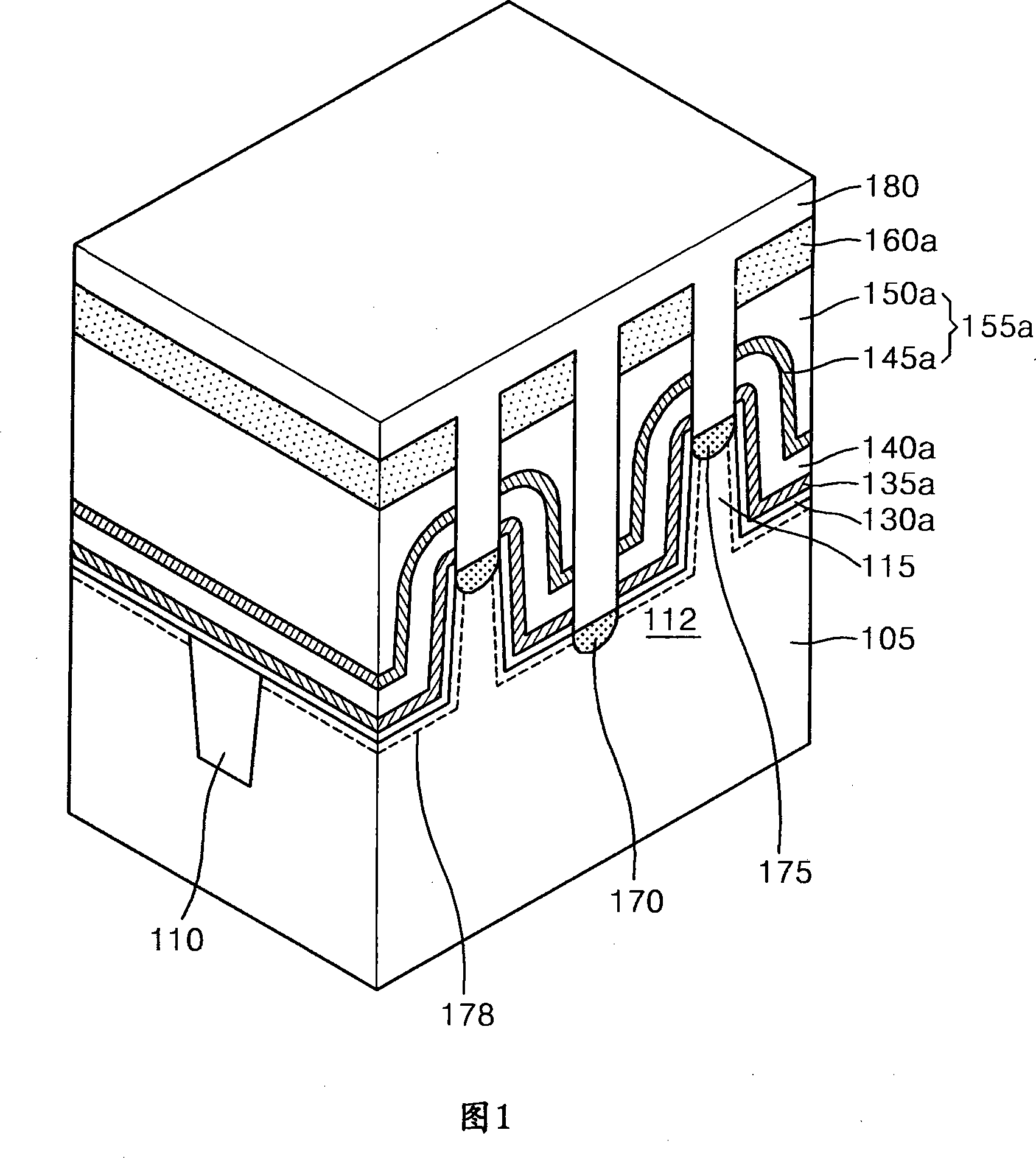

Nonvolatile memory devices and methods of fabricating the same

InactiveCN101246891AIncrease channel lengthHighly integratedSolid-state devicesSemiconductor/solid-state device manufacturingEngineeringSemiconductor

Provided are a nonvolatile memory device and a method of fabricating the same in which a channel length is effectively increased and high-integration may be possible. In the nonvolatile memory device, a semiconductor device may include an active region defined by a device isolation film. The active region may include at least one projecting portion. A pair of control gate electrodes may cover both side surfaces of the at least one projecting portion, and may be spaced apart from each other. A pair of charge storage layers may be between both side surfaces of the at least one projecting portion and the pair of control gate electrodes.

Owner:SAMSUNG ELECTRONICS CO LTD