Patents

Literature

141results about How to "Reduce channel resistance" patented technology

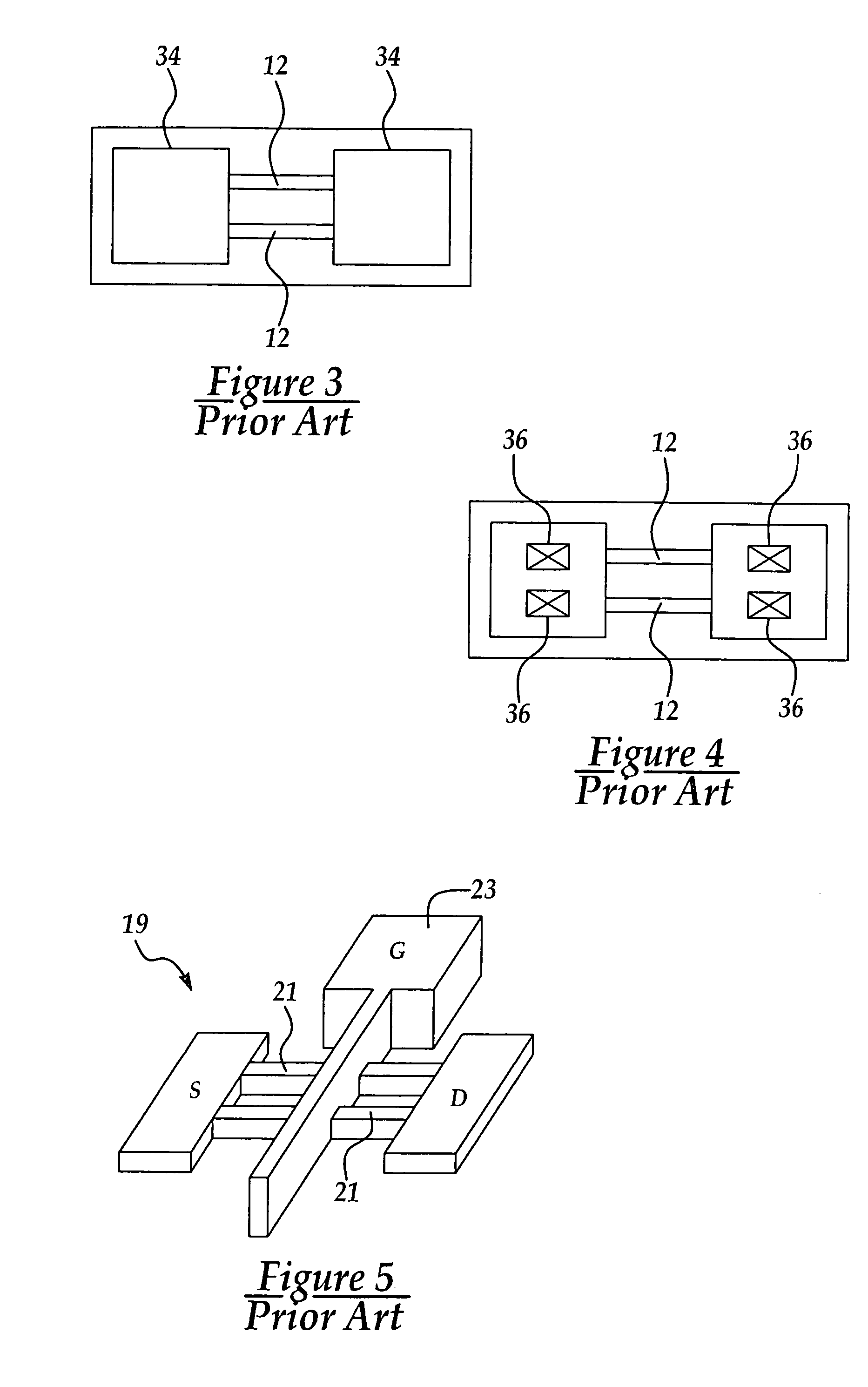

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

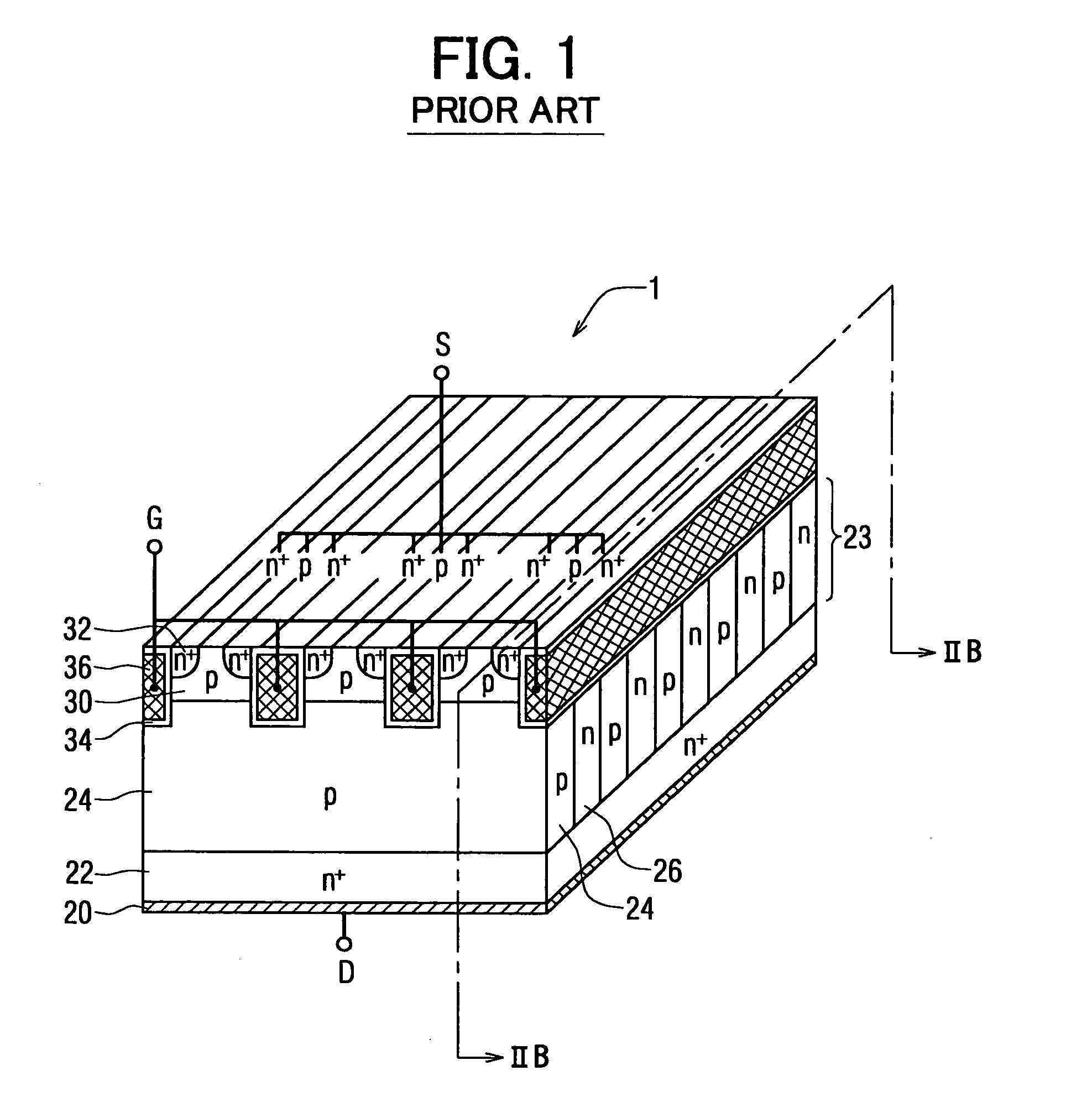

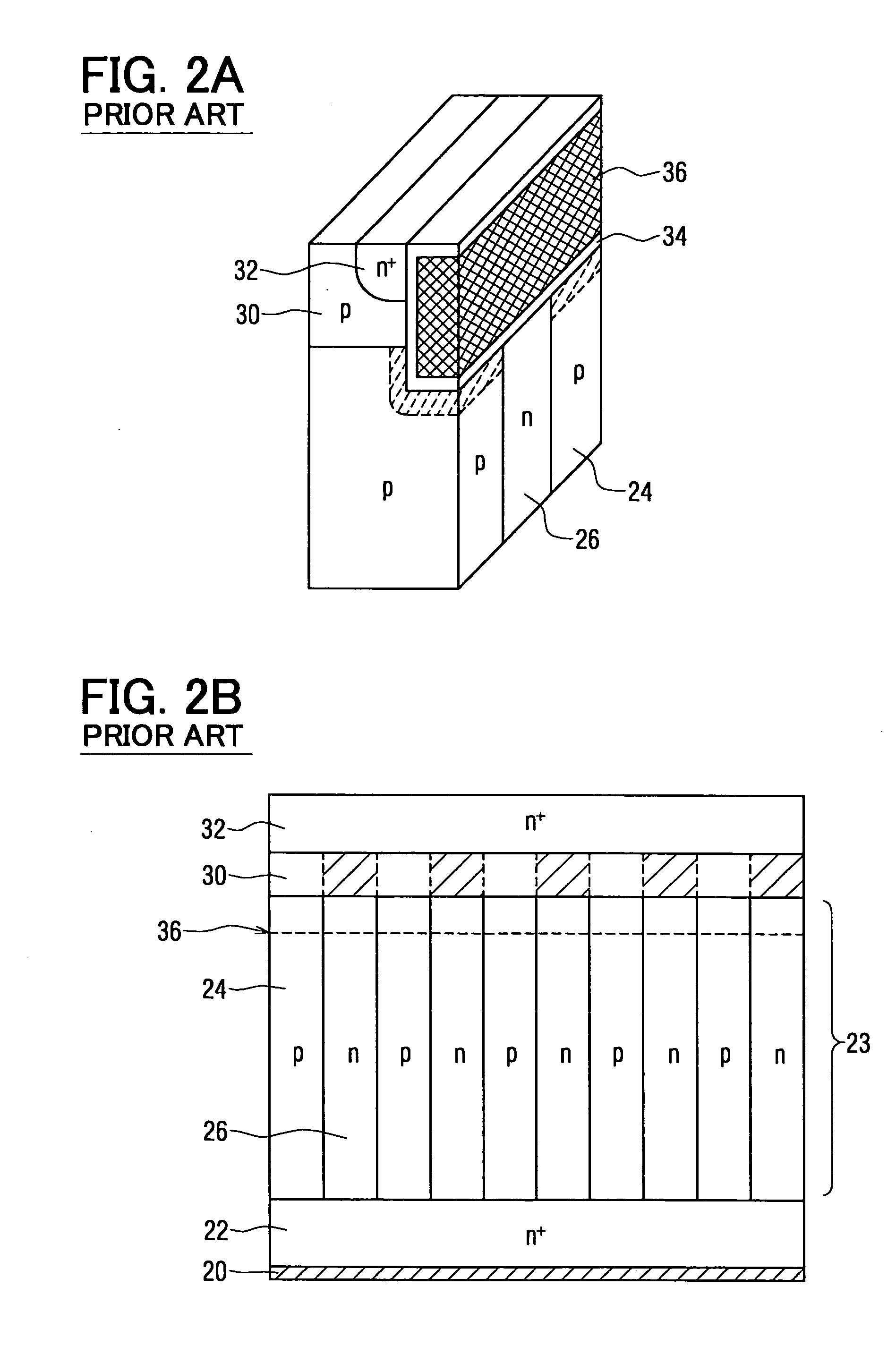

Trench-gate field effect transistors and methods of forming the same

InactiveUS20060273386A1Reduce channel resistanceSemiconductor/solid-state device manufacturingDiodeGate dielectricField-effect transistor

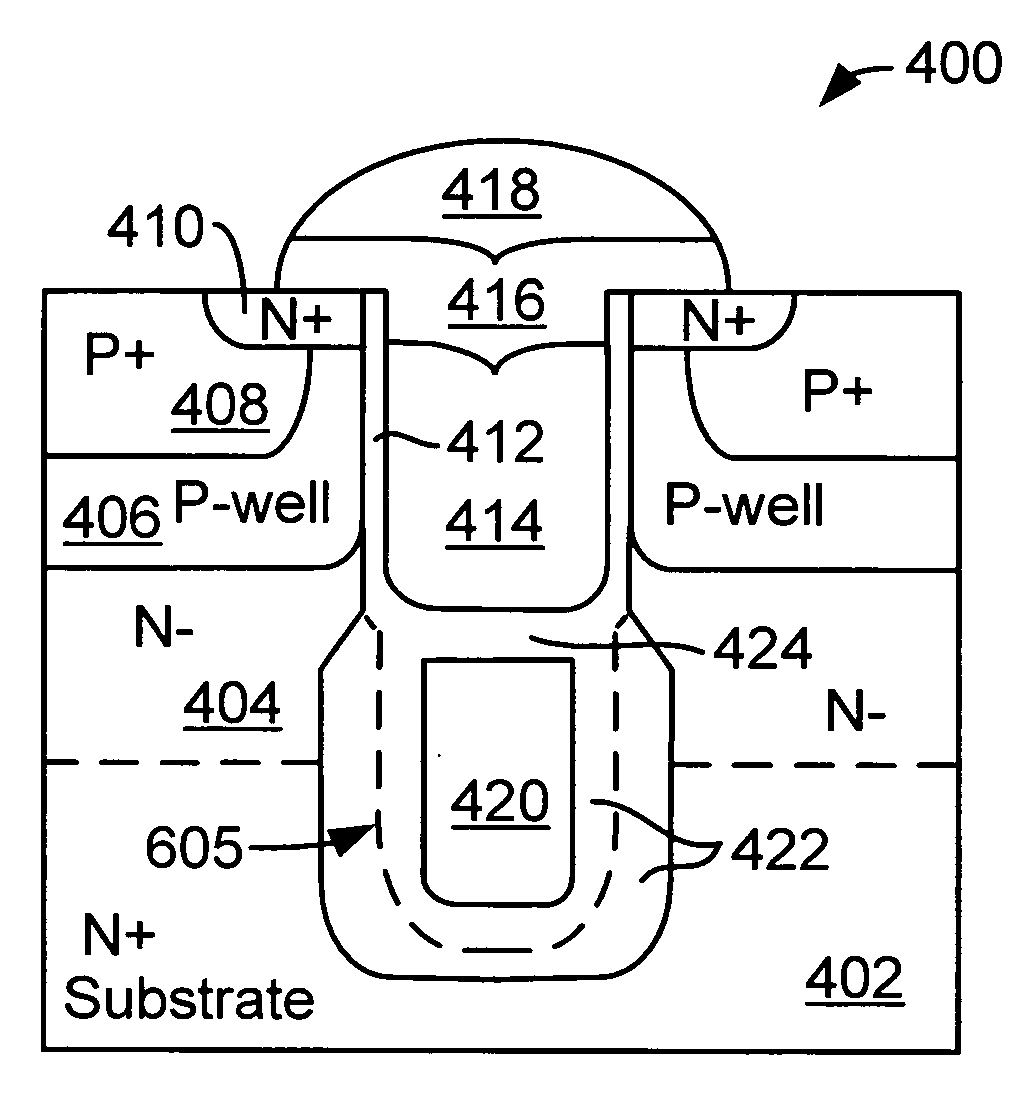

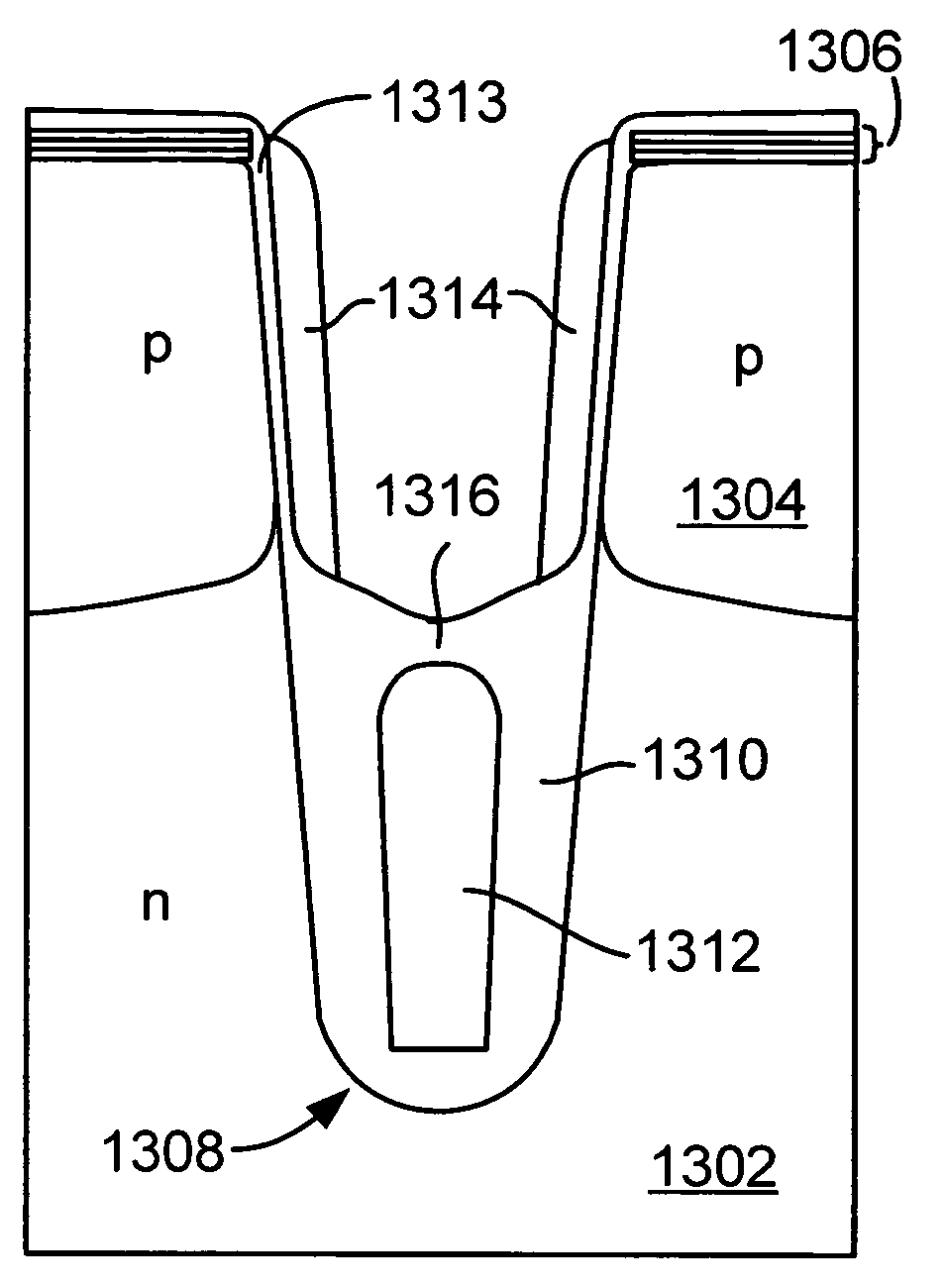

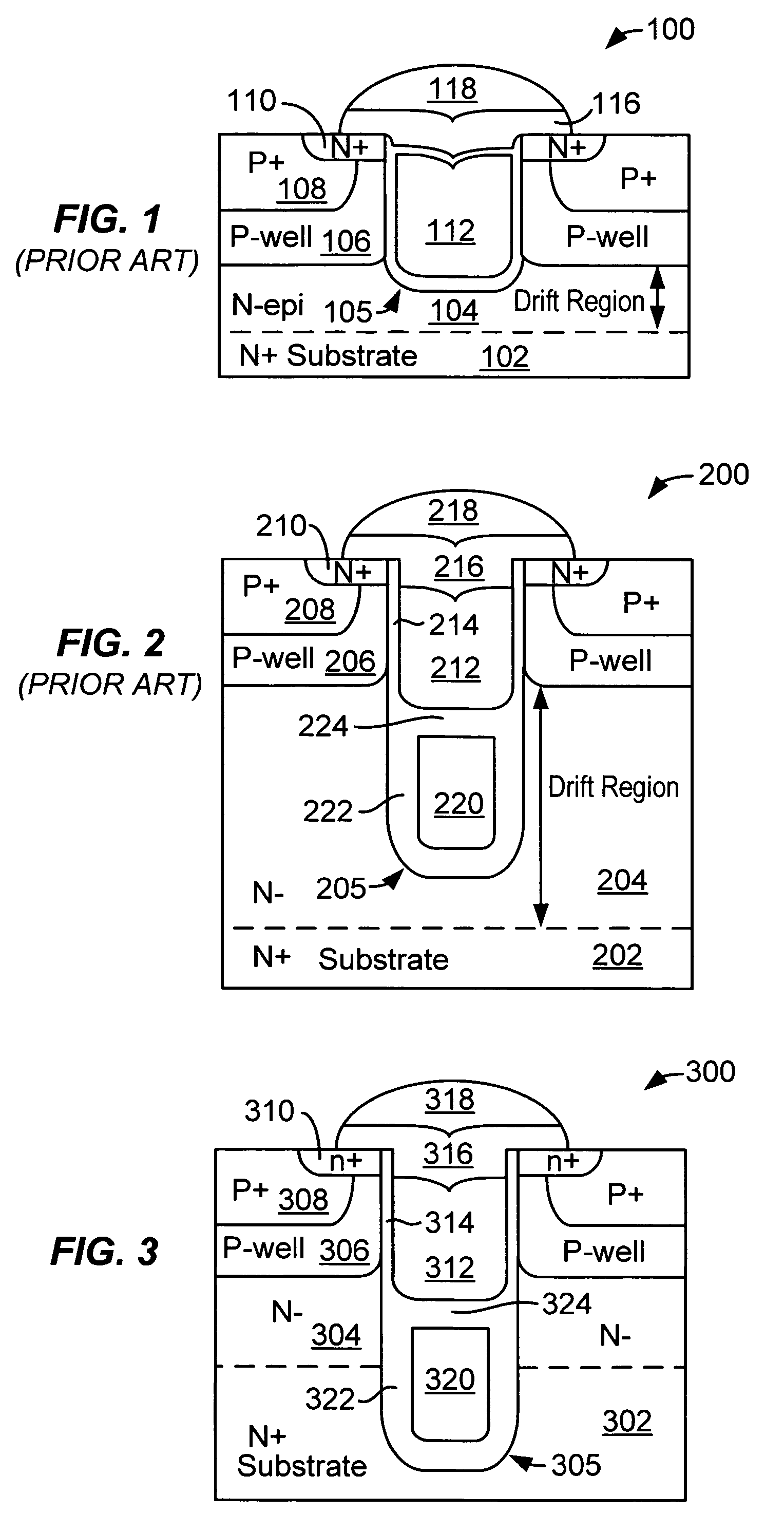

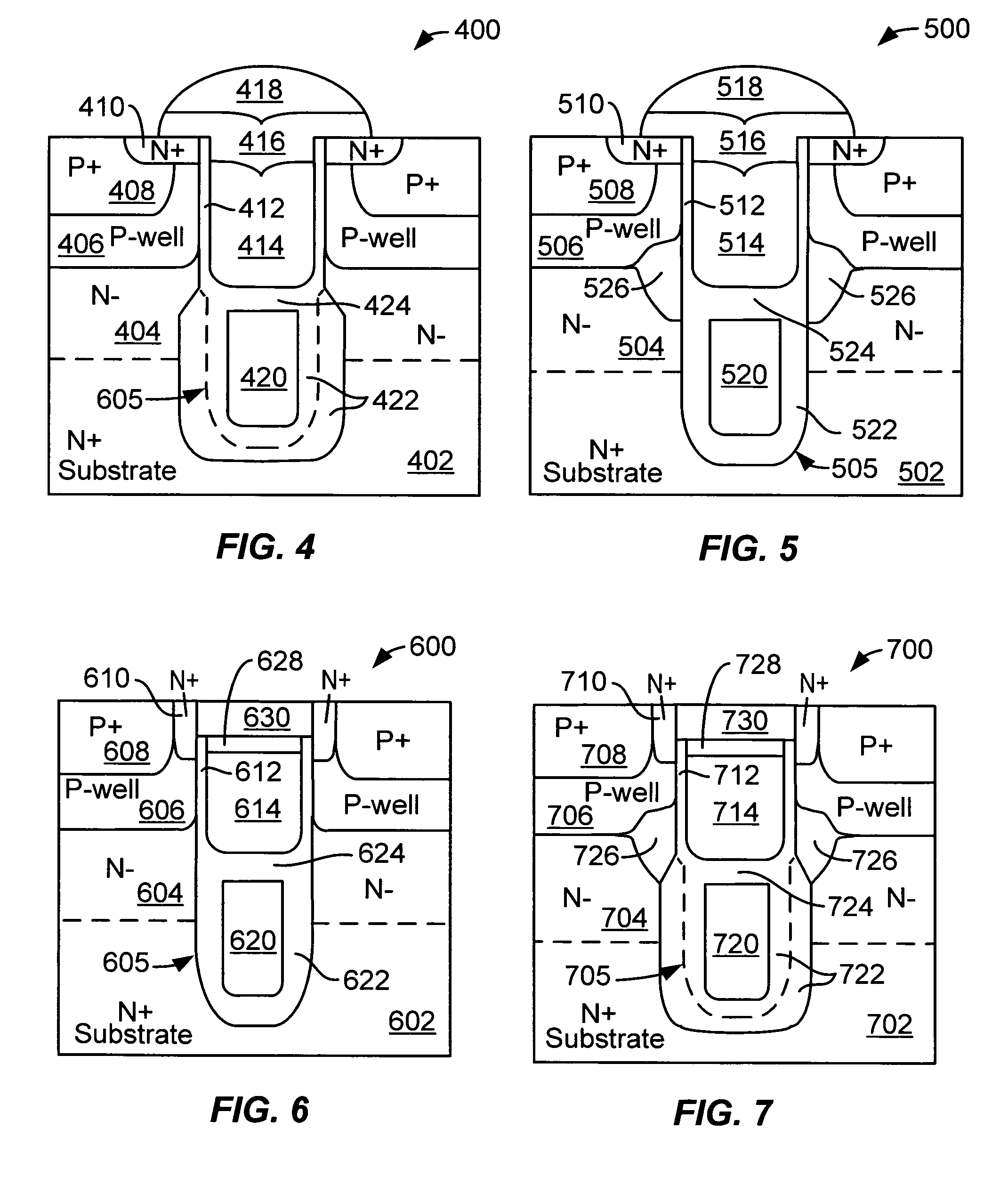

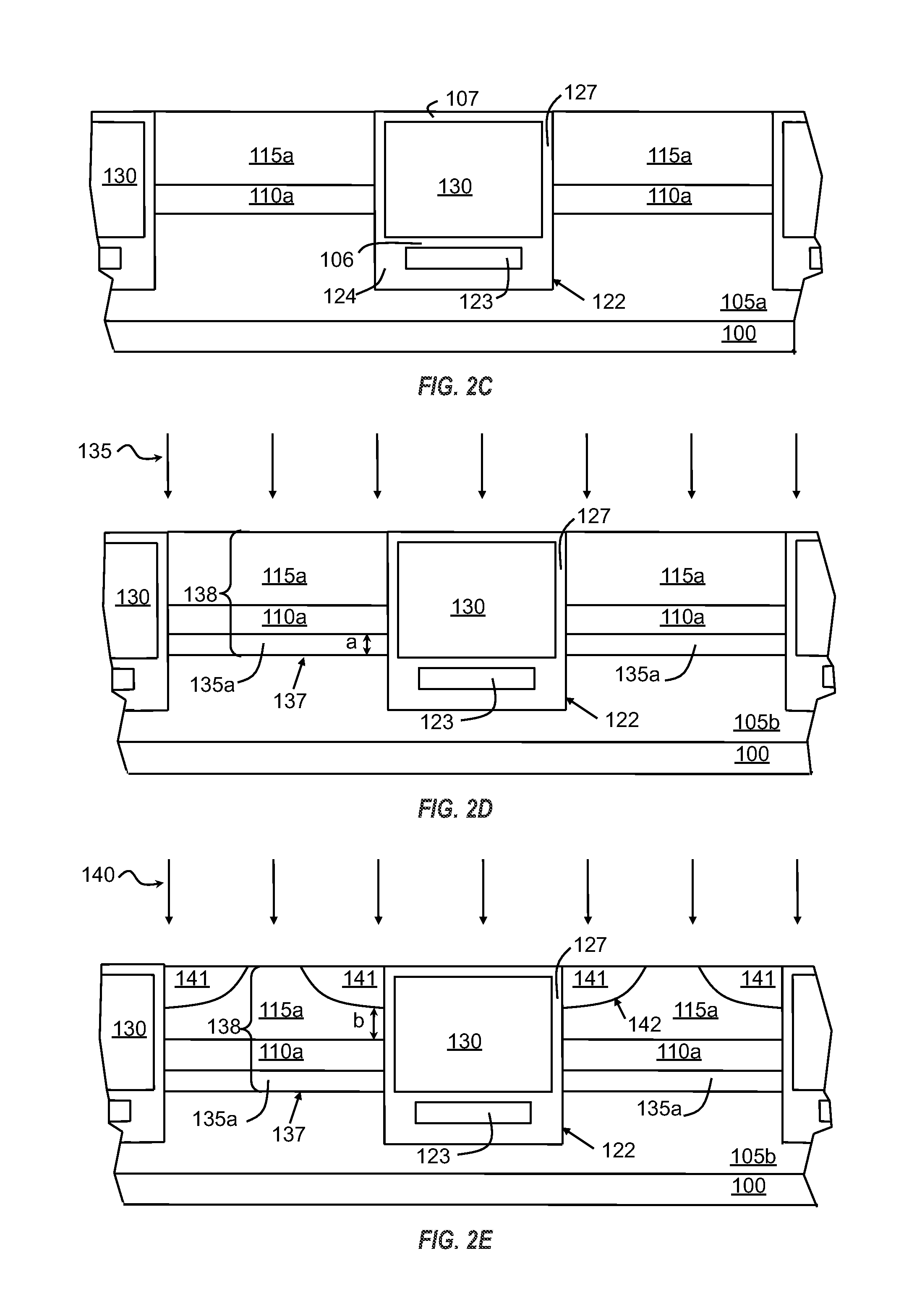

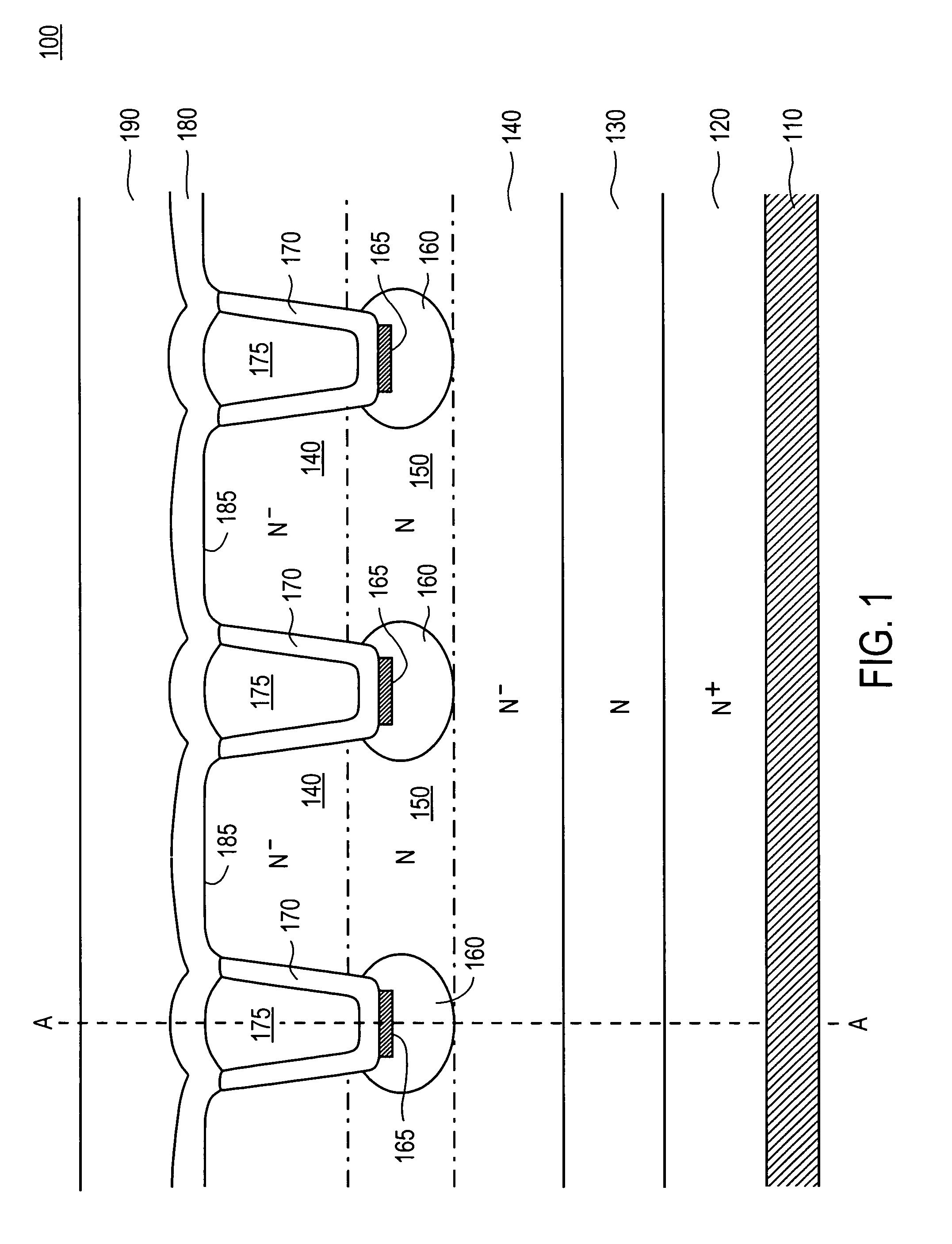

A field effect transistor includes a body region of a first conductivity type over a semiconductor region of a second conductivity type. A gate trench extends through the body region and terminates within the semiconductor region. At least one conductive shield electrode is disposed in the gate trench. A gate electrode is disposed in the gate trench over but insulated from the at least one conductive shield electrode. A shield dielectric layer insulates the at lease one conductive shield electrode from the semiconductor region. A gate dielectric layer insulates the gate electrode from the body region. The shield dielectric layer is formed such that it flares out and extends directly under the body region.

Owner:SEMICON COMPONENTS IND LLC

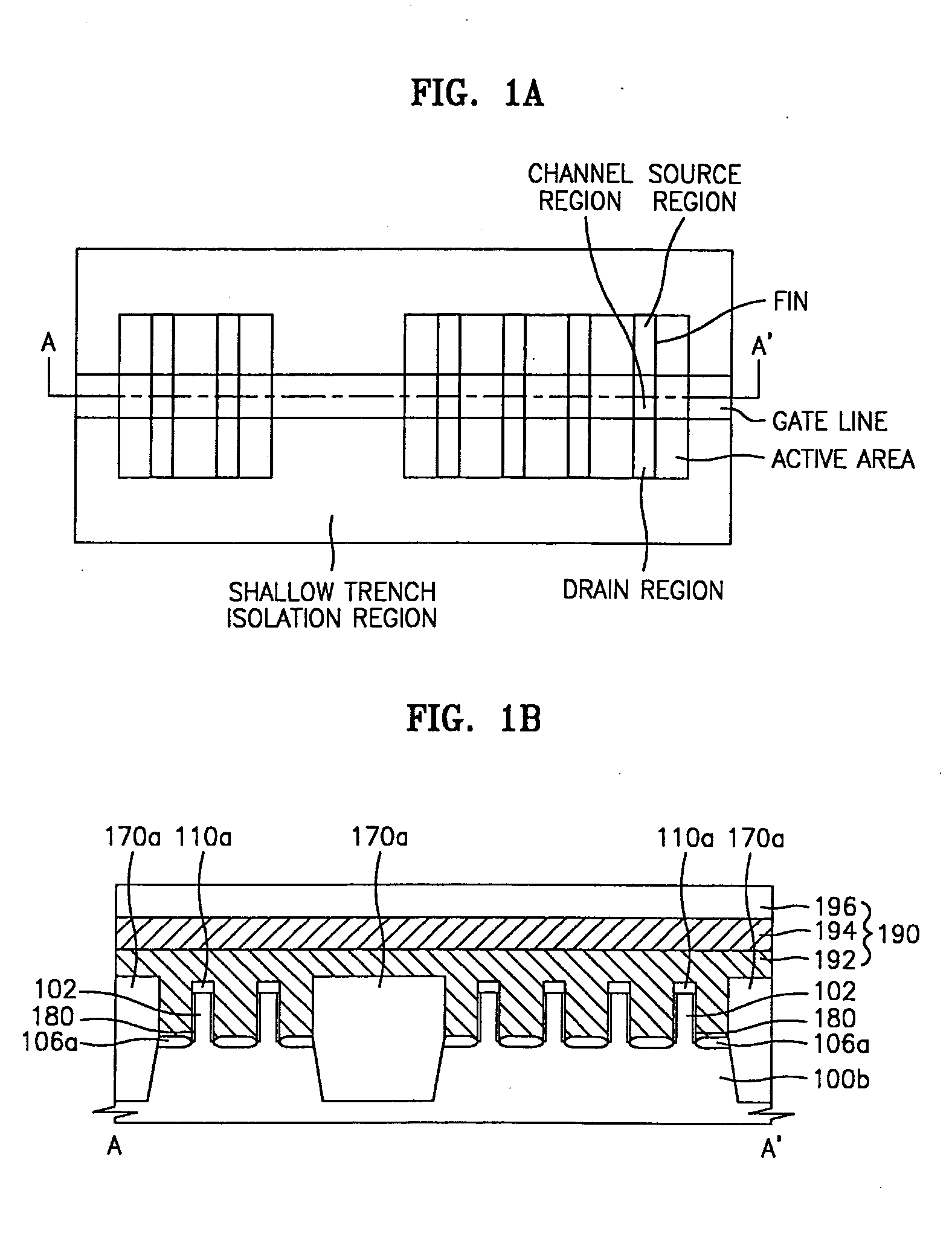

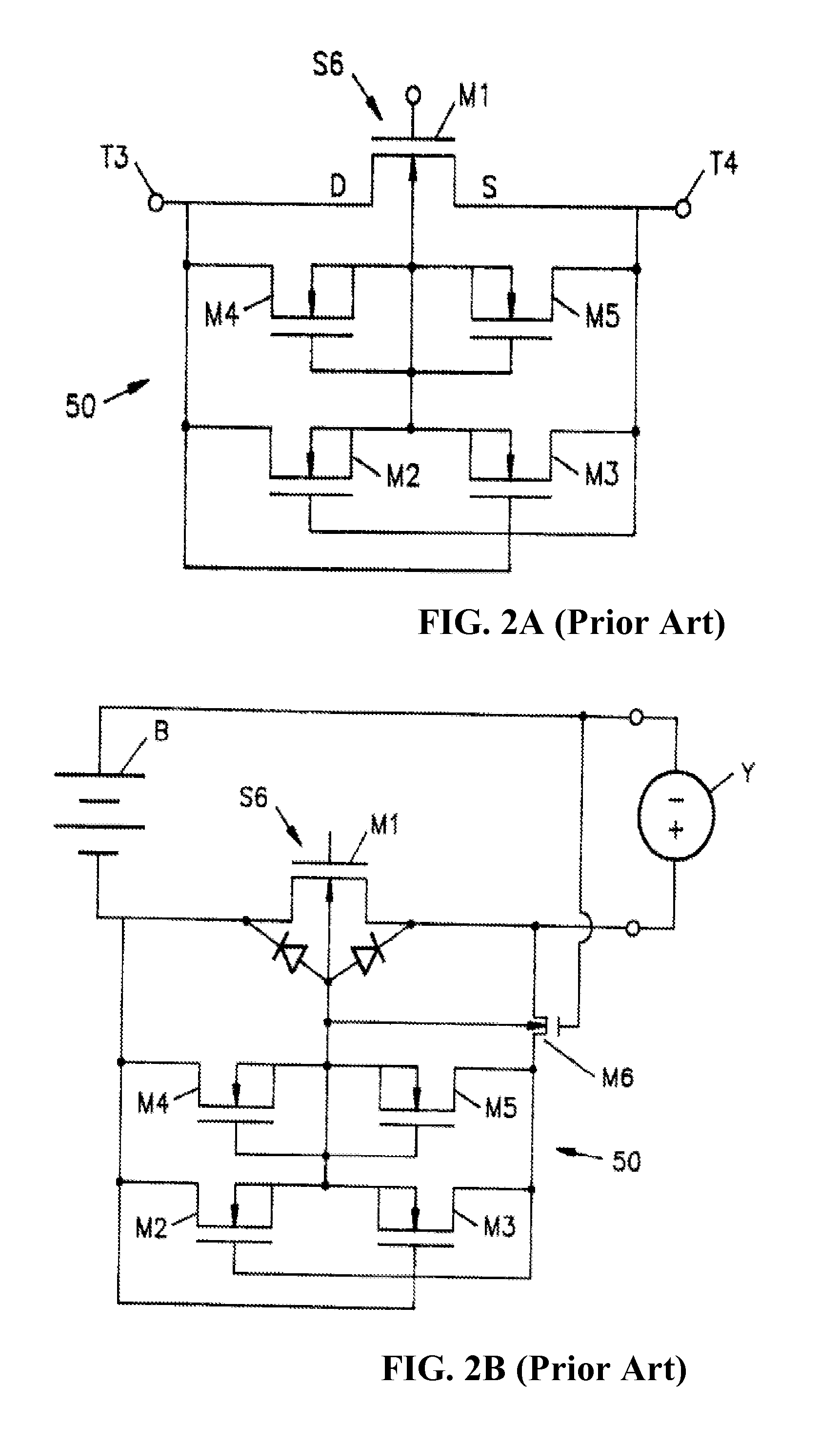

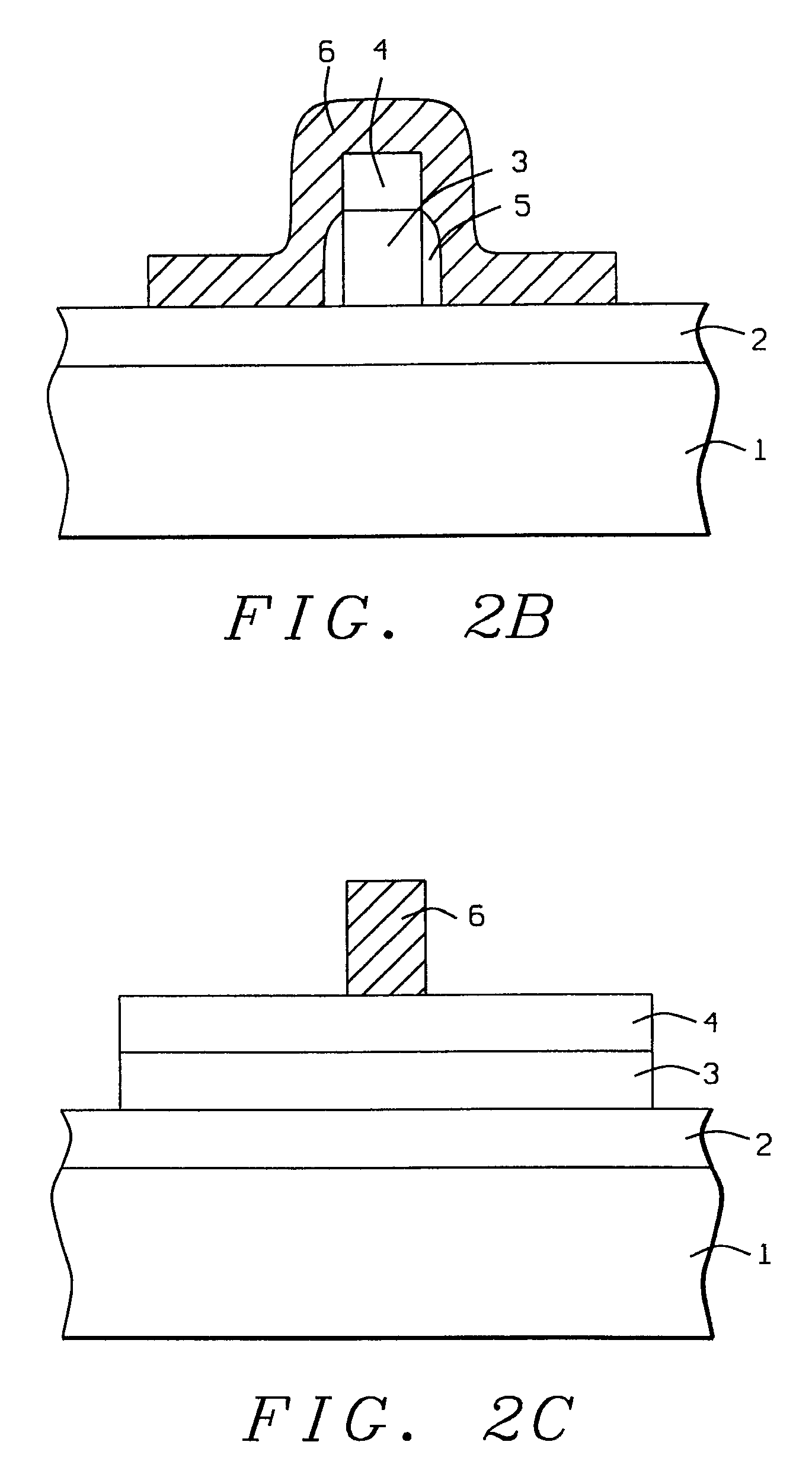

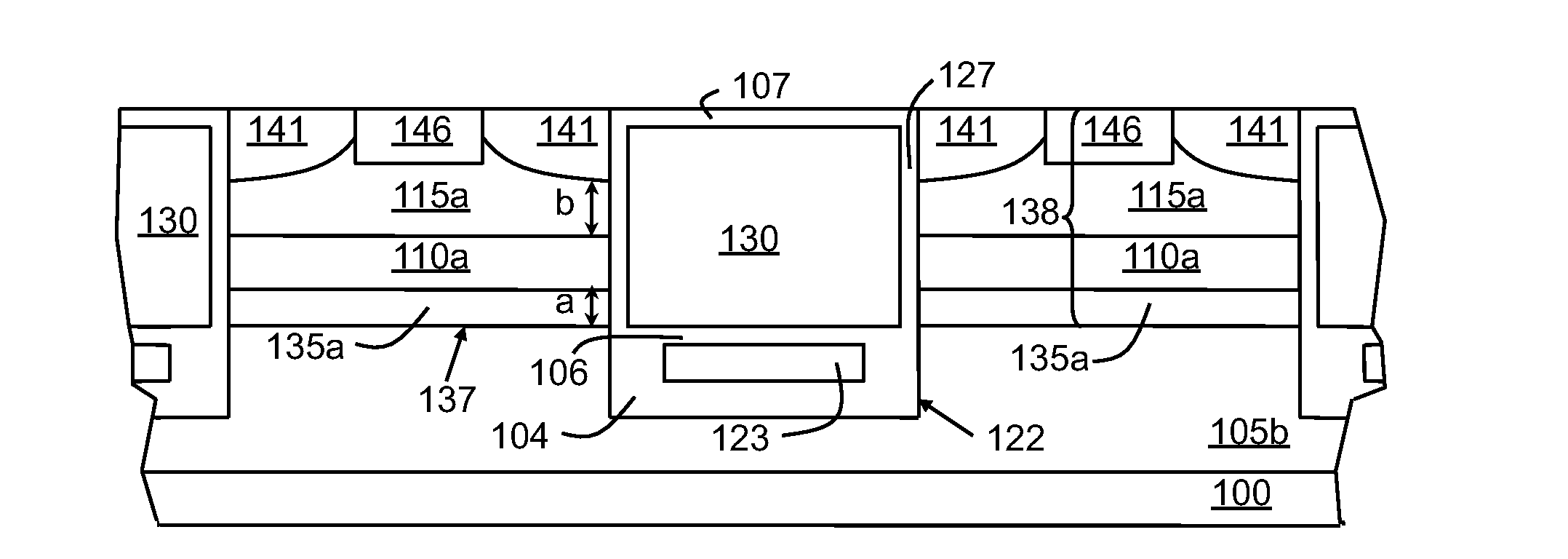

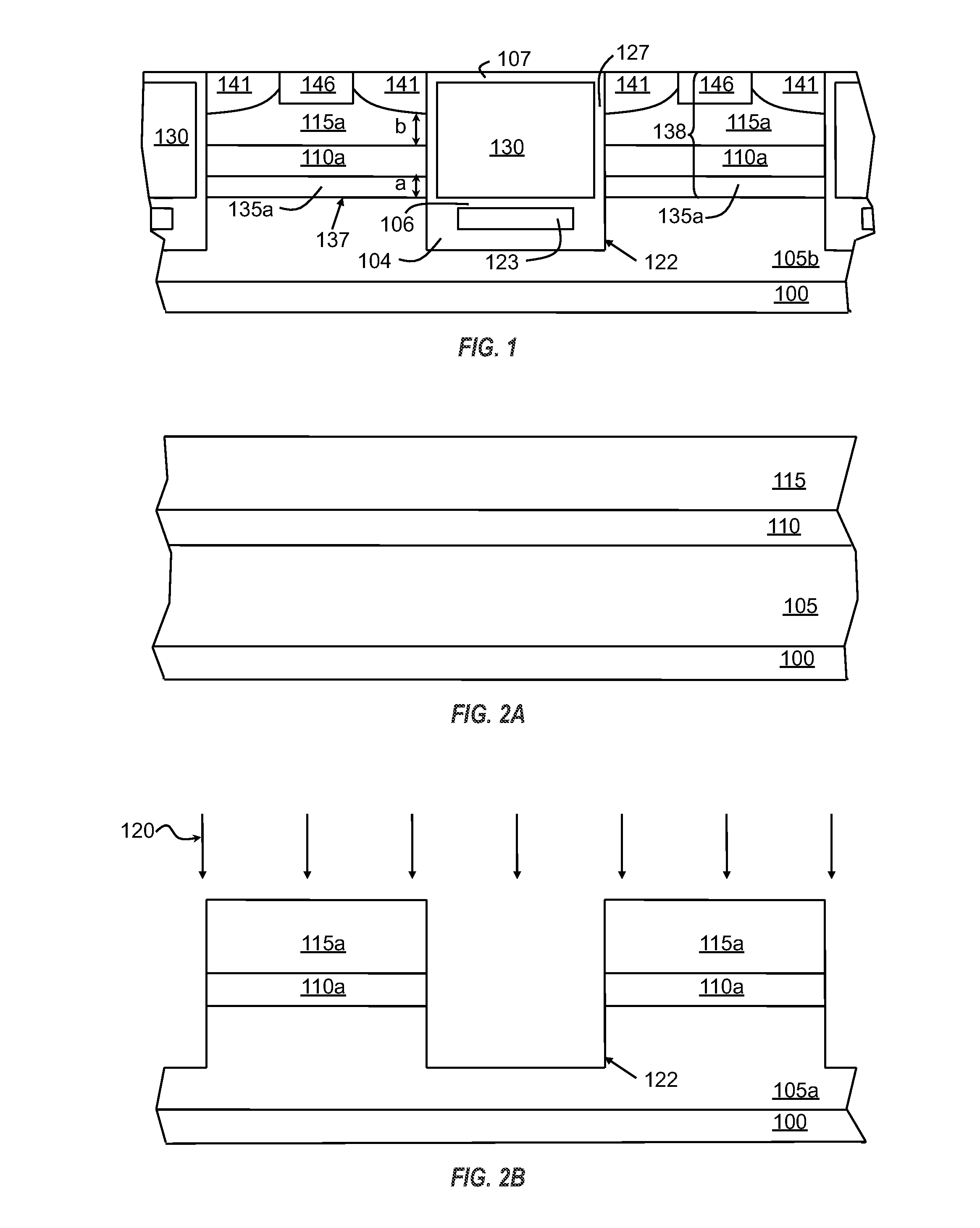

FinFET transistor device on SOI and method of fabrication

ActiveUS7300837B2Thin body”Reduce contact resistanceTransistorSolid-state devicesSilicate glassEngineering

A FinFET transistor on SOI device and method of fabrication is provided. At least two FinFET fins each having an upper poly-silicate glass portion and a lower silicon portion are formed using spacer patterning technology. Each fin is formed on a sacrificial SiN mask layer having a sacrificial support structure. The SiN mask is removed and then a breakthrough etch is applied to remove an underlying pad oxide layer. A PSG layer defining a width of each of the fins on a sidewall of each of the support structures is deposited on each of the support structures. At least two fins each having a narrow fin pitch of about 0.25 μm. are formed. The fins provide a seed layer for at least two selective epitaxially raised source and drain regions, wherein each raised source-drain associated with each fin are interconnected thus forming a source pad and a drain pad.

Owner:TAIWAN SEMICON MFG CO LTD

Trench-gate field effect transistors and methods of forming the same

InactiveUS7504303B2Reduce channel resistanceSemiconductor/solid-state device manufacturingDiodeEngineeringField-effect transistor

A method for forming a shielded gate field effect transistor includes the following steps. Trenches extending into a silicon region are formed using a mask that includes a protective layer. A shield dielectric layer lining sidewalls and bottom of each trench is formed. A shield electrode is formed in a bottom portion of each trench. Protective spacers are formed along upper sidewalls of each trench. An inter-electrode dielectric is formed over the shield electrode. The protective spacers and the protective layer of the mask prevent formation of inter-electrode dielectric along the upper sidewalls of each trench and over mesa surfaces adjacent each trench. A gate electrode is formed in each trench over the inter-electrode dielectric.

Owner:SEMICON COMPONENTS IND LLC

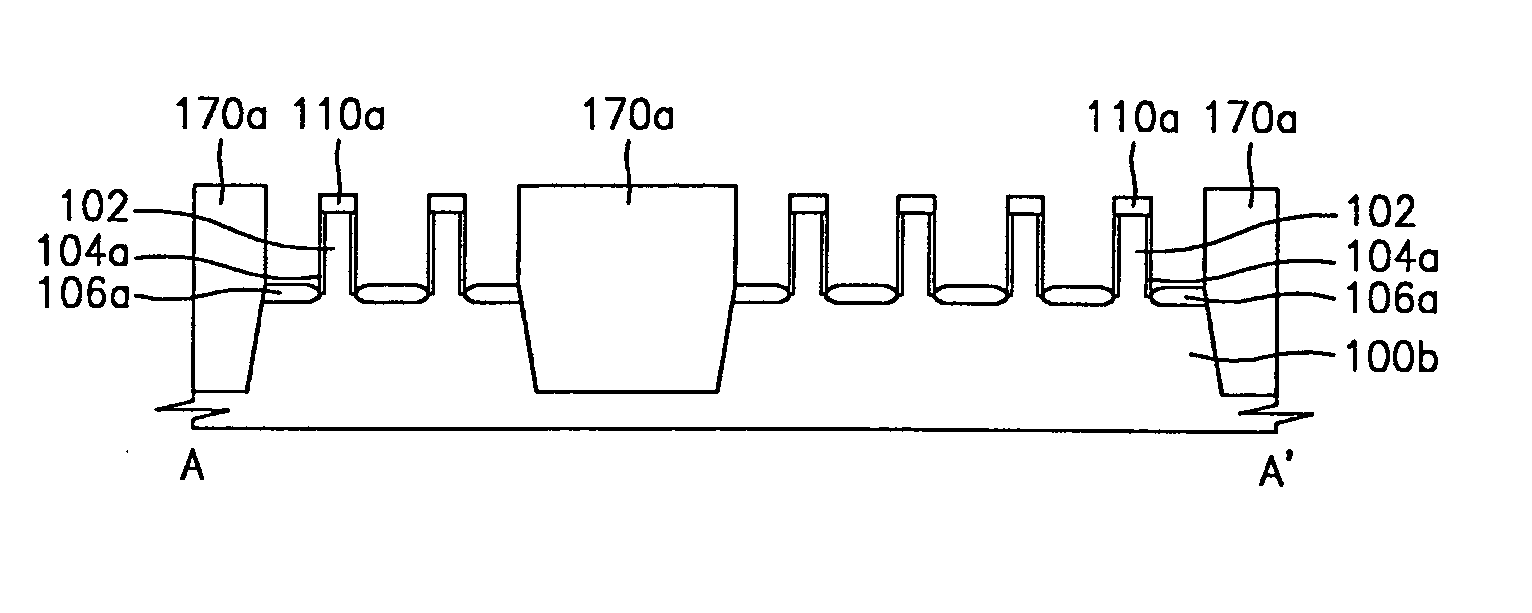

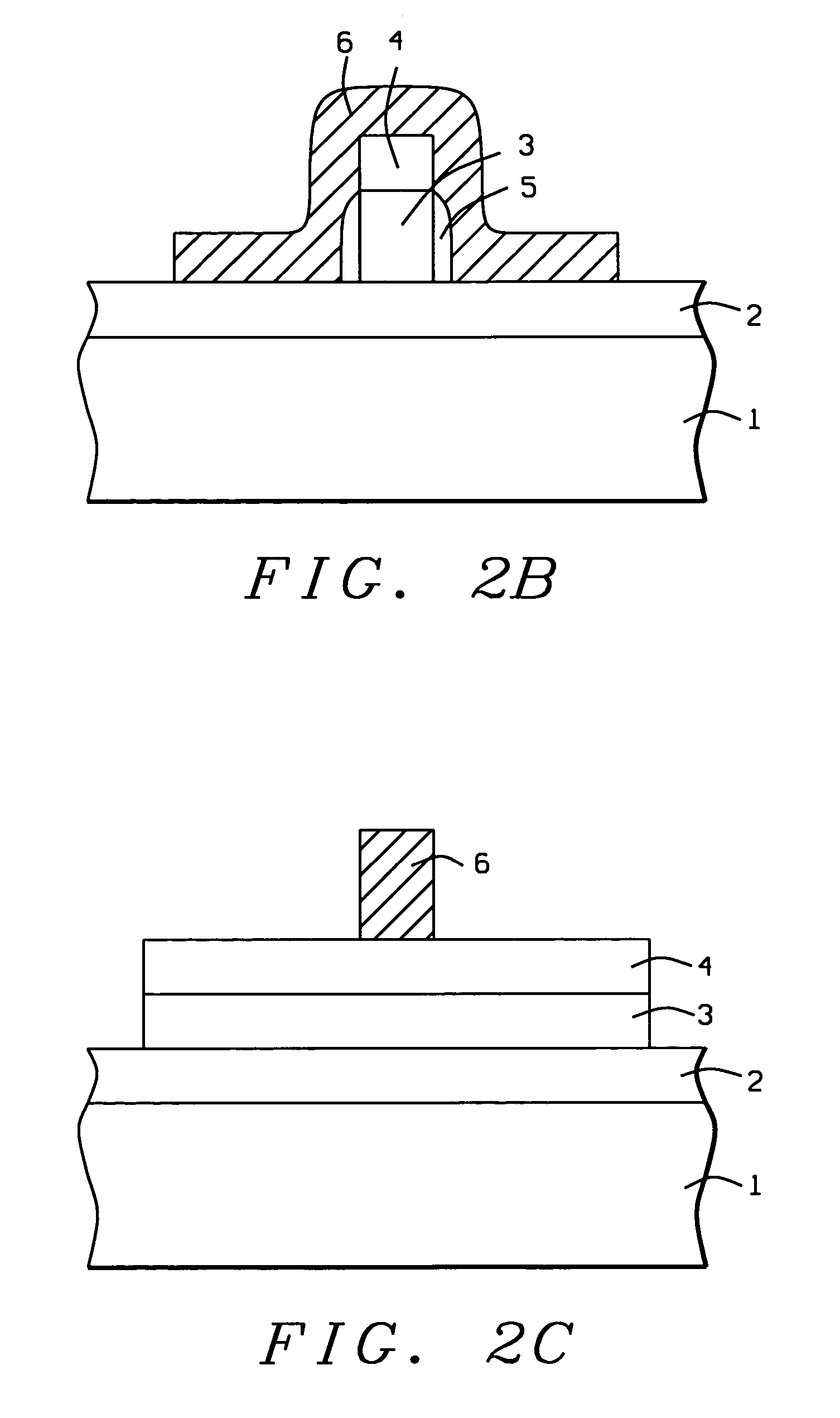

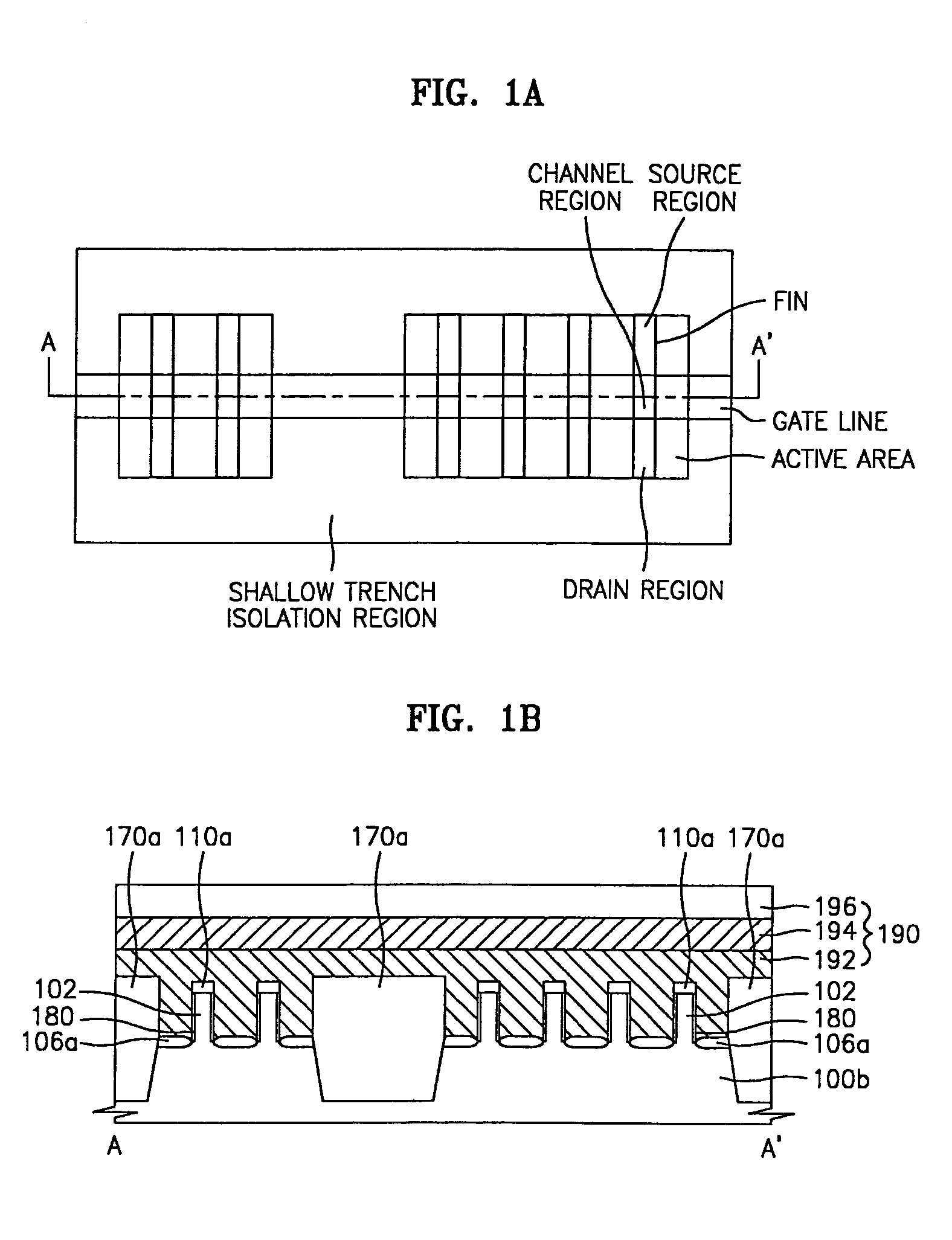

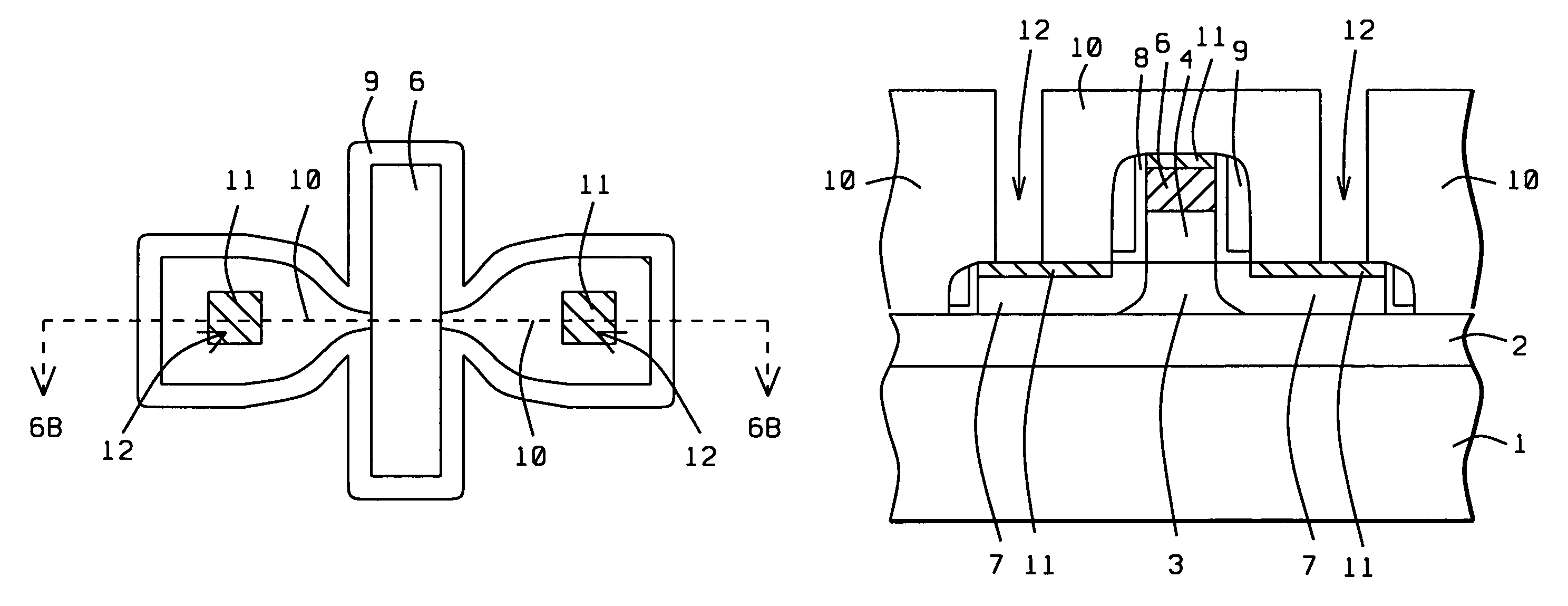

Double gate field effect transistor and method of manufacturing the same

InactiveUS20050056888A1Reduce channel resistanceReduce in quantityTransistorSolid-state devicesSilicon nitrideEngineering

Provided is a double gate field effect transistor and a method of manufacturing the same. The method of manufacturing the double gate field effect transistor comprises forming as many fins as required by etching a silicon substrate, masking the resultant product by an insulating material such as silicon nitride, forming trench regions for device isolation and STI film by using the silicon nitride mask, forming gate oxide films on both faces of the fins after removing the hard mask, and forming a gate line. As such, unnecessary channel formation under the silicon oxide film, when a voltage higher than a threshold voltage is applied to the substrate, is prevented by forming a thick silicon oxide film on the substrate on which no protruding fins are formed.

Owner:SAMSUNG ELECTRONICS CO LTD

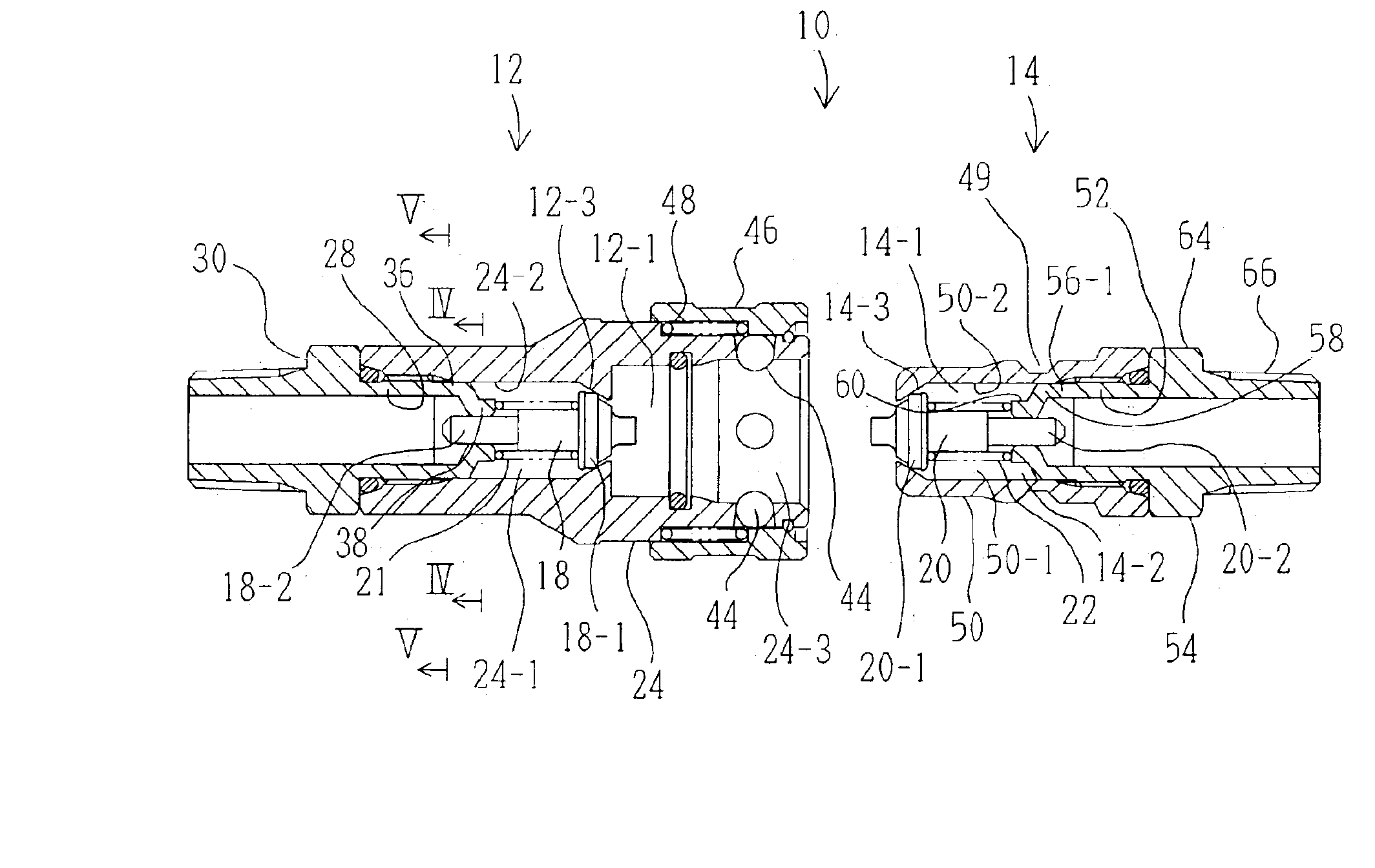

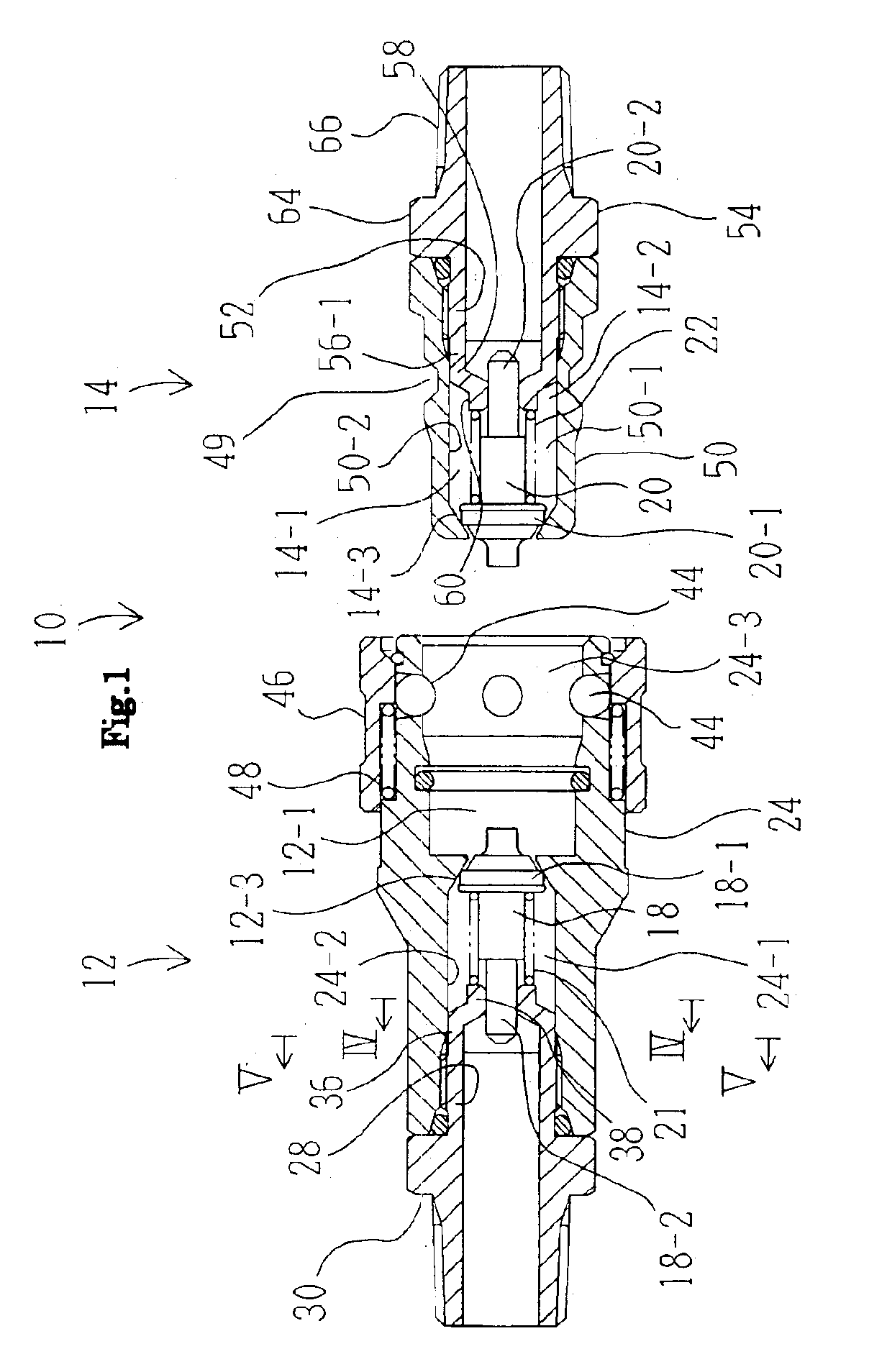

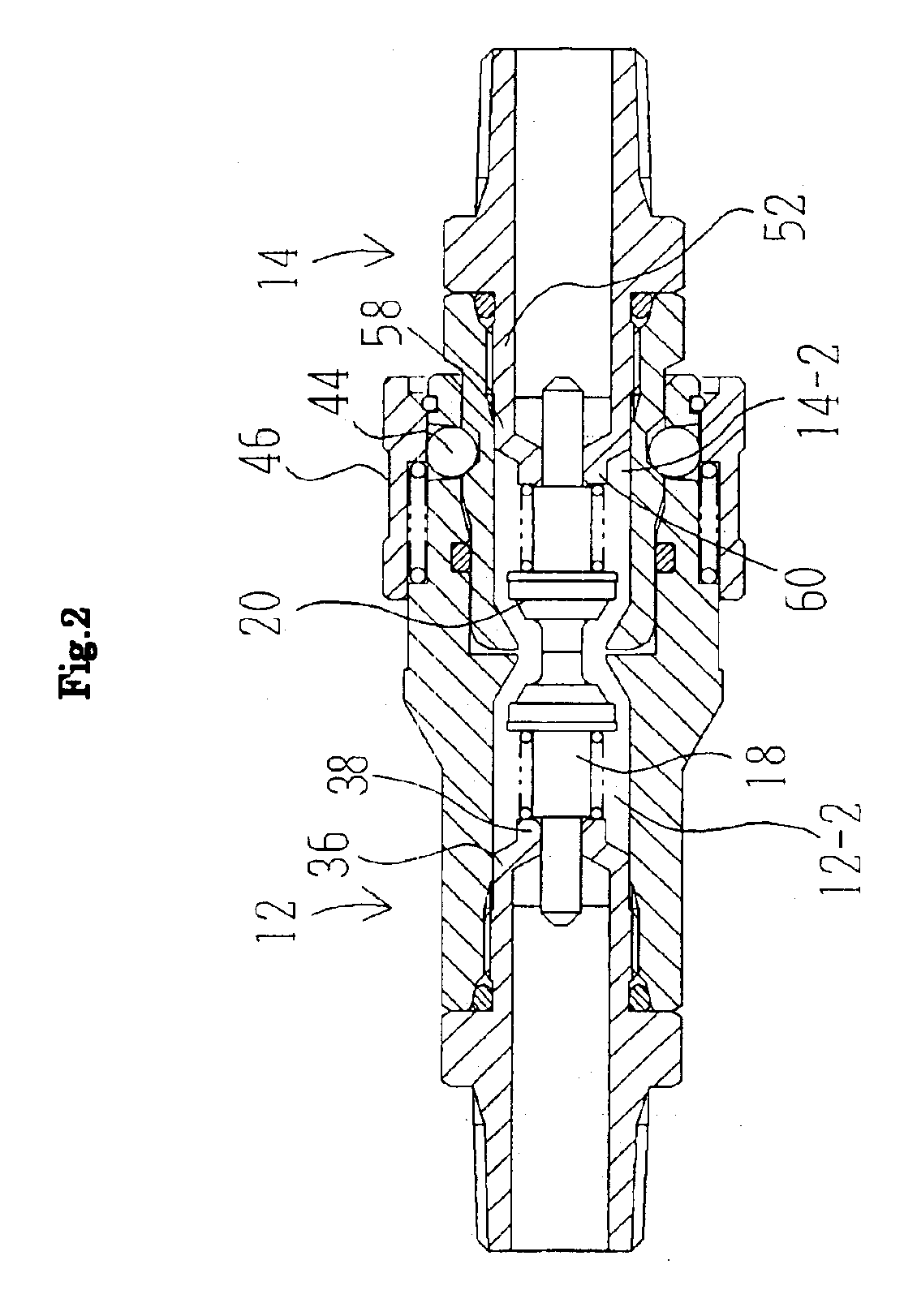

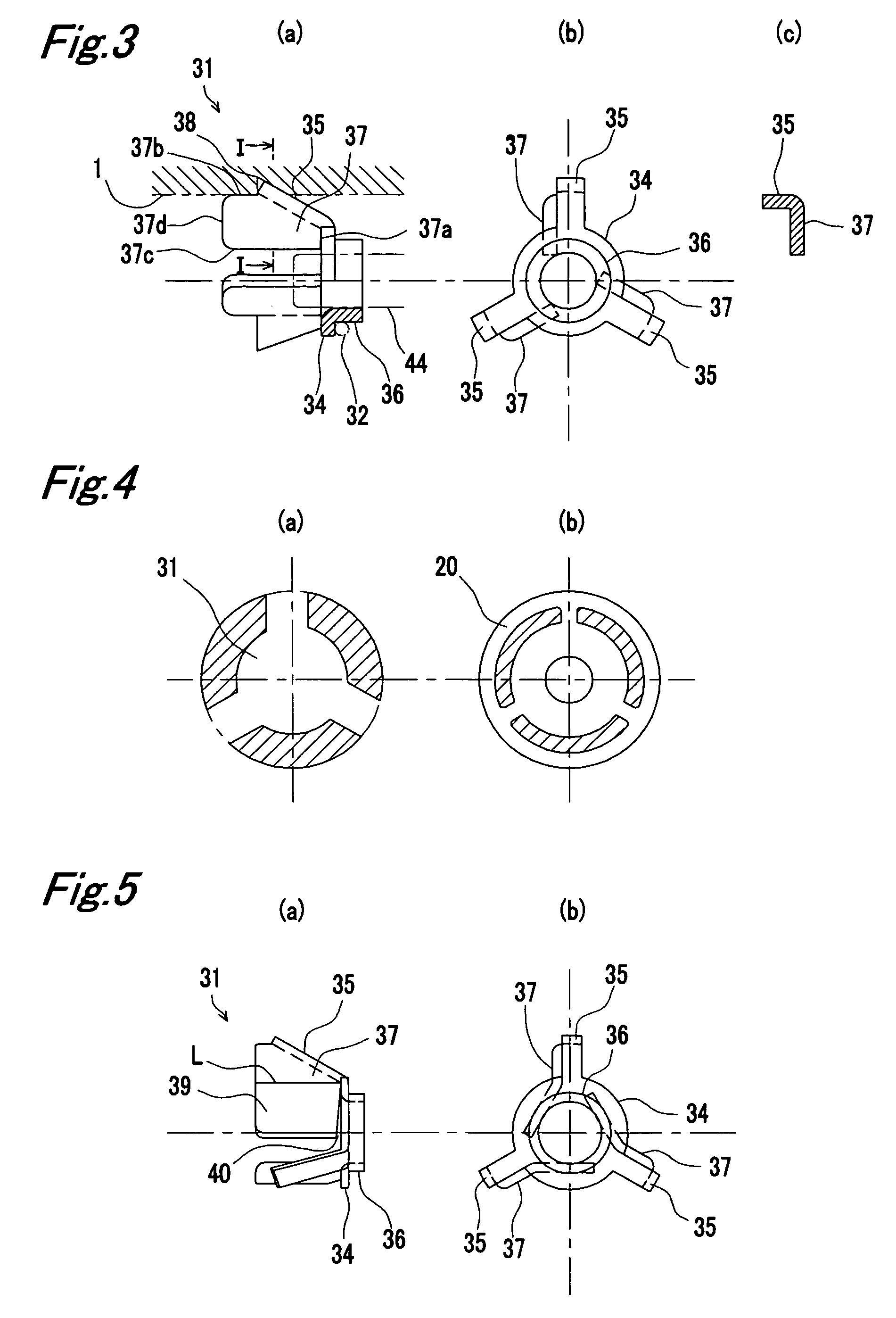

Female and male couplers of pipe coupling

A female coupler and a male coupler of a pipe coupling that are easy to assemble and have a minimized passage resistance are provided. The female coupler includes a cylindrical female coupler body adapted to receive the male coupler from a front end opening thereof. A pipe connection adapter has a cylindrical connecting portion that is inserted into the female coupler body from a rear end opening thereof, and is thus connected to the female coupler body. The pipe connection adapter has two support legs extending from the front end surface of the cylindrical connecting portion. A valve support ring is secured to the distal ends of the support legs. The valve support ring has an outer circumferential surface that has a diameter smaller than the outer diameter of the cylindrical connecting portion, whereby a fluid passage is defined between the outer circumferential surface of the support ring and the wall surface of the through-hole of the female coupler body. The support legs are connected to the valve support ring at the rear end surface thereof. The male coupler has an arrangement similar to the above.

Owner:NITTO KOHKI CO LTD

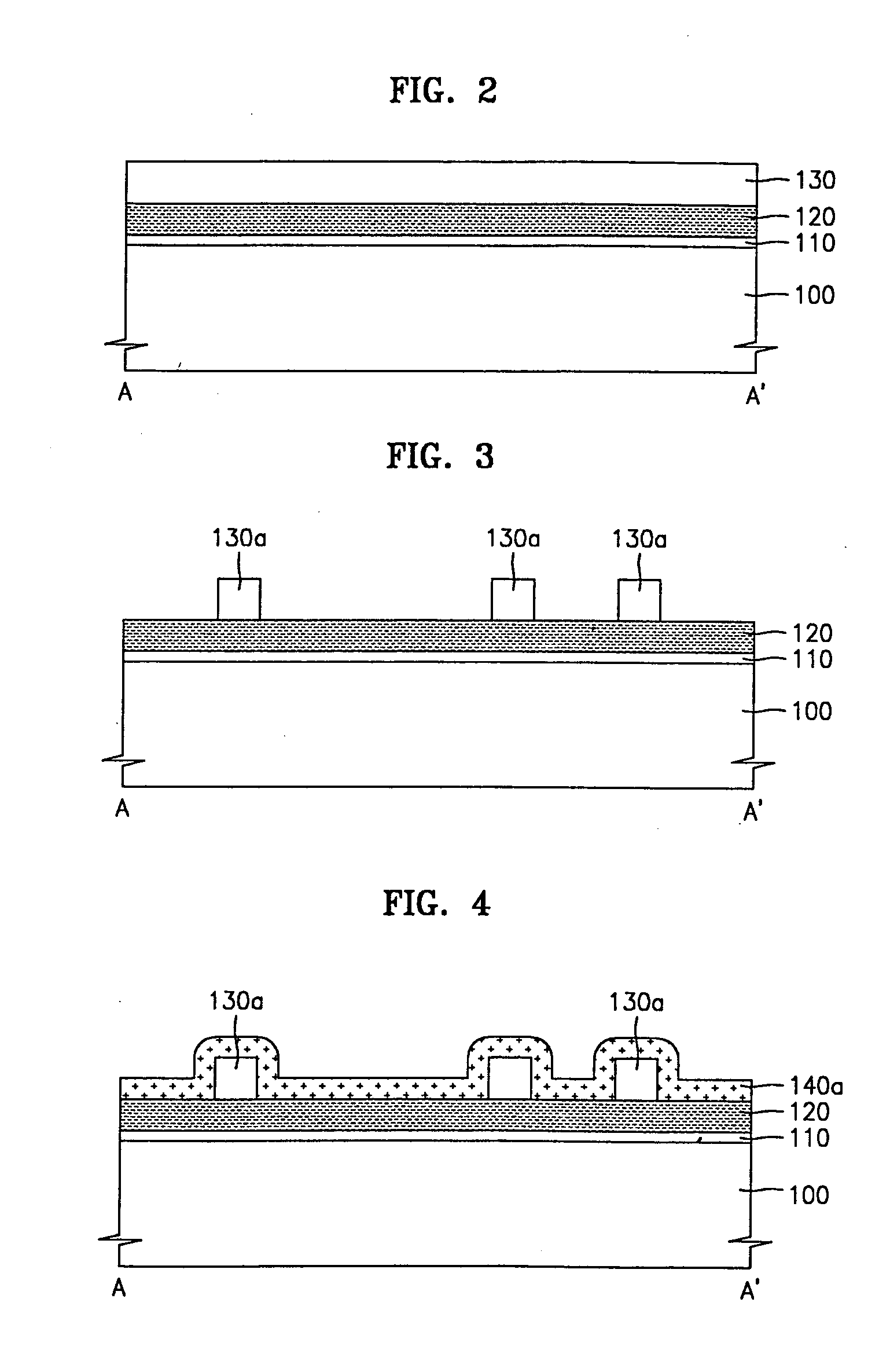

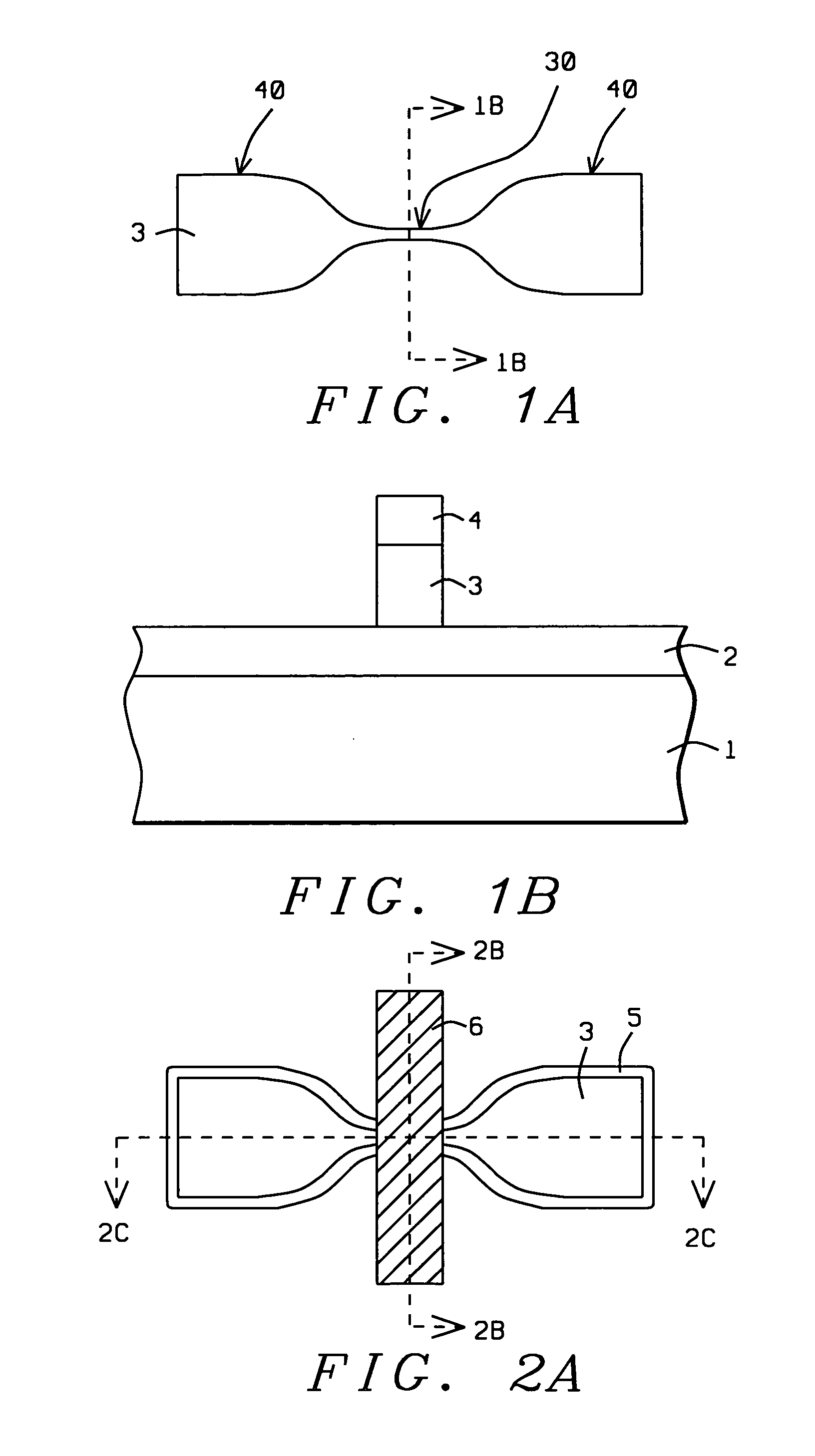

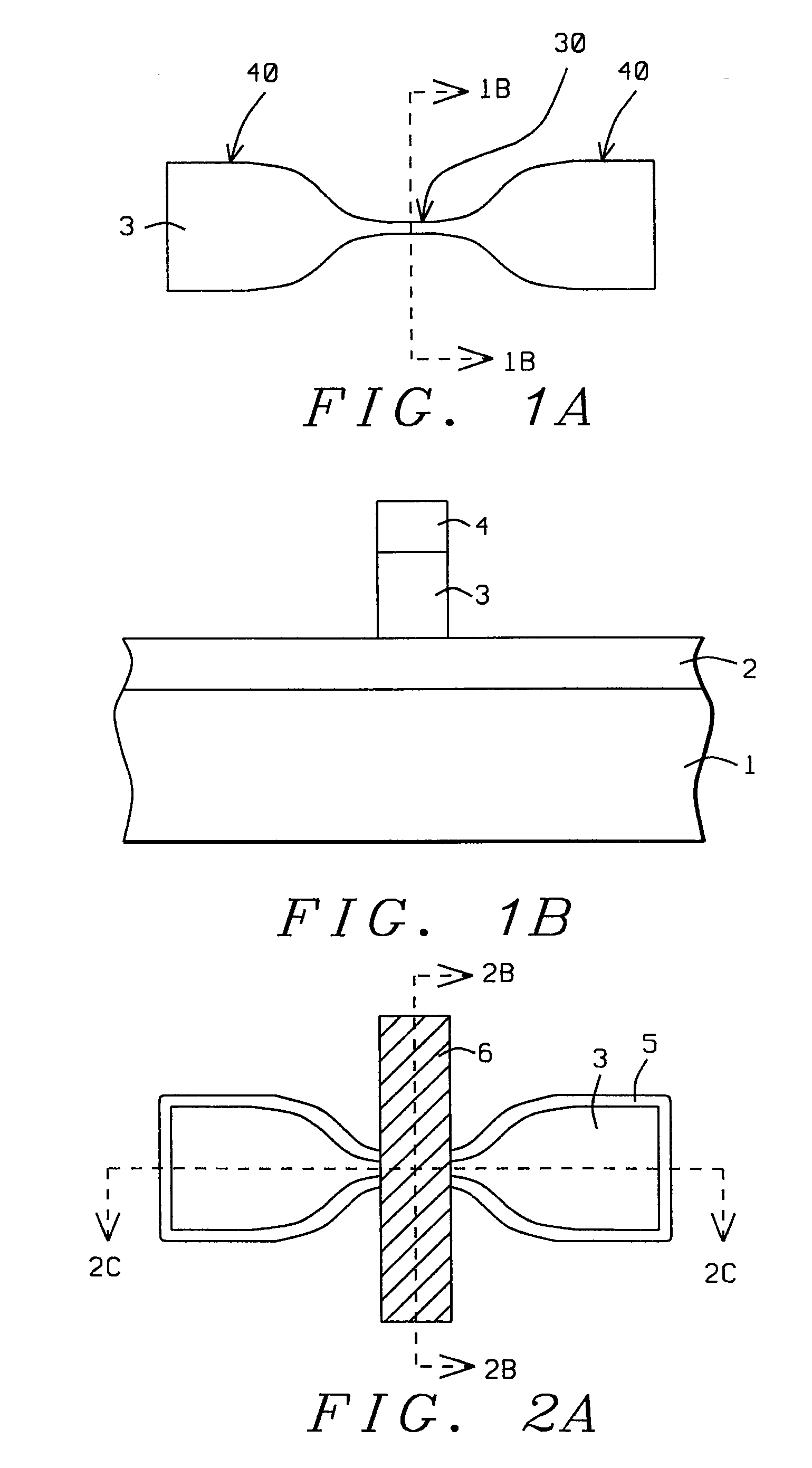

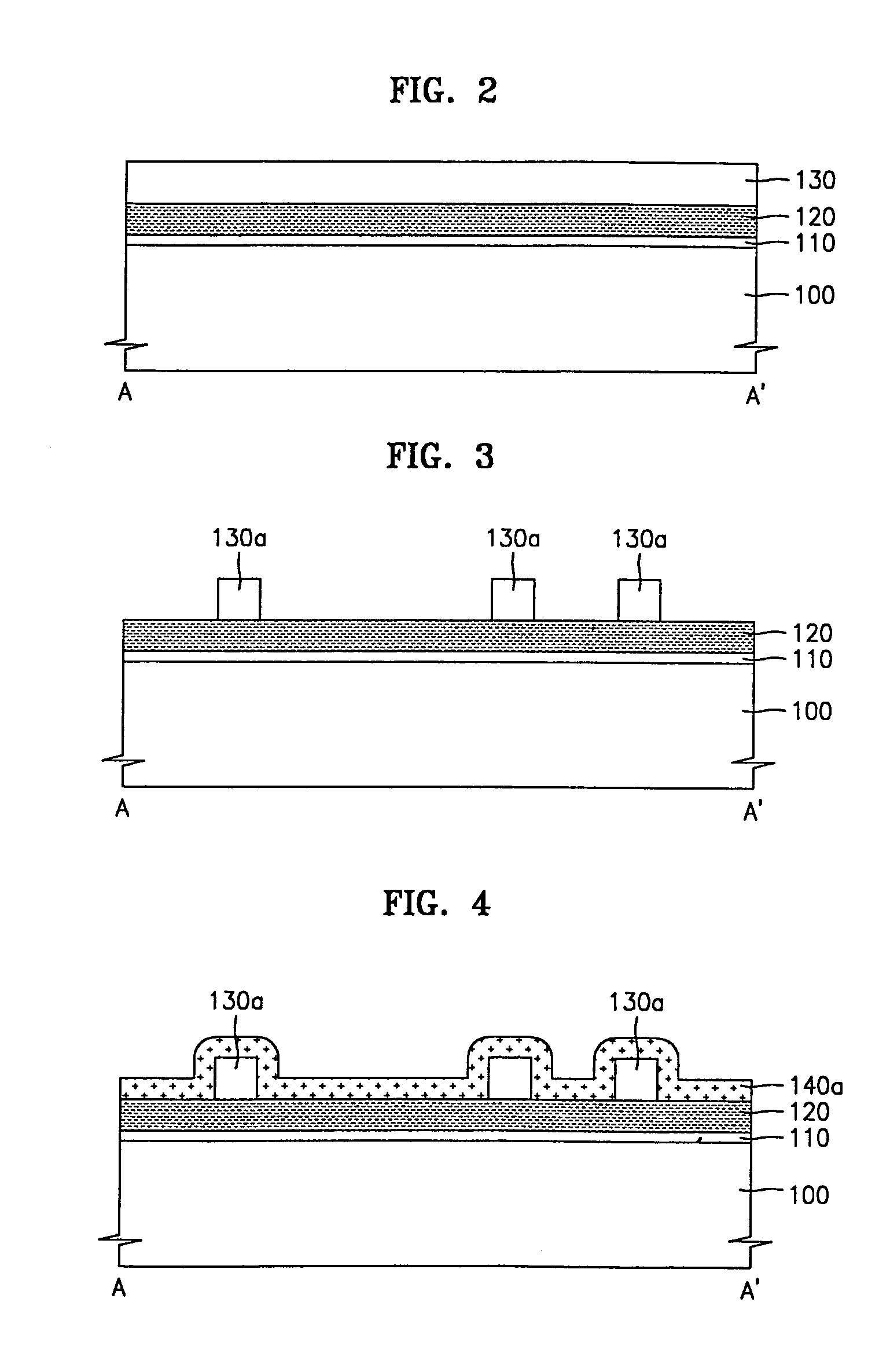

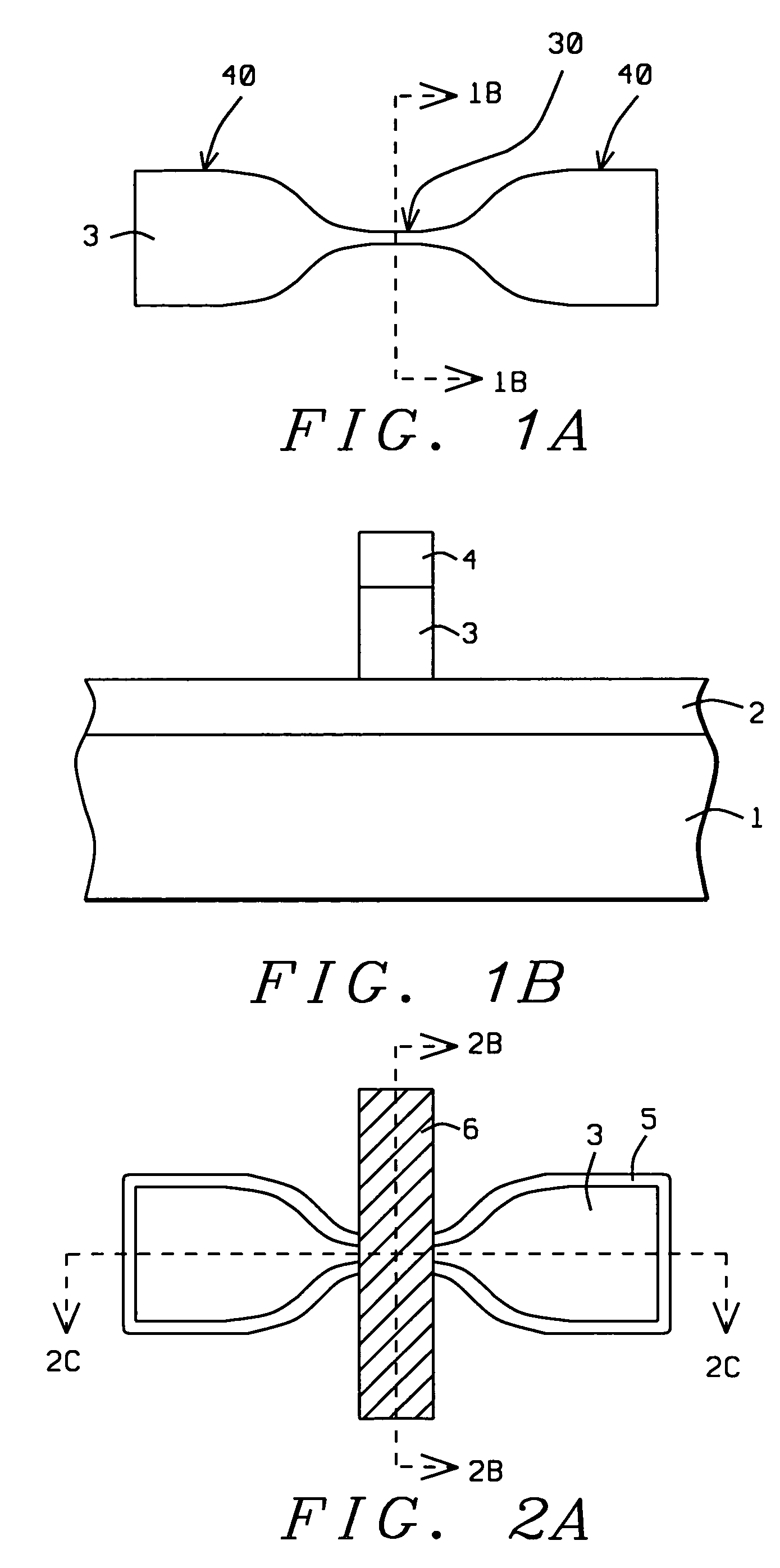

Method of fabricating a necked finfet device

ActiveUS20050253193A1Reduce FINFET channel resistancePrevent silicide formationTransistorSolid-state devicesComposite insulatorsMetal silicide

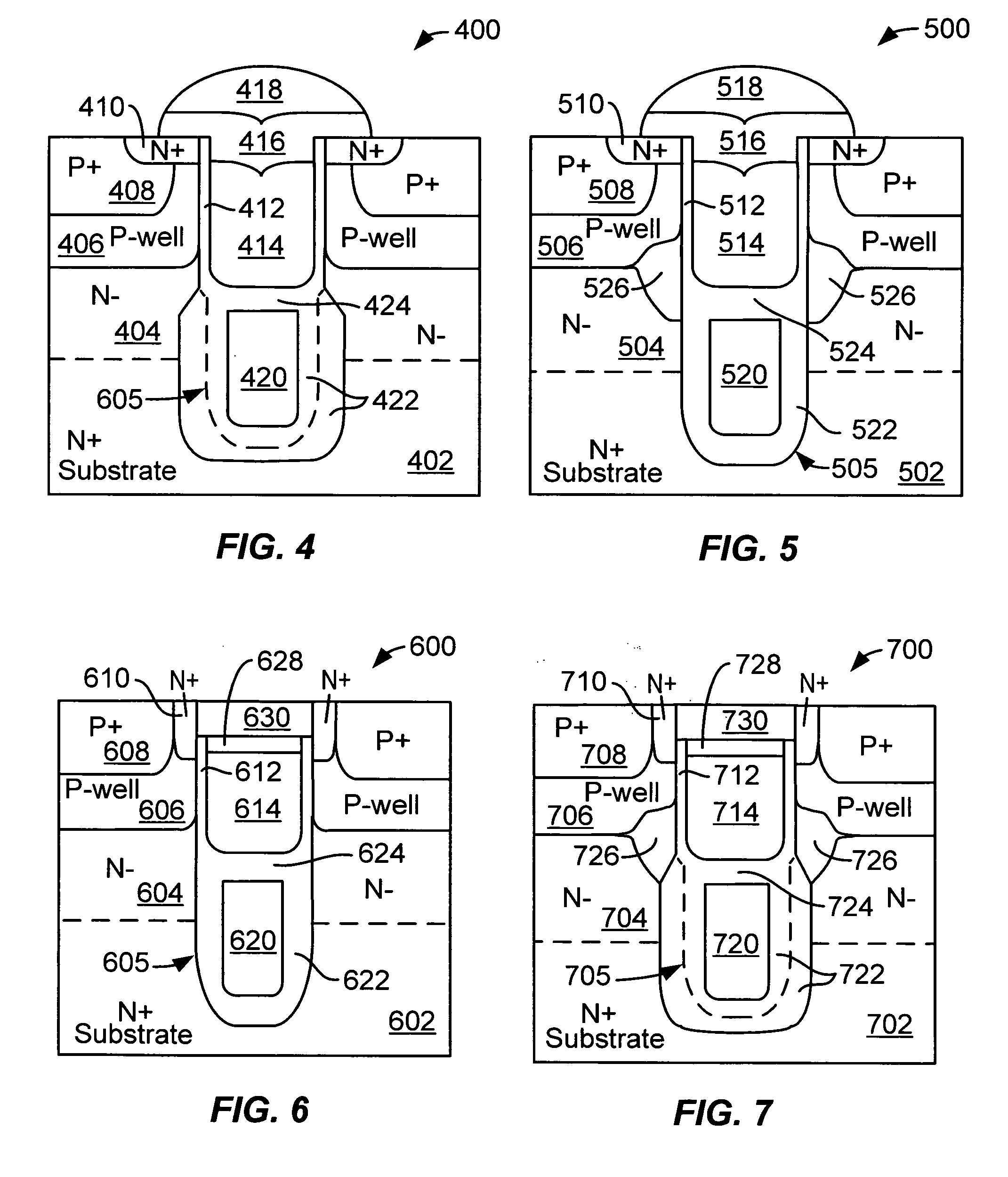

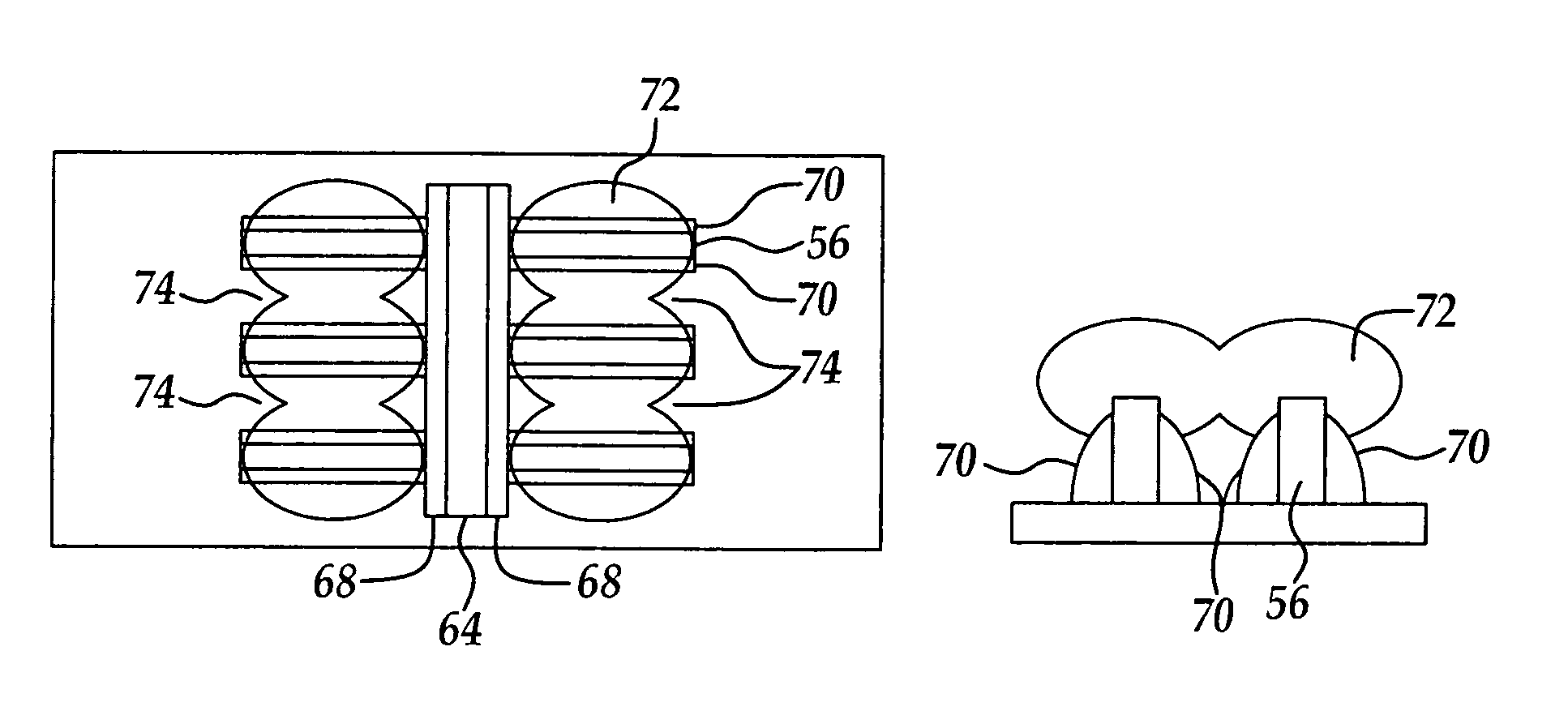

A method of fabricating a double gate, FINFET device structure in a silicon on insulator layer, in which the channel region formed in the SOI layer is defined with a narrowed, or necked shape, and wherein a composite insulator spacer is formed on the sides of the device structure, has been developed. A FINFET device structure shape is formed in an SOI layer via anisotropic RIE procedures, followed by a growth of a silicon dioxide gate insulator layer on the sides of the FINFET device structure shape. A gate structure is fabricated traversing the device structure and overlying the silicon dioxide gate insulator layer located on both sides of the narrowest portion of channel region. After formation of a source / drain region in wider, non-channel regions of the FINFET device structure shape, composite insulator spacers are formed on the sides of the FINFET shape and on the sides of the gate structure. Metal silicide is next formed on source / drain regions resulting in a FINFET device structure featuring a narrow channel region, and surrounded by composite insulator spacers located on the sides of the device structure.

Owner:TAIWAN SEMICON MFG CO LTD

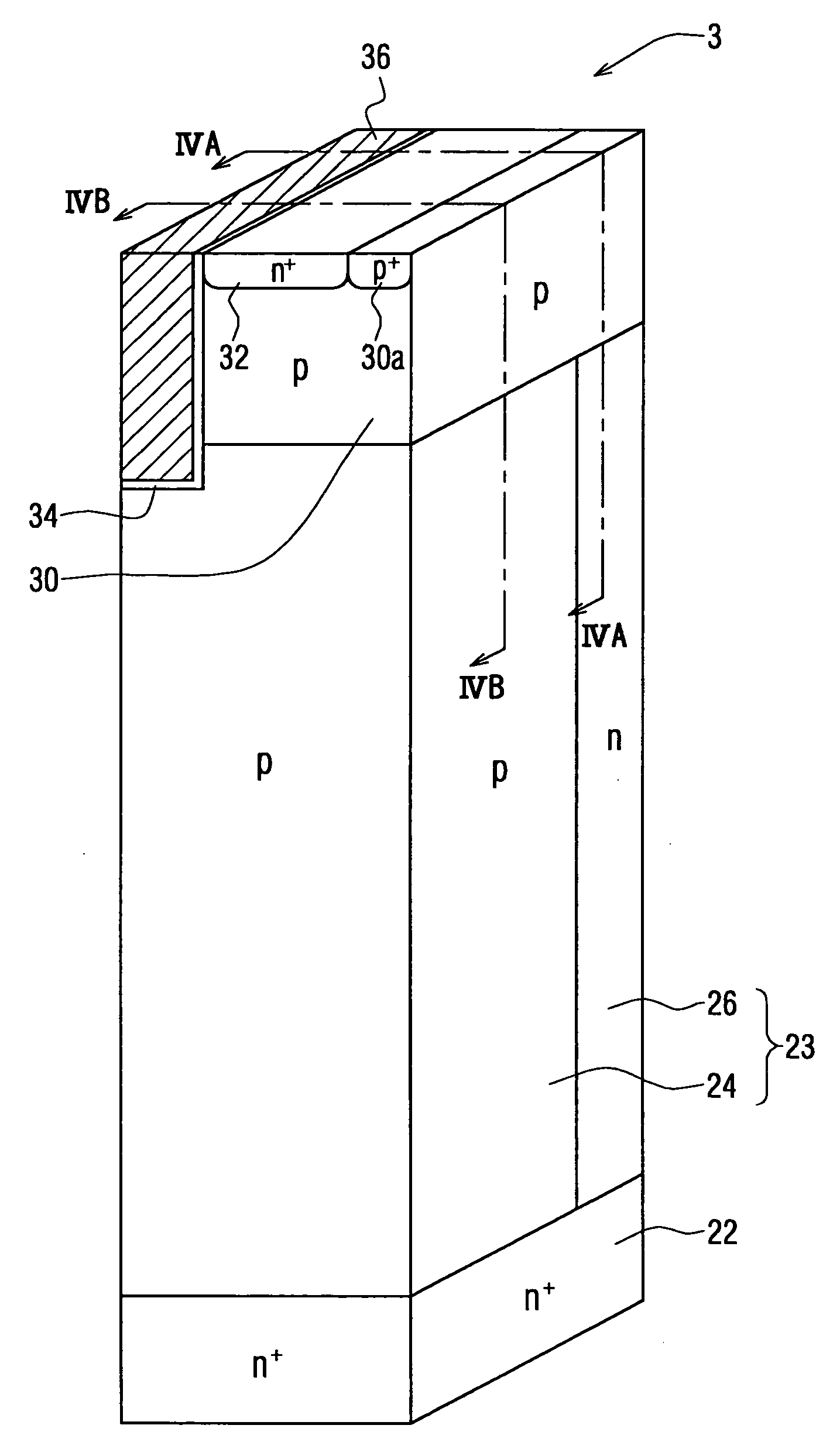

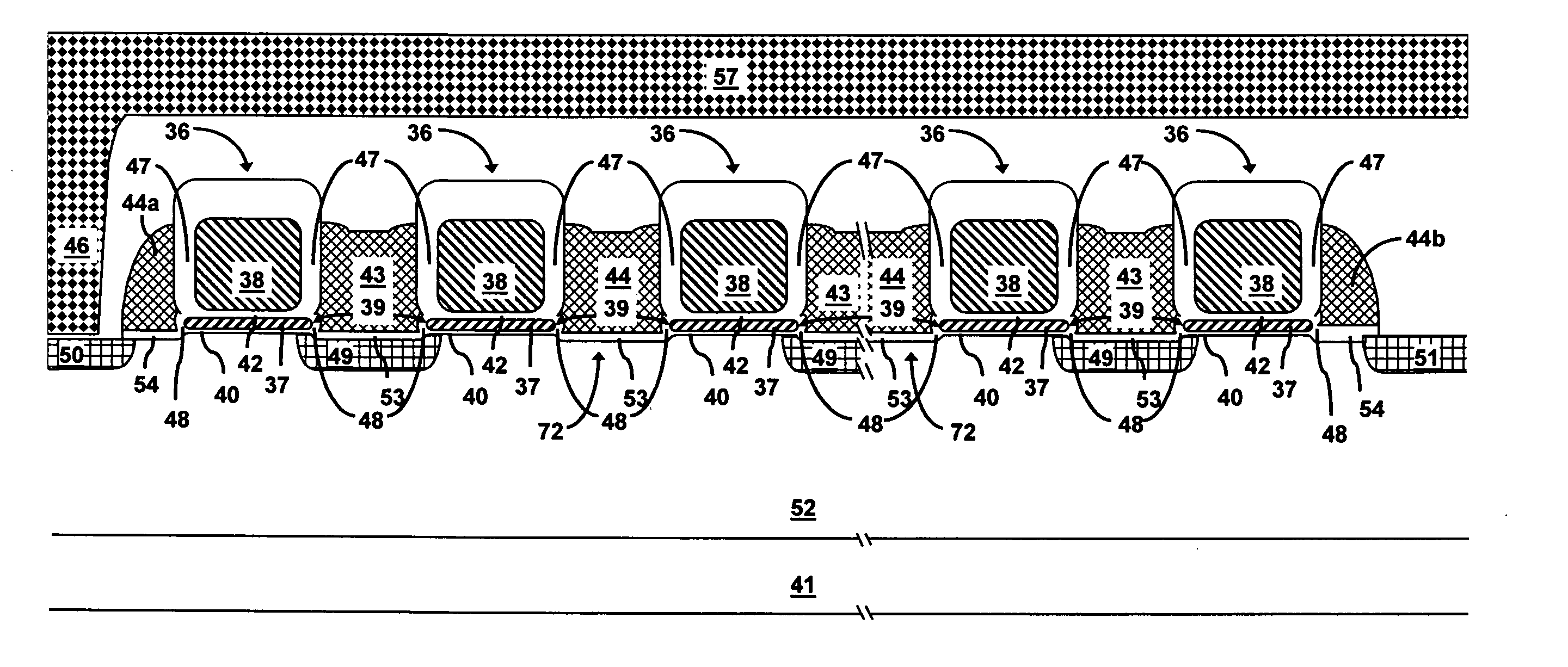

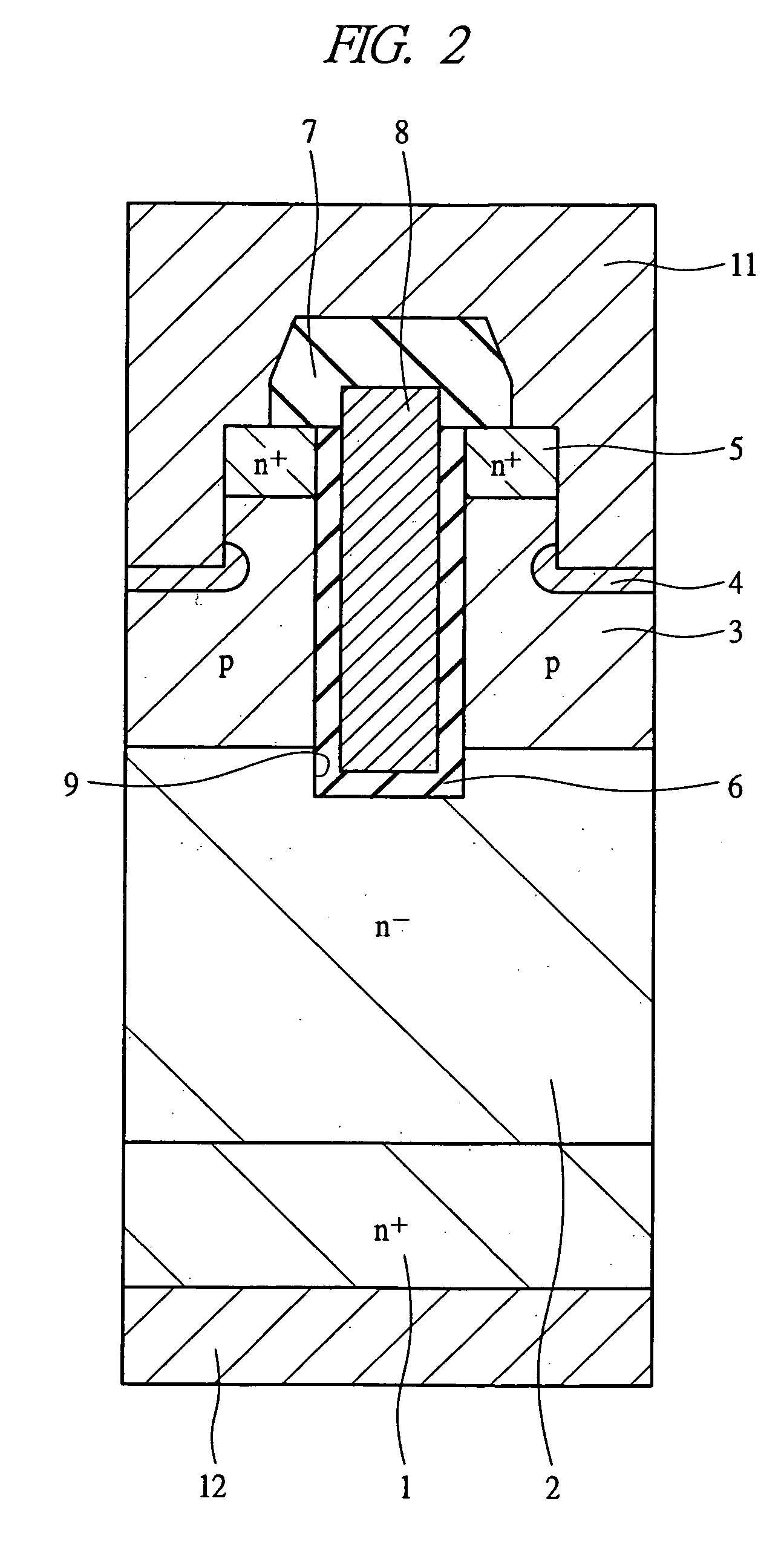

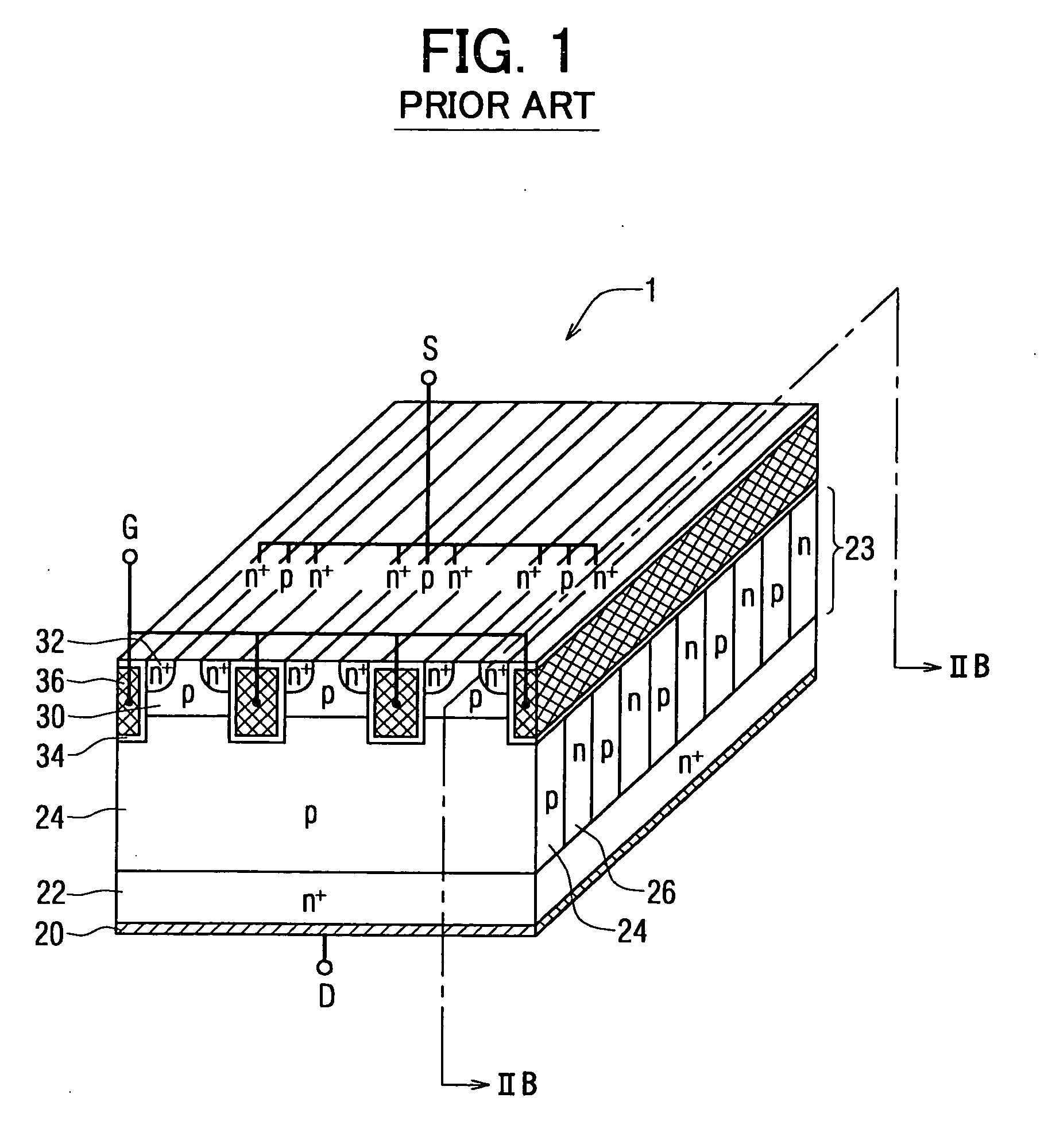

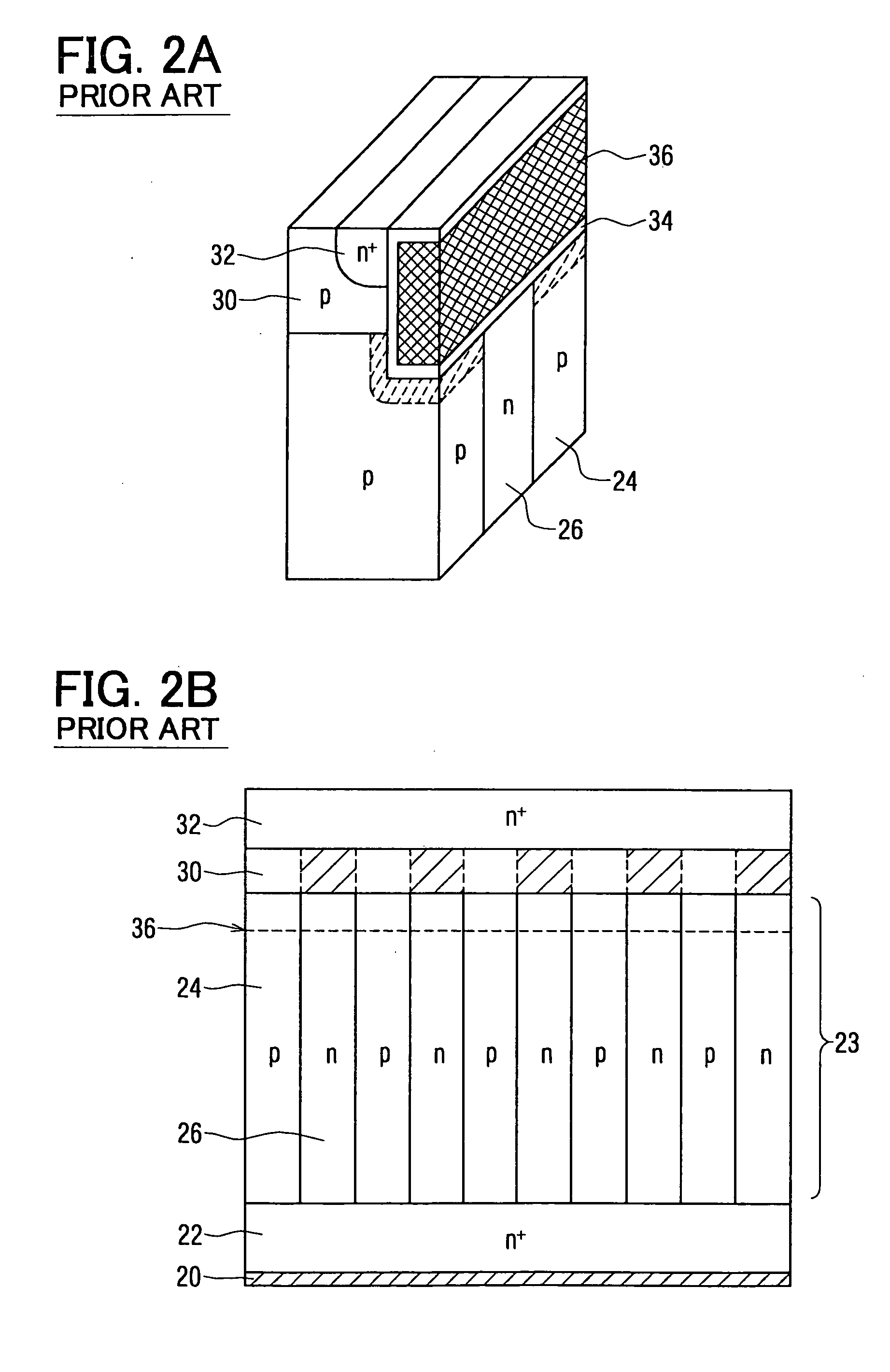

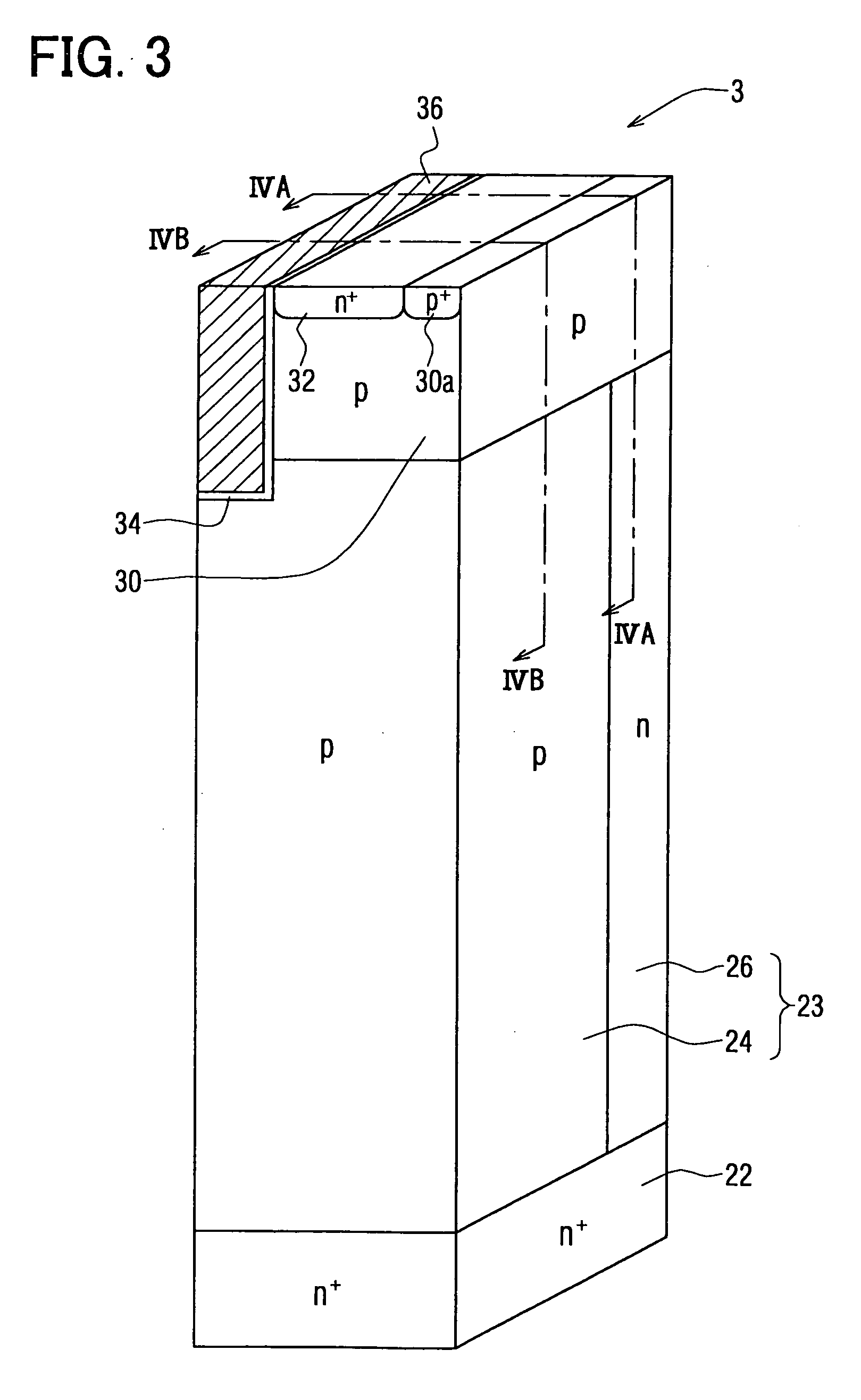

Semiconductor device having super junction construction and method for manufacturing the same

InactiveUS20050006717A1Low manufacturing costStable withstand voltageSemiconductor/solid-state device manufacturingSemiconductor devicesPhysicsBody region

A semiconductor device includes a body region, a drift region having a first part and a second part, and a trench gate electrode. The body region is disposed on the drift region. The first and second parts extend in an extending direction so that the second part is adjacent to the first part. The trench gate electrode penetrates the body region and reaches the drift region so that the trench gate electrode faces the body region and the drift region through an insulation layer. The trench gate electrode extends in a direction crossing with the extending direction of the first and second parts. The first part includes a portion near the trench gate electrode, which has an impurity concentration equal to or lower than that of the body region.

Owner:DENSO CORP

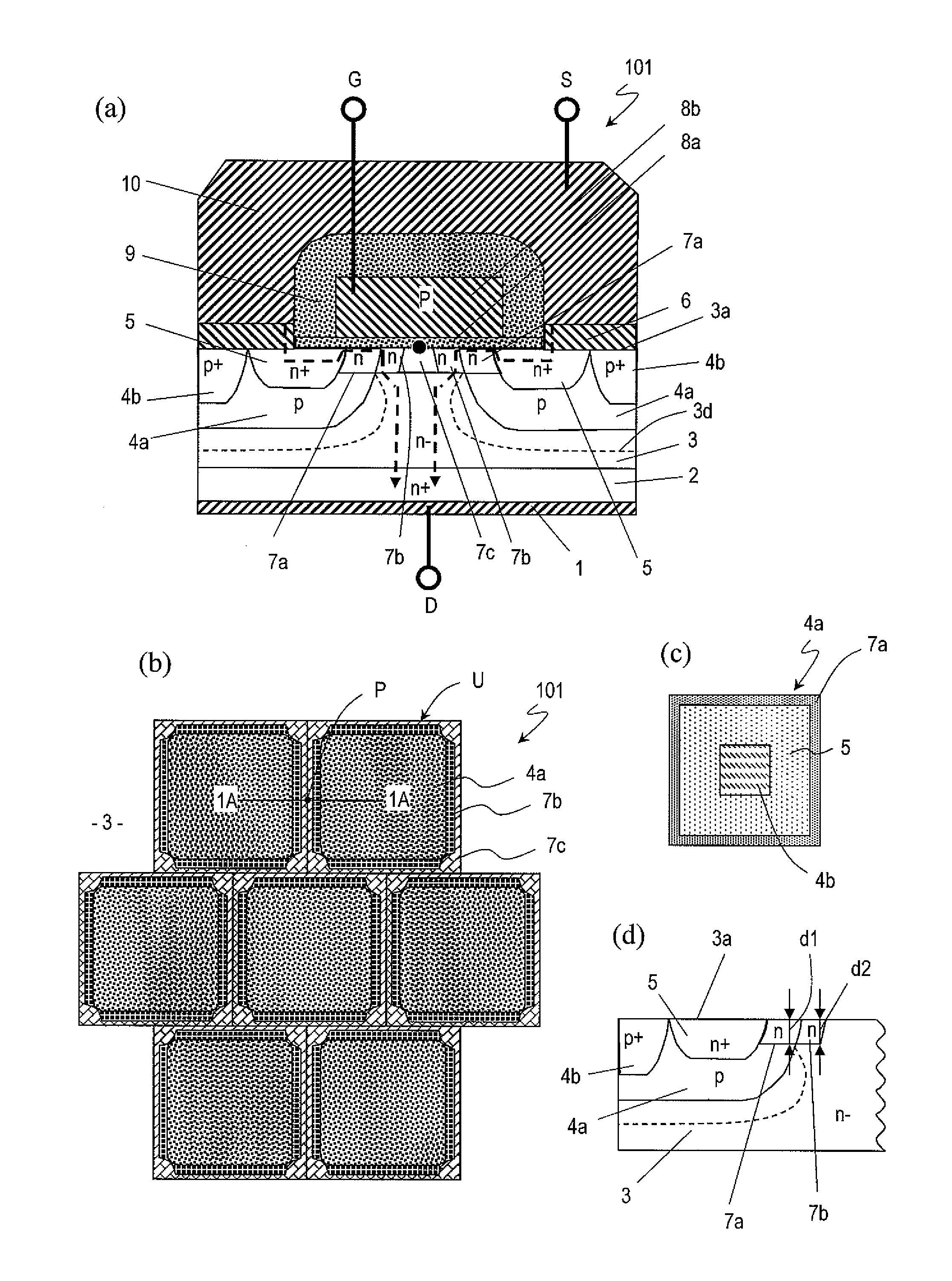

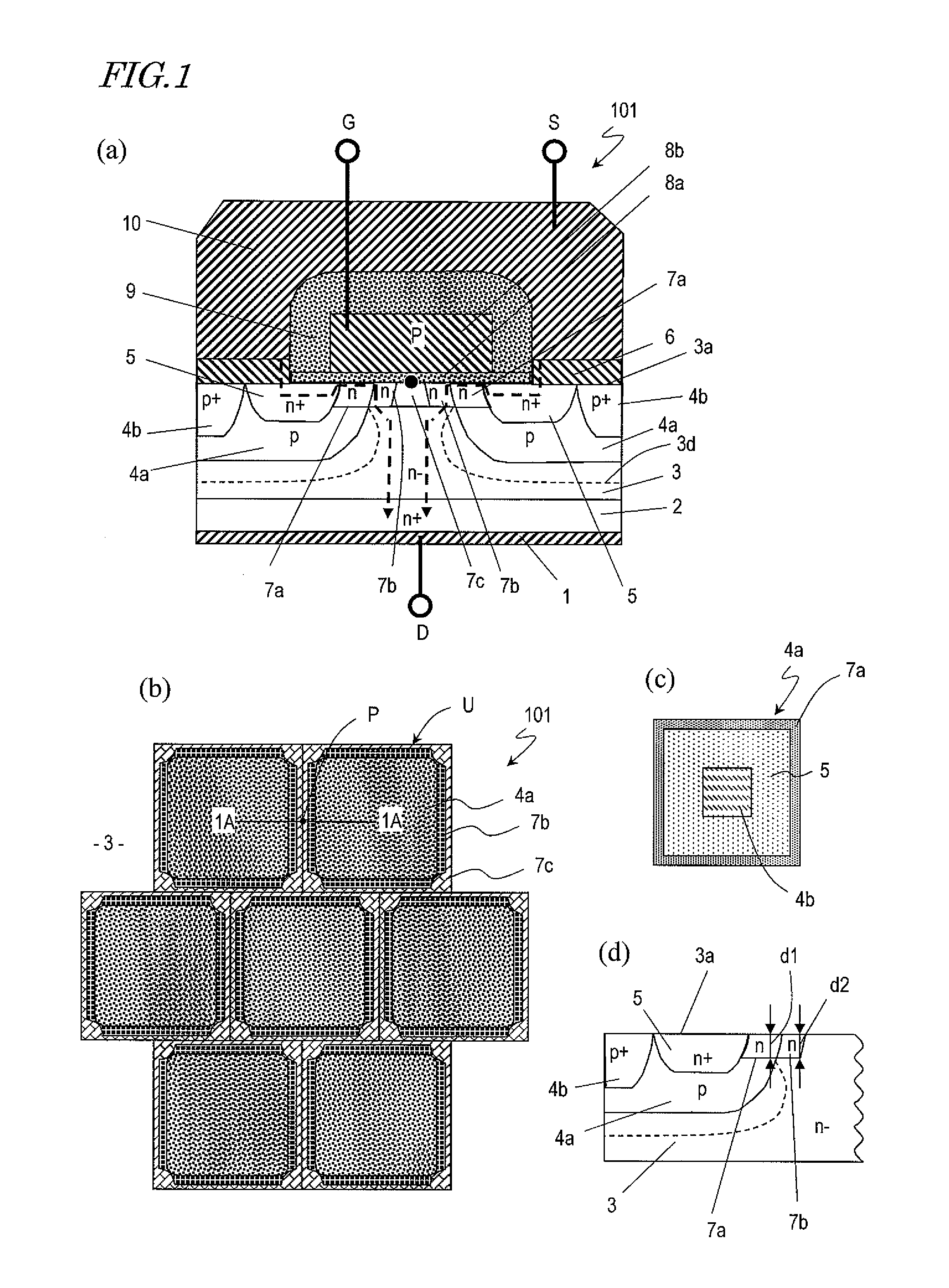

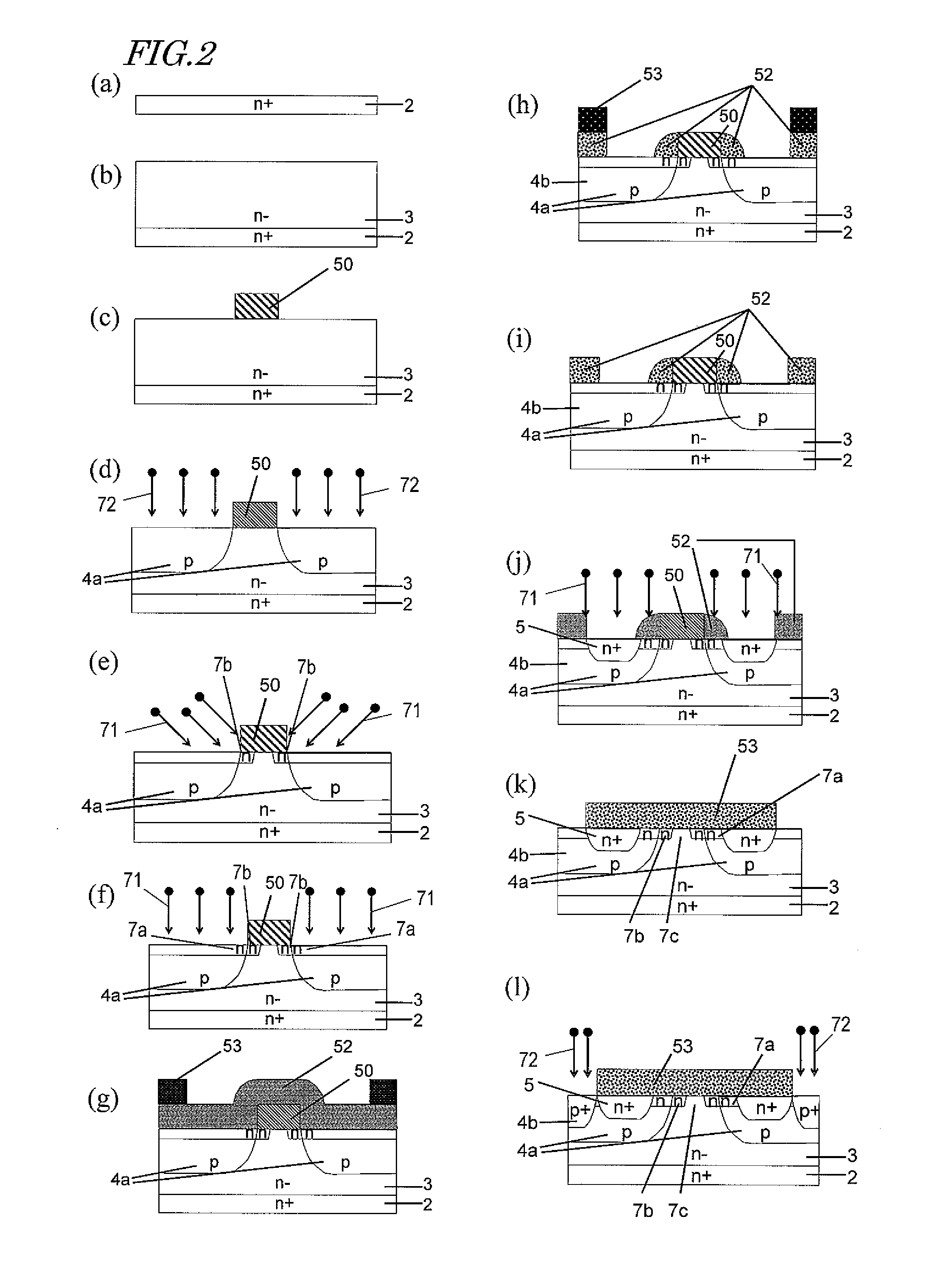

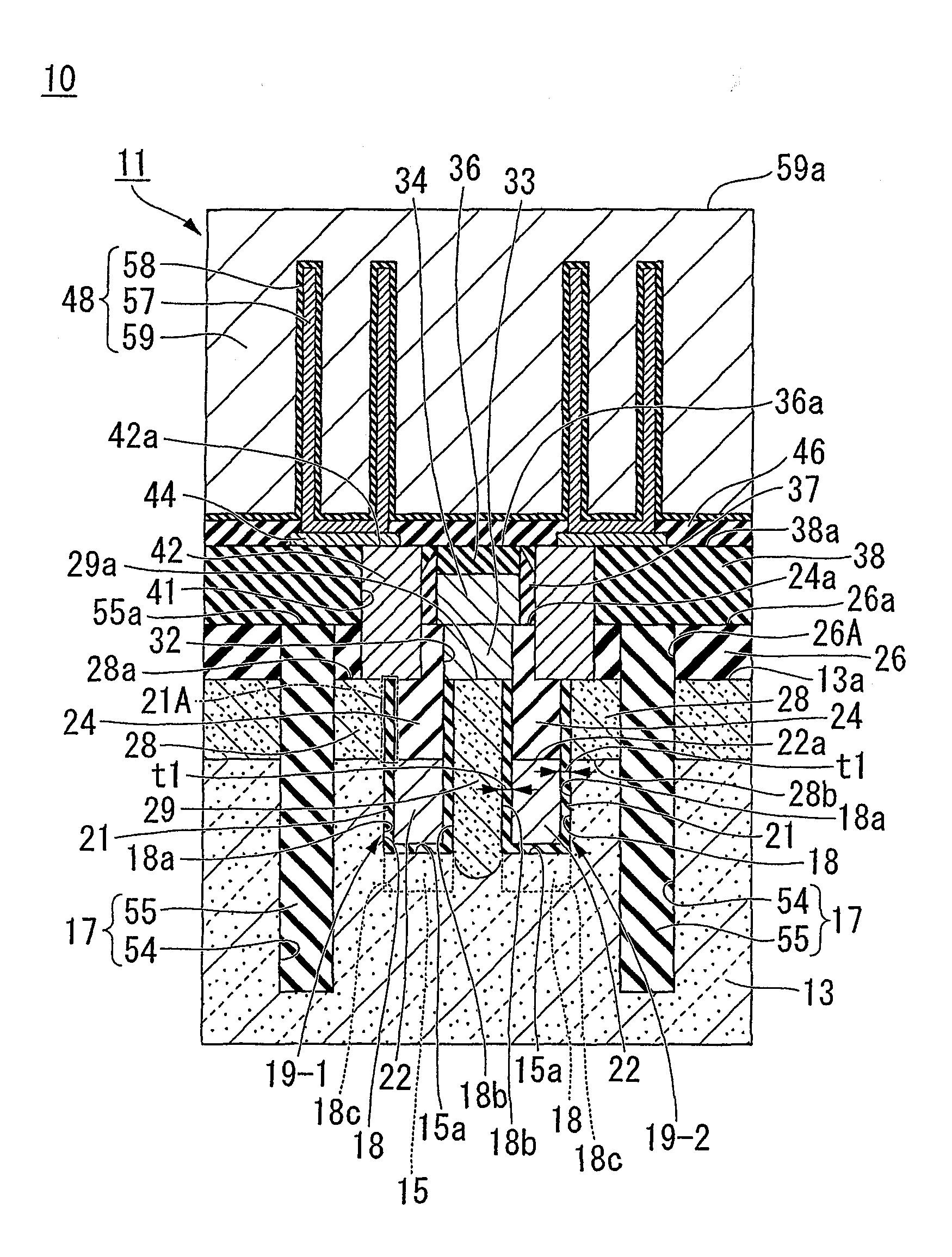

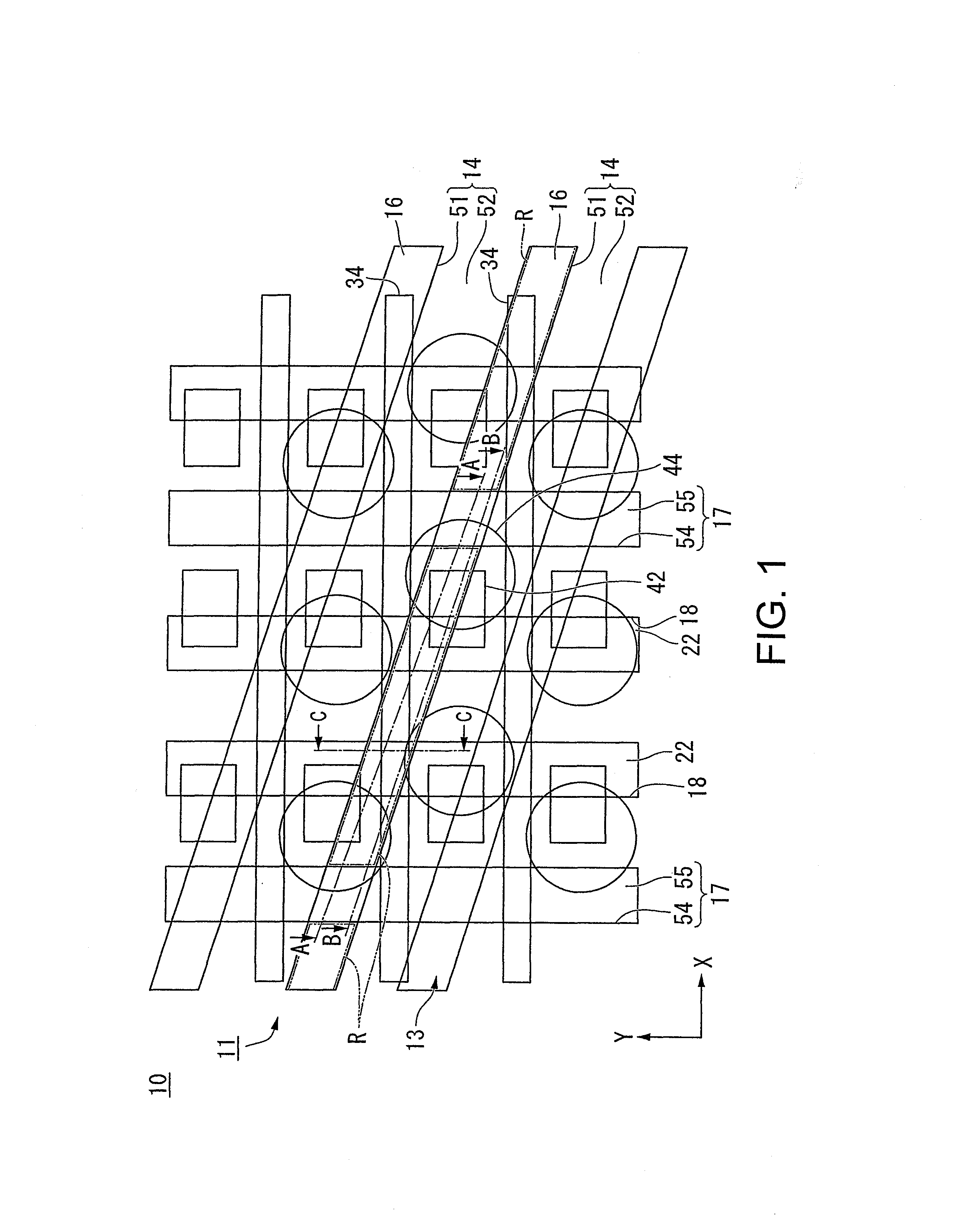

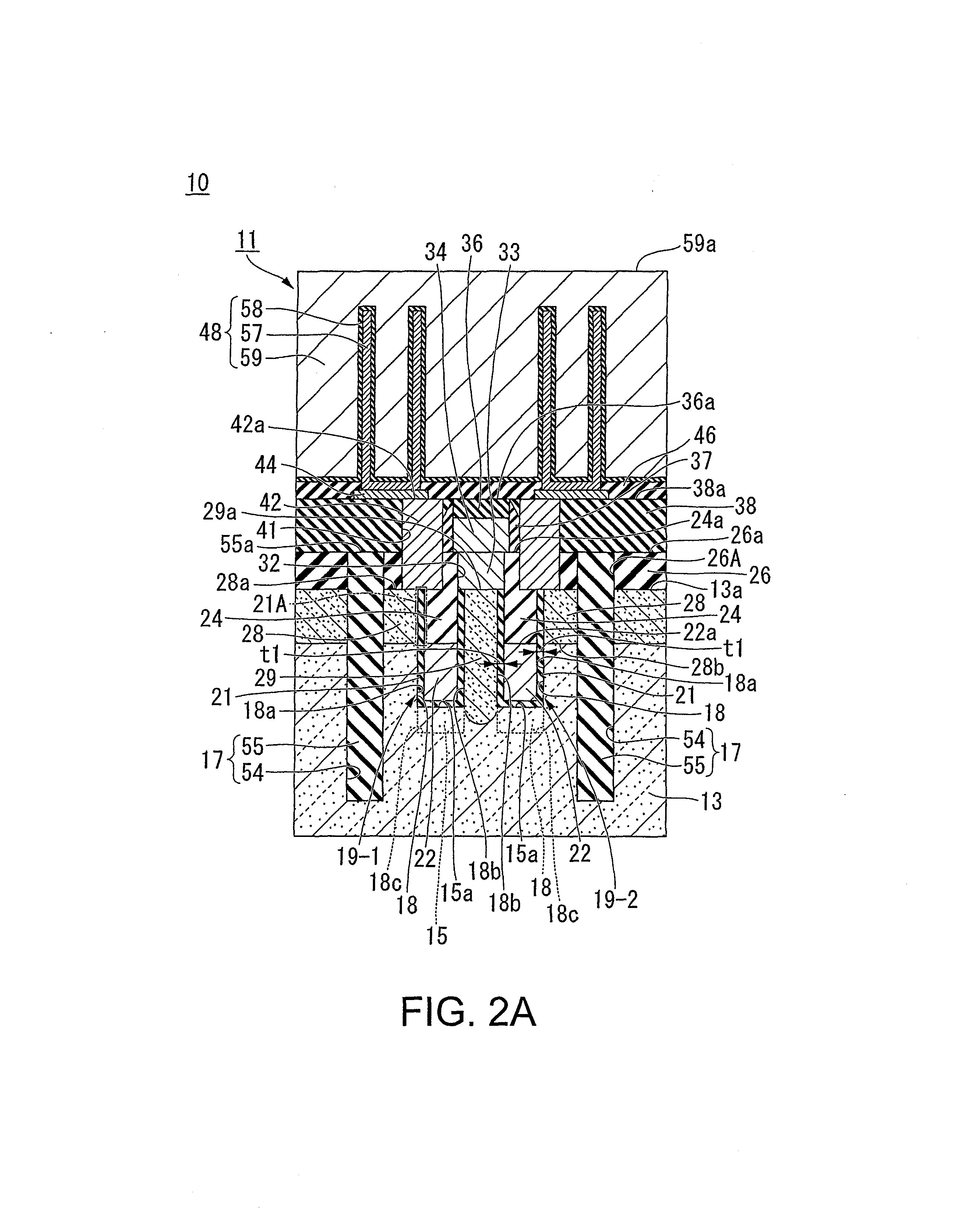

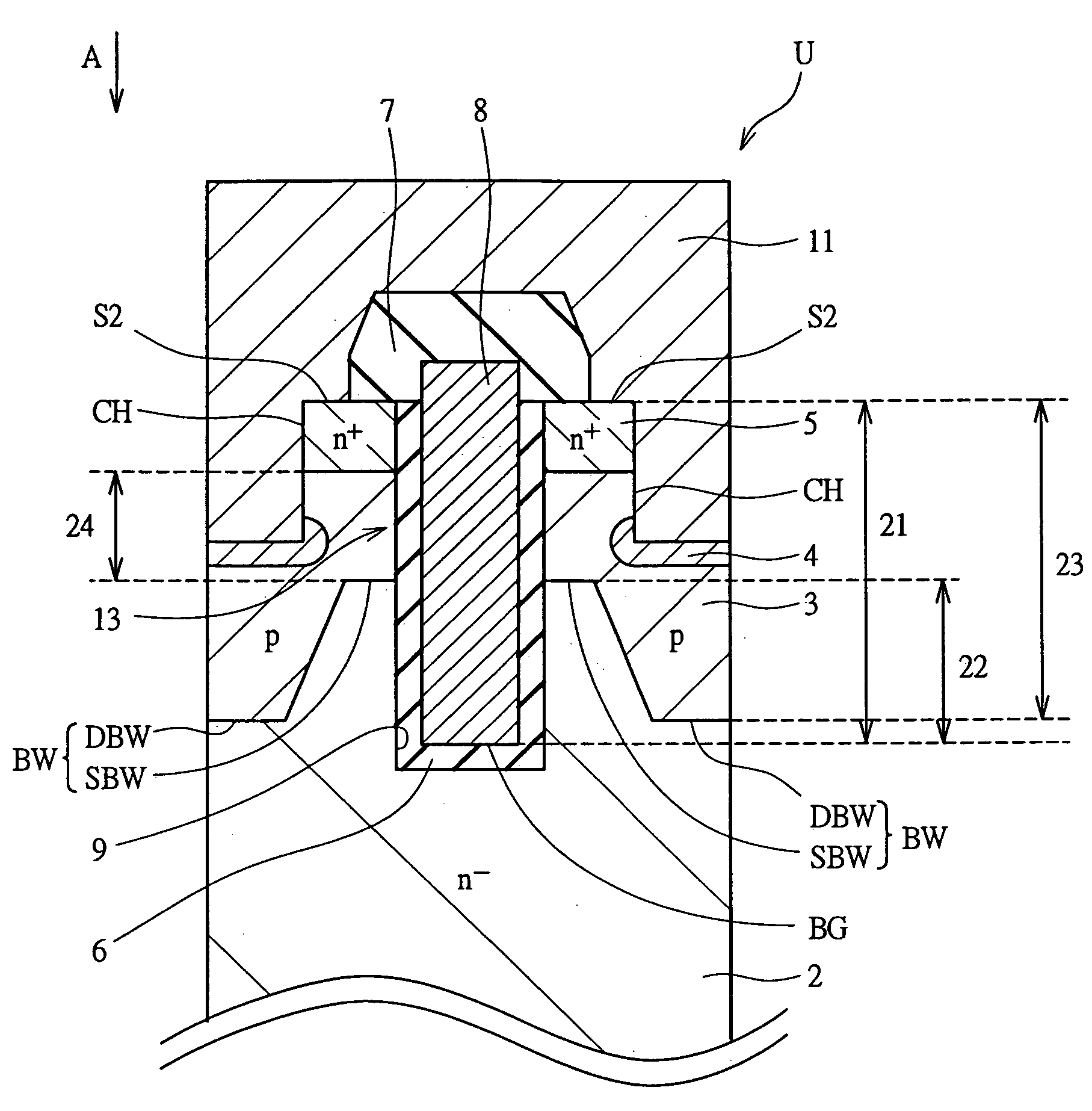

Semiconductor device and process for production thereof

InactiveUS8421151B2Increase channel lengthReduce channel resistanceSemiconductor/solid-state device manufacturingSemiconductor devicesBody regionSemiconductor

Owner:PANASONIC CORP

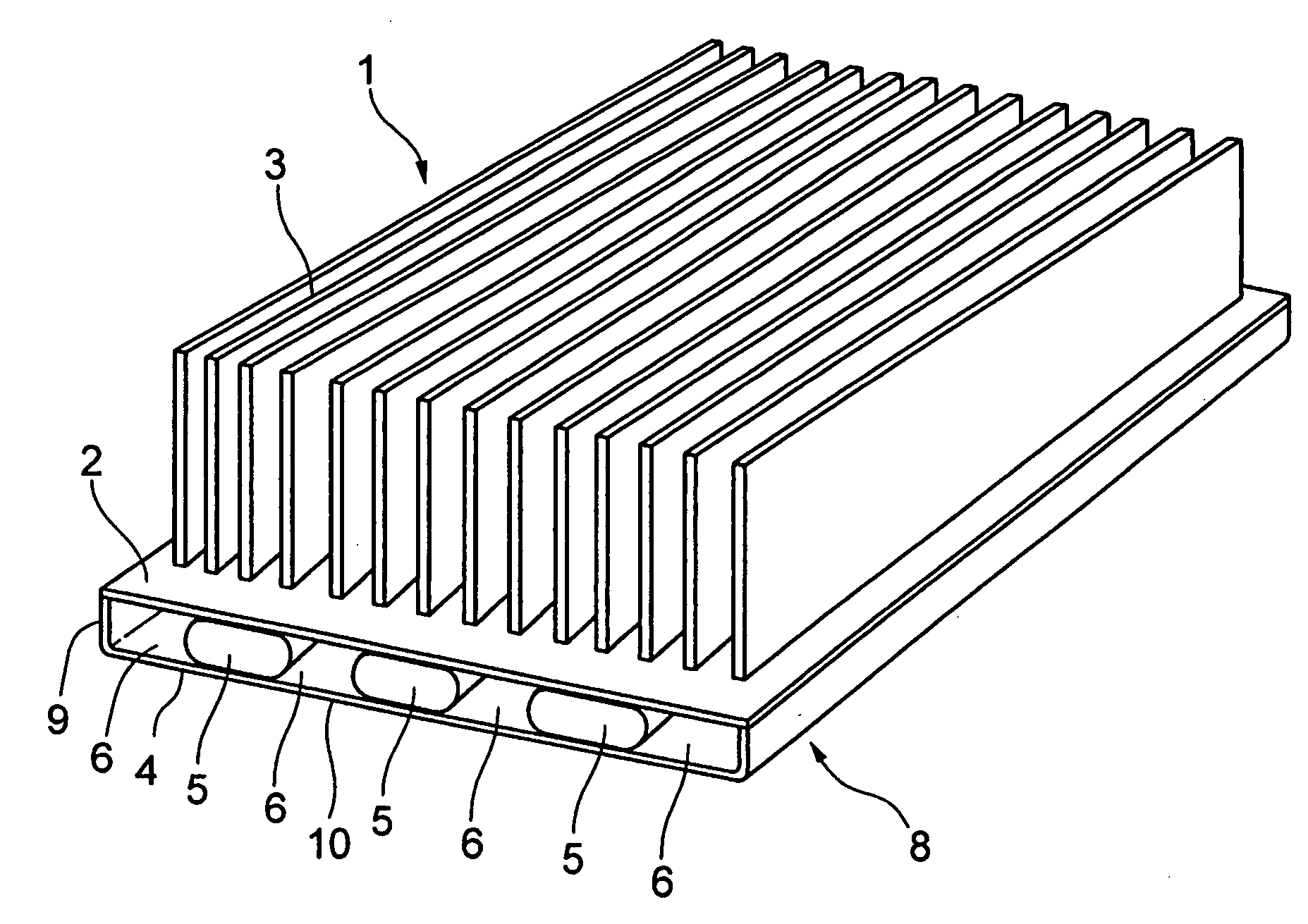

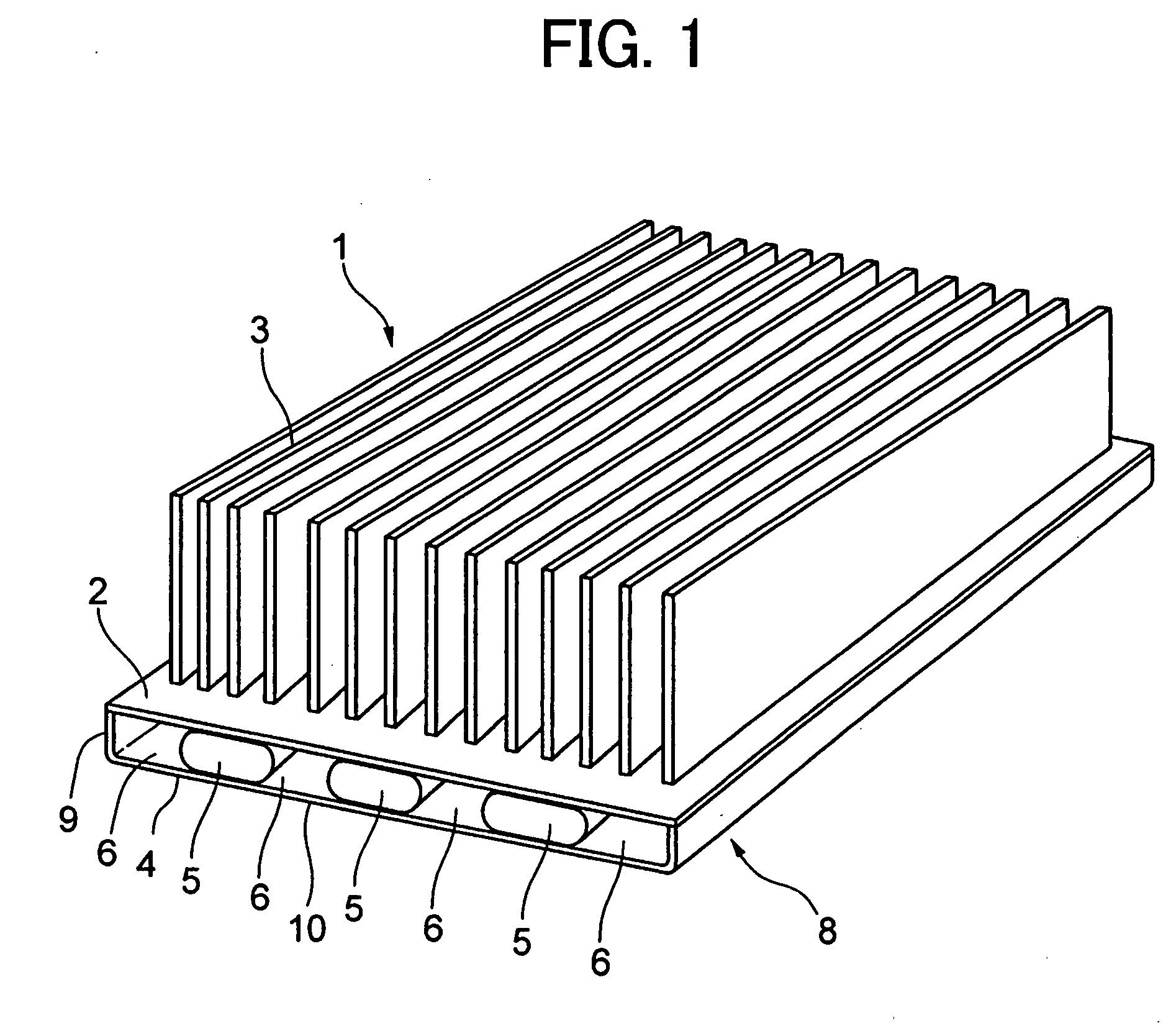

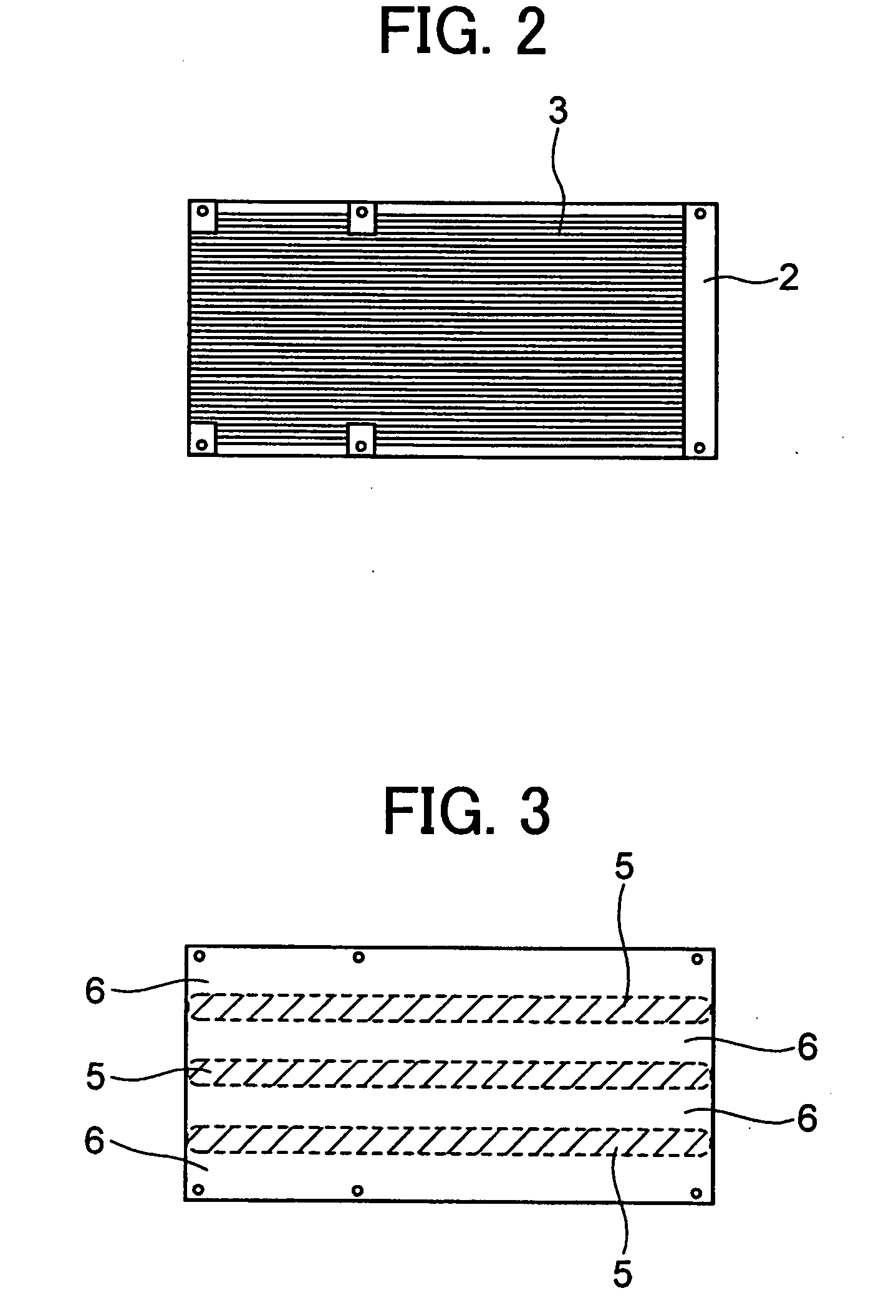

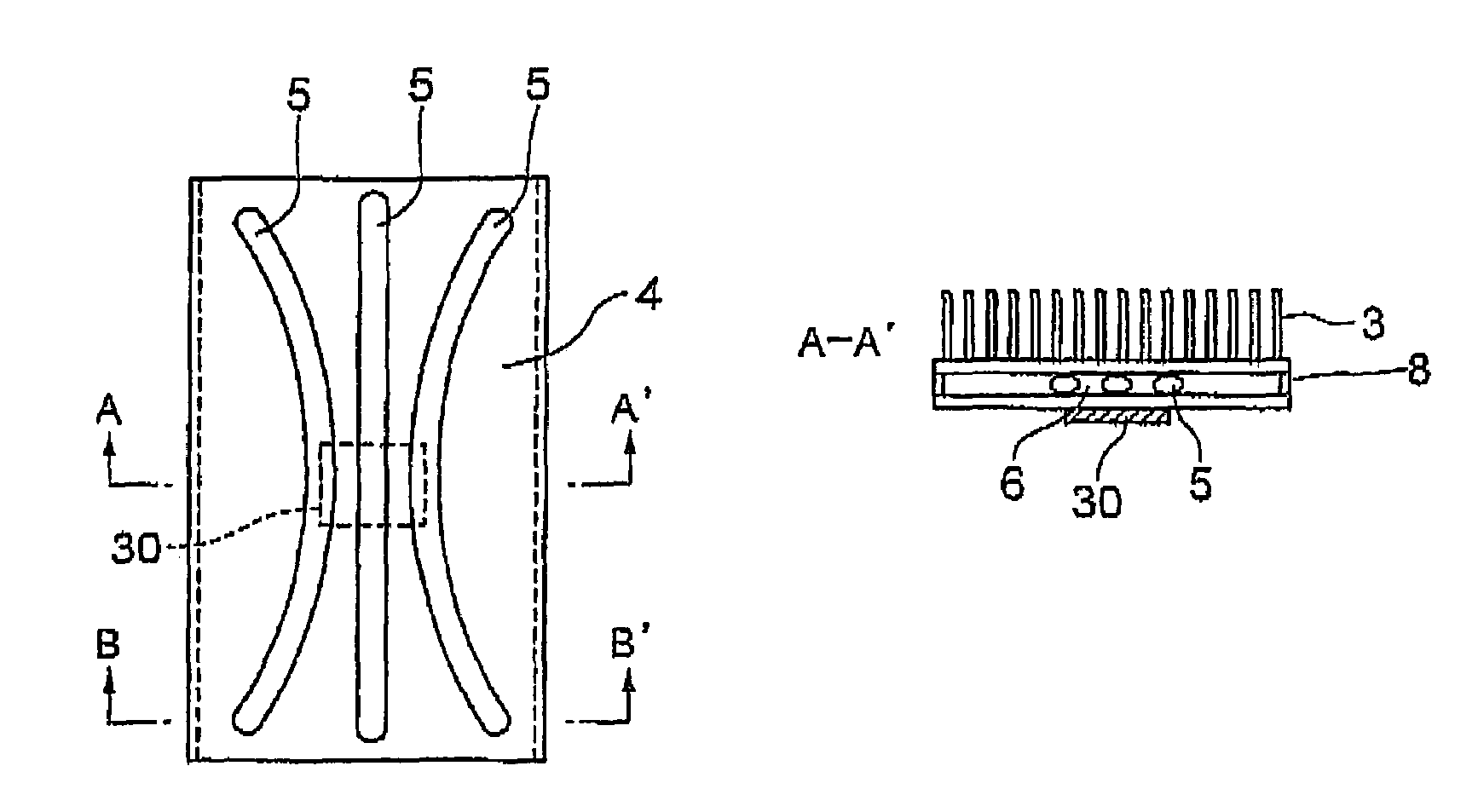

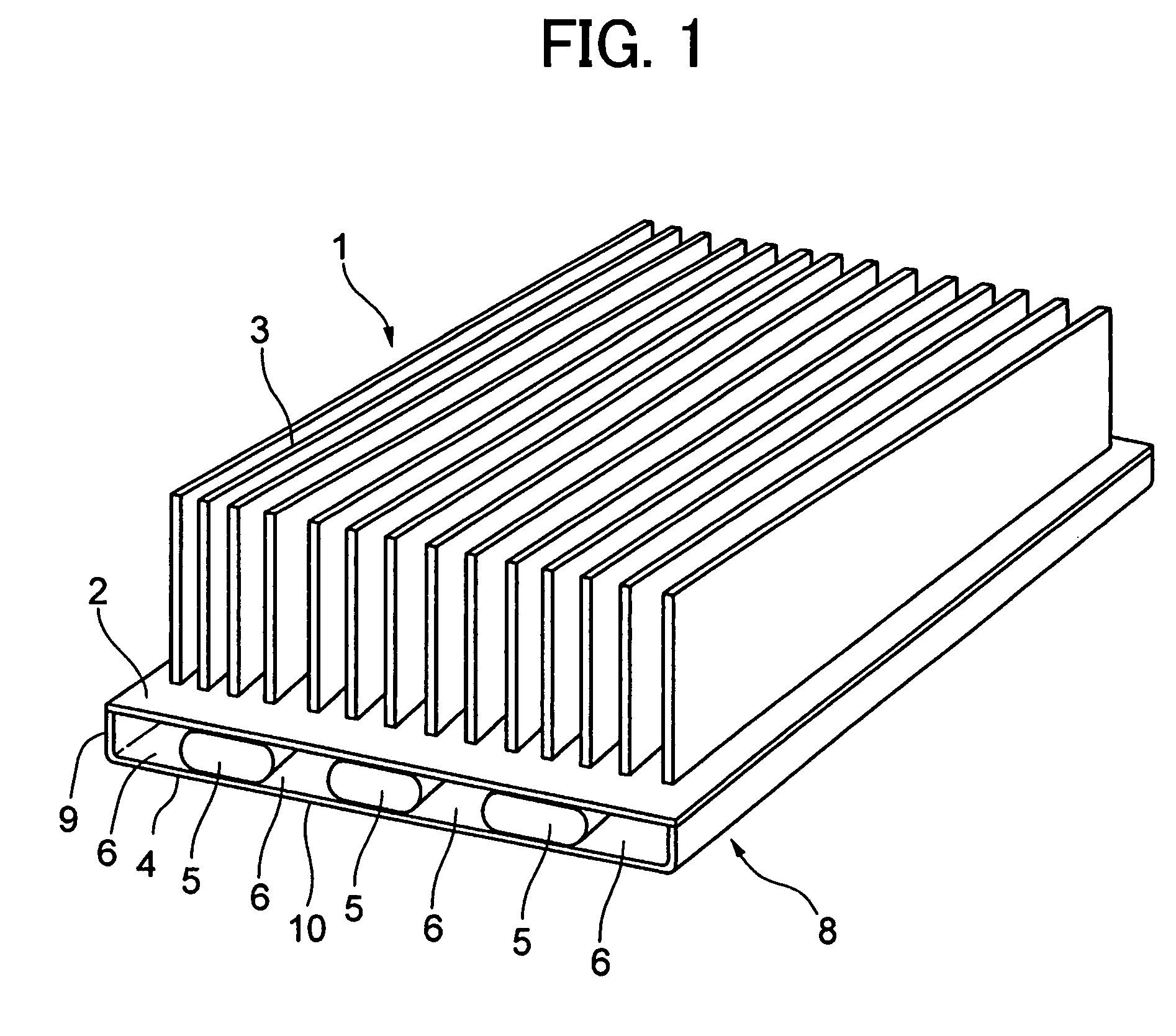

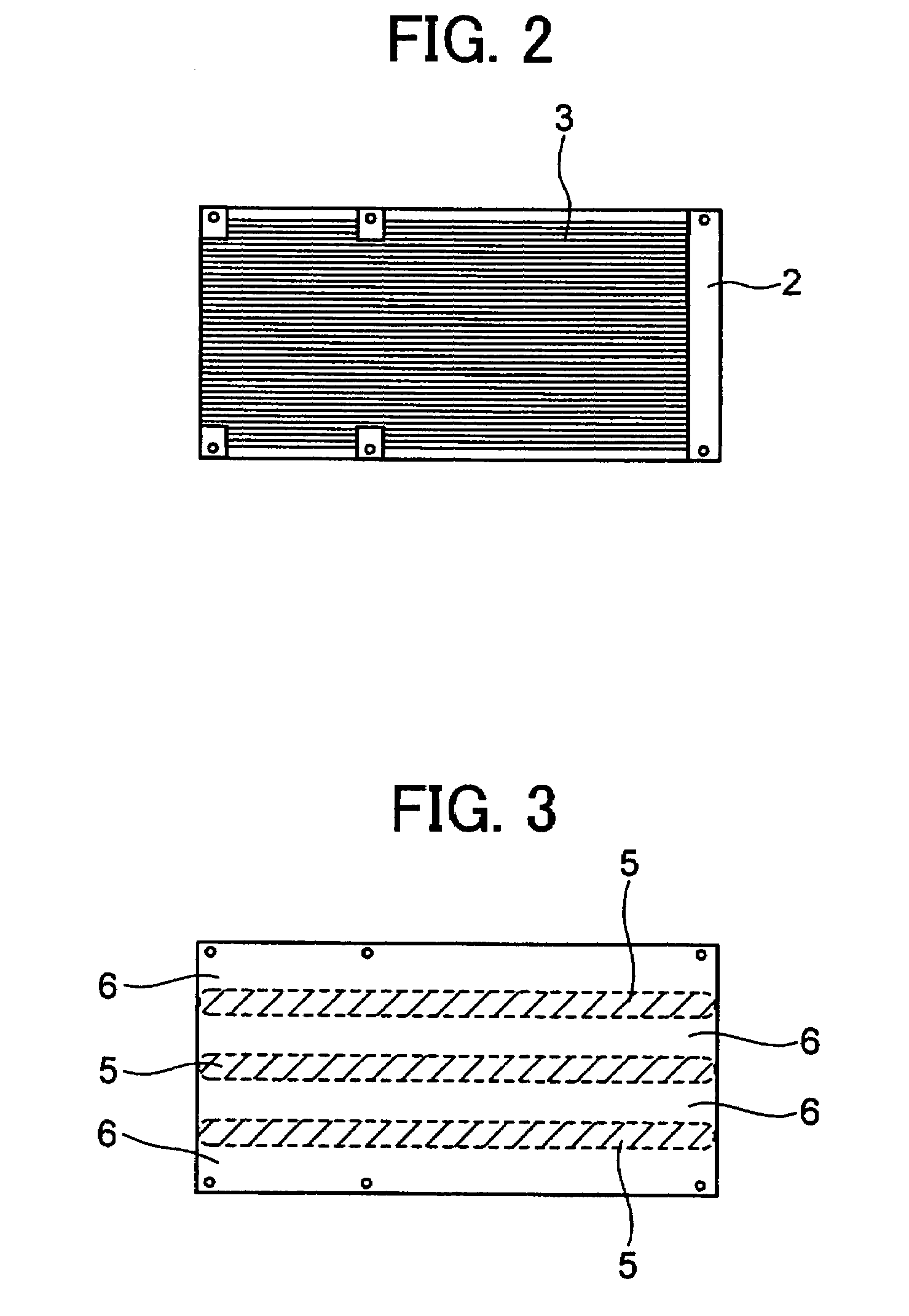

Heat sink with heat pipes and method for manufacturing the same

ActiveUS20070131387A1Reduce weightIncrease volumeSemiconductor/solid-state device detailsSolid-state devicesEngineeringHeat pipe

A heat sink to be used with a heat source can include a base portion and a fin portion. The base portion can include a plurality of heat pipes and a space formed at least partially between adjacent heat pipes. The base portion can also include a first plate thermally connected to the heat source and a second plate thermally connected to the fin portion. The plurality of heat pipes contacts the first plate and the second plate. The plurality of heat pipes can also include a first portion that is closer than a second portion to the heat source. Additionally, a distance between adjacent heat pipes is smaller at the first portion than at the second portion.

Owner:FURUKAWA ELECTRIC CO LTD

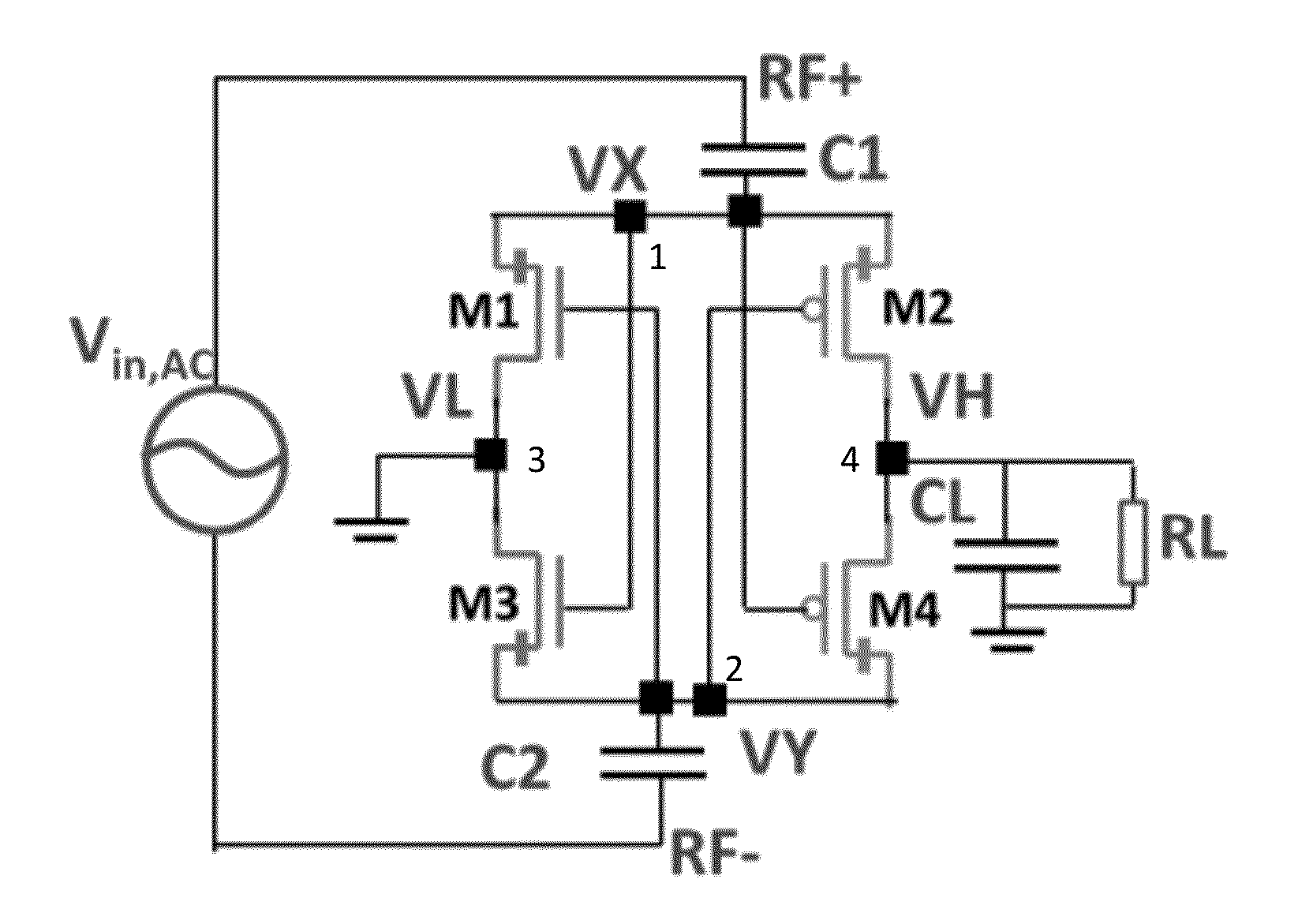

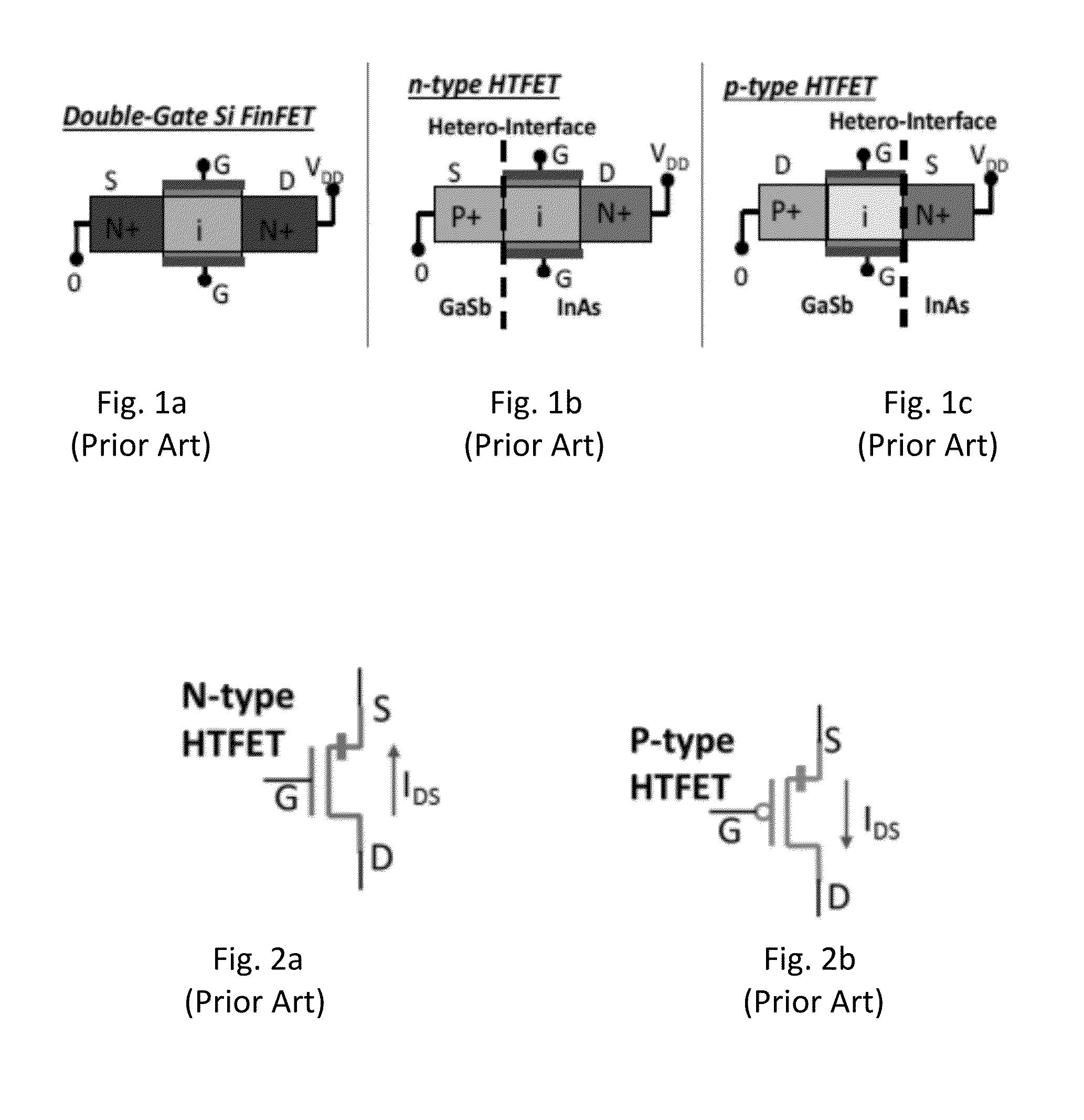

Low Power Nanoelectronics

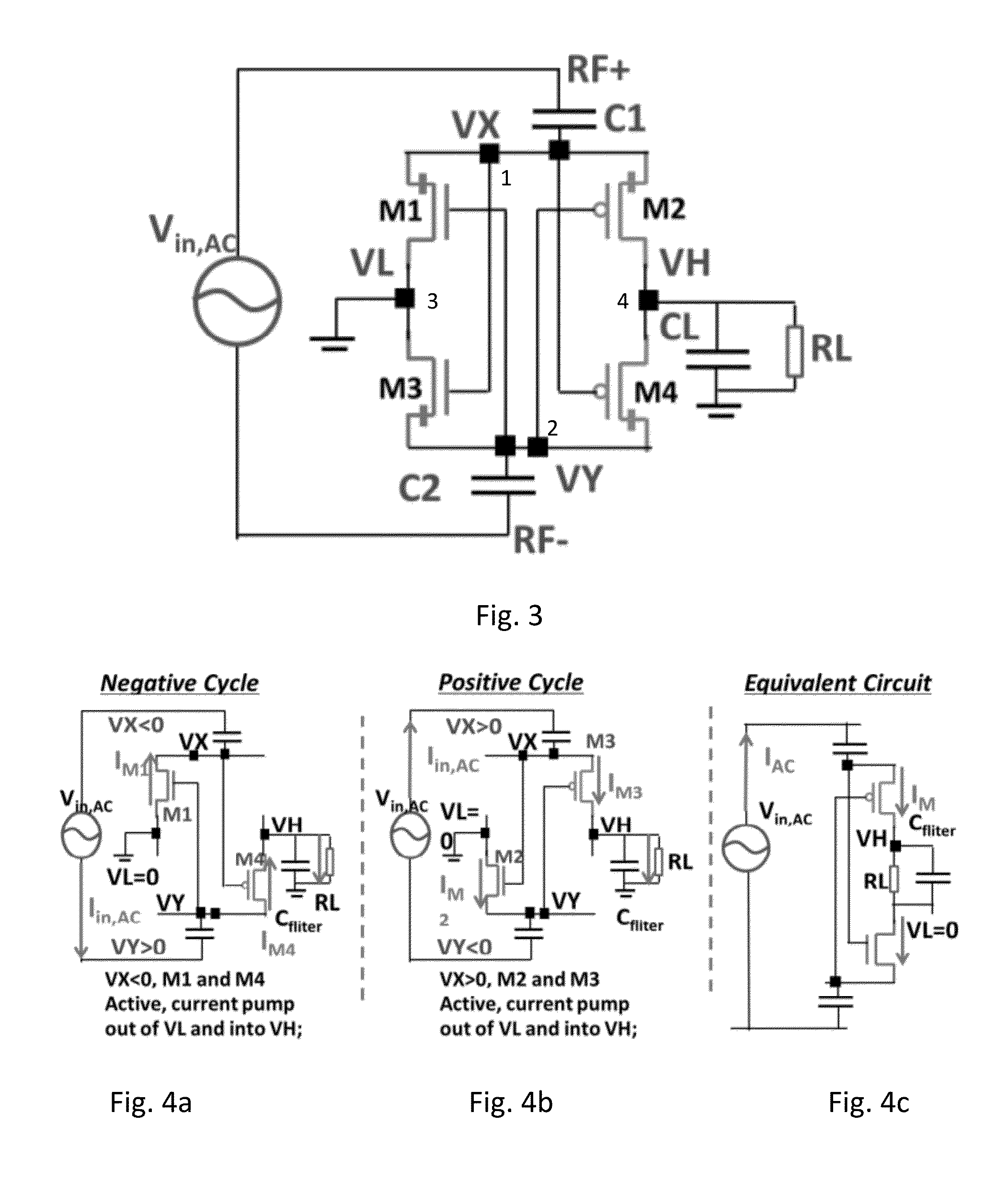

ActiveUS20150333534A1Improve power efficiencyReduce channel resistanceTransformersCircuit arrangementsLow voltageElectric power system

Disclosed are low power electronic devices configured to exploit the sub-threshold swing, unidirectional tunneling, and low-voltage operation of steep slope-tunnel tunnel field-effect transistors (TFET) to improve power-conversion efficiency and power-efficiency of electrical systems incorporating the TFET as an electrical component to perform energy harvesting, signal processing, and related operations. The devices include a HTFET-based rectifier having various topologies, a HTFET-based DC-DC charge pump converter, a HTFET-based amplifier having an amplifier circuit including a telescopic operational transconductance amplifier, and a HTFET-based SAR A / D converter having a HTFET-based transmission gate DFF. Any one of the devices may be used to generate a RF-powered system with improved power conversion efficiencies of power harvesters and power efficiencies of processing components within the system.

Owner:PENN STATE RES FOUND

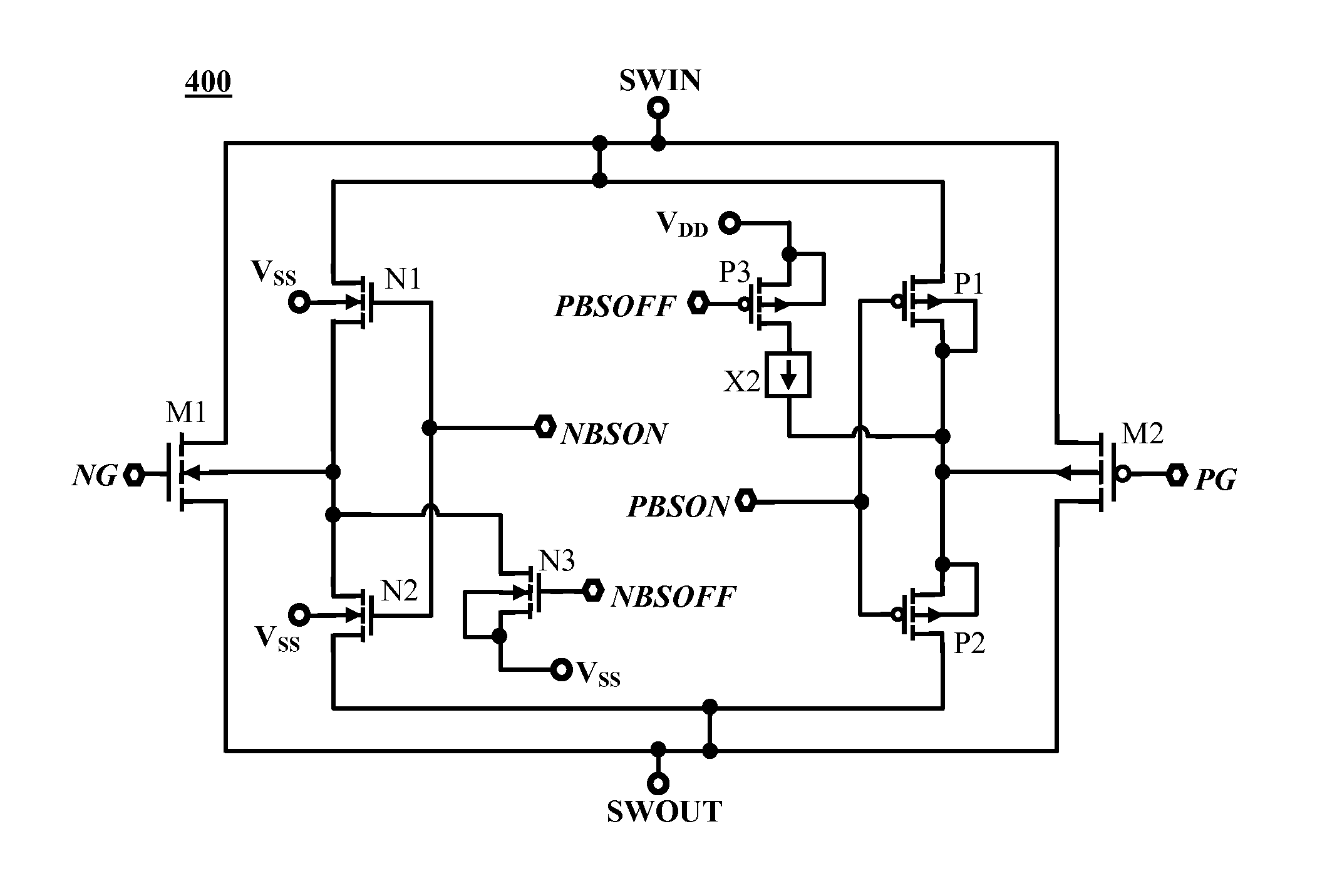

Low leakage dynamic bi-directional body-snatching (lldbbs) scheme for high speed analog switches

ActiveUS20120086499A1Reduce channel resistanceReduce leakage currentElectronic switchingEngineeringField-effect transistor

A bidirectional switch device includes a main pass field effect transistor (FET) connected to an input node and an output node. A body region of the first main pass transistor is tied to a voltage substantially halfway between the voltage at the input node side of the first main pass transistor and the voltage at the output node side of the transistor when the first main pass transistor is in an ON state.

Owner:ALPHA & OMEGA SEMICON CAYMAN

Necked Finfet device

InactiveUS20070063261A1Reduce channel resistanceInhibition formationTransistorSolid-state devicesComposite insulatorsMetal silicide

Owner:TAIWAN SEMICON MFG CO LTD

Double gate field effect transistor and method of manufacturing the same

InactiveUS7015106B2Reduce channel resistanceReduce in quantityTransistorSolid-state devicesEngineeringSilicon oxide

Owner:SAMSUNG ELECTRONICS CO LTD

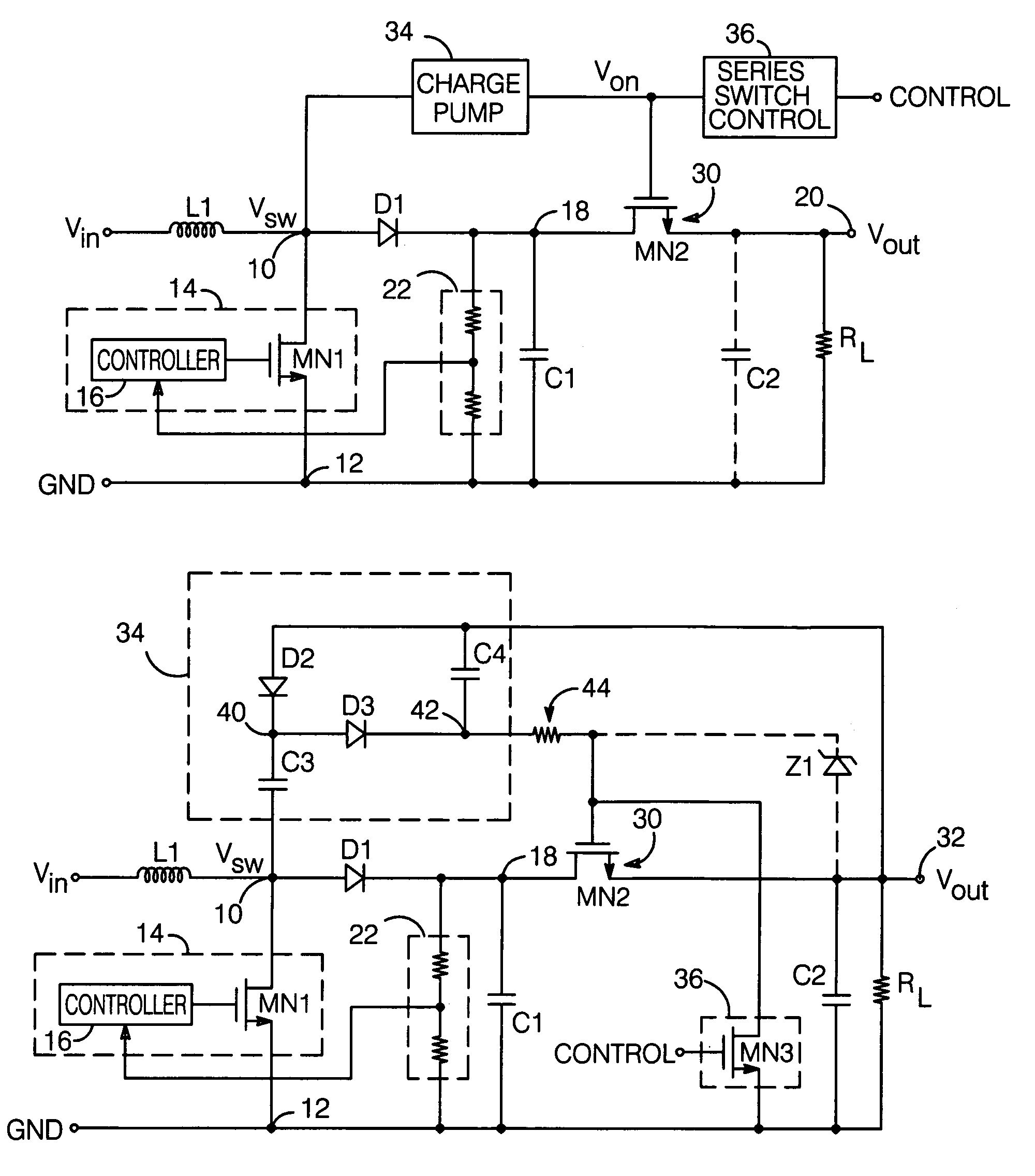

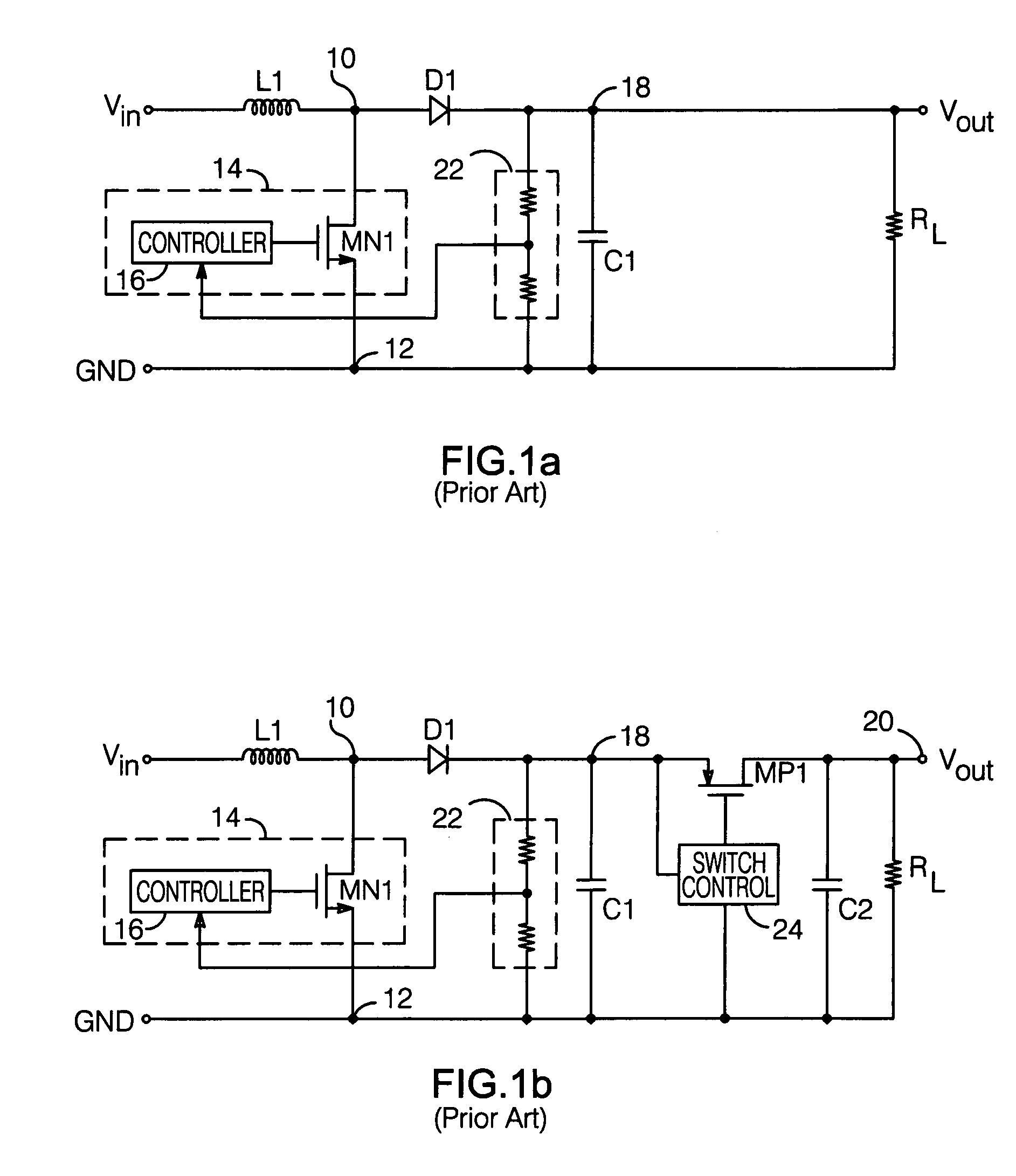

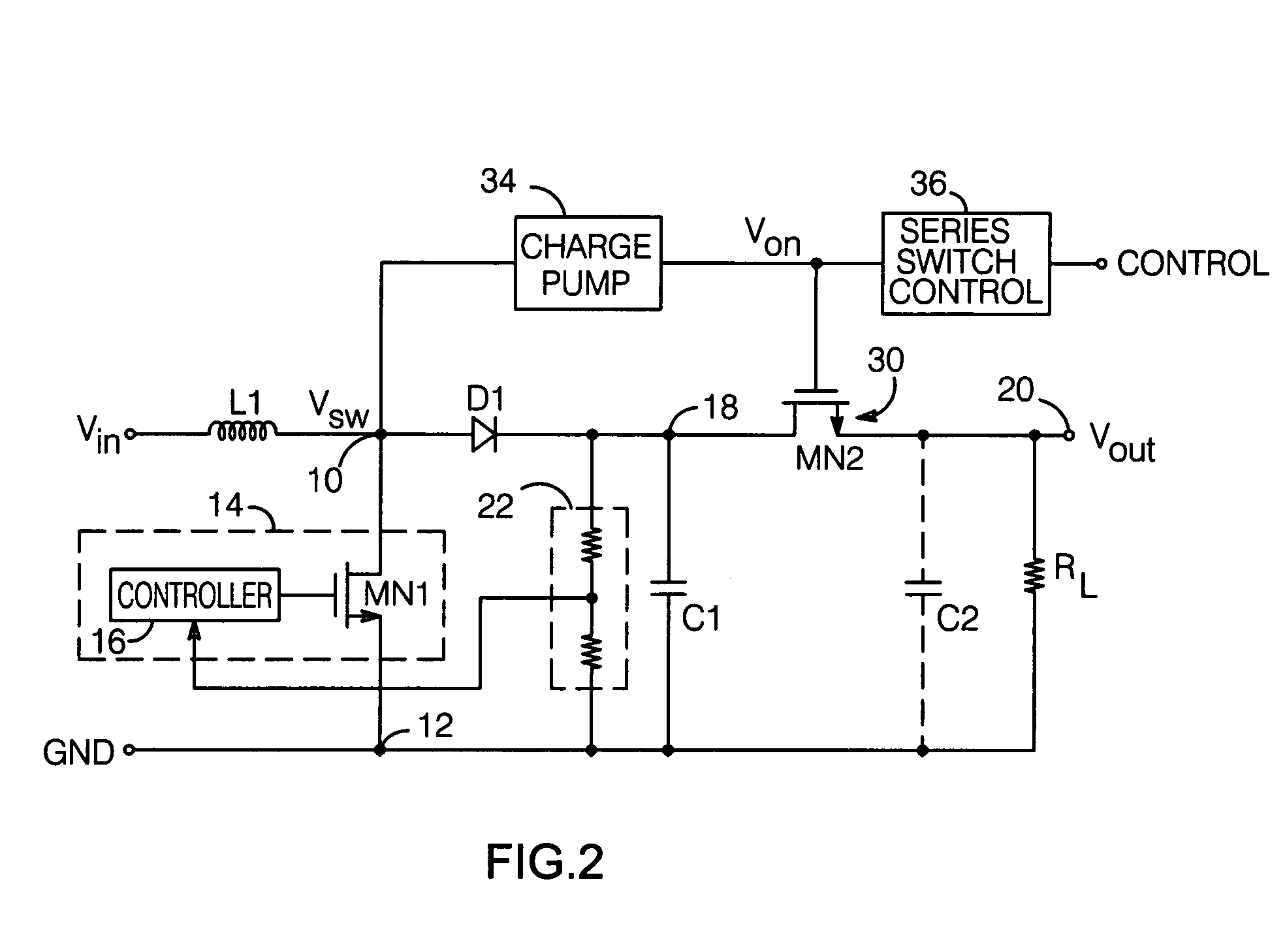

Boost converter with series switch

ActiveUS7098633B1Reduce channel resistanceSmall die sizeElectric variable regulationPower conversion systemsVoltage converterControl signal

A switching voltage converter, suitably a boost converter, employs an n-type transistor, preferably an NMOS FET, as a series switch, with its drain coupled to the cathode of the converter's diode and its source coupled to the converter's output node. A charge pump driven by the converter's switching voltage provides a voltage Von at the NMOS FET's gate input sufficient to turn the FET on. A series switch controller is arranged to, in response to a control signal, hold the NMOS FET off such that the converter's output voltage Vout is approximately zero regardless of the status of input voltage Vin, or allow the NMOS device to be turned on by Von.

Owner:ANALOG DEVICES INC

Method of fabricating a necked FINFET device

ActiveUS7122412B2Reduce channel resistanceInhibition formationTransistorSemiconductor/solid-state device manufacturingComposite insulatorsGate insulator

A method of fabricating a double gate, FINFET device structure in a silicon on insulator layer, in which the channel region formed in the SOI layer is defined with a narrowed, or necked shape, and wherein a composite insulator spacer is formed on the sides of the device structure, has been developed. A FINFET device structure shape is formed in an SOI layer via anisotropic RIE procedures, followed by a growth of a silicon dioxide gate insulator layer on the sides of the FINFET device structure shape. A gate structure is fabricated traversing the device structure and overlying the silicon dioxide gate insulator layer located on both sides of the narrowest portion of channel region. After formation of a source / drain region in wider, non-channel regions of the FINFET device structure shape, composite insulator spacers are formed on the sides of the FINFET shape and on the sides of the gate structure. Metal silicide is next formed on source / drain regions resulting in a FINFET device structure featuring a narrow channel region, and surrounded by composite insulator spacers located on the sides of the device structure.

Owner:TAIWAN SEMICON MFG CO LTD

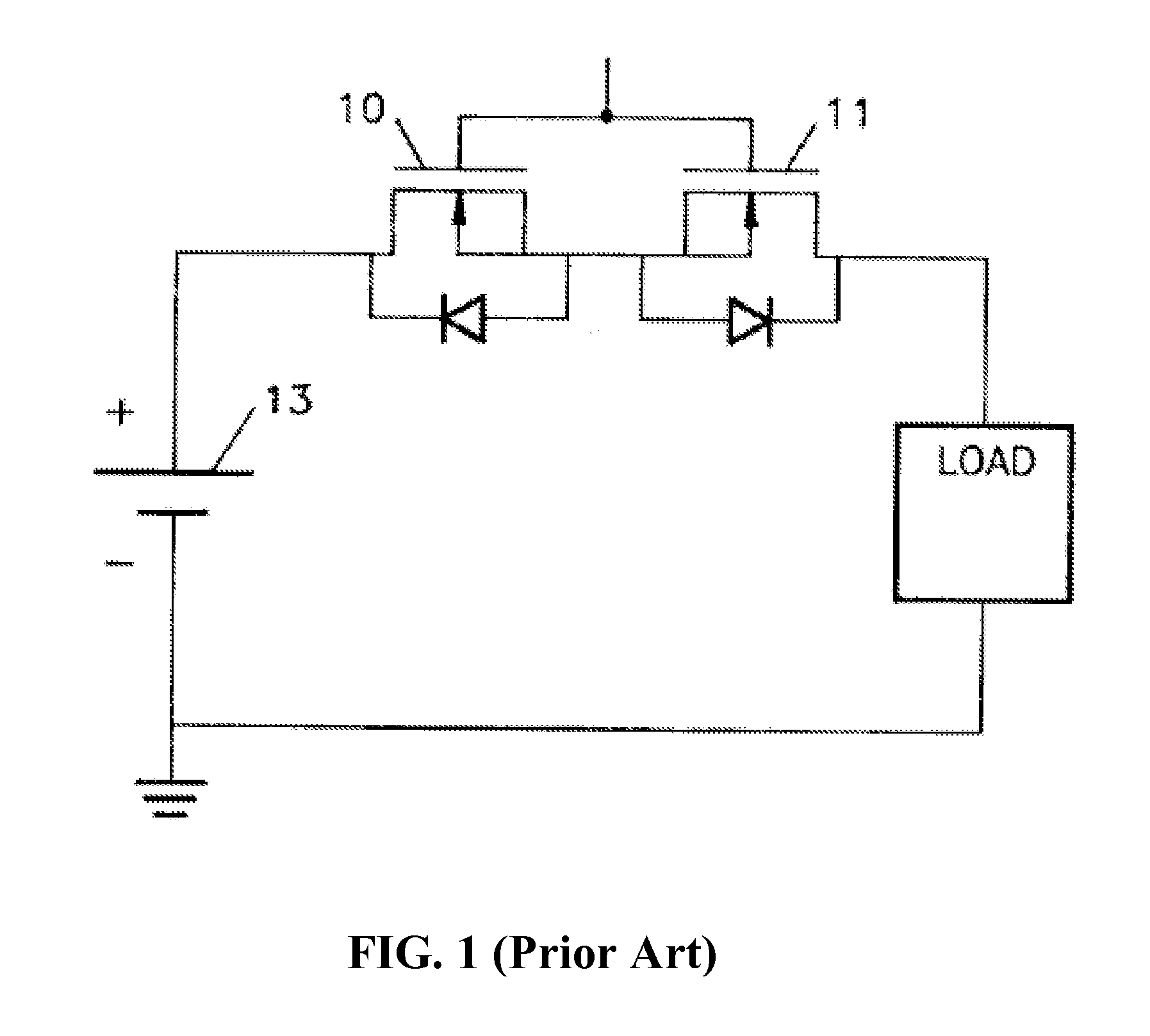

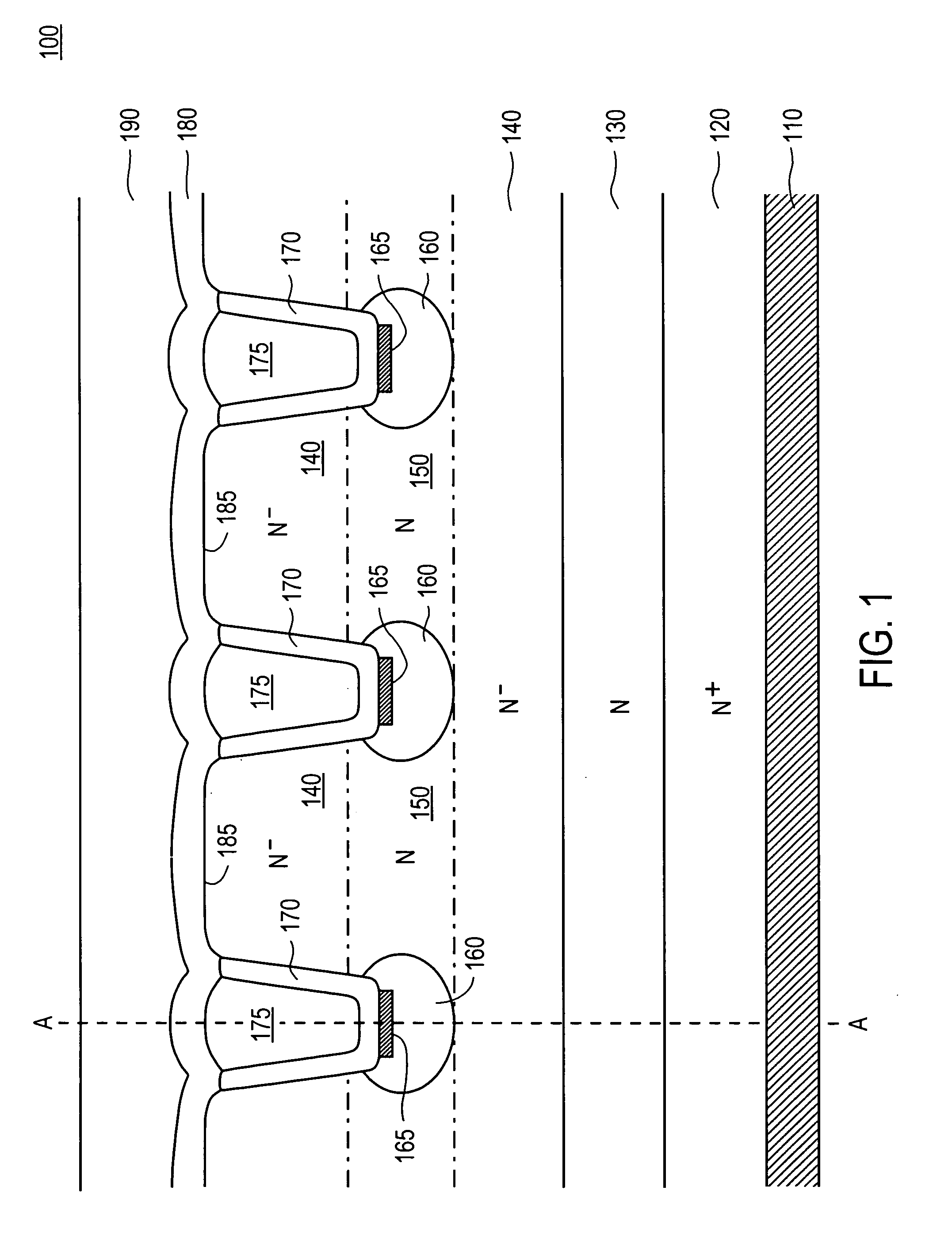

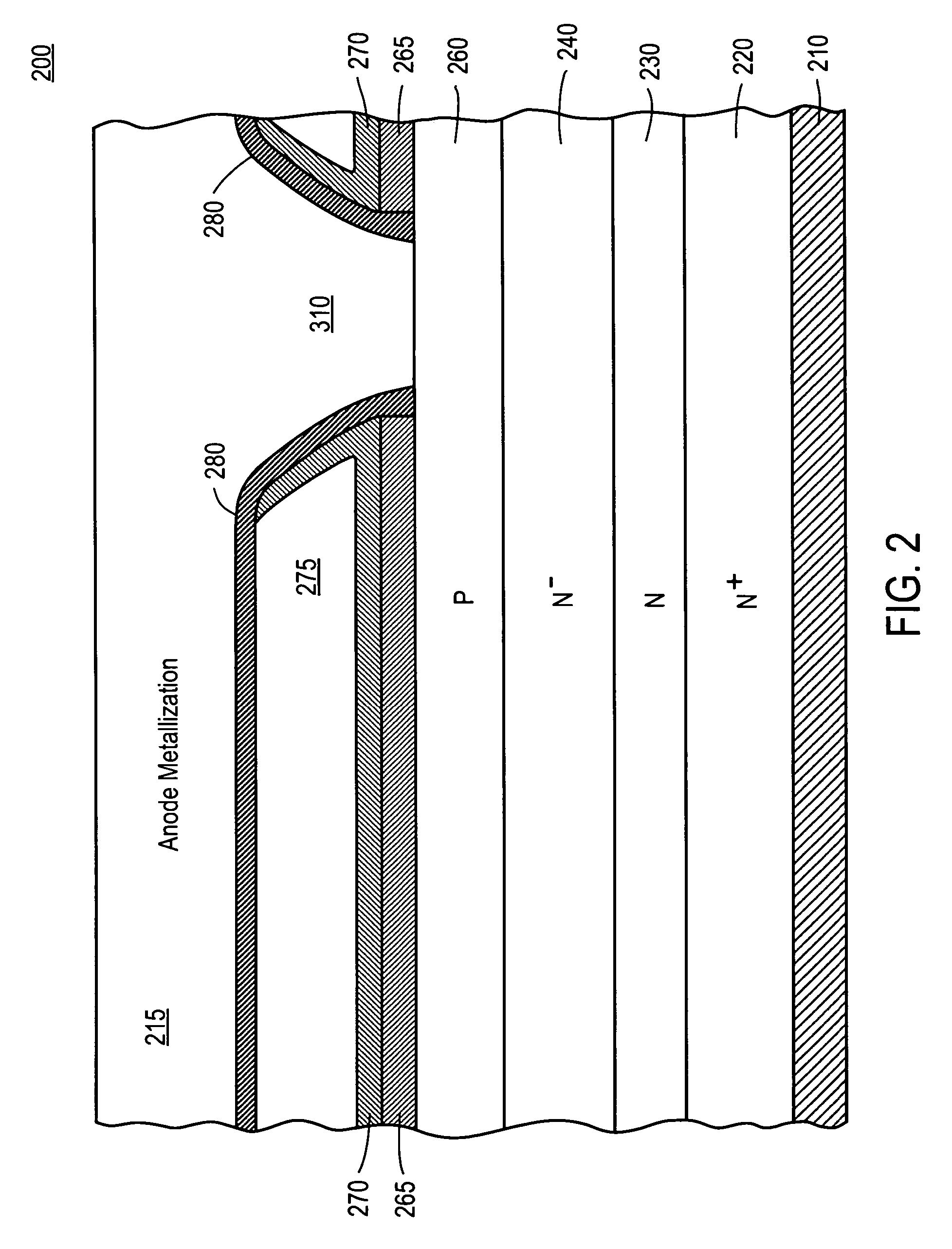

Structure and method for a fast recovery rectifier structure

An apparatus and method for a fast recovery rectifier structure. Specifically, the structure includes a substrate of a first dopant. A first epitaxial layer lightly doped with the first dopant is coupled to the substrate. A first metallization layer is coupled to the first epitaxial layer. A plurality of trenches is recessed into the first epitaxial layer, each of which is coupled to the metallization layer. The device also includes a plurality of wells each doped with a second dopant type, wherein each well is formed beneath and adjacent to a corresponding trench. A plurality of oxide layers is formed on walls and a bottom of a corresponding trench. A plurality of channel regions doped with the first dopant is formed within the first epitaxial layer between two corresponding wells. Each of the plurality of channel regions is more highly doped with the first dopant than the first epitaxial layer.

Owner:POWER INTEGRATIONS INC

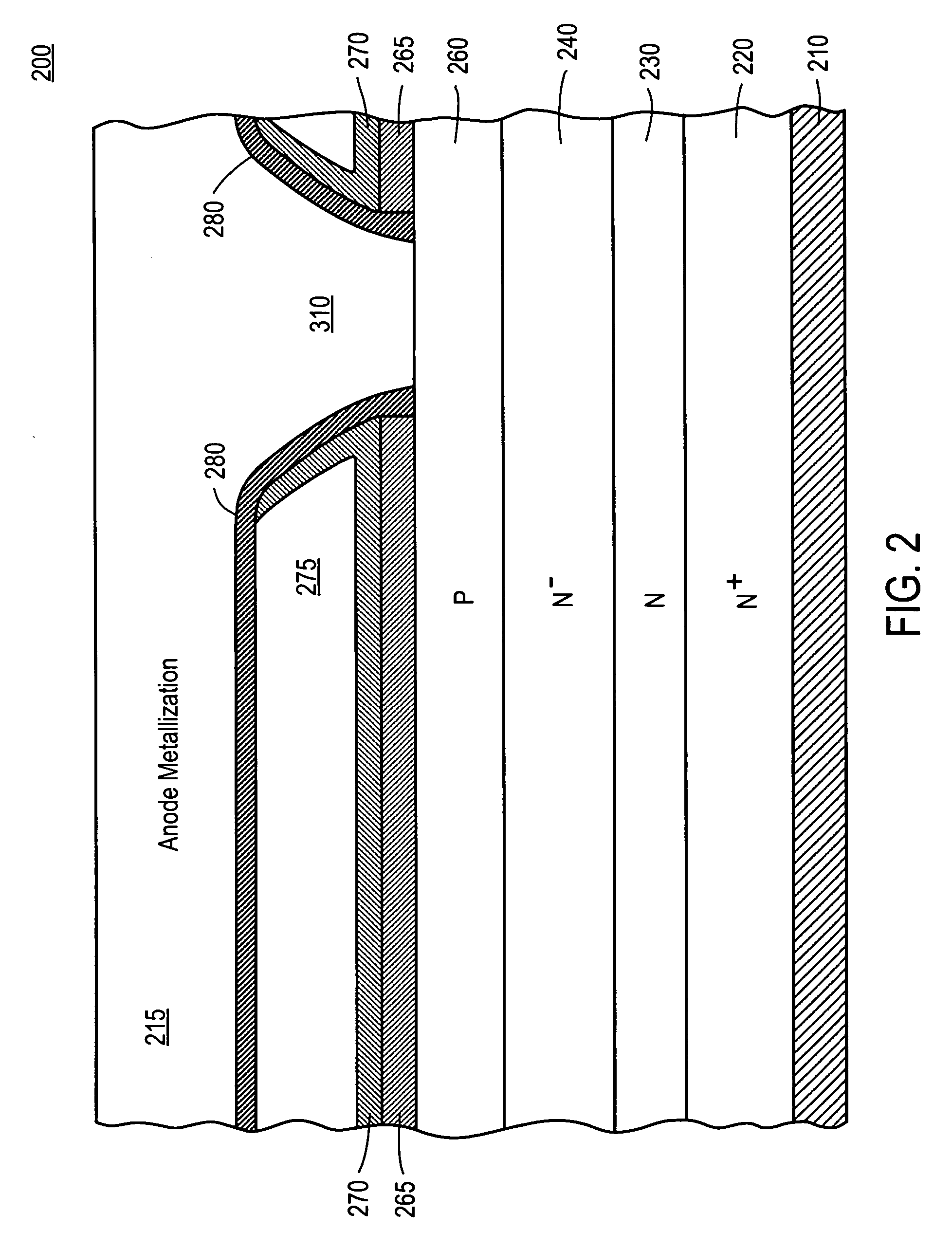

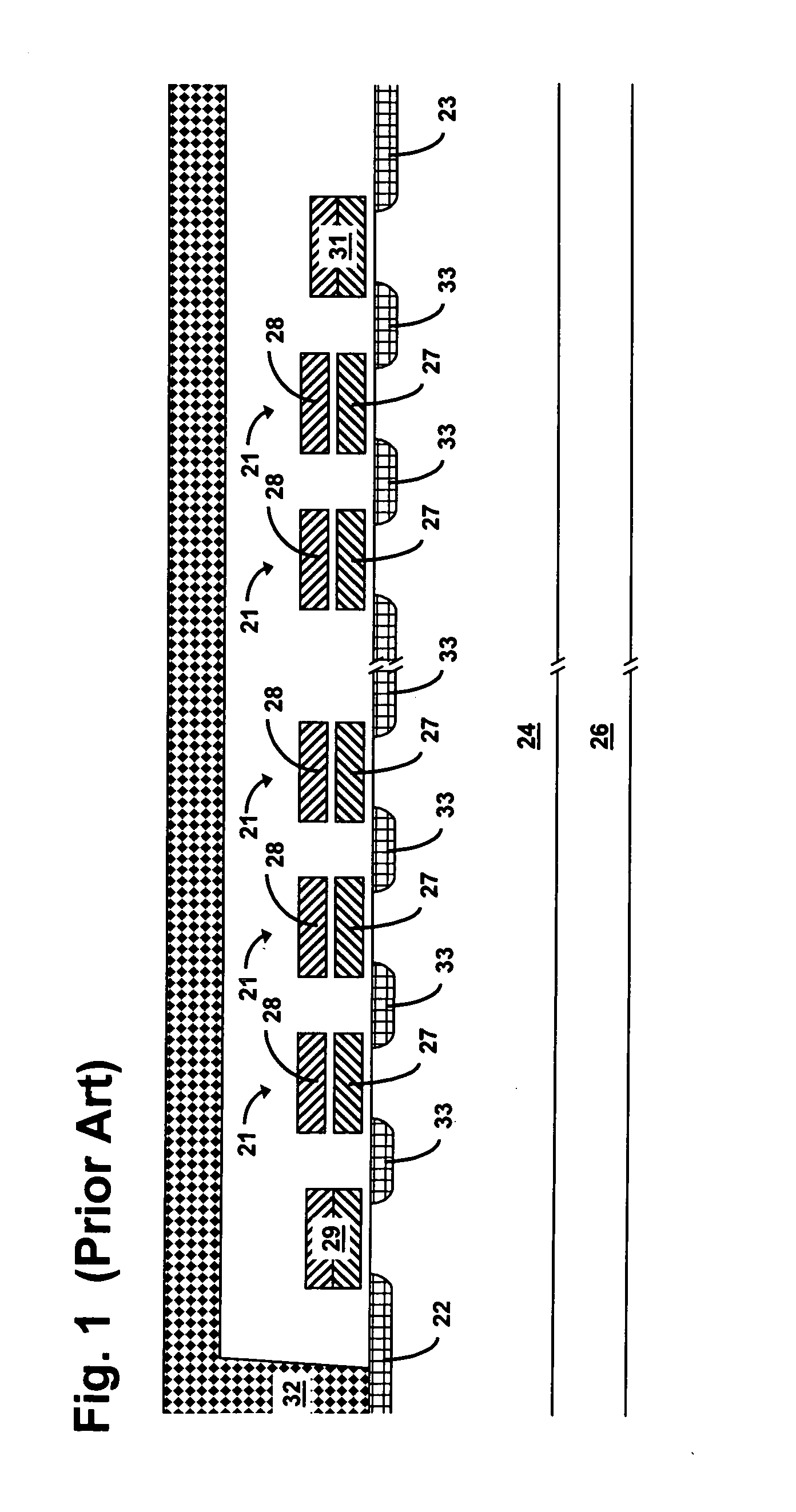

Self-aligned split-gate NAND flash memory and fabrication process

ActiveUS20050207225A1Reduce channel resistanceEnhanced high voltage couplingSolid-state devicesRead-only memoriesBit lineEngineering

Self-aligned split-gate NAND flash memory cell array and process of fabrication in which rows of self-aligned split-gate cells are formed between a bit line diffusion and a common source diffusion in the active area of a substrate. Each cell has control and floating gates which are stacked and self-aligned with each other, and erase and select gates which are split from and self-aligned with the stacked gates, with select gates at both ends of each row which partially overlap the bit line the source diffusions. The channel regions beneath the erase gates are heavily doped to reduce the resistance of the channel between the bit line and source diffusions, and the floating gates are surrounded by the other gates in a manner which provides significantly enhanced high voltage coupling to the floating gates from the other gates. The memory cells are substantially smaller than prior art cells, and the array is biased so that all of the memory cells in it can be erased simultaneously, while programming is bit selectable.

Owner:SILICON STORAGE TECHNOLOGY

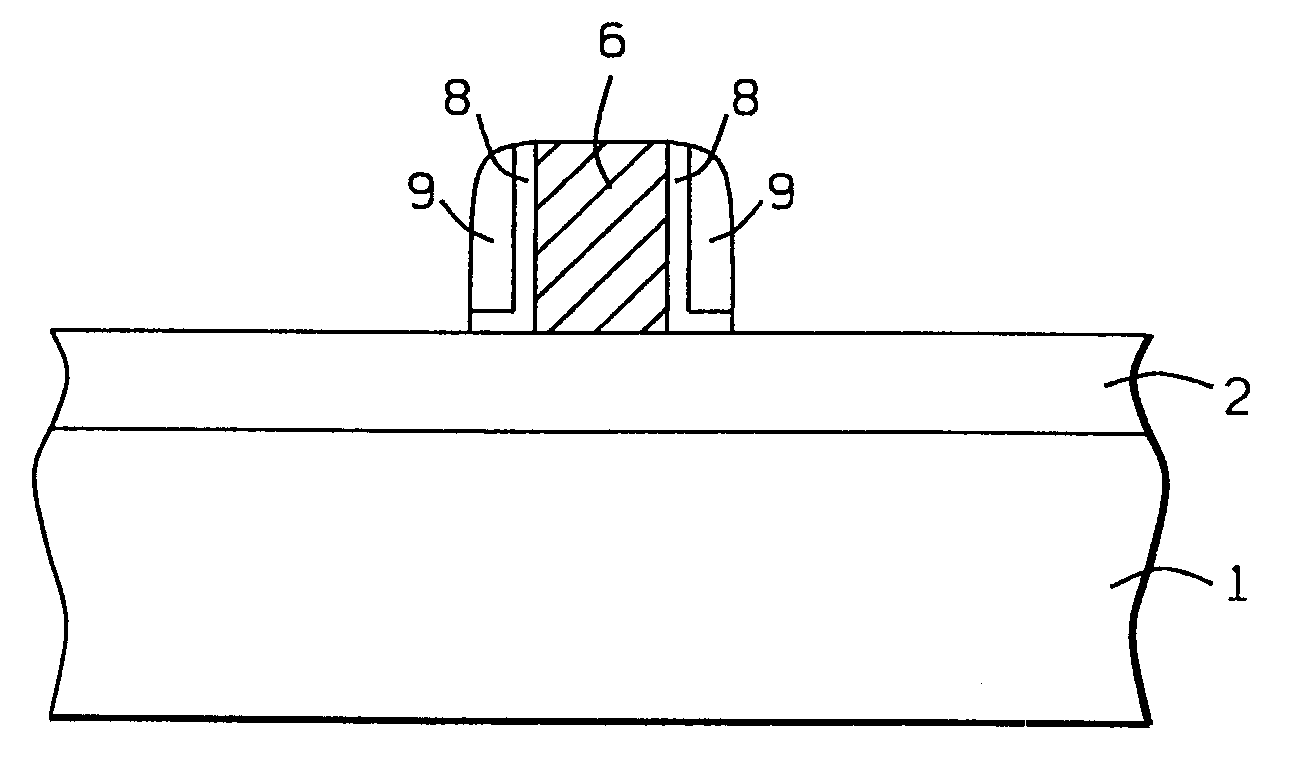

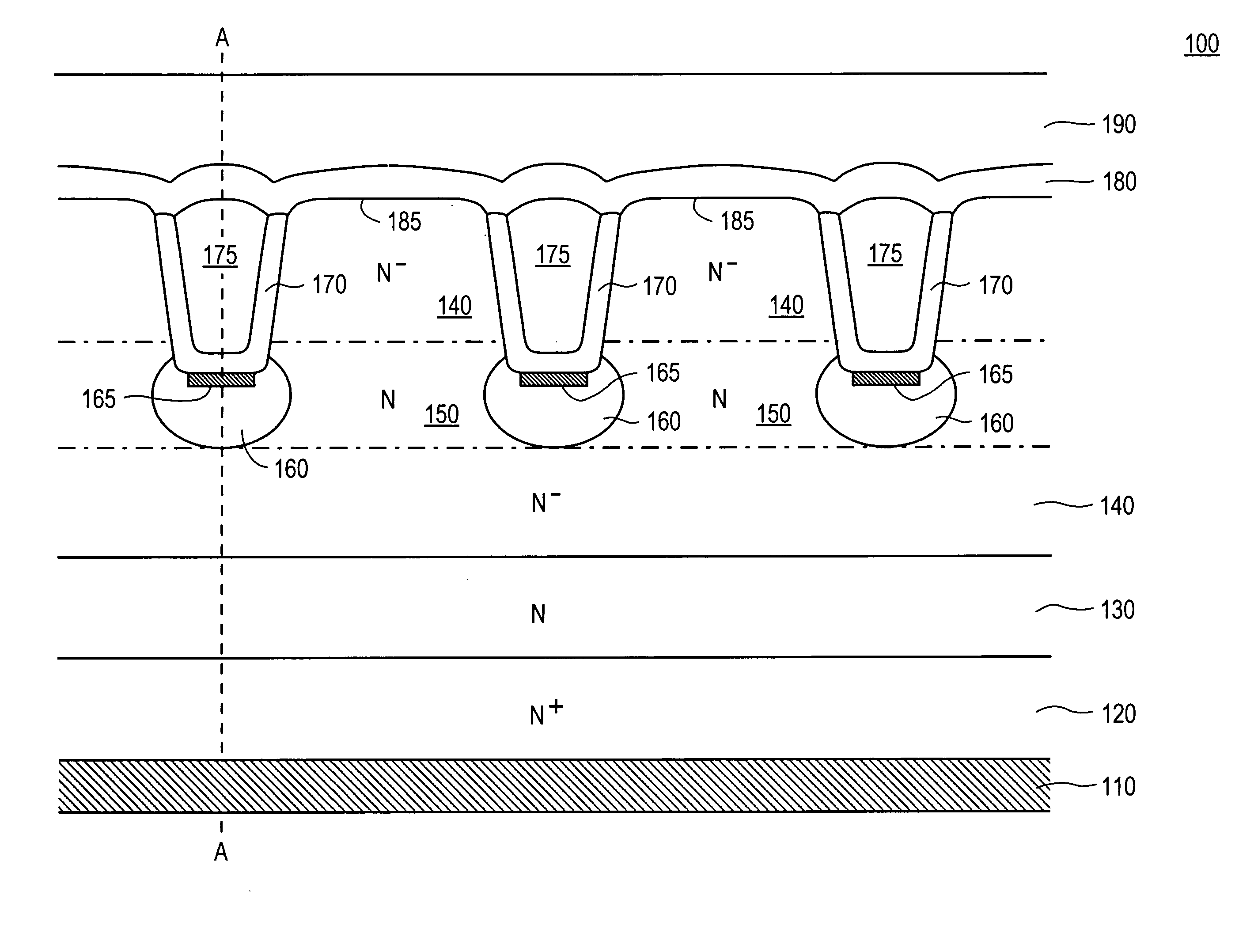

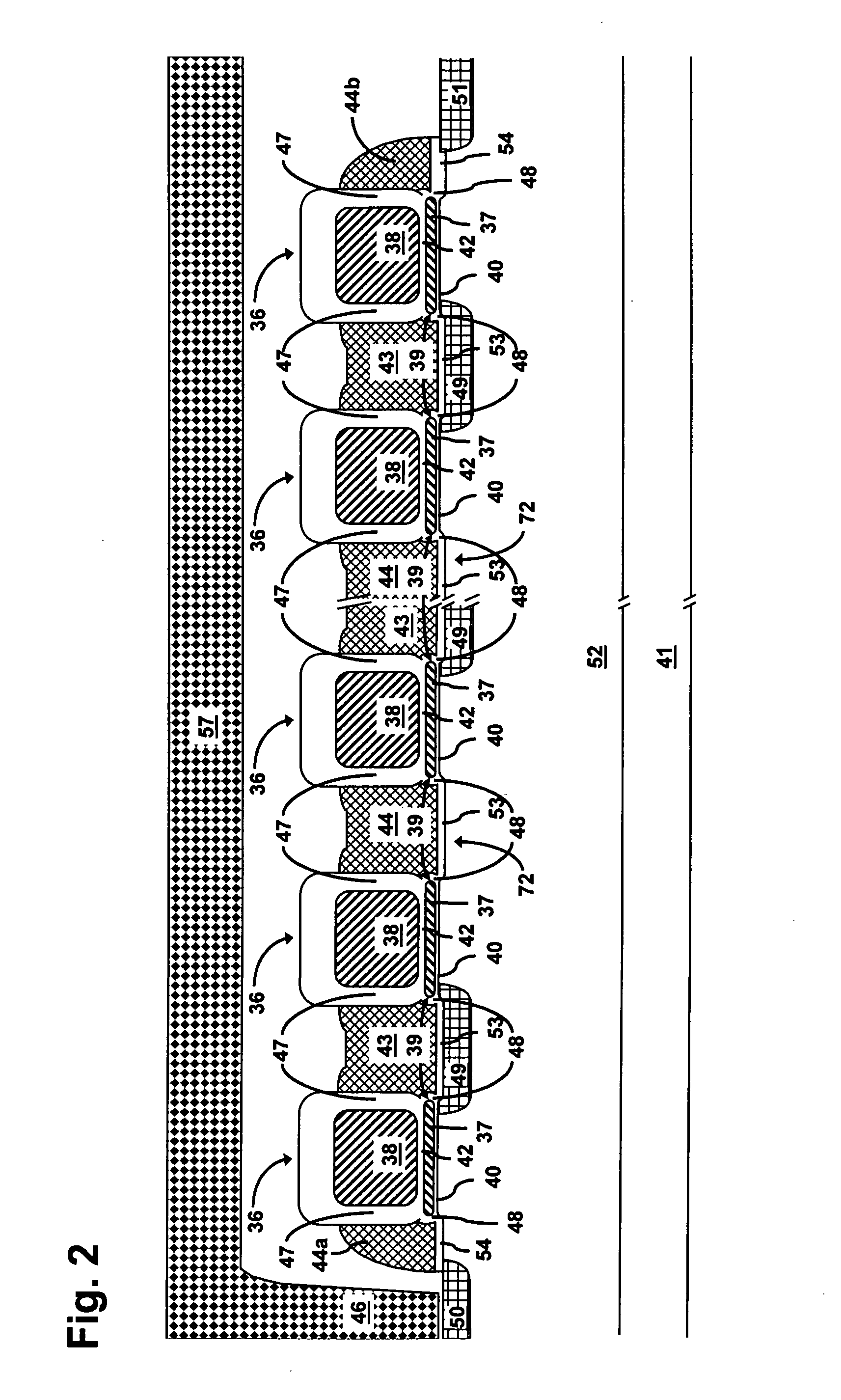

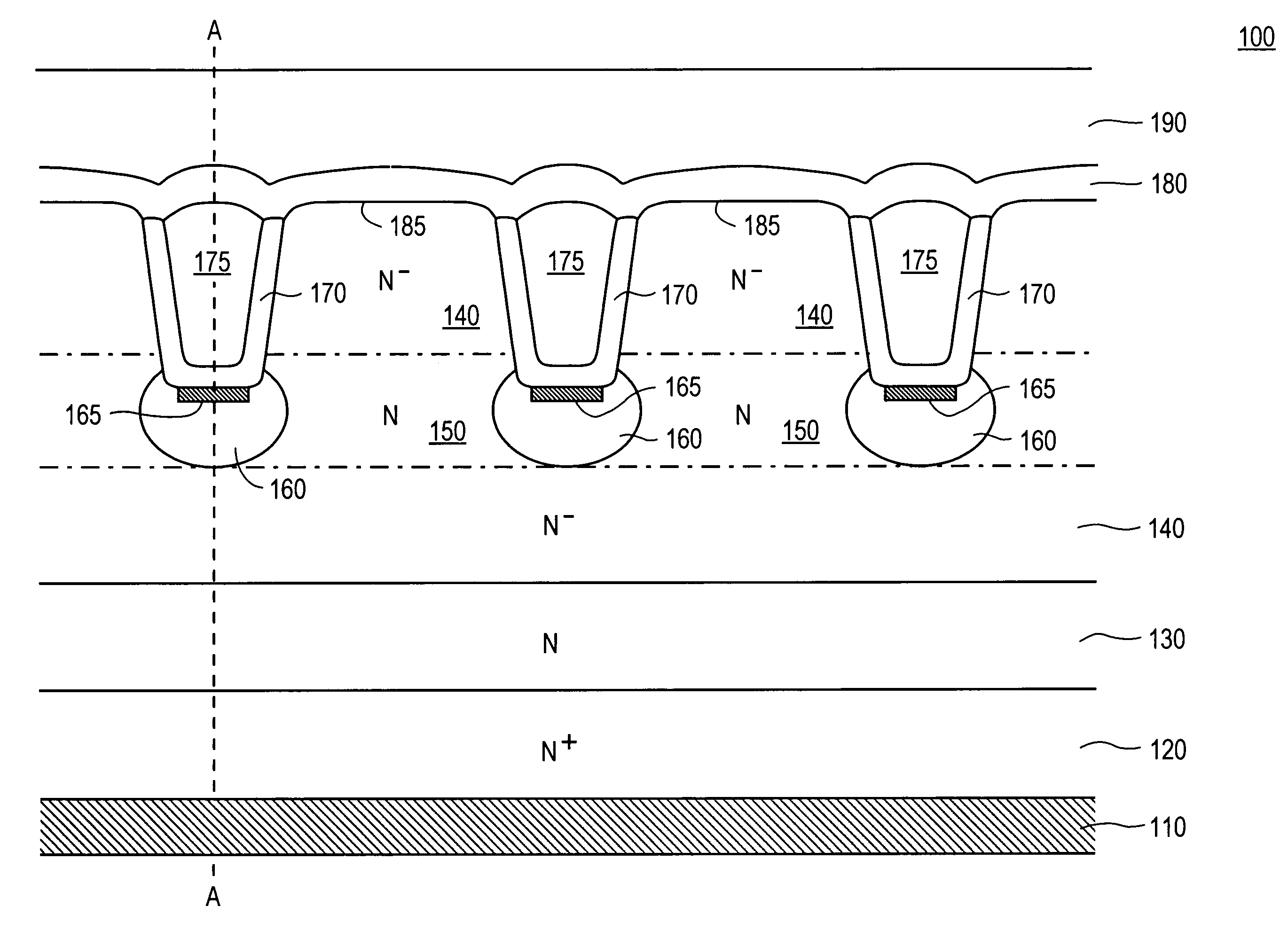

Structure and Method for Forming Field Effect Transistor with Low Resistance Channel Region

ActiveUS20090194811A1Reduce channel resistanceSemiconductor/solid-state device manufacturingSemiconductor devicesBody regionPhysics

A trench-gate field effect transistor includes trenches extending into a silicon region of a first conductivity type, and a gate electrodes in each trench. Body regions of second conductivity type extend over the silicon region between adjacent trenches. Each body region forms a first PN junction with the silicon region, and each body region includes a silicon-germanium layer of the second conductivity type laterally extending between adjacent trenches. Source regions of the first conductivity flank the trenches, and each source region forms a second PN junction with one of the body regions. Channel regions extend in the body regions along sidewalls of the trenches between the source regions and a bottom surface of the body regions. The silicon-germanium layers extend into corresponding channel regions to thereby reduce the channel resistance.

Owner:SEMICON COMPONENTS IND LLC

Semiconductor device

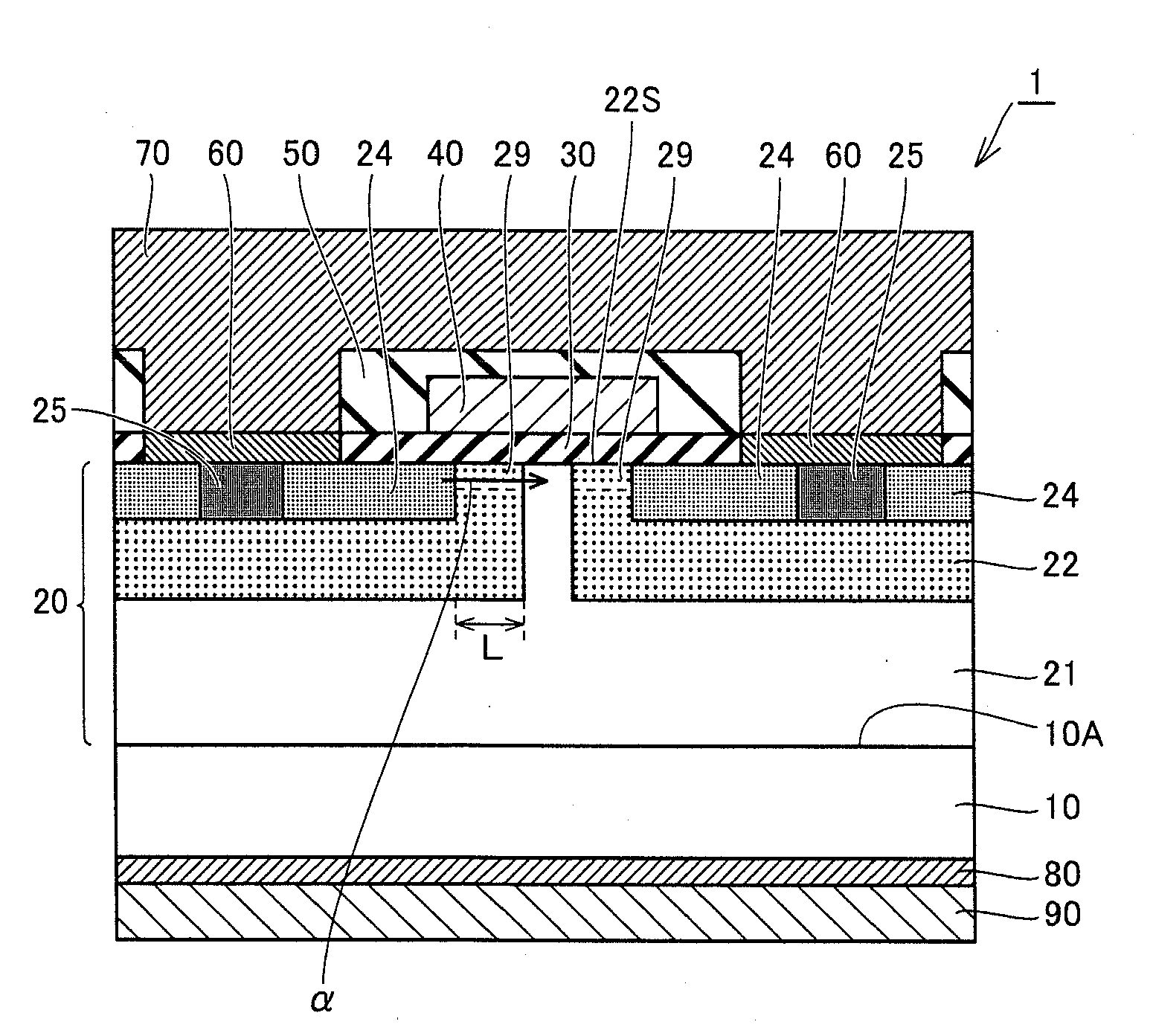

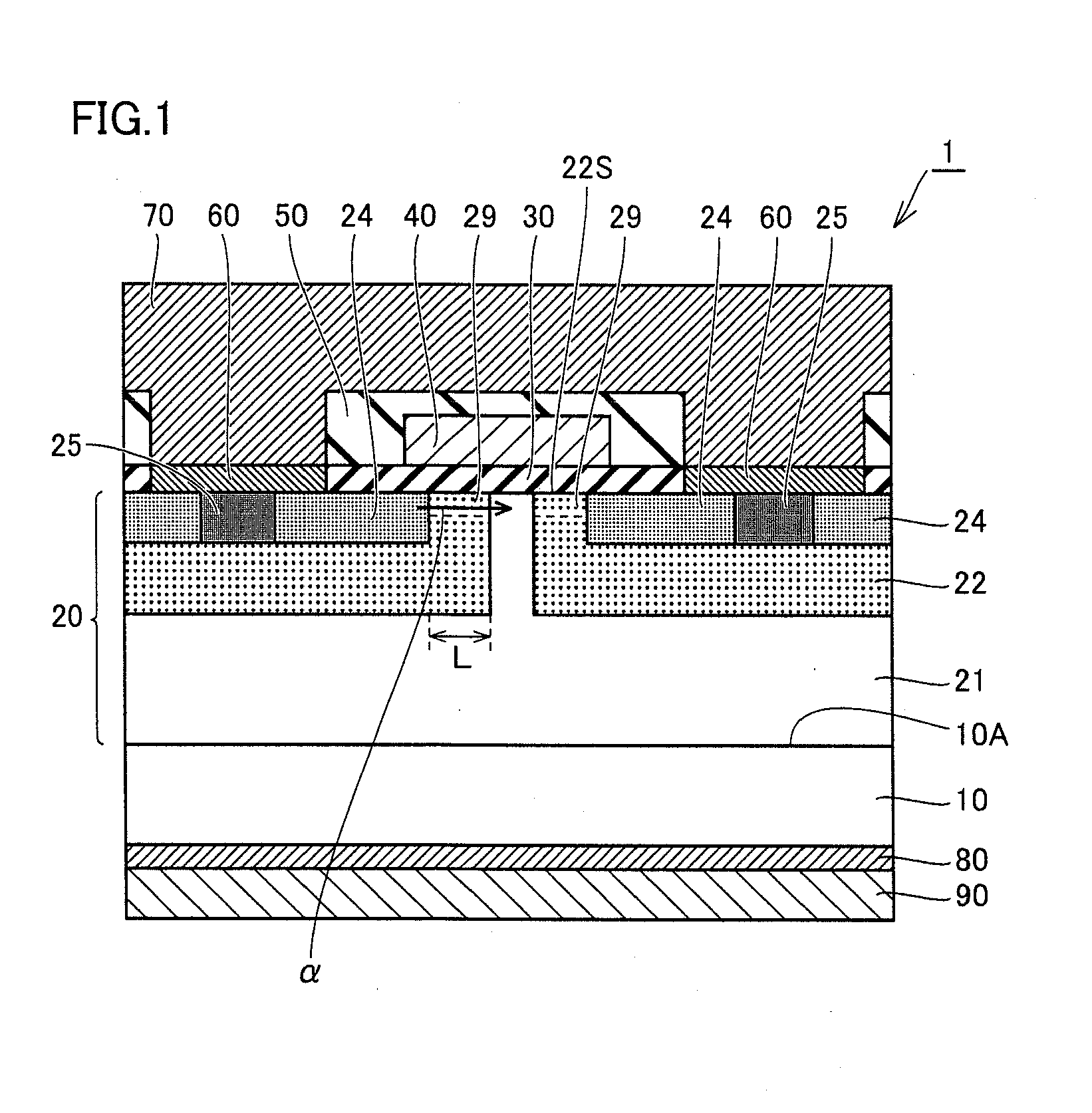

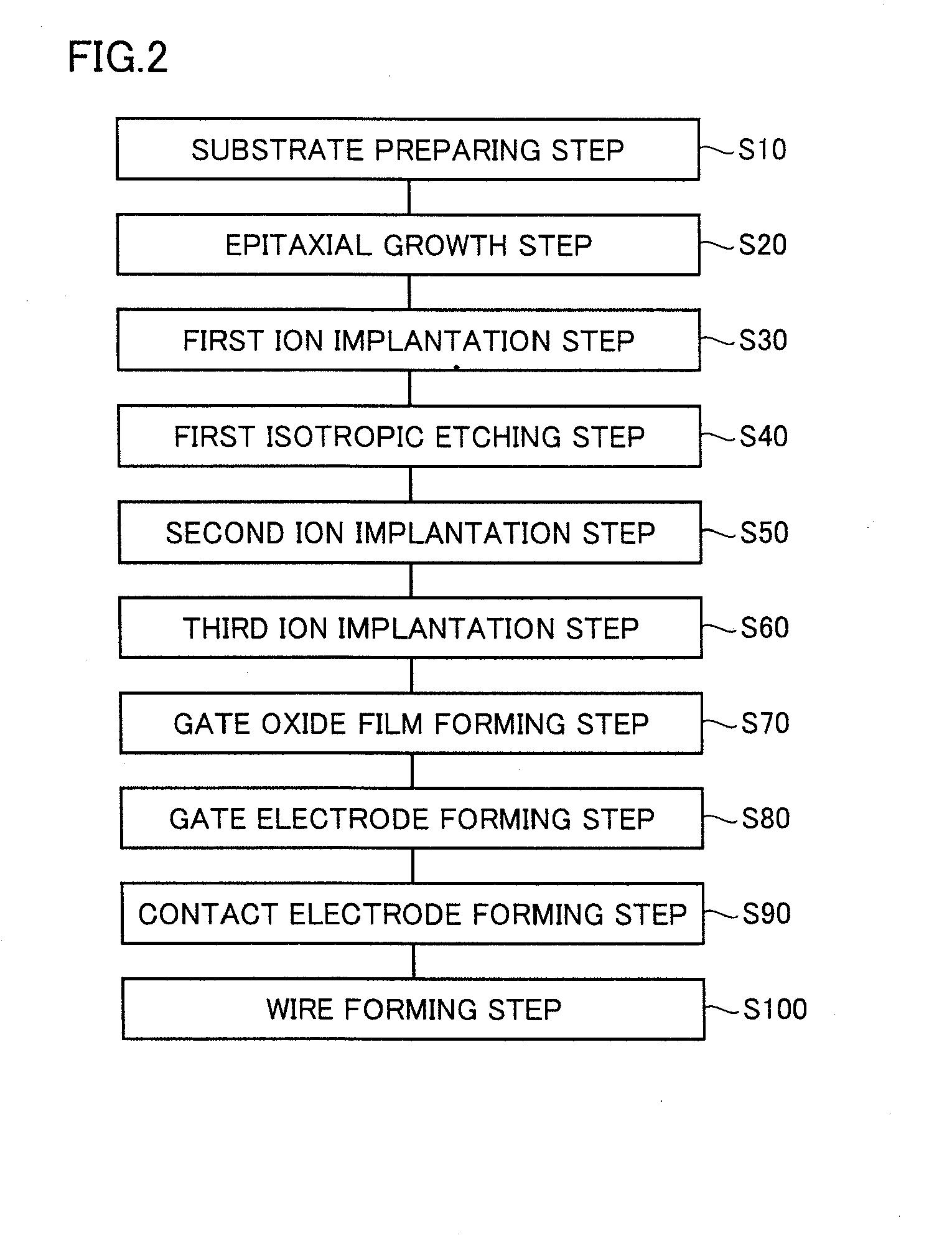

A MOSFET includes a silicon carbide substrate, an active layer, a gate oxide film, and a gate electrode. The active layer includes a p type body region in which an inversion layer is formed when the gate electrode is fed with a voltage. The inversion layer has an electron mobility μ dependent more strongly on an acceptor concentration Na of a channel region of the p type body region, as compared with a dependency of the electron mobility μ being proportional to the reciprocal of the acceptor concentration Na. The acceptor concentration Na in the channel region of the p type body region is not less than 1×1016 cm−3 and not more than 2×1018 cm3. The channel length (L) is equal to or smaller than 0.43 μm. The channel length (L) is equal to or longer than a spreading width d of a depletion layer in the channel region. The spreading width d is expressed by d=D·Na−C.

Owner:SUMITOMO ELECTRIC IND LTD

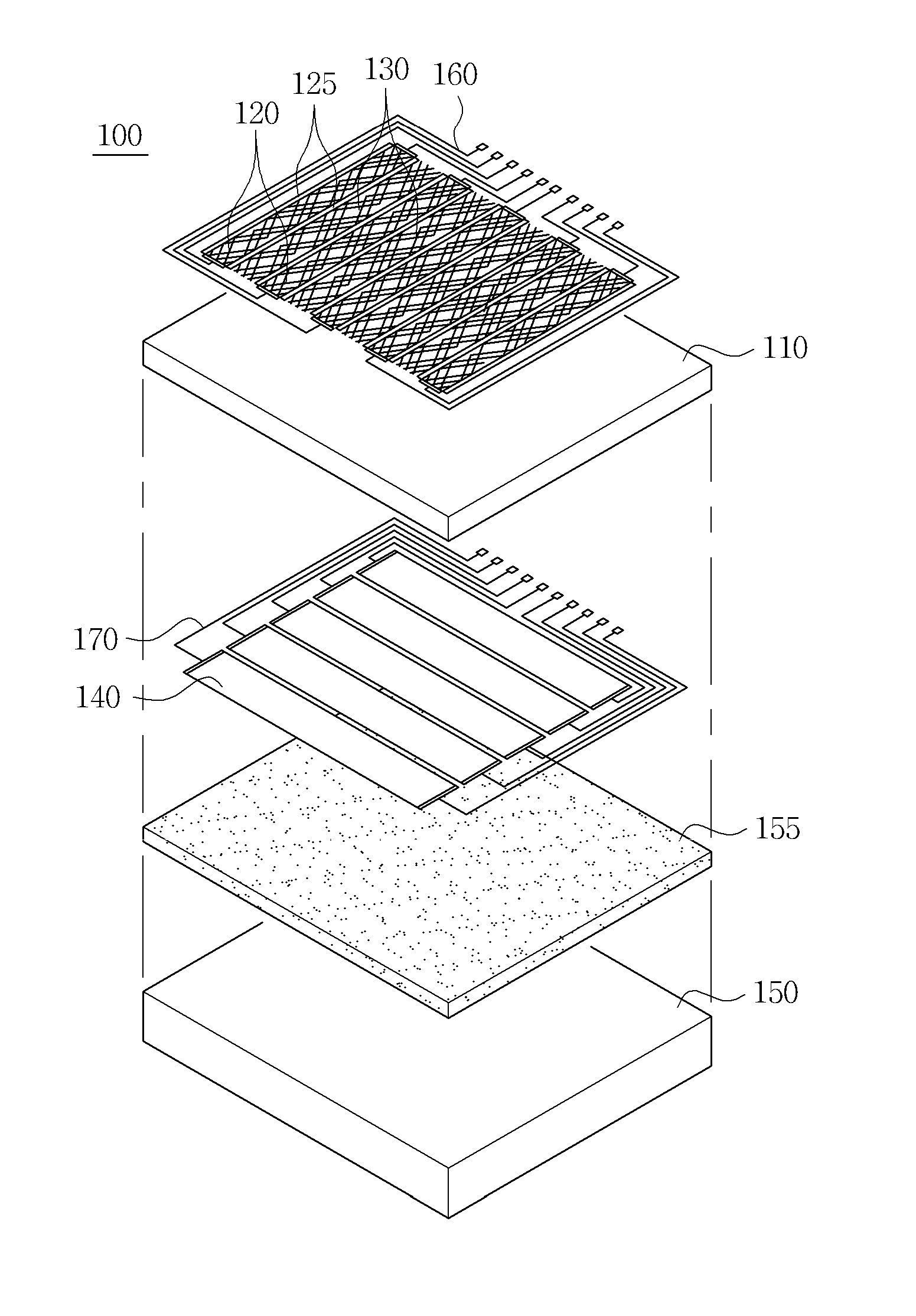

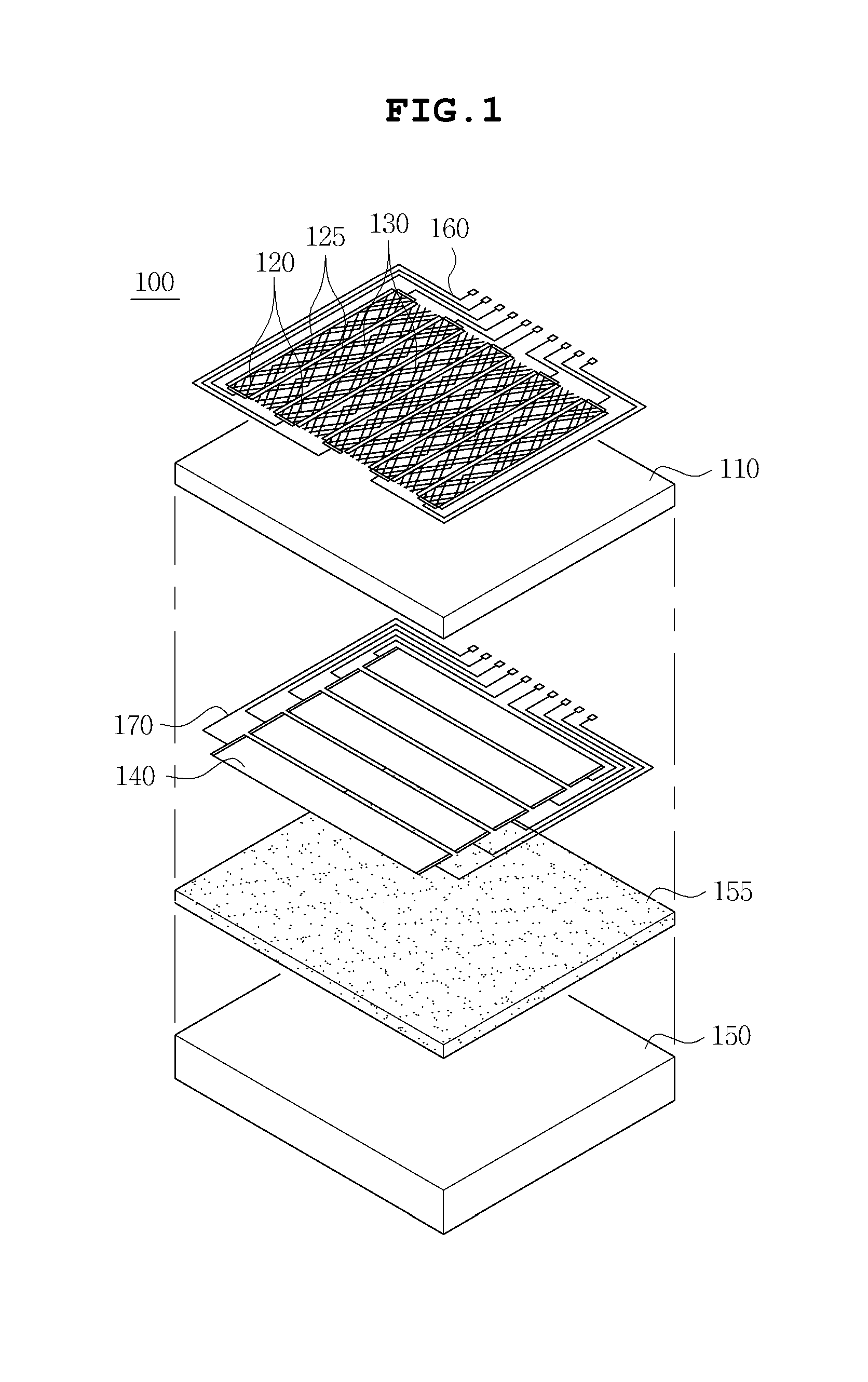

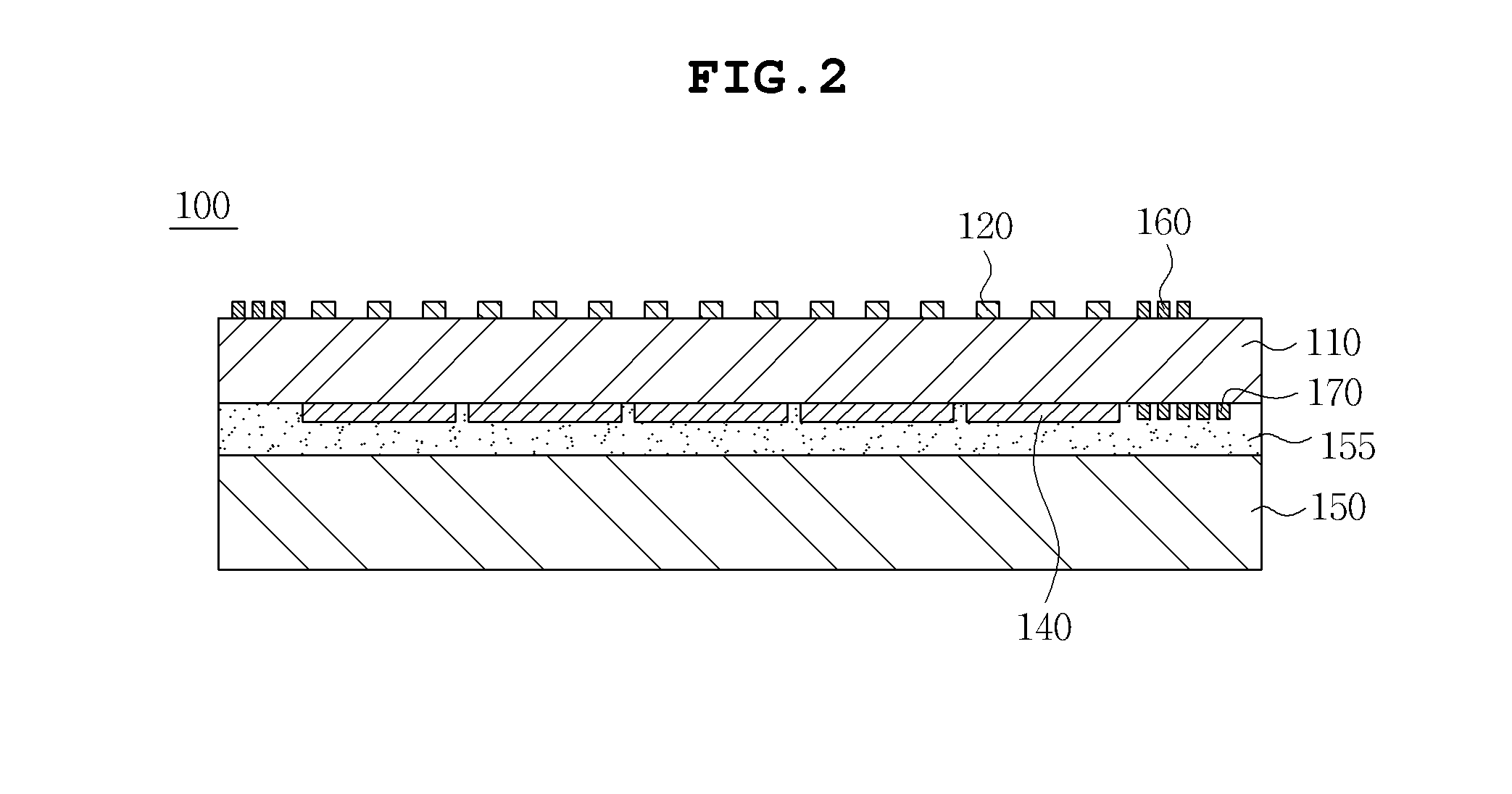

Touch panel

InactiveUS20130169548A1Reduce channel resistanceBlock noise generatedInput/output processes for data processingVisibilityDisplay device

Disclosed herein is a touch panel, including a transparent substrate; first electrode patterns formed in a mesh pattern on one surface of the transparent substrate; second electrode patterns formed in a surface type on the other surface of the transparent substrate; and an image display device provided in a direction of the other surface of the transparent substrate, thereby effectively blocking noise generated in the image display device, lowering a sheet resistance, and improving visibility.

Owner:SAMSUNG ELECTRO MECHANICS CO LTD

Structure and method for a fast recovery rectifier structure

ActiveUS7696540B2Fast recovery rectifier structureReduce channel resistanceTransistorThyristorDopantFast recovery

Owner:POWER INTEGRATIONS INC

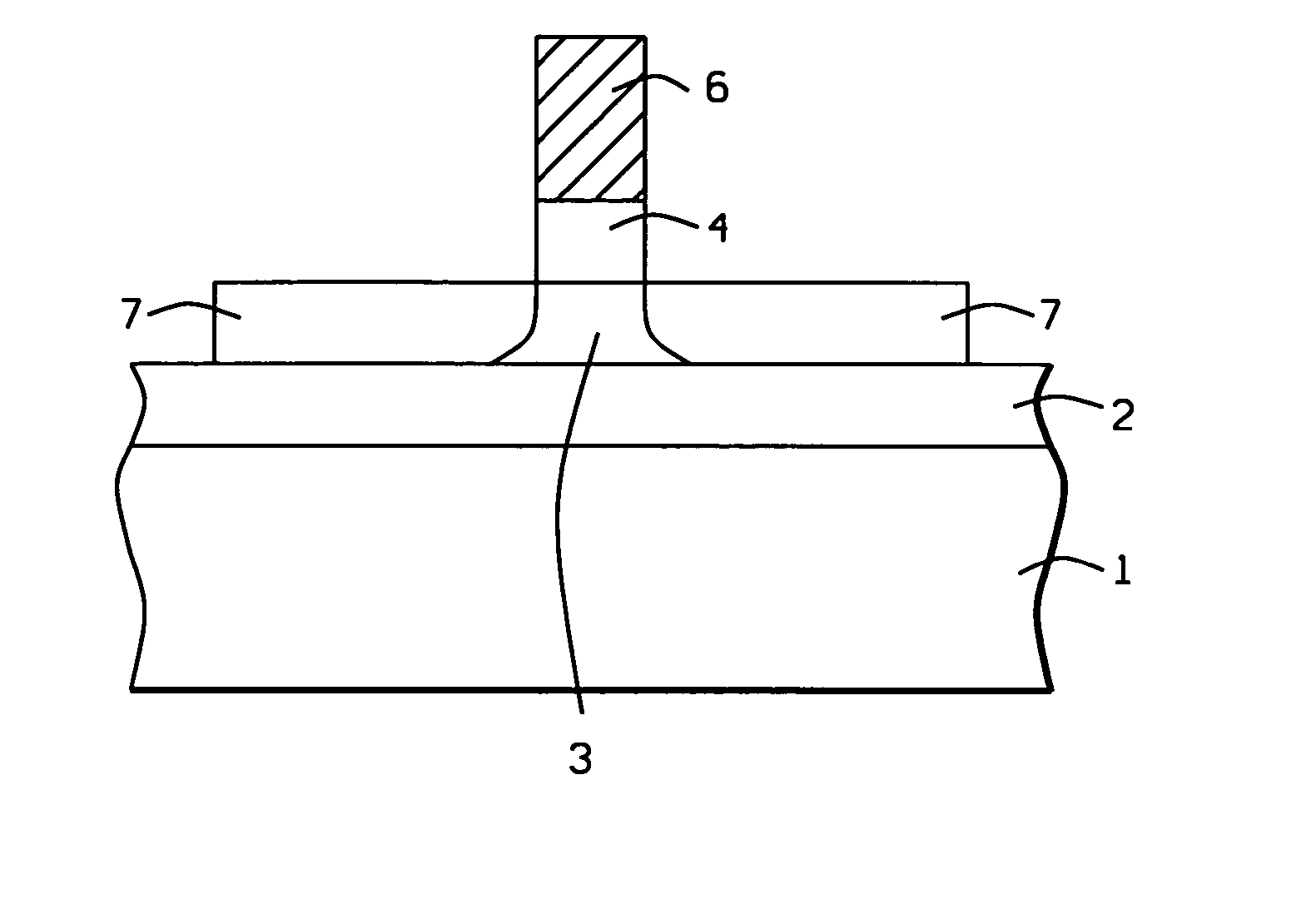

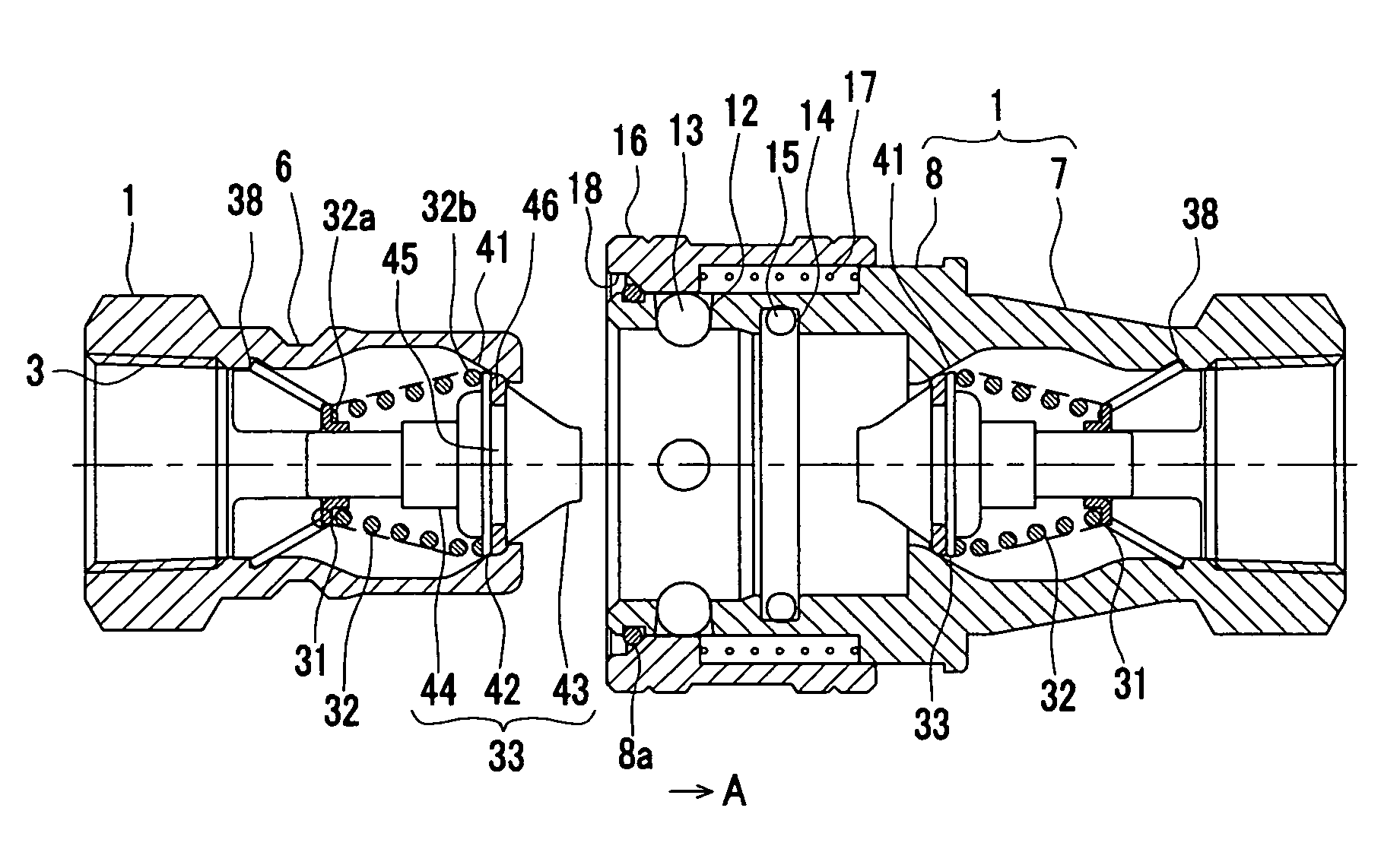

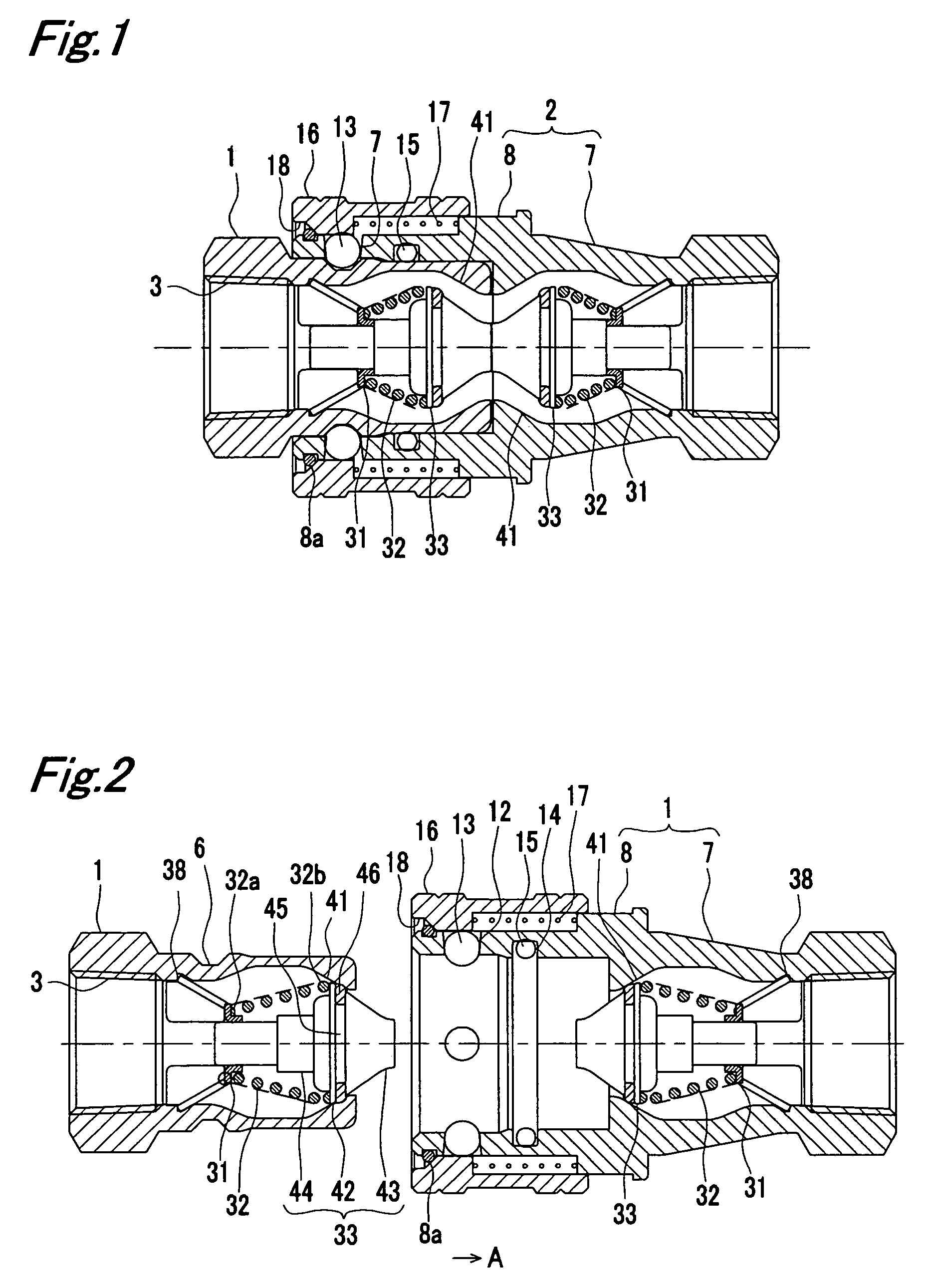

Fluid coupling

ActiveUS7921875B2Reduce total pressure lossReduce channel resistancePipe elementsCouplingsFluid couplingEngineering

In the fluid coupling for connecting the fluid passages of a plug (1) and a socket (2), a valve (33), a valve holder (31) and a spring (32) disposed in a compressed state between the valve (33) and the valve holder (31) are accommodated inside each of the plug (1) and the socket (2) to be connected to each other the plug (1) is inserted into the socket (2), the valve (33) of the plug (1) and the valve (33) of the socket (2) make contact with each other so that the valves (33) are retracted resisting an urging force of the spring (32). This fluid coupling further includes conical members (32, 51) which form a conical external shape along a line connecting the outside diameter portion of the valve (33) and the outside diameter portion of the valve holder (31) when the valve (33) of the plug (1) and the valve (33) of the socket (2) make contact with each other, so that the springs (32) are compressed between the valve (33) and the valve holder (31).

Owner:NAGAHORI SHOKAI

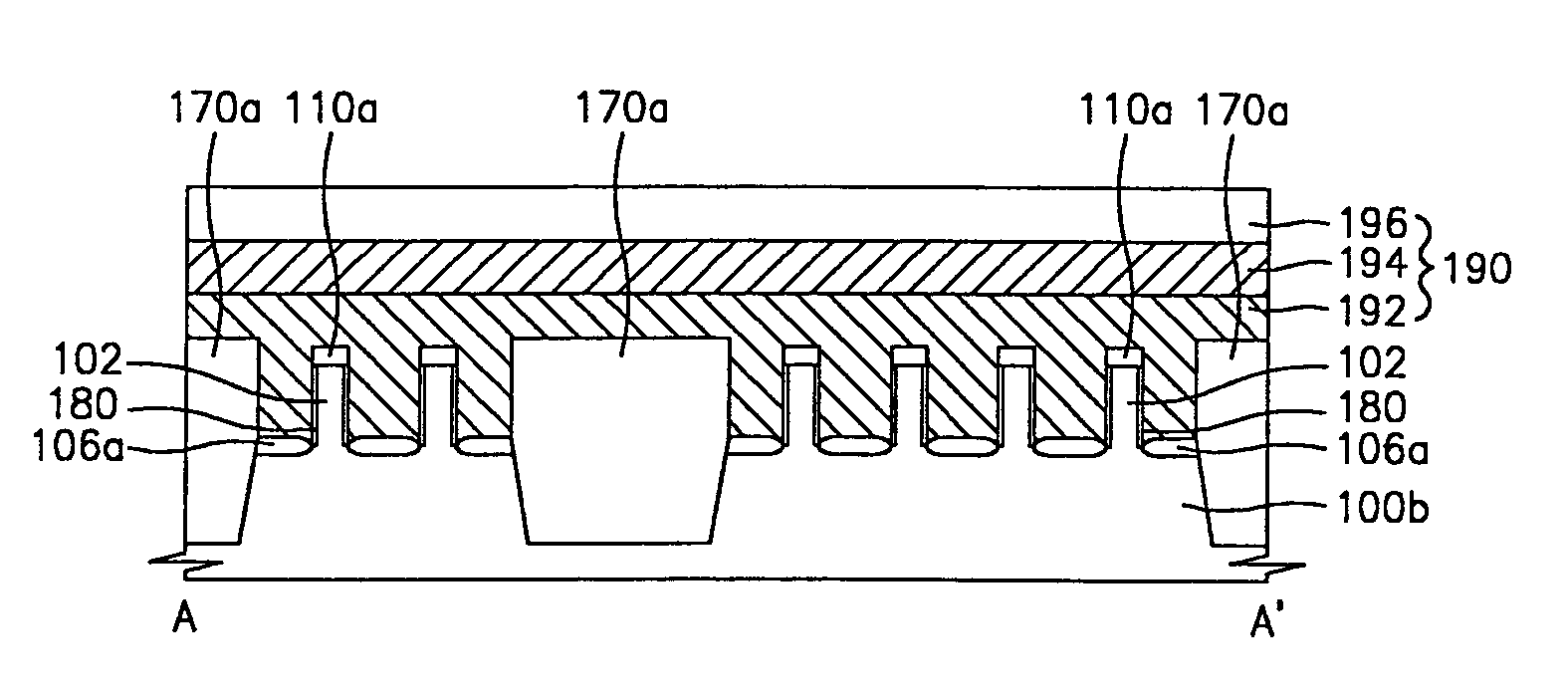

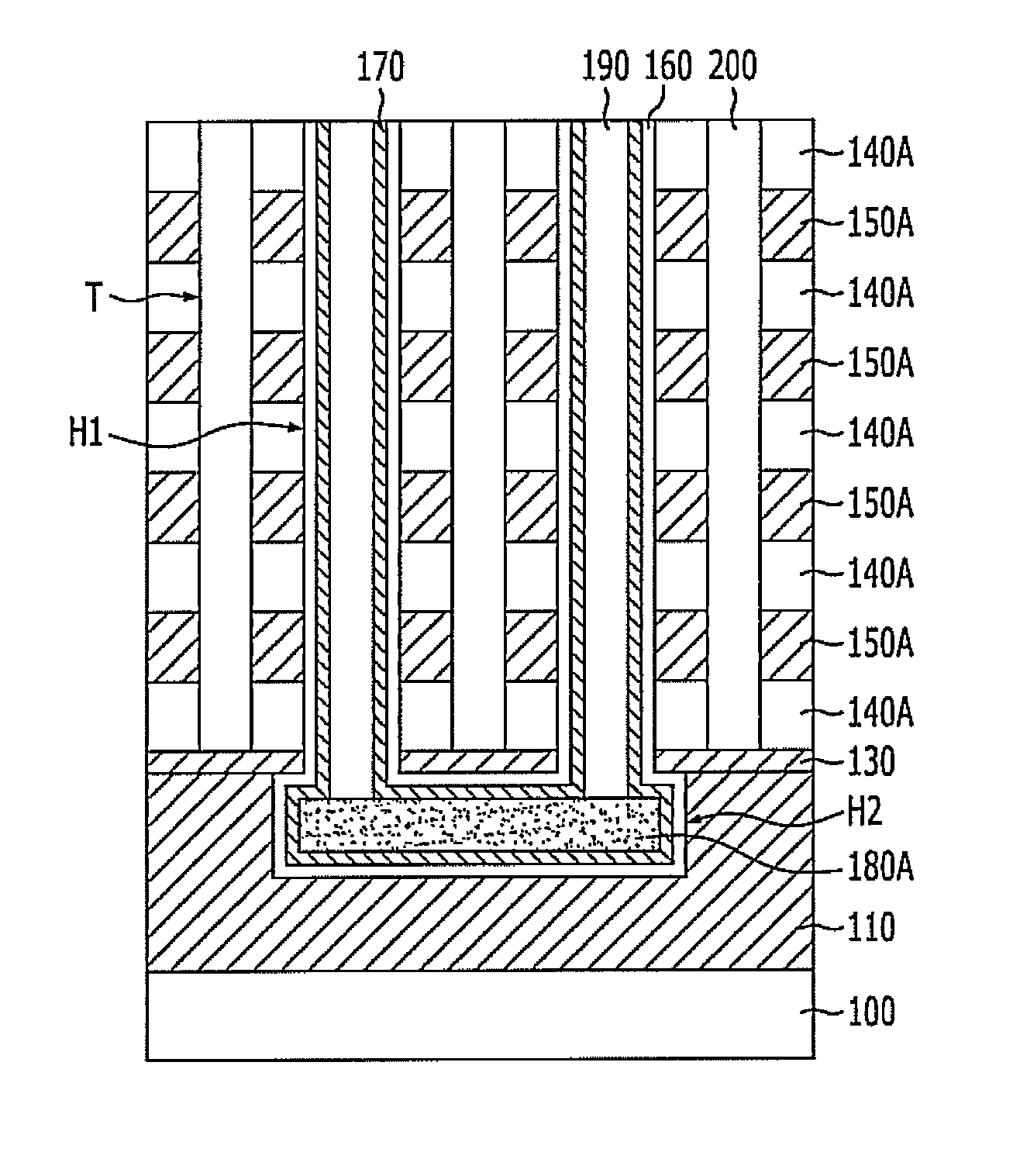

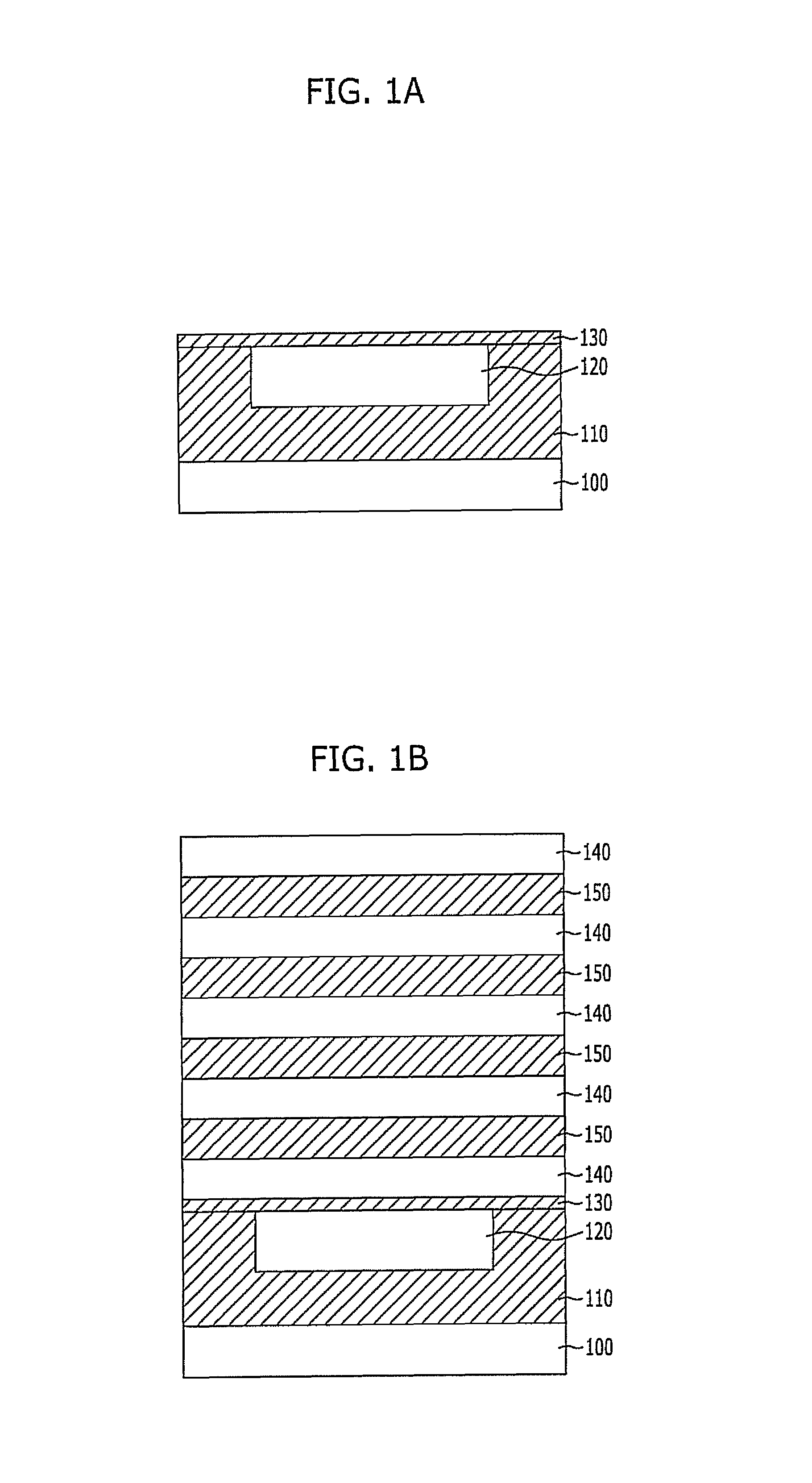

Nonvolatile memory device and method for fabricating the same

ActiveUS8507976B2Reduce channel resistanceStable currentSolid-state devicesRead-only memoriesMain channelDielectric layer

A nonvolatile memory device includes a gate structure in which a plurality of interlayer dielectric layers and a plurality of gate electrodes are alternately stacked; a pass gate electrode lying under the gate structure; a sub channel hole defined in the pass gate electrode; a pair of main channel holes defined through the gate structure and communicating with the sub channel hole; a channel layer formed on inner walls of the pair of main channel holes and the sub channel hole; and a metallic substance layer contacting the channel layer in the sub channel hole.

Owner:SK HYNIX INC

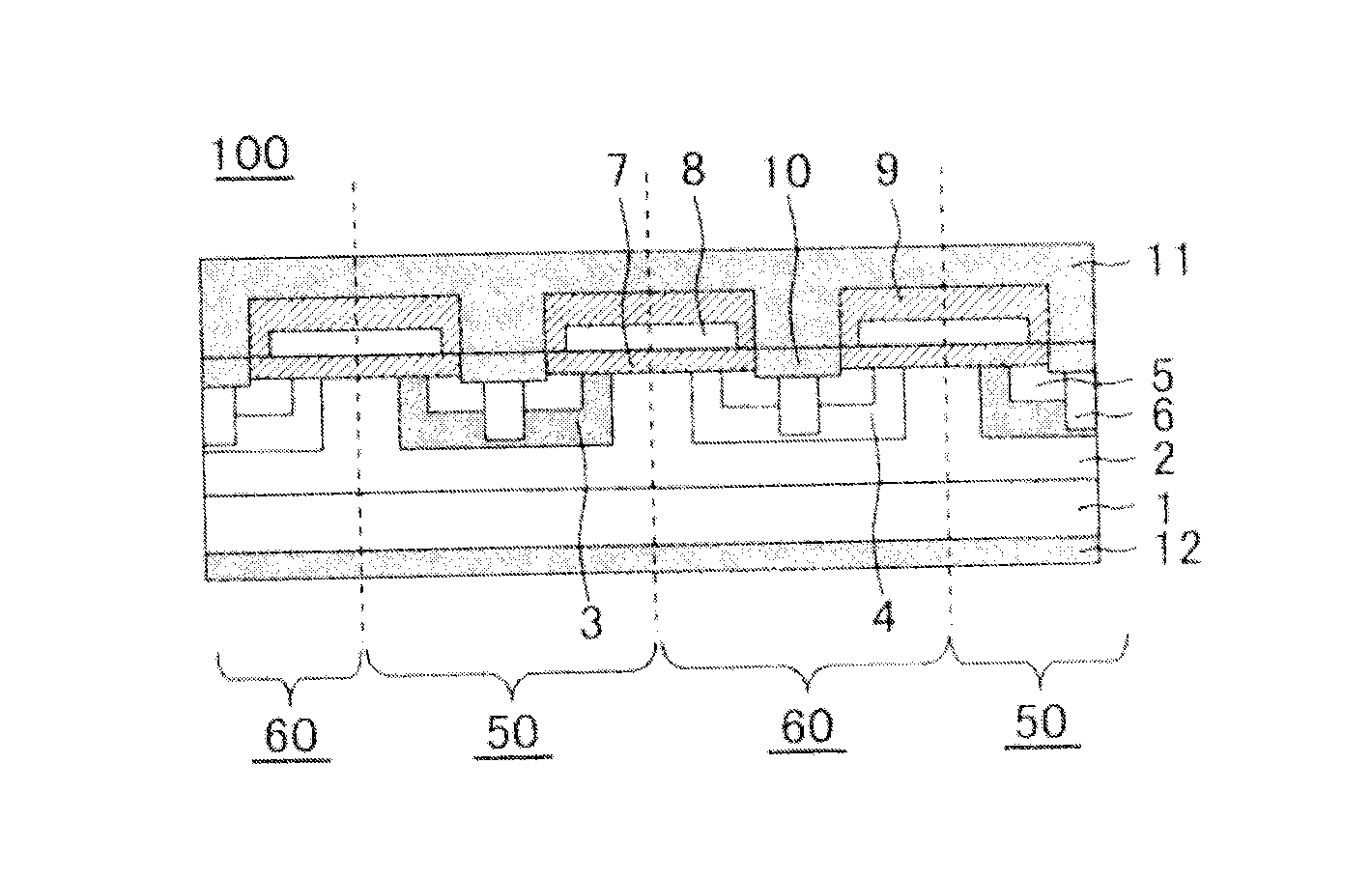

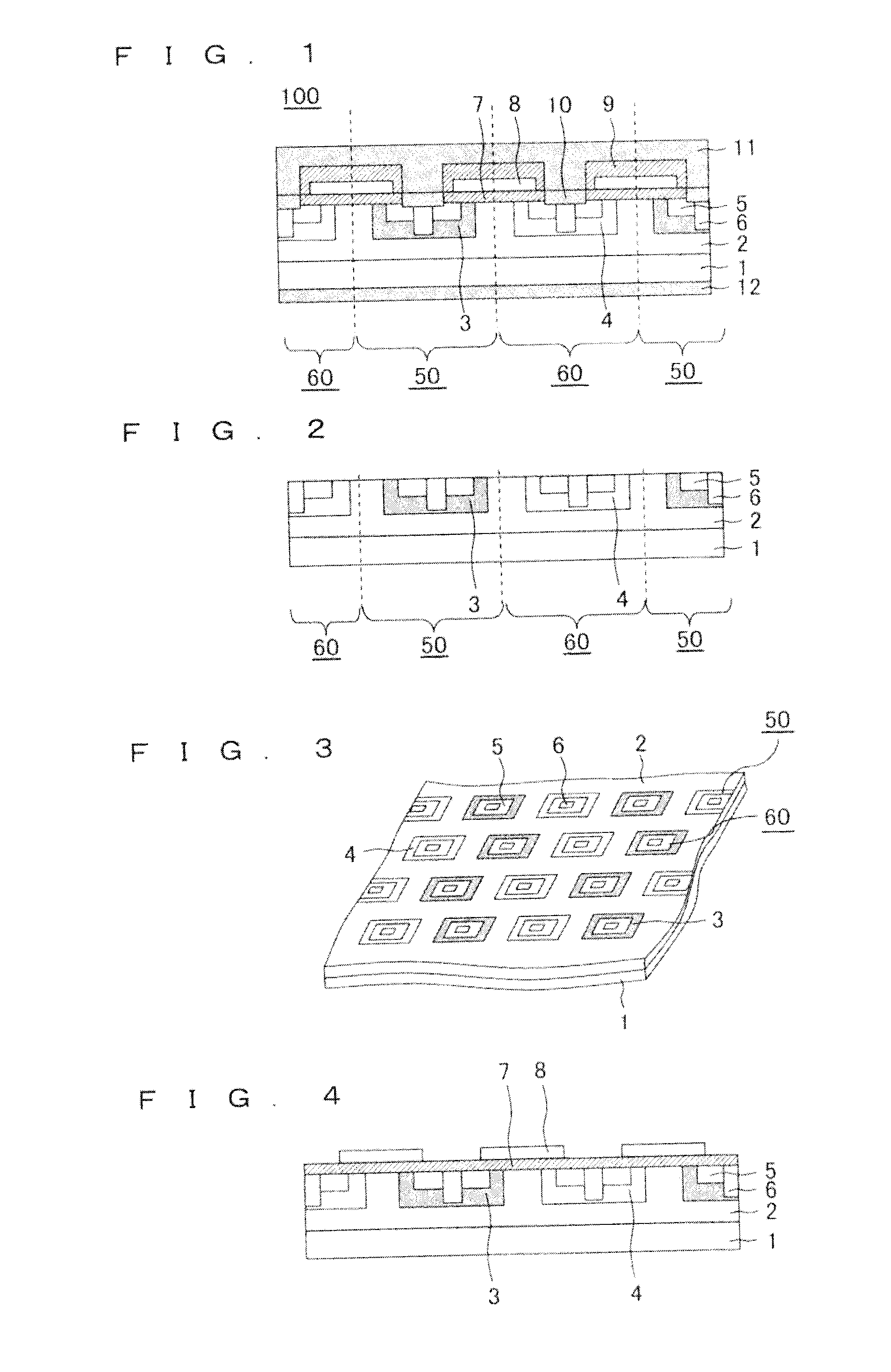

Semiconductor device and manufacturing method thereof

InactiveUS20130181271A1Interfere with their operationReduce channel resistanceTransistorSolid-state devicesImpurity diffusionDevice material

A semiconductor device capable of increasing ON current while reducing channel resistance and allowing transistors to operate independently and stably, having a fin formed to protrude from the bottom of a gate electrode trench, a gate insulating film covering the surfaces of the gate electrode trench and the fin, a gate electrode embedded in a lower part of the gate electrode trench and formed to stride over the fin via the gate insulating film, a first impurity diffusion region arranged on a first side face, and a second impurity diffusion region arranged on a second side face.

Owner:LONGITUDE LICENSING LTD

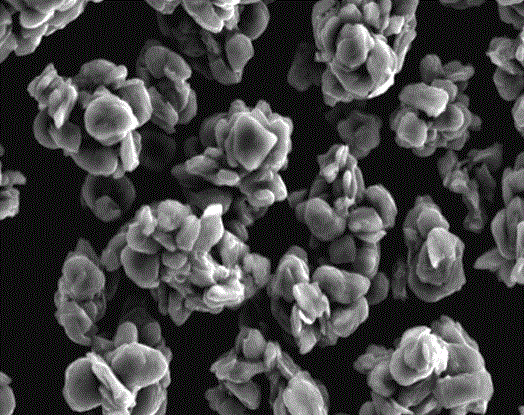

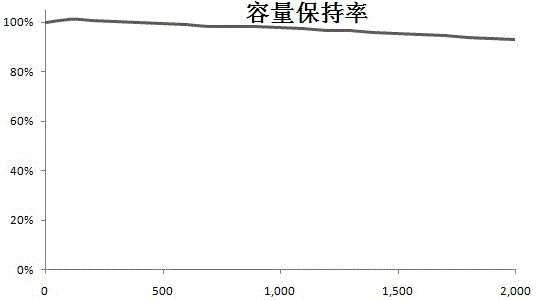

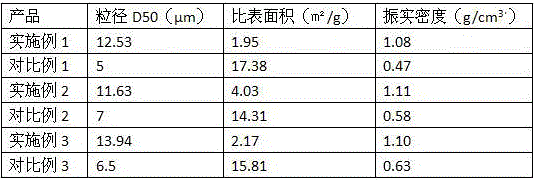

Preparation method for artificial graphite negative electrode material for lithium ion battery

InactiveCN105958070ALow tap densityHigh tap densityCell electrodesSecondary cellsEnvironmental resistanceLithium-ion battery

Disclosed is a preparation method for an artificial graphite negative electrode material for a lithium ion battery. Artificial graphite coke powder with small grain diameter and an organic carbon source are taken as the raw materials; the raw materials are subjected to procedures of mixing, high-temperature treatment, graphitization treatment, sieving and the like; the coke powder and the organic carbon source are mixed in a heating environment, and the effects of coating, mixing and holding, secondary pelleting and the like can be achieved; the small-particle coke powder can form secondary particles under the cohesive action of the organic carbon source; therefore, the problem of anisotropy of the material is solved, and the tap density of the material is improved; meanwhile, the artificial graphite negative electrode material is capable of lowering the material turnover and equipment residual loss, high in yield, simple in procedures, low in energy consumption, environment-friendly, uniform in the coating effect on the surface of the material, and high in consistency; and in addition, the prepared negative electrode material has the characteristics of isotropy, low iron impurity content, low initial irreversible capacity, small volume expansion, high absorbency, high circulation performance, high performance cost ratio, excellent comprehensive performance and the like.

Owner:田东

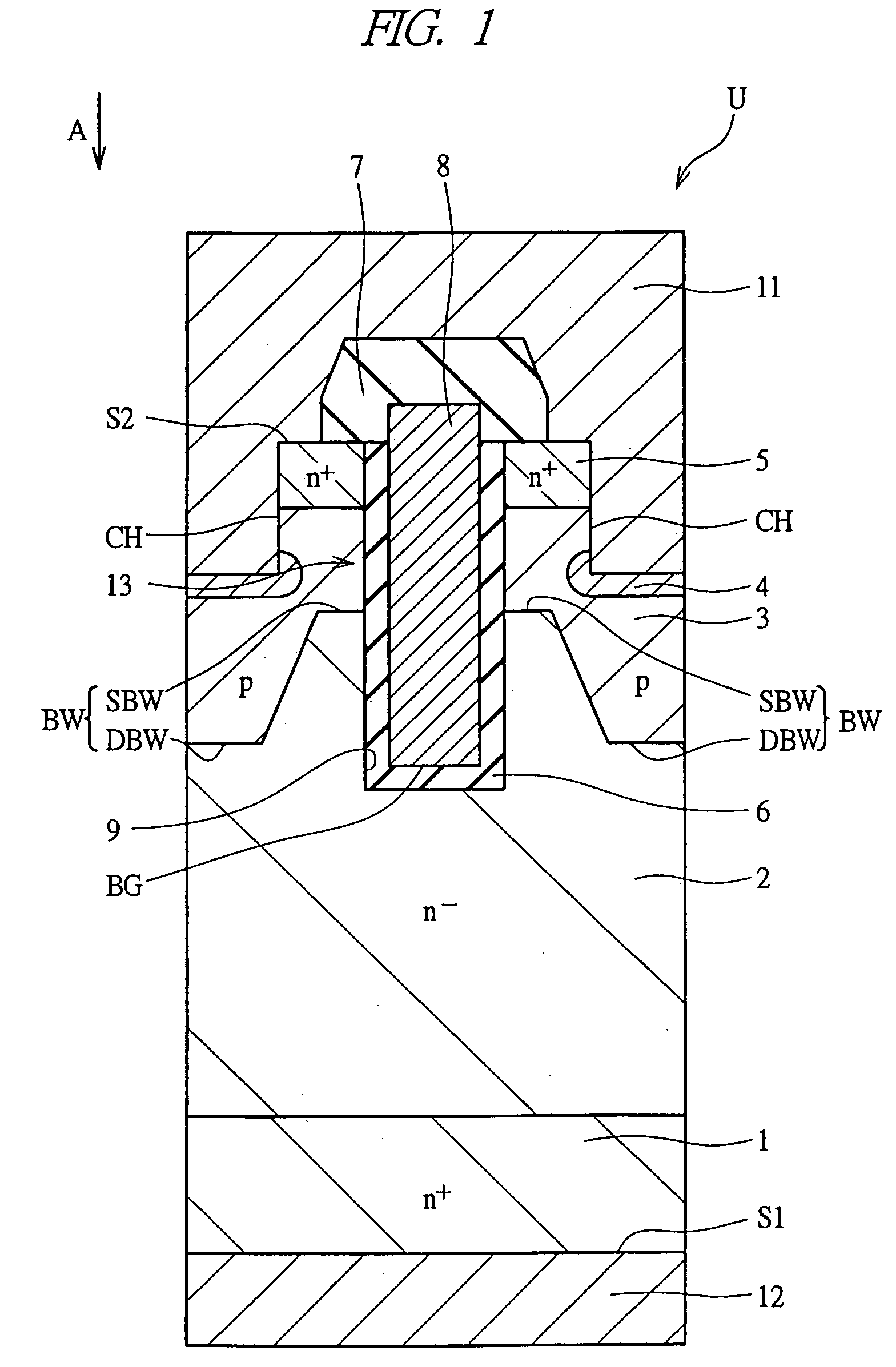

Semiconductor device and manufacturing method thereof and power supply apparatus using the same

InactiveUS20080217684A1Improve performanceReduce channel resistanceTransistorSemiconductor/solid-state device manufacturingEngineeringField-effect transistor

A semiconductor device comprises a trench-gate type field-effect transistor on a semiconductor substrate having a first main surface and a second main surface oppositely positioned in a thickness direction, wherein the trench-gate type field-effect transistor comprises a first semiconductor region at the first main surface side; a second semiconductor region at the second main surface; a semiconductor well region between the first semiconductor region and the second semiconductor region; a trench formed so as to protrude in a first direction intersecting the second main surface; a gate electrode formed on an inner surface of the trench via a gate insulating film, and a bottom of the gate electrode is in the first semiconductor region, and a well bottom has a well deep portion and a well shallow portion, and the well deep portion is in a region more distant from the gate insulating film compared to the well shallow portion.

Owner:RENESAS ELECTRONICS CORP

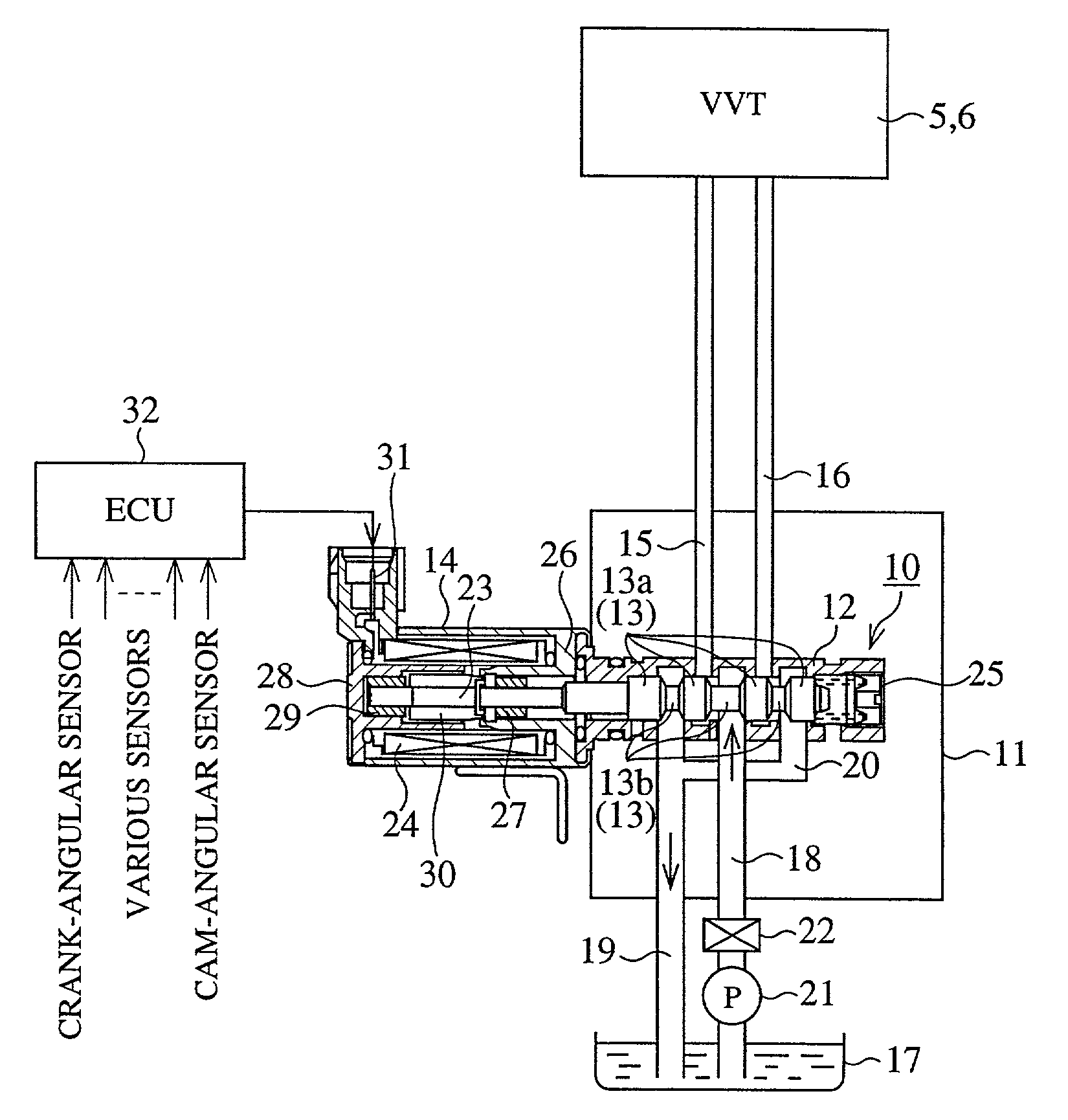

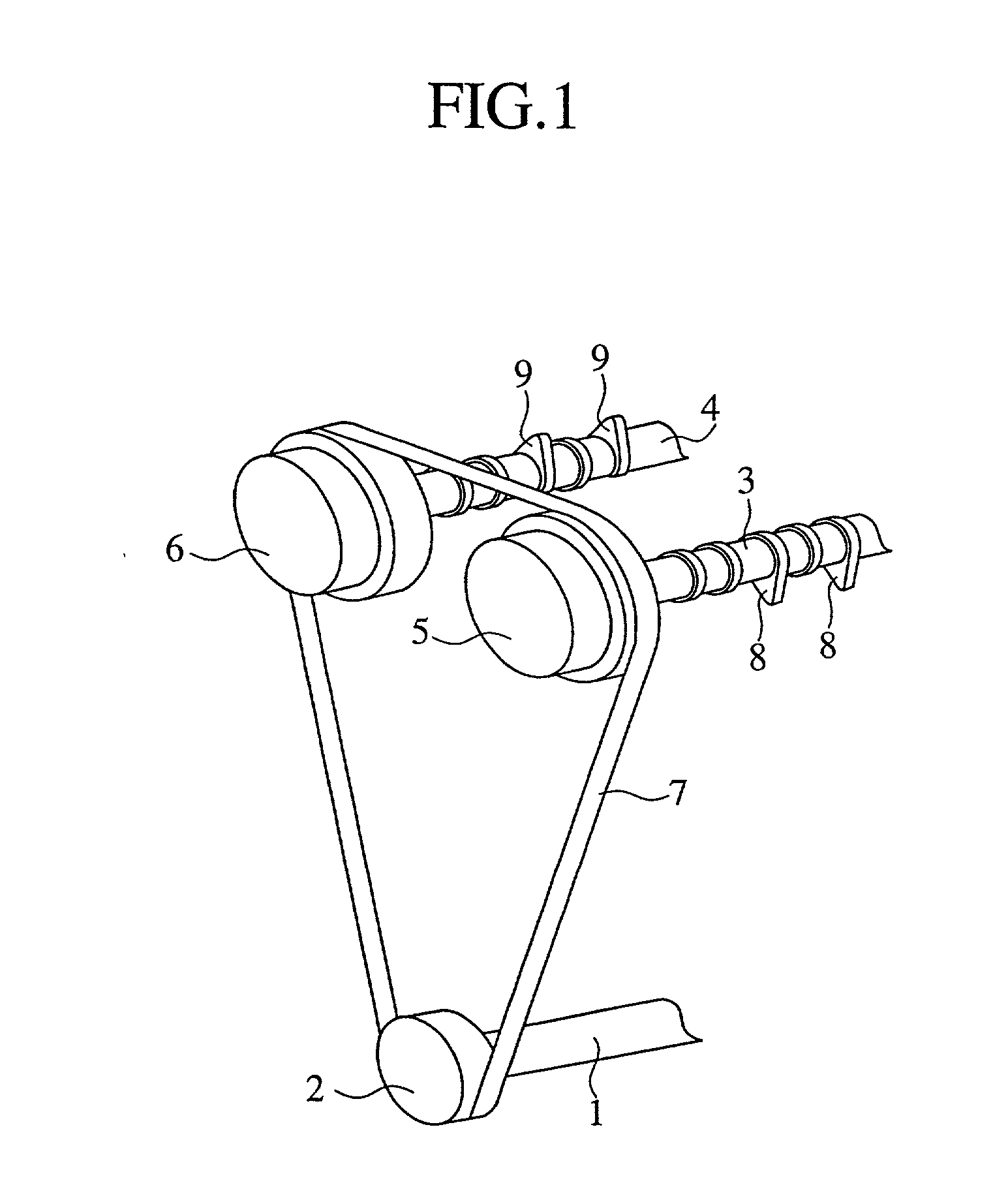

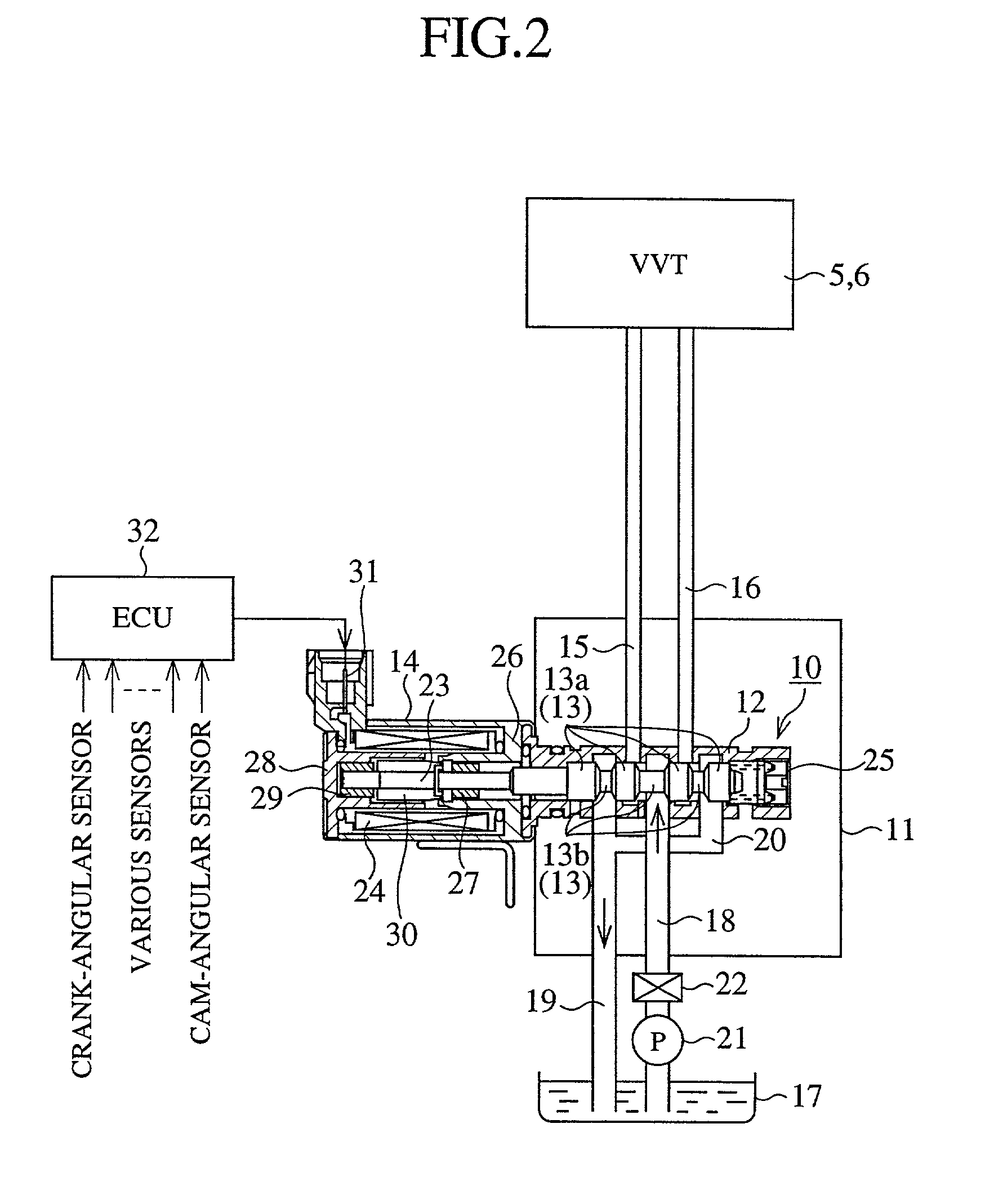

Valve timing control device

InactiveUS20020121253A1Reliable controlEasy to processValve arrangementsMachines/enginesMechanical engineeringHydraulic pressure

A valve timing control device includes a lock member and a push member. The lock member locks a rotor in relation to a case at an approximately intermediate position apart from both of the maximum advanced side position and the maximum retarded side position. At all times, the push member pushes the lock member in a direction-of fitting the lock member in the fitting hole arranged at any one hand of the rotor or the case. A release hydraulic pressure for releasing the fitting state of the lock member in the fitting hole against the push force of the push member is set to be higher than a lock hydraulic pressure for allowing the fitting state of the lock member in the fitting hole.

Owner:MITSUBISHI ELECTRIC CORP

Heat sink with heat pipes and method for manufacturing the same

ActiveUS7621316B2Reduce weightIncrease volumeSemiconductor/solid-state device detailsSolid-state devicesEngineeringHeat pipe

Owner:FURUKAWA ELECTRIC CO LTD

Method for manufacturing semiconductor device having super junction construction

InactiveUS20060138407A1Prevent floatingReduce resistanceSolid-state devicesSemiconductor/solid-state device manufacturingInsulation layerDevice material

A semiconductor device includes a body region, a drift region having a first part and a second part, and a trench gate electrode. The body region is disposed on the drift region. The first and second parts extend in an extending direction so that the second part is adjacent to the first part. The trench gate electrode penetrates the body region and reaches the drift region so that the trench gate electrode faces the body region and the drift region through an insulation layer. The trench gate electrode extends in a direction crossing with the extending direction of the first and second parts. The first part includes a portion near the trench gate electrode, which has an impurity concentration equal to or lower than that of the body region.

Owner:DENSO CORP

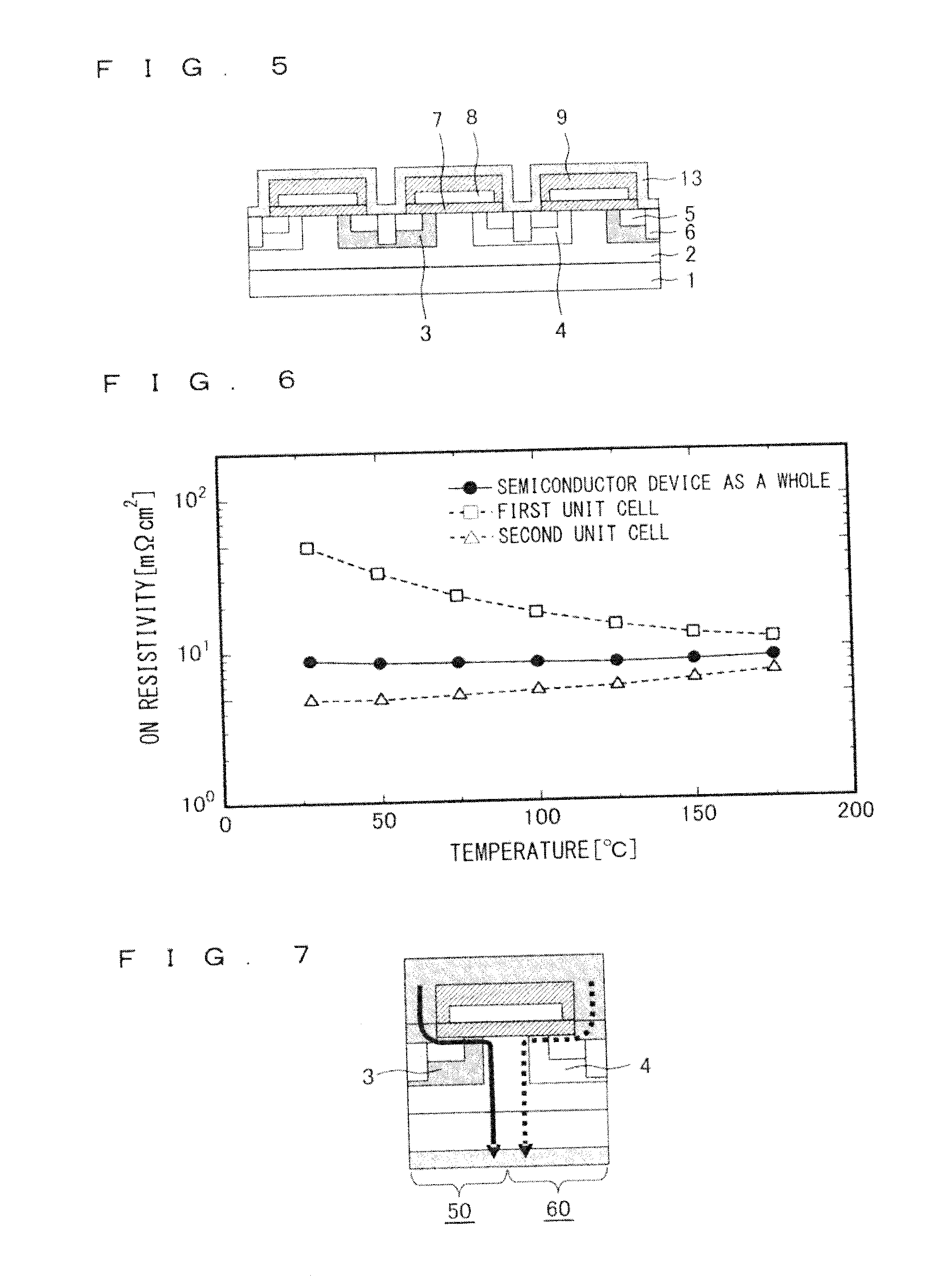

Semiconductor device

ActiveUS20150380494A1Reduce changeIncrease in temperatureSemiconductor/solid-state device manufacturingSemiconductor devicesPhysicsIncrease temperature

A semiconductor device capable of reducing ON-resistance changes with temperature, including a semiconductor substrate of a first conductivity type, a drift layer of the first conductivity type formed on the semiconductor substrate, a first well region of a second conductivity type formed in the front surface of the drift layer, a second well region of the second conductivity type formed in the front surface of the drift layer, and a gate structure that is formed on the front surface of the drift layer and forms a channel in the first well region and a channel in the second well region. A channel resistance of the channel formed in the first well region has a temperature characteristic that the channel resistance decreases with increasing temperature and a channel resistance of the channel formed in the second well region has a temperature characteristic that the channel resistance increases with increasing temperature.

Owner:MITSUBISHI ELECTRIC CORP

Features

- R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

Why Patsnap Eureka

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Social media

Patsnap Eureka Blog

Learn More Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com