Necked Finfet device

a technology of finfet and finfet, which is applied in the direction of semiconductor devices, electrical equipment, transistors, etc., can solve problems affecting device performance, and achieve the effects of reducing finfet channel resistance, preventing silicide formation, and improving device performan

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Benefits of technology

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

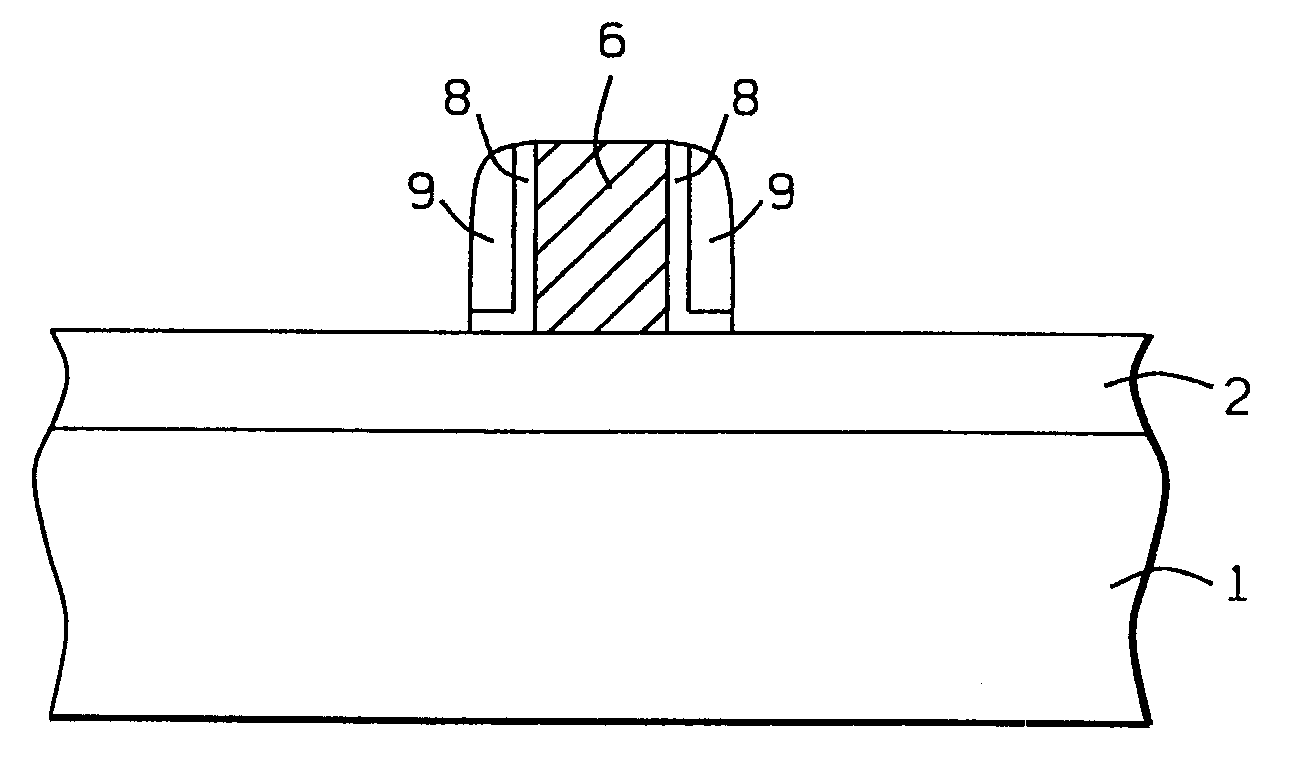

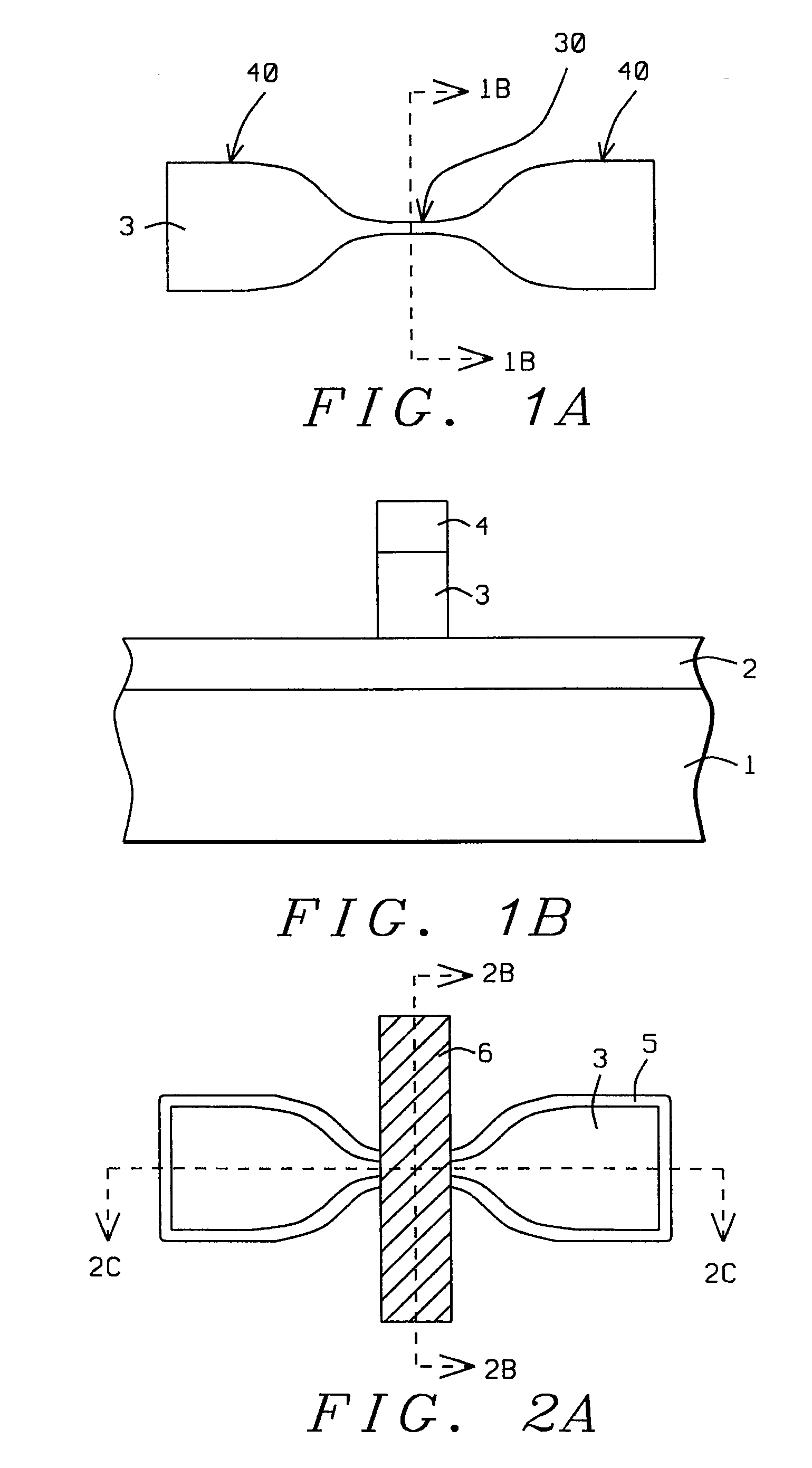

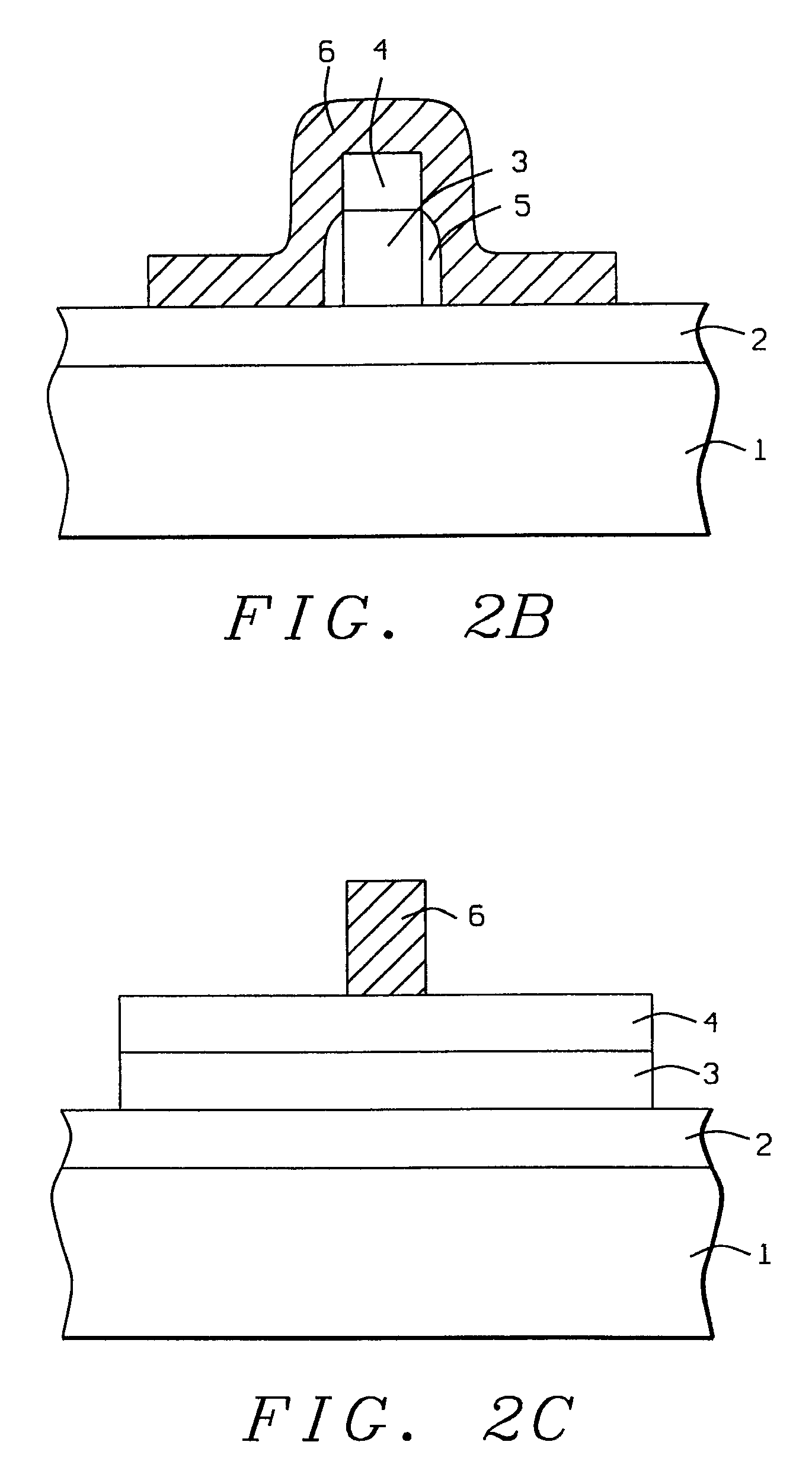

[0014] The method of fabricating a double gate FINFET device structure, defined in an SOI layer, wherein features such as a necked channel region and a wrap up insulator spacer are employed to reduce channel resistance and to prevent silicide formation on the sides of the FINFET device structure, will now be described in detail. Semiconductor substrate 1, comprised of single crystalline silicon with a crystallographic orientation, is used and schematically shown in cross-sectional style in FIG. 1B. Silicon layer 3, the silicon component of SOI layer 3, is formed via oxygen implantation into a portion of semiconductor substrate 1, followed by an anneal procedure which results in the formation of insulator layer 2, underlying an non-implanted, and non-oxidized silicon layer 3. Insulator layer 2, is comprised of silicon dioxide at a thickness between about 100 to 2000 Angstroms, while silicon layer 3, the top portion of semiconductor substrate 1, overlying insulator layer 2, is formed...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More