Patents

Literature

67results about How to "Reduce reverse recovery charge" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

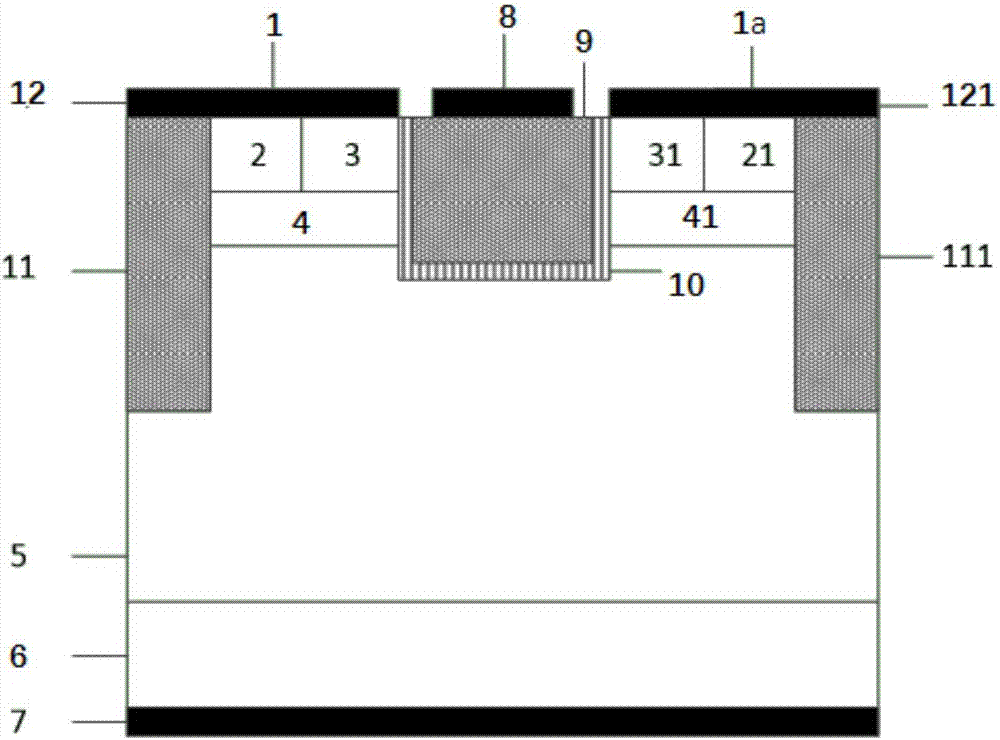

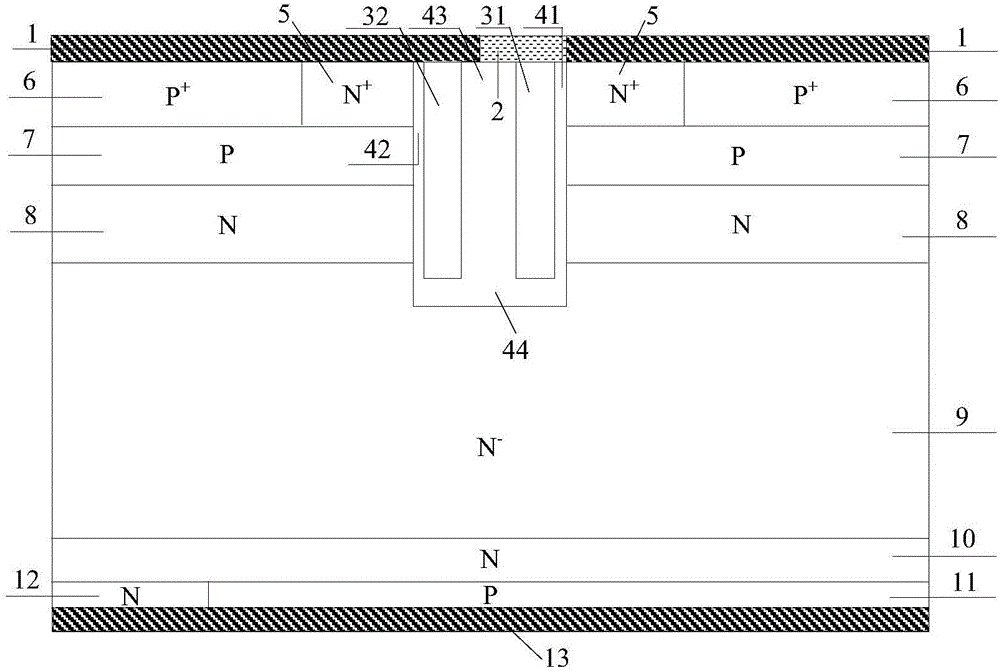

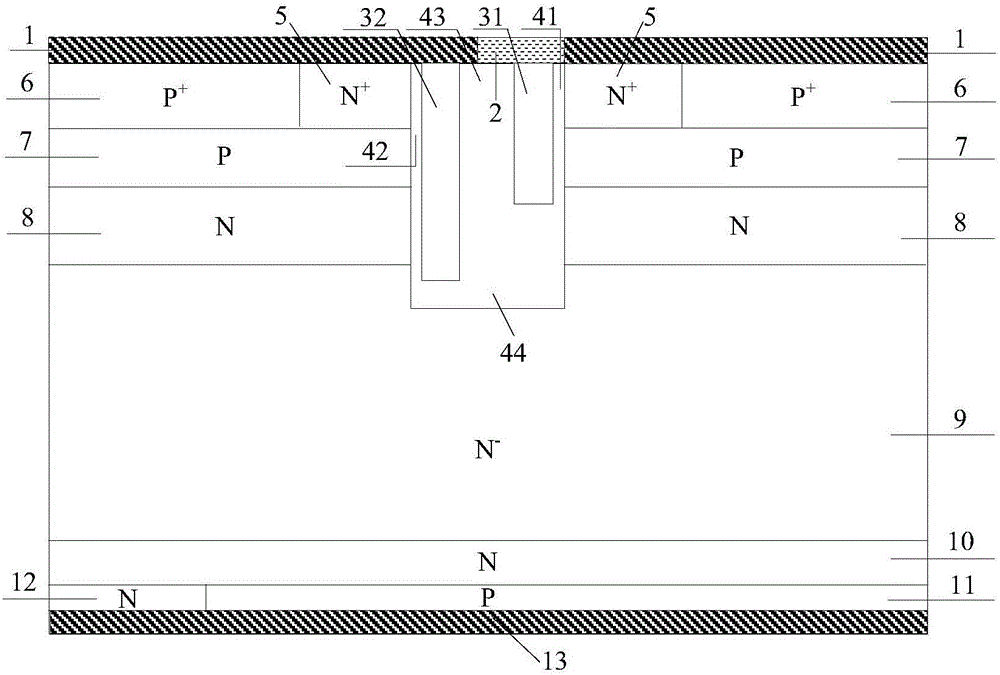

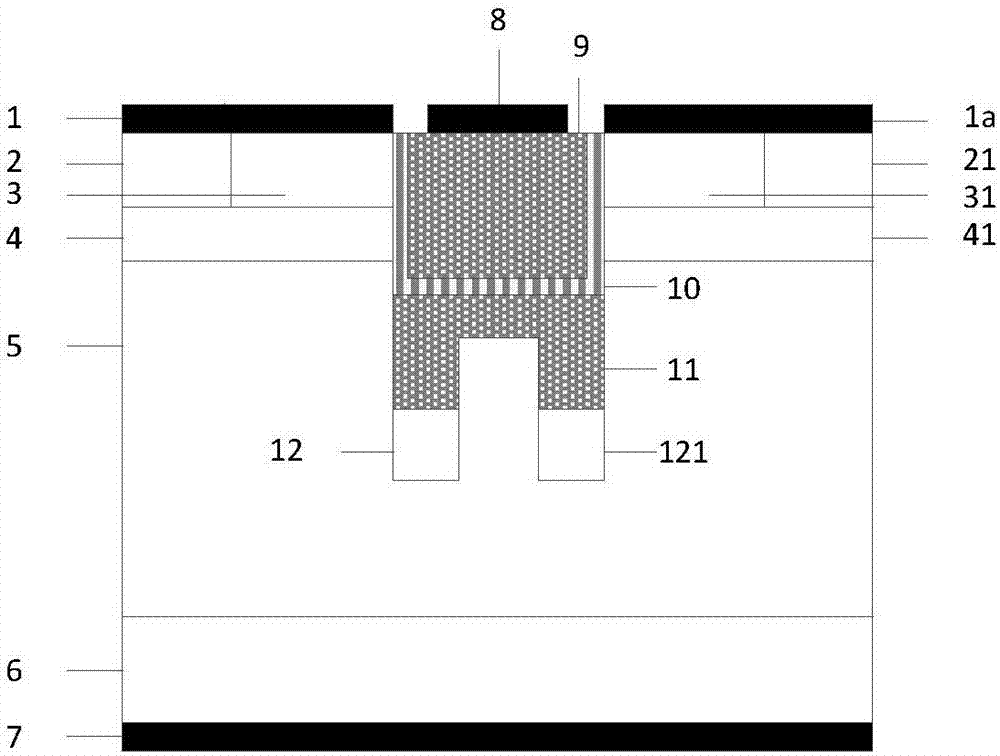

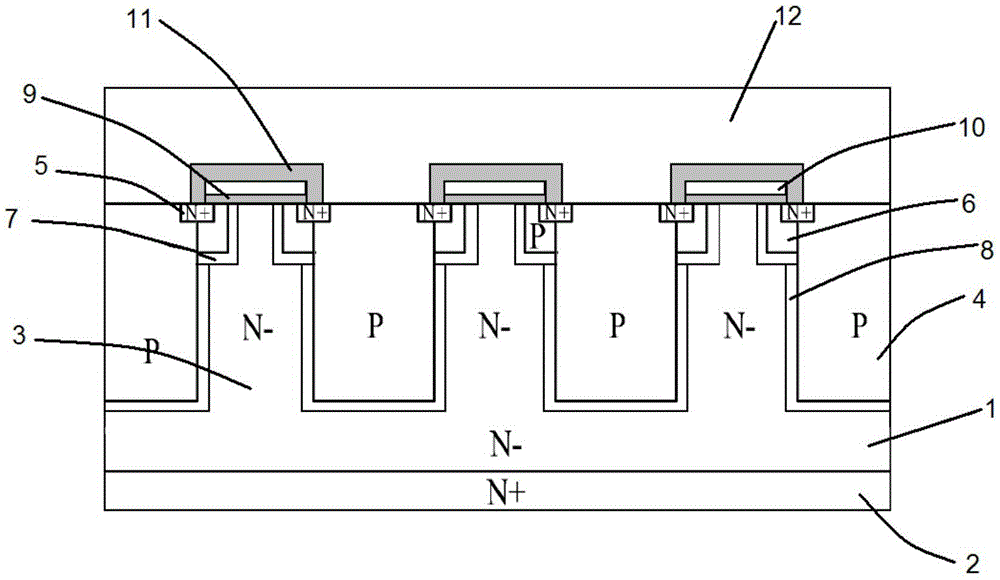

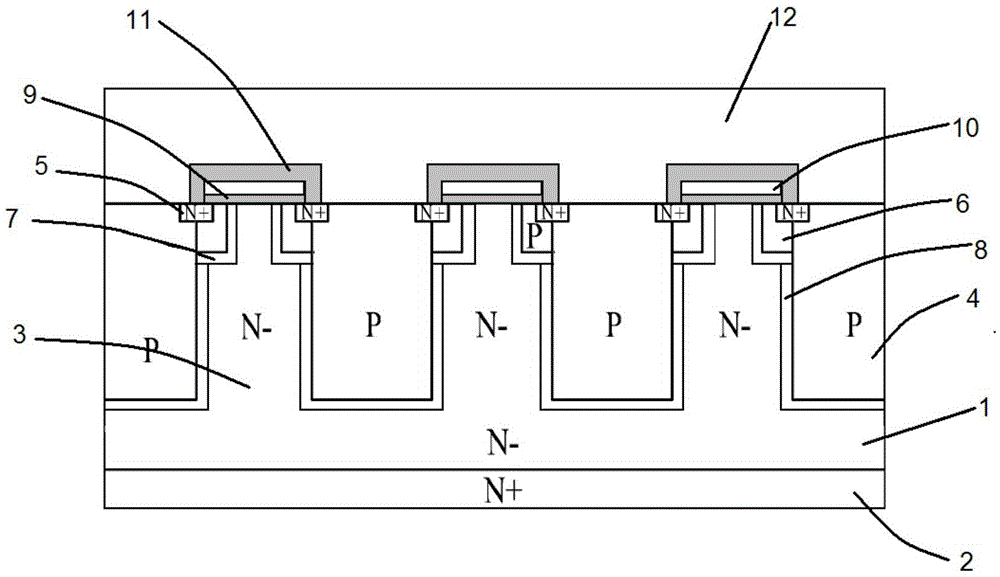

Rapid superjunction longitudinal double-diffusion metal oxide semiconductor transistor

InactiveCN101969073AExpand quicklyImprove pressure resistanceSemiconductor devicesDouble diffusionEngineering

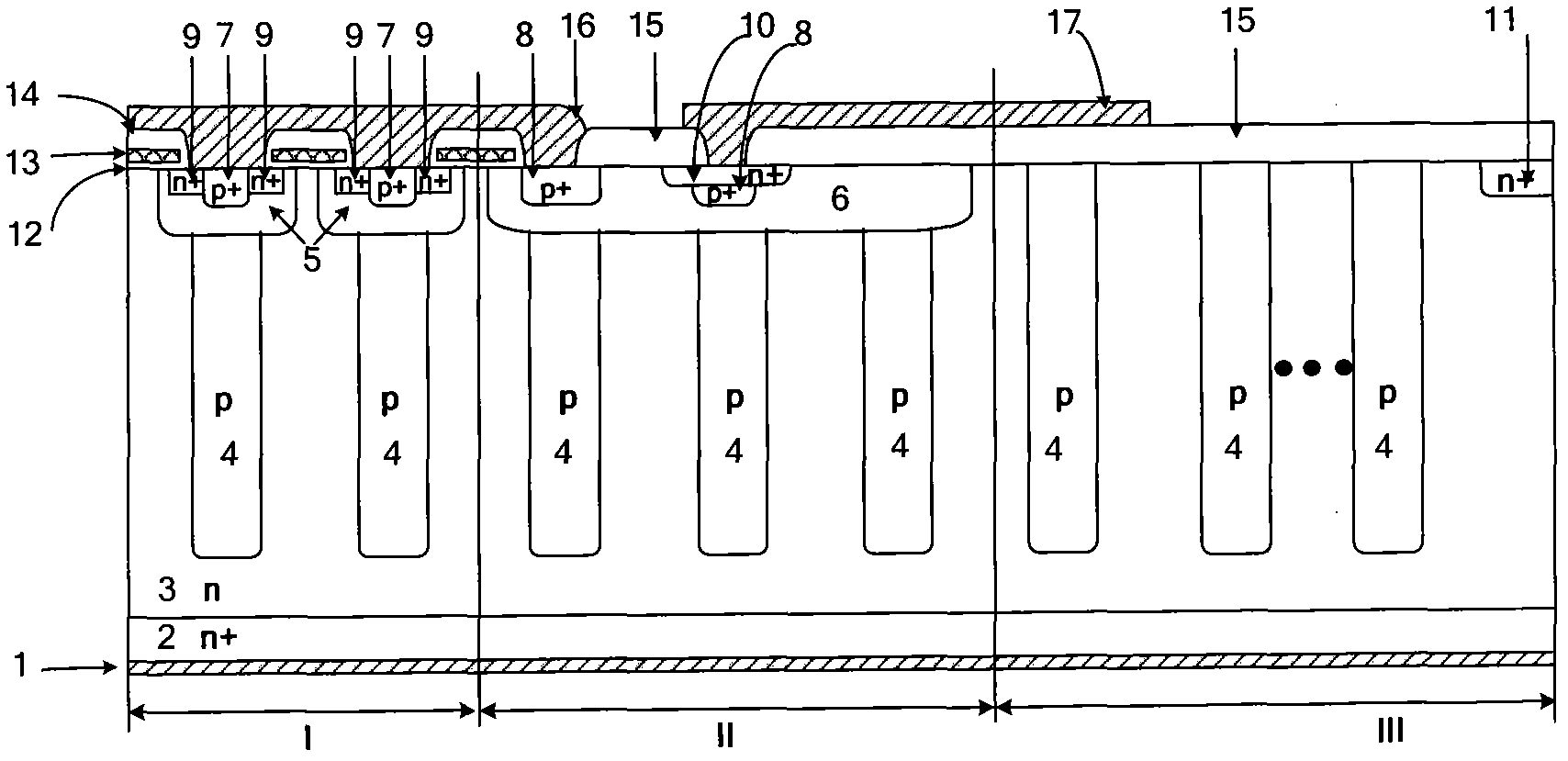

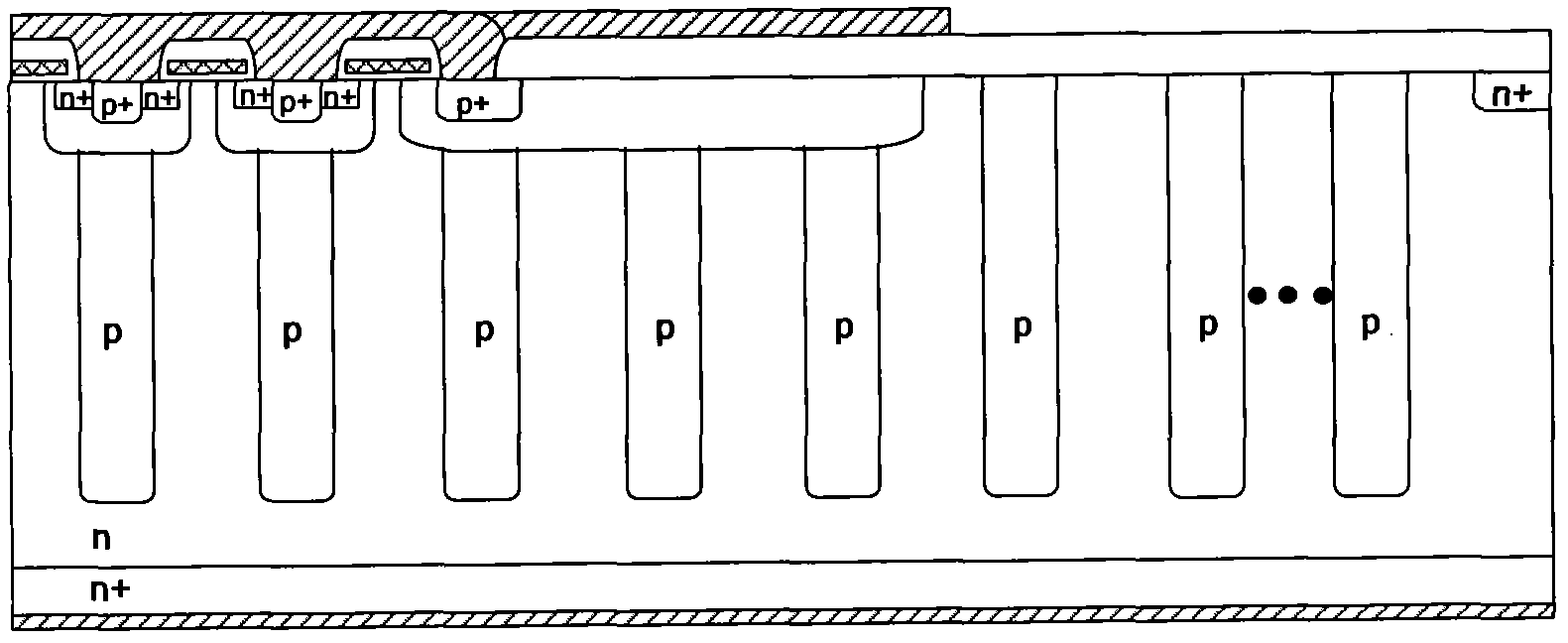

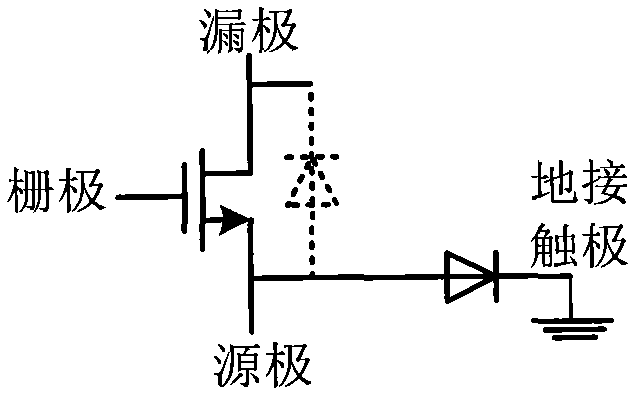

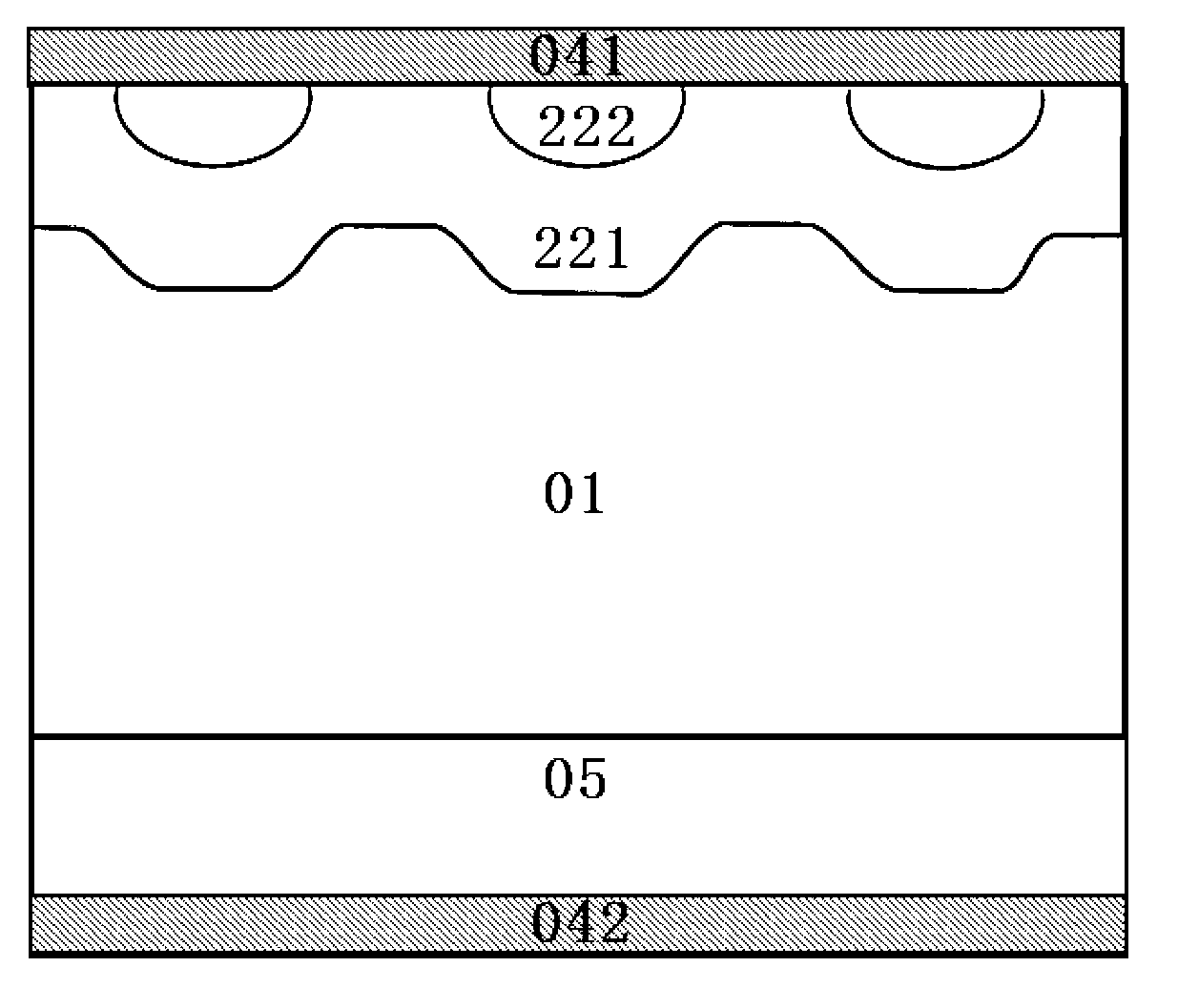

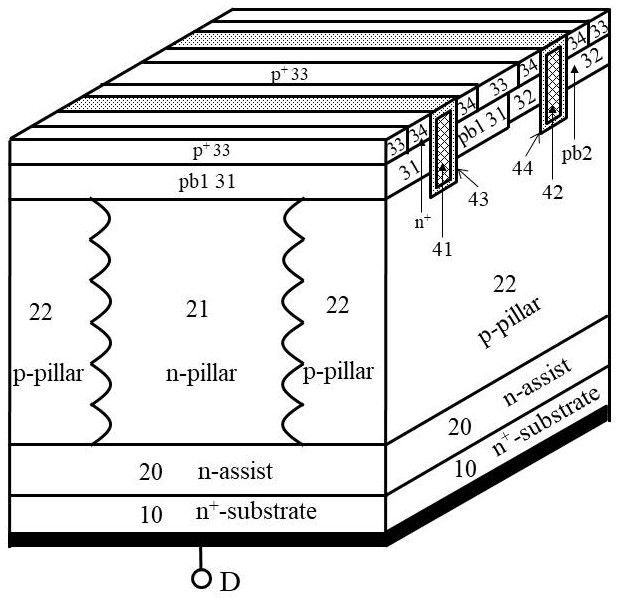

The invention relates to a rapid superjunction longitudinal double-diffusion metal oxide semiconductor transistor which comprises a cell area, a terminal area and a transition area, wherein the terminal area is arranged at the outermost periphery of a chip; the transition area is positioned between the cell area and the terminal area; the bottoms of the cell area, the transition area and the terminal area (III) are provided with drain electrode metal; a heavy doping n-type silicon substrate is arranged on the drain electrode metal and used as a drain area of the chip; an n-type doping epitaxial layer is arranged on the heavy doping n-type silicon substrate; and a discontinuous p-type doping columnar semiconductor area is arranged in the n-type doping epitaxial layer. The rapid superjunction longitudinal double-diffusion metal oxide semiconductor transistor is characterized in that an n-type heavy doping semiconductor area is arranged in a second p-type doping semiconductor area in the transition area, and the surface of the n-type heavy doping semiconductor area is provided with a contact hole which is connected with a metal layer to form a ground contact electrode of the chip. The invention can effectively reduce the reverse recovery charge of a device and improve the reverse recovery characteristics under the conditions of not increasing the process cost or changing the main parameter of the device.

Owner:SOUTHEAST UNIV

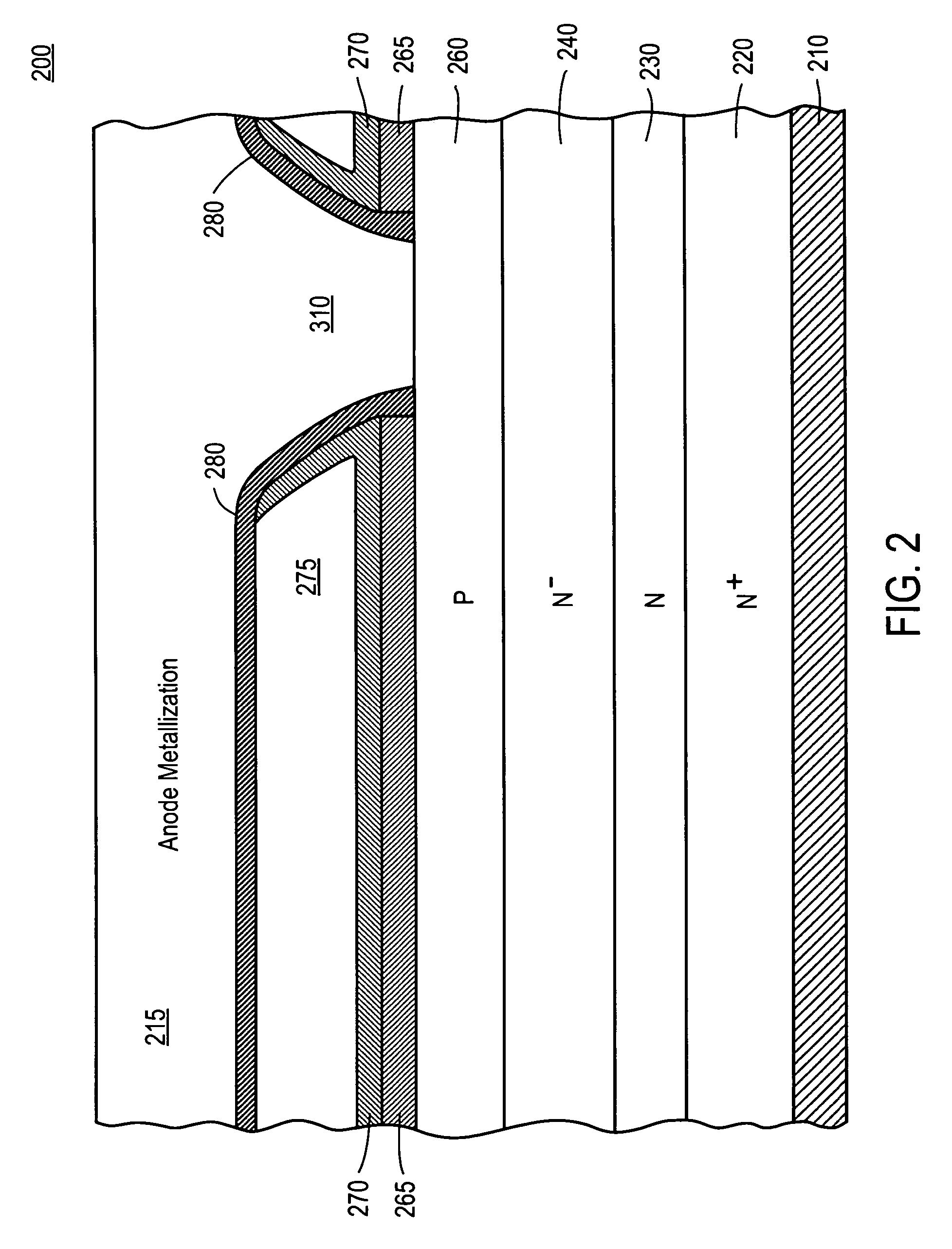

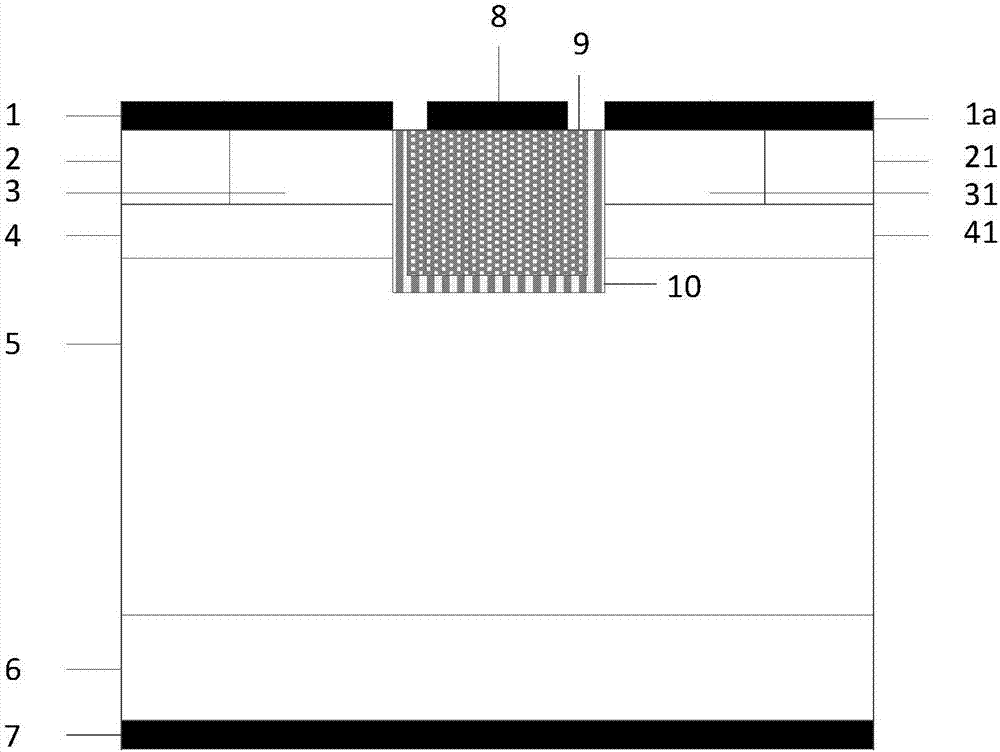

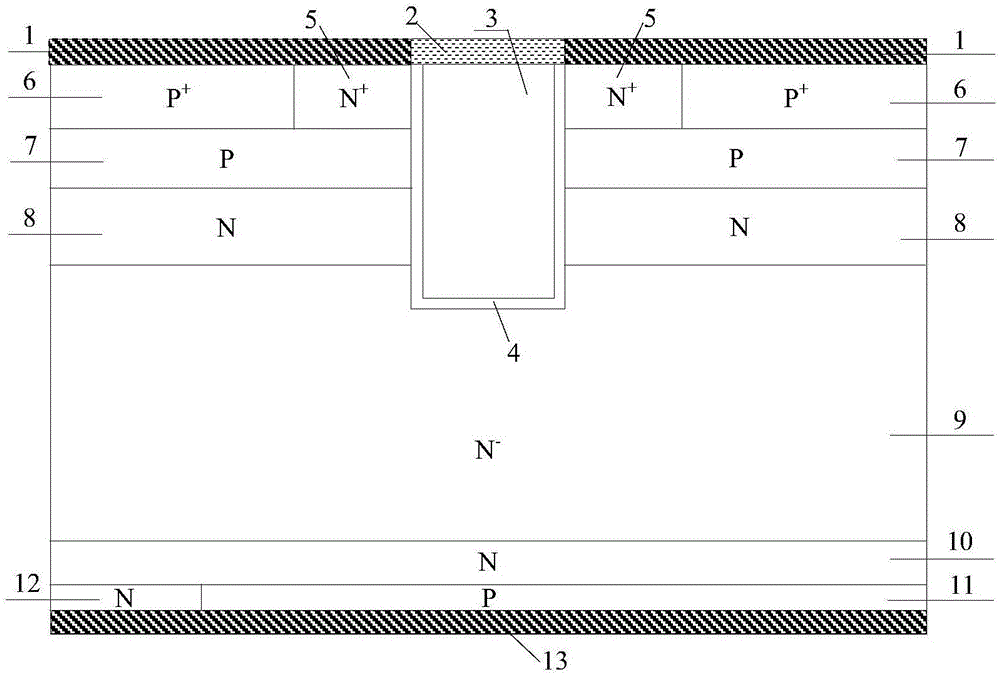

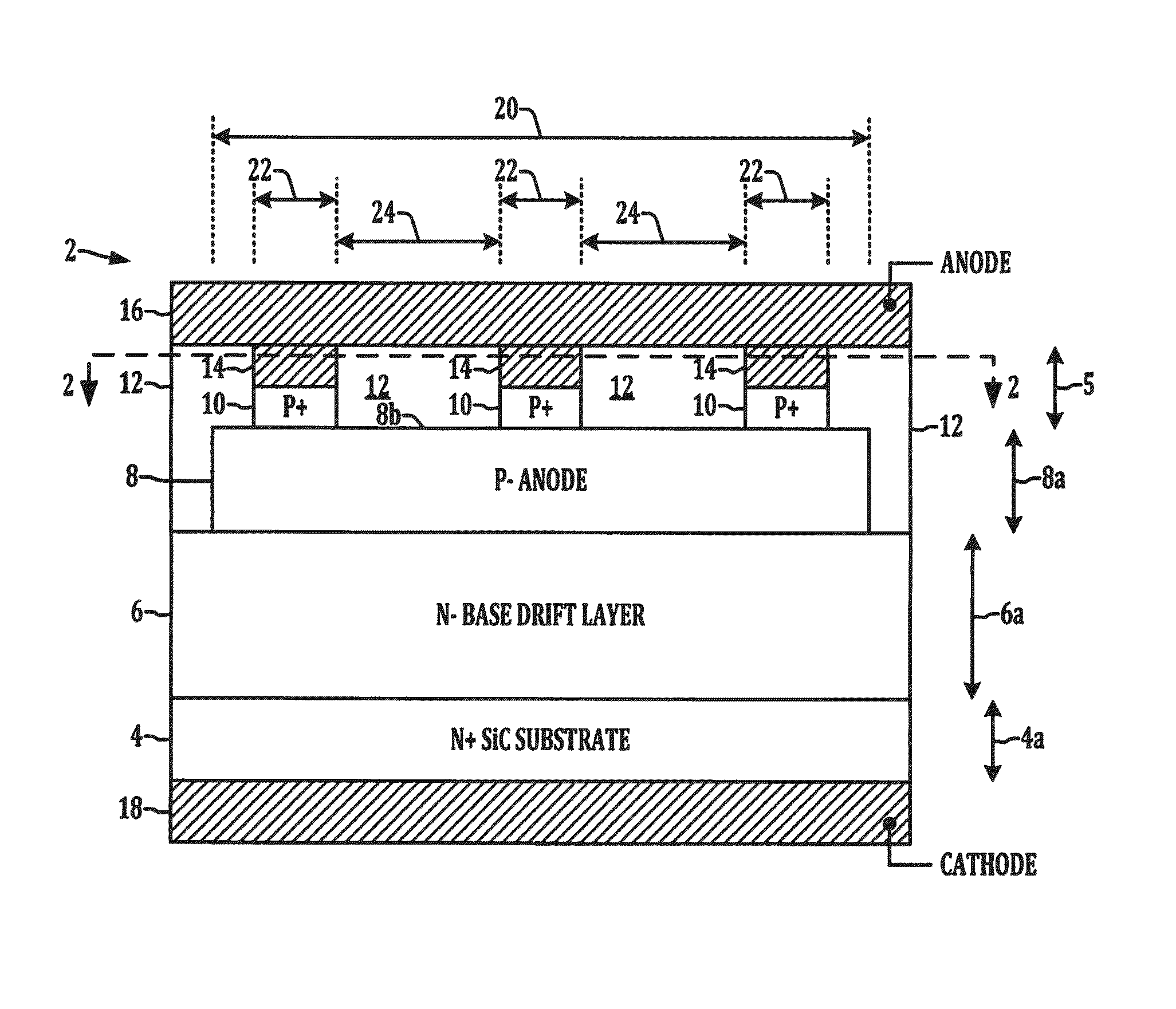

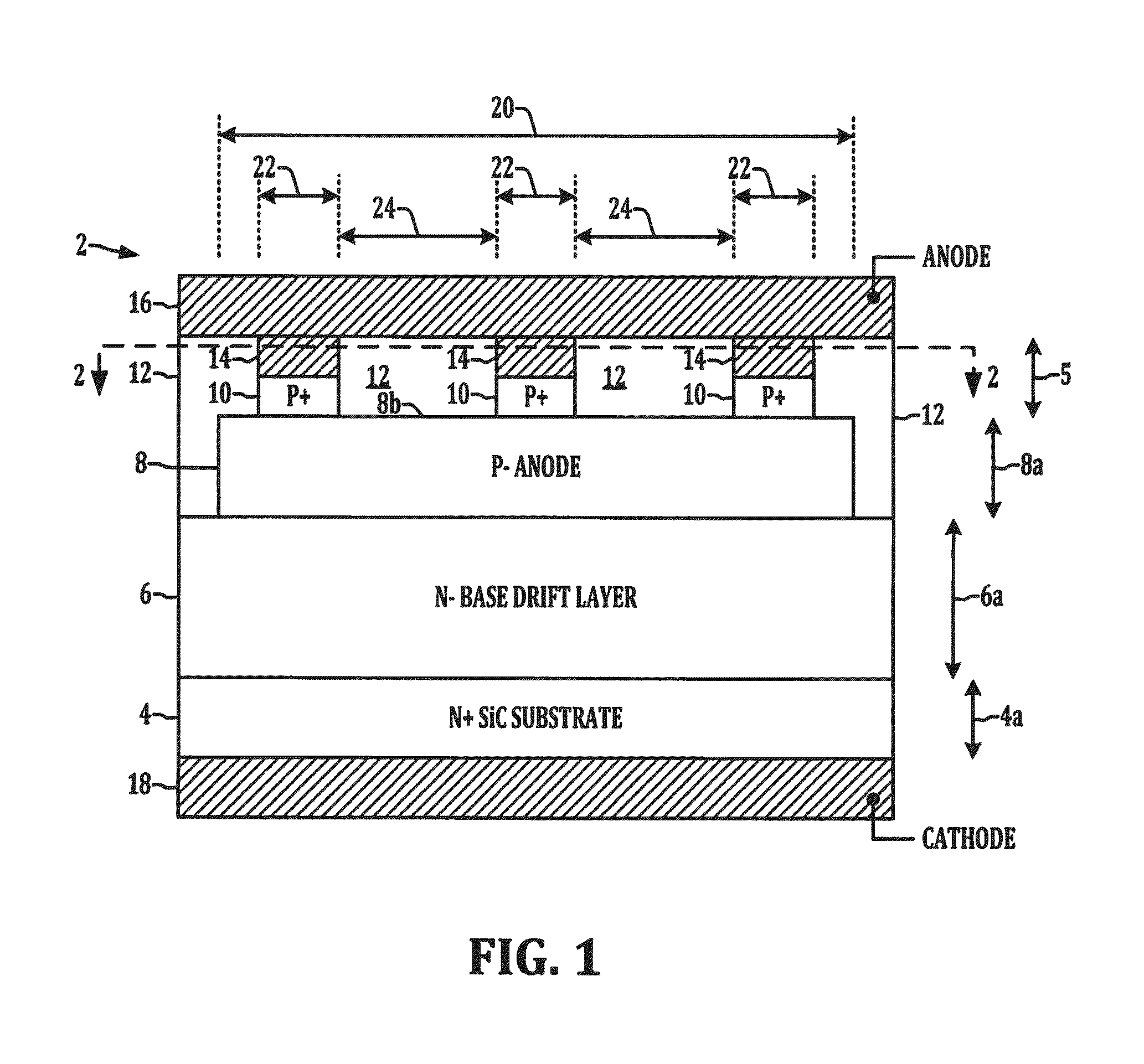

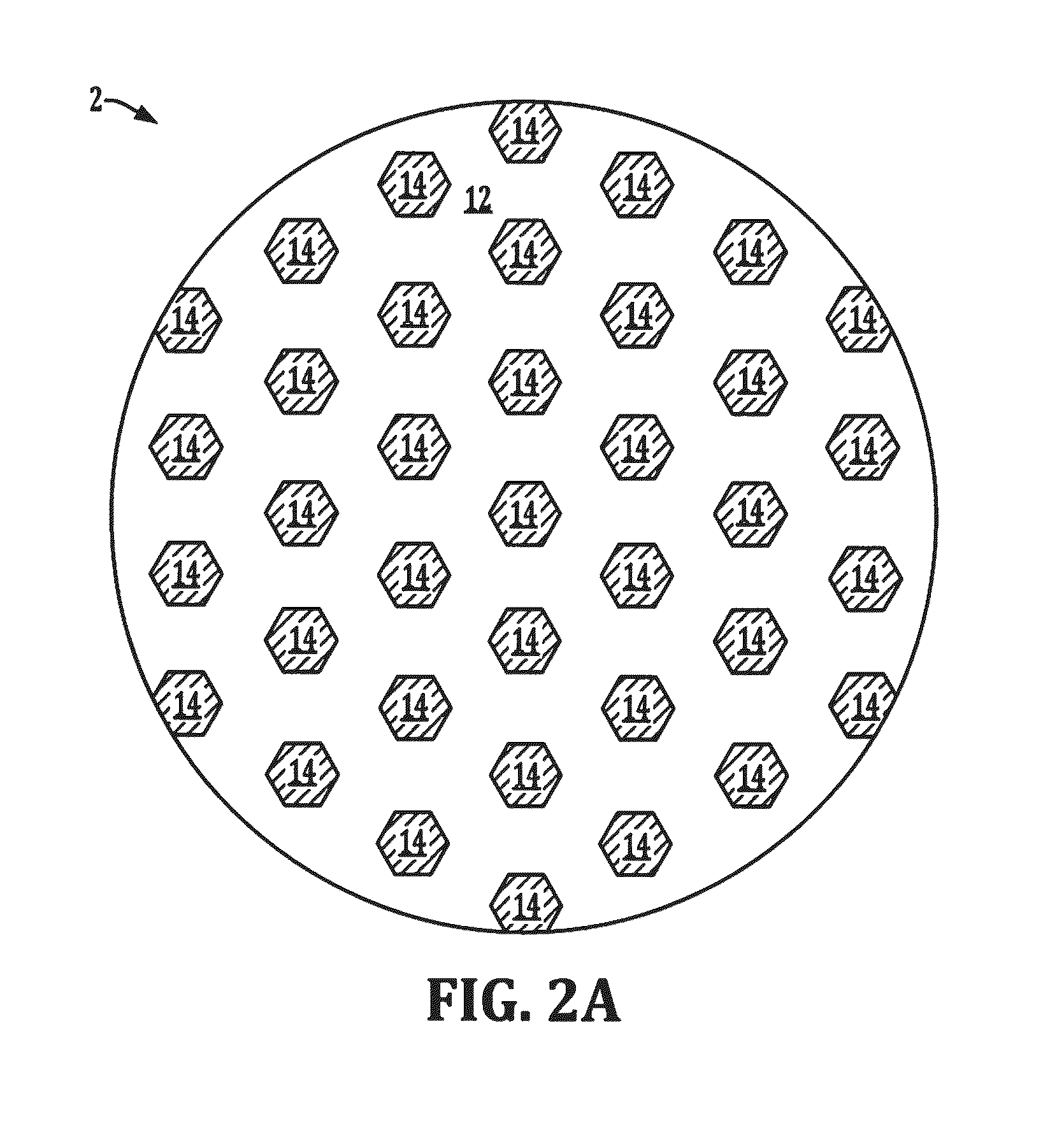

Structure and method for a fast recovery rectifier structure

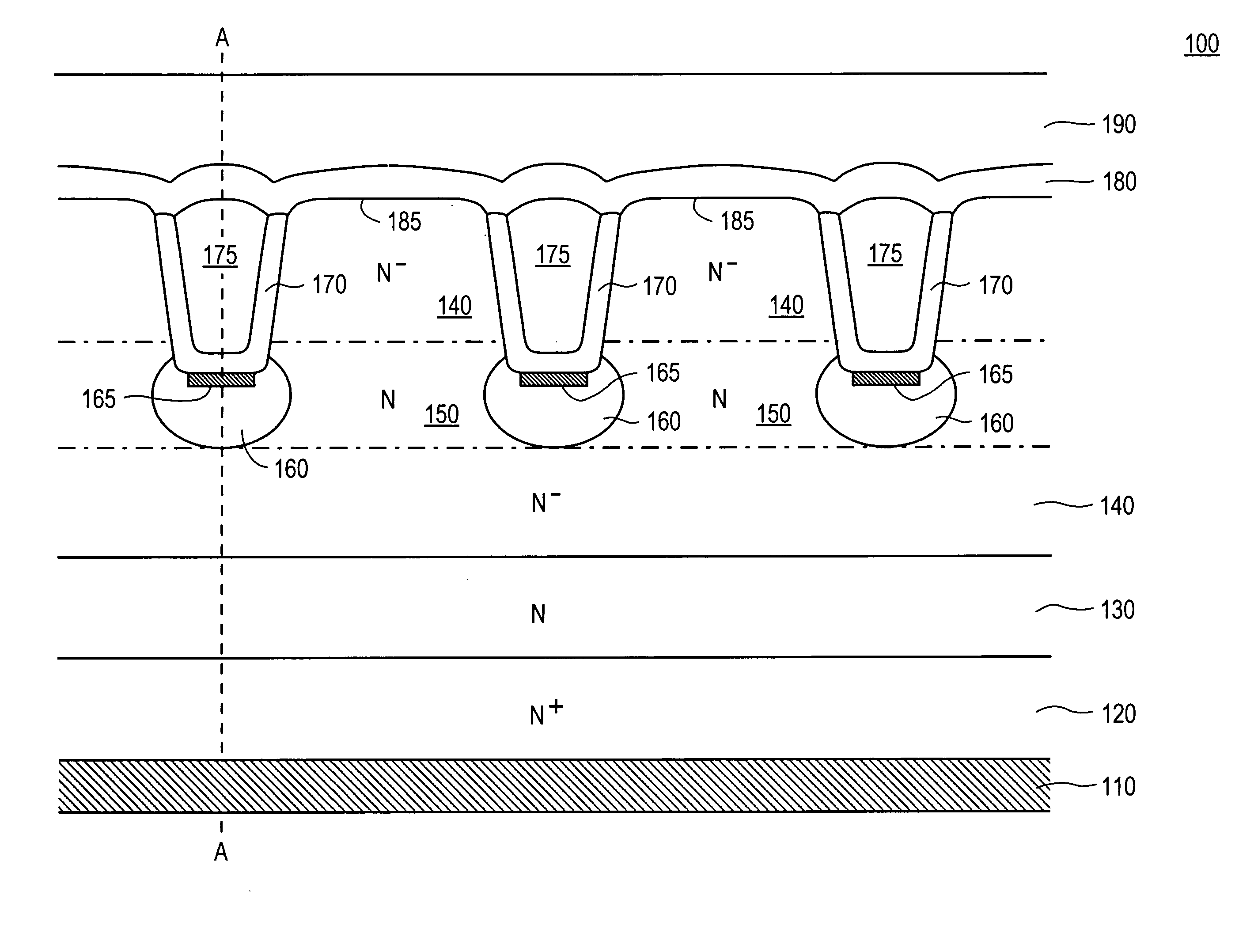

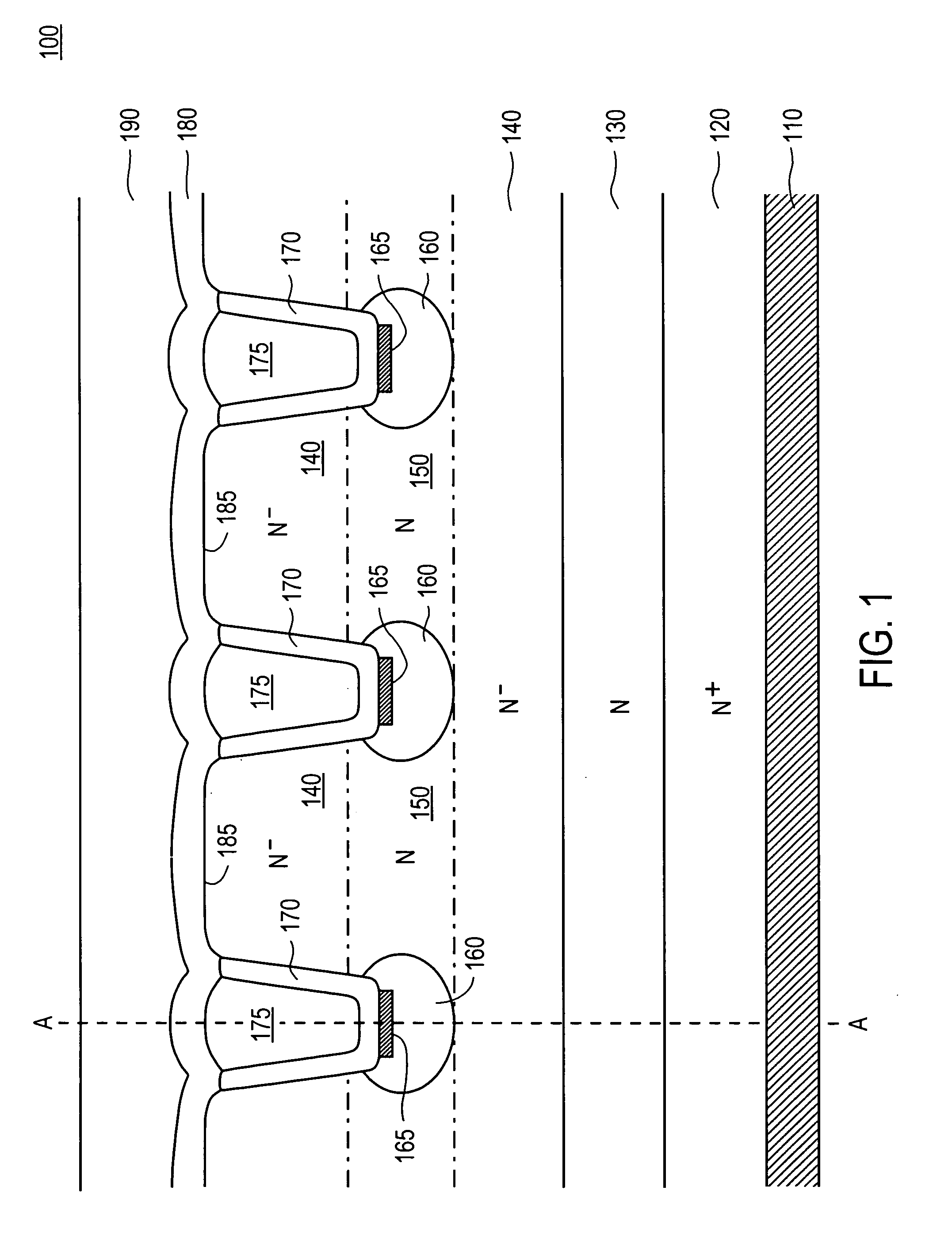

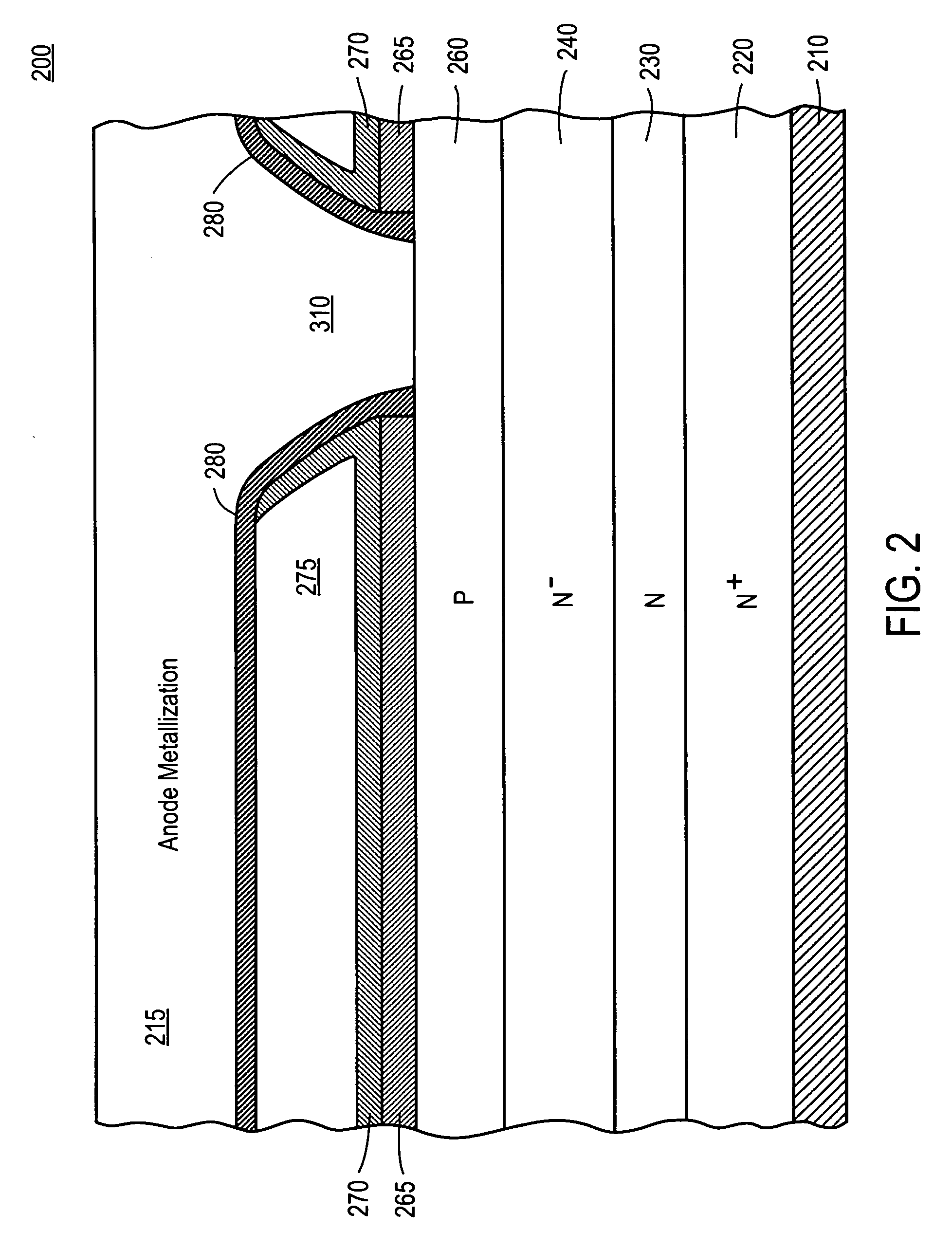

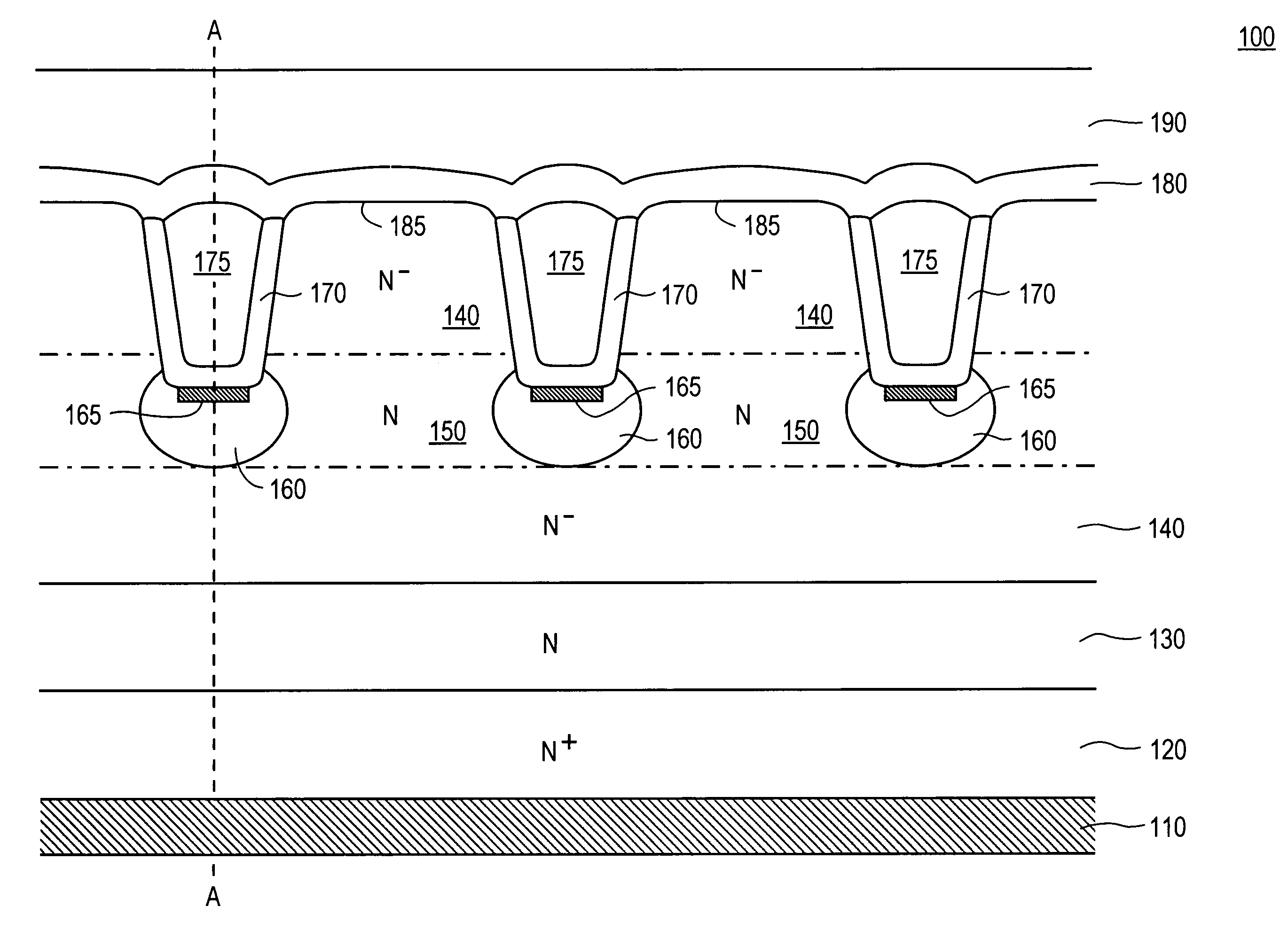

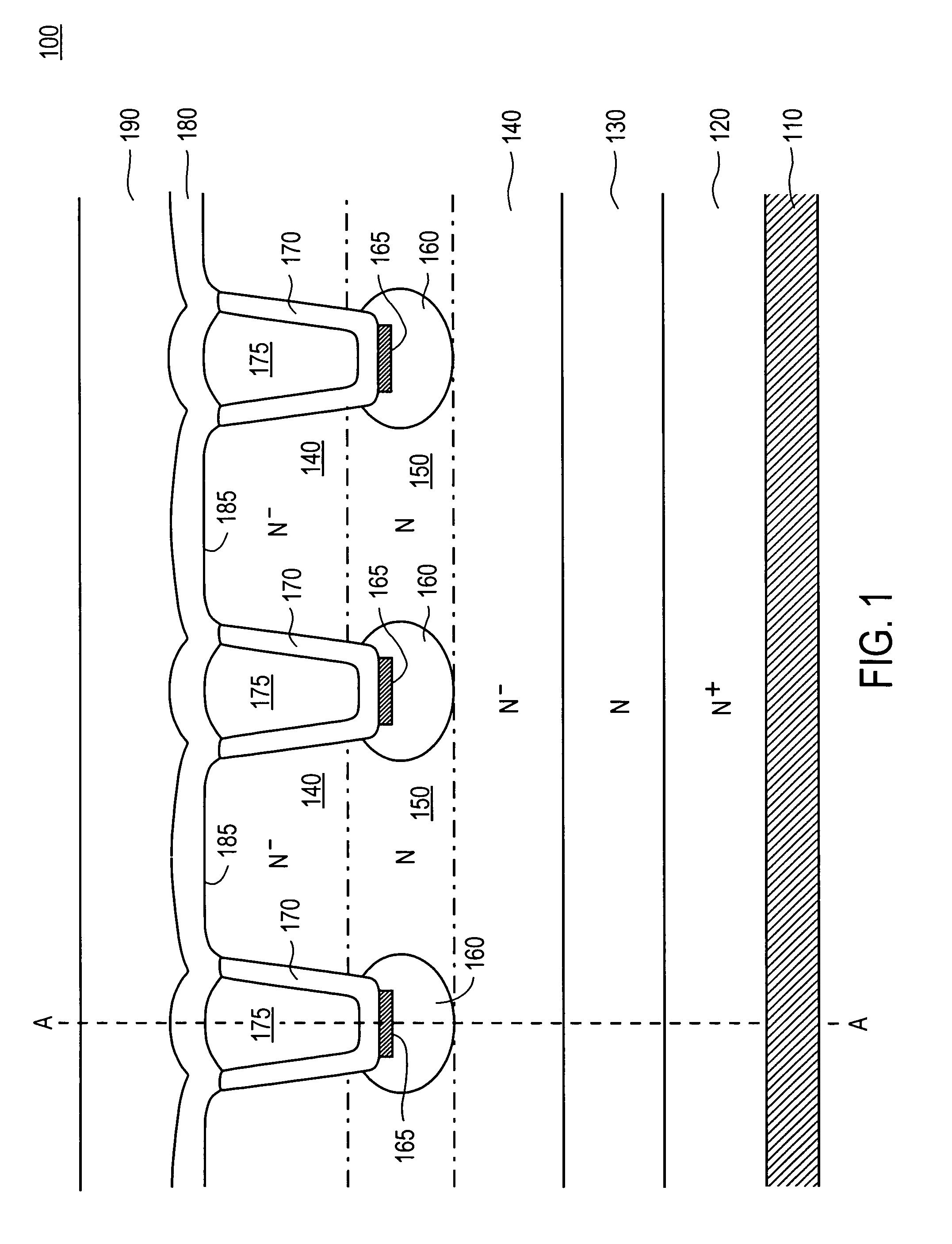

An apparatus and method for a fast recovery rectifier structure. Specifically, the structure includes a substrate of a first dopant. A first epitaxial layer lightly doped with the first dopant is coupled to the substrate. A first metallization layer is coupled to the first epitaxial layer. A plurality of trenches is recessed into the first epitaxial layer, each of which is coupled to the metallization layer. The device also includes a plurality of wells each doped with a second dopant type, wherein each well is formed beneath and adjacent to a corresponding trench. A plurality of oxide layers is formed on walls and a bottom of a corresponding trench. A plurality of channel regions doped with the first dopant is formed within the first epitaxial layer between two corresponding wells. Each of the plurality of channel regions is more highly doped with the first dopant than the first epitaxial layer.

Owner:POWER INTEGRATIONS INC

Structure and method for a fast recovery rectifier structure

ActiveUS7696540B2Fast recovery rectifier structureReduce channel resistanceTransistorThyristorDopantFast recovery

Owner:POWER INTEGRATIONS INC

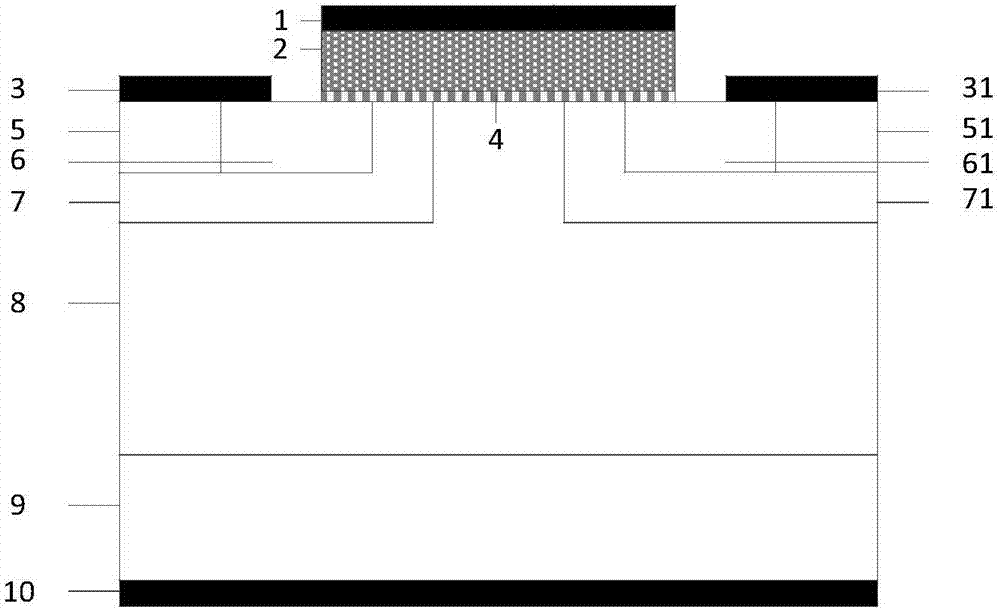

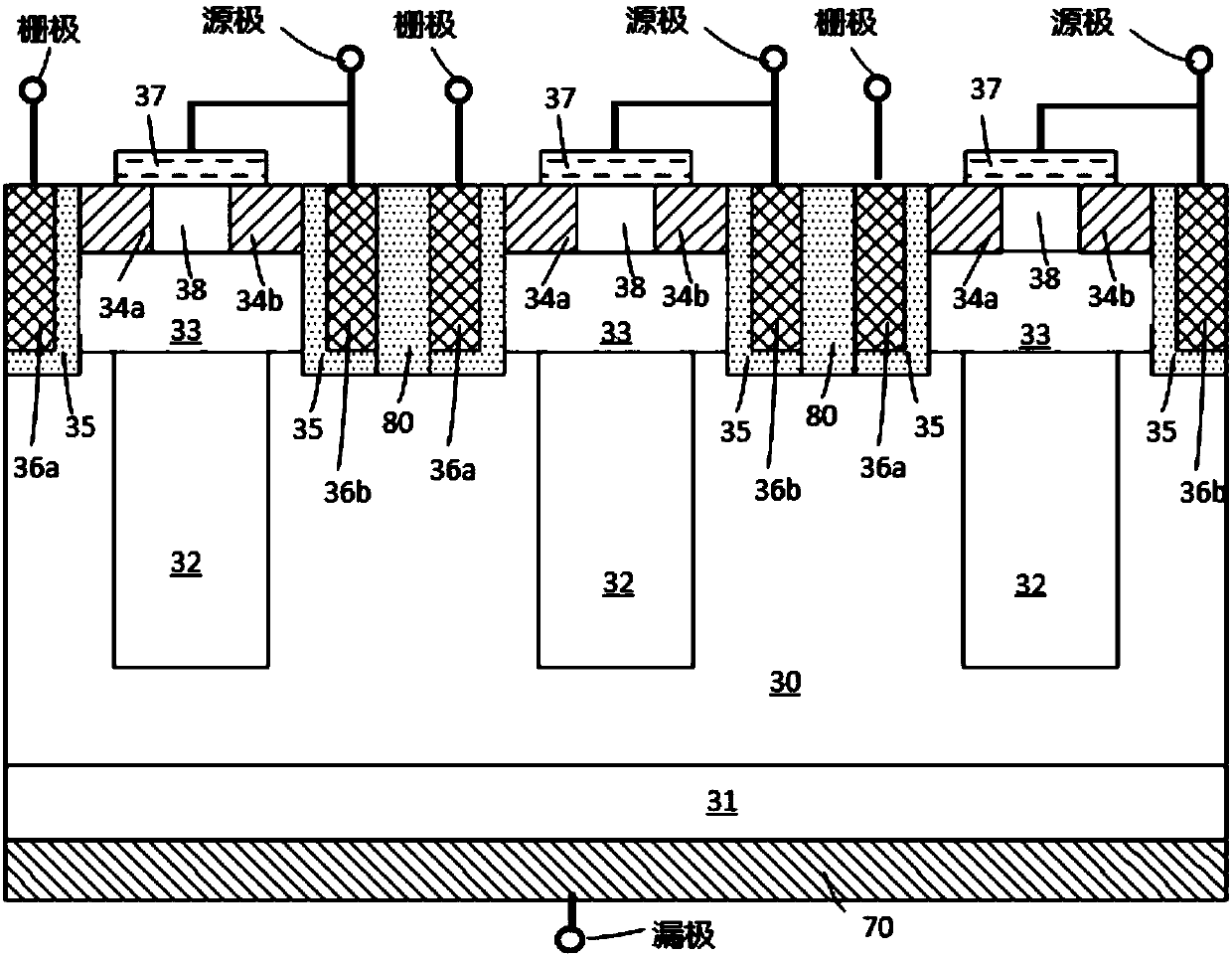

Silicon carbide VDMOS device and manufacturing method thereof

ActiveCN107275407AImprove performanceReduce power lossSemiconductor/solid-state device manufacturingDiodeCapacitanceHeterojunction

The invention discloses a silicon carbide VDMOS device and manufacturing method thereof, and belongs to the technical field of power semiconductors. A trench is etched on a JFET region surface of a traditional silicon carbide VDMOS device, P type doping is introduced into the bottom of the trench, and at the same time, a polycrystalline silicon layer is formed in the trench, so that the polycrystalline silicon layer and a side wall of the trench are in contact to form a Si / SiC heterojunction. A diode is integrated in the device, and the device has the advantages of low conduction voltage drop, fast switching speed and good reverse recovery characteristic in a diode working mode, and has the advantages of high breakdown voltage, small grid capacitance and fast switching speed in an MOS working mode. The proposed device structure optimizes application of the device in the field of inverter circuits, chopper circuits and the like, and has the advantage that the process is simple, and is compatible with a traditional silicon carbide VDMOS device process.

Owner:HANGZHOU SILICON-MAGIC SEMICON TECH CO LTD

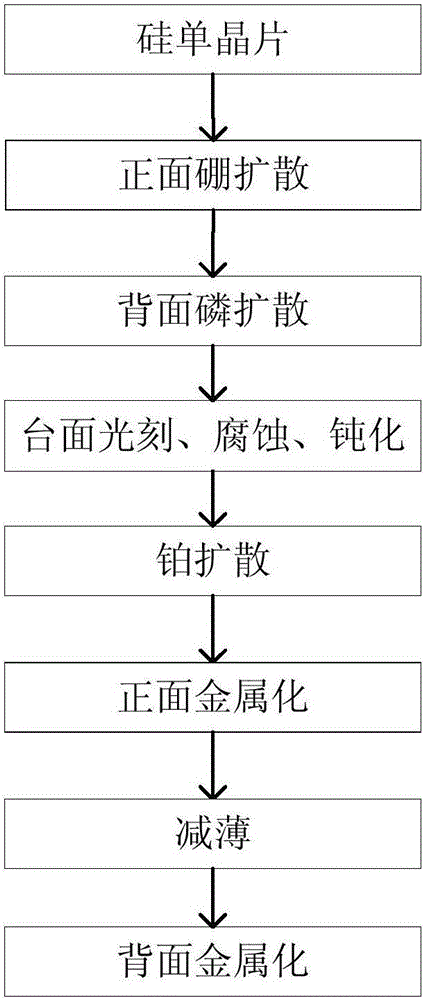

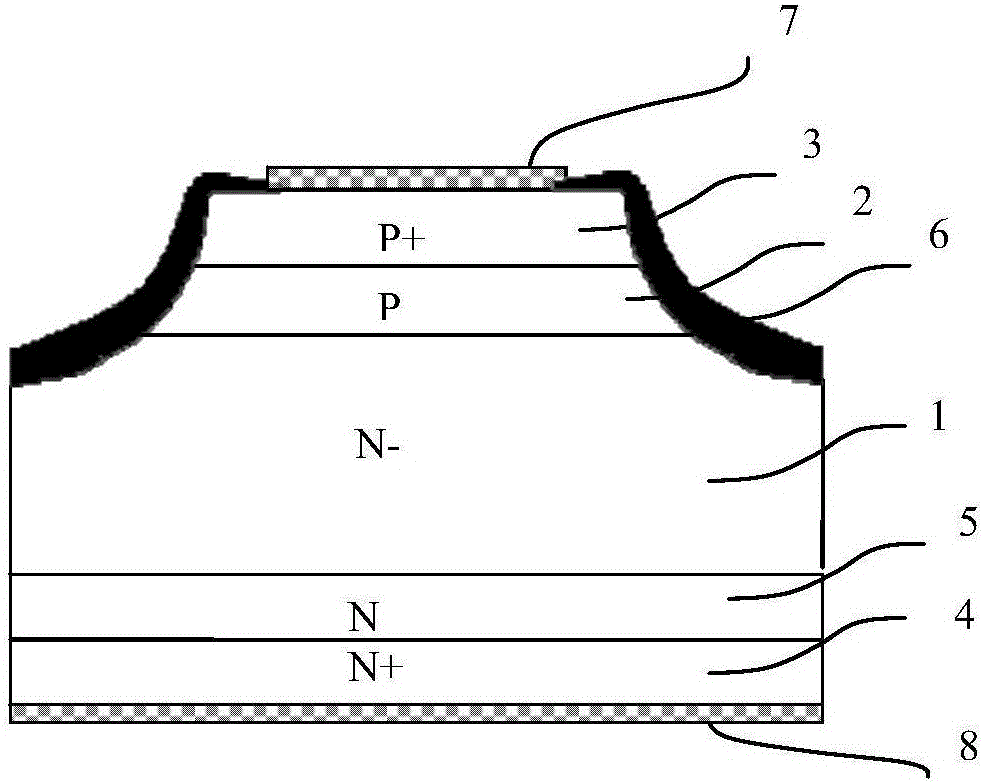

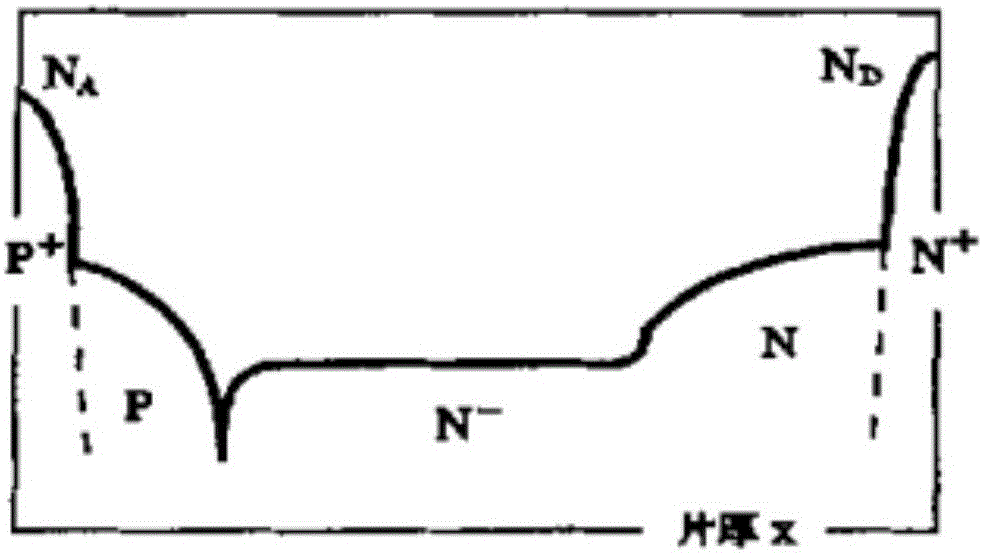

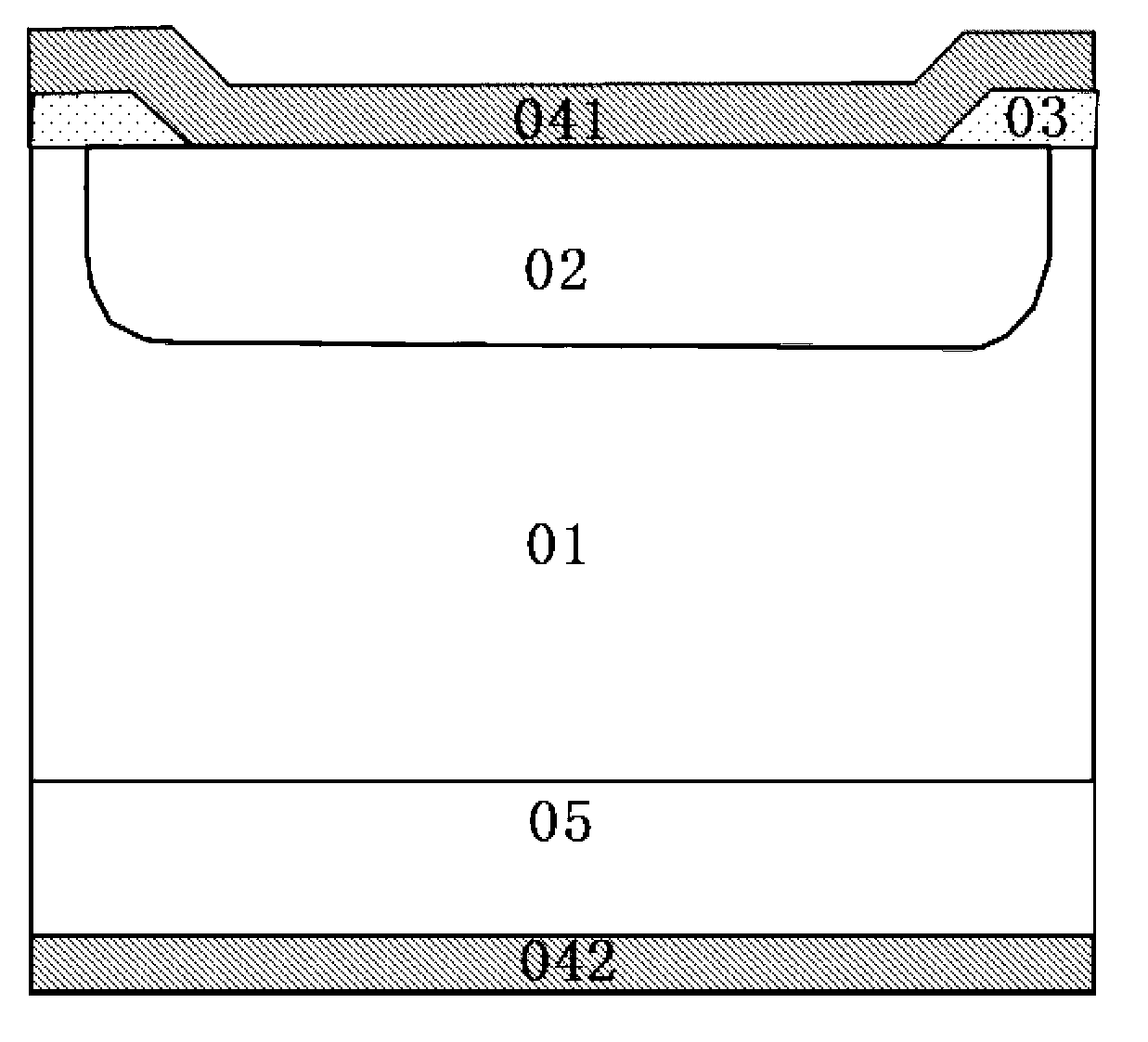

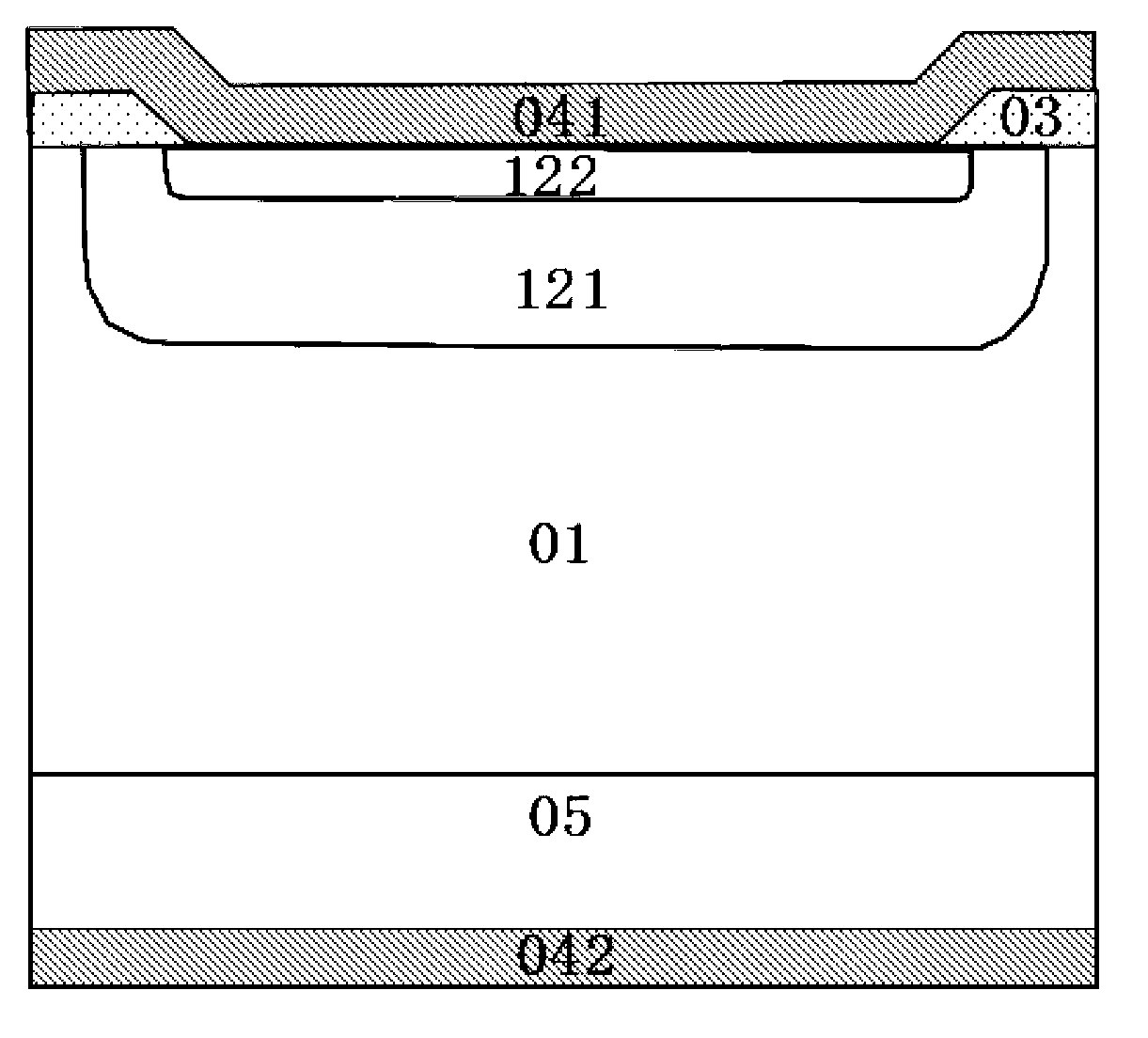

Diffusion-technology-based manufacture method for fast recovery diode chip having double buffering layers

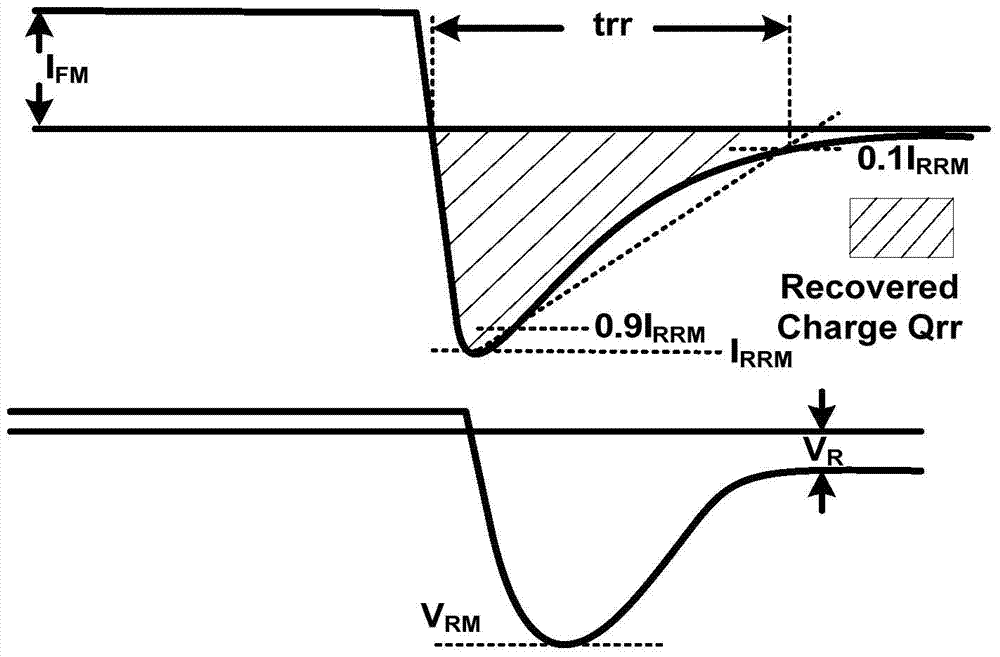

ActiveCN105977154AShort recovery timeHas soft recovery propertiesSemiconductor/solid-state device manufacturingSemiconductor devicesManufacturing technologyPeak current

The invention relates to a diffusion-technology-based manufacture method for a fast recovery diode chip having a double-buffer-layer structure. During a manufacture process, reverse recovery charges and reverse recovery time are reduced and effect of reverse recovery peak current is inhibited. The fast recovery diode is formed by adopting a phosphorus deep diffusion mode and a cathode structure formed by the diffusion is an N+N structure, an N area is a buffering layer which can block expansion of a space charge area, shortens a width of a base area and reduces forward on-state voltage drop; when the diode is reverse, an electric field between an N-N interface and an NN+ interface slows down carrier reverse drawing speed, which enables more charges to be used for recombination and softens the recovery characteristics. The diffusion-technology-based manufacture method adopts the diffusion mode to form the anode and the cathode of the fast recovery diode chip, combines with the platinum diffusion minority carrier life control technology, has a simple manufacture technology process and can manufacture the fast recovery diode chip which is low in cost, high in voltage resistance, short in recovery time and has soft recovery characteristics.

Owner:BEIJING MXTRONICS CORP +1

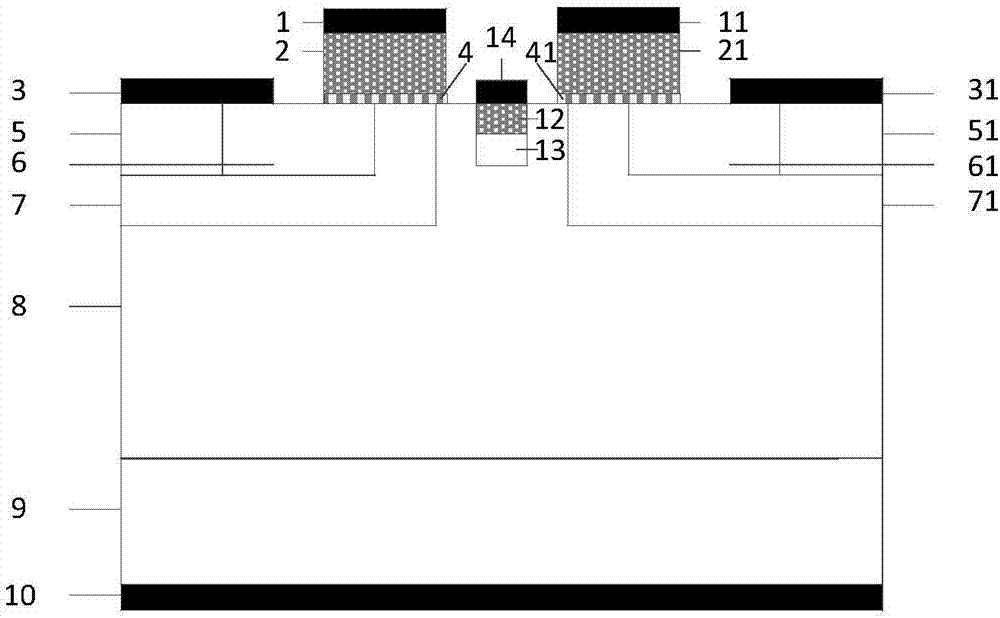

Silicon carbide TrenchMOS device and manufacturing method thereof

ActiveCN107256864AImprove performanceReduce power lossTransistorSolid-state devicesHeterojunctionReverse recovery

The invention discloses a silicon carbide TrenchMOS device and manufacturing method thereof, belonging to the technical field of power semiconductors. Considering the defects of an external anti-parallel fast recovery diode (FRD) and a parasitic diode directly using a silicon carbide TrenchMOS device, a polysilicon area is additionally arranged in the p+ contact area of a conventional device, so that a Si / SiC heterojunction is formed by the polysilicon and silicon carbide epitaxial layer material, and furthermore, a diode is integrated in the device. The junction voltage drop is significantly reduced when a device diode is applied, and the conductive mode during the diode application is converted from bipolar conduction into single polar conduction, so that the silicon carbide TrenchMOS device has the advantages of short reverse recovery time and less reverse recovery charge. The device structure also has the advantages of low parasitic silicon carbide diode reverse leakage, high breakdown voltage and good device temperature stability. Therefore, the silicon carbide TrenchMOS device has wide prospects in circuits such as an inversion circuit and a chopper circuit.

Owner:HANGZHOU SILICON-MAGIC SEMICON TECH CO LTD

Fast recovery diode and manufacturing method thereof

ActiveCN103022154AReduce shockImprove safe work areaSemiconductor/solid-state device manufacturingSemiconductor devicesReverse recoveryIntrinsics

The invention discloses a fast recovery diode and a manufacturing method of the fast recovery diode. The diode disclosed by the invention comprises an anodic diffusion P-type doped region, an evenly-doped intrinsic region, a cathodic diffusion N-type region, anode and cathode metal layers, wherein the anodic diffusion P-type doped region is a P-type doped region provided with alternated high and low concentrations and formed by locally pouring through a mask plate. Compared with the prior art, the diode disclosed by the invention has the characteristics of low inverse peak current IRRM, short reverse recovery time trr and high reverse recovery softness.

Owner:GLOBAL ENERGY INTERCONNECTION RES INST CO LTD +1

System for preventing reverse recovered charges in DUT

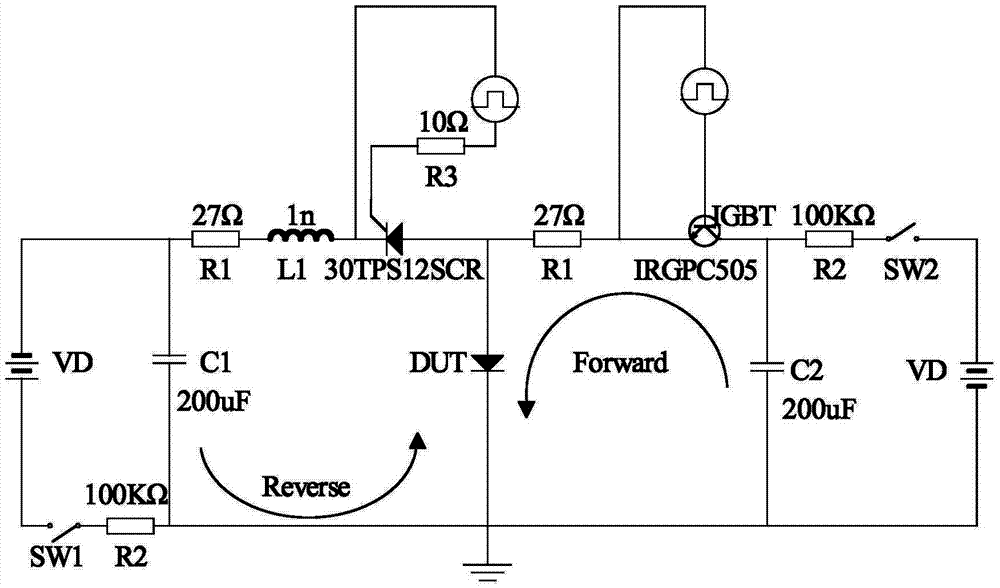

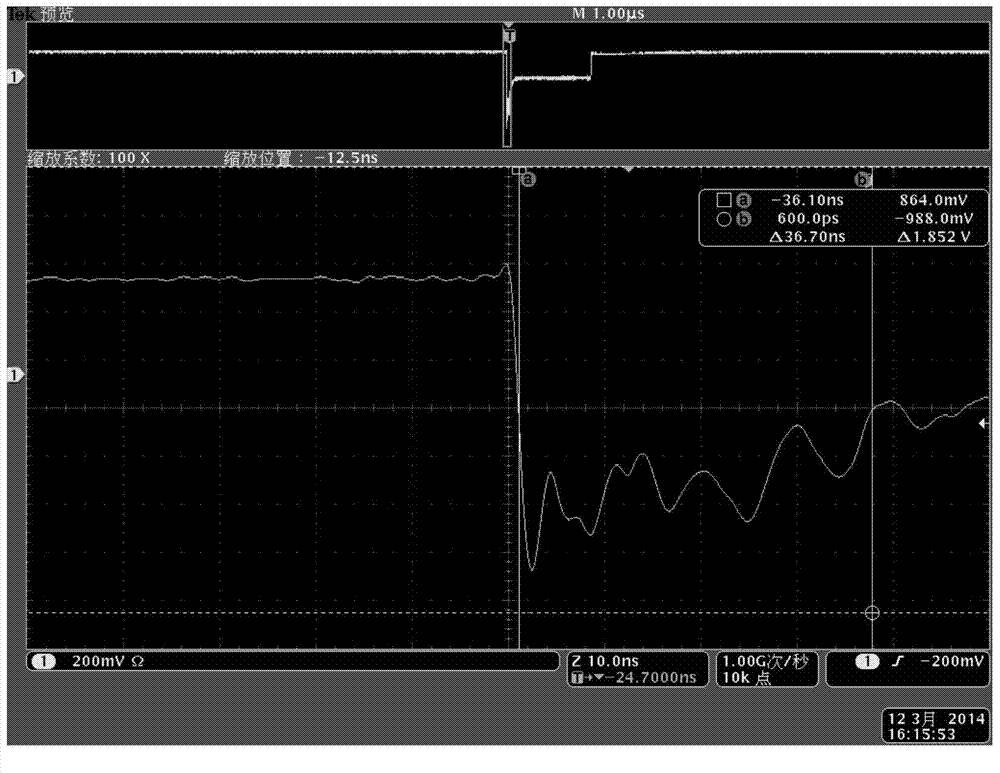

ActiveCN103929156AImproved reverse recovery characteristicsReduce switching lossesPulse shapingReverse recoveryElectromagnetic interference

The invention discloses a system for preventing reverse recovered charges in a DUT. The system is a current injection circuit connected to the two ends of the DUT in a forward bias mode. The injected current circuit comprises a pulse nS-level pulse signal generator formed by an SRD and a pulse edge acceleration circuit formed by a BG2 and a BG1, wherein the pulse edge acceleration circuit is tightly connected with the back of the pulse nS-level pulse signal generator and used for shortening the rising edge time and the falling edge time of pulses. The system has the advantages that the reverse recovered features of the DUT can be improved, the reverse recovered charges can be reduced, and the reverse recovered time can be shortened; meanwhile, switching losses and conduction losses of the DUT can be reduced, electromagnetic interference and surges can be restrained, and efficiency is improved.

Owner:HAIMEN THE YELLOW SEA ENTREPRENEURSHIP PARK SERVICE CO LTD

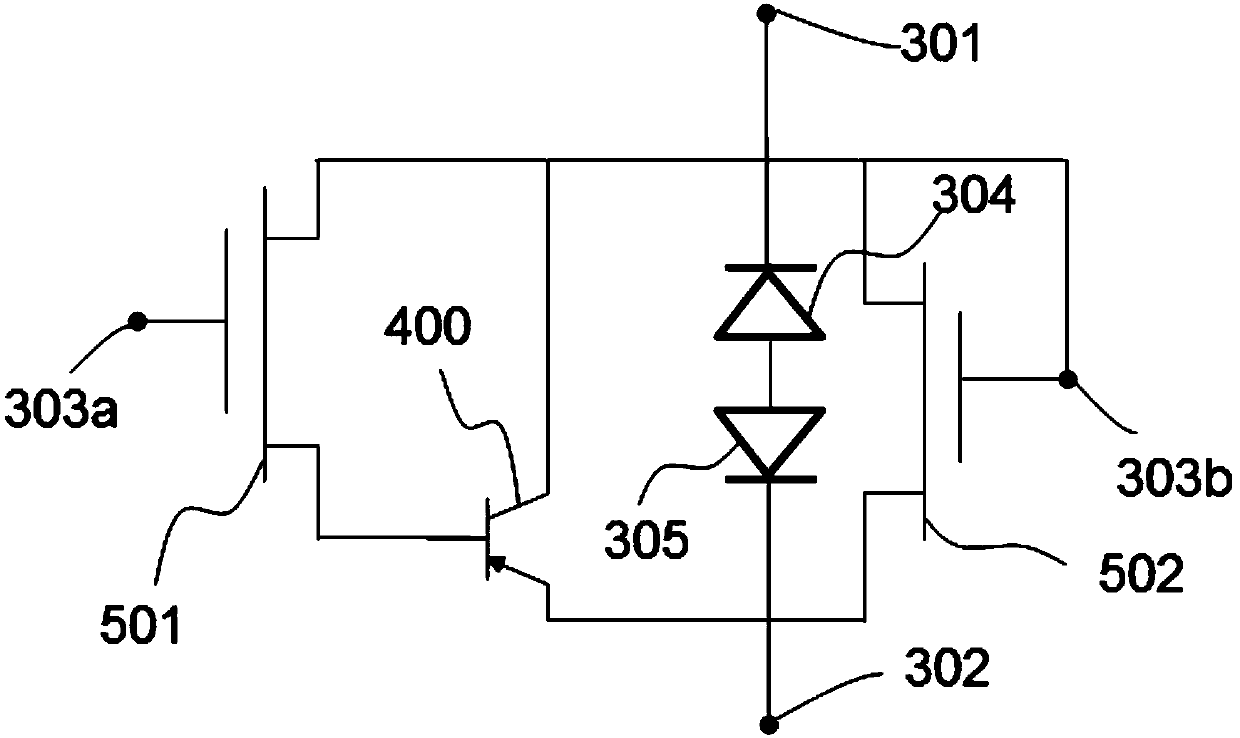

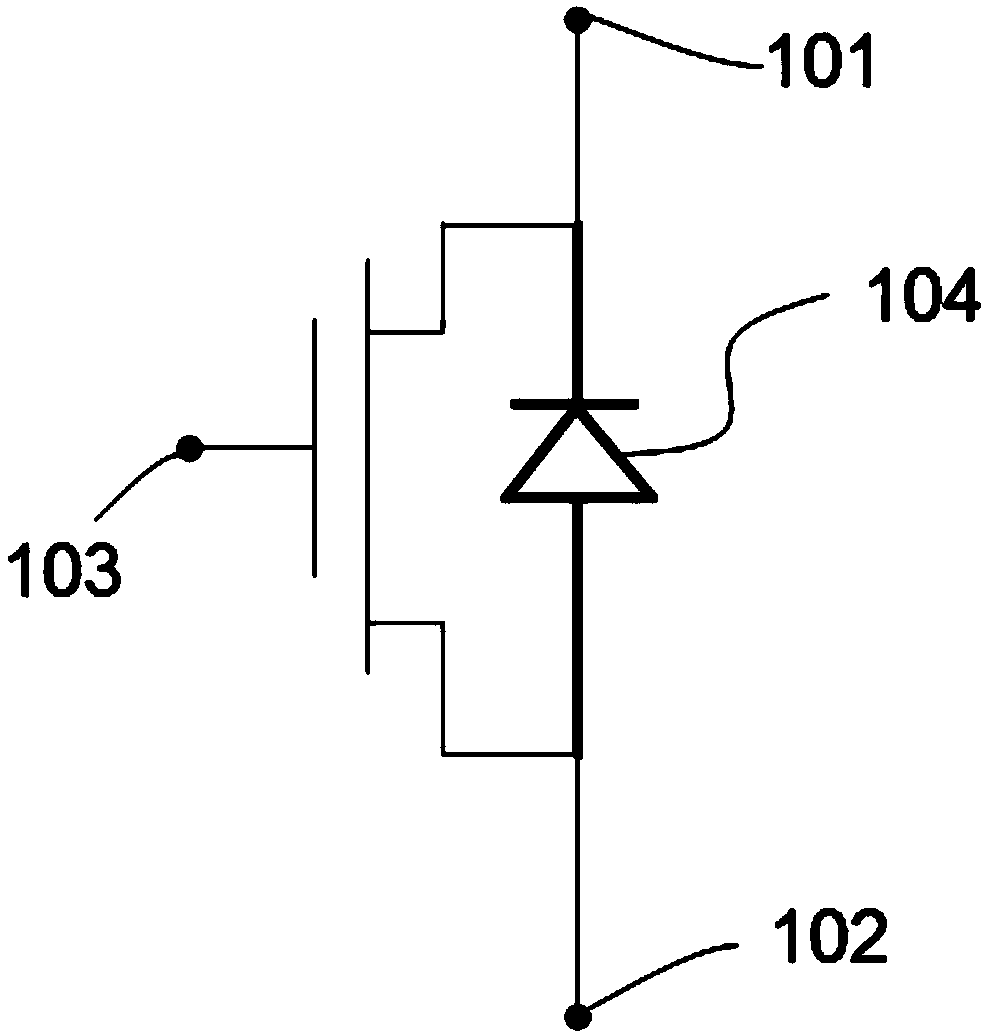

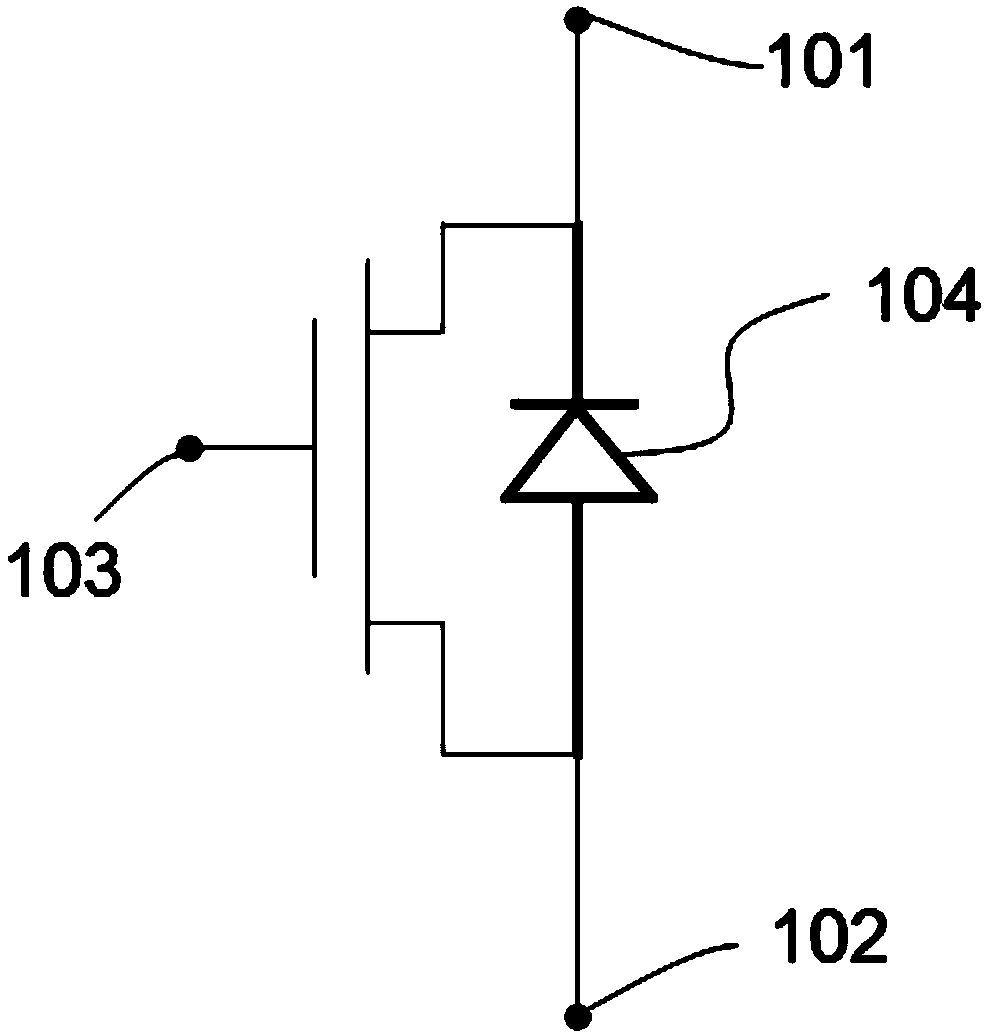

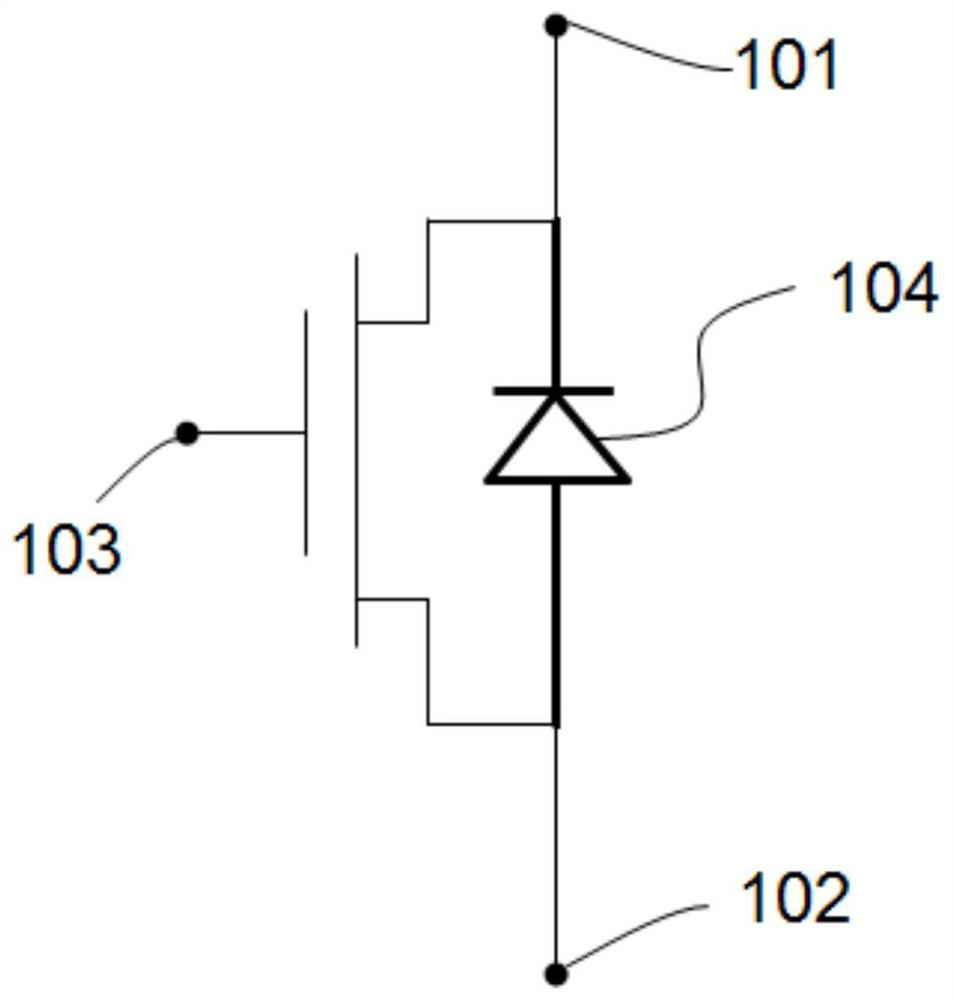

IGBT power device

ActiveCN109755303AReduce reverse recovery chargeReduce reverse currentSemiconductor/solid-state device manufacturingSemiconductor devicesBody contactEngineering

An IGBT power device provided by an embodiment of the invention comprises a bipolar transistor, a first MOS transistor, a second MOS transistor, a body diode, and a body contact diode, wherein the anode of the body contact diode is connected to the anode of the body diode, and the cathode of the body contact diode is connected to the emitter of the bipolar transistor; the first gate of the first MOS transistor controls the first MOS transistor to be turned on or off through the gate voltage of the IGBT power device, the second gate of the second MOS transistor is connected to the emitter of the bipolar transistor, and the second gate of the second MOS transistor controls the second MOS transistor to be turned on or off through the emitter voltage of the IGBT power device.

Owner:SUZHOU ORIENTAL SEMICONDUCTOR CO LTD

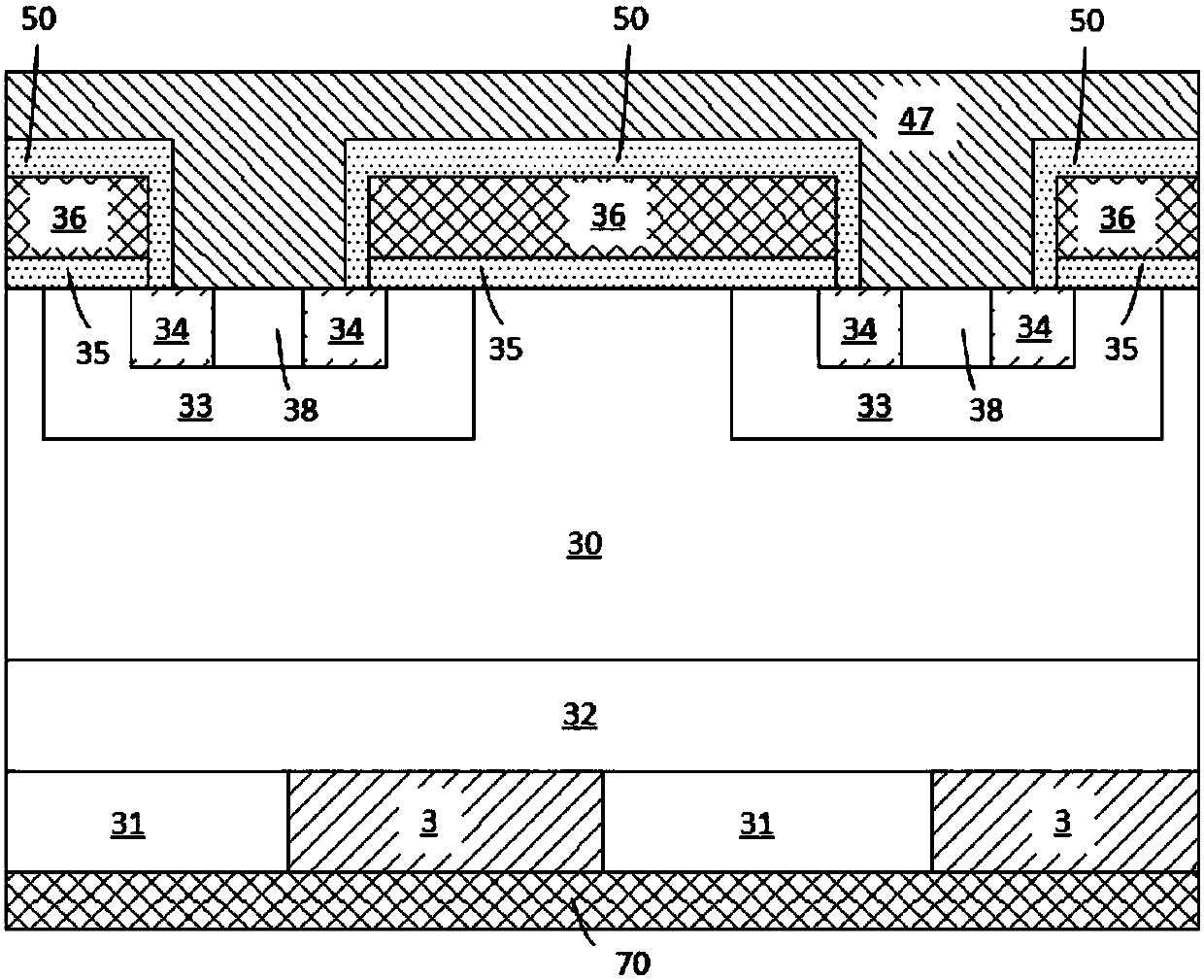

Trench gate charge storage reverse-conducting insulated-gate bipolar transistor (RC-IGBT) and fabrication method thereof

ActiveCN105870179AReduce gate capacitanceLow densitySemiconductor/solid-state device manufacturingSemiconductor devicesCapacitancePower semiconductor device

The invention belongs to the technical field of a power semiconductor device, in particular relates to a reverse-conducting trench gate charge storage insulated-gate bipolar transistor (IGBT). By introducing a side-surfaces split electrode connected with an emitter into a trench on the condition of a certain device trench depth and a certain trench metal oxide semiconductor (MOS) structure density, the gate capacitance of the device is reduced, the switching speed of the device is increased, the switching loss is reduced, and the positive conduction voltage drop and the average switching loss are improved; meanwhile, the density of an MOS channel is reduced, the short-circuit safety working region of the IGBT is improved, and the performance and the reliability of the device are improved; and a reverse freewheeling diode works in multiple submodes in a working mode of the reverse freewheeling diode, the IGBG has low diode conduction voltage drop, and the reverse recovery characteristic of the freewheeling diode is improved.

Owner:UNIV OF ELECTRONIC SCI & TECH OF CHINA

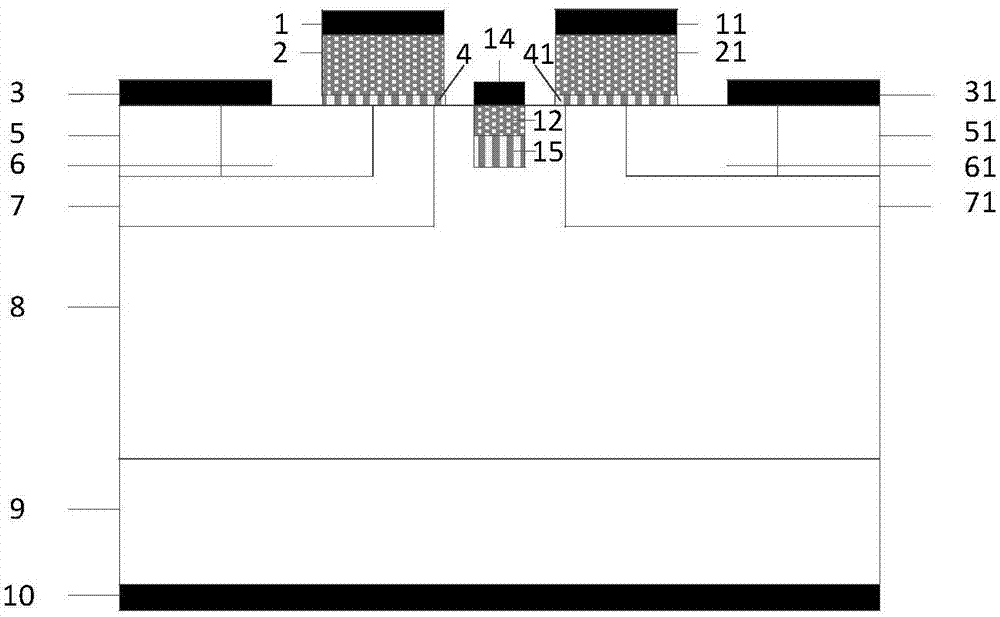

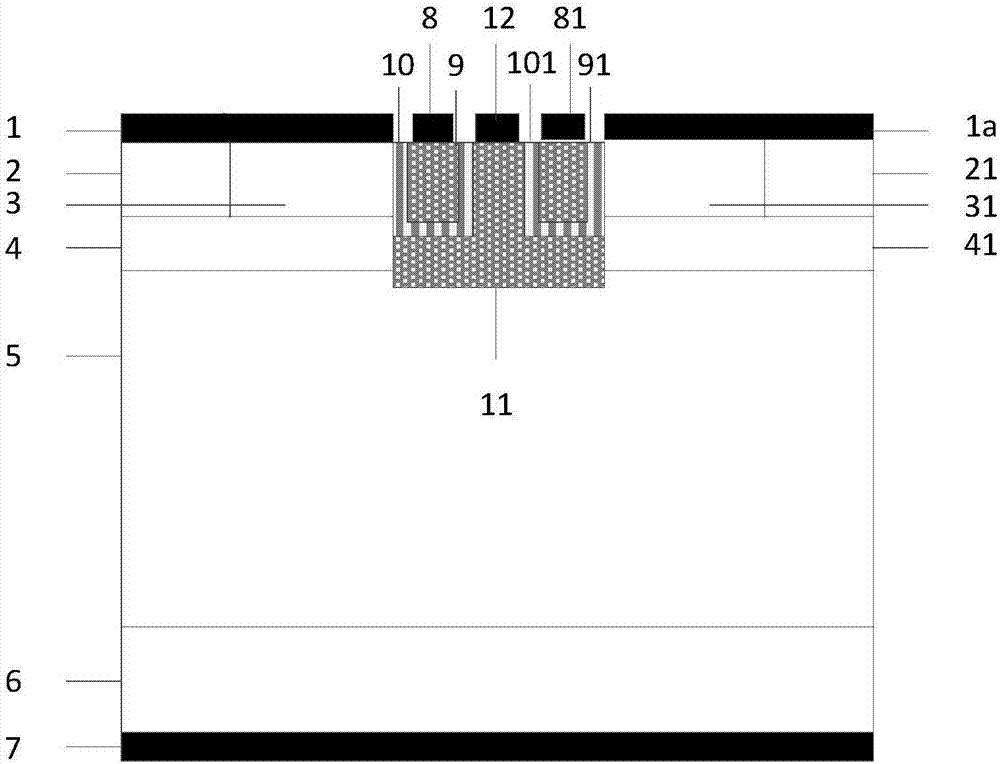

Silicon carbide Trench MOS device and manufacturing method thereof

ActiveCN107425068AImprove performanceReduce power lossSemiconductor/solid-state device manufacturingSemiconductor devicesHeterojunctionReverse recovery

The invention discloses a silicon carbide Trench MOS device and a manufacturing method thereof, and belongs to the technical field of power semiconductors. The method includes: a layer of a polysilicon region distributed in a pi shape is additionally arranged under a trench gate structure of a conventional device, the polysilicon region and an epitaxial layer form a Si / SiC heterojunction, and a diode is integrated in the device. Compared with a parasitic silicon carbide diode which directly employs a silicon carbide Trench MOS, according to the silicon carbide Trench MOS device and the manufacturing method thereof, the junction voltage drop of the device diode during application is substantially reduced, and the switch-on characteristic of the device is improved through large junction area of the heterojunction; moreover, the gate-drain capacitance and the ratio of the gate-drain capacitance to the gate-source capacitance of the device are reduced, and the performance and the reliability of the device MOS during application are enhanced; besides, the silicon carbide Trench MOS device and the manufacturing method thereof are also advantageous in that the reverse recovery time is short, the reverse recovery charges are less, and advantages including low reverse leakage, high breakdown voltage, and good temperature stabilization performance of the conventional silicon carbide Trench MOS device are maintained. In conclusion, according to the silicon carbide Trench MOS device and the manufacturing method thereof, the prospect is wide in circuits such as inversion circuits and chopper circuits etc.

Owner:HANGZHOU SILICON-MAGIC SEMICON TECH CO LTD

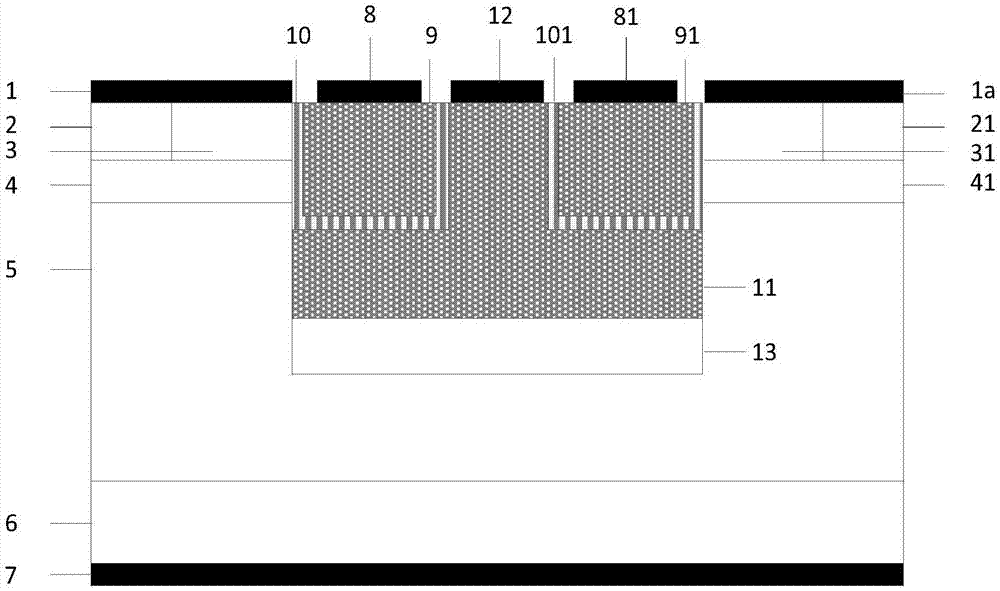

Silicon carbide Trench MOS device and manufacturing method thereof

ActiveCN107275406AImprove performanceReduce power lossSemiconductor/solid-state device manufacturingSemiconductor devicesCapacitanceHeterojunction

The invention discloses a silicon carbide Trench MOS device and manufacturing method thereof, and belongs to the technical field of power semiconductors. A convex polycrystalline silicon region is additionally arranged inside an epitaxial layer, and two independent trench gates are arranged in a groove of the convex polycrystalline silicon region, so that a polycrystalline silicon layer and the epitaxial layer form a Si / SiC heterojunction. Compared with direct utilization of a parasitic silicon carbide diode of a silicon carbide Trench MOS, a junction voltage drop during application of the device diode is remarkably reduced, and a relatively large heterojunction area improves a device conduction characteristic; based on a charge shielding effect of the convex polycrystalline silicon, gate-drain capacitance and a ratio of gate-drain capacitance and gate-source capacitance are reduced, thereby remarkably improving performance and reliability of the device; and the device adopts single-pole electric conduction, thus has relatively good reverse recovery performance and has the advantages of low reverse electric leakage, high breakdown voltage and good device temperature stability performance of a traditional Trench MOS device, and therefore the silicon carbide Trench MOS device provided by the invention has broad prospects in circuits such as an inverter circuit and a chopper circuit.

Owner:HANGZHOU SILICON-MAGIC SEMICON TECH CO LTD

SiC vertical double diffused metal-oxide-semiconductor (VDMOS) device and fabrication method thereof

ActiveCN107248533AImprove performanceReduce power lossSemiconductor/solid-state device manufacturingSemiconductor devicesCapacitanceHeterojunction

The invention discloses a SiC vertical double diffused metal-oxide-semiconductor (VDMOS) device and a fabrication method thereof, and belongs to the technical field of a power semiconductor. A poly-silicon layer is directly deposited on a surface of a junction field-effect transistor (JFET) region of the SiC VDMOS device to form a Si / SiC heterojunction, a diode is further integrated in the device, and the application of the device in the field of an inversion circuit, a chopping circuit and the like is optimized. Compared with the prior art directly employing a VDMOS parasitic SiC diode, the SiC VDMOS device has the advantages of relatively low power loss, relatively fast working speed and relatively high working efficiency, and positive conduction is easier to achieve; compared with the prior art that a fast recovery diode (FRD) is reversely connected with the exterior of the device in parallel, the SiC VDMOS device has the advantages that the usage number of the device is reduced, connection lines between the devices are reduced, and the miniature development of the device is promoted; moreover, the grid width is reduced, the grid capacitance is reduced, and the working speed of the device is further increased; and therefore, the VDMOS device proposed by the invention has wide application prospect in the circuit field of the inversion circuit, the chopping circuit and the like.

Owner:UNIV OF ELECTRONICS SCI & TECH OF CHINA

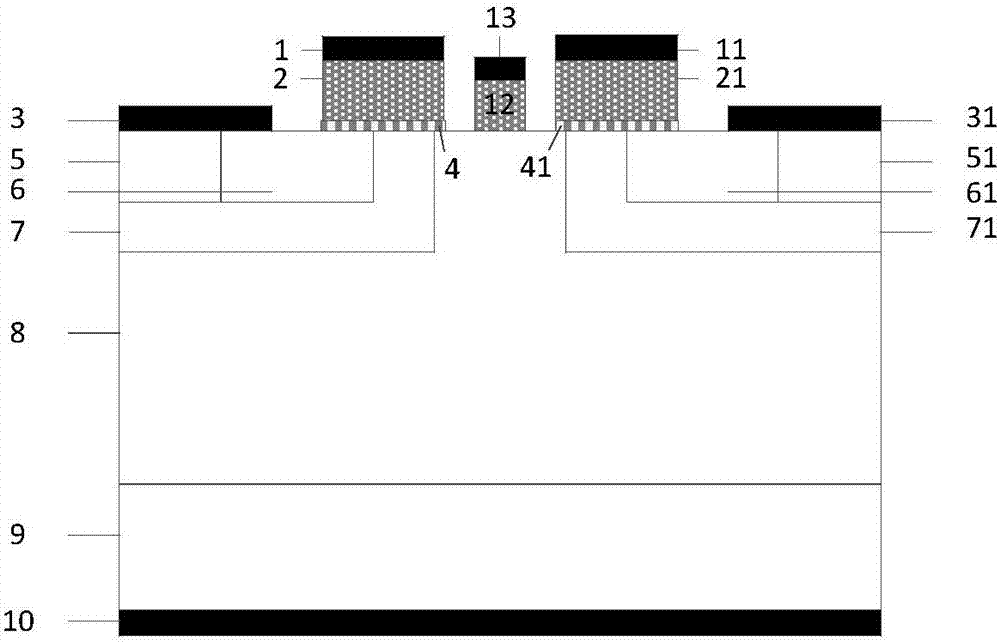

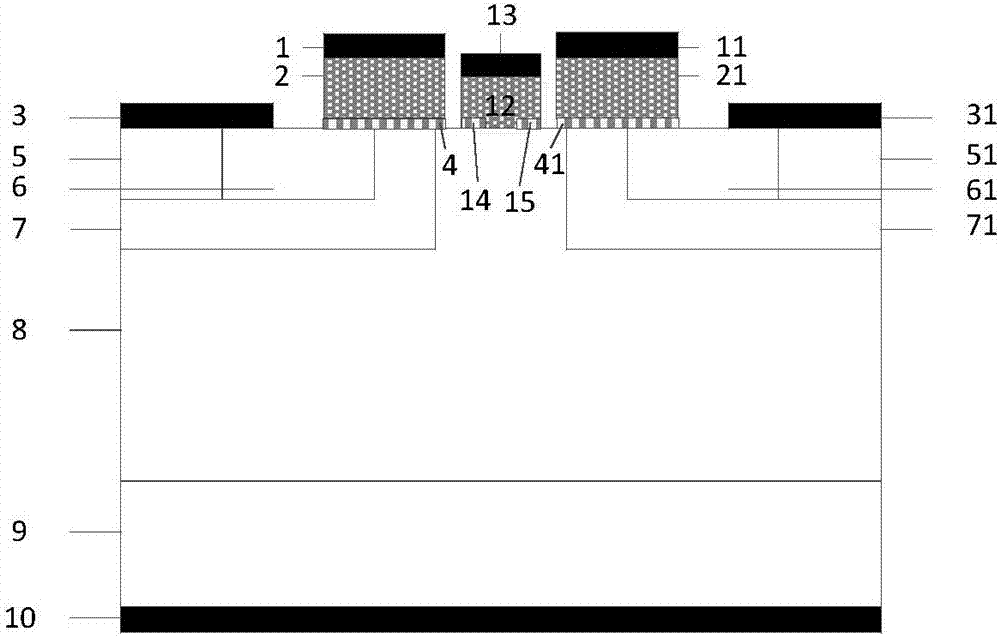

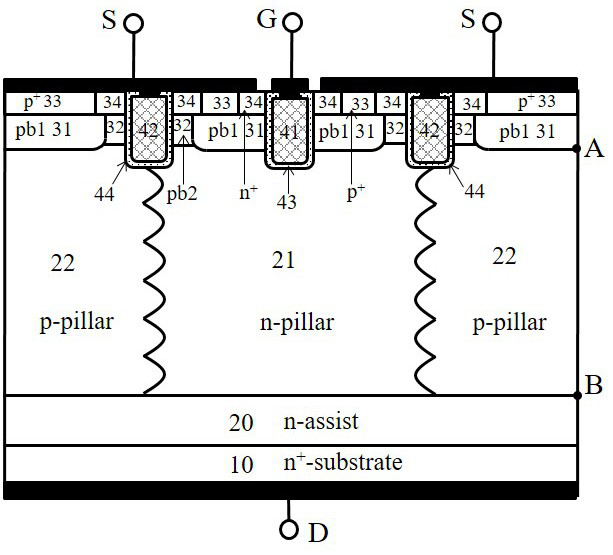

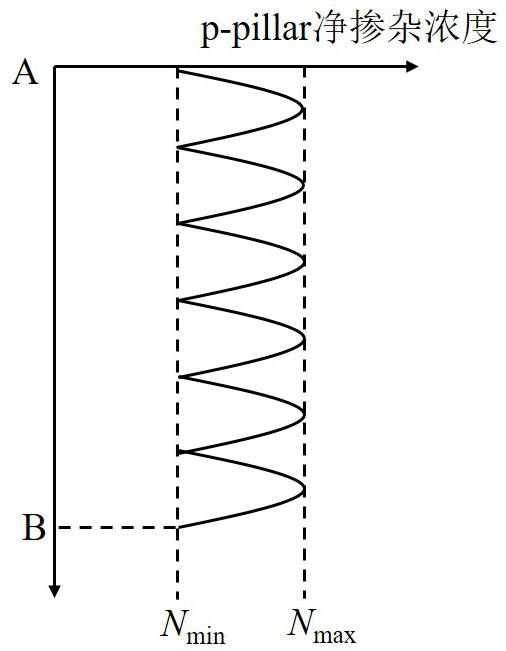

Super junction MOSFET with reverse conductive trench gate structure

The invention provides a super junction MOSFET (Metal-Oxide-Semiconductor Field Effect Transistor) device. Non-uniform doping is adopted in a semiconductor region of a second conductive type in a voltage-withstanding layer to improve the resistance of the region, and a reverse conductive groove type gate structure is introduced to reduce the hole injection efficiency of the body diode. A conductormaterial leading-out end in the groove type gate structure used for reverse conduction is a source electrode of the device, the side face of the conductor material leading-out end is in direct contact with a source region and a lightly-doped base region of the second conductive type, and the bottom of the conductor material leading-out end is in direct contact with the voltage-withstanding layer.Compared with a traditional super junction MOSFET device, the super junction MOSFET device provided by the invention has a more excellent body diode reverse recovery characteristic.

Owner:SICHUAN UNIV

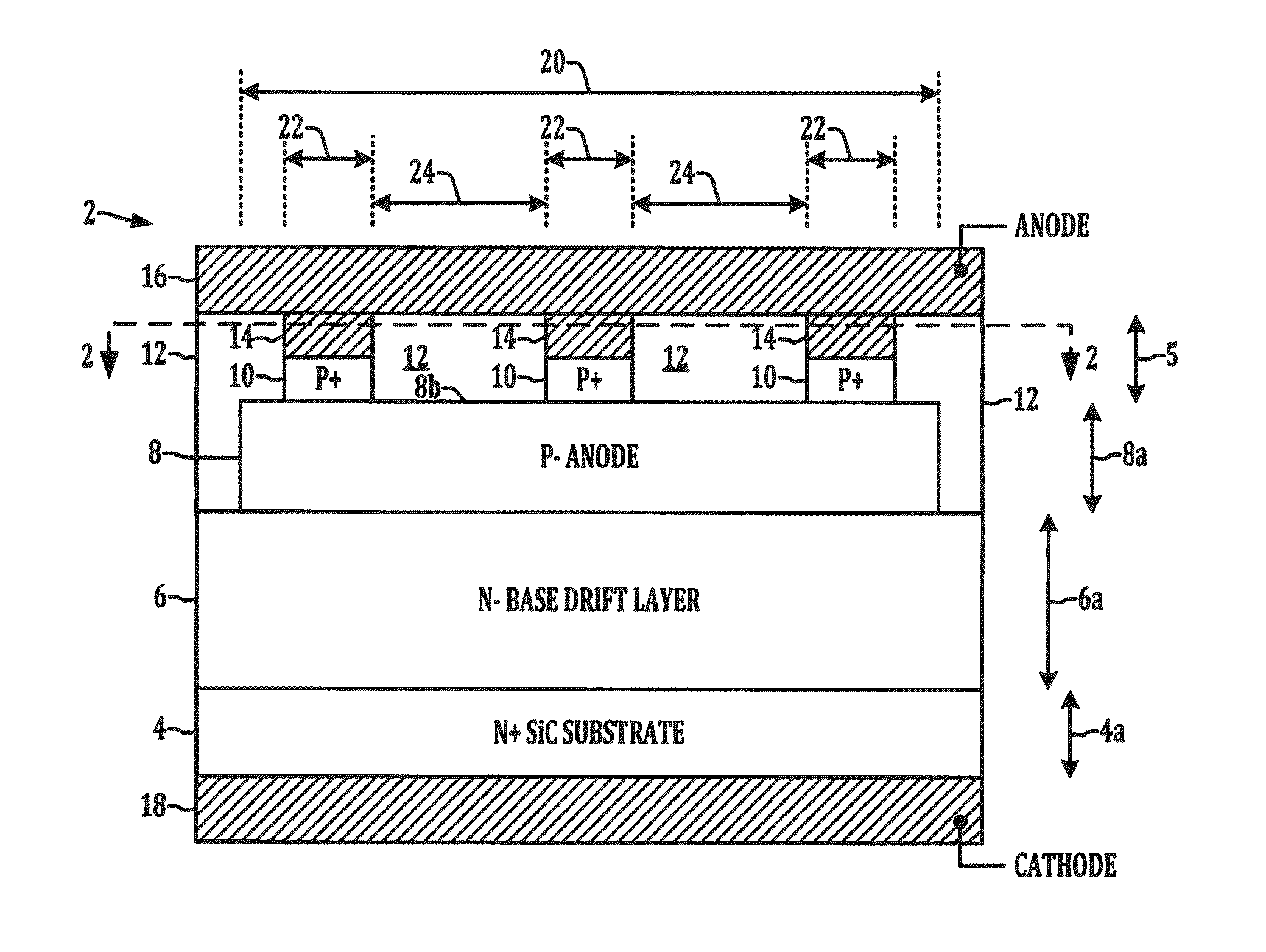

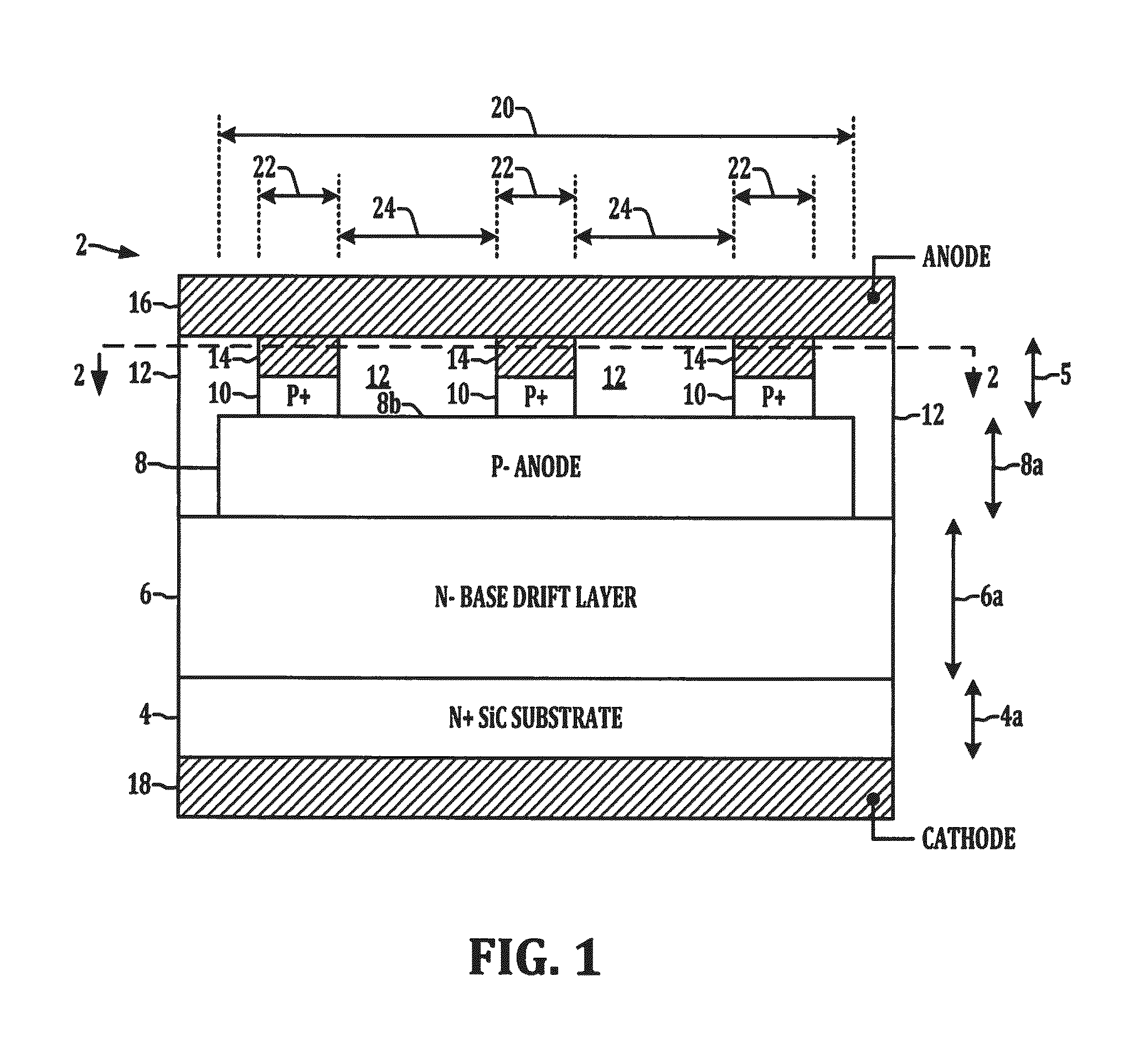

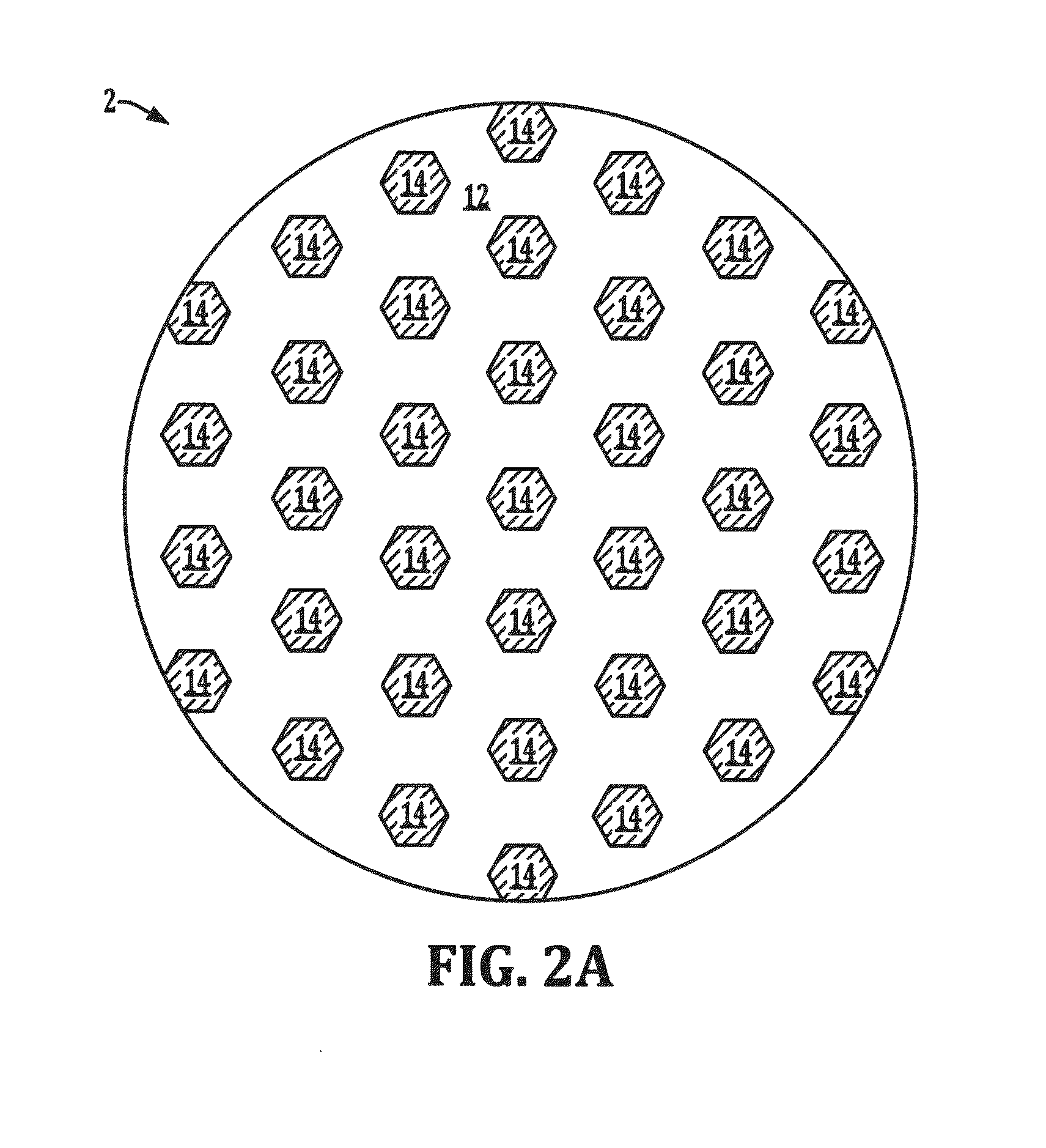

Silicon Carbide Rectifier

ActiveUS20130240905A1Current valueReduce carrier densitySemiconductor/solid-state device manufacturingSemiconductor devicesPower flowNegative temperature

Silicon carbide PiN diodes are presented with reduced temperature coefficient crossover points by limited p type contact area to limit hole injection in the n type drift layer in order to provide a lower current at which the diode shifts from negative temperature coefficient to a positive temperature coefficient of forward voltage for mitigating thermal runaway.

Owner:U S A AS RPRESENTED BY THE SEC OF THE NAVY THE

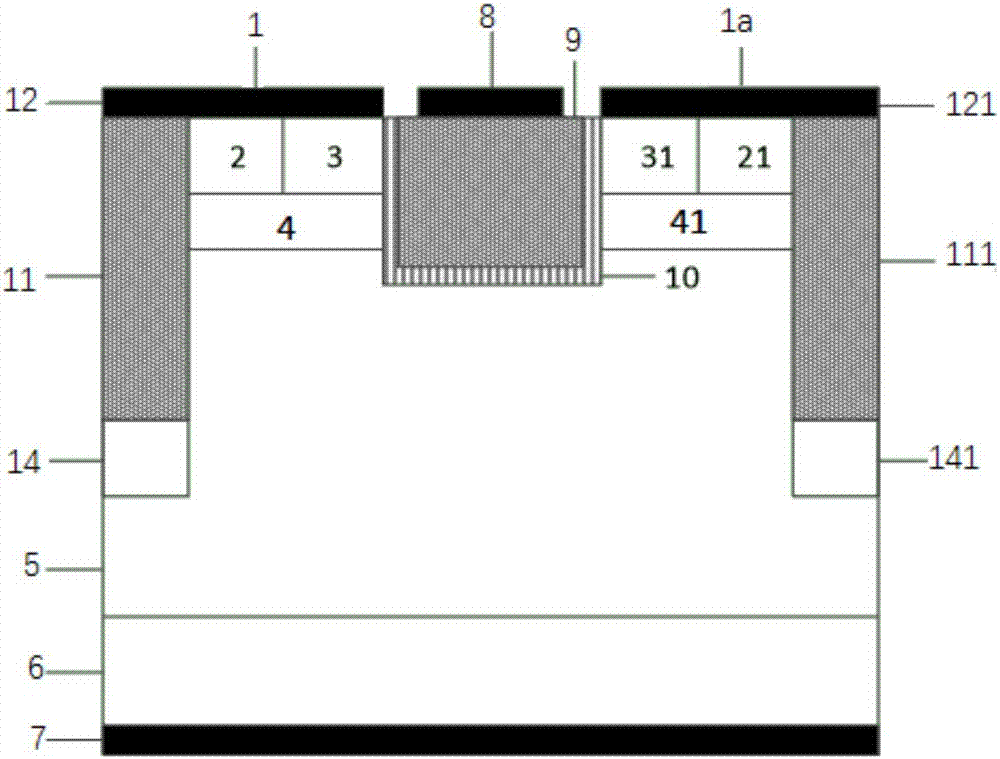

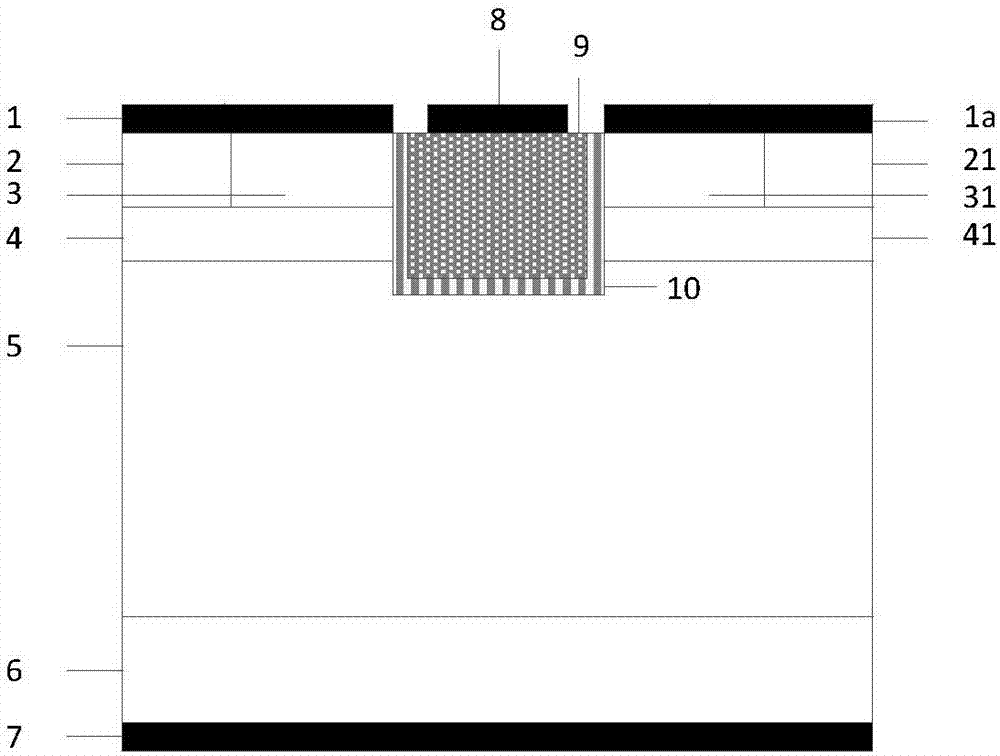

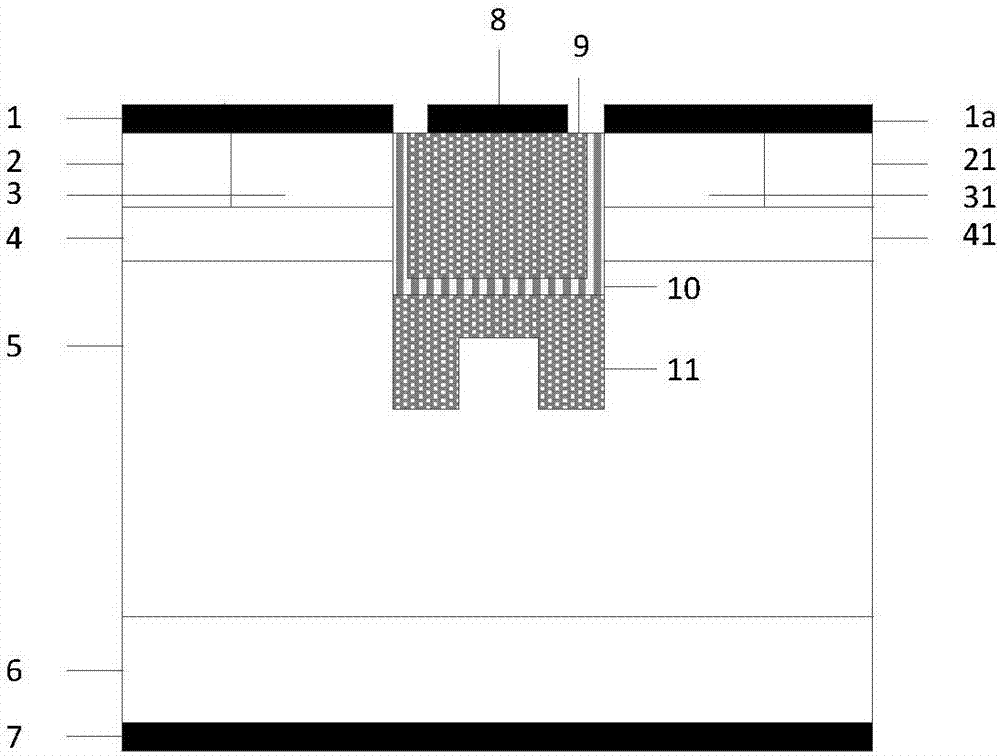

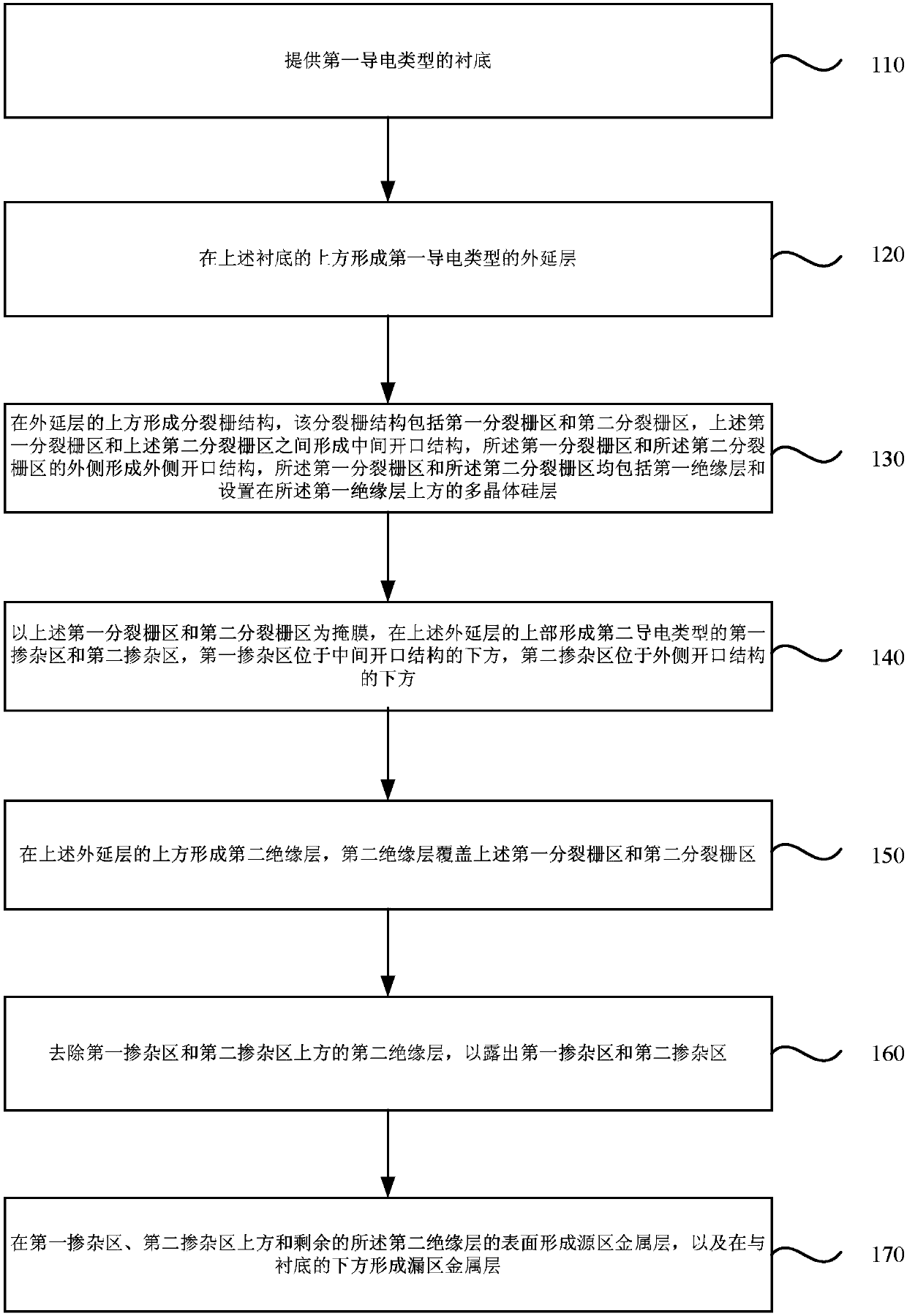

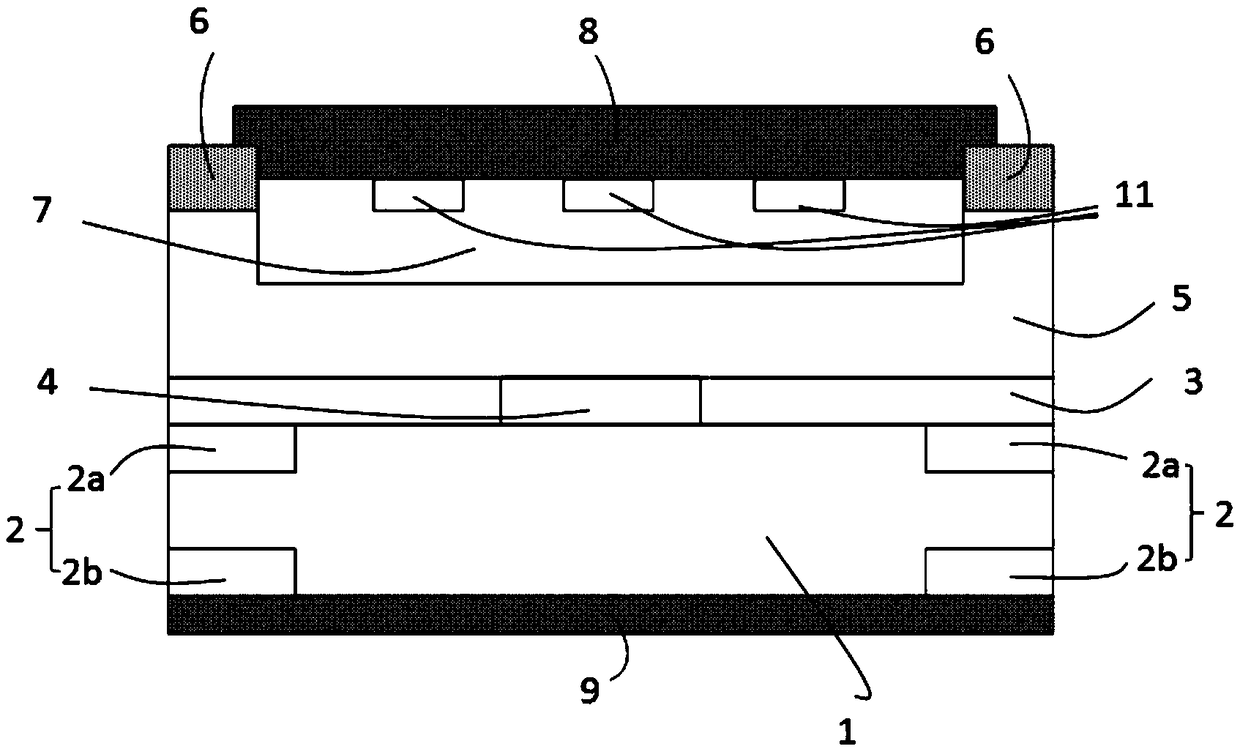

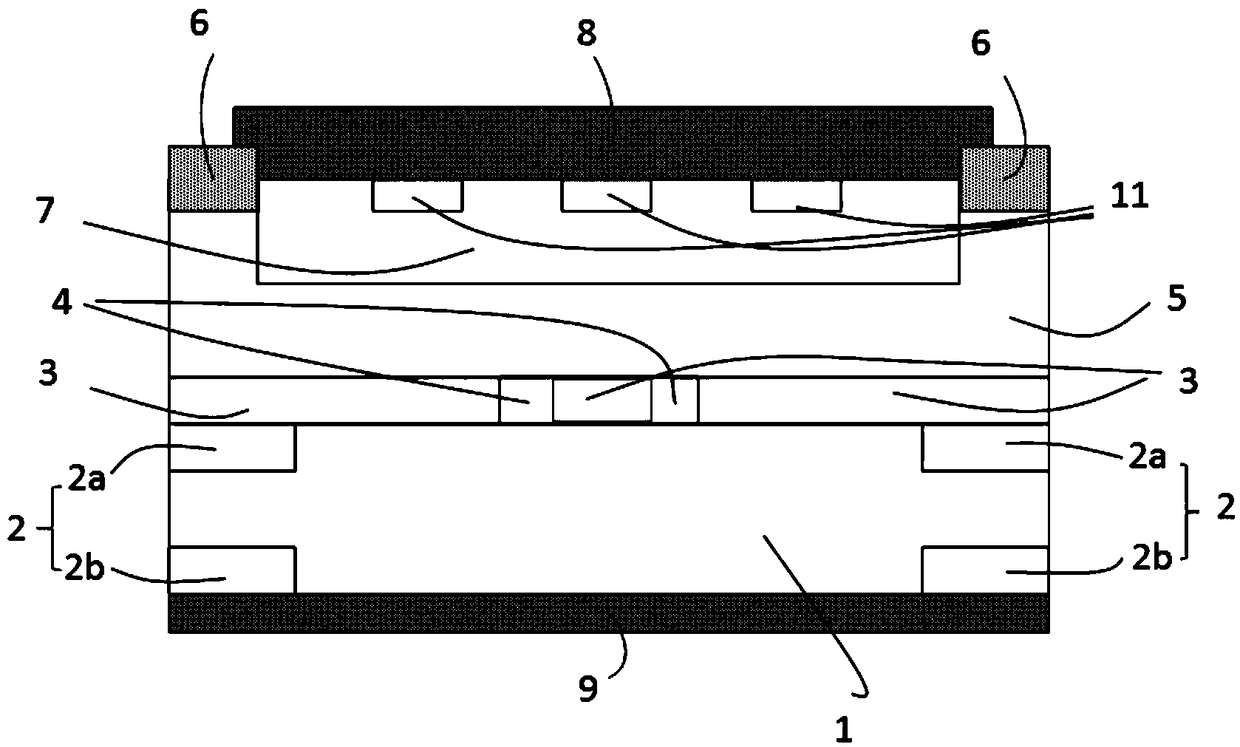

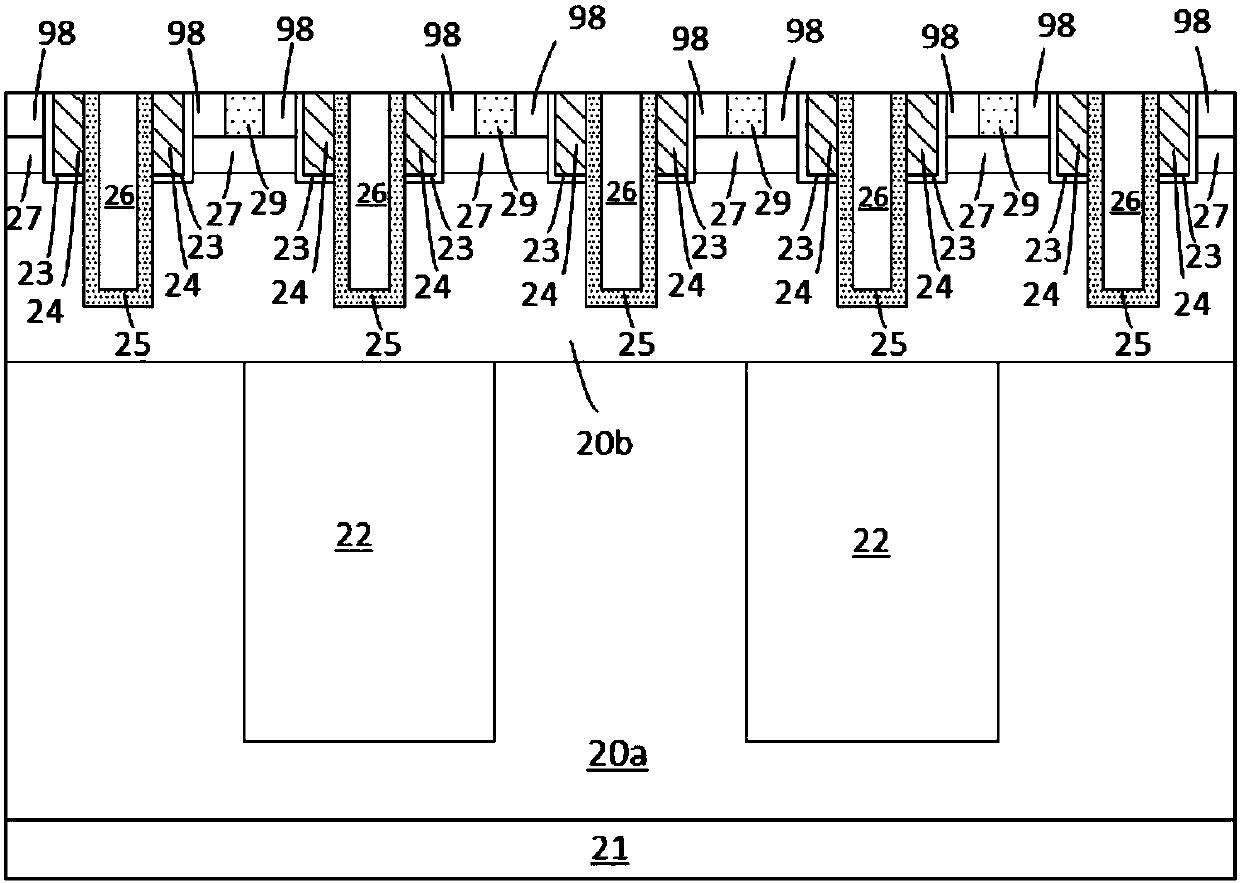

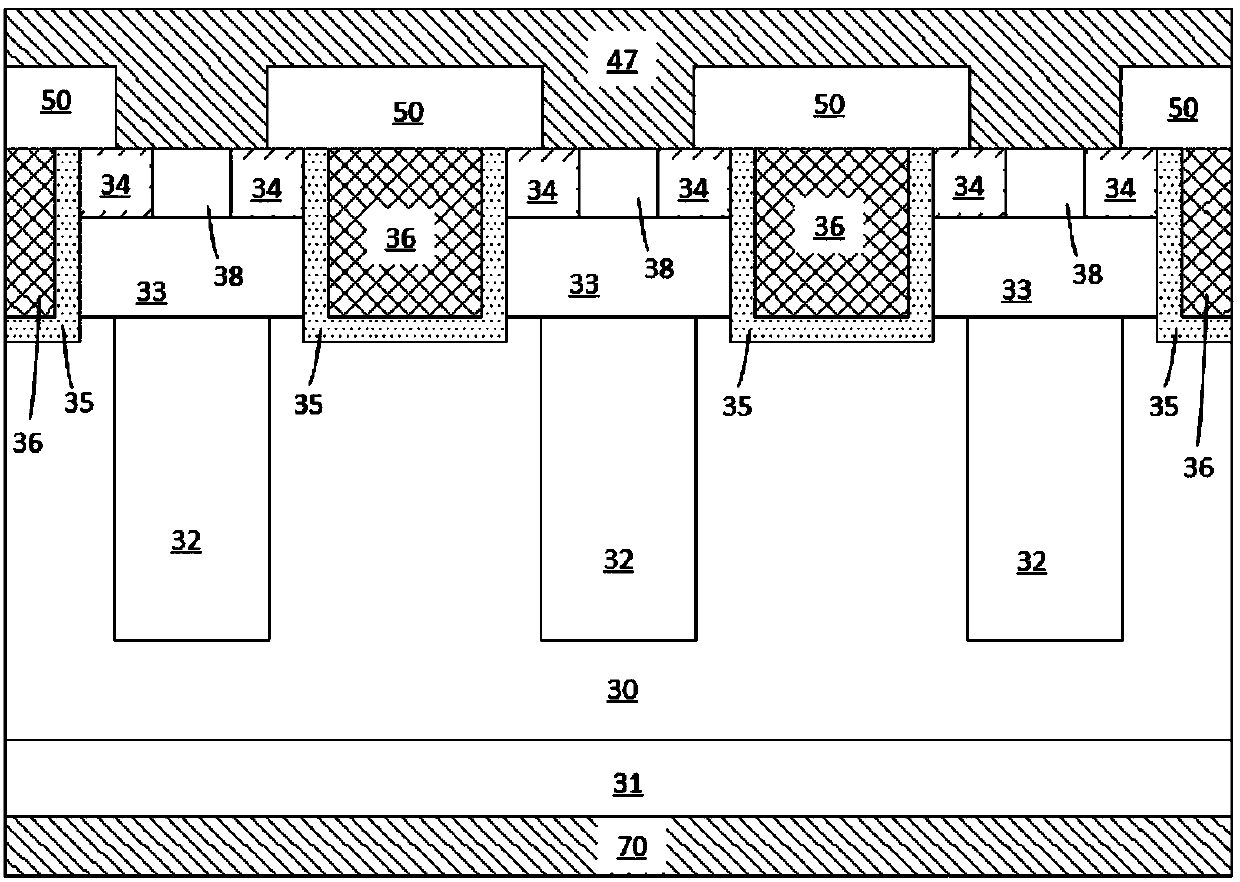

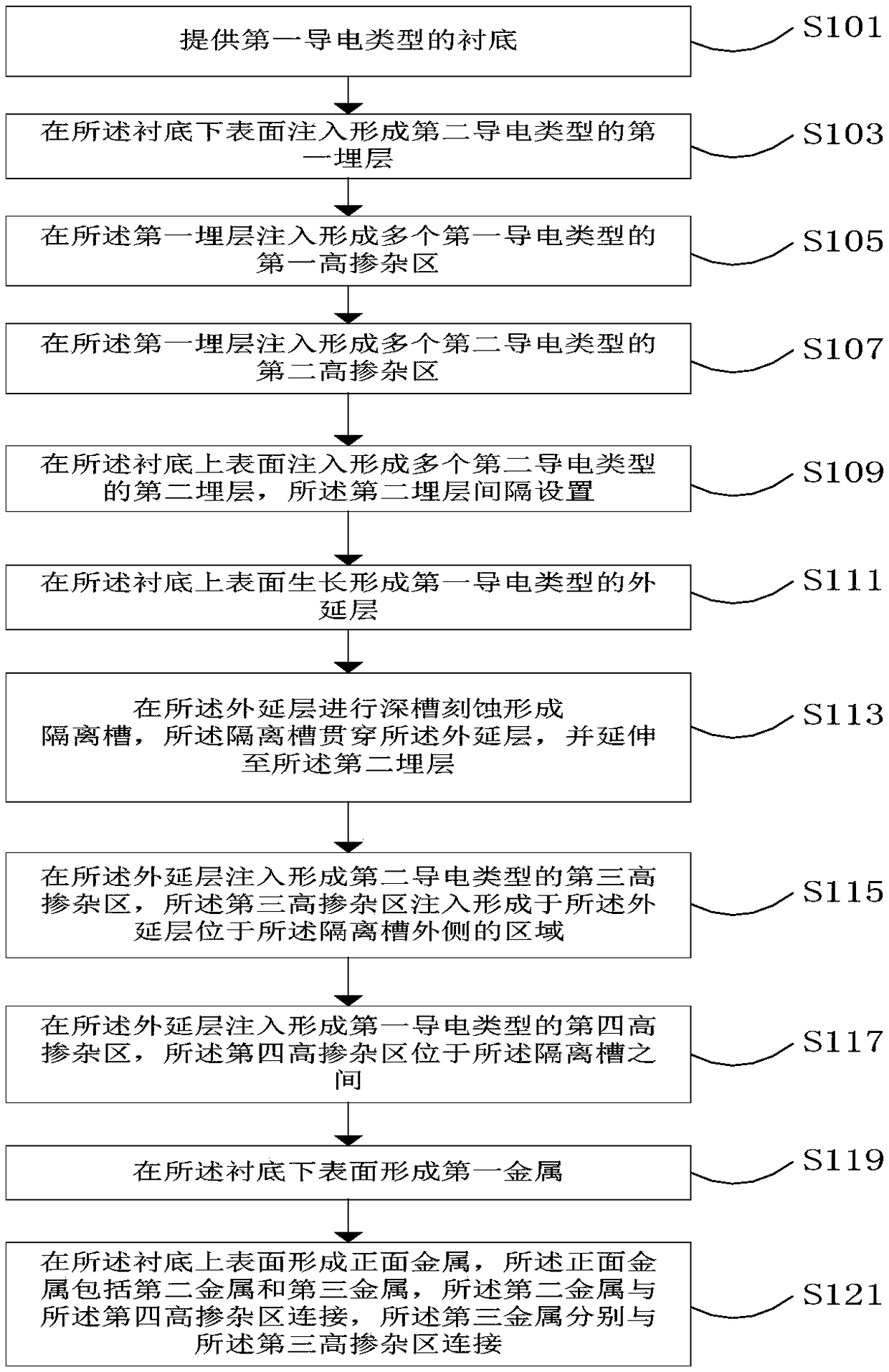

Vertical double-diffusion metal oxide semiconductor device and manufacturing method thereof

InactiveCN107785427AReduce reverse recovery chargeShort switching timeSemiconductor/solid-state device manufacturingSemiconductor devicesCapacitanceDouble diffusion

The embodiments of the invention provide a vertical double-diffusion metal oxide semiconductor device and a manufacturing method thereof. The method comprises the steps of: providing a substrate of afirst conductive type; forming an epitaxial layer of the first conductive type on the substrate; forming a split gate structure on the epitaxial layer, a first split gate region and a second split gate region each comprising a first insulating layer and a polycrystalline silicon layer on the first insulating layer; forming a first doped region and a second doped region of a second conductive typeon the upper surface of the epitaxial layer; forming a second insulating layer on the epitaxial layer, the second insulating layer covering the first split gate region and the second split gate region; and removing the second insulating layer on the first doped region and the second doped region to expose the first doped region and the second doped region. The embodiments of the invention providea manufacturing method and a structure of a vertical double-diffusion metal oxide semiconductor device, which can reduce the reverse capacitance and the switching time of the device and improve the voltage endurance of the device.

Owner:WUXI CHINA RESOURCES HUAJING MICROELECTRONICS

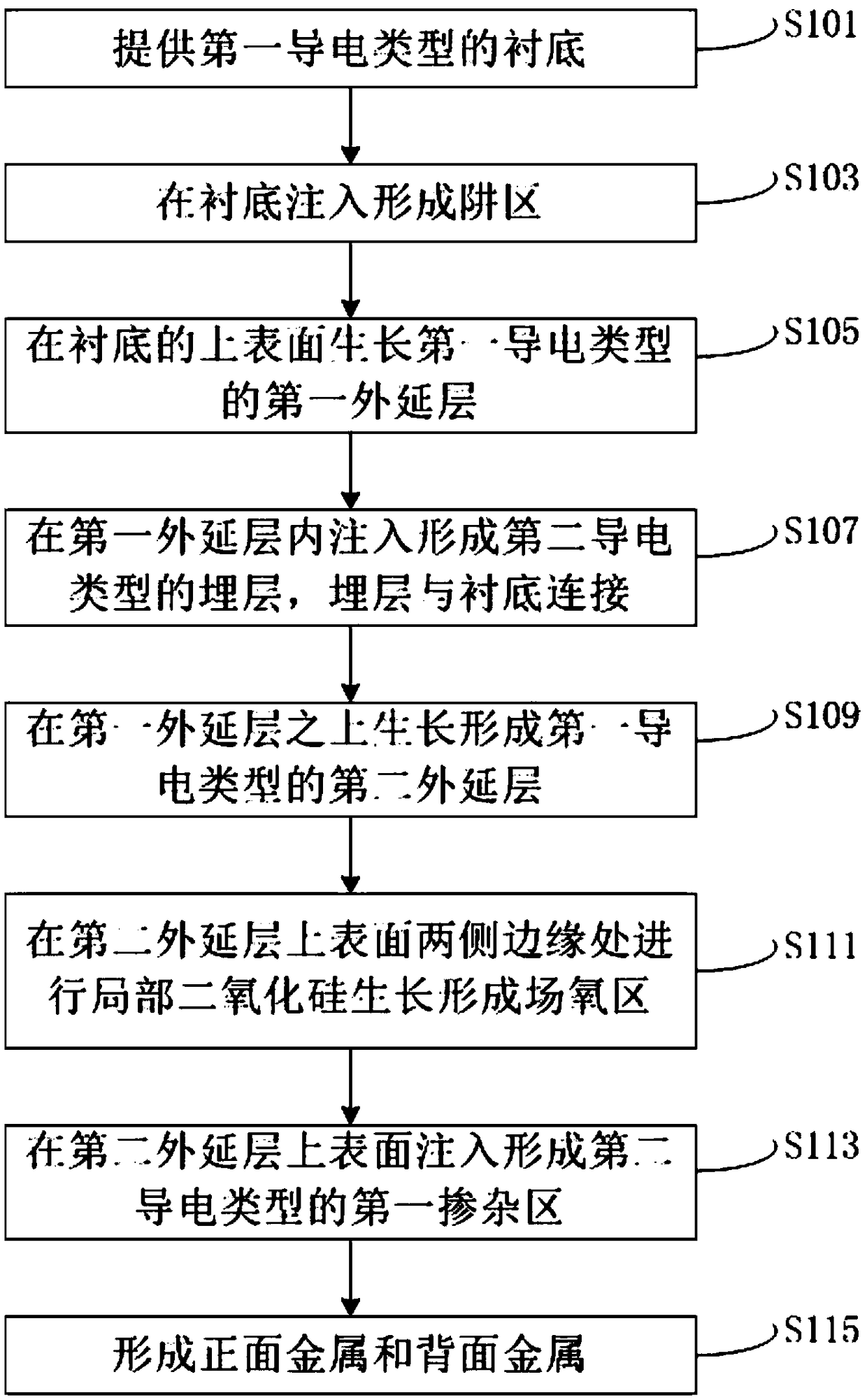

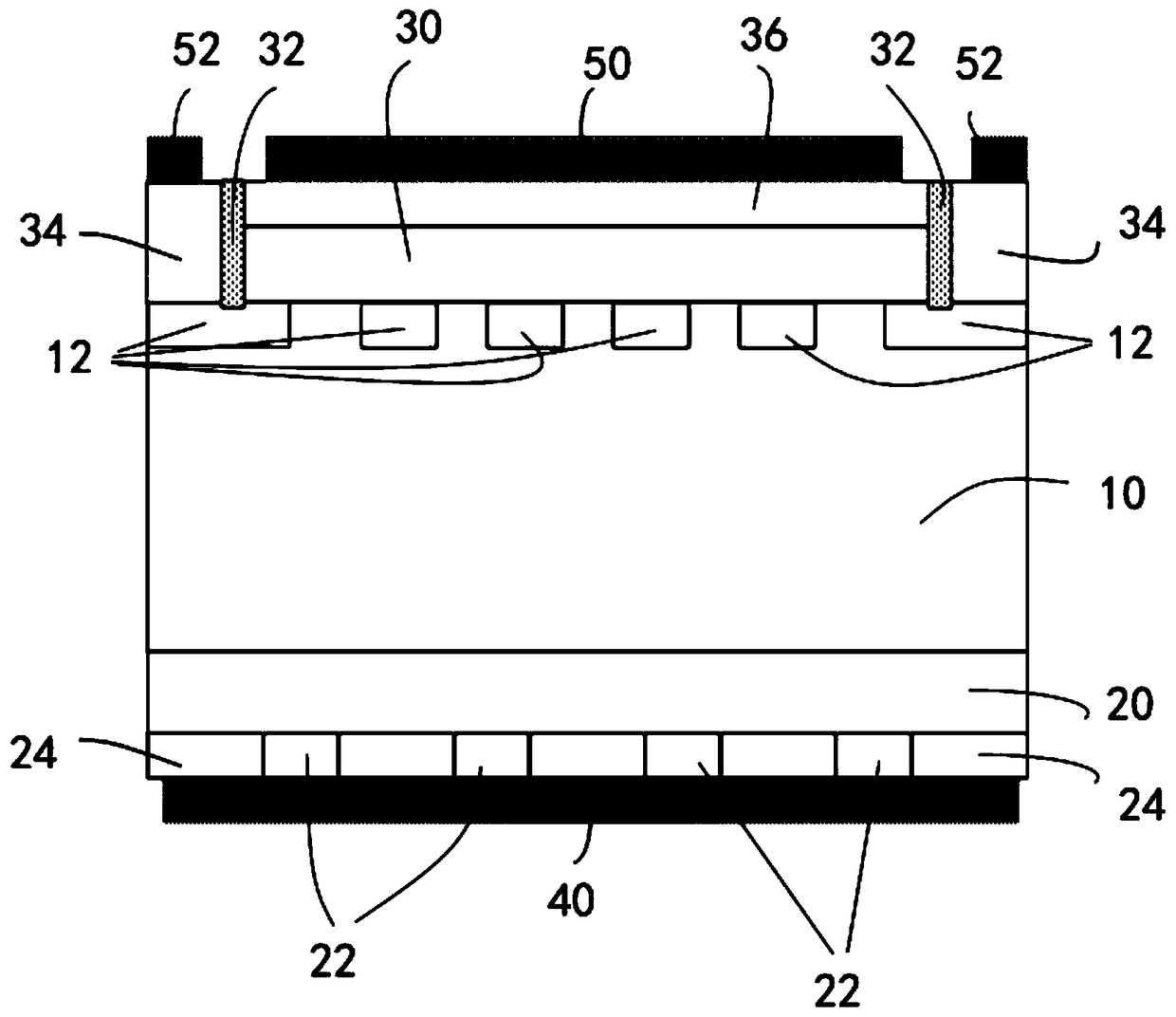

Diode and manufacturing method thereof

ActiveCN109004022ALower breakdown voltageReduce reverse recovery chargeSemiconductor/solid-state device manufacturingSemiconductor devicesReverse recoveryAvalanche diode

A technical scheme of the invention relates to a diode and a manufacturing method thereof. The diode comprises: a substrate of a first conductivity type, well regions of a second conductivity type isformed on edges of two sides of the upper and lower surfaces of the substrate, a first epitaxial layer of a first conductivity type, a buried layer formed on the first epitaxial layer and connected tothe substrate, a second epitaxial layer of the first conductivity type, field oxygen regions formed on edges of two sides on the second epitaxial layer corresponding to the well regions, a first doped region of the second conductivity type, a front metal and a back metal formed in the second epitaxial layer. As the bury layer is provide on the first epitaxial layer, such that a parasitic avalanche diode is formed on the cathode side, As the breakdown voltage is low, the reverse recovery time can be shortened and the soft reverse recovery characteristic can be obtained. Meanwhile, the well regions of the second conductivity type are respectively injected to the upper and lower surfaces of the substrate, and the reverse recovery charge can be reduced by cooperating with the field oxygen regions, the reverse recovery time can be shortened, and the softer reverse recovery characteristic is achieved.

Owner:深圳市天佑照明有限公司

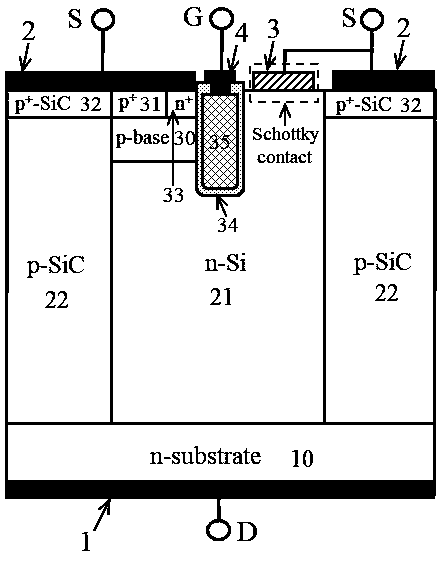

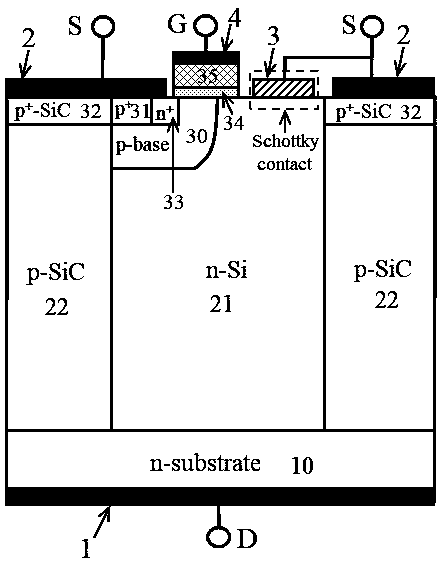

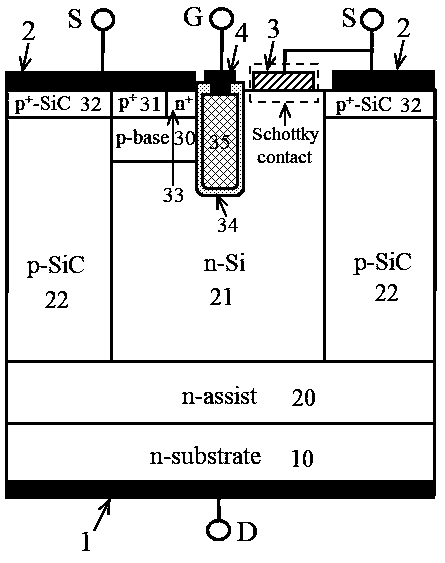

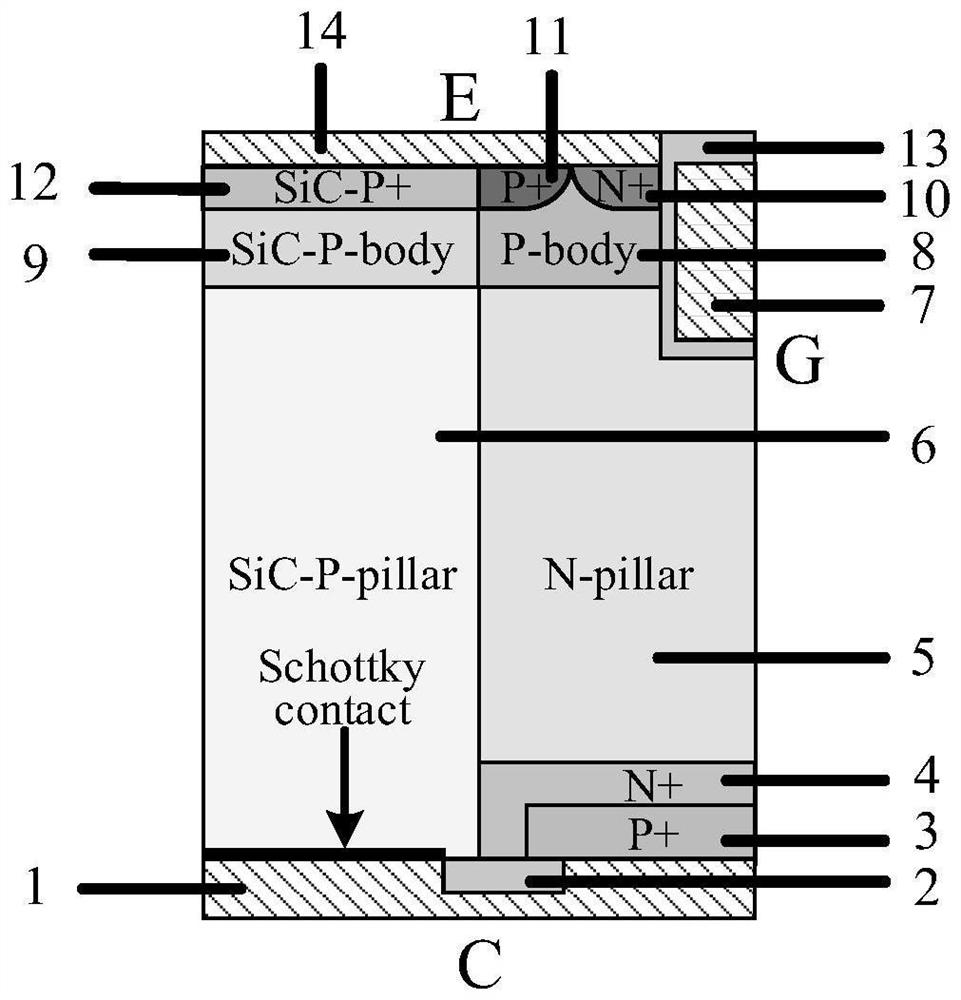

Superjunction metal-oxide-semiconductor field effect transistor (MOSFET) containing p-SiC and integrated with Schottky diode

ActiveCN109755296AReduce reverse recovery chargeReduce shockSolid-state devicesSemiconductor devicesMOSFETElectrical conductor

The invention provides a superjunction metal-oxide-semiconductor field effect transistor (MOSFET) device. A second type of semiconductor area of the second conductive type in a voltage withstanding layer of the MOSFET device can be made of silicon carbide materials, a first type of semiconductor area of the first conductive type in the voltage withstanding layer of the MOSFET device can be made ofsilicon materials, at least part of the upper surface of the first type of semiconductor area of the first conductive type in the voltage withstanding layer makes contact with a conductor to form a Schottky contact electrode, and the Schottky contact electrode is connected with a source electrode through a wire. Compared with a common superjunction MOSFET device, the breakdown voltage of the superjunction MOSFET device is more not prone to being affected by charge non-equilibrium, and the reverse recovery characteristics of a diode are better.

Owner:SICHUAN UNIV

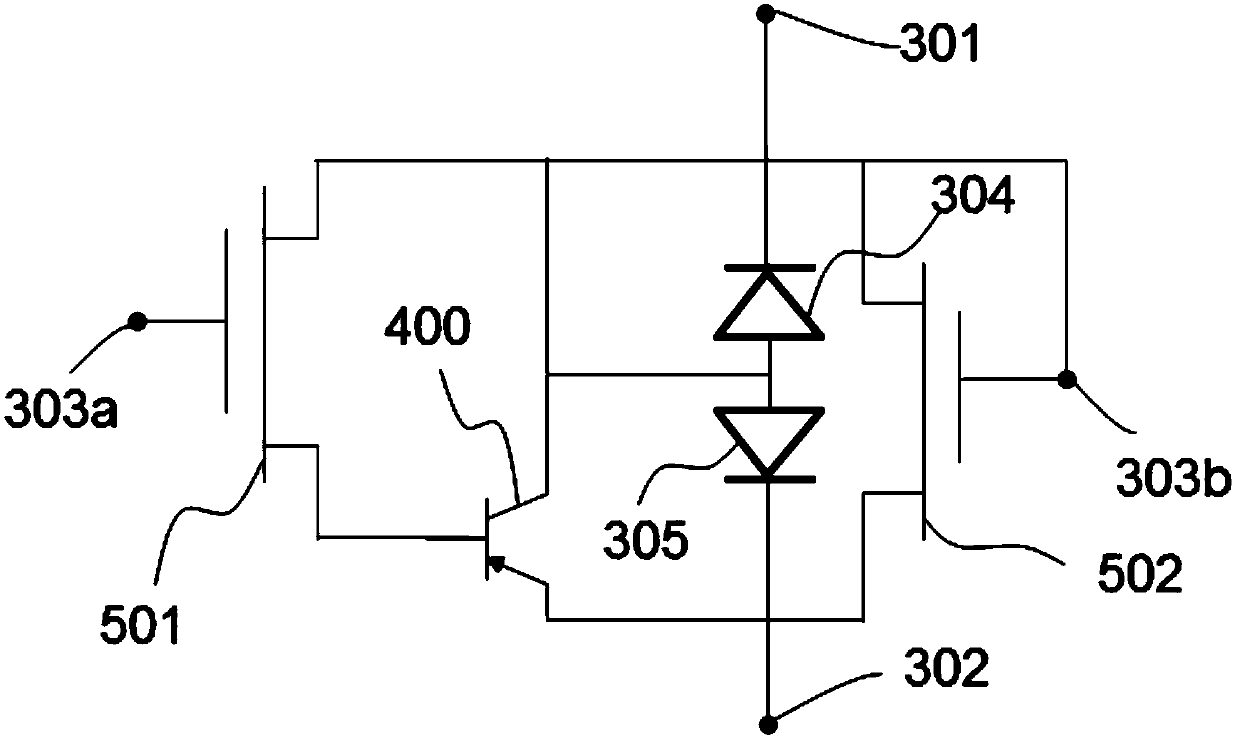

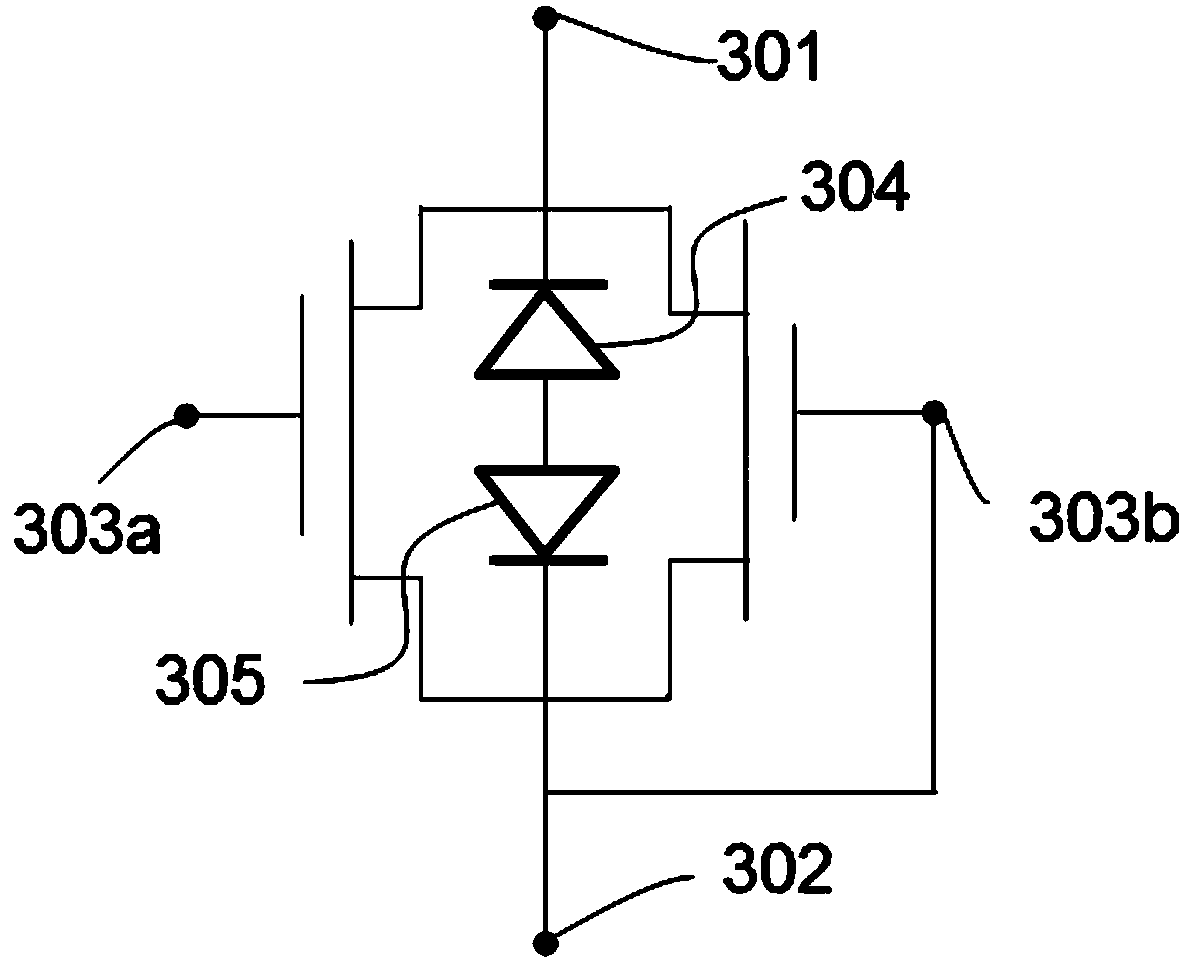

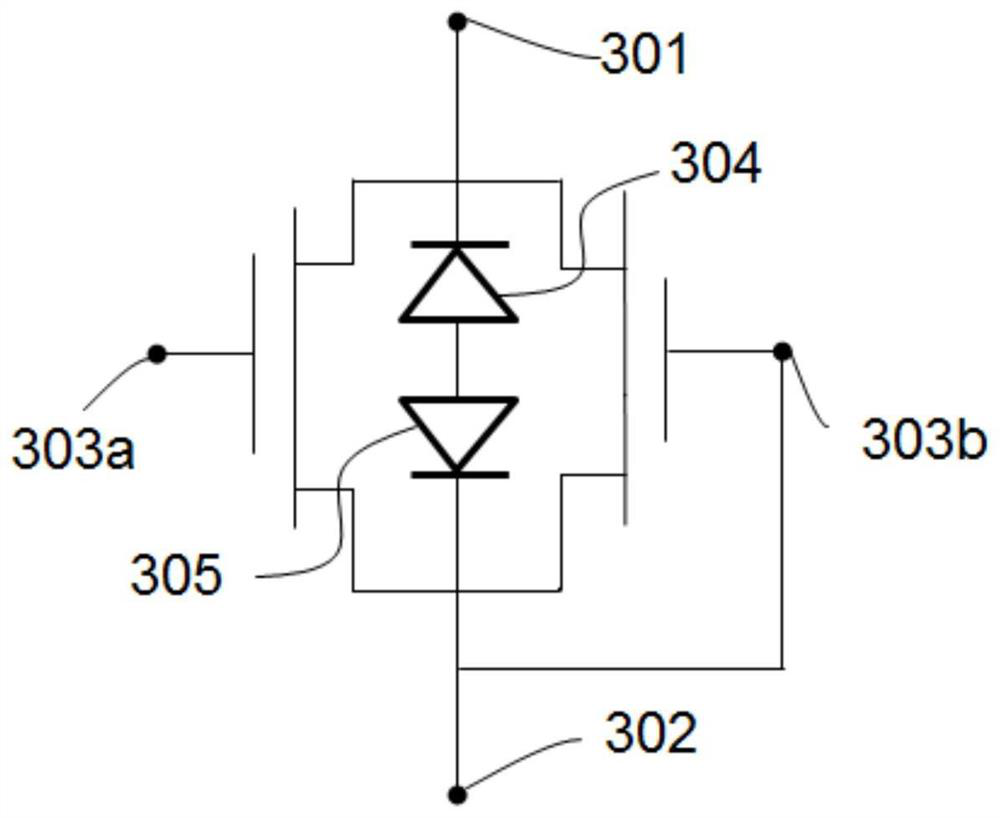

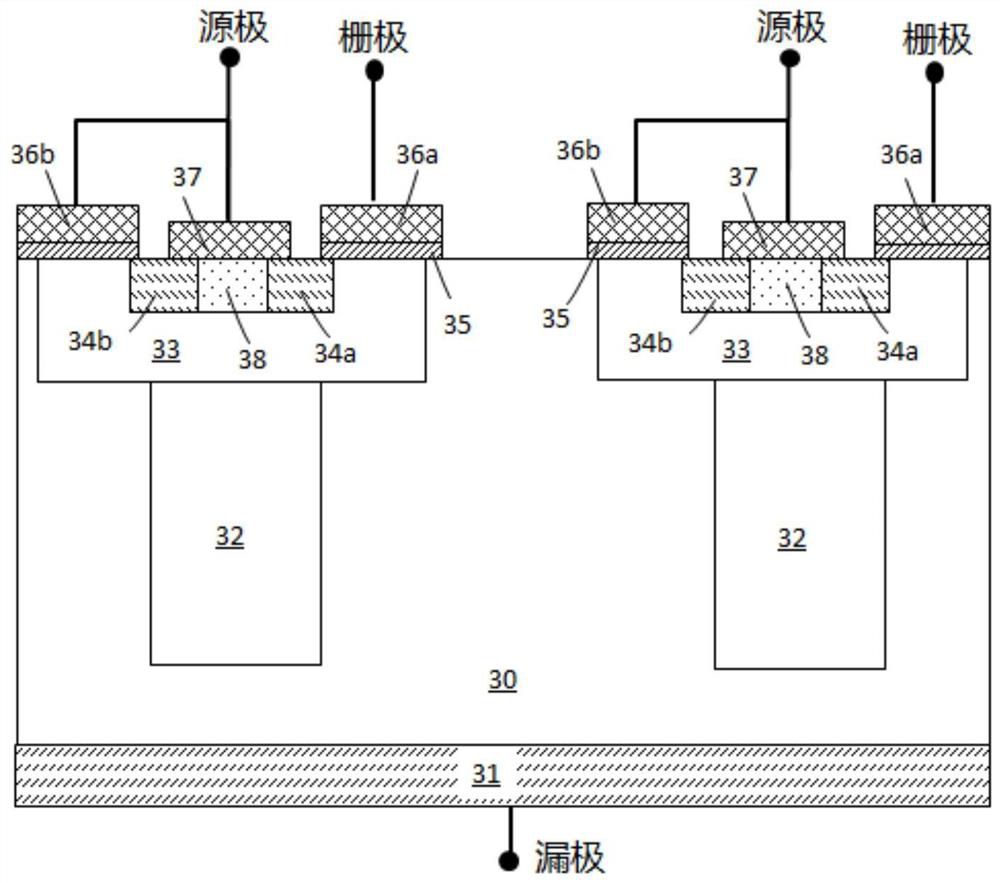

Super junction power device of split gate structure

ActiveCN109755238AReduce reverse recovery chargeReduce reverse recovery timeSolid-state devicesSemiconductor devicesCurrent channelBody contact

Embodiments of the invention disclose a super junction power device of a split gate structure. The device comprises a source, a drain, a first gate, a second gate, a third gate, a body diode and a body contact diode, wherein the cathode of the body diode is connected to the drain, the anode of the body contact diode is connected to the anode of the body diode, the cathode of the body contact diodeis connected to the source, the first gate controls a first current channel between the source and the drain to be turned on or off through the gate voltage, the second gate and a third gate are connected to the source, the second gate controls a second current channel between the source and the drain to be turned on or off through the source voltage, the third gate is a shield gate, and the source voltage is used to increase the withstand voltage of the super junction power device of the split gate structure.

Owner:SUZHOU ORIENTAL SEMICONDUCTOR CO LTD

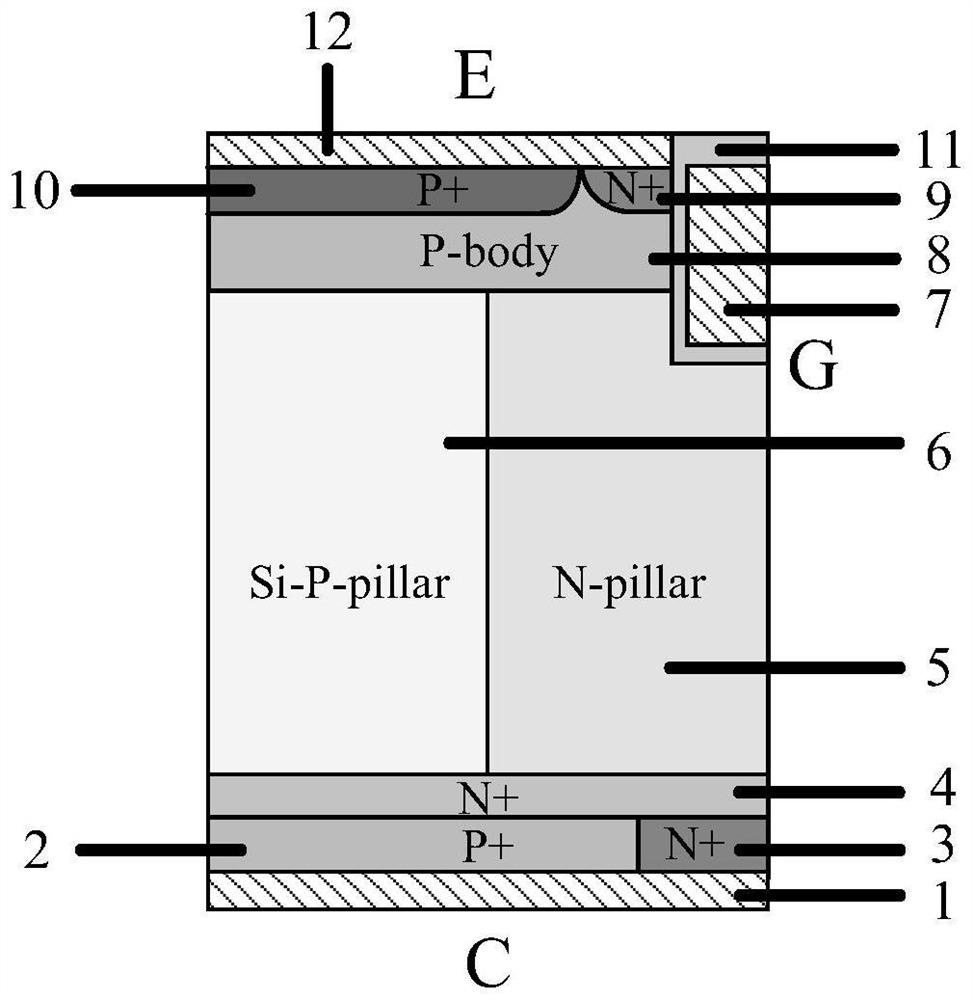

Super-junction reverse conducting IGBT (Insulated Gate Bipolar Translator) with heterojunction

ActiveCN114256331AEliminate the snapback phenomenonReduce reverse recovery chargeEfficient power electronics conversionSemiconductor devicesCarbide siliconHeterojunction

The invention belongs to the technical field of power semiconductors, and particularly relates to a super-junction reverse conducting IGBT (Insulated Gate Bipolar Translator) with a heterojunction. The cell structure of the heterojunction super-junction reverse conducting IGBT comprises a collector electrode structure, a voltage-withstanding layer structure, a grid electrode structure and an emitting electrode structure, compared with a traditional structure, the collector electrode structure is firstly improved, an insulating medium is arranged in the middle of collector electrode metal, a collector electrode region is completely arranged below an N drift region, and the voltage-withstanding layer structure is arranged in the middle of the N drift region; meanwhile, a P drift region on the other side and a P well and a P contact region on the drift region are all made of silicon carbide, so that the snapback phenomenon of a traditional super-junction reverse conducting IGBT during forward conduction is eliminated, and reverse recovery charges can be effectively reduced.

Owner:UNIV OF ELECTRONICS SCI & TECH OF CHINA

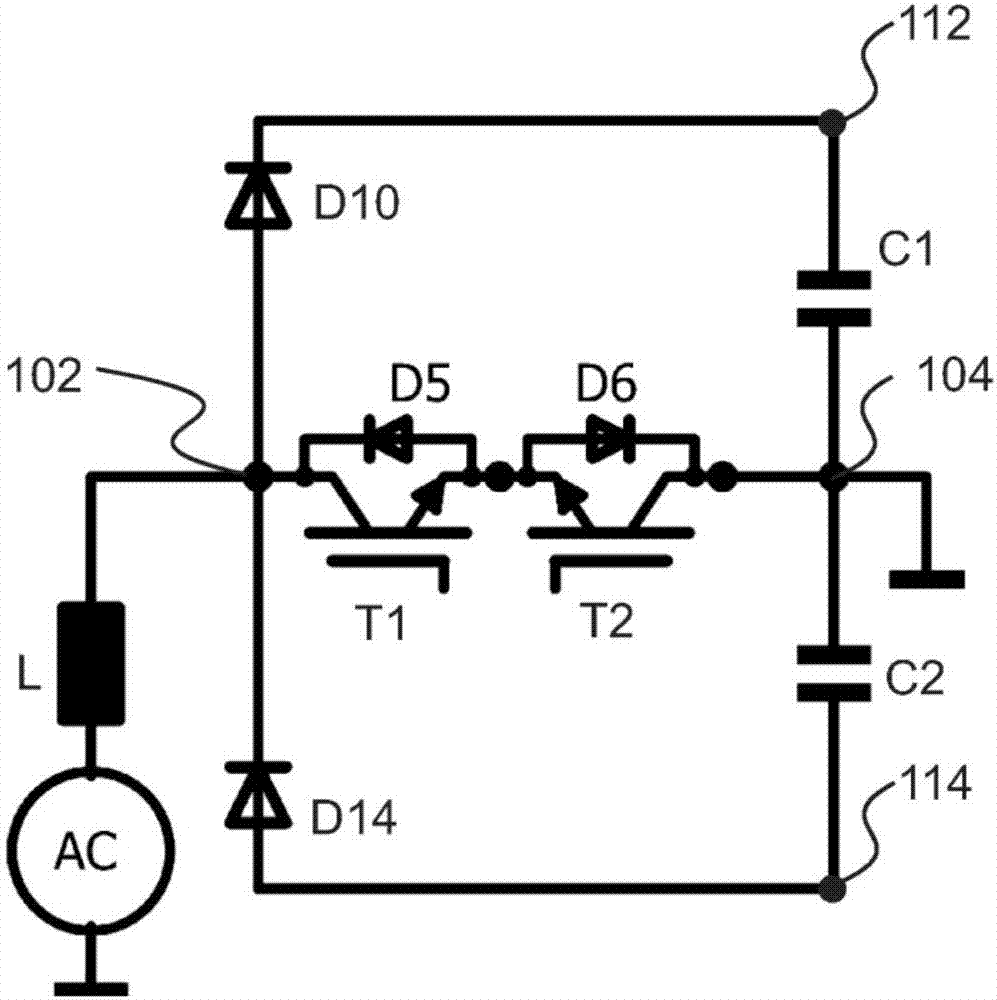

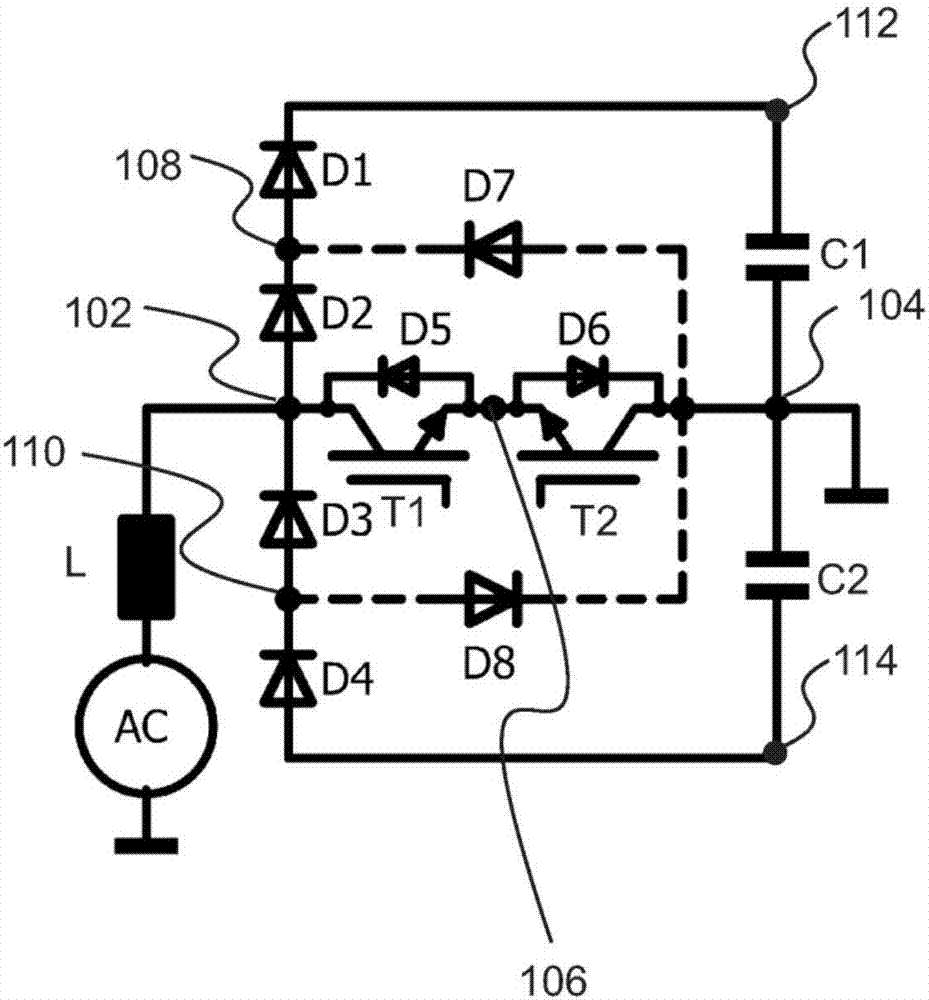

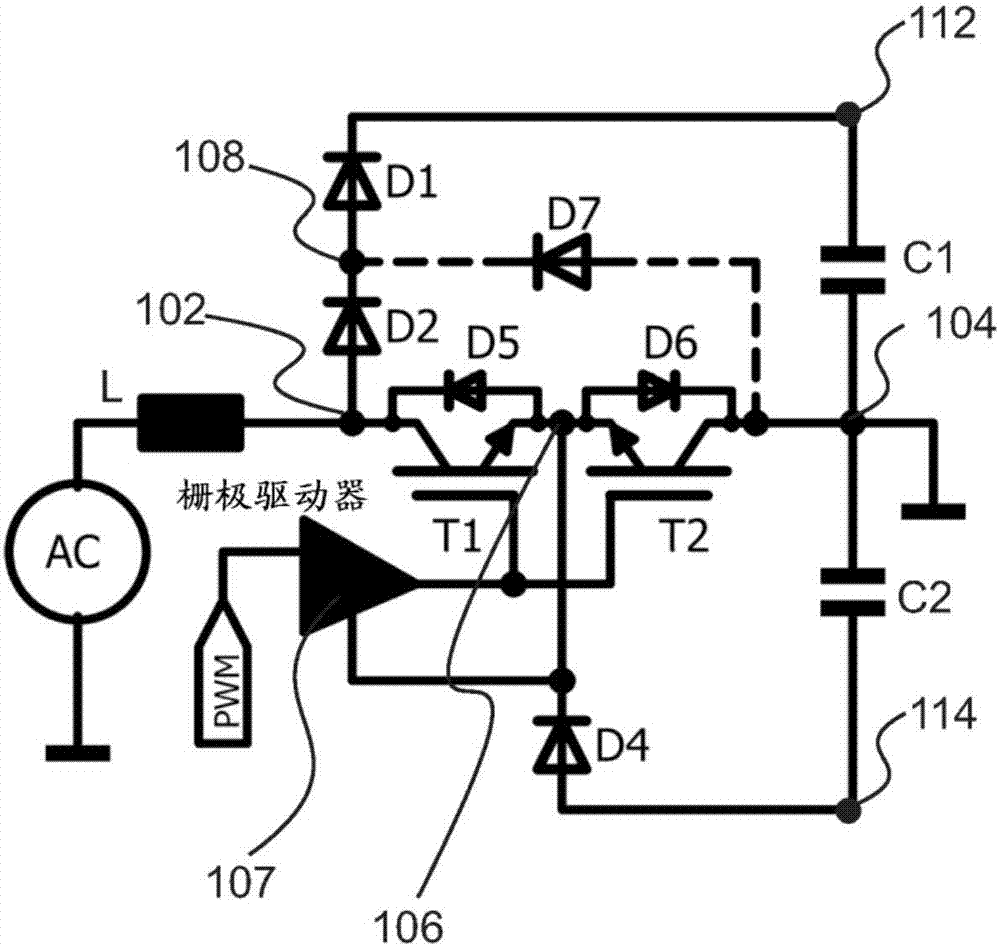

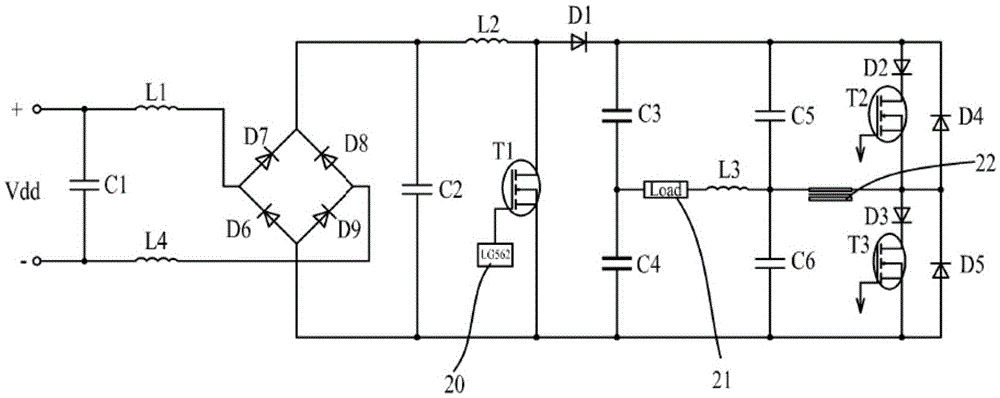

Booster circuit and inverter topology with cascade diode circuit

ActiveCN107546974AReduce lossReduce reverse recovery chargeEfficient power electronics conversionAc-dc conversionPower inverterInverter topology

The invention, as a whole, relates to topology used for a booster circuit, an inverter and a half-bridge circuit. A power factor correction (PFC) booster circuit used for being connected to an AC power supply includes: an AC input node (102) used for being connected to the AC power supply; a reference level node (104) used for being connected to a reference level; and at least a first and second power transistors, which are in series-opposing connection between the AC power supply and the reference level node, wherein the first power transistor (T1) is in reverse parallel connection with a first power diode (D5), and the second power transistor (T2) is in reverse parallel connection with a second power diode (D6). First diode circuits (D1, D2) are connected between the AC input node (102)and a positive output node (112), and include a series connection, different in recovery time, of a first diode element and a second diode element.

Owner:VINCOTECH

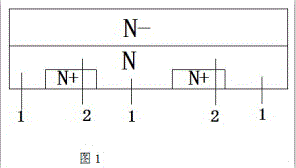

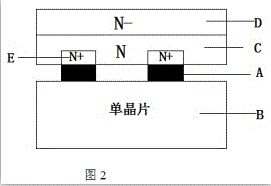

Fast recovery diode material slice structure containing cathode auxiliary part and manufacturing method thereof

InactiveCN105762174ALow costReduce reverse recovery chargeSemiconductor devicesHigh concentrationMachining process

The invention mainly aims to provide a fast recovery diode material slice structure containing a cathode auxiliary part. High-concentration N+ junctions are arranged at intervals and manufactured on the N surface of an N type monocrystalline wafer, and the fast recovery diode material slice structure has a self-modulation effect and has good soft recovery characteristics; according to the material slice, the monocrystalline wafer adheres to the N surface in a silicon oxidation mode, and the wafer is not fragile in the processing process. The manufacturing cost of the structure is lower than that of an epitaxial slice. Compared with the conventional processed epitaxial slice, the fast recovery diode material slice structure containing the cathode auxiliary part has good fast and soft recovery characteristics and is lower in cost.

Owner:上海芯石微电子有限公司

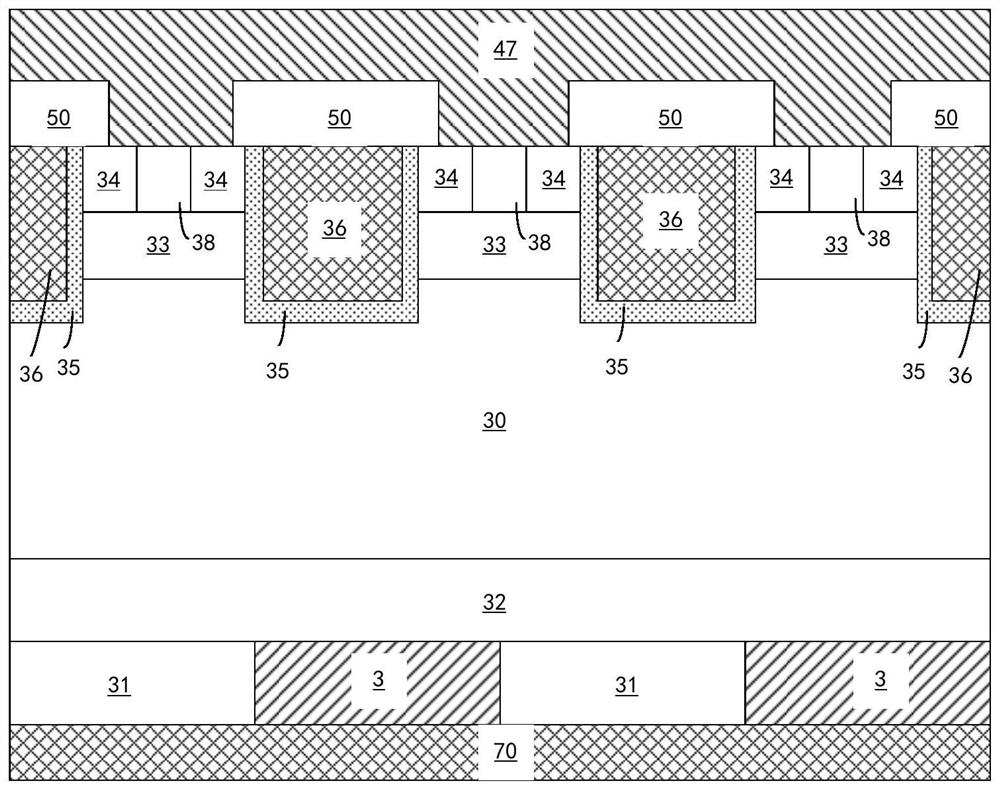

Grooved super junction power device

ActiveCN109755289AReduce reverse recovery chargeReduce reverse recovery timeSemiconductor devicesCurrent channelPower flow

The embodiment of the invention provides a grooved super junction power device. The device comprises sources, a drain, first gates, second gates, body diodes, and p-body contact diodes, wherein each body diode is connected in series with the corresponding p-body contact diode; each first gate controls the on / off of a corresponding first current channel, which is controlled by the first gate, through a gate voltage; and each second gate is connected with the corresponding source, and controls the on / off of a corresponding second current channel, which is controlled by the second gate, through asource voltage. The grooved super junction power device provided by the invention has the advantages that when the device is off, reverse currents flowing through the body diodes can be greatly reduced, so that the number of minority carriers in the body diodes can be greatly decreased, and the grooved super junction power device can achieve a rapid reverse recovery function.

Owner:SUZHOU ORIENTAL SEMICONDUCTOR CO LTD

Static induction thyristor and manufacturing method thereof

InactiveCN109449205AReduce switching lossesReduce power consumptionThyristorSemiconductor/solid-state device manufacturingReverse recoveryVoltage drop

The invention provides a static induction thyristor and a manufacturing method thereof, and solves the problem that an SITH obtained in the prior art cannot meet the latest use requirements. A first highly-doped region is added to a positive electrode region of a device, so that a parasitic transistor is formed; the conduction voltage drop of the SITH is reduced, and meanwhile, the injection efficiency of a positive electrode is reduced by the first highly-doped region of the positive electrode region, so that the reverse recovery time is shortened, and the reverse recovery charge is also obviously reduced; and the final SITH device has a higher switching speed and lower switching loss. An epitaxial layer is also added between a fourth highly-doped region and a substrate, so that the effect of a buffer layer is achieved; during the reverse recovery period, the electric field intensity of the substrate and the epitaxial layer is reduced and the extraction speed of carriers is reduced, so that high-voltage oscillation is remarkably reduced, and a softer recovery characteristic is obtained; and the reverse recovery charge is less, so that the power consumption of the device is furtherreduced.

Owner:中健共创(深圳)大健康产业投资有限公司

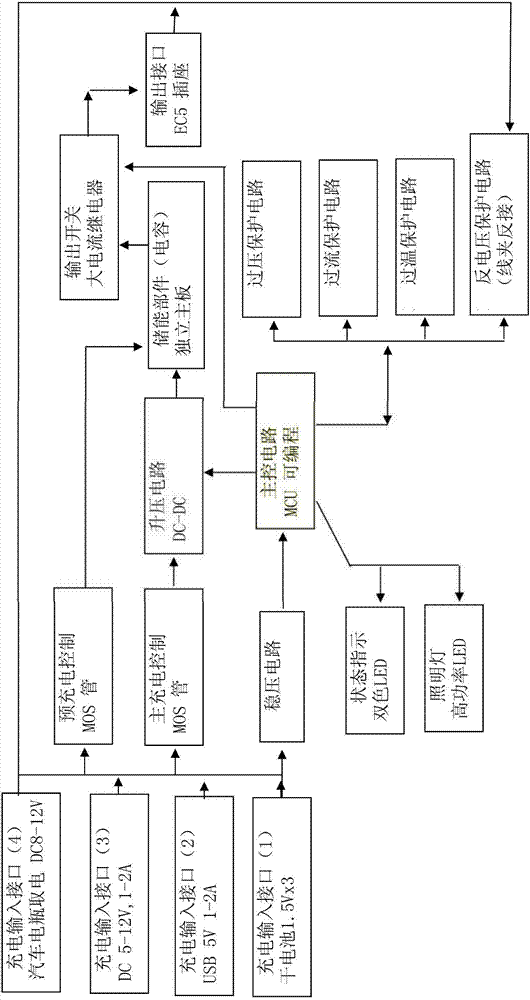

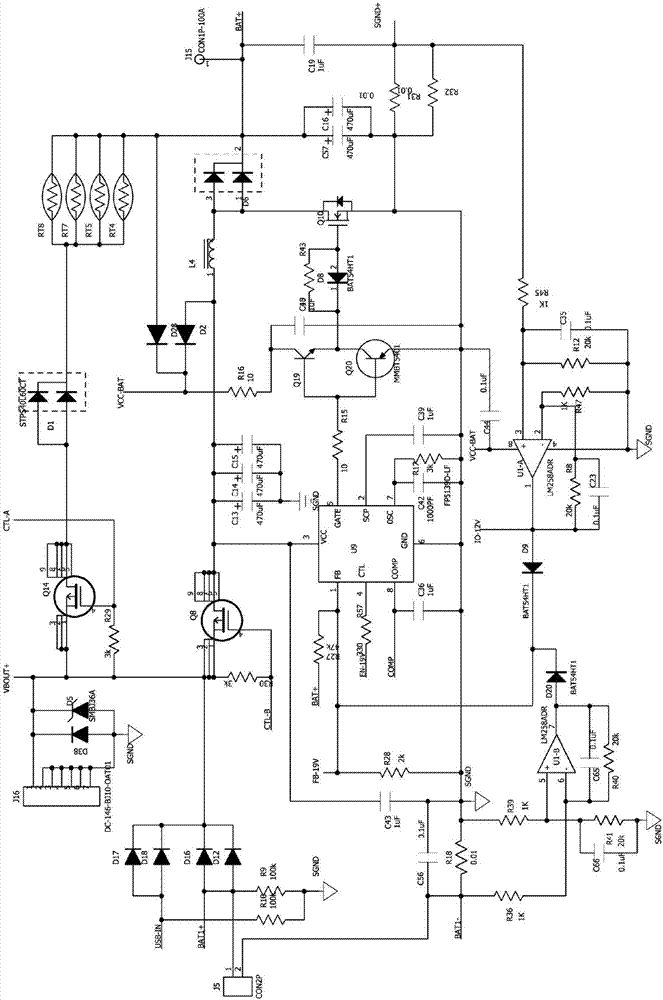

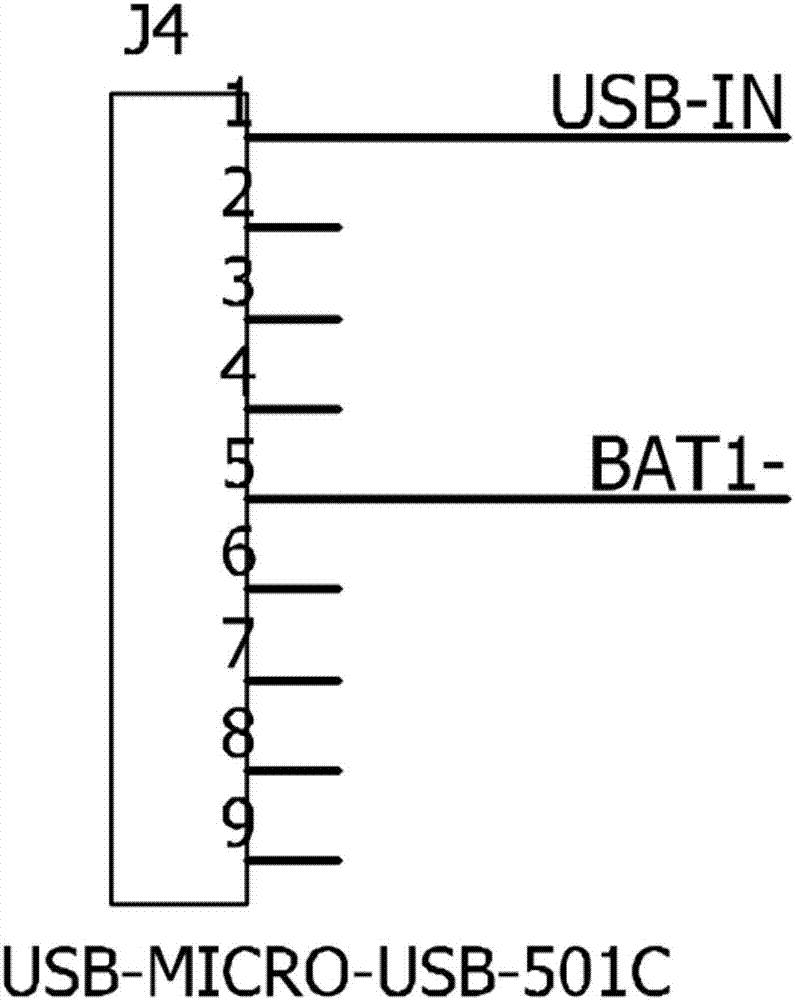

Input and output circuit for car jump starter

PendingCN106936179AReduce reverse recovery chargeFast switching speedIndicating/monitoring circuitsSafety/protection battery circuitsElectricityAlternating current

The invention discloses an input and output circuit for a car jump starter. The input and output circuit comprises a charging input circuit and a power output circuit; the charging input circuit includes four input interfaces, namely, a car storage battery power taking interface, a dry cell charging interface, a USB charging interface and a car cigar lighter interface; and the power output circuit includes a relay. The input and output circuit for the car jump starter includes different types of power interfaces, and is especially suitable for charging mobile power supplies in occasions without AC power supply.

Owner:湖南电将军新能源有限公司

Silicon carbide rectifier

ActiveUS8723218B2Current valueReduce carrier densityThyristorSemiconductor/solid-state device manufacturingPower flowNegative temperature

Owner:U S A AS RPRESENTED BY THE SEC OF THE NAVY THE

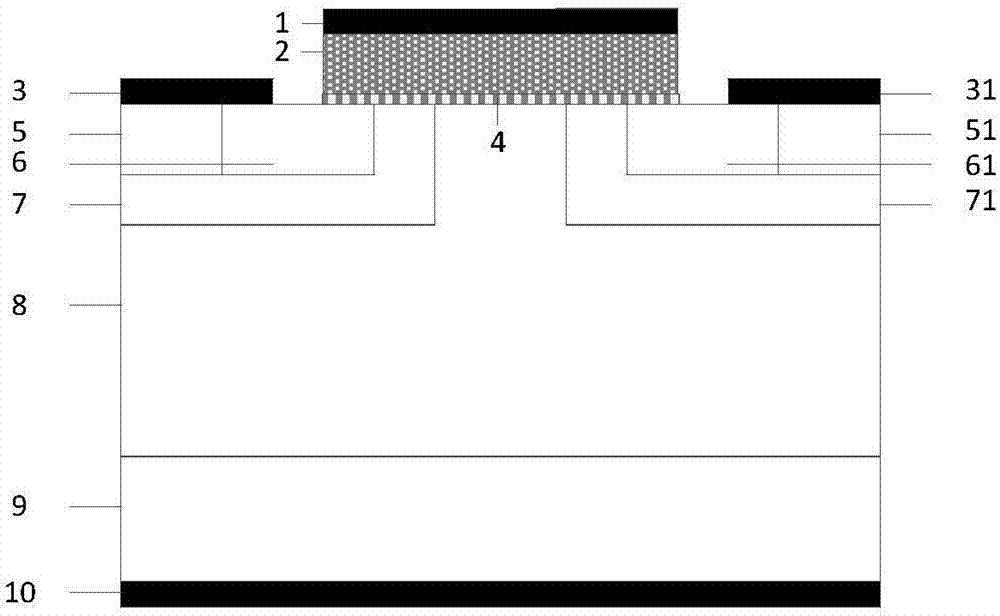

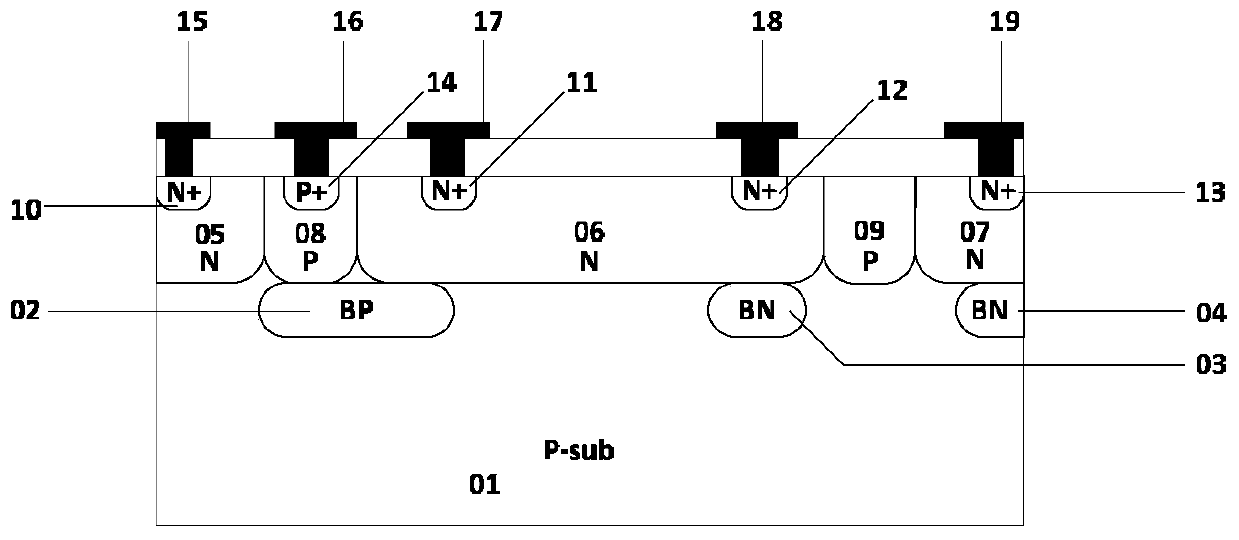

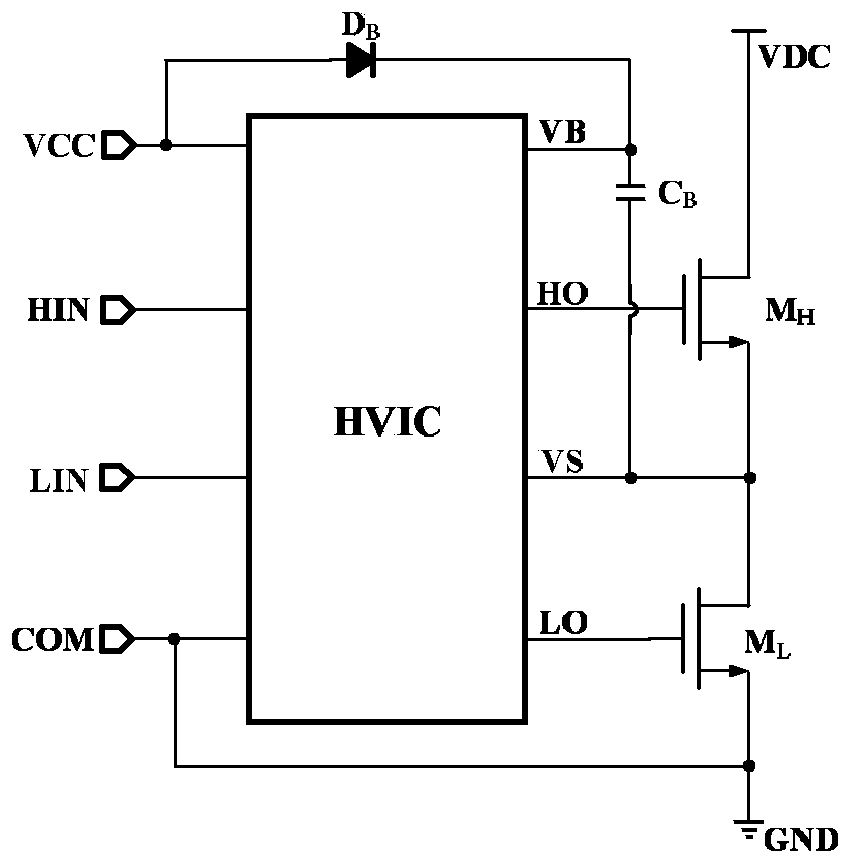

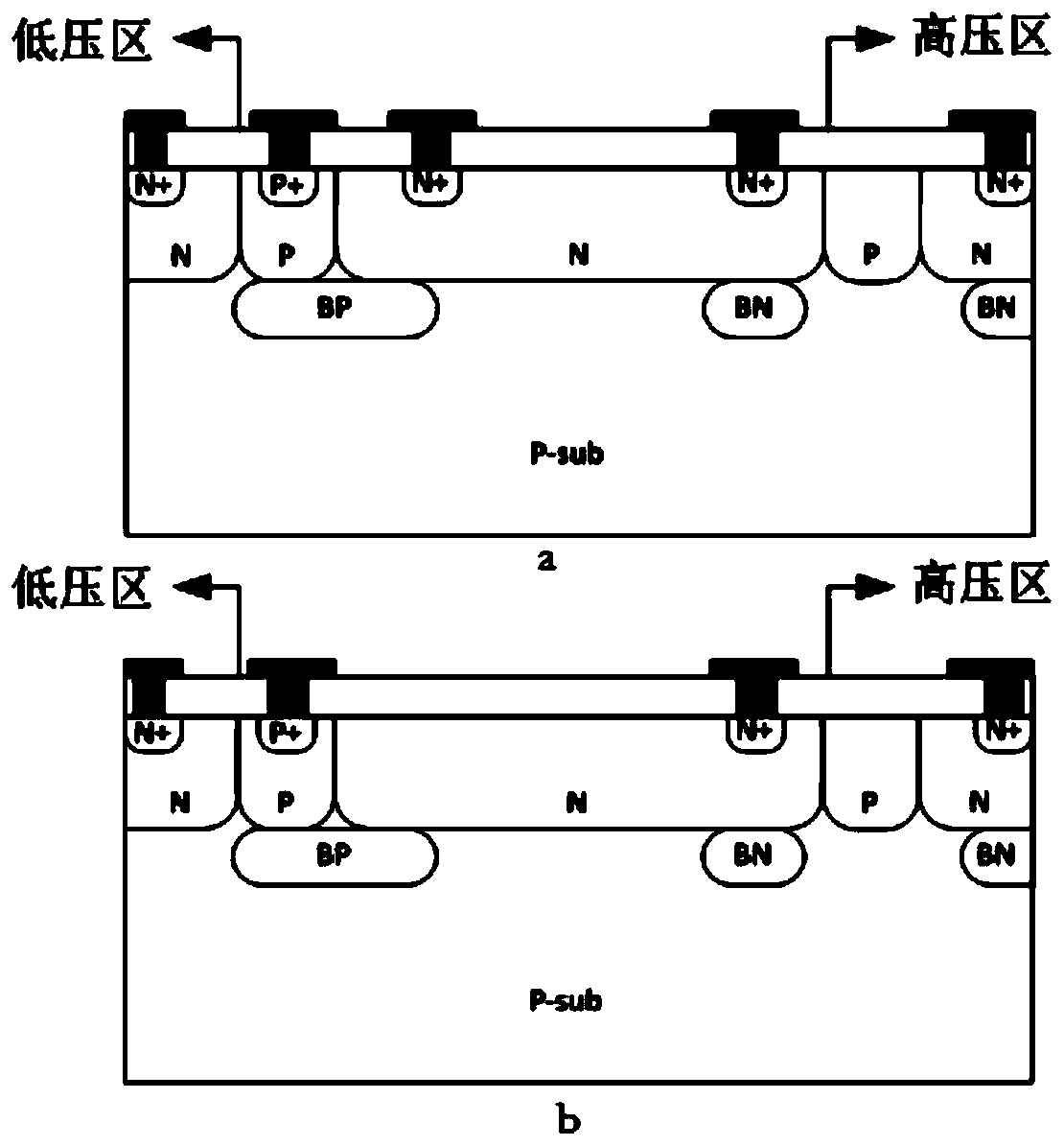

Bootstrap structure and bootstrap circuit integrated on high and low voltage isolation structure

ActiveCN107910326BFunction as a bootstrapSolve reliability problems such as partial breakdownSolid-state devicesSemiconductor devicesCapacitanceLow voltage

The invention relates to a bootstrap structure integrated to a high-and-low-voltage isolation structure and a bootstrap circuit. The bootstrap structure is composed of a first doped type substrate serving as a substrate for a high-and-low-voltage isolation structure, a second doped type drift region serving as a drift region, and a first doped type substrate contact well serving as a substrate contact well. A first doped type substrate contact region as a substrate contact electrode is arranged in the first doped type contact well. A bootstrap structure positive electrode and a bootstrap structure negative electrode are respectively provided in the second doped type drift region; the bootstrap structure positive electrode is one second doped type contact region arranged in the second dopedtype drift region; the bootstrap structure negative electrode is the other second doped type contact region arranged in the second doped type drift region; and the bootstrap structure positive electrode is adjacent to the first doped type contact region. In addition, the bootstrap circuit consists of a bootstrap structure and a bootstrap capacitor; a diode is connected to the bootstrap structurepositive electrode; and the bootstrap capacitor is connected with the bootstrap structure negative electrode.

Owner:SOUTHEAST UNIV

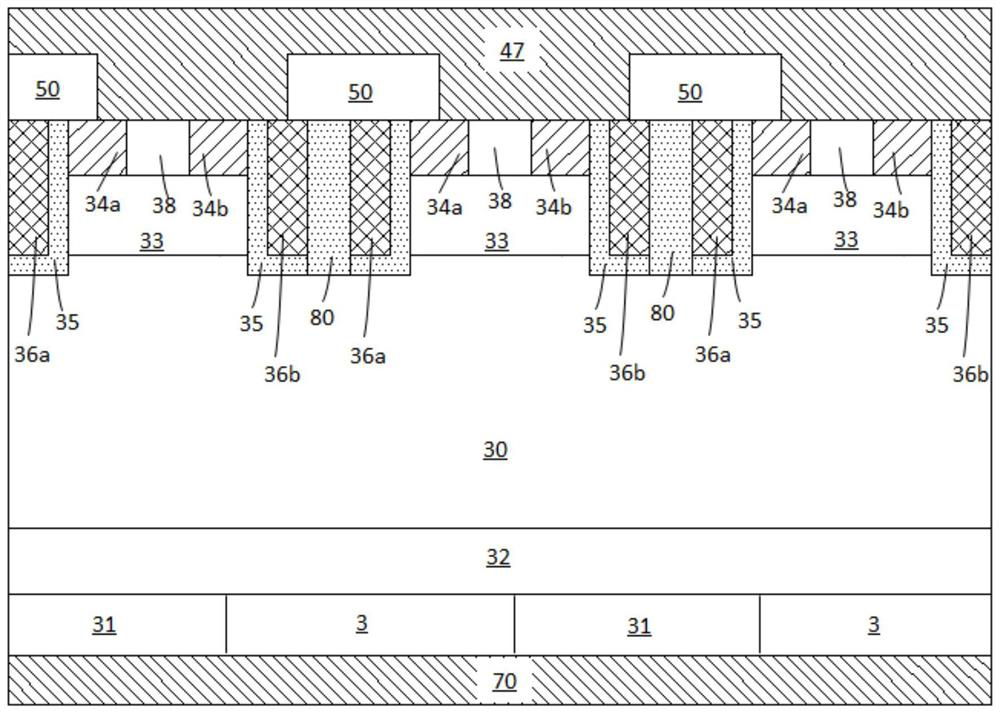

A power mosfet device

ActiveCN109755241BReduce reverse recovery chargeFast reverse recovery functionSolid-state devicesSemiconductor devicesEngineeringPower MOSFET

The present invention provides a power MOSFET device, comprising a source, a drain, a first gate, a second gate, a body diode and a body contact diode, the source, the drain, and the first gate form a first MOSFET structure, the source, drain, and second gate form a second MOSFET structure, the cathode of the body diode is connected to the drain, and the anode of the body contact diode is connected to the anode of the body diode , the cathode of the body contact diode is connected to the source, the first gate controls the opening and closing of the first current channel of the first MOSFET structure through the gate voltage, and the second The gate is connected to the source, and the second gate controls the opening and closing of the second current channel of the second MOSFET structure through the source voltage.

Owner:SUZHOU ORIENTAL SEMICONDUCTOR CO LTD

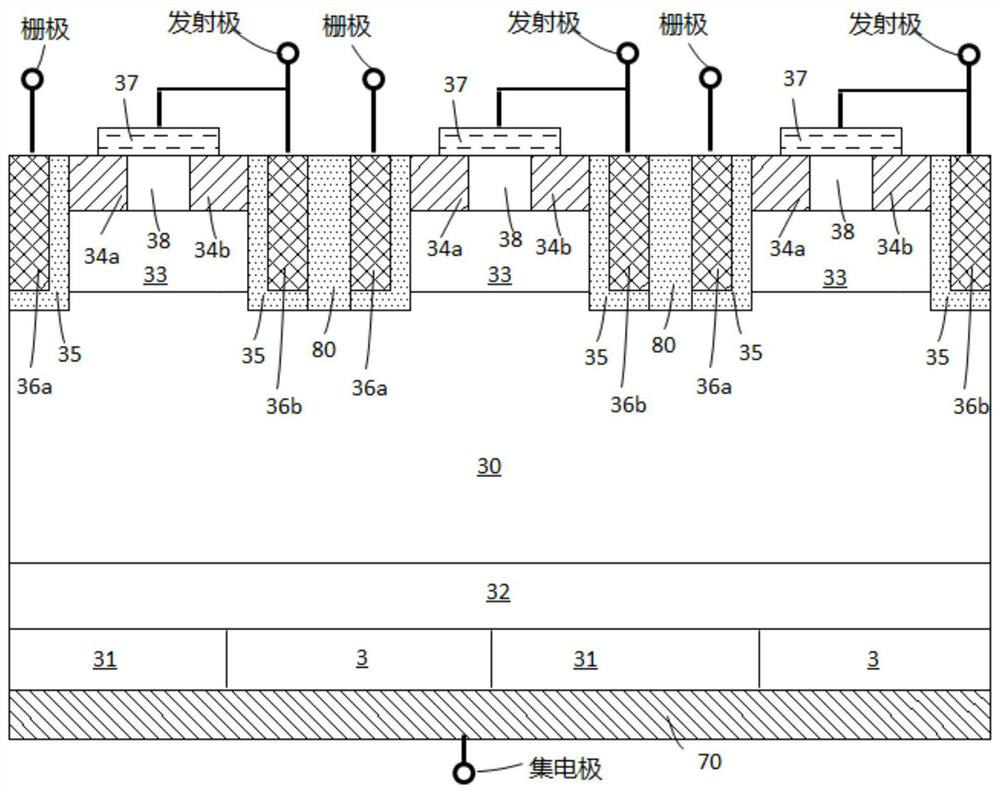

A trench type igbt power device

ActiveCN109755298BReduce reverse recovery chargeFast reverse recovery functionSemiconductor devicesReverse recoveryReverse current

Owner:SUZHOU ORIENTAL SEMICONDUCTOR CO LTD

A kind of superjunction mosfet device and its manufacturing method

ActiveCN103474465BSuitable for mass productionReduce storageSemiconductor/solid-state device manufacturingSemiconductor devicesMOSFETReverse recovery

The invention discloses a super junction MOSFET device and a manufacturing method thereof. A first buffer layer of the first conductivity type adjacent to the body region of the second conductivity type and a second column of the second conductivity type are arranged in the drift layer of the first conductivity type. The second buffer layer of the first conductivity type; the body region of the second conductivity type and the drift layer of the first conductivity type are separated by the first buffer layer of the first conductivity type, and the second column of the second conductivity type is separated from the second column of the first conductivity type. A pillar is isolated by the second buffer layer of the first conductivity type; the impurity concentration of the first buffer layer of the first conductivity type and the second buffer layer of the first conductivity type is greater than that of the first conductivity type drift layer and the first conductivity type The impurity concentration of the first column. The invention has more optimized body diode reverse recovery characteristics, simple process, is compatible with the existing super junction MOSFET manufacturing process, and is suitable for mass production requirements.

Owner:WUXI NCE POWER