Patents

Literature

149results about How to "Short reverse recovery time" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

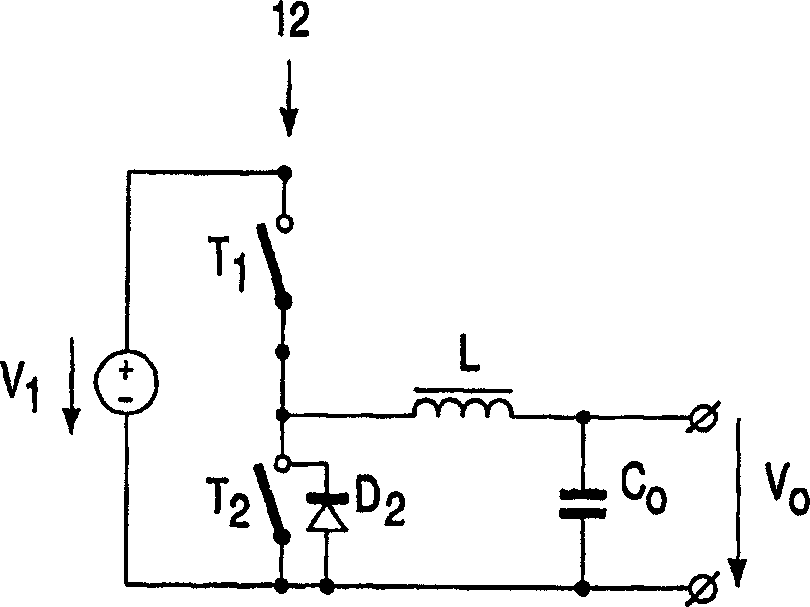

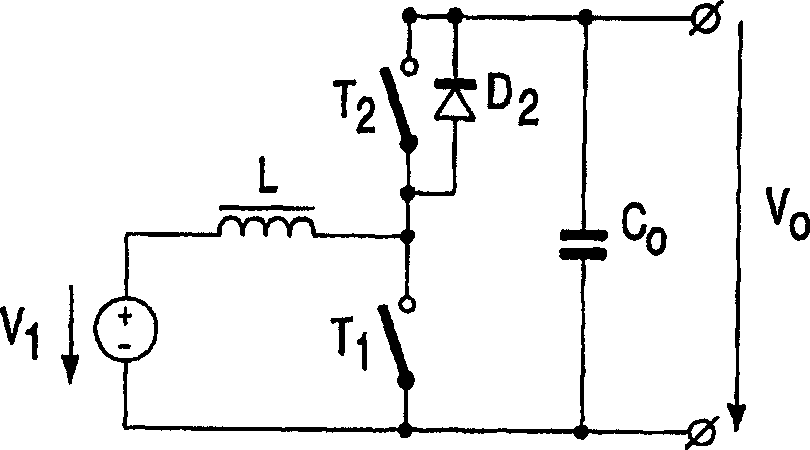

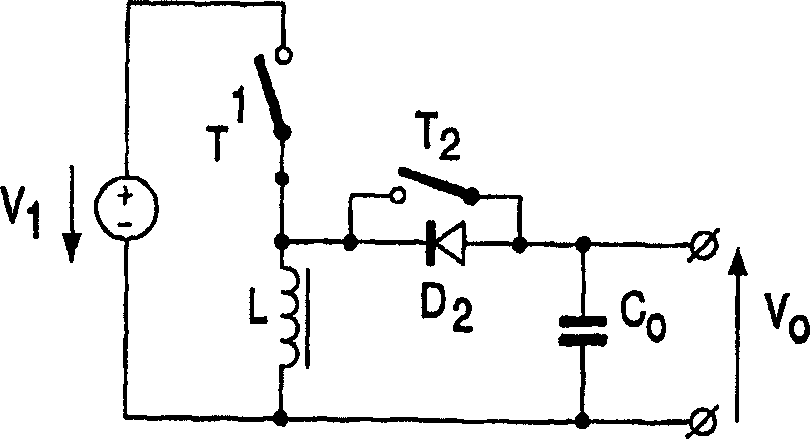

Converter circuit and control method for same

InactiveCN1682445AConduction cancellationShort reverse recovery timeDc-dc conversionElectronic switchingReverse recoveryFlyback diode

In known converter circuits switching losses occur, which are caused by reverse-recovery currents of a freewheeling diode. To reduce said switching losses it is proposed by the invention to drive the switching elements such that, upon switching from the second to the first switching element, the timing is controlled in such a manner that the shoot through currents and the conduction of the freewheeling diode are kept at a low value or, better still, are precluded. As regards the control mechanism, it is proposed to turn on the first switching element later if shoot through currents occur, and to turn on the first switching element sooner if conduction of the freewheeling diode occurs. Here, a time of overlap may be provided during which both switching elements are simultaneously conducting. For the control mechanism, the voltage across a switching element can be used as a measured input value.

Owner:KONINKLIJKE PHILIPS ELECTRONICS NV

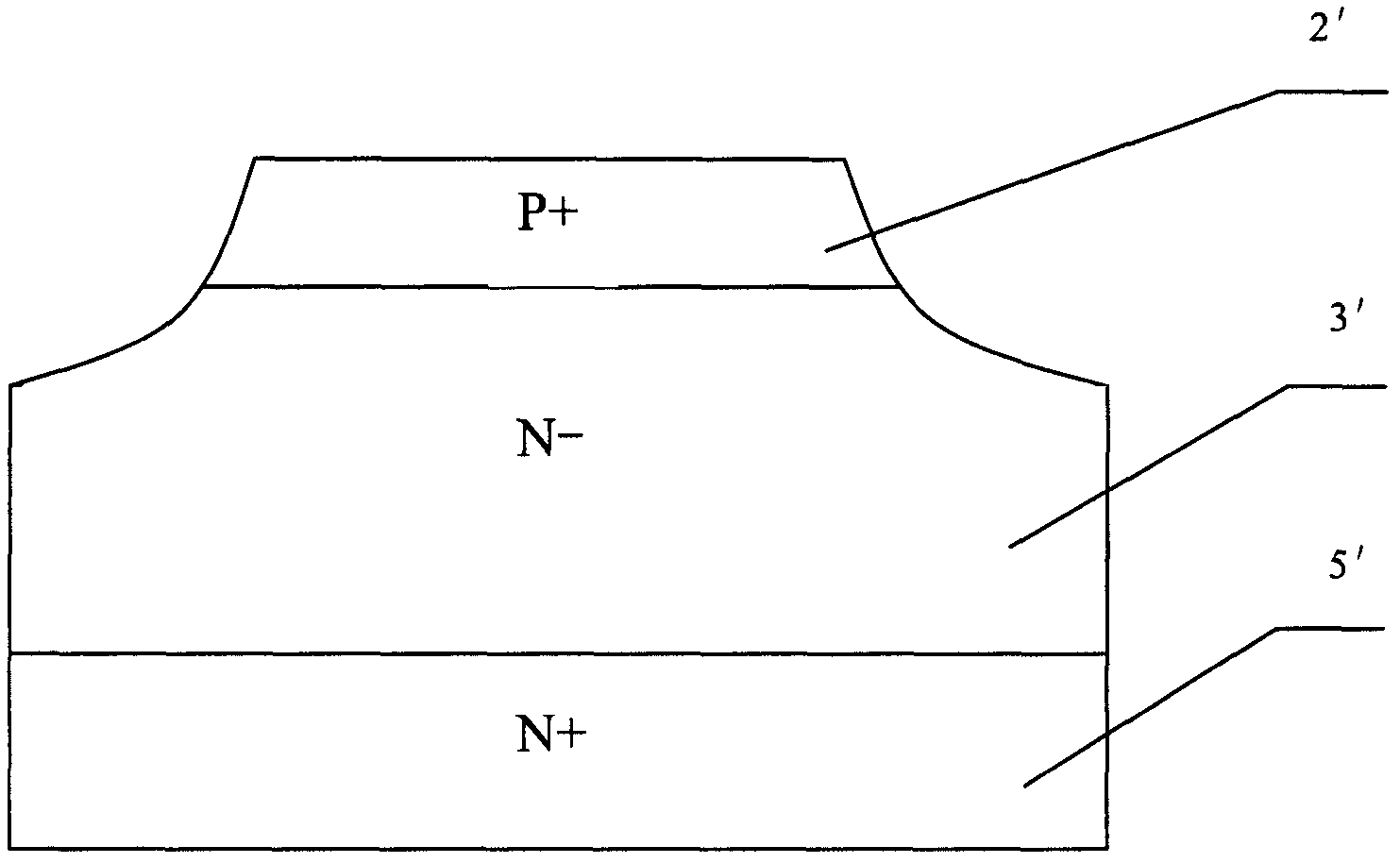

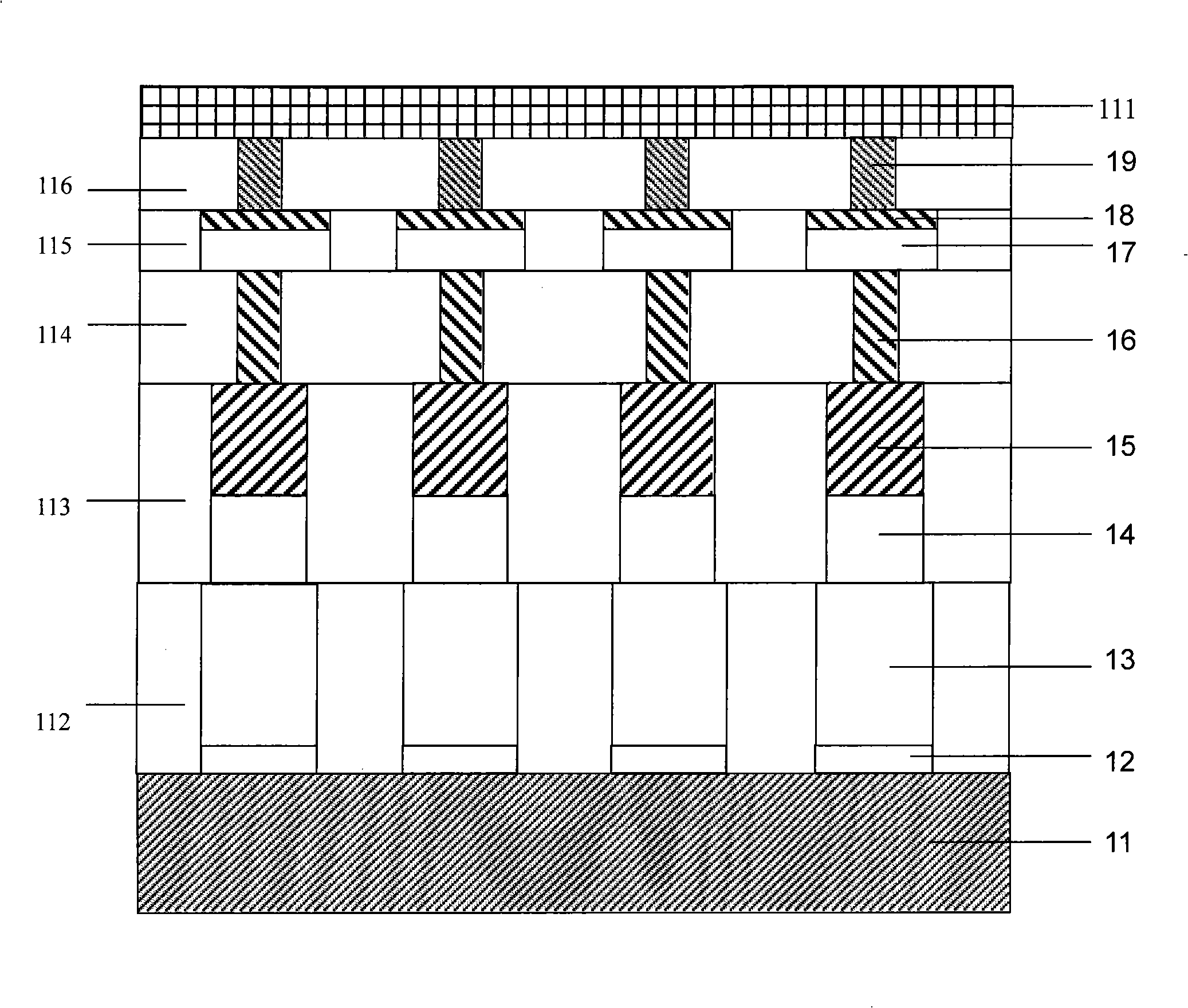

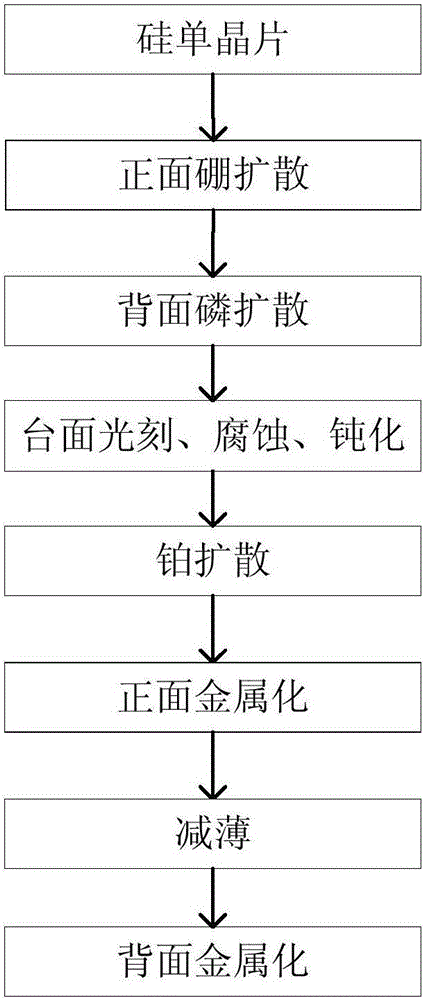

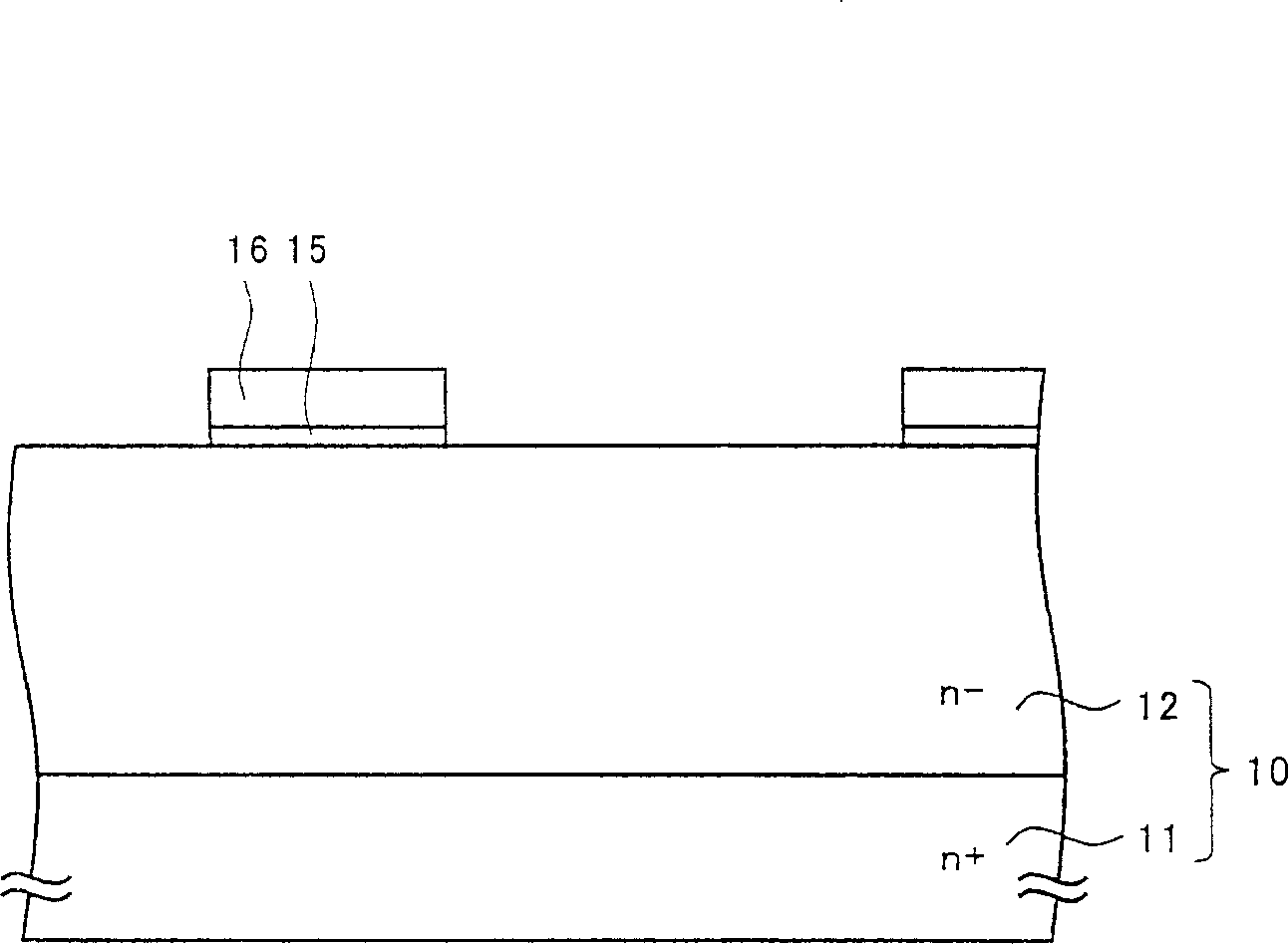

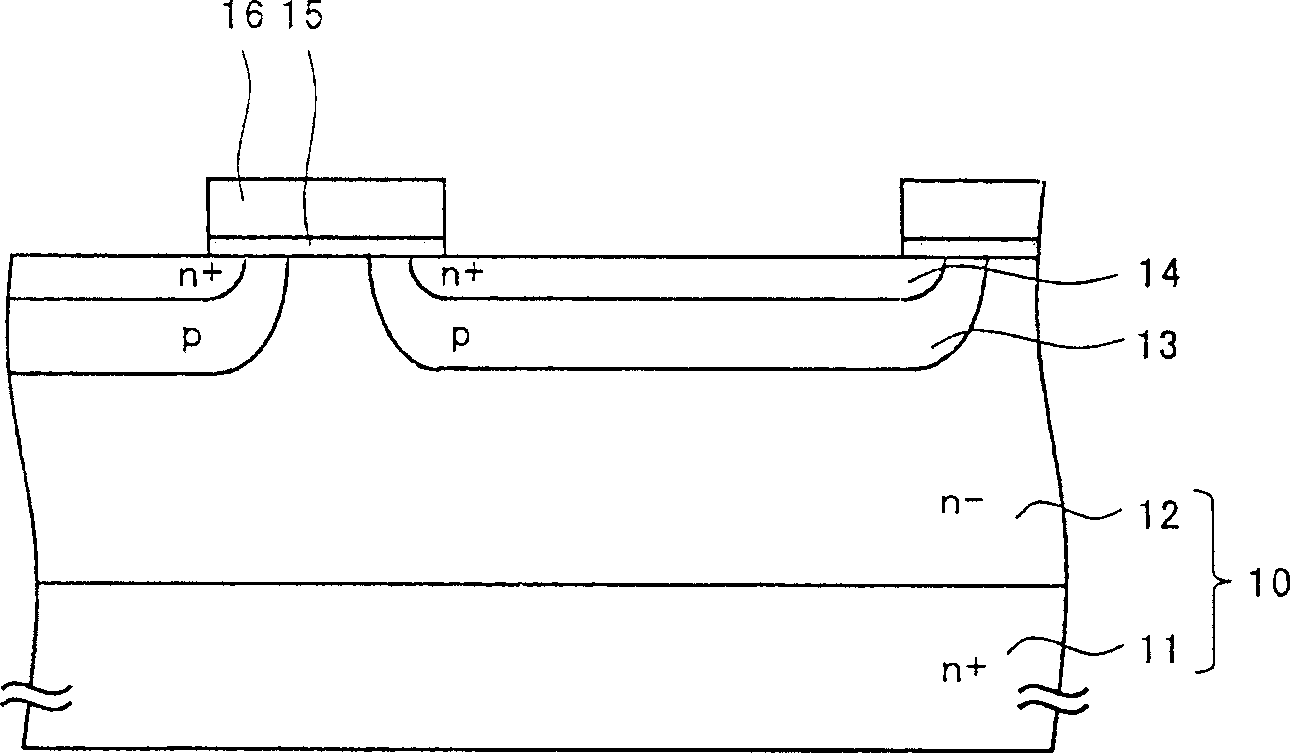

Method for manufacturing planar high-voltage ultrafast soft recovery diode

ActiveCN102569067ALow costMeet the requirements of mass productionSemiconductor/solid-state device manufacturingPlatinumLow leakage

The invention discloses a method for manufacturing a planar high-voltage ultrafast soft recovery diode. The method comprises the following steps of: oxidizing, and photoetching to form an active region and a field limiting ring; doping and pushing; manufacturing a polycrystalline silicon field plate; performing platinum diffusion; thinning; forming an N-type buffer layer; performing contact doping and annealing; and metalizing. The method can be used for manufacturing an ultrafast soft recovery diode chip which is low in cost and short in recovery time and has high-voltage resistance, low leakage current, low forward voltage drop and soft recovery characteristics.

Owner:BEIJING MXTRONICS CORP +1

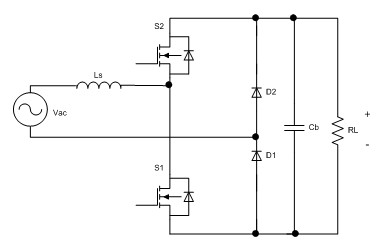

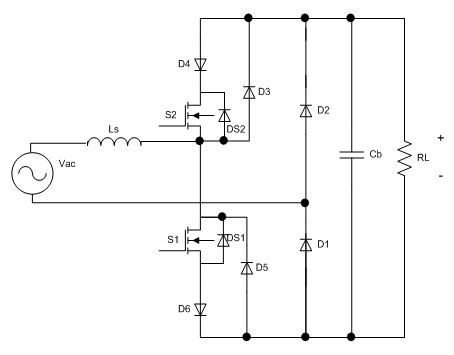

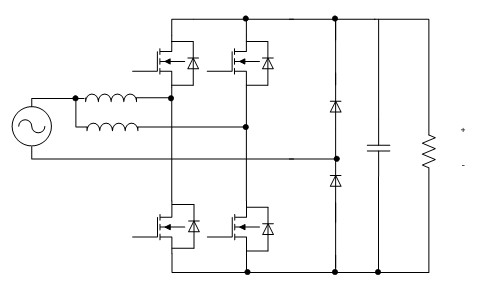

Totem-pole bridgeless power factor correction circuit

InactiveCN102130580AWon't breakShort reverse recovery timeEfficient power electronics conversionEnergy industryPower flowBusbar

The invention discloses a totem-pole bridgeless power factor correction circuit which comprises a switching tube series branch and a rectifier diode series branch, and also comprises two series diodes and two parallel diodes, wherein the switching tube series branch is provided with a first switching tube and a second switching tube, the rectifier diode series branch is provided with a first rectifier diode and a second rectifier diode, the two series diodes are respectively serially connected between the first switching tube and a negative busbar and between the second switching tube and a positive busbar, the two parallel diodes are respectively connected in parallel between a common terminal of the first switching tube and the positive busbar and between the common terminal of the second switching tube and the negative busbar, wherein reverse recovery time of the parallel diodes corresponding to the first switching tube is less than that of the first switching tube, and reverse recovery time of the parallel diodes corresponding to the second switching tube is less than that of the second switching tube. Because reverse recovery characteristics of the parallel diodes are better, a reverse recovery current is smaller without damaging the totem-pole bridgeless power factor correction (PFC) circuit working in a CCM (Coincident-Current Memory) mode.

Owner:EMERSON NETWORK POWER ENERGY SYST NORTH AMERICA

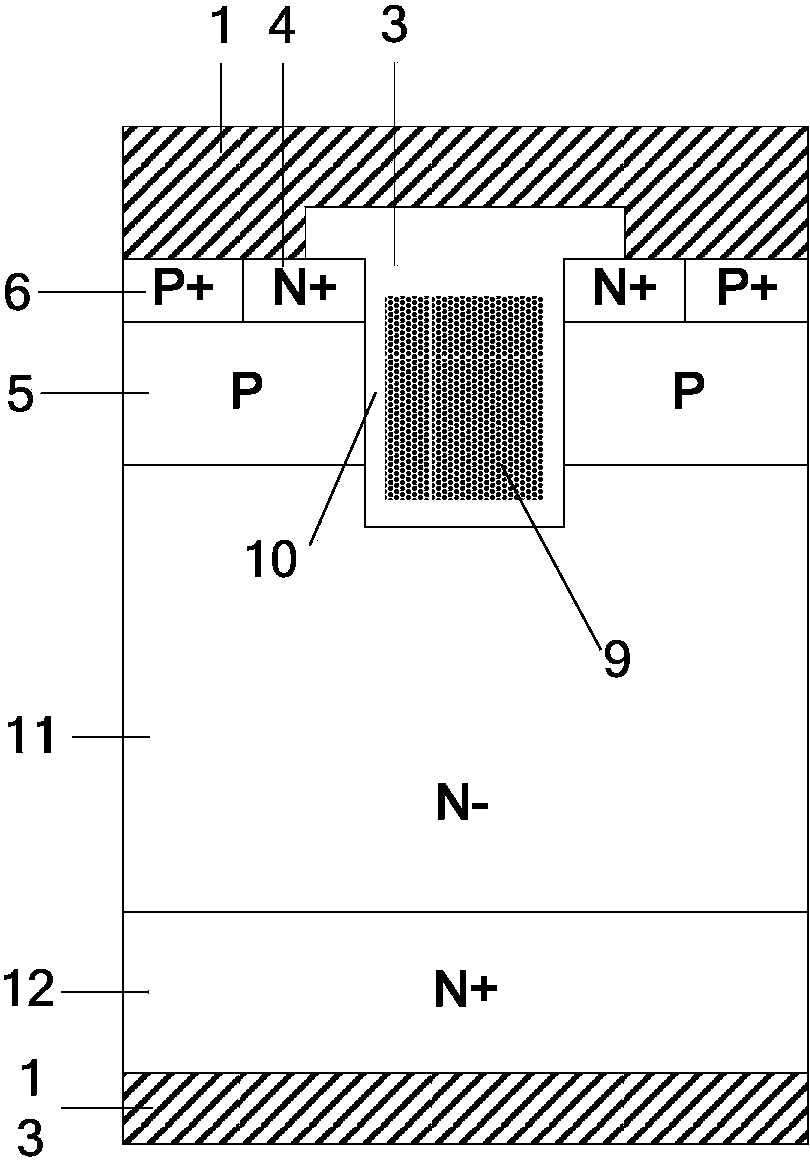

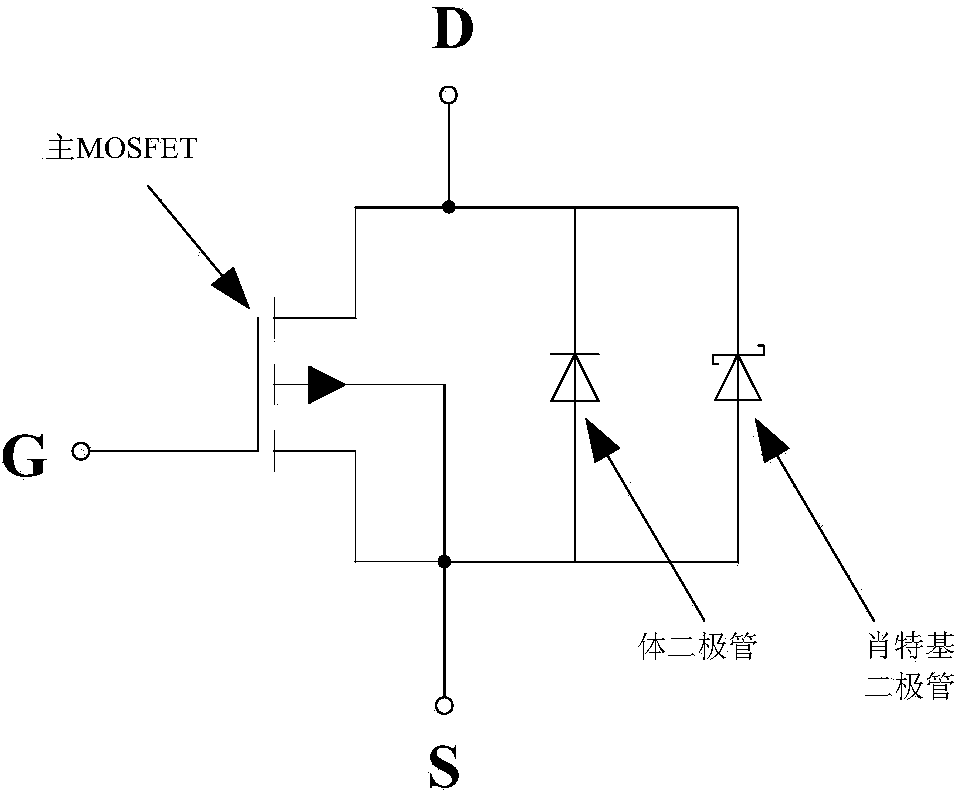

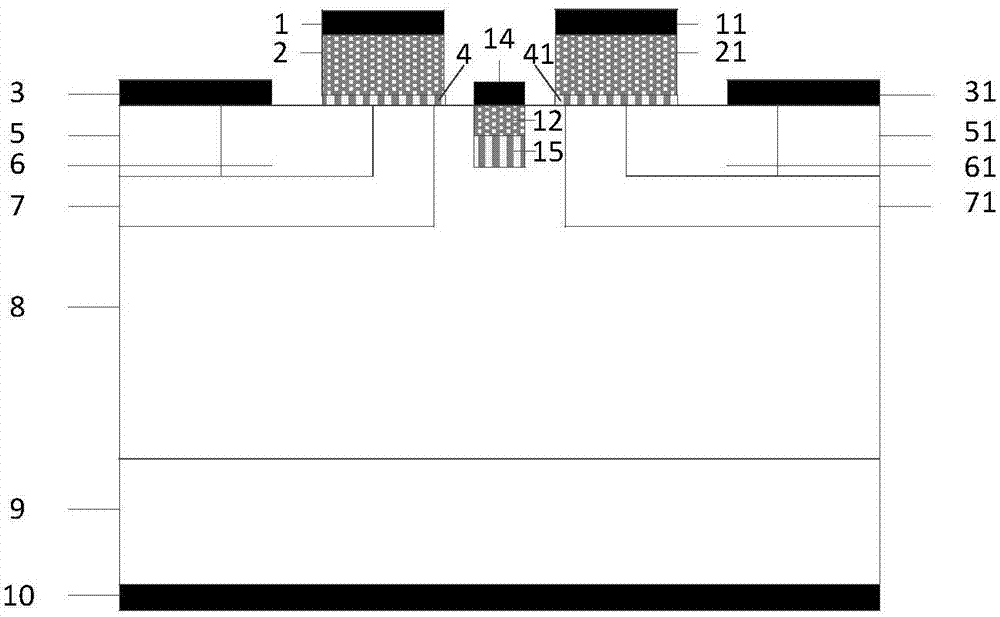

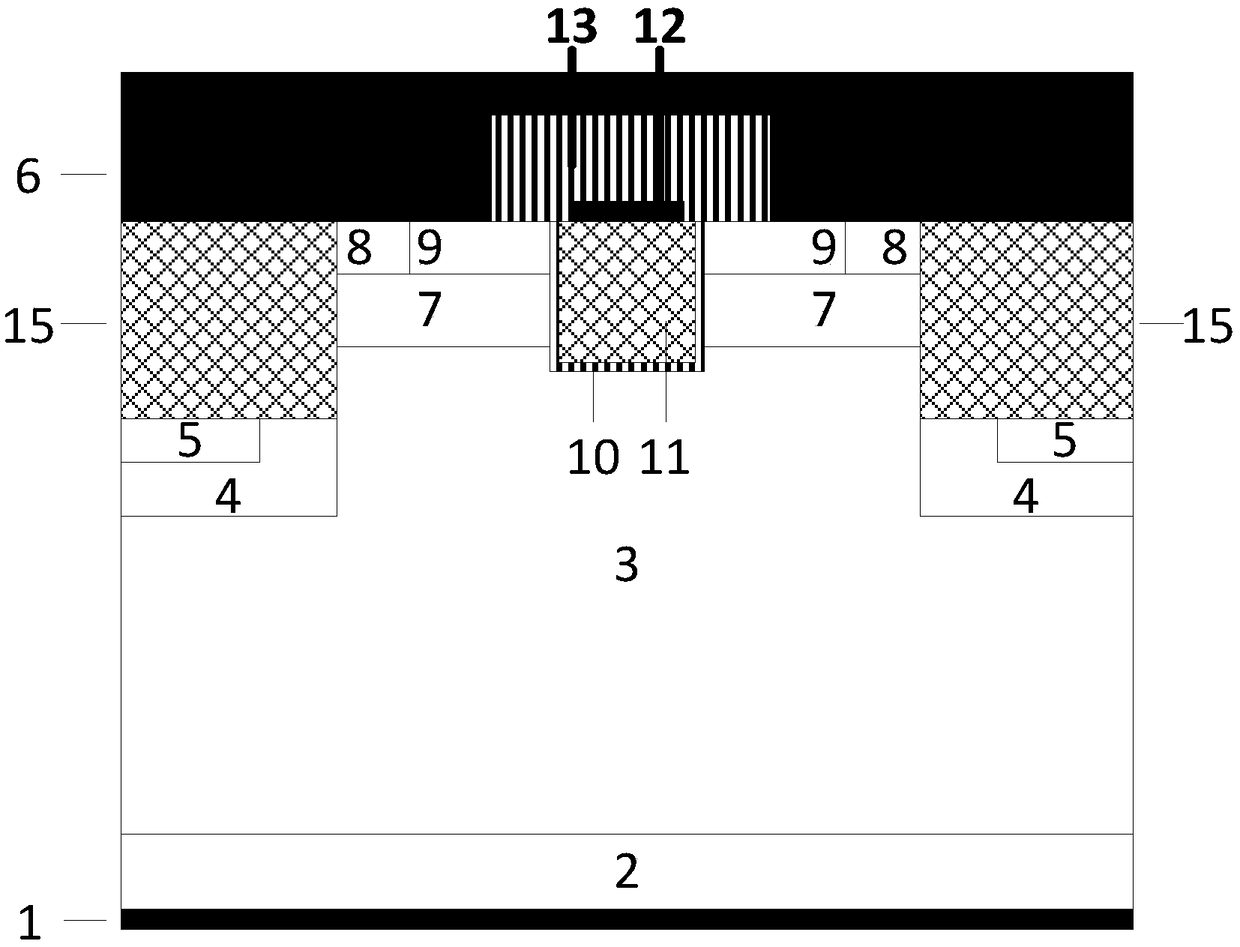

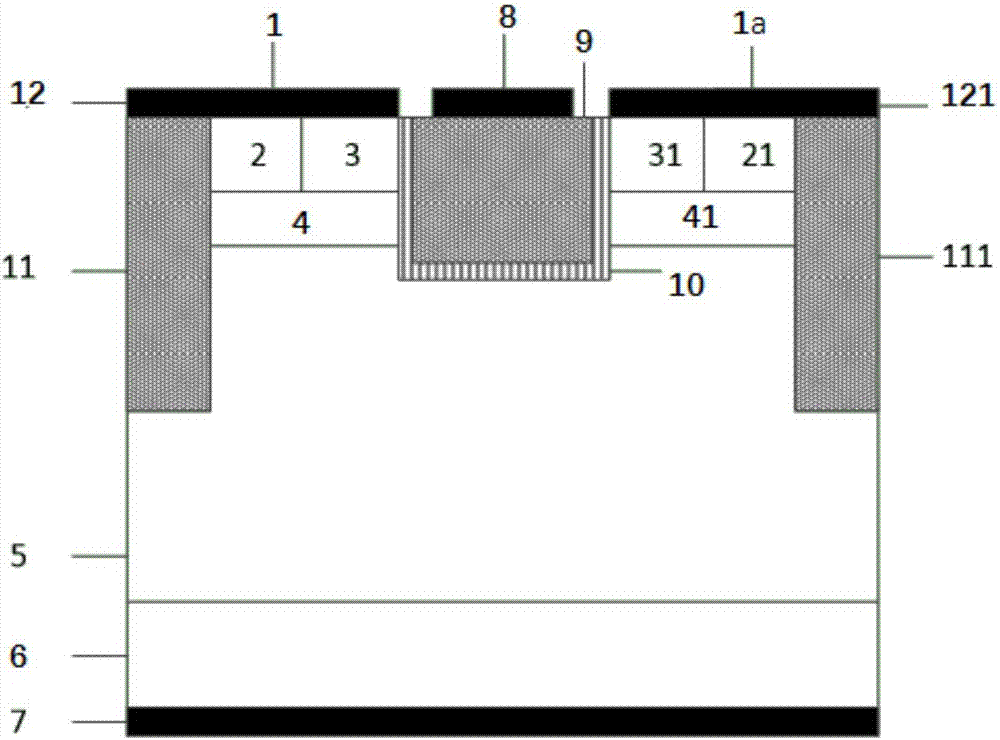

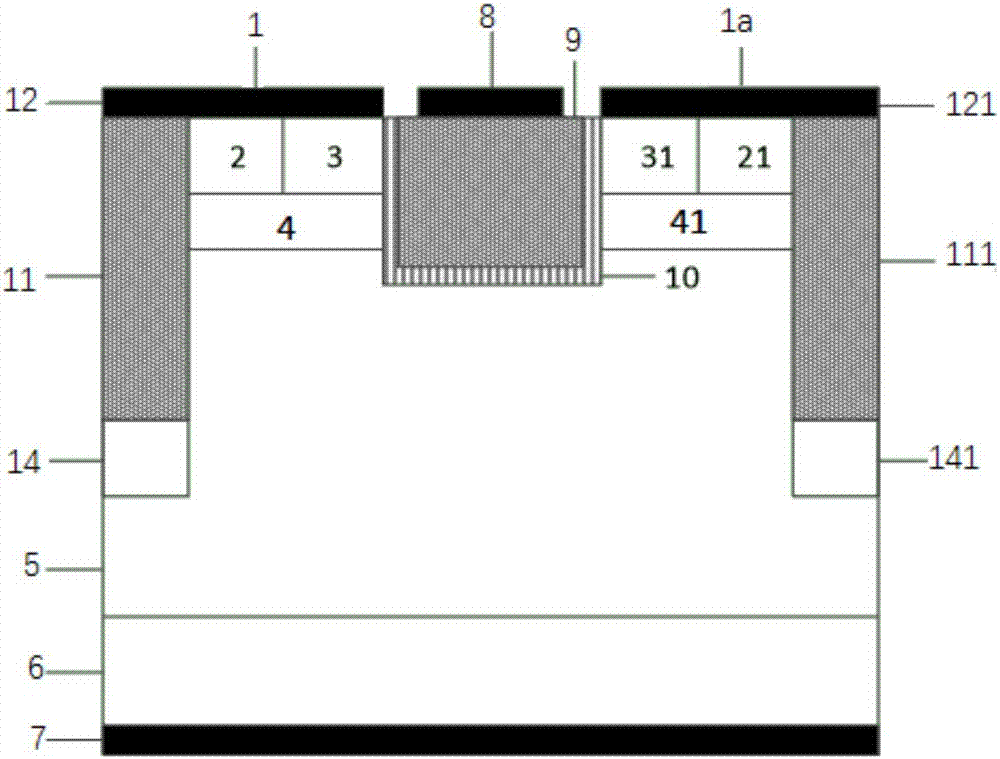

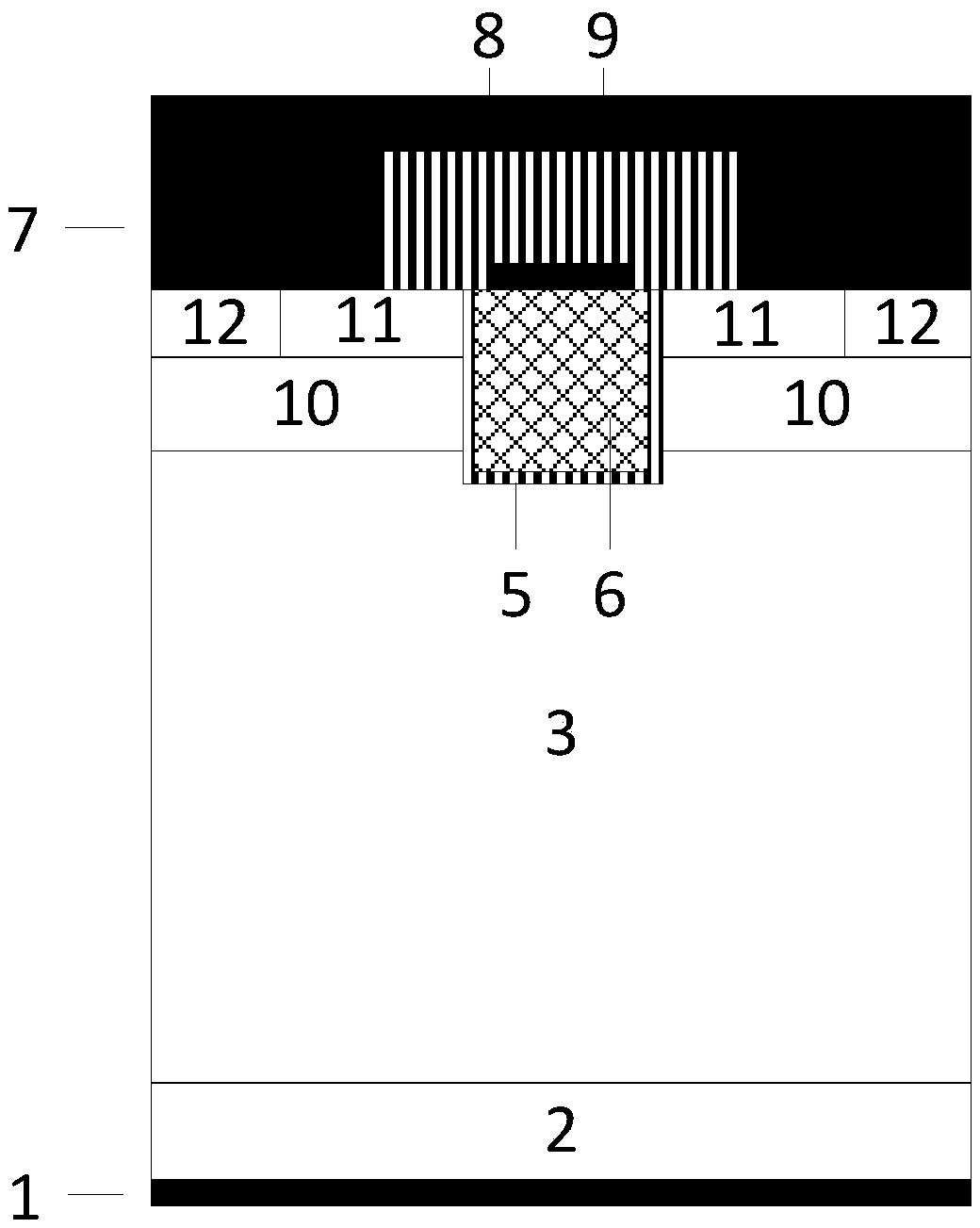

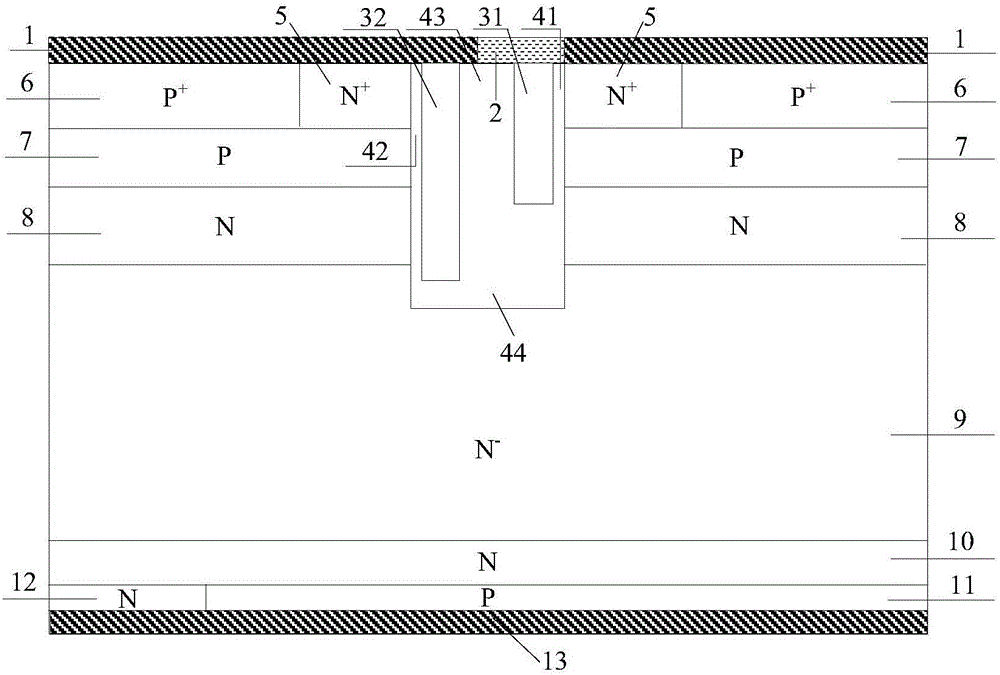

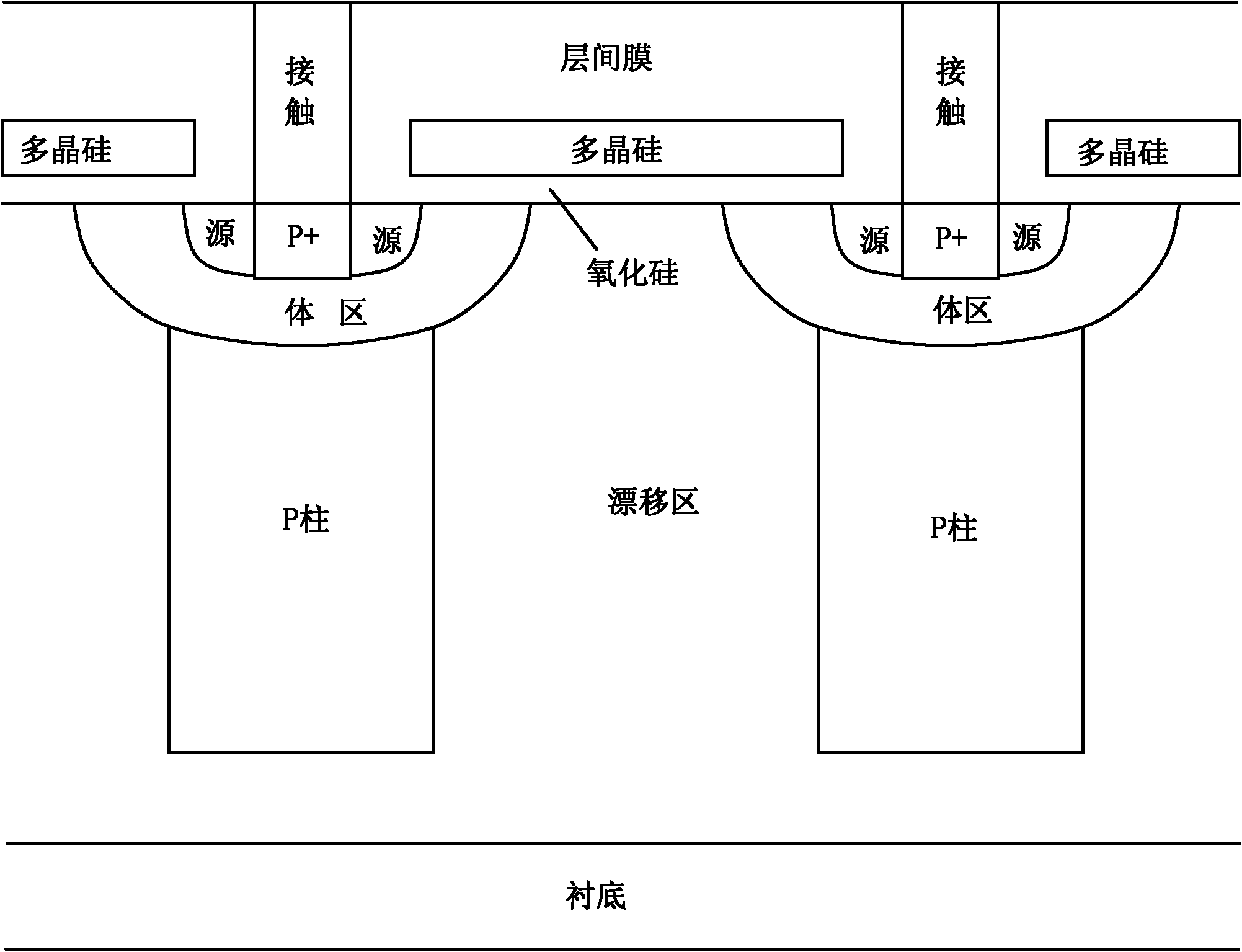

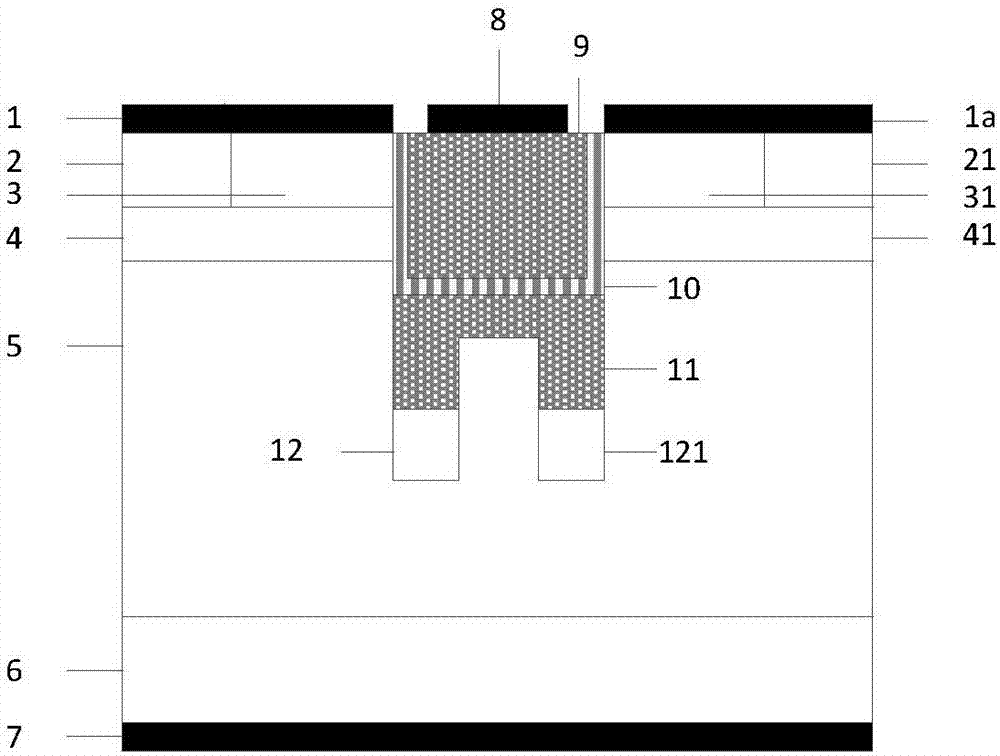

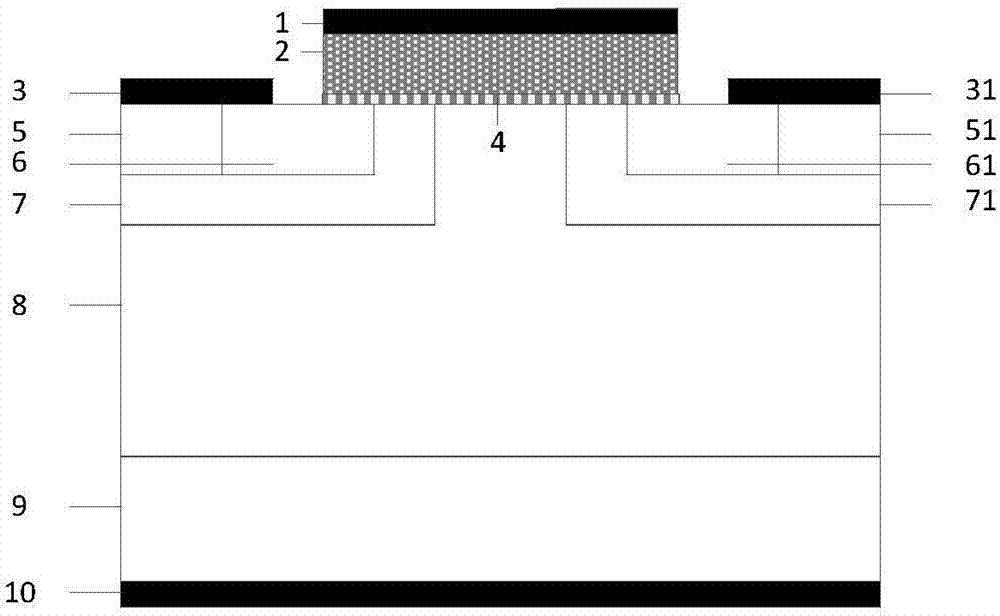

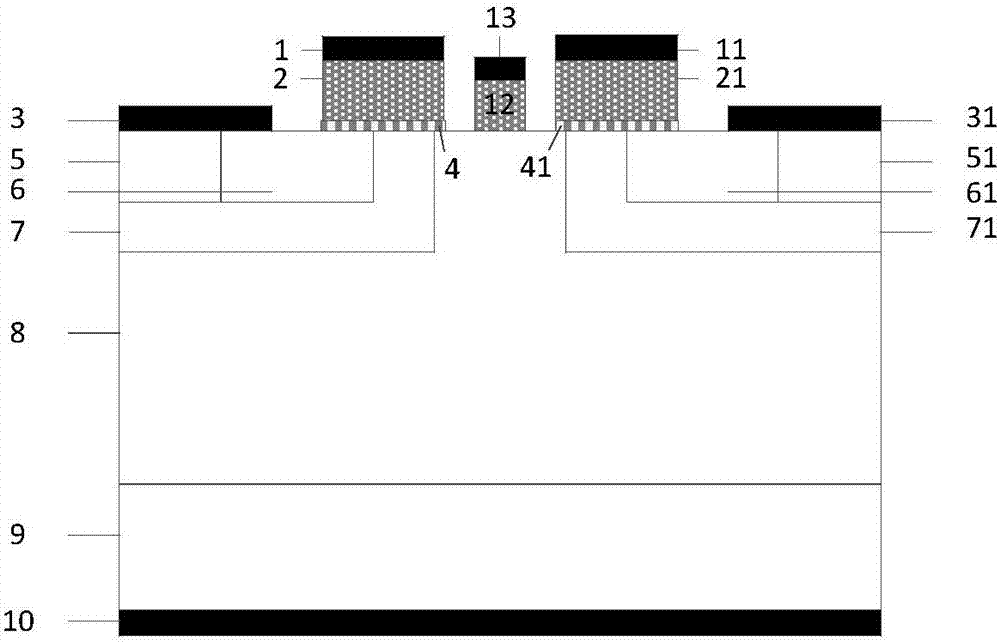

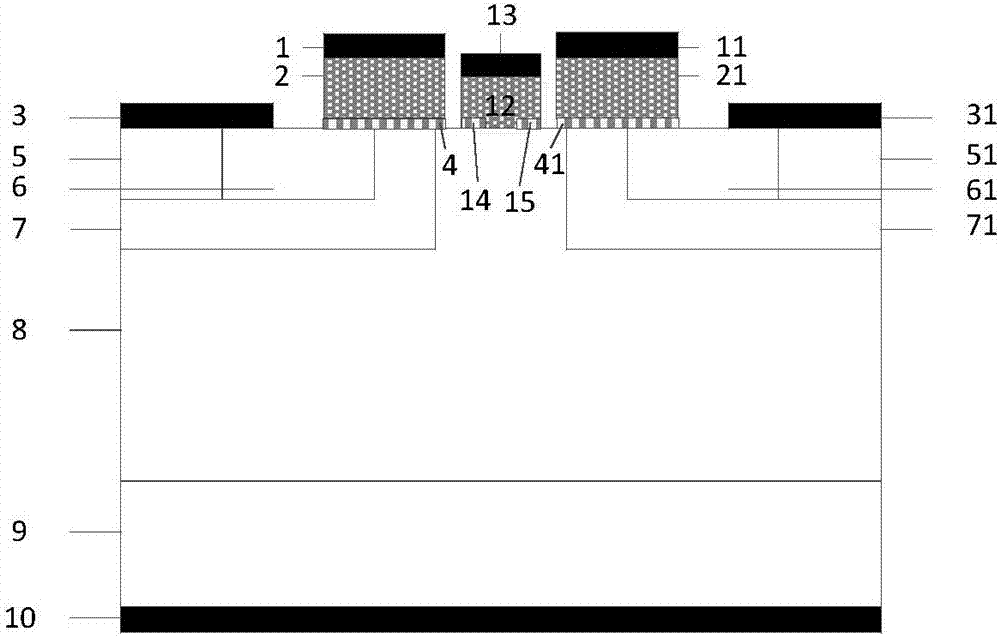

Groove gate VDMOS device integrated with Schottky diode

The invention discloses a groove gate VDMOS device integrated with a Schottky diode and belongs to the technical field of semiconductor devices. According to the groove gate VDMOS device integrated with the Schottky diode, an additional structure composed of a piece of Schottky junction metal and a body electrode conductive material is additionally arranged on each of drift regions on the two sides of a groove gate structure of a conventional groove gate VDMOS device, the upper portion of each piece of Schottky junction metal is in contact with source electrode metal, the lower portion of each piece of Schottky junction metal is in contact with a corresponding body electrode conductive material, and the lower surface and the lateral sides of the each piece Schottky junction metal are in contact with a corresponding drift region to form a Schottky junction; dielectric layers are arranged between the lateral sides of each body electrode conductive material and a corresponding drift region and between the bottom surface of each body electrode conductive material and the corresponding drift region. Compared with a traditional groove gate VDMOS device with the same size, the groove gate VDMOS device integrated with the Schottky diode has the advantages that due to the fact that higher drift region dosage concentration is adopted under the condition of same puncture voltage, turn-on resistance is reduced obviously, and the reverse recovery property of the diode is improved obviously.

Owner:UNIV OF ELECTRONIC SCI & TECH OF CHINA +1

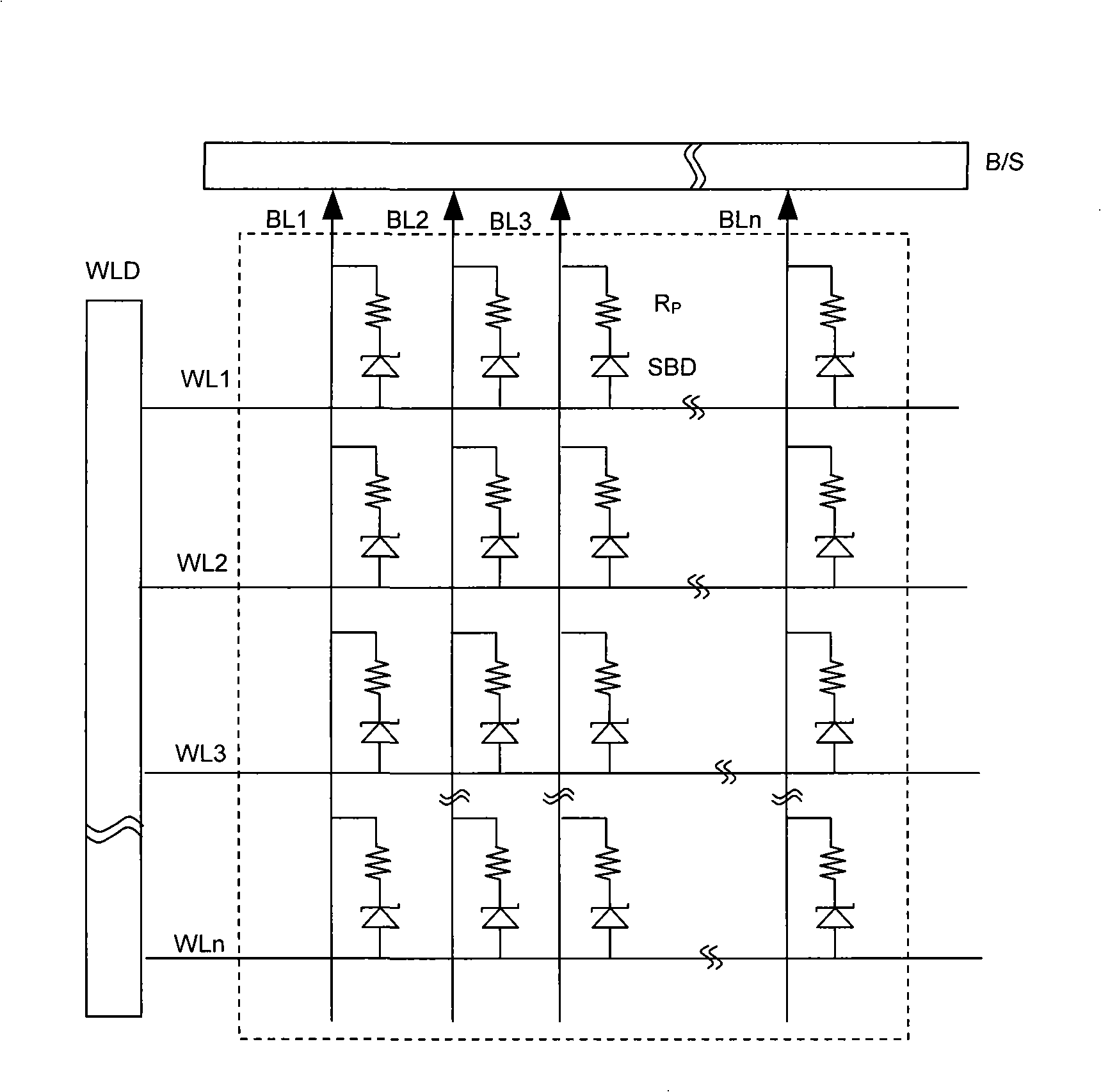

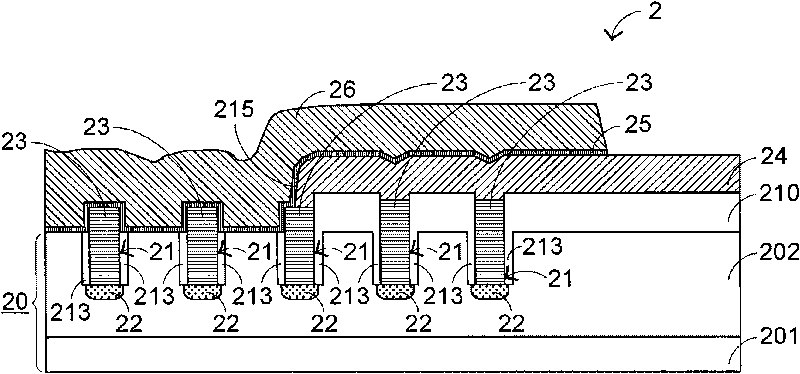

Phase change storage unit using Schottky base diode as selection tube and its making method

InactiveCN101262005AImprove stabilityImprove consistencySemiconductor/solid-state device detailsSolid-state devicesDriving currentPhase-change memory

The invention pertains to the technical field of micro-electronics and discloses a phase change memory device provided with a Schottky diode and a preparation method thereof. The phase change memory device is basically characterized in that a structural unit is composed of the Schottky diode and the phase change memory device; the Schottky diode serves as a gate tube of the phase change memory device; the Schottky diode produces an N-type or P-type Si single crystal film by solid epitaxial technique and the N-type or P-type single crystal film forms a metal semiconductor contact together with a metal film. The Schottky diode prepared by the method has the advantages of stable performance, fast speed and great drive current. The structure disclosed by the invention is characterized in that the structure is applied to highly intense phase change memory devices and can lower the production cost of the phase change memory devices at the same time.

Owner:SHANGHAI INST OF MICROSYSTEM & INFORMATION TECH CHINESE ACAD OF SCI

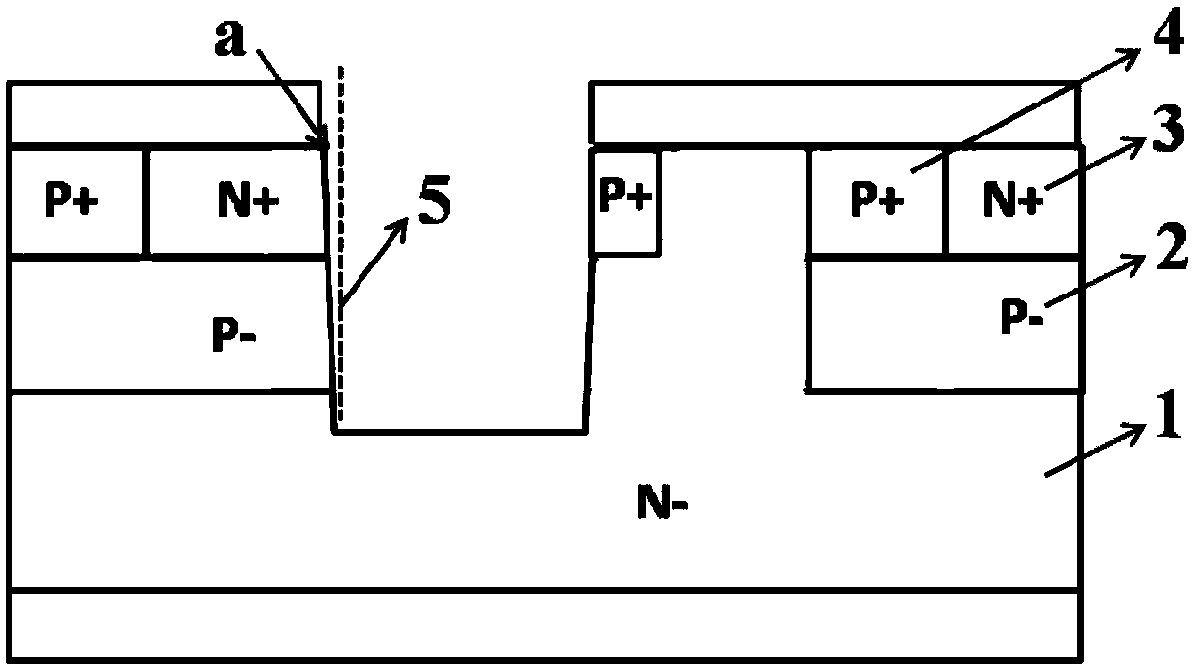

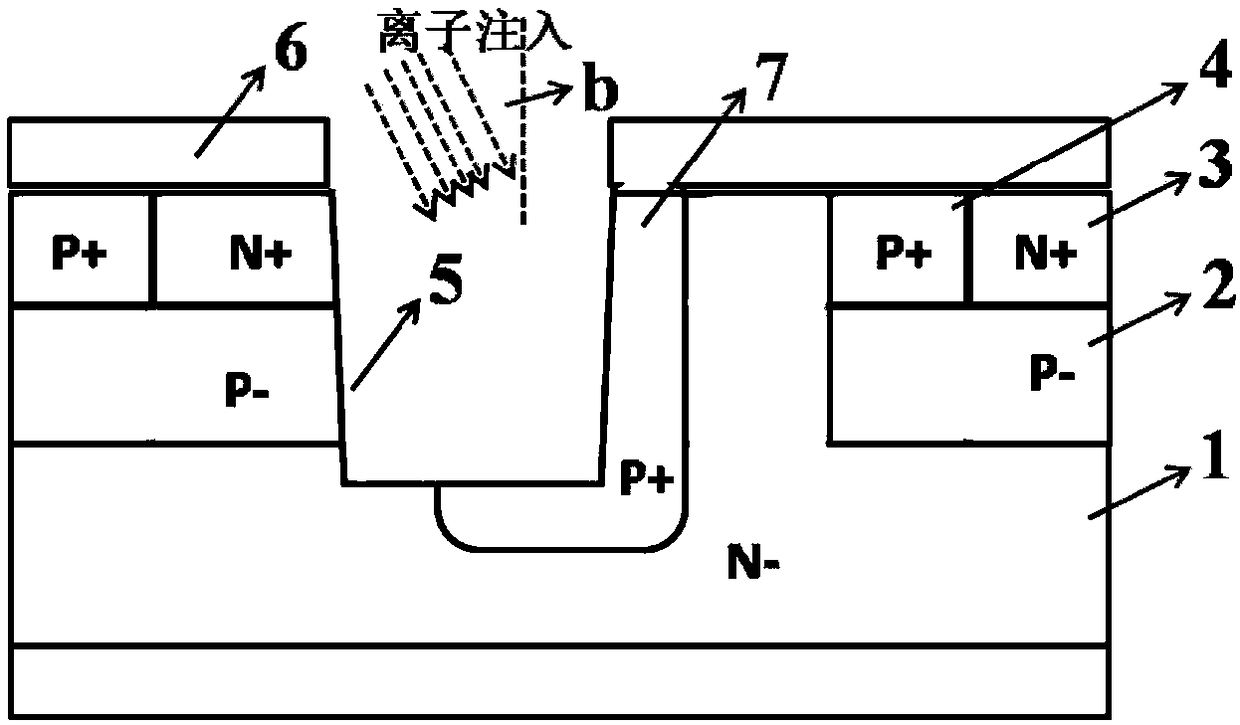

Unilateral MOS-type device manufacturing method integrated with SBD structure

InactiveCN108183131AImprove conduction performanceLow application costSemiconductor/solid-state device manufacturingDiodeMOSFETReverse recovery

The invention discloses a unilateral MOS-type device manufacturing method integrated with an SBD structure. Through introducing a special angle groove manufacturing process, an inclination angle unilateral ion implantation process and a schottky metal process compatible with an ohm process, manufacturing of an SiC groove MOSFET device integrated with an SBD structure is realized. The silicon carbide SBD structure is integrated in the silicon carbide groove-type MOSFET device, a reverse follow current function can be realized well, the reverse recovery time of the MOSFET device can be reduced,and the application cost of a silicon carbide power electronic device can be effectively reduced. In combination of a unilateral high-mobility groove structure with special crystal face etching, whilethe groove mobility is improved, the size of a primitive cell is narrowed, and the device conduction ability is improved.

Owner:NO 55 INST CHINA ELECTRONIC SCI & TECHNOLOGYGROUP CO LTD

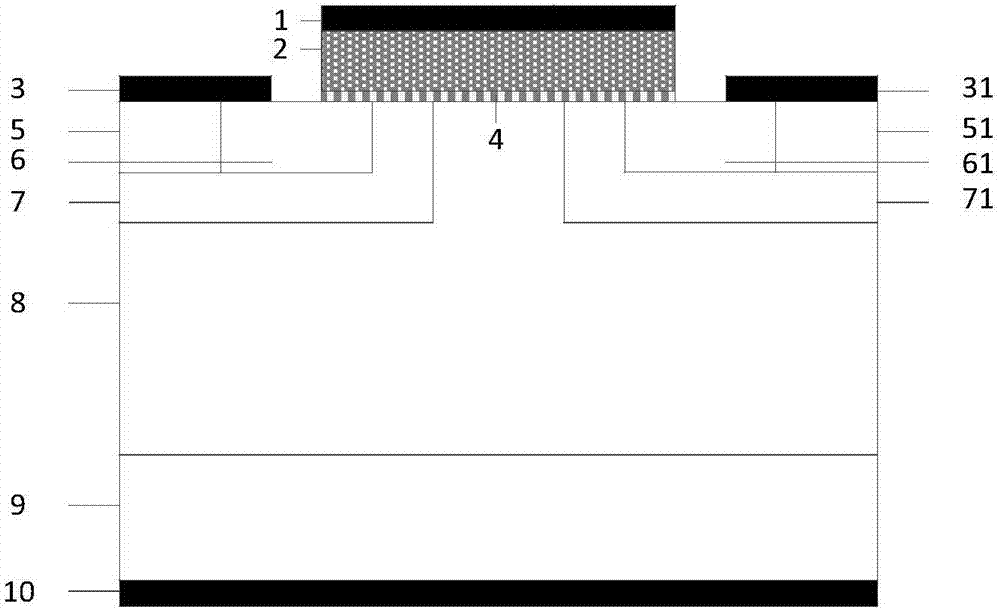

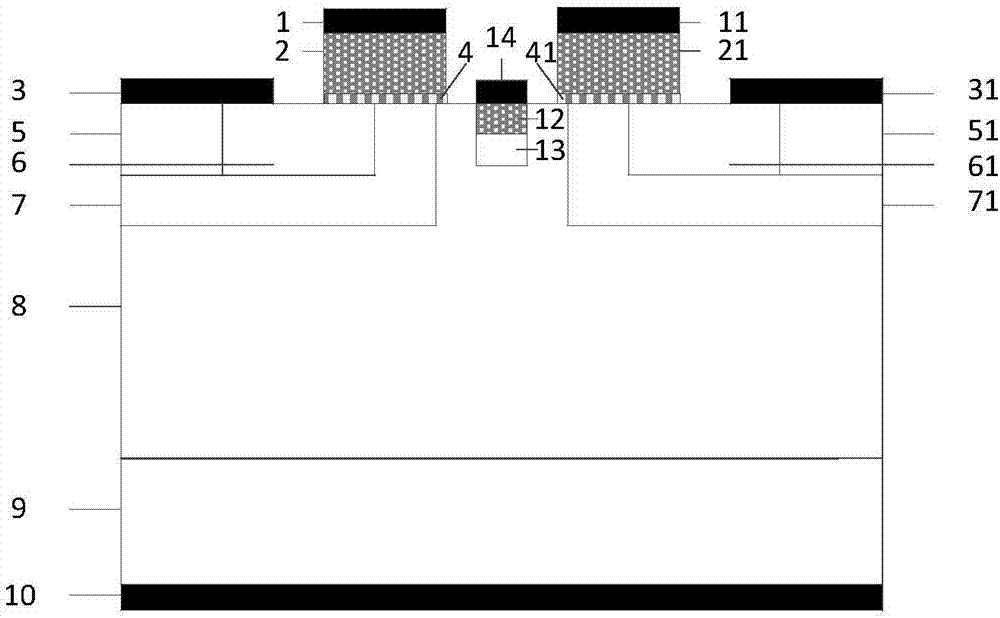

Silicon carbide VDMOS device and manufacturing method thereof

ActiveCN107275407AImprove performanceReduce power lossSemiconductor/solid-state device manufacturingDiodeCapacitanceHeterojunction

The invention discloses a silicon carbide VDMOS device and manufacturing method thereof, and belongs to the technical field of power semiconductors. A trench is etched on a JFET region surface of a traditional silicon carbide VDMOS device, P type doping is introduced into the bottom of the trench, and at the same time, a polycrystalline silicon layer is formed in the trench, so that the polycrystalline silicon layer and a side wall of the trench are in contact to form a Si / SiC heterojunction. A diode is integrated in the device, and the device has the advantages of low conduction voltage drop, fast switching speed and good reverse recovery characteristic in a diode working mode, and has the advantages of high breakdown voltage, small grid capacitance and fast switching speed in an MOS working mode. The proposed device structure optimizes application of the device in the field of inverter circuits, chopper circuits and the like, and has the advantage that the process is simple, and is compatible with a traditional silicon carbide VDMOS device process.

Owner:HANGZHOU SILICON-MAGIC SEMICON TECH CO LTD

Groove-type Schottky diode and manufacture method thereof

ActiveCN101609801ASimple structureLow Reverse Voltage Leakage CurrentSemiconductor/solid-state device manufacturingSemiconductor devicesSputteringElectrical conductor

The invention discloses a groove-type Schottky diode and a manufacture method thereof. The method comprises the following steps of: providing a semiconductor substrate; forming a first mask layer on the semiconductor substrate; forming a multi-groove structure in the semiconductor substrate; forming a gate oxide layer on the surface of the multi-groove structure; forming a polysilicon structure on the gate oxide layer and the first mask layer; etching the polysilicon structure; forming a second mask layer on the part of the polysilicon structure and the part of the first mask layer; forming a metal sputtering layer on the second mask layer and the partial surfaces of the semiconductor substrate, the polysilicon structure and the gate oxide layer; and etching the metal sputtering layer. The structure of the groove-type Schottky diode can be effectively isolated from an external environment, and has lower backward voltage leakage current, lower forward bias voltage, higher backward voltage resistant value and shorter backward recovery time.

Owner:PFC DEVICE HLDG

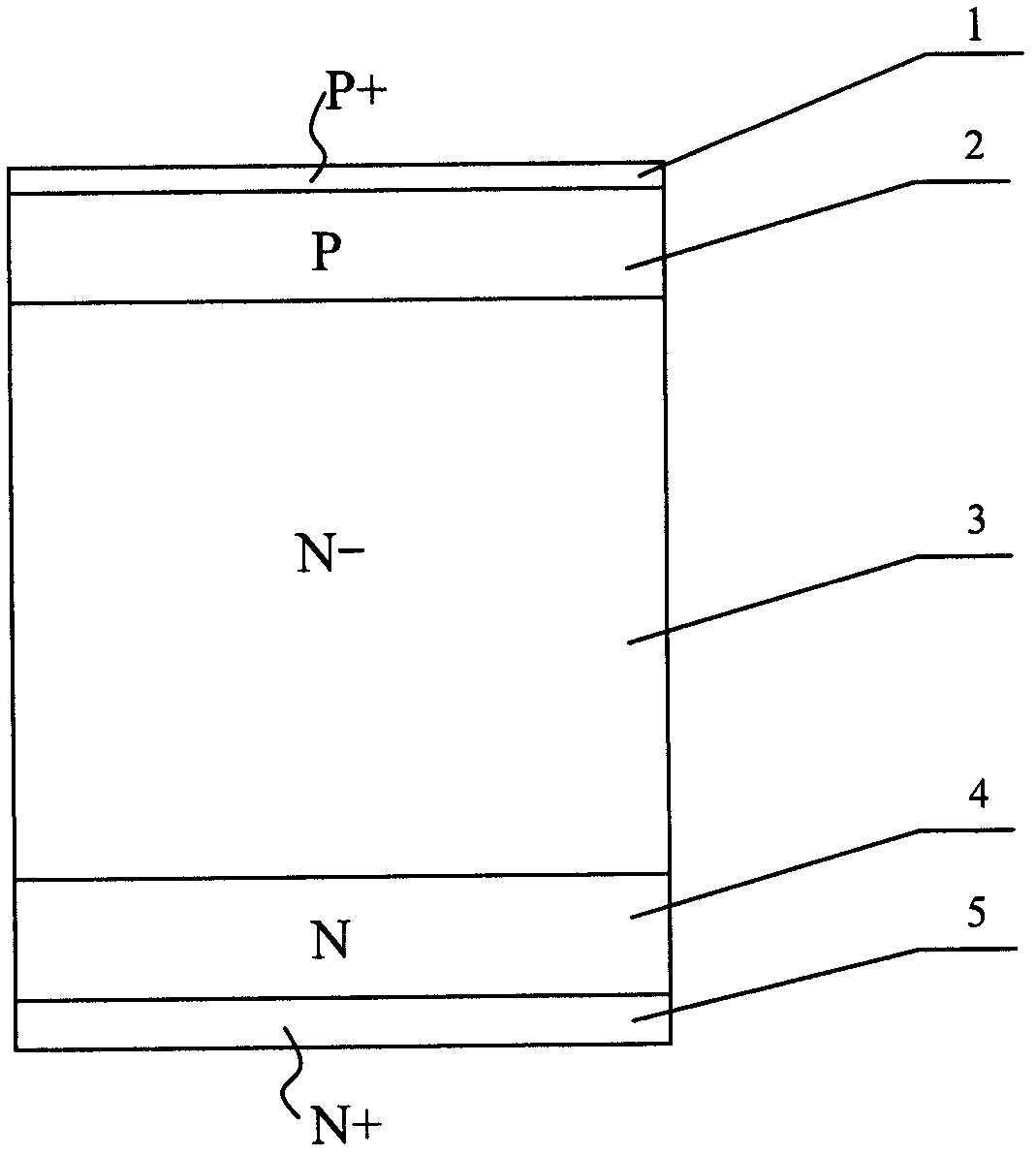

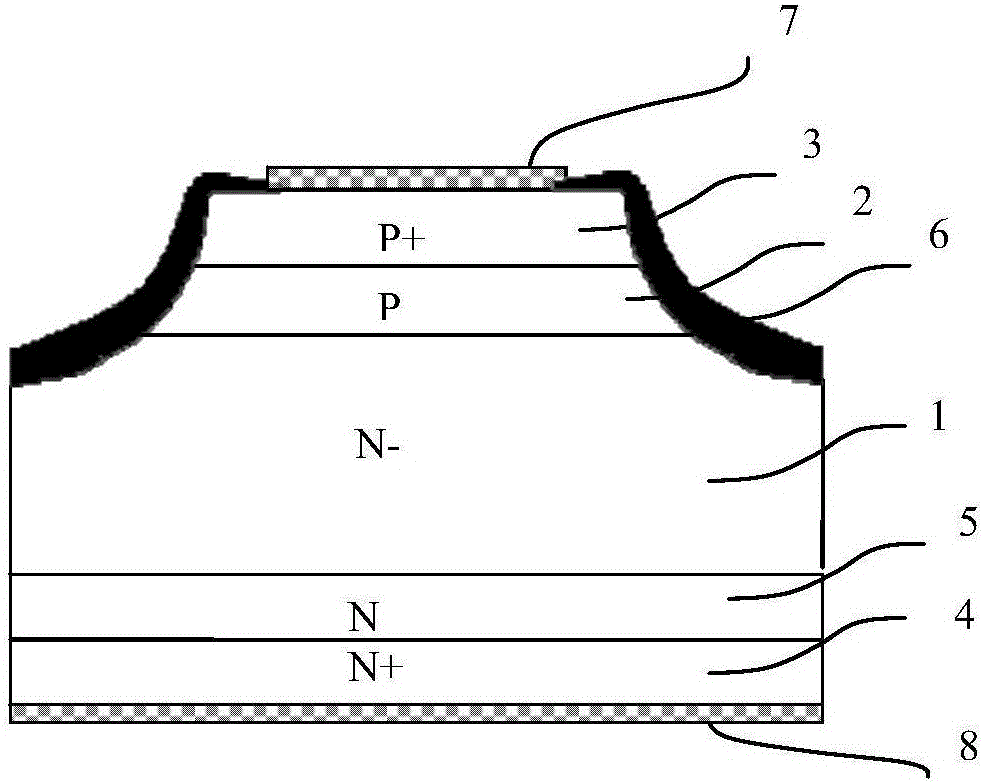

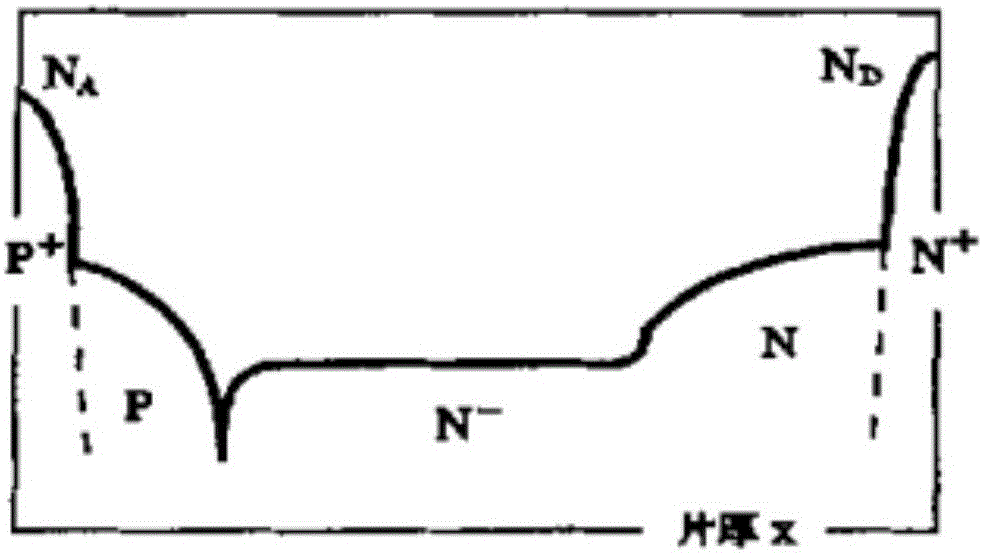

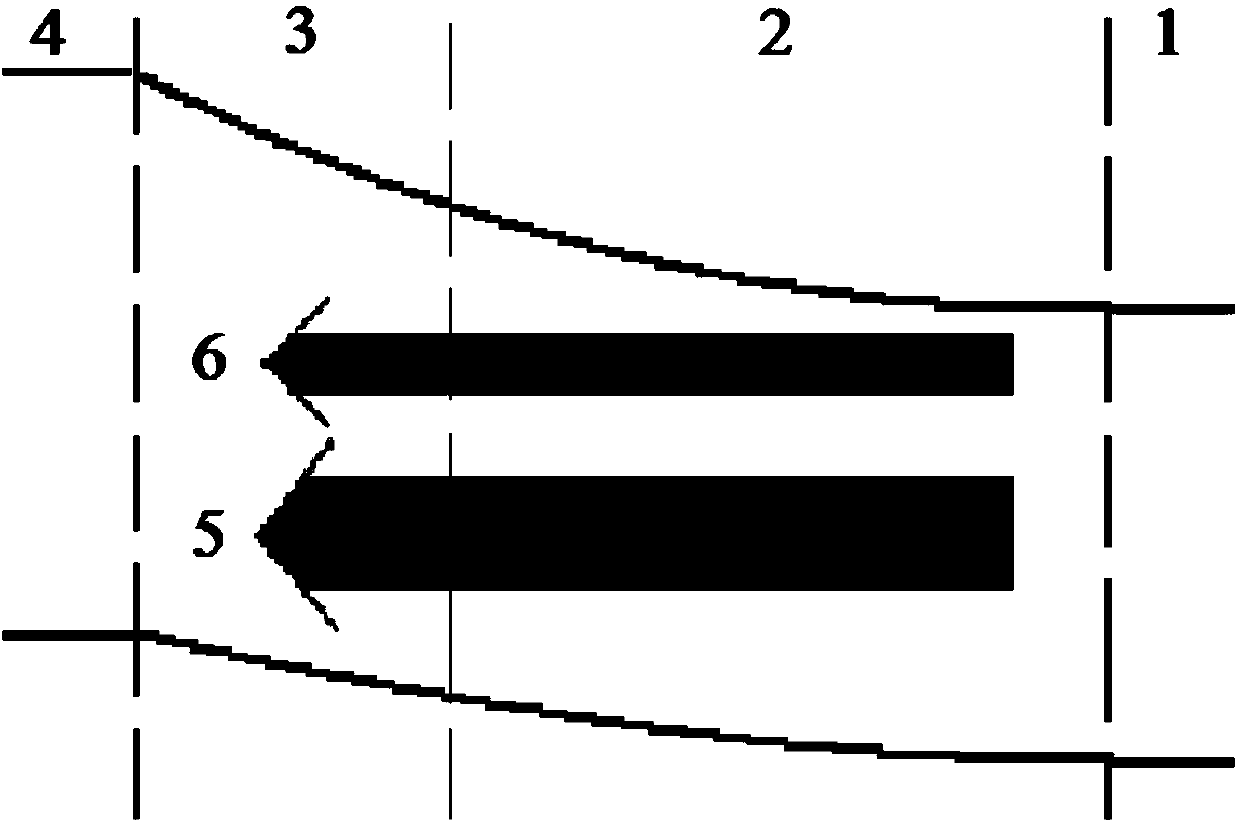

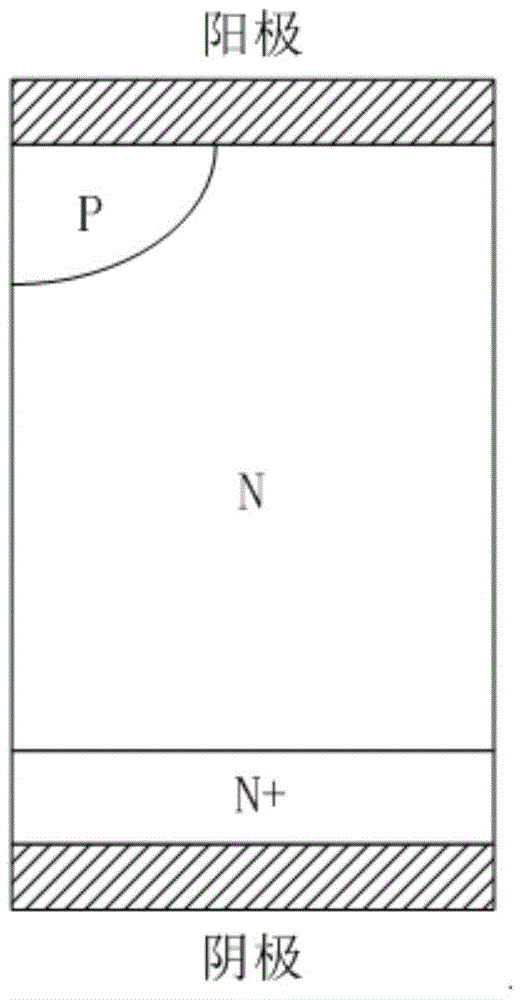

Diffusion-technology-based manufacture method for fast recovery diode chip having double buffering layers

ActiveCN105977154AShort recovery timeHas soft recovery propertiesSemiconductor/solid-state device manufacturingSemiconductor devicesManufacturing technologyPeak current

The invention relates to a diffusion-technology-based manufacture method for a fast recovery diode chip having a double-buffer-layer structure. During a manufacture process, reverse recovery charges and reverse recovery time are reduced and effect of reverse recovery peak current is inhibited. The fast recovery diode is formed by adopting a phosphorus deep diffusion mode and a cathode structure formed by the diffusion is an N+N structure, an N area is a buffering layer which can block expansion of a space charge area, shortens a width of a base area and reduces forward on-state voltage drop; when the diode is reverse, an electric field between an N-N interface and an NN+ interface slows down carrier reverse drawing speed, which enables more charges to be used for recombination and softens the recovery characteristics. The diffusion-technology-based manufacture method adopts the diffusion mode to form the anode and the cathode of the fast recovery diode chip, combines with the platinum diffusion minority carrier life control technology, has a simple manufacture technology process and can manufacture the fast recovery diode chip which is low in cost, high in voltage resistance, short in recovery time and has soft recovery characteristics.

Owner:BEIJING MXTRONICS CORP +1

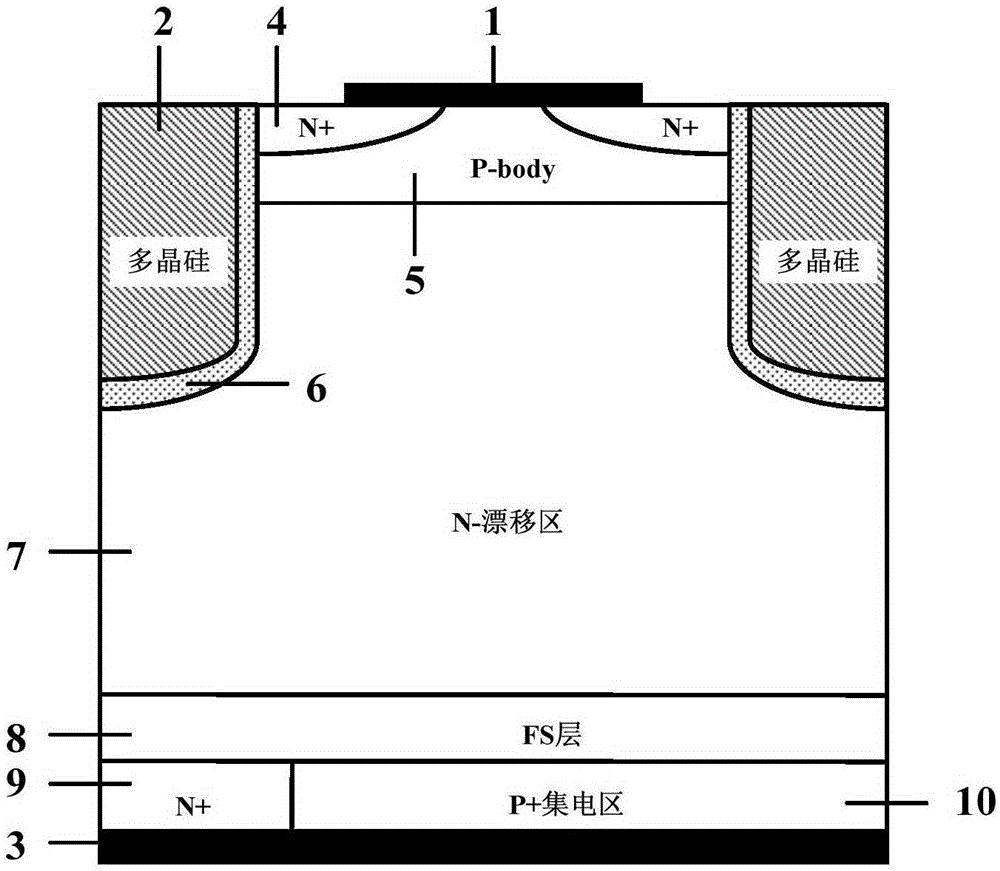

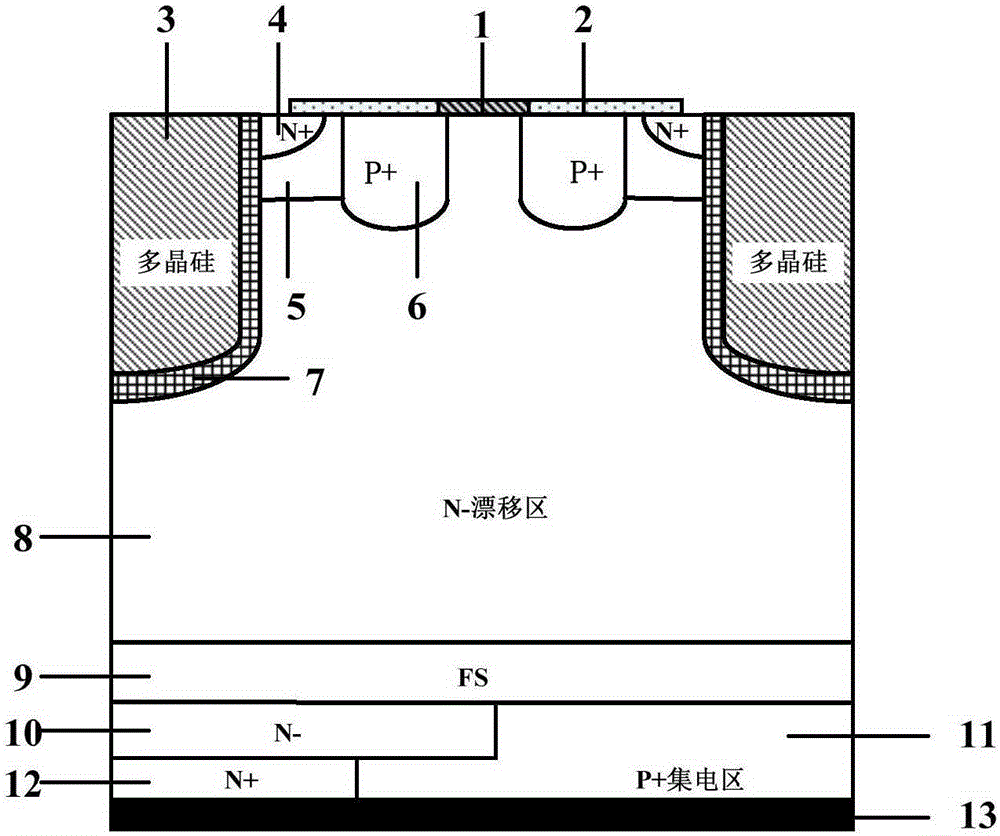

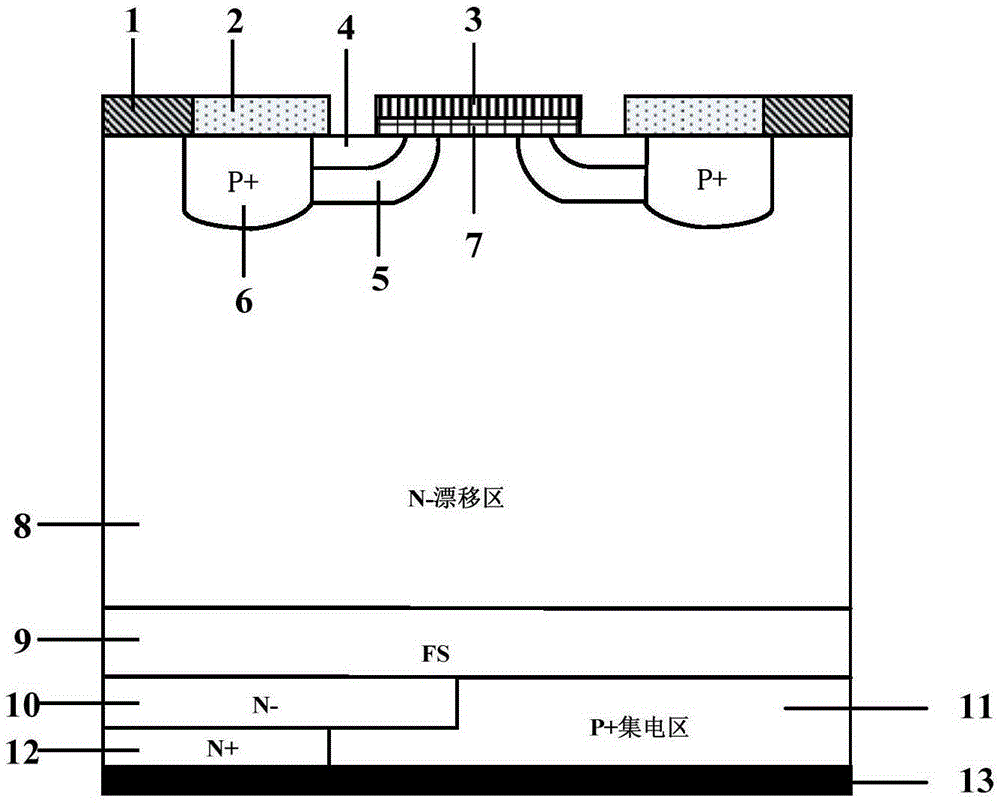

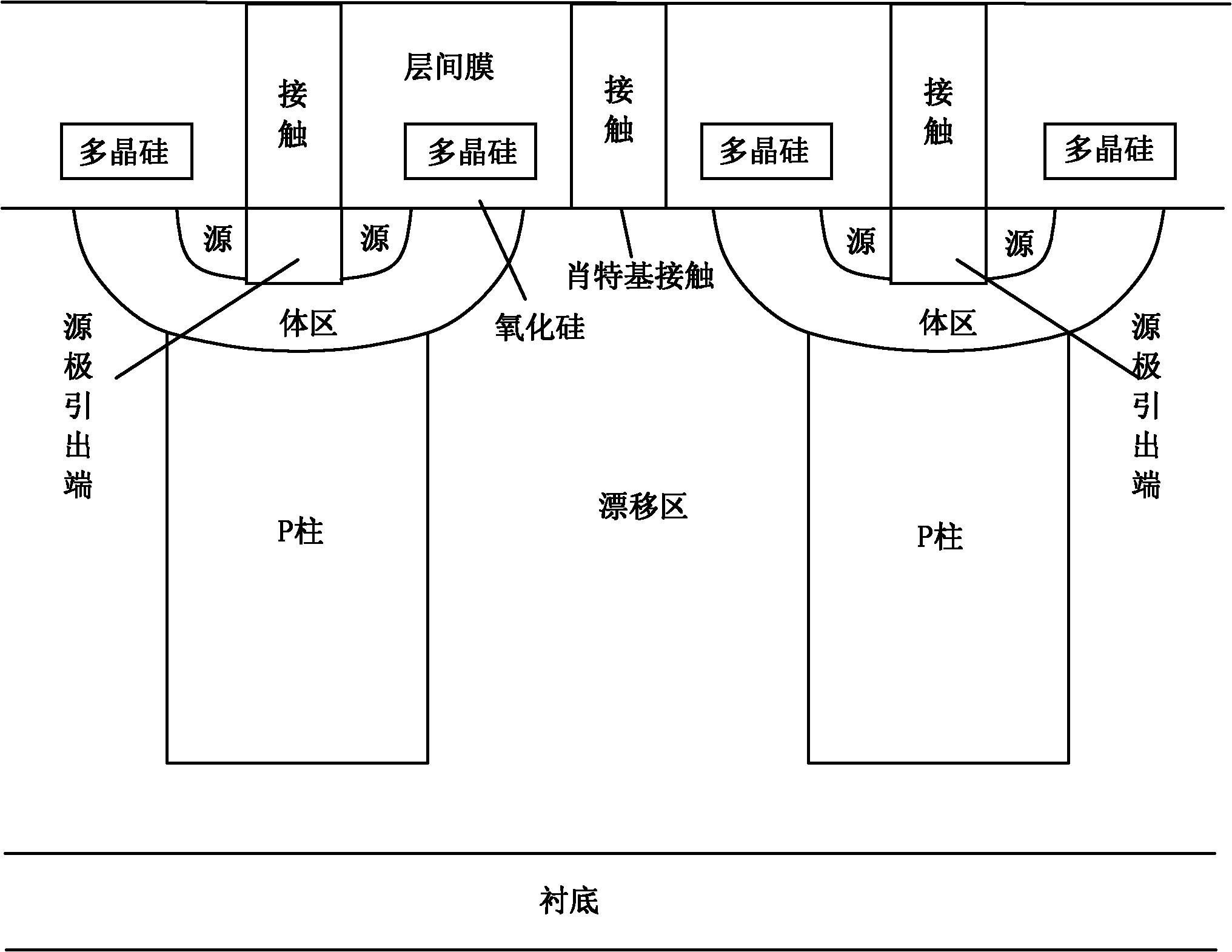

Reverse conducting IGBT device

InactiveCN105206656AShort reverse recovery timeEliminate the snapback phenomenonSemiconductor/solid-state device manufacturingSemiconductor devicesElectric fieldPower semiconductor device

The invention belongs to the technical field of power semiconductor devices, and particularly relates to a reverse conducting IGBT device. Compared with a conventional reverse conducting IGBT structure, emission electrode schottky metal is additionally arranged in source electrode metal, and an N-region is arranged below an N-type electric field stop layer so that a reverse recovery characteristic working under a freewheel diode mode is respectively improved and generation of the snapback phenomenon is suppressed. The beneficial effects of the reverse conducting IGBT device are that the reverse conducting IGBT device has short reverse recovery time, the snapback phenomenon can be eliminated at a shorter back P+ collector region, and the preparation technology of the reverse conducting IGBT device is compatible with the technology of the conventional IGBT device. The invention is especially suitable for the reverse conducting IGBT device.

Owner:UNIV OF ELECTRONIC SCI & TECH OF CHINA

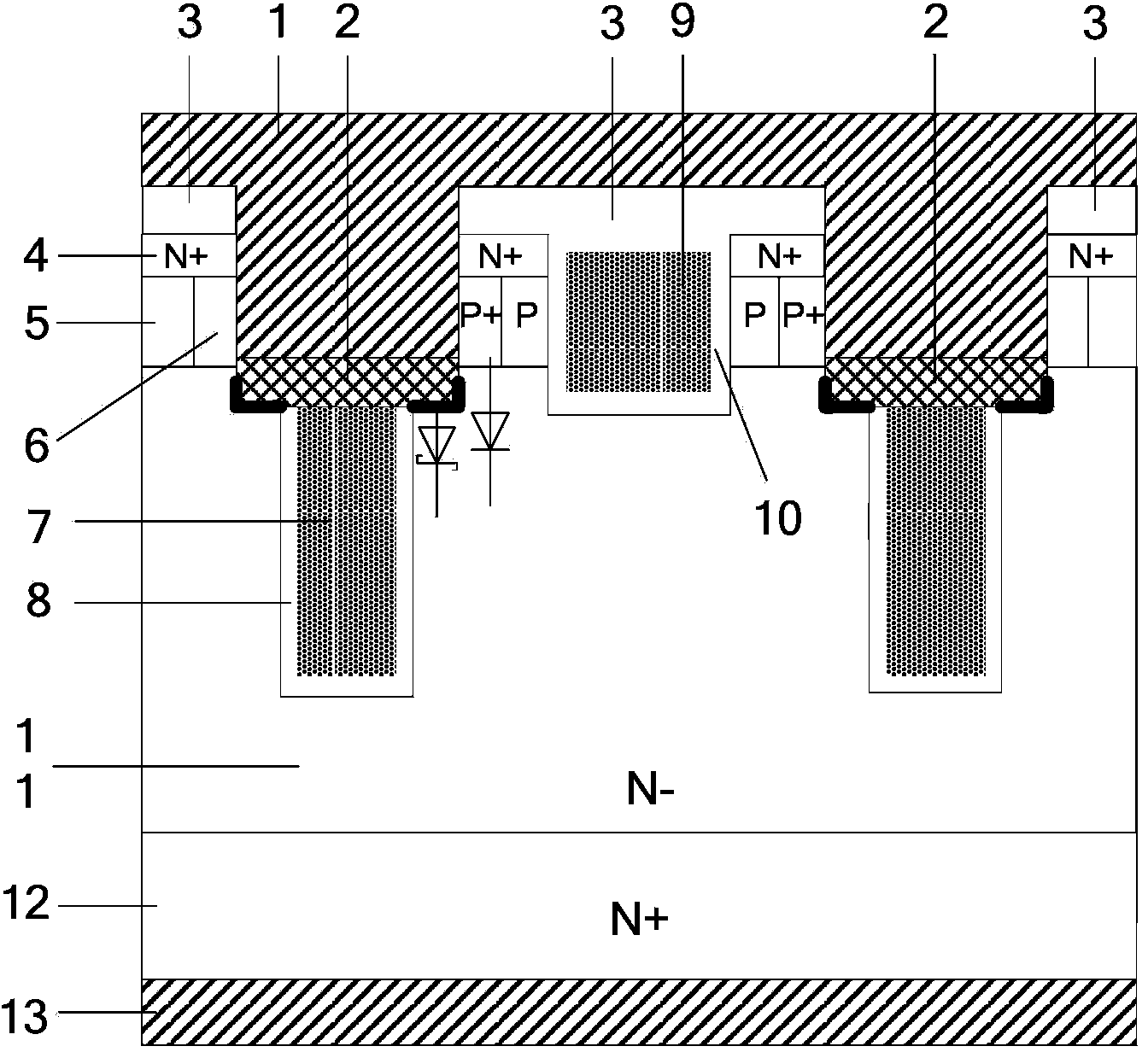

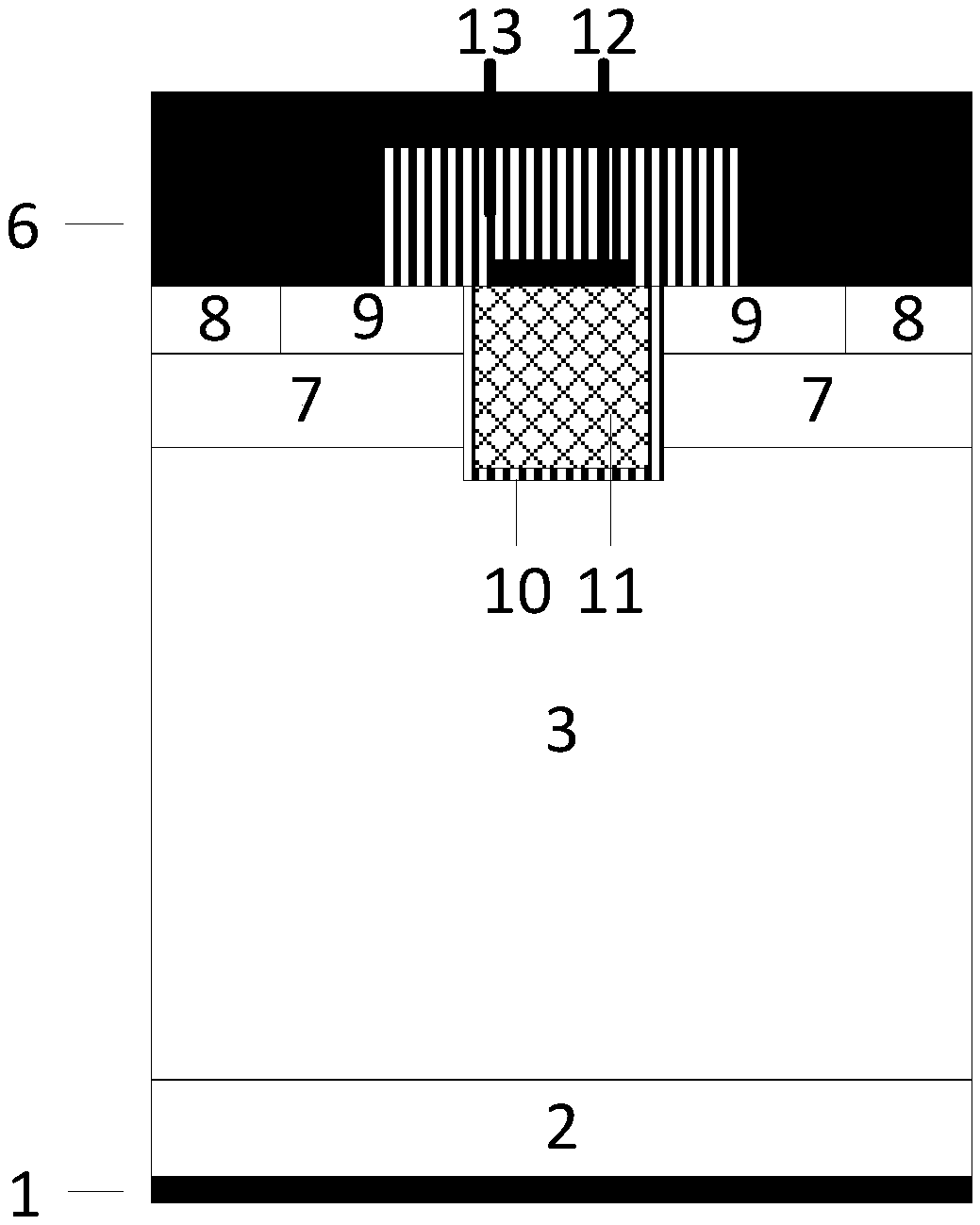

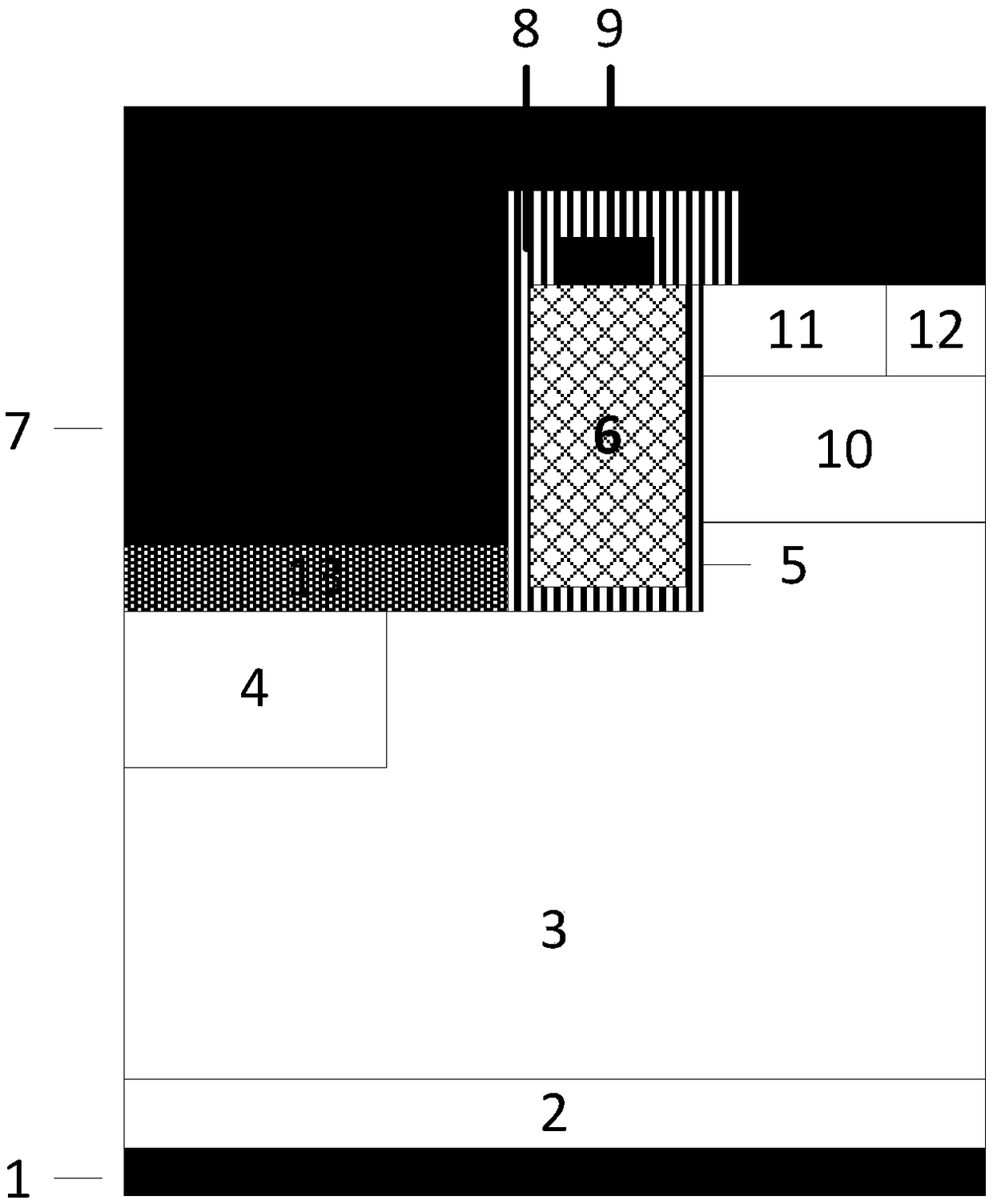

Silicon carbide MOSFET device and manufacturing method thereof

ActiveCN108807504AImprove leakageReduce leakageSemiconductor/solid-state device manufacturingSemiconductor devicesCarbide siliconMOSFET

The invention provides a silicon carbide MOSFET device and a manufacturing method thereof. Silicon carbide deep P injection is performed in a specified region, groove etching and deposition of metal or polysilicon are performed above a silicon carbide deep P doped region, and the deposited metal or polysilicon is in direct contact with the silicon carbide N-epitaxy to form a Schottky contact or aSi / SiC heterojunction contact having rectifying characteristics. Therefore, the integration of multiple sub-rectifiers is achieve while optimizing the basic performance of the conventional silicon carbide UMOSFET, the working performance of the third quadrant of the device is greatly optimized, the gate-drain capacitance of the device is reduced and the switching speed of the device is improved.

Owner:HANGZHOU SILICON-MAGIC SEMICON TECH CO LTD

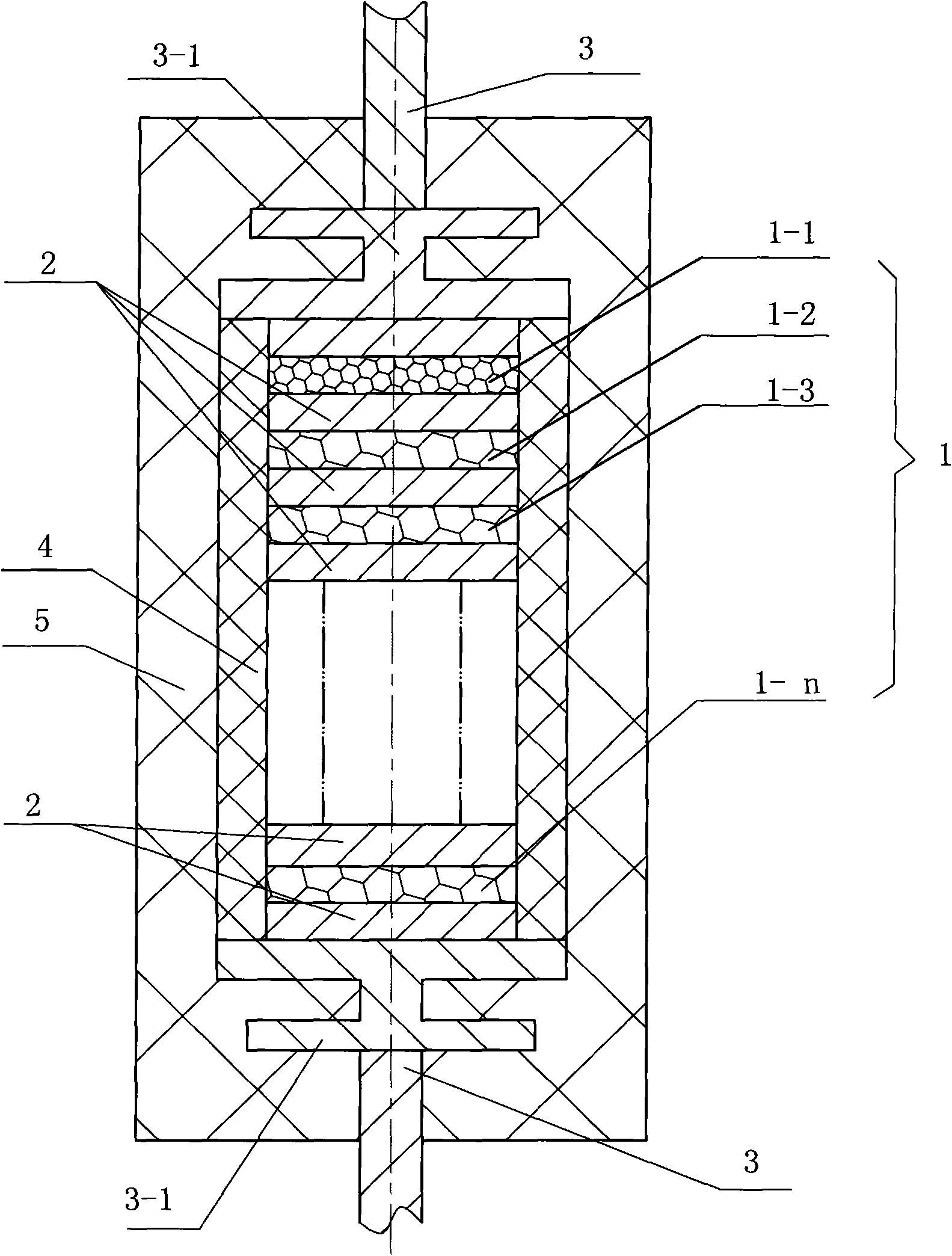

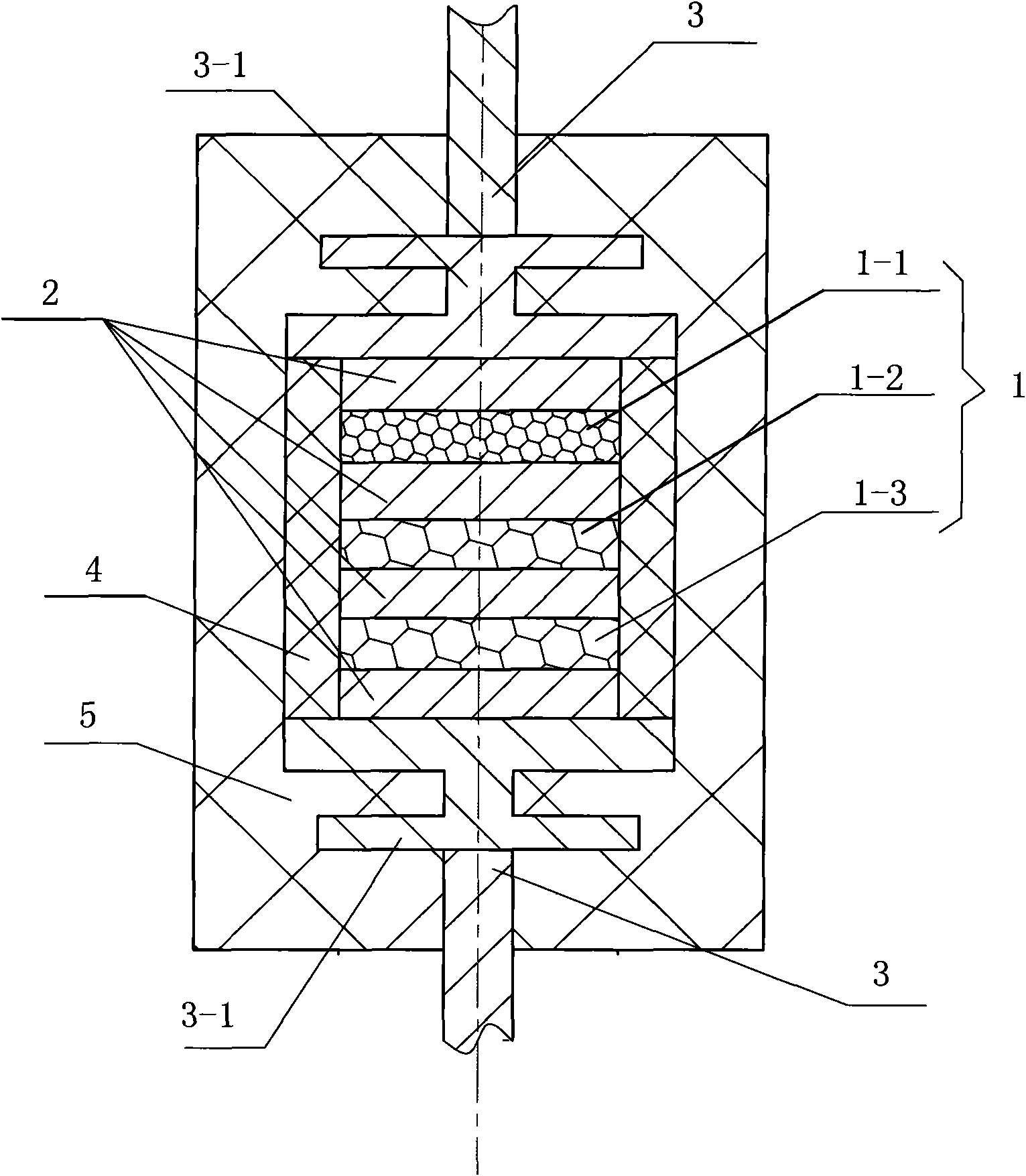

High-frequency quick-recovery diode

InactiveCN101630677AImprove pressure resistanceHigh priceSemiconductor/solid-state device detailsSolid-state devicesReverse recoveryRectifier diodes

The invention relates to a high-frequency quick-recovery diode which comprises a diode chip set, a lug plate, leading wires, lead heads, a packet layer and a plastic-sealed body, wherein the diode chip set comprises n diode chips ranked in the sequence of polarity in the same direction, one to n-1 sheets of chips are quick-recovery diode chips, and the rest chips are common rectifier diode chips, and both sides of each diode chip are respectively provided with a lug plate which is mutually connected with the lug plate; the end surfaces of the lead heads of the two diode leading wires are respectively connected with the lug plates at both ends of the diode chip set; the periphery of the diode chip set and the lug plate is provided with a packet layer; the periphery of the two lead heads and the packet layer is provided with the plastic-sealed body; the plastic-sealed body is a cylinder or a square cylinder. Compared with a traditional high-frequency quick-recovery diode, the invention has the advantages of short reverse recovery time, high pressure-proof performance, low price and convenient purchase, and thereby reducing the production cost of the high-frequency quick-recovery diode. The invention is suitable for industrialized large-scale production.

Owner:CHANGZHOU GIANTION PHOTOELECTRICITY IND DEV

Silicon carbide TrenchMOS device and manufacturing method thereof

ActiveCN107256864AImprove performanceReduce power lossTransistorSolid-state devicesHeterojunctionReverse recovery

The invention discloses a silicon carbide TrenchMOS device and manufacturing method thereof, belonging to the technical field of power semiconductors. Considering the defects of an external anti-parallel fast recovery diode (FRD) and a parasitic diode directly using a silicon carbide TrenchMOS device, a polysilicon area is additionally arranged in the p+ contact area of a conventional device, so that a Si / SiC heterojunction is formed by the polysilicon and silicon carbide epitaxial layer material, and furthermore, a diode is integrated in the device. The junction voltage drop is significantly reduced when a device diode is applied, and the conductive mode during the diode application is converted from bipolar conduction into single polar conduction, so that the silicon carbide TrenchMOS device has the advantages of short reverse recovery time and less reverse recovery charge. The device structure also has the advantages of low parasitic silicon carbide diode reverse leakage, high breakdown voltage and good device temperature stability. Therefore, the silicon carbide TrenchMOS device has wide prospects in circuits such as an inversion circuit and a chopper circuit.

Owner:HANGZHOU SILICON-MAGIC SEMICON TECH CO LTD

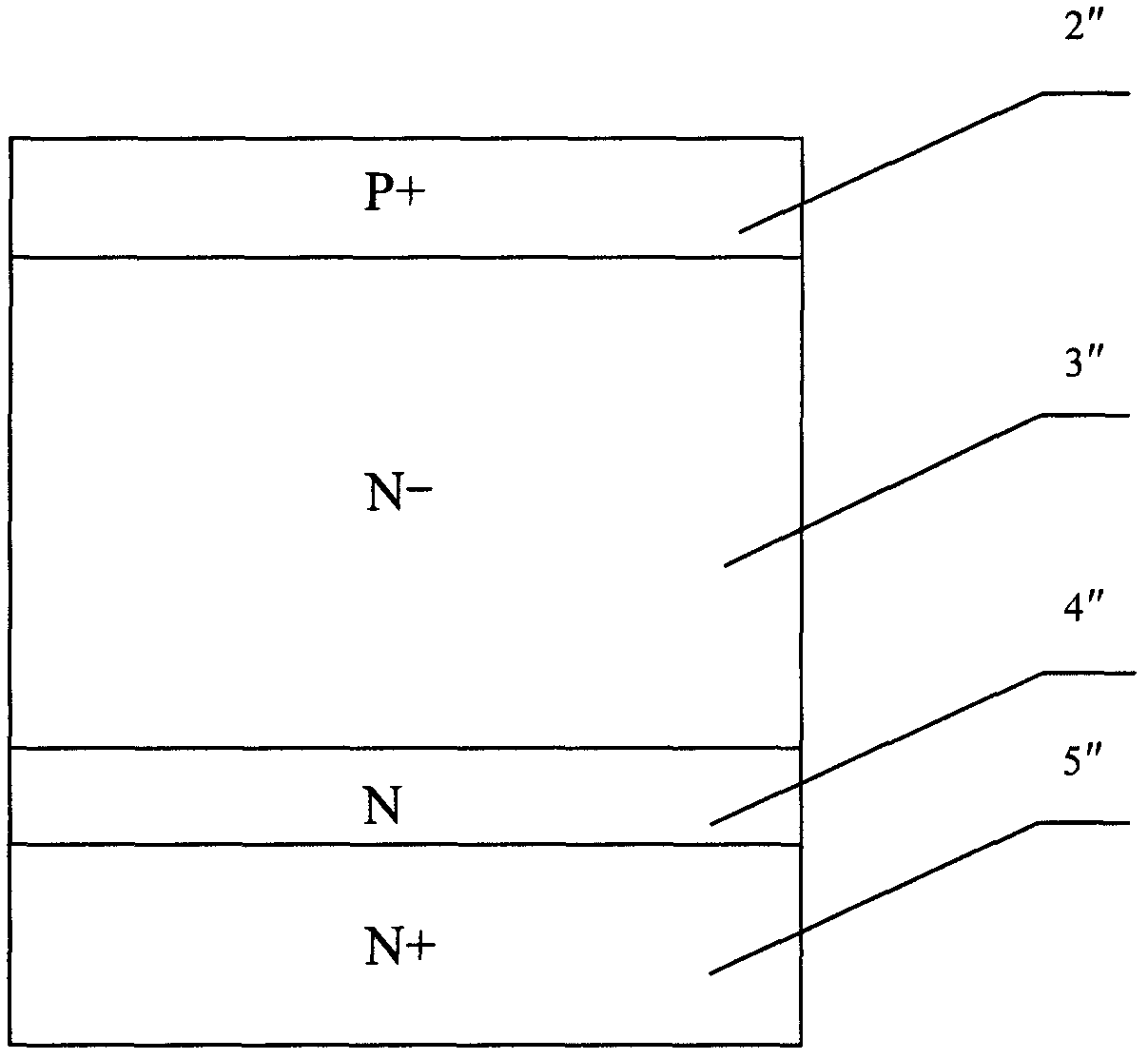

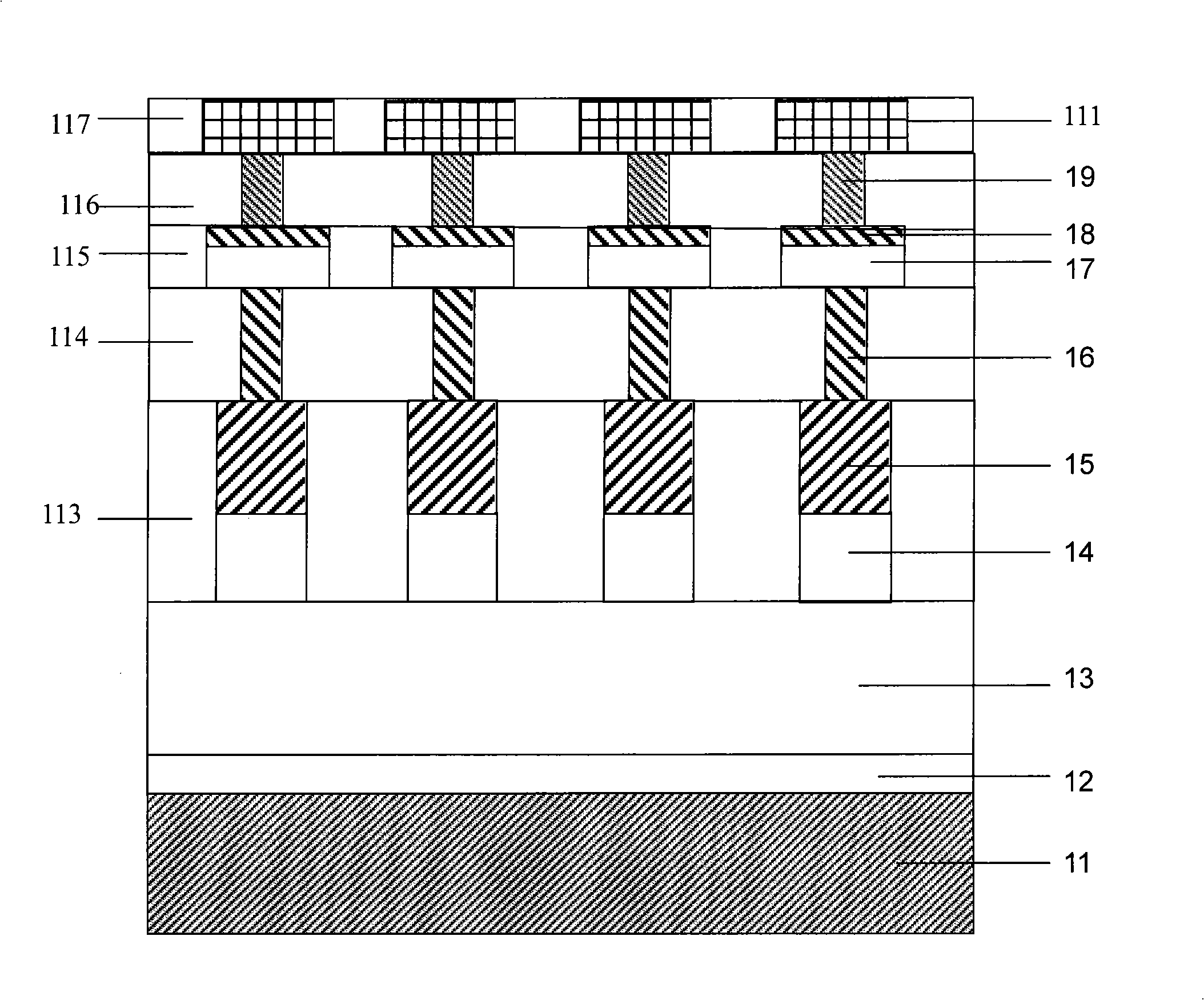

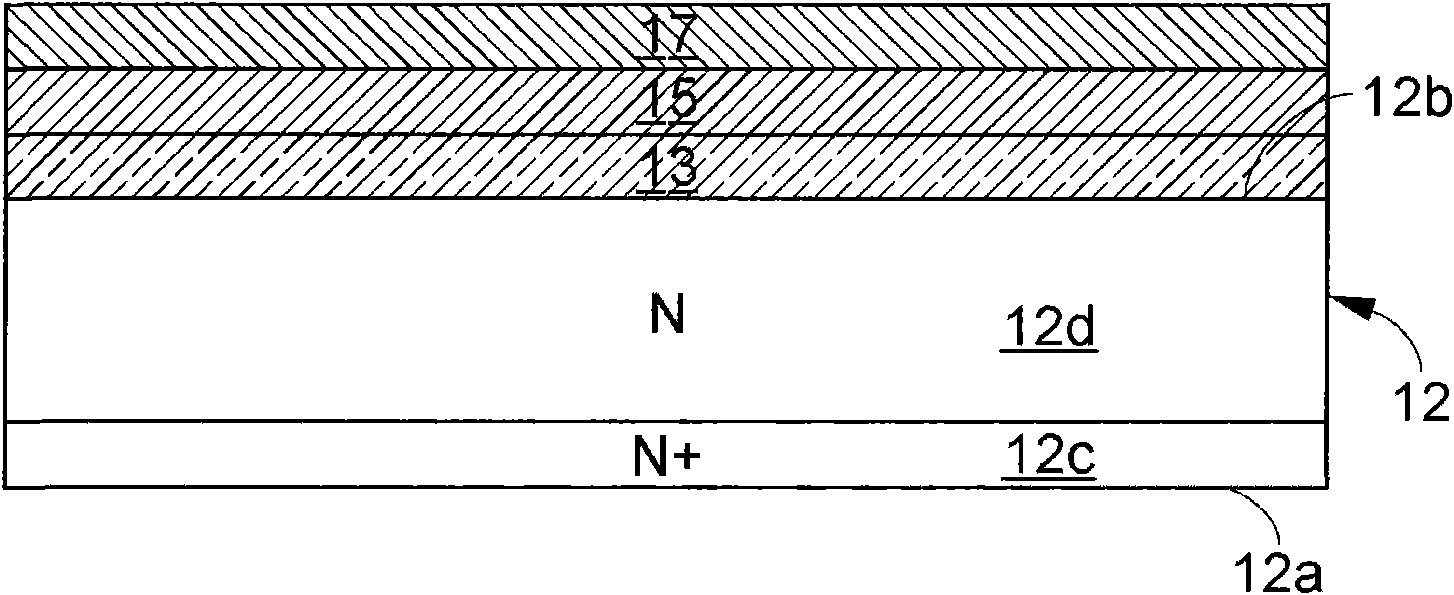

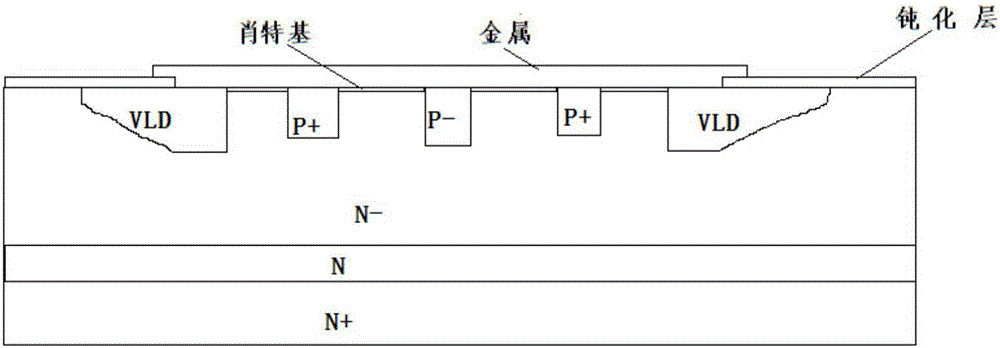

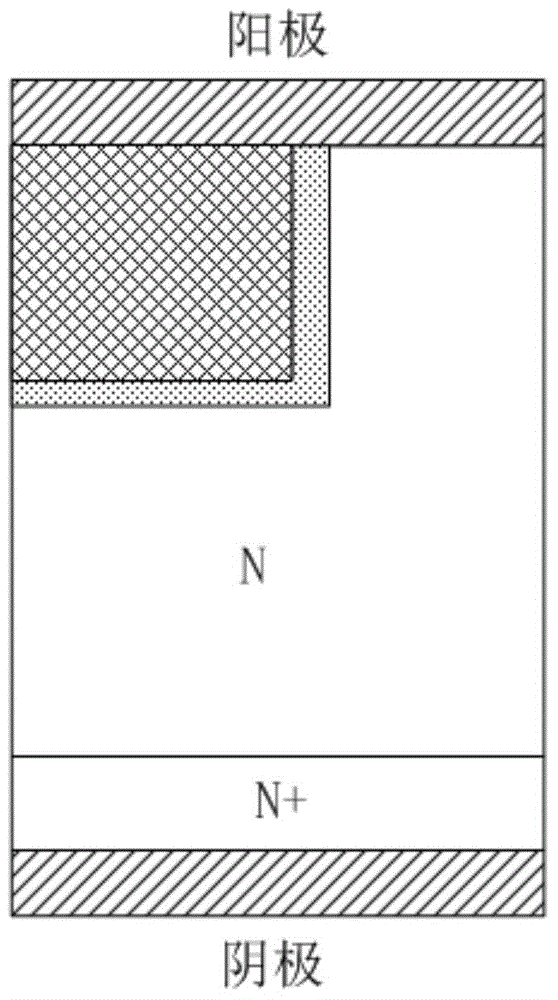

Soft fast recovery diode of multi-mixture structure and preparation method thereof

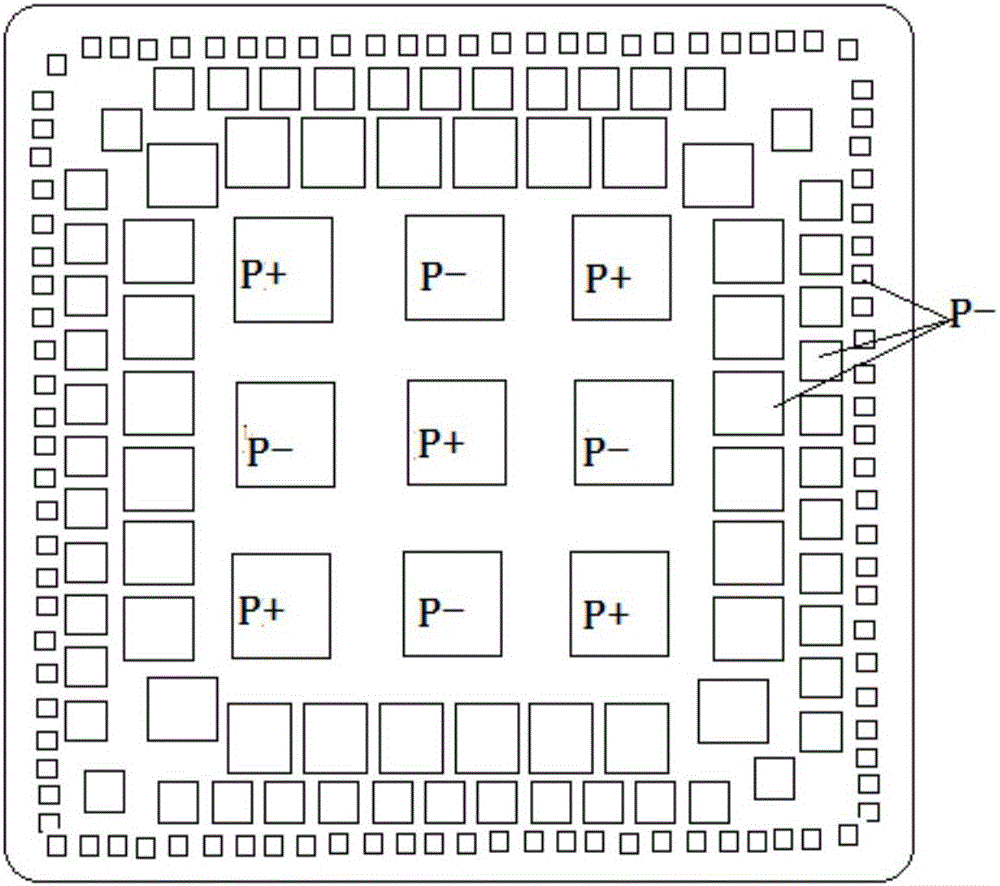

PendingCN105826399AShort reverse recovery timeLow costSemiconductor/solid-state device manufacturingSemiconductor devicesHigh concentrationReverse recovery

The main purpose of the invention is to provide a high-voltage soft fast recovery diode and a preparation method thereof. According to the invention, a structure in which Schottky is mixed with high-concentration and low-concentration PN junctions is adopted, and varied lateral doping (VLD) plane terminal protection is made synchronously. Thus, the breakdown voltage and anti-surge capability are improved, the recovery time is reduced, the soft recovery characteristic is formed, and a good low-leakage effect is achieved. High-concentration P+ / N- junction, Schottky junction, low-concentration P- / N- junction and Schottky junction structures are made and arranged at intervals on N- / N / N+ silicon wafers. By adding the P- / N- structure, the efficiency of hole injection is reduced, the time for reverse recovery is reduced, reduction in barrier height of a Schottky junction is avoided, and soft fast recovery and low leakage are both achieved. The original structure and the added P- / N- structure form a VLD terminal structure, which ensures high voltage and high anti-surge capability, simplifies the manufacturing process, and reduces the cost. Compared with the tradition fast recovery diode of a PIN and MPS structure, the diode of a multi-mixture structure recovers faster, and has a wider application range.

Owner:北海惠科半导体科技有限公司

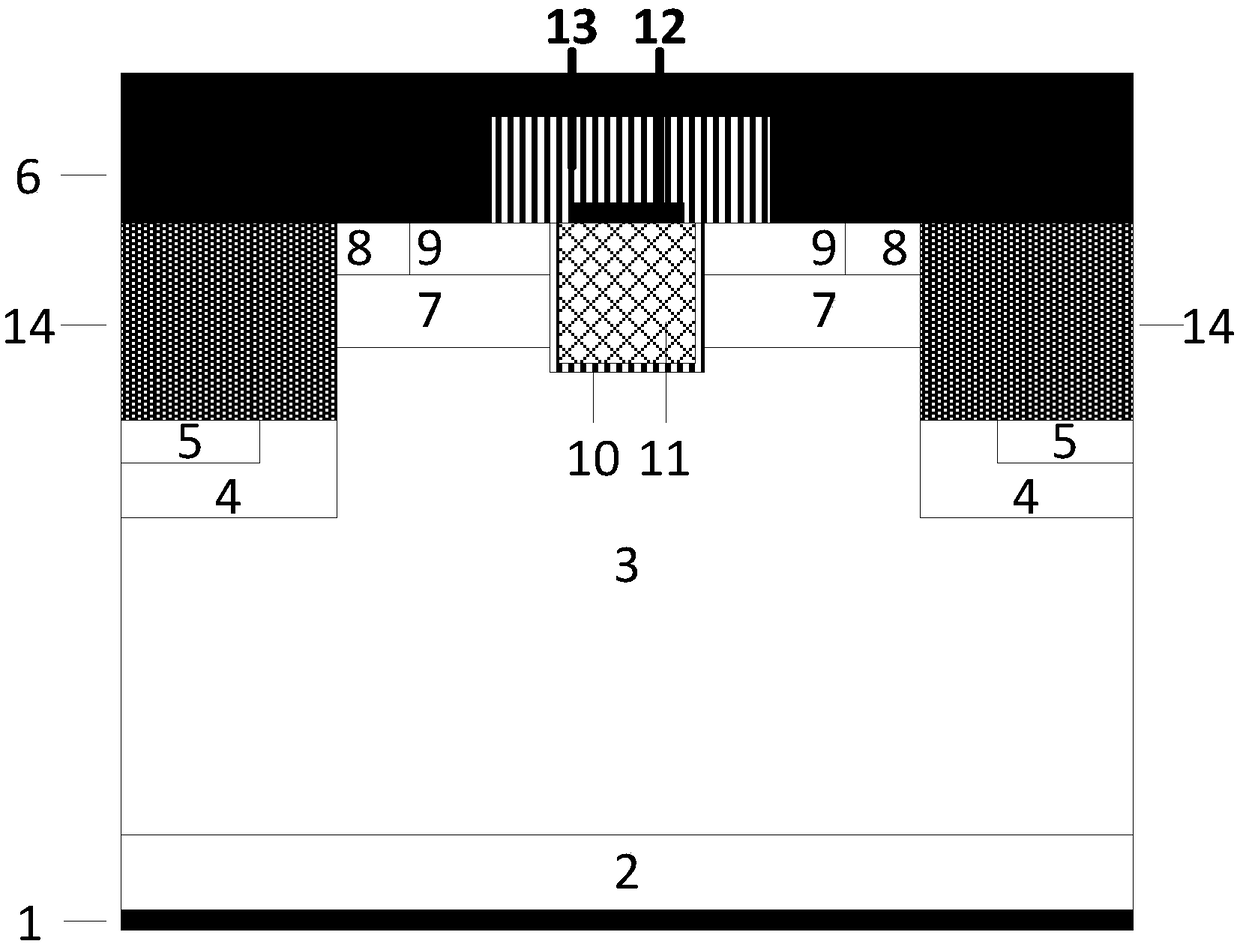

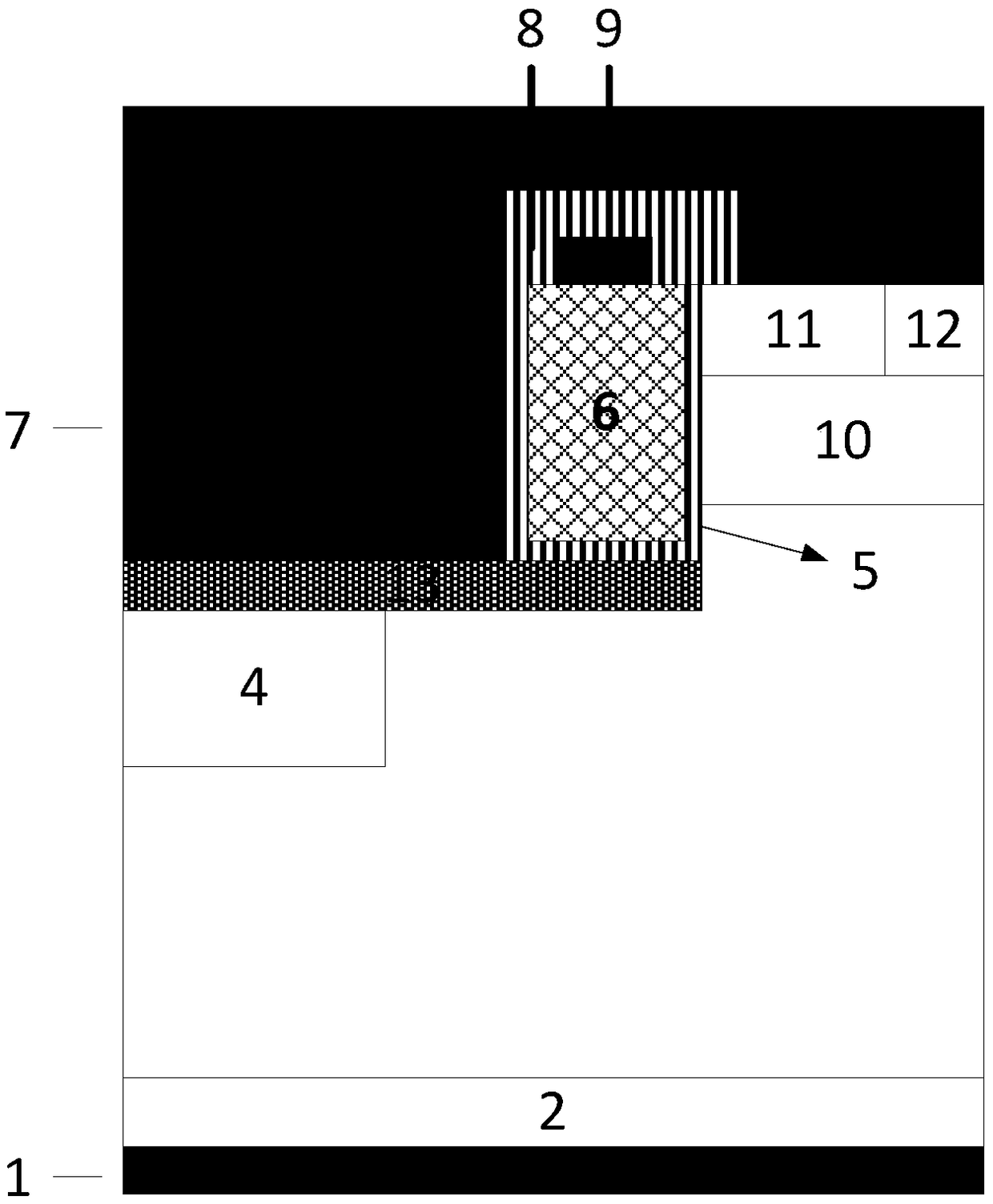

A silicon carbide MOSFET device and a manufacturing method thereof

ActiveCN109192779AGood long-term application reliabilityImprove pressure resistanceSemiconductor/solid-state device manufacturingDiodeMOSFETHeterojunction

The invention provides a silicon carbide MOSFET device and a manufacturing method thereof. The invention improves device structure design and finally integrates Schottky contact or heterojunction contact with rectifying characteristics on the basis of traditional silicon carbide UMOSFET structure. At that same time of optimize the basic characteristics of the traditional silicon carbide UMOSFET structure, the improvement realize the integration of multi-sub rectifier devices, greatly optimizes the work performance of the third quadrant of the device, and in addition, the invention also optimizes the dynamic performance of the device, and has shorter switching time; In addition, the invention also has the characteristics of simple process and easy realization.

Owner:UNIV OF ELECTRONICS SCI & TECH OF CHINA

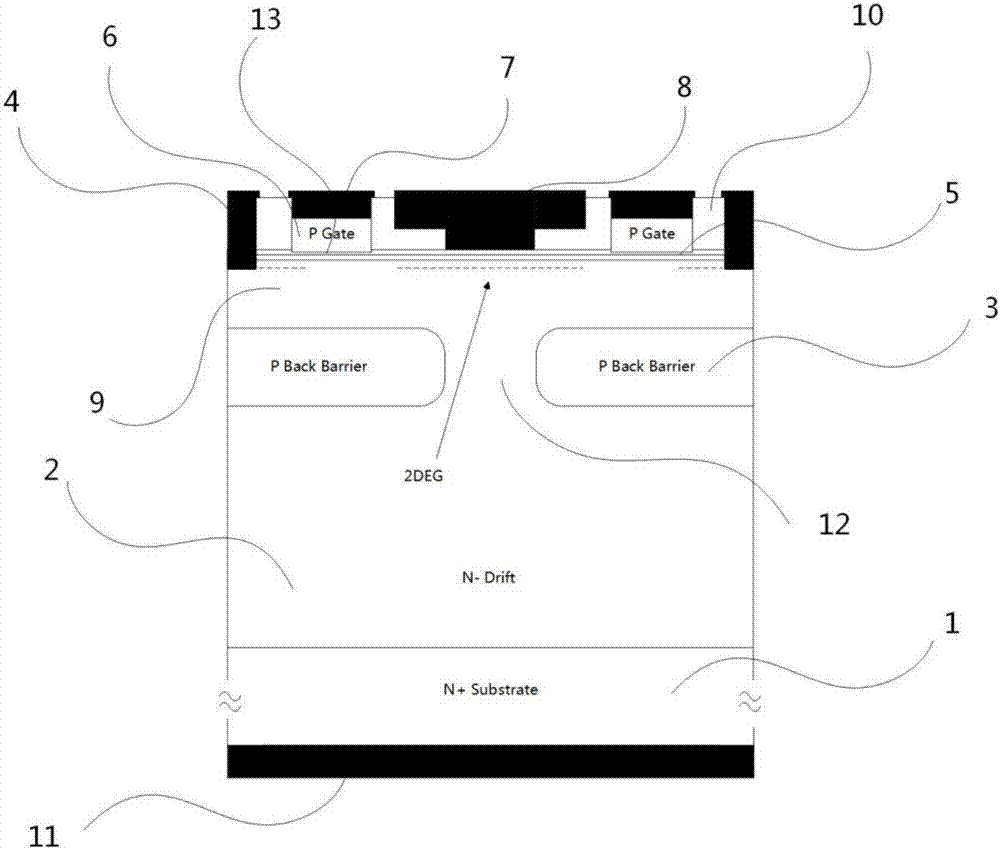

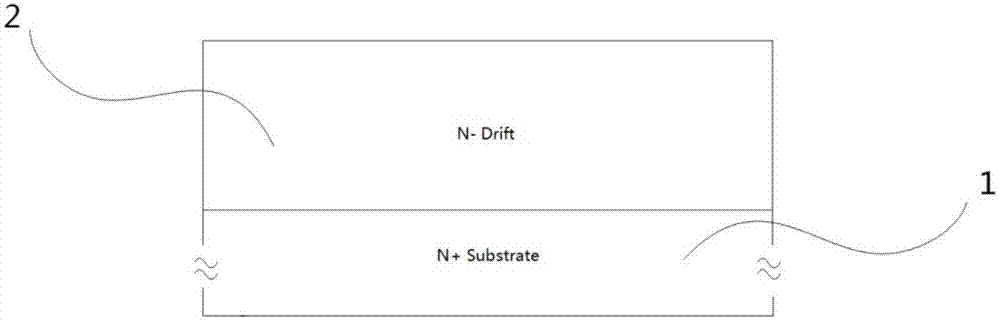

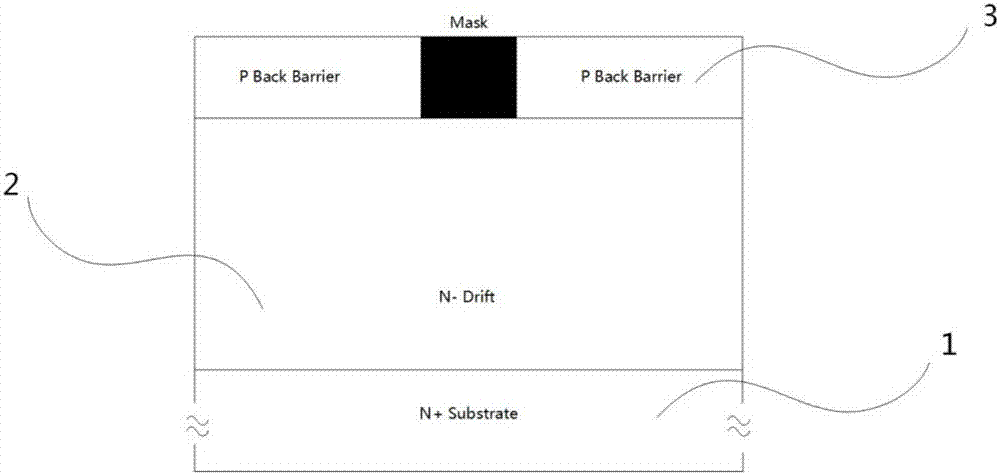

GaN hetero-junction longitudinal inverse-conduction field effect tube

ActiveCN107482059ALower on-resistanceIncrease saturation currentSemiconductor devicesField-effect transistorElectron

The invention relates to the technical field of semiconductor devices, and relates to a GaN hetero-junction inverse-conduction field effect tube. According to the invention, a longitudinal discrete gate structure is adopted; a schottky source electrode is deposited between the gate electrodes so as to form an anode of an inverse-conduction diode; and through the joint action of the back barrier formed in the p-type base region and the p-type gate, the two-dimensional electron gas (2 DEG) below the gate can be depleted; and through the adjustment of the re-growth thickness of the ALMN barrier layer, the threshold voltage can be accurately regulated and controlled. The effect tube has the beneficial effects that under the working state of a forward switch, the threshold voltage is adjustable, that the on-resistance is low, that the saturation current is large, that the off-state withstanding voltage is high, and that working frequency is high and power consumption is low and the like; and under the inverse-conduction working state, the starting voltage is low, the on-resistance is low, the inverse withstanding voltage is large, the inverse recovery time is short, and the power consumption is low and the like. Meanwhile, the manufacturing process is compatible with a traditional GaN hetero-junction HEMT device and is particularly suitable for a GaN hetero-junction longitudinal power field effect tube.

Owner:UNIV OF ELECTRONICS SCI & TECH OF CHINA

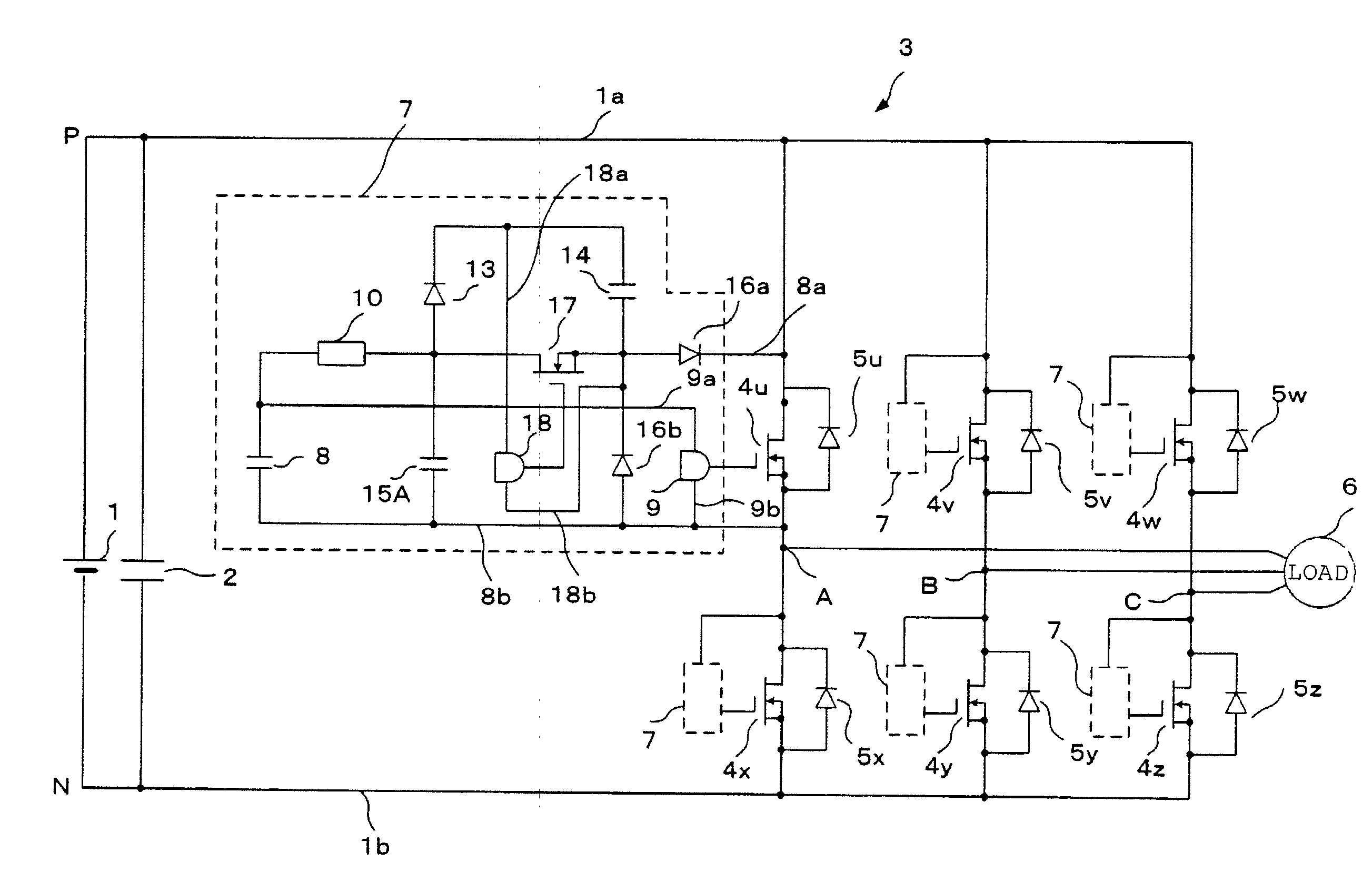

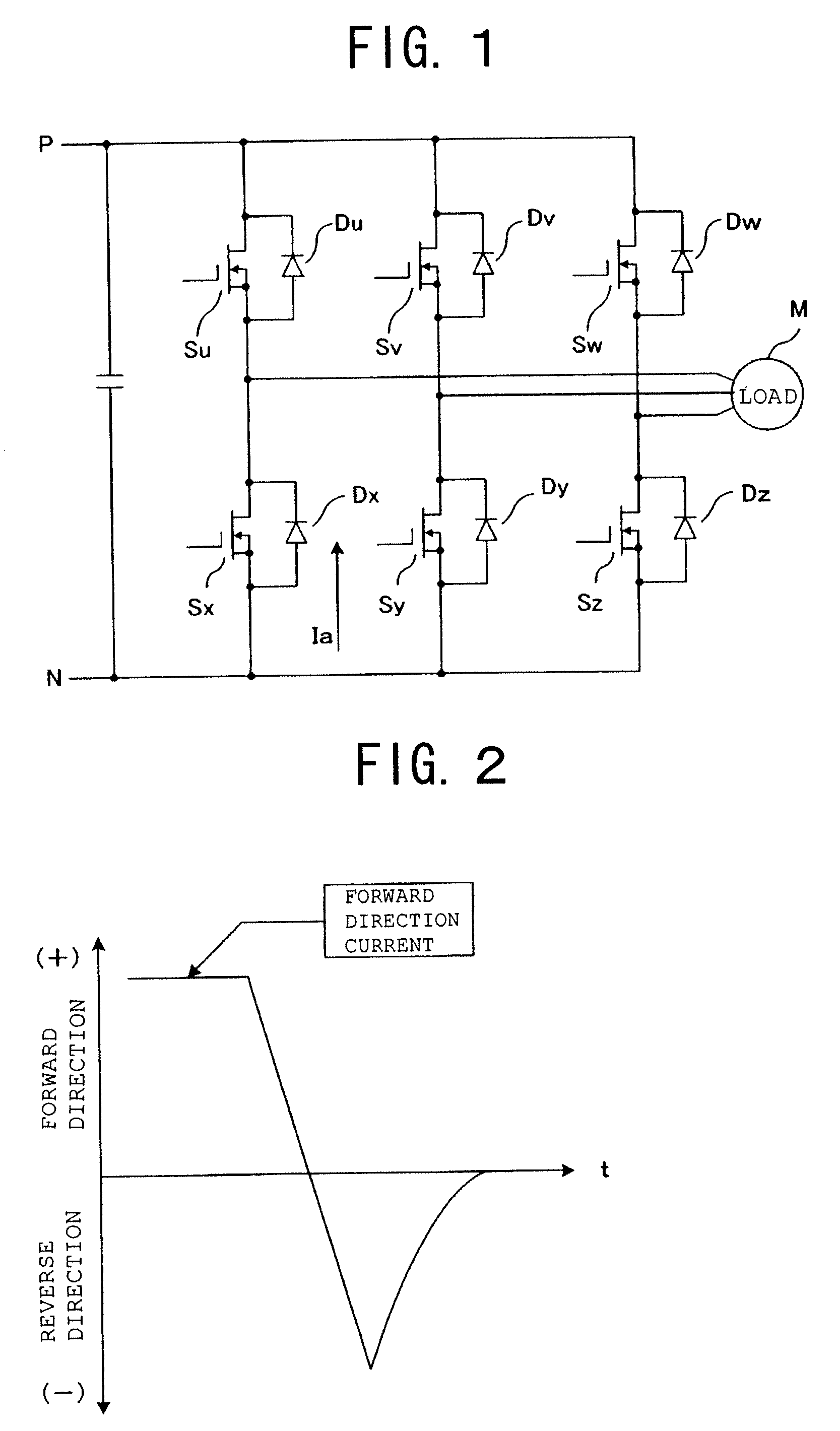

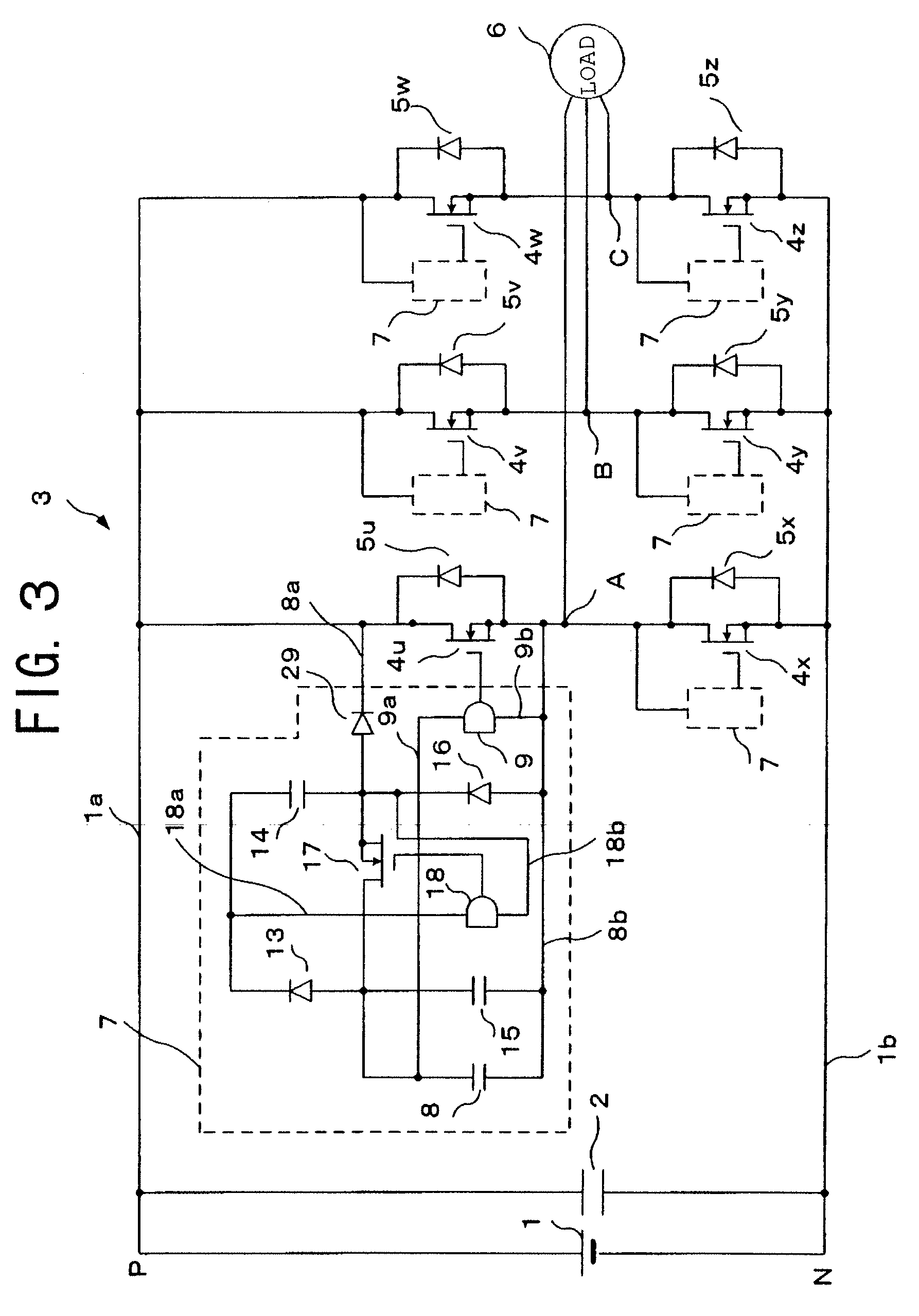

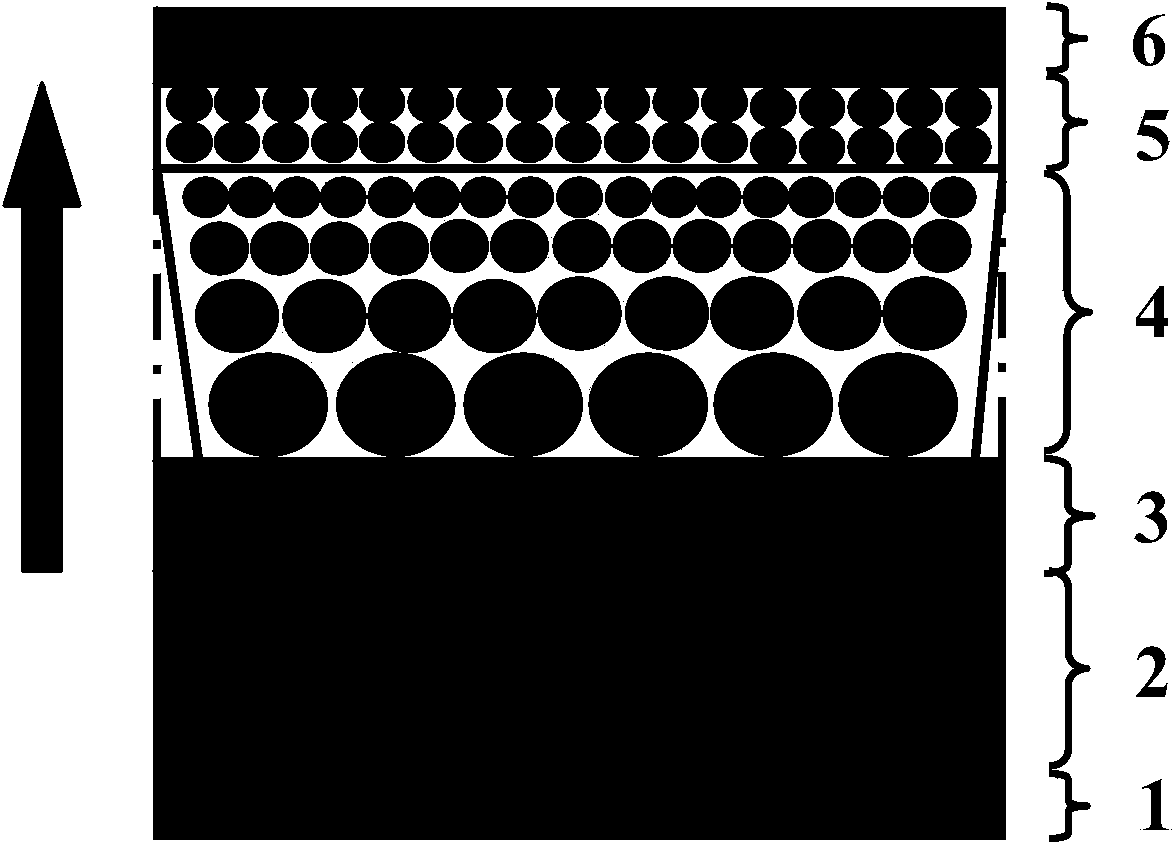

Power Converter

ActiveUS20080253158A1Short reverse recovery timeShort timeEfficient power electronics conversionAc-dc conversionReverse recoveryEngineering

There are provided: sets of pairs of main circuit switching elements (4u), (4x) that supply power to a load, connected in series with a DC power source; free-wheel diodes (5u), (5x) connected in anti-parallel with these main circuit switching elements; and a reverse voltage application circuit (8) that applies reverse voltage smaller than the DC voltage source to the free-wheel diodes when these free-wheel diodes cut off. The reverse voltage application circuit includes a current suppression circuit (10) that suppresses the main circuit current flowing in the low-voltage DC voltage power source on reverse recovery of the free-wheel diodes.

Owner:KK TOSHIBA

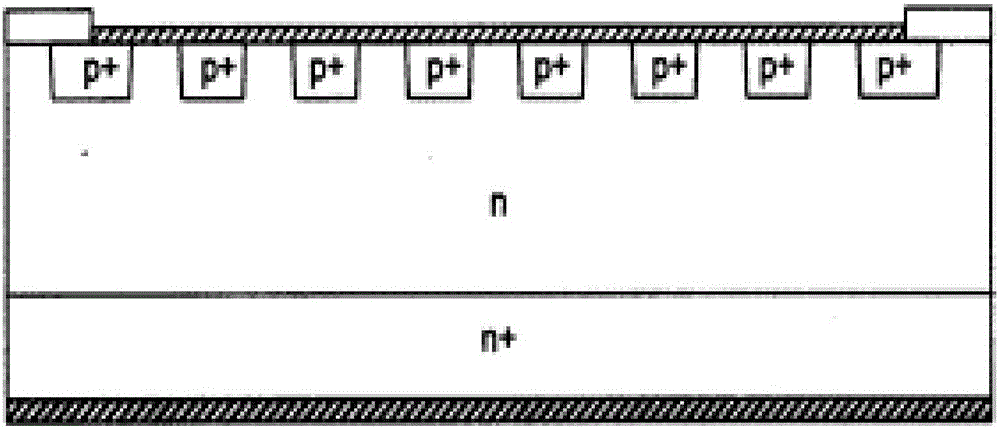

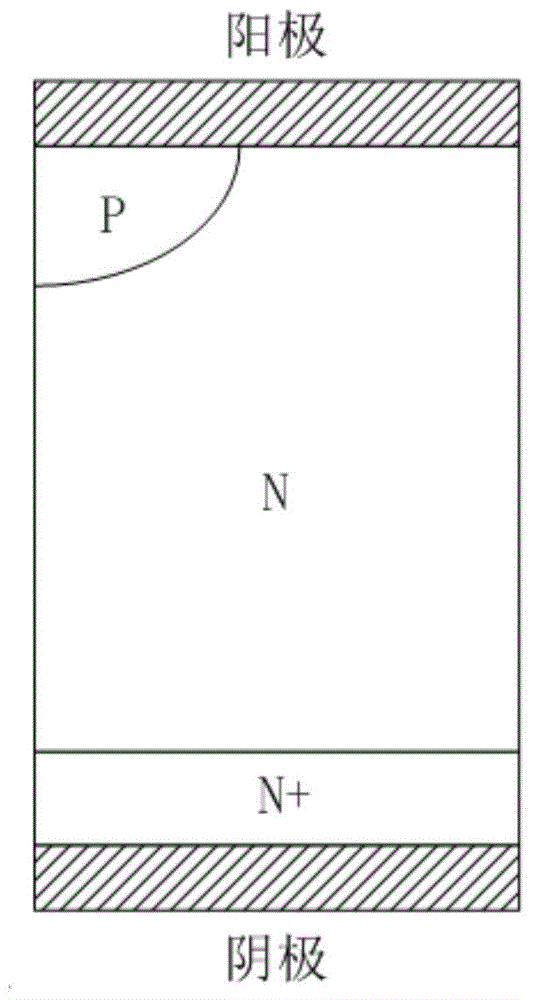

Base region gradient P<+>-N-N<+> type SiC ultrafast recovery diode manufactured on 4H type single crystal silicon carbide epitaxial layer and process

ActiveCN104201211AShort reverse recovery timeSuppress surge currentSemiconductor/solid-state device manufacturingSemiconductor devicesReverse recoveryCarbide

The invention discloses a base region gradient P<+>-N-N<+> type SiC ultrafast recovery diode manufactured on a 4H type single crystal silicon carbide epitaxial layer and a process. An anode / (P<+>)4H-nc-SiC / (N) slowly changes into a 6H-nc-SiC / (N)4H-c-SiC / (N<+>)4H-c-SiC / cathode. The base region gradient P<+>-N-N<+> type SiC ultrafast recovery diode comprises an N<+> type 4H-c-SiC substrate, an N type 4H-c-SiC epitaxial layer, an N type 6H-nc-SiC gradually-doped and grain-gradient multilayer film and a P<+> type 4H-c-SiC single layer film, wherein the outer sides of the N<+> type 4H-c-SiC substrate and the P<+> type 4H-c-SiC single layer film are in ohm connection with an anode NiAu and an anode TiAu respectively. The device structure is made by using a PECVD (Plasma Enhanced Chemical Vapor Deposition) technology. The process has the advantages of shortening the reverse recovery time, inhibiting surge current and lowering the process temperature.

Owner:广州奔瑞电子科技有限公司

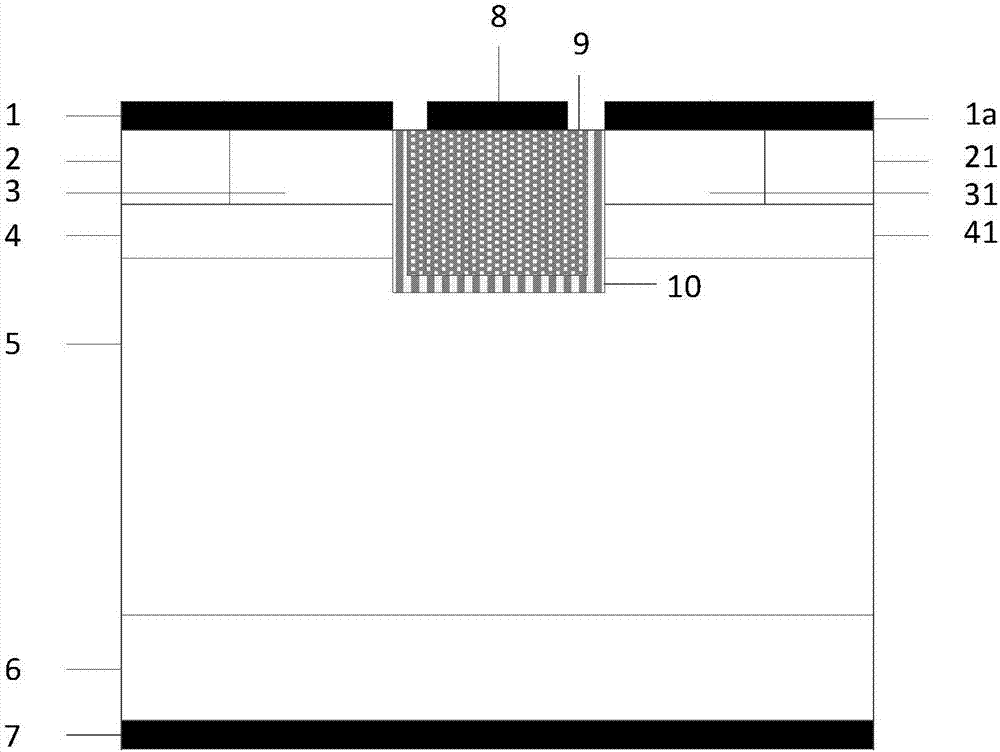

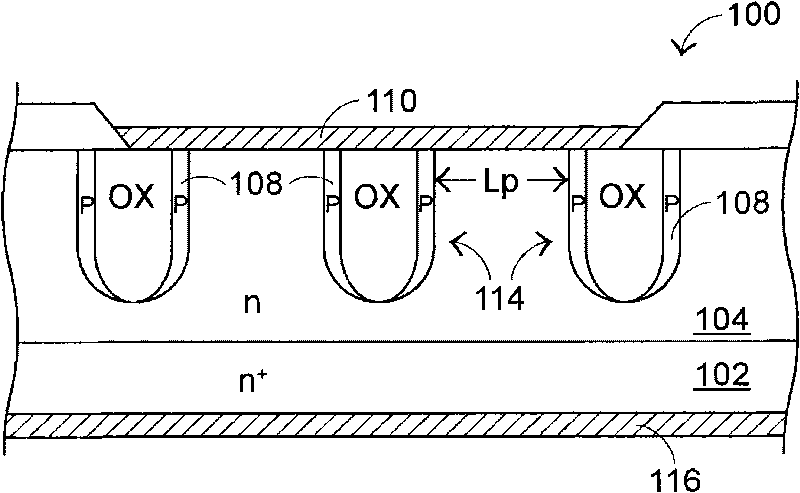

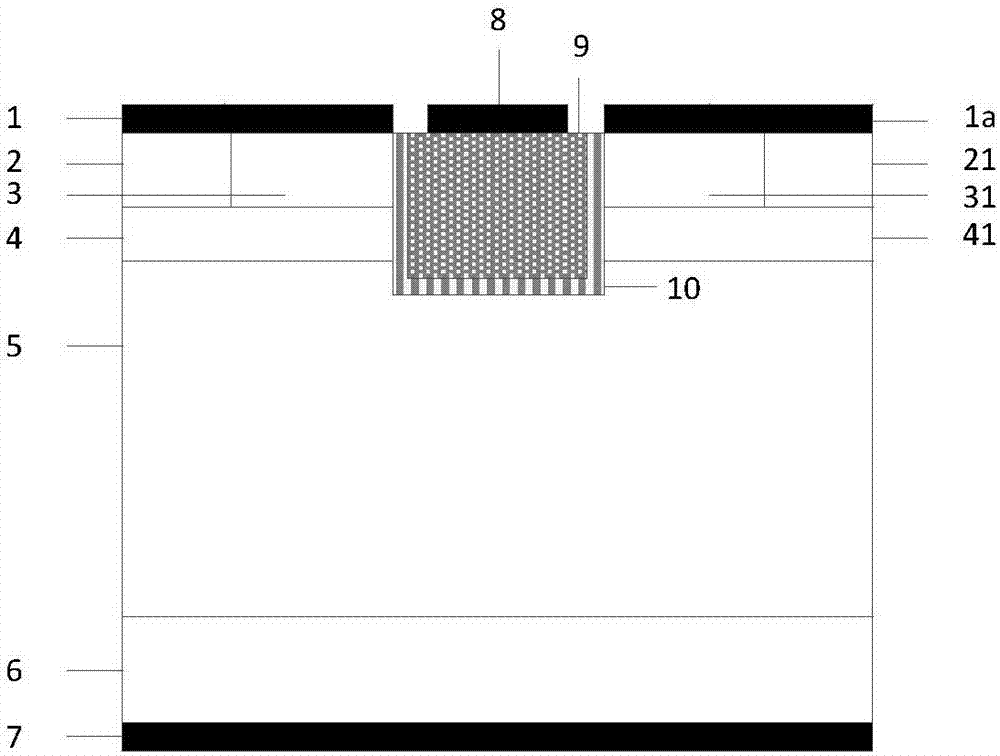

Diode with floating island structure

InactiveCN104409519AReduce conduction voltage dropShort reverse recovery timeSemiconductor devicesReverse recoveryPower semiconductor device

The invention belongs to the technical field of power semiconductor devices, and relates to a diode with a floating island structure. The diode comprises an N-type semiconductor substrate, a cathode arranged at the bottom of the N-type semiconductor substrate, an N-type semiconductor drift region arranged on the upper layer of the N-type semiconductor substrate, a gate oxide layer arranged on the upper layer of the N-type semiconductor drift region, and an anode arranged on the upper layer of the gate oxide layer, wherein the gate oxide layer is of a trench gate structure, and an N-type semiconductor region is arranged between the portions, on the two sides of a trench, of the gate oxide layer. The diode is characterized in that a plurality of doping regions including P-type semiconductor doping regions are arranged in the N-type semiconductor drift region, and therefore the floating island structure is formed. The diode has the advantages that conductive voltage is reduced, the reverse recovery time is short, and the temperature characteristic is good. The diode is particularly suitable for trench type diodes.

Owner:UNIV OF ELECTRONIC SCI & TECH OF CHINA

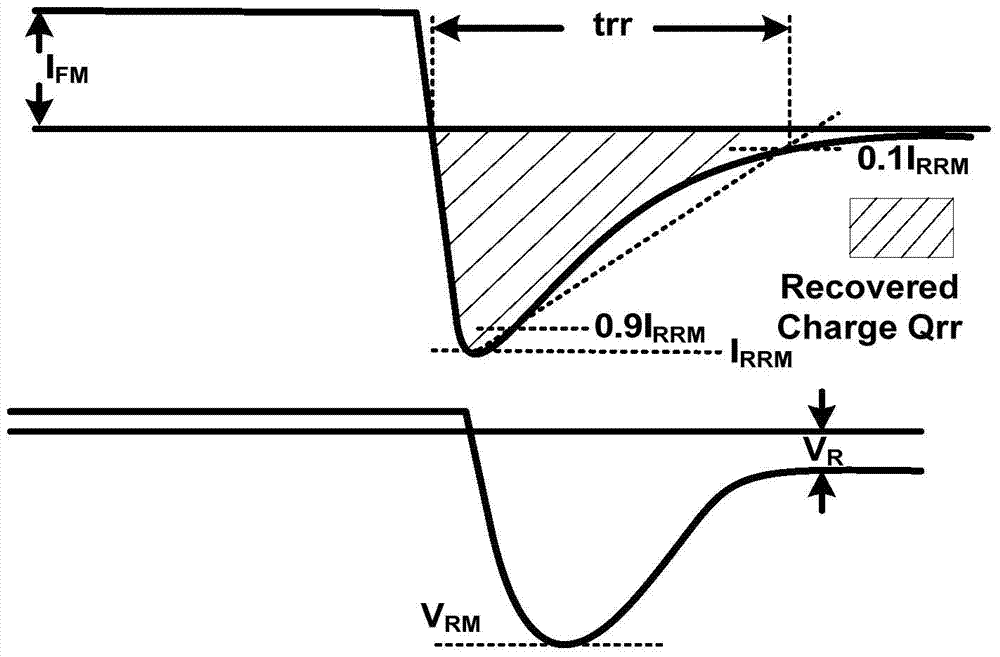

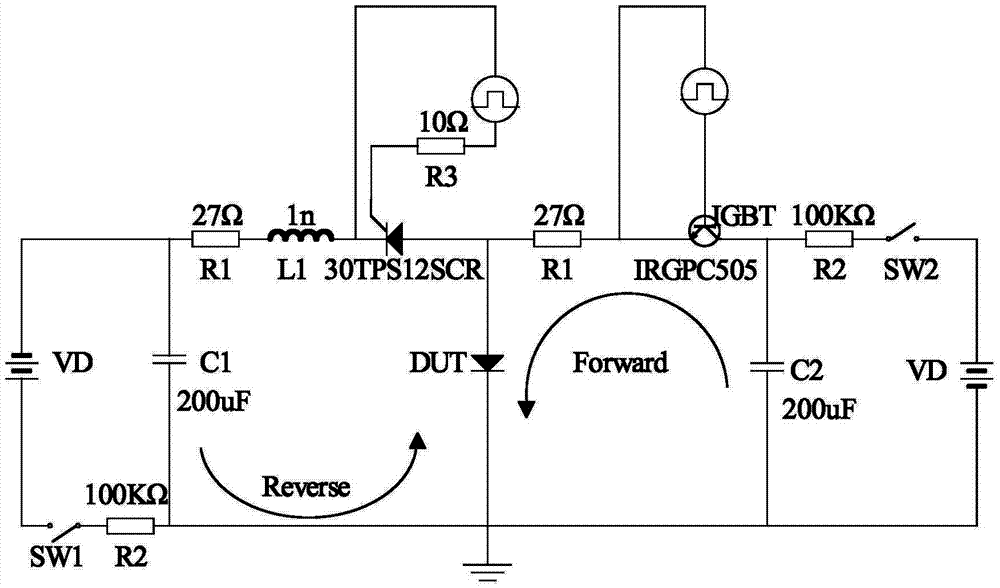

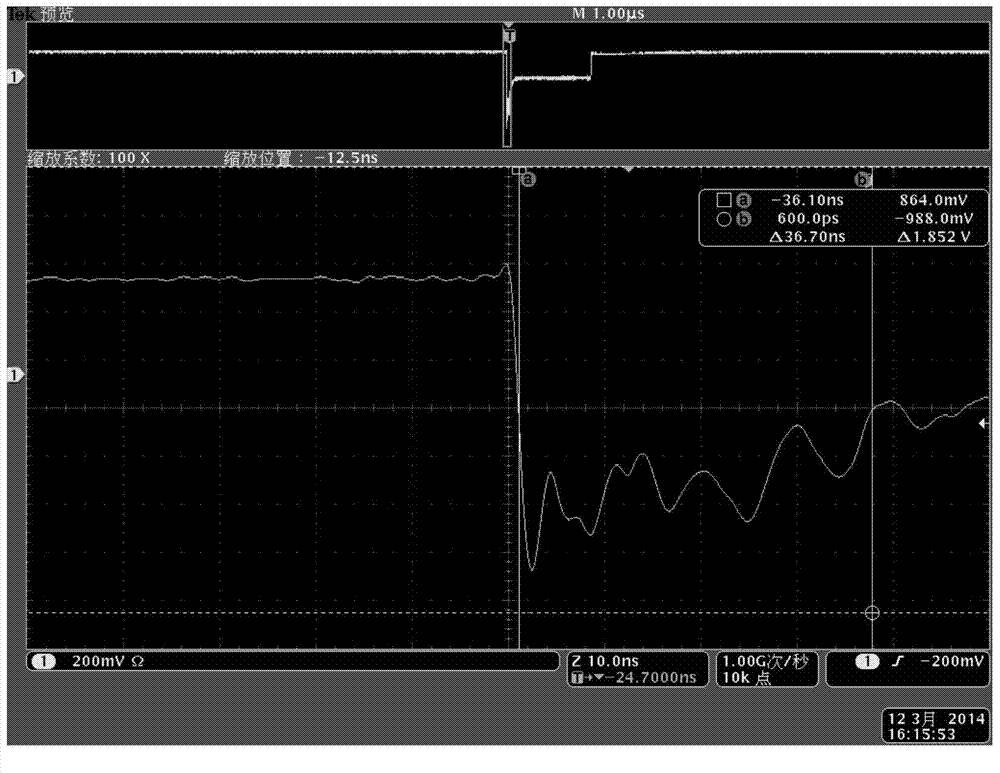

System for preventing reverse recovered charges in DUT

ActiveCN103929156AImproved reverse recovery characteristicsReduce switching lossesPulse shapingReverse recoveryElectromagnetic interference

The invention discloses a system for preventing reverse recovered charges in a DUT. The system is a current injection circuit connected to the two ends of the DUT in a forward bias mode. The injected current circuit comprises a pulse nS-level pulse signal generator formed by an SRD and a pulse edge acceleration circuit formed by a BG2 and a BG1, wherein the pulse edge acceleration circuit is tightly connected with the back of the pulse nS-level pulse signal generator and used for shortening the rising edge time and the falling edge time of pulses. The system has the advantages that the reverse recovered features of the DUT can be improved, the reverse recovered charges can be reduced, and the reverse recovered time can be shortened; meanwhile, switching losses and conduction losses of the DUT can be reduced, electromagnetic interference and surges can be restrained, and efficiency is improved.

Owner:HAIMEN THE YELLOW SEA ENTREPRENEURSHIP PARK SERVICE CO LTD

Manufacture method of diode SF chip

ActiveCN102569044AHigh purityHigh speedSemiconductor/solid-state device manufacturingElectrophoretic coatingsPlatinumHydrofluoric acid

The invention discloses a manufacture method of a diode SF chip, which includes conducting surface processing on a silicon chip, placing the processed silicon chip in a diffusion furnace, introducing a liquid phosphorus source to conduct pre-deposition and spreading propulsion, immersing the silicon chip through hydrofluoric acid, removing an oxidation layer on the surface, controlling the integral thickness of the silicon chip, removing a diffusion junction N+ on one face in abrasion mode, adopting a liquid boron source, controlling temperature in the diffusion furnace for diffusion to form P+, conducting coarsening processing on the surface of the silicon chip, conducting super sand processing and electronic cleaning agent processing on the chip, oxidizing the chip in the furnace, controlling temperature in a platinum diffusion furnace, filling the platinum into the silicon chip, placing the silicon chip after platinum diffusion into electrophoresis liquid for electrophoresis, placing the silicon chip in a sintering furnace for sintering after electrophoresis, immersing the obtained silicon chip through the hydrofluoric acid, conducting ultrasonic washing on the chip through deionized water, conducting twice nickel plated processes and gold plated processes, and dividing the processed silicon chip into single core particles from the platform face groove position to obtain the required diode SF chip.

Owner:CHANGZHOUSR SEA ELECTRONICS

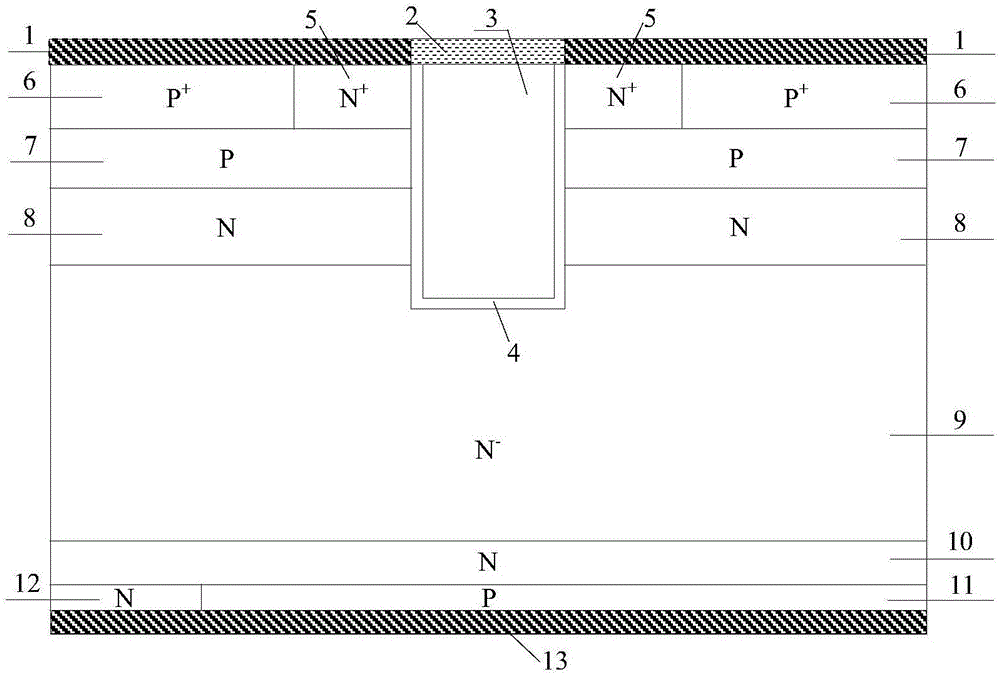

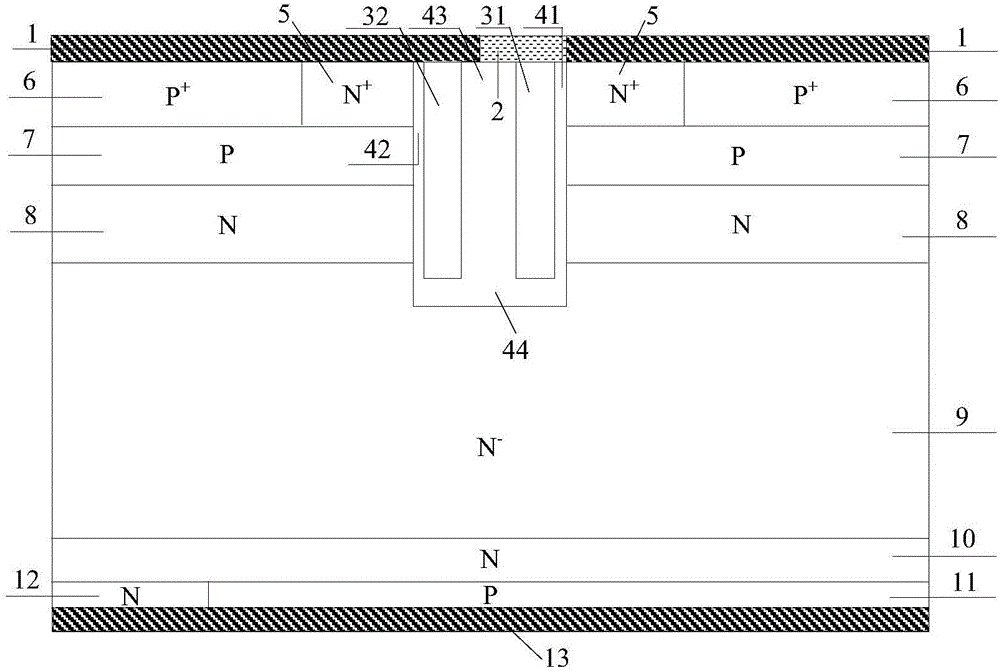

Trench gate charge storage reverse-conducting insulated-gate bipolar transistor (RC-IGBT) and fabrication method thereof

ActiveCN105870179AReduce gate capacitanceLow densitySemiconductor/solid-state device manufacturingSemiconductor devicesCapacitancePower semiconductor device

The invention belongs to the technical field of a power semiconductor device, in particular relates to a reverse-conducting trench gate charge storage insulated-gate bipolar transistor (IGBT). By introducing a side-surfaces split electrode connected with an emitter into a trench on the condition of a certain device trench depth and a certain trench metal oxide semiconductor (MOS) structure density, the gate capacitance of the device is reduced, the switching speed of the device is increased, the switching loss is reduced, and the positive conduction voltage drop and the average switching loss are improved; meanwhile, the density of an MOS channel is reduced, the short-circuit safety working region of the IGBT is improved, and the performance and the reliability of the device are improved; and a reverse freewheeling diode works in multiple submodes in a working mode of the reverse freewheeling diode, the IGBG has low diode conduction voltage drop, and the reverse recovery characteristic of the freewheeling diode is improved.

Owner:UNIV OF ELECTRONIC SCI & TECH OF CHINA

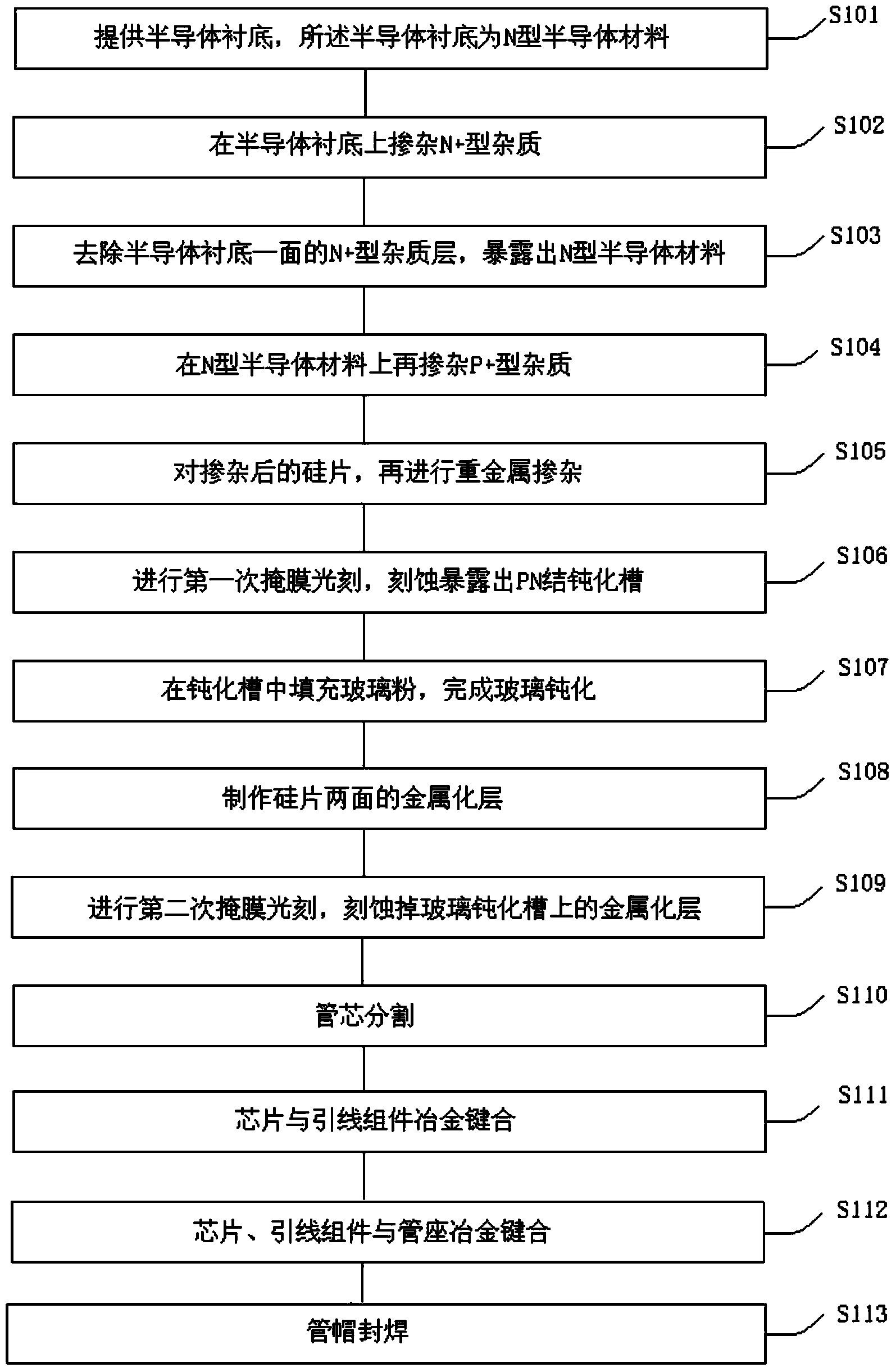

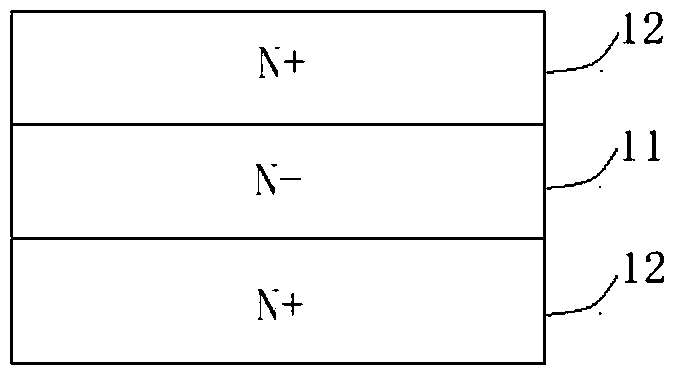

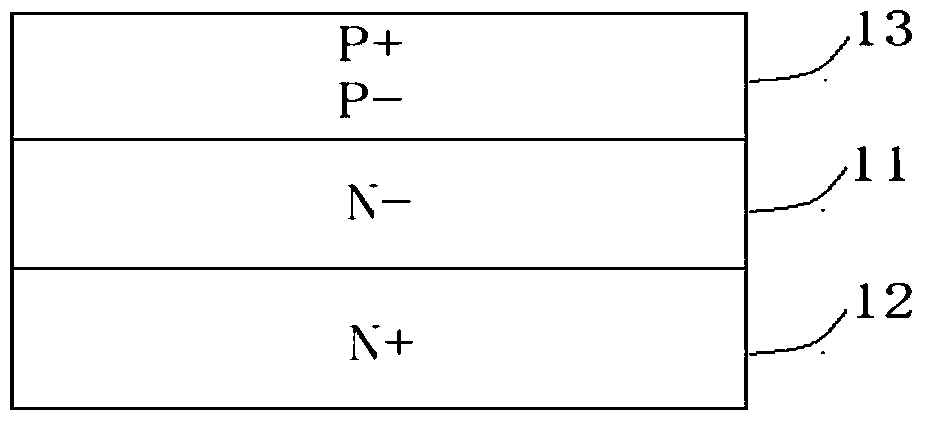

Method for manufacturing 50A high-current fast recovery diode

ActiveCN104269356AReduce reverse leakage currentImprove stabilitySemiconductor/solid-state device manufacturingSemiconductor devicesDiffusion methodsSemiconductor materials

The invention discloses a method for manufacturing a 50A high-current fast recovery diode. The method for manufacturing the 50A high-current fast recovery diode comprises the steps that an N type semiconductor silicon material is provided to serve as a semiconductor substrate; the N type semiconductor substrate is doped with N+ type impurities; the N+ type impurity layer on one side of the semiconductor substrate is removed; an exposed N-type semiconductor material is doped with dual P+ type impurities; heavy metal platinum doping is conducted according to the high-temperature diffusion method; primary mask photoetching is conducted; glass powder is arranged in a passivation groove through knife coating, high-temperature sinter molding is conducted, and then PN junction glass passivation is completed; multiple metallization layers are manufactured on the two sides of a silicon wafer according to the vacuum sputtering method; secondary mask photoetching is conducted; the silicon wafer is divided into independent dies; a chip and a lead component are bonded together; the chip, the lead component and a diode holder are bonded together in a metallurgical mode through sintering; a diode cap and the diode holder are welded together in a sealed mode through percussion welding. According to the method for manufacturing the 50A high-current fast recovery diode, the manufacturing process based on the method is less influenced by the environment, the technology is mature, the stability and the repeatability are high, and the method can be widely used for volume production of high-current fast recovery diodes.

Owner:西安卫光科技有限公司

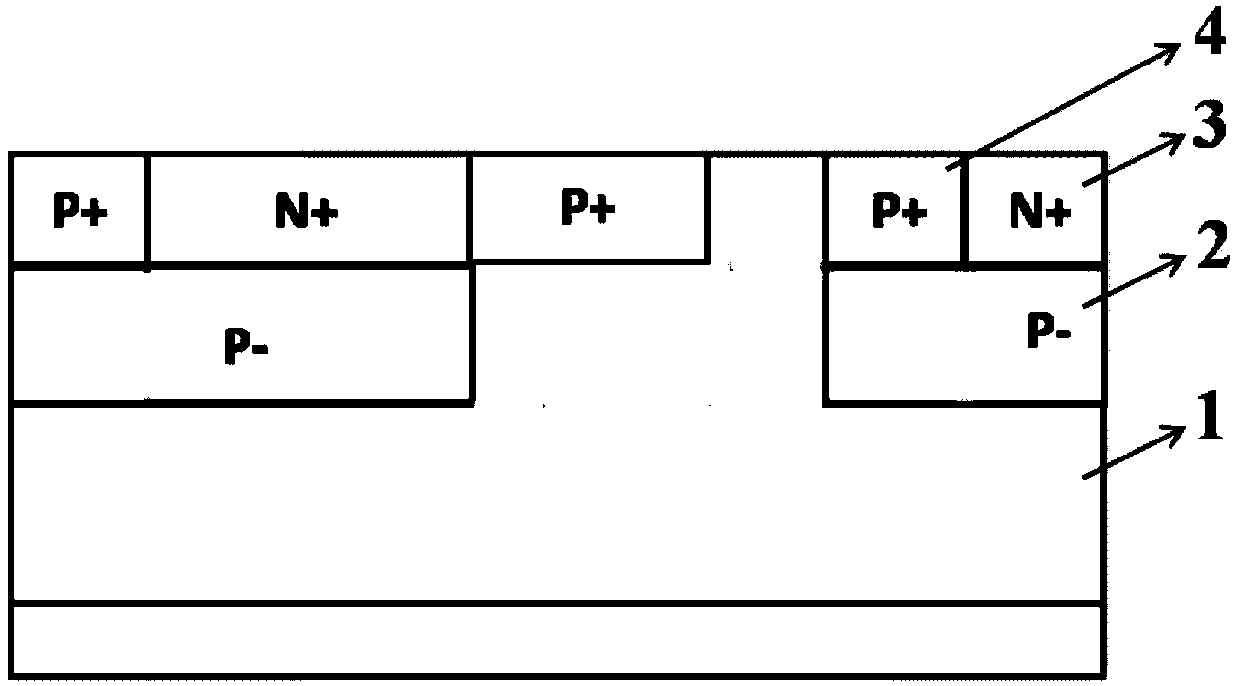

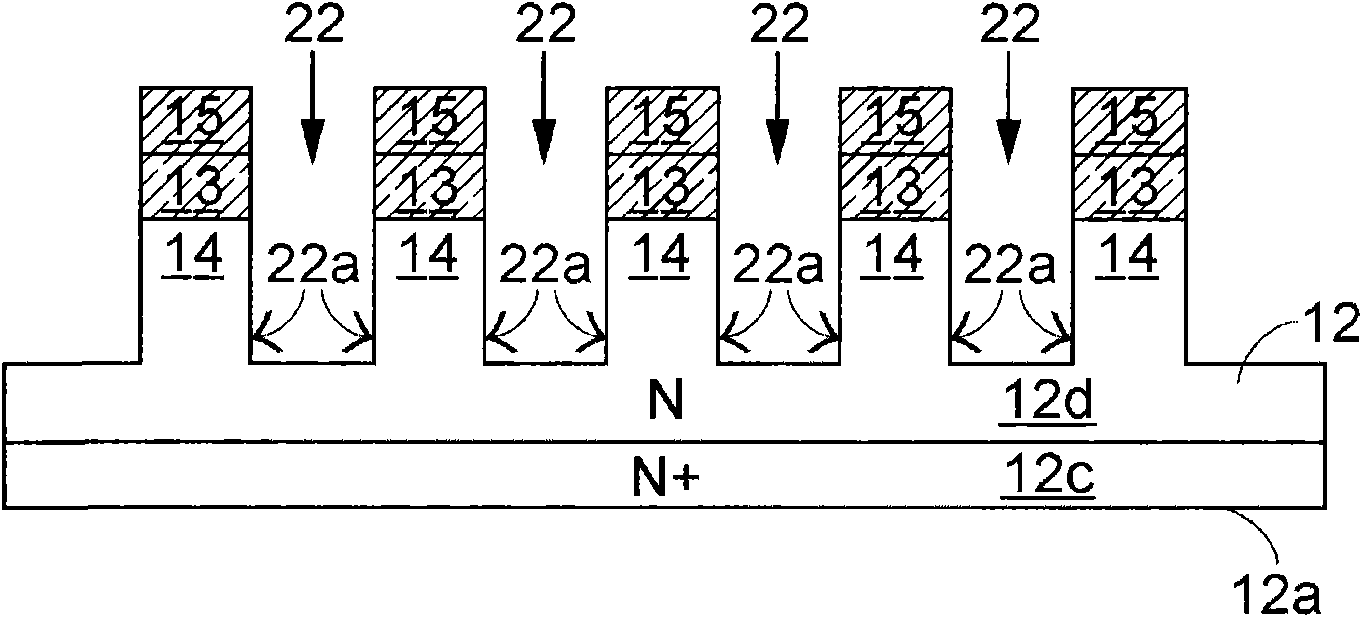

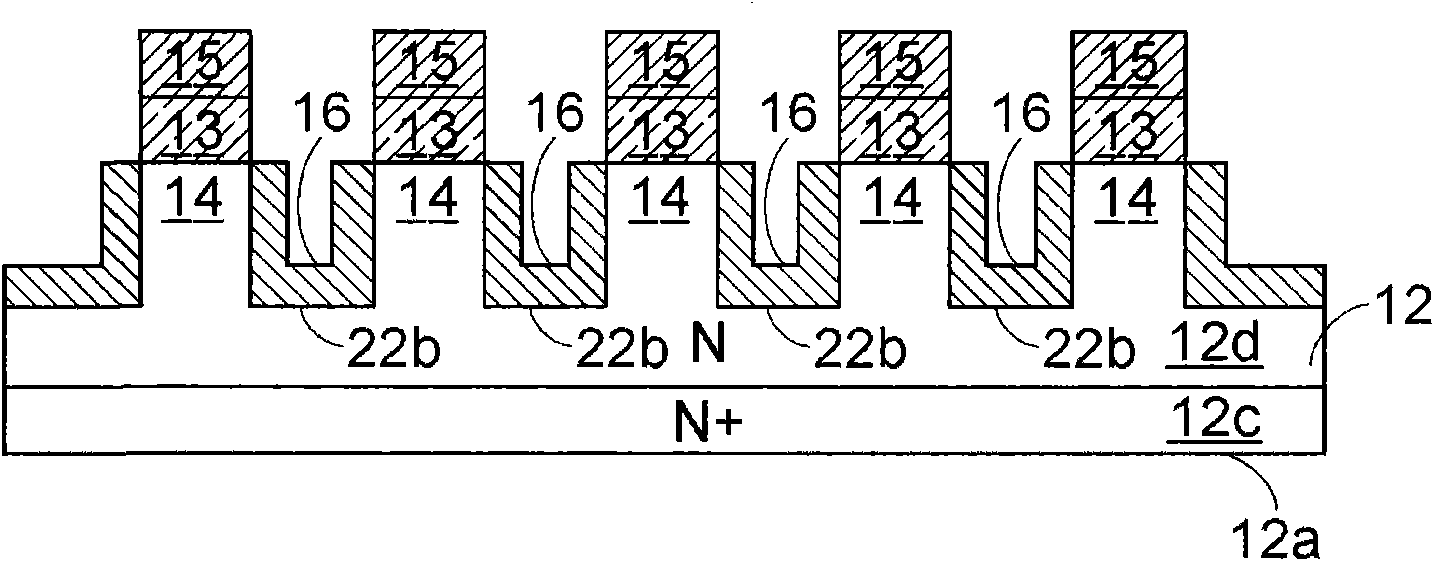

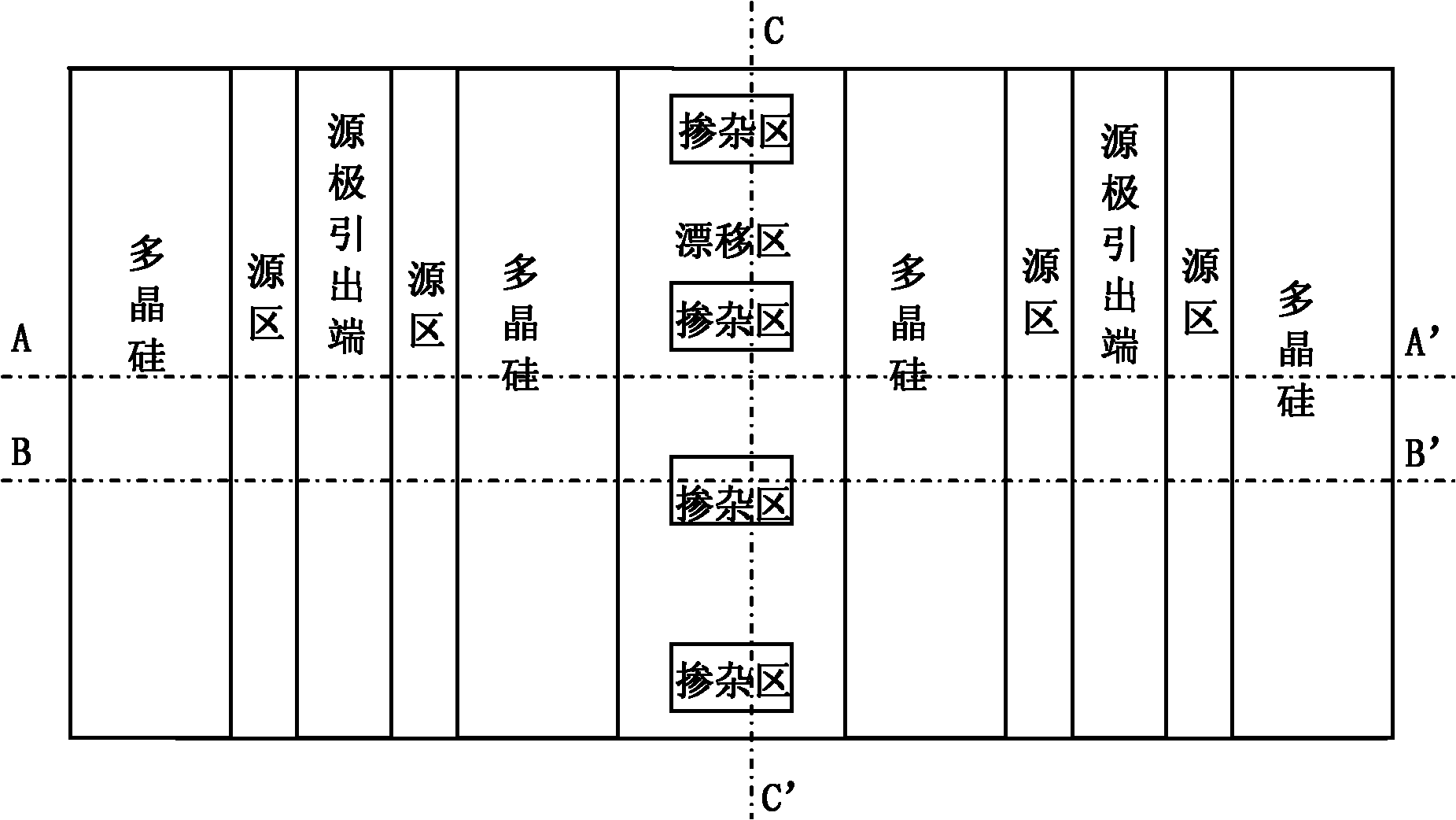

Method for integrating Schottky diode in super-junction MOSFET (metal-oxide-semiconductor field effect transistor)

ActiveCN102610523AReduce reverse leakageReduce intakeSemiconductor/solid-state device manufacturingDiodeMOSFETField-effect transistor

The invention discloses a method for integrating a Schottky diode in a super-junction MOSFET (metal-oxide-semiconductor field effect transistor). In order to connect and combine the Schottky diode consisting of a Schottky contact and a substrate in the super-junction MOSFET in parallel, the anode of the Schottky diode is positioned on a drift area between two body areas at a source end of the super-junction MOSFET element cell area, and is connected with the source end of the super-junction MOSFET; a plurality of doping areas are arranged on the drift area of the anode, the electric conduction types of the doping areas are opposite to the electric conduction type of the drift area, the concentration of impurity is larger than that of impurity in the drift area, and the doping areas are connected with the source end of the super-junction MOSFET; and the cathodes of the Schottky diode share the drain electrode of the super-junction MOSFET. According to the method, the reverse electric leakage amount of the Schottky diode can be reduced.

Owner:SHANGHAI HUAHONG GRACE SEMICON MFG CORP

Channel MOS P-N junction Schottky diode structure and manufacturing method thereof

ActiveCN101699616ALow Reverse Voltage Leakage CurrentLow forward voltage dropSemiconductor/solid-state device manufacturingSemiconductor devicesReverse recoveryP–n junction

The invention discloses a channel MOS P-N junction Schottky diode structure and a manufacturing method thereof. The structure mainly comprises a substrate, a channel structure, a polysilicon layer, an oxide layer, a metal layer and an ion implantation area; and the manufacturing method comprises the following steps: providing the substrate; forming a first mask layer on the substrate; performing a first photoetching process to form the channel structure; growing a gate oxide layer in the channel structure; performing an ion implantation process to form the ion implantation area; forming the polysilicon layer in the channel structure; forming a second mask layer on partial polysilicon layer and the first mask layer; performing a second photoetching process to form a side wall structure and expose the partial polysilicon layer and the substrate; and forming the metal layer on a generating structure. The channel MOS P-N junction Schottky diode structure has the characteristics of low reverse voltage leakage current, low forward voltage drop value, high reverse withstanding voltage value and low reverse recovery time.

Owner:PFC DEVICE HLDG

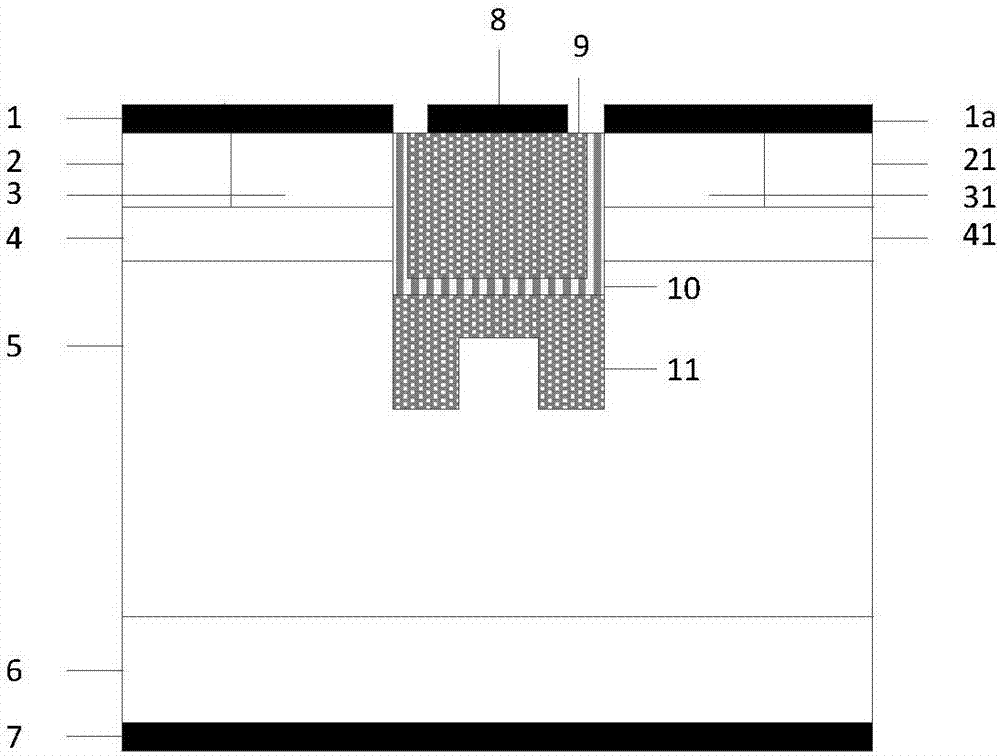

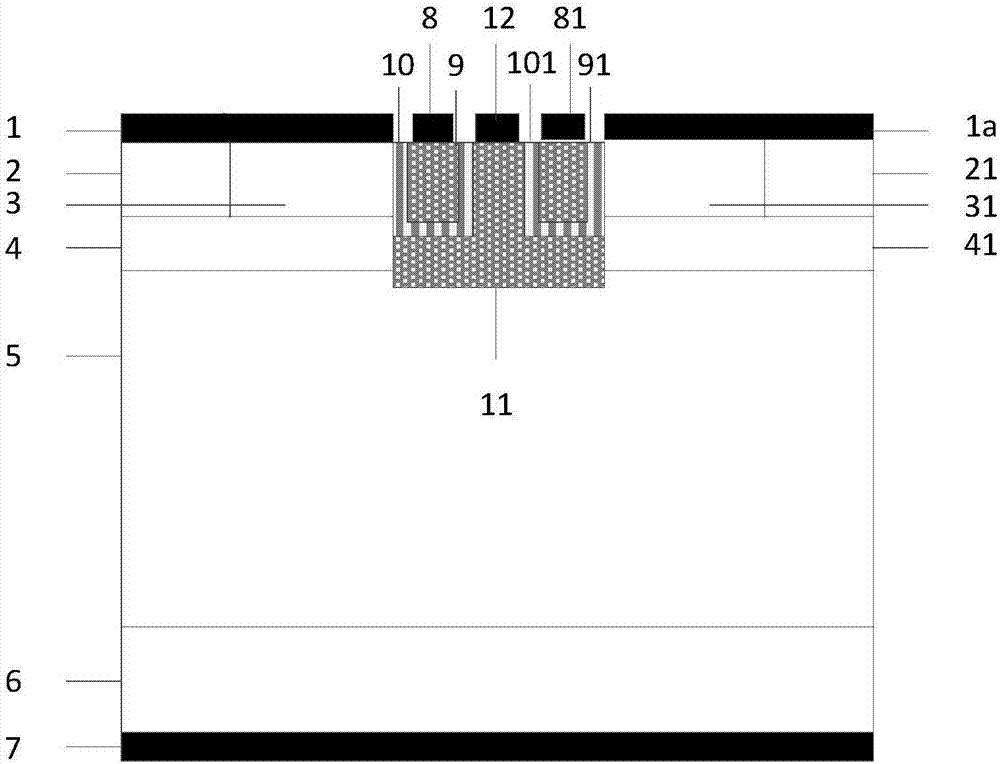

Silicon carbide Trench MOS device and manufacturing method thereof

ActiveCN107425068AImprove performanceReduce power lossSemiconductor/solid-state device manufacturingSemiconductor devicesHeterojunctionReverse recovery

The invention discloses a silicon carbide Trench MOS device and a manufacturing method thereof, and belongs to the technical field of power semiconductors. The method includes: a layer of a polysilicon region distributed in a pi shape is additionally arranged under a trench gate structure of a conventional device, the polysilicon region and an epitaxial layer form a Si / SiC heterojunction, and a diode is integrated in the device. Compared with a parasitic silicon carbide diode which directly employs a silicon carbide Trench MOS, according to the silicon carbide Trench MOS device and the manufacturing method thereof, the junction voltage drop of the device diode during application is substantially reduced, and the switch-on characteristic of the device is improved through large junction area of the heterojunction; moreover, the gate-drain capacitance and the ratio of the gate-drain capacitance to the gate-source capacitance of the device are reduced, and the performance and the reliability of the device MOS during application are enhanced; besides, the silicon carbide Trench MOS device and the manufacturing method thereof are also advantageous in that the reverse recovery time is short, the reverse recovery charges are less, and advantages including low reverse leakage, high breakdown voltage, and good temperature stabilization performance of the conventional silicon carbide Trench MOS device are maintained. In conclusion, according to the silicon carbide Trench MOS device and the manufacturing method thereof, the prospect is wide in circuits such as inversion circuits and chopper circuits etc.

Owner:HANGZHOU SILICON-MAGIC SEMICON TECH CO LTD

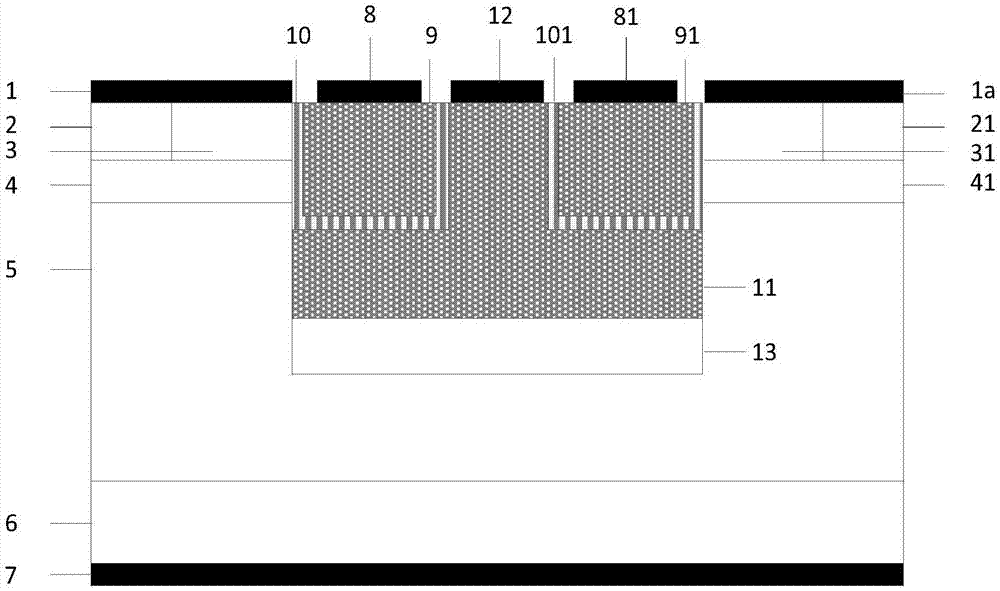

Silicon carbide Trench MOS device and manufacturing method thereof

ActiveCN107275406AImprove performanceReduce power lossSemiconductor/solid-state device manufacturingSemiconductor devicesCapacitanceHeterojunction

The invention discloses a silicon carbide Trench MOS device and manufacturing method thereof, and belongs to the technical field of power semiconductors. A convex polycrystalline silicon region is additionally arranged inside an epitaxial layer, and two independent trench gates are arranged in a groove of the convex polycrystalline silicon region, so that a polycrystalline silicon layer and the epitaxial layer form a Si / SiC heterojunction. Compared with direct utilization of a parasitic silicon carbide diode of a silicon carbide Trench MOS, a junction voltage drop during application of the device diode is remarkably reduced, and a relatively large heterojunction area improves a device conduction characteristic; based on a charge shielding effect of the convex polycrystalline silicon, gate-drain capacitance and a ratio of gate-drain capacitance and gate-source capacitance are reduced, thereby remarkably improving performance and reliability of the device; and the device adopts single-pole electric conduction, thus has relatively good reverse recovery performance and has the advantages of low reverse electric leakage, high breakdown voltage and good device temperature stability performance of a traditional Trench MOS device, and therefore the silicon carbide Trench MOS device provided by the invention has broad prospects in circuits such as an inverter circuit and a chopper circuit.

Owner:HANGZHOU SILICON-MAGIC SEMICON TECH CO LTD

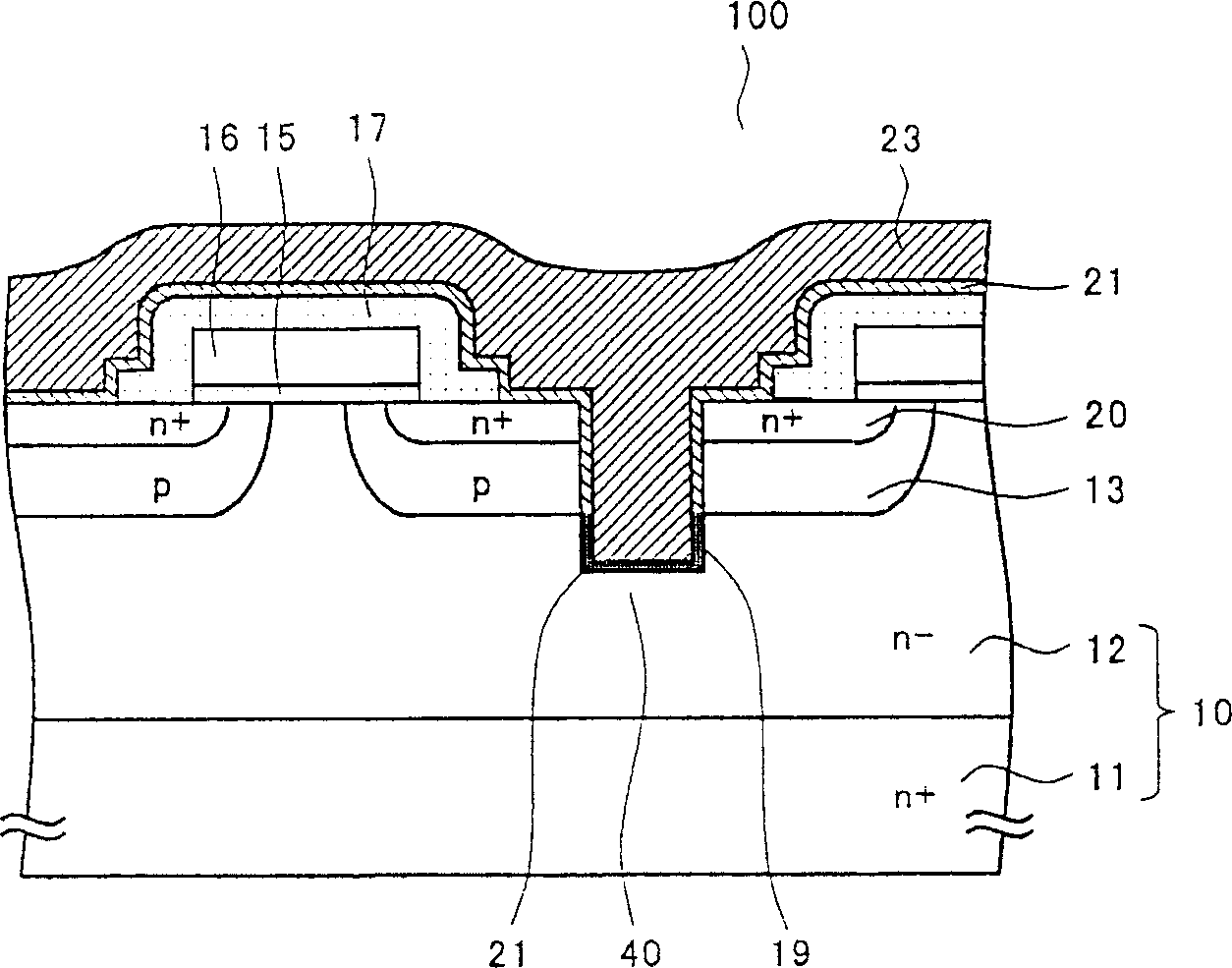

Semiconductor device manufacturing method thereof

InactiveCN1677687AShort reverse recovery timeImprove efficiencyTransistorSolid-state devicesMOSFETSchottky barrier

The invention solves the problem that a device becomes large in size and the number of components increases because a Schottky barrier diode is provided externally, in the case that the MOSFET includes a parasitic pn diode between the source and drain for use as Fast Recovery Diode (FRD), and a pn junction diode becomes a factor for preventing high speed switching operation and low power consumption. A groove is provided through a channel layer between adjacent gate electrodes of the MOSFET and a Schottky metal layer is also provided within the groove. Accordingly, since the bottom of groove is formed with the Schottky barrier diode, the Schottky barrier diode can be comprised within a diffusing region of the MOSFET. Cosequently, reduction in size of device and reduction in the number of components can be realized simultaneously.

Owner:SANYO ELECTRIC CO LTD

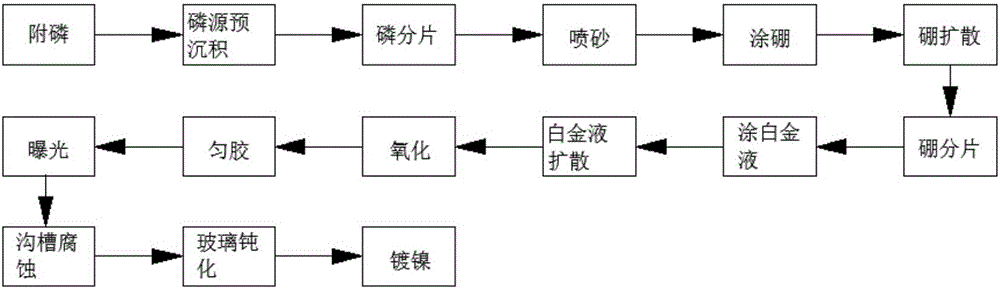

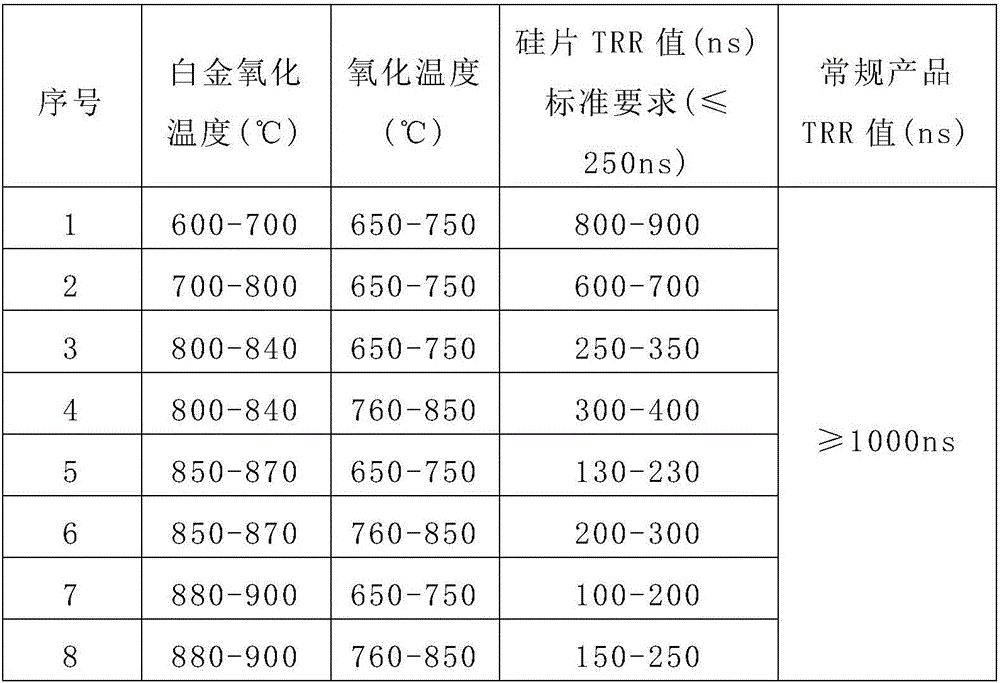

Making process of fast recovery chip

ActiveCN105977155AImprove reliabilityReduce failure rateSemiconductor/solid-state device manufacturingSemiconductor devicesPlatinumSand blasting

The invention provides a making process of a fast recovery chip. The process comprises the following steps: phosphorus attachment, phosphorus source pre-deposition, phosphorus fragmentation, sand blasting, boron coating, boron diffusion, boron fragmentation, platinum liquid coating, platinum diffusion, oxidation, gluing, exposure, groove corrosion, glass passivation and nickel plating. The reverse recovery time of the assembled bridge-type fast recovery chip is shorter than that of a conventional chip, and the fast recovery chip is good in stability and high in client use reliability.

Owner:YANGZHOU HY TECH DEV

SiC vertical double diffused metal-oxide-semiconductor (VDMOS) device and fabrication method thereof

ActiveCN107248533AImprove performanceReduce power lossSemiconductor/solid-state device manufacturingSemiconductor devicesCapacitanceHeterojunction

The invention discloses a SiC vertical double diffused metal-oxide-semiconductor (VDMOS) device and a fabrication method thereof, and belongs to the technical field of a power semiconductor. A poly-silicon layer is directly deposited on a surface of a junction field-effect transistor (JFET) region of the SiC VDMOS device to form a Si / SiC heterojunction, a diode is further integrated in the device, and the application of the device in the field of an inversion circuit, a chopping circuit and the like is optimized. Compared with the prior art directly employing a VDMOS parasitic SiC diode, the SiC VDMOS device has the advantages of relatively low power loss, relatively fast working speed and relatively high working efficiency, and positive conduction is easier to achieve; compared with the prior art that a fast recovery diode (FRD) is reversely connected with the exterior of the device in parallel, the SiC VDMOS device has the advantages that the usage number of the device is reduced, connection lines between the devices are reduced, and the miniature development of the device is promoted; moreover, the grid width is reduced, the grid capacitance is reduced, and the working speed of the device is further increased; and therefore, the VDMOS device proposed by the invention has wide application prospect in the circuit field of the inversion circuit, the chopping circuit and the like.

Owner:UNIV OF ELECTRONICS SCI & TECH OF CHINA

Features

- R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

Why Patsnap Eureka

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Social media

Patsnap Eureka Blog

Learn More Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com