Patents

Literature

1652 results about "Single-core" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

A single-core processor is a microprocessor with a single core on a chip, running a single thread at any one time. The term became common after the emergence of multi-core processors (which have several independent processors on a single chip) to distinguish non-multi-core designs. For example, Intel released a Core 2 Solo and Core 2 Duo, and one would refer to the former as the 'single-core' variant. Most microprocessors prior to the multi-core era are single-core. The class of many-core processors follows on from multi-core, in a progression showing increasing parallelism over time.

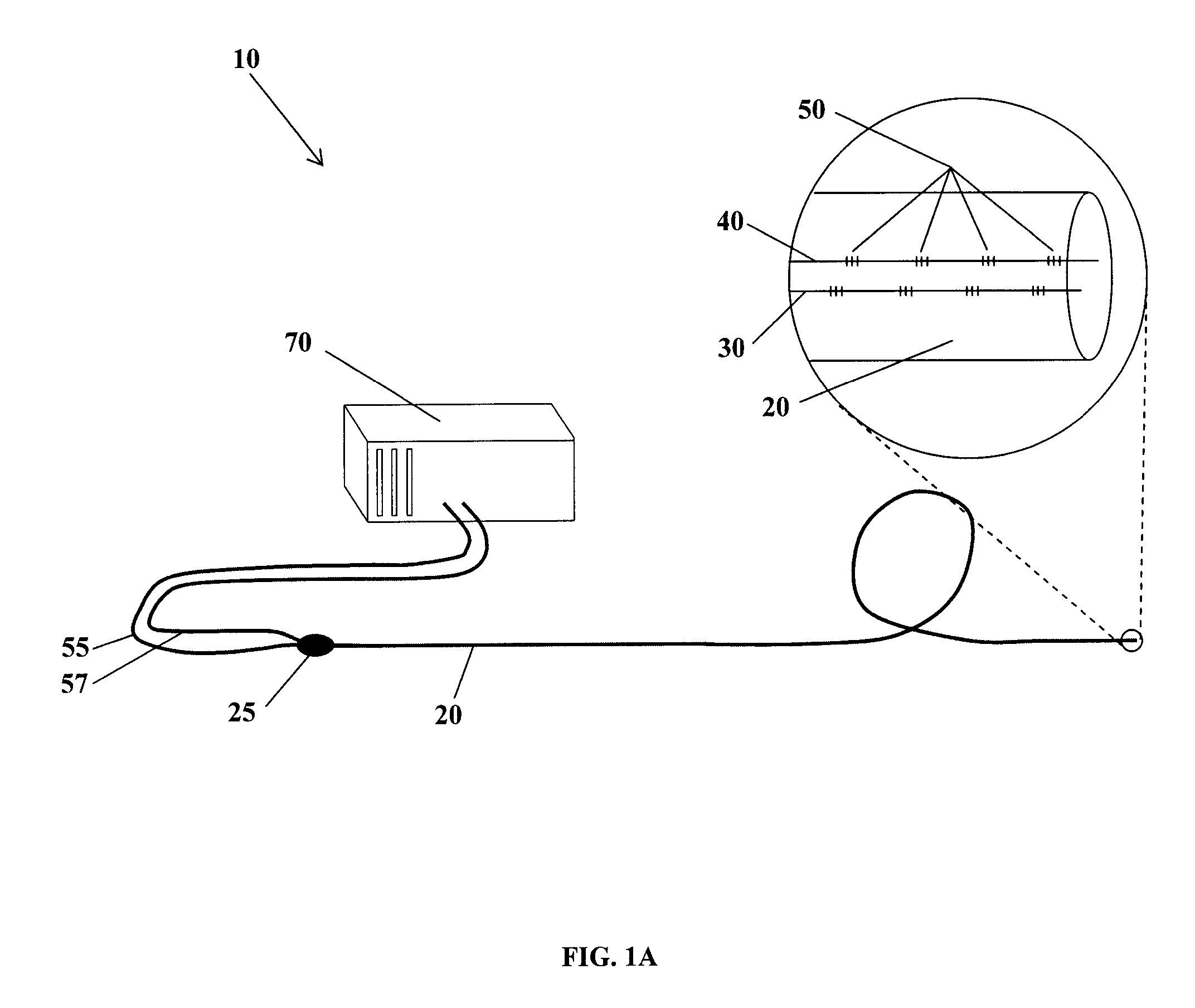

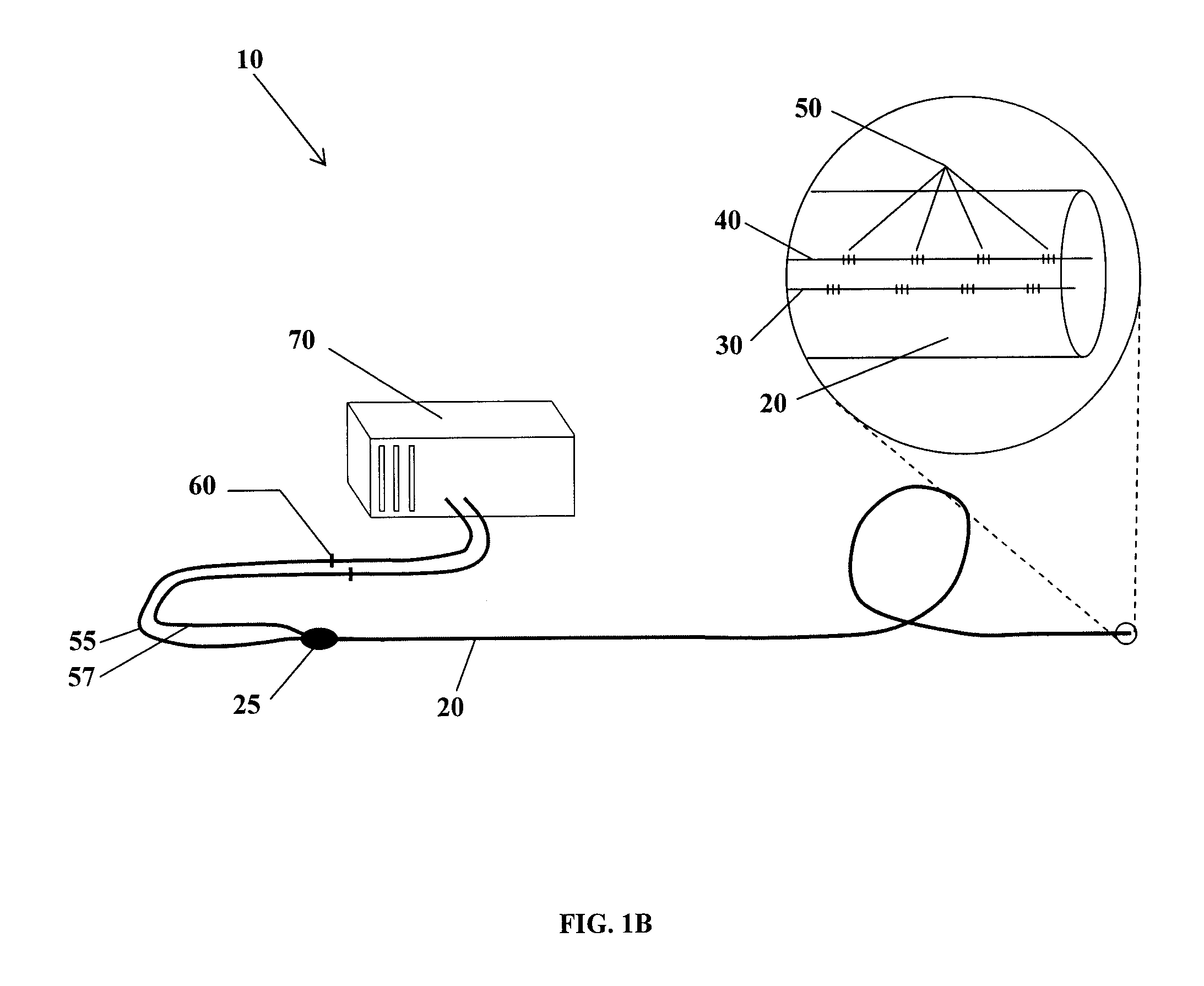

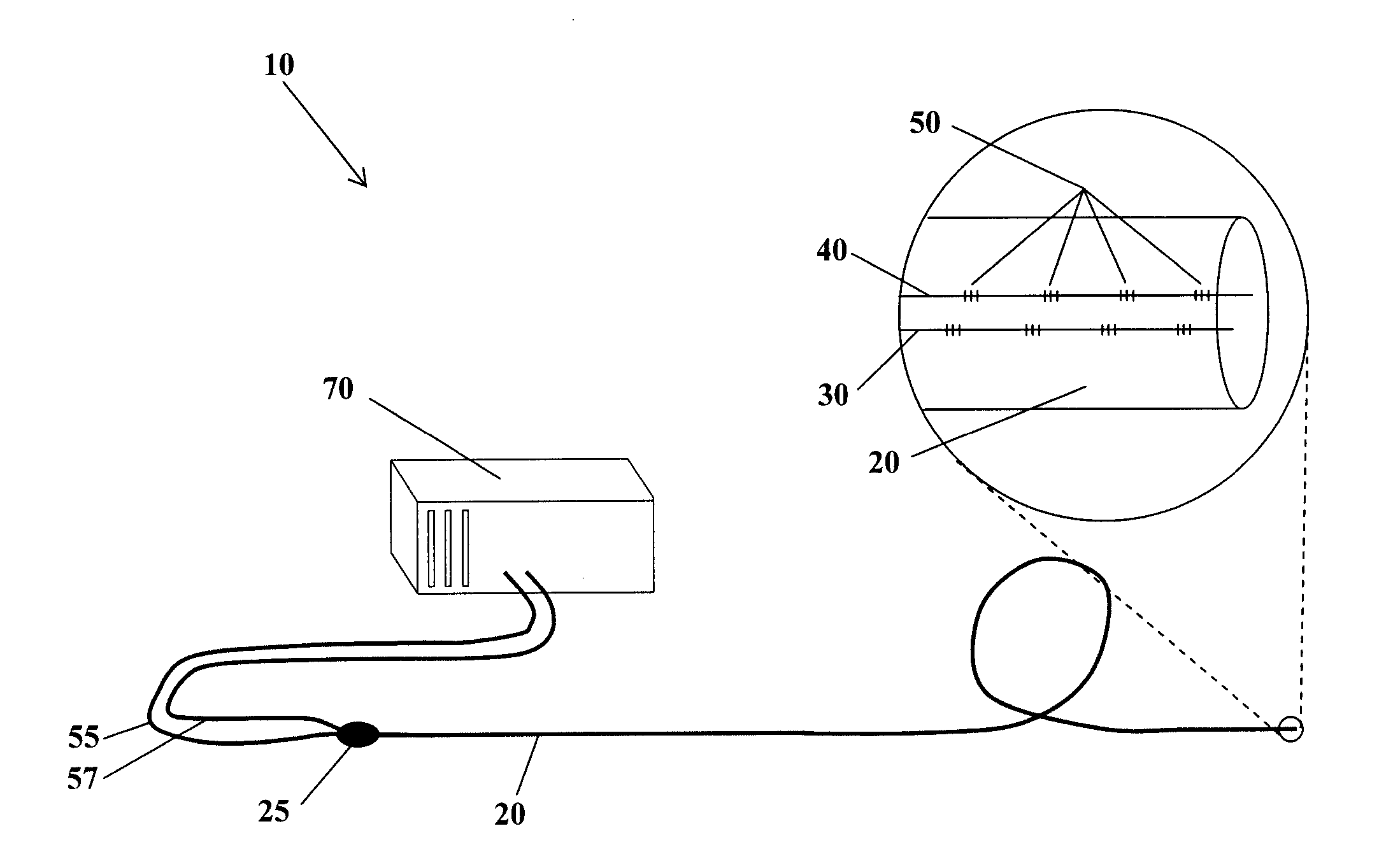

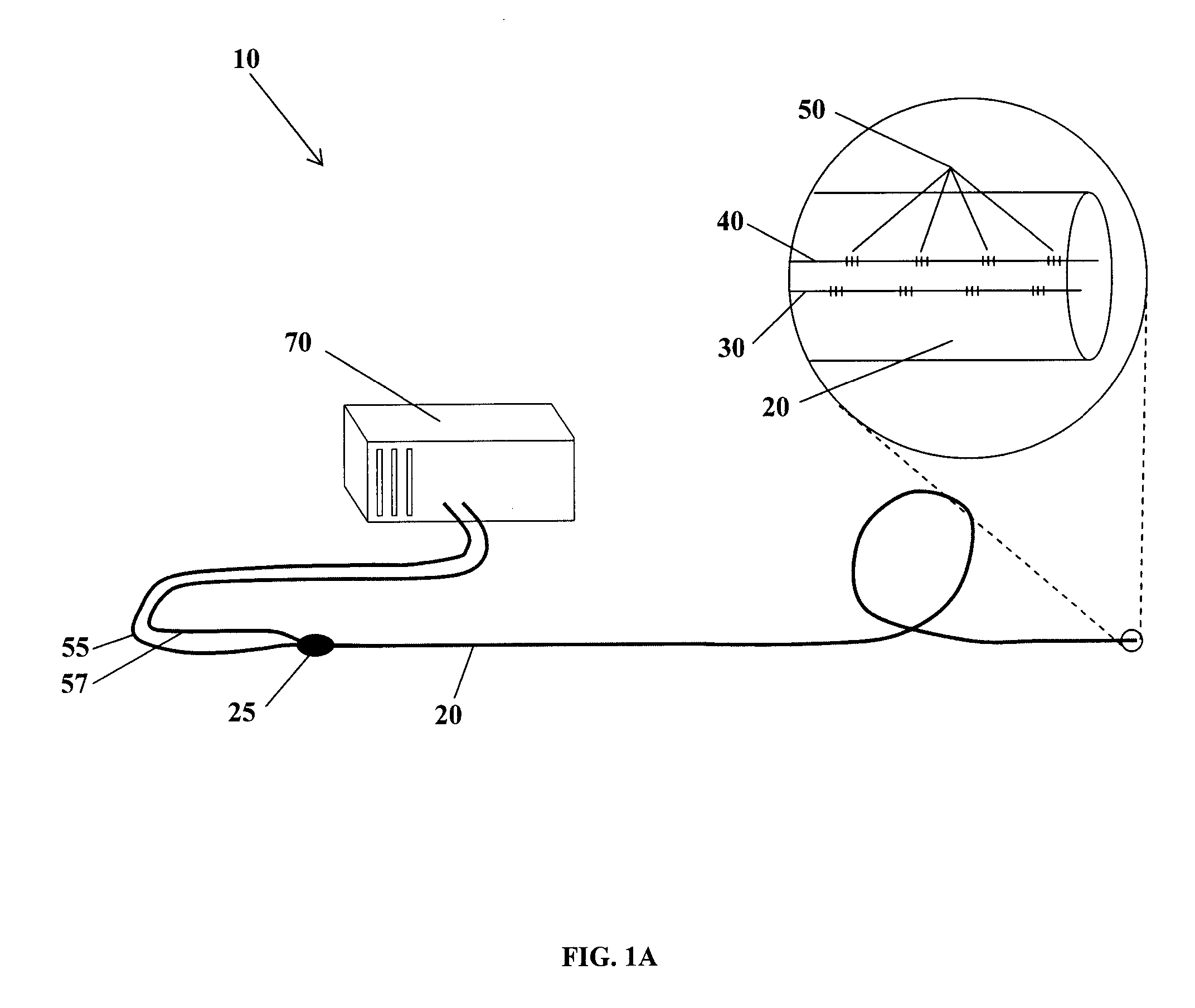

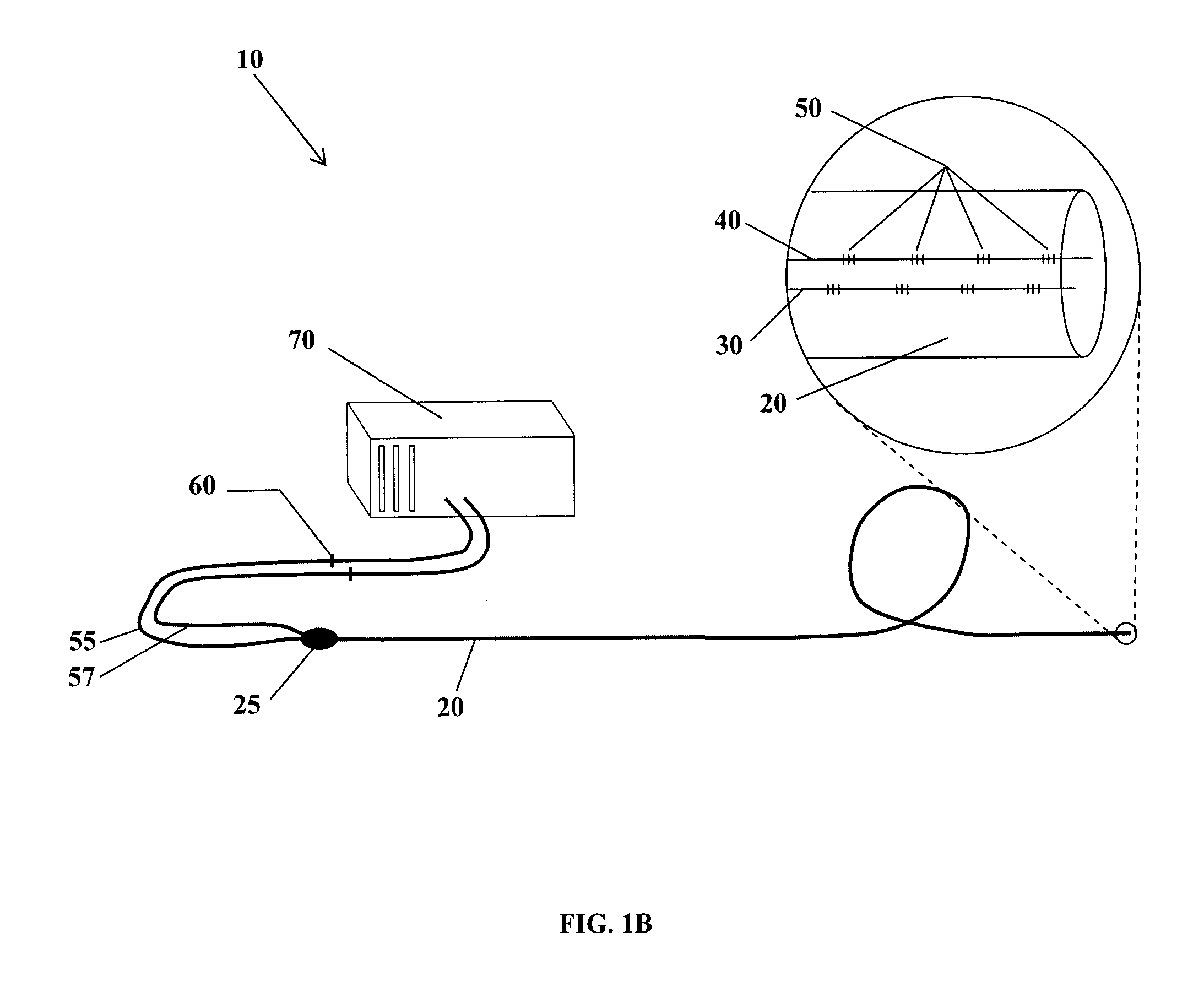

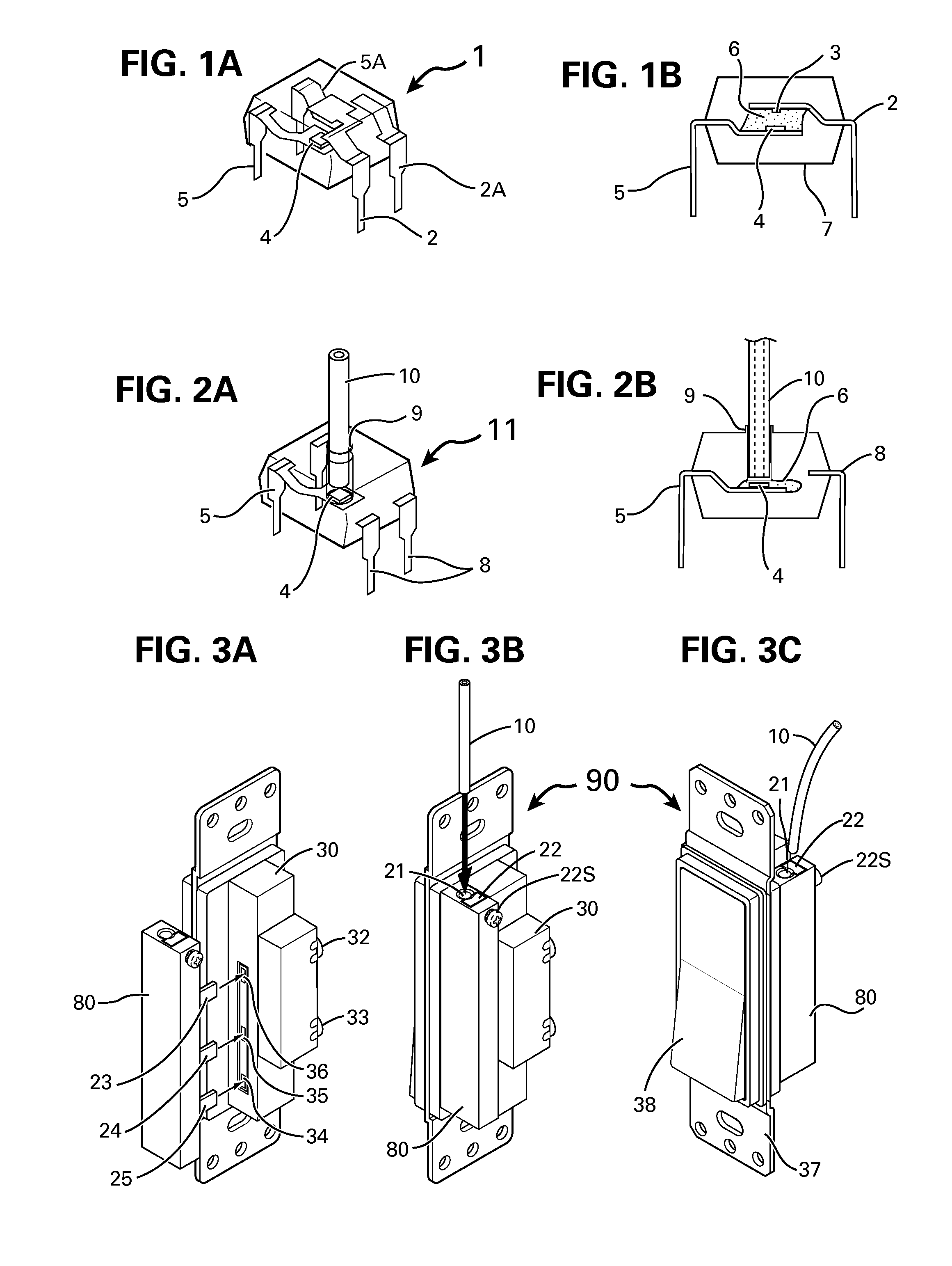

Fiber optic position and shape sensing device and method relating thereto

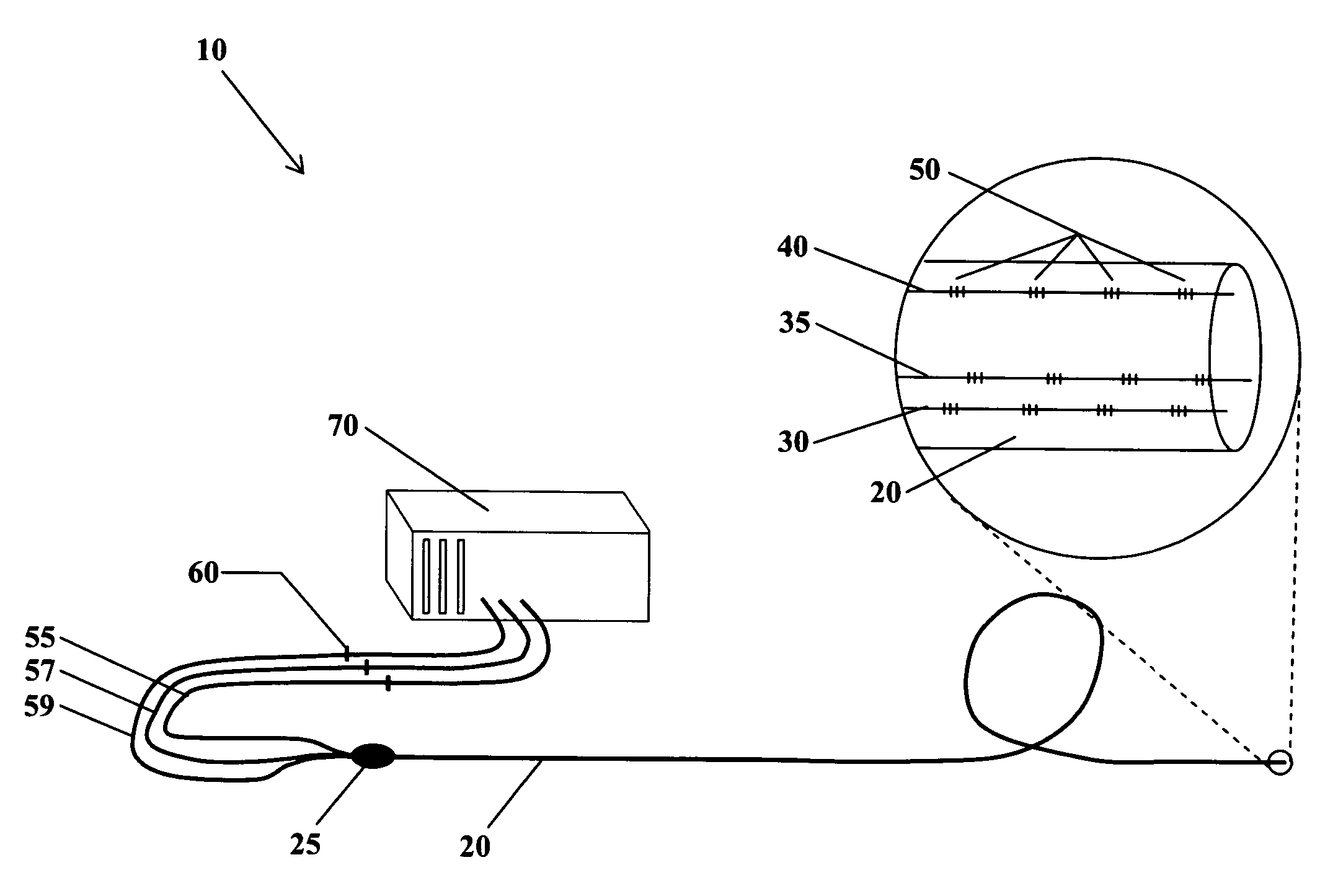

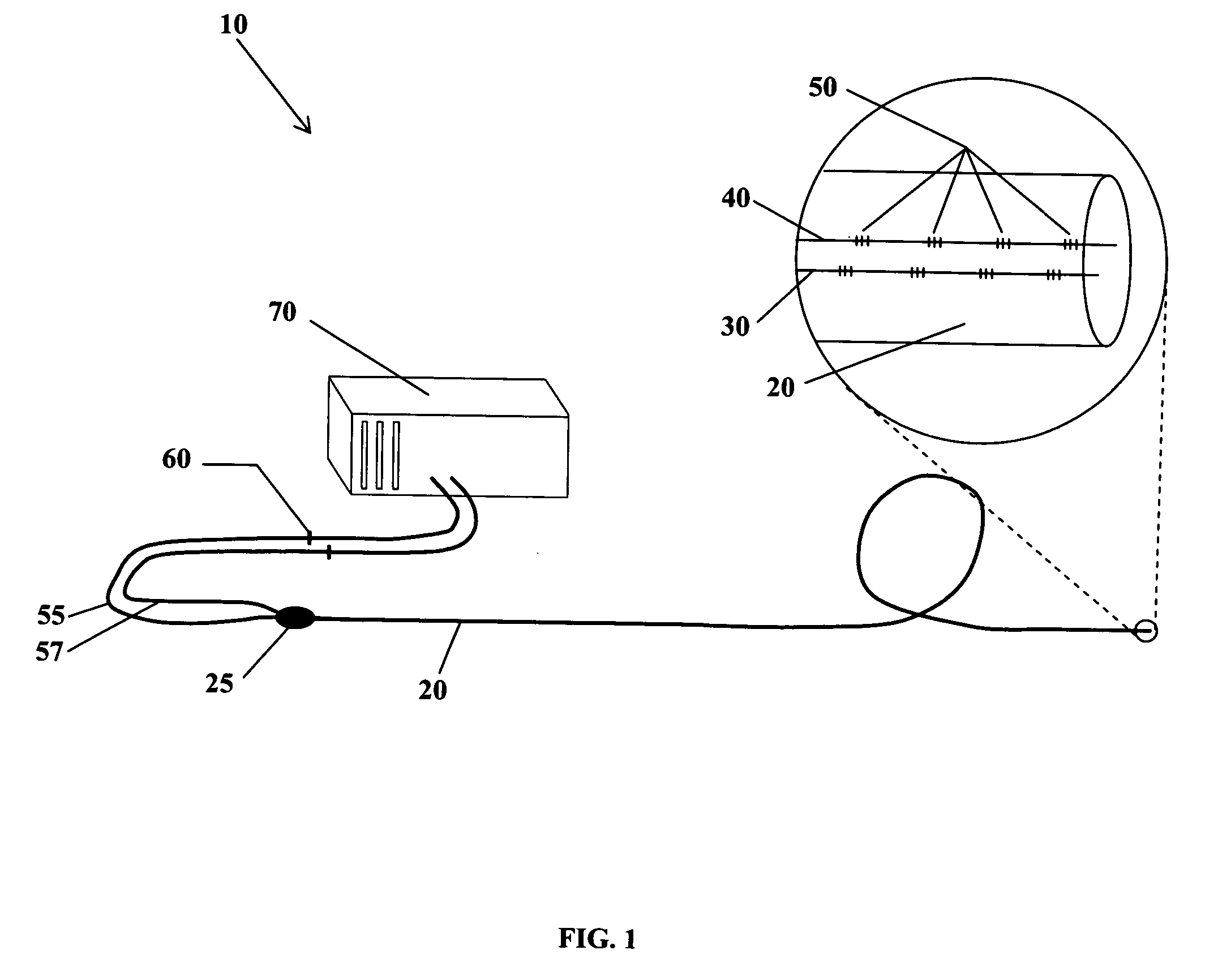

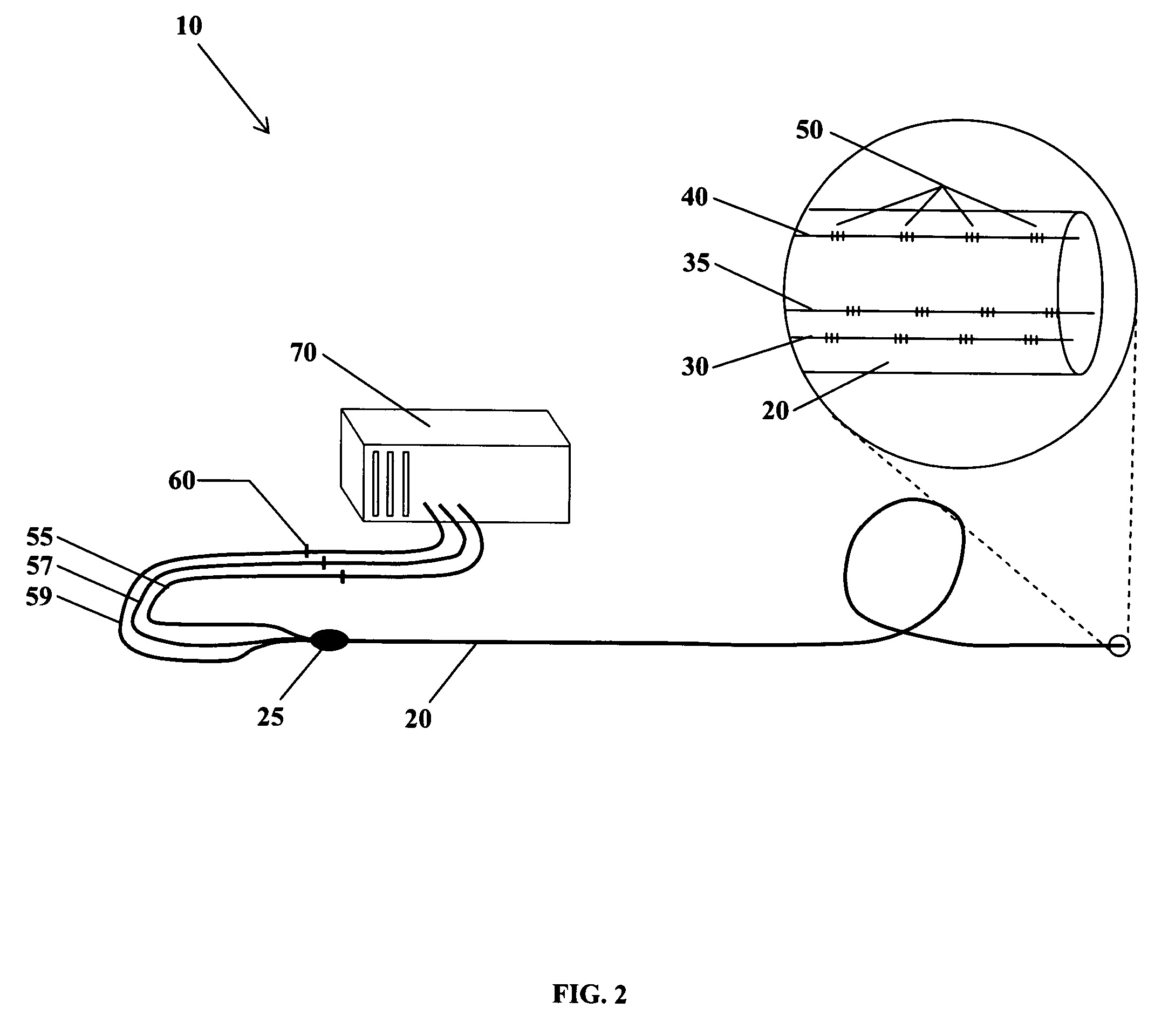

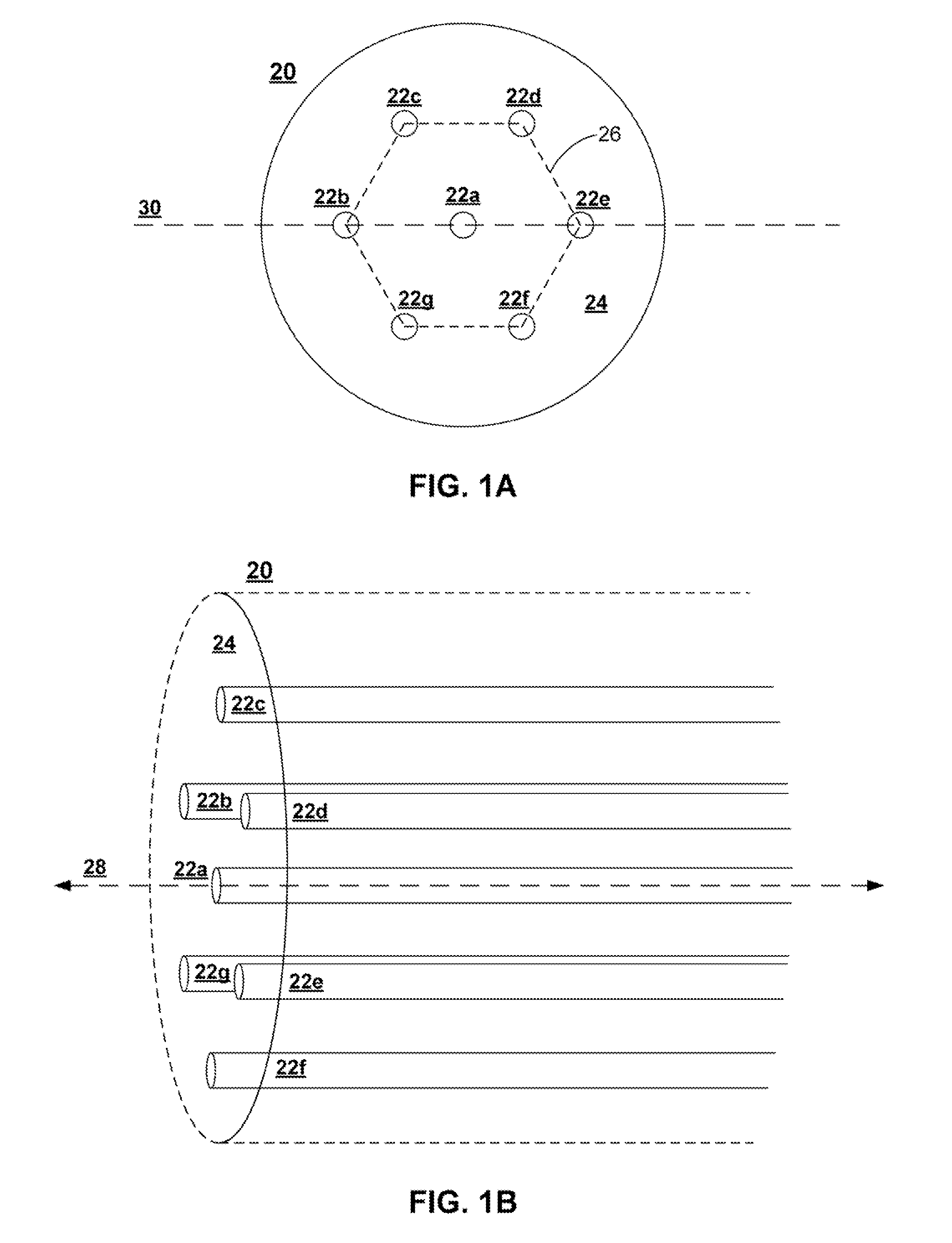

The present invention is directed toward a fiber optic position and shape sensing device and the method of use. The device comprises an optical fiber means. The optical fiber means comprises either at least two single core optical fibers or a multicore optical fiber having at least two fiber cores. In either case, the fiber cores are spaced apart such that mode coupling between the fiber cores is minimized. An array of fiber Bragg gratings are disposed within each fiber core. A broadband reference reflector is positioned in an operable relationship to each fiber Bragg grating wherein an optical path length is established for each reflector / grating relationship. A frequency domain reflectometer is positioned in an operable relationship to the optical fiber means. In use, the device is affixed to an object. Strain on the optical fiber is measured and the strain measurements correlated to local bend measurements. Local bend measurements are integrated to determine position or shape of the object.

Owner:LUNA INNOVATIONS

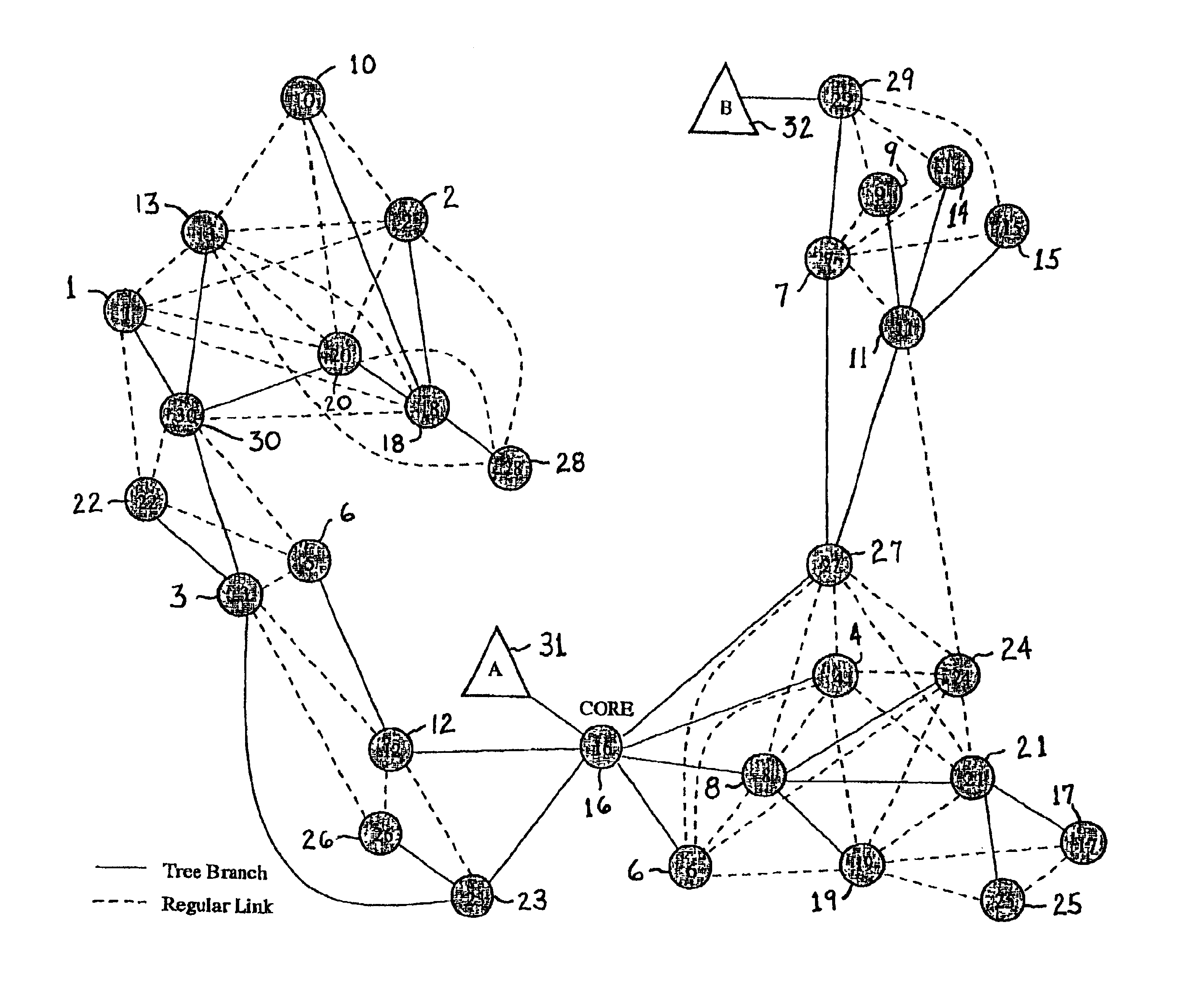

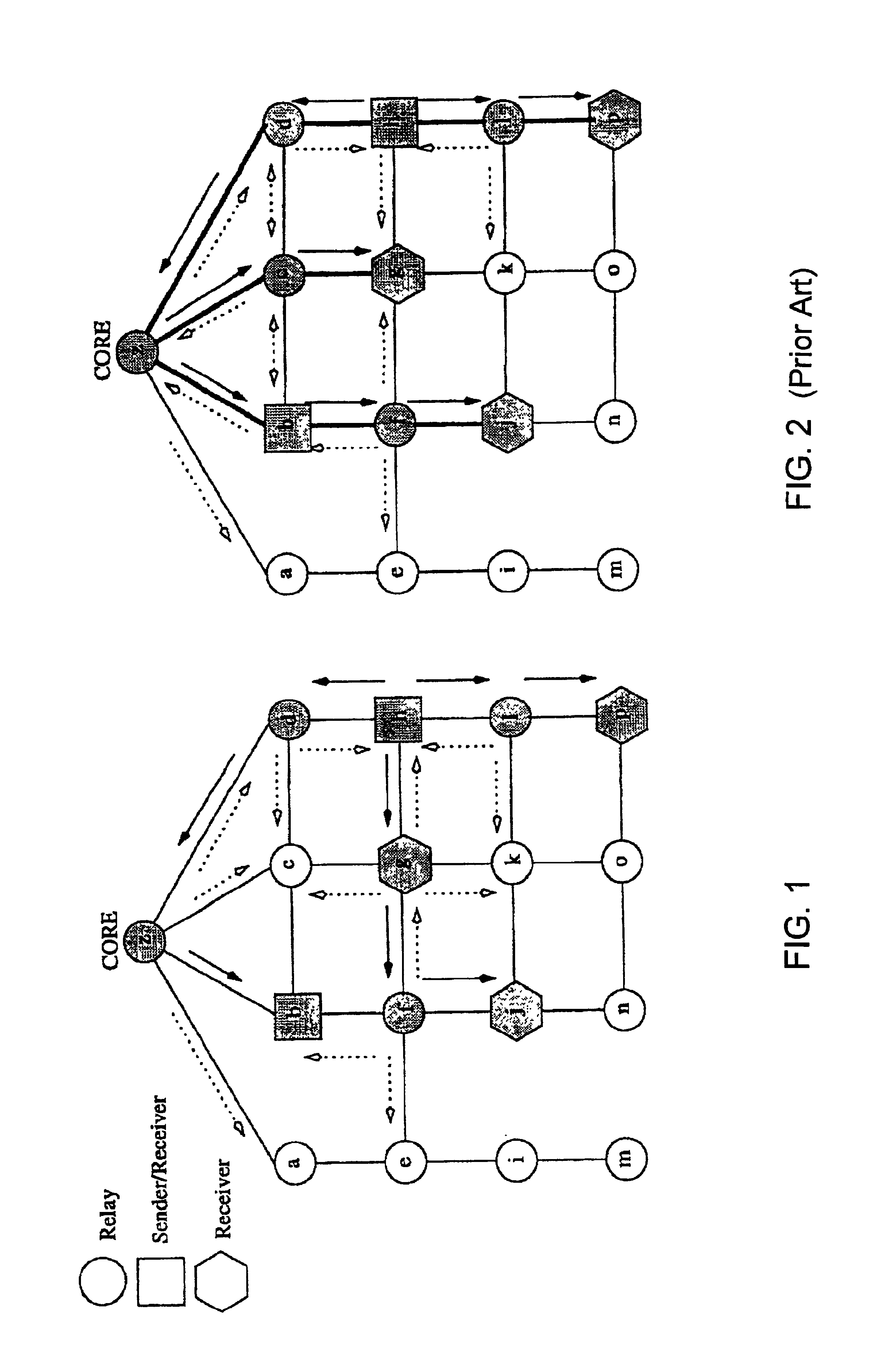

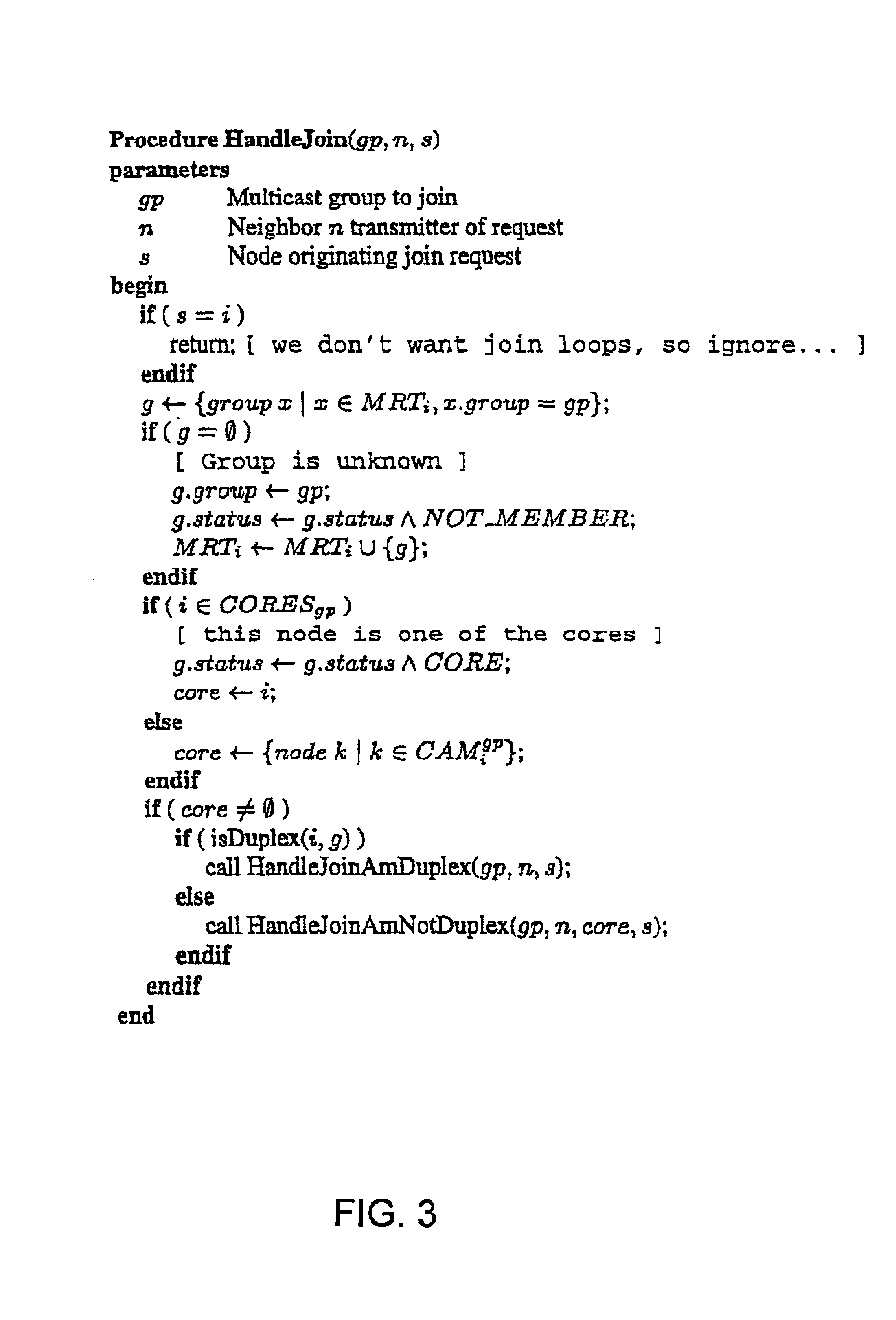

Core assisted mesh protocol for multicast routing in ad-hoc Networks

InactiveUS6917985B2Enrich connectivityStay connectedSpecial service provision for substationError preventionIP multicastBroadcasting

A method of providing multicast routing for use in ad hoc broadcast networks, such as wireless and mobile networks. The method is described within a protocol referred to as core-assisted mesh protocol, or CAMP. The method departs from traditional tree-structured multicast protocols and utilizes multicast meshes in which the network need not be flooded with control or data packets to establish routing paths. Each router configured for CAMP is capable of accepting unique packets arriving from any neighbor in the mesh, wherein packets are forwarded along reverse shortest paths to the receiver. Multiple cores may be defined for a group wherein the loss of a single core does not prevent packet flow. Routers for sender-only hosts are allowed to join the multicast mesh in simplex mode, and in certain cases may join without the sending of a join request.

Owner:RGT UNIV OF CALIFORNIA

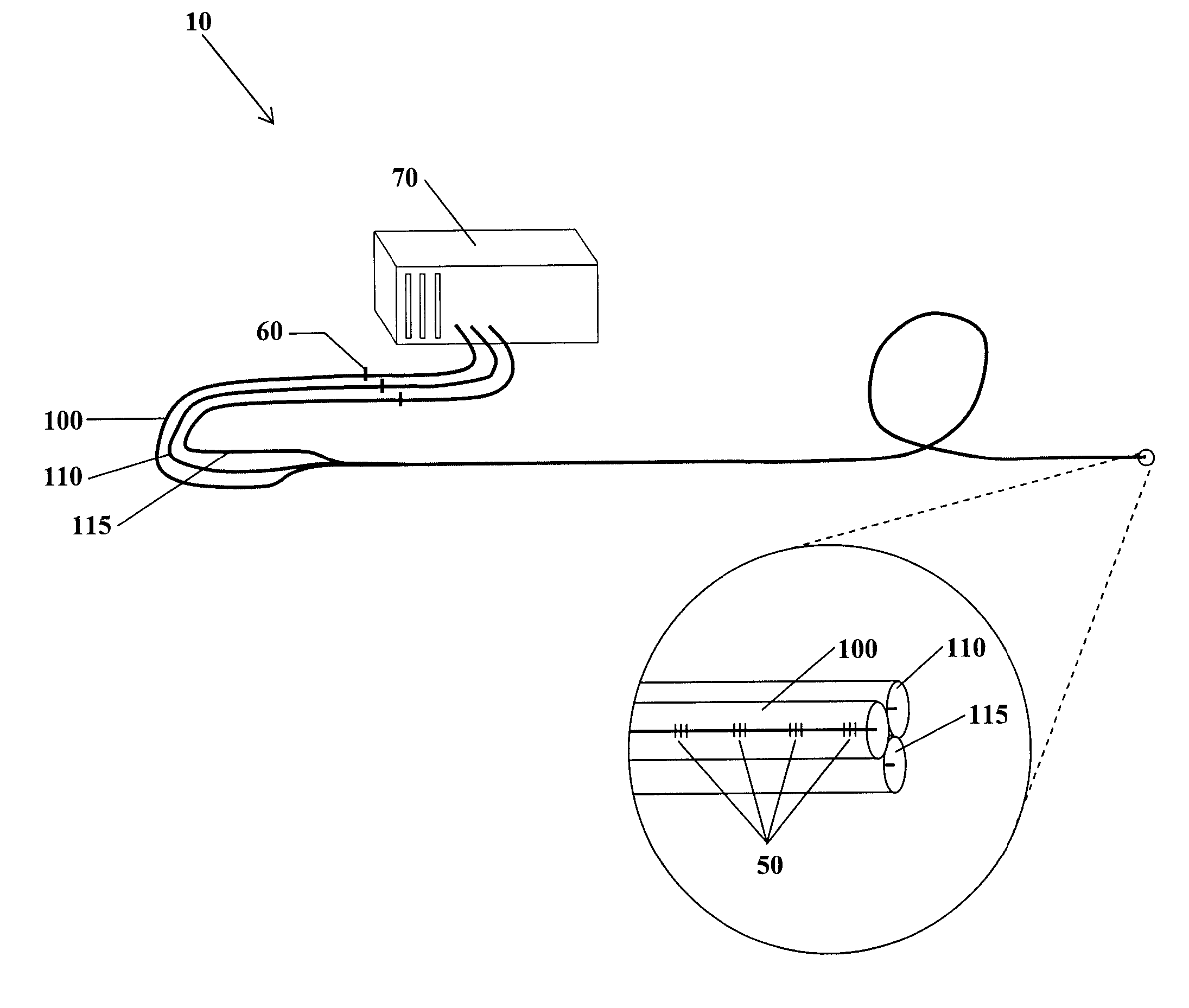

Fiber optic position and shape sensing device and method relating thereto

The present invention is directed toward a fiber optic position and shape sensing device and the method of use. The device comprises an optical fiber means. The optical fiber means comprises either at least two single core optical fibers or a multicore optical fiber having at least two fiber cores. In either case, the fiber cores are spaced apart such that mode coupling between the fiber cores is minimized. An array of fiber Bragg gratings are disposed within each fiber core and a frequency domain reflectometer is positioned in an operable relationship to the optical fiber means. In use, the device is affixed to an object. Strain on the optical fiber is measured and the strain measurements correlated to local bend measurements. Local bend measurements are integrated to determine position and / or shape of the object.

Owner:INTUITIVE SURGICAL OPERATIONS INC

Fiber Optic Position and Shape Sensing Device and Method Relating Thereto

ActiveUS20070065077A1Improve spatial resolutionImprove accuracyRadiation pyrometryEndoscopesFiberGrating

The present invention is directed toward a fiber optic position and shape sensing device and the method of use. The device comprises an optical fiber means. The optical fiber means comprises either at least two single core optical fibers or a multicore optical fiber having at least two fiber cores. In either case, the fiber cores are spaced apart such that mode coupling between the fiber cores is minimized. An array of fiber Bragg gratings are disposed within each fiber core and a frequency domain reflectometer is positioned in an operable relationship to the optical fiber means. In use, the device is affixed to an object. Strain on the optical fiber is measured and the strain measurements correlated to local bend measurements. Local bend measurements are integrated to determine position and / or shape of the object.

Owner:INTUITIVE SURGICAL OPERATIONS INC

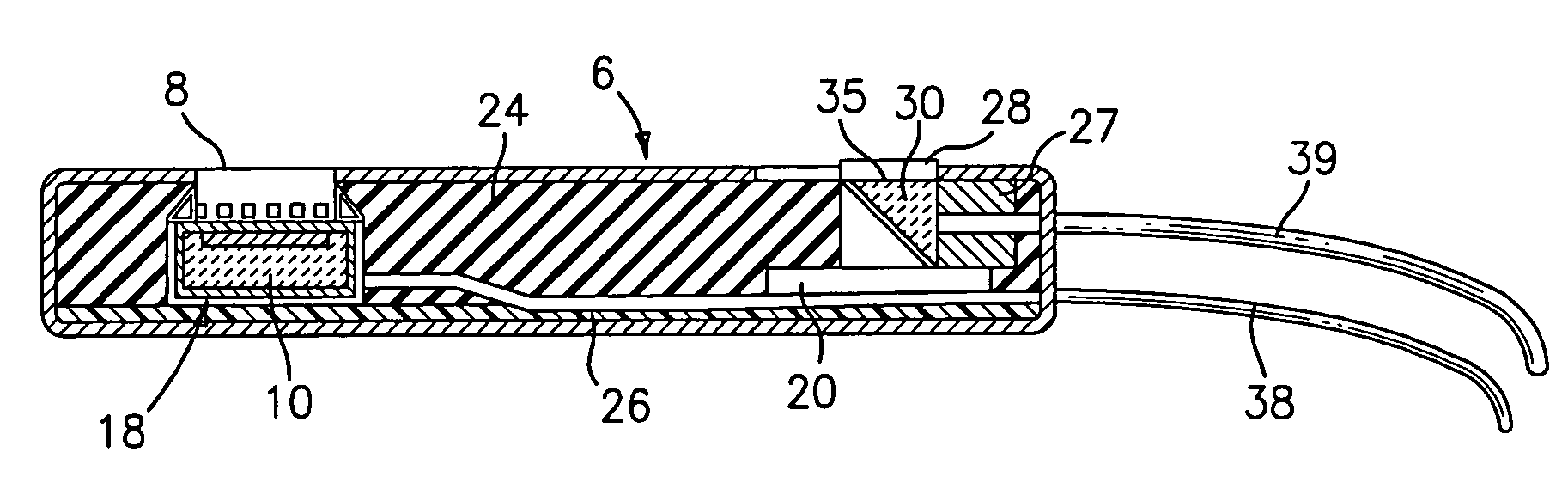

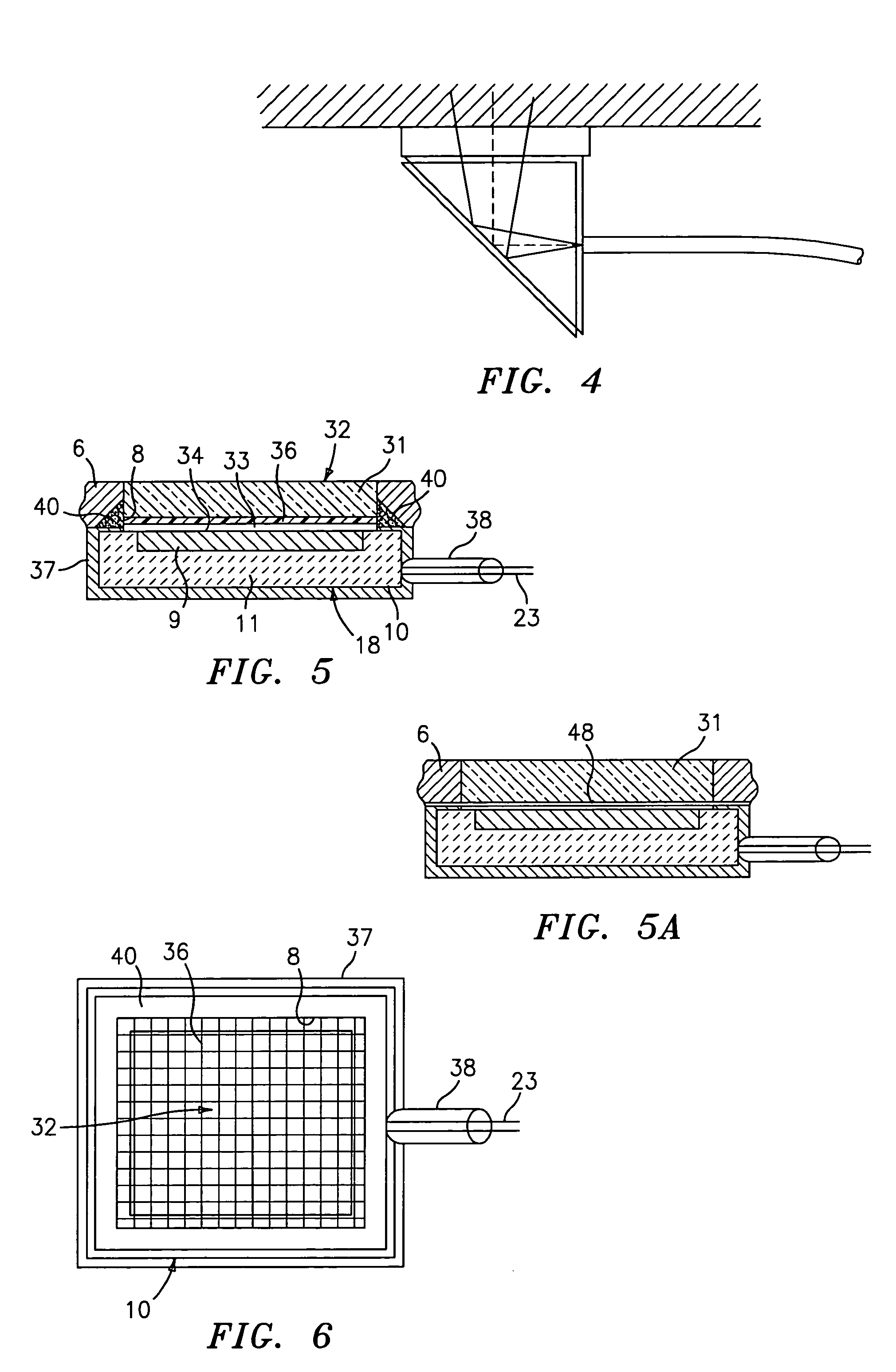

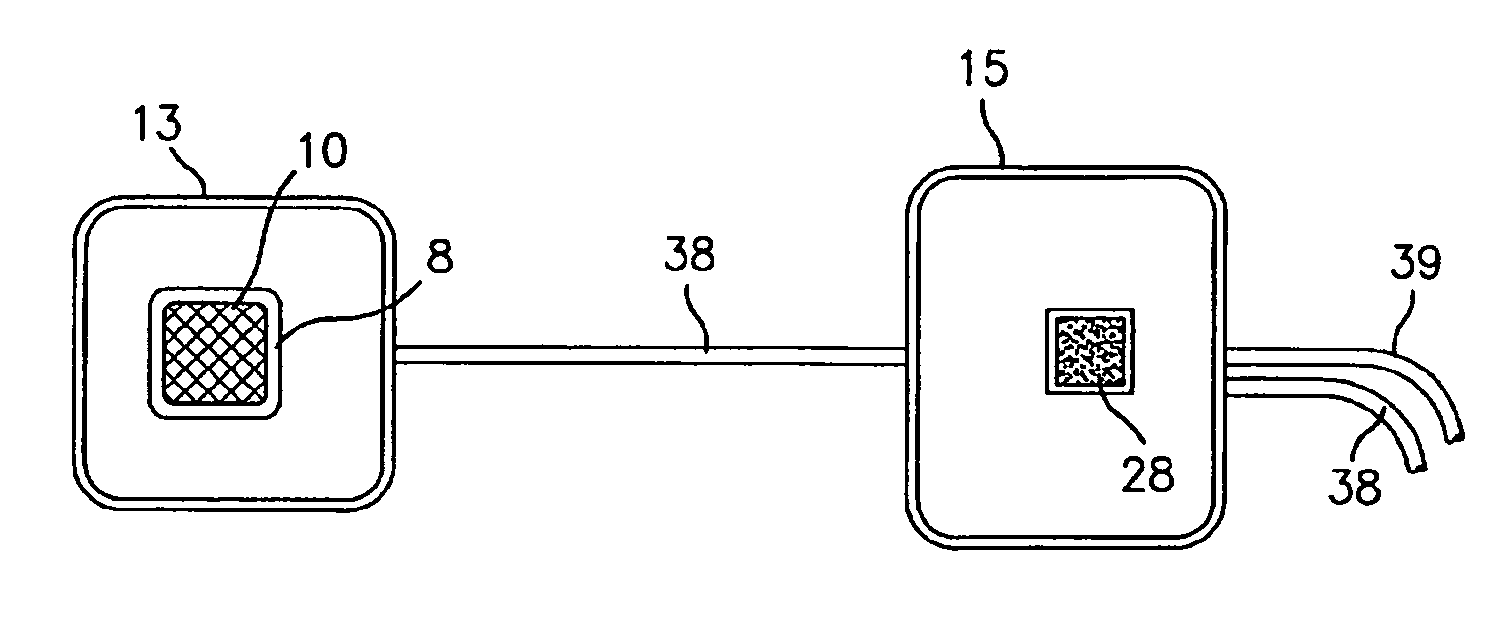

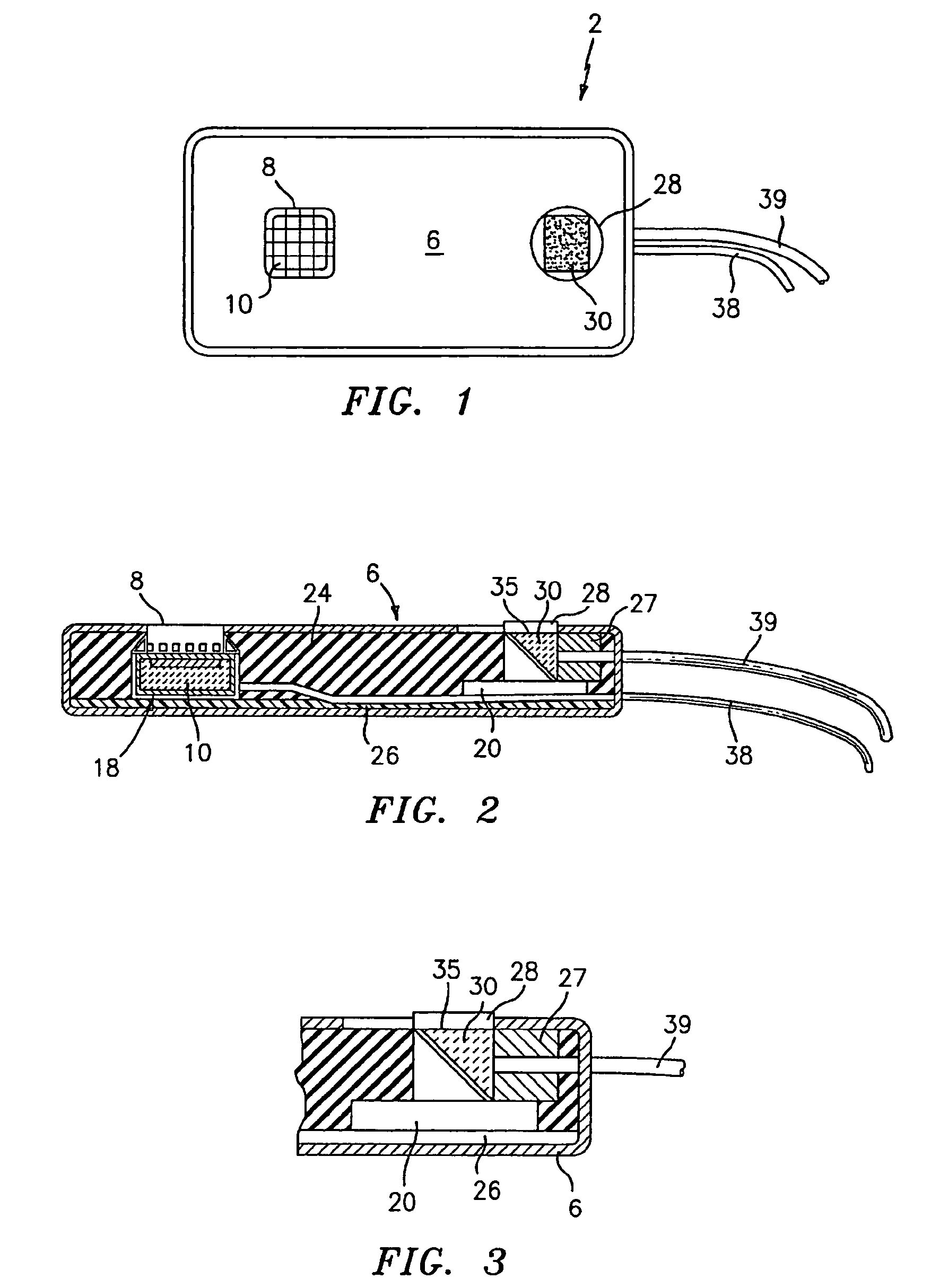

Laser diode optical transducer assembly for non-invasive spectrophotometric blood oxygenation monitoring

InactiveUS7047054B2Easily and securely attachedLight couplingDiagnostic recording/measuringSensorsCapacitanceFiber

A non-invasive near infrared spectrophotometric monitoring transducer assembly includes a housing member, which is adhered directly on a patient's skin. The housing member contains a prism coupled to a flexible and lightweight single core optical light guide, which provides a means of transferring narrow spectral bandwidth light from multiple distant laser diodes of different wavelengths by use of a multi-fiber optic light combining assembly. Different wavelengths are needed to monitor the level of blood oxygenation in the patient. The assembly also contains a planar light guide mounted on the prism located in the housing member, which light guide contacts the patient's skin when the housing member is adhered to the patient's skin. The light guide controls the spacing between the prism and the patient's skin, and therefore controls the intensity of the area on the patient's skin which is illuminated by the laser light. The housing member contains a photodiode assembly, which detects the infrared light at a second location on the skin to determine light absorption. The photodiode assembly is preferably shielded from ambient electromagnetic interference (EMI) by an optically transparent EMI attenuating window. This rigid window placed over the photodiode also provides a planar interface between the assembly and the skin, improving optical coupling and stability as well as reducing the capacitive coupling between skin and the photodiode resulting in further EMI attenuation. The housing may be associated with a disposable sterile hydrogel coated adhesive envelope, or pad, which when applied to the patient's skin will adhere the housing to the patient's skin. The transducer assembly will thus be reusable, and skin-contacting part of the device, i.e., the envelope or pad can be discarded after a single use. The assembly also includes a laser safety interlock means, which is operable to turn off the laser light output in the event that the assembly accidentally becomes detached from the patient's skin.

Owner:CAS MEDICAL SYST

Method and apparatus for coupling optical signal with packaged circuits via optical cables and lightguide couplers

ActiveUS8041221B2Increase speedLow costCoupling light guidesElectromagnetic transmissionFiberShortest distance

Owner:ELBEX VIDEO LTD

Embedded Programmable Intelligent Search Memory

ActiveUS20080140661A1Reduce classification overheadImprove performanceDigital data information retrievalDigital data processing detailsMulti processorMemory architecture

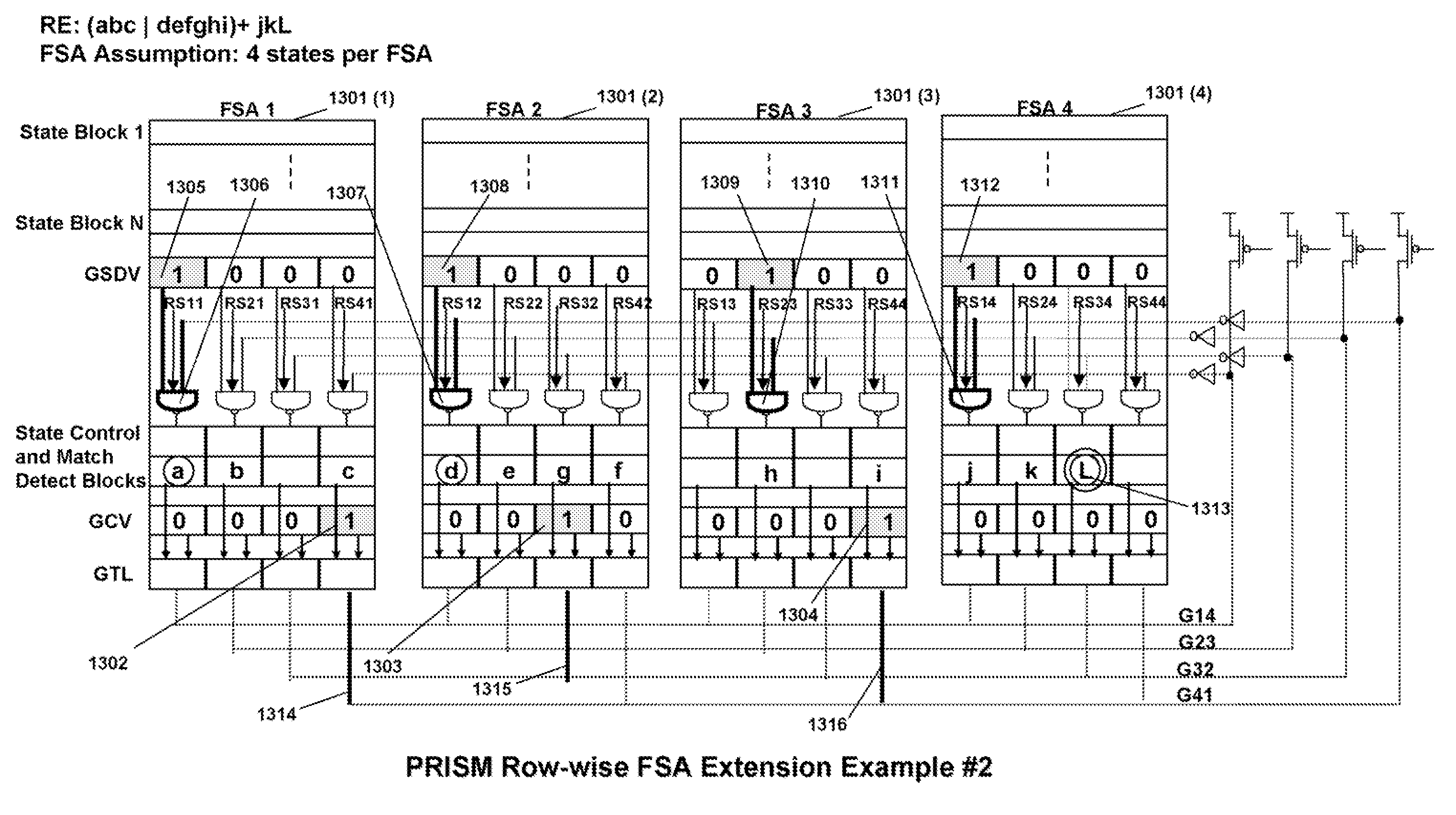

Memory architecture provides capabilities for high performance content search. The architecture creates an innovative memory that can be programmed with content search rules which are used by the memory to evaluate presented content for matching with the programmed rules. When the content being searched matches any of the rules programmed in the Programmable intelligent Search Memory (PRISM) action(s) associated with the matched rule(s) are taken The PRISM content search memory is embedded in a single core or multi-core processors or in multi-processor systems to perform content search. PRISM accelerates content search by offloading the content search tasks from the processors. Content search rules comprise of regular expressions which are converted to finite state automata and then programmed in PRISM for evaluating content with the search rules.

Owner:INFOSIL INC

Laser diode optical transducer assembly for non-invasive spectrophotometric blood oxygenation

A non-invasive near infrared spectrophotometric monitoring transducer assembly includes a housing member, which is adhered directly on a patient's skin. The housing member contains a prism coupled to a flexible and lightweight single core optical light guide, which provides a means of transferring narrow spectral bandwidth light from multiple distant laser diodes of different wavelengths by use of a multi-fiber optic light combining assembly. Different wavelengths are needed to monitor the level of blood oxygenation in the patient. The assembly also contains a planar light guide mounted on the prism located in the housing member, which light guide contacts the patient's skin when the housing member is adhered to the patient's skin. The light guide controls the spacing between the prism and the patient's skin, and therefore controls the intensity of the area on the patient's skin which is illuminated by the laser light. The housing member contains a photodiode assembly, which detects the infrared light at a second location on the skin to determine light absorption. The photodiode assembly is preferably shielded from ambient electromagnetic interference (EMI) by an optically transparent EMI attenuating window. This rigid window placed over the photodiode also provides a planar interface between the assembly and the skin, improving optical coupling and stability as well as reducing the capacitive coupling between skin and the photodiode resulting in further EMI attenuation. The housing may be associated with a disposable sterile hydrogel coated adhesive envelope, or pad, which when applied to the patient's skin will adhere the housing to the patient's skin. The transducer assembly will thus be reusable, and skin-contacting part of the device, i.e., the envelope or pad can be discarded after a single use. The assembly also includes a laser safety interlock means, which is operable to turn off the laser light output in the event that the assembly accidentally becomes detached from the patient's skin.

Owner:EDWARDS LIFESCIENCES CORP

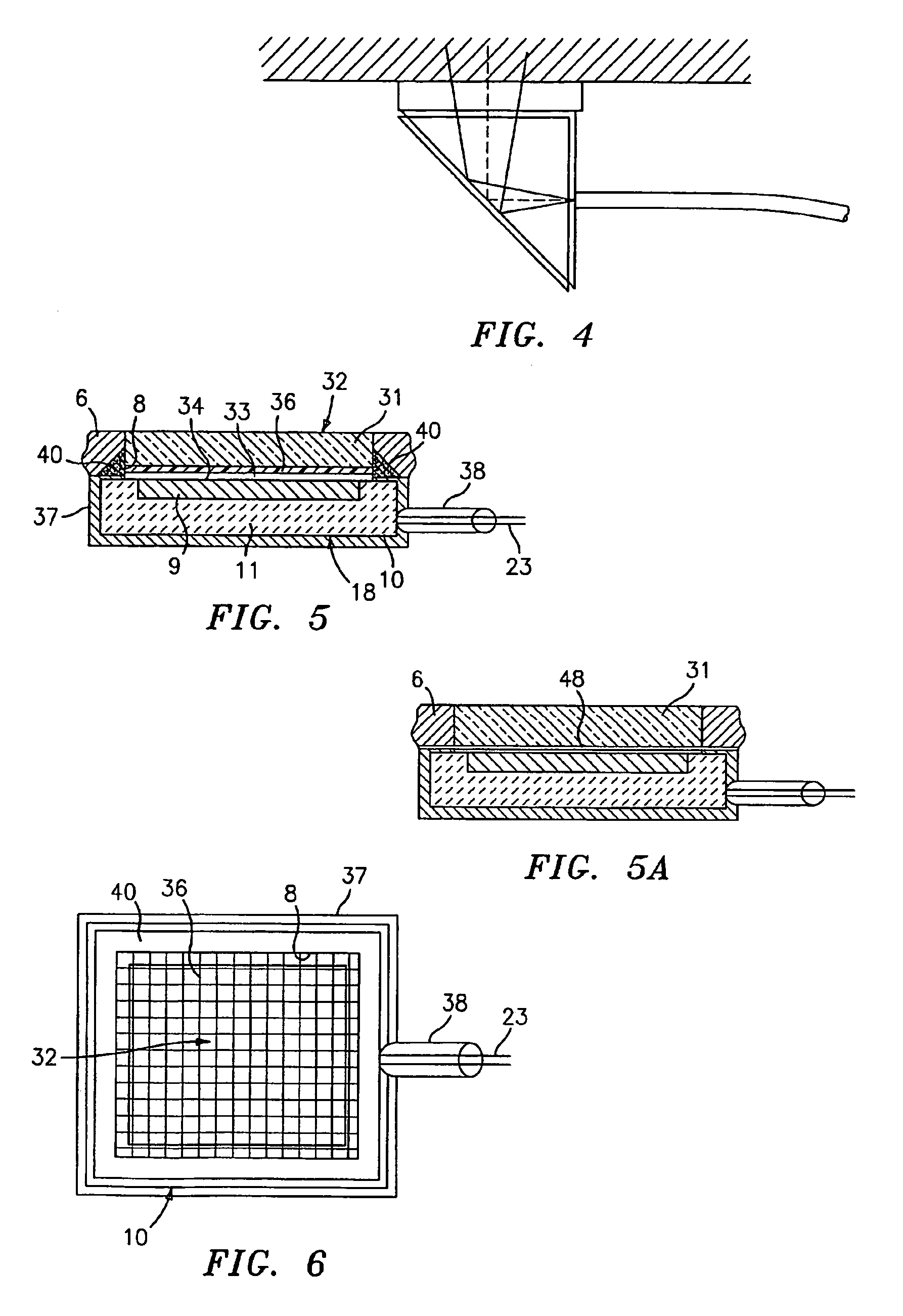

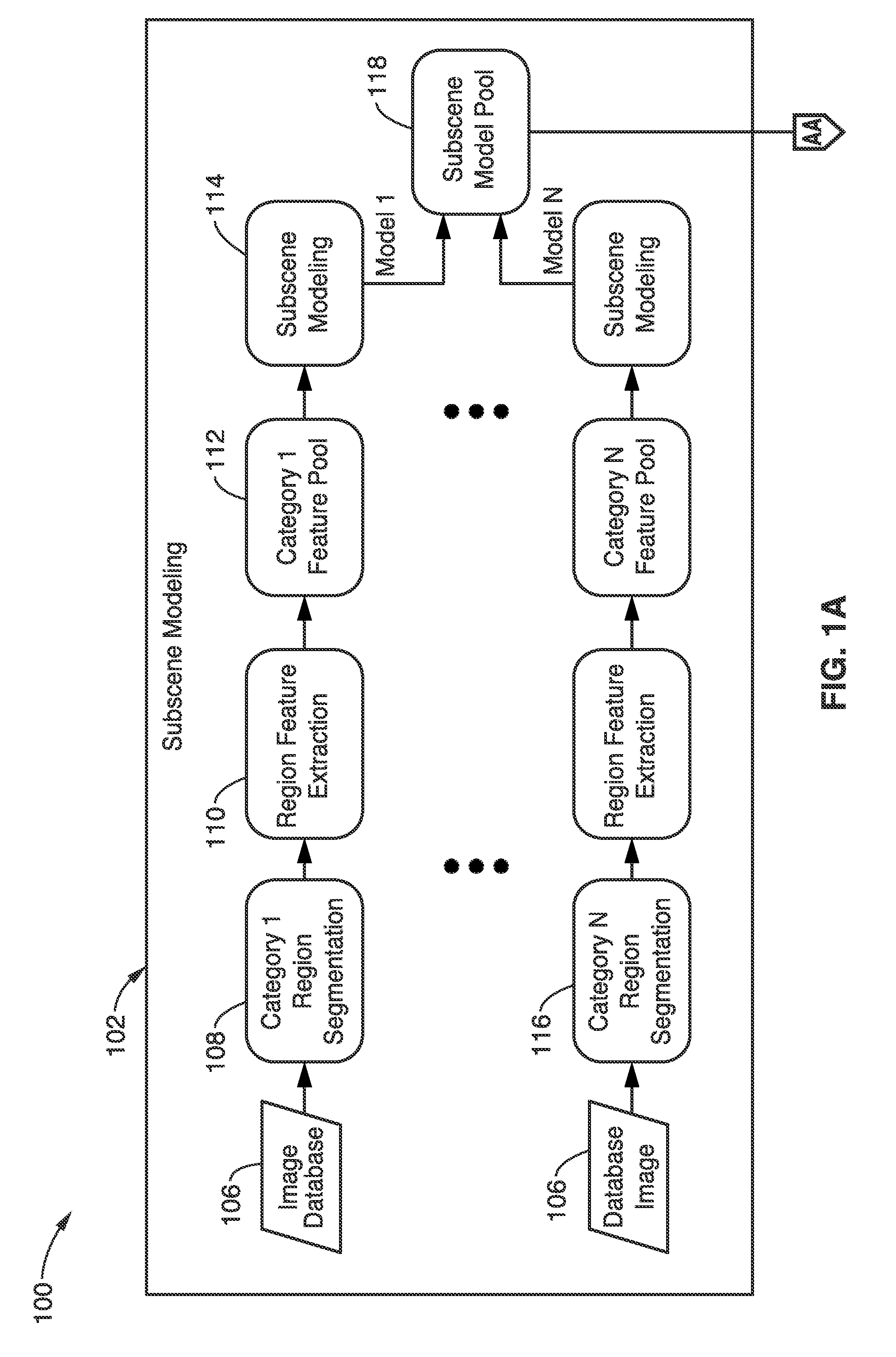

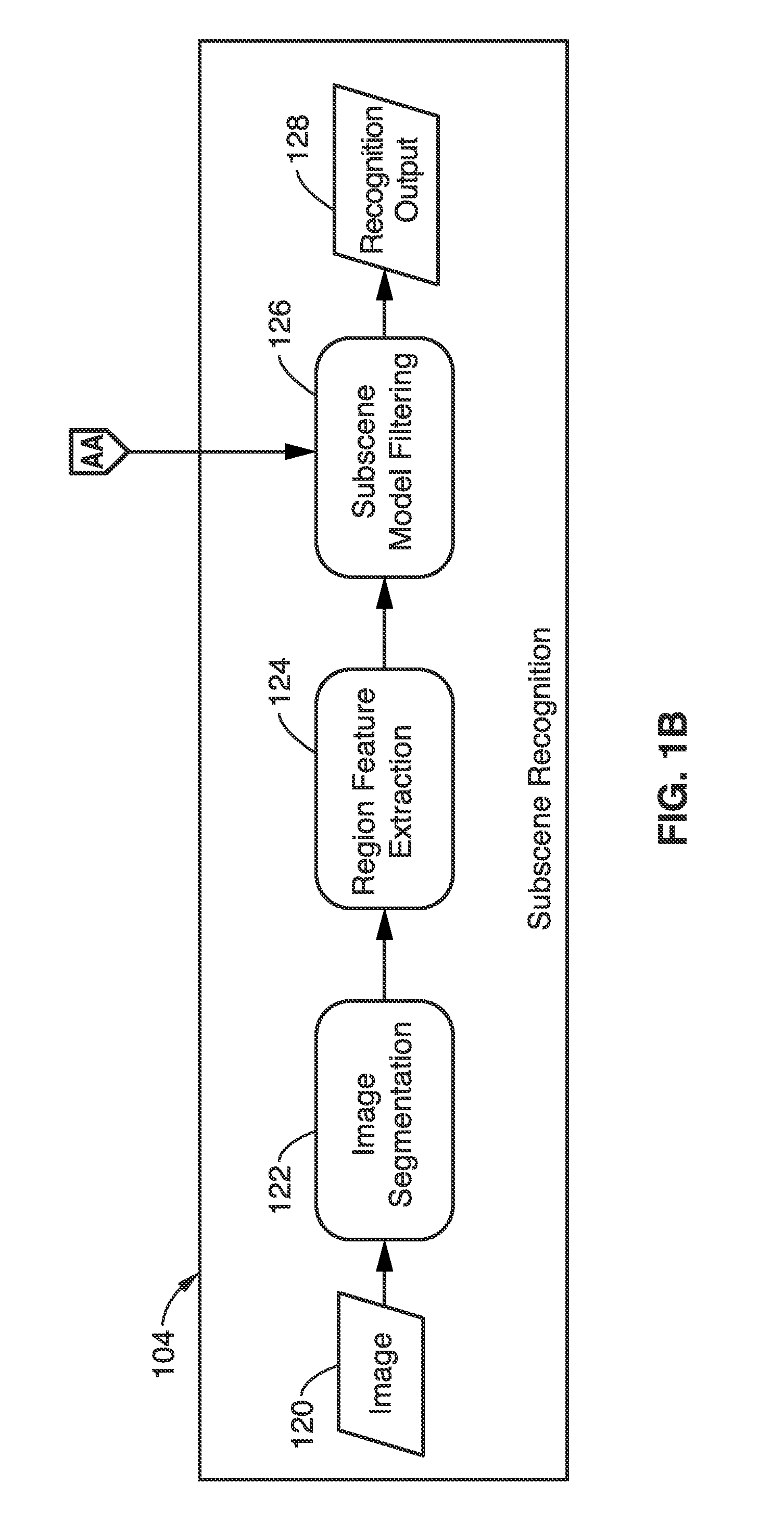

Region description and modeling for image subscene recognition

A method and apparatus is described here that categorizes images by extracting regions and describing the regions with a 16-dimensional subscene feature vector, which is a concatenation of color, texture, and spatial feature vectors. By comparing the spatial feature vectors in images with similarly-obtained feature vectors in a Gaussian mixture based model pool (obtained in a subscene modeling phase), the images may be categorized (in a subscene recognition phase) with probabilities relating to each region or subscene. Higher probabilities are likelier correlations. The device may be a single or multiple core CPU, or parallelized vector processor for characterizing many images. The images may be photographs, videos, or video stills, without restriction. When used real-time, the method may be used for visual searching or sorting.

Owner:SONY CORP

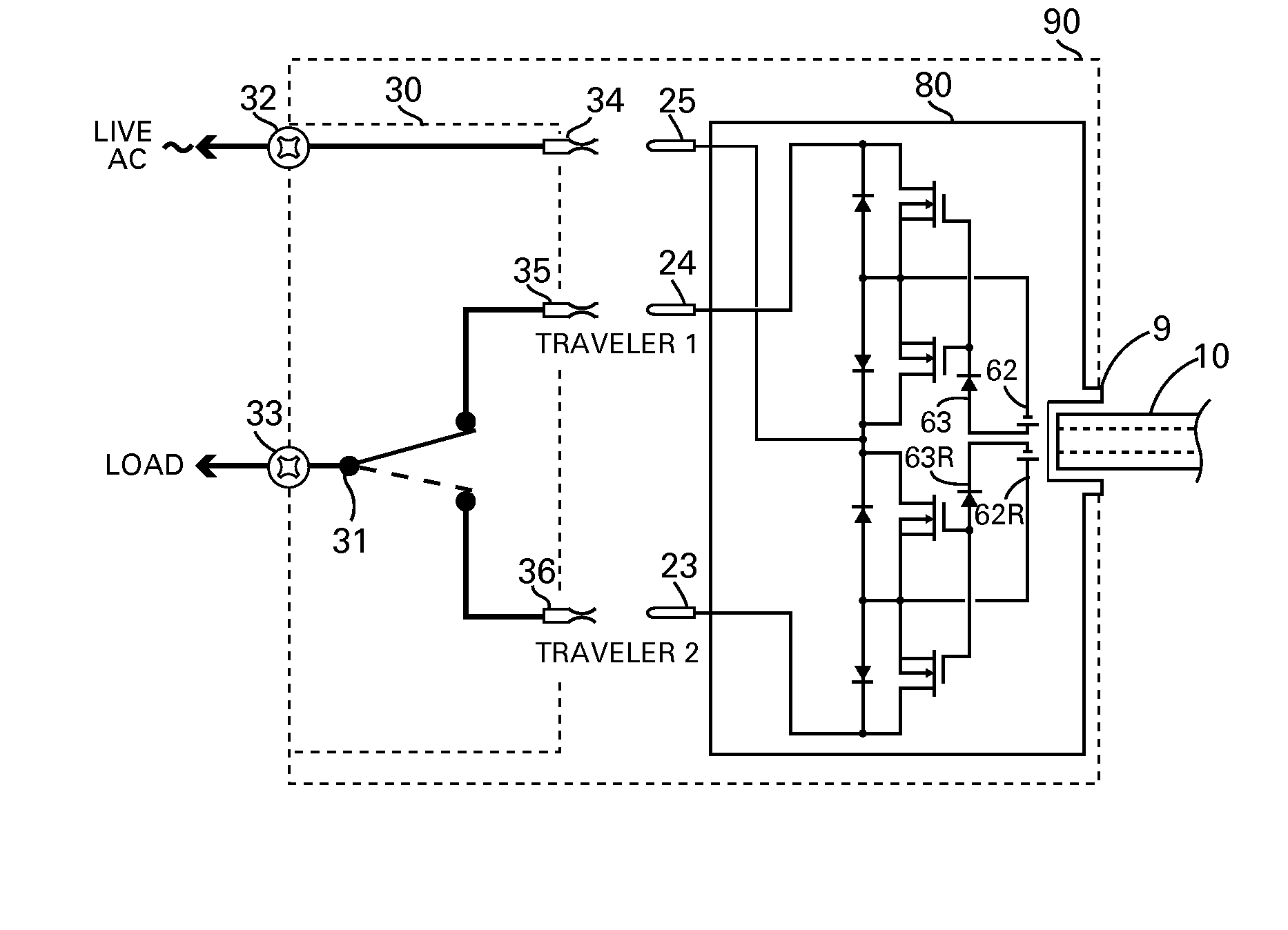

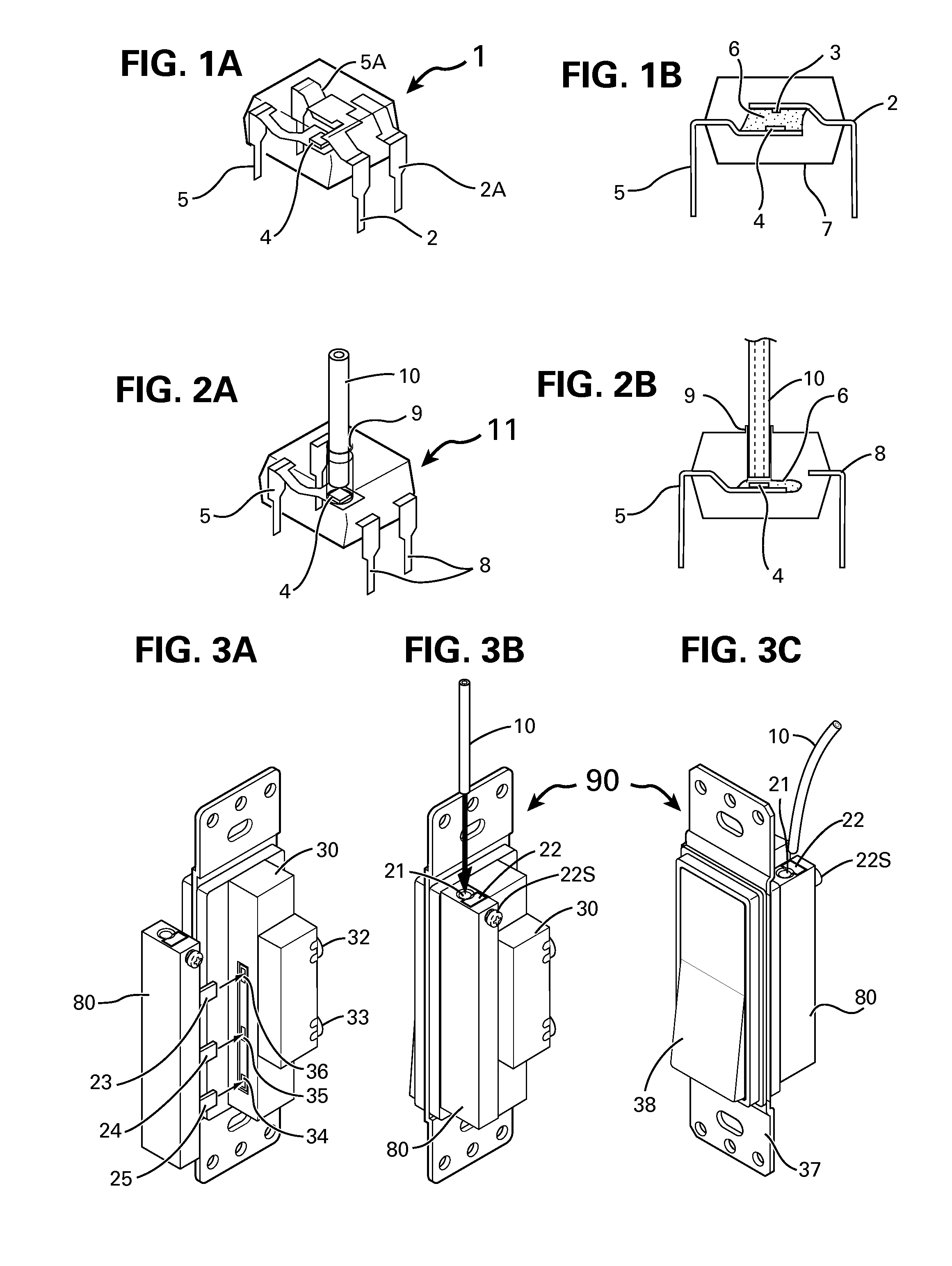

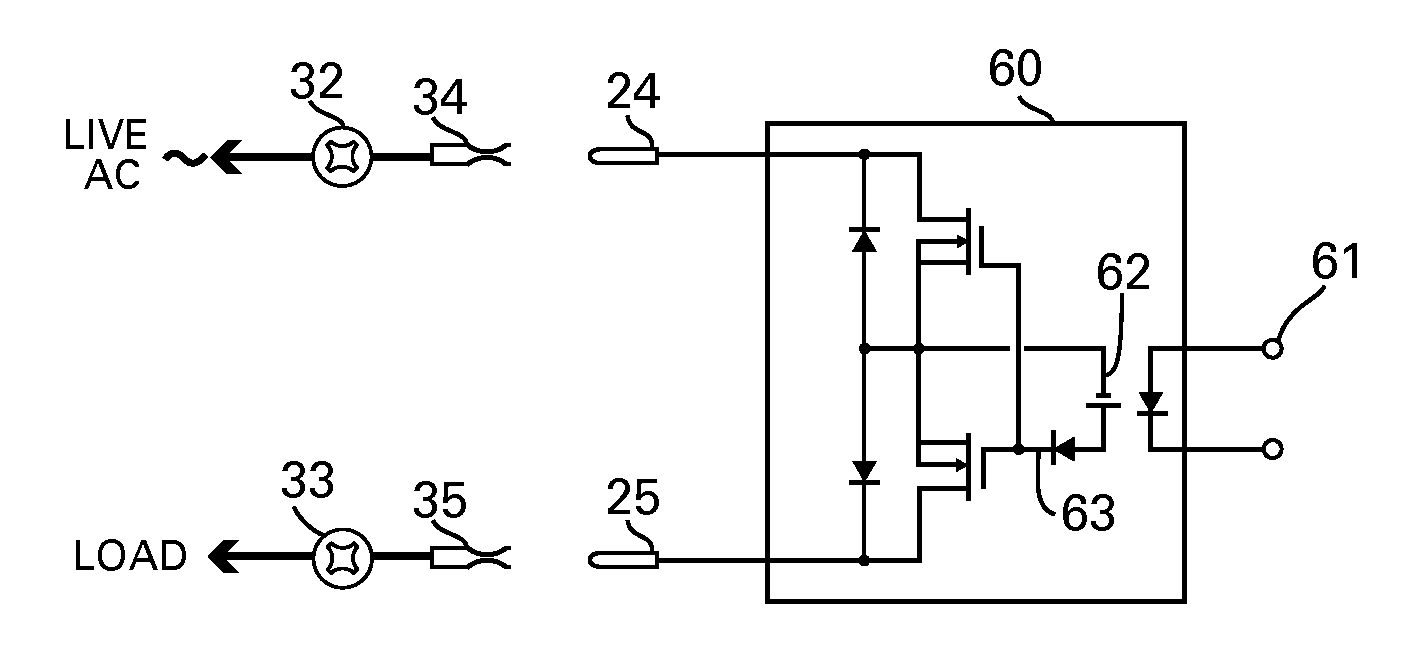

Method and Apparatus for Coupling Optical Signal with Packaged Circuits Via Optical Cables and Lightguide Couplers

ActiveUS20110110673A1Increase speedLow costMaterial analysis by optical meansCoupling light guidesFiberShortest distance

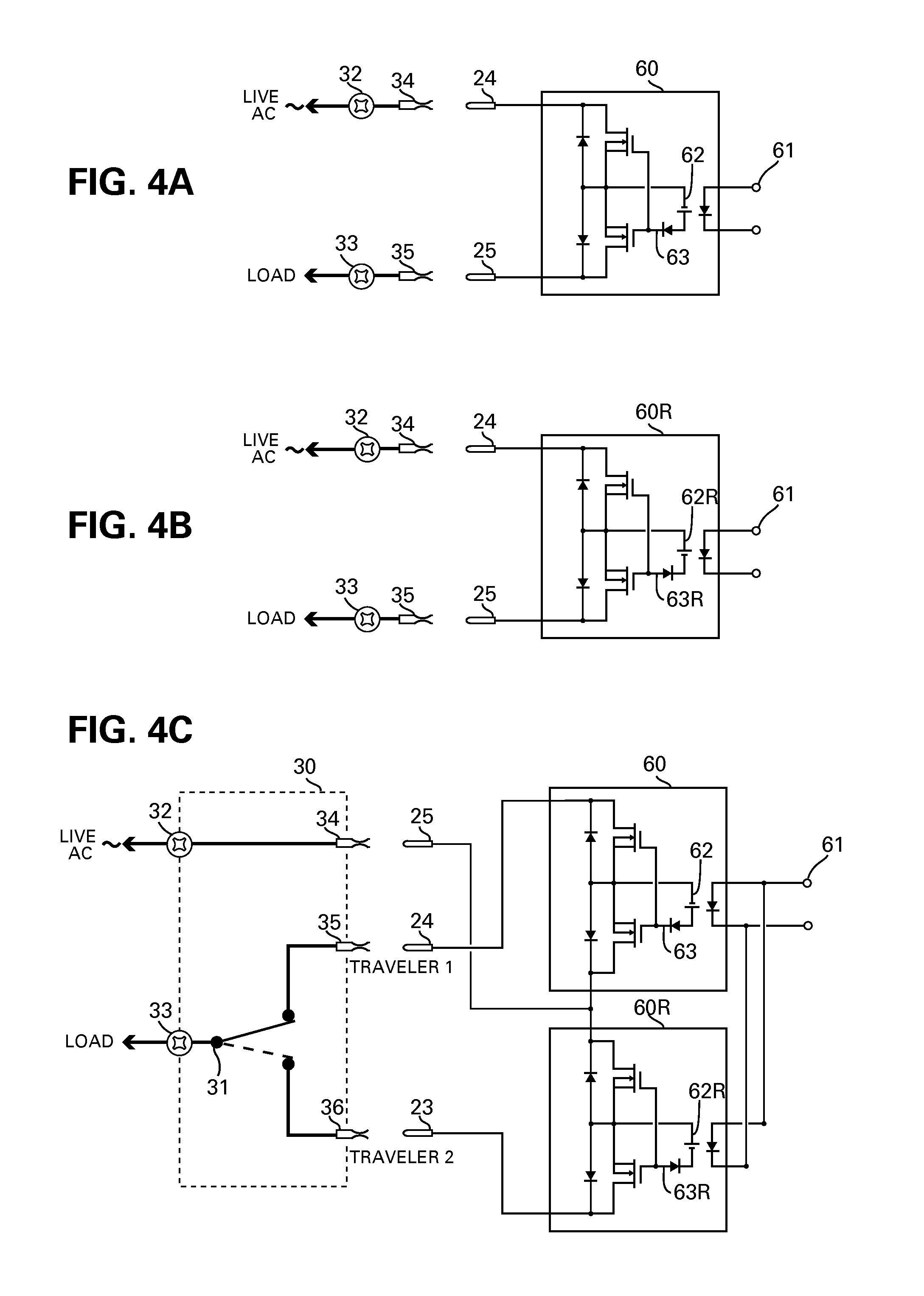

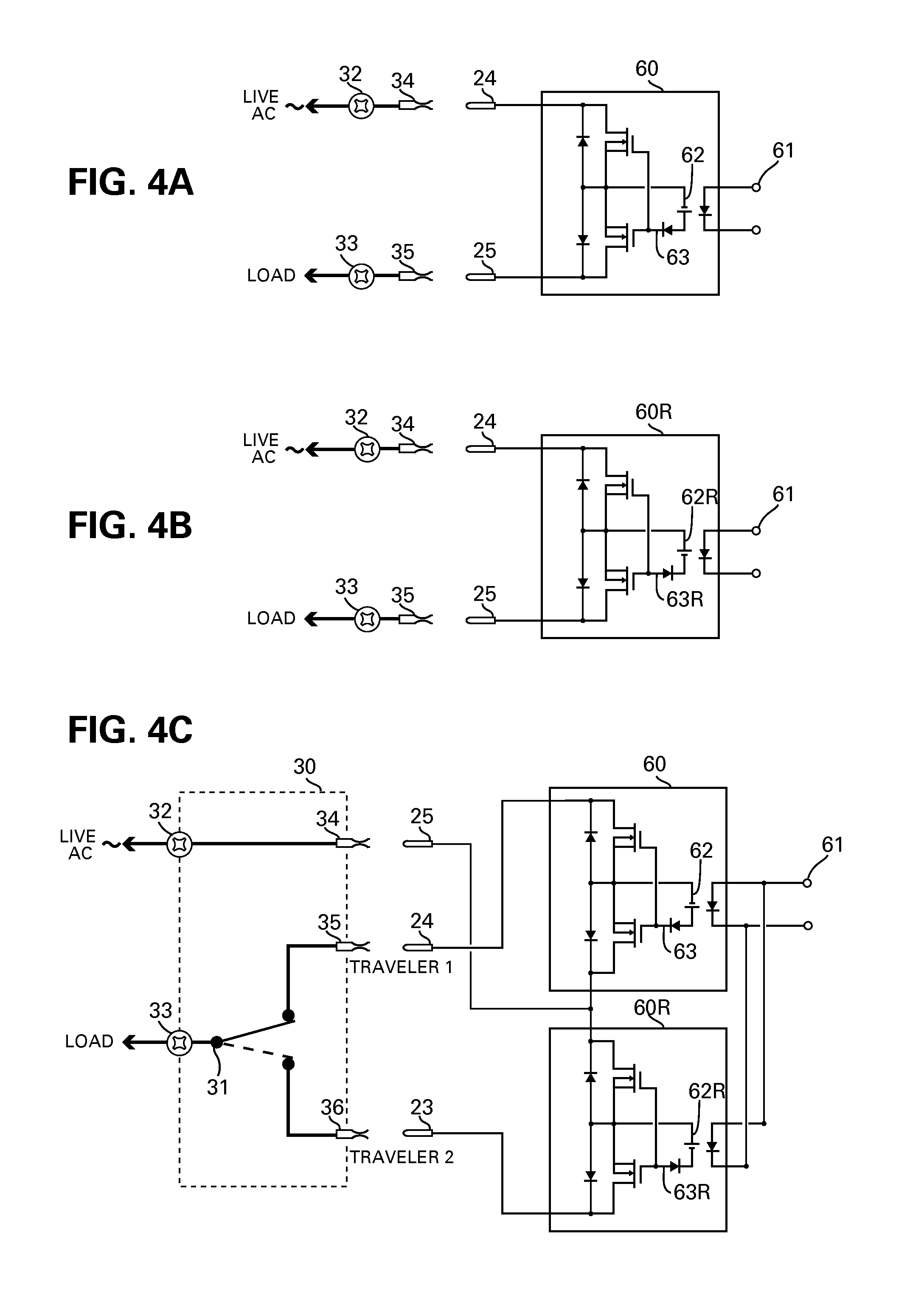

Method and apparatus for coupling electrical and communication circuits, included in a packaged semiconductor comprising photo receivers, photo transmitters and photovoltaic cells, through lightguide and optical fiber cables. The packaged semiconductor combinations comprise one, two or plurality of photo elements for a single or plurality one way optical signal, receive or transmit, and a single or plurality of two way optical signal communications via direct optical links and via optical prisms, filters, half mirrors and lenses. The packaged semiconductor includes at least one optical access to a single or plurality of lightguides or optical fiber with single core and for multicore lightguides. A built-in or attachable holders are used for attaching the different lightguide cables to the one or plurality of optical accesses with the attached cable end is terminated by cutting, trimming and shaping. The packaged circuit comprising electrical switches, current sensors, basic elements such as diodes, transistors and FETs, switches and power switches and different basic electrical circuit and communication, distribution circuits including CPU, DSP and complex semiconductor circuits, as used for communicating within limited short distances through optical network of lightguides and fiber optical cables. A packaged semiconductor of an SPDT power switch circuit is integrated with an SPDT manually activated switch, for providing dual switching for lights and other electrical appliances, via manual action and remotely via the lightguide or the optical fiber.

Owner:ELBEX VIDEO LTD

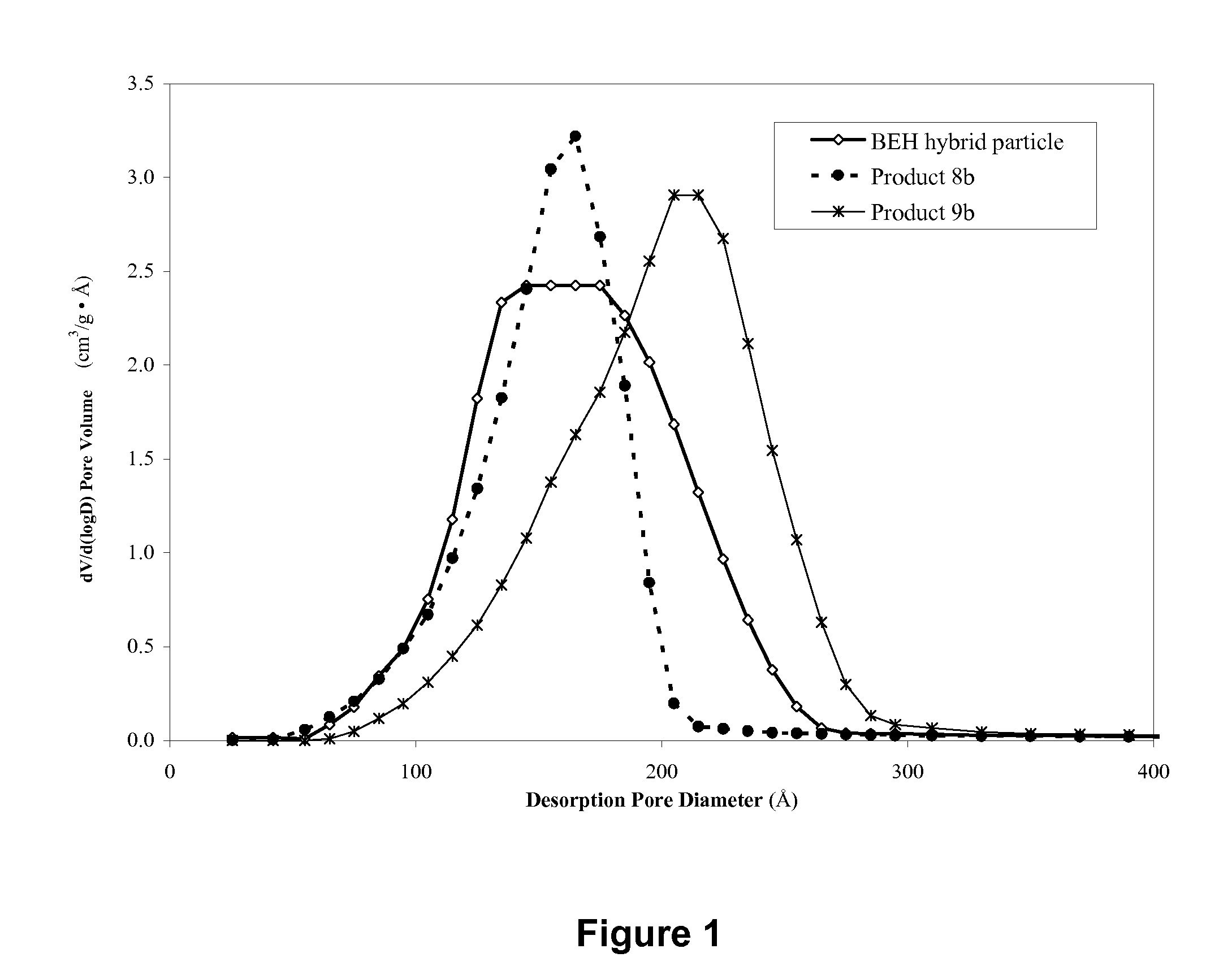

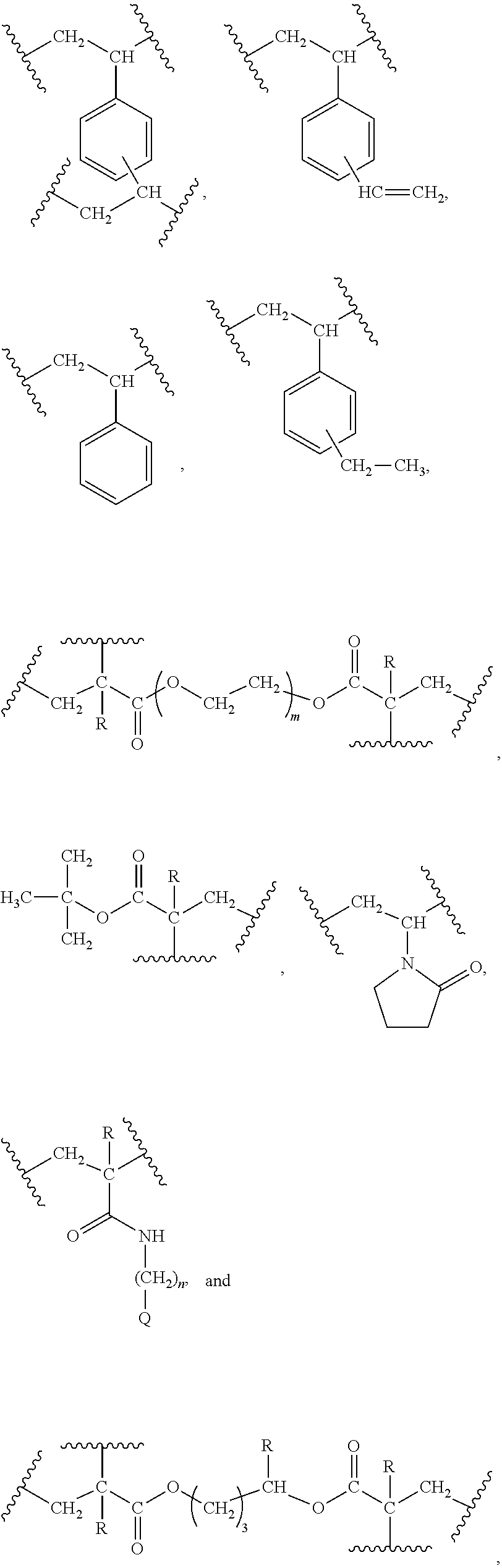

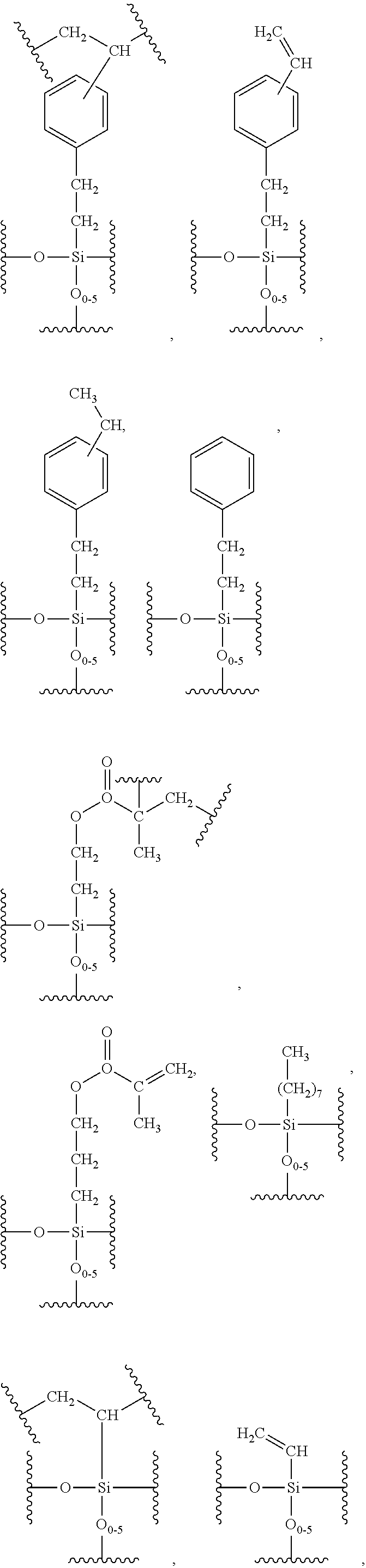

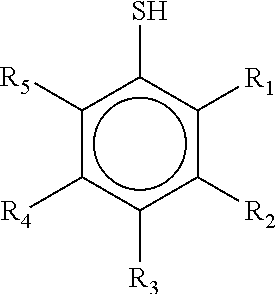

Hybrid inorganic/organic materials having novel surface modification; process for the preparation of inorganic/organic hybrid materials; and use of said particles for chromatographic separations

ActiveUS20120055860A1Enhancing oneMany of characteristicIon-exchange process apparatusSemi-permeable membranesChromatographic separationIon exchange

The present invention provides novel chromatographic materials, e.g., for chromatographic separations, processes for their preparation and separations devices containing the chromatographic materials. The preparation of the inorganic / organic hybrid materials of the invention wherein a surrounding material is condensed on a porous hybrid core material will allow for families of different hybrid packing materials to be prepared from a single core hybrid material. Differences in hydrophobicity, ion-exchange capacity, surface charge or silanol activity of the surrounding material may be used for unique chromatographic separations of small molecules, carbohydrates, antibodies, whole proteins, peptides, and / or DNA.

Owner:WATERS TECH CORP

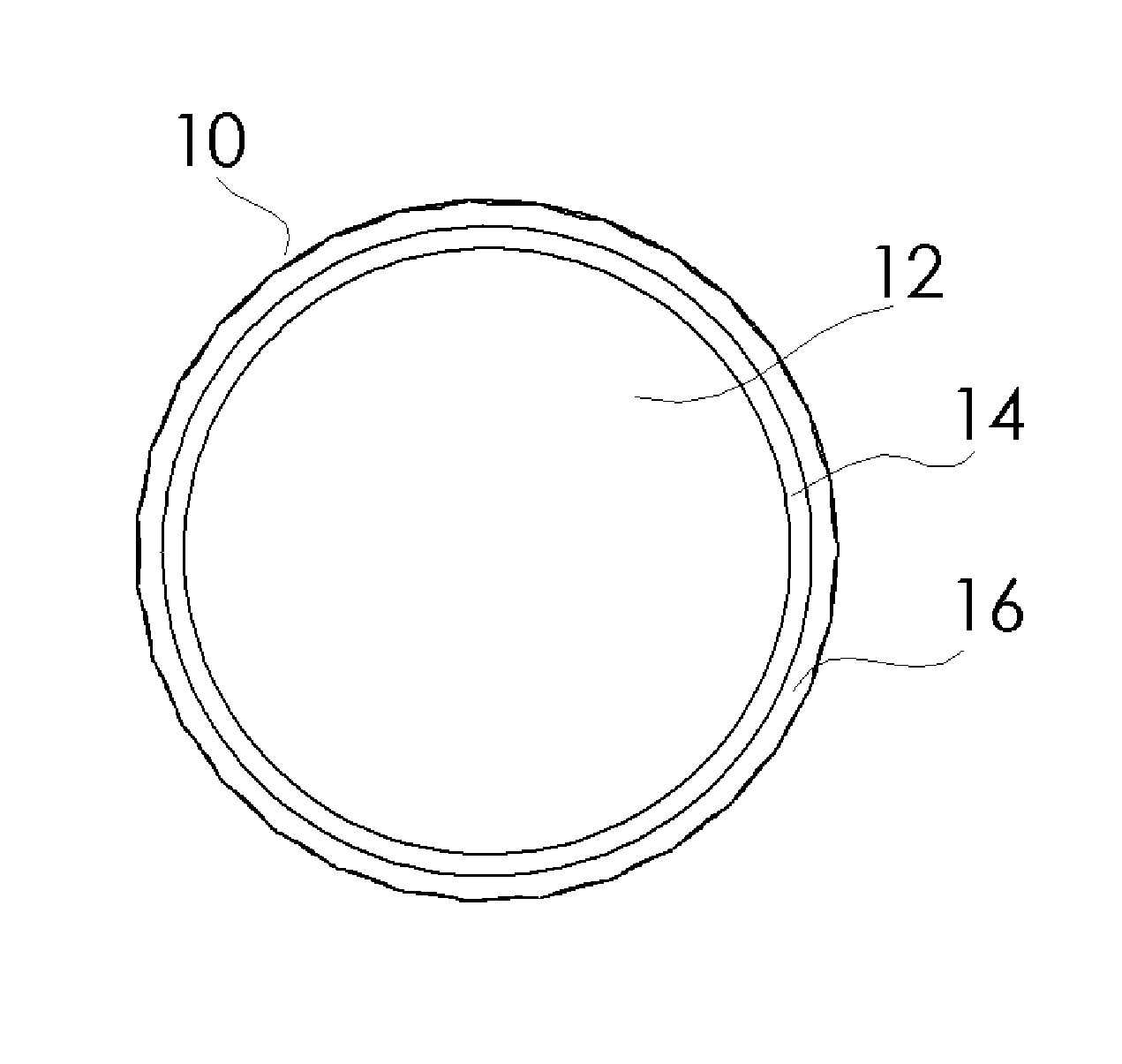

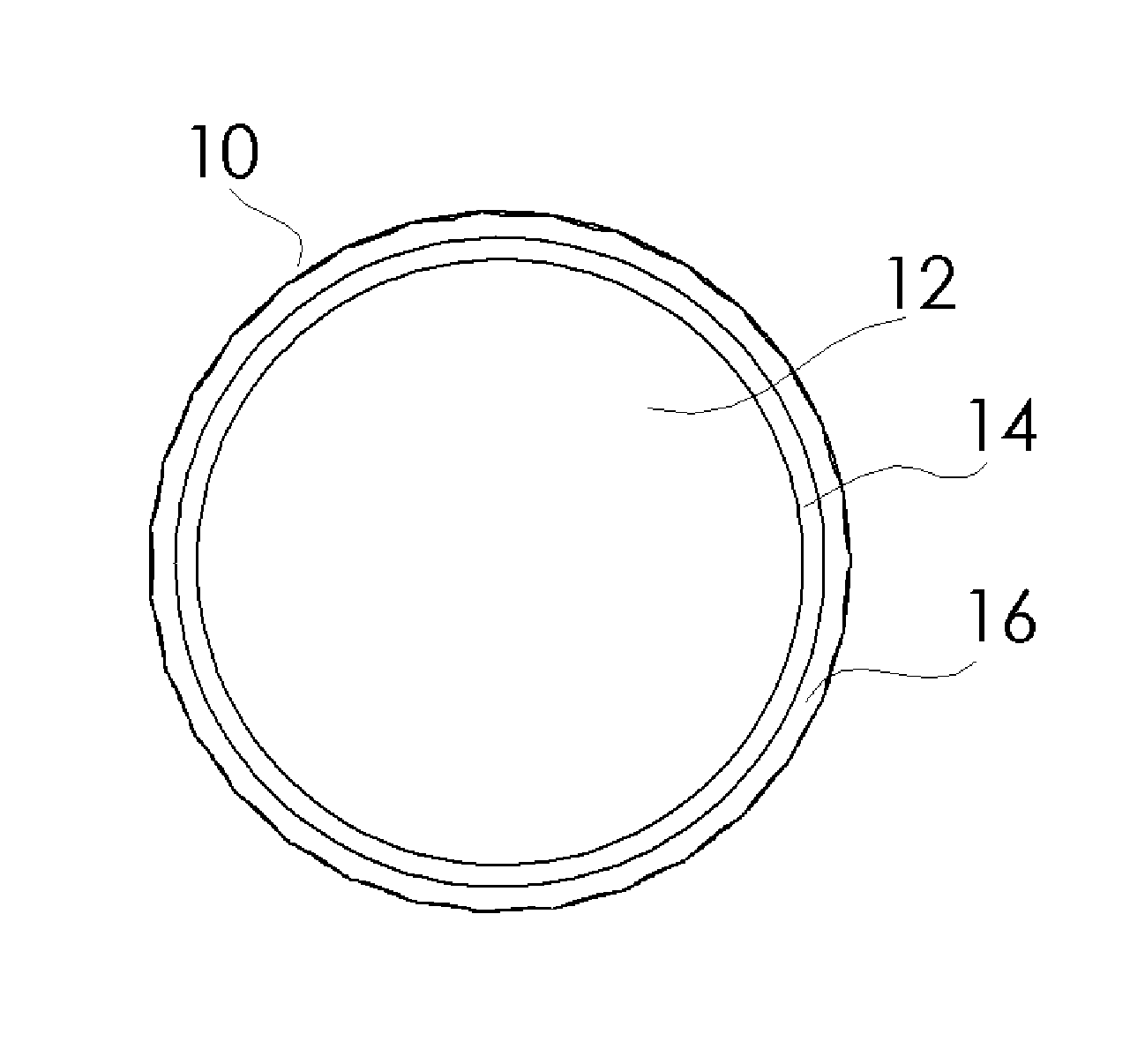

Multi-piece golf ball comprising low hardness gradient core

A golf ball includes a single core formed from a substantially homogenous rubber composition, an inner cover disposed about the core, and an outer cover. The inner cover includes an ionomeric material and has a hardness of about 60 Shore D or greater. The outer cover layer is disposed about the inner cover layer, is formed from a castable polyurea or polyurethane, and has a material hardness of about 60 Shore D or less. The outer surface of the core has a trans content of about 12% or less and a hardness of about 71 to 88 Shore C, the geometric center of the core has a trans content of about 10% or less and a hardness of about 70 to 80 Shore C, and the core surface hardness is greater than the geometric center hardness by about 1 to 10 Shore C to define a shallow positive hardness gradient.

Owner:ACUSHNET CO

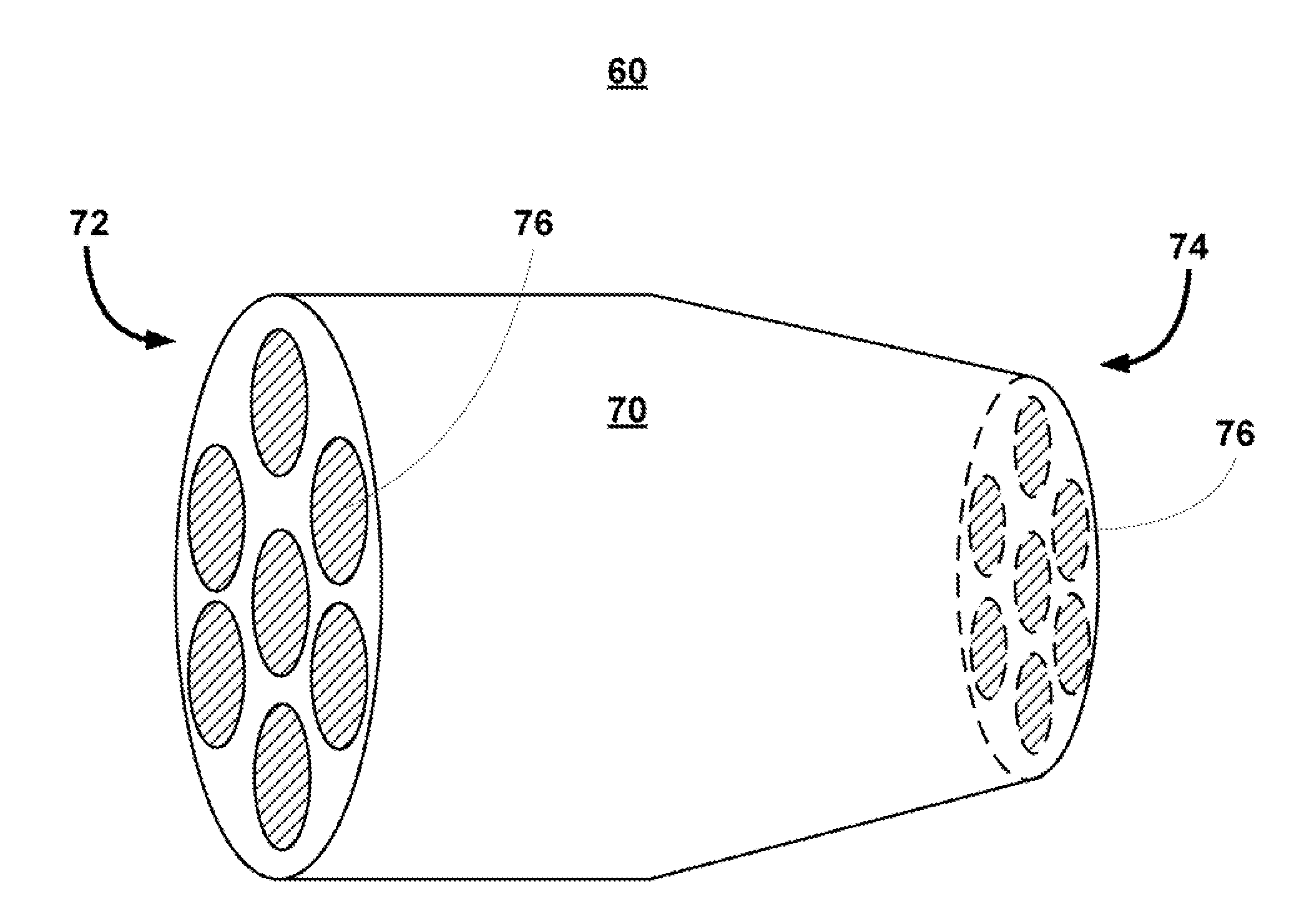

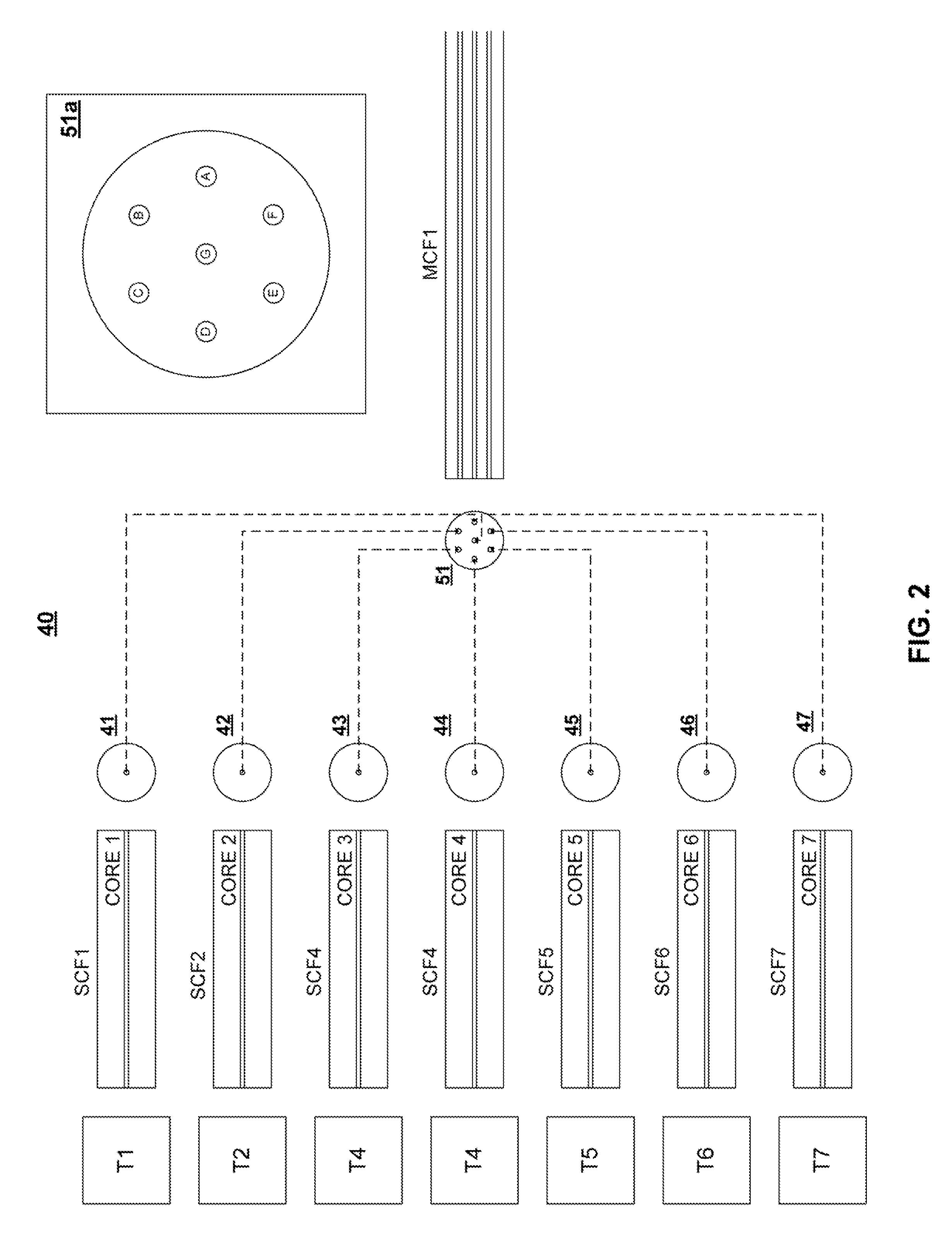

Techniques and devices for low-loss, modefield matched coupling to a multicore fiber

Devices and techniques are described for connecting each of plurality of terminals to respective individual cores of a multicore fiber. Each of the plurality of terminals is provided with a respective length of a single-core fiber. The single-core fibers are configured to maintain modal properties that arc substantially the same, within a tolerance range, at the front and rear ends, as the single-core fiber is tapered. The single-core fibers are assembled together. The front end of the assembly is tapered to form a front cross-section in which the single-core fiber cores are arranged in a configuration matching that of the cores of the multicore fiber.

Owner:OFS FITEL LLC

Method for preparing microcapsule by miniemulsion polymerization

InactiveUS20060281834A1Improve stabilityLow viscosityCoatingsMicroballoon preparationPolymer scienceSingle-core

Provided is a method for preparing uniformly sized and shaped, mono-dispersed microcapsules using miniemulsion polymerization. In microcapsules prepared by the method, a liquid or solid core encapsulated by a polymer shell has 10 to 80% by volume of the microcapsules. Since miniemulsion particles produced at an early stage of the method are stable, an organic material which is well dissolved in monomer particles and has a higher interfacial tension with water, relative to the polymer shell, can be uniformly positioned in polymer particles. Furthermore, when a crosslinking agent is added during the polymerization, single-core microcapsules can be obtained. In addition, use of an oil-soluble initiator can prevent formation of secondary particles and addition of a secondary initiator during the polymerization can increase the yield of the uniformly sized and shaped microcapsules.

Owner:LG CHEM LTD

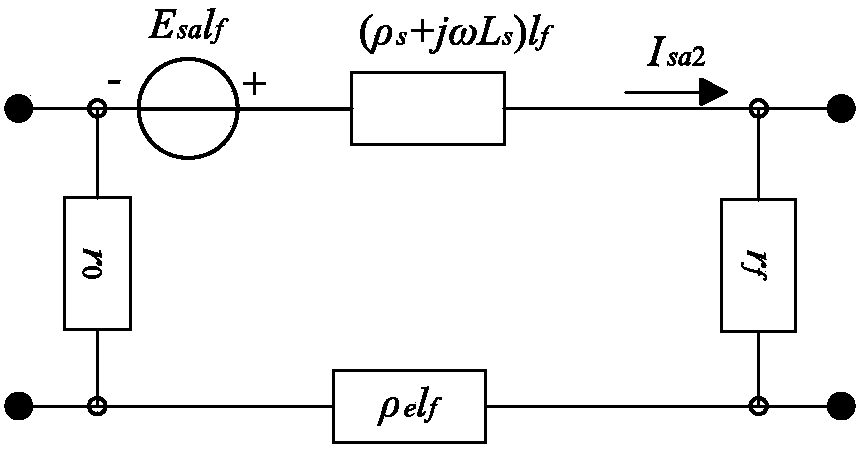

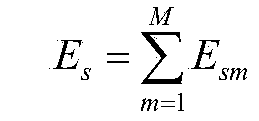

System and method for detecting earth fault of sheath of single-core power cable on basis of circulation measurement

The invention relates to the field of detection on an earth fault of a sheath of a single-core power cable, in particular to a system and a method for detecting the earth fault of the sheath of the single-core power cable on the basis of circulation measurement. Circulation detection is carried out on the sheath of the cable in three earthing modes of single-end earthing, double-end earthing and cross interconnection earthing. Firstly, transformation of additionally arranged switching elements for various earthing boxes of the cable is carried out, so that each earthing mode can be conveniently and safely converted into the single-end earthing mode in the measuring process; then in the state, a circulation value of the sheath is measured; and according to a circuit theory model of a fault sheath circulation loop and experimental data in the single-end earthing mode, circulation characteristics at different fault earthing points are obtained so as to carry out fault judgment and positioning. In the whole process, the detection is simple, the calculated amount is small, and online detection can be realized.

Owner:STATE GRID CORP OF CHINA +1

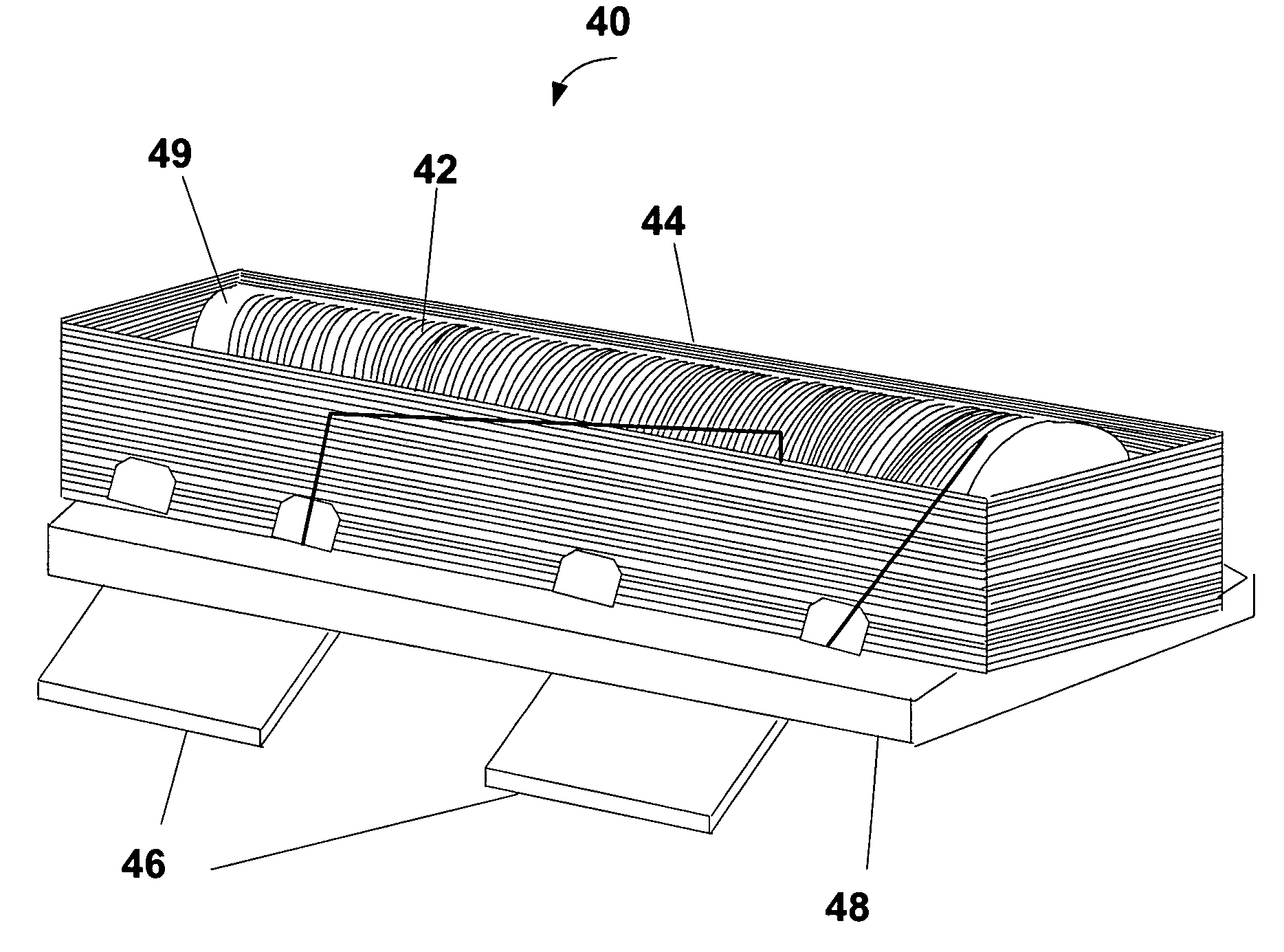

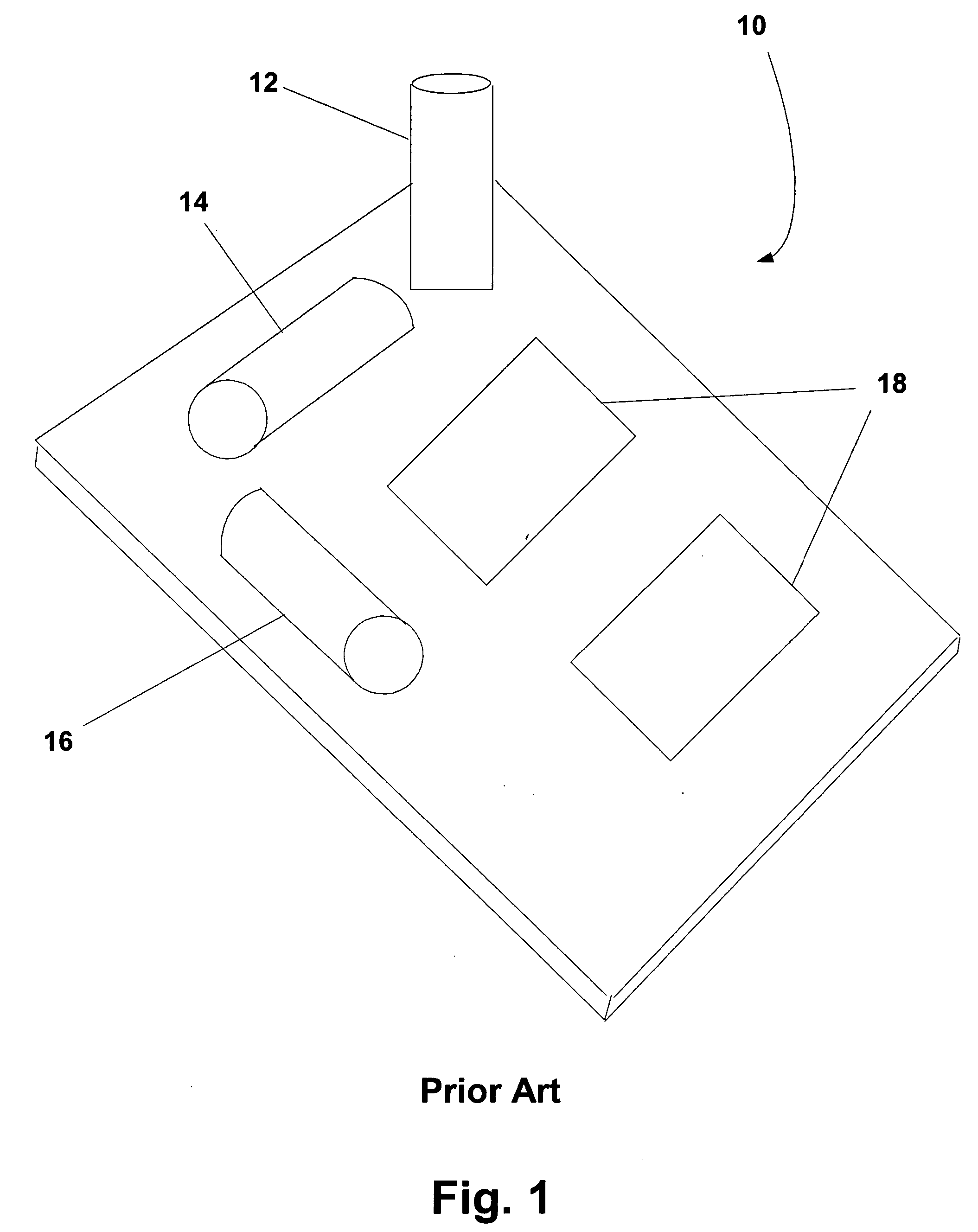

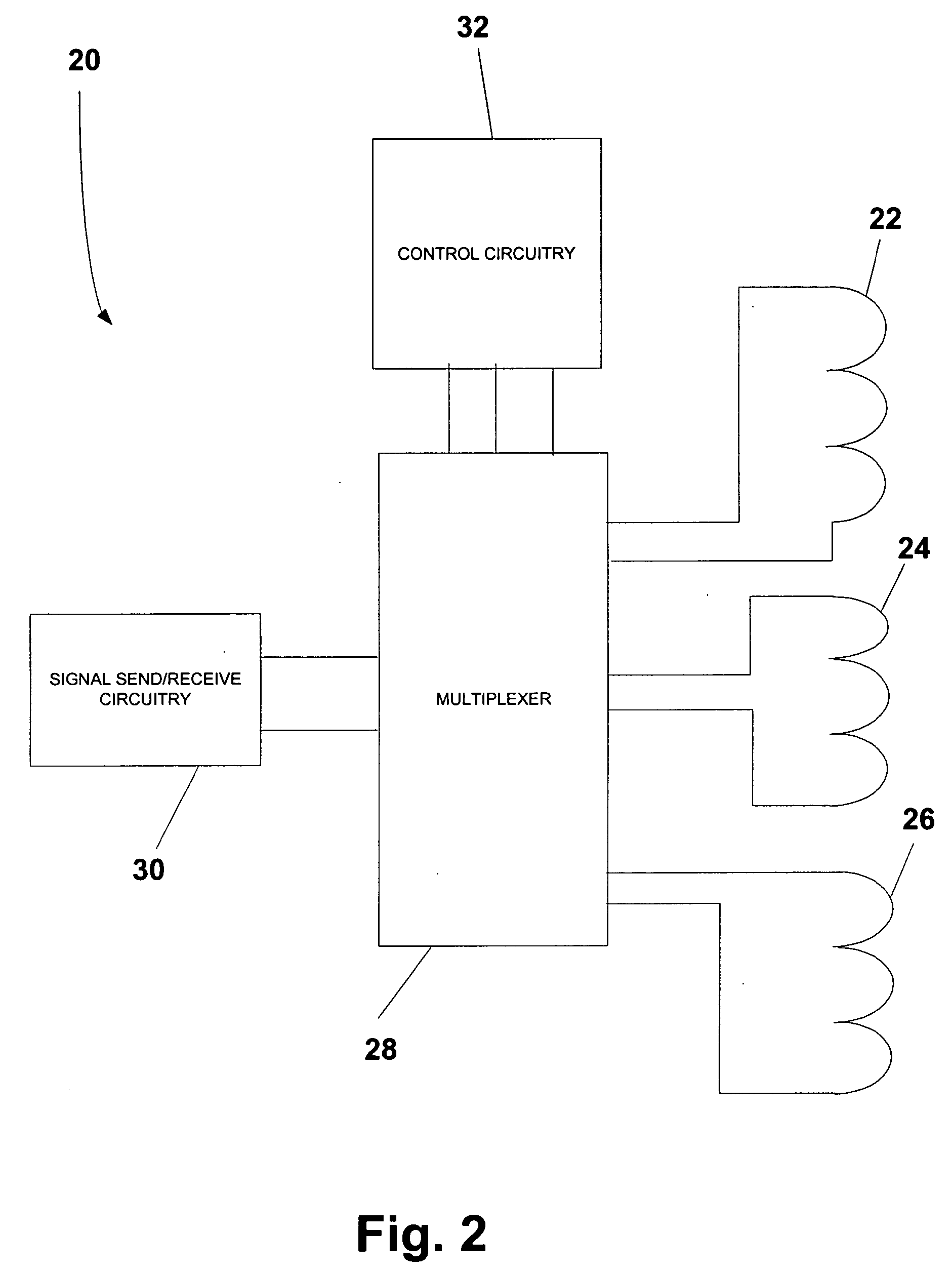

System and method for multiple antennas having a single core

InactiveUS20050088357A1Easy to separateLoop antennas with ferromagnetic coreElectrotherapyBiological activationConductor Coil

A system and method for multiple antennas on a single core. The system may include a first core, a first winding wound about the first core for transmitting / receiving electromagnetic signals, and a second winding for transmitting / receiving electromagnetic signals wound about the first core and the first winding. The first winding and the second winding may be wound such that a direction of a first magnetic field generated by the first winding is different than a direction of a second magnetic field generated by the second winding. The system may also include activation circuitry connected to the first winding and the second winding. The activation circuitry may activate the first winding separately from the second winding. The system may be expanded to three or more coils / antennas disposed on a single core.

Owner:MEDTRONIC MIMIMED INC

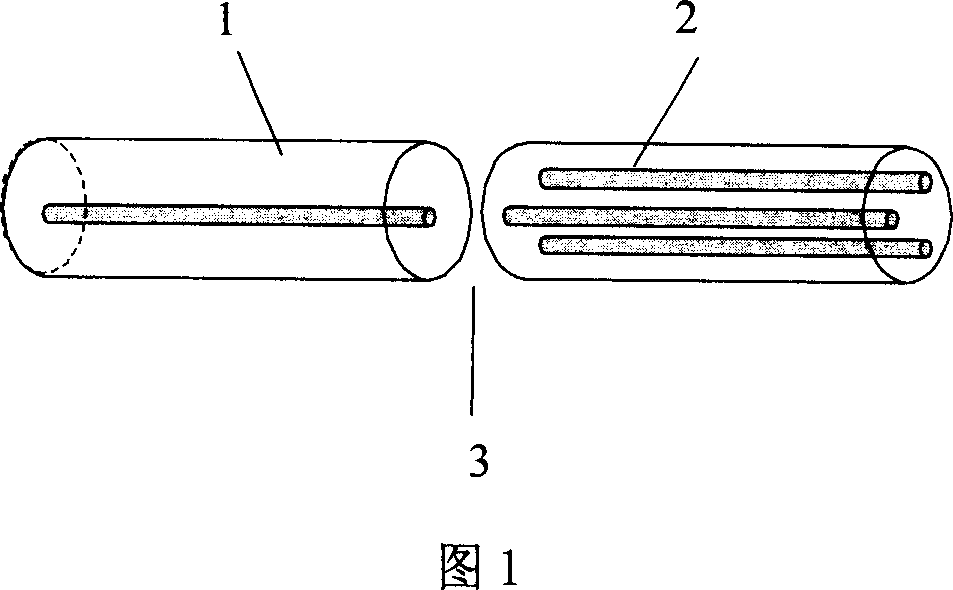

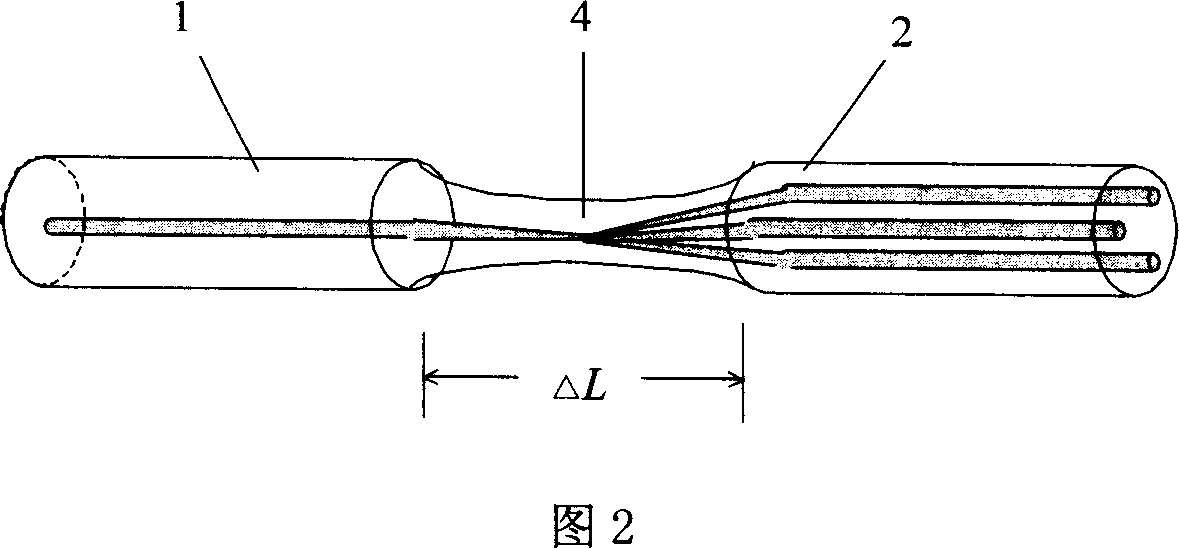

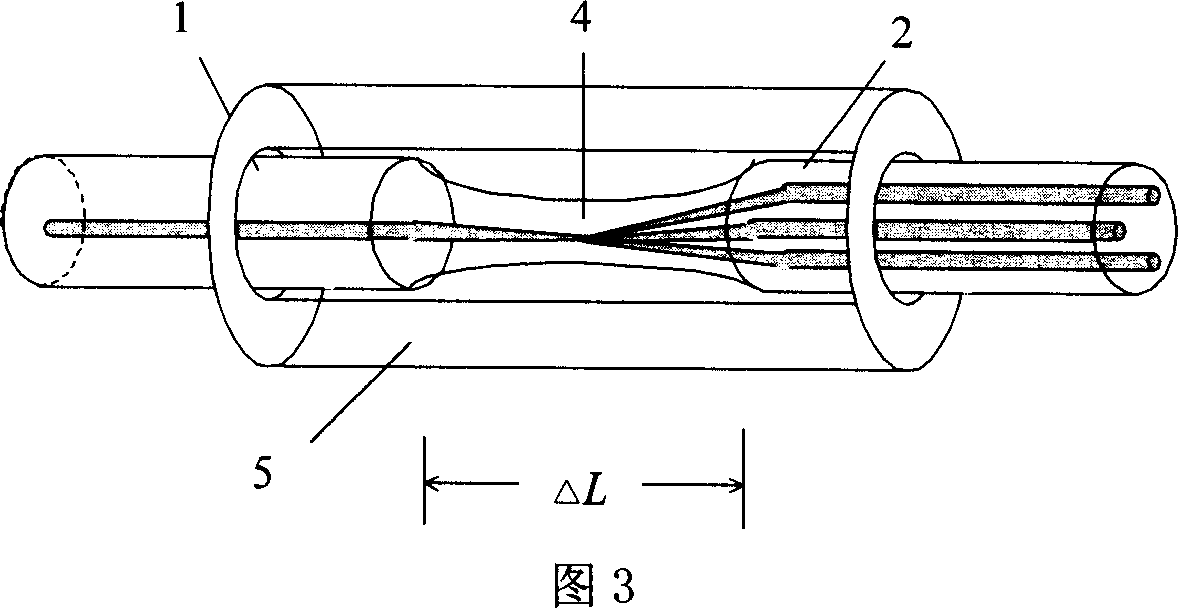

Single fiber and multi-core fiber coupler and fused biconic taper coupling method thereof

InactiveCN1967302ACoupling method improvementsEasy to manufactureCoupling light guidesCouplingOptical power

The invention discloses a single-core and multi-core fiber coupler and fiber access into rafah cone coupling method. It peels the ending coating layer of a single-core optical fibers and a multi-core fiber, direct financial with the fiber welding machine in stripping department, received and in the implementation of solder joint heating department fused biconical taper, monitoring optical power, when cone waist rafah small cone of light power distribution to the target, spectrophotometer stopping widening cone. The method is the technical characteristics of single-core fiber and multi-core fiber fusion welding, the solder joint implemented fused biconical taper, thus forming a cone of light energy distribution, optical power of distribution. The method can be single-core optical fiber distribution of power coupled multi-core optical fiber to each core, or multi-core fiber coupling of light waves to single-core fiber, to achieve optical spectrophotometer and cooperation functions.

Owner:HARBIN ENG UNIV

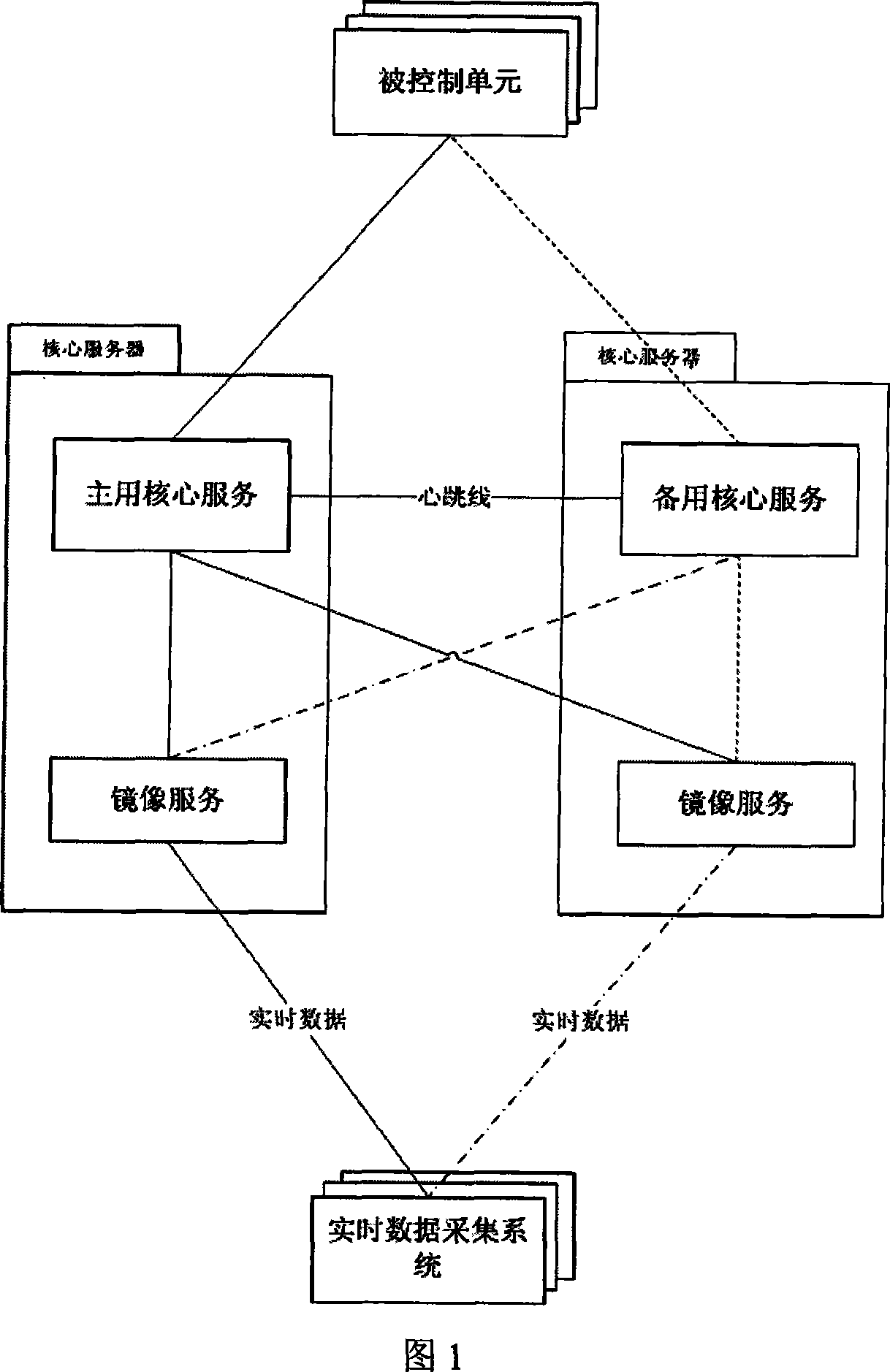

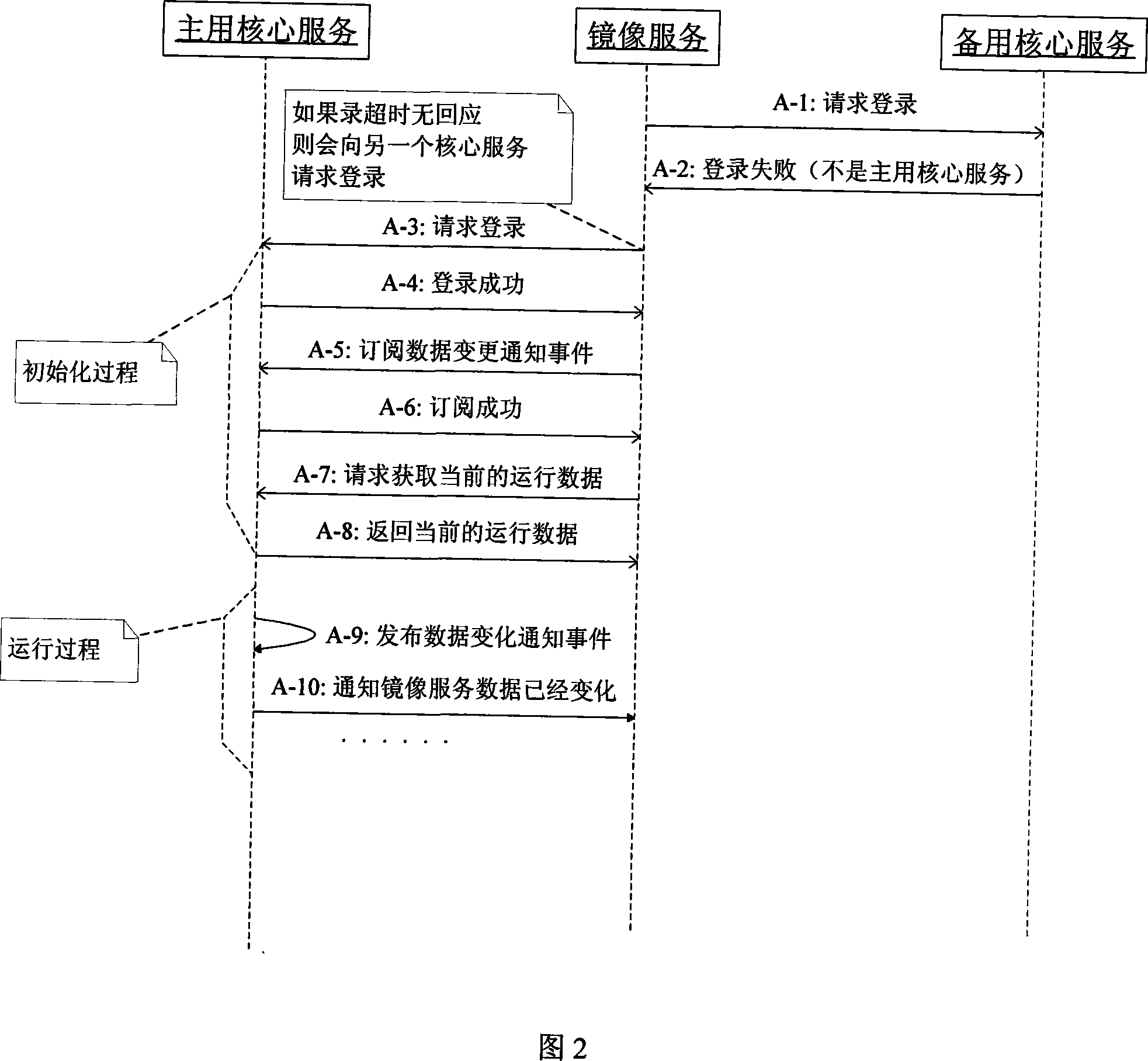

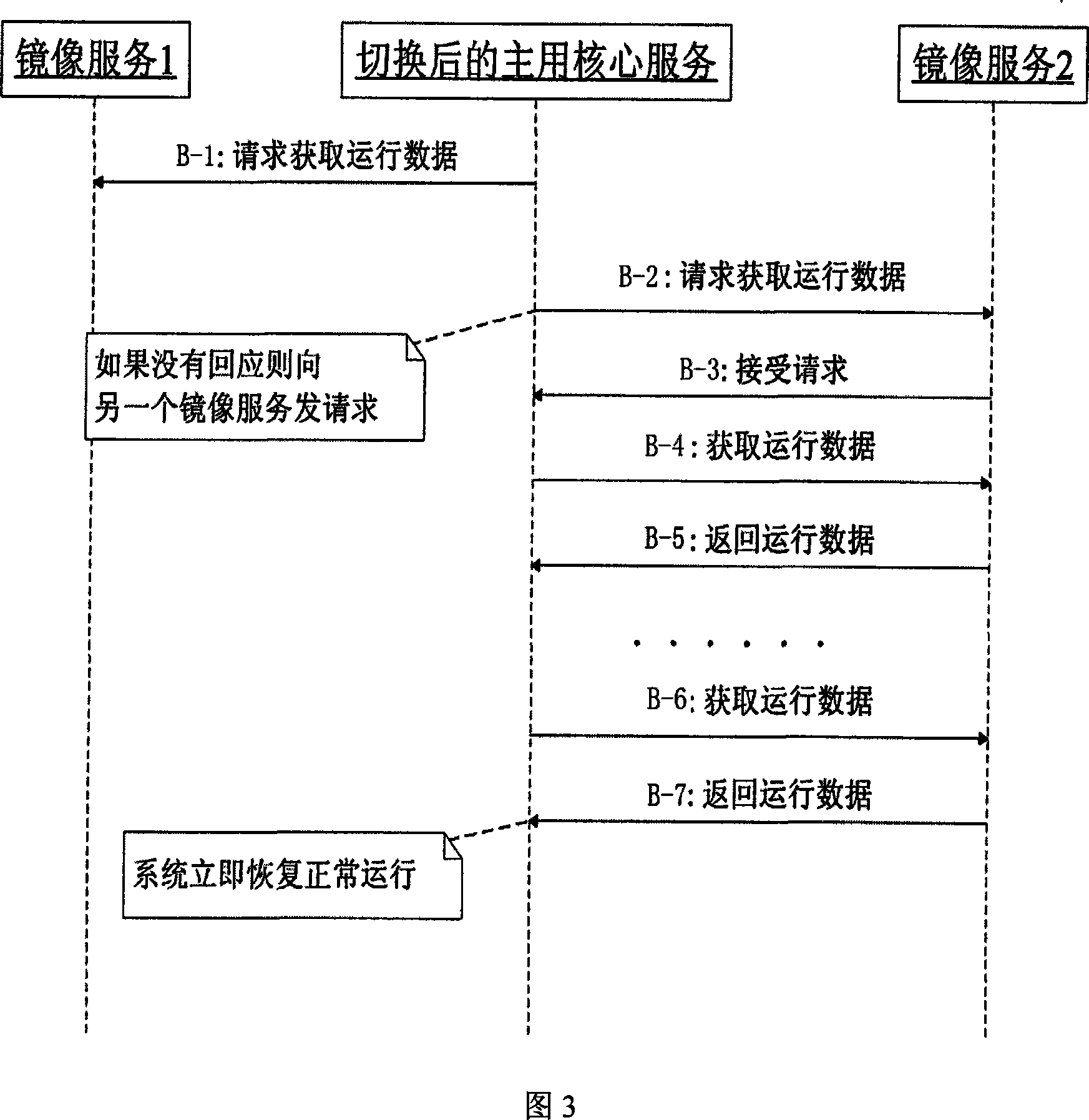

Image backup method for dual-core control of core controlled system

InactiveCN101043310AImprove reliabilityIncrease flexibilityError preventionData switching networksControl systemDual core

The invention relates to the communication technology field, especially relates to two-core control mirror backup method. The method adopts the mechanism of the mirror heat backup, the core service allocates two independent mirror services, and it stores the control data for the core service and provides the data analysis and data acquisition for the core service, and at the same time, it shares the data service of core service to reduce the work of core service. In the system without adopting two-core backup system, when the single core control sever happens fault and refresh resetting, it can obtain the running information from the mirror service to keep the system running cautiously. For the non-core control module, if it needs heating backup or sharing load, the main core service coordinate and control it. The invention adopts the mirror service to help the core service to finish the data backup and data analysis to improve the reliability and the flexibility of whole system.

Owner:BEIJING JIAXUN FEIHONG ELECTRIC CO LTD

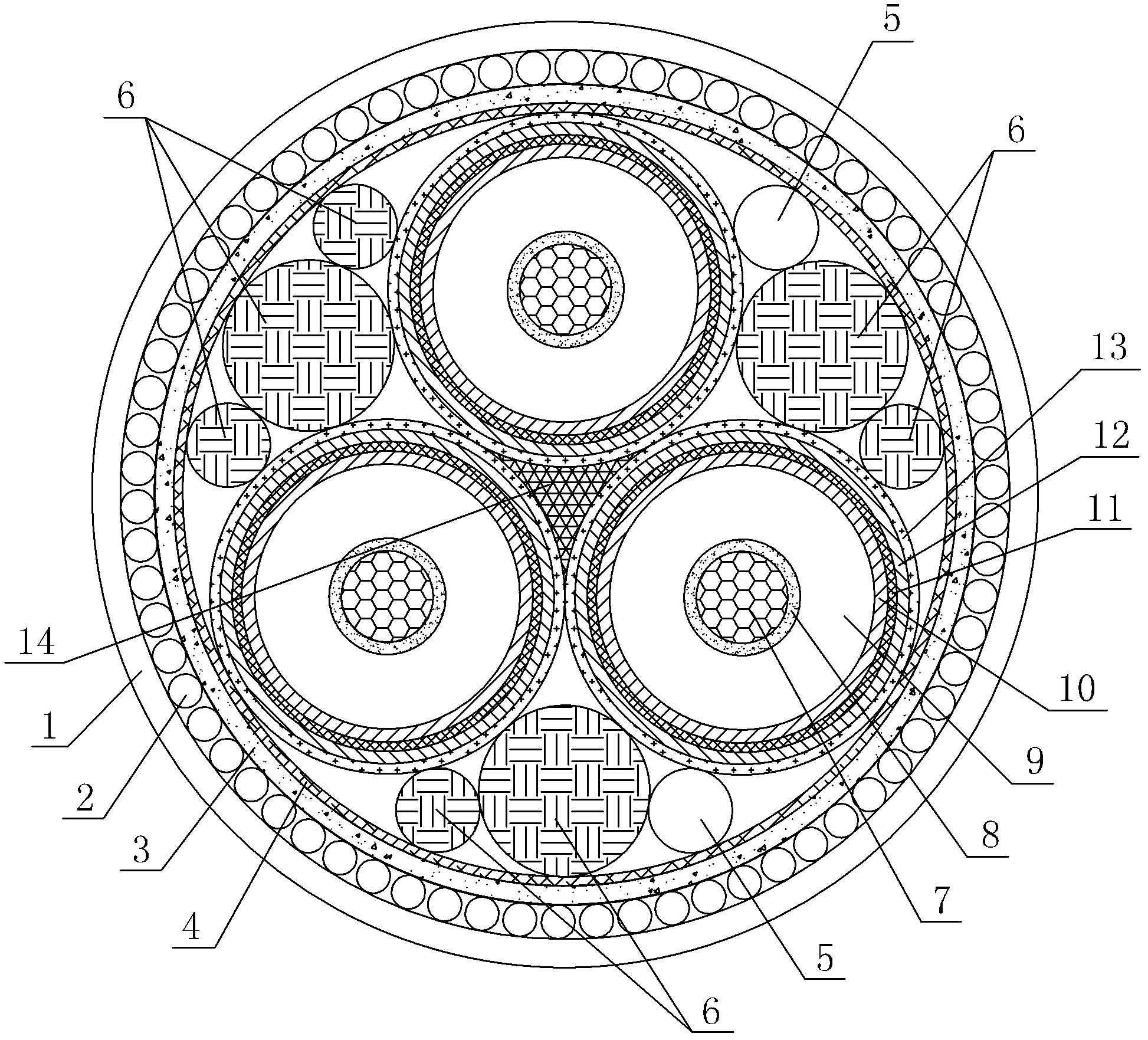

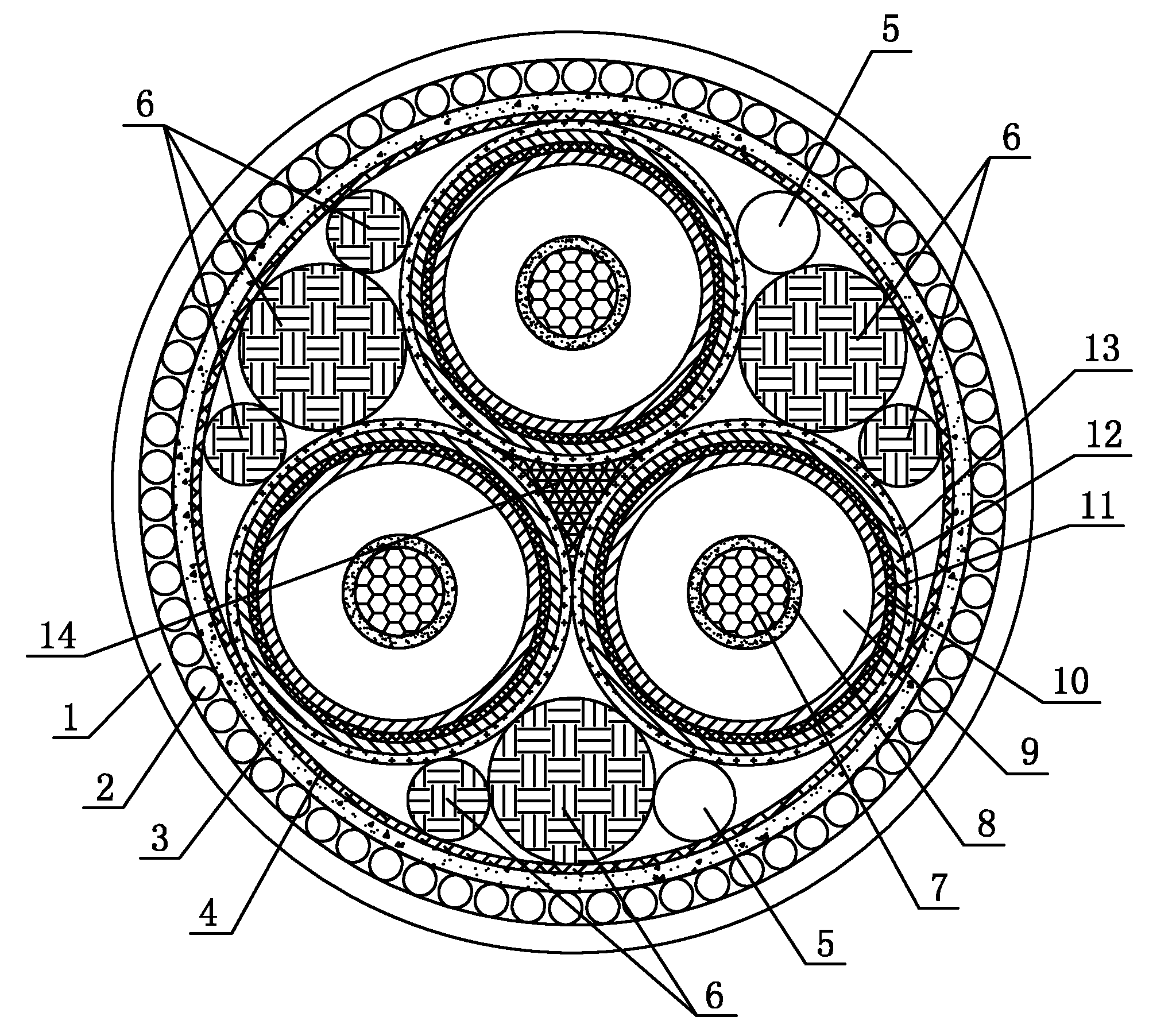

Rated voltage 220kv three-core photoelectric composite submarine cable

ActiveCN102290135ANo magnetic damageImprove effective utilizationPower cables with screens/conductive layersSubmarine cablesElectricityPhase balancing

The invention discloses a three-core photoelectric composite submarine cable with 220kV rated voltage. The cable is characterized by comprising an outer layer, an armor layer and a lining layer which are distributed from outside to inside in turn, wherein three electrical units in which every two units are externally tangential to each other are arranged in the lining layer; a plurality of filling units are filled in three gaps which are enclosed by the electrical units and the lining layer; the three electrical units and all the filling units are stranded into a submarine cable main core part; a gluing cloth tape is lapped outside the stranded submarine cable main core part; and at least one of all the filling units is an optical unit, and the rest filling units are filling ropes. The invention has the advantages that: the three-core photoelectric composite submarine cable with the 220kV rated voltage has a balanced phase during use, does not have requirements on armoring materials, can prevent the magnetic loss of the armor layer and improves the effective utilization rate of power; and the occupied sea area is greatly reduced compared with that of a single-core submarine cable with the same specification.

Owner:宁波东方电缆股份有限公司

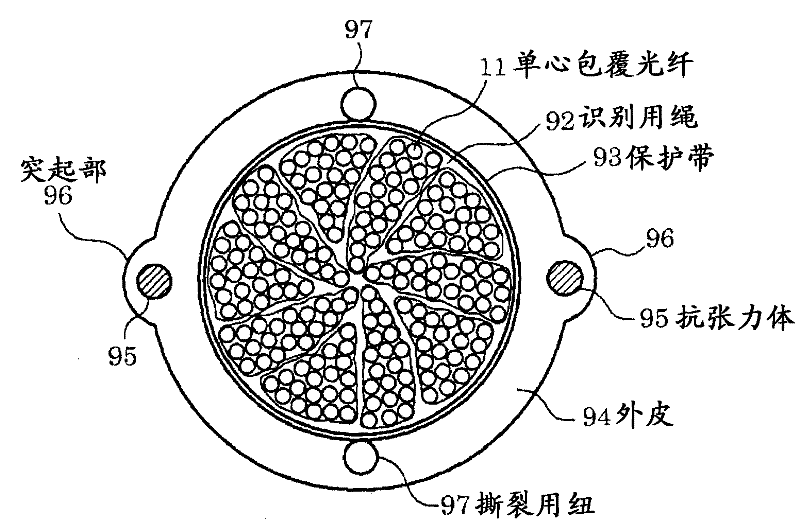

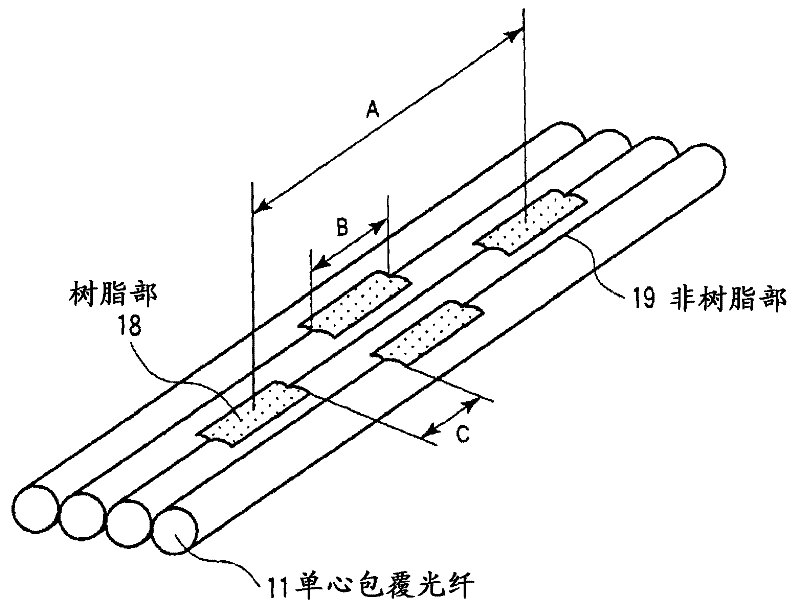

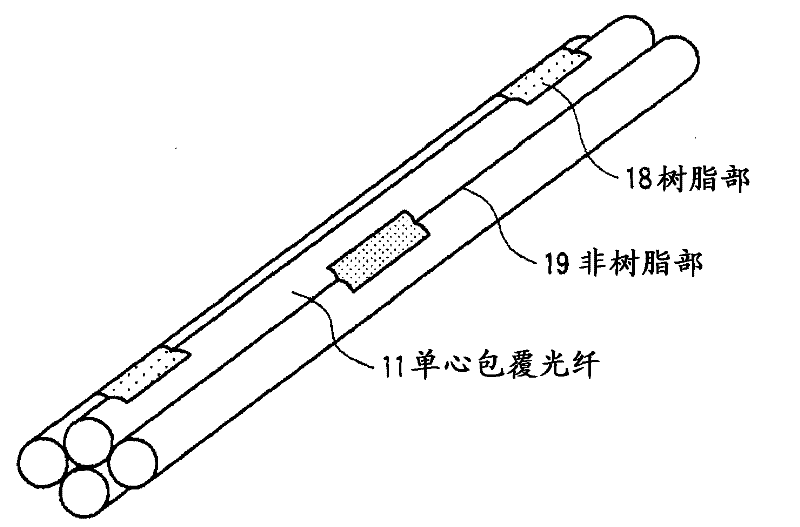

Optical fiber cable and optical fiber tape

ActiveCN102057309ARecognizableExcellent extractabilityFibre mechanical structuresEngineeringBend radius

Provided is a single-core coated optical fiber (11) having such a curve loss characteristic that an optical loss increase at a bending radius 13 mm is 0.2 dB / 10 turn or below. An optical fiber tape conductor includes two-dimensionally arranged resin portions (18) for bonding each two adjacent single-core coated optical fibers (11). The resin portions (18) are arranged apart from one another in the longitudinal direction of the optical fiber tape conductor. An optical fiber cable includes a cable core unit for containing a plurality of sets of the single-core coated optical fibers (11) constituting the optical fiber tape conductor which are twisted together.

Owner:NIPPON TELEGRAPH & TELEPHONE CORP

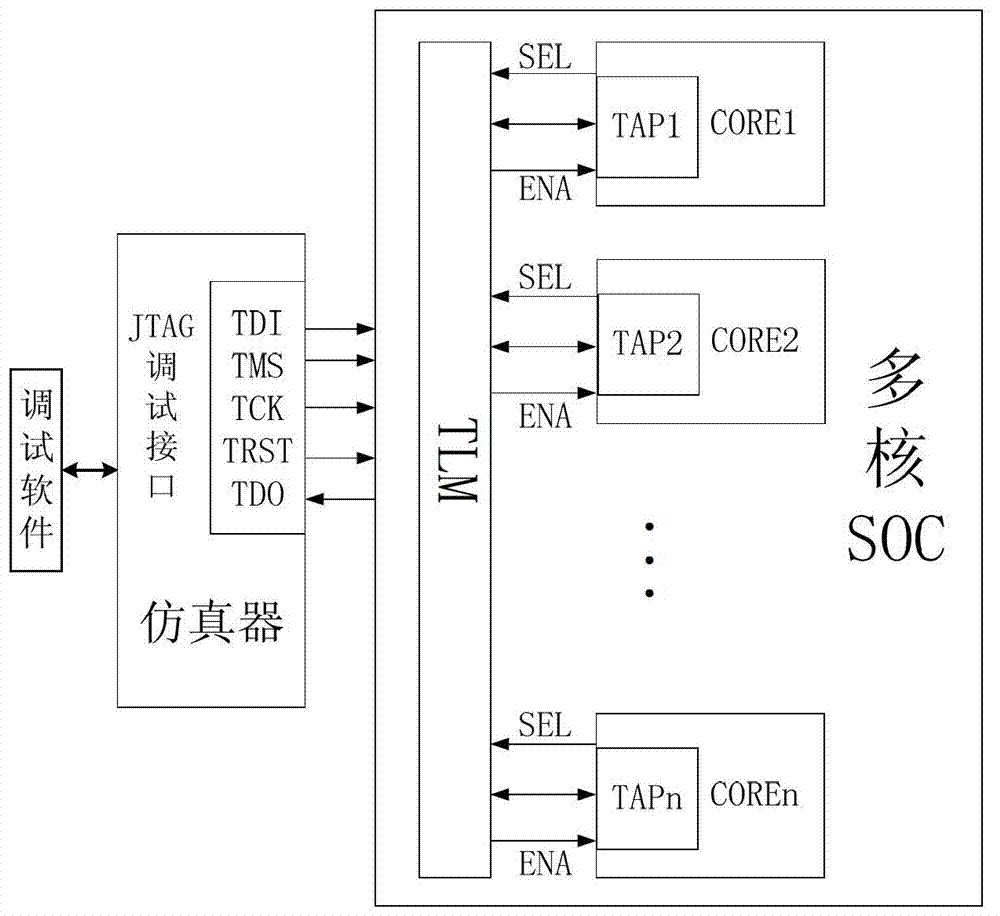

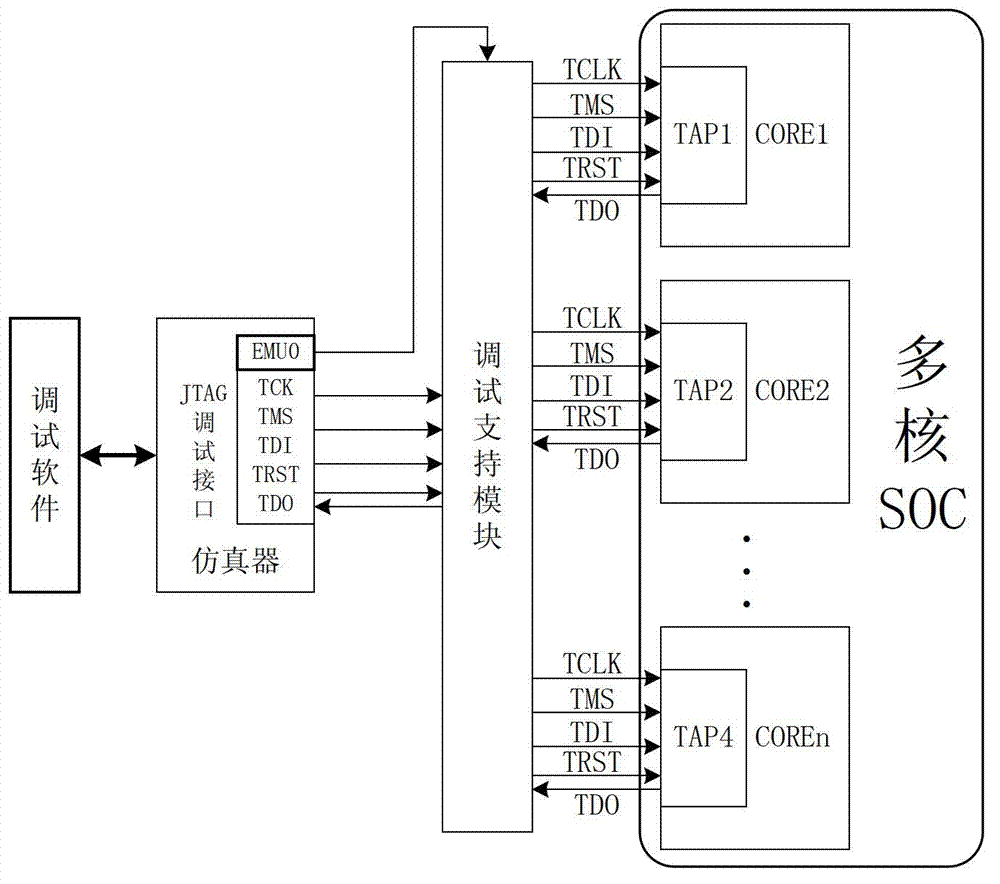

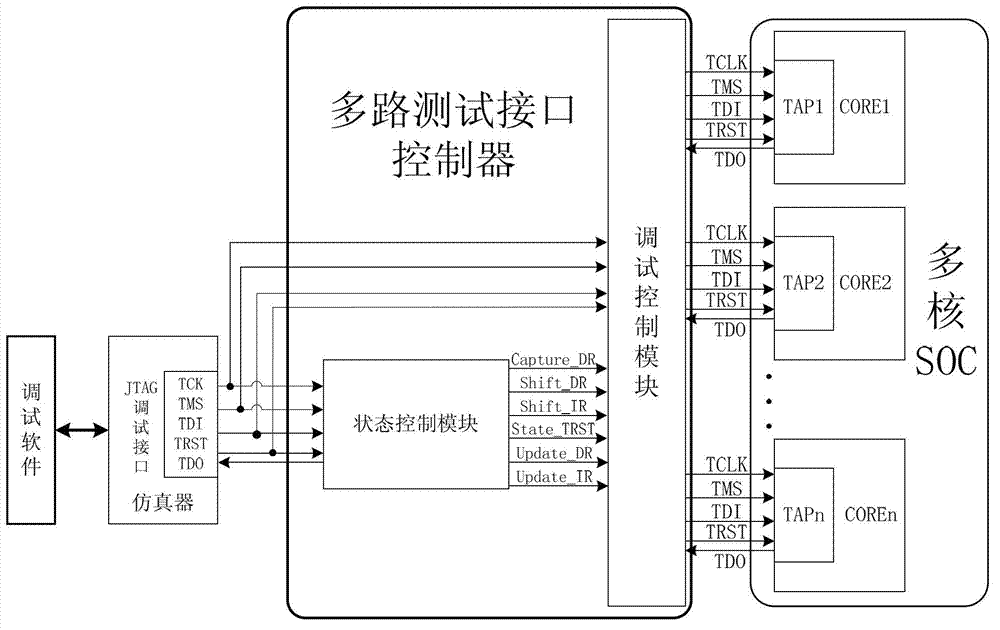

JTAG (joint test action group) debug method of multi-core processor

The invention provides a JTAG (joint test action group) debug method of a multi-core processor. A multichannel test interface controller is connected between a standard test access port controller and a simulator JTAG debug interface of every processor core. The debug method comprises the following steps that: firstly, a system is electrified, and the functional state machine of the multichannel test access port controller enters the state of test logic reset; secondly, a debug command is sent, and specific TCK (testing clock), TDI (testing data input) and TMS (testing method select) signals are output through the simulator JTAG debug interface, so that state control modules enter states in sequence; thirdly, selective signals are sent, and a control register is configured; fourthly, after one-clock cycle of delay, the information in the control register is loaded to a state register; and fifthly, after finishing the selection of the processor cores, the debug command is sent, and the debug procedure of a single-core processor is carried out. The invention effectively completes the selection and the control of every processor core and the storage and the feedback of debug information, so that the reliability is promoted.

Owner:C SKY MICROSYST CO LTD

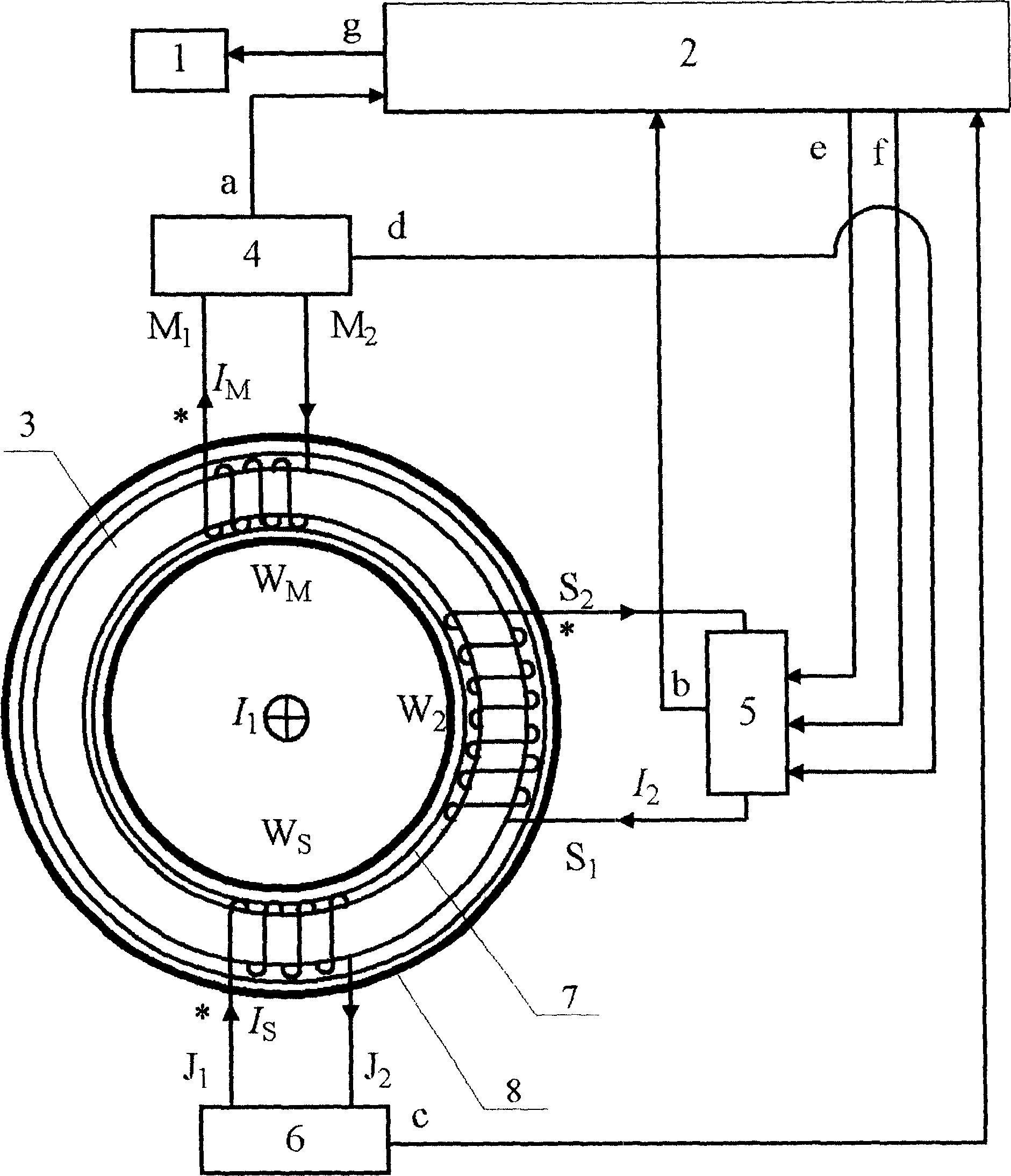

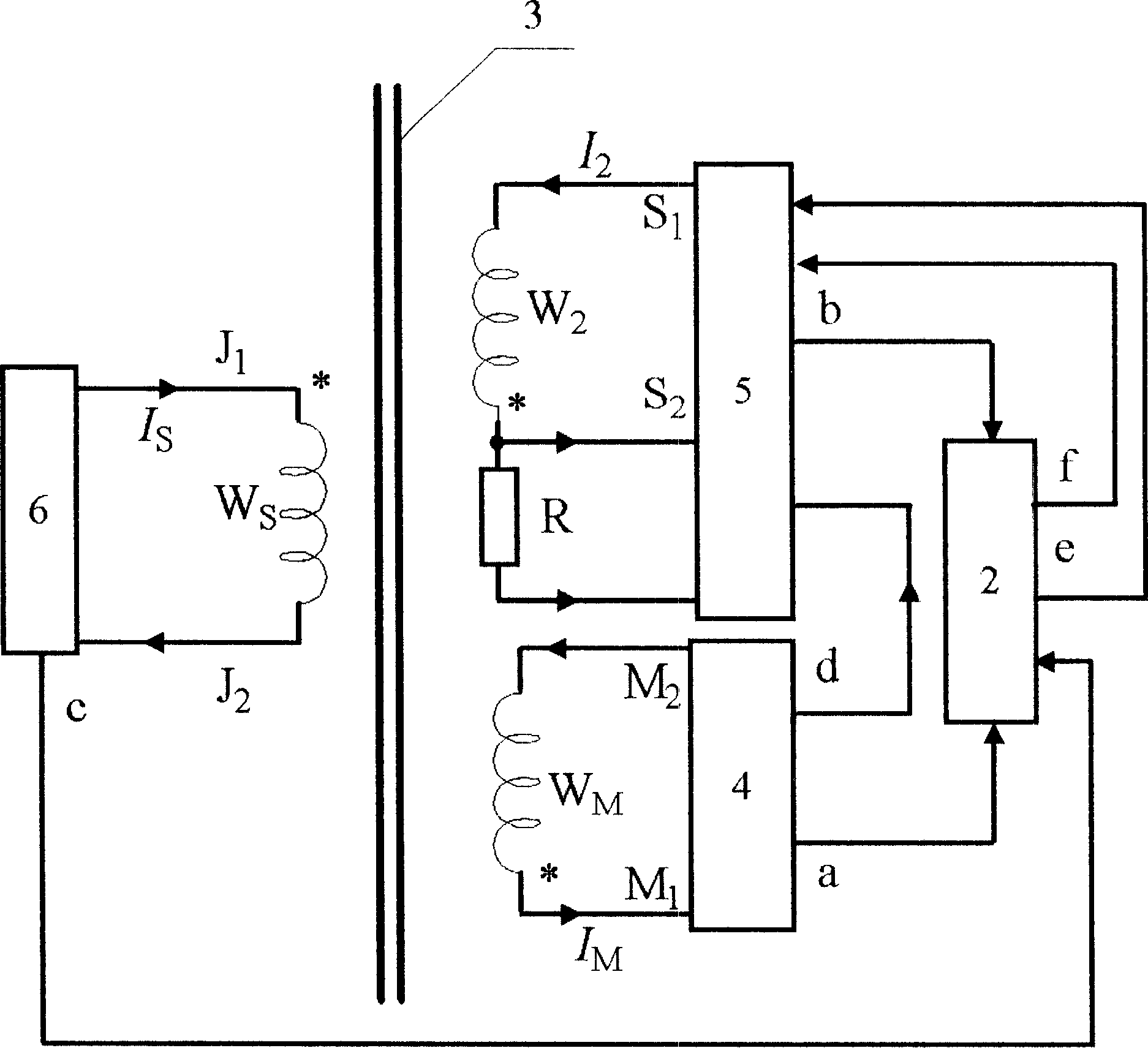

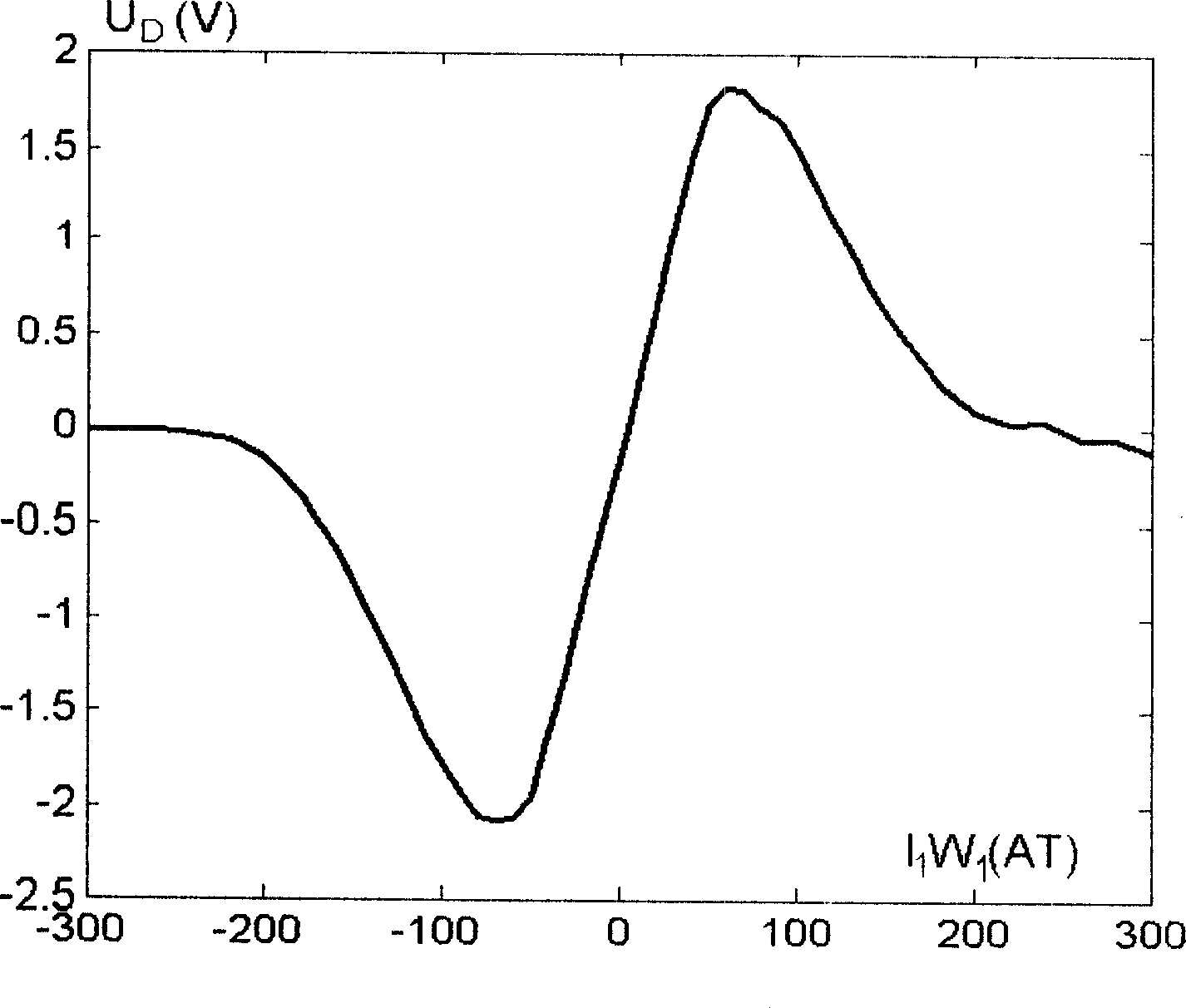

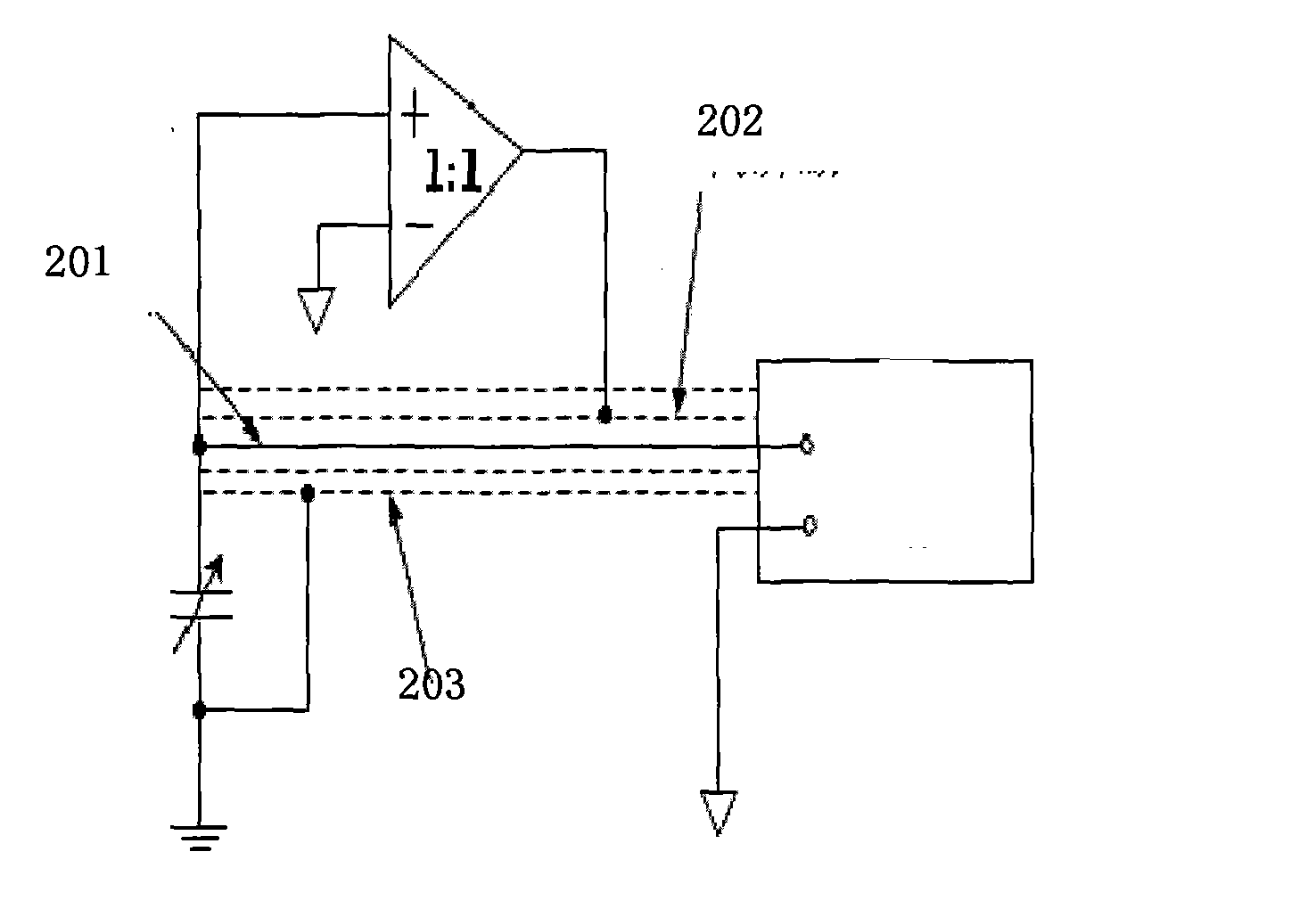

Direct current sensor

The present invention discloses a DC curren sensor. In said sensor a detection coil is added, said sensor adopts single-core three-winding structure, when a DC bias magnet is existed in the magnetic core, the induced potential obtained by detection coil can produce positive-negative half-wave unsmmetrical waveforms, said waveforms can be converted into the voltage signal of difference of positive-negative half-wave effective values, after voltage / current conversio, said signal can be fed into feedback winding, said feedback winding cap produce the DC magnetic potential whose direction is opposite to that of magnetic patential produced by detected direct current to balance the bias magnetic potential produced by detected direct current to form 'null-flux' state, so that it can obtain the detected direct current intensity so as to implement the detection of direct current.

Owner:HUAZHONG UNIV OF SCI & TECH

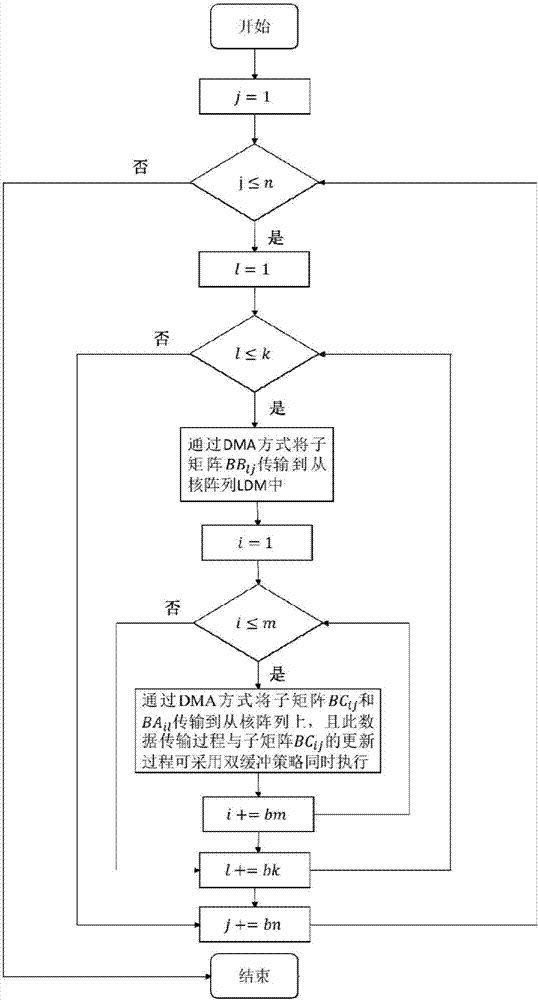

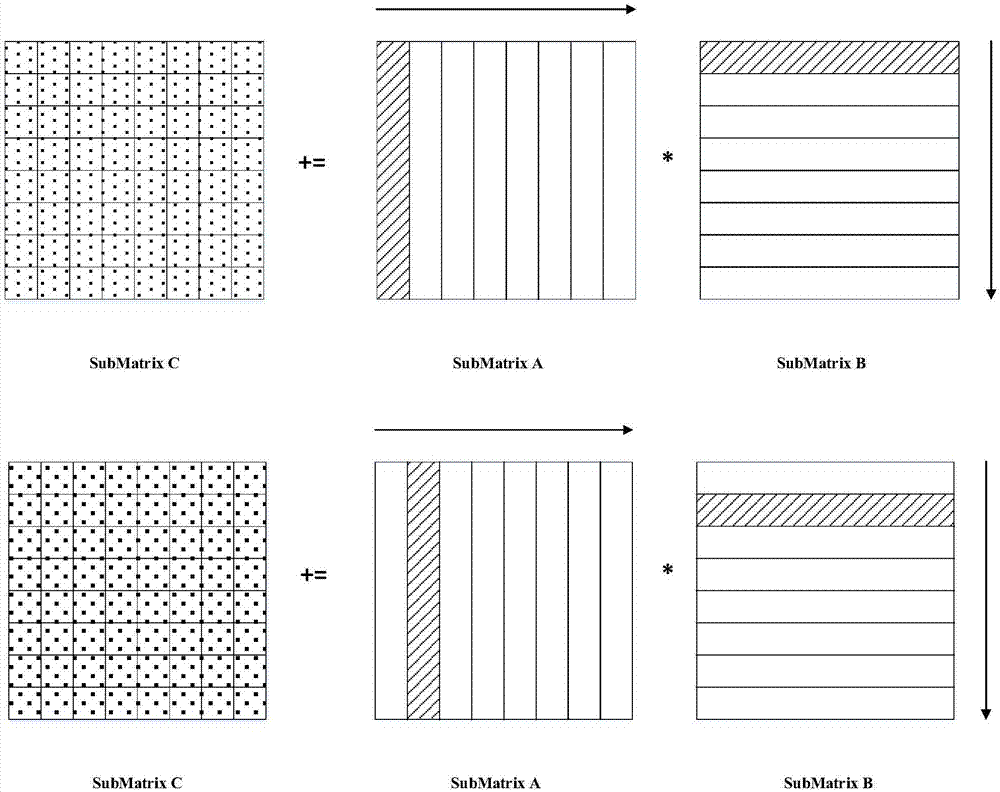

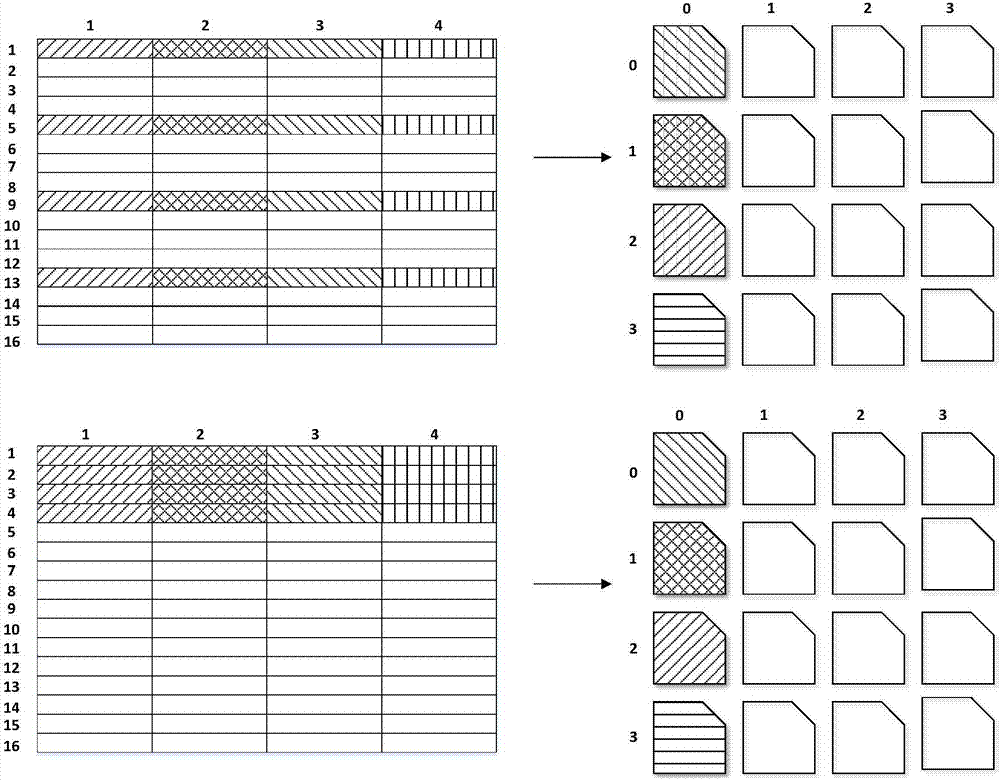

A GEMM (general matrix-matrix multiplication) high-performance realization method based on a domestic SW 26010 many-core CPU

ActiveCN107168683ASolve the problem that the computing power of slave cores cannot be fully utilizedImprove performanceRegister arrangementsConcurrent instruction executionFunction optimizationAssembly line

The invention provides a GEMM (general matrix-matrix multiplication) high-performance realization method based on a domestic SW 26010 many-core CPU. For a domestic SW many-core processor 26010, based on the platform characteristics of storage structures, memory access, hardware assembly lines and register level communication mechanisms, a matrix partitioning and inter-core data mapping method is optimized and a top-down there-level partitioning parallel block matrix multiplication algorithm is designed; a slave core computing resource data sharing method is designed based on the register level communication mechanisms, and a computing and memory access overlap double buffering strategy is designed by using a master-slave core asynchronous DMA data transmission mechanism; for a single slave core, a loop unrolling strategy and a software assembly line arrangement method are designed; function optimization is achieved by using a highly-efficient register partitioning mode and an SIMD vectoring and multiplication and addition instruction. Compared with a single-core open-source BLAS math library GotoBLAS, the function performance of the high-performance GEMM has an average speed-up ratio of 227. 94 and a highest speed-up ratio of 296.93.

Owner:INST OF SOFTWARE - CHINESE ACAD OF SCI +1

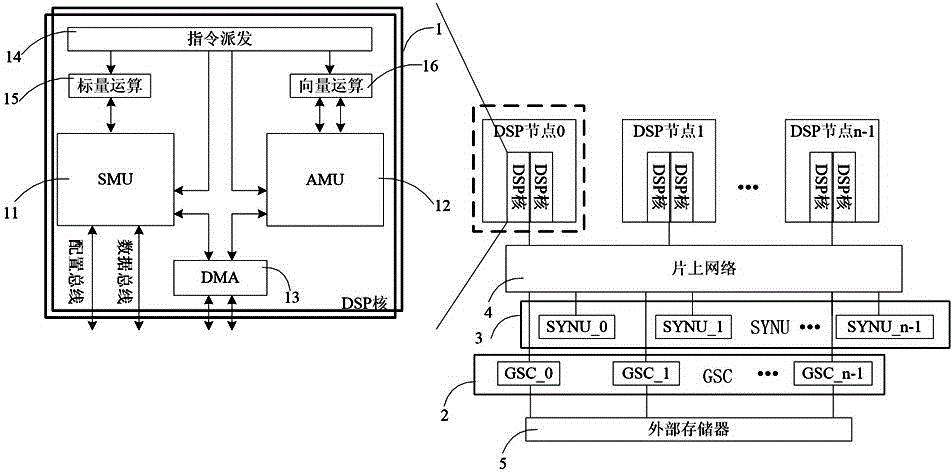

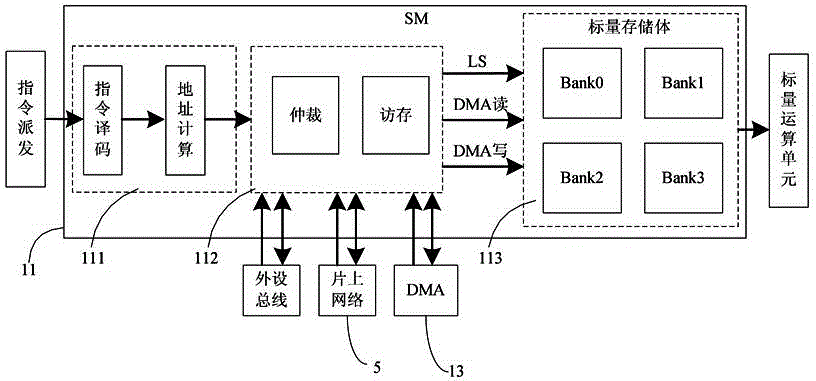

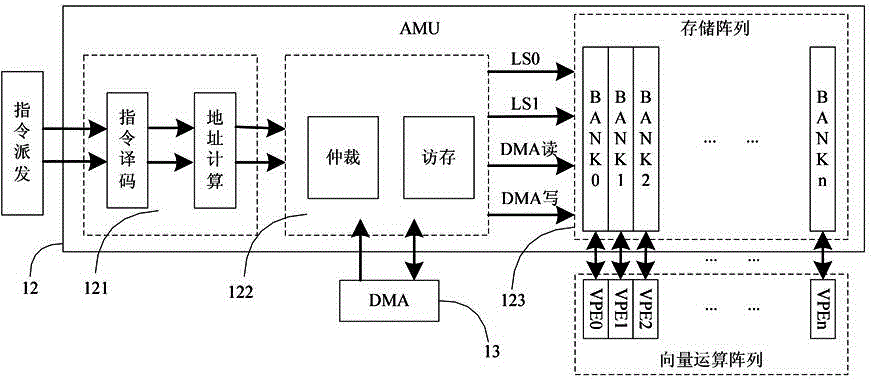

Storage device and fetching method for multilayered cooperation and sharing in GPDSP (General-Purpose Digital Signal Processor)

ActiveCN104699631AAchieving Data Transfer LatencyAvoid Computational Performance ImpactsMemory adressing/allocation/relocationGeneral purposeNetworks on chip

The invention discloses a storage device and a fetching method for multilayered cooperation and sharing in a GPDSP (General-Purpose Digital Signal Processor). The device comprises a plurality of DSP (Digital Signal Processor) cores and an overall sharing caching unit for caching off-chip storage data, wherein each DSP core is connected with the overall sharing caching unit by an on-chip network; each DSP core comprises a scalar storage unit and a vector array storage unit which are parallel to each other; each DSP core is used for carrying out in-core data fetching through the respective scalar storage unit and vector array storage unit, and sharing data through the overall sharing caching unit. The method can be used for uniformly addressing through the scalar storage units and the vector array storage units, and fetching the scalar storage units according to data type configurations. By the aid of the device and the method, the efficient fetching of the data in the single core and the efficient sharing of the inter-core data in the GPDSP can be realized; the device and the method have the advantages of high accessing efficiency, small hardware cost and flexible configuration.

Owner:NAT UNIV OF DEFENSE TECH

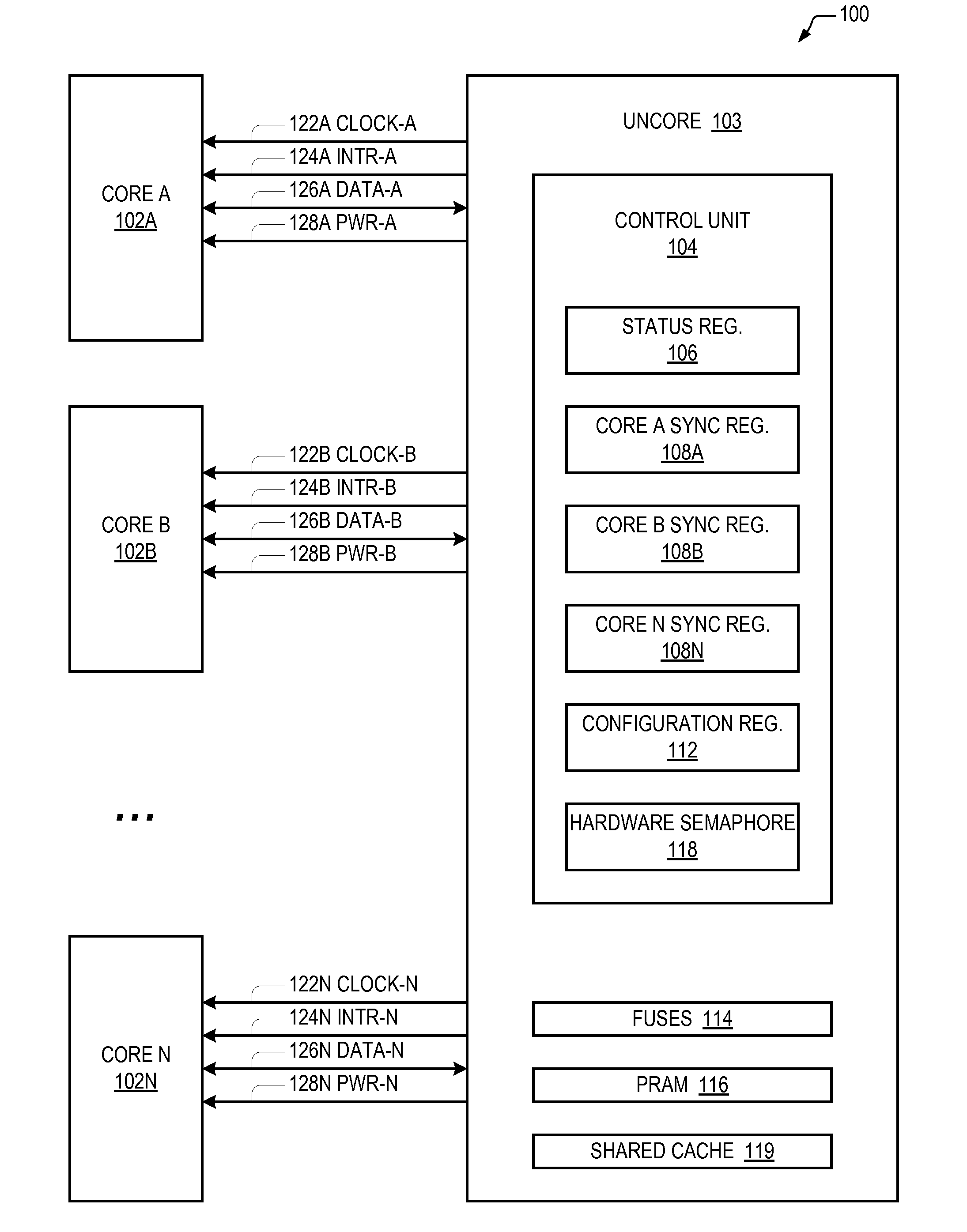

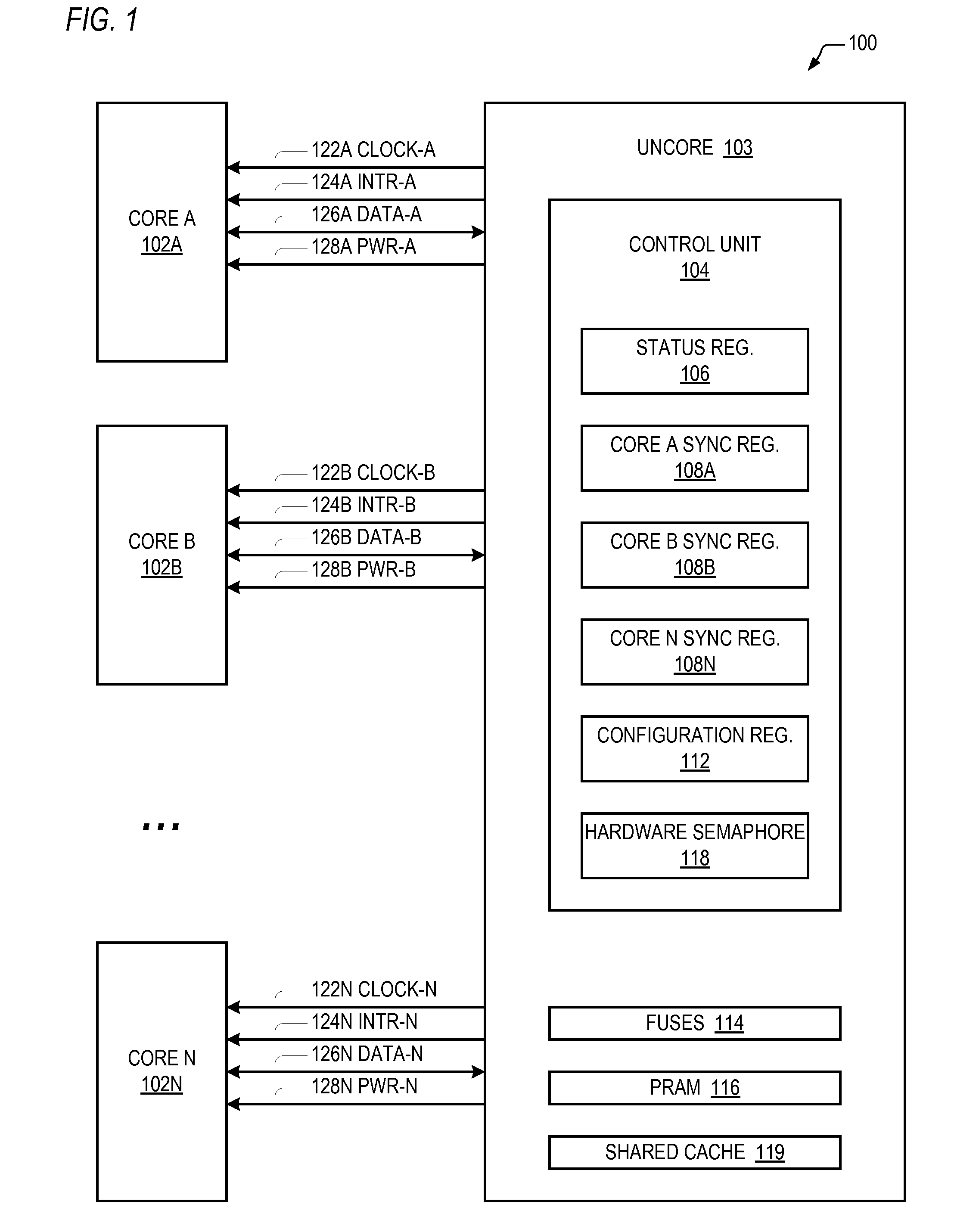

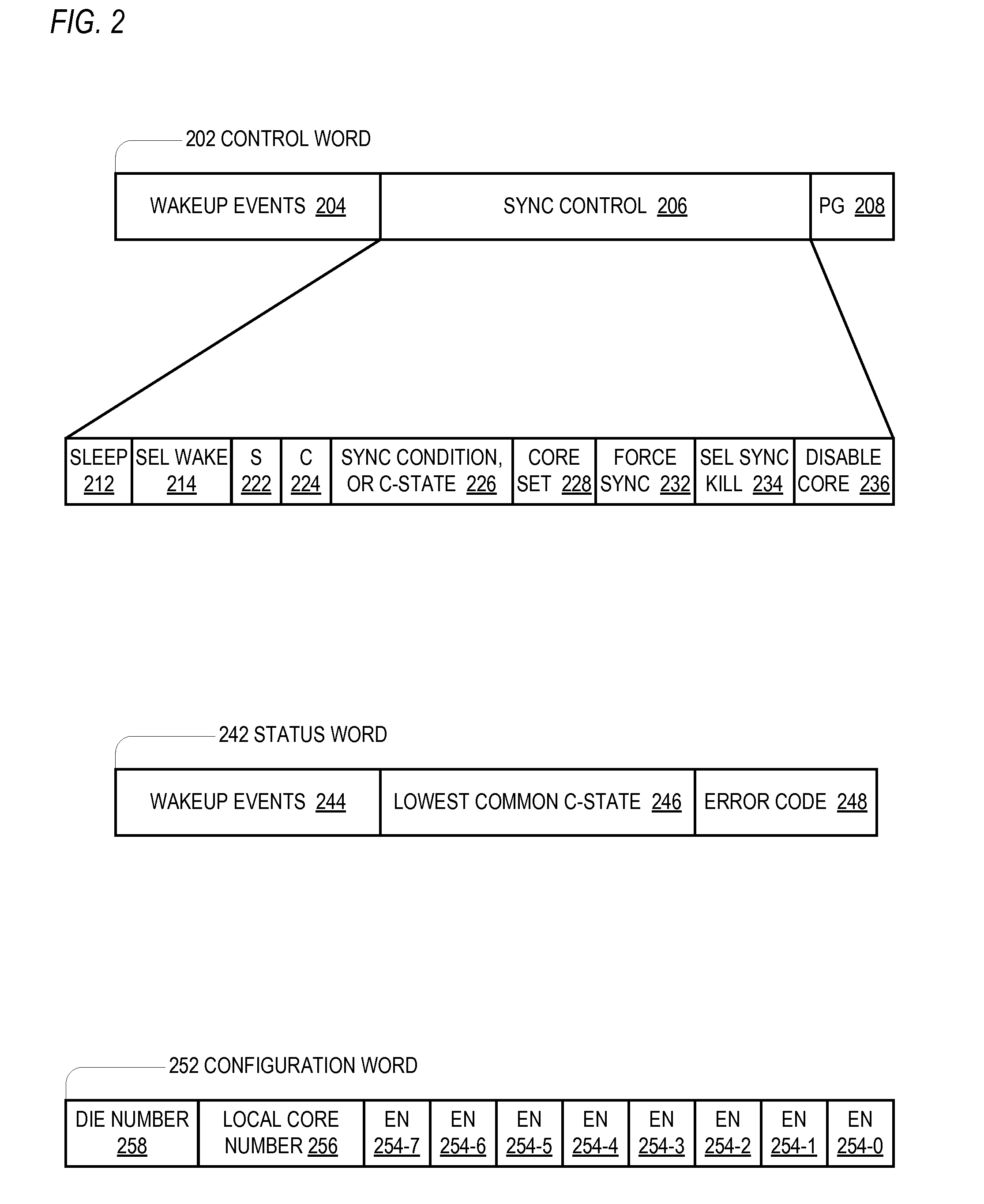

Single-core wakeup multi-core synchronization mechanism

ActiveUS20150067214A1Memory architecture accessing/allocationMemory adressing/allocation/relocationSingle-coreControl unit

A microprocessor includes a plurality of cores, a shared cache memory, and a control unit that individually puts each core to sleep by stopping its clock signal. Each core executes a sleep instruction and responsively makes a respective request of the control unit to put the core to sleep, which the control unit responsively does, and detects when all the cores have made the respective request and responsively wakes up only the last requesting cores. The last core writes back and invalidates the shared cache memory and indicates it has been invalidated and makes a request to the control unit to put the last core back to sleep. The control unit puts the last core back to sleep and continuously keeps the other cores asleep while the last core writes back and invalidates the shared cache memory, indicates the shared cache memory was invalidated, and is put back to sleep.

Owner:VIA TECH INC

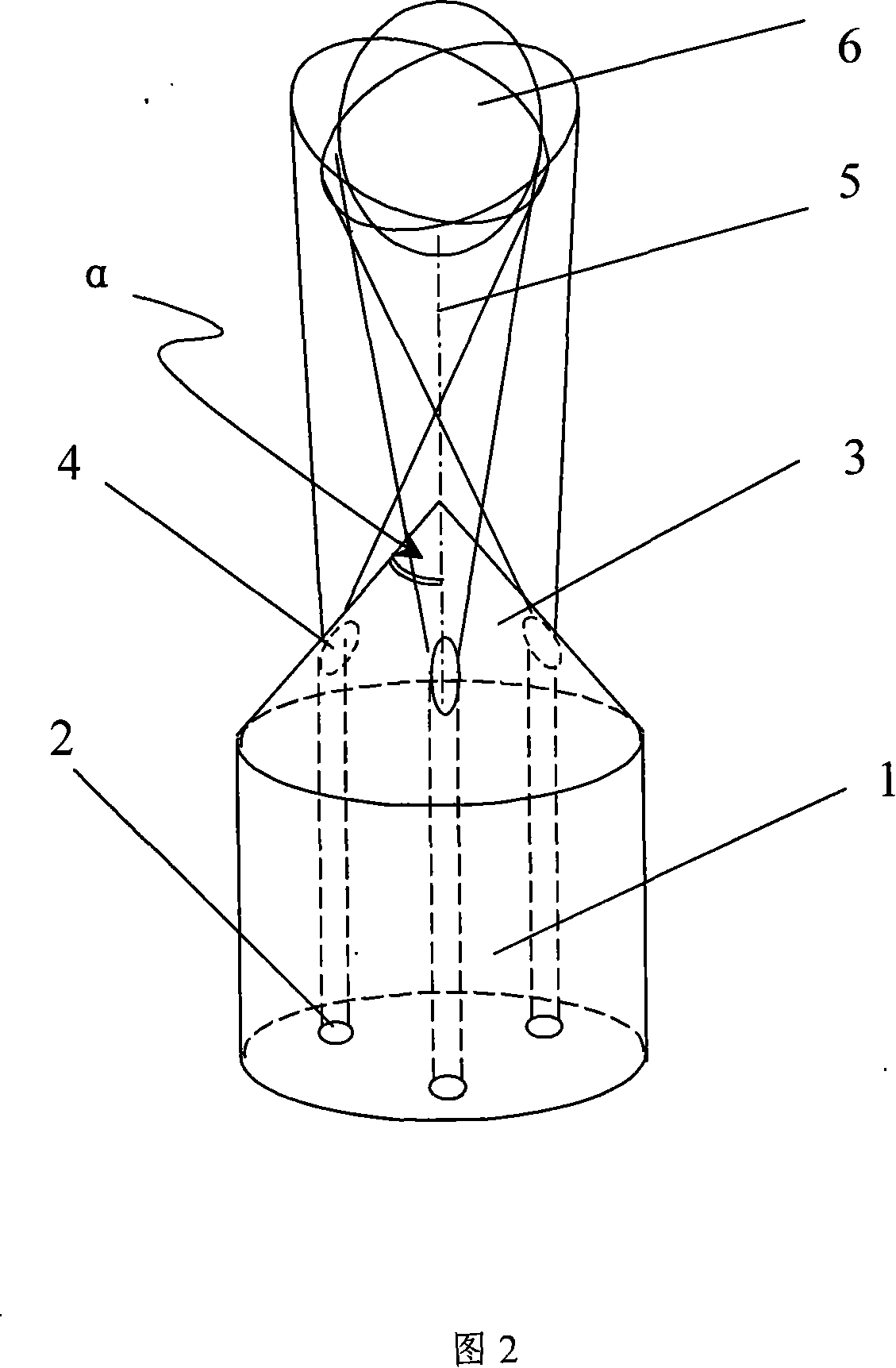

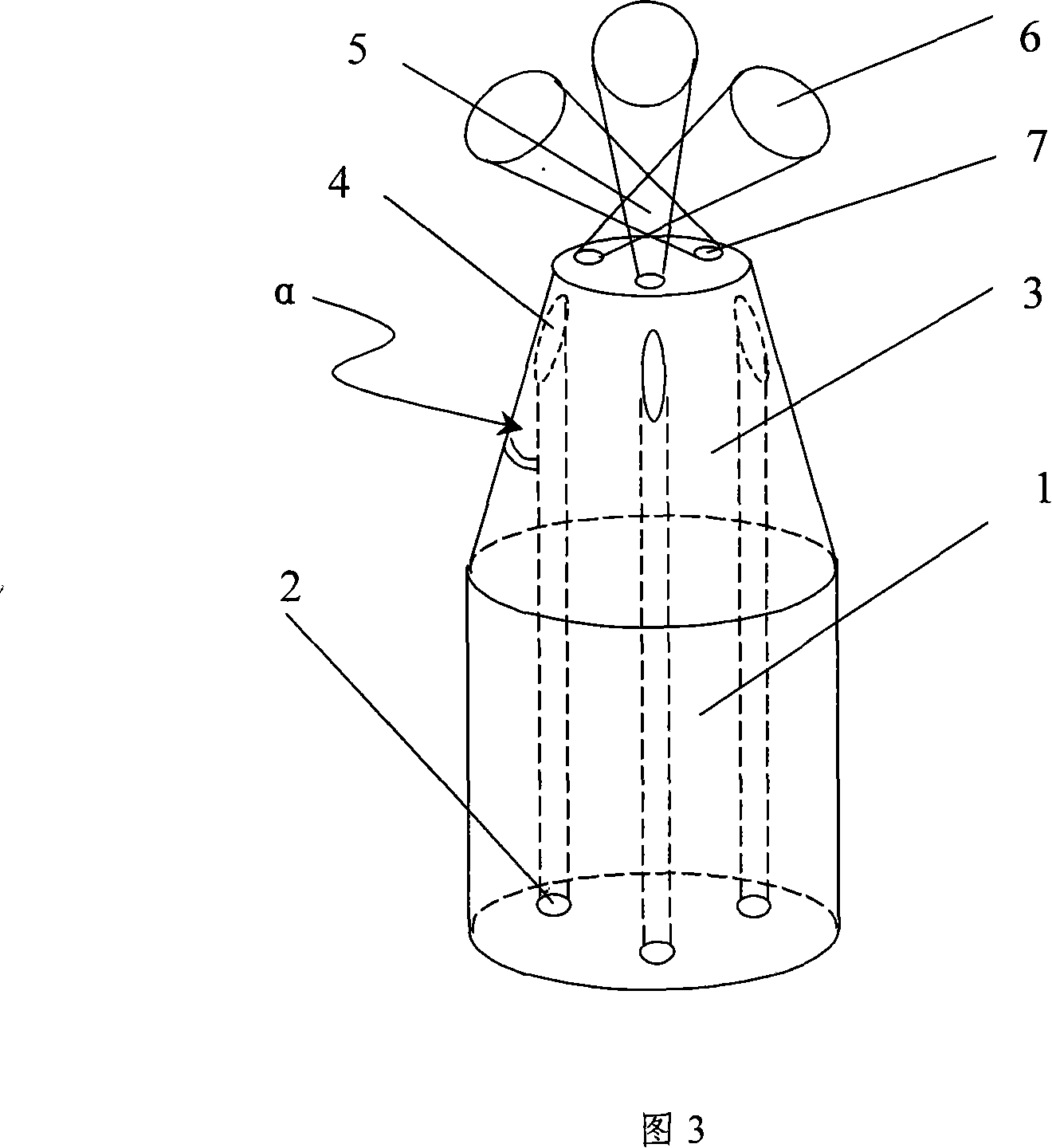

Optical microhand based on three-core optical fibre

InactiveCN101236274AAchieve captureEasy to moveRadiation/particle handlingOptical fibre with multilayer core/claddingFiberTrapping

The invention provides an optical micro-hand based on a three-core fiber and a method for preparing the same. The fiber comprises a three-core fiber and a single-core fiber which is in coupled connection with the rear of the three-core fiber and the connection between the three-core fiber and the single-core fiber is realized by applying heating, fusing and tapering the welding point after welding. The other end of the three-core fiber is made into a cone by sintering at the sharp end after grinding or heating the ends of the fiber and applying fusing and tapering. Aiming at the defect and deficiency in the prior art, the optical micro-hand discloses an optical micro-hand based on a three-core fiber which can form a cross combination light field by grinding or tapering the ends of the fiber based on the three-core fiber by making use of the joint action among external refraction, internal reflection and external refraction as well as a cone gradual wave guide and further form a three dimensional gradient force potential trough at the convergence point of combination light fields so as to realize three dimensional trapping of tiny particles.

Owner:HARBIN ENG UNIV

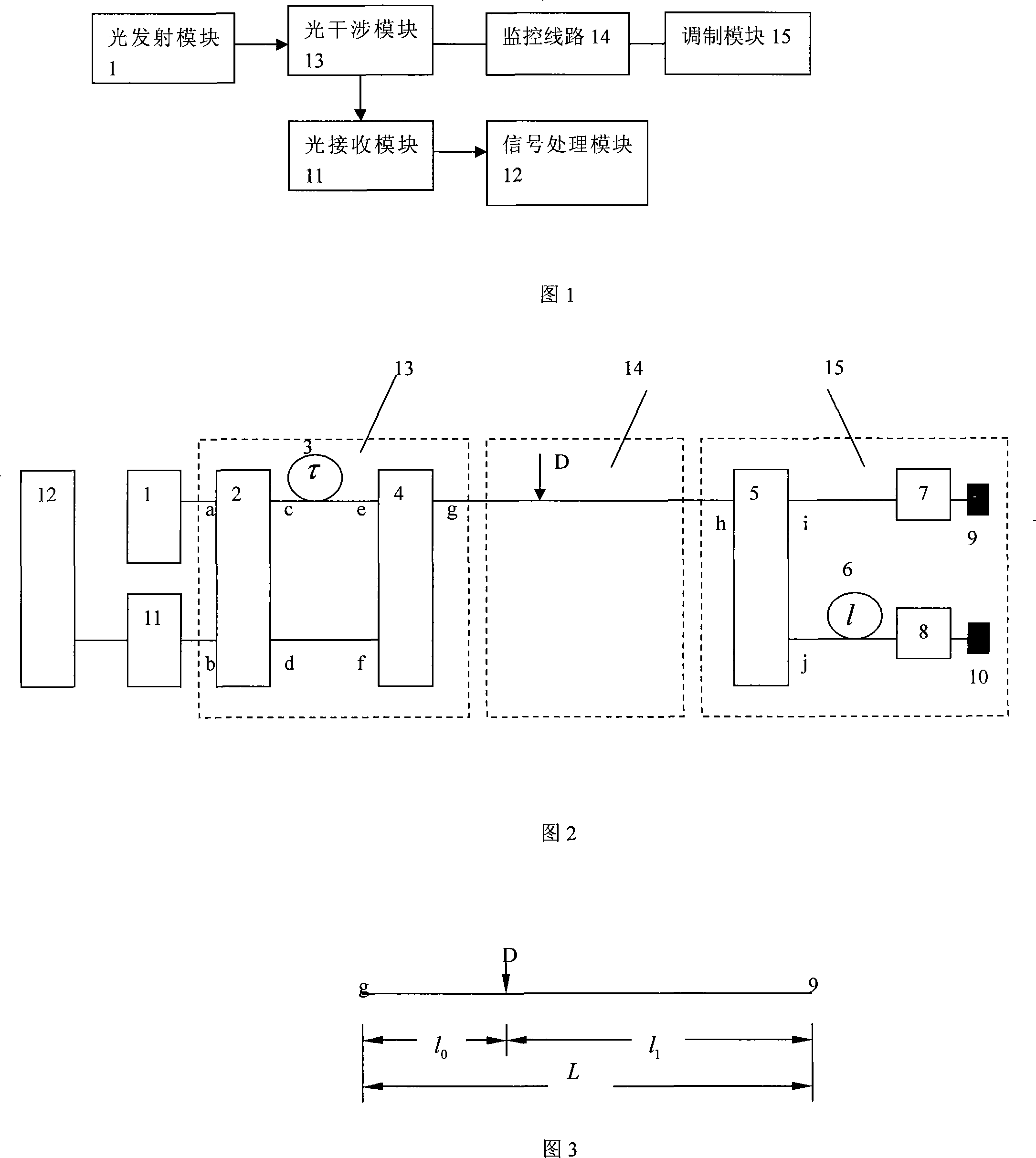

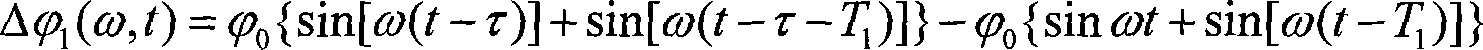

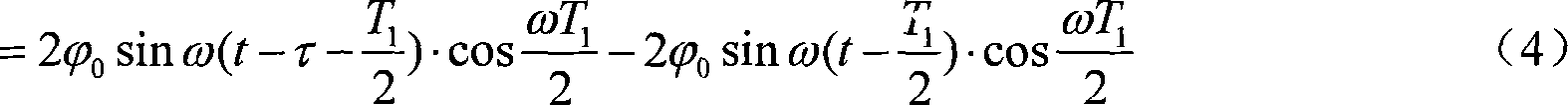

An optical fiber pipe monitoring system

ActiveCN101242224AEliminate differencesSimple structureElectromagnetic transmissionFiberFrequency spectrum

The invention pertains to the pipeline monitoring technology, particularly a fiber pipeline monitoring system. The system is composed of an optical transmitter module, an optical interferometer module, a monitoring line, a modulator module, an optical receiver module and a signal processing module. The system can get two signals corresponding to different optical path positions of the same vibration though multiplexing a fiber interference system, compare the spectrum characteristics of the two signals, and eliminate the interference of the position information caused by the vibration information so as to obtain the accurate vibration position information under the condition that the system adds no photoelectric detector. The position information is obtained through the medium value of the spectrum amplitude ratio of the two signals, and the difference caused by the instability of the detection signal is eliminated, thus the accuracy of the location is greatly improved. The location function is realized with single-core fiber under the condition of not constituting a loop, thus the location monitoring can be realized by paving equal-distance main line along the petroleum pipe line, which has strong environmental applicability.

Owner:东莞先进光纤应用技术研究院有限公司

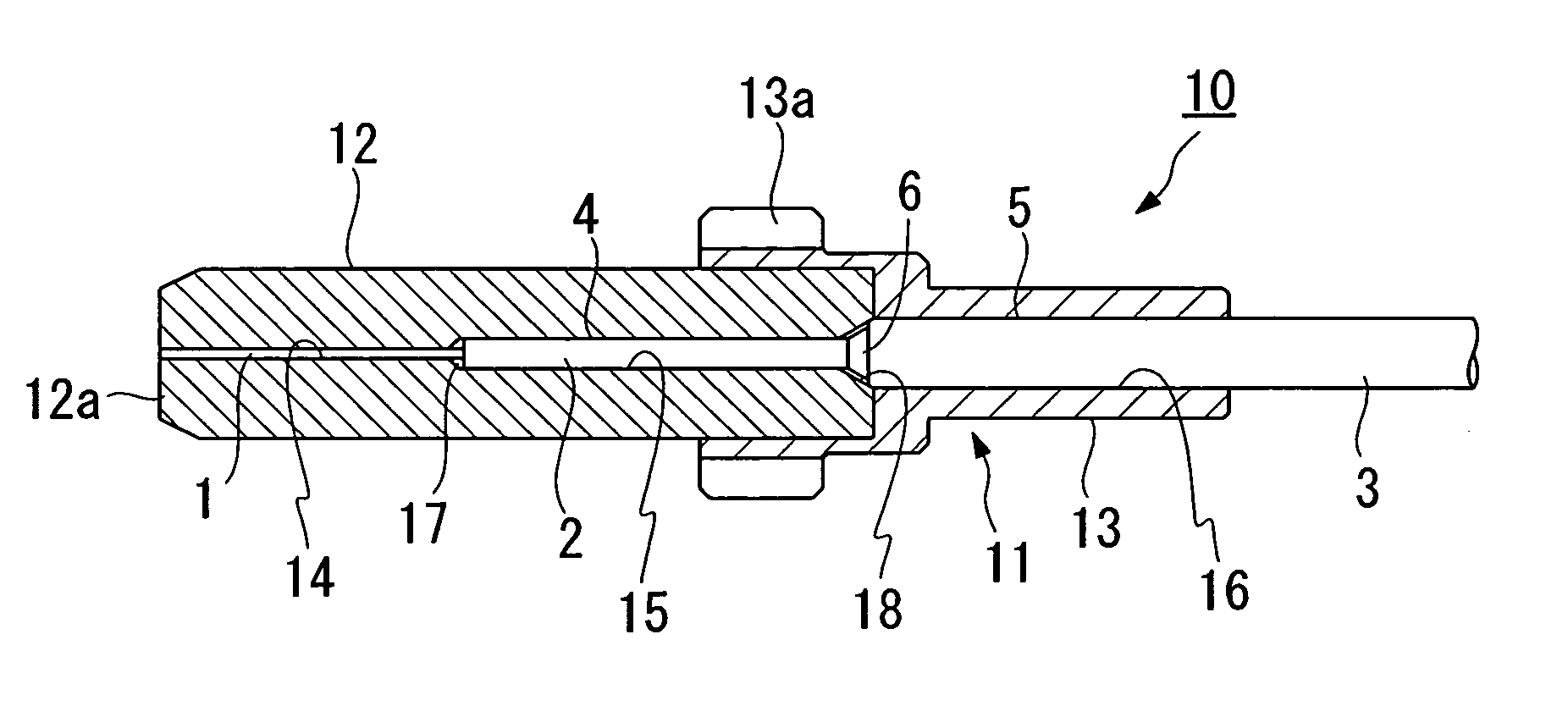

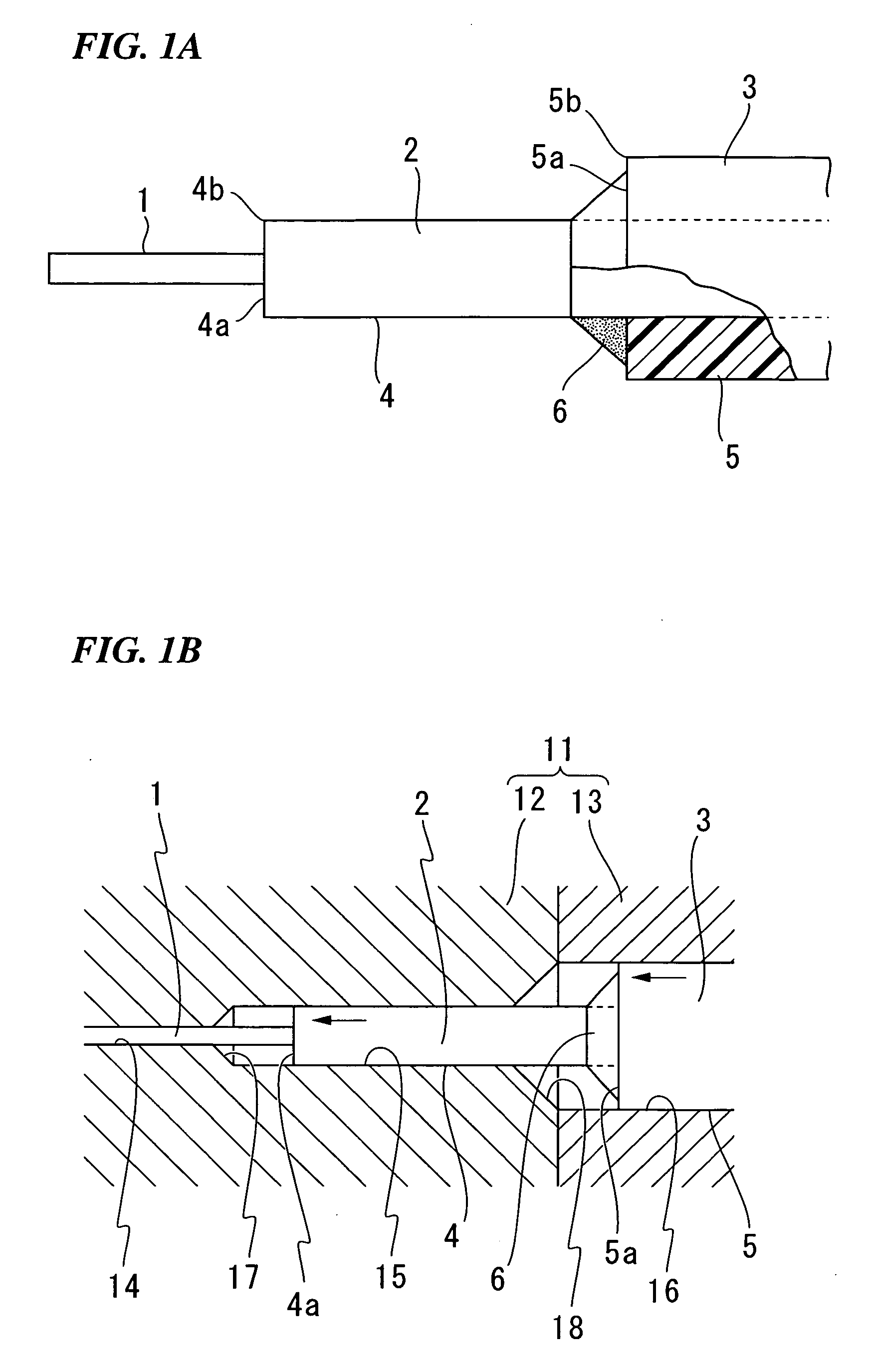

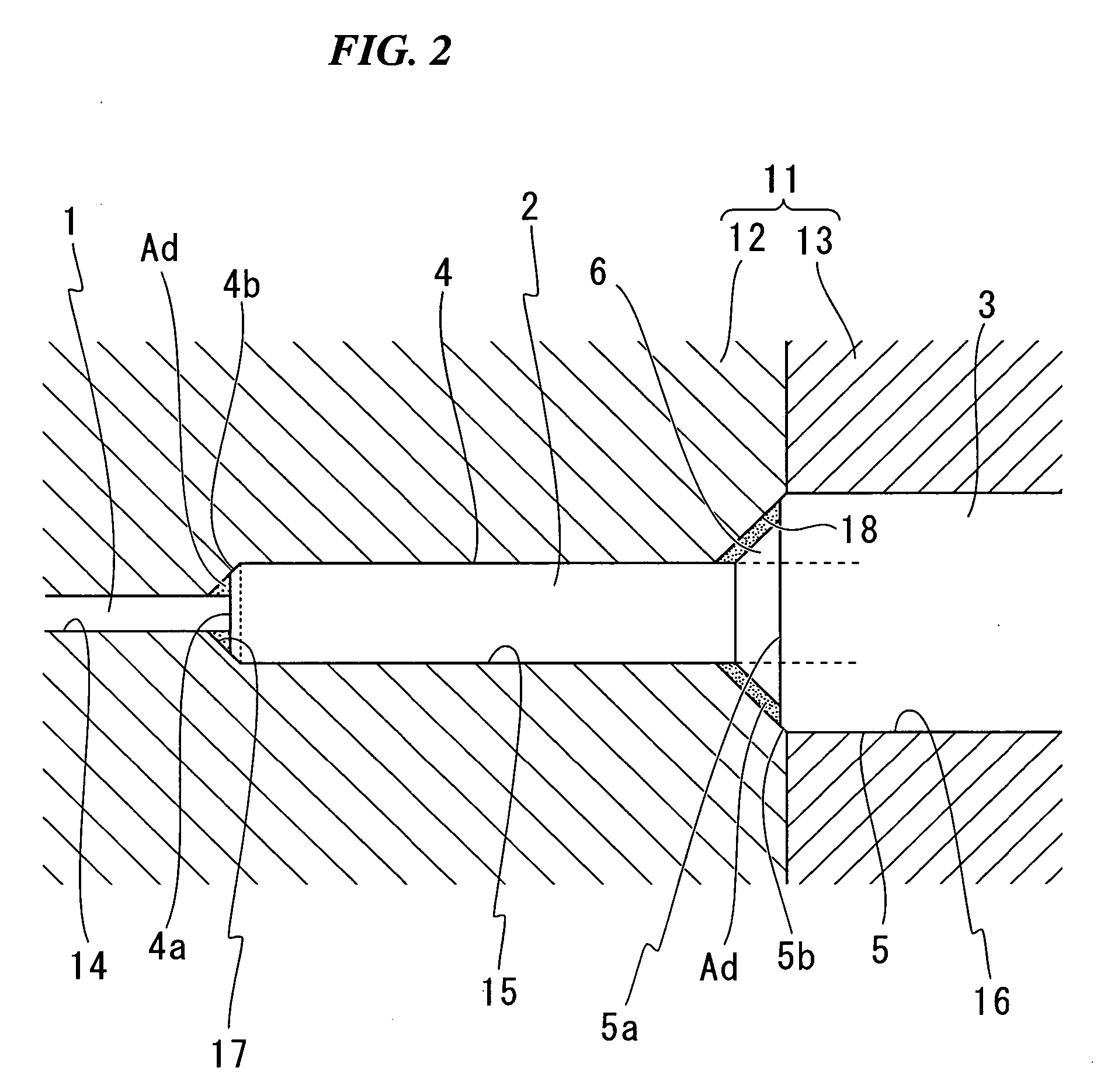

Method of producing a ferrule with an optical fiber

ActiveUS20060269192A1Control worsening of characteristicReduce the amount requiredCoupling light guidesFiberAdhesive

In a state in which a front end of a single-core fiber is passed through an end surface portion of a reinforcing pipe, an inner surface of the reinforcing pipe and an outer peripheral surface of the single-core fiber are glued together by means of adhesive. By using the same adhesive, an adhesive portion is formed by curing it so as to protrude and taper from the end surface portion of the reinforcing pipe toward the front end of the single-core fiber. Thereafter, a coated optical fiber formed with the adhesive portion is inserted in a ferrule until an end surface portion of the coating of the single-core fiber abuts against the first tapered hole and until the end surface portion of the reinforcing pipe abuts against the second tapered hole. Then, the optical fiber is glued in the ferrule by means of adhesive.

Owner:FUJIKURA AUTOMOTIVE ASIA

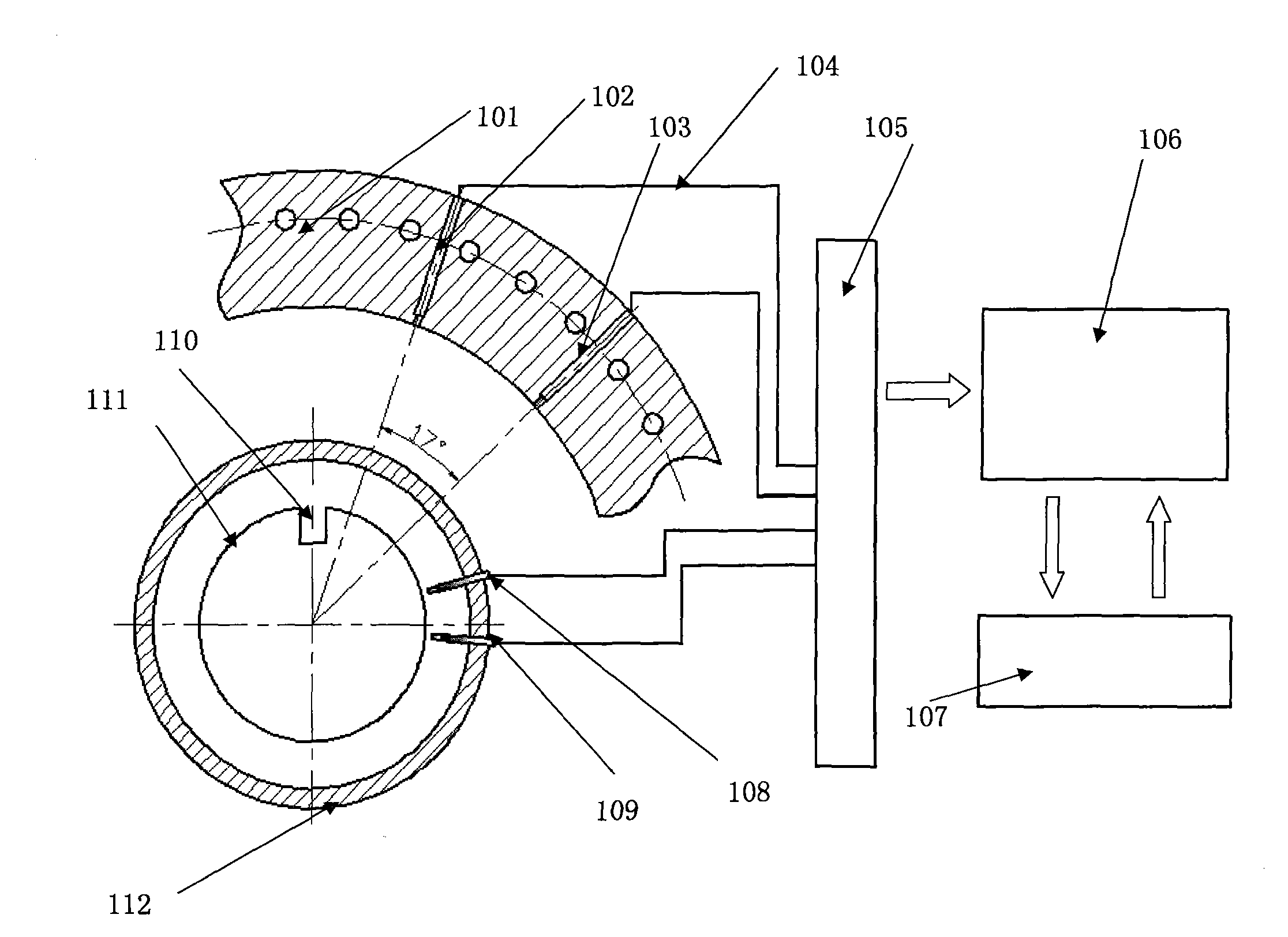

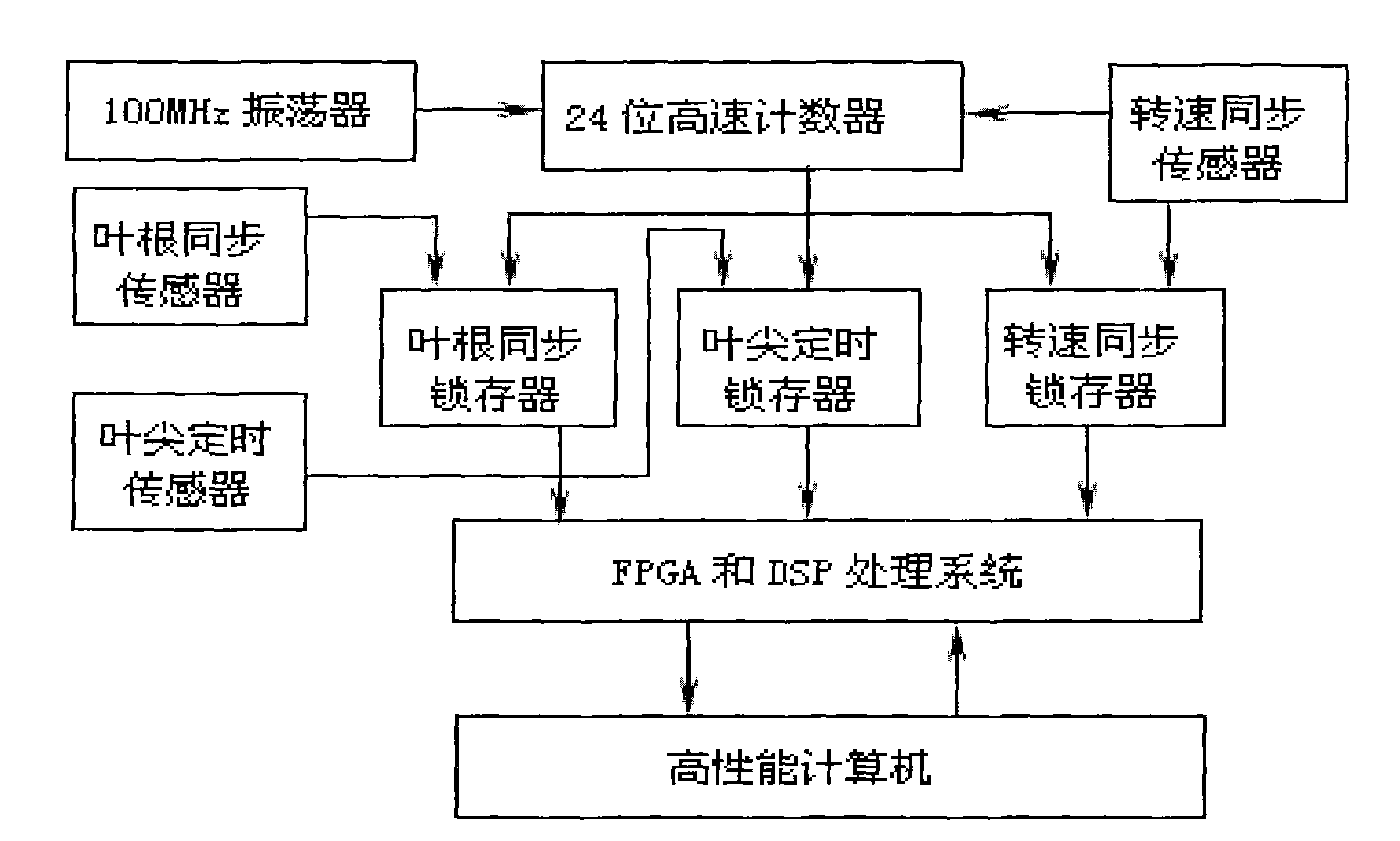

Real-time on-line monitoring apparatus of blade vibration of flue gas turbine

InactiveCN102735326AReal-time monitoring of vibrationHigh precisionSubsonic/sonic/ultrasonic wave measurementUsing electrical meansCapacitanceFlue gas

The invention relates to a real-time on-line monitoring apparatus of blade vibration of a flue gas turbine. The monitoring apparatus comprises blade tip timing sensors, an angle reference sensor, a rotating speed synchronization sensor, a preprocessing system, a data integrated processing card, and a computer. The blade tip timing sensors, the angle reference sensor, and the rotating speed synchronization sensor are connected with the preprocessing system that is connected with the data integrated processing card; and the data integrated processing card is connected with the computer. According to the invention, the sensors employ double-shielded capacitance impulsers; single-core double-shielded wires are utilized as transmission lines of output signals; and a driving cable technology is utilized to effectively reduce a random error introduced by an environmental interference; and a charge amplification circuit is used to extract a capacitance pulse signal, thereby eliminating the system error basically and improving the measurement accuracy of the system.

Owner:CHINA SPECIAL EQUIP INSPECTION & RES INST

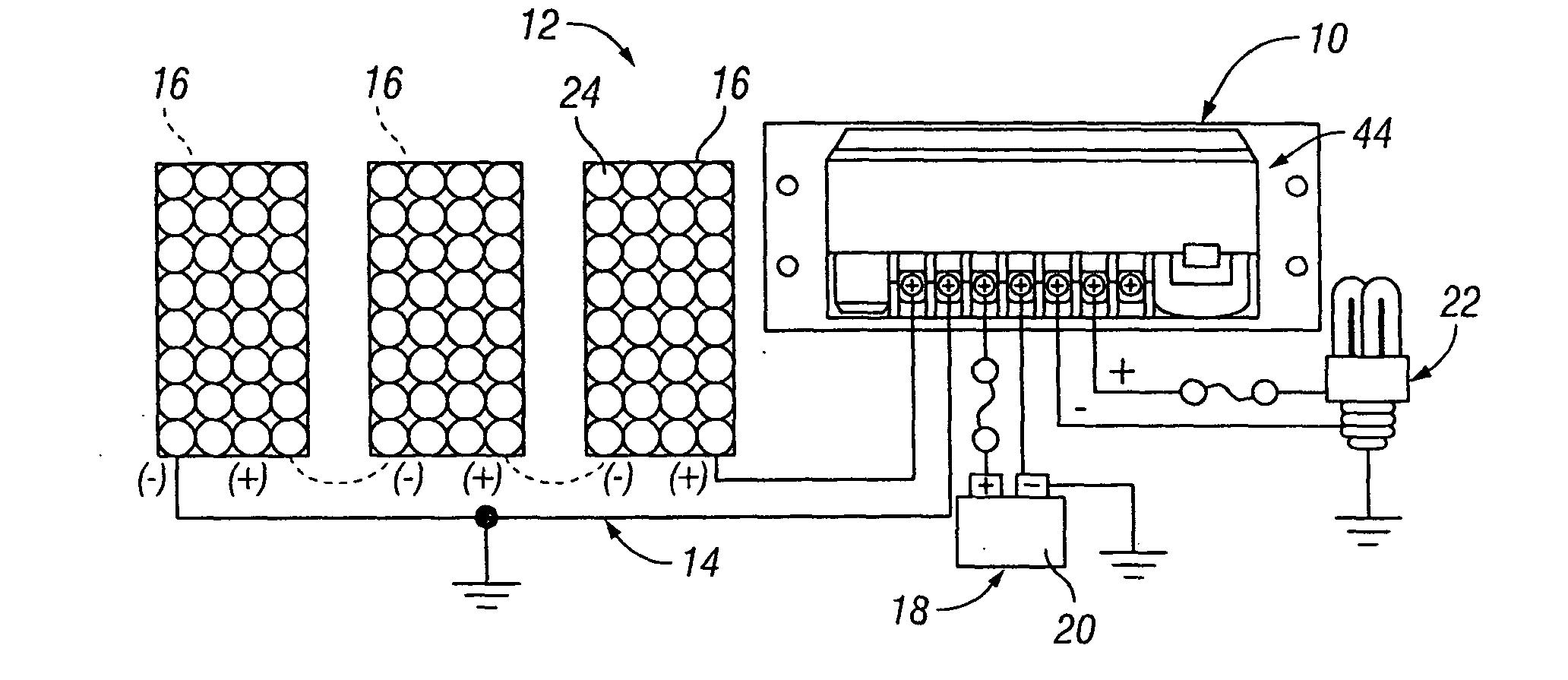

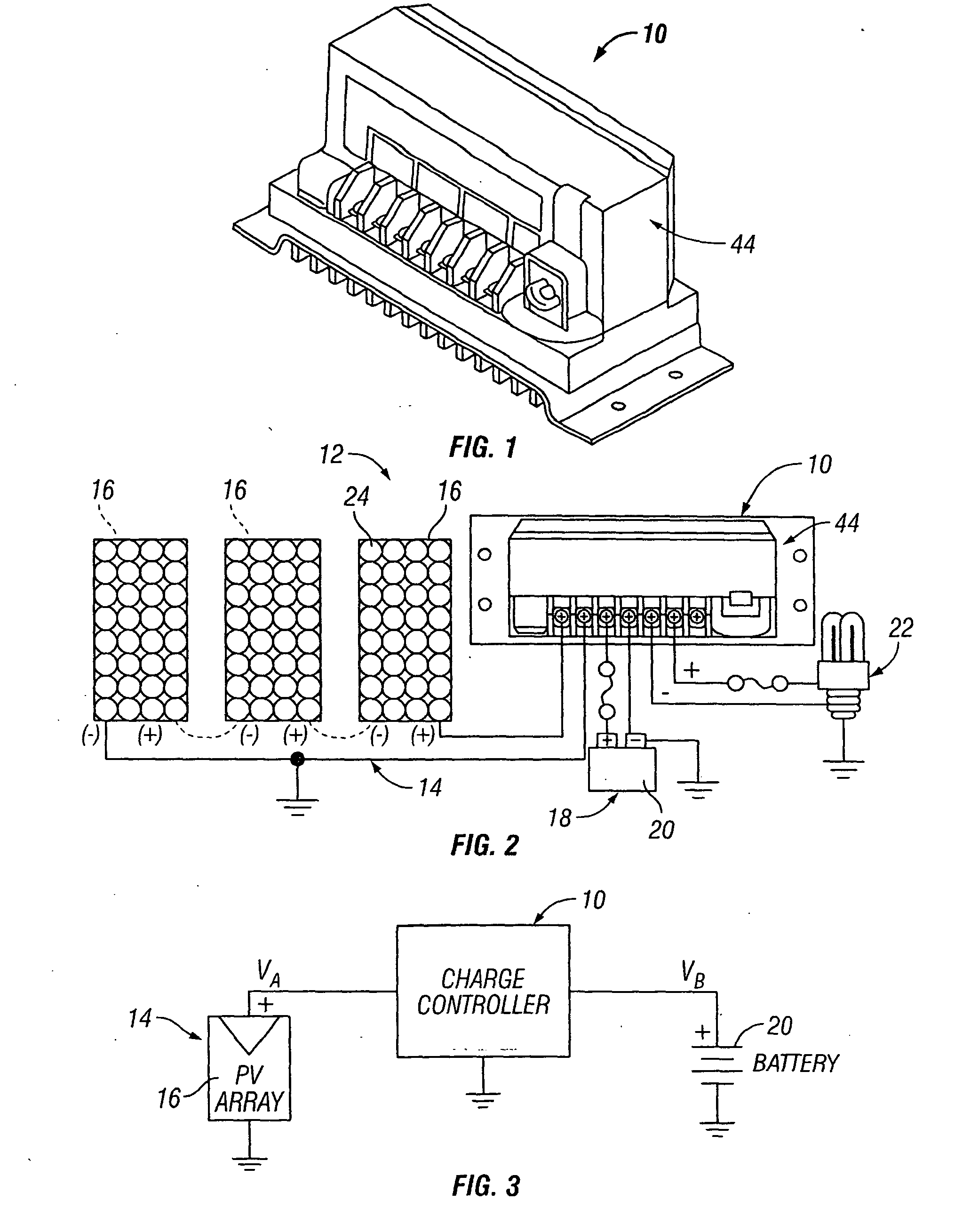

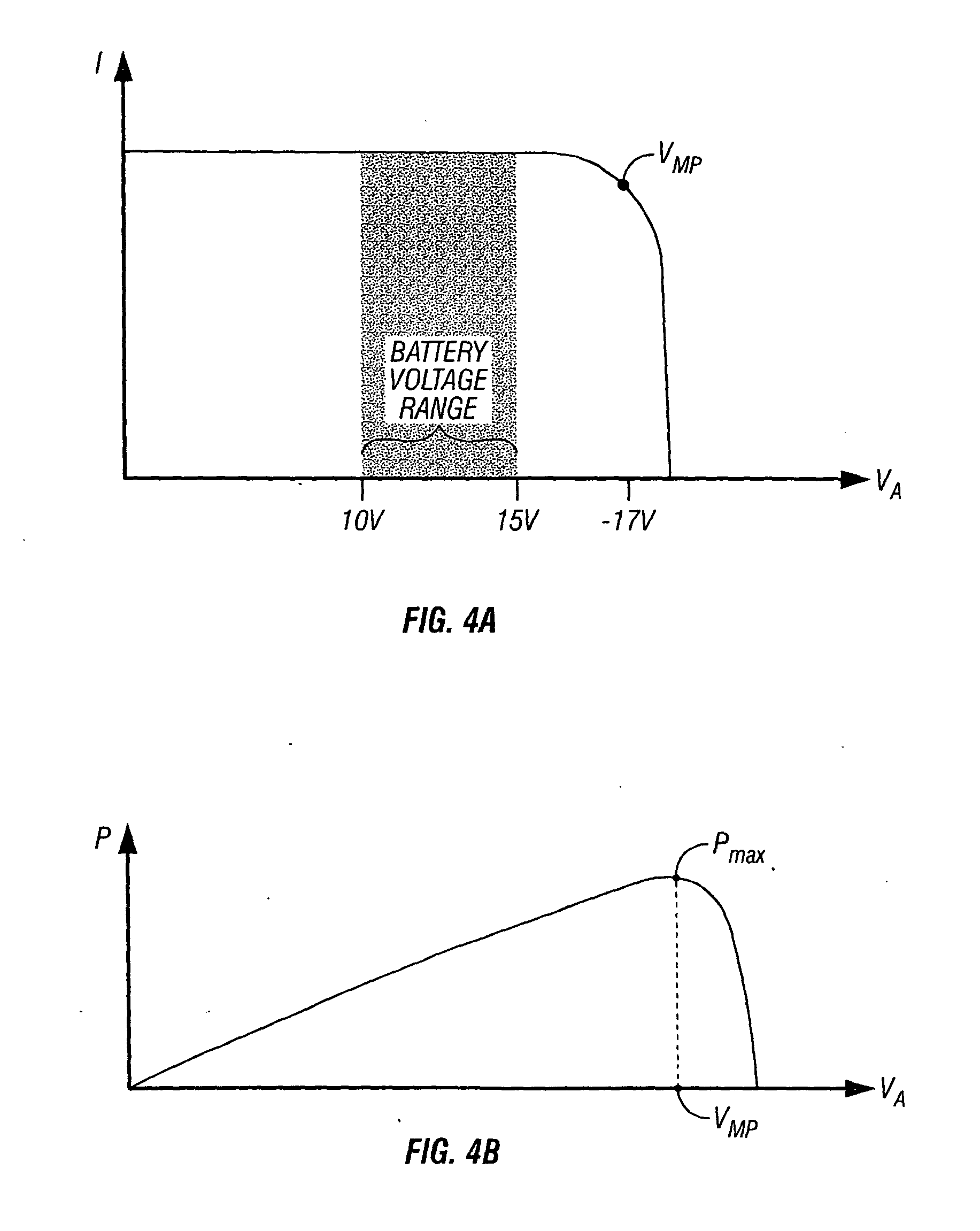

Maximum Power Point Tracking Charge Controller with Coupled Inductor Multi-phase Converter

A maximum power point tracking (MPPT) charge controller for photovoltaic (PV) systems employs a maximum power point tracking algorithm for tracking the maximum power point voltage of a PV array at which the PV array produces maximum power voltage, and a buck converter for converting the maximum power voltage to the voltage required to charge one or more batteries. The buck converter includes multiple buck converter phase configurations phase shifted from one another. Each of the buck converter phase configurations has a phase inductor, and the phase inductors are combined on a single core to form a coupled inductor. One of the buck converter phase configurations is intentionally temporarily shut down when the output power is low. A first switch or a second switch of the buck converter phase configuration that is intentionally temporarily shut down is turned on to conduct electrical current when predetermined conditions are satisfied. A method of controlling battery charging in a photovoltaic system involves operating a coupled inductor multi-phase buck converter of a charge controller so that one of the buck converter phase configurations is intentionally temporarily shut down when the power output is below a predetermined value.

Owner:MORNINGSTAR CORP