JTAG (joint test action group) debug method of multi-core processor

A technology of multi-core processor and debugging method, which is applied in the detection of faulty computer hardware and functional inspection, etc., can solve problems such as poor reliability, inability to effectively complete selection control and debugging information storage feedback, etc., to improve the reuse rate, simple The effect of transplantation

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

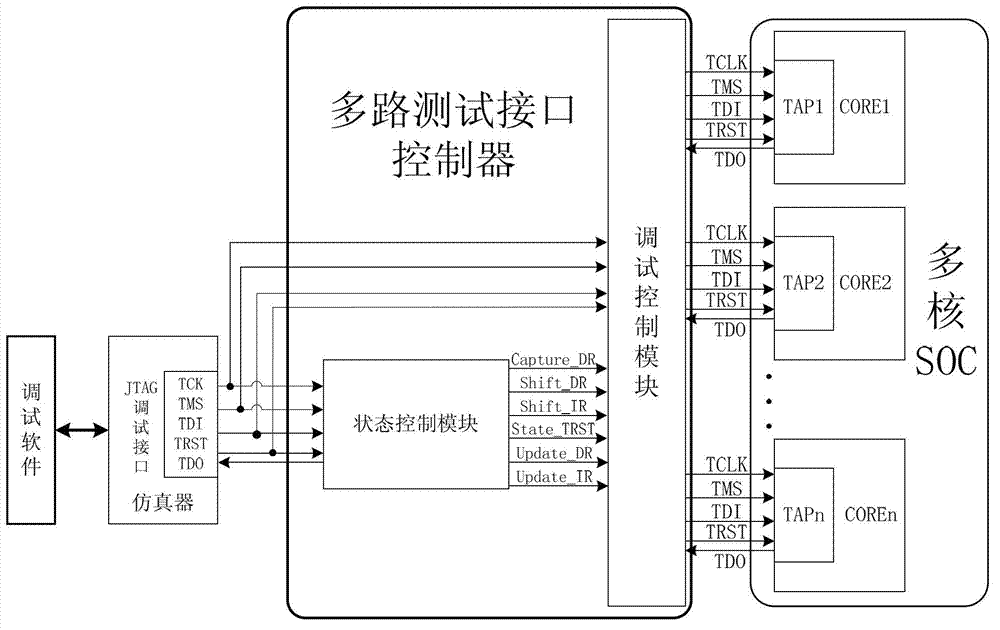

[0030] The present invention will be further described below in conjunction with the accompanying drawings.

[0031] refer to Figure 3~Figure 5 , a kind of JTAG debugging method of multi-core processor, comprises the steps:

[0032] Step 1: The system is powered on, and the functional state machine of the multi-channel test access port controller enters the Test-Logic Reset (test logic reset) state.

[0033] Step 2: The debugging software sends debugging instructions, and outputs specific TCK, TDI, and TMS signals through the JTAG debugging interface of the emulator, so that the state control module of the multi-channel interface test module enters in turn: Run-Test / Idle (testing) state, Select-DR-Scan (select data scan register) status, Select-IR-Scan (select instruction scan register) status, Capture-IR (capture instruction) status, Shift-IR (move into instruction) status, Exit1-IR (exit instruction 1) Status, Update-IR (update instruction) status, and finally return to R...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More