Patents

Literature

426results about How to "Good process compatibility" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

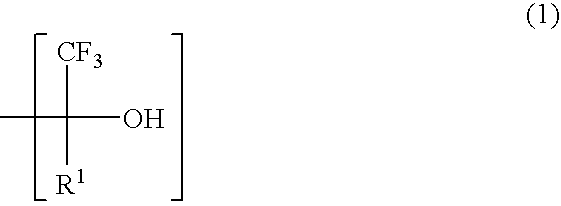

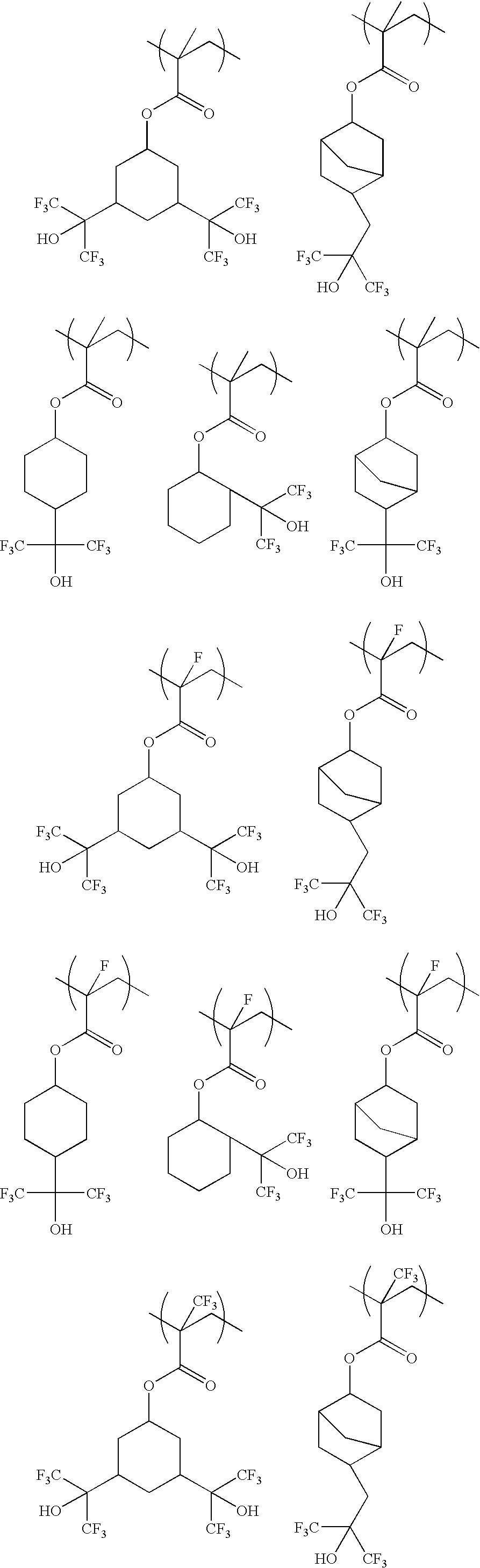

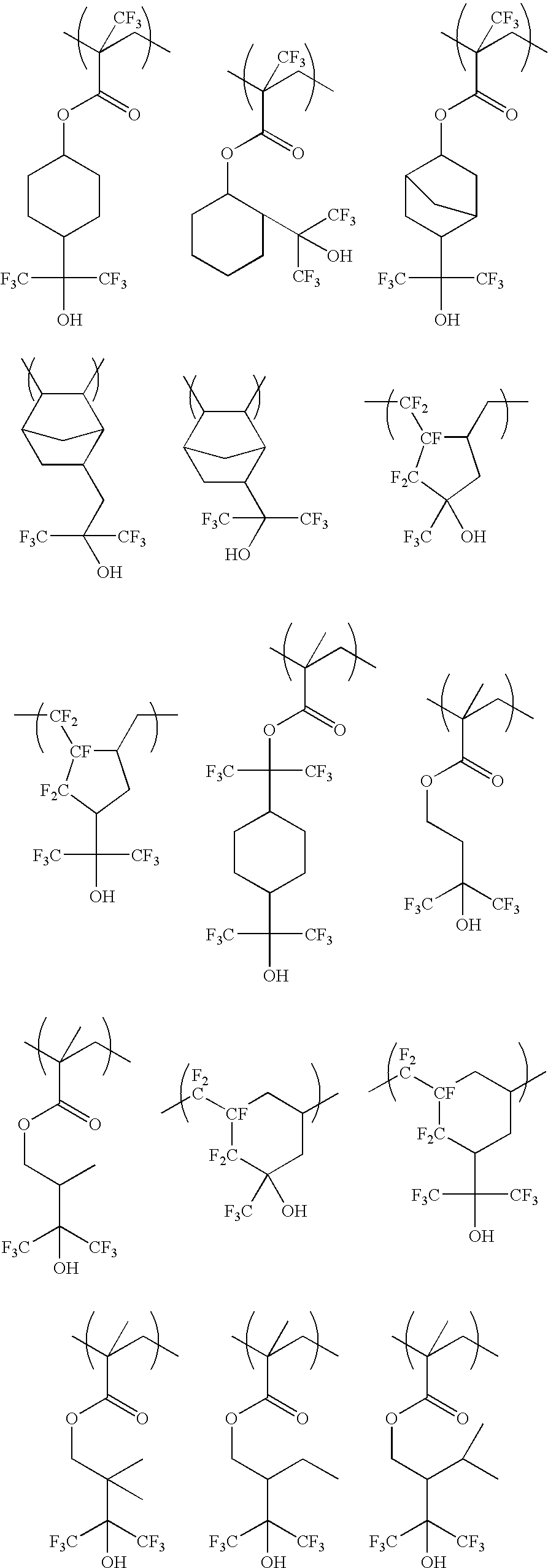

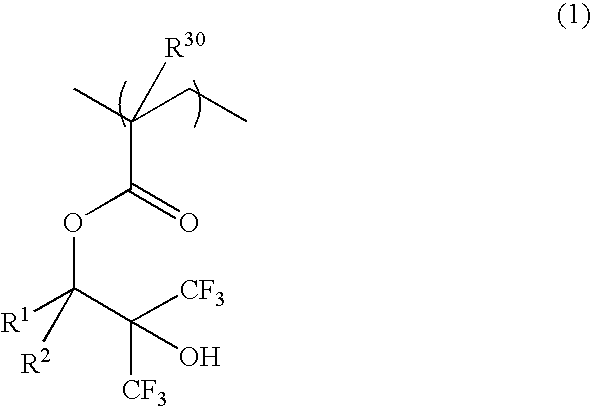

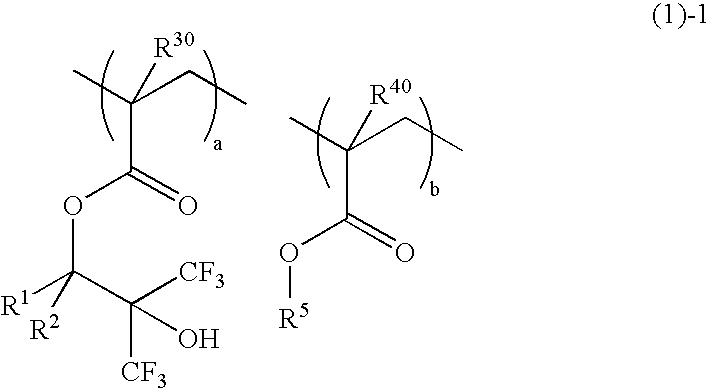

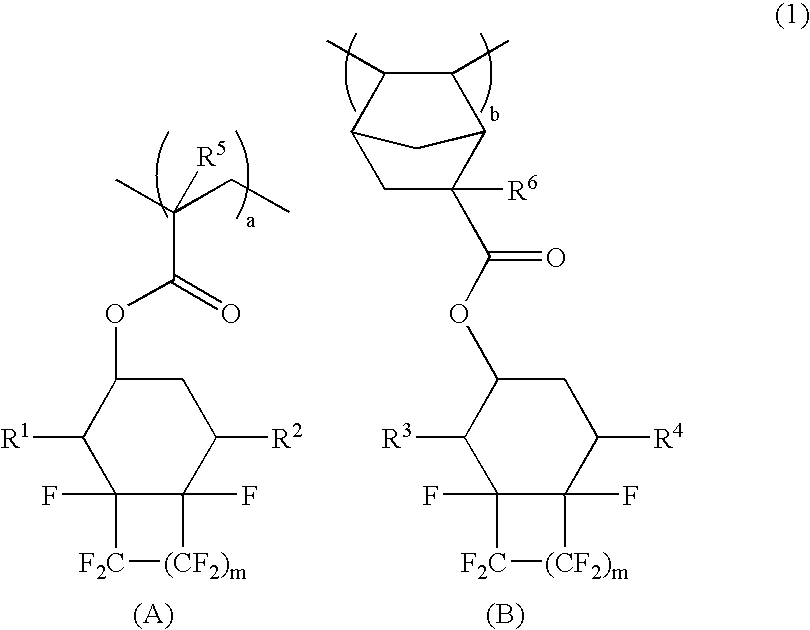

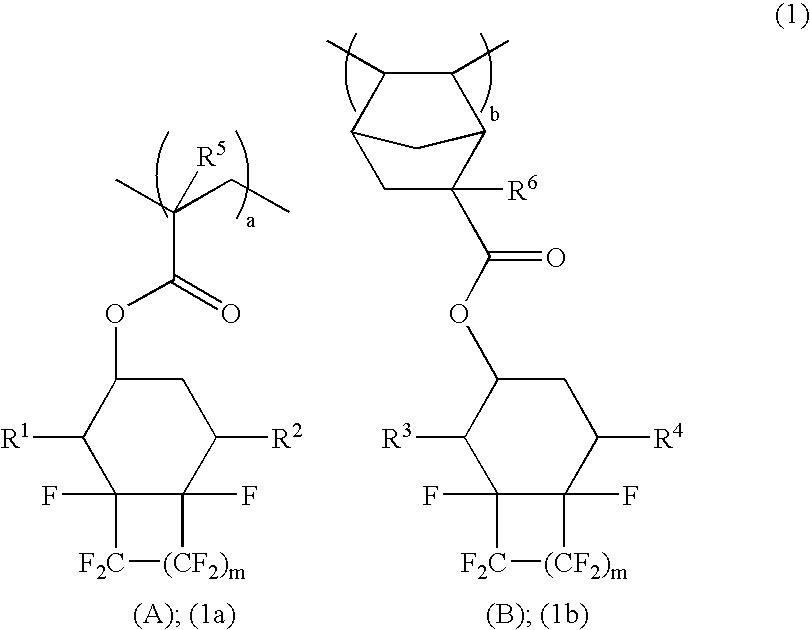

Polymer, resist protective coating material, and patterning process

ActiveUS20070178407A1Efficient formationGood process compatibilityPhotosensitive materialsPhotosensitive materials for photomechanical apparatusHydrogenWater insoluble

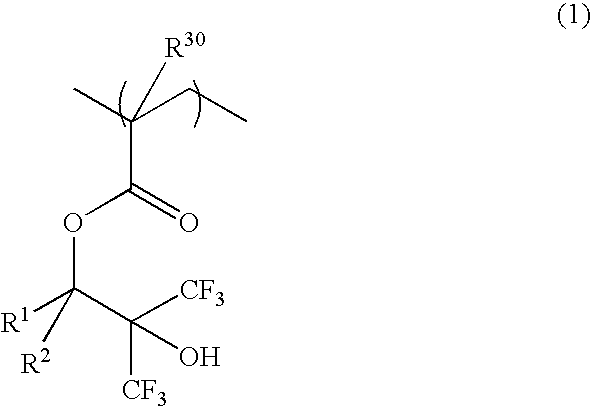

A polymer comprising repeat units having formula (1) wherein R1 and R2 are hydrogen or C1-C12 alkyl, or R1 and R2 may bond together to form a ring, and R30 is hydrogen or methyl is used to formulate a resist protective coating material. A protective coating formed therefrom on a resist film is water-insoluble, dissolvable in alkali aqueous solution or alkaline developer, and immiscible with the resist film so that the immersion lithography can be conducted in a satisfactory manner. During alkali development, development of the resist film and removal of the protective coating can be simultaneously achieved.

Owner:SHIN ETSU CHEM IND CO LTD

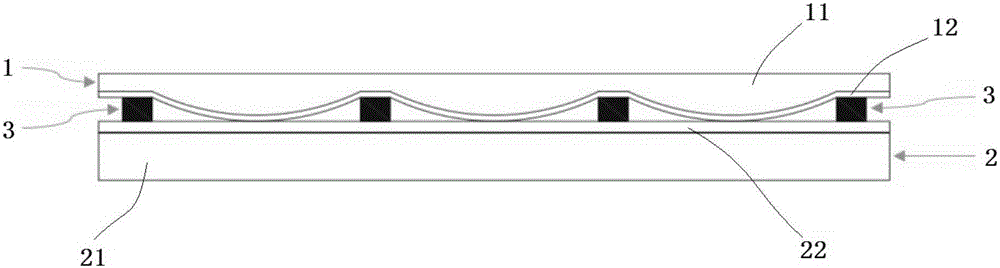

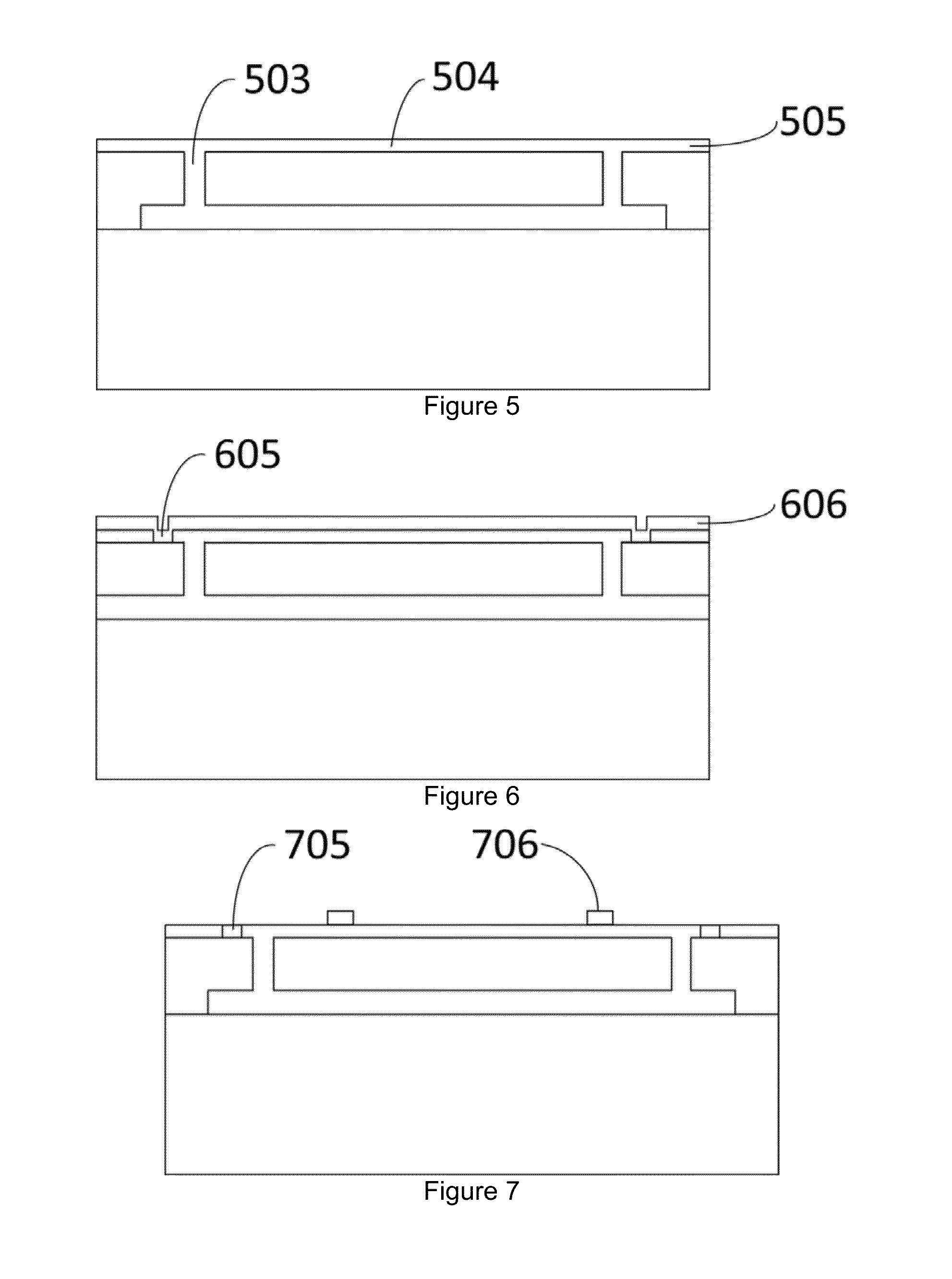

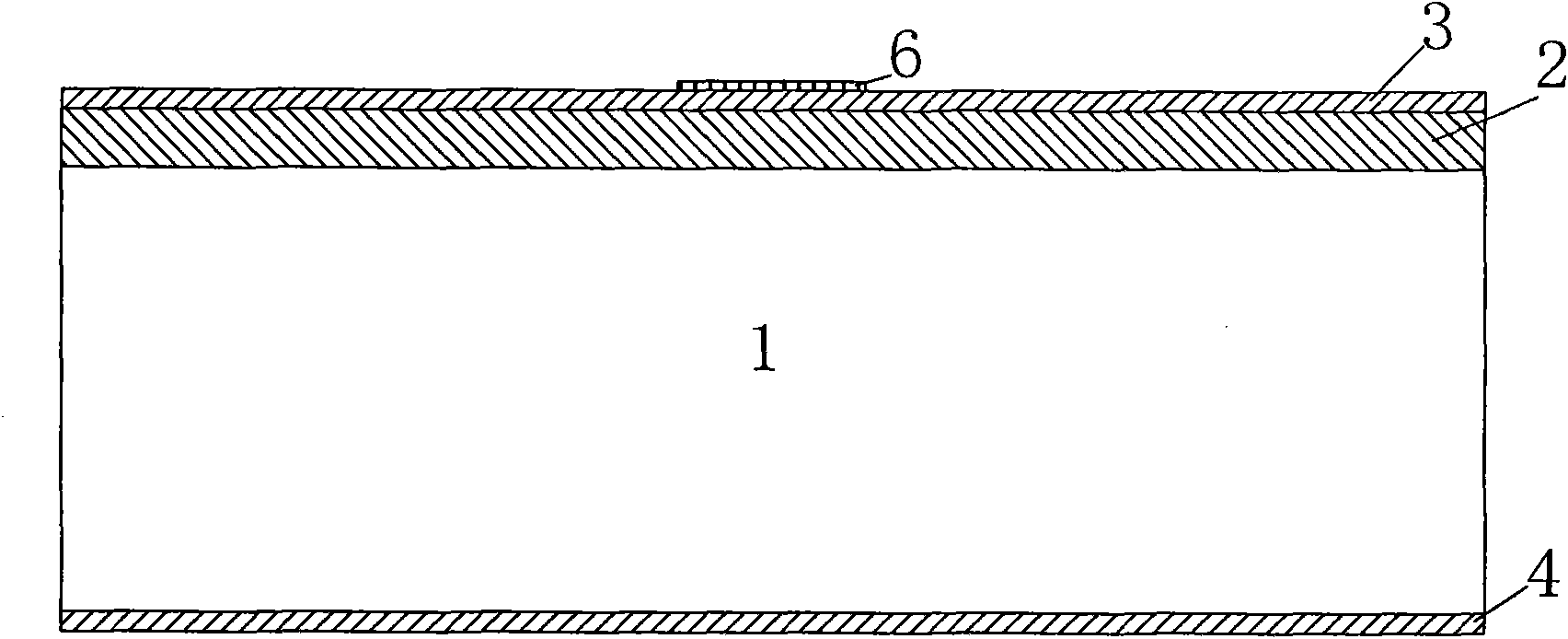

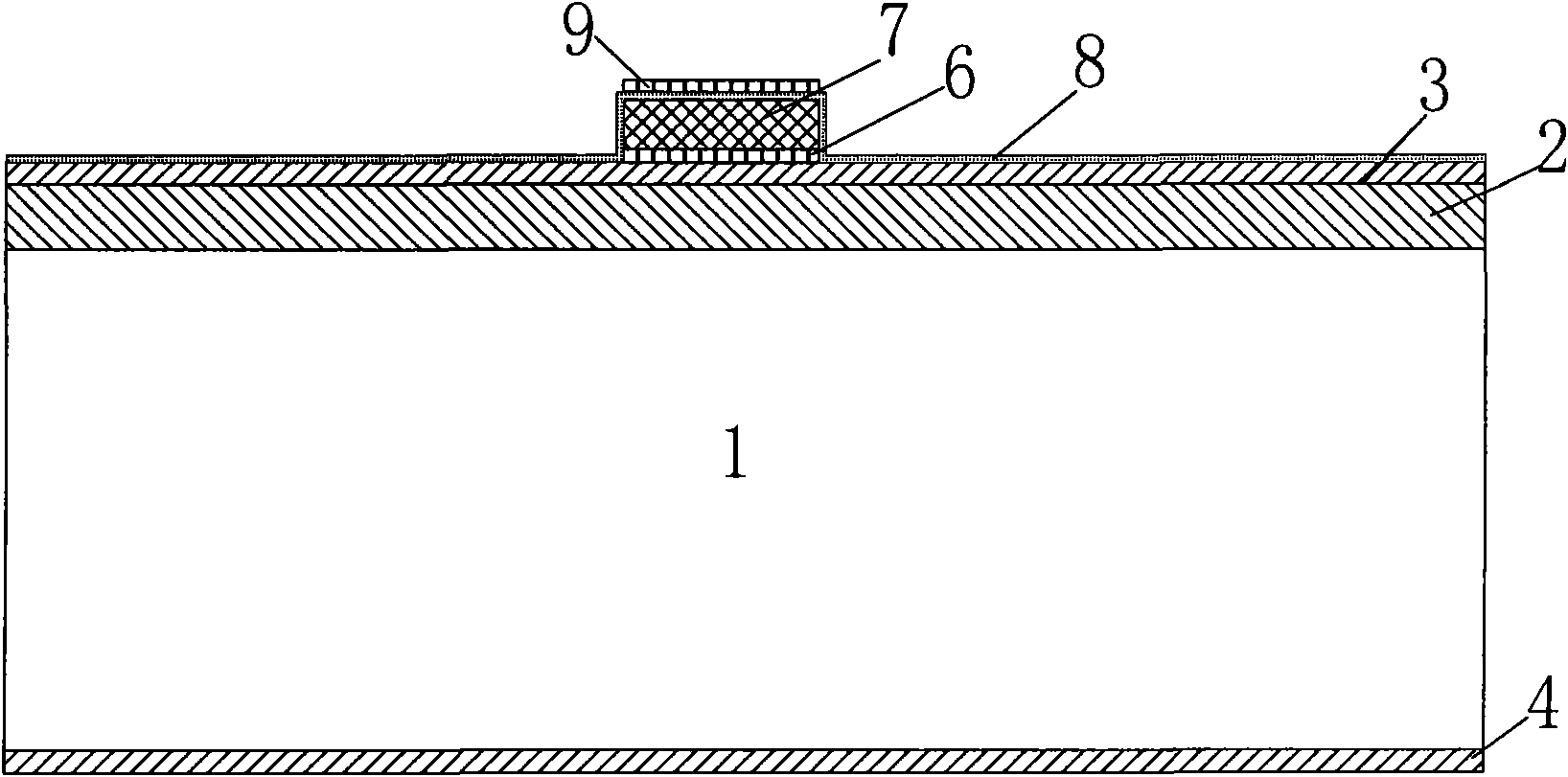

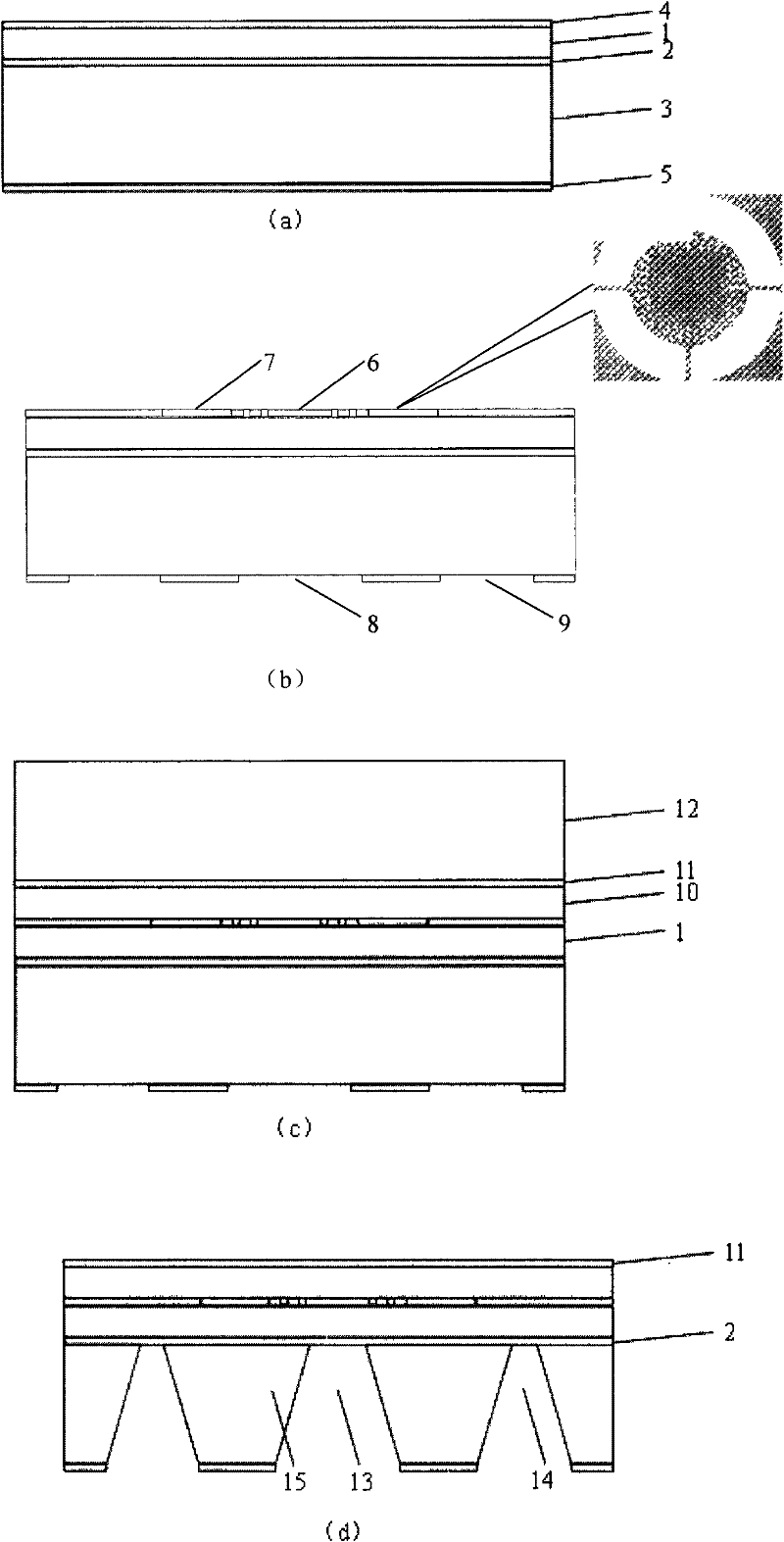

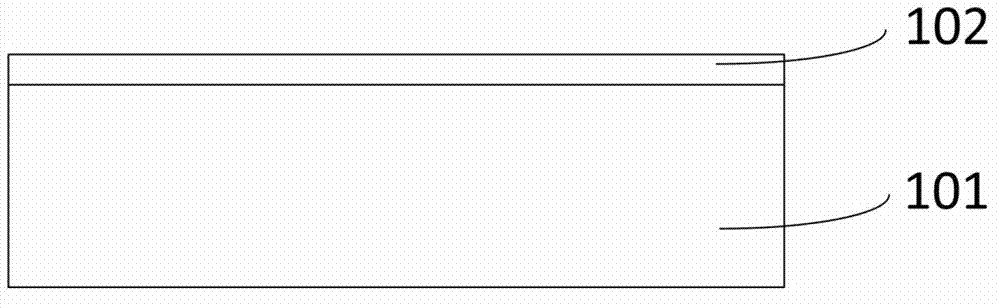

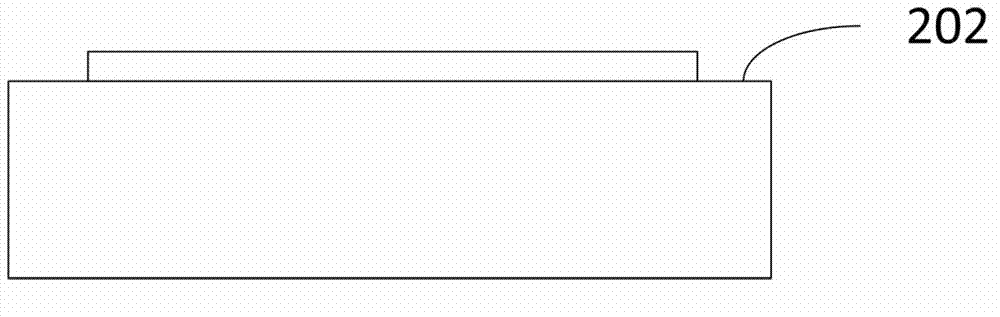

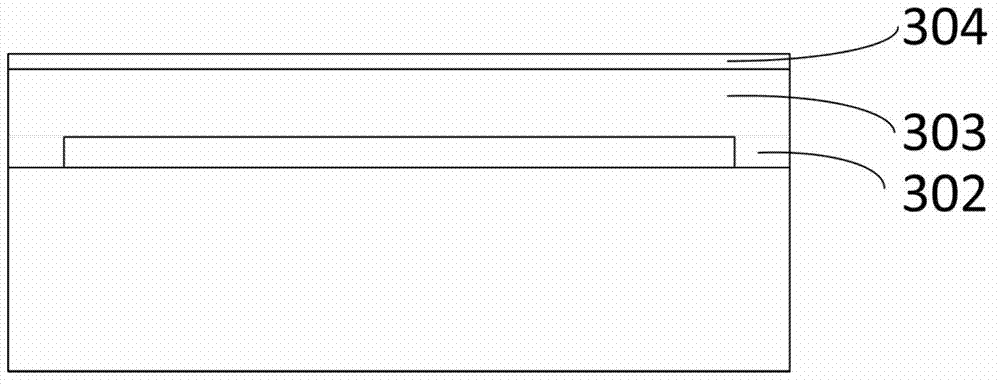

Flexible pressure sensor and preparation method thereof

ActiveCN106197772AHigh sensitivityImprove reliabilityForce measurement using piezo-resistive materialsElectrical resistance and conductanceIsolation layer

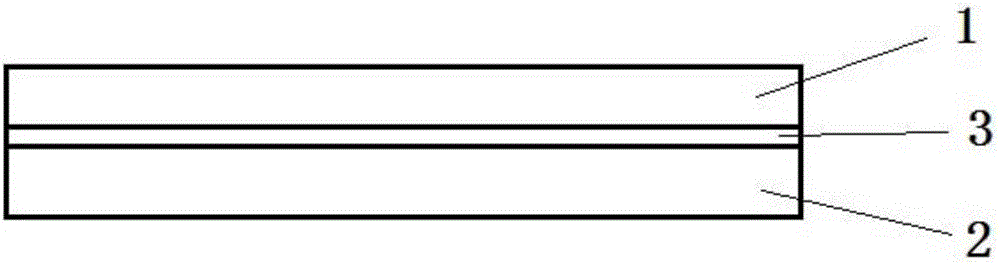

The invention discloses a flexible pressure sensor which comprises an induction layer, a substrate layer, an isolation layer and electrodes. The isolation layer is positioned between the induction layer and the substrate layer and bonded to the induction layer and the substrate layer, and enables electric contact between the induction layer and the substrate layer to be isolated discontinuously; the surface of the induction layer is provided with a first conductive layer, the surface of the substrate layer is provided with a second conductive layer, and the first and second conductive layers are bonded to the isolation layer in opposite directions; and the electrodes are led out of the first or second conductive layer and connected with an external circuit. The flexible pressure sensor is used to detect the size and fluctuation of pressure, a flexible conductive material on the specific substrate is bonded to other conductive substrate, the electrodes are led out, change of resistance between the electrodes is measured, and the size and fluctuation of the pressure is detected in directly. The pressure sensor of high flexibility and high reliability can be applied to a flexible bearing body, technology is simple, and the sensor can be compatible with a present processing technology of a resistant screen to realize scaled production and application.

Owner:常州第六元素半导体有限公司

Resist protective coating material and patterning process

InactiveUS20070122741A1Good process compatibilityAdversely affecting the pattern profile and process marginPhotosensitive materialsPhotosensitive materials for photomechanical apparatusWater insolubleEther

A pattern-forming process uses a resist protective coating material comprising a C8-C12 ether compound as a solvent. A resist protective coating formed on a resist film is water-insoluble, soluble in an alkaline developer, and unmixable with the resist film, and thus the immersion lithography can be performed. During alkaline development, development of the resist film and removal of the protective coating can be achieved in a single step at the same time.

Owner:SHIN ETSU CHEM IND CO LTD

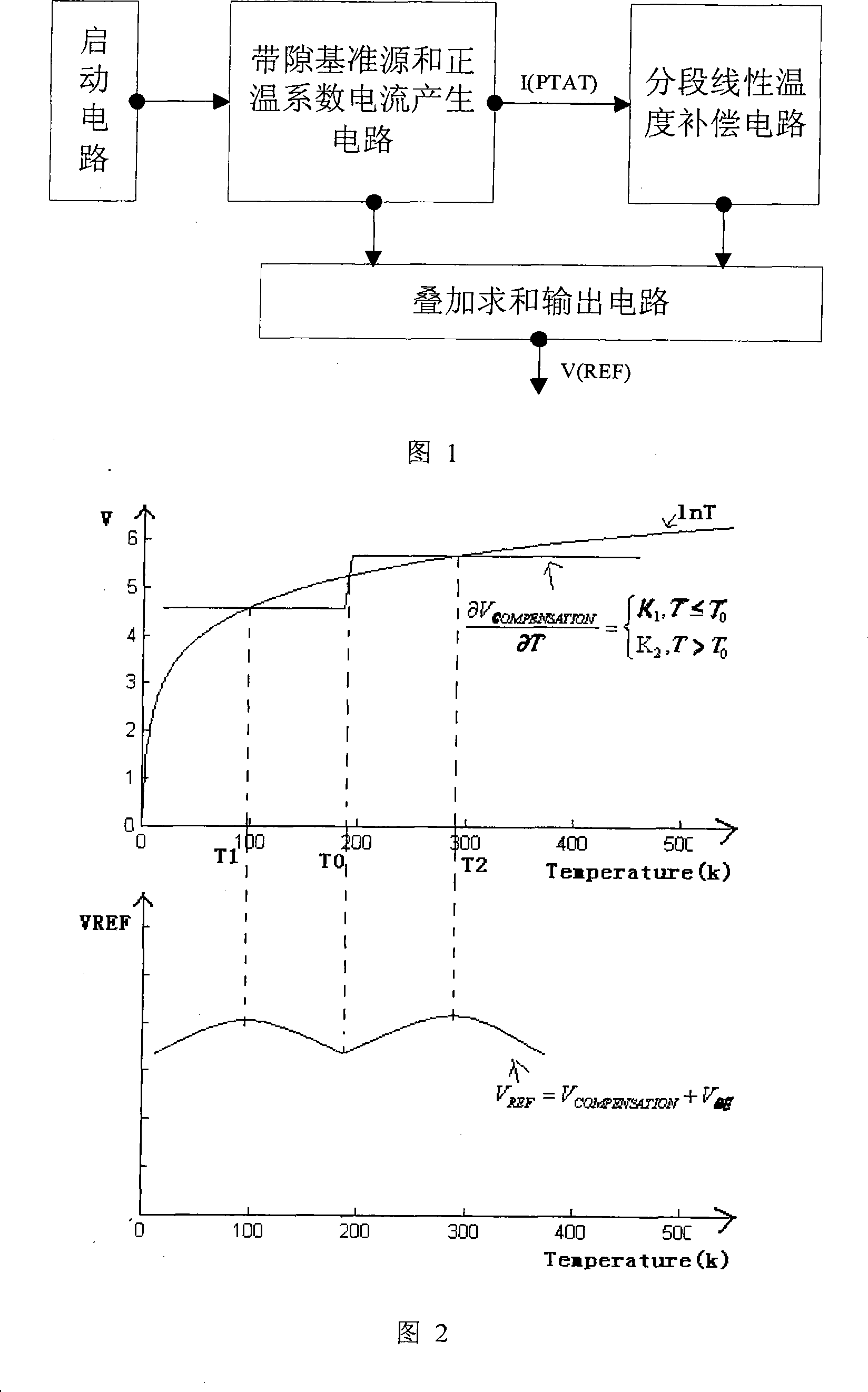

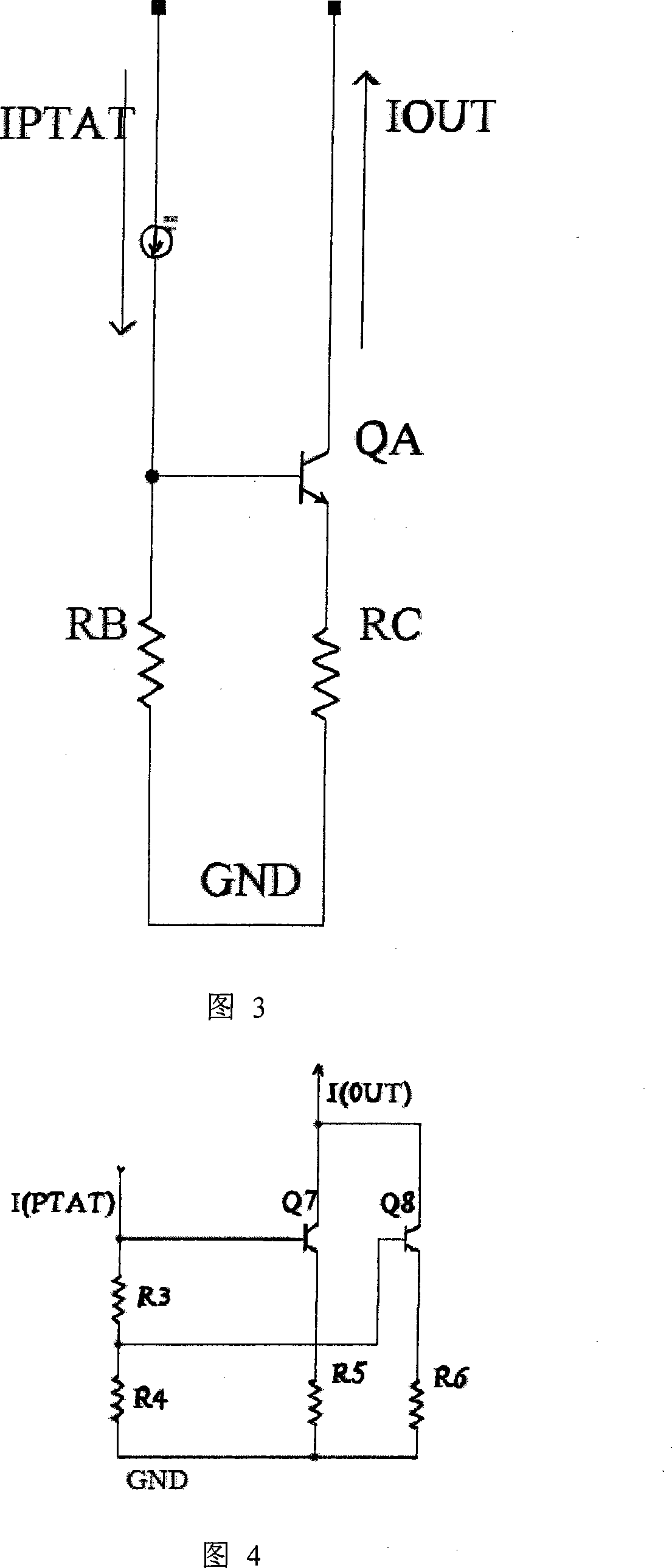

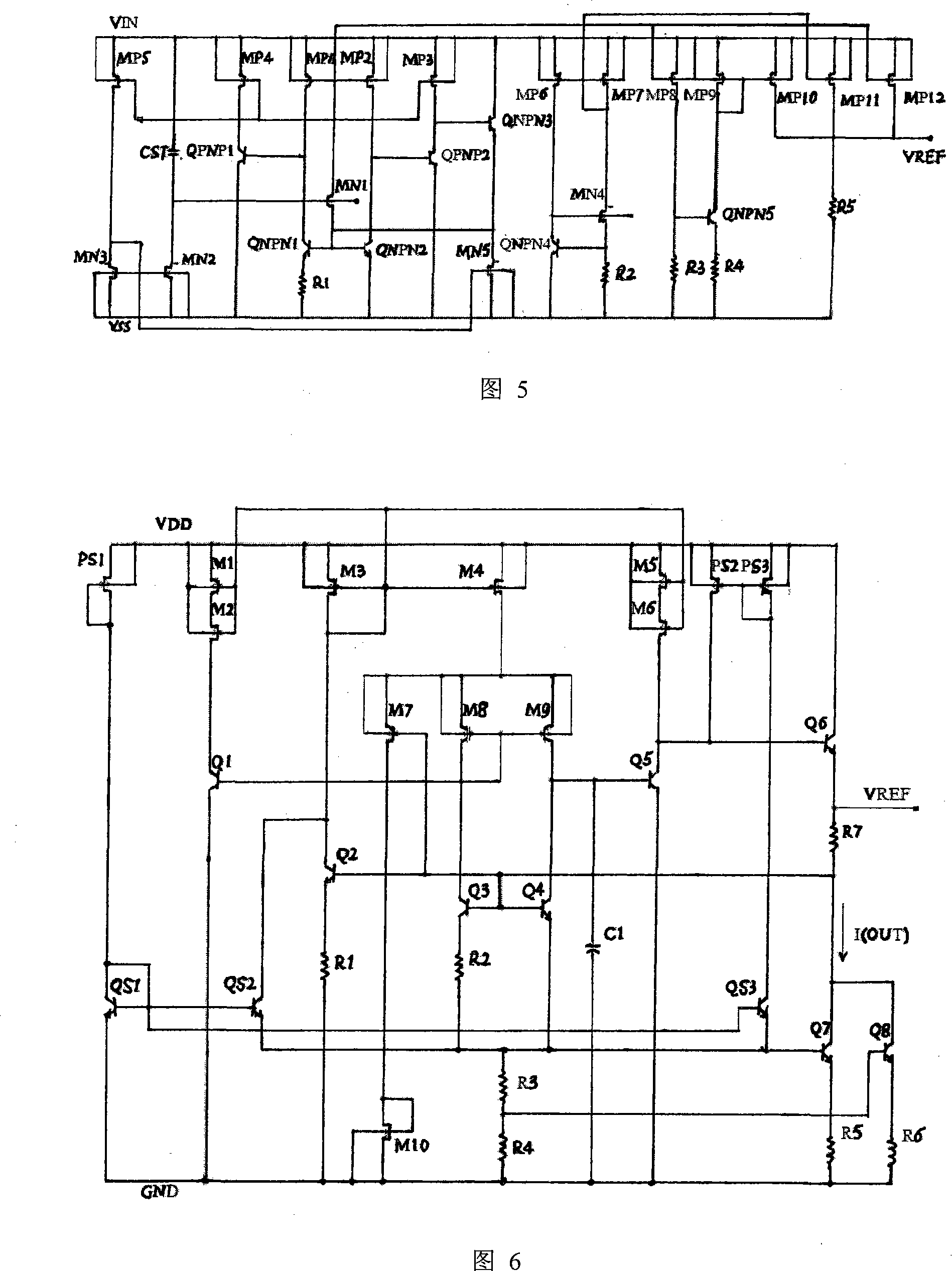

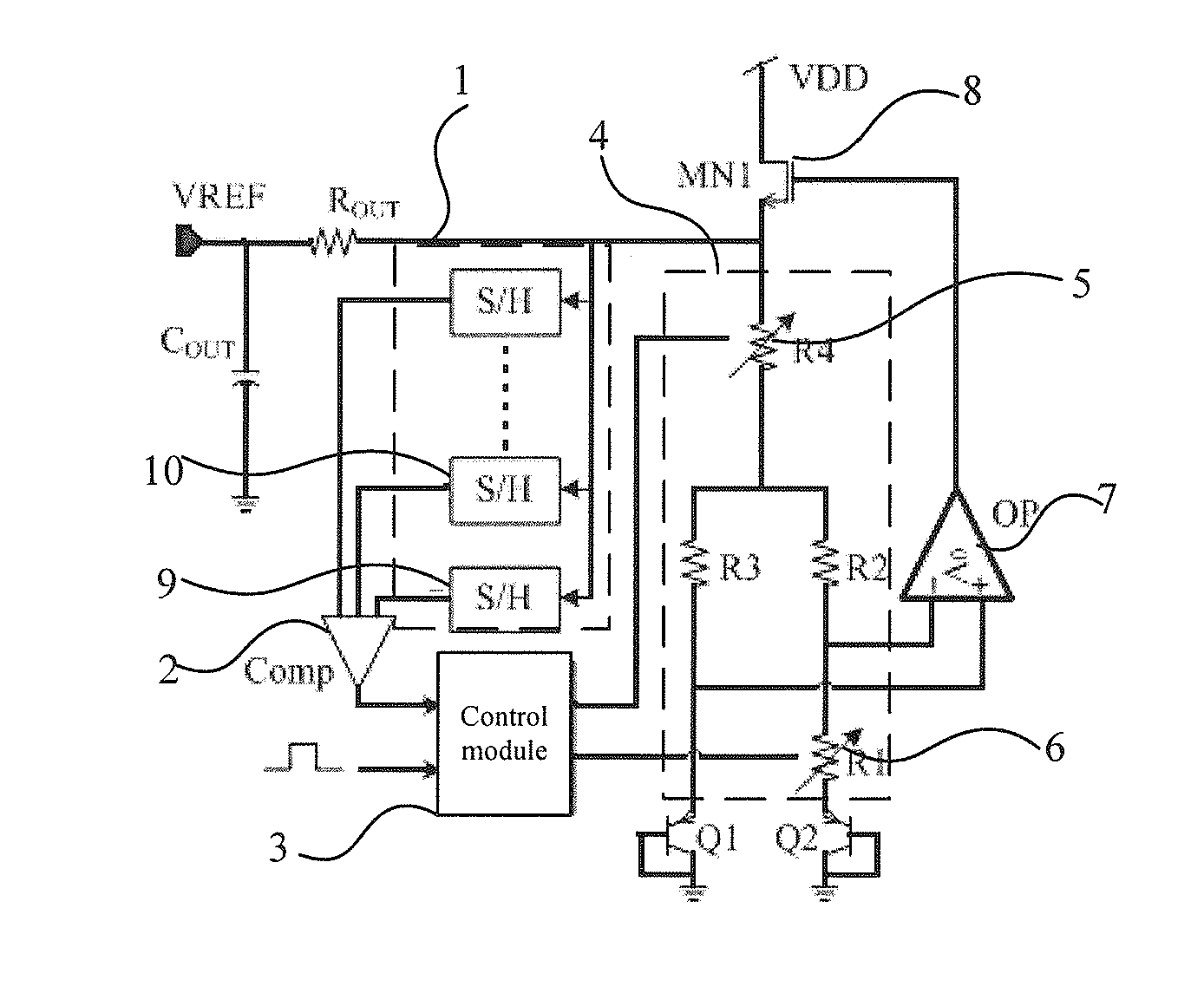

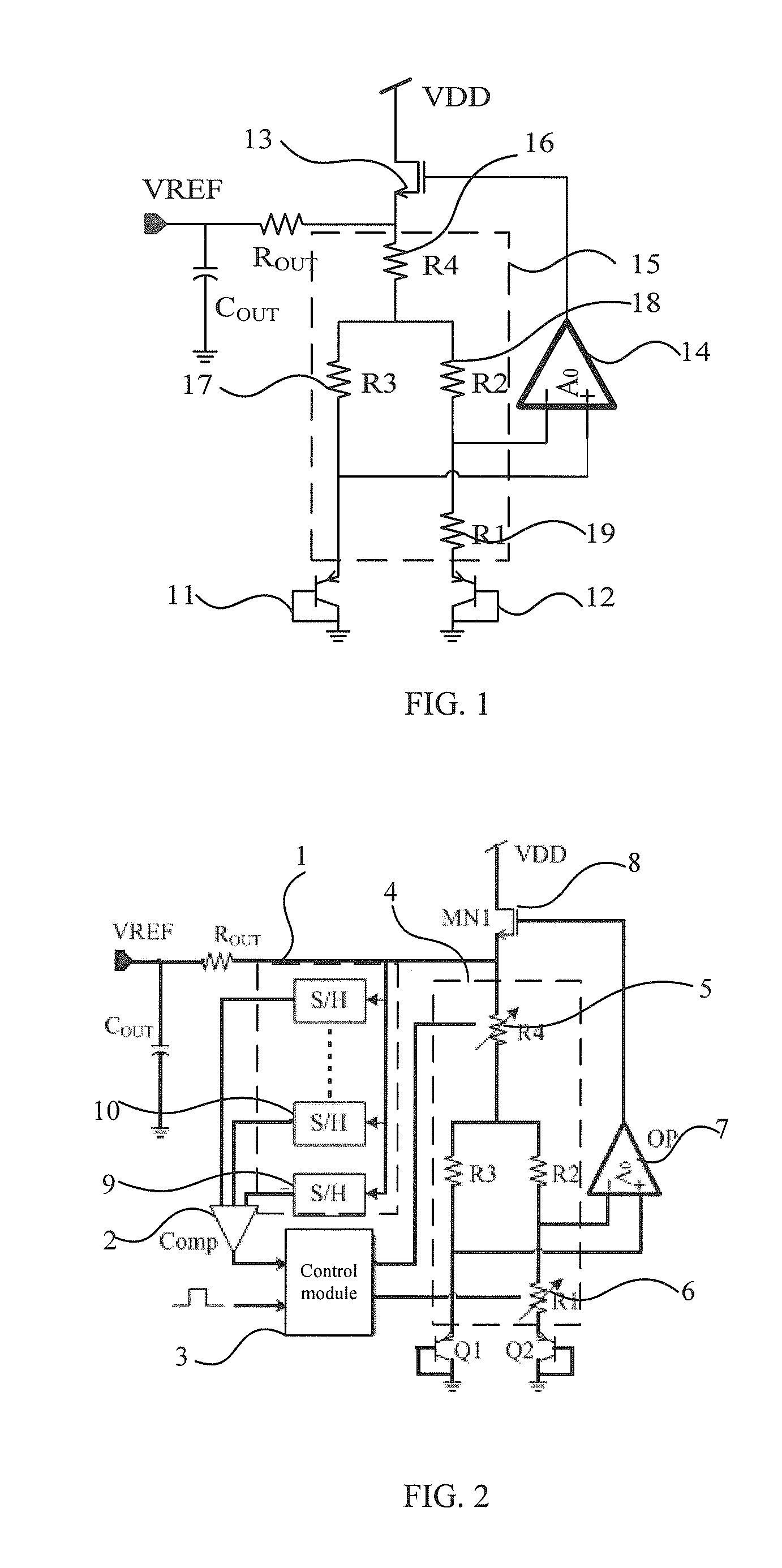

Piecewise linear temperature compensating circuit and temperature compensation voltage reference source

InactiveCN101216718AReduce the impactImprove temperature stabilityElectric variable regulationElectrical resistance and conductanceEngineering

The invention discloses a sectional linear temperature compensating circuit and a temperature compensating voltage reference source. The sectional linear temperature compensating circuit consists of resistances and a triode, wherein the number of resistances is at least two; the base electrode of the triode is connected with the input port to constitute an input end. One end of a first resistance is connected with the input port, and the other end is connected with a ground wire; the emitting electrode of the triode is connected with the ground wire through a second resistance, and the collector electrode of the triode constitutes an output end. In the voltage reference source, the band-gap reference source and the input end of a positive-temperature coefficient electric current generating circuit are connected with a summing output circuit and a sectional linear temperature compensation circuit respectively. The output end of the sectional linear temperature compensating circuit is connected with the summing output circuit. The invention reduces the impact of resistance temperature on the output amount and has good process compatibility and temperature stability.

Owner:UNIV OF ELECTRONICS SCI & TECH OF CHINA

Wire bonding of aluminum-free metallization layers by surface conditioning

InactiveUS20090166861A1Reduce contact failureHigh similaritySemiconductor/solid-state device detailsSolid-state devicesLead bondingEngineering

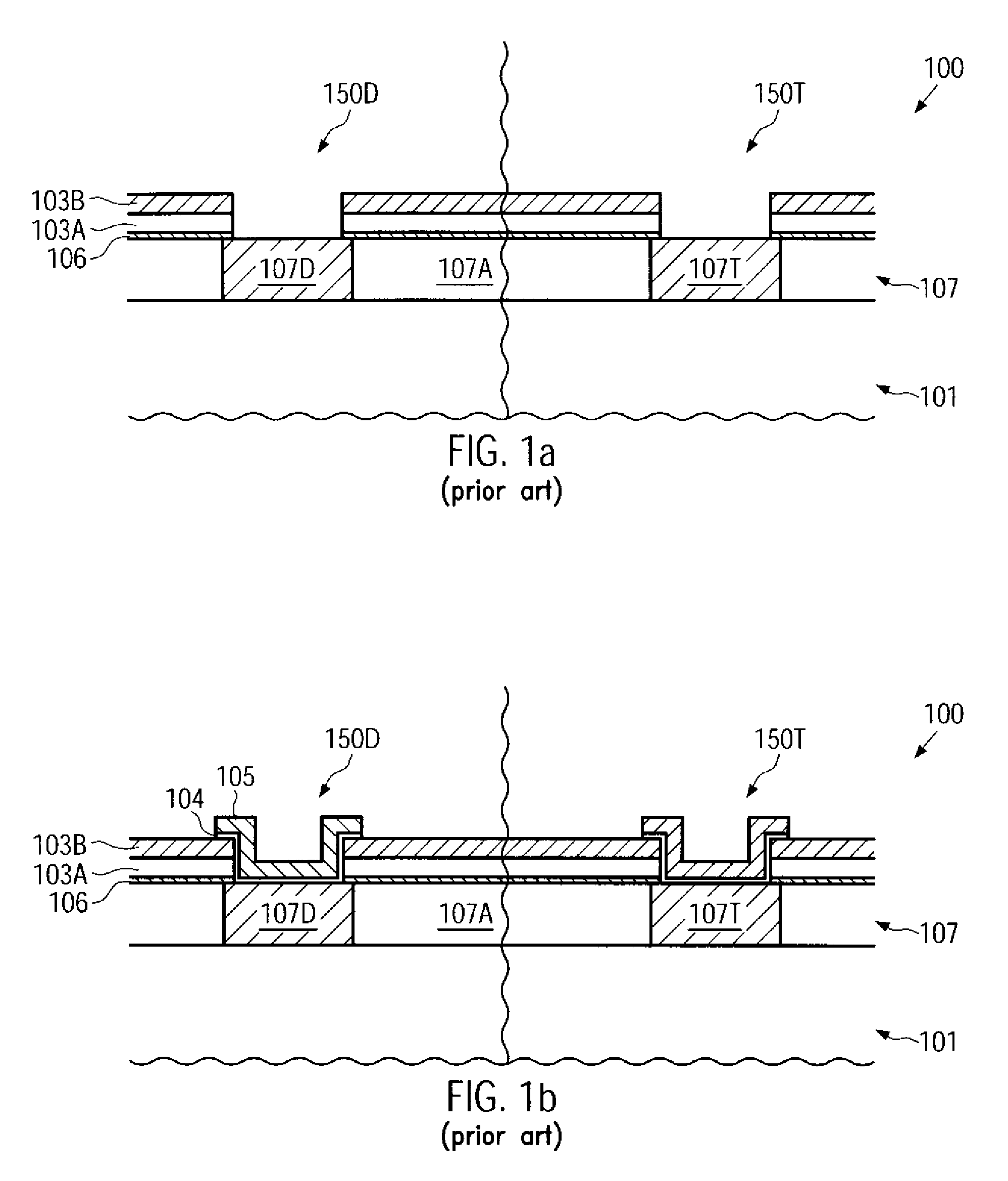

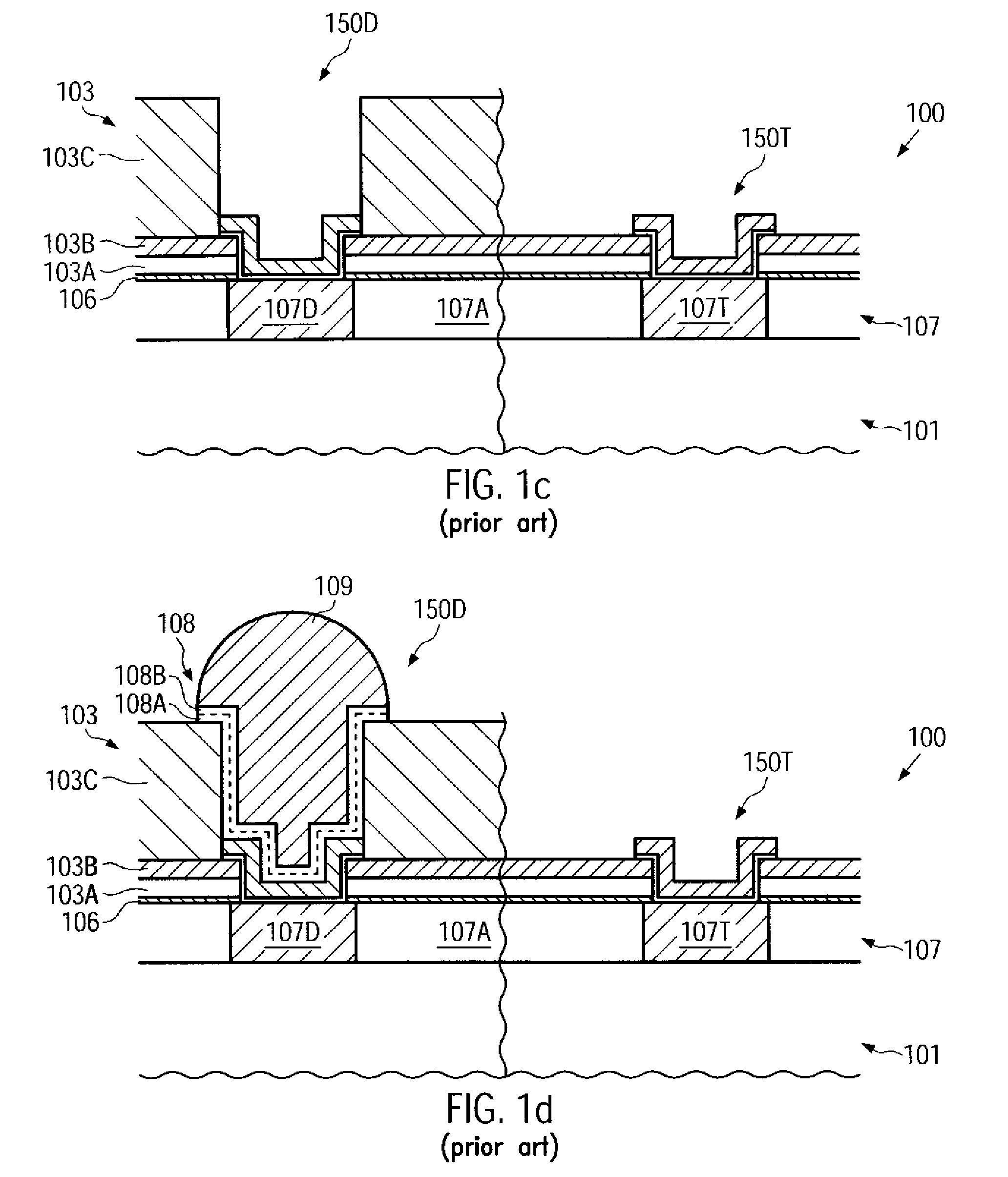

In sophisticated semiconductor devices including copper-based metallization systems, a substantially aluminum-free bump structure in device regions and a substantially aluminum-free wire bond structure in test regions may be formed on the basis of a manufacturing process resulting in identical final dielectric layer stacks in these device areas. Moreover, reliable wire bond connections may be obtained by providing a protection layer, such as an oxide layer, after exposing the respective contact metal, such as copper, nickel and the like, thereby providing highly uniform process conditions during the subsequent wire bonding process. The number of process steps may be reduced by making a decision as to whether a substrate is to become a product substrate or test substrate for estimating the reliability of actual semiconductor devices. For example, nickel contact elements may be formed above copper-based contact areas wherein the nickel may provide a base for wire bonding or forming a bump material thereon.

Owner:GLOBALFOUNDRIES INC

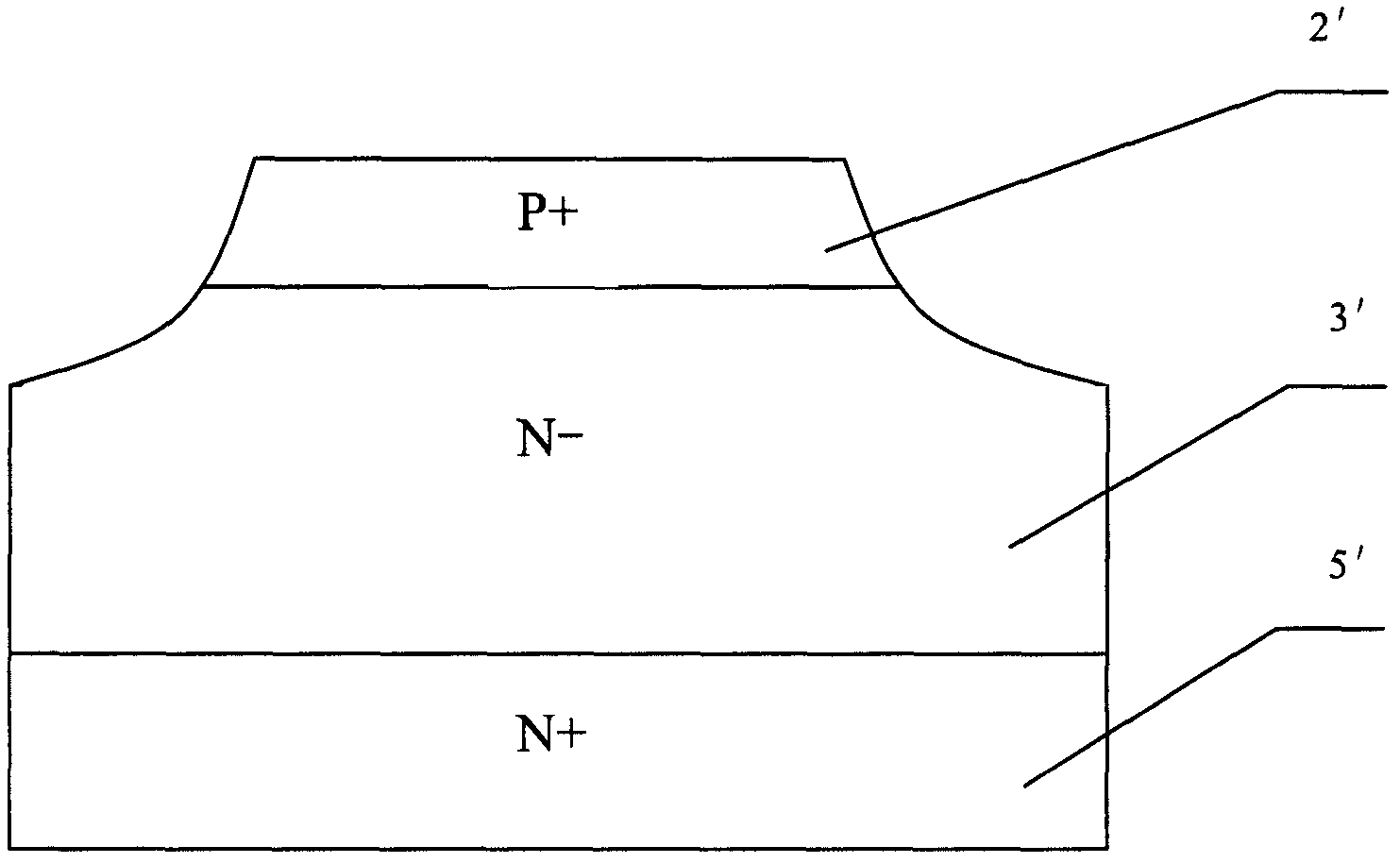

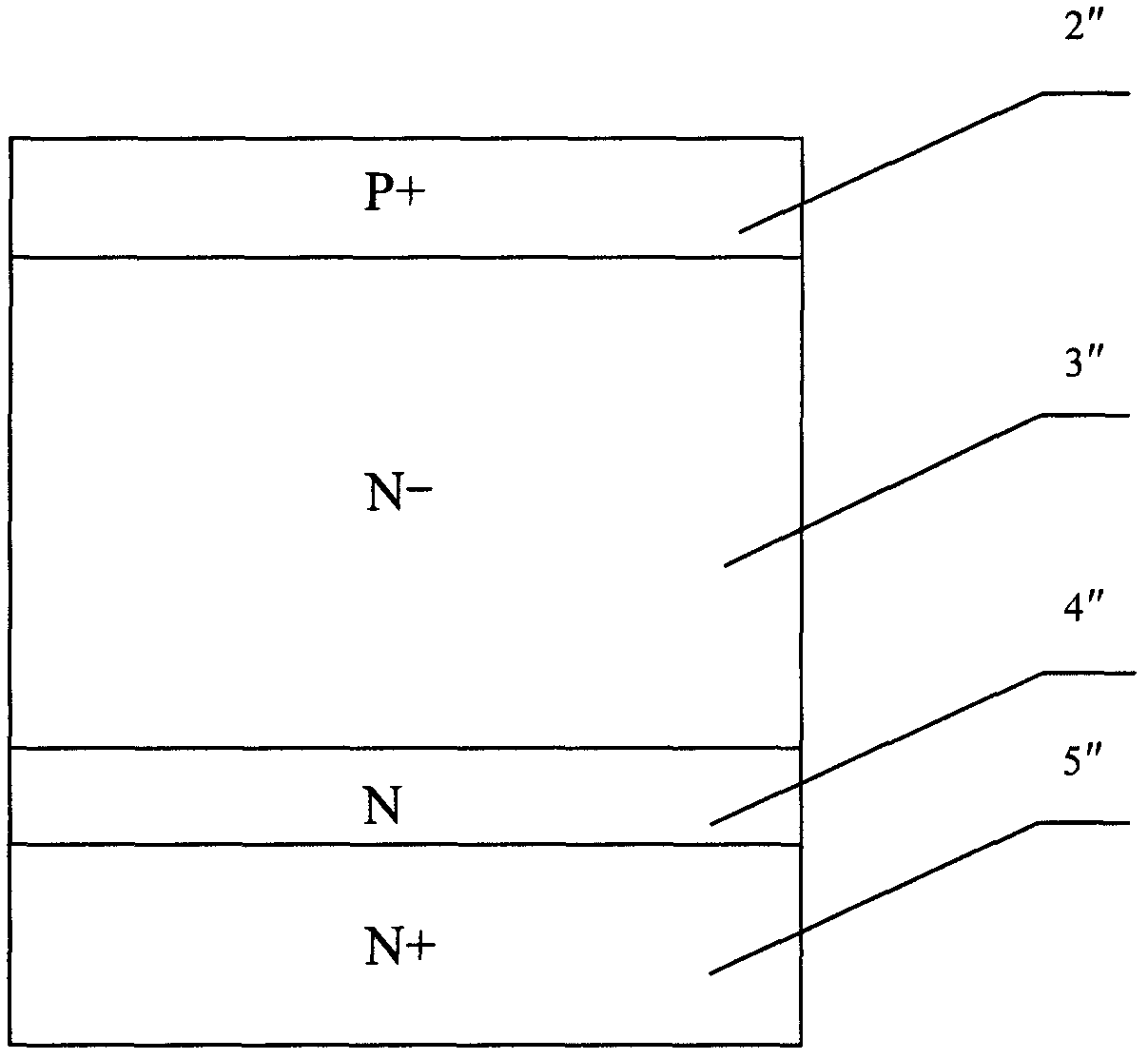

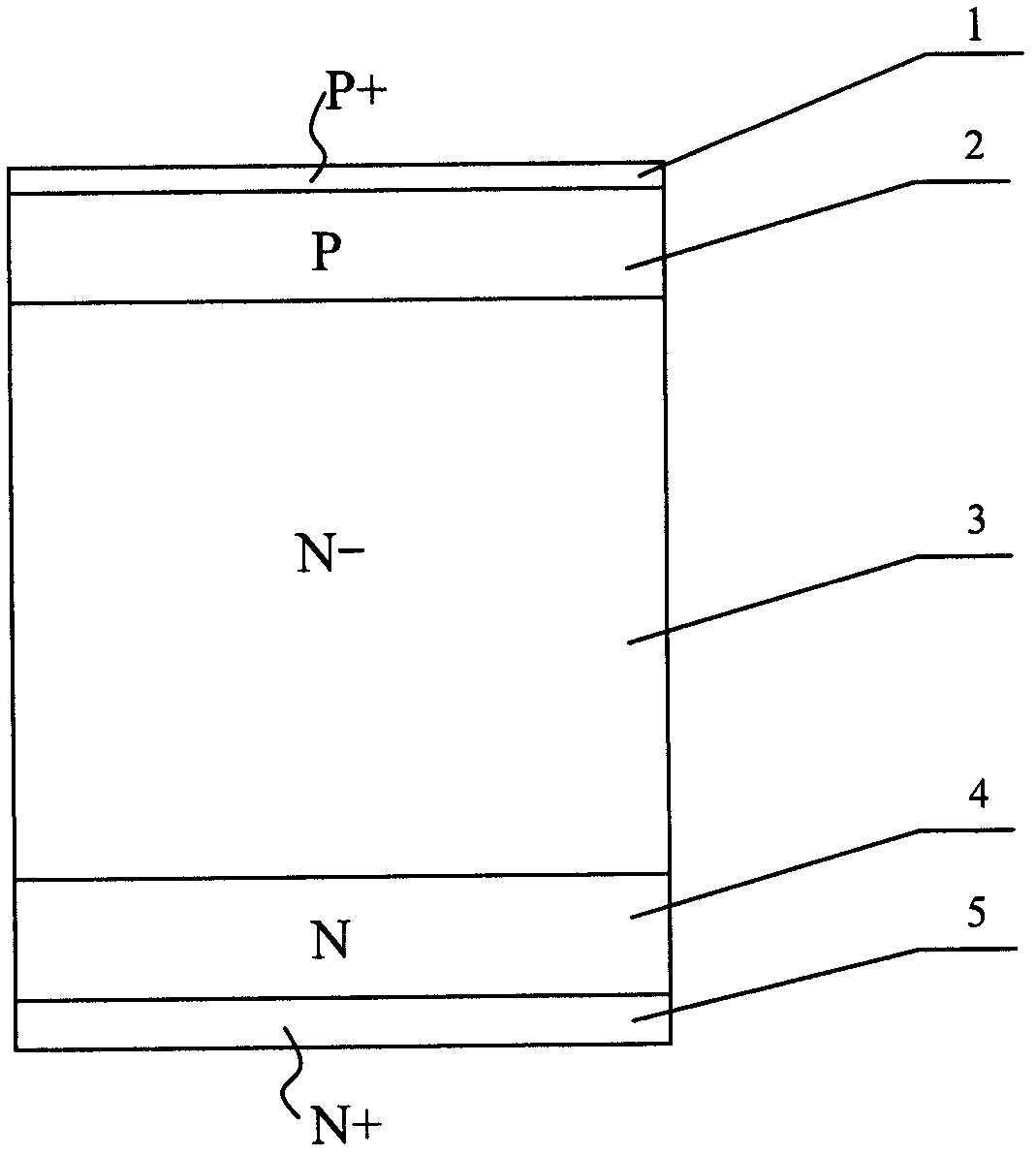

Method for manufacturing planar high-voltage ultrafast soft recovery diode

ActiveCN102569067ALow costMeet the requirements of mass productionSemiconductor/solid-state device manufacturingPlatinumLow leakage

The invention discloses a method for manufacturing a planar high-voltage ultrafast soft recovery diode. The method comprises the following steps of: oxidizing, and photoetching to form an active region and a field limiting ring; doping and pushing; manufacturing a polycrystalline silicon field plate; performing platinum diffusion; thinning; forming an N-type buffer layer; performing contact doping and annealing; and metalizing. The method can be used for manufacturing an ultrafast soft recovery diode chip which is low in cost and short in recovery time and has high-voltage resistance, low leakage current, low forward voltage drop and soft recovery characteristics.

Owner:BEIJING MXTRONICS CORP +1

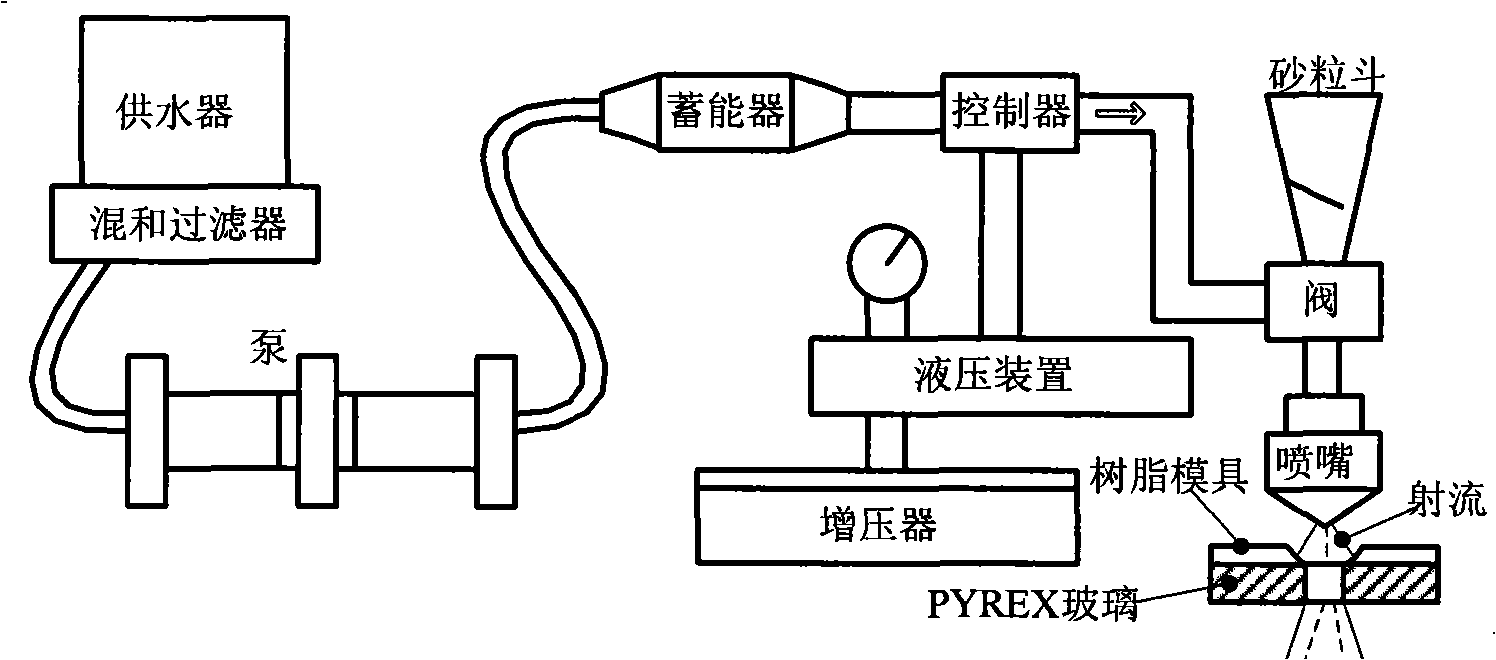

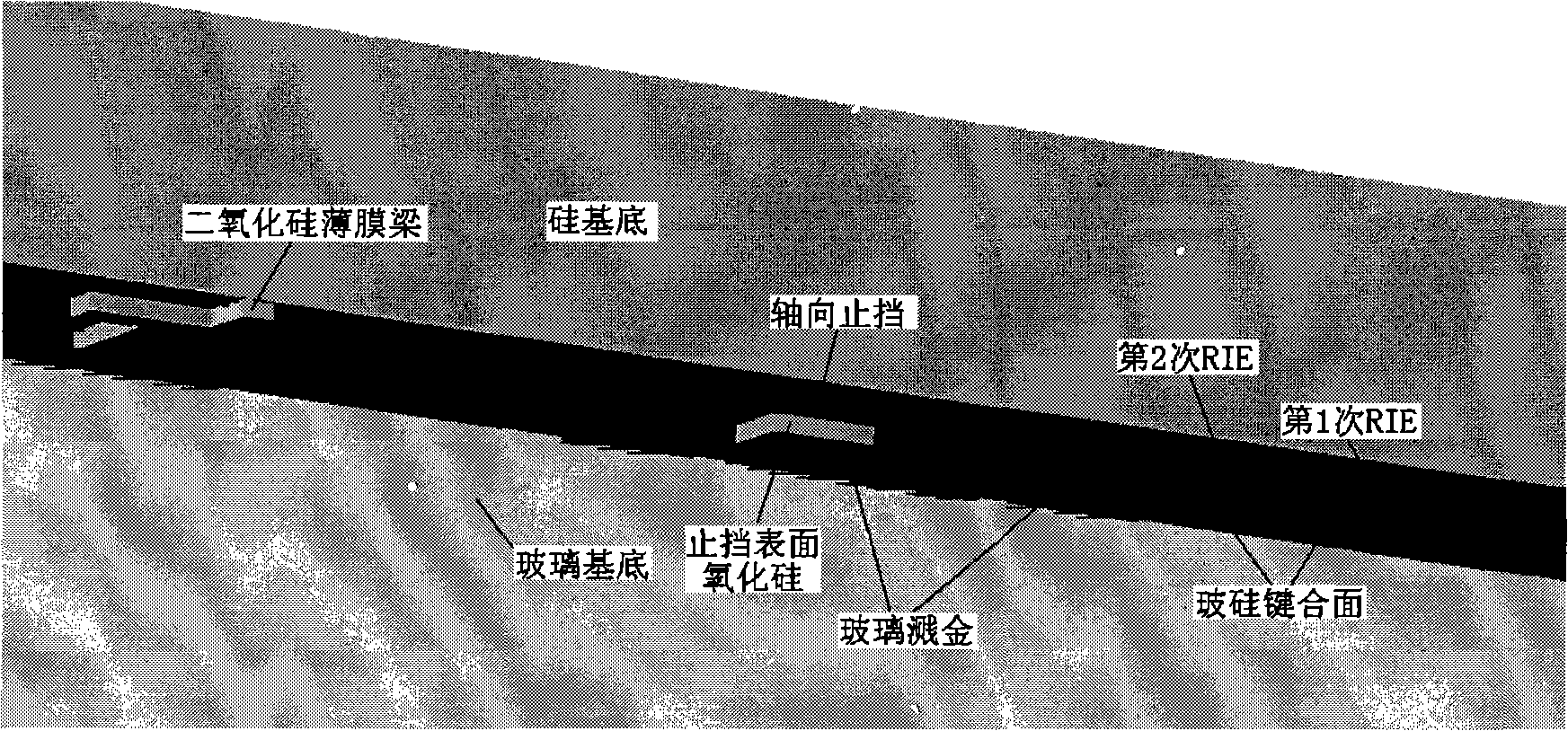

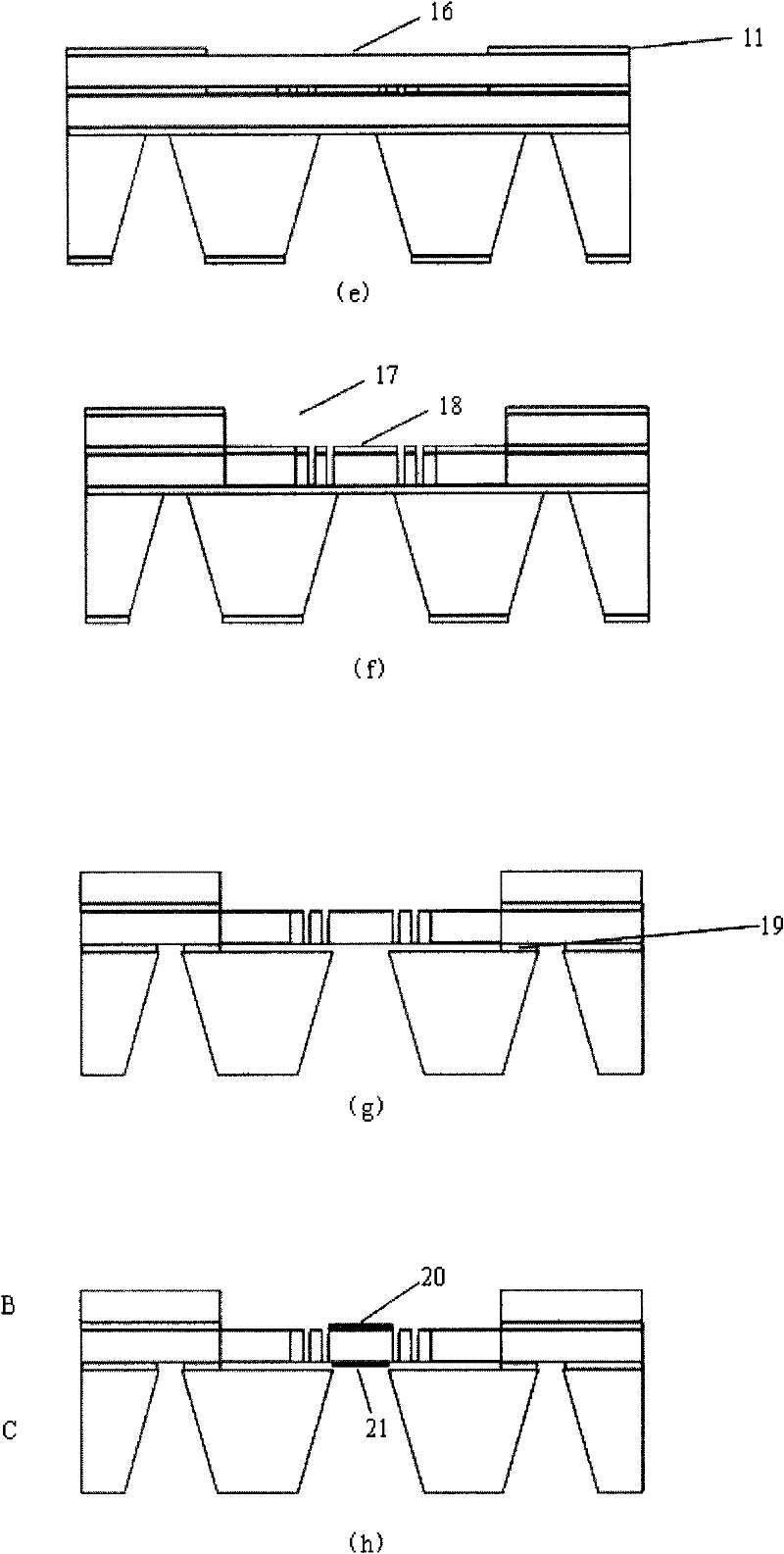

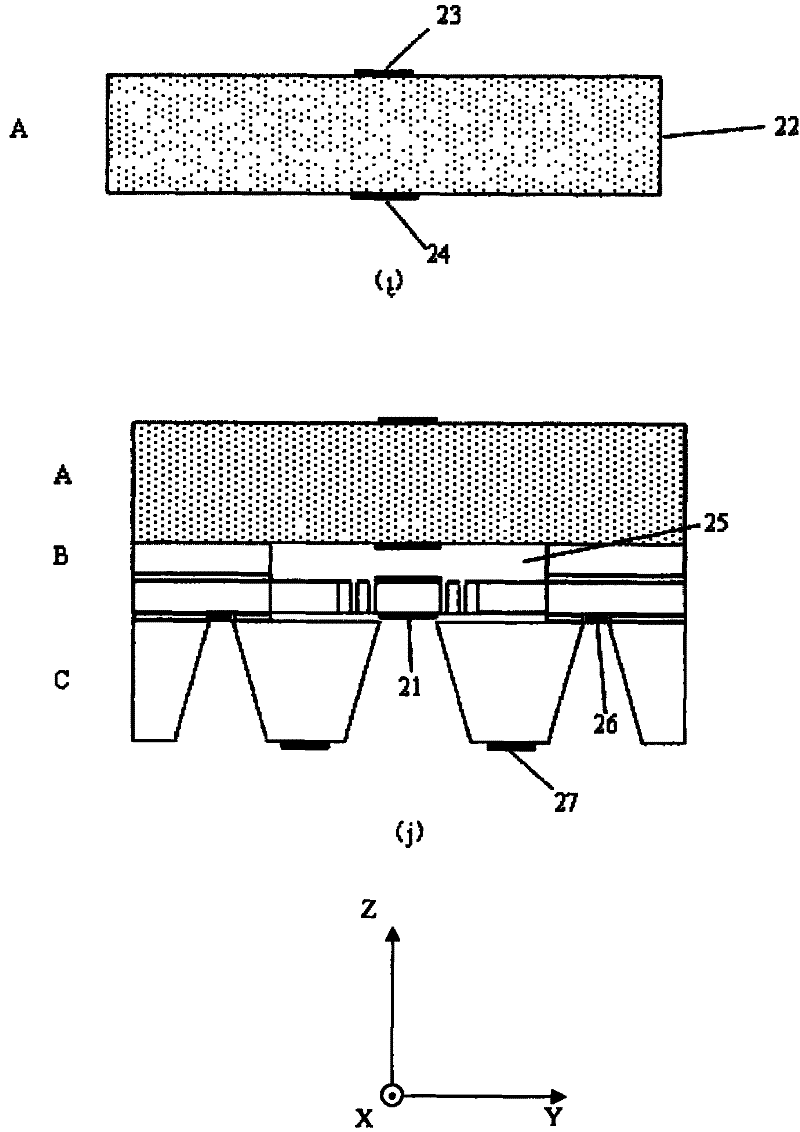

Manufacturing method for floating type micro-silicon electrostatic gyro/accelerometer sensitive structure

InactiveCN101279713AInhibit sheddingThickness loss is negligibleAcceleration measurement using interia forcesDecorative surface effectsLevitationAccelerometer

The invention relates to a method for preparing a levitation-type micro-silicon electrostatic gyro / accelerometer sensitive structure, which belongs to the technical field of silicon structure processing. The method comprises the steps: glass etching; glass gold splashing: a metal layer raising 400-600 tenthmeters higher than a glass surface; perforating the glass; a first and a second RIE etching for the silicon slice; film beam process: high-temperature dry oxidation and surface corrosion; a first electrostatic bonding for glass and silicon; thinning and polishing to the silicon slice; ICP etching for the silicon slice; a third RIE etching for the silicon slice; a fourth RIE etching for the silicon slice; a second electrostatic bonding for glass and silicon; ICP removal for film beam to prepare the levitation-type micro-silicon electrostatic gyro / accelerometer sensitive structure. The method adopts the proposal of sandblasting perforating for perforating the glass, introduces the silicon dioxide film beam as a sacrificial layer and adopts the ICP film beam removal process; the method can effectively solve the problem of adherence of a sandwich microstructure in the second electrostatic bonding and does not need post treatment so that the method has higher efficiency and better compatibility with the MEMS process.

Owner:TSINGHUA UNIV +1

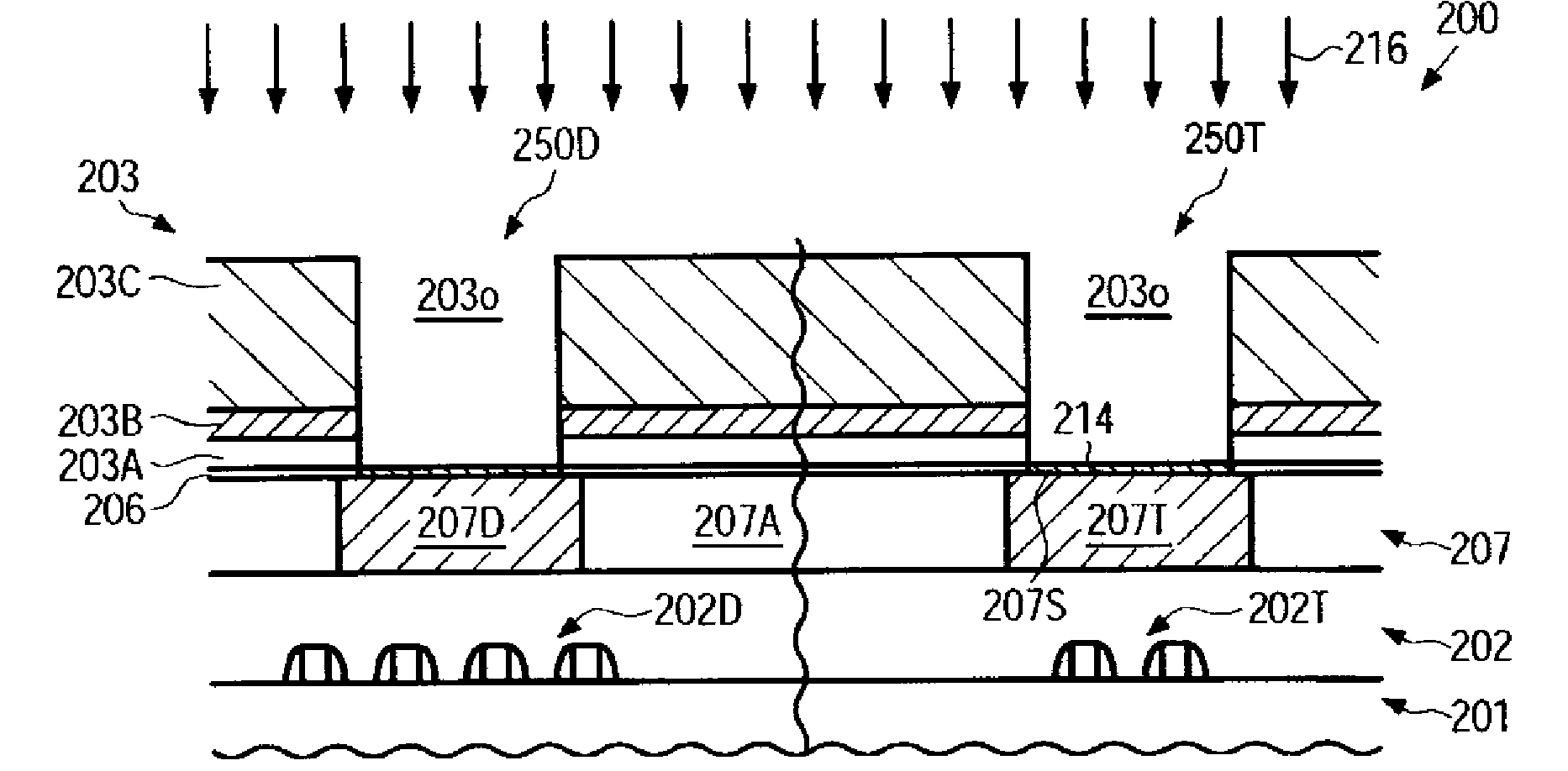

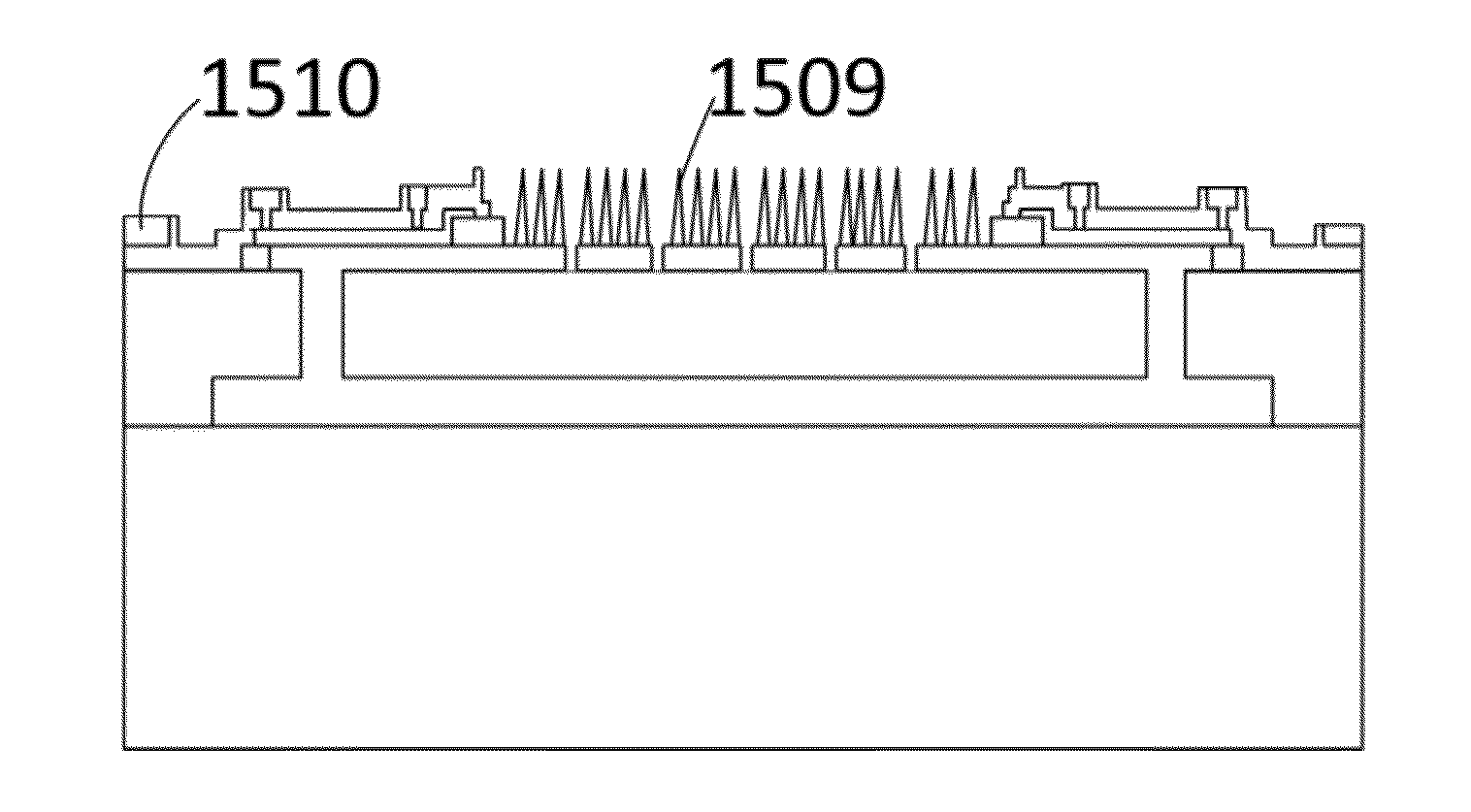

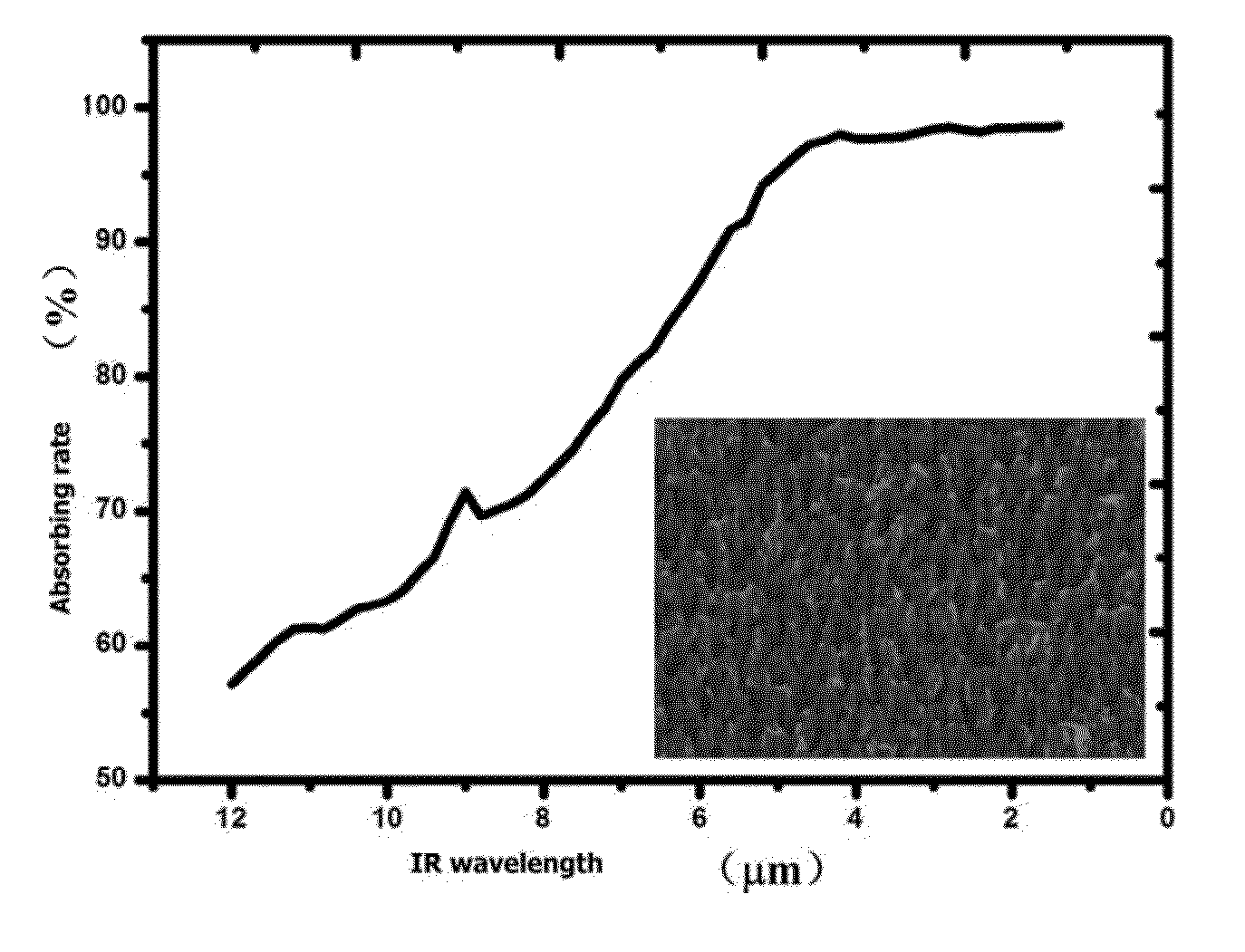

Black silicon-based high-performance MEMS thermopile ir detector and fabrication method

ActiveUS20150168221A1Good process compatibilityEasy of device structureTelevision system detailsPiezoelectric/electrostriction/magnetostriction machinesPhysicsIr detector

This invention involves structure and fabrication method of a black silicon-based MEMS thermopile IR detector. The high-performance black silicon-based MEMS thermopile IR detector includes a substrate; a releasing barrier band on the substrate; a thermal isolation cavity constructed by the releasing barrier band; a black silicon-based IR absorber located right above the thermal isolation cavity; a number of thermocouples are set around the lateral sides of the black silicon-based IR absorber. The thermopiles around the black silicon-based IR absorber are electrically connected in series thus to form a thermopile. Metallic electrodes are located beside the electrically-connected thermopiles for signal output. The cold junctions of the thermopile are connected to the substrate through the first thermal-conductive-electrical-isolated structures, the heat conductor is located at the lateral sides of the thermal isolation cavity. The hot junctions of the thermopile are in contact with the IR absorber through the second thermal-conductive-electrical-isolated structures, and the second thermal-conductive-electrical-isolated structures are located above the releasing barrier band. The structure of such detector is simple, and it is easy to implement and can also be monolithicly integrated. Such detector has high responsivity and detection rate, and is CMOS-compatible, thus can be used widely in a safe and reliable manner.

Owner:ZHONGKE FUTURE OF CHIP MICROELECTRONICS TECH CHENGDU CO LTD

Soft support bridge type silicon micro-piezoelectric ultrasonic transducer chip and prepration method thereof

InactiveCN101645484AHigh sensitivityGood process compatibilityPiezoelectric/electrostrictive device manufacture/assemblyPiezoelectric/electrostrictive device material selectionVertical projectionUltrasonic sensor

The invention relates to a soft support bridge type silicon micro-piezoelectric ultrasonic transducer chip which comprises a silicon substrate with a square conical hole which is small at the top andbig at the bottom in the center; a silicon layer and a first oxidation layer are sequentially covered on the front surface of the silicon substrate, and a second oxidation layer is covered on the backsurface; the corresponding silicon layer and the first oxidation layer above the square hole of the front surface of the silicon substrate constitute a square vibration membrane, one pair of oppositesides of the square vibration membrane respectively etch a vertical narrow slot, and the vertical projection of each narrow slot is positioned on the inner side of the hole edge above the front surface of the silicon substrate; a lower electrode, a piezoelectric membrane and an upper electrode are sequentially deposited on the square vibration membrane; a polyimide membrane is deposited on various parts on the front surface of the silicon substrate; and the square vibration membrane which is etched with the vertical narrow slots and the polyimide membrane commonly constitute a soft support anti-sound leakage bridge type vibration membrane. The anti-sound leakage bridge type structure is used on the vibration membrane of the transducer; in order to avoid sound leakage through the narrow slots, the soft polyimide membrane is deposited on the narrow slots, which has little effect on vibration of the vibration membrane and can still keep high sensitivity.

Owner:INST OF ACOUSTICS CHINESE ACAD OF SCI

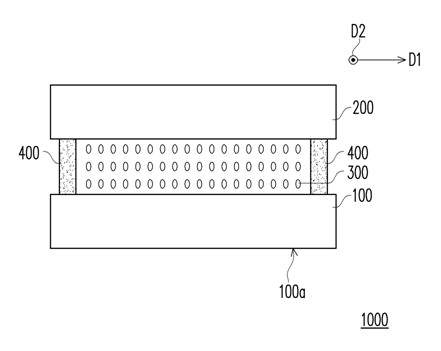

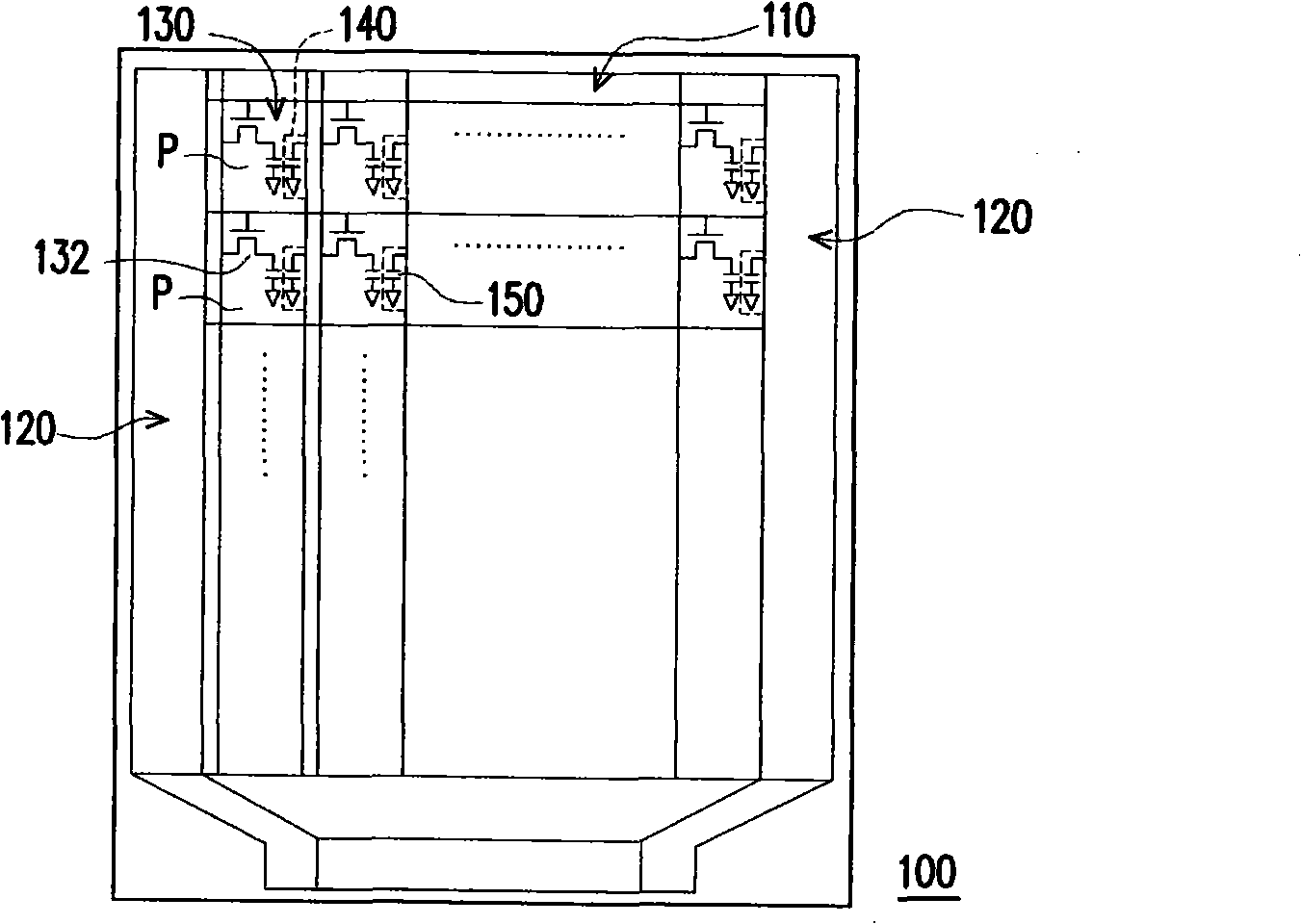

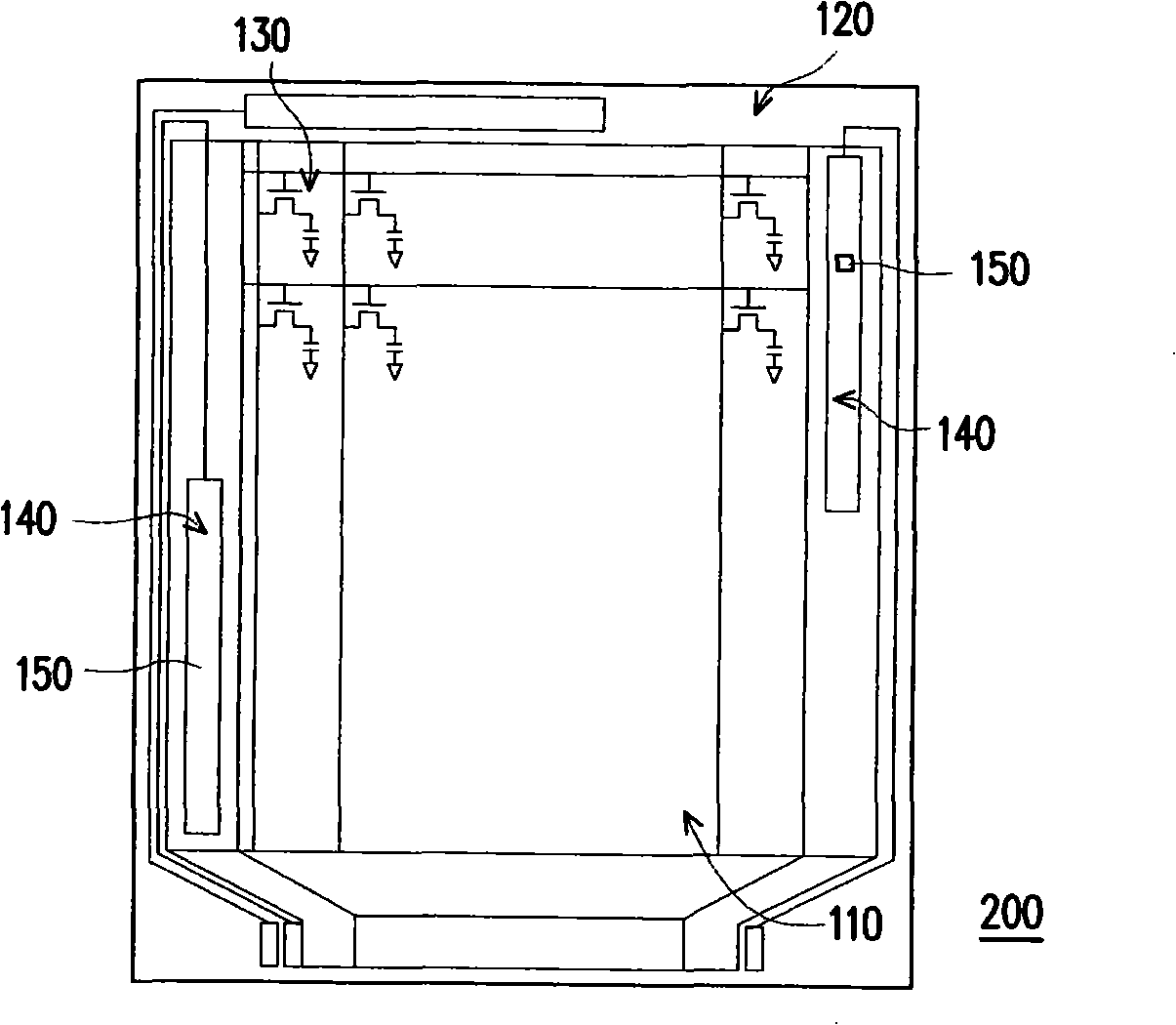

Pixel array substrate display panel

InactiveCN102183860AReduce the chance of electrostatic damageAvoid problems such as uneven hardeningSolid-state devicesNon-linear opticsArray data structureComputer science

The invention relates to a pixel array substrate which comprises a substrate, a plurality of pixel structures, a plurality of first routings and second routings, wherein the substrate comprises a display area and a peripheral circuit area out of the display area, the pixel structure array is arranged in the display area, the plurality of first routings and second routings are located at the peripheral circuit area, and respectively electrically connected with the corresponding pixel structure; the second routing is above the first routing and electrically insulated from the first routing; the first routing and the second routing are respectively extended along a column direction from the display area and alternatively arranged on a line direction; the projections of each first routing and one of the adjacent second routing are crossed and overlapped with each other by means of inclined parts with the same slope so as to form a set of double-layer routing; and furthermore, the invention provides a display panel with the pixel array substrate. The narrow side of the pixel array substrate can be framed so as to improve the problem of static damage of two adjacent peripheral routings in the traditional pixel array substrate.

Owner:CPT TECH GRP +1

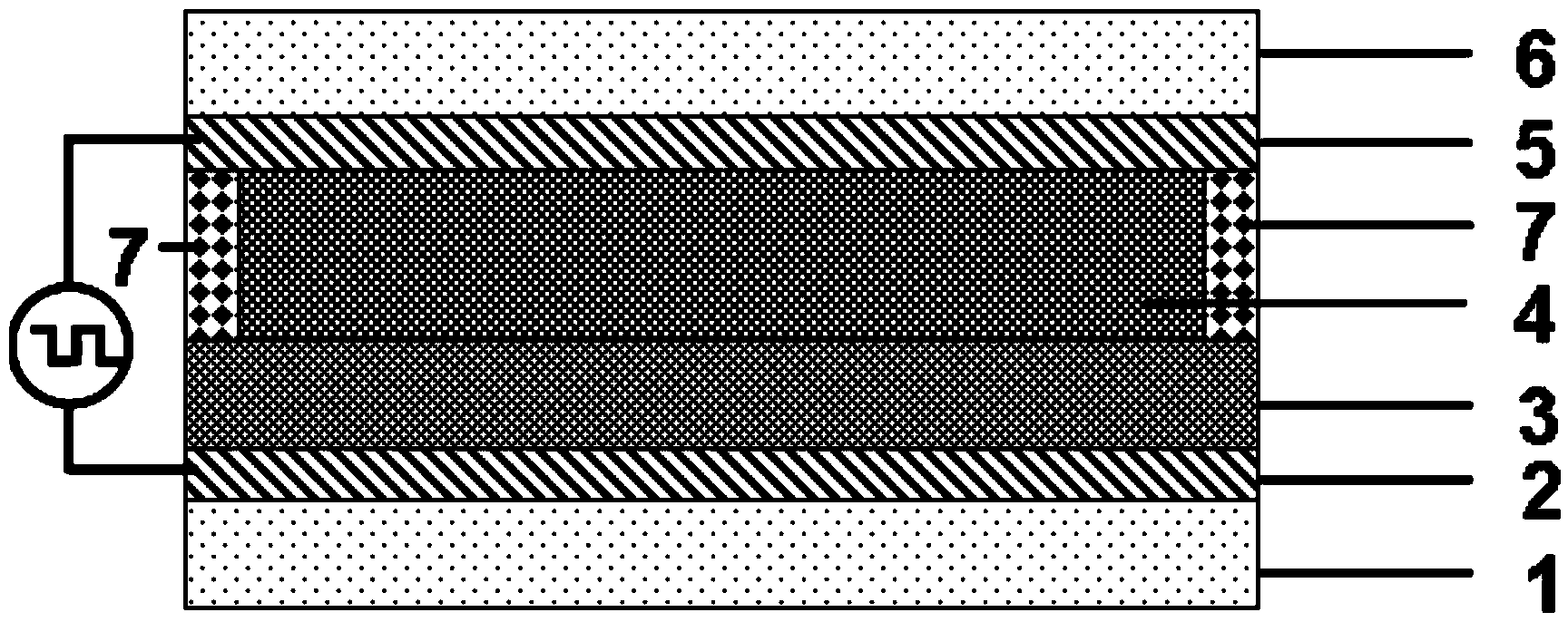

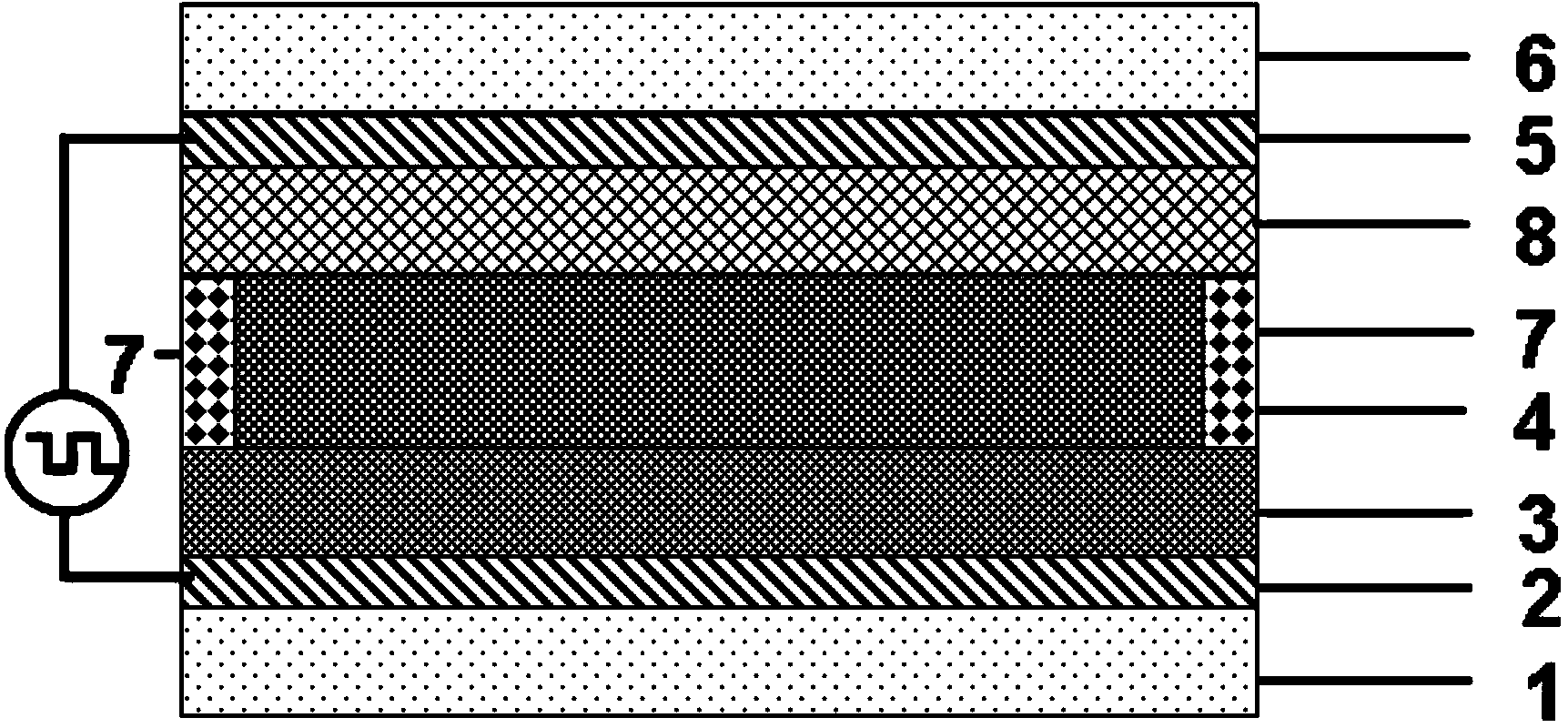

Electrochromic device and manufacturing method thereof

ActiveCN104076569AReduce manufacturing costLow costNon-linear opticsSolid state electrolyteComposite film

The invention discloses an electrochromic device and a manufacturing method of the electrochromic device. The electrochromic device comprises a transparent conducting layer, an electrochromic layer and an electrolyte layer, and the electrolyte layer is a transparent nano-particle film filled with electrolyte solutions with Li ions. An anode electrochromic layer or a cathode electrochromic layer is adopted as the electrochromic layer, and the electrochromic behaviors of four colors (orange-yellow-green-blue) can be achieved under the multi-step electric potential ([-3.0, +3.0] V). The inorganic oxide nano-particle film is manufactured based on the plasma enhanced chemical vapor deposition technology and is fully soaked in the electrolyte solutions with the Li ions to form an inorganic-organic composite film as the solid electrolyte layer, cost is low, the electrochemical deposition technology, the PECVD technology, the magnetron sputtering technology and the like are adopted in the manufacturing process of the electrochromic device, deposition is carried out at the room temperature, large-size growth can be achieved easily, compared with an existing electronic device, process compatibility is good, large-scale industrialization is easy to achieve, and therefore the manufacturing cost of the device can be greatly lowered.

Owner:CHANGZHOU DEEP BLUE COATING TECH

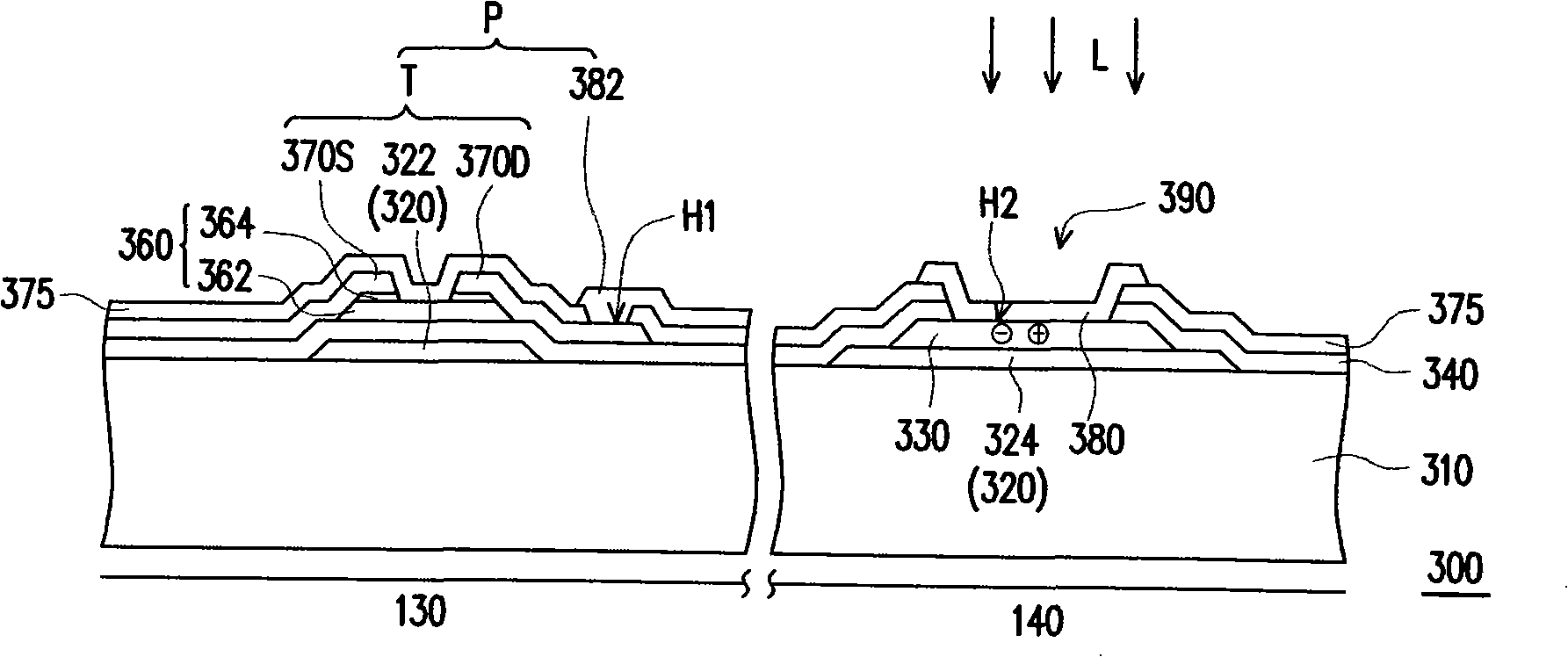

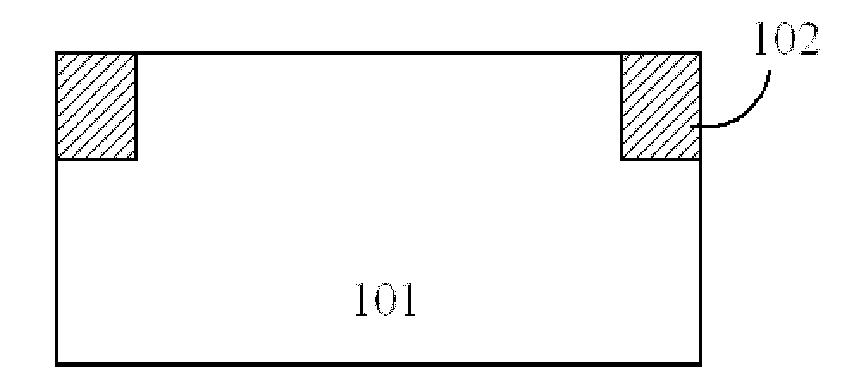

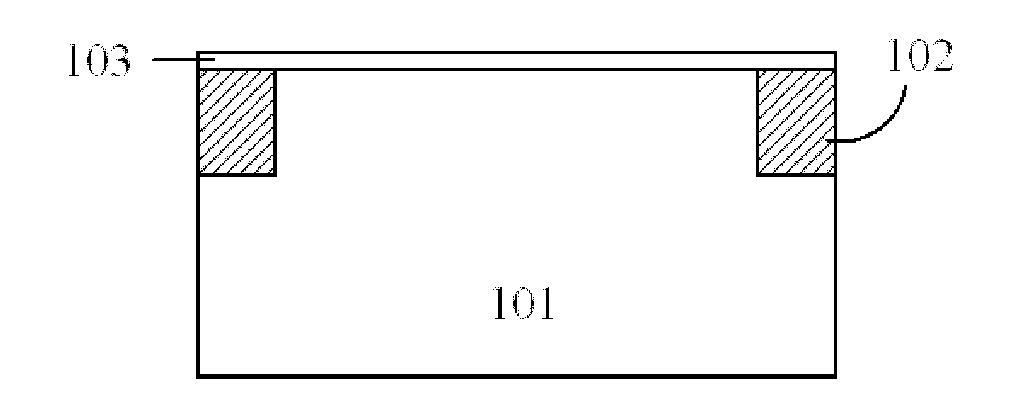

Thin-film transistor array substrate and preparation method thereof

ActiveCN101325181AIncrease photocurrentIncrease the performance of photoelectric characteristicsSemiconductor/solid-state device manufacturingRadiation controlled devicesLight sensingDielectric layer

The invention discloses a thin-film transistor array substrate and a manufacturing method thereof. The method comprises the following steps of: (1) providing a substrate with a pixel region and a light sensing region; (2) forming a first patterned conducting layer on the substrate, wherein the first patterned conducting layer comprises a grid electrode positioned in the pixel region and a first electrode positioned in the light sensing region, and forming a light sensing dielectric layer on the first electrode; (3) forming a grid electrode insulating layer on the substrate to cover the grid electrode, the light sensing dielectric layer and the first electrode; (4) forming a patterned semiconductor layer on the grid electrode insulating layer above the grid electrode; (5) forming a source electrode and a drain electrode on the patterned semiconductor layer at two sides of the grid electrode, wherein the grid electrode, the source electrode and the drain electrode form a thin-film transistor; and (6) forming a second electrode on the light sensing dielectric layer.

Owner:AU OPTRONICS CORP

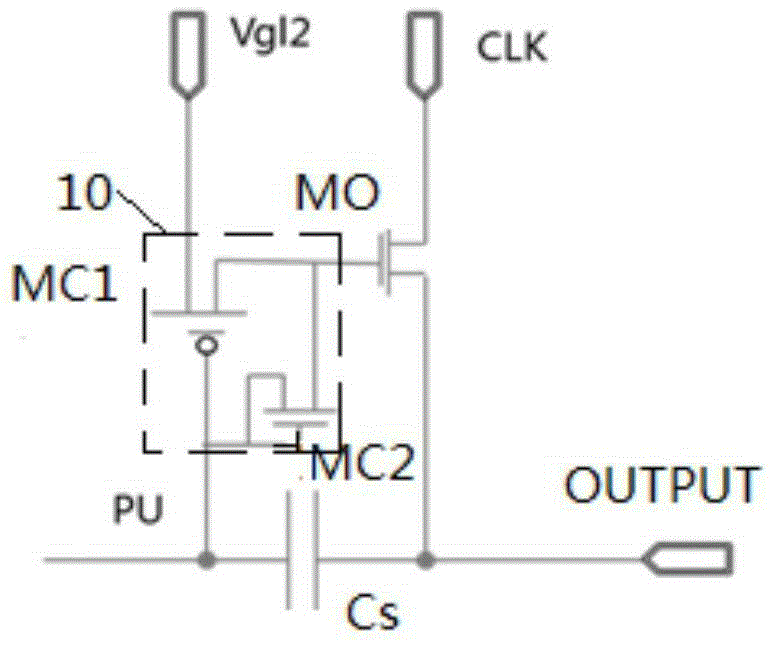

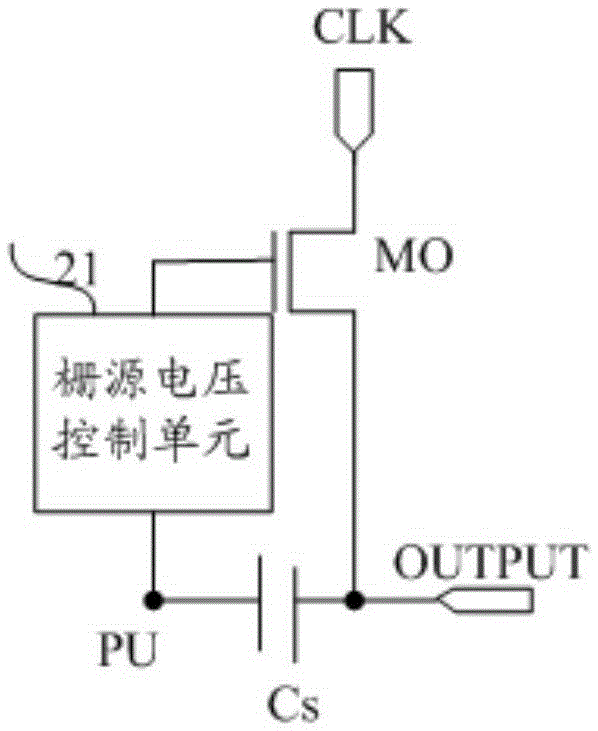

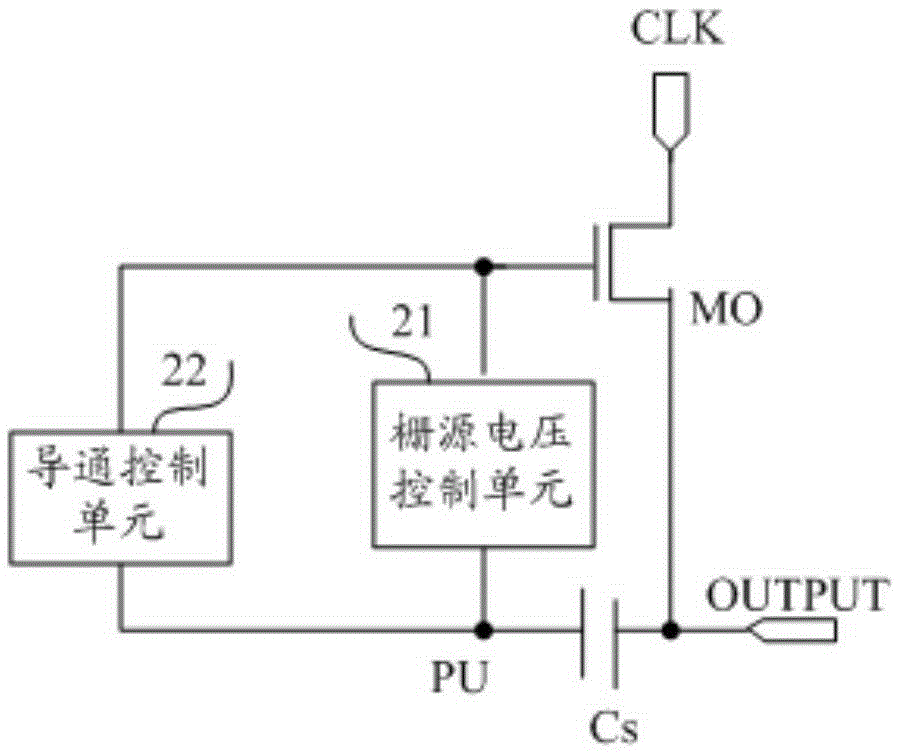

Voltage control circuit and method, grid driving circuit, and display apparatus

ActiveCN105427793ASolve the problem of high temperature abnormal displayGood process compatibilityStatic indicating devicesDigital storageElectricityEngineering

The invention provides a voltage control circuit and method, a grid driving circuit, and a display apparatus. The voltage control circuit comprises a grid source voltage control unit which is connected with a grid of an output transistor and an upper-drawing node for controlling grid source voltage of the output transistor to be smaller than preset grid source voltage through controlling grid level of the output transistor when level of the upper-drawing node is low in an output cut-off maintenance time period of each display period, wherein the preset grid source voltage is smaller than or equal to zero. All transistors included by the grid source voltage control unit are n-type transistors. In each display period, the output cut-off maintenance time period is set after an output time period. All the transistors included in the grid source voltage control unit included by the voltage control circuit provided by the invention are all n-type transistors. The voltage control circuit can improve the technical compatibility while solving the problem of high-temperature abnormal display caused by too large reverse cut-off grid source voltage.

Owner:BOE TECH GRP CO LTD +1

Polymer, resist protective coating material, and patterning process

ActiveUS7642034B2Efficient formationGood process compatibilityPhotosensitive materialsPhotosensitive materials for photomechanical apparatusTectorial membraneHydrogen

A polymer comprising repeat units having formula (1) wherein R1 and R2 are hydrogen or C1-C12 alkyl, or R1 and R2 may bond together to form a ring, and R30 is hydrogen or methyl is used to formulate a resist protective coating material. A protective coating formed therefrom on a resist film is water-insoluble, dissolvable in alkali aqueous solution or alkaline developer, and immiscible with the resist film so that the immersion lithography can be conducted in a satisfactory manner. During alkali development, development of the resist film and removal of the protective coating can be simultaneously achieved.

Owner:SHIN ETSU CHEM IND CO LTD

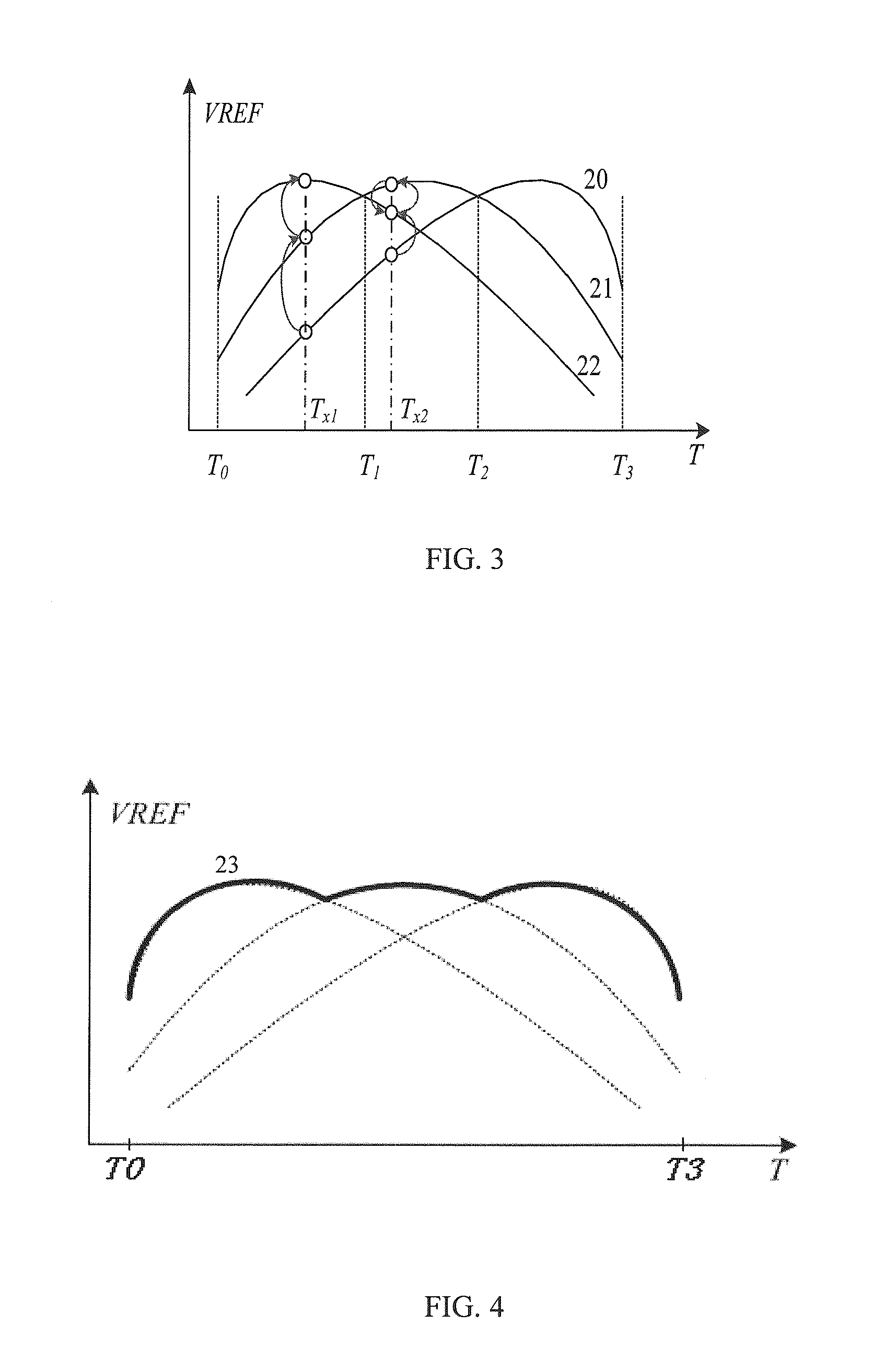

Temperature adaptive bandgap reference circuit

InactiveUS20130314068A1Good process compatibilitySmall coefficientPower supply linesElectric variable regulationHemt circuitsControl theory

This invention involves a bandgap reference circuit in IC. The temperature coefficient of conventional bandgap reference is large and the higher order compensation is difficult to implement. This invention provides an adaptive compensated bandgap reference which solves the problem only using lower order (first order) temperature coefficient compensation. The invention adopts segmental compensation circuit to realize adaptive segmental compensation of bandgap reference with low temperature coefficient. The technical solution includes traditional bandgap voltage reference circuit and adaptive feedback compensation circuit which consists of sample and hold circuit, voltage comparator and control module. This invention controls the bandgap voltage reference through systematical view and it has high process compatibility. This invention can find the best temperature characteristic curve adaptively, the output voltage has low temperature coefficient, meeting the requirement of fabrication process, the implementation is simple with small area. This invention relates to integrated circuits.

Owner:UNIV OF ELECTRONIC SCI & TECH OF CHINA

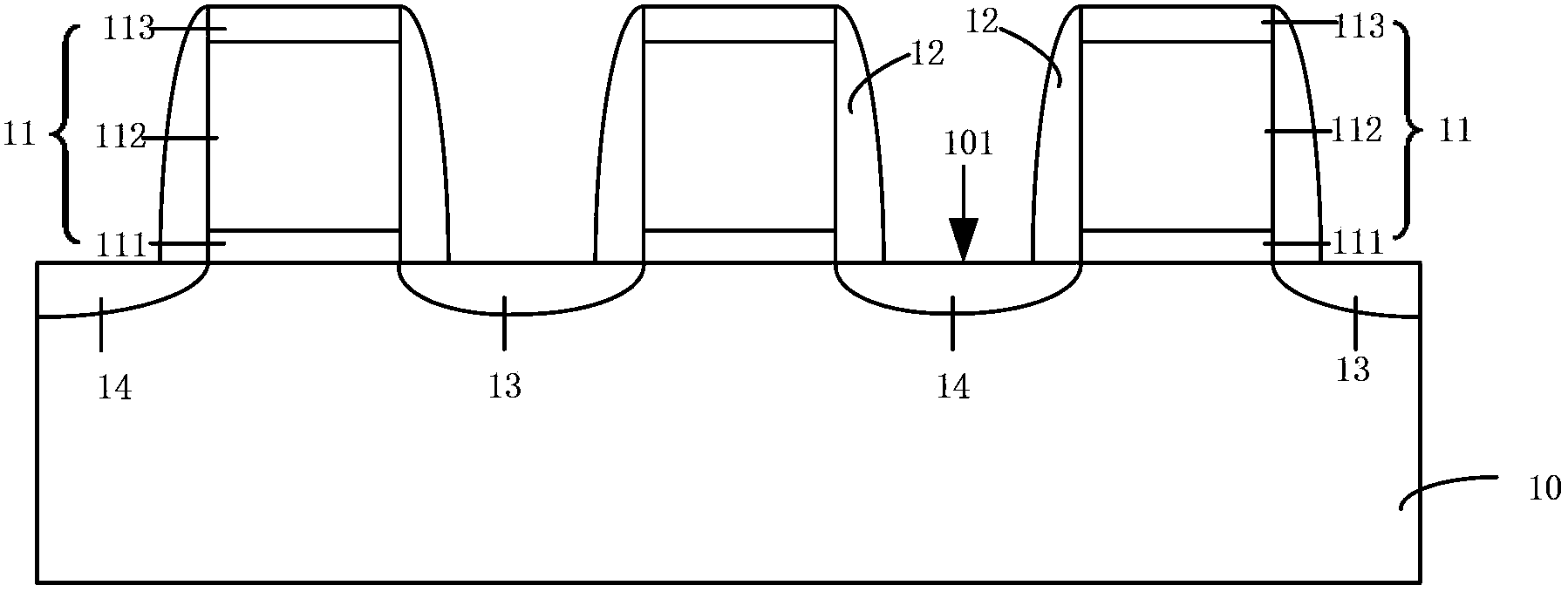

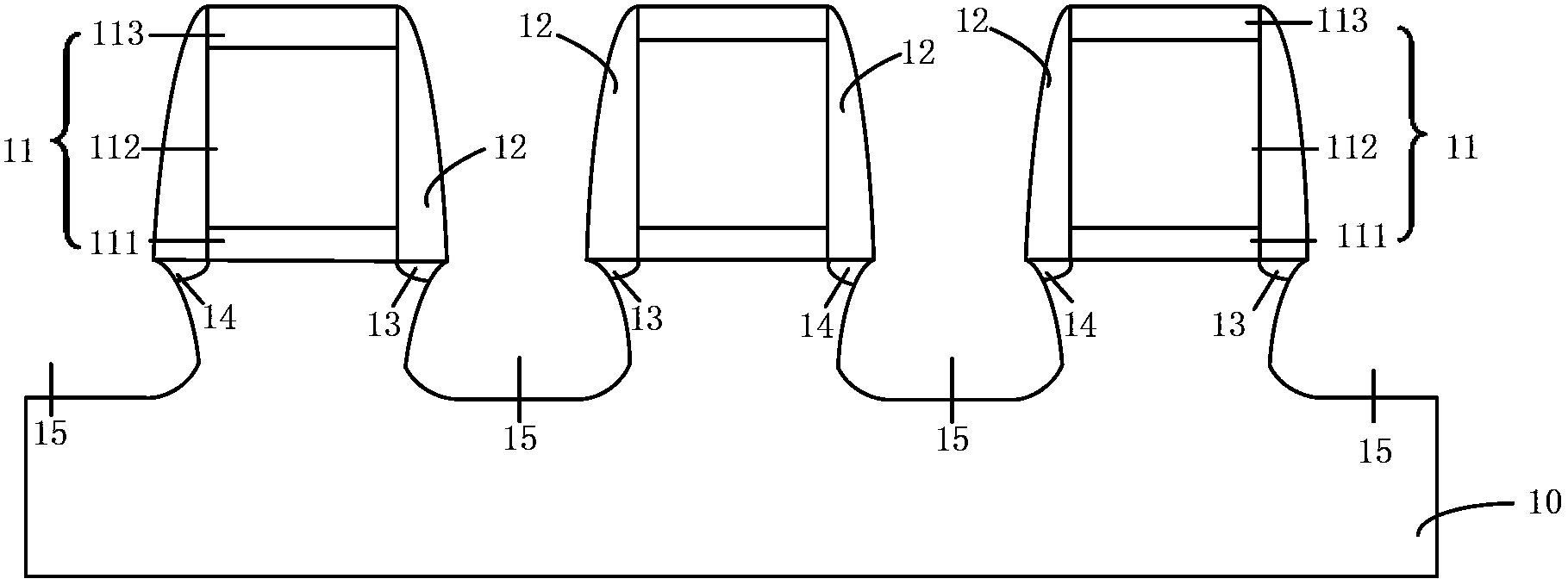

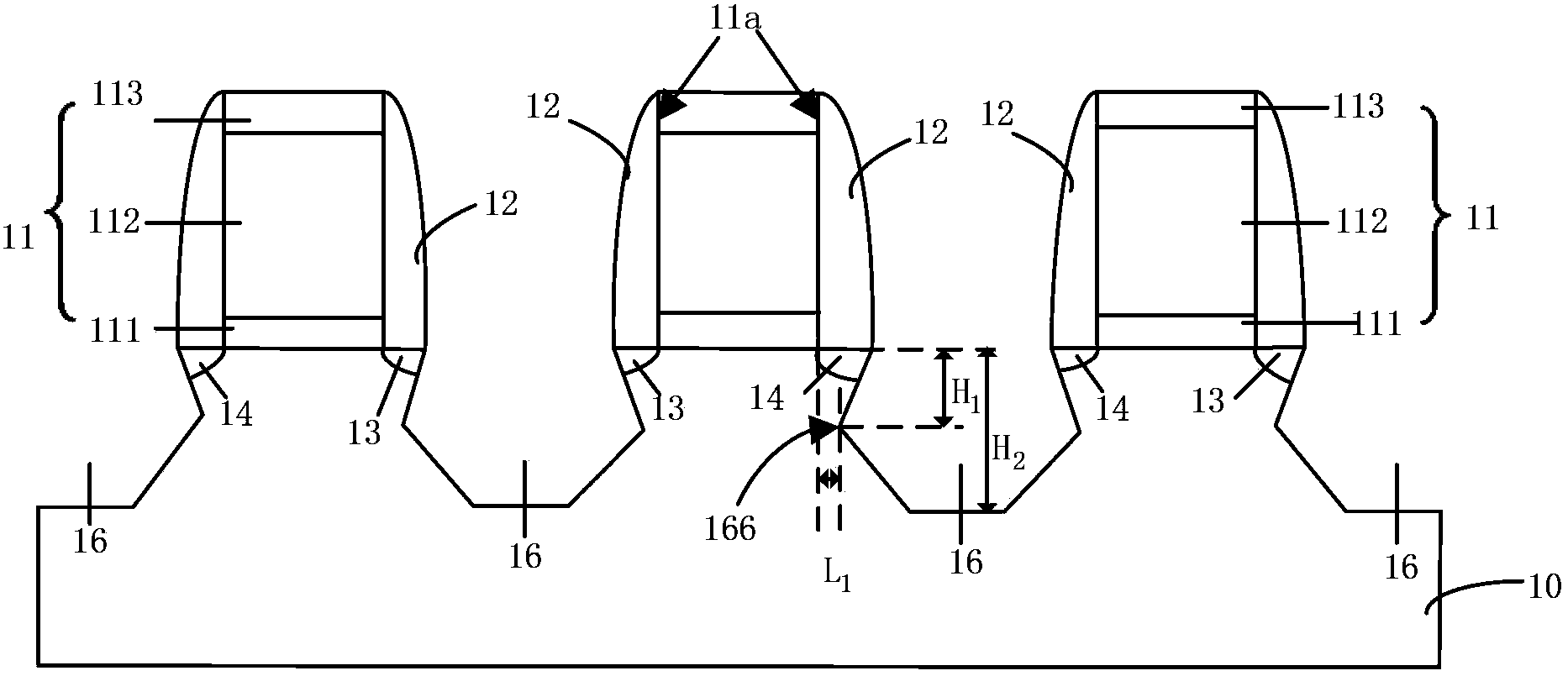

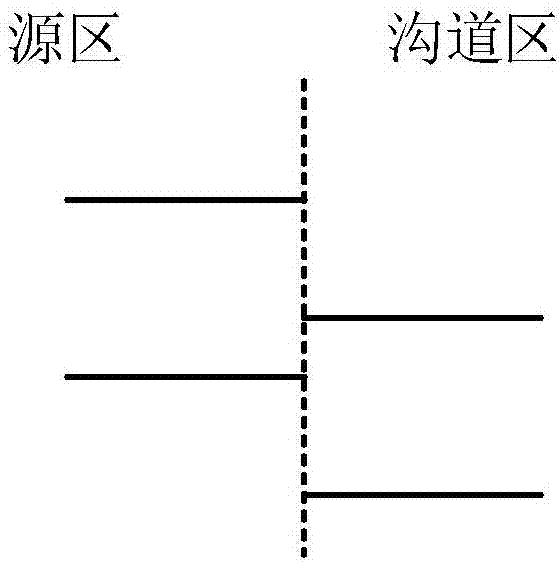

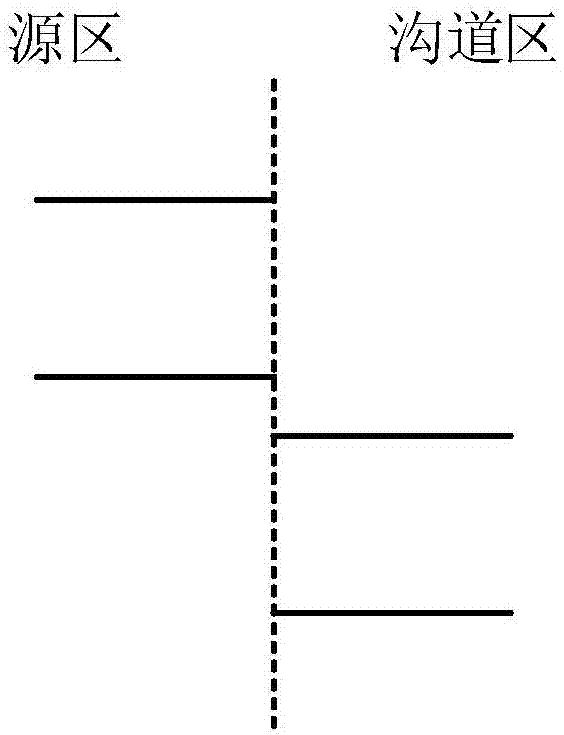

Manufacturing method for PMOS transistor and manufacturing method for NMOS transistor

ActiveCN104103515AIncrease compressive stressIncrease the tensile stressTransistorSemiconductor/solid-state device manufacturingEngineeringElectron

The invention provides a manufacturing method for a PMOS transistor and a manufacturing method for an NMOS transistor. According to the aforementioned manufacturing methods, multiple laminated sigma-shaped grooves (at least two), i.e. stepped sigma-shaped grooves, are formed in source electrode and drain electrode regions in a direction of being perpendicular to the surface of a silicon substrate. In the direction from the surface of the silicon substrate into the silicon substrate, the groove tip, which stretches into a channel, of each sigma-shaped groove presents to be away from the channel gradually. Then a) as for the PMOS transistor, silicon germanium material is filled in the stepped sigma-shaped grooves so that pressure stress is applied to the channel, b) and as for the NMOS transistor, silicon carbide material is filled in the stepped sigma-shaped grooves so that pulling stress is applied to the channel. Therefore, capacity of the stepped sigma-shaped grooves is larger, and more silicon germanium material or silicon carbide material can be accommodated. Correspondingly, pressure stress or pulling stress to the channel is increased so that migration rate of hole carriers or electron carriers is improved.

Owner:SEMICON MFG INT (SHANGHAI) CORP

Manufacturing method of adjustable FP (filter pass) optical filter based on MEMS (micro electro mechanical system) process

InactiveCN102225739AImprove yieldGood process compatibilityDecorative surface effectsChemical vapor deposition coatingAcid etchingEvaporation

The invention relates to a manufacturing method of an adjustable FP (filter pass) optical filter based on an MEMS (micro electro mechanical system) process, which is characterized in that the etching window of all graphs is manufactured by adopting the etching twice; the manufacturing of a middle FP air cavity and a movable reflector surface structure is finished by adopting the plasma silicon etching once; a movable silicon membrane reflector is manufactured by adopting the processes such as the silicon-silicon bonding, the plasma dry etching, the HF (hydrogen fluoride) acid etching and the silicon oxide layer releasing once; the high-reflection membrane and anti-reflection membrane of the two reflectors in the FP cavity are manufactured by adopting a method for selecting evaporation through a hard template; and a final FP cavity filter is formed by adopting the silicon-glass bonding once. In the manufacturing method provided by the invention, the process procedures are greatly simplified; the mirror finish and parallelism of the FP cavity are guaranteed; and the optical technical index and chip yield of the manufactured FP filter are improved. Compared with the existing like product manufacturing process, the manufacturing method provided by the invention has the advantages of good process compatibility and maneuverability, low driving voltage and good optical tuning repeatability and stability and can be widely applied to an optical communication WDM (wavelength division multiplex) system.

Owner:SHANGHAI INST OF MICROSYSTEM & INFORMATION TECH CHINESE ACAD OF SCI

Manufacturing method for FinFETs (fin field effect transistors)

ActiveCN102651320AOvercoming heatingOvercome the floating body effectSemiconductor/solid-state device manufacturingSemiconductor devicesFloating body effectOrganic field-effect transistor

The invention discloses a manufacturing method for FinFETs (fin field effect transistors), which includes the following steps: forming Omega-shaped fins on a semiconductor substrate; forming grid stacking structures at the tops and on the lateral surfaces of the Omega-shaped fins; forming source / leakage structures in the Omega-shaped fins on the two sides of the grid stacking structures; and performing metallization, wherein except that the bottoms of the Omega-shaped fins are connected with the semiconductor substrate through a narrower silicon strip, the other parts of the grid stacking structures are separated from the semiconductor substrate through a separation dielectric layer. The manufacturing method provided by the invention eliminates the self-heating effect and the floating body effect existing in an SOI device, has lower cost, overcomes the defects that the common bulk FinFET has big creepage current and better SCE (short-channel effect), is excellently compatible with the CMOS (complementary metal oxide semiconductor) plane technology, and is simple to integrate.

Owner:SOI MICRO CO LTD

Full-color semiconductor light emitting micro display and manufacturing process thereof

ActiveCN107195654ALow costEasy to manufactureSolid-state devicesSemiconductor/solid-state device manufacturingDisplay deviceOrganic compound

The invention discloses a structure of a full-color semiconductor light emitting micro display and a manufacturing process thereof. The full-color semiconductor light emitting micro display comprises a silicon substrate, micro light emitting diodes arranged in an array and a transparent substrate with a color filter layer; each micro light emitting diode at least comprises a first electrode, a plurality of layers of non-organic compounds and a second electrode; the color filter layer is produced on the surface of the transparent substrate; the transparent substrate is adhered to the silicon substrate; the micro light emitting diodes are driven by a current provided by a driving circuit and emit first light; the color filter layer comprises a plurality of color filter points; and the color filter points cover the micro light emitting diodes in a vertical direction and convert the first light emitted by the micro light emitting diodes into second light. The manufacturing process of the full-color semiconductor light emitting micro display comprises the process of producing the driving circuit on the silicon substrate, producing the micro light emitting diodes on the silicon substrate on which the driving circuit is produced and adhering the transparent substrate on which the color filter layer is produced to the silicon substrate.

Owner:南京昀光科技有限公司

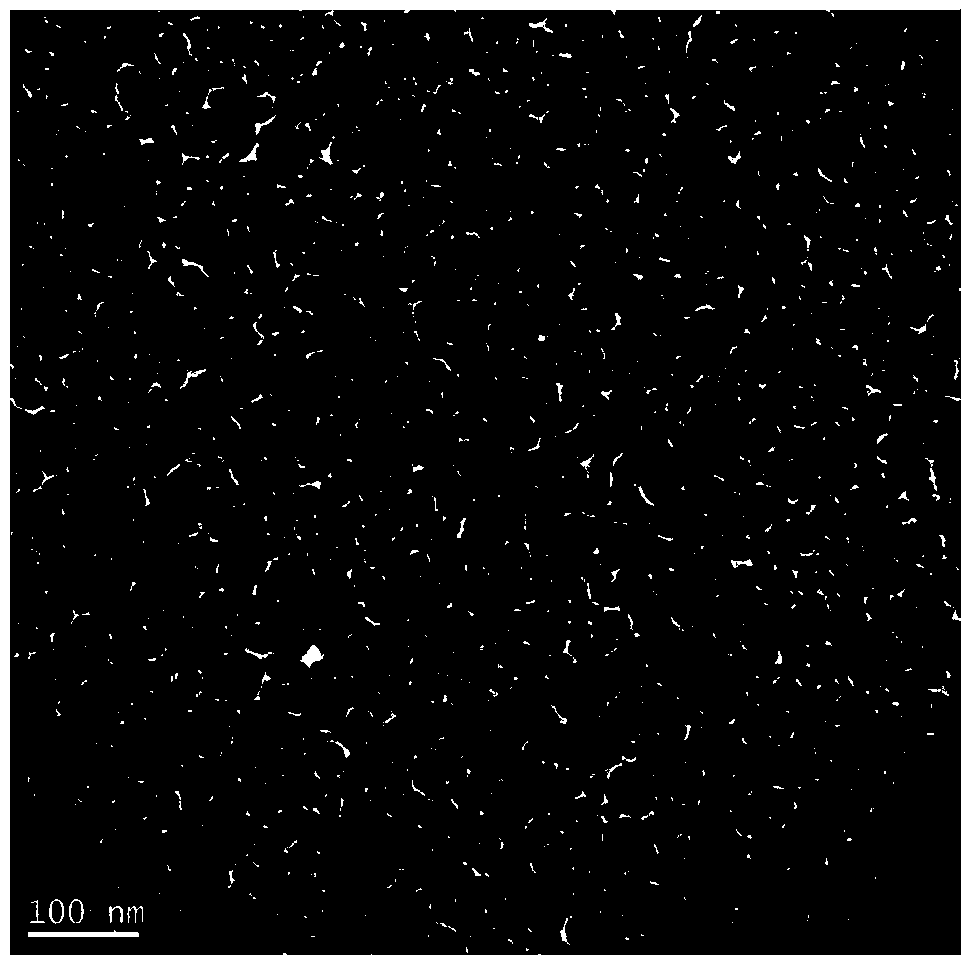

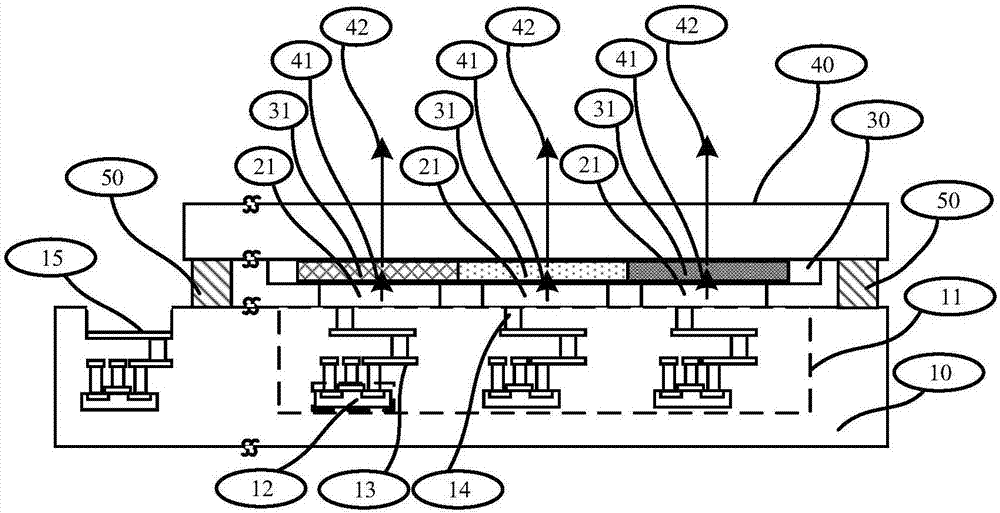

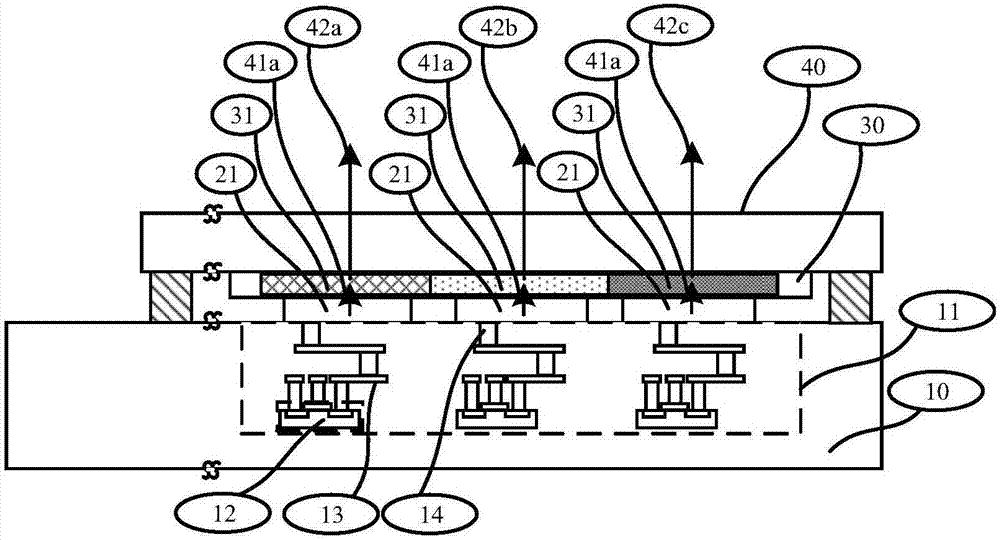

High-performance MEMS (Micro Electro Mechanical System) thermopile infrared detector based on black silicon and preparation method thereof

ActiveCN102829880AImprove response rateImprove the detection rateDecorative surface effectsChemical vapor deposition coatingThermopileEngineering

The invention relates to a high-performance MEMS (Micro Electro Mechanical System) thermopile infrared detector based on black silicon and a preparation method thereof. The high-performance MEMS thermopile infrared detector comprises a substrate, wherein the substrate is provided with a release barrier strip, a heat isolation cavity is arranged in the release barrier strip, a black silicon infrared absorption region is arranged above the heat isolation cavity, thermopiles are arranged on the outer side of the black silicon infrared absorption region, after the thermopiles on the outer side of the black silicon infrared absorption region are connected in series, the thermopiles are electrically connected to a whole body, and the thermopiles, which are connected in series, are provided with metal electrodes for outputting a detection result; the detection cold ends of the thermopiles are connected with the substrate through a first heat conduction and electric isolation structure, and a heat conductor is located on the outer side of a heat isolation cavity; and the detection heat ends of the thermopiles are in contact with the black silicon infrared absorption region through a second heat conduction and electric isolation structure. The high-performance MEMS thermopile infrared detector, provided by the invention, has the advantages of simple and easy implementation, convenience for monolithic integration, high response rate and detection rate, compatibility with a CMOS (Complementary Metal Oxide Semiconductor) process, wide application range, safety and reliable.

Owner:BEIJING ZHONGKE MICRO INVESTMENT MANAGEMENT CO LTD

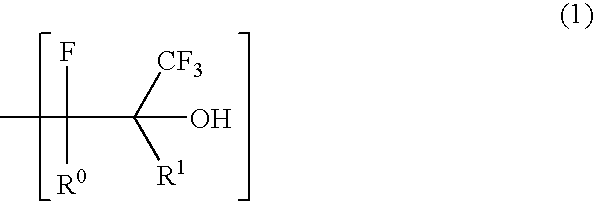

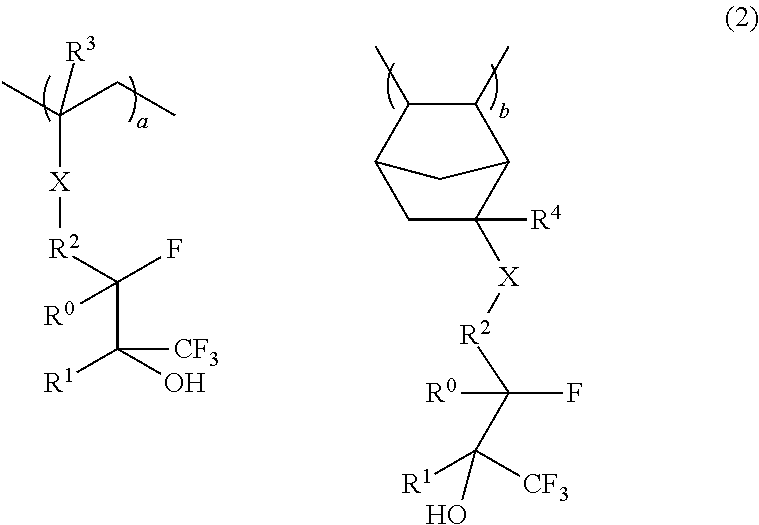

Resist protective coating material and patterning process

ActiveUS20070026341A1Effective pattern formationGood process compatibilityPhotosensitive materialsRadiation applicationsNorborneneWater insoluble

A resist protective coating material is provided comprising an α-trifluoromethylacrylic acid / norbornene copolymer having cyclic perfluoroalkyl groups as pendant. In a pattern-forming process, the material forms on a resist film a protective coating which is water-insoluble, dissolvable in alkaline developer and immiscible with the resist film, allowing for effective implementation of immersion lithography.

Owner:PANASONIC CORP +2

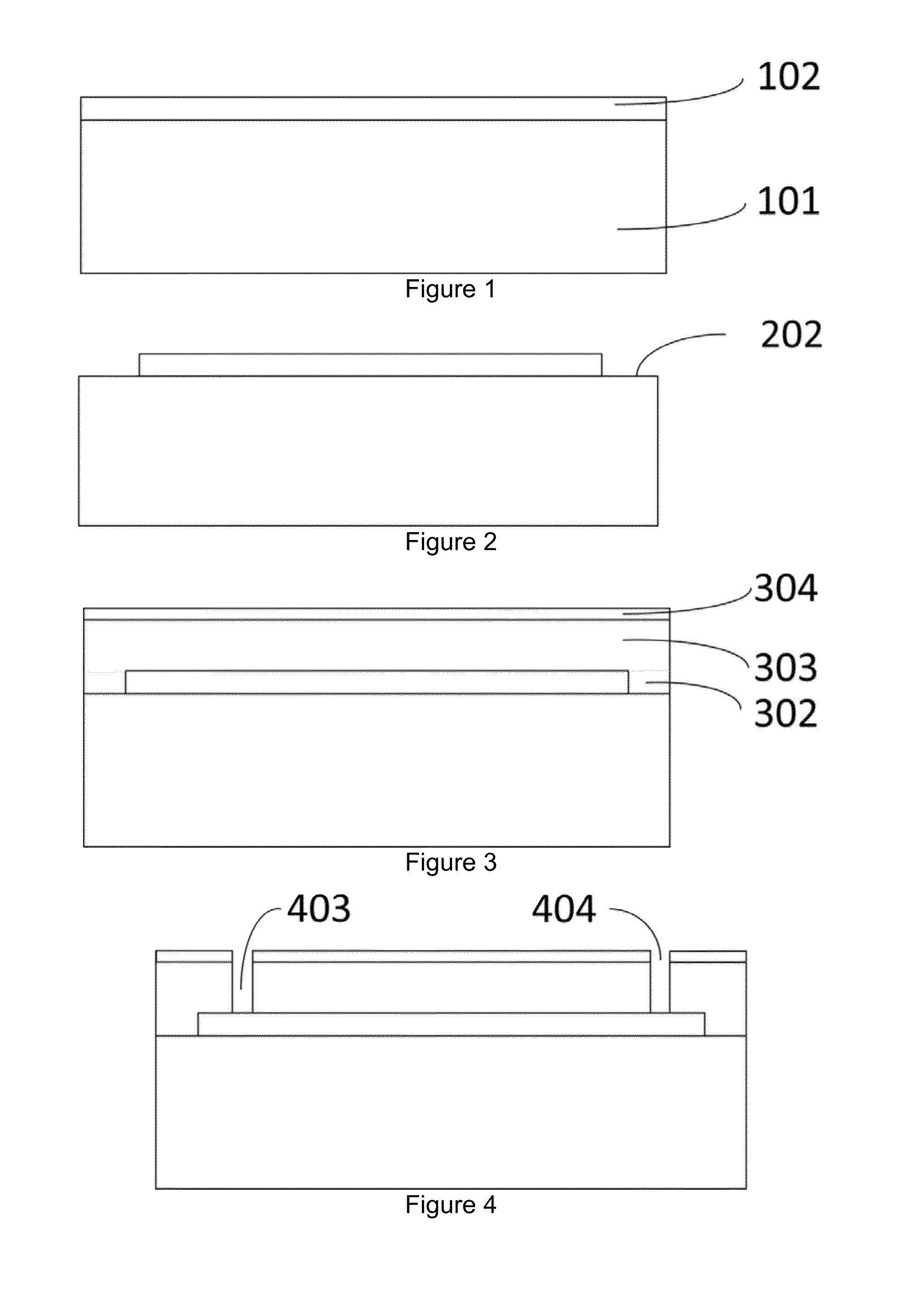

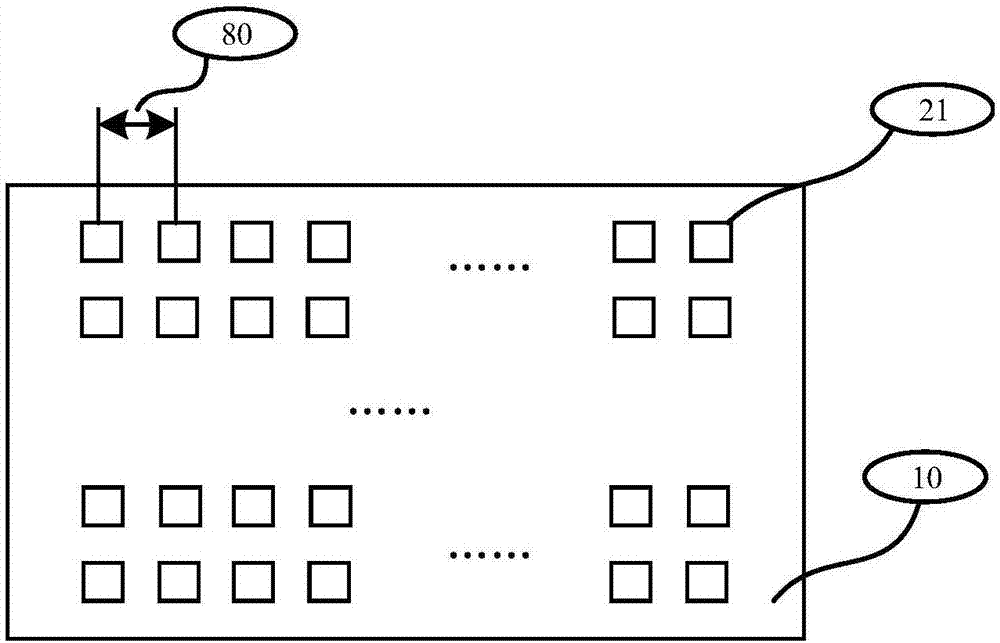

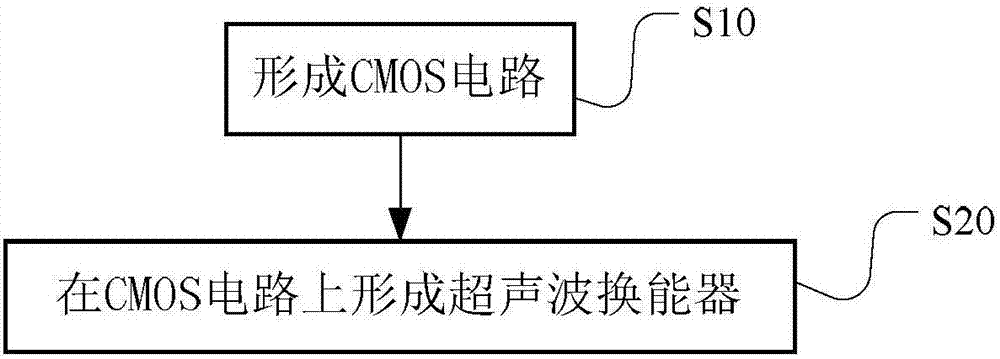

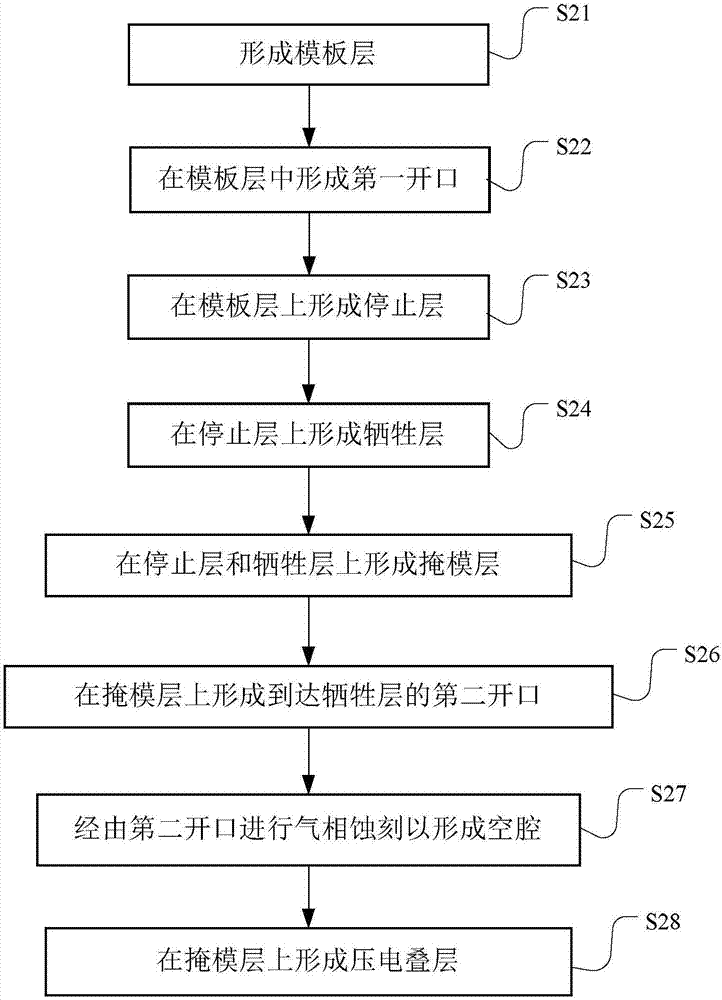

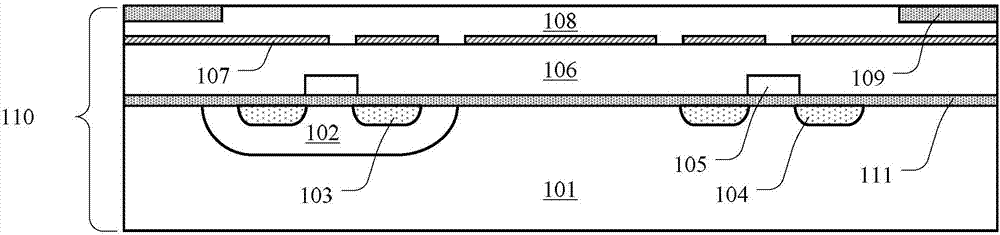

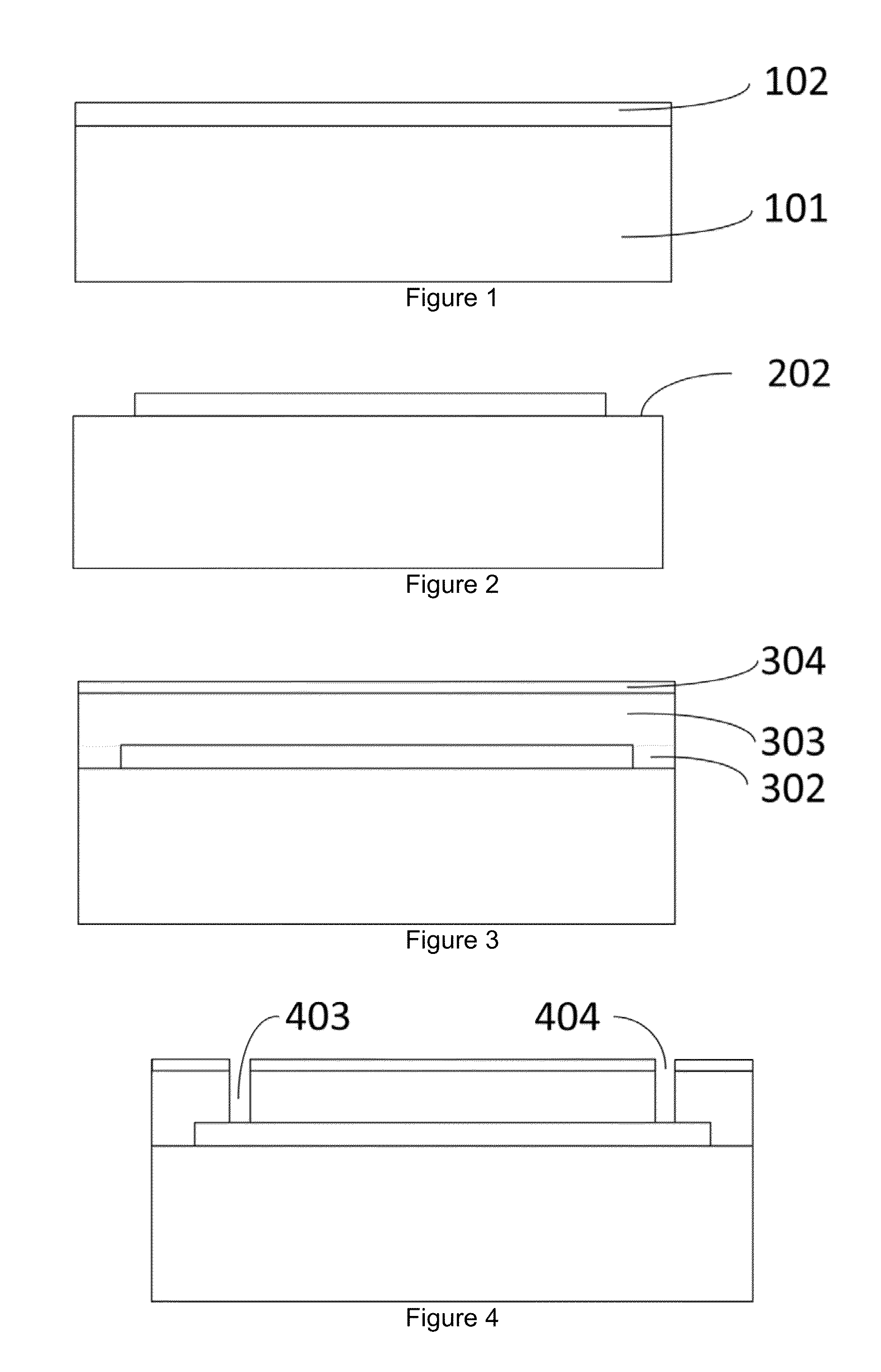

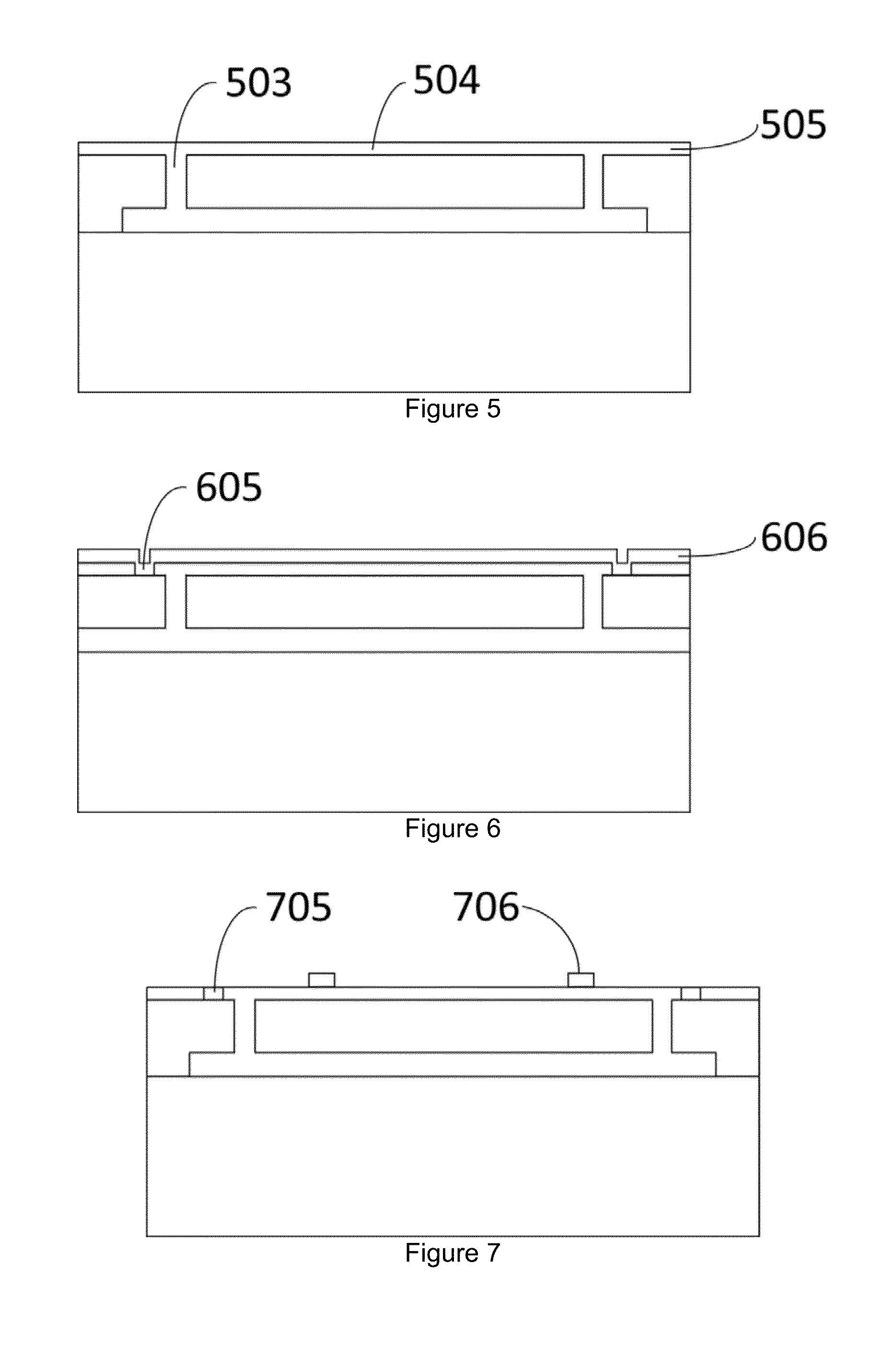

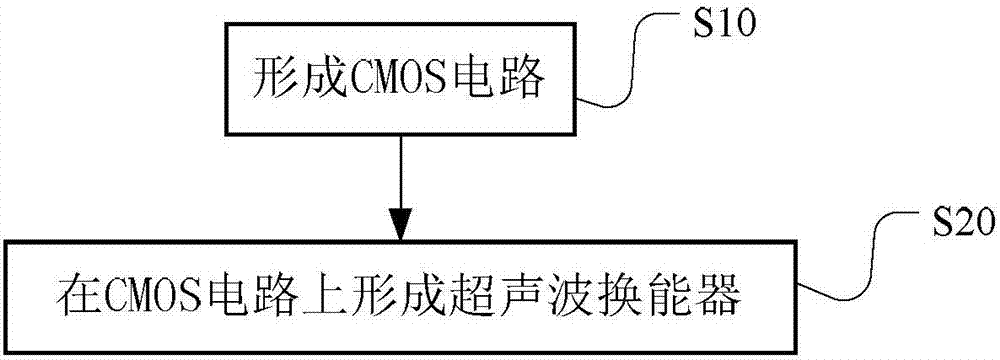

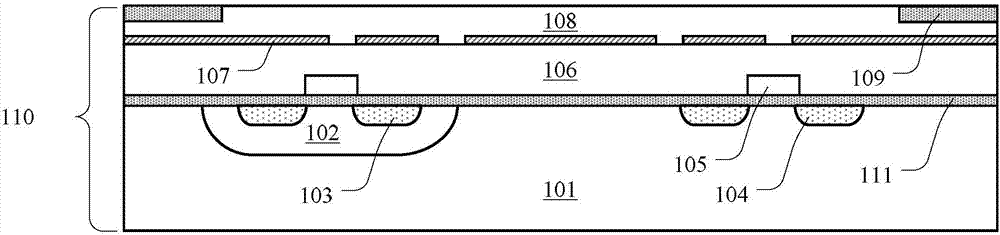

Ultrasonic fingerprint sensor and manufacturing method thereof

ActiveCN107092880AReduce difficultyLimited sizeSolid-state devicesSemiconductor/solid-state device manufacturingManufacturing cost reductionCMOS

The invention discloses an ultrasonic fingerprint sensor and a manufacturing method thereof. According to the method, a CMOS circuit is formed; an ultrasonic transducer is formed on the CMOS circuit. The manufacturing method of the ultrasonic fingerprint sensor comprises steps that a template layer is formed; a first opening is formed on the template layer; a stop layer is formed on the template layer, and the stop layer covers the template layer in a conformal mode; a sacrificial layer is formed on the stop layer, and the first opening is filled by the sacrificial layer; a mask layer is formed on the stop layer and the sacrificial layer, and the mask layer covers the sacrificial layer; at least one second opening arriving the sacrificial layer is formed on the mask layer; the sacrificial layer is removed through the at least one second opening to form a chamber, and a piezoelectric lamination layer is formed on the mask layer. The method is advantaged in that the template layer and the stop layer are utilized to form the chamber, so reduction of manufacturing cost and improvement of performance of sensors can be realized.

Owner:HANGZHOU SILAN MICROELECTRONICS

Structure and fabrication method of a high performance MEMS thermopile ir detector

ActiveUS20150137304A1Good process compatibilitySimple equipment structureSolid-state devicesSemiconductor/solid-state device manufacturingThermal isolationThermopile

The invention involves structure and fabrication method of a high performance IR detector. The structure comprises a substrate; a releasing barrier band on the substrate; a thermal isolation chamber constructed by the releasing barrier band; a black silicon-based IR absorber located right above the thermal isolation chamber and the black silicon-based IR absorber is set on the releasing barrier band; a number of thermocouples are set around the lateral sides of the black silicon-based IR absorber. The thermopiles around the black silicon-based IR absorber are electrically connected in series. The cold junctions of the thermopile are connected to the substrate through the first thermal-conductive-electrical-isolated structures as well as the heat conductor under the first thermal-conductive-electrical-isolated structures. The hot junctions of the thermopile are in contact with the IR absorber through the second thermal-conductive-electrical-isolated structures, and the second thermal-conductive-electrical-isolated structures are located above the releasing barrier band. The structure of such detector is simple, and it is easy to implement and can also be monolithicly integrated. Such detector has high responsivity and detection rate, and is CMOS-compatible, thus can be used widely in a safe and reliable manner.

Owner:ZHONGKE FUTURE OF CHIP MICROELECTRONICS TECH CHENGDU CO LTD

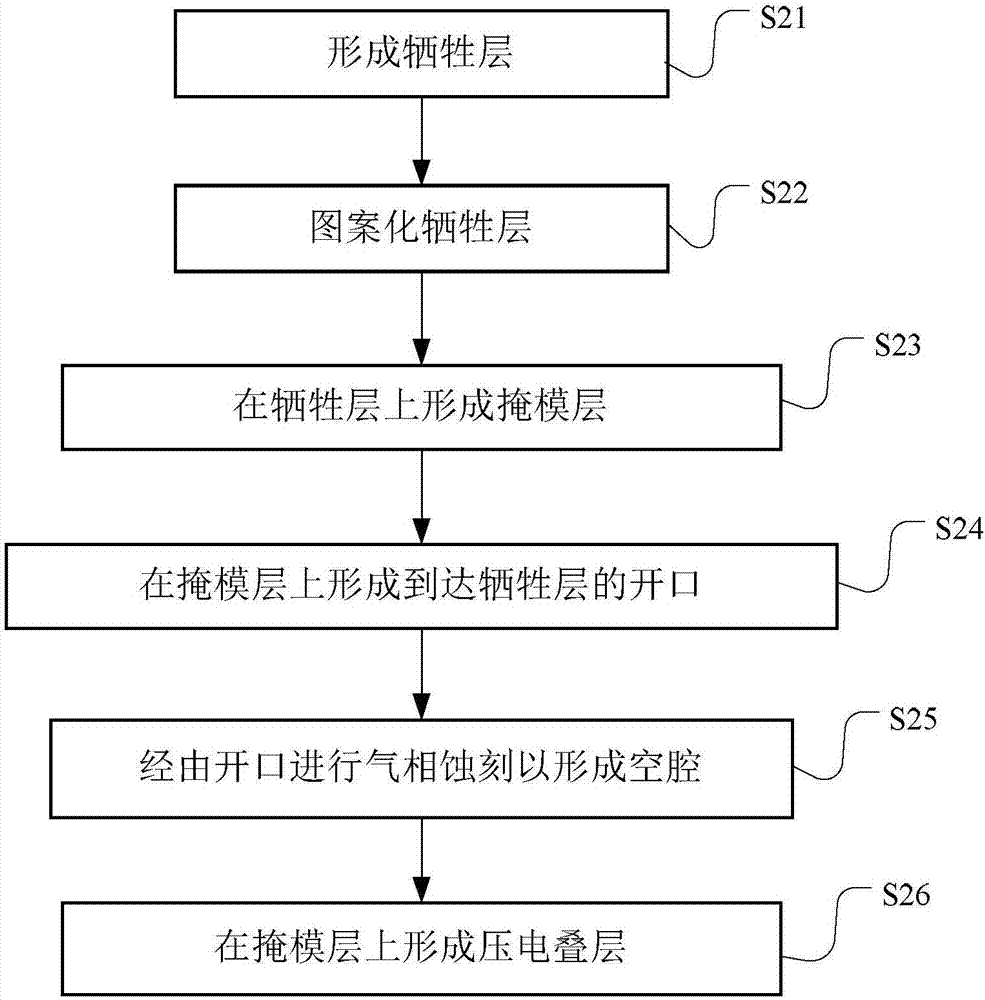

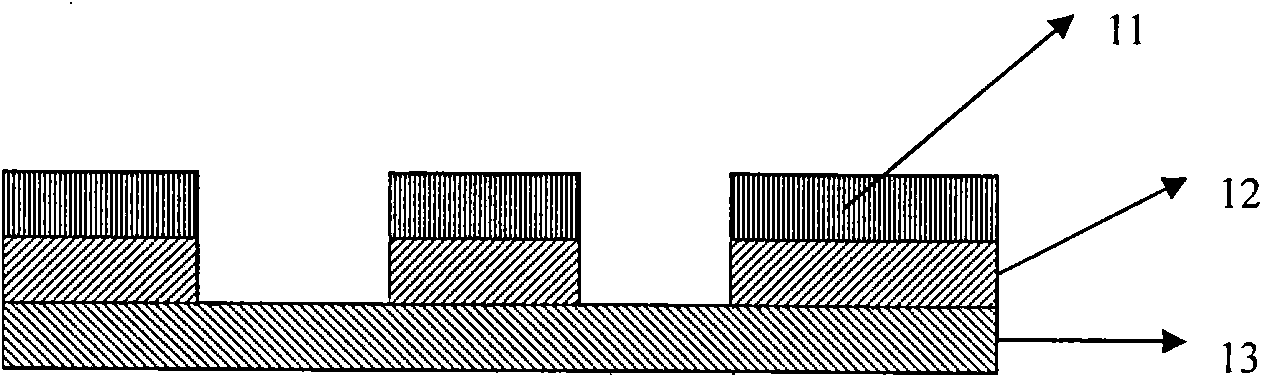

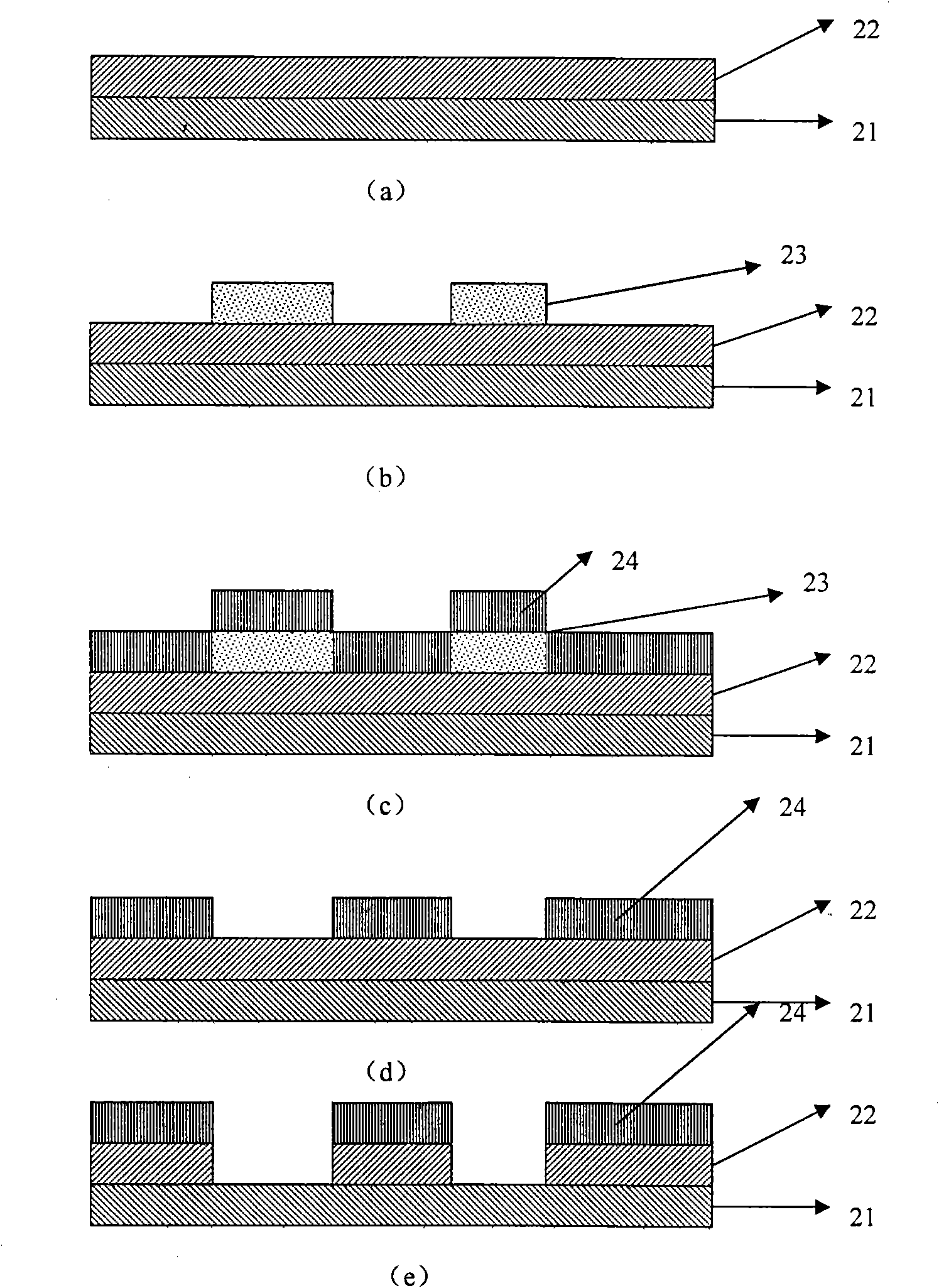

Ultrasonic transducer, ultrasonic fingerprint sensor and manufacturing method of ultrasonic transducer

ActiveCN107199169AHigh sensitivityGood process compatibilityMechanical vibrations separationPrint image acquisitionManufacturing cost reductionCMOS

The invention discloses an ultrasonic transducer, an ultrasonic fingerprint sensor and a manufacturing method of the ultrasonic transducer. The method comprises the steps that a CMOS circuit is formed, and the ultrasonic transducer is formed on the CMOS circuit. In the method, the forming process of the ultrasonic transducer comprises the steps that a sacrificial layer is formed; the sacrificial layer is patterned; a mask layer is formed on the sacrificial layer, and the mask layer covers and surrounds the sacrificial layer; an opening for reaching the sacrificial layer is formed on the mask layer; gas phase etching is carried out through the opening, and therefore the sacrificial layer is removed to form a cavity; and a piezoelectric stack is formed on the mask layer. The cavity is formed by patterning the sacrificial layer, accordingly, the manufacturing cost can be reduced, and the performance of the sensor can be improved.

Owner:HANGZHOU SILAN MICROELECTRONICS

Polymer composite material embedded microcapacitor and preparation method thereof

InactiveCN101944434AHigh dielectric constantIncrease the areaFixed capacitor dielectricStacked capacitorsIn situ polymerizationCopper

The invention relates to a polymer composite material embedded microcapacitor and a preparation method thereof, belonging to the technical field of the novel microelectronic material and element. The microcapacitor comprises an upper electrode, a dielectric film and a lower electrode which are stacked in turn, wherein the dielectric film is prepared from polyimide / barium titanate (PI / BT) composite material. The method of the invention comprises the following steps: adopting the in-situ polymerization method to disperse BT nanoparticles in PI and prepare the PI / BT composite material of the dielectric film; adopting the casting method to stick the PI / BT composite material to a copper plate substrate, coating a layer of photoresist on the obtained dielectric film, performing ultraviolet exposure according to a template drawing to obtain patterned photoresist; sputtering a metal layer on the dielectric film and photoresist; soaking in acetone solution to form the patterned upper electrode; performing RIE treatment in the mixed gas of oxygen and trifluoromethane, and cleaning with ultrasonic wave to obtain the microcapacitor. By using the method of the invention, the uniform and dense dielectric film with large area can be obtained; and the microcapacitor can work stably at a higher temperature or a lower temperature.

Owner:TSINGHUA UNIV +1

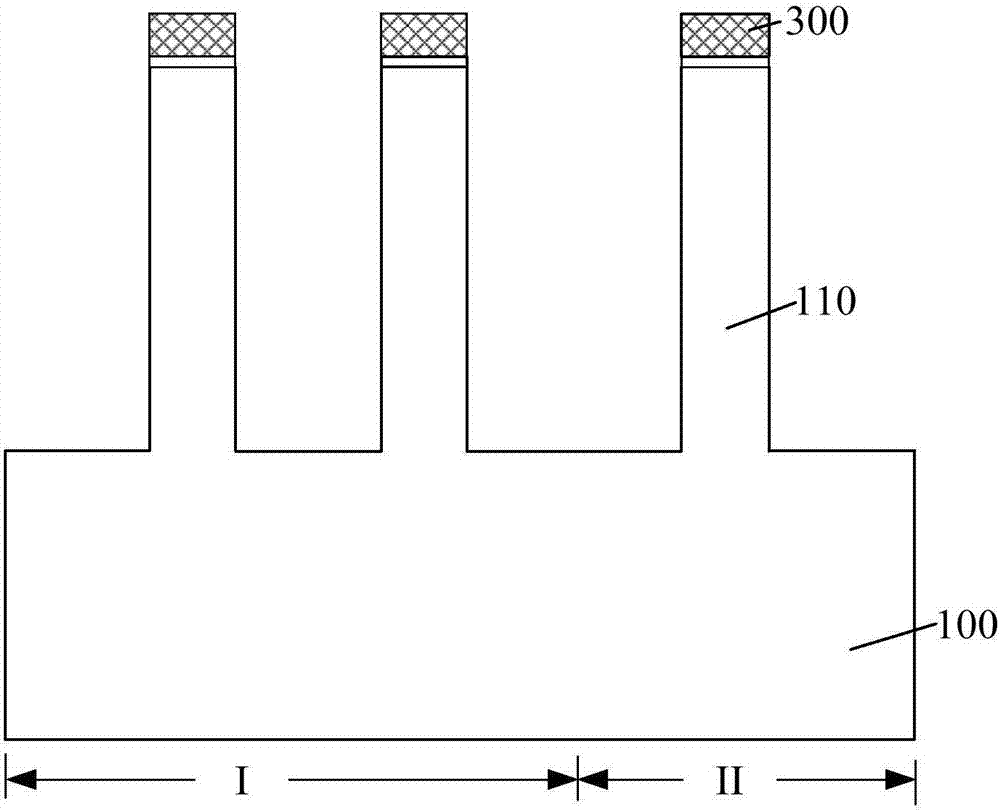

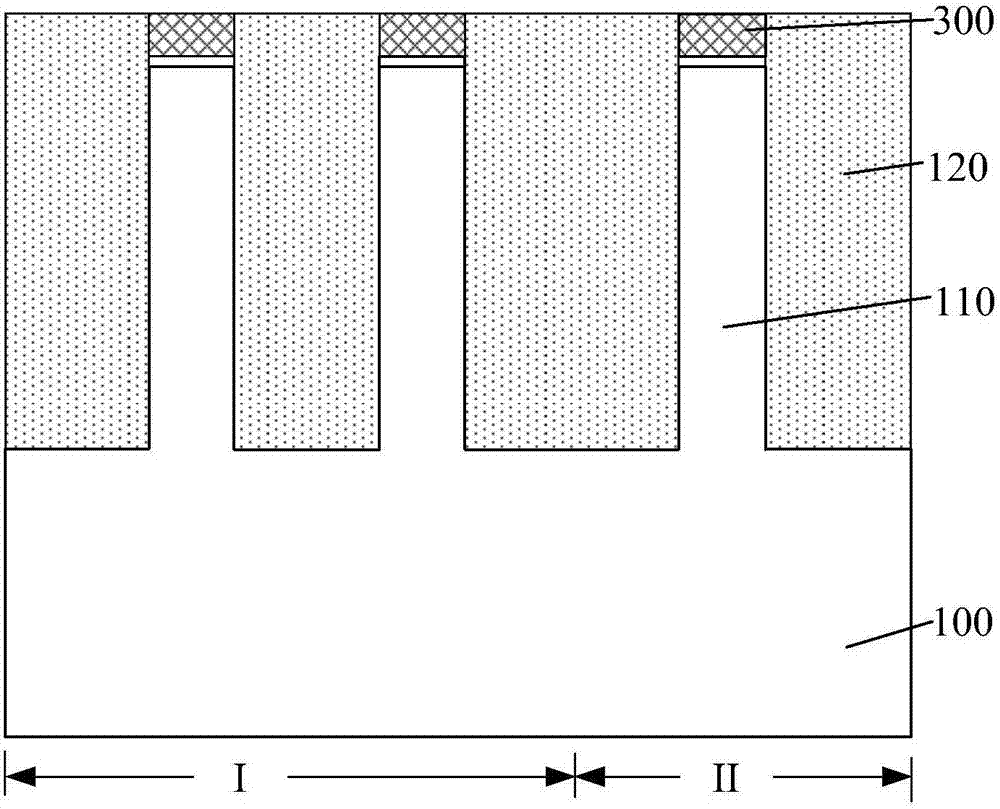

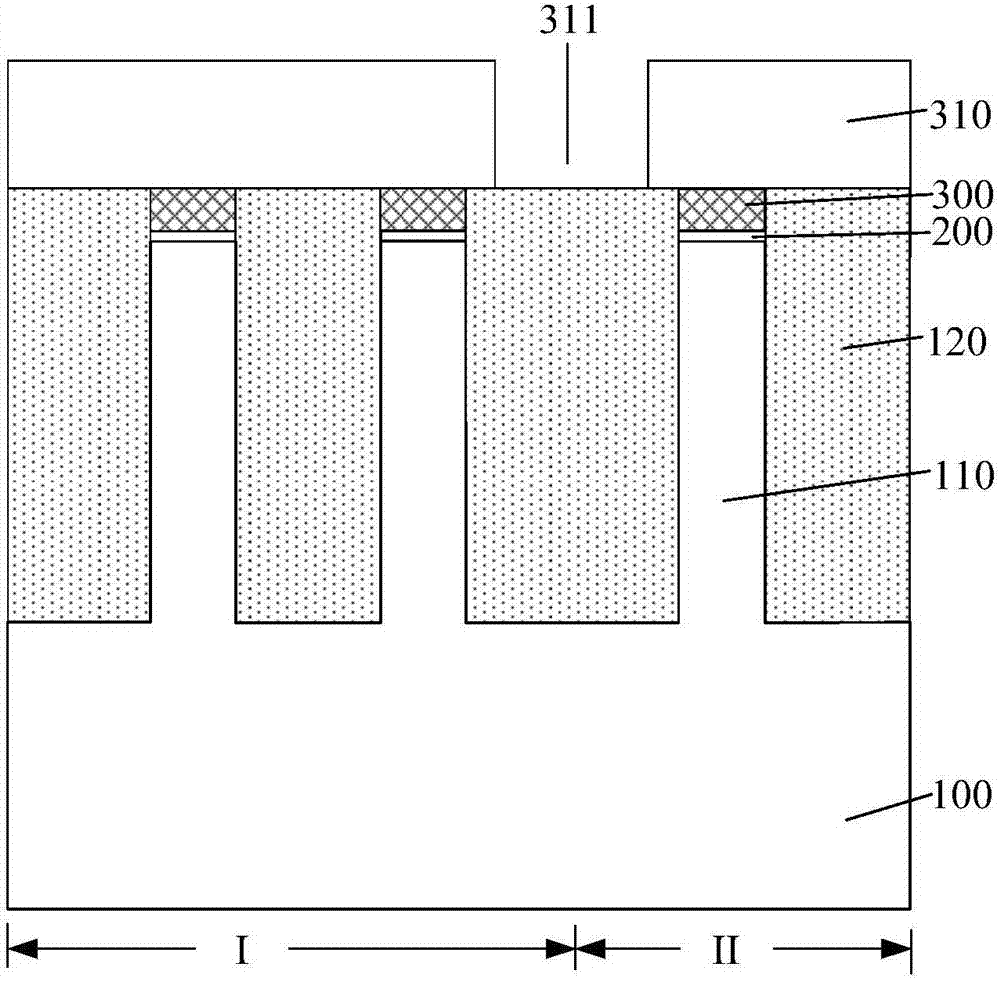

Semiconductor structure and manufacturing method thereof

ActiveCN107346759AAvoid lossImprove electrical performanceSolid-state devicesSemiconductor/solid-state device manufacturingSemiconductor structureIsolation layer

The invention provides a semiconductor structure and a manufacturing method thereof. The manufacturing method comprises the steps of: providing a base which comprises a substrate and fin portions protruding out of the substrate, wherein the substrate comprises a first region and a second region; forming a first initial isolating layer on the substrate; patterning the first initial isolating layer, and forming a first opening through which the substrate is exposed in a junction of the first region and the second region; forming a side wall protective layer which is made of a material different from that of the substrate and the fin portions on the side wall of the first opening; etching the substrate along the first opening, and forming a second opening in the substrate; forming a second initial isolating layer which fills up the second opening and the first opening; and removing a partial thickness of the second initial isolating layer, the side wall protective layer and the first initial isolating layer, so as to expose the fin portions. According to the semiconductor structure and the manufacturing method thereof, the first opening is formed in the first initial isolating layer at first, then the side wall protective layer is formed on the side wall of the first opening, and the substrate is etched along the first opening; and the side wall protective layer can protect the fin portions on two sides of the first opening, thereby preventing the fin portions from being damaged by the process of etching the substrate.

Owner:SEMICON MFG INT (SHANGHAI) CORP +1

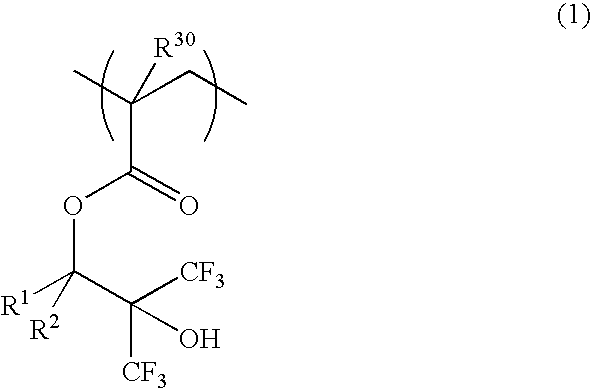

Resist protective coating material and patterning process

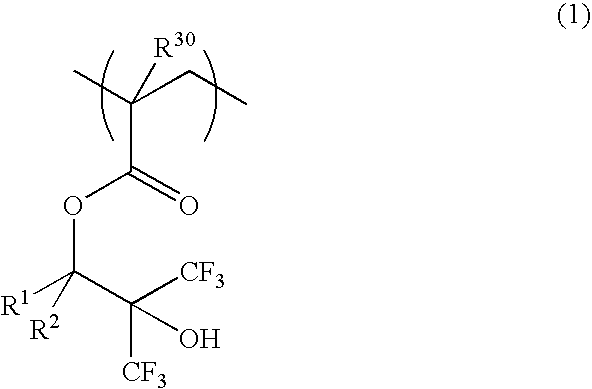

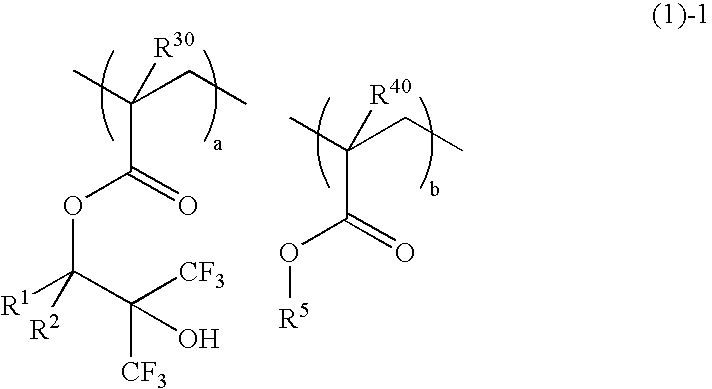

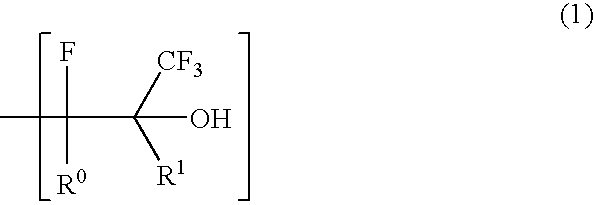

ActiveUS8323872B2Efficient formationGood process compatibilityPhotosensitive materialsPhotosensitive materials for photomechanical apparatusWater insolublePolymer chemistry

A resist protective coating material is provided comprising a polymer having a partial structure of formula (1) wherein R0 is H, F, alkyl or alkylene, and R1 is fluorinated alkyl or alkylene. In a pattern-forming process, the material forms on a resist film a protective coating which is water-insoluble, dissolvable in alkaline developer and immiscible with the resist film, allowing for effective implementation of immersion lithography. During alkali development, development of the resist film and removal of the protective coating can be simultaneously achieved.

Owner:SHIN ETSU CHEM IND CO LTD

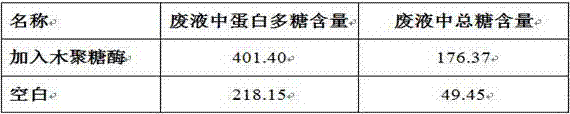

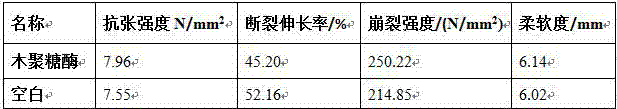

Animal hide fiber loosening method based on xylanase effect

ActiveCN107312896AReduce dosageReduce processing difficultyPre-tanning chemical treatmentFiberDepilations

The invention discloses an animal hide fiber loosening method based on the xylanase effect and relates to the field of production of leather and fur leather. The method is characterized in that xylanase is added as a hide fiber loosening additive during the steps such as water soaking, depilation, softening and pickling of leather making or during the steps such as water soaking, softening and pickling of fur leather making. By means of the method, the components such as proteoglycan and glycosaminoglycan, which have a cohesive effect on hide fiber, in the animal hide can be efficiently and specifically destroyed. Hide protein ingredients cannot be destructed. The method has wide applicability and is suitable for the manufacturing process of all-purpose leather or fur leather with various kinds of animal hides as raw materials. The effects of promoting loosening of hide fiber and improving the softness, hand feeling and physical and mechanical properties of finished leather products are achieved. Through the method in the leather making process, pollutants such as lime and sodium sulfide are reduced, and the depilation effect is improved.

Owner:SICHUAN UNIV

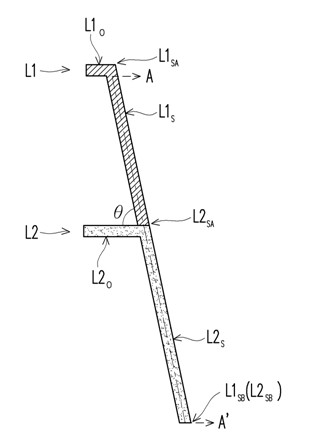

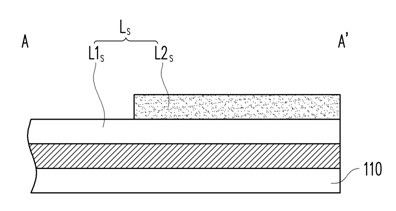

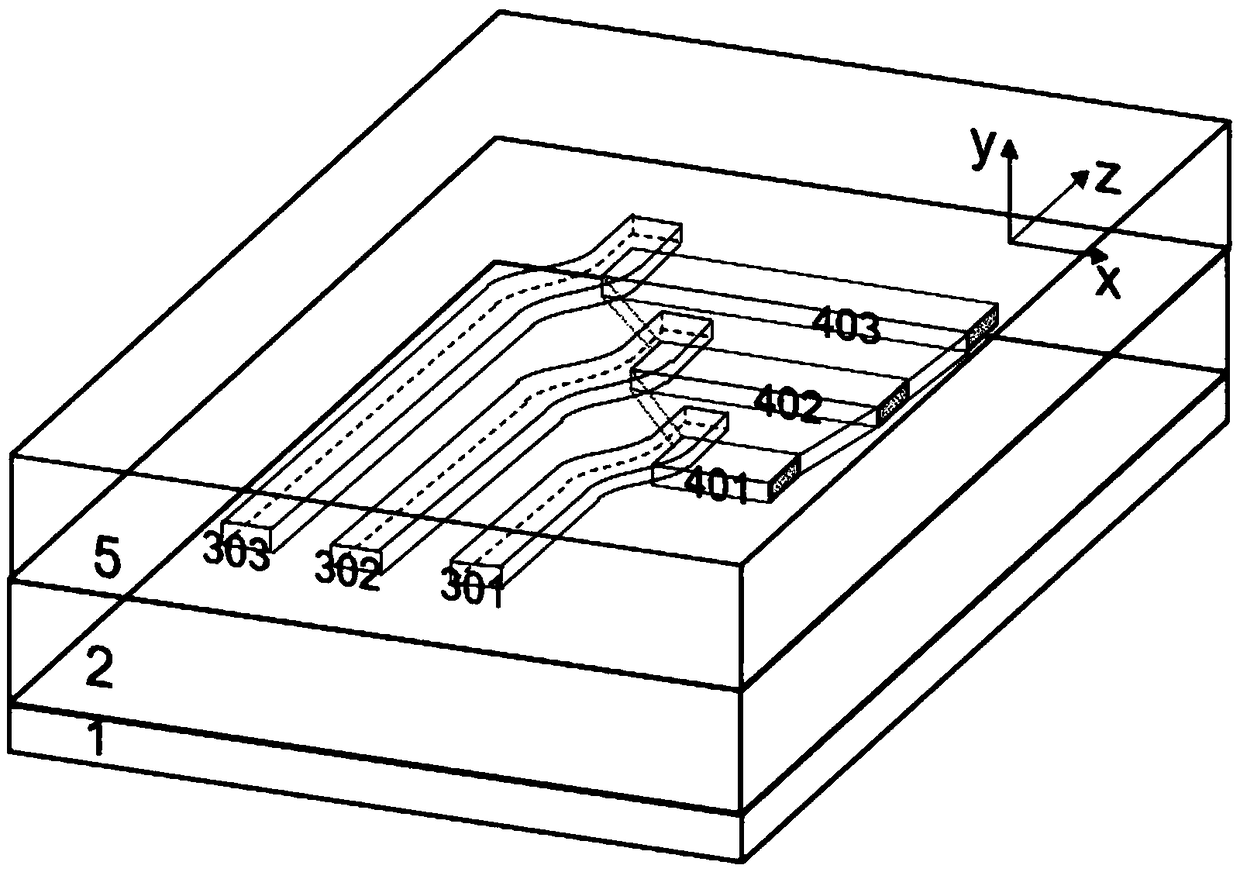

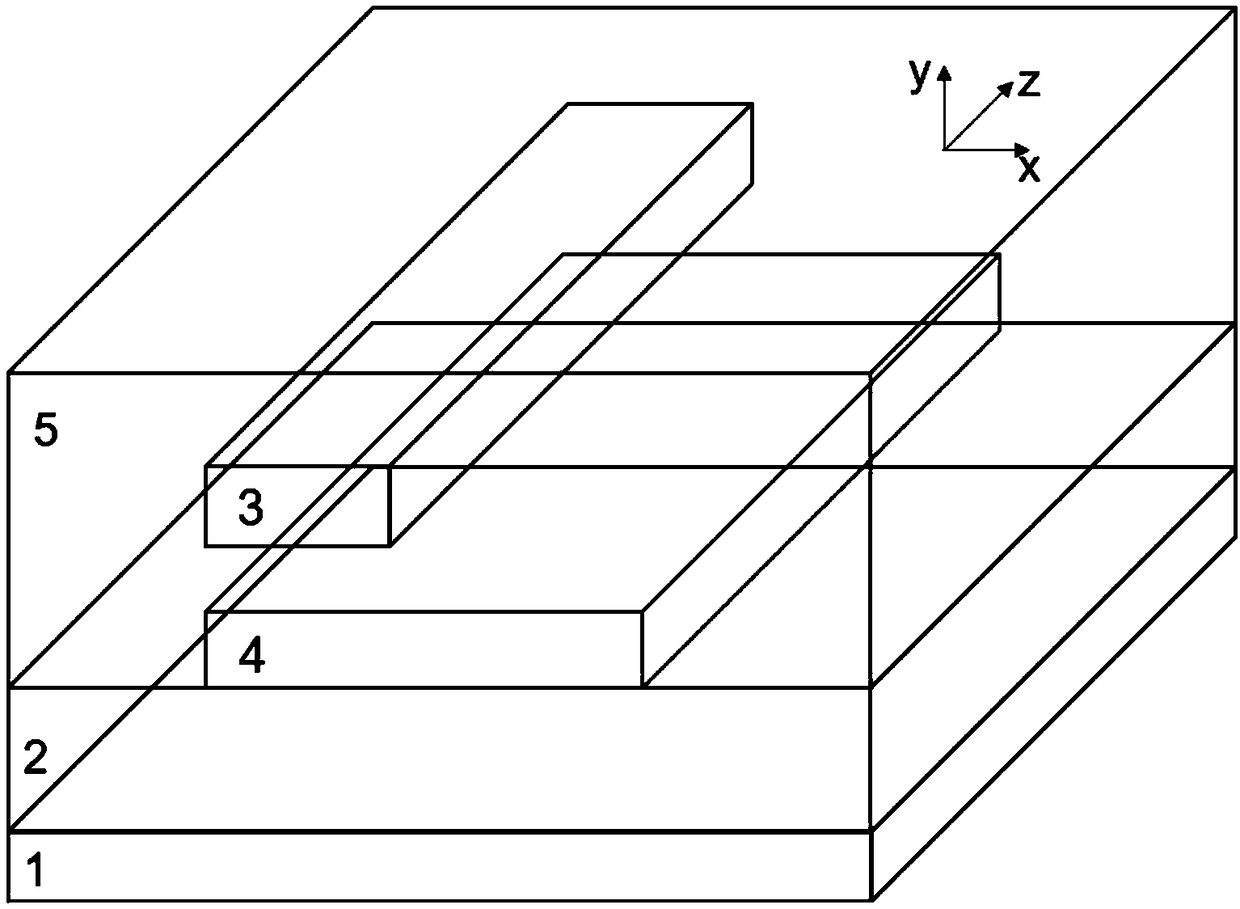

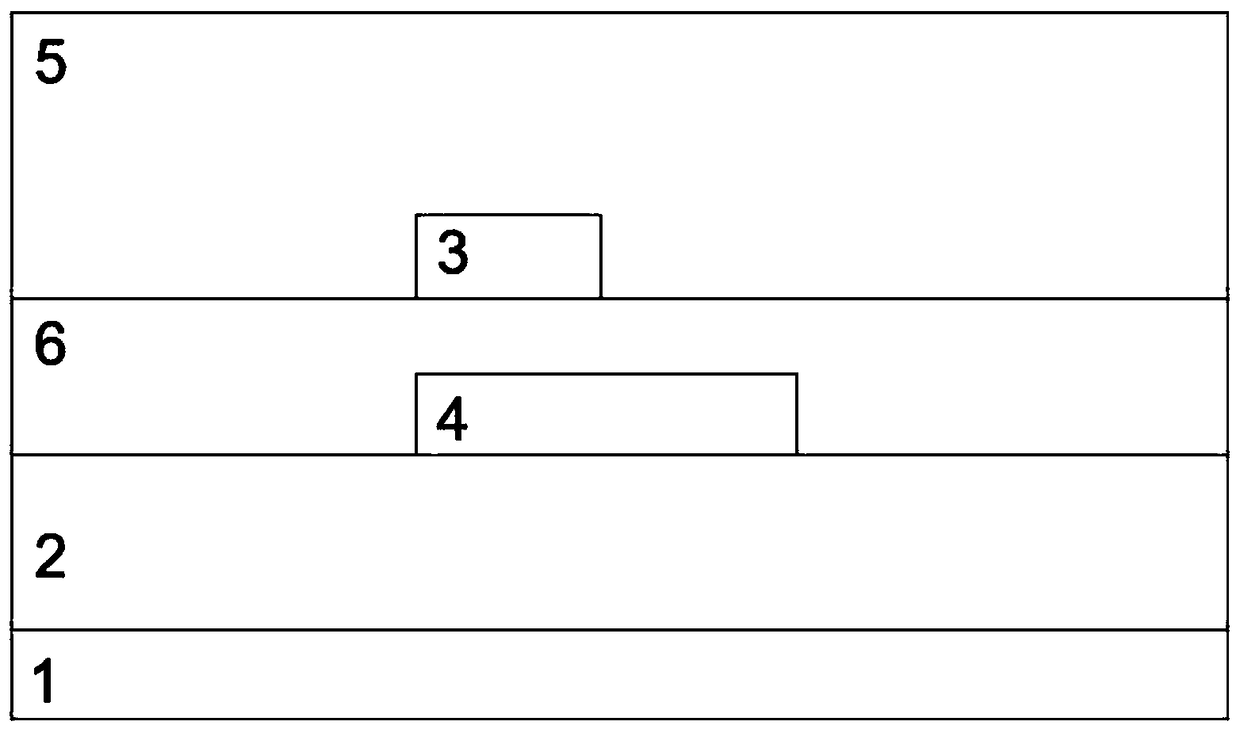

Three-dimensional multilayer waveguide mode multiplexing and de-multiplexing device and preparation method thereof

PendingCN108761637AIncrease the dimension of integrationHighly integratedOptical waveguide light guideMultiplexerDirect coupling

The invention relates to a three-dimensional multilayer waveguide mode multiplexing and de-multiplexing device and a preparation method thereof and belongs to the optical communication device technical field, in particular, a mode division multiplexing system. According to the three-dimensional multilayer waveguide mode multiplexing and de-multiplexing device and the preparation method thereof ofthe invention, a three-dimensional multilayer waveguide integrated structure is adopted, and therefore, the limitations of a traditional two-dimensional planar waveguide structure can be eliminated, the integration dimensions of the device can be increased, the integration and flexibility of the device can be enhanced, and the communication capacity of a system can be improved. The boundary of anyone side of the upper-layer waveguide of the three-dimensional waveguide is aligned with the boundary of any one side of the lower-layer waveguide of the three-dimensional waveguide, so that the direct three-dimensional coupling of a fundamental mode and a high-order mode is realized, and therefore, a defect that a traditional three-dimensional mode multiplexer fails to realize direct coupling ofmodes can be eliminated, and the structure and complexity of the device can be simplified. The device of the invention is prepared based on a mature CMOS process, so that high efficiency, low cost and mass production of the device can be realized. With the three-dimensional multilayer waveguide mode multiplexing and de-multiplexing device and the preparation method thereof of the invention adopted, the flexible three-dimensional coupling of the modes can be realized, a solid foundation is laid for on-chip mode multiplexing technology. The three-dimensional multilayer waveguide mode multiplexing and de-multiplexing device and the preparation method thereof can be further applied to the flexible mode routing of a mode division multiplexing network.

Owner:NANJING UNIV OF POSTS & TELECOMM

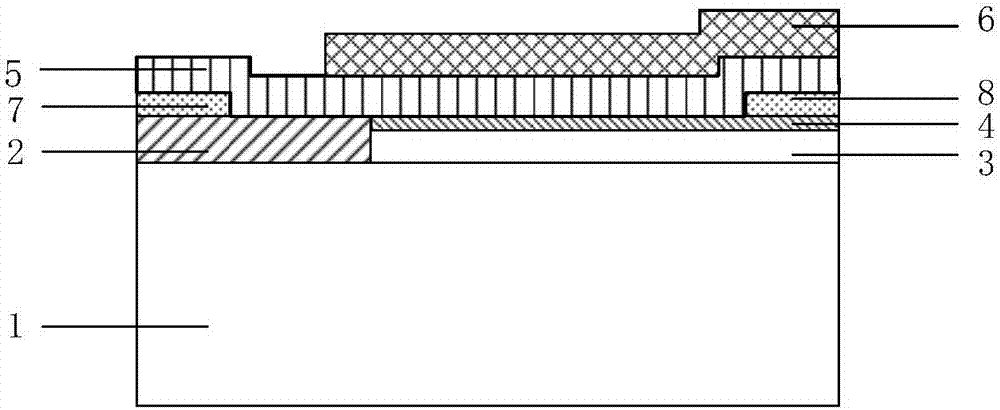

Two-dimensional material/semiconductor hetero-junction tunneling transistor and preparation method thereof

ActiveCN107104140AEffective tunnelingDirect tunnelingSemiconductor/solid-state device manufacturingSemiconductor devicesSemiconductor materialsPower flow

The invention discloses a tunneling field effect transistor based on a two-dimensional material / semiconductor hetero-junction and a preparation method thereof. A device forms an interleaved energy band structure in the off state through the energy band design, namely, a tunneling window is inexistent between the two-dimensional material and the semiconductor material, and the ultra-low off-state current can be acquired; the grid voltage can be applied to regulate an energy band alignment way at the two-dimensional material / semiconductor hetero-junction so that the device can form the staggered energy band structure in the on-state, and the effective tunneling barrier height is a negative value; and meanwhile, the current carrier tunnels to a channel region from a source region to realize the direct tunneling, thereby acquiring large on-state current. The device adopts the highly-doped three-dimensional semiconductor material as the source region material, and the three-dimensional semiconductor material and the metal source electrode are unipotential; since the thickness of the two-dimensional material is ultra-thin, the grid voltage can regulate the two-dimensional material and the energy band at the two-dimensional material / semiconductor hetero-junction interface, thereby acquiring an ideal grid control capacity. The tunneling field effect transistor disclosed by the invention is simple in process, and large in compatibility with the traditional semiconductor process.

Owner:PEKING UNIV