Patents

Literature

351results about How to "Reduce conduction voltage drop" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

Method for producing a pn-junction for a semiconductor device of SiC

InactiveUS6083814AShort timeNumber of processing stepSemiconductor/solid-state device manufacturingSemiconductor devicesOhmic contactEngineering

A method for producing a pn-junction for a semiconductor device of SiC intended to have at least one lateral zone of junction termination with a lower doping concentration of a first conductivity type than a main zone for smearing out the electrical field at said junction comprising at least the step of applying a first layer of SiC over the entire surface and on top of a second layer of SiC. A mask is applied on the first layer over a portion thereof where said main zone and an ohmic contact are to be formed. It is after that etched through the first layer to the second layer while leaving a main zone of said first layer and a contact layer thereof under said mask.

Owner:CREE INC

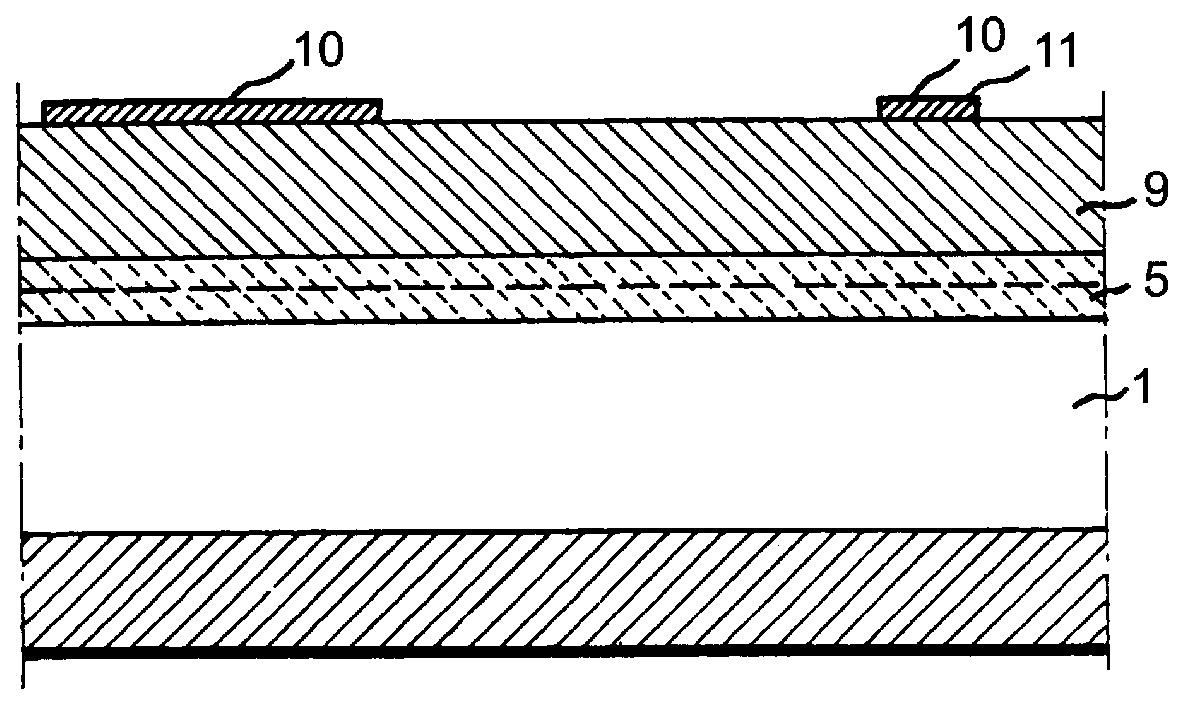

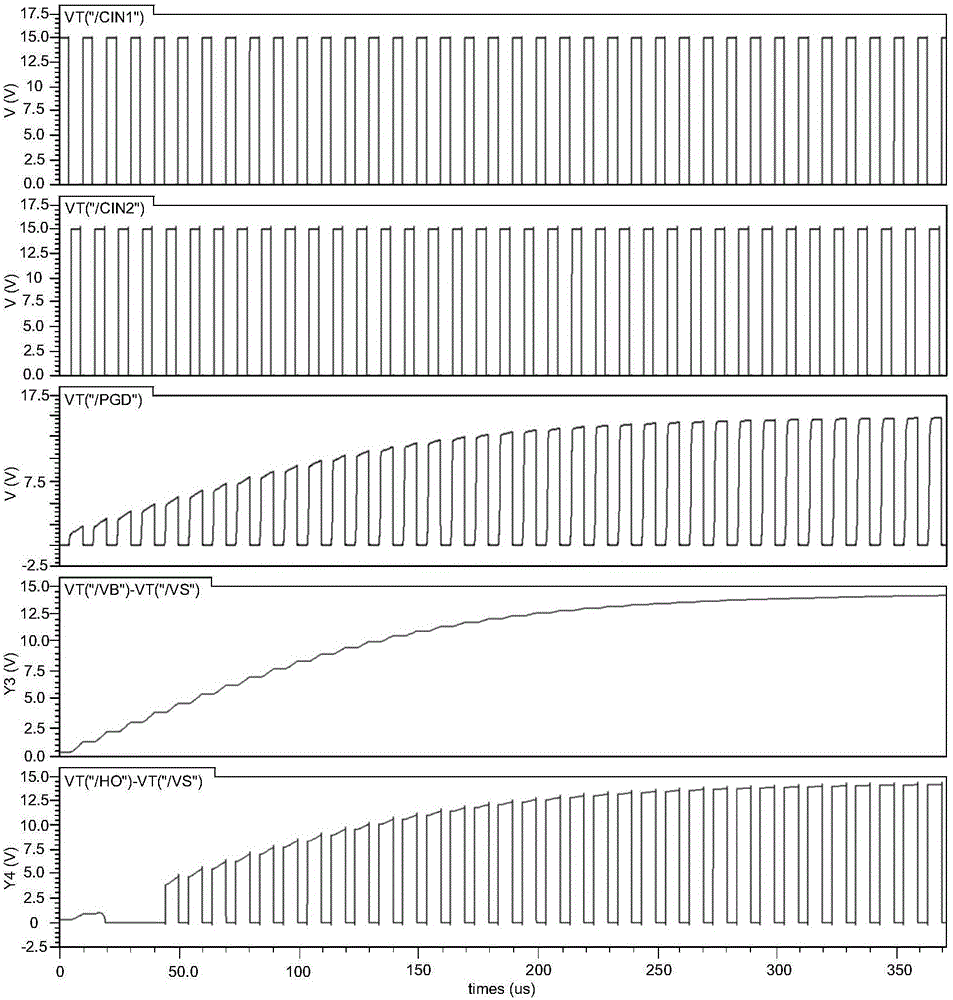

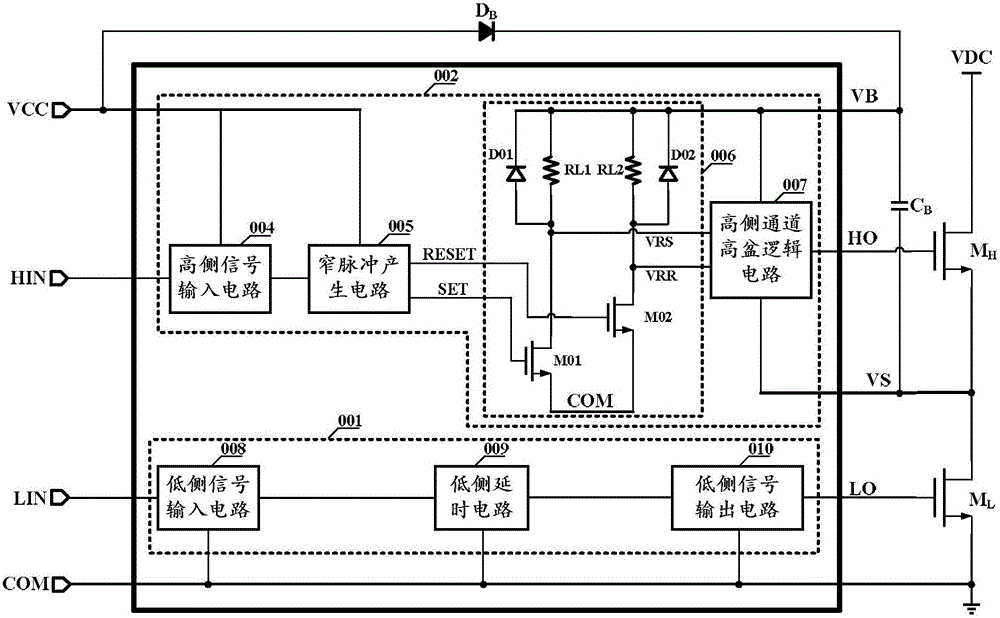

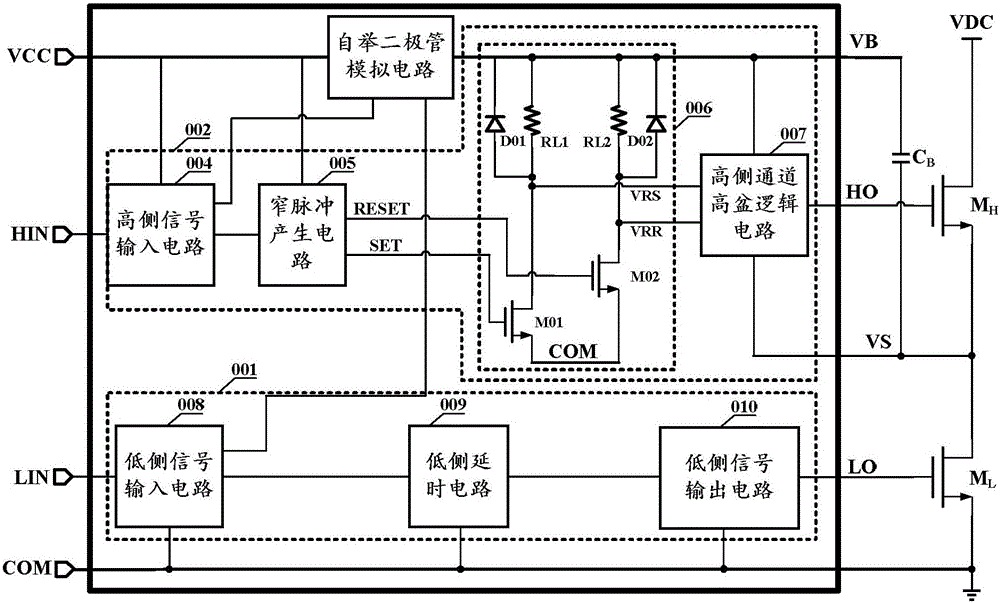

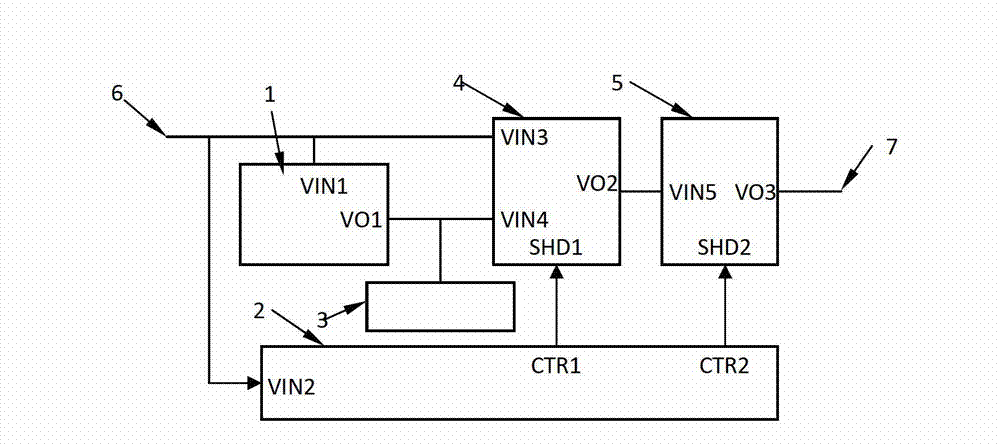

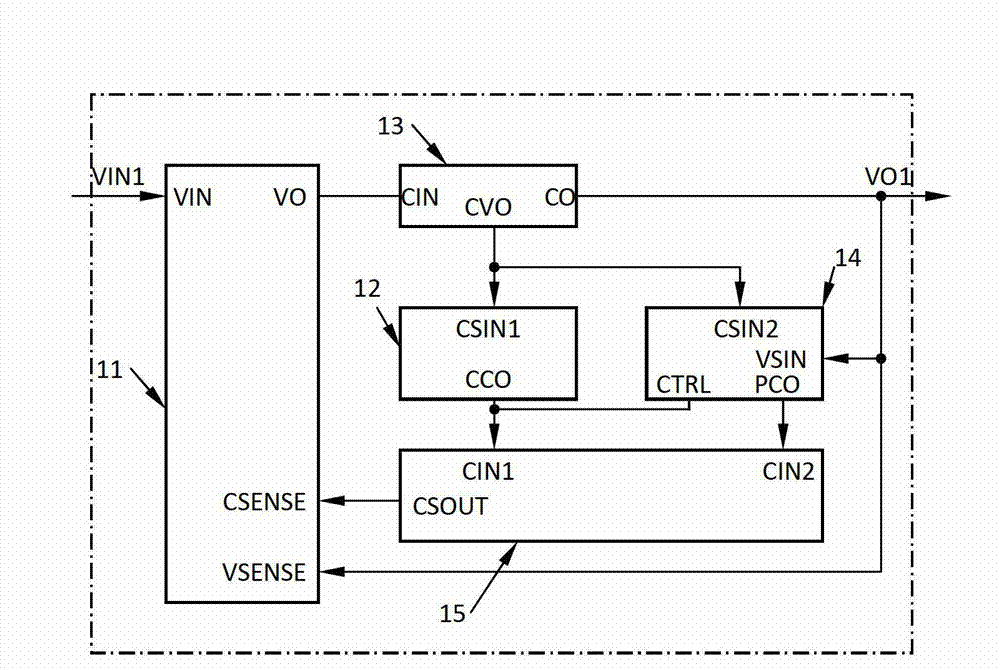

Integrated bootstrap high voltage driving chip and technological structure thereof

ActiveCN105827223ASimple structureReduce areaTransistorLogic circuits coupling/interface using field-effect transistorsCapacitanceElectricity

The invention discloses an integrated bootstrap high voltage driving chip and a technological structure thereof. Parasitic high voltage diodes realized by the integration technology in a high voltage level shift circuit are ingeniously utilized to charge a bootstrap capacitor, wherein the power terminal of the high voltage level shift circuit is a high side floating power supply VB, and the reference ground is floating voltage PGD. The PGD is controlled by a bootstrap control circuit. A first parasitic diode and a second parasitic diode are arranged between the VB and the PGD. The bootstrap control circuit is controlled by a high side signal and a low side signal. When the low side output signal LO is high level and the high side output signal HO is low level or the low side output signal LO is low level and the high side output signal HO is low level, the output PGD of the bootstrap control circuit is high level VCC. The VCC performs unidirectional charging to an external bootstrap capacitor through the first parasitic diode and the second parasitic diode. The integrated bootstrap high voltage driving chip is high in charging speed, high in charging efficiency, simple in circuit structure and low in cost.

Owner:SOUTHEAST UNIV +1

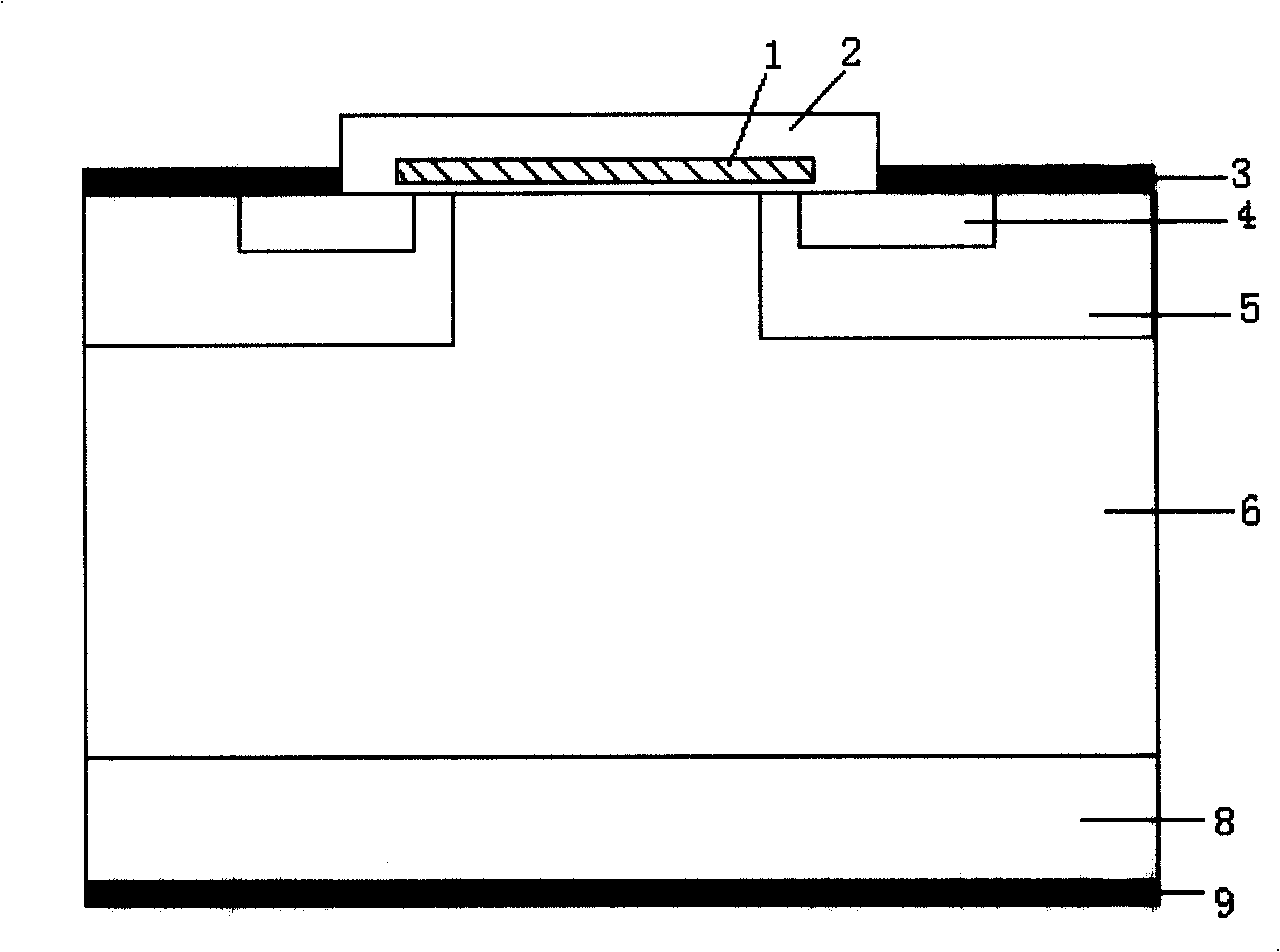

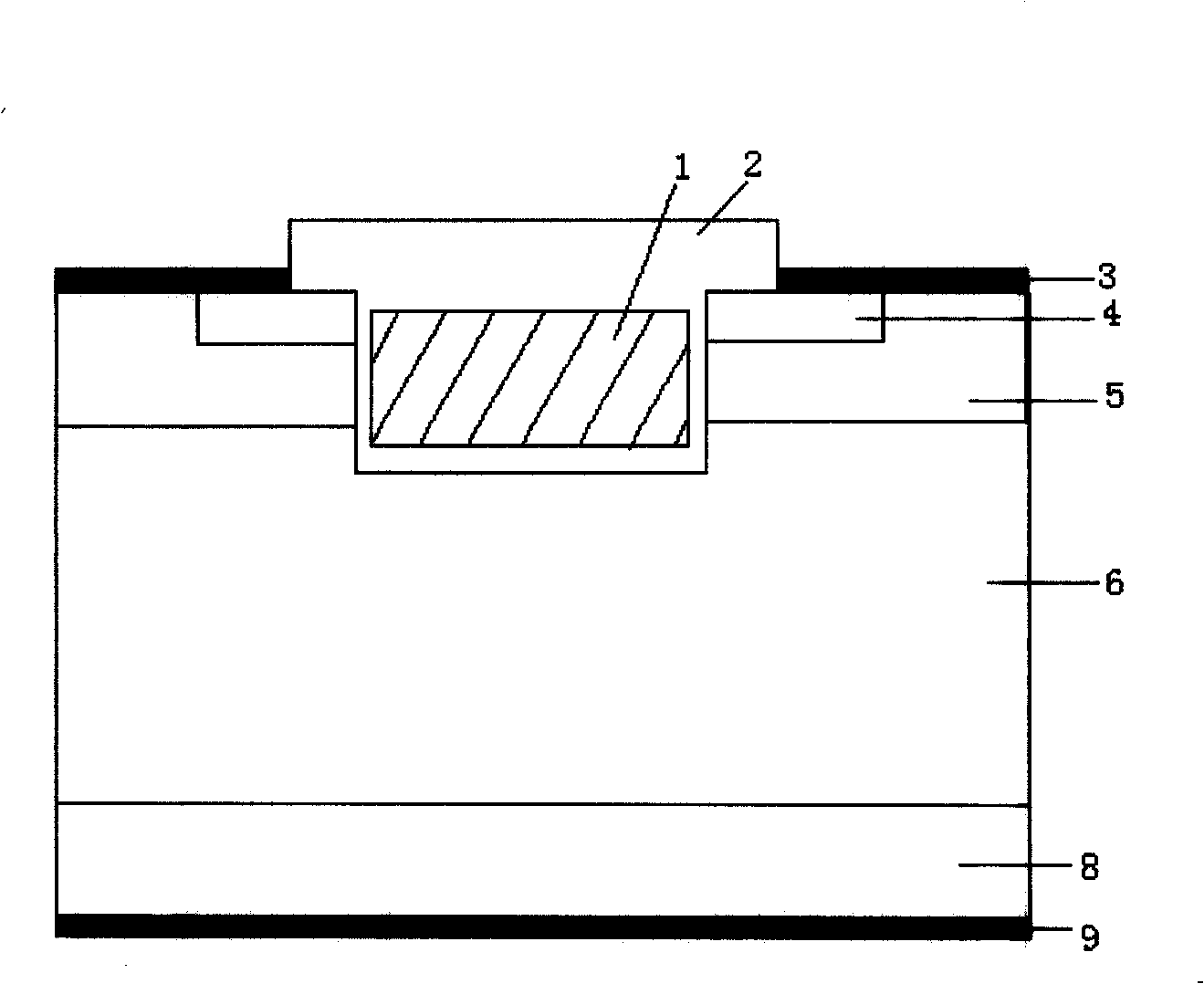

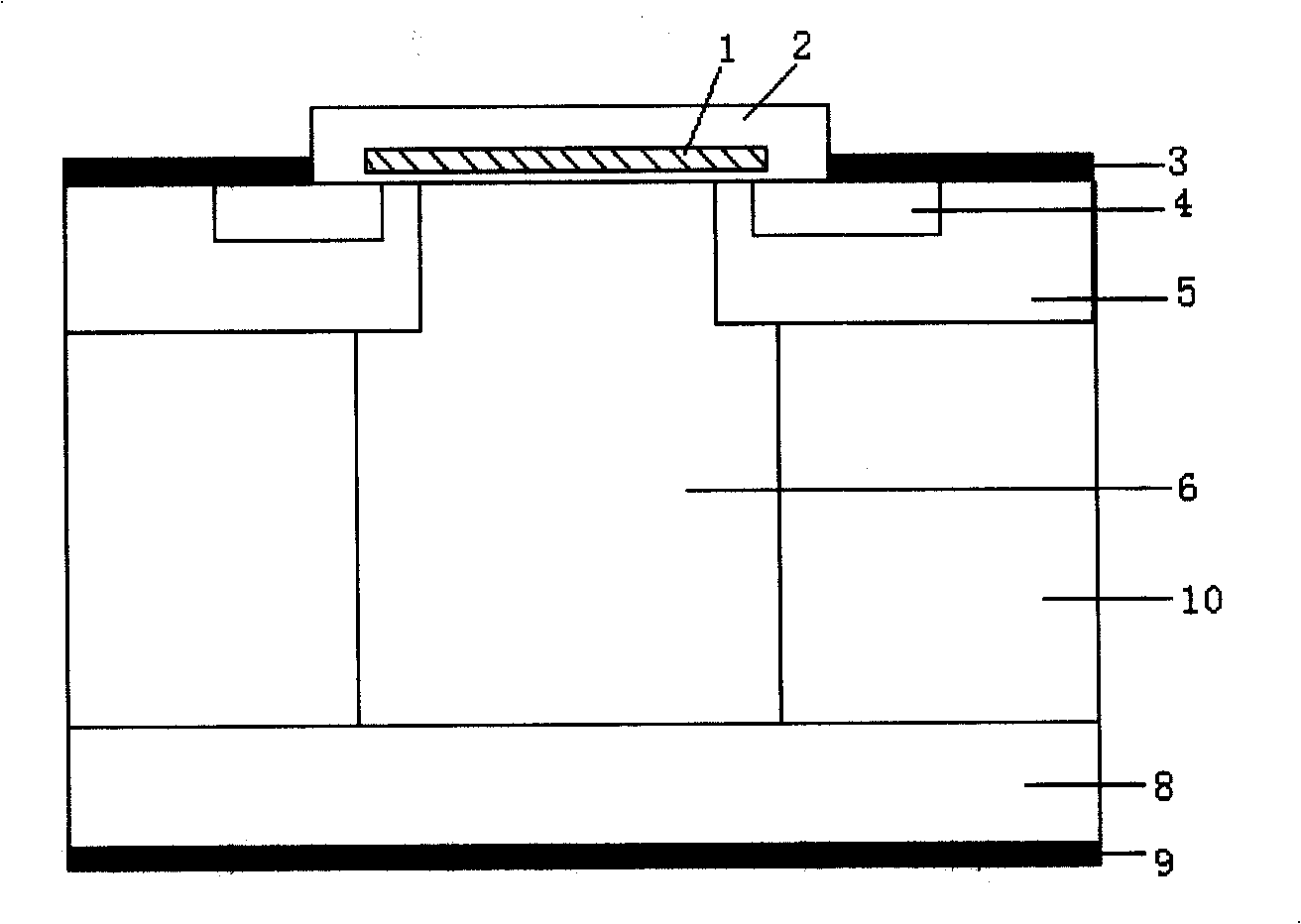

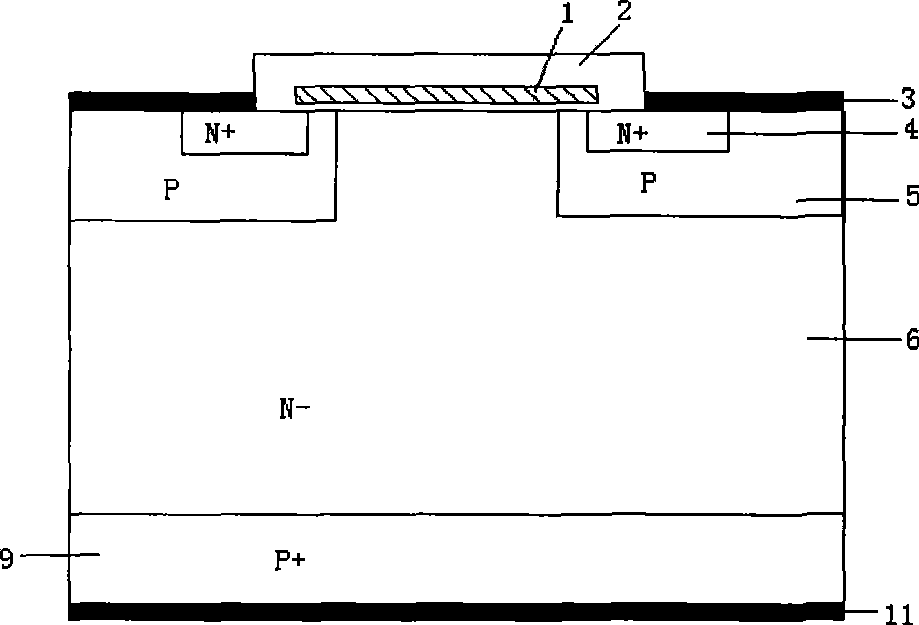

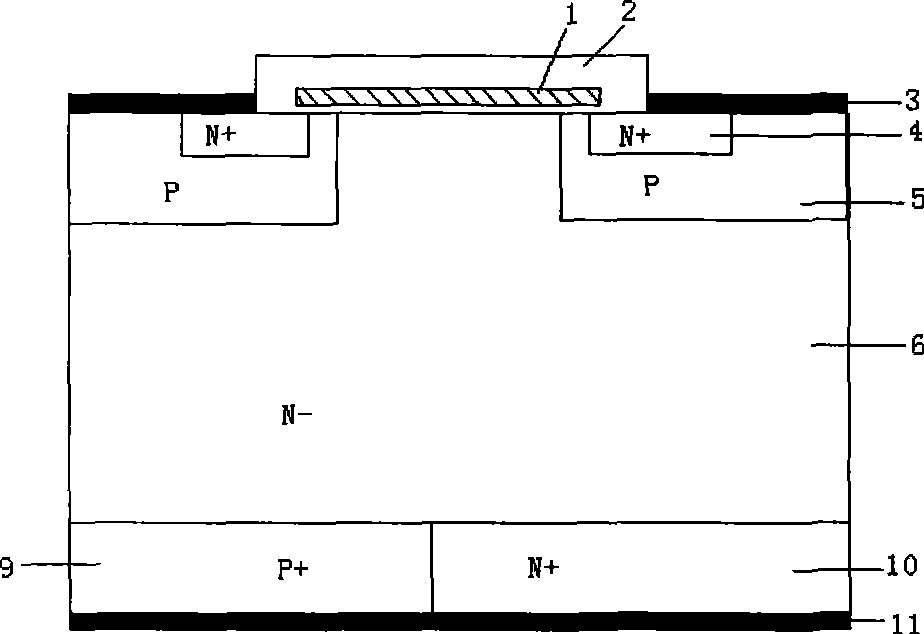

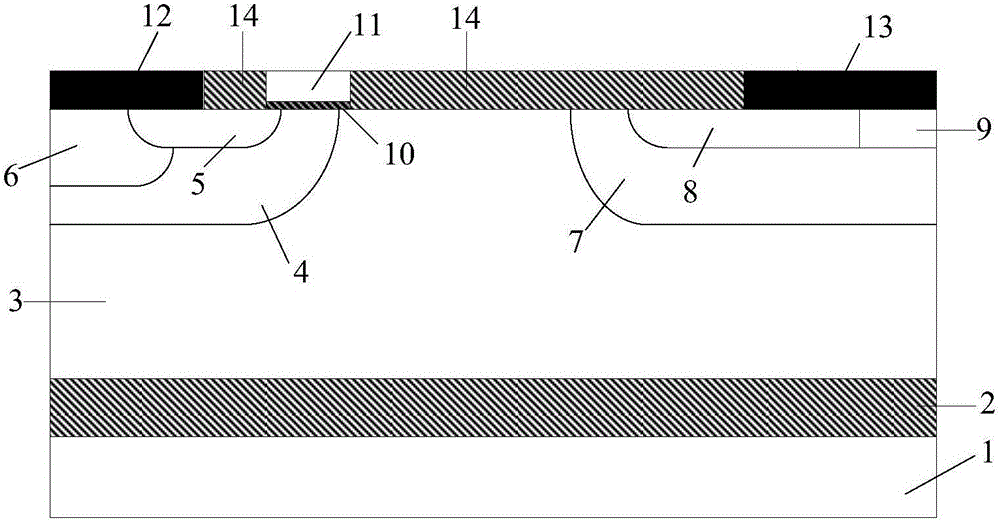

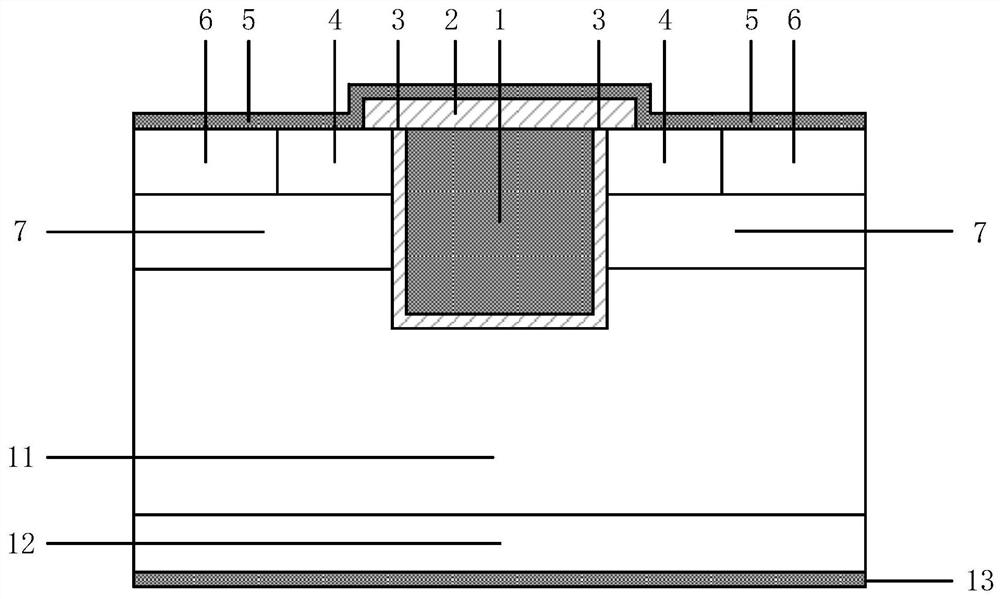

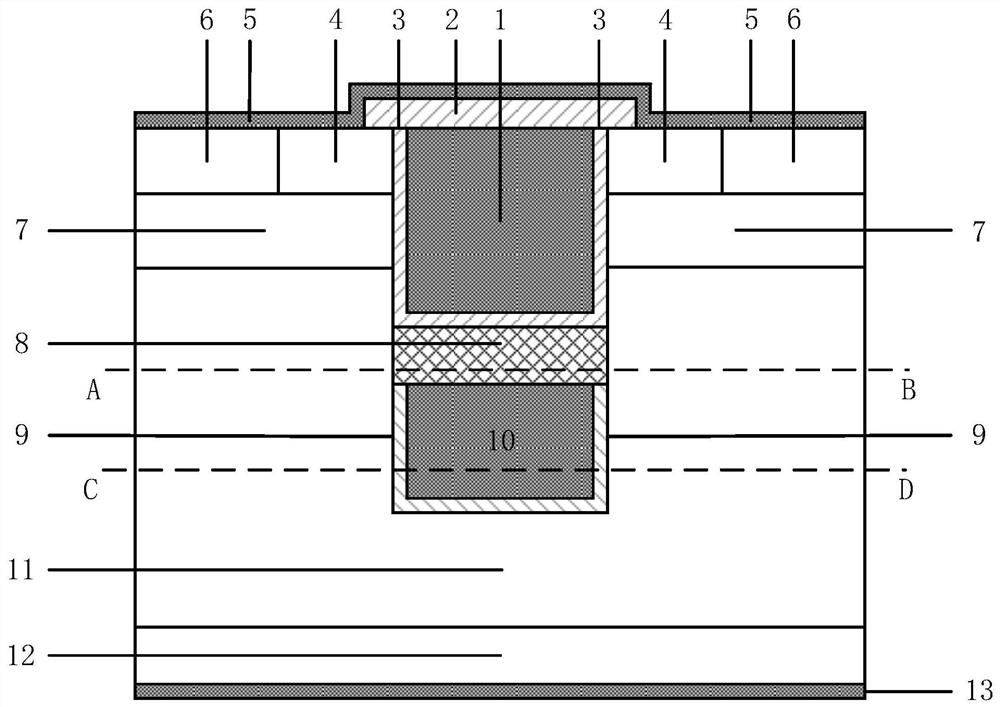

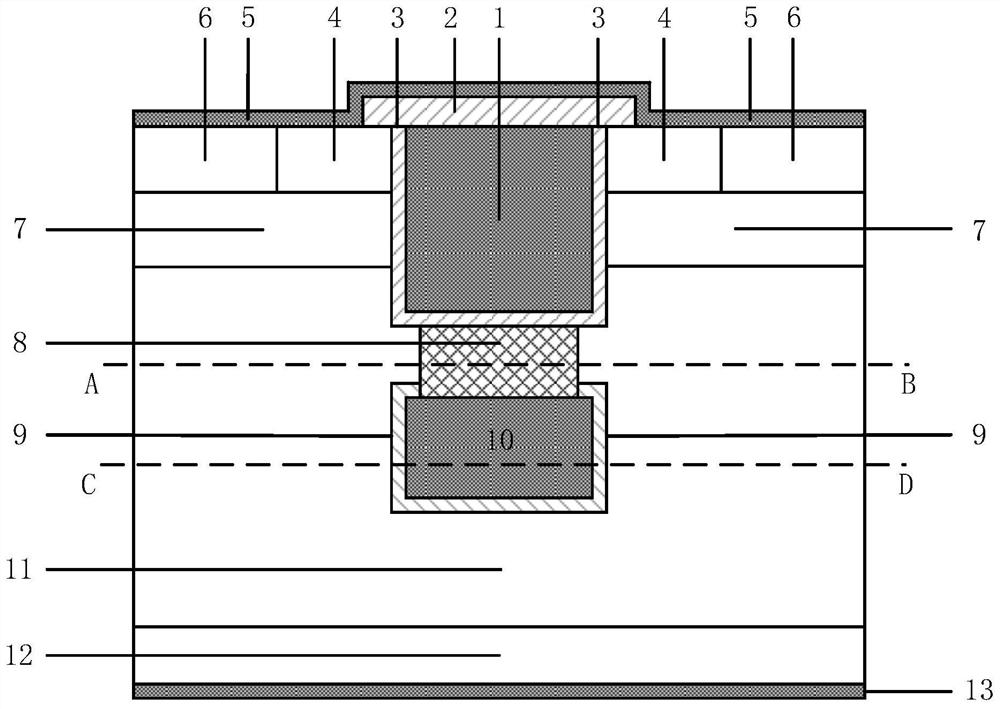

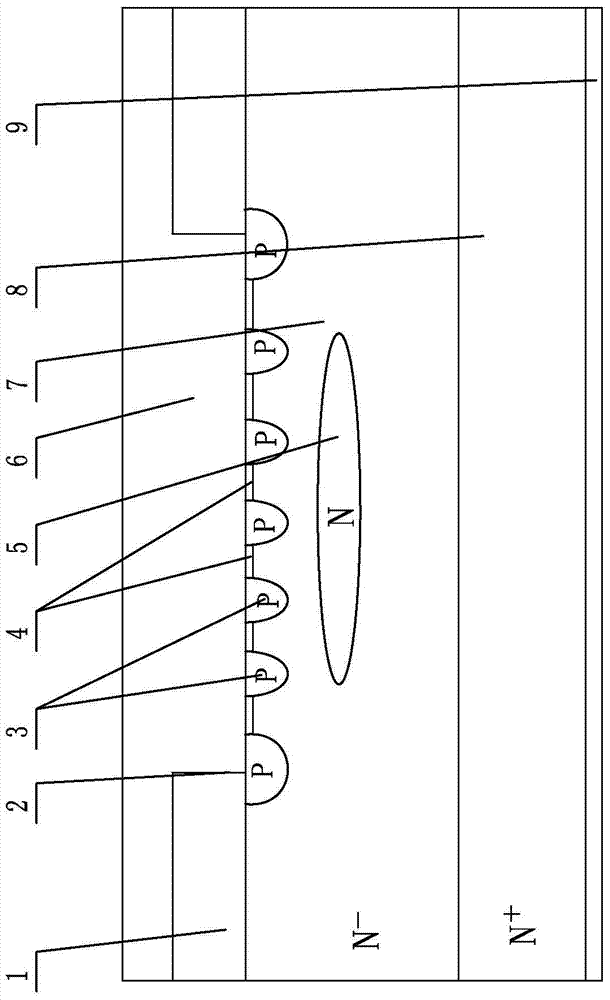

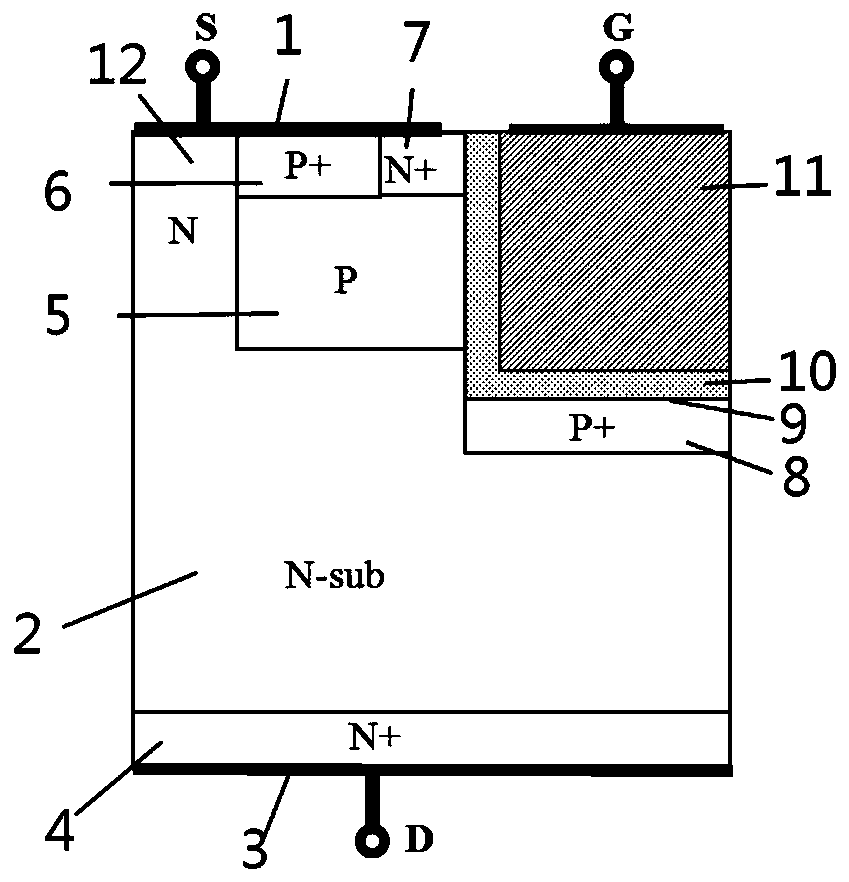

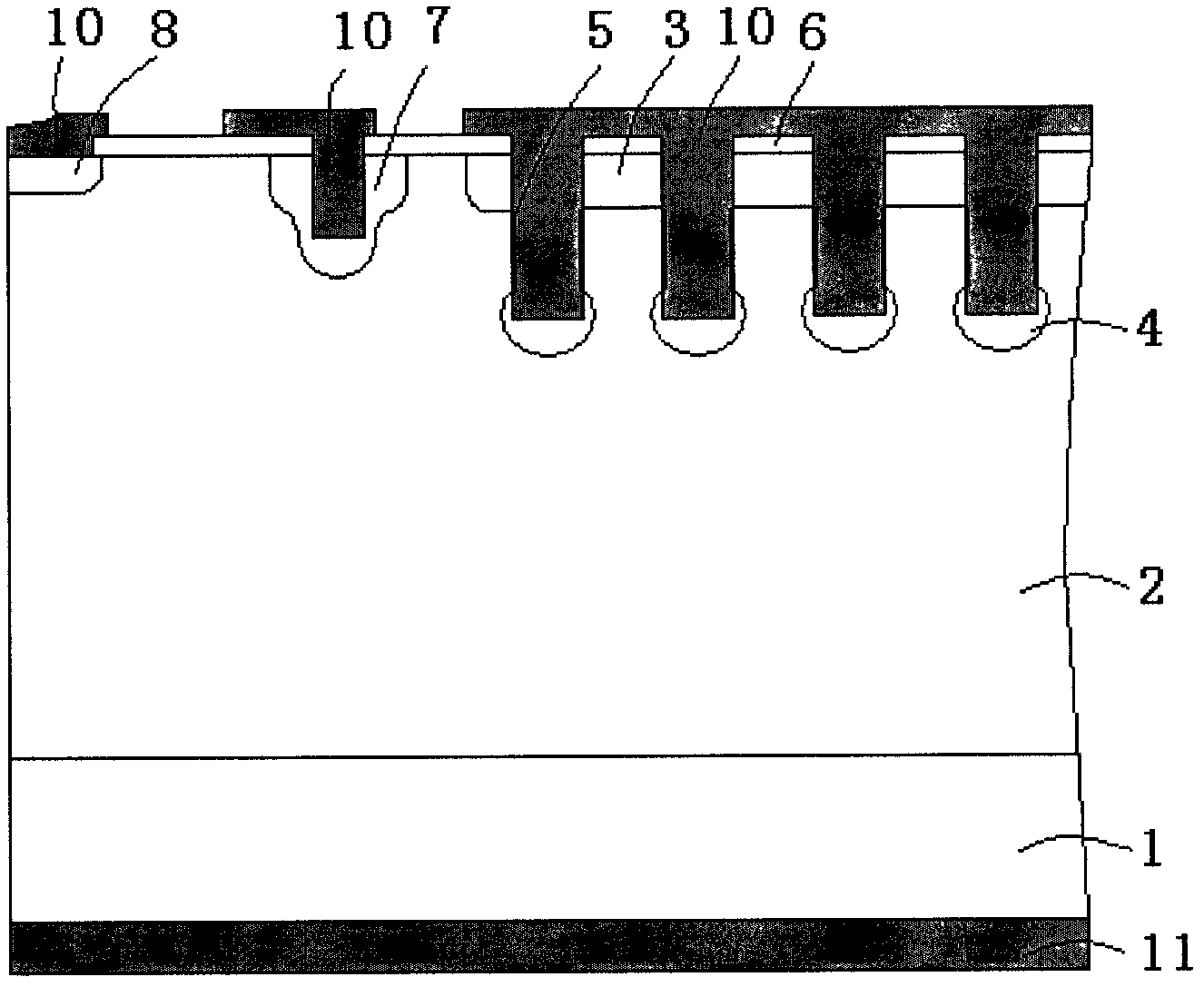

VDMOS device

InactiveCN101404292AReduce forward voltage dropIncrease the cross-sectional areaSemiconductor devicesElectronic systemsReverse recovery

A VDMOS device belongs to the technical field of semiconductor power devices. A doped layer is introduced into a conventional VDMOS device; for an N-channel VDMOS device, the doped layer is an N<+> layer (7) positioned between a P-typed base region (5) and an N<-> drift region (6); for a P-channel VDMOS device, the doped layer is a P<+> layer (7') positioned between an N-typed base region (5') and a P<-> drift region (6'). Compared with the conventional VDMOS device, sectional area where the electrons flow passes through is enlarged by adding the doped layer between the base region and the drift region, thus obtaining lower conduction loss, optimizing positive conduction voltage drop and reverse recovery property of a VDMOS intrinsic diode, and reducing the reverse recovery time to a certain extent while reducing the positive conduction voltage drop. The VDMOS device also has the advantages of simple fabrication process and lower process difficulty. Compared with the conventional VDMOS devices, the VDMOS device satisfies the application requirement of power electronic systems more easily.

Owner:UNIV OF ELECTRONICS SCI & TECH OF CHINA

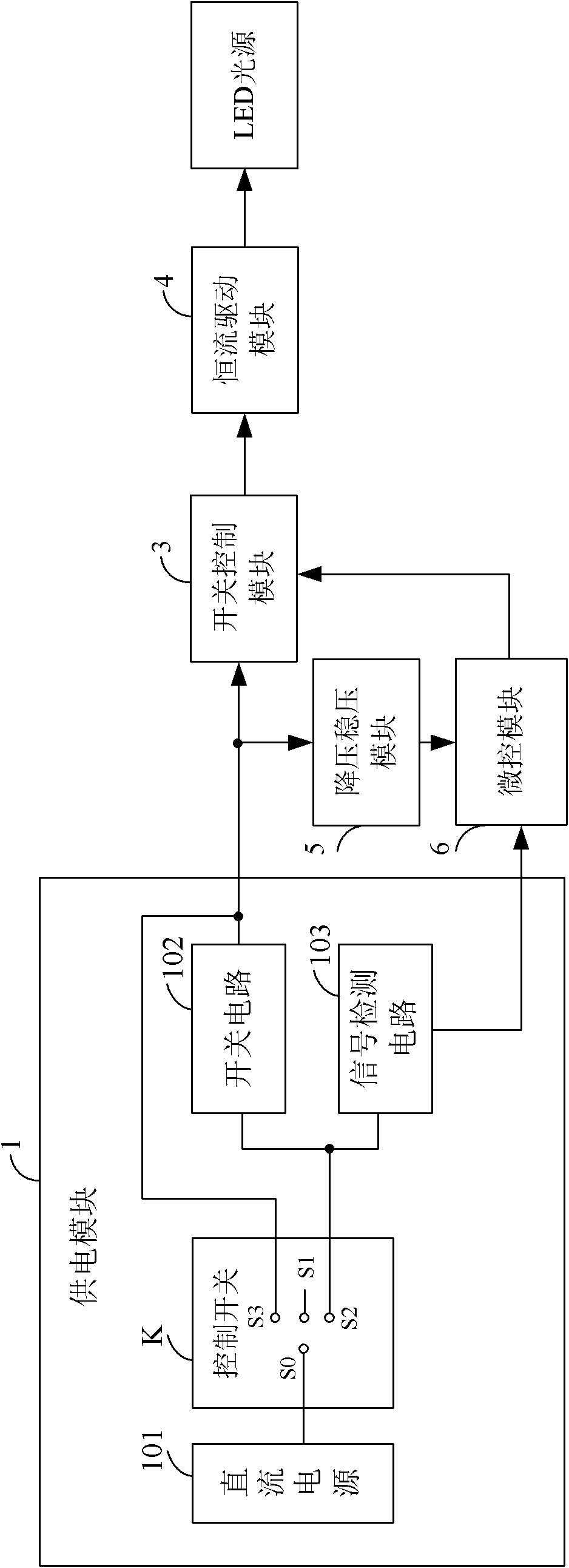

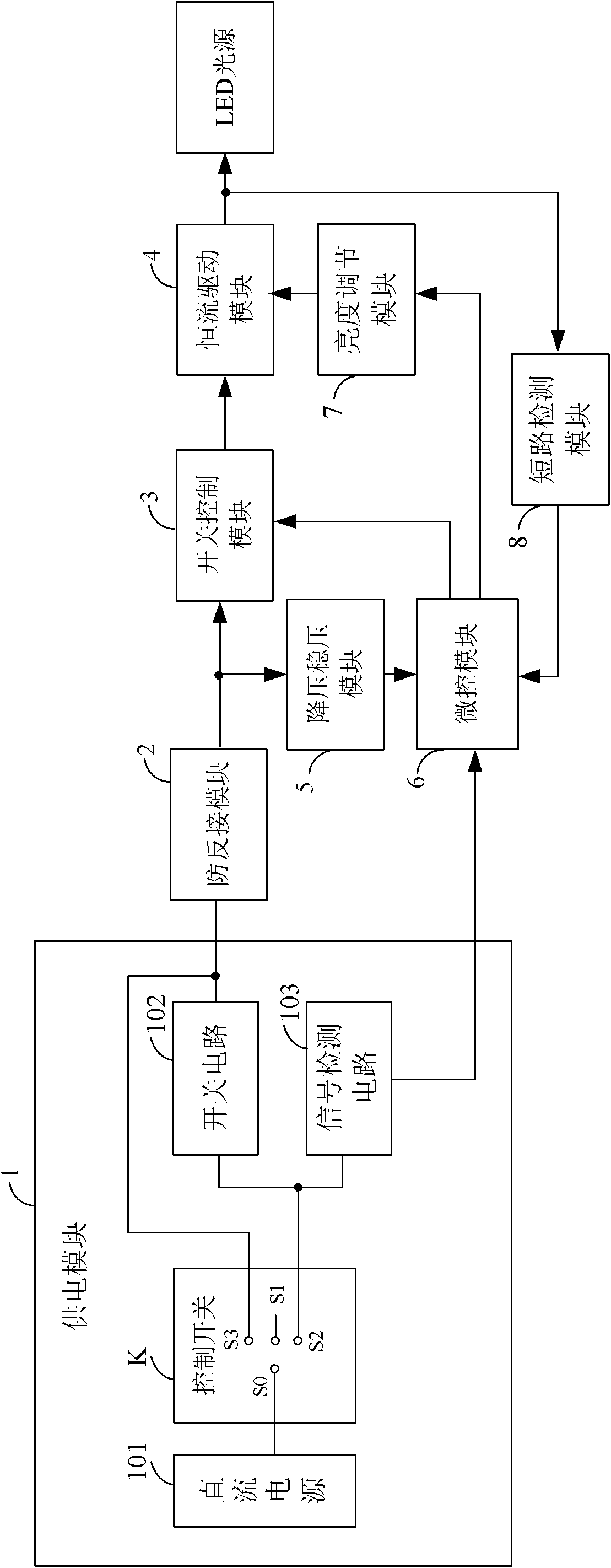

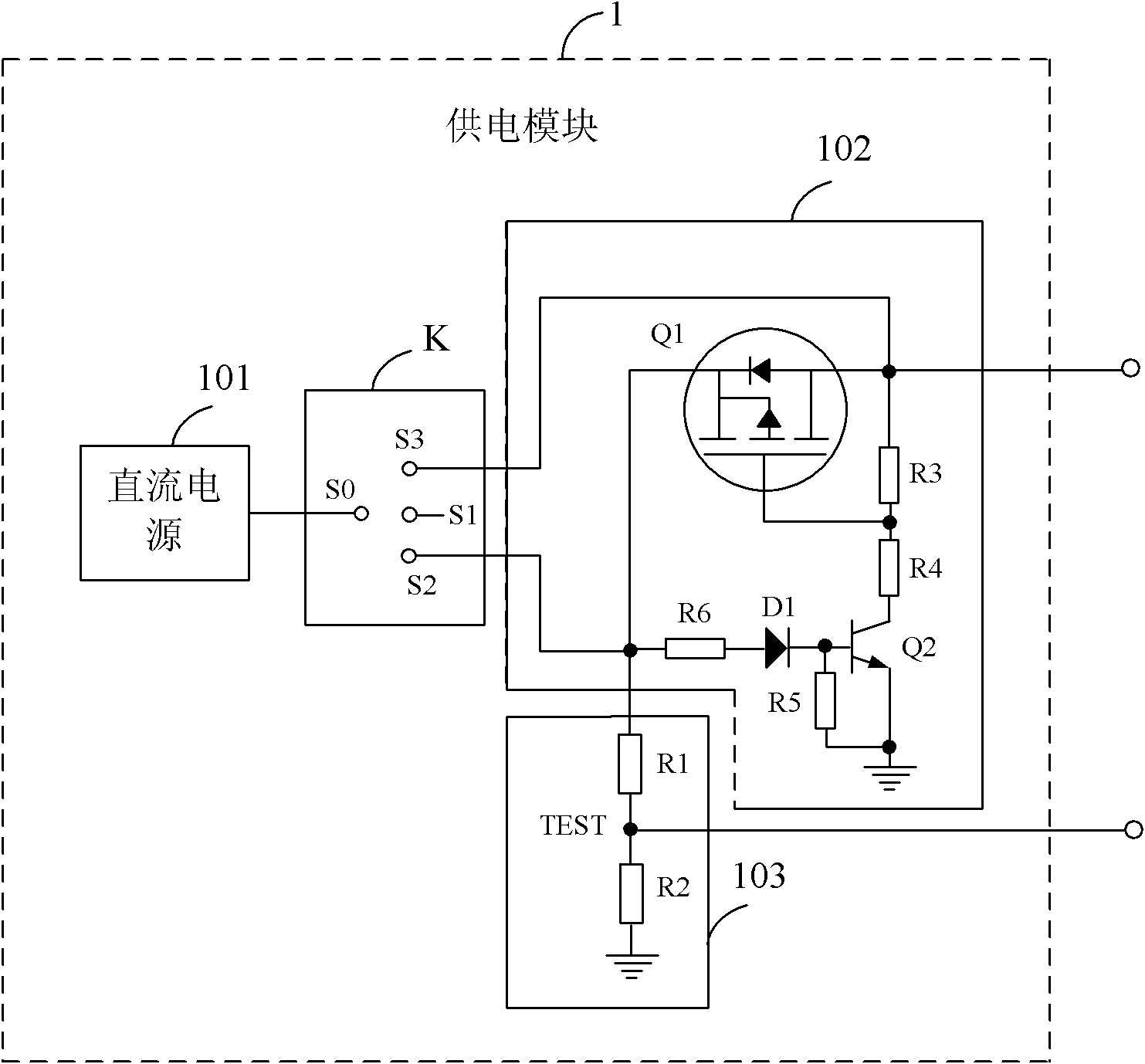

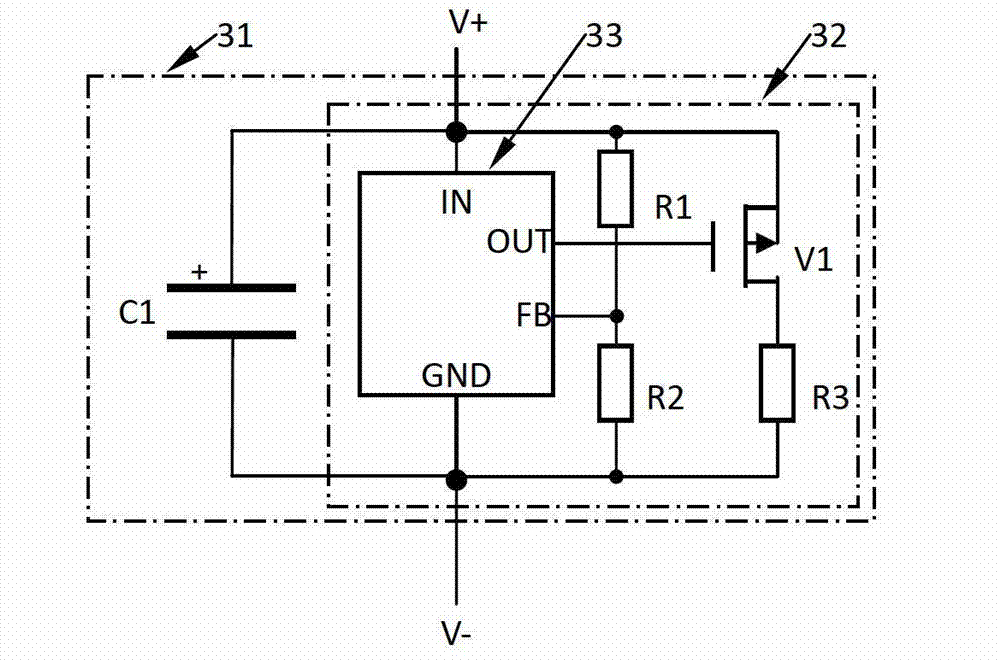

LED lamp control circuit and LED lamp

ActiveCN101848580ASave powerReduce conduction voltage dropPoint-like light sourceElectric circuit arrangementsComputer moduleVoltage drop

The invention relates to an LED lamp control circuit and an LED lamp. The LED lamp control circuit comprises a power supply module, a switch control module, a constant current driving module, a voltage drop and stabilization module and a micro-control module, The power supply module comprises a direct current power supply, a control switch, a switch circuit and a signal detection circuit, whereinthe control switch is used for controlling the direct current power supply to switch on or switch off, the switch circuit is switched on or switched off according to electrical signals on the controlswitch, and the signal detection circuit generates a detection signal according to the electrical signals on the control switch. The micro-control module controls the switch module to generate a first output voltage or the second output voltage according to the detection signals. The constant current driving module generates a first constant current or a second constant current according to the first output voltage or the second output voltage so that an LED light source works in a high light mode or a low light mode. In the invention, when the LED light source is extinguished, the direct current power supply does not need to supply power for the micro-control module, thereby the electric quantity is saved, and the LED light source can be switched between the high light mode and the low light weight.

Owner:OCEANS KING LIGHTING SCI&TECH CO LTD +1

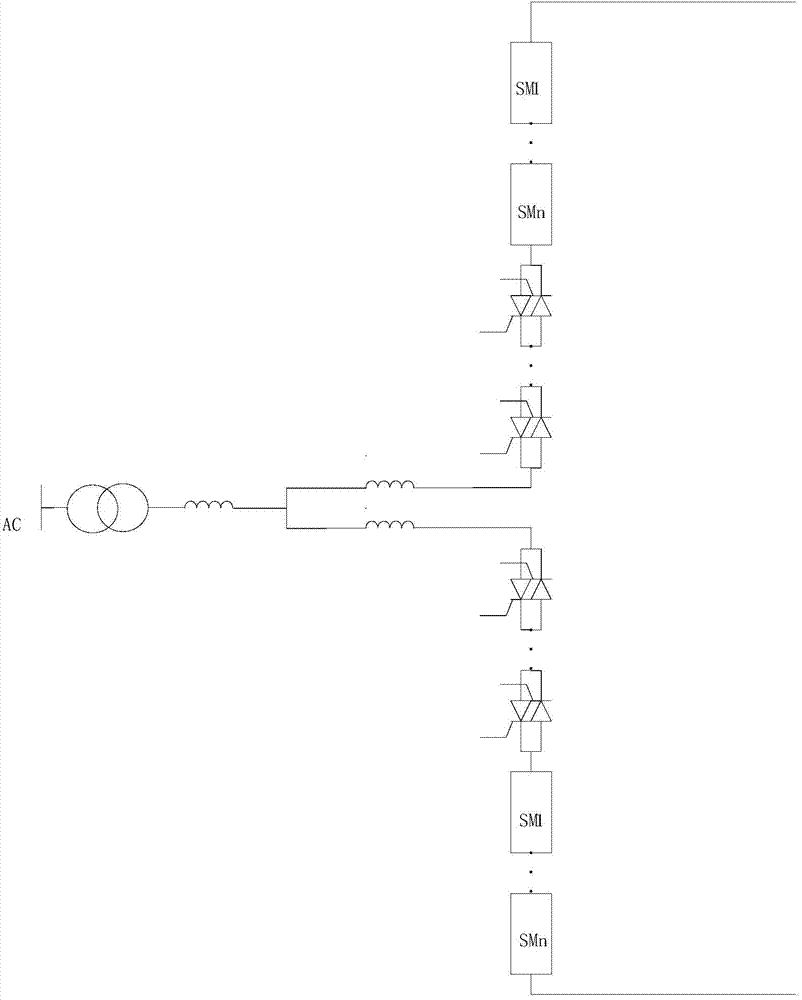

Multi-level voltage source current converter and control method thereof

InactiveCN103580521AReduce harmonic contentLow costEmergency protective circuit arrangementsAc-dc conversionComputer moduleEngineering

The invention discloses a multi-level voltage source current converter comprises at least one phase unit. Each phase unit comprises an upper bridge arm, a lower bridge arm and a current conversion electric reactor, wherein the upper bridge arm and the lower bridge arm respectively comprise at least two sub-modules, a switch loop and a bridge arm electric reactor all of which are sequentially connected in series; all sub-modules in the same bridge arm are connected in series in the same direction; the sub-modules, connected with the switch loop, in the upper bridge arm are opposite to the sub-modules, connected with the switch loop, in the lower bridge arm in polarity; one end, connected with the electric reactor in series, of the upper bridge arm and one end, connected with the electric reactor in series, of the lower bridge arm are connected and have access to an alternating current network through the current conversion electric reactor; the other end of the upper bridge arm and the other end of the lower bridge arm serve as a first direct current endpoint and a second direct current endpoint of the phase unit respectively to have access to a direct current network. Each switch loop comprises a plurality of anti-parallel thyristor pairs which are connected in series. The multi-level voltage source current converter is applied to flexible direct-current transmission and the like, and has the advantages of being small in number of the sub-modules, low in cost, small in consumption, capable of effectively blocking fault currents when the direct current side breaks down, and the like. The invention further discloses a control method of the multi-level voltage source current converter.

Owner:NR ELECTRIC CO LTD +1

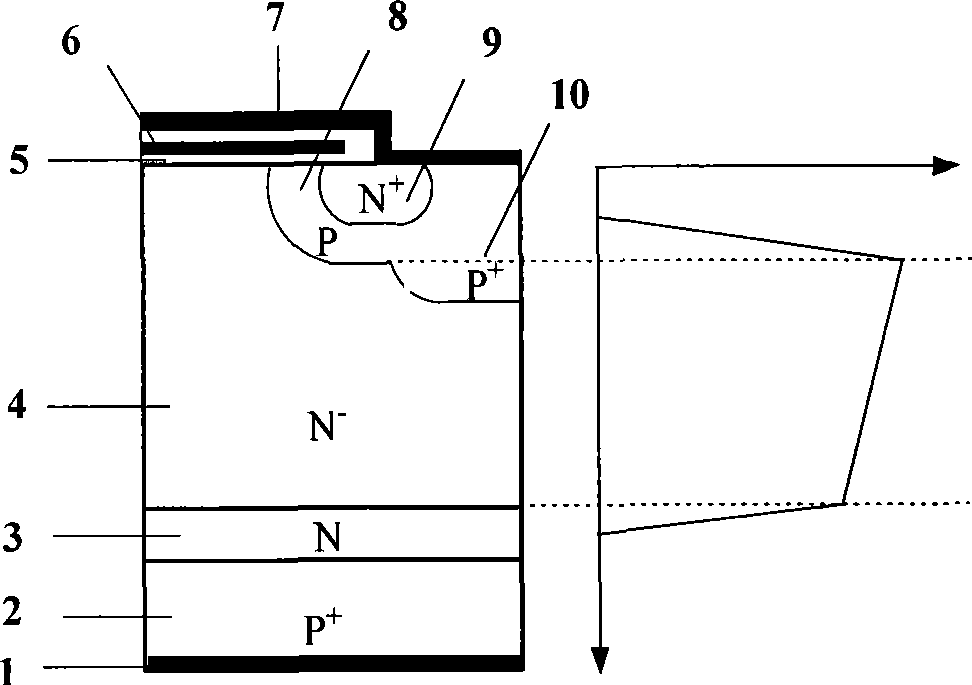

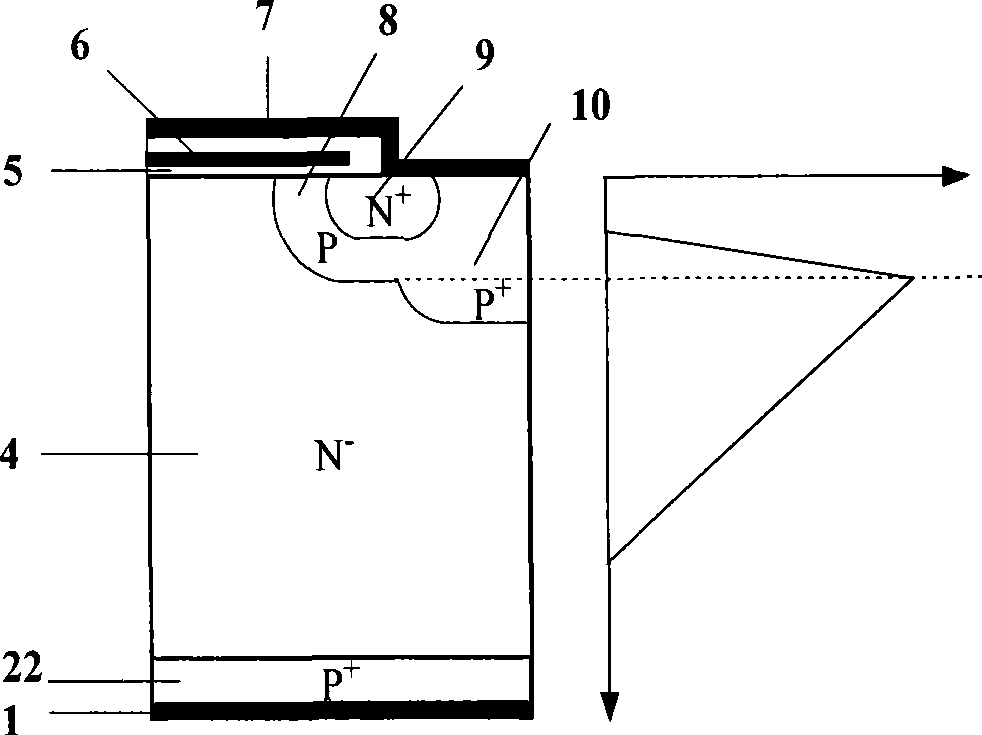

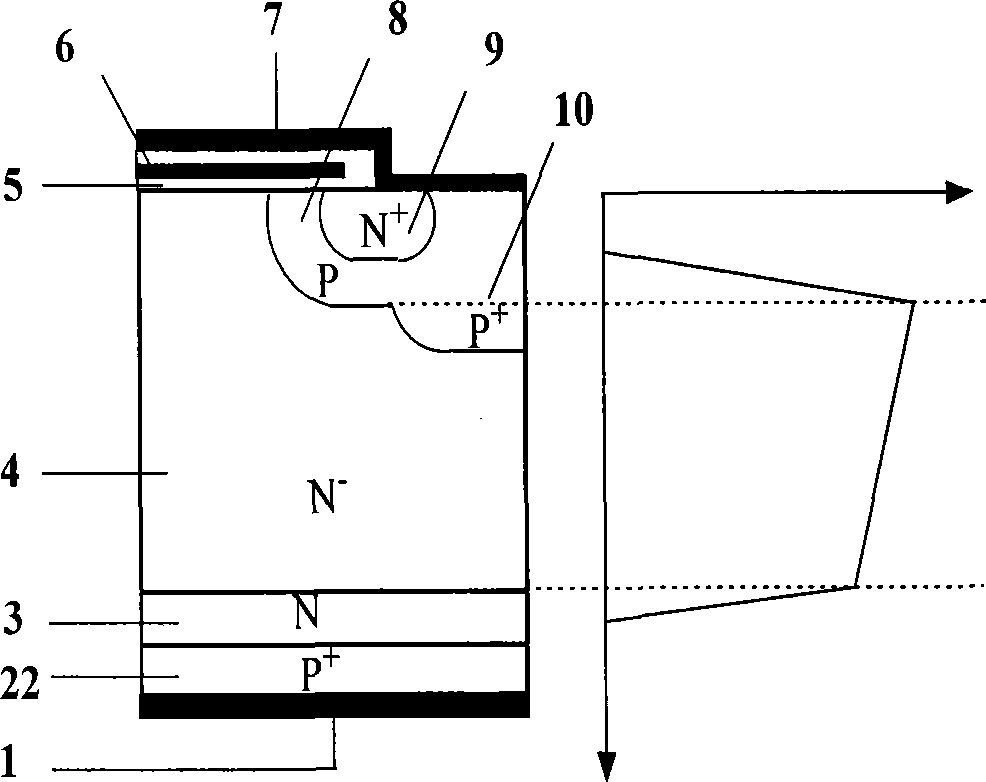

Tunnel IGBT with anode in short circuit

InactiveCN101393928AImprove conduction characteristicsShorten off timeSemiconductor devicesVoltage dropEngineering

An anode-short tunnel pump IGBT belongs to the technical field of semiconductor power devices. With an anode-short structure and a tunnel pump structure simultaneously introduced into a traditional IGBT, or a tunnel pump structure into an anode-short IGBT, or an anode-short structure into a tunnel pump IGBT, the invention gives the advantages of both the anode-short IGBT and the tunnel pump IGBT to the anode-short tunnel pump IGBT so as to improve the turn-off characteristic of the device and lower the conductive voltage drop of the device. The invention can better reconcile the positive saturation voltage drop with the turn-off time, and optimize the conductive characteristic of the device, so that the invention is suitable in particular for application environments characterized by high voltage, heavy current and high frequency.

Owner:UNIV OF ELECTRONICS SCI & TECH OF CHINA

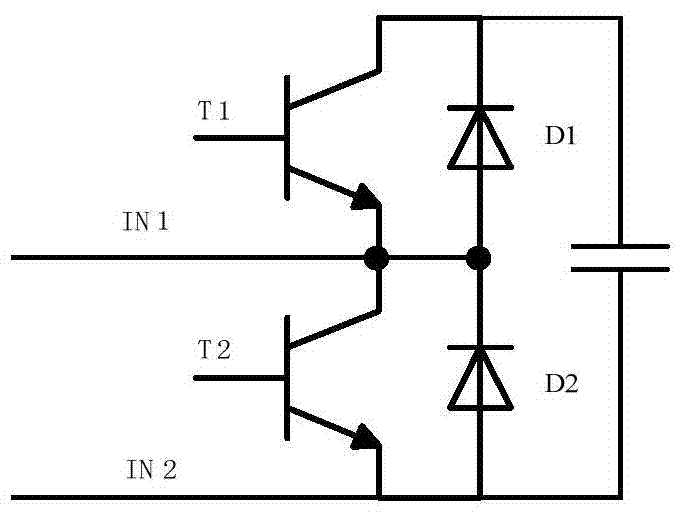

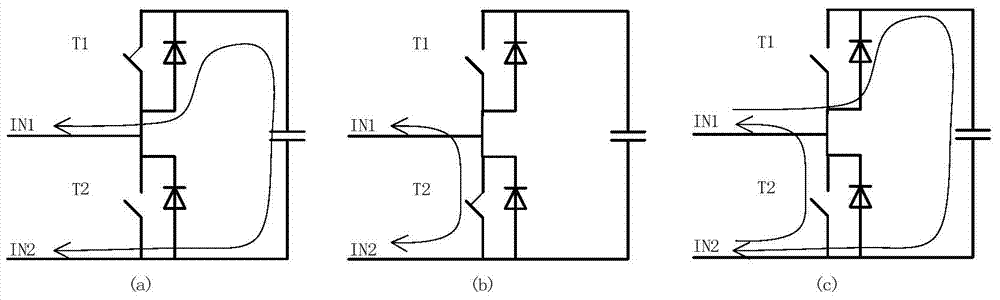

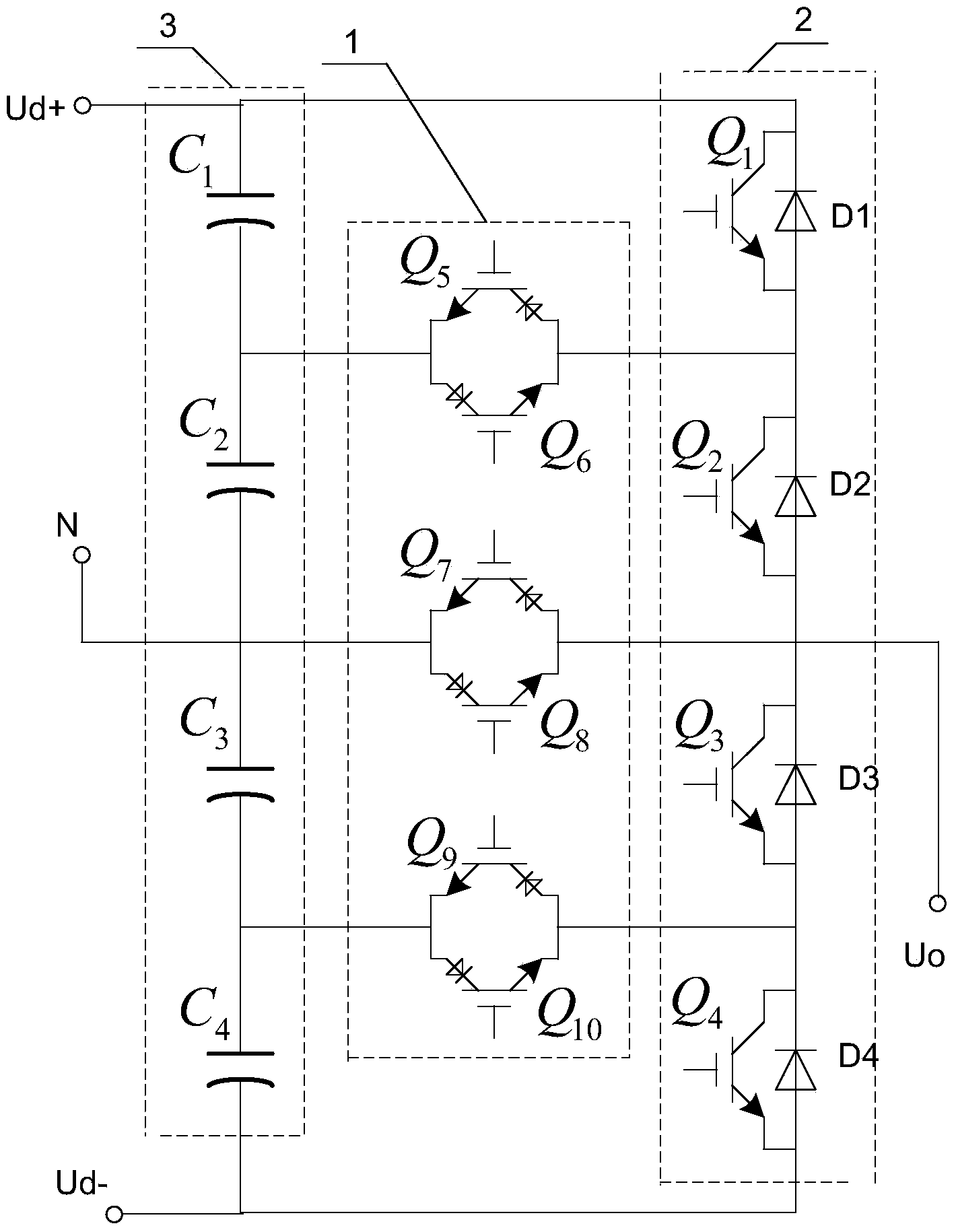

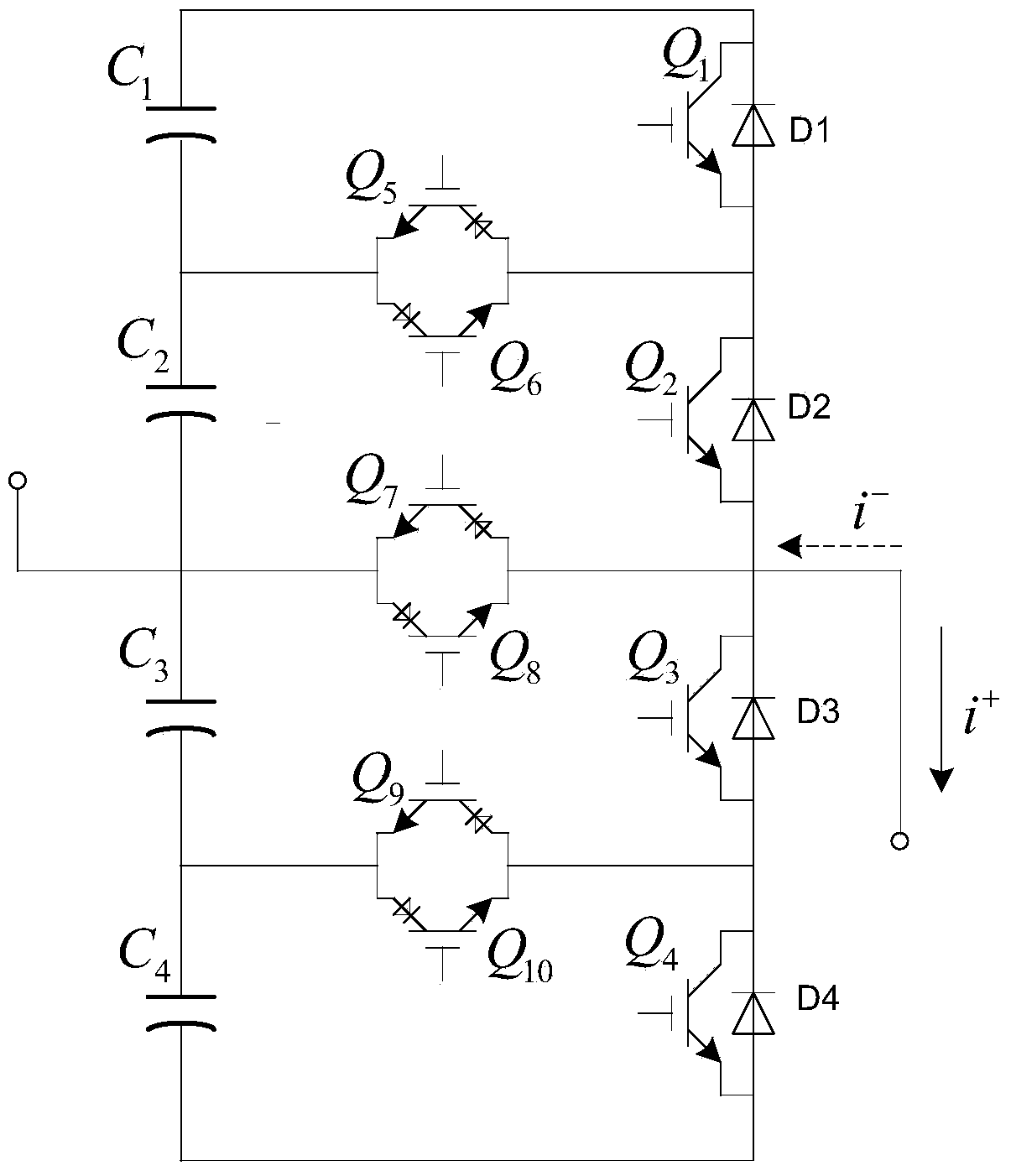

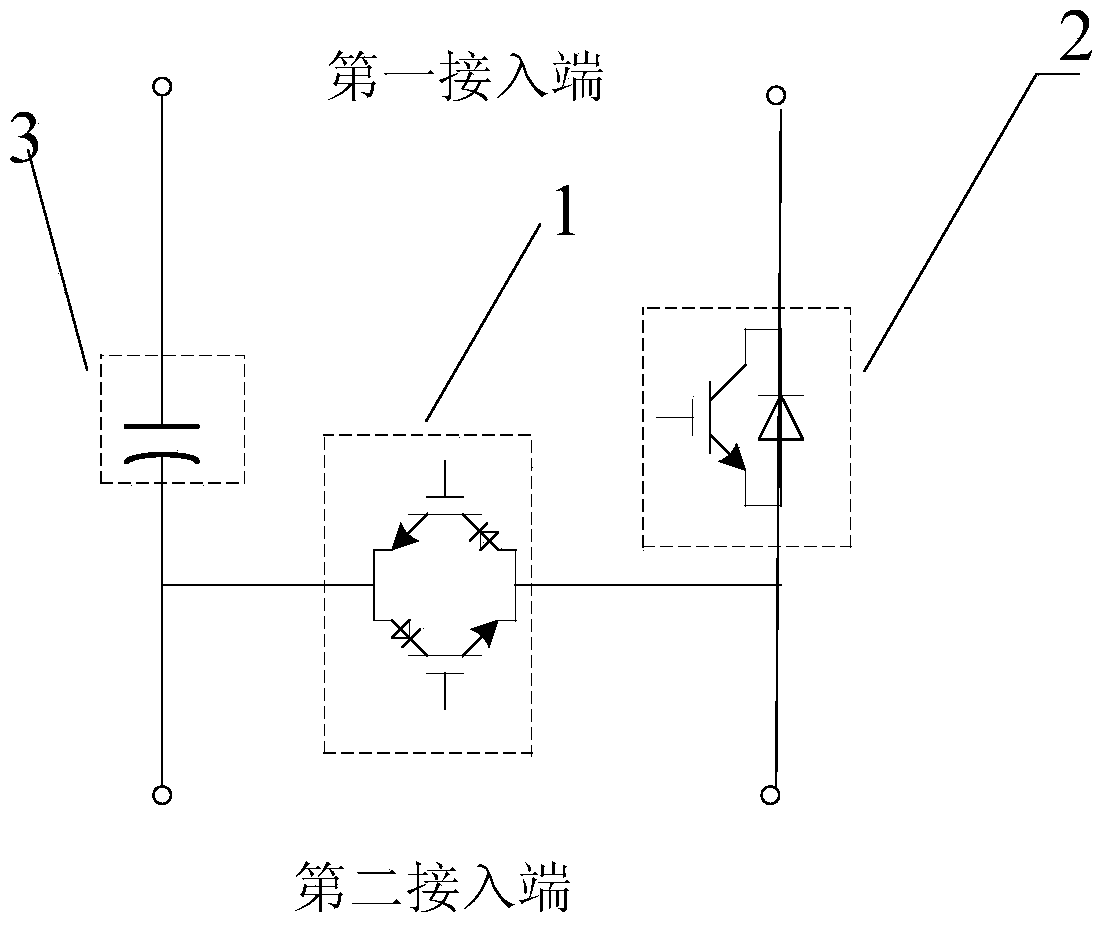

T-shaped multi-level inverter circuit based on reverse blocking IGBT antiparallel connection

ActiveCN104038090AImprove Harmonic DistortionImprove scalabilityAc-dc conversionCapacitanceDc capacitor

The invention discloses a T-shaped multi-level inverter circuit based on reverse blocking IGBT (Insulated Gate Bipolar Transistor) antiparallel connection. The T-shaped multi-level inverter circuit comprises a two-way controllable switch (1), a power device (2) and a direct-current capacitor (3); the two-way controllable switch (1) comprises a plurality of reverse blocking IGBTs which are in antiparallel connection with each other in pairs; one side of a connecting wire of the reverse blocking IGBTs in antiparallel connection with each other in pairs after being connected in parallel is connected with a power switch tube, while the other side of the connecting wire is connected with the direct-current capacitor (3). The T-shaped multi-level inverter circuit is characterized in that after the reverse blocking IGBTs are in antiparallel connection with each other to form the two-way controllable switch, the antiparallel reverse blocking IGBTs are connected at the midpoints of a plurality of series capacitors without increasing the conduction loss, and then a plurality of midpoint voltage clamping circuits to realize five-level outputs, and with the increase of the number of output levels, the harmonic distortion of an output voltage is improved, the desired filter inductance is lower or the switching frequency can be reduced accordingly.

Owner:JIANGSU WEIFAN INTELLIGENT ELECTRICAL TECH

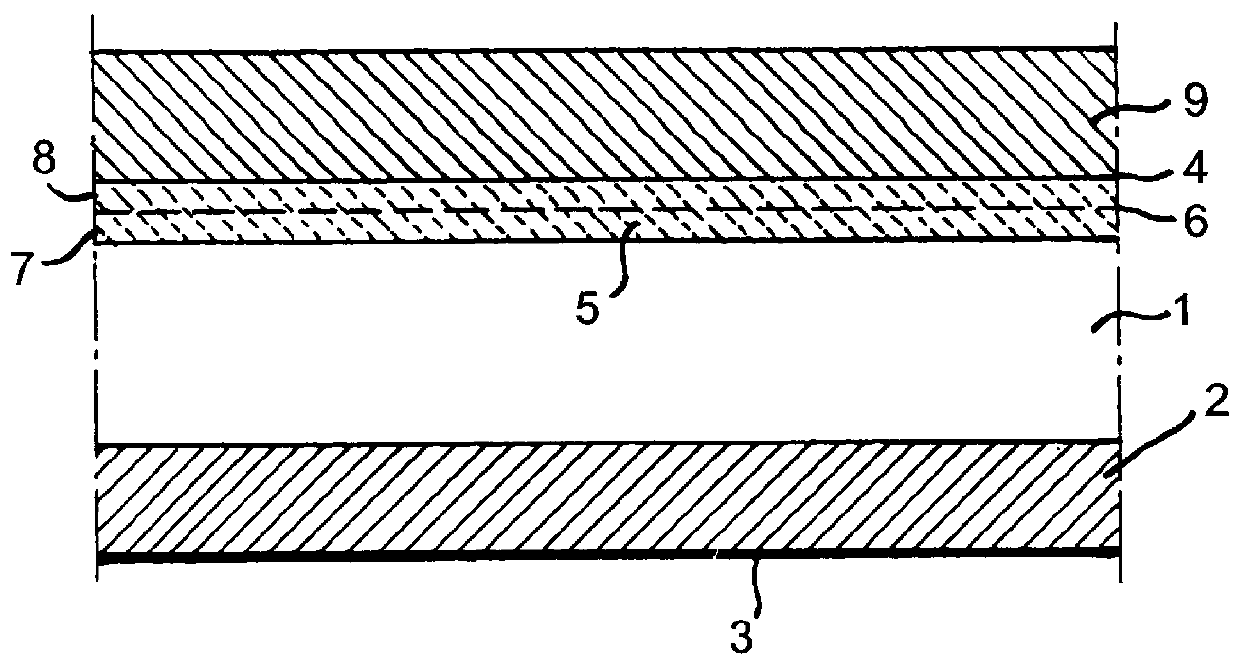

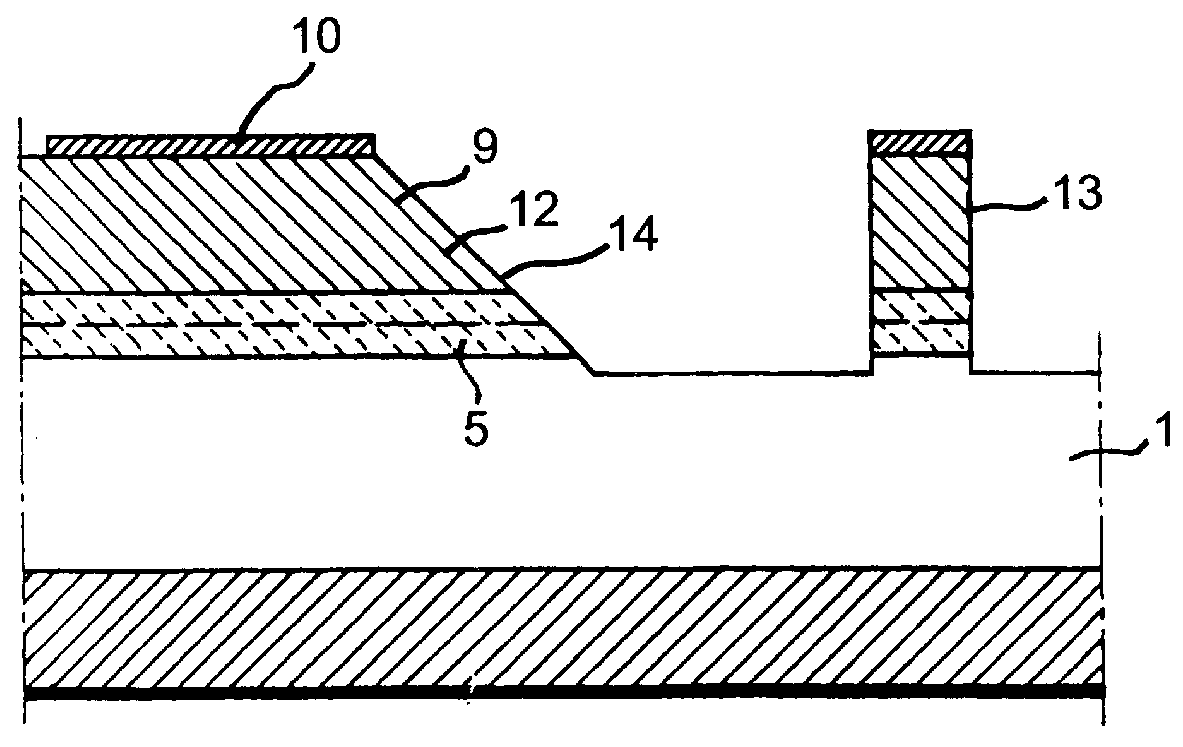

Accumulation layer controlled insulation gate type bipolar transistor

InactiveCN101393927AIncreased saturation current densityElimination of parasitic thyristor effectsSemiconductor devicesElectron flowParasitic bipolar transistor

Insulated gate bipolar transistors controlled by an accumulation layer belong to the technical field of semiconductor power devices. The transistors include a channel insulated gate bipolar transistor, a plane insulated gate bipolar transistor and a transverse insulated gate bipolar transistor. According to the invention, when a device is in the blocking state, a built-in electric field formed by a P body region (10) and an N base region (4) forms part of an electron barrier which stops electrons flowing from an N source region (9) into the N base region(4) with the voltage-resistance of the device improved; when the device is in the conductive state, the accumulation layer is formed between the N source region (4) and a gate oxide layer (5), and the electrons can flow from the N source region (9) to the N base region (4) through the accumulation layer so as to control the normal operation of the device. With the accumulation layer rather than a P-type base region and an MOS inversion channel of a traditional insulated gate bipolar transistor, the invention can achieve lower conductive voltage drop and greater saturation current density, thereby avoiding parasitic thyristor effect, and ensuring that the safe operating area, the reliability and the high-temperature working characteristics of the device can be greatly promoted.

Owner:UNIV OF ELECTRONICS SCI & TECH OF CHINA

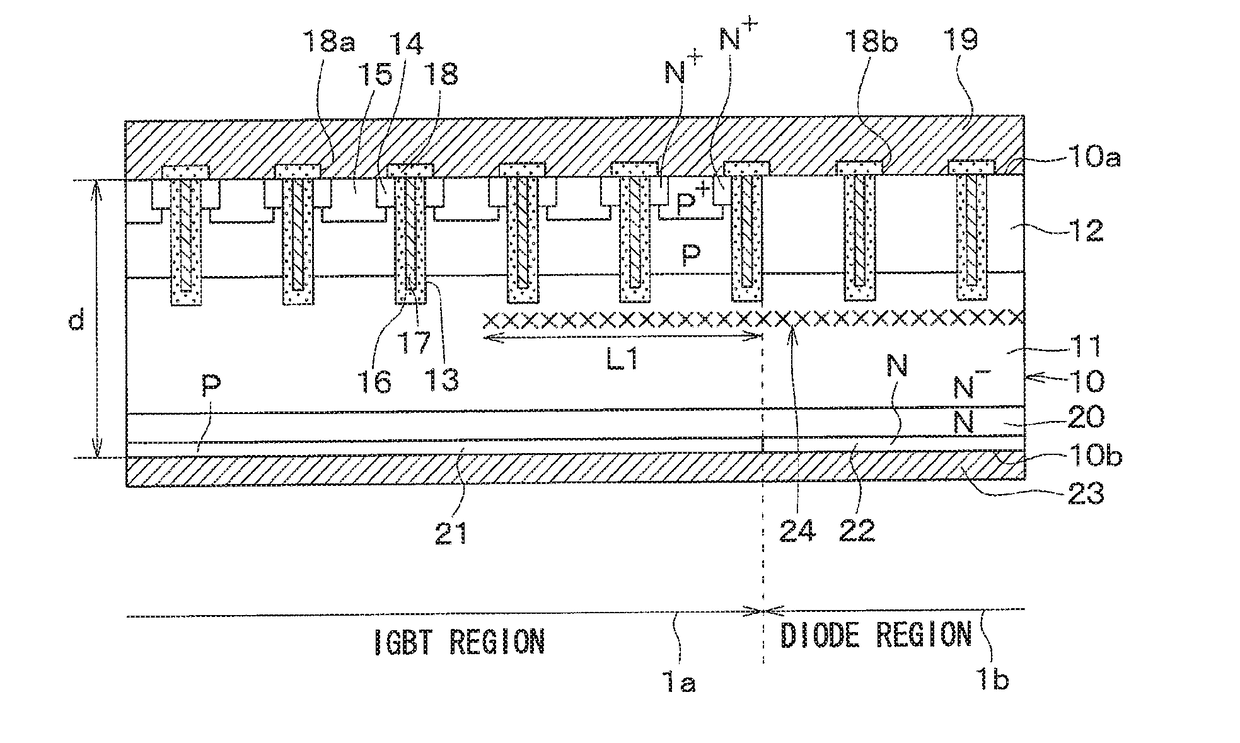

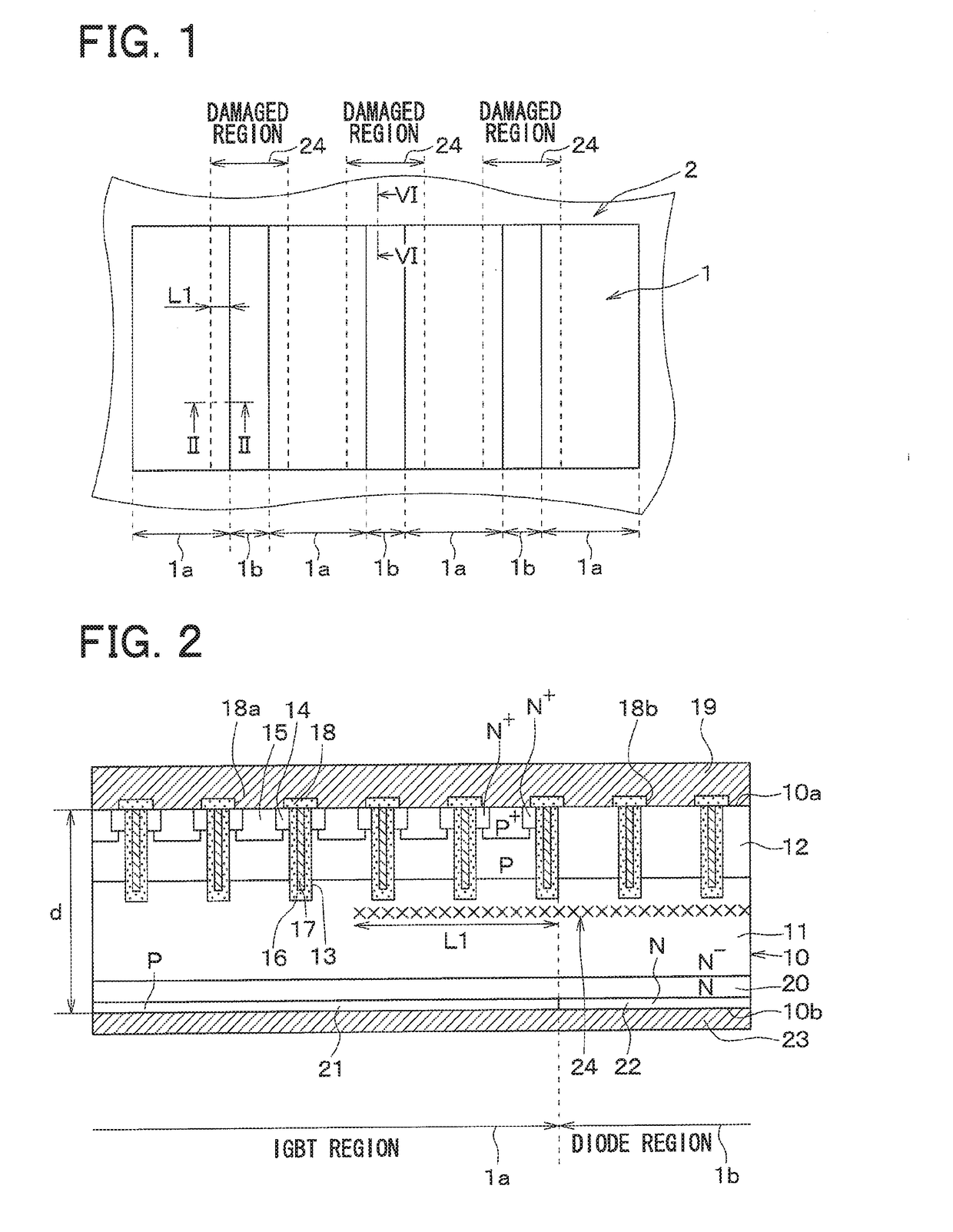

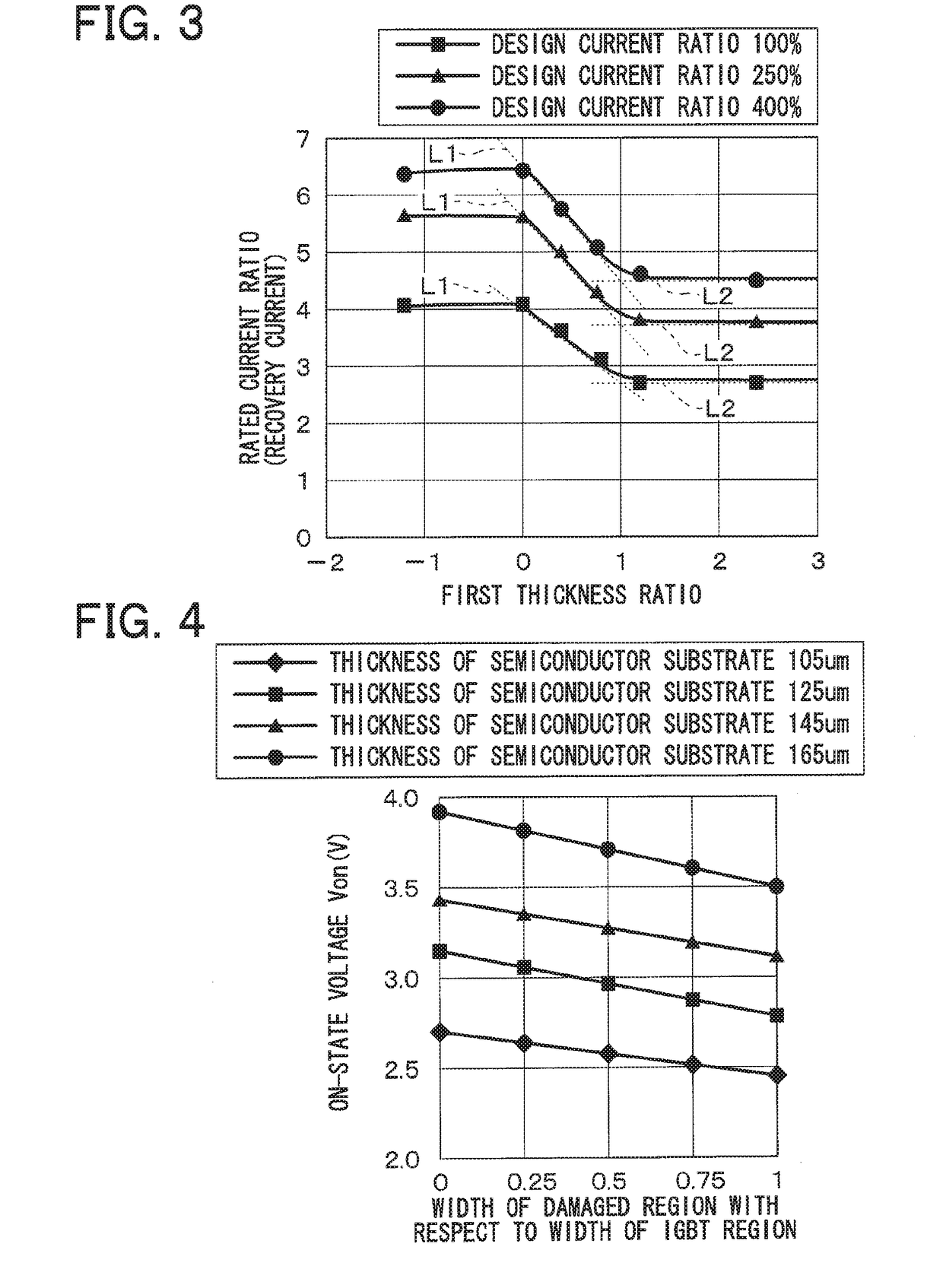

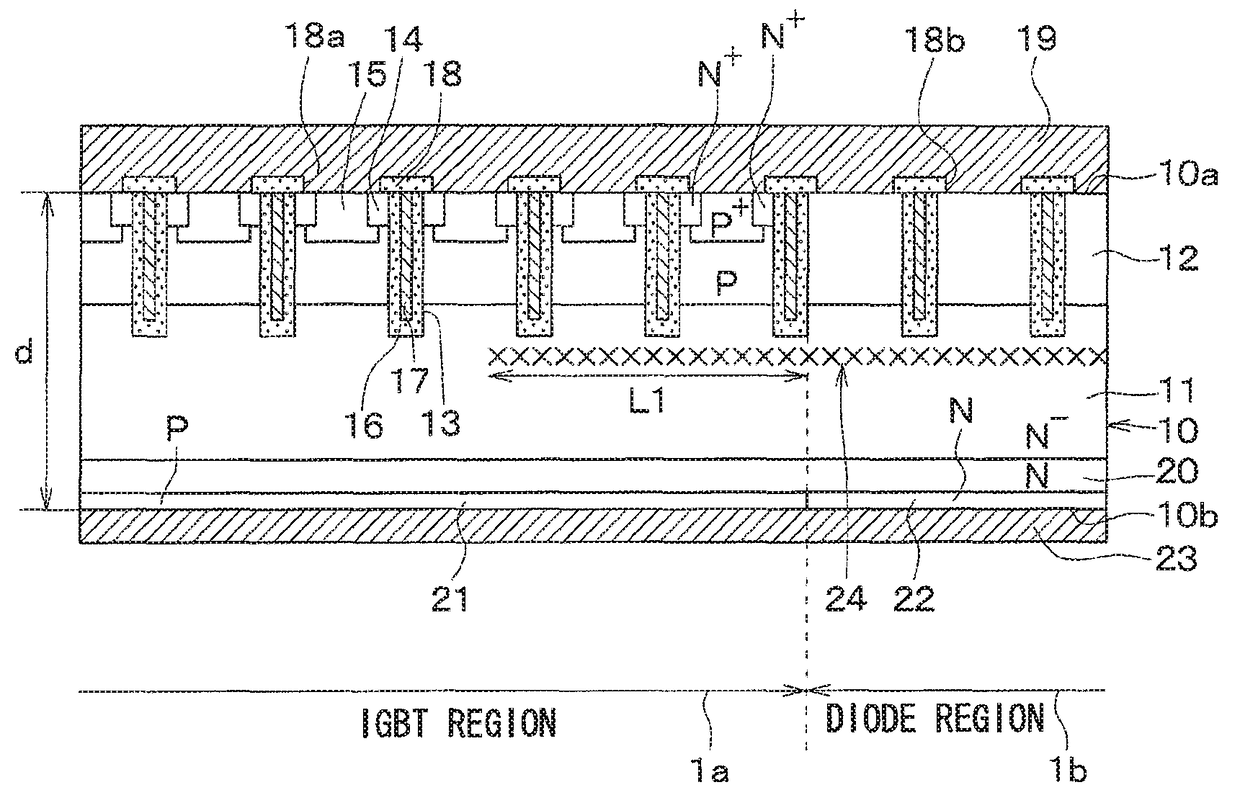

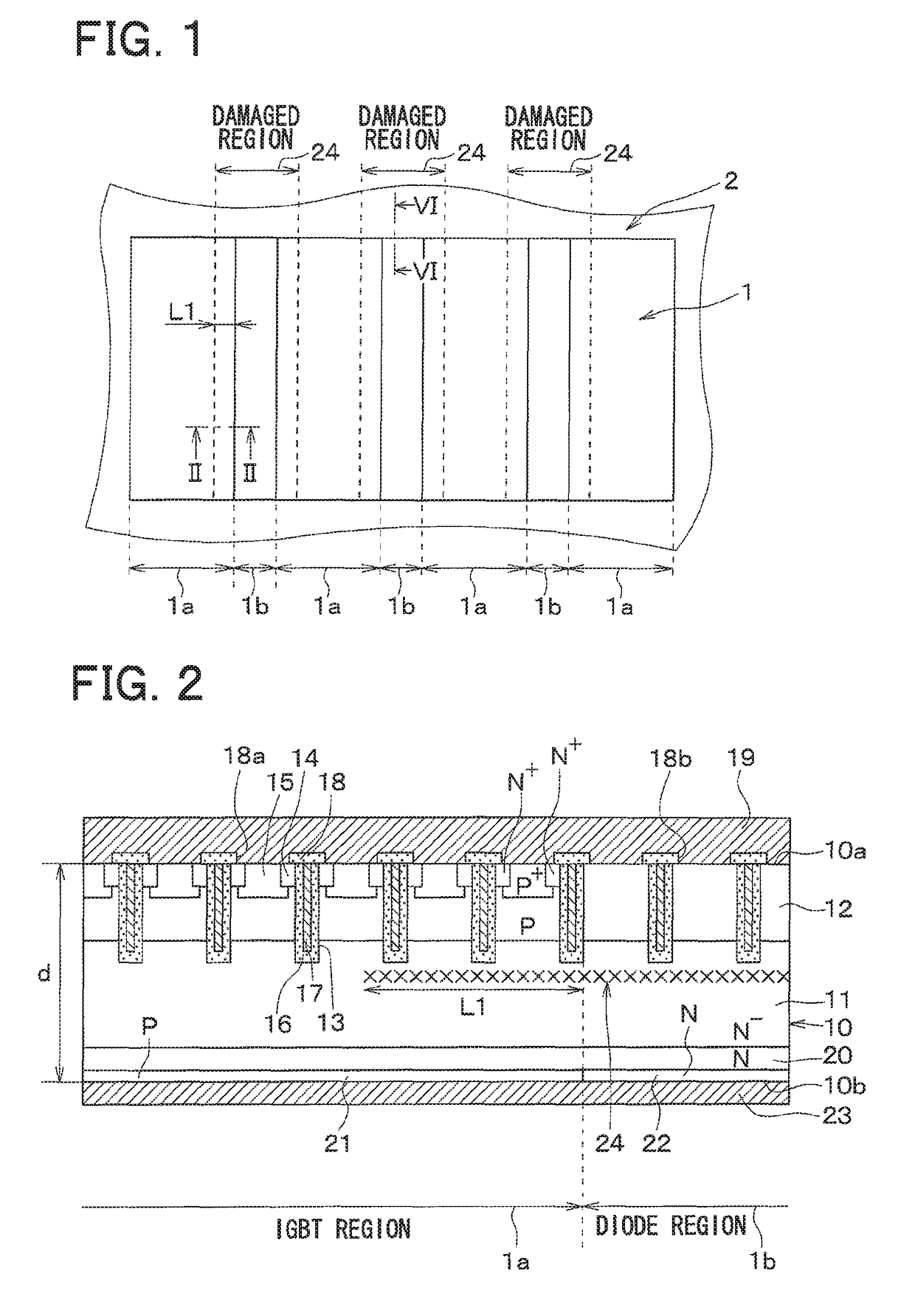

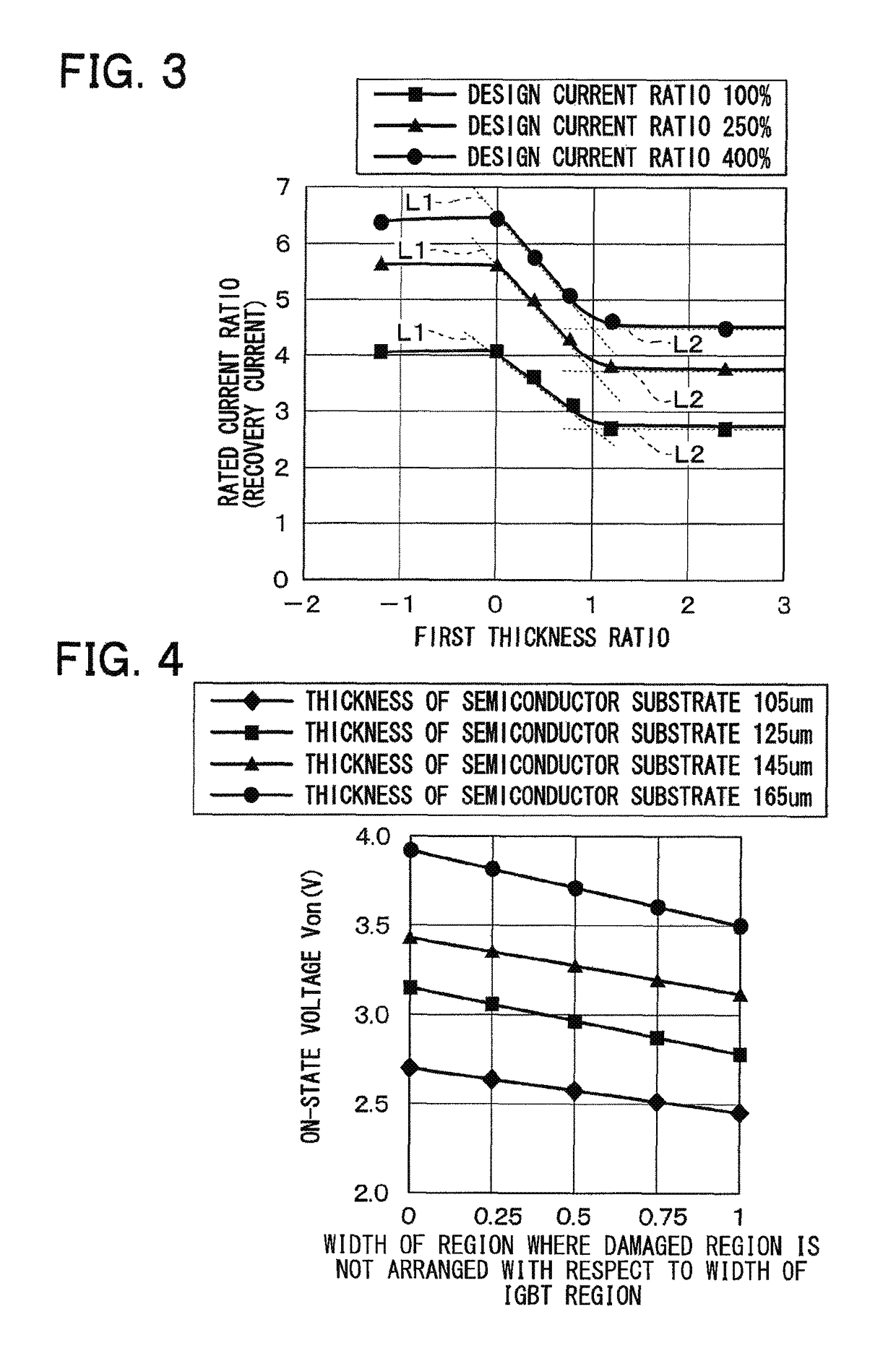

Semiconductor device

ActiveUS20170077216A1Improve featuresImproved recovery propertiesTransistorConversion constructional detailsSemiconductorSemiconductor device

A semiconductor device includes a semiconductor substrate with: a drift layer; a base layer; and a collector layer and a cathode layer. In the semiconductor substrate, when a region operating as an IGBT device is an IGBT region and a region operating as a diode device is a diode region, the IGBT and diode regions are arranged alternately in a repetitive manner; a damaged region is arranged on a surface portion of the diode region in the semiconductor substrate. The IGBT and diode regions are demarcated by a boundary between the collector and cathode layers; and a surface portion of the IGBT region includes: a portion having the damaged region at a boundary side with the diode region; and another portion without the damaged region arranged closer to an inner periphery side relative to the boundary side.

Owner:DENSO CORP

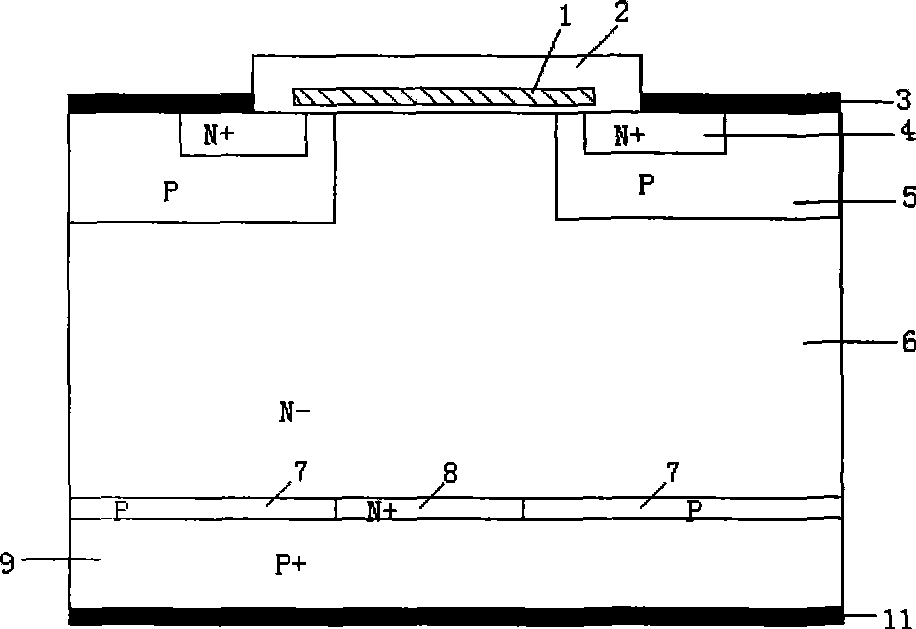

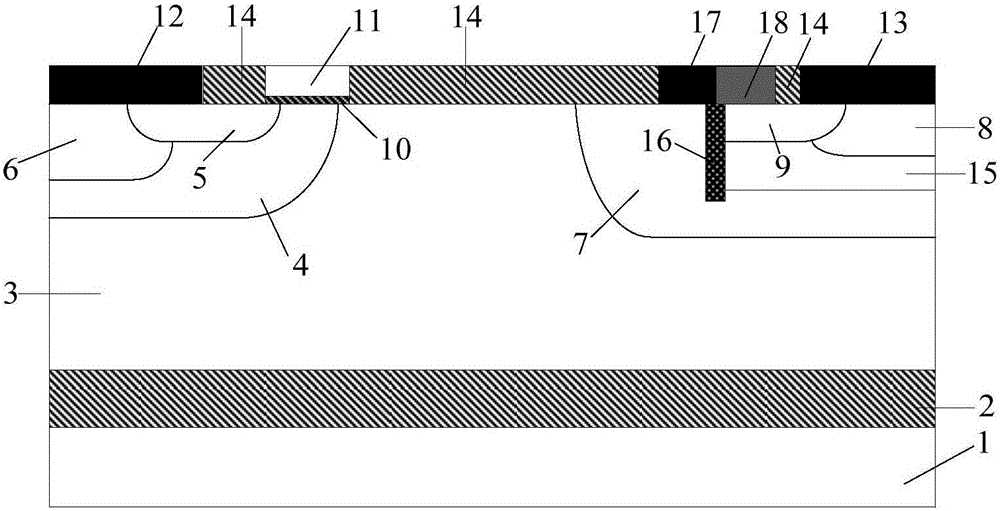

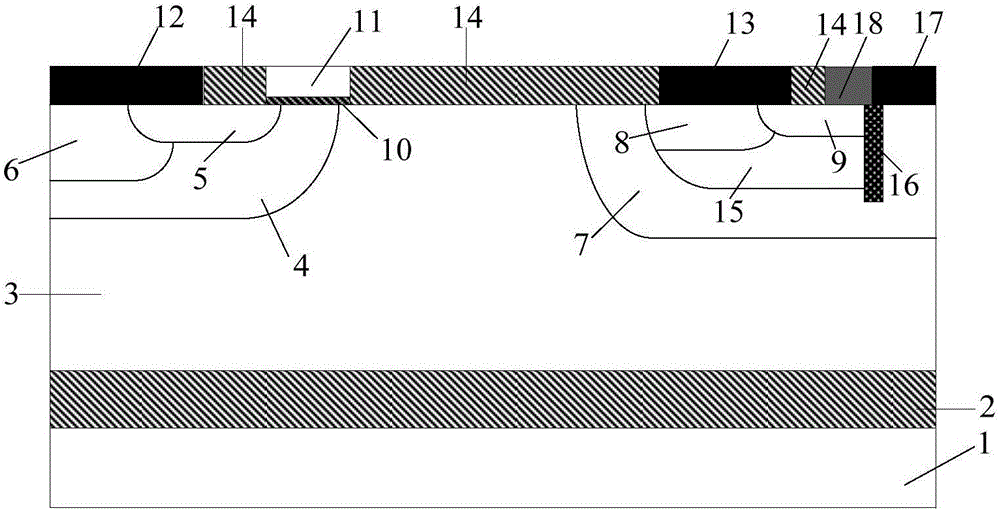

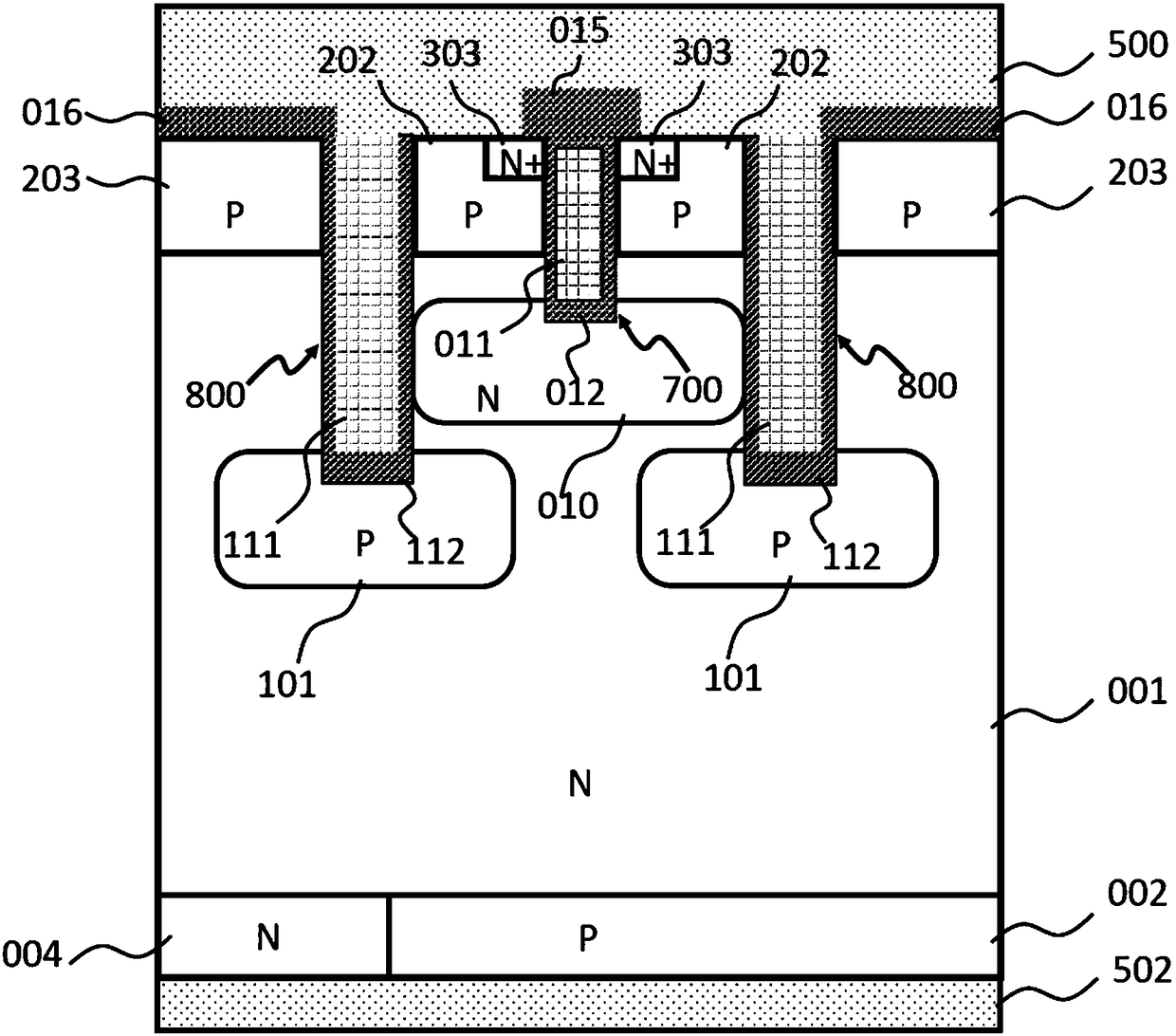

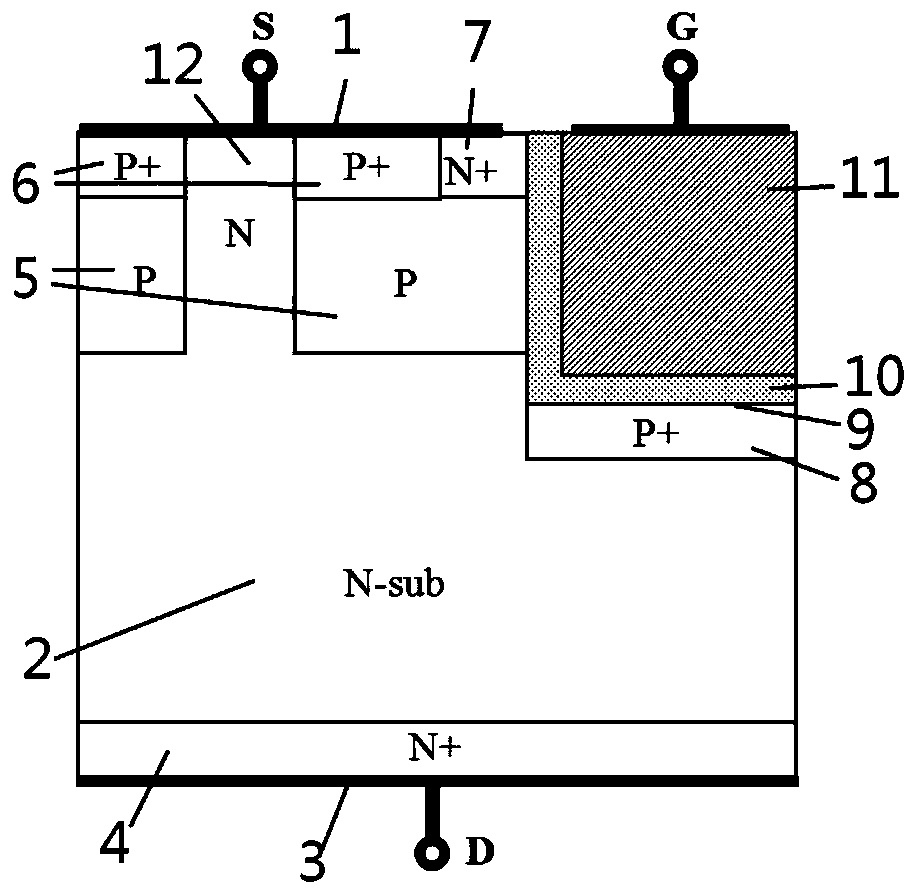

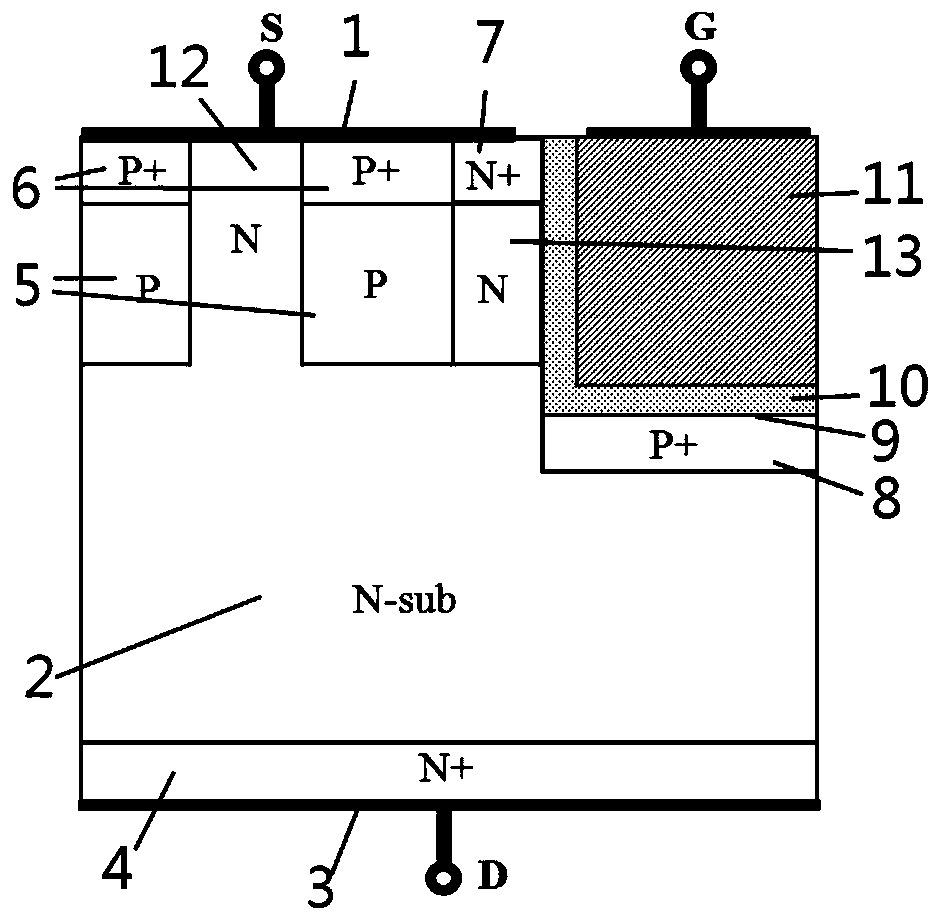

Binary channel RC-LIGBT device and manufacturing method therefor

InactiveCN106067480AImprove stabilityImprove reliabilitySemiconductor/solid-state device manufacturingSemiconductor devicesVoltage dropEngineering

A binary channel RC-LIGBT device and a manufacturing method therefor are disclosed. The invention belongs to the field of power semiconductor integrated circuits and specifically relates to a reverse conducting-LIGBT / RC-LIGBT and a manufacturing method therefor that are used for suppressing snapback phenomena of a conventional RC-LIGBT device, improving characteristics of backward diodes and improving device stability and reliability. The RC-LIGBT device disclosed in the invention has a unilateral electric conduction path having binary channels, the unilateral electric conduction path is formed by introducing a composite structure at a collector electrode end of the device, impact exerted on conduction characteristics by an N type collecting zone can be completely shielded in a forward direction LIGBT work mode, the snapback phenomena can be completely eliminated, the RC-LIGBT device disclosed in the invention has the same low conduction voltage drop as the conventional LIGBT, device stability and reliability can be improved, two freewheel channels are provided at the collector electrode end in a backward diode freewheel work mode, freewheeling capacity of the RC-LIGBT device is optimized, and the RC-LIGBT device is enabled to have a small conduction voltage drop.

Owner:UNIV OF ELECTRONICS SCI & TECH OF CHINA

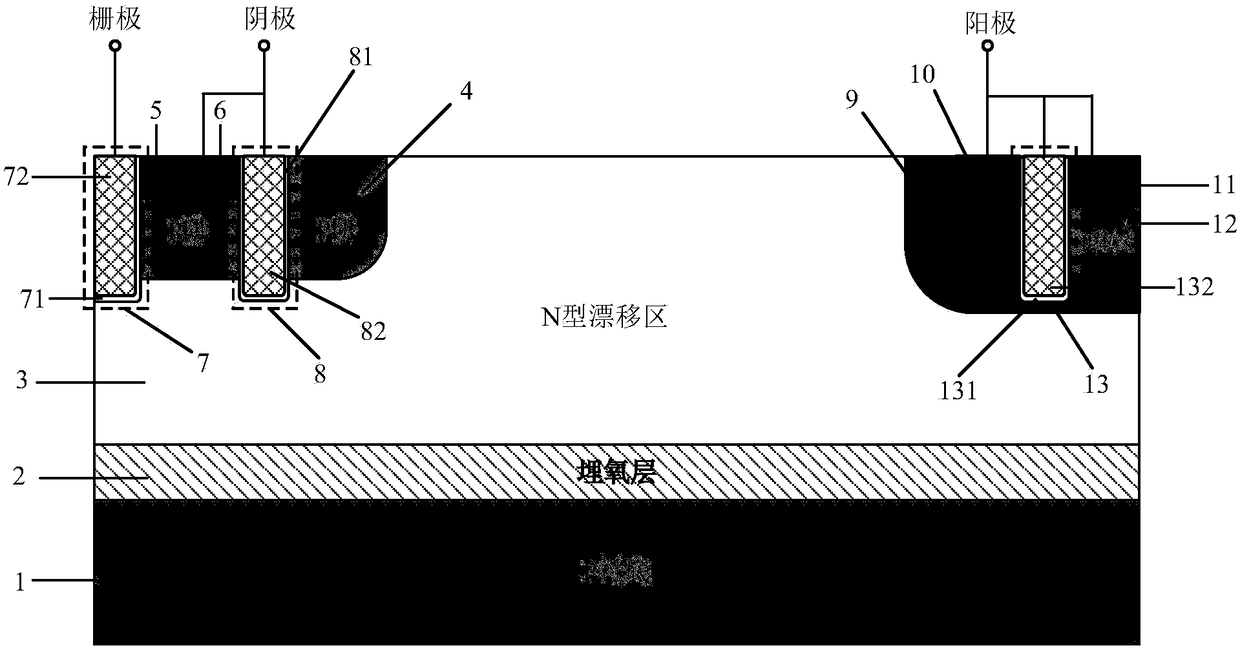

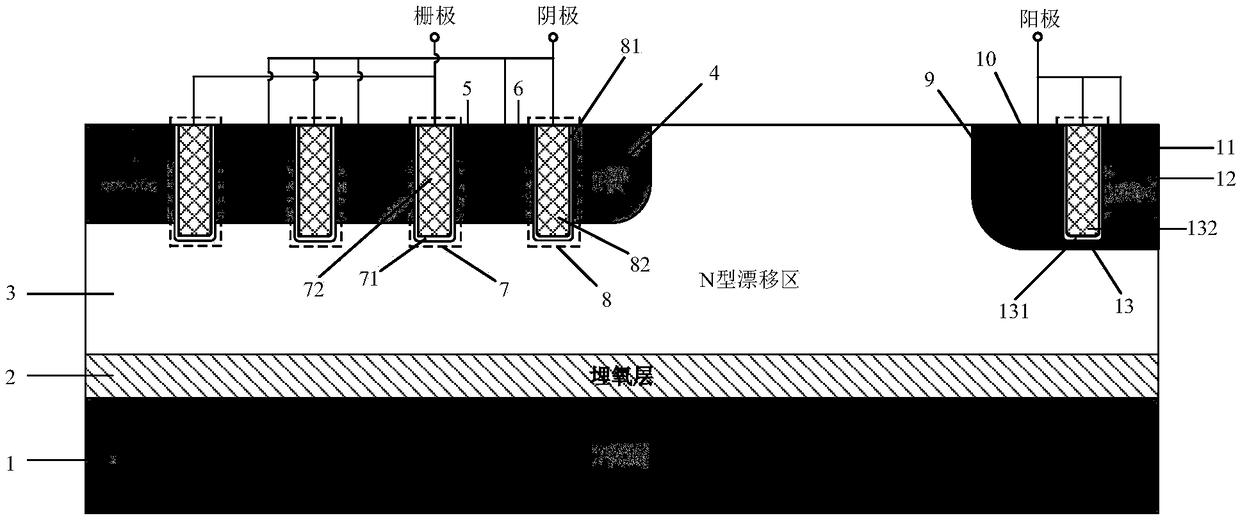

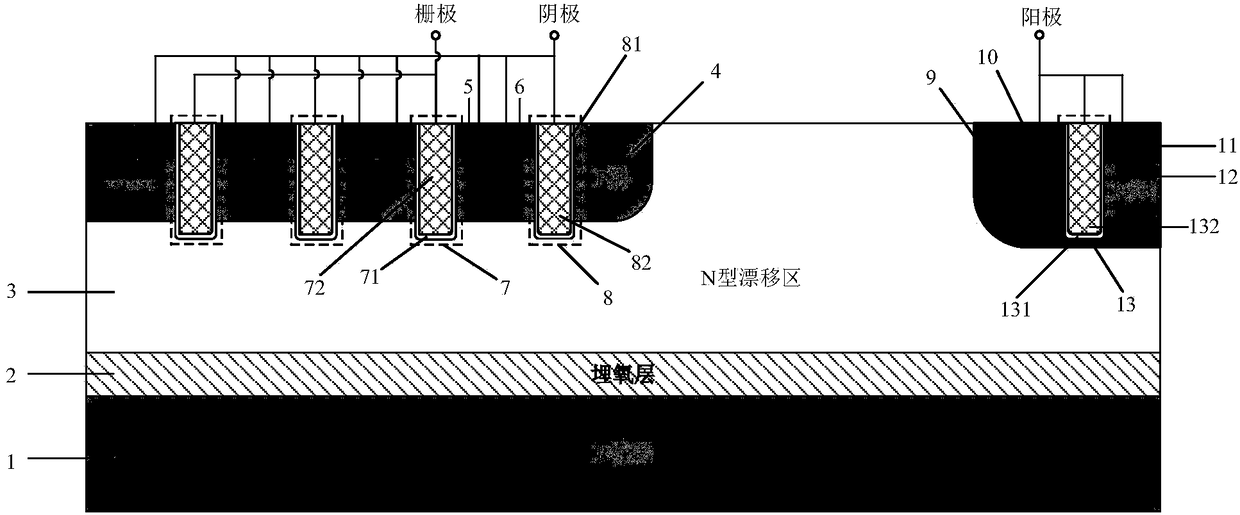

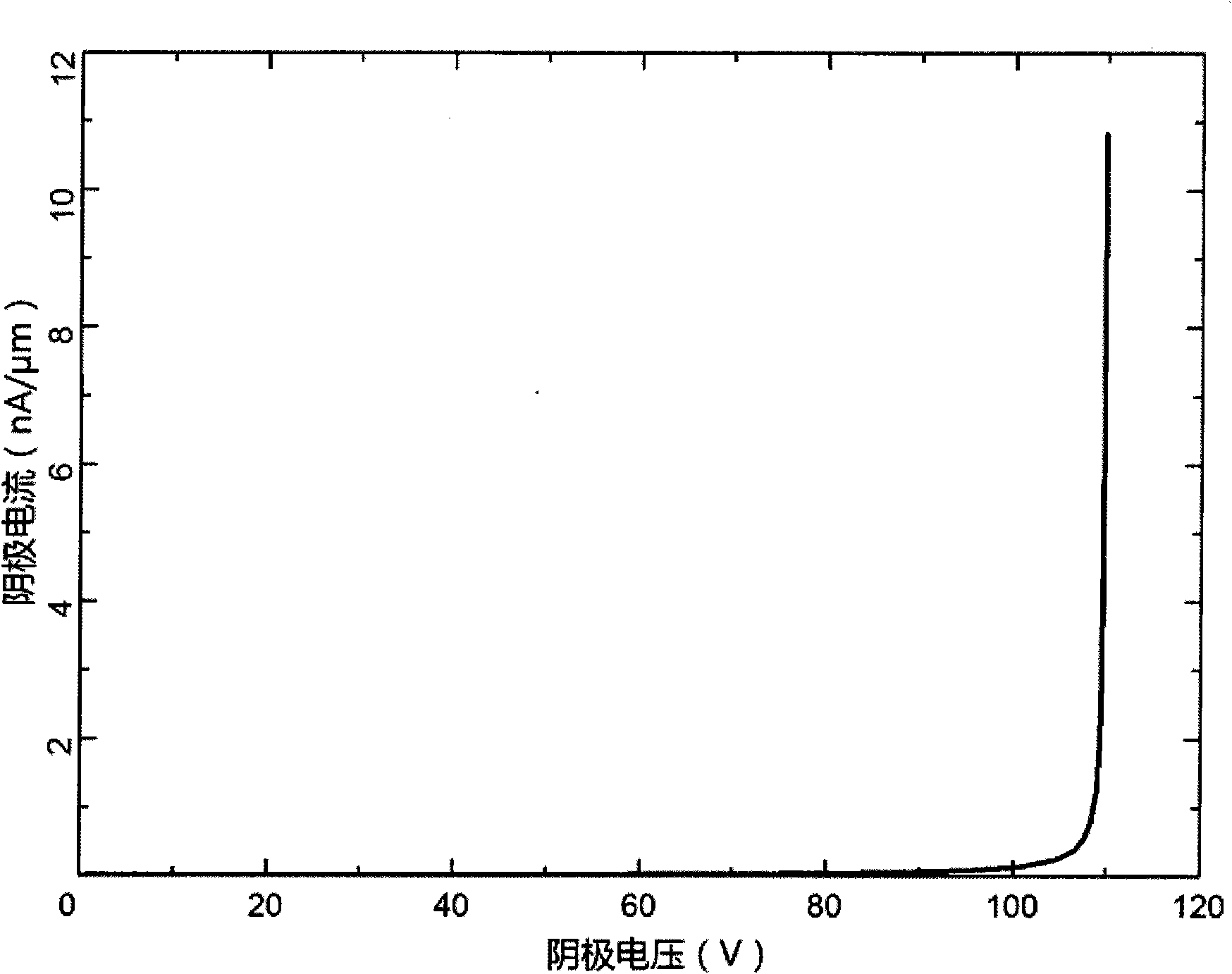

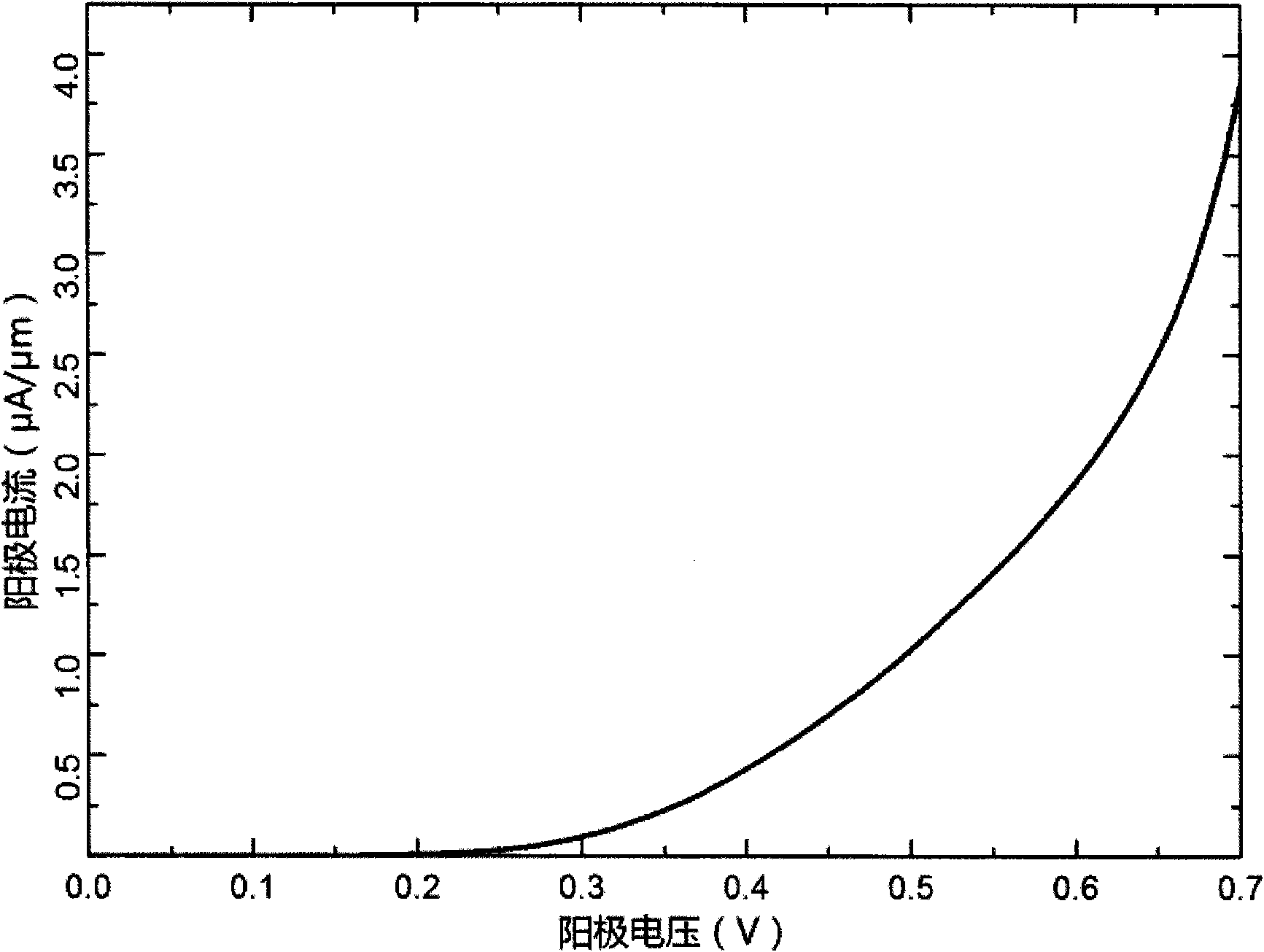

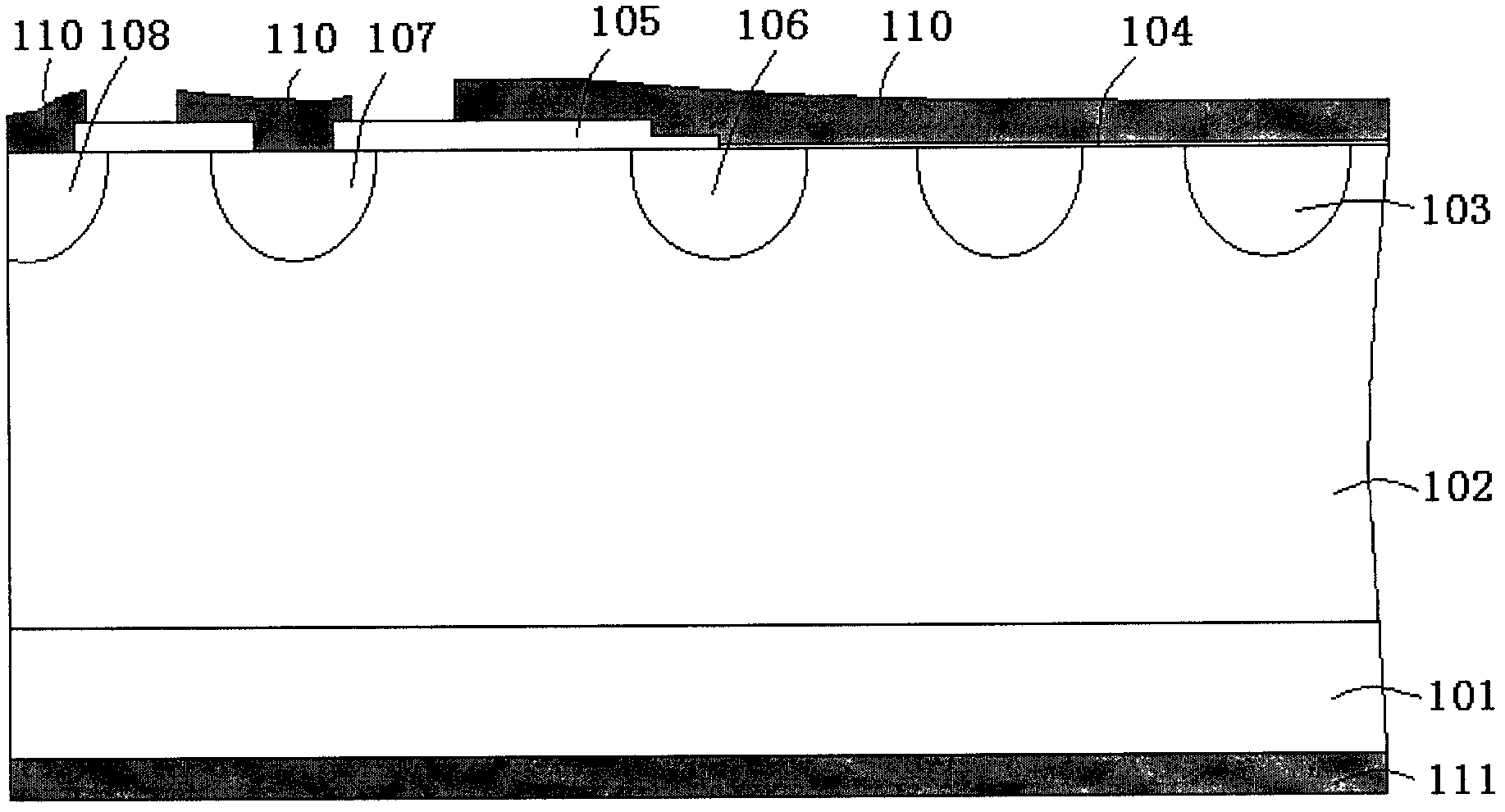

Grooved gate short circuit anode SOI LIGBT

The invention belongs to the technical field of power semiconductors and relates to a grooved gate short circuit anode SOI LIGBT. In comparison with the traditional short circuit anode LIGBT, anode grooves connected to anode potential are introduced at an anode end, and a P body area is introduced right below an N+ anode area; and grooved gates and cathode grooves connected with a cathode are introduced in a cathode area. When the device is turned off, the anode groove is connected to high potential, an NMOS in the anode area is started automatically, extraction of electrons stored in a driftarea is quickened, and the turn-off time and the turn-off energy loss are reduced; when the device is in a high-voltage high-current state, the cathode groove forms a hole bypass, and happening of latch-up effects is suppressed; when the device is conducted, under blocking of an electronic barrier in the P body area, electron current in the drift region is not easy to be collected by the N+ anode,voltage reentry effects are eliminated, and as the grooved gate structures of the cathode are in parallel connection, the channel density is increased and the conduction voltage drop is reduced. Thegrooved gate short circuit anode SOI LIGBT has the beneficial effects that in comparison with the traditional short circuit anode LIGBT, a voltage reentry phenomenon is eliminated under a smaller transverse cell size, and the conduction voltage drop is lower.

Owner:UNIV OF ELECTRONICS SCI & TECH OF CHINA

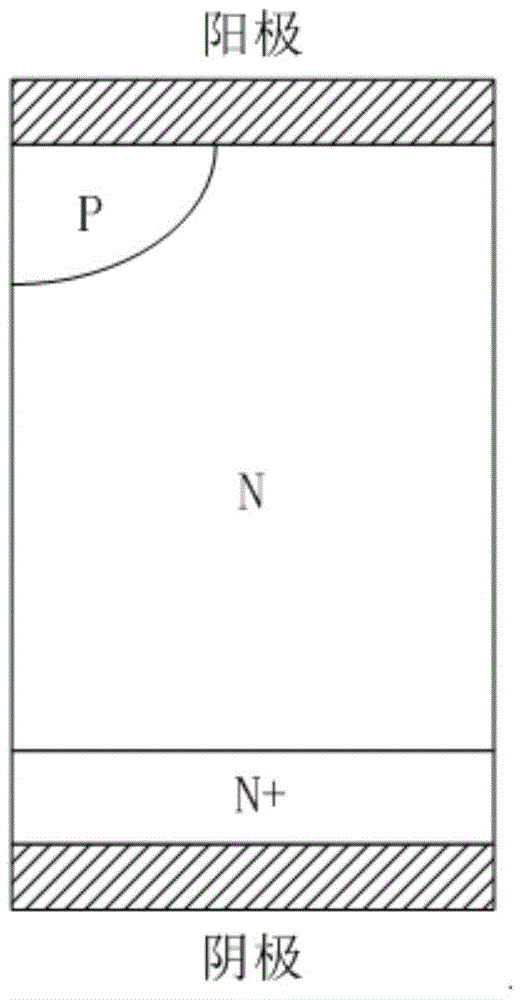

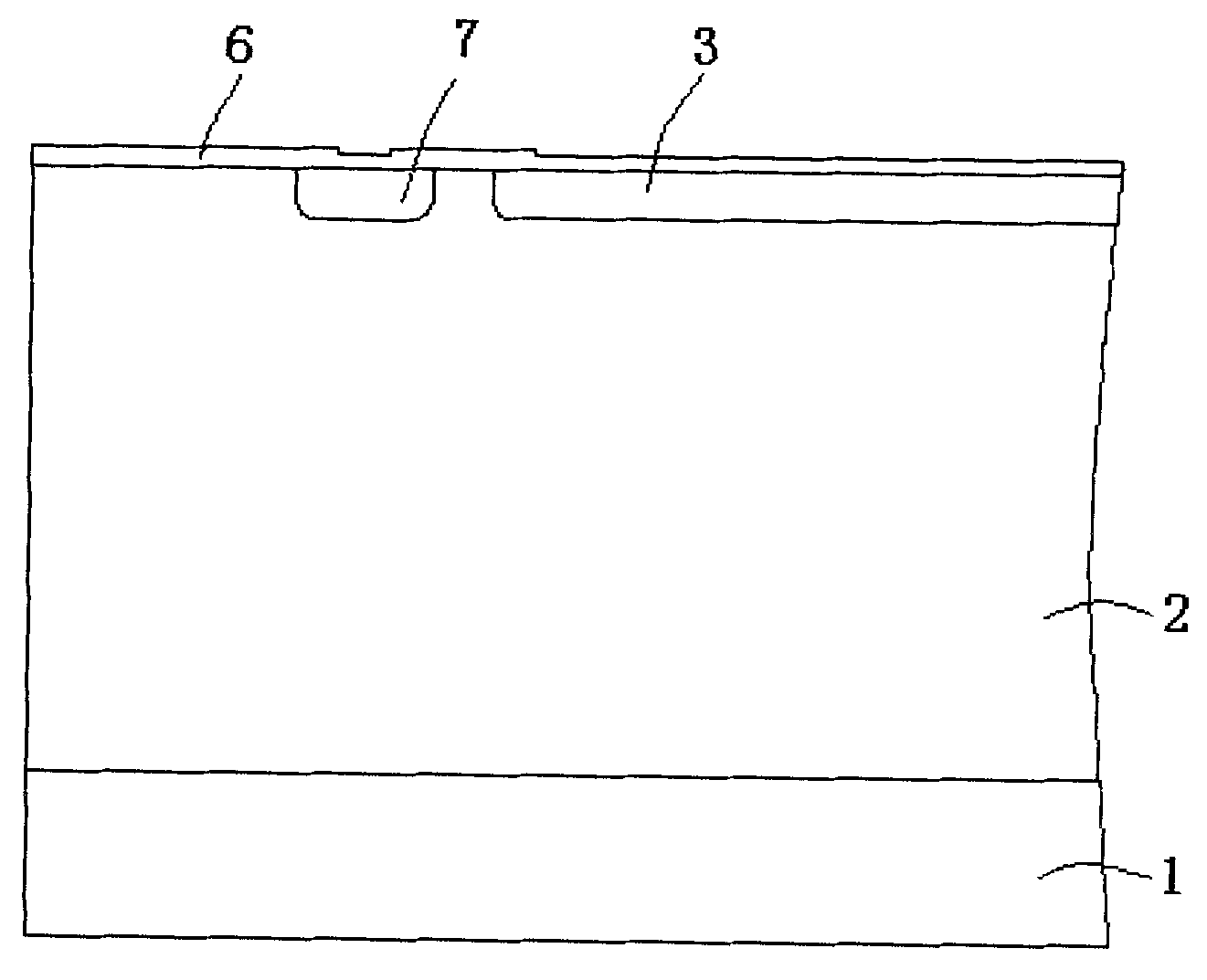

Shallow-slot metal oxide semiconductor diode

InactiveCN102064201AReduce conduction voltage dropAccelerated pinch offSemiconductor devicesSilicon dioxideJFET

The invention discloses a shallow-slot metal oxide semiconductor diode for solving reducing the forward conduction voltage drop of the diode, increasing reverse breakdown voltage and reducing leakage current. The shallow-slot metal oxide semiconductor diode provided by the invention comprises a metallized cathode, an N-type heavily-doped monocrystalline silicon substrate region, an N-epitaxial layer, two deep P regions located on two sides, shallow slots located on the deep P regions, N-type heavily-doped regions on the inner sides of the shallow slots, a silicon dioxide gate oxide layer, a polycrystalline silicon gate electrode and a metallized anode, which are arranged in sequence from the bottom layer to the top. Compared with the prior art, by adopting the electron accumulation layer structure and the junction field-effect tube structure, the invention can obtain extremely low conduction voltage drop, greatly improve the breakdown voltage, and reduce the leakage current. Under reverse voltage, the thin gate oxide layer accelerates the pinch-off of a conducting channel on a semiconductor surface, and the compromise between forward conduction voltage drop and reverse recovery time is better realized, and therefore, the shallow-slot metal oxide semiconductor diode provided by the invention has better compromise between forward conduction voltage drop and reverse recovery time.

Owner:深圳市芯威科技有限公司

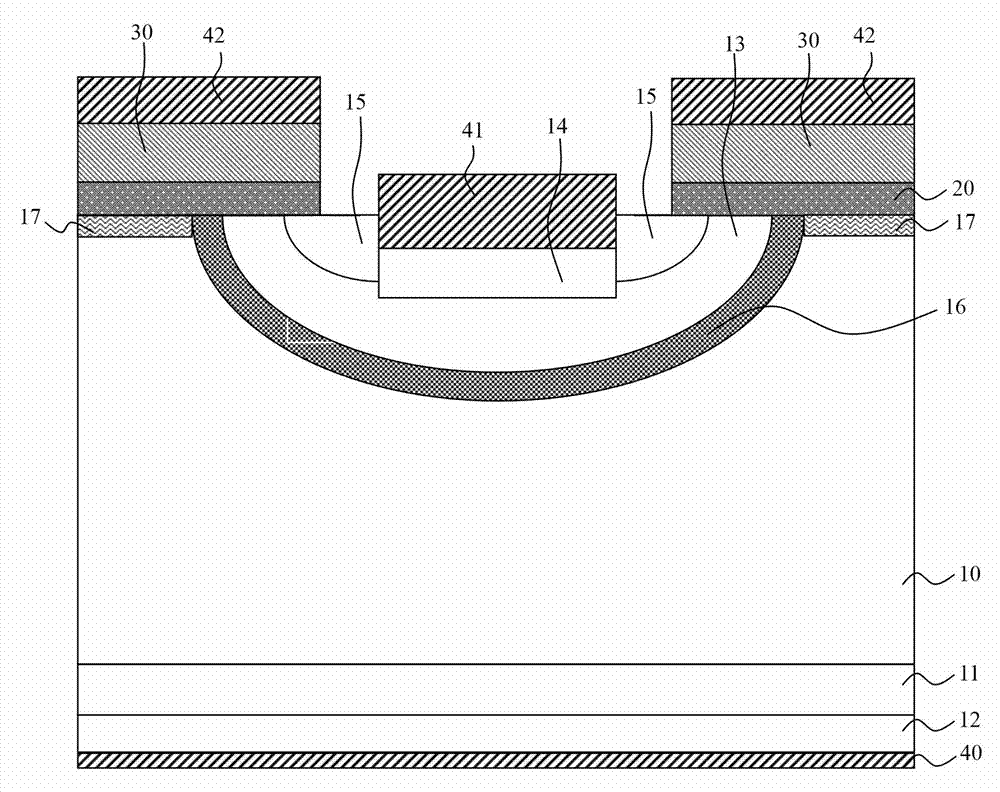

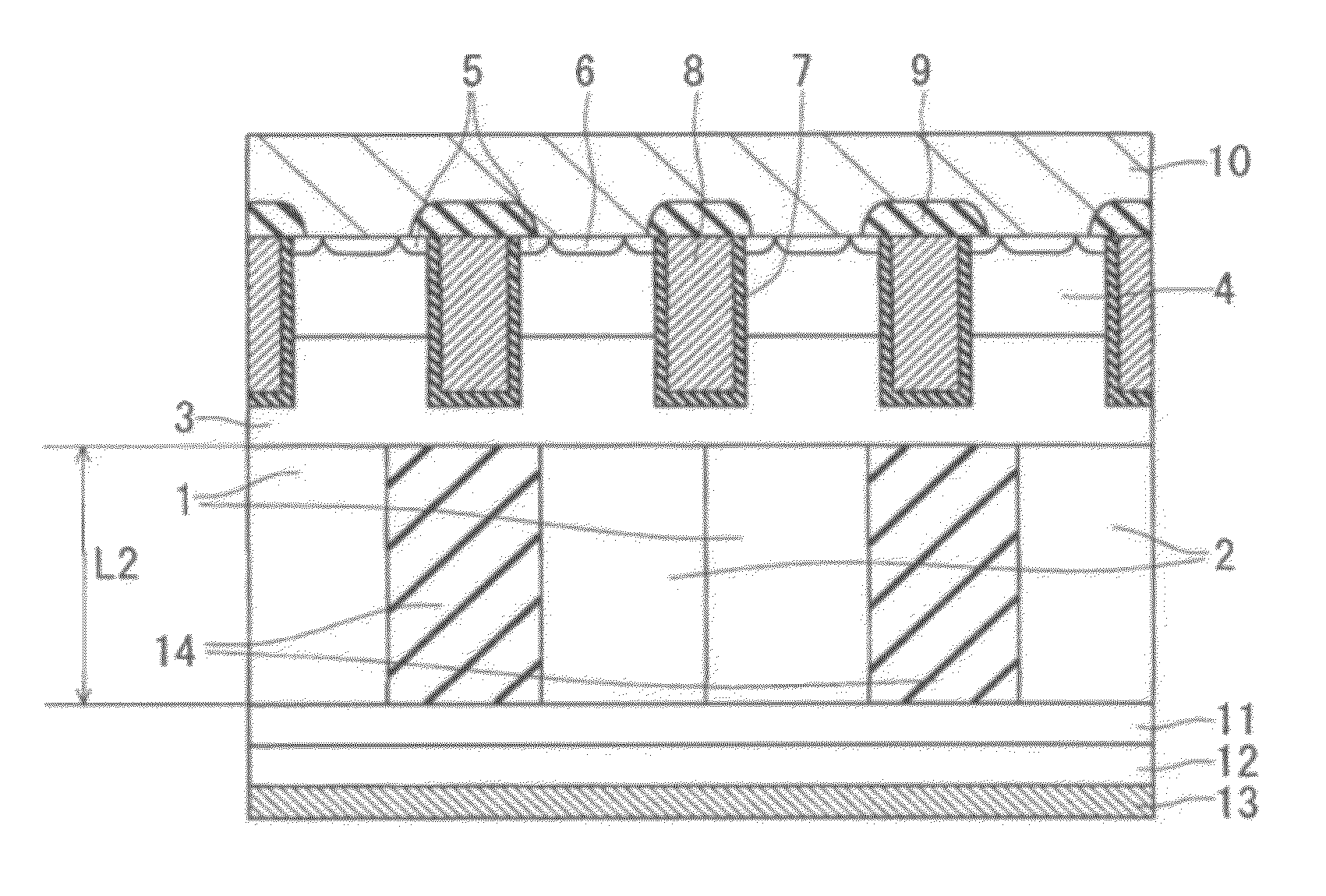

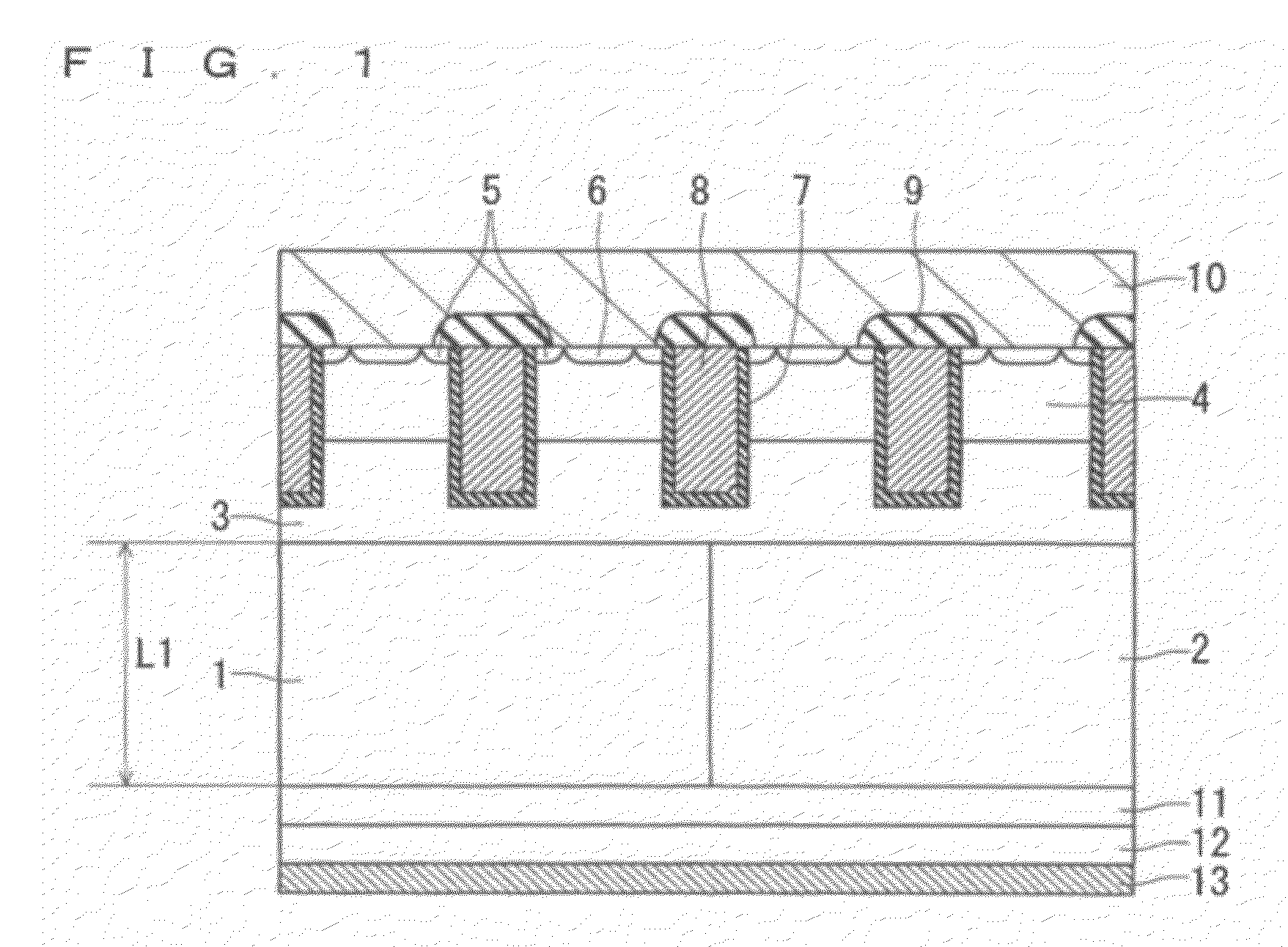

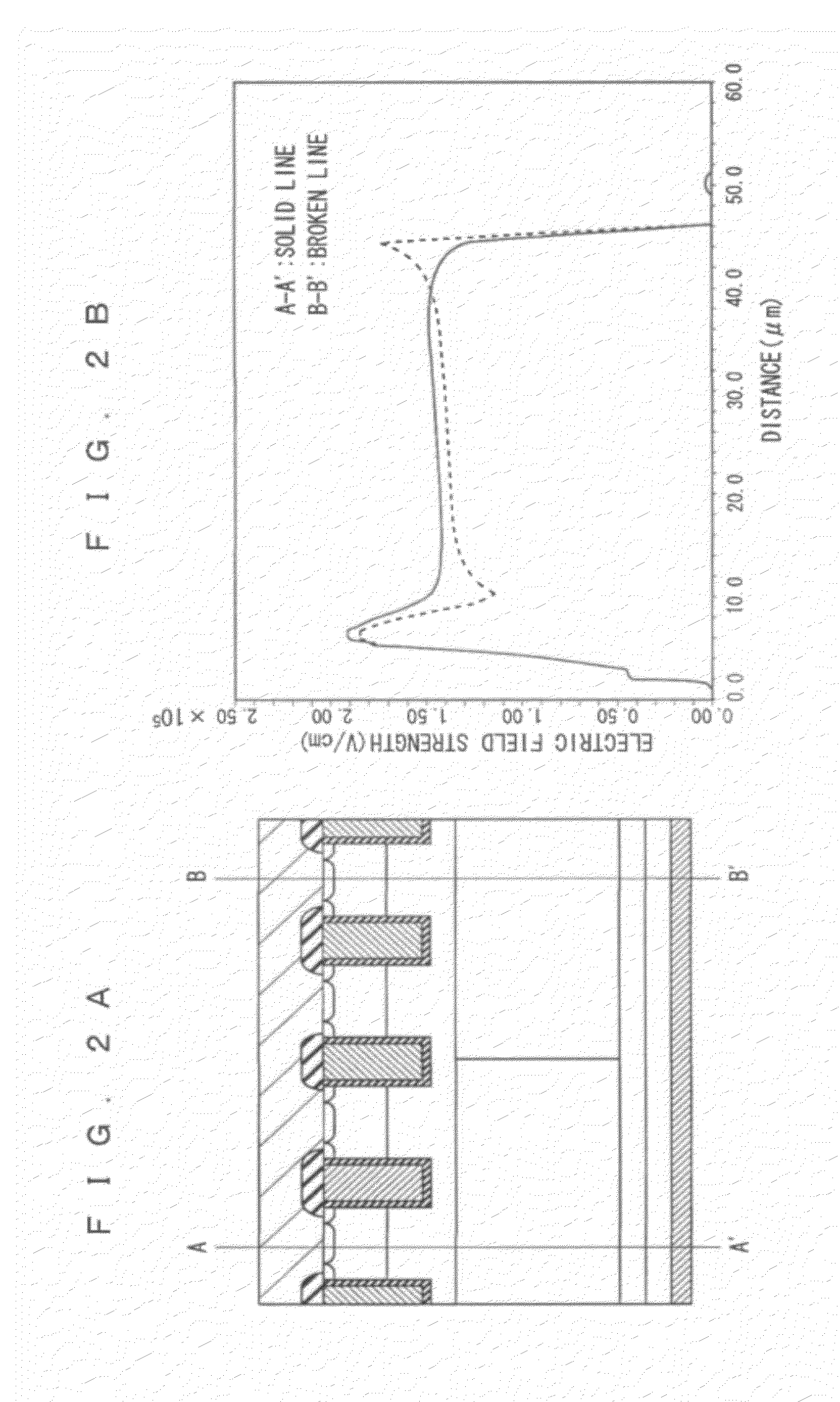

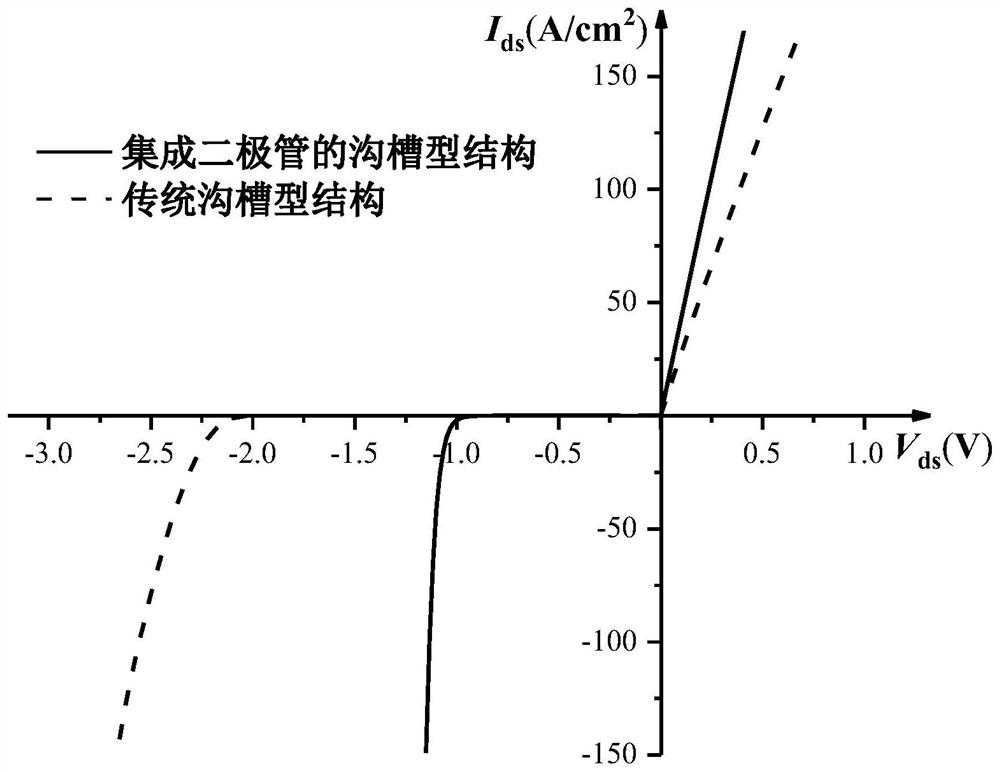

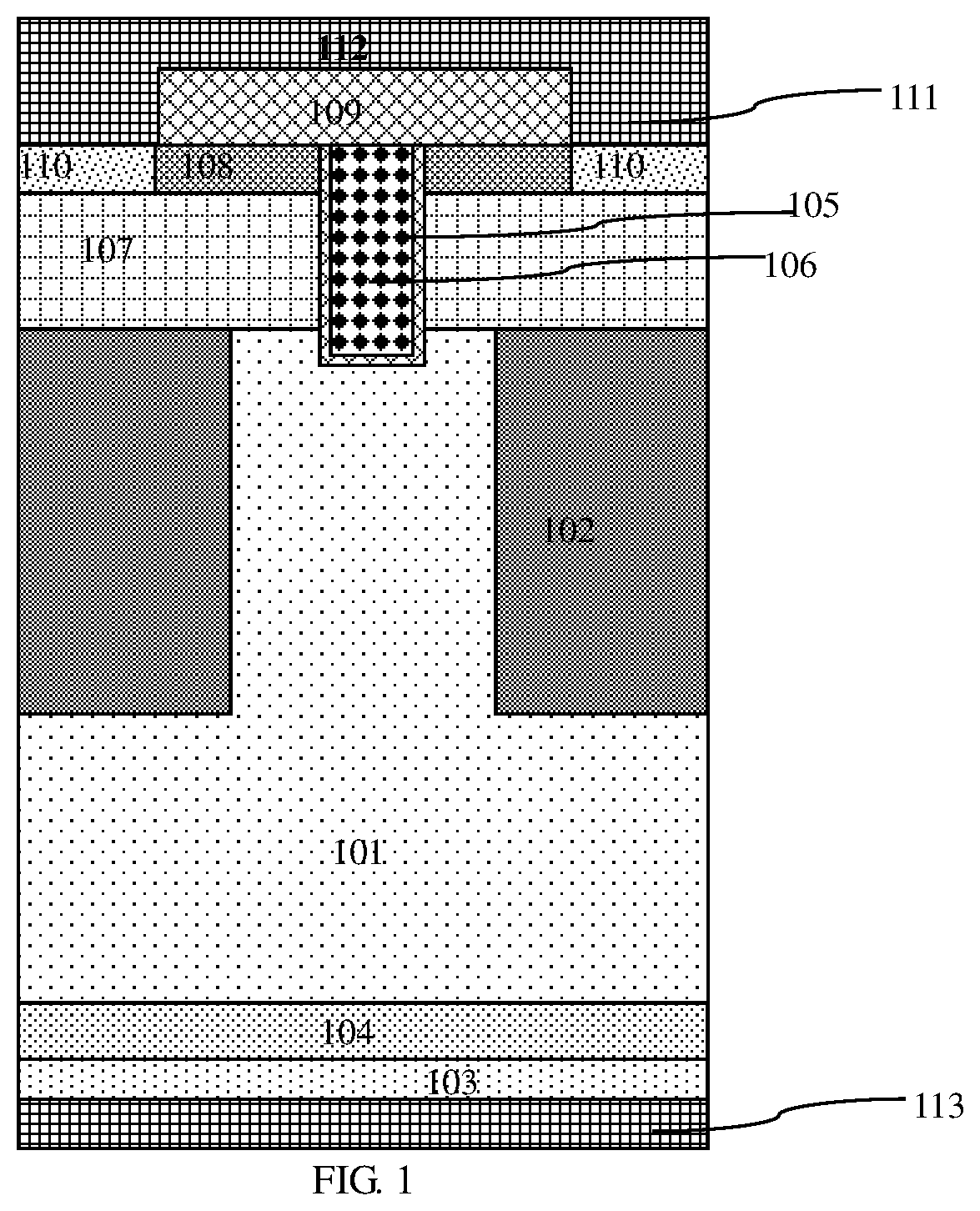

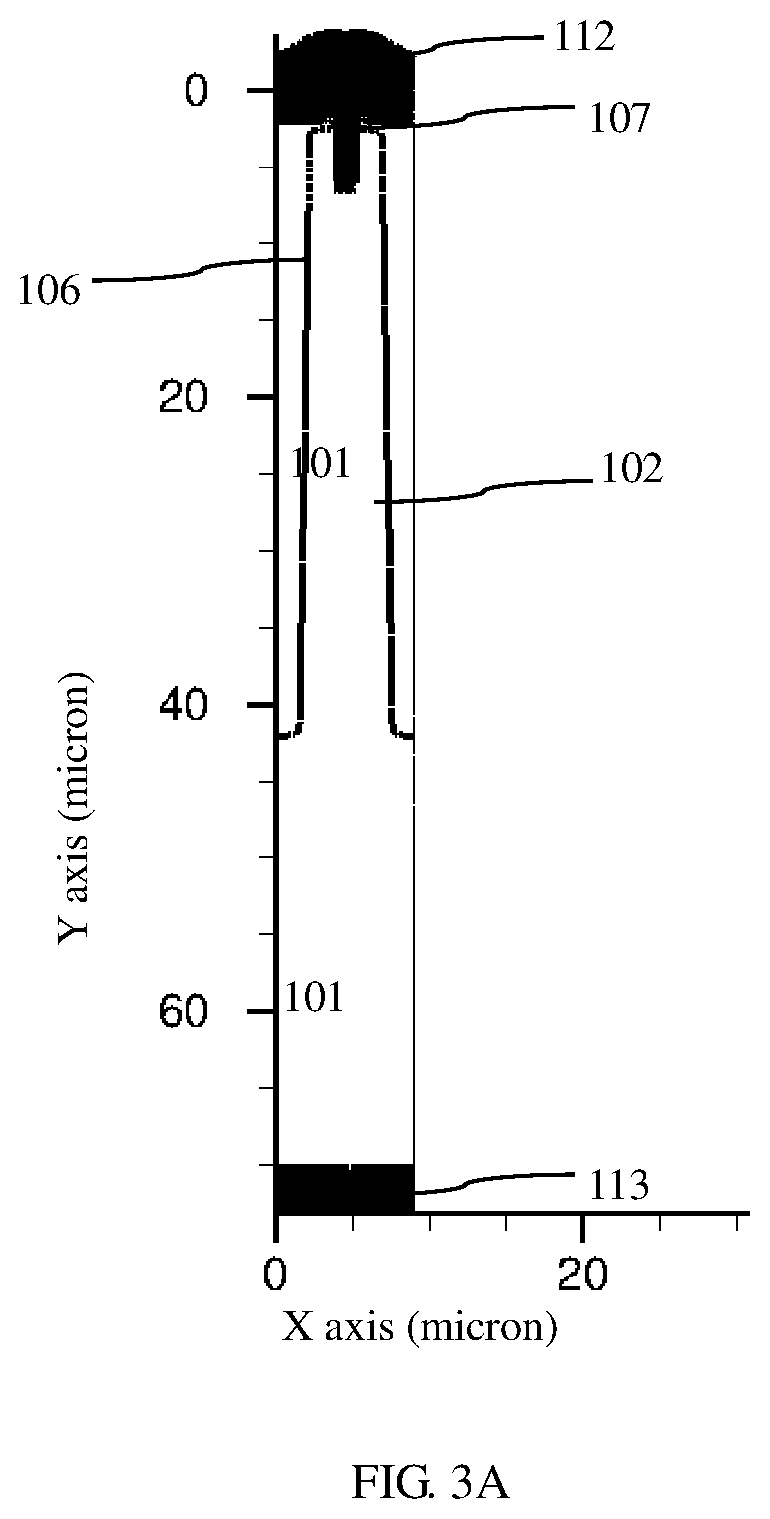

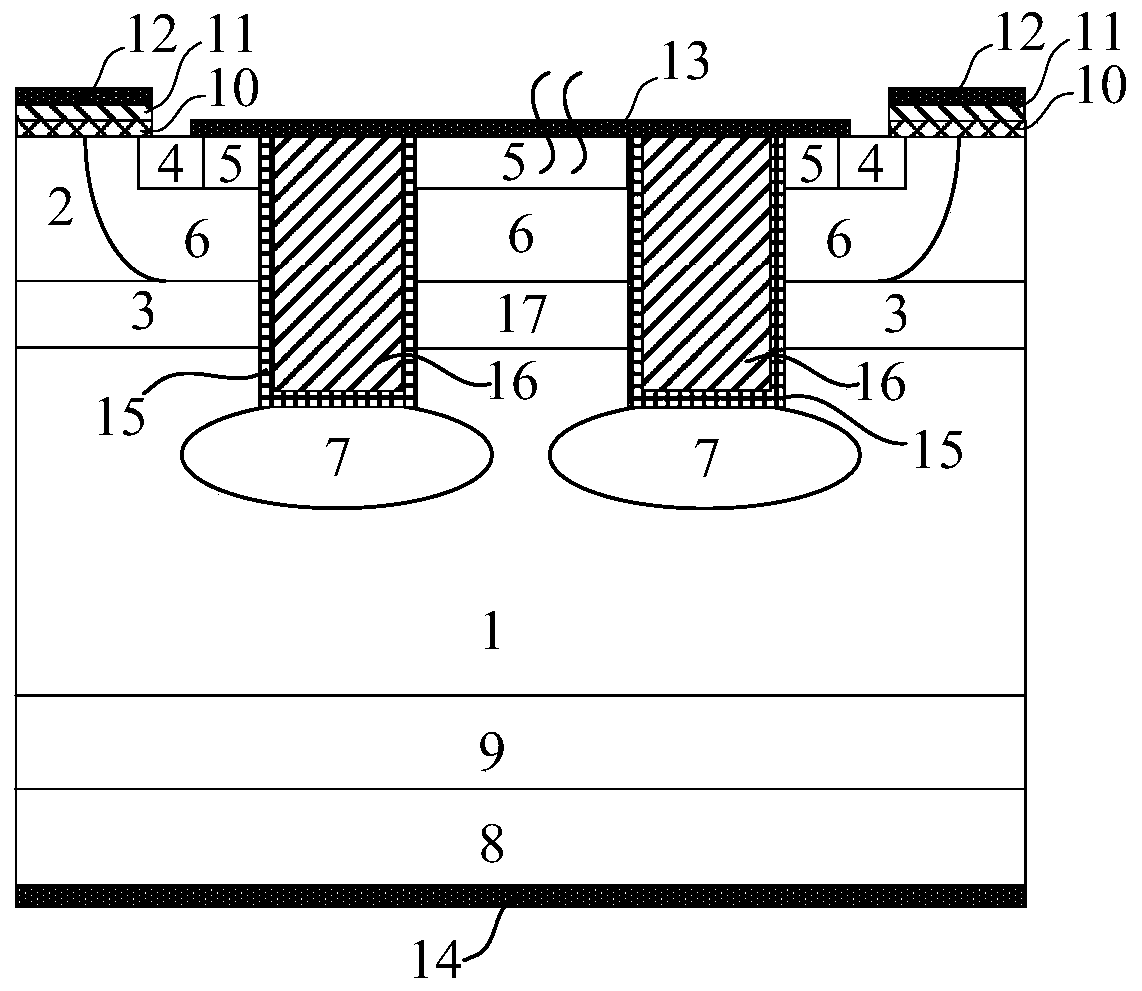

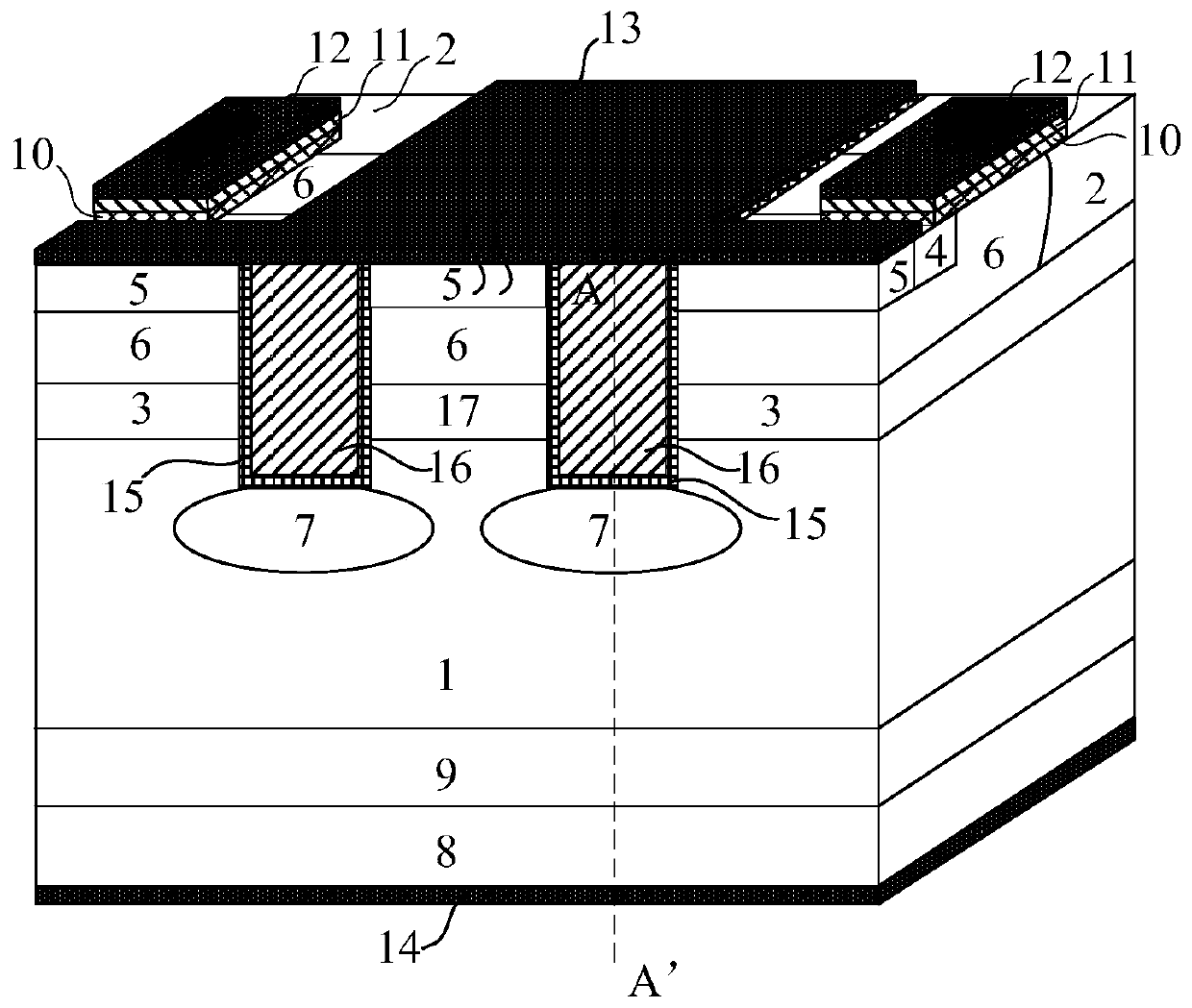

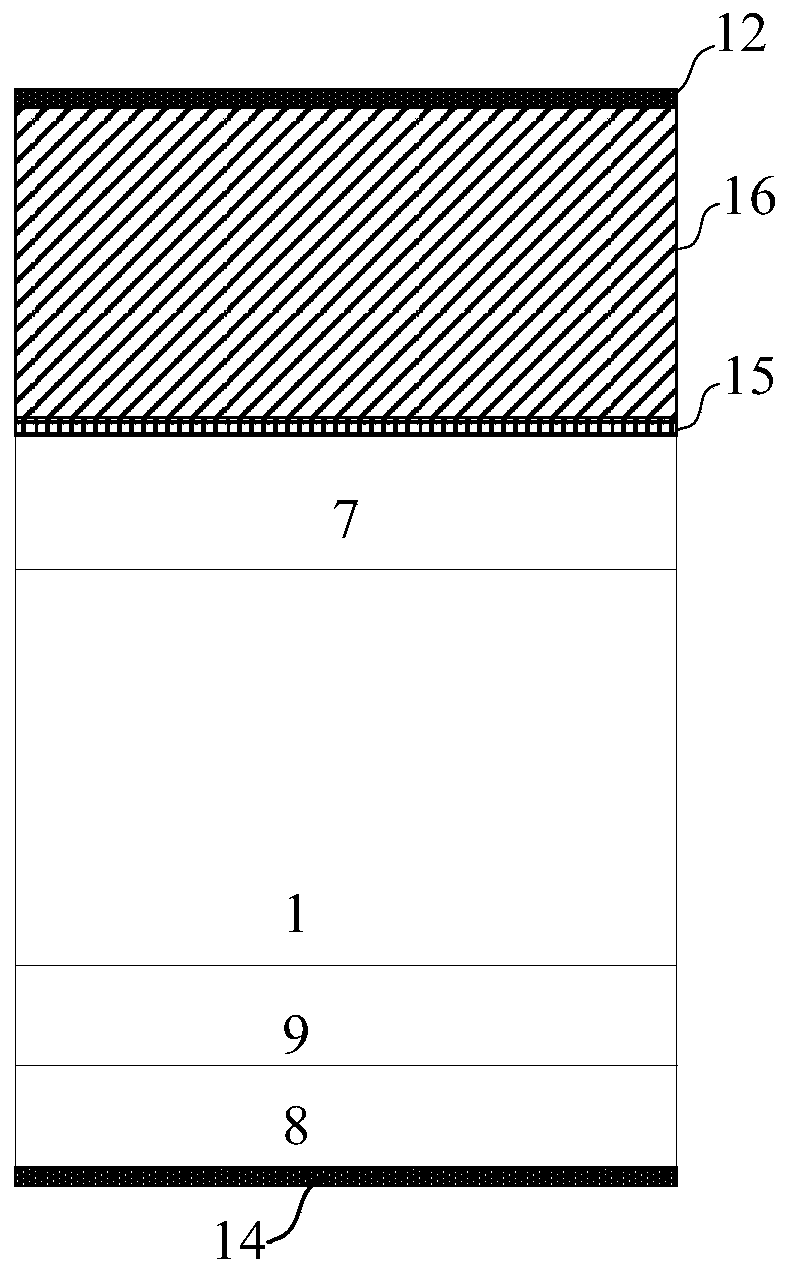

SiC trench gate power MOSFET device and preparation method thereof

ActiveCN111697077AReduce conduction voltage dropWill not increase the areaSemiconductor/solid-state device manufacturingDiodeCapacitanceDielectric

The invention relates to a SiC trench gate power MOSFET device, and belongs to the technical field of power semiconductors. The SiC trench gate power MOSFET device comprises a trench source structure,a P-type polycrystalline silicon and a trench gate structure which are manufactured in a trench. The trench source structure can reduce gate-drain capacitance (Cgd) and switching loss, when a sourcedielectric layer is made of a high-K dielectric material, the electric field intensity of a source dielectric can be effectively reduced, the P-type polycrystalline silicon realizes integration of anHJD in the N-channel SiC trench gate power MOSFET, the HJD has lower forward conduction voltage drop, conduction of a body diode is inhibited, a reliability problem caused by bipolar degradation is avoided, and the integrated HJD does not additionally increase the area of a chip. The integrated SiCHJD is a unipolar device, the reverse recovery characteristic is superior to that of a bipolar body diode, and stability is better due to the fact that parasitic parameters brought by an external diode lead are avoided, in addition, the device is simple and controllable in manufacturing process and high in compatibility with an existing process.

Owner:HANGZHOU SILICON-MAGIC SEMICON TECH CO LTD

A superjunction IGBT with a shielded gate and a manufacturing method thereof

PendingCN109037312AReduce lossLow resistivitySemiconductor/solid-state device manufacturingSemiconductor devicesCapacitanceCell region

The invention discloses a superjunction IGBT with a shield gate and a manufacturing method thereof. The superjunction IGBT comprises a semiconductor substrate, a cell region and a terminal protectionarea. The semiconductor substrate comprises a second conductivity type collector region, a first conductivity type field termination layer and at least one first conductivity type epitaxial layer. Thecell region comprises a plurality of cells connected in parallel with each other, which includes a plurality of cell trenches and a gate conductive polysilicon and a shield gate filled in the cell trenches, A seventh oxide layer is arranged on both sides and sidewalls of the notch of the cell trench opposite to the gate conductive polysilicon, a fifth oxide layer is arranged between the gate conductive polysilicon and the shield gate, and a fourth oxide layer is arranged on the bottom and sidewalls of the cell trench opposite to the shield gate. A P-pillar is also provided in the first conductivity type epitaxial layer, one end of the P-pillar is connected to the second conductivity type well layer, and the other end extends toward the first conductivity type field termination layer. Theinvention adopts the shielding gate structure, reduces the Miller capacitance, thereby reducing the switching loss.

Owner:无锡市乾野微纳科技有限公司

Plane gate type IGBT (Insulated Gate Bipolar Translator) chip production method

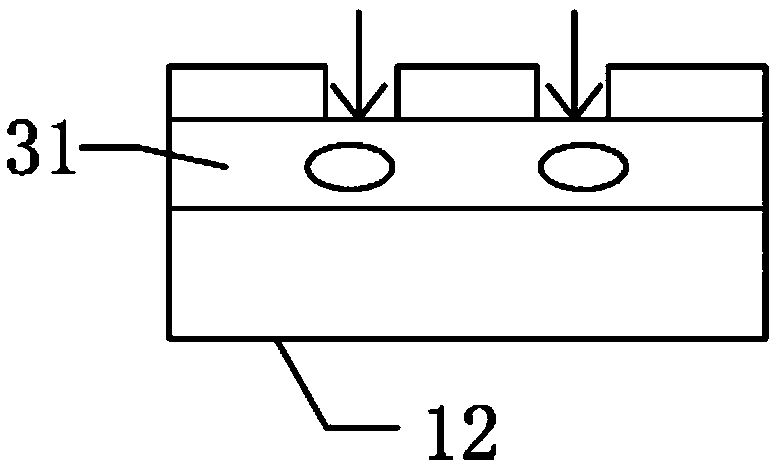

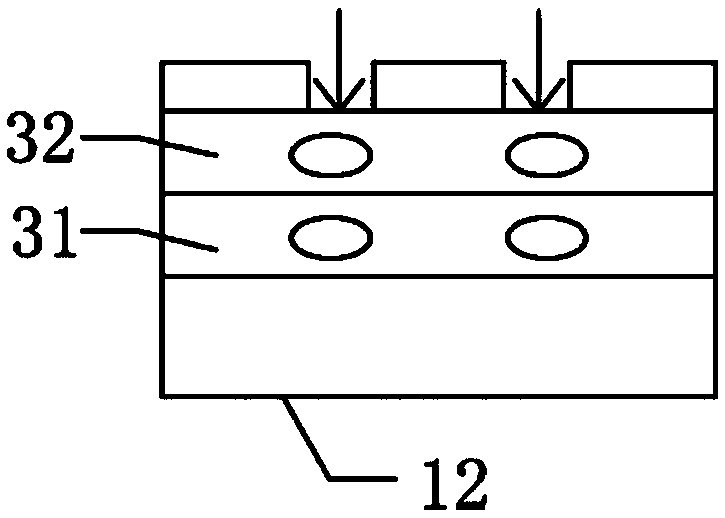

ActiveCN102969243AIncrease hole concentrationImprove injection efficiencySemiconductor/solid-state device manufacturingPhysicsInsulated-gate bipolar transistor

The invention discloses a plane gate type IGBT (Insulated Gate Bipolar Translator) chip production method. The method comprises the steps: firstly carrying out front side processing, and injecting and annealing a second N type current carrier buried layer to a semiconductor substrate; etching, injecting and annealing a first N type current carrier buried layer injection window; etching a first N type current carrier buried layer; removing an oxidization layer on the surface of the semiconductor substrate; depositing an insulating material on the outer surface of the first N type current carrier buried layer, and photoetching and etching the deposited insulating material to form a media buried layer; completing the remaining front side processing technology; conducting back side processing, thinning the back side part to the needed thickness; injecting, doping and propelling and annealing an N buffer layer; injecting, doping and propelling and annealing a P+ collector electrode region; and producing a metal collector electrode. According to the plane gate type IGBT chip production method, the drop voltage of an IGBT chip is reduced, the compromise relation of the turn-off loss can be optimized, and lower power consumption can be realized, so that the power density, operating junction temperature and reliability of the IGBT chip can be improved.

Owner:ZHUZHOU CRRC TIMES SEMICON CO LTD

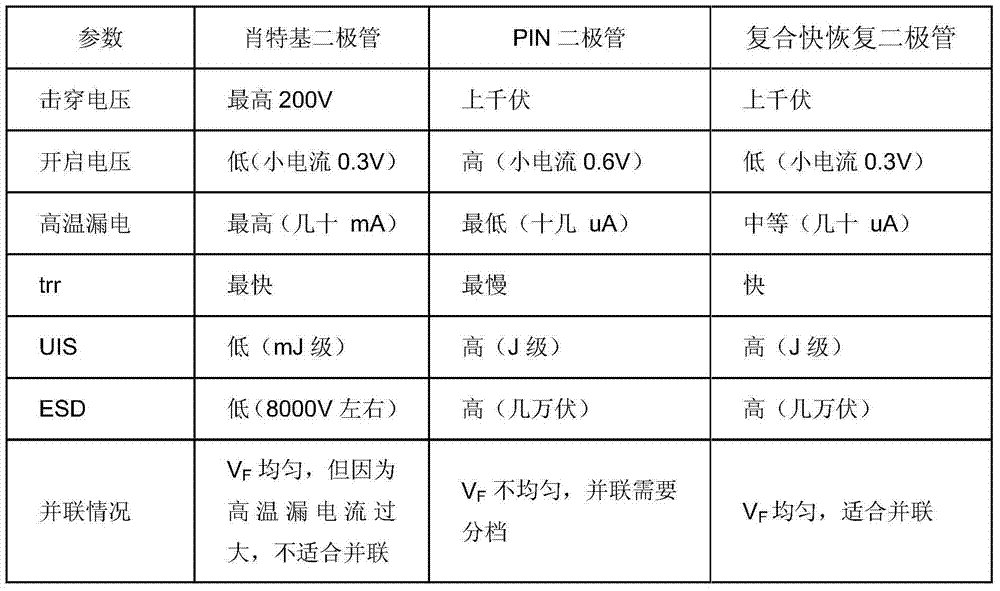

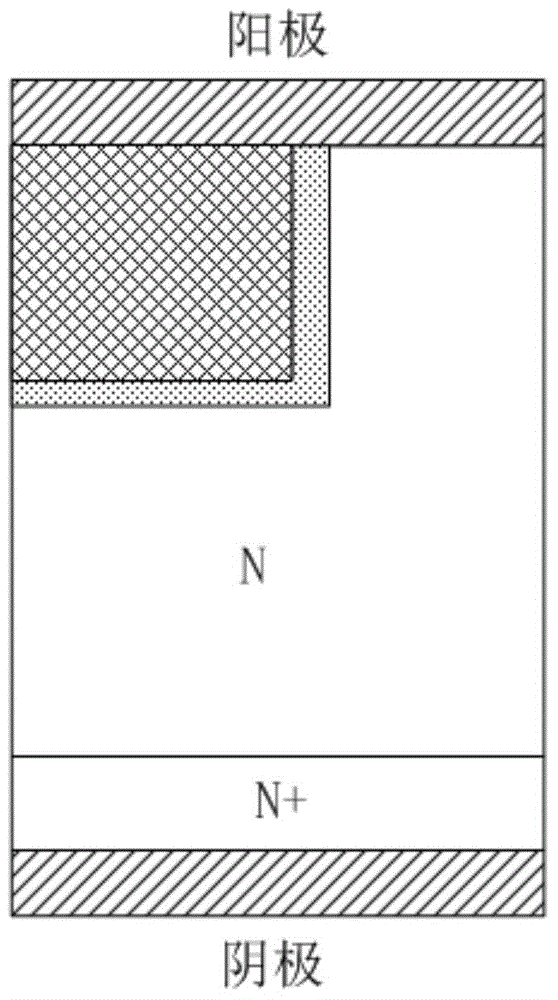

Composite fast recovery diode and preparation method thereof

ActiveCN104716038AImproved Forward Voltage Drop ConsistencyImprove consistencySemiconductor/solid-state device manufacturingSemiconductor devicesImpurity ionsForward voltage

The invention relates to a preparation method for a composite fast recovery diode. The method comprises the steps that 1, an active area is subjected to oxidization and photoetching; 2, N-typed impurity ions are injected; 3, N knot pushing is conducted; 4, P-area injection windows are formed; 5, P-typed impurity ions are injected; 6, knot pushing is conducted; 7, Schottky areas are formed; 8, metal film deposition is conducted; 9, back reduction is conducted; 10, back metallization is conducted to obtain the composite fast recovery diode. The composite fast recovery diode has the advantages that the forward voltage drop consistence is good, the avalanche tolerance capacity is high and the recovery property is good.

Owner:MACMIC SCIENCE & TECHNOLOGY CO LTD

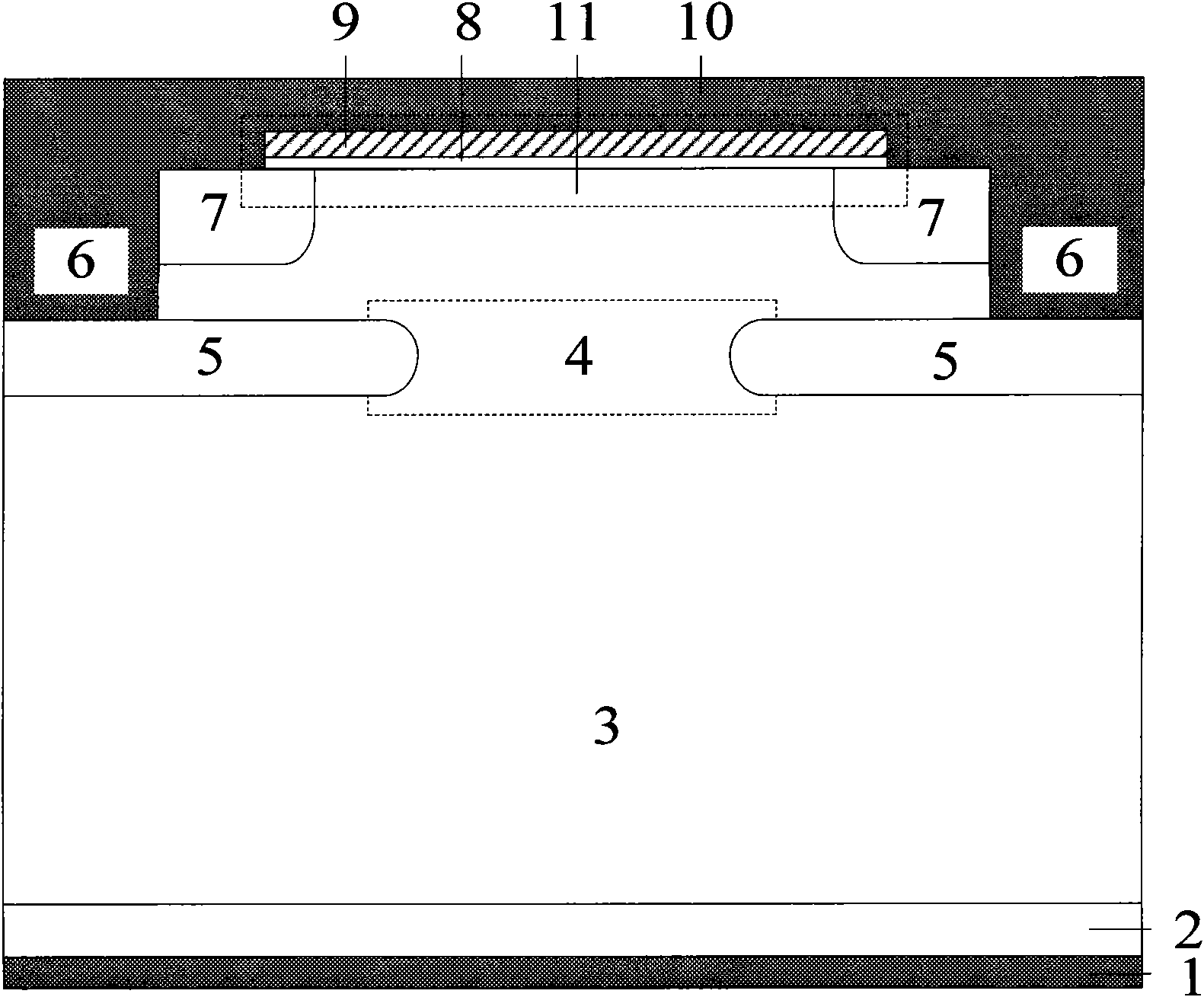

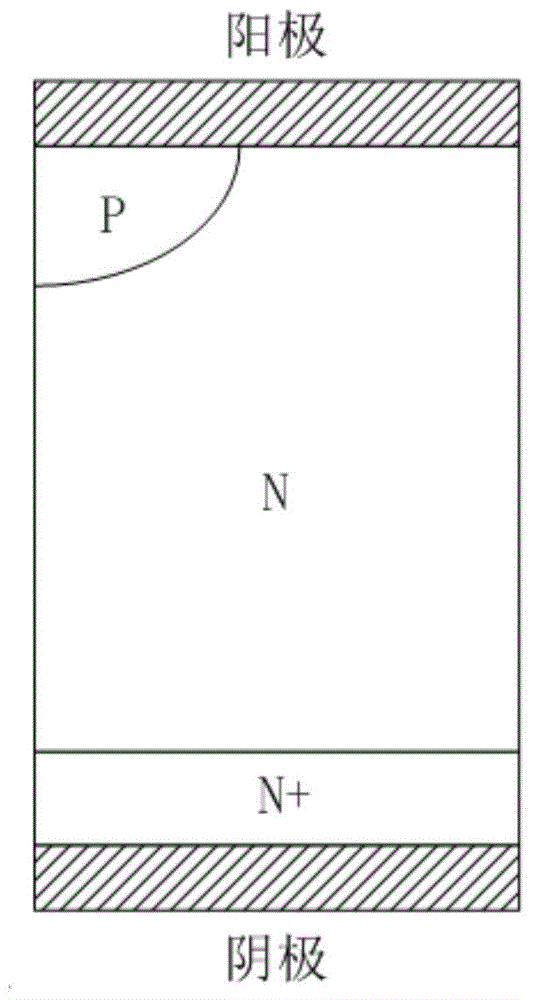

Diode with floating island structure

InactiveCN104409519AReduce conduction voltage dropShort reverse recovery timeSemiconductor devicesReverse recoveryPower semiconductor device

The invention belongs to the technical field of power semiconductor devices, and relates to a diode with a floating island structure. The diode comprises an N-type semiconductor substrate, a cathode arranged at the bottom of the N-type semiconductor substrate, an N-type semiconductor drift region arranged on the upper layer of the N-type semiconductor substrate, a gate oxide layer arranged on the upper layer of the N-type semiconductor drift region, and an anode arranged on the upper layer of the gate oxide layer, wherein the gate oxide layer is of a trench gate structure, and an N-type semiconductor region is arranged between the portions, on the two sides of a trench, of the gate oxide layer. The diode is characterized in that a plurality of doping regions including P-type semiconductor doping regions are arranged in the N-type semiconductor drift region, and therefore the floating island structure is formed. The diode has the advantages that conductive voltage is reduced, the reverse recovery time is short, and the temperature characteristic is good. The diode is particularly suitable for trench type diodes.

Owner:UNIV OF ELECTRONIC SCI & TECH OF CHINA

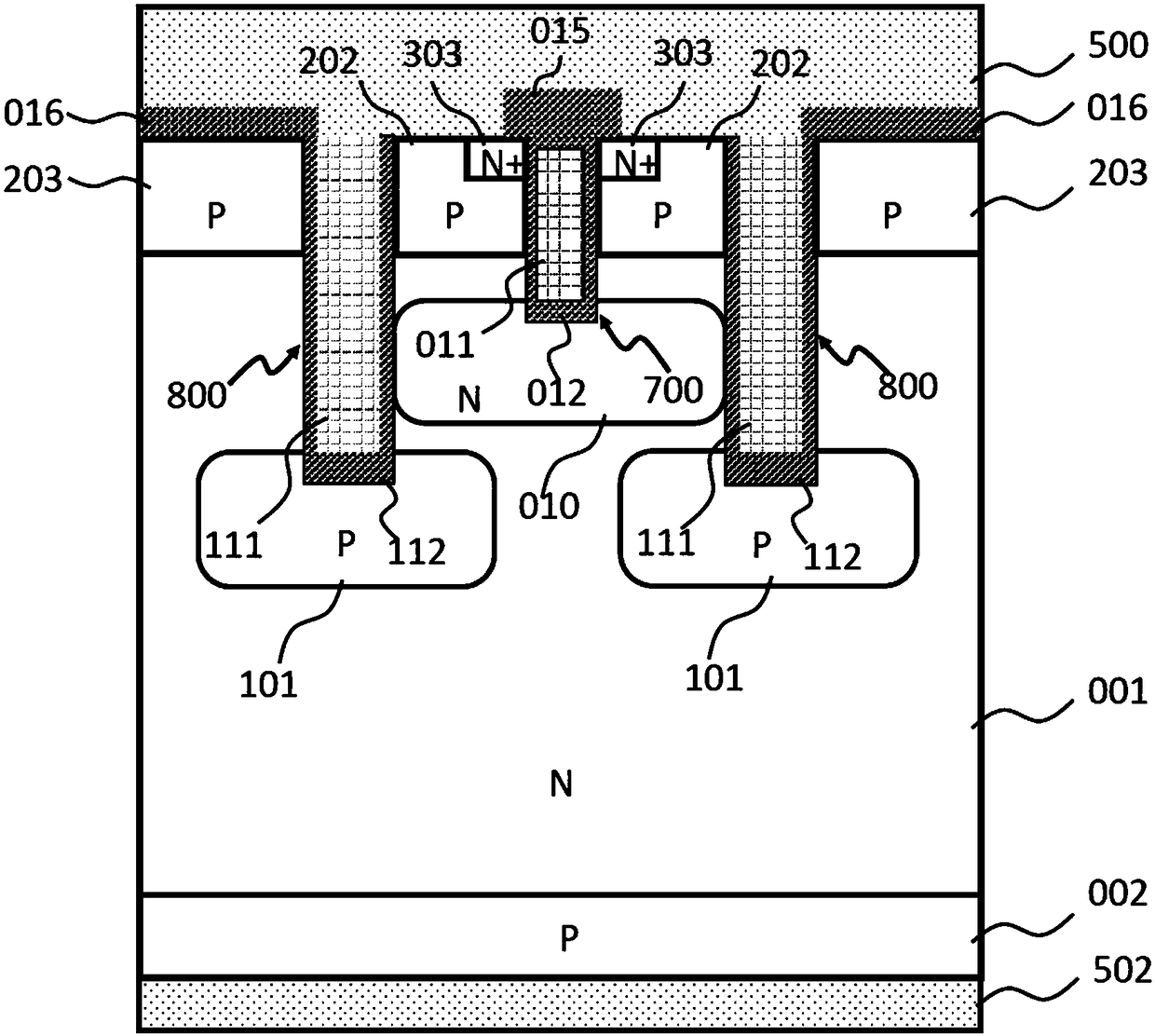

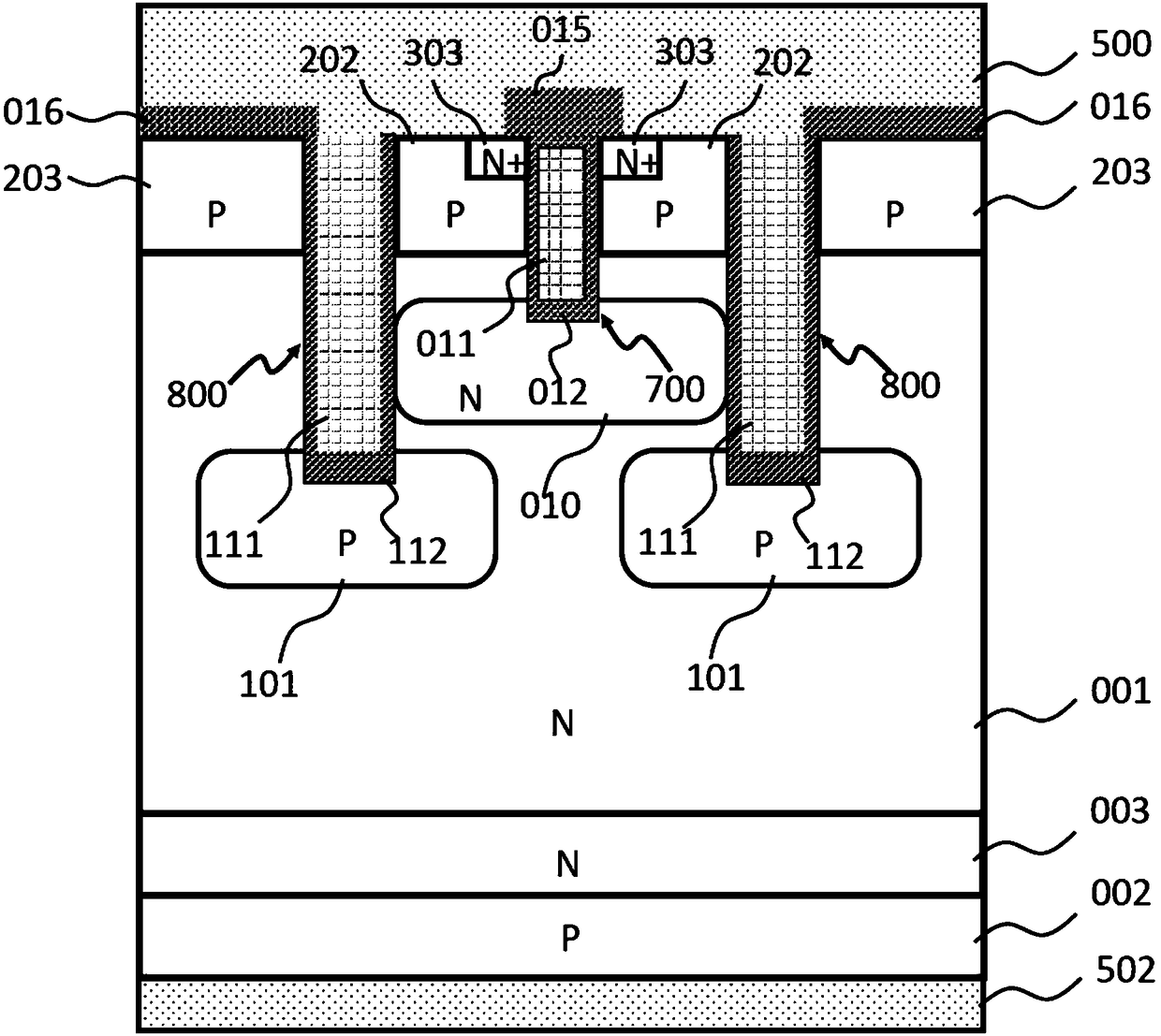

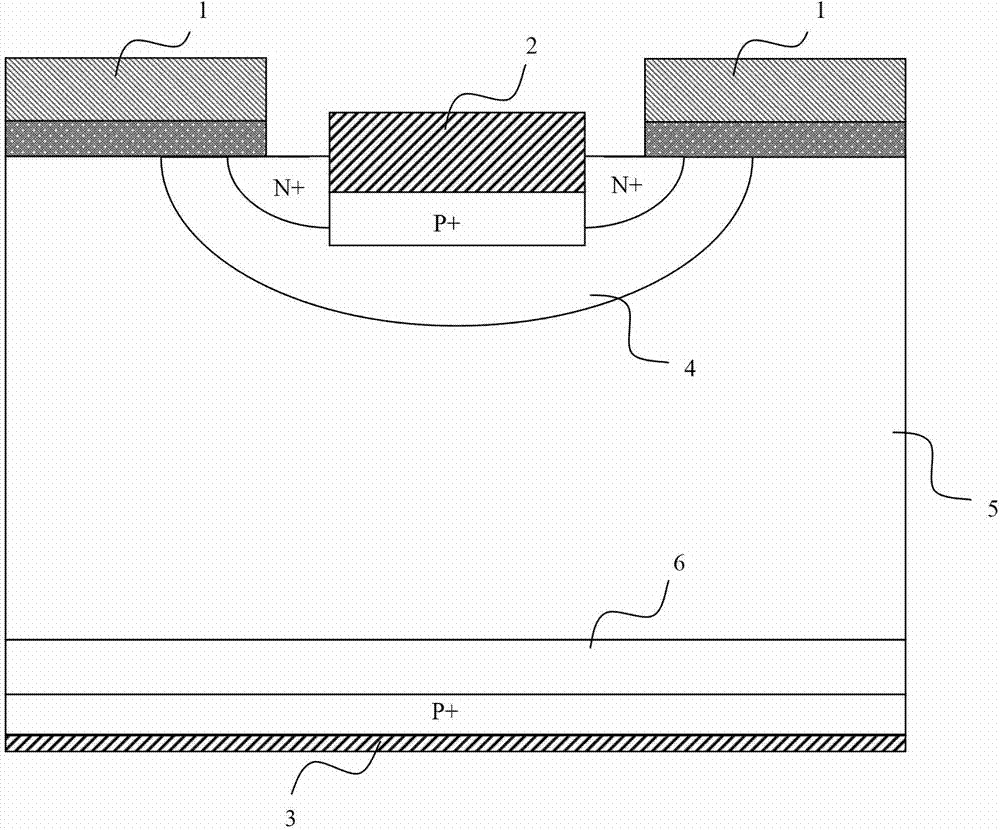

Semiconductor device

Disclosed is a semiconductor device. The semiconductor device comprises at least one cell, and the structure of any cell comprises an N-type substrate, at least one N-type carrier barrier region, andat least one P-type electric field shielding region, wherein at least one first groove unit and at least one second groove unit are included on one side of the N-type substrate; at least one P-type semiconductor region is arranged on the other side of the N-type substrate, wherein the P-type semiconductor region is referred to as an anode region. The invention aims to provide the semiconductor device, wherein the semiconductor device has a novel cellular structure so as to obtain a large safe operating area, and the anti-short-circuit capability; the effect of a parasitic thyristor is eliminated; the low-grid-collector charges (QGC) are adopted to obtain the maximum anti-dv / dt capability; the emitter side electric conduction modulation is added, so that a relatively large current density and an extremely low conducting voltage drop can be obtained; and relatively turn-off loss and relatively low process complexity are achieved.

Owner:NANJING SINNOPOWER TECH CO LTD

Semiconductor device

ActiveUS10056450B2Improved recovery propertiesReduce conduction voltage dropTransistorConversion constructional detailsSemiconductorSemiconductor device

A semiconductor device includes a semiconductor substrate with: a drift layer; a base layer; and a collector layer and a cathode layer. In the semiconductor substrate, when a region operating as an IGBT device is an IGBT region and a region operating as a diode device is a diode region, the IGBT and diode regions are arranged alternately in a repetitive manner; a damaged region is arranged on a surface portion of the diode region in the semiconductor substrate. The IGBT and diode regions are demarcated by a boundary between the collector and cathode layers; and a surface portion of the IGBT region includes: a portion having the damaged region at a boundary side with the diode region; and another portion without the damaged region arranged closer to an inner periphery side relative to the boundary side.

Owner:DENSO CORP

Insulated gate bipolar transistor and manufacturing method thereof

InactiveUS20120153348A1Reduce conduction voltage dropTransistorSemiconductor/solid-state device manufacturingOptoelectronicsTrench gate

A trench gate IGBT designed to reduce on-state voltage while maintaining the withstand voltage, including a first drift layer formed on a first main surface of a buffer layer, a second drift layer of the first conductivity type formed on said first drift layer, a base layer of a second conductivity type formed on the second drift layer, an emitter layer of the first conductivity type selectively formed in the surface of the base layer, and a gate electrode buried from the surface of the emitter layer through into the second drift layer with a gate insulating film therebetween, wherein said first drift layer has a structure in which a first layer of the first conductivity type and a second layer of the second conductivity type are repeated in a horizontal direction.

Owner:MITSUBISHI ELECTRIC CORP

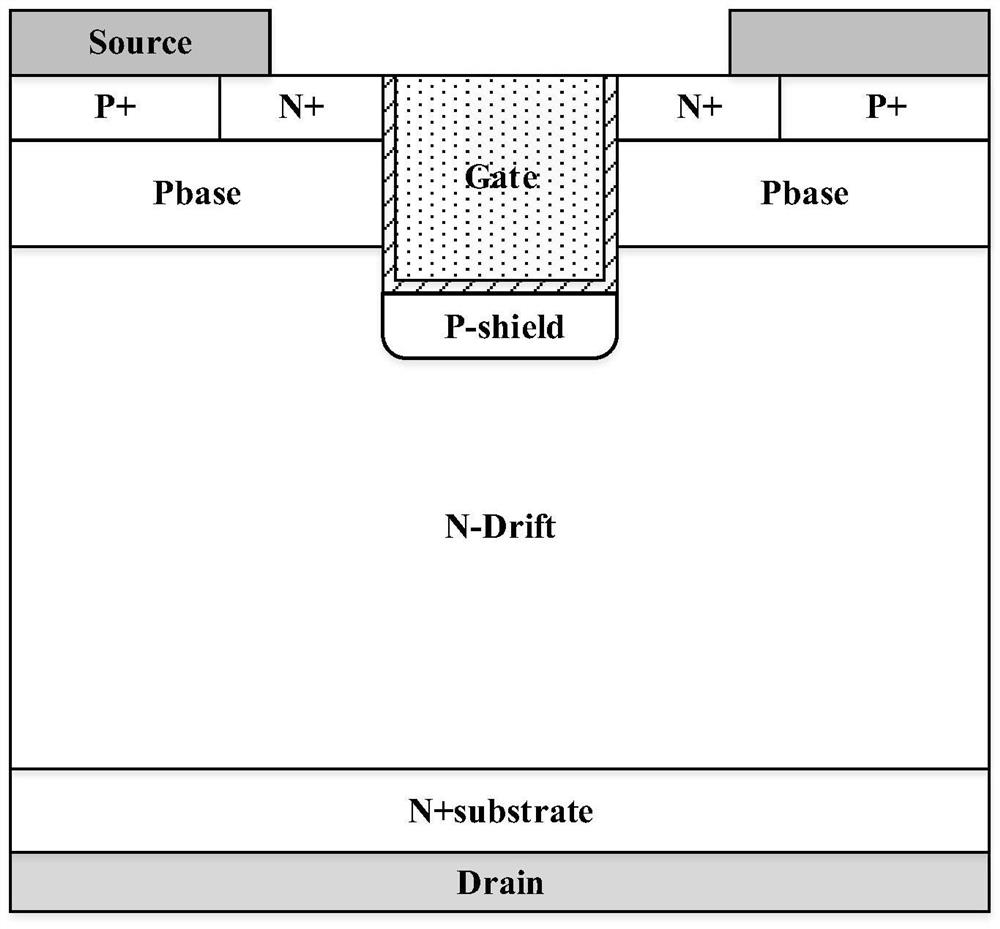

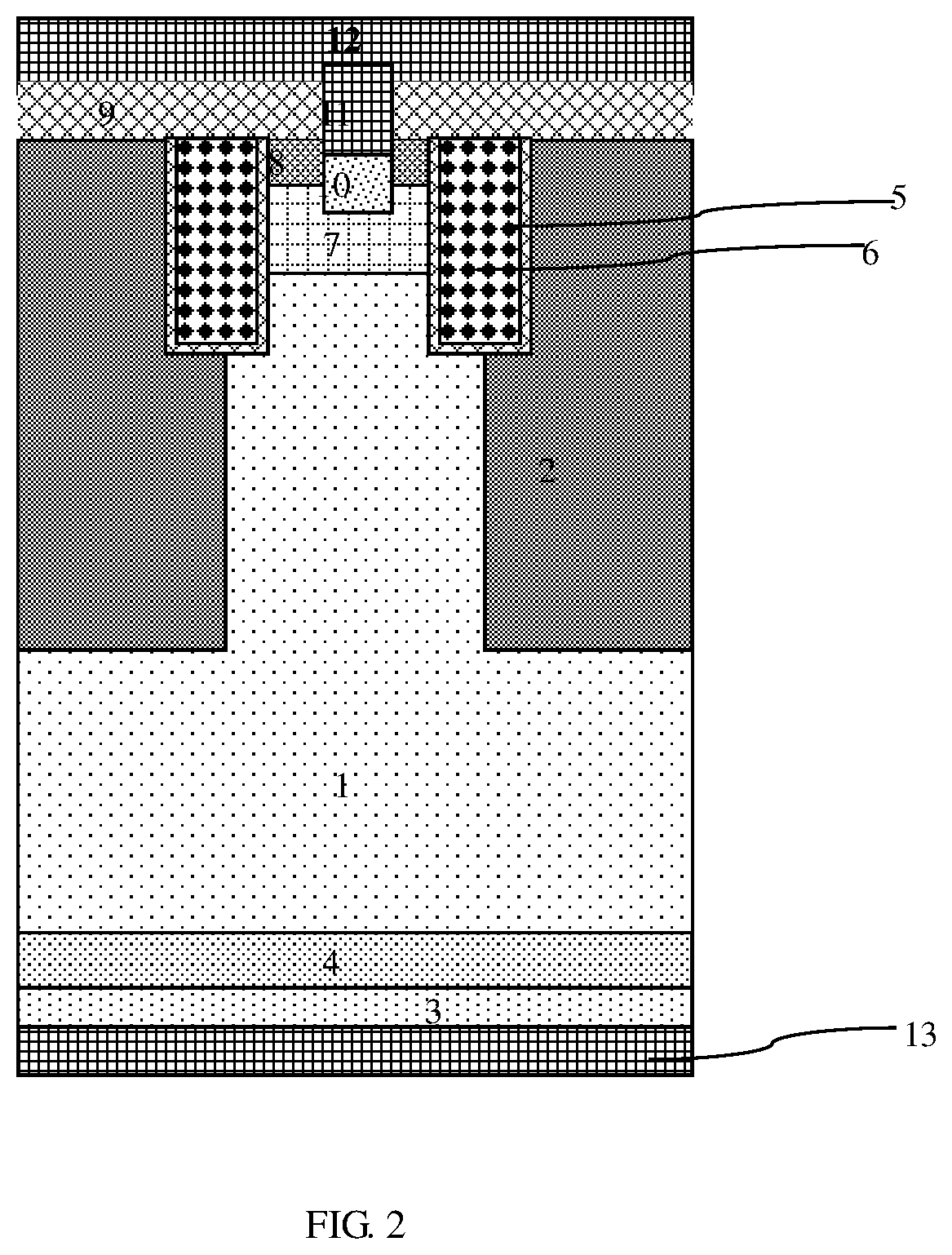

Silicon carbide MOSFET (Metal-Oxide -Semiconductor Field Effect Transistor) device capable of integrating with high-speed reverse free-wheeling diode

ActiveCN109904155ALower channel resistanceLower characteristic resistanceSolid-state devicesSemiconductor devicesMOSFETPower semiconductor device

The invention belongs to the technical field of semiconductor power devices, and relates to a silicon carbide semiconductor device, in particular to a silicon carbide MOSFET (Metal-Oxide-SemiconductorField Effect Transistor) device capable of integrating with a high-speed reverse free-wheeling diode for realizing the integration of the silicon carbide semiconductor device and the reverse free-wheeling diode. Compared with the original body diode of silicon carbide MOSFET, the integrated Schottky barrier FWD (Free-Wheeling Diode) can realize low diode conduction pressure drop and reduce reverse recovery time and loss. By use of the device, the application cost of the silicon carbide power semiconductor device and the number of peripheral devices when the device is applied can be favorablylowered, and therefore, the device has a large application value.

Owner:UNIV OF ELECTRONICS SCI & TECH OF CHINA

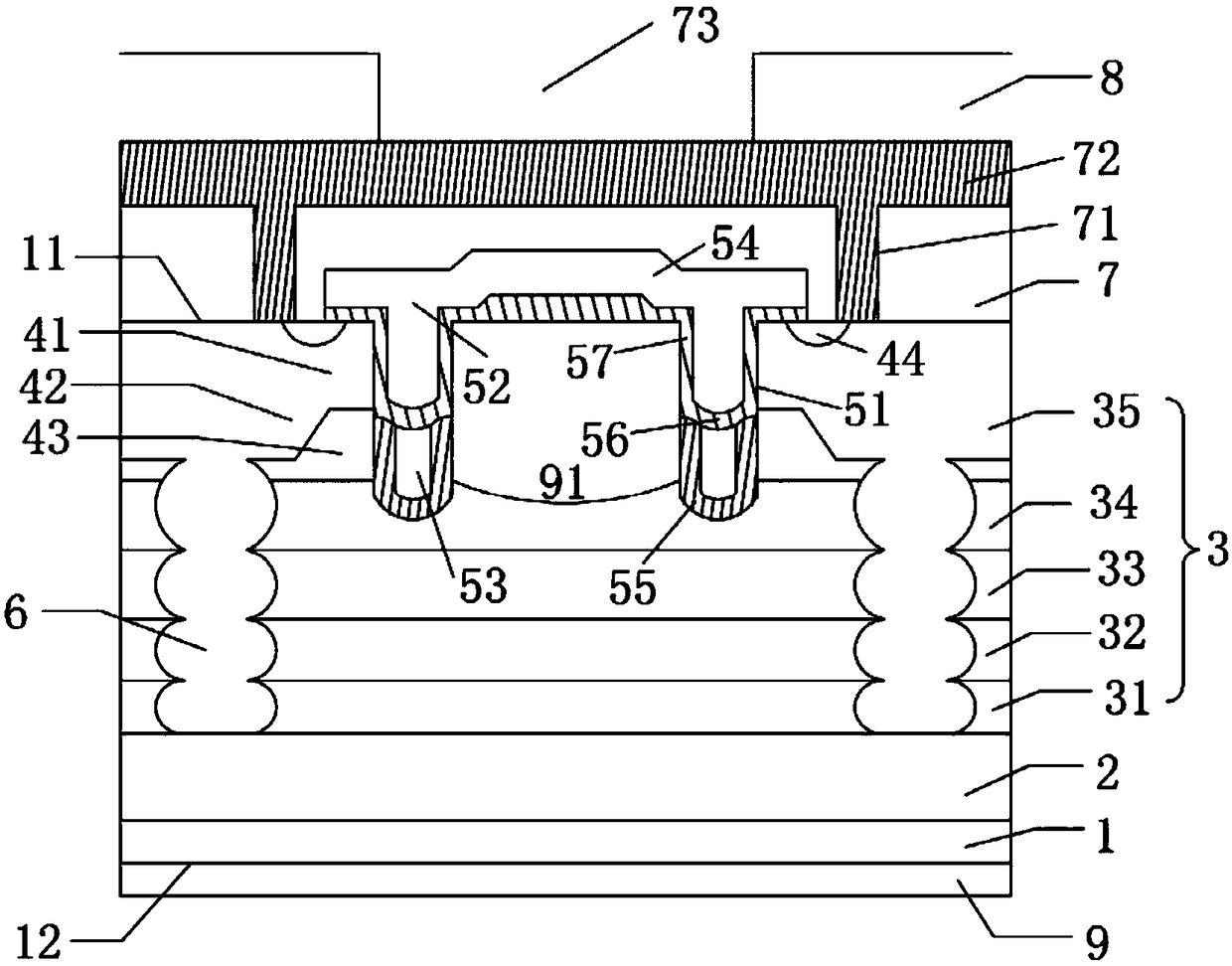

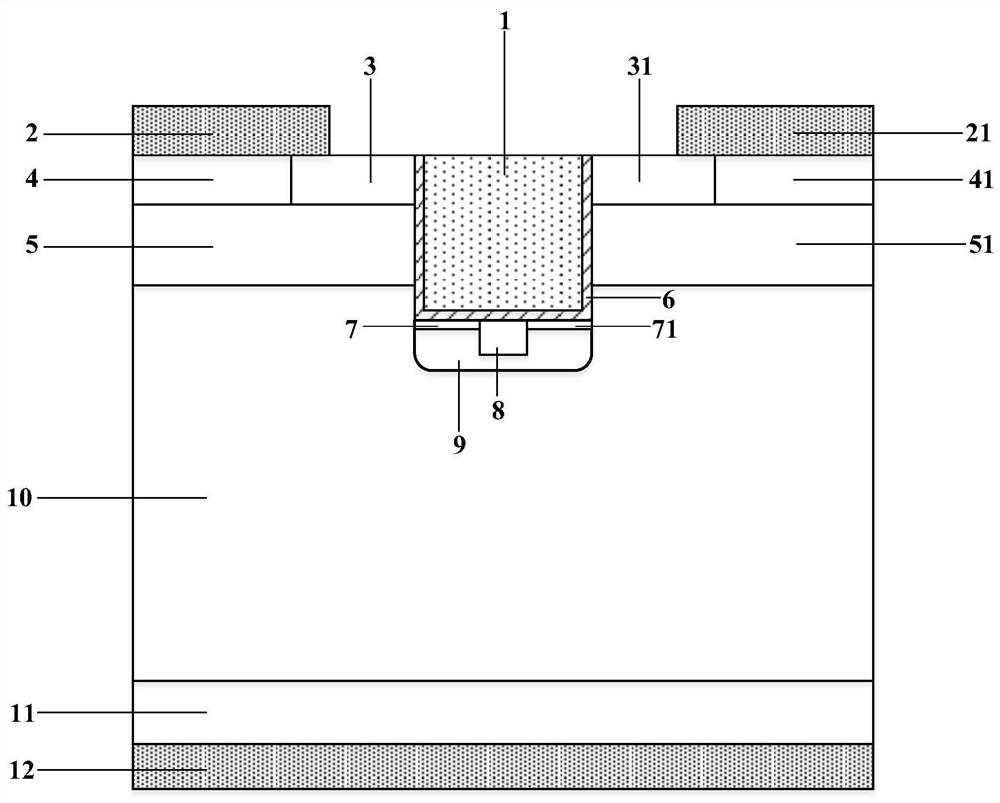

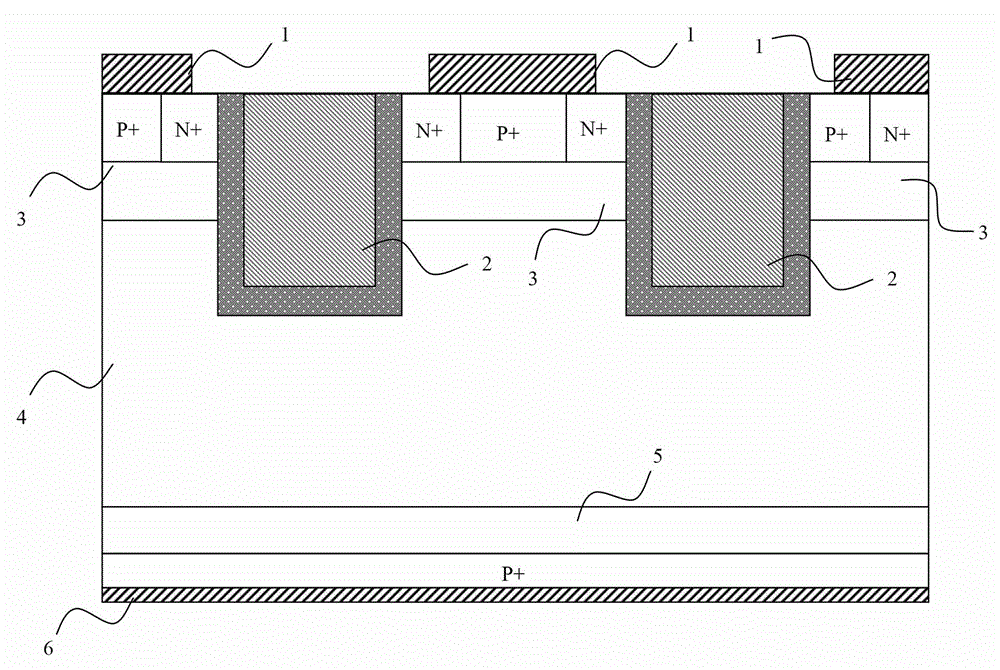

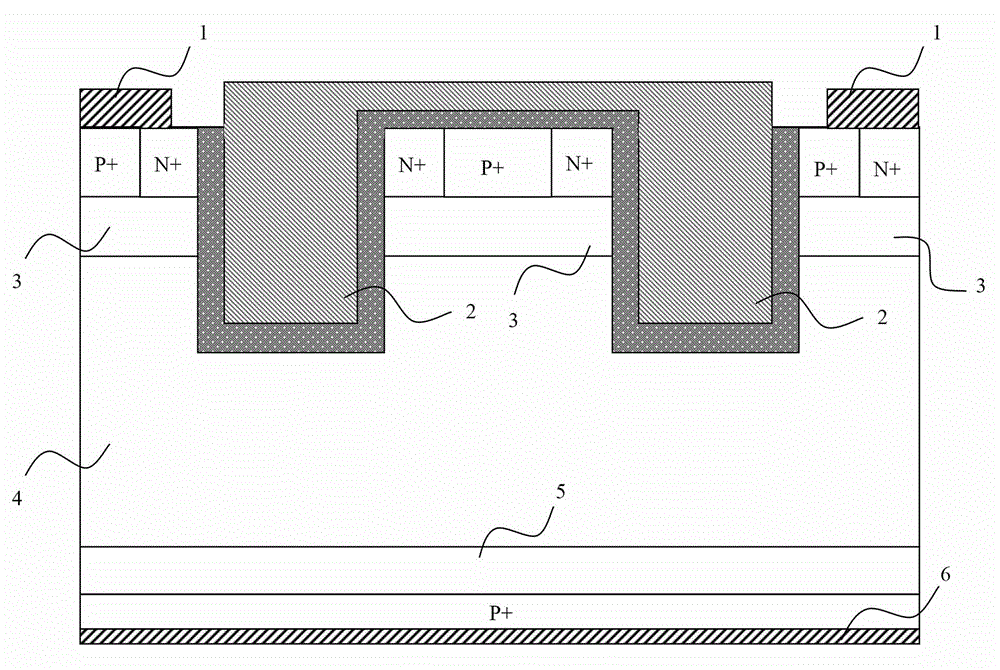

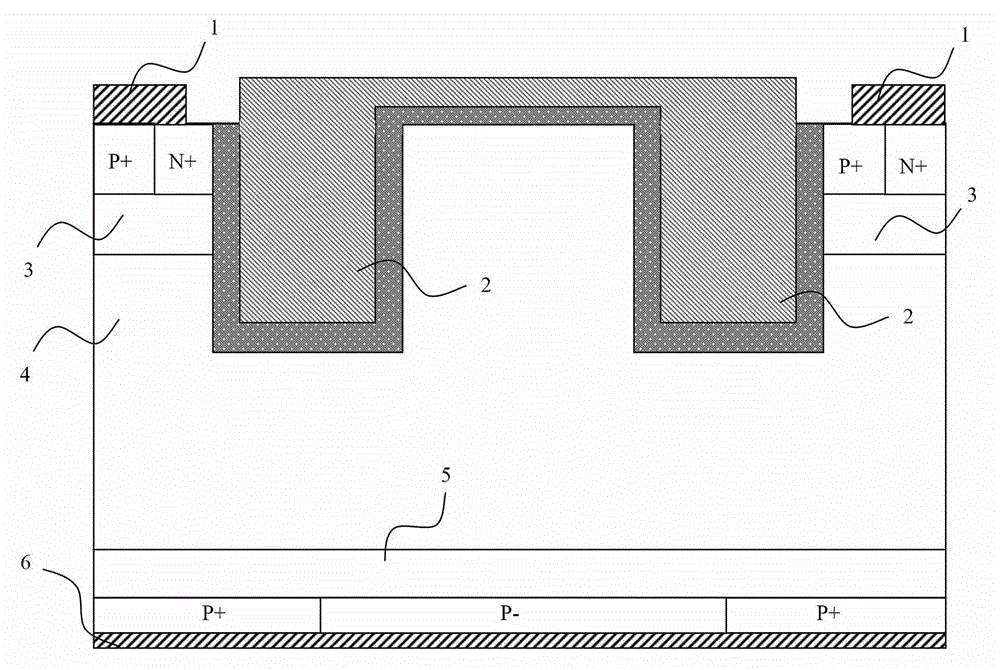

Silicon carbide MOSFET device with integrated diode and manufacturing method

PendingCN114122139AReduce areaImprove reliabilitySolid-state devicesSemiconductor/solid-state device manufacturingMOSFETGate dielectric

The invention provides a silicon carbide MOSFET (Metal-Oxide-Semiconductor Field Effect Transistor) device with an integrated diode and a manufacturing method. The device comprises a source ohmic contact region, a drain ohmic contact region, an N + substrate, an N-drift region, a P-type base region, a P + source region, an N + source region, a P-type shielding layer, a shielding layer N + source region, an N-type channel region, a gate dielectric layer and a polysilicon gate. According to the trench type silicon carbide MOSFET device provided by the invention, the chip area is greatly saved in a mode of integrating the diodes in the chip. The N-type channel region is introduced to the bottom of the trench, so that the electron barrier height at the interface of the oxide layer is adjusted, the third quadrant characteristic of the device is remarkably improved, the low third quadrant turn-on voltage is realized, and the bipolar degradation effect is avoided; multiple channels are connected in parallel, so that the forward current capability of the device is improved, and the on-resistance is reduced; and the P-type shielding layer wraps and protects the gate groove, so that the electric field of the gate oxide layer is reduced, and the reliability of the device oxide layer is enhanced.

Owner:UNIV OF ELECTRONICS SCI & TECH OF CHINA

Method for manufacturing trench gate type IGBT (insulated gate bipolar transistor) chip

ActiveCN102945804AIncrease hole concentrationImprove injection efficiencySemiconductor/solid-state device manufacturingNitric oxideInsulated-gate bipolar transistor

The invention discloses a method for manufacturing a trench gate type IGBT (insulated gate bipolar transistor) chip, which comprises the following steps: selecting two N-shaped semiconductor substrates, and carrying out oxidation or deposition on one of the substrates, so that insulating materials including silicon oxides or nitric oxides are formed on the surface of the substrate; carrying out photoetching and etching on the insulating materials on the surface of the substrate so as to form a dielectric buried layer; carrying out photoetching and etching on the other substrates so as to form a figure coincided with the concave-convex surface of the dielectric buried layer; carrying out concave-convex surface butt-joint on the dielectric buried layer and the figure, and bonding the two substrates together at high temperature; according to voltage-withstanding requirements and machining allowances, respectively carrying out thinning processing on the two substrates, and controlling the dielectric buried layer at a design depth, so that a chip manufacturing intermediate is formed; and completing the manufacturing process of a trench gate type IGBT chip. According to the invention, the drop voltage of the chip is reduced, a compromising relation with shut-off loss is optimized, and the lower power consumption is realized, thereby improving the power density, operating junction temperature and reliability of the IGBT chip.

Owner:ZHUZHOU CRRC TIMES SEMICON CO LTD

Fast recovery diode and manufacturing method thereof

InactiveCN102867849AIncreased Schottky areaReduce conduction voltage dropSemiconductor/solid-state device manufacturingSemiconductor devicesHigh current densitySchottky barrier

The invention relates to a fast recovery diode device, and also relates to a manufacturing method of the fast recovery diode device. According to the invention, a groove structure is added into a traditional Schottky barrier rectifier (MPS) structure intruding into a PN junction. Compared with the traditional MPS device, the fast recovery diode device disclosed by the invention has the advantages of lower forward voltage drop and higher current density.

Owner:盛况

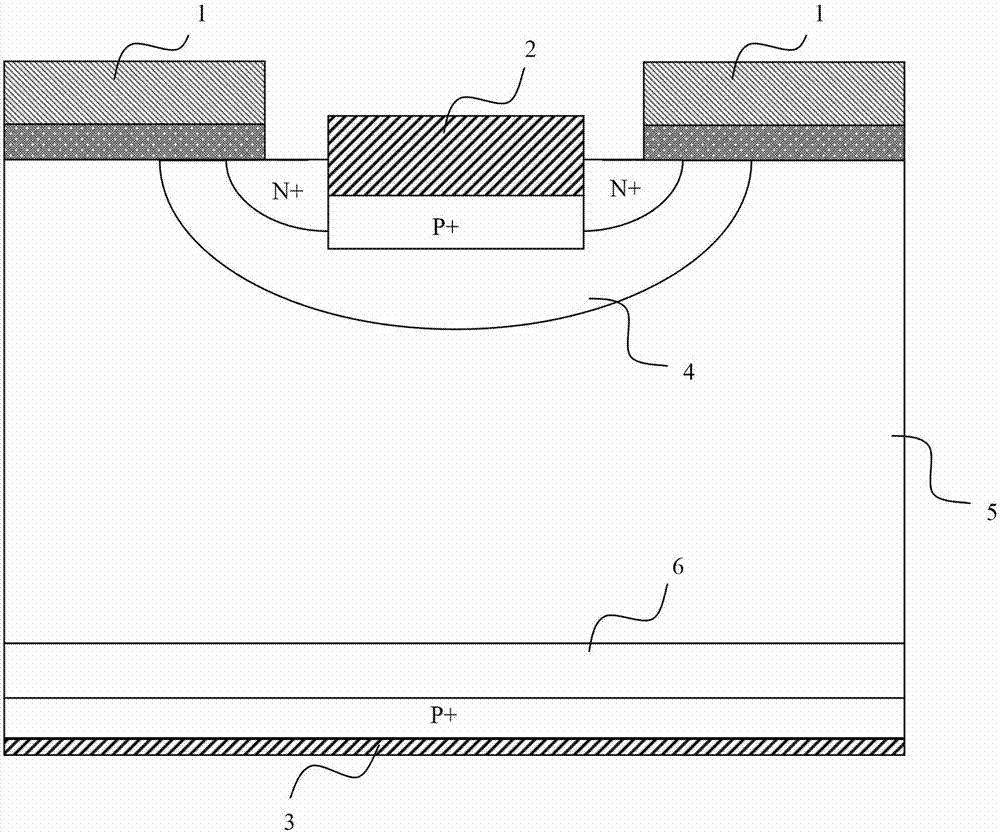

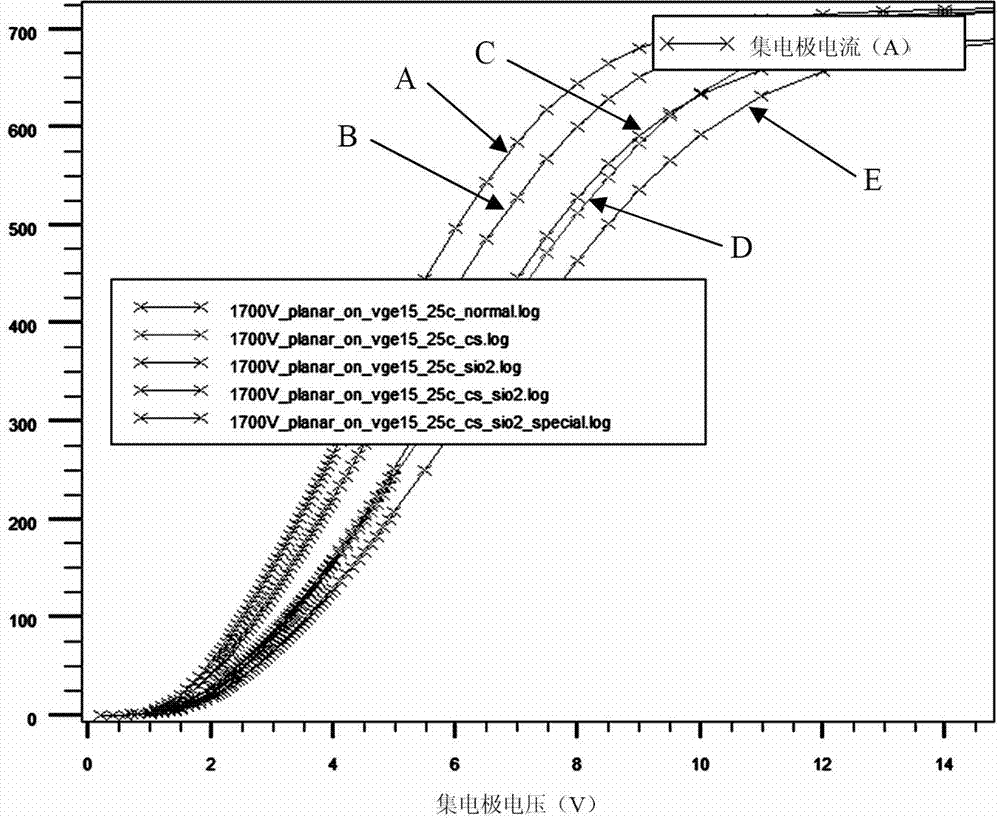

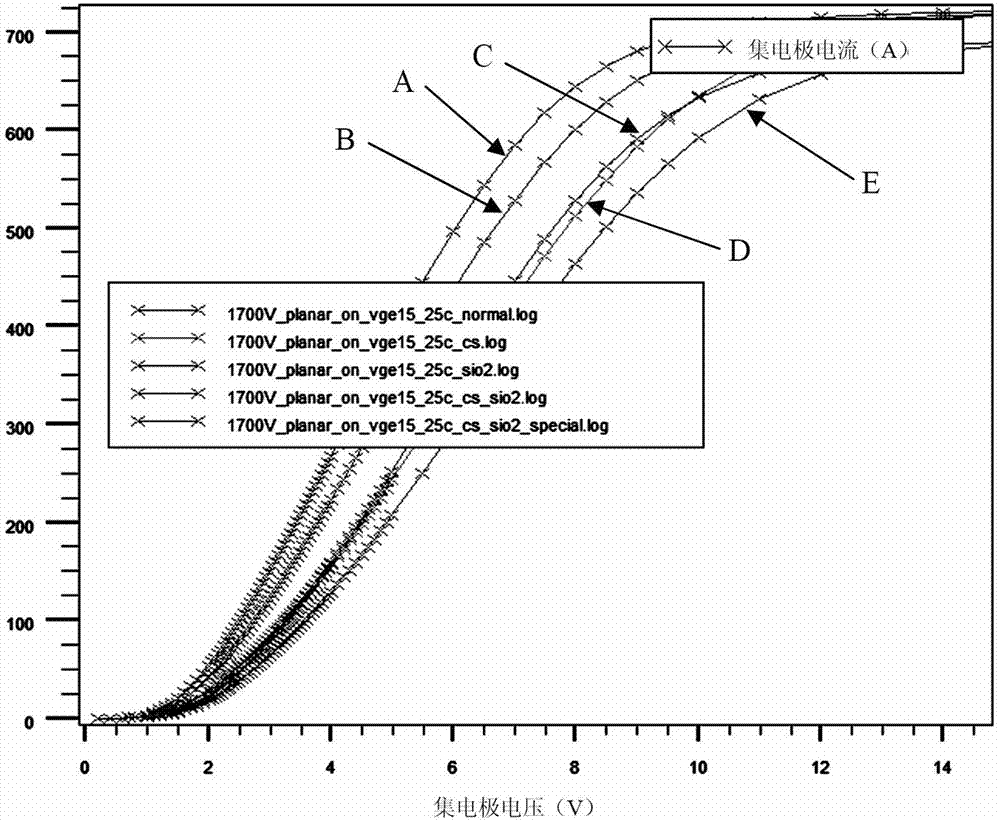

Planar gate IGBT (Insulated Gate Bipolar Transistor) chip

ActiveCN102969351AReduce conduction voltage dropImprove the conduction voltage dropSemiconductor devicesOhmic contactCharge carrier

The invention discloses a planar gate IGBT (Insulated Gate Bipolar Transistor) chip, which comprises a collector metal electrode, a P+ collector region, an N- drift region, a P- base region, a P+ ohmic contact region, an N+ source region, a gate oxide layer, a polysilicon gate and a gate metal electrode which are arranged successively, and an emitter metal electrode arranged above the P+ ohmic contact region, wherein the polysilicon gate of the planar gate IGBT chip adopts a planar gate structure. The planar gate IGBT chip also comprises a first N-type carrier buried layer and / or a second N-type carrier buried layer. The first N-type carrier buried layer is located below the P- base region. The second N-type carrier buried layer is located below the gate oxide layer and at both sides of the P- base region. The planar gate IGBT chip has the beneficial effects that the compromise relation between conduction pressure drop and turn-off loss of the IGBT is reduced, lower power consumption is realized, and thus the power density, the operating junction temperature and the long-term reliability of the IGBT chip are increased.

Owner:ZHUZHOU CRRC TIMES SEMICON CO LTD

Aviation onboard recorder independent power supply

ActiveCN103036284ANo maintenanceImprove storage efficiencyBatteries circuit arrangementsElectric powerAviationCapacitance

The invention belongs to avionics technology, is applied to the technical field of avionics, and particularly relates to an aviation onboard recorder independent power supply. The aviation onboard recorder independent power supply comprises a charging circuit 1, a control unit 2, an energy storage unit 3, a power supply voting unit 4 and a boosted circuit 5. As a super-capacitor is adopted as the energy storage unit, compared with a charging battery, the aviation onboard recorder independent power supply has the advantages that the cycle life is more than 100 times that of the charging battery, maintenance-free of the energy storage unit of the recorder independent power supply in a full life circle is achieved, large-current charging and discharging can be borne, self-heating quantity is small, energy storage efficiency can be improved conveniently, and the heat dissipation design can be simplified conveniently. The aviation onboard recorder independent power supply is designed according to requirements of the TSO-C155 airworthiness standard, adopts the super-capacitor for energy storage, and is capable of providing a 12 W back up power supply which can last 10 minutes for a recorder after being charged for 15 minutes when a main power supply of an aircraft is cut off.

Owner:SHAANXI QIANSHAN AVIONICS

Super-junction IGBT device and method for manufacturing same

A super-junction IGBT device comprises a plurality of N-type pillars and a plurality of P-type pillars which are alternately arrayed in a horizontal direction. Device cell structures are formed at tops of super-junction cells and each comprise a trench gate having a gate trench striding across an interface of the corresponding P-type pillar and the corresponding N-type pillar. A body region is formed at a top of the corresponding N-type pillar, and a source region is formed on a surface of the body region. The top of each N-type pillar is provided with one body region and two trench gates located on two sides of the body region, and each body region is isolated from the P-type pillars on the two sides of the body region through the corresponding trench gates. The invention further discloses a method for manufacturing a super-junction IGBT device. Self-isolation of the P-type pillars is realized, the on-state current capacity of the device is improved, and the on-state voltage drop of the device is reduced.

Owner:SHANGHAI HUAHONG GRACE SEMICON MFG CORP

Method for manufacturing non-punch-through (NPT) type groove IGBT (Insulated Gate Bipolar Transistor) with field stop structure

InactiveCN102184855AImprove pressure resistanceReduce conduction voltage dropSemiconductor/solid-state device manufacturingSilicon oxideMaterials science

The invention discloses a method for manufacturing a non-punch-through (NPT) type groove IGBT (Insulated Gate Bipolar Transistor) with a field stop structure, and the method comprises the following steps: in a groove at a surface celluar area on a silicon chip, based on a silicon nitride insulating medium membrane serving as groove side wall protection, forming a thick silicon oxide insulating medium membrane at the bottom of the groove by twice thermal oxide growth, and forming a thin silicon oxide insulating medium membrane at the side wall of the groove by once thermal oxide growth; forming a composite field limiting ring outside a celluar area through twice ion implantation and thermal treatment, forming a composite field plate through polycrystalline silicon, metal deposition and corrosion, and forming one or more pressure rings by the composite field limiting ring and the composite field plate; and at the lower surface of the silicon chip, forming a field stop layer and a current collector region through twice ion implantation and shallow junction thermal treatment. The determined manufacturing method is low in cost and easy to implement; the manufactured IGBT area is small, the switching speed is fast, and the IGBT manufactured by the method has the performance characteristics of low power consumption, enhanced anti-electromagnetic interference and radiation-resistance capability, and the like, thus meeting the demand of the market on high quality of IGBT products.

Owner:TIANJIN HUANXIN TECH DEV

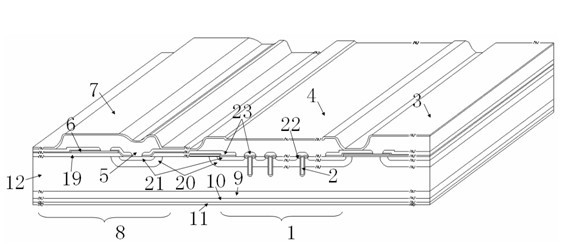

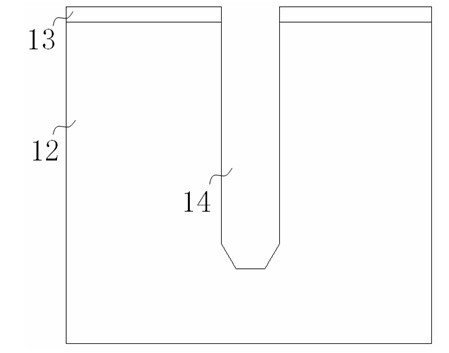

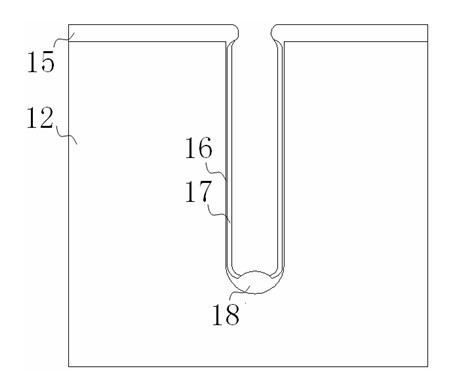

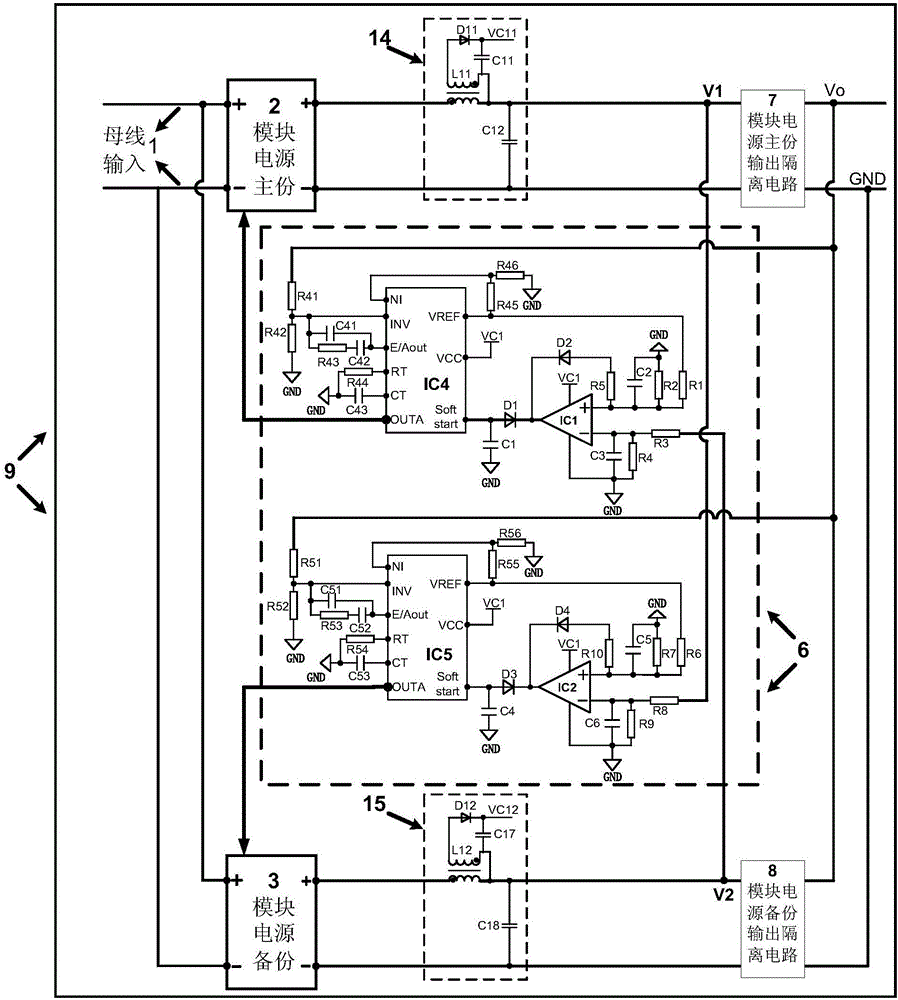

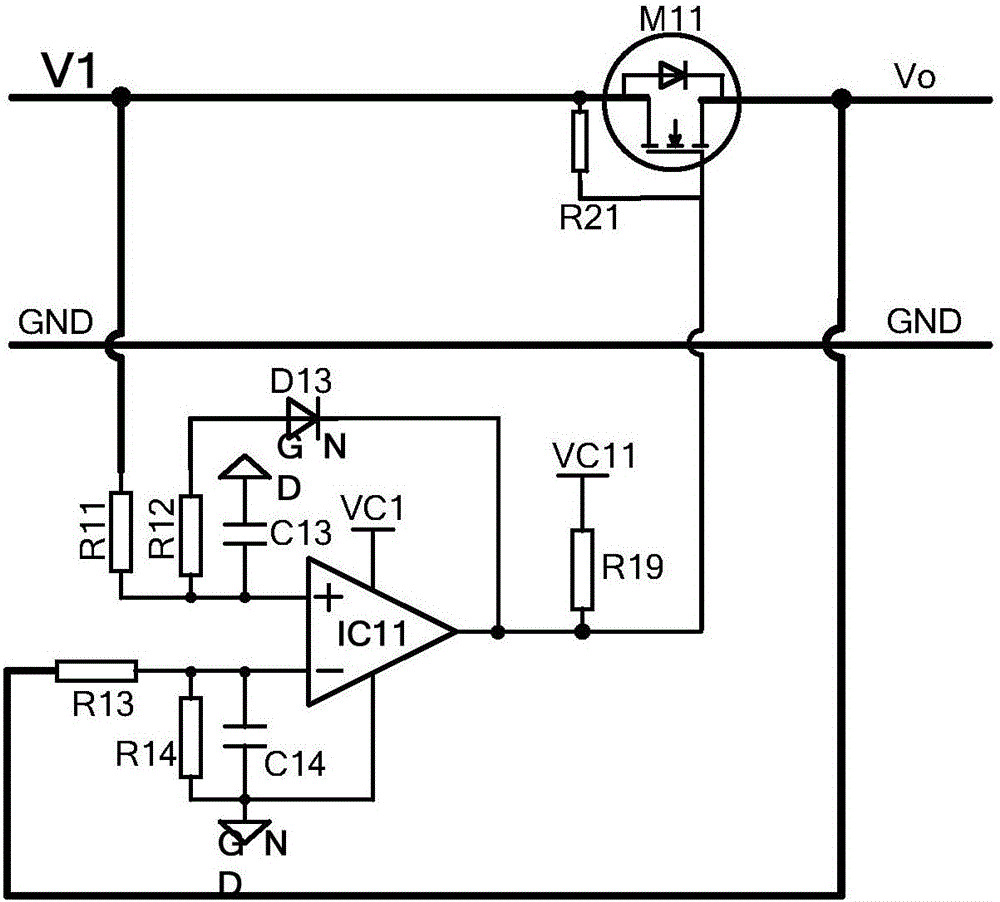

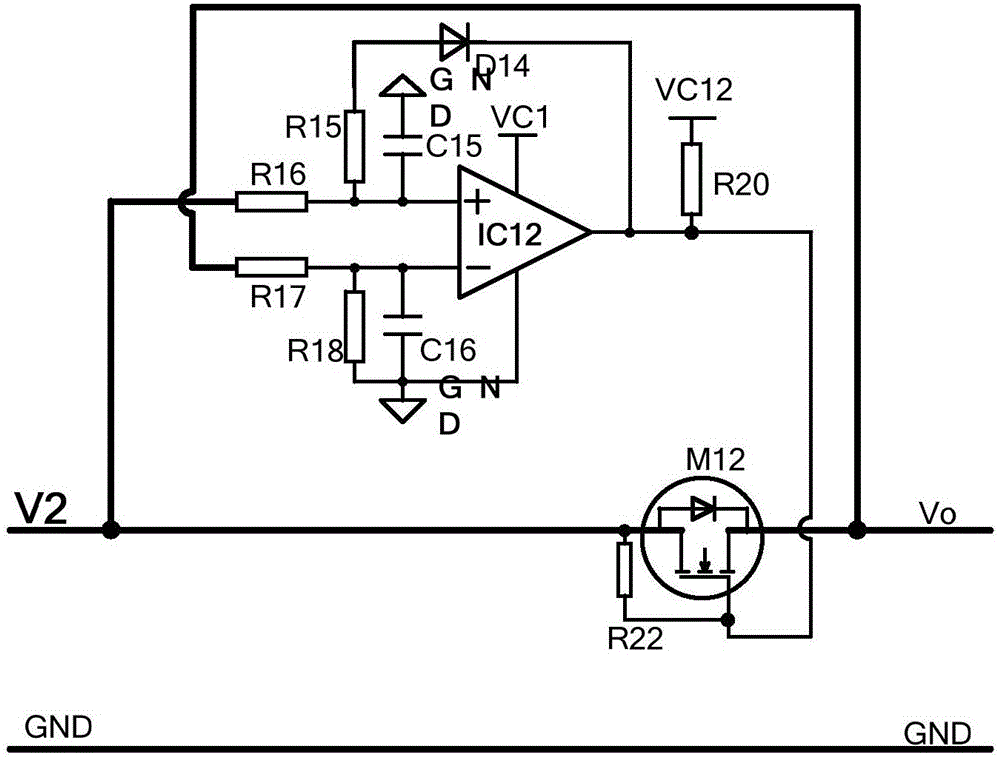

Main and backup power supply fault detection and automatic switching control circuit

ActiveCN106549487AImprove reliabilityReduce the difficulty of mechanical designEmergency power supply arrangementsElectricityComputer module

The invention discloses a main and backup power supply fault detection and automatic switching control circuit which comprises a main module power supply and a backup module power supply, wherein the main module power supply and the backup module power supply are connected in parallel with each other; the output ends of the main module power supply and the backup module power supply are both cascaded with isolation circuits of completely identical circuit structures, so that parallel redundancy between two modules of a power supply is realized; the main and backup power supply fault detection and automatic switching control circuit can monitor working states of the main and backup power supplies in real time and realize automatic fault detection and switching between the power supply modules; compared with the conventional relay-control main and backup switching circuit, the main and backup power supply fault detection and automatic switching control circuit has the advantages that the mechanical design difficulty of the module power supplies is reduced, and the reliability of the module power supplies is improved; and the main module power supply and the backup module power supply are mutually controlled, so that the requirement that the main power supply is powered on first under a condition that the module power supplies work normally is met, and a power-on time sequence control circuit is eliminated.

Owner:BEIJING SATELLITE MFG FACTORY

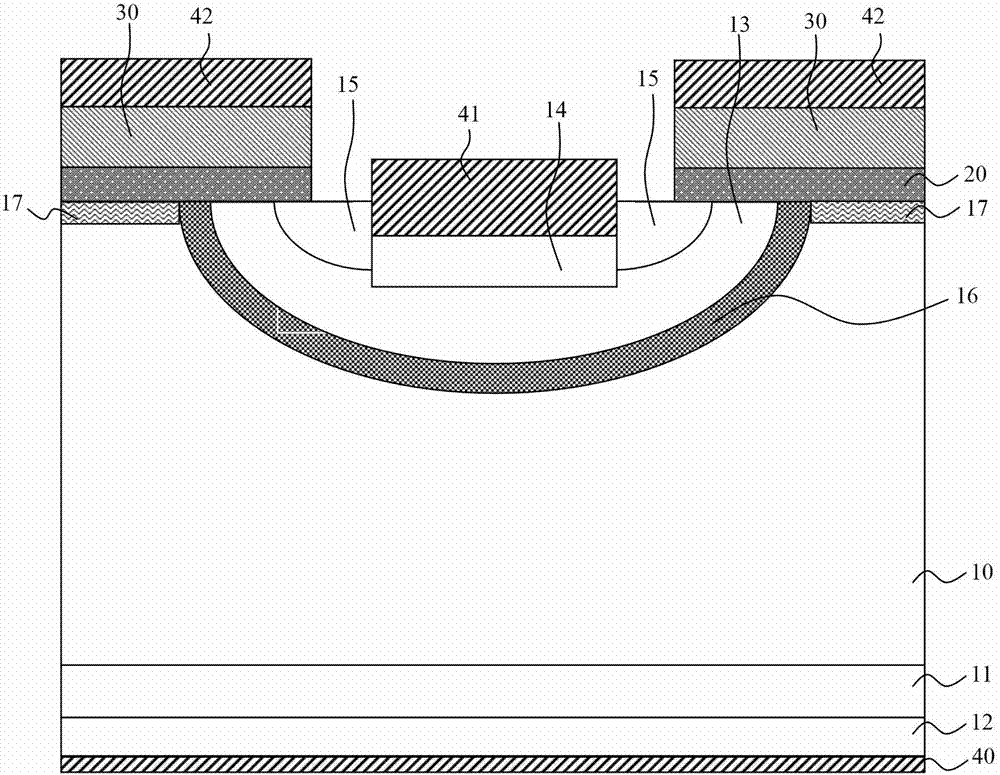

Planar gate IGBT device with deep trench electric field shielding structure

ActiveCN109728084AImprove safe work areaIncrease concentrationSemiconductor devicesCharge carrierEngineering

The invention relates to the field of power semiconductors, and provides a planar gate IGBT device with a deep trench electric field shielding structure, which is used for overcoming the problems thata current groove-gate IGBT gate with a carrier storage layer is too large in drive charges and small in short-circuit safety working region and is limited in the concentration of the CSL layer. The deep groove used for manufacturing the groove-gate IGBT channel traditionally and a P-type buried layer at the bottom portion of the groove are combined to form an electric field shielding structure toachieve clamping of the potential of the carrier storage layer; one IGBT cell is internally provided with a plurality of deep grooves to improve the concentration of the carrier storage layer of theIGBT compared to a traditional IGBT, have the higher cathode injection efficiency, and obtain the better trade-off relation of the on-state voltage and the turn-off loss. A planar gate and an electricfield shielding structure are employed, the IGBT has lower gate drive power consumption and lower saturation current density so as to improve the safety working region of the IGBT.

Owner:UNIV OF ELECTRONICS SCI & TECH OF CHINA