Accumulation layer controlled insulation gate type bipolar transistor

A technology of bipolar transistors and accumulation layers, applied in semiconductor devices, electrical components, circuits, etc., can solve the problems of increased amplification factor of PNP transistors, increased resistance of P-type base area 8, and reduced safe operating area, etc., to achieve Improved reliability and high-temperature operating characteristics, good turn-off loss, and reduced manufacturing costs

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0041] By adopting the accumulation layer control structure of the present invention, an insulated gate bipolar transistor with low conduction voltage drop, high current density, large safe operating area, low cost, and a better compromise between conduction voltage drop and turn-off loss can be obtained . It can be applied to planar gate structure, trench gate structure and lateral structure, etc. With the development of semiconductor technology, more power devices with low voltage drop, high current and high reliability can be produced by adopting the invention.

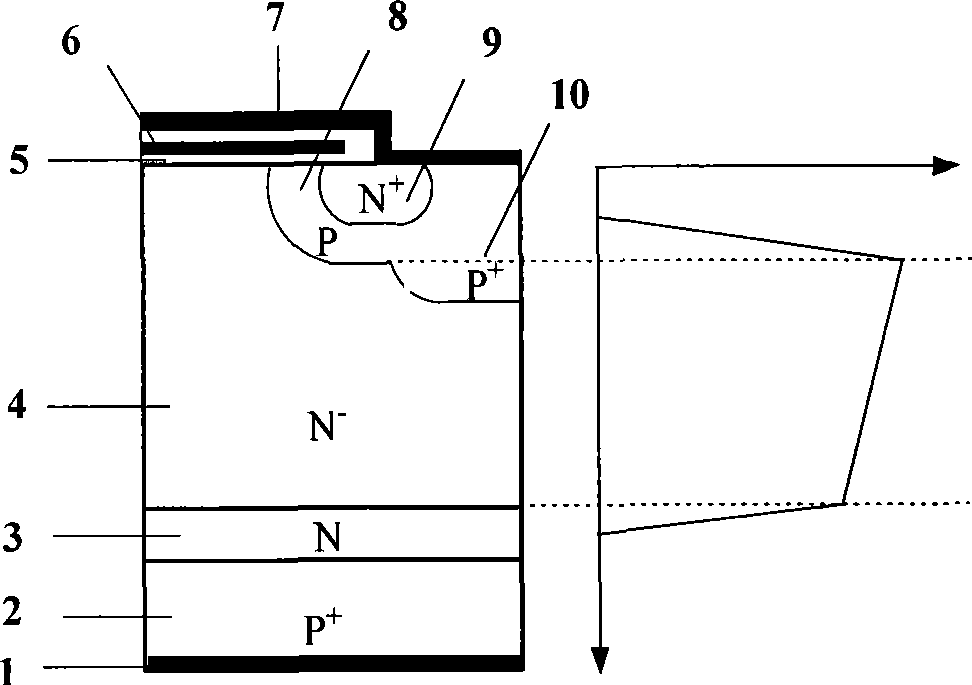

[0042] Trench insulated gate bipolar transistors that introduce accumulation layer control structures, such as Figure 5 shown, including collector 1, P-type collector 23, N - Base region 4, gate oxide layer 5, polysilicon gate 6, emitter 7, N + Source region 9, P + body area 10.

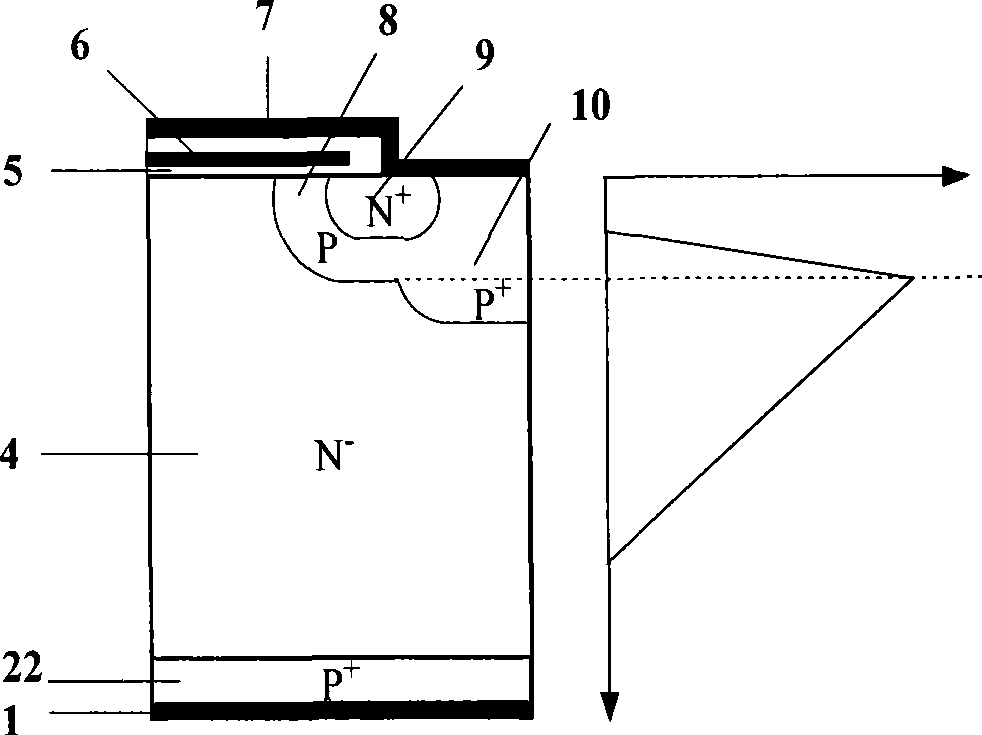

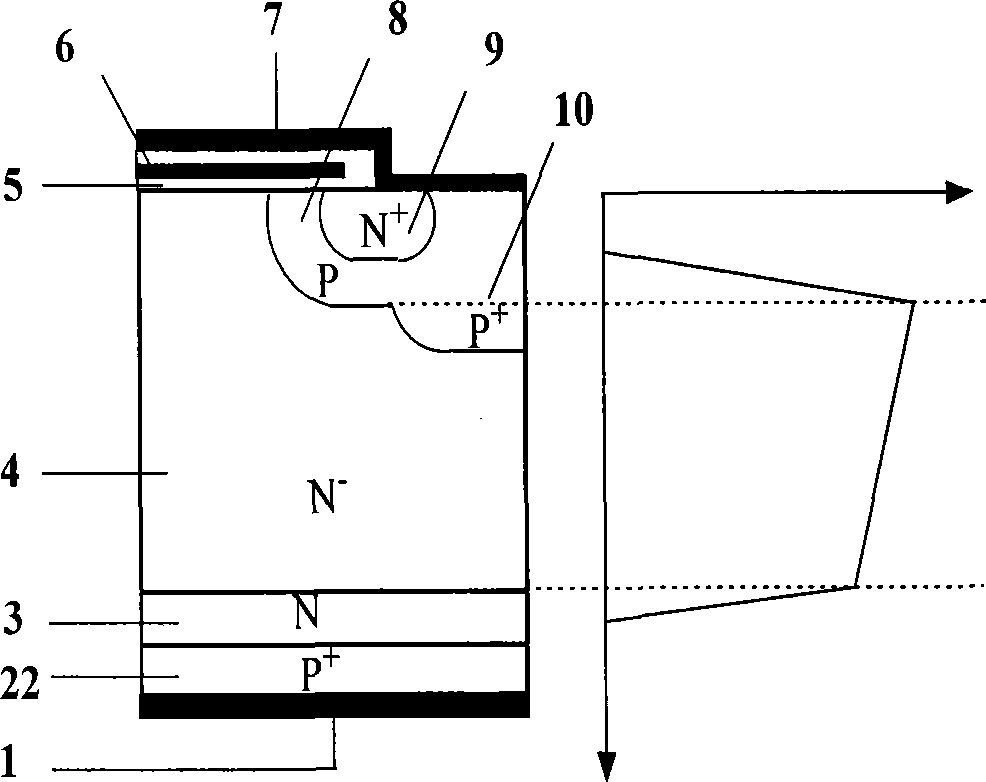

[0043] An accumulation layer controlled planar gate insulated gate bipolar transistor, such as Image 6 shown, including collecto...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More