Monolithic integrated phase inverter based on GaN-based enhanced device and preparation method thereof

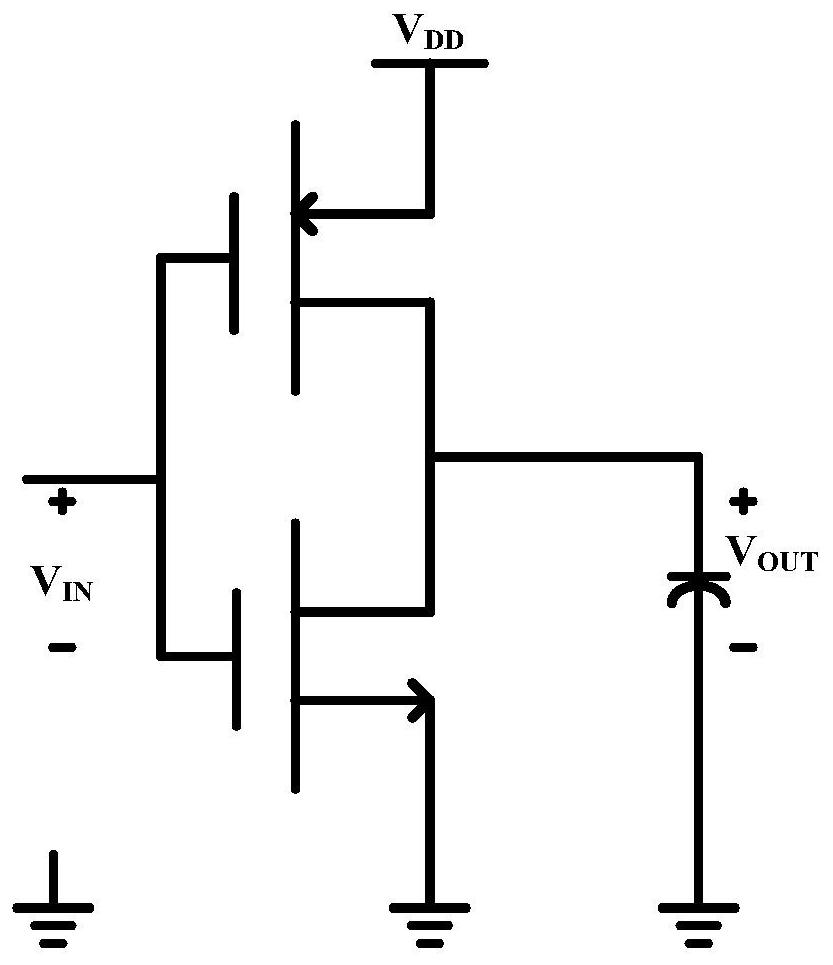

A monolithic integrated, enhancement-mode technology, applied in semiconductor/solid-state device manufacturing, semiconductor devices, electrical components, etc., can solve the problem of high on-resistance of p-channel enhancement-mode heterostructure field effect transistors, hindering GaN-based inversion It can improve the hole mobility, increase the threshold voltage, and reduce the on-resistance due to problems such as the application of devices and monolithic integrated circuits, and the large leakage of the gate electrode.

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

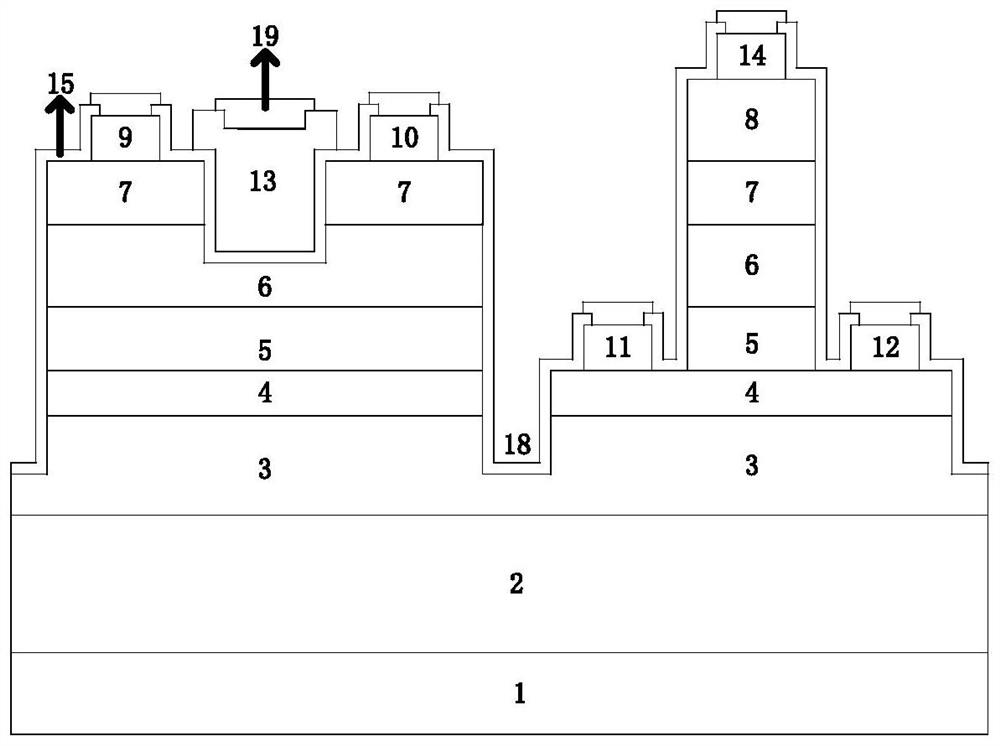

[0042] See figure 2 , figure 2 It is a schematic structural diagram of a monolithic integrated inverter based on a GaN-based enhancement device provided by an embodiment of the present invention, which sequentially includes a substrate 1, a buffer layer 2, a UID-GaN layer 3, and an AlGaN barrier layer from bottom to top 4. The UID-InGaN layer 5 and the p-InGaN layer 6. An isolation groove 18 as deep as the UID-GaN layer is provided in the middle of the device to divide the device into left and right parts; wherein,

[0043] The p-InGaN layer 6 on the left side of the device is provided with a first source electrode 9 and a first drain electrode 10, and a first gate as deep as the p-InGaN layer 6 is provided between the first source electrode 9 and the first drain electrode 10. An electrode 13 to form a p-channel enhancement type heterostructure field effect transistor;

[0044] A second source electrode 11 and a second drain electrode 12 are provided on the AlGaN barrier l...

Embodiment 2

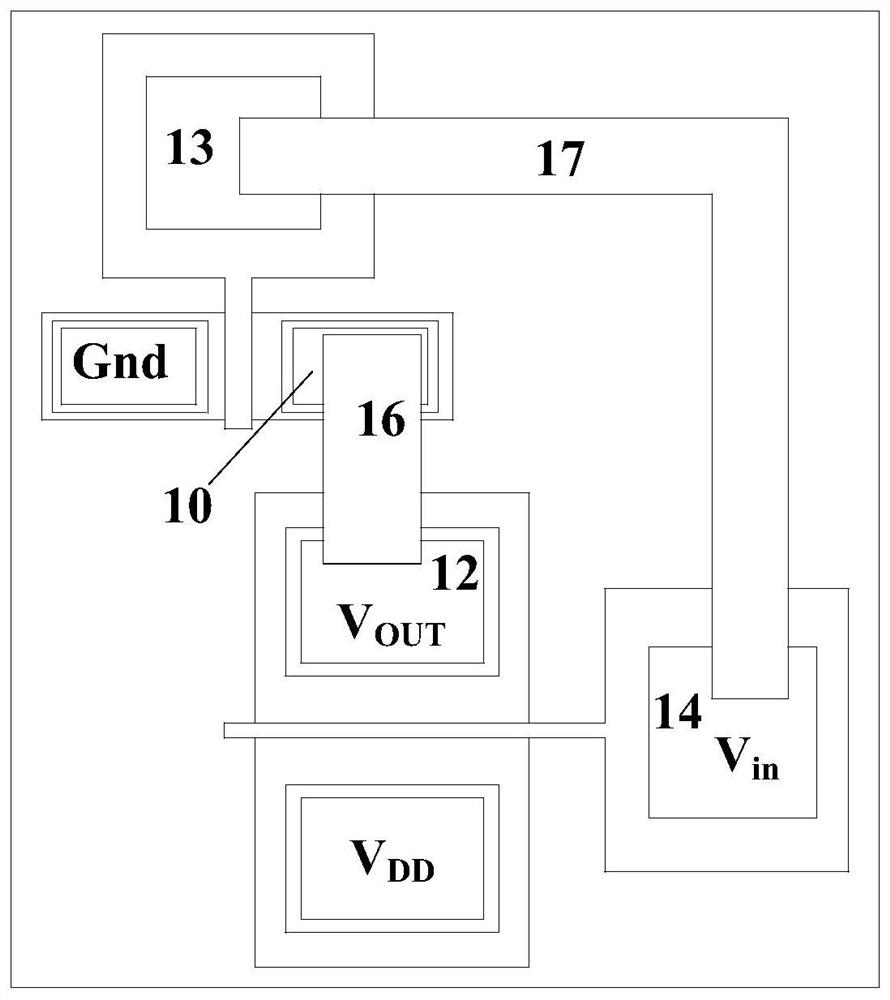

[0058] On the basis of the first embodiment above, this embodiment provides a method for manufacturing a monolithic integrated inverter based on p-channel and n-channel GaN-based enhancement devices. See Figure 4 , Figure 4 It is a flow chart of a method for manufacturing a monolithic integrated inverter based on a GaN-based enhancement device provided by an embodiment of the present invention, specifically including:

[0059] Step 1: Epitaxial buffer layer, UID-GaN layer, AlGaN barrier layer, UID-InGaN layer and p-InGaN layer on the substrate in sequence.

[0060] Specifically, in this embodiment, a metal-organic chemical vapor deposition process is used to sequentially grow various layer structures on a silicon substrate to obtain a silicon substrate.

[0061] Step 2: Etching the right side of the substrate to form the gate region of the n-channel enhancement type heterostructure field effect transistor.

[0062] Specifically, photolithography and inductively coupled pl...

Embodiment 3

[0092] The process of the preparation method provided by the present invention will be described in detail below in conjunction with the accompanying drawings.

[0093] See Figures 5a-5m , Figures 5a-5m It is a process schematic diagram of a method for manufacturing a monolithic integrated inverter based on a GaN-based enhancement device provided by an embodiment of the present invention. This embodiment includes UID-InGaN layer, p-InGaN layer, p + -InGaN layer and n-GaN layer devices are taken as examples to introduce the preparation process, which specifically includes the following steps:

[0094] S1: Prepare n-GaN / p-InGaN / AlGaN / GaN / silicon substrate substrate.

[0095] Using metal organic chemical vapor deposition process, epitaxial GaN buffer layer, UID-GaN, AlGaN barrier layer, UID-InGaN, p-InGaN layer, p + -InGaN layer and n-GaN layer to obtain n-GaN / p-InGaN / AlGaN / GaN / silicon substrate substrate, such as Figure 5a shown.

[0096] S2: n-GaN etching

[0097] Usi...

PUM

| Property | Measurement | Unit |

|---|---|---|

| thickness | aaaaa | aaaaa |

| thickness | aaaaa | aaaaa |

| thickness | aaaaa | aaaaa |

Abstract

Description

Claims

Application Information

Login to View More

Login to View More