Patents

Literature

74results about How to "Improve conduction characteristics" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

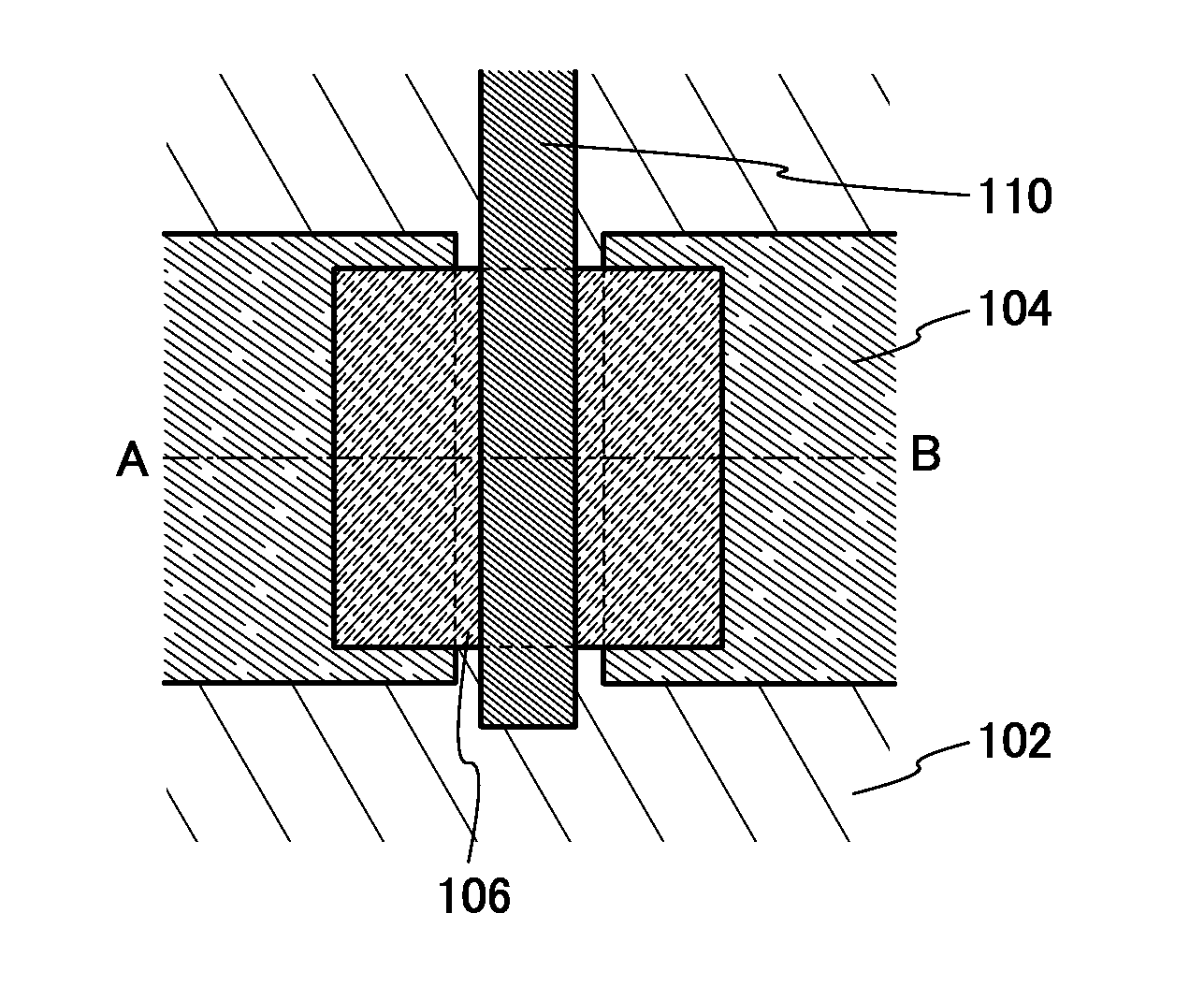

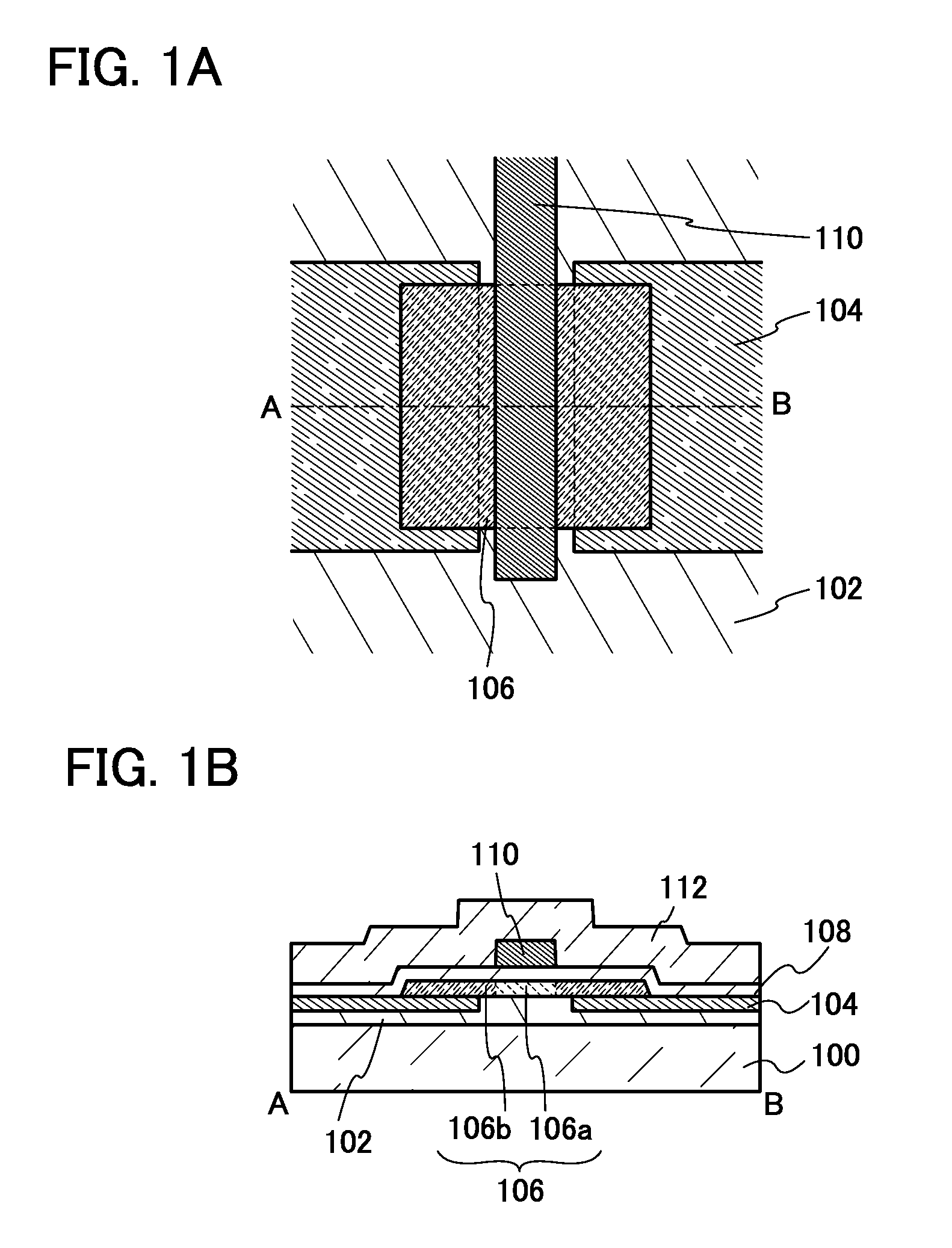

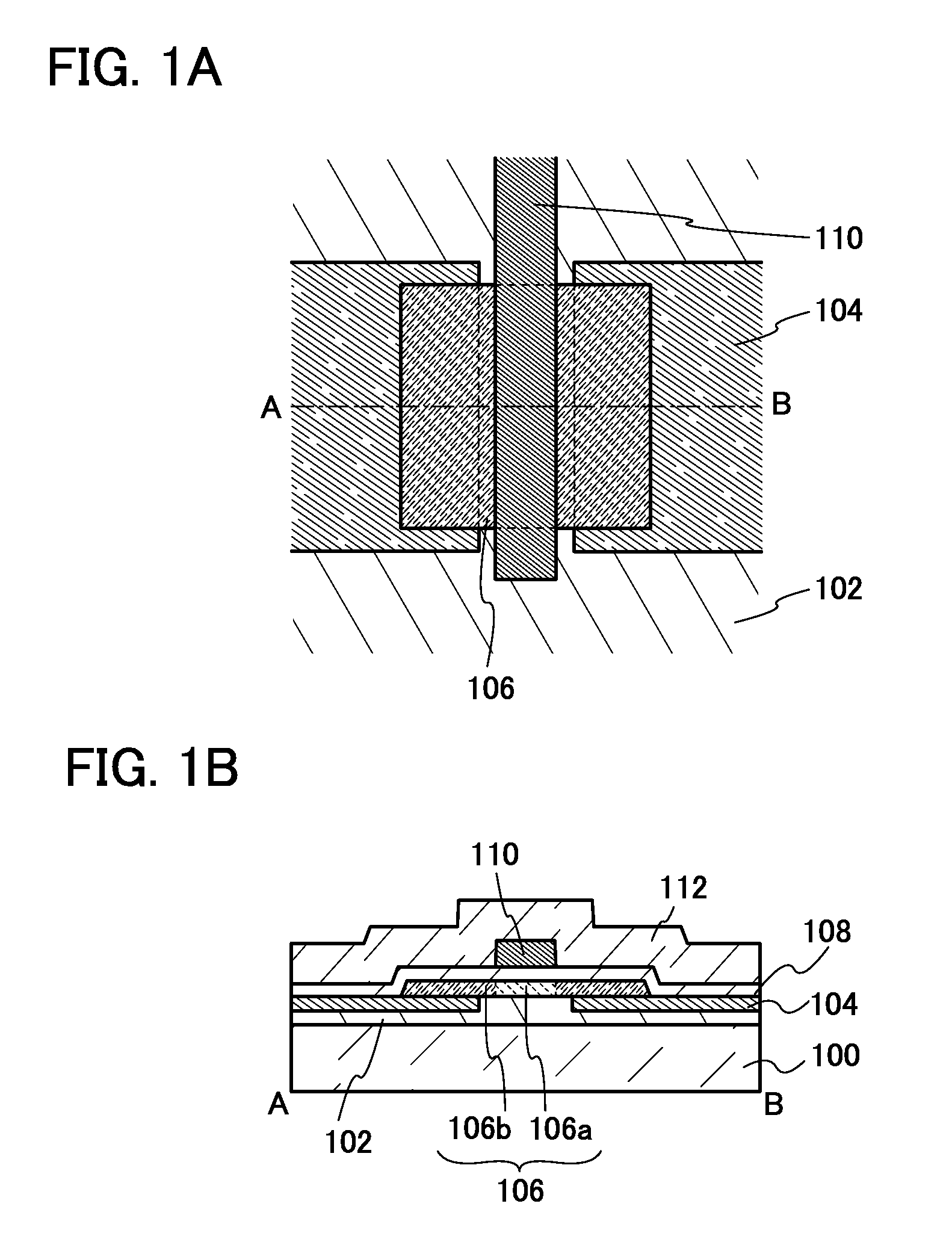

Semiconductor device and method for manufacturing the same

ActiveUS20120319114A1Improve conduction characteristicsRapid responseTransistorSemiconductor/solid-state device manufacturingDopantPower semiconductor device

A transistor including an oxide semiconductor layer and having electric characteristics required depending on an intended use, and a semiconductor device including the transistor are provided. In a transistor in which a semiconductor layer, a source electrode layer and a drain electrode layer, a gate insulating film, and a gate electrode layer are stacked in this order over an oxide insulating film, an oxide semiconductor stack composed of at least two oxide semiconductor layers having different energy gaps is used as the semiconductor layer. Oxygen and / or a dopant may be introduced into the oxide semiconductor stack.

Owner:SEMICON ENERGY LAB CO LTD

Heat-conducting polymer material and its prepn

InactiveCN1388202AImprove conduction characteristicsReduce paddingHeat-exchange elementsPolyolefinPolymer science

The heat-conducting polymer material includes polyolefin, heat-conducting assistant, environmental stress crack resisting assistant and impact resisting modifier. It is prepared through addition of crosslinking agent into heat-conducting assistant for surface treatment, or high temperature sintering and surface treatment of heat-conducting assistant after or without puffing treatment; mixing polyolefin with antioxidant; mixing all the material; fusion and extrusion in a double-screw extruder; cooling, drawing and slicing. The material of the present invention has excellent mechanical property, high conductivity and good welding property.

Owner:杭州华电华源环境工程有限公司

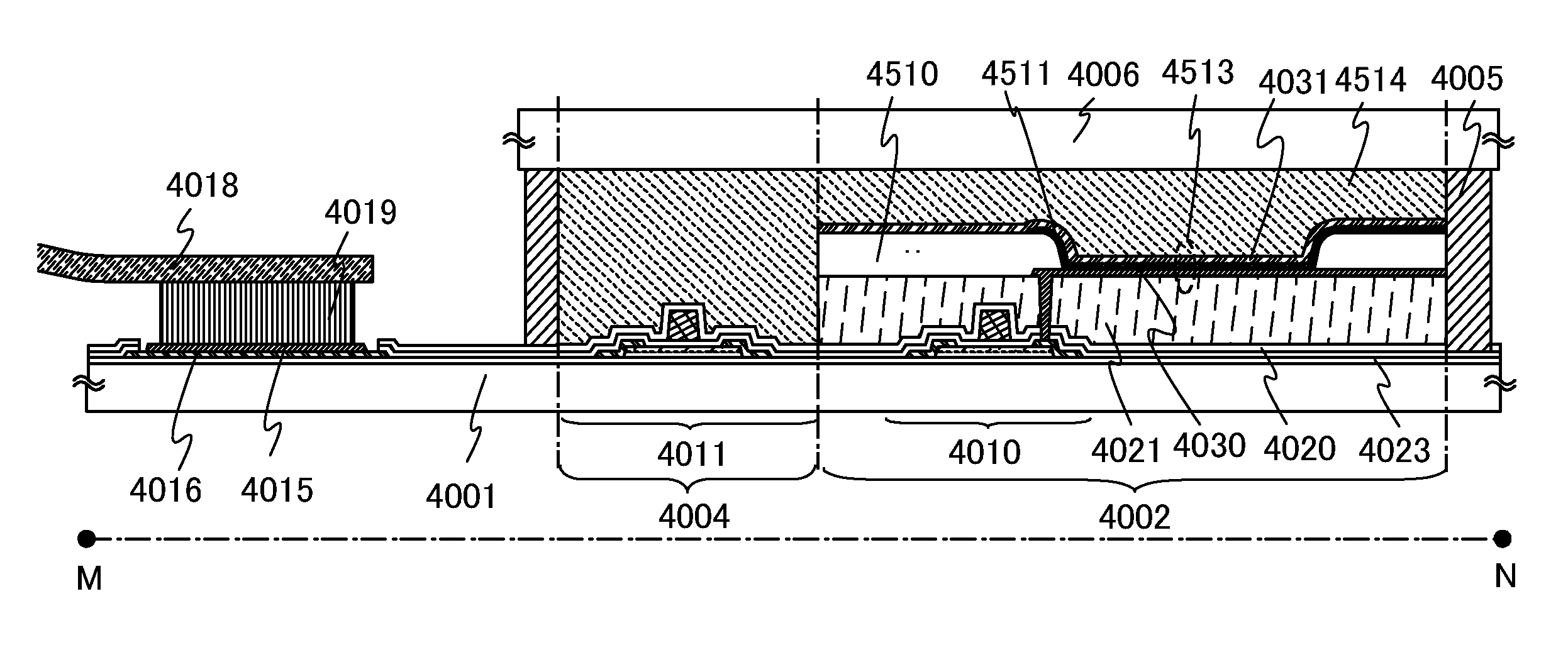

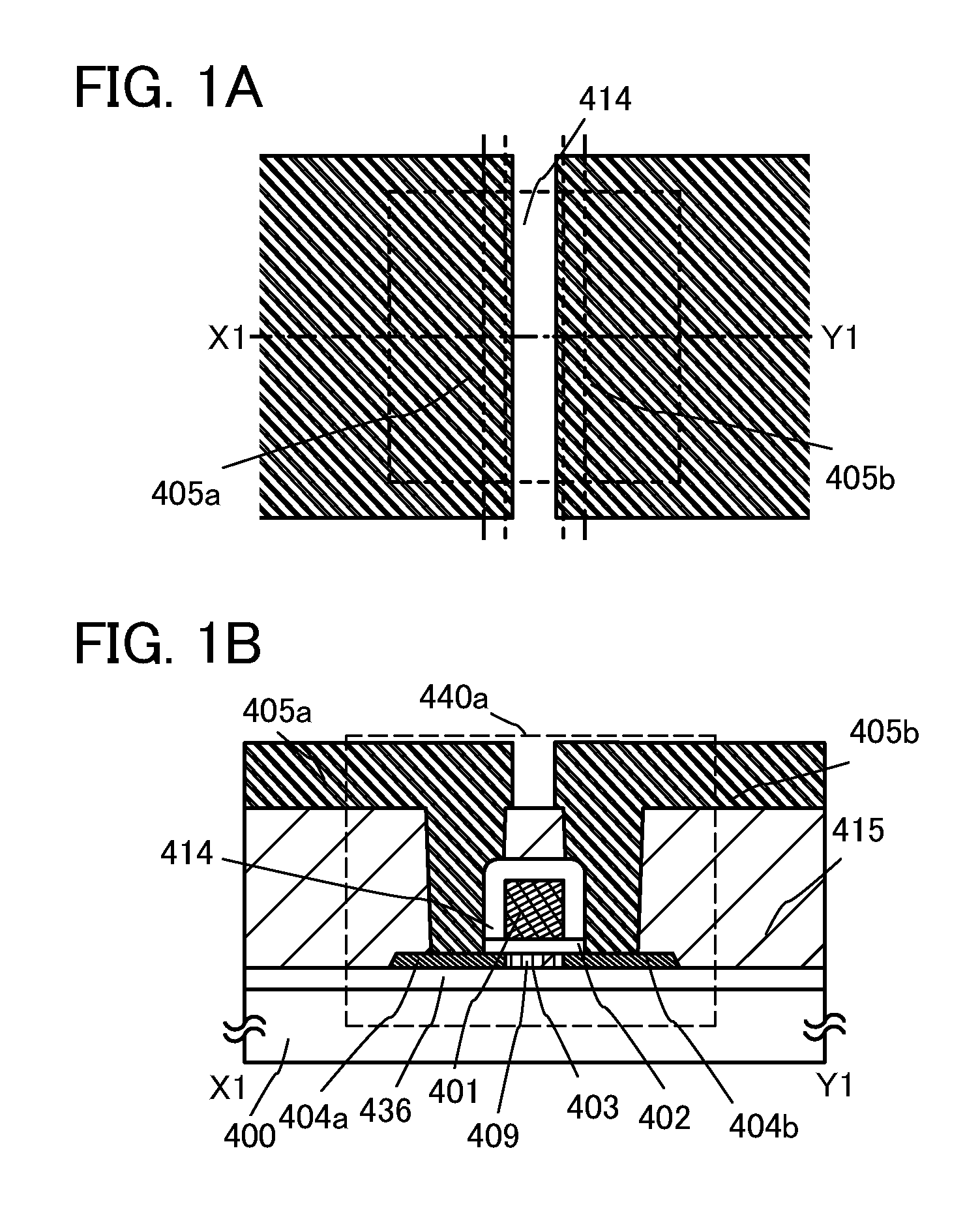

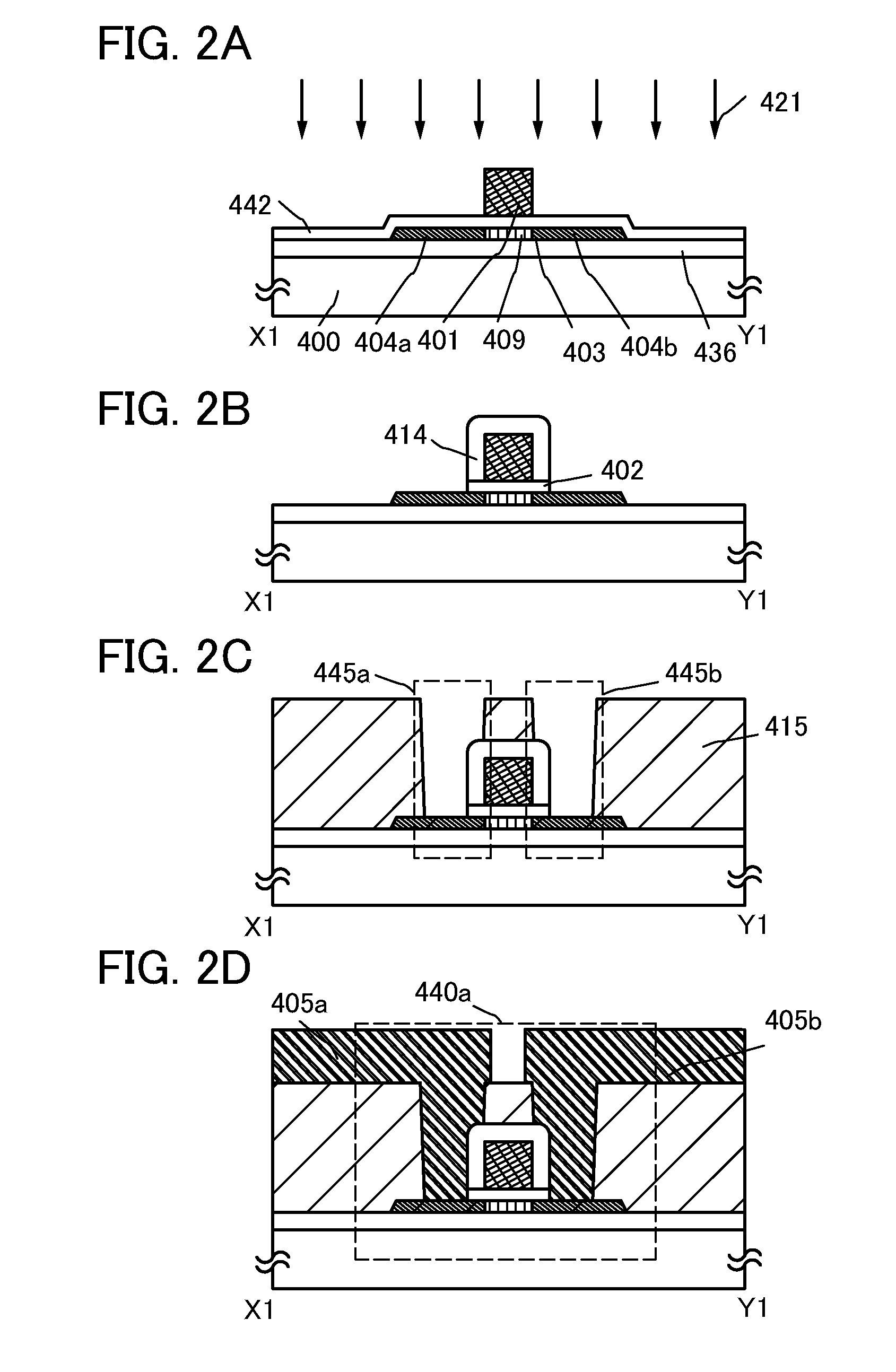

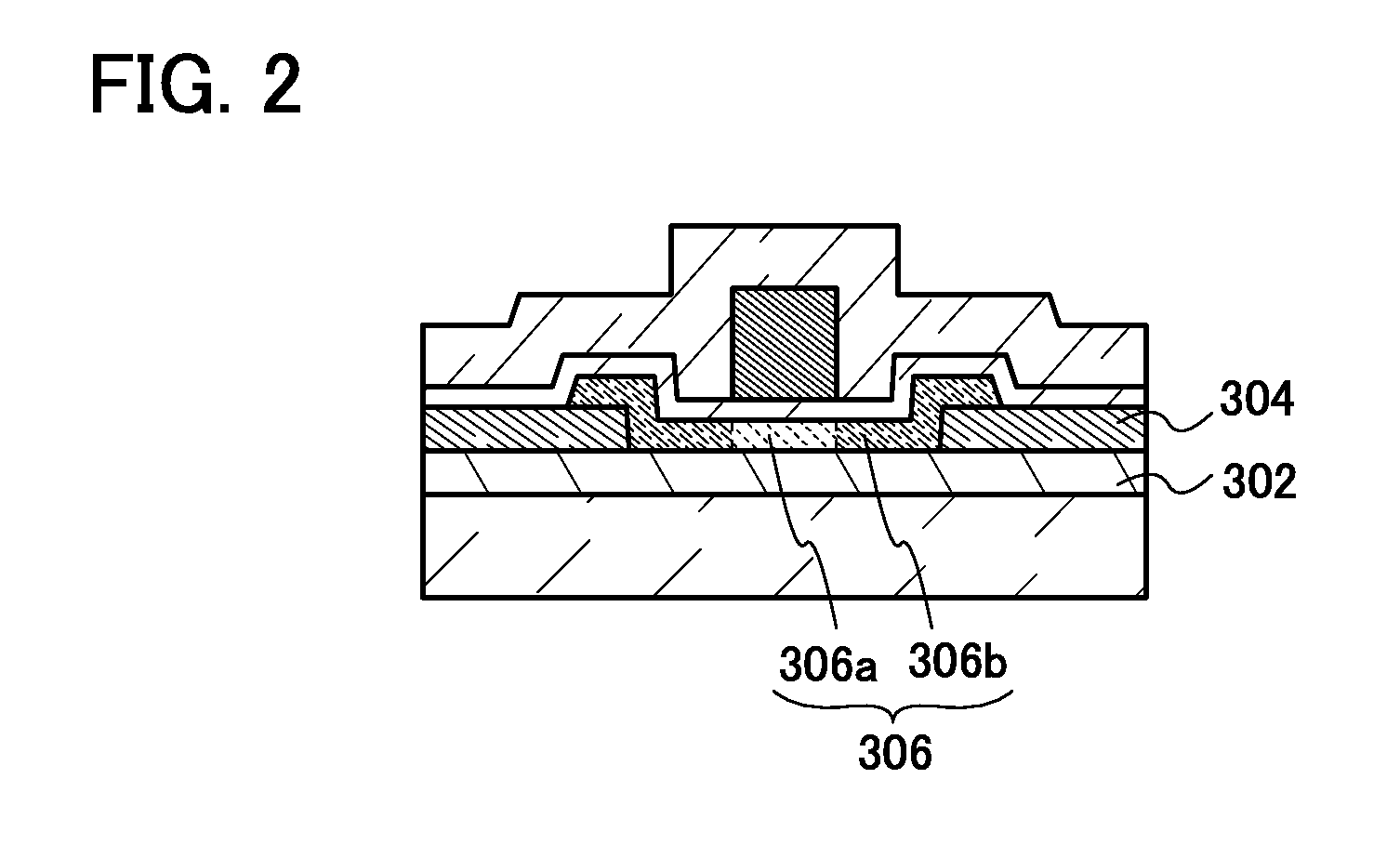

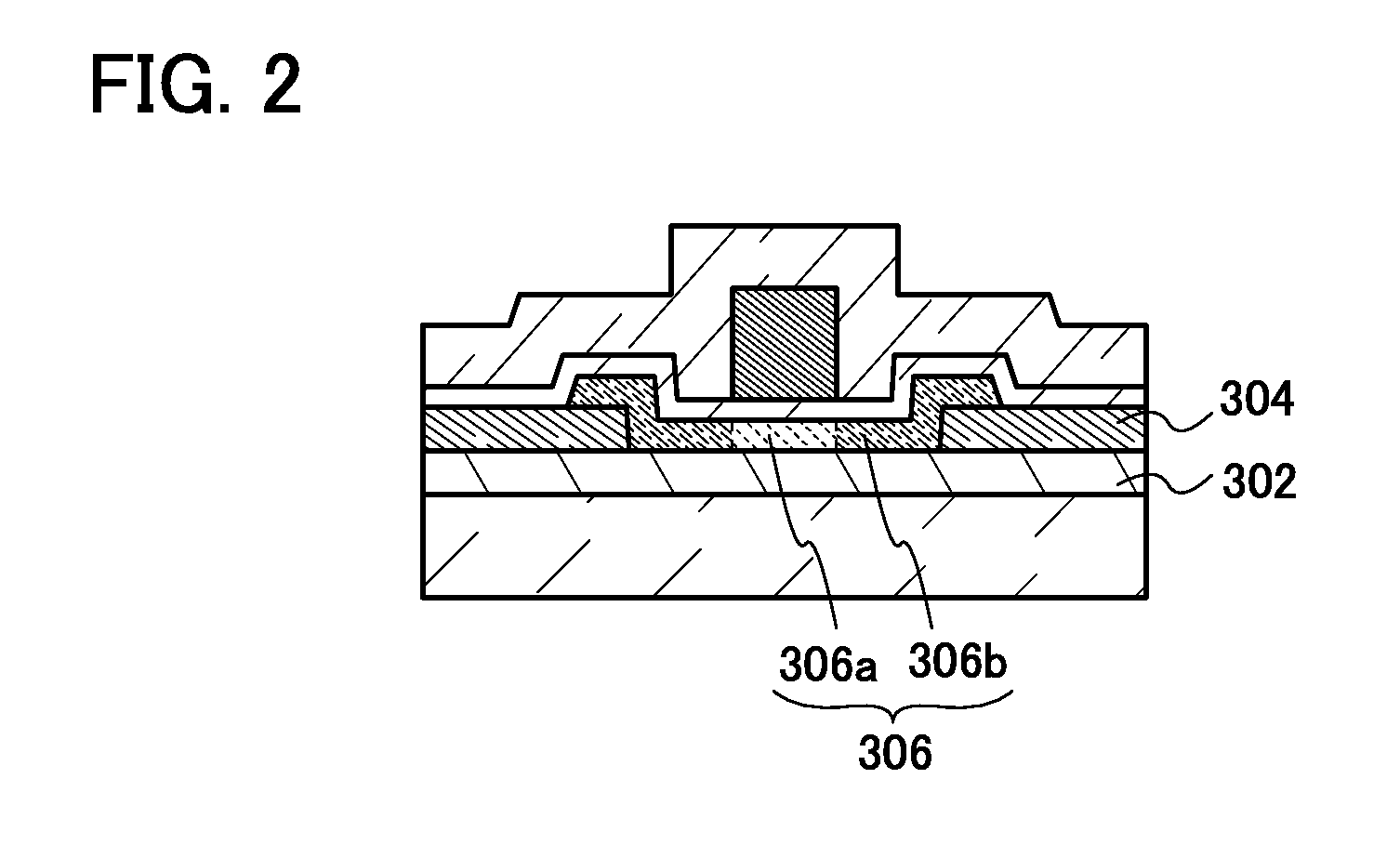

Semiconductor device and method for manufacturing semiconductor device

ActiveUS20130092924A1Excellent electrical propertiesImprove reliabilityTransistorSolid-state devicesProduction rateDevice material

A miniaturized transistor having excellent electrical characteristics is provided with high yield. Further, a semiconductor device including the transistor and having high performance and high reliability is manufactured with high productivity. In a semiconductor device including a transistor in which an oxide semiconductor film including a channel formation region and low-resistance regions between which the channel formation region is sandwiched, a gate insulating film, and a gate electrode layer whose top surface and side surface are covered with an insulating film including an aluminum oxide film are stacked, a source electrode layer and a drain electrode layer are in contact with part of the oxide semiconductor film and the top surface and a side surface of the insulating film including an aluminum oxide film.

Owner:SEMICON ENERGY LAB CO LTD

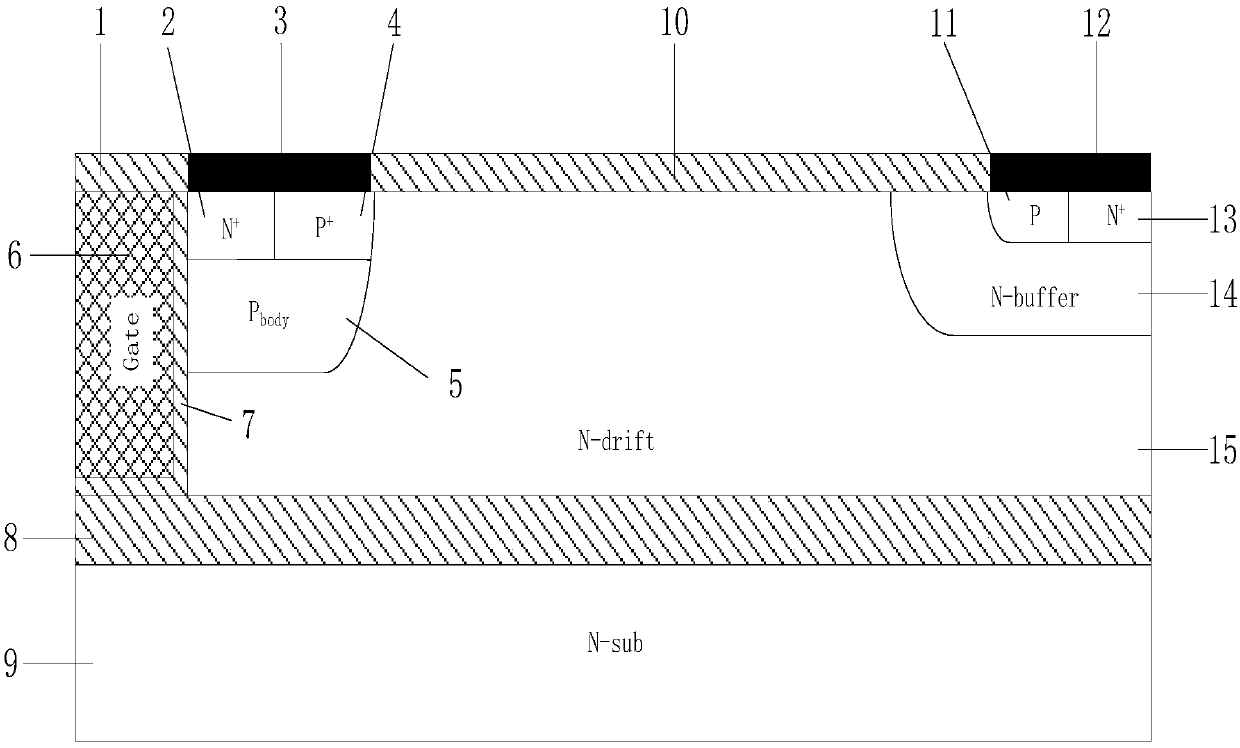

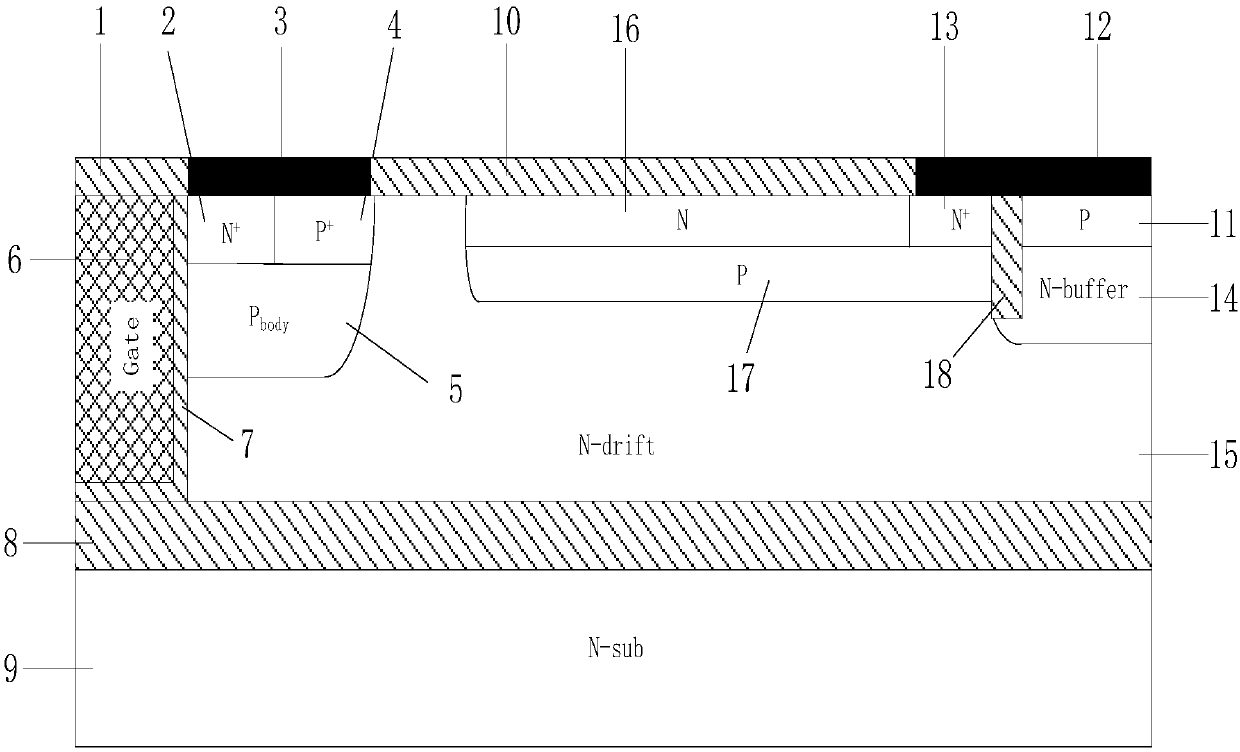

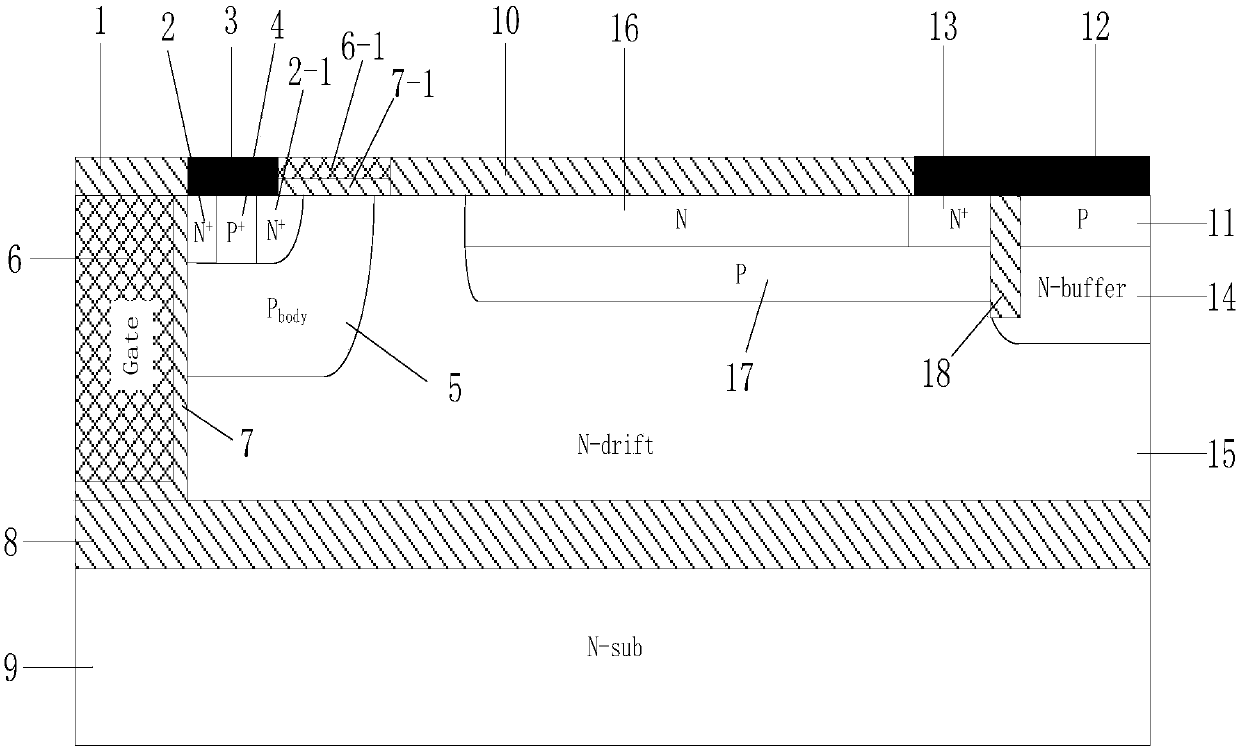

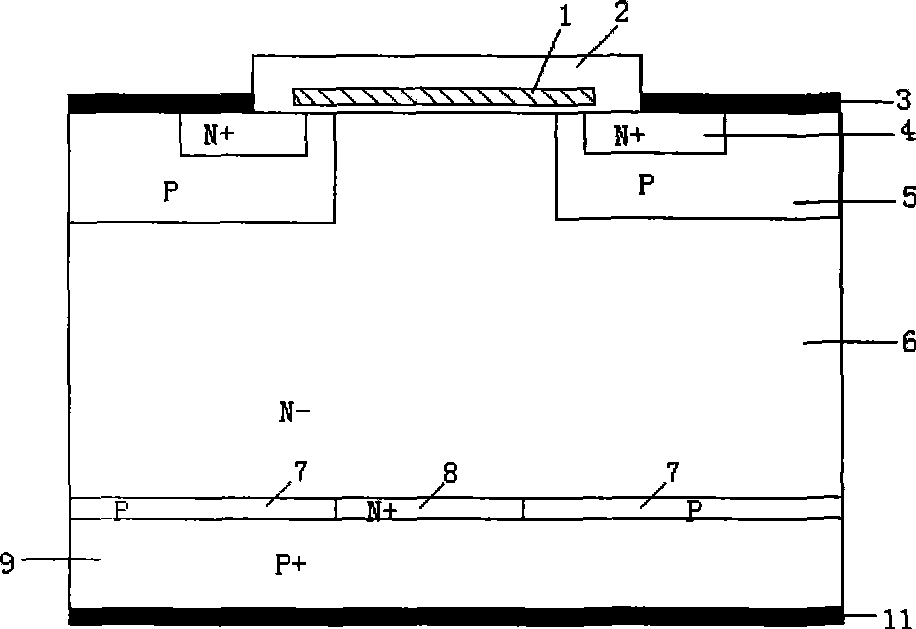

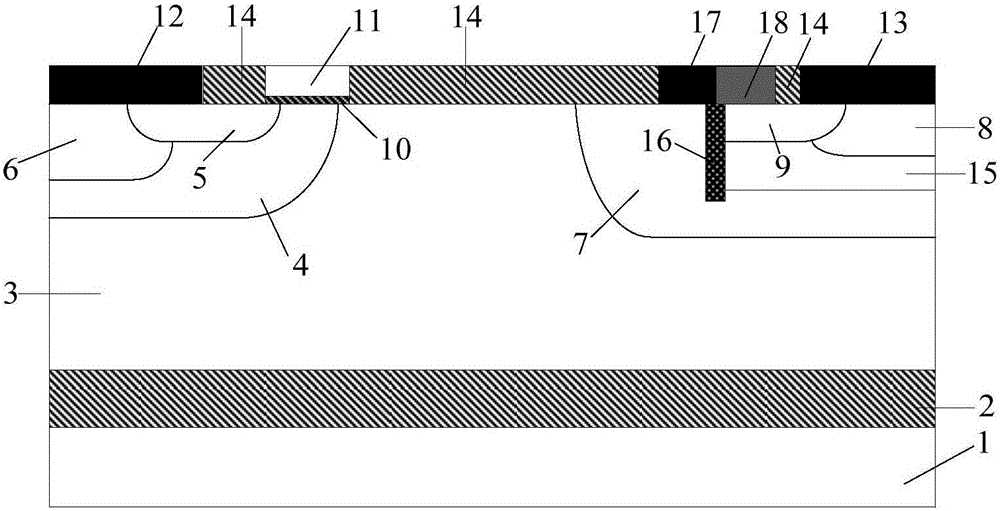

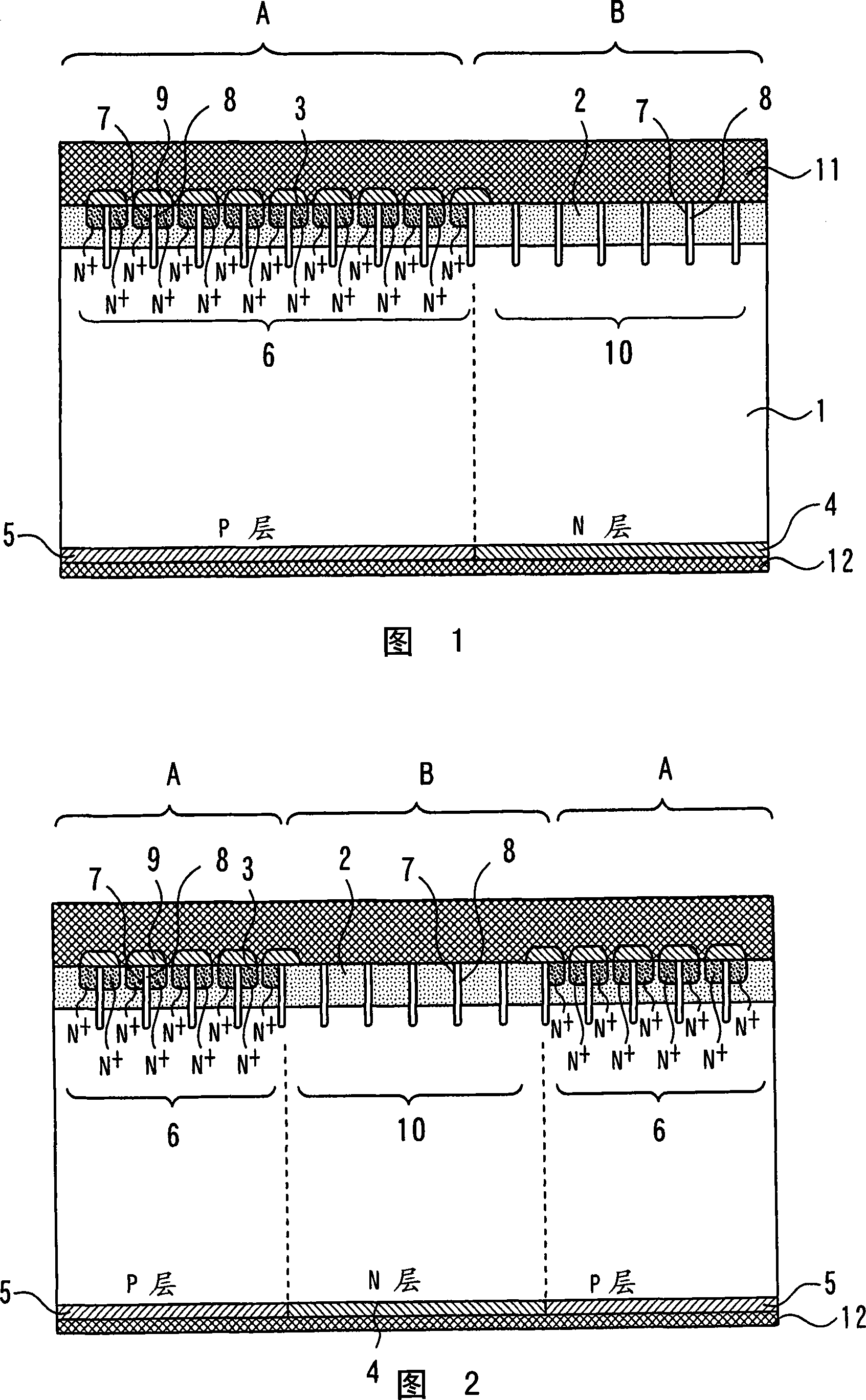

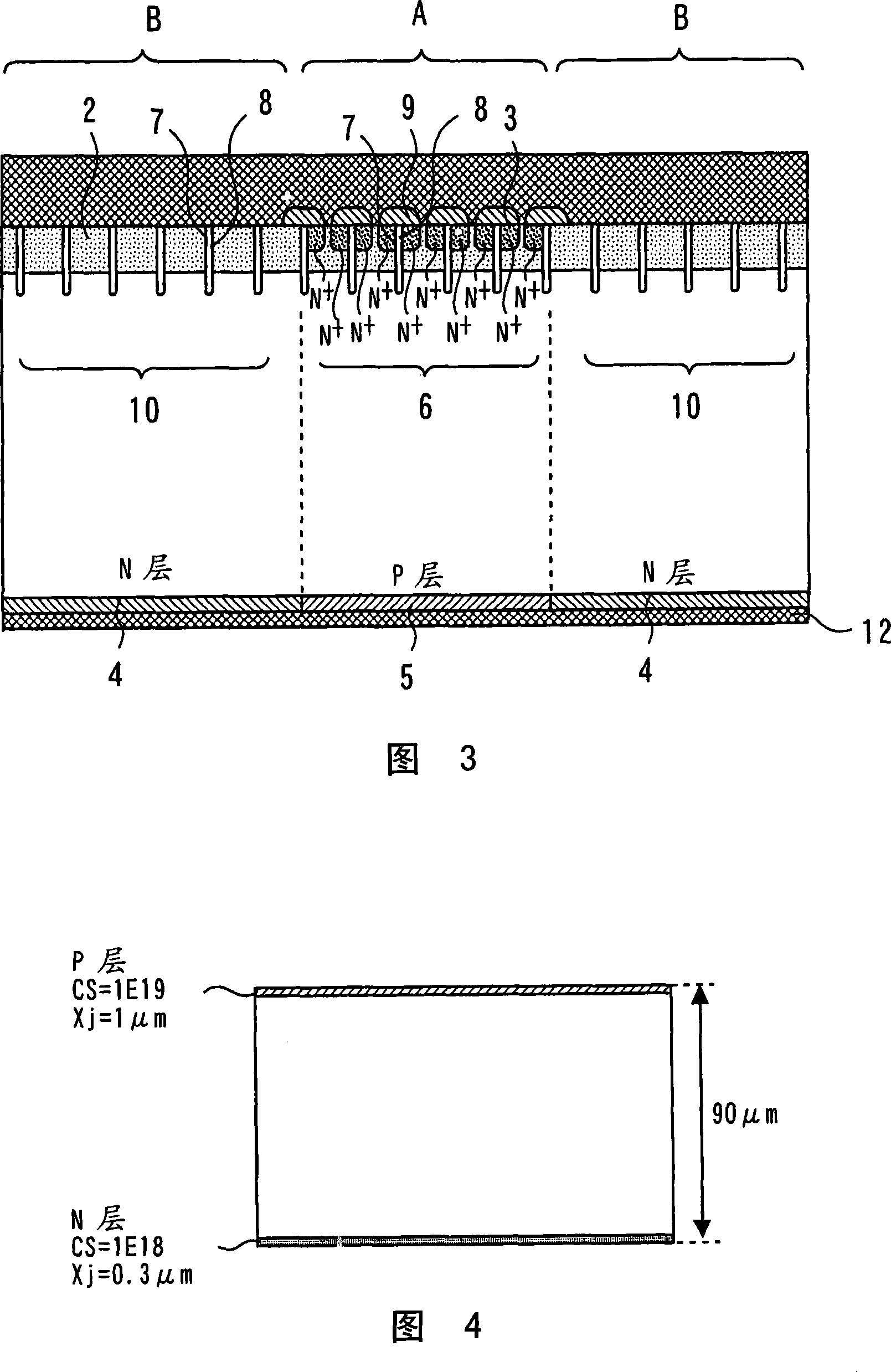

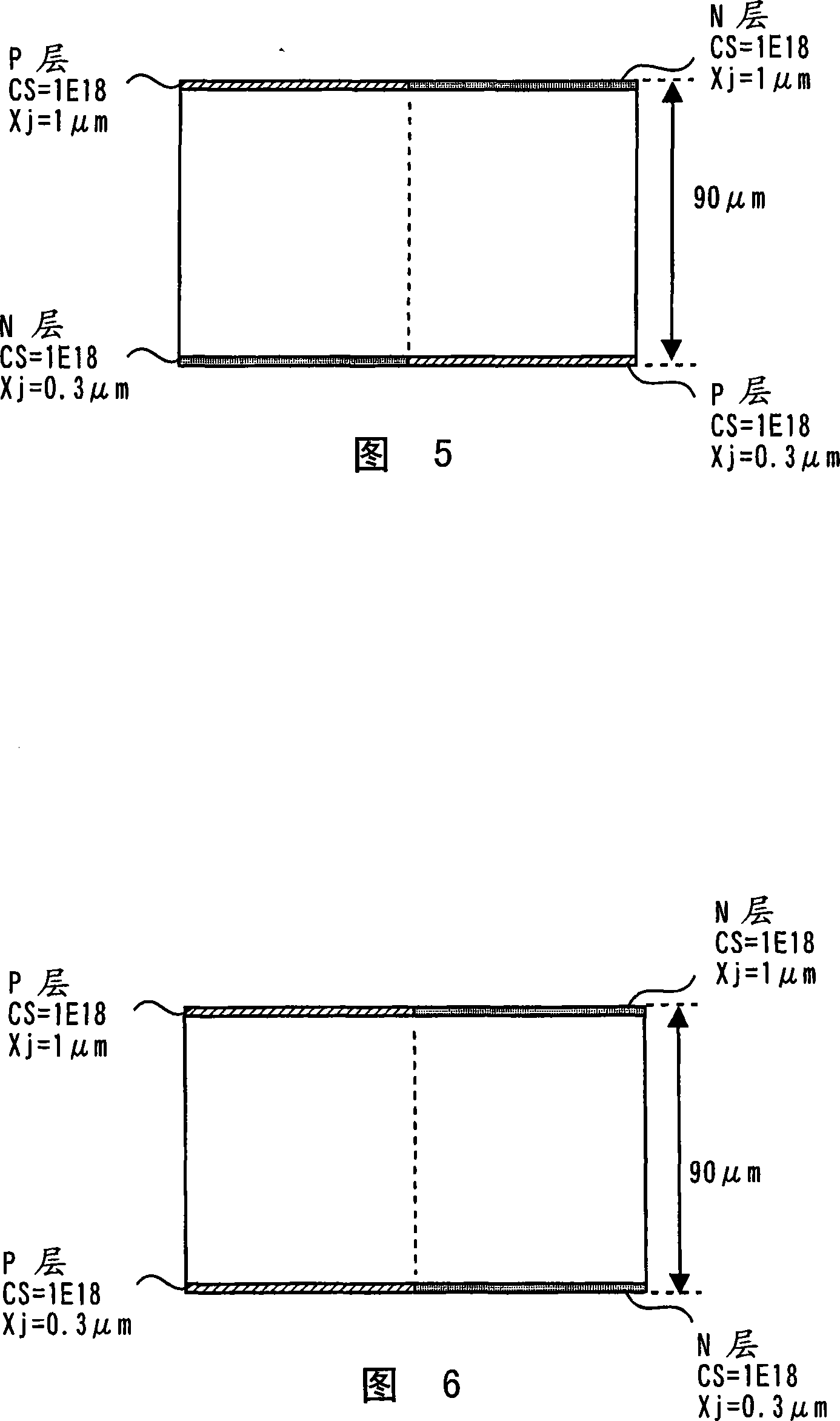

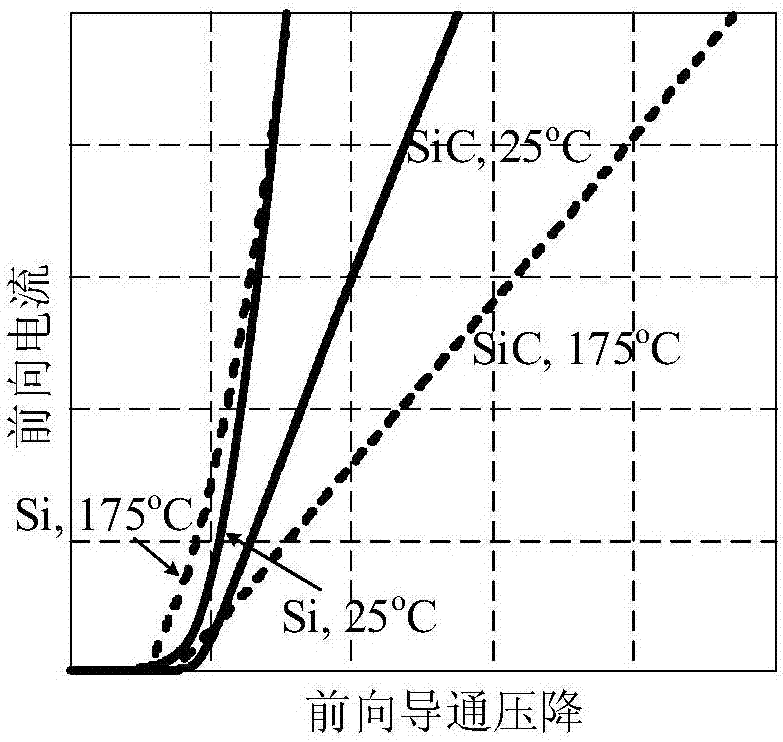

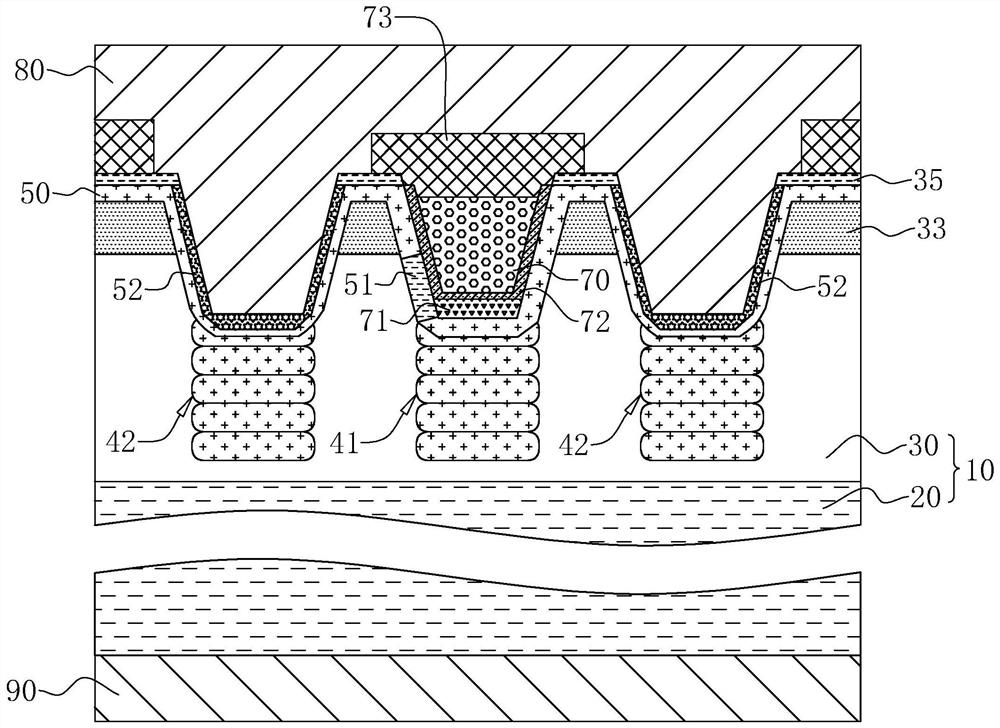

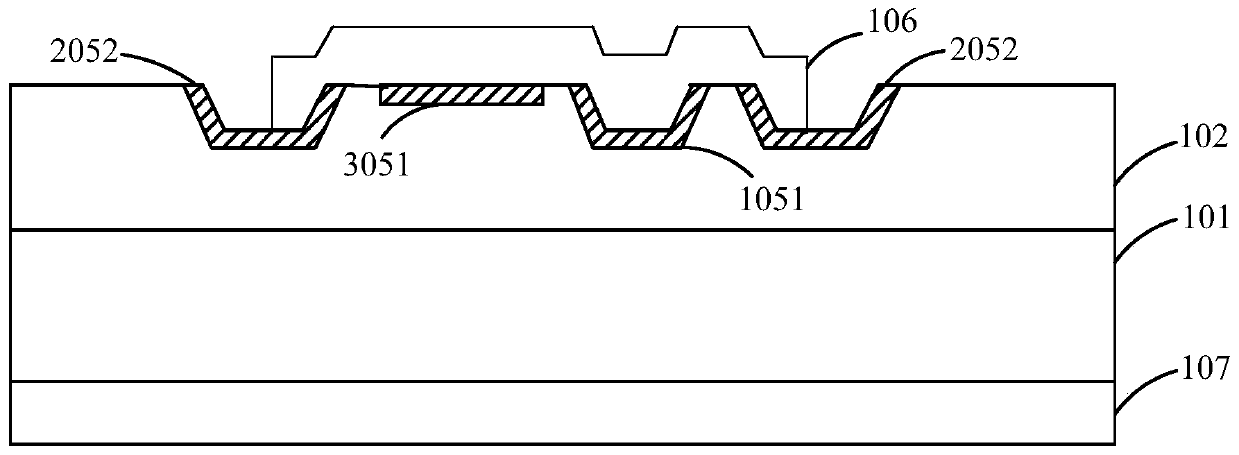

SOI-RC-LIGBT device and preparation method thereof

ActiveCN107785415AImprove breakdown voltageLower on-resistanceSemiconductor/solid-state device manufacturingSemiconductor devicesReverse recoveryVoltage drop

The invention provides an SOI-RC-LIGBT device and a preparation method thereof. The SOI-RC-LIGBT device comprises an N-type substrate, a buried oxide layer, an N-type drift region, a trench gate structure, a P-type base region, an N+ source region, a P+ contact region, an emitting electrode, an oxide layer, an N-type buffer region and a P-type collector region; an N-type strip is arranged on the surface of the portion, between the P-type base region and the N-type buffer region, of the N-type drift region, and a P-type buried layer is arranged in the portion, below the N-type strip, of the drift region; a medium trench structure is arranged between the right sides of the N-type strip and the P-type buried layer and the left sides of the N-type buffer region and the P-type collector region;an N+ collector region is arranged between the N-type strip and the medium trench structure. According to the SOI-RC-LIGBT device, while the IGBT conduction characteristic snapback phenomena are eliminated, the breakdown voltage of the device is improved, the forward conduction voltage drop of the device is reduced, the shutoff speed is increased, the shutoff loss is reduced, and meanwhile, the reverse recovery characteristics of an integrated free-wheeling diode are improved.

Owner:UNIV OF ELECTRONICS SCI & TECH OF CHINA

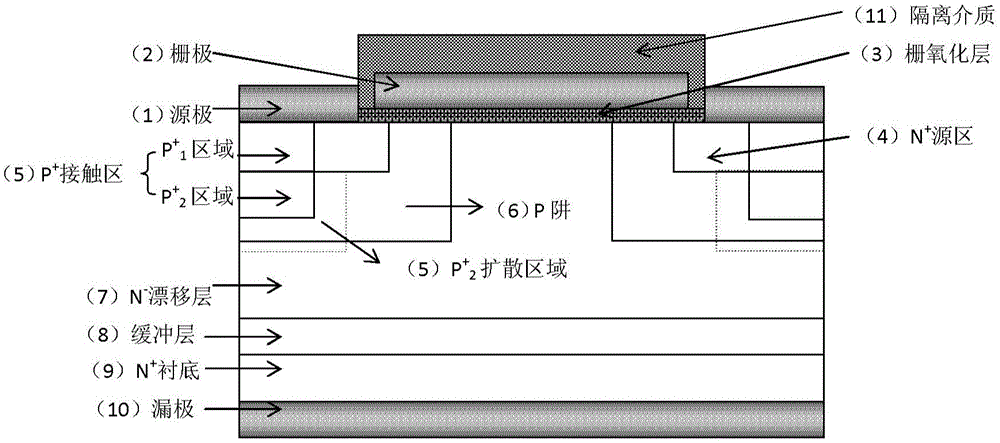

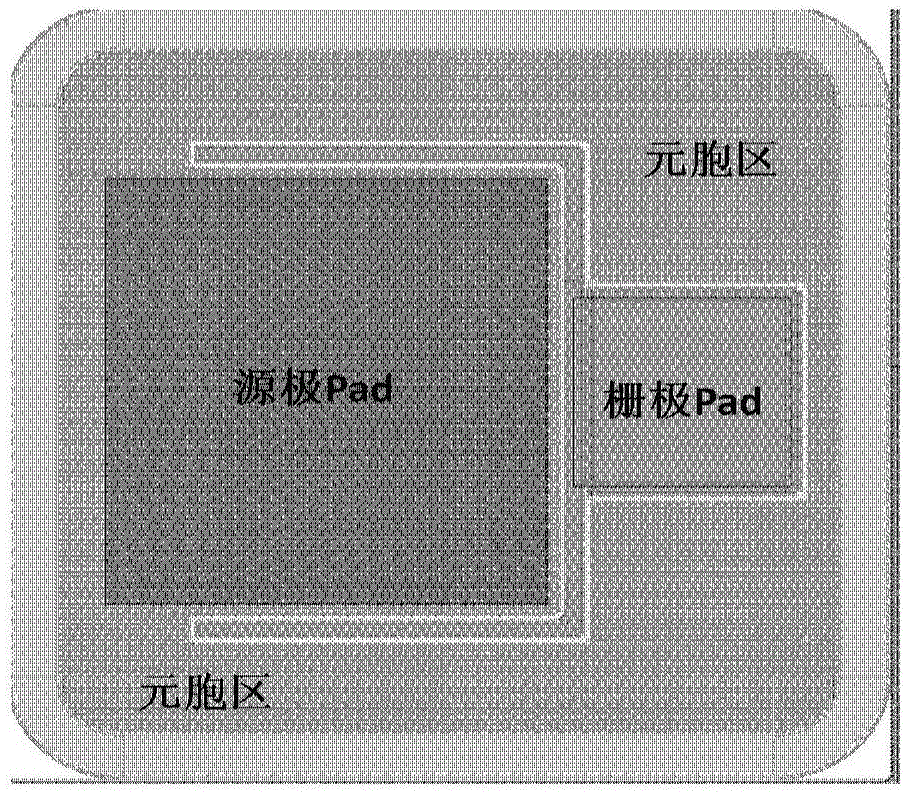

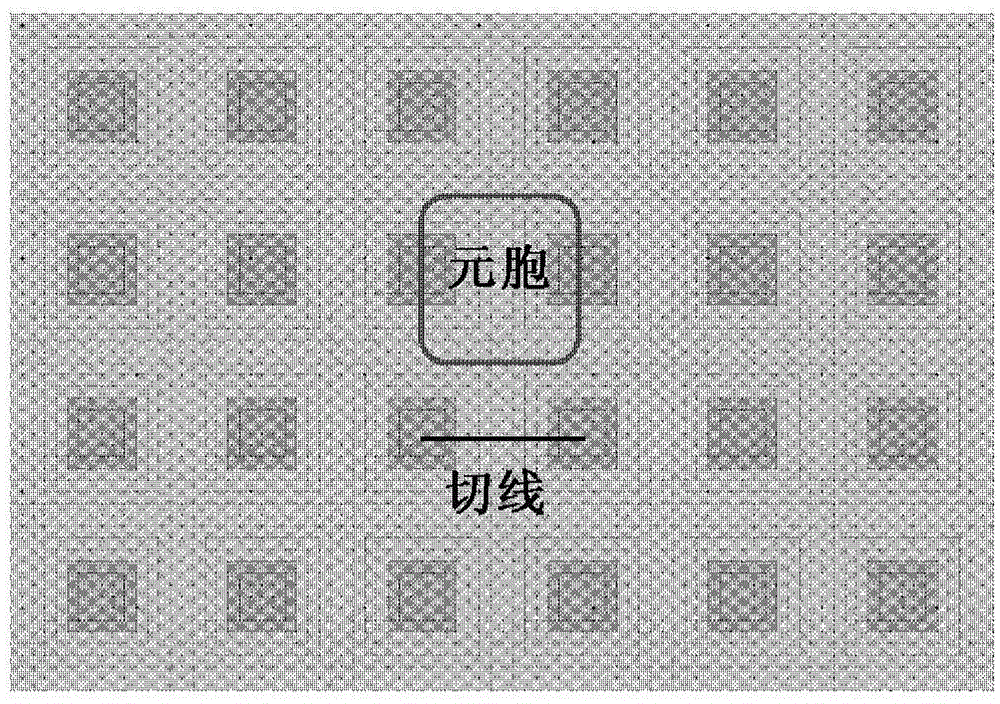

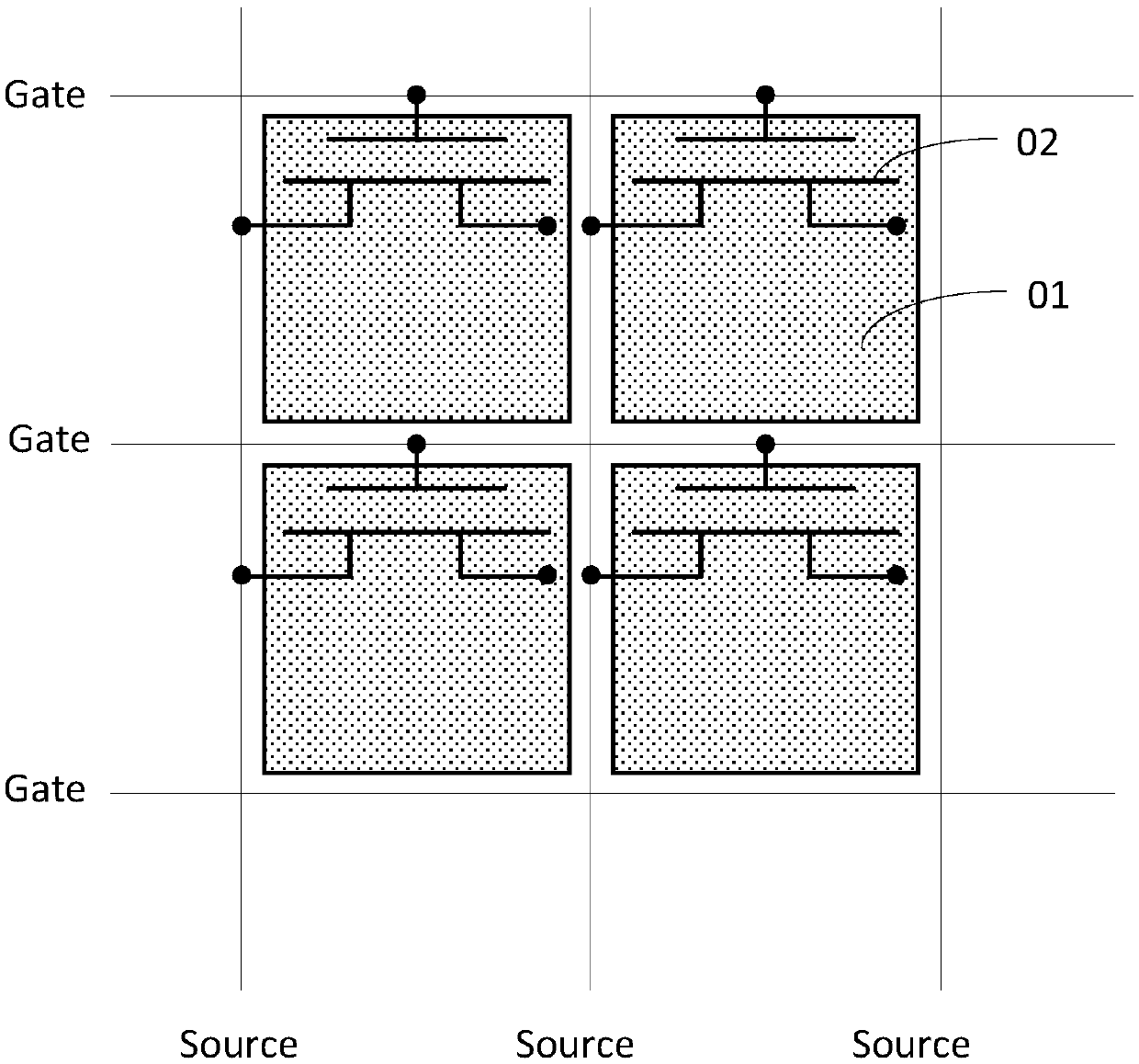

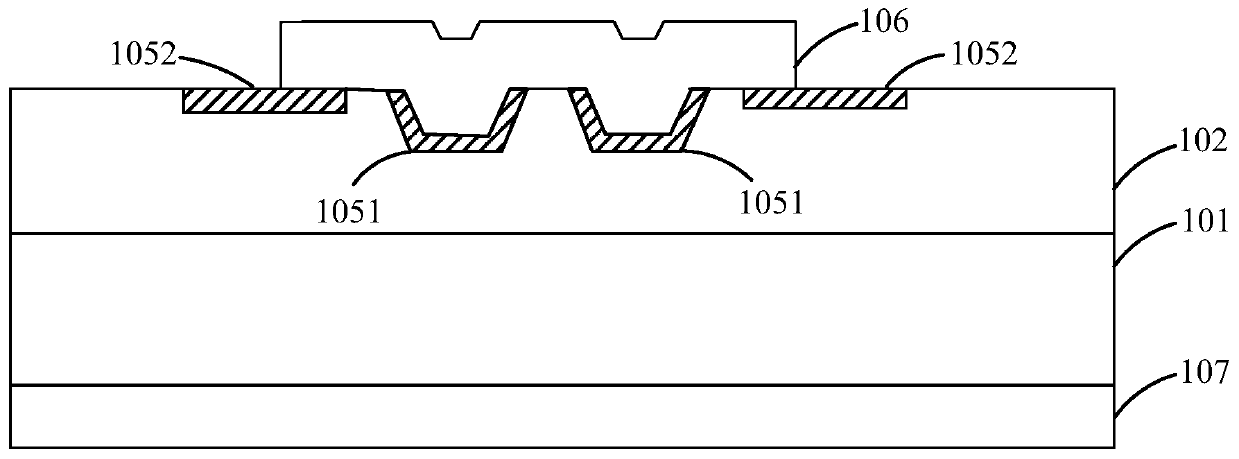

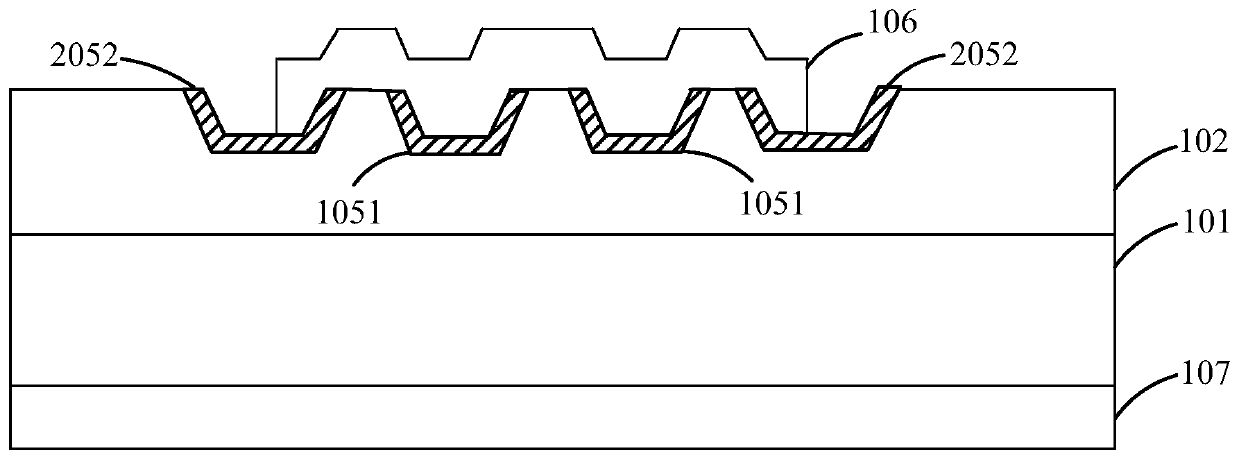

Silicon carbide metal-oxide-semiconductor field-effect-transistor (MOSFET) device and fabrication method thereof

ActiveCN105161539AAvoid avalanche breakdownGood source ohmic contactSemiconductor/solid-state device manufacturingSemiconductor devicesField-effect transistorPower MOSFET

The invention discloses a self-aligned silicon carbide metal-oxide-semiconductor field-effect-transistor (MOSFET) device with an optimized P<+> region and a fabrication method of the self-aligned silicon carbide MOSFET device. The self-aligned silicon carbide MOSFET device is formed by connecting a plurality of same cells in parallel, and the cells of the silicon carbide MOSFET device are uniformly arranged. Each cell of the silicon carbide MOSFET device comprises two sources, a grid, a grid oxide layer, two N<+> source regions, two P<+> contact regions, two P pits, an N<-> drift layer, a buffer layer, an N<+> substrate, a drain and an isolation dielectric layer. By optimizing the P<+> region, favorable source ohmic contact is formed, the on resistance is reduced, meanwhile, the source and the P pits are in short connection, parasitic negative-positive-negative (PNP) and a parasitic transistor effect of PiN are prevented, the conduction property and the breakdown property of the device can be compatible, and the device can be used in a high-voltage and high-frequency silicon carbide MOSFET device. A self-aligned fabrication method is adopted by the invention, the process is simplified, the channel size is accurately controlled, and a transverse or longitudinal power MOSFET can be fabricated.

Owner:INST OF MICROELECTRONICS CHINESE ACAD OF SCI +1

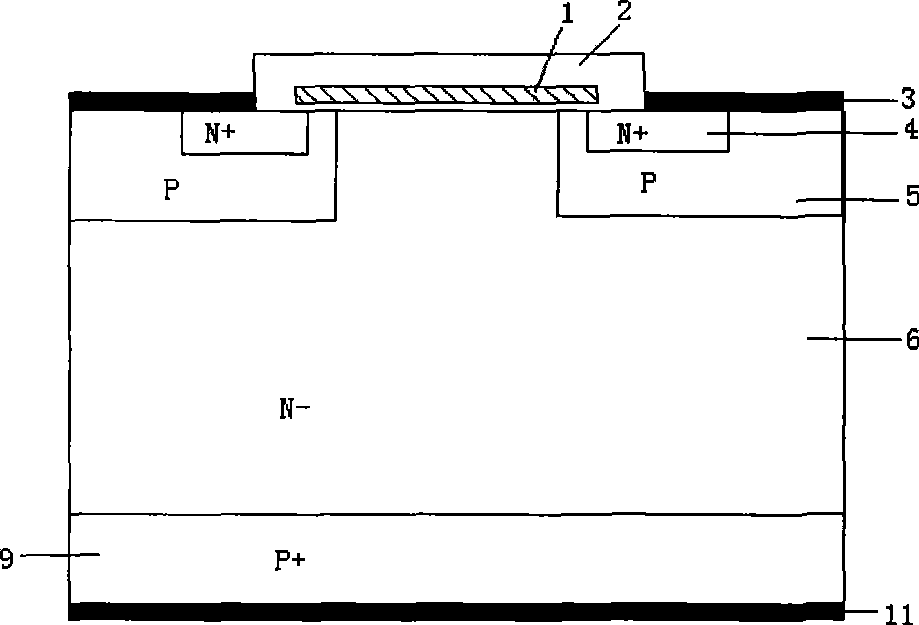

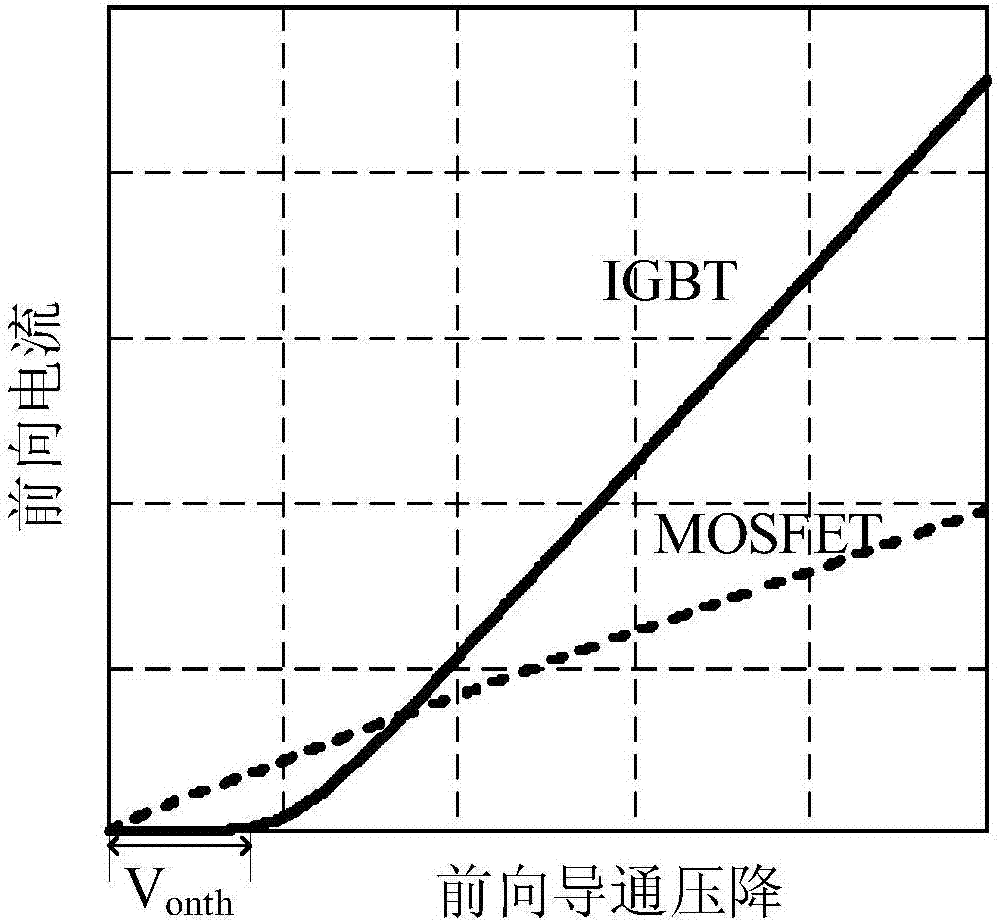

Tunnel IGBT with anode in short circuit

InactiveCN101393928AImprove conduction characteristicsShorten off timeSemiconductor devicesVoltage dropEngineering

An anode-short tunnel pump IGBT belongs to the technical field of semiconductor power devices. With an anode-short structure and a tunnel pump structure simultaneously introduced into a traditional IGBT, or a tunnel pump structure into an anode-short IGBT, or an anode-short structure into a tunnel pump IGBT, the invention gives the advantages of both the anode-short IGBT and the tunnel pump IGBT to the anode-short tunnel pump IGBT so as to improve the turn-off characteristic of the device and lower the conductive voltage drop of the device. The invention can better reconcile the positive saturation voltage drop with the turn-off time, and optimize the conductive characteristic of the device, so that the invention is suitable in particular for application environments characterized by high voltage, heavy current and high frequency.

Owner:UNIV OF ELECTRONICS SCI & TECH OF CHINA

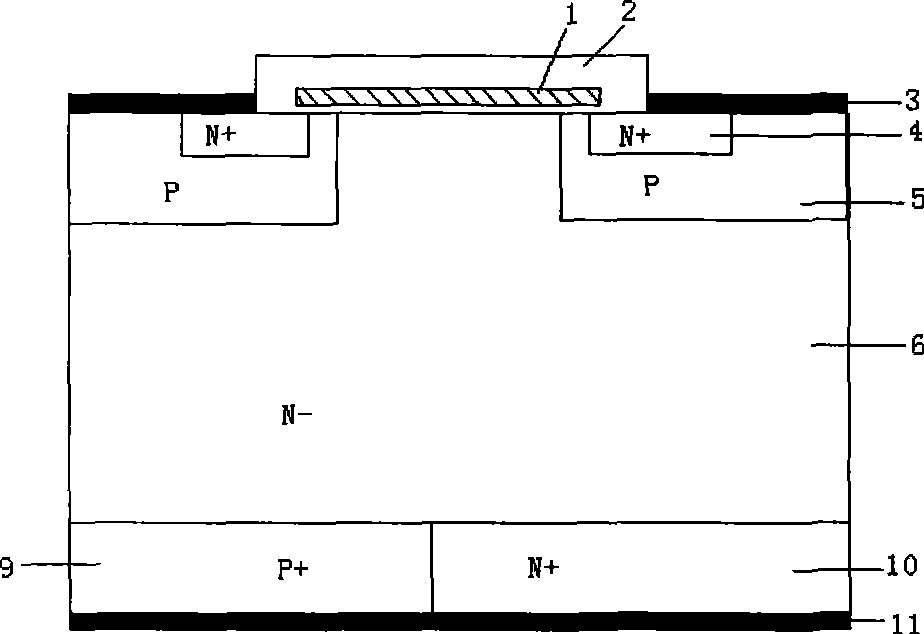

Binary channel RC-LIGBT device and manufacturing method therefor

InactiveCN106067480AImprove stabilityImprove reliabilitySemiconductor/solid-state device manufacturingSemiconductor devicesVoltage dropEngineering

A binary channel RC-LIGBT device and a manufacturing method therefor are disclosed. The invention belongs to the field of power semiconductor integrated circuits and specifically relates to a reverse conducting-LIGBT / RC-LIGBT and a manufacturing method therefor that are used for suppressing snapback phenomena of a conventional RC-LIGBT device, improving characteristics of backward diodes and improving device stability and reliability. The RC-LIGBT device disclosed in the invention has a unilateral electric conduction path having binary channels, the unilateral electric conduction path is formed by introducing a composite structure at a collector electrode end of the device, impact exerted on conduction characteristics by an N type collecting zone can be completely shielded in a forward direction LIGBT work mode, the snapback phenomena can be completely eliminated, the RC-LIGBT device disclosed in the invention has the same low conduction voltage drop as the conventional LIGBT, device stability and reliability can be improved, two freewheel channels are provided at the collector electrode end in a backward diode freewheel work mode, freewheeling capacity of the RC-LIGBT device is optimized, and the RC-LIGBT device is enabled to have a small conduction voltage drop.

Owner:UNIV OF ELECTRONICS SCI & TECH OF CHINA

Insulated gate semiconductor device and method for manufacturing the same

InactiveCN101136405ASuppression of forward voltage VfRecovery current risesTransistorSolid-state devicesSemiconductorForward voltage

Owner:MITSUBISHI ELECTRIC CORP

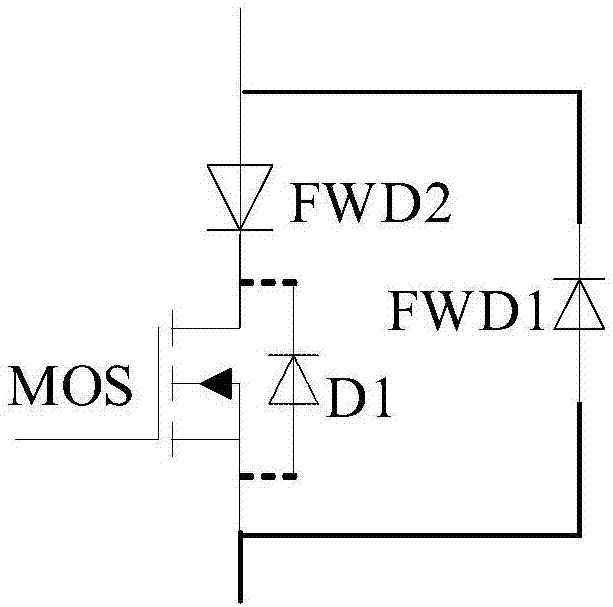

Semiconductor device, control method and converter

ActiveCN106936298AReduce conduction lossReasonable optimization of capacity allocationElectronic switchingPower conversion systemsPower semiconductor deviceLow voltage

The embodiment of the invention discloses a semiconductor device and a converter. The semiconductor device provided by the invention comprises a low-voltage switch device, a first diode and a second diode, wherein the low-voltage switch device and the first diode form a series structure, the second diode is connected in parallel with two ends of the series structure formed by the low-voltage switch device and the first diode, the current passing directions of the first diode and the second diode are consistent, the first diode is a low-conduction voltage drop diode, and the second diode is a low-reverse recovery diode. When the semiconductor device is in a conduction state, control equipment controls the low-voltage switch device to be conducted, and simultaneous follow current is performed by the first diode and the second diode to reduce conduction voltage drop of the semiconductor device; and when the semiconductor device is switched off, the control equipment controls the low-voltage switch device to be switched off in advance of preset time, so that a load current is completely transferred to the second diode, and current exchange is achieved by the second diode and a complementary device to reduce a reverse recovery current of the semiconductor device.

Owner:HUAWEI DIGITAL POWER TECH CO LTD

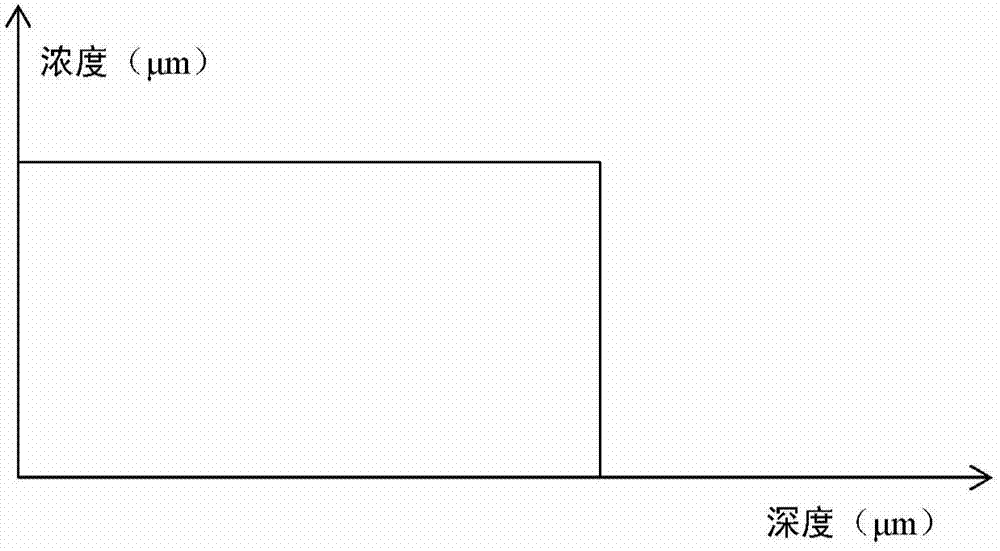

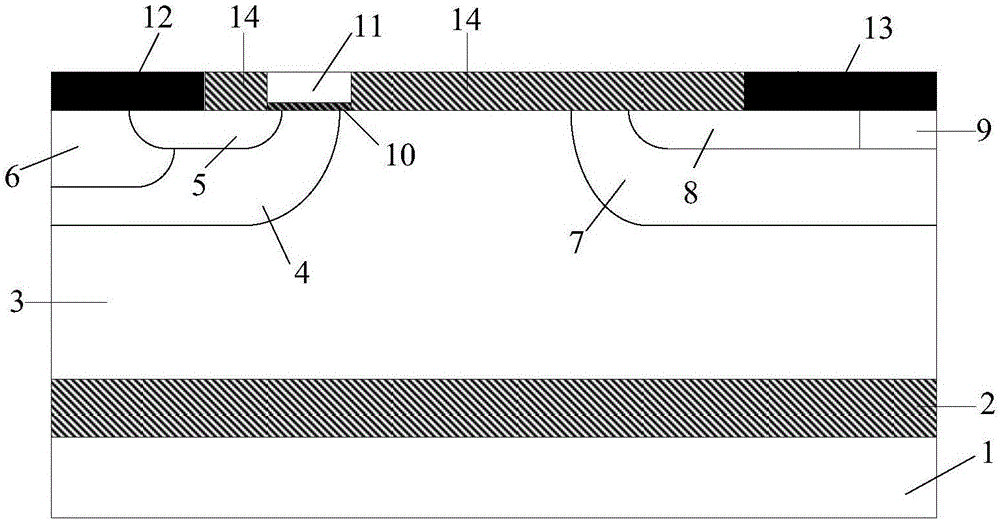

SiC metal oxide semiconductor field effect transistor and production method thereof

ActiveCN104241338AReduce Design ComplexityReduce the possibility of introducing adverse influence factorsSemiconductor/solid-state device manufacturingSemiconductor devicesDielectricEnergy integration

The invention discloses an SiC metal oxide semiconductor field effect transistor and a production method thereof. The SiC metal oxide semiconductor transistor comprises a source electrode, a gate electrode, an SiO2 oxide media dielectric, an N+ source region, a P+ contact region, an optimized doped P well, an optimized doped main junction, an N- epitaxial layer, a buffer layer, an N+ substrate, a drain electrode, optimized doped field limiting rings, a cut-off region and an isolation dielectric. According to the production method of the SiC metal oxide semiconductor field effect transistor, the SiC metal oxide semiconductor field effect transistor of a P- well and terminal structure in optimized concentration distribution is formed by means of Al injection with less energy integration, the production process is relatively simple, and conduction and breakdown characteristics of the transistor are taken into consideration. The SiC metal oxide semiconductor field effect transistor produced by the method can be used for power-switch power supply circuits, DC / DC, AC / DC and DC / AC converters and the like.

Owner:INST OF MICROELECTRONICS CHINESE ACAD OF SCI

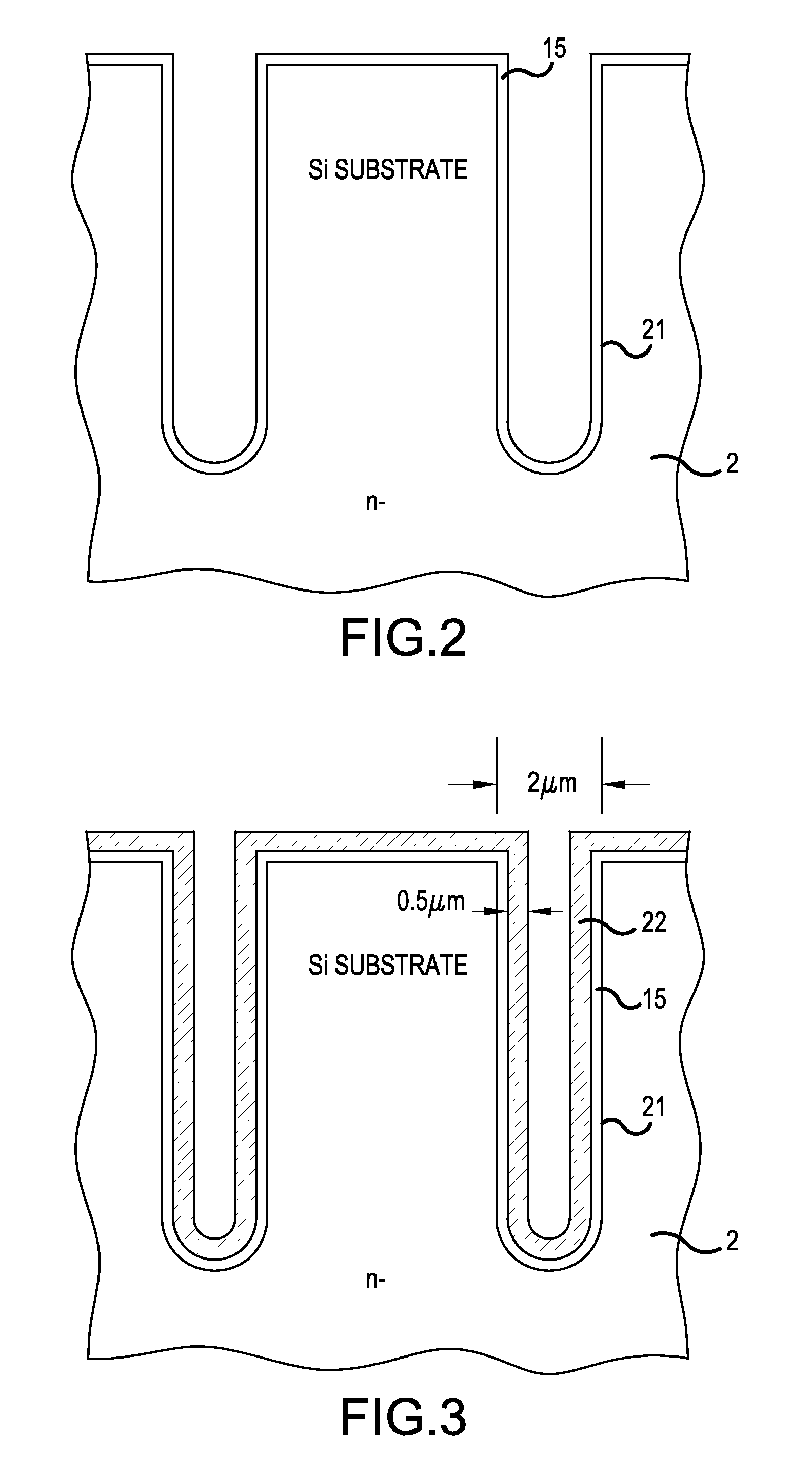

Trench silicon carbide power device with low on-resistance and manufacturing process thereof

ActiveCN111668312AImprove process precisionReduce processing difficultySemiconductor/solid-state device manufacturingSemiconductor devicesElectrical resistance and conductanceManufacturing technology

The invention provides a trench silicon carbide power device with low on-resistance and a manufacturing process thereof. The cell of the trench silicon carbide power device comprises an N-type substrate, an N-type epitaxial layer and a trench, wherein the trench is internally provided with a gate oxide layer and a polysilicon gate, a P-type body region, an N-type source region and a P+ body contact region are arranged on the two sides of the trench, a P shielding layer is arranged below the trench, and an N-type buried layer is arranged on the side of the P shielding layer. The manufacturing process of the N-type buried layer comprises the steps of epitaxially growing a first part of an N-type drift region on the N-type substrate, forming a P shielding layer and an N-type buried layer on the first part of the N-type drift region by adopting an ion implantation process, continuing to epitaxially form a second part of the N-type drift region, and carrying out a subsequent process flow. According to the invention, two sides of the P shielding layer are provided with the N-type buried layers, the electric field peak is moved downwards, the trench corner electric field is reduced, the interface state density and defects are reduced, and the reliability of the gate oxide layer is improved; and an N-type buried layer below is eliminated, the gate charge of the device is reduced, the switching characteristic is improved, and the withstand voltage of the device is further improved.

Owner:SOUTHEAST UNIV

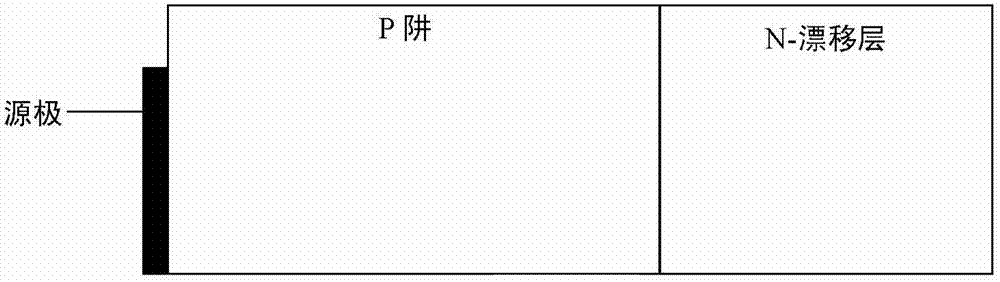

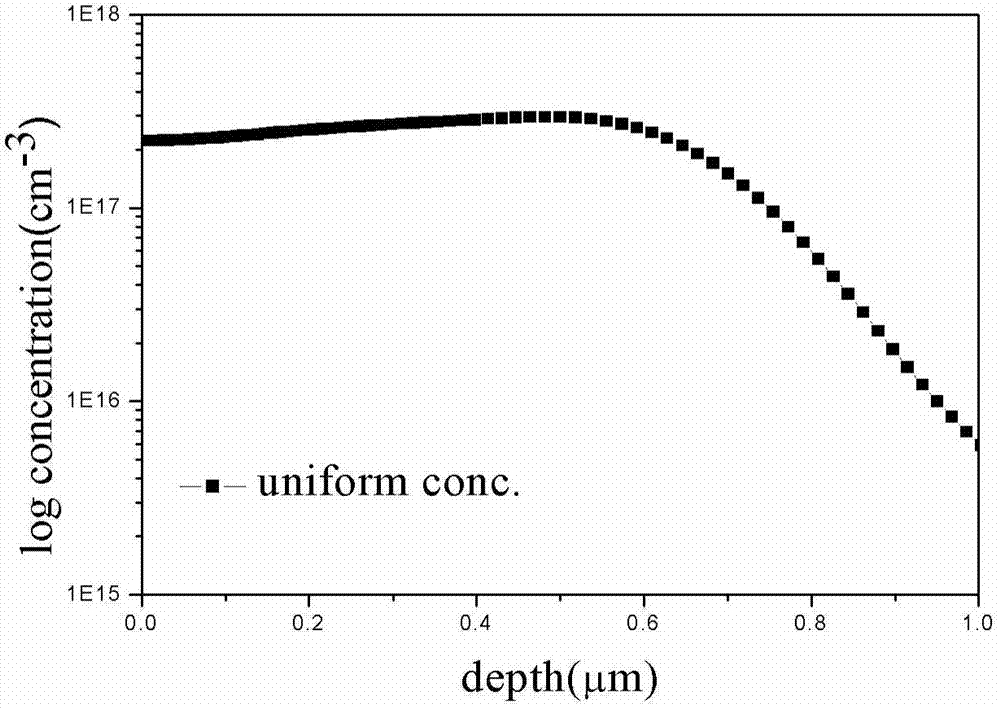

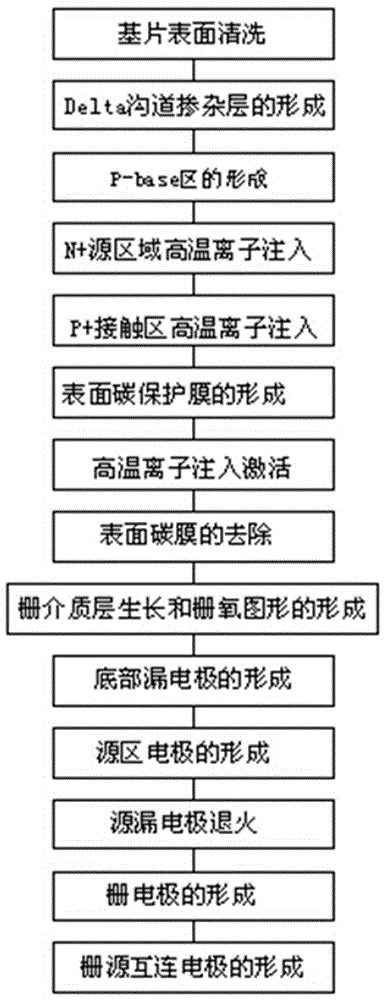

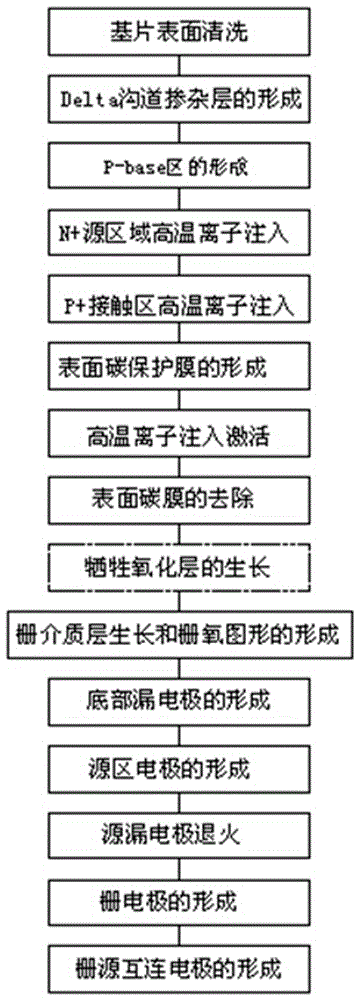

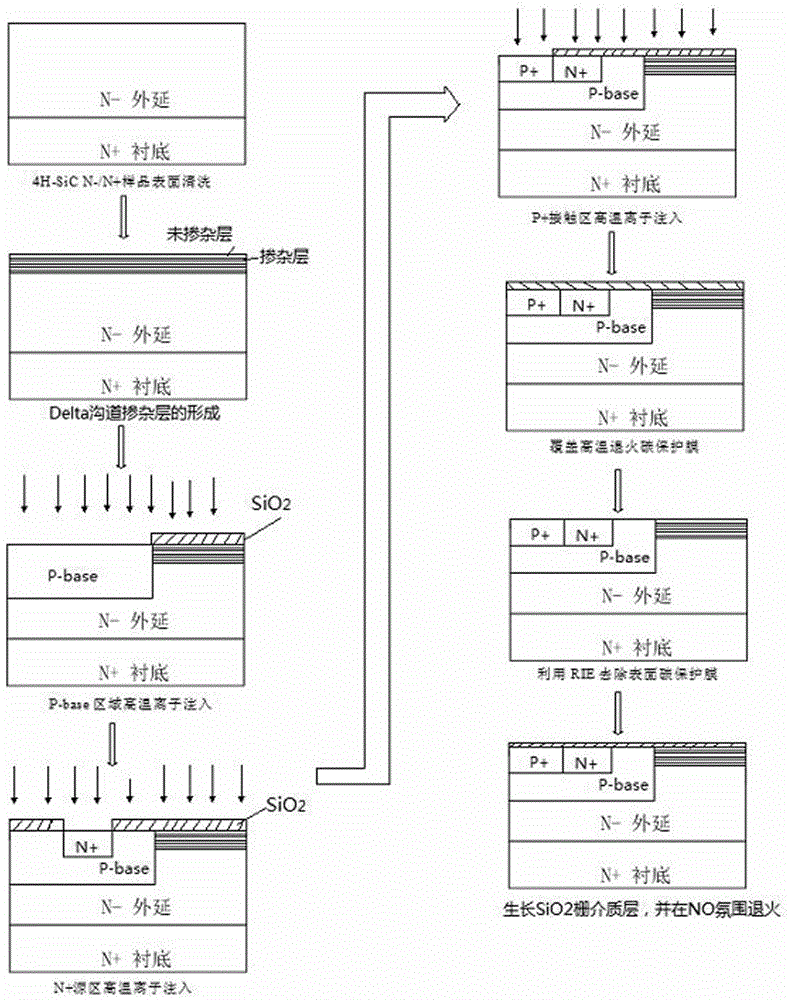

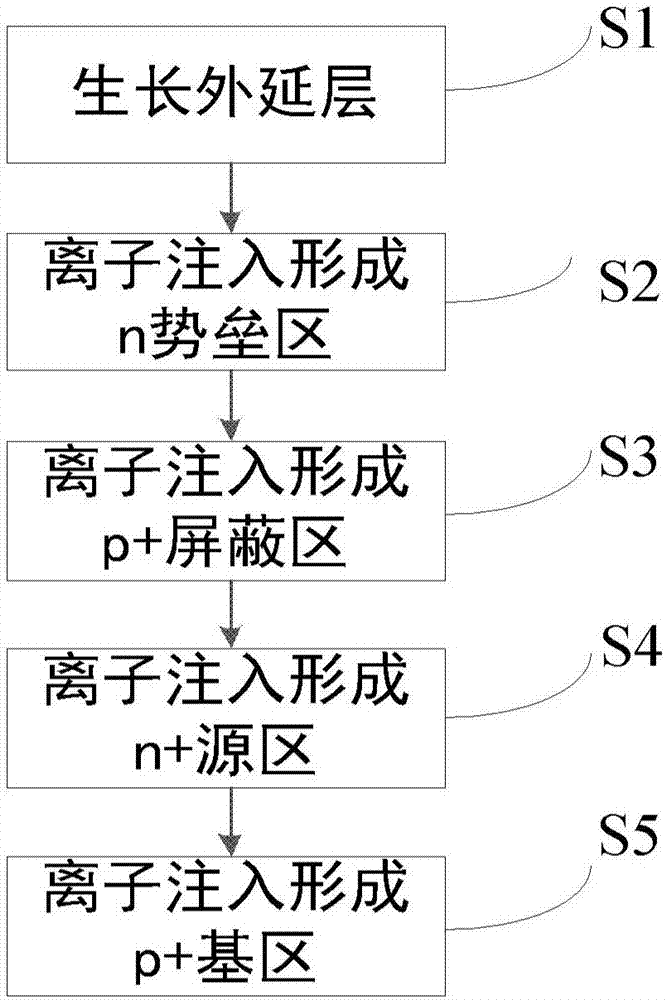

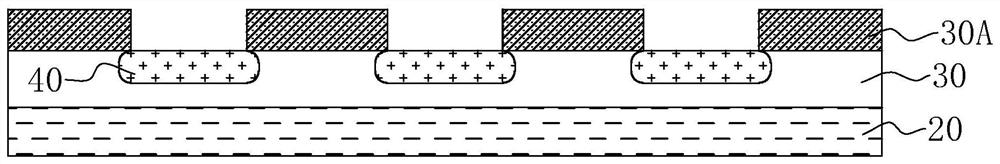

Delta channel doping SiC vertical power MOS device manufacturing method

ActiveCN105470288AImprove channel mobilityImprove conduction characteristicsSemiconductor devicesCarbon filmIron injection

The invention provides a Delta channel doping SiC vertical power MOS device manufacturing method. The method comprises the steps of: cleaning the surface of an N- / N+ type SiC epitaxial wafer; carrying out layered doping in a CVD furnace; etching out a P-base region and injecting high temperature Al irons; etching out an N+ doping source region and injecting high temperature N irons; etching out a P+ contact region and injecting high temperature Al irons; forming a carbon protection film on the surface of the N- / N+ type SiC epitaxial wafer; annealing high temperature iron injection; removing the surface carbon film; carrying out acid cleaning; growing a SiO2 insulating layer; growing a bottom drain electrode; smearing stripping glue and a photoresist, etching out a source contact hole, carrying out source metal deposition, and stripping the source metal to form a source pattern; annealing source and drain electrodes; forming a grid electrode; and forming a grid and source interconnection electrode. According to the invention, the channel effective migration rate of the vertical power MOS device is effectively improved, the threshold voltage of the device is reduced, and the conduction characteristic of the vertical power device is improved.

Owner:XIDIAN NINGBO INFORMATION TECH INST

Two-channel RC-LIGBT device and manufacturing method thereof

ActiveCN106098764AImprove stabilityImprove reliabilitySemiconductor/solid-state device manufacturingSemiconductor devicesCurrent channelVoltage drop

The invention belongs to the power semiconductor integration circuit field and especially relates to a transverse reverse conducting insulated gate bipolar transistor (Reverse Conducting-LIGBT, RC-LIGBT) and a manufacturing method thereof. The device and the method are used for restraining a snapback phenomenon of a traditional RC-LIGBT device, simultaneously improving a reverse direction diode characteristic and increasing stability and reliability of the device. By using the RC-LIGBT device, through introducing a composite structure into a collector electrode terminal of the device to form a one-way conductive path possessing two channels, under a forward direction LIGBT work mode, an influence of an N-type collecting zone on a conduction characteristic is completely shielded, the snapback phenomenon is completely eliminated, a low conduction voltage drop which is the same with the voltage drop of a traditional LIGBT is possessed and stability and reliability of the device are increased. Simultaneously, under a reverse direction diode follow current work mode, two follow current channels are provided on the collector electrode terminal, a follow current capability is optimized and a small conduction voltage drop is possessed.

Owner:UNIV OF ELECTRONICS SCI & TECH OF CHINA

Semiconductor device and method of manufacturing semiconductor device

ActiveUS20130119377A1Improve reliabilityIncrease in contact resistanceTransistorSemiconductor/solid-state device manufacturingOxide semiconductorPlasma treatment

By reducing the contact resistance between an oxide semiconductor film and a metal film, a transistor that uses an oxide semiconductor film and has excellent on-state characteristics is provided. A semiconductor device includes a pair of electrodes over an insulating surface; an oxide semiconductor film in contact with the pair of electrodes; a gate insulating film over the oxide semiconductor film; and a gate electrode overlapping with the oxide semiconductor film with the gate insulating film interposed therebetween. In the semiconductor device, the pair of electrodes contains a halogen element in a region in contact with the oxide semiconductor film. Further, plasma treatment in an atmosphere containing fluorine can be performed so that the pair of electrodes contains the halogen element in a region in contact with the oxide semiconductor film.

Owner:SEMICON ENERGY LAB CO LTD

Normally-closed GaN-based MOSFET structure with high threshold voltage and high conduction performance and fabrication method thereof

PendingCN107768252ARaise the threshold voltageImprove stabilitySemiconductor/solid-state device manufacturingSemiconductor devicesMOSFETEngineering

The invention relates to the technical field of semiconductor, in particular to a normally-closed GaN-based MOSFET structure with a high threshold voltage and high conduction performance and a fabrication method thereof. The fabrication method of the normally-closed GaN-based MOSFET structure with the high threshold voltage and high conduction performance comprises the following steps of firstly,providing a required substrate, sequentially and epitaxially growing a stress buffer layer, a GaN buffer layer, an AIN thin layer and an AlGaN thin layer on the substrate, and reserving the AlN thin layer and the AlGaN thin layer on a grid region by etching to obtain a substrate for epitaxy of a selection region; secondly, sequentially selecting a regional epitaxial GaN channel layer, a AIN insertion layer and a AIGaN barrier layer on the substrate to form a groove structure; and finally, depositing a grid dielectric layer, covering grid metal on a groove channel grid dielectric layer, and covering two ends of the grid with metal to form a source and a drain. By the fabrication method, the threshold voltage and the grid region mobility can be effectively improved, the channel resistance isreduced, and the conduction performance of the GaN MOSFET device is improved.

Owner:SUN YAT SEN UNIV

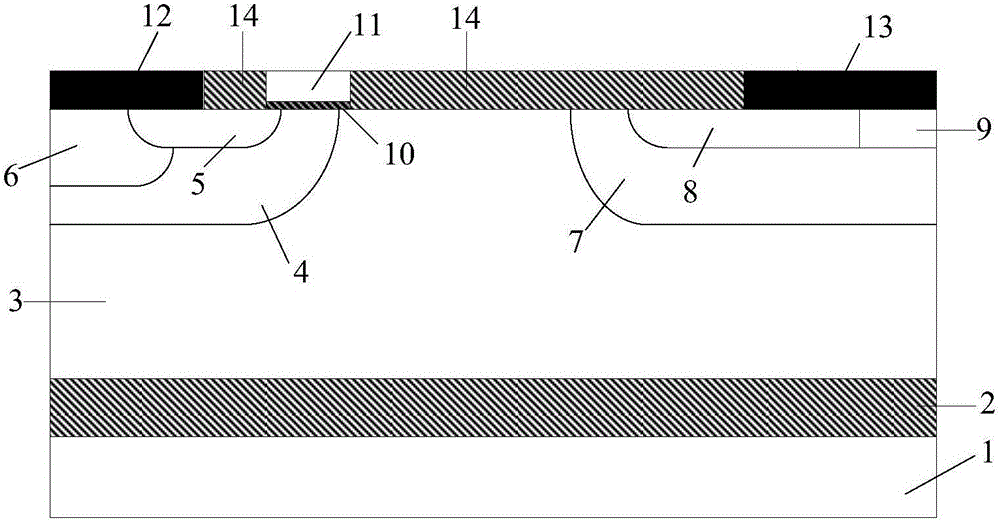

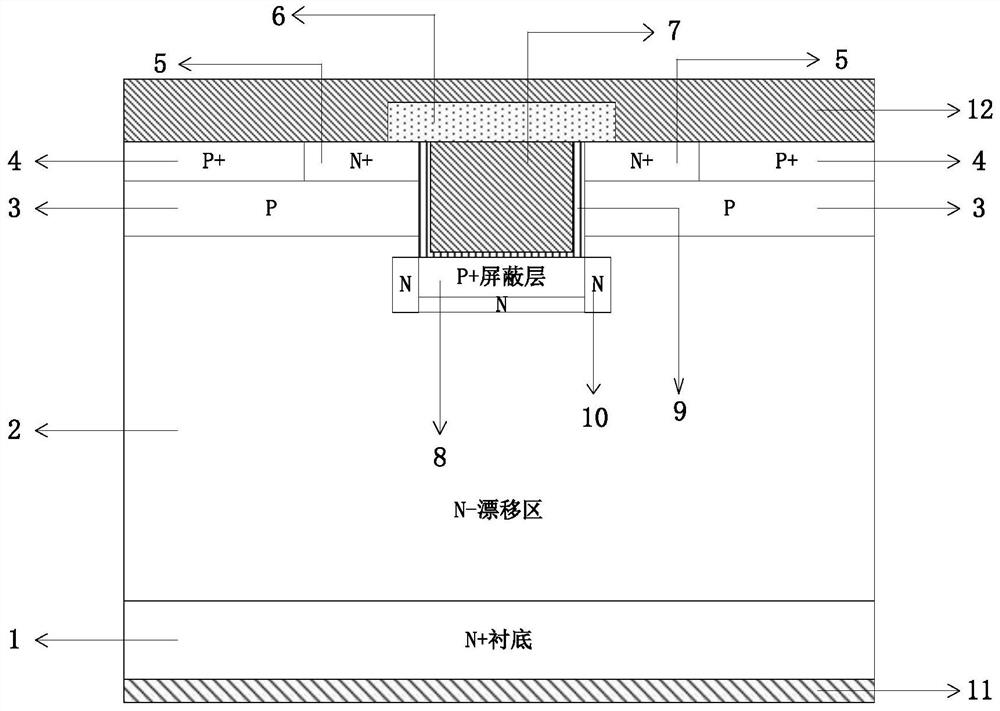

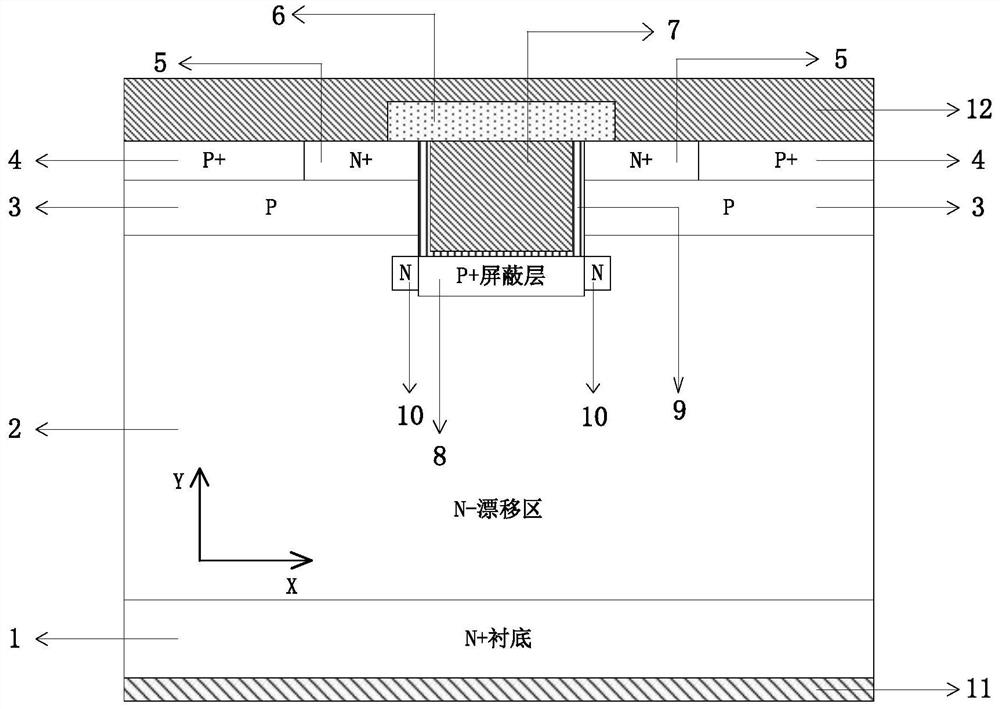

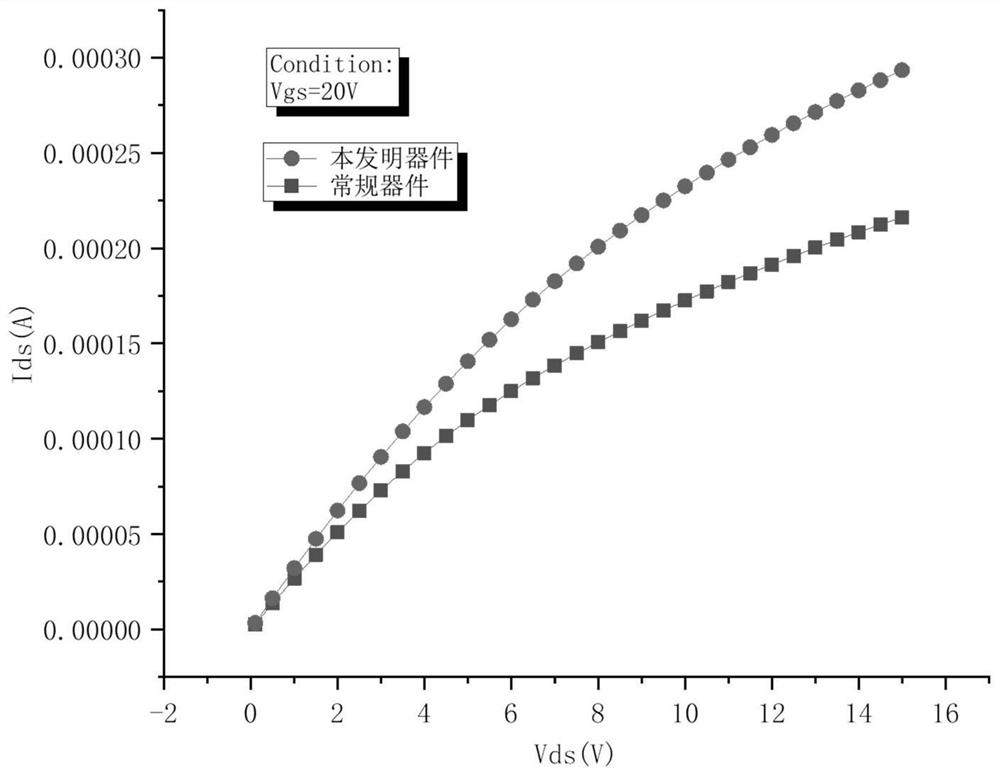

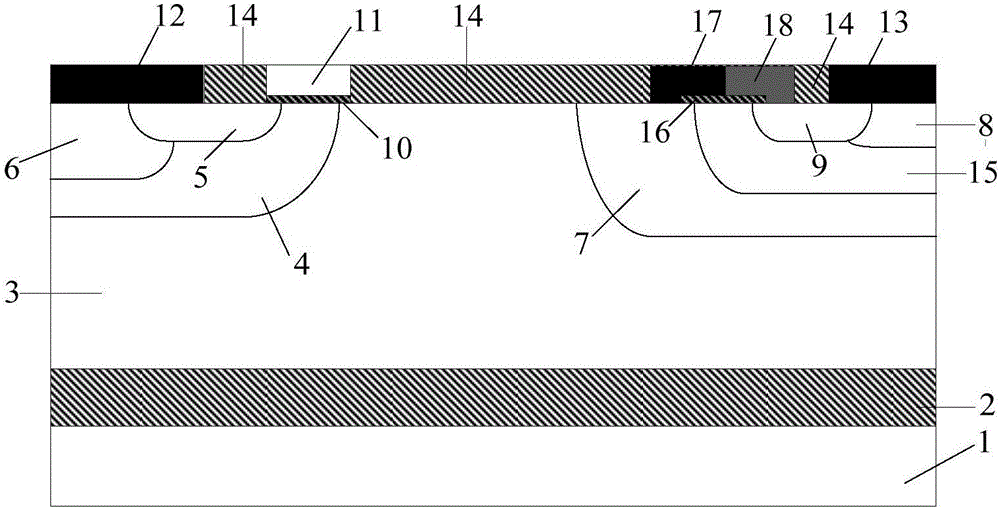

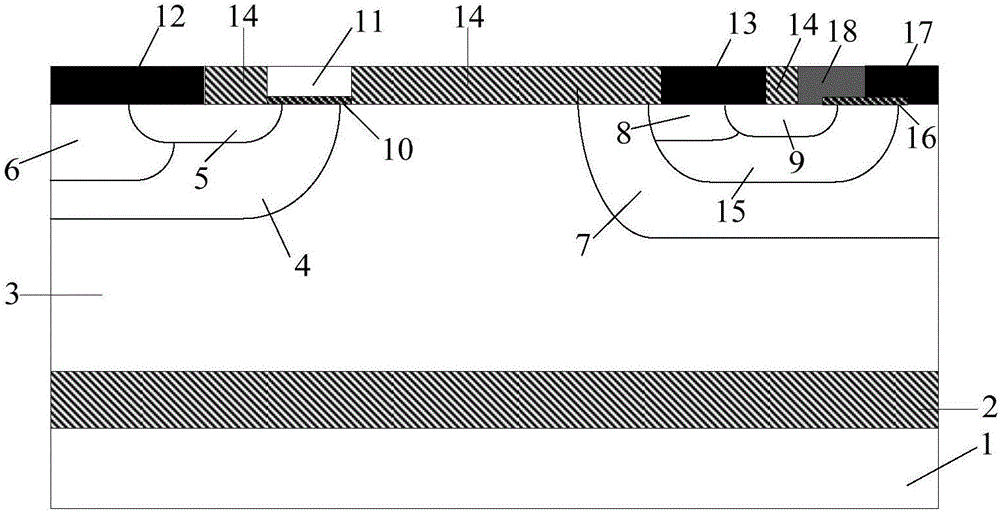

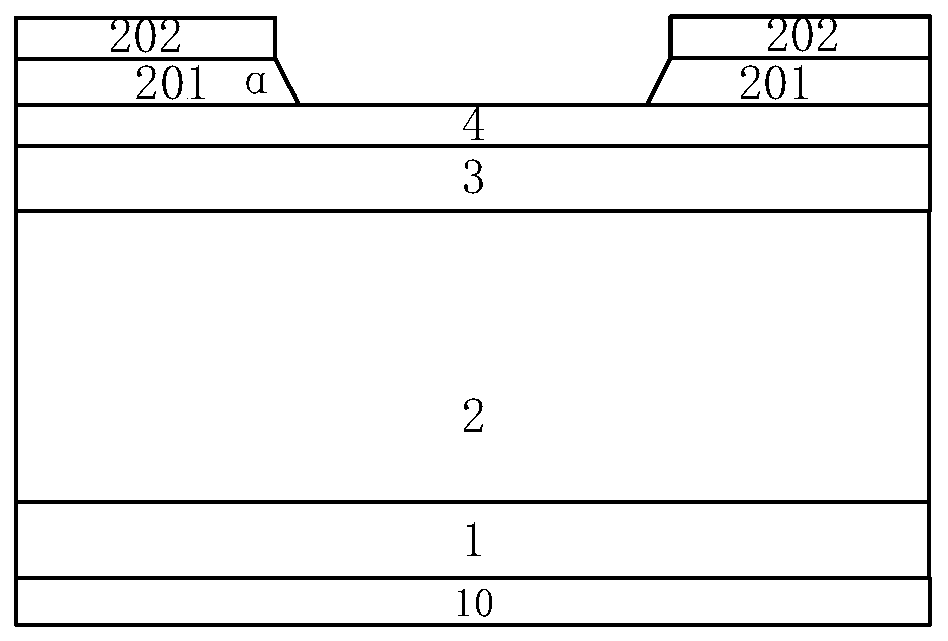

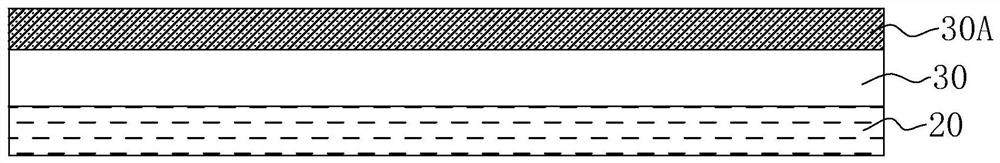

Silicon carbide trench MOSFET device and manufacturing method thereof

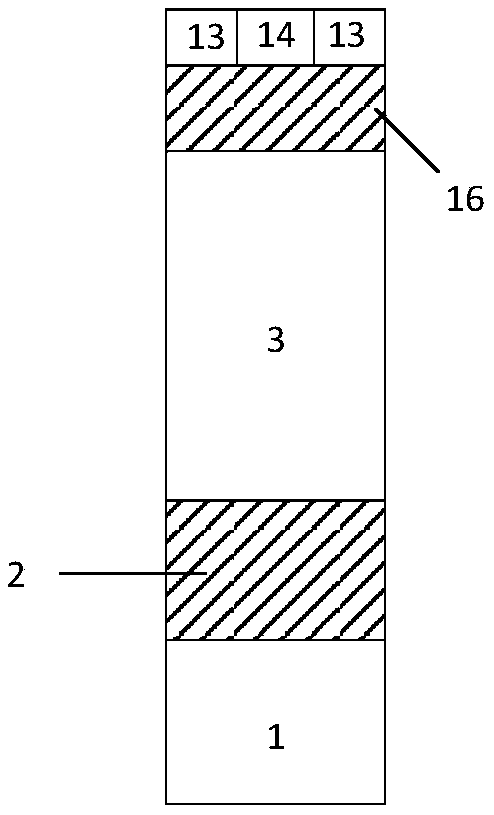

InactiveCN111081778AImprove conduction characteristicsImprove blocking propertiesSemiconductor/solid-state device manufacturingSemiconductor devicesCarbide siliconGate dielectric

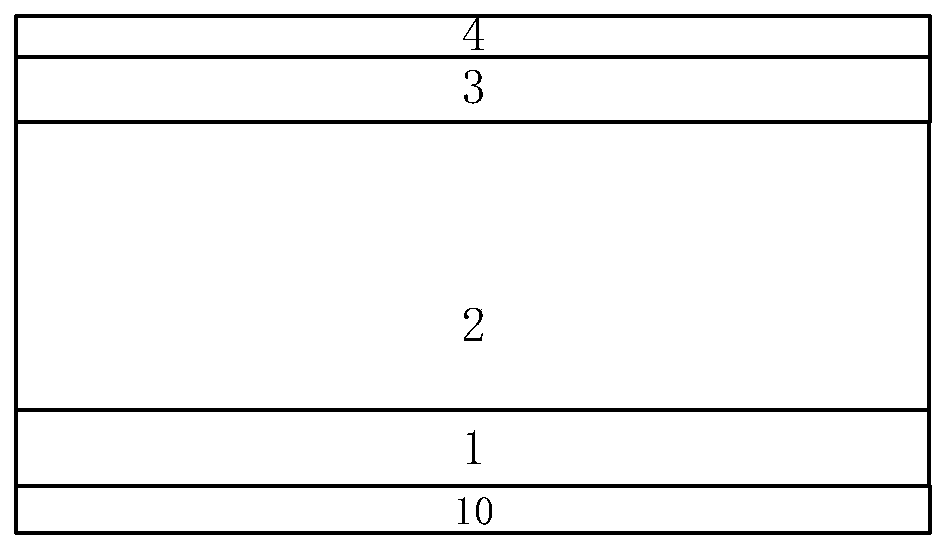

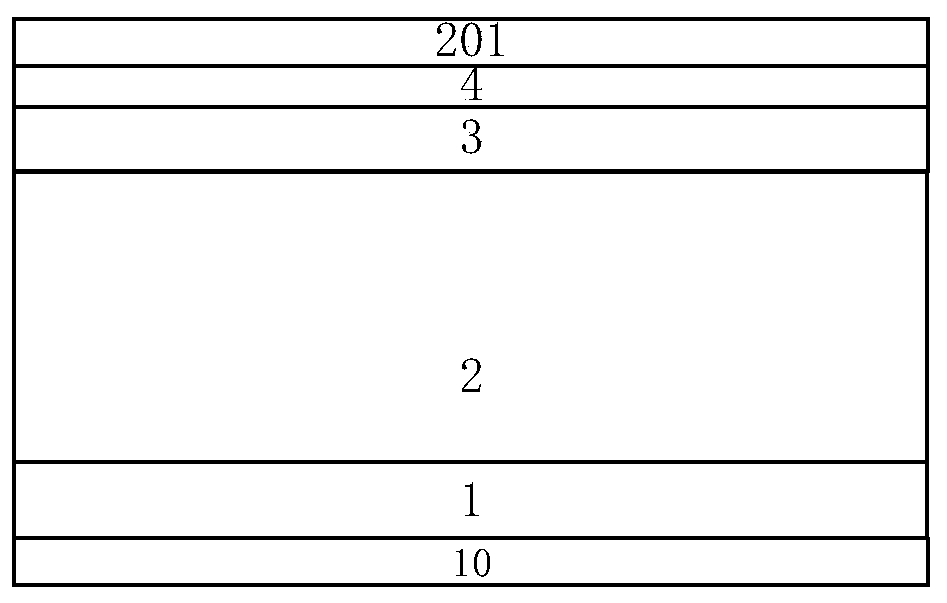

The invention discloses a silicon carbide trench type MOSFET device and a preparation method thereof. The structure of the device mainly comprises an N+ type silicon carbide substrate 1; an N- type drift region 2, a P type base region 3 and an N+ type source region 4 are sequentially arranged on the N+ type silicon carbide substrate 1; a drain electrode 10 is arranged on the lower portion of the N+ type silicon carbide substrate 1, and an inverted trapezoidal deep groove is formed in the top of the N- type epitaxial layer and comprises a gate dielectric layer 6 and a gate electrode 7; and thedeep groove divides each of the P type base region 3 and the N+ type source region 4 into two parts. According to the silicon carbide trench type MOSFET device and the preparation method thereof of the invention, on the basis of a characteristic that silicon carbide {0-33-8} plane systems have the highest channel carrier mobility, the conduction characteristic of the device is improved by introducing the inverted trapezoidal deep trench structure; A base region is implanted with ions after groove etching, so that a V-shaped deep trench gate dielectric layer is protected in a blocking state, and therefore, the blocking characteristic of the device is improved; a characteristic that the oxidation rates of different crystal surfaces of silicon carbide are different, the structure enables theside wall gate dielectric layer of the trench to be thinner, and the bottom gate dielectric layer of the trench to be thicker can be realized more conveniently, and therefore, the device has reasonable threshold voltage and higher blocking voltage at the same time.

Owner:SHENZHEN INST OF WIDE BANDGAP SEMICON

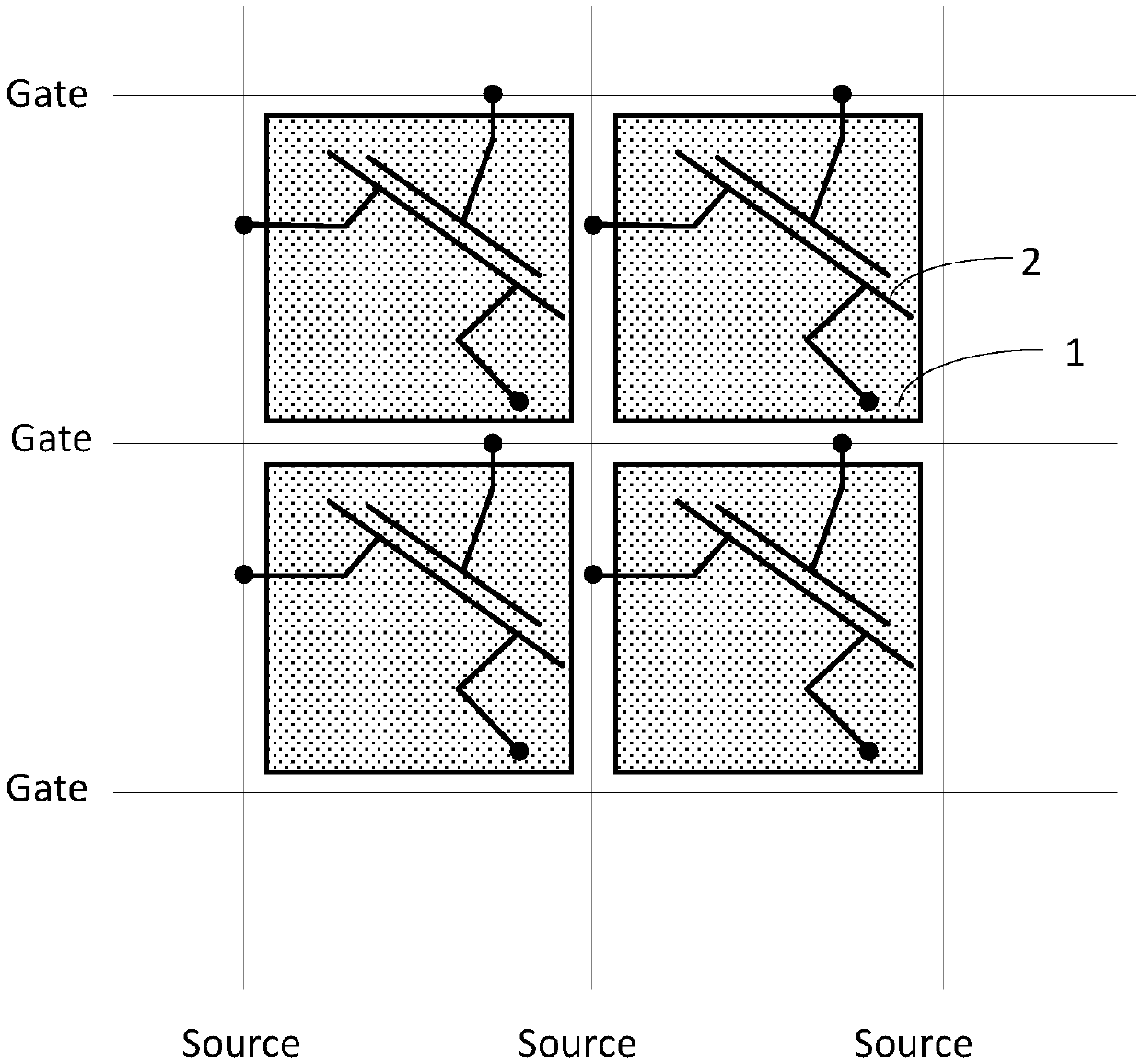

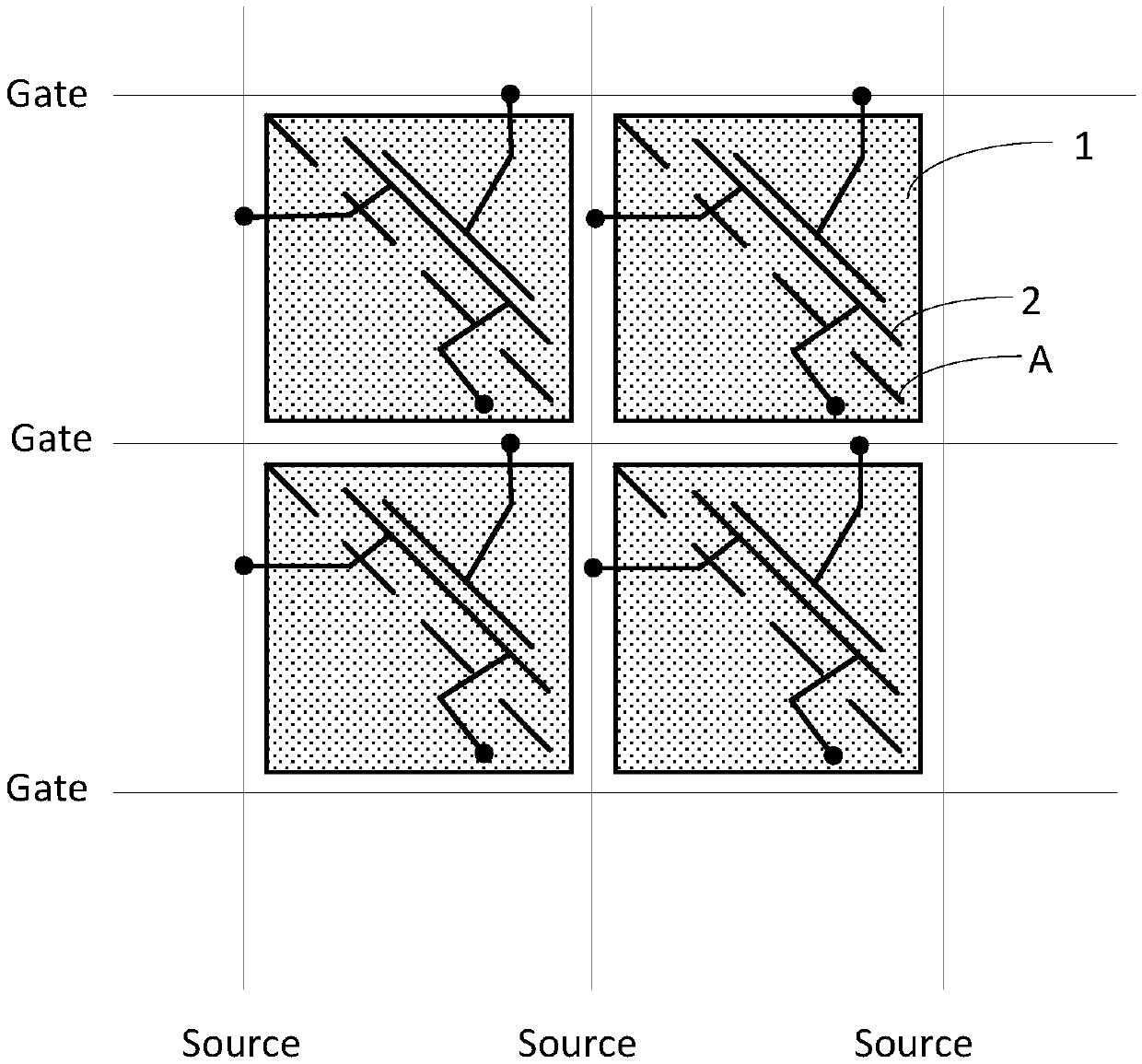

Array substrate and micro total analysis device

ActiveCN109659326AImprove conduction characteristicsIncrease the lengthSolid-state devicesLaboratory glasswaresOptoelectronicsActive layer

The invention discloses an array substrate and a micro total analysis device. The array substrate includes a substrate, a plurality of pixel regions which are arranged on the substrate and limited bycrossing of a data line and a grid line, and driving transistors in the pixel regions, wherein each driving transistor includes an active layer graph, and a first preset angle is displayed between theextending direction of the active layer graph and the grid line, and the active layer graph strides the pixel region in an inclined manner in the first preset angle direction; and the source and drain electrodes of each driving transistor are connected to the active layer graph in the first preset angle direction. By setting the first preset angle between the extending direction of active layer graph and the grid line, compared with a conventional device which sets the extending direction of the active layer to be parallel with the grid line, the array substrate can increase the length of theactive layer graph in the extending direction, thus increasing the length breadth ratio of the active layer graph while not increasing the area of the occupied pixel area, so as to improve the conductivity of the driving transistors while realizing high pixel design.

Owner:BOE TECH GRP CO LTD

Resonant isolating transformer with ultra-wide voltage regulating range

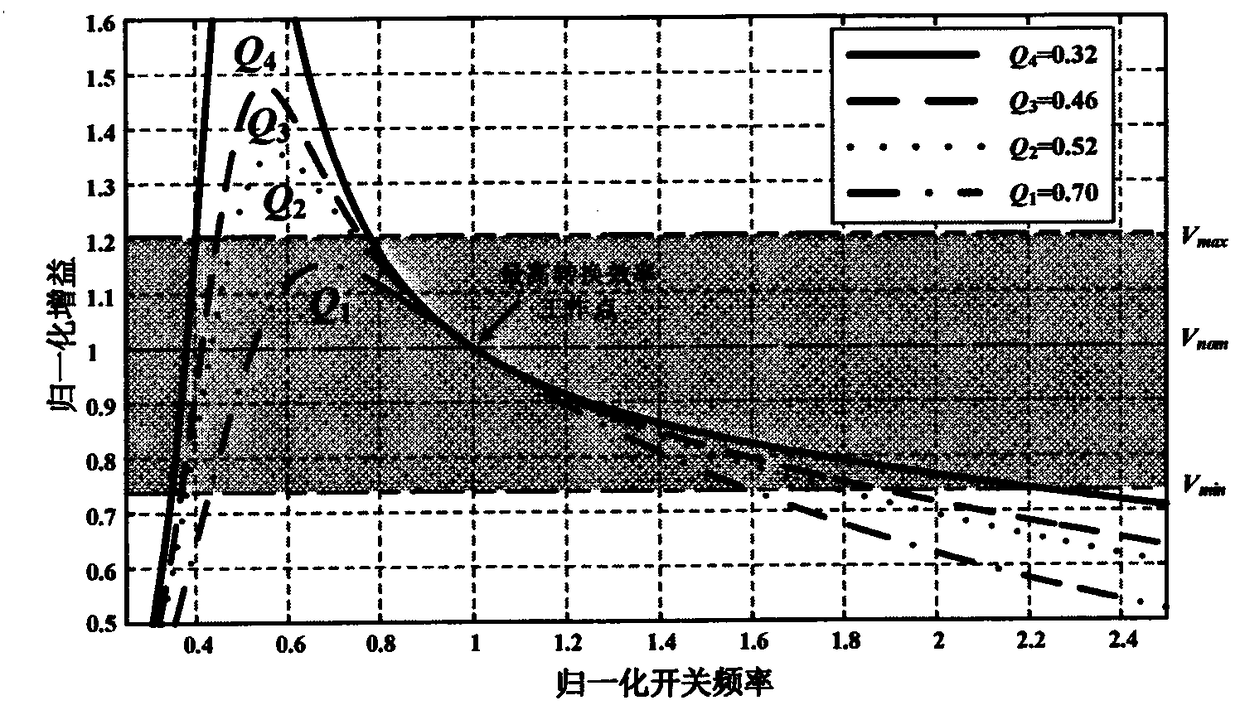

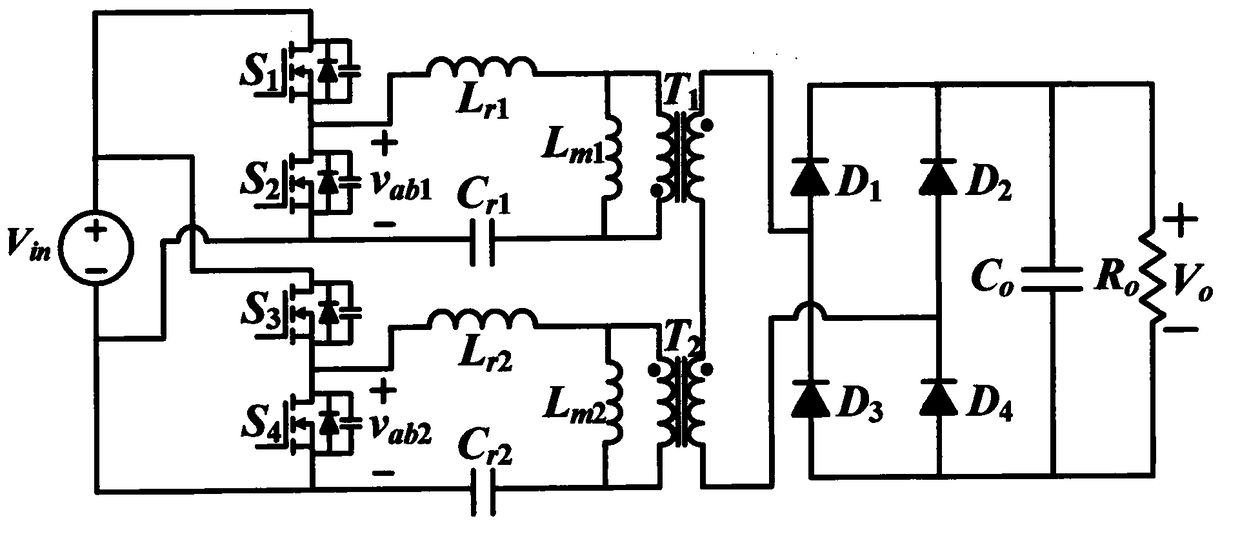

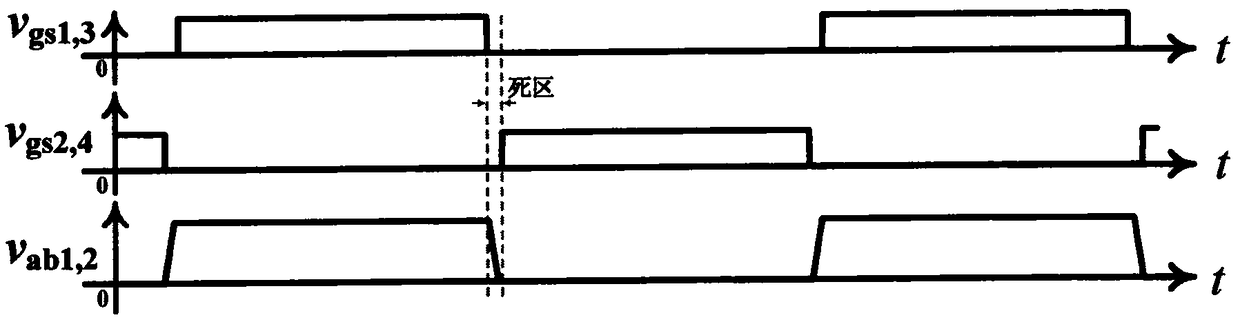

ActiveCN108900090AImprove conduction characteristicsGood blood pressure effectEfficient power electronics conversionDc-dc conversionTransformerEngineering

The invention provides a resonant isolating transformer with an ultra-wide voltage regulating range. The resonant isolating transformer is characterized by comprising a first half-bridge LLC resonantnetwork with a first transformer and a second half-bridge LLC resonant network with a second transformer, wherein the sub edge of the first transformer is the output end of the first half-bridge LLC resonant network; the sub edge of the second transformer is the output end of the second half-bridge LLC resonant network; the input voltage is simultaneously input into the first half-bridge LLC resonant network and the second half-bridge LLC resonant network; the output end of the first half-bridge LLC resonant network and the output end of the second half-bridge LLC resonant network are connected in series, are then sequentially connected with a rectifying circuit and a filter circuit and are then connected with a load. The voltage reduction capability of an LLC resonant circuit is greatly improved; the voltage can be reduced to 0 under any load condition; the zero voltage conduction characteristic of a raw edge switch is greatly improved.

Owner:SHANGHAI TECH UNIV

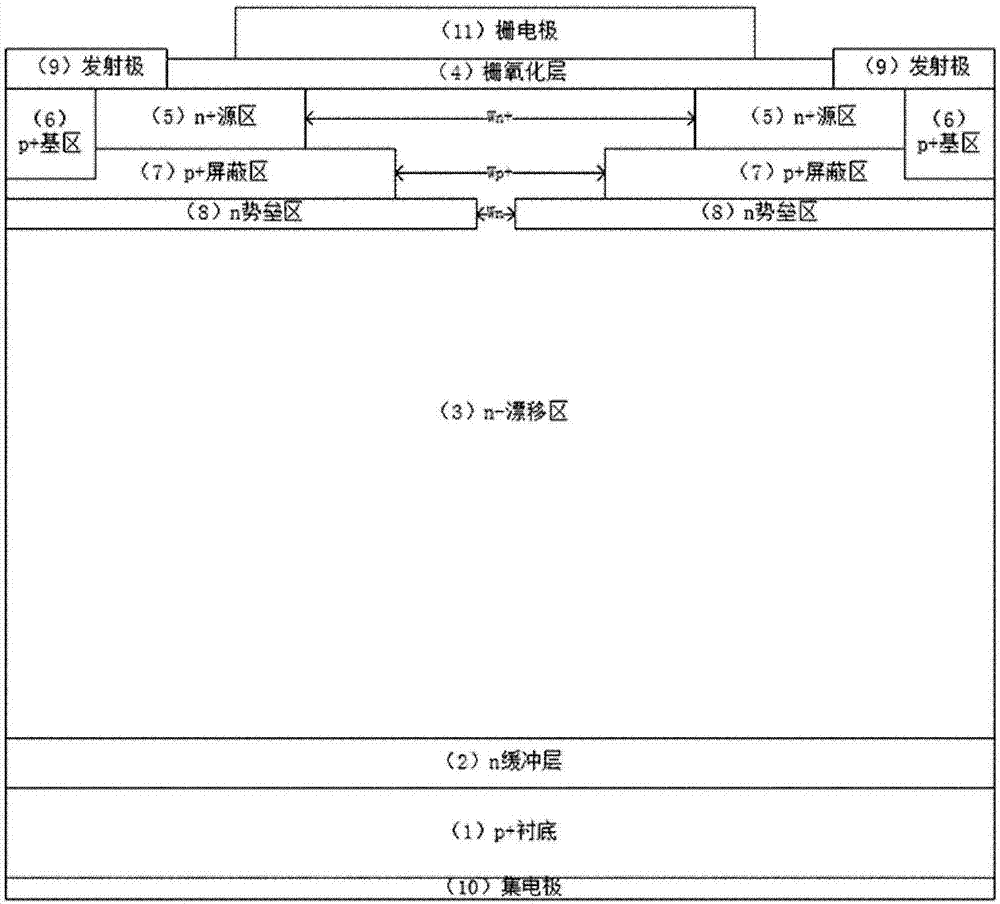

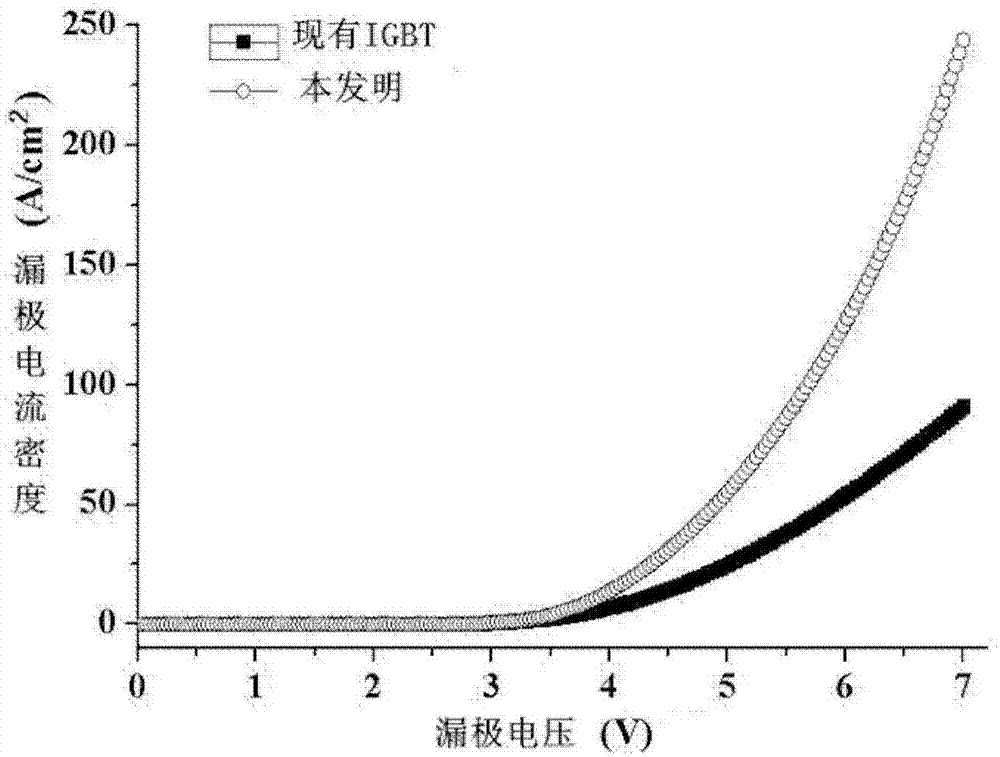

Silicon carbide semiconductor device and preparation method therefor

ActiveCN106876255AImprove featuresImprove switching characteristicsSemiconductor/solid-state device manufacturingSemiconductor devicesGate oxideHigh pressure

The invention provides a silicon carbide semiconductor device which can be applied to a high-voltage field. The silicon carbide semiconductor device is formed by a plurality of cells in a parallel-connection manner; the structure of each cell comprises a p<+> substrate, an epitaxial layer, two ion injection n barrier regions, two ion injection p<+> shielding regions, two p<+> base regions, two n<+> source regions, a collector layer, two emitters, a gate oxide layer and a gate electrode, wherein the epitaxial layer is positioned on the substrate; the two ion injection n barrier regions are arranged on the two sides of the epitaxial layer respectively in an overlaying manner; the two ion injection p<+> shielding regions are arranged on the respective n barrier regions respectively in an overlaying manner; the two p<+> base regions are adjacent to the respective p<+> shielding regions respectively; the two n<+> source regions are arranged on the respective p<+> base regions in an overlaying manner respectively, and are adjacent to the p<+> base regions; the collector layer is positioned below the substrate; the two emitters are positioned on the respective p<+> base regions and the n<+> source regions respectively; the gate oxide layer is positioned on the two n<+> source regions; and the gate electrode is positioned on the gate oxide layer. In addition, the invention also provides a preparation method for the silicon carbide semiconductor device. Through ion injection, hole barrier is formed in the device, so that injection ratio of the emitters is improved and the conduction performance of the device is greatly improved.

Owner:ZHEJIANG XINKE SEMICON CO LTD

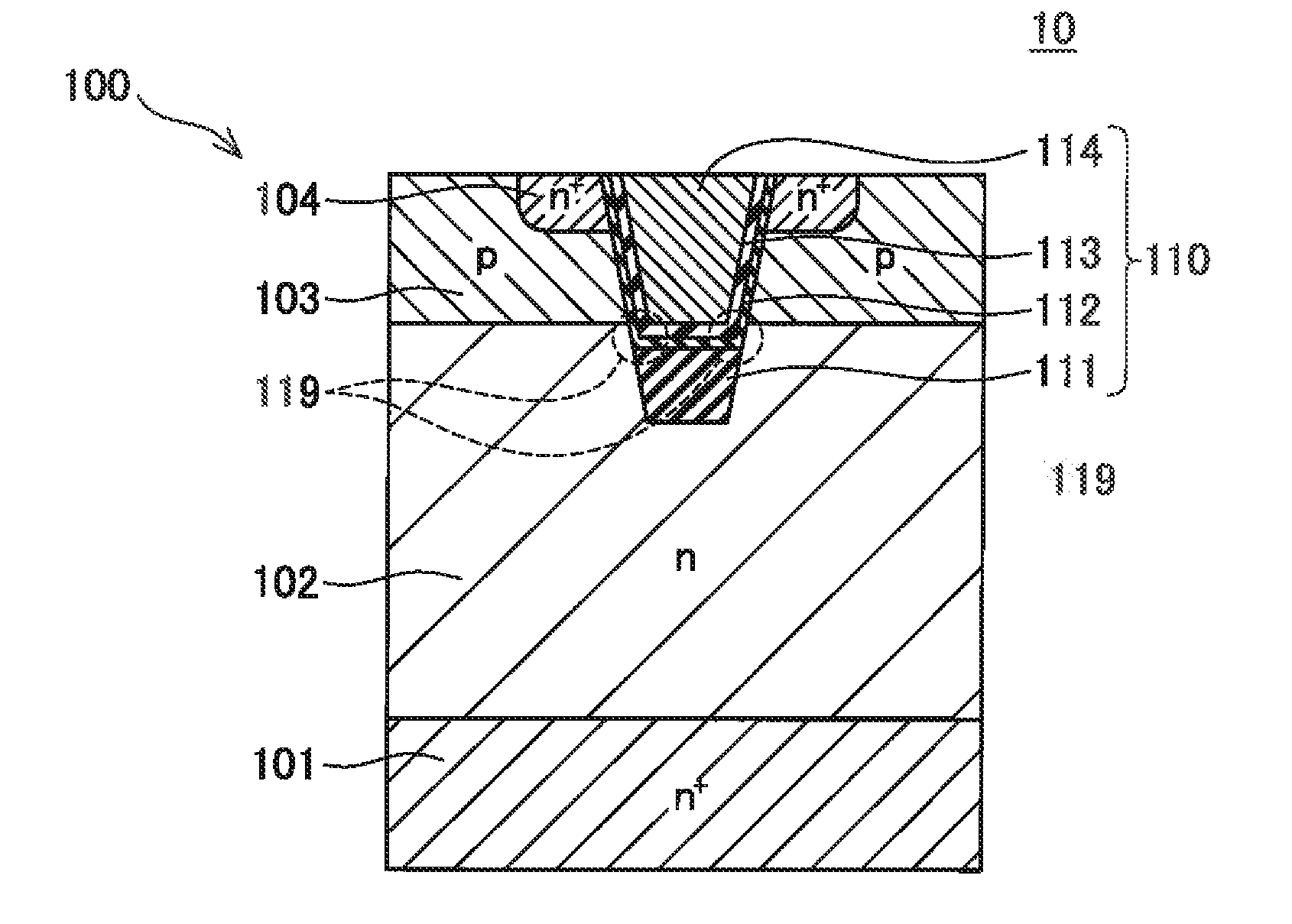

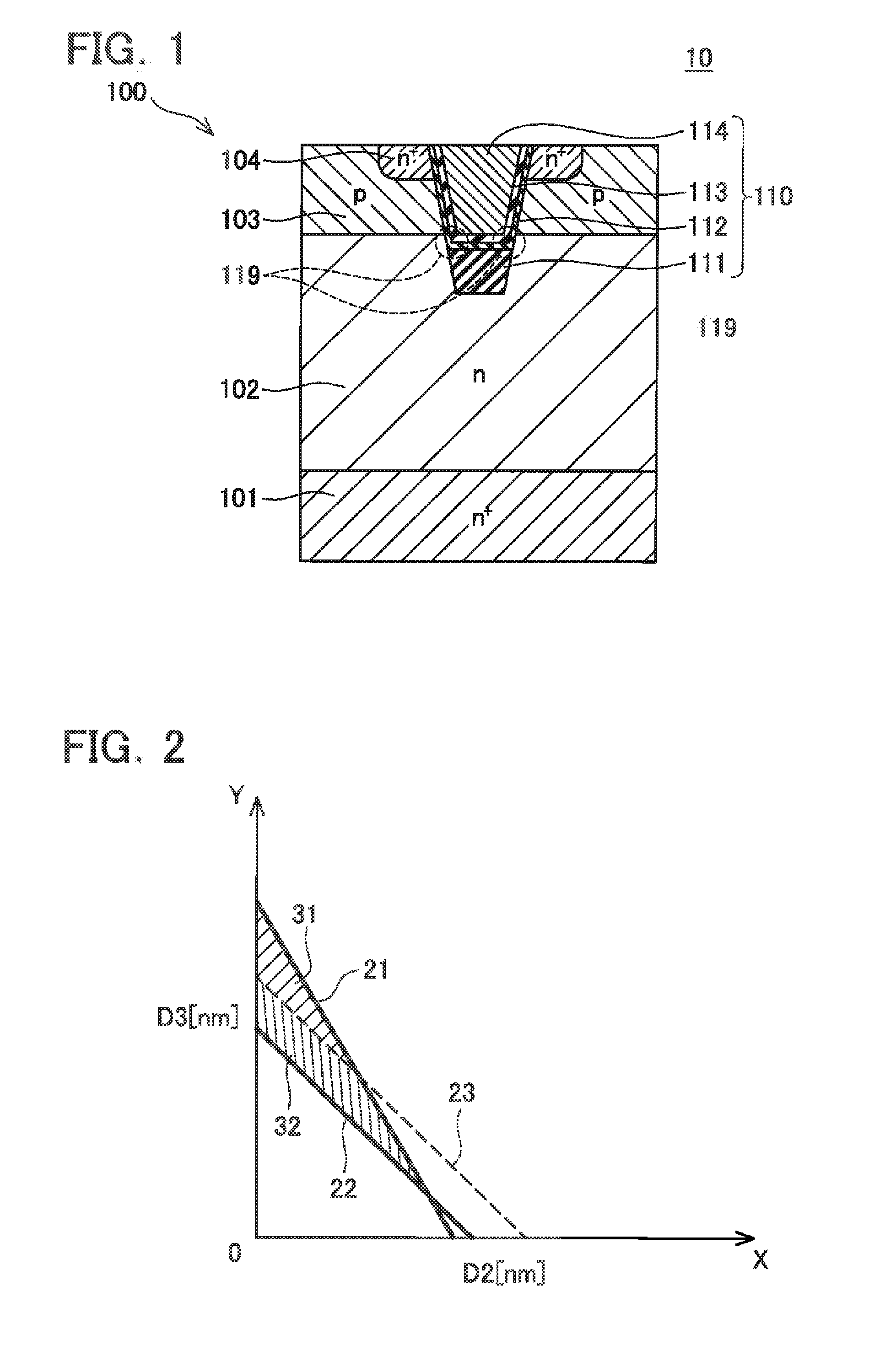

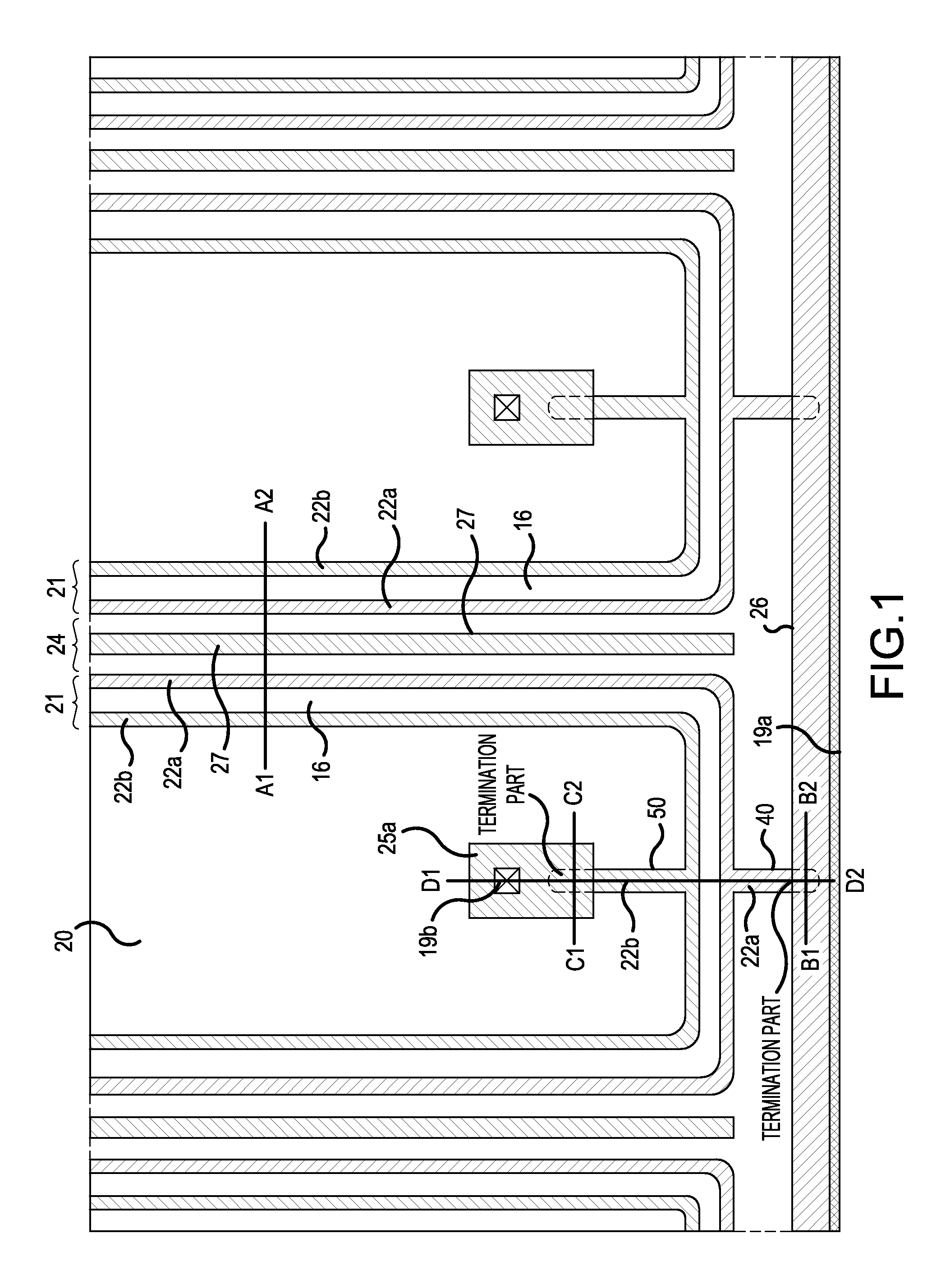

Semiconductor device

InactiveUS20140346592A1Avoid insulation breakdownIncreasing the thicknessSemiconductor devicesMOSFETDielectric

A vertical MOSFET includes: a semiconductor substrate comprising a drain layer, a drift layer, a body layer, and a source layer; and a trench gate penetrating through the source layer and the body layer from an upper surface of the semiconductor substrate and reaching the drift layer. The trench gate includes a gate electrode; a first insulating film disposed on a bottom surface of a trench formed in the semiconductor substrate; a second insulating film disposed at least on a side surface of the trench, and in contact with the body layer; and a third insulating film disposed between the gate electrode and the second insulating film, and formed of a material of which dielectric constant is higher than a dielectric constant of the second insulating film.

Owner:TOYOTA JIDOSHA KK +1

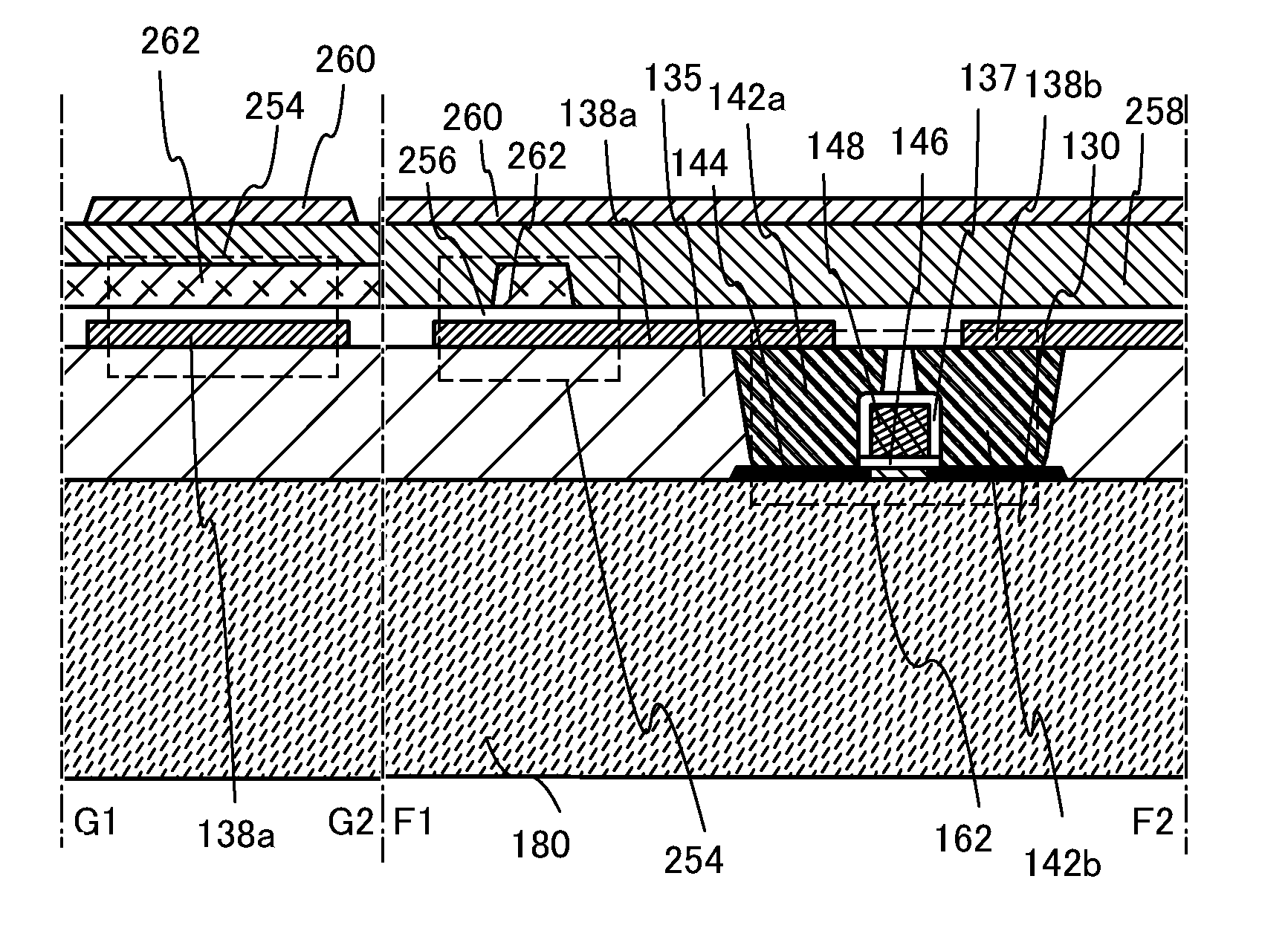

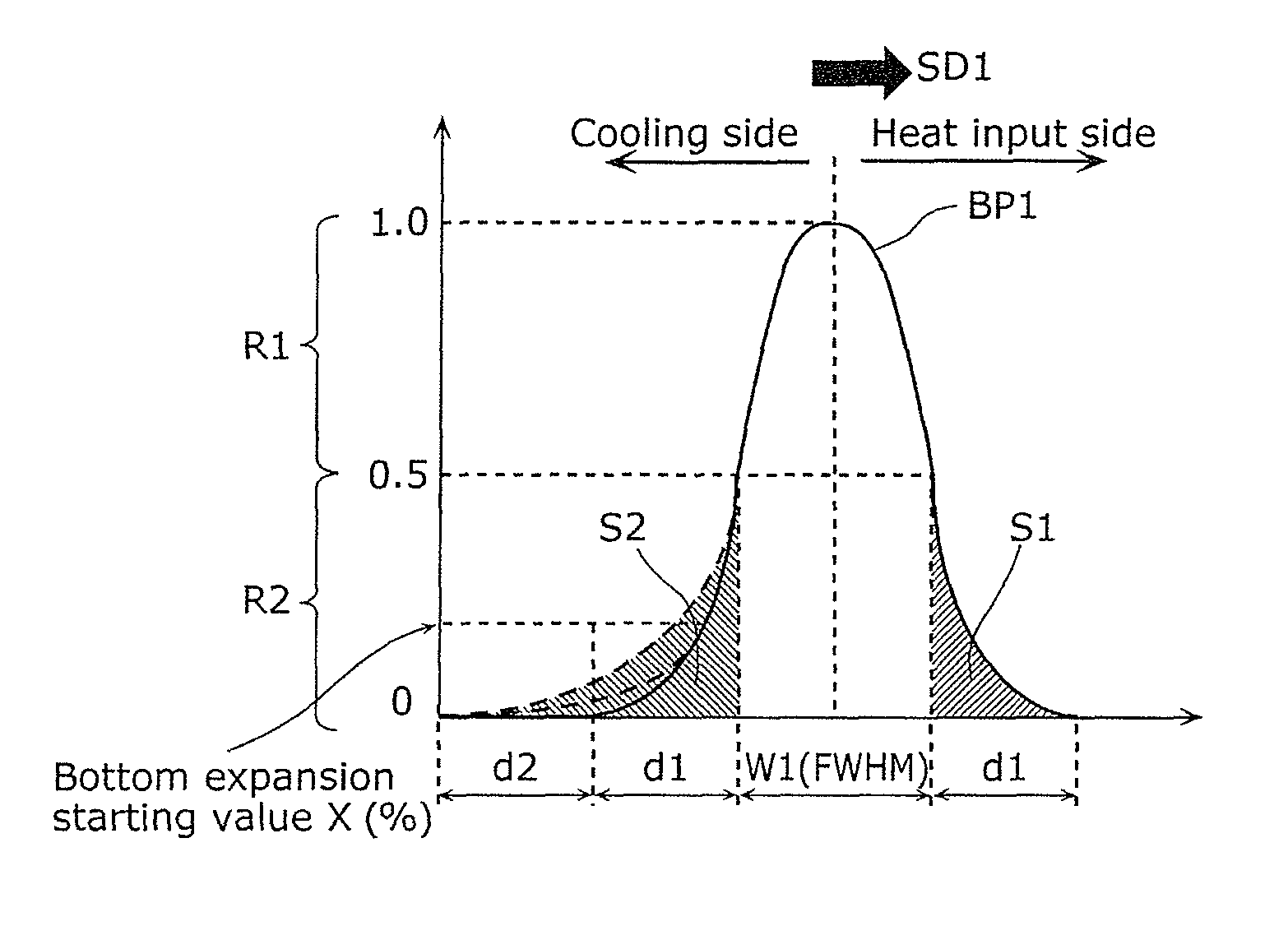

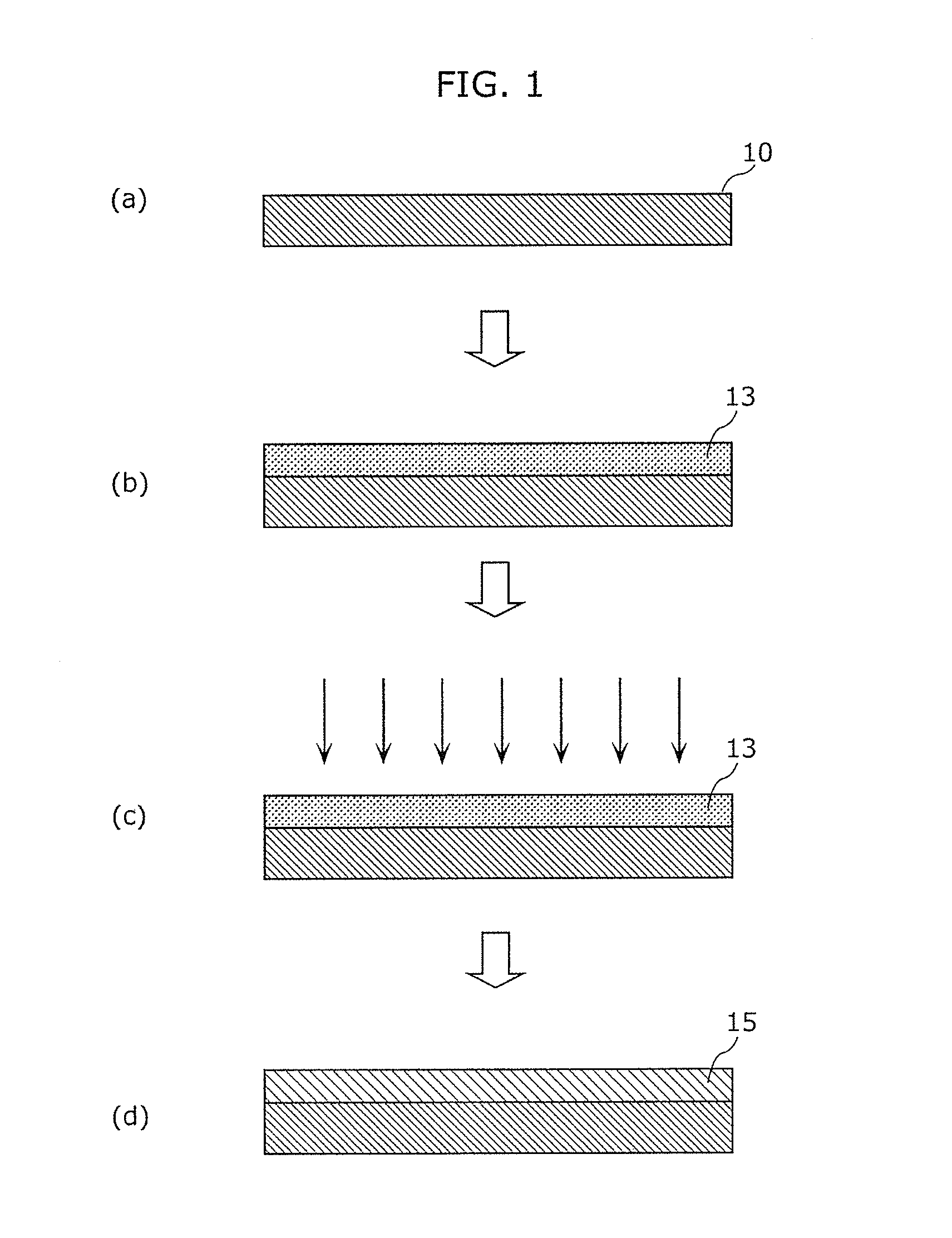

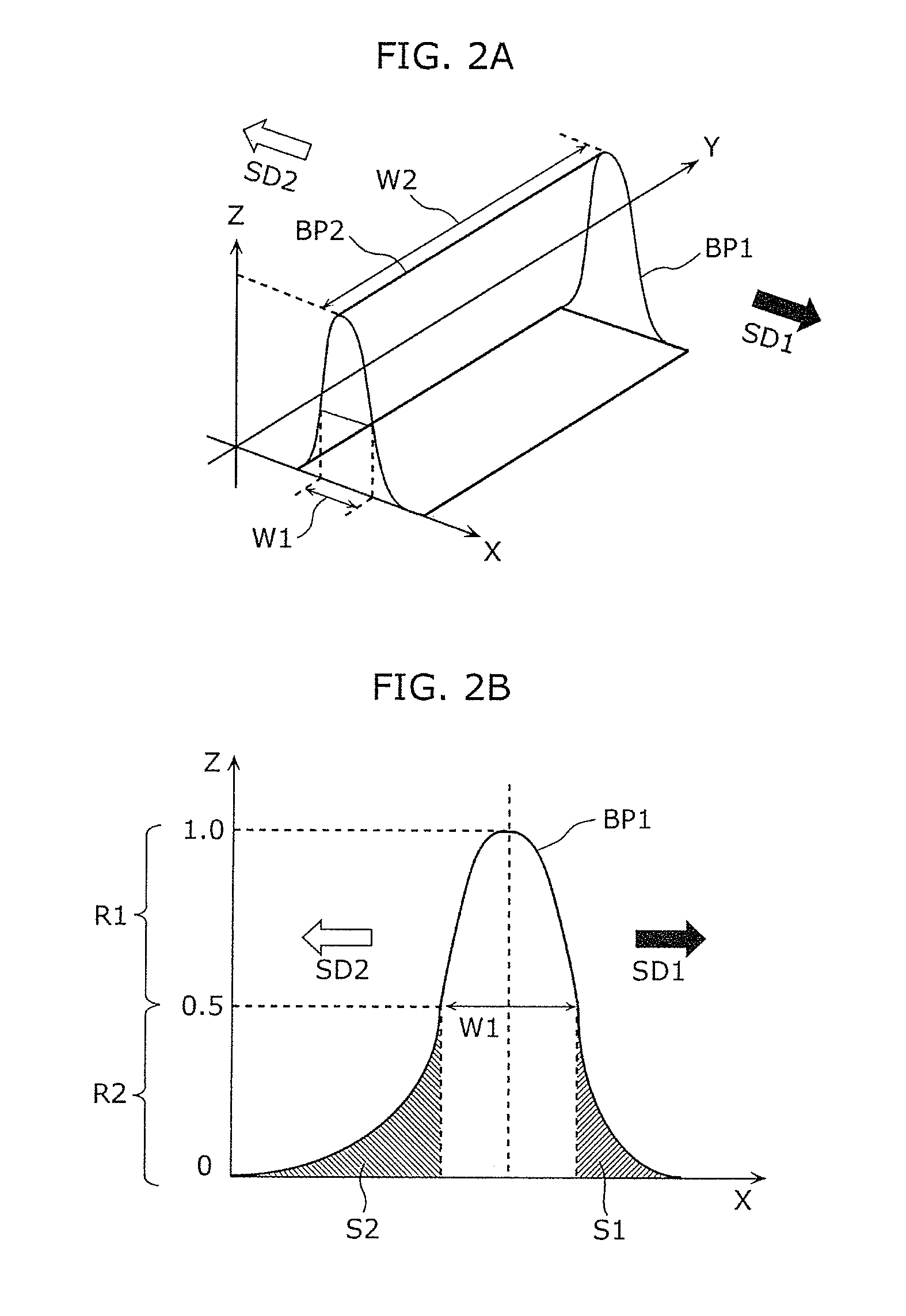

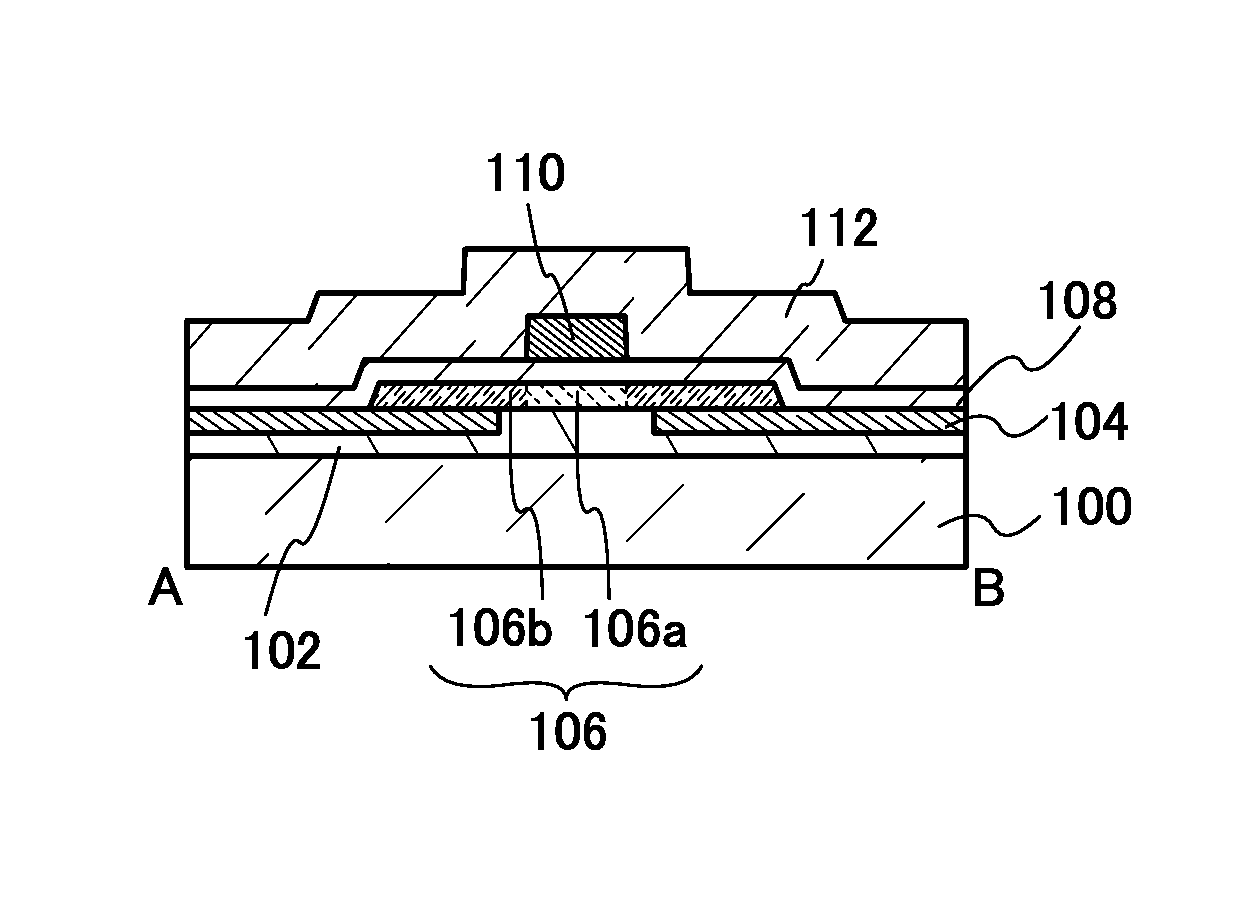

Manufacturing method for thin film semiconductor device, manufacturing method for thin film semiconductor array substrate, method of forming crystalline silicon thin film, and apparatus for forming crystalline silicon thin film

InactiveUS8735233B2Improve conduction characteristicsDrive fastSolid-state devicesMaterial analysis by optical meansLight beamSilicon thin film

A crystalline silicon thin film is formed by irradiating a silicon thin film with a laser beam. The laser beam is a continuous wave laser beam. An intensity distribution of the laser beam in a first region about a center of the intensity distribution is symmetric on an anterior side and a posterior side of the center. The intensity distribution in a second region about the center is asymmetric on the anterior side and the posterior side. The first region is from the maximum intensity of the laser beam at the center to an intensity half of the maximum intensity. The second region is at most equal to the half of the maximum intensity of the laser beam. In the second region, an integral intensity value on the posterior side is larger than on the anterior side.

Owner:JOLED INC

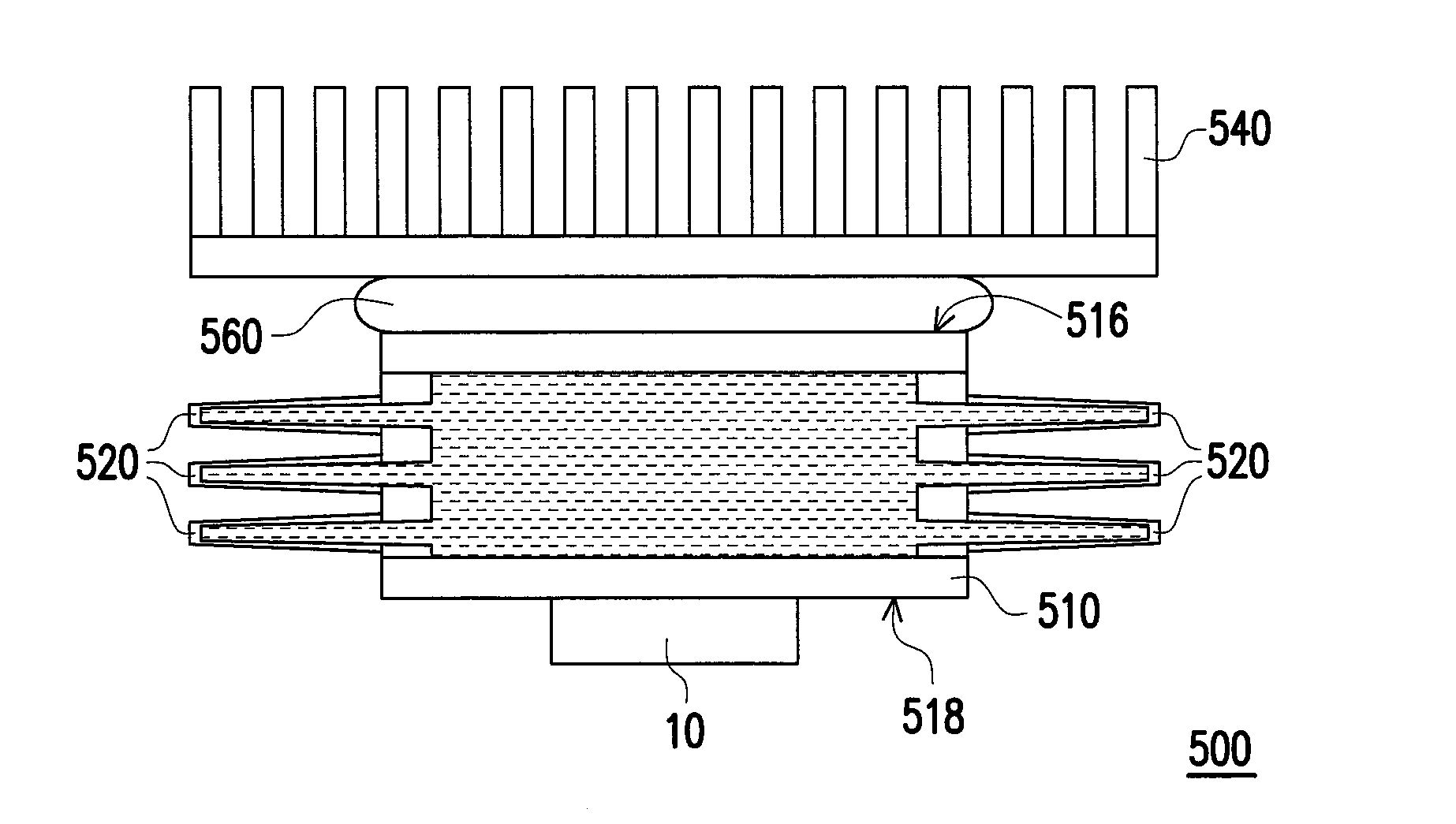

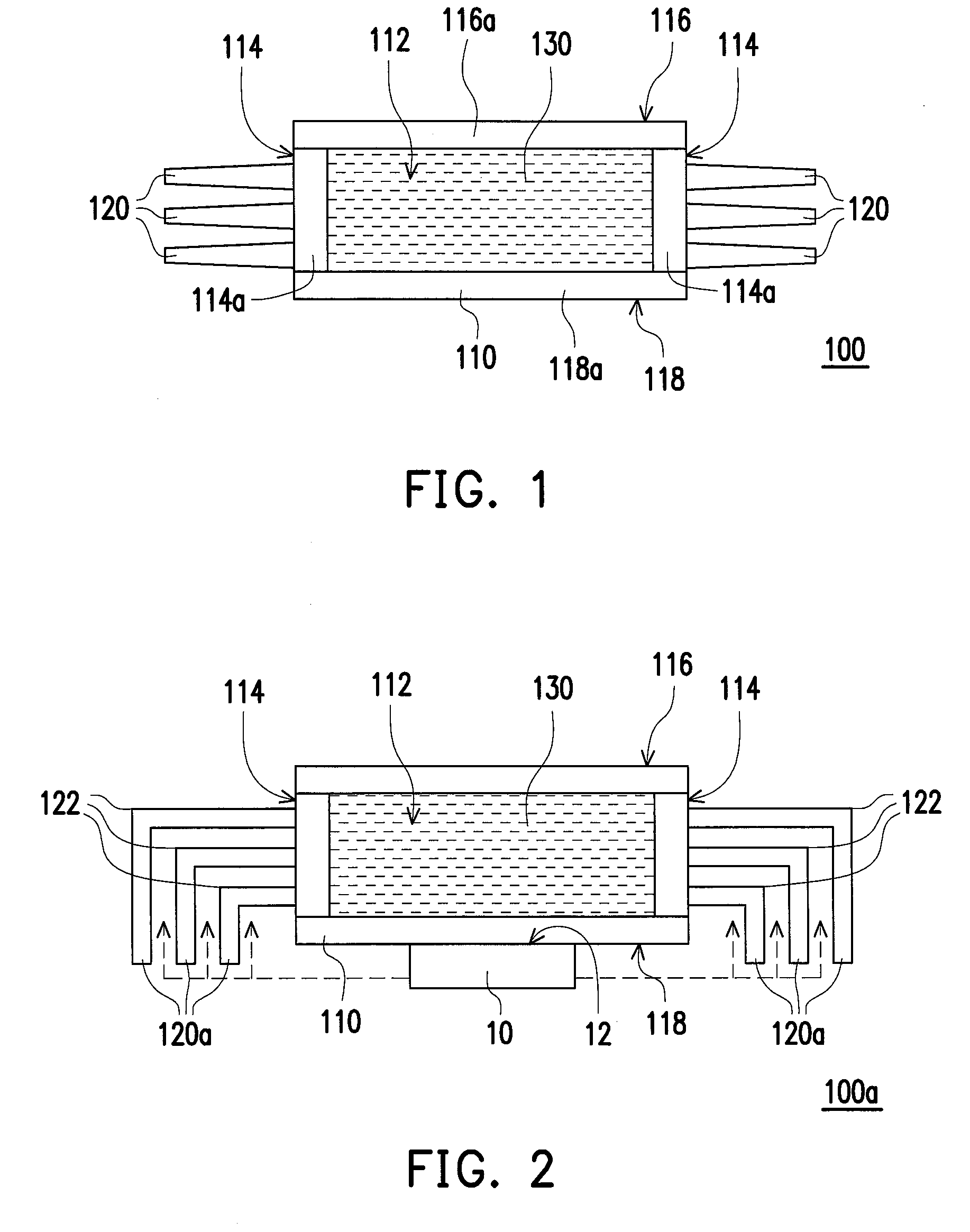

Heat dissipation module

InactiveUS20160095256A1Improve cooling efficiencyReduce the temperatureSemiconductor/solid-state device detailsIndirect heat exchangersComputer engineeringSpecific heat

A heat dissipation module includes a hollow housing, a plurality of heat dissipation fins and heat dissipation liquid. The hollow housing includes a chamber, a side surface, a top surface and a bottom surface opposite to the top surface. The side surface is connected to the top surface and the bottom surface. The heat dissipation fins are disposed on the side surface. The heat dissipation liquid is contained within the chamber, and a specific heat of the heat dissipation liquid is substantially greater than or equal to 1 cal / g° C.

Owner:SUBTRON TECH

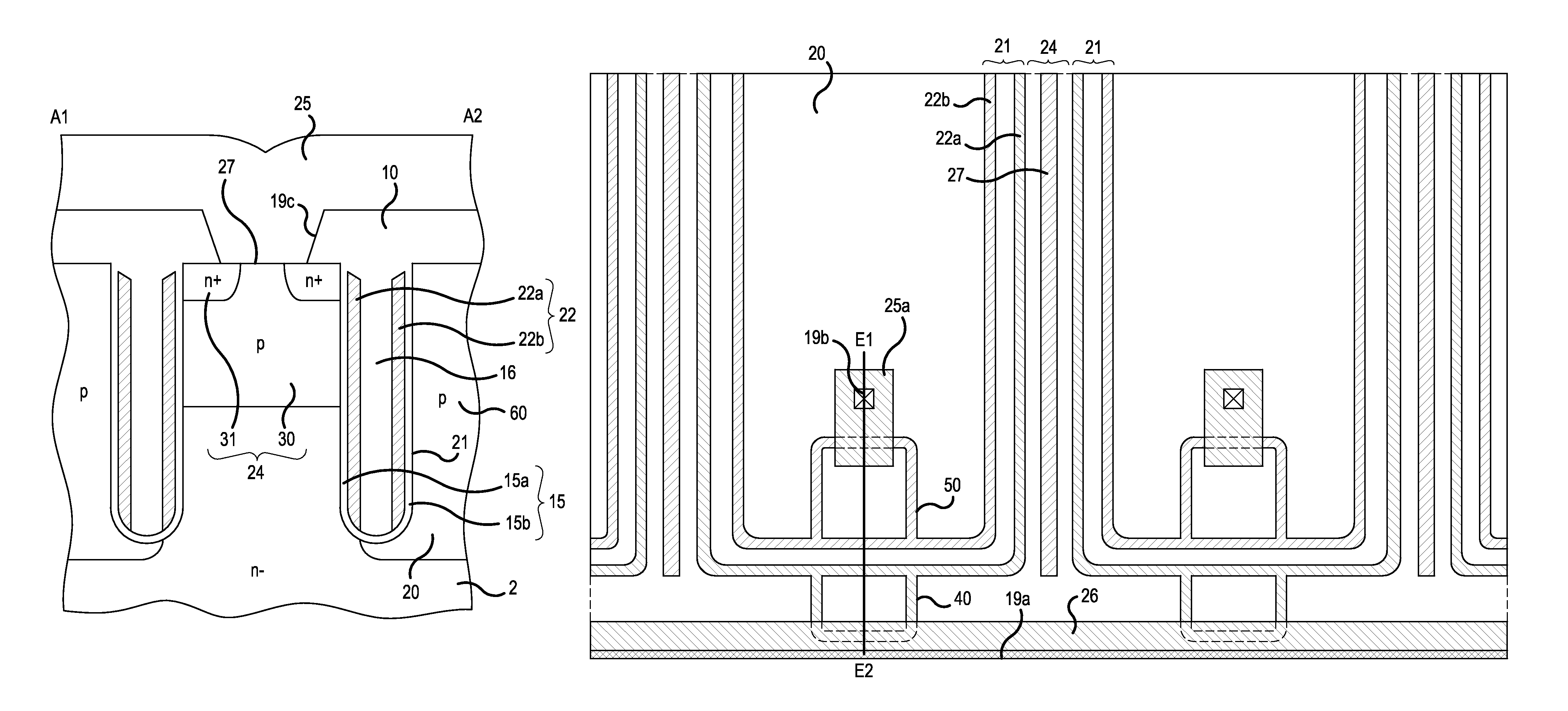

Semiconductor device

ActiveUS9054154B2Improve conduction characteristicsIncrease the number ofSemiconductor devicesPower semiconductor deviceSemiconductor

A semiconductor device includes a first gate electrode that is provided on a first insulating film along one side wall of a first trench and is provided in a second trench, a shield electrode that is provided on a second insulating film along the other side wall of the first trench and is provided in a third trench, a gate runner that is an extended portion of the second trench, has a portion which is provided on the first gate electrode, and is connected to the first gate electrode, and an emitter polysilicon layer that is an extended portion of the third trench, has a portion which is provided on the shield electrode, and is connected to the shield electrode. The semiconductor device has improved turn-on characteristics with a slight increase in the number of process steps, while preventing increase in costs and reduction in yield.

Owner:FUJI ELECTRIC CO LTD

Silicon carbide MOSFET device with improved gate bottom charge balance and manufacturing method thereof

ActiveCN114242768APrevent penetrationFix stability issuesSemiconductor/solid-state device manufacturingSemiconductor devicesMOSFETCarbide silicon

The invention relates to a silicon carbide MOSFET (Metal-Oxide-Semiconductor Field Effect Transistor) device with improved gate bottom charge balance and a manufacturing method thereof, the device comprises an epitaxial wafer structure with a charge balance column, an embedded gate structure, a source electrode structure positioned on the top layer and a drain electrode structure positioned on the bottom layer, and a grooved channel compliant layer is formed on a silicon carbide epitaxial layer of the epitaxial wafer structure. Non-planar ohmic contact is formed by the source electrode structure and the epitaxial wafer structure through the contact grooves located in the two sides of the grid electrode structure. A charge balance column located below a gate trench and a contact trench and basically formed by a preset laminated well is utilized to prevent the charge balance column from penetrating into a silicon carbide substrate of an epitaxial wafer structure. The method has the effect of standardizing the bottom depth and appearance of the gate bottom charge balance junction to be in a relatively good section column shape, so that the defects that the injection concentration of the charge balance junction cannot be adjusted, a junction side column cannot be formed and the electrical performance is unstable due to the fact that the depth of the junction bottom changes along with the depth of the groove on the basis of the arrangement of the channel compliant layer are overcome.

Owner:深圳真茂佳半导体有限公司

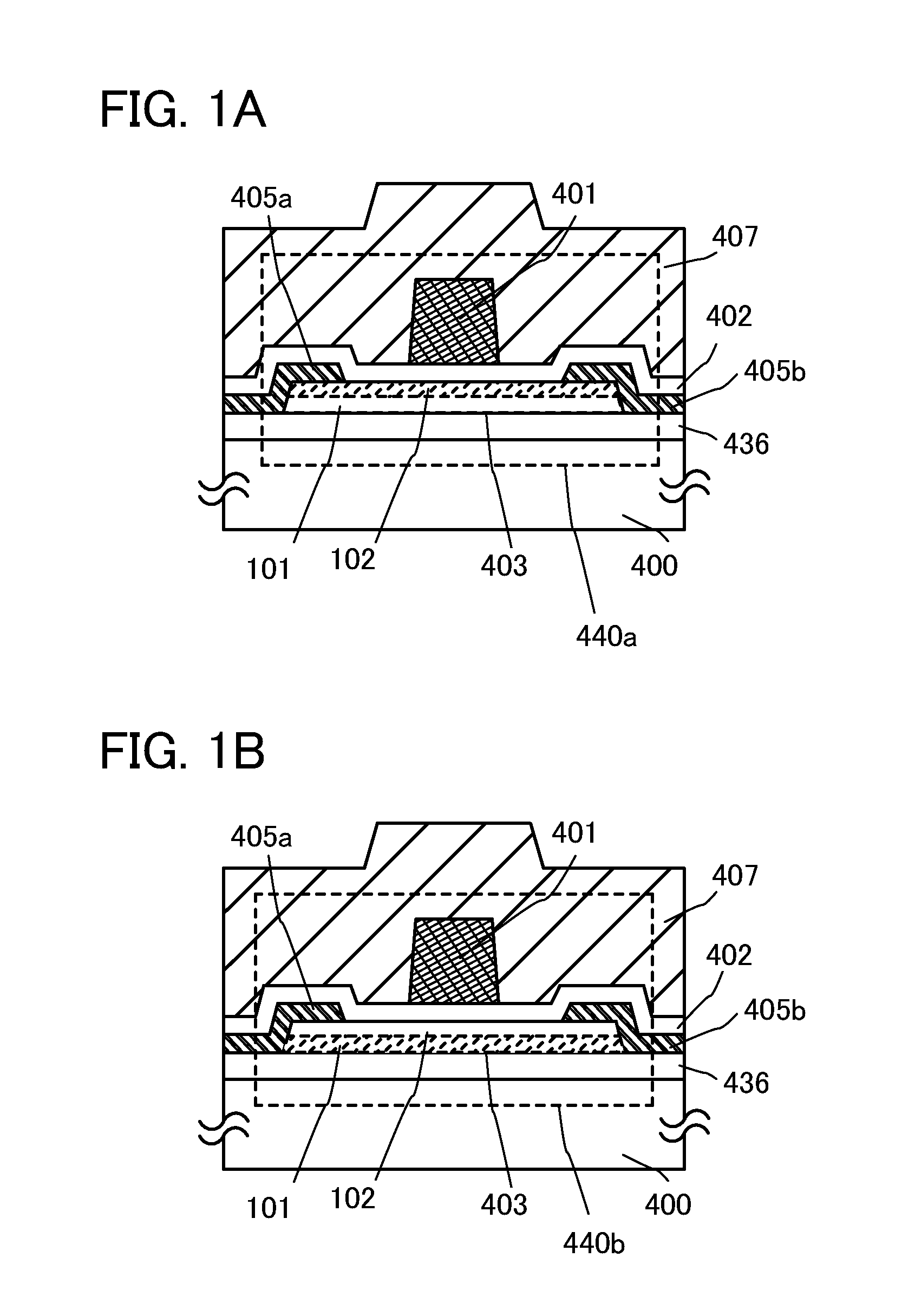

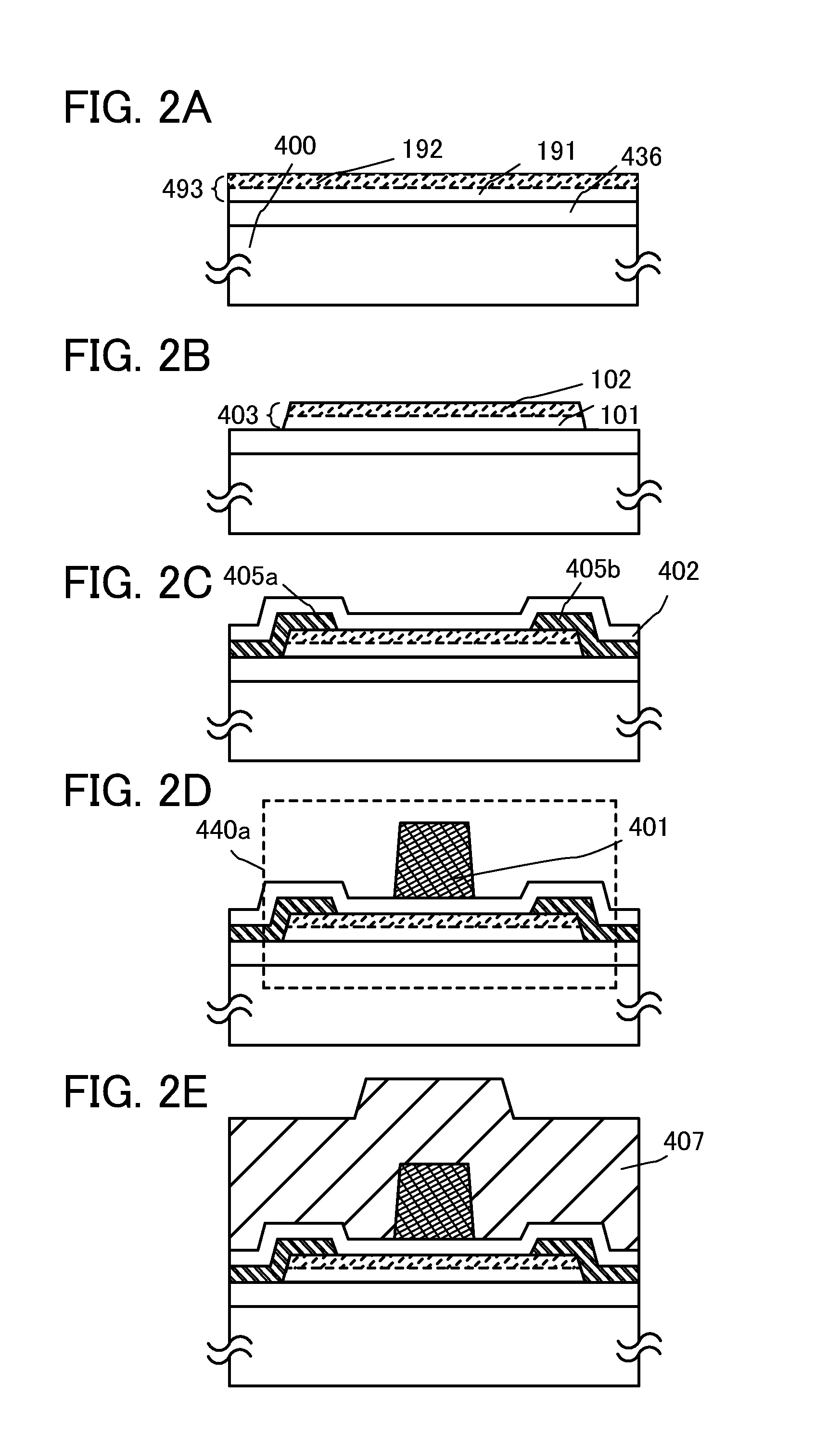

Semiconductor device and method of manufacturing semiconductor device

ActiveUS9123692B2Reduced characteristicsImprove conduction characteristicsTransistorSemiconductor/solid-state device manufacturingEngineeringContact resistance

By reducing the contact resistance between an oxide semiconductor film and a metal film, a transistor that uses an oxide semiconductor film and has excellent on-state characteristics is provided. A semiconductor device includes a pair of electrodes over an insulating surface; an oxide semiconductor film in contact with the pair of electrodes; a gate insulating film over the oxide semiconductor film; and a gate electrode overlapping with the oxide semiconductor film with the gate insulating film interposed therebetween. In the semiconductor device, the pair of electrodes contains a halogen element in a region in contact with the oxide semiconductor film. Further, plasma treatment in an atmosphere containing fluorine can be performed so that the pair of electrodes contains the halogen element in a region in contact with the oxide semiconductor film.

Owner:SEMICON ENERGY LAB CO LTD

Schottky diode and preparation method thereof

PendingCN111146294AReduce reverse leakageImprove breakdown characteristics and conduction characteristicsSemiconductor/solid-state device manufacturingSemiconductor devicesPhysicsAnode

The invention relates to the field of semiconductors, in particular to a Schottky diode and a preparation method thereof. The Schottky diode comprises: a substrate; an n-type gallium oxide layer formed on the substrate, wherein the n-type gallium oxide layer comprises at least one first thermal oxidation region and two second thermal oxidation regions; an anode metal layer which is formed on the n-type gallium oxide layer; the first thermal oxidation region located below the anode metal layer, wherein the second thermal oxidation regions are partially located below the anode metal layer; a cathode metal layer which is formed on the back surface of the substrate, wherein at least one first thermal oxidation region is provided with a groove structure. Compared with an existing Schottky diode, the Schottky diode has the advantages that the electric field at the anode junction is better, and the high-voltage resistance characteristic and the conduction characteristic are better.

Owner:THE 13TH RES INST OF CHINA ELECTRONICS TECH GRP CORP

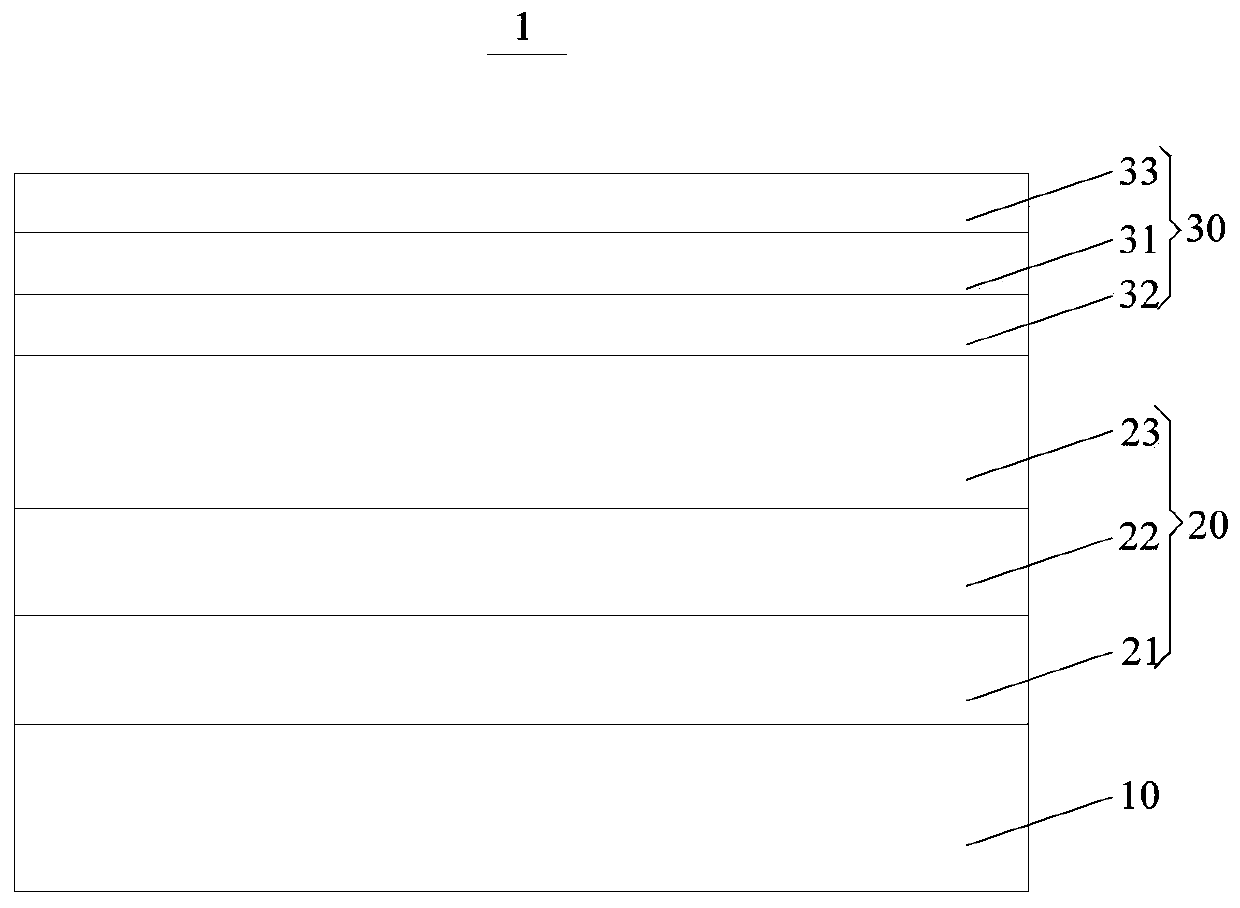

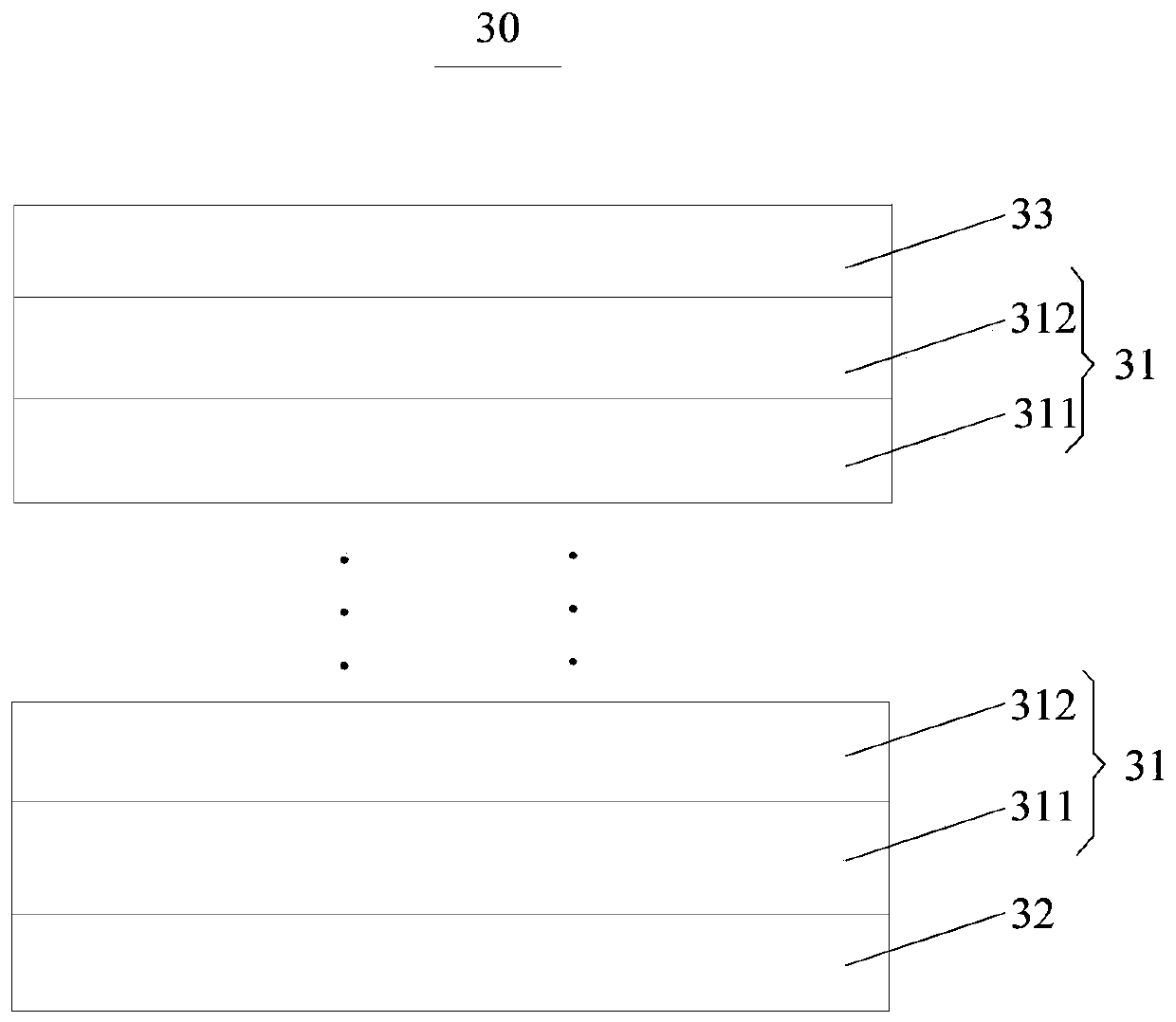

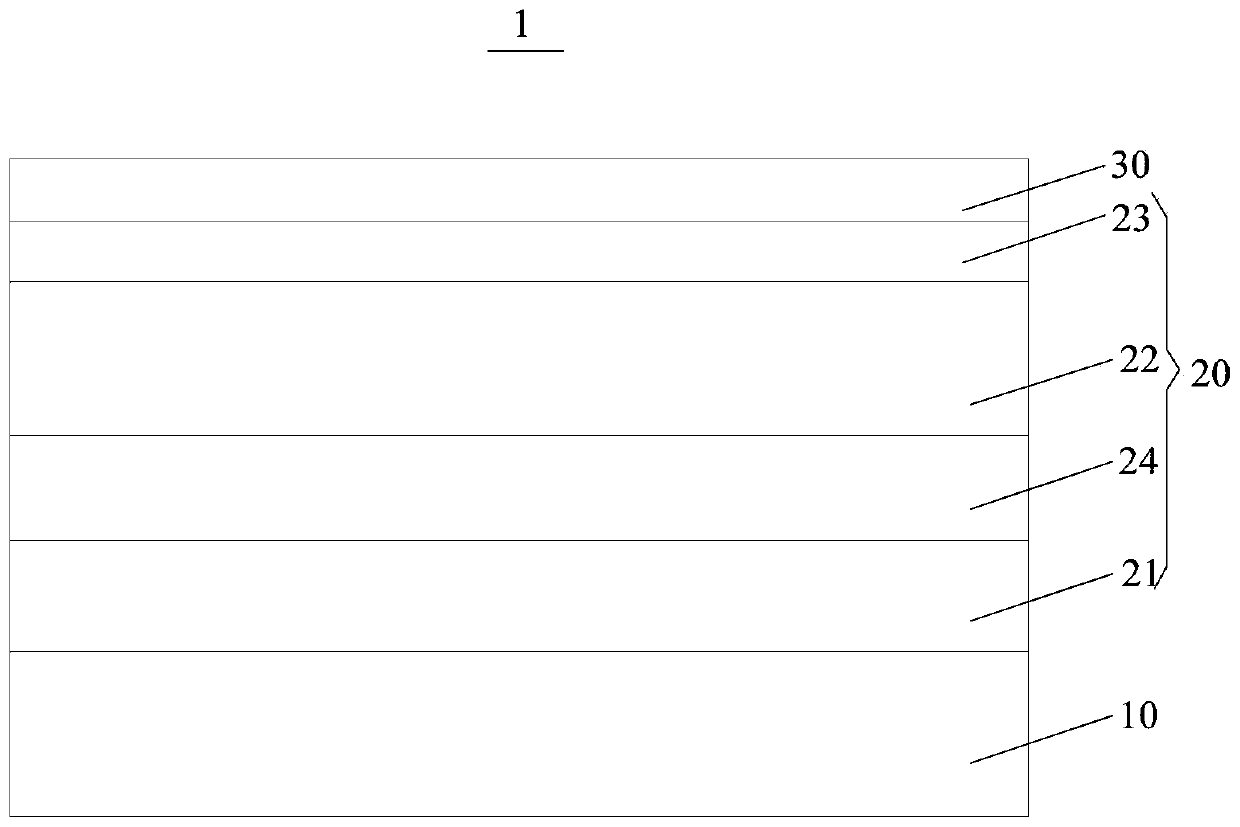

GaN-based semiconductor device and manufacturing method thereof

ActiveCN110600547AImprove conduction characteristicsReduced inverse piezoelectric deformationSemiconductor/solid-state device manufacturingSemiconductor devicesHigh pressureGas concentration

The invention provides a GaN-based semiconductor device and a manufacturing method thereof. The GaN-based semiconductor device comprises a substrate, a nitride semiconductor layer formed based on oneside of the substrate, and a composite barrier layer formed based on one side of the nitride semiconductor layer away from the substrate. The composite barrier layer comprises at least two groups of superlattice barrier layers which are arranged in a stacked manner, each group of superlattice barrier layers comprises a first barrier layer and a second barrier layer which are arranged in a stackedmanner, and Al component content in the first barrier layer is higher than that in the second barrier layer. Thus, the two-dimensional electron gas concentration of a channel is guaranteed through thefirst barrier layer with the higher Al component content to improve the conduction characteristic of the device, the equivalent piezoelectric polarization coefficients of the superlattice barrier layers are reduced through the second barrier layer with the lower Al component content, so that the inverse piezoelectric deformation of the device under a high voltage is reduced, and the reliability of the device is improved.

Owner:XIAMEN SANAN INTEGRATED CIRCUIT

Display panel and preparation method thereof

ActiveCN111293127AImprove and optimize continuityIncrease edge contact yieldSolid-state devicesSemiconductor/solid-state device manufacturingInsulation layerElectrical conductor

The invention provides a display panel and a preparation method thereof. The display panel comprises a substrate layer, a shading metal layer and the first polar plate of a storage capacitor which arepositioned on the substrate layer, a buffer layer which is located on the substrate layer and covers the shading metal layer and the first polar plate, an active layer and the second polar plate of the storage capacitor which are located on the buffer layer, , a gate insulation layer which is located on the buffer layer and the active layer, and a source electrode, a gate electrode and a drain electrode which are located on the gate insulation layer. The width of the source electrode and the width of the drain electrode are both smaller than the width of the active layer. According to the invention, by increasing the conductor area of the active layer, edge contact paths between the active layer and the source electrode and between the active layer and the drain electrode are increased; the edge contact yield of the source electrode, the drain electrode and the active layer is increased by means of the transverse diffusion phenomenon during conductor of the active layer; and the conduction characteristic of a thin film transistor device is greatly improved.

Owner:SHENZHEN CHINA STAR OPTOELECTRONICS SEMICON DISPLAY TECH CO LTD

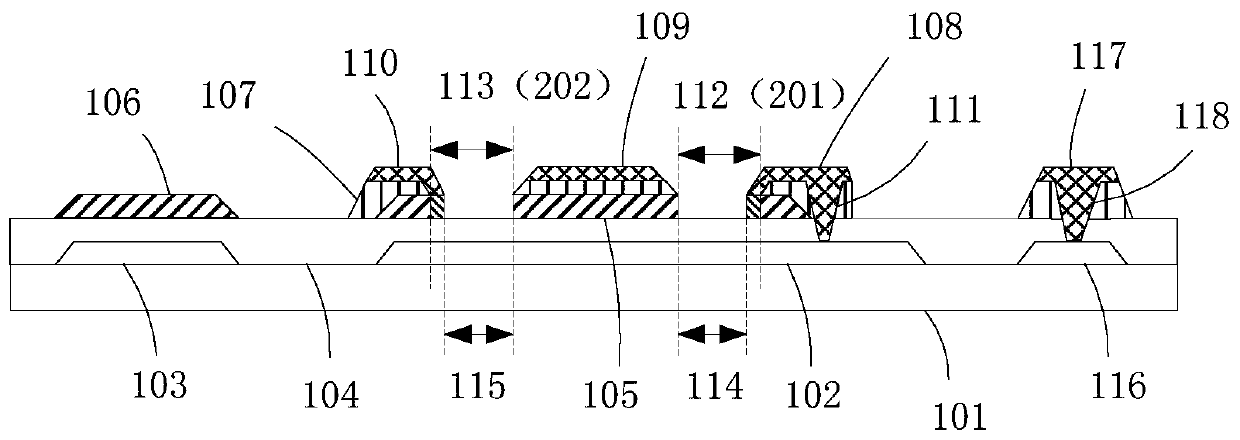

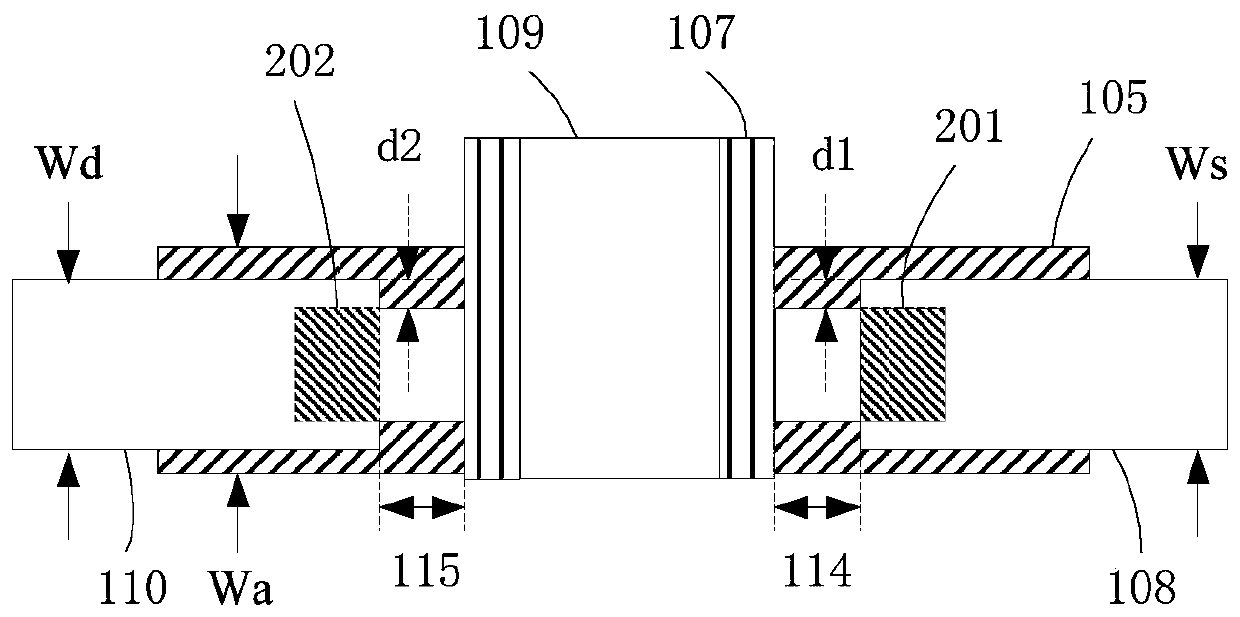

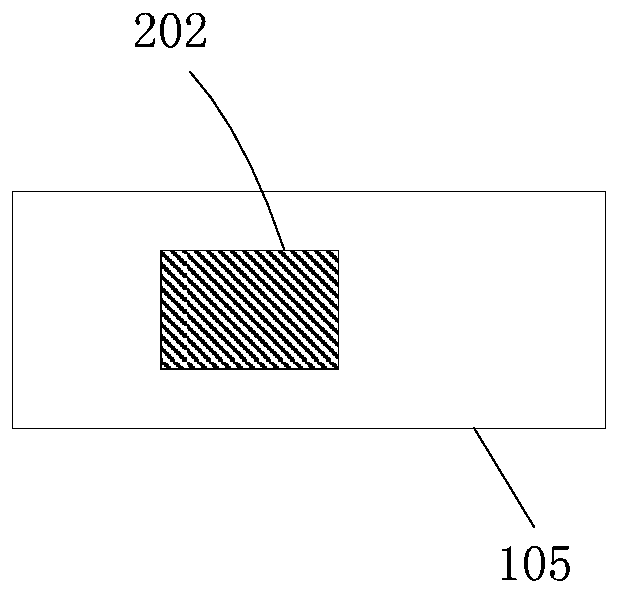

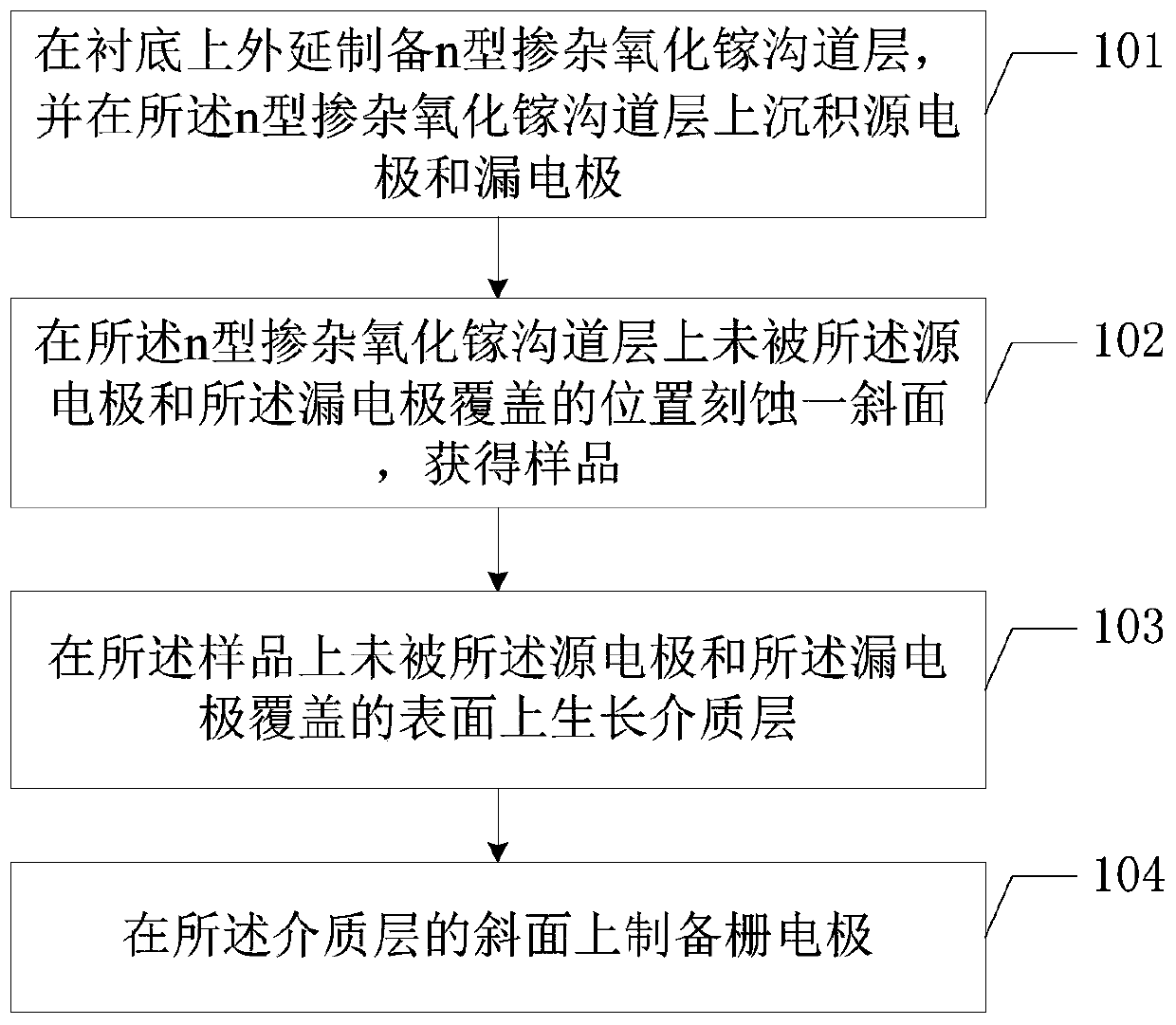

Gallium oxide field effect transistor and preparation method thereof

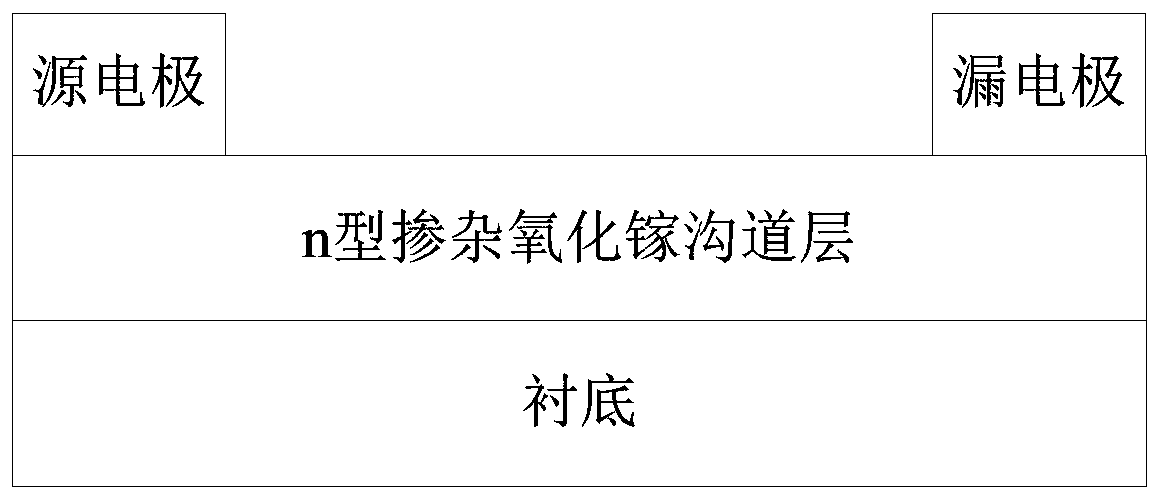

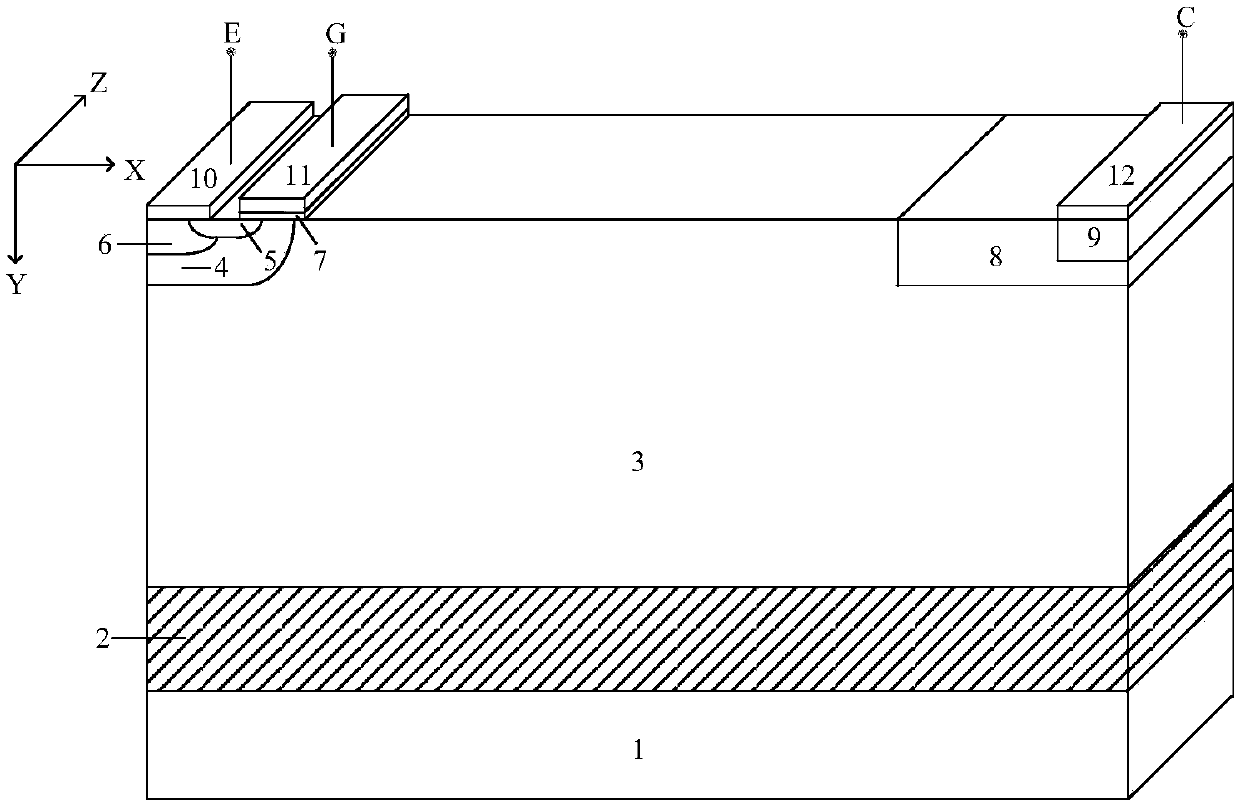

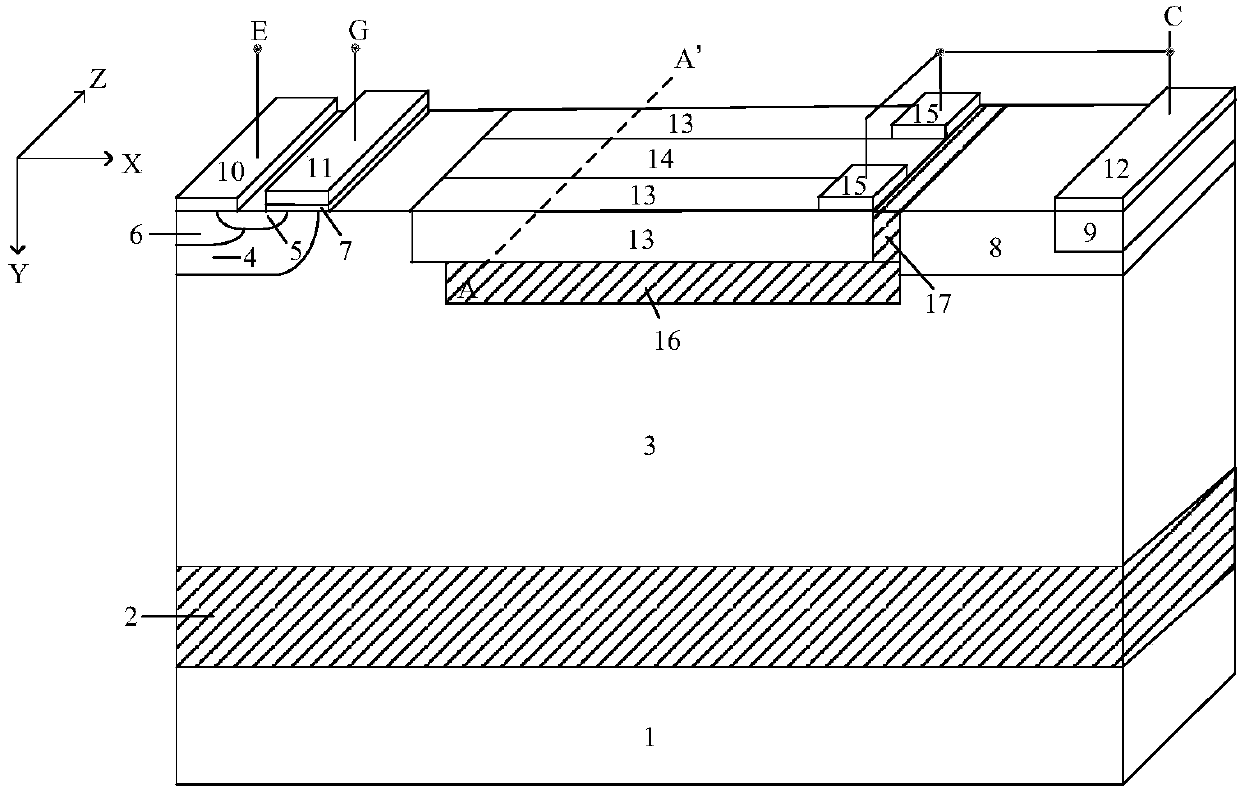

ActiveCN110808212AImprove breakdown voltageImprove conduction characteristicsSemiconductor/solid-state device manufacturingSemiconductor devicesEtchingField effect

The invention is applicable to the technical field of semiconductor manufacturing, and provides a gallium oxide field effect transistor and a preparation method thereof. The preparation method comprises the steps: an n-type doped gallium oxide channel layer is prepared on a substrate in an epitaxial mode, and a source and a drain are deposited on the n-type doped gallium oxide channel layer; a position, which is not covered by the source and the drain, on the n-type doped gallium oxide channel layer is etched into an inclined plane to obtain a sample; a dielectric layer grows on the surface, which is not covered by the source and the drain of the sample; and a gate electrode is prepared on the inclined surface of the dielectric layer. The gate can be located on one inclined plane in an inclined plane etching mode, the angle of the end point, close to the drain, of the gate is increased, a lower peak electric field of the gate is effectively restrained, electric field distribution is more uniform, and therefore the breakdown voltage of the gallium oxide field effect transistor is greatly increased, and the conduction characteristic of the gallium oxide field effect transistor is improved.

Owner:THE 13TH RES INST OF CHINA ELECTRONICS TECH GRP CORP

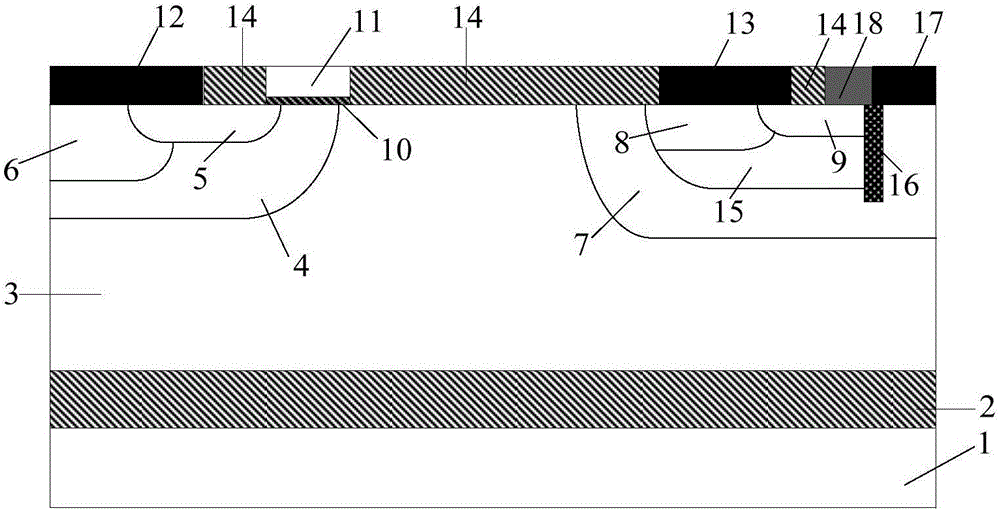

Transverse power device with mixed conductive pattern and preparation method thereof

ActiveCN107785414AReduce conduction voltage dropFast shutdownSemiconductor/solid-state device manufacturingSemiconductor devicesLDMOSVoltage drop

The invention provides a transverse power device with a mixed conductive pattern and a preparation method thereof. The transverse power device includes a P-type liner, a buried oxidation layer, an N-type drift area, a P-type basic area, an N-type buffer area, an N-type source area, a P-type contact area, a P-type collecting electrode area, an emitting electrode, a collecting electrode, a gate medium layer and a gate electrode; the surface of the N-type drift area is provided with N-type strips and P-type strips, the N-type strips and the P-type strips are arrayed on the surface of the drift area of the device body in the direction perpendicular to the length direction of a gutter alternatively, and the drift area below the N-type strips and the P-type strips is internally provided with a medium burying layer; medium groove structures are arranged among the N-type strips, the P-type strips, the medium burying layer and the N-type buffer area; the concentration of the N-type strips and the P-type strips is higher than that of the N-type drift area. According to the transverse power device, mixed conduction of an SJ-LDMOS and an LIGBT at the surface is achieved, a lower conduction voltage drop, a higher endurable voltage, higher switch-on and switch-off speed and lower switch-off loss can be obtained, a snapback effect is eliminated, and the performance of the device is greatly improved.

Owner:UNIV OF ELECTRONICS SCI & TECH OF CHINA