Delta channel doping SiC vertical power MOS device manufacturing method

A technology of MOS device and manufacturing method, applied in the field of microelectronics

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

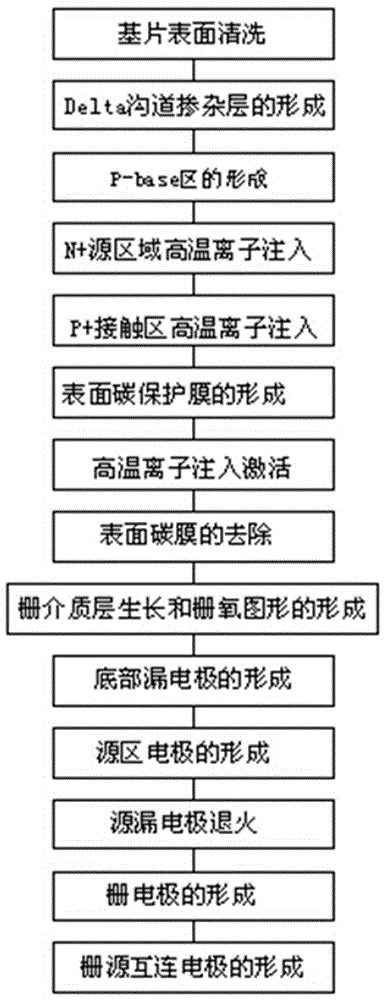

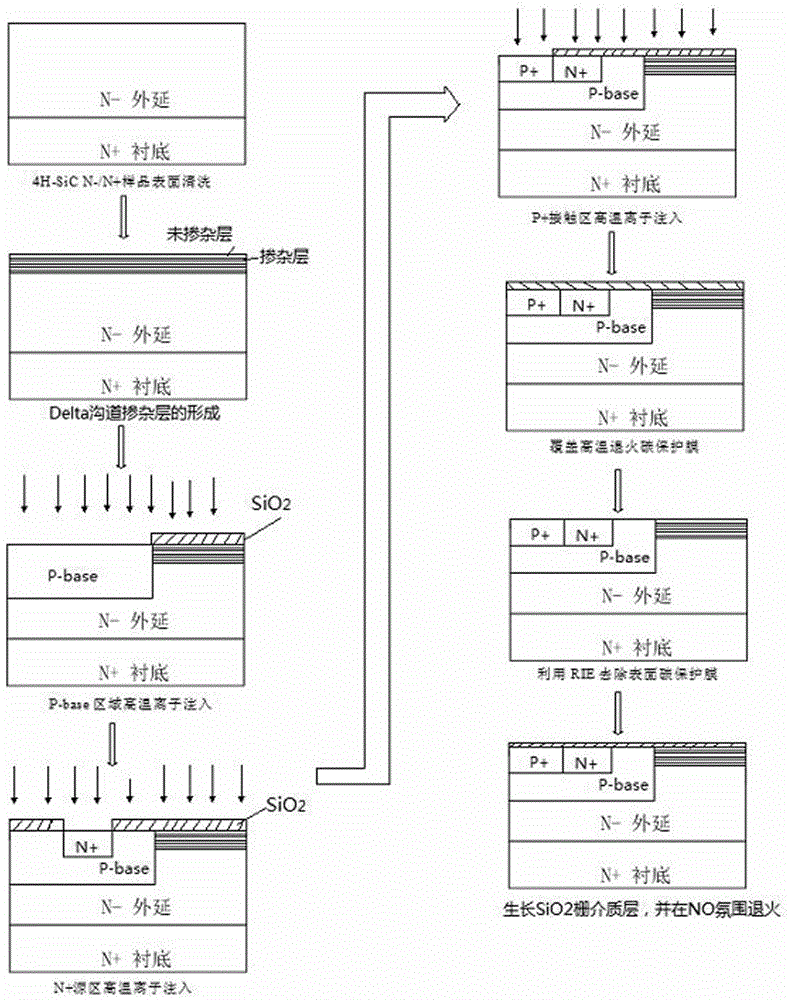

[0095] refer to figure 1 , image 3 and Figure 4 , the preparation and implementation steps of the first embodiment of the present invention are as follows:

[0096] Step 1. Use the standard cleaning method RCA to clean the surface of the 4H-SiCN- / N+ type SiC epitaxial wafer. The specific cleaning process is as follows:

[0097] (1a) Soak the 4H-SiCN- / N+ type SiC epitaxial wafer in acetone and absolute ethanol for 5 minutes each, and then rinse with deionized water to remove the grease on the surface of the SiC epitaxial wafer;

[0098] (1b) Place the SiC epitaxial wafer after the first cleaning in H 2 SO 4 :H 2 o 2 =1:1 (volume ratio) solution soaked for 15min, H 2 SO 4 The concentration is 98%, H 2 o 2 The concentration is 27%, then rinse with deionized water;

[0099] (1c) Place the SiC epitaxial wafer after the second cleaning in HF:H 2 Soak in the solution of O=1:10 (volume ratio) for 1min to rinse off the natural oxide layer, the concentration of HF acid is ...

Embodiment 2

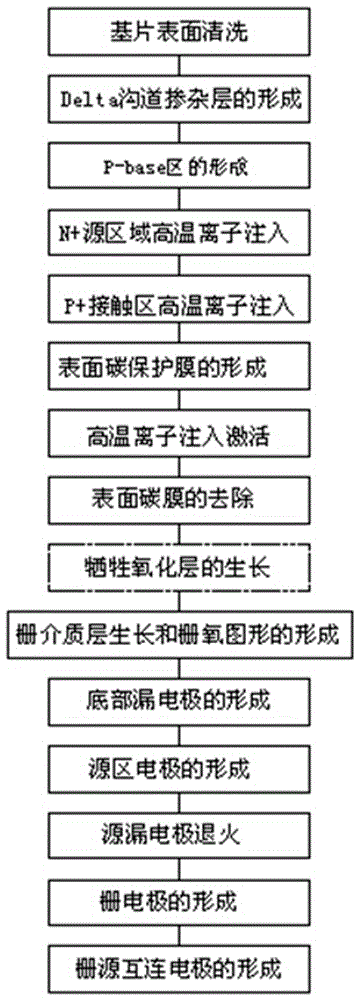

[0228] Compared with Example 1, this example is based on Example 1, after removing the carbon protective film on the front of the N- / N+ SiC epitaxy and growing SiO over a large area 2A growth process of a sacrificial oxide layer is added between the gate dielectric layers, which can more effectively reduce the interface damage caused by high-temperature ion implantation annealing, and effectively improve the flatness of the interface.

[0229] Such as figure 2 , Figure 5 and Image 6 As shown, the implementation steps of this embodiment 2 are as follows (other process contents not mentioned are the same as the previous embodiment):

[0230] Step I, growth of sacrificial oxide layer:

[0231] (Ia) Put the SiC epitaxial wafer that has undergone high-temperature annealing into a high-temperature oxidation furnace, oxidize the surface of the SiC epitaxial wafer under pure dry oxygen at 1200 ° C for 30 minutes, and generate SiO with a thickness of 20 nm on the front side of th...

PUM

| Property | Measurement | Unit |

|---|---|---|

| thickness | aaaaa | aaaaa |

| thickness | aaaaa | aaaaa |

| thickness | aaaaa | aaaaa |

Abstract

Description

Claims

Application Information

Login to View More

Login to View More