Trench silicon carbide power device with low on-resistance and manufacturing process thereof

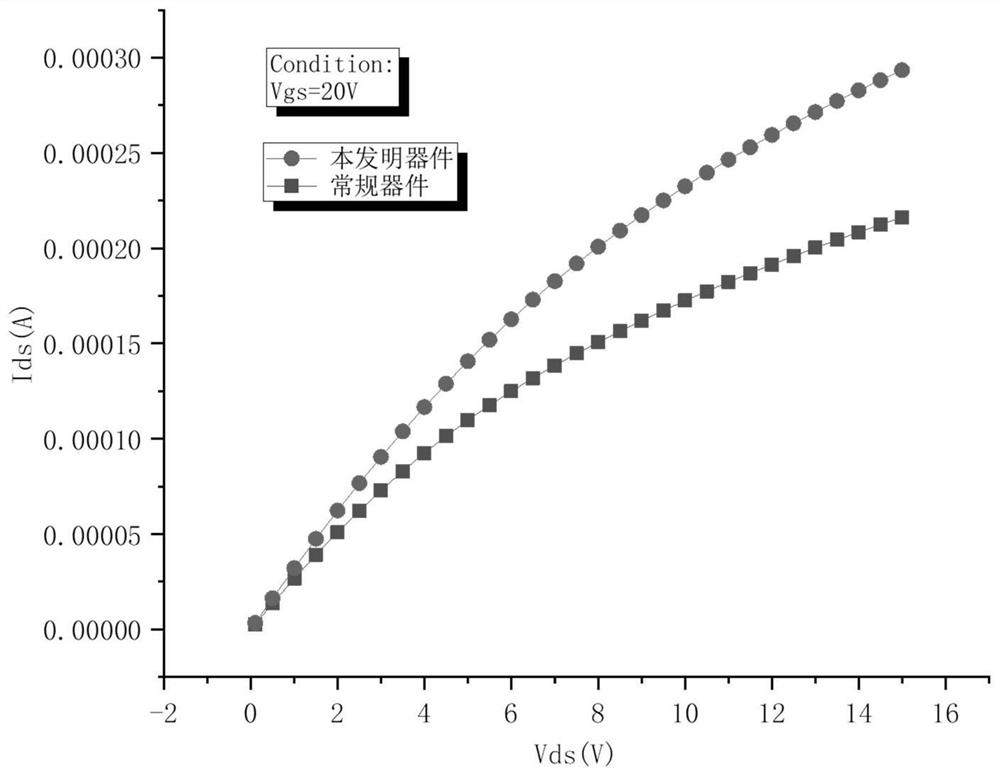

A low on-resistance, power device technology, applied in the field of silicon carbide trench MOS devices and their manufacturing processes, can solve the problems of complex process flow, high interface state density, device failure gate leakage, etc. Process difficulty and effect on equipment requirements

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

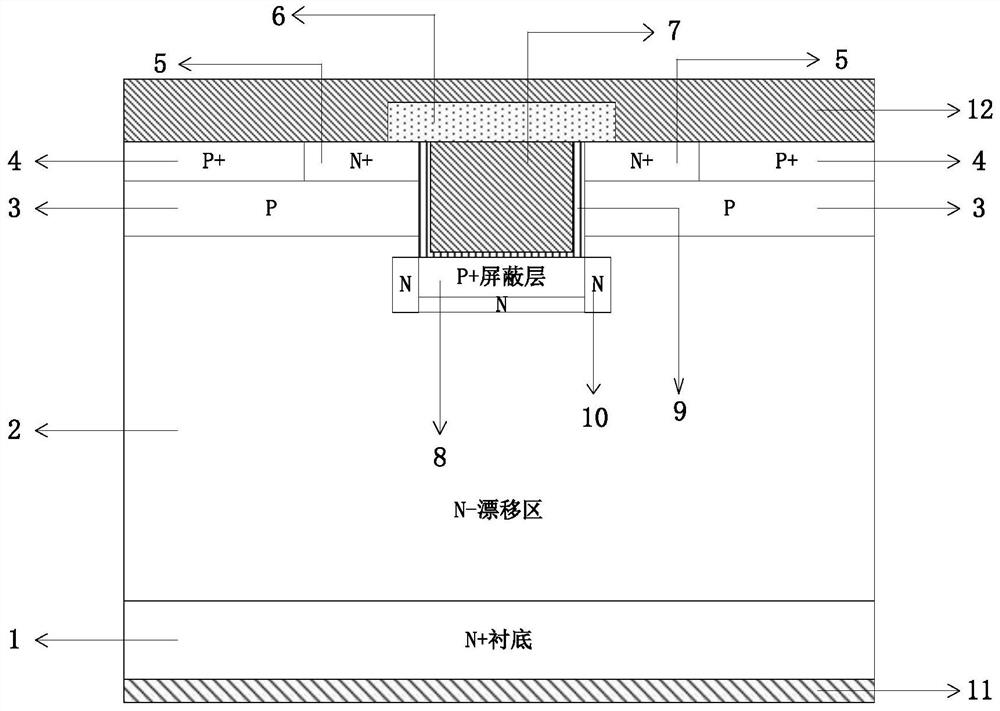

[0034]A trench silicon carbide power device with low on-resistance, comprising: an N-type substrate 1, a drain metal 11 is provided on one side of the N-type substrate 1, and a drain metal 11 is provided on the other side of the N-type substrate 1. The N-type epitaxial layer 2 is provided with a P-type body region 3 on the N-type epitaxial layer 2, and an N-type source region 5 and a P-type body contact region 4 are arranged on the P-type body region 3, and the P-type body contact region 4 is located outside the N-type source region 5, and a trench is opened on the N-type source region 5. The trench passes through the N-type source region 5 and the P-type body contact region 4 and enters the N-type epitaxial layer 2. A gate oxide layer 9 is provided on the bottom and inner walls, a polysilicon gate 7 is provided in the gate oxide layer 9, a passivation layer 6 is covered on the top of the trench, a P-type shielding layer 8 is provided under the trench, and a P-type shielding la...

Embodiment 2

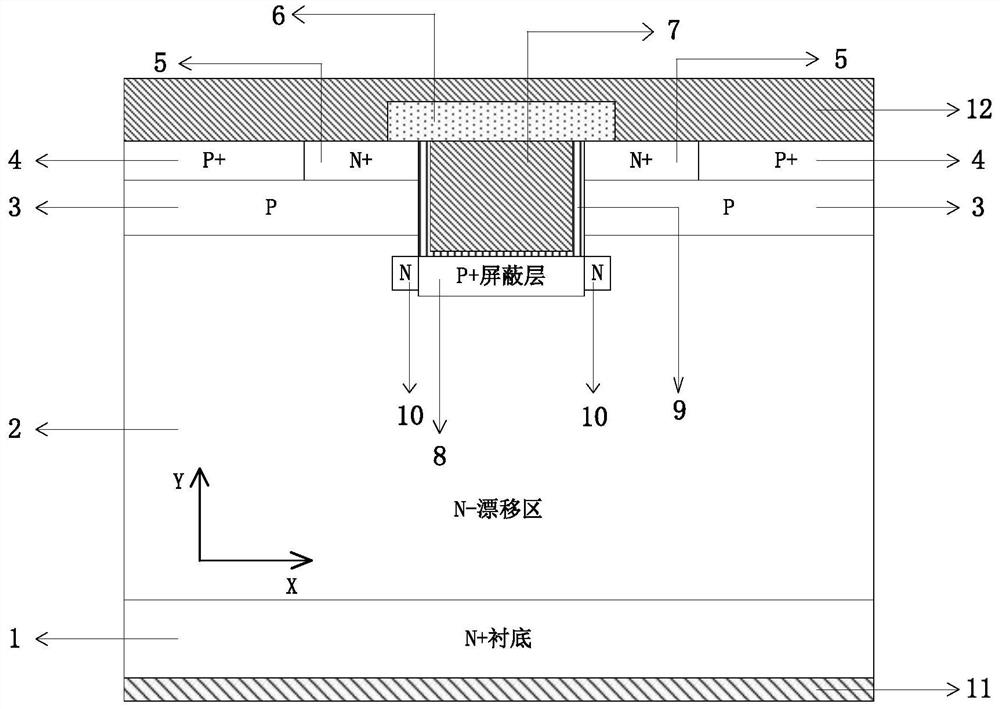

[0037] A manufacturing process of trench silicon carbide power devices with low on-resistance, with figure 2 The XY axis shown is the reference, including the following steps:

[0038] Take an N-type substrate 1, and make an N-type epitaxial layer 2 on one surface of the N-type substrate 1. The N-type epitaxial layer 2 is made by epitaxially growing a part of the N-type epitaxial layer on the N-type substrate 1. On the grown N-type epitaxial layer, ion implantation is used to form a P-type shielding layer 8 and an N-type buried layer 10, and then another part of the N-type epitaxial layer is epitaxially grown, and the two parts of the N-type epitaxial layer are stacked to form a complete N-type epitaxial layer. type epitaxial layer 2;

[0039] Prepare the P-type body region 3, the N-type source region 5, and the P-type body contact region 4 on the other N-type epitaxial layer according to this, and then perform groove etching on the N-type source region 5, and the groove As...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More