Formation method of semiconductor structure

一种半导体、栅极结构的技术,应用在半导体结构的形成领域,能够解决抬高源/漏区缺陷等问题

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0035] When the prior art adopts the raised source / drain region formed by the selective epitaxy process, especially when forming the carbon silicon source / drain region, the process is difficult to control, and the formed carbon silicon source / drain region has many defects and relatively high resistance. Big.

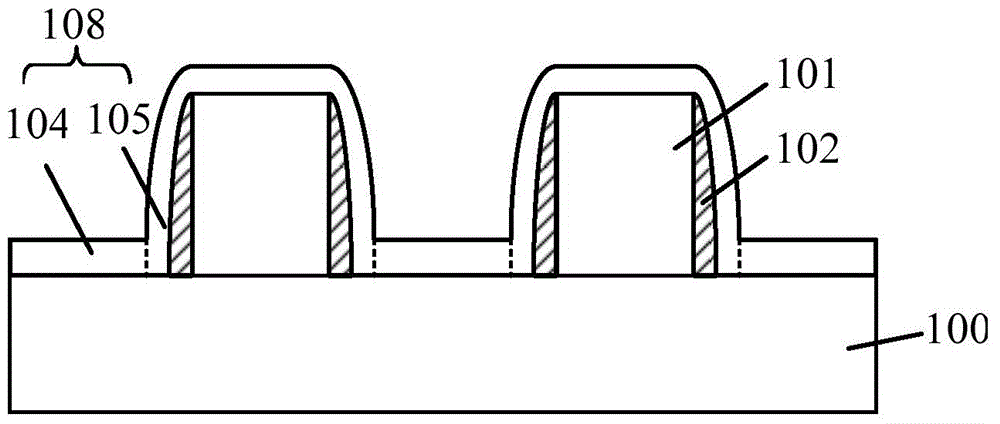

[0036] In order to solve the above problems, an embodiment of the present invention provides a method for forming raised source / drain regions, please refer to Figure 1 ~ Figure 3 , first refer to figure 1 A semiconductor substrate 100 is provided, the material of the semiconductor substrate 100 is a single crystal silicon layer, a gate structure 101 is formed on the semiconductor substrate 100, and sidewalls 102 are formed on both sidewall surfaces of the gate structure 101, so The material of the sidewall 102 is silicon nitride, and grooves (not shown in the figure) may be formed in the semiconductor substrate 100 on both sides of the gate structure 101; figure 1 , ...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More