Silicon carbide trench MOSFET device and manufacturing method thereof

A technology of silicon carbide trenches and manufacturing methods, which is applied in semiconductor/solid-state device manufacturing, semiconductor devices, electrical components, etc., and can solve problems such as unfavorable device conduction characteristics, gate dielectric layer breakdown, and high device on-resistance

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0048] In order to make the object, technical solution and advantages of the present invention clearer, the present invention will be further described in detail below in conjunction with specific embodiments and with reference to the accompanying drawings.

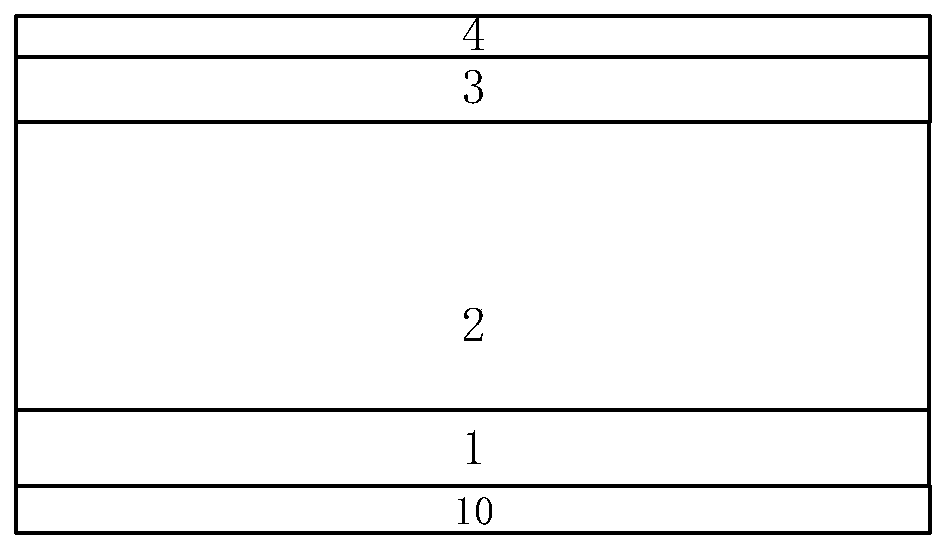

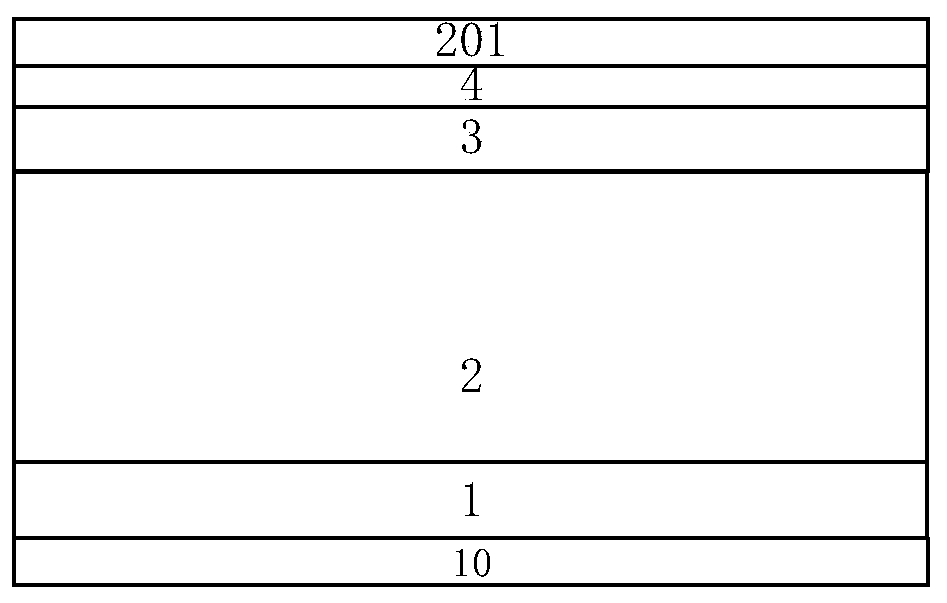

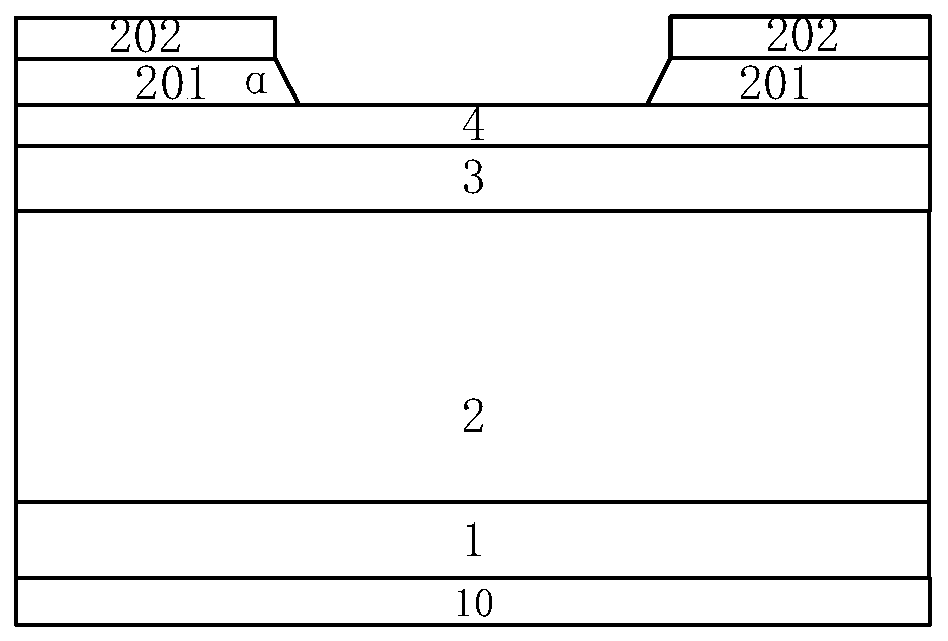

[0049] One aspect of the embodiments of the present invention provides a silicon carbide trench MOSFET device structure. The device structure of the silicon carbide trench MOSFET device includes an N+ type silicon carbide substrate 1, above which is an N-type drift Region 2, P-type base region 3, N+ type source region 4. There is a drain electrode 10 at the bottom of the N+ type substrate 1, and an inverted trapezoidal deep trench is arranged on the top of the N-type epitaxial layer, the trench includes a gate dielectric layer 6 and a gate electrode 7, and the inclination angle θ of the trench is 54.74°. The sidewall of the trench is the {0-33-8} plane system, and the epitaxial growth plane selected for the N+ type silico...

PUM

| Property | Measurement | Unit |

|---|---|---|

| angle | aaaaa | aaaaa |

| thickness | aaaaa | aaaaa |

| thickness | aaaaa | aaaaa |

Abstract

Description

Claims

Application Information

Login to View More

Login to View More