Silicon carbide MOSFET device and manufacturing method thereof

A silicon carbide and device technology, applied in semiconductor/solid-state device manufacturing, semiconductor devices, electrical components, etc., can solve problems such as low work efficiency, high power loss, and poor robustness

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

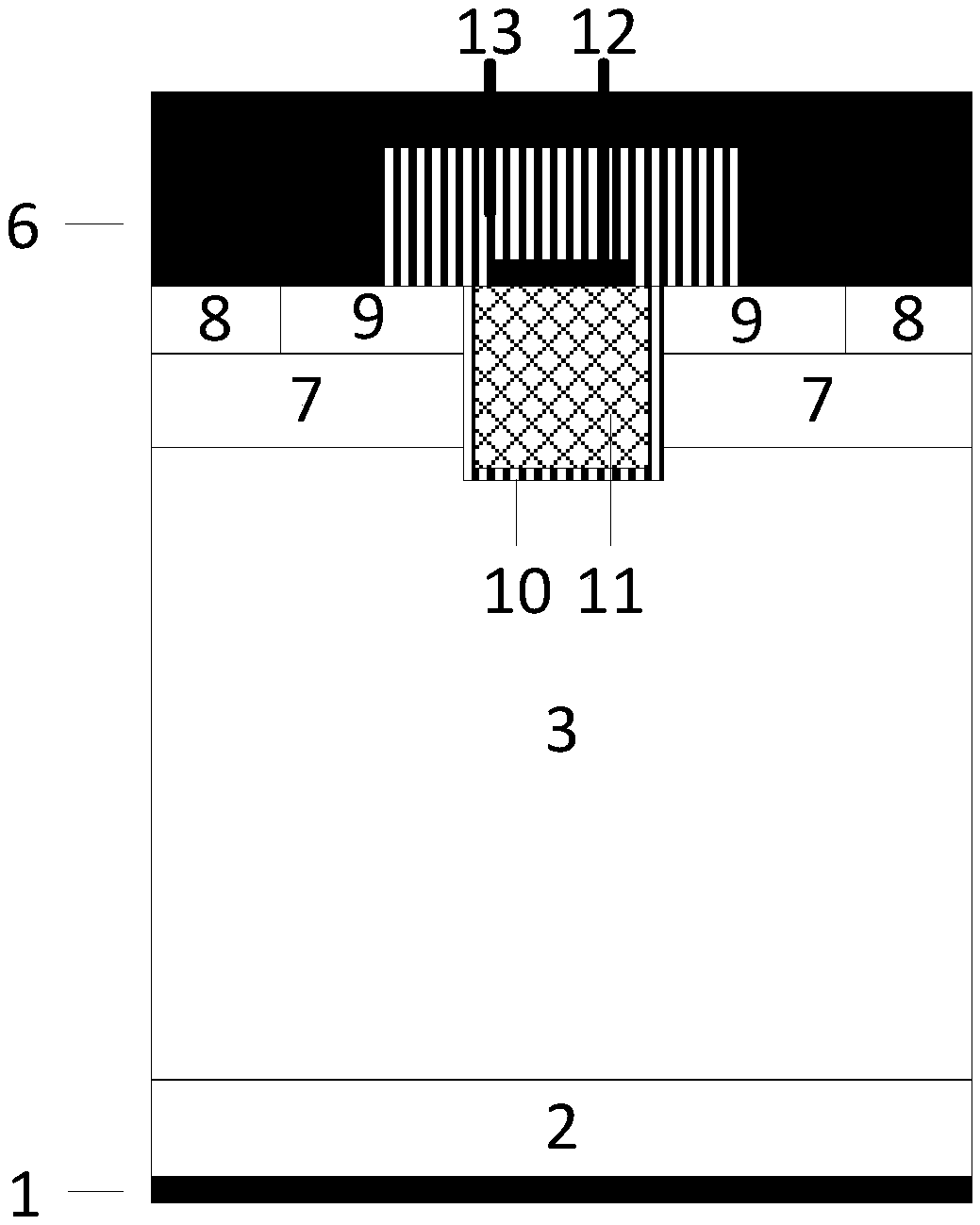

Embodiment 1

[0140] A silicon carbide MOSFET device, the cell structure of its basic structure is as follows figure 2 As shown, it includes metal drain 1, silicon carbide N + Substrate 2 and SiC N - epitaxial layer 3; the silicon carbide N - There is a first source trench on the upper left of the epitaxial layer 3, and there are silicon carbide P+ doped regions 5 and silicon carbide P-type doped regions 4 below the first source trench from top to bottom; the silicon carbide N - There is a second source trench on the upper right of the epitaxial layer 3, and there are silicon carbide P+ doped regions 5 and silicon carbide P-type doped regions 4 below the second source trench from top to bottom; both the first and second source trenches are filled Schottky contact metal 14 is formed; there is a gate trench above the silicon carbide N- epitaxial layer 3, the depth of which is shallower than the two source trenches, and a gate structure is formed inside and on the surface of the gate trench...

Embodiment 2

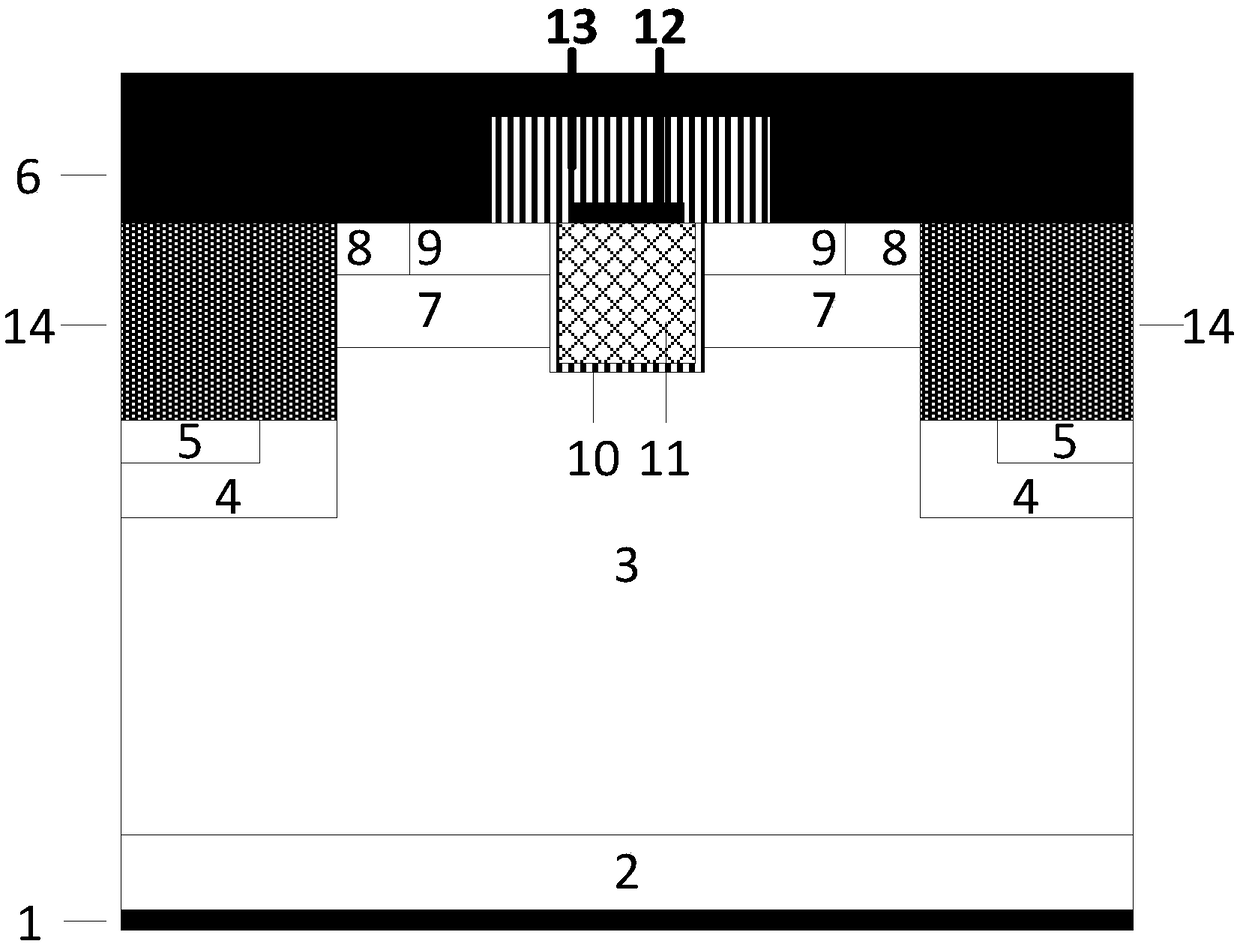

[0143] The structure of this embodiment is roughly the same as that of Embodiment 1, except that the Schottky contact metal 14 used is replaced by polysilicon 15, as image 3 shown. Also, a Si / SiC heterojunction structure with a rectifying contact is formed on the sidewall at the bottom of the source trench and the silicon carbide N-epitaxy 3 . The forward conduction voltage drop Von of the heterojunction structure is about 1.1V, which also has a greater effect on the operation of the third quadrant of the device. At the same time, since the heterojunction is a multi-sub-device, the diode has good reverse recovery performance.

Embodiment 3

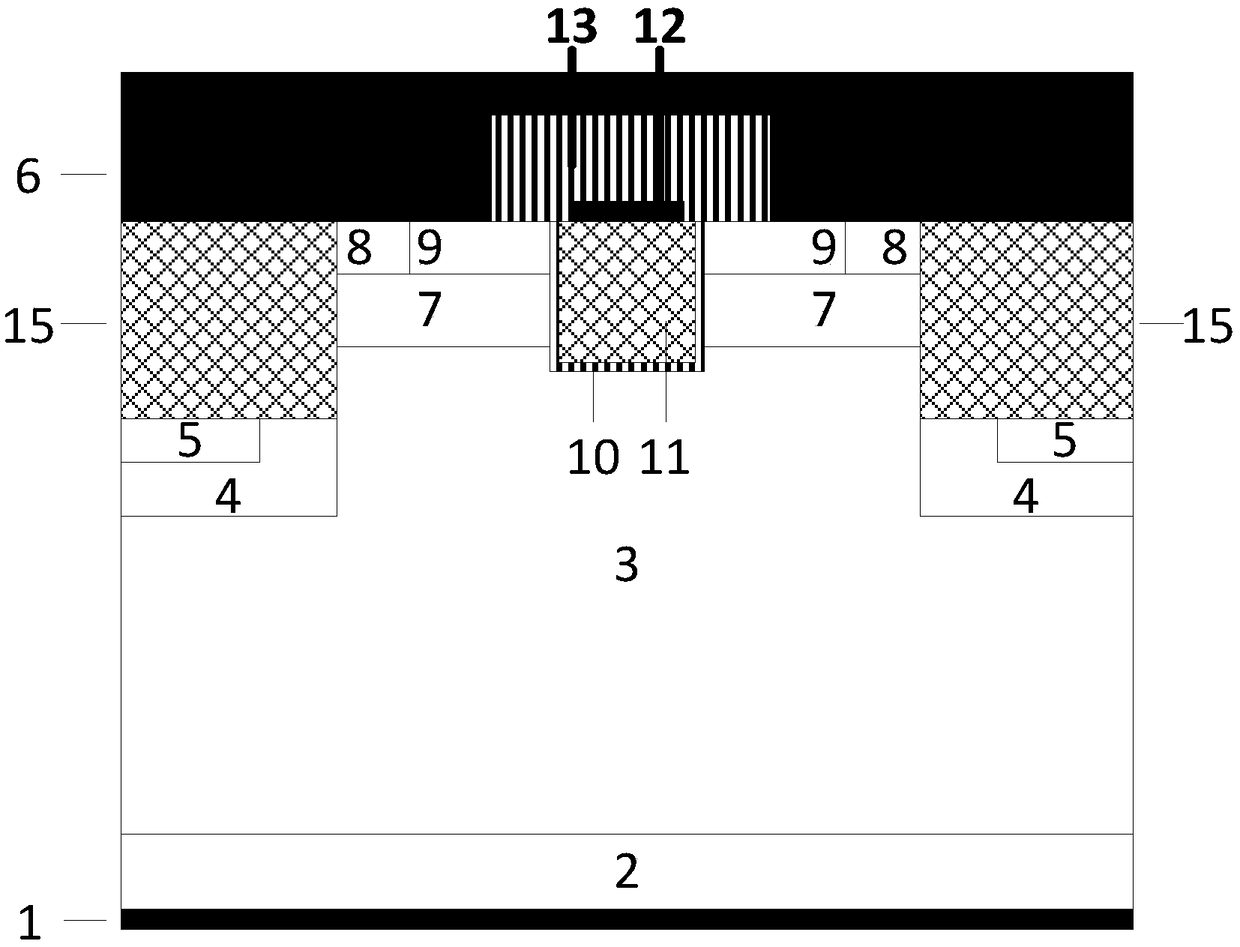

[0145] The difference between this embodiment and Embodiment 1 is that the bottom region of the gate structure has a split-gate structure, such as Figure 4shown. The split-gate structure includes a split-gate polysilicon 16 and a gate dielectric layer 10 surrounding the split-gate polysilicon 16 . The split-gate polysilicon 16 is led out by a metal lead at the back, which can be grounded or shorted to the source. This method significantly reduces the gate drain charge of the device, thereby reducing the Miller capacitance, and has a great optimization effect on improving the switching speed of the device.

PUM

| Property | Measurement | Unit |

|---|---|---|

| thickness | aaaaa | aaaaa |

| width | aaaaa | aaaaa |

| width | aaaaa | aaaaa |

Abstract

Description

Claims

Application Information

Login to View More

Login to View More