Patents

Literature

943 results about "Electron-beam lithography" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

Electron-beam lithography (often abbreviated as e-beam lithography, EBL) is the practice of scanning a focused beam of electrons to draw custom shapes on a surface covered with an electron-sensitive film called a resist (exposing). The electron beam changes the solubility of the resist, enabling selective removal of either the exposed or non-exposed regions of the resist by immersing it in a solvent (developing). The purpose, as with photolithography, is to create very small structures in the resist that can subsequently be transferred to the substrate material, often by etching.

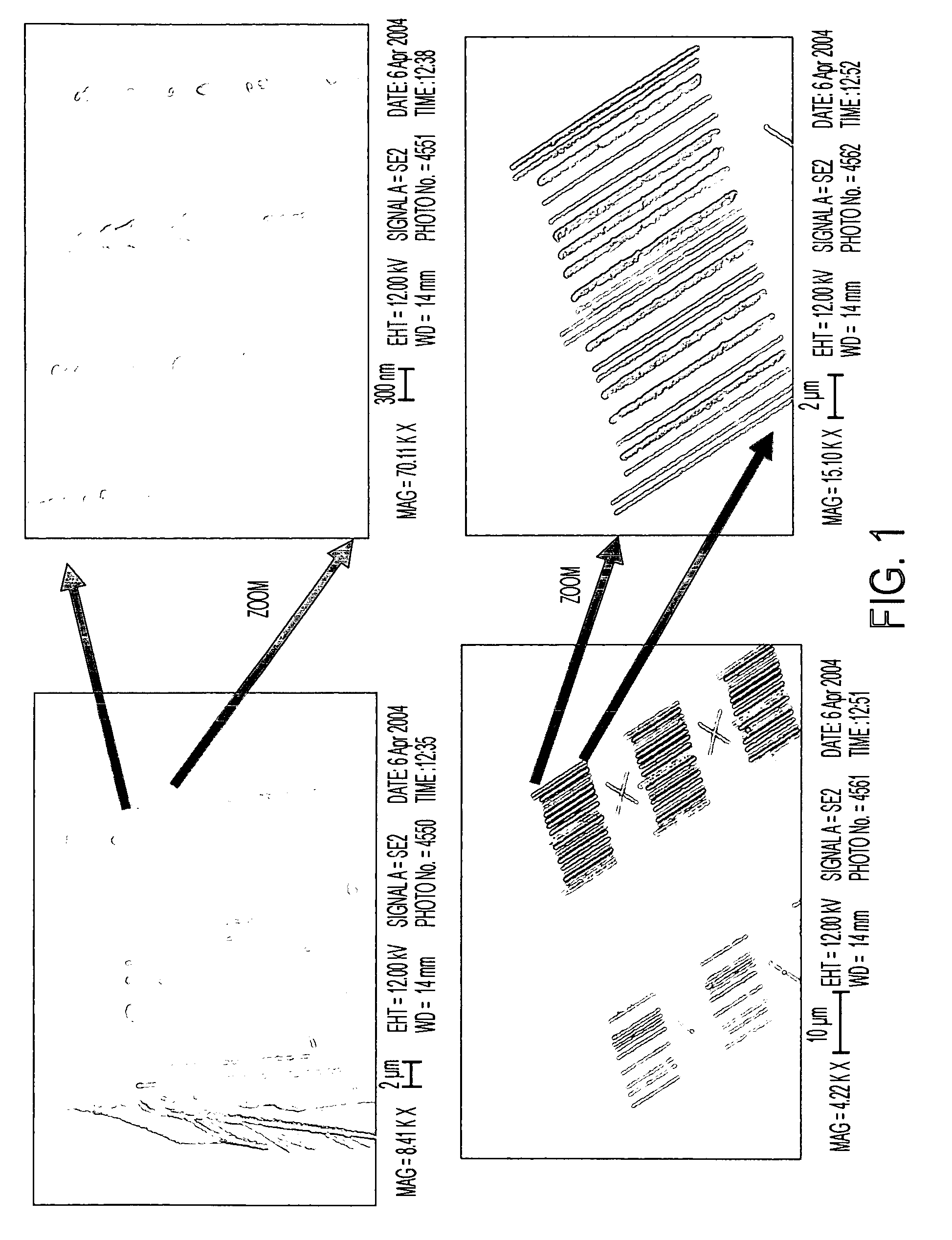

Fabrication of sub-50 nm solid-state nanostructures based on nanolithography

InactiveUS20060014001A1High resolutionMaterial nanotechnologyDecorative surface effectsResistDip-pen nanolithography

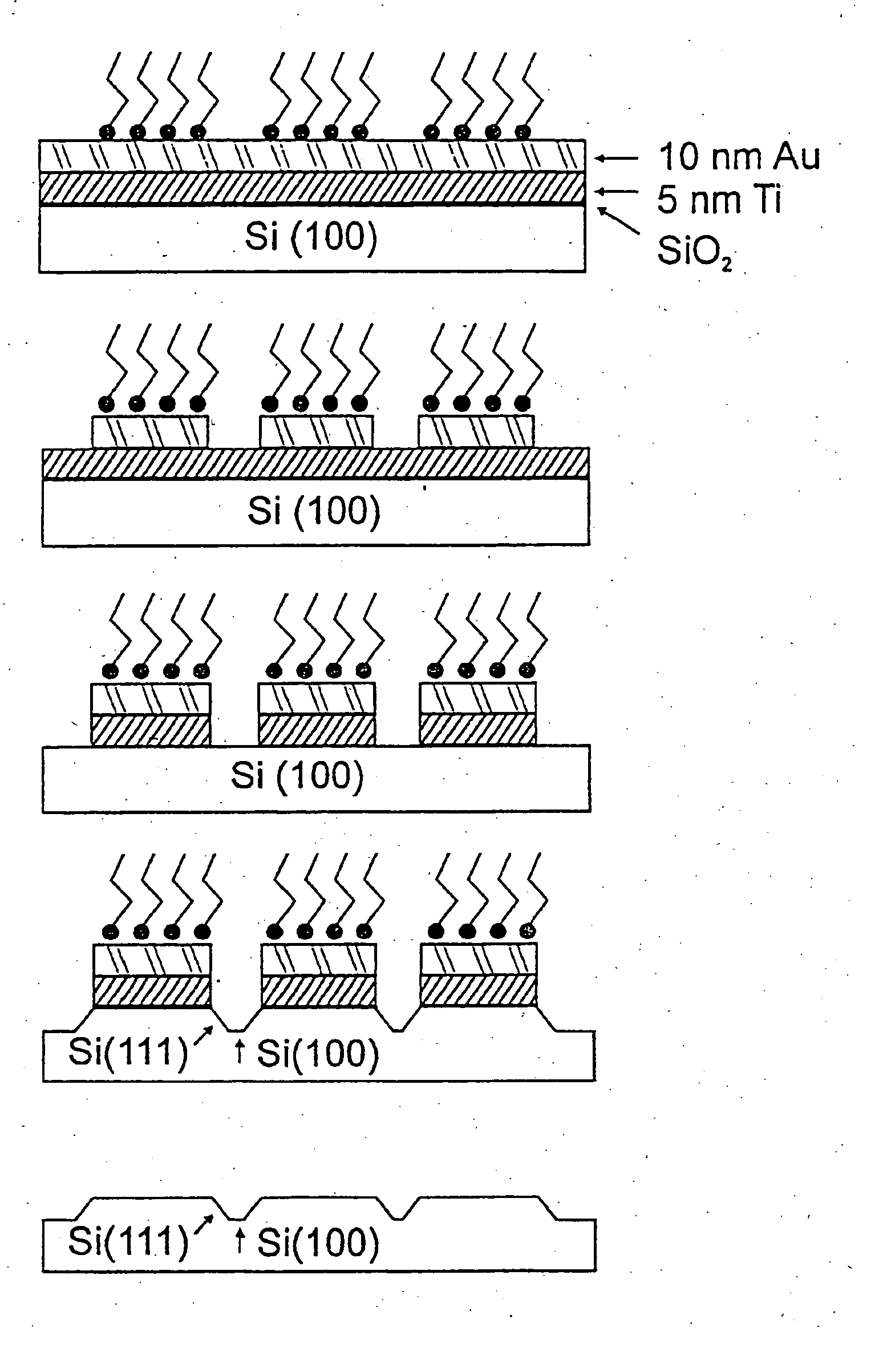

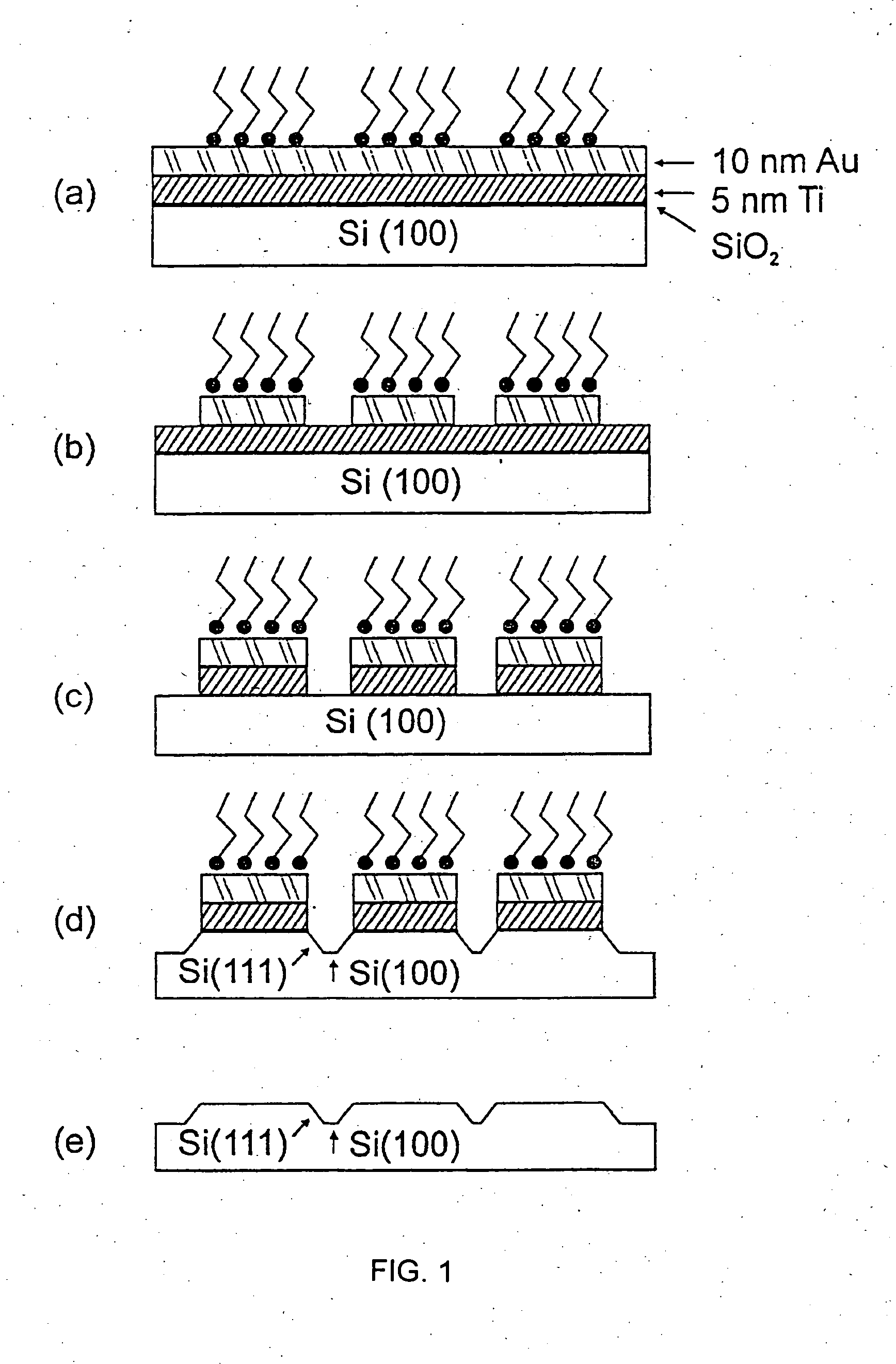

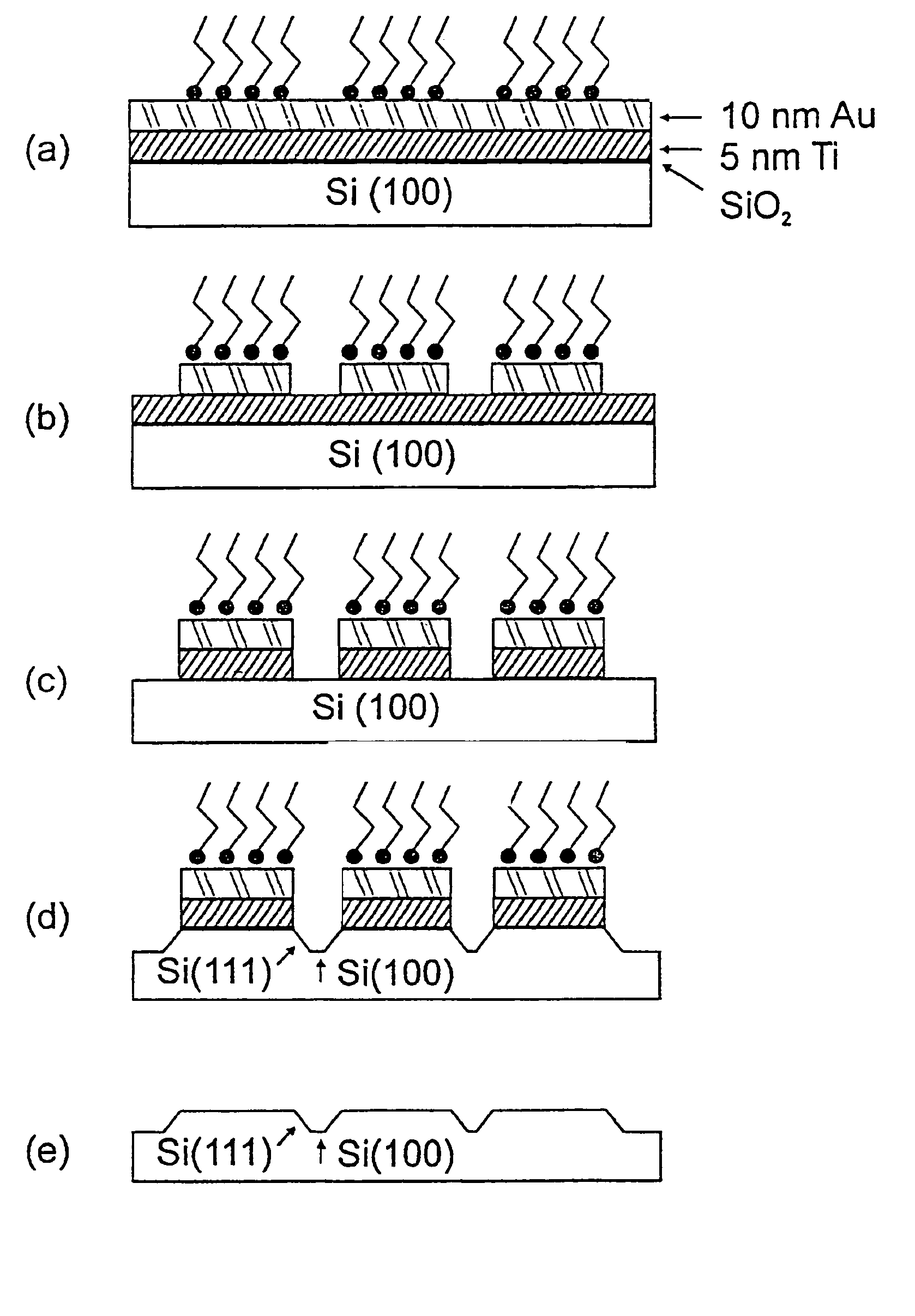

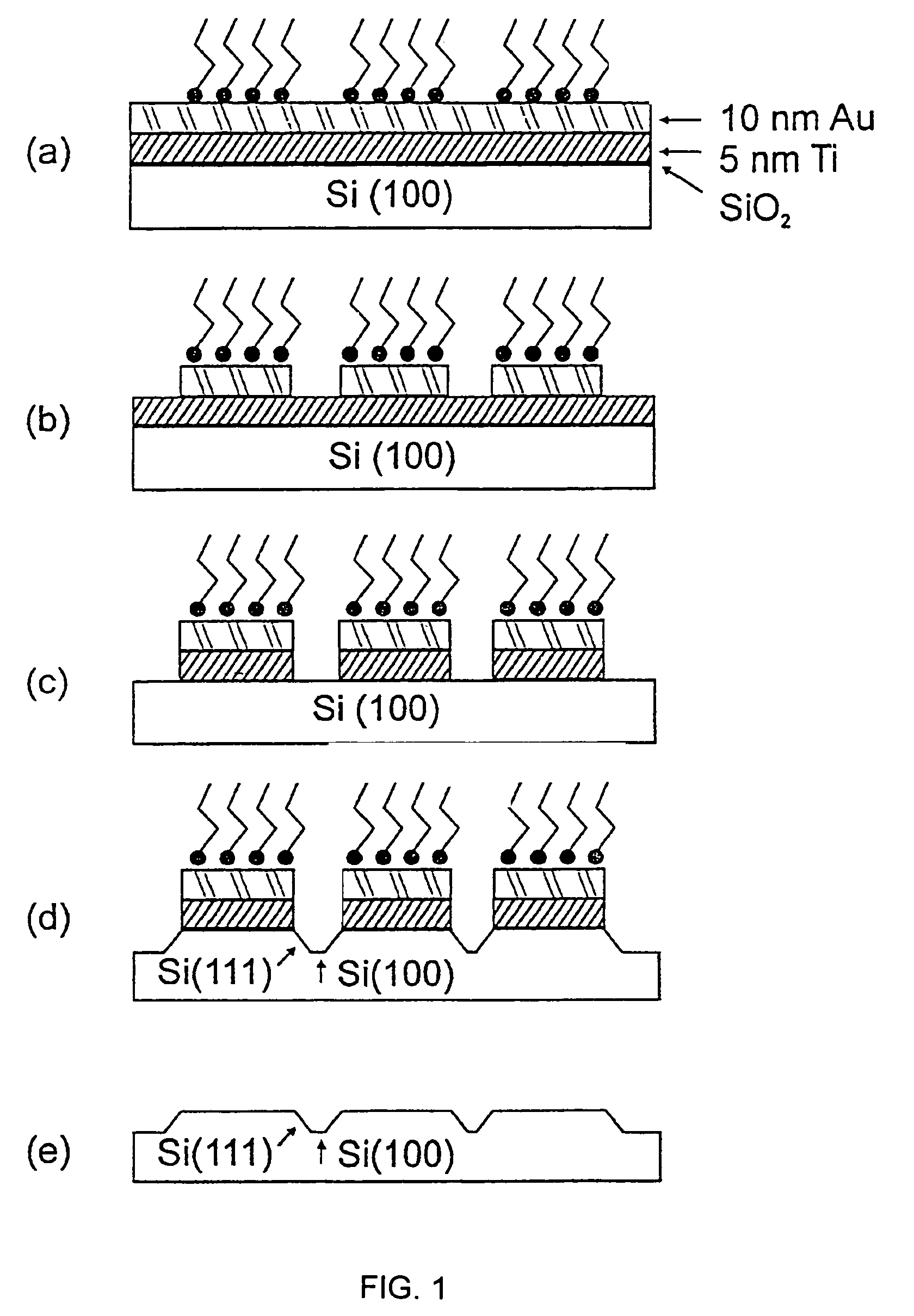

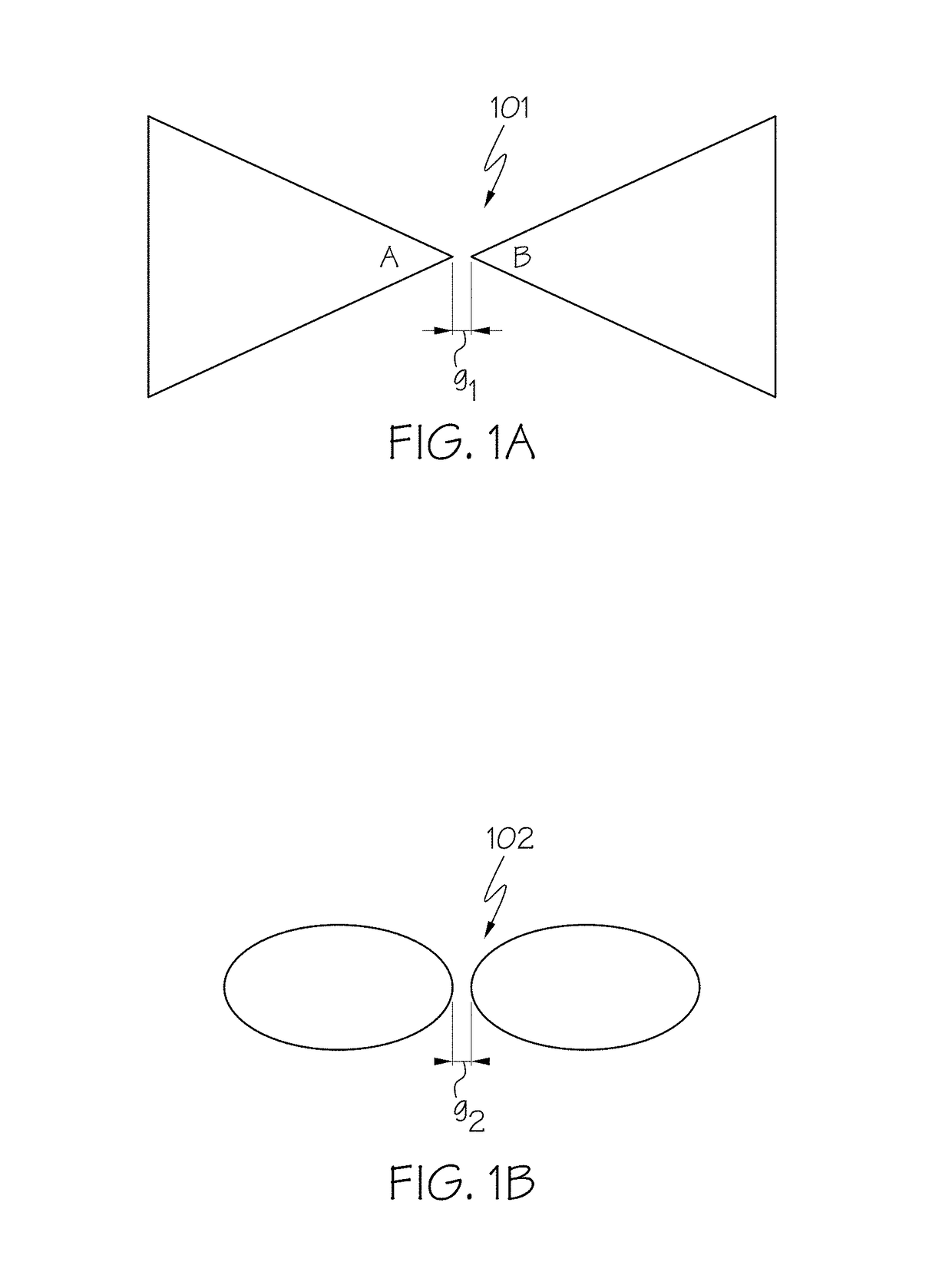

Combination of nanolithography and wet chemical etching including the fabrication of nanoarrays of sub-50 nm gold dots and line structures with deliberately designed approximately 12-100 nm gaps. These structures were made by initially using direct write nanolithography to pattern the etch resist, 16-mercaptohexadecanoic acid (MHA), on Au / Ti / SiOx / Si substrates and then wet chemical etching to remove the exposed gold. These are the smallest Au structures prepared by a wet chemical etching strategy. Also, Dip-Pen Nanolithography (DPN) has been used to generate resist layers on Au, Ag, and Pd that when combined with wet chemical etching can lead to nanostructures with deliberately designed shapes and sizes. Monolayers of mercaptohexadecanoic acid (MHA) or octadecanethiol (ODT), patterned by DPN, were explored as etch resists. They work comparably well on Au and Ag, but ODT is the superior material for Pd. MHA seems to attract the FeCl3 etchant and results in nonuniform etching of the underlying Pd substrate. Dots, lines, triangles and circles, ranging in size from sub-100 to several hundred nm have been fabricated on these substrates. These results show how one can use DPN as an alternative to more complex and costly procedures like electron beam lithography to generate nanostructures from inorganic materials.

Owner:NORTHWESTERN UNIV

Semiconductor device and a manufacturing method of the same

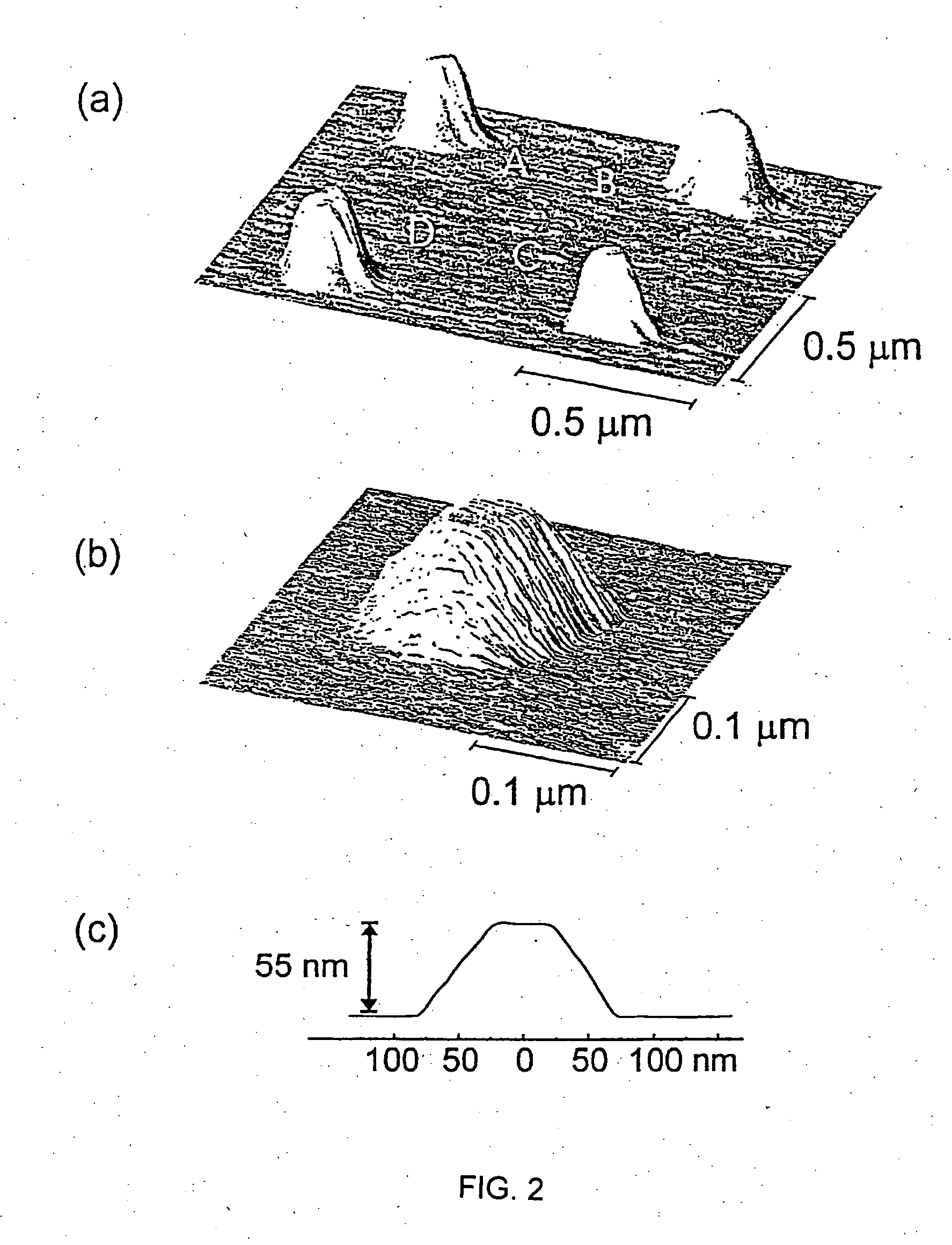

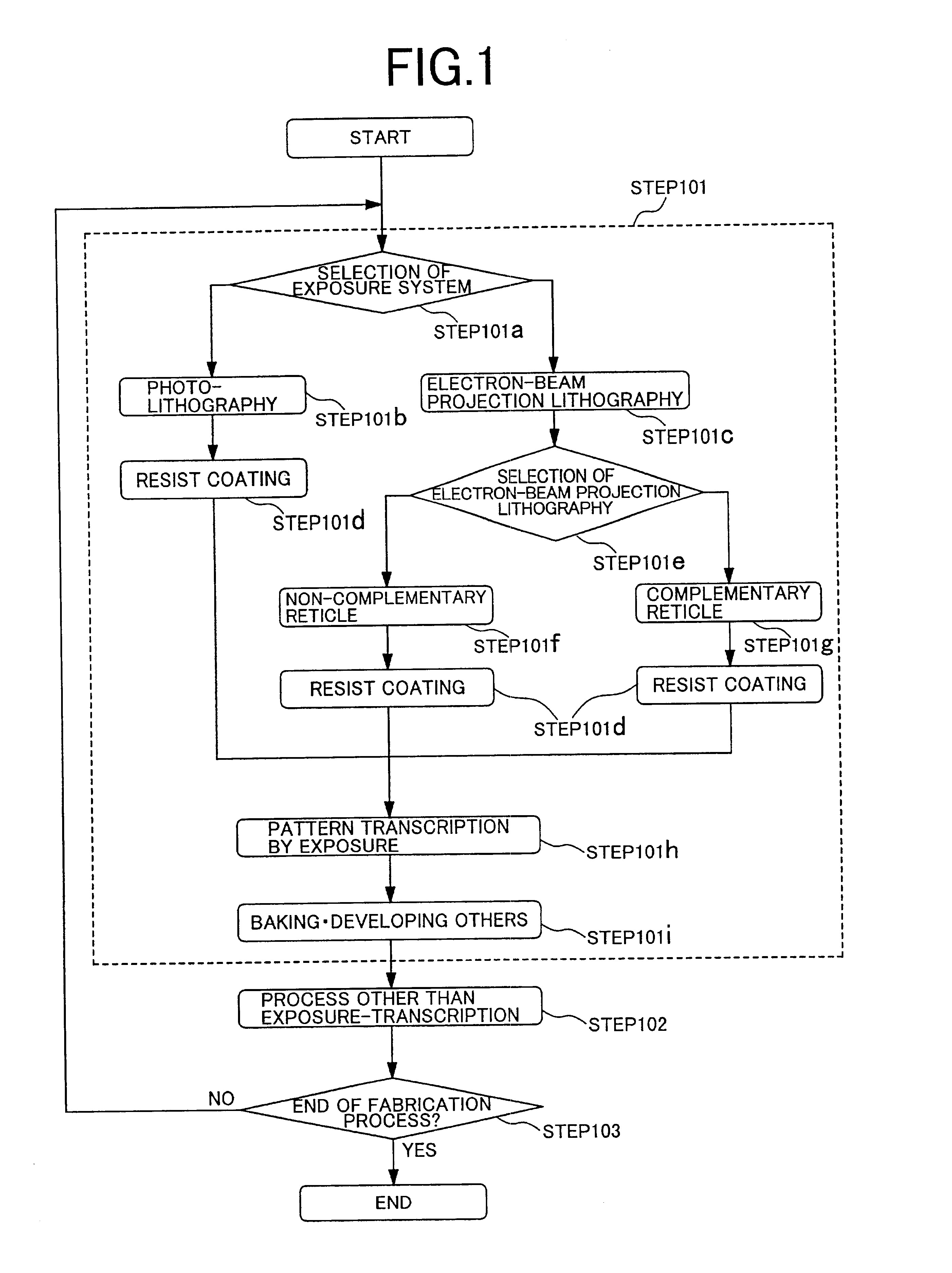

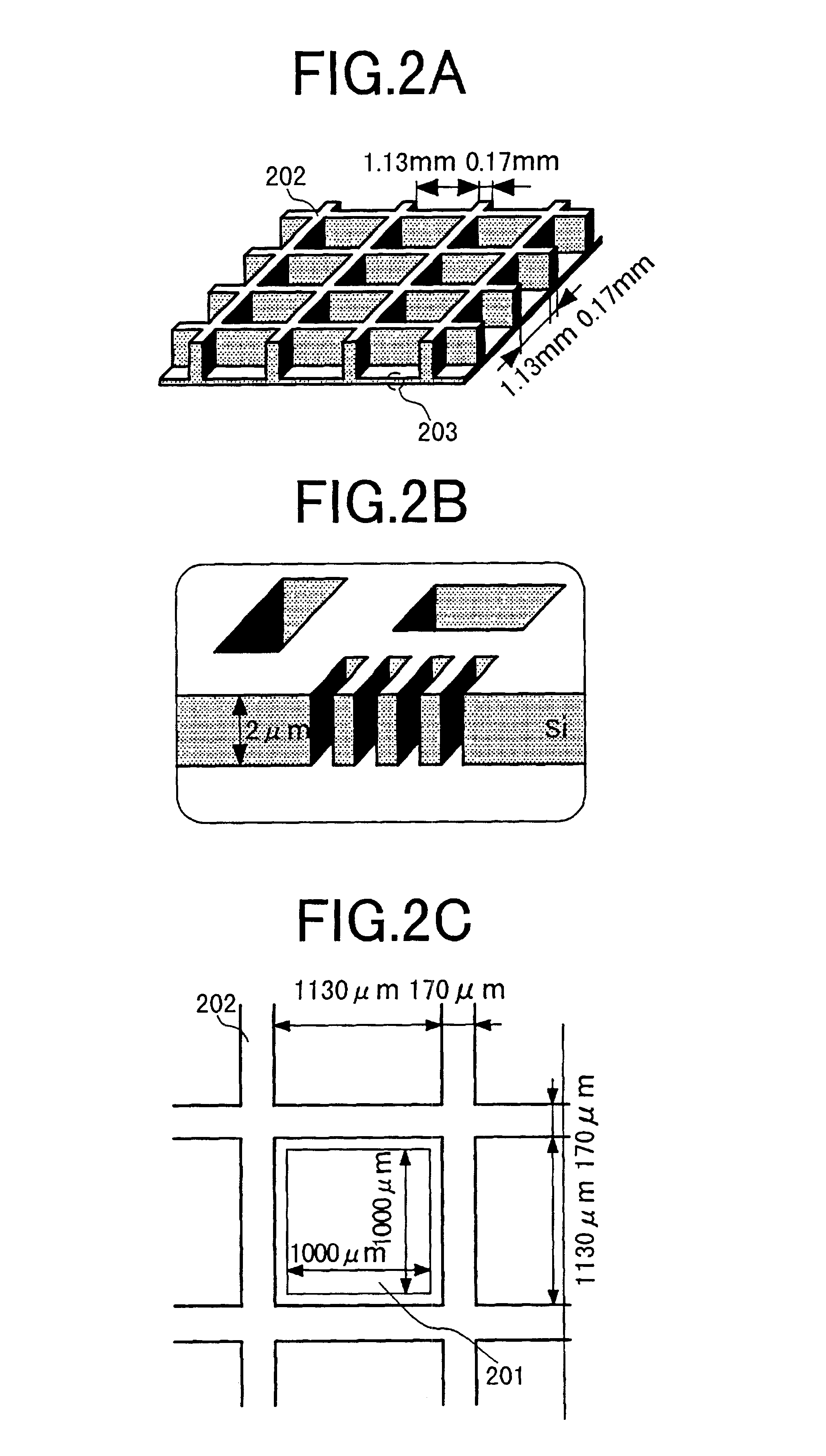

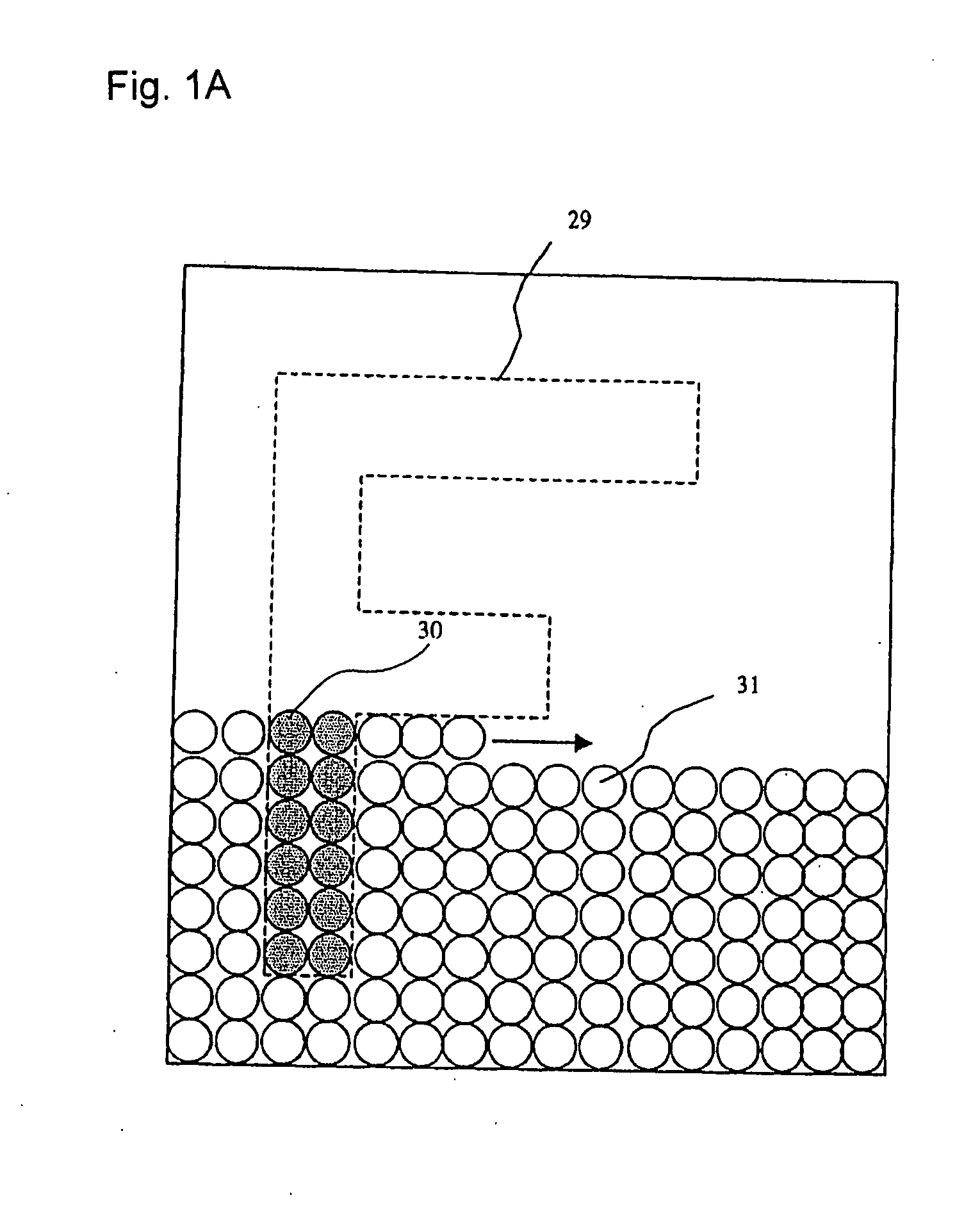

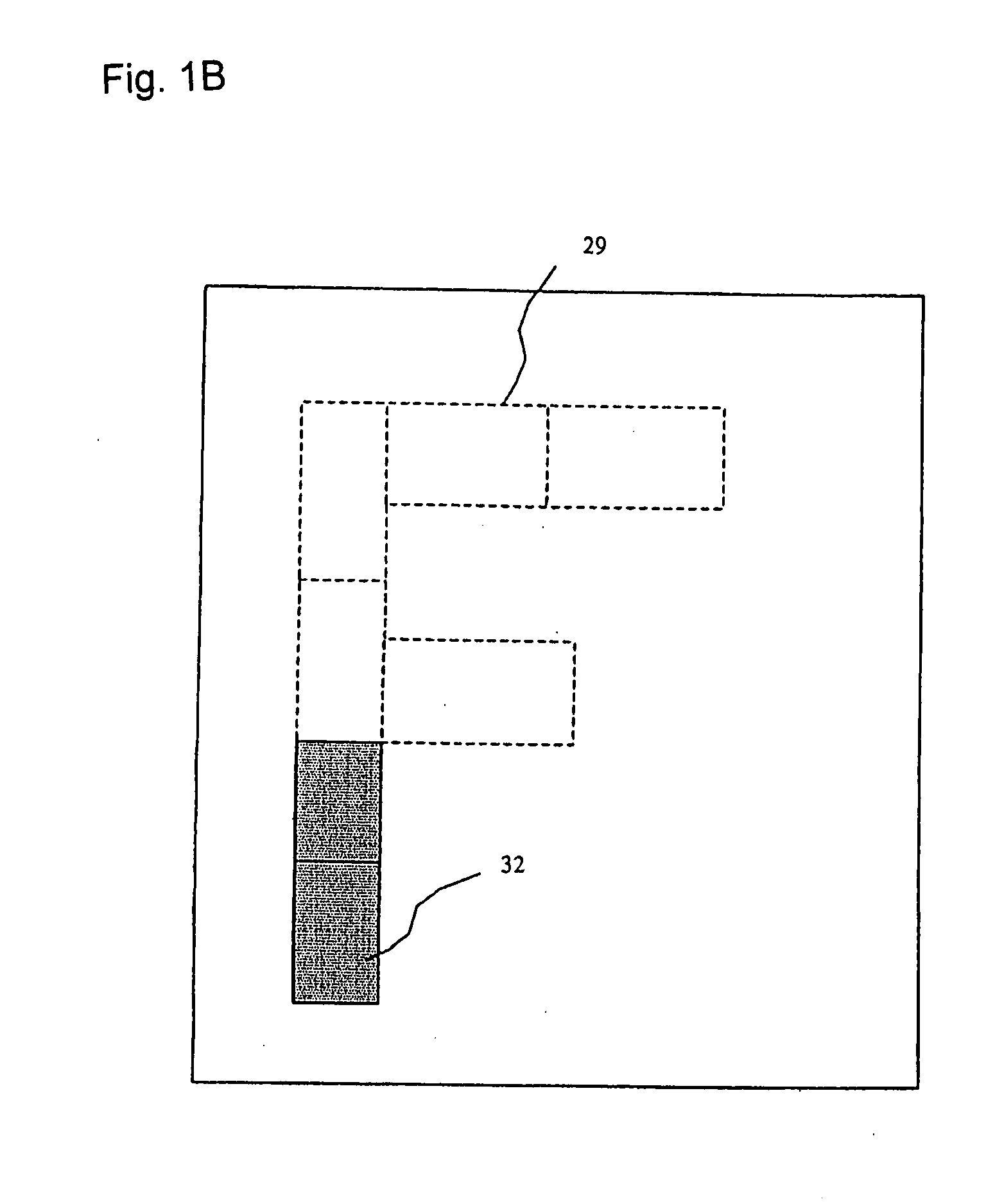

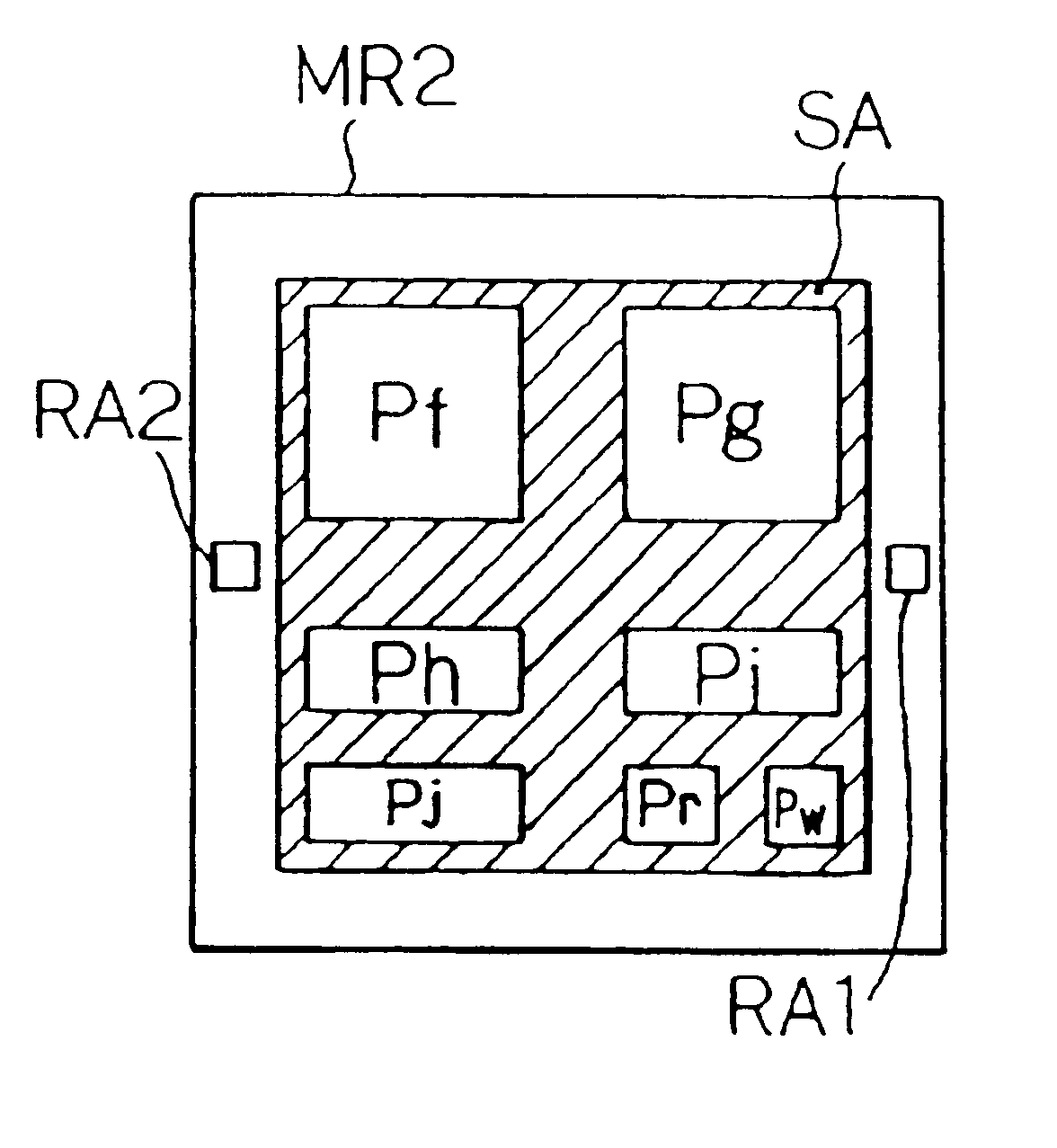

There is disclosed a method for forming micro patterns in a semiconductor integrated circuit device with high productivity and high accuracy. A photolithography having high throughput and electron beam lithography using a reticle and having relatively high throughput and high resolution are selectively used so as to obtain highest throughput while satisfying accuracy and resolution required for each product / layer. In the case of using the electron beam lithography, a non-complementary reticle and a complementary reticle are selectively used so as to obtain highest throughput while satisfying required accuracy and resolution. Thus, productivity and integration can be improved for the semiconductor integrated circuit device.

Owner:HITACHI LTD +1

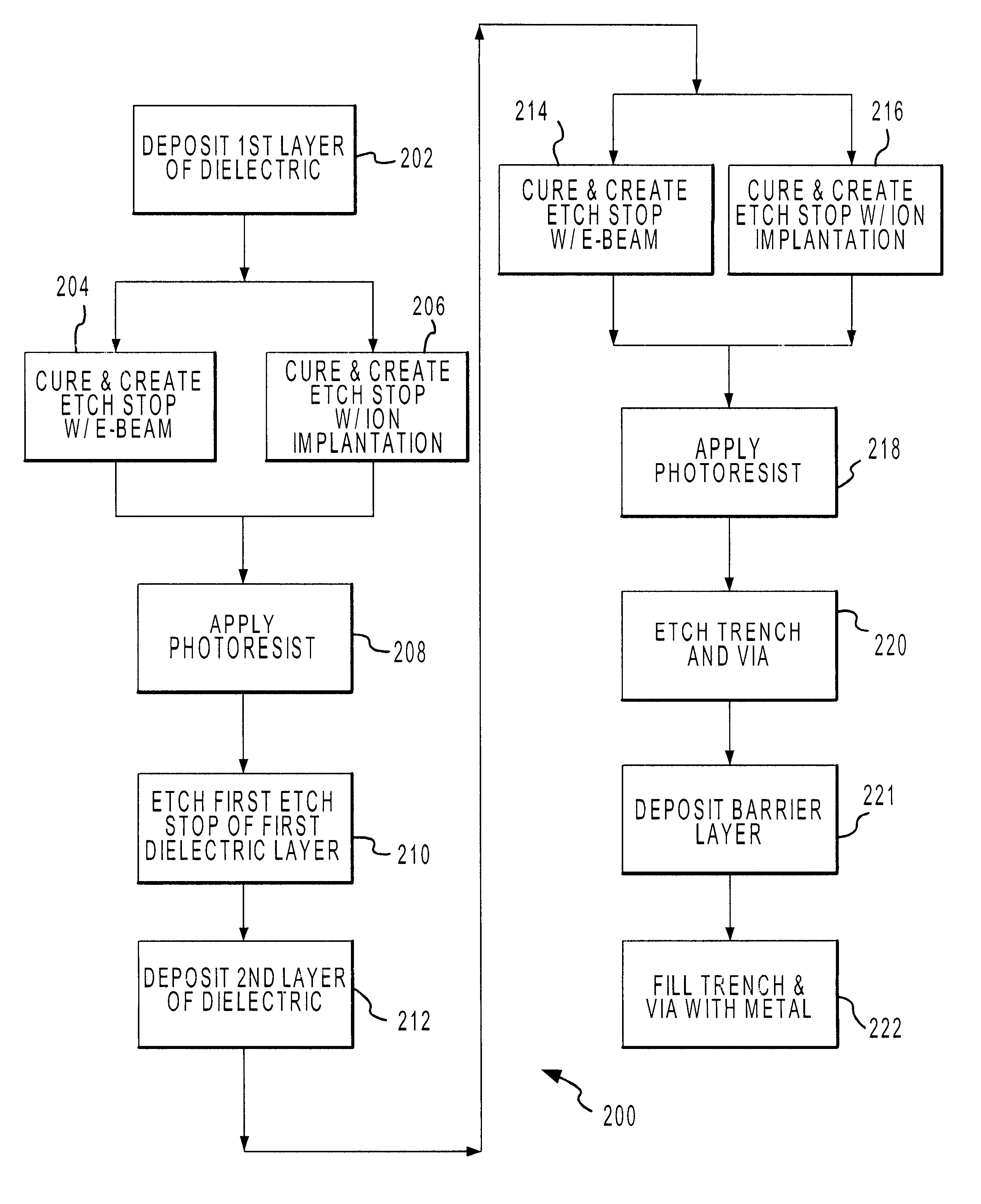

Method for dual damascene process using electron beam and ion implantation cure methods for low dielectric constant materials

InactiveUS6271127B1Semiconductor/solid-state device manufacturingSemiconductor devicesElectron-beam lithographySemiconductor

Owner:NEWPORT FAB

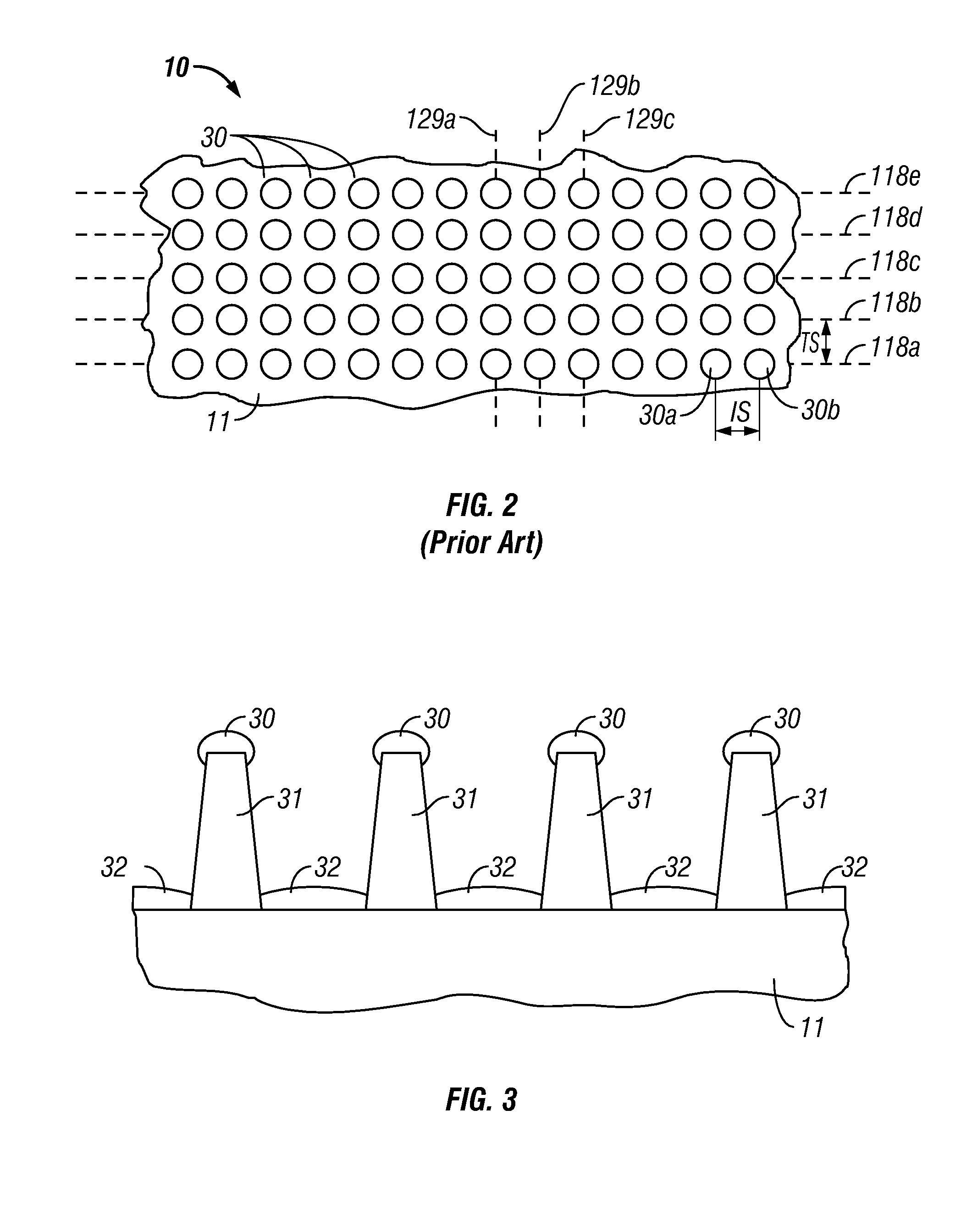

Methods for nanoscale structures from optical lithography and subsequent lateral growth

InactiveUS20070029643A1Reduce defect densityReduce dislocationMaterial nanotechnologyDecorative surface effectsLithographic artistPhotonics

Methods, and structures formed thereby, are disclosed for forming laterally grown structures with nanoscale dimensions from nanoscale arrays which can be patterned from nanoscale lithography. The structures and methods disclosed herein have applications with electronic, photonic, molecular electronic, spintronic, microfluidic or nano-mechanical (NEMS) technologies. The spacing between laterally grown structures can be a nanoscale measurement, for example with a spacing distance which can be approximately 1-50 nm, and more particularly can be from approximately 3-5 nm. This spacing is appropriate for integration of molecular electronic devices. The pitch between posts can be less than the average distance characteristic between dislocation defects for example in GaN (ρ=1010 / cm2→d=0.1 μm) resulting an overall reduction in defect density. Large-scale integration of nanoscale devices can be achieved using lithographic equipment that is orders of magnitude less expensive that that used for advanced lithographic techniques, such as electron beam lithography.

Owner:NORTH CAROLINA STATE UNIV

Fabrication of sub-50 nm solid-state nanostructures based on nanolithography

Combination of nanolithography and wet chemical etching including the fabrication of nanoarrays of sub-50 nm gold dots and line structures with deliberately designed approximately 12-100 nm gaps. These structures were made by initially using direct write nanolithography to pattern the etch resist, 16-mercaptohexadecanoic acid (MHA), on Au / Ti / SiOx / Si substrates and then wet chemical etching to remove the exposed gold. These are the smallest Au structures prepared by a wet chemical etching strategy. Also, Dip-Pen Nanolithography (DPN) has been used to generate resist layers on Au, Ag, and Pd that when combined with wet chemical etching can lead to nanostructures with deliberately designed shapes and sizes. Monolayers of mercaptohexadecanoic acid (MHA) or octadecanethiol (ODT), patterned by DPN, were explored as etch resists. They work comparably well on Au and Ag, but ODT is the superior material for Pd. MHA seems to attract the FeCl3 etchant and results in nonuniform etching of the underlying Pd substrate. Dots, lines, triangles and circles, ranging in size from sub-100 to several hundred nm have been fabricated on these substrates. These results show how one can use DPN as an alternative to more complex and costly procedures like electron beam lithography to generate nanostructures from inorganic materials.

Owner:NORTHWESTERN UNIV

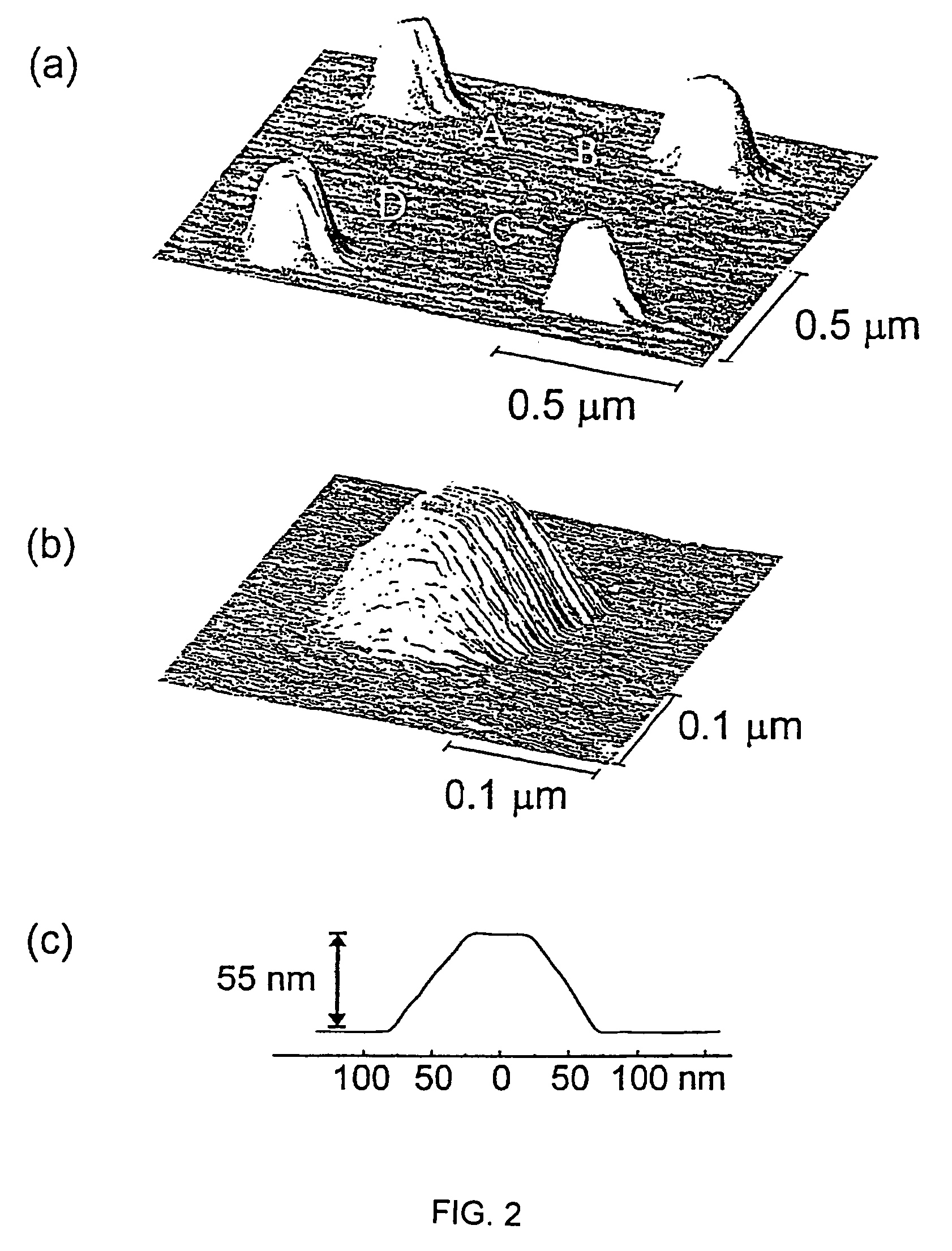

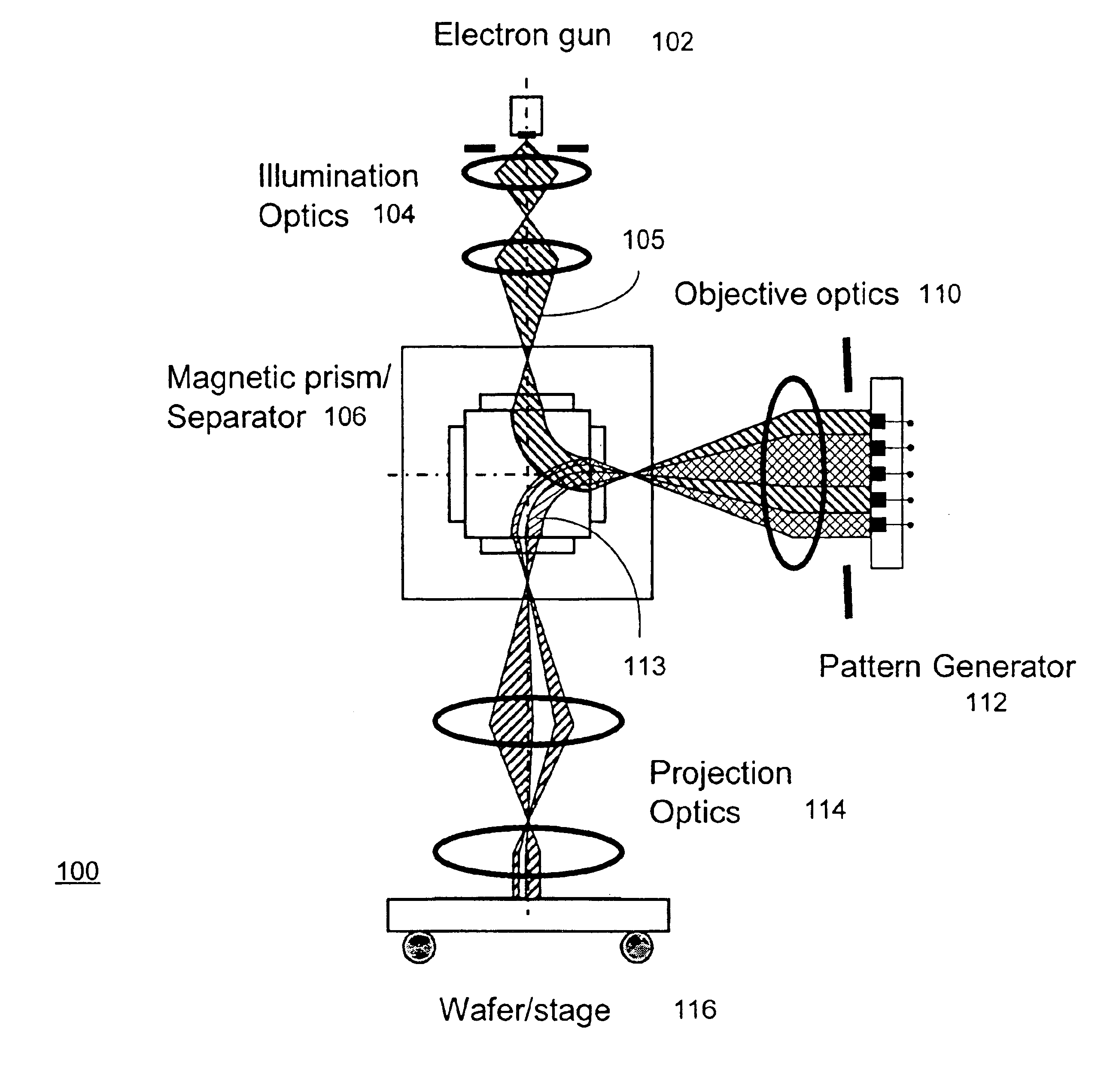

Maskless reflection electron beam projection lithography

One embodiment disclosed relates to an apparatus for reflection electron beam lithography. An electron source is configured to emit electrons. The electrons are reflected to a target substrate by portions of an electron-opaque patterned structure having a lower voltage level and are absorbed by portions of the structure having a higher voltage level. Another embodiment relates to a novel method of electron beam lithography. An incident electron beam is formed and directed to an opaque patterned structure. Electrons are reflected from portions of the structure having a lower voltage level applied thereto and are absorbed by portions of the structure having a higher voltage level applied thereto. The reflected electrons are directed towards a target substrate to form an image and expose a lithographic pattern.

Owner:KLA TENCOR TECH CORP

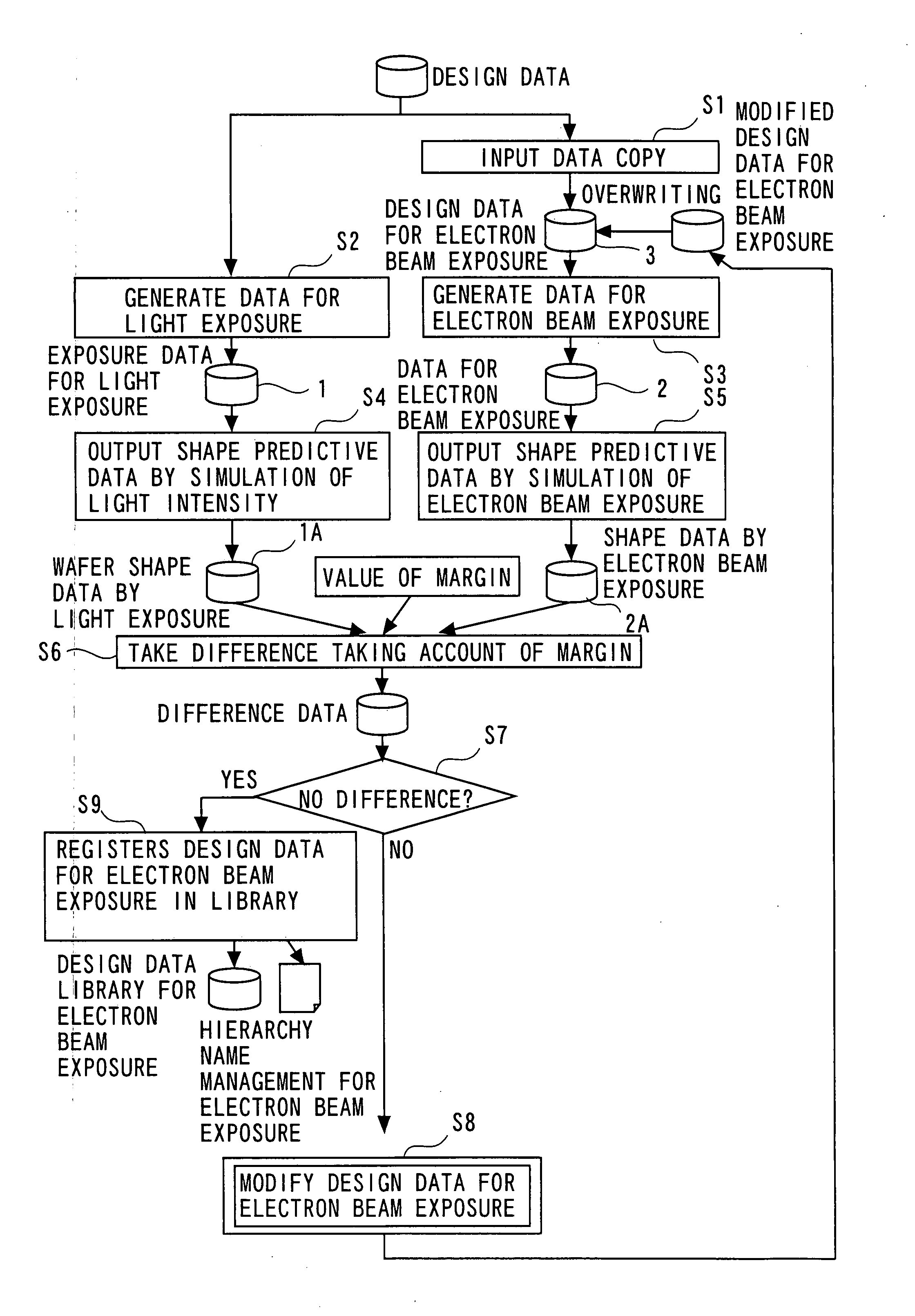

Semiconductor device manufacturing method, data generating apparatus, data generating method and recording medium readable by computer recoded with data generating program

A semiconductor manufacturing method comprising, a data generating process including, acquiring a simulation light pattern that simulates a shape of a light exposure pattern formed on a substrate on the basis of design data of a semiconductor device, acquiring a simulation electron beam exposure pattern that simulates a shape of an electron beam exposure pattern formed by an electron beam exposure on the substrate on the basis of the design data, extracting difference information representing a shape difference portion between the simulation light pattern and the simulation electron beam exposure pattern, acquiring changed design data for modifying shape by changing the design data in accordance with the difference information, conducting the electron beam exposure on the substrate by use of the changed design data for modifying the shape.

Owner:FUJITSU LTD

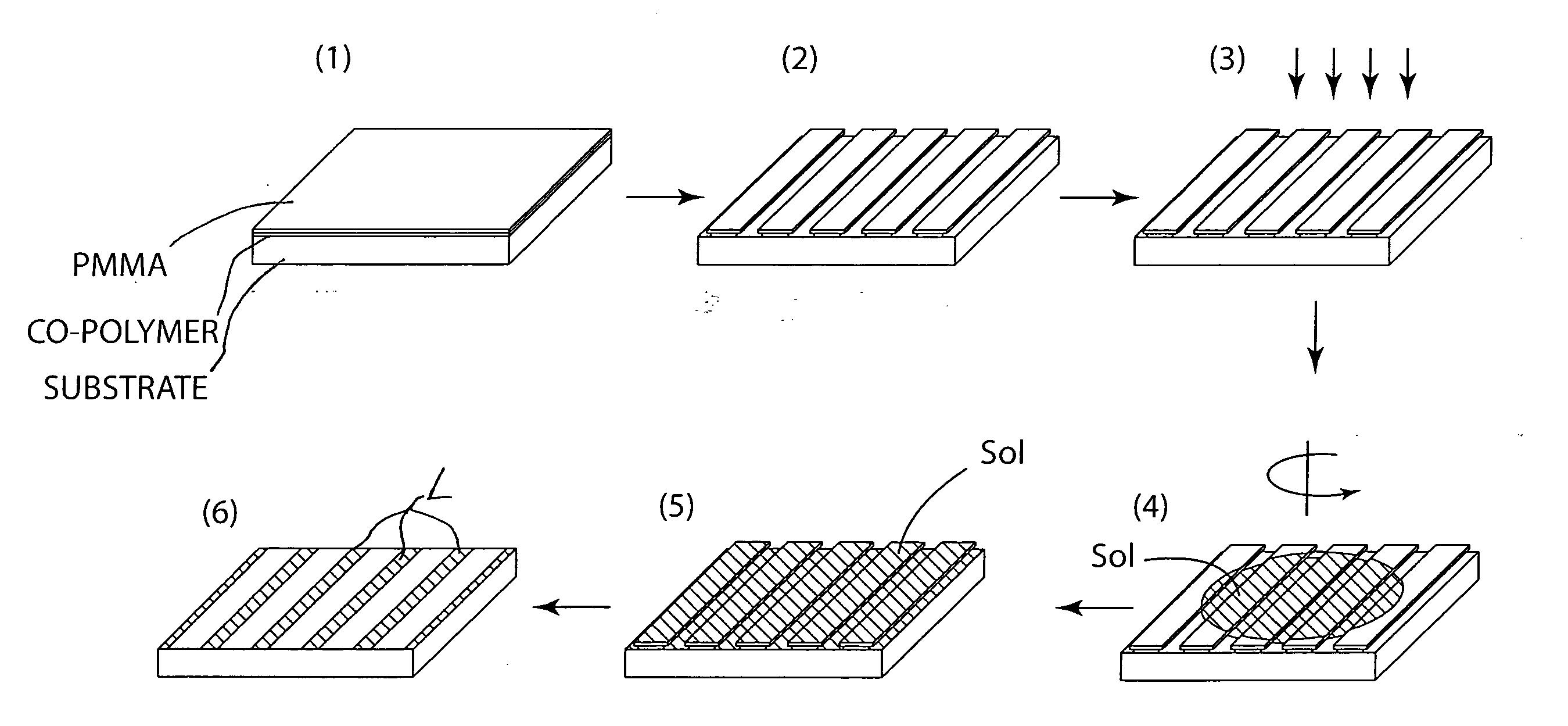

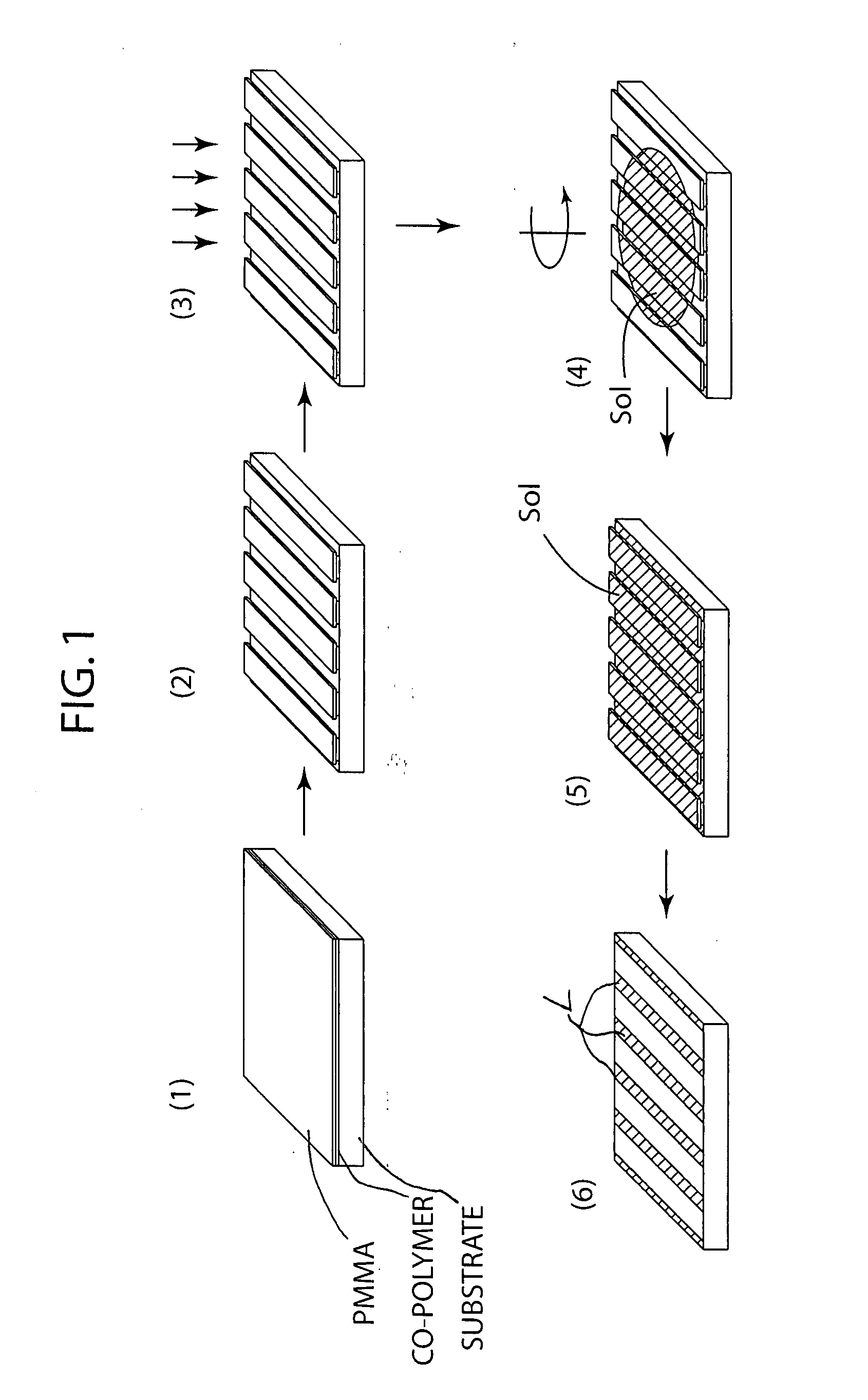

Method using block copolymers for making a master mold with high bit-aspect-ratio for nanoimprinting patterned magnetic recording disks

ActiveUS20090308837A1Decorative surface effectsSemiconductor/solid-state device manufacturingResistEngineering

The invention is a method for making a master mold to be used for nanoimprinting patterned-media magnetic recording disks. The method uses conventional optical or e-beam lithography to form a pattern of generally radial stripes on a substrate, with the stripes being grouped into annular zones or bands. A block copolymer material is deposited on the pattern, resulting in guided self-assembly of the block copolymer into its components to multiply the generally radial stripes into generally radial lines of alternating block copolymer components. The radial lines of one of the components are removed and the radial lines of the remaining component are used as an etch mask to etch the substrate. Conventional lithography is used to form concentric rings over the generally radial lines. After etching and resist removal, the master mold has pillars arranged in circular rings, with the rings grouped into annular bands.

Owner:WESTERN DIGITAL TECH INC

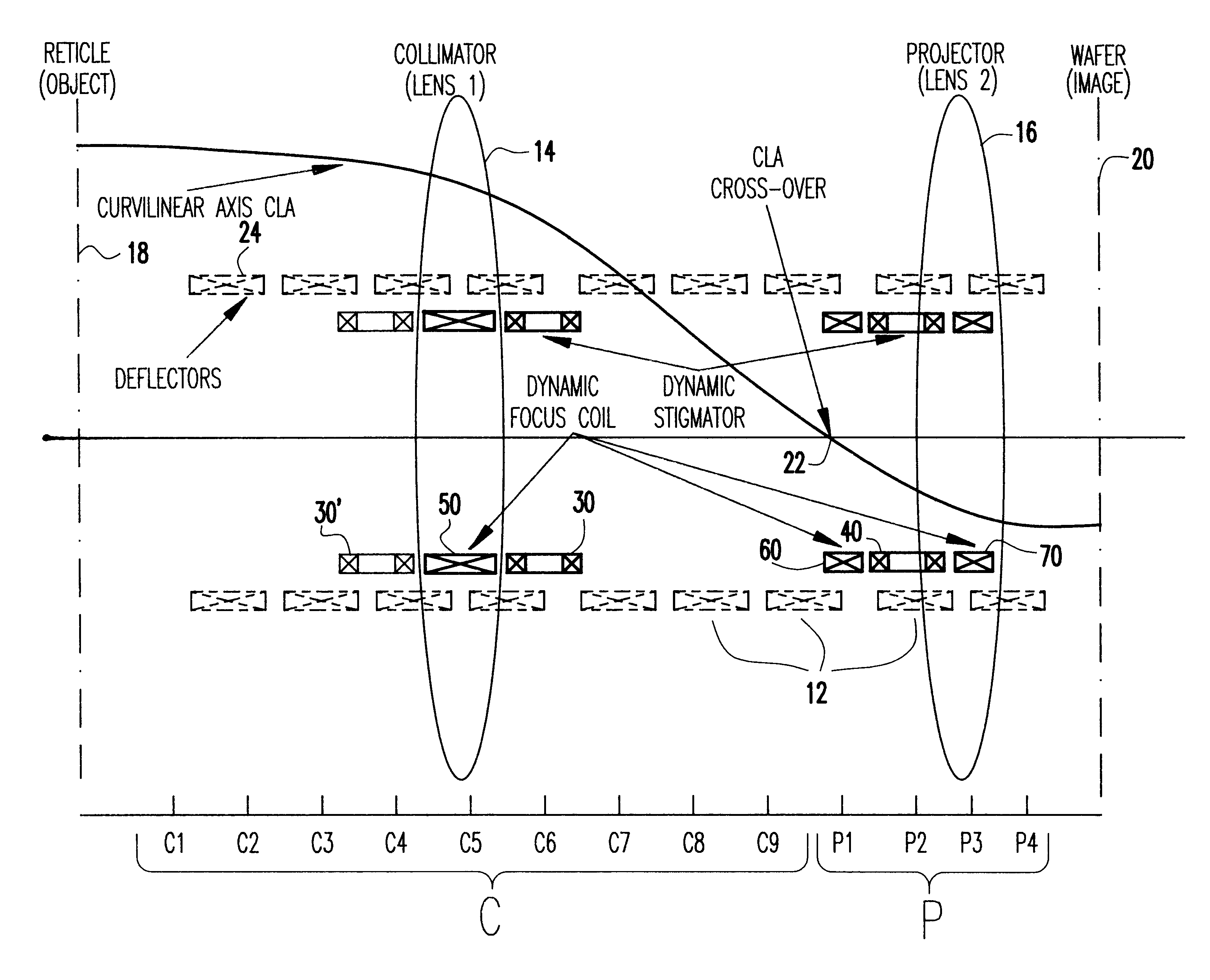

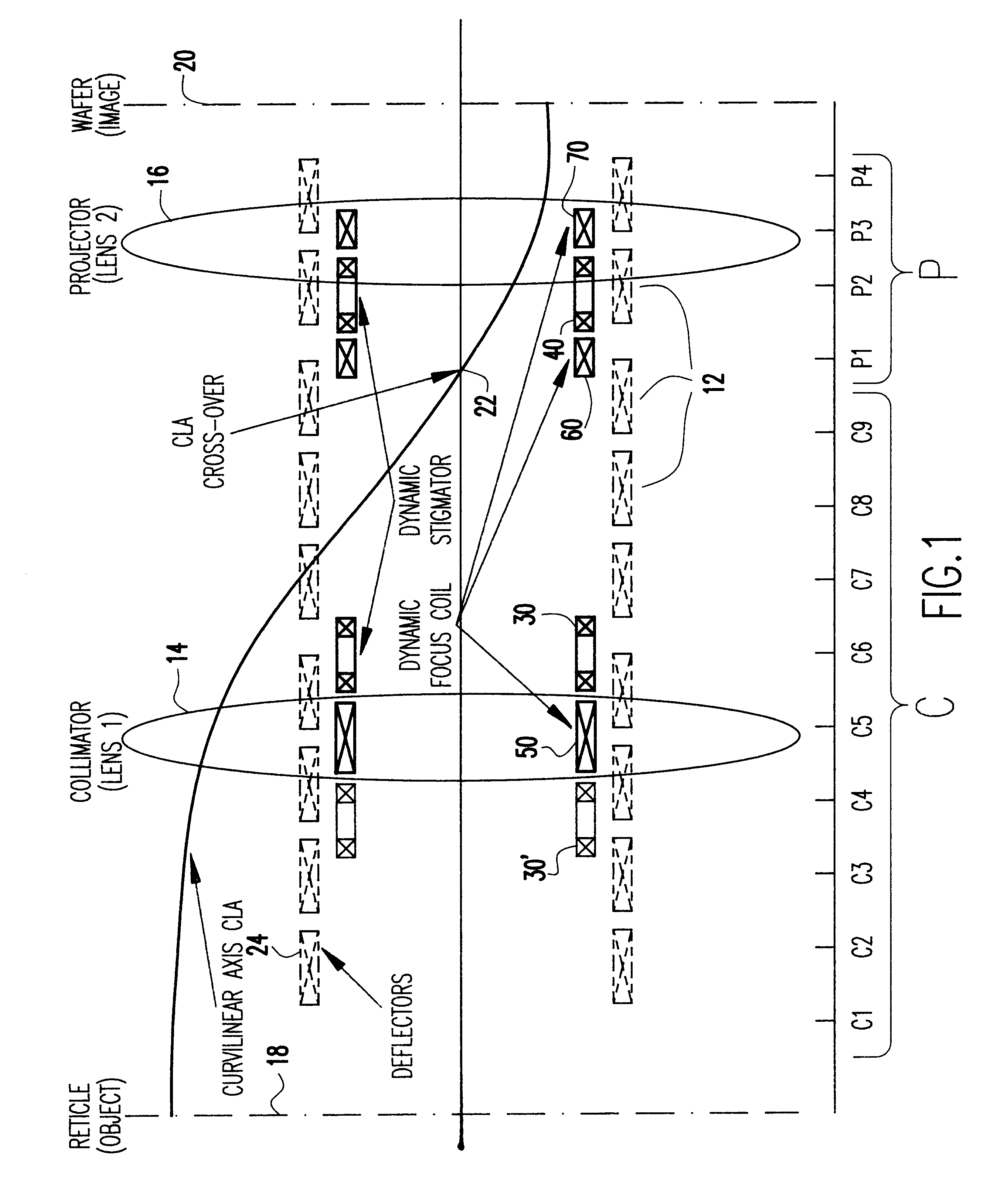

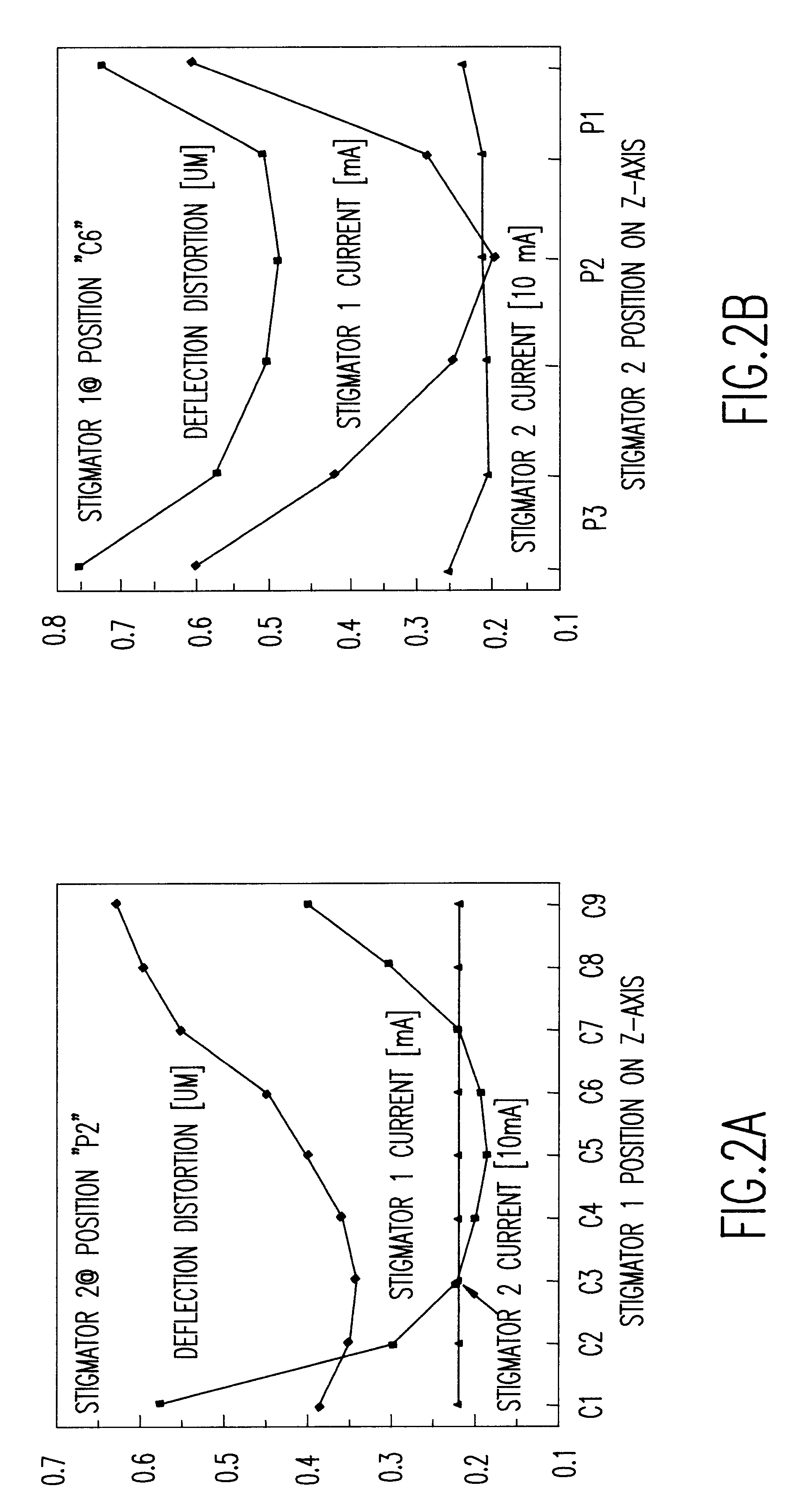

Multi-element deflection aberration correction for electron beam lithography

InactiveUS6180947B1Adjust focusStability-of-path spectrometersBeam/ray focussing/reflecting arrangementsProjection opticsLithographic artist

A method of optimizing locations of correction elements of a charged particle beam system determines respective corrector element currents to achieve optimum correction as a function of individual corrector location. Substantially complete dynamic correction of FSD and SFD can be obtained consistent with efficiency of operation and minimization of deflection distortion. In particular, FSD and SFD corrections can be sufficiently separated for substantially complete correction of SFD and FSD simultaneously with two stigmators. Both of these types of correction can be provided in complex charged particle beam systems employing curvilinear axis (CVA) particle trajectories and or large area reduction projection optics (LARPO) which cause complex hybrid aberrations in order to achieve high throughput consistent with extremely high resolution supporting one-tenth micron minimum feature size lithography regimes and smaller.

Owner:NIKON CORP

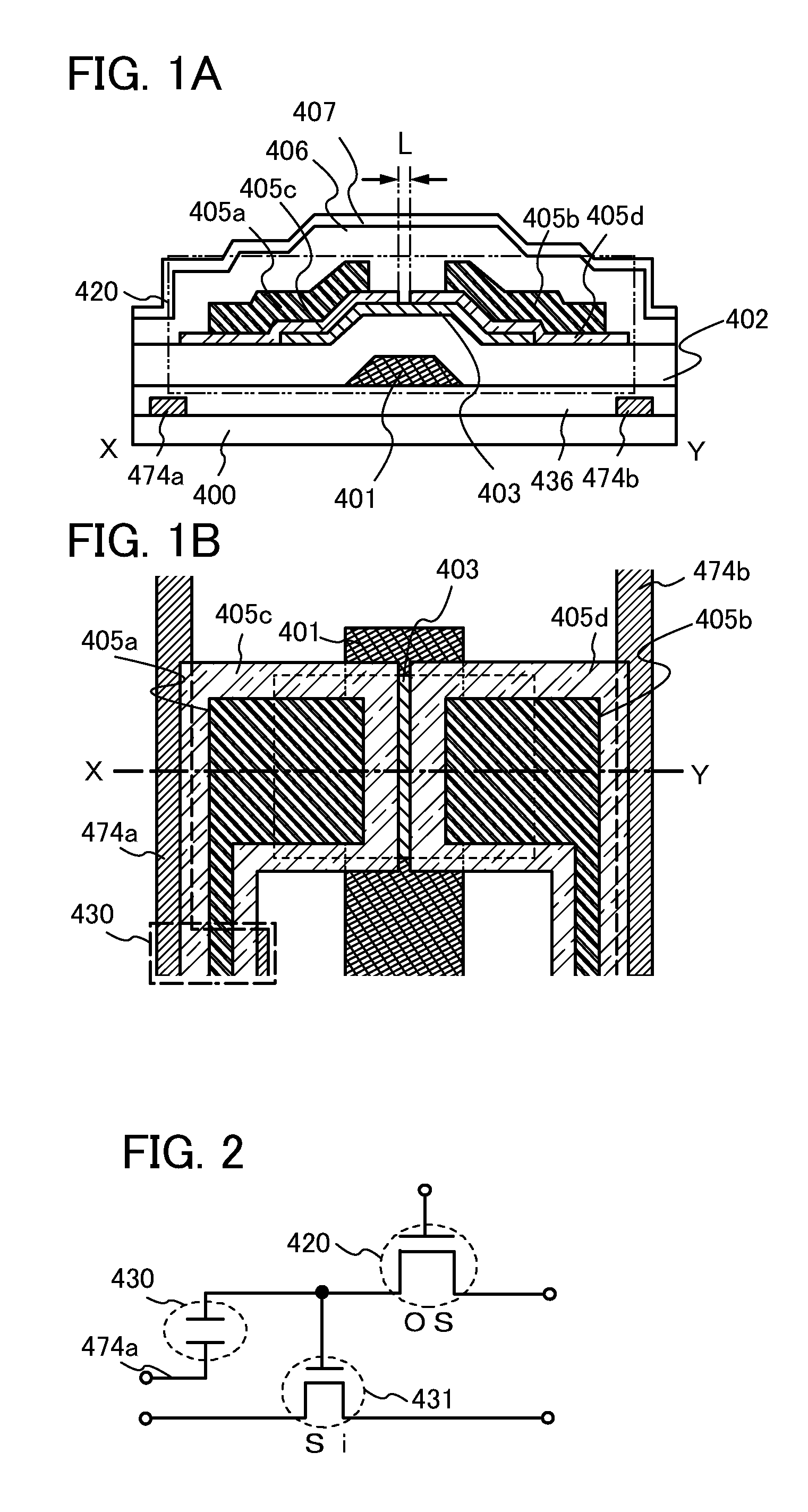

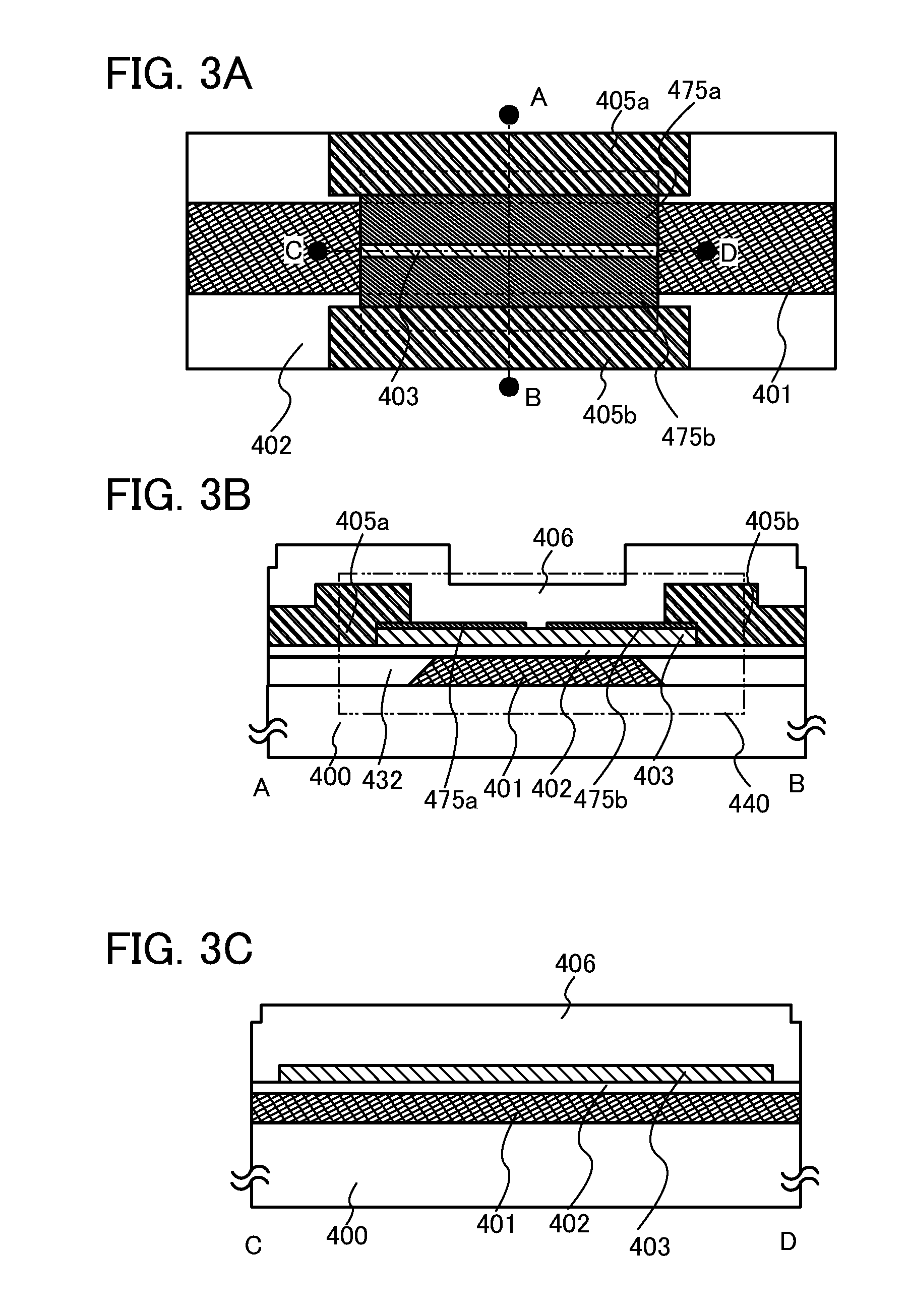

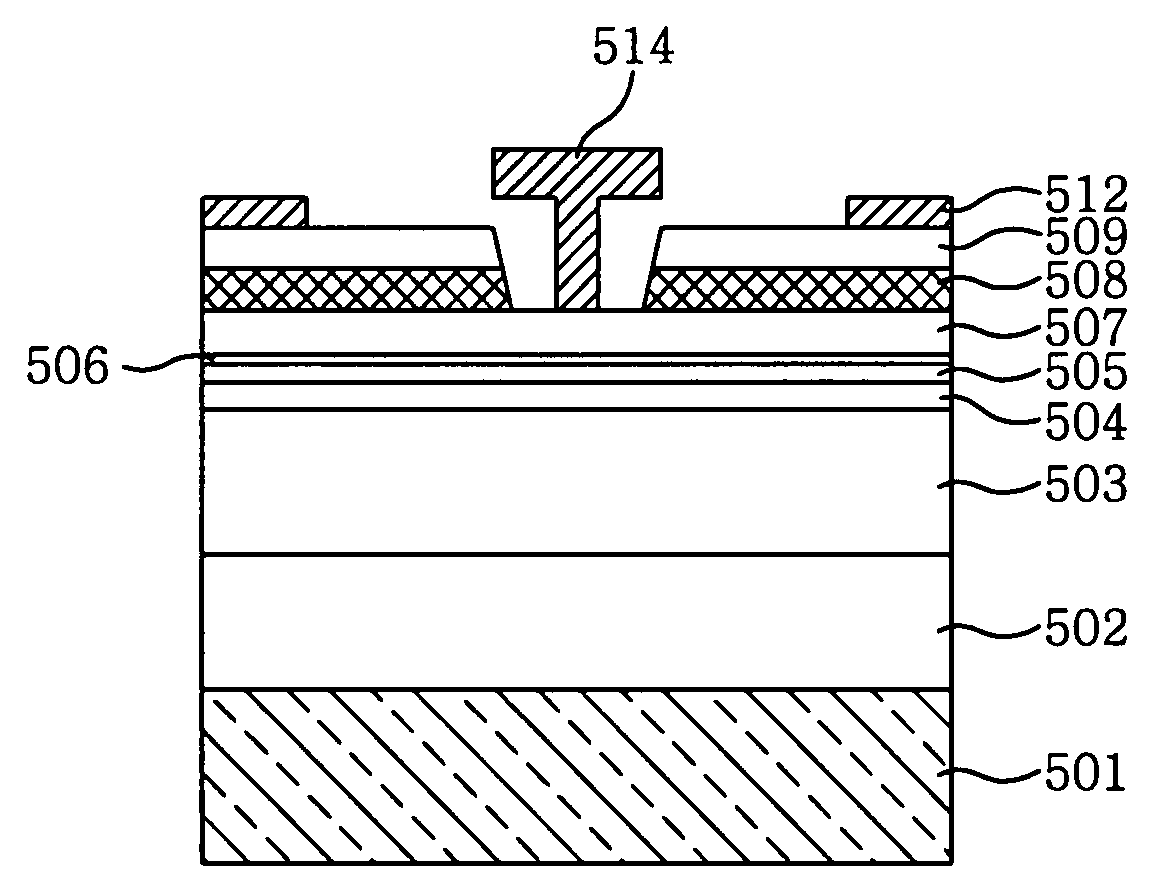

Semiconductor device and method for manufacturing the same

ActiveUS20130140554A1Reduce leakageShort channel lengthTransistorSemiconductor/solid-state device manufacturingResistElectron-beam lithography

A semiconductor device including a minute transistor with a short channel length is provided. A gate insulating layer is formed over a gate electrode layer; an oxide semiconductor layer is formed over the gate insulating layer; a first conductive layer and a second conductive layer are formed over the oxide semiconductor layer; a conductive film is formed over the first conductive layer and the second conductive layer; a resist mask is formed over the conductive film by performing electron beam exposure; and then a third conductive layer and a fourth conductive layer are formed over and in contact with the first conductive layer and the second conductive layer, respectively, by selectively etching the conductive film.

Owner:SEMICON ENERGY LAB CO LTD

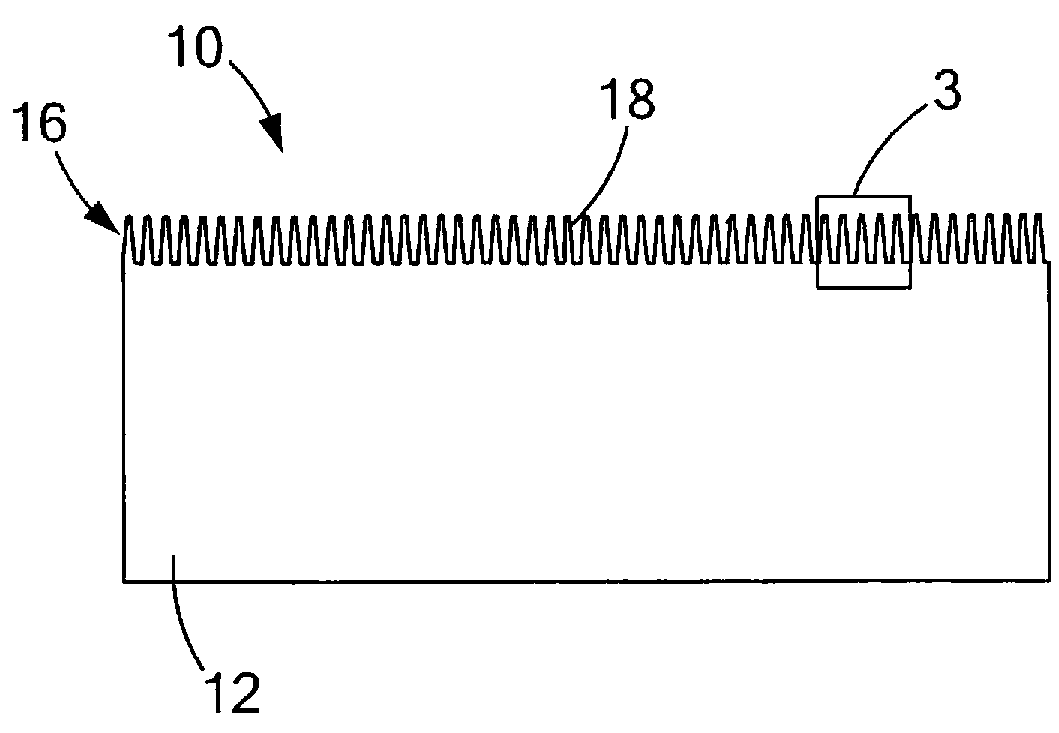

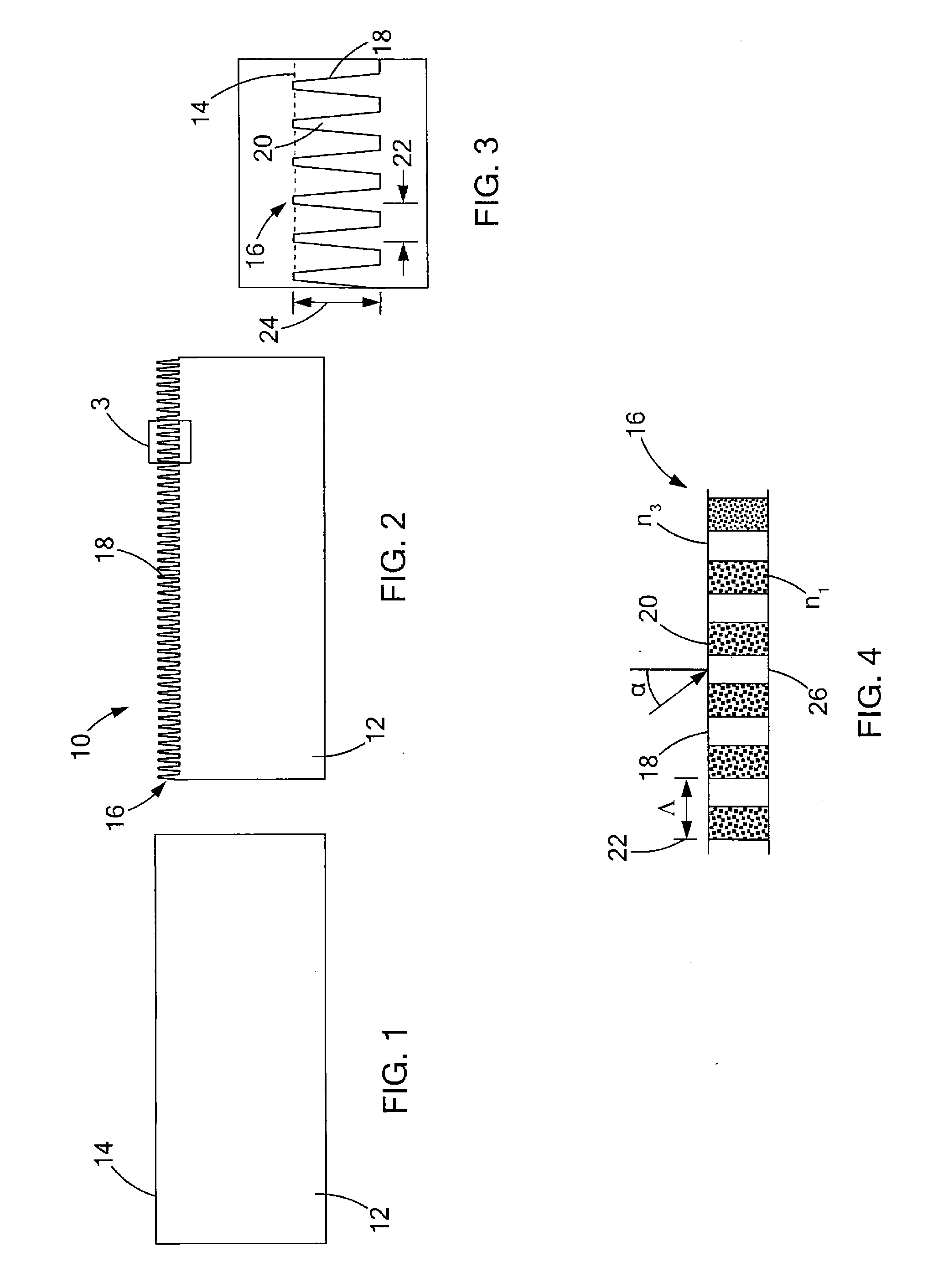

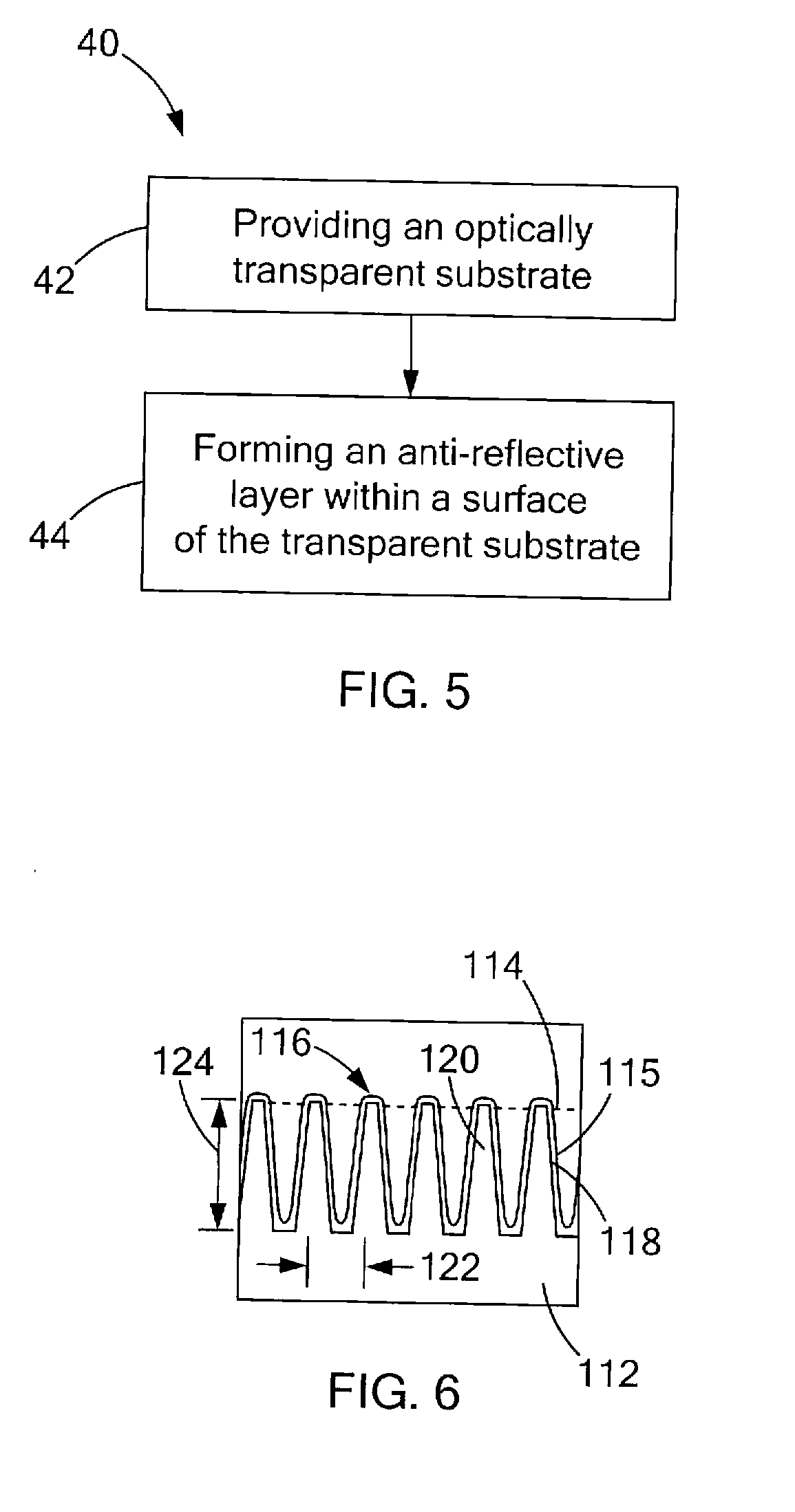

Transparent Anti-reflective article and method of fabricating same

InactiveUS20090231714A1Minimize light diffractionSimilar shapeElectric discharge tubesSemiconductor/solid-state device manufacturingNano structuringRefractive index

A transparent anti-reflective article includes a transparent substrate having a first refractive index and a first surface. An anti-reflective layer is formed within the first surface of the transparent substrate through use of one of nanosphere lithography, deep ultra-violet photolithography, electron beam lithography, and nano-imprinting. The anti-reflective layer includes a subwavelength nano-structured second surface including a plurality of protuberances. Such protuberances have a predetermined maximum distance between adjacent protuberances and a predetermined height for a given wavelength such that the anti-reflective layer includes a second refractive index lower than the first refractive index to minimize light diffraction and random scattering therethrough. The predetermined height is approximately equal to a quarter of the given wavelength divided by the second refractive index.

Owner:WAYNE STATE UNIV

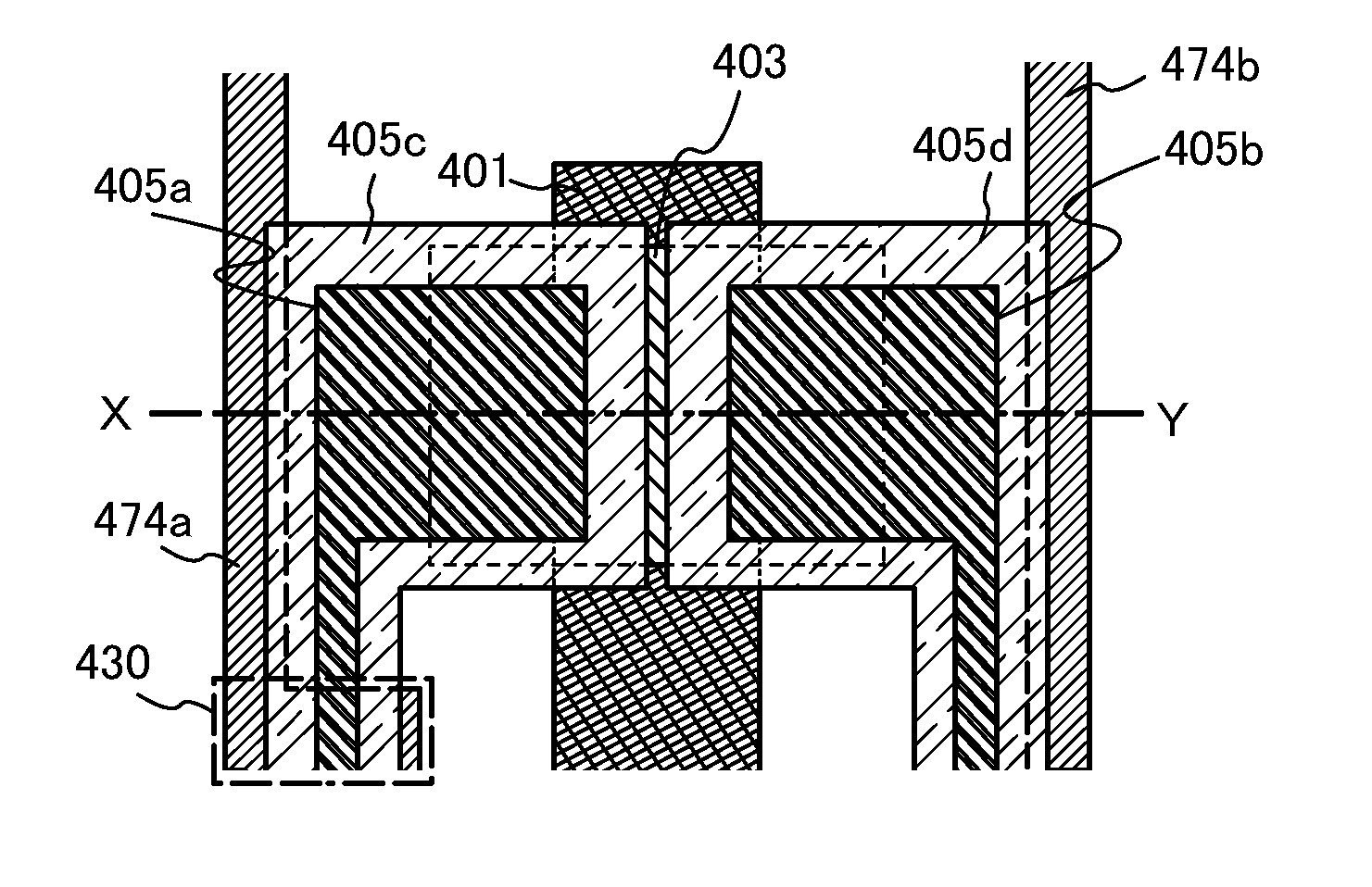

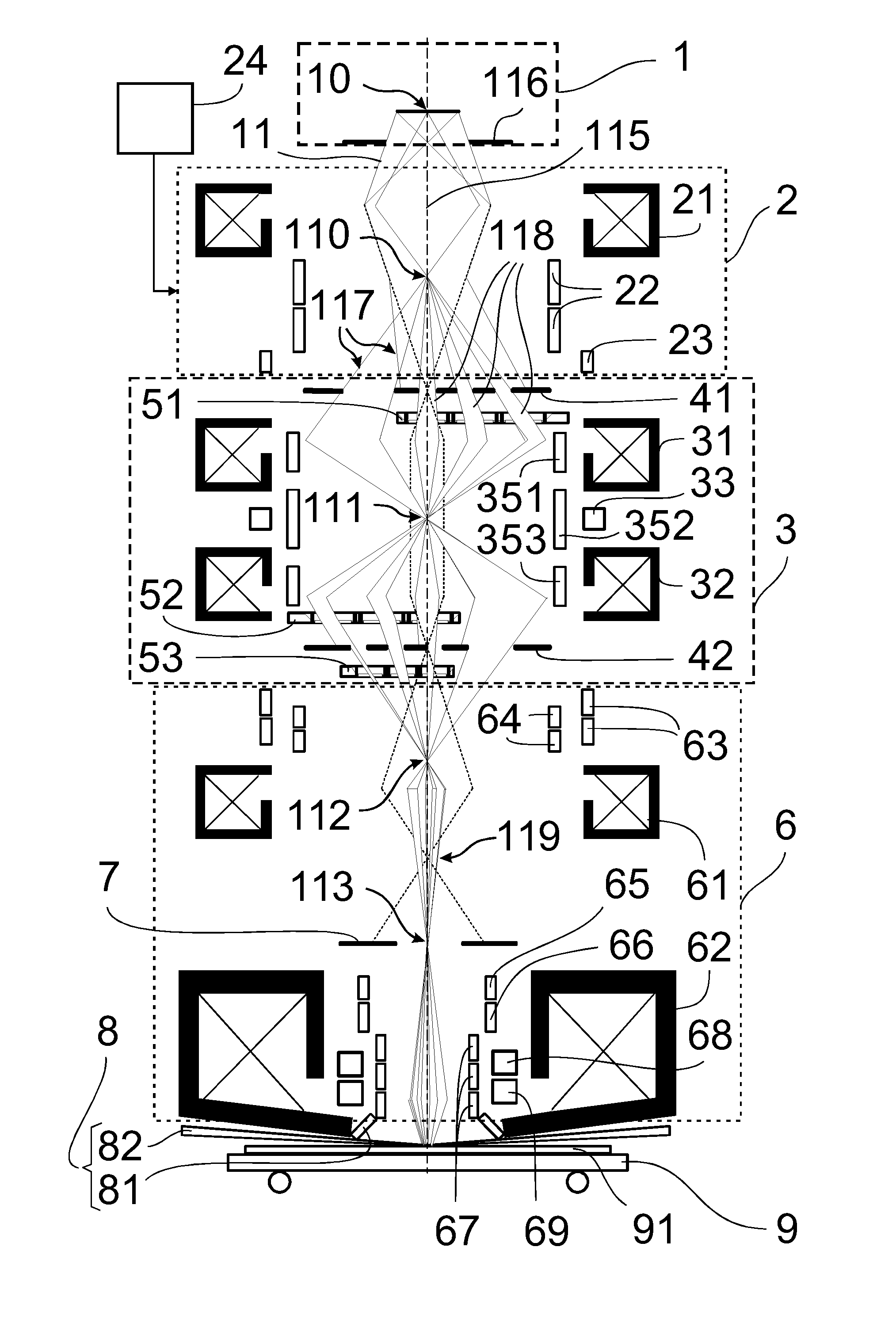

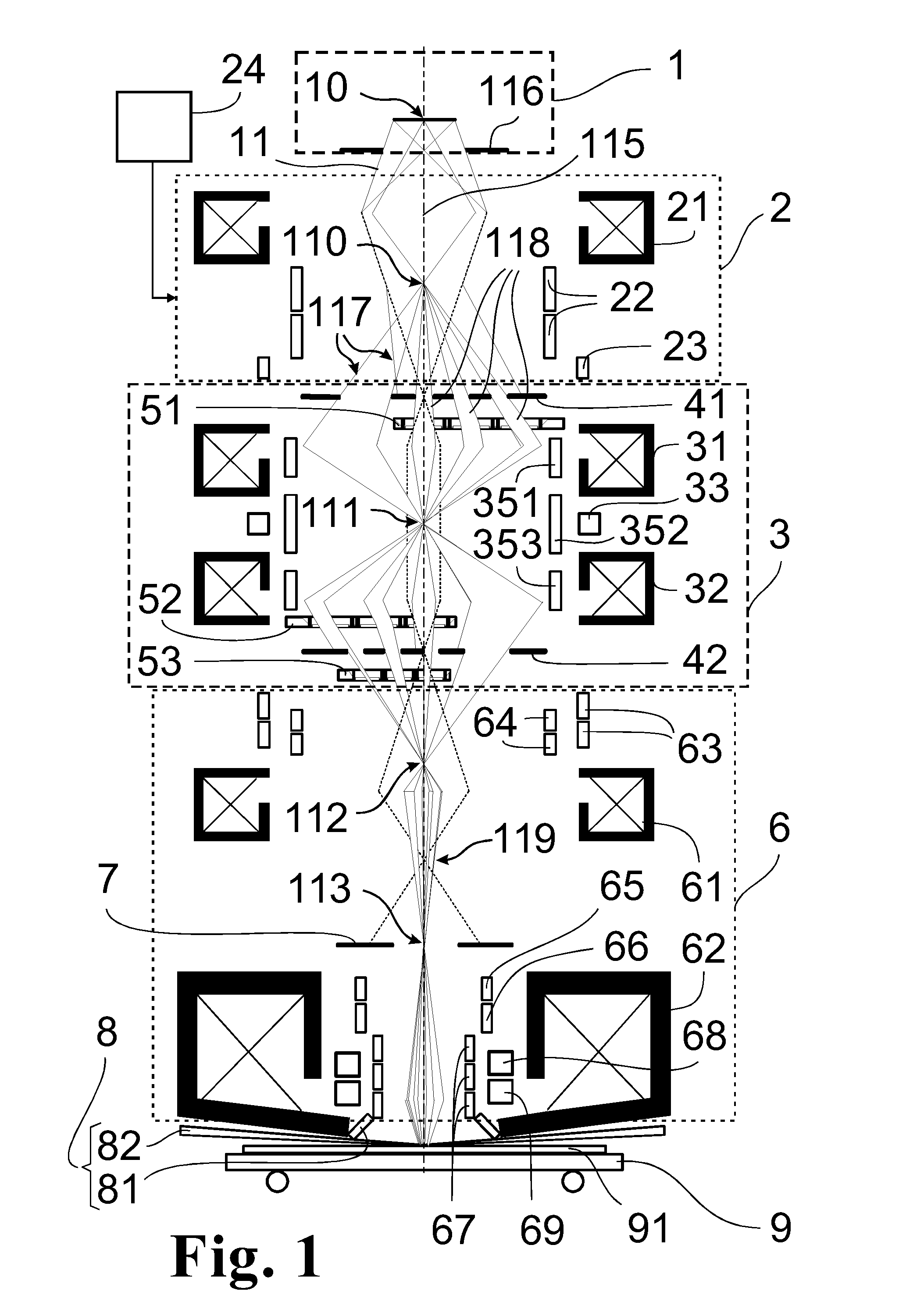

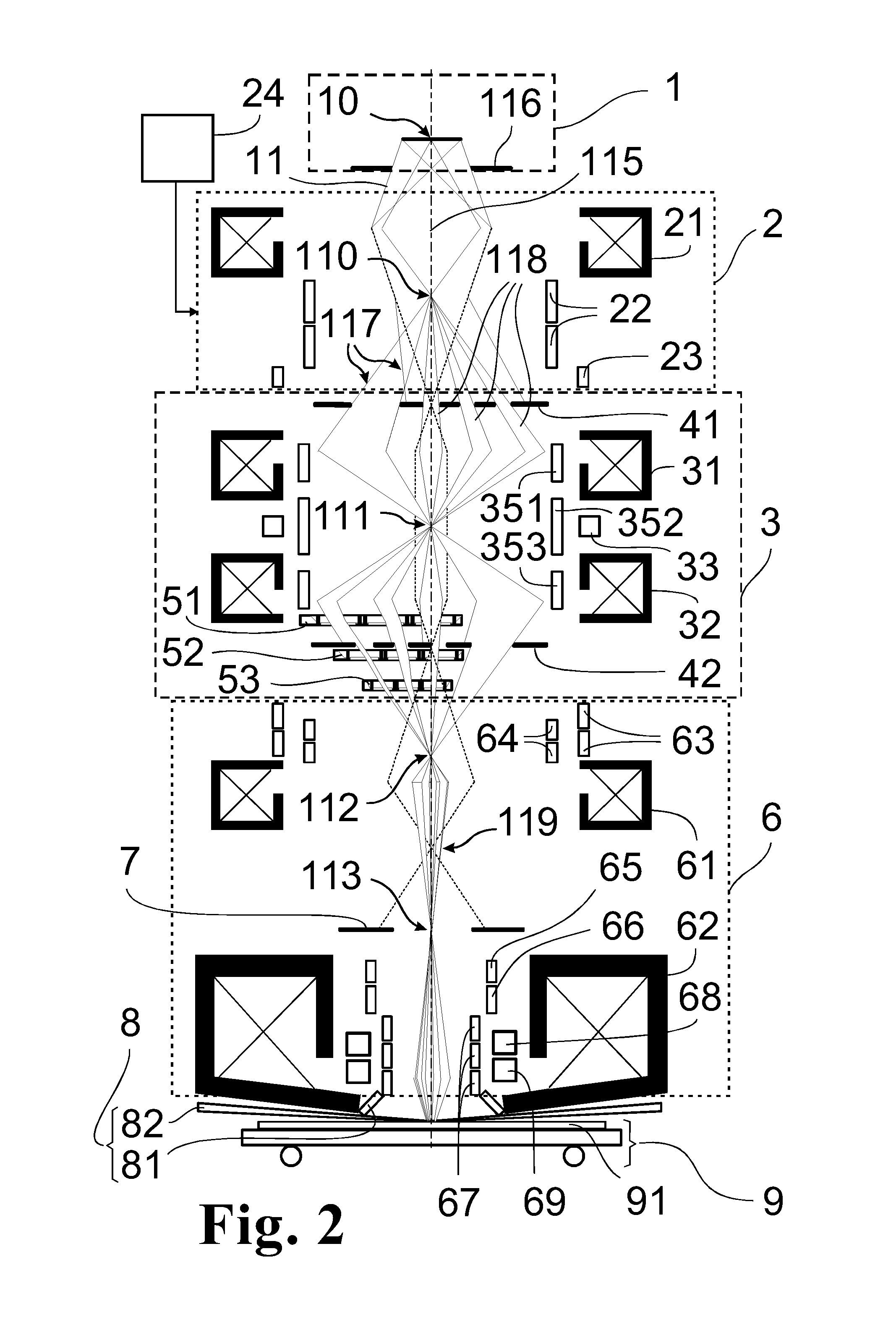

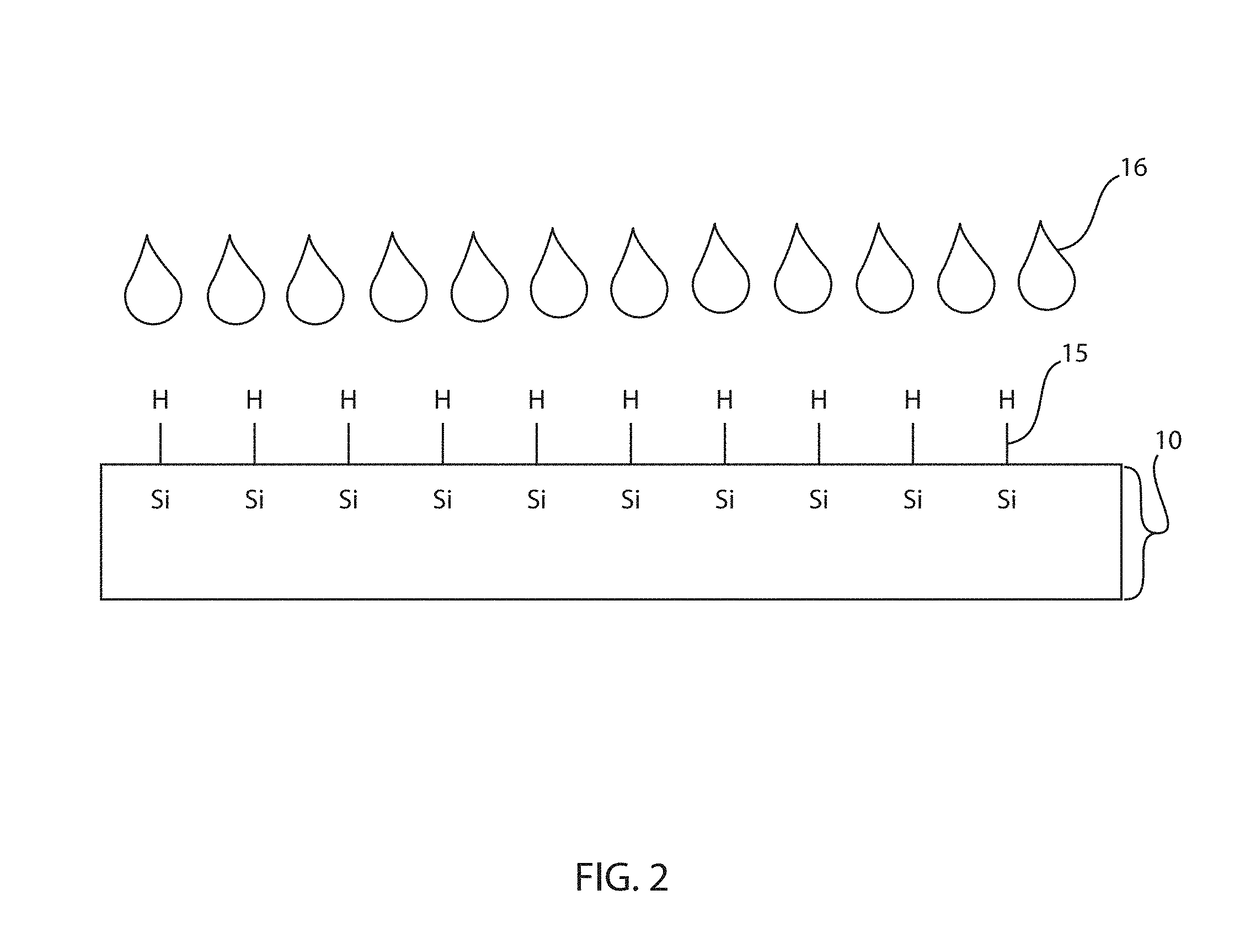

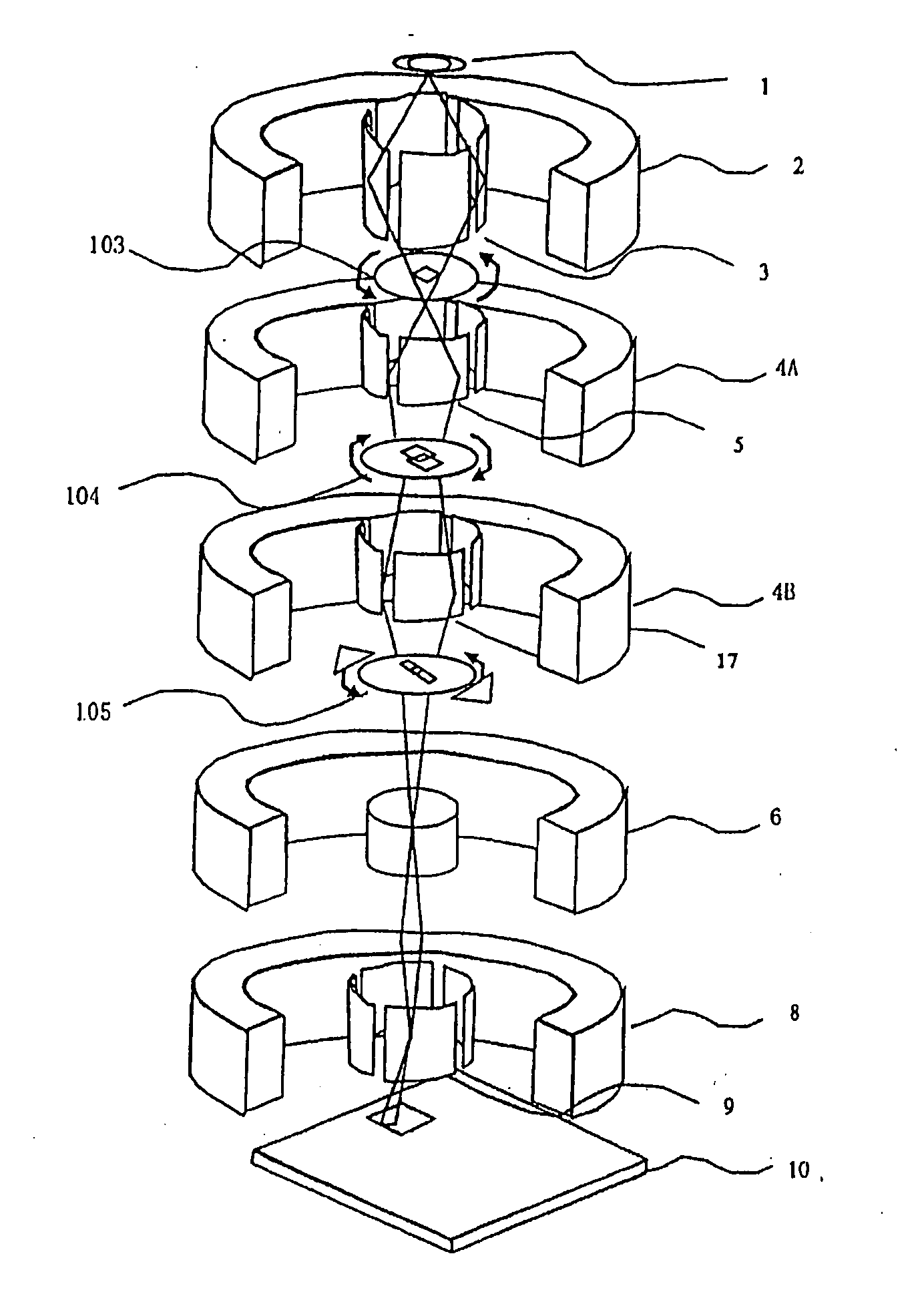

Arrangement for the Illumination of a Substrate with a Plurality of Individually Shaped Particle Beams for High-Resolution Lithography of Structure Patterns

ActiveUS20100148087A1High substrate throughputIncrease structural flexibilityThermometer detailsStability-of-path spectrometersParticle beamLight beam

The invention is directed to an arrangement for the illumination of a substrate with a plurality of individually shaped, controllable particle beams, particularly for electron beam lithography in the semiconductor industry. It is the object of the invention to find a novel possibility for illuminating a substrate (91) with a plurality of individually shaped, controllable particle beamlets (118) which permits a high-resolution structuring of substrates with a high substrate throughput without limiting the flexibility of the applicable structure patterns or limiting the high substrate throughput due to a required flexibility. According to the invention, this object is met in that a first aperture diaphragm array and a second aperture diaphragm array are constructed as multiple-format diaphragm arrays (41, 42) for generating particle beamlets (118) with different beam cross sections, and at least three multibeam deflector arrays (51, 52, 53) for individual deflection of the particle beamlets (118) are associated with the first multiple-format diaphragm array (41) and with the second multiple-format diaphragm array (42), wherein at least one multibeam deflector array (51) is arranged between the first multiple-format diaphragm array (41) and the second multiple-format diaphragm array (42) in order to generate different cross sections of the particle beamlets (118), at least a second multibeam deflector array (52) is arranged in the vicinity of the second multiple-format diaphragm array (42) in order to blank or deflect individual particle beamlets (118) into individual crossovers, and at least a third multibeam deflector array (53) is arranged downstream of the second multiple-format diaphragm array (42) at a distance of 10-20% of the distance to the next crossover (112) in order to generate different positions of the particle beamlets (118) on the substrate (91).

Owner:VISTEC ELECTRON BEAM

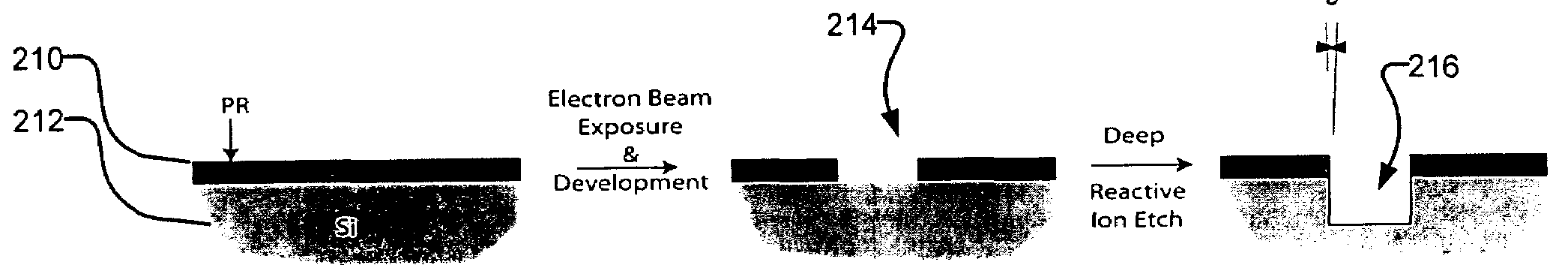

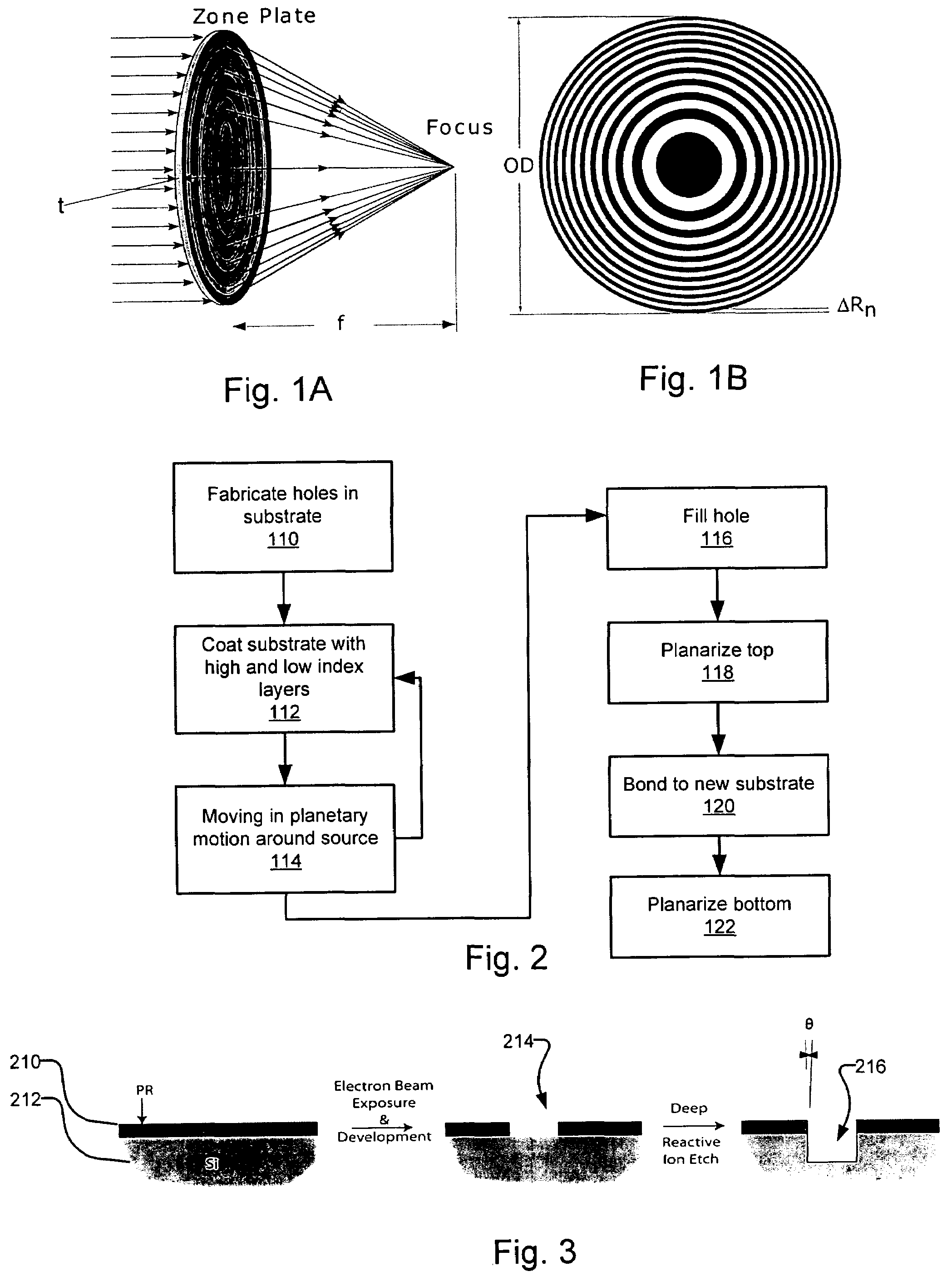

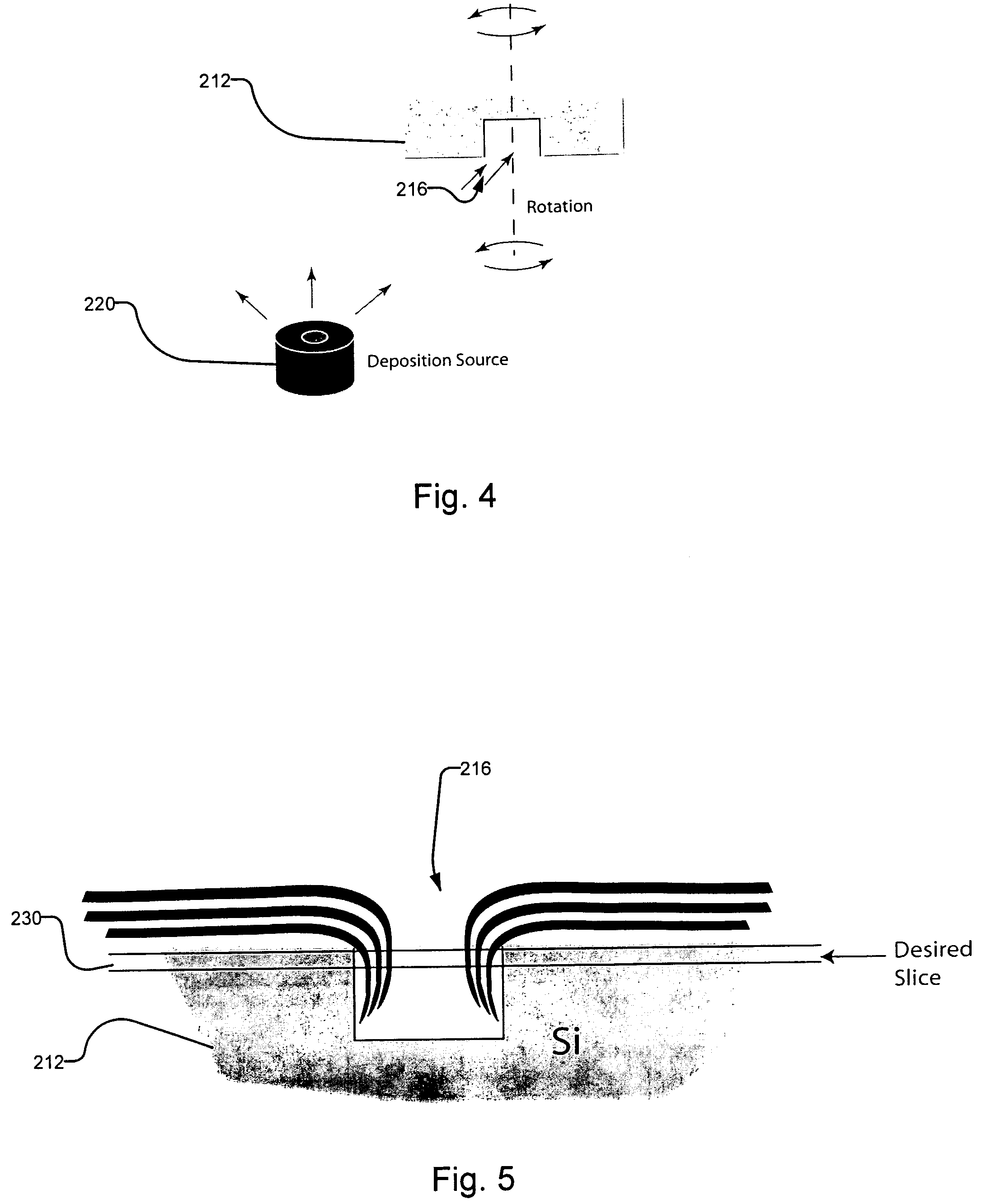

Fast x-ray lenses and fabrication method therefor

A fabrication process for zone plate lenses is based on controlled thin layer deposition for fabricating structures as small as 2 nanometers (nm) in width, and potentially smaller. The substrate for deposition will take the form of a precision hole, fabricated in a substrate, such as silicon by electron beam lithography and subsequent reactive ion etching. A controlled layer deposition is then used to form the required zone plate structure. A subsequent thinning process is used to section the hole and produce a zone plate with the required layer thicknesses.

Owner:CARL ZEISS X RAY MICROSCOPY

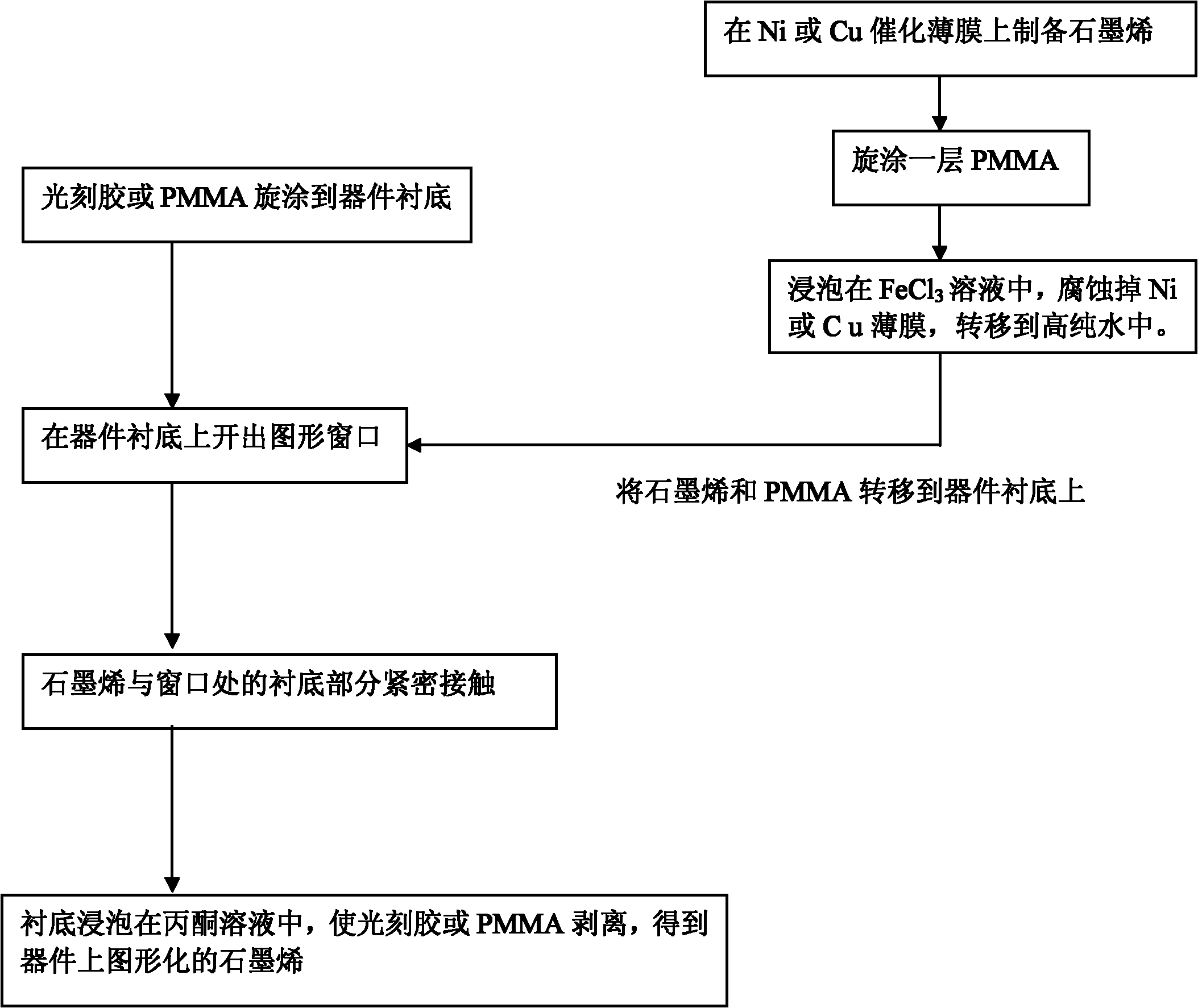

Method for preparing patterned graphene

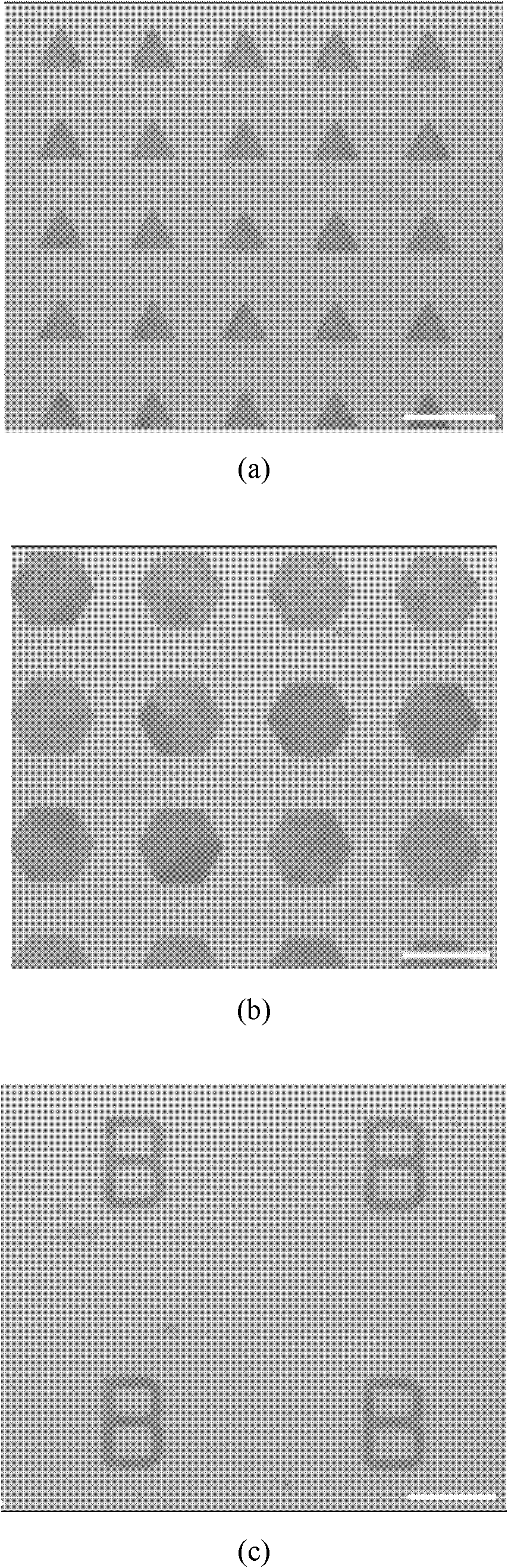

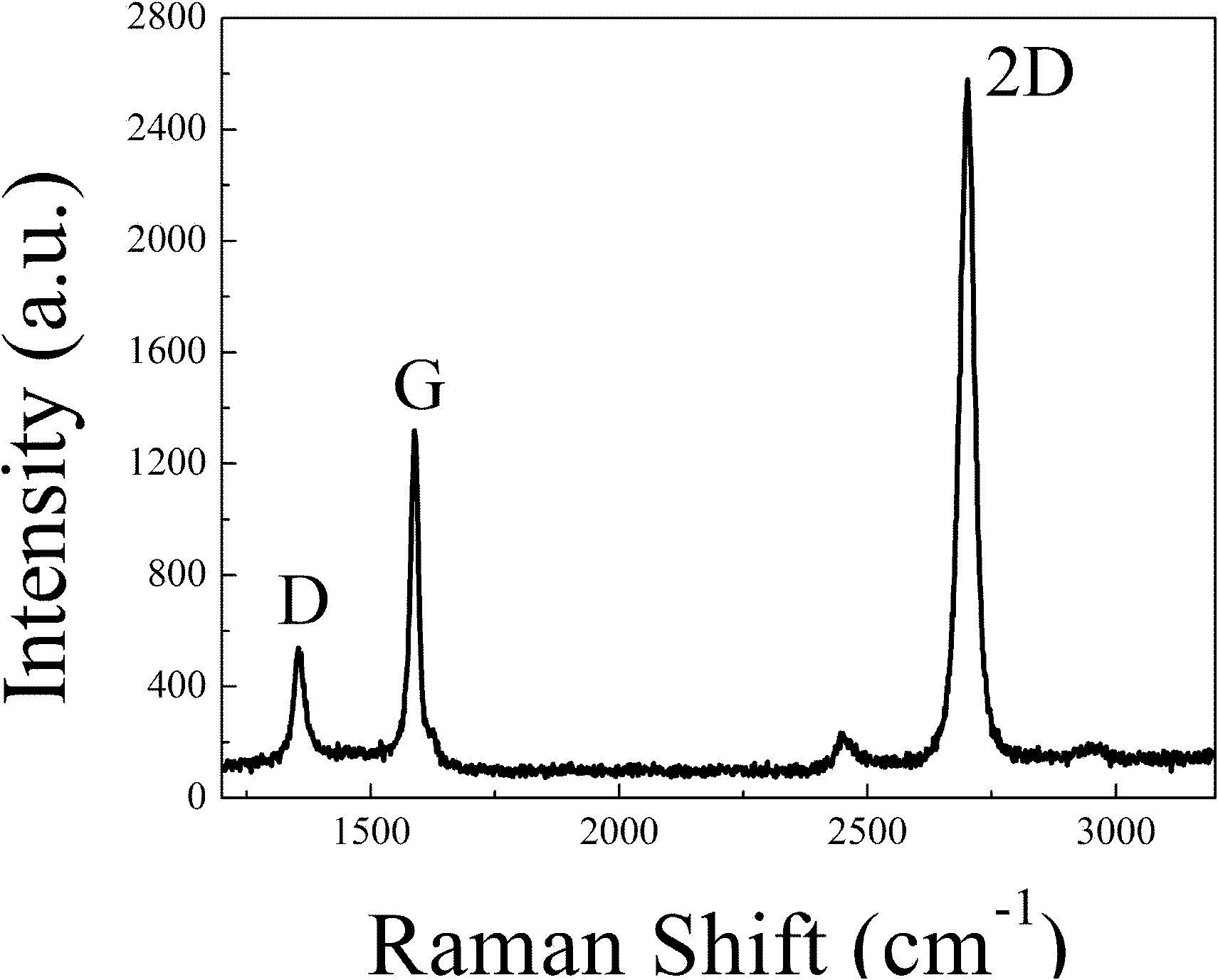

InactiveCN101872120AReduce performancePrecise positioningPhotomechanical apparatusLithographic artistOxygen plasma etching

The invention discloses a method for preparing patterned graphene. In the method, a photoresist is patterned on a device substrate by a microelectronic process such as UV lithography and electron beam lithography, and windows are formed at positions needing graphene; by a graphene transfer method, large-area graphene is transferred onto the patterned photoresist; and the photoresist and the graphene thereon are stripped by an acetone immersion method so as to obtain the patterned graphene required by the device. Compared with the prior art, the method has the advantages of accurate positioning, and does not require etching or manufacturing an imprint template so as to have low cost. Through the method, the patterned graphene is accurately positioned, and the integration of large-area devices is easy to realize. Besides, by exposure and stripping methods, an oxygen plasma-etching step is avoided, so the reduction of the device performance caused by radiation damage is avoided.

Owner:PEKING UNIV

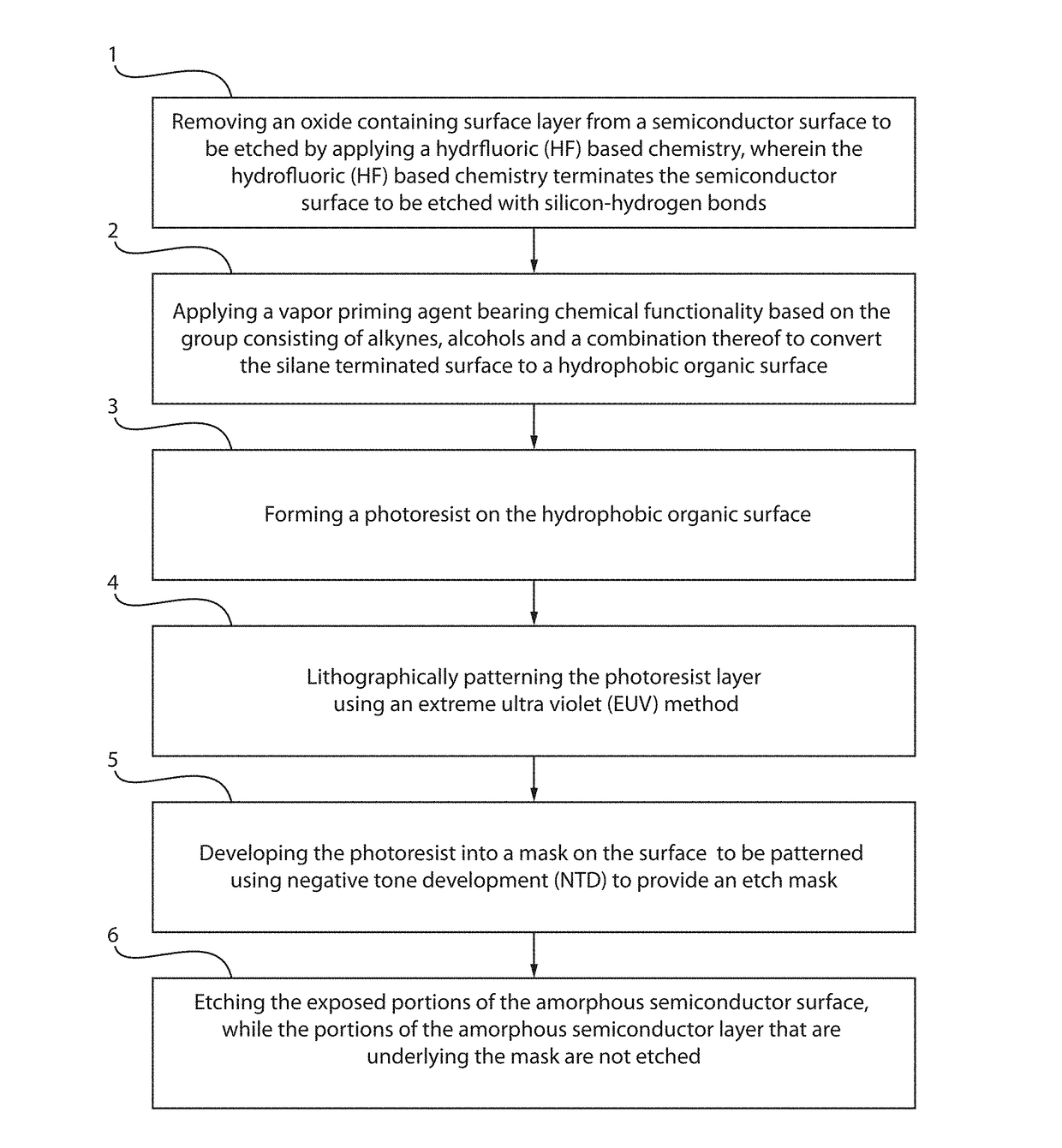

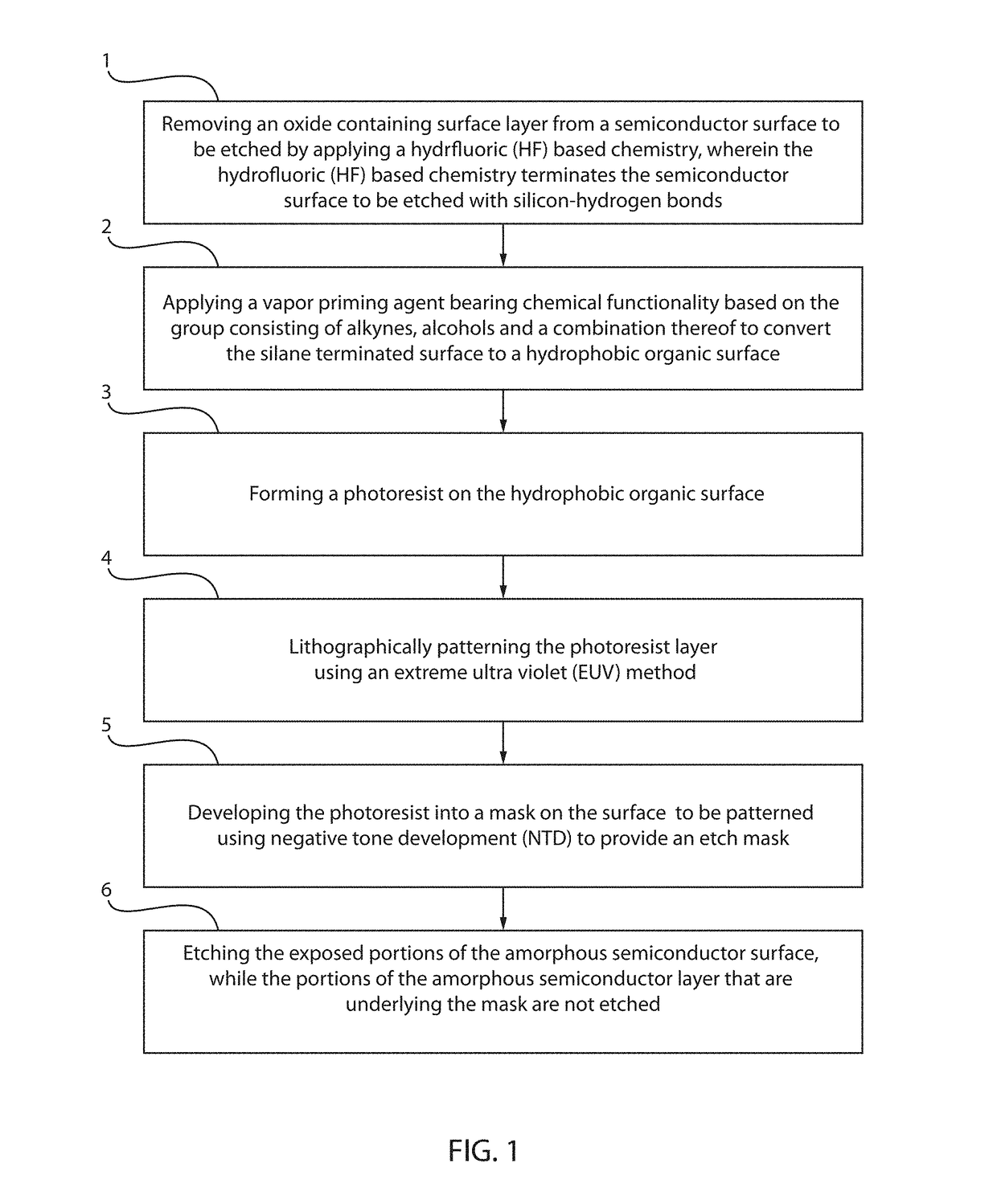

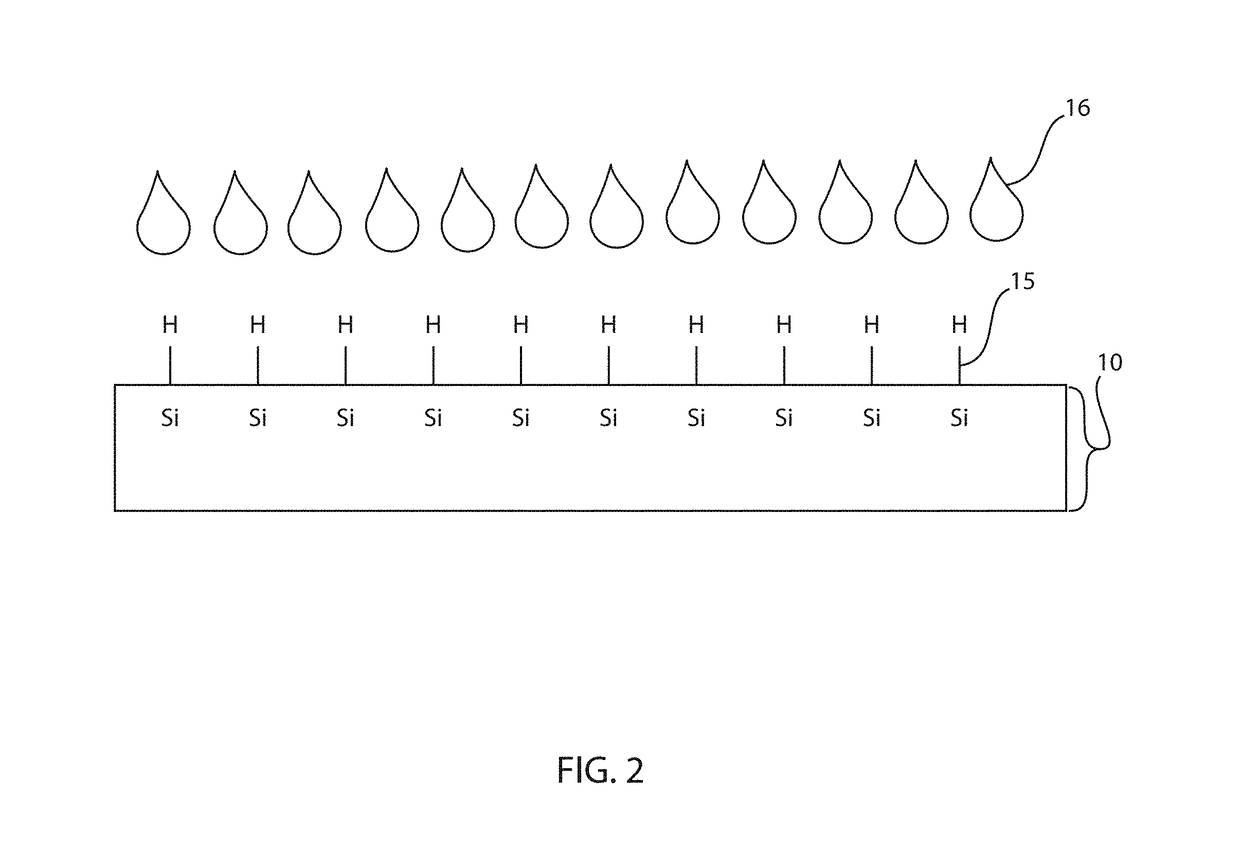

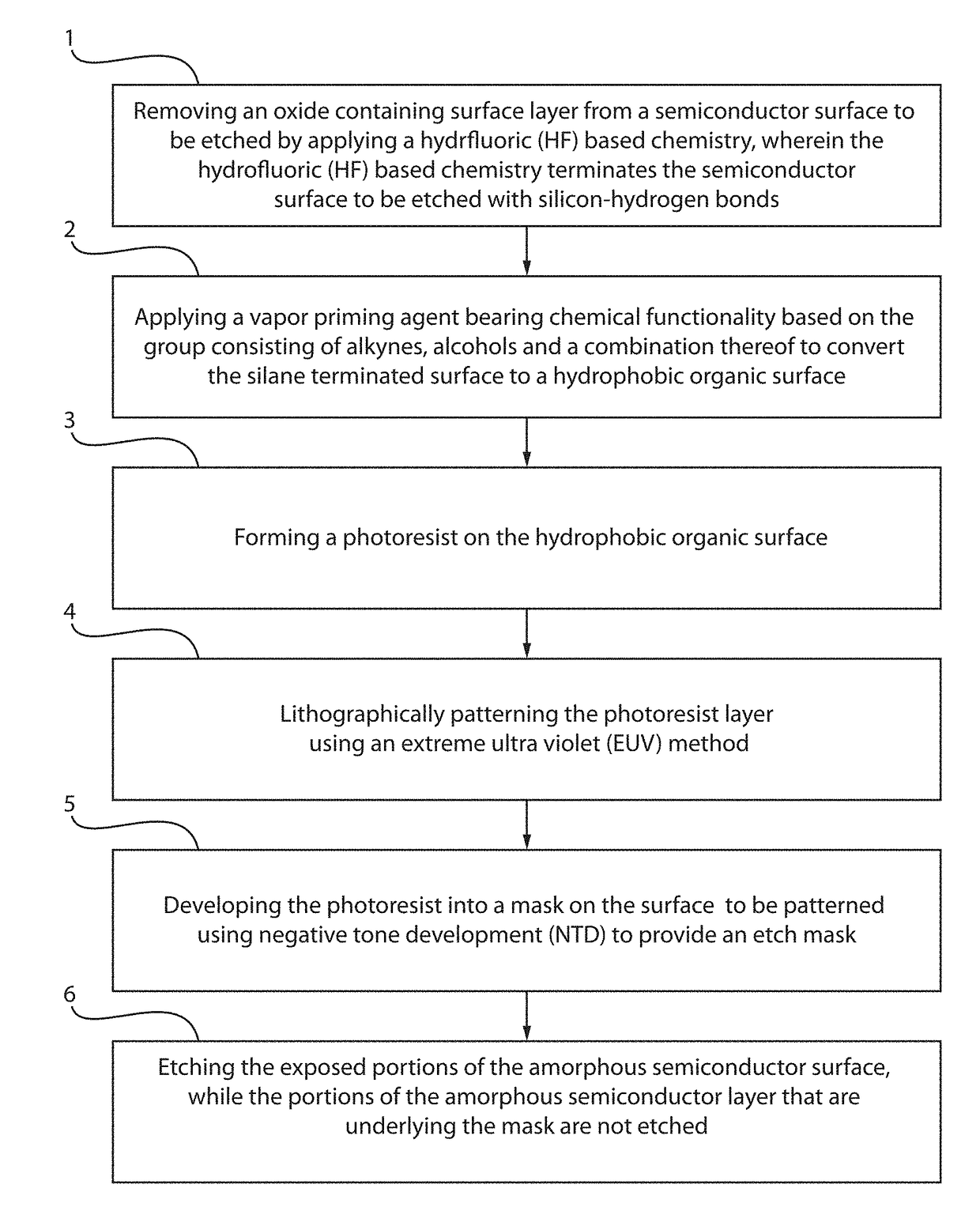

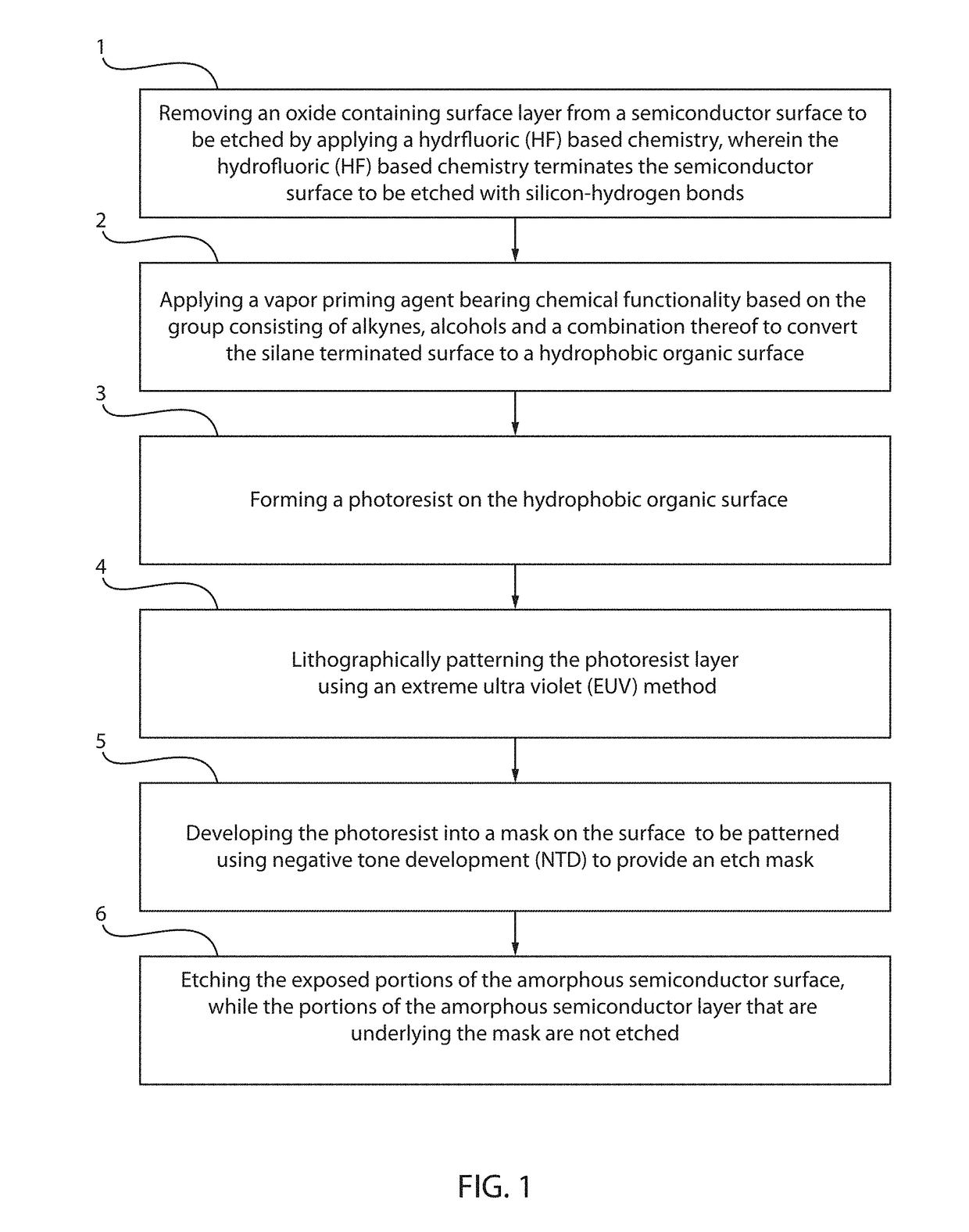

Method to improve adhesion of photoresist on silicon substrate for extreme ultraviolet and electron beam lithography

ActiveUS20180233363A1Improve adhesionImproved patterning fidelitySemiconductor/solid-state device manufacturingPhotomechanical coating apparatusSilanesAlkyne

An etch process that includes removing an oxide containing surface layer from a semiconductor surface to be etched by applying a hydrofluoric (HF) based chemistry, wherein the hydrofluoric (HF) based chemistry terminates the semiconductor surface to be etched with silicon-hydrogen bonds, and applying a vapor priming agent bearing chemical functionality based on the group consisting of alkynes, alcohols and a combination thereof to convert the silane terminated surface to a hydrophobic organic surface. The method continues with forming a photoresist layer on the hydrophobic organic surface; and patterning the photoresist layer. Thereafter, the patterned portions of the photoresist are developed to provide an etch mask. The portions of the semiconductor surface exposed by the etch mask are then etched.

Owner:IBM CORP

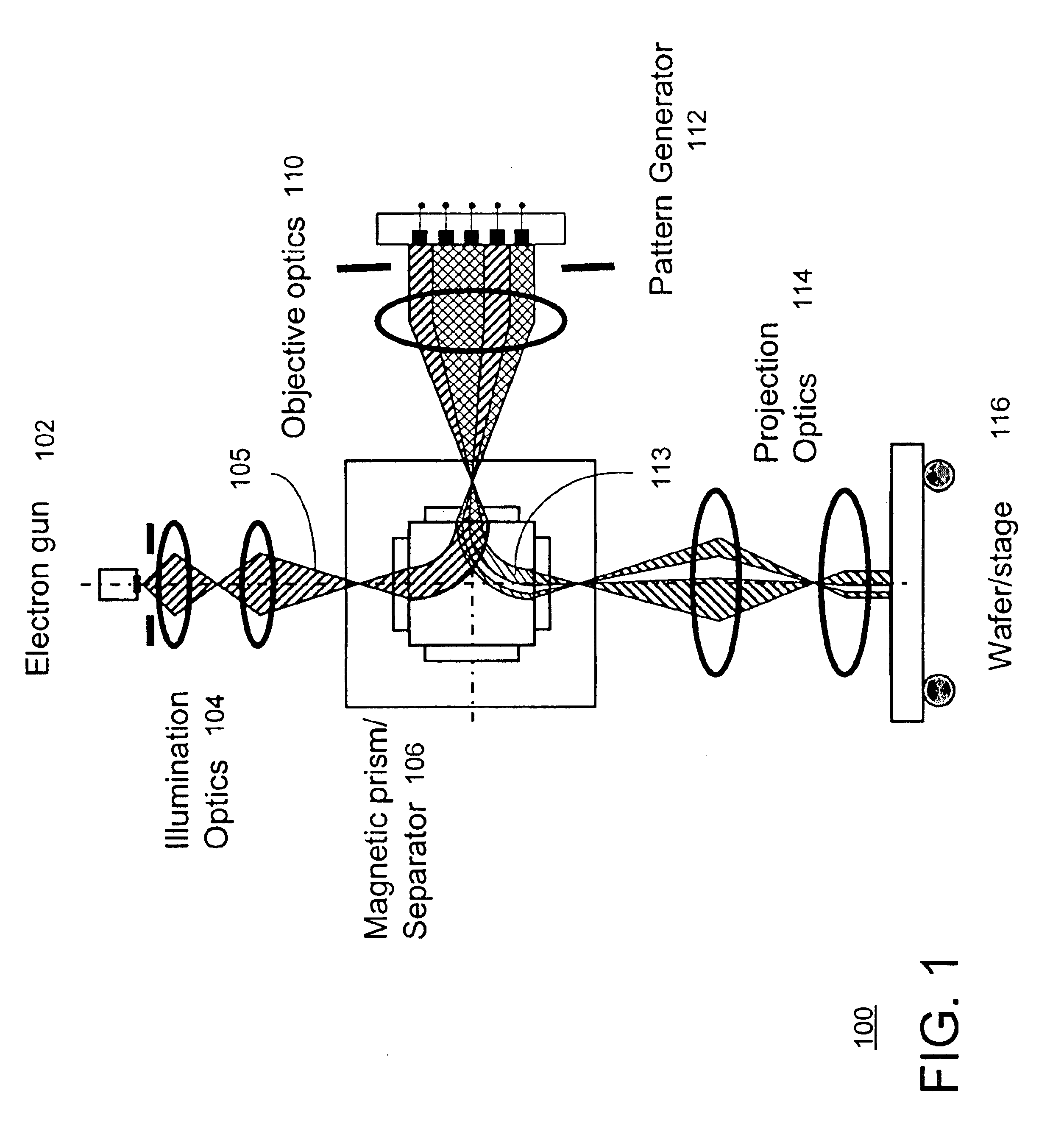

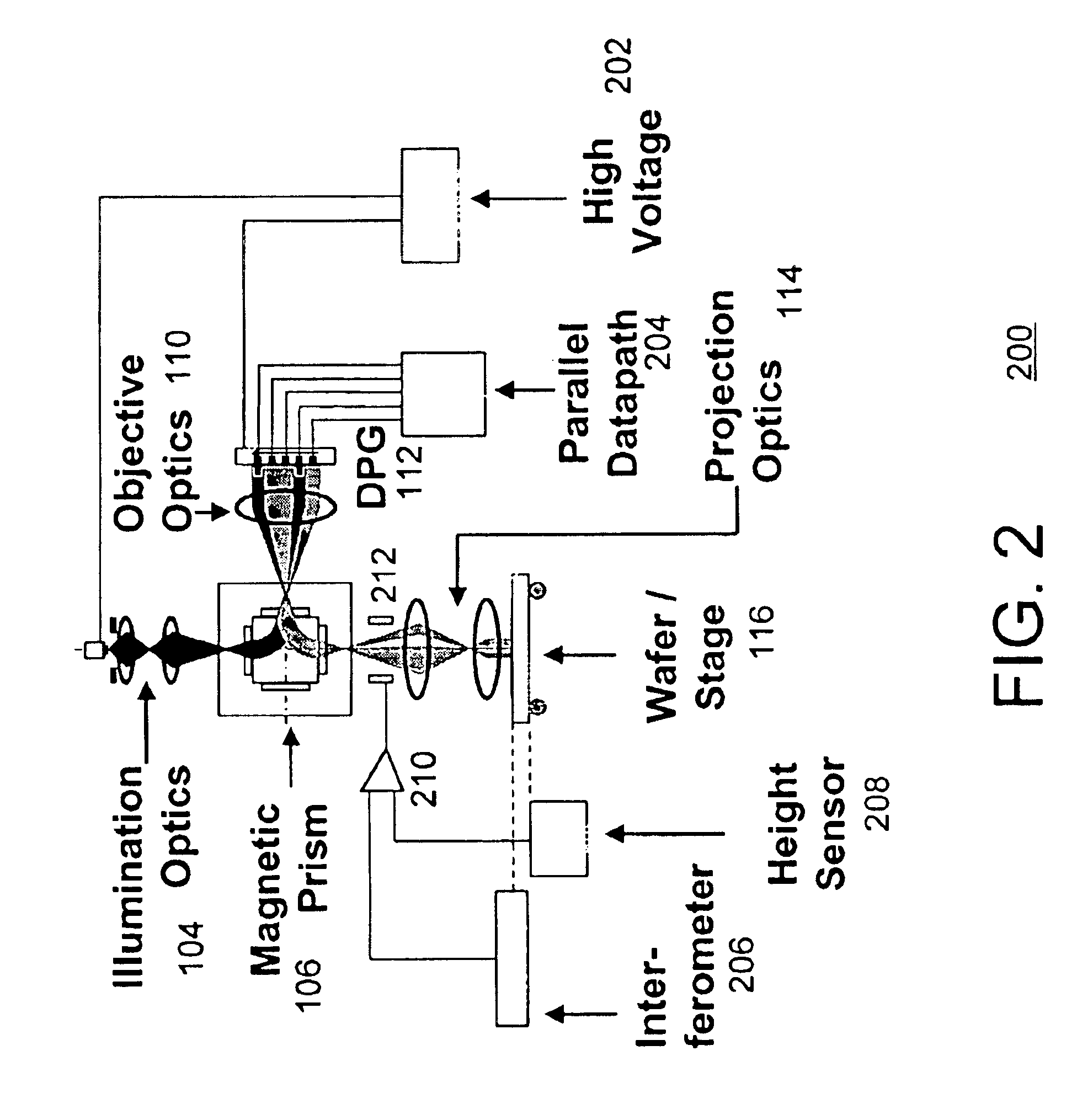

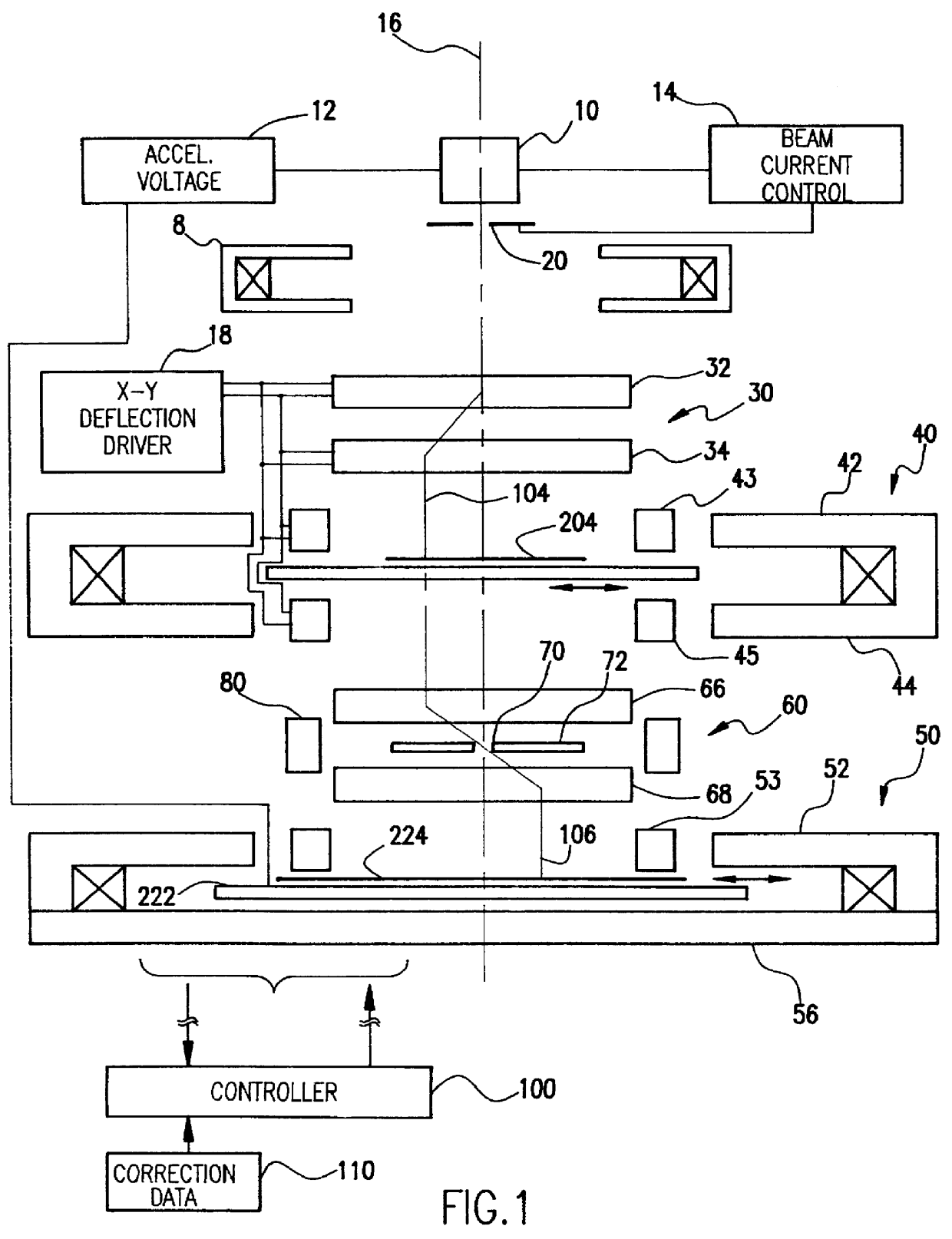

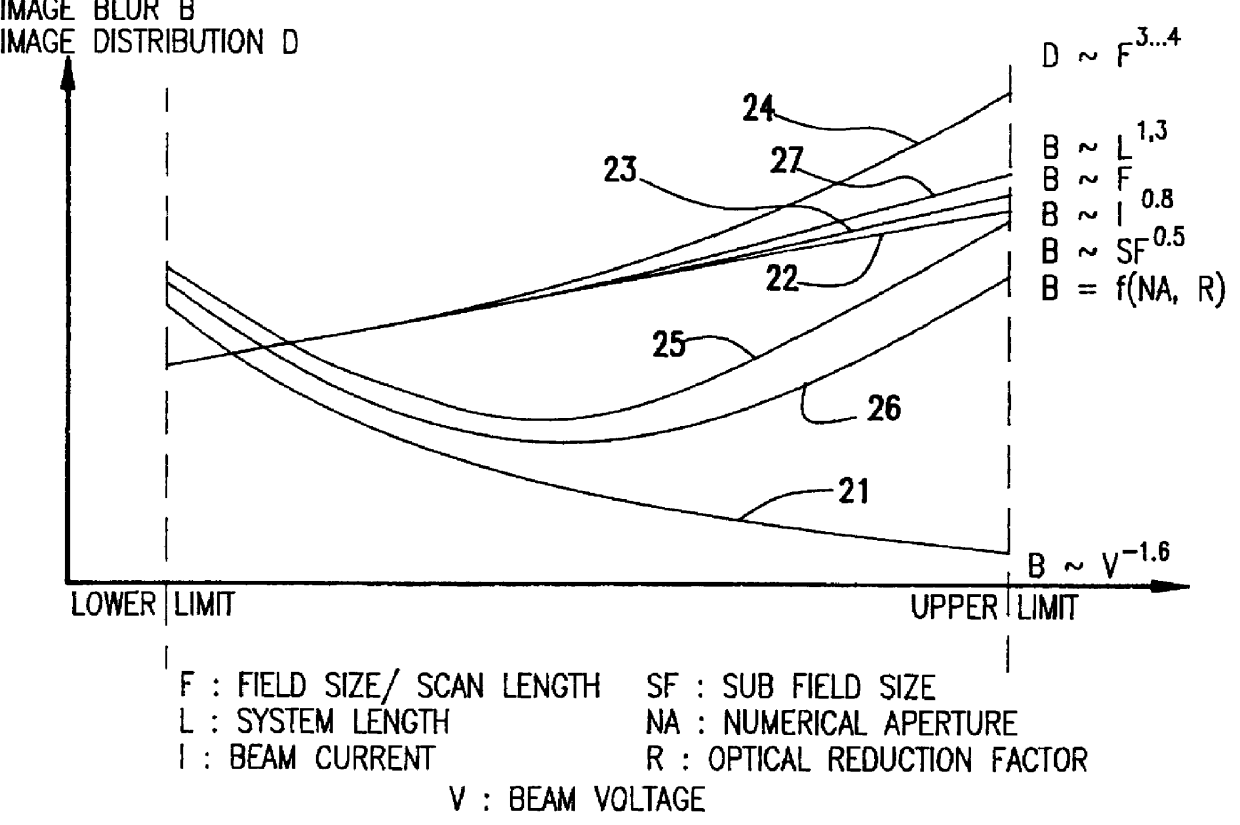

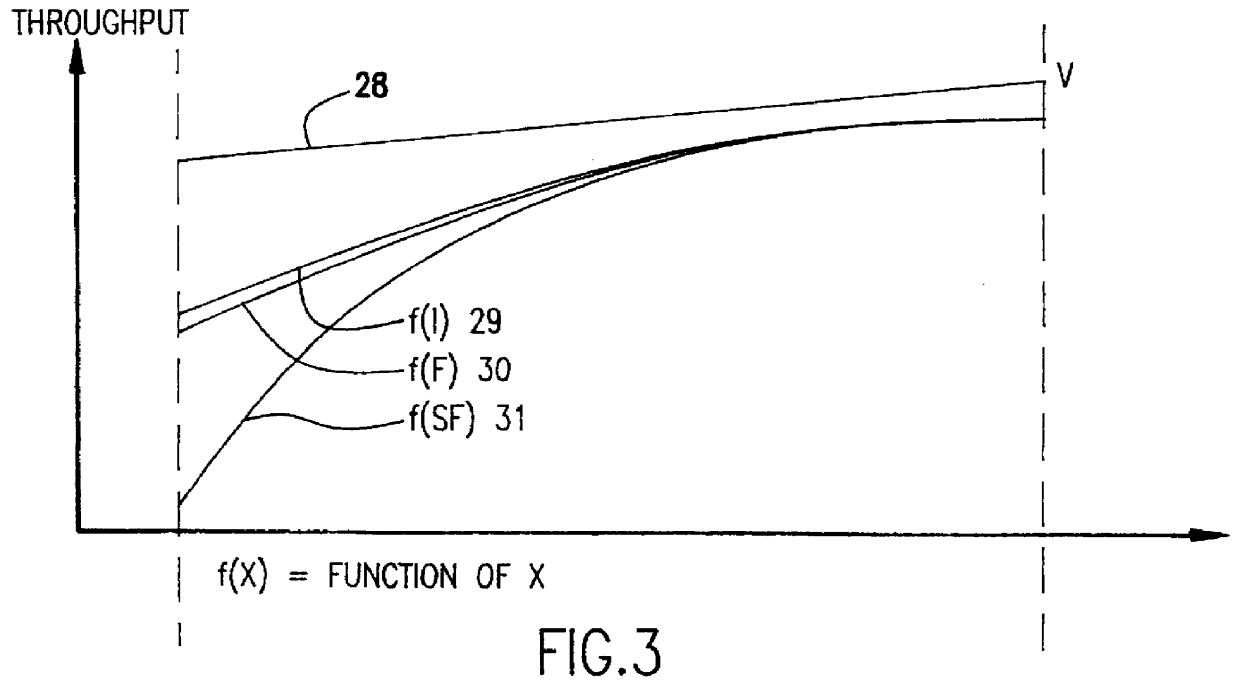

Electron beam projection lithography system (EBPS)

InactiveUS6069684AHigh resolutionImprove throughputElectric discharge tubesNanoinformaticsBeam energyBeam trajectory

Numerous largely unpredictable criticalities of operating parameters arise in electron beam projection lithography systems to maintain throughput comparable to optical projection lithography systems as minimum feature size is reduced below one-half micron and resolution requirements are increased. Using an electron beam projection lithography system having a high emittance electron source, variable axis lenses, curvilinear beam trajectory and constant reticle and / or target motion in a dual scanning mode wherein the target and / or wafer is constantly moved orthogonally to the direction of beam scan, high throughput is obtained consistent with 0.1 mu m feature size ground rules utilizing a column length of greater than 400 mm, a beam current of between about 4 and 35 mu A, a beam energy of between about 75 and 175 kV, a sub-field size between about 0.1 and 0.5 mm at the target at an optical reduction factor between about 3:1 and 5:1, a numerical aperture greater than 2 mrad and preferably between about 3 and 8 mrad and a scan length between about 20 mm and 55 mm. Reticle and target speed preferably differ by about the optical reduction factor.

Owner:IBM CORP

Method to improve adhesion of photoresist on silicon substrate for extreme ultraviolet and electron beam lithography

ActiveUS20180233362A1Improve adhesionImproved patterning fidelitySemiconductor/solid-state device manufacturingPhotomechanical coating apparatusSilanesAlkyne

An etch process that includes removing an oxide containing surface layer from a semiconductor surface to be etched by applying a hydrofluoric (HF) based chemistry, wherein the hydrofluoric (HF) based chemistry terminates the semiconductor surface to be etched with silicon-hydrogen bonds, and applying a vapor priming agent bearing chemical functionality based on the group consisting of alkynes, alcohols and a combination thereof to convert the silane terminated surface to a hydrophobic organic surface. The method continues with forming a photoresist layer on the hydrophobic organic surface; and patterning the photoresist layer. Thereafter, the patterned portions of the photoresist are developed to provide an etch mask. The portions of the semiconductor surface exposed by the etch mask are then etched.

Owner:IBM CORP

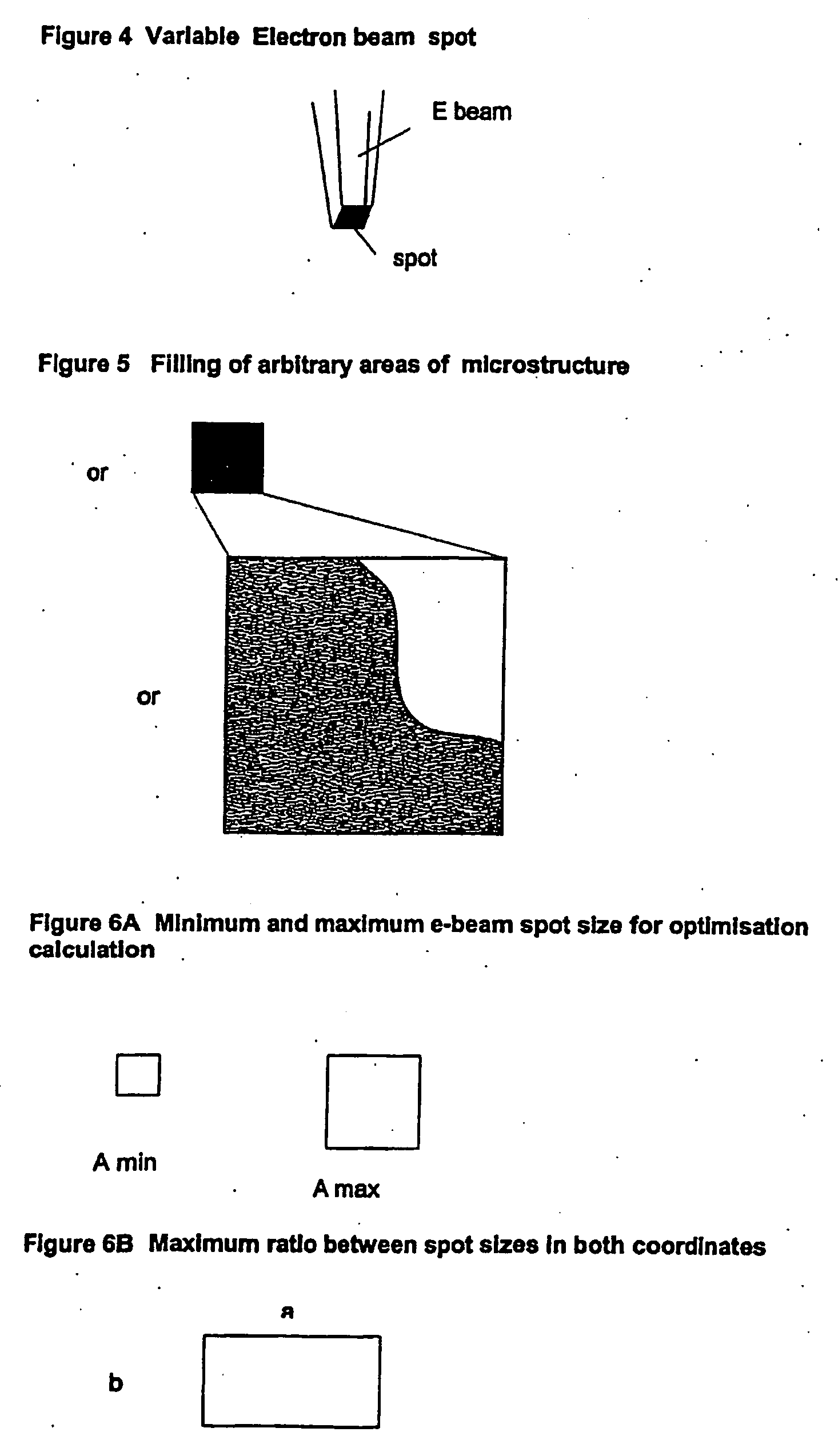

Variable shaped electron beam lithography system and method for manufacturing substrate

InactiveUS20080054196A1Reduce drawing timeDrawn preciselyMaterial analysis using wave/particle radiationElectric discharge tubesSingle electronOptical axis

This VSB lithography system includes a first, second and third aperture for forming a single electron beam in each of the rectangular opening portion that are provided, and draws a figure pattern using the single electron beam formed by passing the beam through the first, second and third aperture in sequence. Each of the first, second and third aperture has a mechanism for rotationally driving the aperture around an optical axis up to an arbitrary angle from 0 to 360°. Further, in the third aperture, a mechanism for varying the opening slit width of the rectangular opening portion is provided.

Owner:LONGITUDE SEMICON S A R L

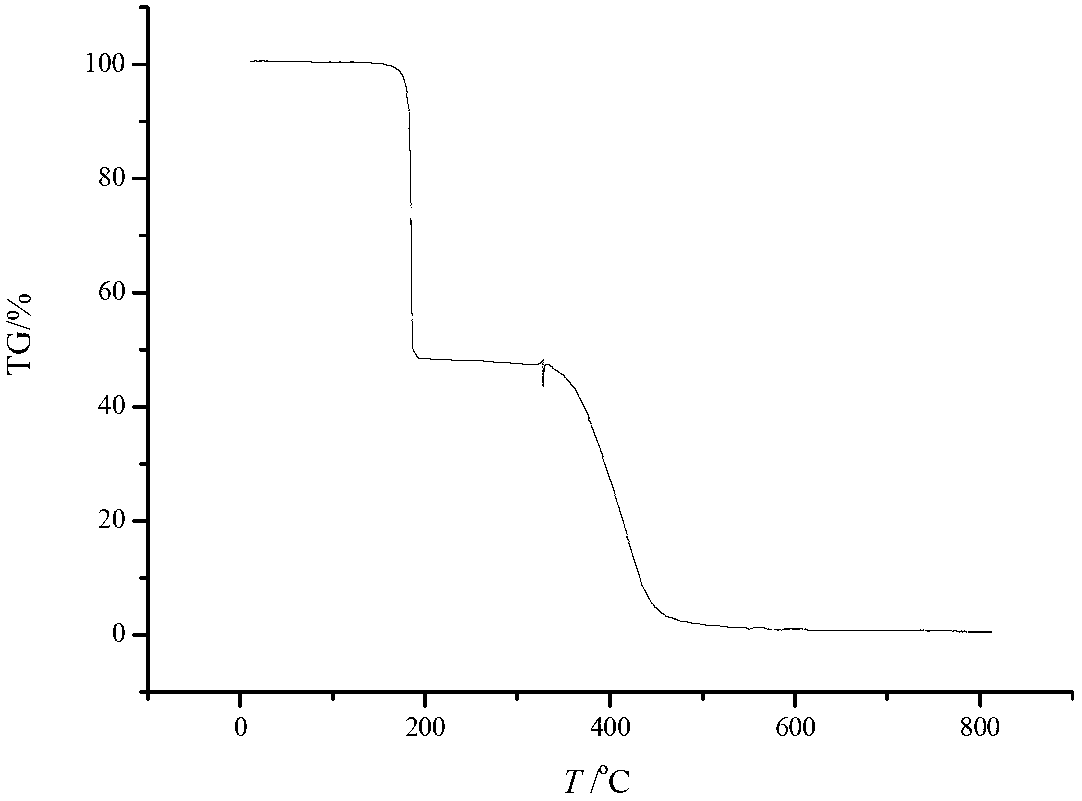

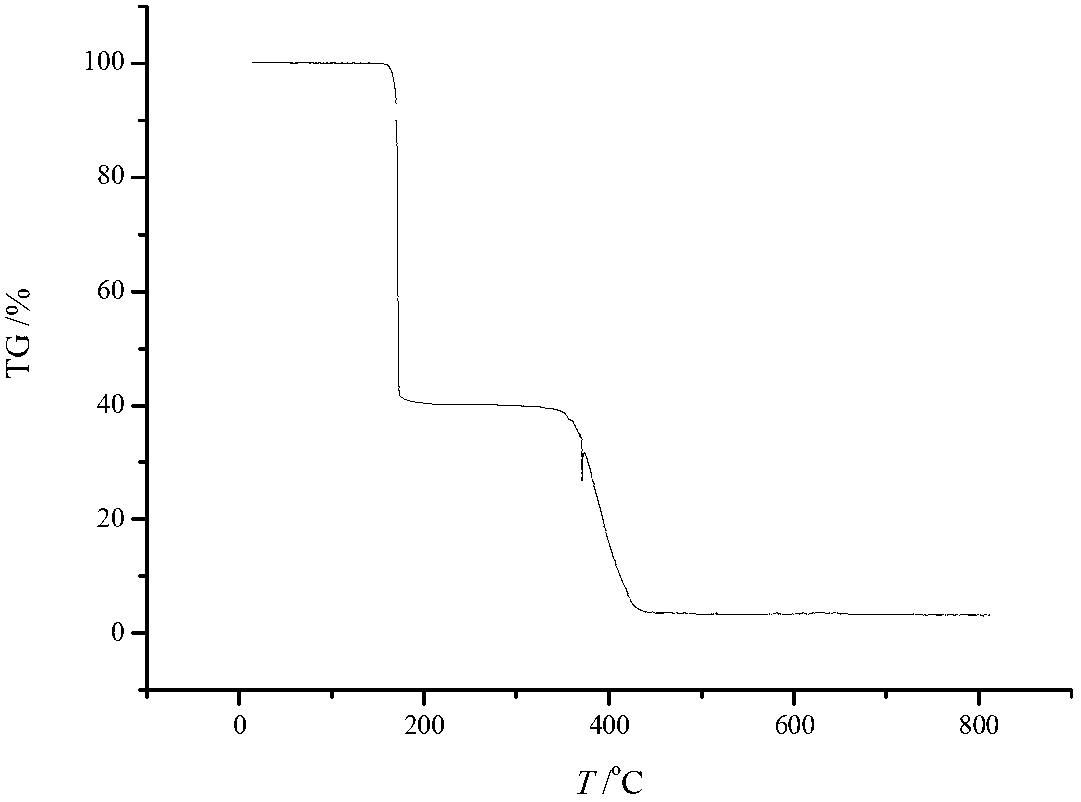

Molecular glass photoresist containing bisphenol A skeleton structure as well as preparation method and application thereof

ActiveCN103304385AOrganic compound preparationPhotomechanical coating apparatusSolventNanoimprint lithography

The invention relates to a series of molecular glass photoresists (I and II) based on bisphenol A as a main body structure and a preparation method thereof. The molecular glass photoresists are compounded with a photo-acid generator, a crosslinking agent, a photoresist solvent and other additives to produce positive or negative photoresists; the positive or negative photoresists are placed on a silicon wafer through a spin coating method to prepare a photoresist coating layer with uniform thickness. The photoresist formula can be used in modern lithography technologies, such as 248nm lithography, 193nm lithography, extreme ultraviolet lithography, nanoimprinting lithography and electron beam lithography, and is especially suitable for an extreme ultraviolet (EUV) photo-lithographic process.

Owner:GUOKE TIANJI (BEIJING) NEW MATERIAL TECH CO LTD

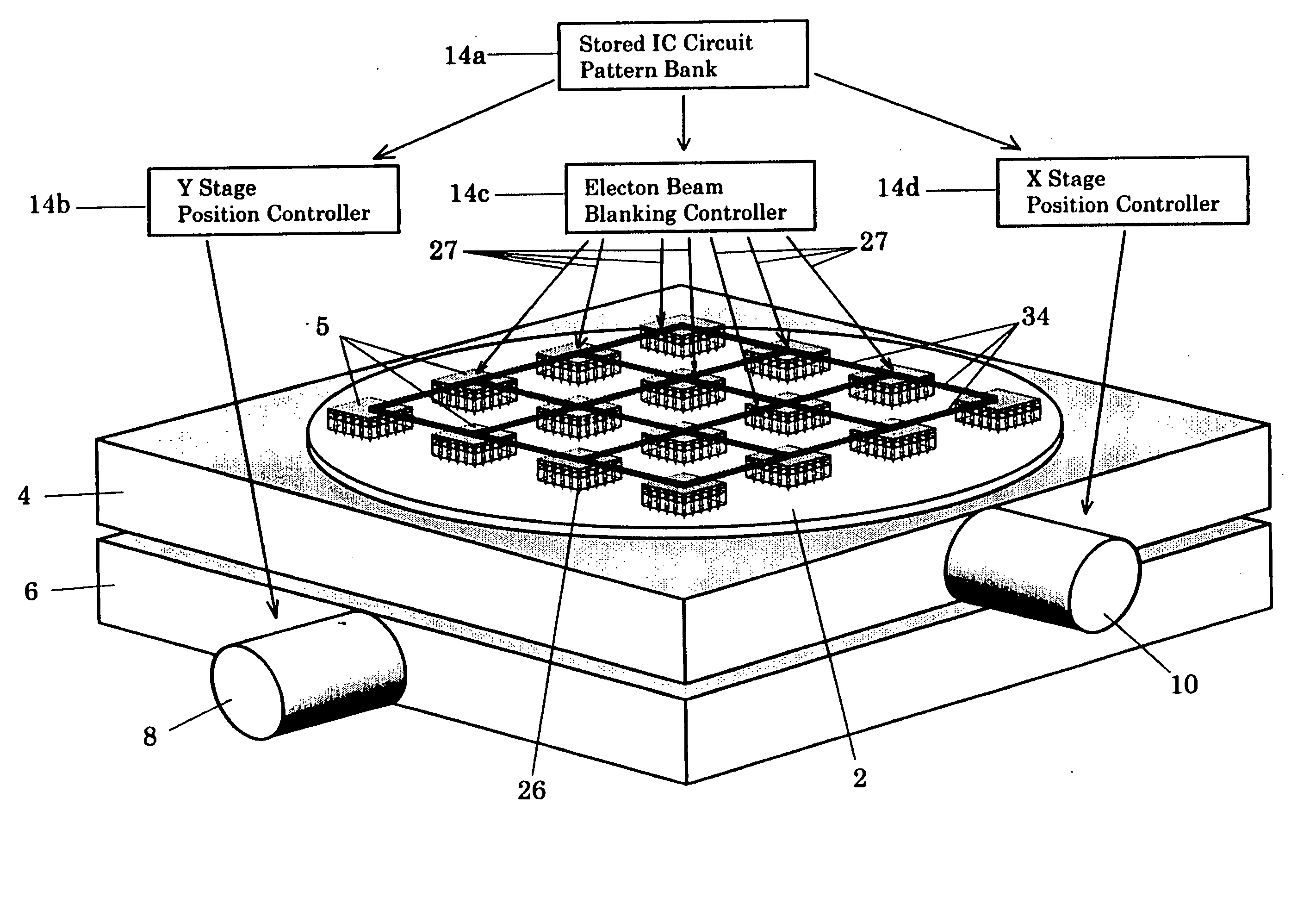

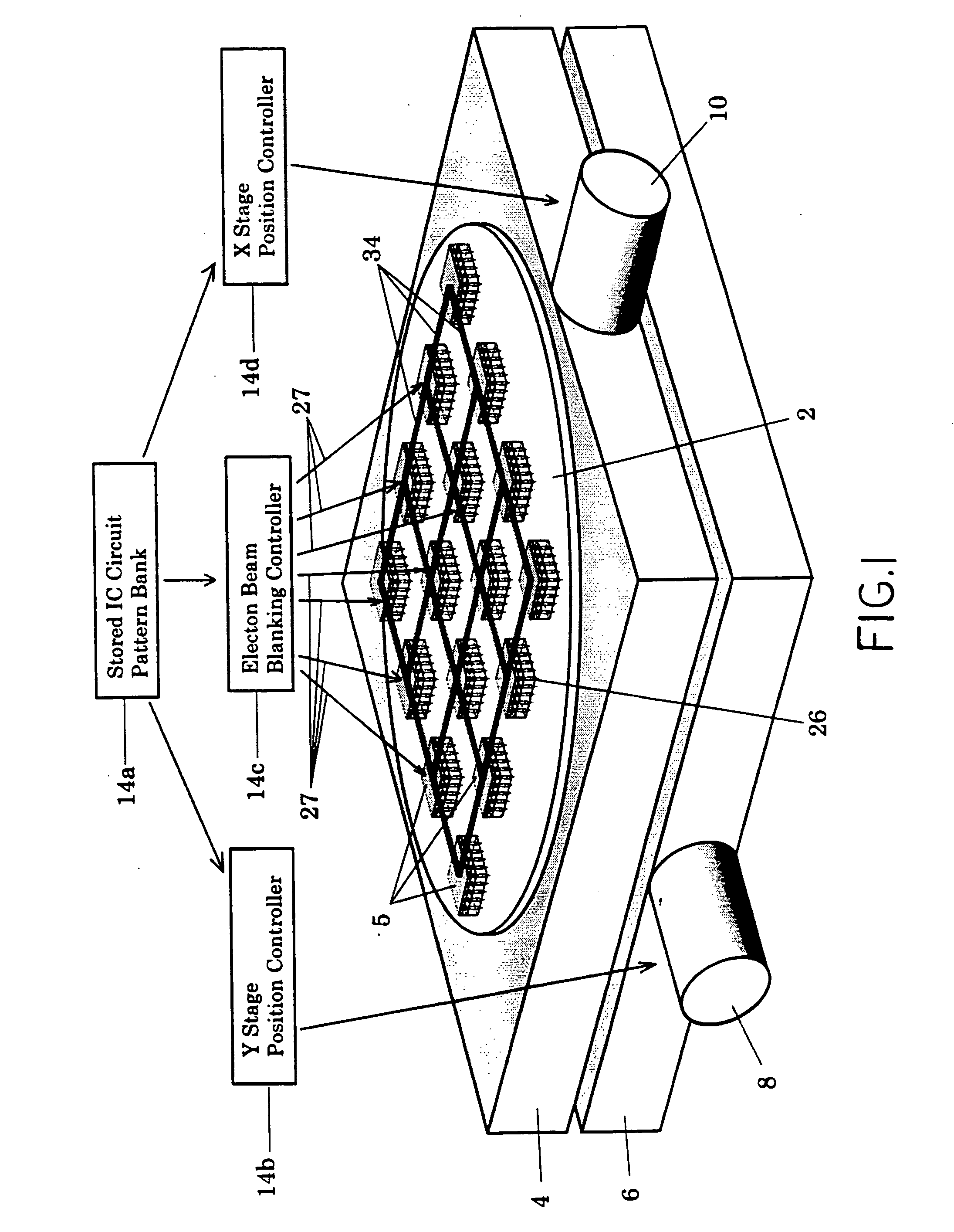

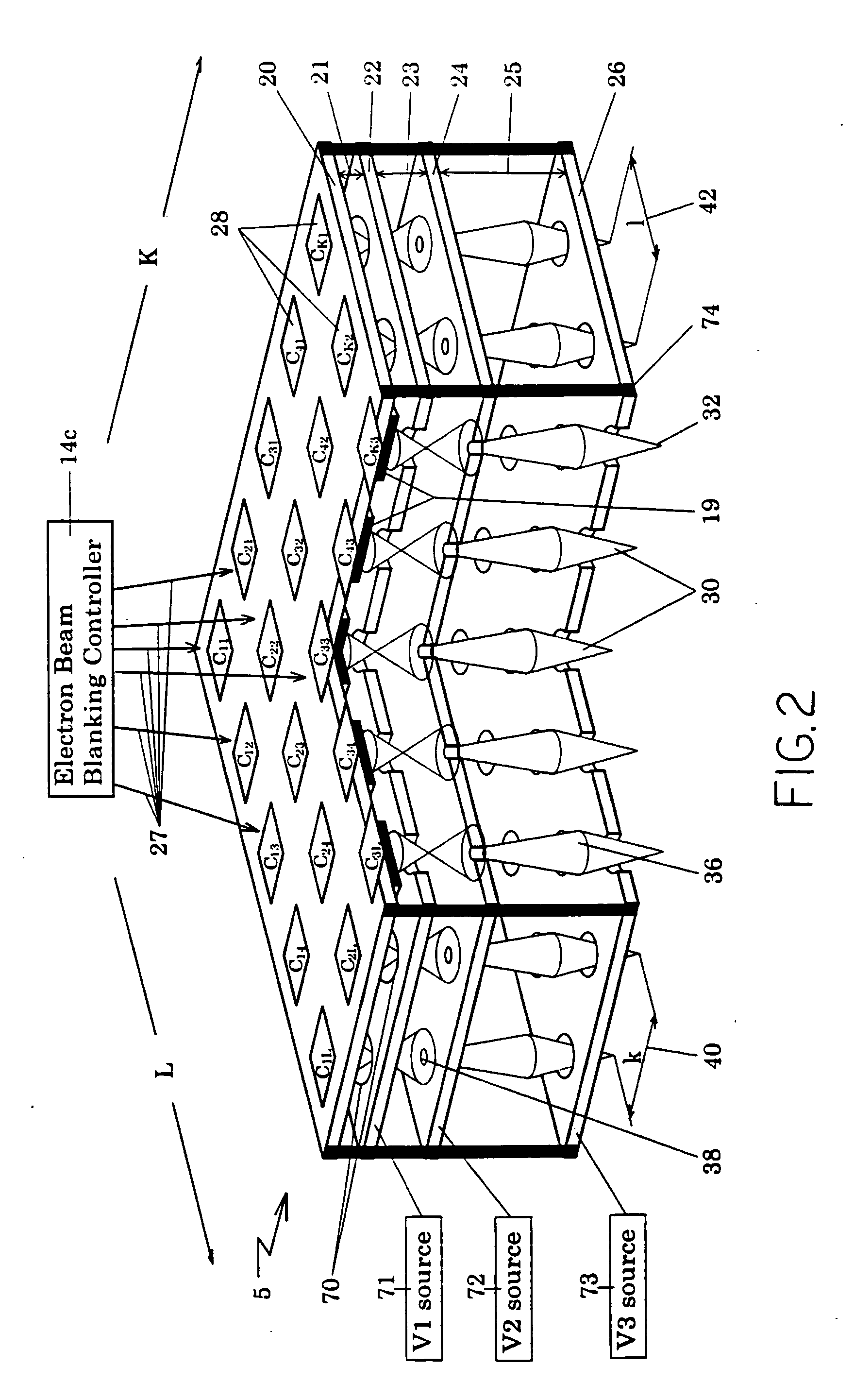

Parallel multi-electron beam lithography for IC fabrication with precise X-Y translation

InactiveUS20050253093A1Low costReduce decreaseMaterial analysis using wave/particle radiationElectric discharge tubesLithographic artistLight beam

A maskless, direct write electron lithography apparatus for accurately and simultaneously writing plural sub-micron patterns on a silicon substrate employs plural parallel electron beams with precise X-Y mechanical translation of the substrate to provide low cost, high throughput integrated circuit (IC) fabrication. Plural compact micro electron gun assemblies arranged in a I×J rectangular grid each simultaneously expose one IC pattern on the substrate, with each electron gun assembly including a K×L array of individually controlled electron guns emitting K×L electron beams. The regular, small spacing between electron beams in each array, i.e., approximately 1 mm or less, requires a correspondingly small X-Y translation of the substrate to write the entire wafer. Each electron gun array includes plural AC blanked cathodes and DC biased plates having plural aligned beam passing apertures. A computer controlled pattern generator synchronized with wafer X-Y translation controls the duration and timing of the cathode blanking signals.

Owner:GORSKI RICHARD M +2

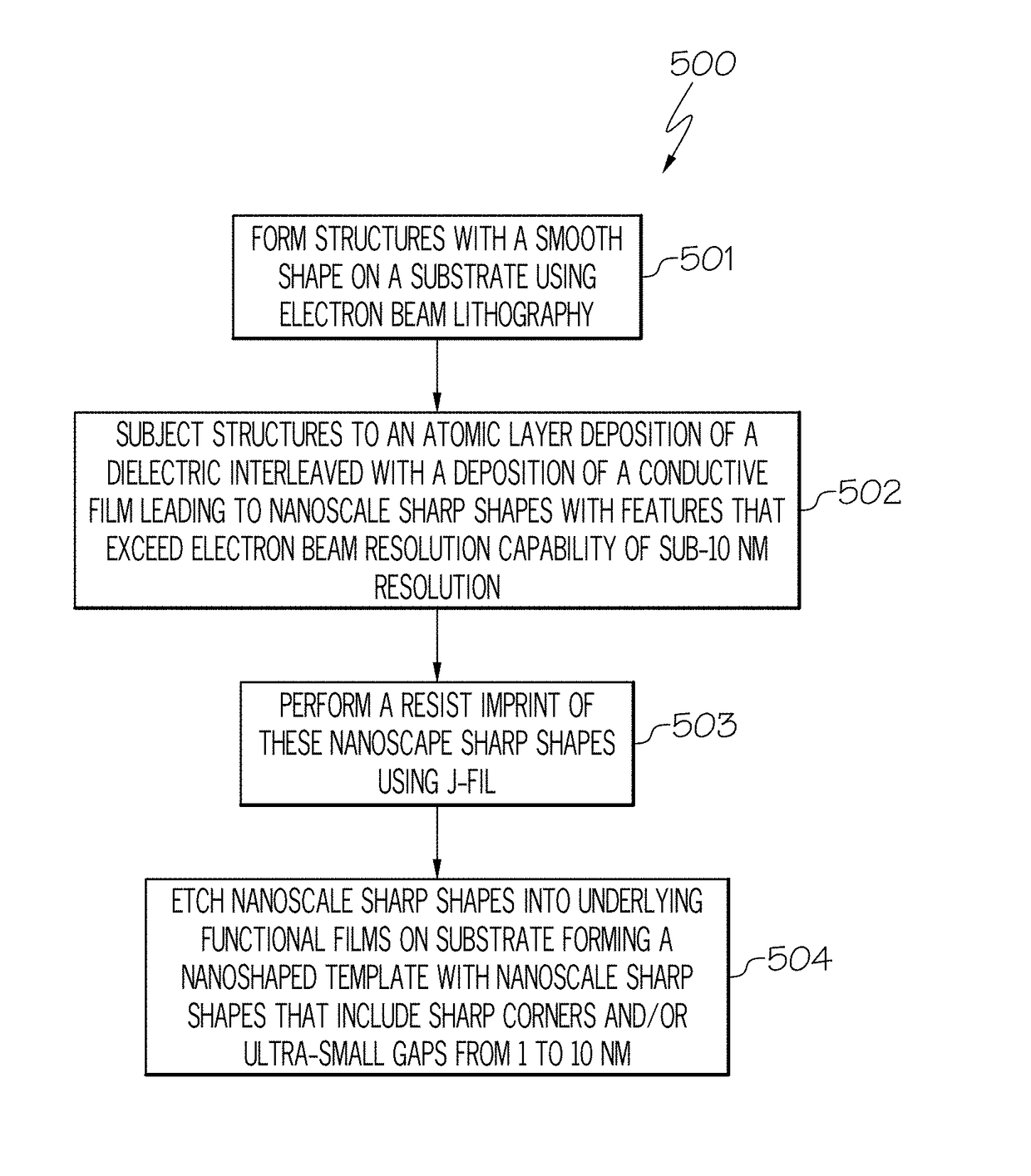

Nanoshape patterning techniques that allow high-speed and low-cost fabrication of nanoshape structures

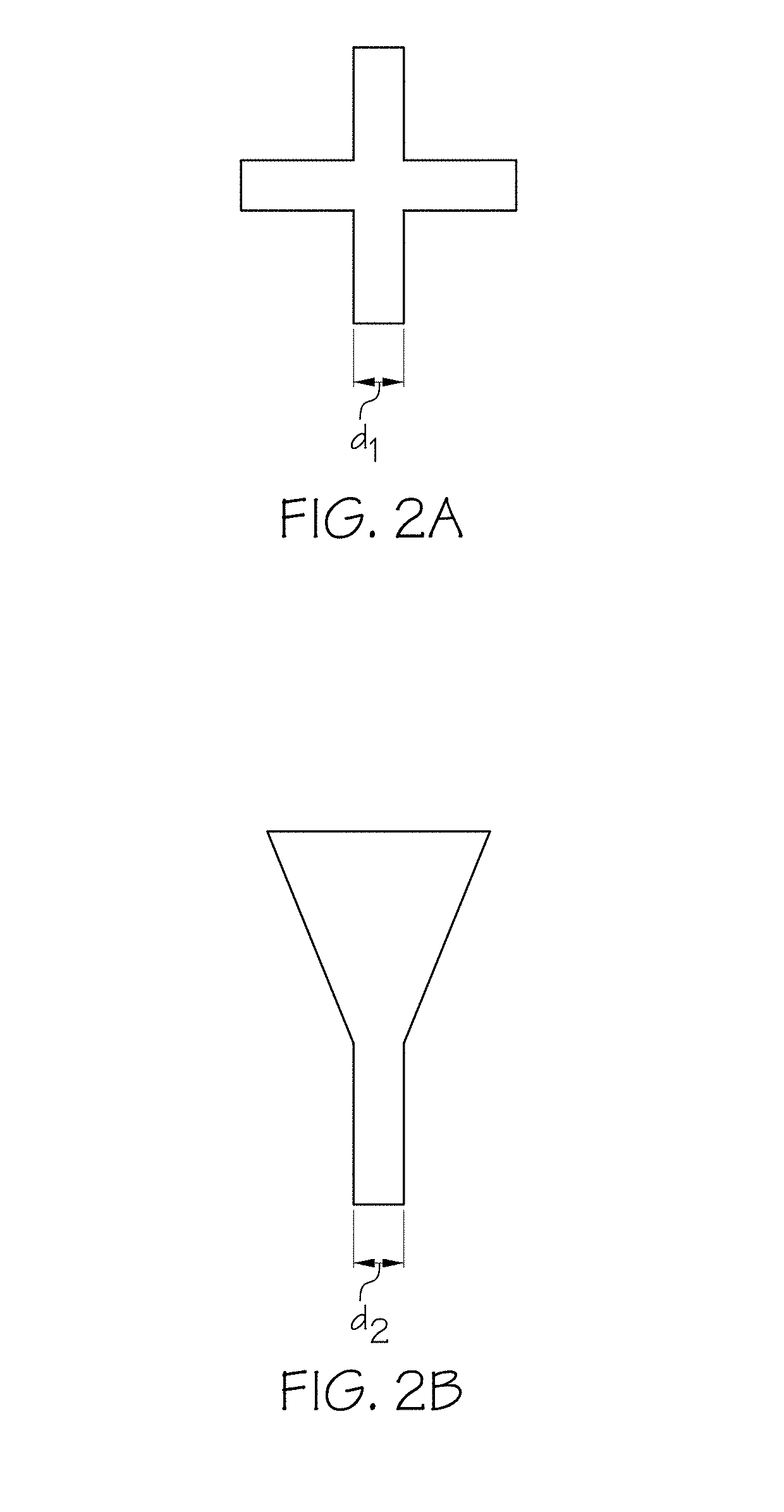

A method for template fabrication of ultra-precise nanoscale shapes. Structures with a smooth shape (e.g., circular cross-section pillars) are formed on a substrate using electron beam lithography. The structures are subject to an atomic layer deposition of a dielectric interleaved with a deposition of a conductive film leading to nanoscale sharp shapes with features that exceed electron beam resolution capability of sub-10 nm resolution. A resist imprint of the nanoscale sharp shapes is performed using J-FIL. The nanoscale sharp shapes are etched into underlying functional films on the substrate forming a nansohaped template with nanoscale sharp shapes that include sharp corners and / or ultra-small gaps. In this manner, sharp shapes can be retained at the nanoscale level. Furthermore, in this manner, imprint based shape control for novel shapes beyond elementary nanoscale structures, such as dots and lines, can occur at the nanoscale level.

Owner:BOARD OF RGT THE UNIV OF TEXAS SYST

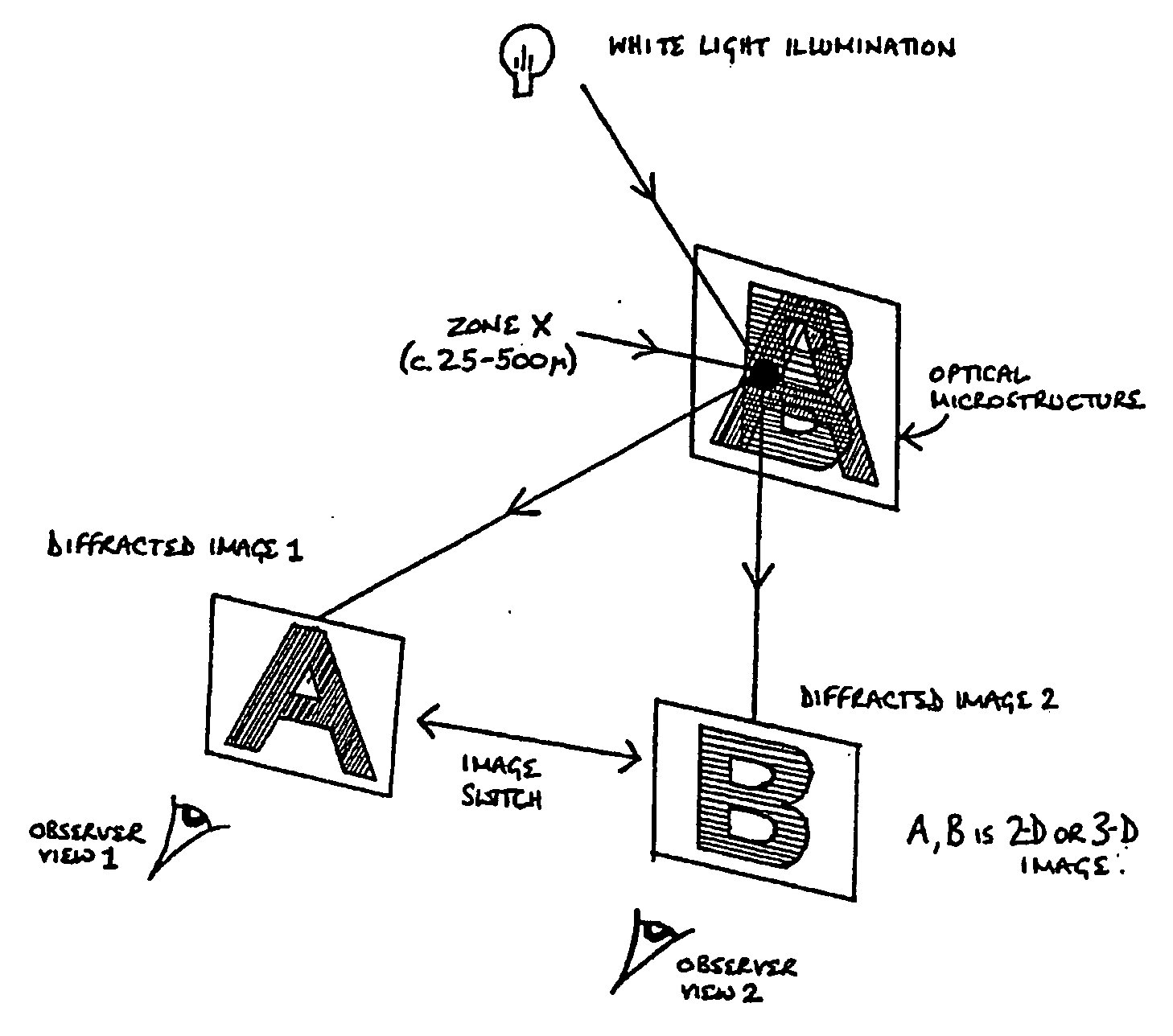

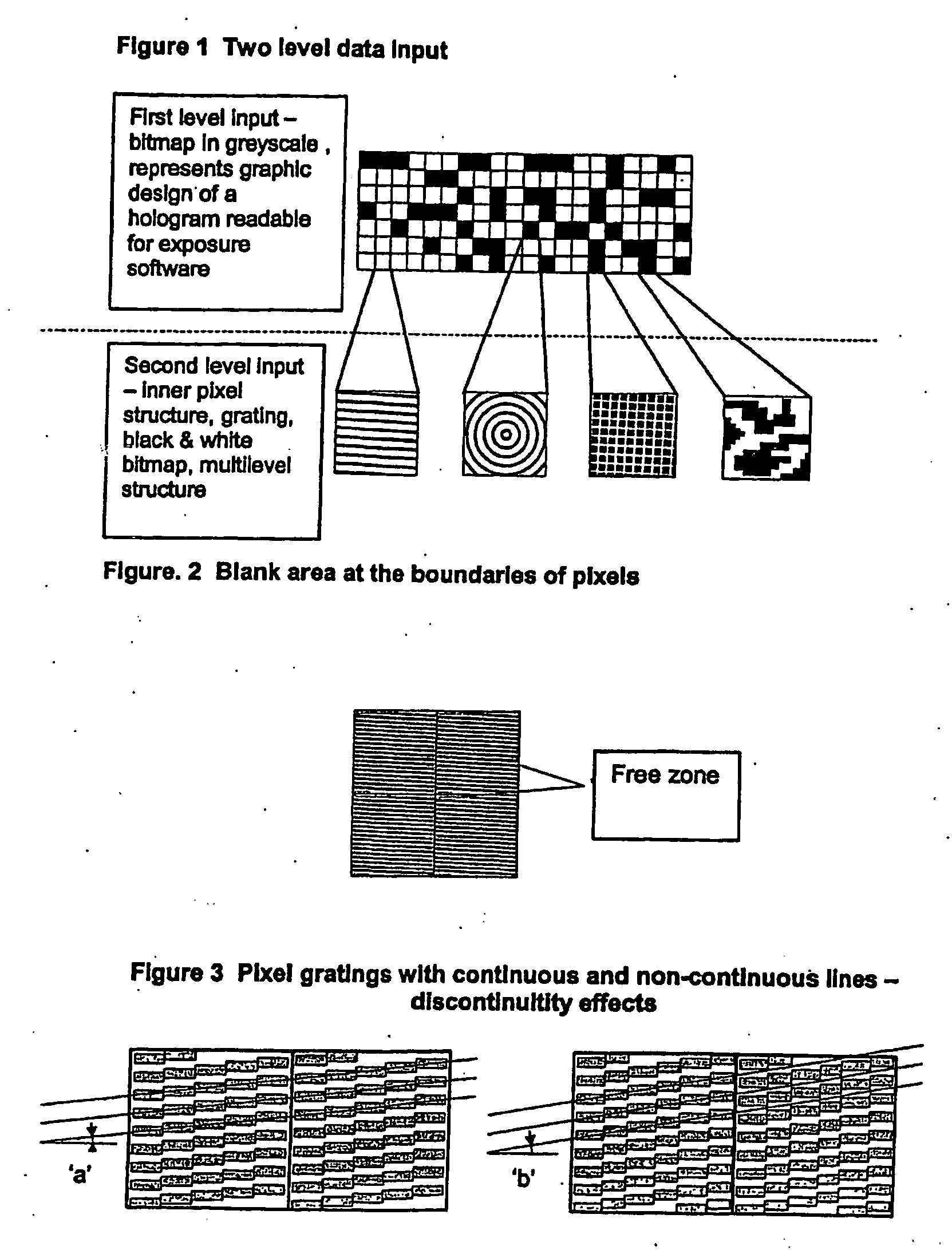

Optical device and method of manufacture

InactiveUS20070284546A1Unlimited flexibilityImprove the immunityDigitally marking record carriersMirrorsElectron-beam lithographyElectron bunches

The present invention provides for a method of producing an optical device by means of electron beam lithography and including the step of varying the characteristics of the electron beam spot during formation of the device and also an apparatus for producing diffractive optical devices and / or holographic devices by means of electron beam lithography and including an electron beam lithograph, controlling and processing means, means for varying the characteristics of the electron beam spot during formation of the device, and wherein the processing means is arranged for compiling and pre-processing data and for providing optimisation and allocation control and to optical devices such as those produced thereby.

Owner:OPTAGLIO

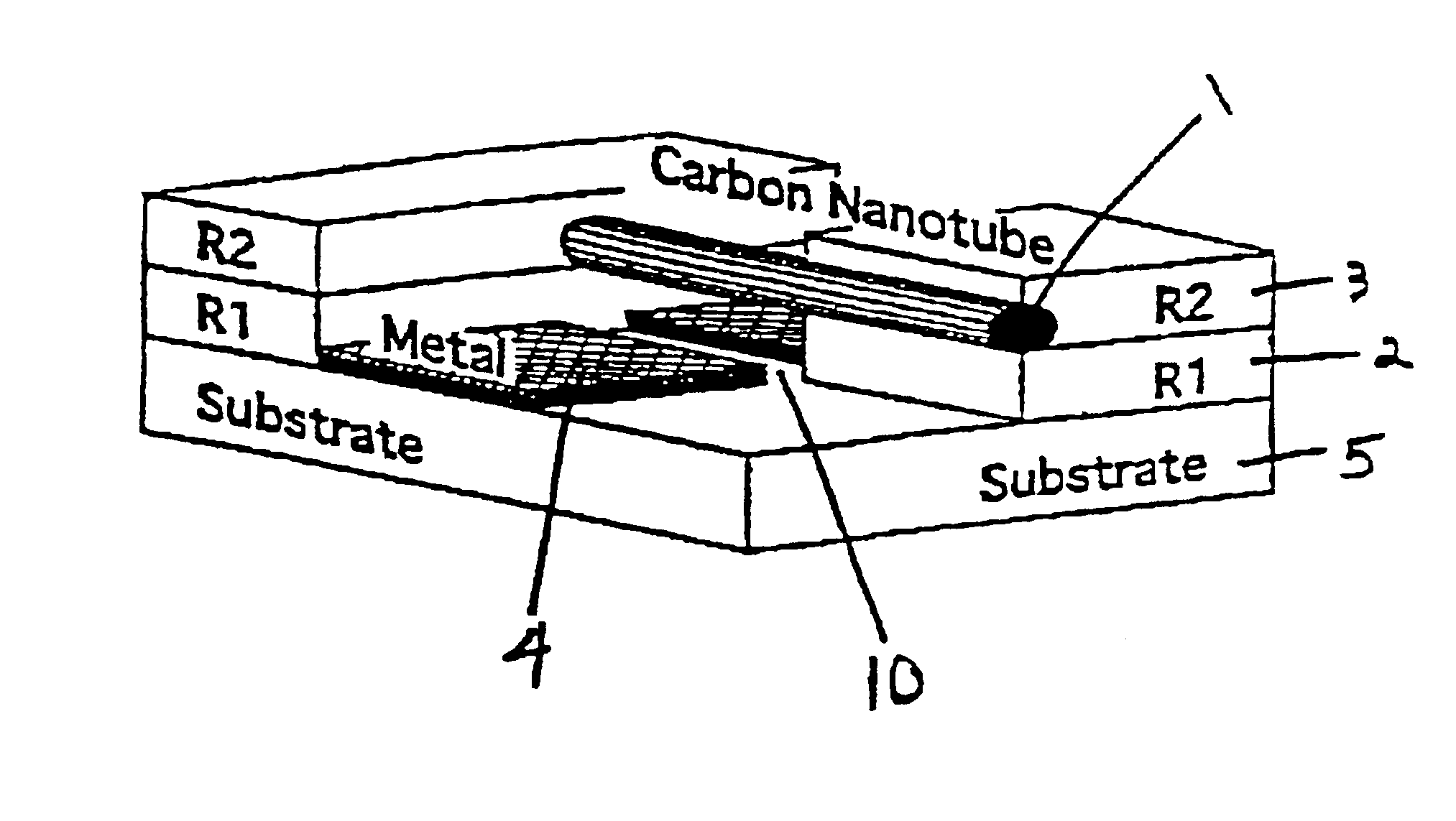

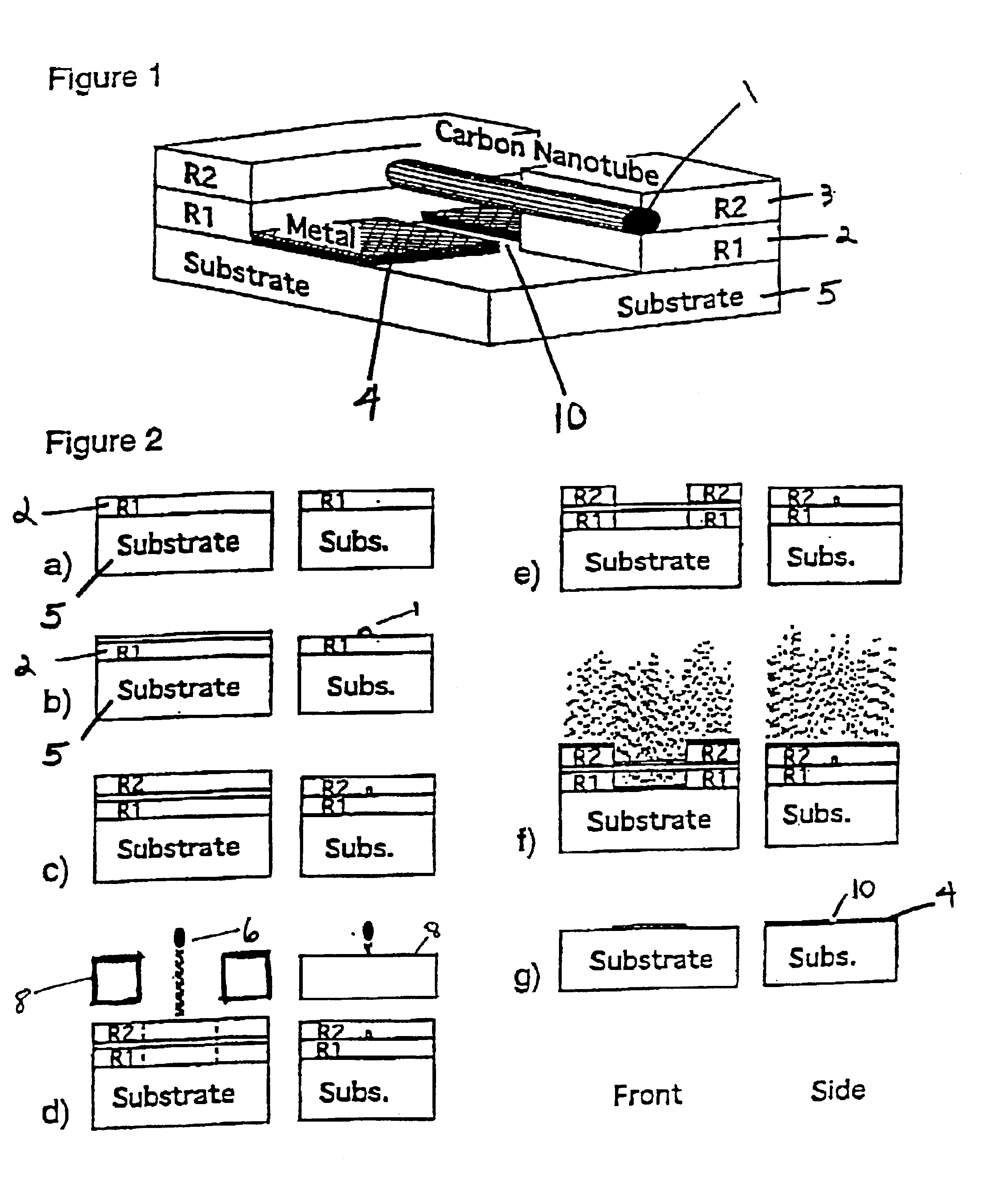

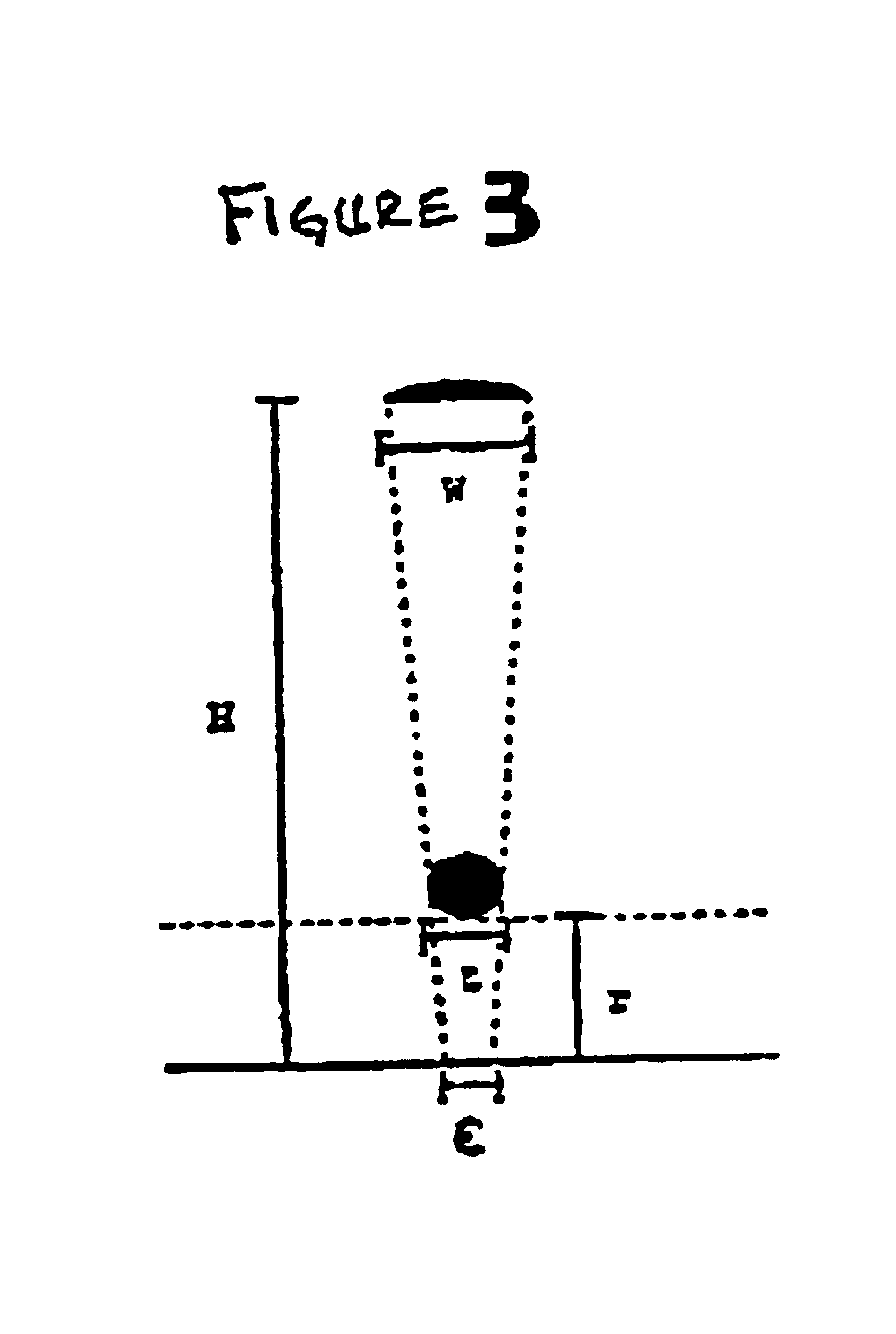

Fabrication of nanometer size gaps on an electrode

InactiveUS6897009B2Photo-taking processesNanoinformaticsField-effect transistorElectron-beam lithography

A shadow mask method to fabricate electrodes with nanometer scale separation utilizes nanotubes (NTs). Metal wires with gaps are made by incorporating multi-wall carbon nanotubes (MWNTs) or single-wall carbon nanotubes (SWNTs) (or bundles thereof) into a tri-layer electron beam lithography process. The simple, highly controllable, and scaleable method can be used to make gaps with widths between 1 and 100 nm. Electronic transport measurements performed on individual SWNTs bridge nanogaps smaller than 30 nm. Metallic SWNTs exhibit quantum dot behavior with an 80 meV charging energy and a 20 meV energy level splitting. Semiconducting SWNTs show an anomalous field effect transistor behavior.

Owner:THE TRUSTEES OF THE UNIV OF PENNSYLVANIA

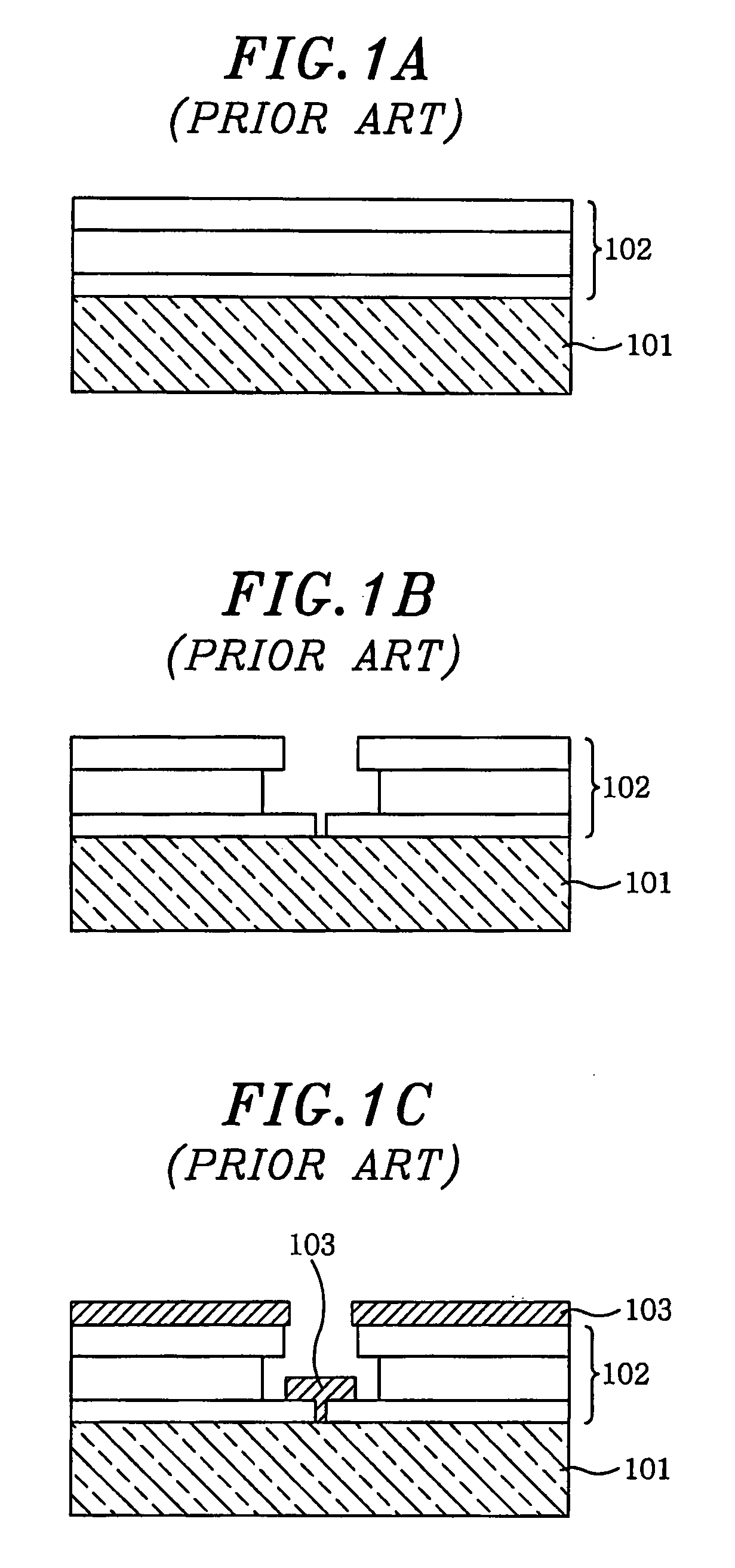

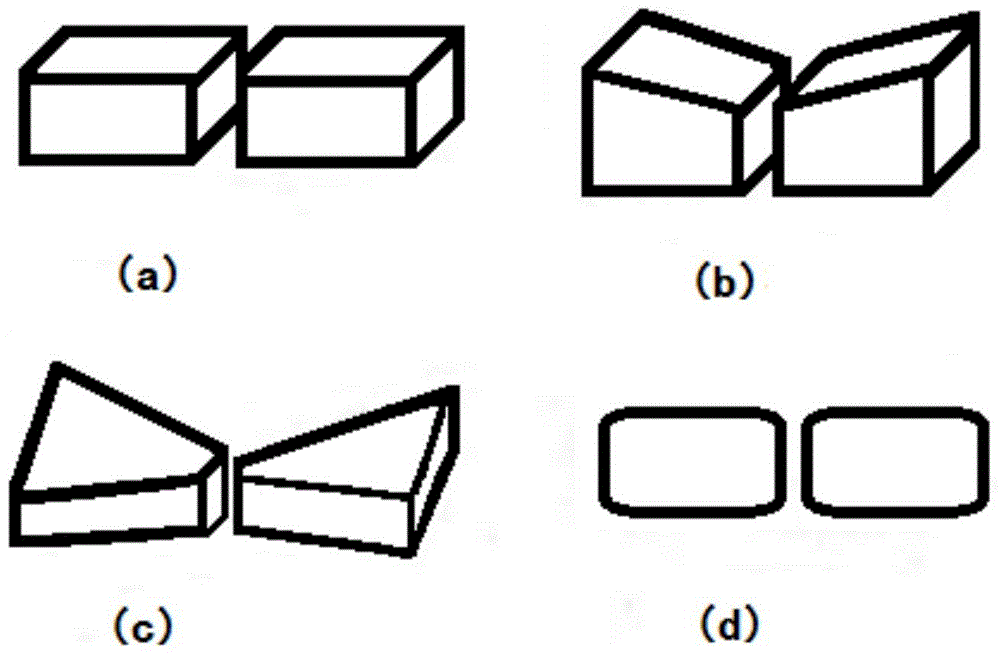

T-gate forming method and metamorphic high electron mobility transistor fabricating method using the same

InactiveUS20080182369A1Reduce physical impactImprove performanceSemiconductor/solid-state device manufacturingSemiconductor devicesResistMetamorphic high electron mobility transistor

A method for forming a T-gate of a metamorphic high electron mobility transistor is provided. The method includes sequentially laminating a plurality of resist films on a substrate; forming a T-shaped pattern in the laminated resist films using electron beam lithography; forming a gate metal layer on the substrate where the T-shaped pattern has been formed; attaching an adhesion member to the gate metal layer formed on a top surface of the laminated resist films and detaching the adhesion member to thereby remove the gate metal layer; and removing the laminated resist films.

Owner:POSTECH ACAD IND FOUND

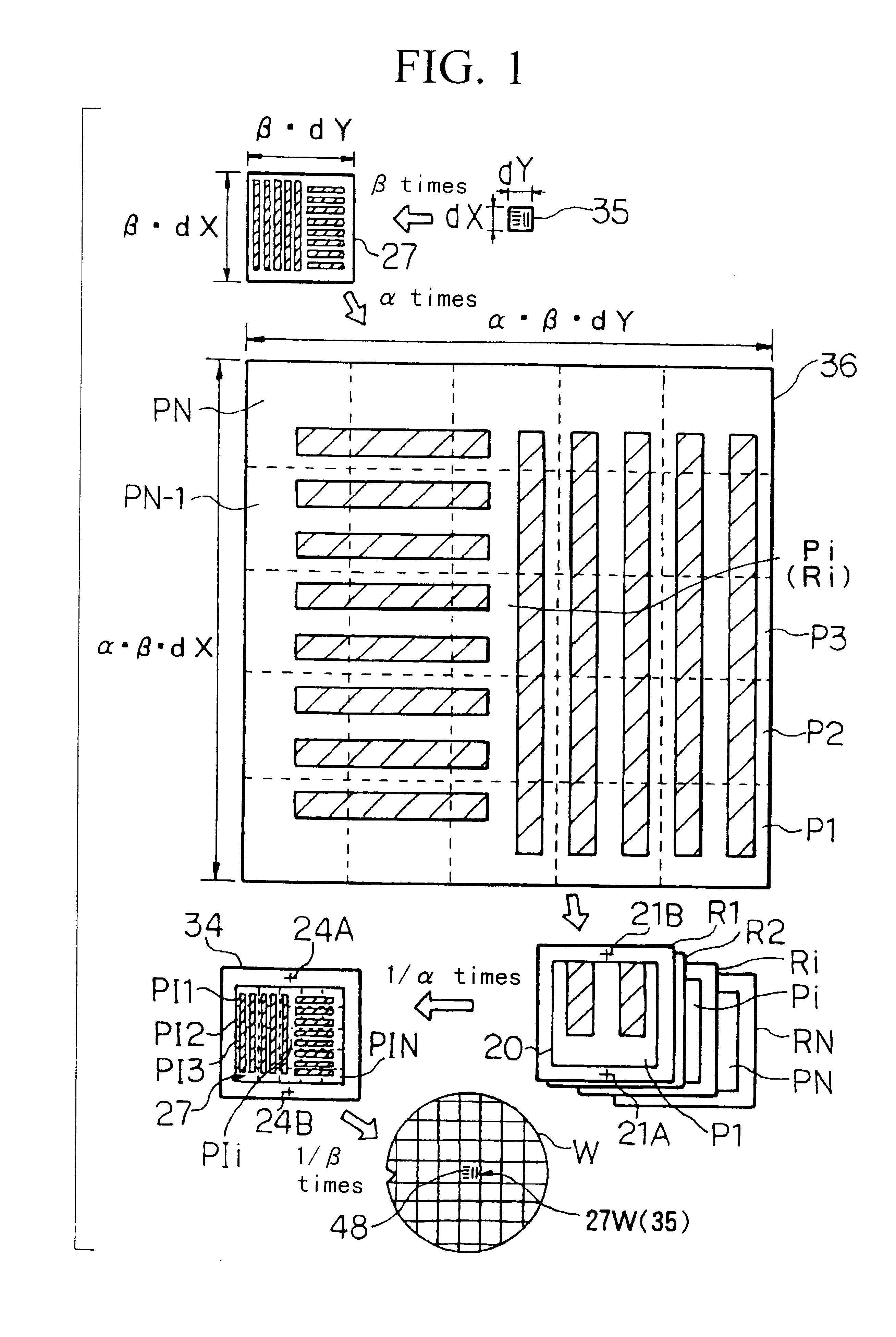

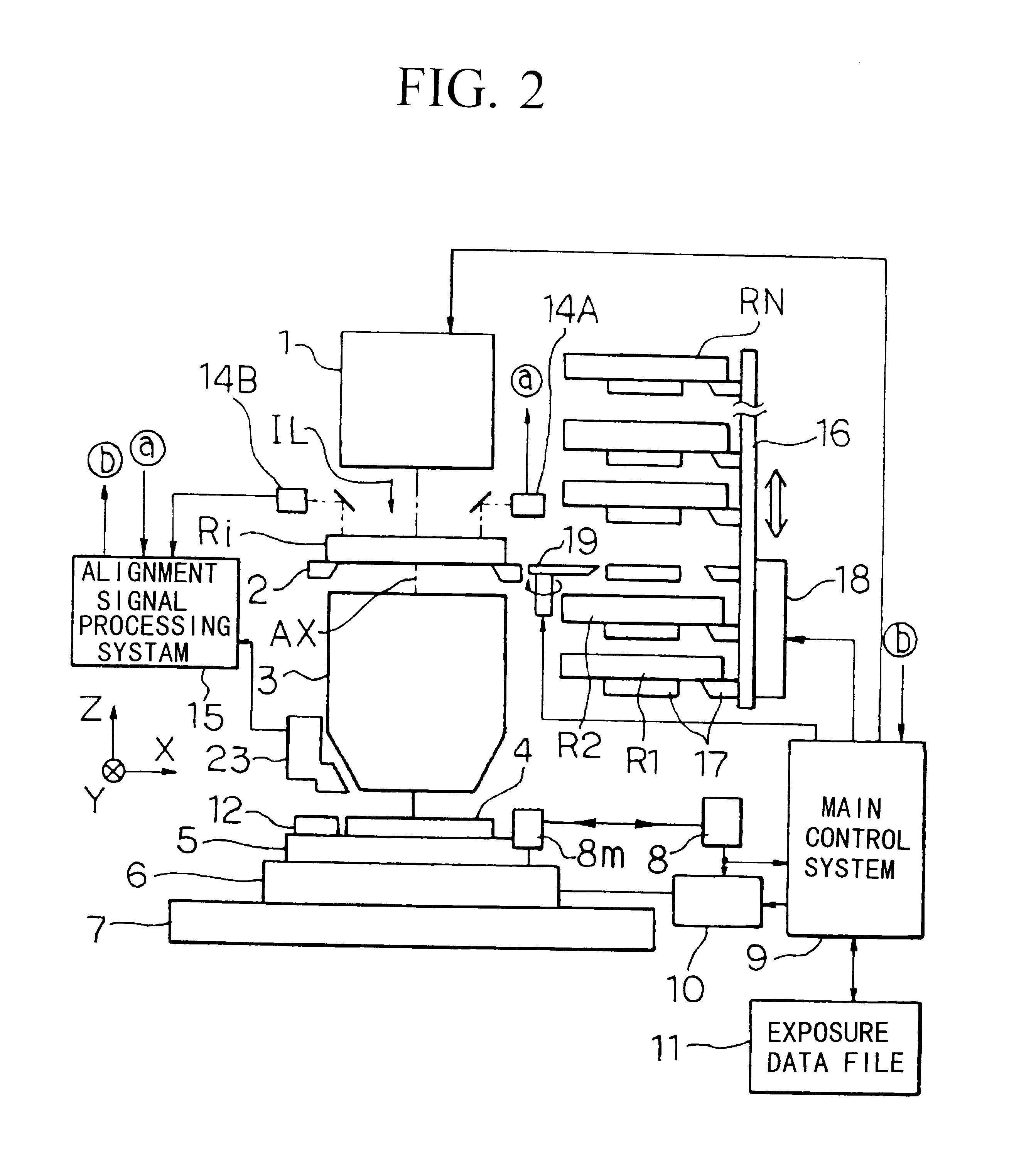

Photomask producing method and apparatus and device manufacturing method

InactiveUS6677088B2Effect of writing errorPhoto-taking processesElectric discharge tubesComputational physicsMagnification

Owner:NIKON CORP

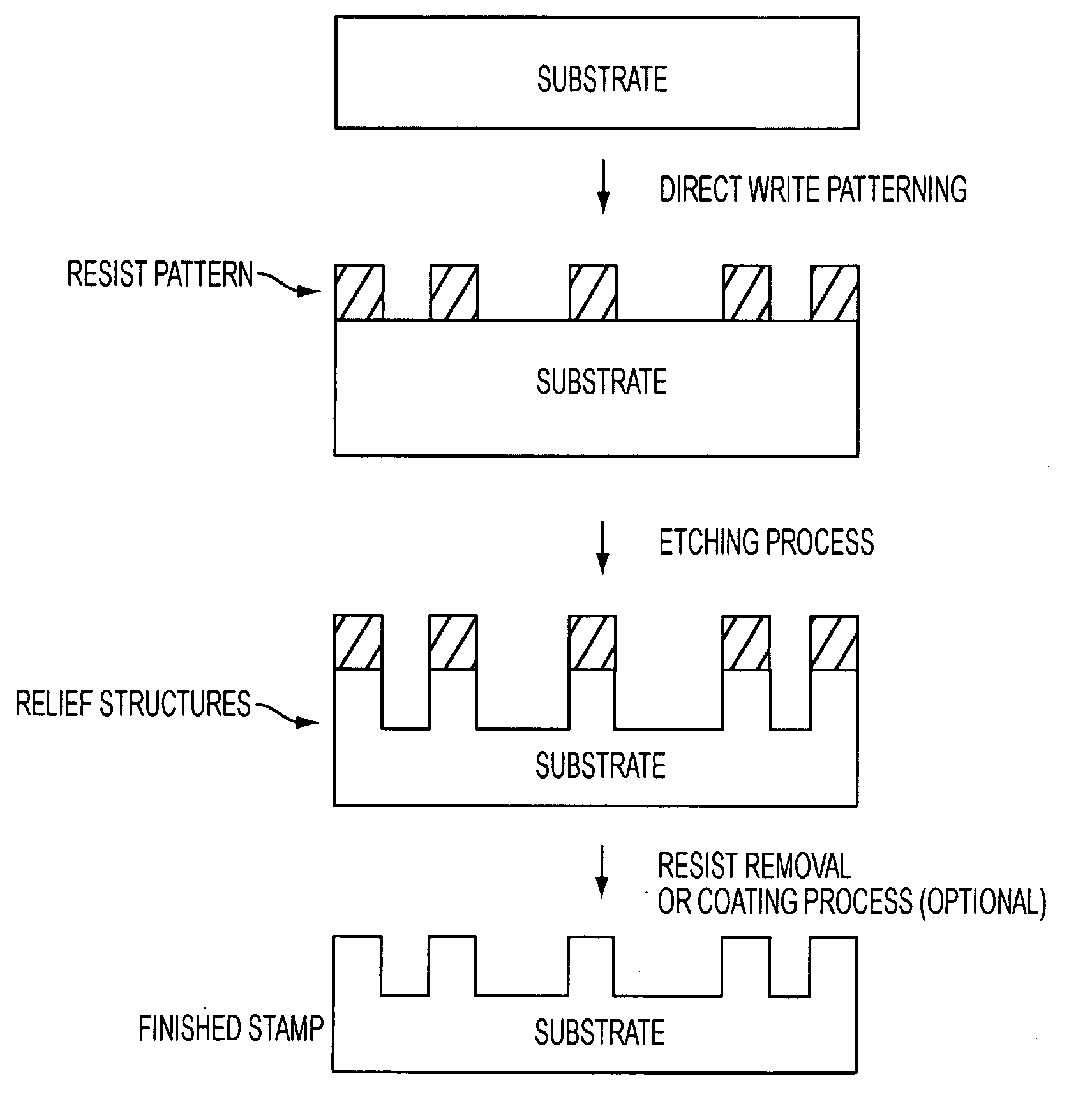

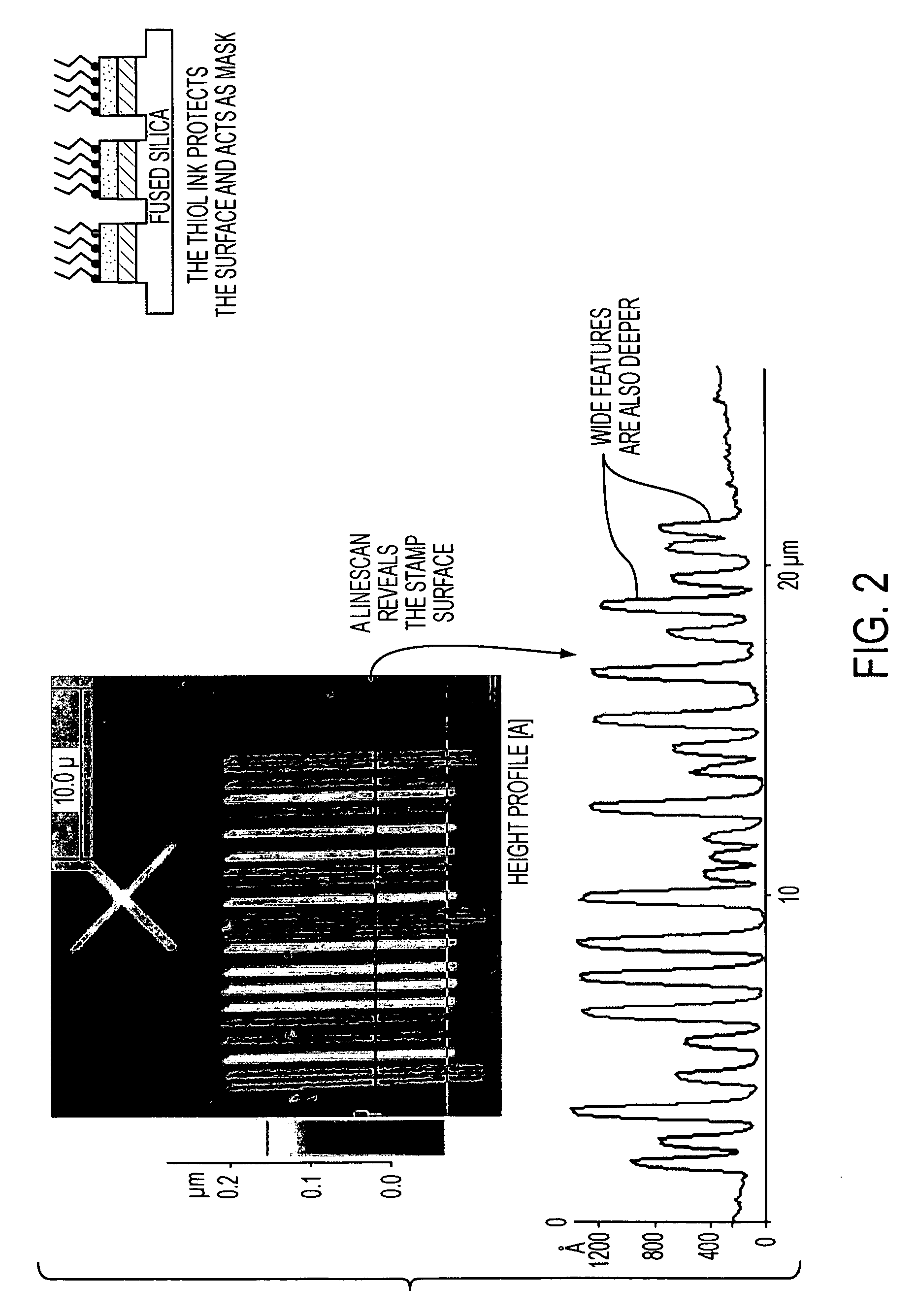

Stamps with micrometer-and nanometer-scale features and methods of fabrication thereof

InactiveUS20100294146A1Digitally marking record carriersMechanical working/deformationMicrometerElectron-beam lithography

Stamps and methods of making stamps for applications in anti-counterfeiting and authentication. The stamps are relatively small in size and feature nanoscale and microscale identification regions and features. High throughput manufacturing and high resolution methods are used to make the stamps including electron beam lithography and optical lithography. Anti-fouling coatings can be applied.

Owner:NANOINK INC +1

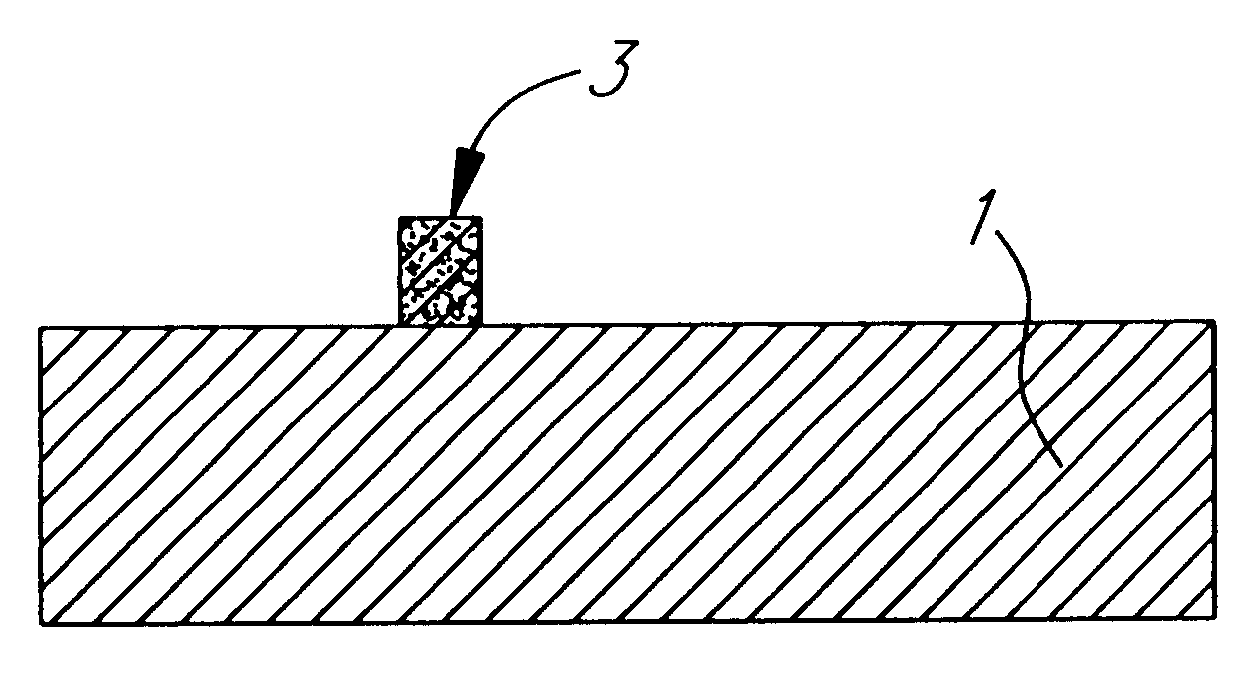

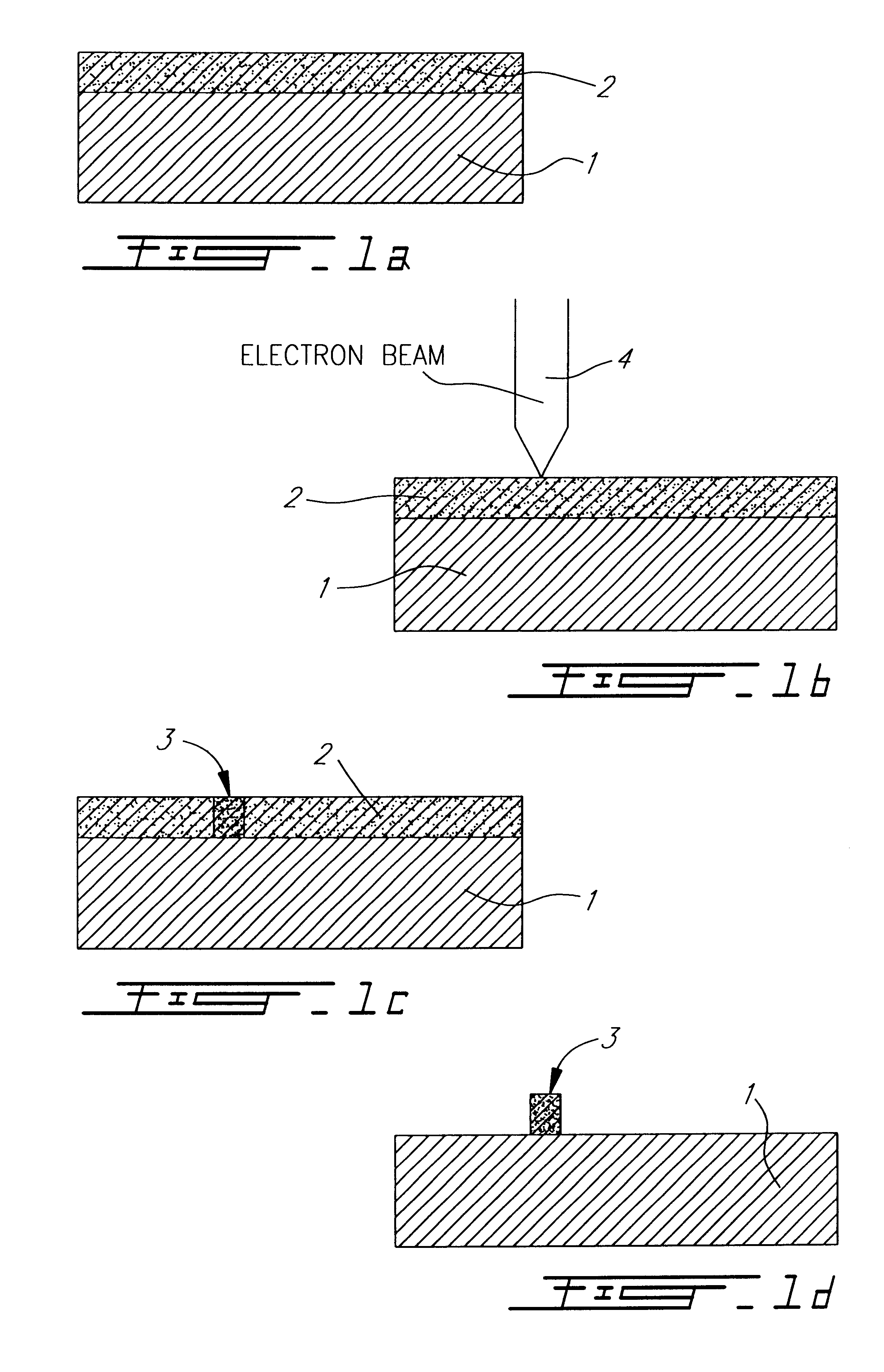

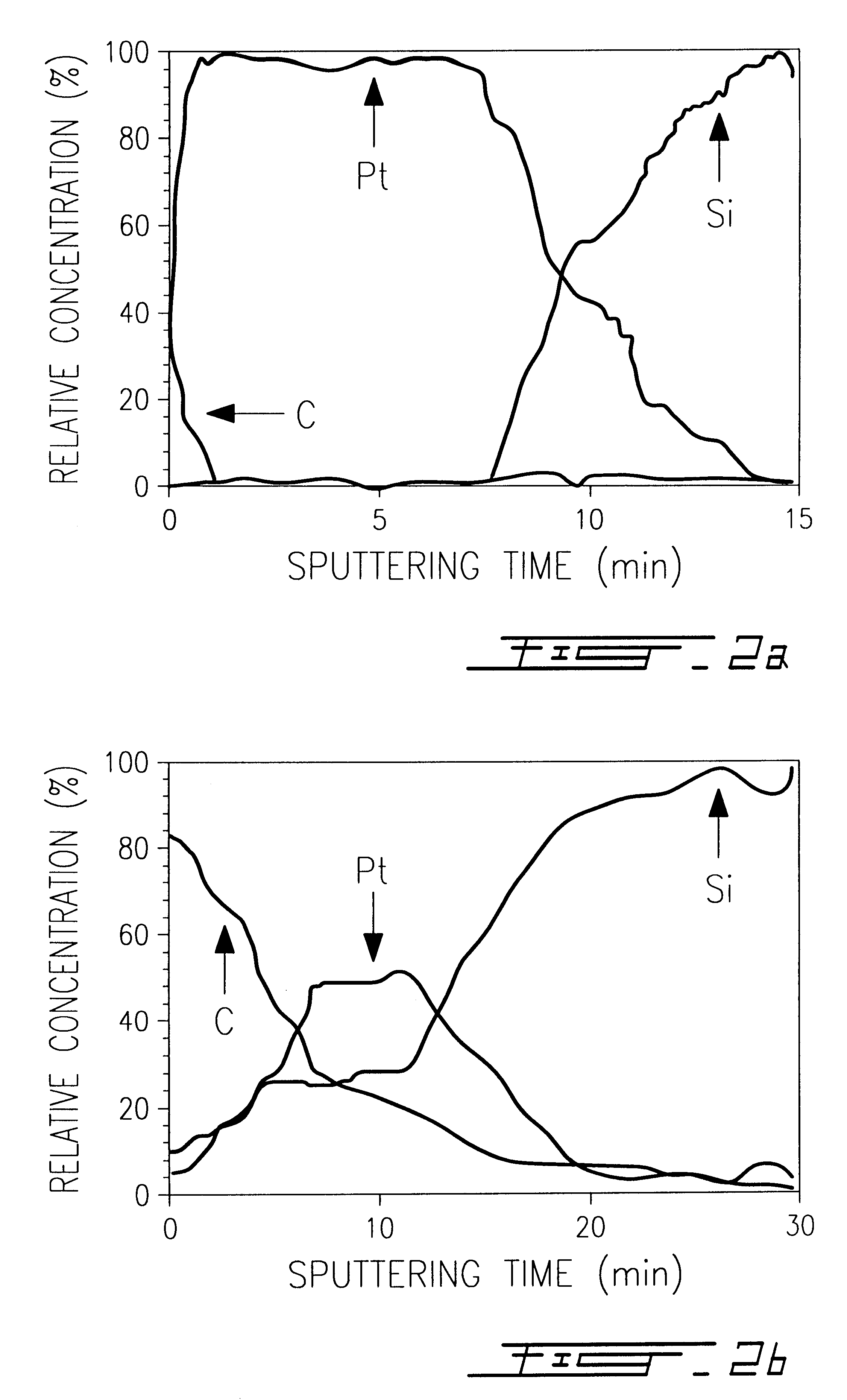

Fabrication of sub-micron etch-resistant metal/semiconductor structures using resistless electron beam lithography

InactiveUS6261938B1NanoinformaticsSemiconductor/solid-state device manufacturingSemiconductor materialsSemiconductor structure

A method for fabricating a sub-micron structure of etch-resistant metal / semiconductor compound on a substrate of semiconductor material comprises the step of depositing onto the substrate a layer of metal capable of reacting with the semiconductor material to form etch-resistant metal / semiconductor compound, and the step of producing a focused electron beam. The focused electron beam is applied to the layer of metal to locally heat the metal and semiconductor material and cause diffusion of the metal and semiconductor material in each other to form etch-resistant metal / semiconductor compound. The focused electron beam is displaced onto the layer of metal to form the structure of etch-resistant metal / semiconductor compound. Finally, the layer of metal is wet etched to leave on the substrate only the structure of metal / semiconductor compound. Following wet etching of the layer of metal, an oxygen plasma etch can be conducted to remove a carbon deposit formed at the surface of the structure of etch-resistant metal / semiconductor compound. Also, the substrate may be subsequently etched to remove a thin layer of metal rich semiconductor material formed at the surface of the substrate by reaction, at room temperature, of the metal and semiconductor material with each other.

Owner:SCOPRA SCI & GENIE SEC

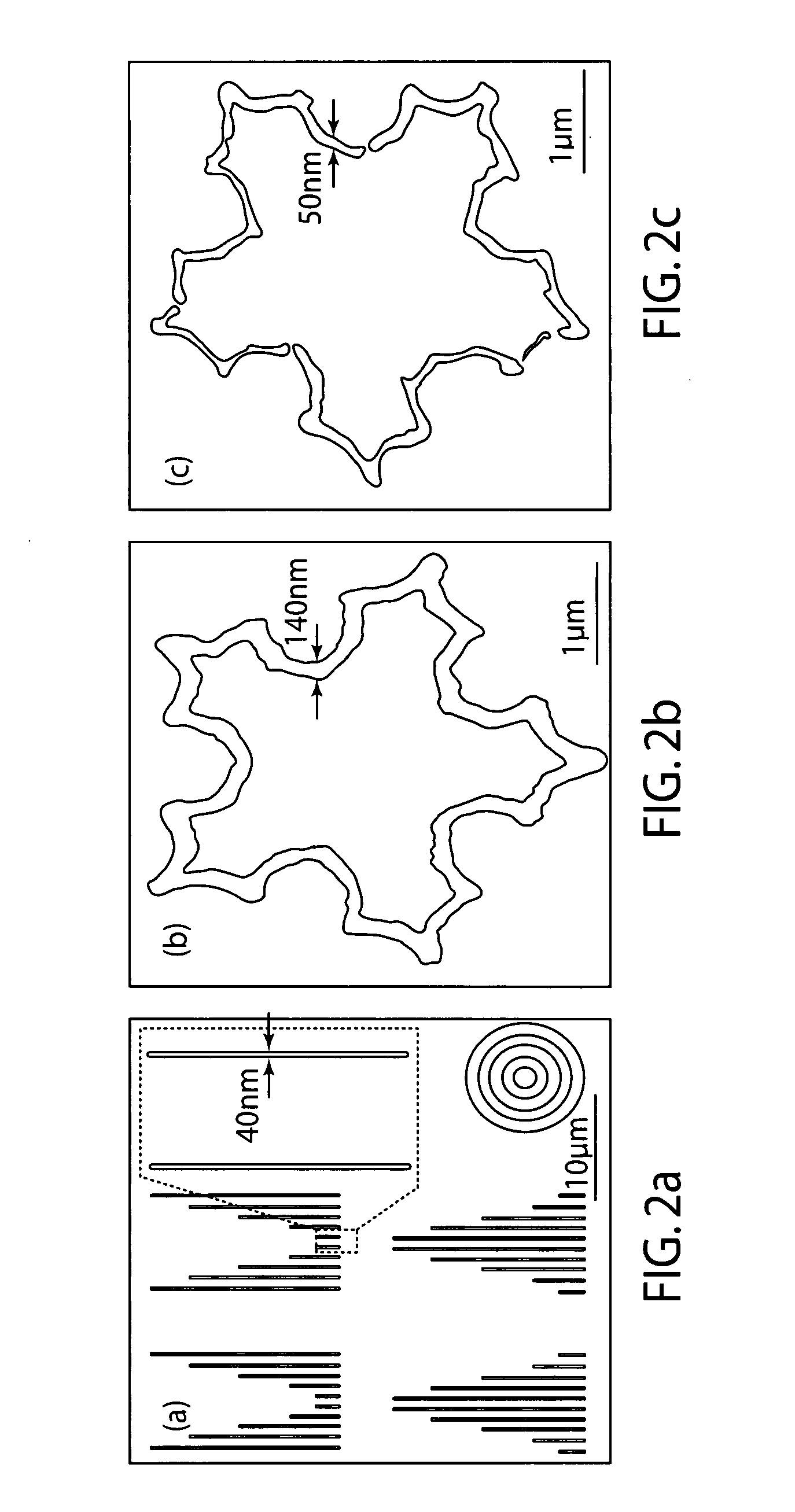

Method of making nanopatterns and nanostructures and nanopatterned functional oxide materials

InactiveUS20080070010A1High patterning speedHigh-throughput processingElectric discharge tubesDecorative surface effectsMulti materialNanostructure

Method for nanopatterning of inorganic materials, such as ceramic (e.g. metal oxide) materials, and organic materials, such as polymer materials, on a variety of substrates to form nanopatterns and / or nanostructures with control of dimensions and location, all without the need for etching the materials and without the need for re-alignment between multiple patterning steps in forming nanostructures, such as heterostructures comprising multiple materials. The method involves patterning a resist-coated substrate using electron beam lithography, removing a portion of the resist to provide a patterned resist-coated substrate, and spin coating the patterned resist-coated substrate with a liquid precursor, such as a sol precursor, of the inorganic or organic material. The remaining resist is removed and the spin coated substrate is heated at an elevated temperature to crystallize the deposited precursor material.

Owner:NORTHWESTERN UNIV

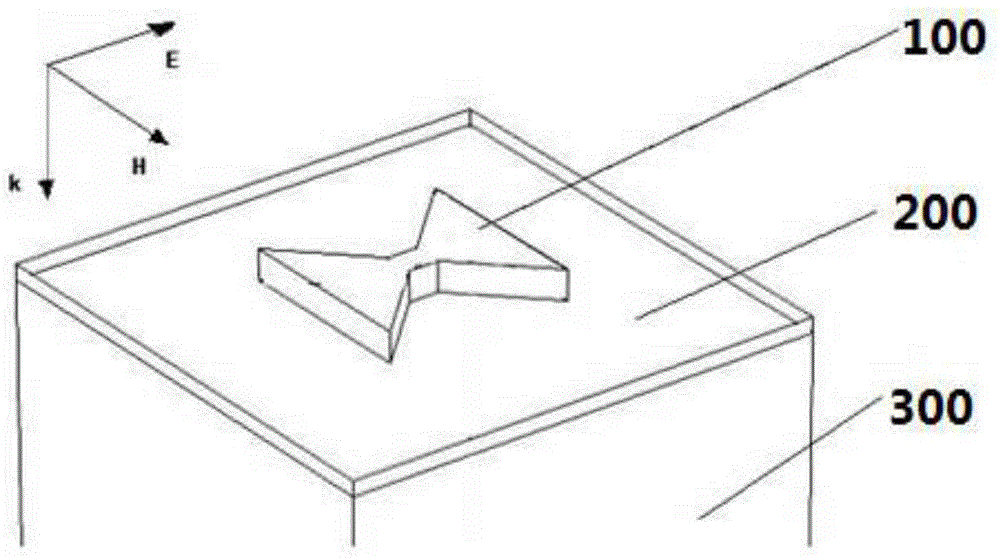

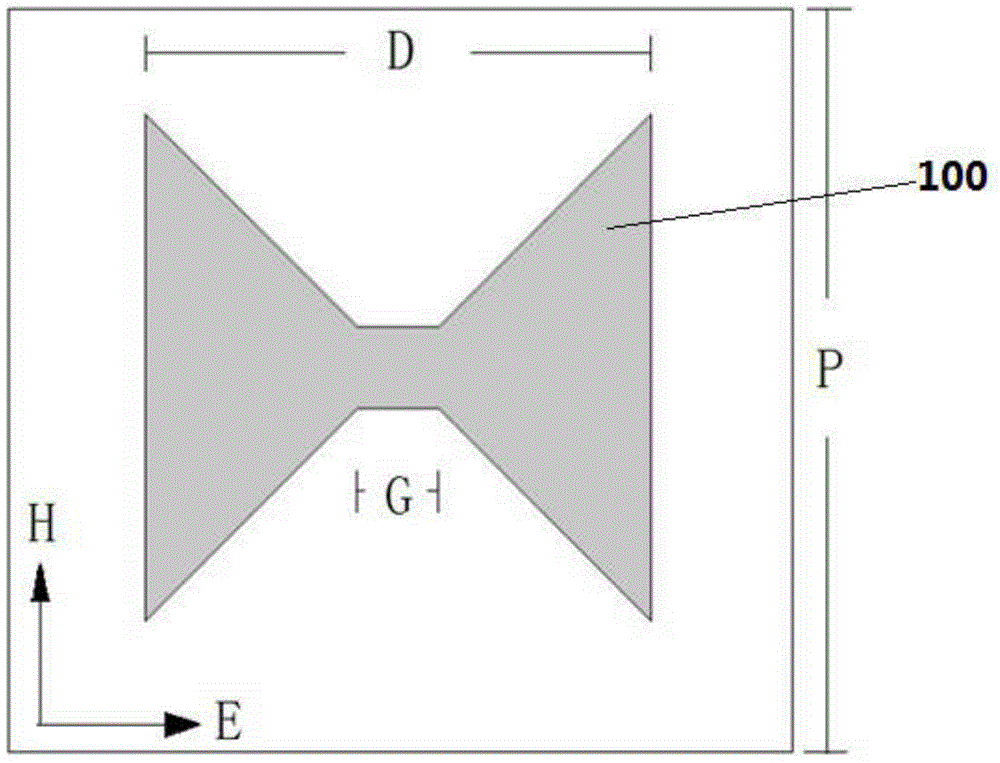

Tunable nanometer antenna and preparation method thereof

InactiveCN104319471ASmall sizeIncrease signal strengthMaterial nanotechnologyRadiating elements structural formsResistIsosceles trapezoid

The invention provides a tunable nanometer antenna and a preparation method thereof. The tunable nanometer antenna comprises three layers which comprise an upper layer metal structure, a middle layer single-layer grapheme and bottom substrate materials; the upper layer metal structure is a bowknot structure; the bowknot structure is formed by two isosceles trapezoids and a square. The preparation method of the tunable nanometer antenna comprises the following steps of covering the layer of single-layer grapheme on a silicon dioxide substrate through a chemical vapor deposition method; coating resist coating in a rotary mode on the single-layer grapheme; achieving structural corrosion and developing through the electron beam lithography technology; achieving evaporation of a golden layer through the vacuum electron beam evaporation technology; obtaining a final nanometer optical antenna through a lift-off process. The tunable nanometer antenna has the advantages of being small in size due to the fact that the thickness of a metamaterial structure is in the dozens of nanometer level and beneficial to application in integration optics; being high in signal intensity due to the fact that magnetic field enhance through the nanometer optical antenna can achieve more than 20000 times under illumination of incident light under specific frequency; being obvious in modulation effect.

Owner:HARBIN INST OF TECH SHENZHEN GRADUATE SCHOOL

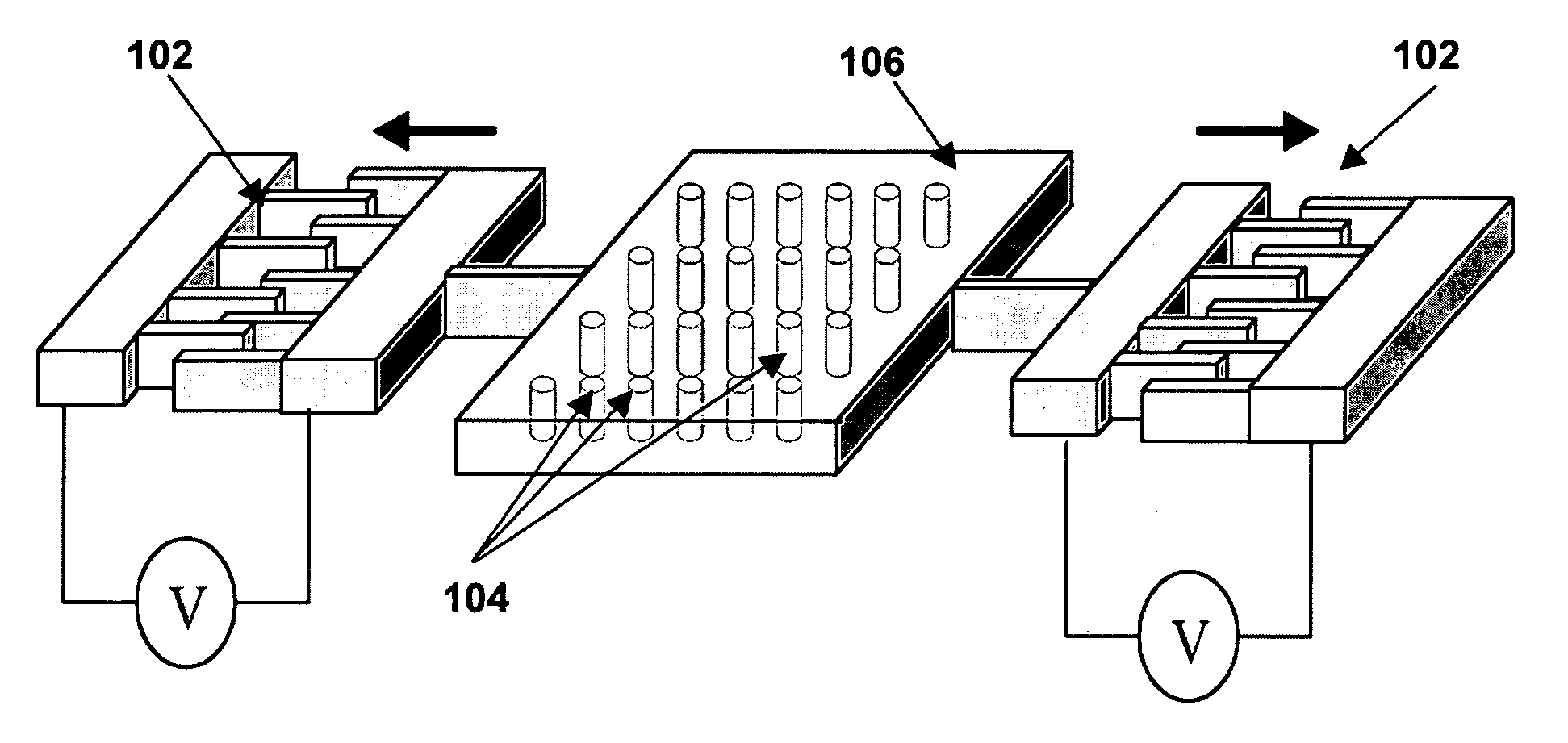

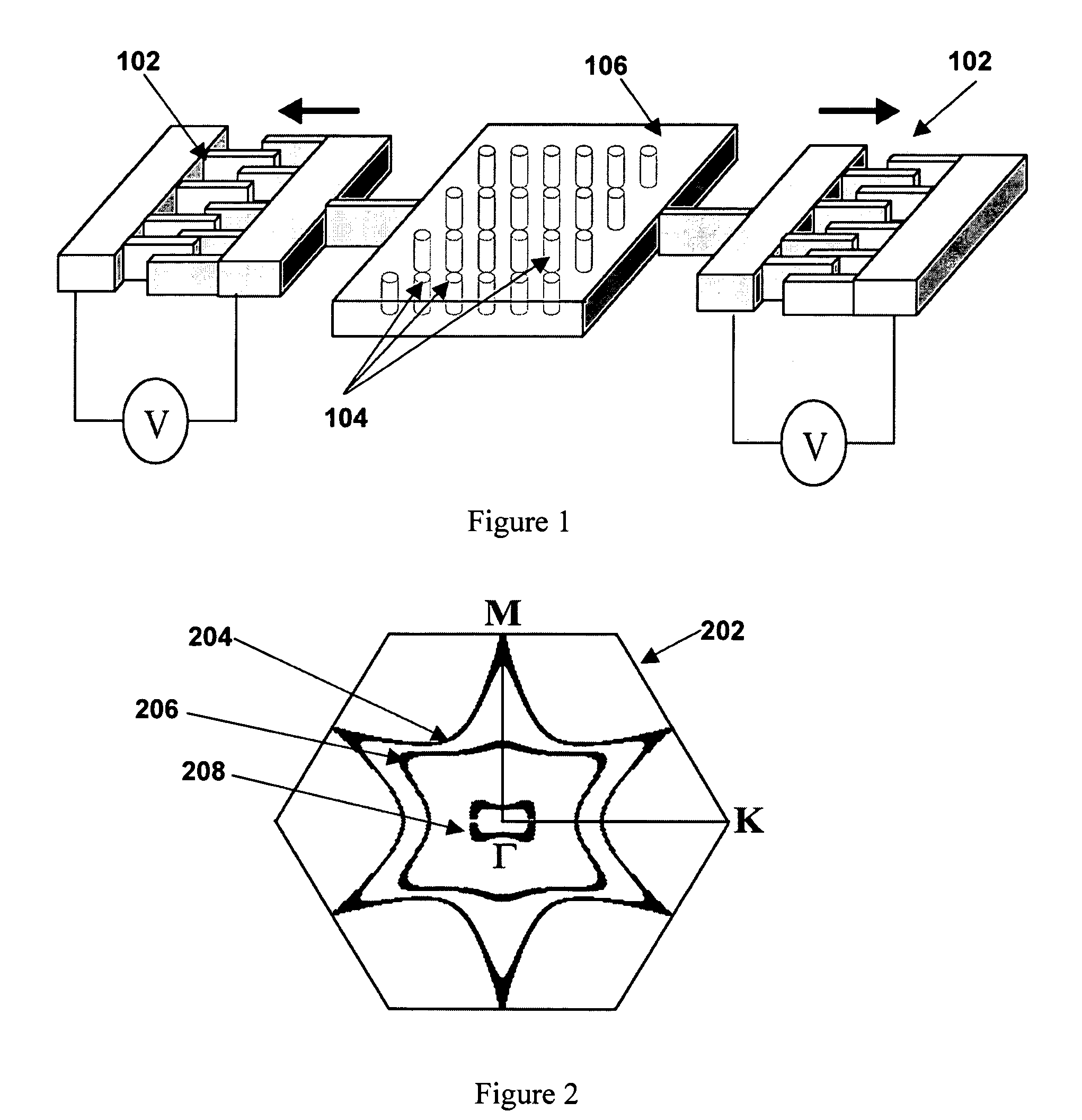

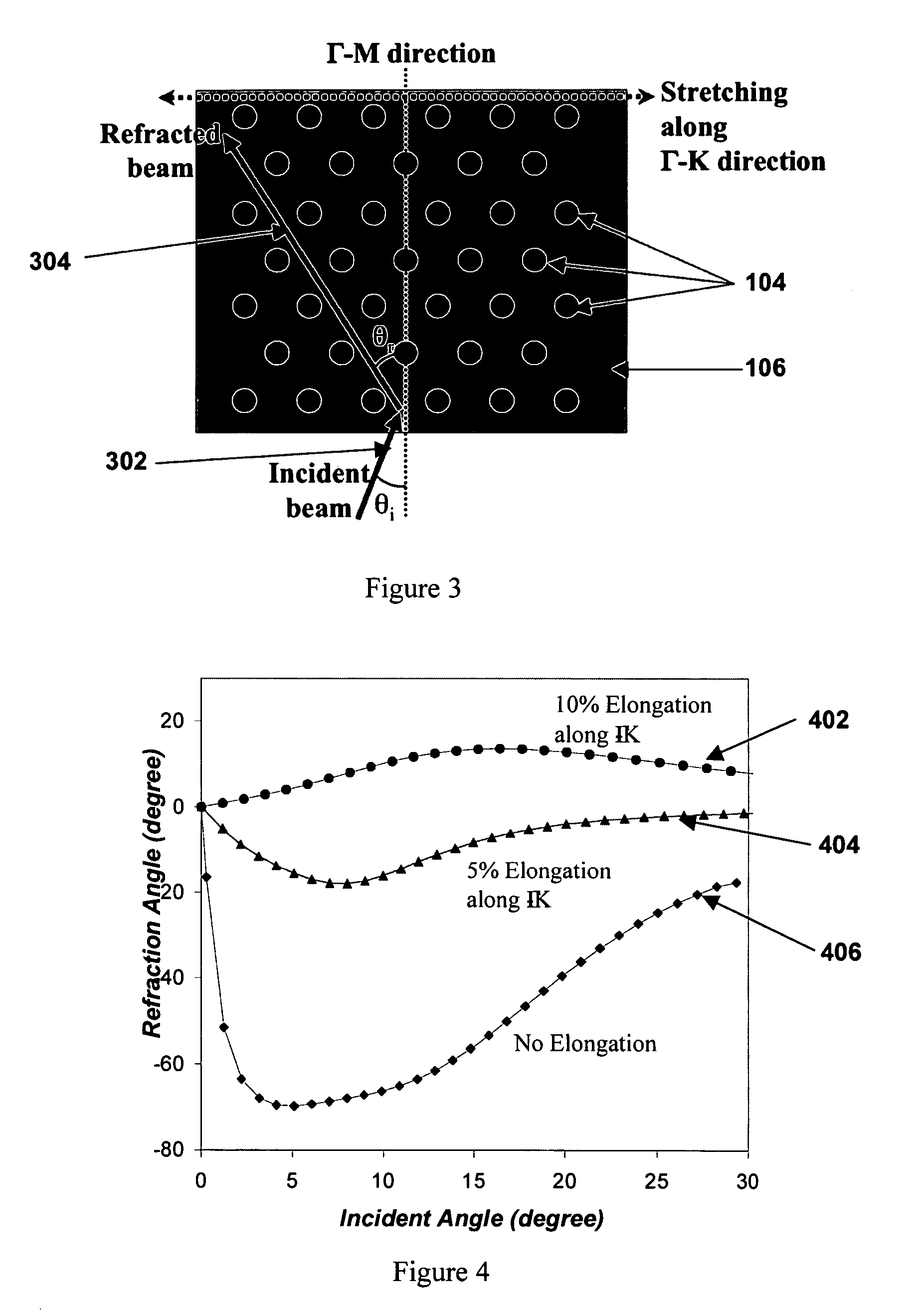

Strain tunable, flexible photonic crystals

A device is described based on flexible photonic crystal, which is comprised of a periodic array of high index dielectric material embedded in a flexible polymer. Dynamic, real time tunability is achieved by the application of a variable force with a MEMS actuator or other means. The force induces changes in the crystal structure of the photonic crystal, and consequently modifies the photonic band structure. The concept was demonstrated by a theoretical investigation on the effect of mechanical stress on the anomalous refraction behavior of the flexible PC, and a very wide tunability in beam propagation direction was observed. Experimental studies on fabrication and characterizations of the flexible photonic crystal structures were also carried out. High quality flexible PC structures were fabricated by e-beam lithography and anisotropic etching processes.

Owner:UNIV OF COLORADO THE REGENTS OF +1