Patents

Literature

5737results about How to "Reduce performance" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

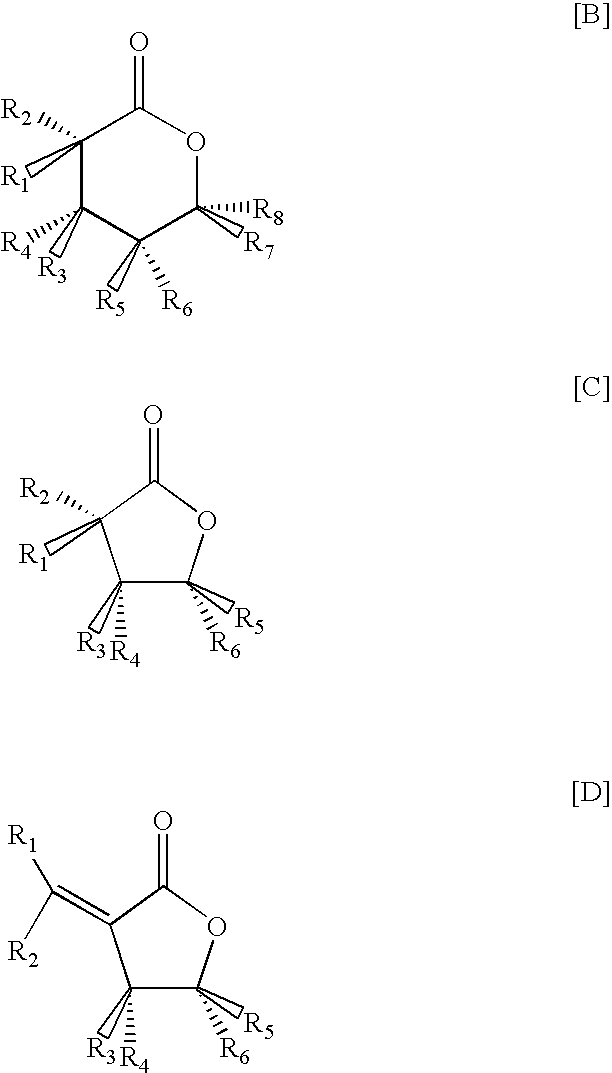

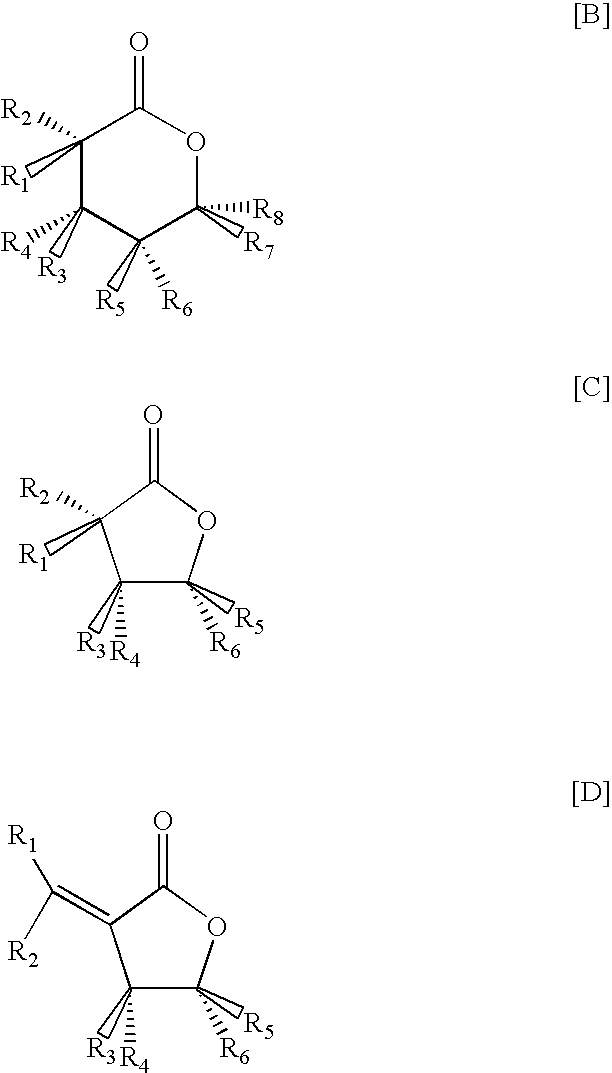

Compositions comprising a fluoroolefin

InactiveUS20060243944A1Reduce performanceReduce flammabilityOther chemical processesTransportation and packagingPhysicsChemistry

The present invention relates to compositions for use in refrigeration, air-conditioning, and heat pump systems wherein the composition comprises a fluoroolefin and at least one other component. The compositions of the present invention are useful in processes for producing cooling or heat, as heat transfer fluids, foam blowing agents, aerosol propellants, and fire suppression and fire extinguishing agents.

Owner:EI DU PONT DE NEMOURS & CO

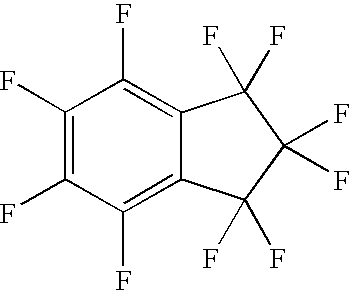

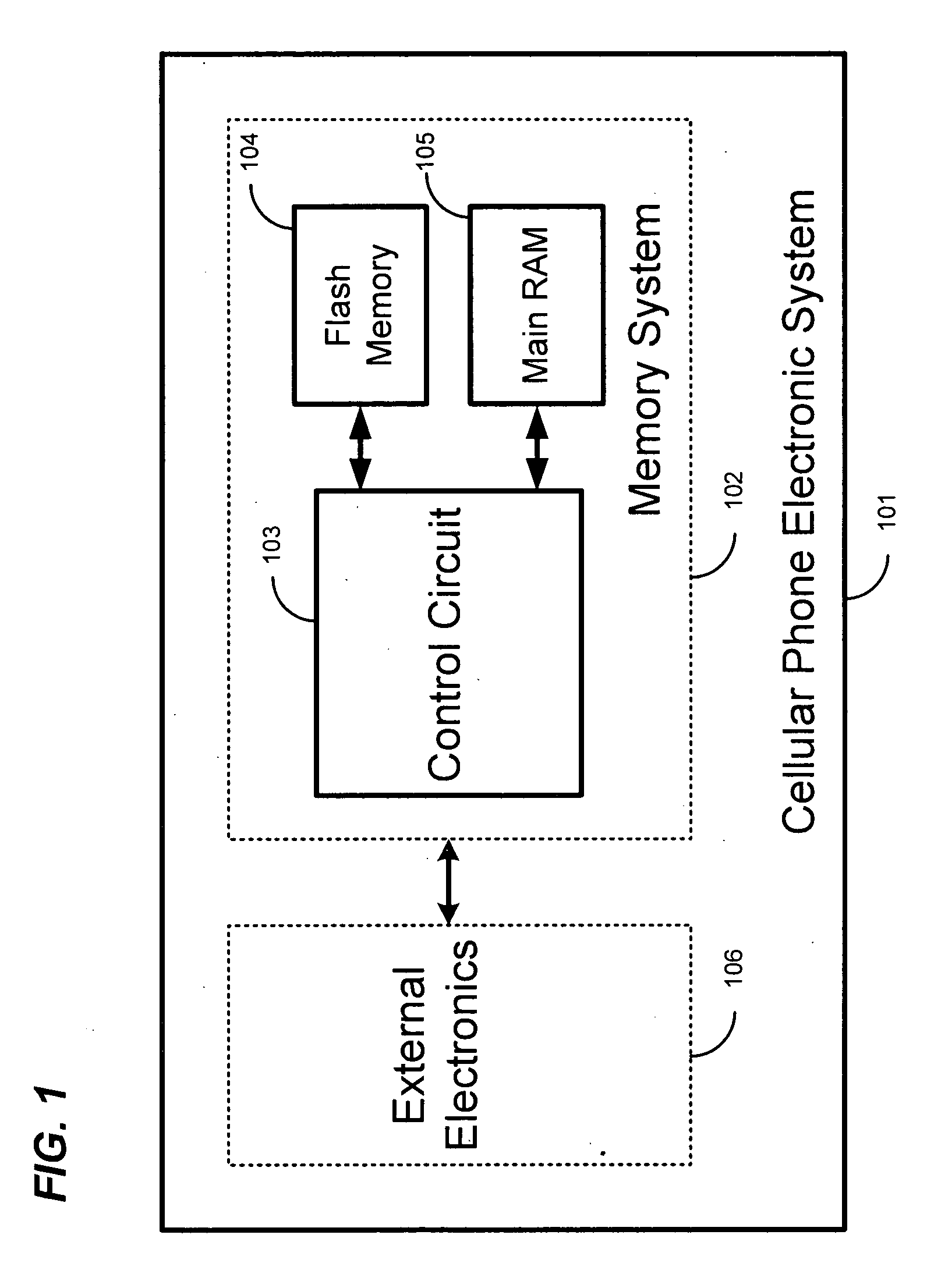

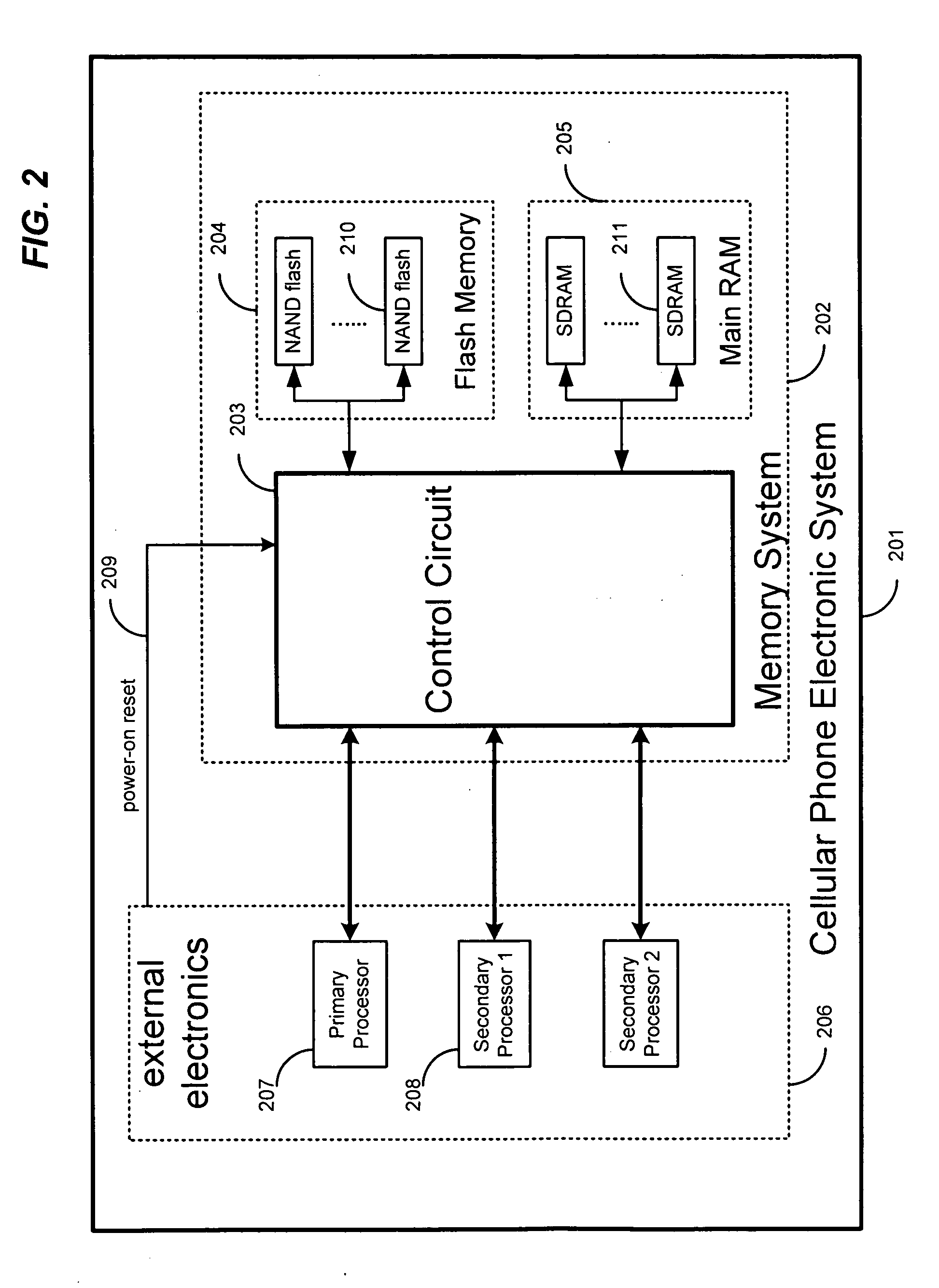

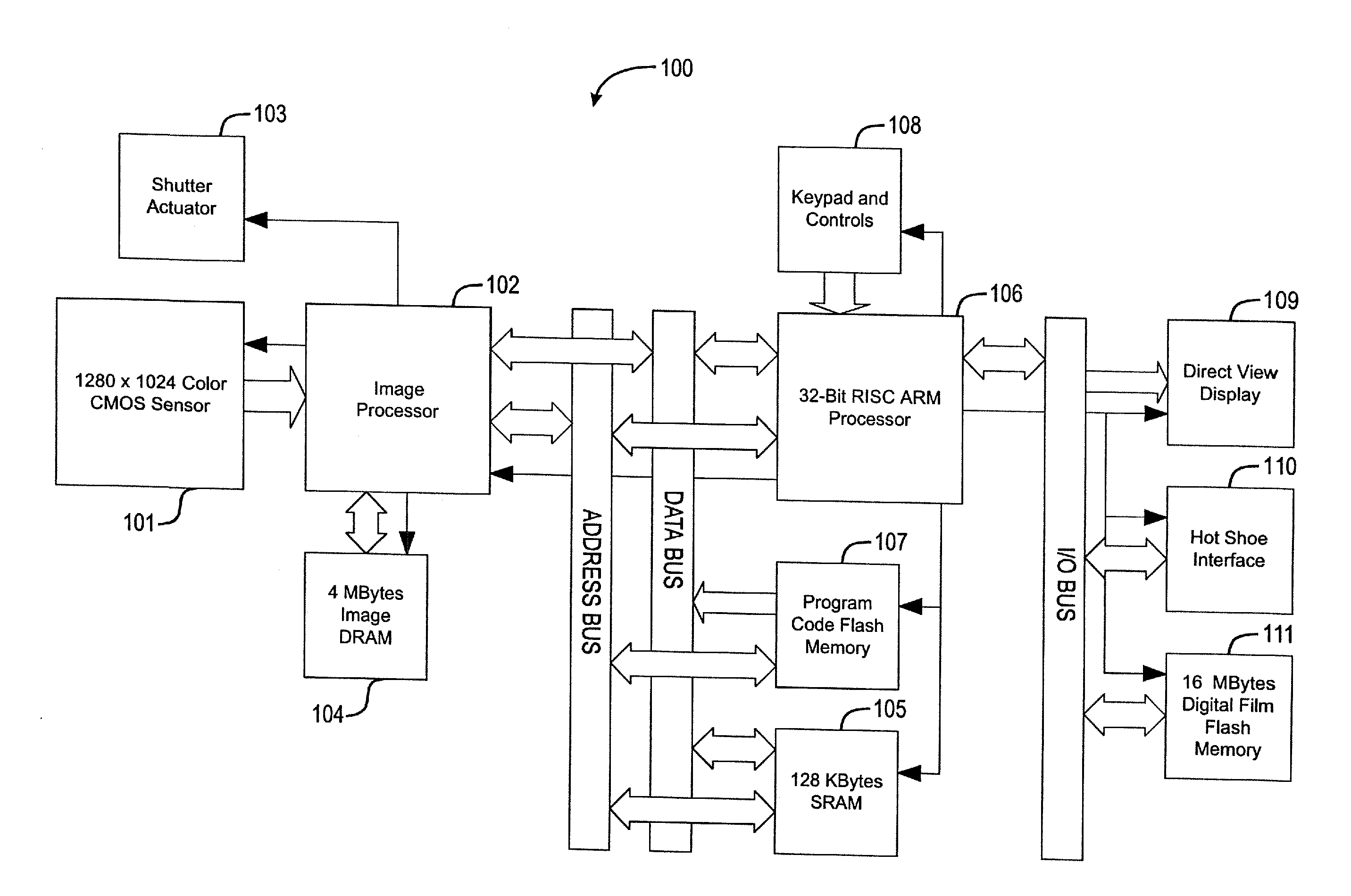

Systems and methods for providing nonvolatile memory management in wireless phones

ActiveUS20060053246A1Low costSmall sizeUnauthorized memory use protectionDigital storageMemory controllerInterface circuits

The present invention is related to memory management, and in particular, to methods and systems for accessing and managing nonvolatile, such as in a wireless phone. A wireless phone memory controller is disclosed that, comprises a first interface circuit configured to be coupled to wireless phone nonvolatile memory, a second interface circuit configured to be coupled to wireless phone volatile memory, a first processor interface configured to be coupled to a first wireless phone processor, wherein the first processor interface is configured to provide the first processor with access to the wireless phone volatile memory, a second processor interface configured to be coupled to a second wireless phone processor, and a controller circuit configured to copy at least a portion of wireless phone nonvolatile memory data to the wireless phone volatile memory.

Owner:GOOGLE LLC

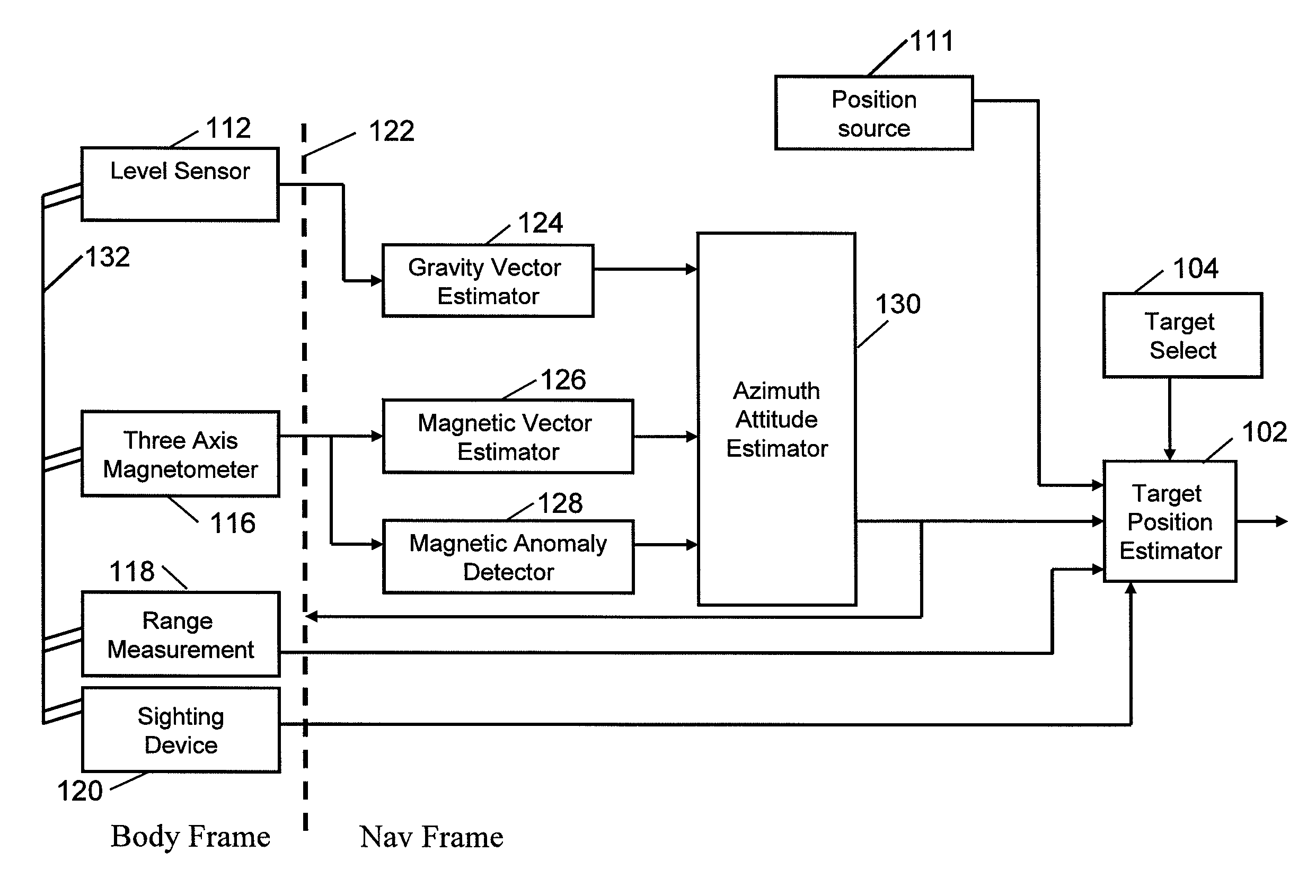

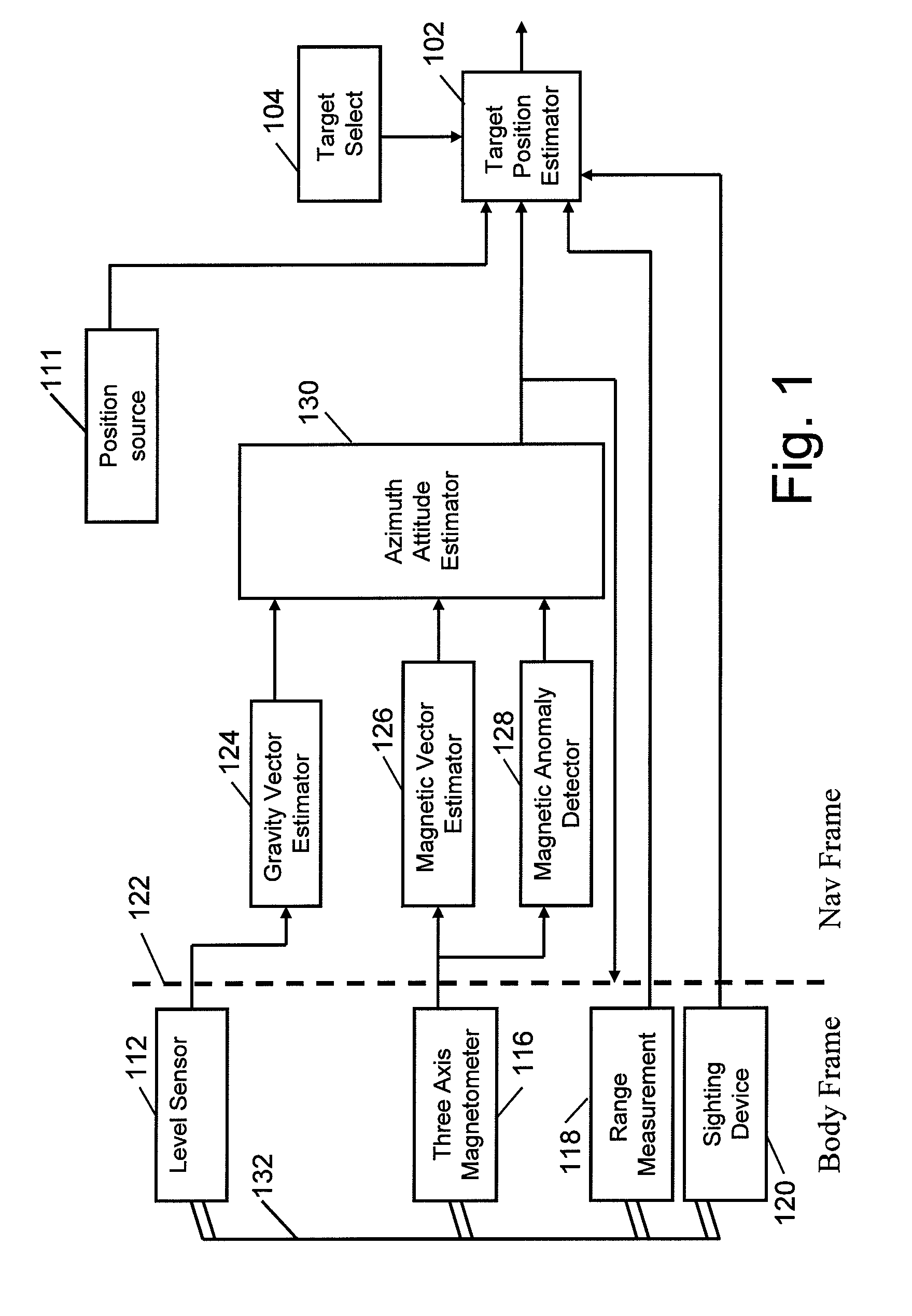

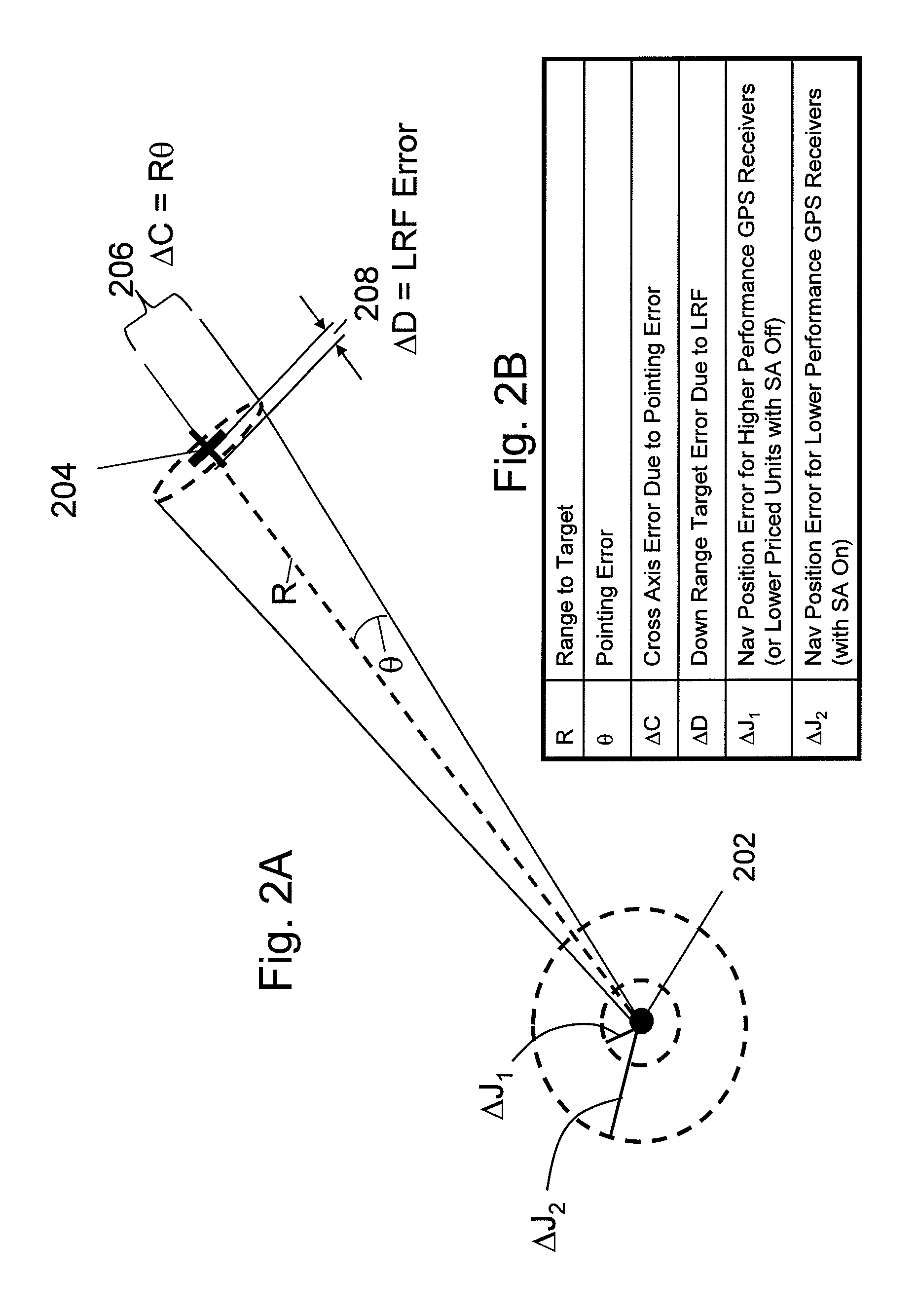

Magnetically stabilized forward observation platform

ActiveUS8275544B1Improved rapid initializationImprove operationDigital computer detailsNavigation by speed/acceleration measurementsMagnetic stabilizationGps receiver

A system and method for determining a position of a remote object comprising inertial sensors and three axis magnetic sensor, together with a target sighting device aligned with the observation platform to determine a target line of sight and a target range finder to determine a distance to the target along the line of sight. A GPS receiver may be included for determining an observation platform position and orientation, The three axis magnetic sensor provides both magnetic north and vertical attitude information for improved rapid initialization and operation in motion. Magnetic anomaly information is detected by comparing IMU and magnetic navigation information and by other methods. Target identification may be determined by a human operator and / or by computer. The system may be integrated with a weapon system to use weapon system sights. The system may be networked to provide target location and / or location error information to another identical unit or a command information system.

Owner:GENERAL ATOMICS

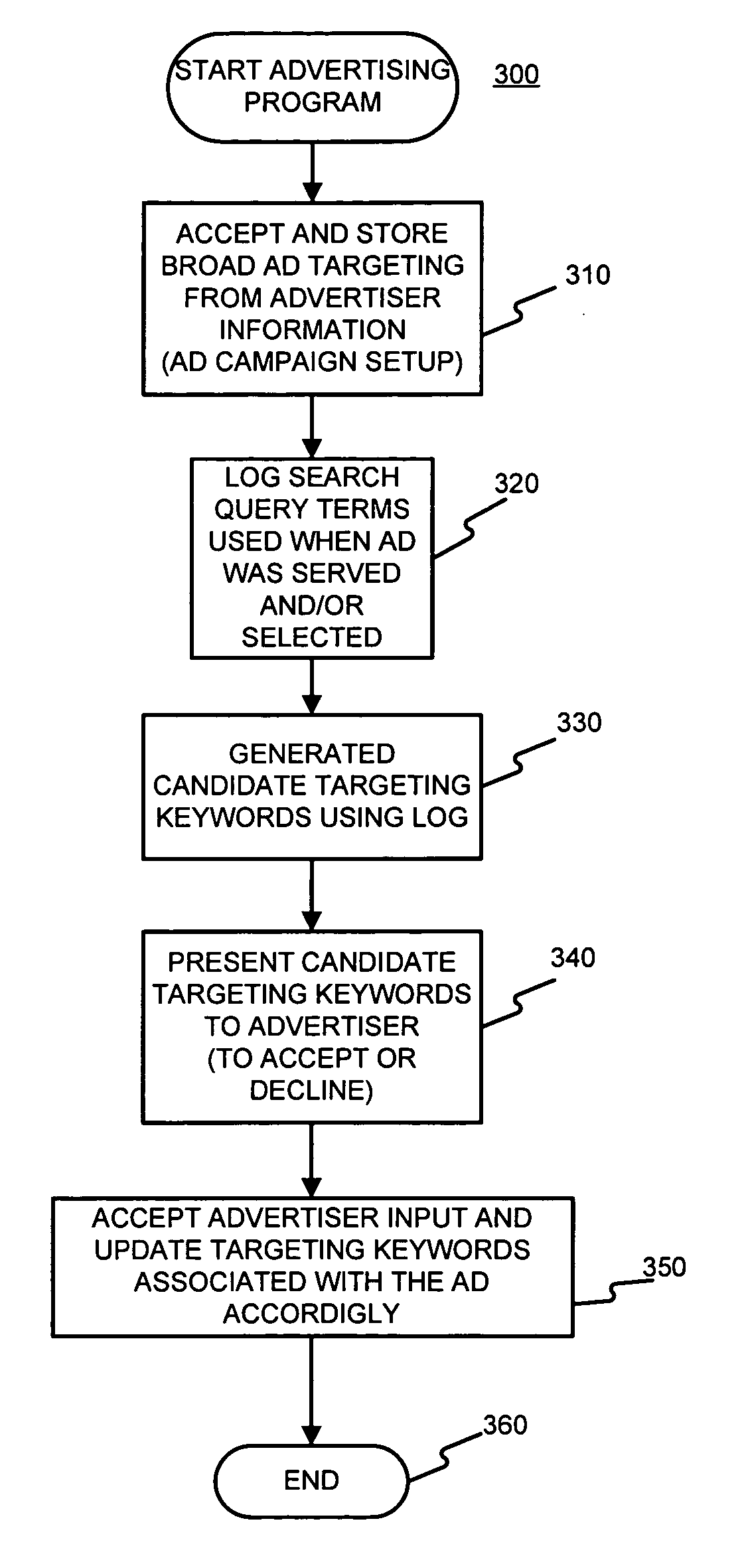

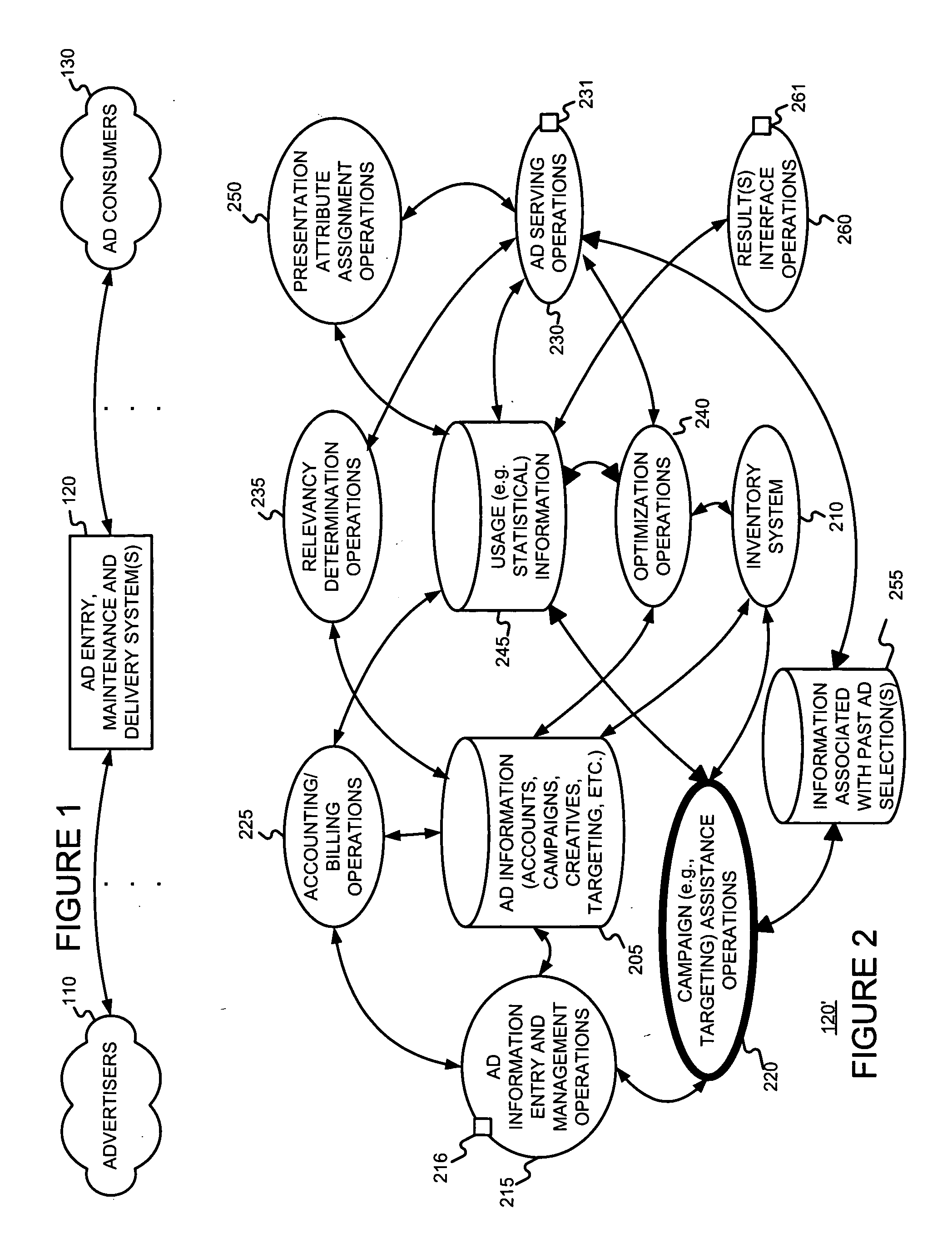

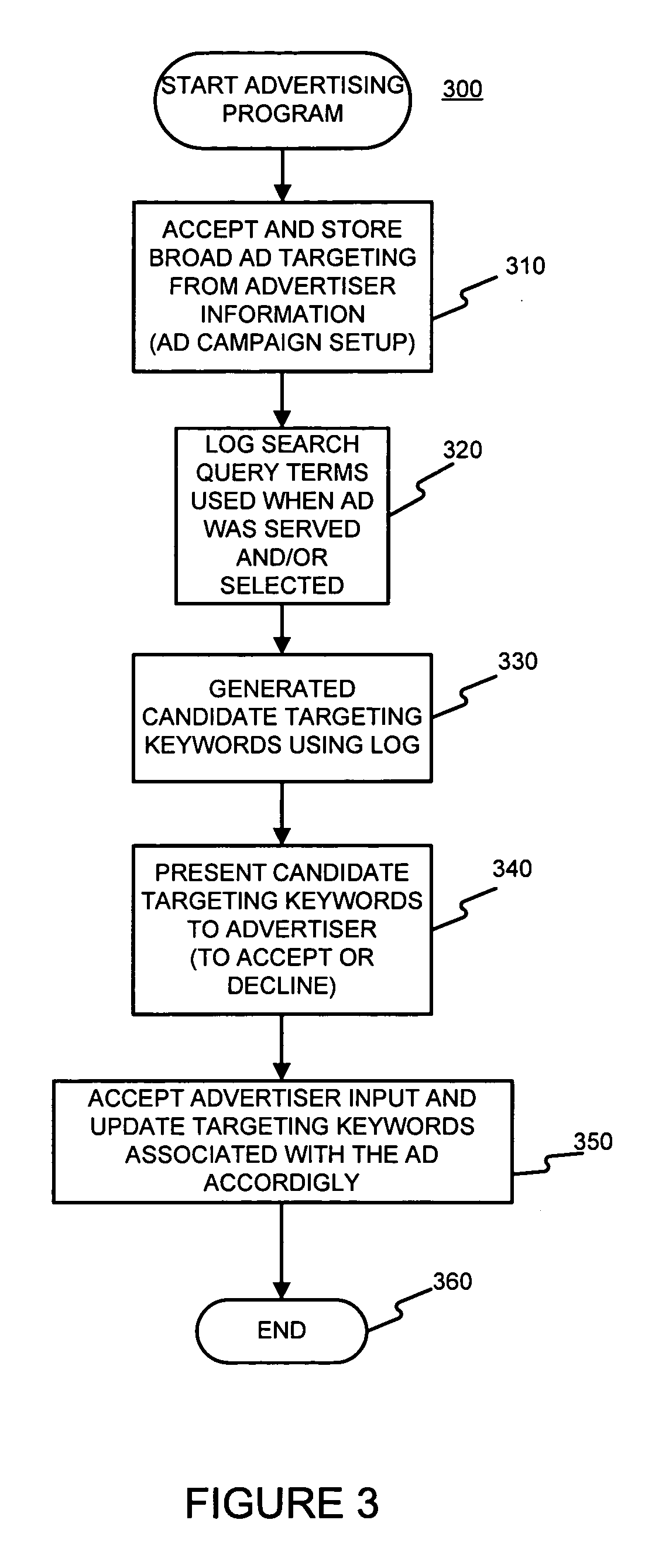

Suggesting and/or providing targeting information for advertisements

InactiveUS20060149625A1Improve performanceSlows sale cycleMarketingInformation provisionInformation retrieval

The relevancy of ads may be increased, and opportunities to serve an ad that might otherwise be missed may be exploited by (i) accepting broad targeting information, to be used for serving an ad, from an advertiser, (ii) serving the ad using the broad targeting information, (iii) logging search query terms (or some other information, such as concepts, concept keywords, etc.) associated with the serving of the ad, and (iv) generating one or more candidate targeting keywords or phrases for the ad using the logged search query terms. At least one of the candidate targeting keywords or phrases may be provided as targeting information for the ad. Alternatively, at least one of the candidate targeting keywords or phrases may be presented to the advertiser. Advertiser input with respect to the candidate targeting keyword(s) or phrase(s) presented may then be accepted. Zero or more of the candidate targeting keyword(s) or phrase(s) may be provided as targeting information for the ad, in accordance with the accepted advertiser input. Cost information (e.g., average cost per selection, average cost per conversion, total costs, etc.) may be presented in association with the candidate targeting information.

Owner:GOOGLE LLC

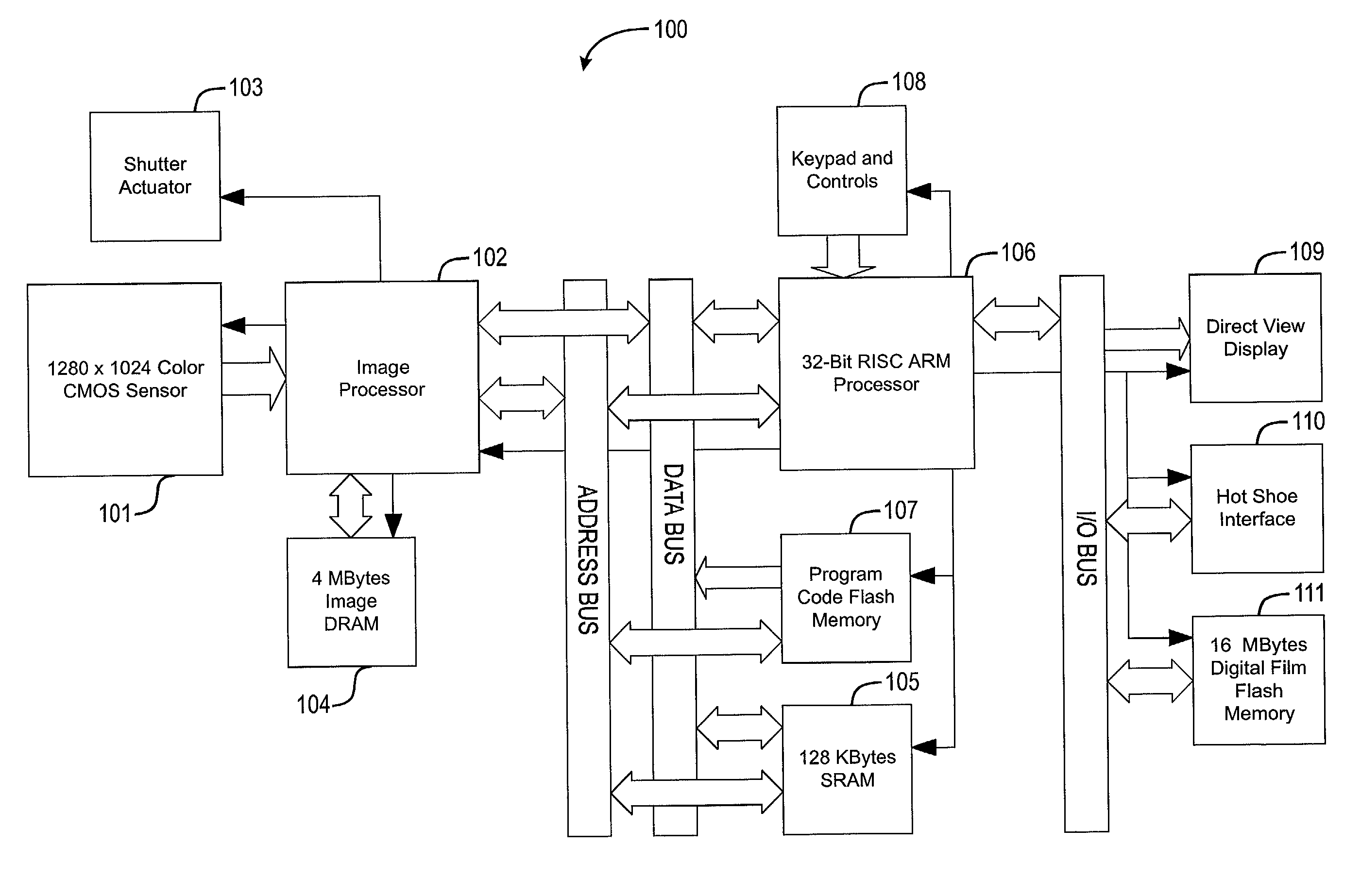

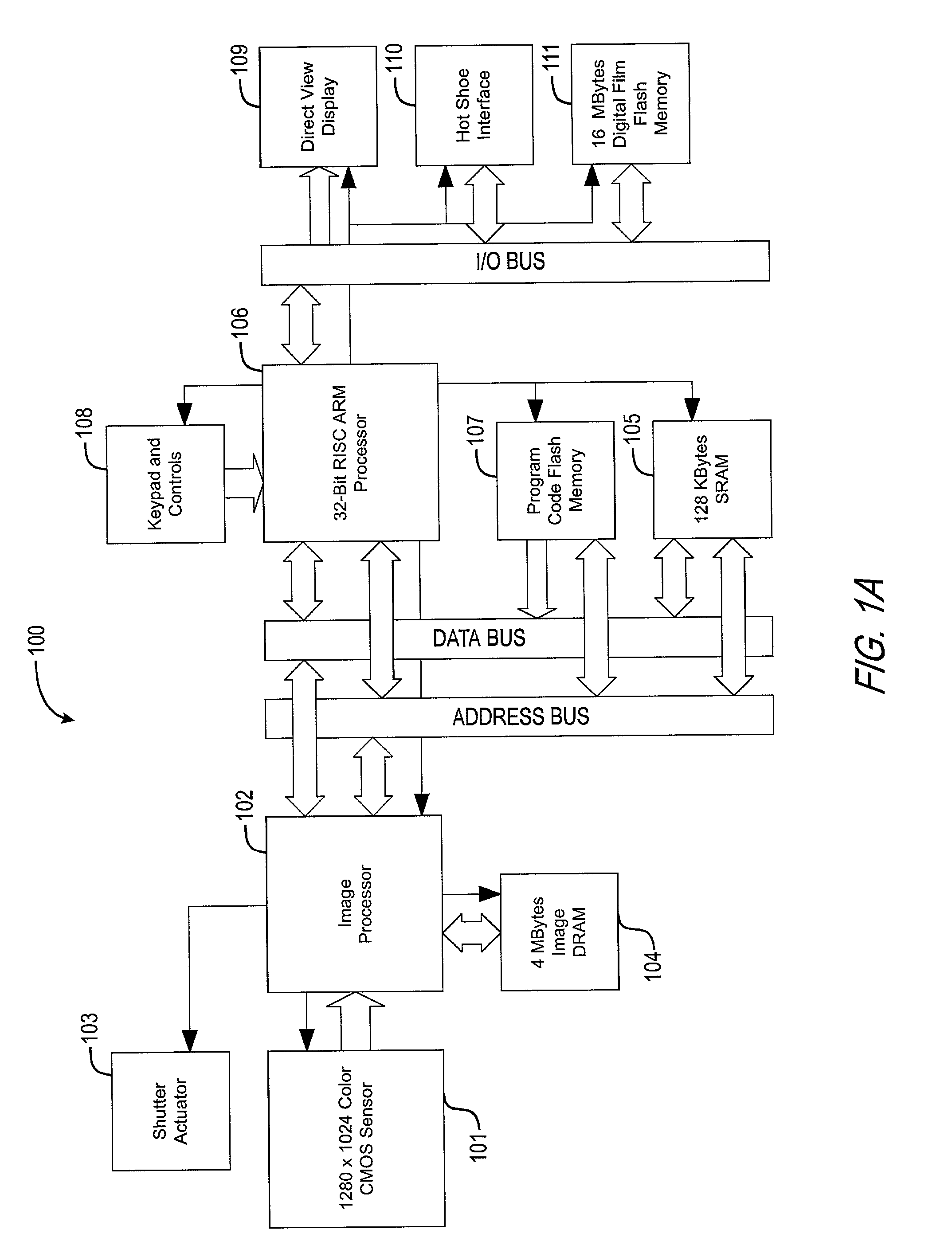

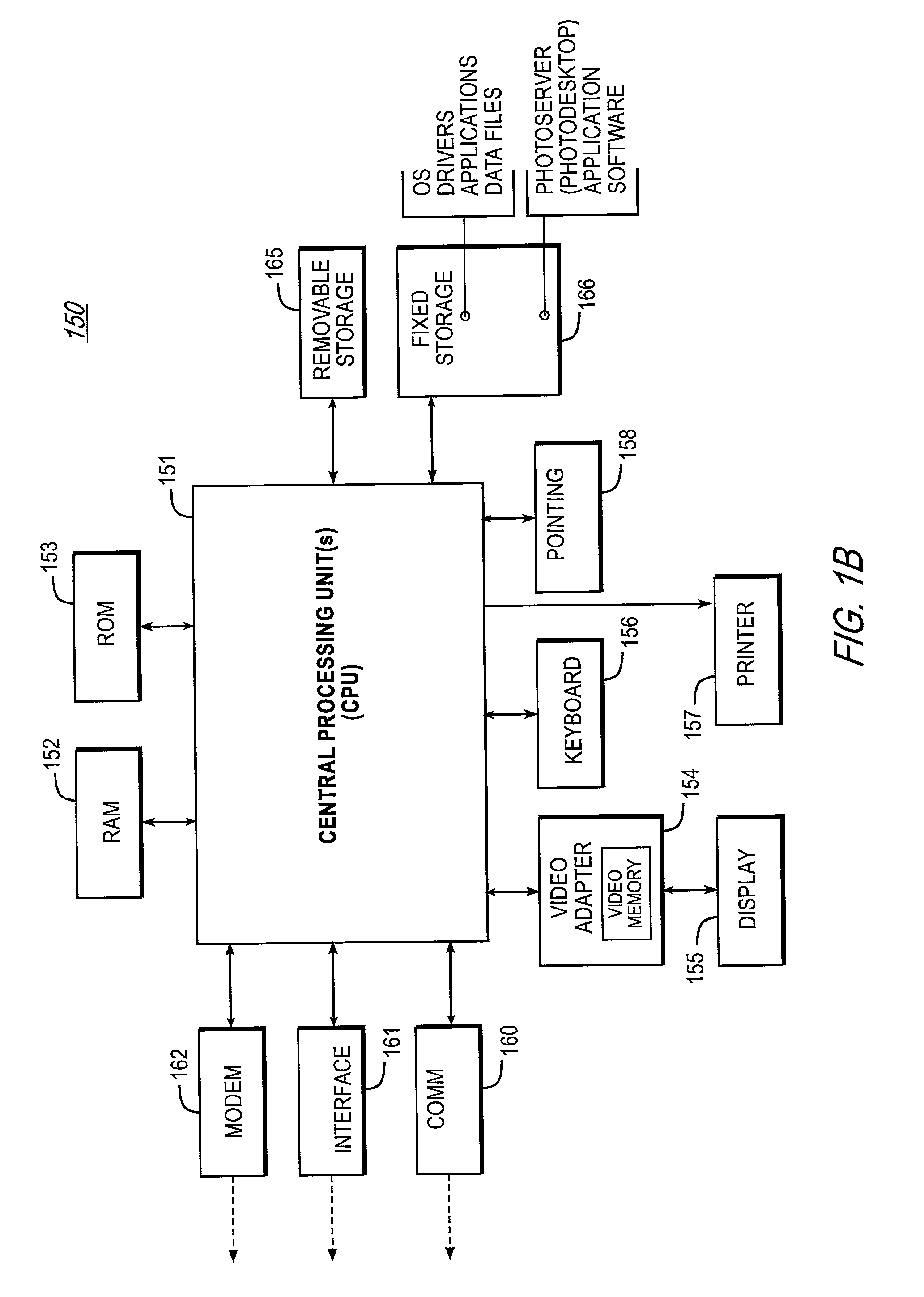

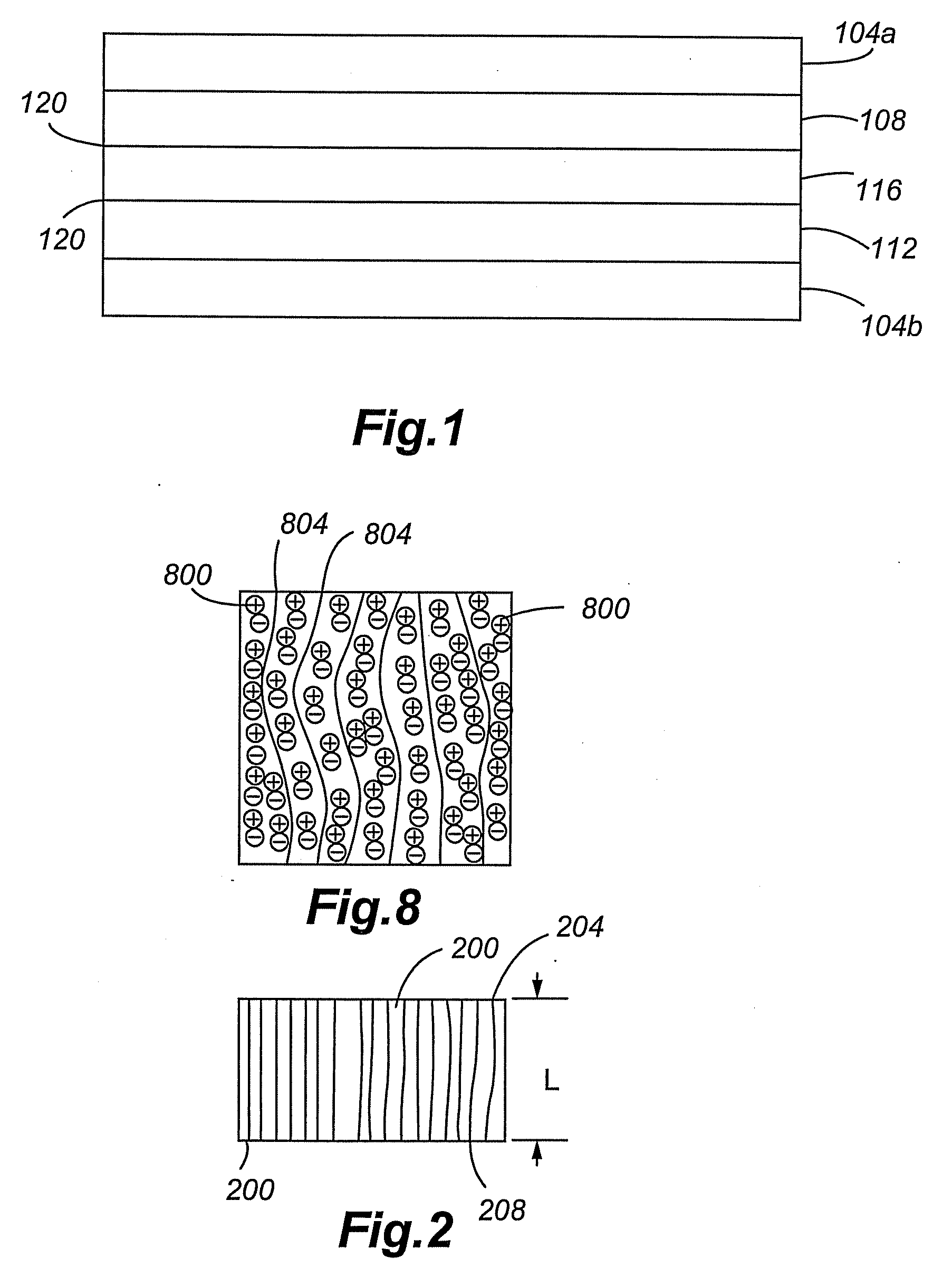

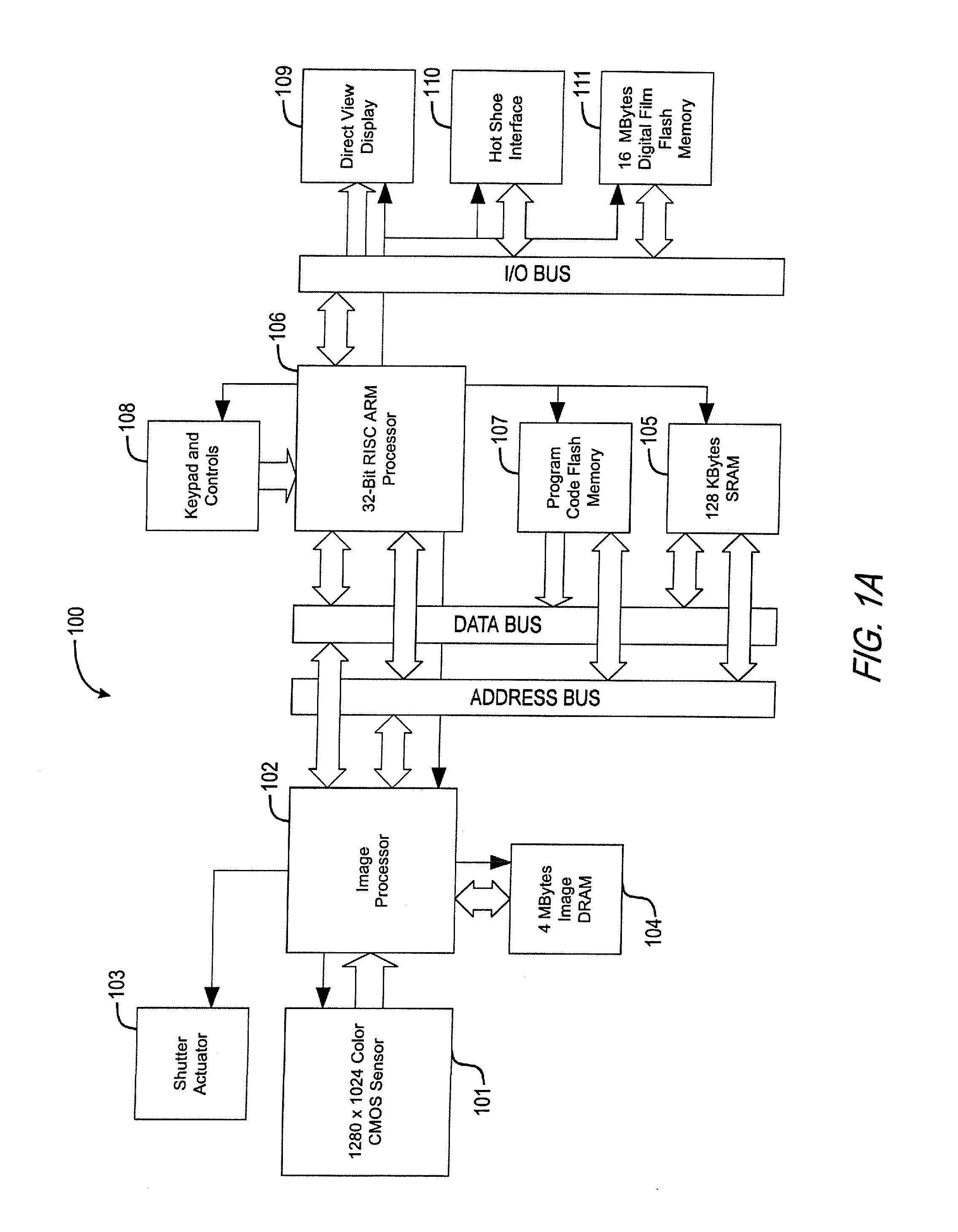

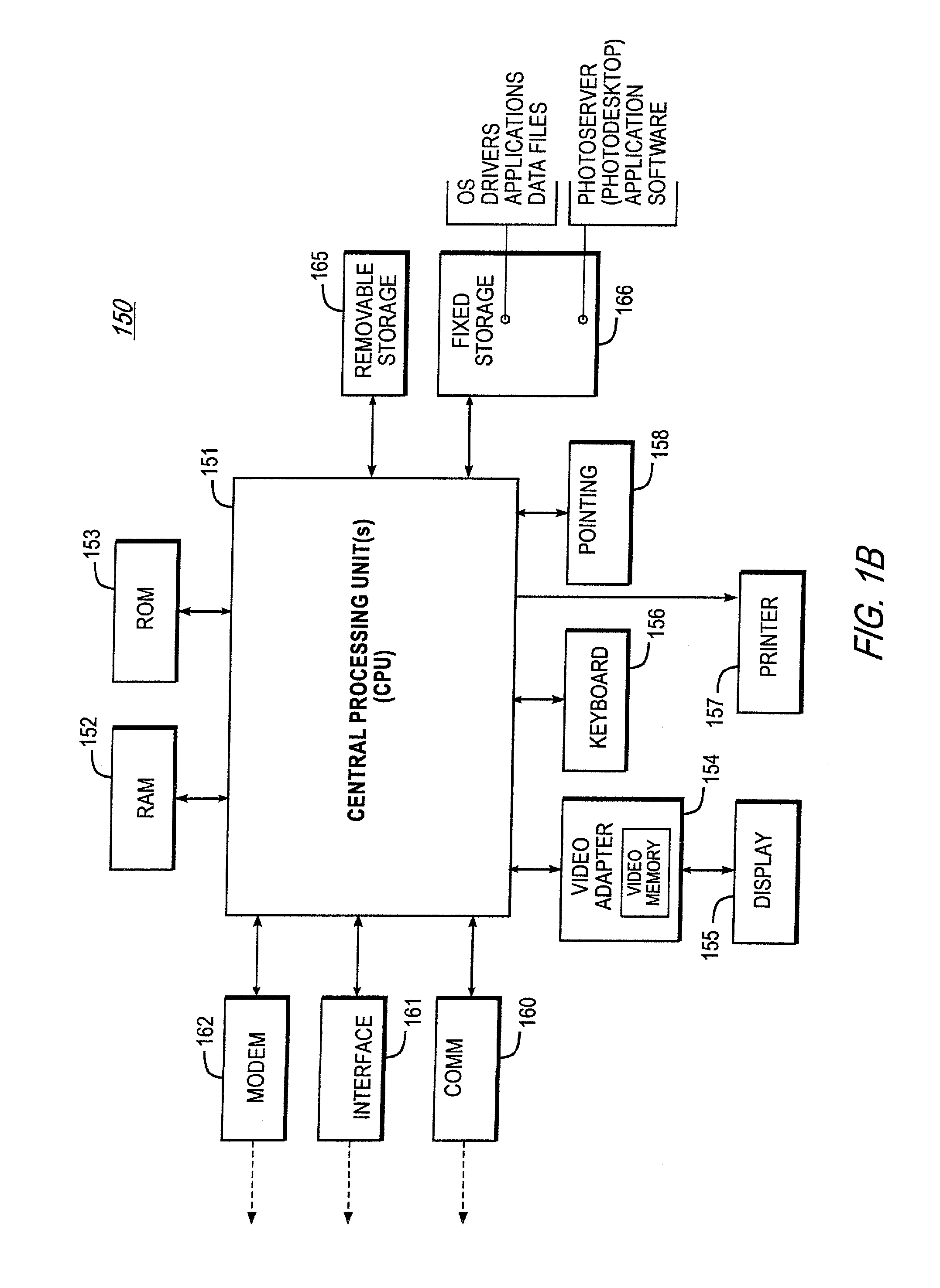

Digital camera device providing improved methodology for rapidly taking successive pictures

InactiveUS7369161B2Extended latencyAvailable storageTelevision system detailsColor television with pulse code modulationLuminosityDigital image

An in-camera two-stage compression implementation is described that reduces the latency between snapshots to a fraction of that otherwise required by other systems that either process complete compression following each snapshot or that incorporate heavy, bulky, and expensive RAM hardware capable of maintaining several raw luminosity records (unprocessed file containing a digital image). In the 1st stage compression the raw luminosity record is quickly, yet partially, compressed to available RAM buffer space to allow a user to expeditiously capture a succeeding image. When the higher-priority processes, the user shooting pictures, and stage one compression subside, a 2nd stage compression, which is slower but more effective, decompresses the earlier partially-compressed images, and re-compresses them for saving in flash memory until they are distributed to a remote platform to be finally converted to the JPEG2000 format.

Owner:RPX CORP

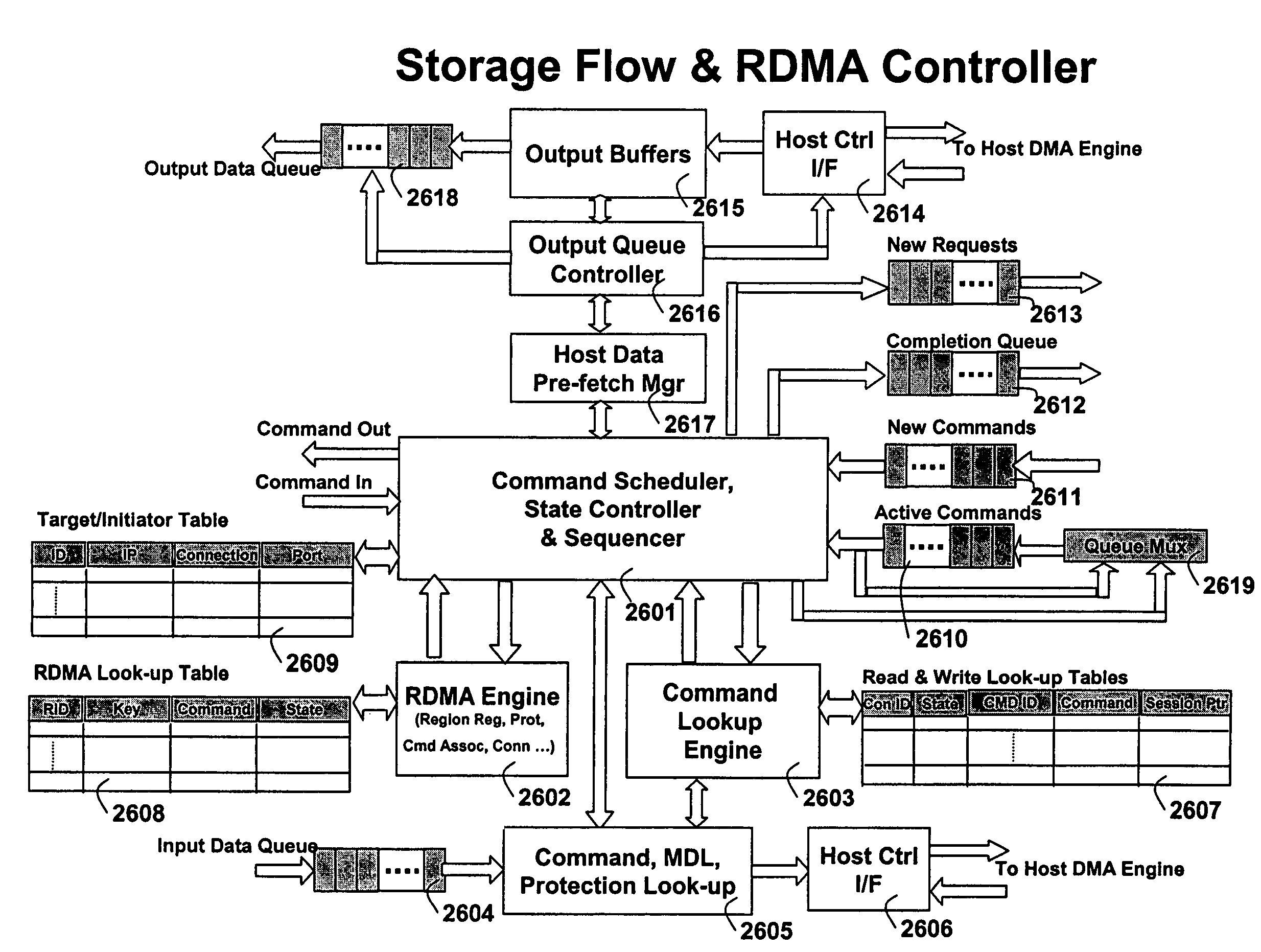

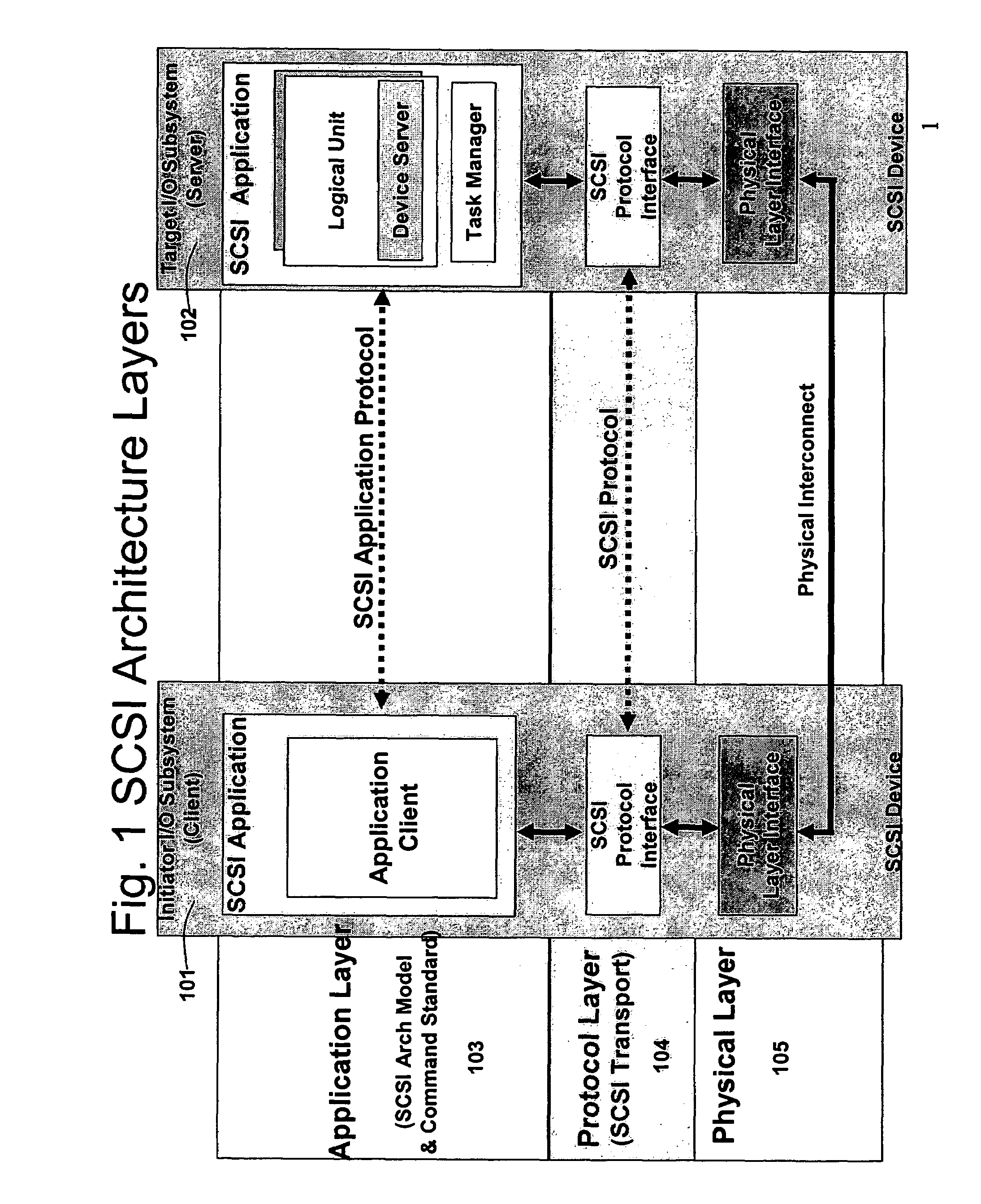

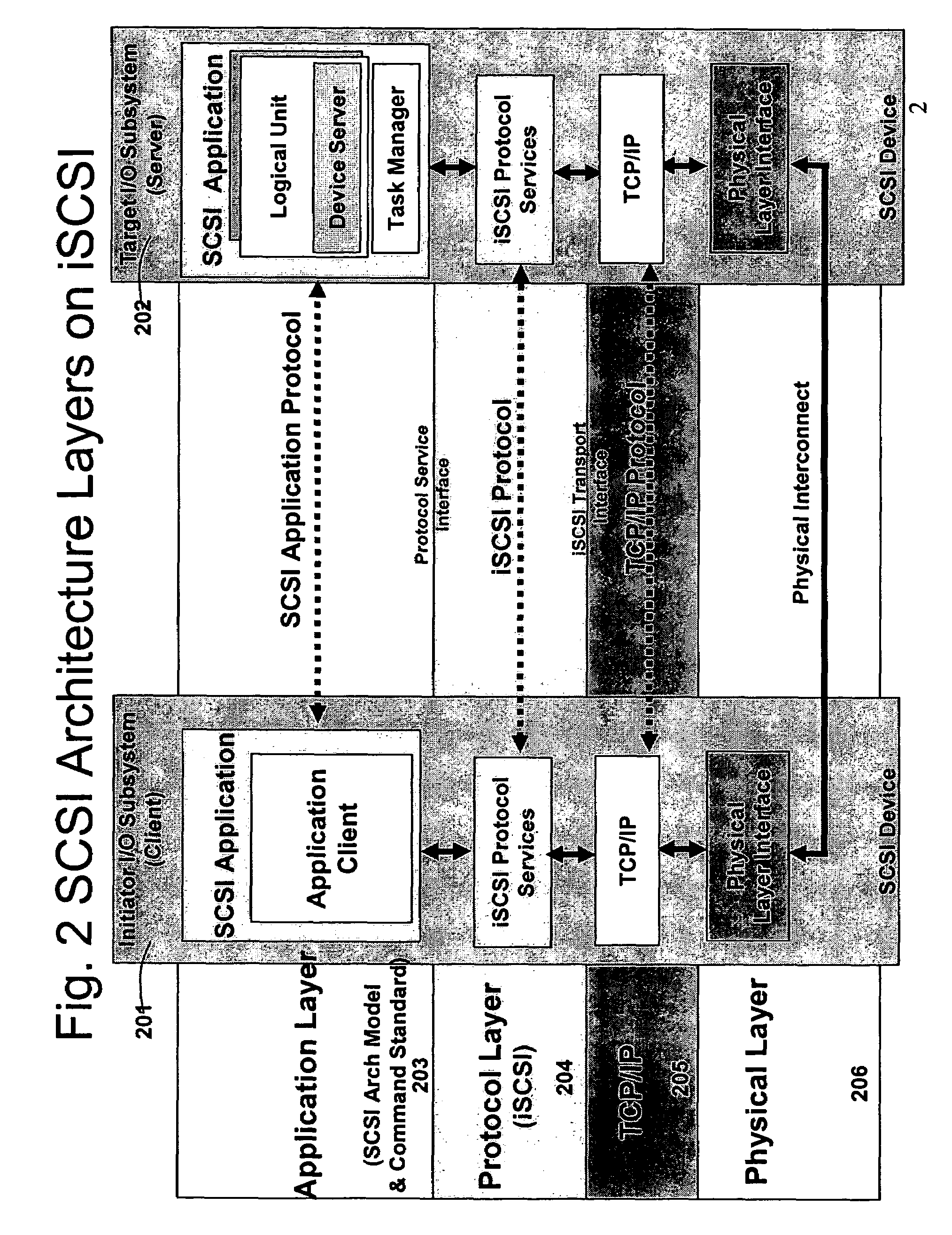

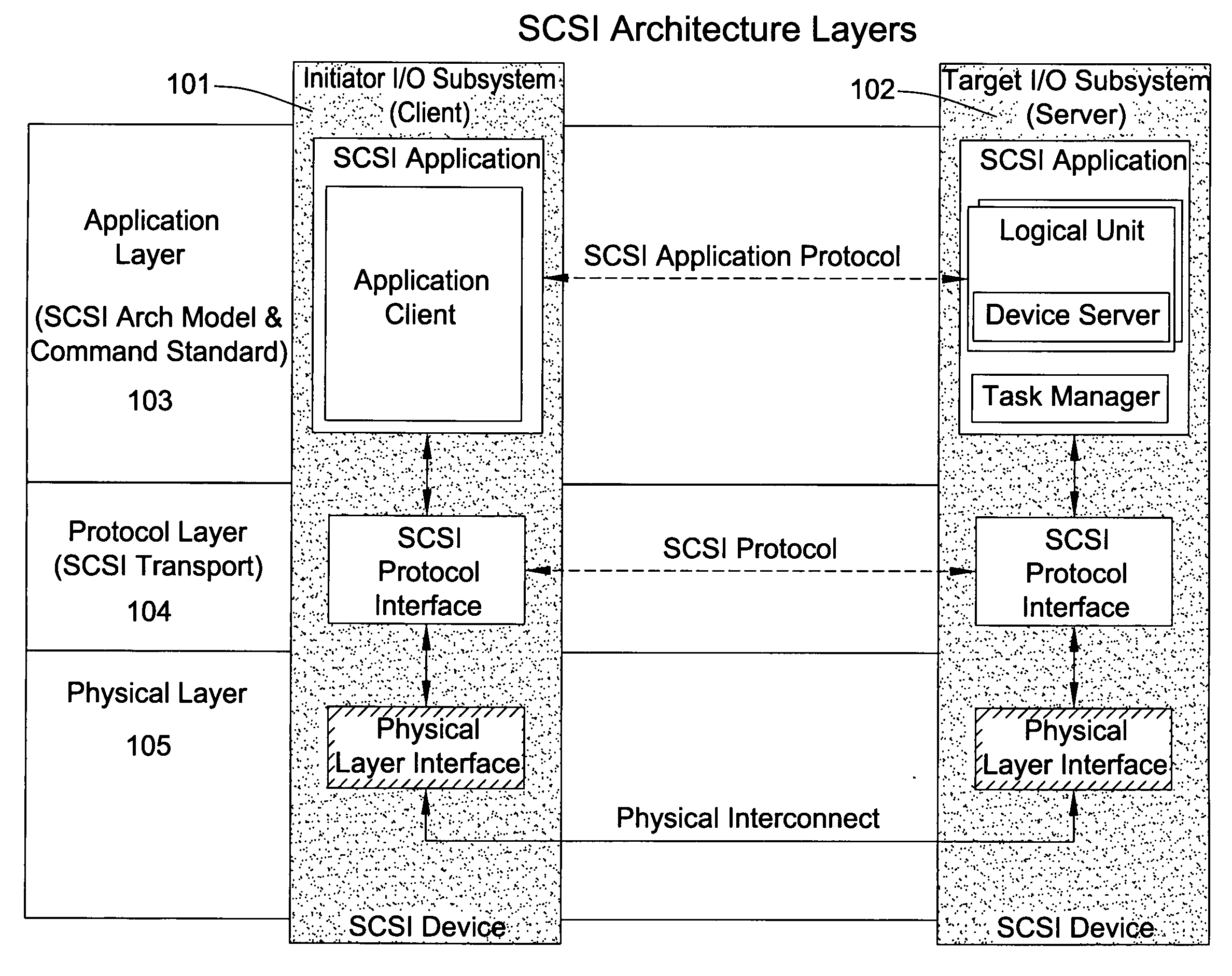

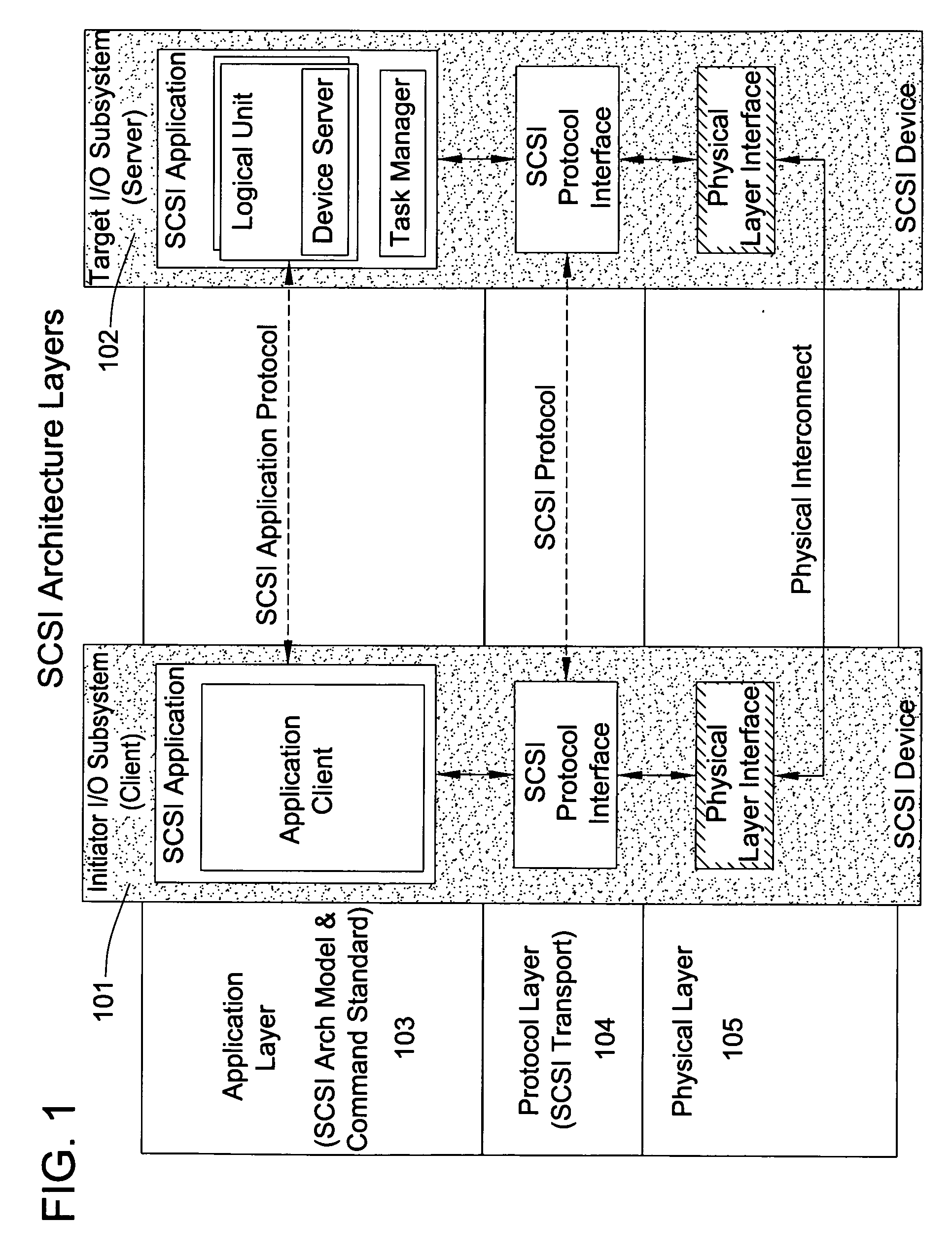

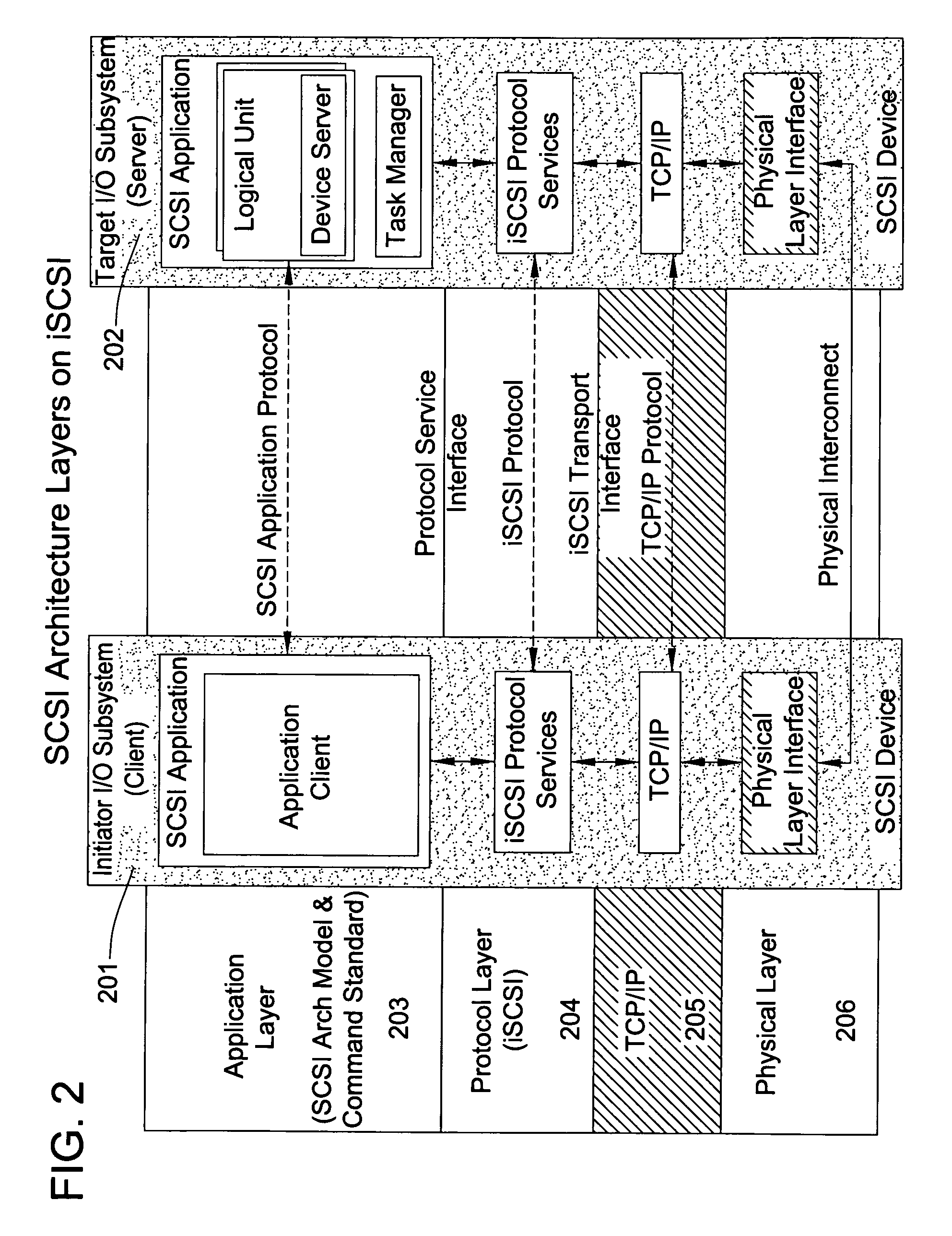

TCP/IP processor and engine using RDMA

ActiveUS7376755B2Sharply reduces TCP/IP protocol stack overheadImprove performanceMultiplex system selection arrangementsMemory adressing/allocation/relocationTransmission protocolInternal memory

A TCP / IP processor and data processing engines for use in the TCP / IP processor is disclosed. The TCP / IP processor can transport data payloads of Internet Protocol (IP) data packets using an architecture that provides capabilities to transport and process Internet Protocol (IP) packets from Layer 2 through transport protocol layer and may also provide packet inspection through Layer 7. The engines may perform pass-through packet classification, policy processing and / or security processing enabling packet streaming through the architecture at nearly the full line rate. A scheduler schedules packets to packet processors for processing. An internal memory or local session database cache stores a TCP / IP session information database and may also store a storage information session database for a certain number of active sessions. The session information that is not in the internal memory is stored and retrieved to / from an additional memory. An application running on an initiator or target can in certain instantiations register a region of memory, which is made available to its peer(s) for access directly without substantial host intervention through RDMA data transfer.

Owner:MEMORY ACCESS TECH LLC

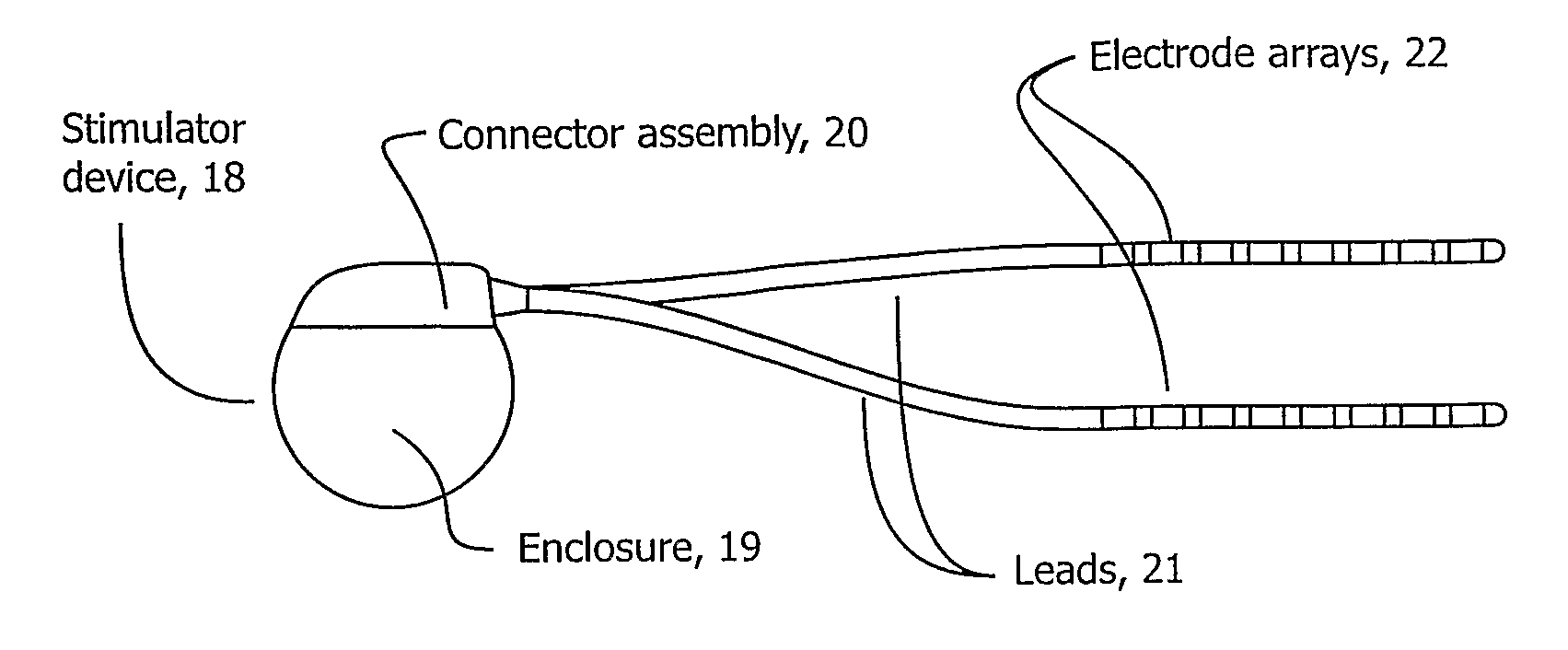

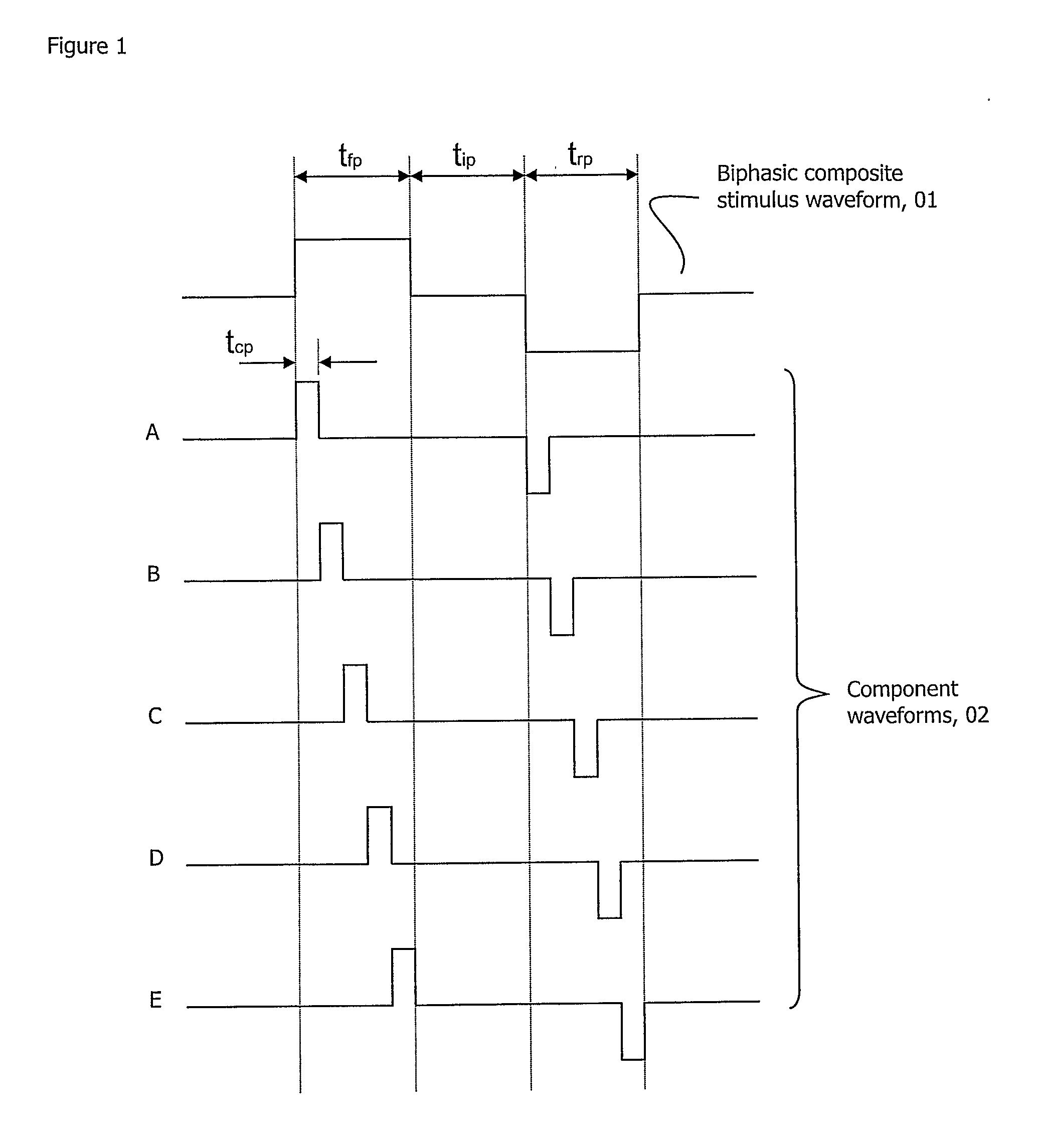

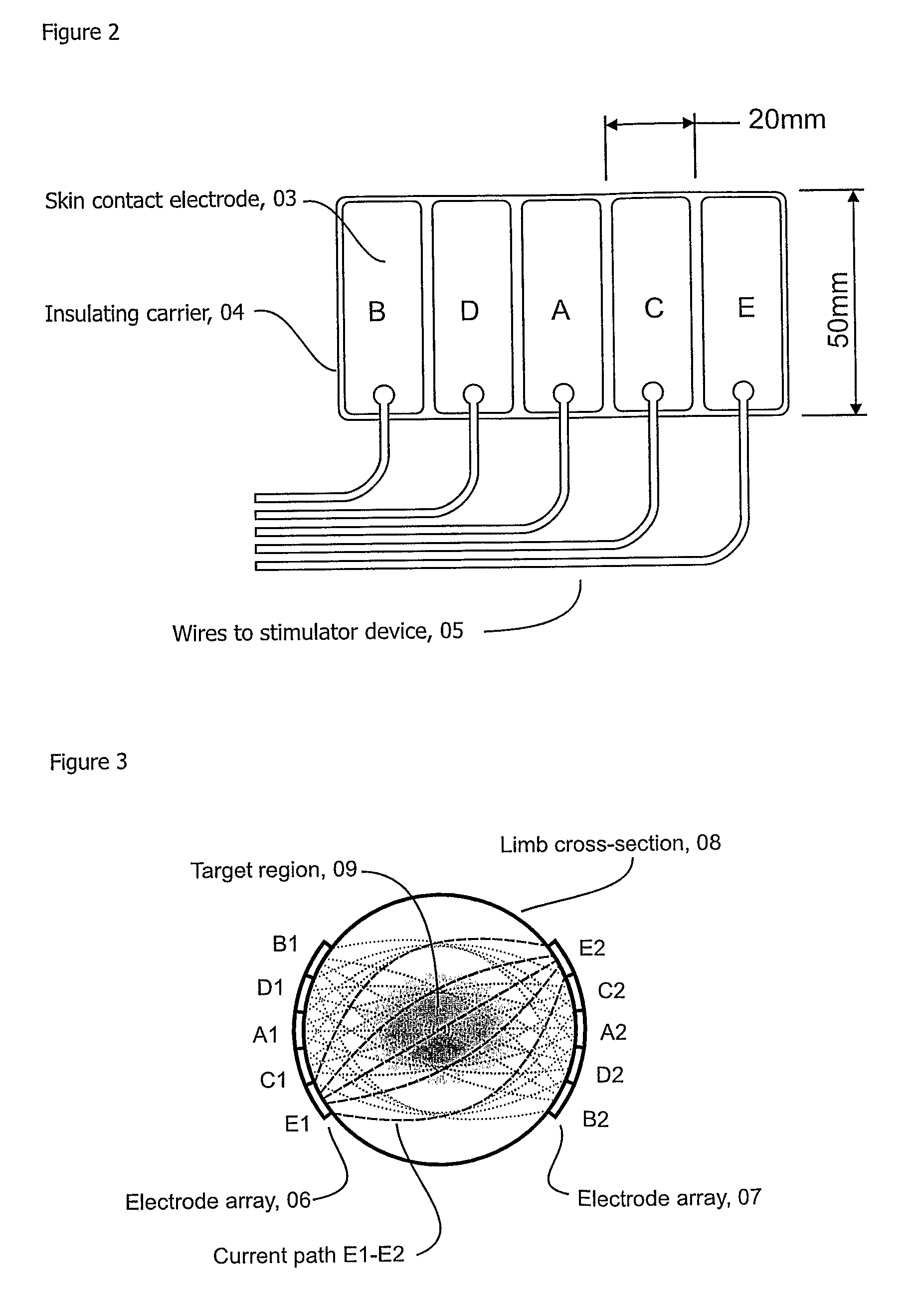

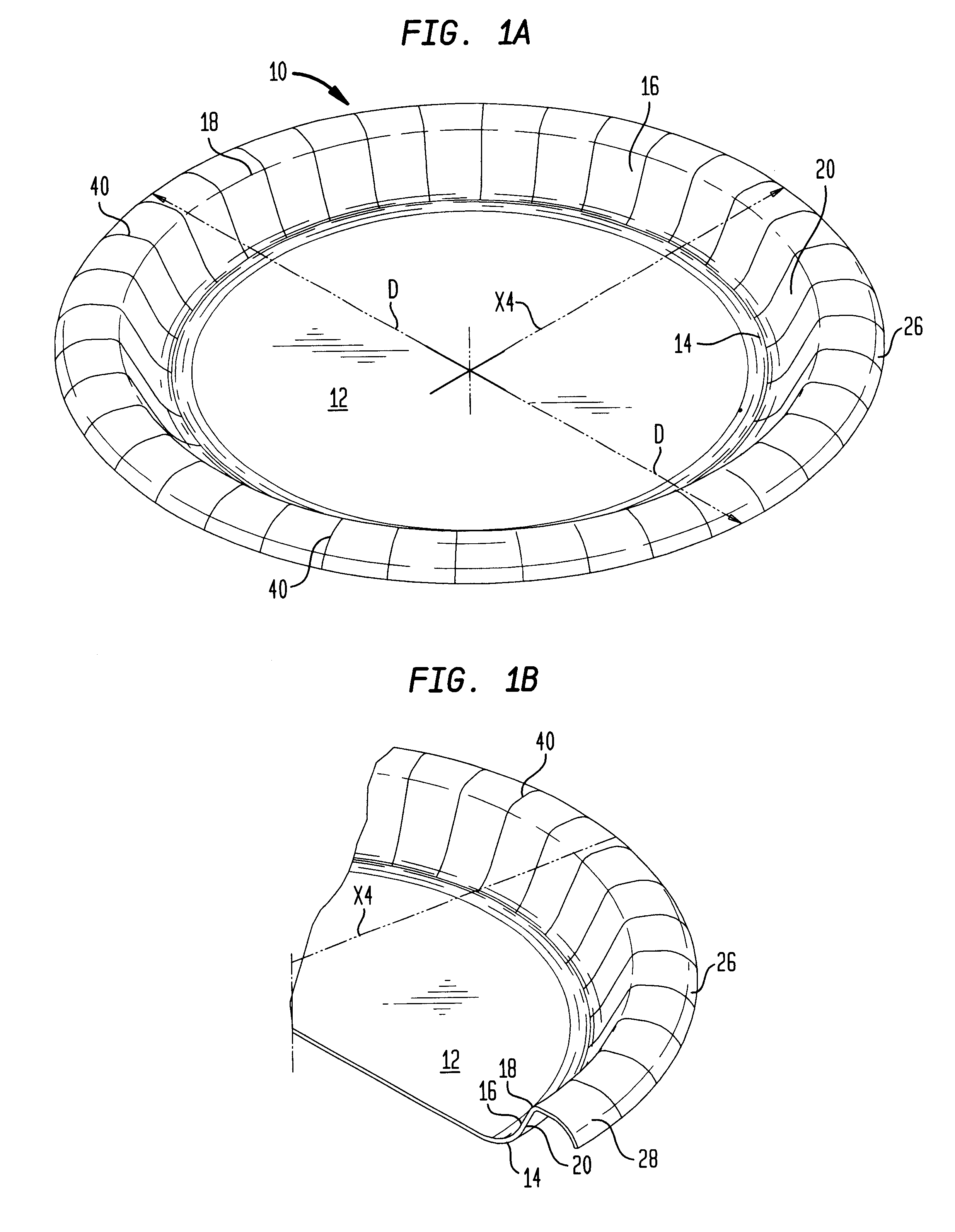

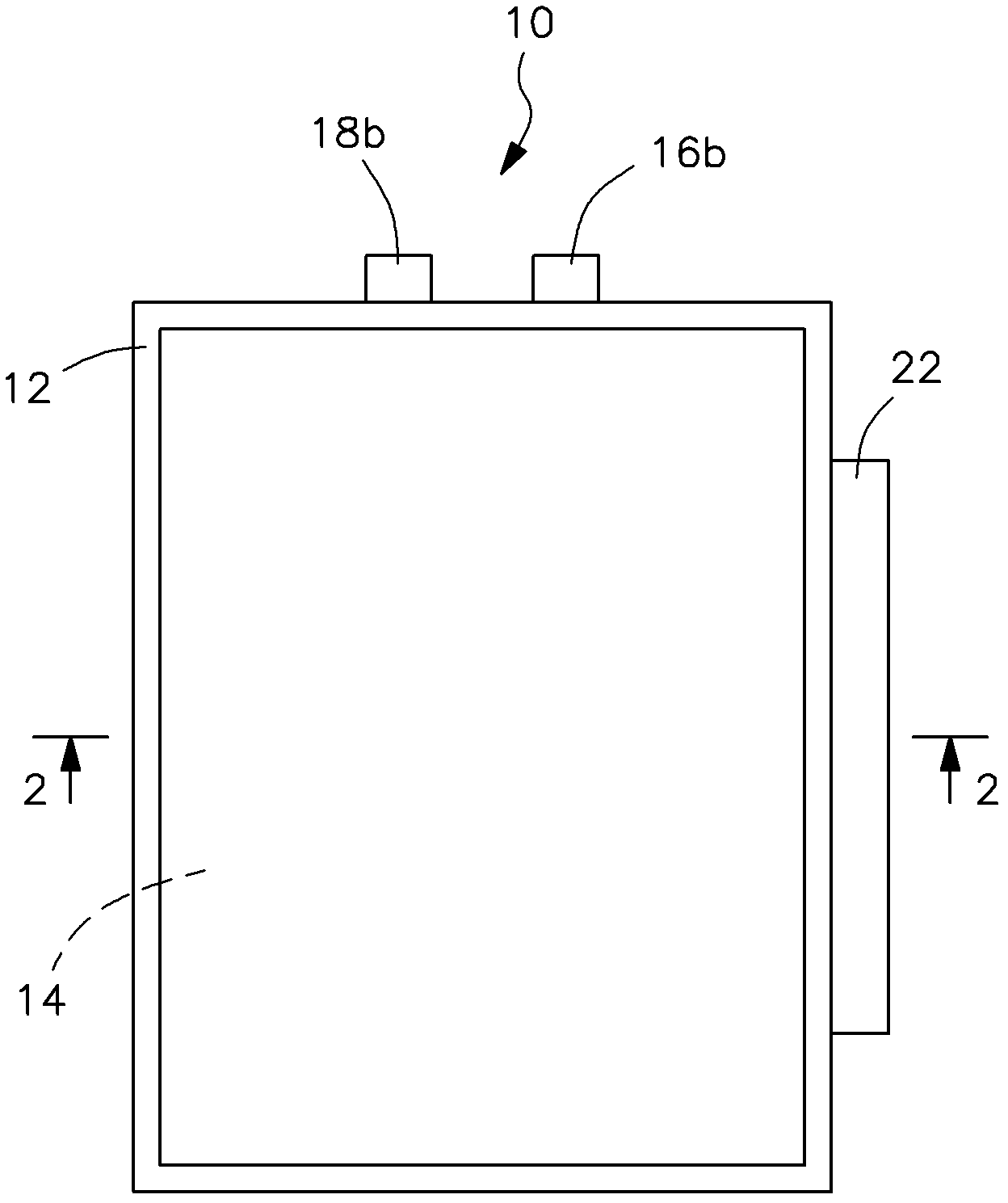

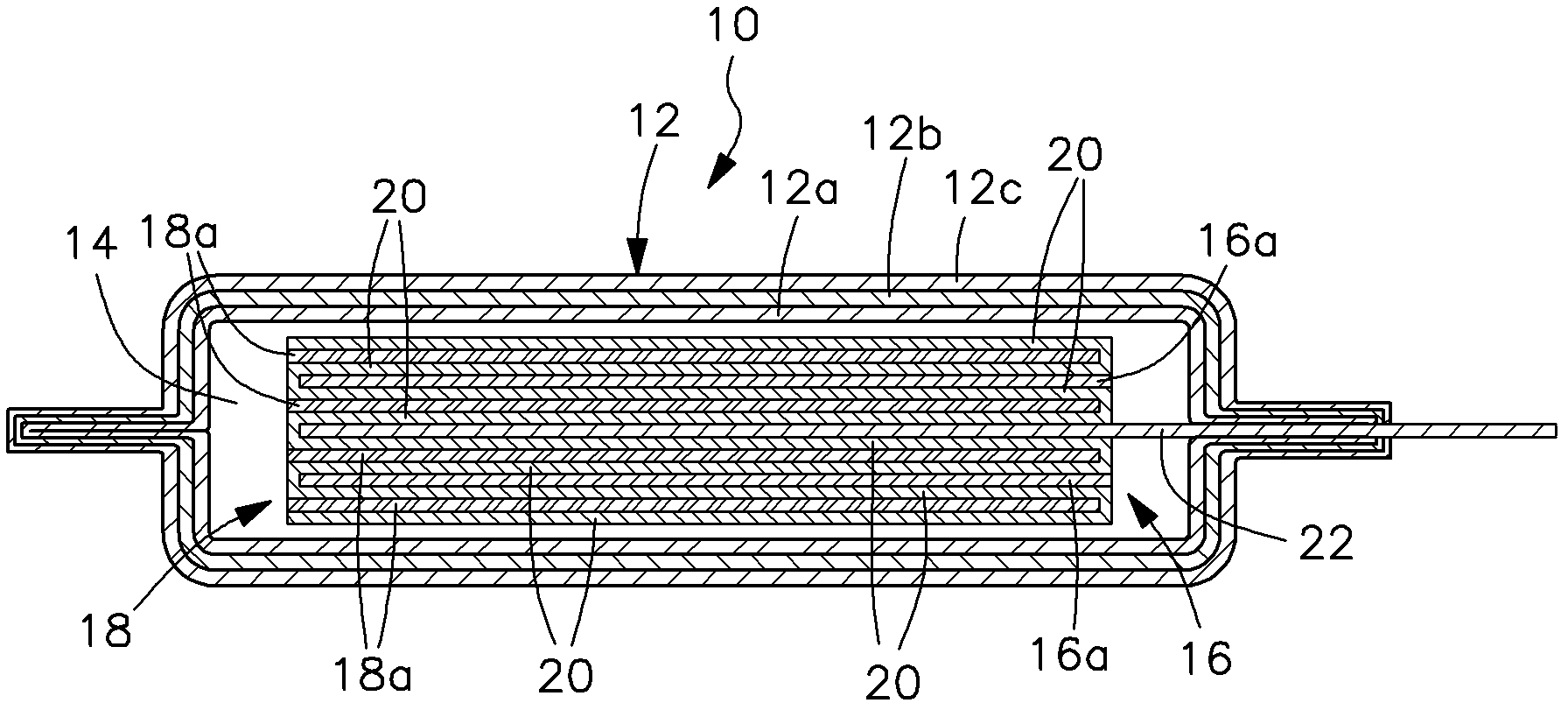

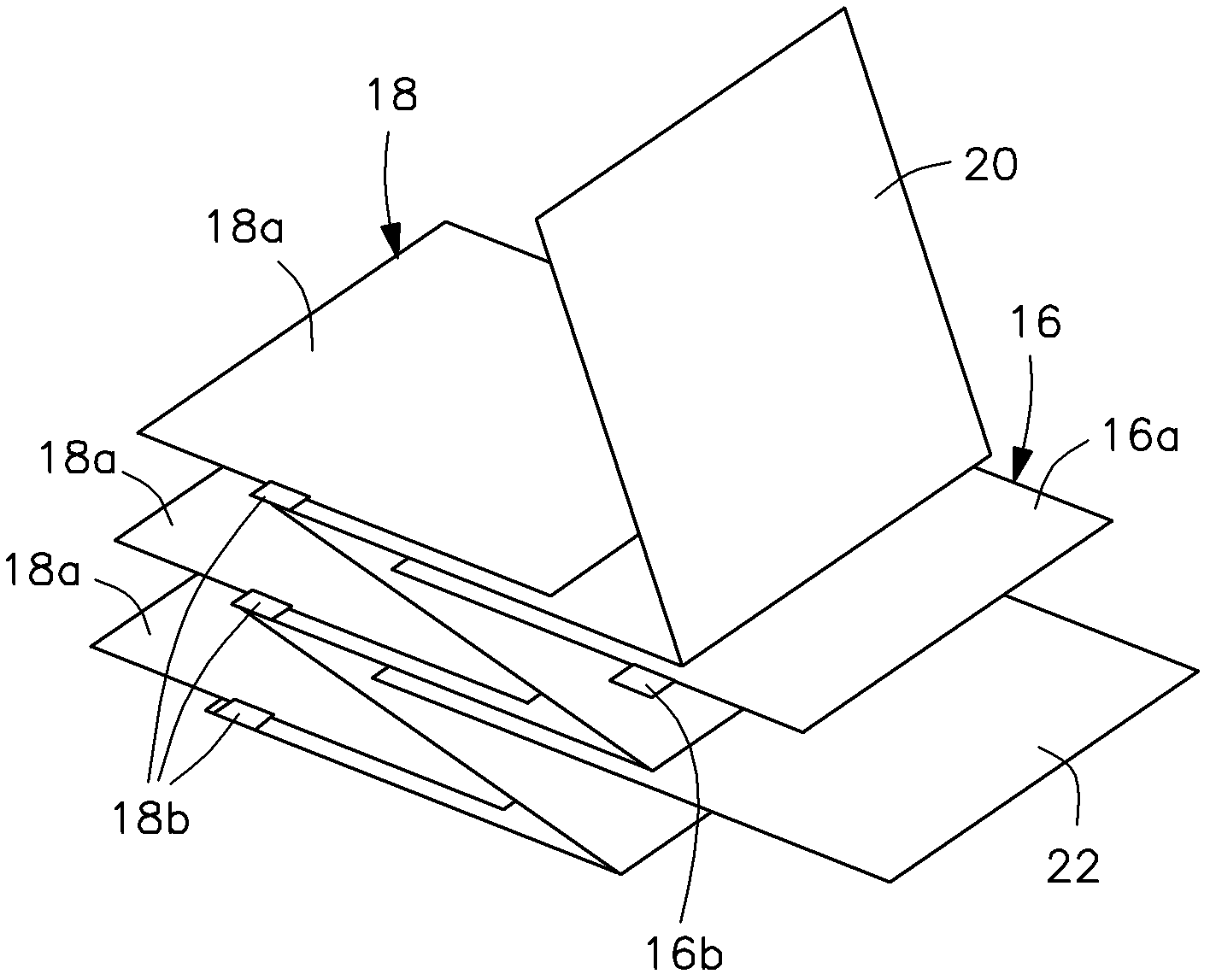

Array Stimulator

ActiveUS20100152817A1Simplify designLow bandwidthSpinal electrodesExternal electrodesNervous systemShort duration

An array stimulator has a plurality of electrodes in an array (22), the electrodes forming a plurality of electrode pairs, and a signal generator (18) for generating signals to the electrodes so as to generate electrical pulse in a patient to which the stimulator has been applied either transcutaneously or by implantation. Those electrical pulses form a composite pulse in the patient which stimulates the nervous system of the patient. The composite pulse has a duration between 4 μs and 1500 μs and a maximum voltage between 2V and 50V when the stimulator is implanted, and 15V to 500V when applied transcutaneously. The electrical pulses themselves are significantly shorter duration than the composite pulse, so they stimulate the nervous system of the patient much less than the composite pulse or not at all.

Owner:GILLBE IVOR STEPHEN

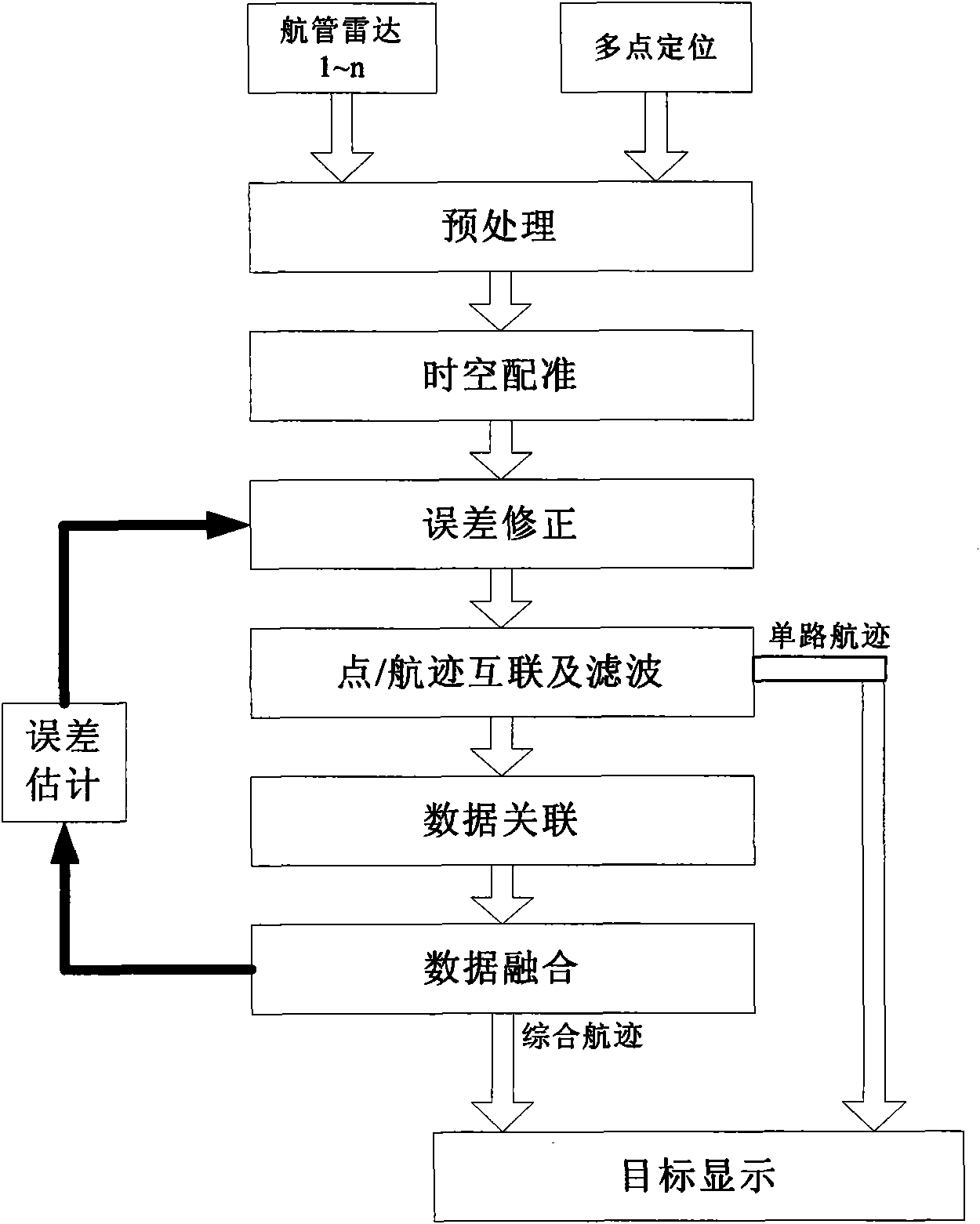

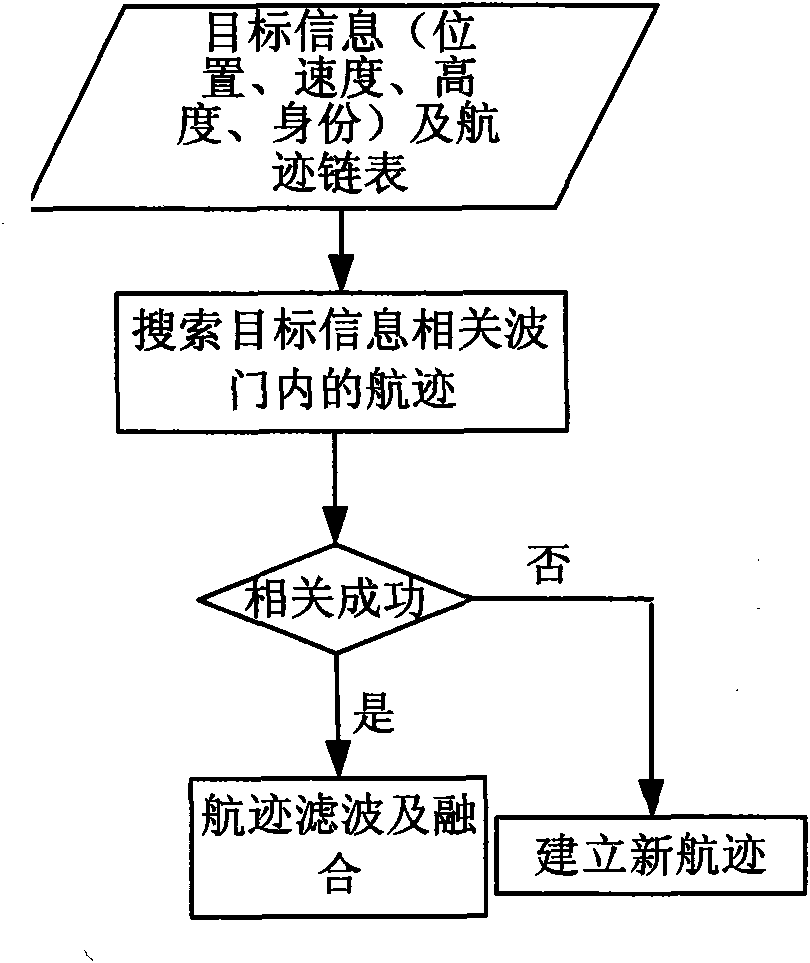

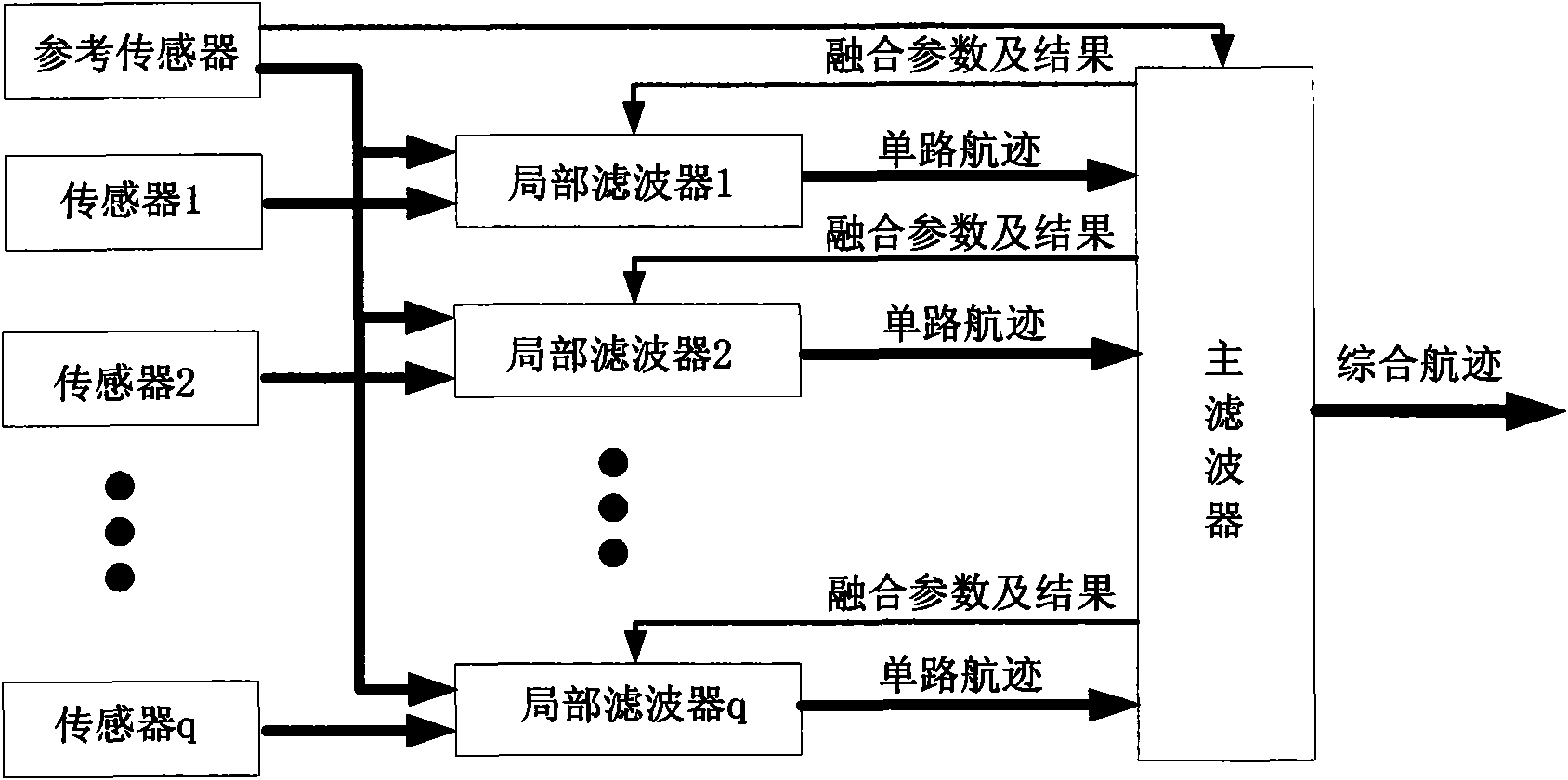

Federated Kalman filtering-based method for fusing multilateration data and radar data

InactiveCN101655561AReduce performanceCorrection errorRadio wave reradiation/reflectionRadarFiltration

The invention relates to a Federated Kalman filtering-based method for fusing multilateration data and radar data, comprising seven processes: pretreatment, time and space registration, error correction, single-sensor line tracking or airborne trace interconnection and filtration, data association, data fusion as well as error estimation. On the basis of multiclass monitoring information, the technical scheme of the invention establishes data association mapping relations among all classes of targets, constructs a process method fusing the multilateration system data and the radar data, realizes deep fusion of all classes of information and comprehensive utilization on effective information, ensures high updating rate of a multilateration system and the whole precision of system monitoringwhen period is less than or equal to 1sec, reduces impact of radar measuring error on system monitoring precision, and significantly improves the tracking precision of the system.

Owner:NANJING LES INFORMATION TECH

High performance ultracapacitors with carbon nanomaterials and ionic liquids

InactiveUS20080192407A1Excellent electrolyte accessibilityImprove performanceHybrid capacitor electrolytesElectrolytic capacitorsSupercapacitorCarbon nanomaterials

The present invention is directed to the use of carbon nanotubes and / or electrolyte structures comprising ionic liquids in various electrochemical devices, such as ultracapacitors.

Owner:ADA TECH

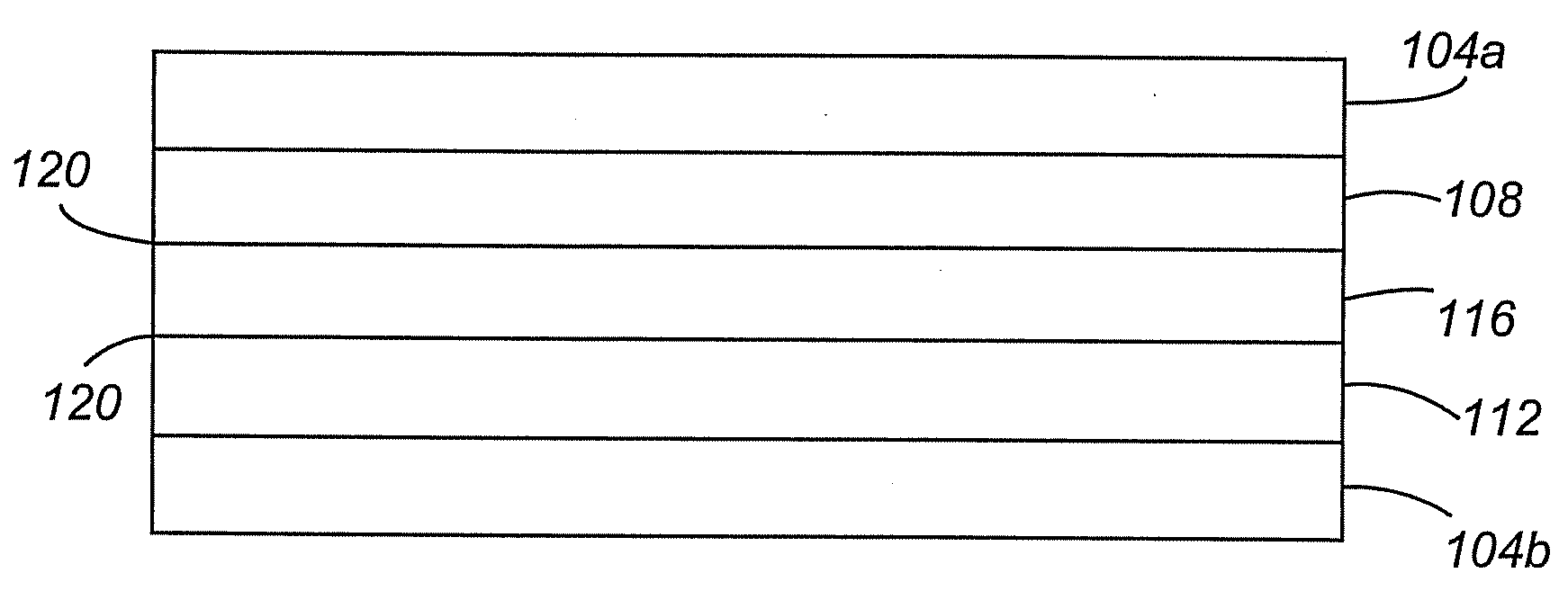

Digital Camera Device Providing Improved Methodology for Rapidly Taking Successive Pictures

InactiveUS20080239093A1Extended latencyAvailable storageTelevision system detailsColor television with pulse code modulationComputer graphics (images)Engineering

An in-camera two-stage compression implementation is described that reduces the latency between snapshots to a fraction of that otherwise required by other systems that either process complete compression following each snapshot or that incorporate heavy, bulky, and expensive RAM hardware capable of maintaining several raw luminosity records (unprocessed file containing a digital image). In the 1st stage compression the raw luminosity record is quickly, yet partially, compressed to available RAM buffer space to allow a user to expeditiously capture a succeeding image. When the higher-priority processes, the user shooting pictures, and stage one compression subside, a 2nd stage compression, which is slower but more effective, decompresses the earlier partially-compressed images, and re-compresses them for saving in flash memory until they are distributed to a remote platform to be finally converted to the JPEG2000 format.

Owner:RPX CORP

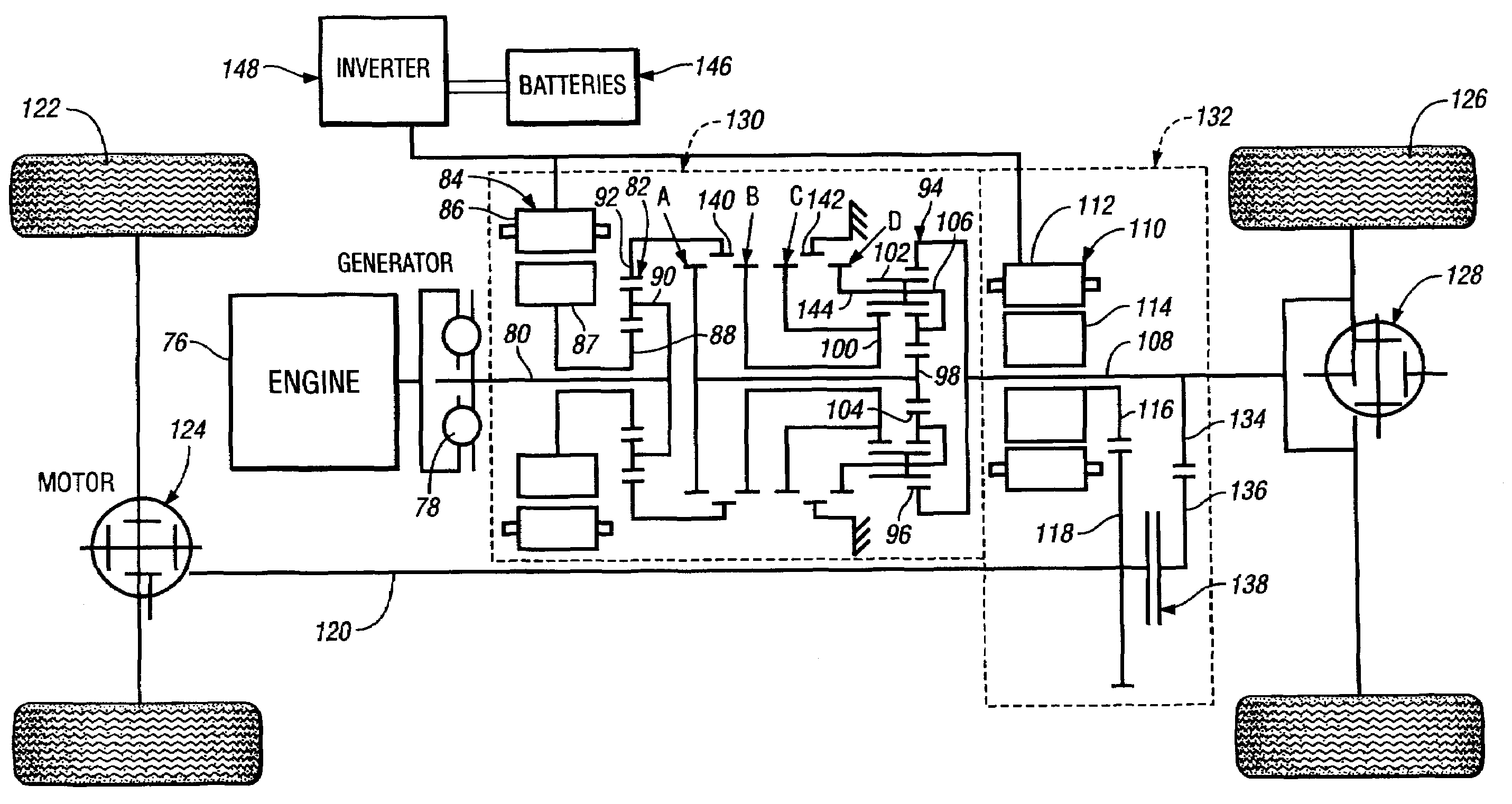

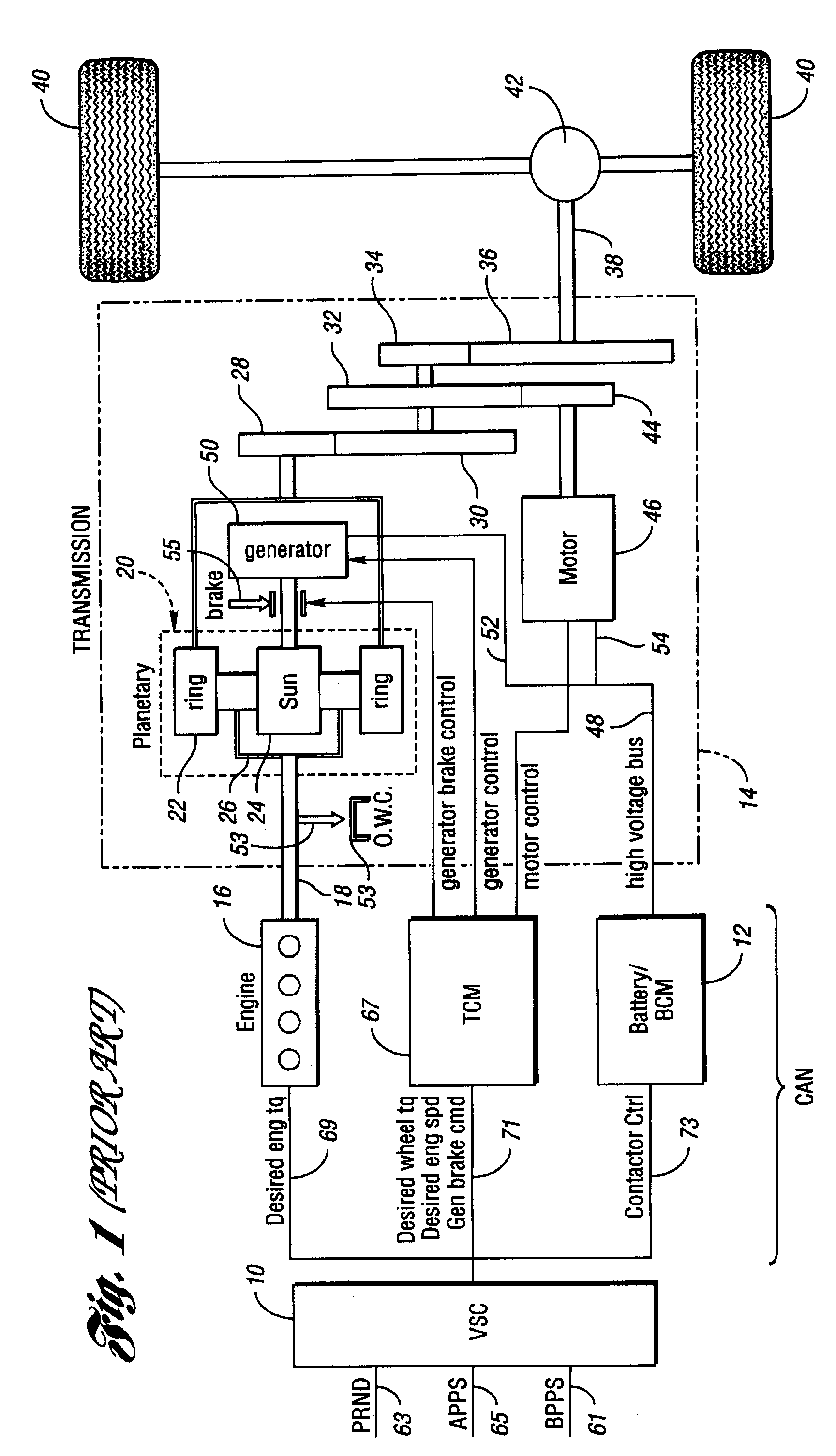

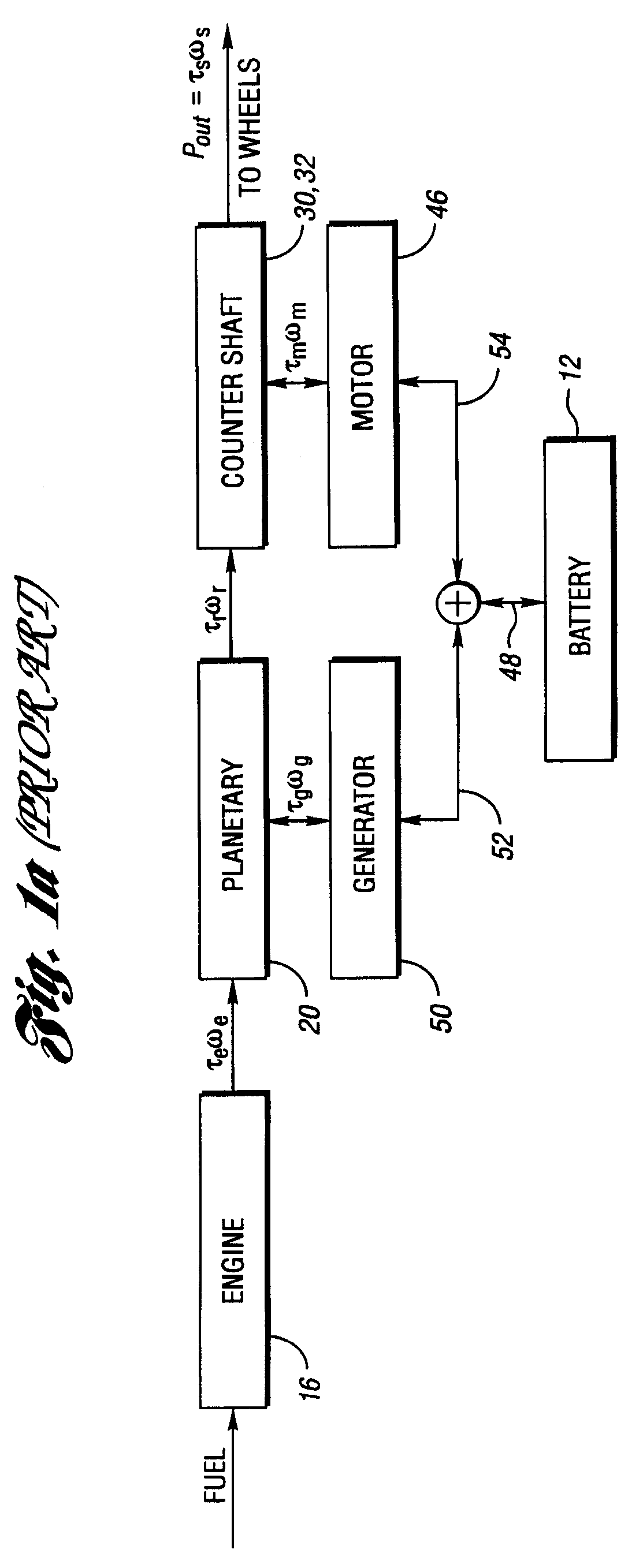

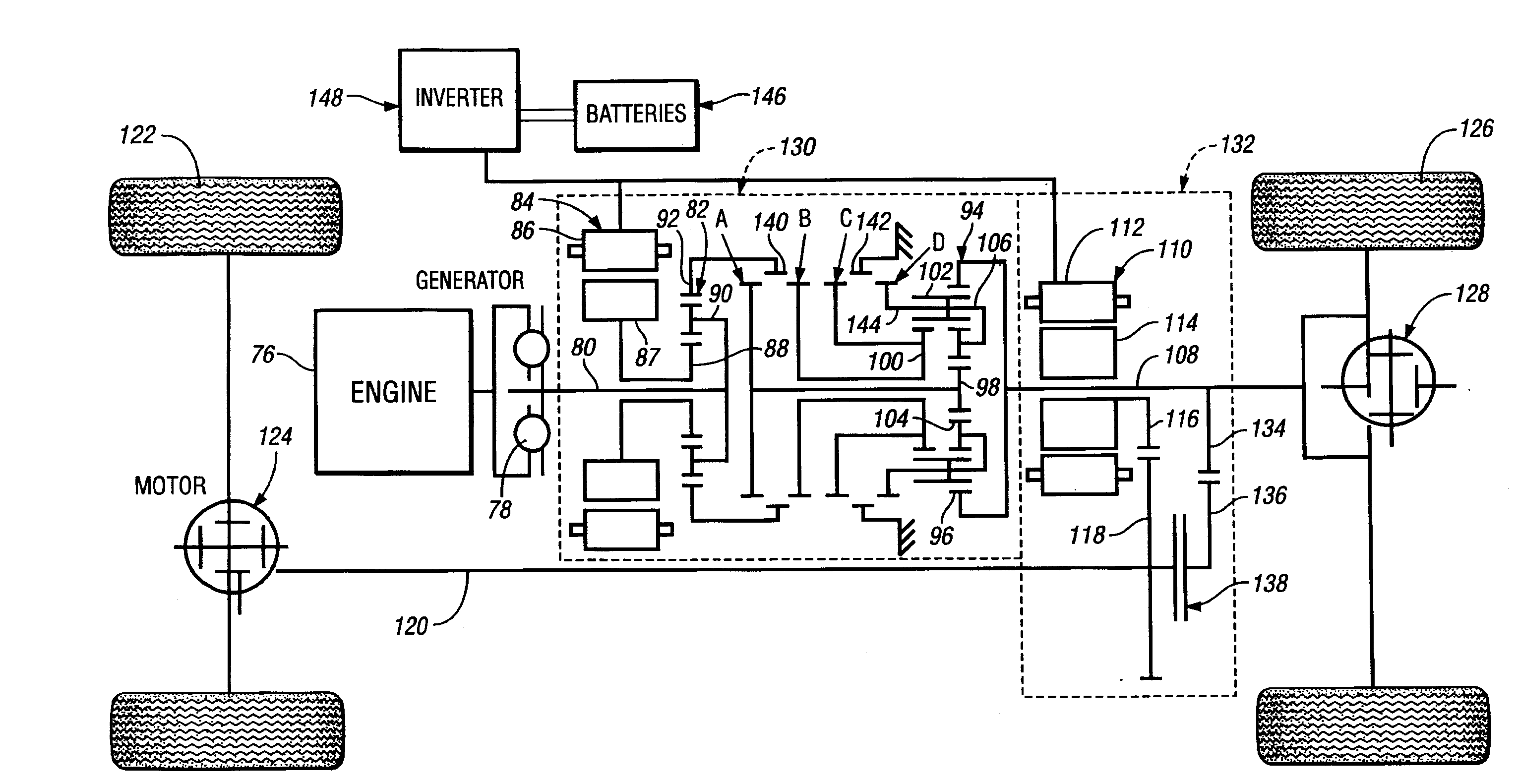

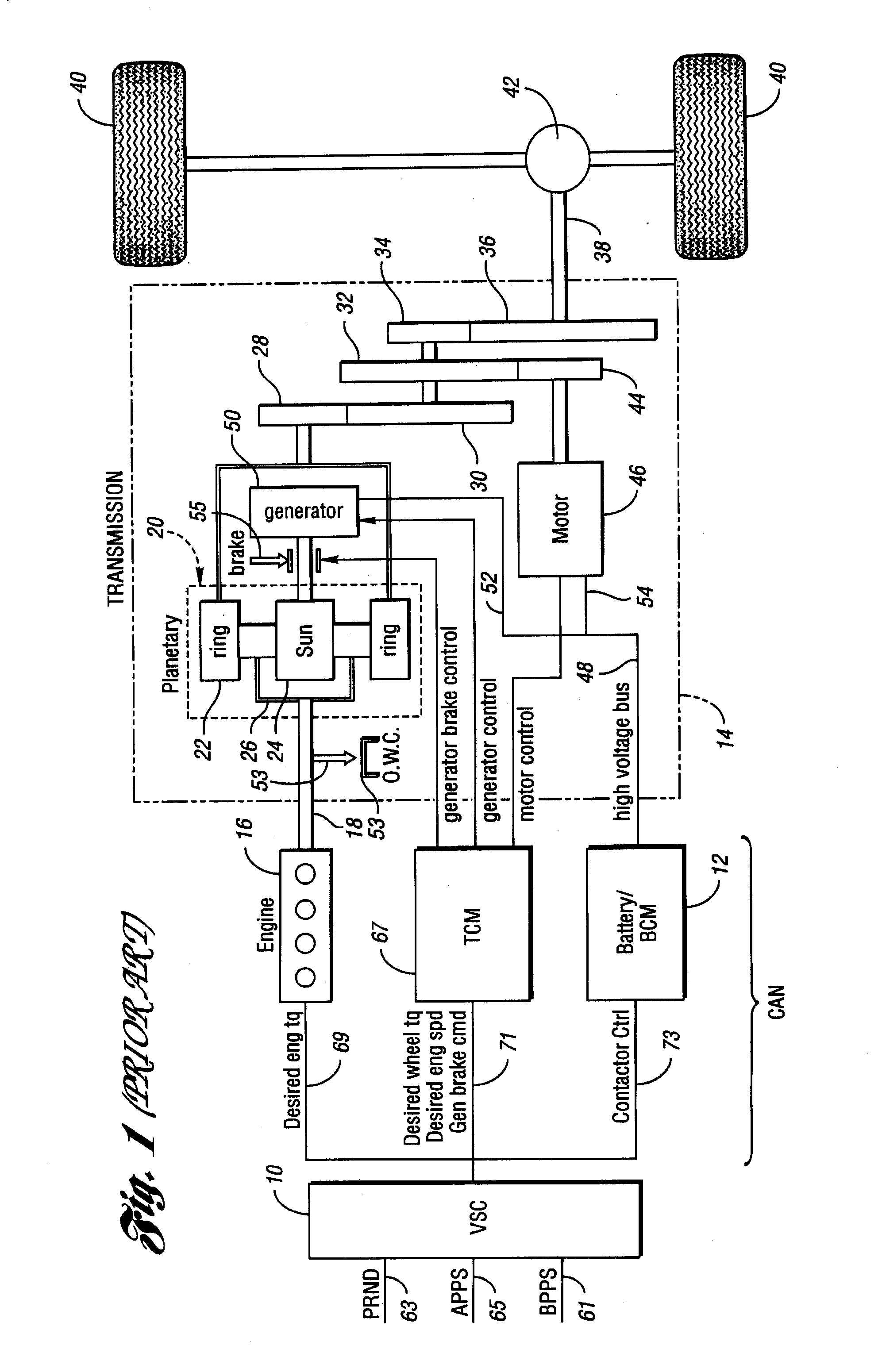

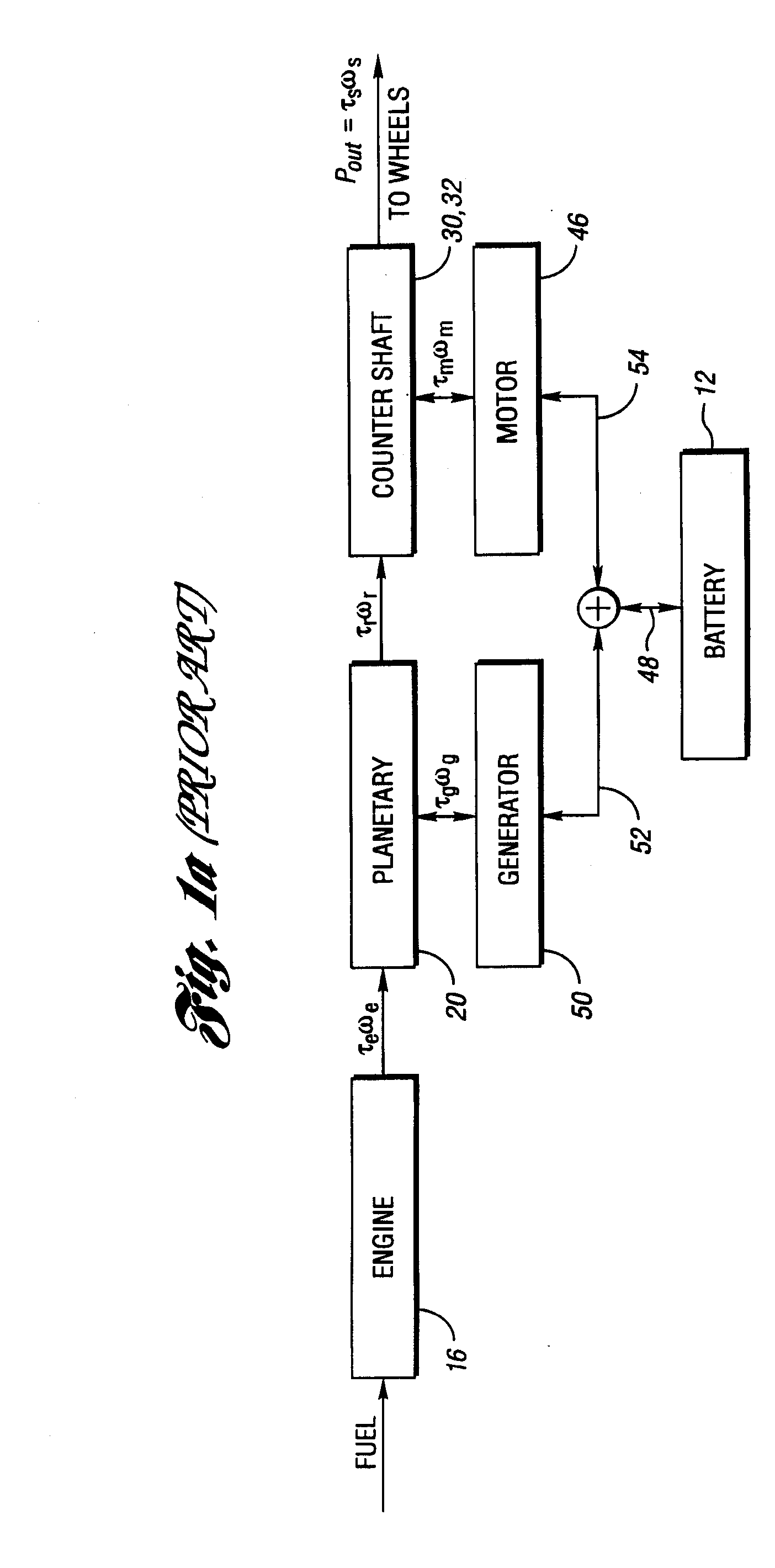

Electric hybrid powertrain system

InactiveUS7572201B2Improve climbing abilityImprove drivabilityAuxillary drivesTransmission elementsPower flowElectric vehicle

A hybrid electric vehicle powertrain having an engine and an electric motor and generator sub-system, which establish mechanical and electric power flow paths. Multiple-ratio gearing in a power flow path for forward drive enhances vehicle traction torque for heavy-duty vehicle applications. Reverse drive performance is enhanced by torque multiplying gearing in a reverse drive power delivery path.

Owner:FORD GLOBAL TECH LLC

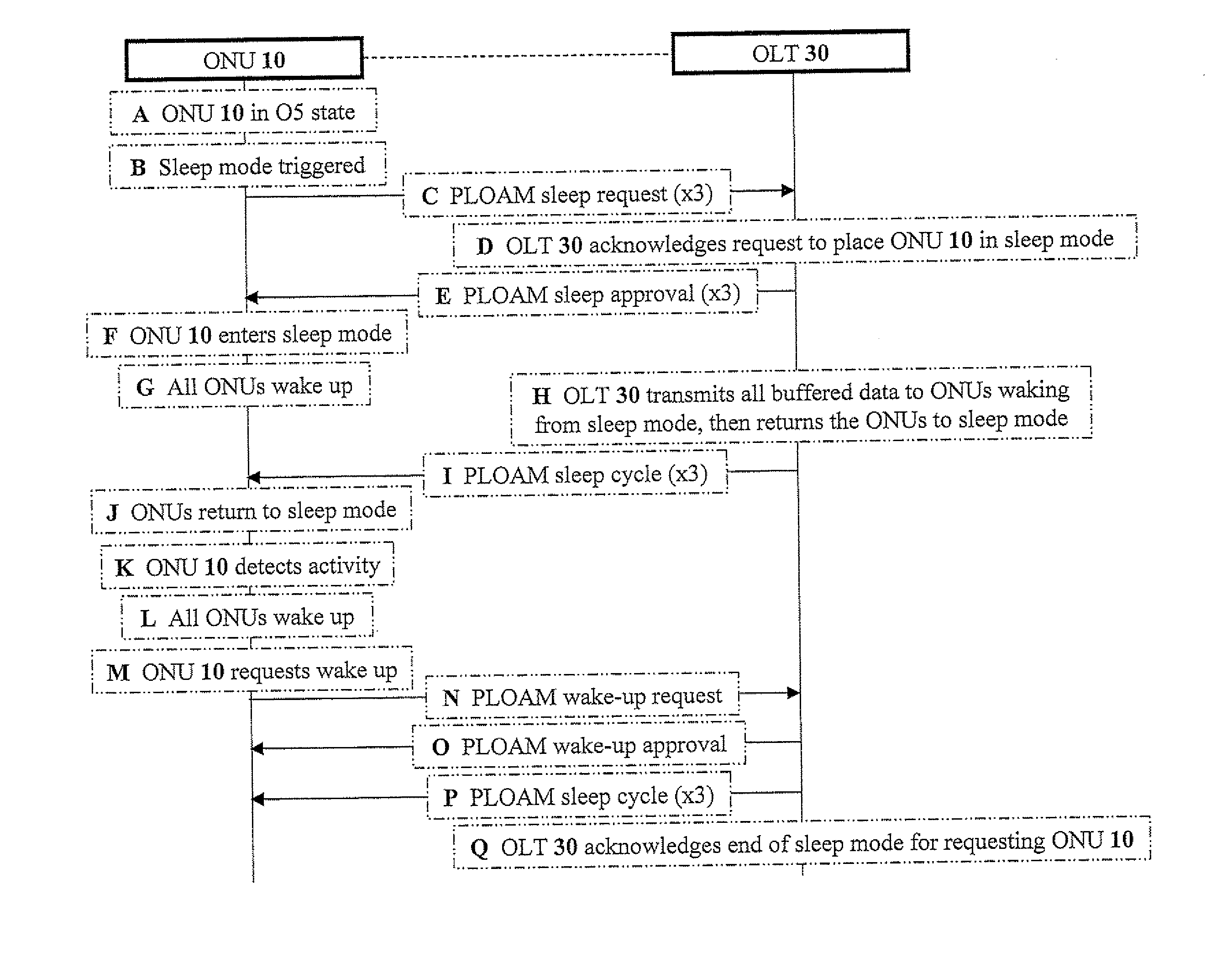

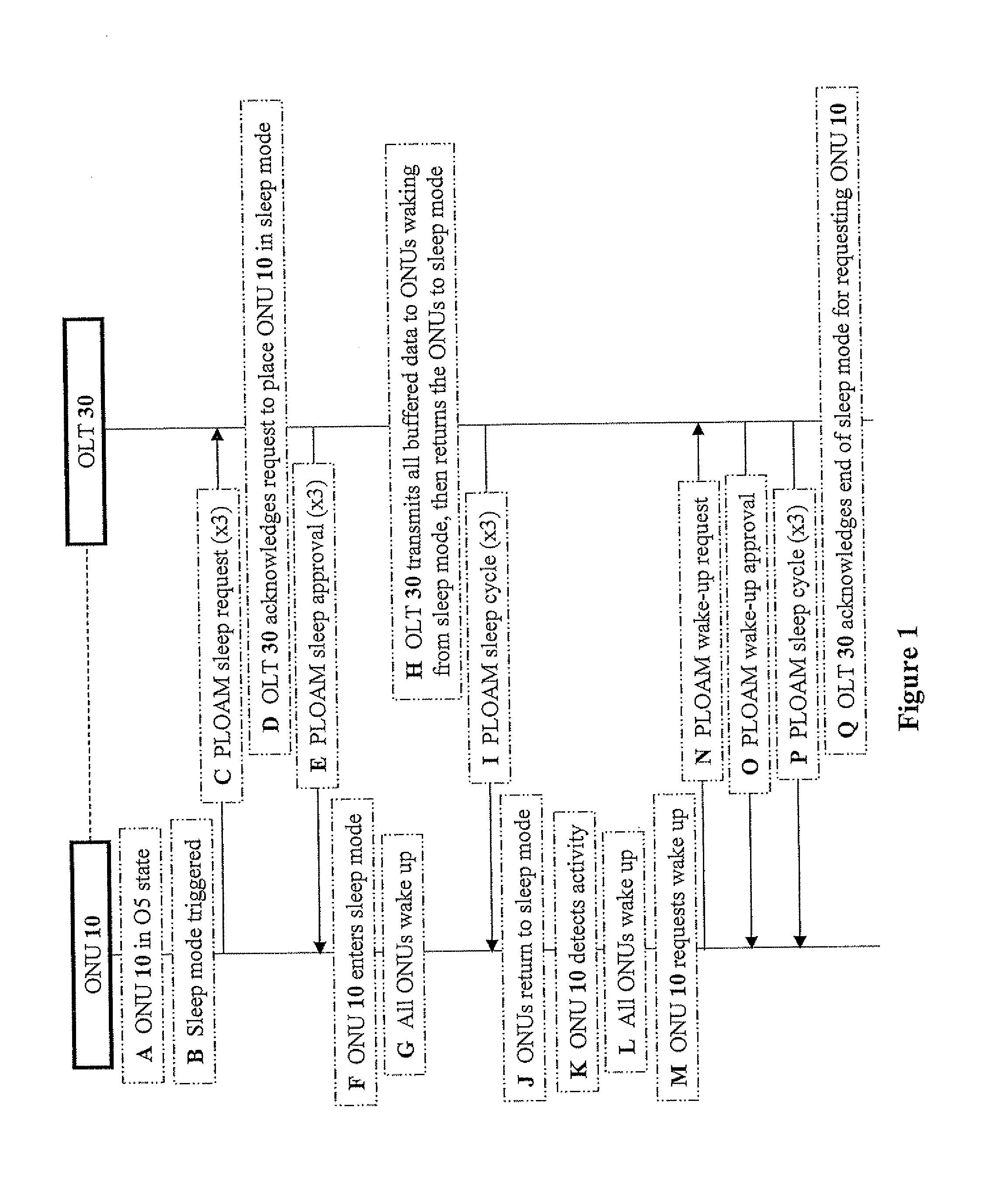

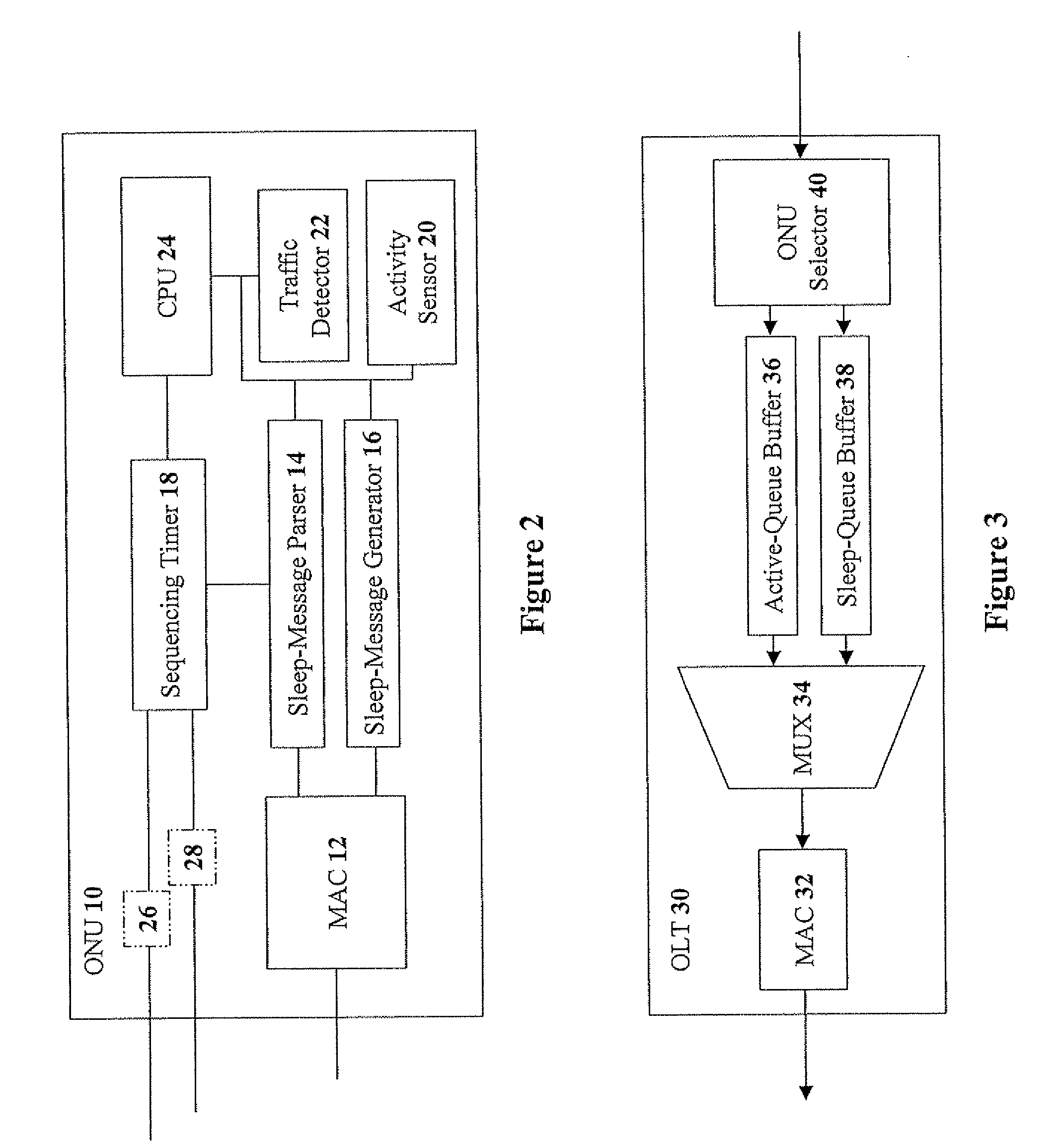

Methods and devices for reducing power consumption in a passive optical network while maintaining service continuity

ActiveUS20090263127A1Reduce power consumptionMaintain continuityMultiplex system selection arrangementsTransmission monitoringData trafficComputer science

The present invention discloses methods for reducing power consumption in a PON while maintaining service continuity, the method including the steps of: providing an OLT operationally connected to at least one ONU; triggering a sleep request for at least one requesting ONU; upon receiving a sleep acknowledgement, activating a sleep mode for at least one requesting ONU according to a sleep period designated in the sleep request; and terminating the sleep mode according to the sleep period. Preferably, the sleep acknowledgement is transmitted from the OLT to the requesting ONU. Preferably, the sleep period is executed by a sleep command in the sleep acknowledgement. Preferably, the method further includes the step of: upon completion of the sleep period, transmitting buffered data traffic from the OLT to a sleeping ONU. Preferably, the step of transmitting is performed without the sleeping ONU being re-registered and without causing packet reordering.

Owner:MICROSEMI ISRAEL STORAGE SOLUTIONS LTD

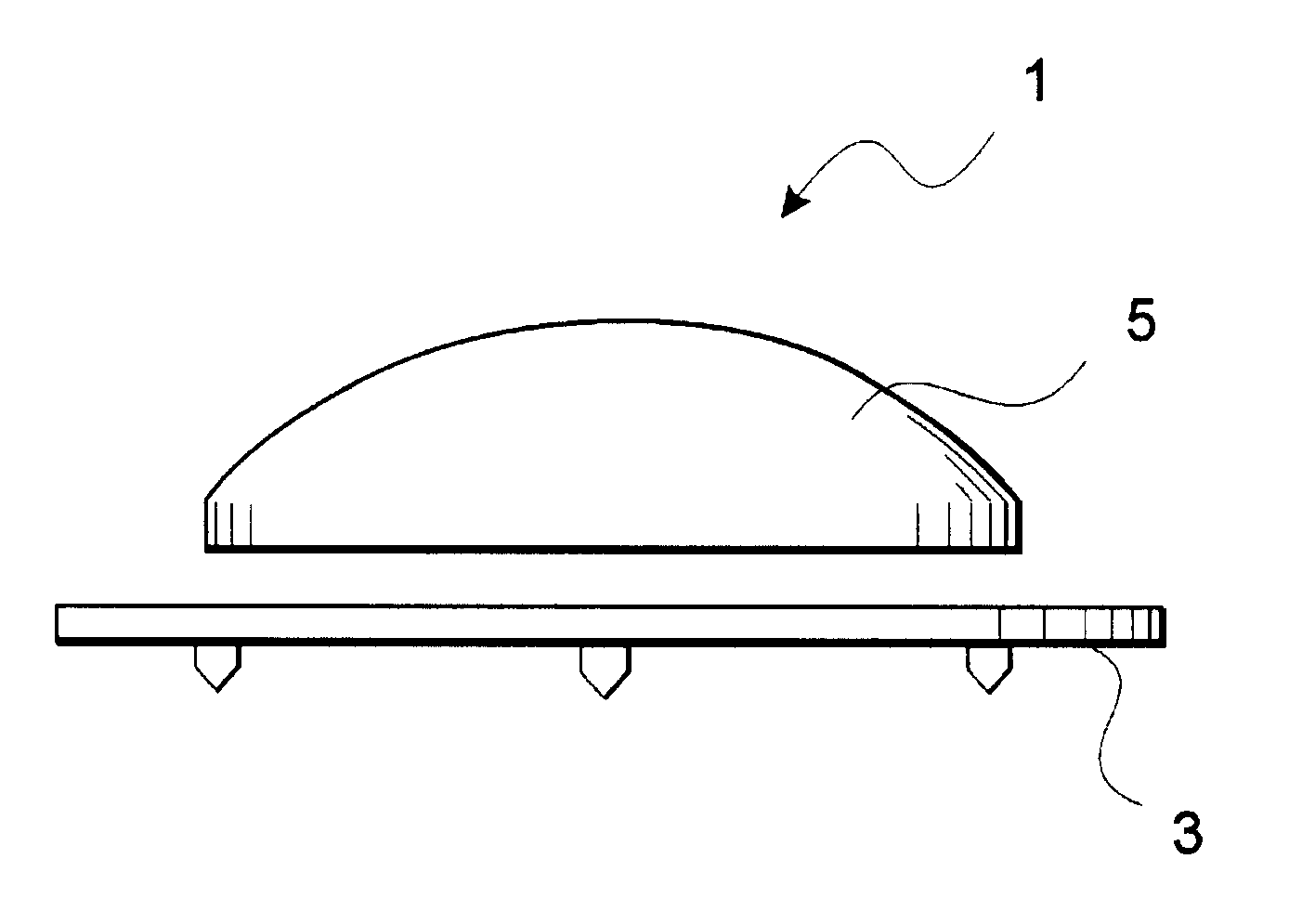

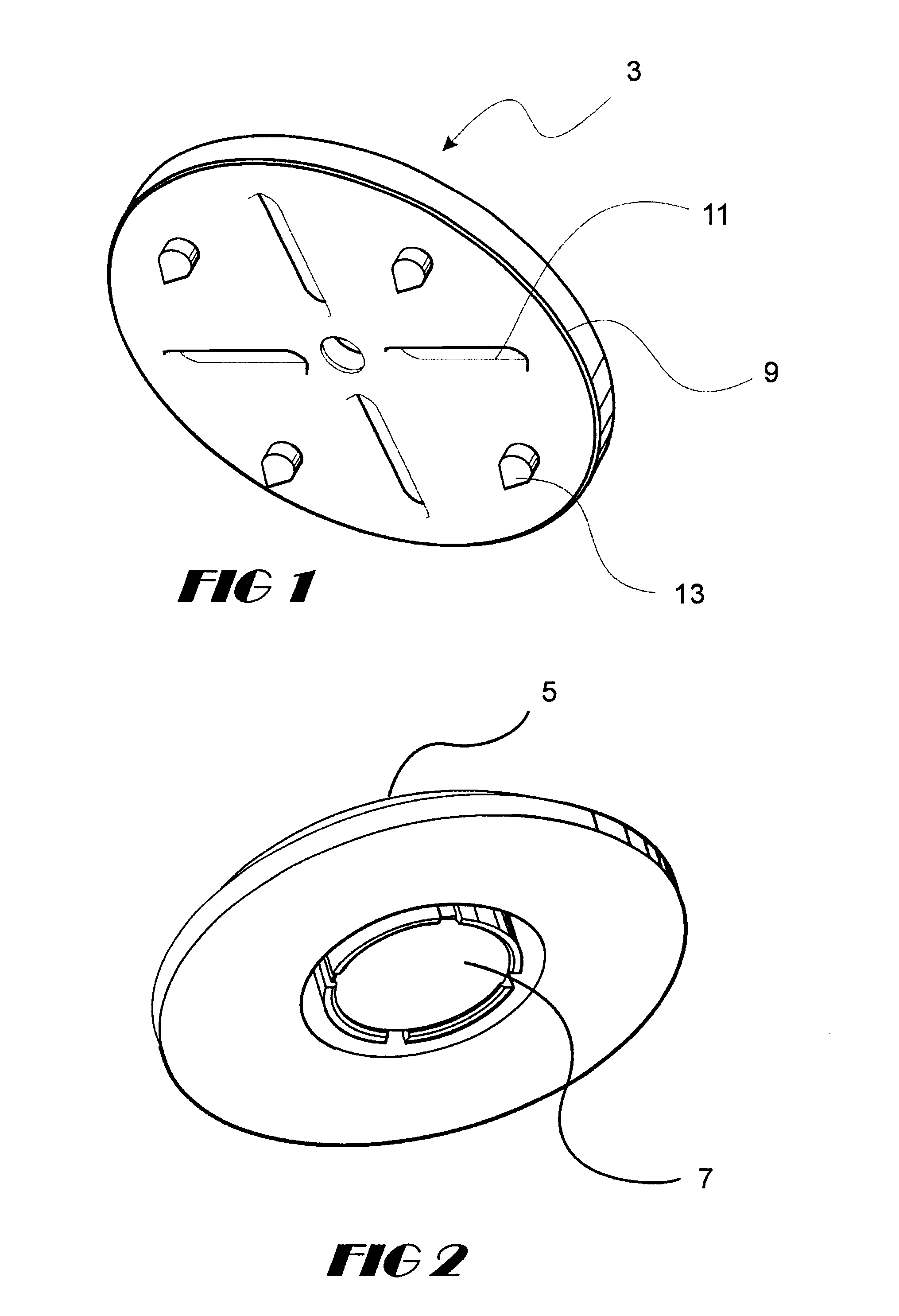

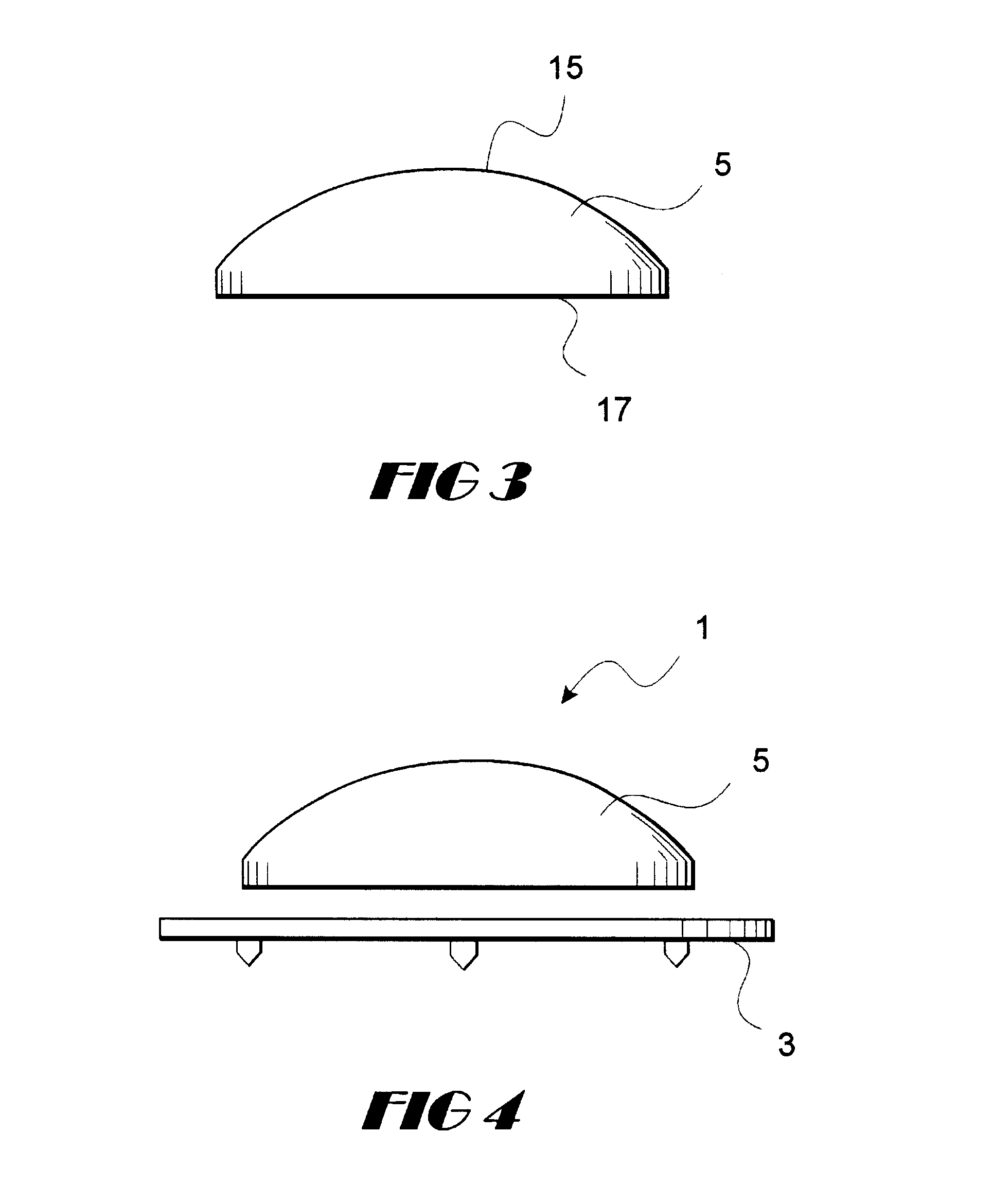

Patellar alignment device

InactiveUS6589248B1Accurately locate proper positionReduce performanceDiagnosticsJoint implantsPatella prosthesisEngineering

A patellar alignment device for determining the position of a patella prosthesis. The device comprises two components-a baseplate and a mobile component which is preferably magnetically attached to the baseplate. During a surgical procedure to replace the knee, the baseplate is temporarily attached to the back of the patella. The baseplate may contain spikes or prongs to secure it to the patella. The baseplate further includes a series of slots for marking the patella. The mobile component resembles a patella and is placed on the baseplate. The patella with the alignment device in place is then placed in position on the knee and trialed. Because the mobile component is free to move on the baseplate, it finds the position that is most amenable to a natural knee movement. The alignment device is then exposed and the patella is marked at the position of the mobile component. Since the baseplate contains a series of slots, the patella can be easily marked at several locations around the mobile component. The entire patella alignment assembly is then removed and the final prosthetic device can be inserted at the marked location.

Owner:HUGHES JOE L

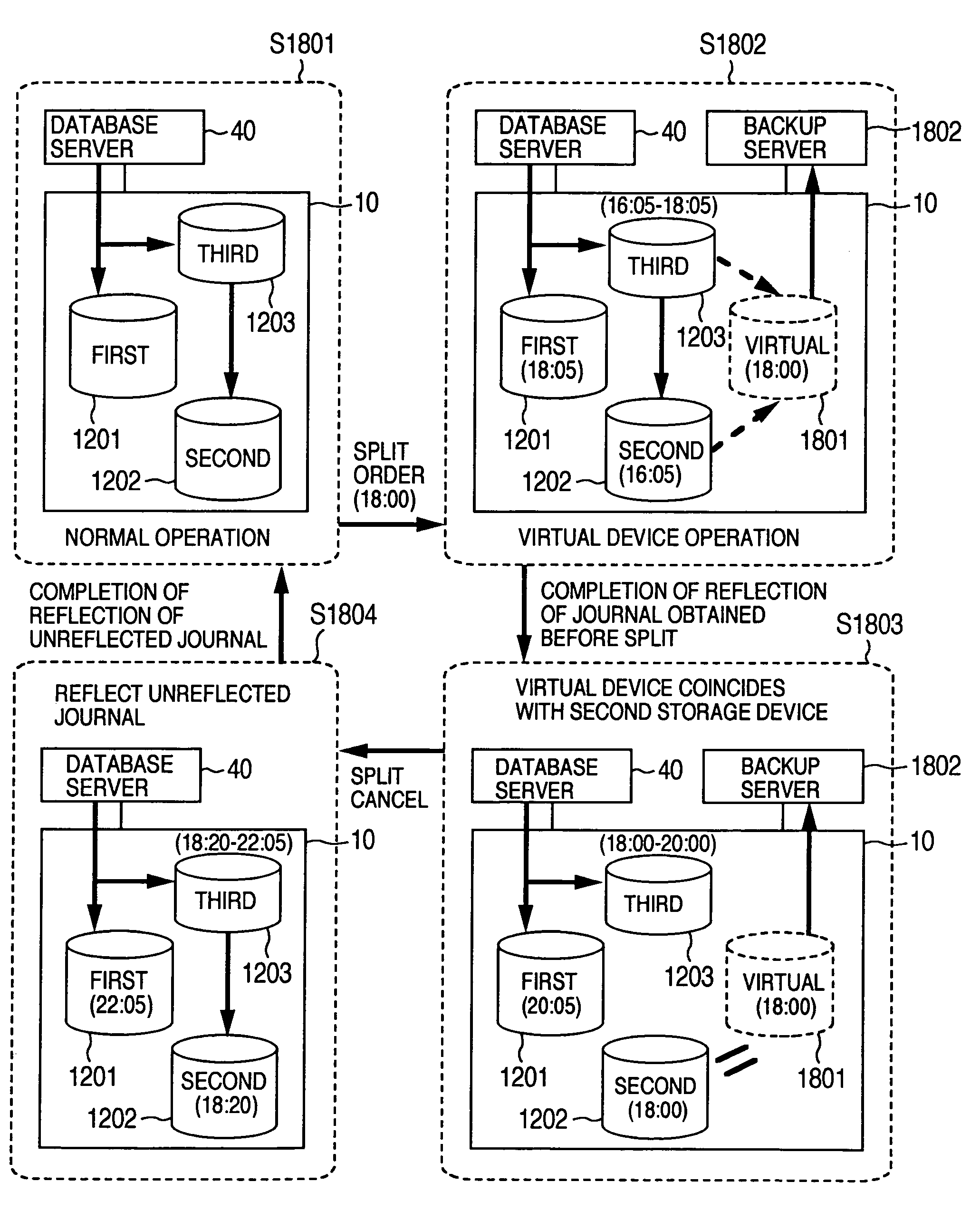

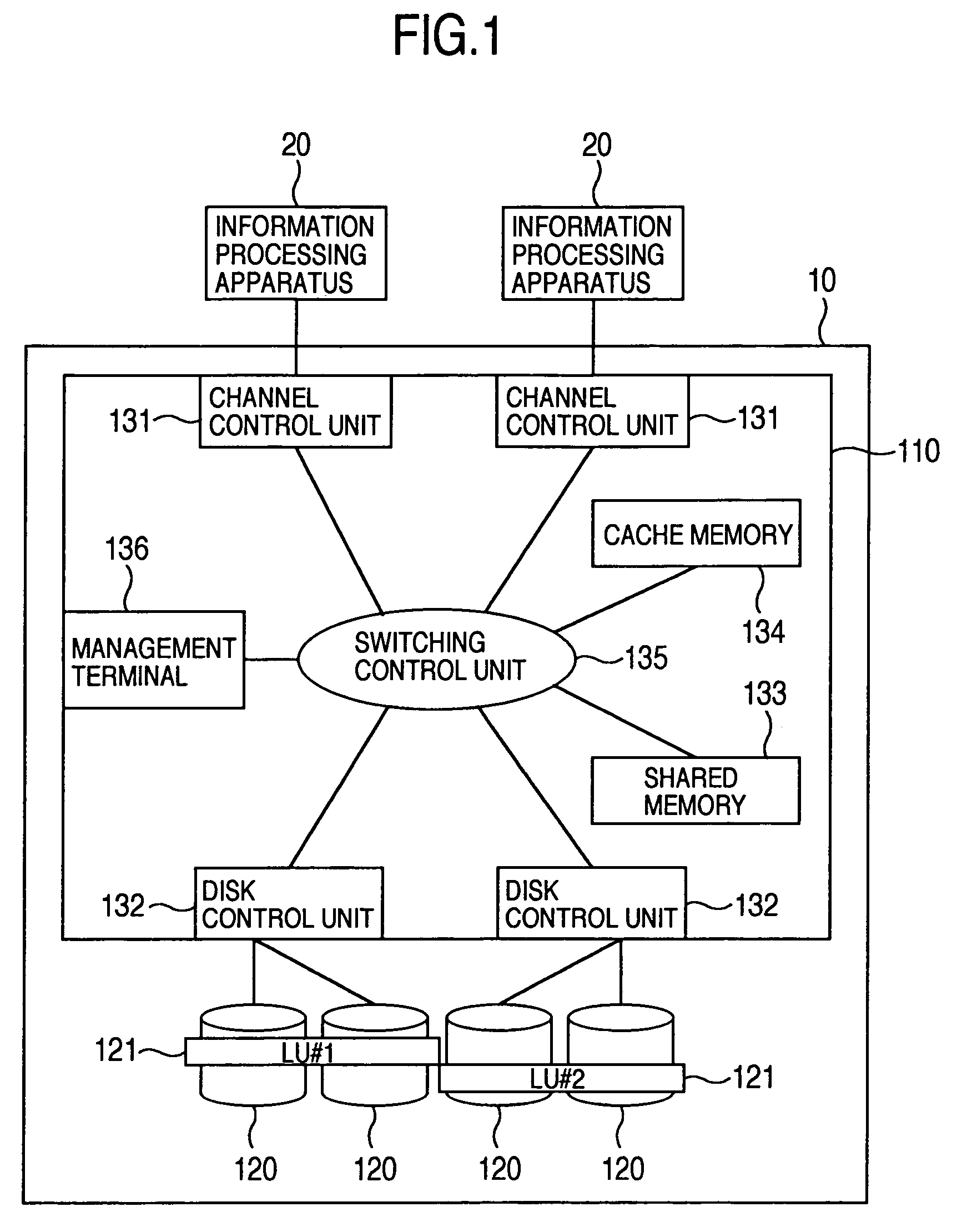

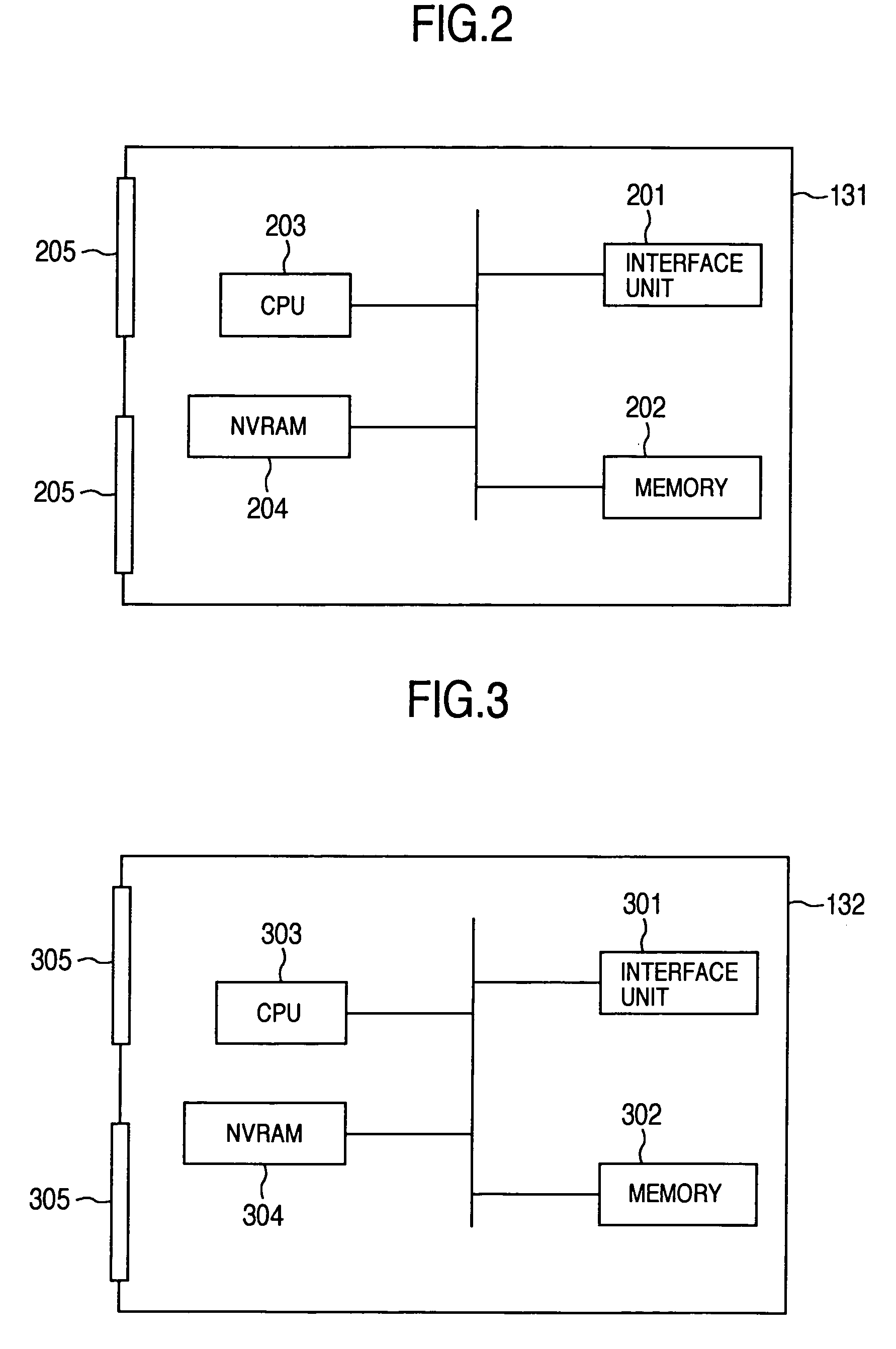

Disk array apparatus and disk array apparatus control method

InactiveUS7017003B2Reduce storage capacityPromote recoveryInput/output to record carriersMemory loss protectionRenewal timeDisk array

A journal write unit writes journal data into a third storage device. The journal data includes an identifier of a logical volume in a first storage device into which data has been written, information of a location in which the data is stored in the logical volume, update time which is current time acquired from a timing mechanism, and the data. A second write unit refers to update time of the journal data stored in the third storage device, selects journal data for which a difference between current time acquired from the timing mechanism and the update time is longer than a detection time stored in the third storage device, and writes the data into a place indicated by the location information, in a logical volume in the second storage device in the order of update time in the selected journal data.

Owner:HITACHI LTD

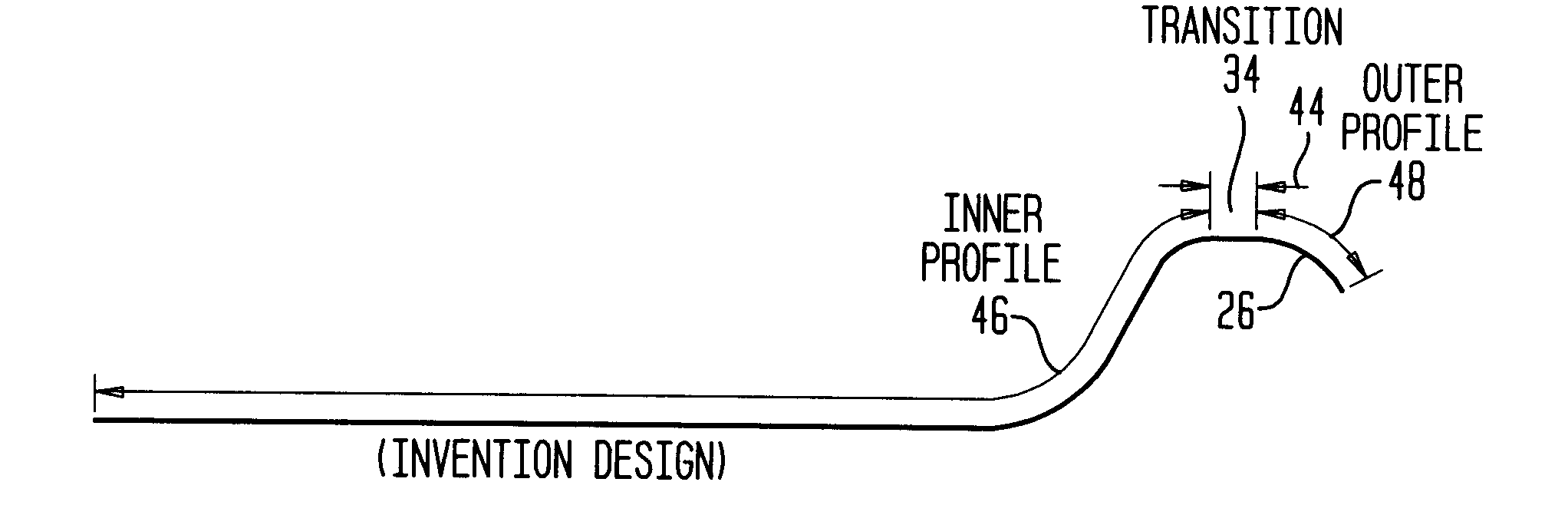

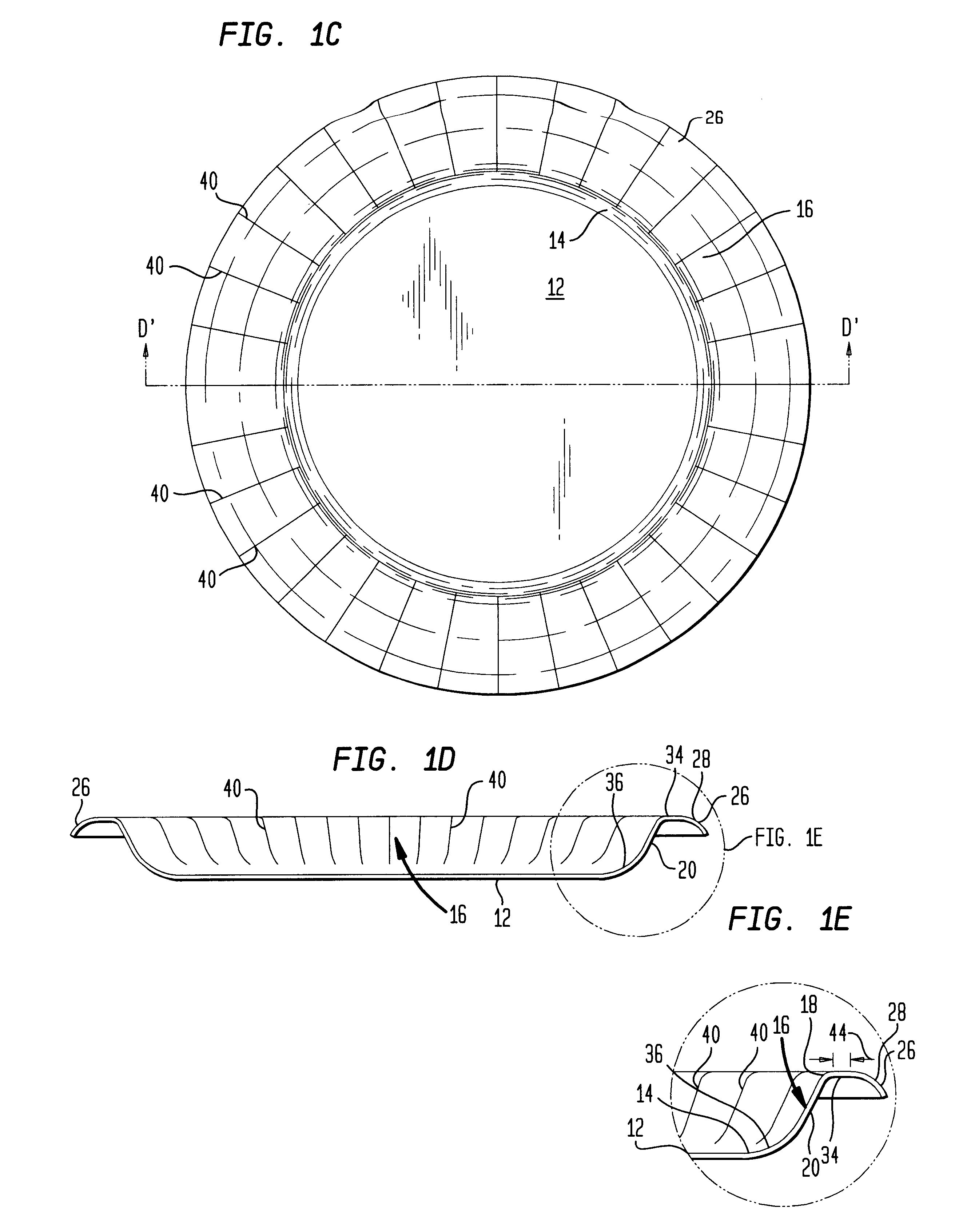

Disposable food container with a linear sidewall profile and an arcuate outer flange

InactiveUS6715630B2Good physical propertiesLose weightEnvelopes/bags making machinerySpecial paperEngineeringUltimate tensile strength

The present invention is directed to rigid disposable food containers provided with a relatively steep sidewall with a generally linear profile and an outwardly flared arcuate flange portion. The containers are further characterized by a flange outer vertical drop wherein the ratio of the length of the vertical drop to the characteristic diameter of the container is greater than about 0.01. By virtue of unique geometry, the containers of the invention exhibit improved rigidity and / or rim stiffness yet have favorable runnability in pressware manufacturing systems characteristic of plates of lower strength.

Owner:GPCP IP HLDG LLC

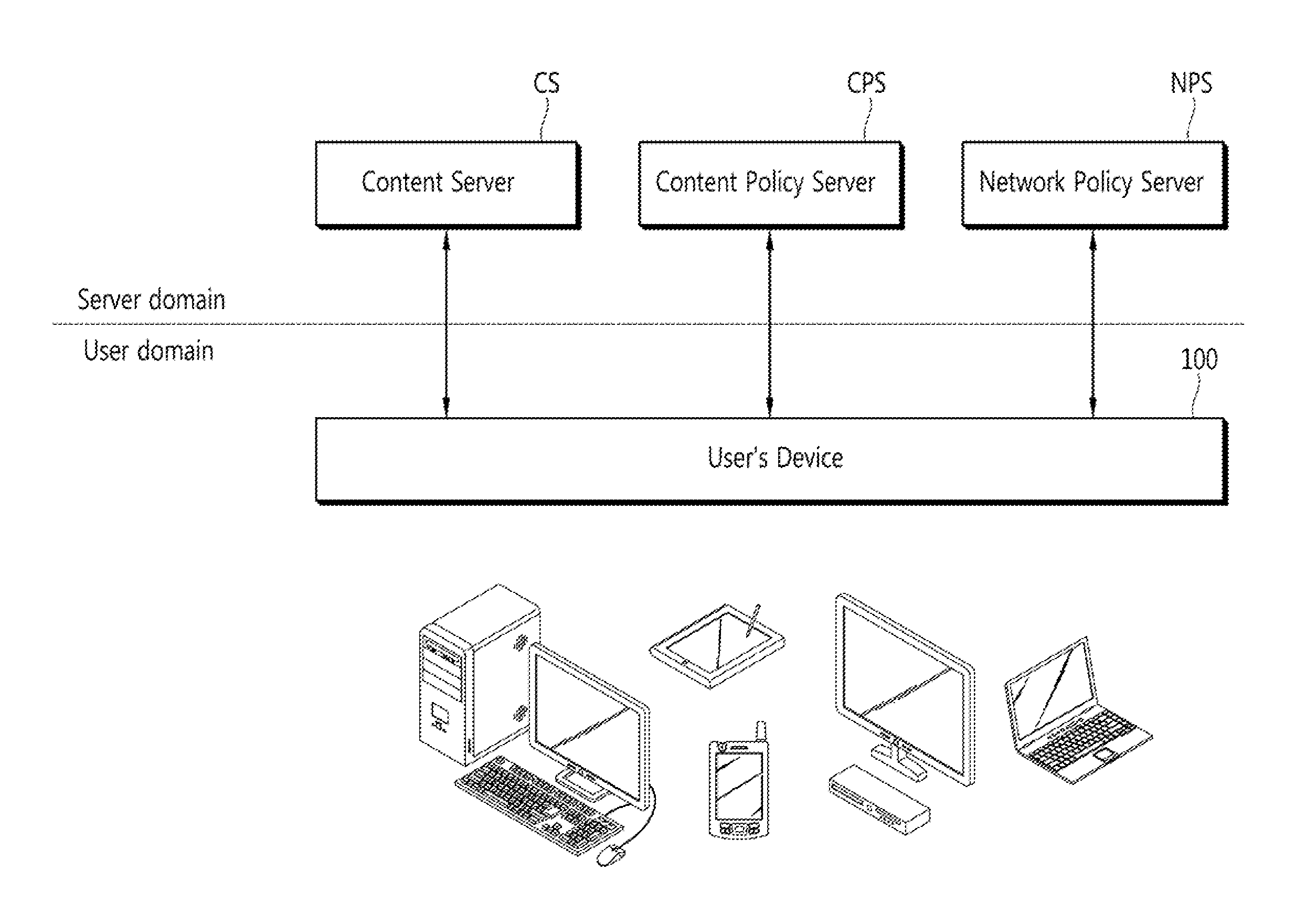

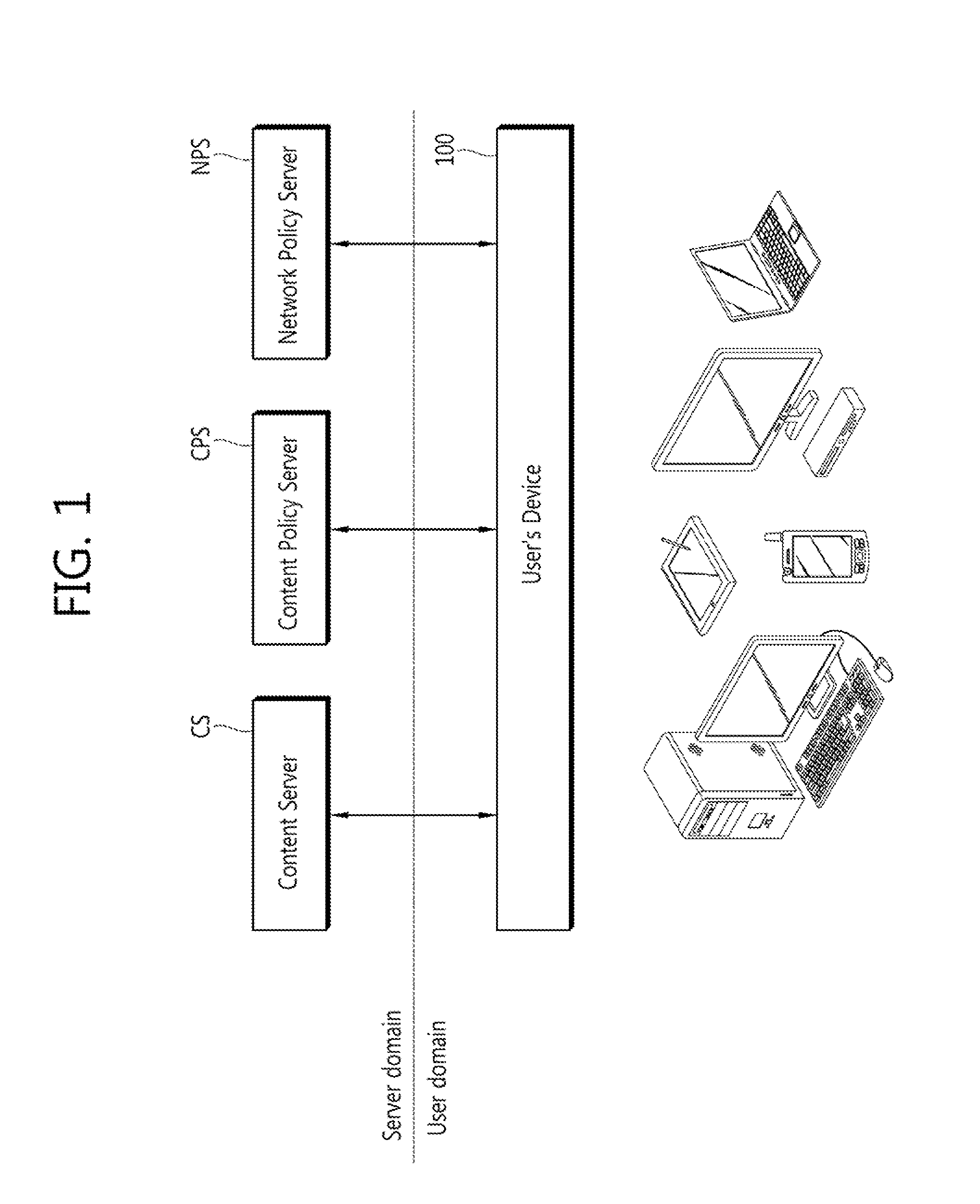

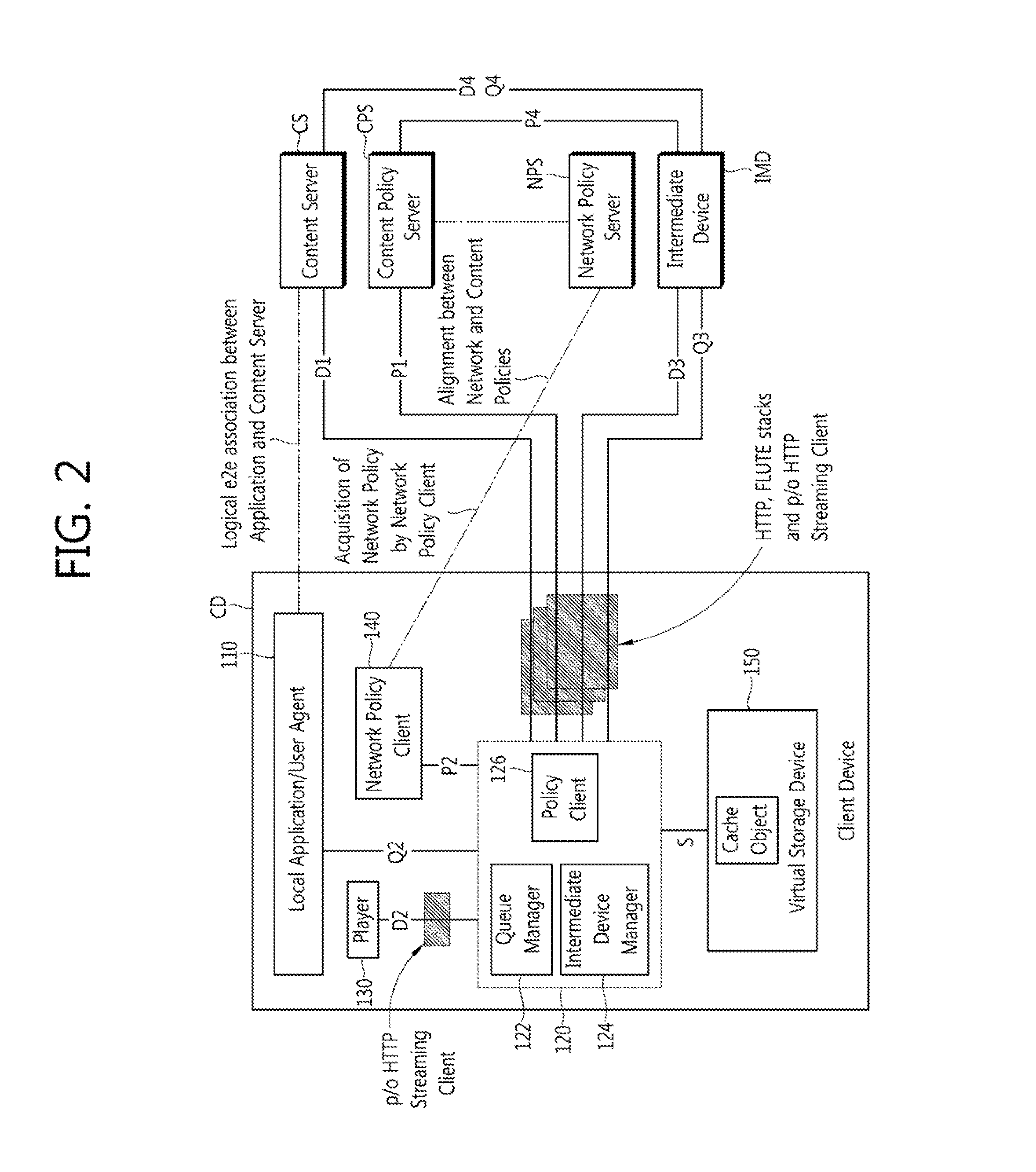

Method and apparatus for downloading content using NFC

ActiveUS20150133049A1Reduction procedureReduced resourceNear-field transmissionMobile application execution environmentsNetwork-attached storageSmart device

Disclosed are a method and apparatus for downloading content using NFC. The content-downloading method of the present invention is performed by a first device, and comprises the steps of: transmitting a content-downloading request for requesting a download of content using a second device; receiving a confirmation to the content-downloading request from the device which has received the content-downloading request; receiving a wake-up request from the second device; and receiving, from the second device, the content downloaded to the second device in response to the content-downloading request. Accordingly, a user may support a download reservation and transmission by simply placing NFC-supporting devices in contact, support a queue download request and list management using NFC between network attached storage (NAS) and a smart device, and support a queue request and caching using a home network after establishing an NFC link.

Owner:LG ELECTRONICS INC

Electric hybrid powertrain system

InactiveUS20070093341A1Improves reverse low gear performanceImprove drive performanceAuxillary drivesTransmission elementsElectric vehicleElectric generator

A hybrid electric vehicle powertrain having an engine and an electric motor and generator sub-system, which establish mechanical and electric power flow paths. Multiple-ratio gearing in a power flow path for forward drive enhances vehicle traction torque for heavy-duty vehicle applications. Reverse drive performance is enhanced by torque multiplying gearing in a reverse drive power delivery path.

Owner:FORD GLOBAL TECH LLC

Tcp/ip processor and engine using rdma

InactiveUS20080253395A1Sharply reduces TCP/IP protocol stack overheadImprove performanceDigital computer detailsTime-division multiplexInternal memoryTransmission protocol

A TCP / IP processor and data processing engines for use in the TCP / IP processor is disclosed. The TCP / IP processor can transport data payloads of Internet Protocol (IP) data packets using an architecture that provides capabilities to transport and process Internet Protocol (IP) packets from Layer 2 through transport protocol layer and may also provide packet inspection through Layer 7. The engines may perform pass-through packet classification, policy processing and / or security processing enabling packet streaming through the architecture at nearly the full line rate. A scheduler schedules packets to packet processors for processing. An internal memory or local session database cache stores a TCP / IP session information database and may also store a storage information session database for a certain number of active sessions. The session information that is not in the internal memory is stored and retrieved to / from an additional memory. An application running on an initiator or target can in certain instantiations register a region of memory, which is made available to its peer(s) for access directly without substantial host intervention through RDMA data transfer.

Owner:MEMORY ACCESS TECH LLC

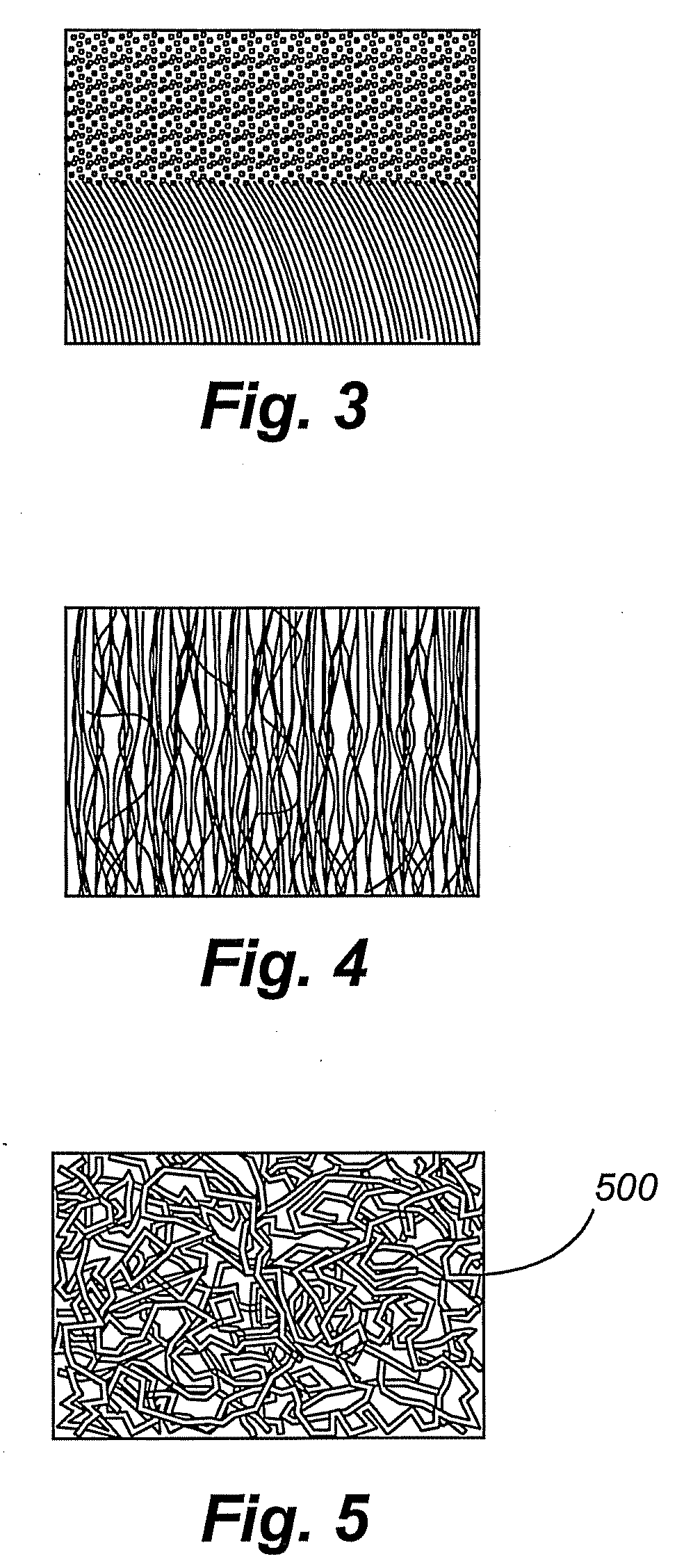

Carbon nanotube containing materials and articles containing such materials for altering electromagnetic radiation

InactiveUS20050272856A1Reduce performanceImprove performanceMaterial nanotechnologyMagnetic/electric field screeningCarbon nanotubeElectromagnetic radiation

Disclosed herein is a material for altering electromagnetic radiation incident on the material. The material disclosed herein comprises carbon nanotubes having a length (L) that meets the following formula (1): L≧½λ (1) where λ is the wavelength of the electromagnetic radiation incident on the material. Also disclosed herein are methods of altering electromagnetic radiation, including mitigating, intensifying, or absorbing and re-transmitting electromagnetic radiation using the disclosed material.

Owner:MULTIPURE INT

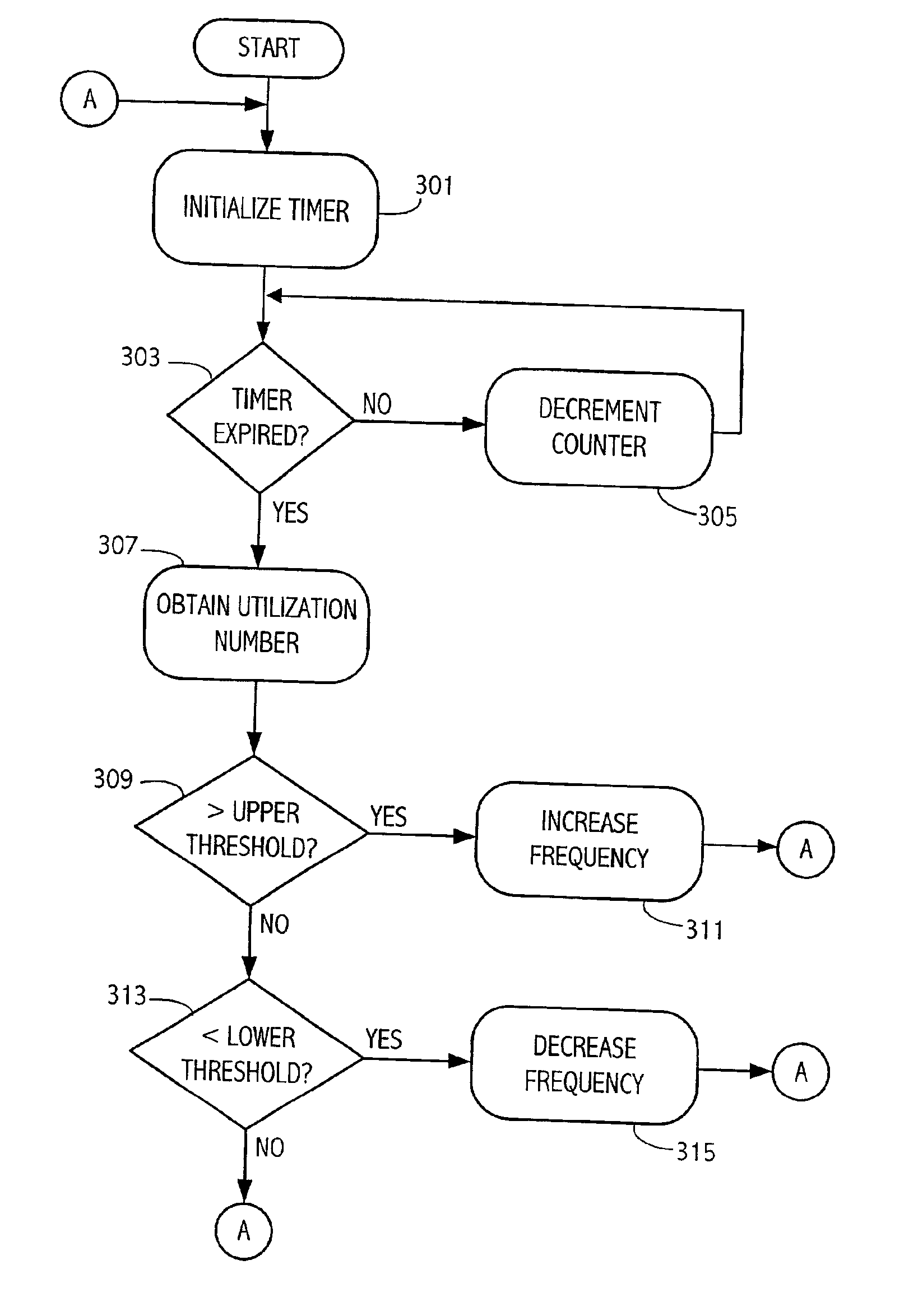

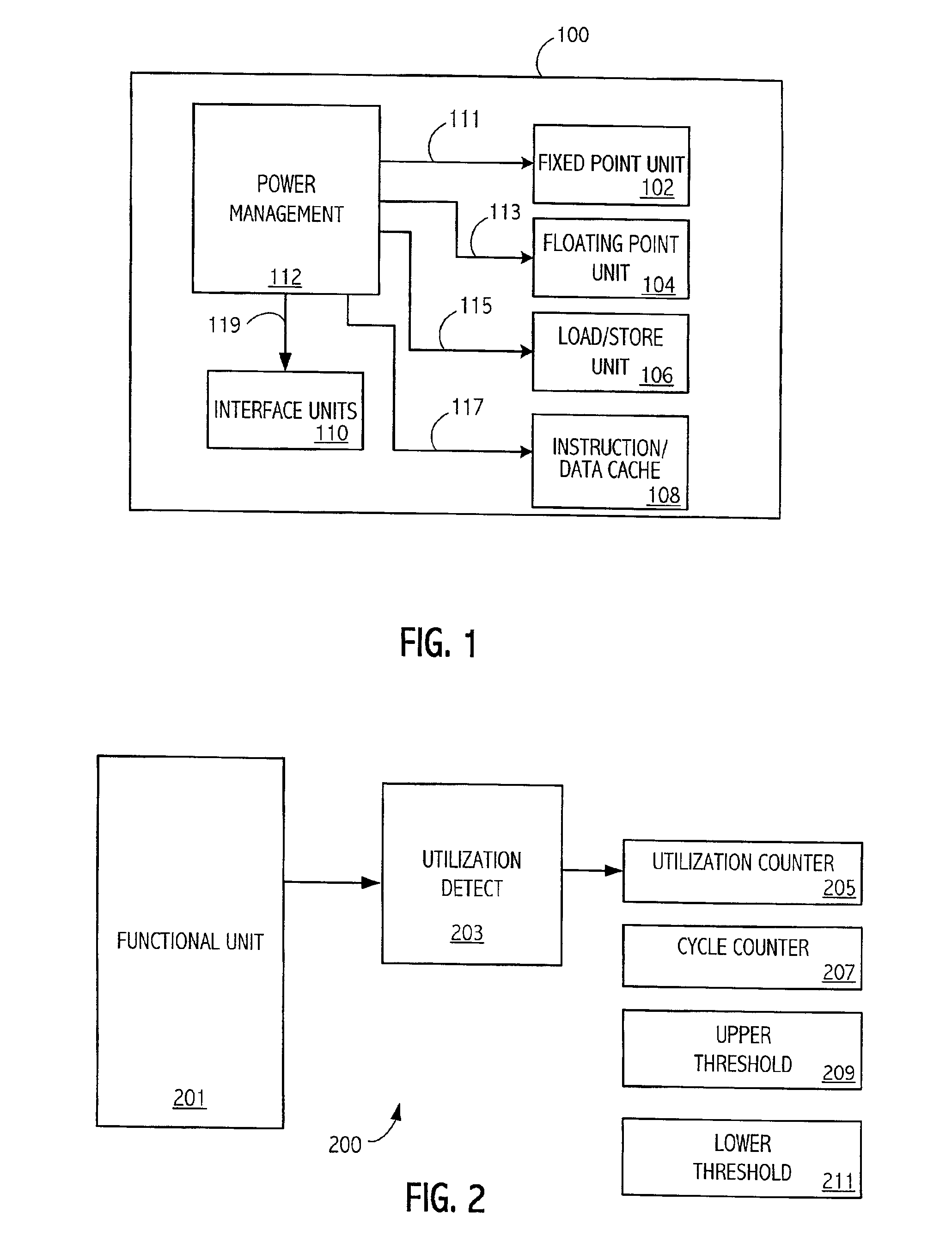

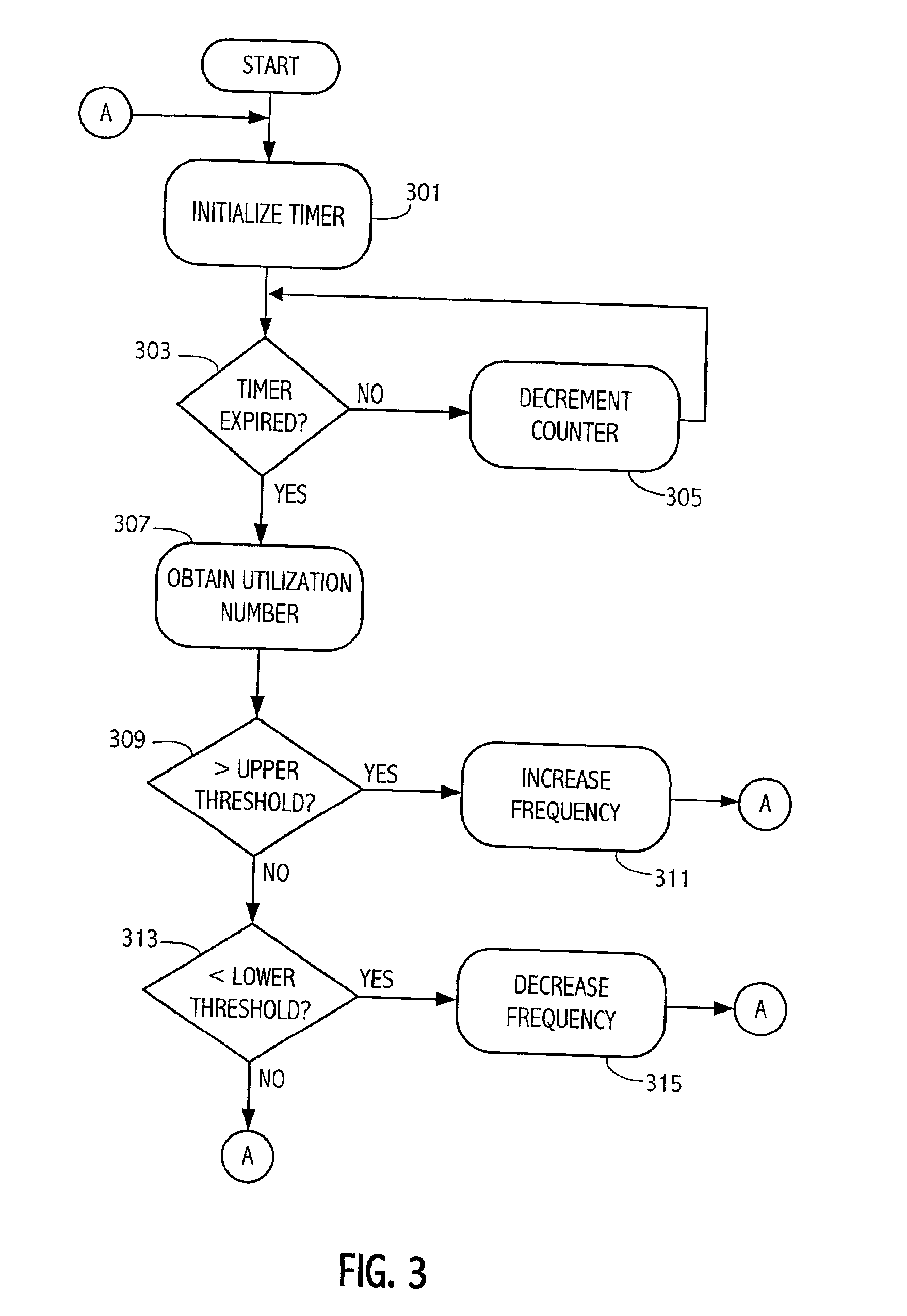

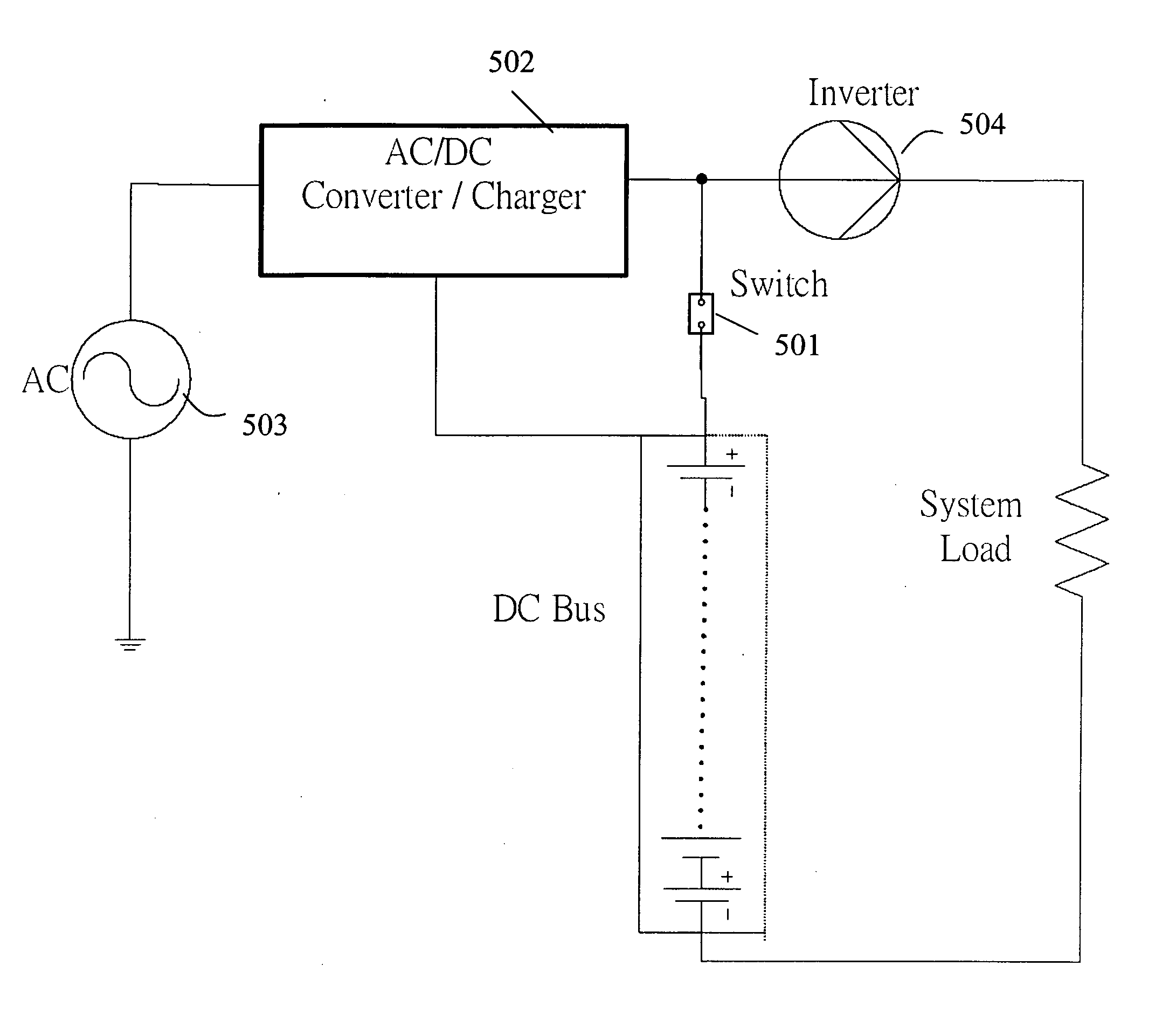

Performance and power optimization via block oriented performance measurement and control

InactiveUS6895520B1Improve the level ofIncrease power consumptionEnergy efficient ICTVolume/mass flow measurementEngineeringIntegrated circuit

An integrated circuit includes a plurality of functional blocks. Utilization information for the various functional blocks is generated. Based on that information, the power consumption and thus the performance levels of the functional blocks can be tuned. Thus, when a functional block is heavily loaded by an application, the performance level and thus power consumption of that particular functional block is increased. At the same time, other functional blocks that are not being heavily utilized and thus have lower performance requirements can be kept at a relatively low power consumption level. Thus, power consumption can be reduced overall without unduly impacting performance.

Owner:ADVANCED MICRO DEVICES INC

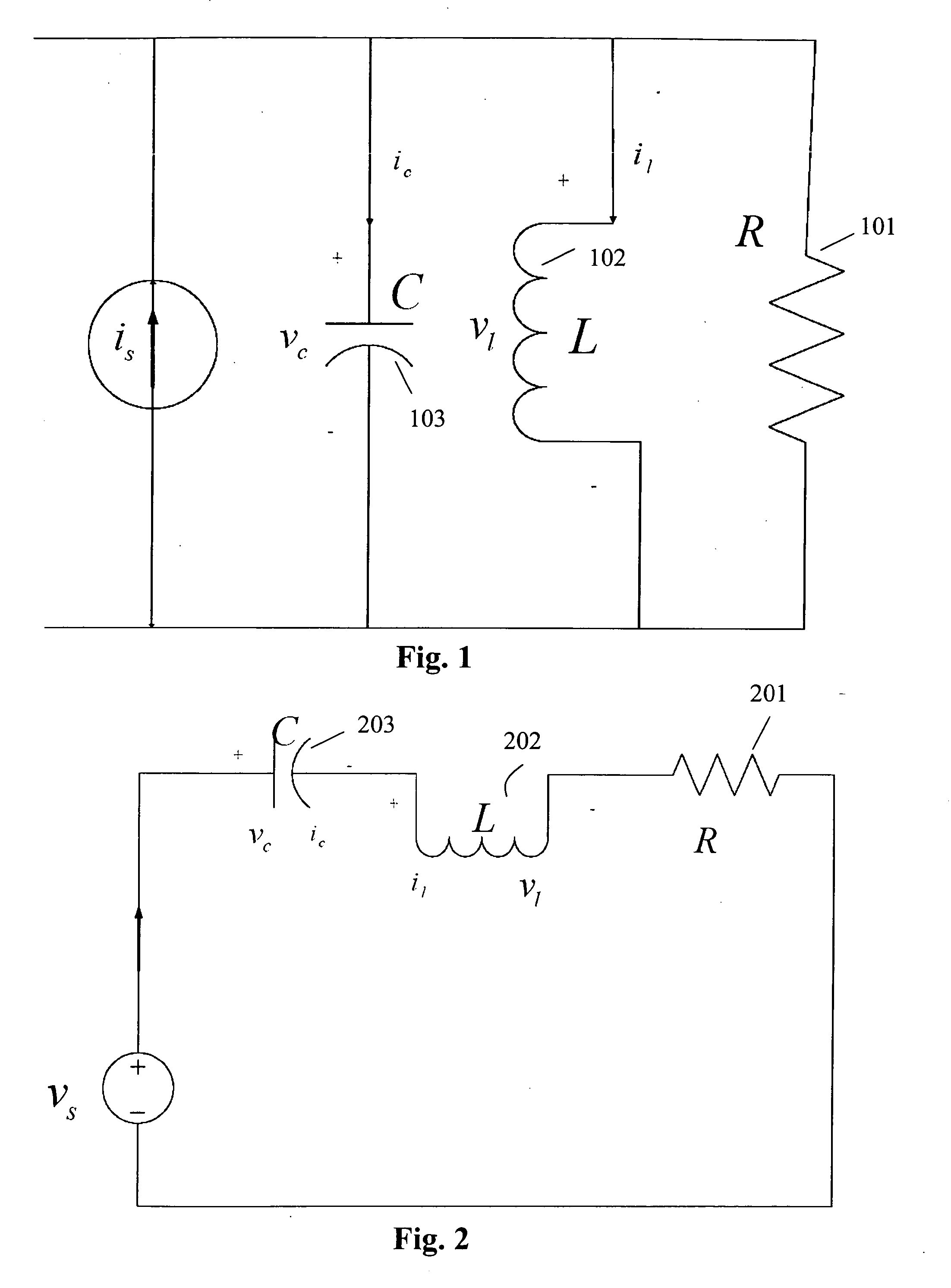

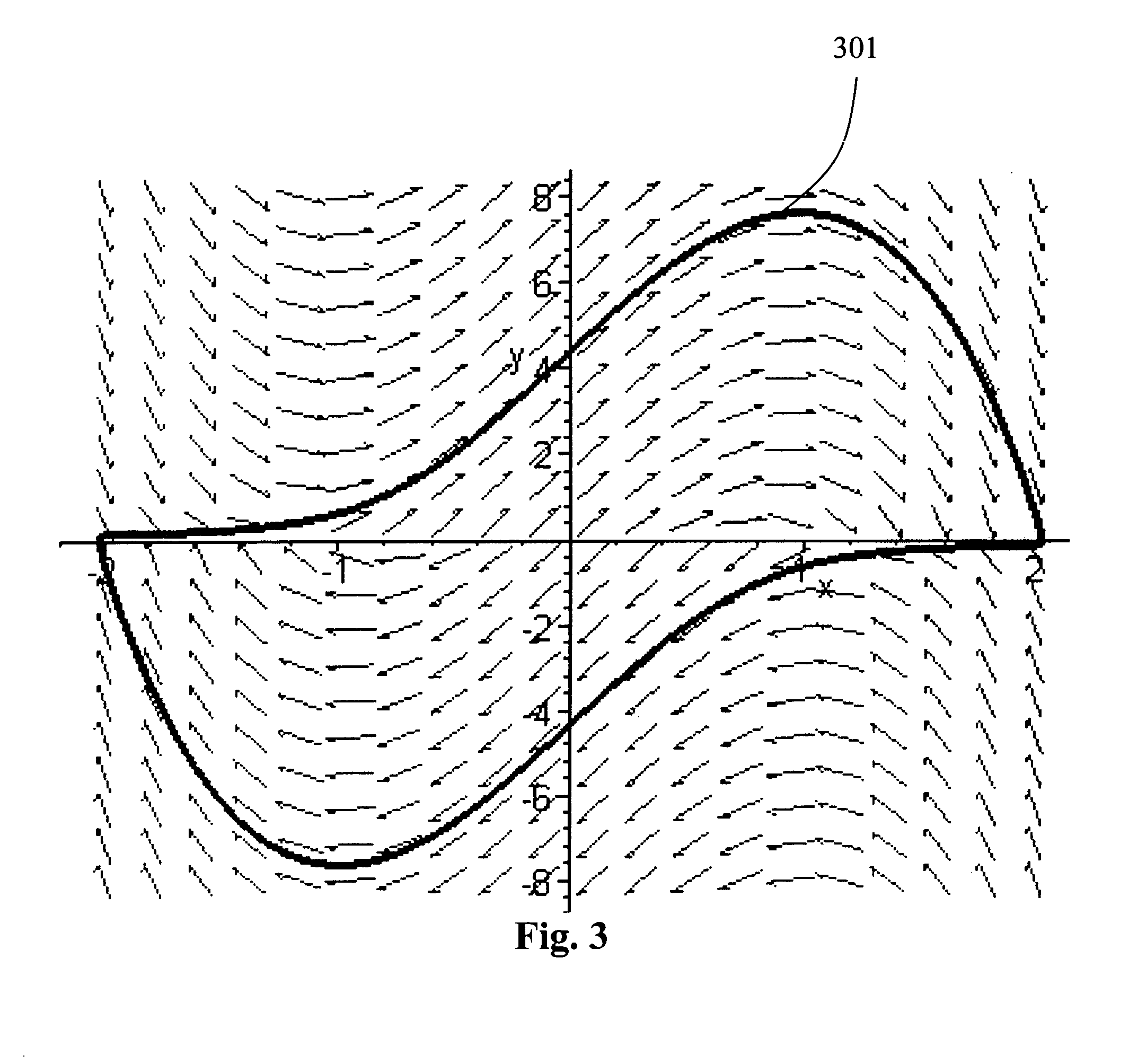

Spectral resistor, spectral capacitor, order-infinity resonant tank, EM wave absorbing material, and applications thereof

InactiveUS20070170910A1Improve power qualityReduce performanceOther resistor networksMultiple-port networksElectricityElectric power system

A spectral resistor based on the constitute law of “elasticity of electricity” derived from the Riemann-Lebesgue lemma is provided to build a substantial order-∞ resonant tank. The substantial order-∞ resonant tank according to embodiments of the present invention can function as many different roles such as an electric filter, a harmonic and sub-harmonic power waveform distortion filter, a dynamic damper, a dynamic impedance matching circuit and a kind of electromagnetic wave absorbing material. By attaching an order-∞ resonant tank according to the present invention to an ordinary system with equivalent inductance in a suitable topology as an electric filter, a substantial snubber network, or so-called DeLenzor, is obtained. The duality of an electric system can be handled by coupling the system with an order-∞ resonant tank according to the present invention, and thus the disadvantageous effects caused by the duality of the system can be canceled immediately without any drawbacks. Furthermore, the reactive (or so-called regenerated) power caused by the duality of the electric system can be recycled according to embodiments of the present invention.

Owner:CHANG MING HOO +3

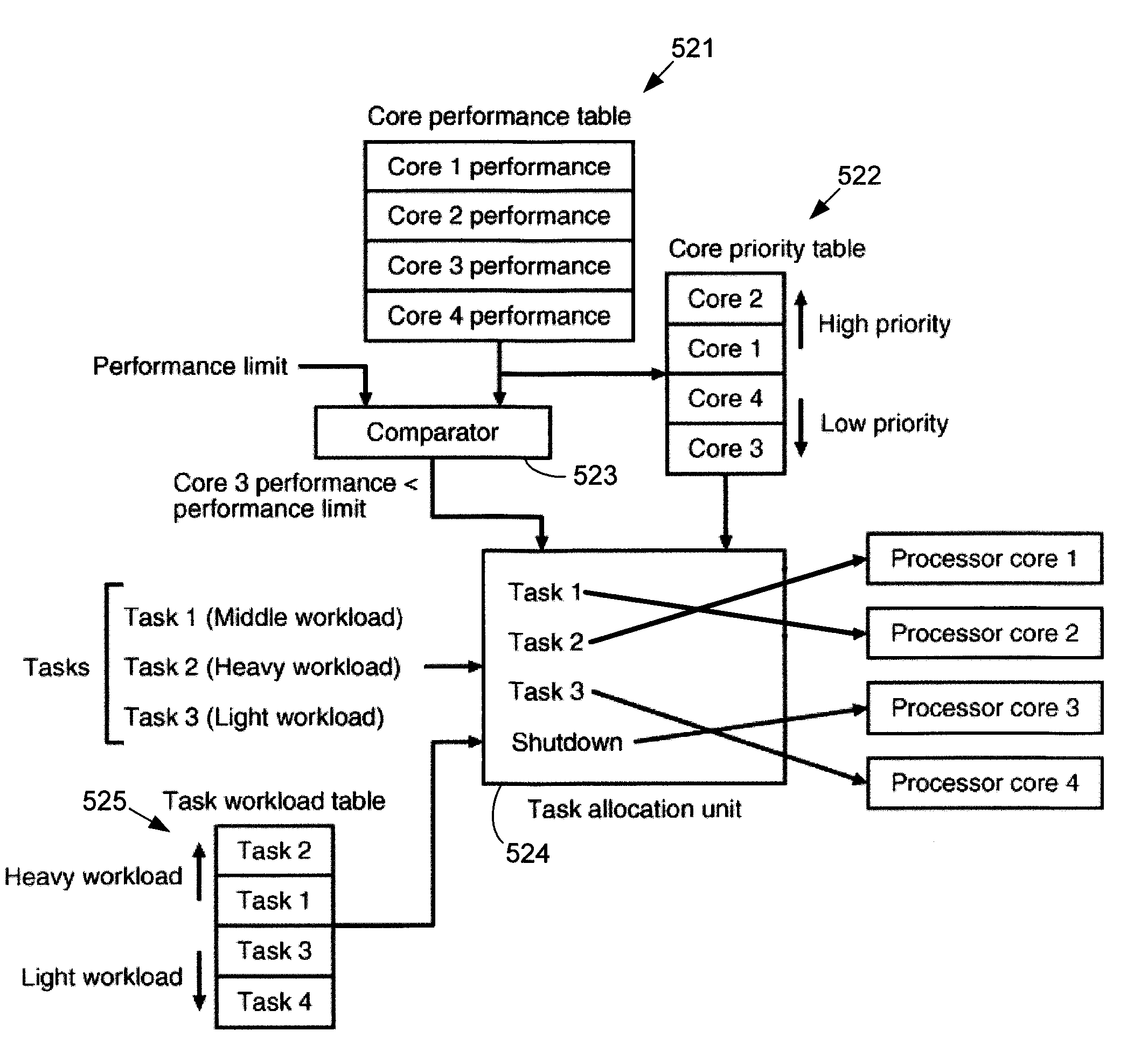

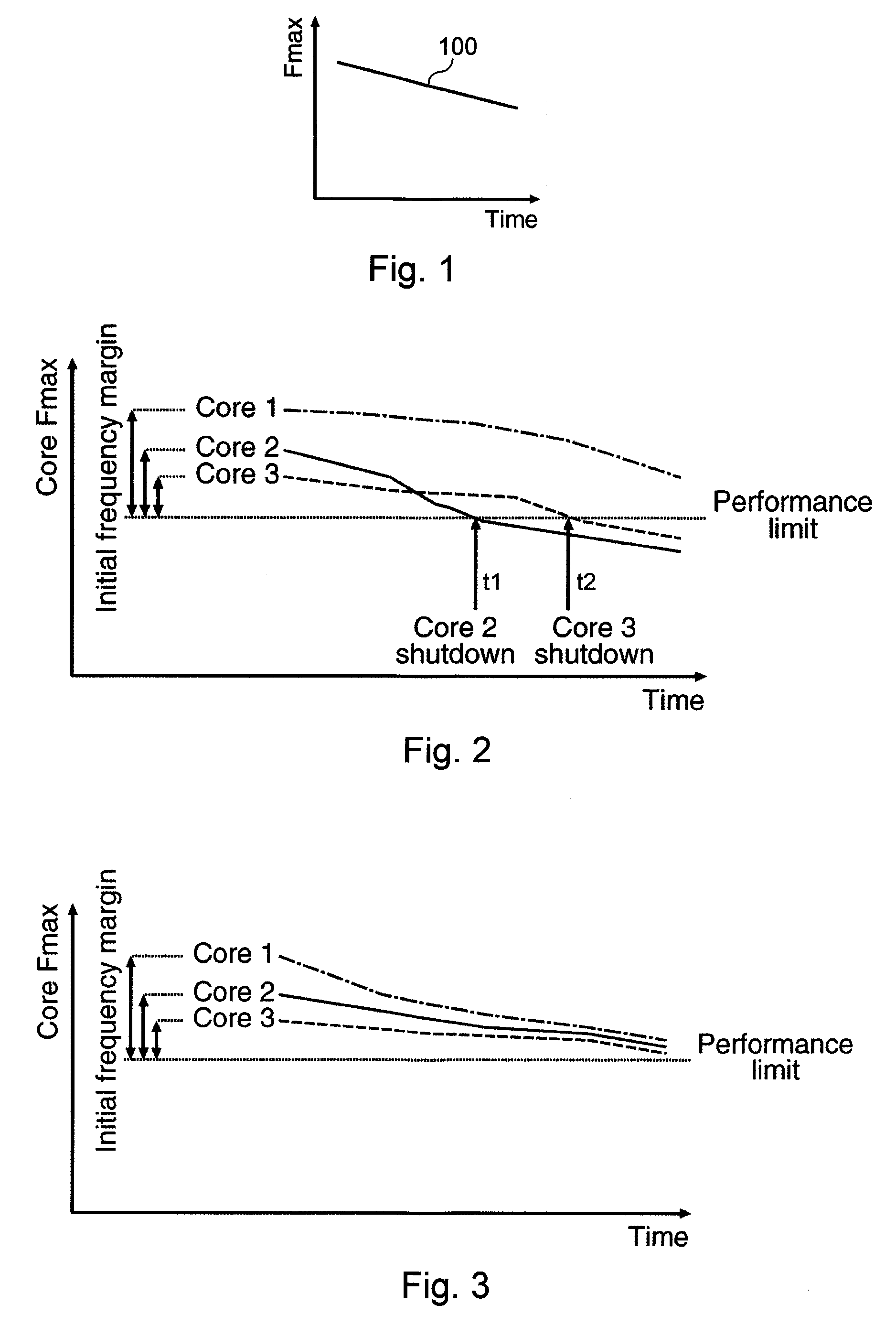

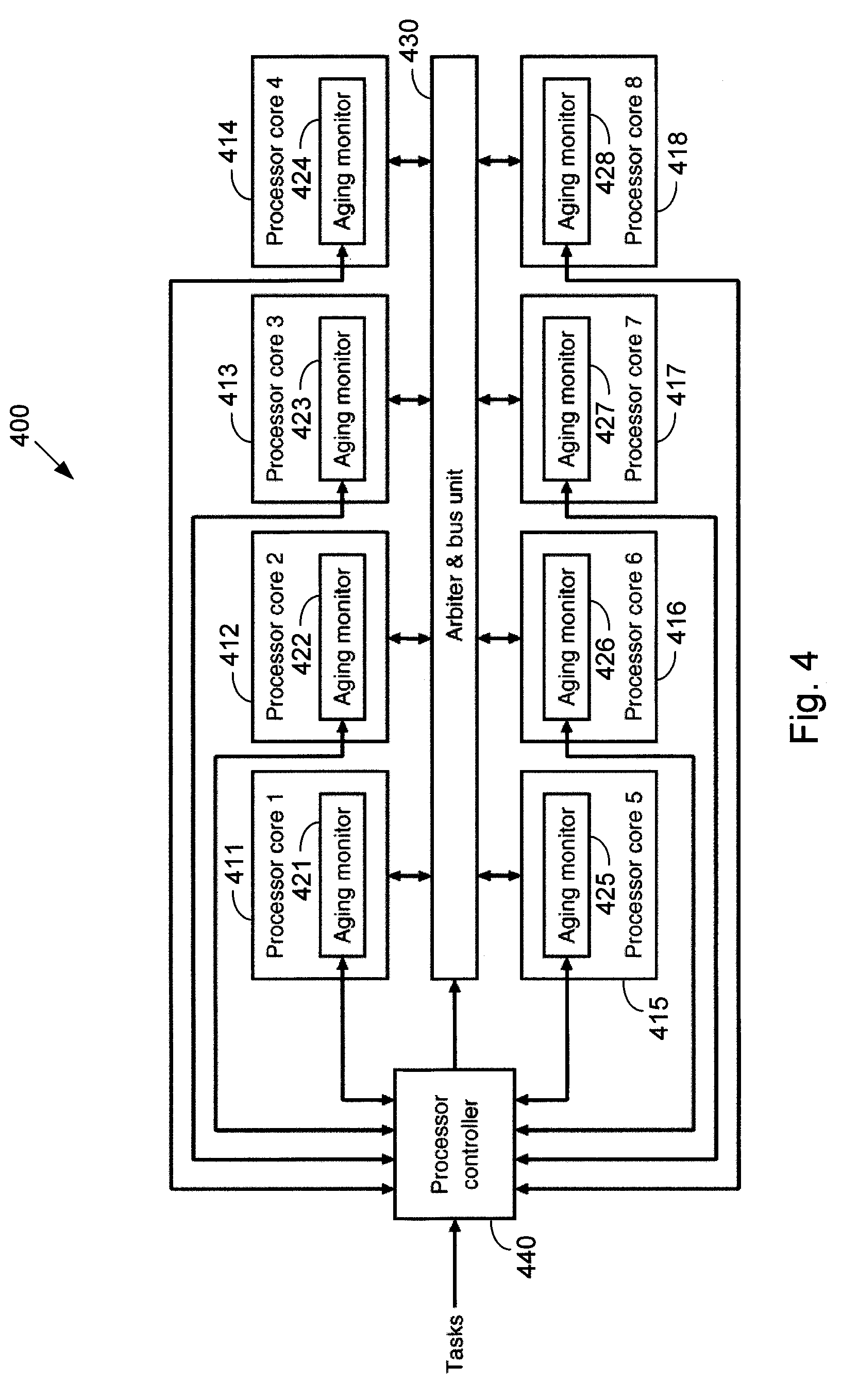

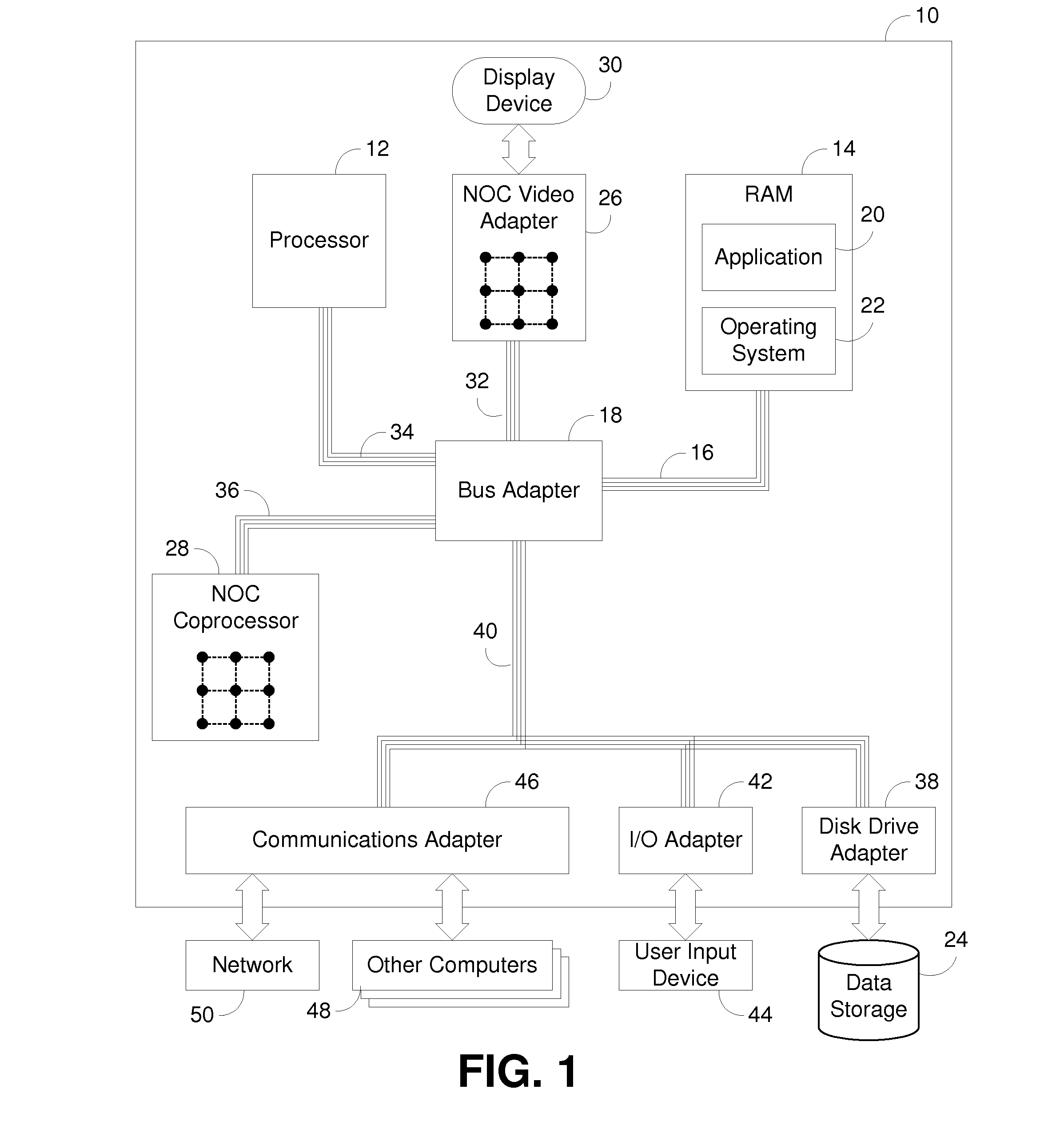

Systems and Methods for Improving the Reliability of a Multi-Core Processor

InactiveUS20090288092A1Improve reliabilityDelay agingResource allocationMemory systemsMulti processorBelow threshold level

Systems and methods for improving the reliability of multiprocessors by reducing the aging of processor cores that have lower performance. One embodiment comprises a method implemented in a multiprocessor system having a plurality of processor cores. The method includes determining performance levels for each of the processor cores and determining an allocation of the tasks to the processor cores that substantially minimizes aging of a lowest-performing one of the operating processor cores. The allocation may be based on task priority, task weight, heat generated, or combinations of these factors. The method may also include identifying processor cores whose performance levels are below a threshold level and shutting down these processor cores. If the number of processor cores that are still active is less than a threshold number, the multiprocessor system may be shut down, or a warning may be provided to a user.

Owner:KK TOSHIBA

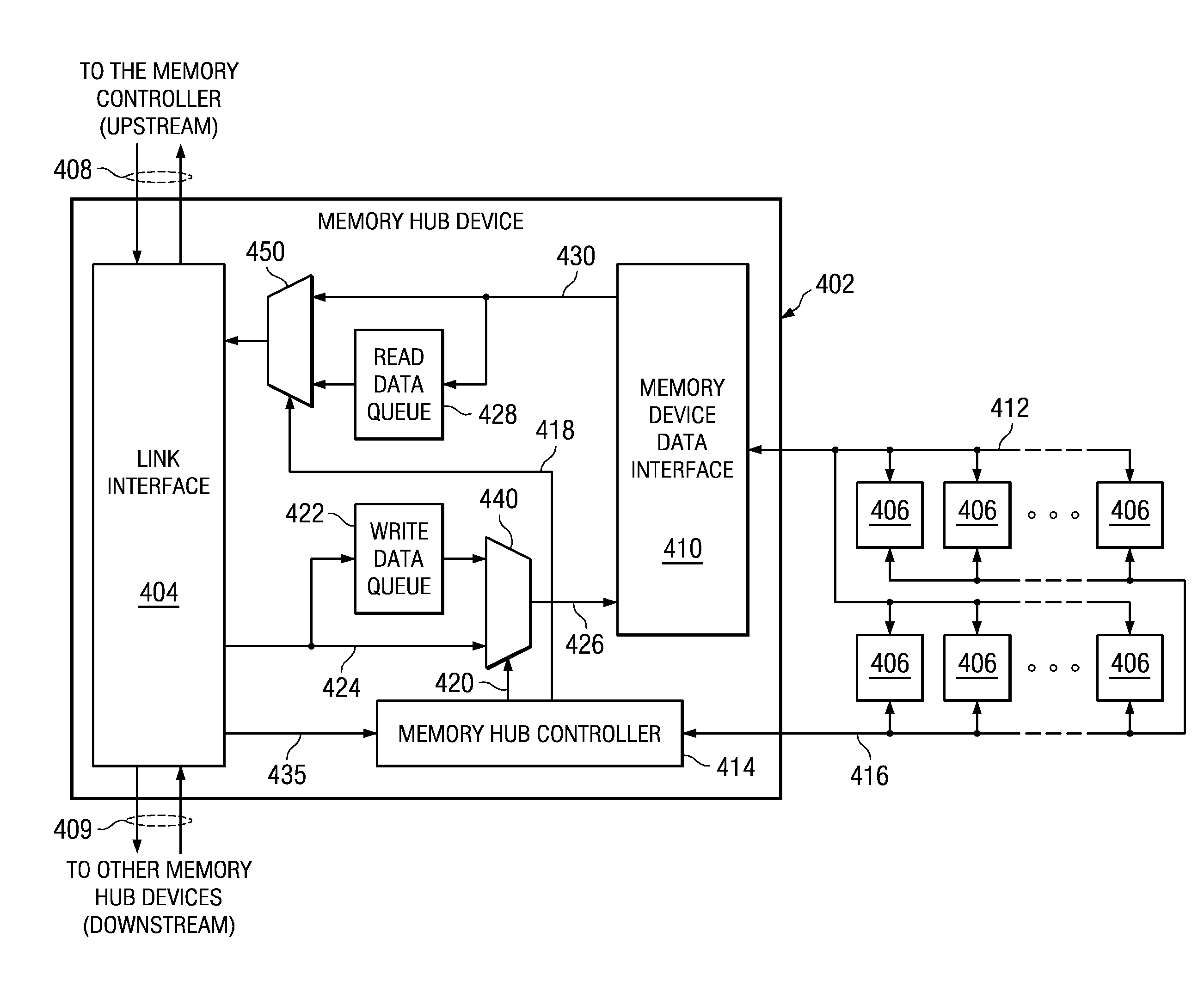

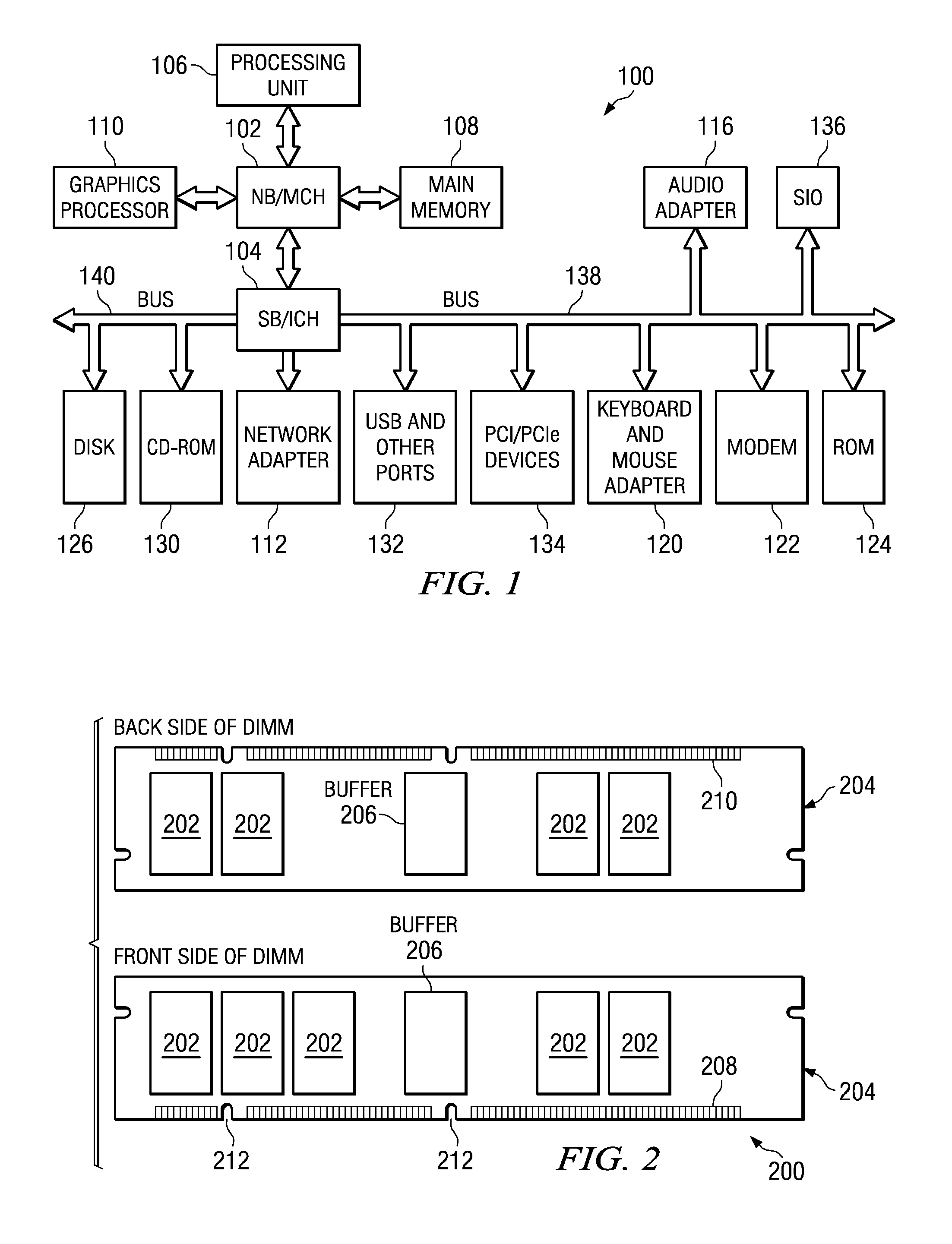

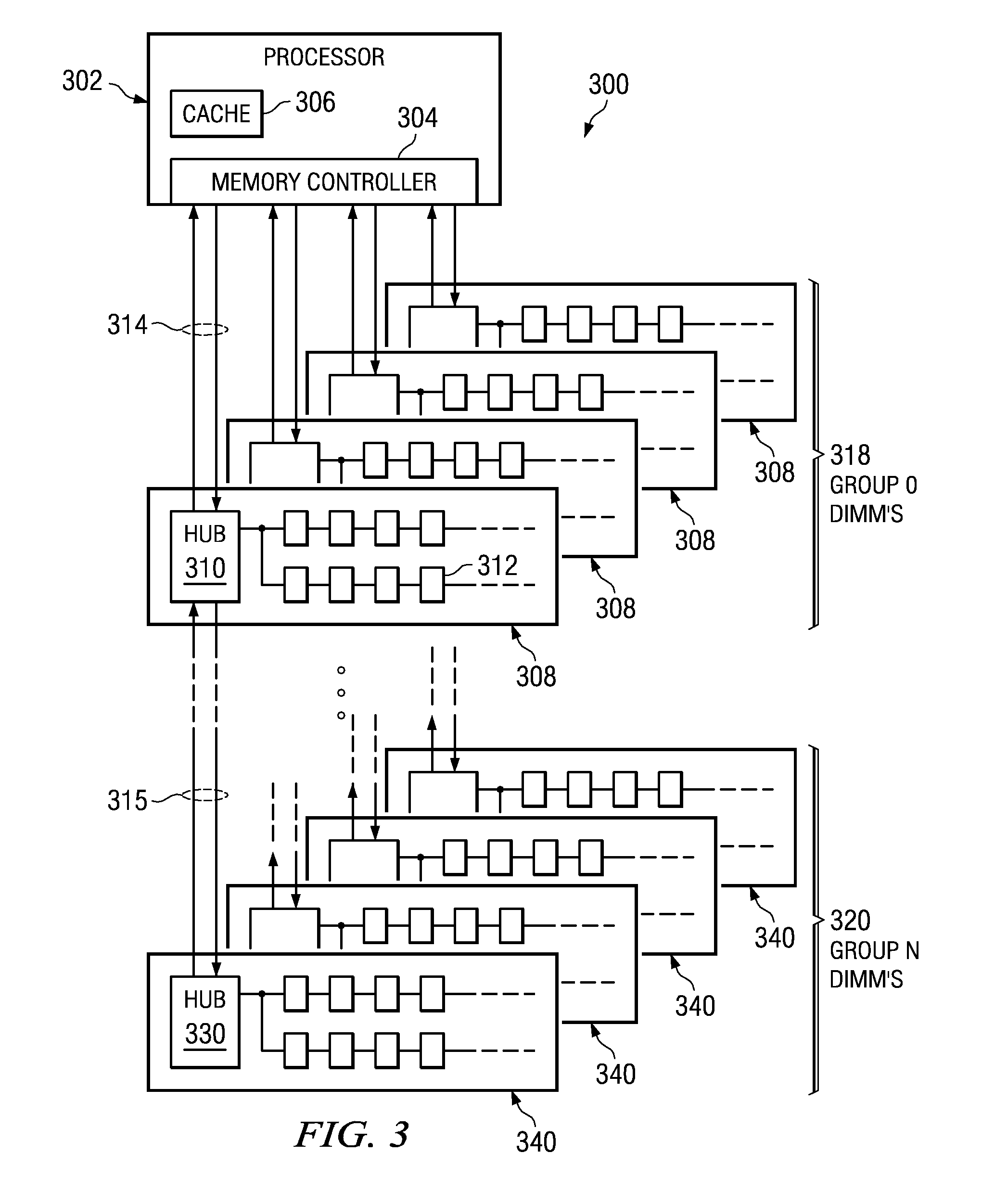

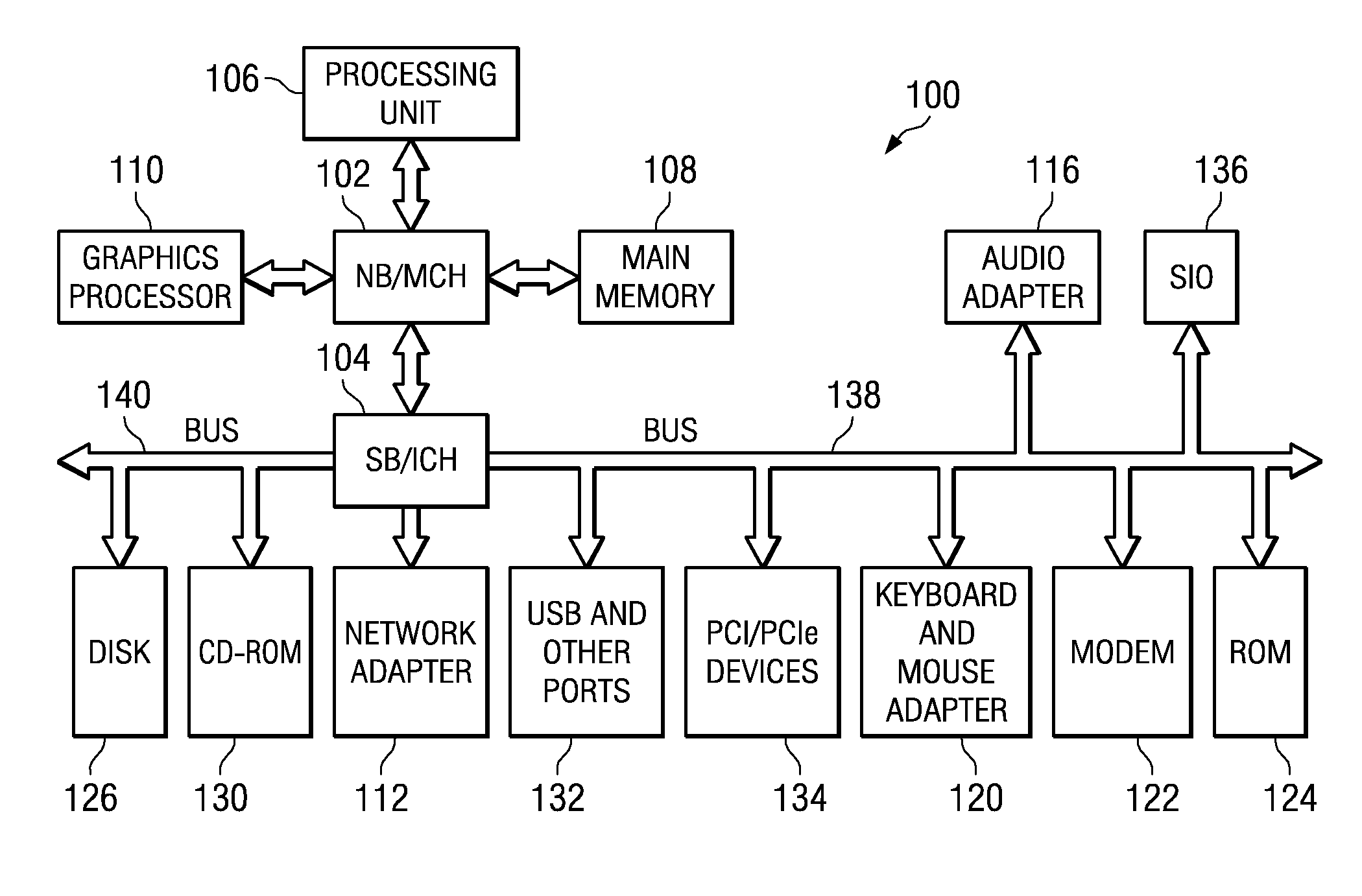

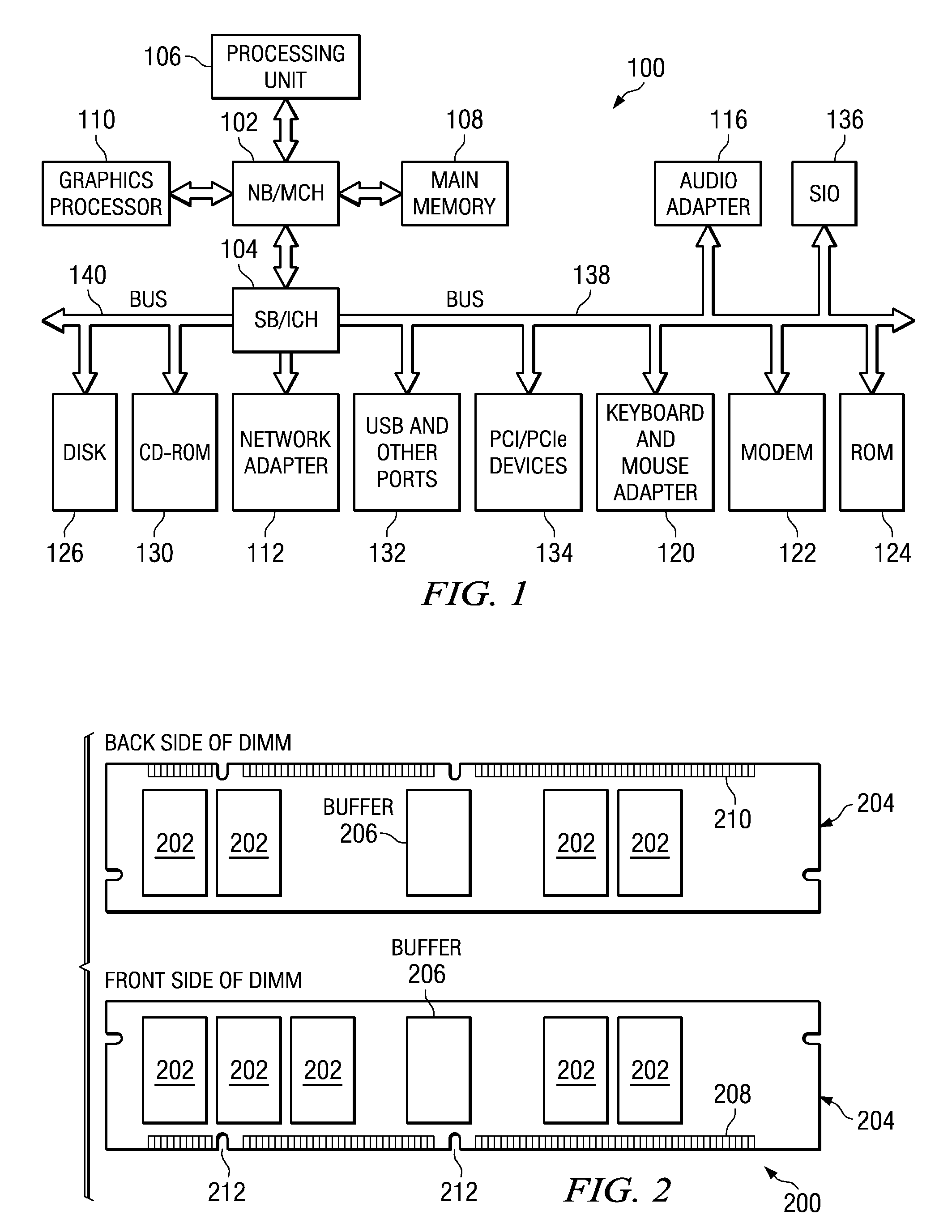

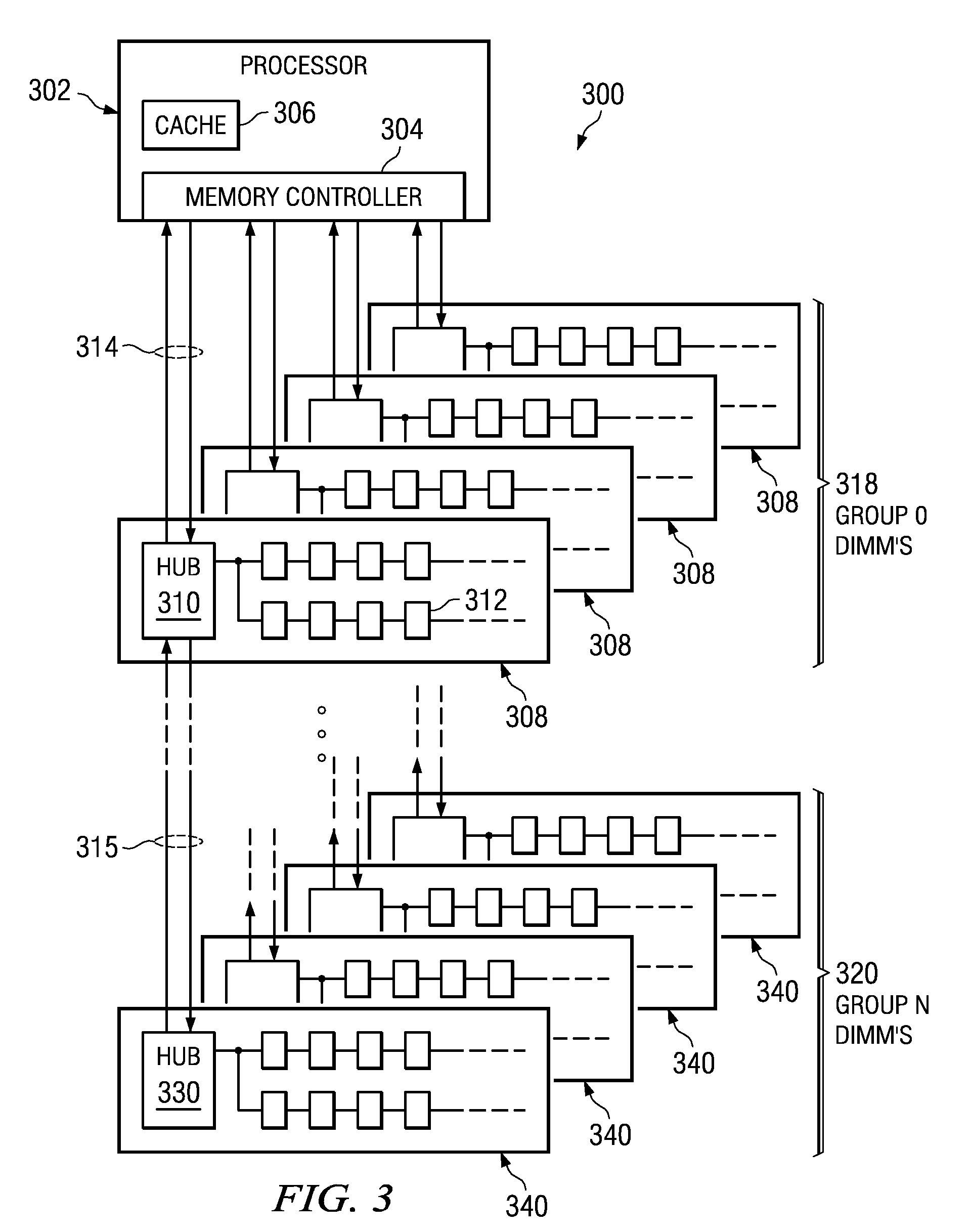

System to Increase the Overall Bandwidth of a Memory Channel By Allowing the Memory Channel to Operate at a Frequency Independent from a Memory Device Frequency

InactiveUS20090193201A1High bandwidthReduce operating frequencyDigital data processing detailsMemory systemsExternal storageMemory controller

A memory system is provided that increases the overall bandwidth of a memory channel by operating the memory channel at a independent frequency. The memory system comprises a memory hub device integrated in a memory module. The memory hub device comprises a command queue that receives a memory access command from an external memory controller via a memory channel at a first operating frequency. The memory system also comprises a memory hub controller integrated in the memory hub device. The memory hub controller reads the memory access command from the command queue at a second operating frequency. By receiving the memory access command at the first operating frequency and reading the memory access command at the second operating frequency an asynchronous boundary is implemented. Using the asynchronous boundary, the memory channel operates at a maximum designed operating bandwidth, which is independent of the second operating frequency.

Owner:IBM CORP

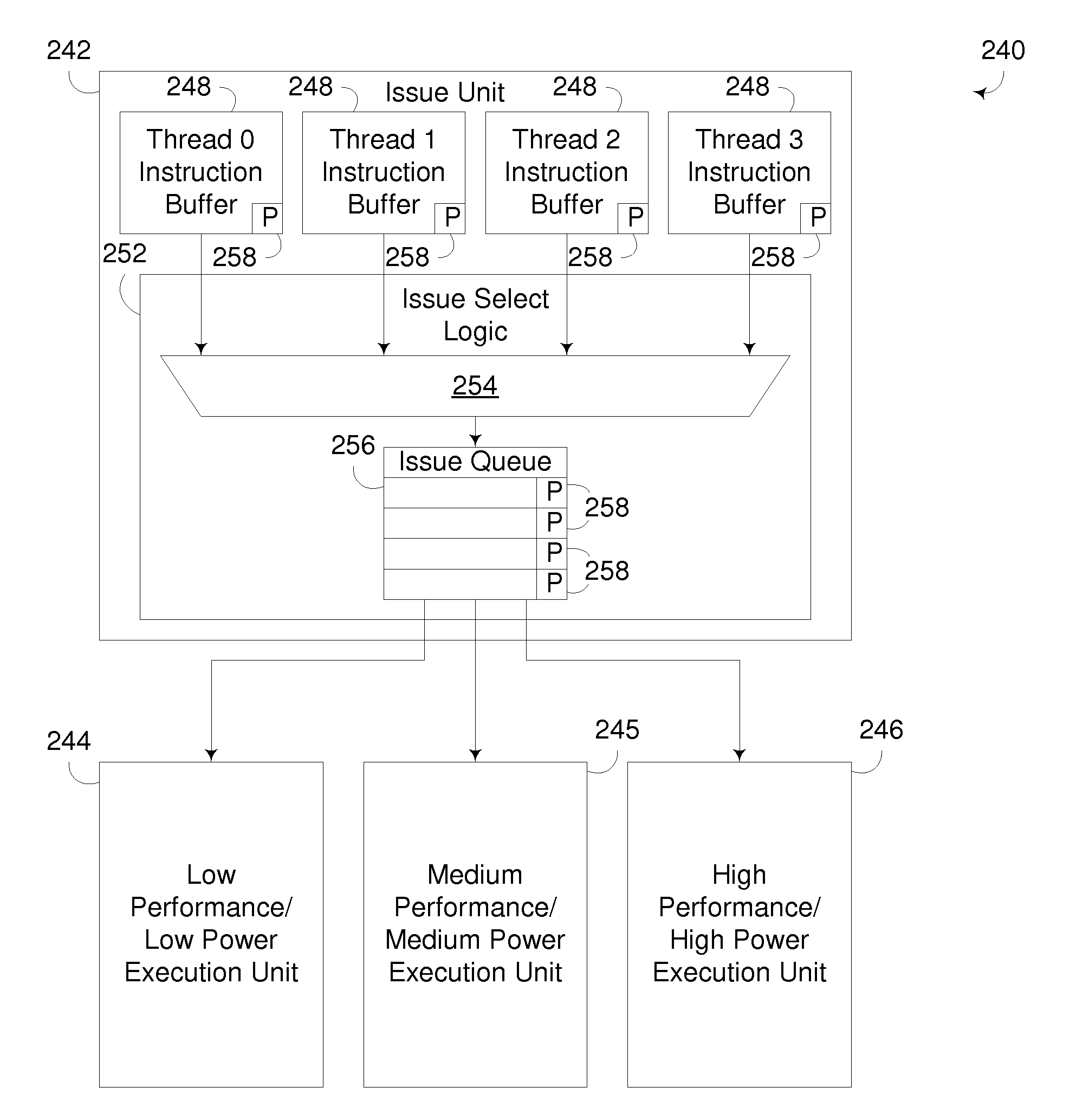

Structural Power Reduction in Multithreaded Processor

InactiveUS20090293061A1Improve performancePerformance maximizationEnergy efficient ICTVolume/mass flow measurementParallel computingExecution unit

A circuit arrangement and method utilize a plurality of execution units having different power and performance characteristics and capabilities within a multithreaded processor core, and selectively route instructions having different performance requirements to different execution units based upon those performance requirements. As such, instructions that have high performance requirements, such as instructions associated with primary tasks or time sensitive tasks, can be routed to a higher performance execution unit to maximize performance when executing those instructions, while instructions that have low performance requirements, such as instructions associated with background tasks or non-time sensitive tasks, can be routed to a reduced power execution unit to reduce the power consumption (and associated heat generation) associated with executing those instructions.

Owner:IBM CORP

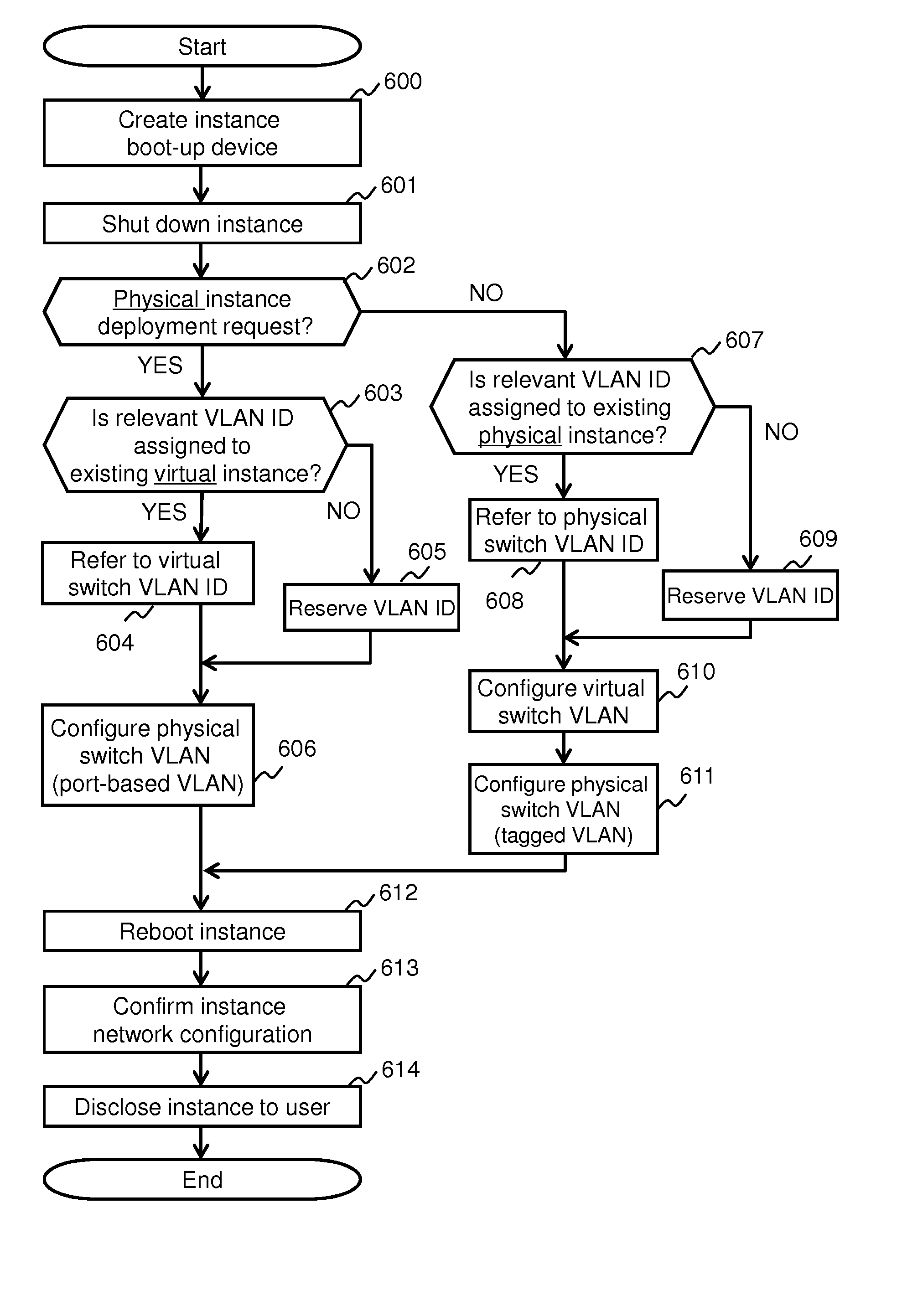

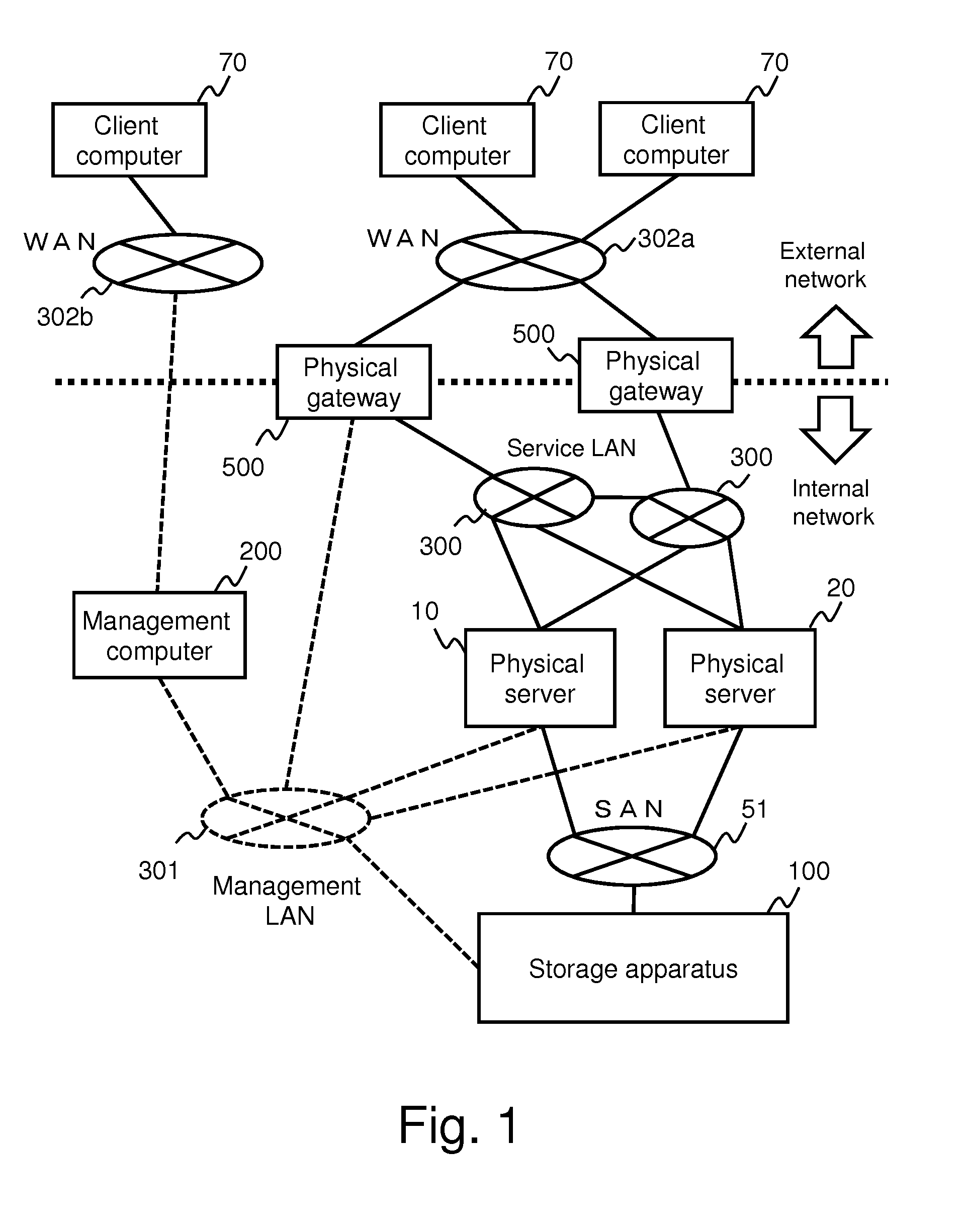

Method of managing tenant network configuration in environment where virtual server and non-virtual server coexist

ActiveUS9575798B2Good informationCostNetworks interconnectionSoftware simulation/interpretation/emulationVirtualizationVirtual switch

A non-virtual server and a virtual server make up the same tenant in an environment, in which virtual servers created by dividing a single physical server into a plurality of computer environments coexist with a non-virtual server that directly uses a single physical server as a computer environment without using server virtualization. A management computer is provided with virtual switch management information that shows a correlation between the virtual servers and an internal network to which a relevant virtual server connects, and physical switch management information that shows a correlation between the non-virtual server and an internal network to which the non-virtual server connects. The management computer creates a virtual server that belongs to the same tenant as a physical instance, identifies a first internal network to which the non-virtual server connects, and configures the tenant so that the relevant virtual server is connected to the first internal network.

Owner:HITACHI LTD

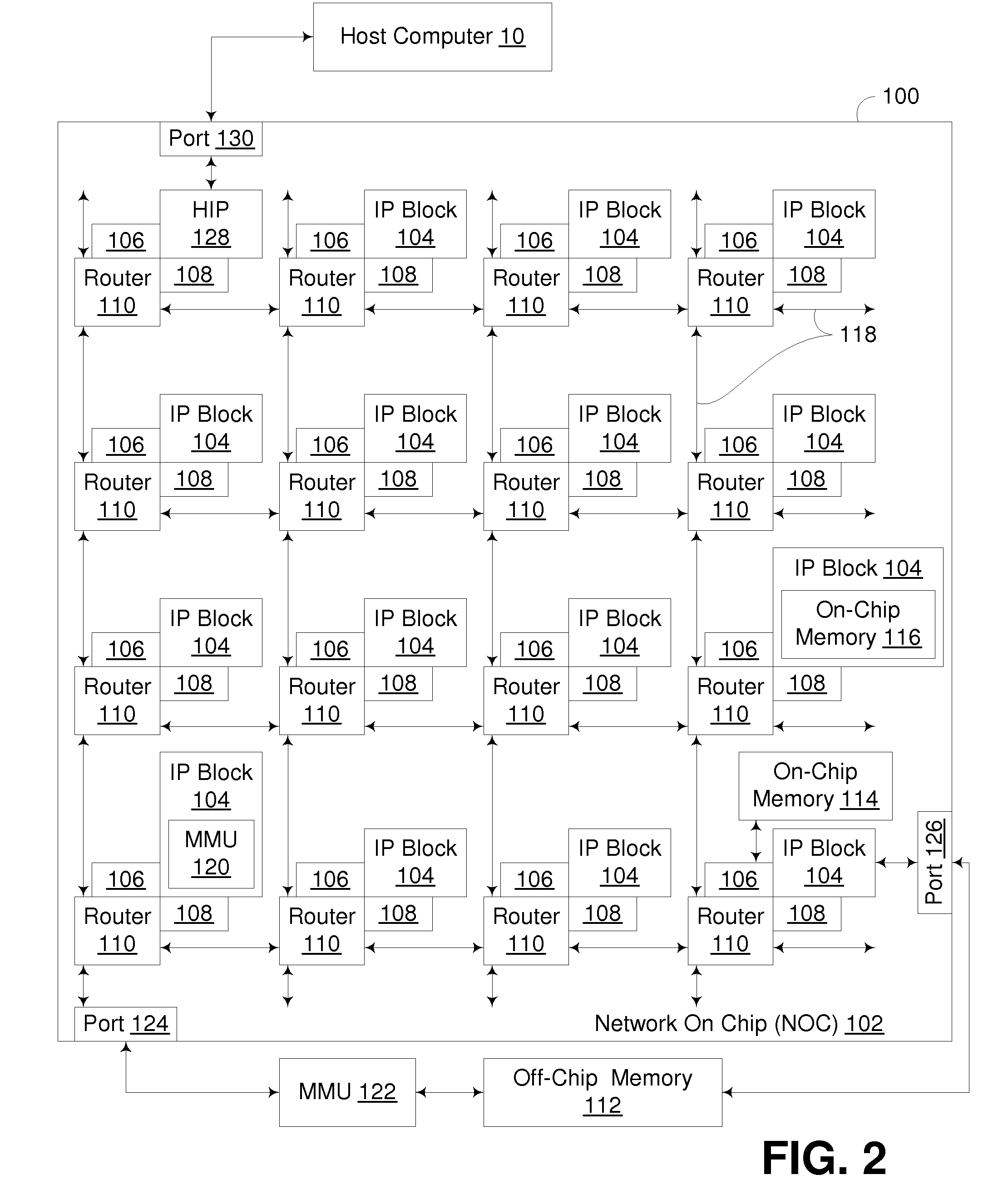

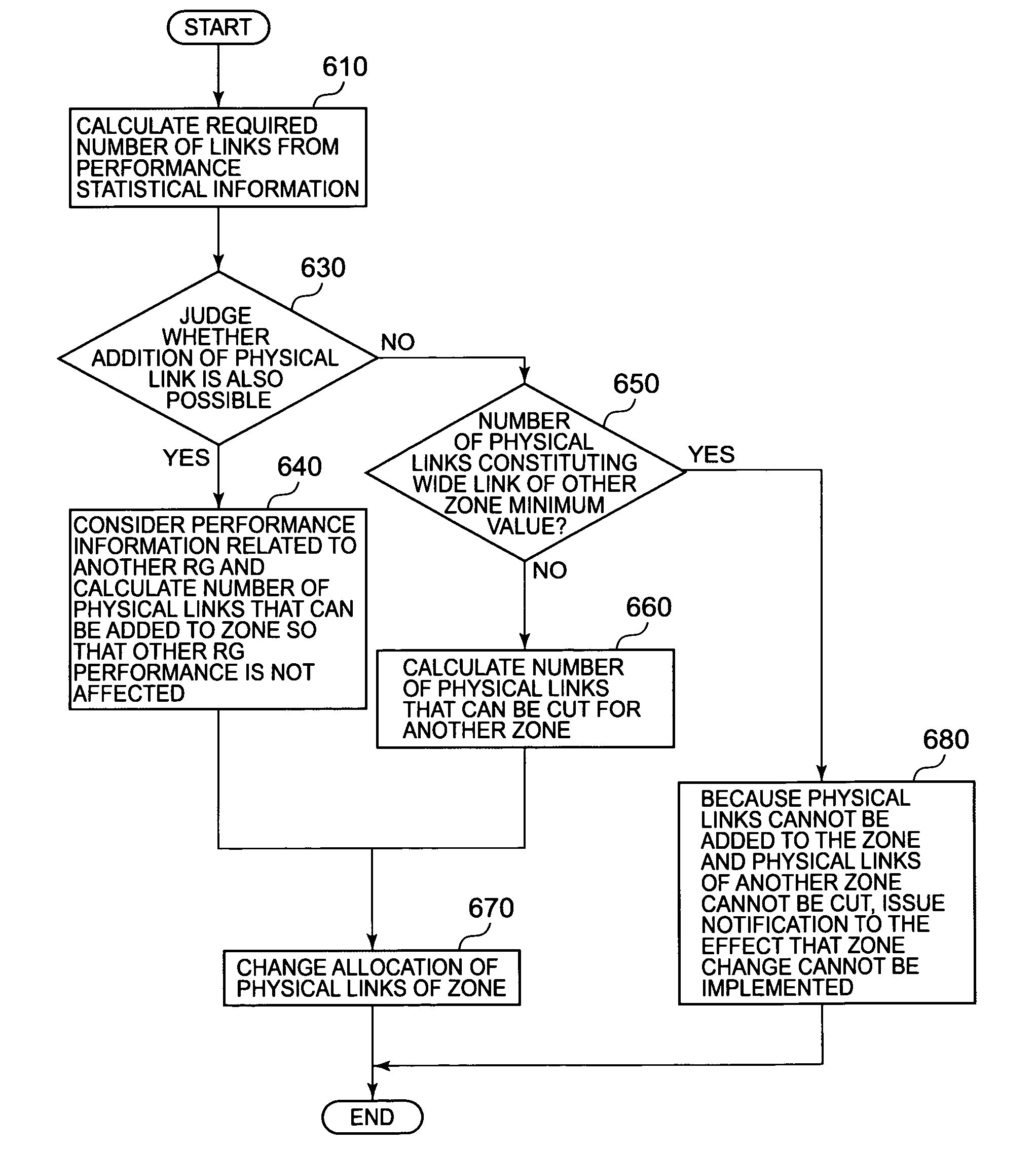

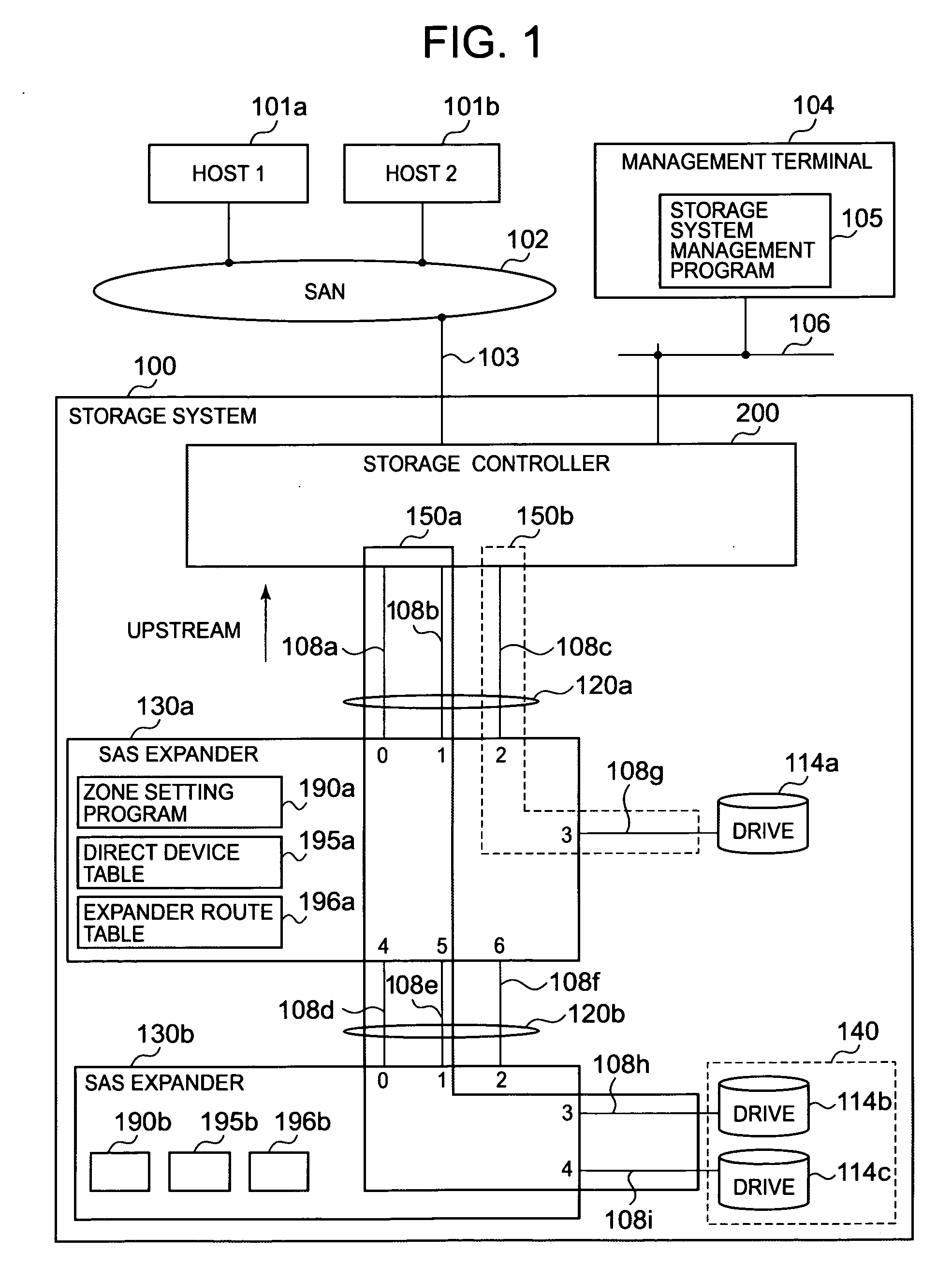

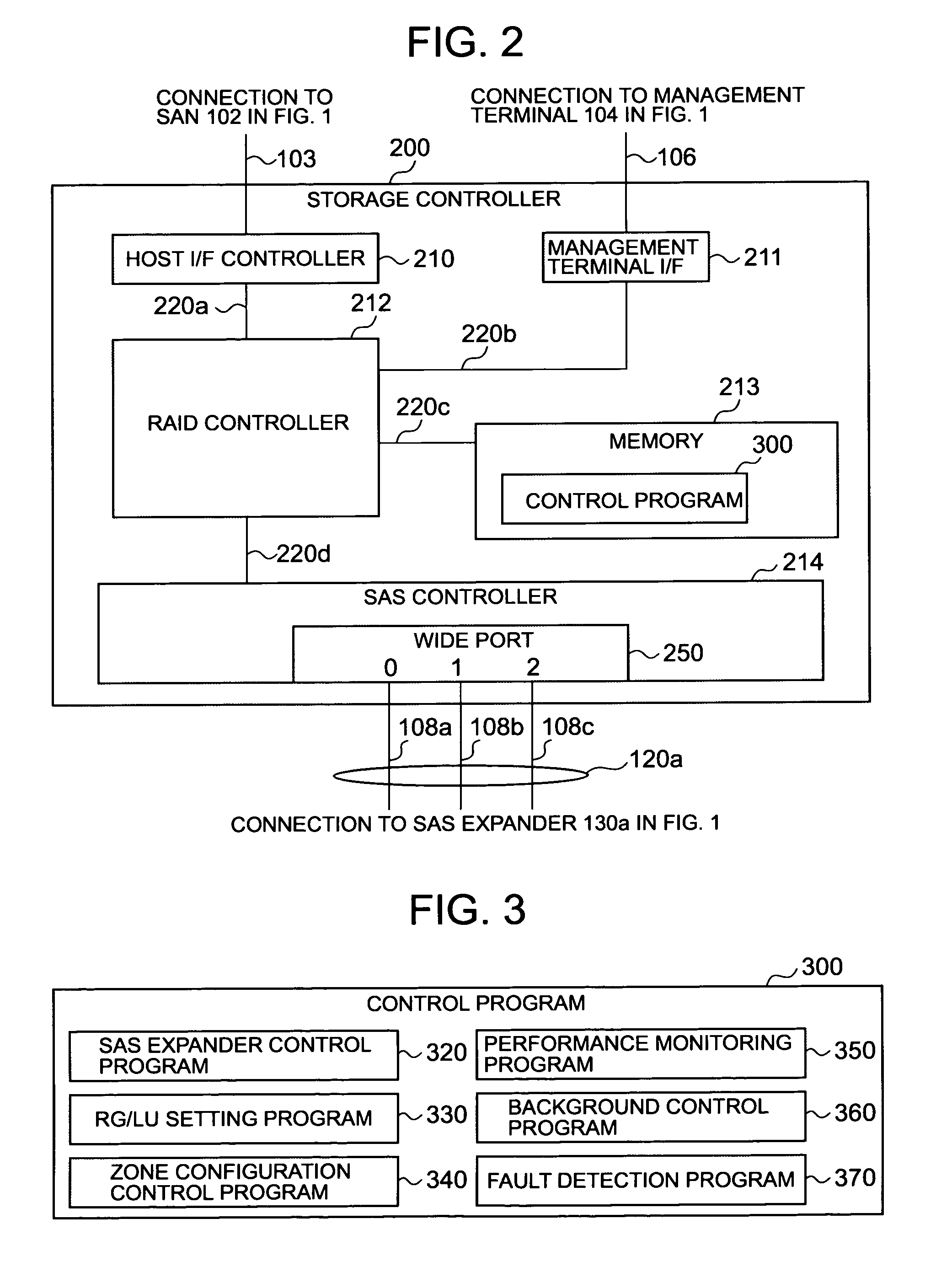

Computer system for controlling allocation of physical links and method thereof

InactiveUS20070220204A1Prevent drop in throughputImprove performanceMemory loss protectionMultiple digital computer combinationsEngineering

The computer system of the present invention has a plurality of SAS target devices, an SAS initiator device, and a service delivery subsystem that is connected to each SAS target device by means of a physical link that is physical wiring and connected to the SAS initiator device by means of a wide link constituted by a plurality of physical links. The SAS initiator device controls how many physical links in the wide link are allocated to a particular SAS target device, whereby access from the SAS initiator device to the SAS target device is made via a physical link that is allocated to the SAS target device and is not made via a physical link that is not allocated to the SAS target device.

Owner:HITACHI LTD

System to Reduce Latency by Running a Memory Channel Frequency Fully Asynchronous from a Memory Device Frequency

InactiveUS20090193203A1High bandwidthReduce operating frequencyDigital data processing detailsMemory systemsExternal storageMemory controller

A memory system is provided that reduces latency by running a memory channel fully asynchronous from a memory device frequency. The memory system comprises a memory hub device integrated in a memory module. The memory hub device comprises a command queue that receives a memory access command from an external memory controller via a memory channel at a first operating frequency. The memory system also comprises a memory hub controller integrated in the memory hub device. The memory hub controller reads the memory access command from the command queue at a second operating frequency. By receiving the memory access command at the first operating frequency and reading the memory access command at the second operating frequency an asynchronous boundary is implemented. The first operating frequency is a maximum designed operating frequency of the memory channel and the first operating frequency is independent of the second operating frequency.

Owner:IBM CORP

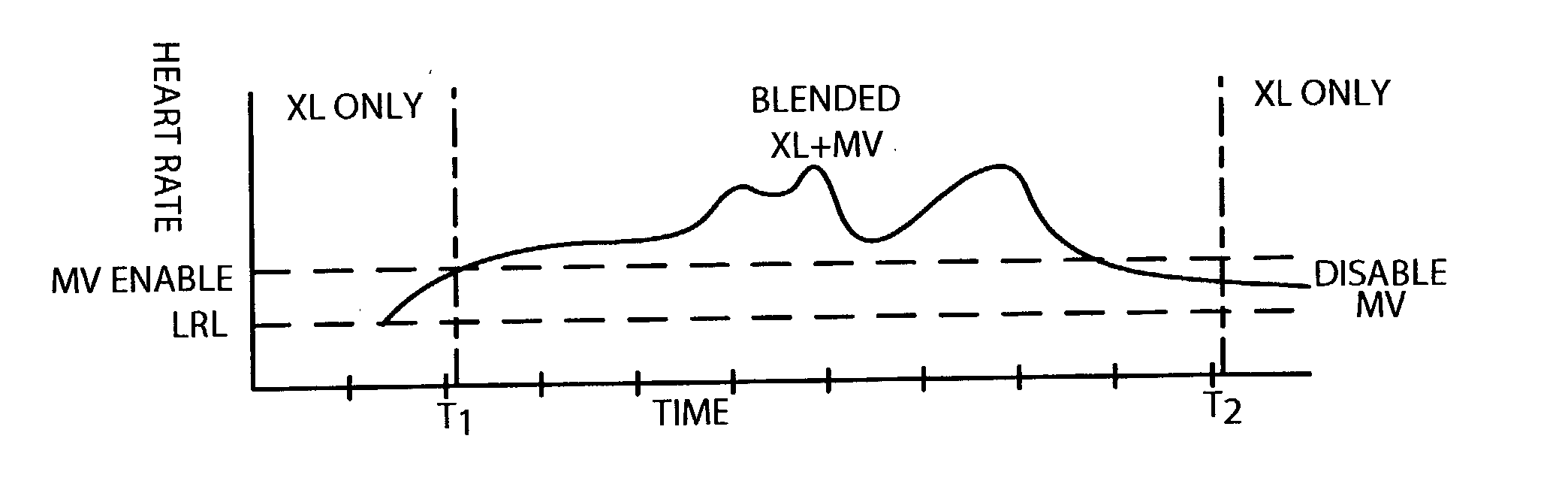

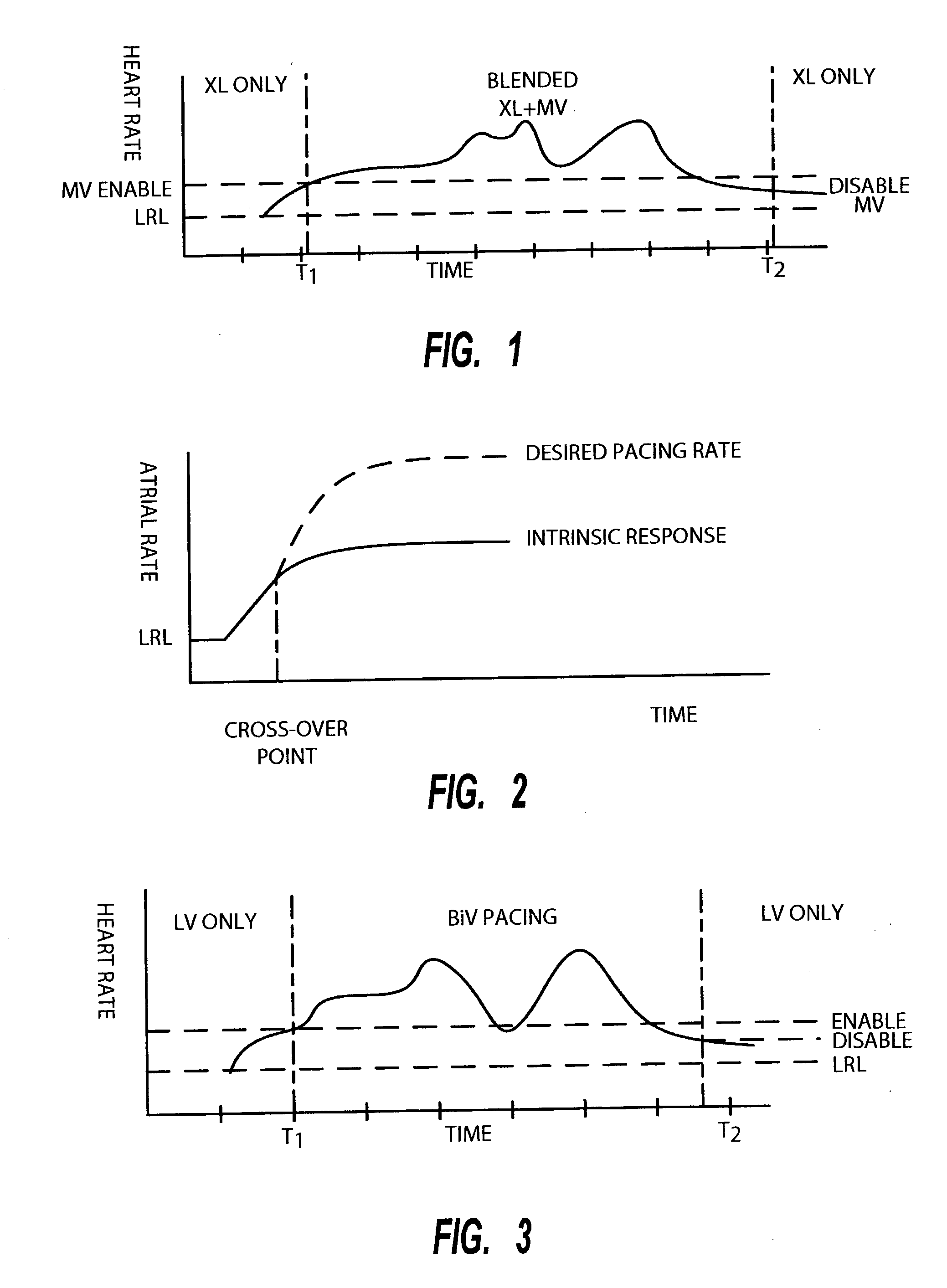

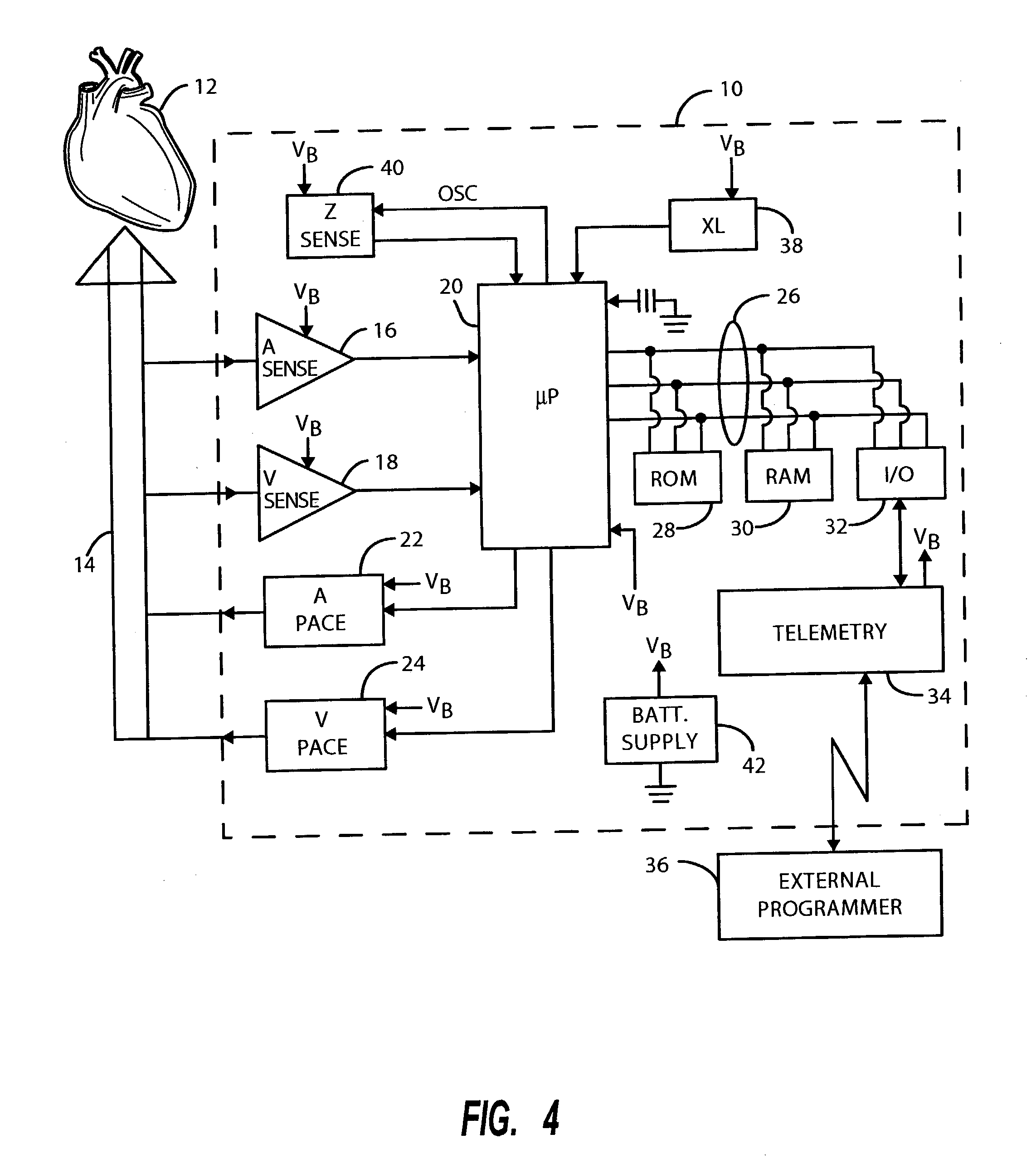

Method of operating implantable medical devices to prolong battery life

ActiveUS20040098060A1Alters Cardiac FunctionHigh incidenceHeart stimulatorsPhysical medicine and rehabilitationElectrical battery

A method of conserving power and extending the life of a battery in an implantable rate-responsive cardiac rhythm management device. In accordance with the preferred embodiment, a first physiologic sensor is used to enable a power consuming feature only when the first sensor produces an output falling within a predetermined range and subsequently disables the power consuming feature when the output of the first sensor falls back outside the predetermined range. The first sensor may measure heart rate, physical movement, posture or other parameters and the power consuming feature may comprise further physiologic sensors, a different mode of pacing or a combination thereof

Owner:CARDIAC PACEMAKERS INC

Lithium battery core capable of radiating heat by directly conducting heat from internal to external

InactiveCN103165952AReduce performanceAvoid damageFinal product manufactureCell temperature controlEngineeringHeat sink

The invention relates to a lithium battery core capable of radiating heat by directly conducting heat from internal to external. The lithium battery core comprises a packaging bag for accommodating a positive electrode, a negative electrode, a separator membrane for separating the positive electrode and the negative electrode, and an electrolyte solution. The packaging bag is also provided with at least one heat radiation fin; and at least one side of the heat radiation fin protrudes out of one side of the packaging bag. Heat produced from the positive electrode and the negative electrode is transmitted to the heat radiation fin through the electrolyte solution, so that efficiency reduction or damage caused by overheating of the lithium battery core can be prevented. Besides, the lithium battery core can be operated in cooperation with a fan or a cooling system, so that heat can be continuously removed from the heat radiation fin, and heat radiation efficiency is increased.

Owner:LOROM INDAL

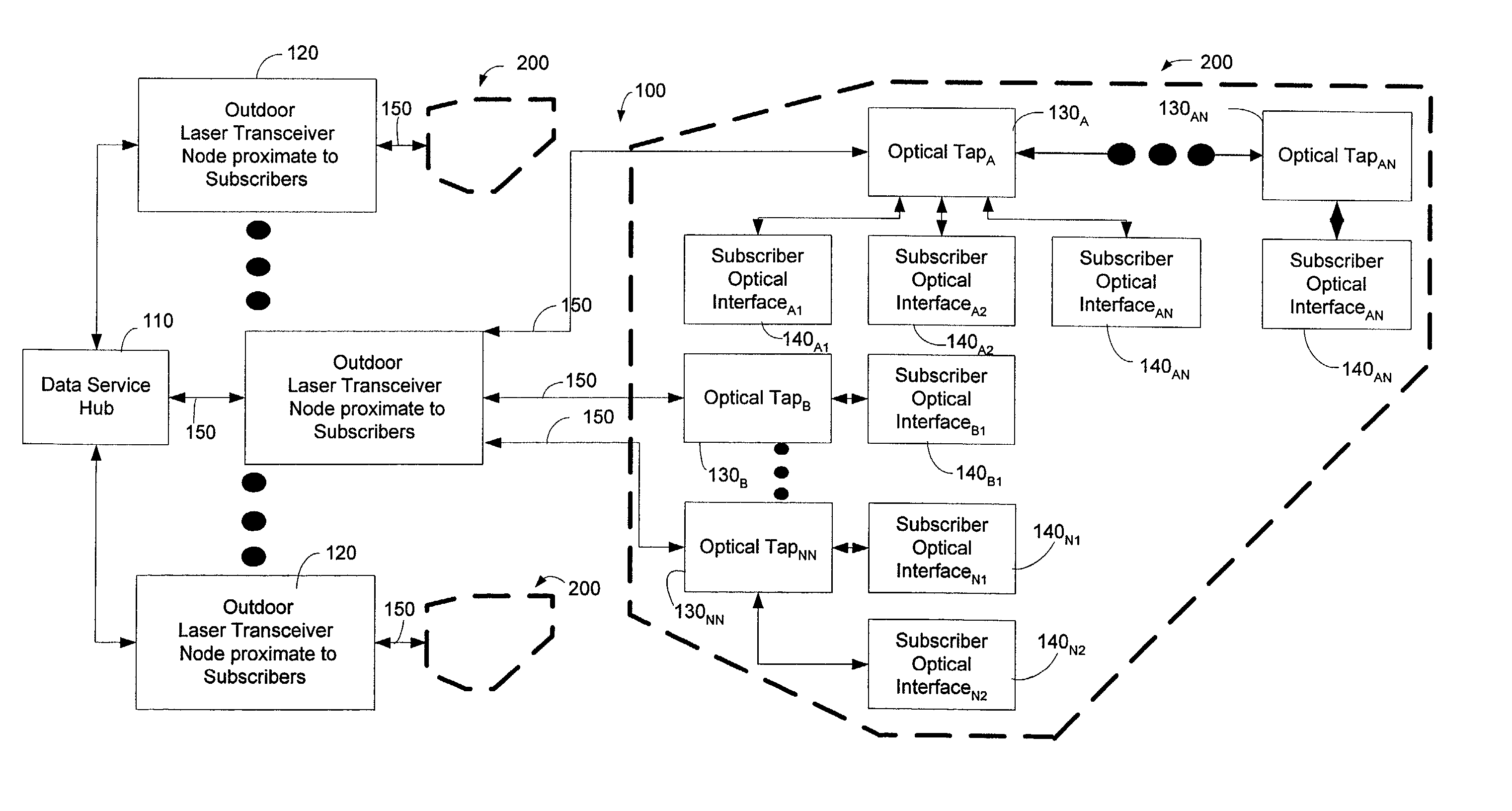

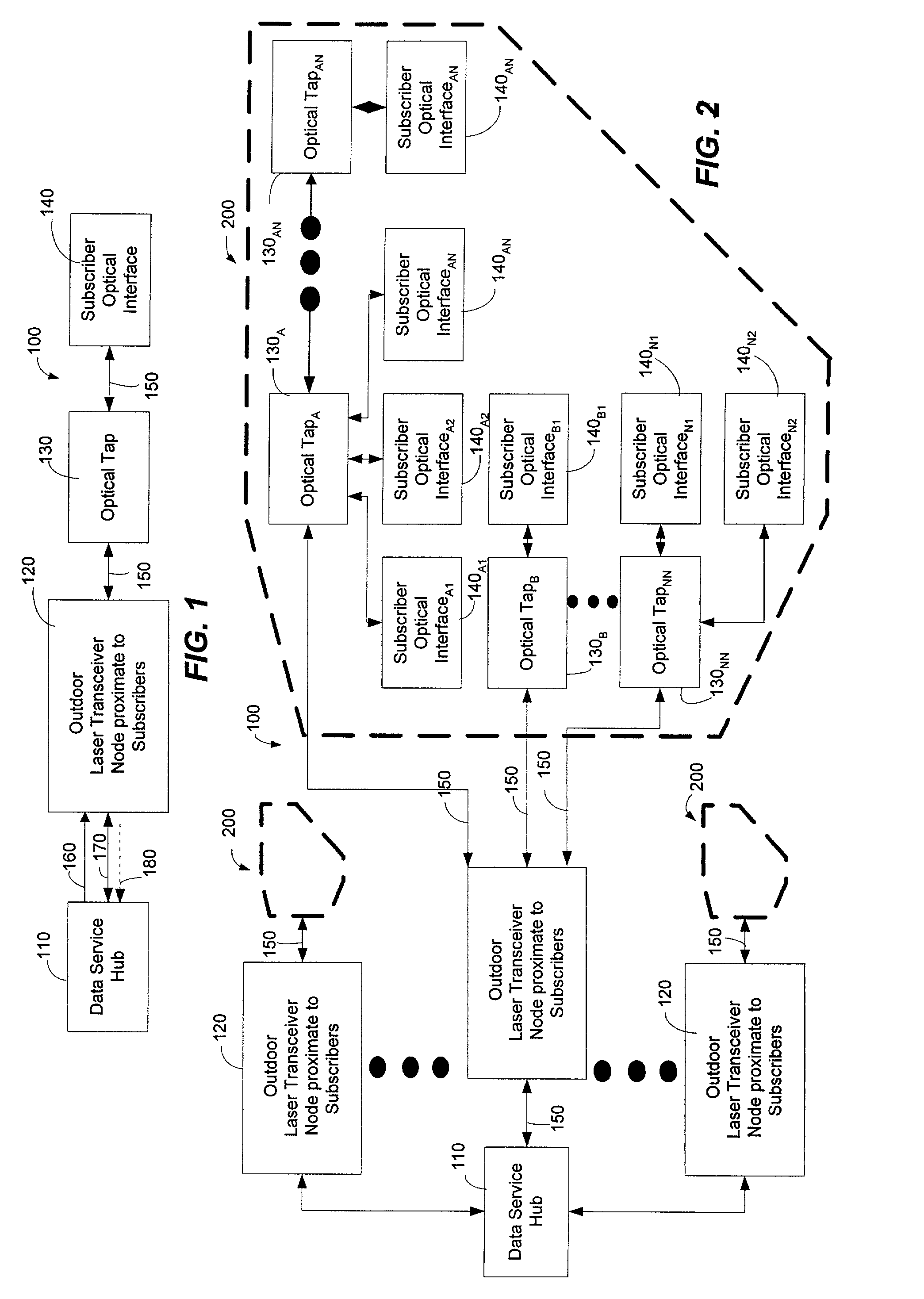

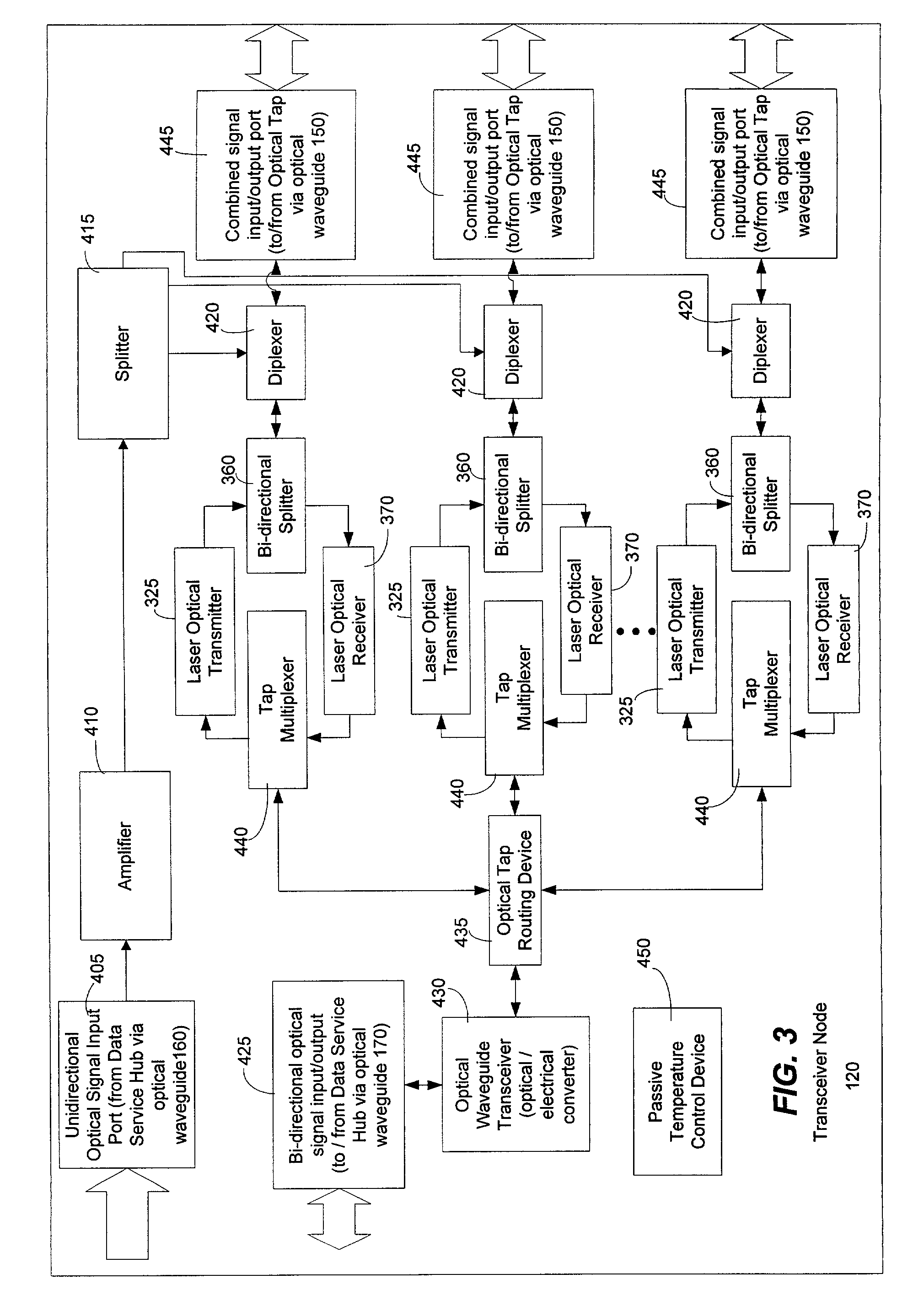

Method and system for processing upstream packets of an optical network

InactiveUS7085281B2Avoid collisionReduce performanceMultiplex system selection arrangementsTime-division optical multiplex systemsGeneral purposeTransceiver

A protocol for an optical network can control the time at which subscriber optical interfaces of an optical network are permitted to transmit data to a transceiver node. The protocol can prevent collisions of upstream transmissions between the subscriber optical interfaces of a particular subscriber group. With the protocol, a transceiver node close to the subscriber can allocate additional or reduced upstream bandwidth based upon the demand of one or more subscribers. That is, a transceiver node close to a subscriber can monitor (or police) and adjust a subscriber's upstream bandwidth on a subscription basis or on an as-needed basis. The protocol can account for aggregates of packets rather than individual packets. By performing calculation on aggregates of packets, the algorithm can execute less frequently which, in turn, permits its implementation in lower performance and lower cost devices, such as software executing in a general purpose microprocessor.

Owner:ARRIS ENTERPRISES LLC