Patents

Literature

192 results about "Pn diode" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

Printable electronic display

InactiveUS6980196B1Easy to manufactureLow costElectromagnetic wave systemStatic indicating devicesMicroparticleNonlinear element

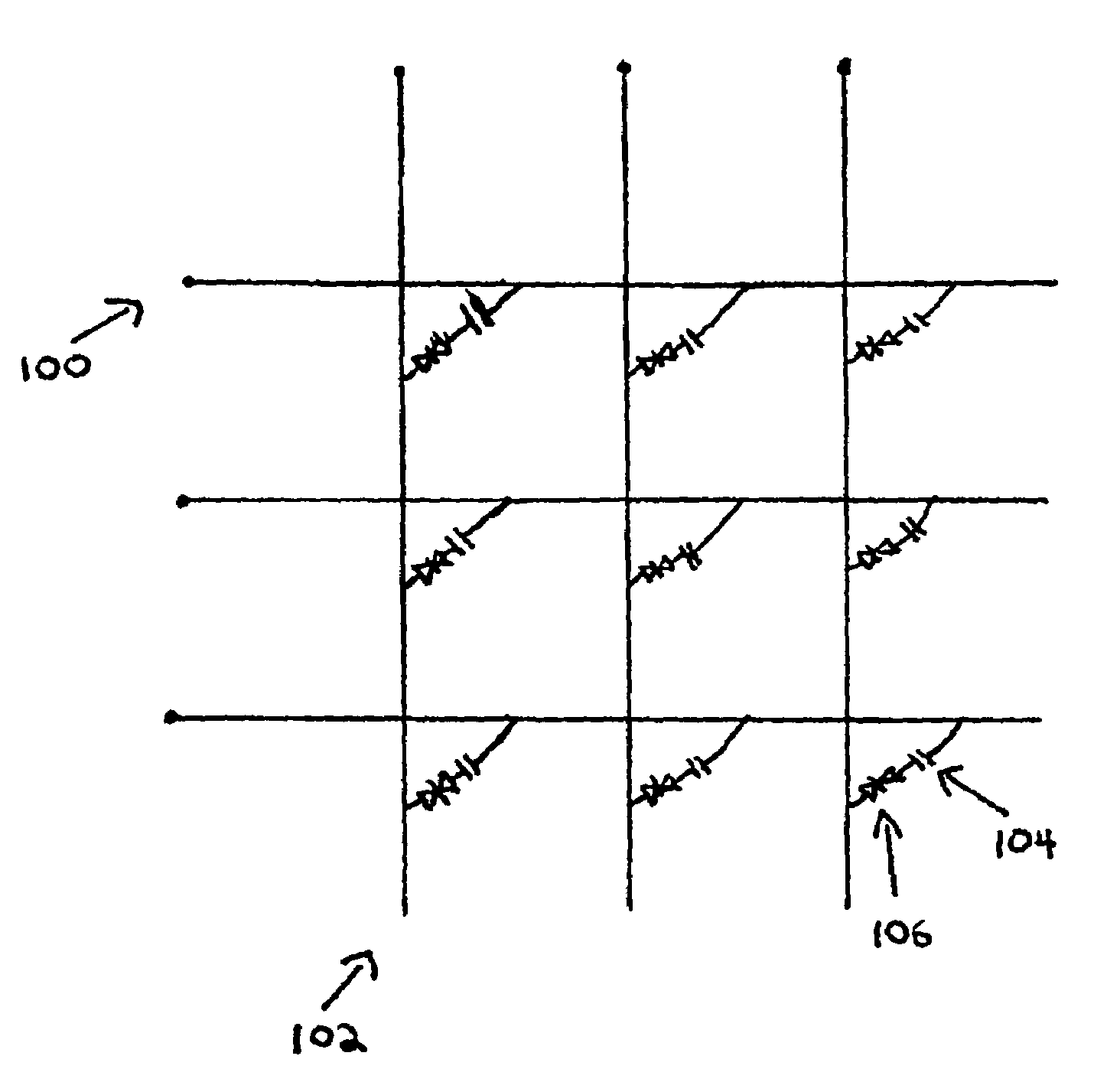

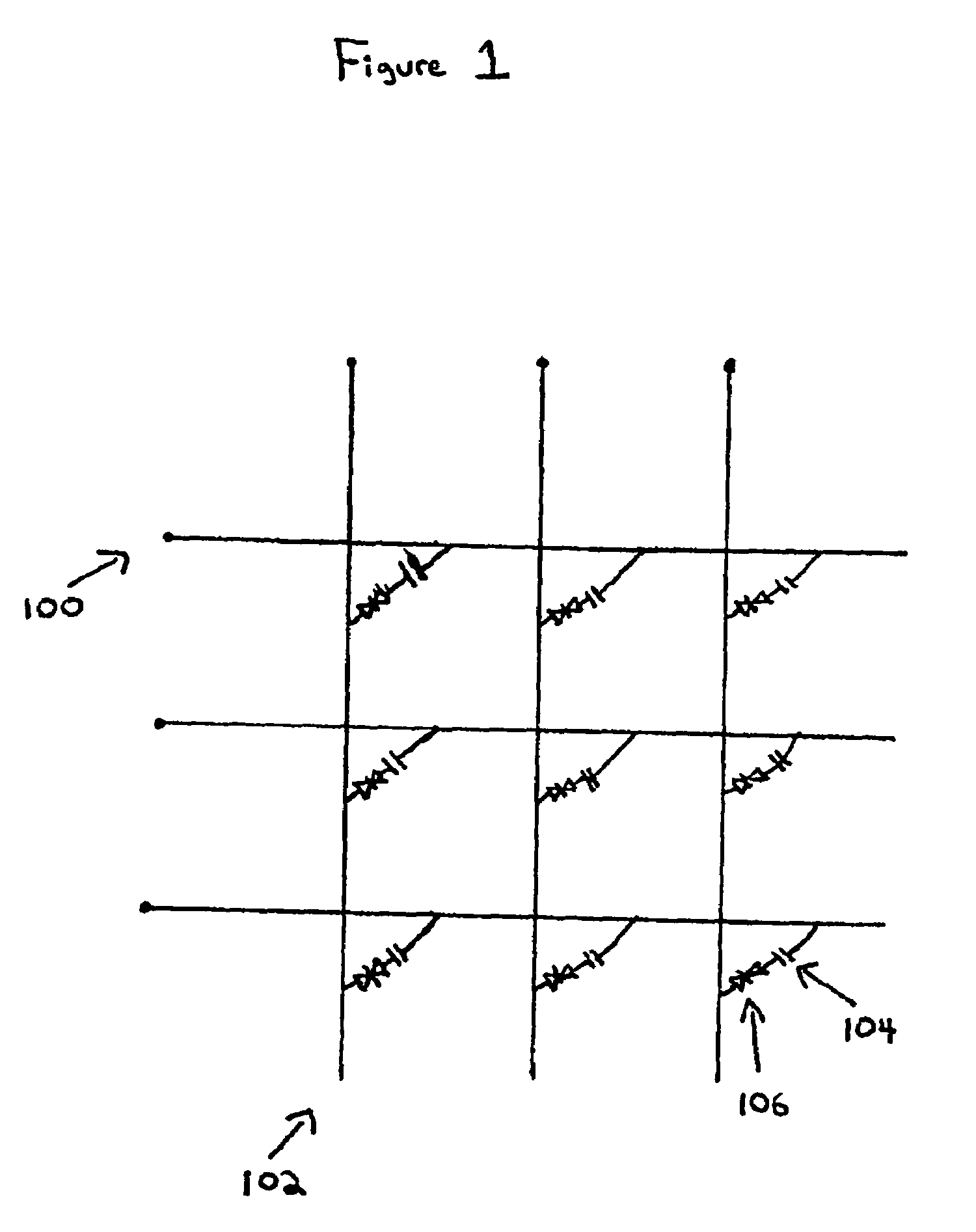

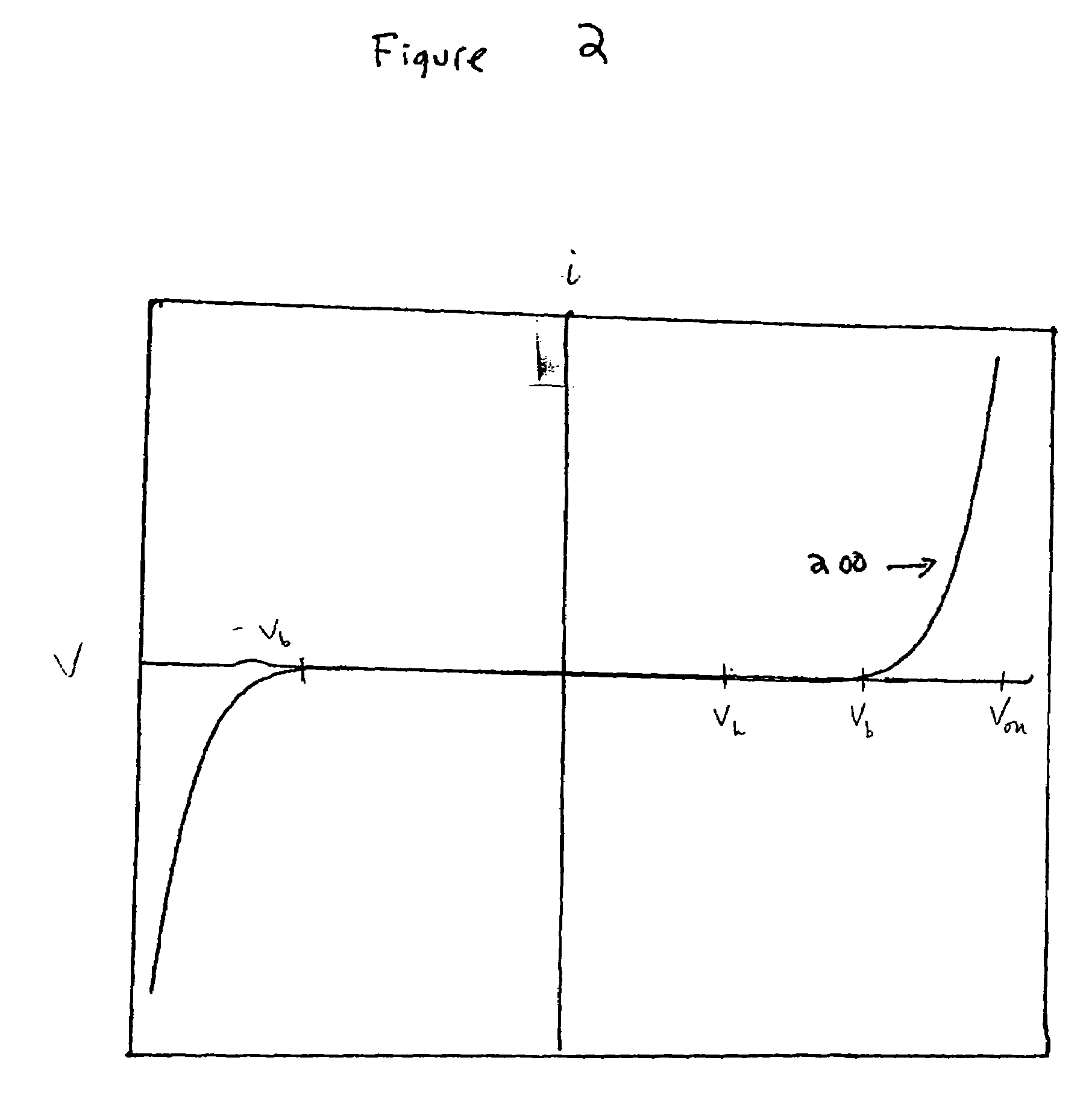

A display system includes a substrate upon which the display system is fabricated; a printable electrooptic display material, such as a microencapsulated electrophoretic suspension; electrodes (typically based on a transparent, conductive ink) arranged in an intersecting pattern to allow specific elements or regions of the display material to be addressed; insulating layers, as necessary, deposited by printing; and an array of nonlinear elements that facilitate matrix addressing. The nonlinear devices may include printed, particulate Schottky diodes, particulate PN diodes, particulate varistor material, silicon films formed by chemical reduction, or polymer semiconductor films. All elements of the display system may be deposited using a printing process.

Owner:MASSACHUSETTS INST OF TECH

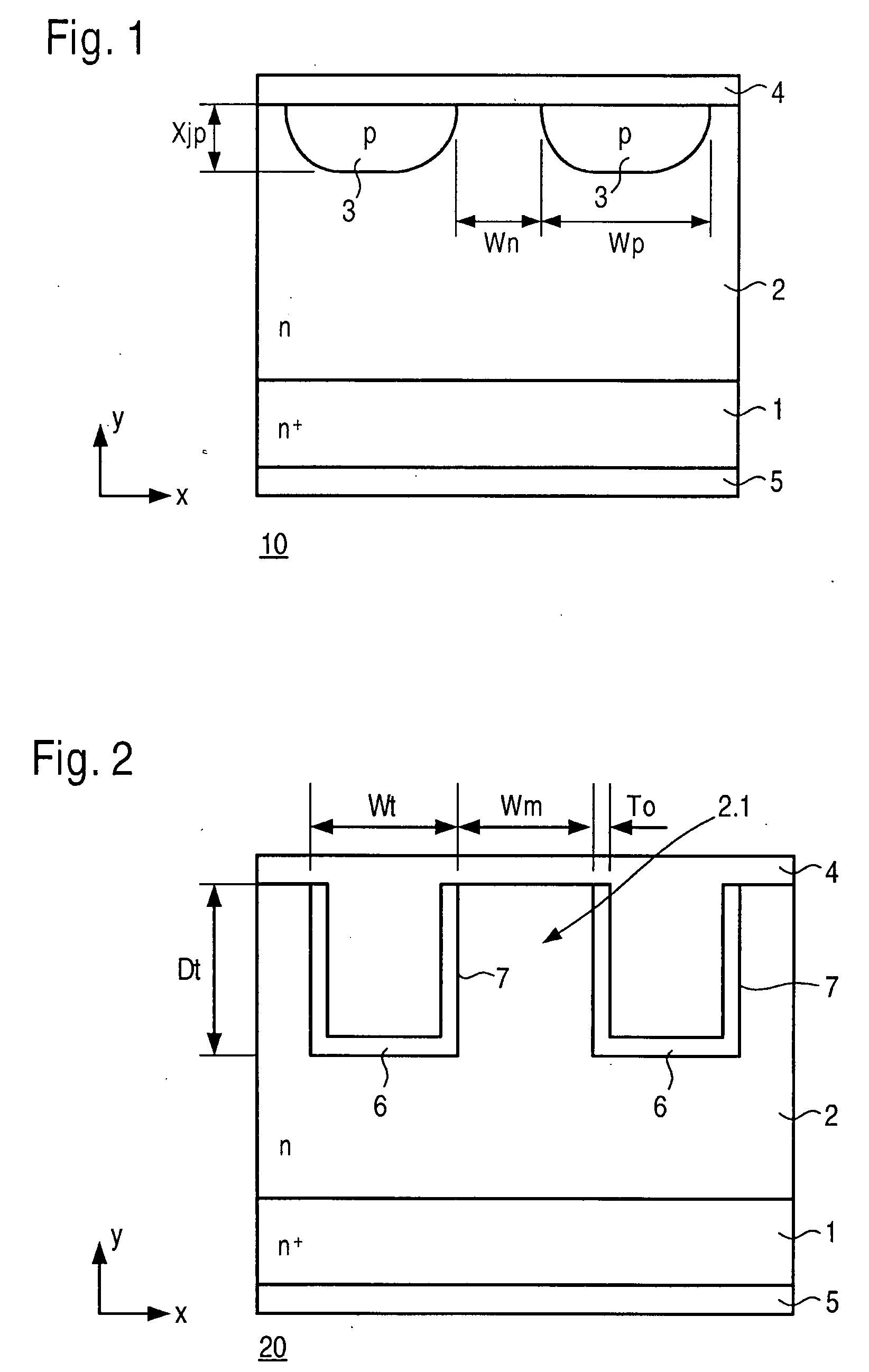

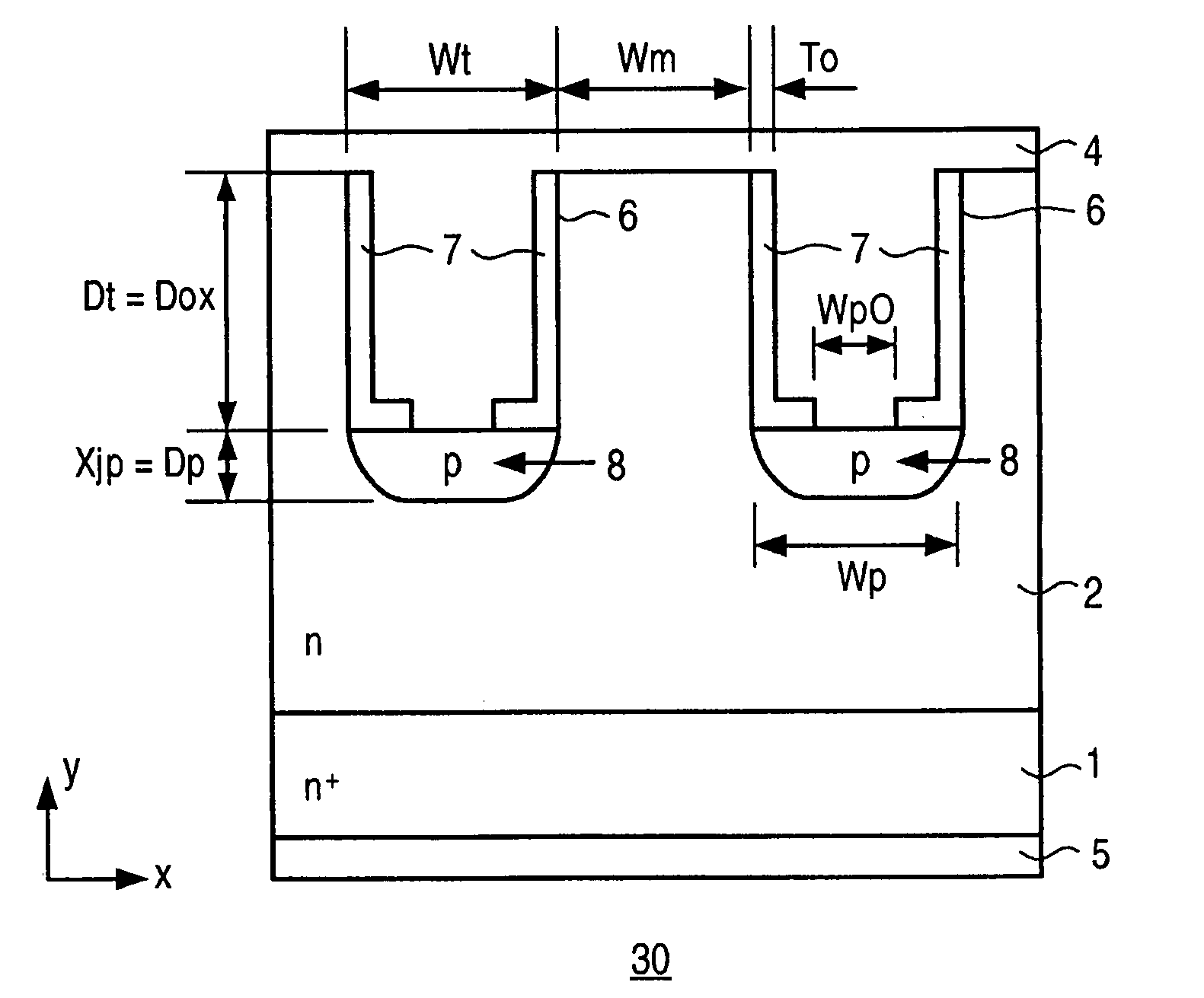

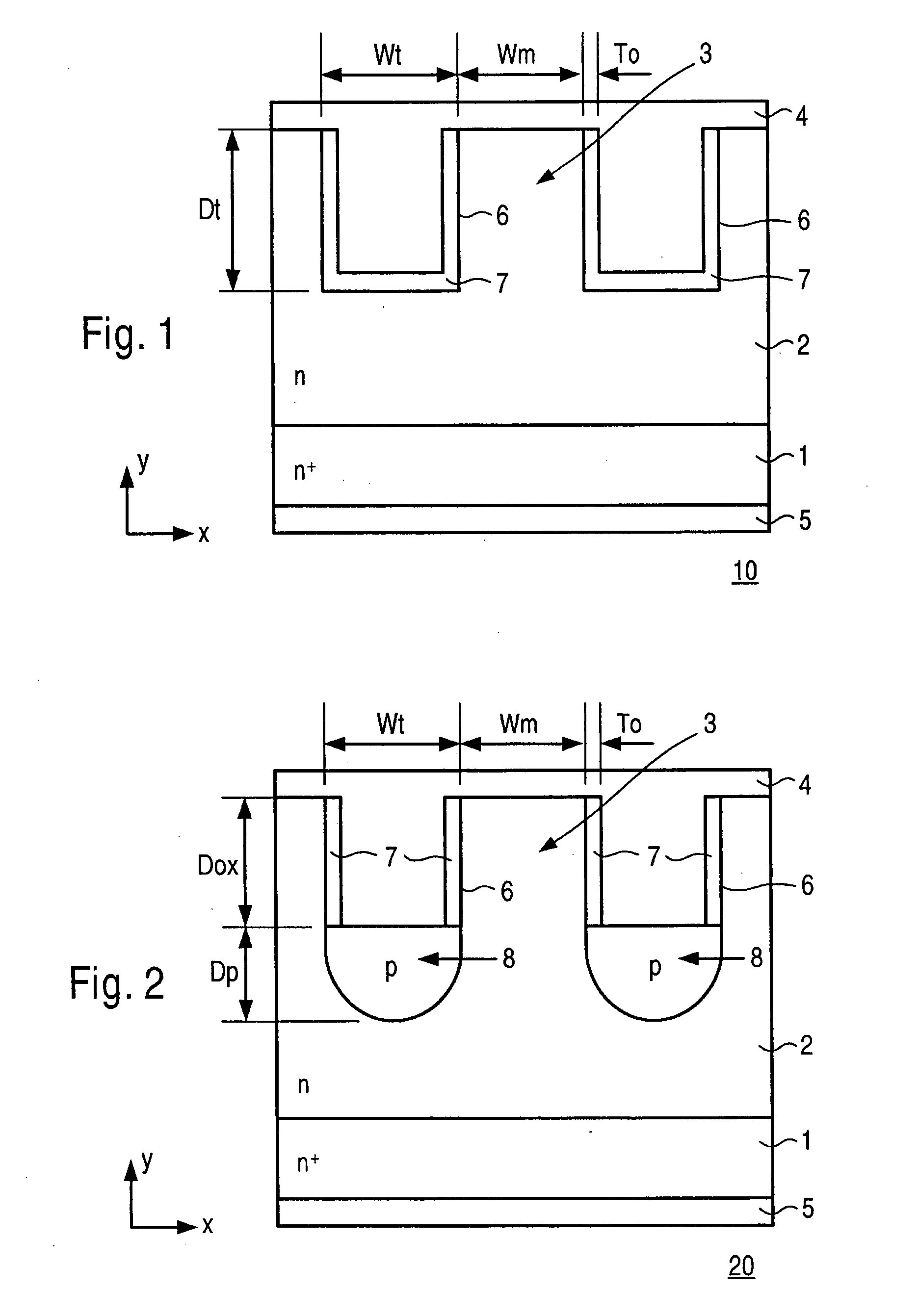

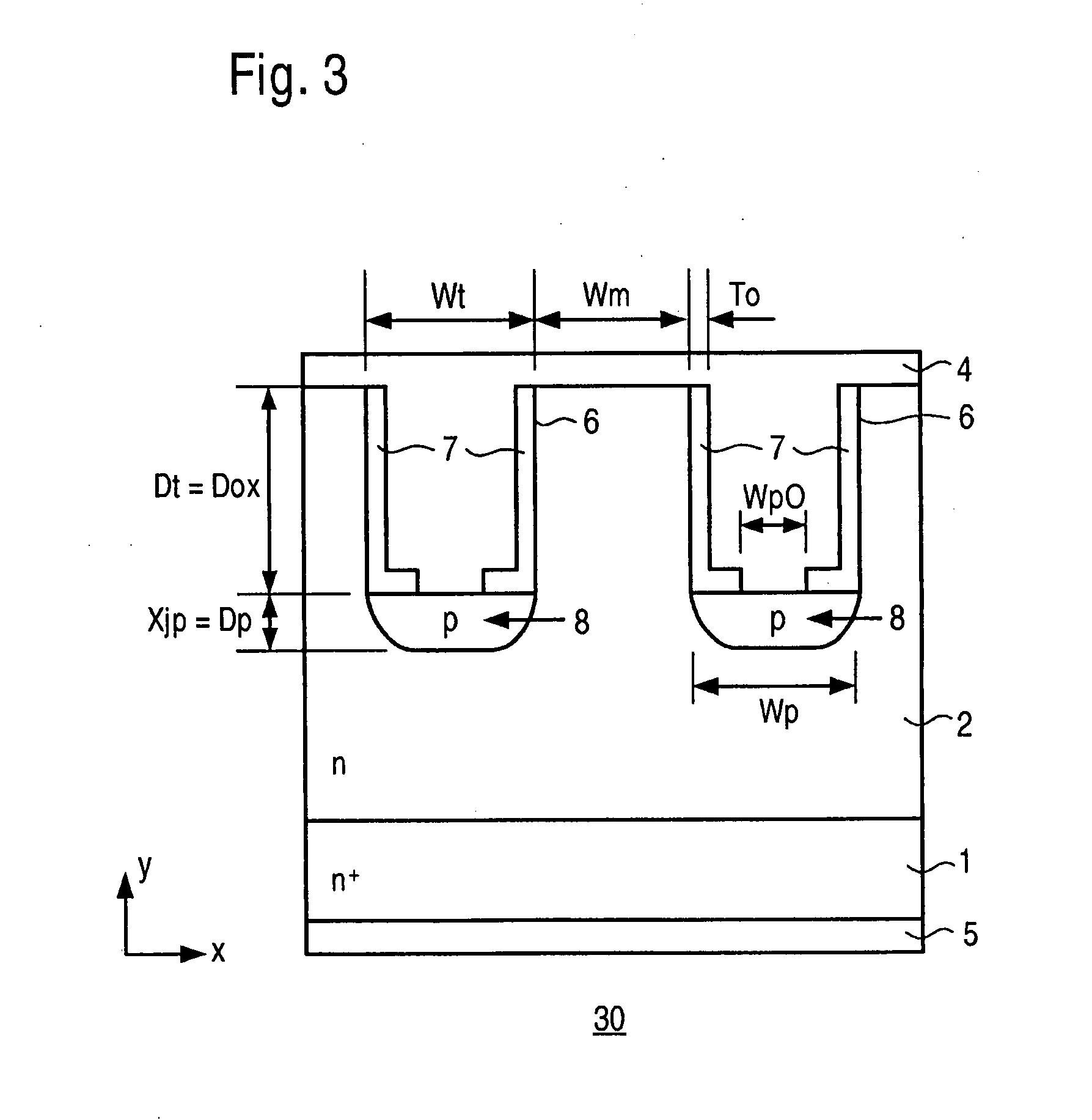

Semiconductor Device And Method For Manufacturing Same

ActiveUS20080197439A1Lower forward voltageImprove sturdinessSemiconductor/solid-state device manufacturingSemiconductor devicesEngineeringContact layer

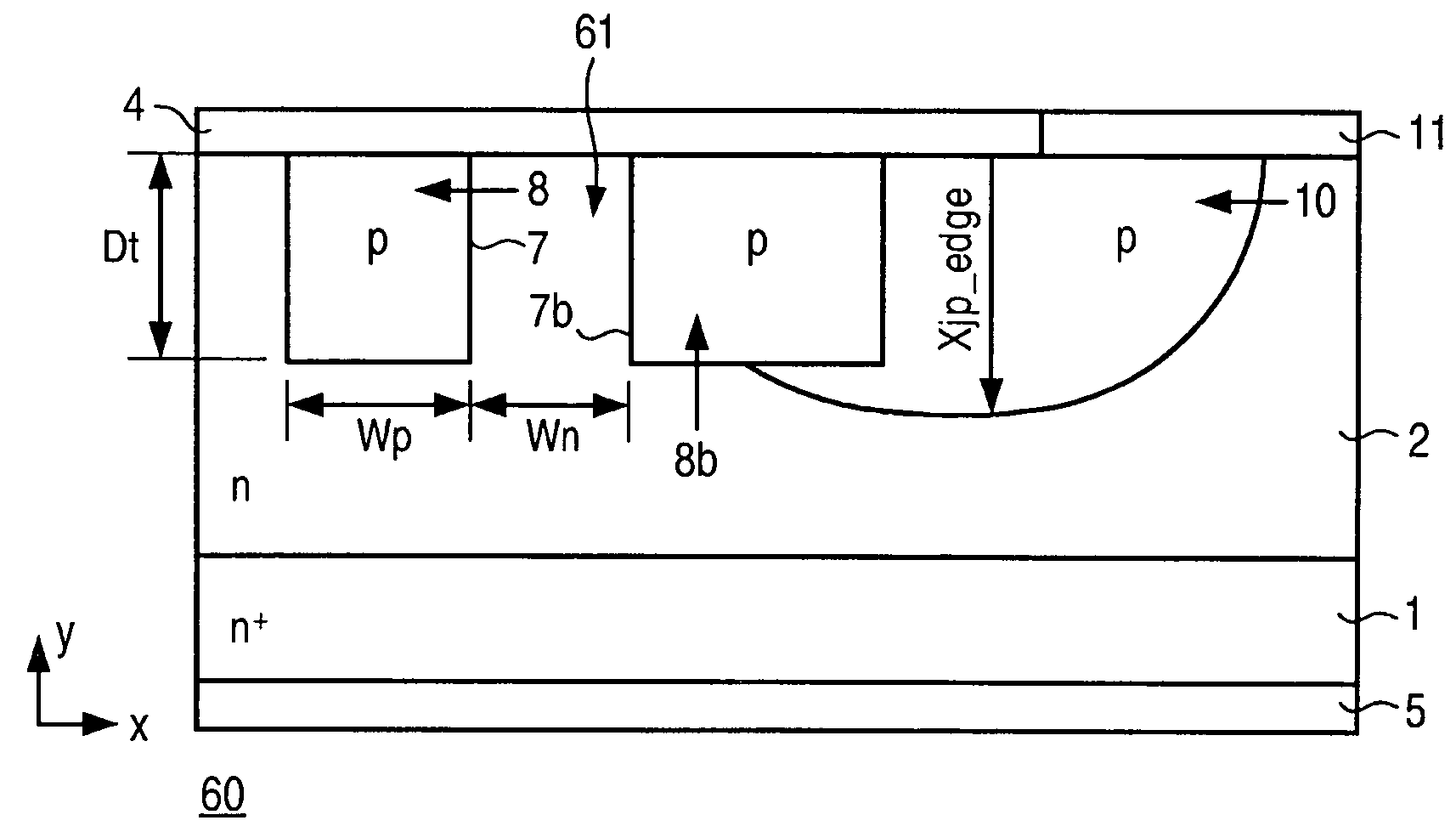

A semiconductor device including a Schottky diode of the trench-junction-barrier type having an integrated PN diode, and a corresponding method for manufacturing the device, are provided. An n layer is provided on an nt substrate, and trenches are provided in the n layer. The trenches are provided with p-doped regions. The nt substrate and the n layer carry a contact layer.

Owner:ROBERT BOSCH GMBH

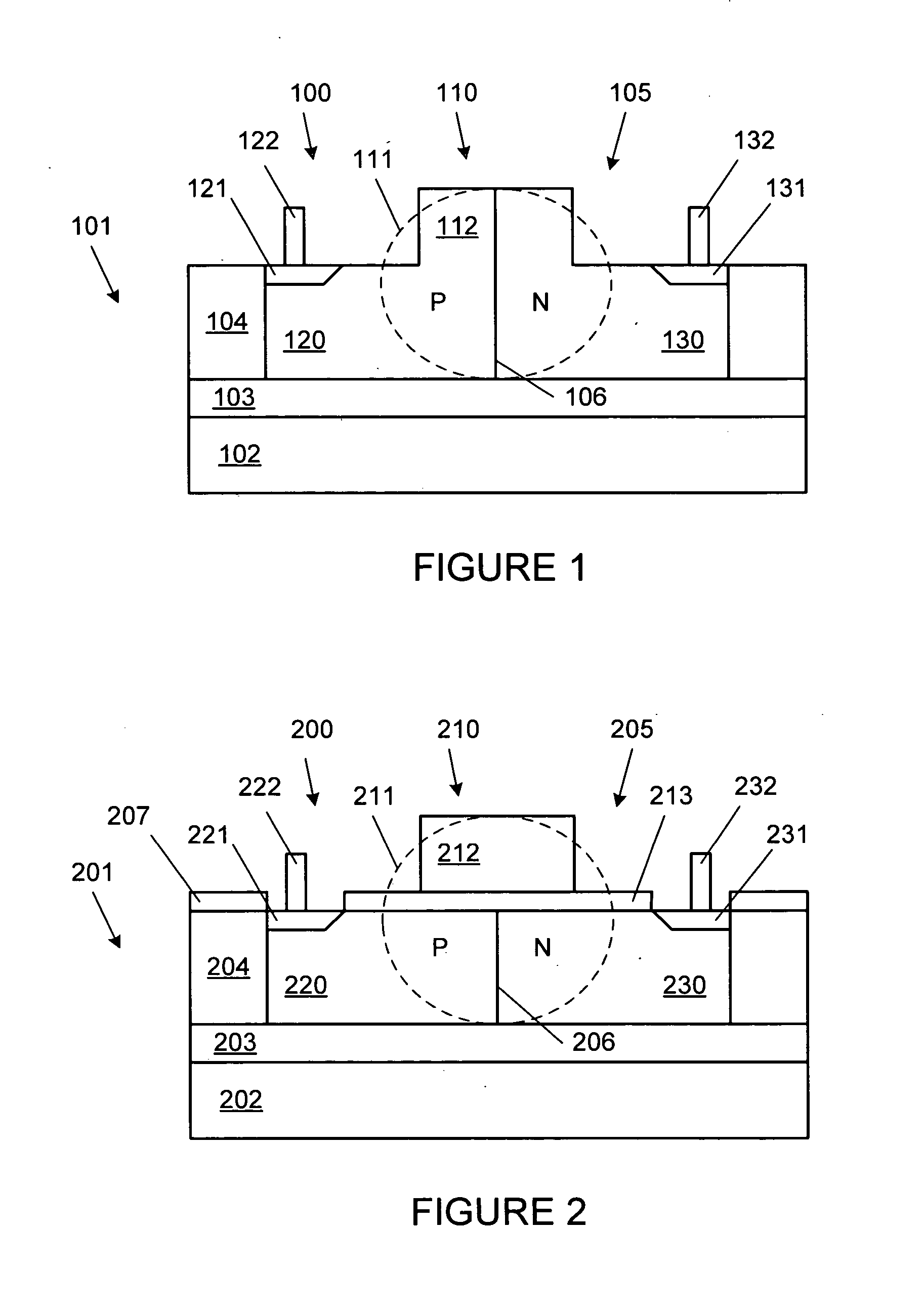

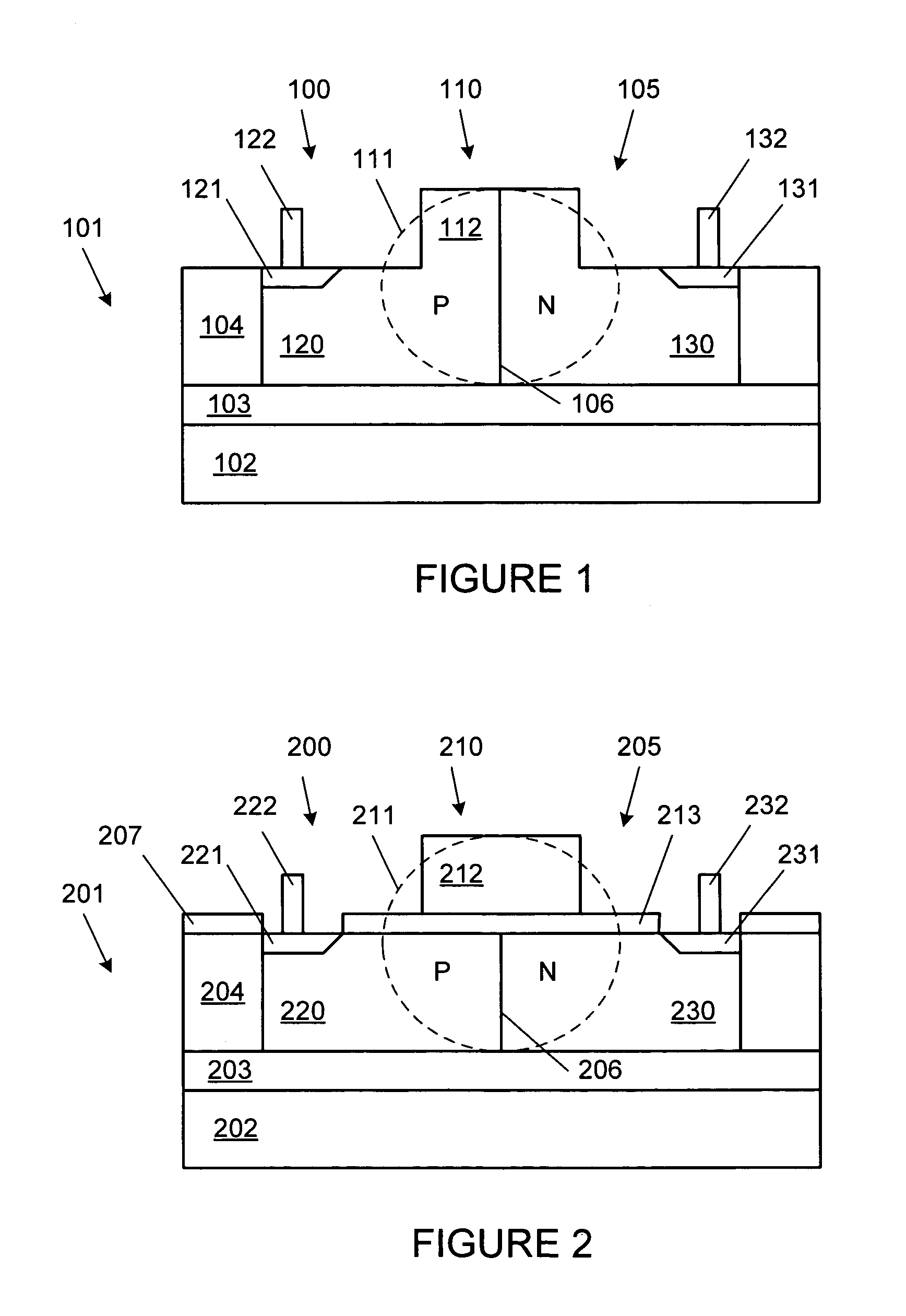

PN diode optical modulators fabricated in rib waveguides

ActiveUS20060008223A1Reduce speedSemiconductor/solid-state device manufacturingOptical waveguide light guideLow speedPhase shifted

Owner:CISCO TECH INC

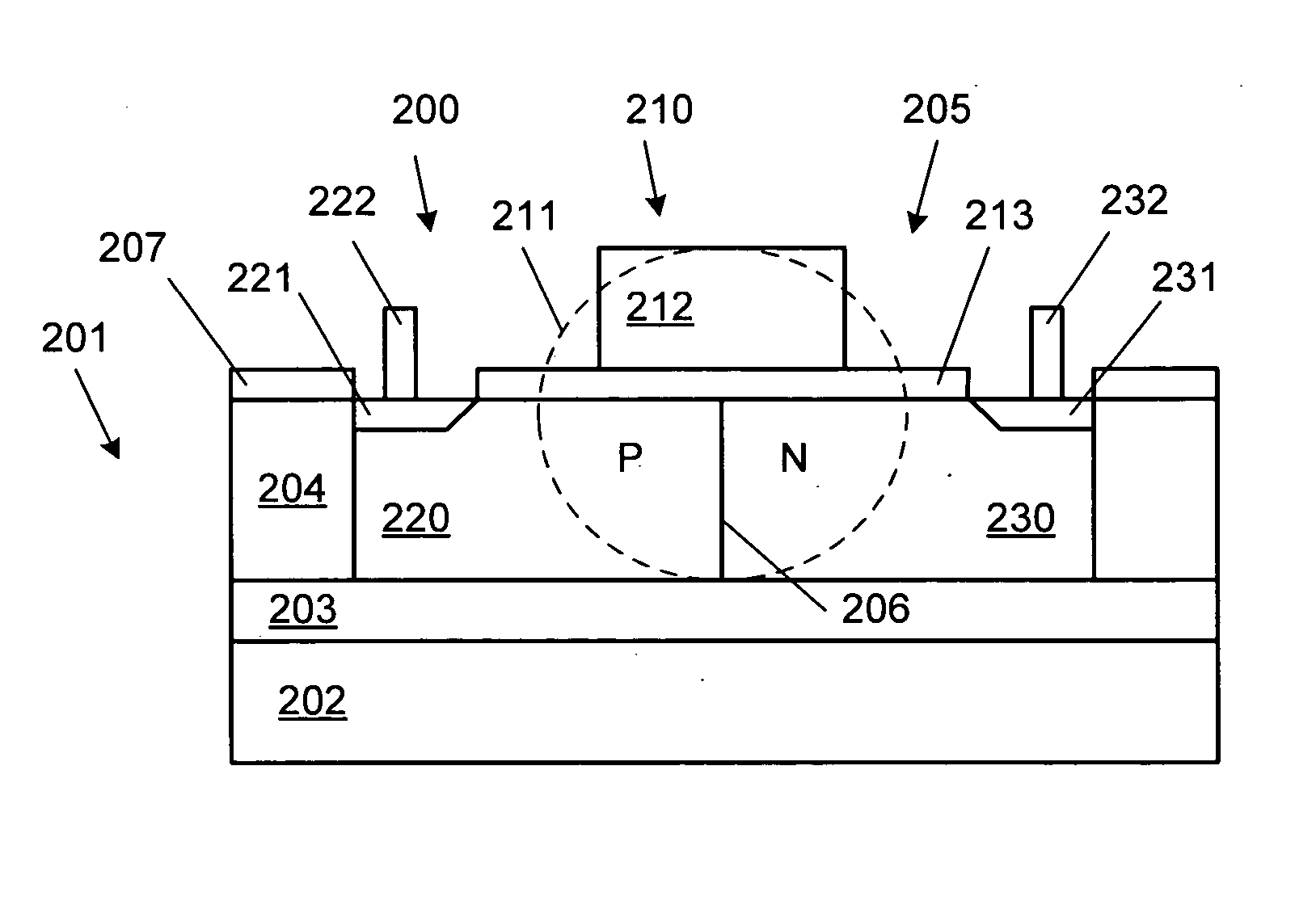

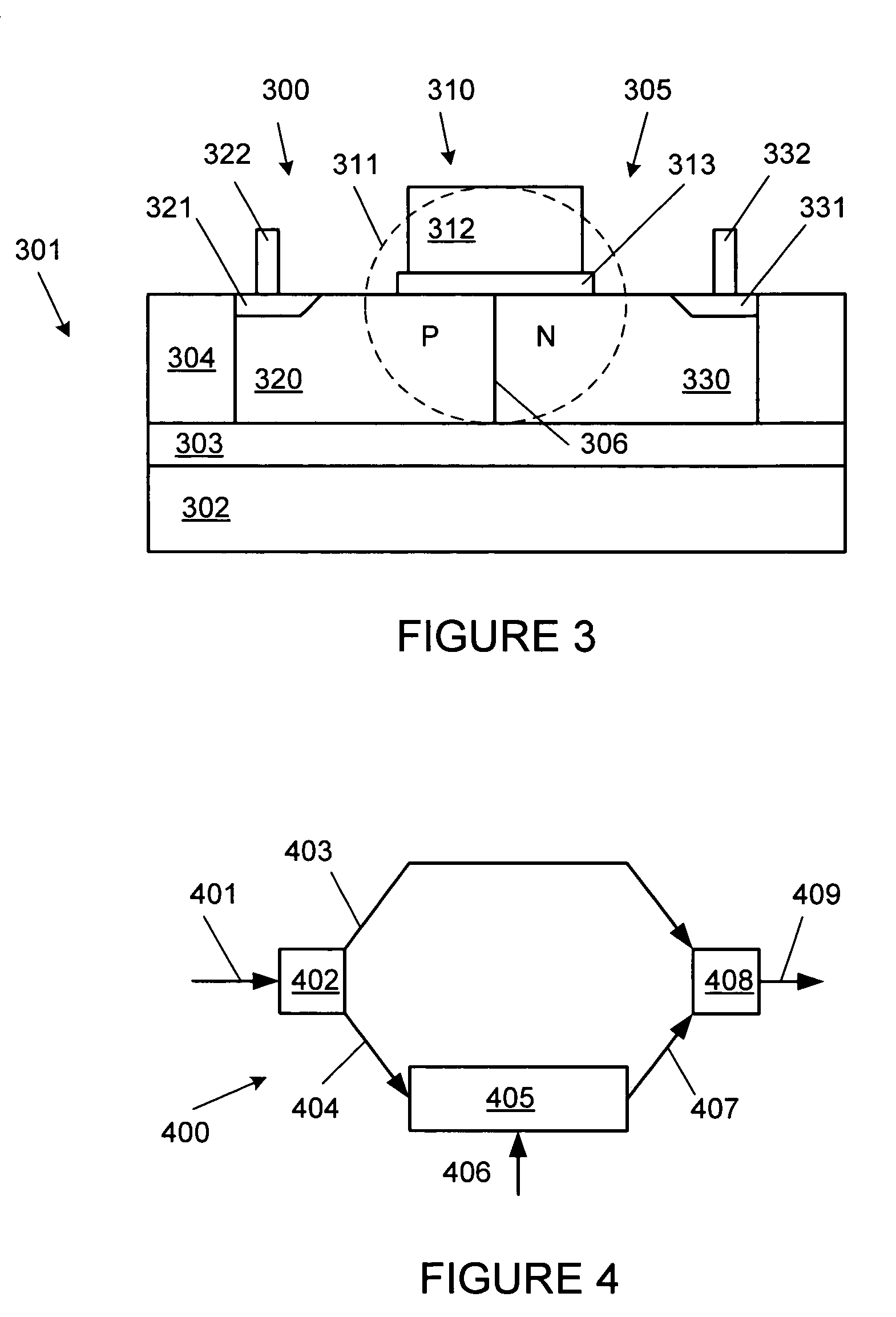

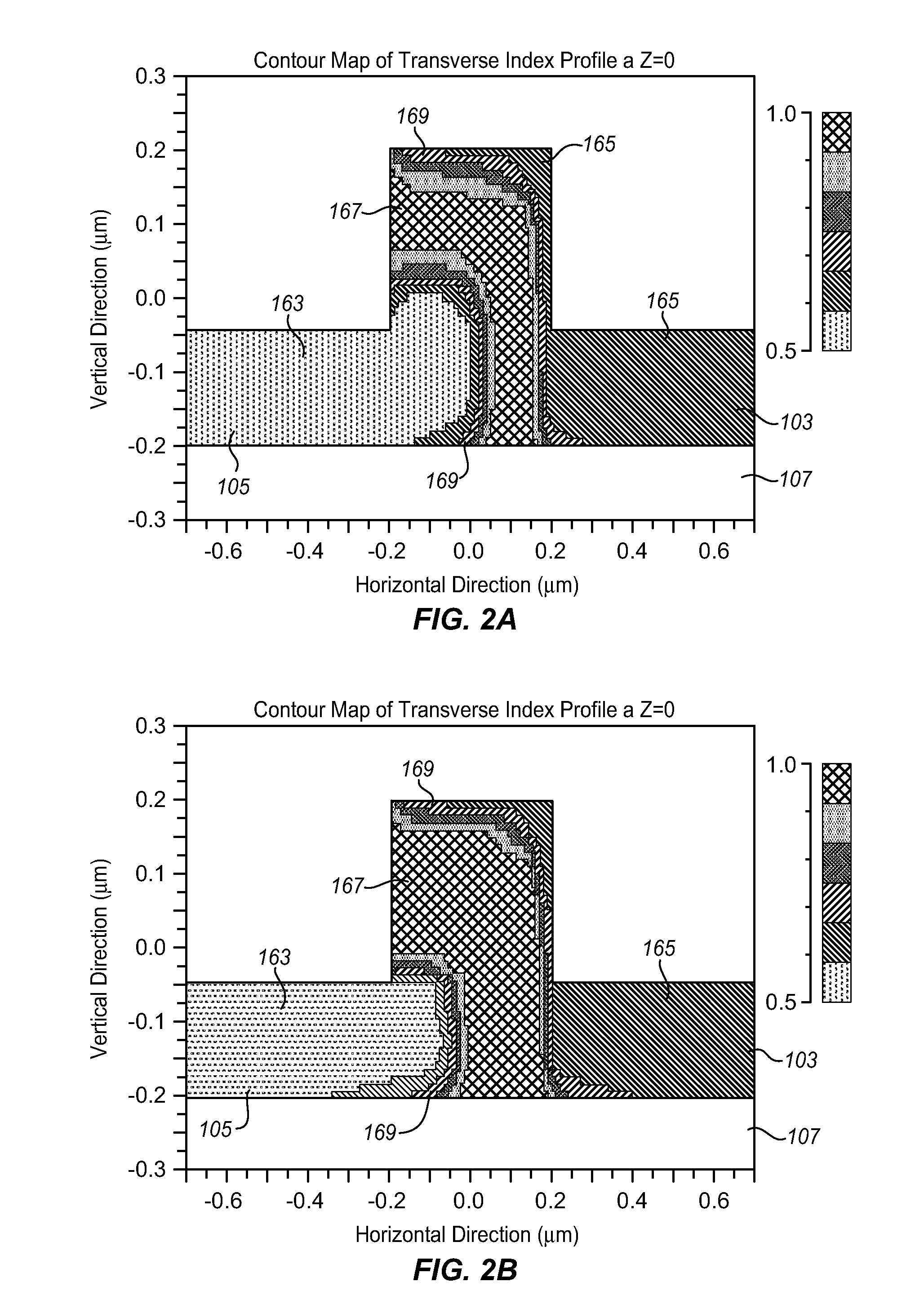

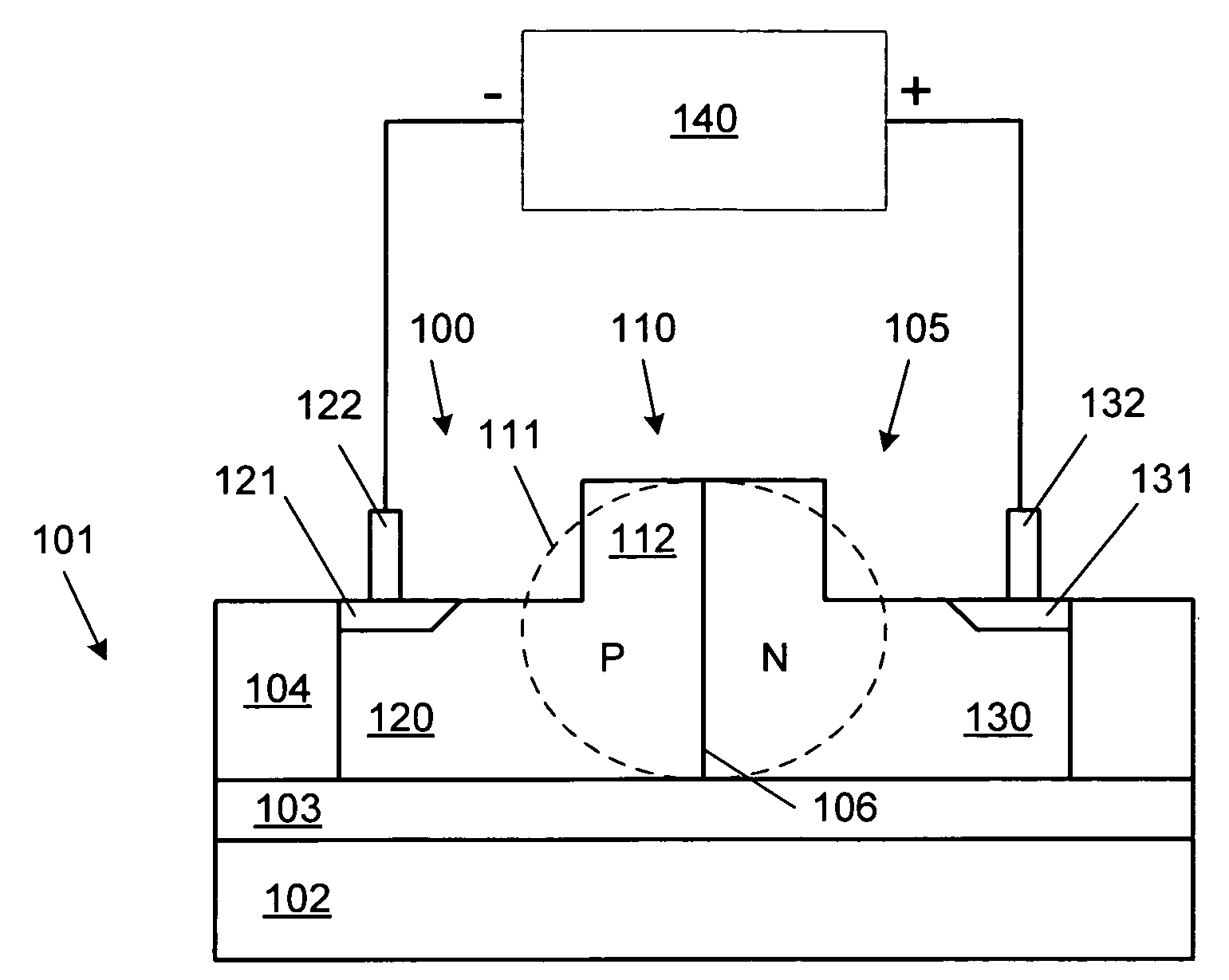

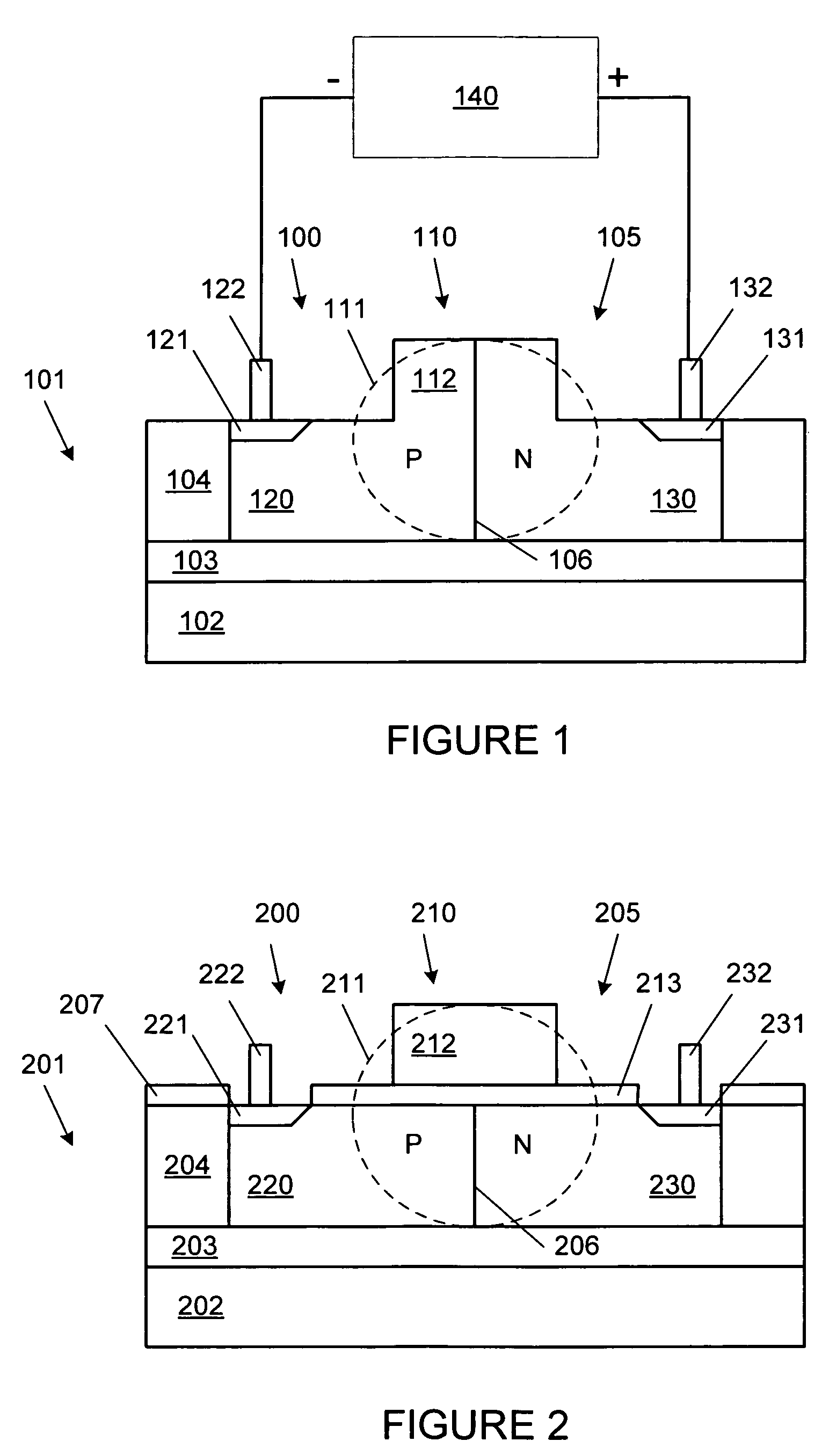

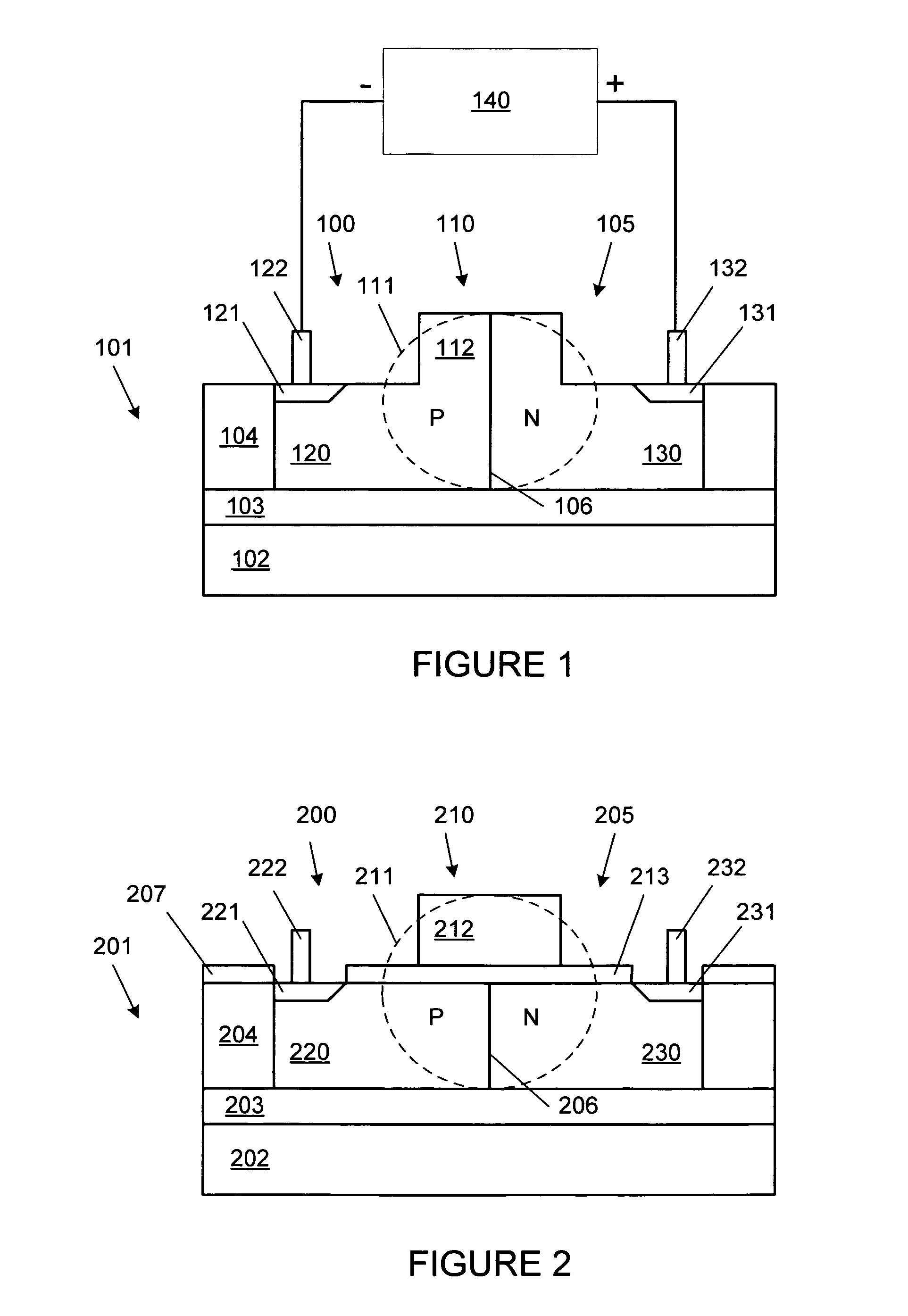

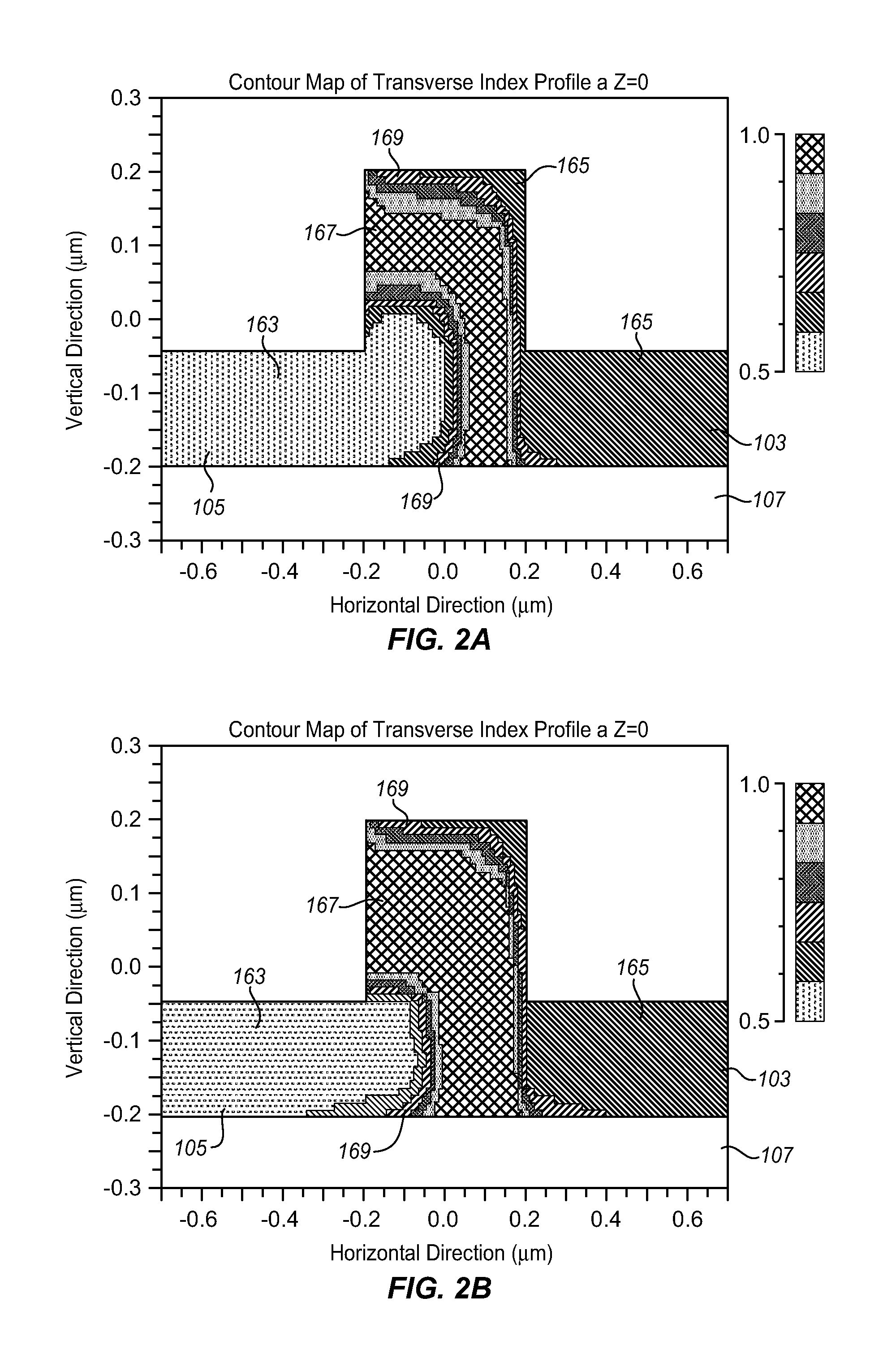

Doping profiles in PN diode optical modulators

ActiveUS7085443B1Coupling light guidesOptical waveguide light guideElectrical resistance and conductanceDopant

High speed optical modulators can be made of a lateral PN diode formed in a silicon optical waveguide, disposed on a SOI or other silicon based substrate. A PN junction is formed at the boundary of the P and N doped regions. The depletion region at the PN junction overlaps with the center of a guided optical mode propagating through the waveguide. Electrically modulating a lateral PN diode causes a phase shift in an optical wave propagating through the waveguide. Each of the doped regions can have a stepped or gradient doping profile within it or several doped sections with different doping concentrations. Forming the doped regions of a PN diode modulator with stepped or gradient doping profiles can optimize the trade off between the series resistance of the PN diode and the optical loss in the center of the waveguide due to the presence of dopants.

Owner:CISCO TECH INC

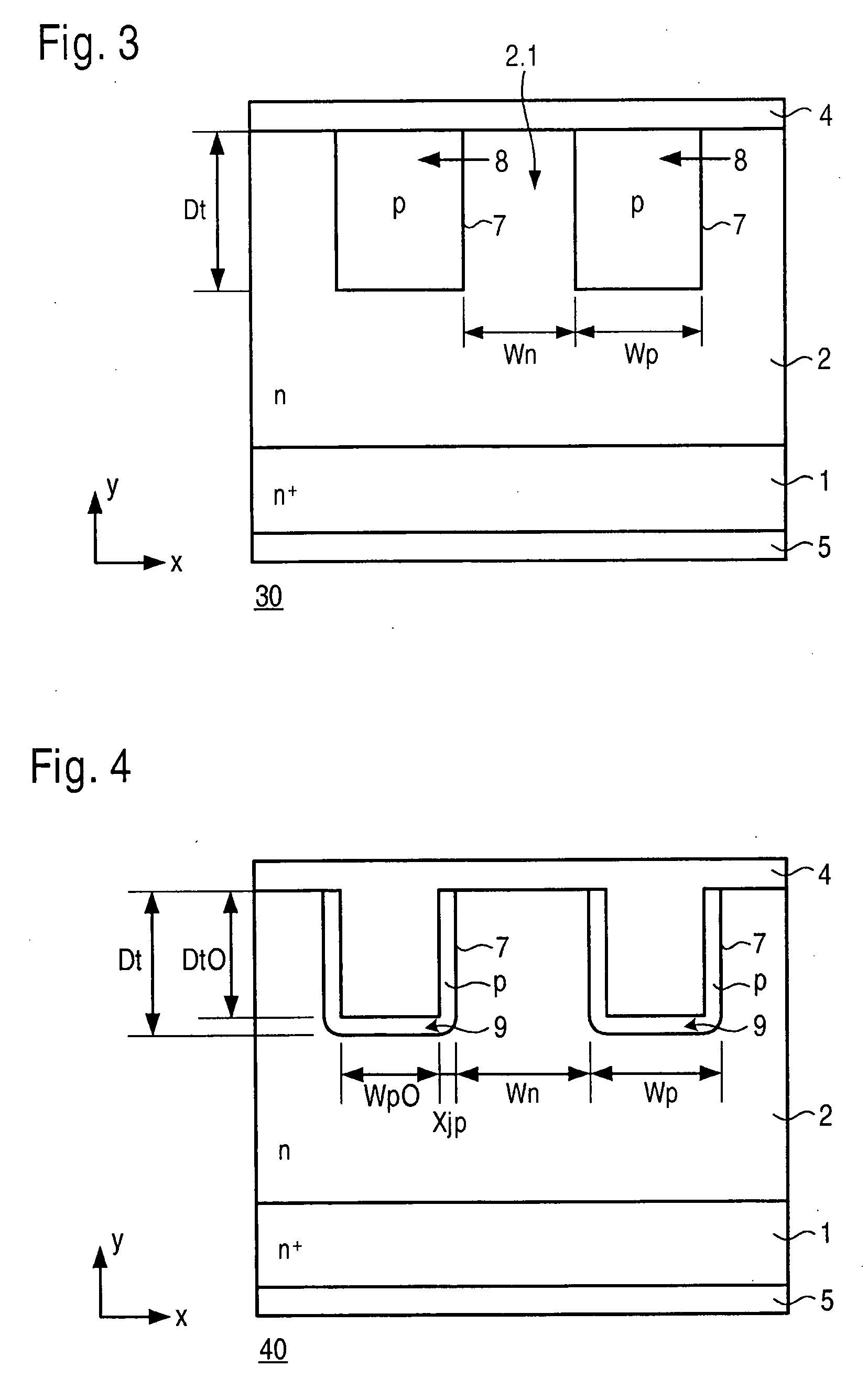

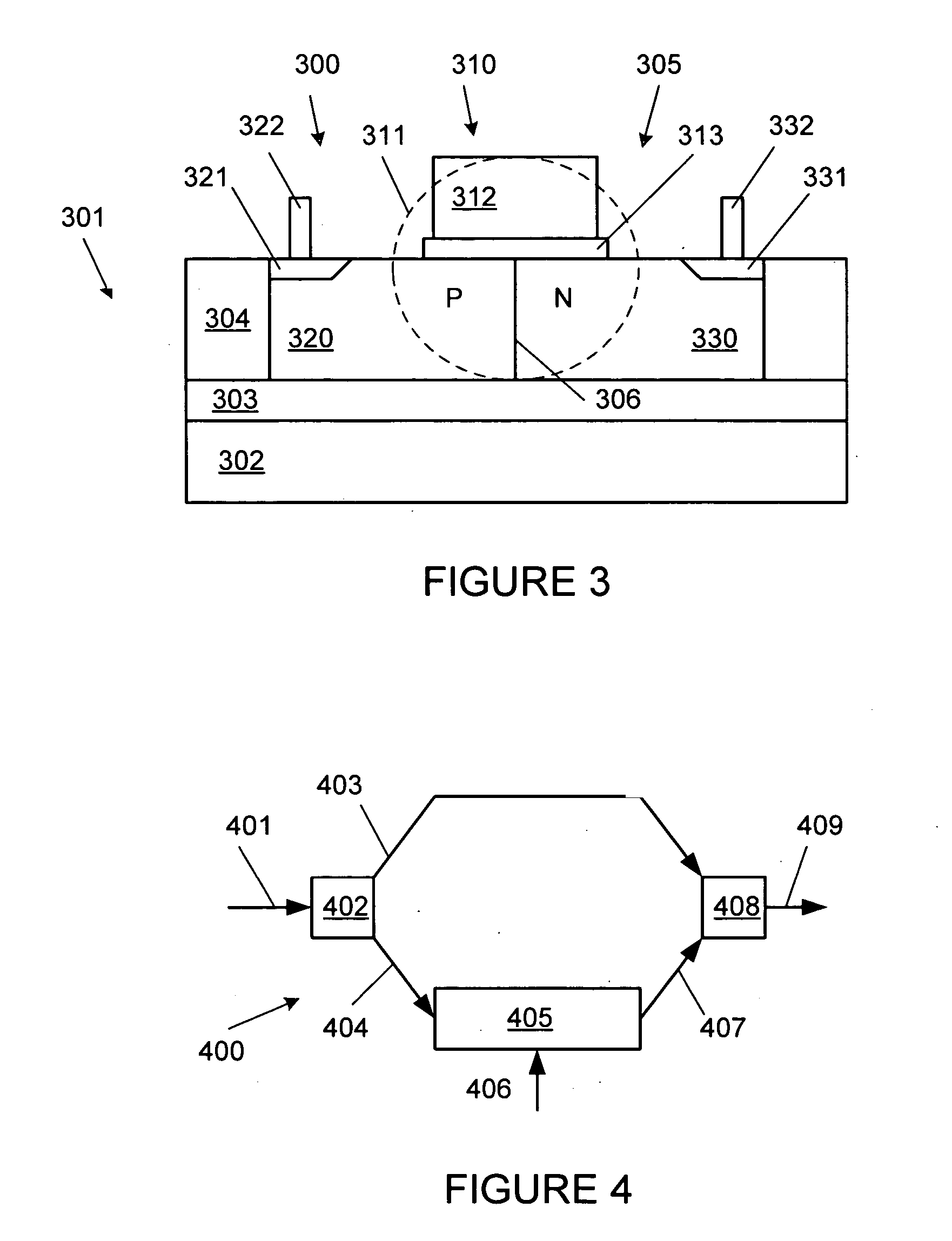

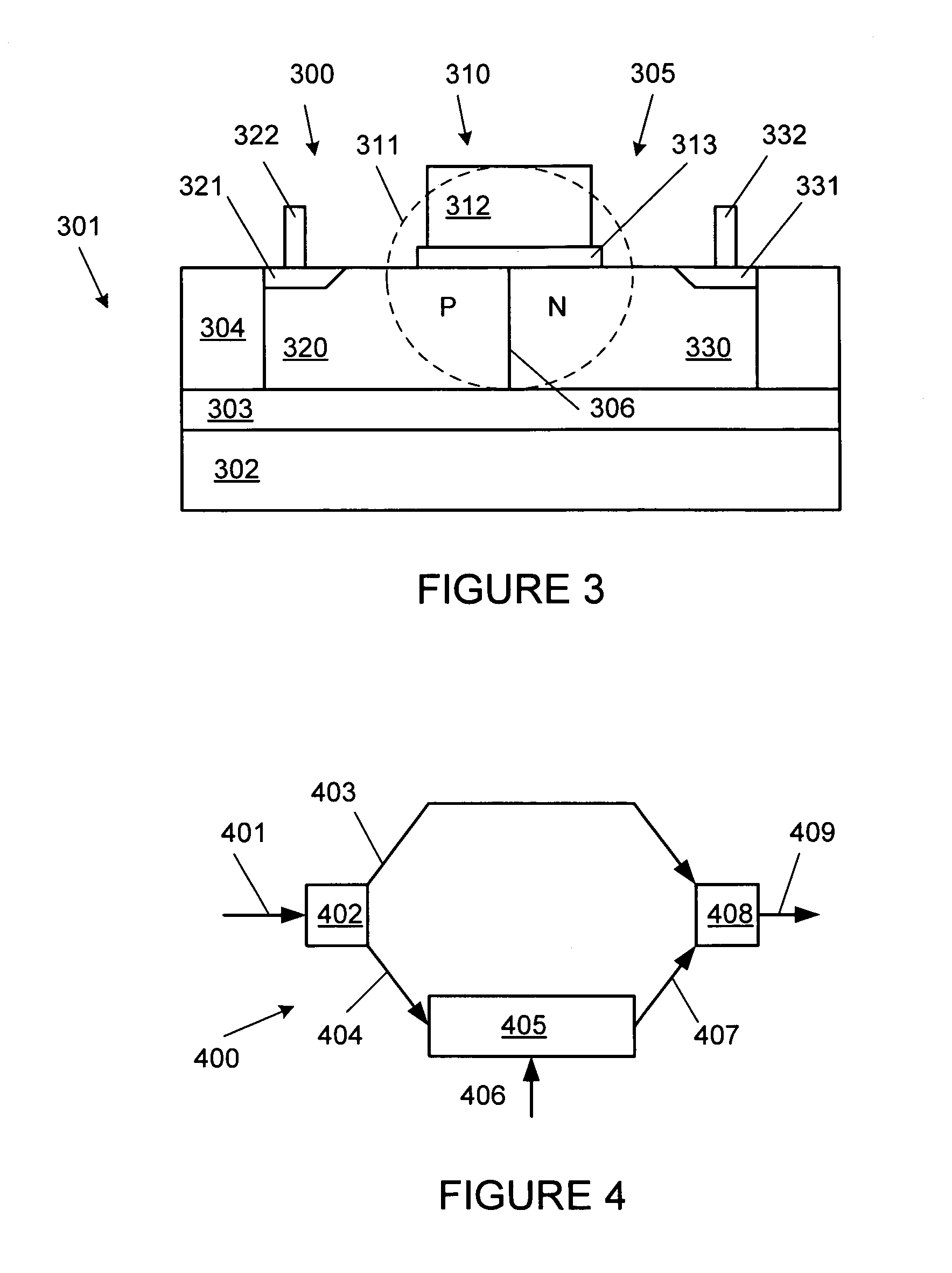

Method and Apparatus for High Speed Silicon Optical Modulation Using PN Diode

InactiveUS20100080504A1Coupling light guidesOptical waveguide light guideWaveguidePerpendicular direction

A method and apparatus for high speed silicon optical modulation is described using a PN diode. In one example, an optical waveguide has adjoining first and second doped semiconductor regions. The first and second regions have opposite doping types and the first doped region extends in two perpendicular directions through the waveguide.

Owner:INTEL CORP

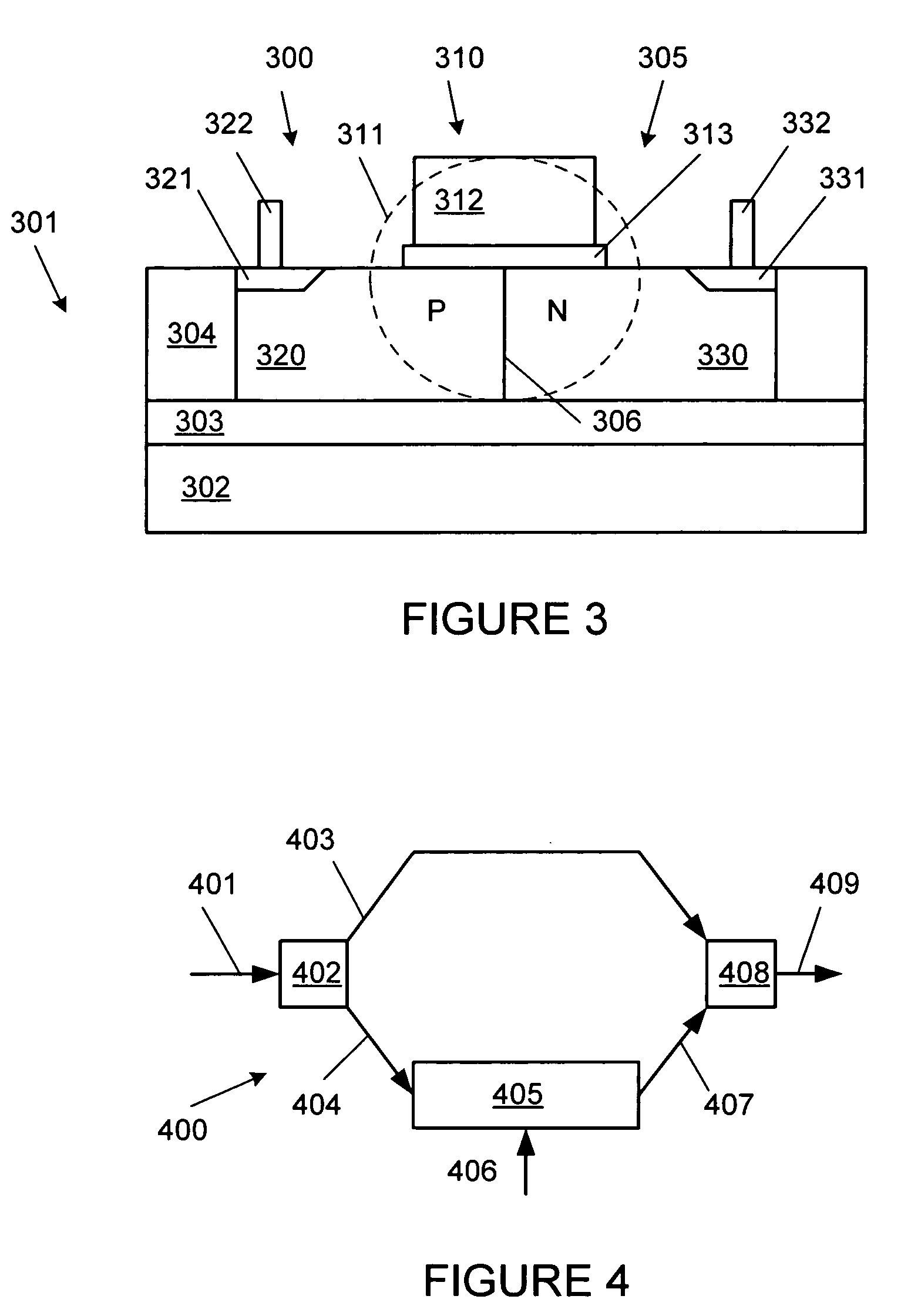

PN diode optical modulators fabricated in strip loaded waveguides

ActiveUS7136544B1Minimal impactDifficult to controlOptical waveguide light guideNon-linear opticsPhase shiftedWaveguide

High speed optical modulators can be made of a lateral PN diode formed in a strip loaded optical waveguide on a SOI or other silicon based substrate. A PN junction is formed at the boundary of the P and N doped regions. The depletion region at the PN junction overlaps with the center of a guided optical mode propagating through the waveguide. Electrically modulating a lateral PN diode causes a phase shift in an optical wave propagating through the waveguide. Due to differences in fabrication methods, forming strip loaded waveguides with consistent properties for use in PN diode optical modulators is much easier than fabricating similar rib waveguides.

Owner:CISCO TECH INC

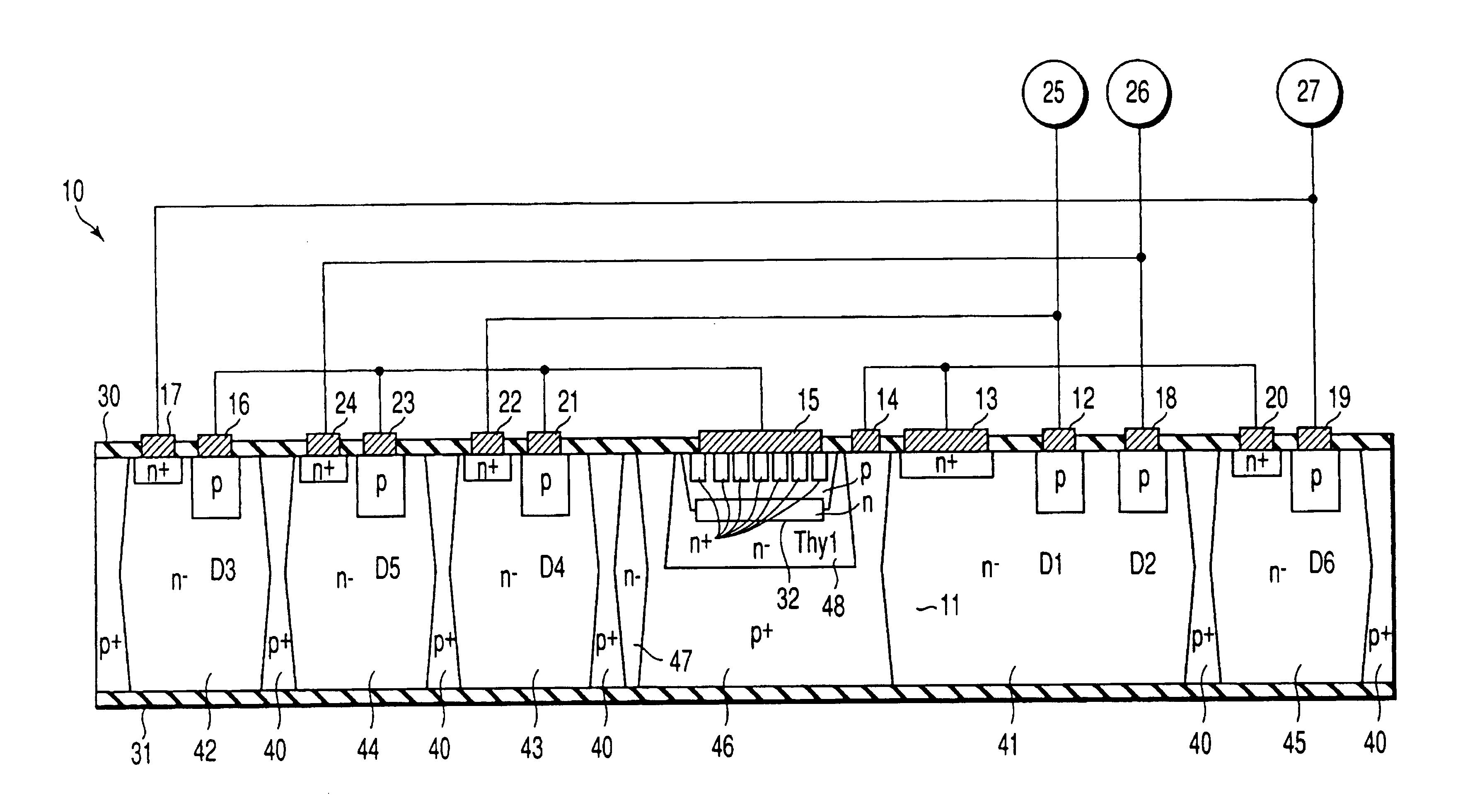

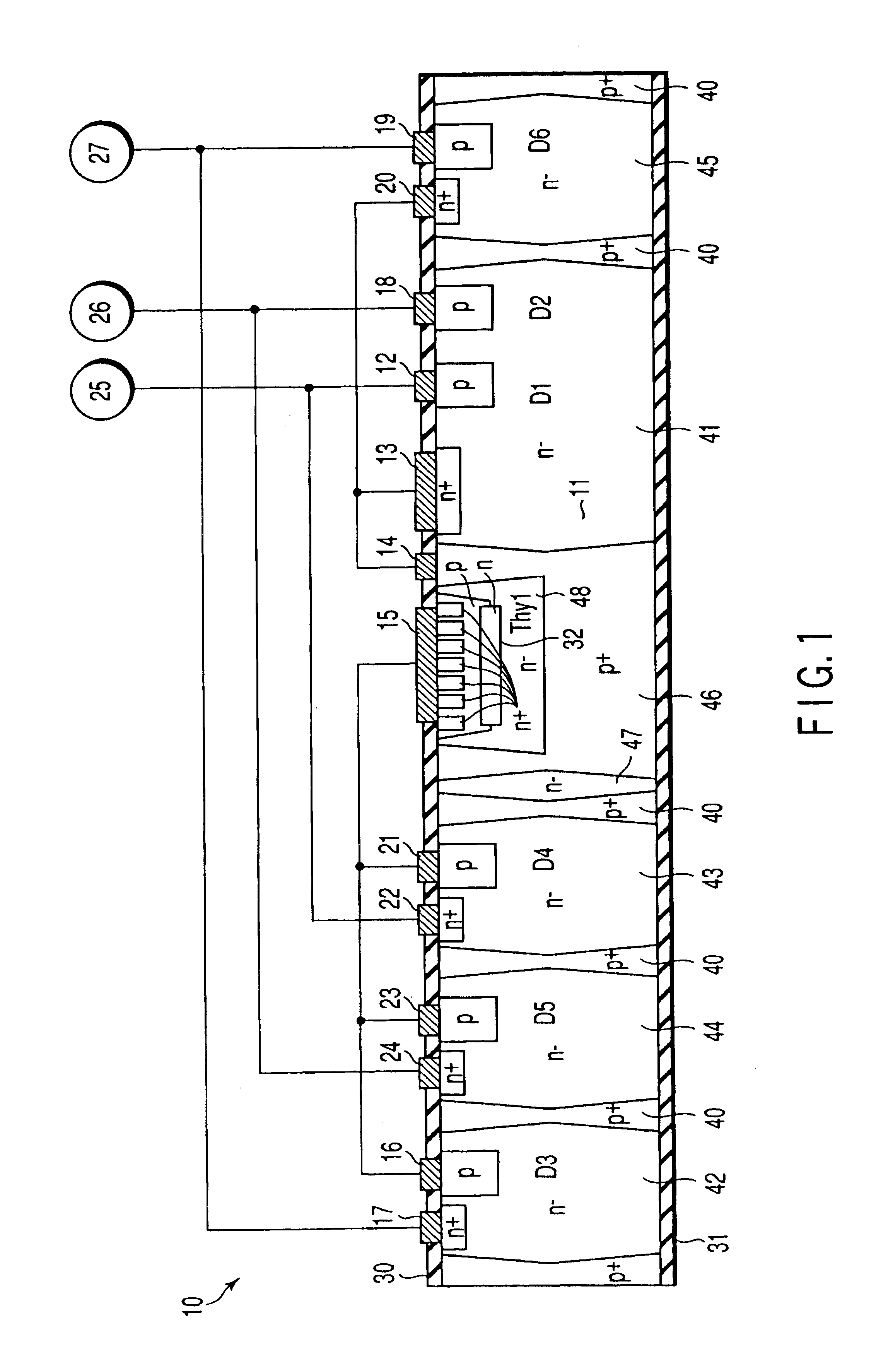

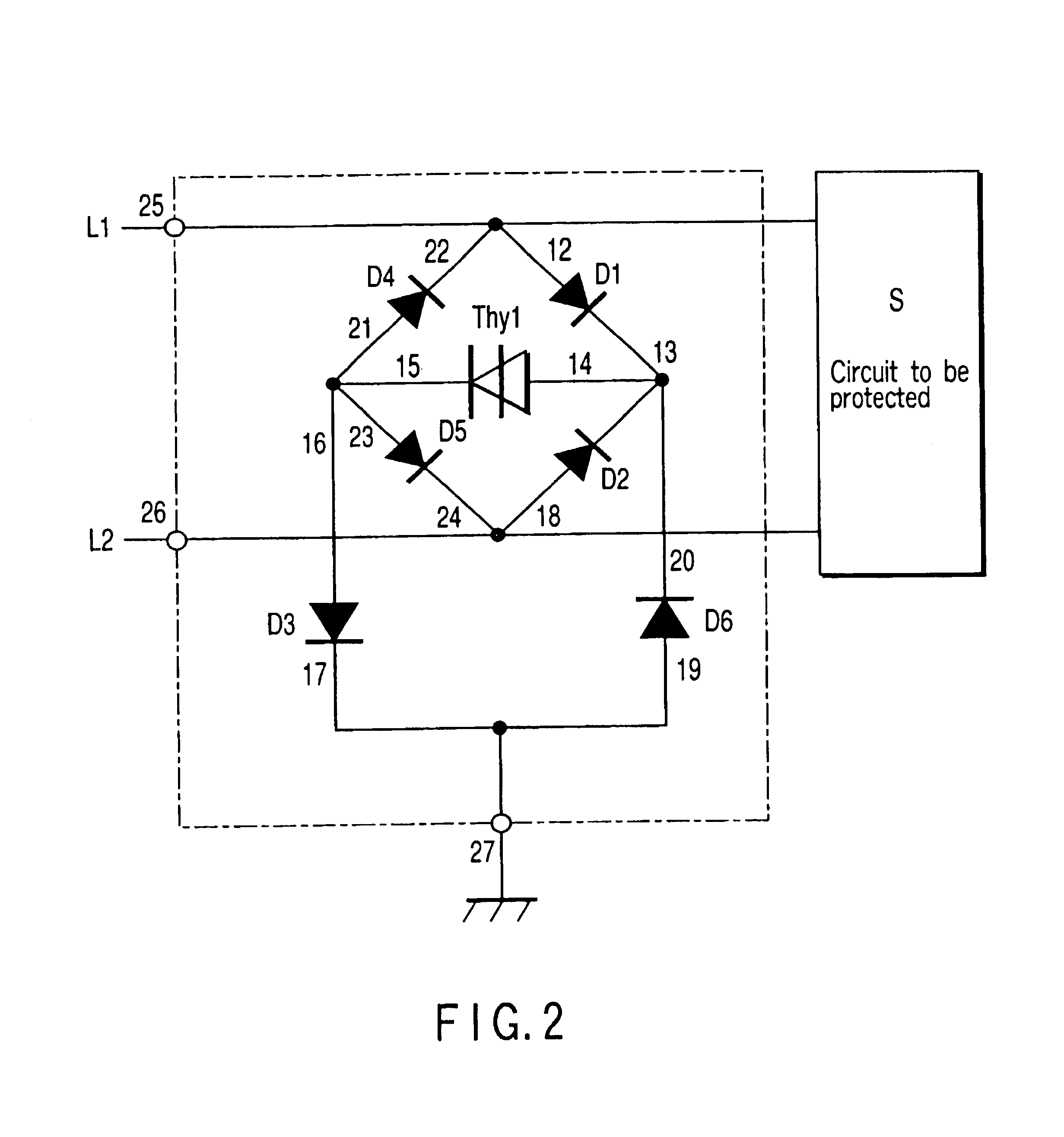

Surge protection semiconductor device

A pnpn thyristor element Thy1 and six pn diode elements D1, D2, D3, D4, D5, and D6 are formed in a semiconductor substrate of a first conductivity type, and separated into six regions by a diffusion layer of a second conductivity type which also functions as the anode of the thyristor element Thy1. A double isolation diffusion layer is disposed between the region of the thyristor element Thy1 and three pn diode elements D1 ·D2 and D6, and the region of the three remaining pn diodes D3, D4, and D5. Surface connection is performed to provide a balance type surge protection circuit.

Owner:SHINDENGEN ELECTRIC MFG CO LTD

Doping profiles in PN diode optical modulators

ActiveUS7251408B1Coupling light guidesOptical waveguide light guideDopantElectrical resistance and conductance

High speed optical modulators can be made of a lateral PN diode formed in a silicon optical rib waveguide, disposed on a SOI or other silicon based substrate. A PN junction is formed at the boundary of the P and N doped regions. The depletion region at the PN junction overlaps with the center of a guided optical mode propagating through the waveguide. Electrically modulating a lateral PN diode causes a phase shift in an optical wave propagating through the waveguide. Each of the doped regions can have a stepped or gradient doping profile within it or several doped sections with different doping concentrations. Forming the doped regions of a PN diode modulator with stepped or gradient doping profiles can optimize the trade off between the series resistance of the PN diode and the optical loss in the center of the waveguide due to the presence of dopants.

Owner:CISCO TECH INC

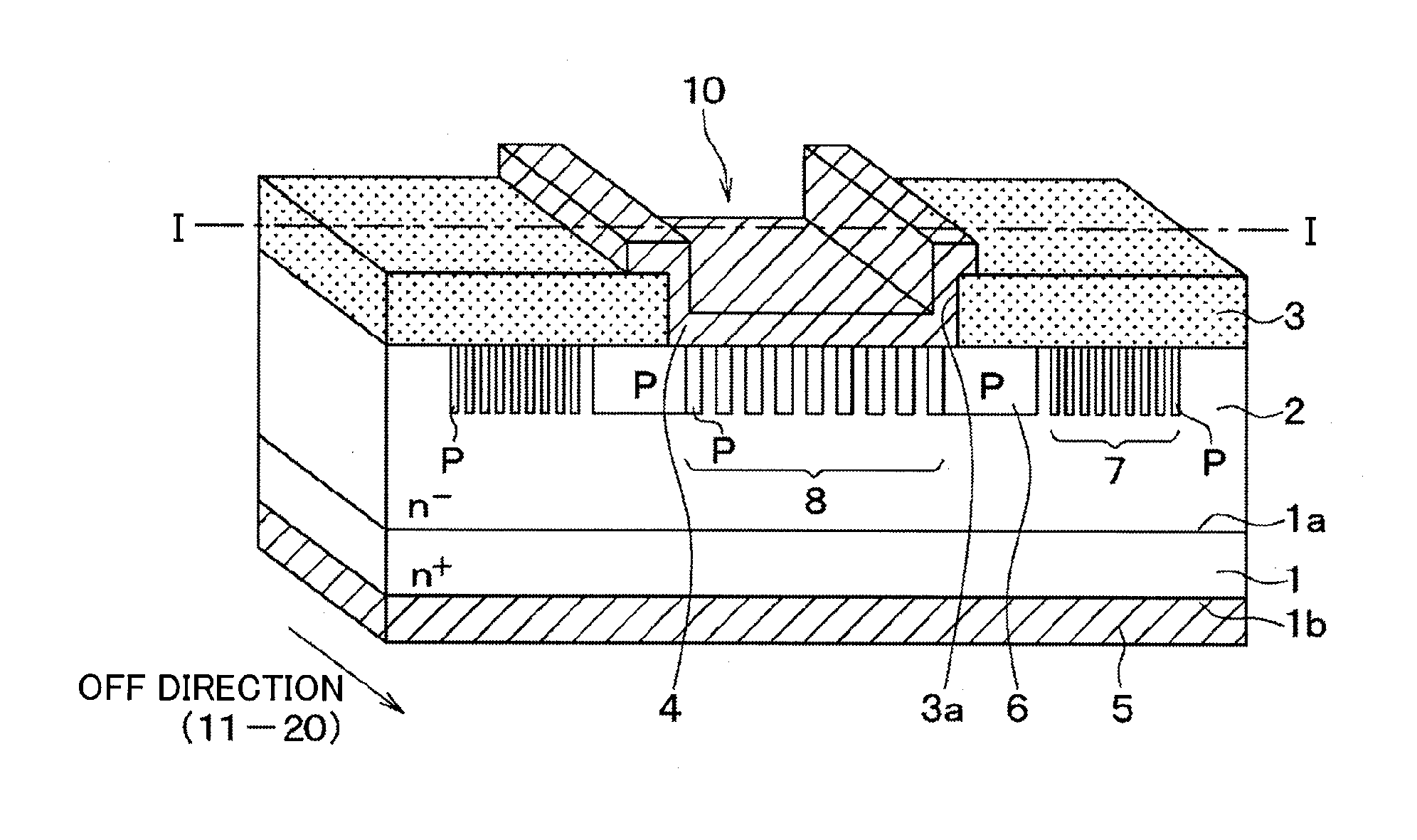

Semiconductor device with large blocking voltage

InactiveUS20090014719A1Large noise marginRaise the threshold voltageTransistorSolid-state devicesNoise marginSemiconductor

A junction FET having a large gate noise margin is provided. The junction FET comprises an n− layer forming a drift region of the junction FET formed over a main surface of an n+ substrate made of silicon carbide, a p+ layer forming a gate region formed in contact with the n− layer forming the drift region and a gate electrode provided in an upper layer of the n+ substrate. The junction FET further incorporates pn diodes formed over the main surface of the n+ substrate and electrically connecting the p+ layer forming the gate region and the gate electrode.

Owner:RENESAS ELECTRONICS CORP

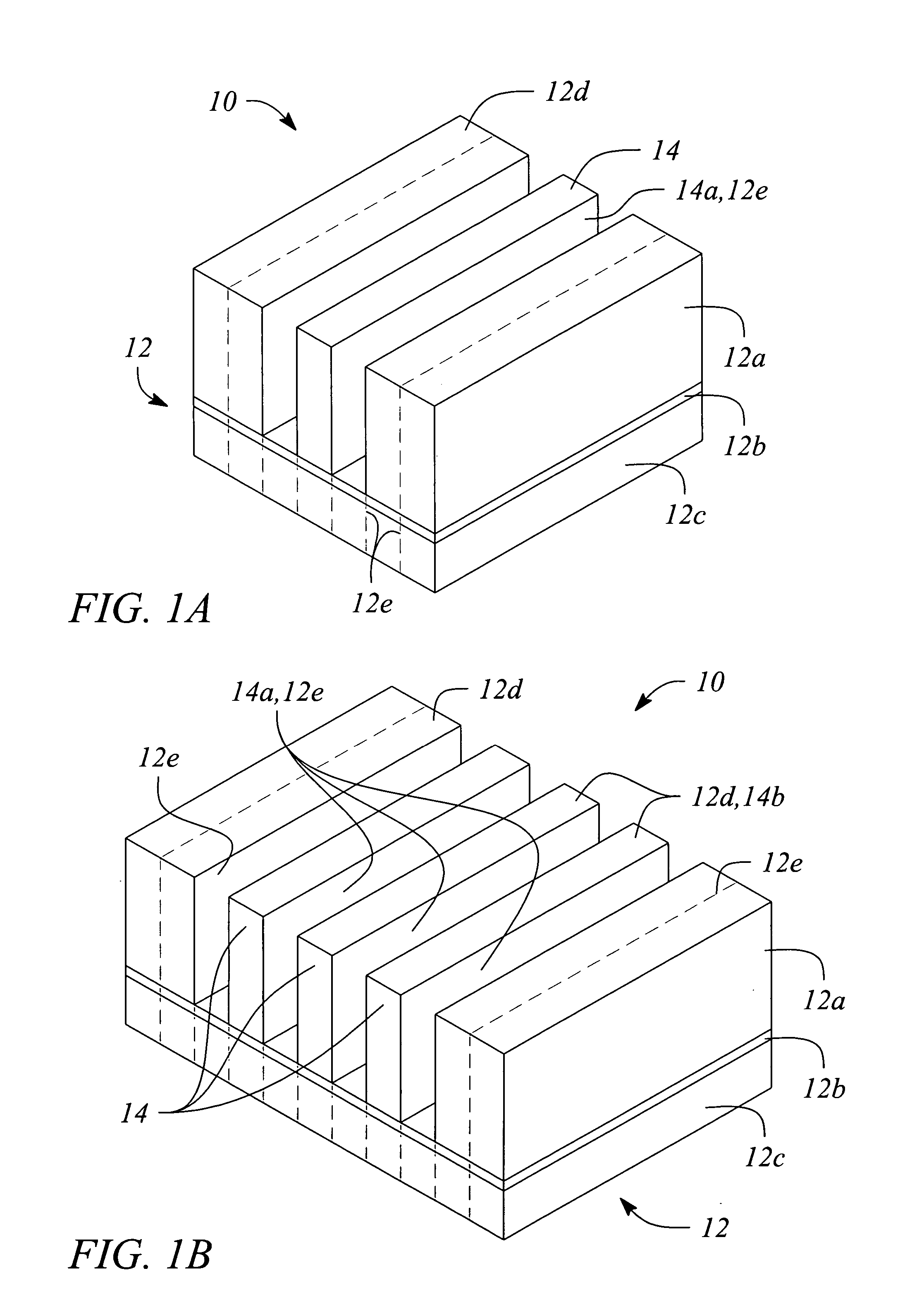

Nanowire device with (111) vertical sidewalls and method of fabrication

A nano-scale device and method of fabrication provide a nanowire having (111) vertical sidewalls. The nano-scale device includes a semiconductor-on-insulator substrate polished in a [110] direction, the nanowire, and an electrical contact at opposite ends of the nanowire. The method includes wet etching a semiconductor layer of the semiconductor-on-insulator substrate to form the nanowire extending between a pair of islands in the semiconductor layer. The method further includes depositing an electrically conductive material on the pair of islands to form the electrical contacts. A nano-pn diode includes the nanowire as a first nano-electrode, a pn-junction vertically stacked on the nanowire, and a second nano-electrode on a (110) horizontal planar end of the pn-junction. The nano-pn diode may be fabricated in an array of the diodes on the semiconductor-on-insulator substrate.

Owner:HEWLETT PACKARD DEV CO LP

SIS semiconductor having junction barrier schottky device

A semiconductor device having a junction barrier Schottky diode includes: a SiC substrate; a drift layer on the substrate; an insulation film on the drift layer having an opening in a cell region; a Schottky barrier diode having a Schottky electrode contacting the drift layer through the opening of the insulation film and an ohmic electrode on the substrate; a terminal structure having a RESURF layer surrounding the cell region; and multiple second conductive type layers on an inner side of the RESURF layer. The second conductive type layers and the drift layer provide a PN diode. The Schottky electrode includes a first Schottky electrode contacting the second conductive type layers with ohmic contact and a second Schottky electrode contacting the drift layer with Schottky contact.

Owner:DENSO CORP

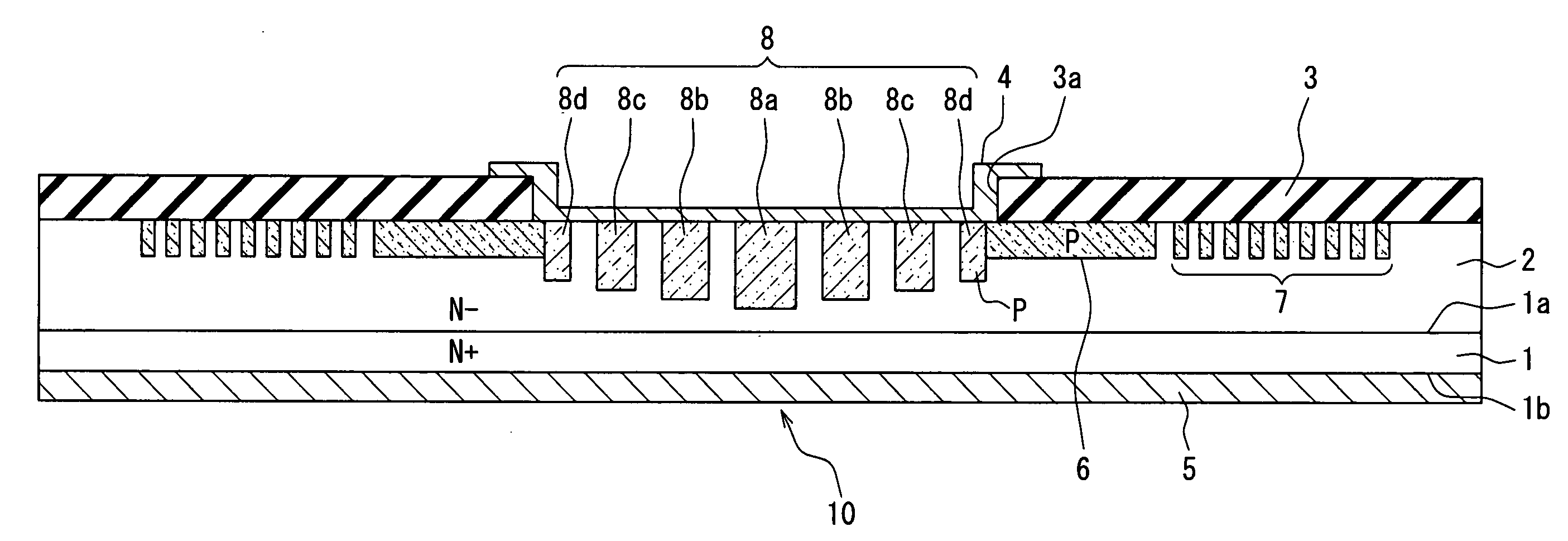

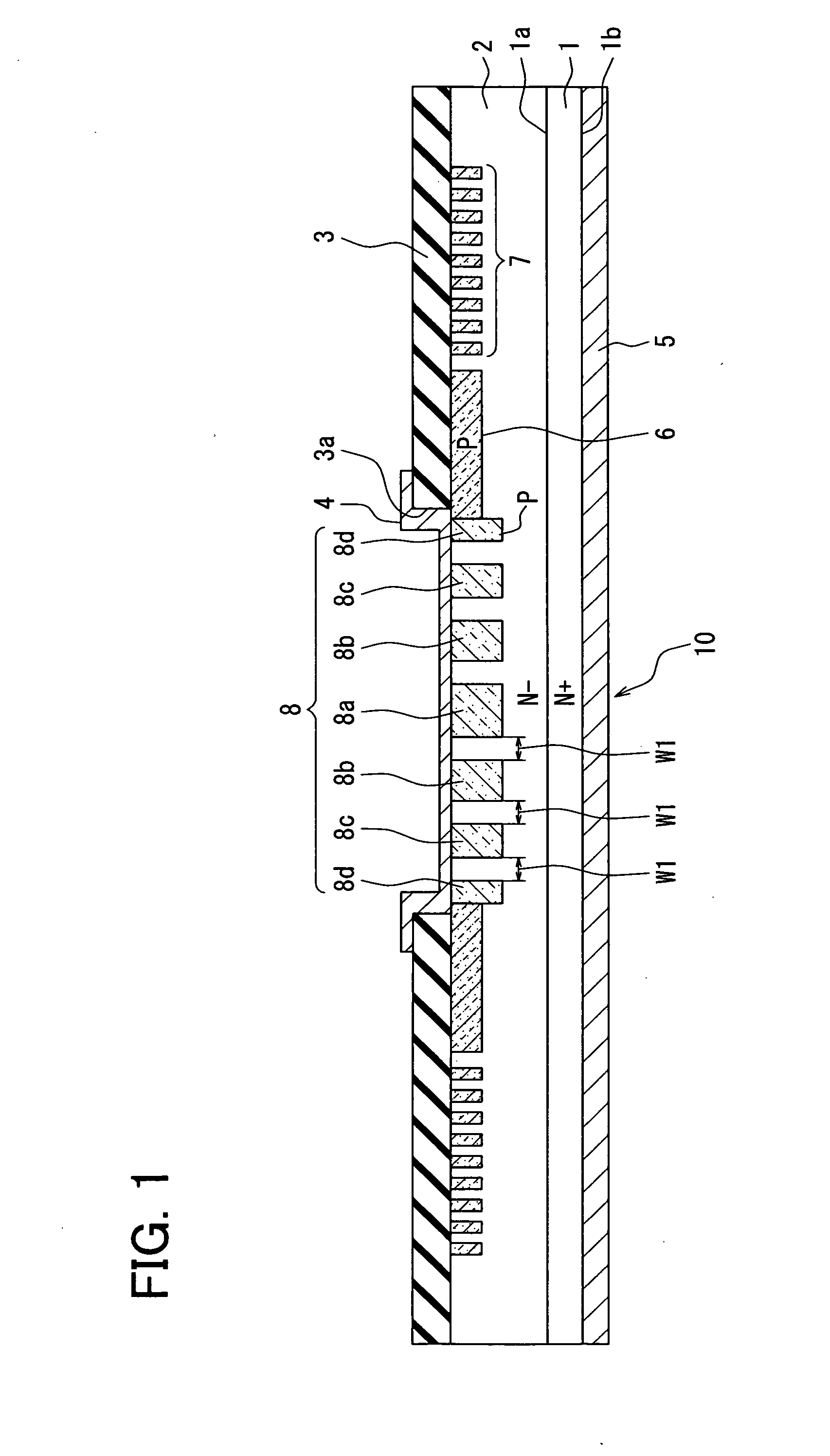

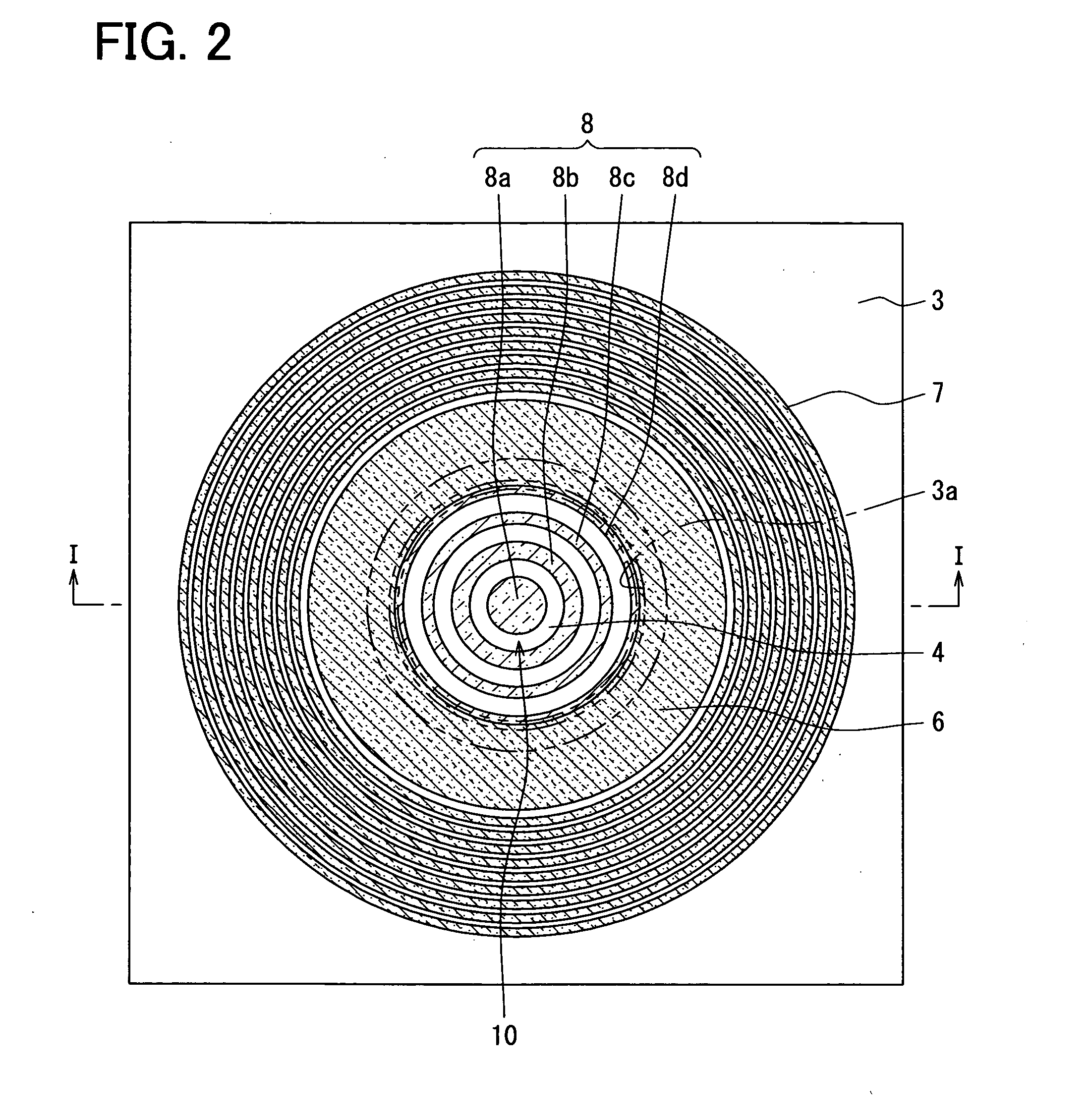

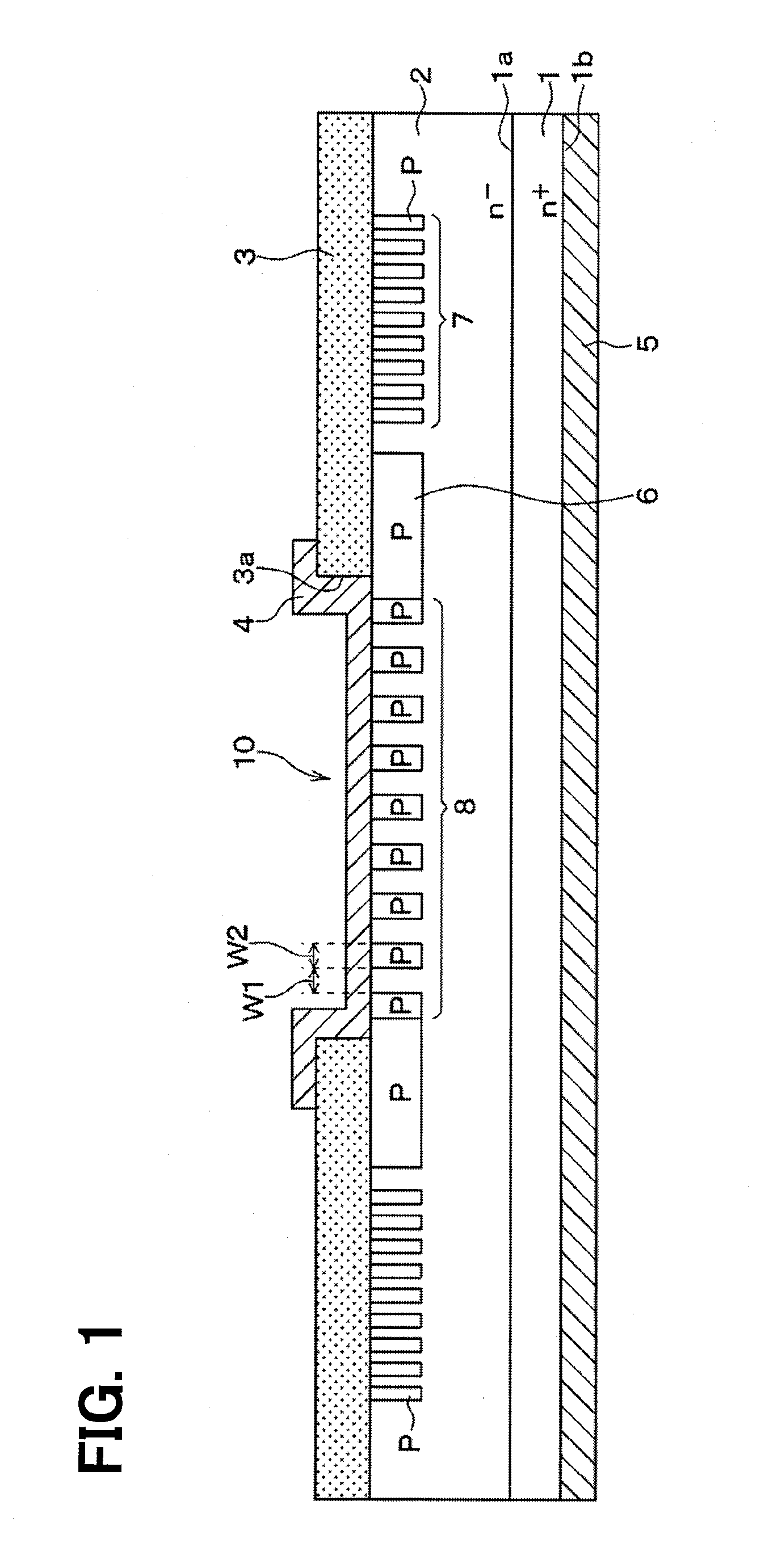

Silicon carbide semiconductor device having junction barrier schottky diode

A silicon carbide semiconductor device includes a drift layer having first conductive type on a substrate, a cell region in the drift layer, a schottky electrode on the drift layer and multiple second conductive type layers in the cell region. The second conductive type layers are separated from each other and contact the schottky electrode. A size and an impurity concentration of the second conductive type layers and a size and an impurity concentration of a portion of the drift layer sandwiched between the second conductive type layers are determined so that a charge quantity of the second conductive type layers is equal to a charge quantity of the portion. Hereby, the pressure-proof JBS and low resistivity second conductive type layers arranged on a surface of the drift layer to provide a PN diode, can be obtained.

Owner:DENSO CORP

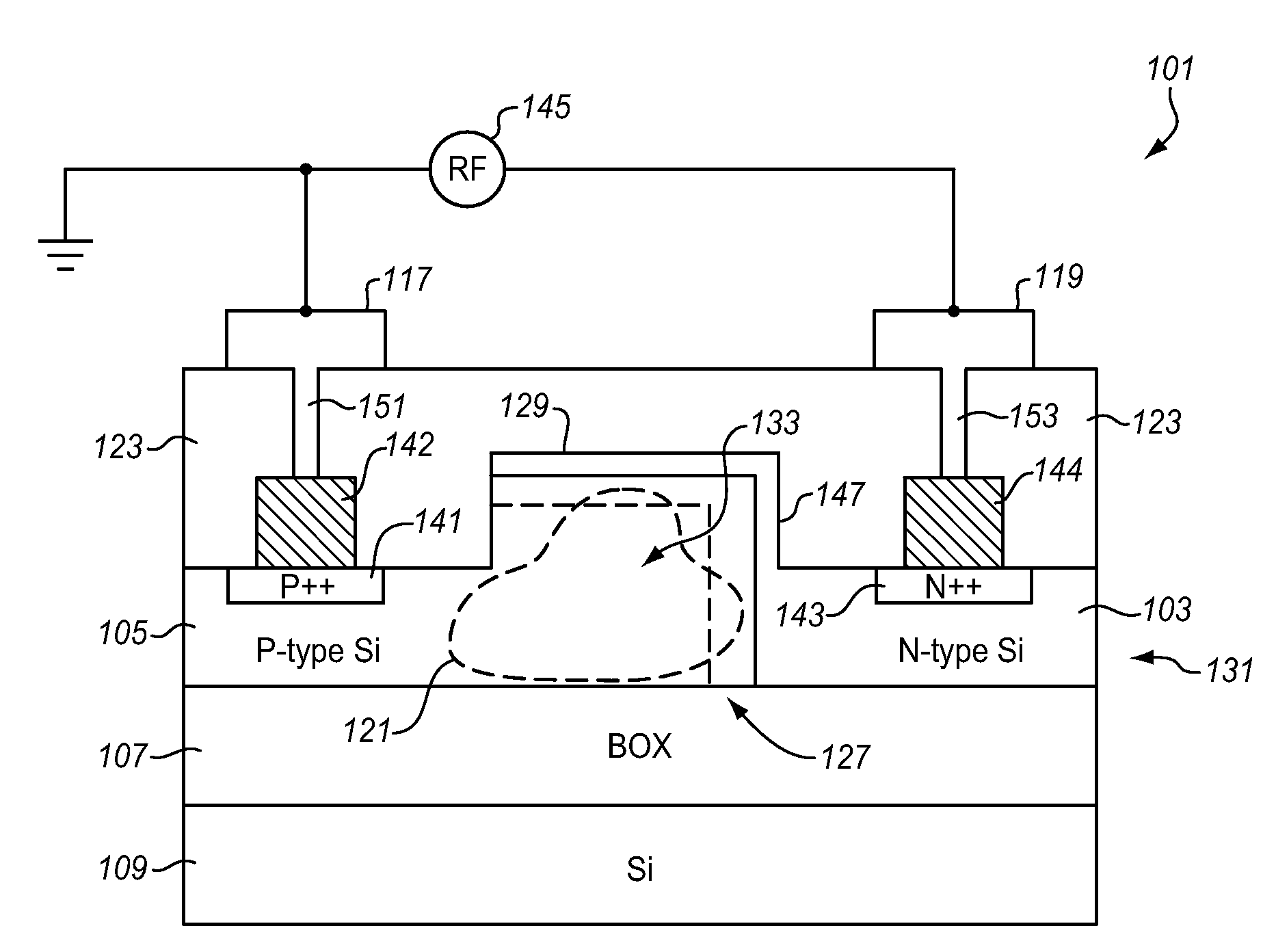

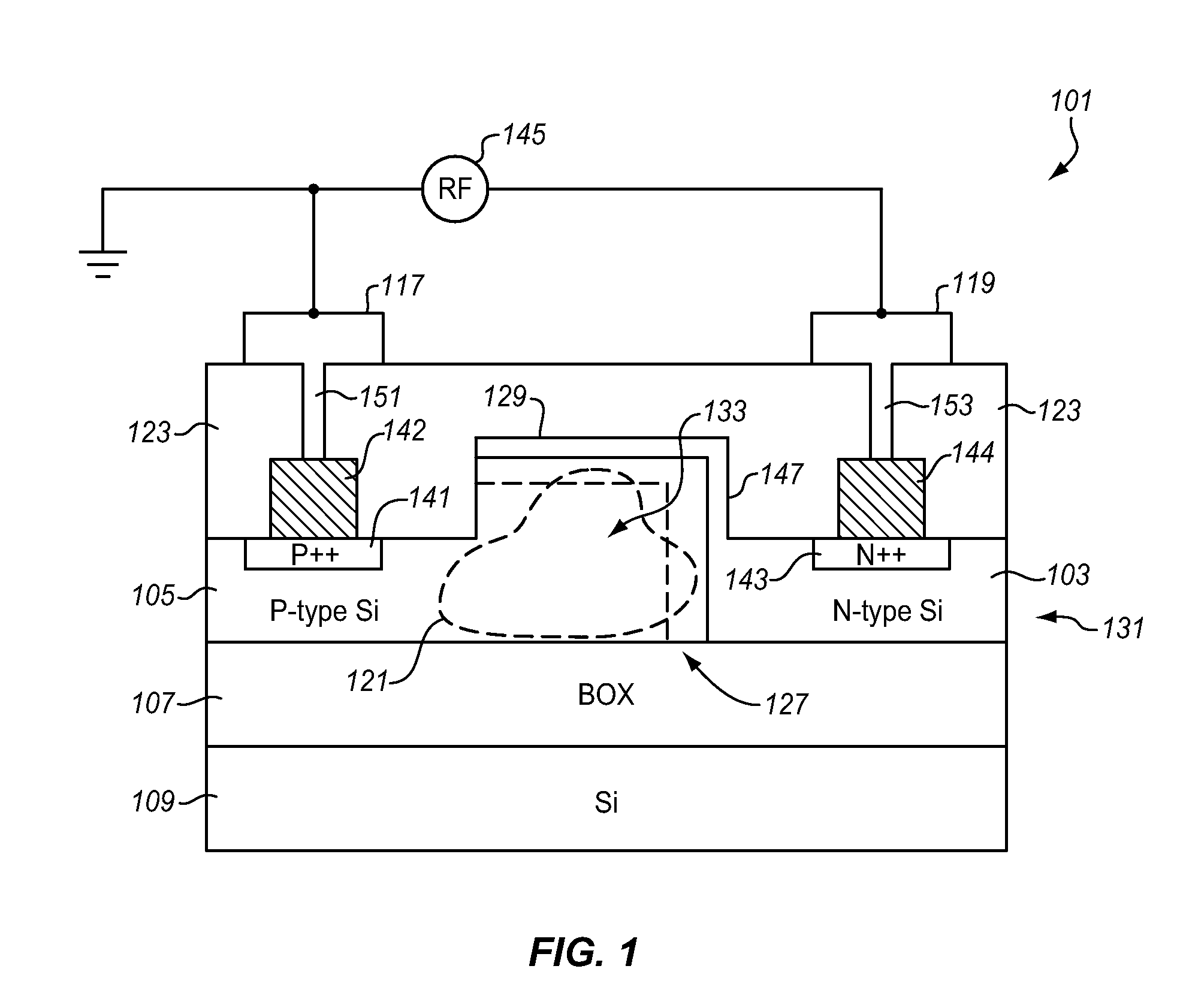

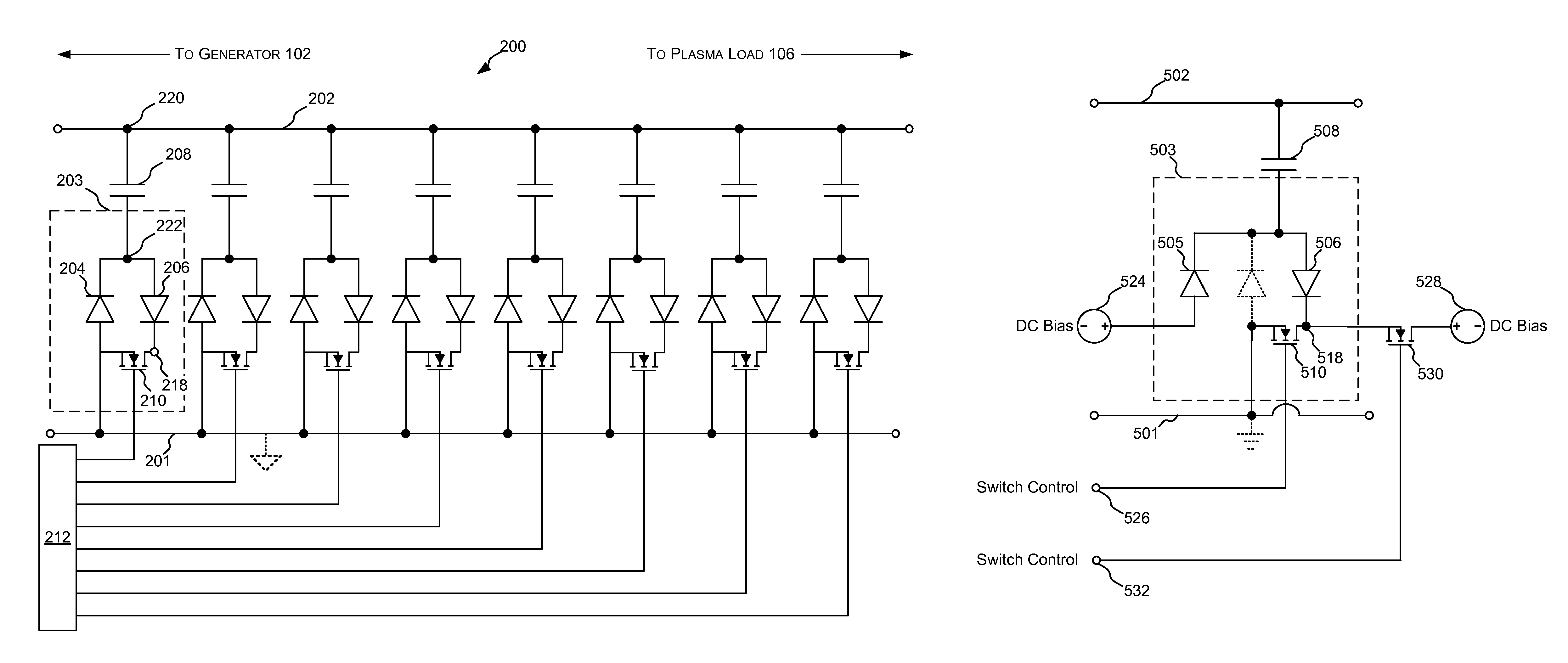

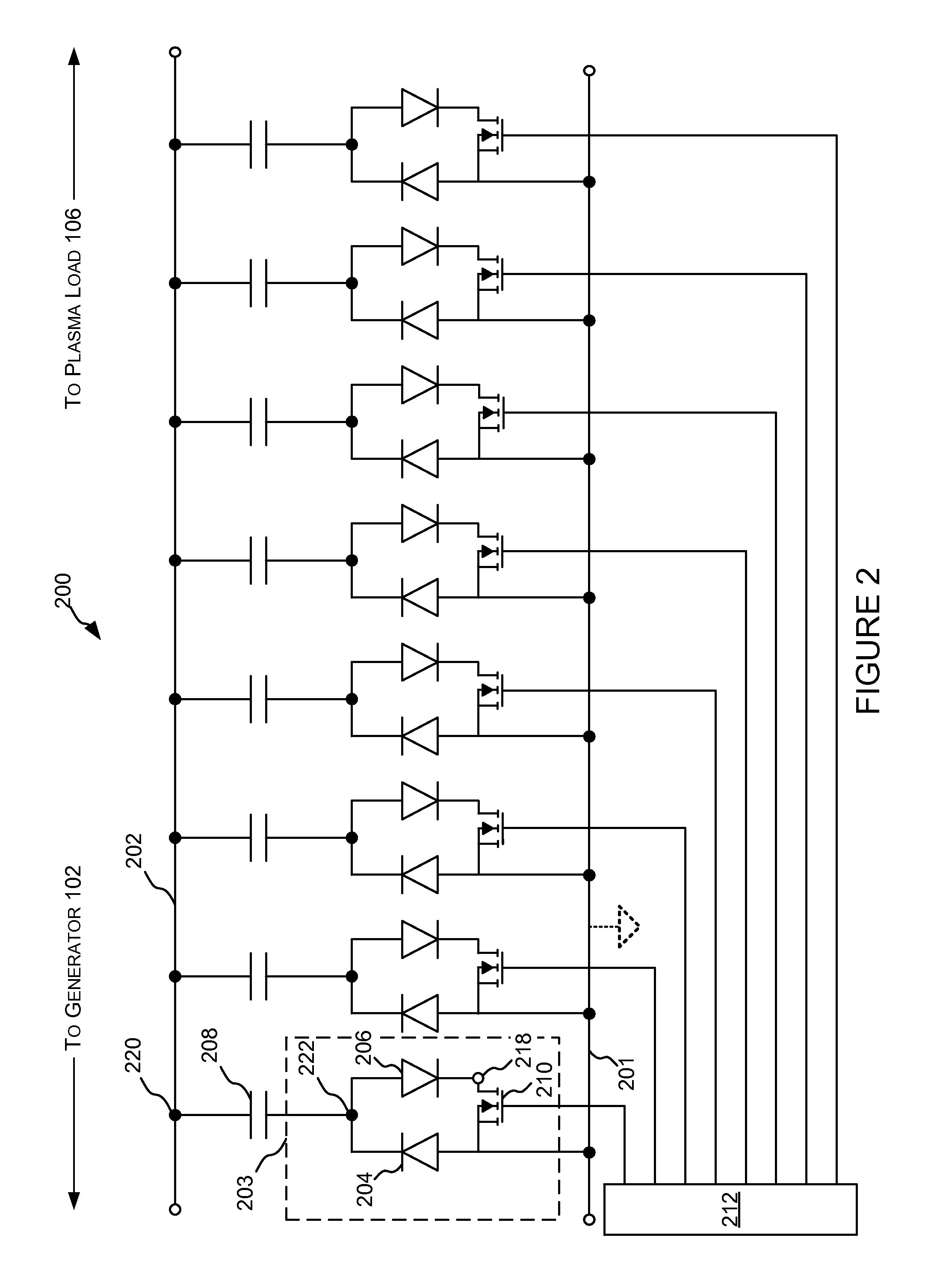

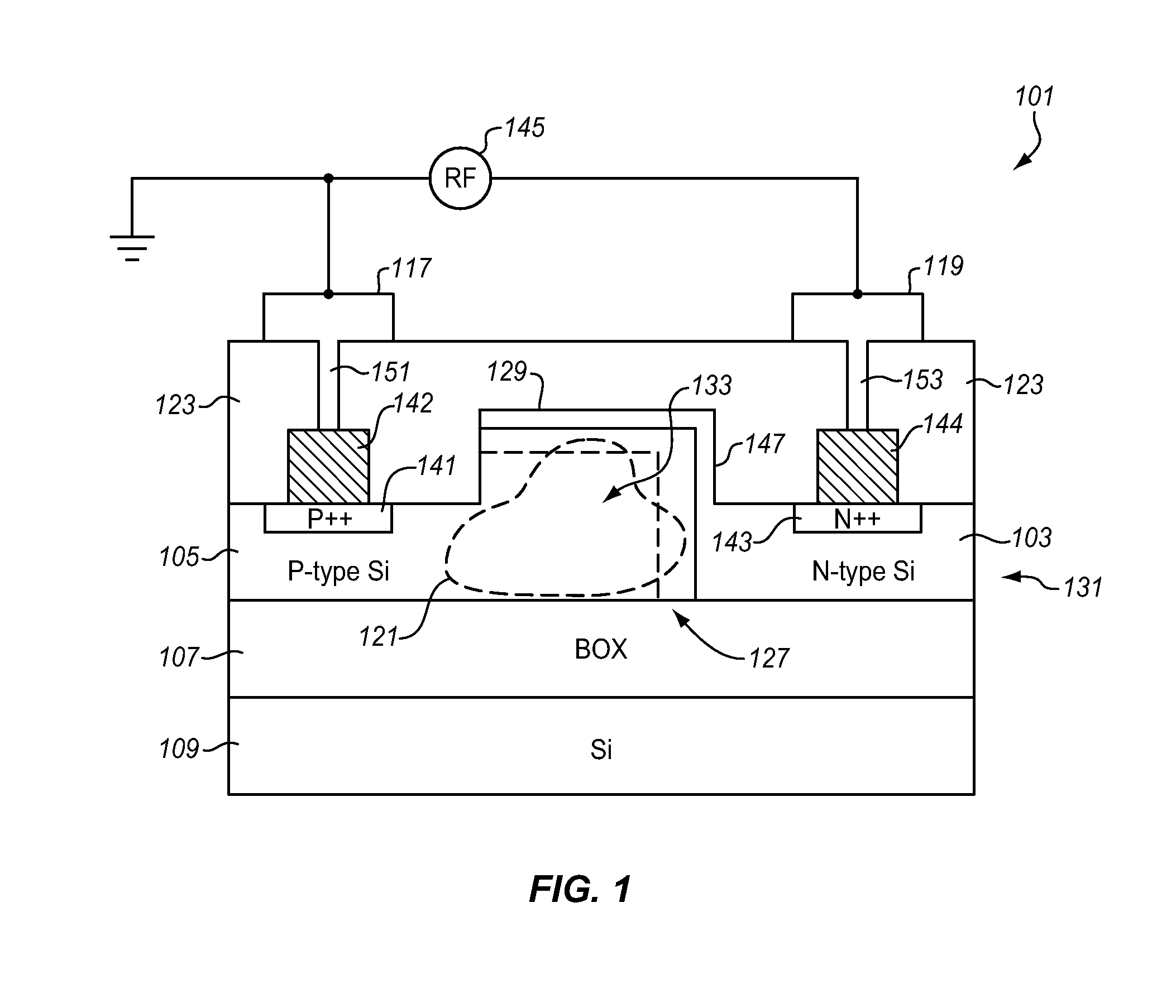

High frequency solid state switching for impedance matching

ActiveUS8436643B2Reliability increasing modificationsMultiple-port networksImpedance matchingEngineering

Owner:AES GLOBAL HLDG PTE LTD

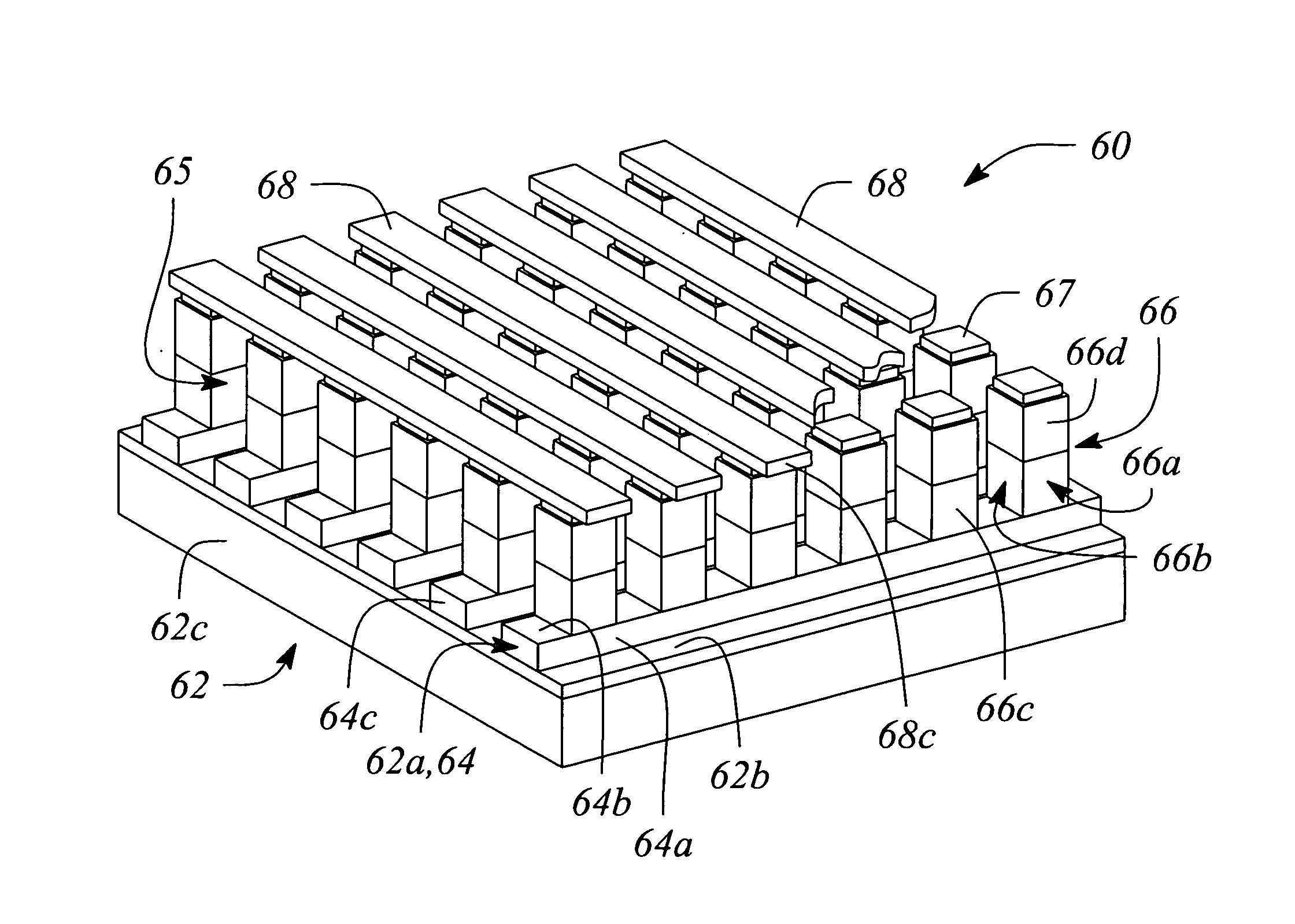

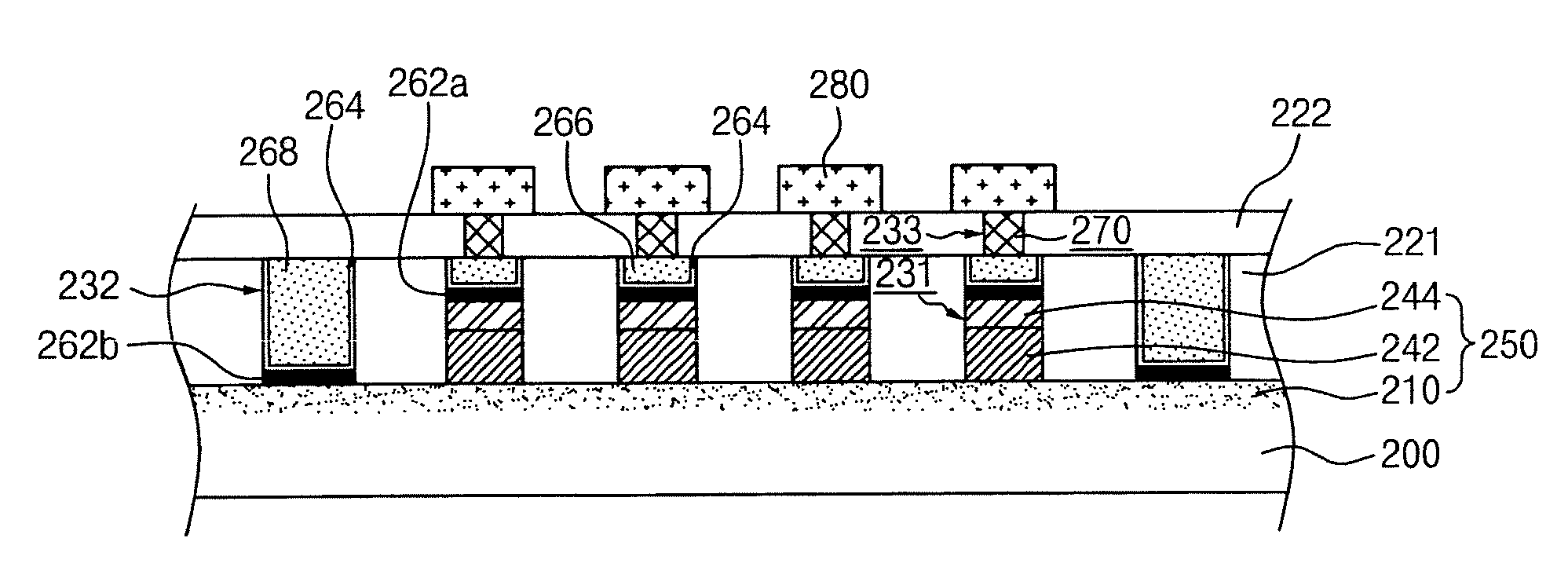

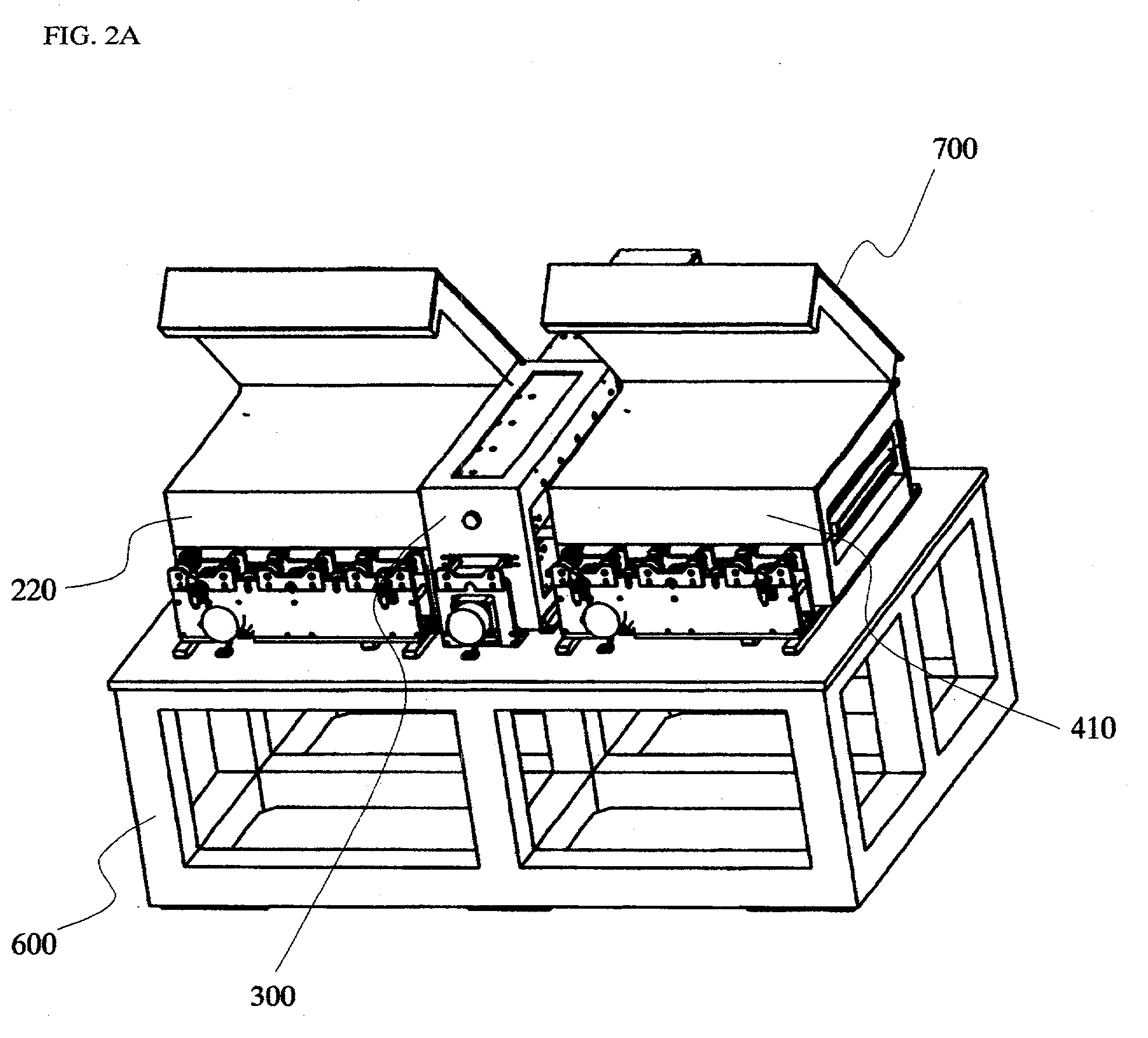

Phase change memory device and method for manufacturing the same

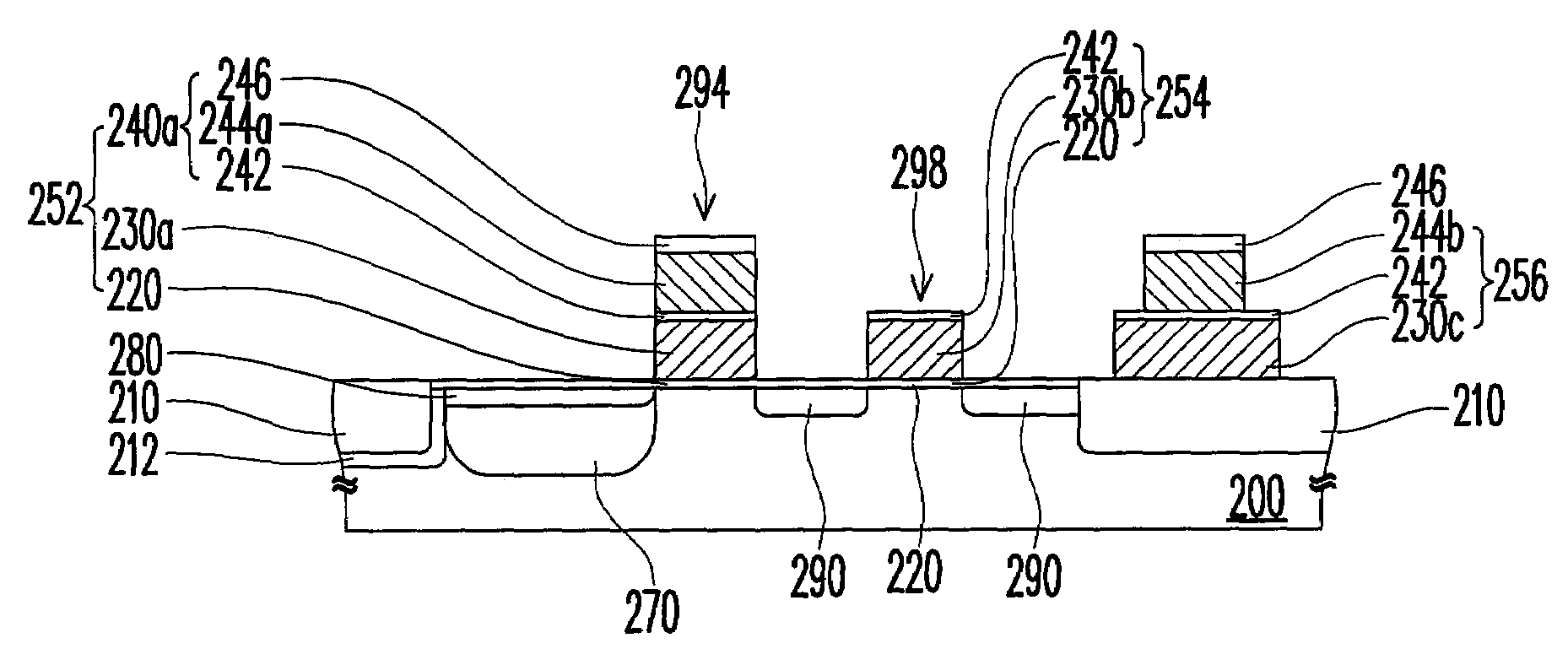

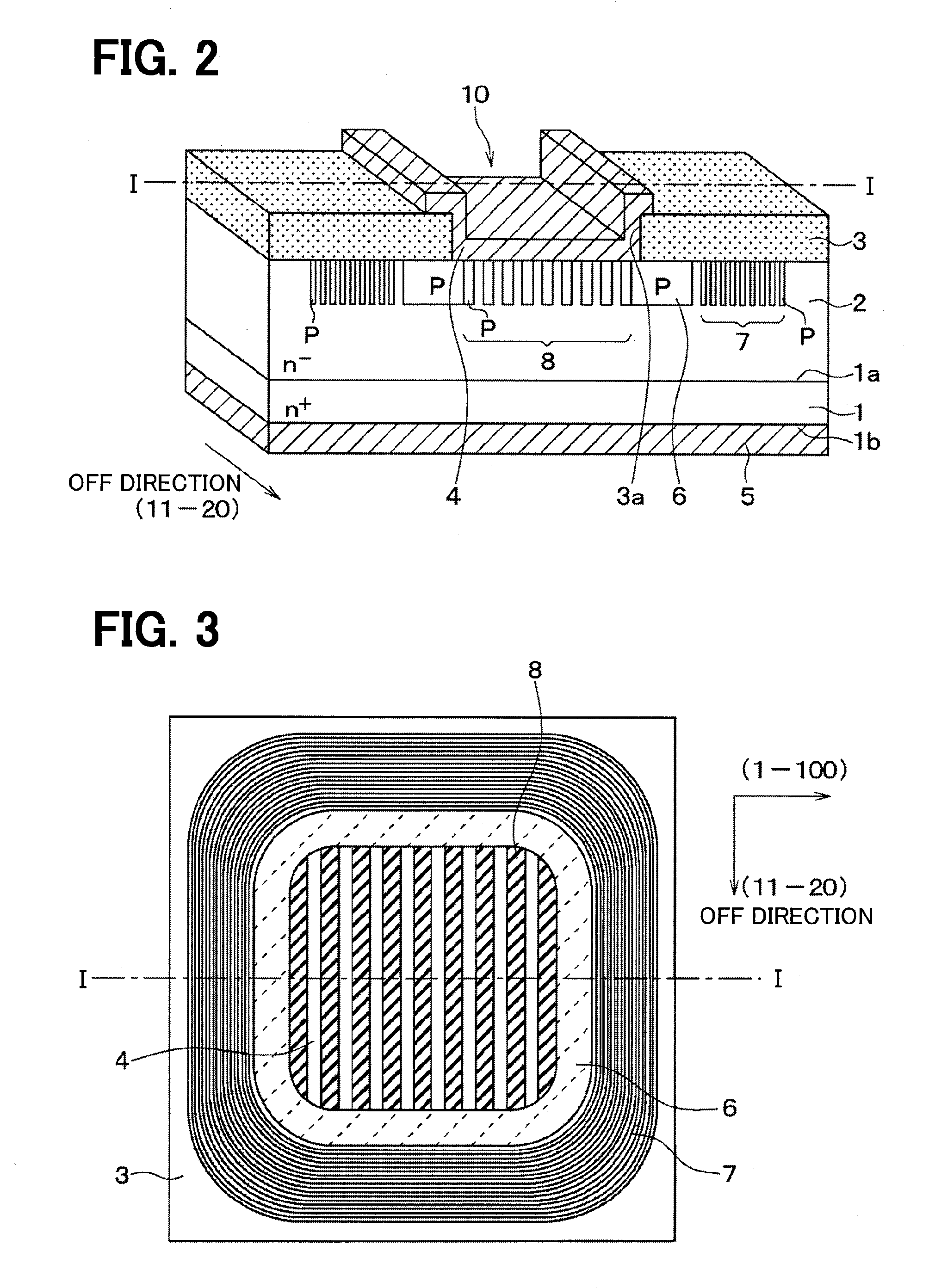

InactiveUS20090039333A1Rapid coolingImprove operating characteristicsSolid-state devicesSemiconductor/solid-state device manufacturingInsulation layerPhase-change memory

A phase change memory device includes a silicon substrate having a bar-type active region and an N-type impurity region formed in a surface of the active region. A first insulation layer is formed on the silicon substrate, and the first insulation layer includes a plurality of first contact holes and second contact holes. PN diodes are formed in the first contact holes. Heat sinks are formed in the first contact holes on the PN diodes, and contact plugs fill the second contact holes. A second insulation layer having third contact holes is formed on the first insulation layer. Heaters fill the third contact holes. A stack pattern of a phase change layer and a top electrode is formed to contact the heaters. The heat sink quickly cools heat transferred from the heater to the phase change layer.

Owner:SK HYNIX INC

PN diode optical modulators fabricated in rib waveguides

ActiveUS7116853B2Semiconductor/solid-state device manufacturingOptical waveguide light guideElectricityLow speed

Owner:CISCO TECH INC

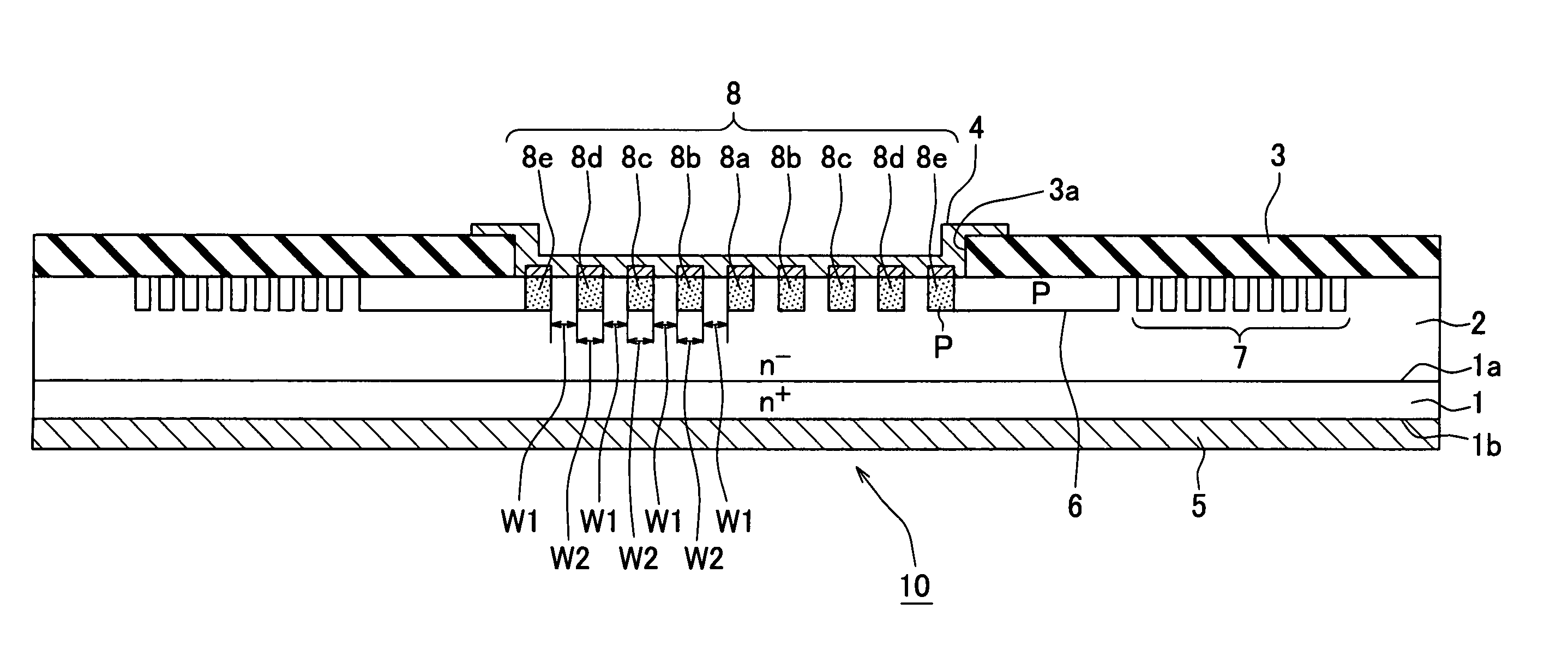

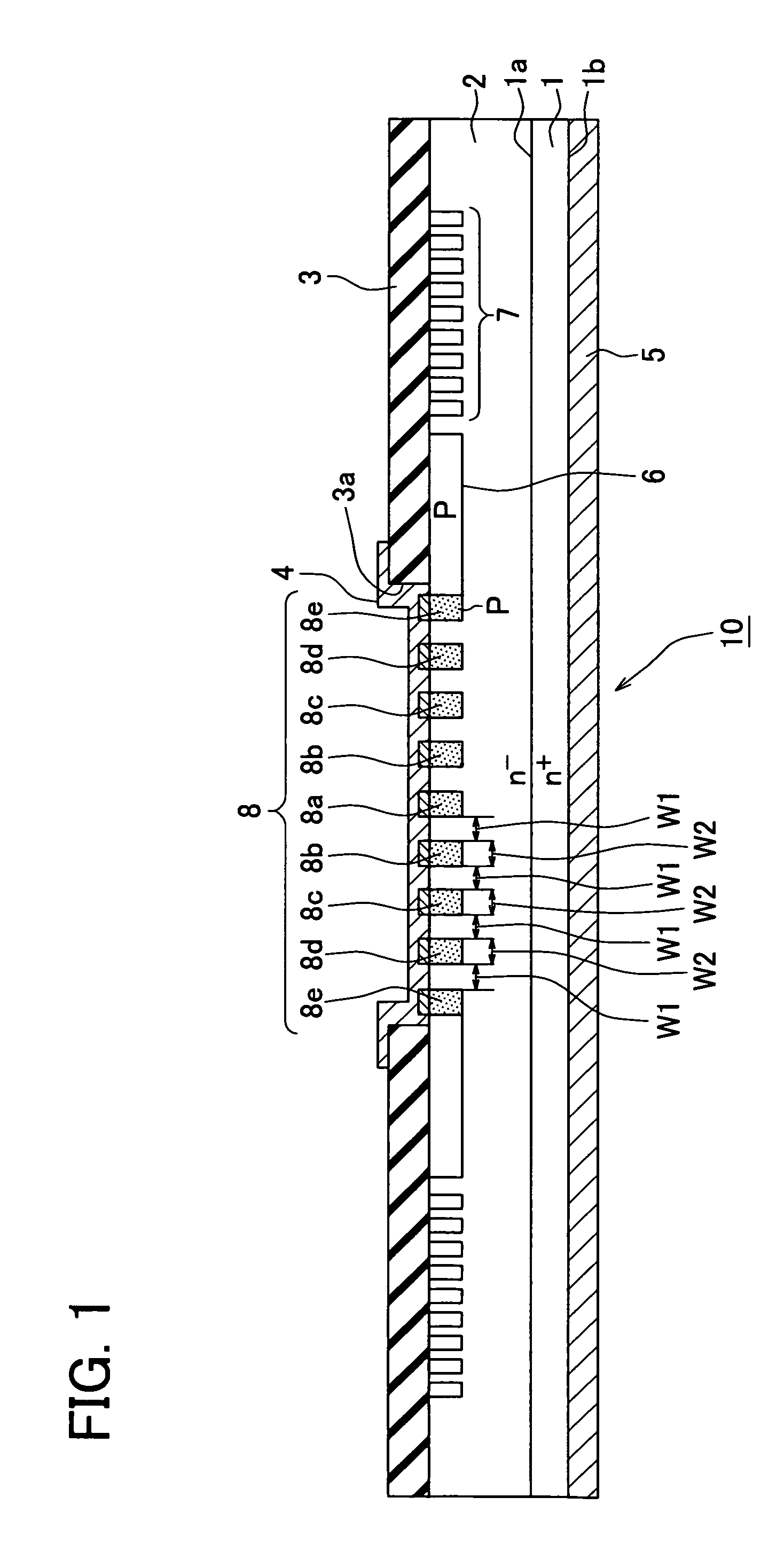

Silicon carbide semiconductor device having junction barrier schottky diode

InactiveUS20080296587A1Improve breakdown voltageDifficulty concentratingSemiconductor/solid-state device manufacturingSemiconductor devicesSchottky diodeSemiconductor

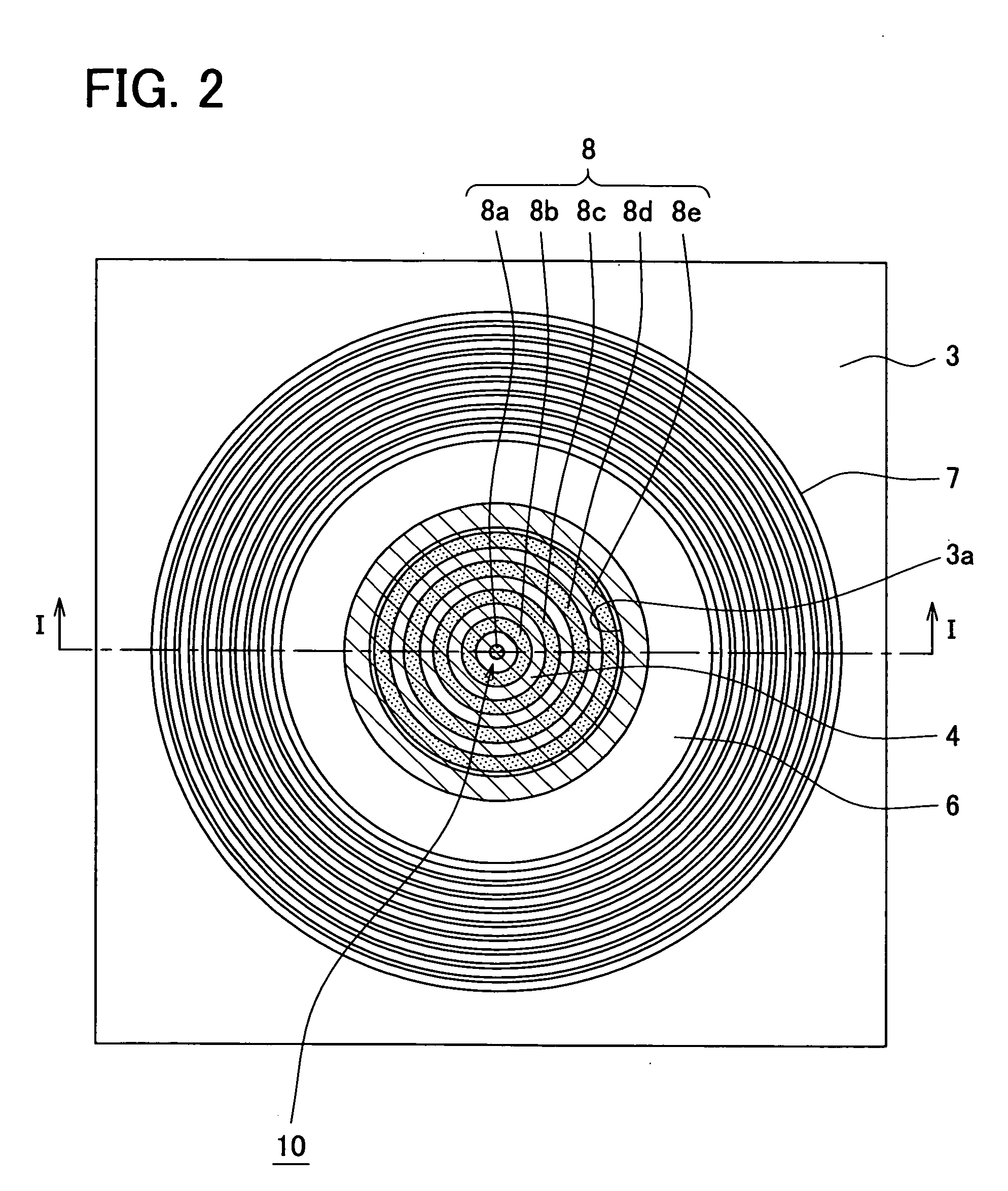

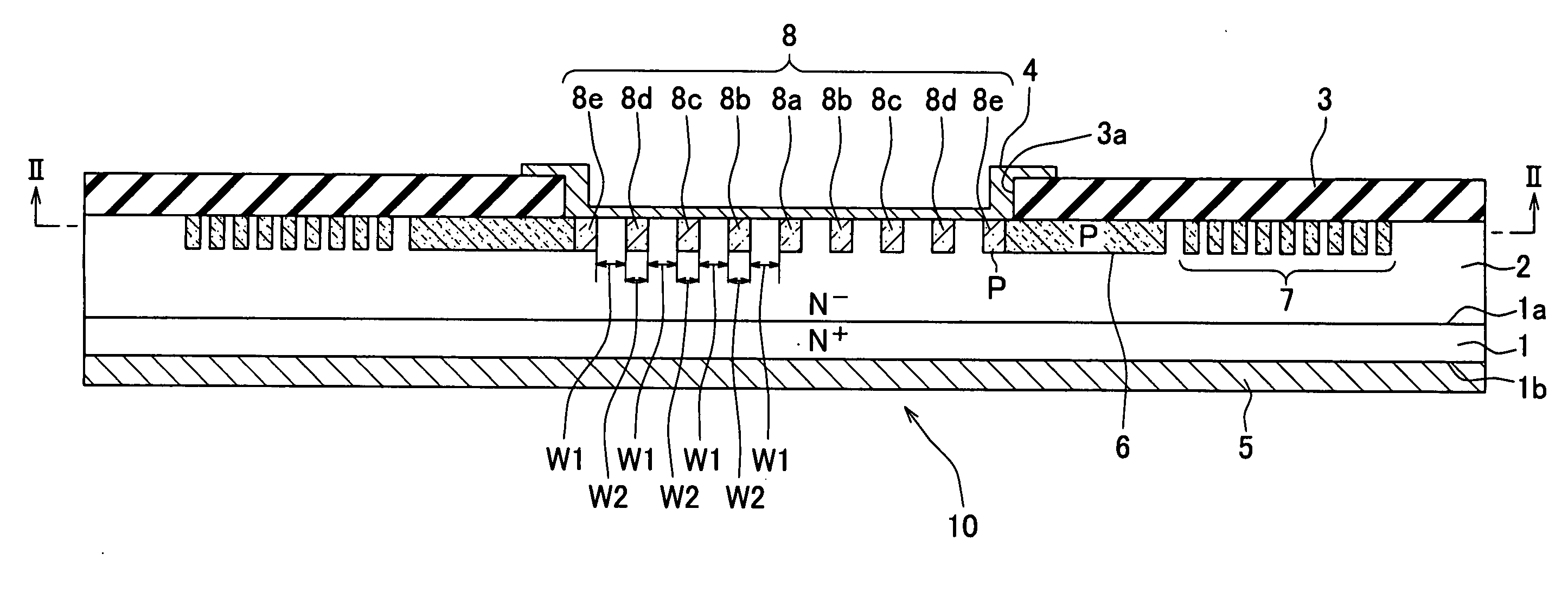

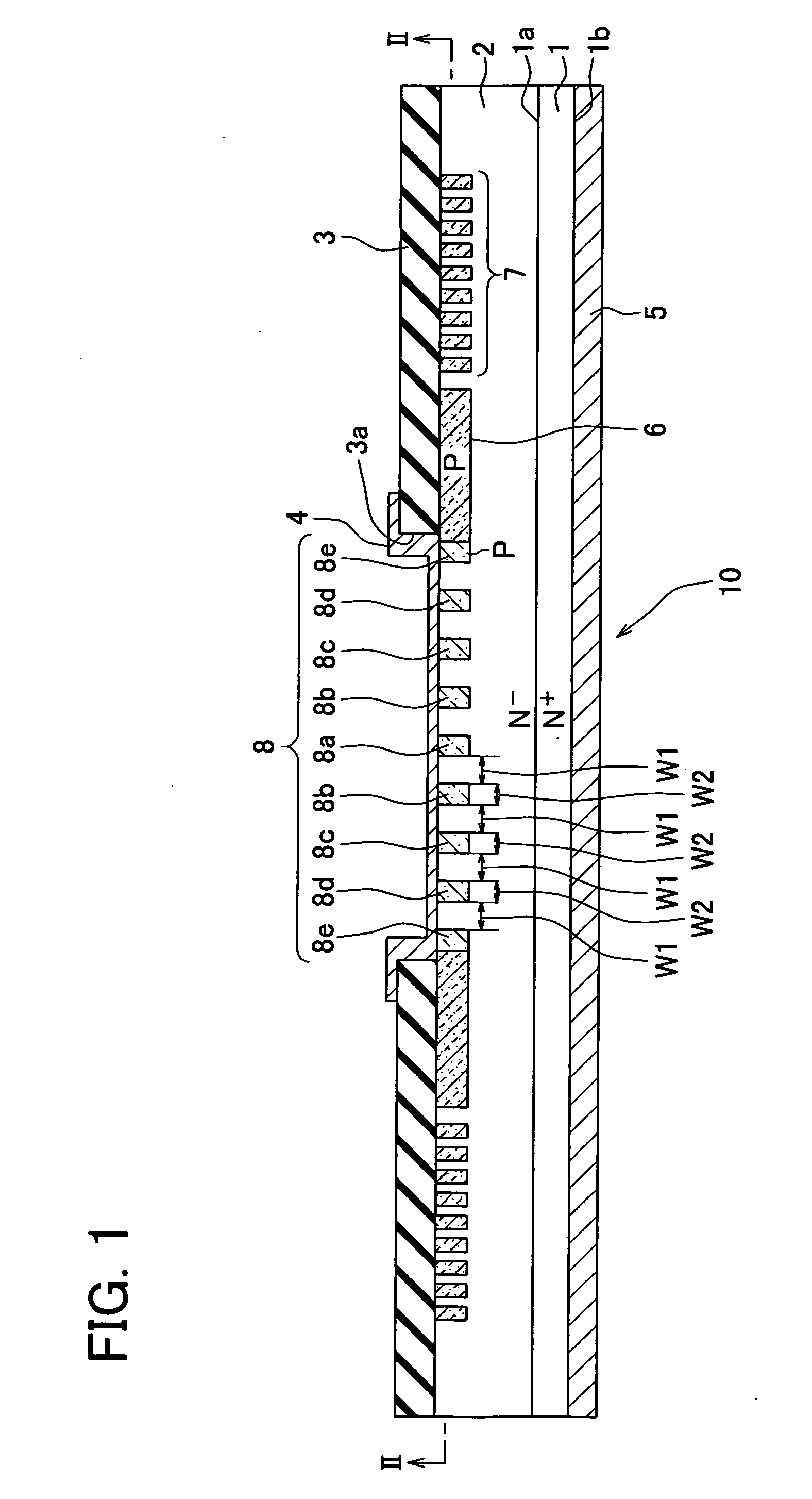

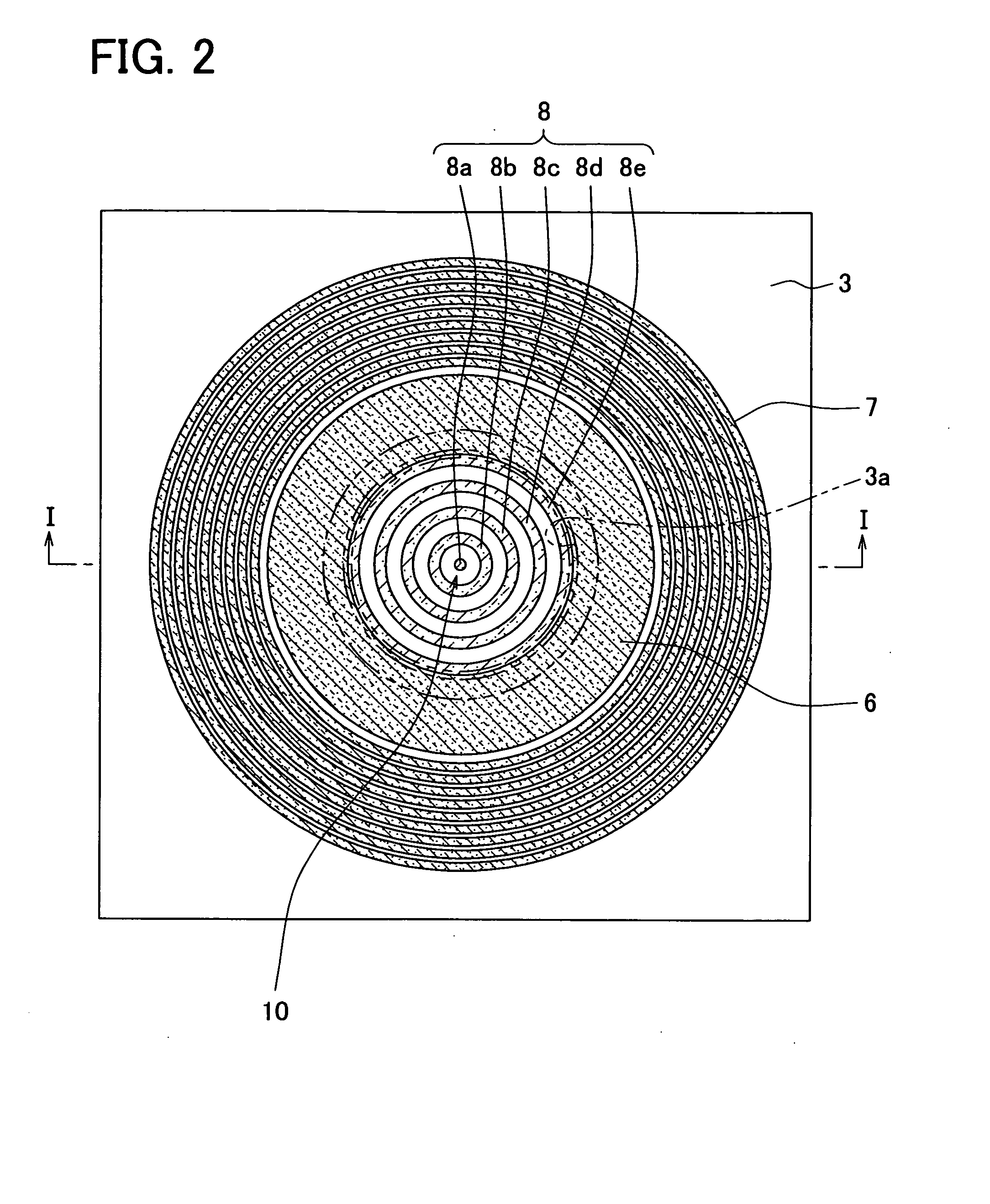

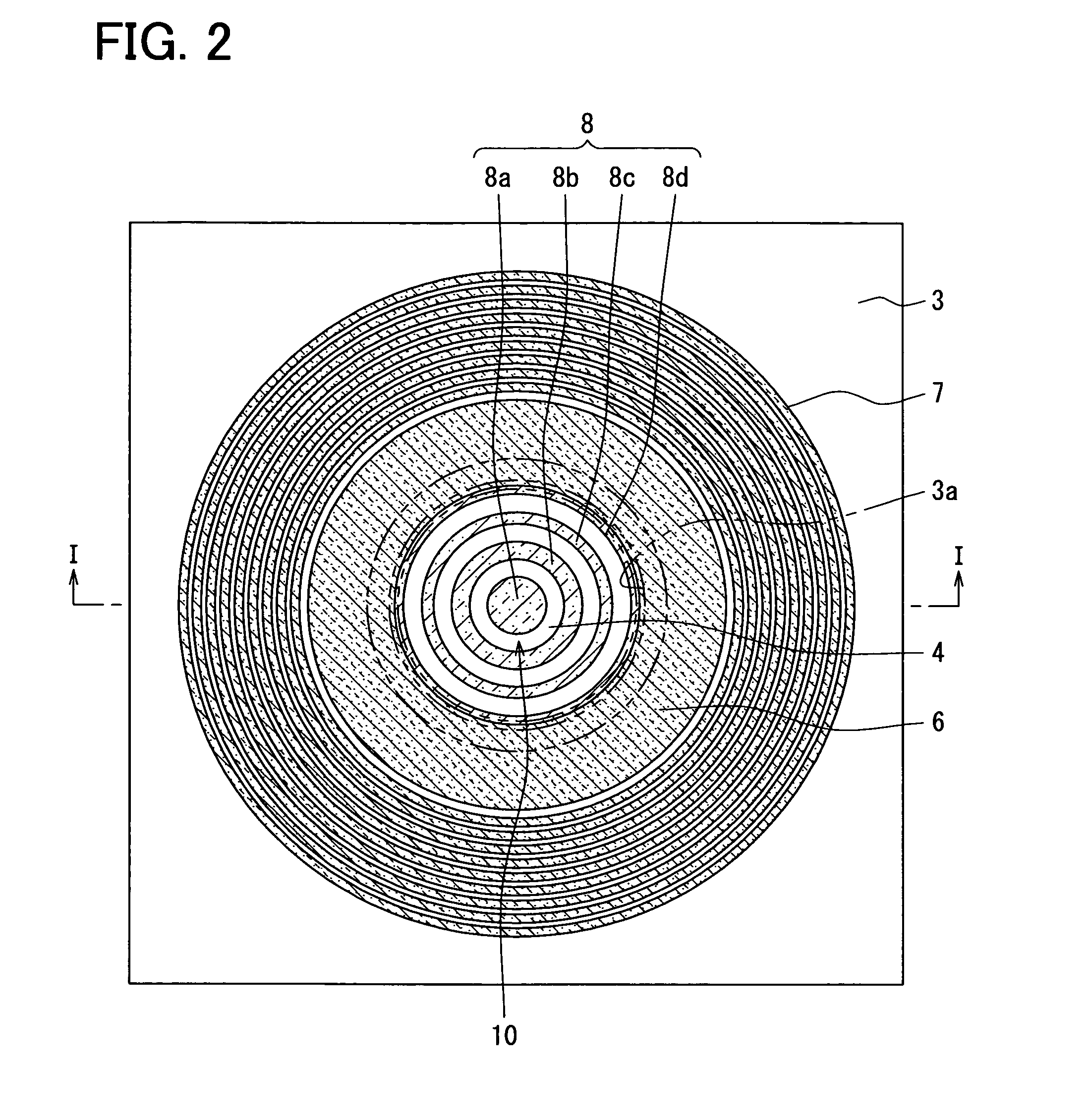

A silicon carbide semiconductor device includes a substrate; a drift layer having a first conductivity type; an insulating layer; a Schottky electrode; an ohmic electrode; a resurf layer; and second conductivity type layers. The drift layer and the second conductivity type layers provide multiple PN diodes. Each second conductivity type layer has a radial width with respect to a center of a contact region between the Schottky electrode and the drift layer. A radial width of one of the second conductivity type layers is smaller than that of another one of the second conductivity type layers, which is disposed closer to the center of the contact region than the one of the second conductivity type layers.

Owner:DENSO CORP

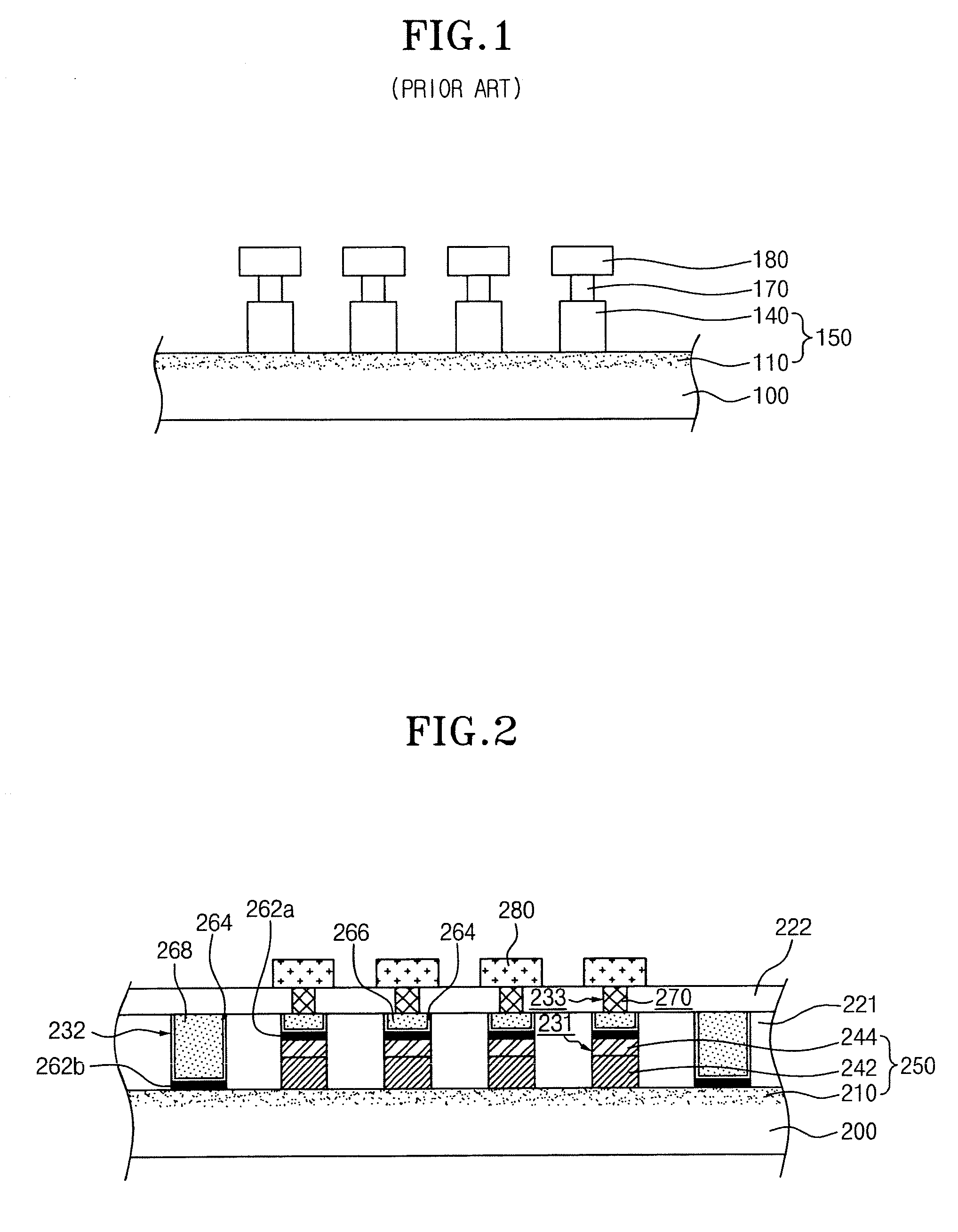

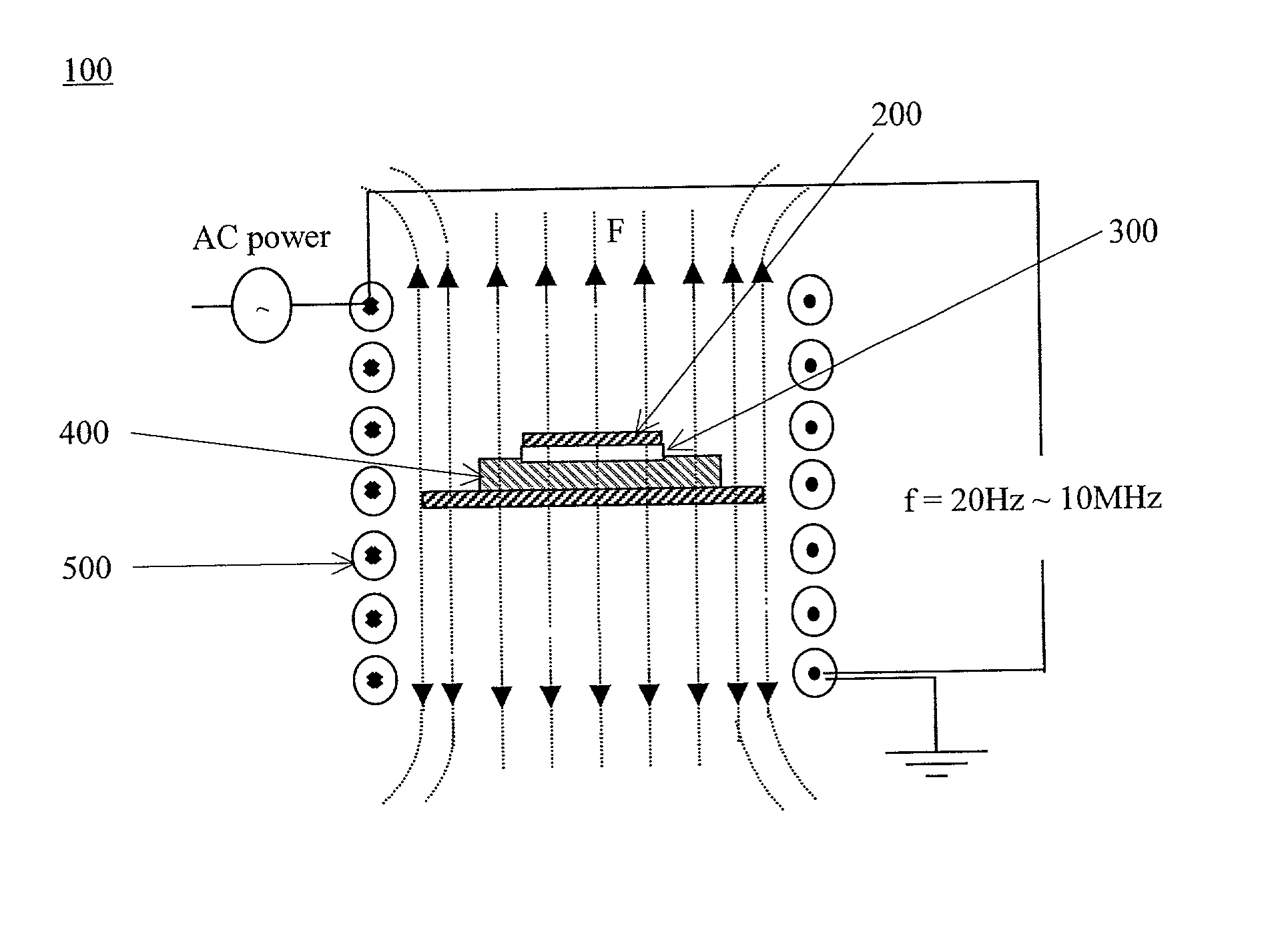

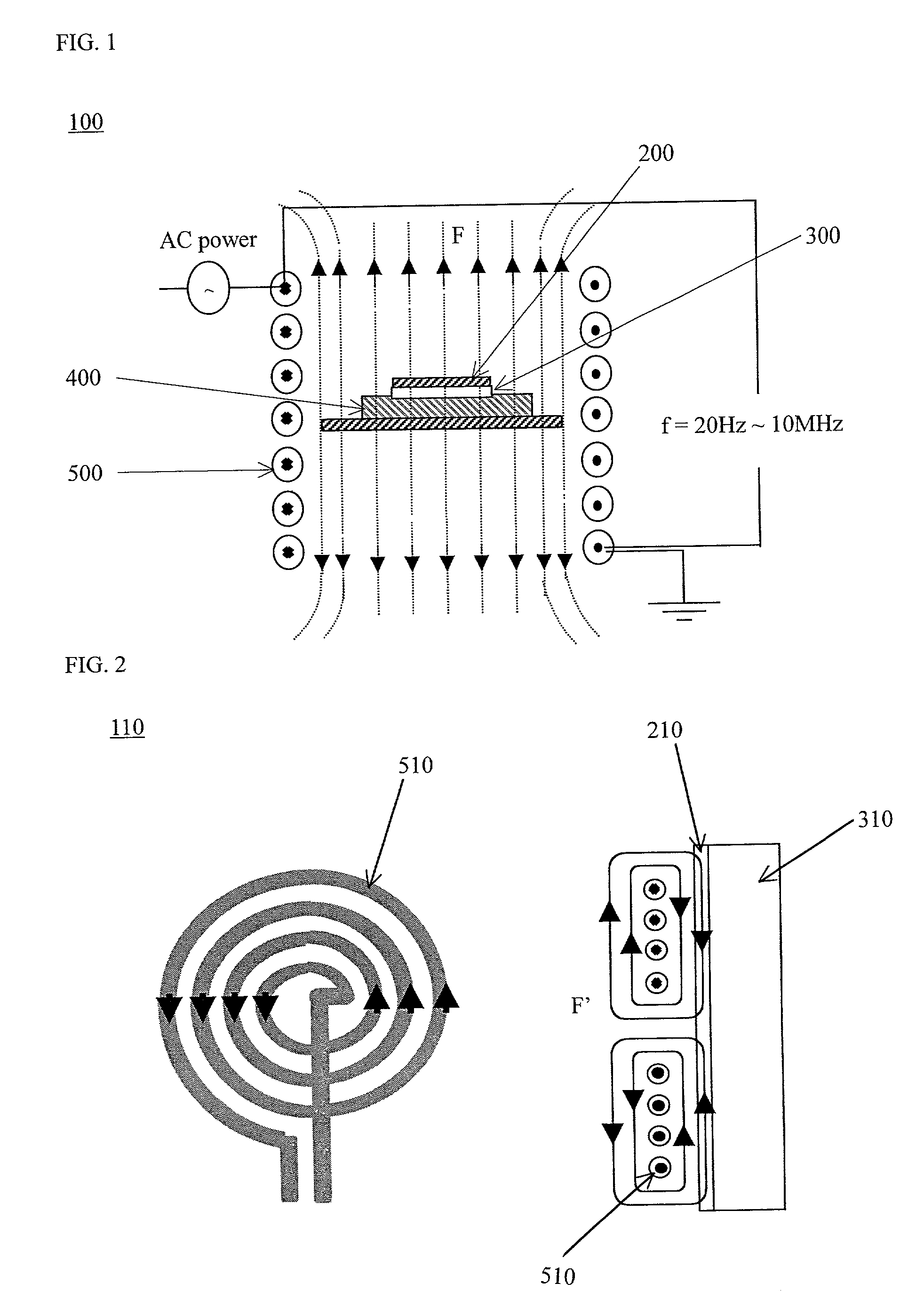

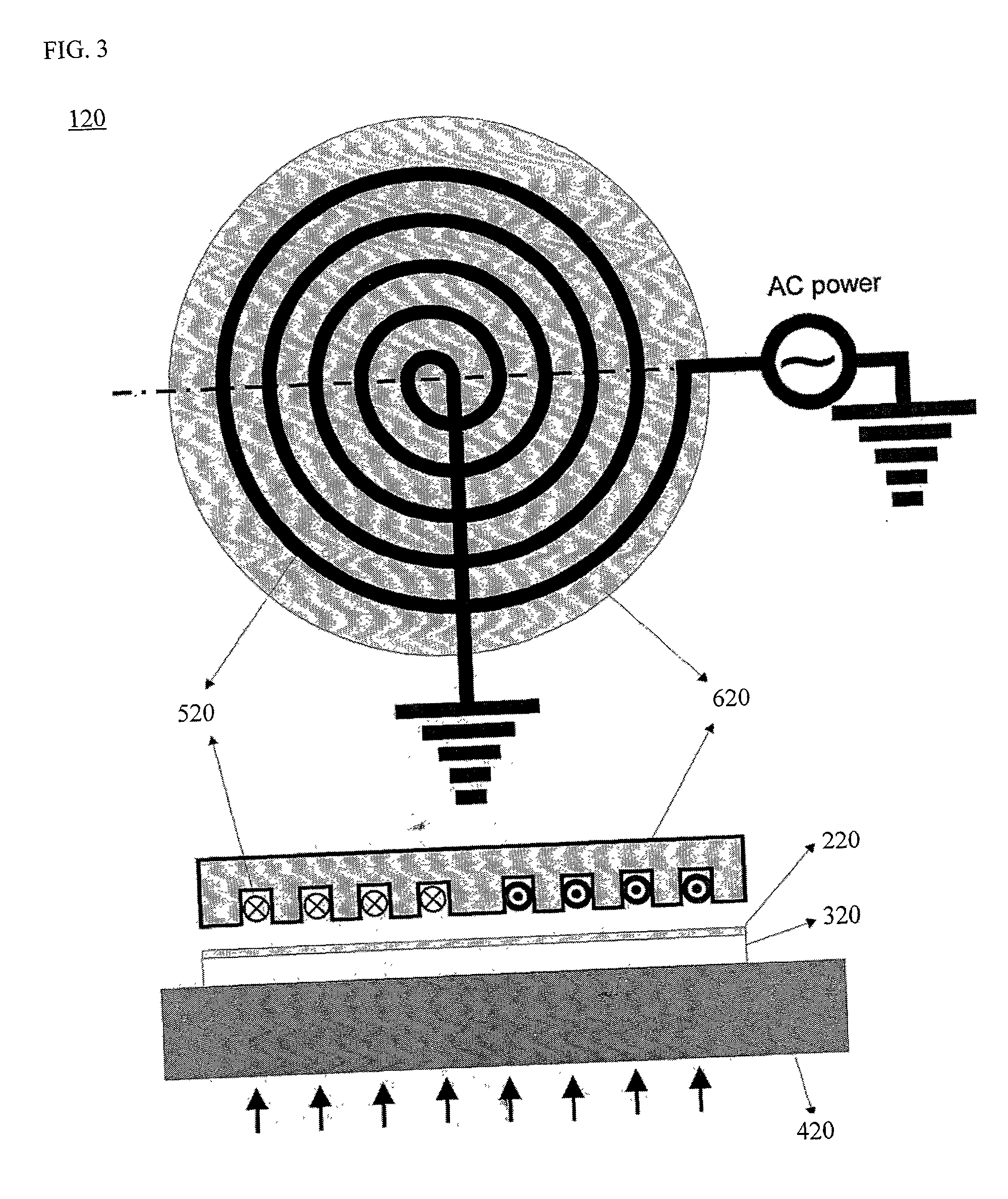

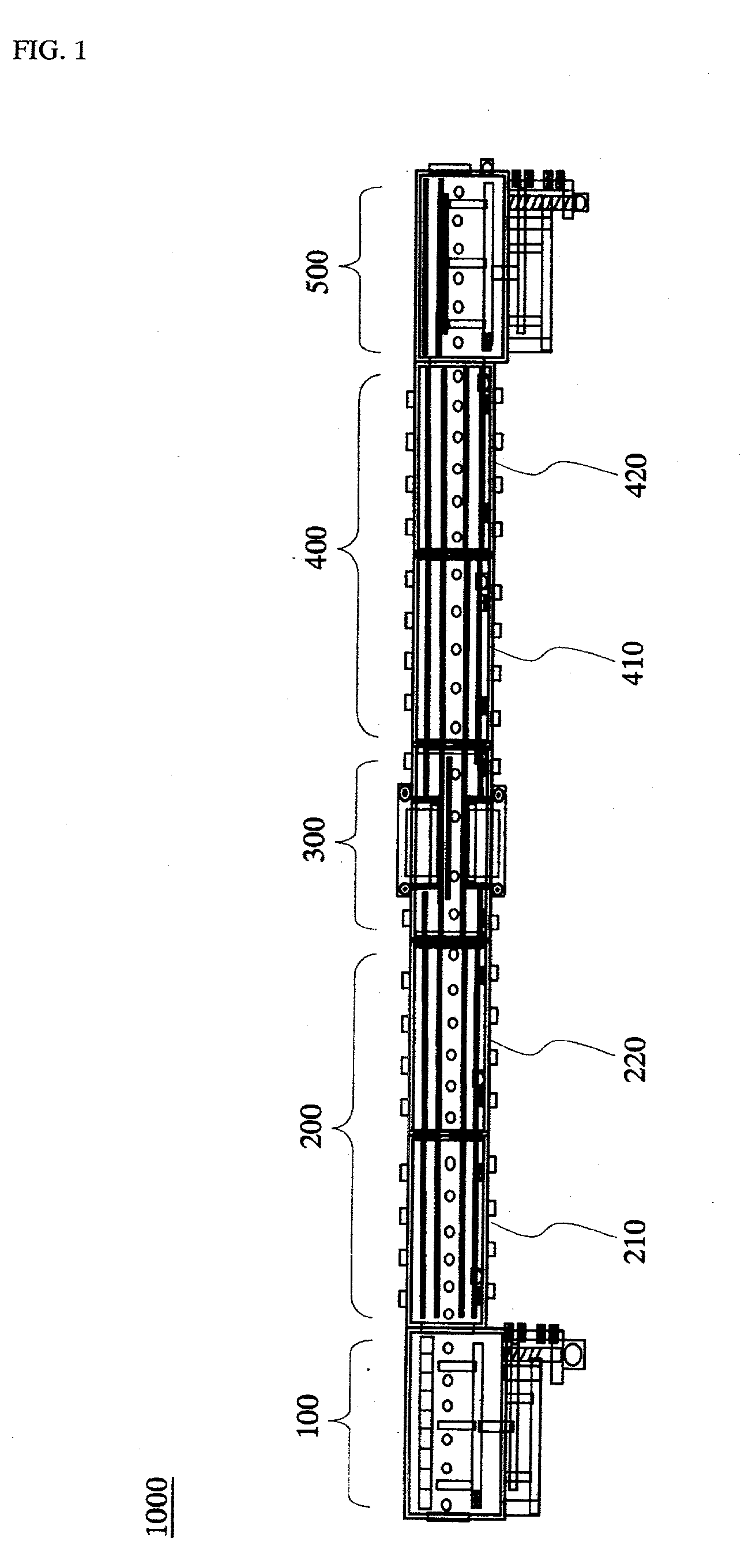

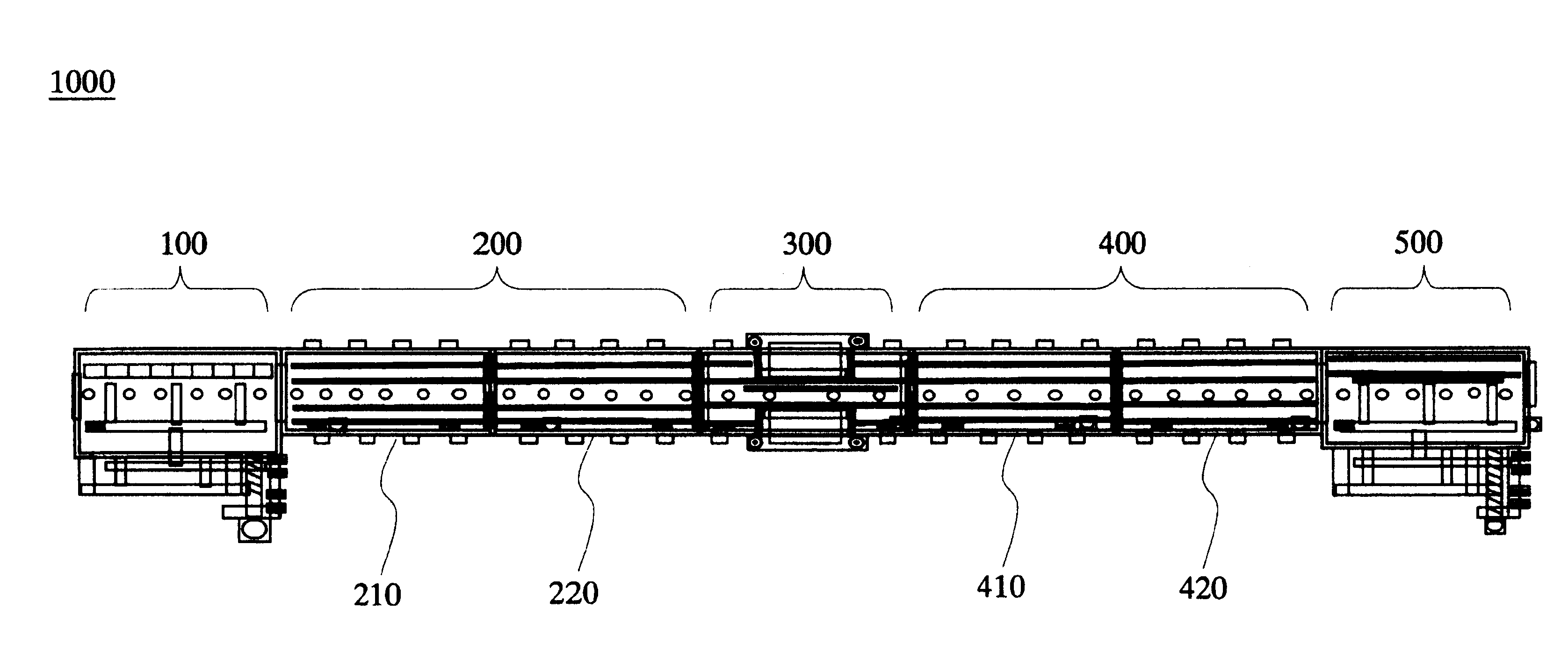

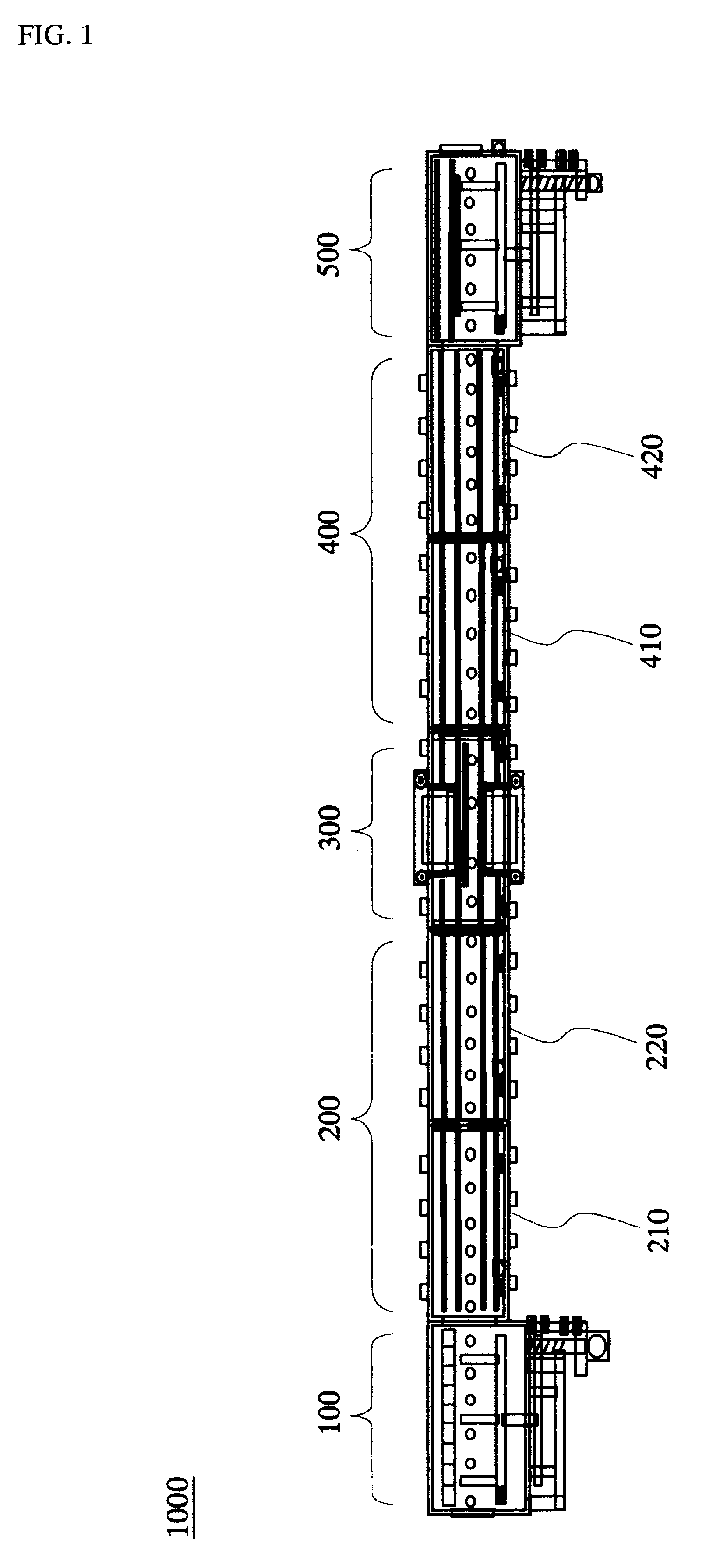

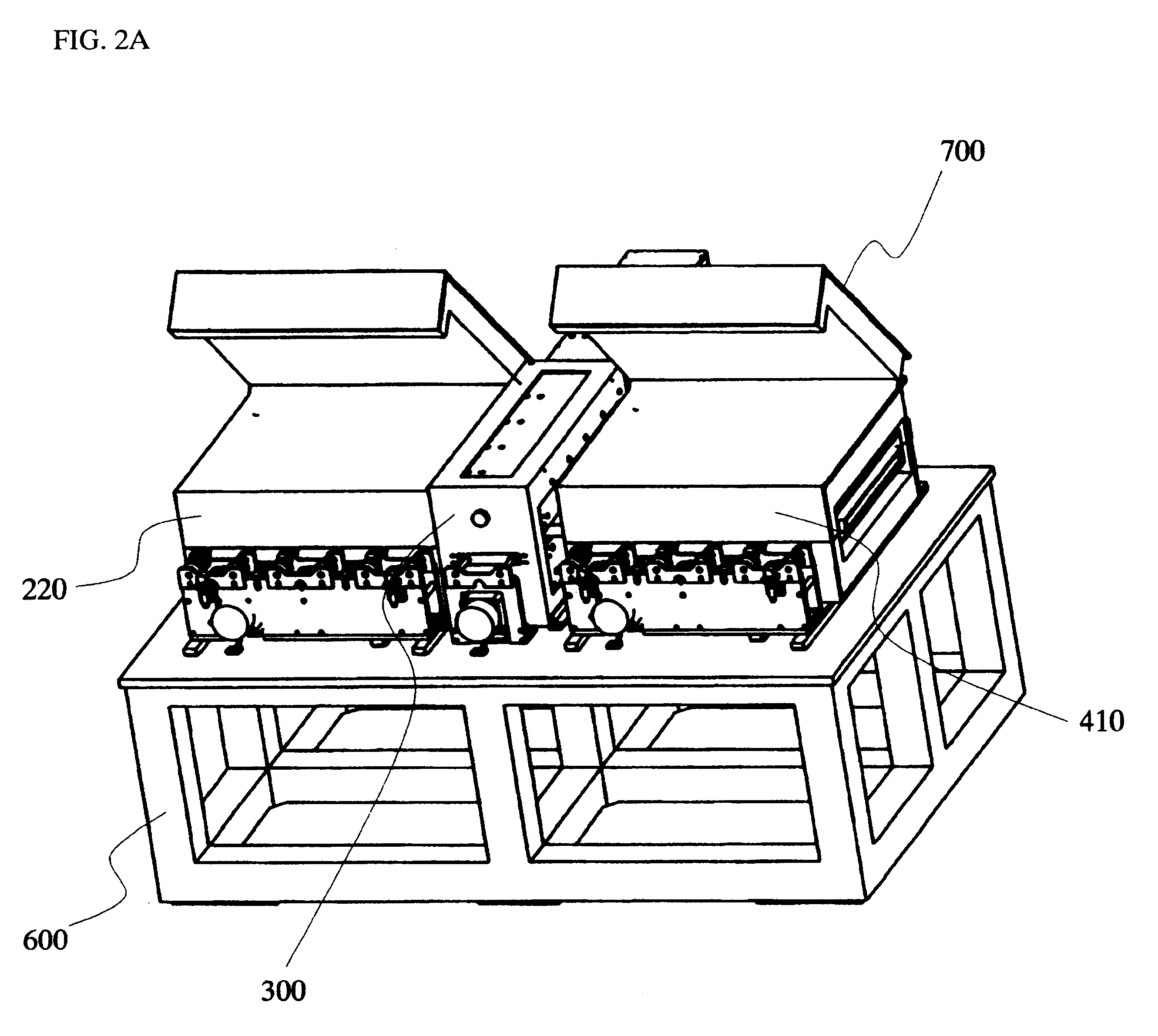

Methods and apparatuses for heat treatment of semiconductor films upon thermally susceptible non-conducting substrates

InactiveUS20030010775A1Improve uniformityMaximize goalFurnaces without endless coreTransistorEngineeringSolar cell

The present invention relates to methods and apparatuses for heat treatment of semiconductor films upon thermally susceptible non-conducting substrates at a minimum thermal budget are required, and more particularly, to a polycrystalline silicon thin-film transistors (poly-Si TFTs) and PN diodes on glass substrates for various applications of liquid crystal displays (LCDs), organic light emitting diodes (OLEDs), and solar cells. According to the methods and apparatus of the present invention, the semiconductor films can be heat-treated without damaging the thermally susceptible substrates; e.g., crystallization of amorphous silicon films at the minimum thermal budget acceptable for the use of glass, enhancing kinetics of dopant activation at the minimum thermal budget acceptable for the use of glass.

Owner:KIM HYOUNG JUNE

Method and apparatus for high speed silicon optical modulation using PN diode

InactiveUS7747122B2Coupling light guidesOptical waveguide light guidePerpendicular directionWaveguide

A method and apparatus for high speed silicon optical modulation is described using a PN diode. In one example, an optical waveguide has adjoining first and second doped semiconductor regions. The first and second regions have opposite doping types and the first doped region extends in two perpendicular directions through the waveguide.

Owner:INTEL CORP

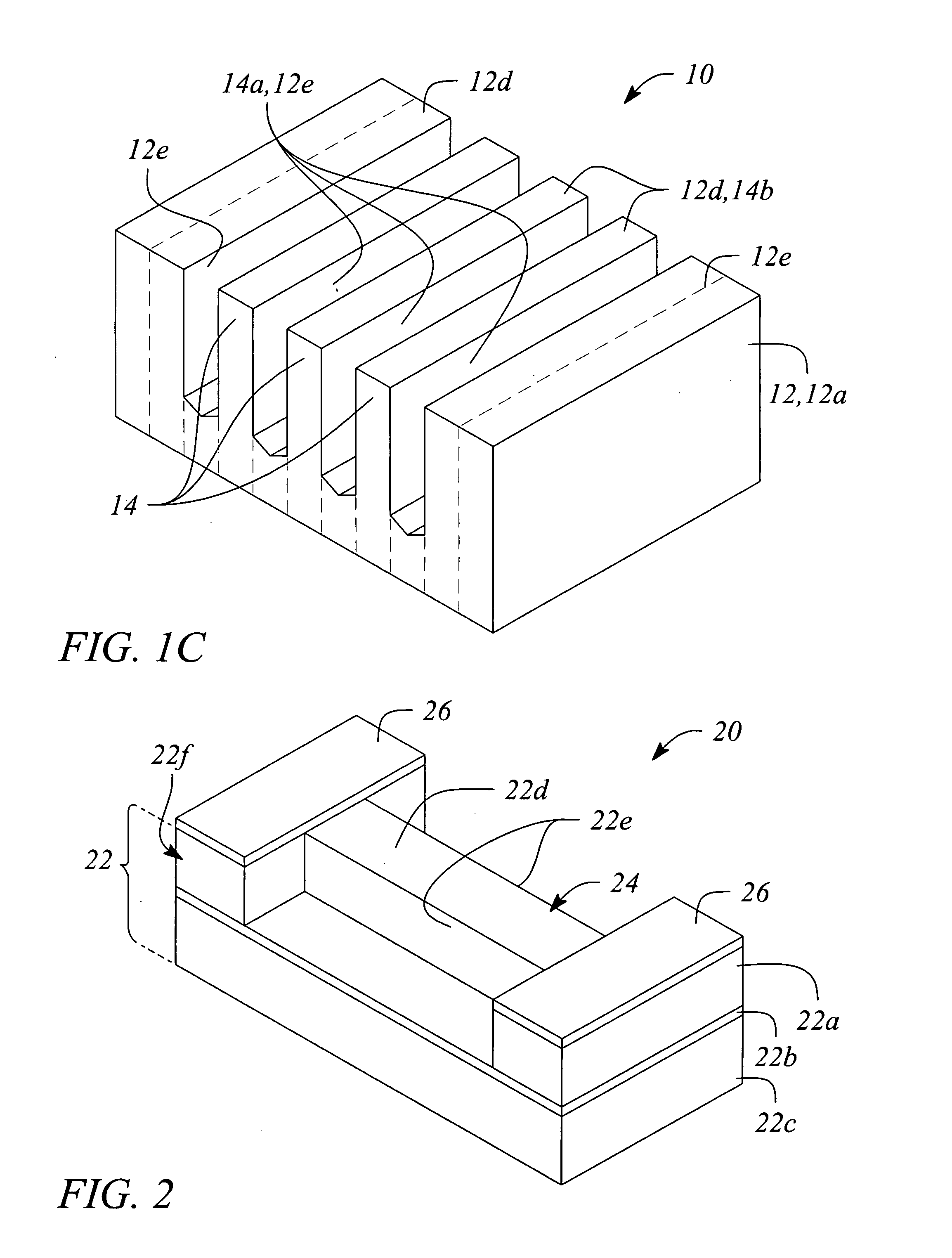

Semiconductor Device And Method For Manufacturing Same

InactiveUS20080128850A1Increase field strengthImprove sturdinessSemiconductor/solid-state device manufacturingSemiconductor devicesEngineeringSchottky diode

A semiconductor device (20) comprising a trench MOS barrier Schottky diode having an integrated PN diode and a method for manufacturing same are described.

Owner:ROBERT BOSCH GMBH

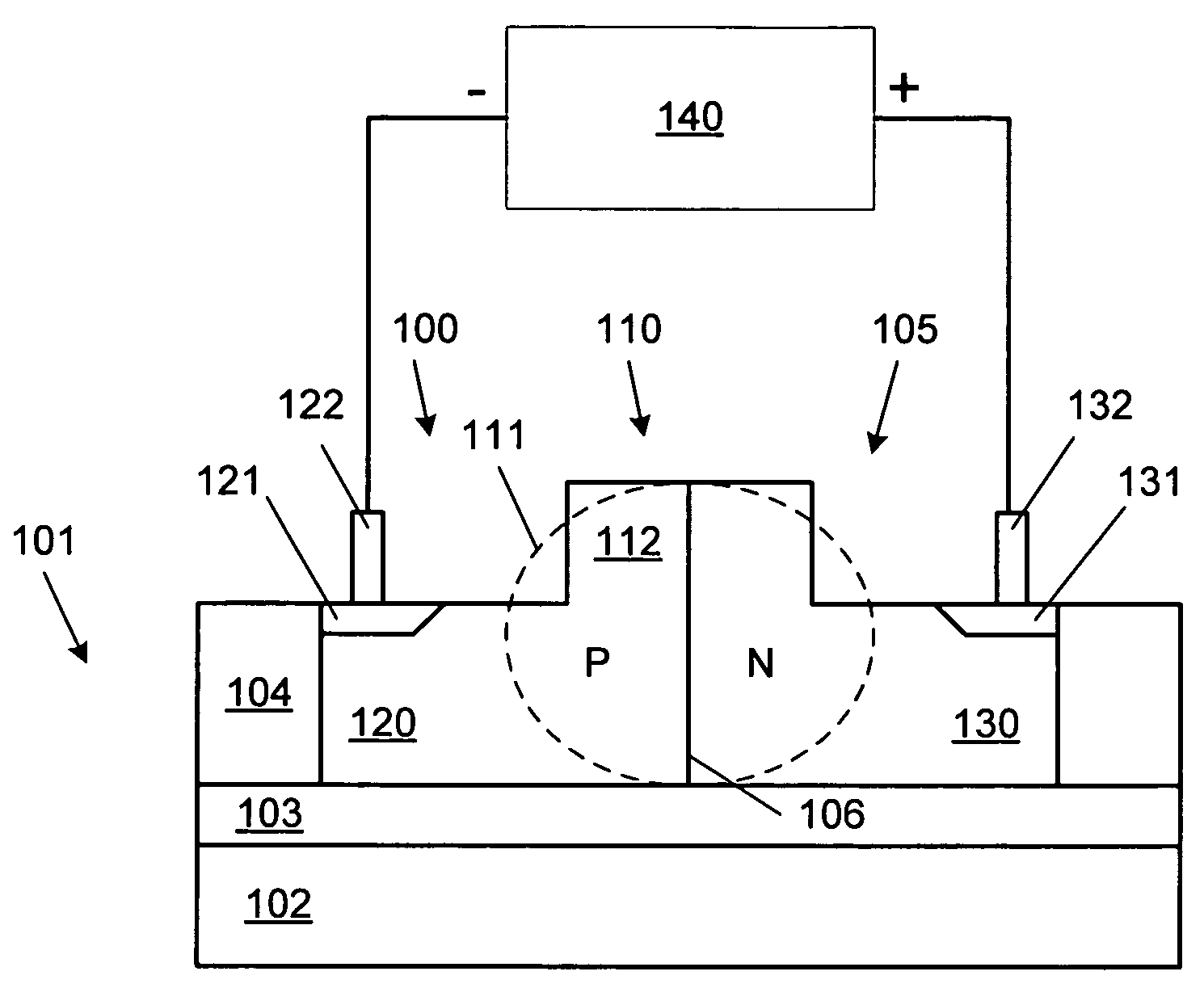

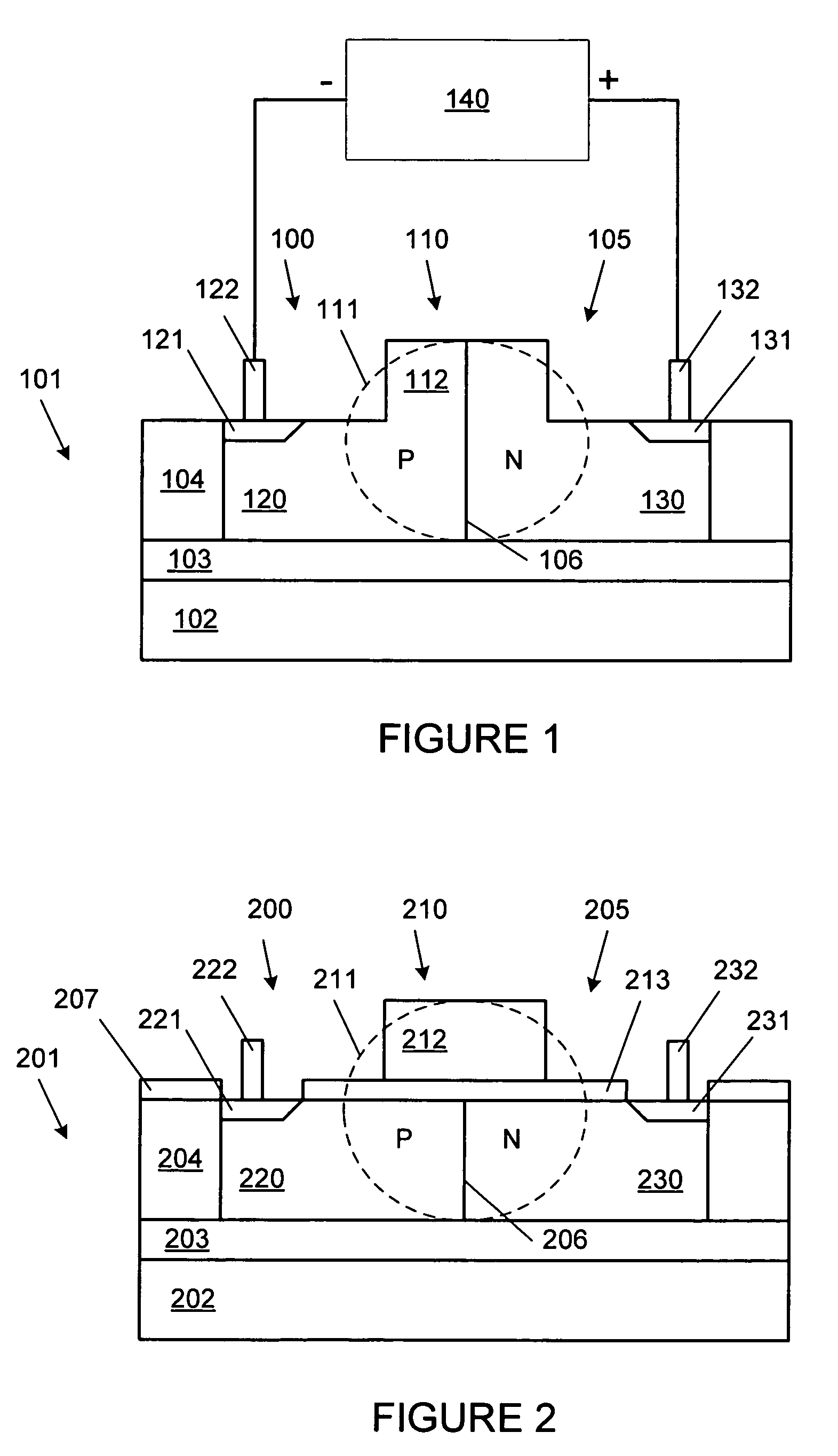

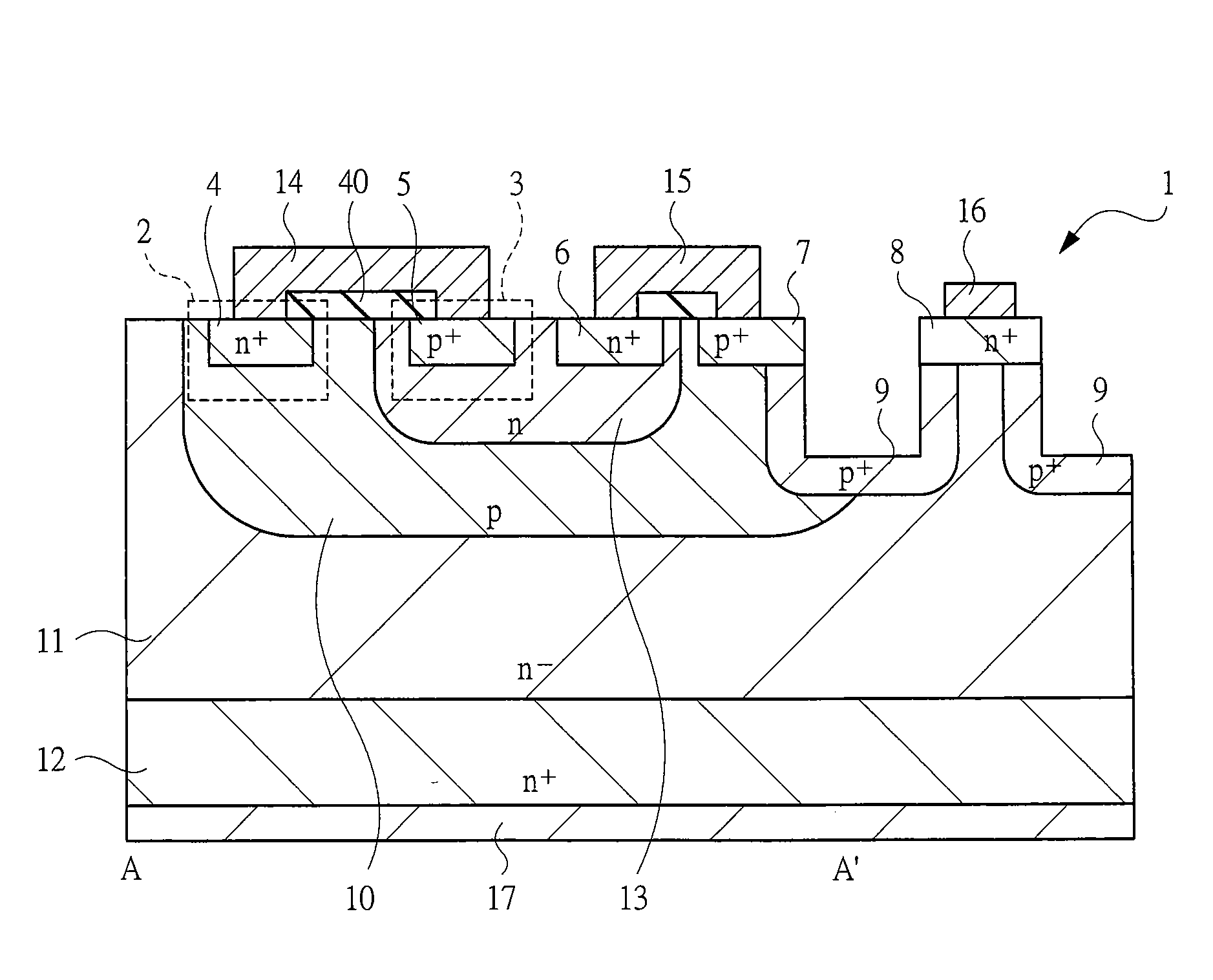

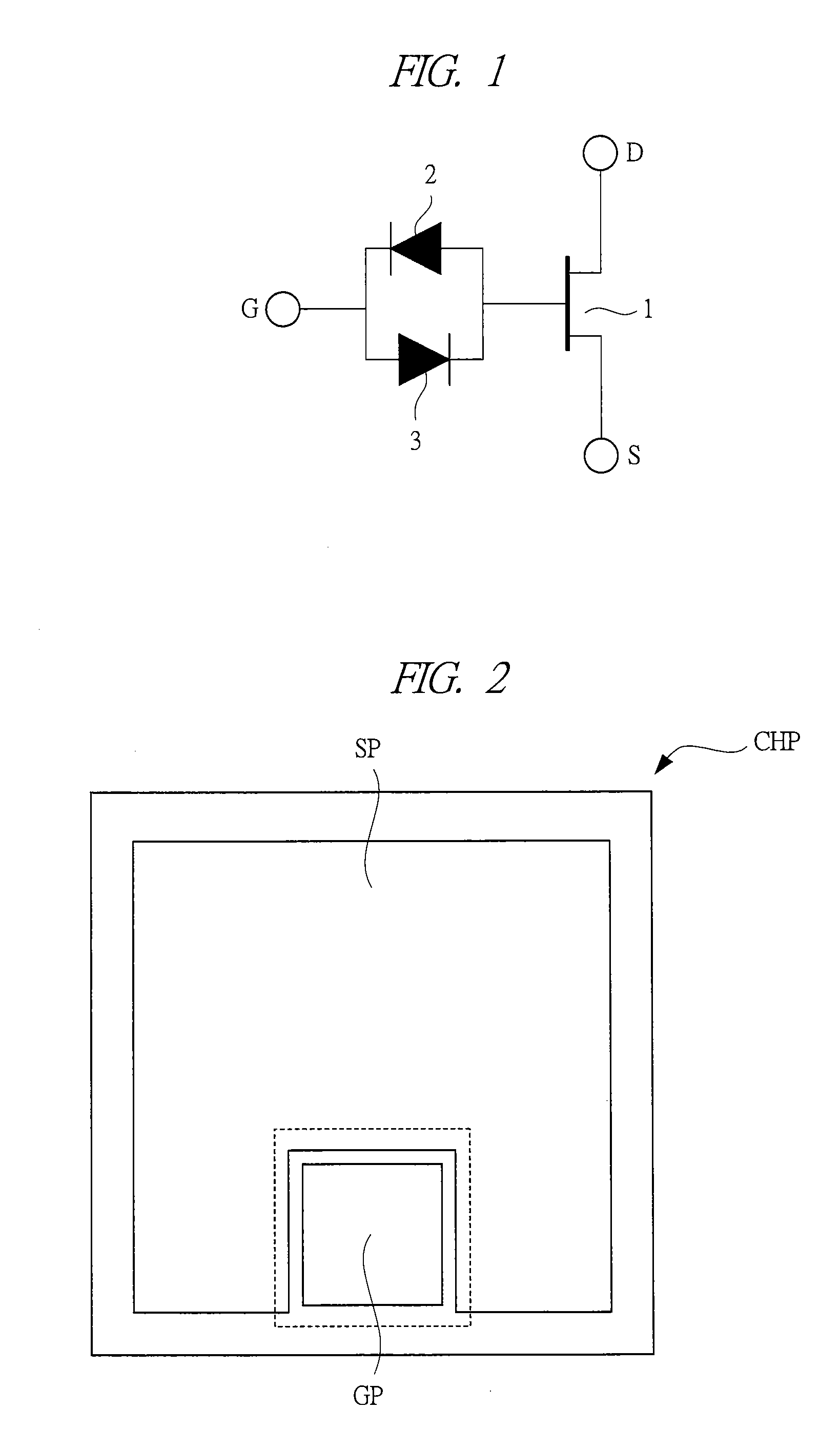

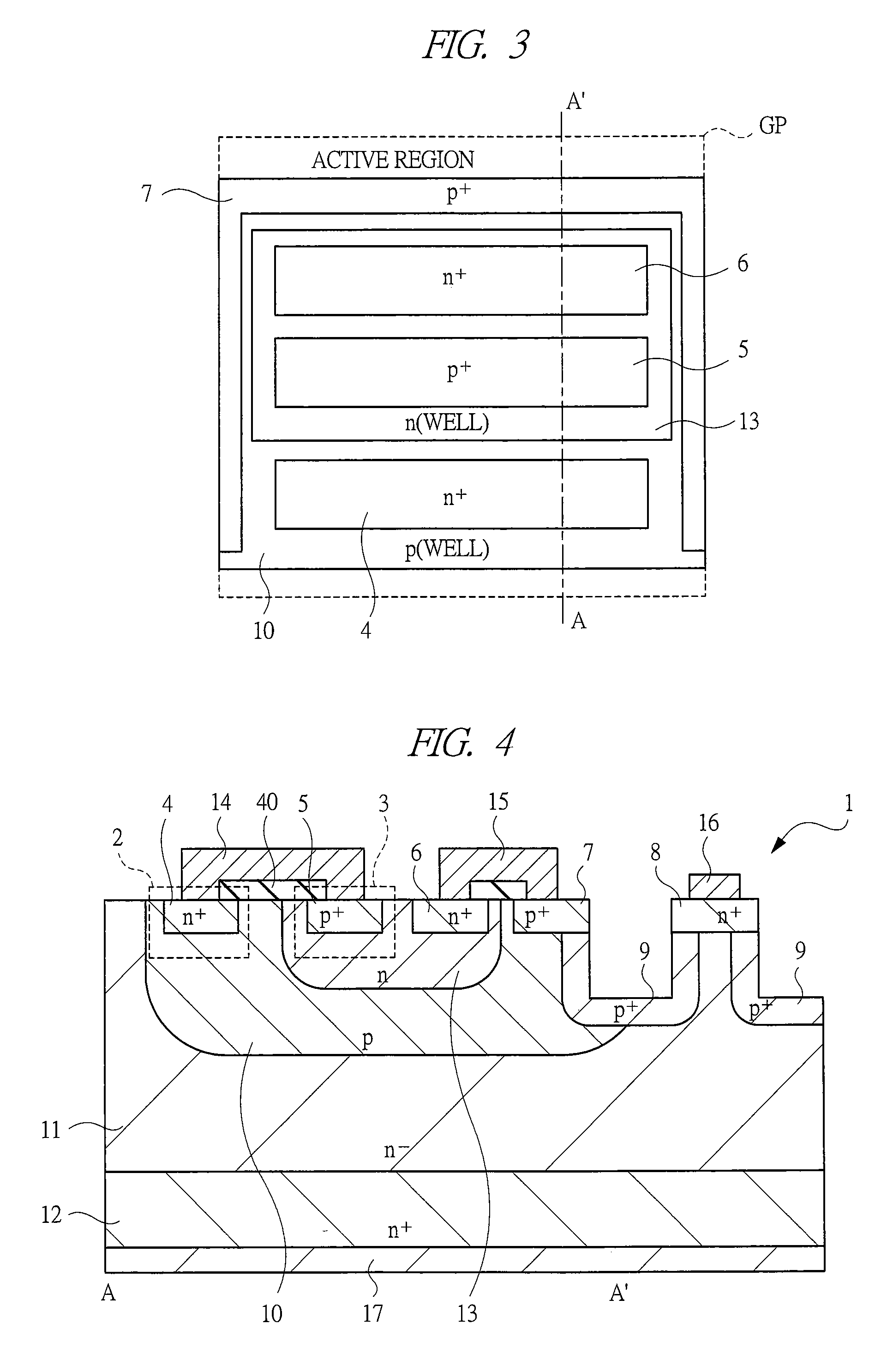

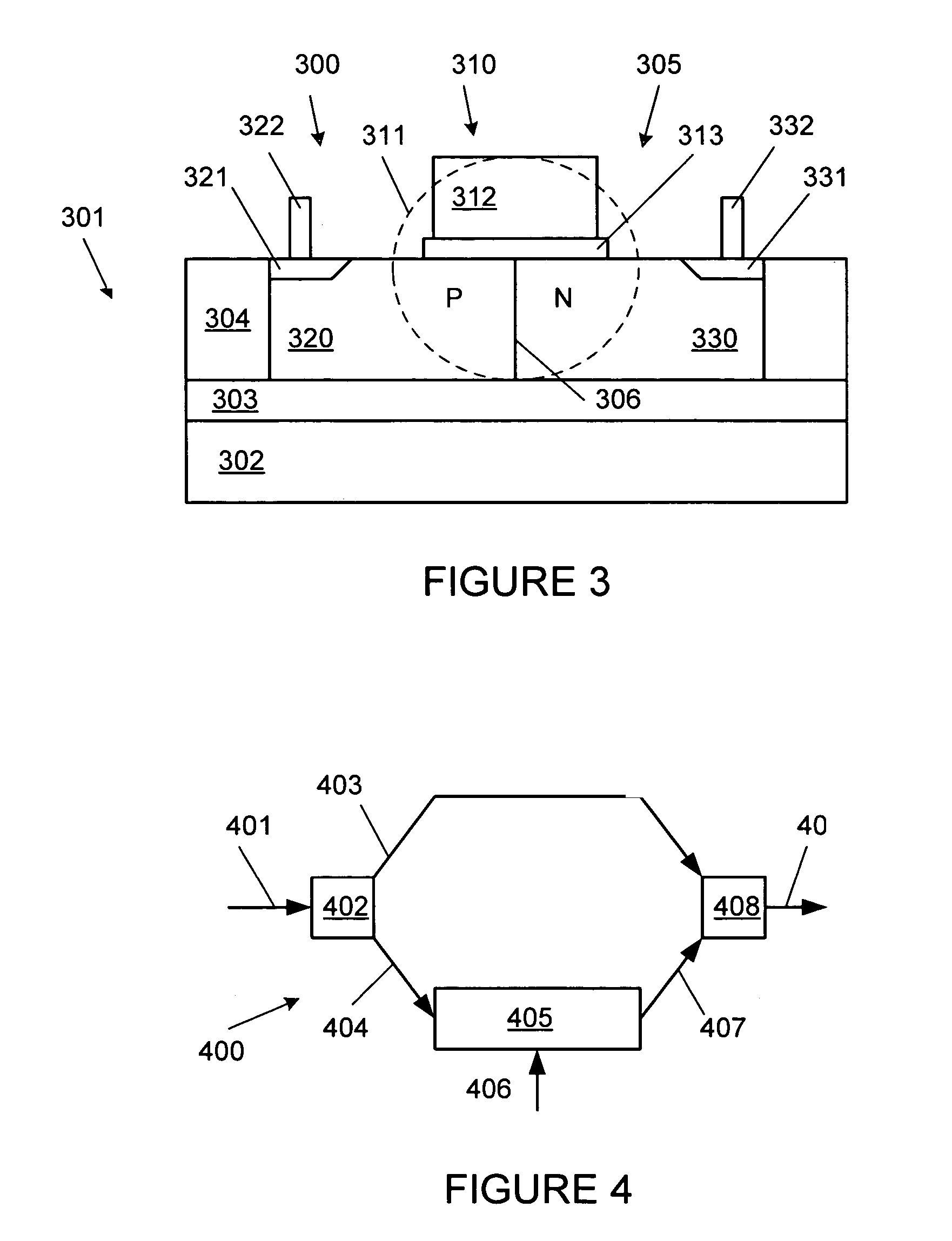

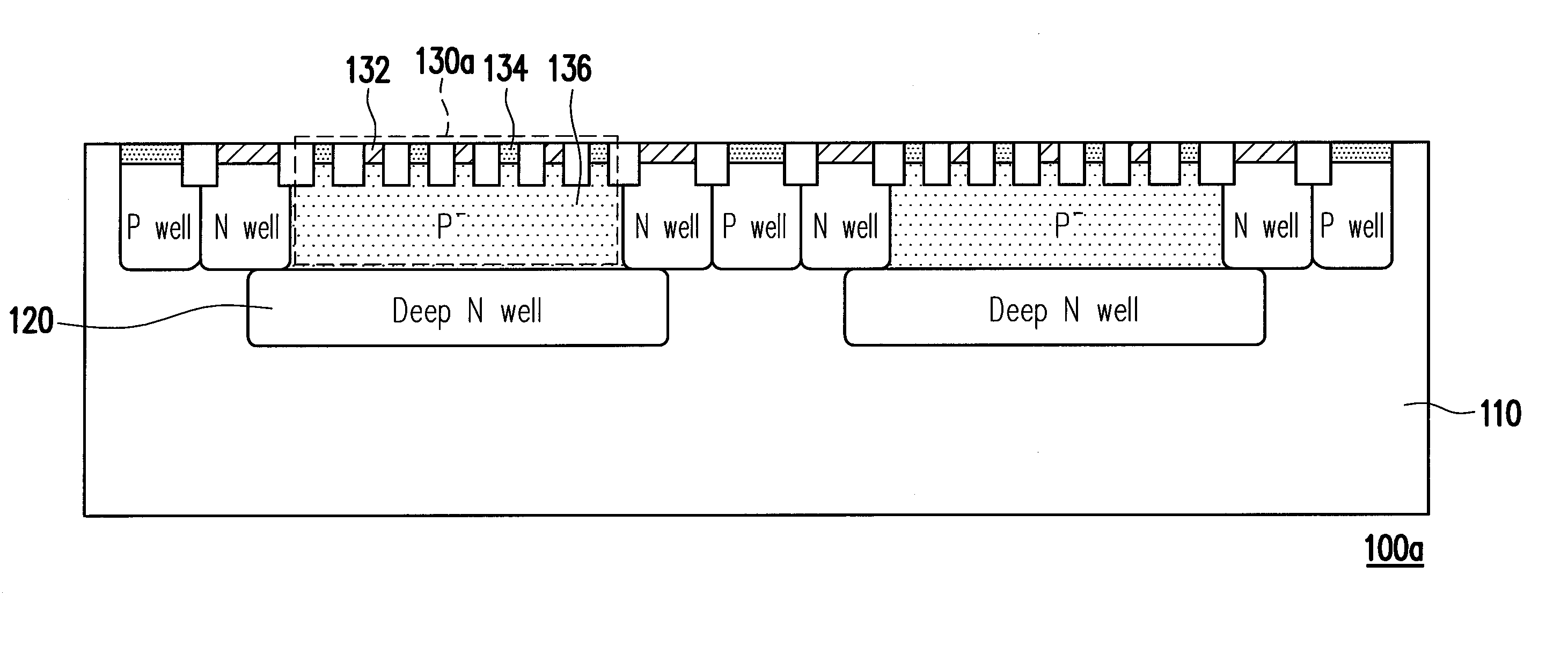

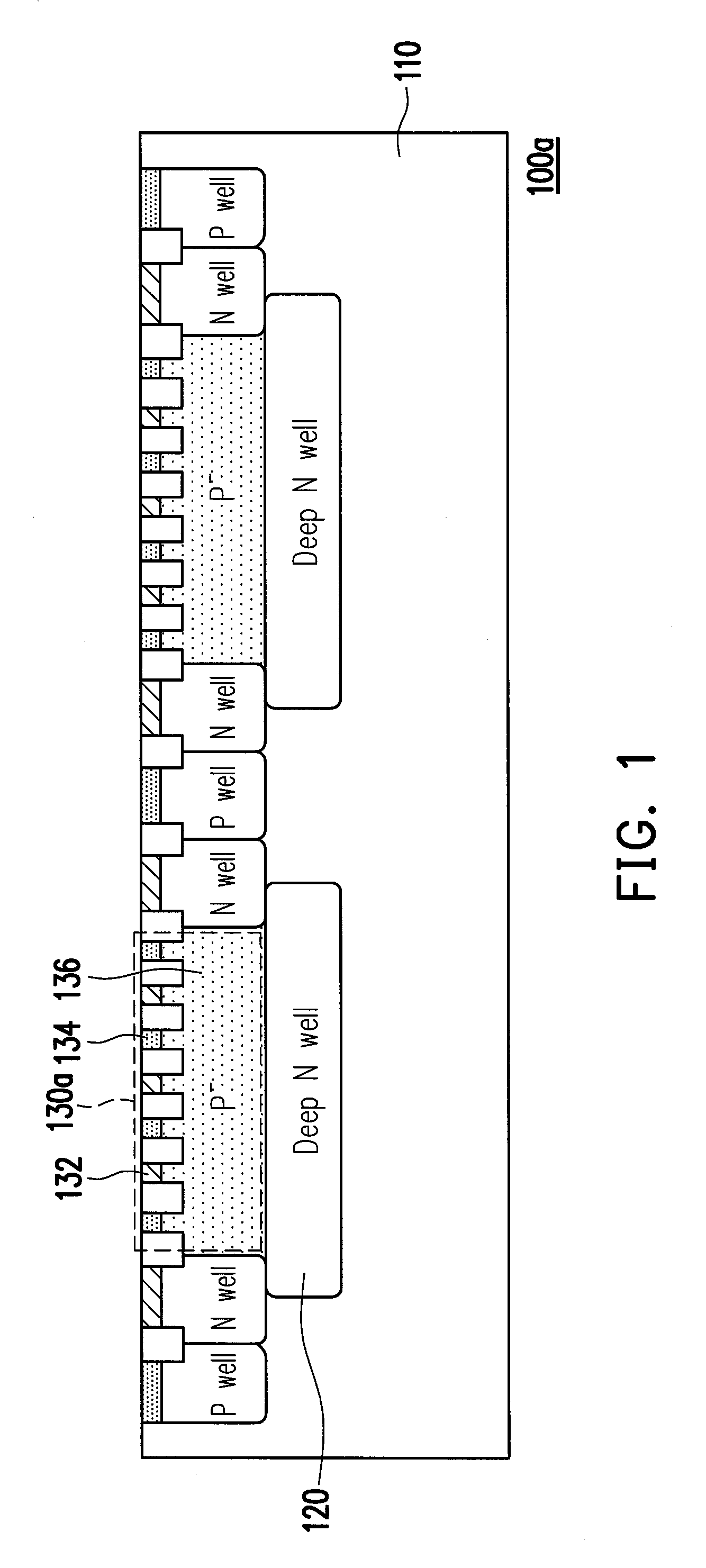

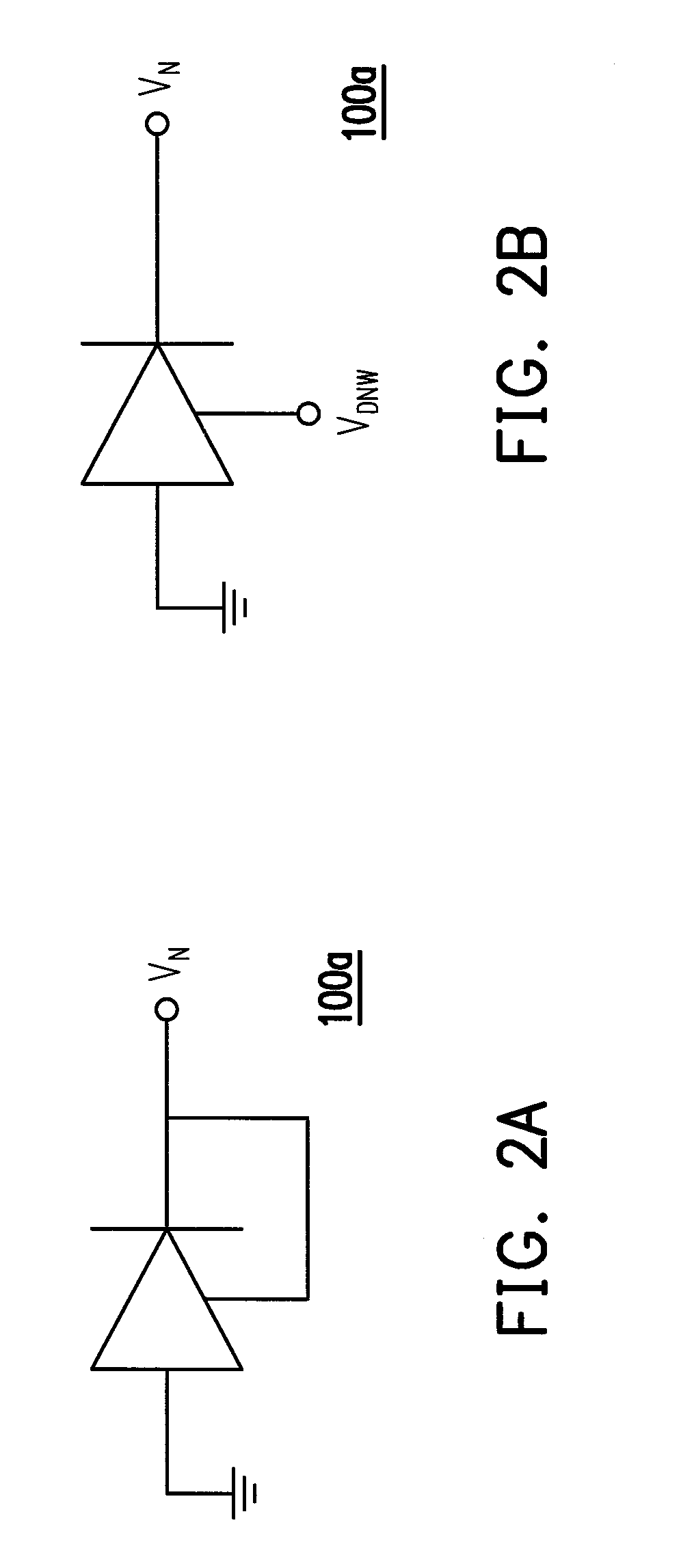

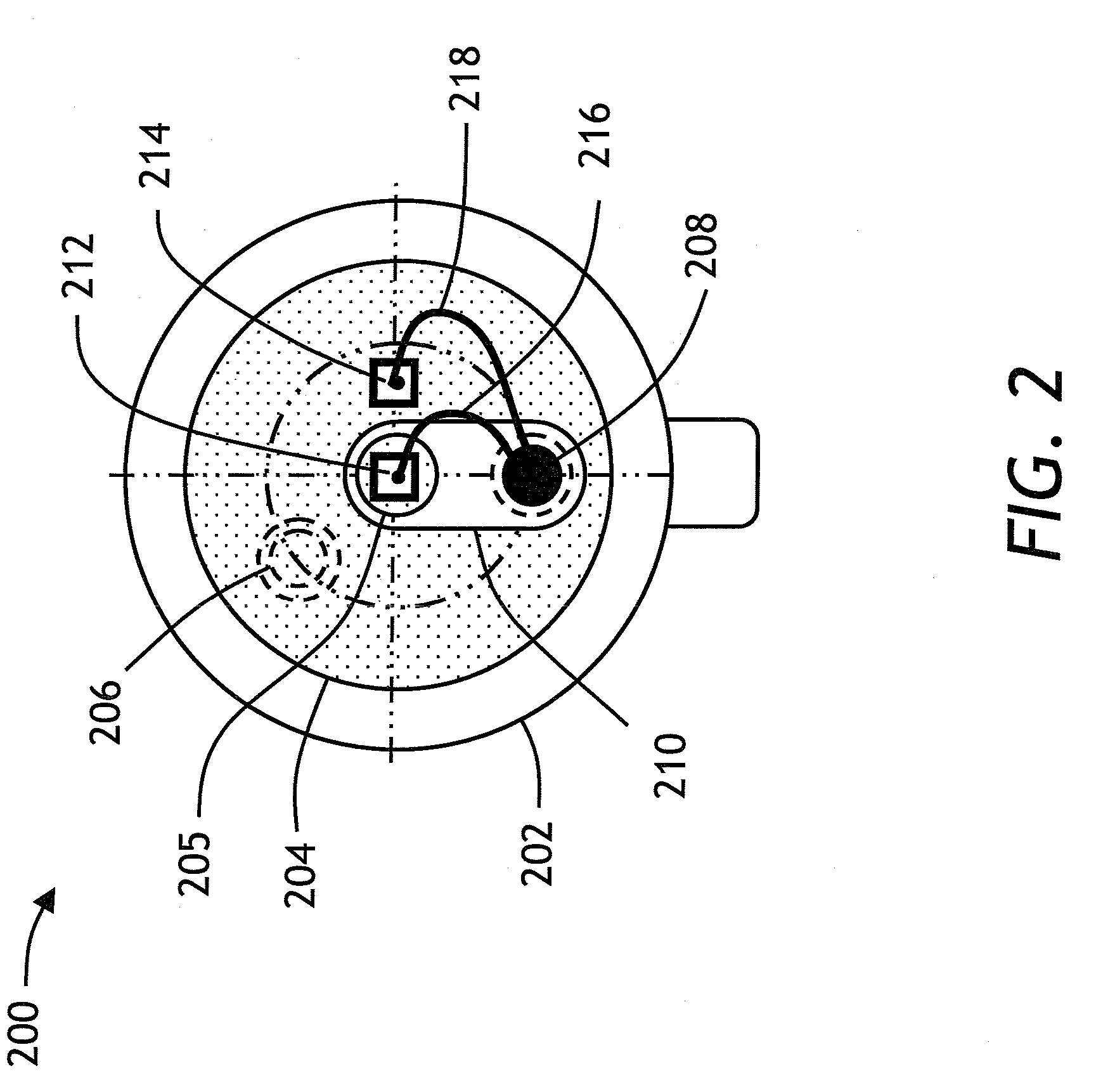

Si photodiode with symmetry layout and deep well bias in CMOS technology

InactiveUS8598639B2Increase frequency bandwidthImprove response speedSolid-state devicesSemiconductor devicesCMOSSoi cmos technology

A silicon photodiode with symmetry layout and deep well bias in CMOS technology is provided. The silicon photodiode includes a substrate, a deep well, and a PN diode structure. The deep well is disposed on the substrate, where an extra bias is applied to the deep well. The region surrounded by the deep well forms the main body of the silicon photodiode. The PN diode structure is located in the region surrounded by the deep well, where the silicon photodiode has a symmetry layout. The deep well is adopted when fabricating the silicon photodiode, and the extra bias is applied to the deep well to eliminate the interference and effect of the substrate absorbing light, and further greatly improve speed and bandwidth. Furthermore, the silicon photodiode has a symmetry layout, so that uniform electric field distribution is achieved, and the interference of the substrate noise is also reduced.

Owner:NAT CENT UNIV

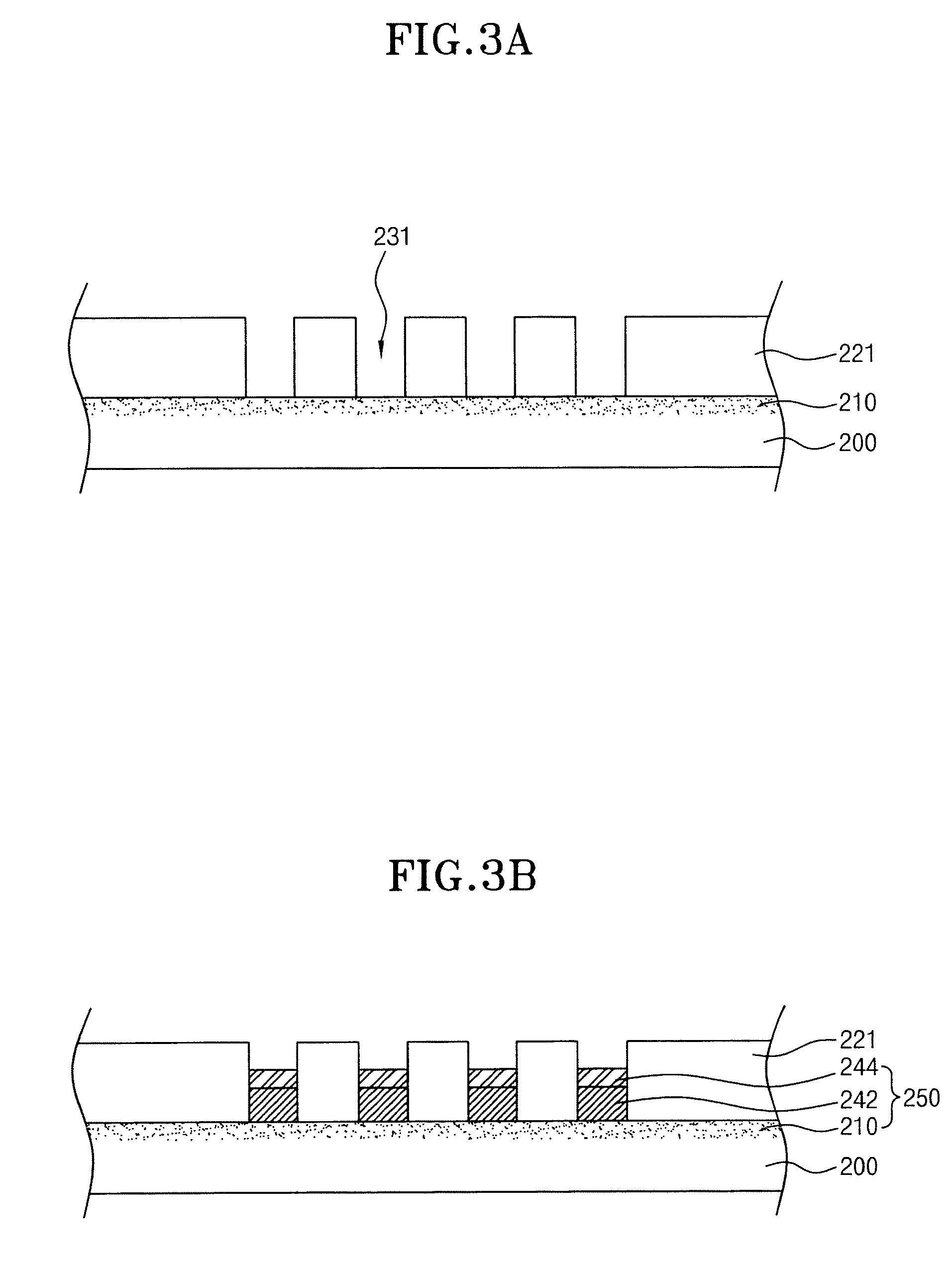

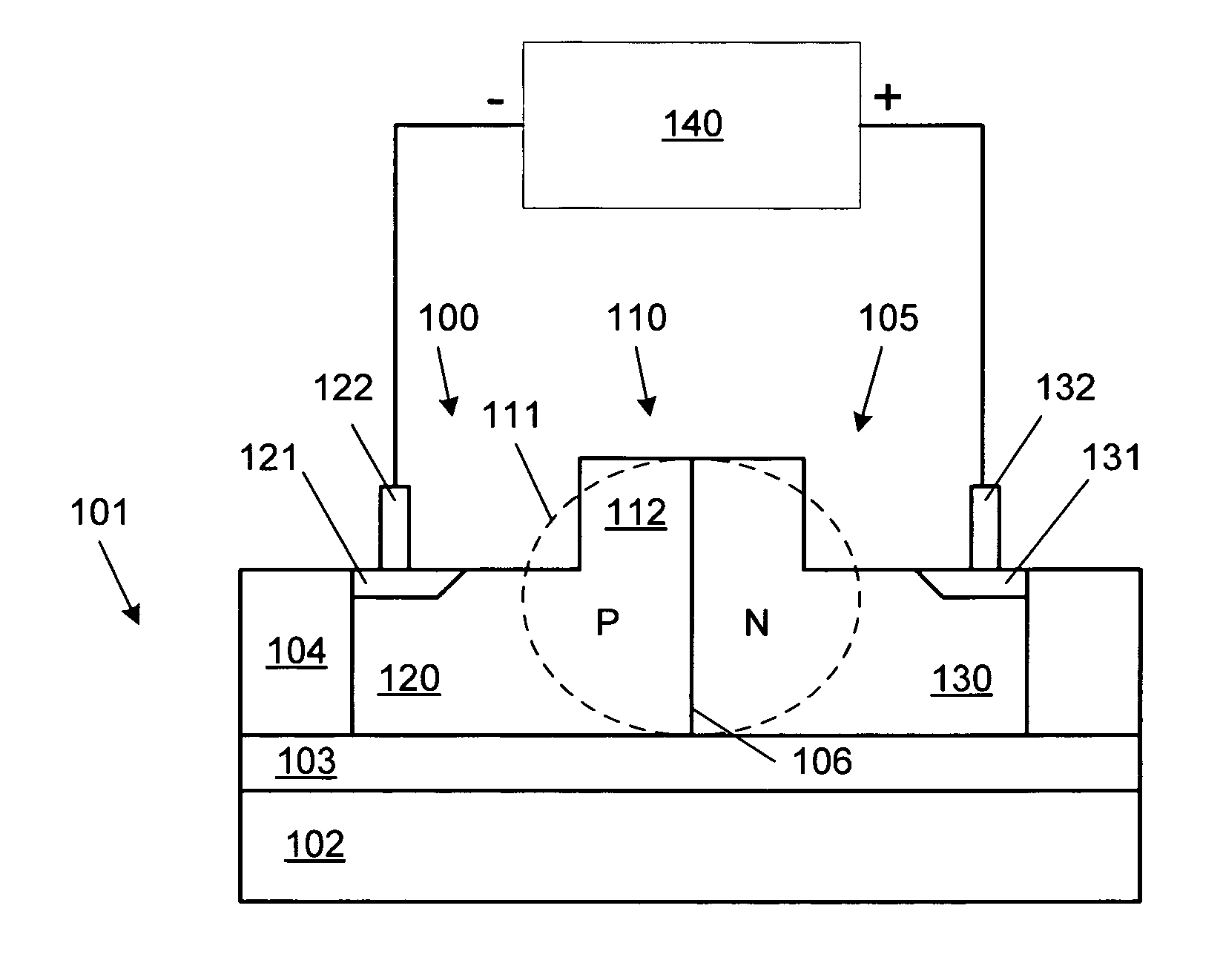

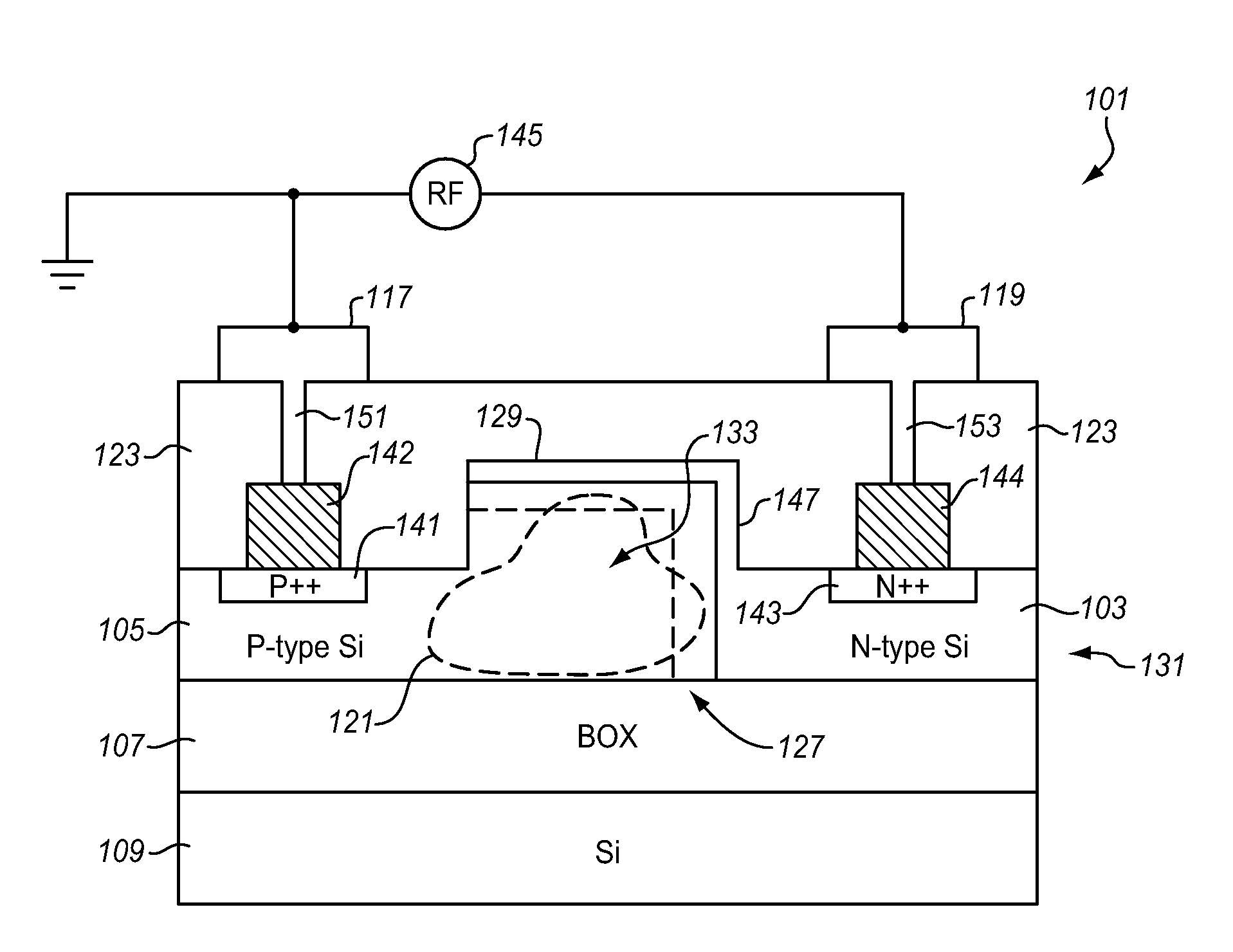

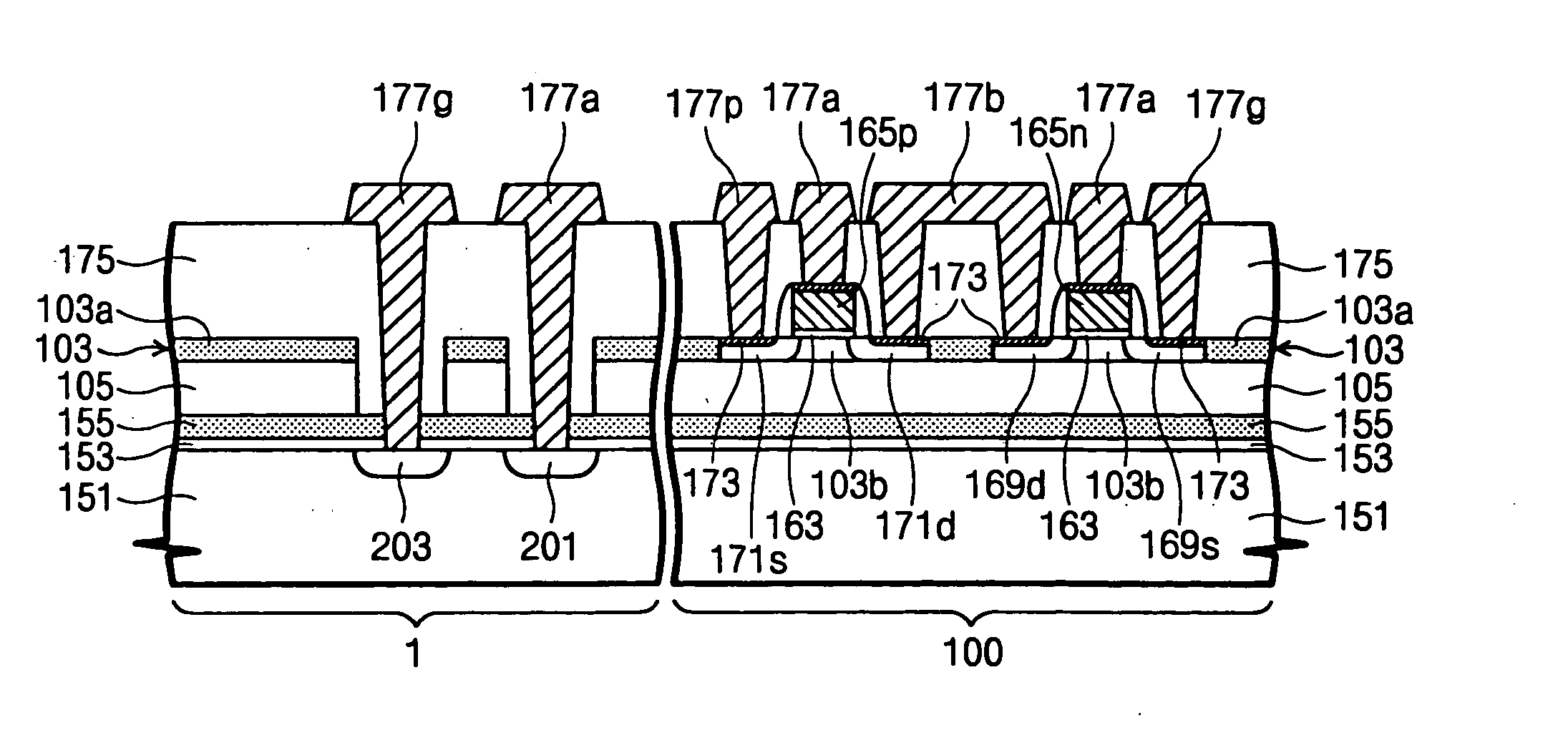

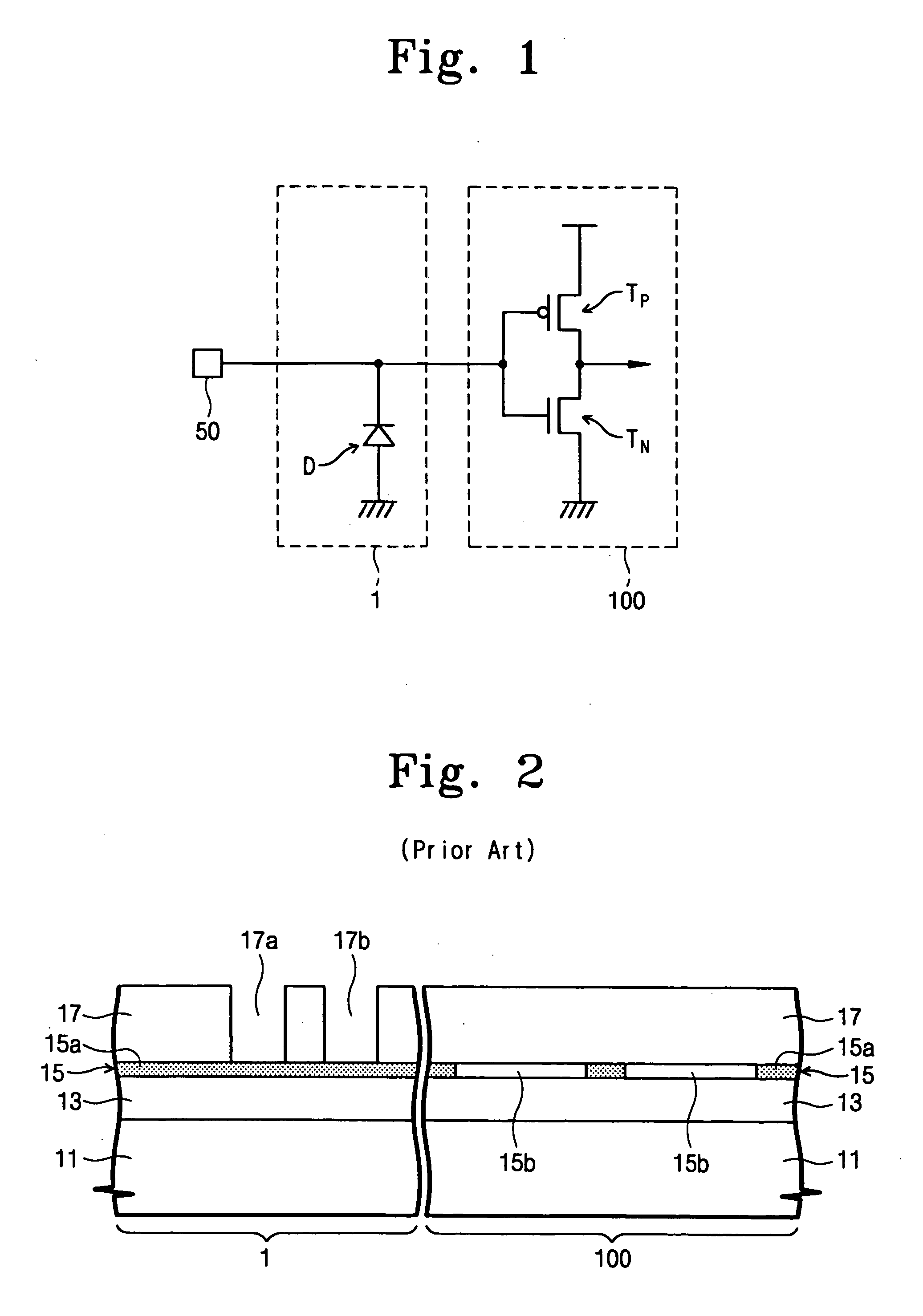

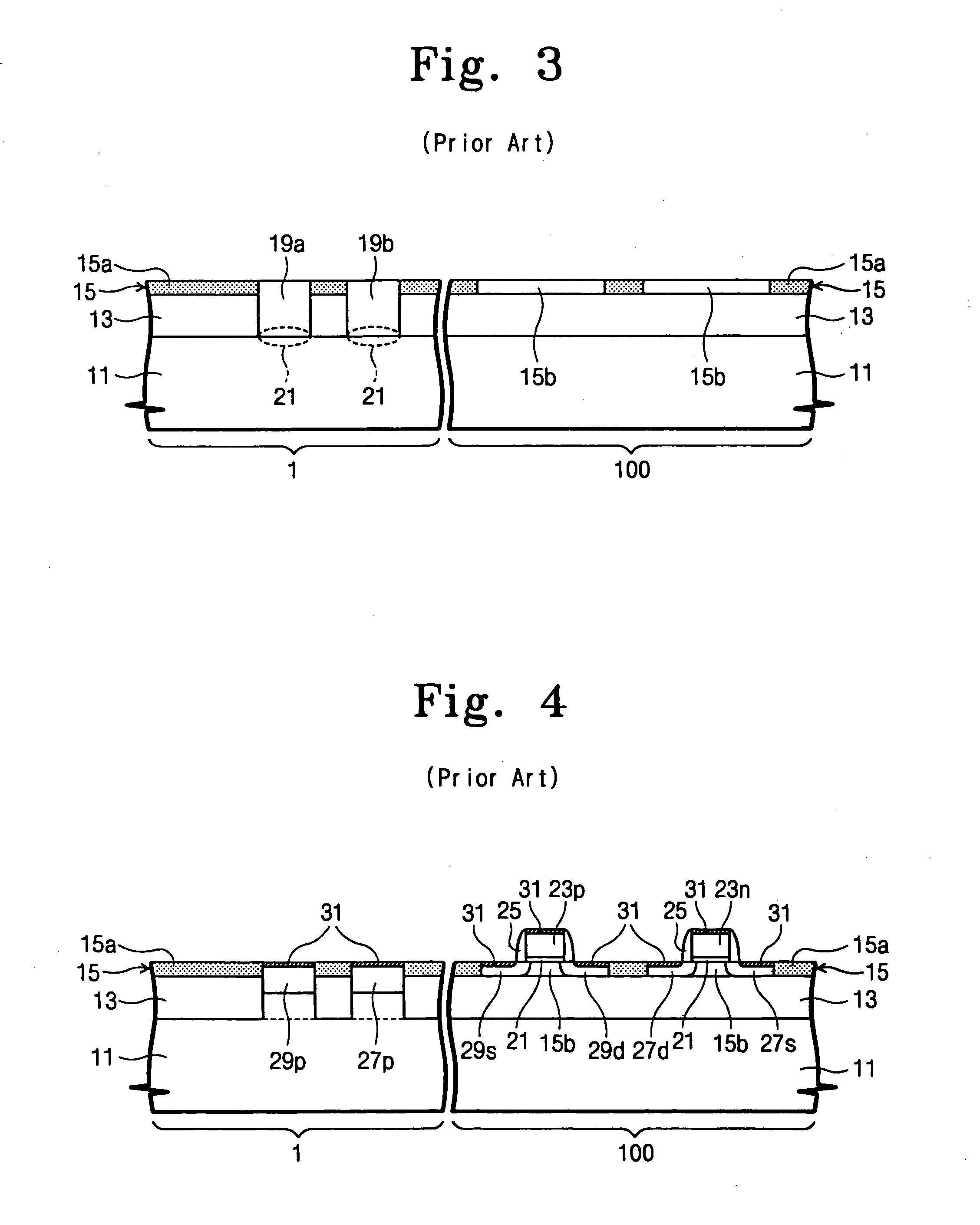

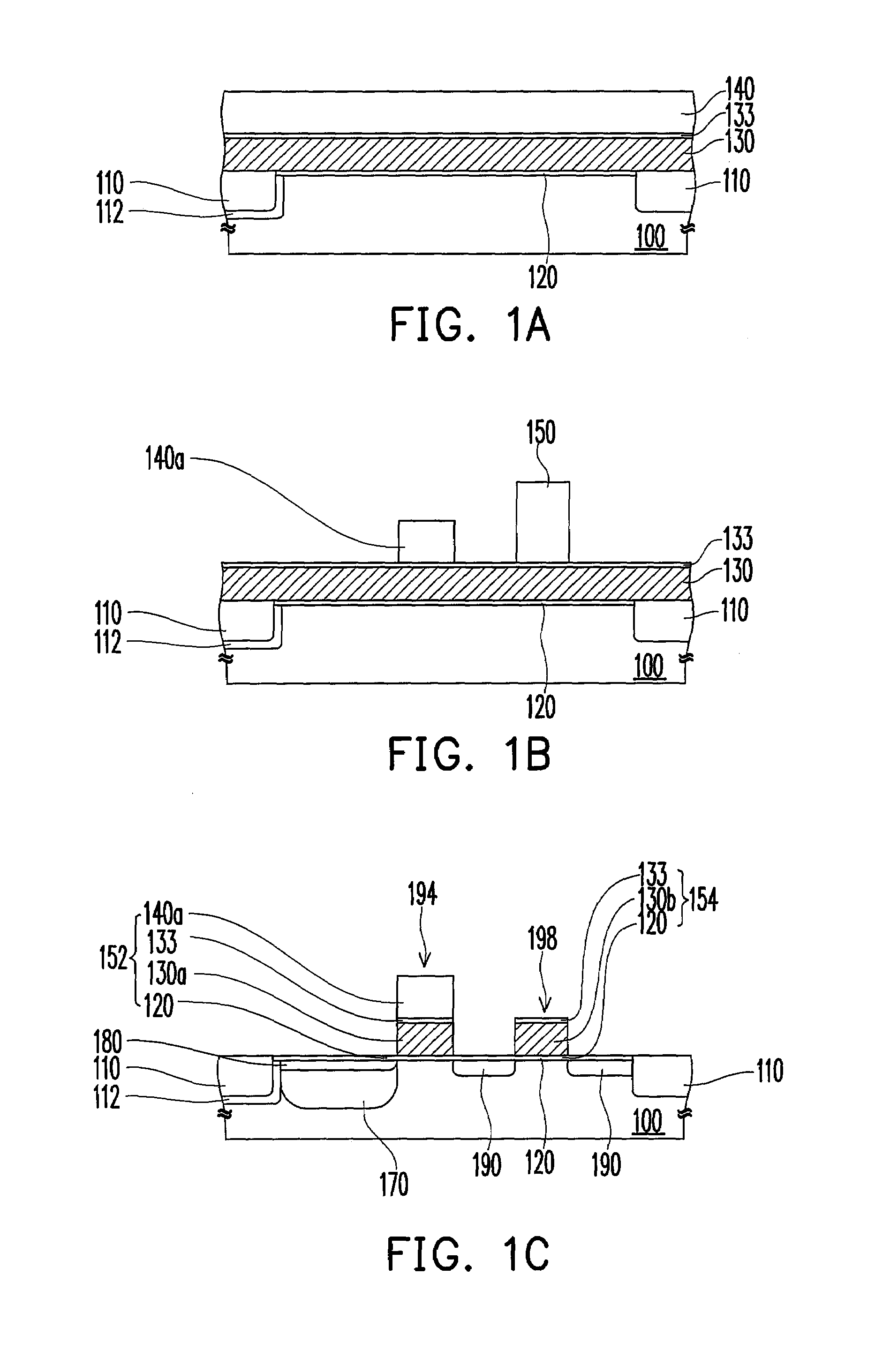

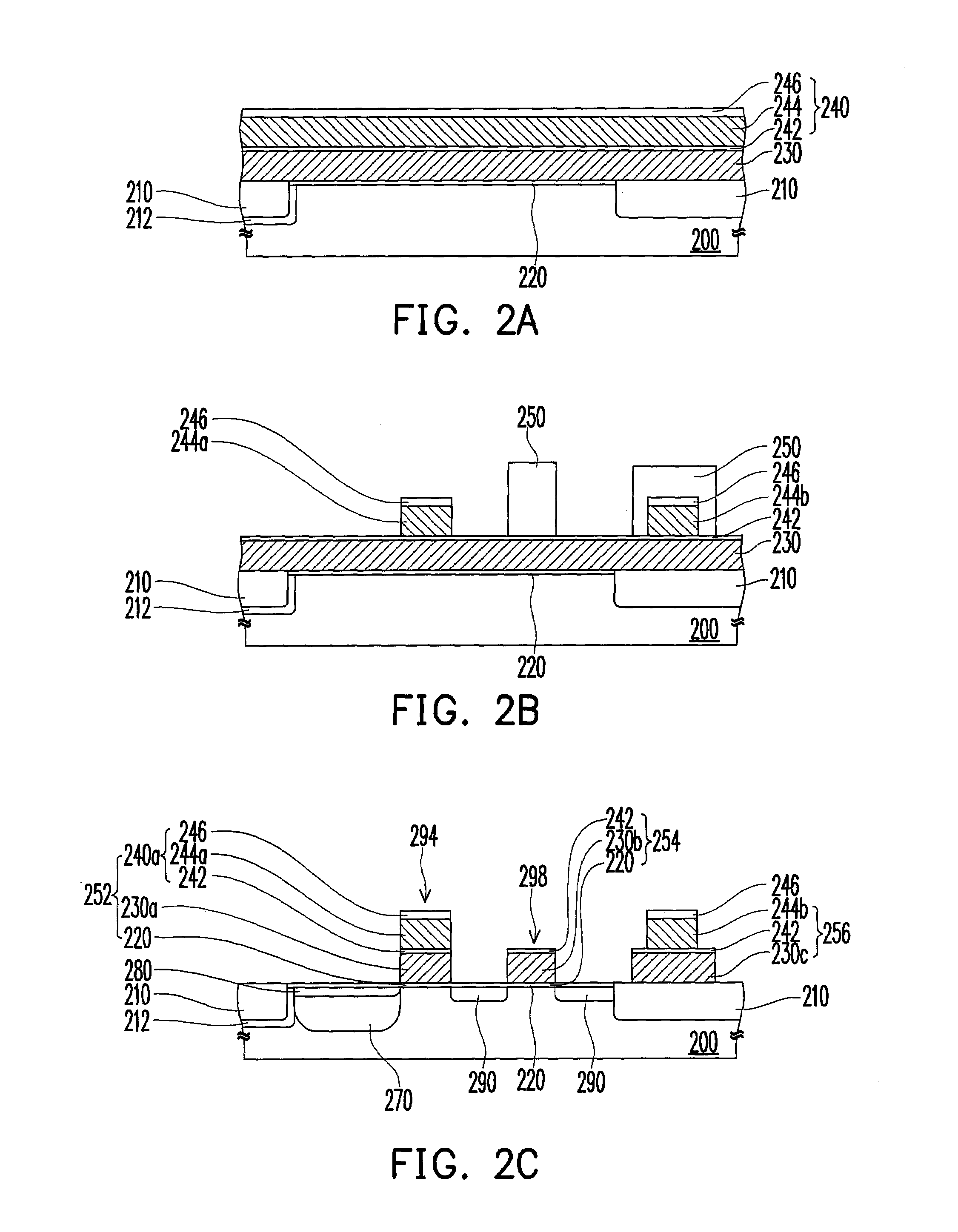

SOI substrate having an etch stop layer, and fabrication method thereof, SOI integrated circuit fabricated thereon, and method of fabricating SOI integrated circuit using the same

InactiveUS20040099910A1TransistorSemiconductor/solid-state device detailsIsolation layerSingle crystal

A SOI substrate having an etch stopping layer, a SOI integrated circuit fabricated on the SOI substrate, and a method of fabricating both are provided. The SOI substrate includes a supporting substrate, an etch stopping layer staked on the supporting substrate, a buried oxide layer and a semiconductor layer sequentially stacked on the etch stopping layer. The etch stopping layer preferably has an etch selectivity with respect to the buried oxide layer. A device isolation layer is preferably formed to define active regions. The device isolation, buried oxide and etch-stop layers are selectively removed to form first and second holes exposing the supporting substrate without damaging it. Semiconductor epitaxial layers grown on the exposed supporting substrate therefore have single crystalline structures without crystalline defects. Thus, when impurity regions are formed at surfaces of the epitaxial layers, a high performance PN diode having a superior leakage current characteristic may be formed.

Owner:SAMSUNG ELECTRONICS CO LTD

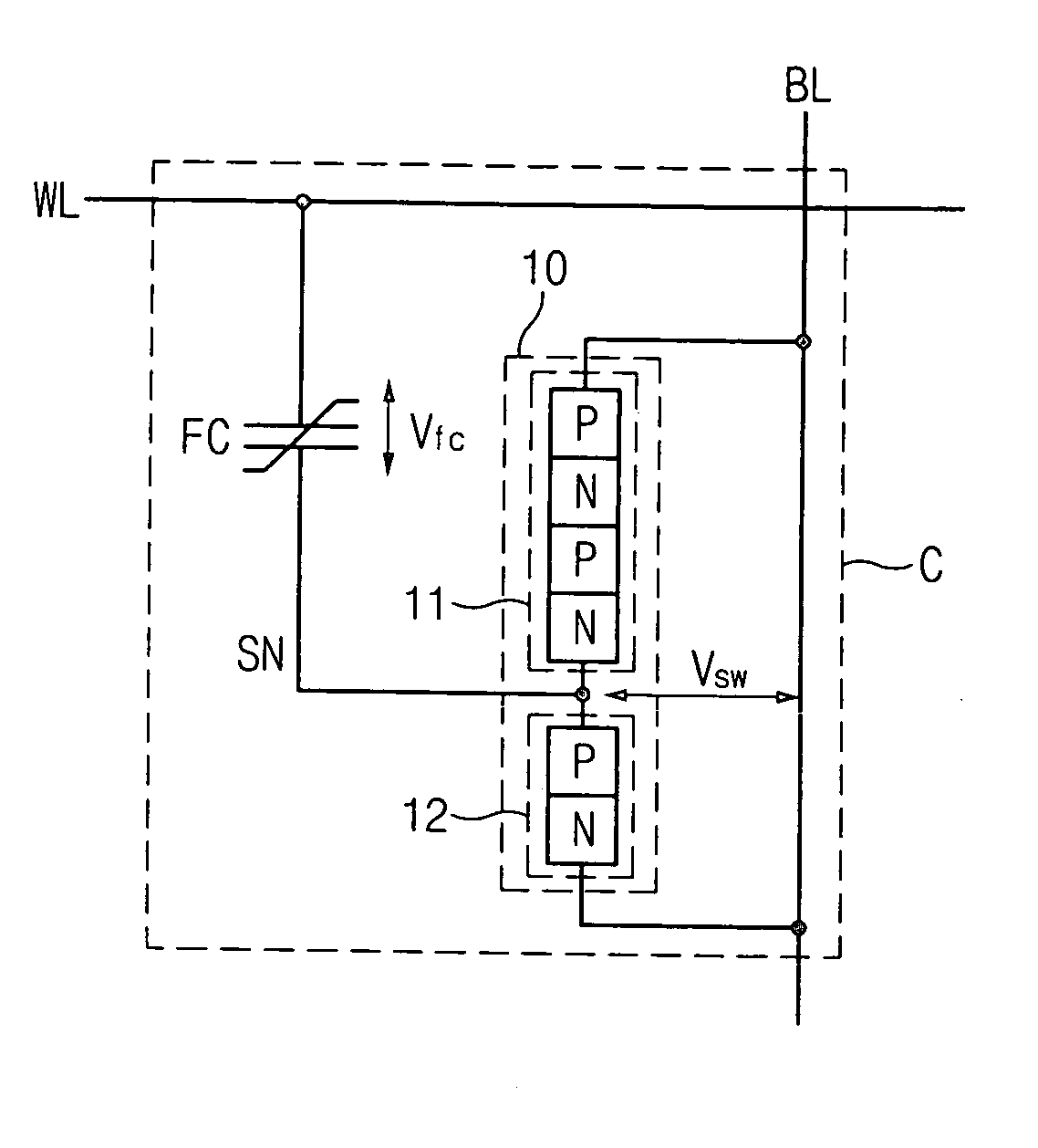

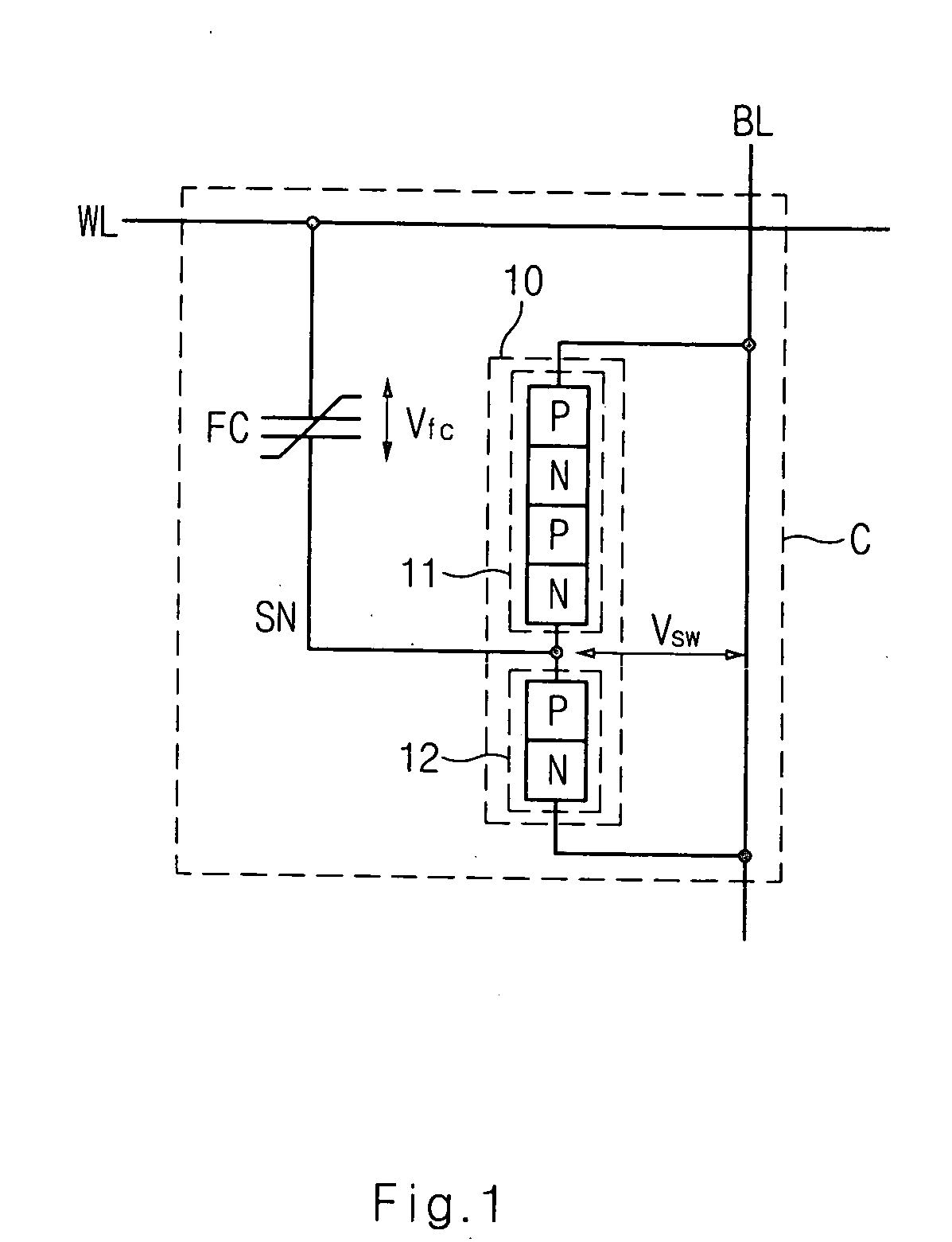

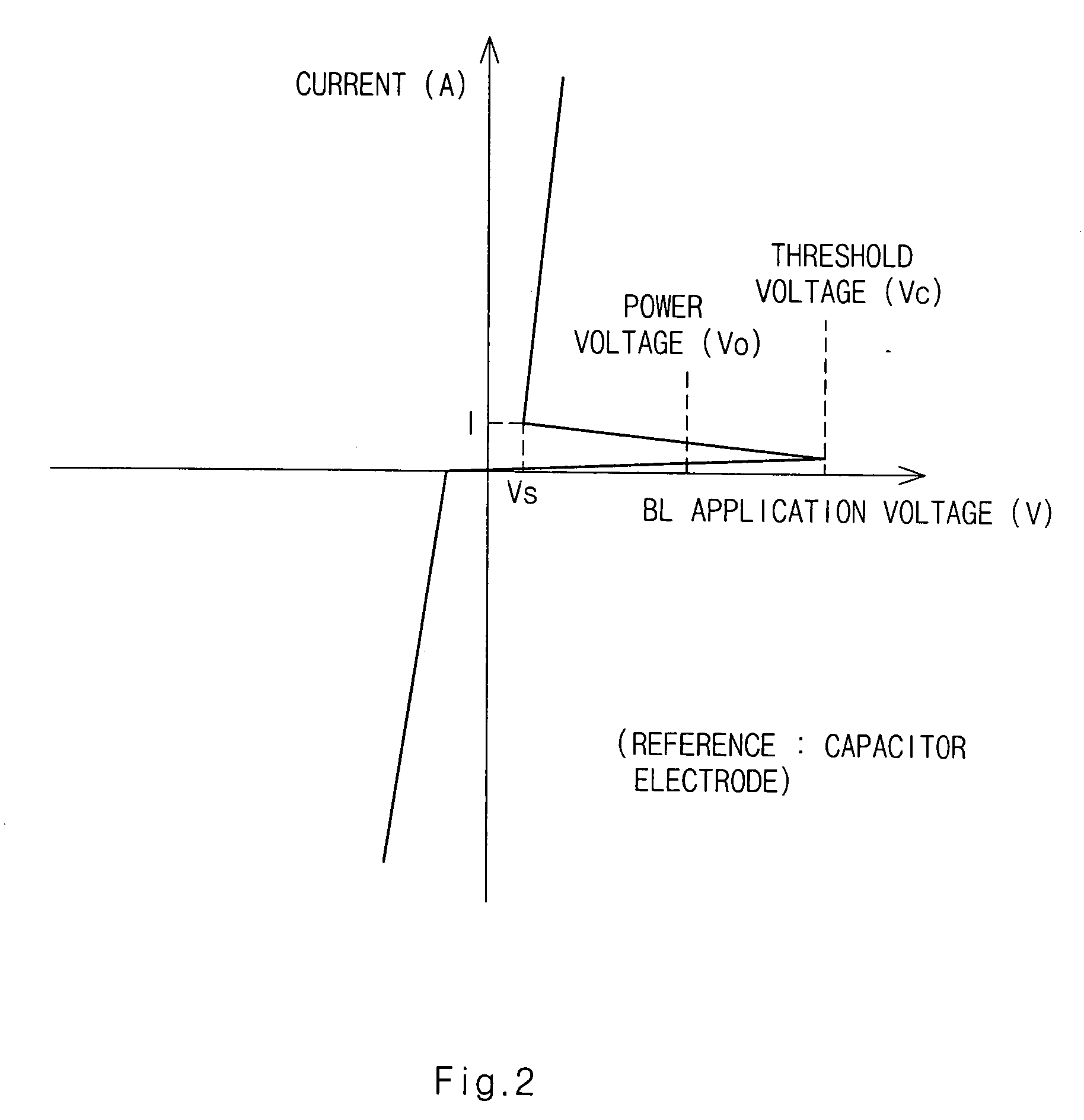

Nonvolatile ferroelectric perpendicular electrode cell, FeRAM having the cell and method for manufacturing the cell

InactiveUS20050237779A1Simple structureSolid-state devicesSemiconductor/solid-state device manufacturingBit lineFerroelectric capacitor

A nonvolatile ferroelectric perpendicular electrode cell comprises a ferroelectric capacitor and a serial PN diode switch. The ferroelectric capacitor includes a word line perpendicular electrode as a first electrode and a storage perpendicular electrode as a second electrode apart at a predetermined interval from the word line perpendicular electrode to have a column type, where a ferroelectric material is filled in a space where the first electrode are separated from the second electrode. The serial PN diode switch, which is connected between a bit line and the ferroelectric capacitor, selectively switches a current direction between the bit line and the ferroelectric capacitor depending on voltage change between the bit line and the ferroelectric capacitor.

Owner:SK HYNIX INC

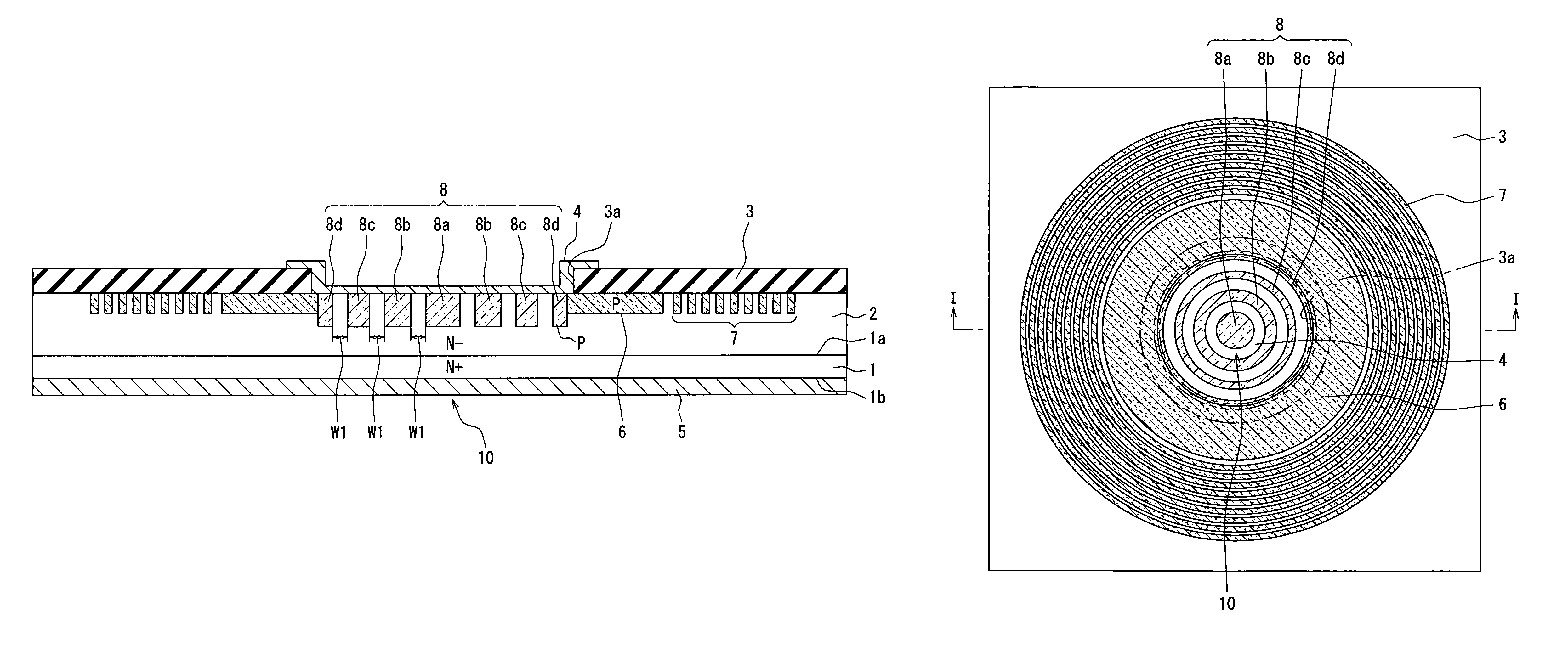

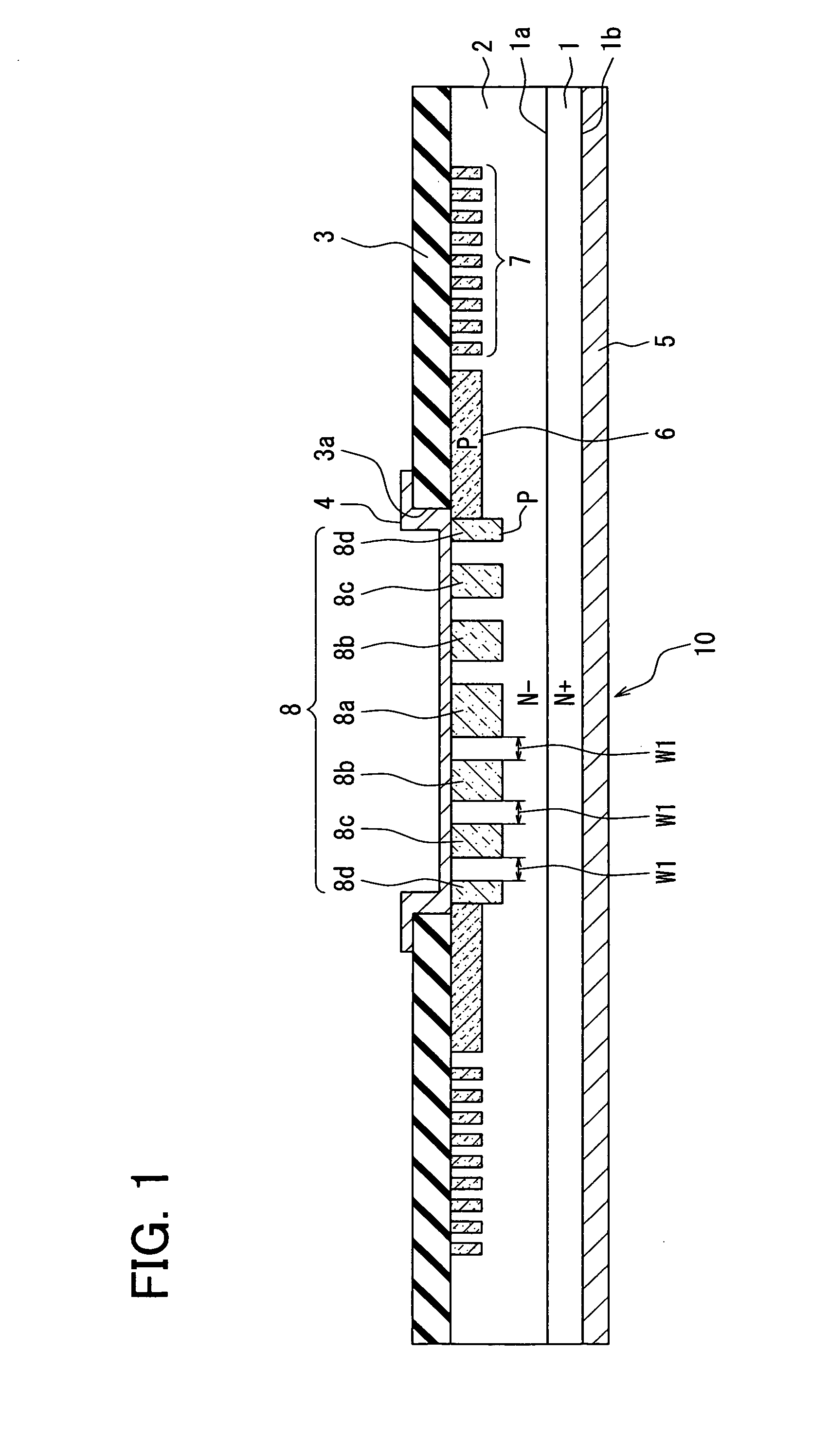

Silicon carbide semiconductor device having junction barrier Schottky diode

InactiveUS7893467B2Improve breakdown voltageDifficulty concentratingSemiconductor/solid-state device manufacturingSemiconductor devicesSchottky diodeSemiconductor

A silicon carbide semiconductor device includes a substrate; a drift layer having a first conductivity type; an insulating layer; a Schottky electrode; an ohmic electrode; a resurf layer; and second conductivity type layers. The drift layer and the second conductivity type layers provide multiple PN diodes. Each second conductivity type layer has a radial width with respect to a center of a contact region between the Schottky electrode and the drift layer. A radial width of one of the second conductivity type layers is smaller than that of another one of the second conductivity type layers, which is disposed closer to the center of the contact region than the one of the second conductivity type layers.

Owner:DENSO CORP

CMOS image sensor process and structure

ActiveUS20080121951A1Reduce dark currentIncrease contrastSolid-state devicesSemiconductor/solid-state device manufacturingCMOSGate dielectric

A CMOS image sensor (CIS) process is described. A semiconductor substrate is provided, and then a gate dielectric layer, a gate material layer and a thickening layer are sequentially formed on the substrate, wherein the thickening layer includes at least a hard mask layer. The thickening layer is defined to form a transfer-gate pattern, and then the transfer-gate pattern is used as an etching mask to pattern the gate material layer and form a transfer gate. Ion implantation is then conducted to form a PN diode in the substrate with the transfer-gate pattern and the transfer gate as a mask.

Owner:UNITED MICROELECTRONICS CORP

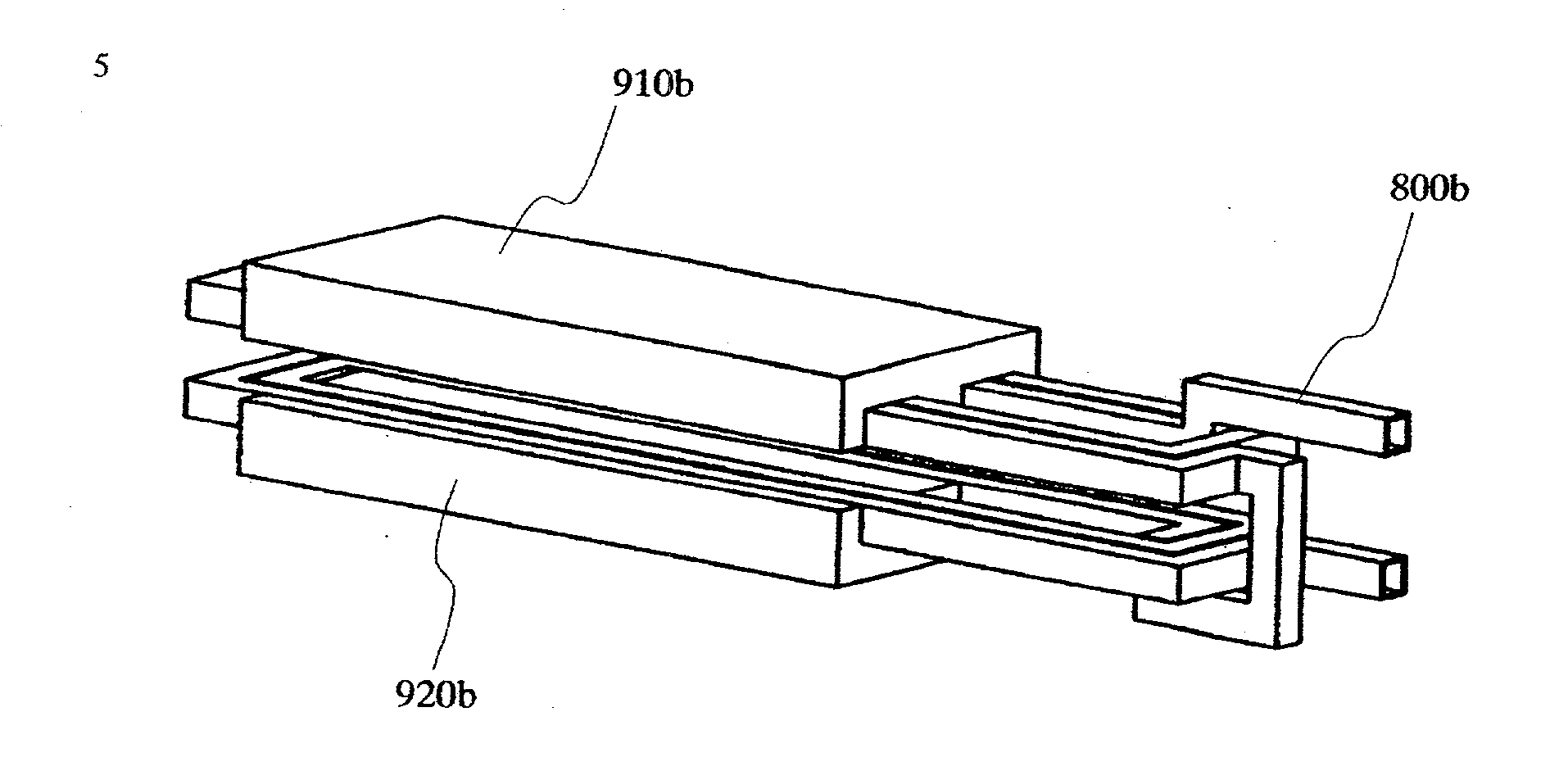

Apparatuses for heat-treatment of semiconductor films under low temperature

InactiveUS20030197007A1Increase the magnetic field strengthEfficient heat treatmentCoil arrangementsSemiconductor/solid-state device manufacturingHeat sensitiveSolar cell

Owner:VIATRON TECH INC

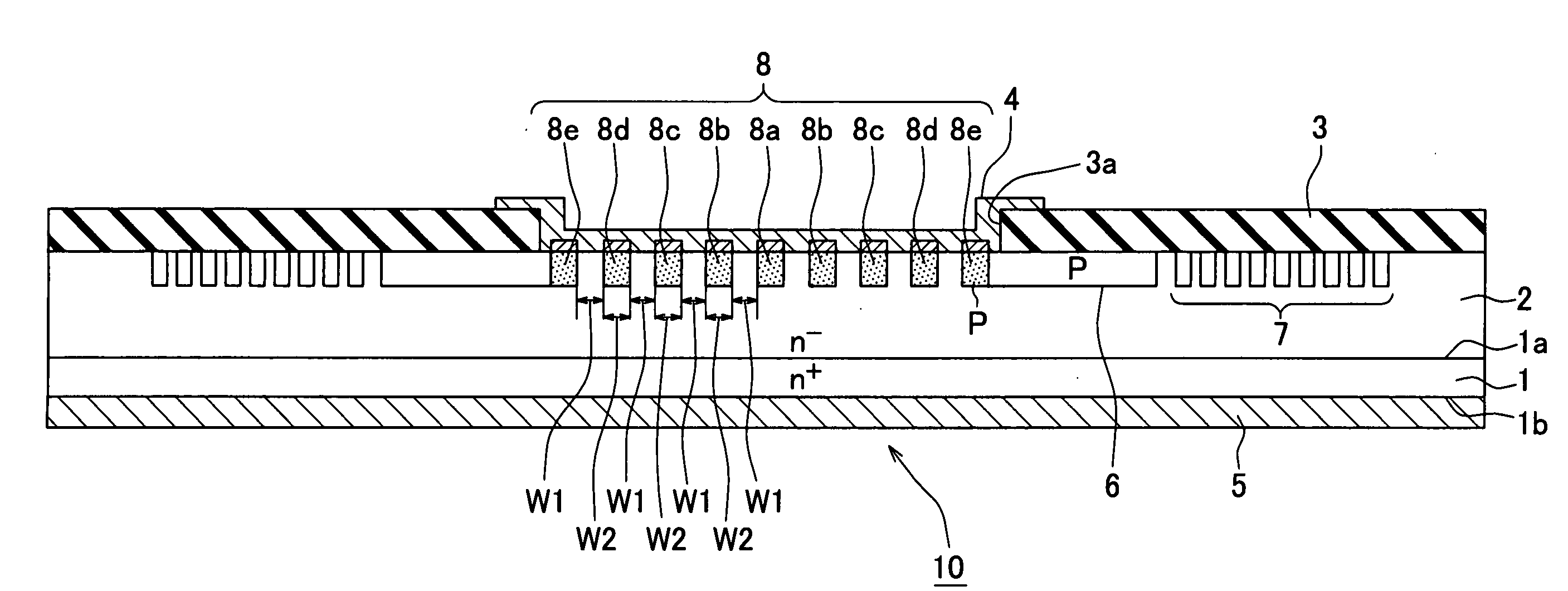

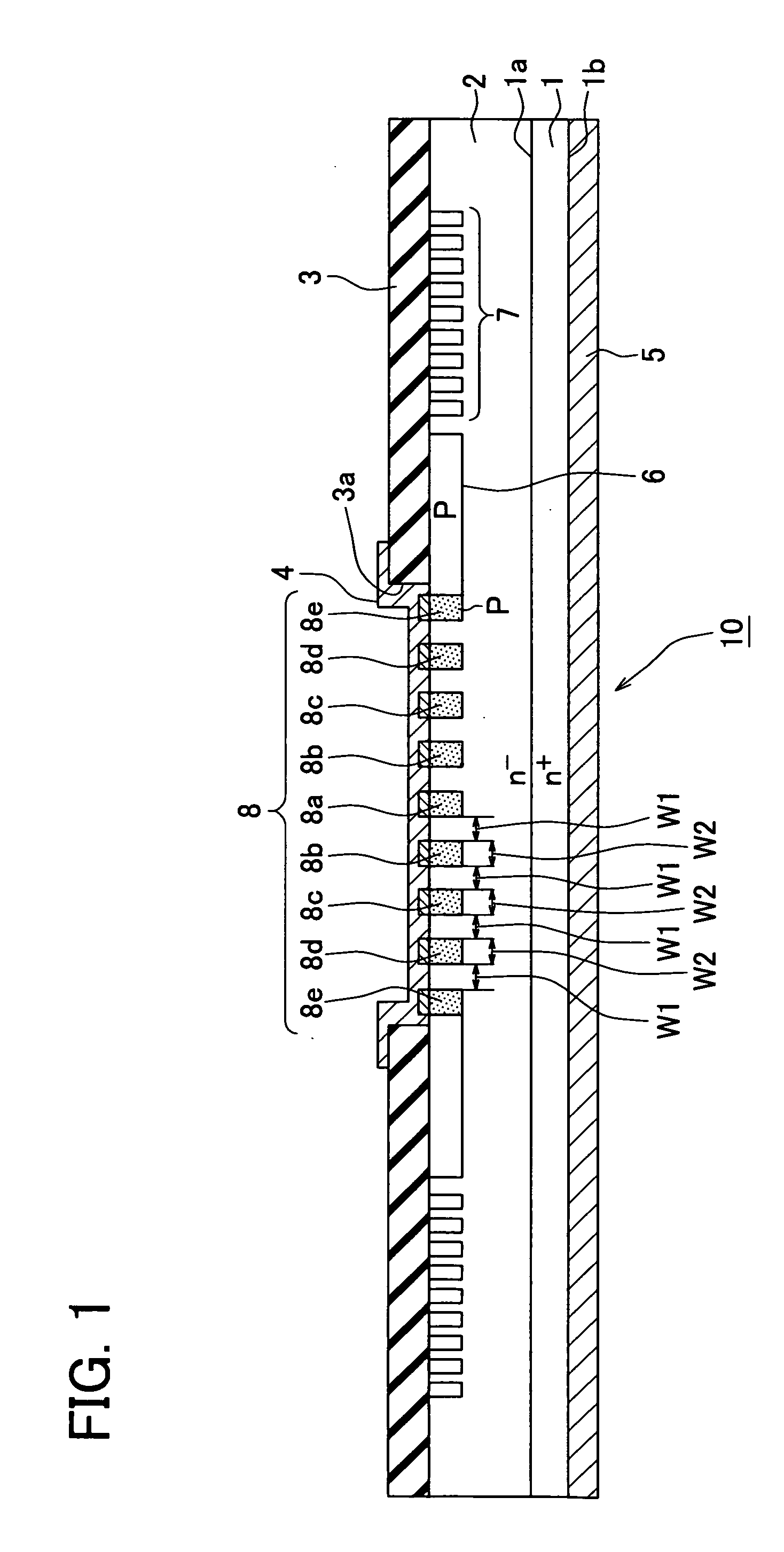

Silicon carbide semiconductor device having junction barrier schottky diode

ActiveUS20150206941A1Improve device yieldTotal current dropSemiconductor/solid-state device manufacturingSemiconductor devicesSchottky barrierStacking fault

A silicon carbide semiconductor device includes a junction barrier Schottky diode including a substrate, a drift layer, an insulating film, a Schottky barrier diode, and a plurality of second conductivity type layers. The Schottky barrier diode includes a Schottky electrode and an ohmic electrode. A PN diode is configured by the plurality of second conductivity type layers and the drift layer, and the plurality of second conductivity type layers is formed in stripes only in a direction parallel to a rod-shaped stacking fault.

Owner:DENSO CORP

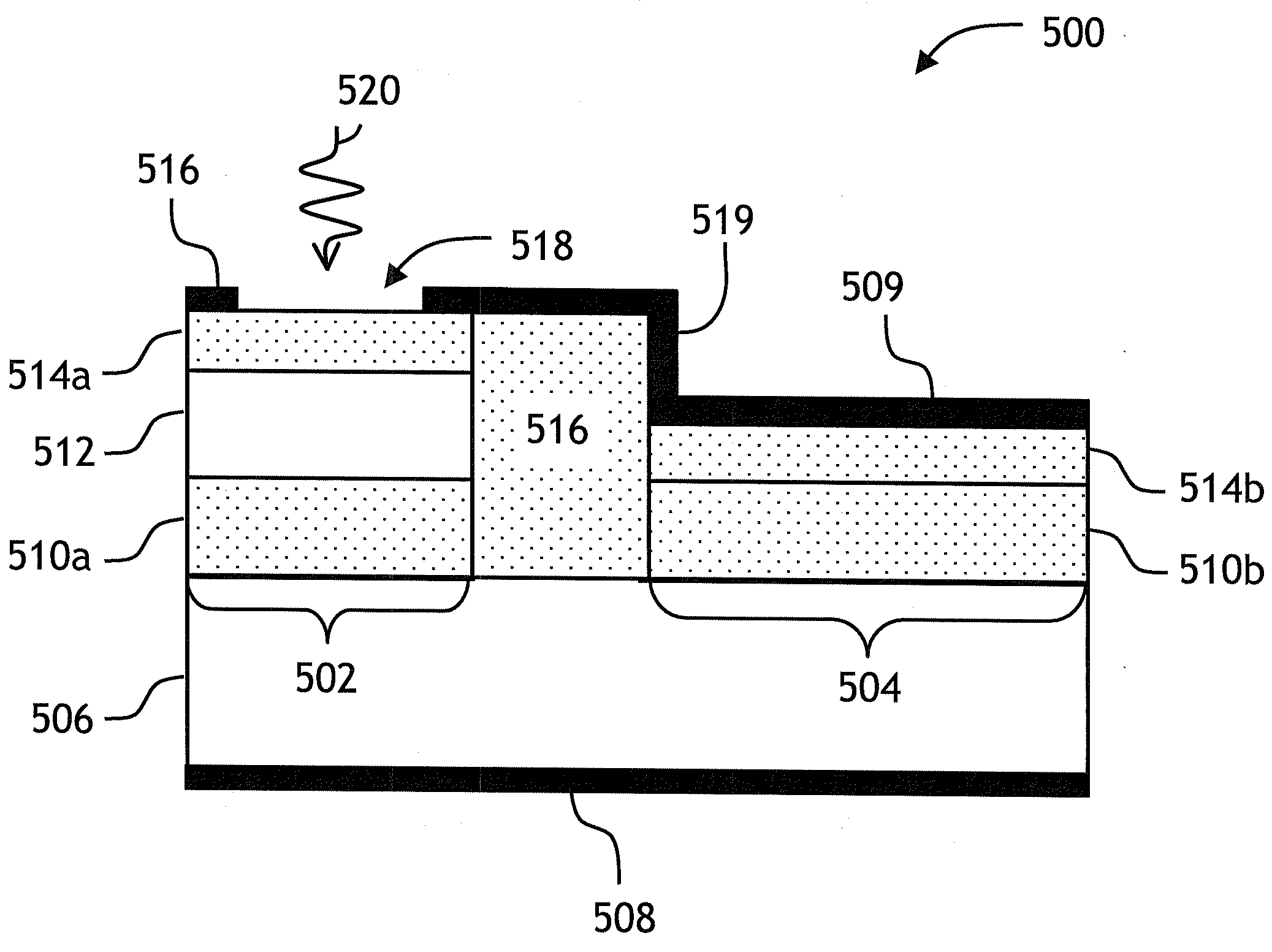

Photodiode Assembly With Improved Electrostatic Discharge Damage Threshold

A photodiode with an improved electrostatic damage threshold is disclosed. A Zener or an avalanche diode is connected in parallel to a photodiode. Both diodes are integrated into the same photodiode housing. The diodes can be mounted on a common header or onto each other. An avalanche photodiode and an avalanche diode can be fabricated on a common semiconductor substrate. A regular p-n diode connected in series, cathode-to-cathode or anode-to-anode, to a Zener diode, forms a protection circuit which, when connected in parallel to a photodiode, provides a smaller electrical capacity increase as compared to a simpler circuit consisting just of a Zener or an avalanche diode.

Owner:JDS UNIPHASE CORP

Apparatuses for heat-treatment of semiconductor films under low temperature

InactiveUS6747254B2Improved kineticsHeat-treated continuously and efficientlyCoil arrangementsSemiconductor/solid-state device manufacturingHeat sensitiveSolar cell

Owner:VIATRON TECH INC

SIC semiconductor having junction barrier Schottky diode

Owner:DENSO CORP

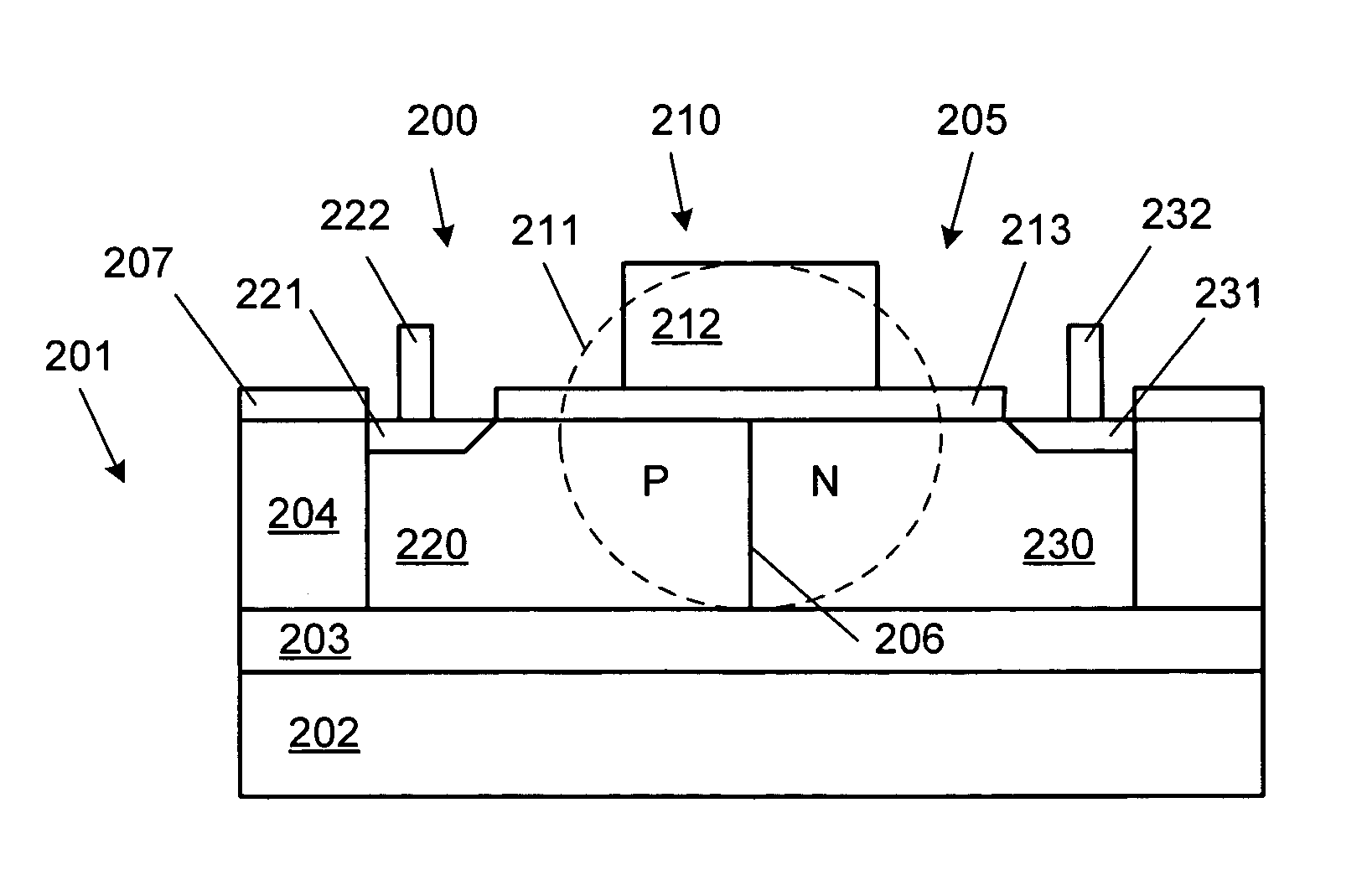

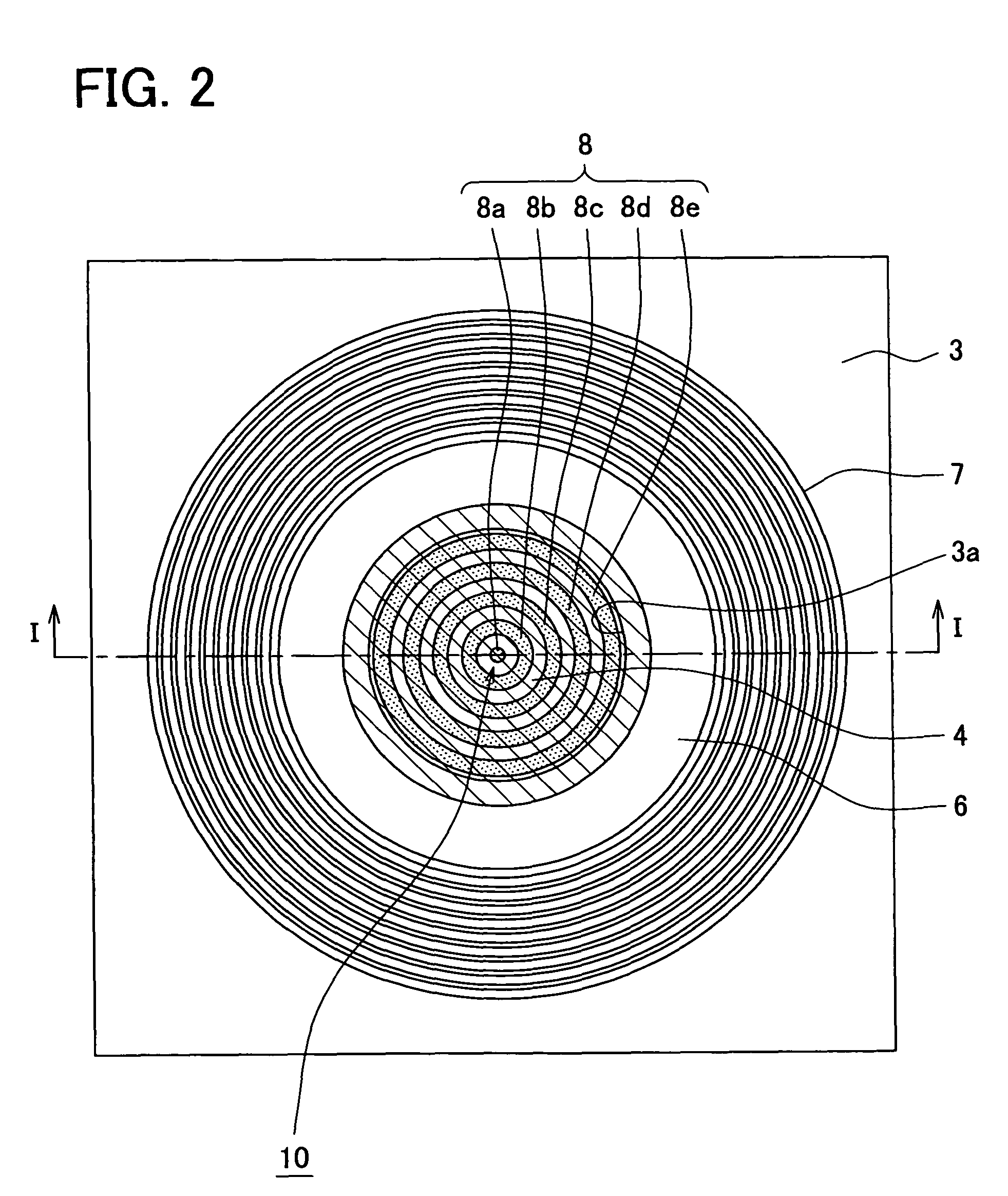

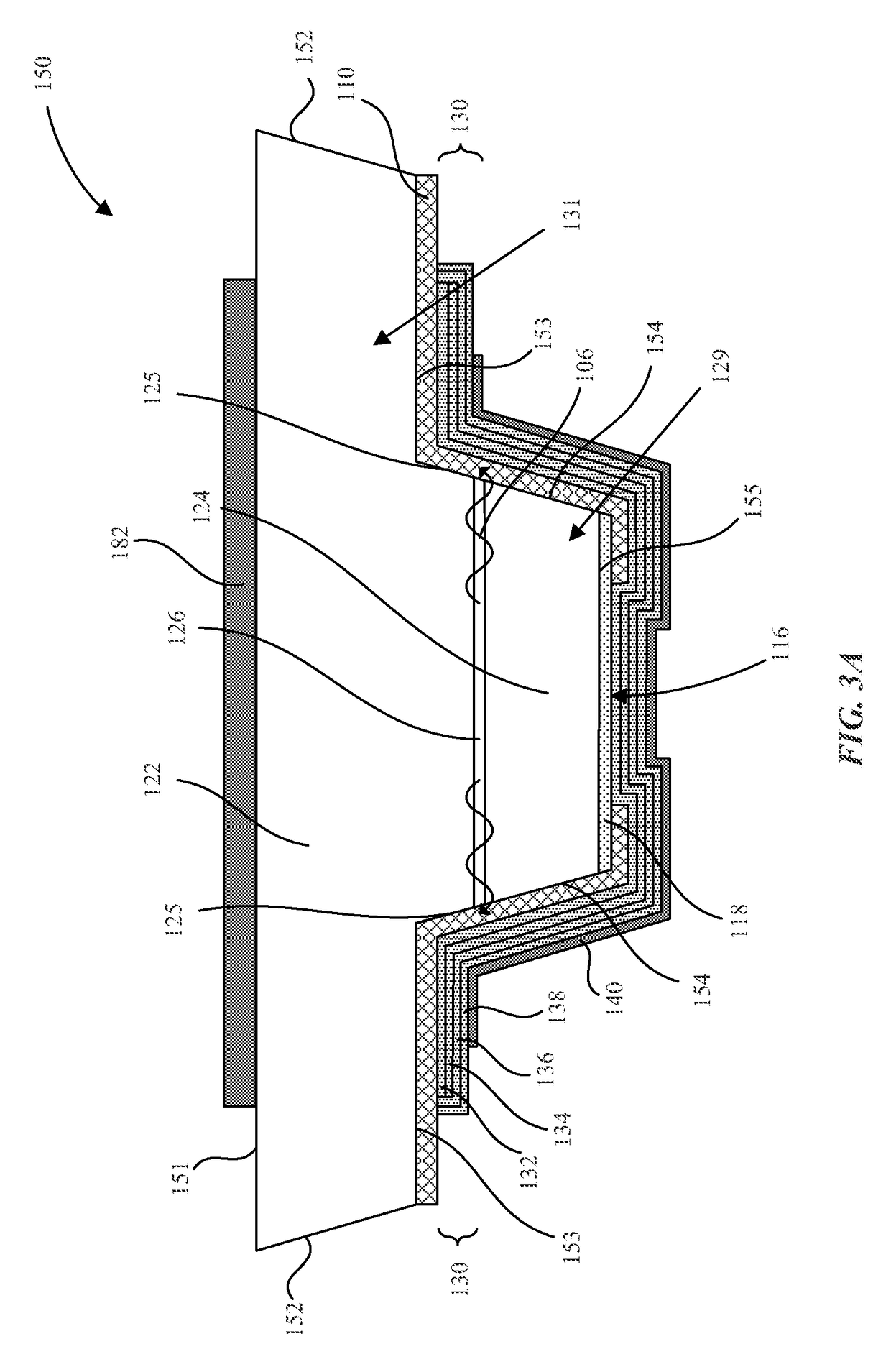

Micro-light emitting diode with metal side mirror

Light emitting diodes and display systems are disclosed. In an embodiment a light emitting diode (150) includes a p-n diode (120) including a mesa structure (129) that protrudes from a base structure (131). A reflective metallization (130) laterally surrounds the mesa structure, which also includes a quantum well layer of the p-n diode.

Owner:APPLE INC