Patents

Literature

182 results about "Noise margin" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

In electrical engineering, noise margin is the maximum voltage amplitude of extraneous signal that can be algebraically added to the noise-free worst-case input level without causing the output voltage to deviate from the allowable logic voltage level.

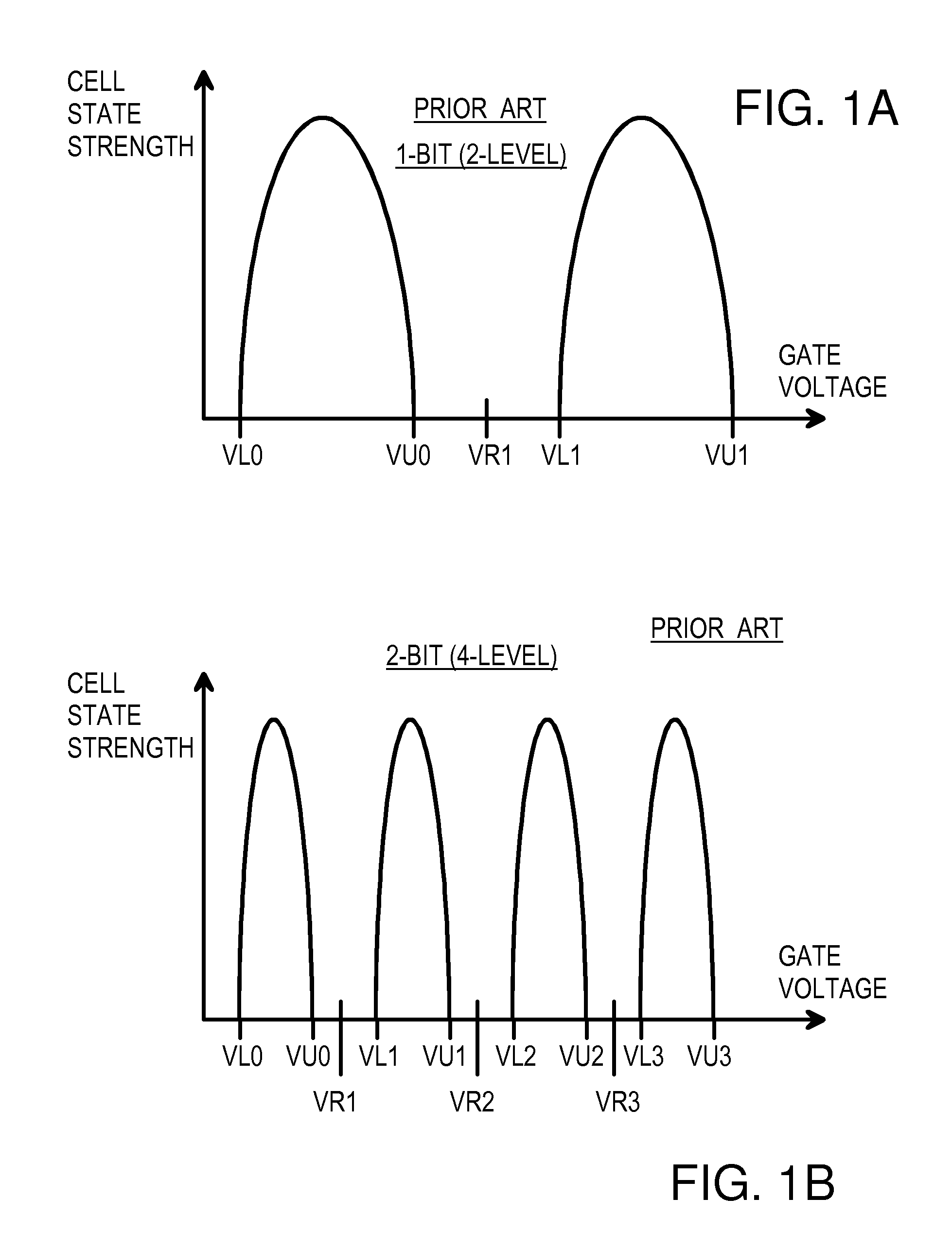

Cell-Downgrading and Reference-Voltage Adjustment for a Multi-Bit-Cell Flash Memory

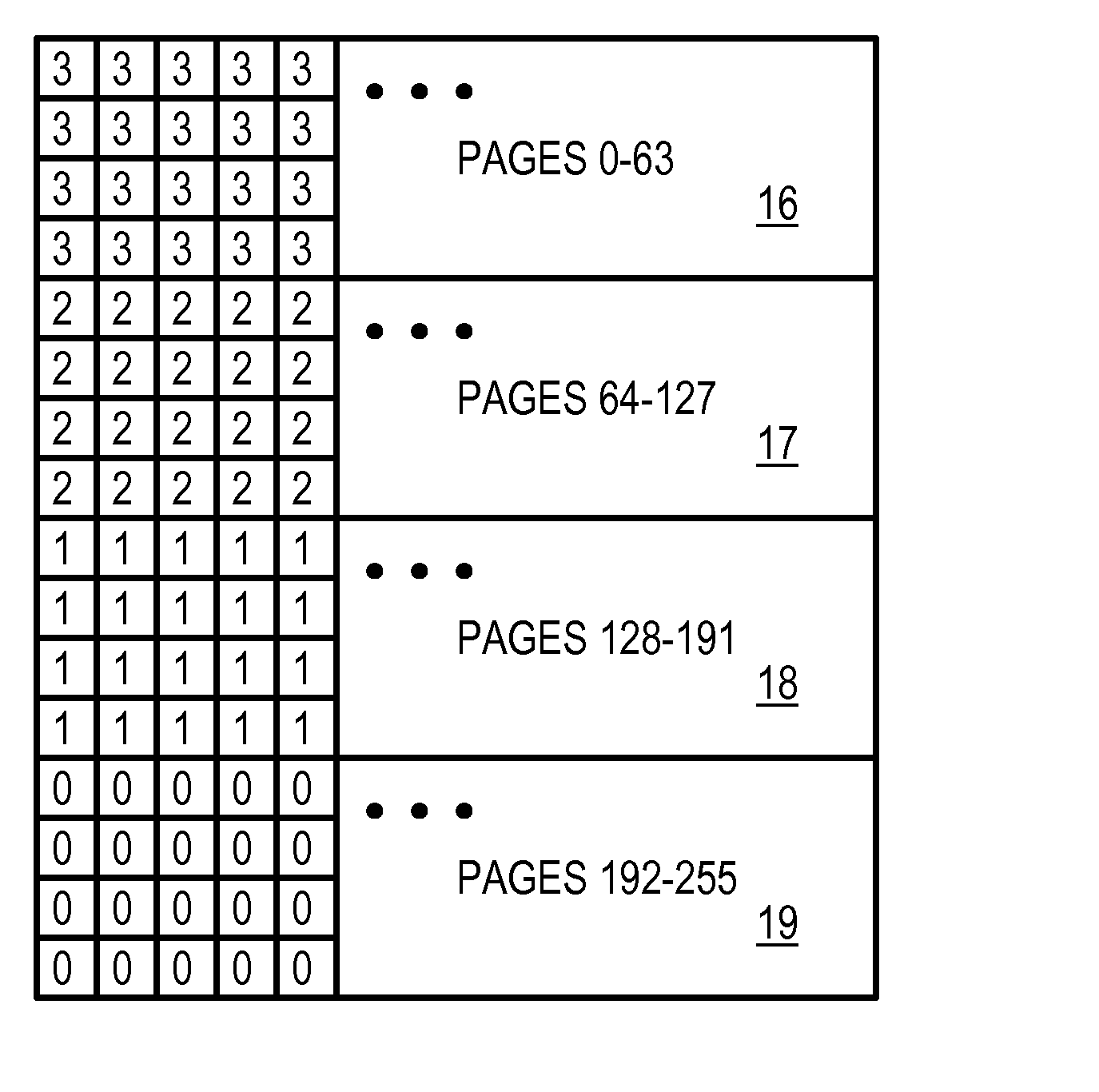

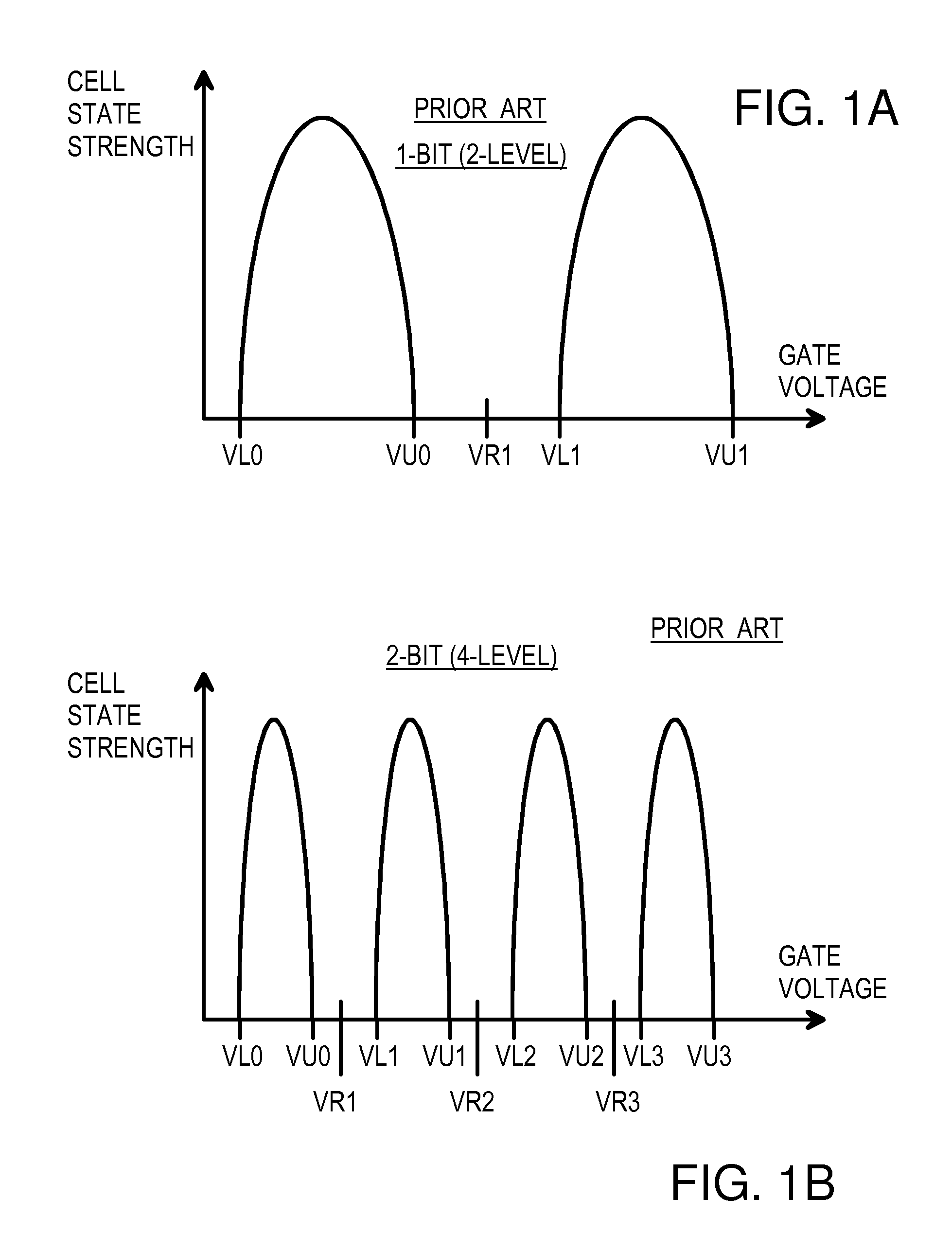

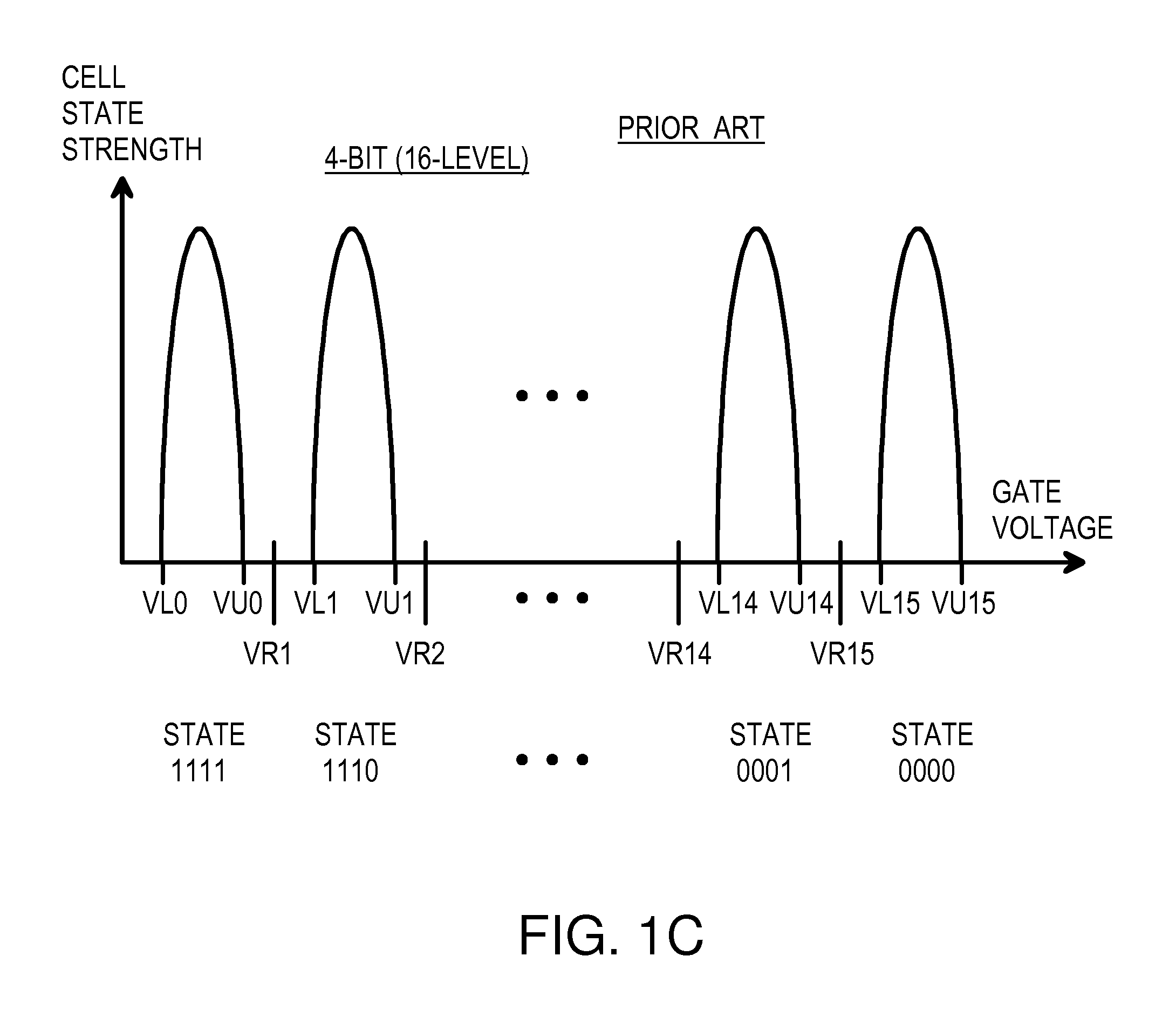

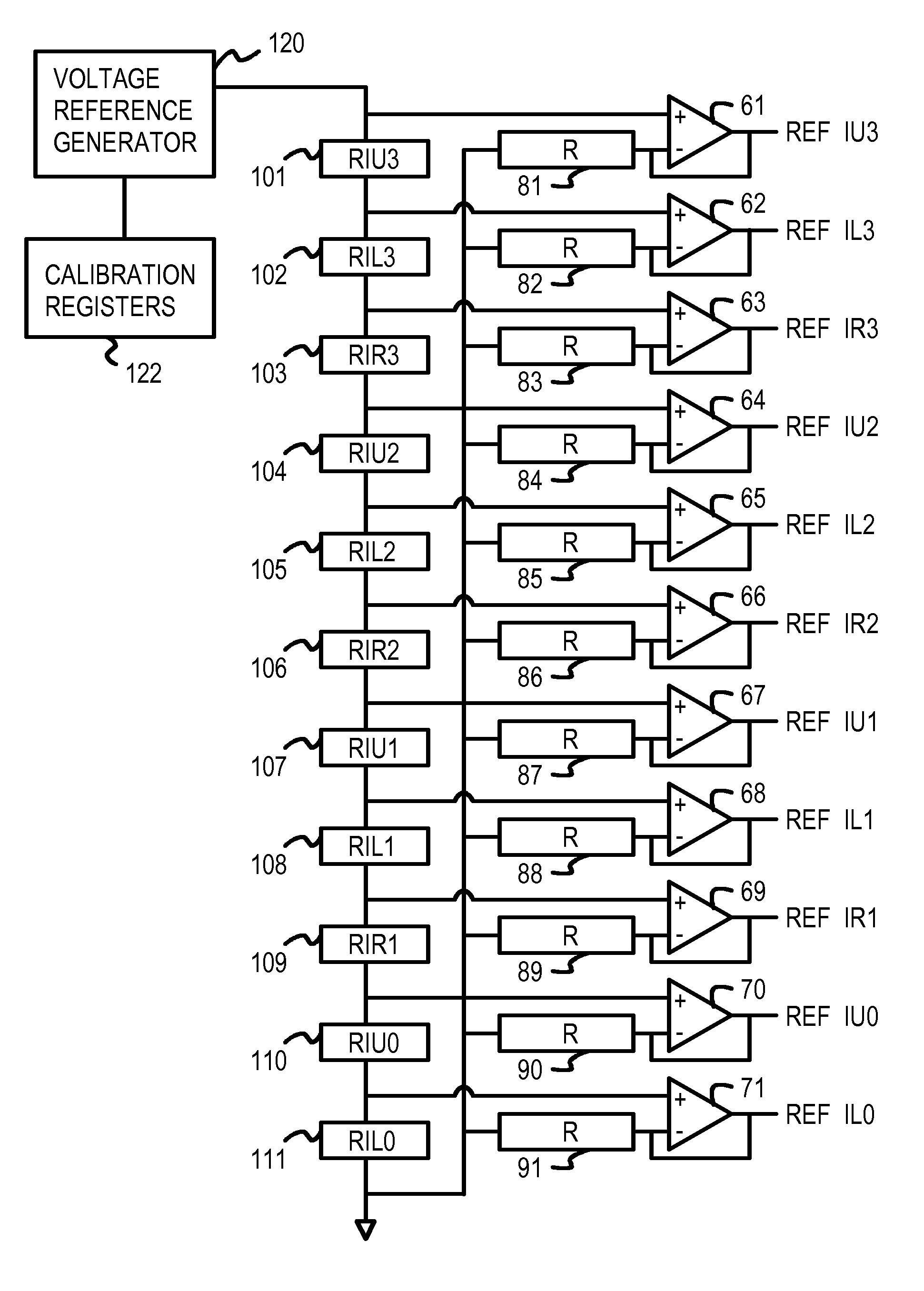

A flash memory has multi-level cells (MLC) that can each store multiple bits per cell. Blocks of cells can be downgraded to fewer bits / cell when errors occur, or for storing critical data such as boot code. The bits from a single MLC are partitioned among multiple pages to improve error correctability using Error Correction Code (ECC). An upper reference voltage is generated by a voltage reference generator in response to calibration registers that can be programmed to alter the upper reference voltage. A series of decreasing references are generated from the upper reference voltage and are compared to a bit-line voltage. Compare results are translated by translation logic that generates read data and over- and under-programming signals. Downgraded cells use the same truth table but generate fewer read data bits. Noise margins are asymmetrically improved by using the same sub-states for reading downgraded and full-density MLC cells.

Owner:SUPER TALENT TECH CORP

Cell-downgrading and reference-voltage adjustment for a multi-bit-cell flash memory

A flash memory has multi-level cells (MLC) that can each store multiple bits per cell. Blocks of cells can be downgraded to fewer bits / cell when errors occur, or for storing critical data such as boot code. The bits from a single MLC are partitioned among multiple pages to improve error correctability using Error Correction Code (ECC). An upper reference voltage is generated by a voltage reference generator in response to calibration registers that can be programmed to alter the upper reference voltage. A series of decreasing references are generated from the upper reference voltage and are compared to a bit-line voltage. Compare results are translated by translation logic that generates read data and over- and under-programming signals. Downgraded cells use the same truth table but generate fewer read data bits. Noise margins are asymmetrically improved by using the same sub-states for reading downgraded and full-density MLC cells.

Owner:SUPER TALENT TECH CORP

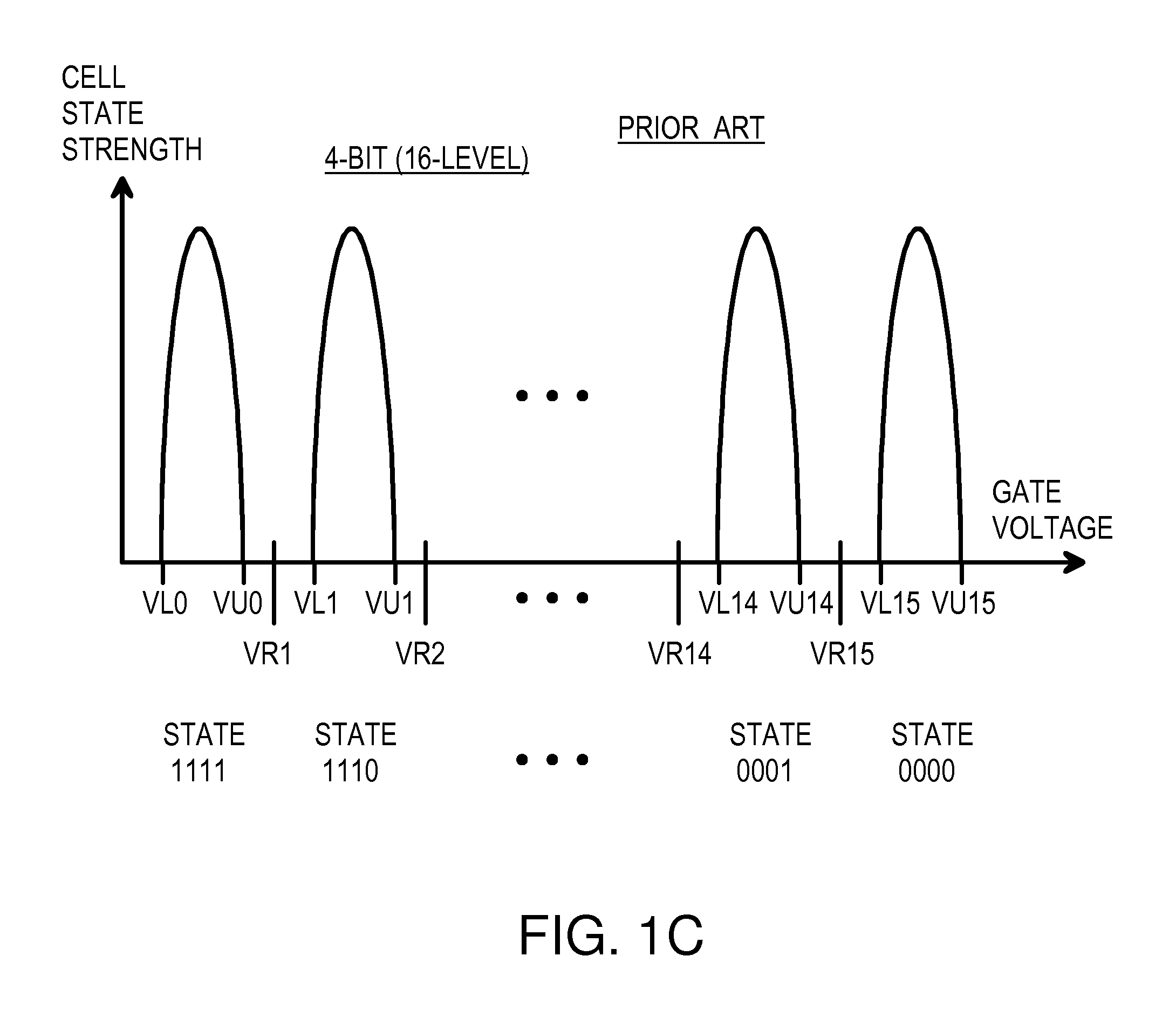

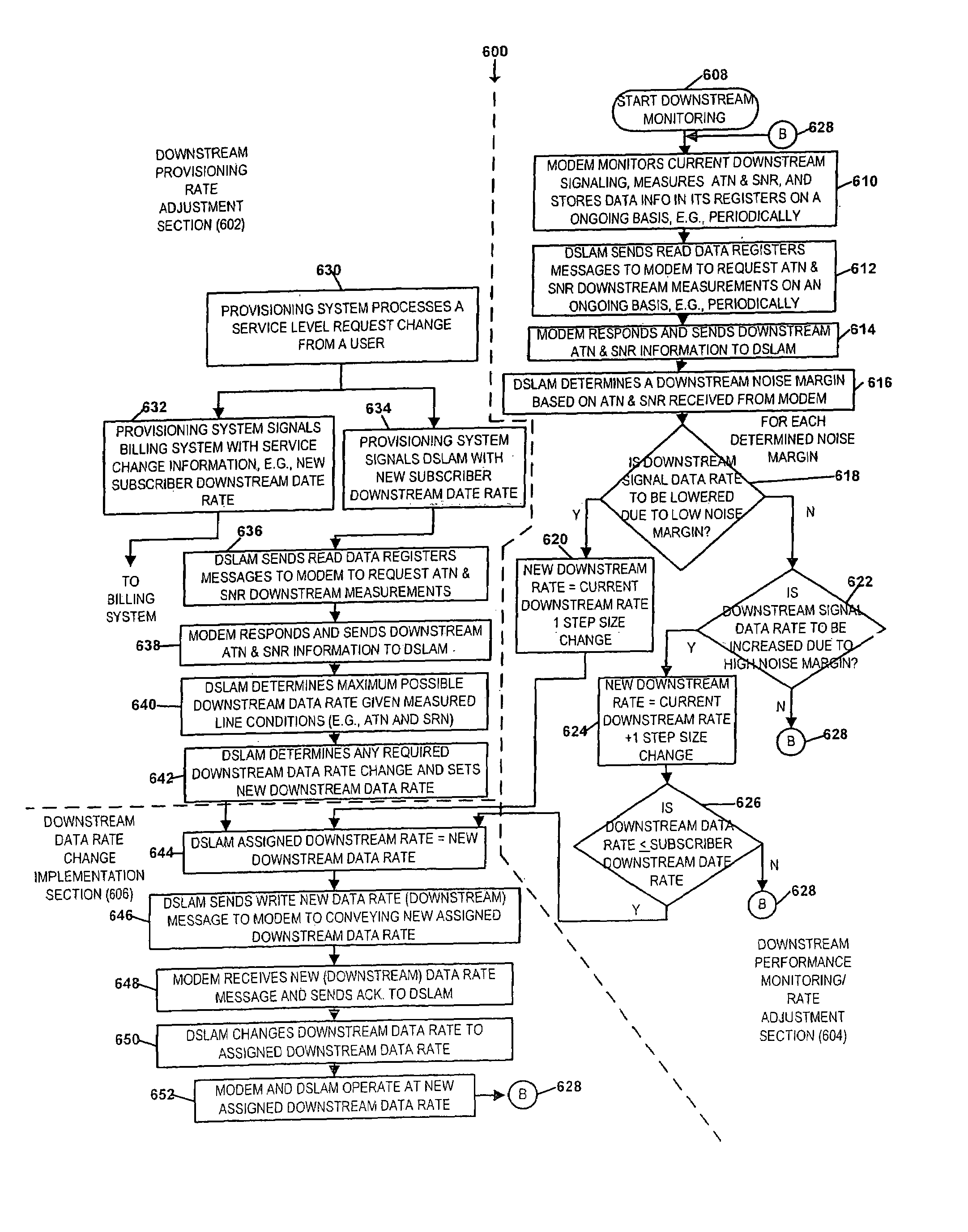

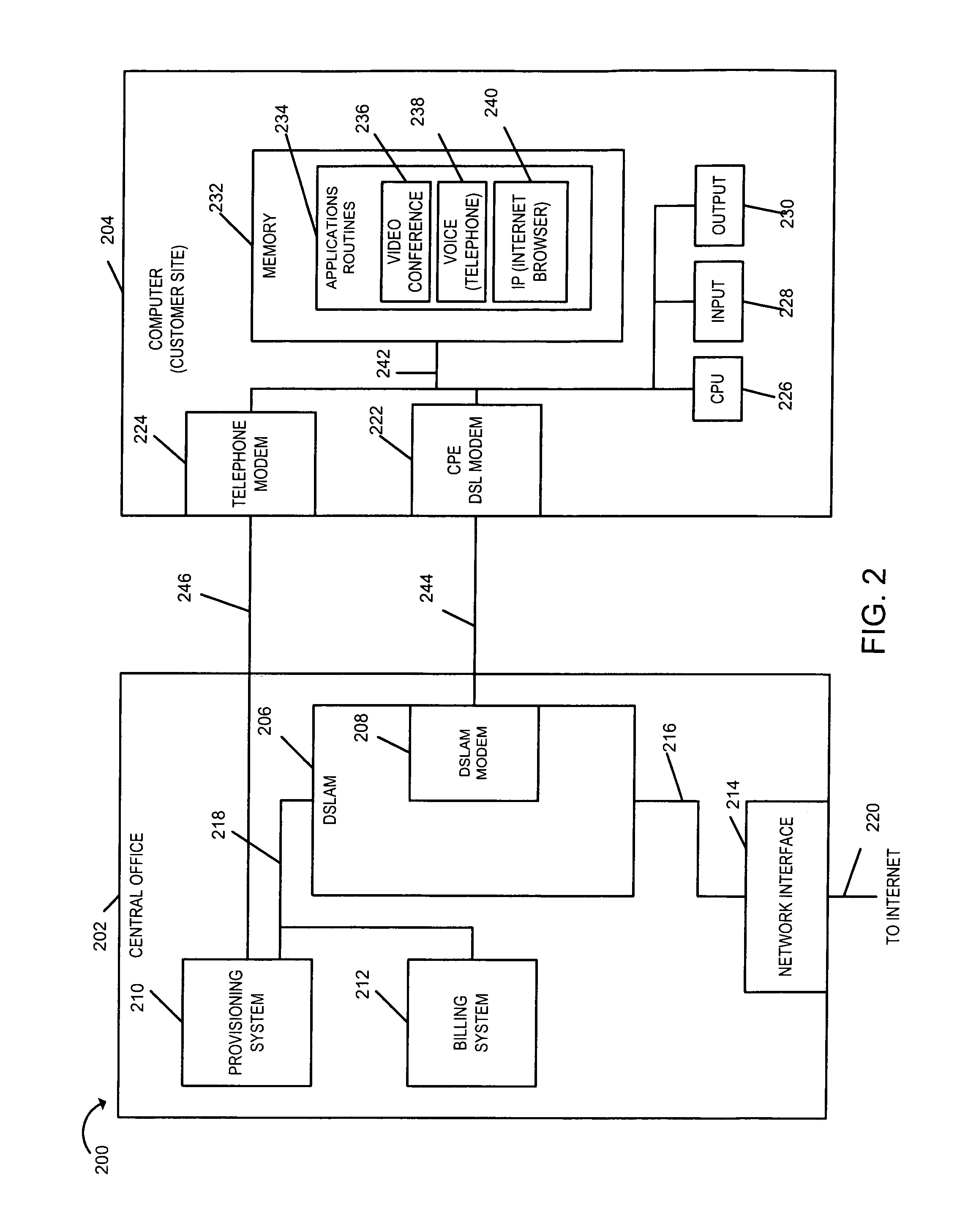

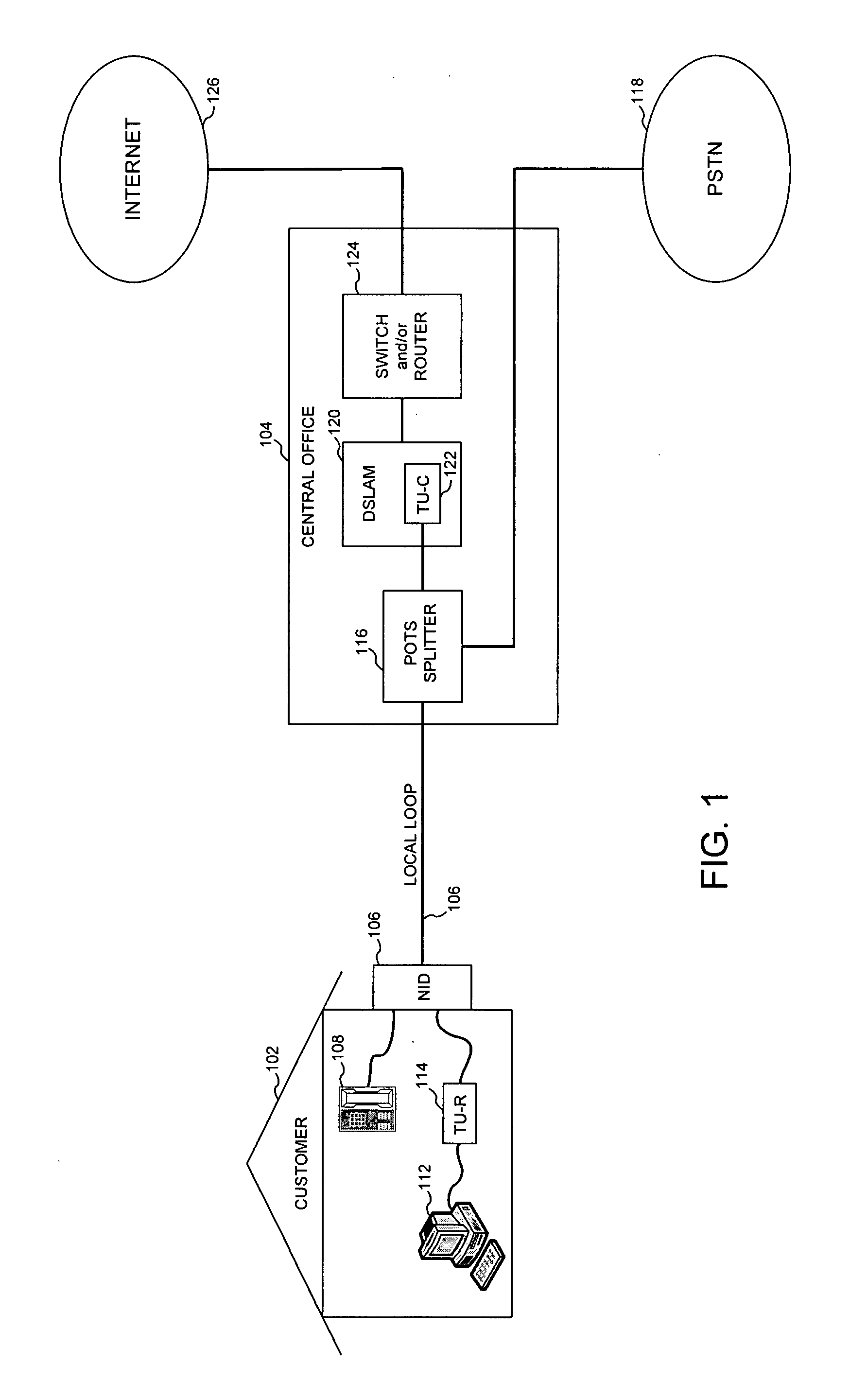

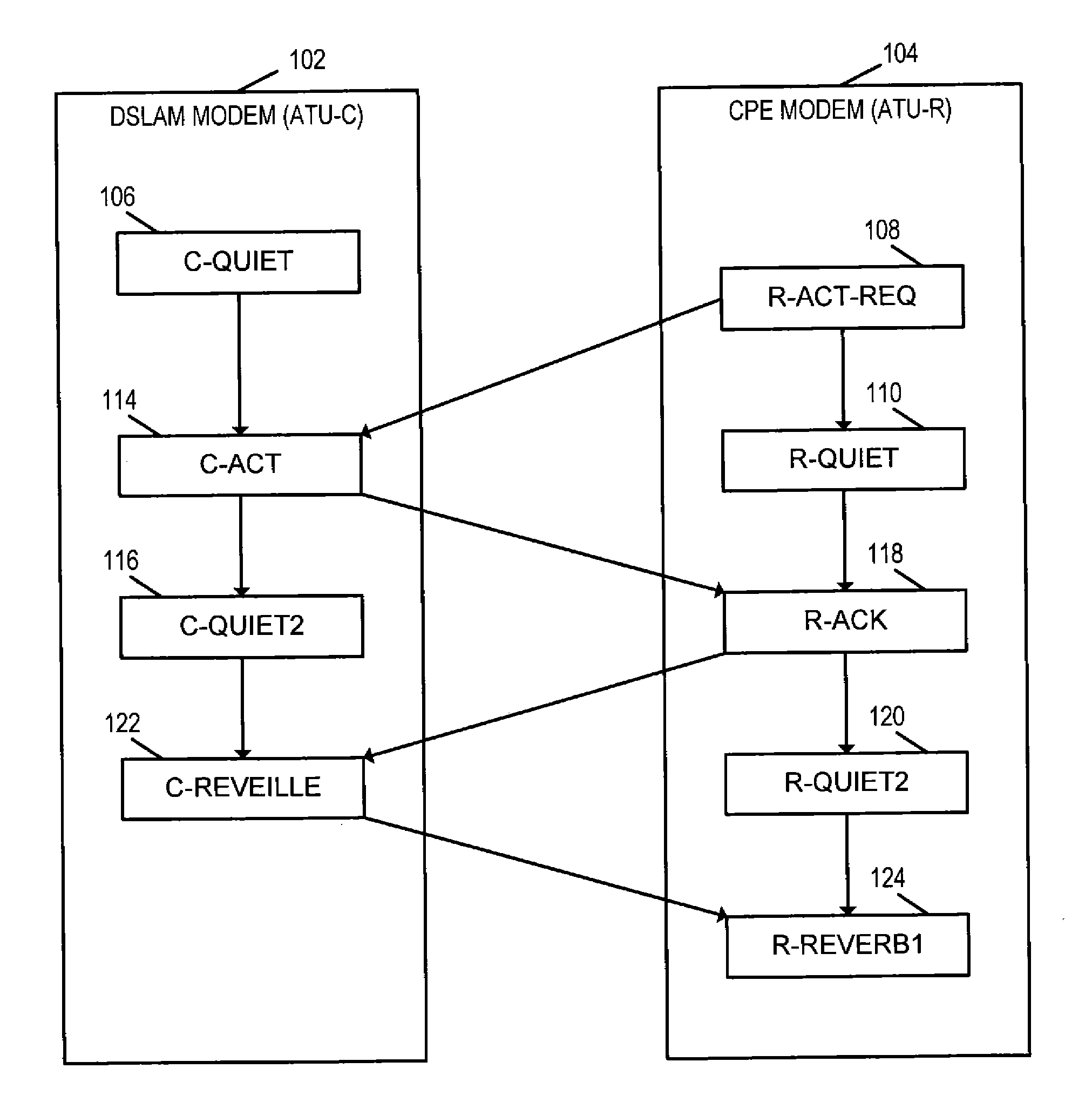

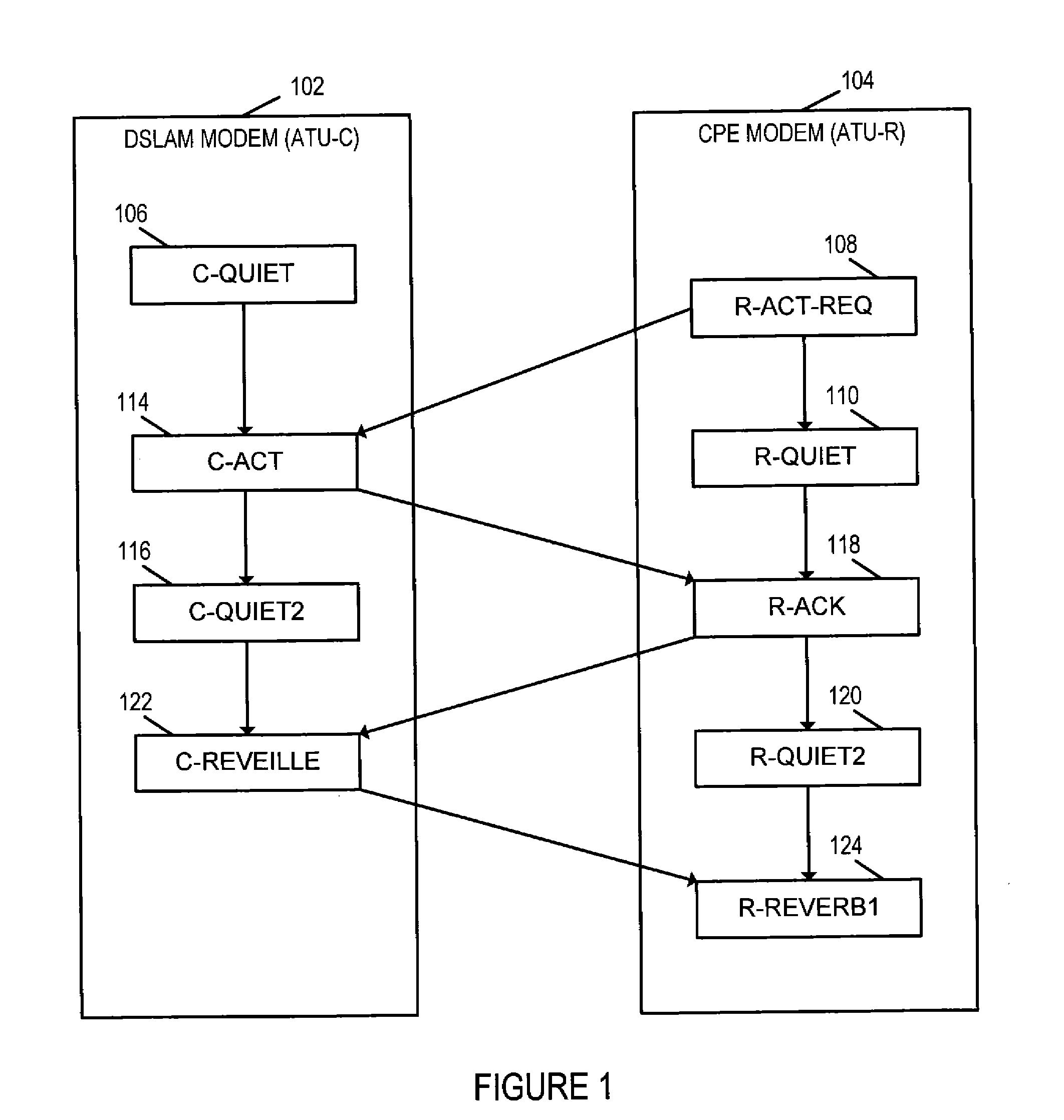

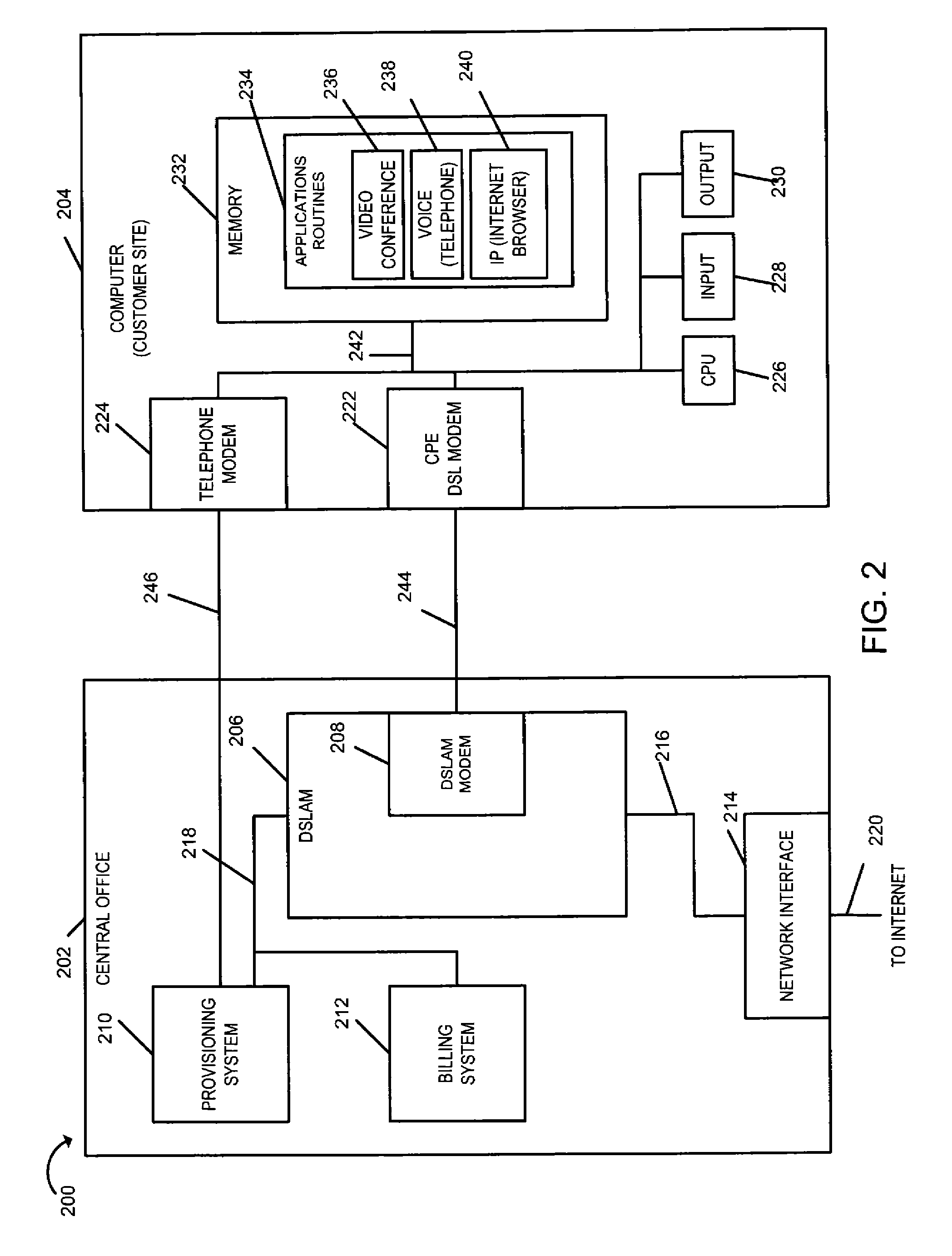

Rate agile rate-adaptive digital subscriber line

ActiveUS7317754B1Line rate can be increasedHigh achievable data rateEnergy efficient ICTSignal allocationModem deviceRate change

Methods and apparatus for maintaining the maximum achievable data rate on a DSL line, up to and including a rate to which a user subscribes is described. Performance monitoring is conducted on the DSL line on an ongoing basis to determine noise margins in each direction. Each noise margin is compared against pre-determined decreasing / increasing thresholds to determine whether the line characteristics dictate a data rate change without loss of synchronization. The invention supports dynamic provisioning changes including application driven service level change requests, e.g., new bandwidth-on demand services. In some embodiments, a combination of existing and new embedded operations channel (EOC) messages are used to implement the modem data rate changes. New EOC messages may be implemented using some of the reserved and / or vendor proprietary Opcodes currently permitted. Modem assigned data rate changes are implemented without a disruption of service, e.g., without the need for re-initialization and / or re-synchronization.

Owner:INTELLECTUAL VENTURES II

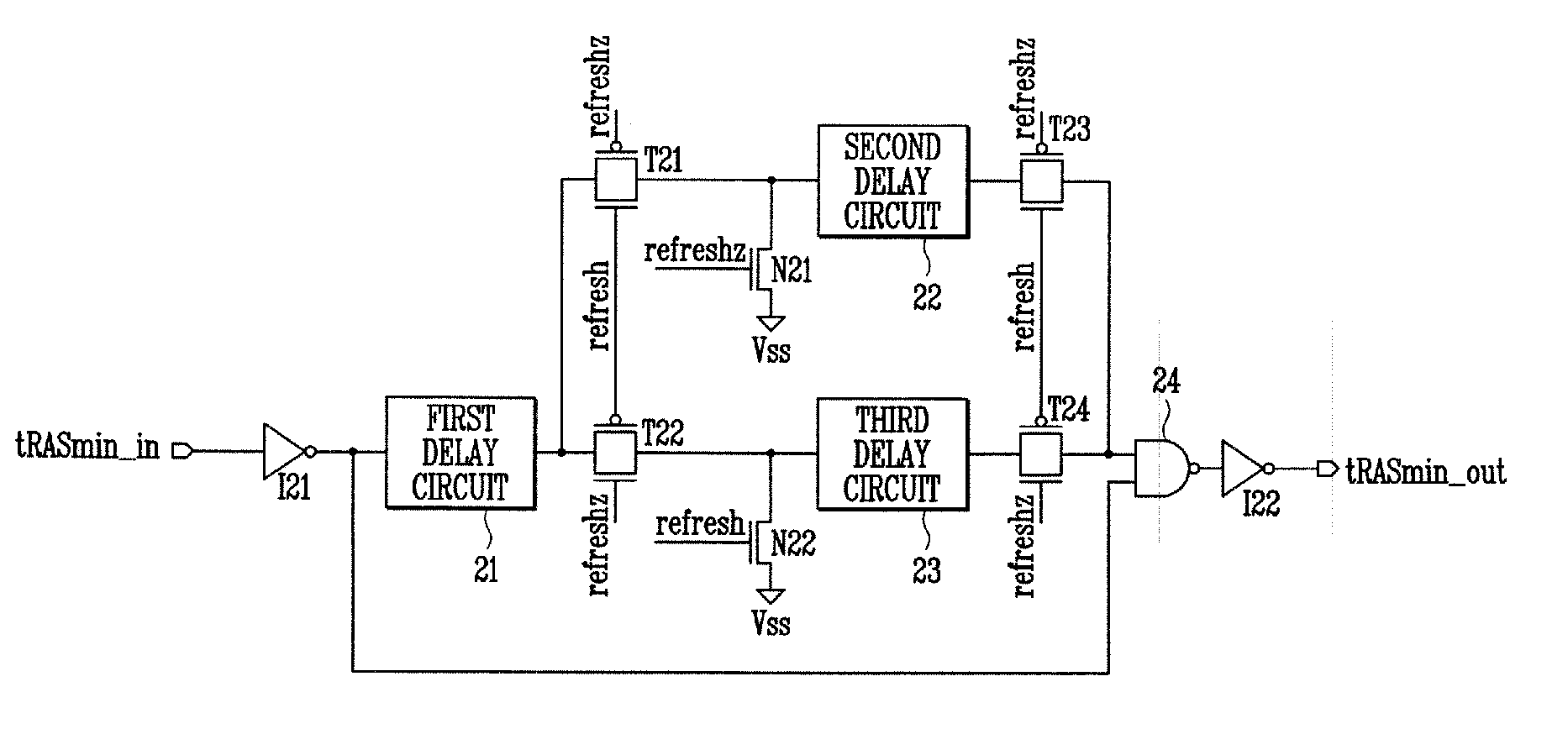

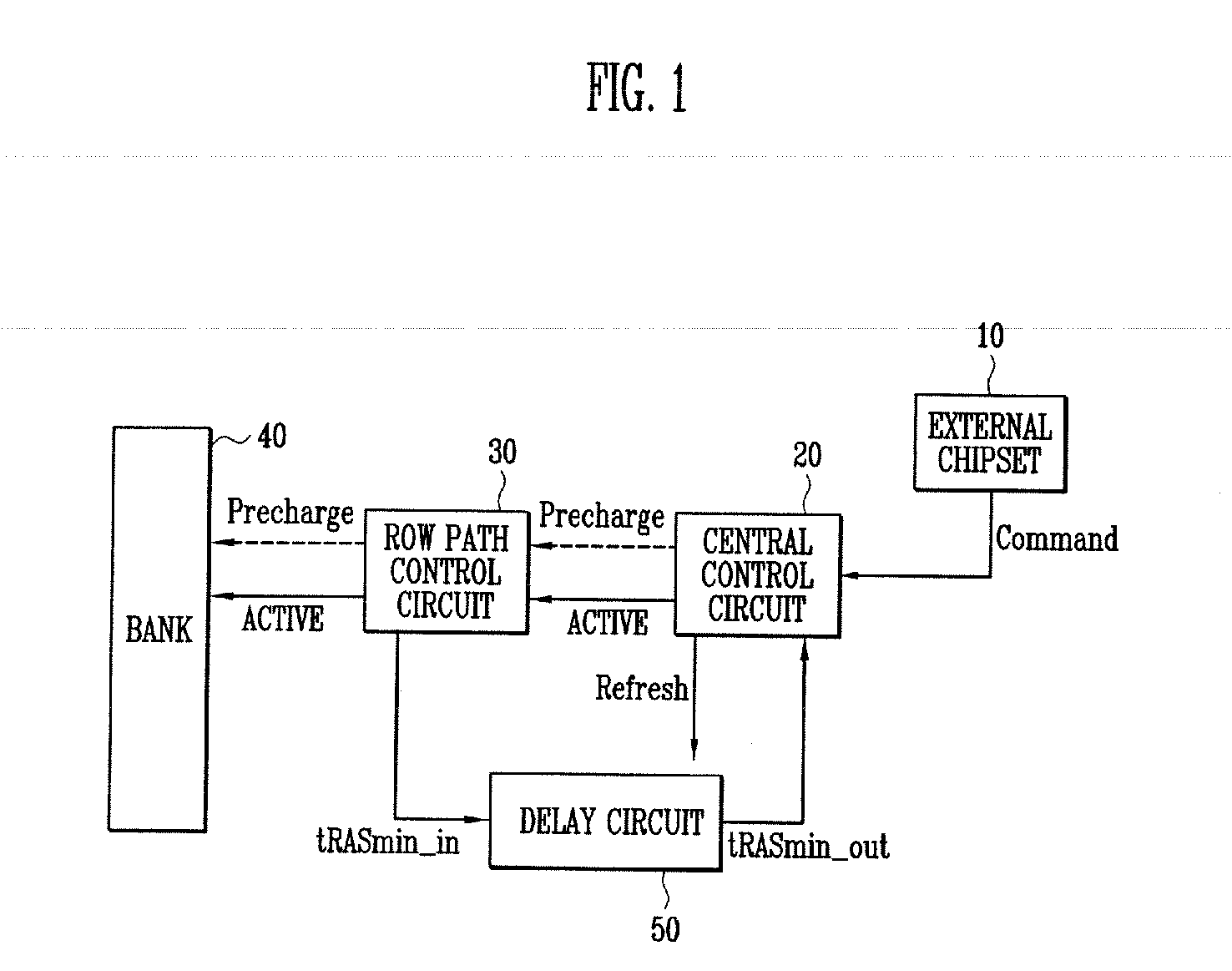

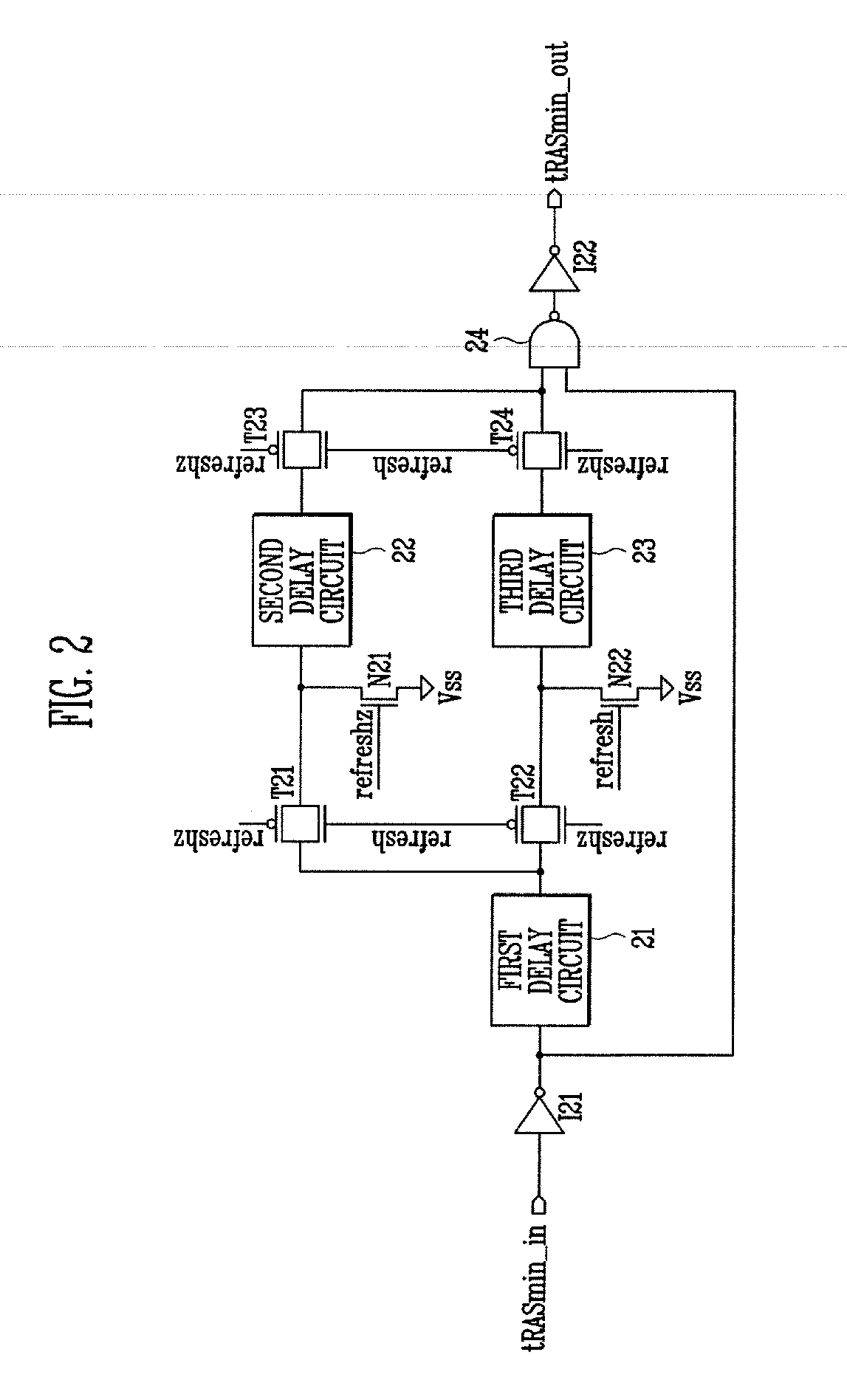

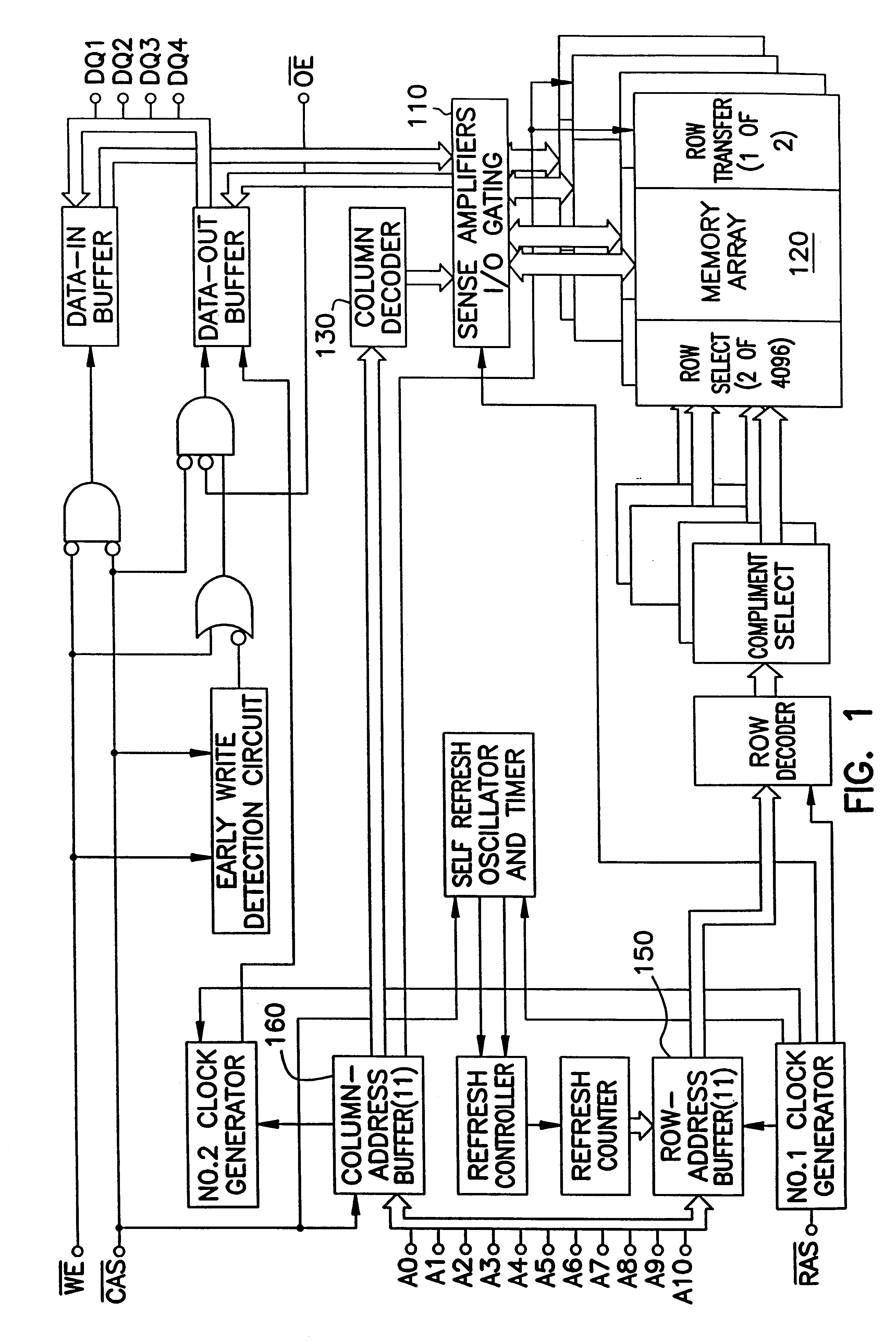

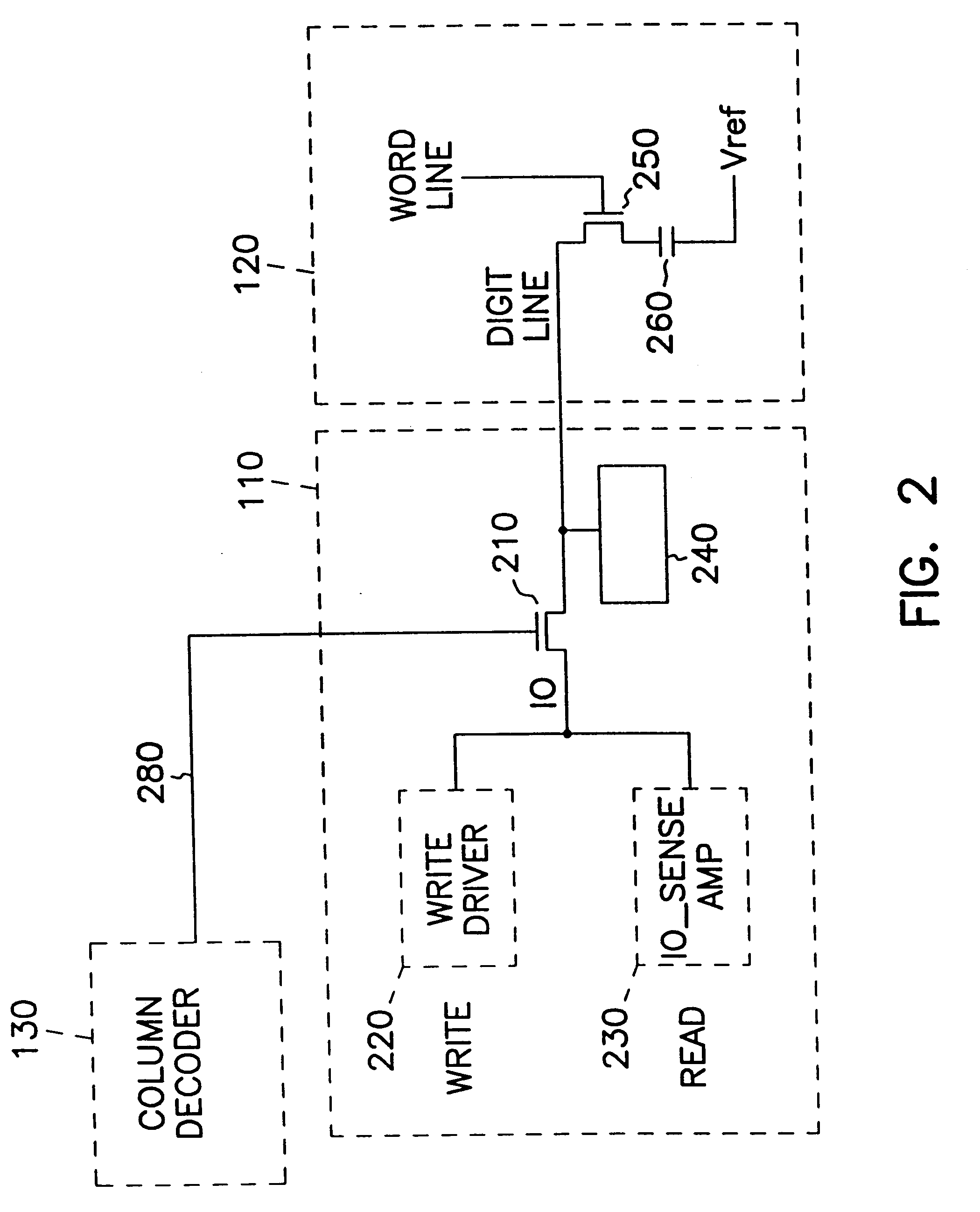

Semiconductor memory device

ActiveUS20050232049A1Better noise marginReduce failure rateConstruction fastening devicesDigital storageNoise marginDelayed time

The present invention relates to a semiconductor memory device. According to the present invention, a delay circuit is constructed in order for a refresh operation and a normal operation to have different delay paths such that a minimum tRAS (Active to Precharge command period) delay time of the refresh operation to which tRFC (Auto Referesh to Active / Auto Referesh command period) is applied is longer than a minimum tRAS delay time of a normal operation to which tRC (Active to Active / Auto Refresh command period) is applied. Thus, a greater noise margin is secured in tRFC in a refresh operation being the worst situation of a DRAM. Accordingly, the probability that fail can occur is reduced and the yield upon test is thus improved.

Owner:SK HYNIX INC

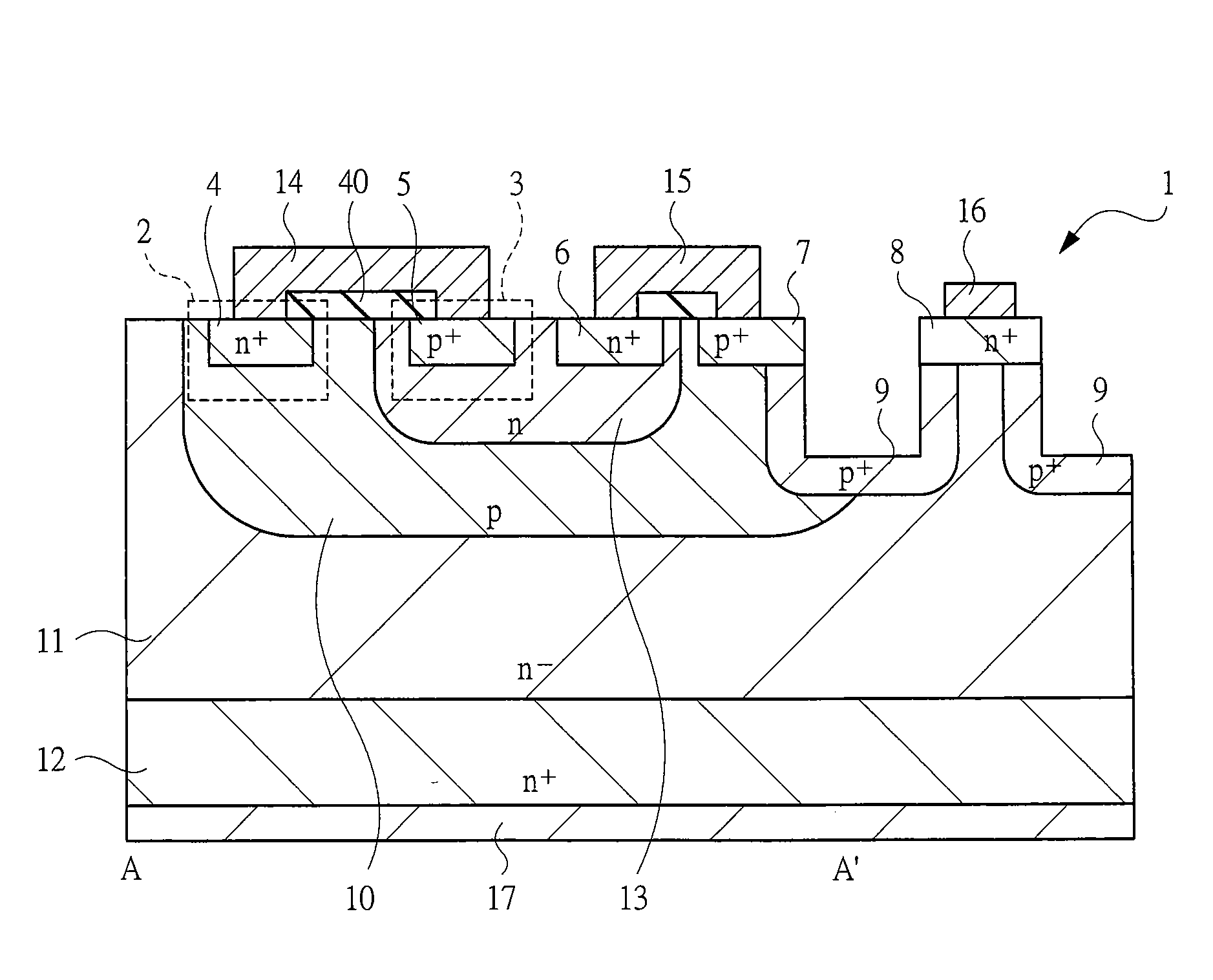

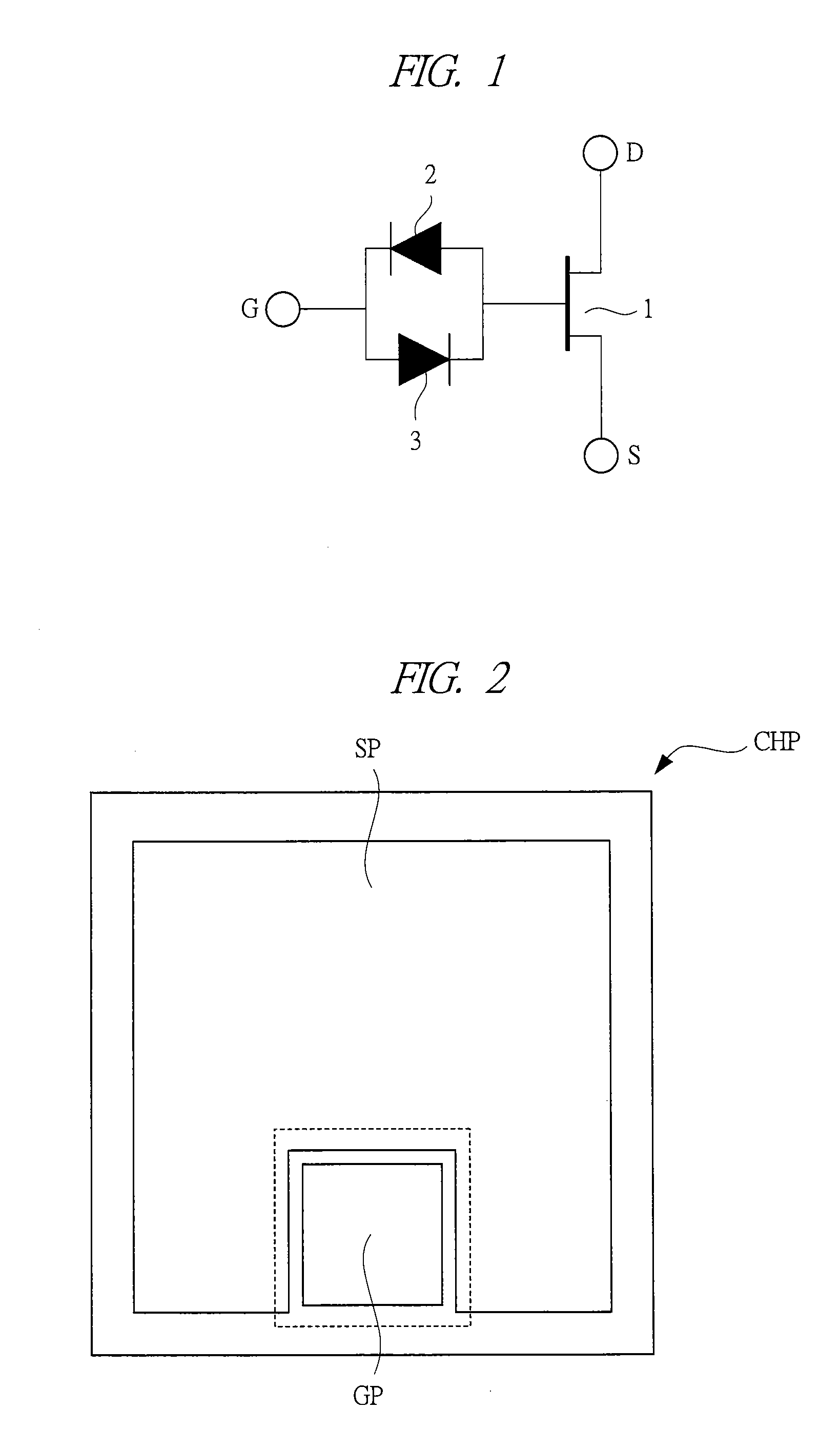

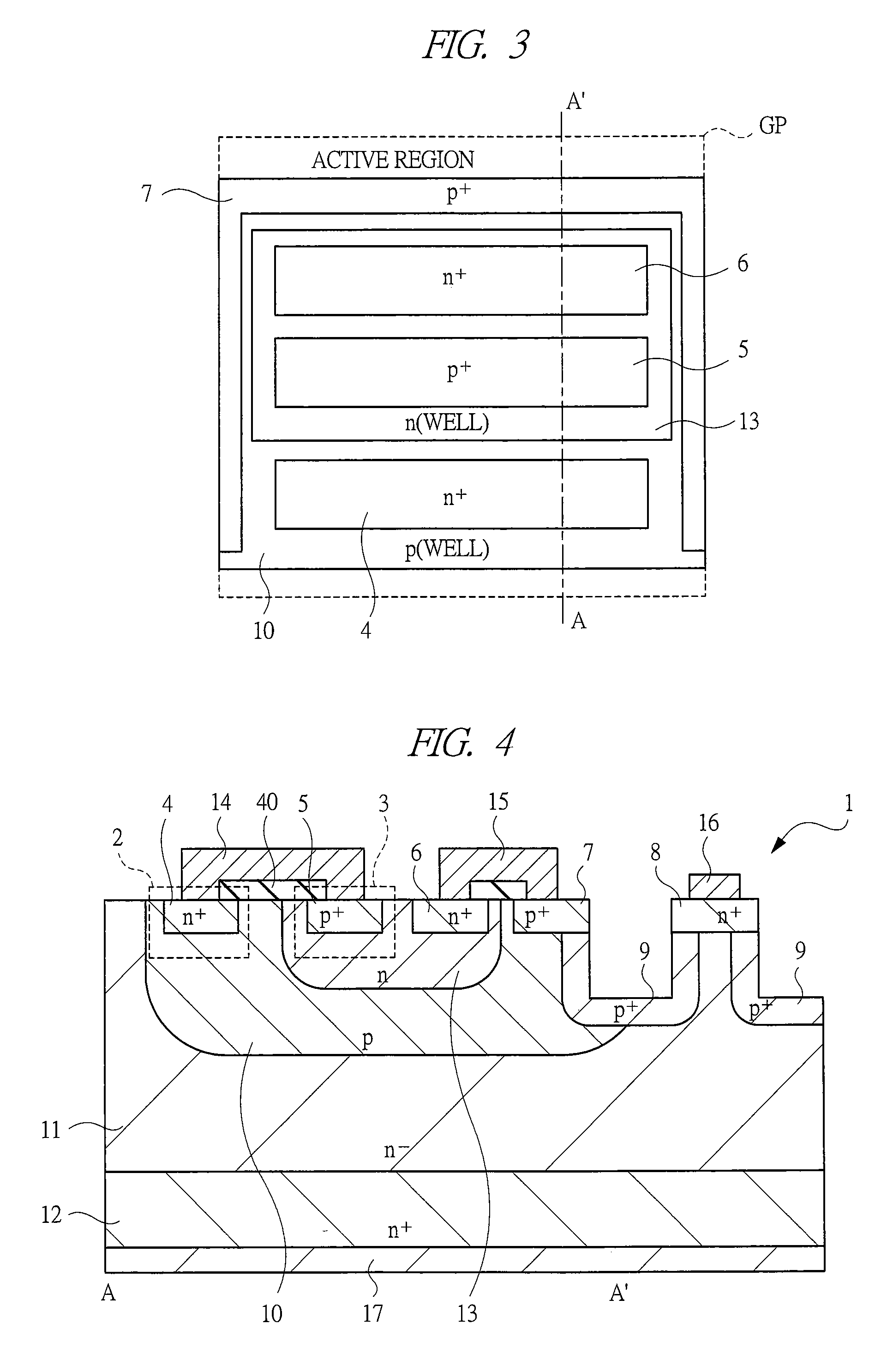

Semiconductor device with large blocking voltage

InactiveUS20090014719A1Large noise marginRaise the threshold voltageTransistorSolid-state devicesNoise marginSemiconductor

A junction FET having a large gate noise margin is provided. The junction FET comprises an n− layer forming a drift region of the junction FET formed over a main surface of an n+ substrate made of silicon carbide, a p+ layer forming a gate region formed in contact with the n− layer forming the drift region and a gate electrode provided in an upper layer of the n+ substrate. The junction FET further incorporates pn diodes formed over the main surface of the n+ substrate and electrically connecting the p+ layer forming the gate region and the gate electrode.

Owner:RENESAS ELECTRONICS CORP

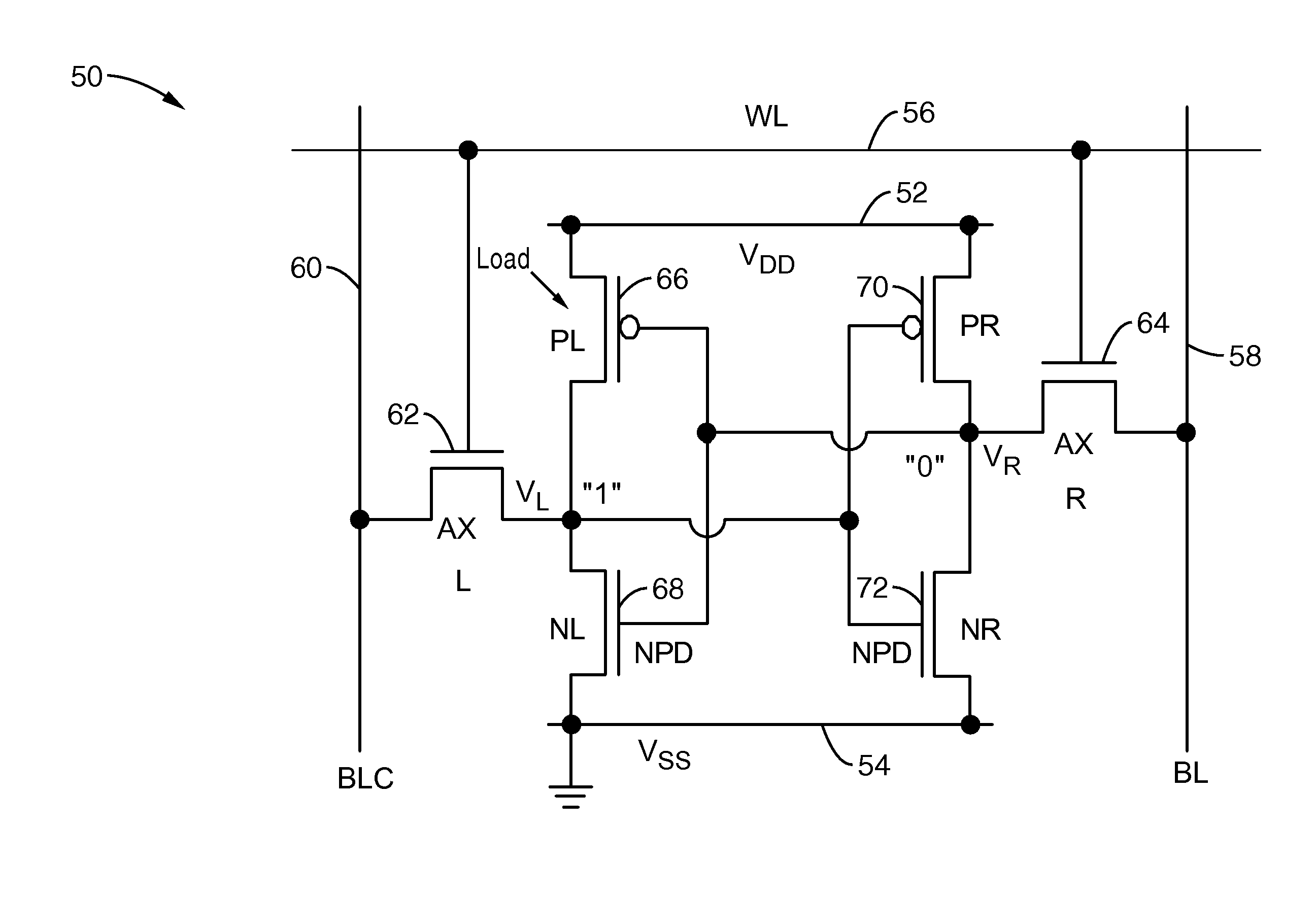

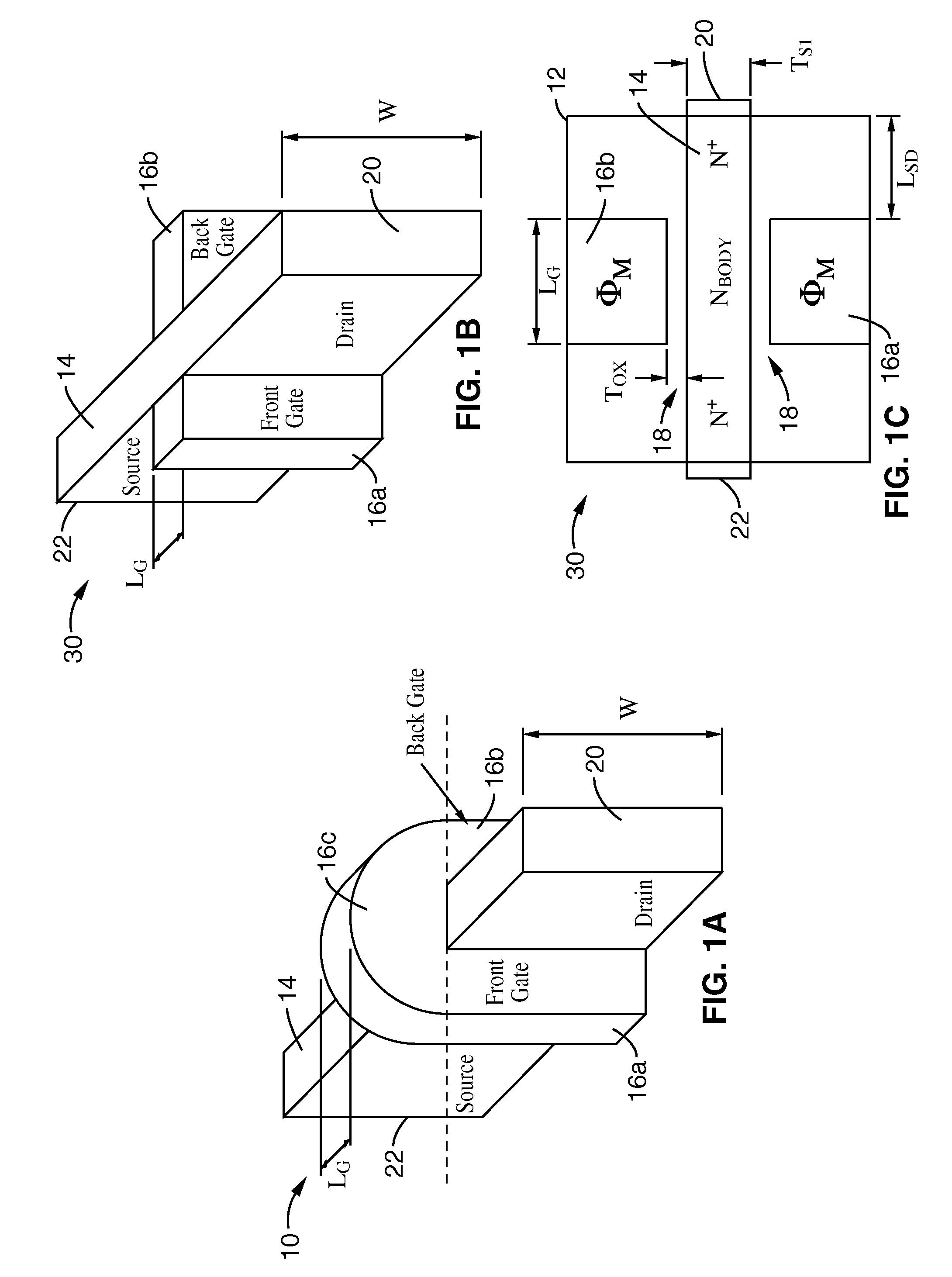

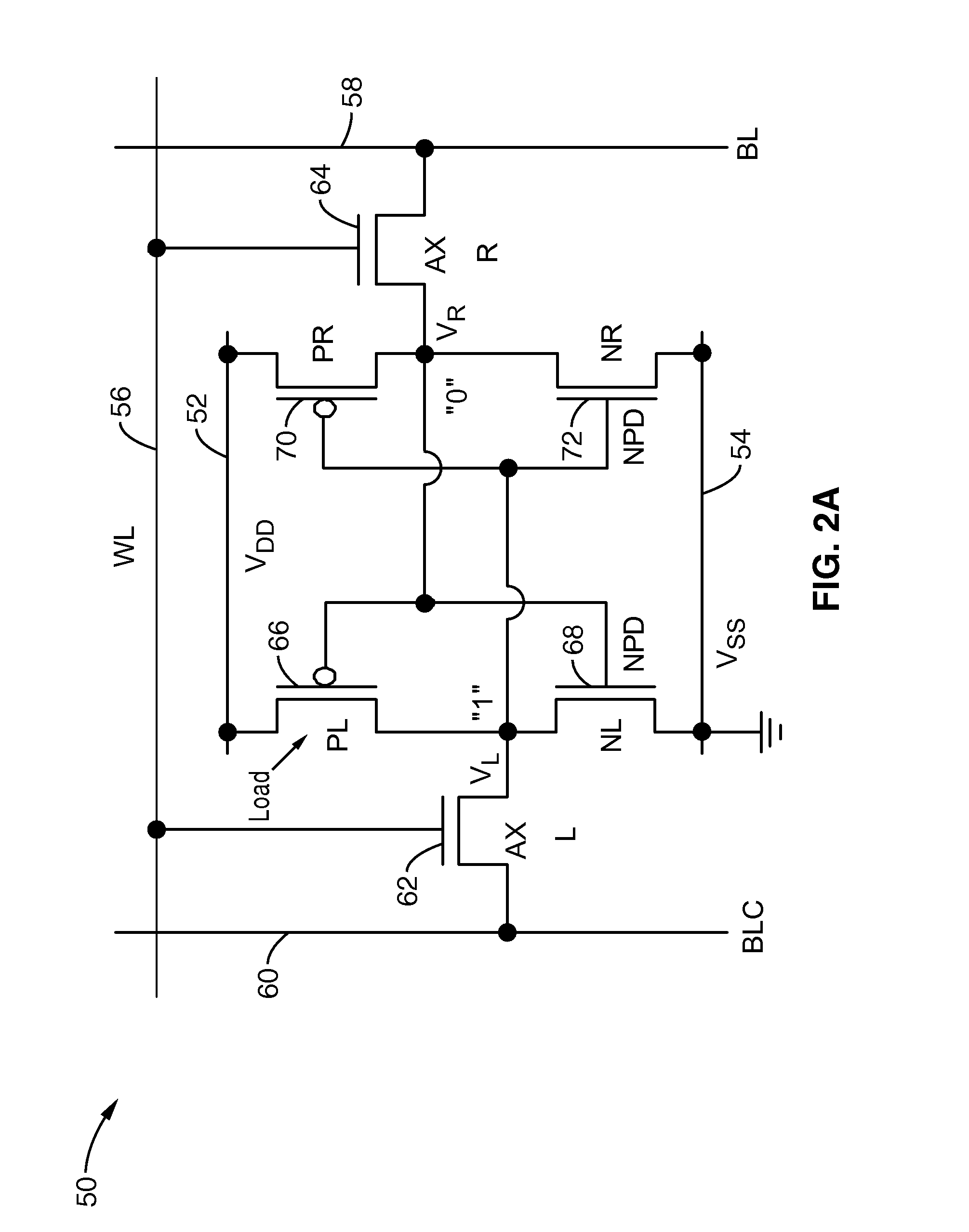

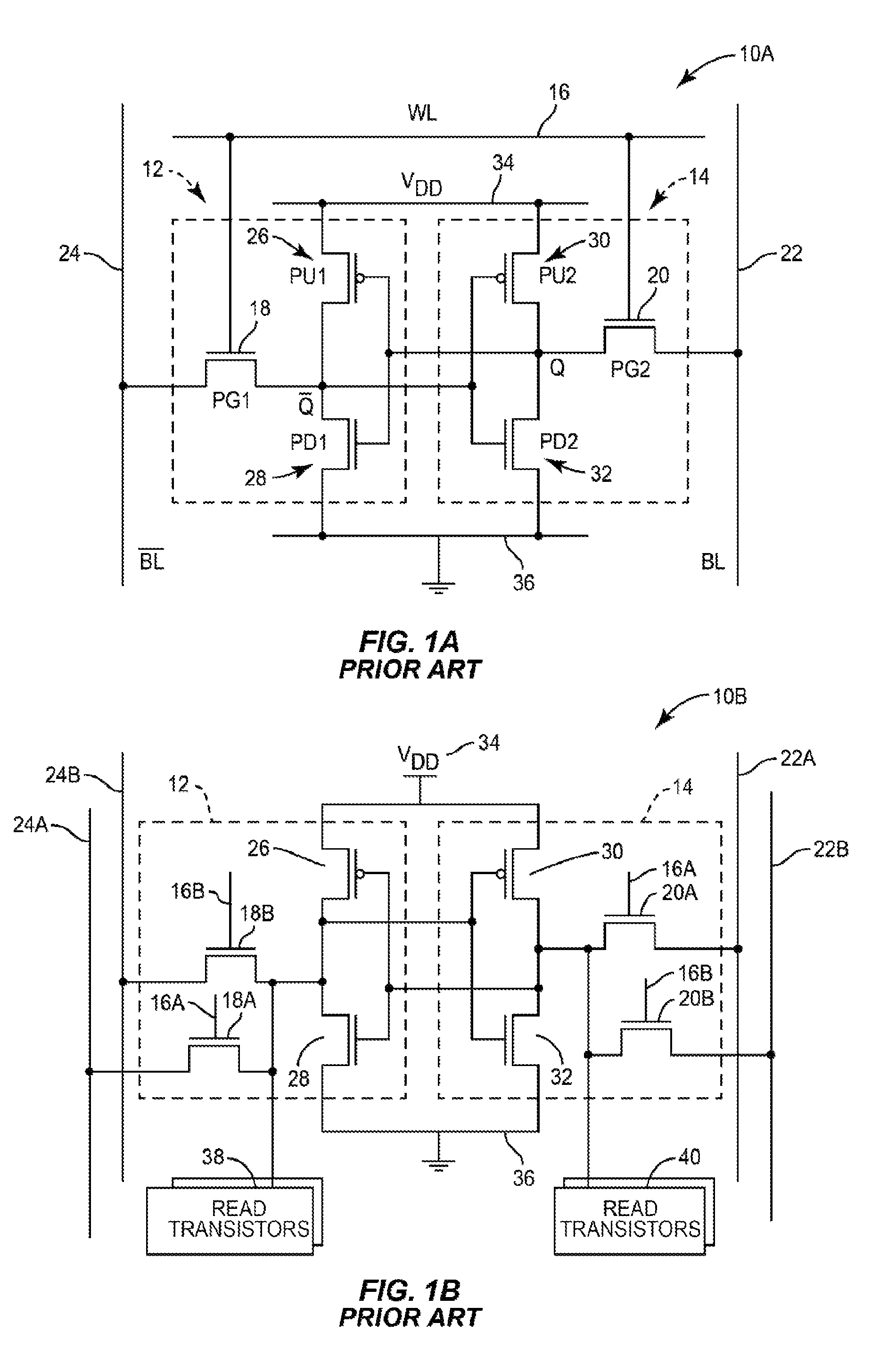

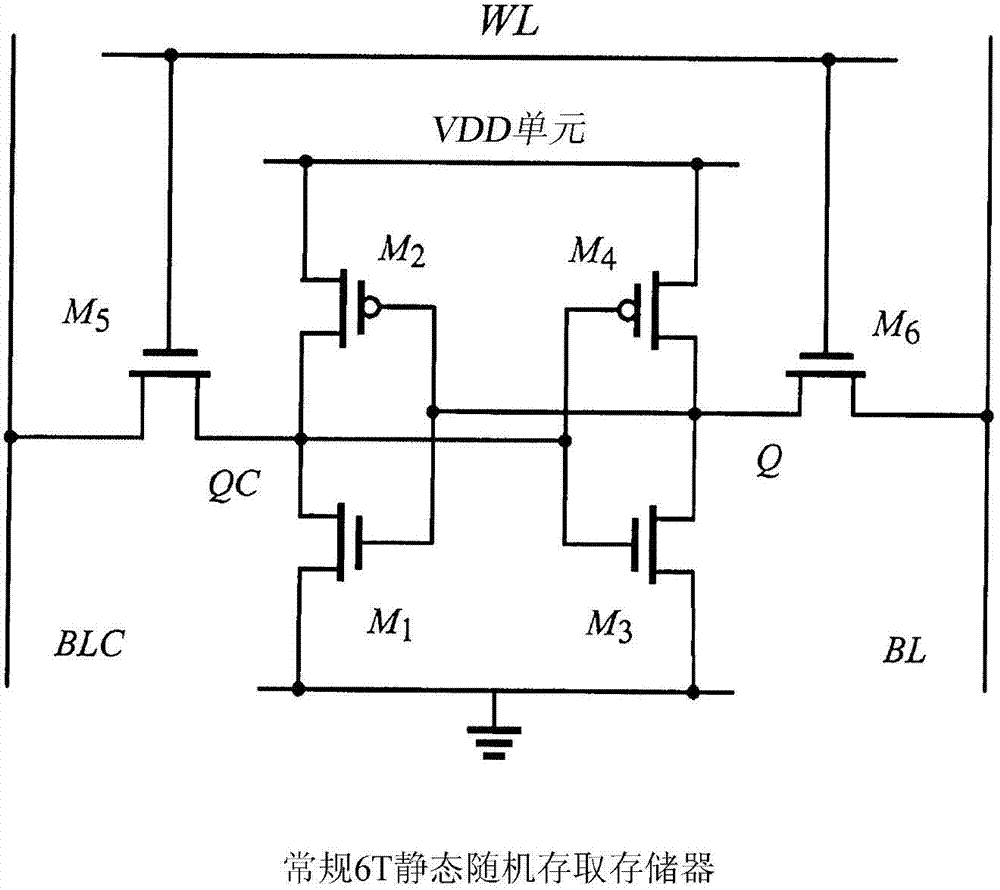

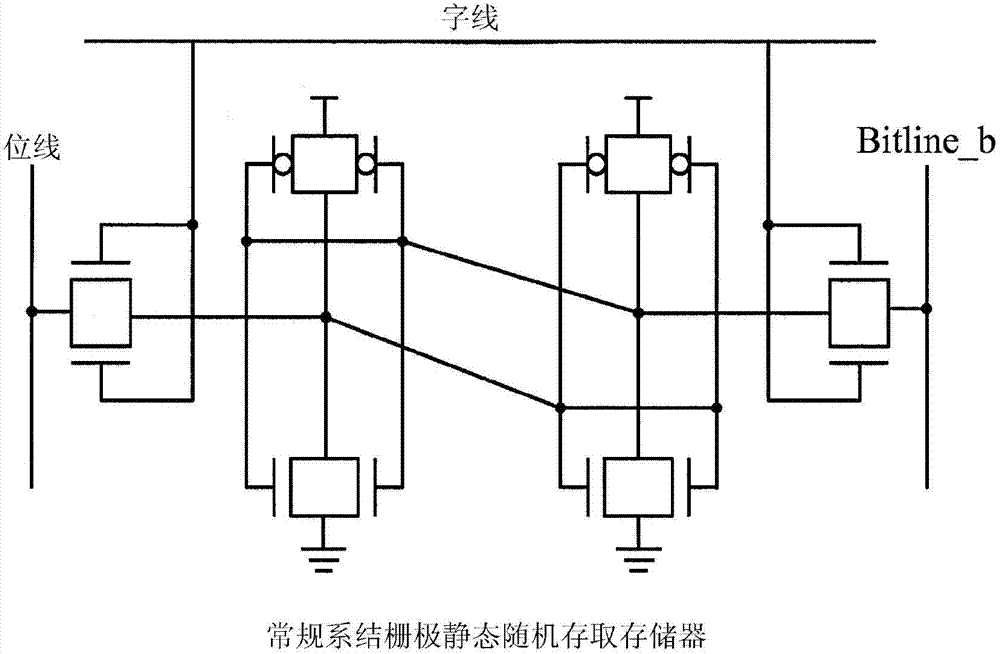

Finfet-based SRAM with feedback

InactiveUS20070183185A1Adequate noise marginReduce leakage currentTransistorSolid-state devicesNoise marginCell design

Intrinsic variations and challenging leakage control in current bulk-Si MOSFETs force undesired tradeoffs to be made and limit the scaling of SRAM circuits. Circuits and mechanisms are taught herein which improve leakage and noise margin in SRAM cells, such as those comprising either six-transistor (6-T) SRAM cell designs, or four-transistor (4-T) SRAM cell designs. The inventive SRAM cells utilize a feedback means coupling a portion of the storage node to a back-gate of an access transistor. Preferably feedback is coupled in this manner to both access transistors. SRAM cells designed with this built-in feedback achieve significant improvements in cell static noise margin (SNM) without area penalty. Use of the feedback scheme also results in the creation of a practical 4-T FinFET-based SRAM cell that achieves sub-100 pA per-cell standby current and offers similar improvements in SNM as the 6-T cell with feedback.

Owner:RGT UNIV OF CALIFORNIA

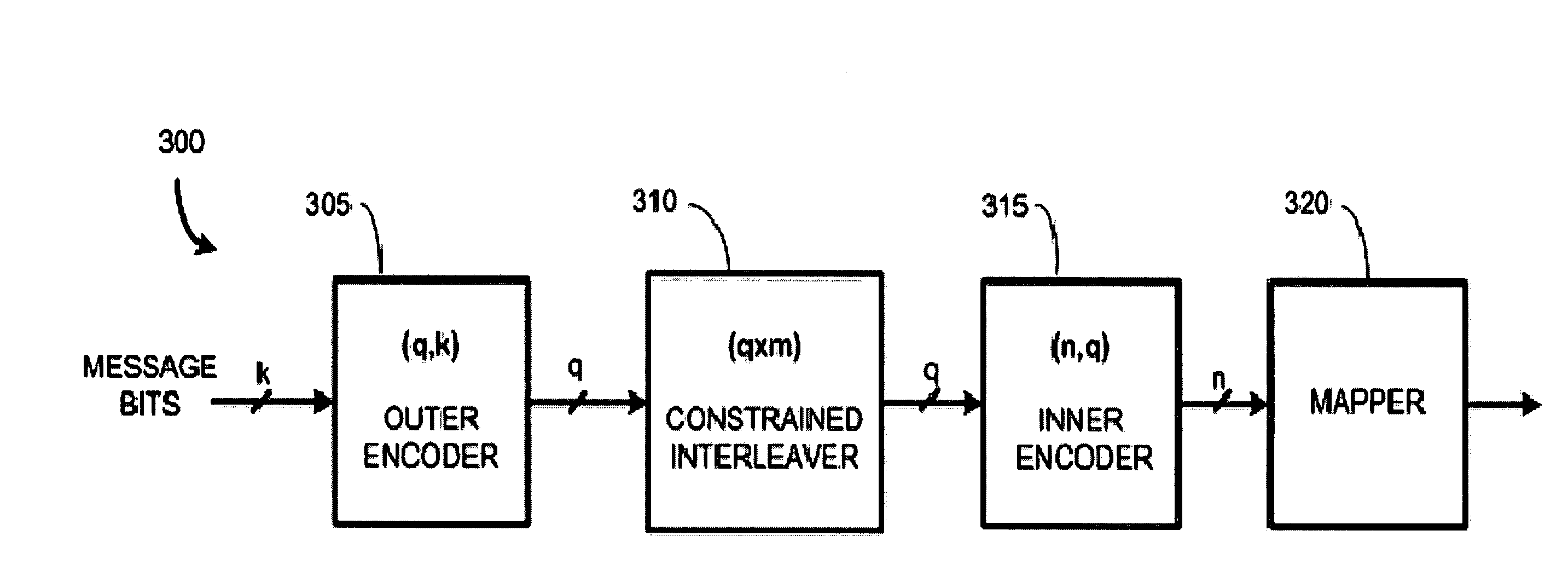

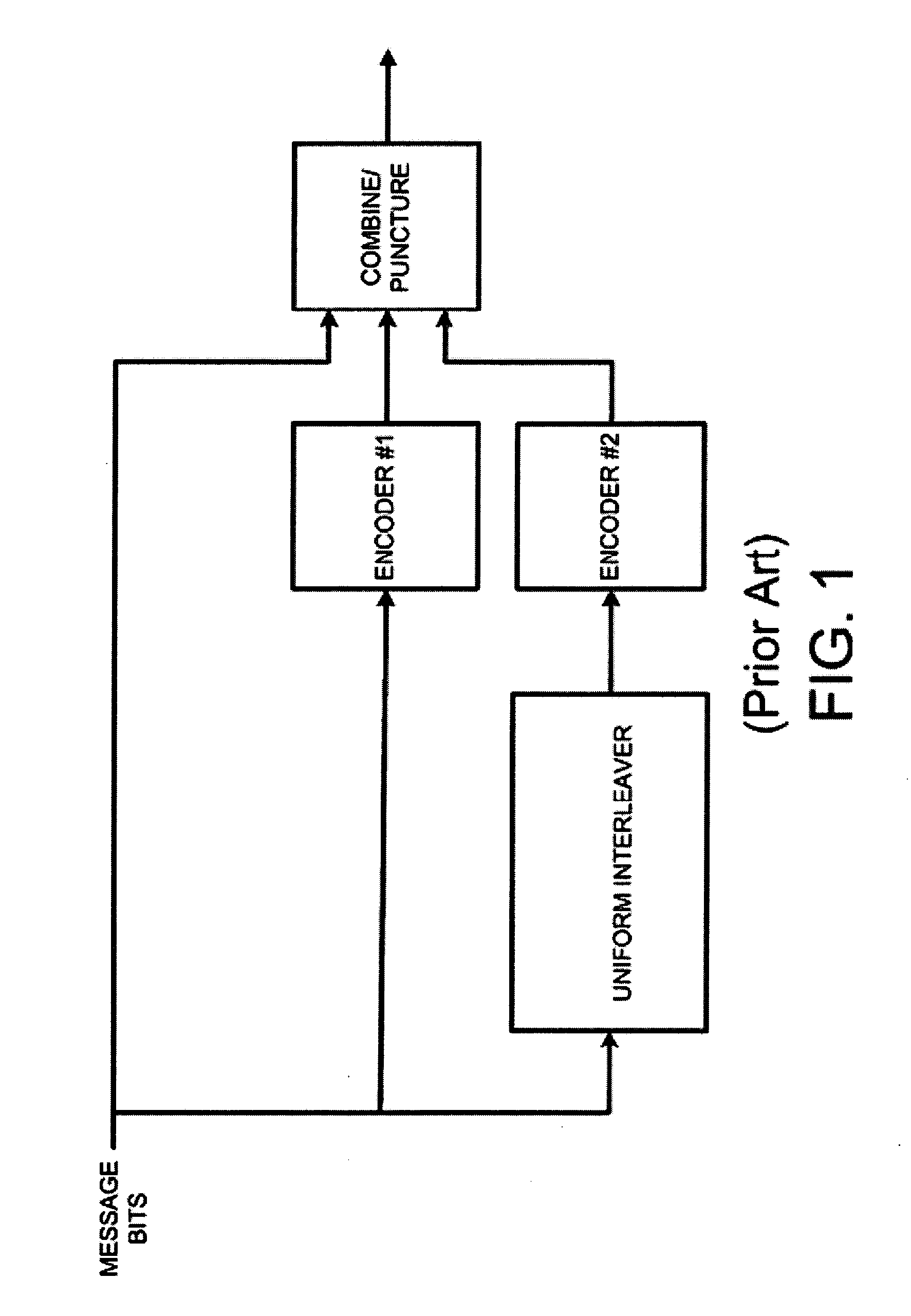

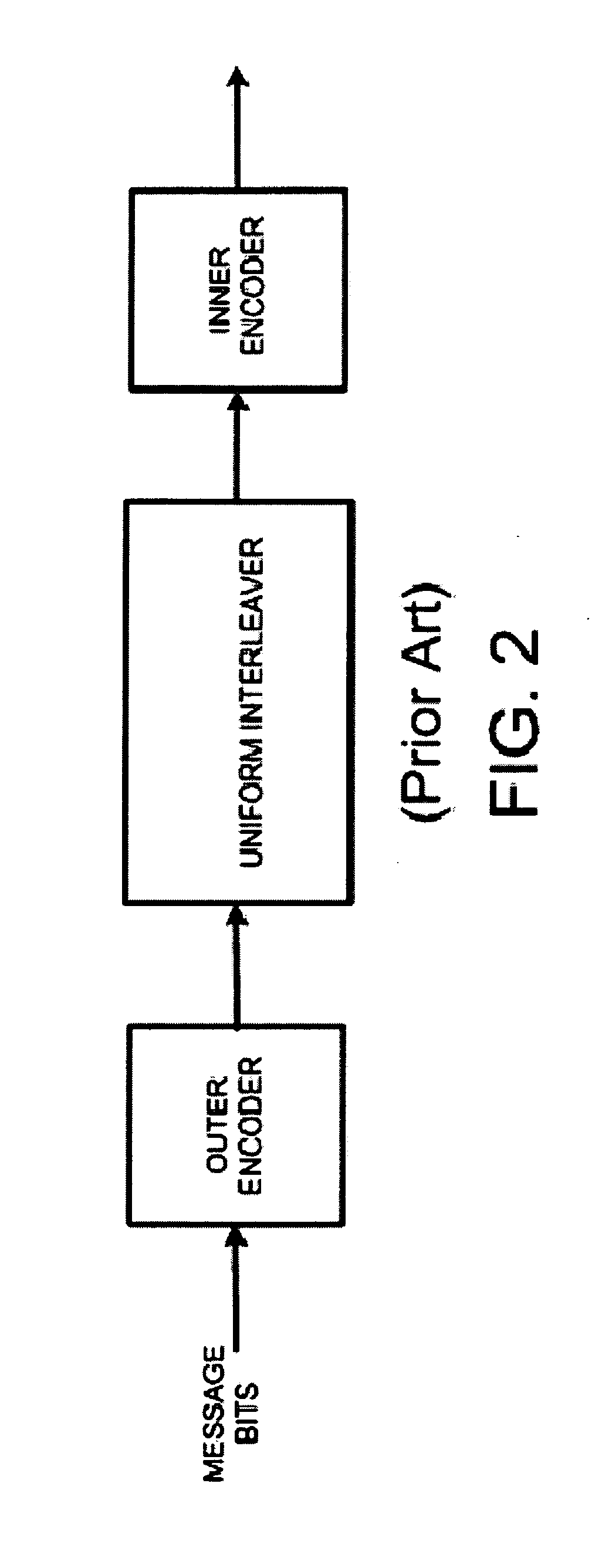

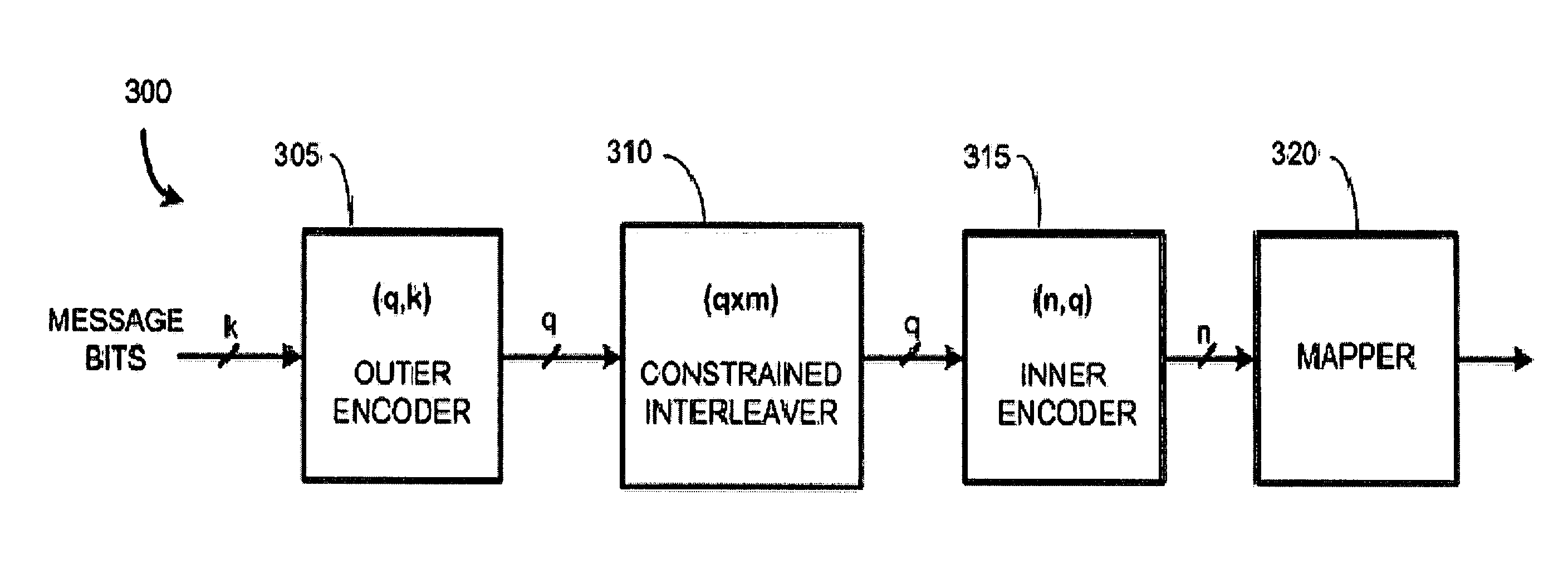

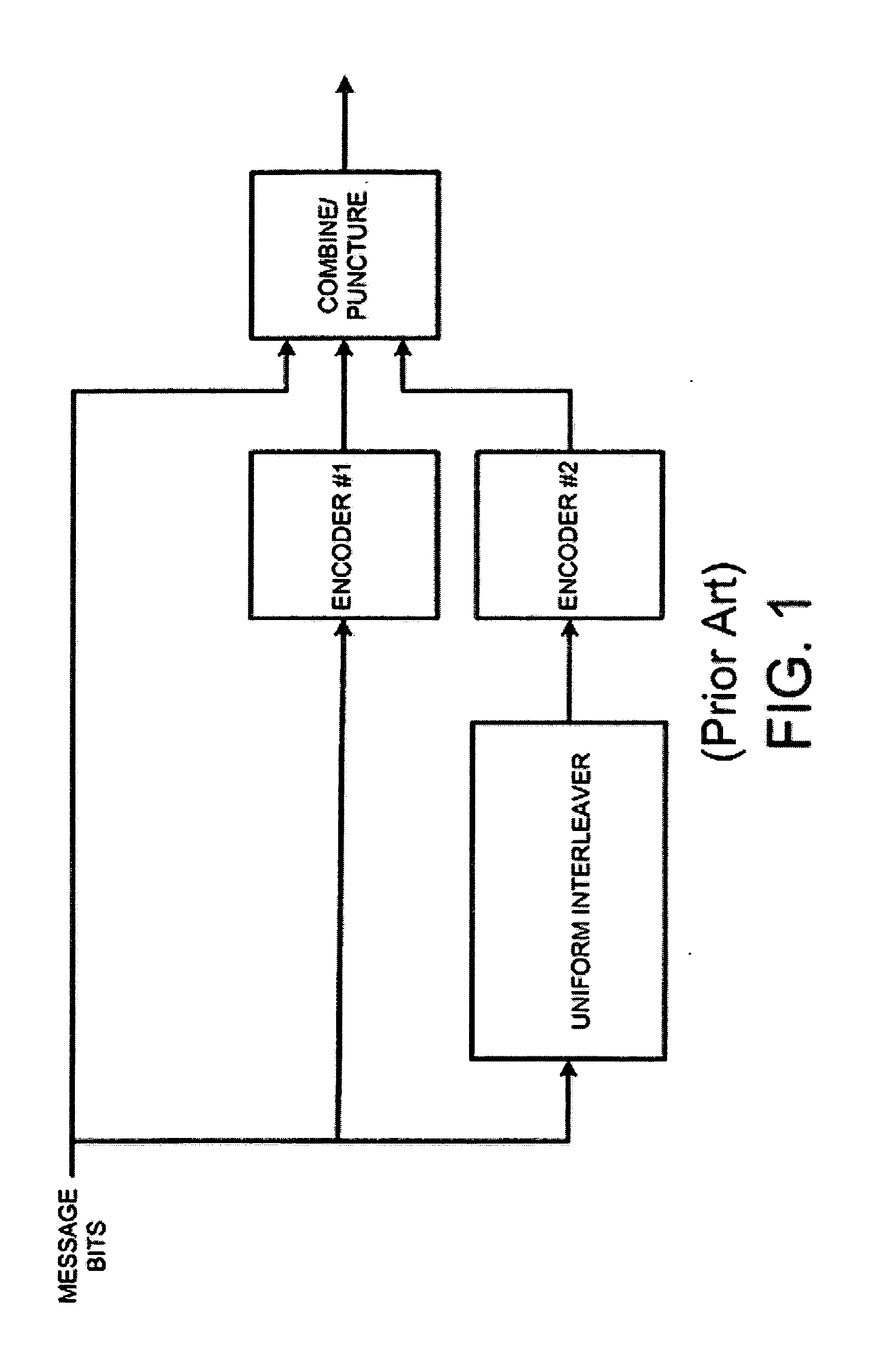

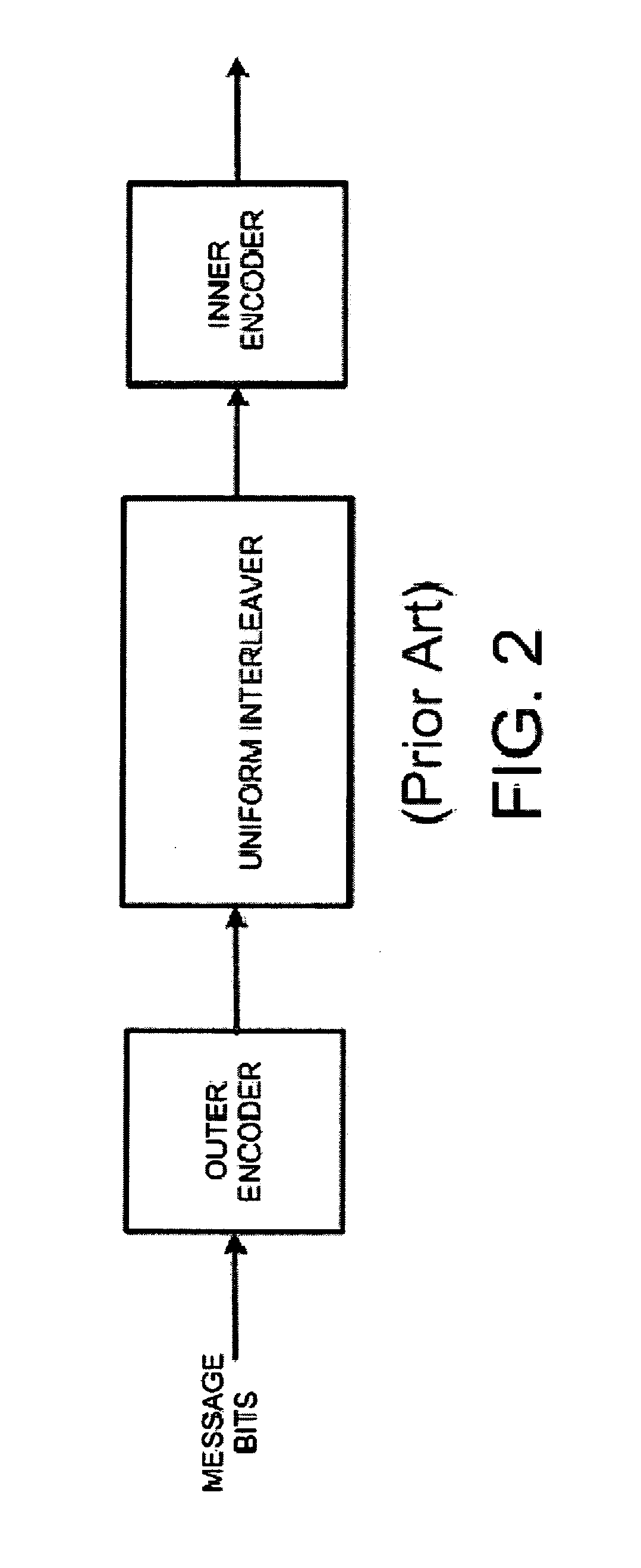

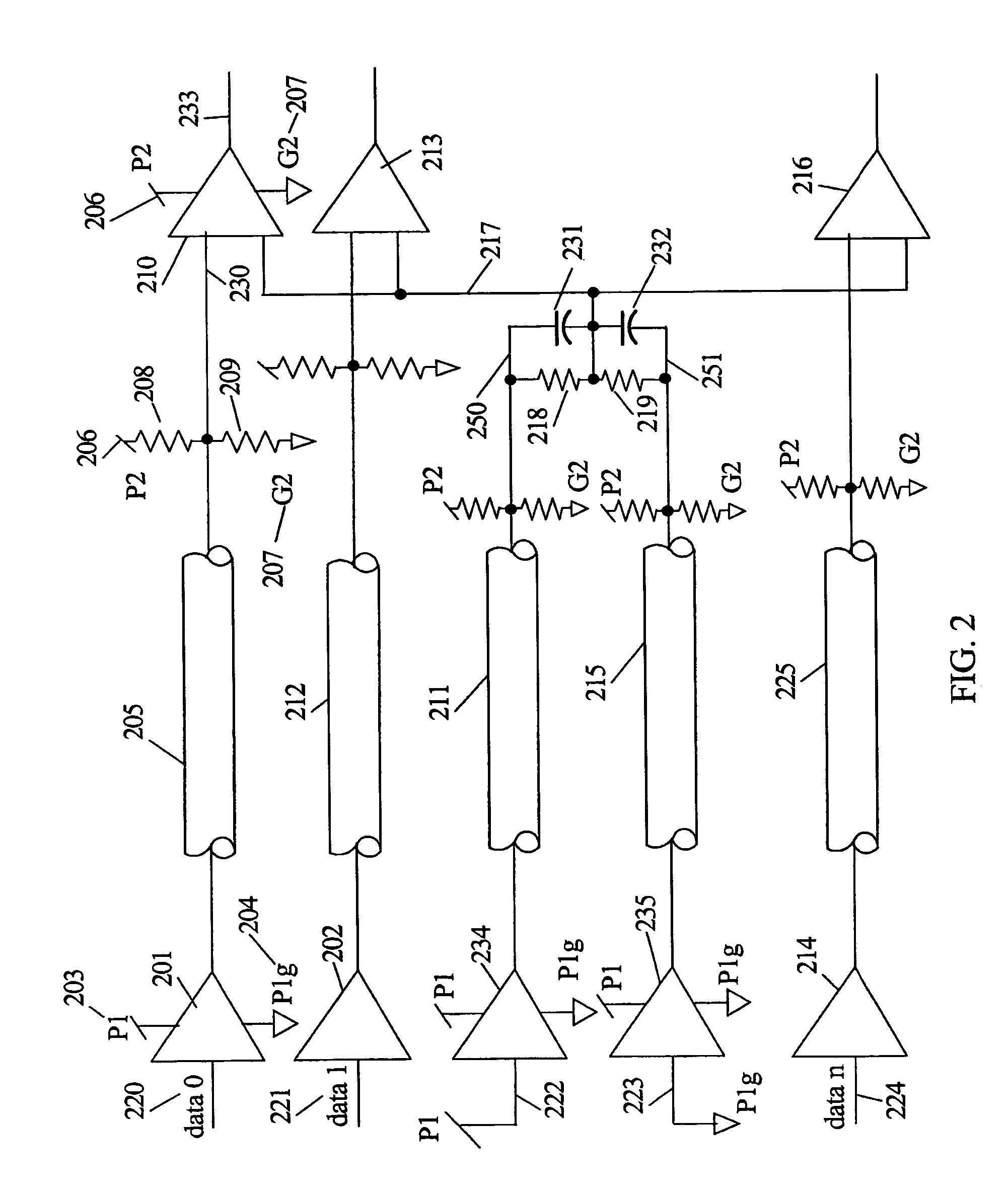

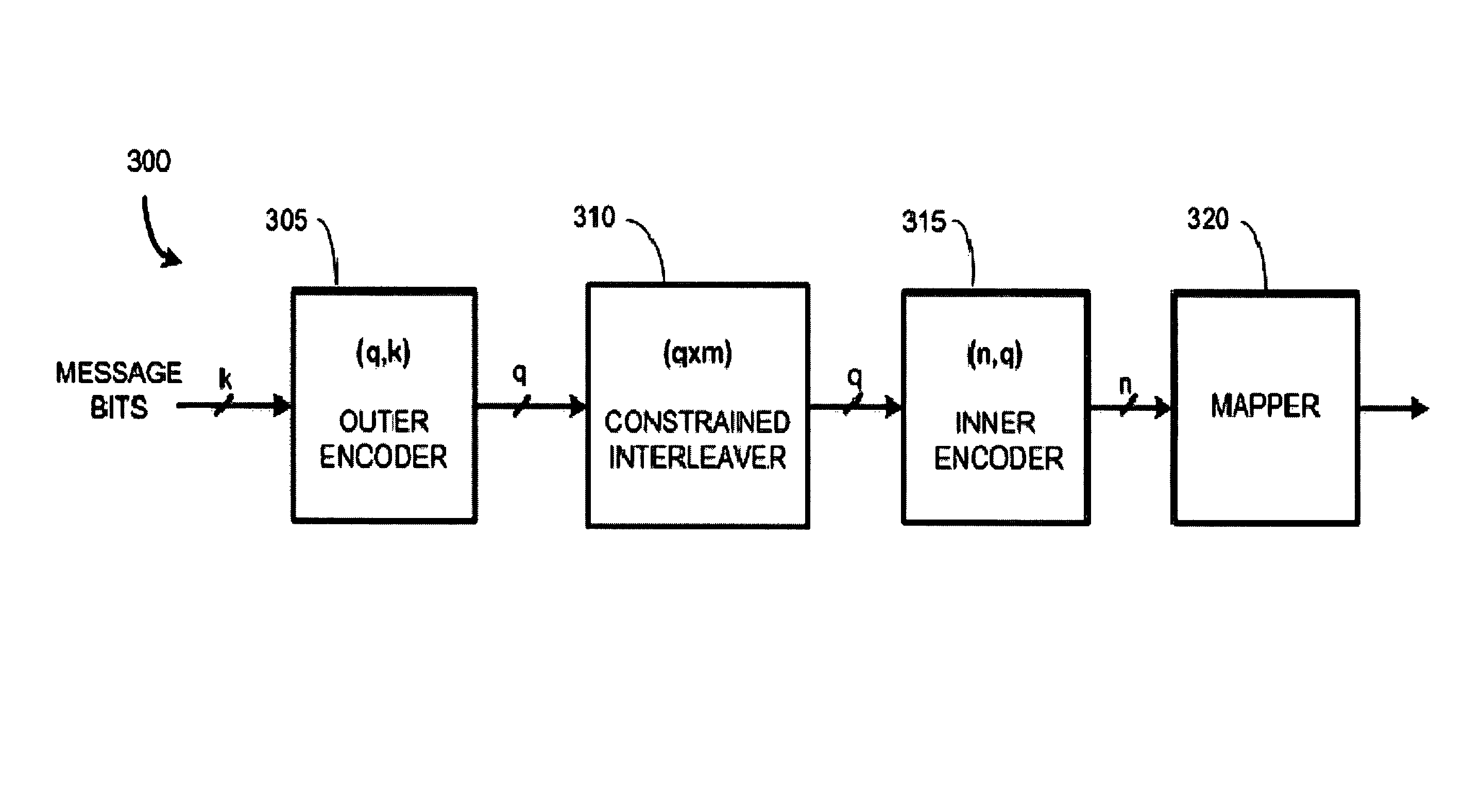

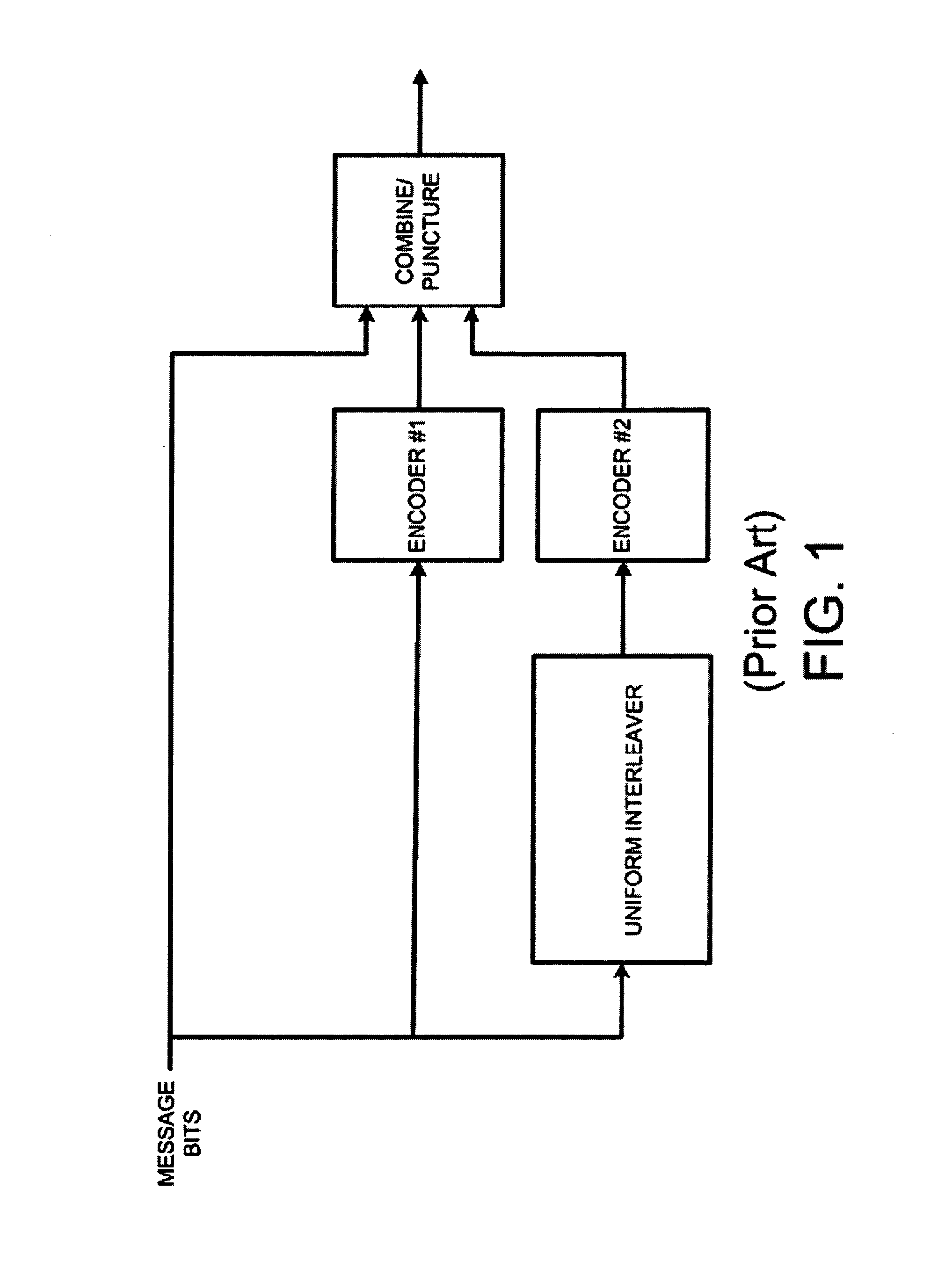

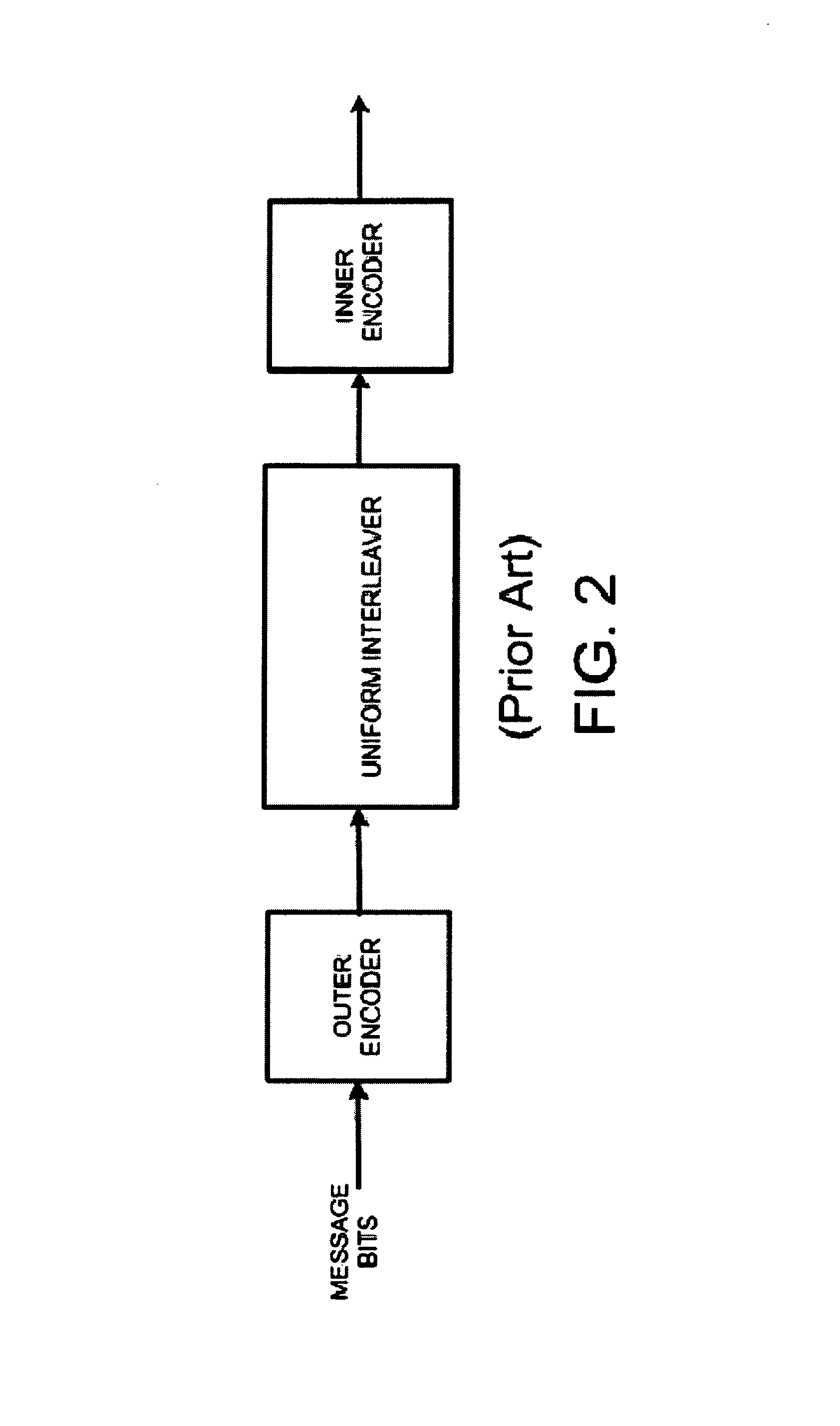

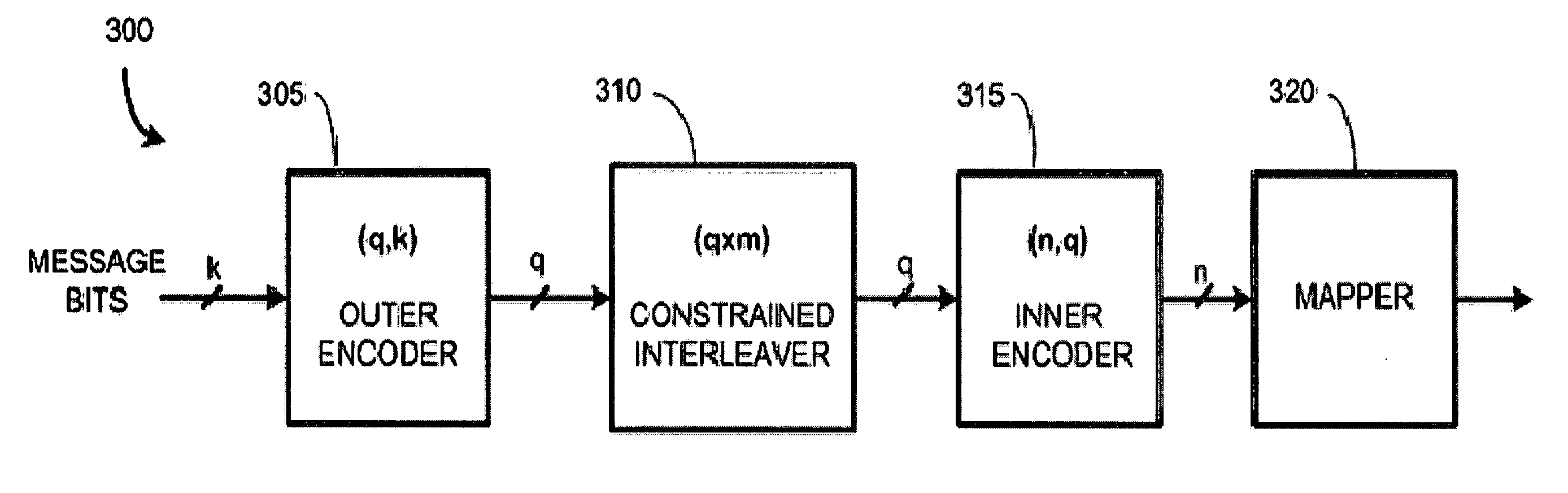

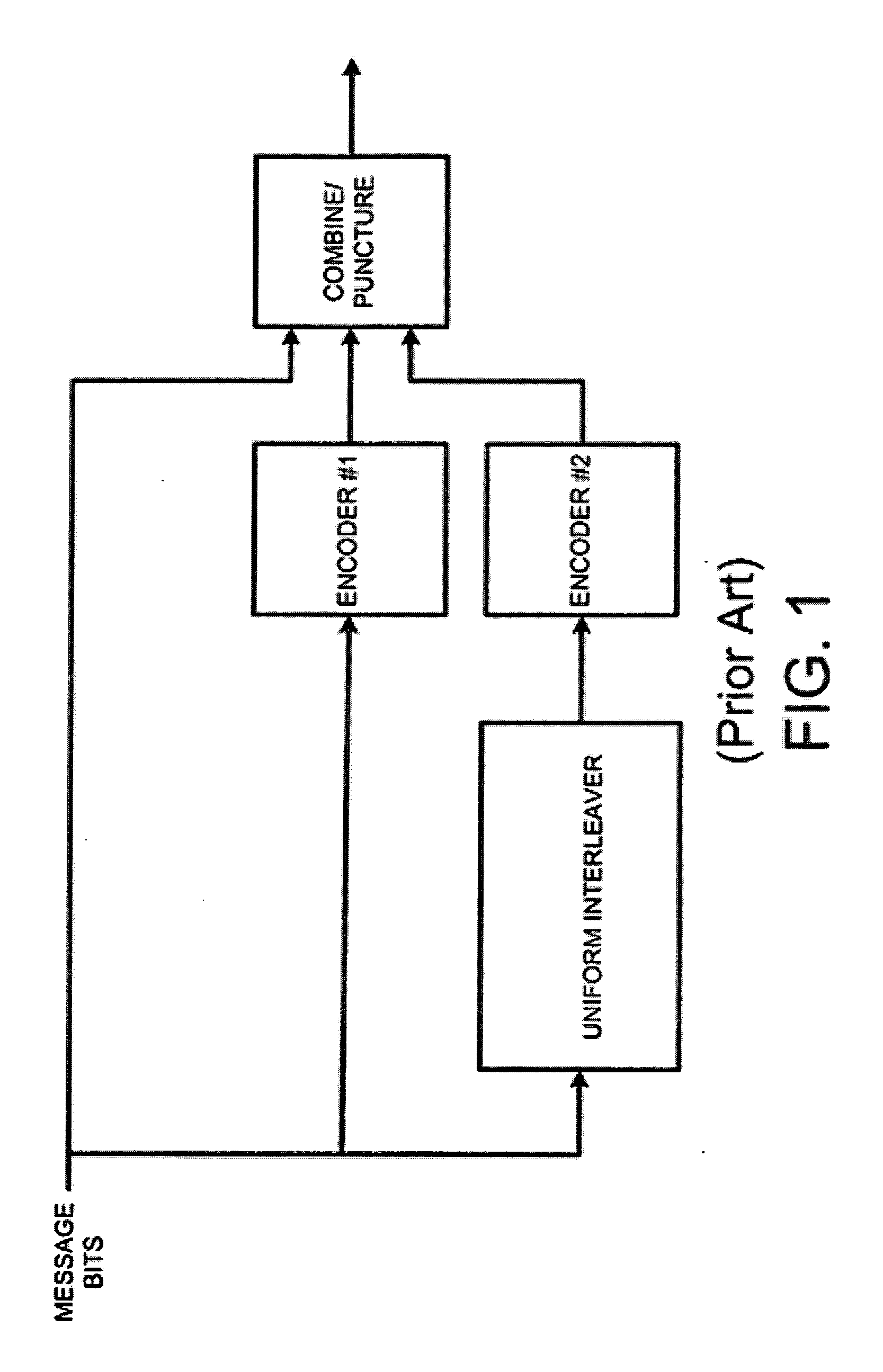

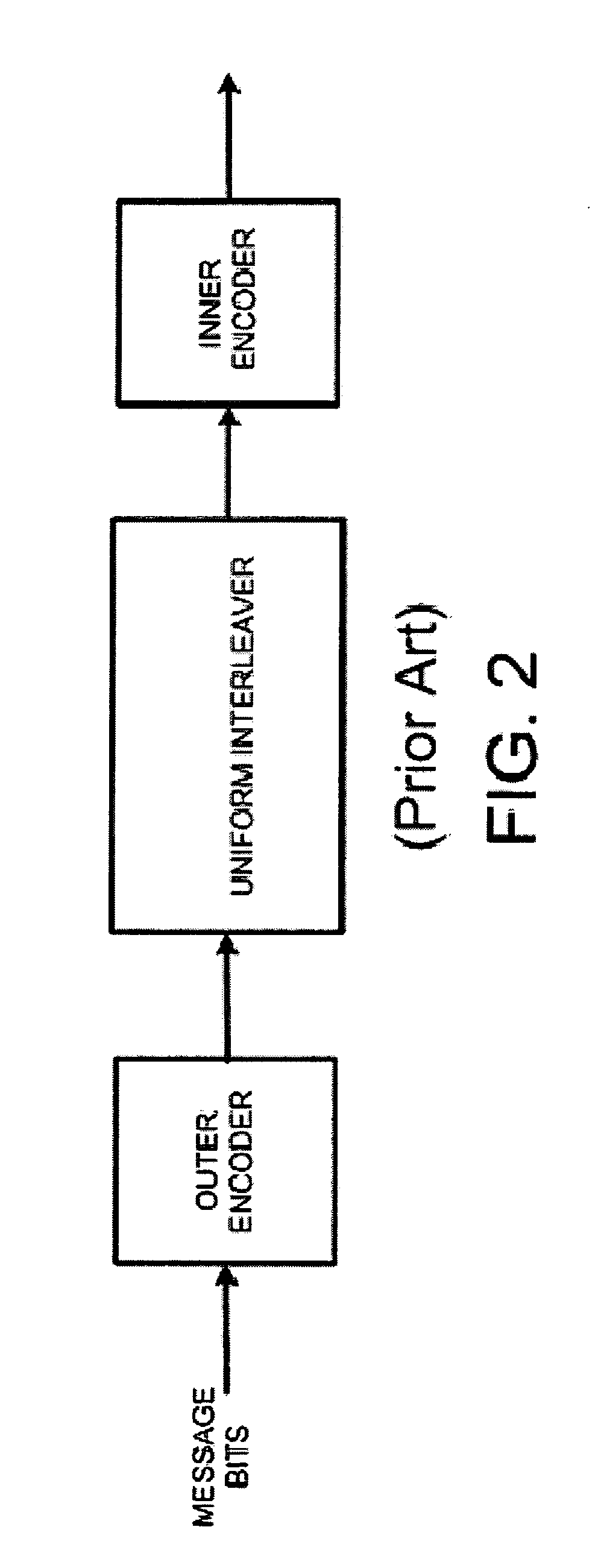

Encoding and decoding using constrained interleaving

InactiveUS20120063533A1Reduce measurementEfficient implementationAmplitude-modulated carrier systemsAmplitude demodulationSimple componentNoise margin

Serially-concatenated codes are formed in accordance with the present invention using a constrained interleaver. The constrained interleaver cause the minimum distance of the serial concatenated code to increase above the minimum distance of the inner code alone by adding a constraint that forces some or all of the distance of the outer code onto the serially-concatenated code. This allows the serially-concatenated code to be jointly optimized in terms of both minimum distance and error coefficient to provide significant performance advantages. These performance advantages allow a noise margin target to be achieved using simpler component codes and a much shorter interleaver than was needed when using prior art codes such as Turbo codes. Decoders are also provided. Both encoding and decoding complexity can be lowered, and interleavers can be made much shorter, thereby shortening the block lengths needed in receiver elements such as equalizers and other decision-directed loops. Also, other advantages are provided such as the elimination of a error floor present in prior art serially-concatenated codes. That allows the present invention to achieve much higher performance at lower error rates such as are needed in optical communication systems.

Owner:TRELLIS PHASE COMM LP

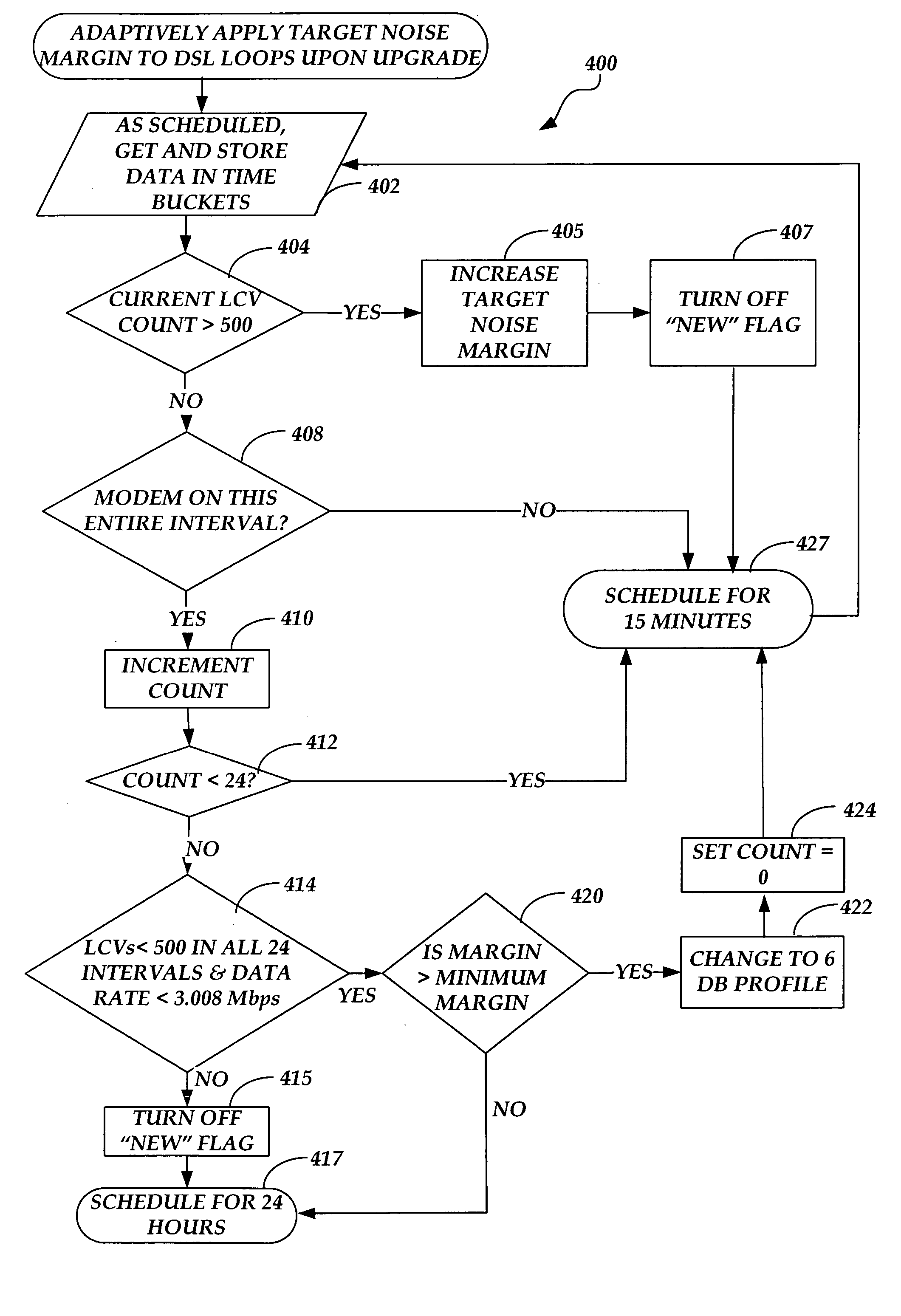

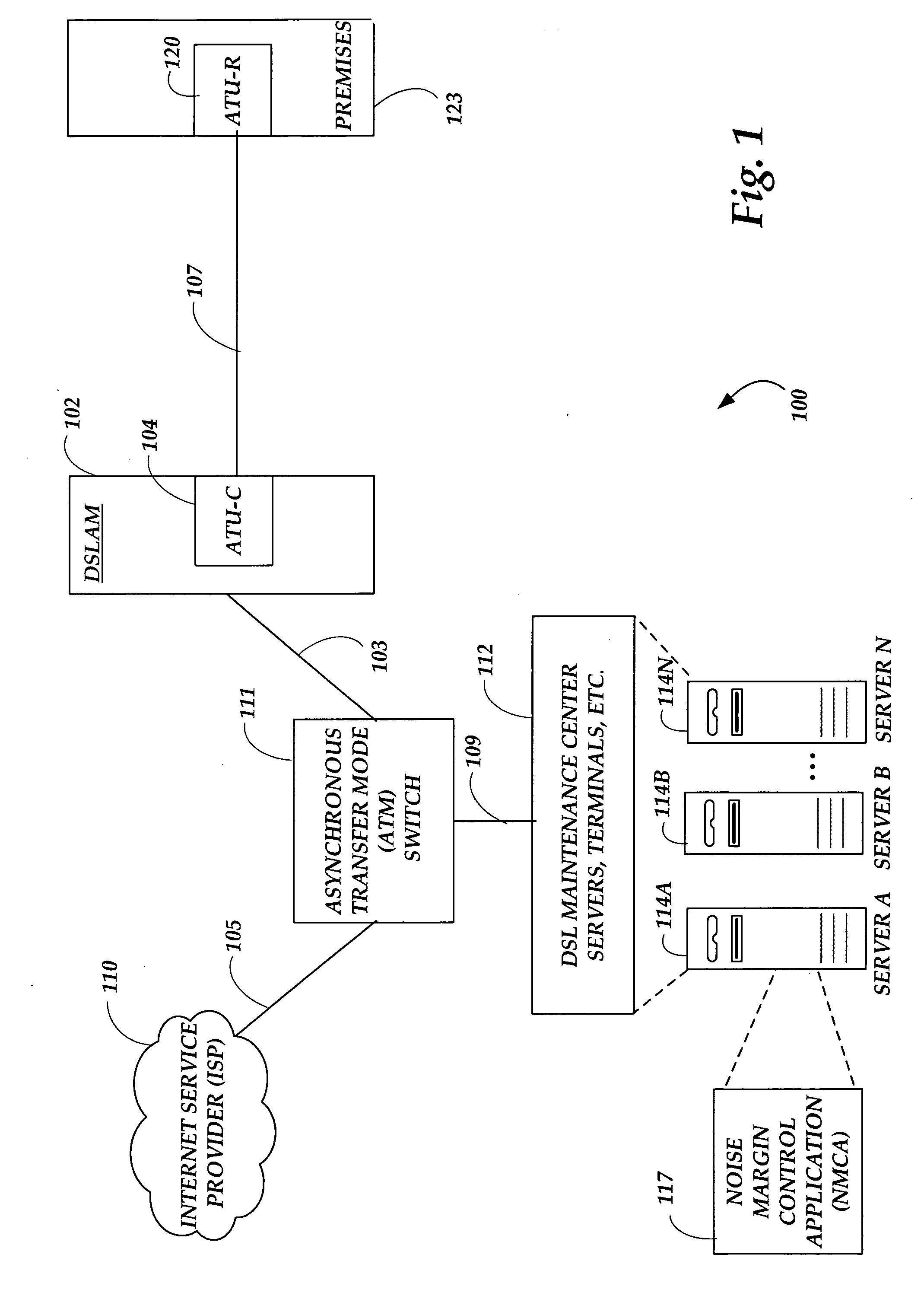

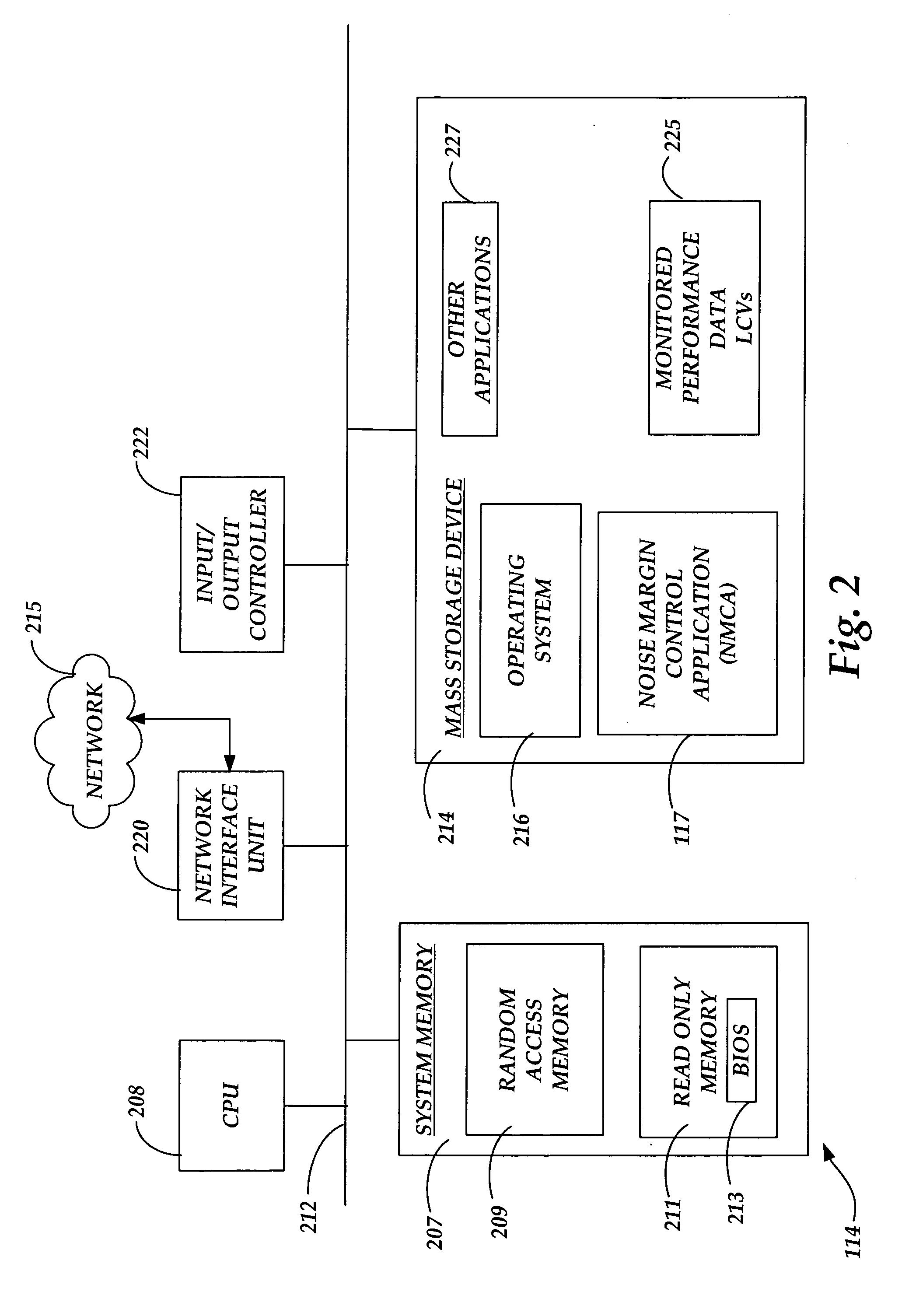

Adaptively applying a target noise margin to a DSL loop for DSL data rate establishment

InactiveUS20050237940A1Increase target noise marginLarge data-rateError preventionTransmission systemsData rateNoise margin

Methods, systems, and computer program products adaptively apply a target noise margin to a DSL loop to establish a DSL data rate on the DSL loop. A method involves receiving performance data associated with a quantity of errors detected over a period of time on the DSL loop and adjusting the target noise margin for the DSL loop based on the performance data. The target noise margin is inversely associated with the DSL data rate that can be established and is adjusted in order to maximize the DSL data rate while minimizing the quantity of errors detected over the period of time. Thus, embodiments of the present invention allow a maximum data rate that can be sustained on a DSL loop without an excessive quantity of errors.

Owner:AT&T INTPROP I L P

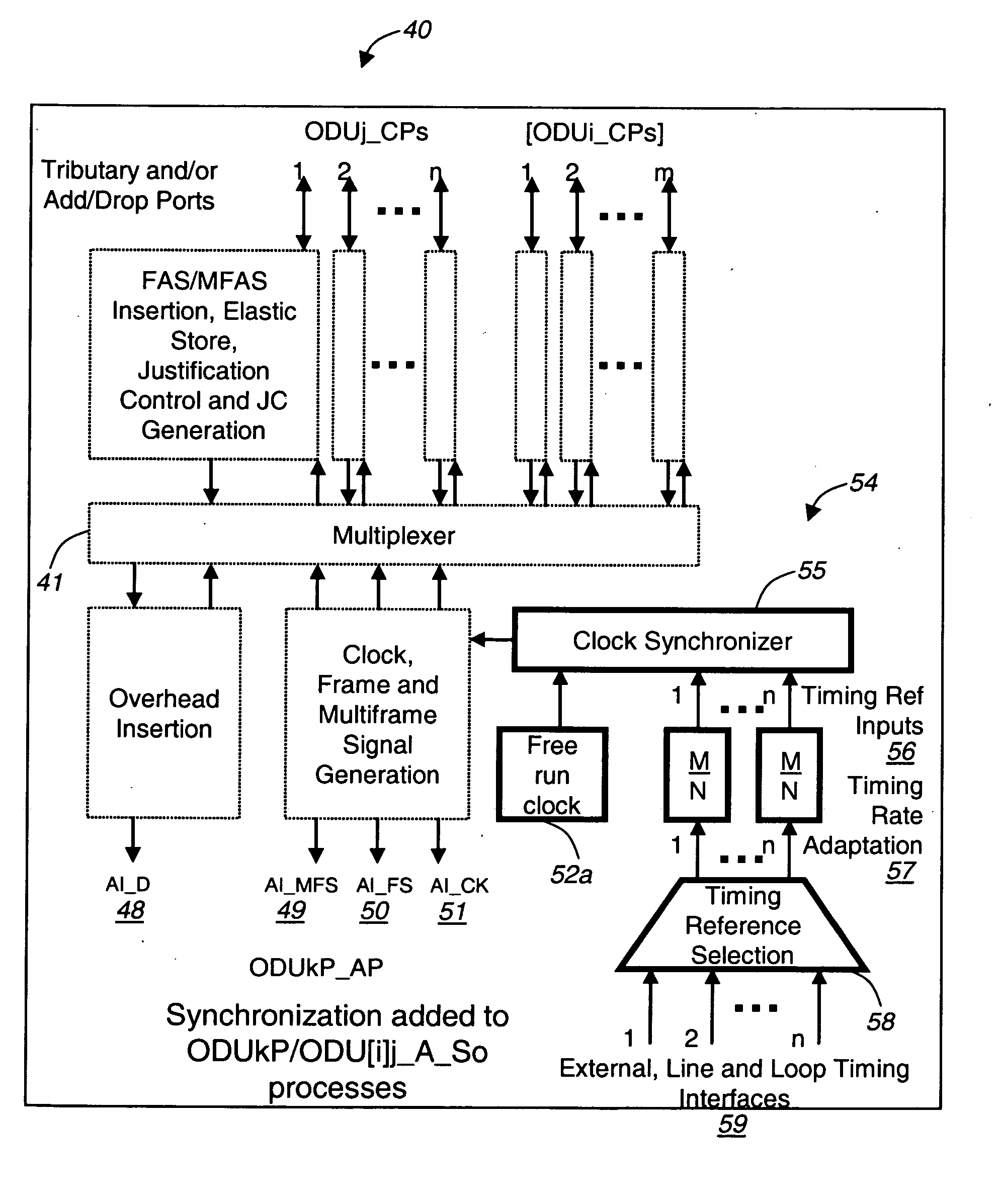

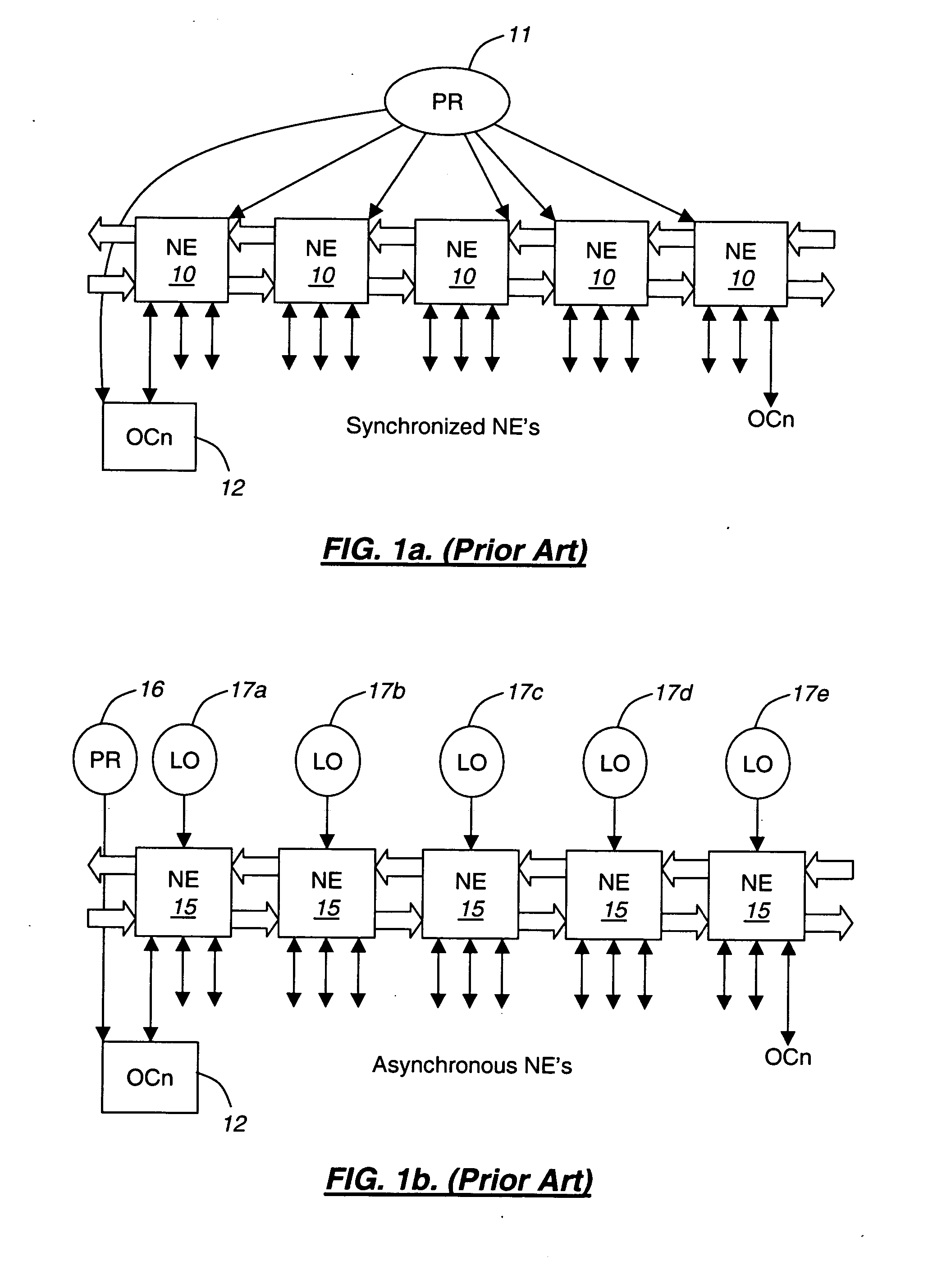

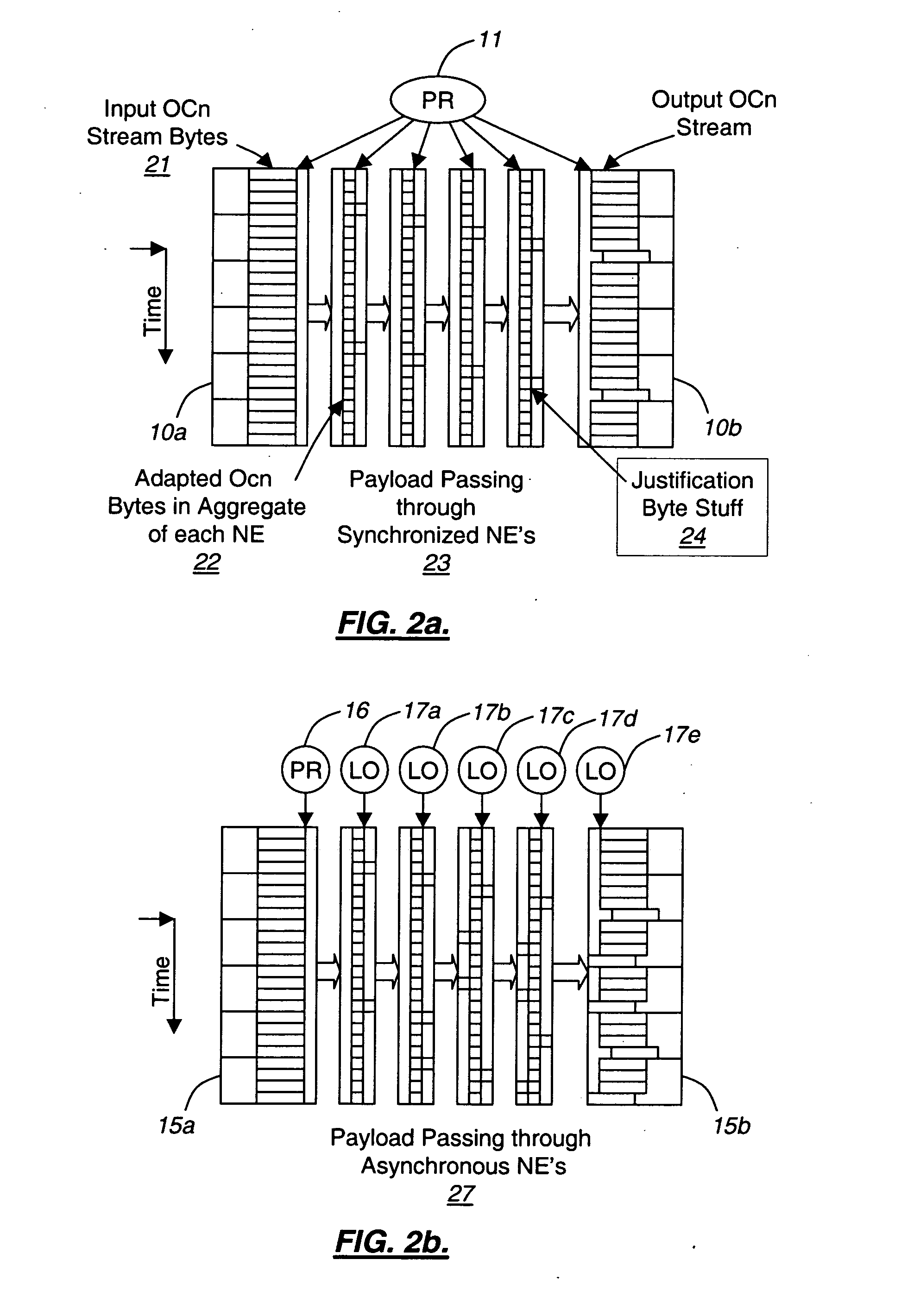

Externally synchronized optical transport network systems and associated methods

ActiveUS20070116061A1Less jitterLess wander build-upTime-division multiplexData switching by path configurationExternal referenceNoise margin

The present invention utilizes external synchronization to generate a completely standardized or functionally standardized optical transmission unit of level k (OTUk[V]) signal providing less jitter and wander build-up through a network of optical transport network (OTN) elements. This increases noise margins of transported signals and payloads. The present invention provides stratum-level synchronization utilizing a standards-based approach. In one embodiment of the present invention, rate adapters are included to provide m / n scaling of OTUk[V] signals to rates common in SONET and SDH synchronizers to provide line and loop distribution of timing through OTUk[V] signals. The present invention provides a choice of external synchronization sources including building integrated timing source (BITS), line, and loop timing sources. In another exemplary embodiment, the present invention provides multiple external references and automated timing protection switching for redundancy and reliability.

Owner:CIENA

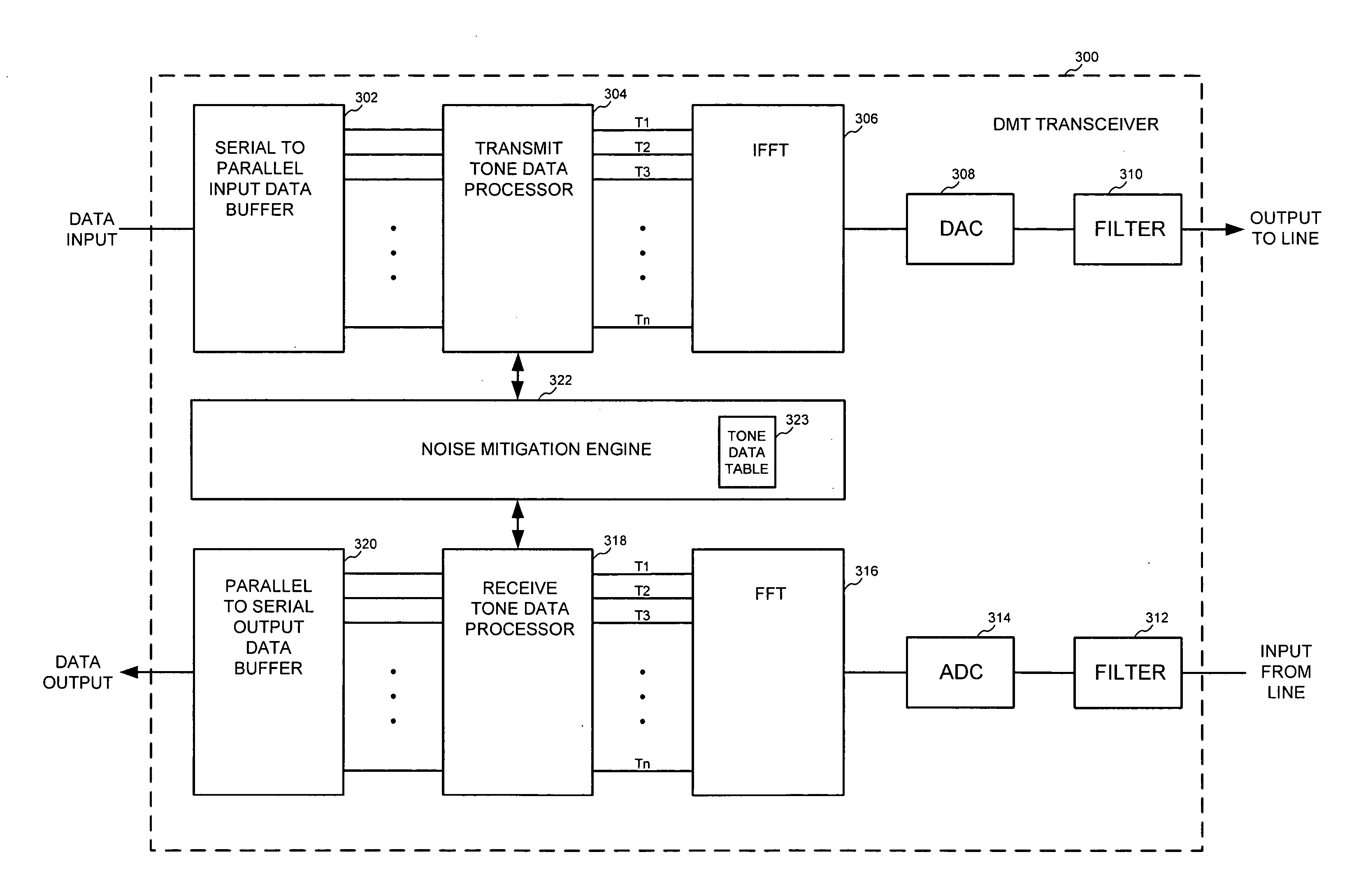

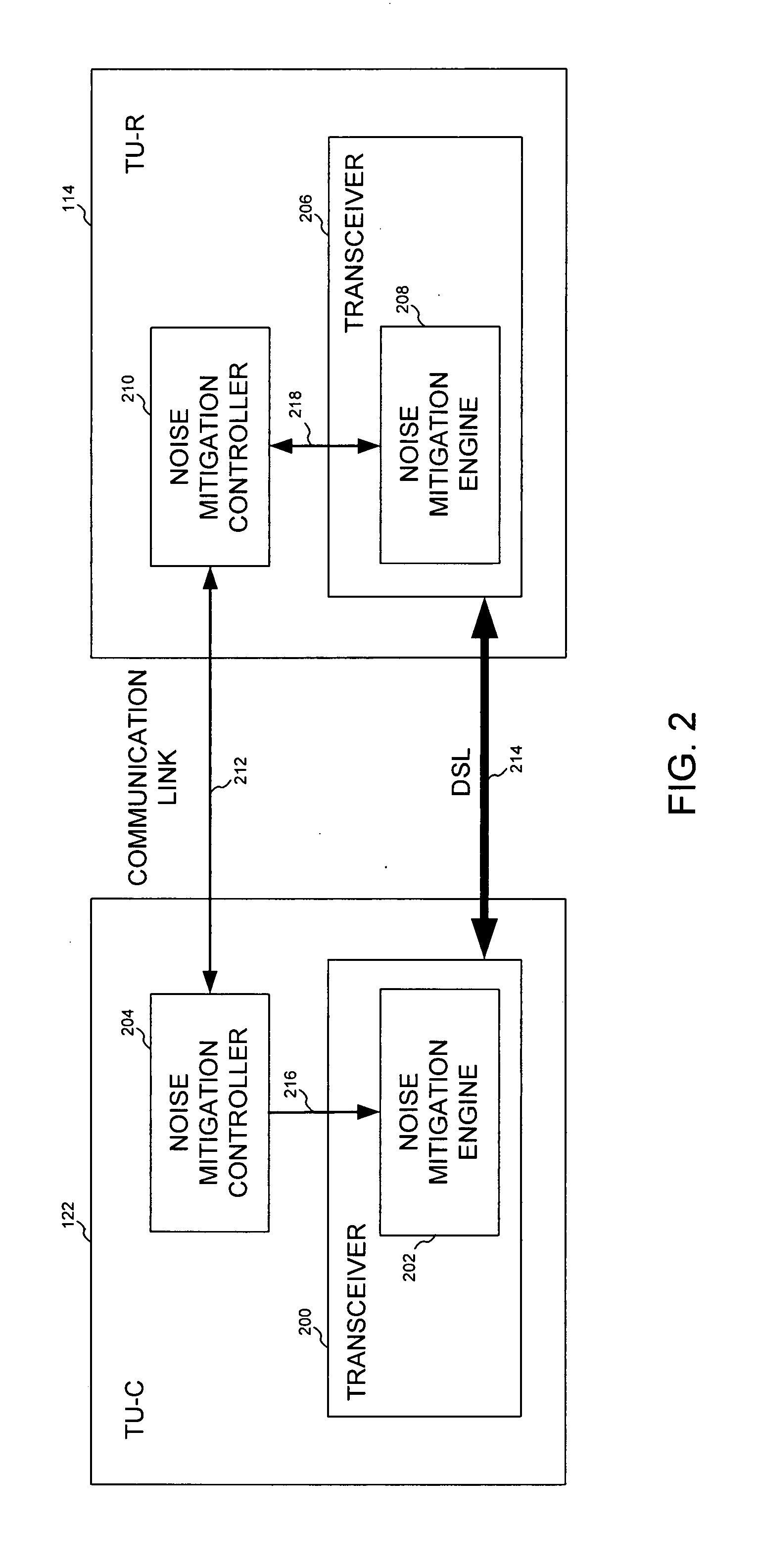

Digital subscriber line noise mitigation techniques, and applications thereof

InactiveUS20070230548A1Reduce the impactImproved noise measurementError detection/prevention using signal quality detectorTransmission path divisionNoise monitoringDigital subscriber line

The present invention provides digital subscriber line noise mitigation techniques, and applications thereof. In an embodiment, the present invention provides a toolbox of methods and techniques for mitigating the effects of noise in xDSL systems. These methods and techniques are controllable and locatable at one or both ends of a DSL communication link (e.g., within a central office transceiver unit or a remote transceiver unit). These novel methods and techniques include: (1) per tone noise margin modification, (2) data framer constraints modification, (3) improved noise measurements; (4) more robust on-line reconfiguration processes, (5) worst case noise monitoring, (6) induced bit rate limitations, and (7) distortion noise mitigation. These methods and techniques are particularly useful for mitigating the effects of time-varying noise and impulse noise.

Owner:AVAGO TECH INT SALES PTE LTD

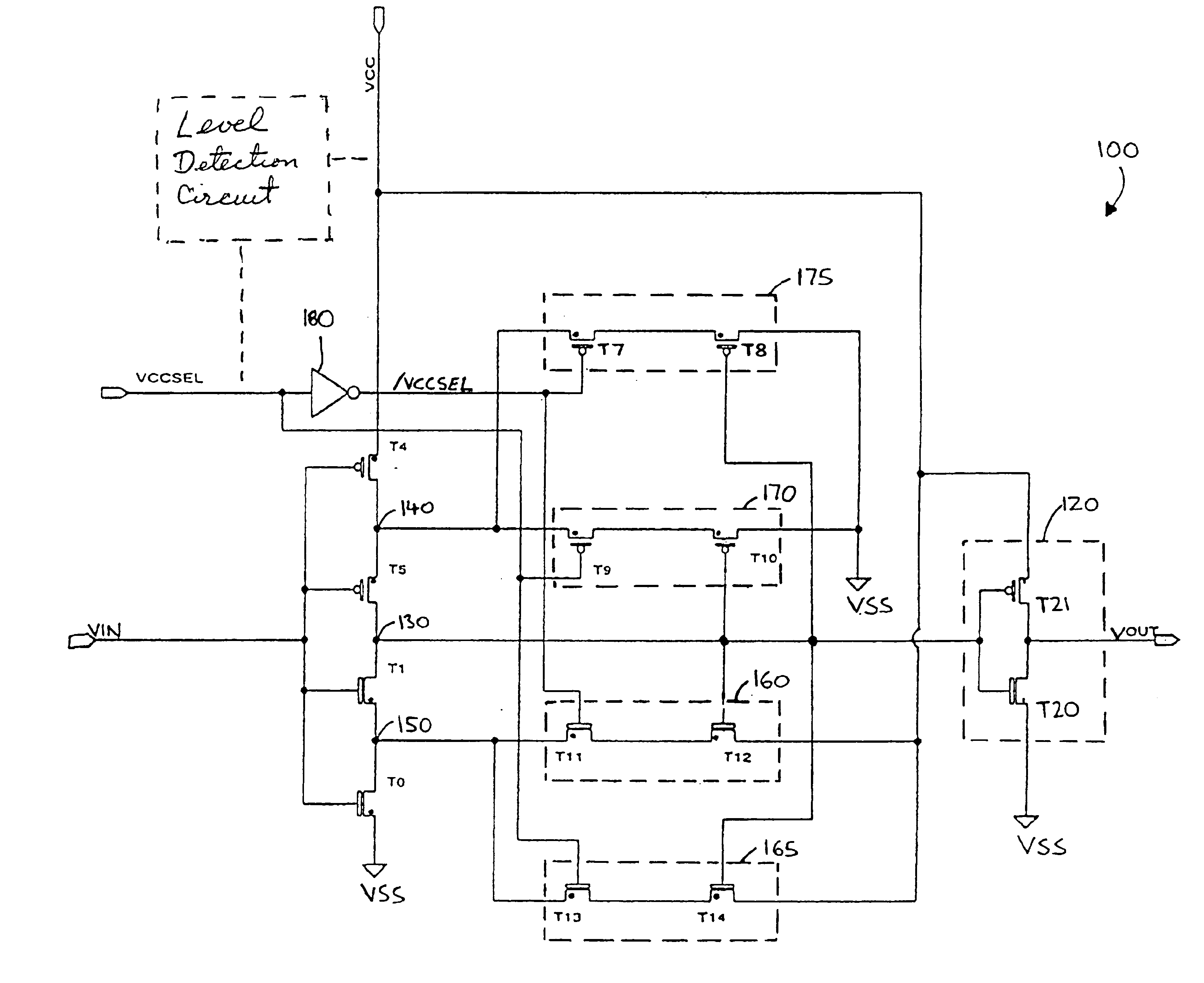

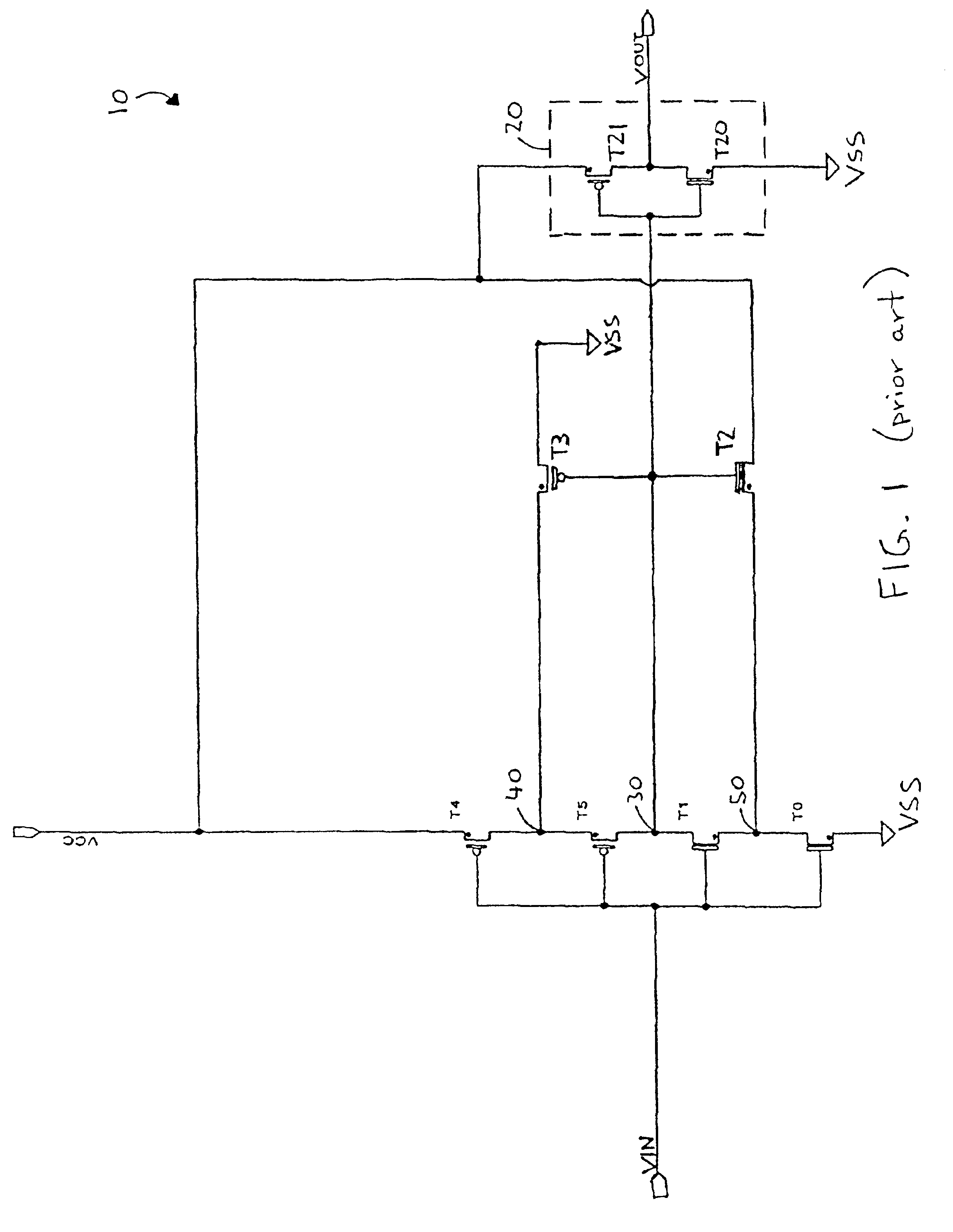

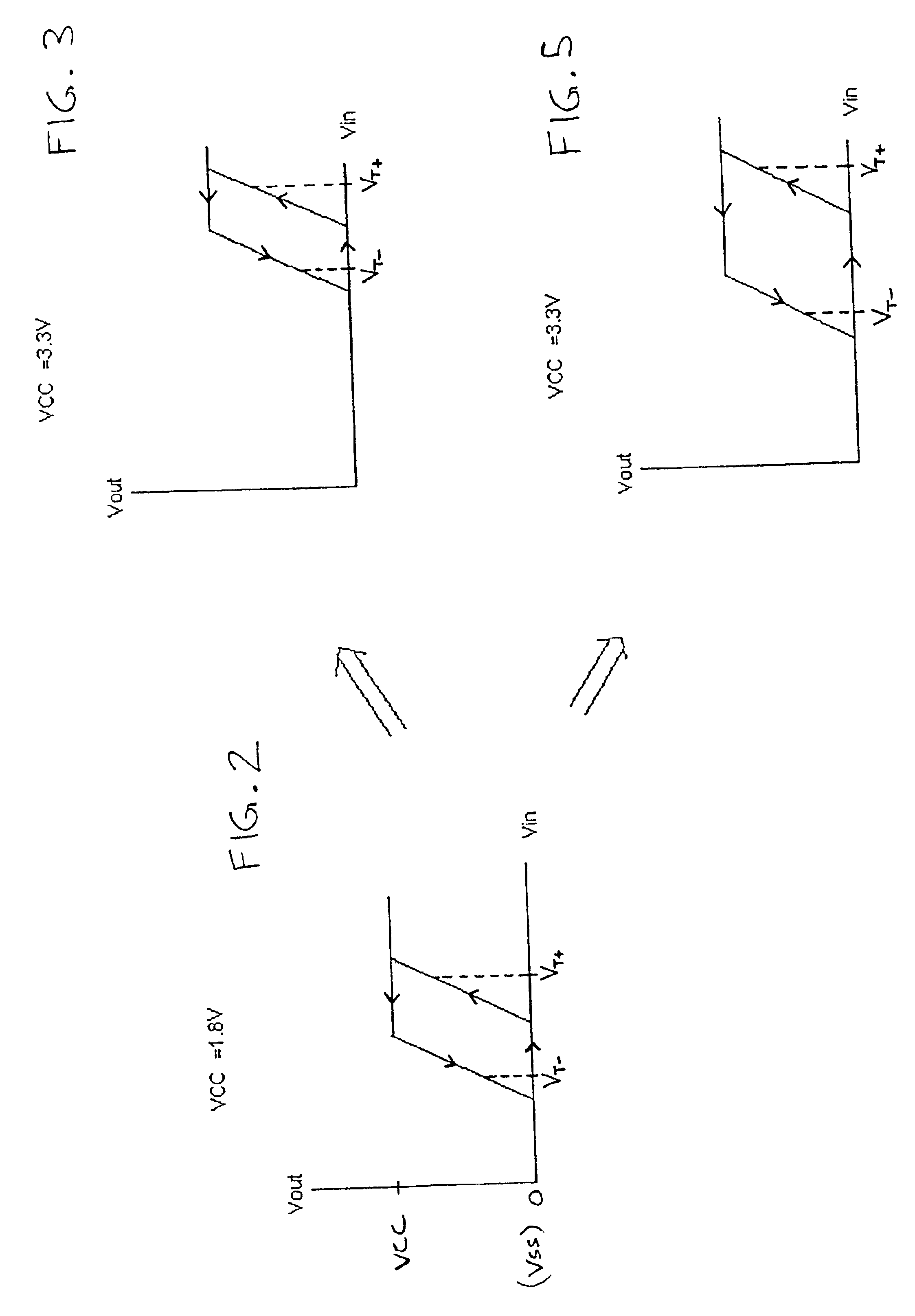

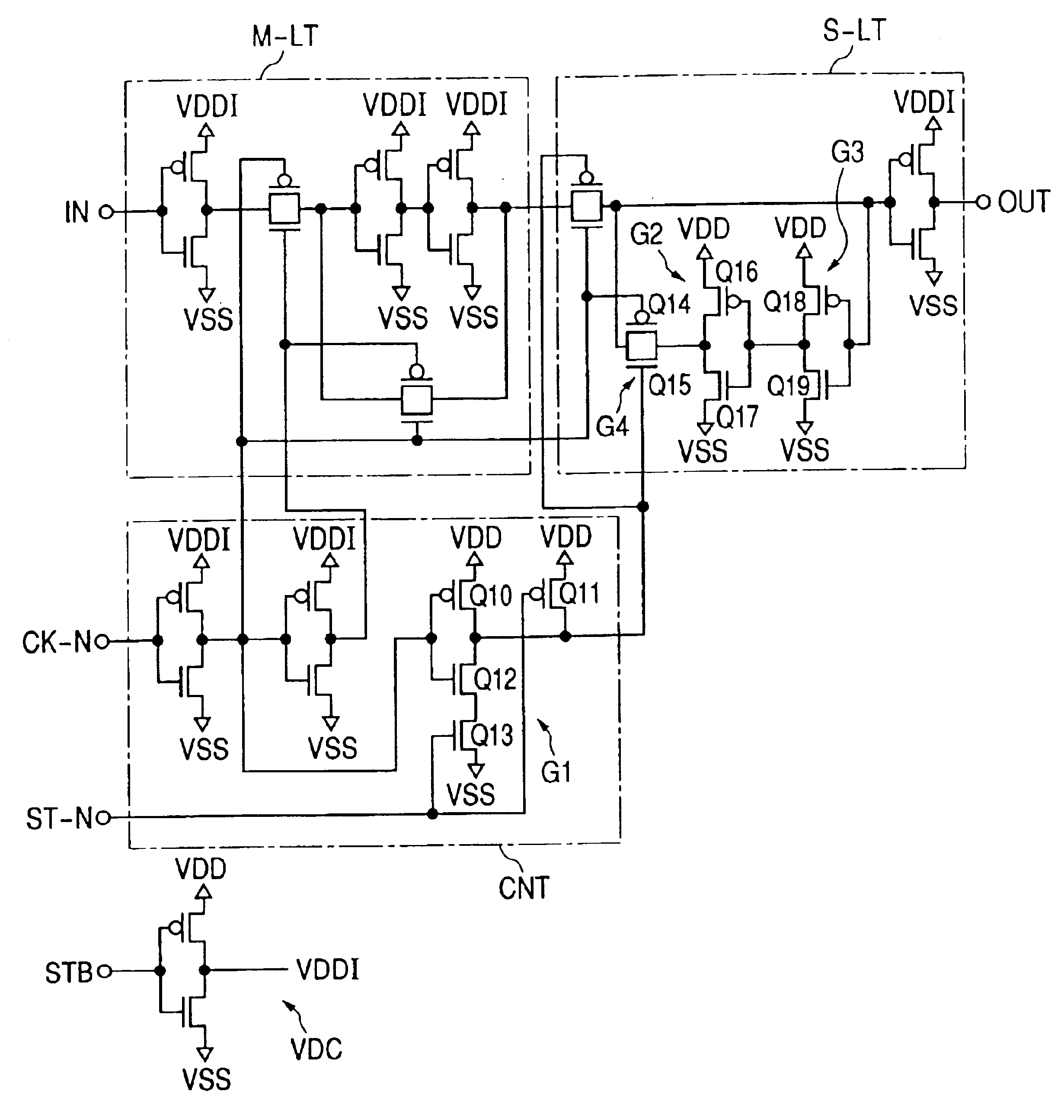

Schmitt trigger circuit with adjustable trip point voltages

A Schmitt trigger circuit has an adjustable hysteresis characteristic by providing a plurality of feedback circuits that differently affect at least one, and preferably both, of the circuit's upper trip point level and lower trip point level. The upper trip point level can be adjusted by selecting a desired feedback circuit from a first set of feedback circuits, and / or the lower trip point level can be adjusted by selecting a desired feedback circuit from a second set of feedback circuits. Feedback circuit selection is achieved by one or more control signals that may be programmable. The hysteresis characteristic can be adjusted to meet desired noise margin, delay, and input recognition criteria at different VCC levels. The Schmitt trigger circuit may be a CMOS Schmitt trigger with two input stage NMOS, two input stage PMOS transistors, a first set of NMOS feedback circuits, and a second set of PMOS feedback circuits.

Owner:ALTERA CORP

Rate agile rate-adaptive digital subscriber line

ActiveUS20080095188A1High achievable data rateEasy to adjustEnergy efficient ICTInterconnection arrangementsModem deviceRate change

Methods and apparatus for maintaining the maximum achievable data rate on a DSL line, up to and including a rate to which a user subscribes is described. Performance monitoring is conducted on the DSL line on an ongoing basis to determine noise margins in each direction. Each noise margin is compared against pre-determined decreasing / increasing thresholds to determine whether the line characteristics dictate a data rate change without loss of synchronization. The invention supports dynamic provisioning changes including application driven service level change requests, e.g., new bandwidth-on demand services. In some embodiments, a combination of existing and new embedded operations channel (EOC) messages are used to implement the modem data rate changes. New EOC messages may be implemented using some of the reserved and / or vendor proprietary Opcodes currently permitted. Modem assigned data rate changes are implemented without a disruption of service, e.g., without the need for re-initialization and / or re-synchronization.

Owner:INTELLECTUAL VENTURES II

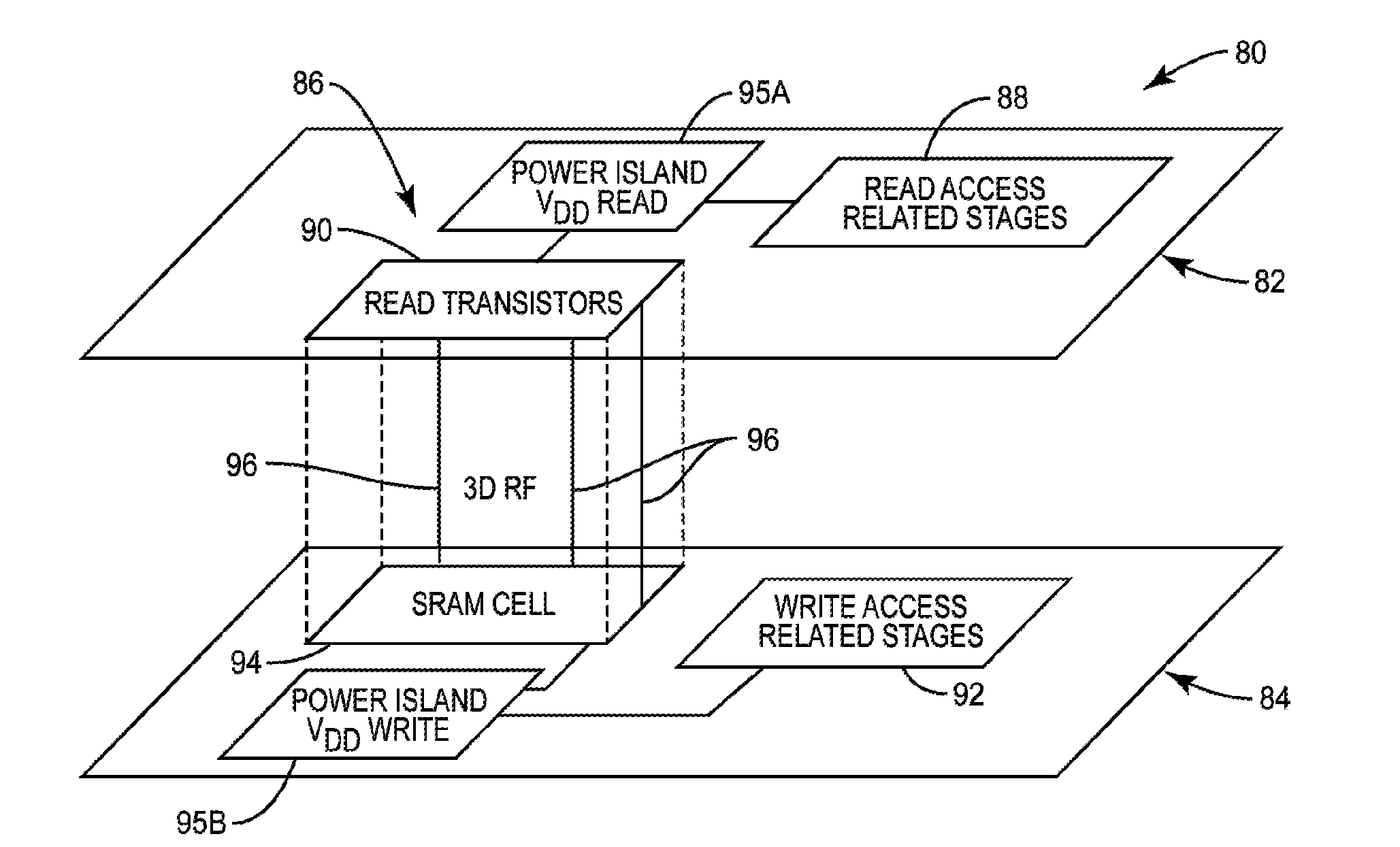

Three-dimensional (3D) memory cell separation among 3D integrated circuit (IC) tiers, and related 3D integrated circuits (3DICS), 3Dic processor cores, and methods

ActiveUS20140269022A1High device packing densityLower latencyTransistorSemiconductor/solid-state device details3d integrated circuitComputer architecture

A three-dimensional (3D) memory cell separation among 3D integrated circuit (IC) (3DIC) tiers is disclosed. Related 3DICs, 3DIC processor cores, and methods are also disclosed. In embodiments disclosed herein, memory read access ports of a memory block are separated from a memory cell in different tiers of a 3DIC. 3DICs achieve higher device packing density, lower interconnect delays, and lower costs. In this manner, different supply voltages can be provided for the read access ports and the memory cell to be able to lower supply voltage for the read access ports. Static noise margins and read / write noise margins in the memory cell may be provided as a result. Providing multiple power supply rails inside a non-separated memory block that increases area can also be avoided.

Owner:QUALCOMM INC

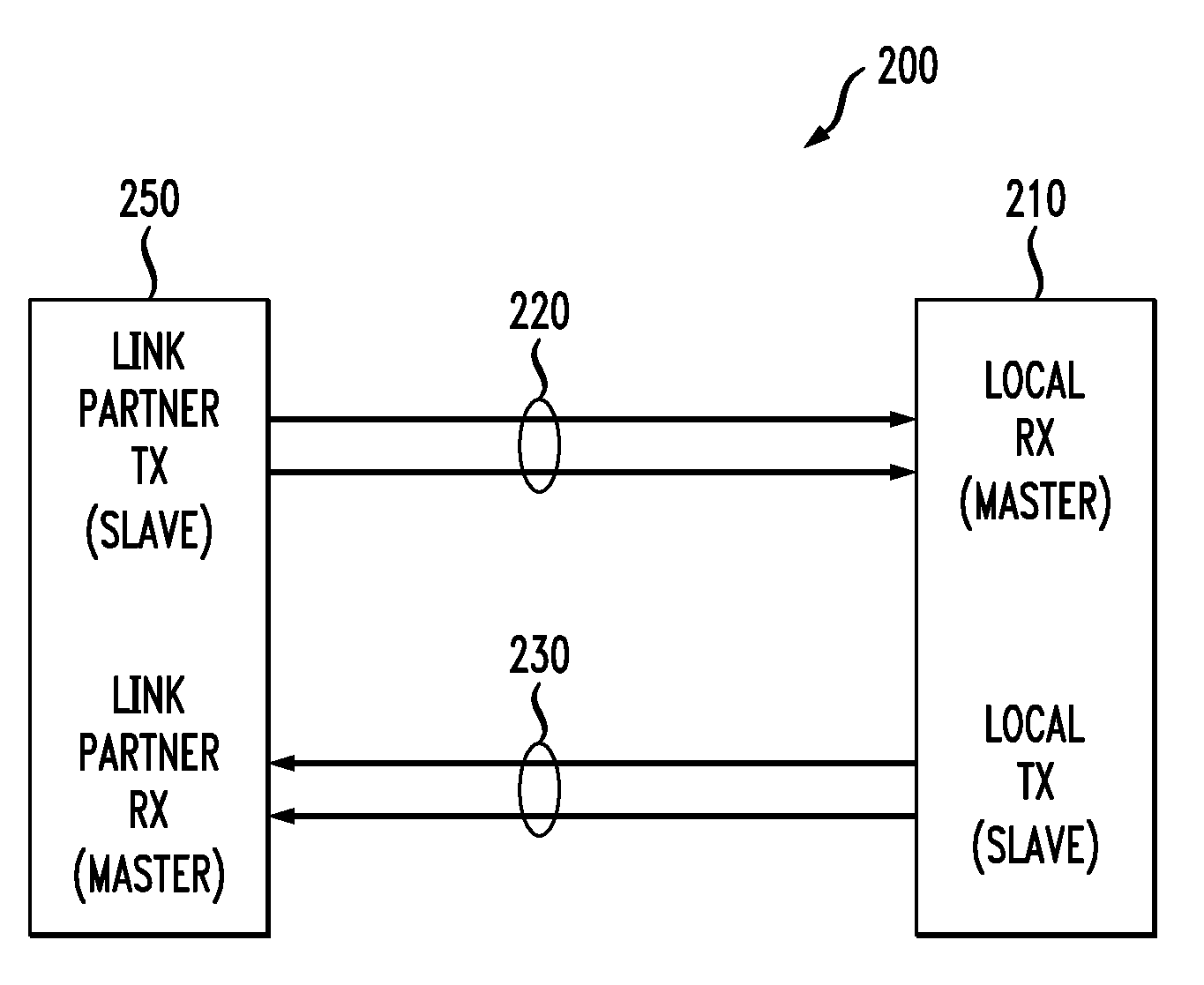

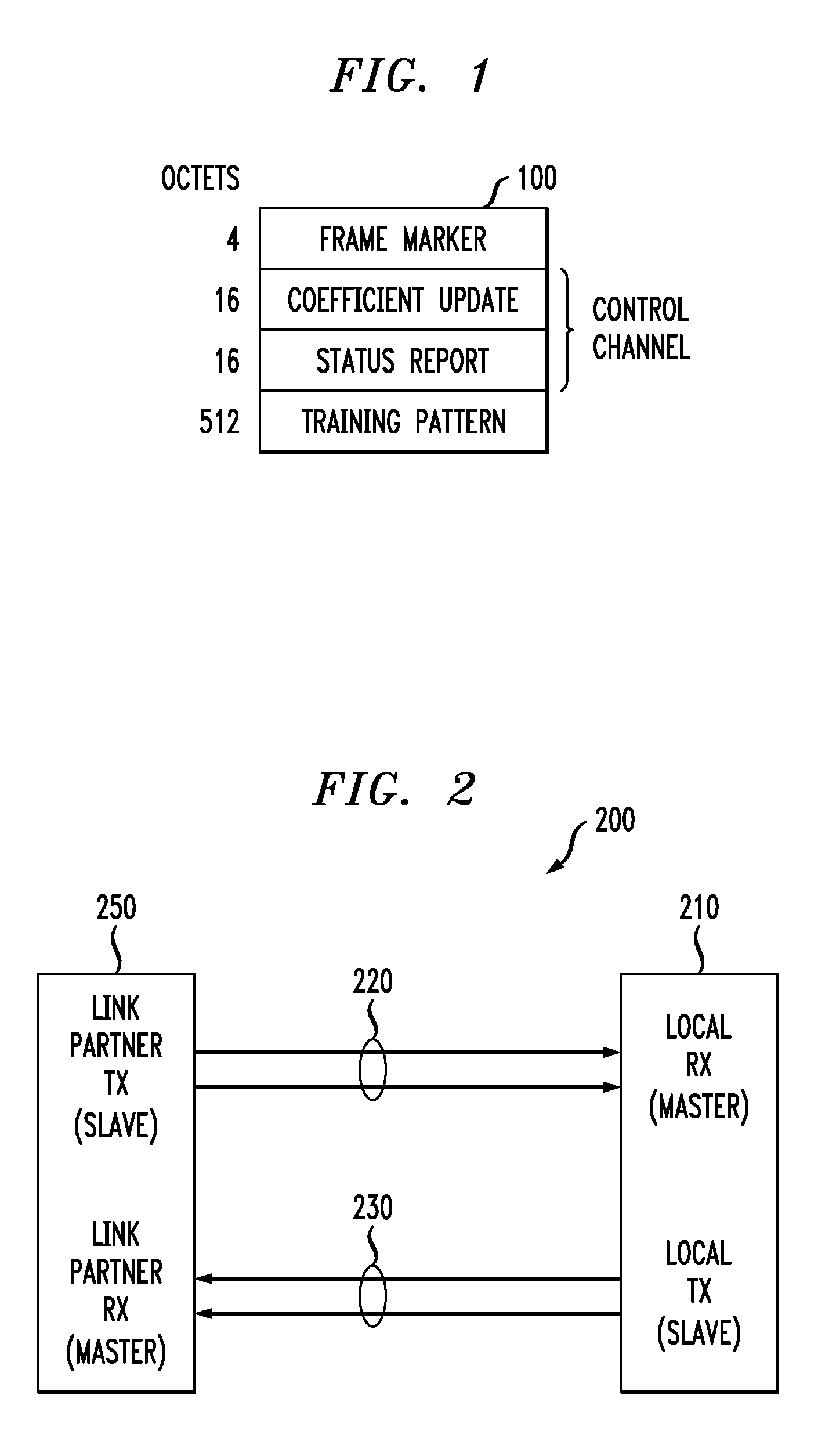

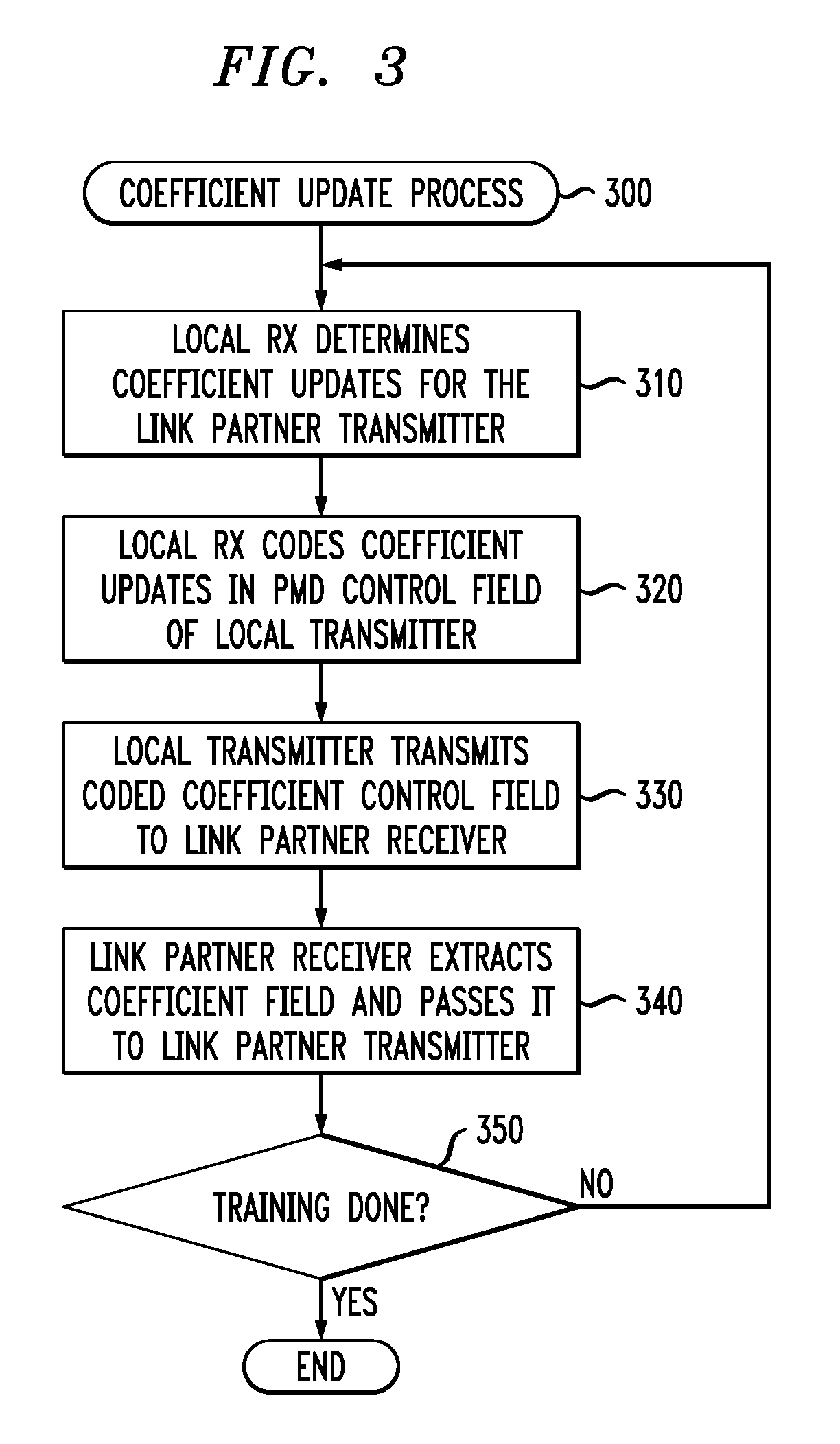

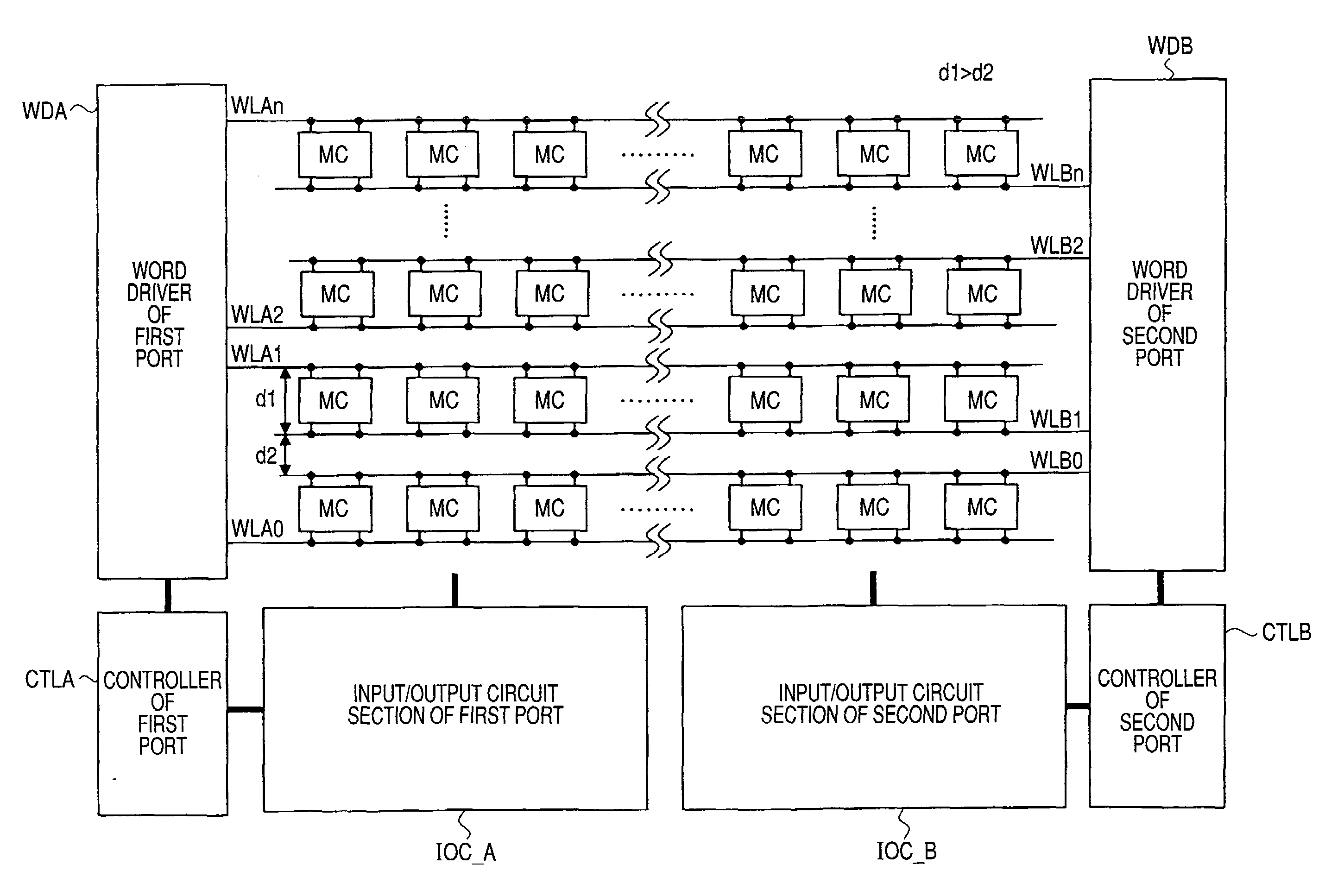

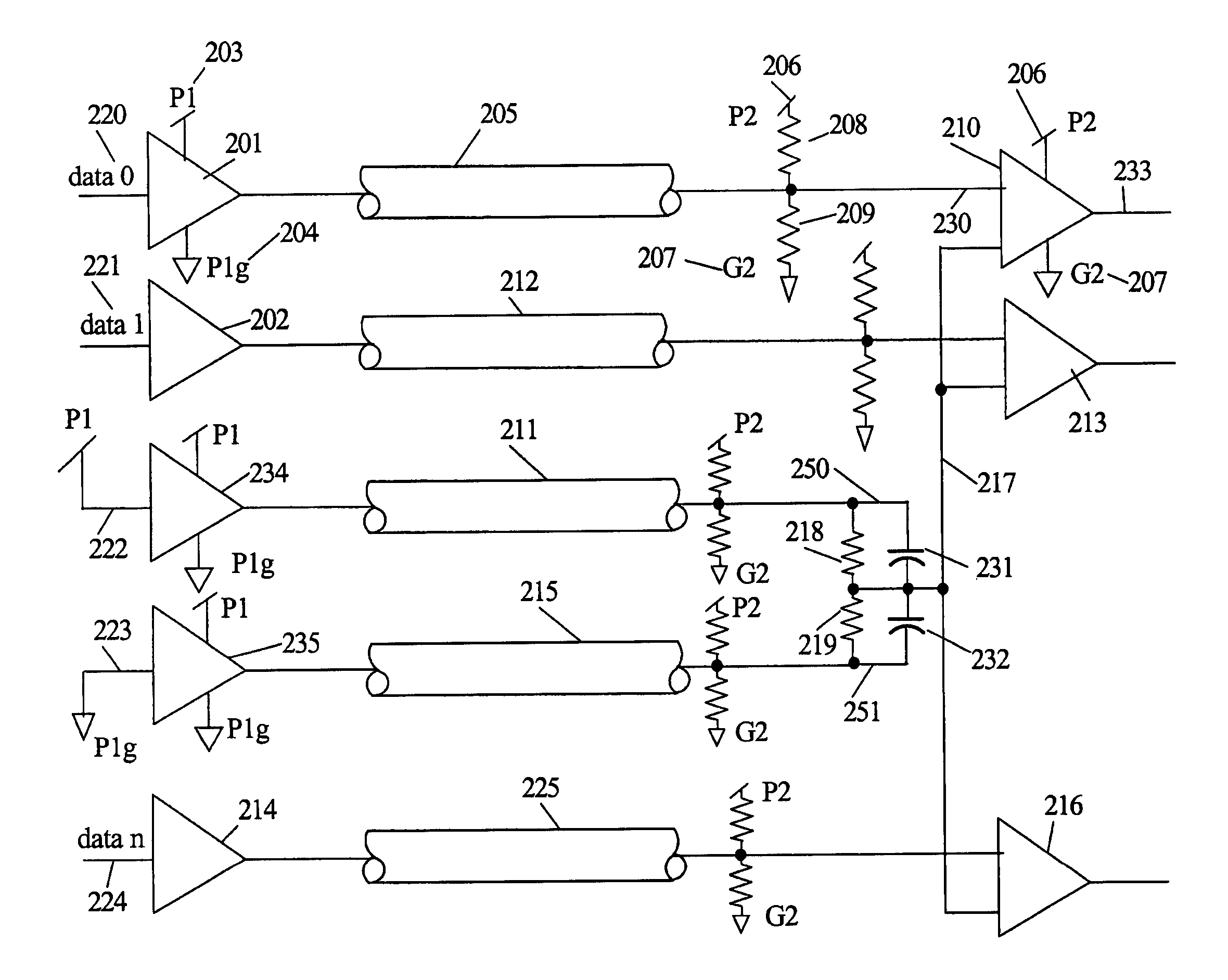

Methods And Apparatus For Adaptive Link Partner Transmitter Equalization

Methods and apparatus are provided for adaptive link partner transmitter equalization. According to one aspect of the invention, a local transceiver adapts one ox more equalization parameters of a link partner by receiving a training frame over a channel between the link partner and the local transceiver, wherein the training frame is comprised of a predefined training pattern; adjusting one or more of the equalization parameters of the link partner; and determining whether the equalization of the channel satisfies one or more predefined criteria based on whether the predefined training pattern is properly received by the local transceiver The predefined training pattern can be a pseudo random pattern, such as a PN11 pattern. Noise margins and jitters margins for the channel can optionally be improved.

Owner:AVAGO TECH INT SALES PTE LTD

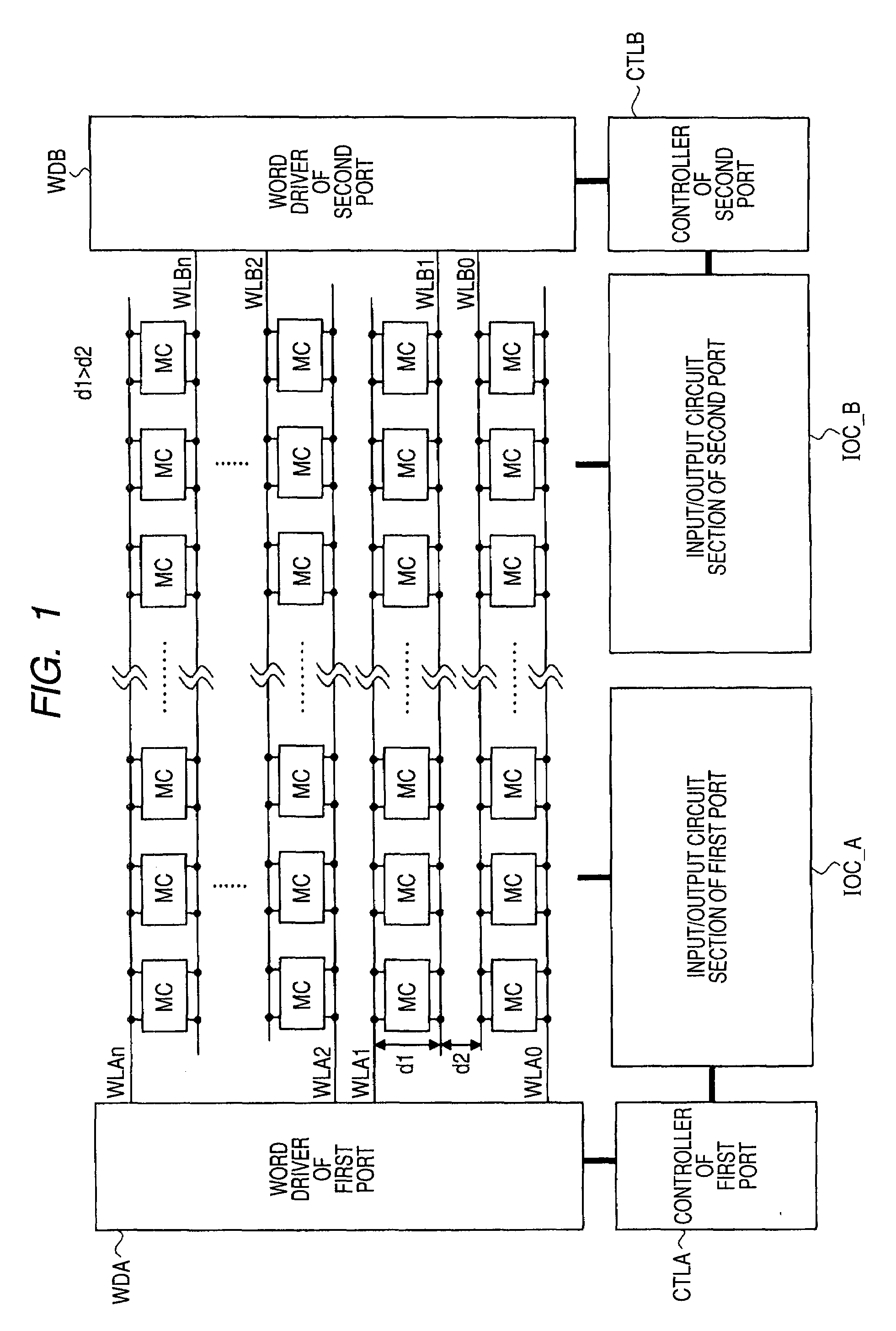

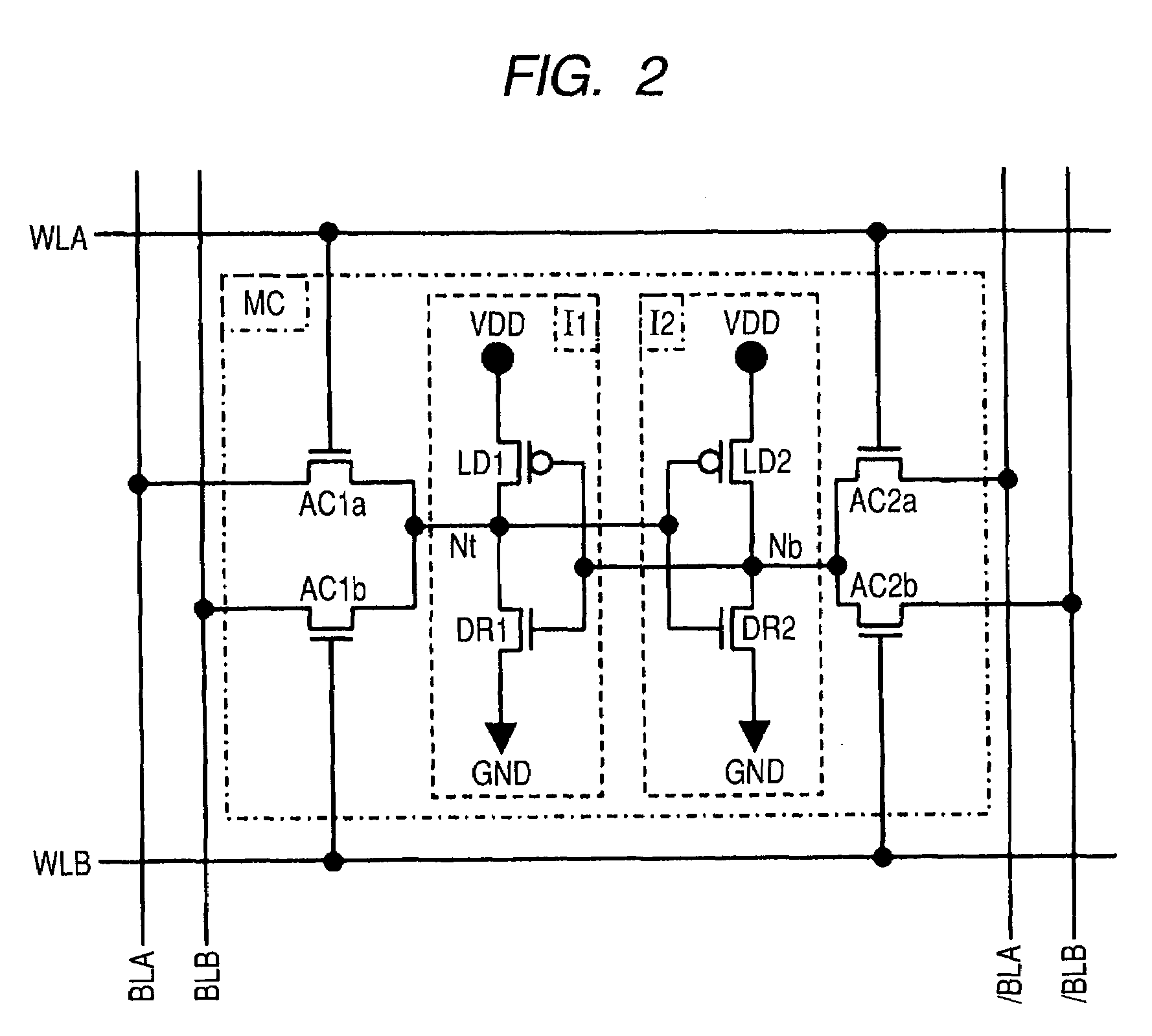

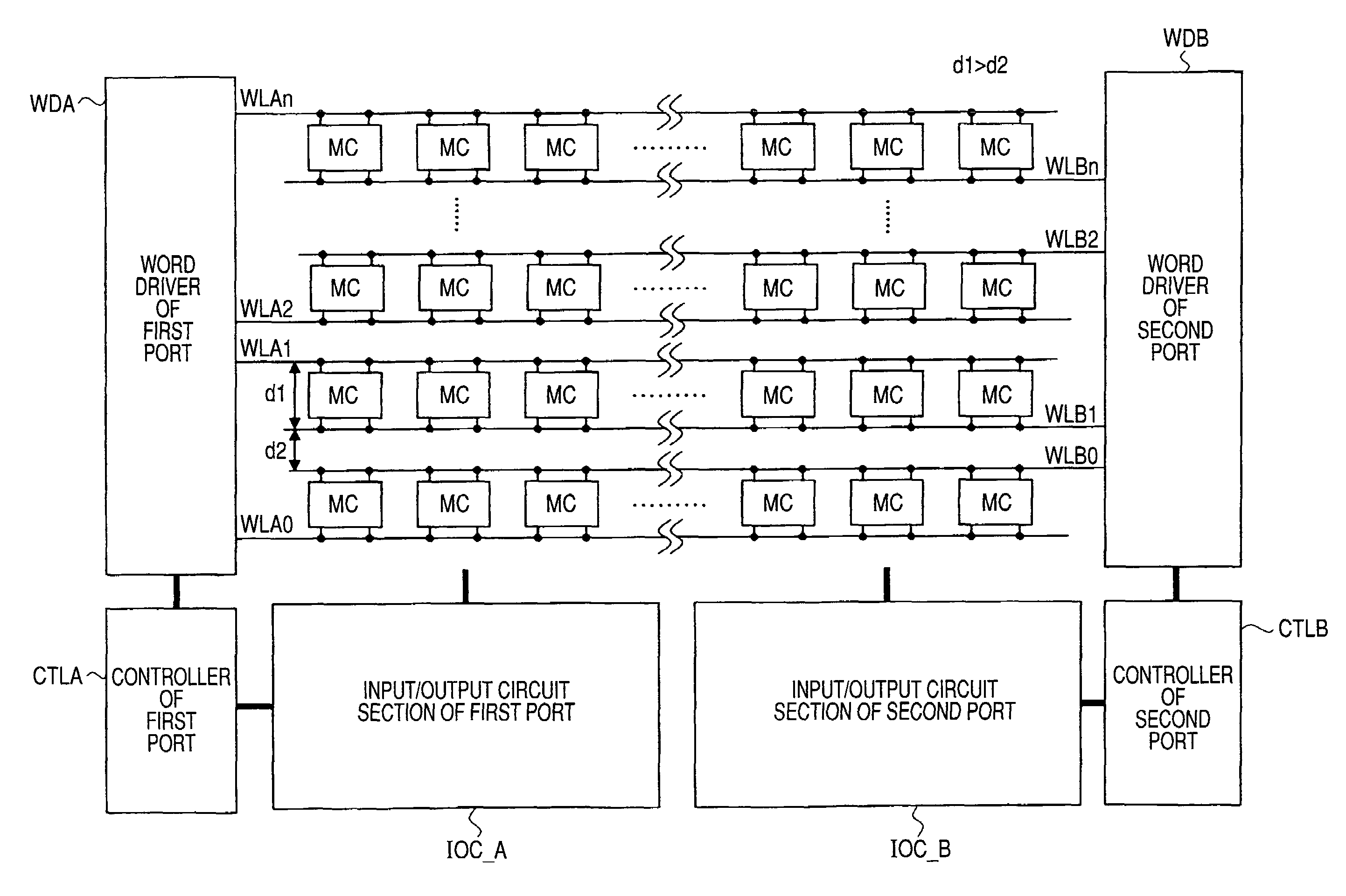

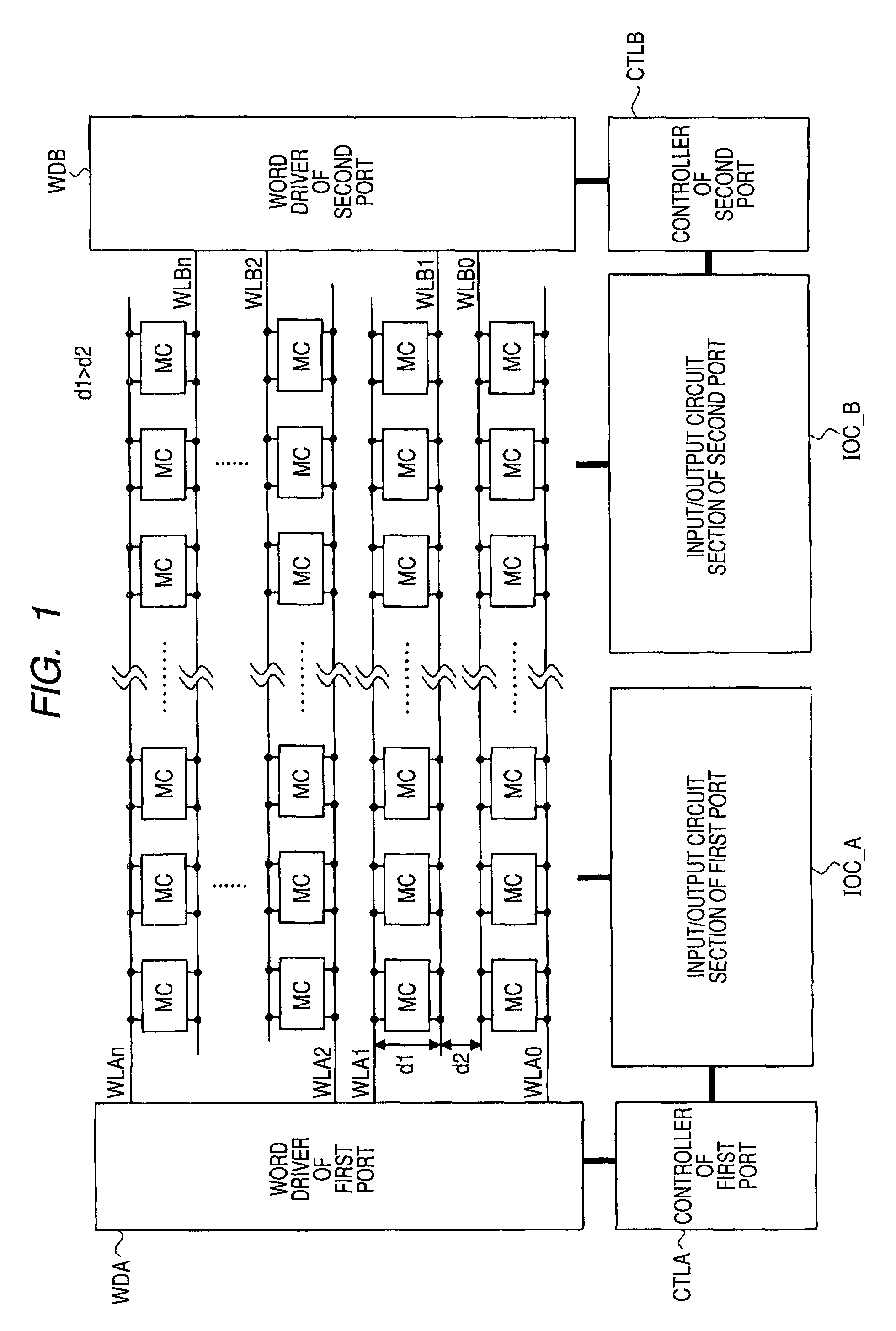

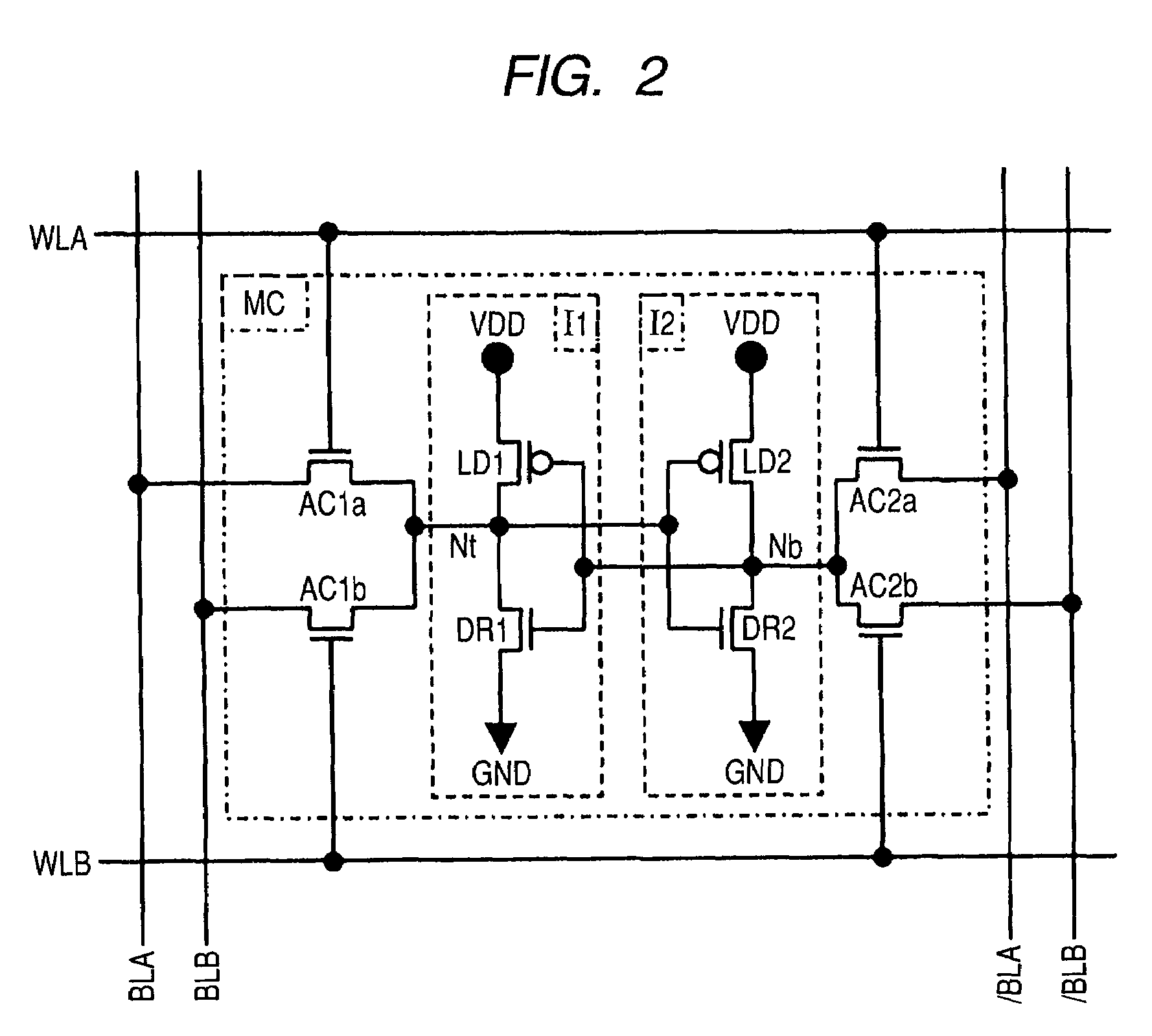

Semiconductor device having multiport memory

ActiveUS20090059640A1Reduce distractionsImprove noise marginTransistorSolid-state devicesNoise marginComputer science

A semiconductor device enabling expansion of a noise margin. For example, in a memory area in which each memory cell MC is coupled to a word line WLA for a first port and a word line WLB for a second port, and a plurality of memory cells MC is disposed in a matrix shape, each word line is disposed in the order like WLA0, WLB0, WLB1, WLA1, WLA2, . . . . Further, a pitch d2 between WLA-WLA and between WLB-WLB is made smaller than a pitch d1 between WLA-WLB. As such, the word lines of an identical port are disposed at the pitch d2 on one of both sides of a certain word line as a criterion, while the word lines of different ports are disposed at the pitch d1 on the other. With the above configuration, for example, as compared with a case of alternately disposing WLA and WLB, interference between ports can be reduced even with a small area, and the noise margin can be expanded.

Owner:RENESAS ELECTRONICS CORP

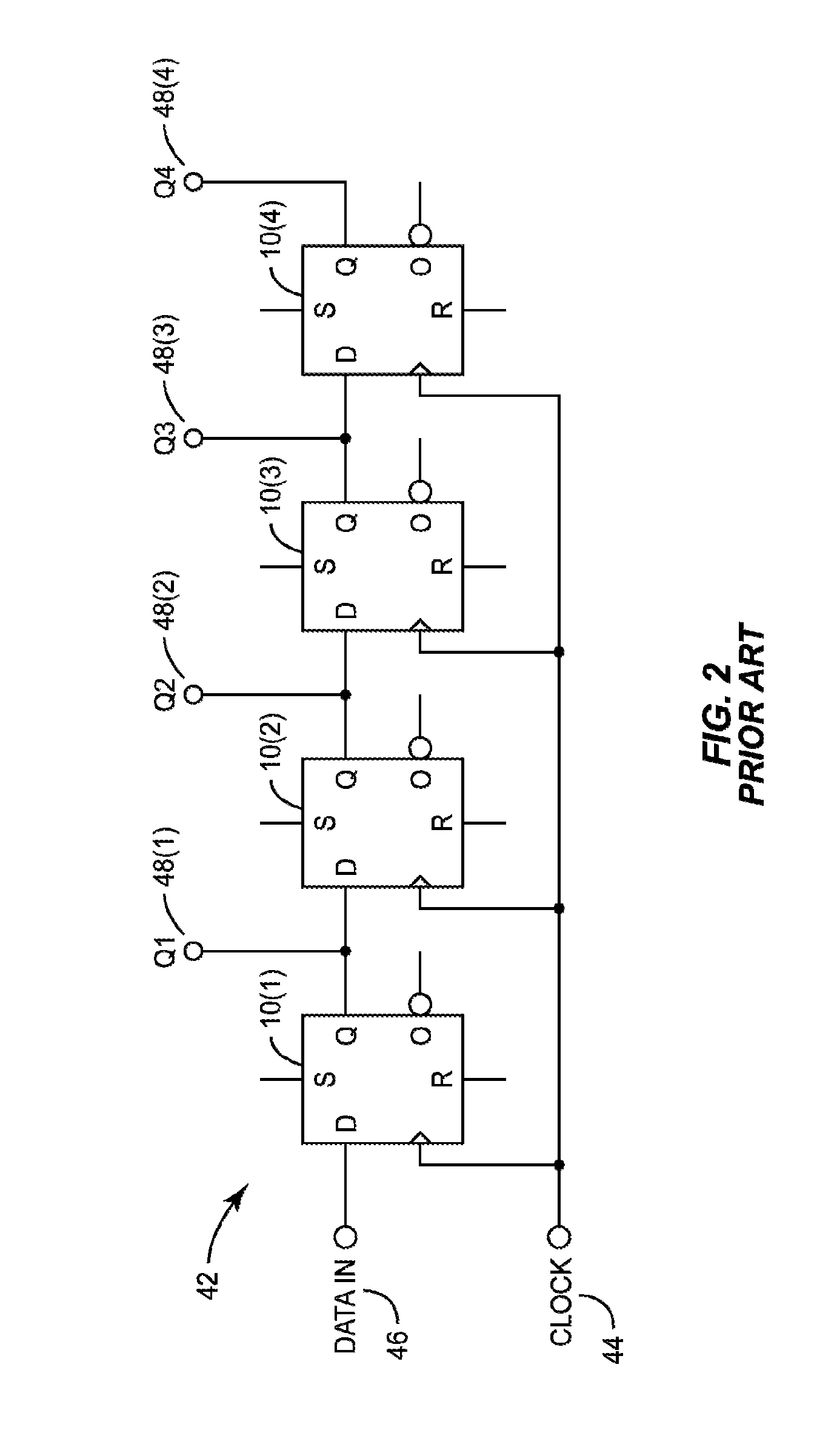

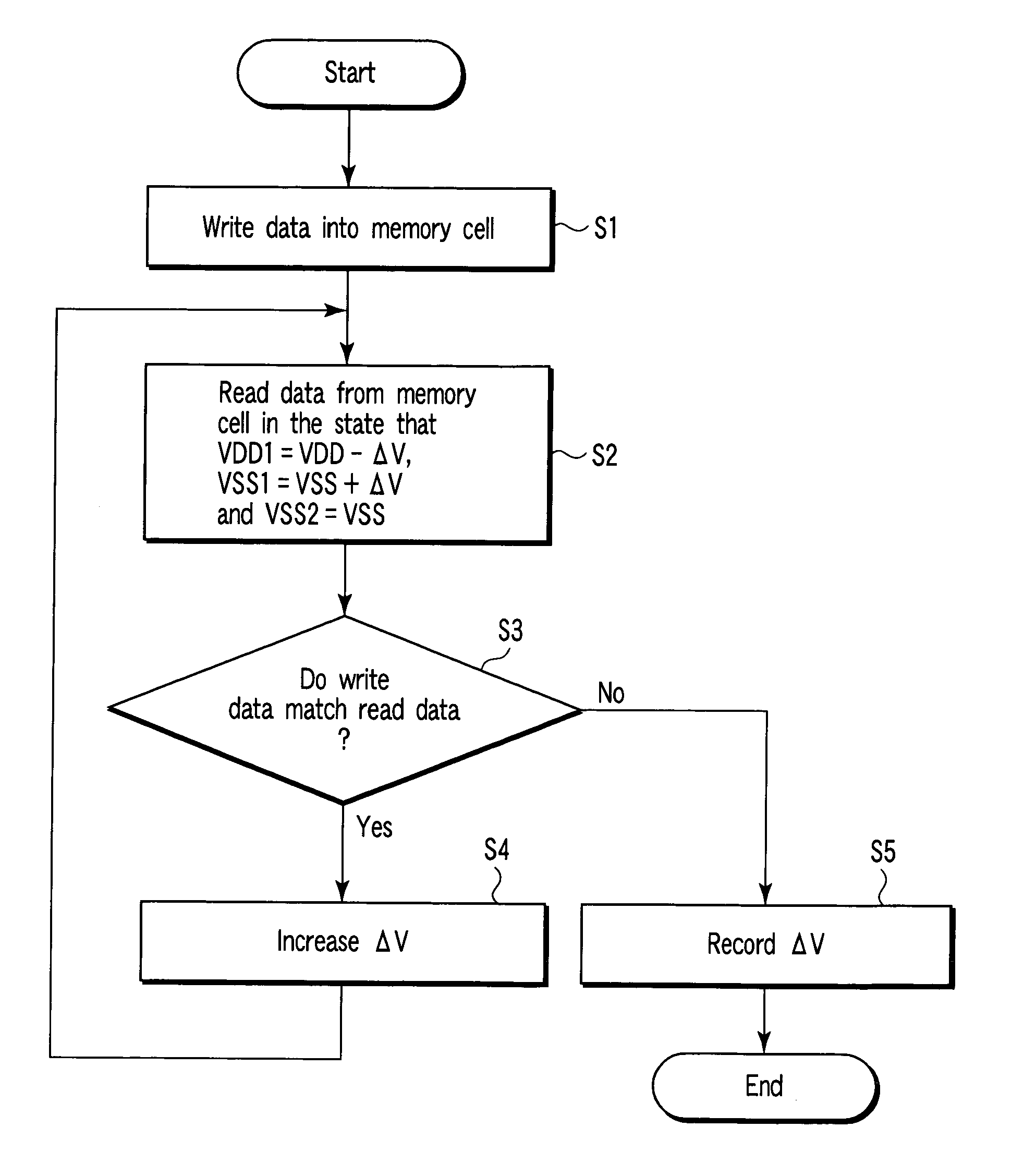

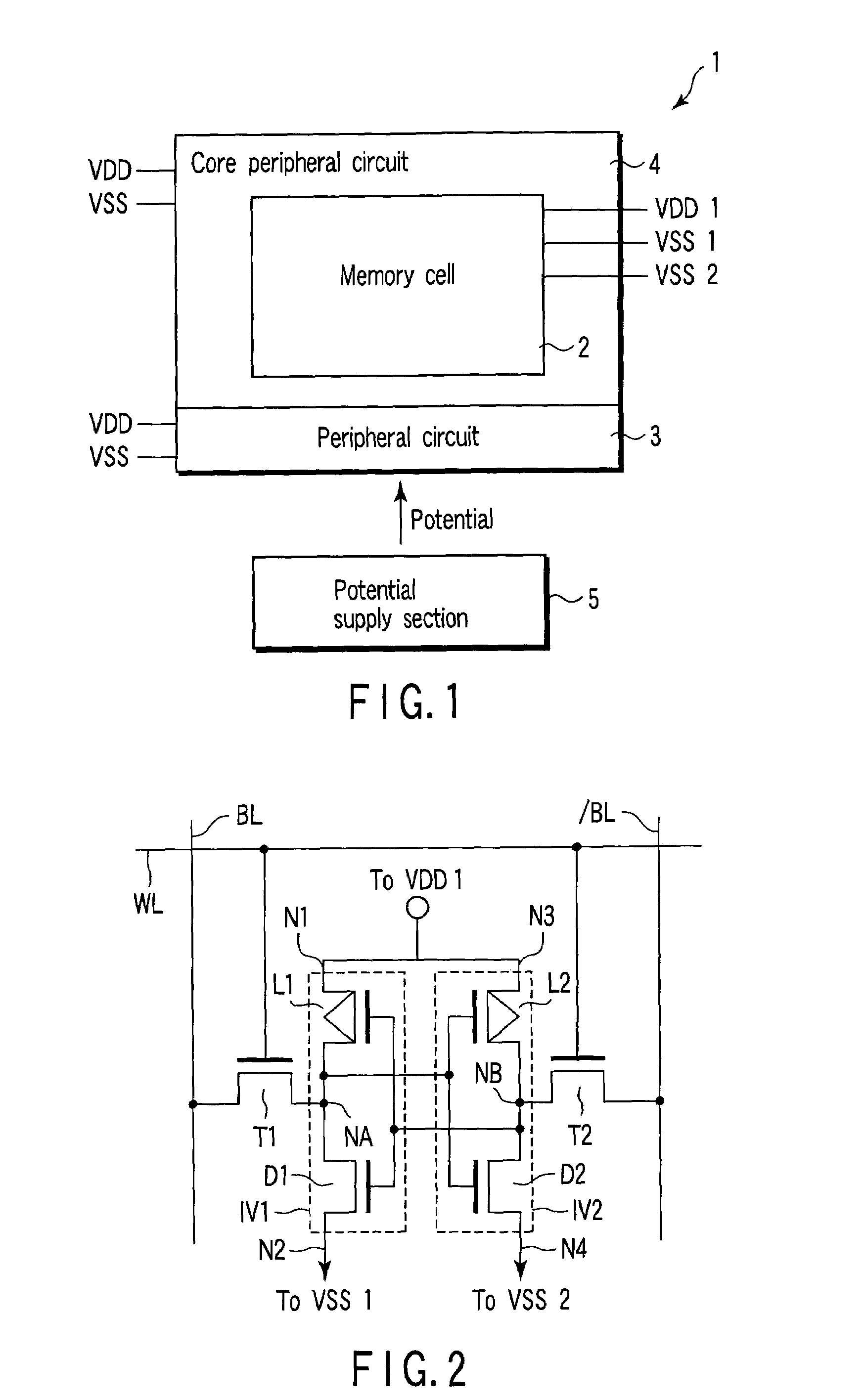

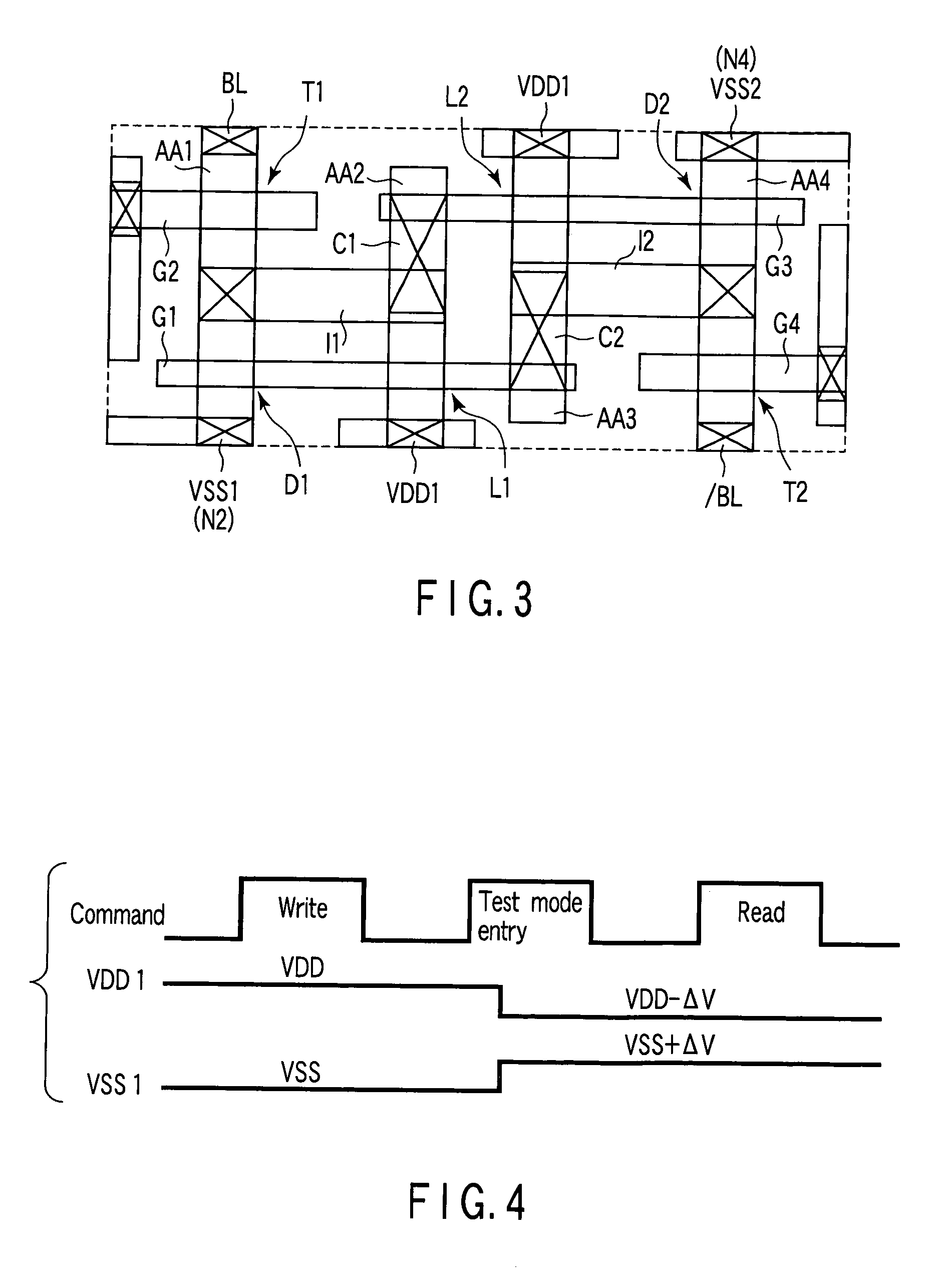

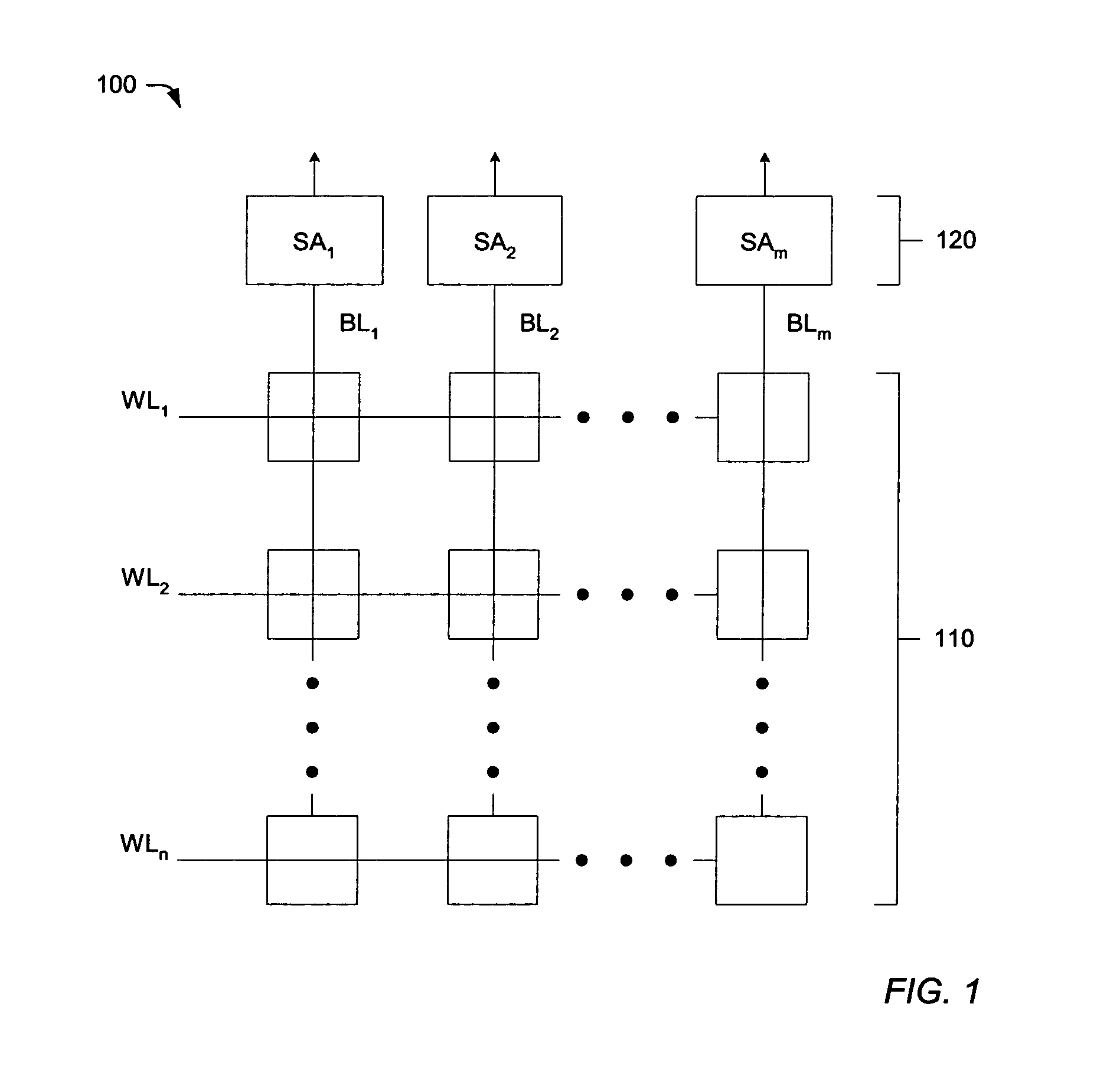

Static random access memory and pseudo-static noise margin measuring method

A first inverter includes a first load element and a first transistor, which are connected between first and second terminals in series, a first input terminal and a first output terminal. A second inverter includes a second load element and a second transistor, which are connected between third and fourth terminals in series, a second input terminal and a second output terminal. A first transfer transistor selectively and electrically connects the first output terminal and a first bit line. A second transfer transistor selectively and electrically connects the second output terminal and a second bit line. When data are read from the memory cell which comprises the first and second inverters and the first and second transfer transistors, a first potential is applied to the second terminal and a second potential different from the first potential is applied to the fourth terminal.

Owner:KK TOSHIBA

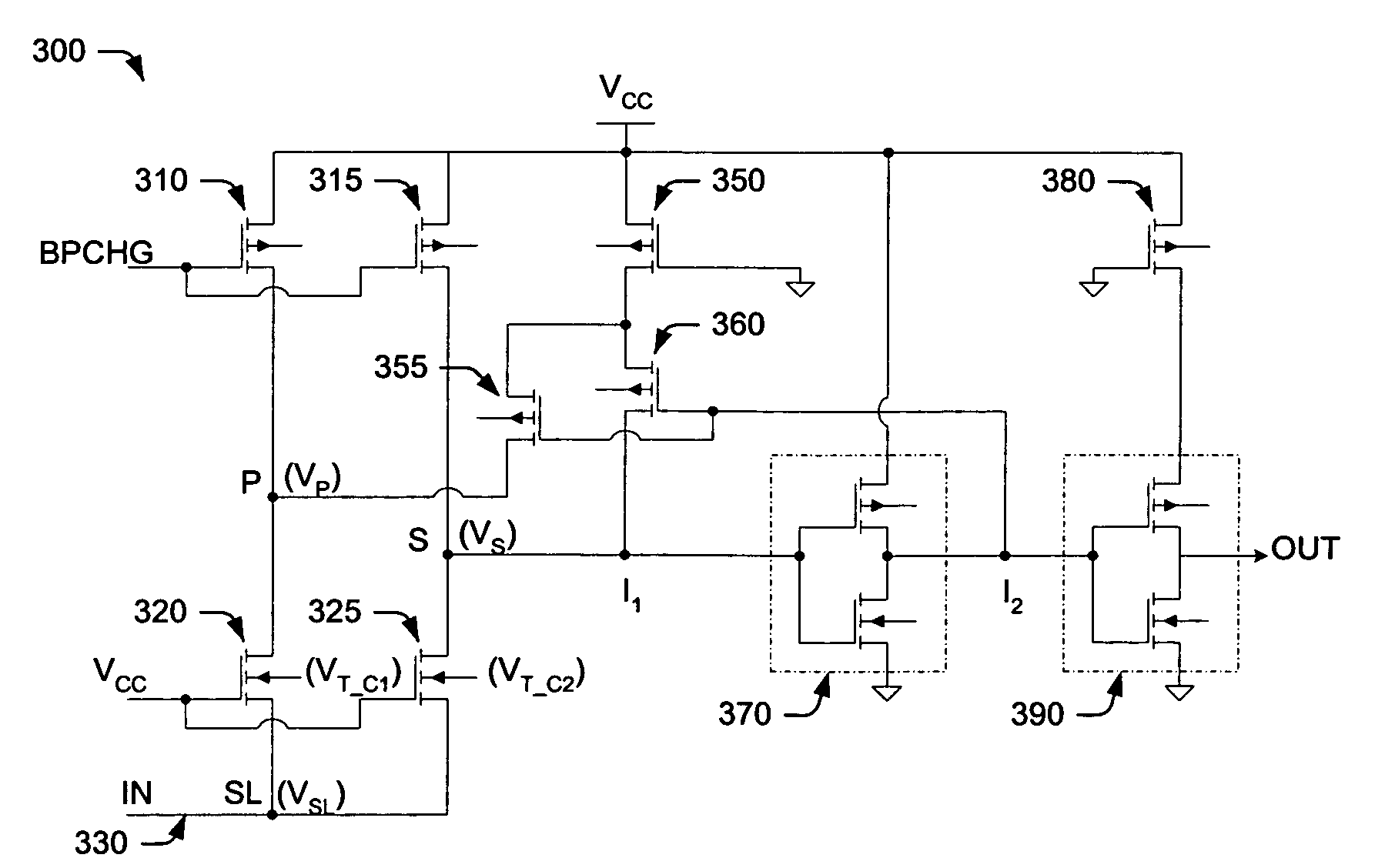

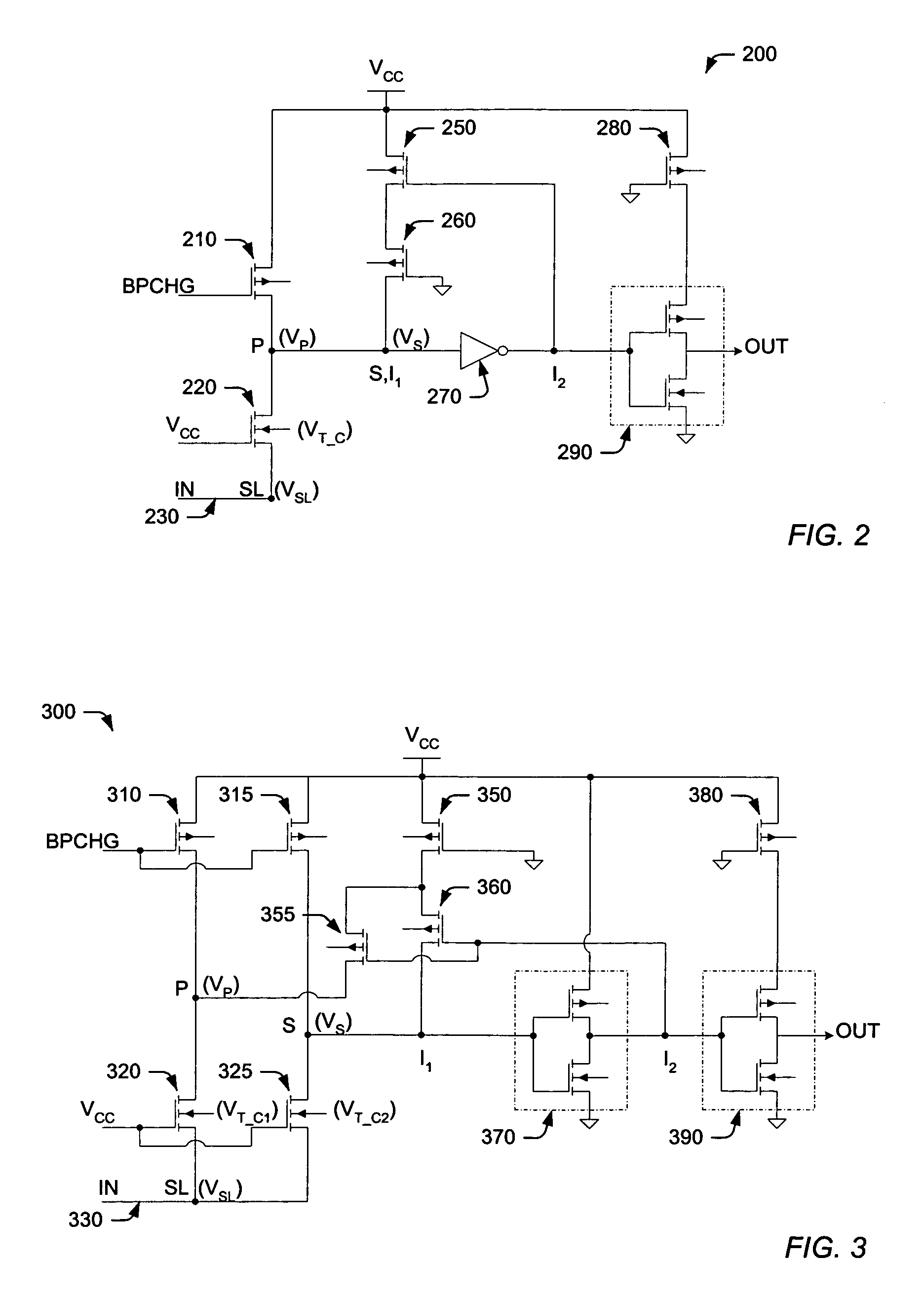

Sense amplifier with dual cascode transistors and improved noise margin

ActiveUS7126869B1Acceptable noise marginImprove the sense of speedDigital storageAudio power amplifierNoise margin

A sense amplifier, system and methods for increasing a noise margin of the sense amplifier are contemplated herein. In general, the sense amplifier includes a pair of cascode transistors coupled in parallel between a power supply node and a sense line of the sense amplifier. The sense amplifier also includes a precharge node coupled to the power supply node through a first precharge transistor, and a sense node coupled to the power supply node through a second precharge transistor. The sense amplifier described herein functions to separate the sense node from the precharge node with the pair of cascode transistors, which in turn, increases the noise margin of the sense amplifier by decoupling the sense node from any voltage fluctuations that may be present on the sense line during a sensing state.

Owner:MONTEREY RES LLC

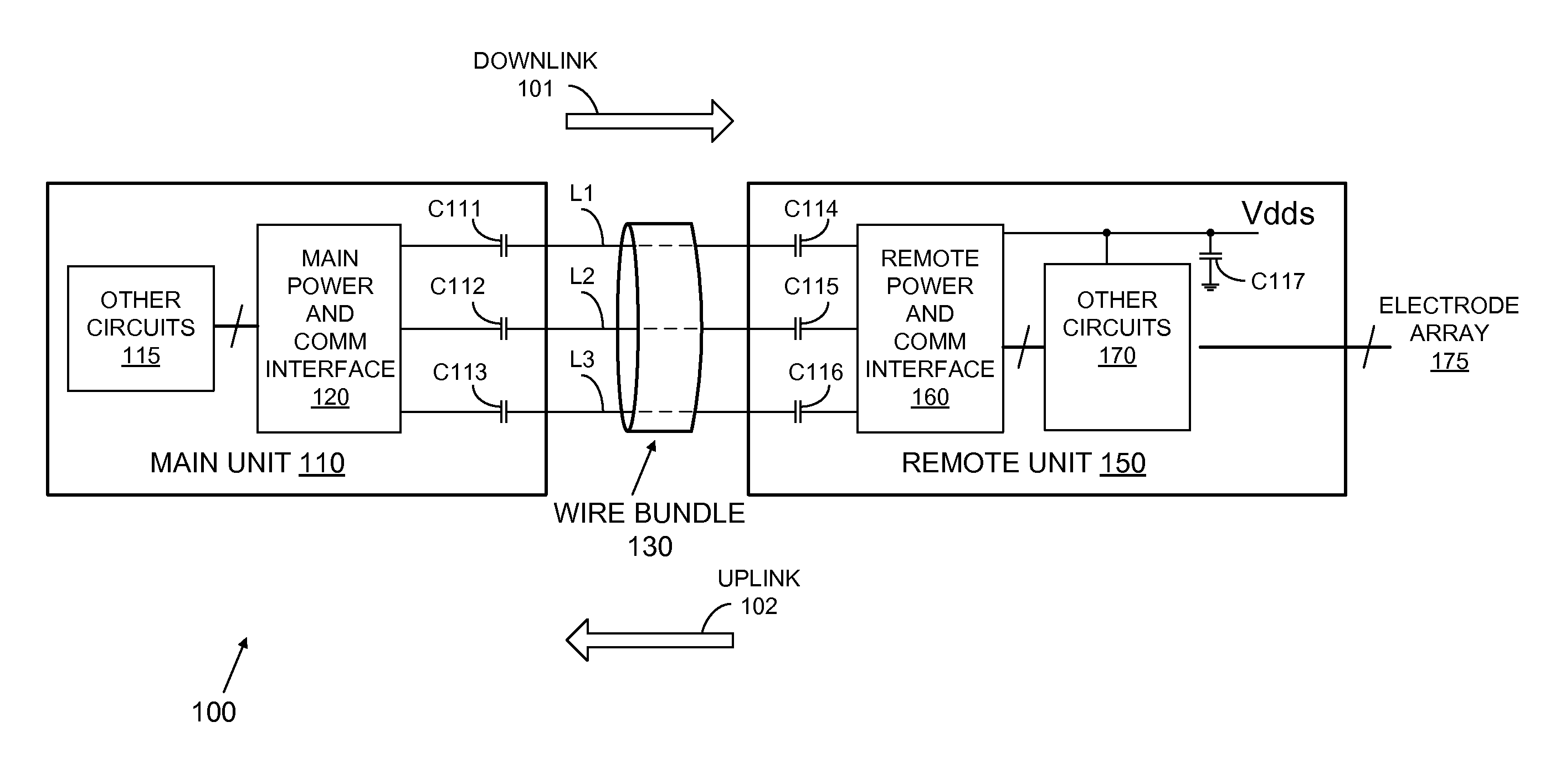

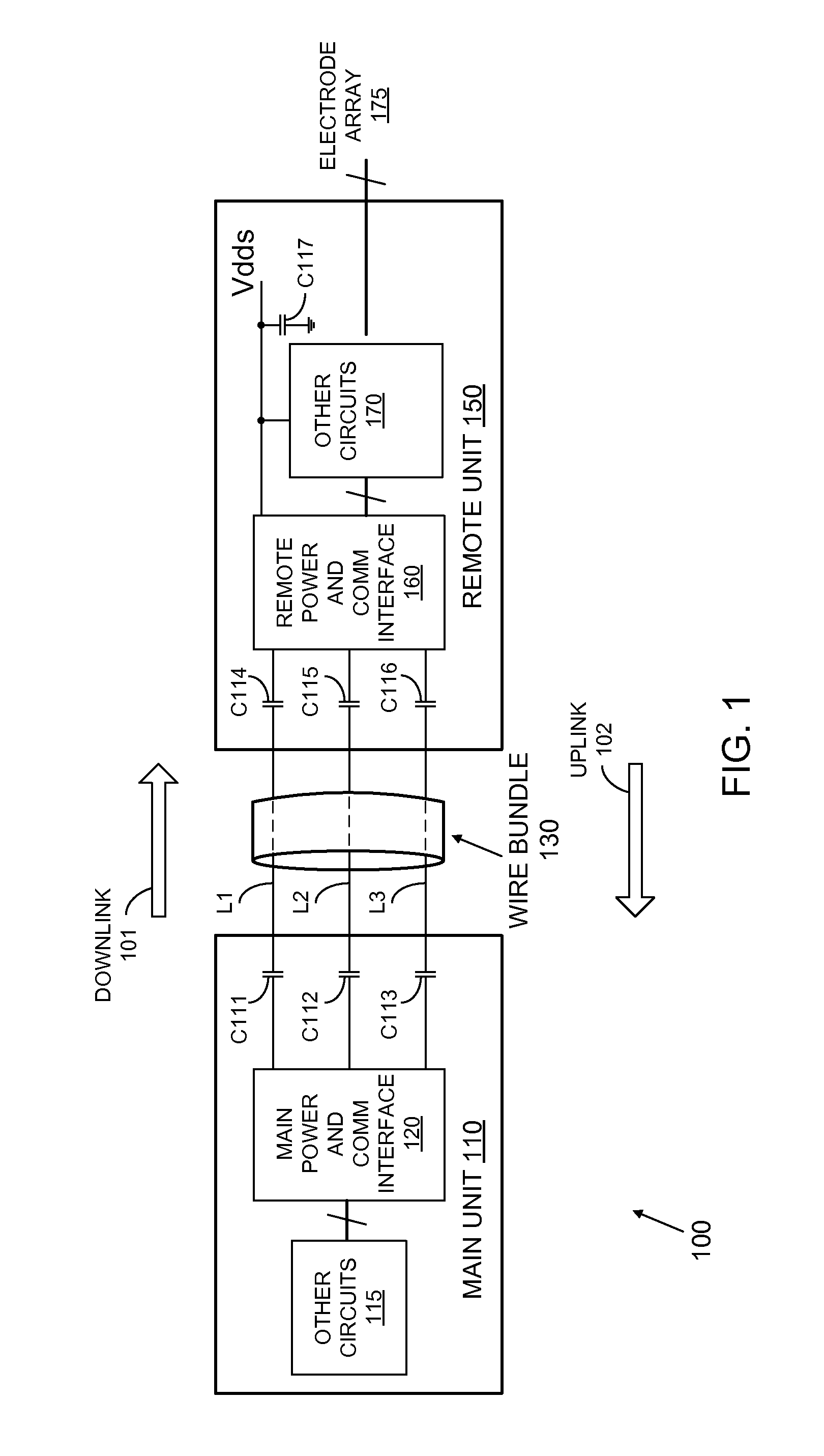

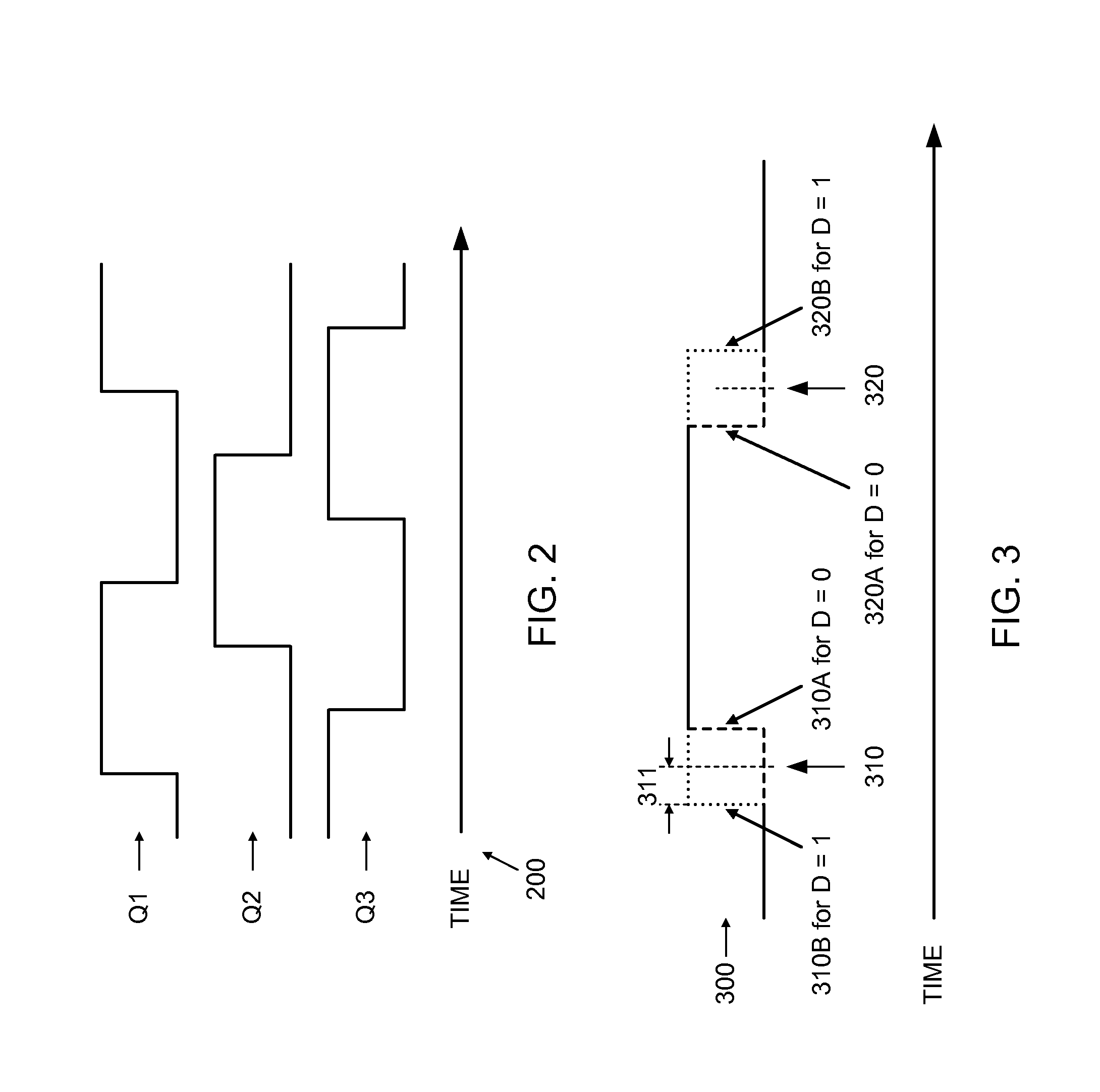

Power and bidirectional data transmission

ActiveUS20120287984A1Increase output impedanceReliability increasing modificationsElectric signal transmission systemsUplink transmissionTime segment

Systems and methods for power and bidirectional data transmission using a plurality of wires. A multiphase digital signal is downlinked from a main unit to a remote unit over the plurality of wires and is converted to a DC power signal used to power the remote unit. Uplink data is sent from the remote to the main over one selected wire during a predetermined time period for an uplink transmission by amplitude modulating the received digital signal at the remote. During an uplink, the output impedance of the line driver in the main unit connected to the wire selected for the uplink is increased to allow for the uplink amplitude modulation. The modulated signal is maintained within the noise margins of the digital circuits in the main and remote units.

Owner:ALFRED E MANN FOUND FOR SCI RES

Encoding and decoding using constrained interleaving

InactiveUS20150039966A1Reduce measurementEfficient implementationCode conversionError correction/detection by combining multiple code structuresNoise marginSimple component

Serially-concatenated codes are formed in accordance with the present invention using a constrained interleaver. The constrained interleaver cause the minimum distance of the serial concatenated code to increase above the minimum distance of the inner code alone by adding a constraint that forces some or all of the distance of the outer code onto the serially-concatenated code. This allows the serially-concatenated code to be jointly optimized in terms of both minimum distance and error coefficient to provide significant performance advantages. These performance advantages allow a noise margin target to be achieved using simpler component codes and a much shorter interleaver than was needed when using prior art codes such as Turbo codes. Decoders are also provided. Both encoding and decoding complexity can be lowered, and interleavers can be made much shorter, thereby shortening the block lengths needed in receiver elements such as equalizers and other decision-directed loops. Also, other advantages are provided such as the elimination of a error floor present in prior art serially-concatenated codes. That allows the present invention to achieve much higher performance at lower error rates such as are needed in optical communication systems.

Owner:TRELLIS PHASE COMM LP

Semiconductor device having multiport memory

ActiveUS7940542B2Reduce distractionsImprove noise marginTransistorSolid-state devicesNoise marginComputer science

A semiconductor device enabling expansion of a noise margin. For example, in a memory area in which each memory cell MC is coupled to a word line WLA for a first port and a word line WLB for a second port, and a plurality of memory cells MC is disposed in a matrix shape, each word line is disposed in the order like WLA0, WLB0, WLB1, WLA1, WLA2, . . . . Further, a pitch d2 between WLA-WLA and between WLB-WLB is made smaller than a pitch d1 between WLA-WLB. As such, the word lines of an identical port are disposed at the pitch d2 on one of both sides of a certain word line as a criterion, while the word lines of different ports are disposed at the pitch d1 on the other. With the above configuration, for example, as compared with a case of alternately disposing WLA and WLB, interference between ports can be reduced even with a small area, and the noise margin can be expanded.

Owner:RENESAS ELECTRONICS CORP

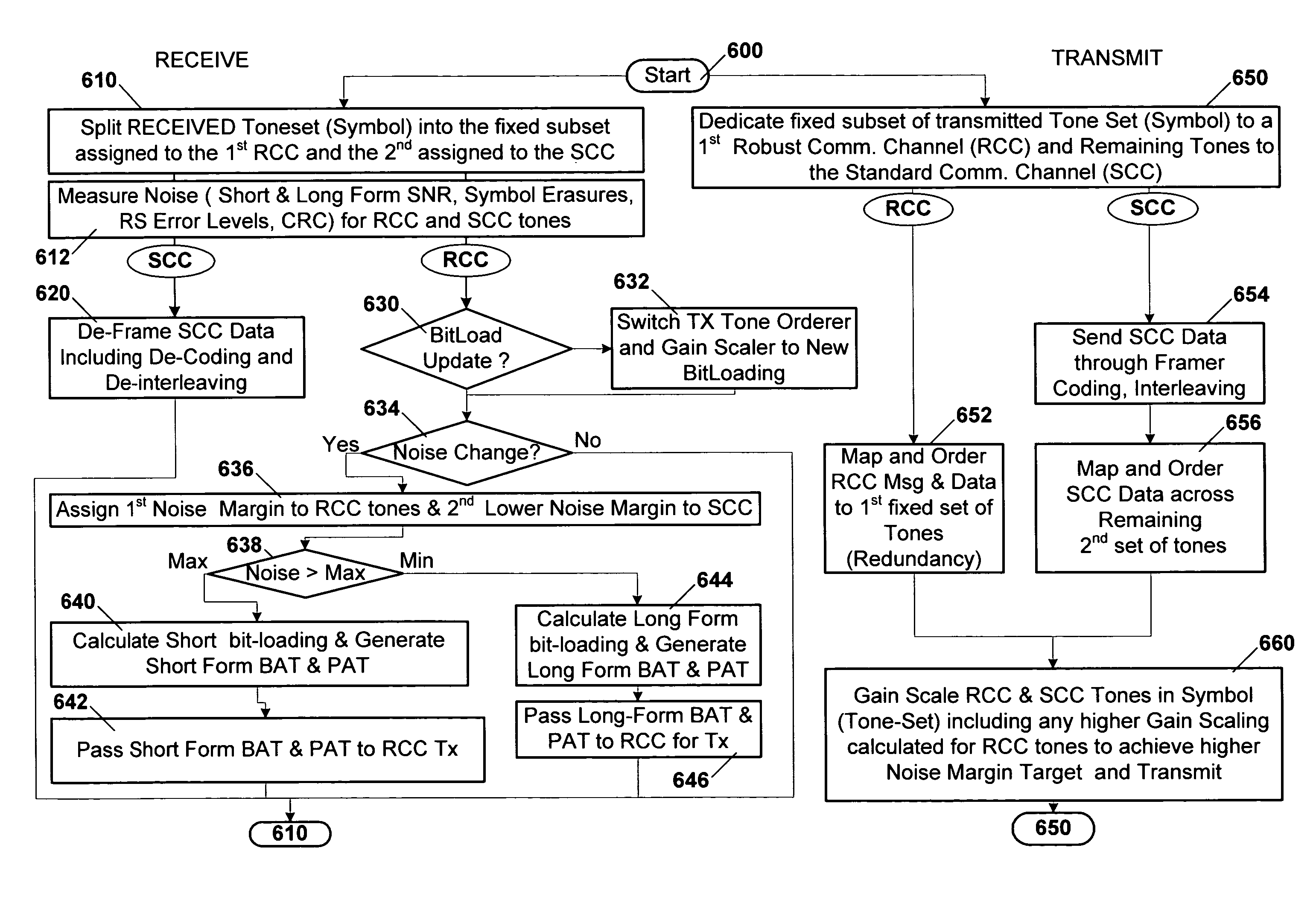

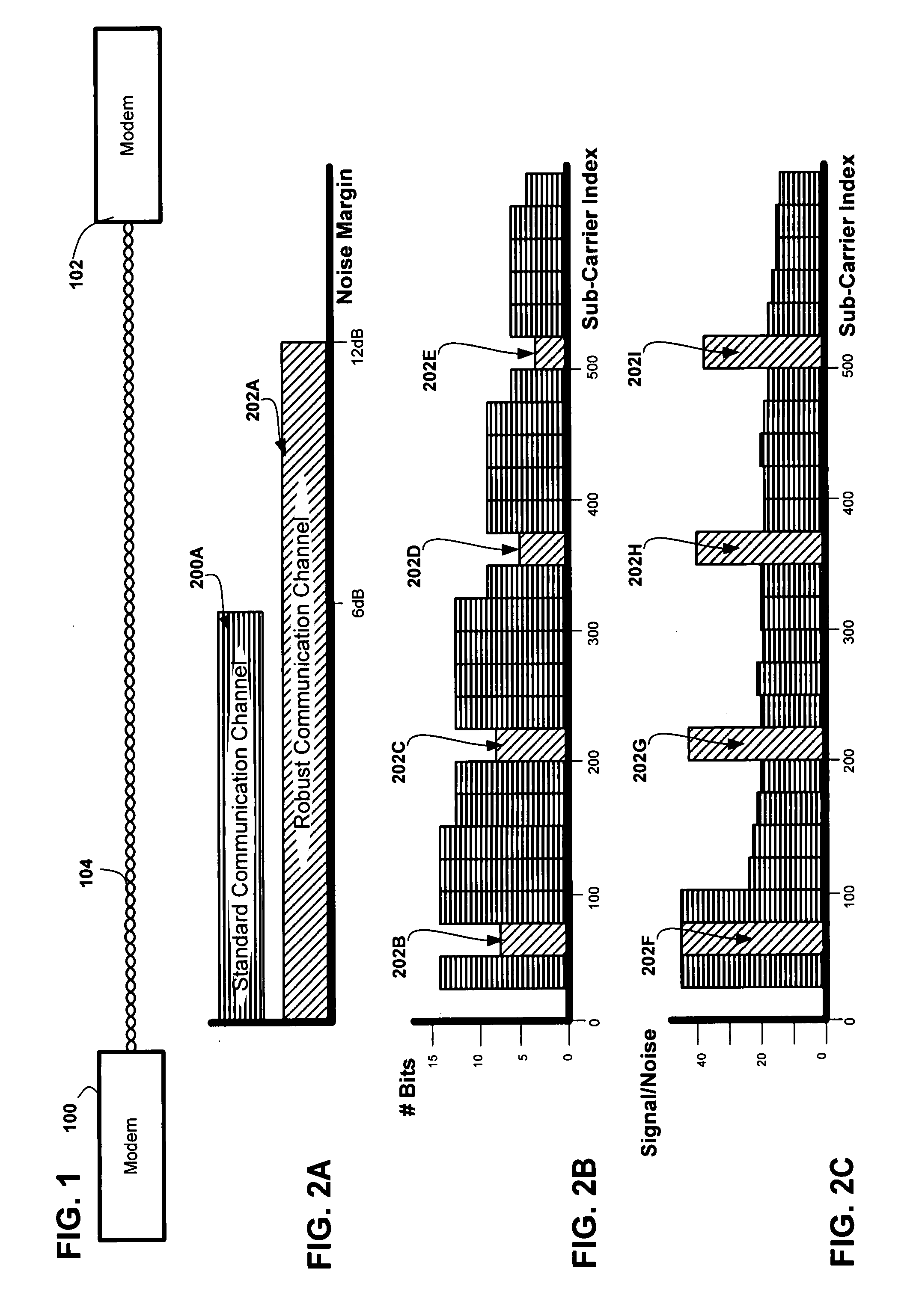

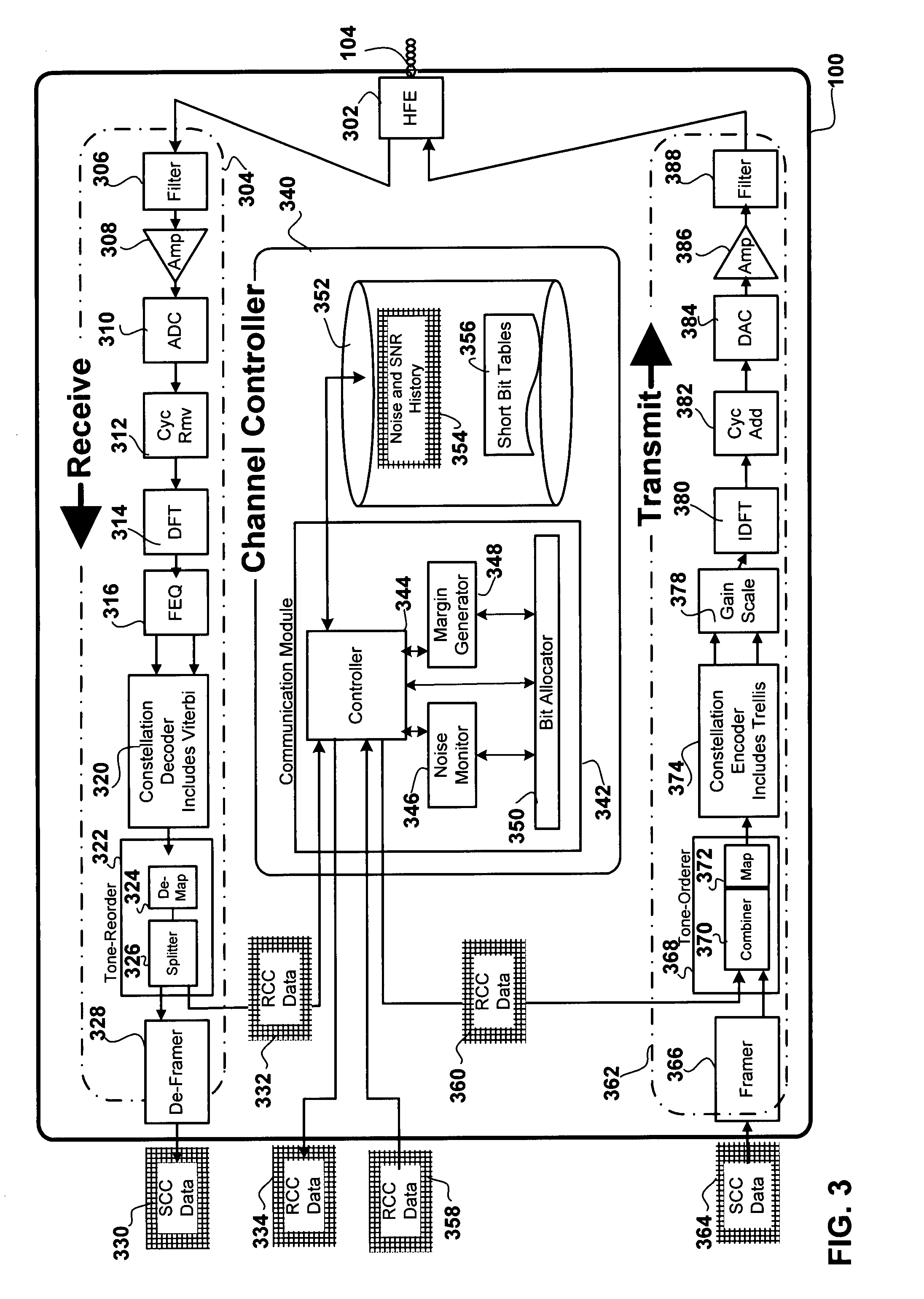

Method and apparatus for differentiated communication channel robustness in a multi-tone transceiver

A multi-tone transceiver including: a channel controller and a plurality of components forming a transmit path and a receive path. The channel controller configured to determine bit-loading for each successive symbol or tone set based on a 1st noise margin target for a first subset of tones in each tone set dedicated to transport of a robust communications channel (RCC) and based on a 2nd noise margin target less than the 1st noise margin target for remaining tones in each tone set dedicated to a standard communications channel (SCC). The plurality of components forming the transmit and receive paths are responsive to the channel controller to select for data modulated on a given tone at least one of smaller constellations and higher gain scaling levels when the given tone corresponds to an RCC tone as compared to an SCC tone, whereby the first set of tones dedicated to the RCC exhibit greater immunity to noise variations than the remaining tones dedicated to the SCC.

Owner:IKANOS COMMUNICATIONS

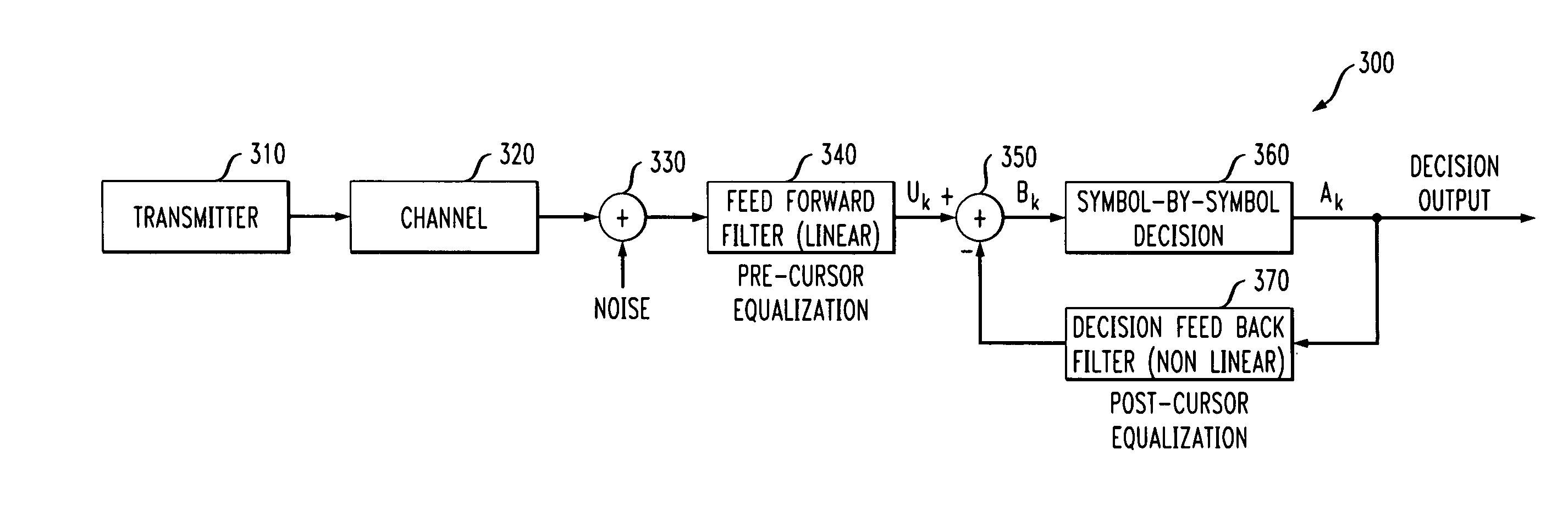

Method and apparatus for determining a position of an offset latch employed for decision-feedback equalization

InactiveUS20070253477A1Improve noise marginMultiple-port networksDelay line applicationsNoise marginEngineering

Methods and apparatus are provided for determining a position of an offset latch employed for decision-feedback equalization. The position of an offset latch is determined by obtaining a plurality of samples of a data eye associated with a signal, the data eye comprised of a plurality of trajectories for transitions out of a given binary state; determining an amplitude of at least two of the trajectories based on the samples; and determining a position of an offset latch based on the determined amplitudes. The initial position of the offset latch can be placed, for example, approximately in the middle of the determined amplitudes for at least two of the trajectories. The initial position of the offset latch can be optionally skewed by a predefined amount to improve the noise margin.

Owner:AVAGO TECH INT SALES PTE LTD

Circuit for generating a tracking reference voltage

InactiveUS7208972B2Low pass filteringReduce noiseReliability increasing modificationsDc level restoring means or bias distort correctionDifferential signalingNoise margin

Two or more integrated circuit (IC) chips are separated by a significant distance relative to their communication frequency such that pseudo-differential signaling is used to improve signal detection. A derived reference voltage is generated that tracks the variations of the driver and receiver side power supply variations that normally reduce noise margins. The derived reference voltage is filtered to reduce high frequency response and coupled as the reference to differential receivers used to detect the logic levels of the communication signals.

Owner:IBM CORP

Encoding and decoding using constrained interleaving

InactiveUS8537919B2Improve bit error rate performanceReduce the numberAmplitude-modulated carrier systemsAmplitude demodulationRound complexitySimple component

Serially-concatenated codes are formed in accordance with the present invention using a constrained interleaver. The constrained interleaver cause the minimum distance of the serial concatenated code to increase above the minimum distance of the inner code alone by adding a constraint that forces some or all of the distance of the outer code onto the serially-concatenated code. This allows the serially-concatenated code to be jointly optimized in terms of both minimum distance and error coefficient to provide significant performance advantages. These performance advantages allow a noise margin target to be achieved using simpler component codes and a much shorter interleaver than was needed when using prior art codes such as Turbo codes. Decoders are also provided. Both encoding and decoding complexity can be lowered, and interleavers can be made much shorter, thereby shortening the block lengths needed in receiver elements such as equalizers and other decision-directed loops. Also, other advantages are provided such as the elimination of a error floor present in prior art serially-concatenated codes. That allows the present invention to achieve much higher performance at lower error rates such as are needed in optical communication systems.

Owner:TRELLIS PHASE COMM LP

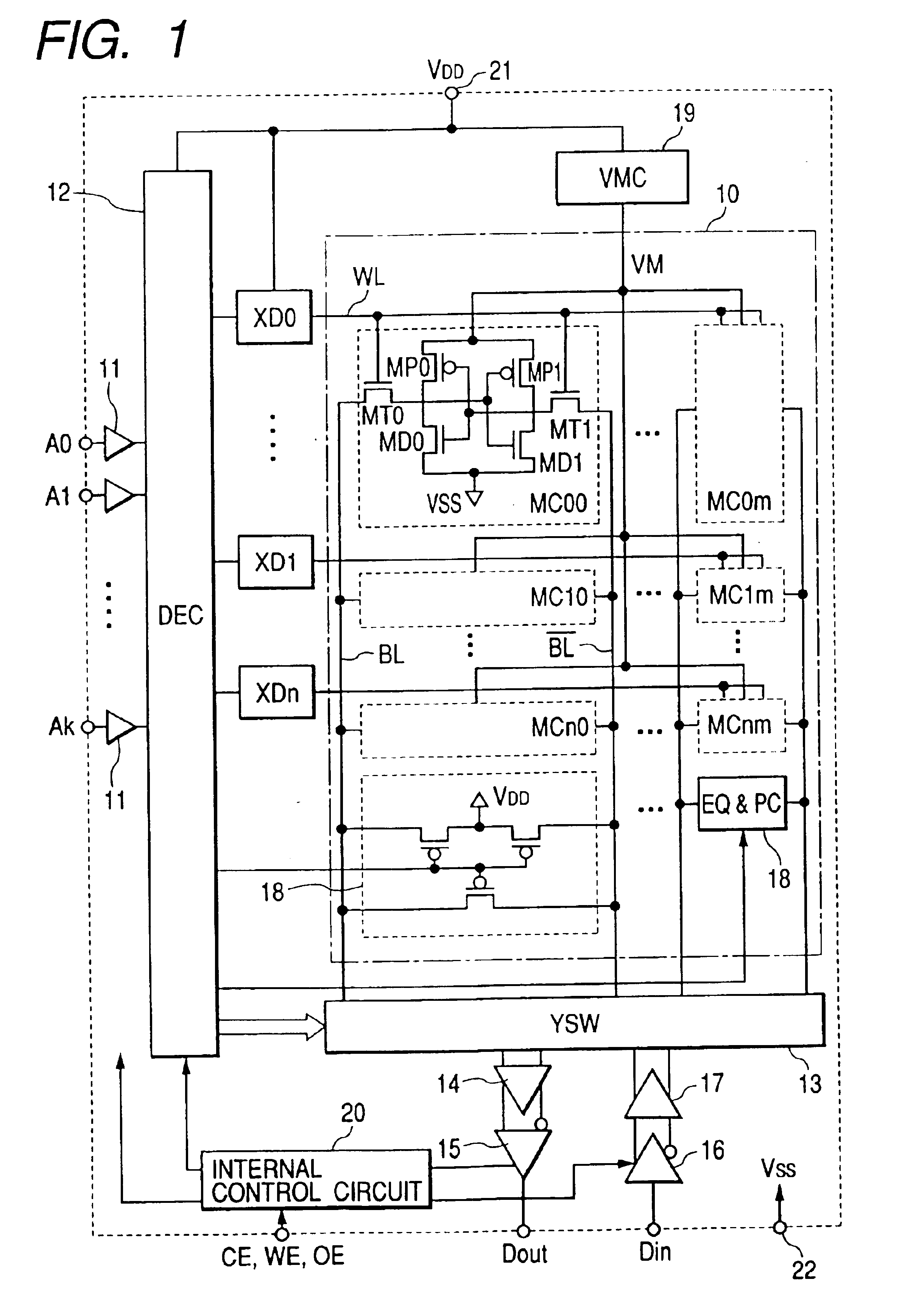

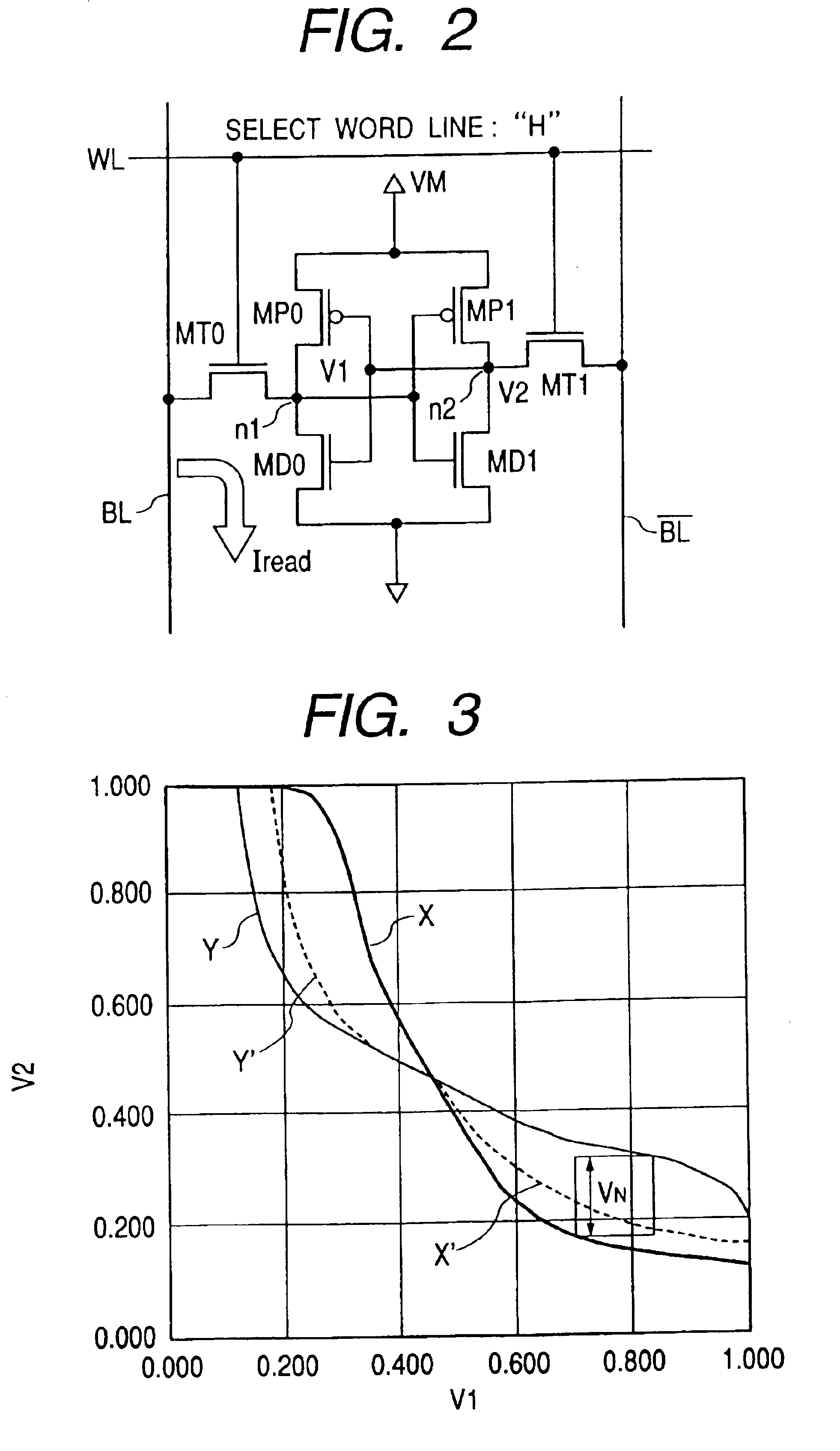

Semiconductor memory device

InactiveUS6876573B2Reduce rateIncrease currentSolid-state devicesSemiconductor/solid-state device manufacturingCMOSNoise margin

A semiconductor memory device having a memory array comprising CMOS flip-flop circuit type memory cells, which is capable of improving a noise margin, making a read rate fast and reducing power consumption. In the semiconductor memory device, an operating voltage of the memory cell is set higher than an operating voltage of each of peripheral circuits. Threshold voltages of MOS transistors that constitute the memory cell, are set higher than those of MOS transistors constituting the peripheral circuit. A gate insulting film for the MOS transistors that constitute the memory cell, is formed so as to be regarded as thicker than a gate insulting film for the MOS transistors constituting the peripheral circuit when converted to an insulating film of the same material. Further, a word-line selection level and a bit-line precharge level are set identical to the level of the operating voltage of the peripheral circuit.

Owner:HITACHI LTD

Encoding and decoding using constrained interleaving

InactiveUS20150039963A1Reduce measurementEfficient implementationError correction/detection using concatenated codesError correction/detection using trellis codingNoise marginSimple component

Serially-concatenated codes are formed in accordance with the present invention using a constrained interleaver. The constrained interleaver cause the minimum distance of the serial concatenated code to increase above the minimum distance of the inner code alone by adding a constraint that forces some or all of the distance of the outer code onto the serially-concatenated code. This allows the serially-concatenated code to be jointly optimized in terms of both minimum distance and error coefficient to provide significant performance advantages. These performance advantages allow a noise margin target to be achieved using simpler component codes and a much shorter interleaver than was needed when using prior art codes such as Turbo codes. Decoders are also provided. Both encoding and decoding complexity can be lowered, and interleavers can be made much shorter, thereby shortening the block lengths needed in receiver elements such as equalizers and other decision-directed loops. Also, other advantages are provided such as the elimination of a error floor present in prior art serially-concatenated codes. That allows the present invention to achieve much higher performance at lower error rates such as are needed in optical communication systems.

Owner:TRELLIS PHASE COMM LP

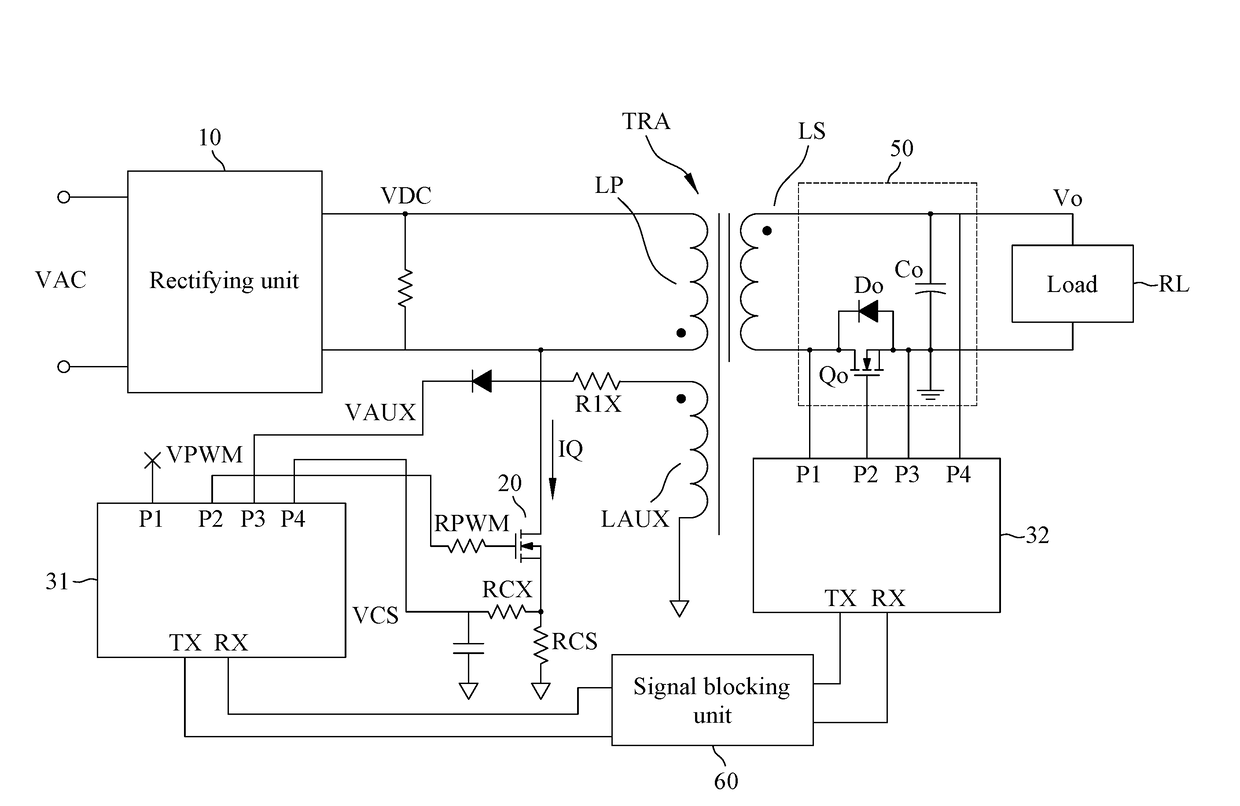

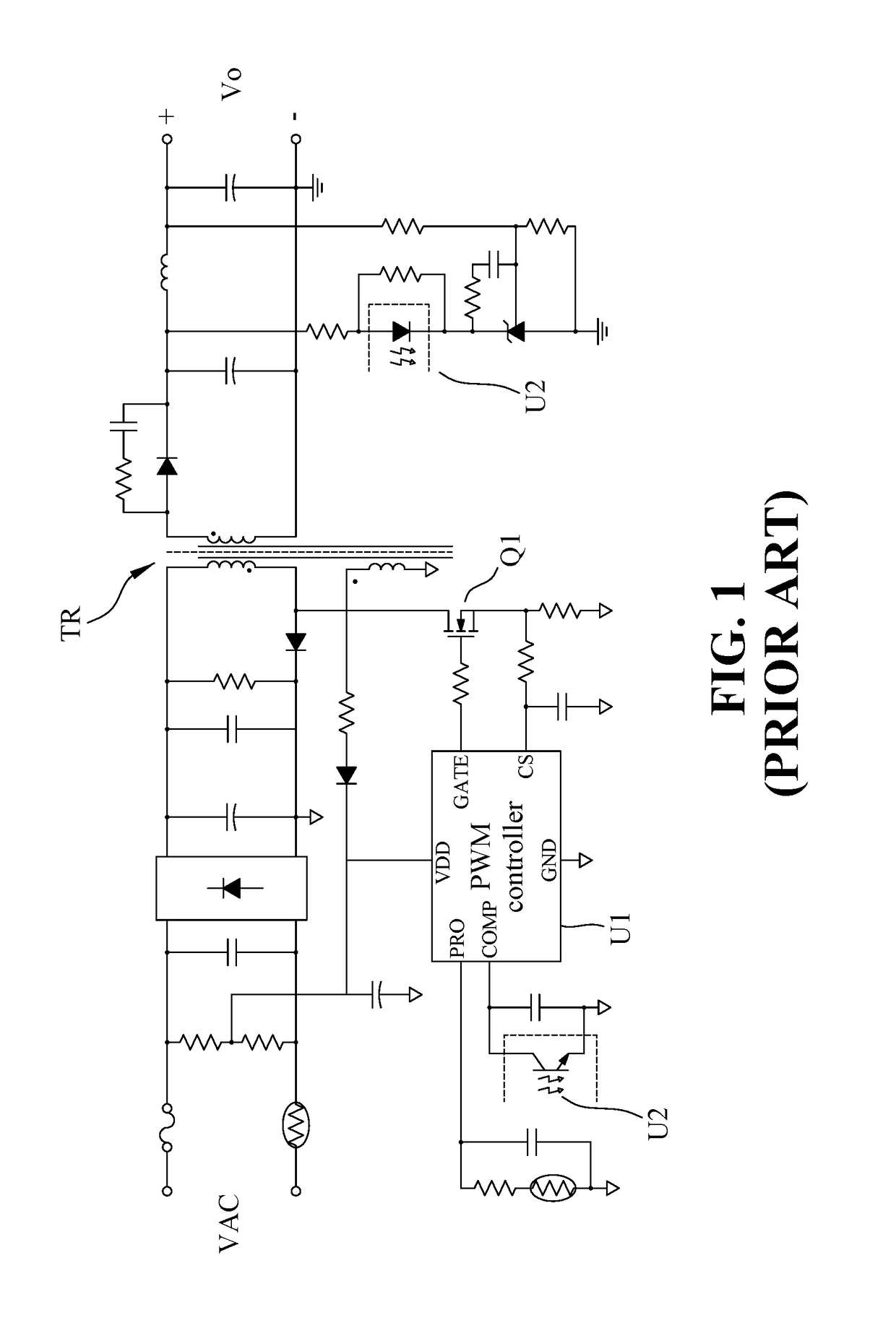

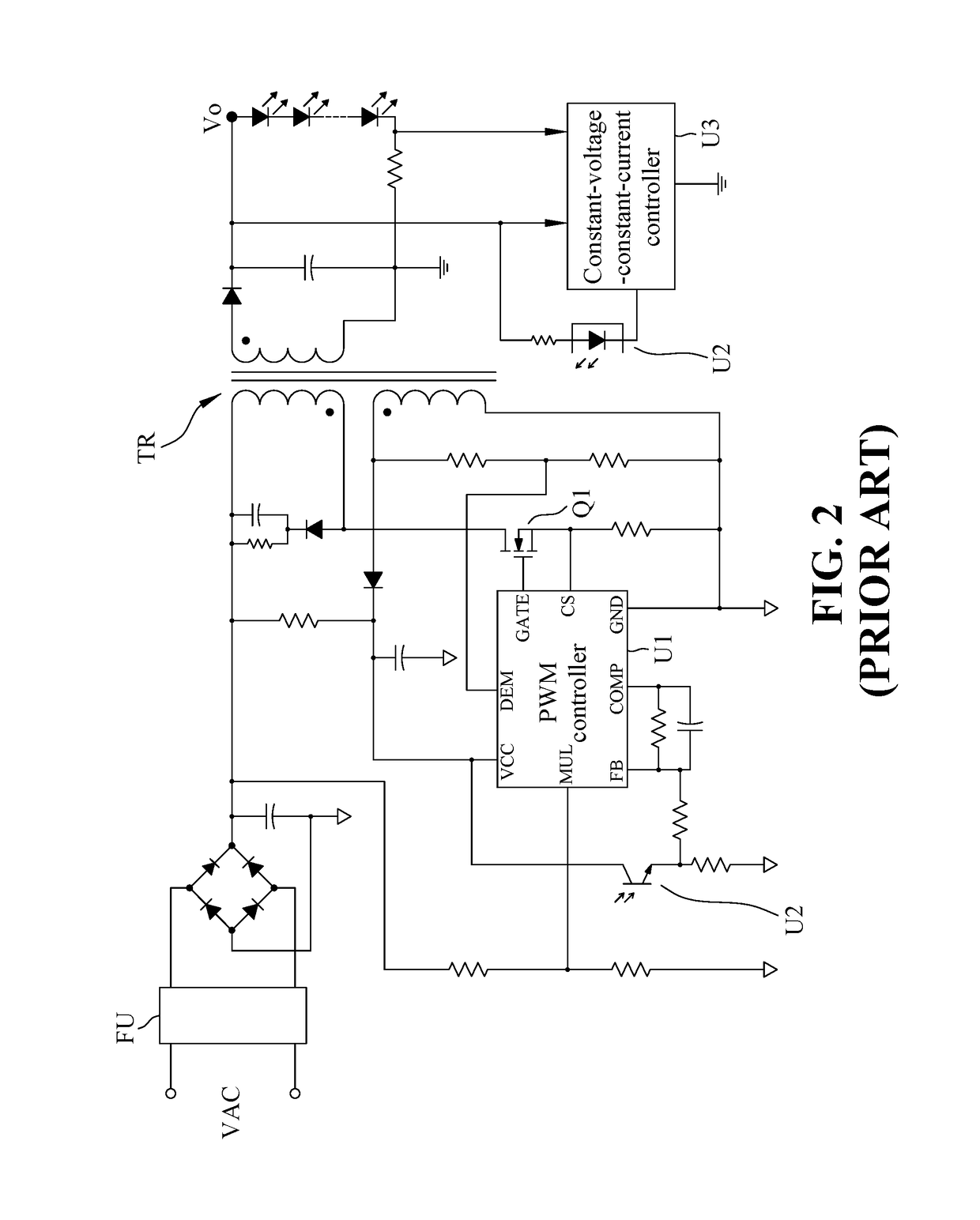

Isolated power conversion system

InactiveUS20170214322A1Improve abilitiesImprove stabilityEfficient power electronics conversionDc-dc conversionTransformerNoise margin

Disclosed is an isolated power conversion system for providing a function of isolated power conversion by converting an AC power into a DC output power, and a rectifying unit, a transformer, a switching transistor, a first pulse width modulation (PWM) controller, a second PWM controller, an output unit and a signal blocking unit are included. The signal blocking unit is employed as a connection interface between the first and second PWM controllers to provide digital signal for communication. Noise margin and stability of electrical operation are improved to avoid malfunction. Overall, the present invention greatly enhances stability of power conversion and secures quality of electrical signal.

Owner:INNOTECH CO LTD

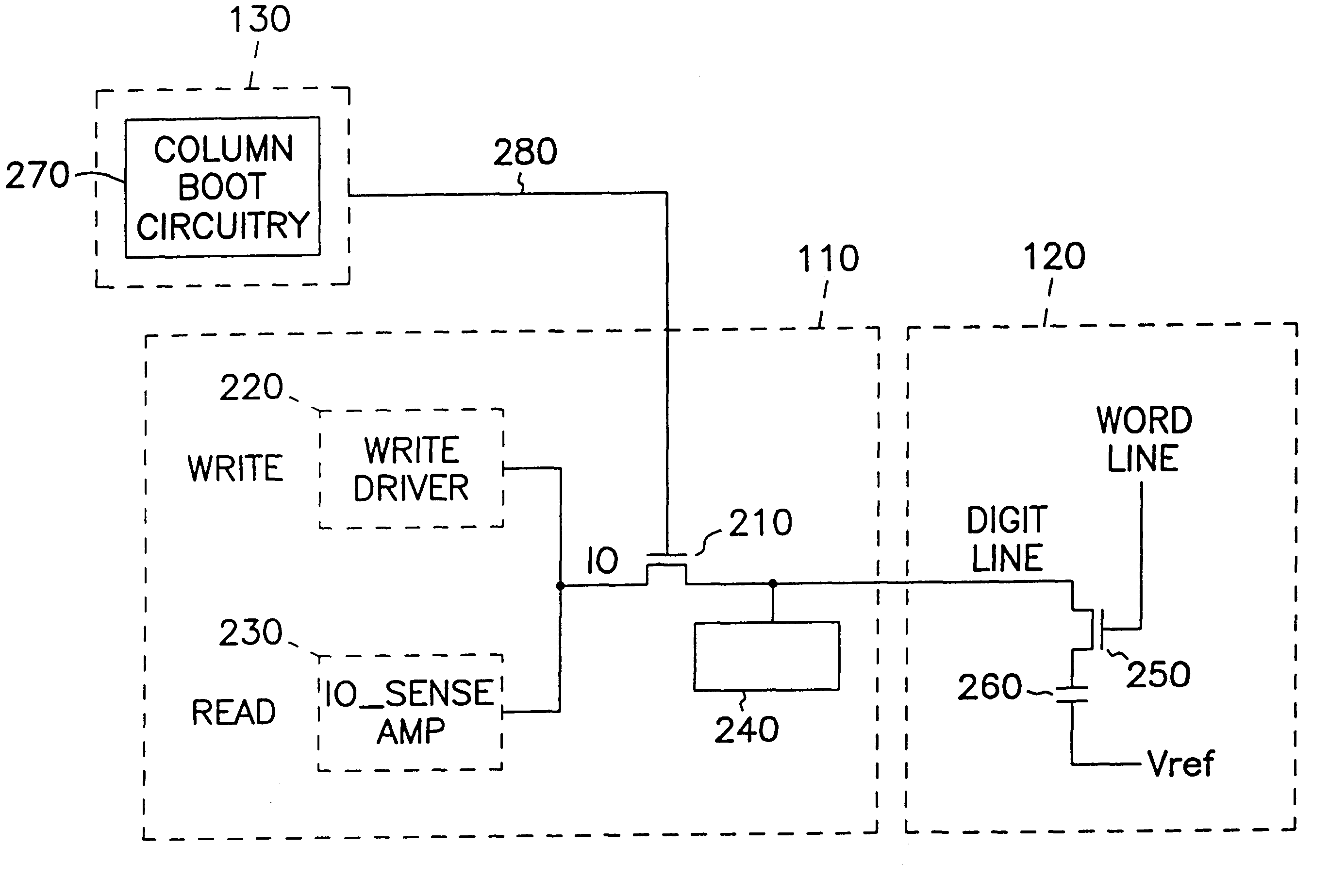

System for improved memory cell access

A voltage booting circuit for booting the switching signal applied to a column access passgate is employed to reduce the voltage drop across the passgate. Reduction of the voltage dropped across the passgate results in faster read and write times and improved noise margin. In one application the booted voltage is used only during a write operation, but not during a read. In another application, the booted voltage is used during both operations.

Owner:MICRON TECH INC

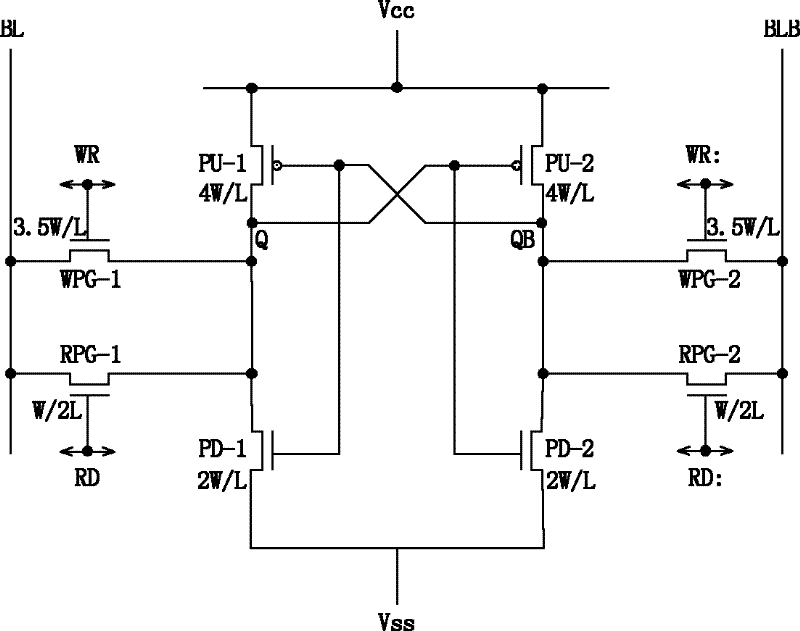

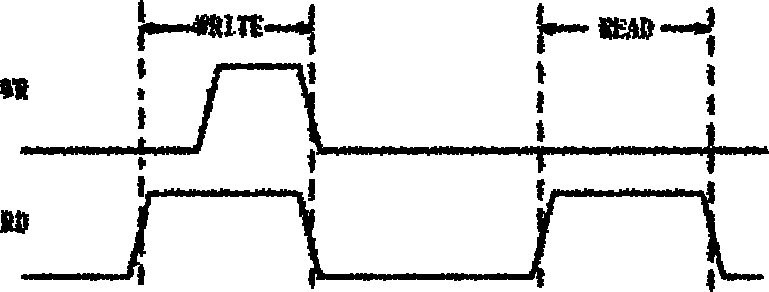

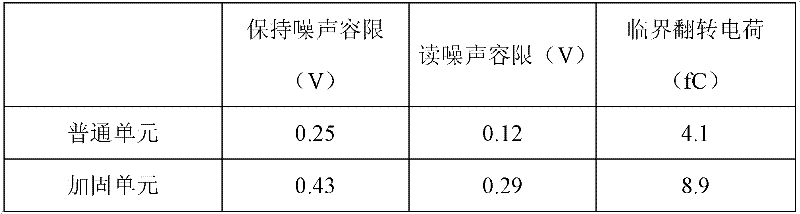

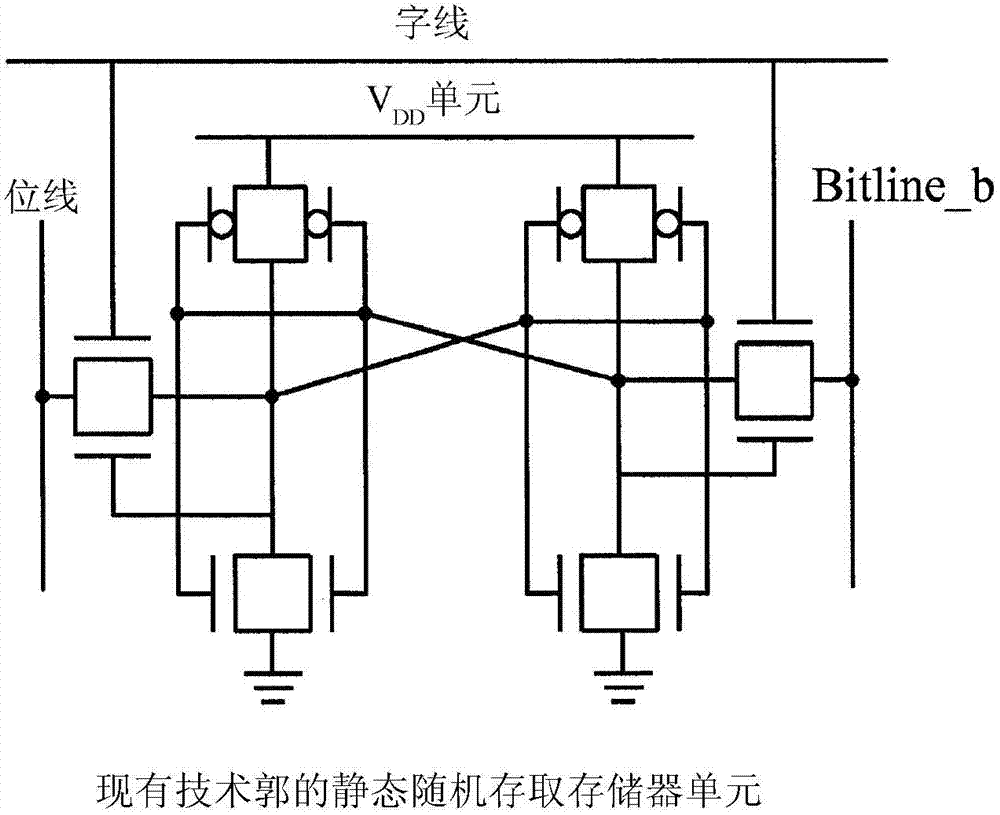

High-reliability static storage cell and application method thereof

The invention discloses a high-reliability static storage cell and an application method thereof. The high-reliability static storage cell comprises a first pull-up transistor PU-1, a second pull-up transistor PU-2, a first pull-down transistor PD-1, a second pull-down transistor PD-2, a first read access transistor RPG-1, a second read access transistor RPG-2, a first write access transistor WPG-1 and a second write access transistor WPG-2, wherein the grids of the first read access transistor RPG-1 and the second read access transistor RPG-2 are connected on a read access control signal RD, and the first write access transistor WPG-1 and the second write access transistor WPG-2 are connected on a write access control signal WR. By applying the storage cell and the application method thereof, the problems that a read noise margin is increasingly serious due to that a process is improved and a power supply voltage is reduced and the noise margin and single event upset are maintained can be solved, and the reliability of the static storage cell is improved.

Owner:NO 771 INST OF NO 9 RES INST CHINA AEROSPACE SCI & TECH

Stable SRAM bitcell design utilizing independent gate FinFET

ActiveCN103201797ASolid-state devicesSemiconductor/solid-state device manufacturingBit lineStatic random-access memory

Stable SRAM cells utilizing Independent Gate FinFET architectures provide improvements over conventional SRAM cells in device parameters such as Read Static Noise Margin (RSNM) and Write Noise Margin (WNM). Exemplary SRAM cells comprise a pair of storage nodes, a pair of bit lines, a pair of pull-up devices, a pair of pull-down devices and a pair of pass-gate devices. A first control signal and a second control signal are configured to adjust drive strengths of the pass-gate devices, and a third control signal is configured to adjust drive strengths of the pull-up devices, wherein the first control signal is routed orthogonal to a bit line direction, and the second and third control signals are routed in a direction same as the bit line direction. RSNM and WNM are improved by adjusting drive strengths of the pull-up and pass-gate devices during read and write operations.

Owner:QUALCOMM INC