High-reliability static storage cell and application method thereof

A static storage, reliable technology, applied in the direction of static storage, information storage, digital storage information, etc.

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0016] The present invention is described in further detail below in conjunction with accompanying drawing:

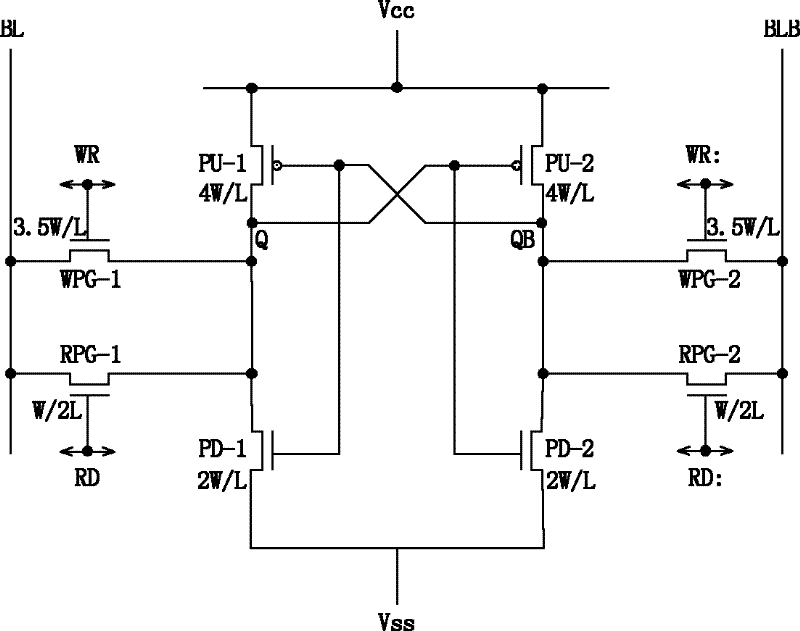

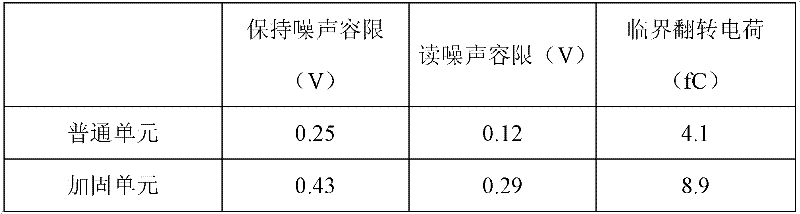

[0017] see Figure 1-2 , a highly reliable static memory unit, including a first pull-up transistor PU-1, a second pull-up transistor PU-2, a first pull-down transistor PD-1, a second pull-down transistor PD-2, a first read access transistor RPG-1, the second read access transistor RPG-2, the first write access transistor WPG-1 and the second write access transistor WPG-2; wherein the first read access transistor RPG-1 and the second read access transistor RPG-2 The gate is connected to the read access control signal RD, and the first write access transistor WPG-1 and the second write access transistor WPG-2 are connected to the write access control signal WR.

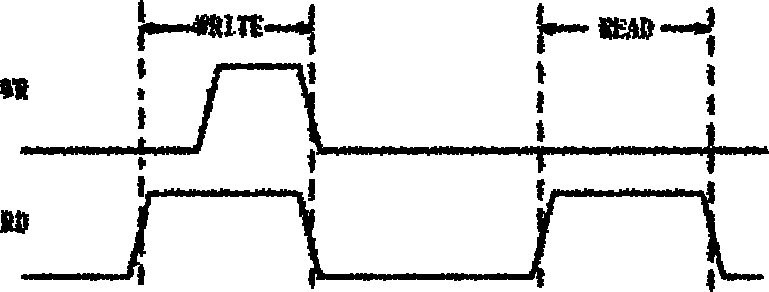

[0018] figure 1 It is a schematic diagram and transistor size of an 8T-SRAM according to an embodiment of the present invention. The specific implementation examples of its read and write access control sign...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More