Patents

Literature

577 results about "User Error" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

The term use error has recently been introduced to replace the commonly used terms human error and user error. The new term, which has already been adopted by international standards organizations for medical devices (see #Use errors in health care below for references), suggests that accidents should be attributed to the circumstances, rather than to the human beings who happened to be there.

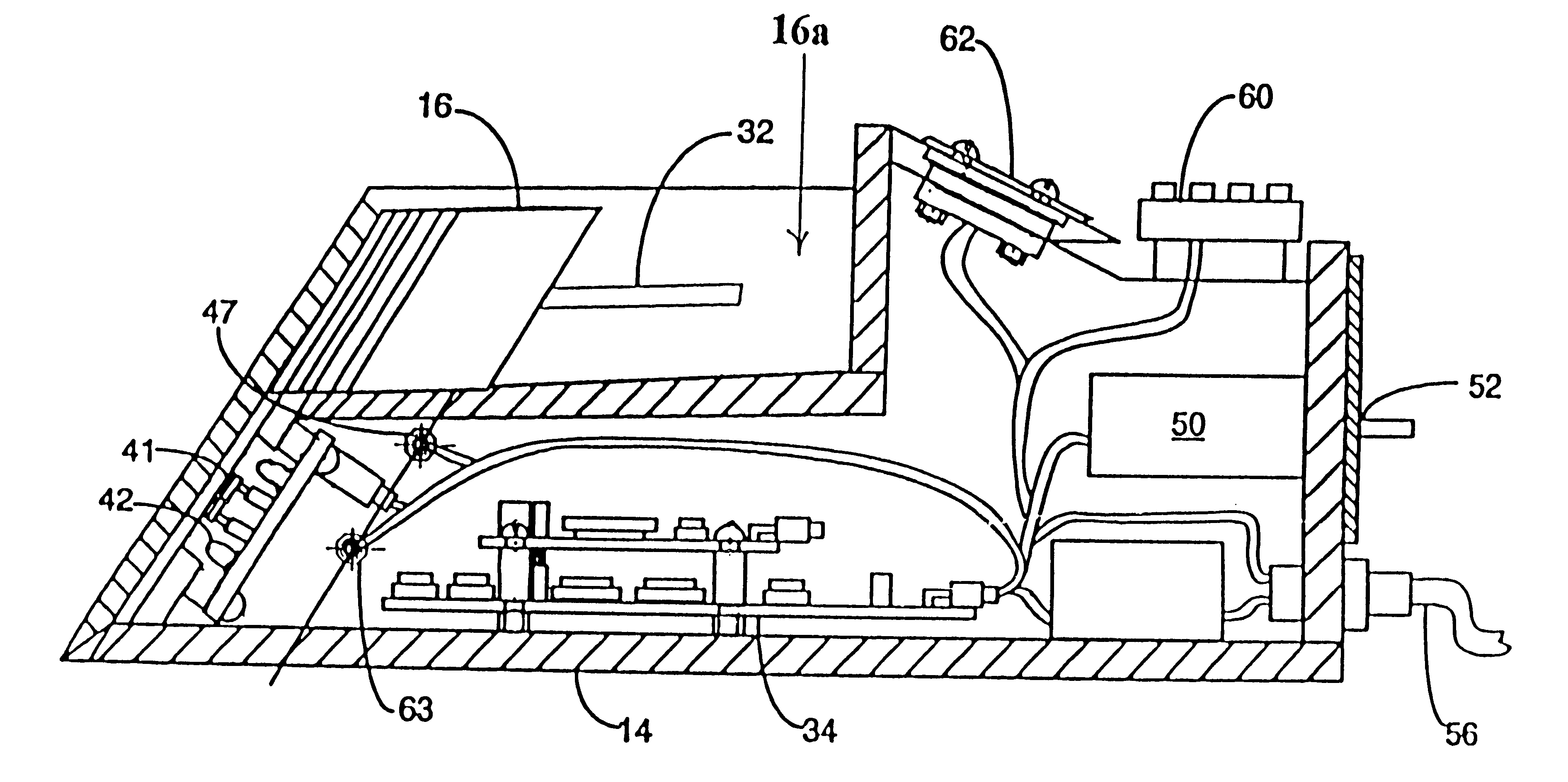

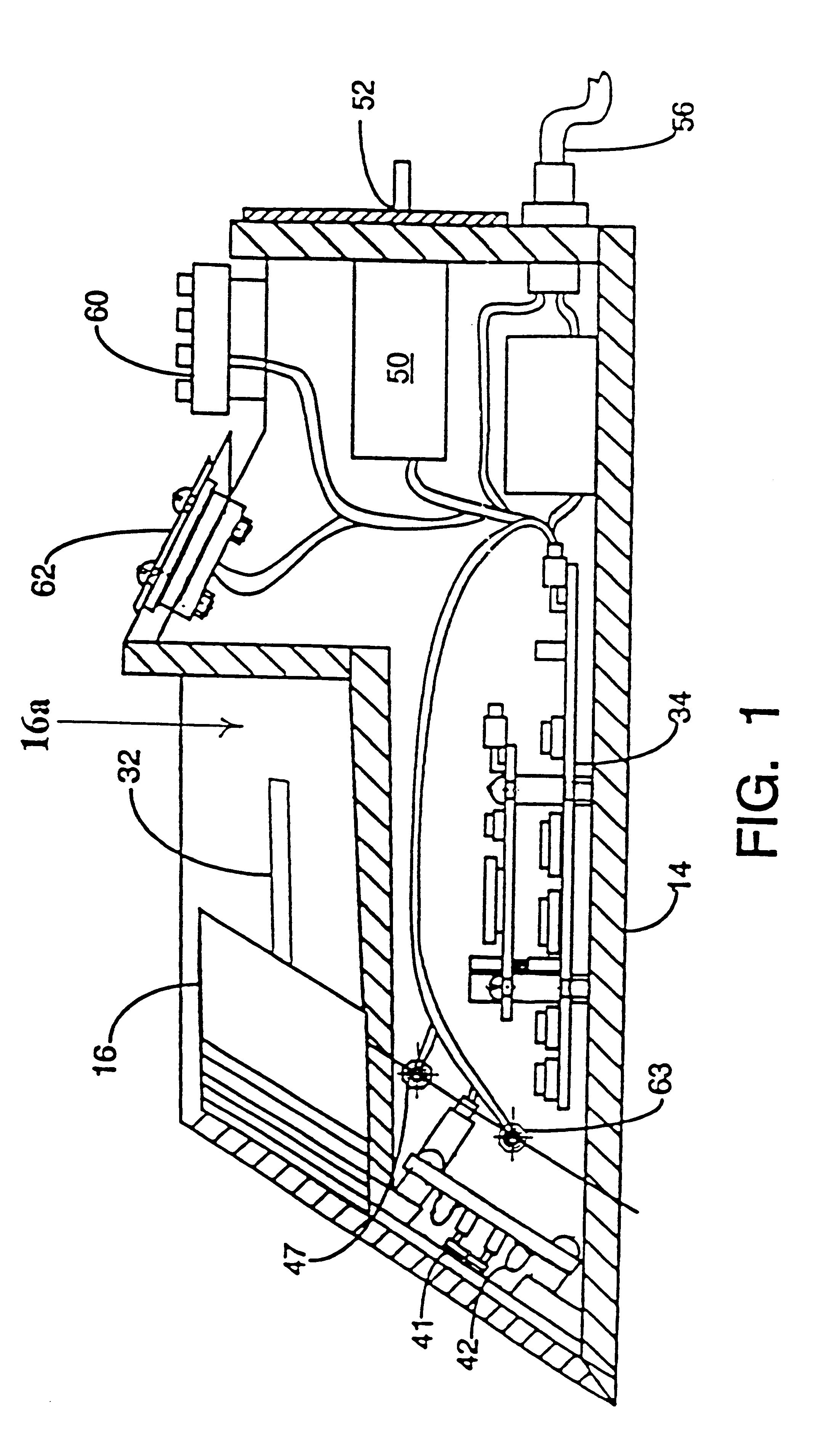

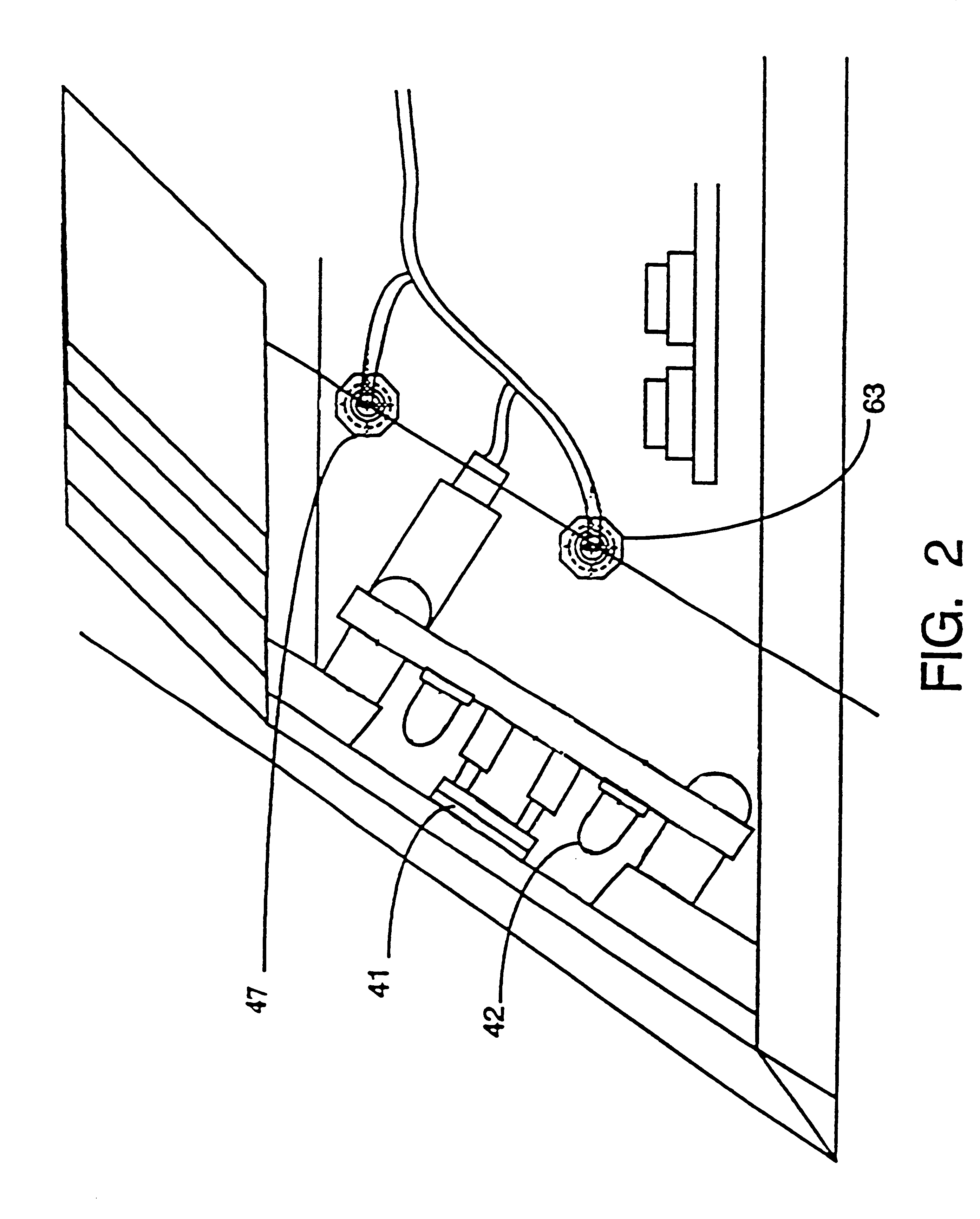

Card dispensing shoe with scanner apparatus, system and method therefor

The present invention is directed to a playing card dispensing shoe apparatus, system and method wherein the shoe has a card scanner which scans the indicia on a playing card as the card moves along and out of a chute of the shoe by operation of the dealer. The scanner comprises an optical-sensor used in combination with a neural network which is trained using error back-propagation to recognize the card suits and card values of the playing cards as they are moved past the scanner. The scanning process in combination with a central processing unit (CPU) determines the progress of the play of the game and, by identifying card counting systems or basic playing strategies in use by the players of the game, provides means to limit or prevent casino losses and calculate the Theoretical Win of the casino, thus also providing an accurate quality method of the amount of comps to be given a particular player. The shoe is also provided with additional devices which make it simple and easy to access, record and display other data relevant to the play of the game. These include means for acconunodating a "customer-tracking card" which reads each player's account information from a magnetic stripe on the card, thus providing access to the player's customer data file stored on the casino's computer system, and one or more alpha-numeric keyboards and LCD displays used to enter and retrieve player and game information. Also included are keyboards on the game table so that each player can individually select various playing or wagering options using their own keyboard.

Owner:PROGRESSIVE GAMING INT

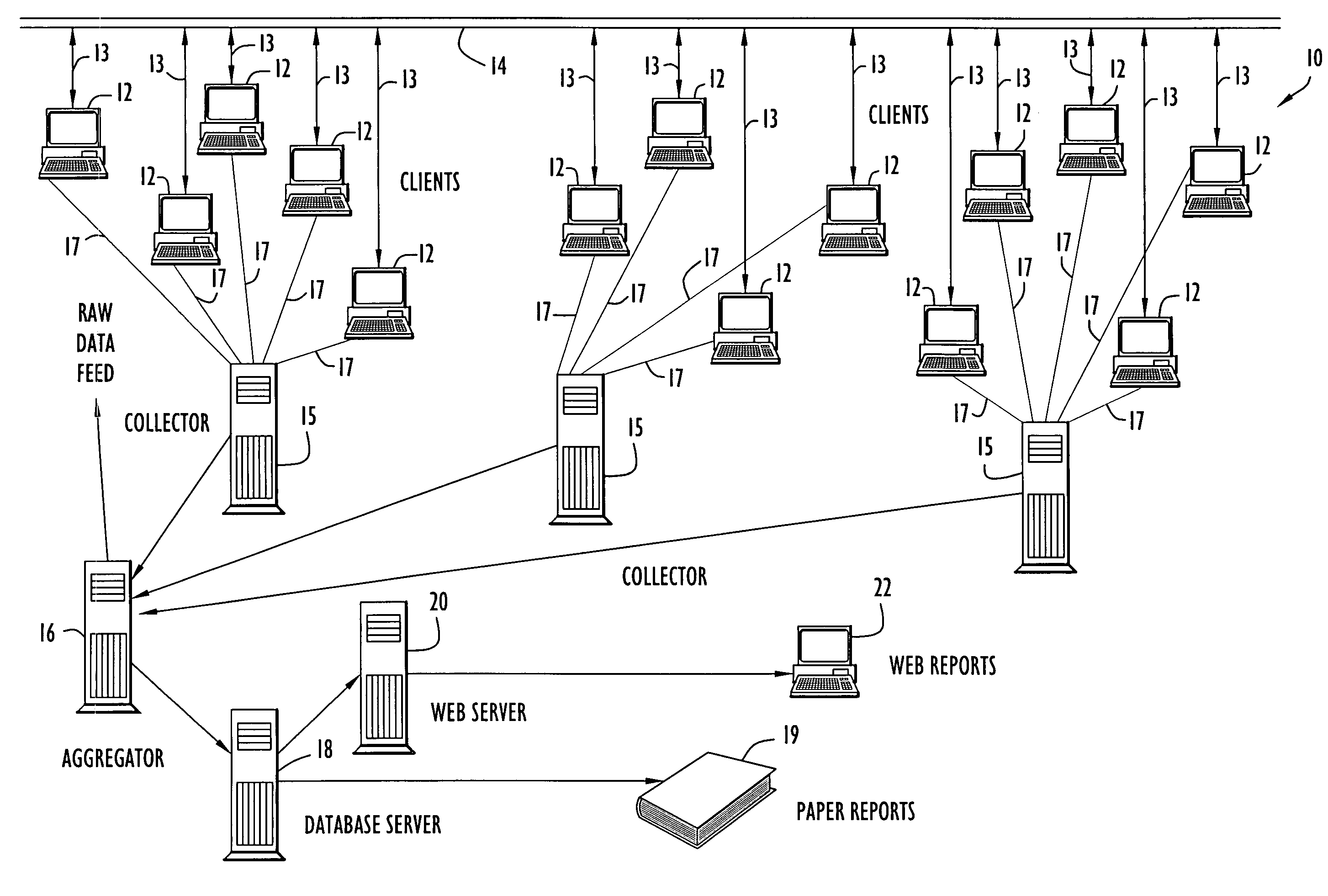

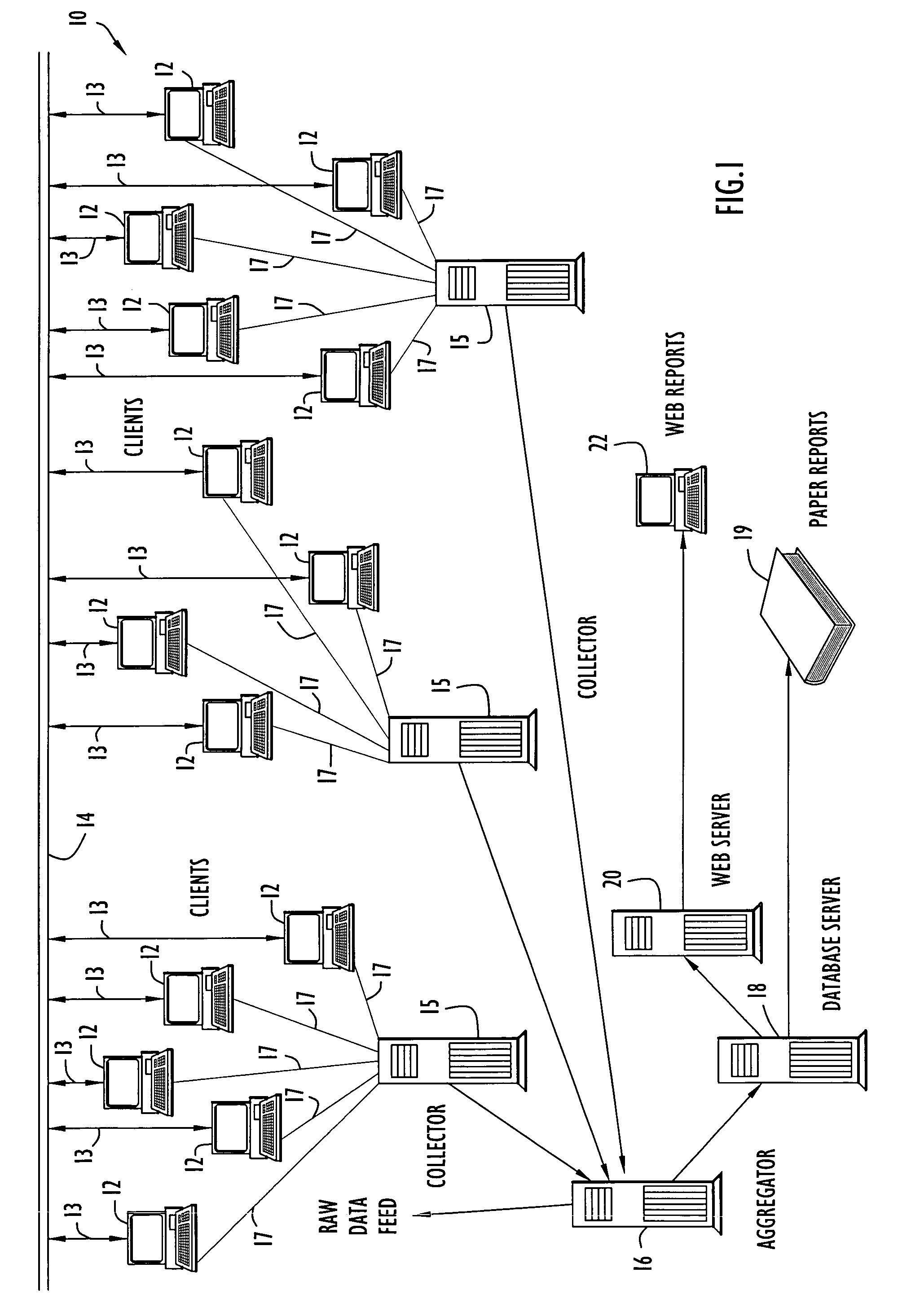

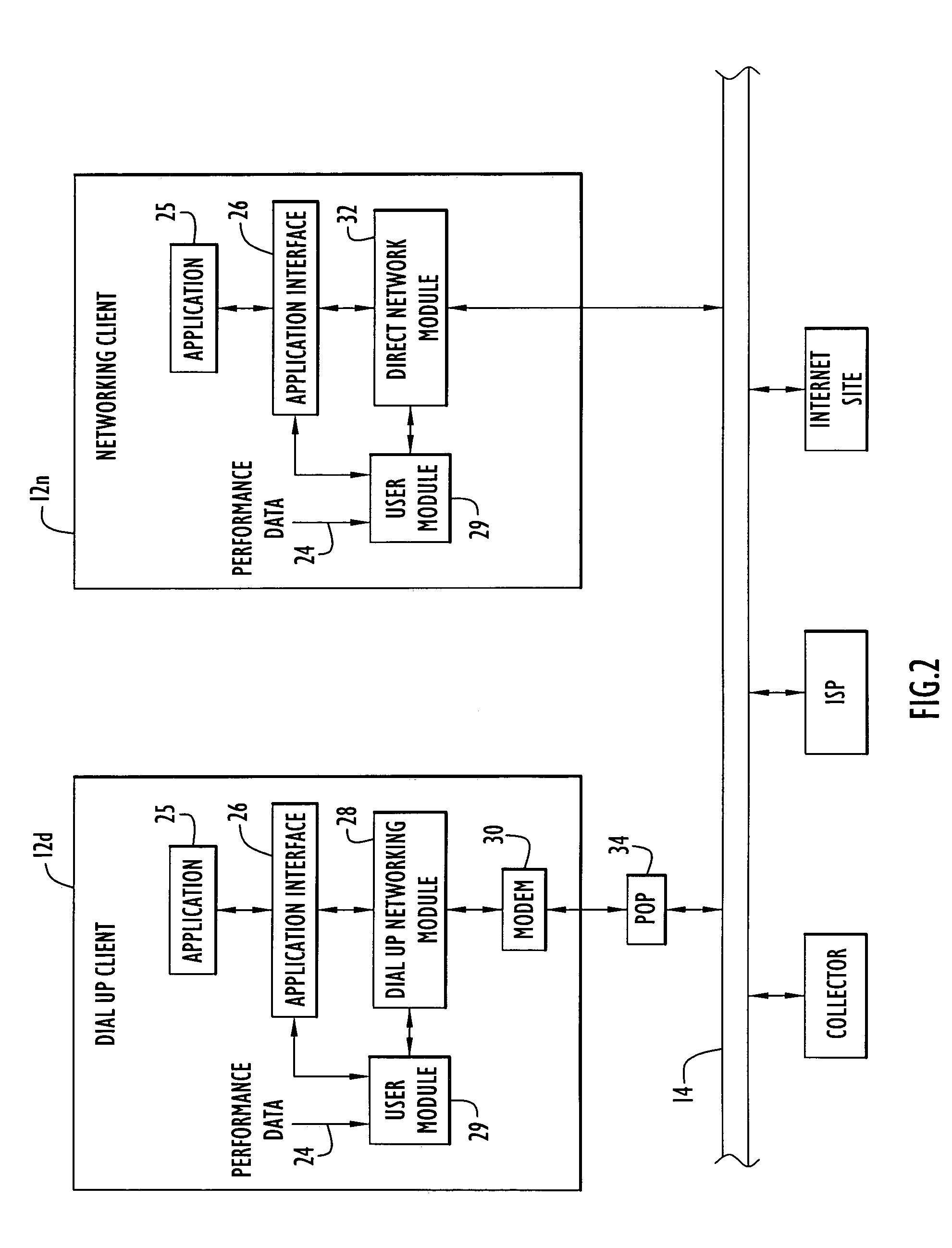

Methods and apparatus for monitoring end-user experience in a distributed network

InactiveUS6970924B1Accurate assessmentAccurately determineMultiple digital computer combinationsProgram loading/initiatingMonitoring systemSystem usage

A network performance monitoring system uses a plurality of user modules, each user operating on a unique user machine coupled to one or more provider servers and an experience test server for collecting data from the plurality of user modules. The collected data includes at least one performance datum relating to user experience with a link from the user machine to the provider server. The system also cleanses the collected data to account for variable user configurations, user errors and the like.

Owner:INVERSE NETWORK TECH INC +1

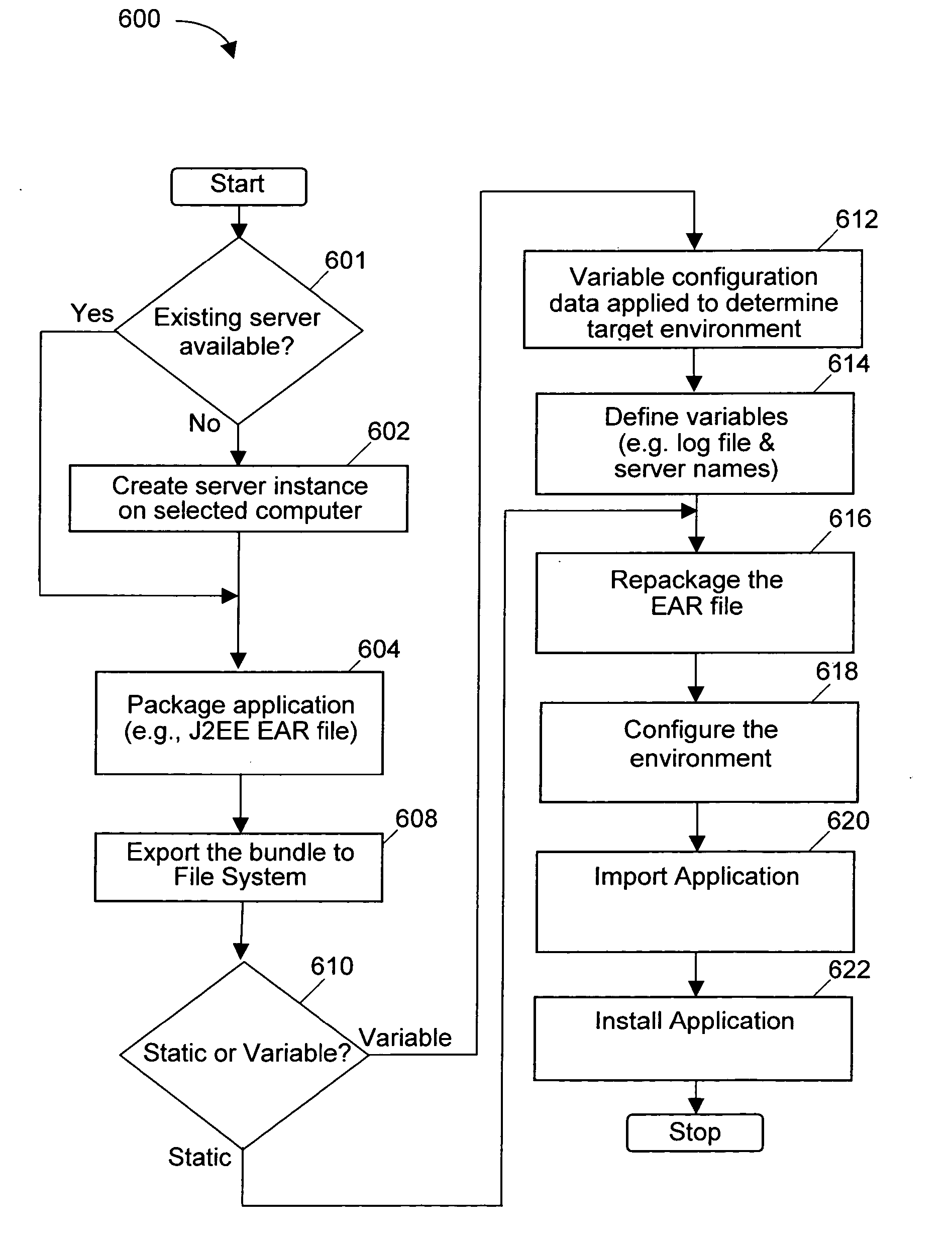

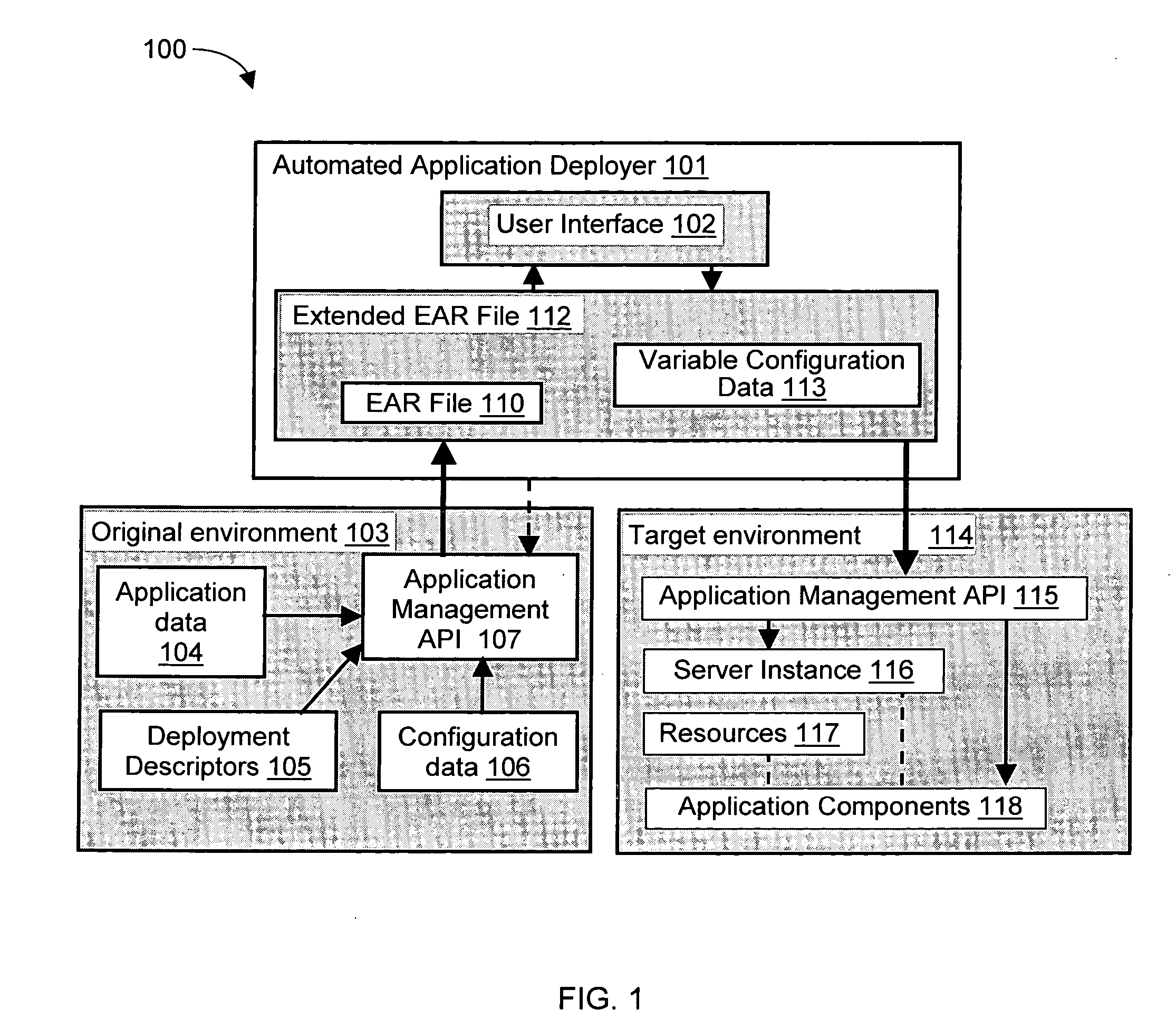

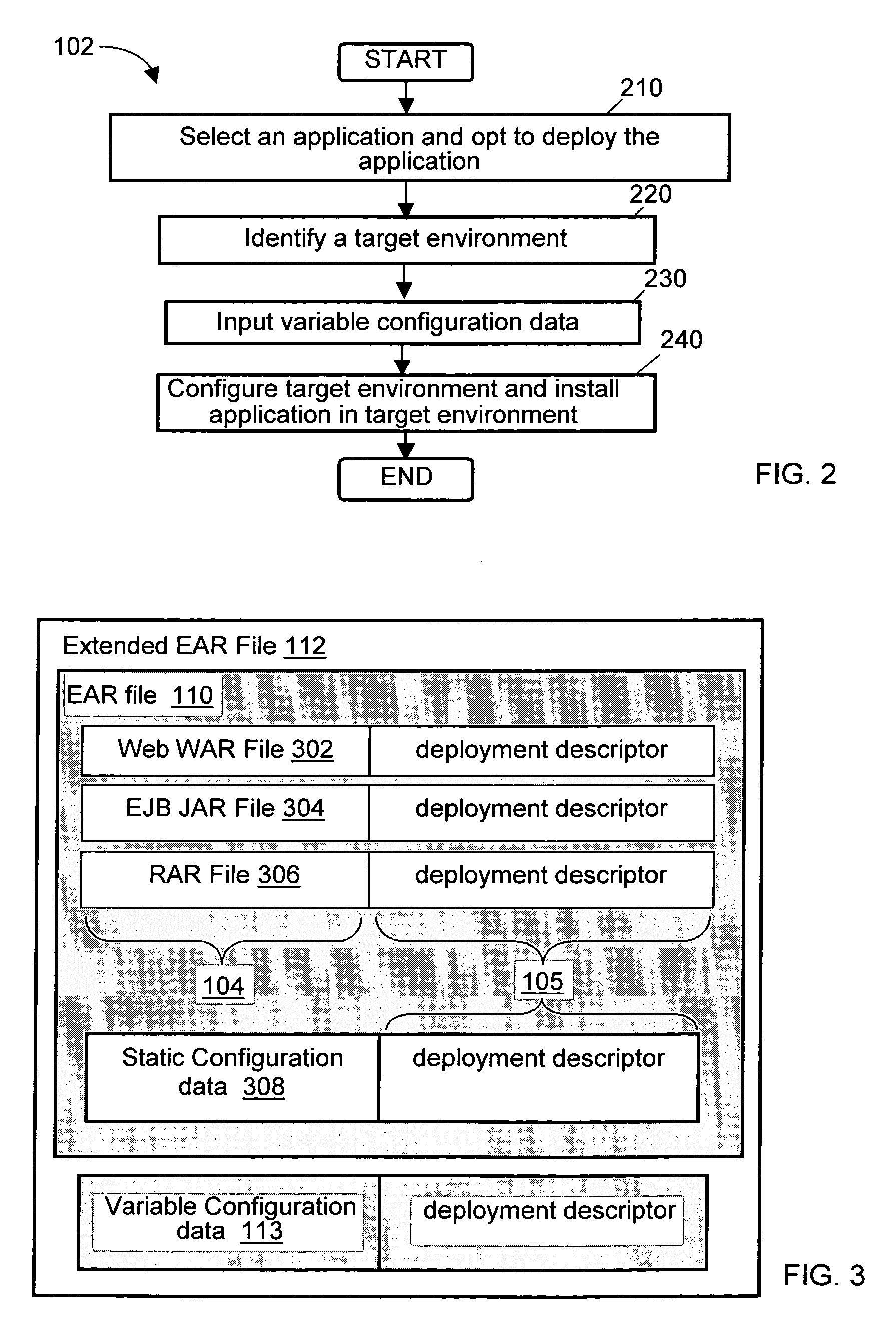

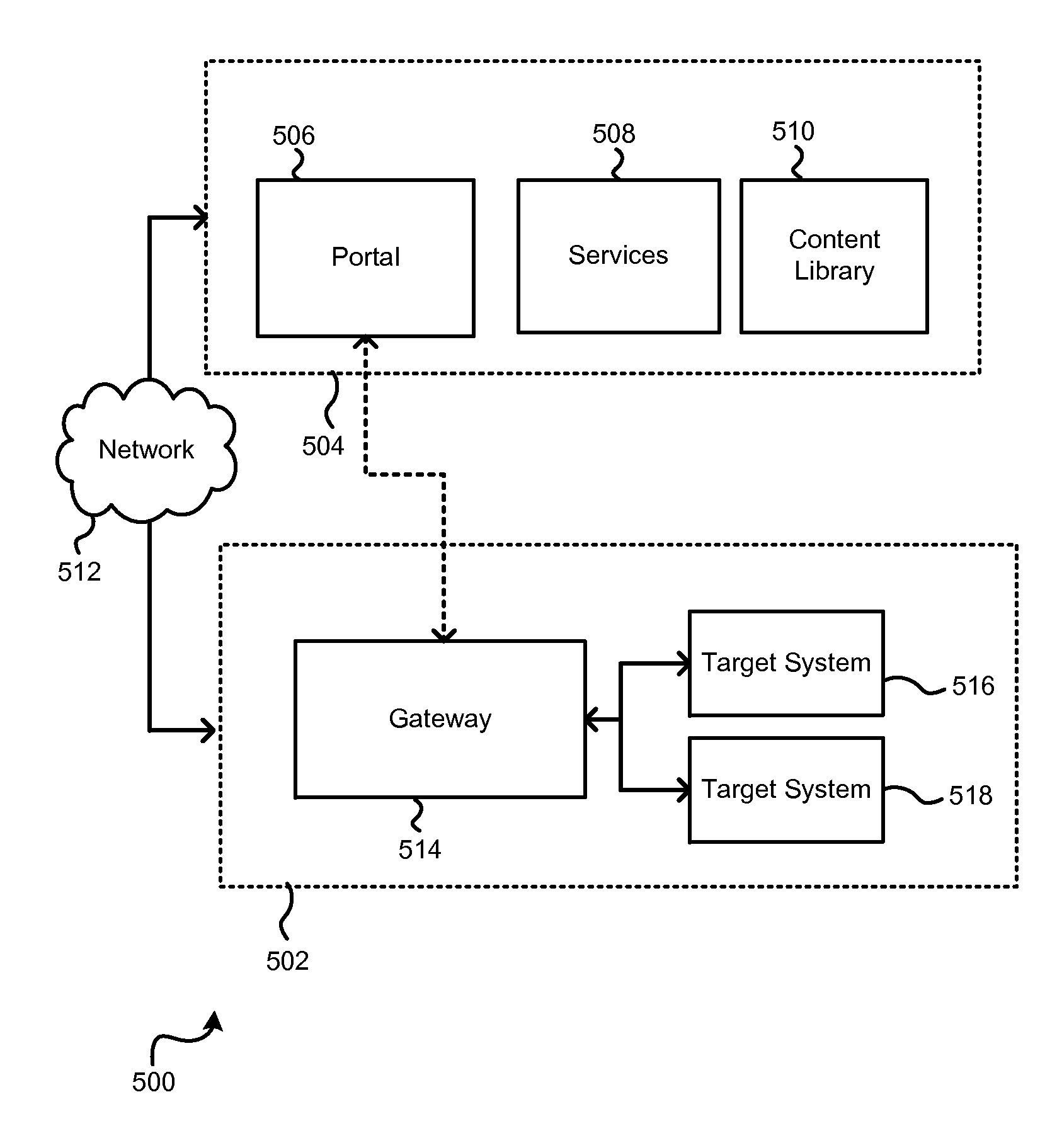

Automated deployment of an application

Methods, systems, and media to automatically deploy an, e.g., a JS2EE file between environments are disclosed. Embodiments include hardware and / or software for selecting one or more applications in an original system for export. The applications along with their corresponding application data, configuration data, and descriptor files, are compressed into one or more archive files such as Enterprise Archives (EARs). Variable configuration data associated with the target environment is identified so the values of the variable configuration data can be adapted for the target environment. Then, the target environment is adapted for installation of the application and the application is installed in the target environment. Advantageously, this deployment of the application may reduce the chance of user error, require less J2EE knowledge and script maintenance, and complete faster than deployments effected manually.

Owner:IBM CORP

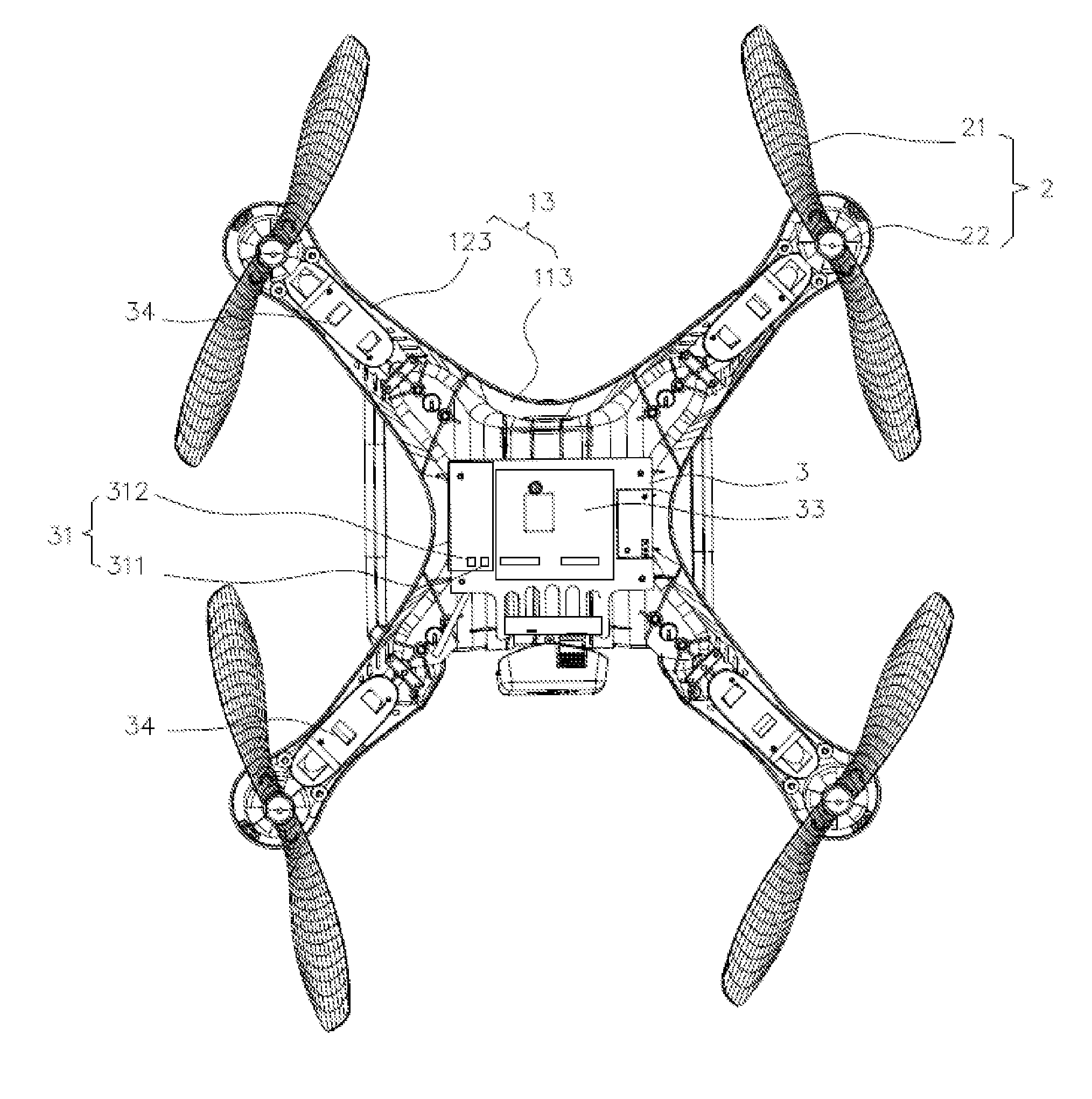

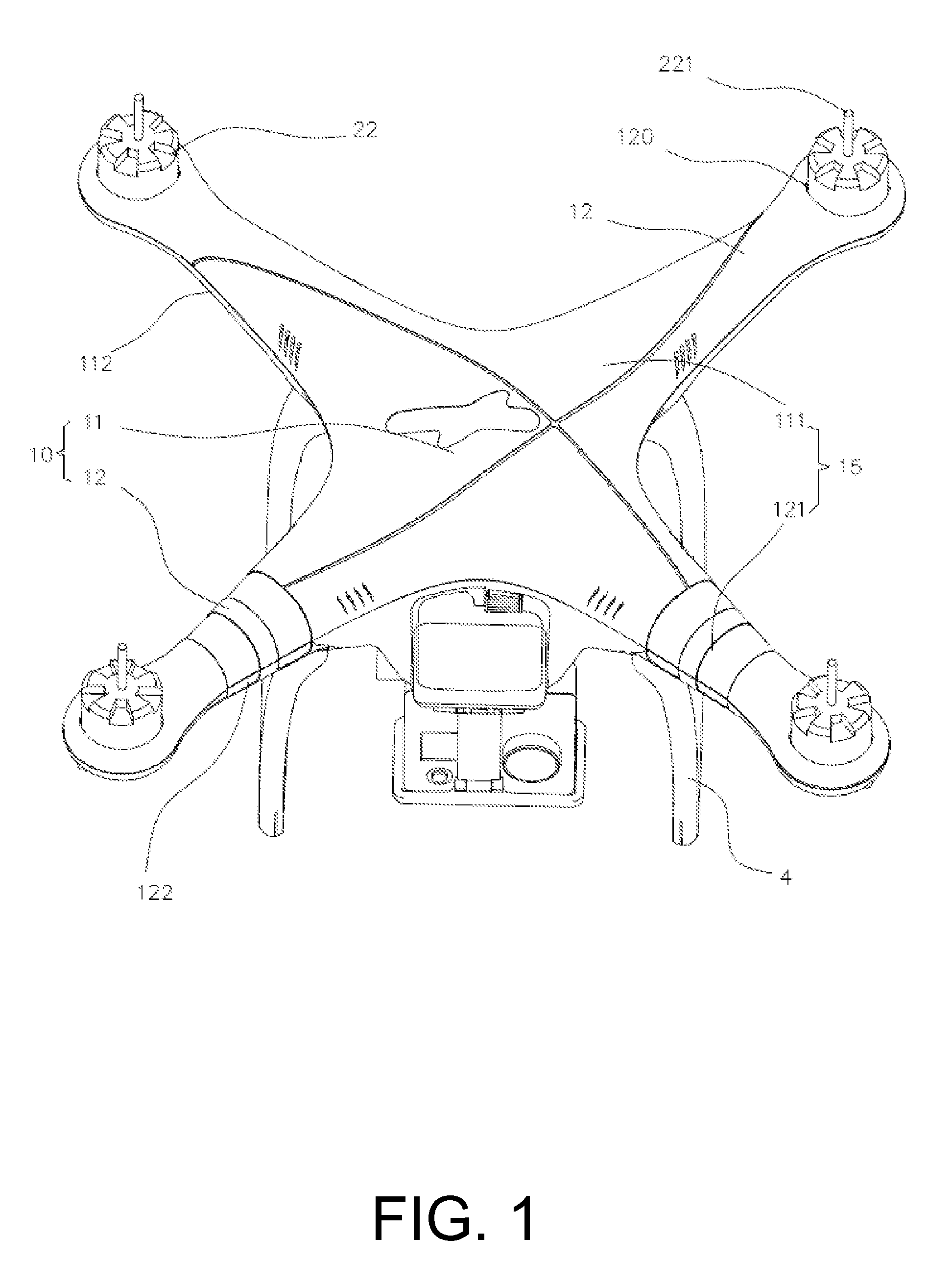

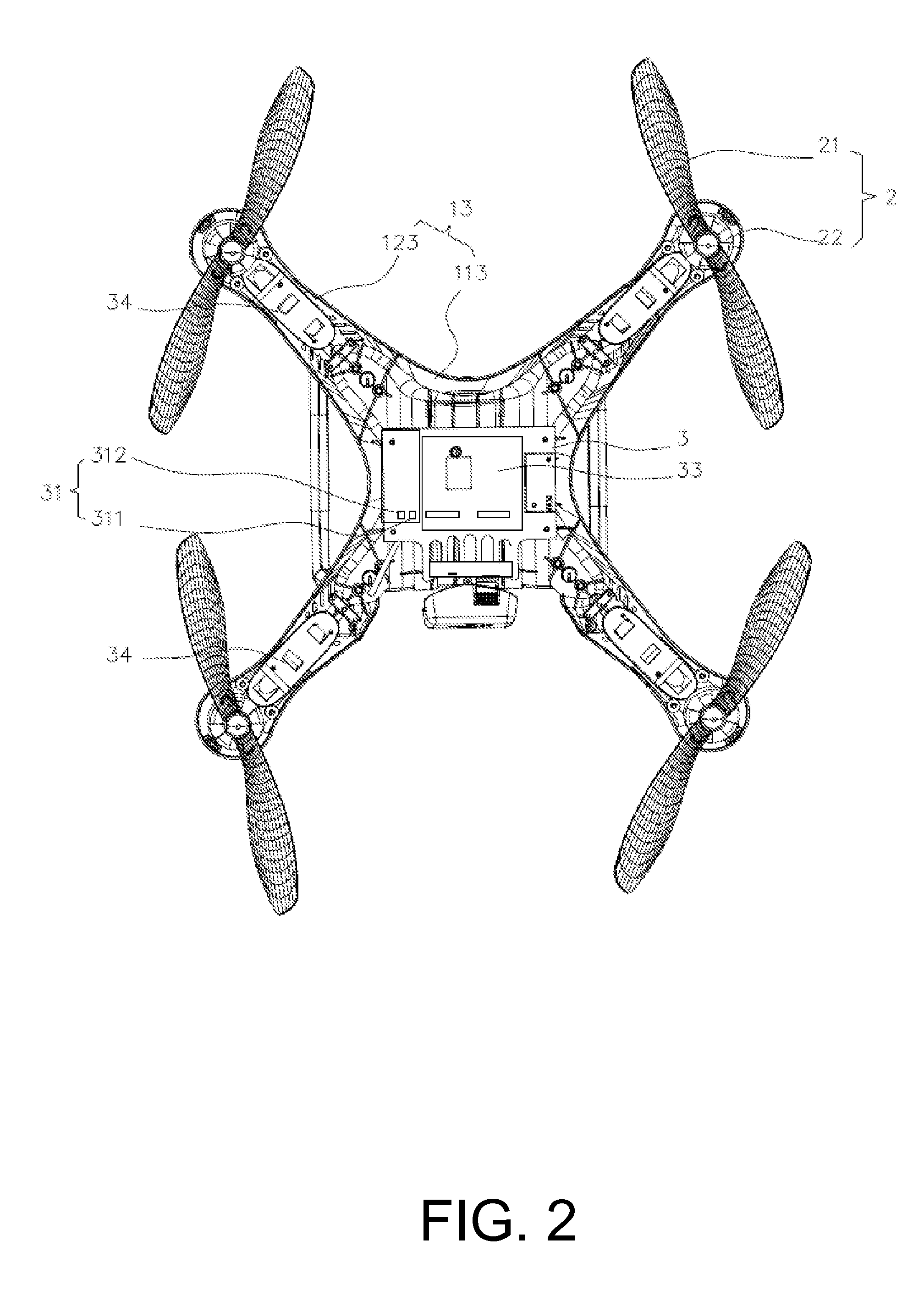

Unmanned aerial vehicle and operations thereof

ActiveUS20140131510A1Reduce distractionsAircraft power plantsMagnetic sensor packagingEngineeringDependability

The present invention provides methods and apparatus for unmanned aerial vehicles (UAVs) with improved reliability. According to one aspect of the invention, interference experienced by onboard sensors from onboard electrical components is reduced. According to another aspect of the invention, user-configuration or assembly of electrical components is minimized to reduce user errors.

Owner:SZ DJI TECH CO LTD

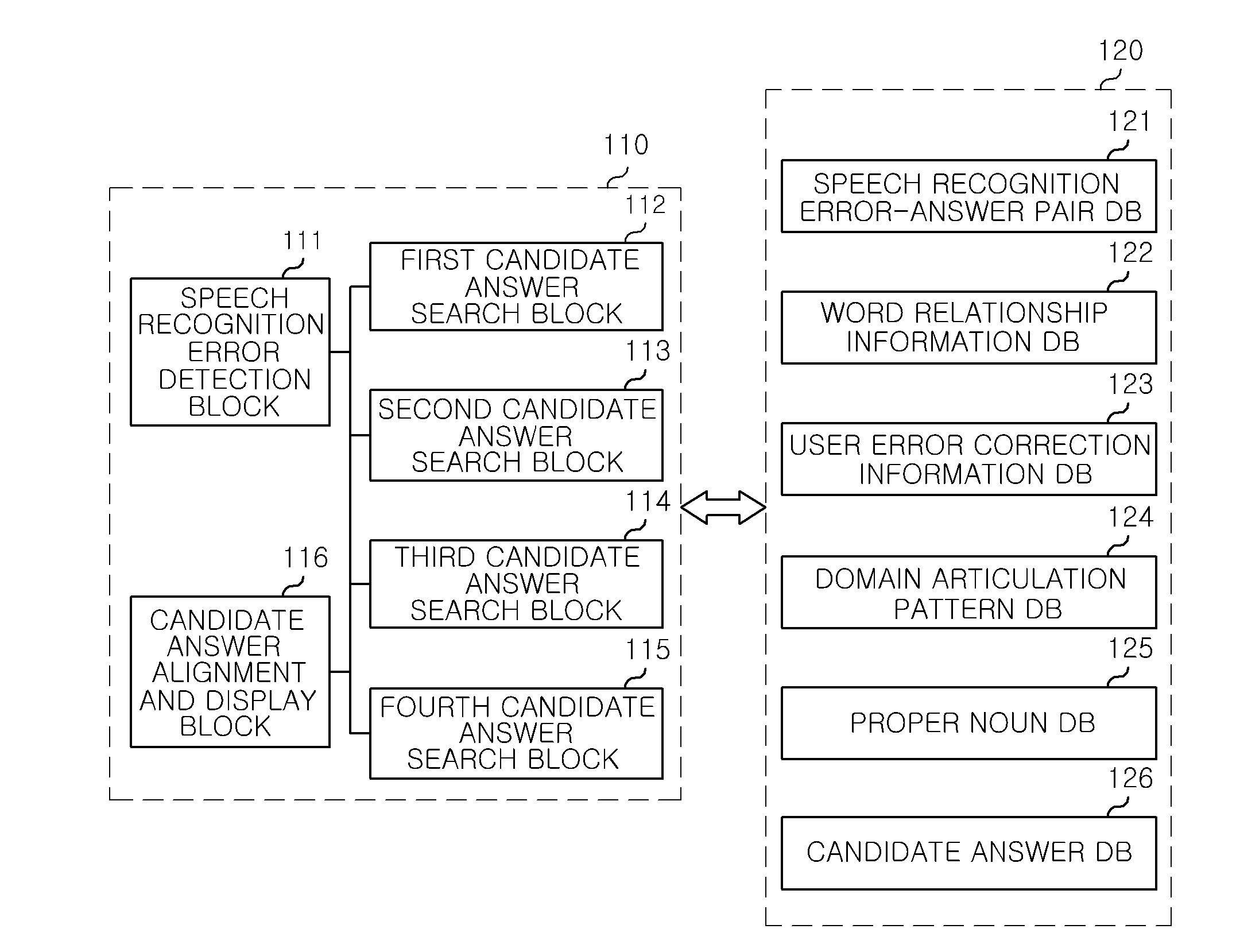

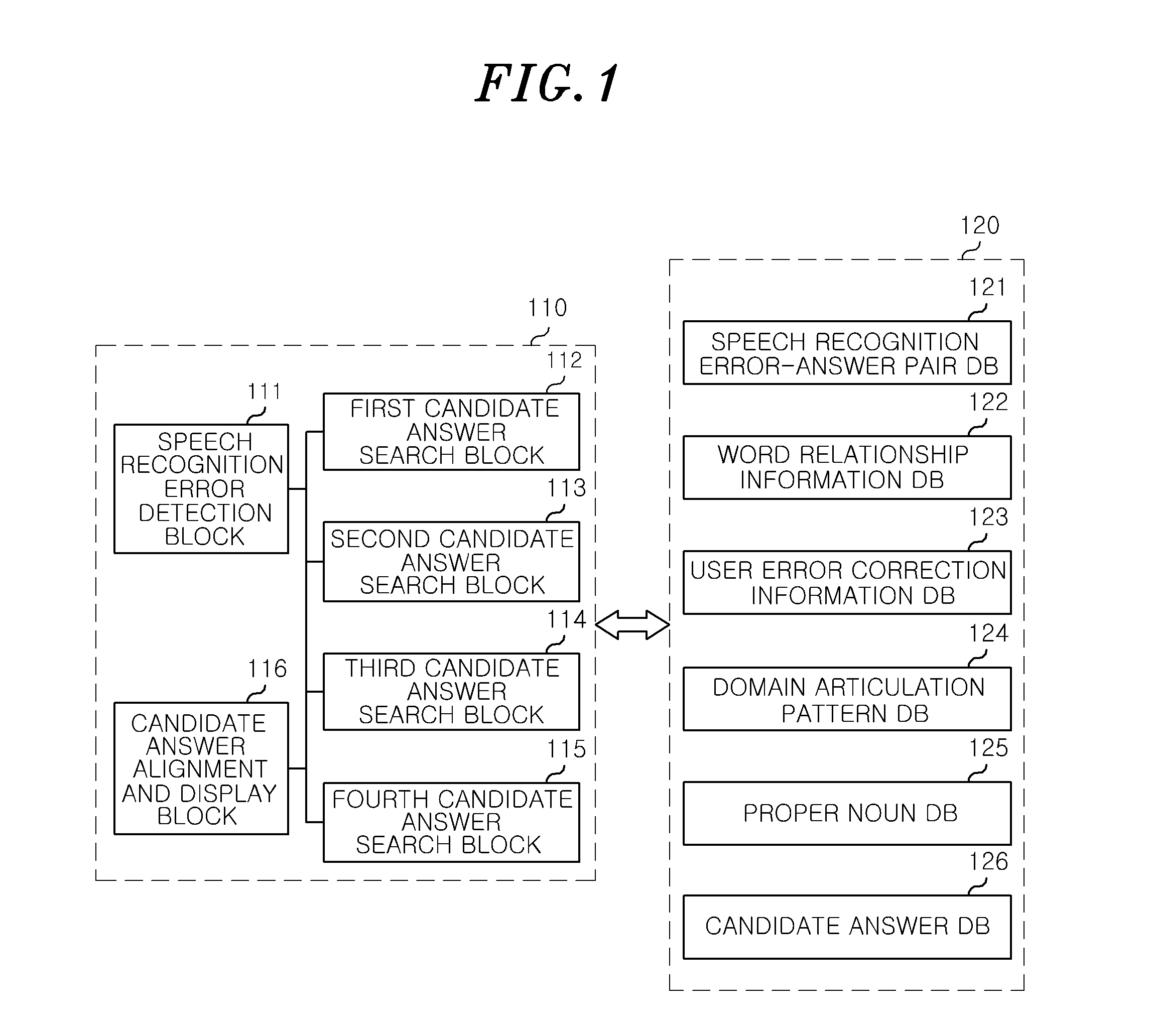

Method and apparatus for correcting error in speech recognition system

InactiveUS20140195226A1Easy to handleImprove user convenienceMetal sawing devicesSpeech recognitionSpeech identificationA domain

A method of correcting errors in a speech recognition system includes a process of searching a speech recognition error-answer pair DB based on a sound model for a first candidate answer group for a speech recognition error, a process of searching a word relationship information DB for a second candidate answer group for the speech recognition error, a process of searching a user error correction information DB for a third candidate answer group for the speech recognition error, a process of searching a domain articulation pattern DB and a proper noun DB for a fourth candidate answer group for the speech recognition error, and a process of aligning candidate answers within each of the retrieved candidate answer groups and displaying the aligned candidate answers.

Owner:ELECTRONICS & TELECOMM RES INST

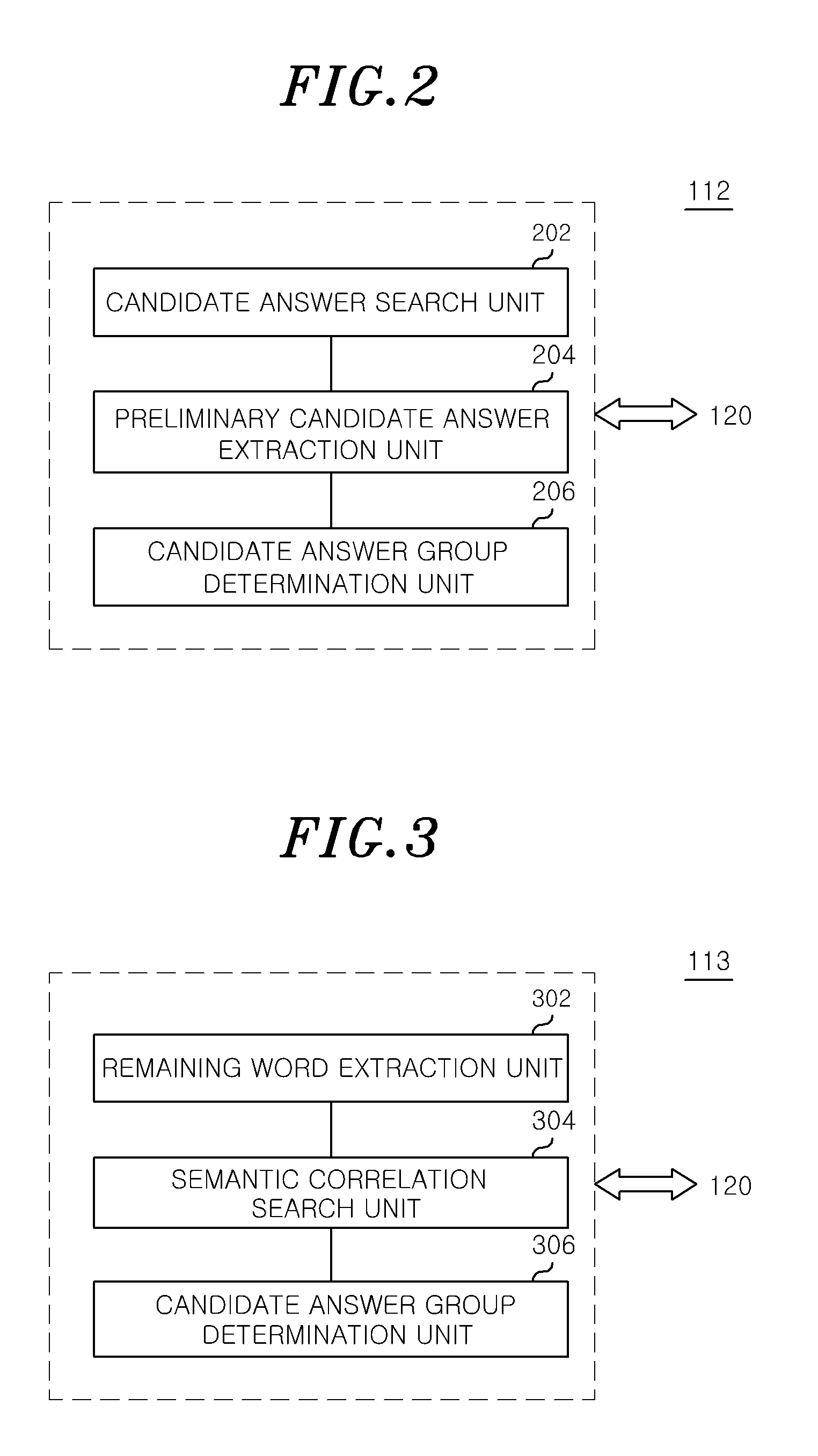

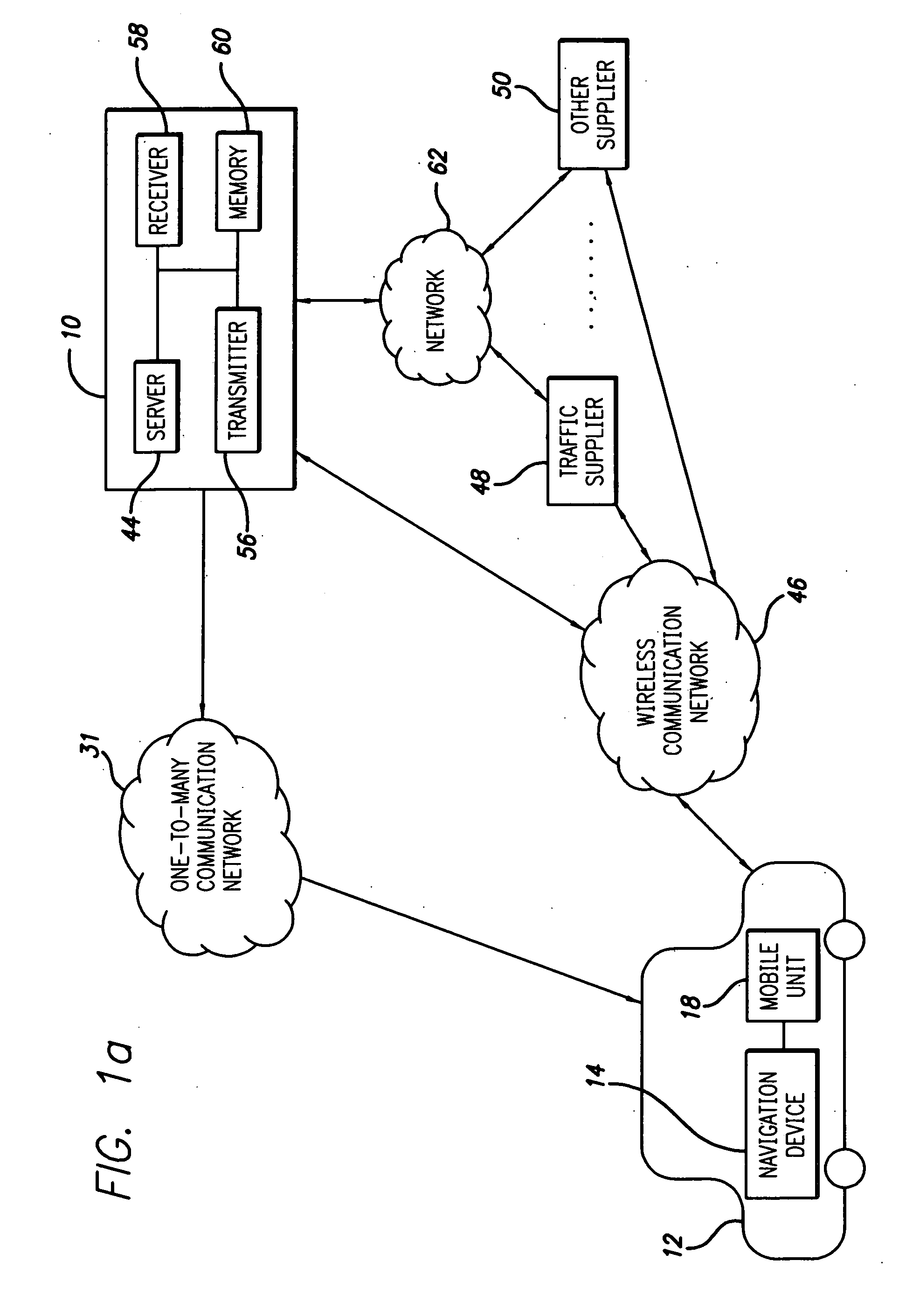

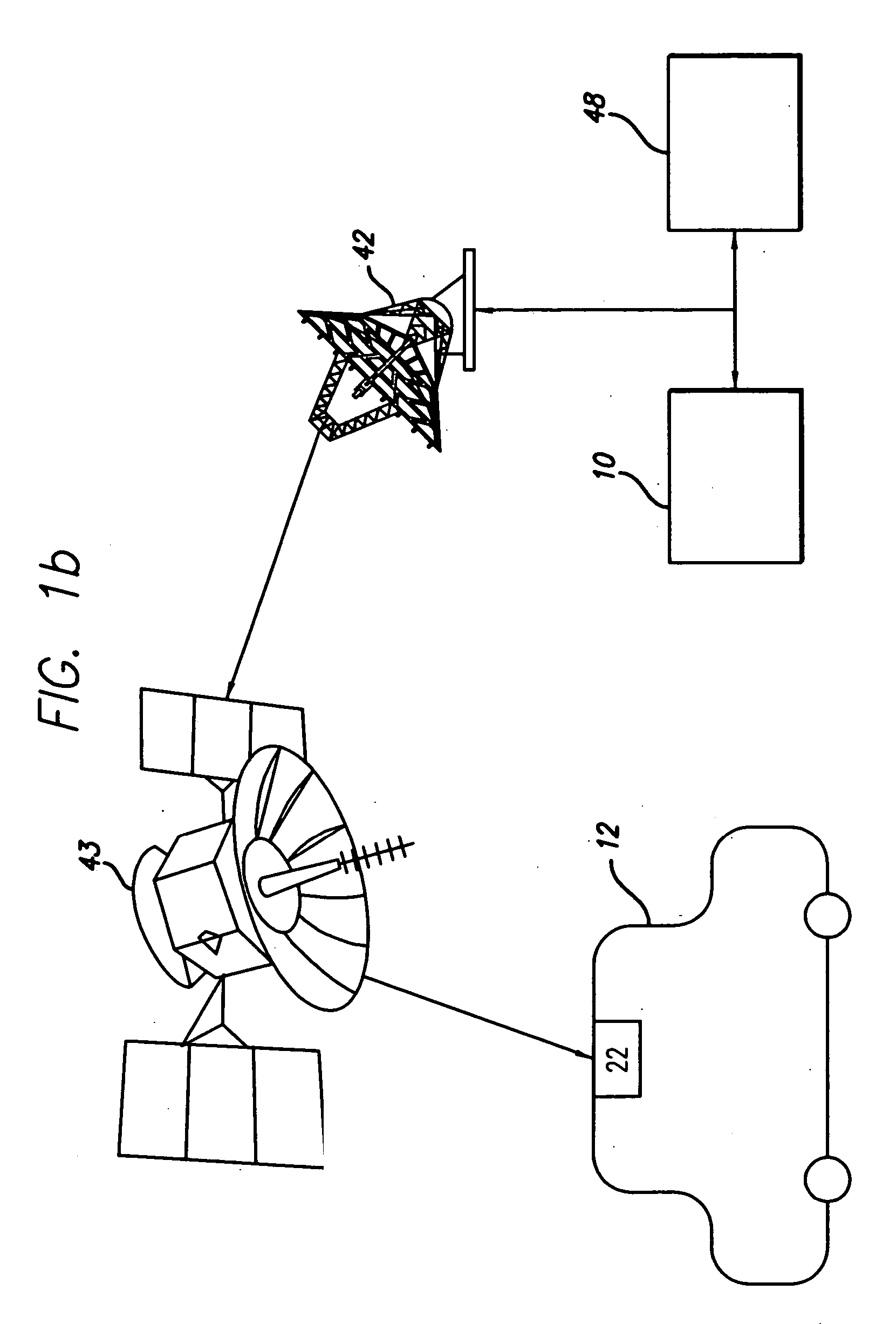

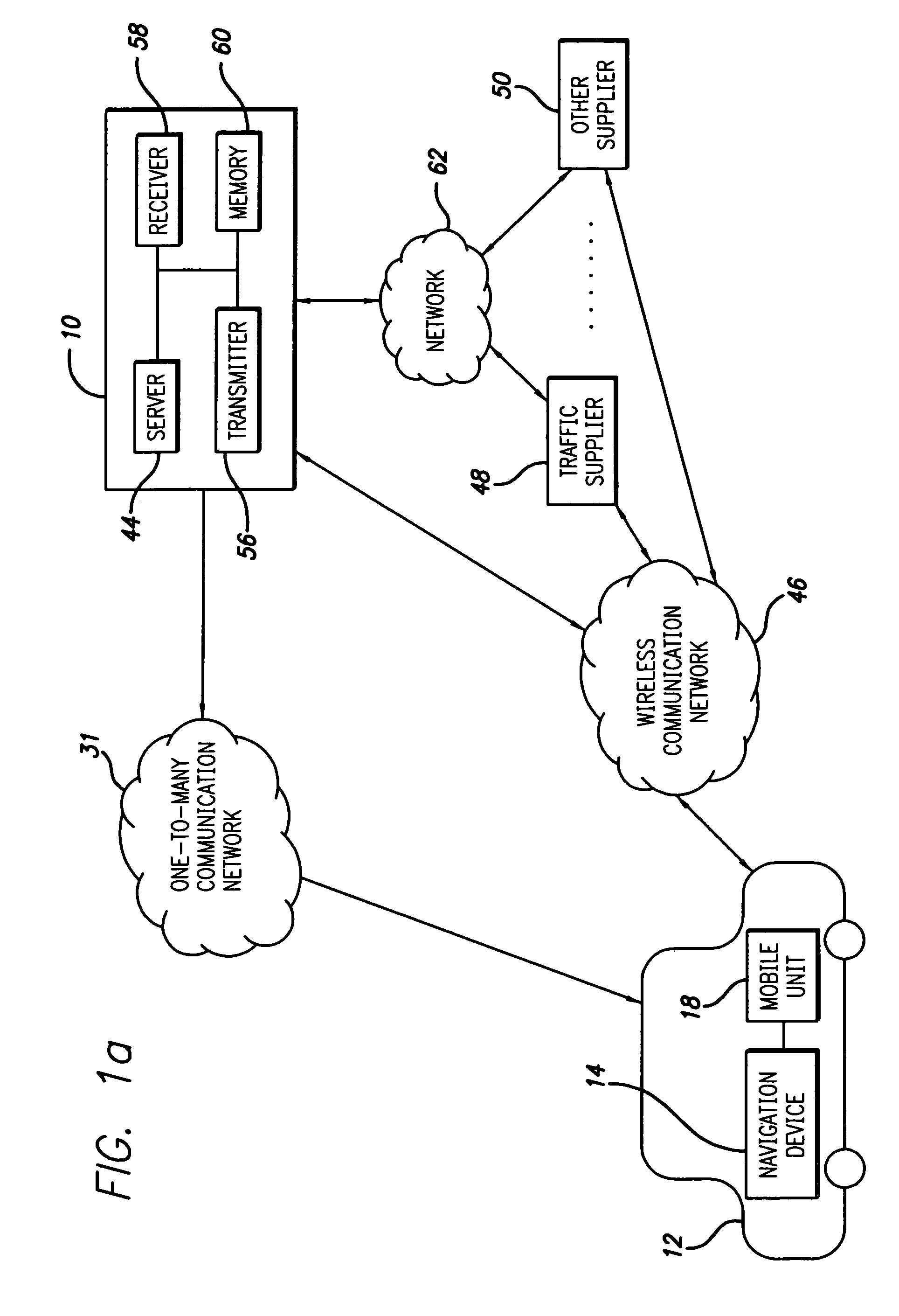

Route calculation method for a vehicle navigation system

ActiveUS20050222764A1Increase route calculationIncrease and decrease broadcastInstruments for road network navigationRoad vehicles traffic controlNavigation systemReceipt

Traffic information, including flow information and incident information, obtained through a traffic management system for providing and facilitating the exchange of traffic information between a remote location and a vehicle may be used in route calculation by a navigation device. The navigation device may recalculate a route based on anticipated user error. Alternatively, the navigation device may recalculate a route using received traffic information triggered by the receipt of a traffic information update, or triggered by the passage of an amount of time. The broadcast rate of traffic information updates may vary temporally (providing more frequent updates during peak commute times) or geographically (providing more frequent updates to metropolitan areas with increased traffic information needs). If route calculation is triggered by an elapsed amount of time, the amount of time may vary to be shorter during peak commute times. Additional route calculation techniques allow the incorporation of historical traffic information or the use of the most recent traffic information if incomplete traffic information is available. Still further route calculation techniques may calculate a best route by avoiding zigzagging or evaluating an assigned cost of a potential route.

Owner:HONDA MOTOR CO LTD

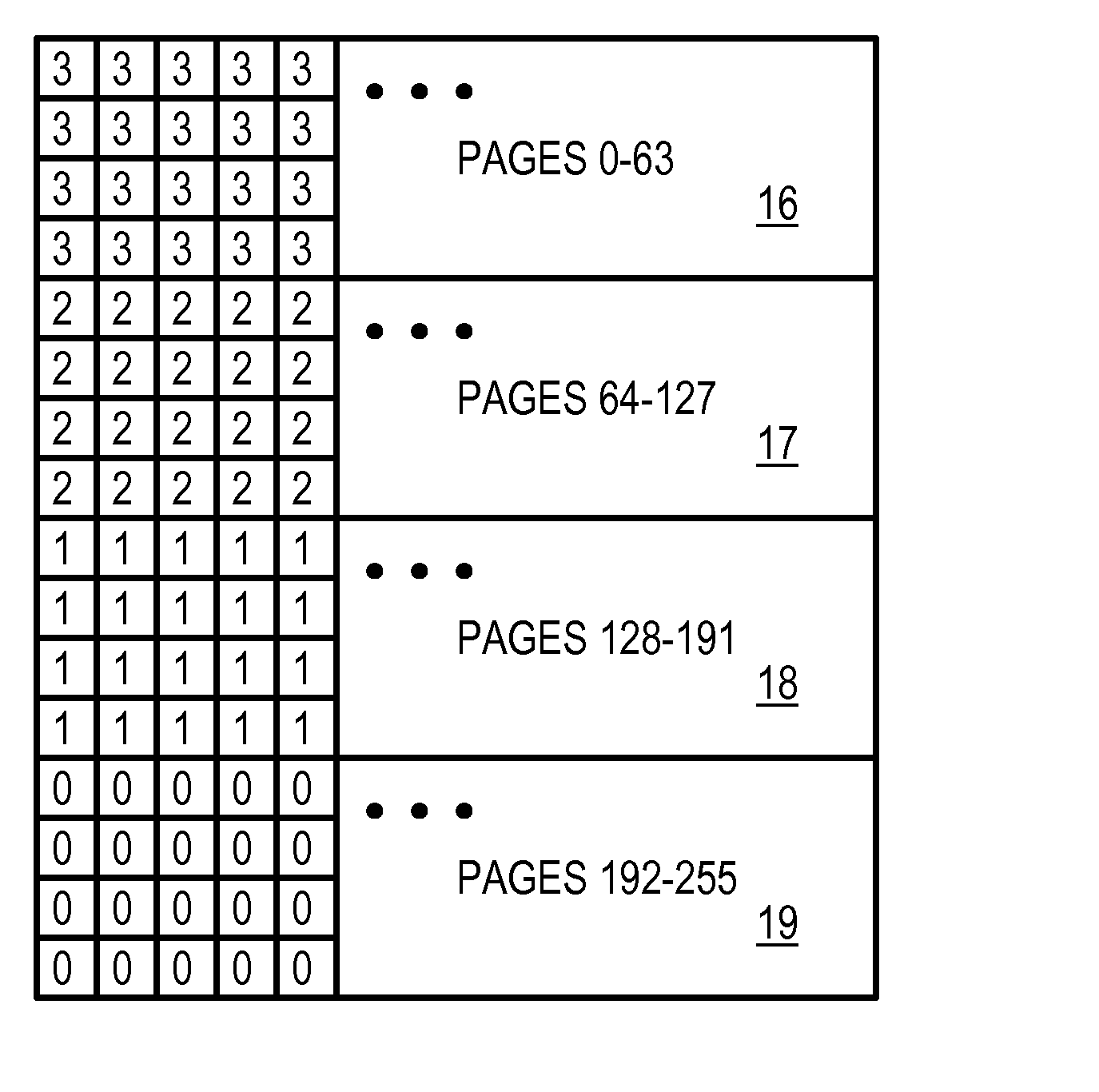

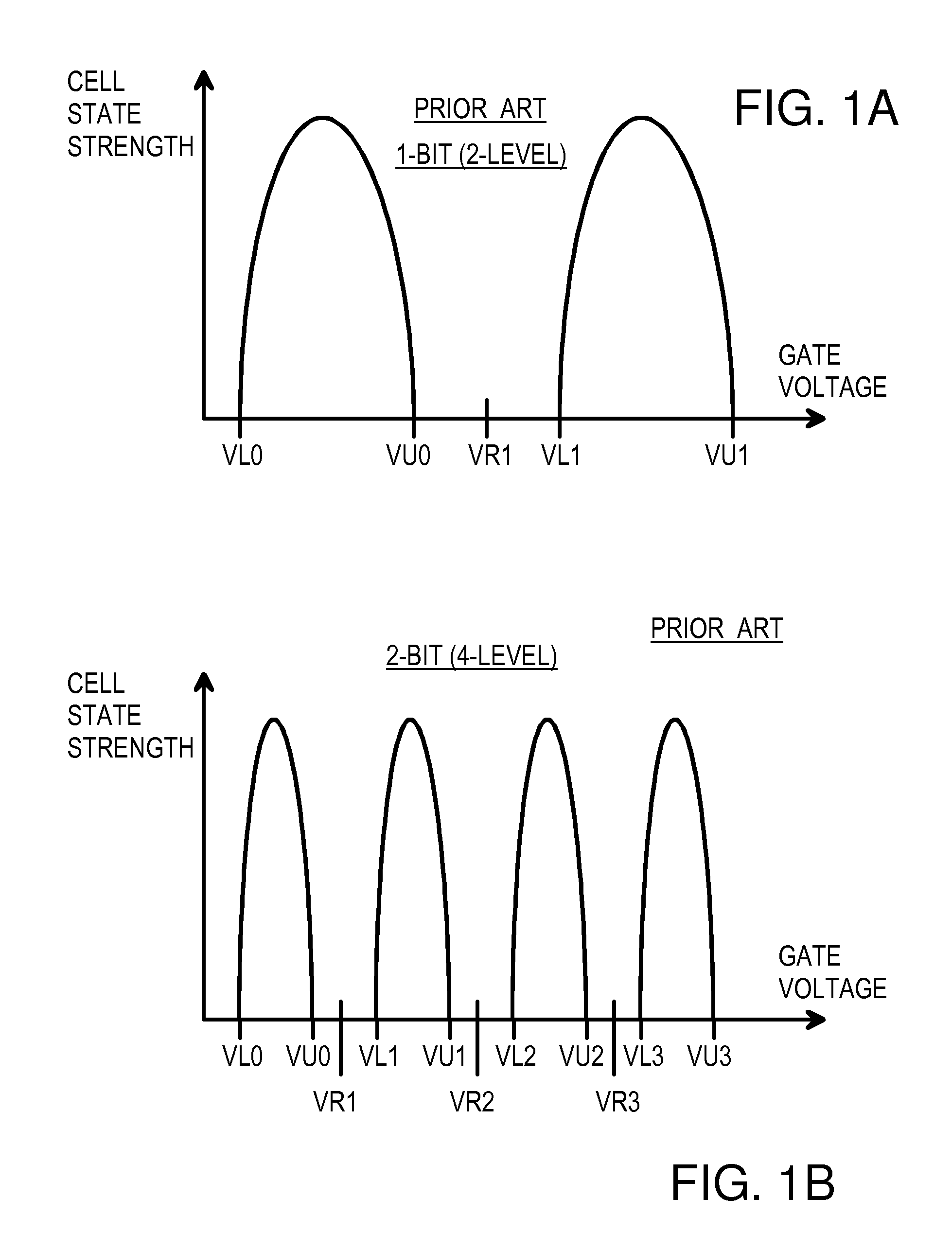

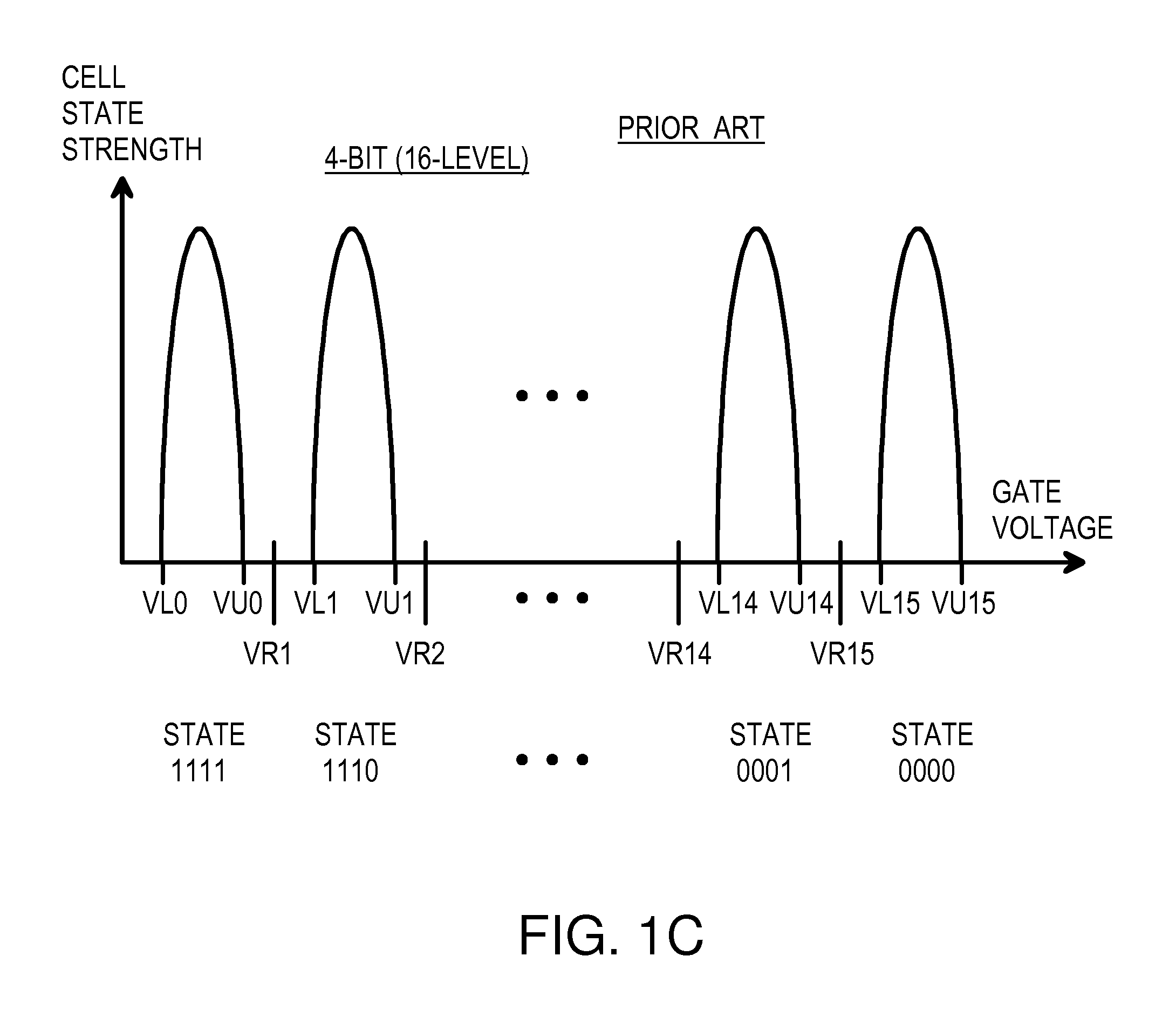

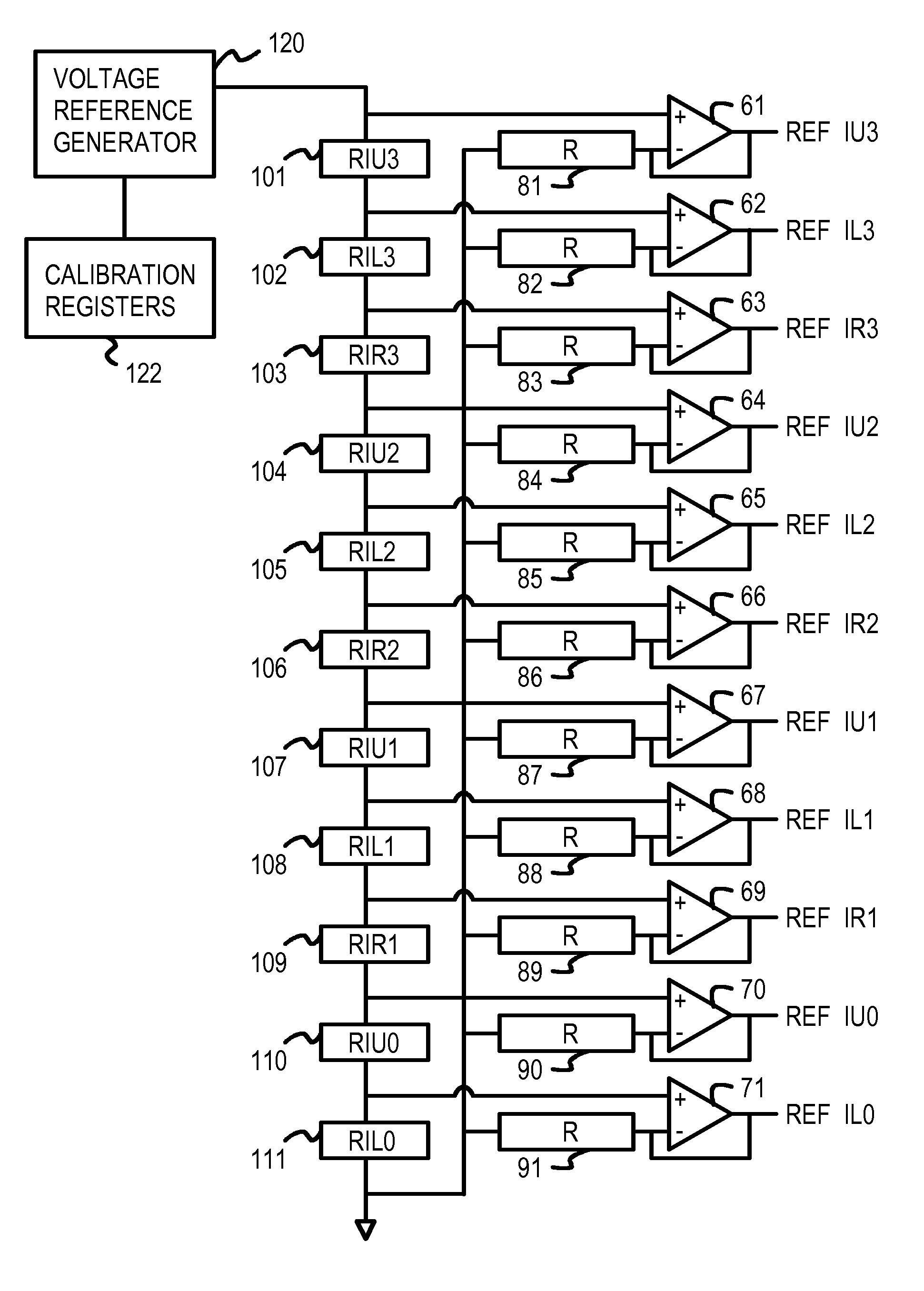

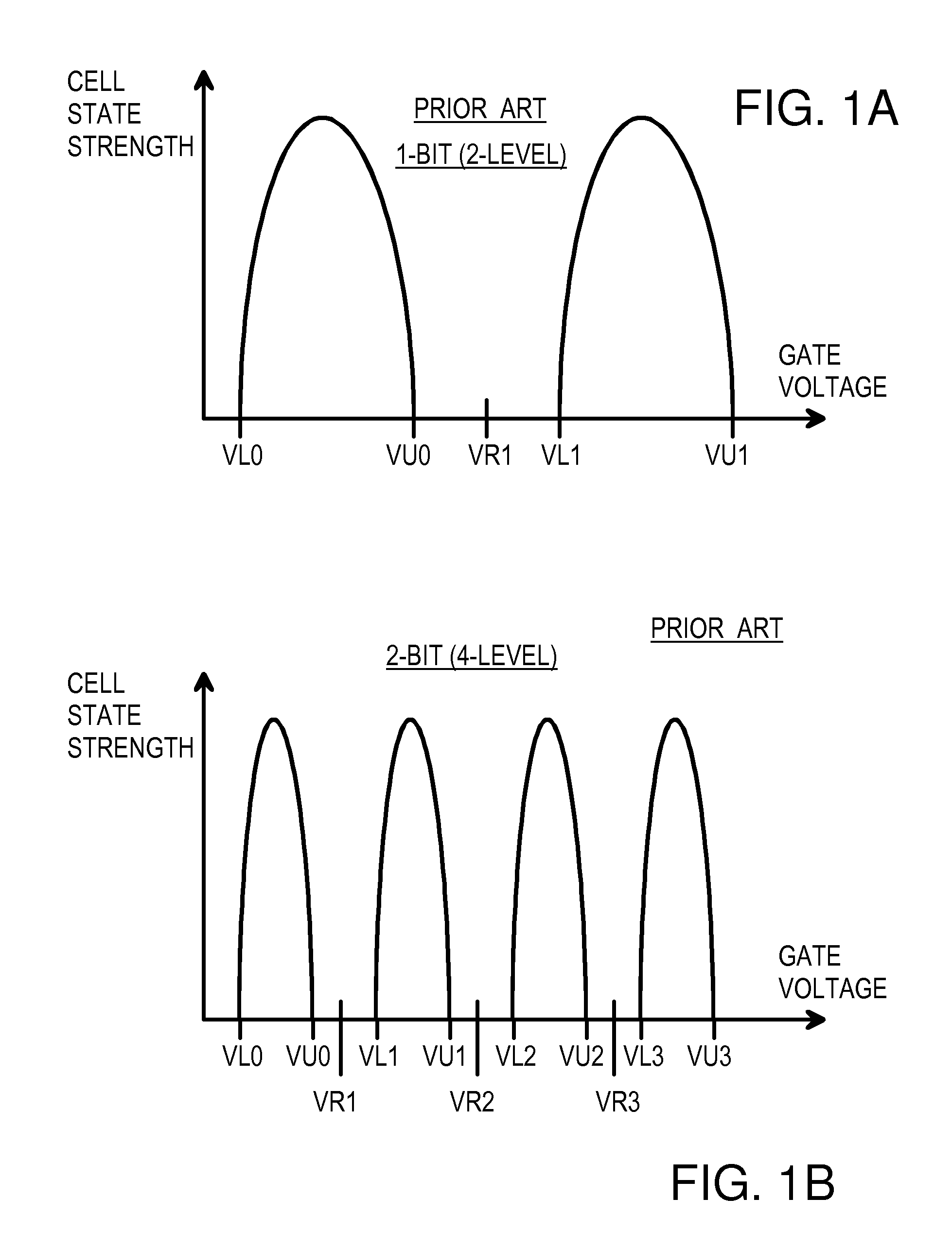

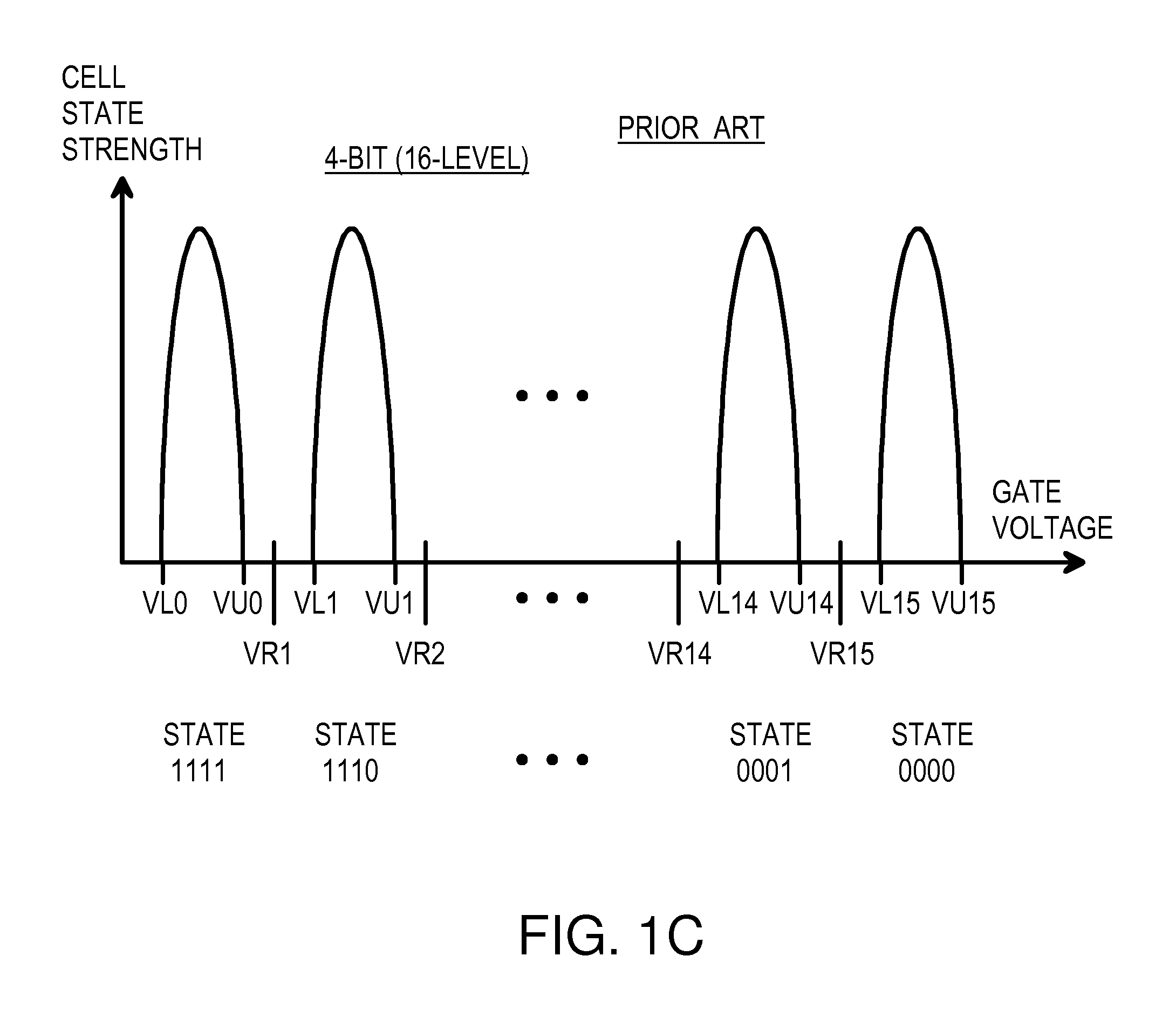

Cell-Downgrading and Reference-Voltage Adjustment for a Multi-Bit-Cell Flash Memory

A flash memory has multi-level cells (MLC) that can each store multiple bits per cell. Blocks of cells can be downgraded to fewer bits / cell when errors occur, or for storing critical data such as boot code. The bits from a single MLC are partitioned among multiple pages to improve error correctability using Error Correction Code (ECC). An upper reference voltage is generated by a voltage reference generator in response to calibration registers that can be programmed to alter the upper reference voltage. A series of decreasing references are generated from the upper reference voltage and are compared to a bit-line voltage. Compare results are translated by translation logic that generates read data and over- and under-programming signals. Downgraded cells use the same truth table but generate fewer read data bits. Noise margins are asymmetrically improved by using the same sub-states for reading downgraded and full-density MLC cells.

Owner:SUPER TALENT TECH CORP

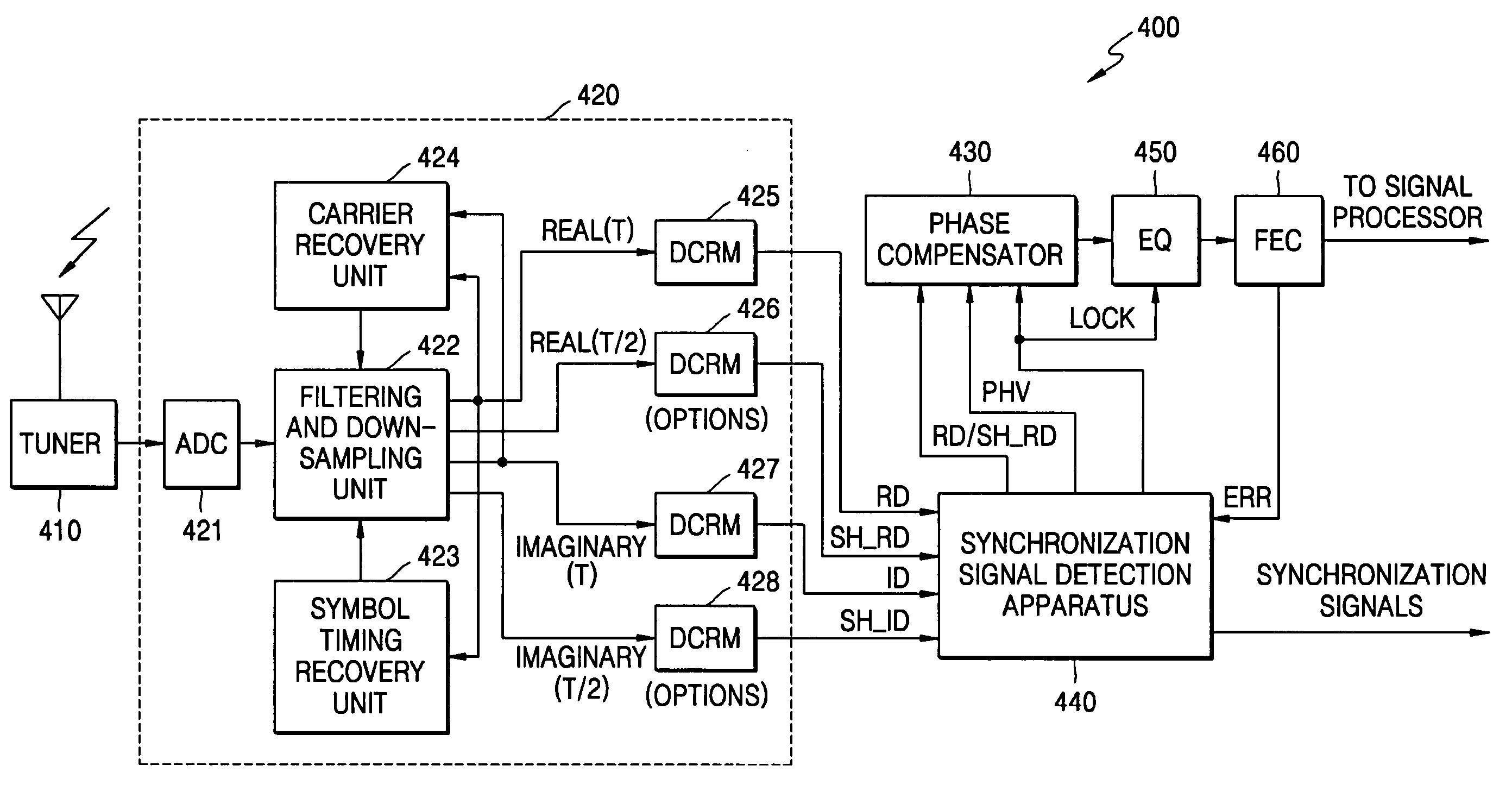

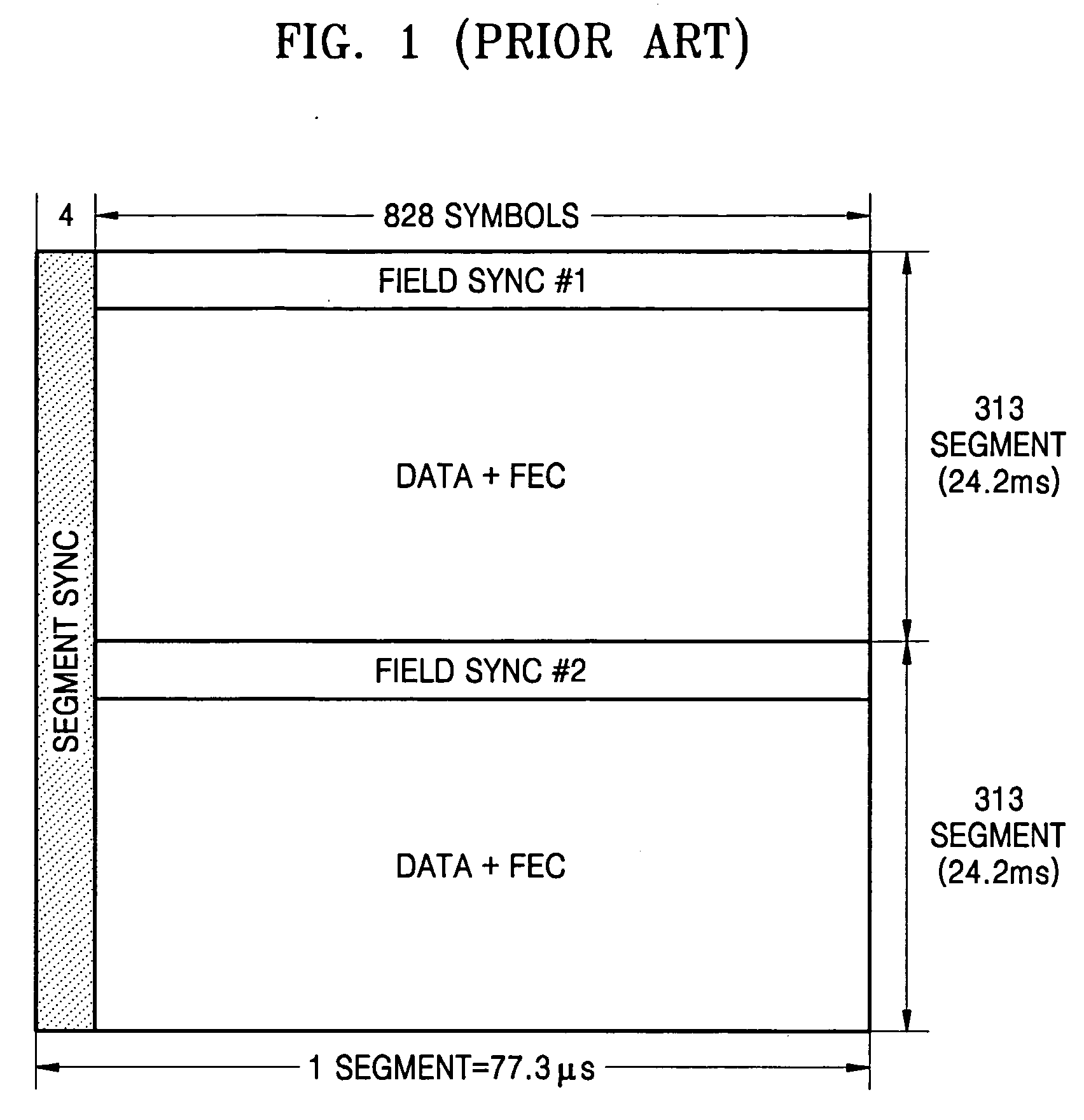

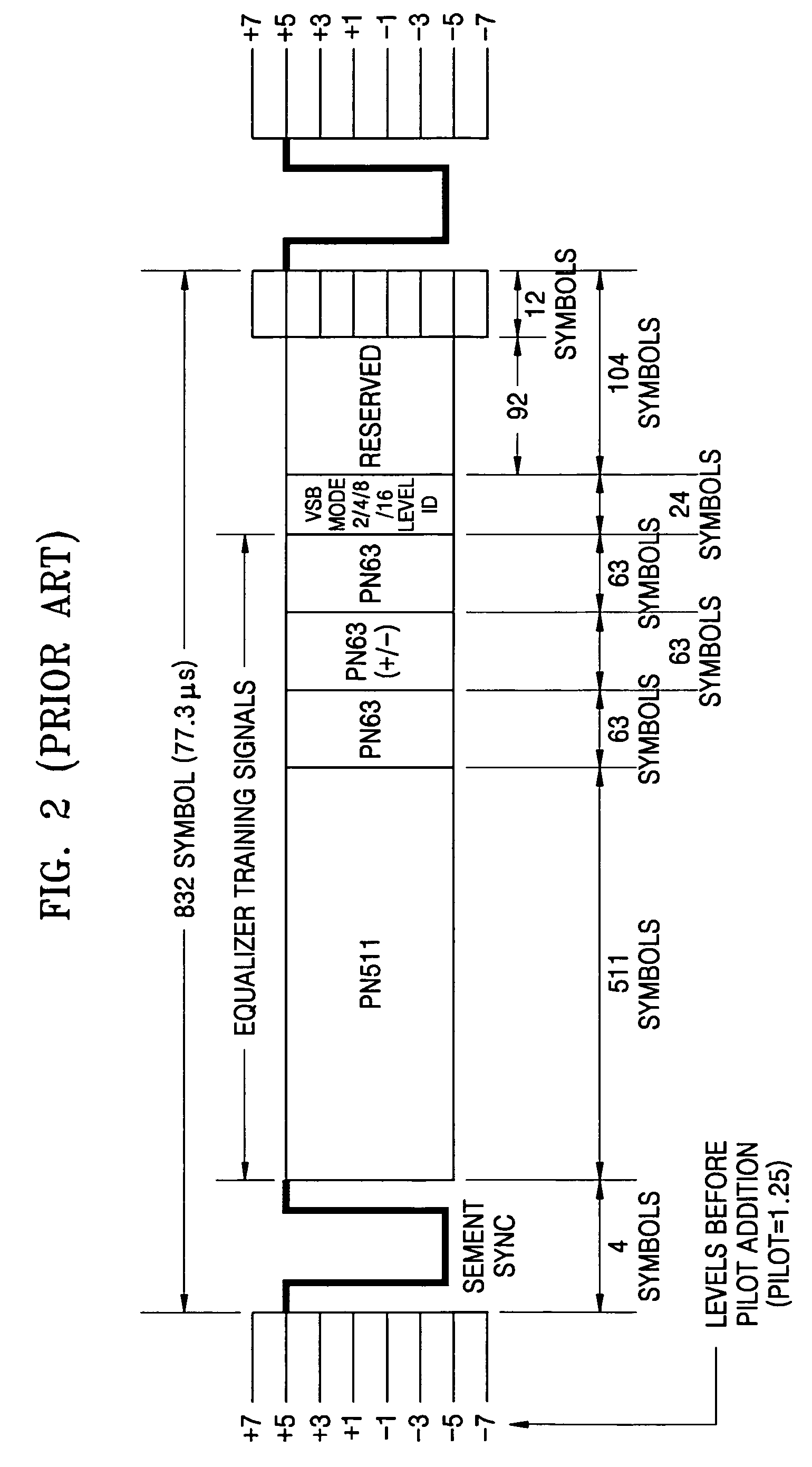

Synchronization signal detection circuit and method of digital television (DTV) receiver

InactiveUS20060078072A1Guaranteed uptimeStable operation can be assuredTelevision system detailsColor burst signal generation/insertionControl signalDTV receiver

A synchronization signal detection circuit and method of a digital TV (DTV) receiver are provided. The synchronization signal detection circuit determines a precise main path by determining powers in consideration of the influence of multiple paths near signals located at a peak value location and guarantees a stable operation of an equalizer by using error values output from a decoder to generate a synchronization locking control signal. A power signal based on the correlation of the received signal with a PN511 sequence is filtered to compensate for a dynamic multipath distortion (e.g., due to other multipath signals near signals located at a peak value location). The magnitude of the filtered power signal is then compared (e.g., with a predetermined threshold value) to determine the position of the main path (e.g., at the peak value location, or at a pre or post multipath signal location).

Owner:SAMSUNG ELECTRONICS CO LTD

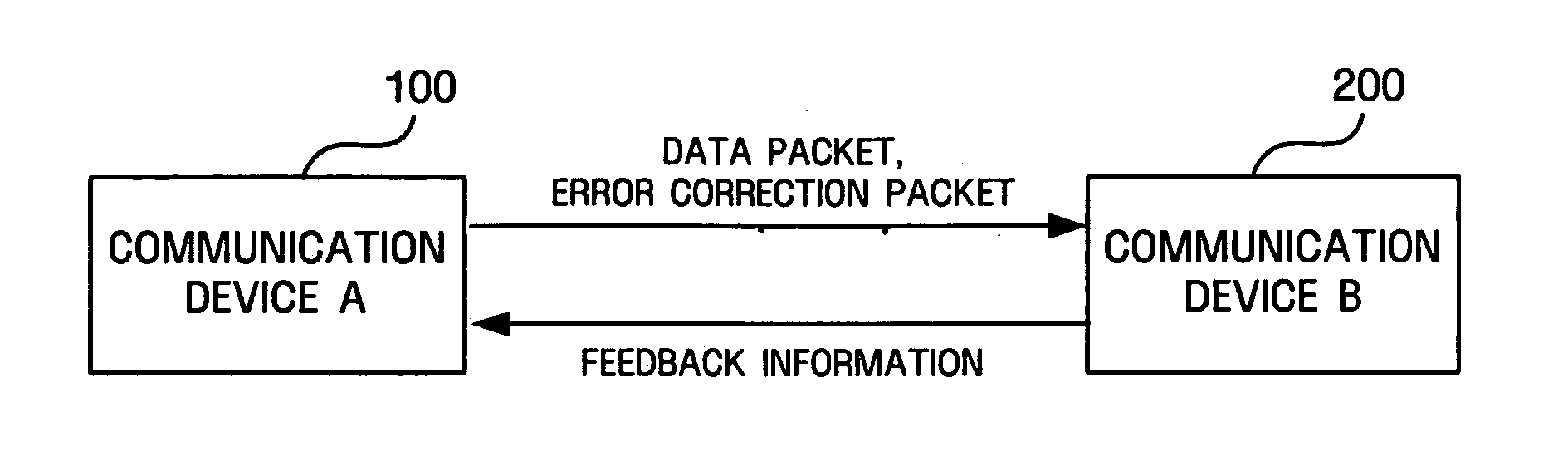

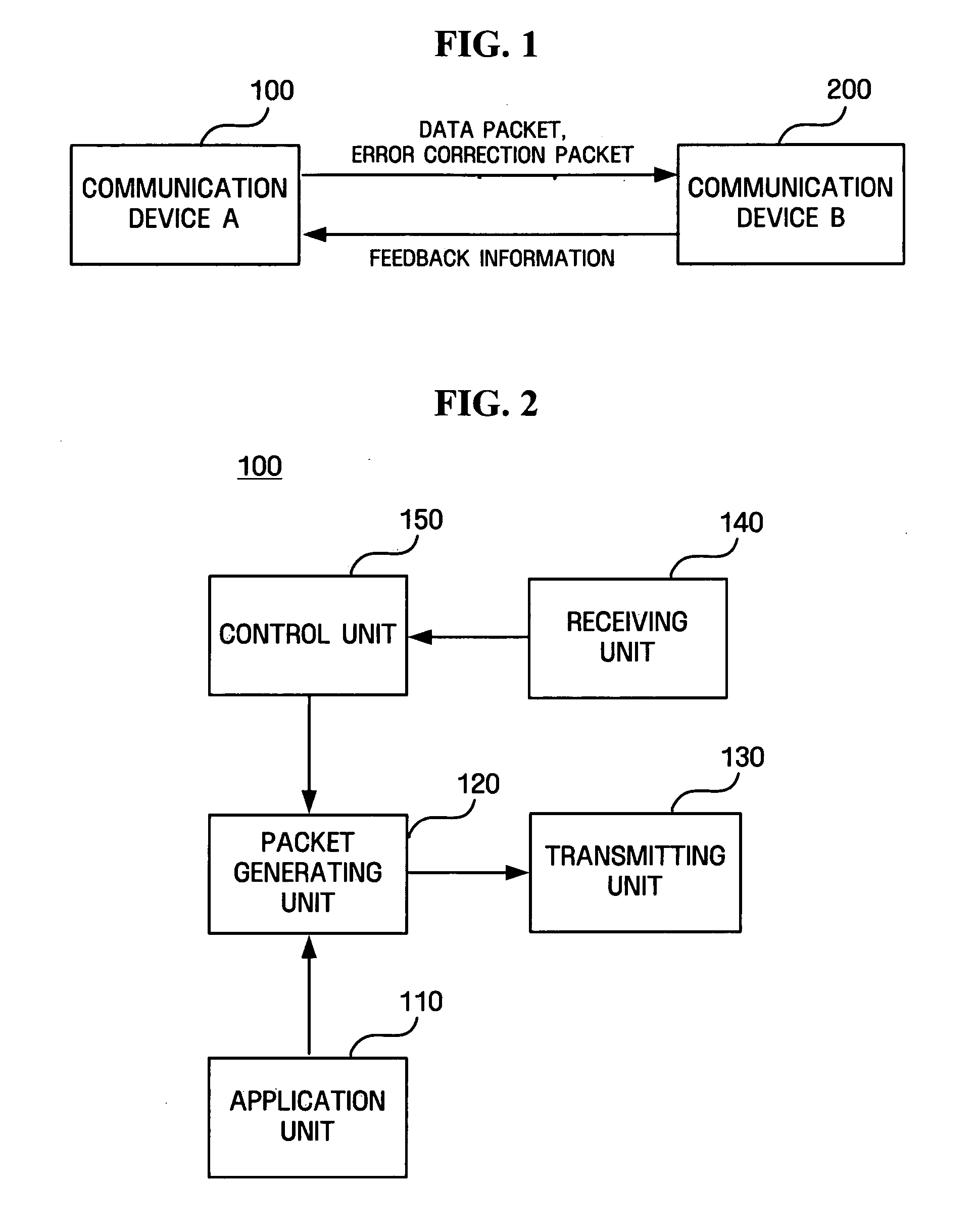

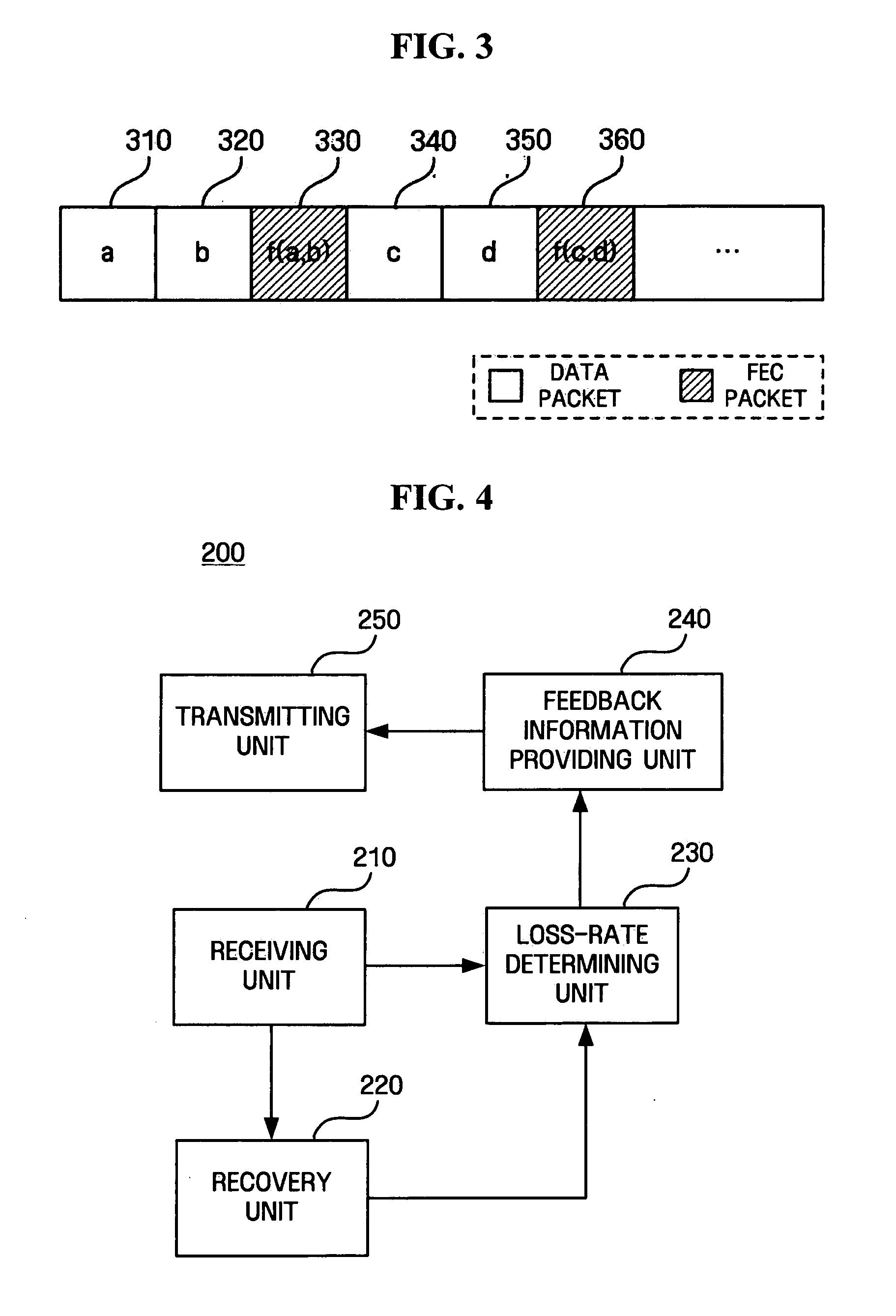

Method of controlling transmission rate by using error correction packets and communication apparatus using the same

ActiveUS20060280205A1Increase percentageReduce percentageEnergy efficient ICTTime-division multiplexCommunication deviceUser Error

A method of controlling transmission rate by using error correction packets and a communication apparatus using the same are provided. According to an embodiment of the present invention, the method of controlling transmission rate by using error correction packets includes transmitting a first packet group composed in a predetermined ratio of data packets and error correction packets, transmitting a second packet group composed of the data packets and the error correction packets in a ratio adjusted based on feedback information about the first packet group, and controlling the transmission rate based on the feedback information about the second packet group.

Owner:SAMSUNG ELECTRONICS CO LTD

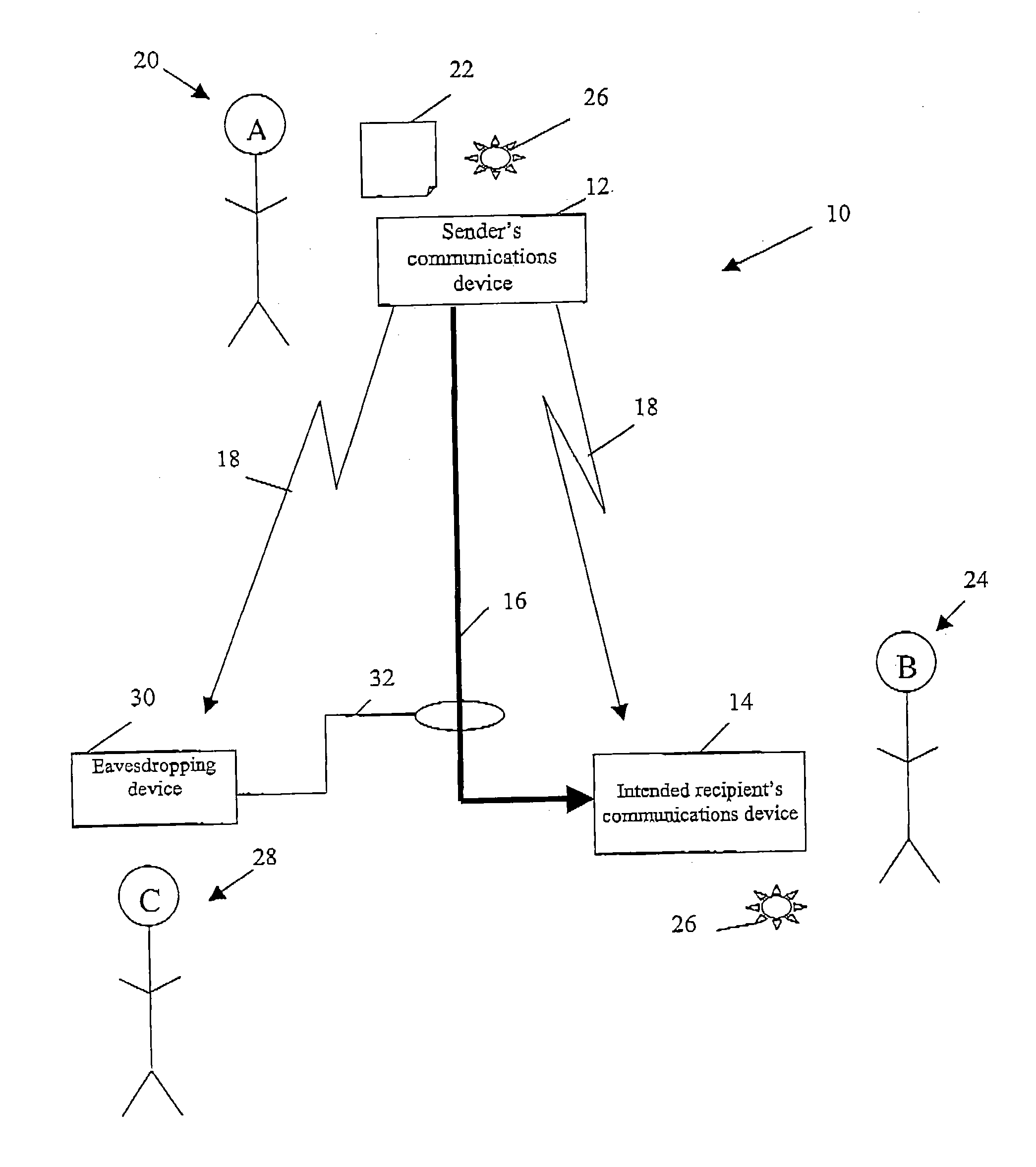

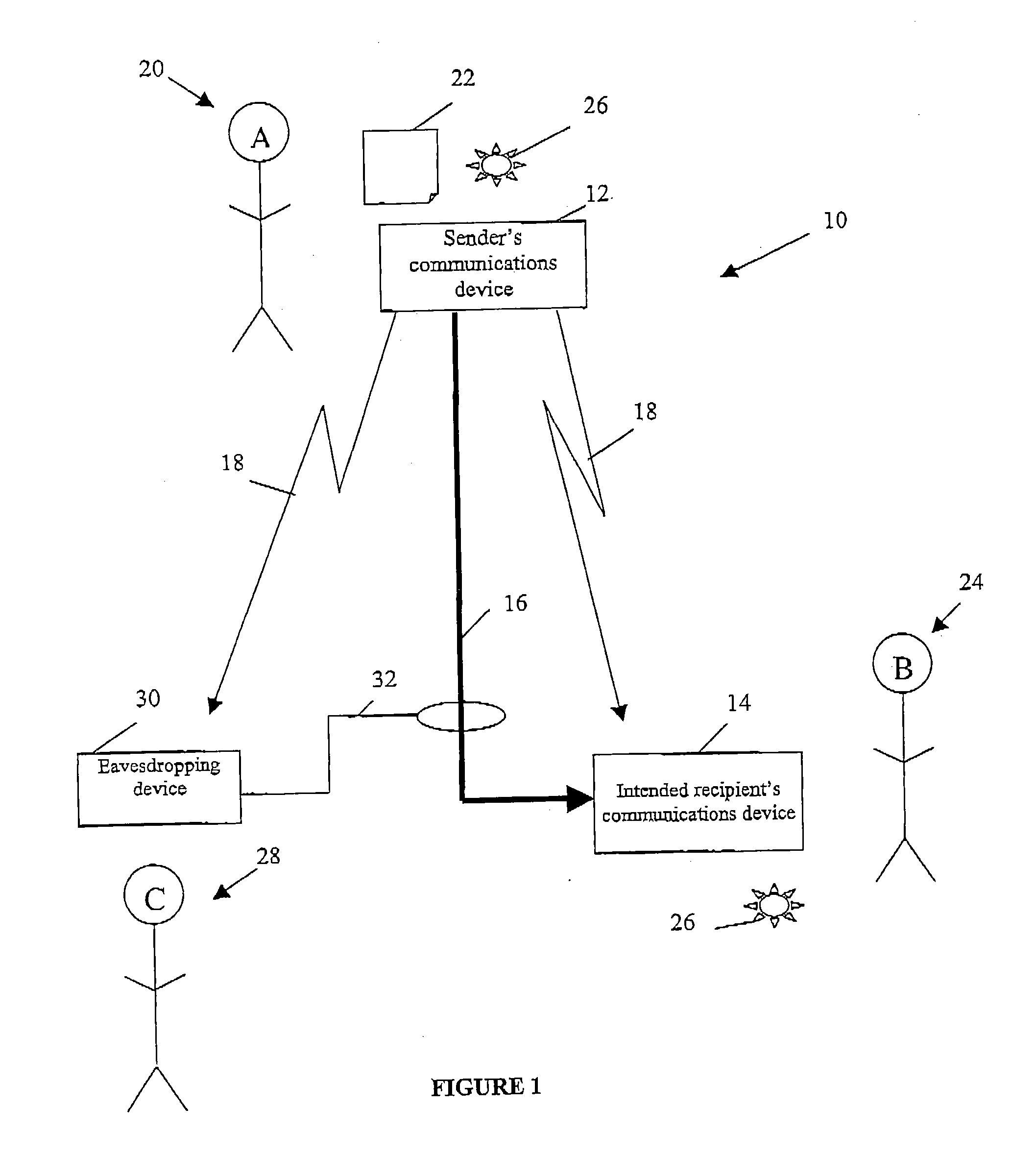

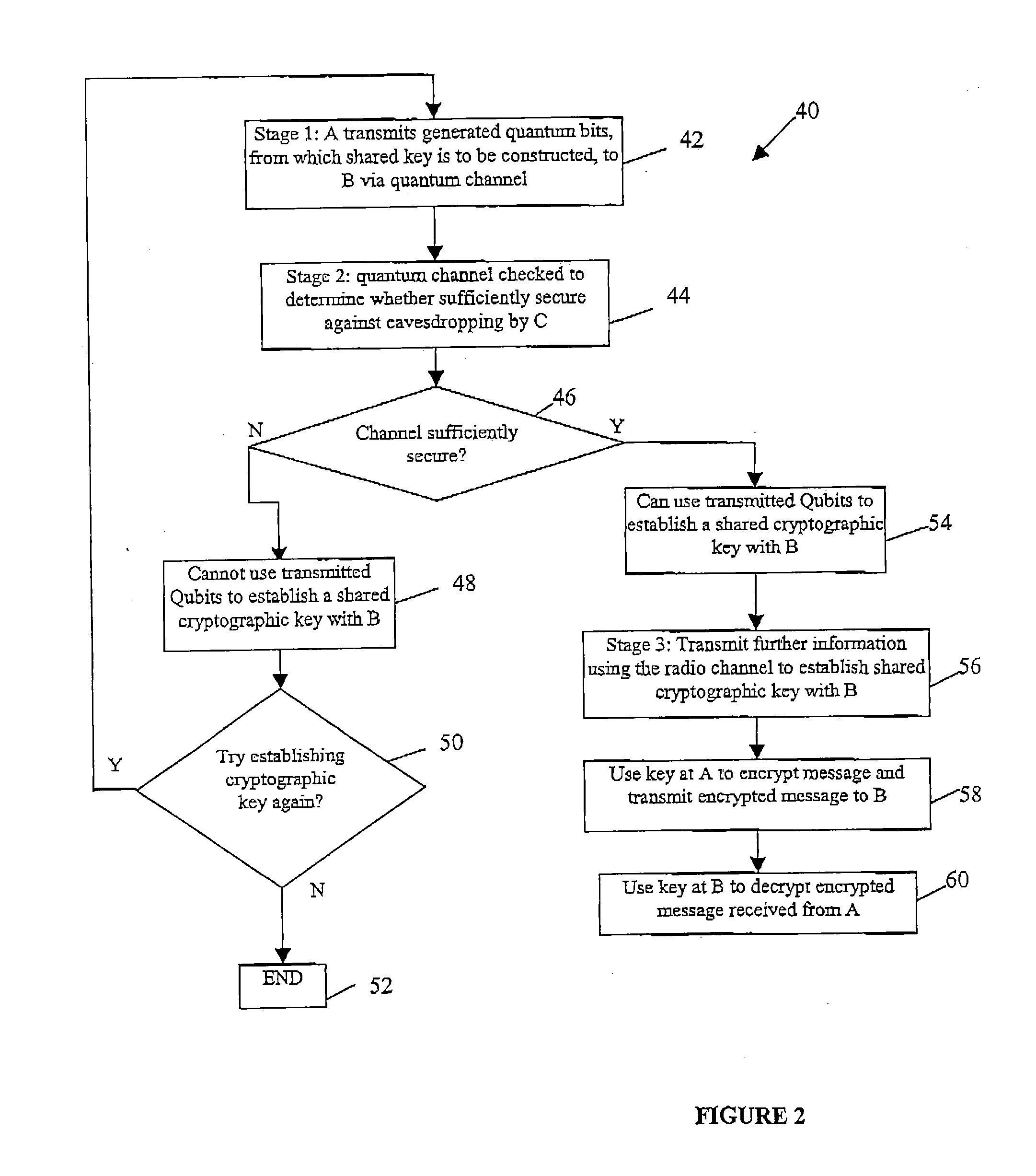

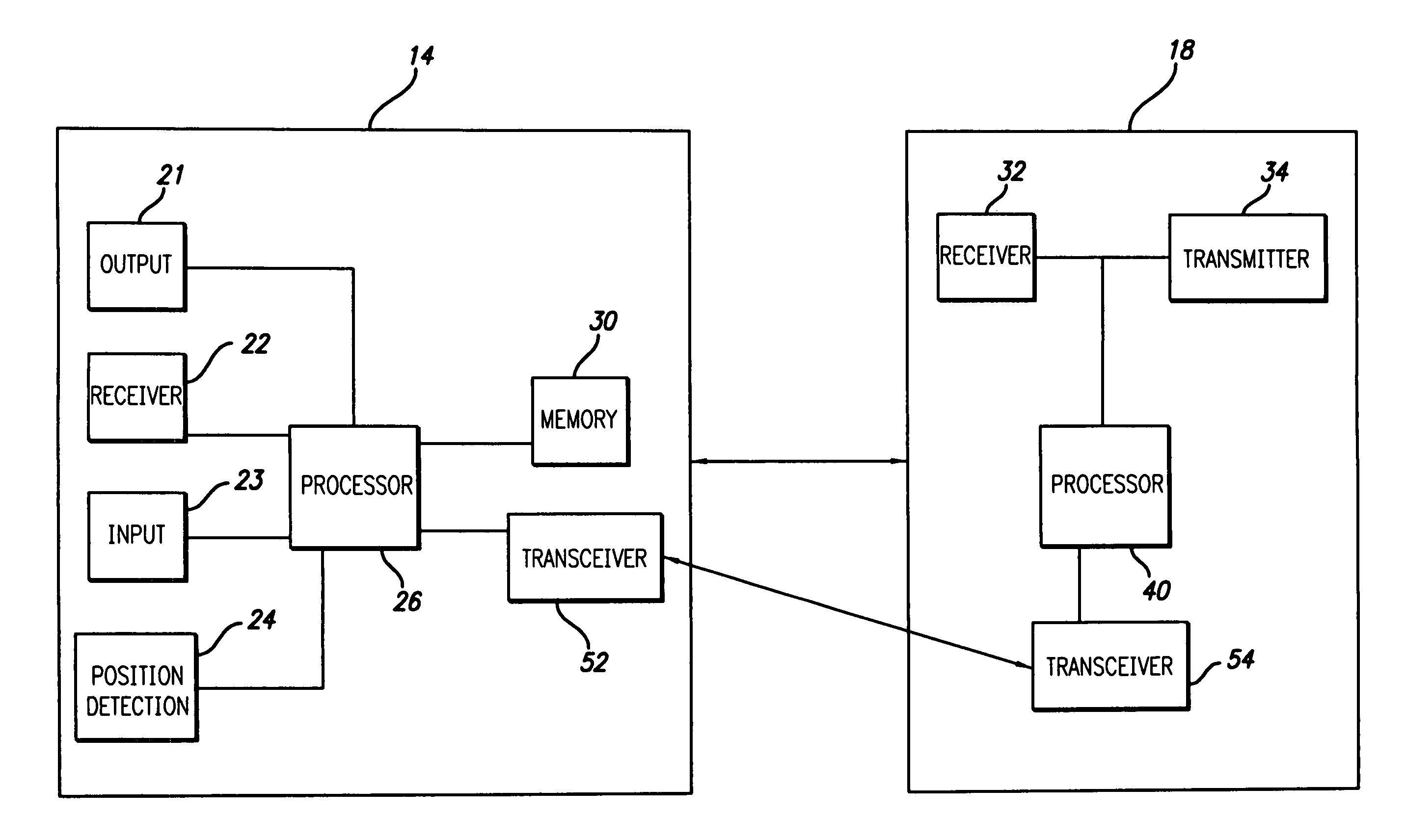

Quantum cryptography

ActiveUS20050036624A1Reduce bitrateIncrease bitrateKey distribution for secure communicationQuantum channelHilbert space

A method of establishing a shared secret random cryptographic key between a sender and a recipient using a quantum communications channel is described. The method comprises: generating a plurality of random quantum states of a quantum entity, each random state being defined by a randomly selected one of a first plurality of bases in Hilbert space, transmitting the plurality of random quantum states of the quantum entity via the quantum channel to a recipient, measuring the quantum state of each of the received quantum states of the quantum entity with respect to a randomly selected one of a second plurality of bases in Hilbert space, transmitting to the recipient composition information describing a subset of the plurality of random quantum states, analysing the received composition information and the measured quantum states corresponding to the subset to derive a first statistical distribution describing the subset of transmitted quantum states and a second statistical distribution describing the corresponding measured quantum states, establishing the level of confidence in the validity of the plurality of transmitted random quantum states by verifying that the first and second statistical distributions are sufficiently similar, deriving a first binary sting and a second binary string, correlated to the first binary string, respectively from the transmitted and received plurality of quantum states not in the subset, and carrying out a reconciliation of the second binary string to the first binary string by using error correction techniques to establish the shared secret random cryptographic key from the first and second binary strings.

Owner:HEWLETT-PACKARD ENTERPRISE DEV LP +1

Route calculation method for a vehicle navigation system

ActiveUS7680596B2Increase and decrease broadcastReduce twistInstruments for road network navigationRoad vehicles traffic controlNavigation systemReceipt

Traffic information, including flow information and incident information, obtained through a traffic management system for providing and facilitating the exchange of traffic information between a remote location and a vehicle may be used in route calculation by a navigation device. The navigation device may recalculate a route based on anticipated user error. Alternatively, the navigation device may recalculate a route using received traffic information triggered by the receipt of a traffic information update, or triggered by the passage of an amount of time. The broadcast rate of traffic information updates may vary temporally (providing more frequent updates during peak commute times) or geographically (providing more frequent updates to metropolitan areas with increased traffic information needs). If route calculation is triggered by an elapsed amount of time, the amount of time may vary to be shorter during peak commute times. Additional route calculation techniques allow the incorporation of historical traffic information or the use of the most recent traffic information if incomplete traffic information is available. Still further route calculation techniques may calculate a best route by avoiding zigzagging or evaluating an assigned cost of a potential route.

Owner:HONDA MOTOR CO LTD

Cell-downgrading and reference-voltage adjustment for a multi-bit-cell flash memory

A flash memory has multi-level cells (MLC) that can each store multiple bits per cell. Blocks of cells can be downgraded to fewer bits / cell when errors occur, or for storing critical data such as boot code. The bits from a single MLC are partitioned among multiple pages to improve error correctability using Error Correction Code (ECC). An upper reference voltage is generated by a voltage reference generator in response to calibration registers that can be programmed to alter the upper reference voltage. A series of decreasing references are generated from the upper reference voltage and are compared to a bit-line voltage. Compare results are translated by translation logic that generates read data and over- and under-programming signals. Downgraded cells use the same truth table but generate fewer read data bits. Noise margins are asymmetrically improved by using the same sub-states for reading downgraded and full-density MLC cells.

Owner:SUPER TALENT TECH CORP

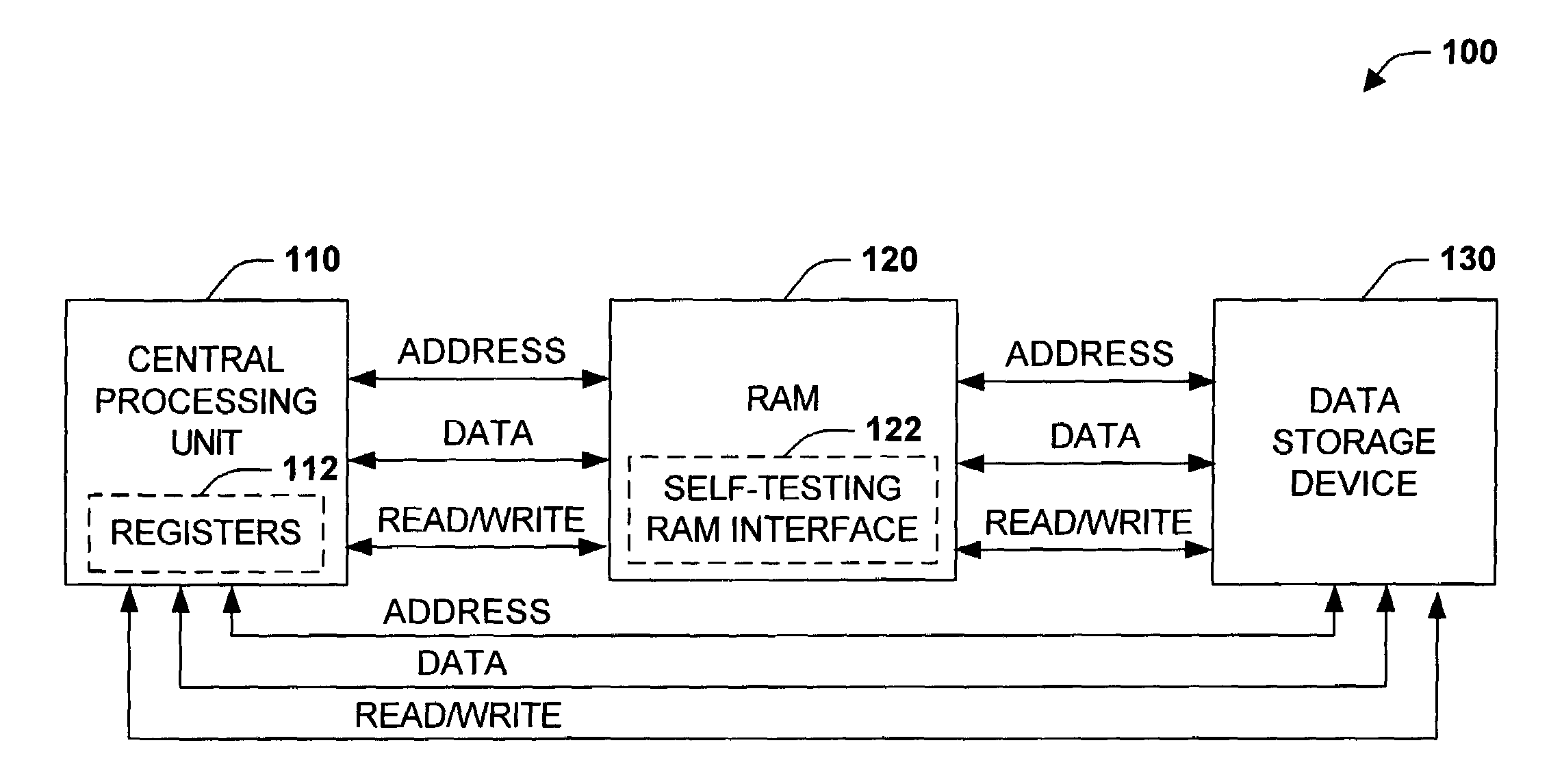

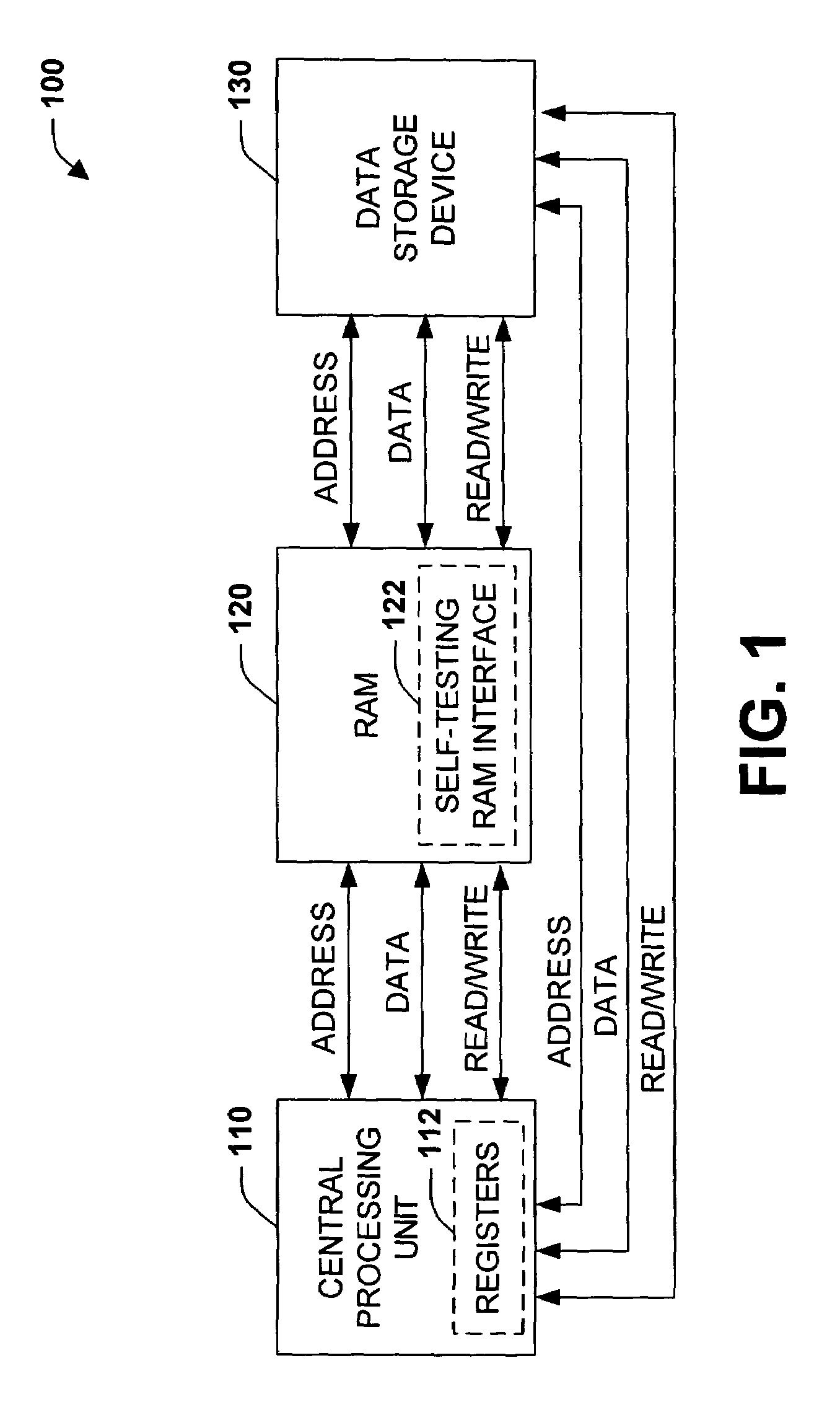

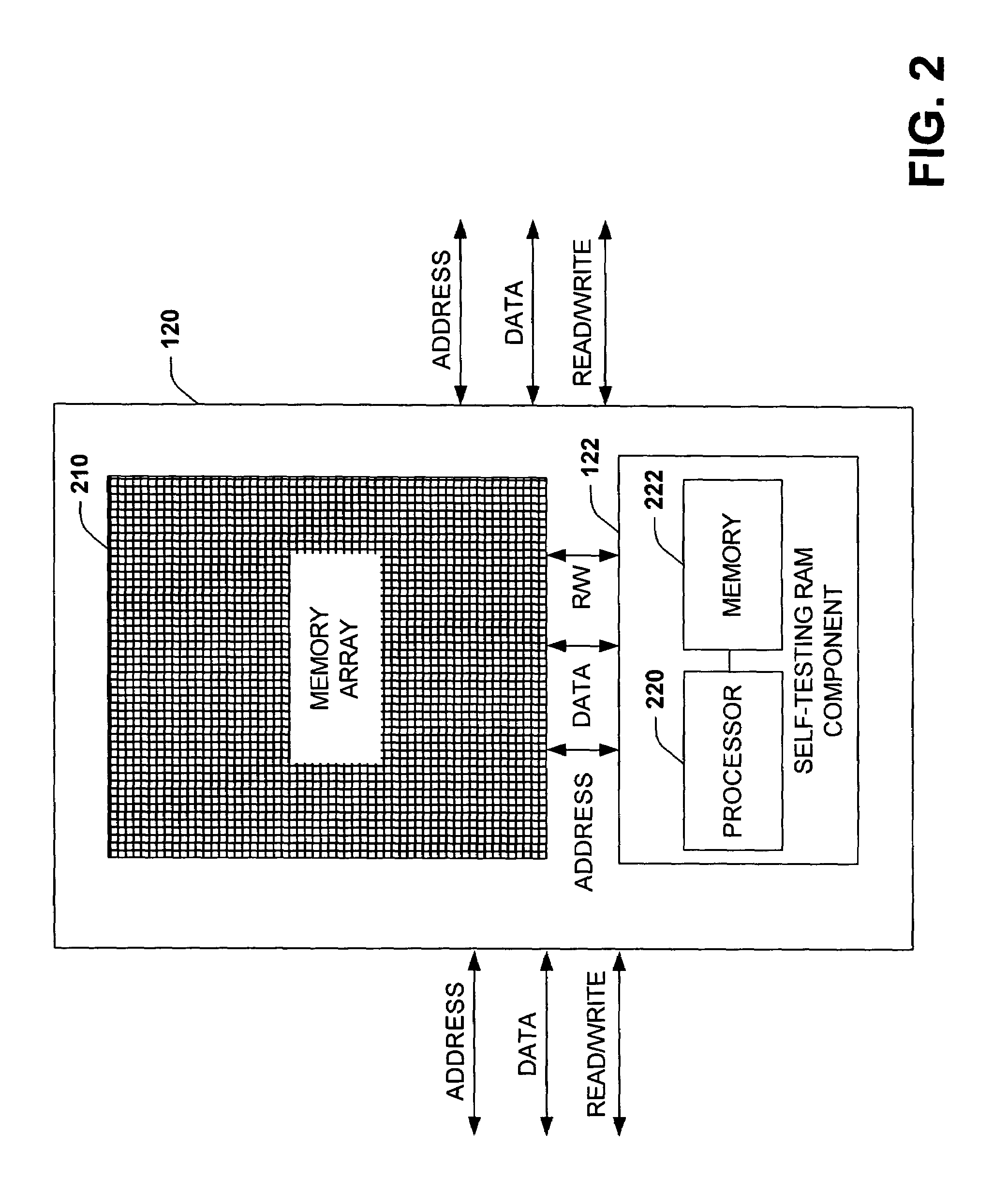

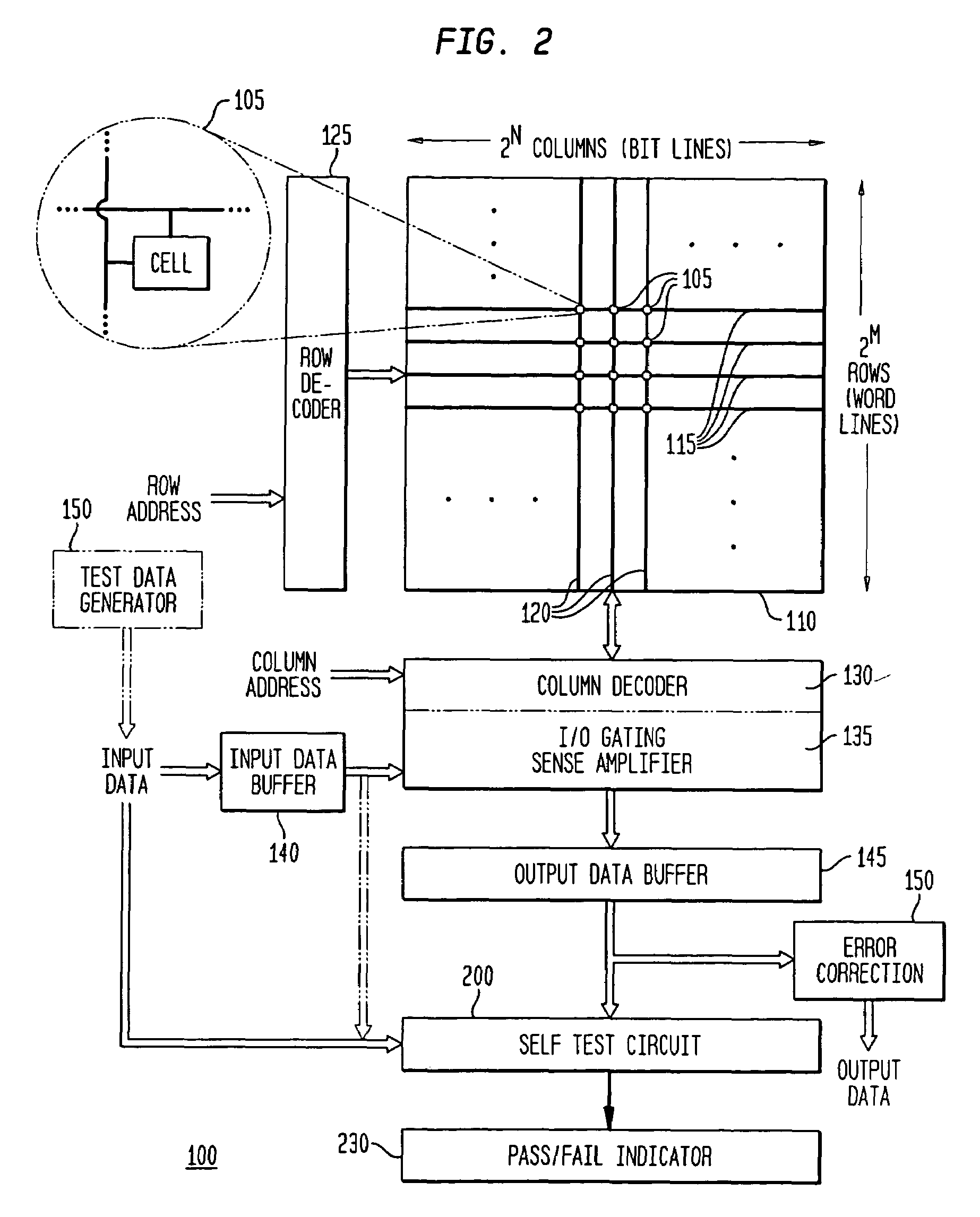

Self-testing RAM system and method

ActiveUS7334159B1Easy to testTedious to testUnauthorized memory use protectionDigital storageData integrityMemory interface

A self-testing and correcting random access memory (RAM) device and methodology is disclosed herein. The device includes at least one array of memory to enable data storage and self-testing RAM interface for evaluating, correcting, and / or compensating for memory cell errors. The RAM device, via the self-testing RAM interface, supports interaction with a central processing unit (CPU) to facilitate testing of the CPU to memory interface as well as the device memory array. Upon detection of memory errors, the self-testing RAM interface can notify the CPU, notify an exception handler, correct, and / or compensate for the errors. Error correction can be accomplished using error correction codes (ECCs) alone or in combination with retrieval and replacement of erroneous data with correct data stored in different locations. Memory cells that are physically defective and incapable of maintaining data integrity can be compensated for by mapping defective cells to a plurality of reserved replacement cells.

Owner:XENOGENIC DEV LLC

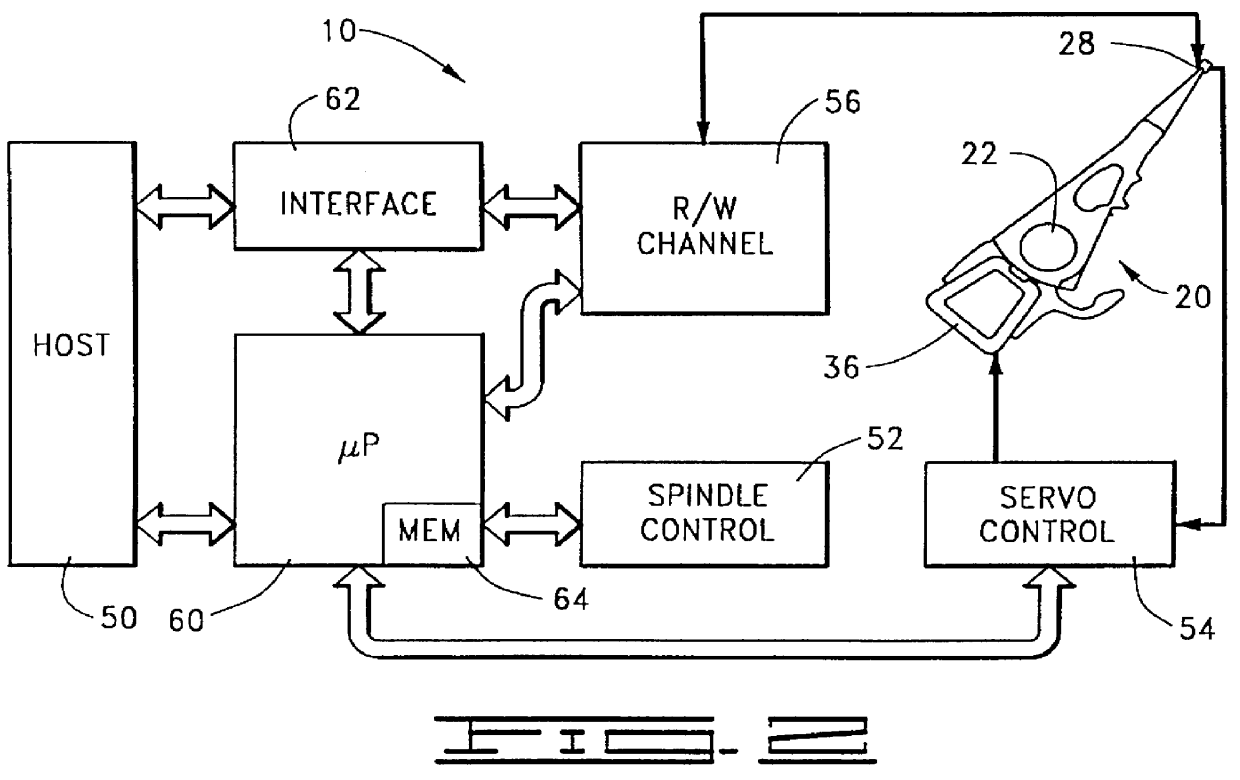

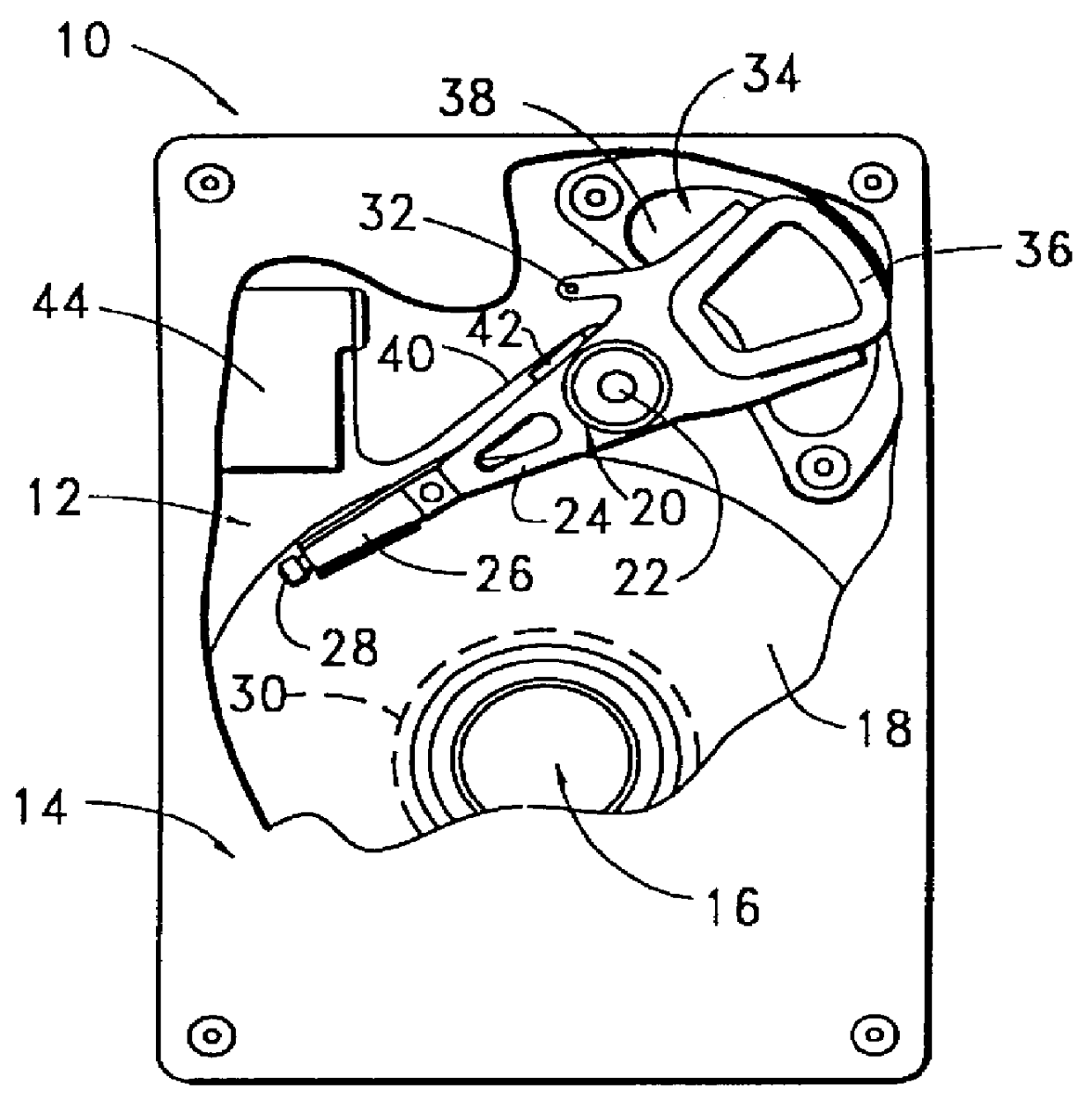

Read error recovery utilizing ECC and read channel quality indicators

PCT No. PCT / US97 / 04906 Sec. 371 Date Oct. 21, 1997 Sec. 102(e) Date Oct. 21, 1997 PCT Filed Mar. 27, 1997 PCT Pub. No. WO97 / 43835 PCT Pub. Date Nov. 20, 1997An apparatus and method for recovering from read errors detected by a read channel (70) in a sequence of data read from a disc (18) of a disc drive (10) by using read channel quality indicators to determine the appropriateness of using error correction in combination with other corrective actions utilized in the recovery process. Upon the detection of an uncorrected error in the retrieved data, the disc drive (10) enters a read error recovery routine wherein one or more corrective actions (102, 122) are applied in an effort to resolve the error. One of the channel quality indicators comprises a channel quality measurement (108, 128) determined as the sum of the square of the sampled data bit error values recovered during the read operation. When the channel quality measurement is at or below a threshold value indicative that the probability of passing undetected erroneous data is at an acceptable level (110, 130), error correction is applied to the data (112, 138); otherwise, error correction is disallowed (118, 140). Additional channel quality indicators comprise erasure pointers (132) which identify a particular set of symbols that are suspected of containing a read error. In such a case, the disc drive determines that the total number of symbols identified by the erasure pointers is below a predetermined erasure threshold before applying error correction (134, 136, 138), the erasure threshold selected to be within the correction capability of error correction circuitry 90.

Owner:SEAGATE TECH LLC

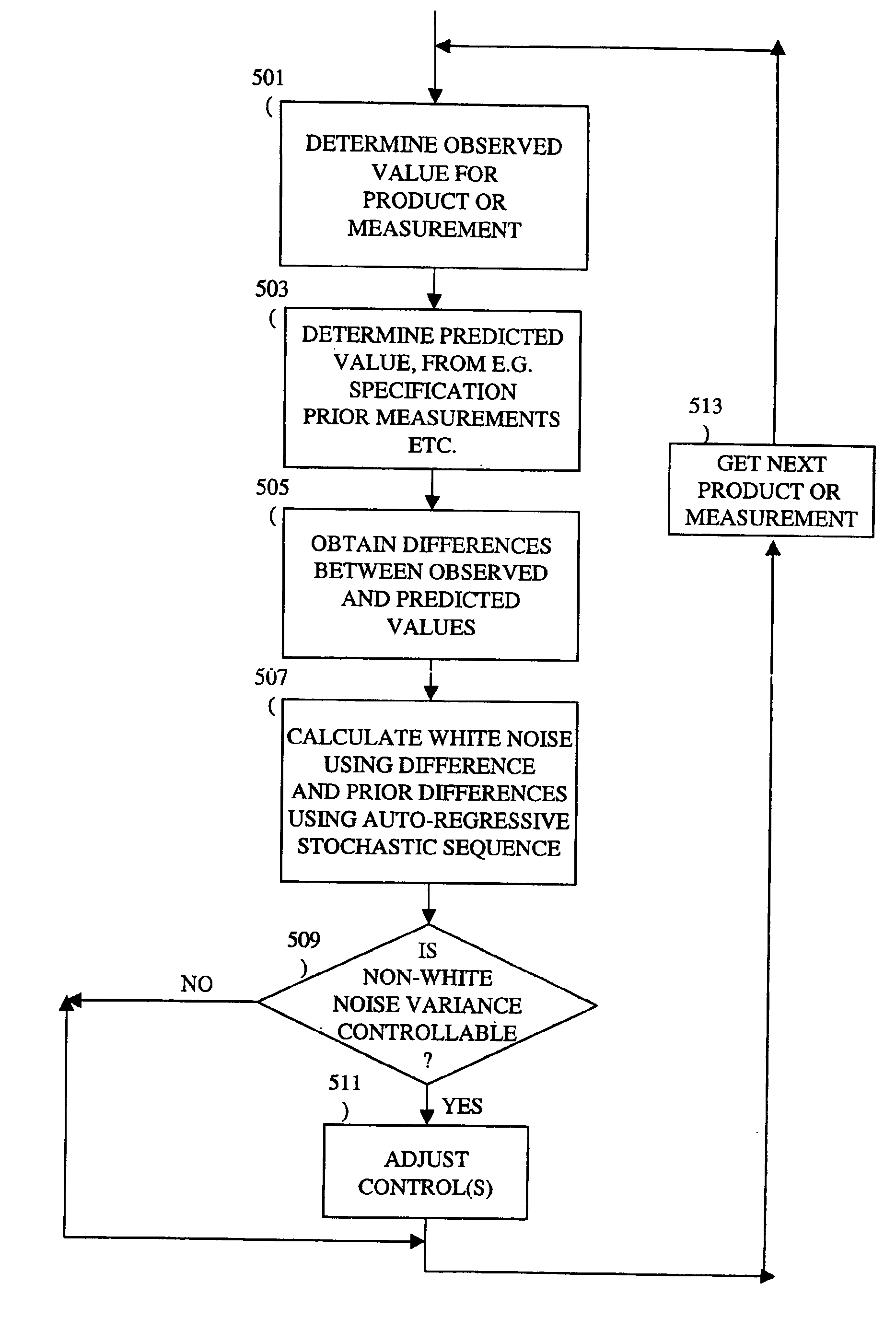

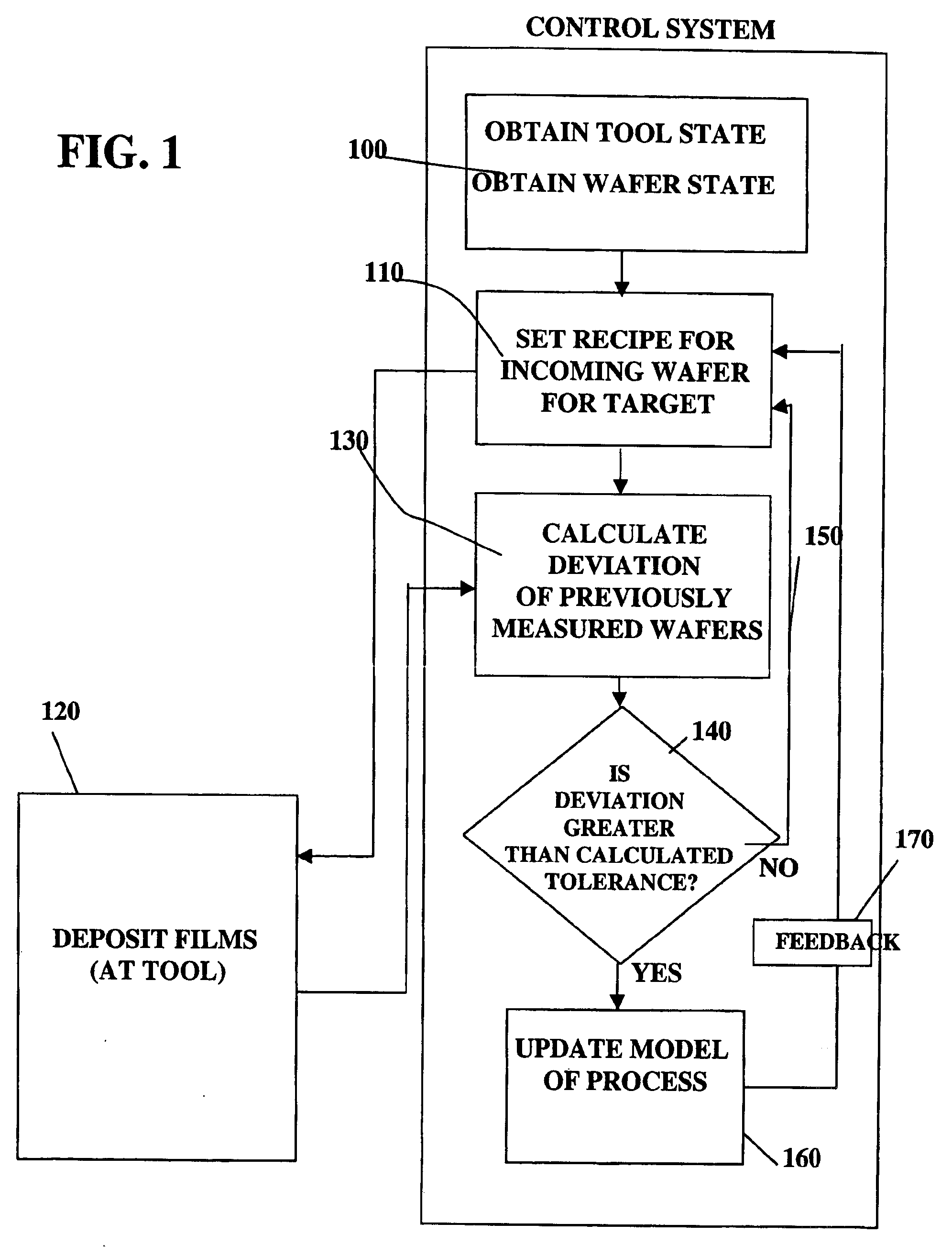

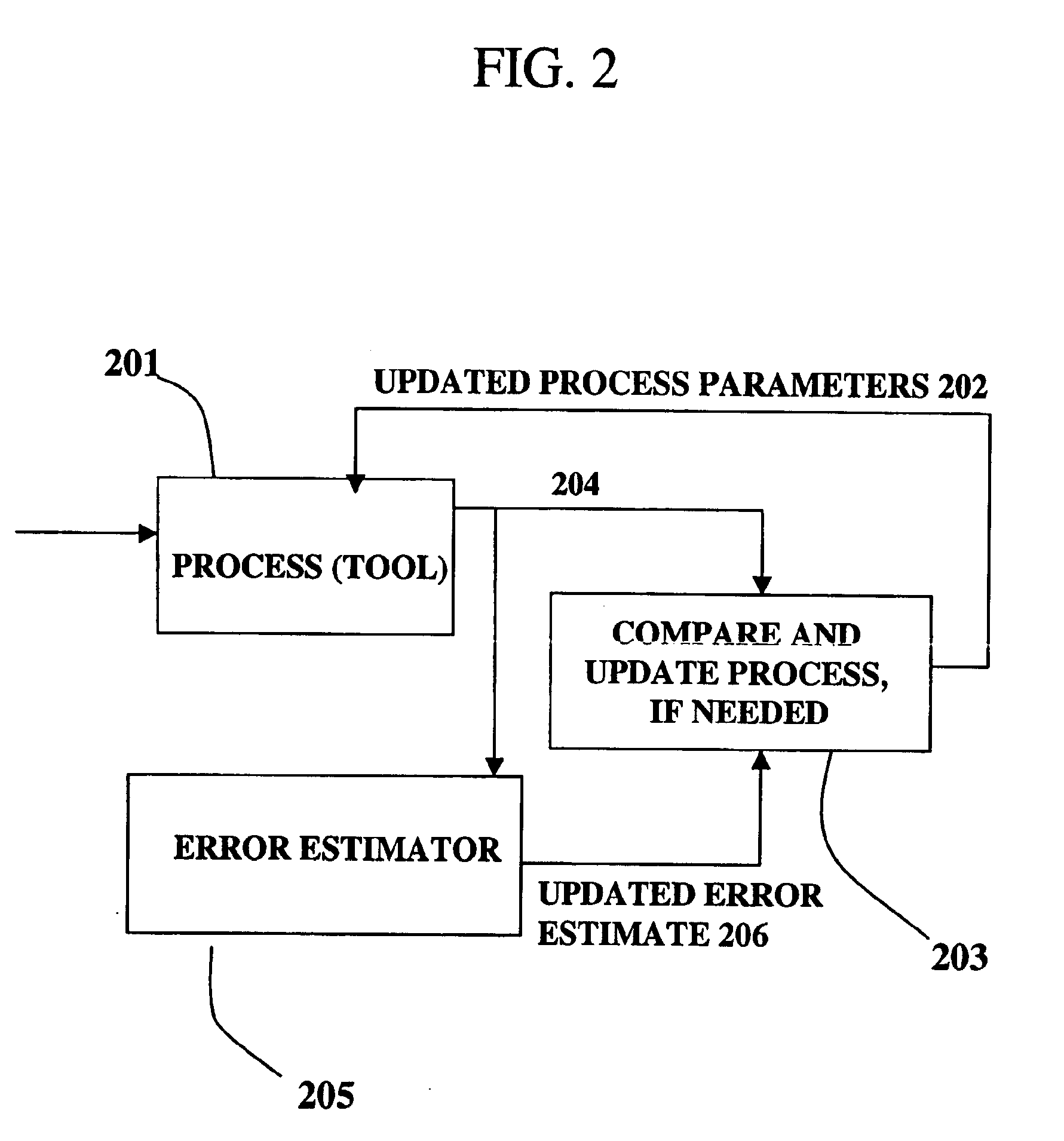

Dynamic offset and feedback threshold

InactiveUS6961626B1Strict controlNon-controllableTotal factory controlSpecial data processing applicationsProcess varianceSemiconductor chip

A method, system and medium are provided for enabling improved feedback and feedforward control. An error, or deviation from target result, is observed during manufacture of semi conductor chips. The error within standard deviation is caused by two components: a white noise component and a signal component (such as systematic errors). The white noise component is random noise and therefore is relatively non-controllable. The systematic error, in contrast, may be controlled by changing the control parameters. A ratio between the two components is calculated autoregressively. Based on the ratio and using the observed or measured error, the actual value of the error caused by the signal component is calculated utilizing an autoregressive stochastic sequence. The actual value of the error is then used in determining when and how to change the control parameters. The autoregressive stochastic sequence addresses the issue of real-time control of the effects of run-to-run deviations, and provides a mechanism that can extract white noise from the statistical process variance in real time. This results in an ability to provide tighter control of feedback and feedforward variations.

Owner:APPLIED MATERIALS INC

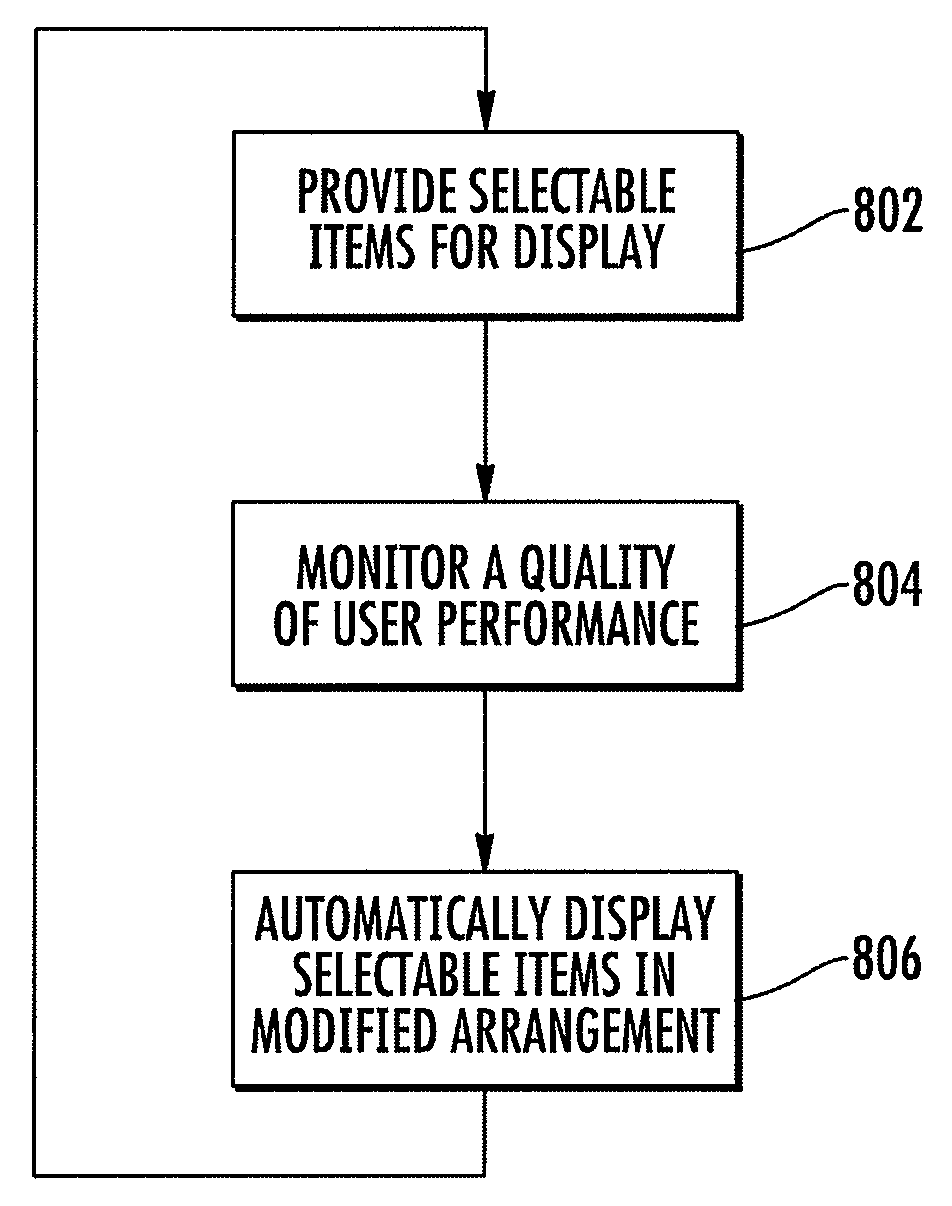

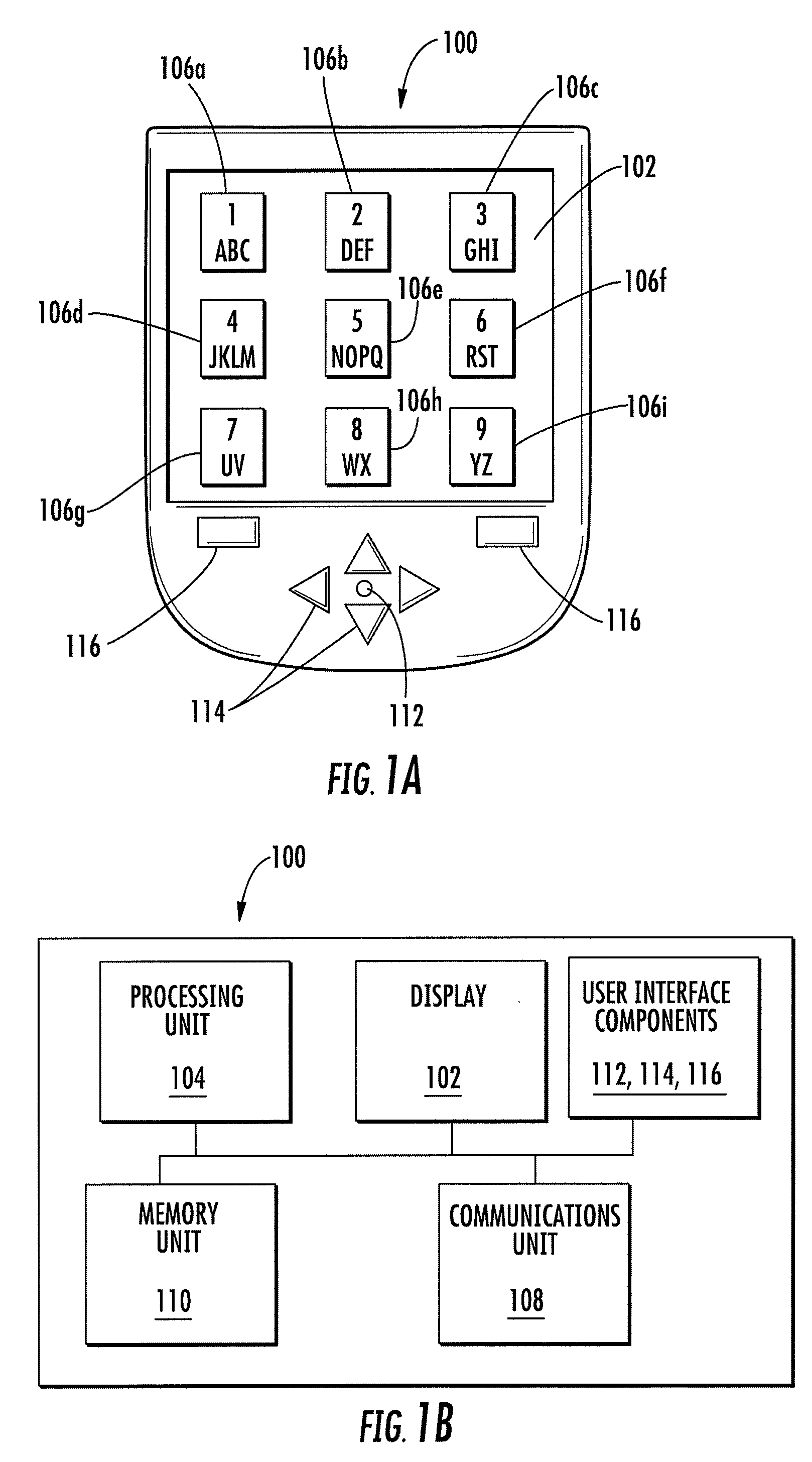

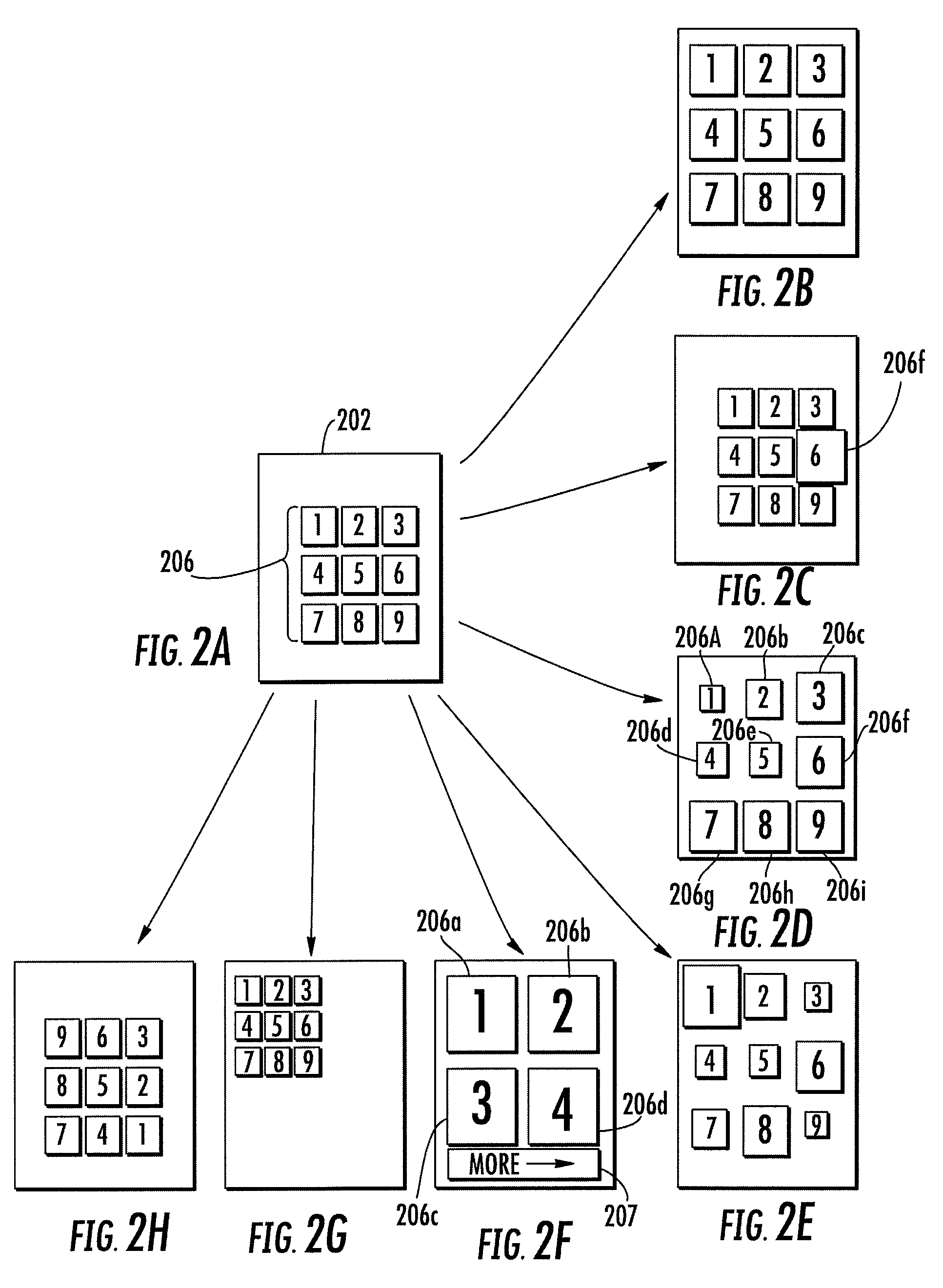

Apparatus, method, and computer program product for affecting an arrangement of selectable items

ActiveUS20090106694A1Overcome disadvantagesInput/output for user-computer interactionGraph readingDisplay deviceHuman–computer interaction

Provided is an apparatus that includes a processing unit configured to monitor a quality of user performance in selecting one or more selectable items that are presented on a display. The processing unit is further configured to cause the one or more selectable items to be presented on the display in a modified arrangement based at least in part on the quality of user performance in respectively selecting the one or more selectable items. For example, the processing unit can be configured to cause the selectable items to be presented in a modified arrangement based at least in part on noted frequency of user error in respectively selecting the selectable items and / or on noted rate of user selection in respectively selecting the selectable items. Also provided are corresponding methods and computer program products.

Owner:RPX CORP

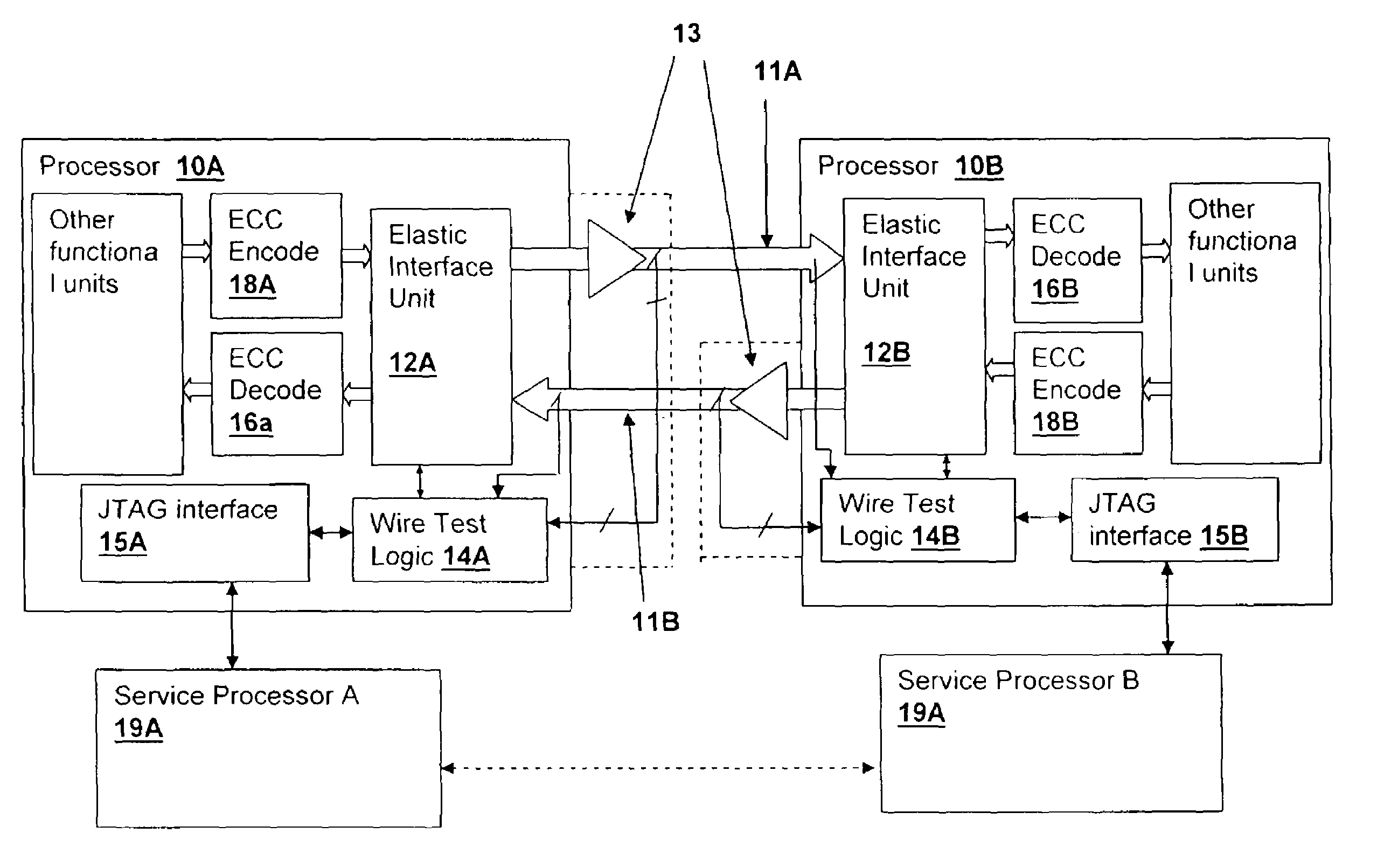

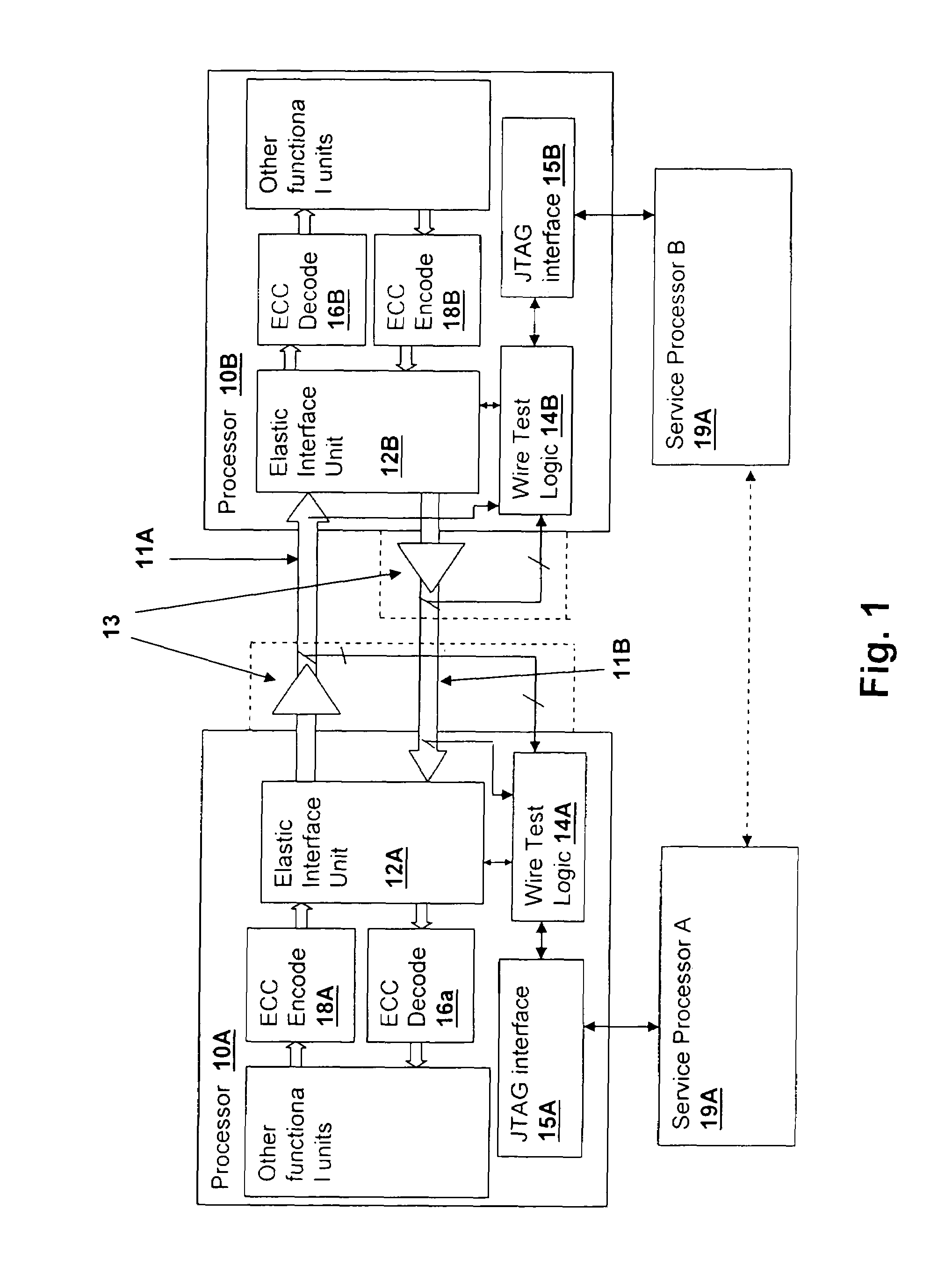

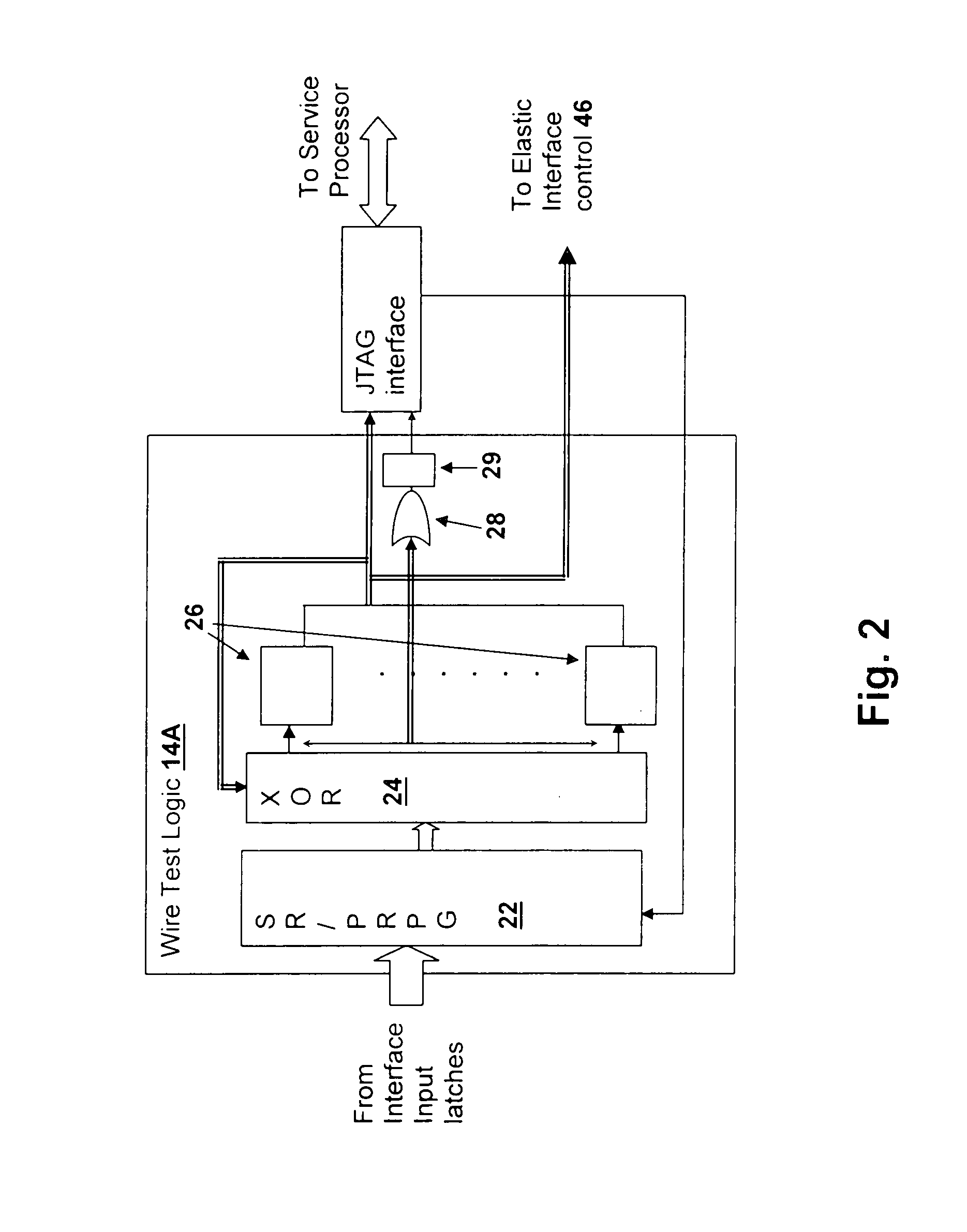

Method and apparatus for interface failure survivability using error correction

ActiveUS7080288B2Correct operation testingDetecting faulty computer hardwareSurvivabilityForward error correction

A method an apparatus for interface failure survivability using error correction provides operation of an interface when a number of bits of the interface less than or equal to available error correction depth are present. Initialization tests are used to determine whether the interface errors due to failed interconnects or circuits can be corrected, or whether the interface must be disabled. Subsequent alignment at initialization or during operation idle periods may be disabled for any failed bit paths. The failed bit path indications are determined and maintained in hardware, and used to bypass subsequent calibrations that could otherwise corrupt the interface. A fault indication specifying total failure may be generated and used to shut down the interface and / or connected subsystem in response to an uncorrectable condition and request immediate repair. A second fault indication specifying correctable failure may be generated and used to indicate a need for eventual repair.

Owner:INT BUSINESS MASCH CORP

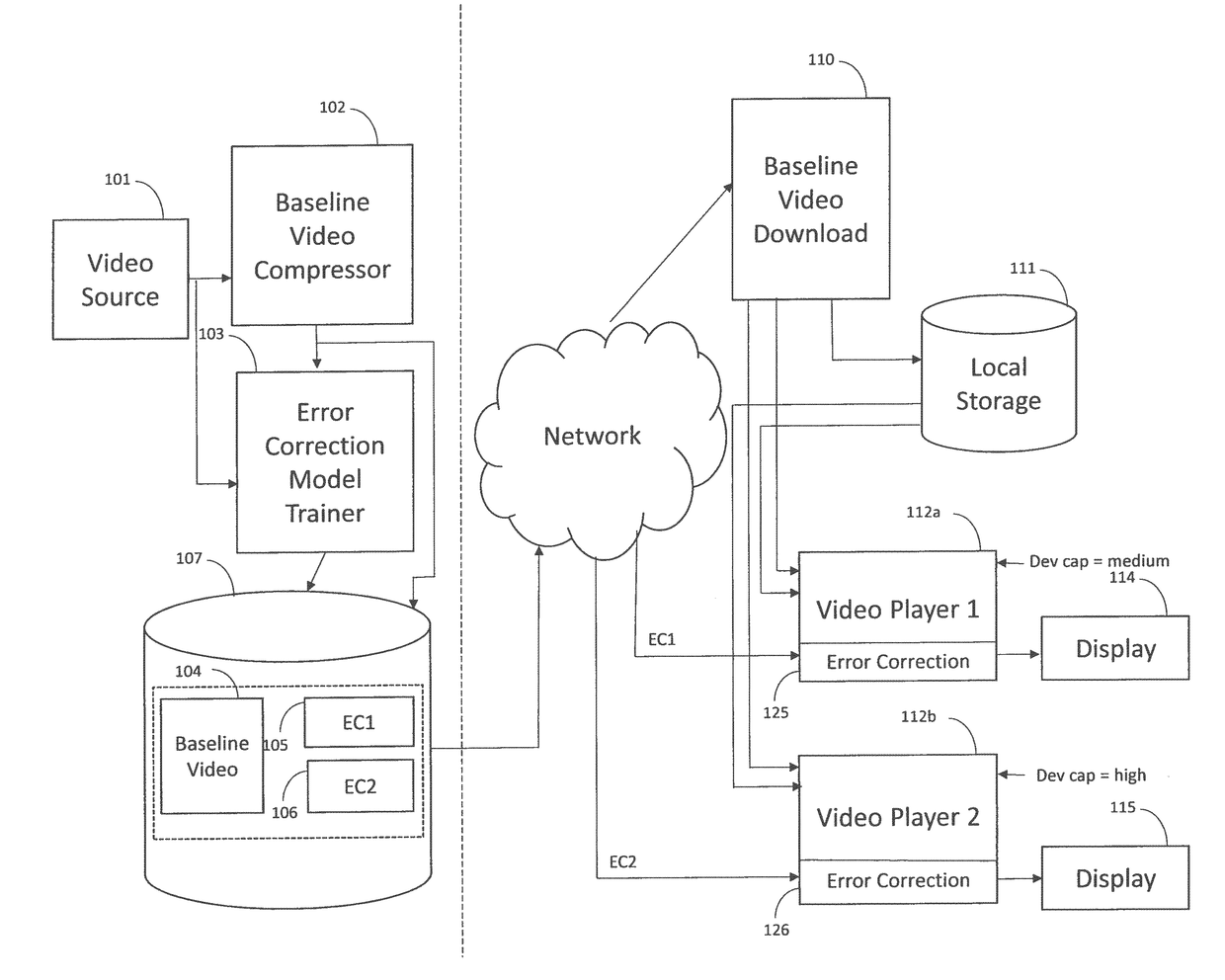

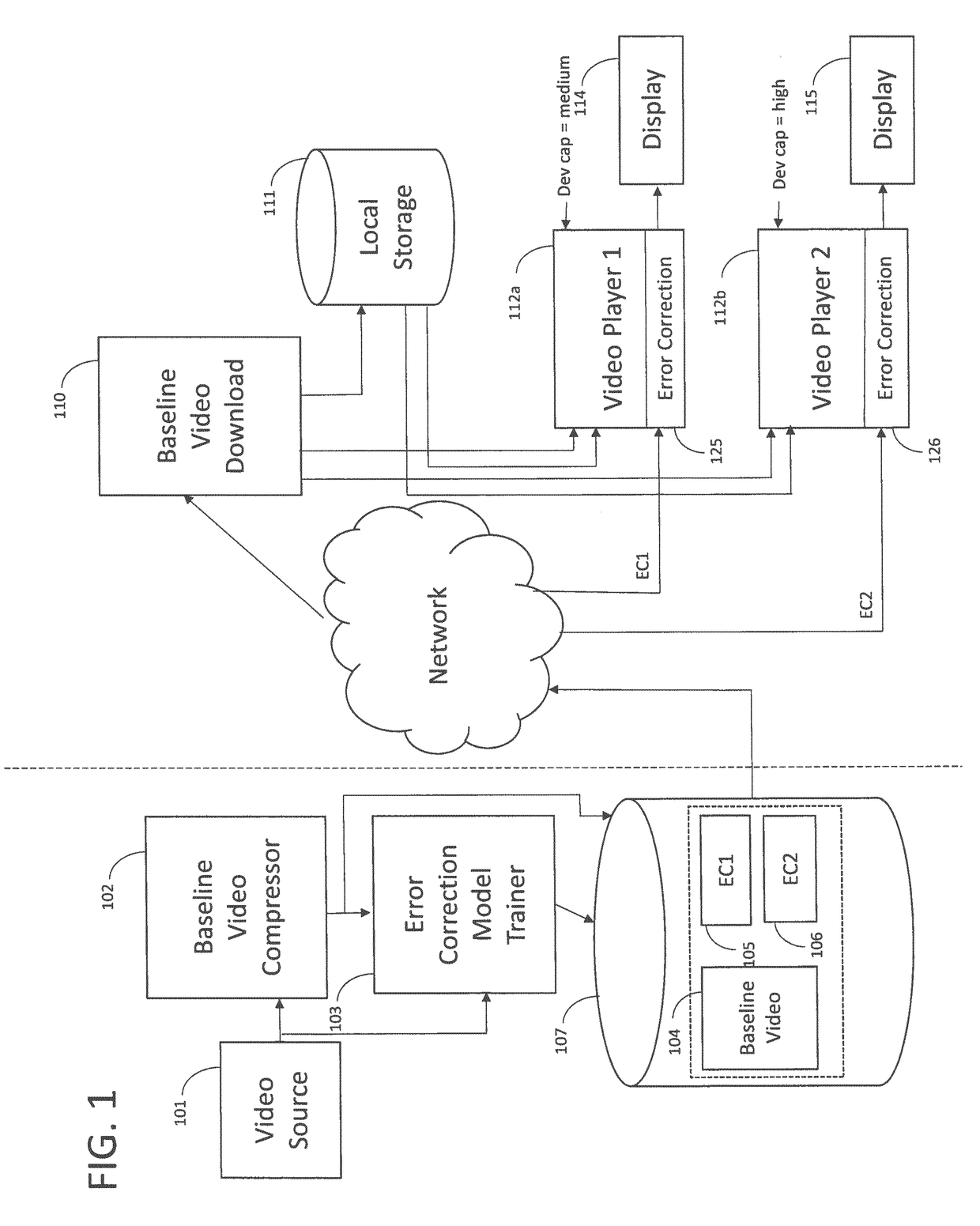

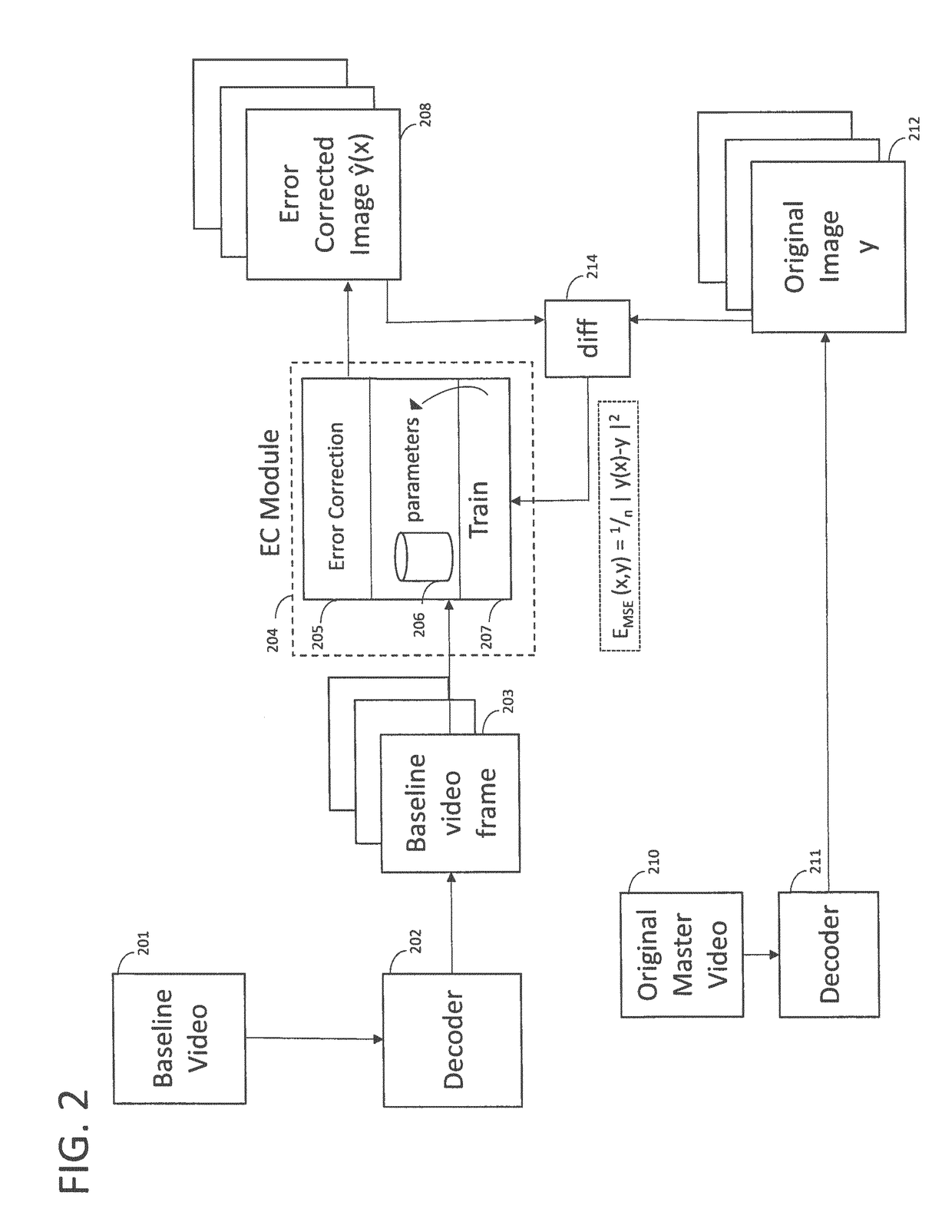

Improved video stream delivery via adaptive quality enhancement using error correction models

ActiveUS20180288440A1Attenuation bandwidthReduce duplicationCharacter and pattern recognitionImage codingComputer hardwareSelf adaptive

There is disclosed a technique for providing multimedia content comprising: compressing a multimedia stream; and generating an error correction model for providing an alternative version of the compressed multimedia stream by: decompressing the compressed multimedia stream; determining errors in the decompressed version by comparing to the input multimedia stream; and correcting the errors to minimise the difference between the decompressed version and the input multimedia stream.

Owner:PRJ HLDG CO LLC

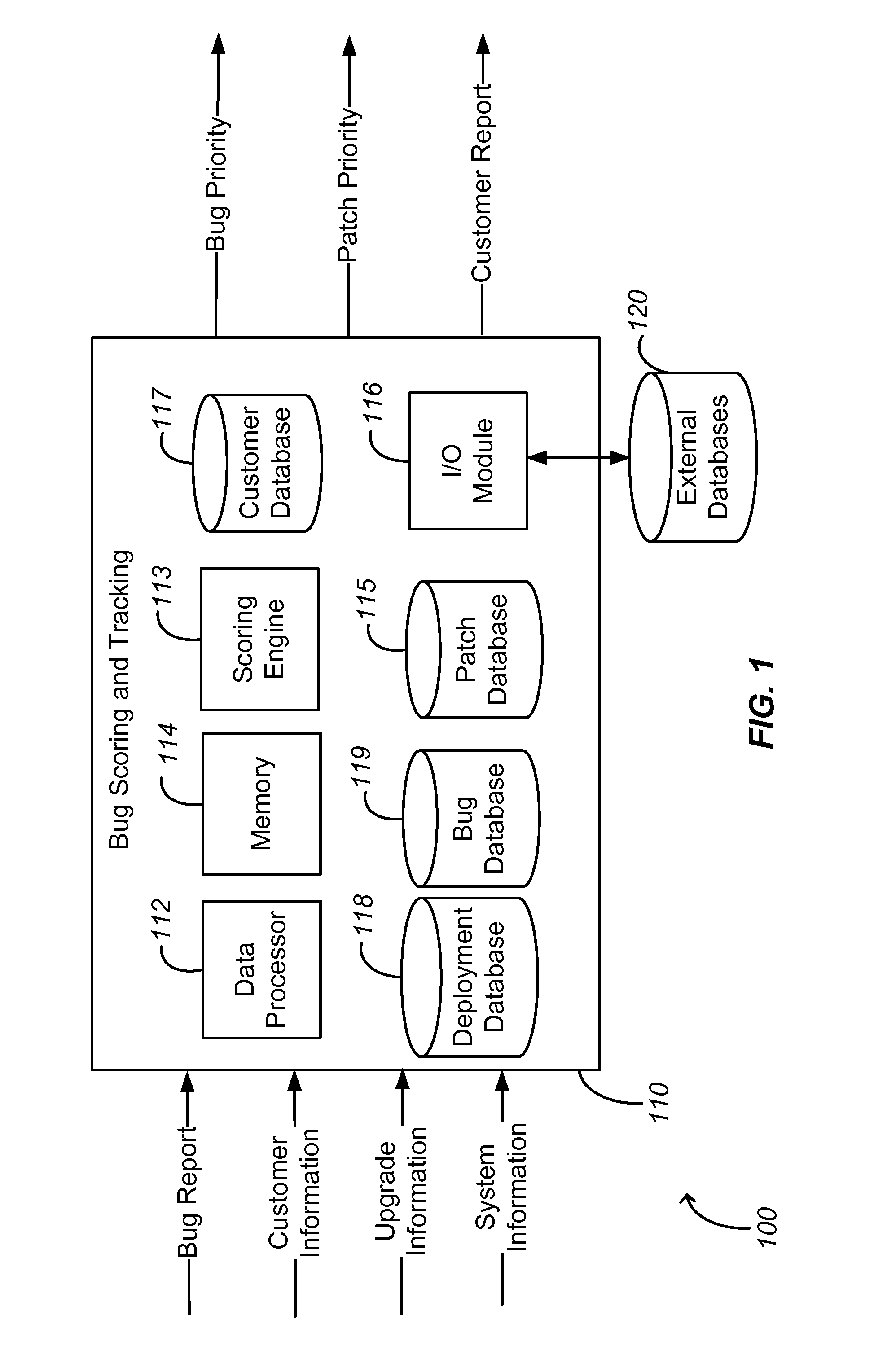

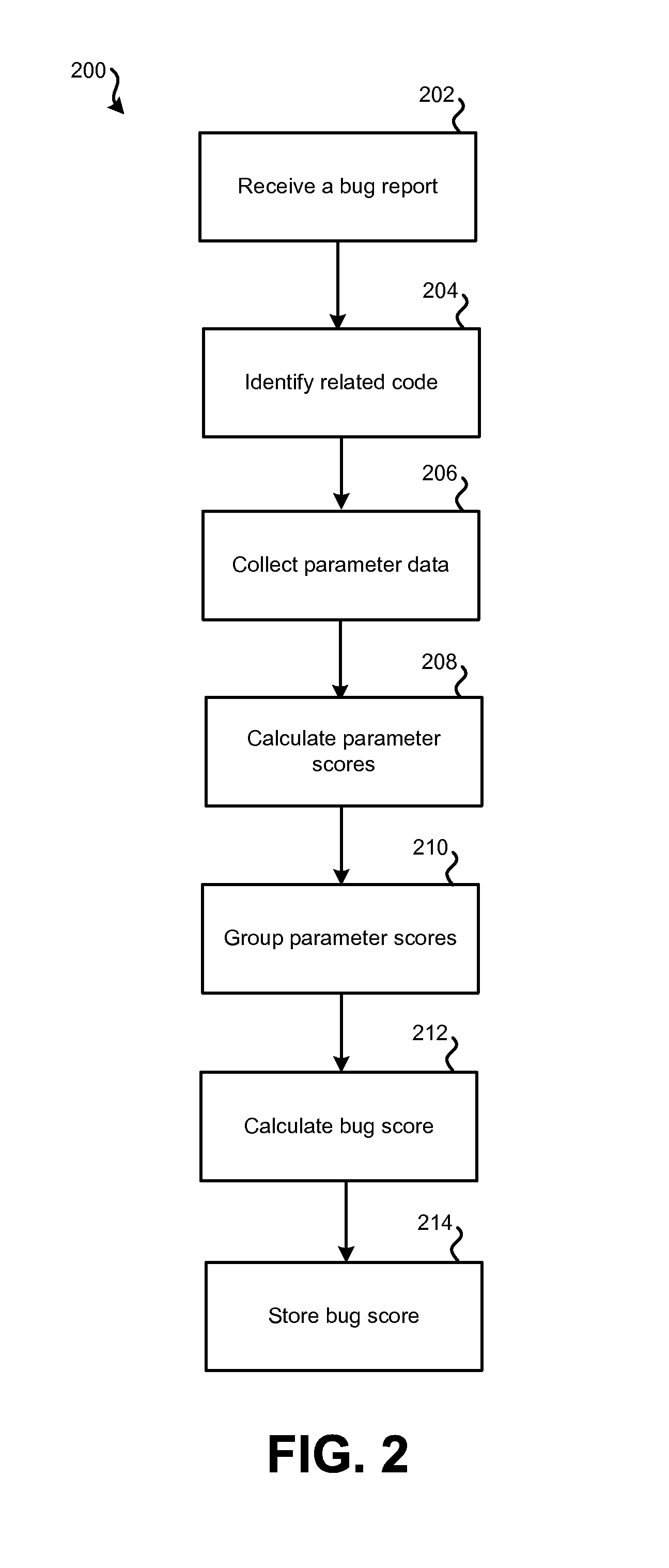

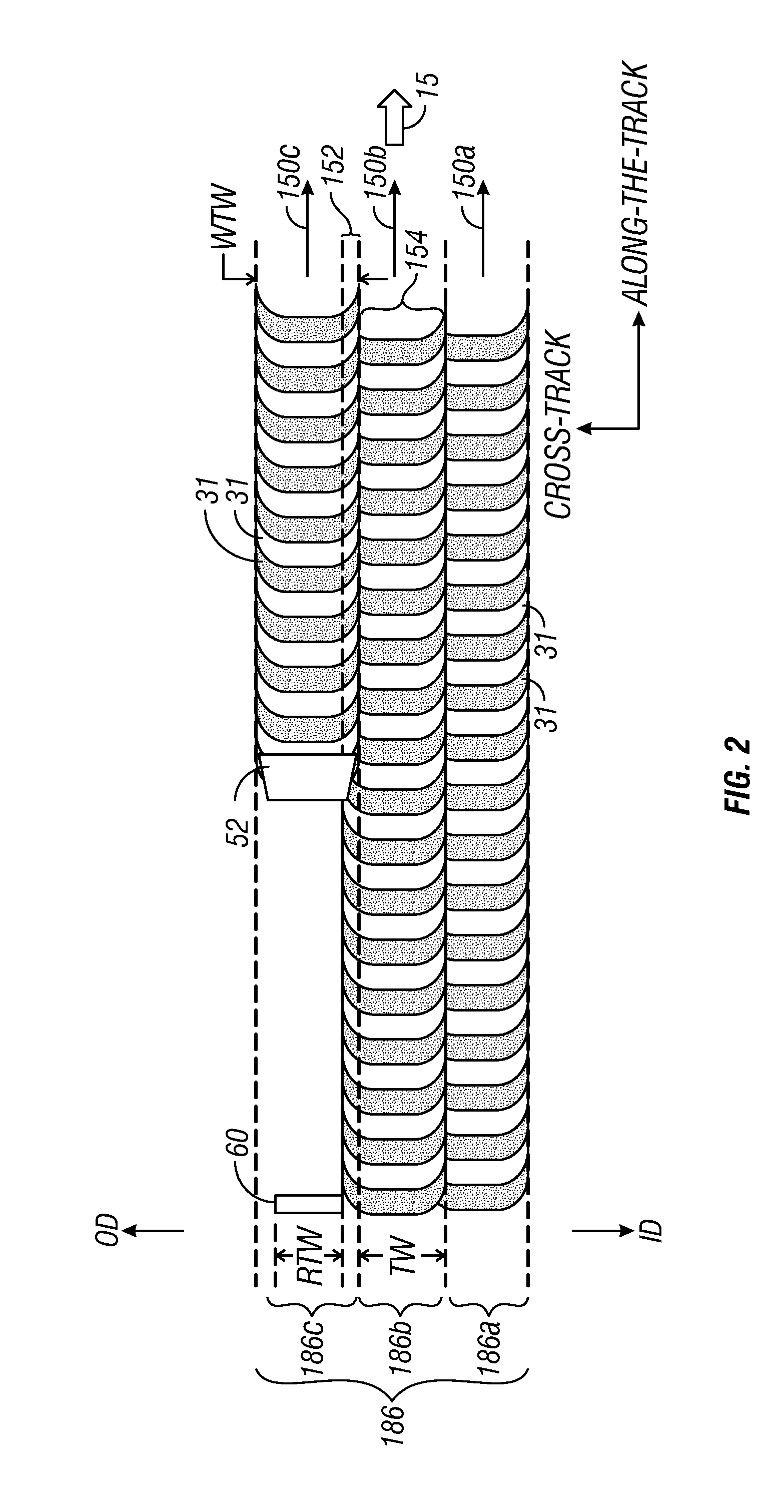

Method and system for reducing instability when upgrading software

ActiveUS20150019564A1Easy to addThe process is fast and accurateDigital data information retrievalError detection/correctionSoftware bugInstability

A system and a method of rating software bugs using a bug scoring and tracking system is presented. The system and method may use automated scoring of the bugs to determine the impact of the bug. The system and method may connect to one or more databases to determine the extent of the deployment of the software, the impact of the bug, and / or the history of the bug. Scoring is used to prioritize the bugs and the scoring is extensible and adjustable allowing easy addition of new parameters and allowing the system to be modified for different bug types, software, or customers.

Owner:ORACLE INT CORP

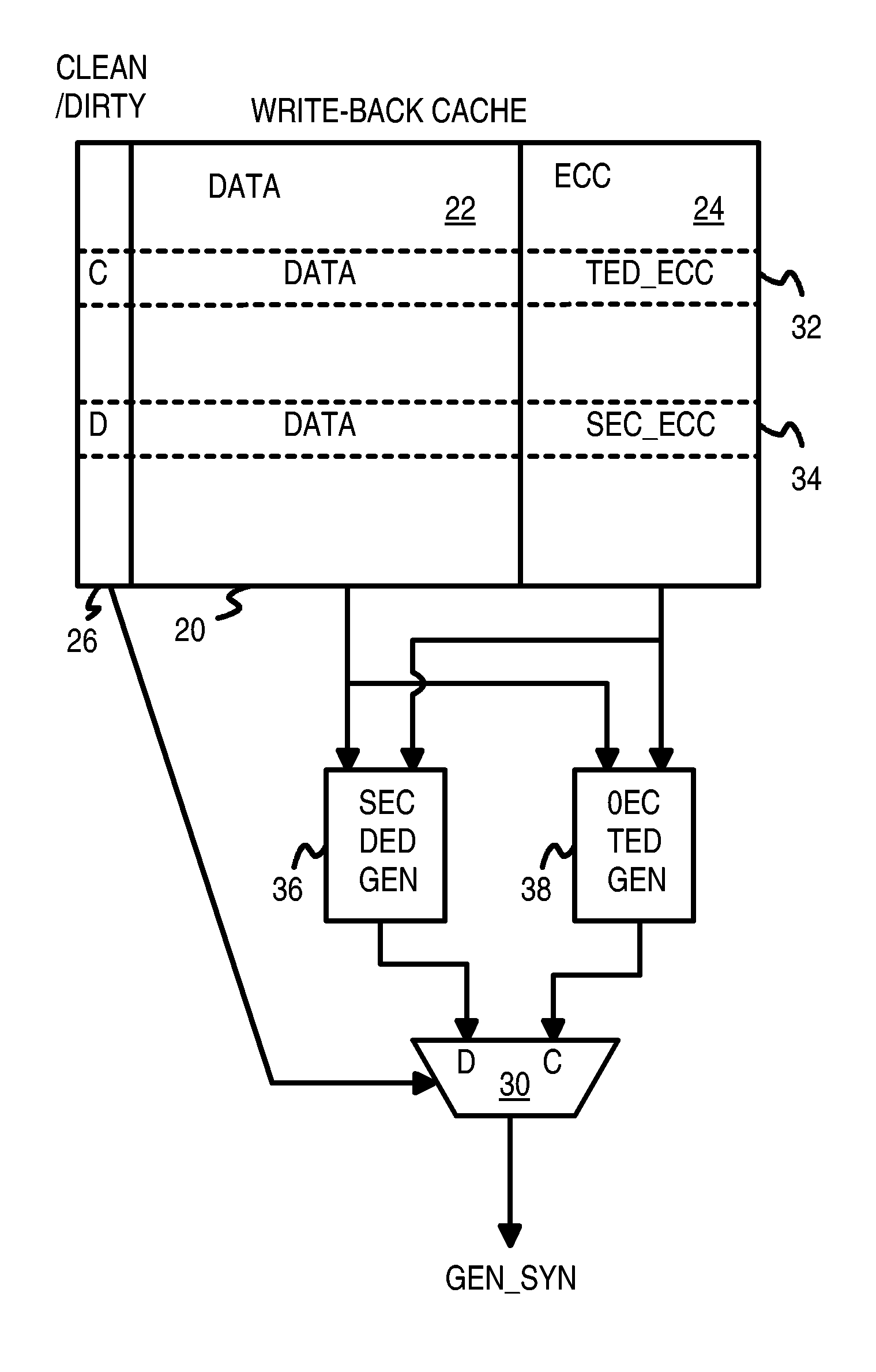

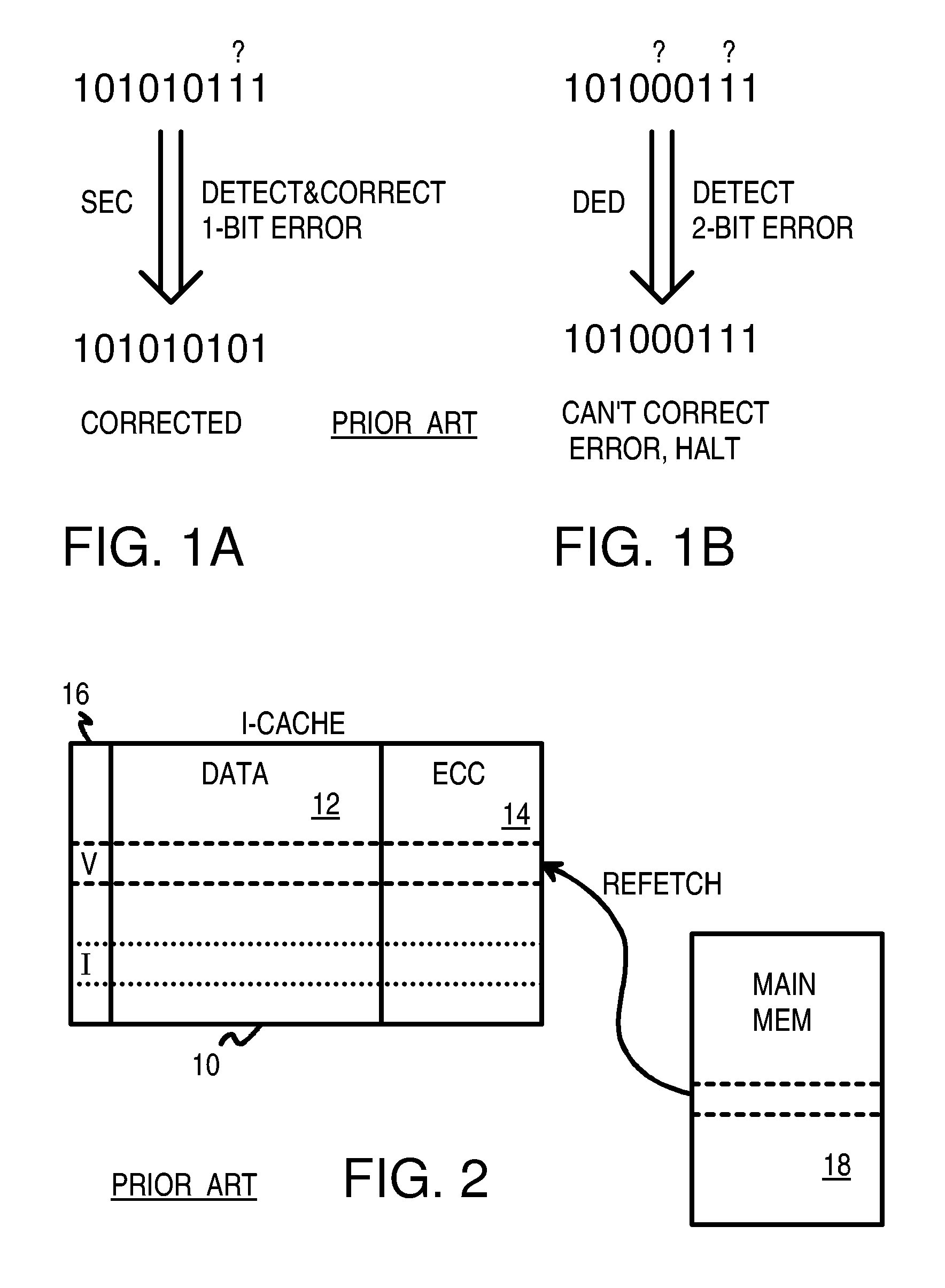

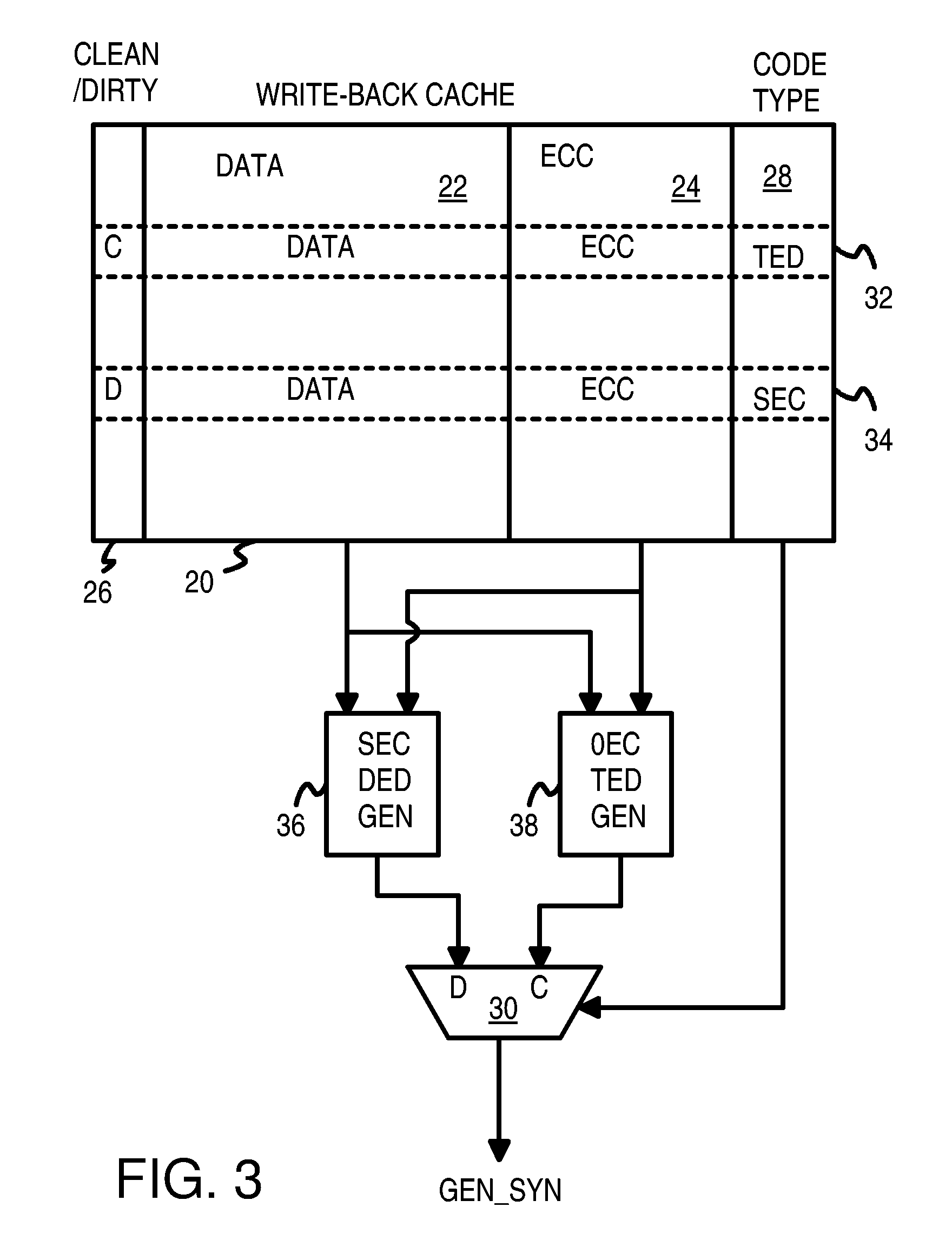

Write-back cache with different ECC codings for clean and dirty lines with refetching of uncorrectable clean lines

ActiveUS7437597B1Static storageRedundant data error correctionParallel computingError detection coding

A write-back cache has error-correction code (ECC) fields storing ECC bits for cache lines. Clean cache lines are re-fetched from memory when an ECC error is detected. Dirty cache lines are corrected using the ECC bits or signal an uncorrectable error. The type of ECC code stored is different for clean and dirty lines. Clean lines use an error-detection code that can detect longer multi-bit errors than the error correction code used by dirty lines. Dirty lines use a correction code that can correct a bit error in the dirty line, while the detection code for clean lines may not be able to correct any errors. Dirty lines' ECC is optimized for correction while clean lines' ECC is optimized for detection. A single-error-correction, double-error-detection (SECDED) code may be used for dirty lines while a triple-error-detection code is used for clean lines.

Owner:AZUL SYSTEMS

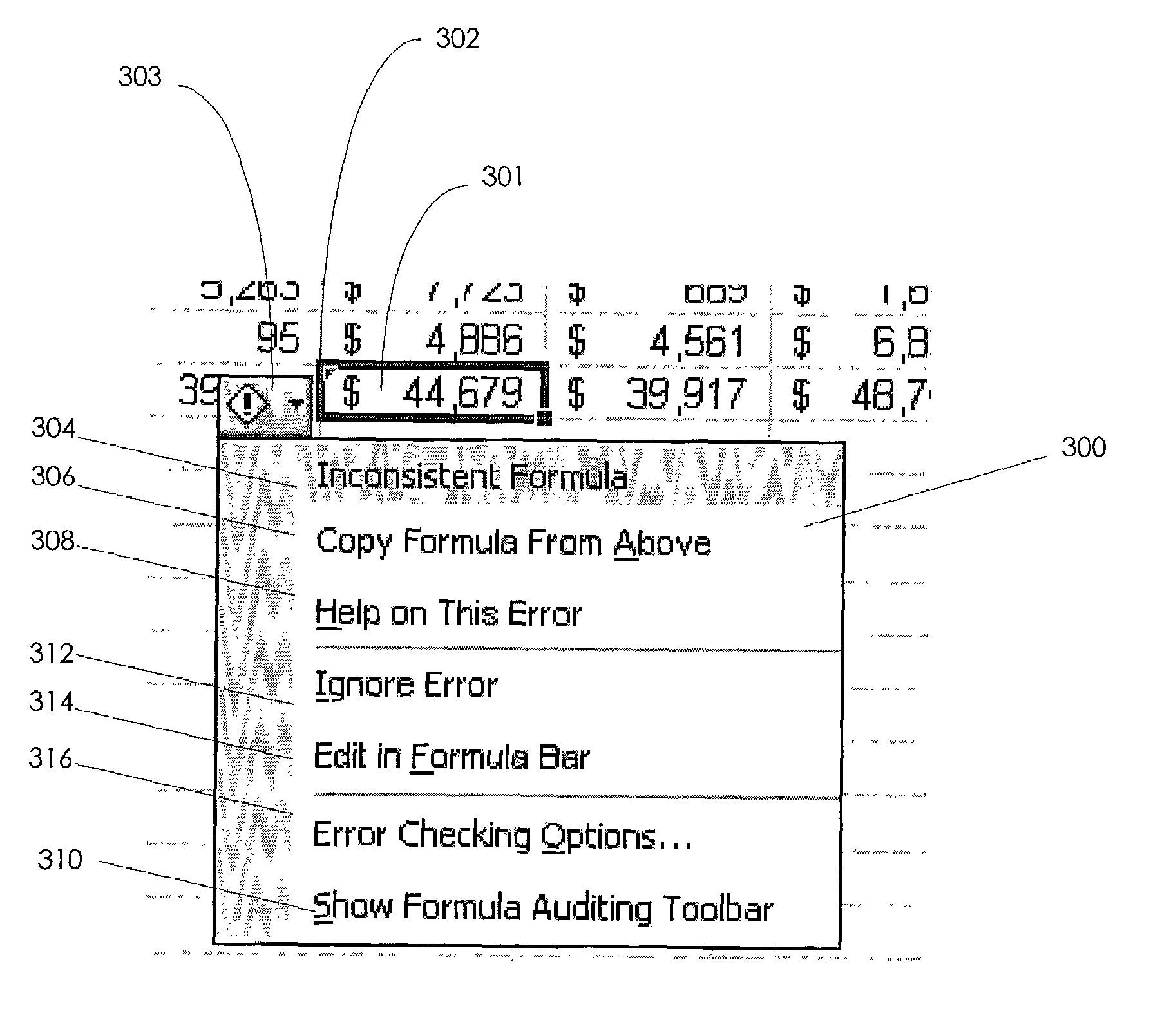

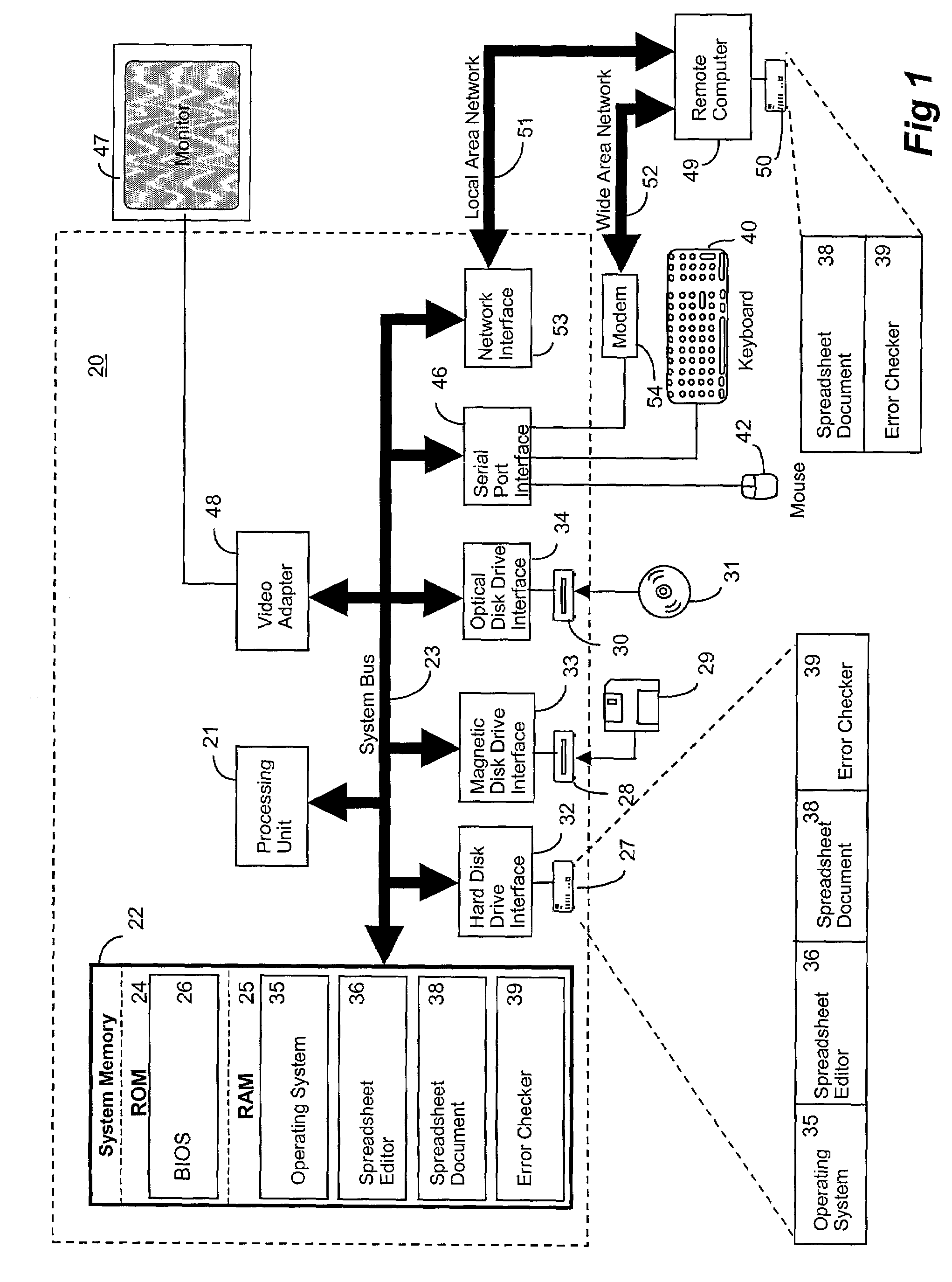

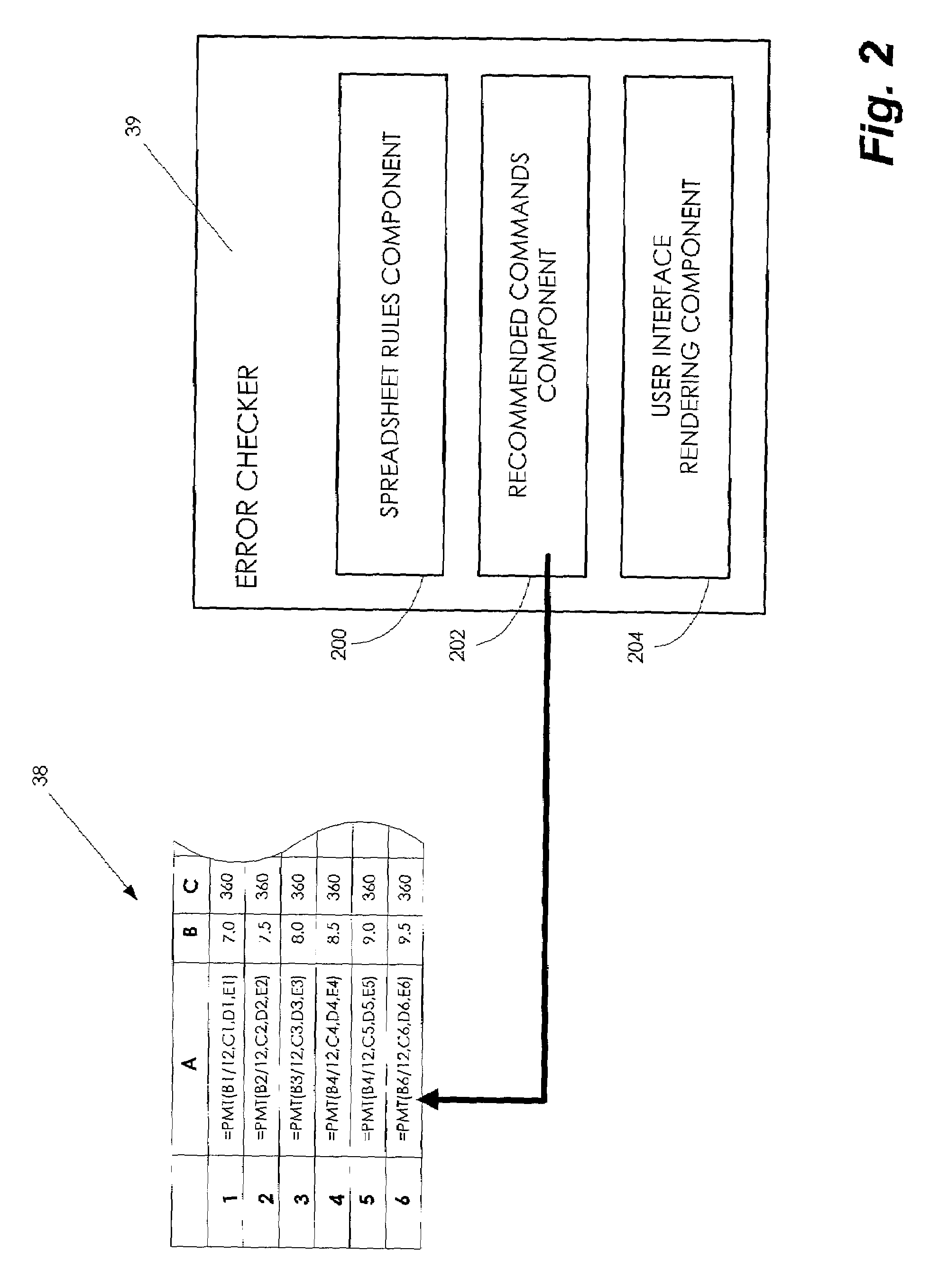

Spreadsheet error checker

An error checker identifies spreadsheet errors by traversing a spreadsheet cell-by-cell and comparing each cell's contents to a list of error rules. When a cell's contents satisfy an error rules, then the cell is identified as containing a potential spreadsheet error. The error checker identifies potential spreadsheet errors and marks the cells containing the potential errors with an error indicator. A drop-down menu is provided that includes an element identifying the error rule that was invoked by the cell's contents and may include one or more recommended actions to resolve the identified error.

Owner:MICROSOFT TECH LICENSING LLC

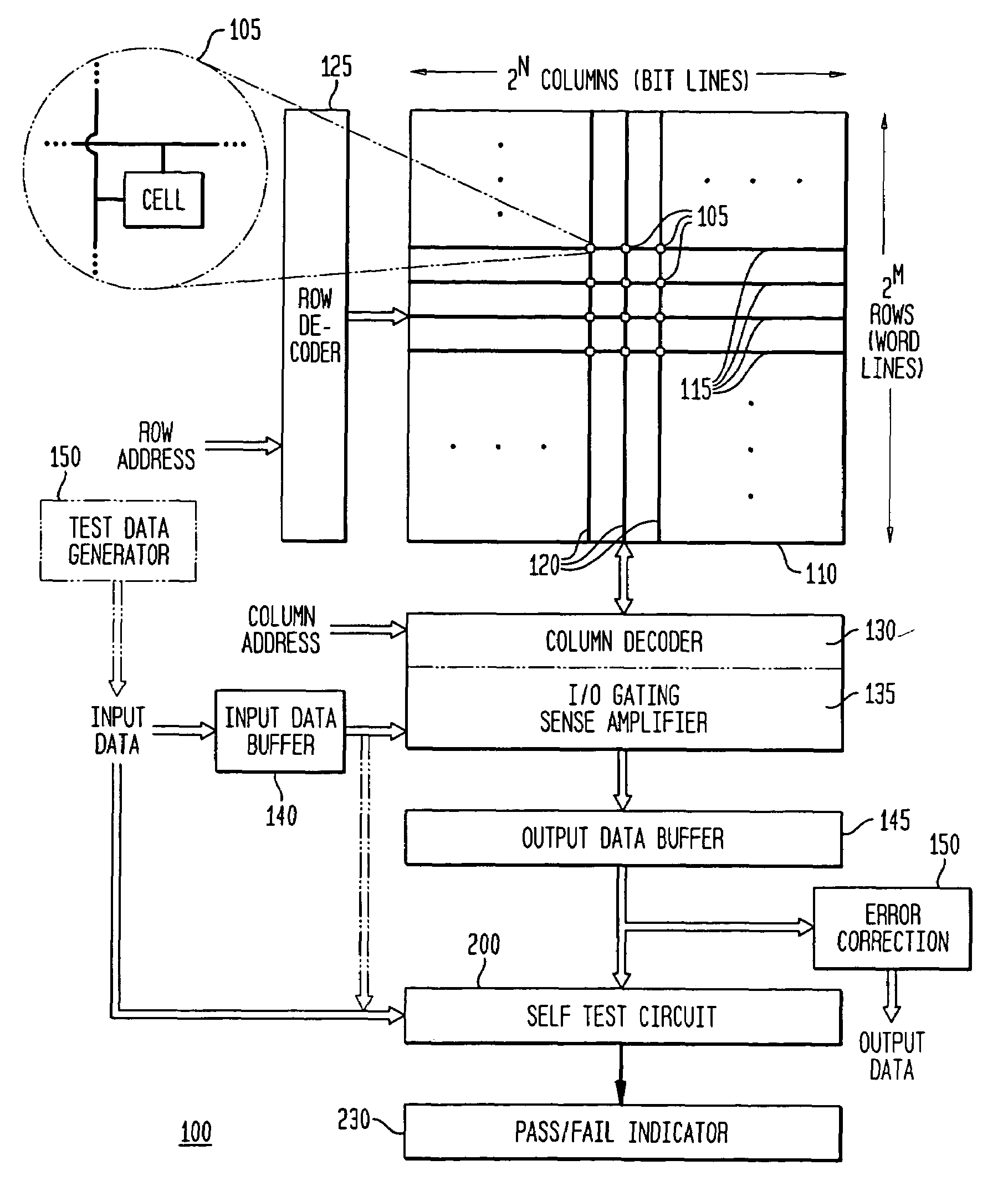

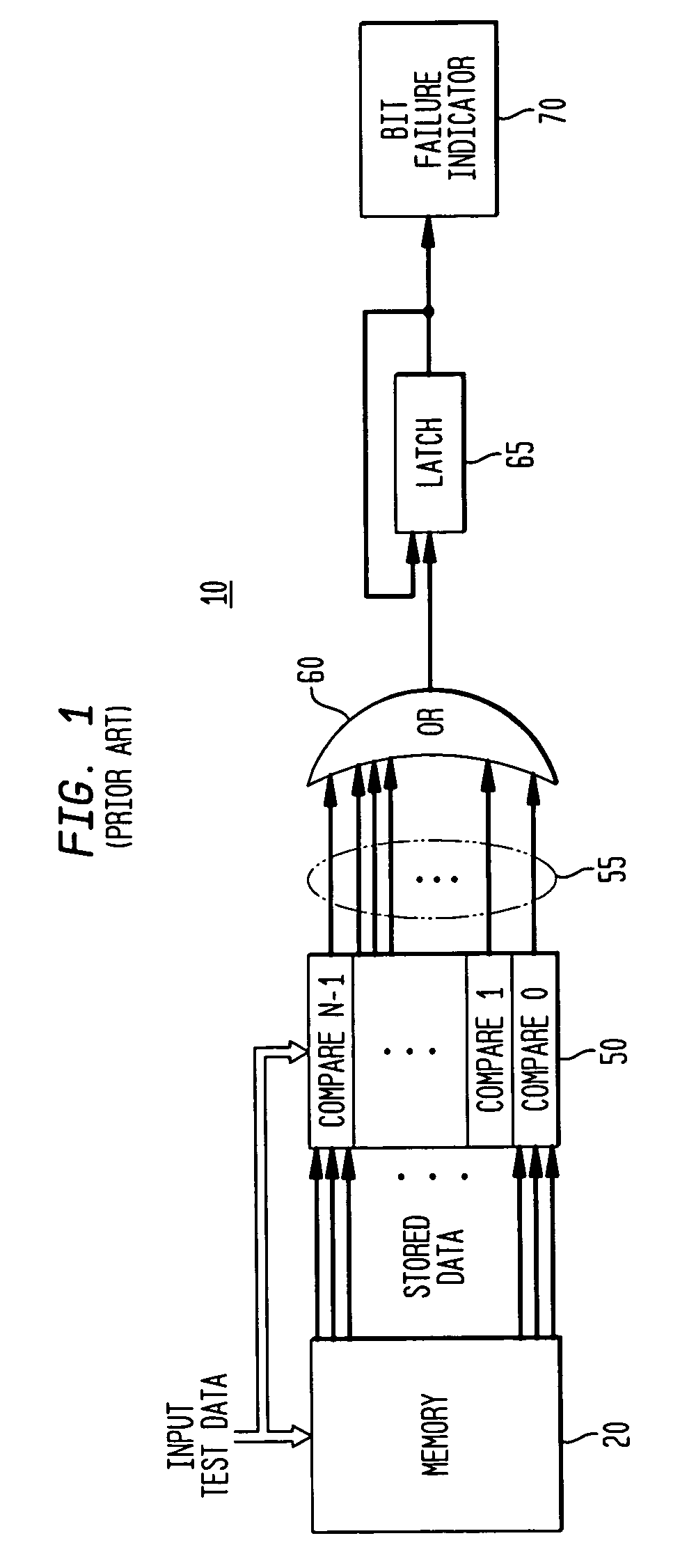

Built-in self test for memory arrays using error correction coding

InactiveUS7254763B2Increased and improved IC manufacturing yieldShorten test timeElectronic circuit testingError detection/correctionIntegratorControl circuit

A memory self-testing system, apparatus, and method are provided which allow for testing for a plurality of bit errors and passing memory arrays having an error level which is correctable using selected error correction coding. An exemplary system embodiment includes a memory array, a comparator, an integrator, and a test control circuit. The memory array is adapted to store input test data and output stored test data during a plurality of memory read and write test operations. The comparator compares the input test data and the stored test data for a plurality of bit positions, and provides a corresponding error signal when the stored test data is not identical to the input test data for each bit position of the plurality of bit positions. The integrator receives the corresponding error signal and maintains the corresponding error signal for each bit position during the plurality of test operations. The test control circuit provides a fail signal when a predetermined level of corresponding error signals have been provided for the plurality of bit positions.

Owner:AVAGO TECH INT SALES PTE LTD

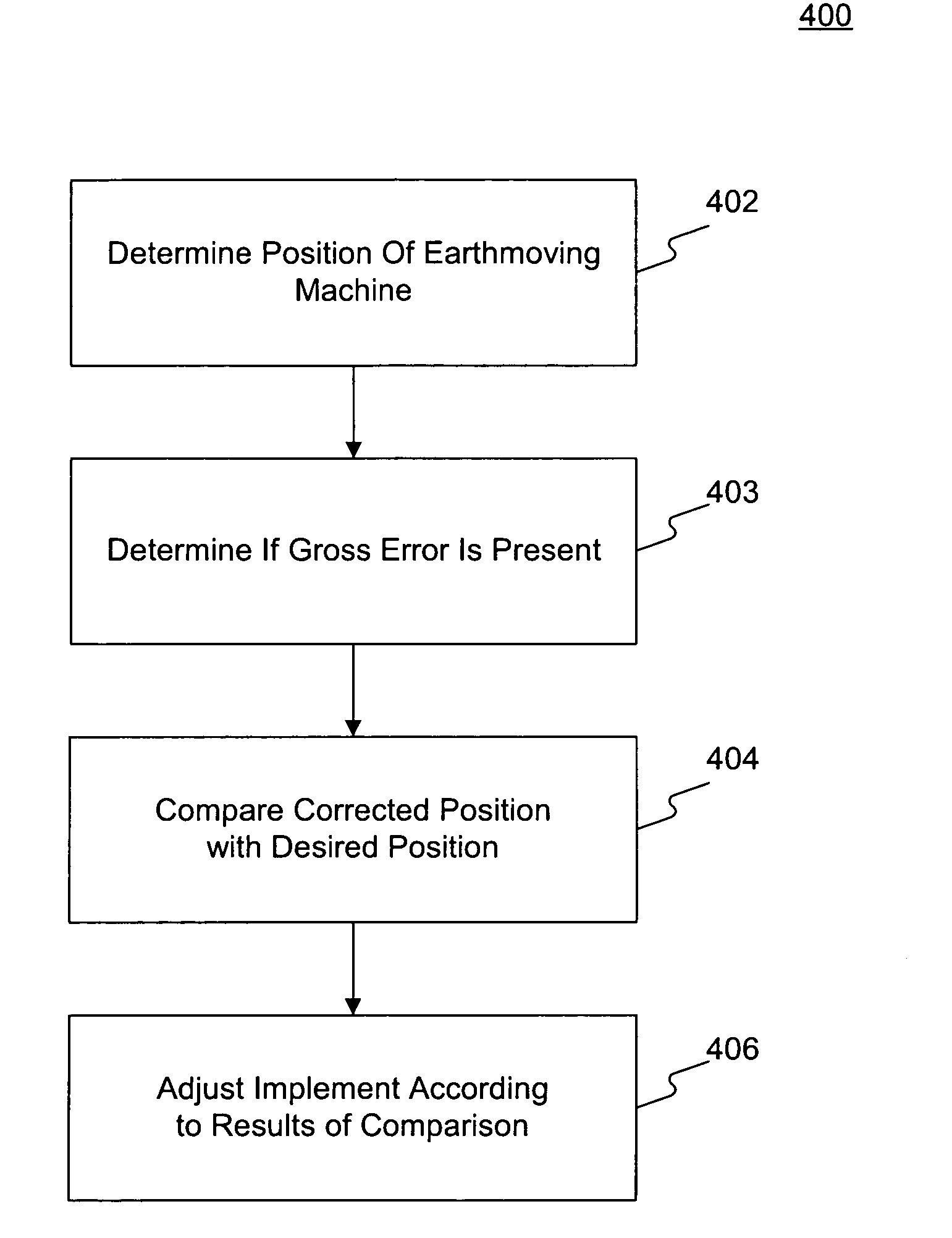

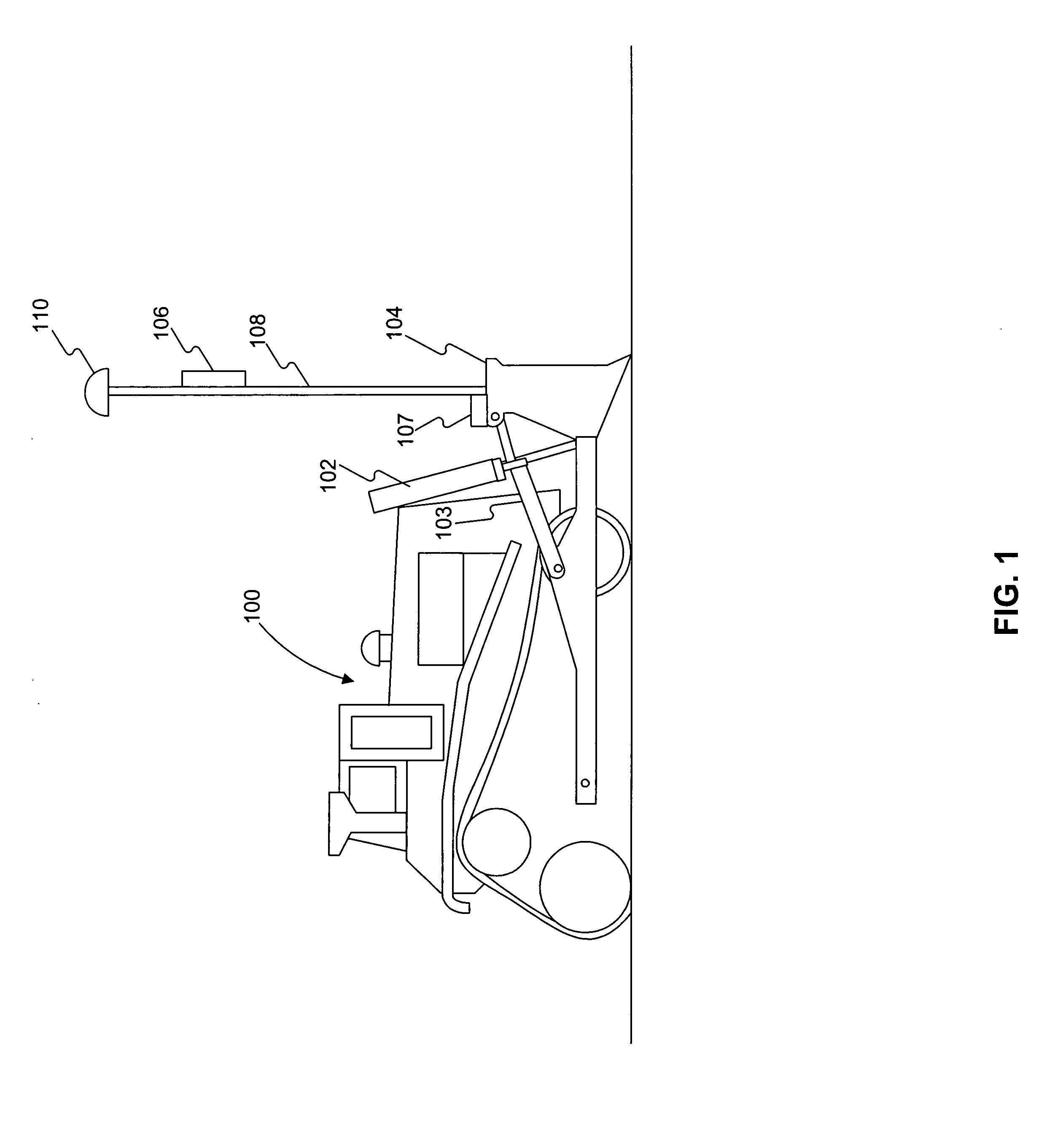

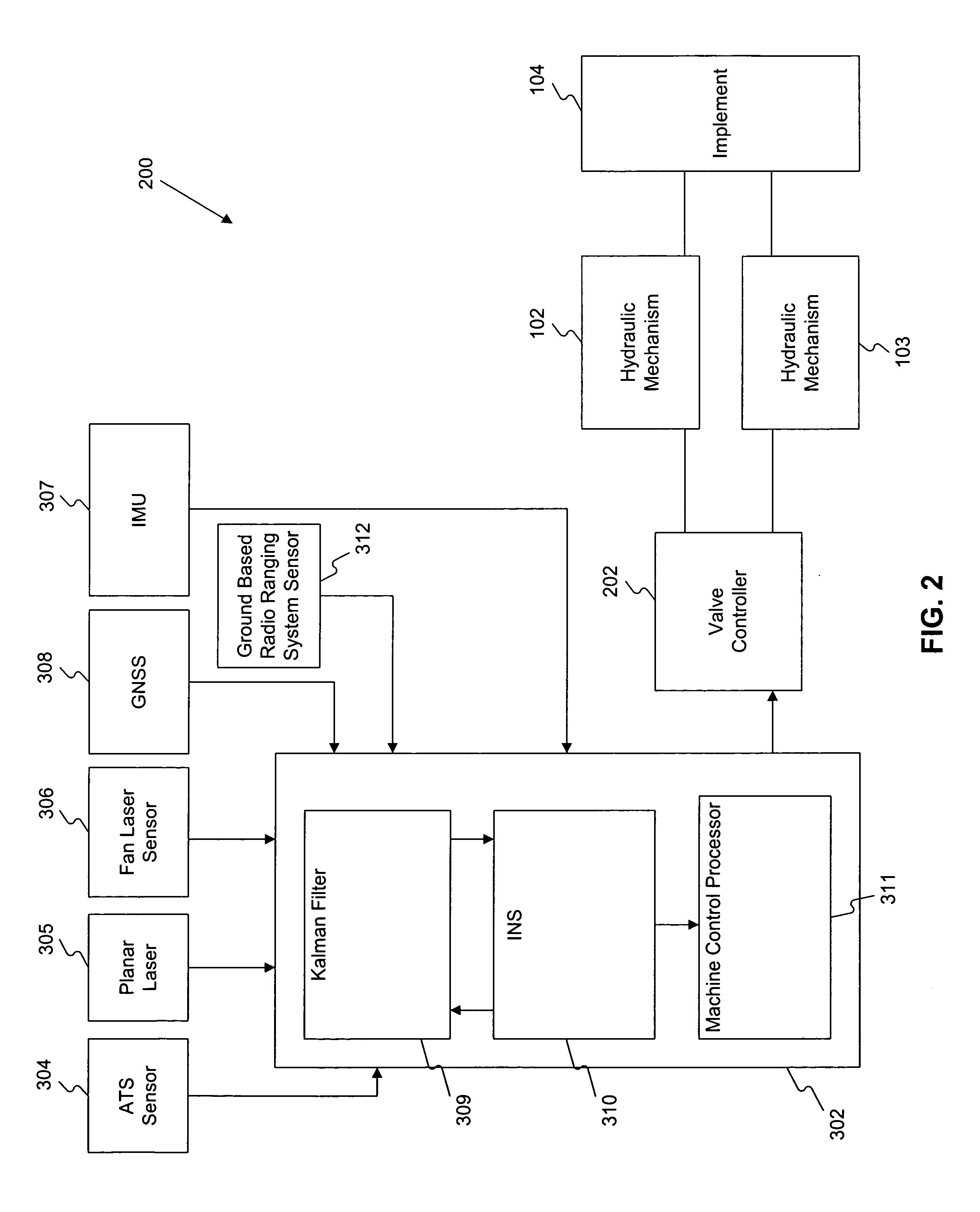

Systems and methods for augmenting an inertial navigation system

ActiveUS20080109141A1Analogue computers for trafficNavigation by speed/acceleration measurementsKaiman filterTotal station

Systems and methods for augmenting an inertial navigation system (INS) include outputting from the INS position information associated with the implement and adjusting the implement based upon a comparison of the position information of the implement and a desired position of the implement. The INS is periodically re-initialized using error estimates generated by a kalman filter as a function of position information from one or more positioning (or measuring) devices, such as a fan laser, an automatic total station (ATS), a GNSS receiver, or a ground based radio positioning system, to correct a drift of the position information that may be caused by inherent characteristics of the INS.

Owner:CATERPILLAR TRIMBLE CONTROL TECH

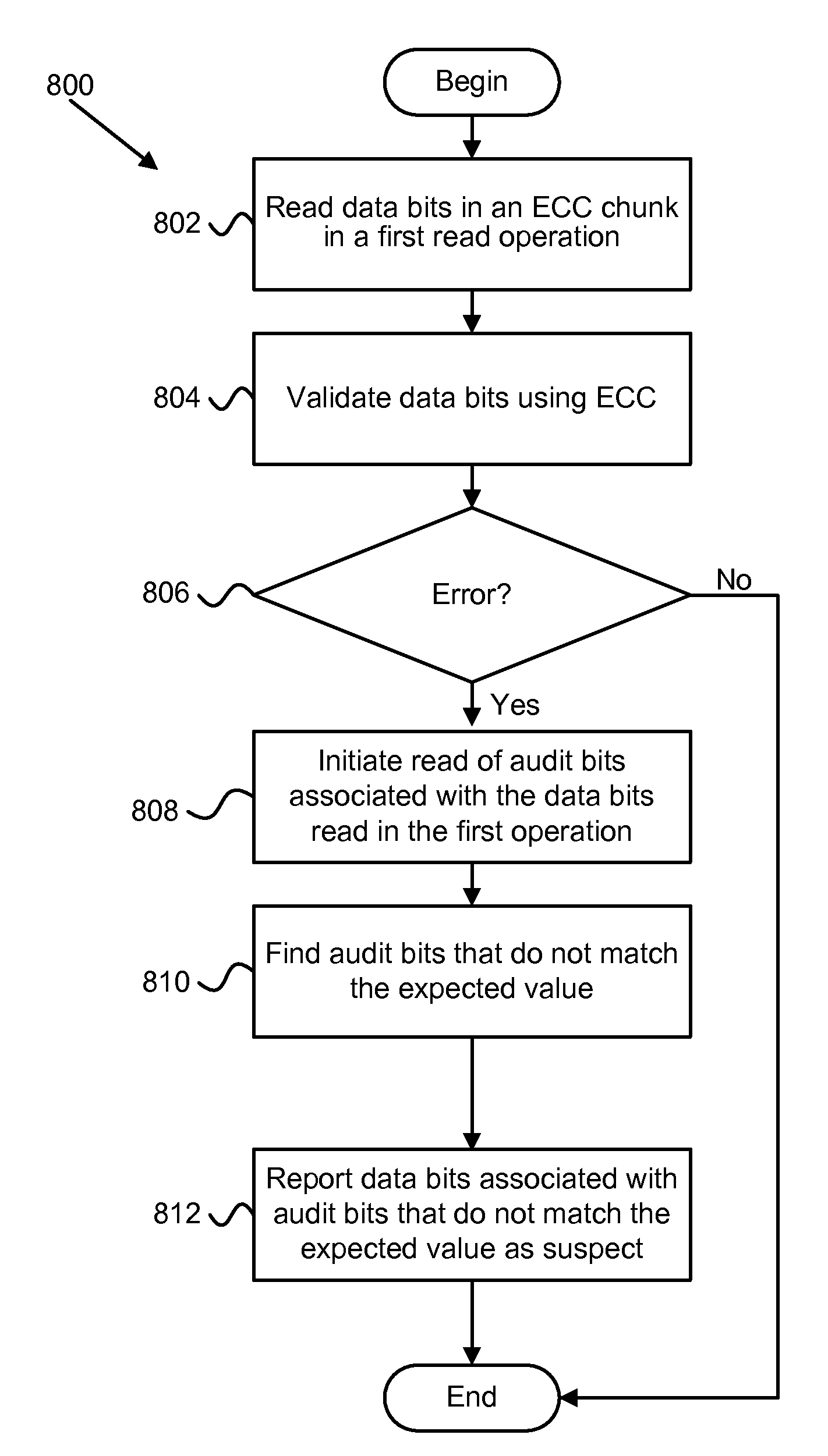

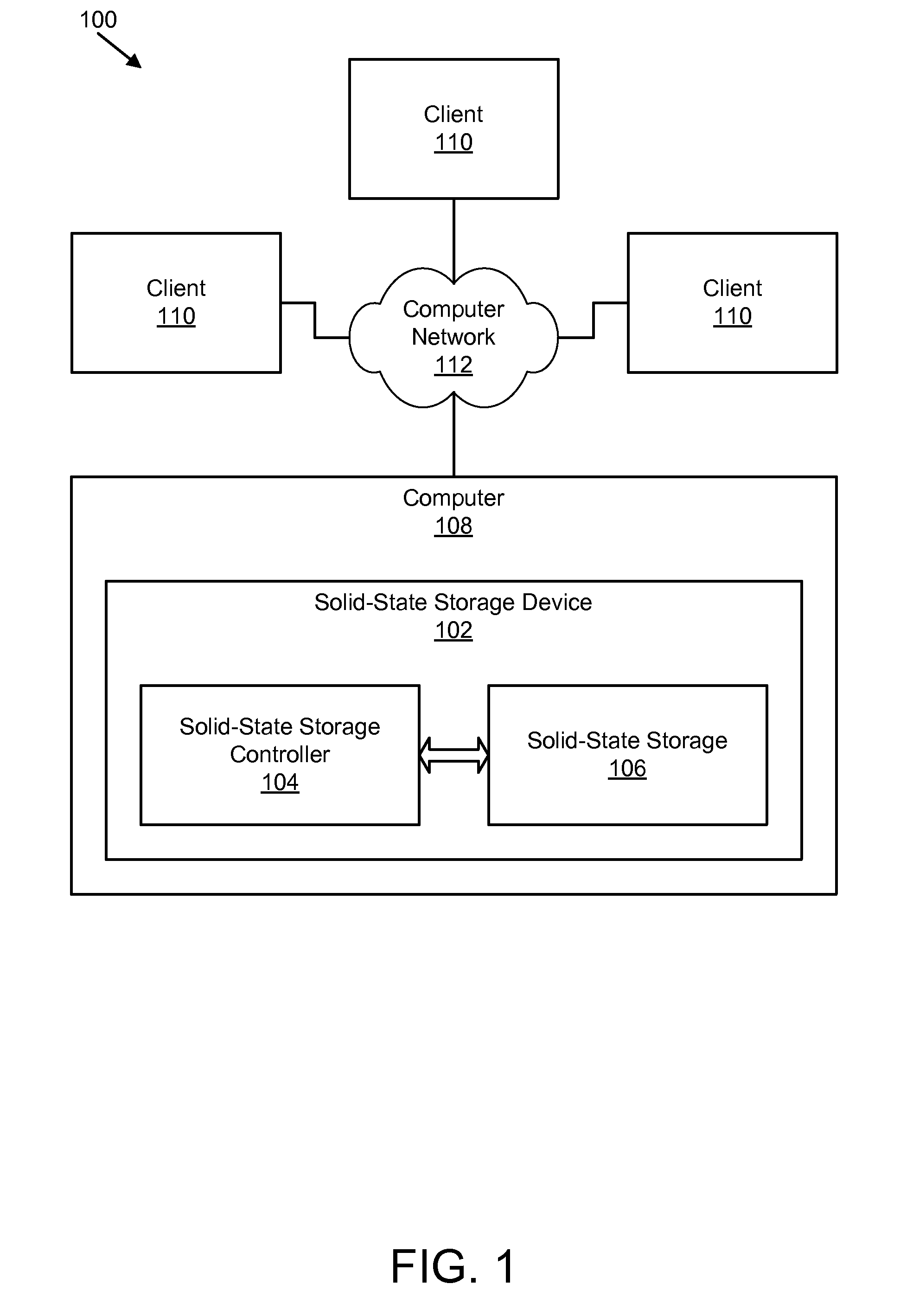

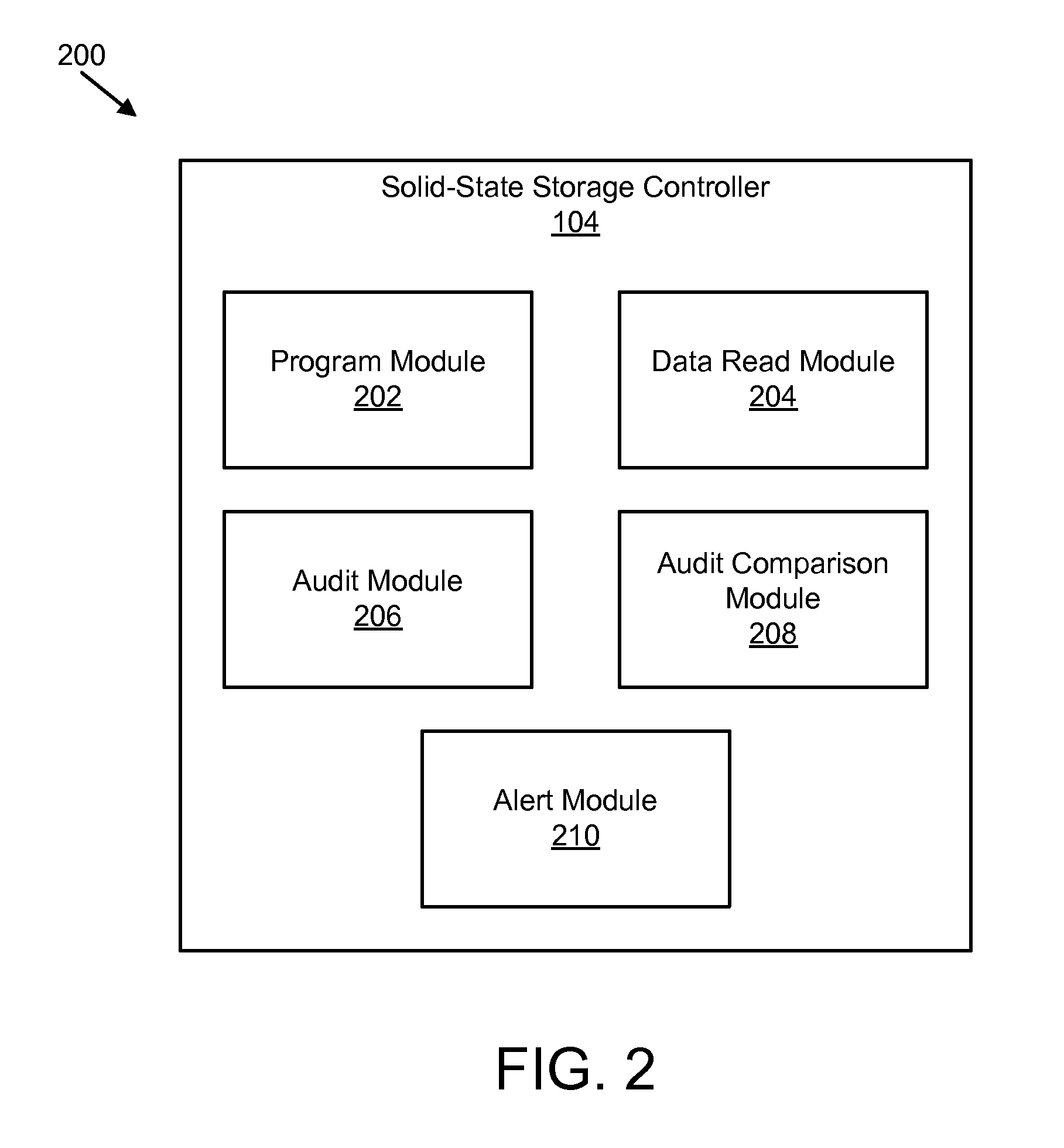

Apparatus, system, and method for using multi-level cell solid-state storage as single-level cell solid-state storage

ActiveUS20100235715A1Increase guard bandLow reliabilityMemory loss protectionRead-only memoriesSolid-state storageMultilevel memory

An apparatus, system, and method are disclosed for storing information in a storage device that includes multi-level memory cells. The method involves storing data that is written to the storage device in the LSBs of the multi-level memory cells, and storing audit data in the MSBs of the multi-level memory cells. The audit data can be read separately from the data and used to determine whether or not there has been any unintended drift between states in the multi-level cells. The audit data may be used to correct data when the errors in the data are too numerous to be corrected using error correction code (ECC). The audit data may also be used to monitor the general health of the storage device. The monitoring process may run as a background process on the storage device. The storage device may transition the multi-level memory cells to operate as single-level memory cells.

Owner:SANDISK TECH LLC

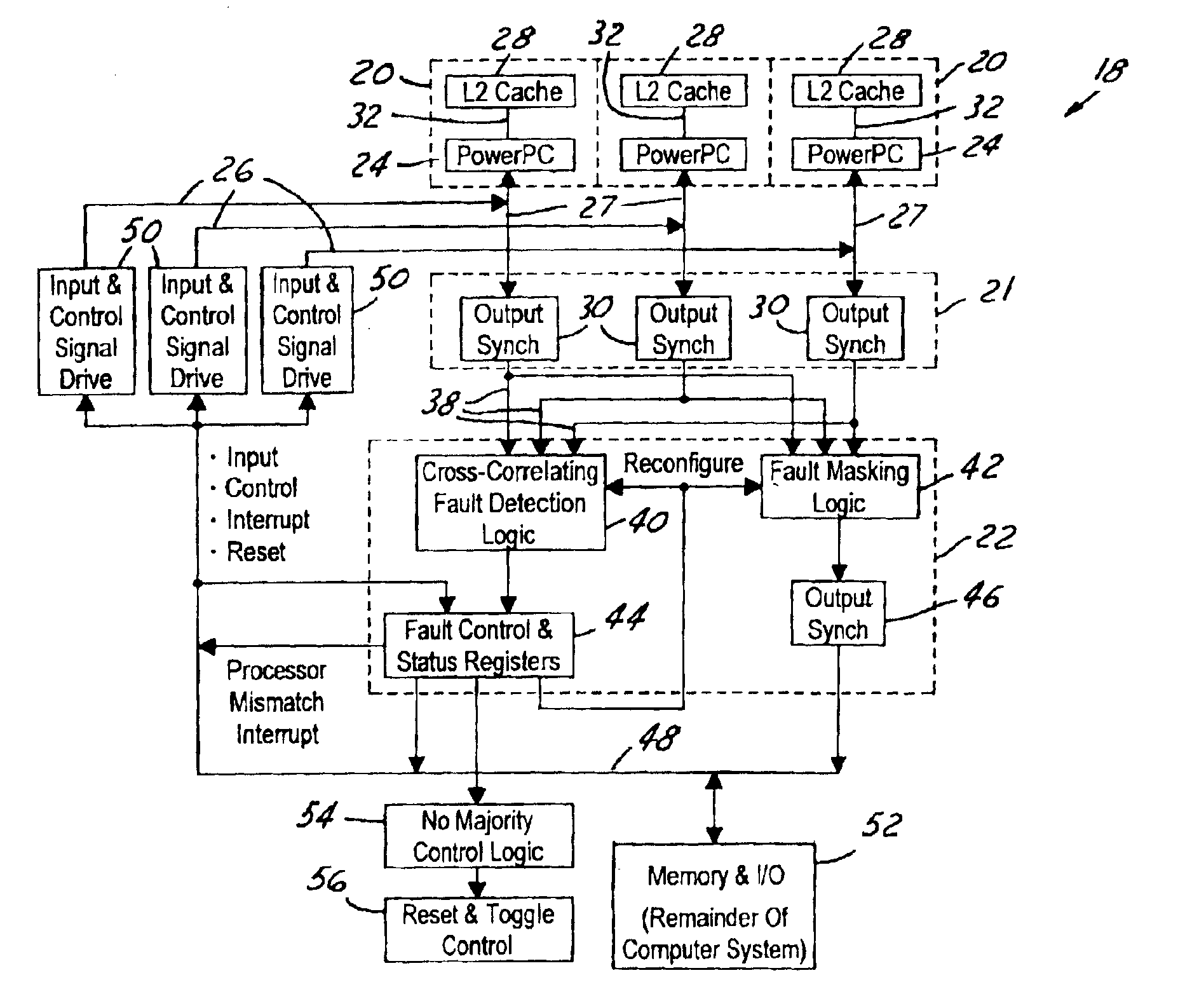

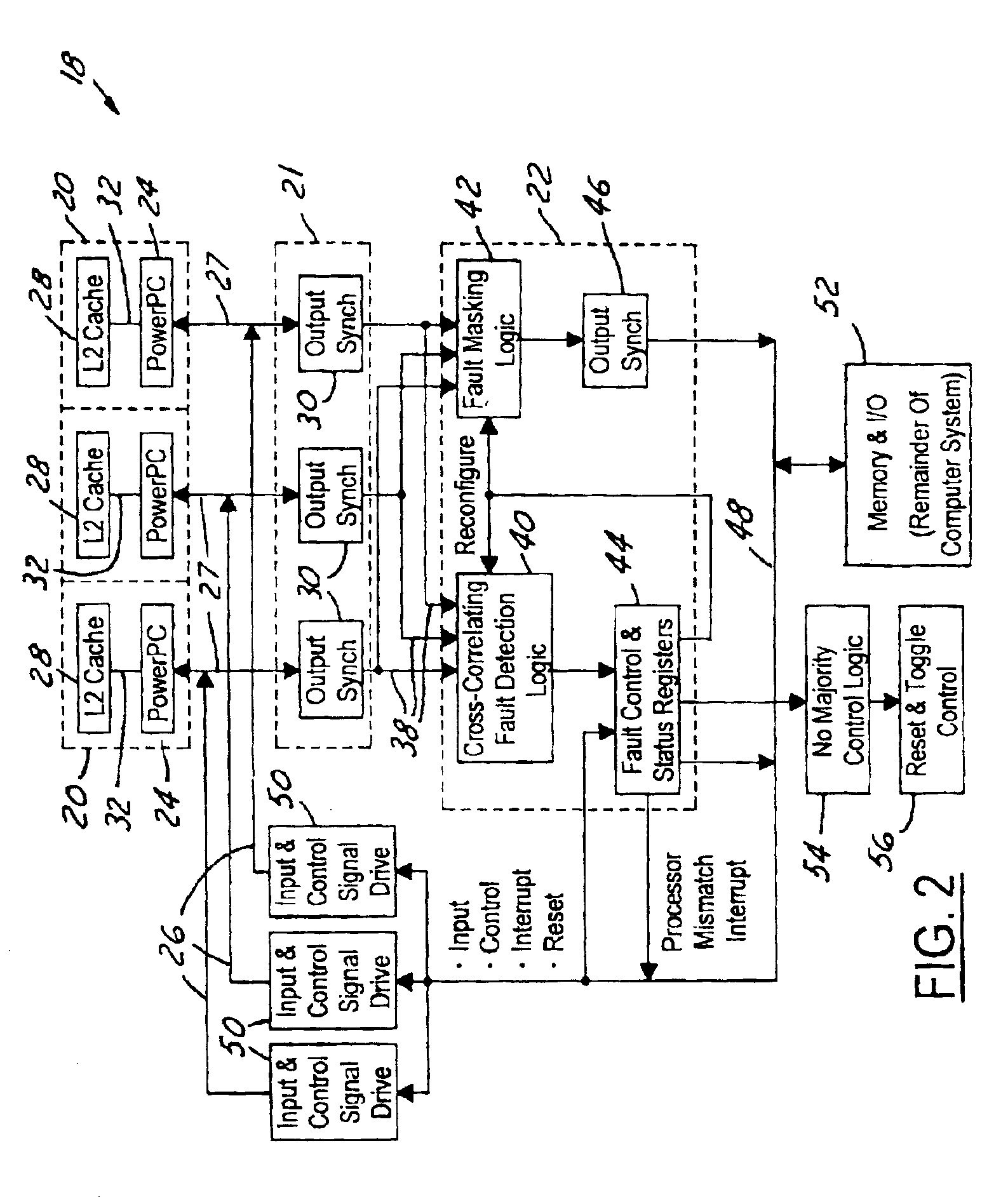

Fault tolerant processing architecture

InactiveUS6938183B2Hinders its propagationRestoring normal computational behaviorError preventionRedundant data error correctionComputer scienceLogic circuitry

A fault tolerant processing circuit comprising at least three processor groupings, a synchronizing circuit and a fault logic circuit. Each of the processor groupings have a plurality of processor grouping inputs and a plurality of processor grouping outputs. The synchronizing circuit comprises a plurality of output synchronizers, wherein each output synchronizer communicates with a corresponding respective processor grouping for synchronizing the output of each processor grouping. A fault logic circuit communicates with the synchronizing circuit. The fault logic circuit comprises a fault detection circuit and a fault mask circuit. The fault logic circuit compares the plurality of processor group outputs to detect errors in any one of the plurality of processor group outputs. An error is detected when none of the at least three processor groups is in a majority of the processor groups. Upon a detected fault, the fault mask circuit masks the output of the respective processor grouping associated with a detected error and signals a detected error. The error signal latch is then used to reset the processor groupings.

Owner:THE BOEING CO

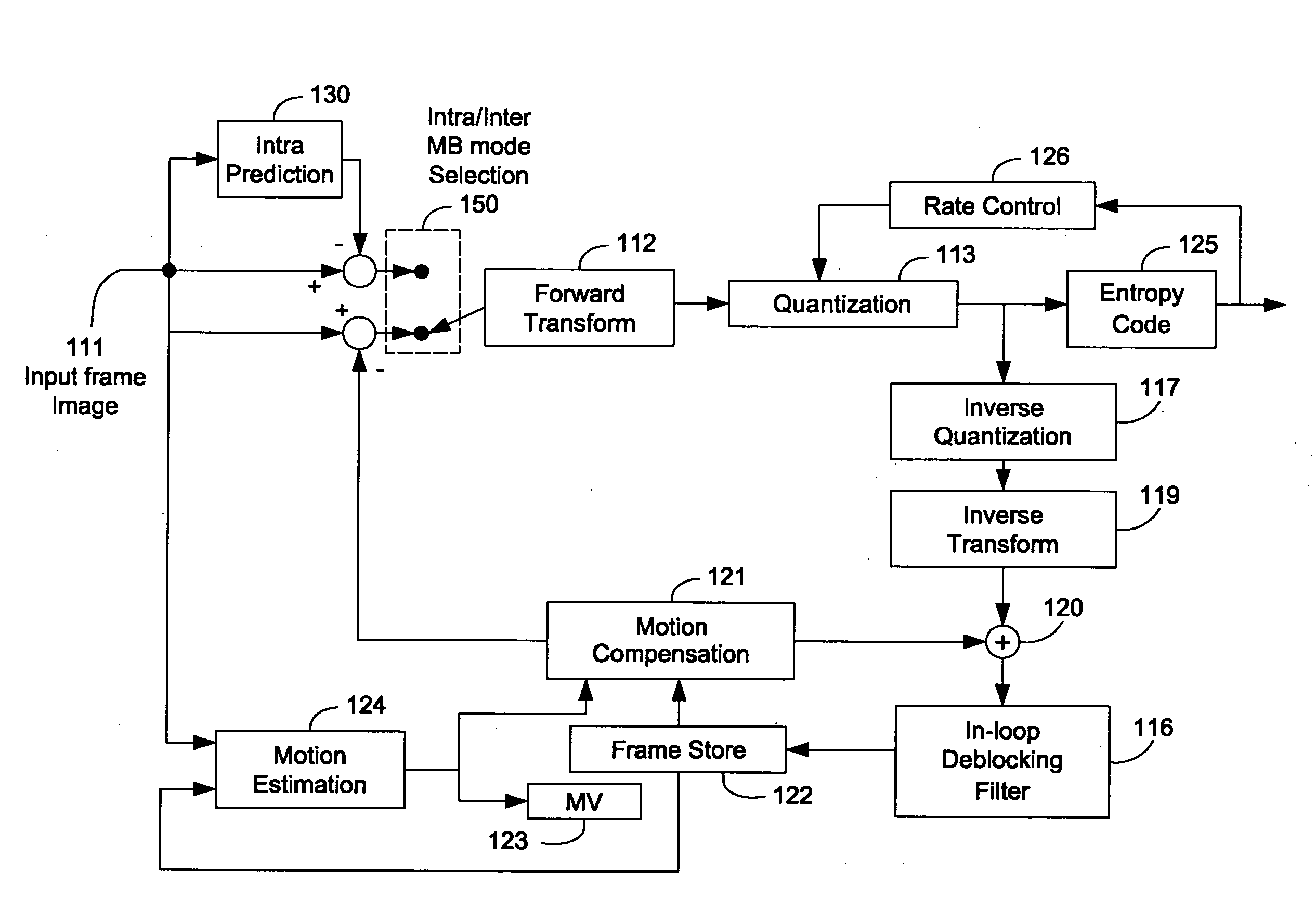

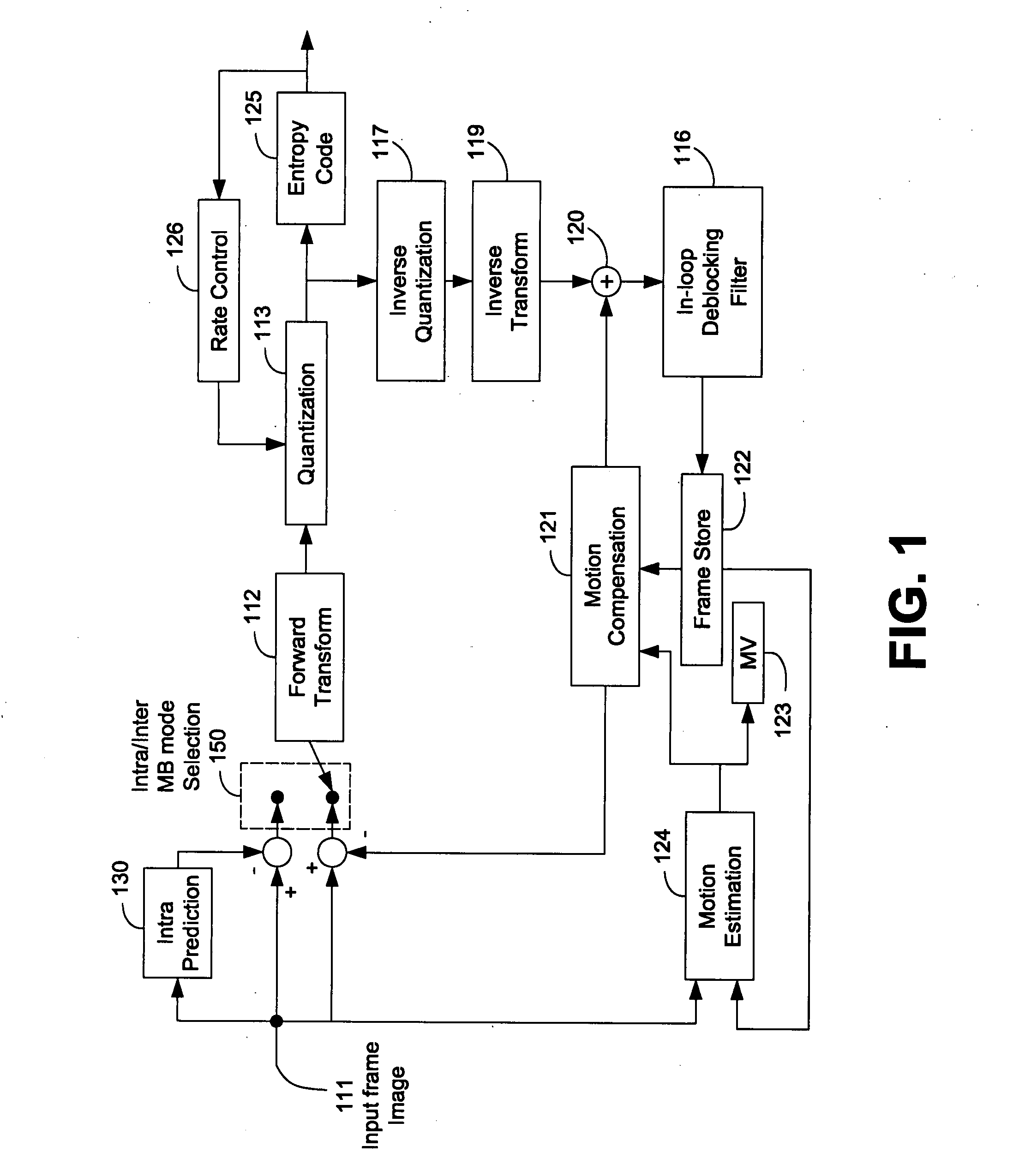

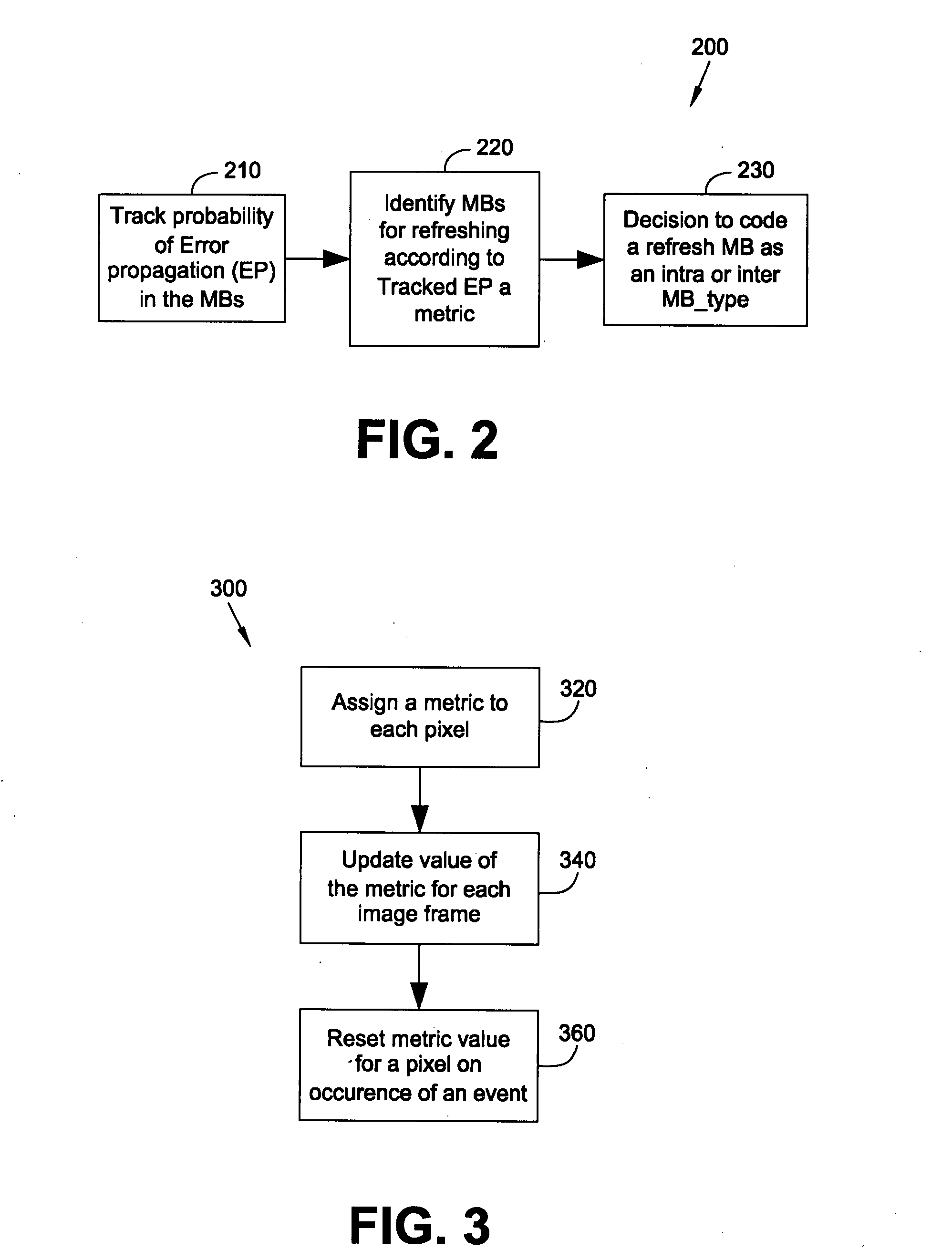

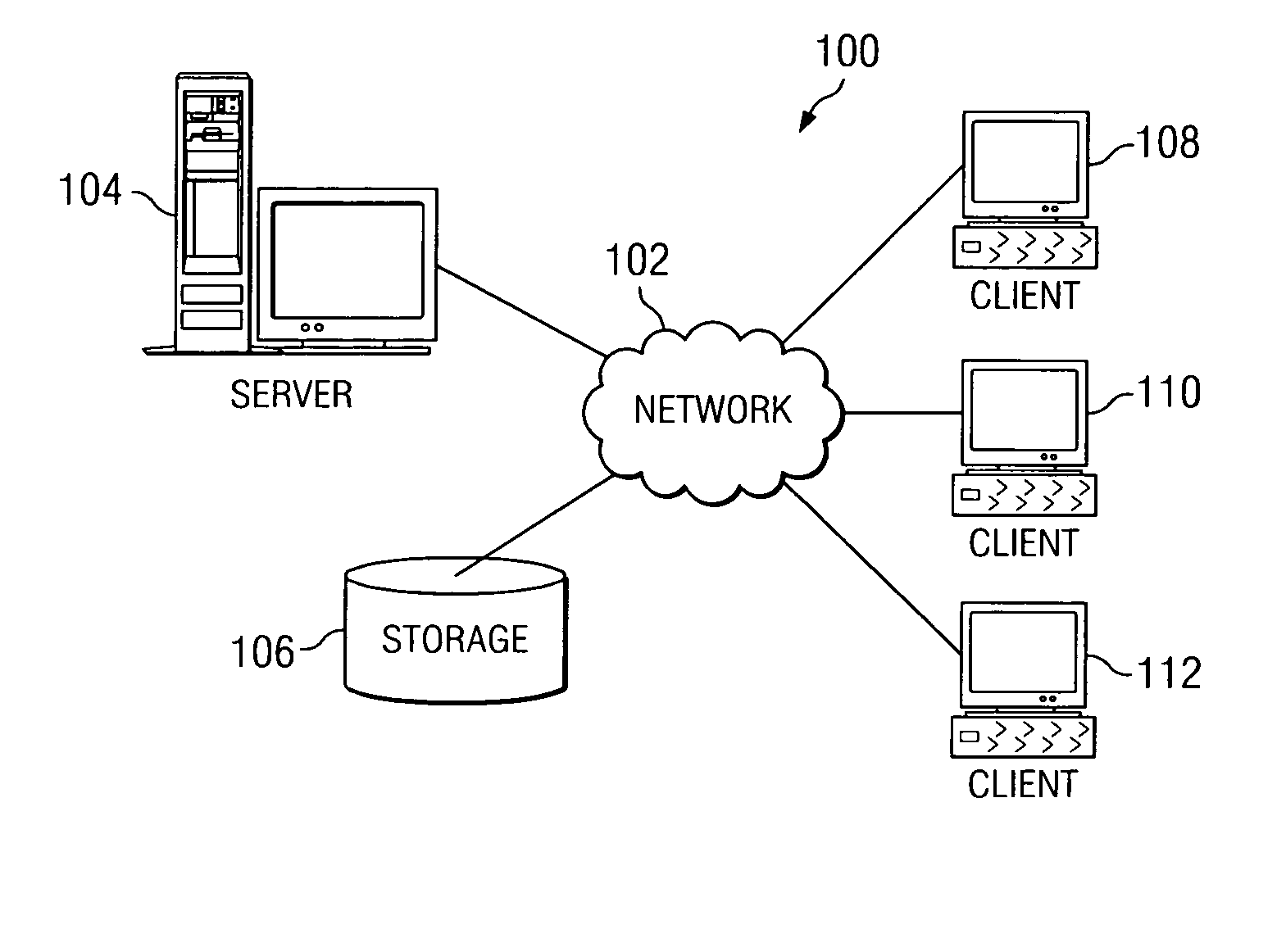

Method and device for tracking error propagation and refreshing a video stream

ActiveUS20080247469A1Reduce probabilityError propagationColor television with pulse code modulationColor television with bandwidth reductionPacket lossInterframe coding

A method and device for tracking error propagation and refreshing a video stream is provided. The proposed subject matter comprises of an error propagation tracking method that works in the sub-sampled domain to reduce computational cycles and memory bandwidth. Further, the tracking based update of the error propagation metric is done differently for static and non-static regions to avoid unnecessary refresh of static areas. Through suitable thresholding of the metric at a macroblock (MB) level, a set of refresh MBs are selected for each frame. These refresh MBs are coded either as an intra MB or as an inter MB that is predicted from one or more reliable reference frames (—frames that are known to be available at the decoder with negligible errors—). Such inter coding of refresh MBs improves the compression efficiency when compared to pure intra coding of refresh MBs. Further, variants to the threshold selection are presented that result in temporally uniform distribution of the number of refresh MBs and a strict refresh scheme wherein all MBs are guaranteed to be with negligible errors following a packet loss within a committed refresh period. In addition, to using the error propagation metric, spatial connectivity to already chosen refresh MBs is used in the selection of additional refresh MBs within a frame and across frames; this reduces the rate of error propagation due to part of a macroblock predicting from older, erroneous neighboring MBs and in turn requiring more refresh MBs on the average per frame.

Owner:ITTIAM SYST P

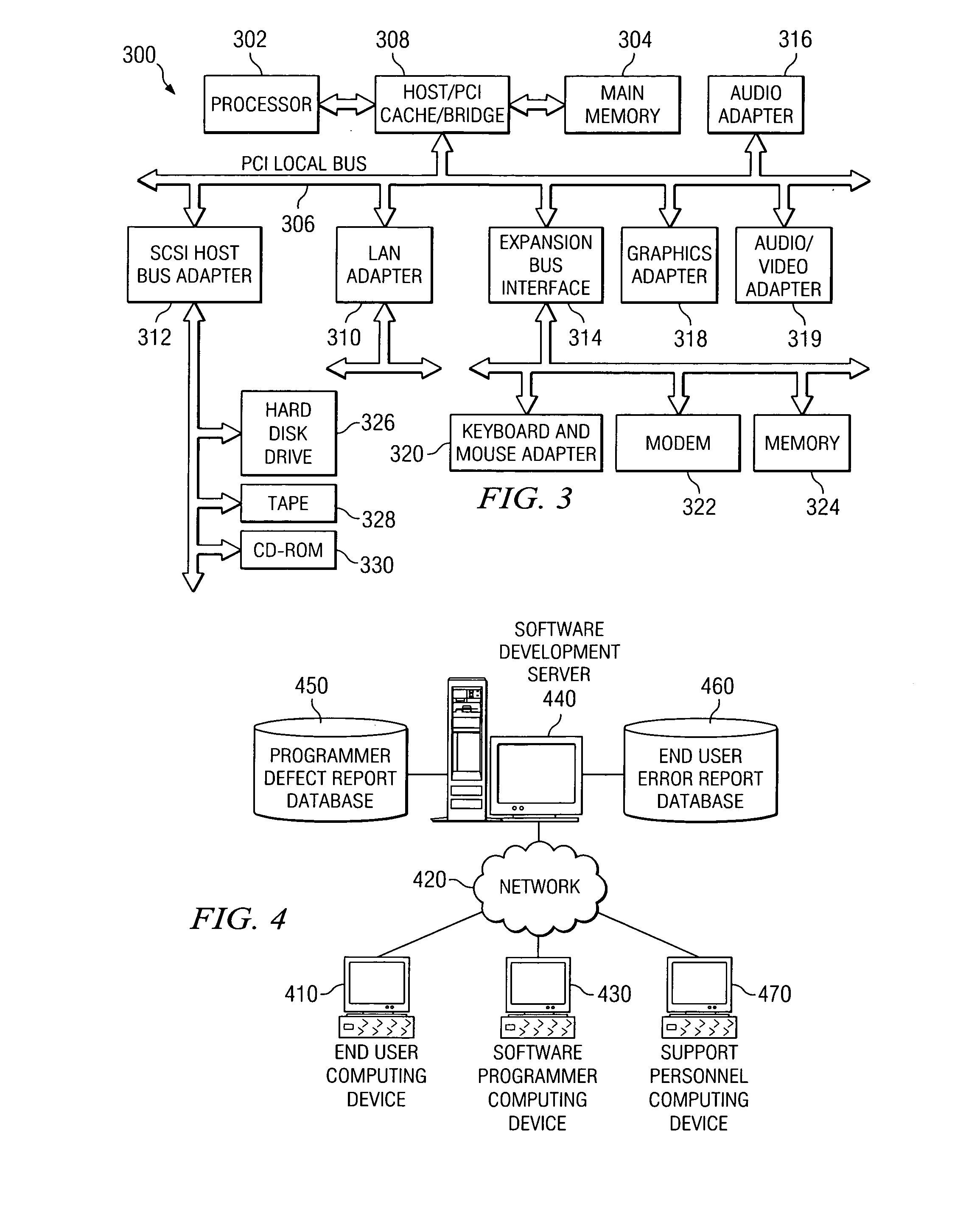

System and method for updating end user error reports using programmer defect logs

ActiveUS20060156077A1Error detection/correctionSpecial data processing applicationsSoftware developmentData mining

A system and method for correlating end user error reports with software developer defect logs to thereby update the end user error reports with information from the developer defect logs. With the system and method, when support personnel open an end user error report to address the problem encountered by the user, the mechanisms of the system and method search a defect report database to determine if there is any defect report related to the same error that is the subject of the opened end user error report. If so, the end user error report is updated to include information from the defect report. This information may include, for example, the identity of the source of the problem generating the error, the identity of the fix or patch that solves the problem generating the error encountered by the end user, if any, and the like.

Owner:IBM CORP

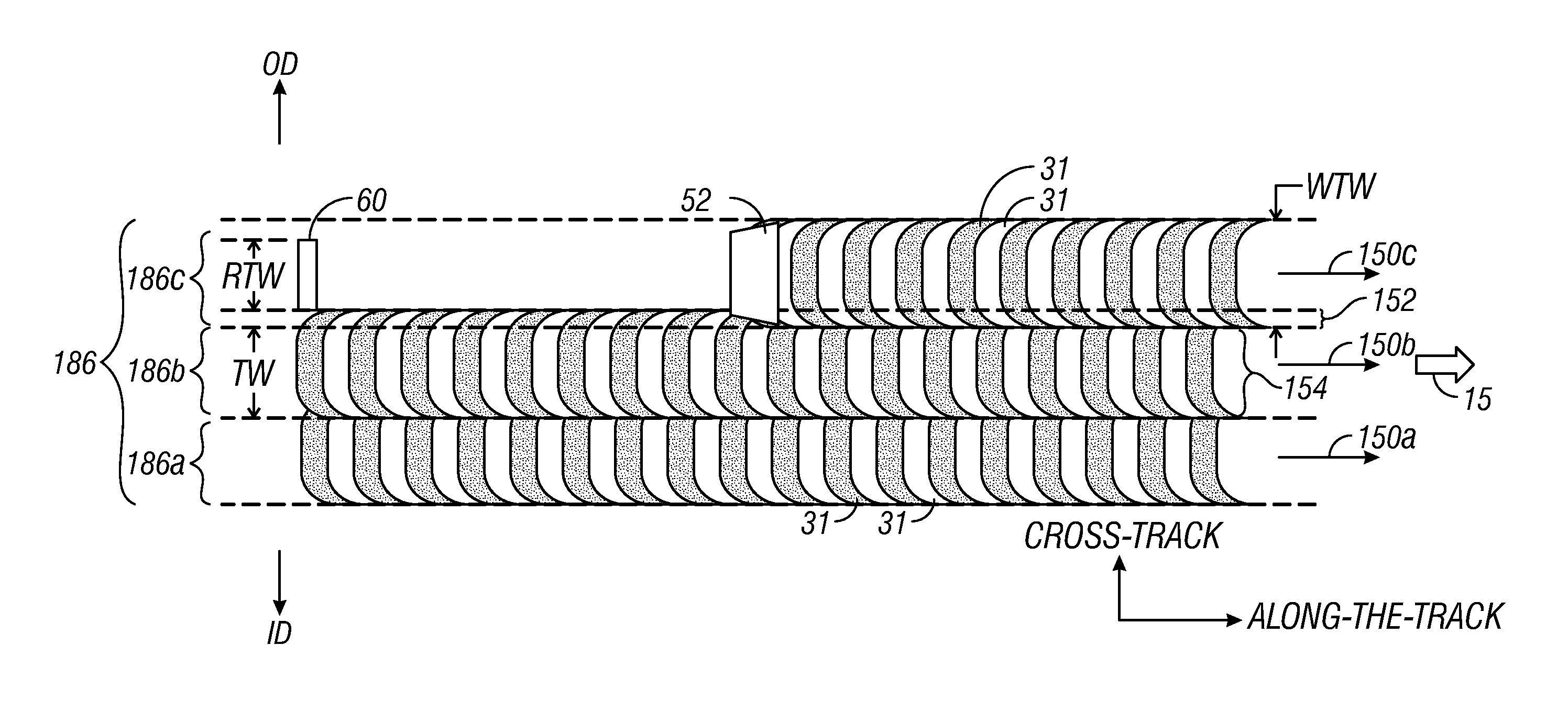

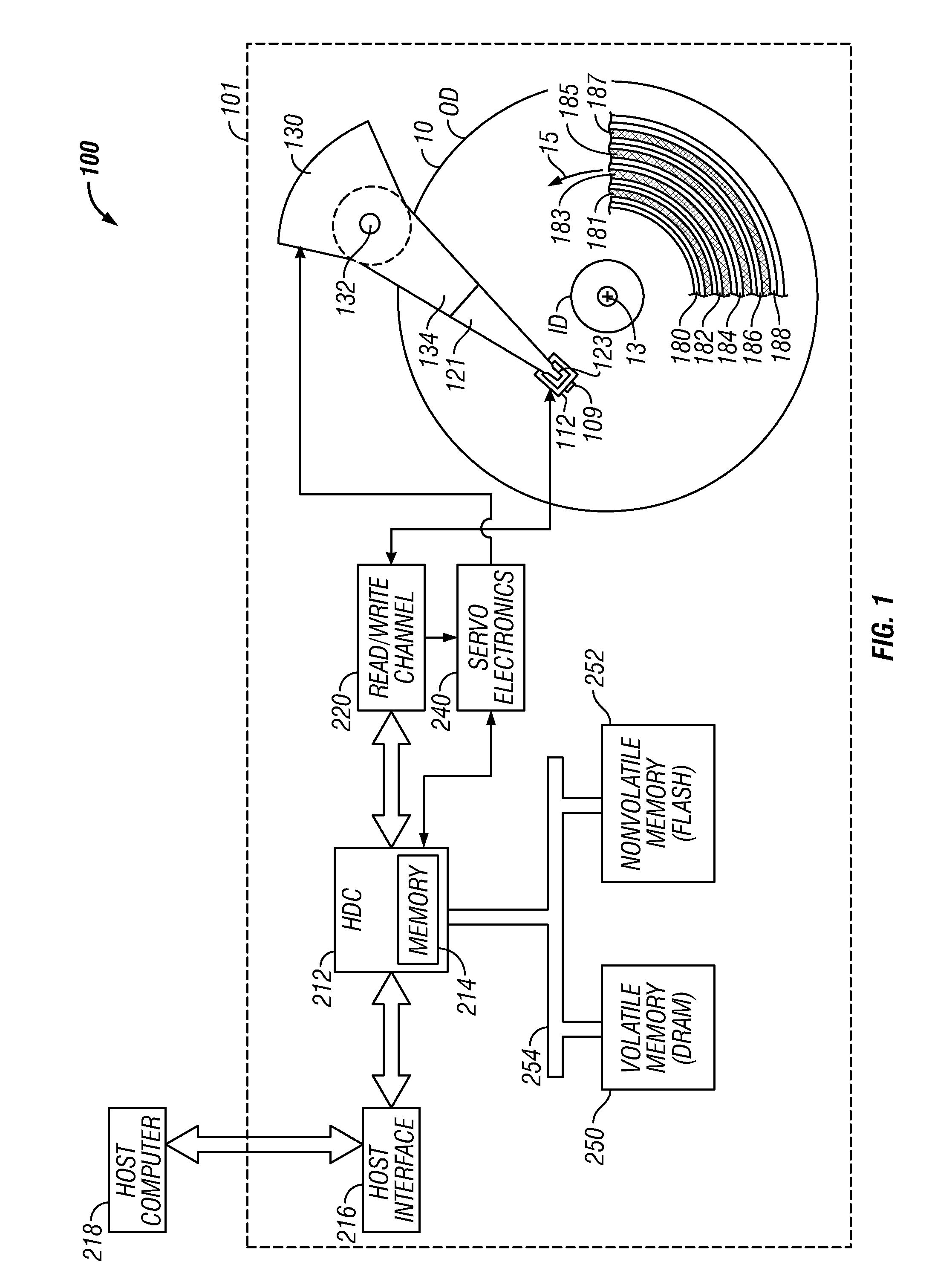

Shingled magnetic recording (SMR) disk drive with verification of written data

ActiveUS20130148225A1Improve writing efficiencyTrack density can not be increasedRecord information storageCarrier monitoringData validationShingled magnetic recording

A “write-squeeze-verify” method is used for verification of the data that has been written in the annular bands of a shingled magnetic recording disk drive. The writing of data along a track overwrites a portion of the previously written track and thus “squeezes” the data of the previously written track to thereby form a “shingled data track” (SDT). The data in each SDT is read back and verified by performing an error correction check using error correction bits associated with the data written in the SDT, or by comparing the readback data with the data stored in memory. If the data read back is not verified, a write error counter is incremented and a write error frequency is calculated. One or more attempts to write the data can be performed. If the data in the SDT cannot be verified after the attempted rewrite(s), then a “re-try fail” is reported.

Owner:WESTERN DIGITAL TECH INC

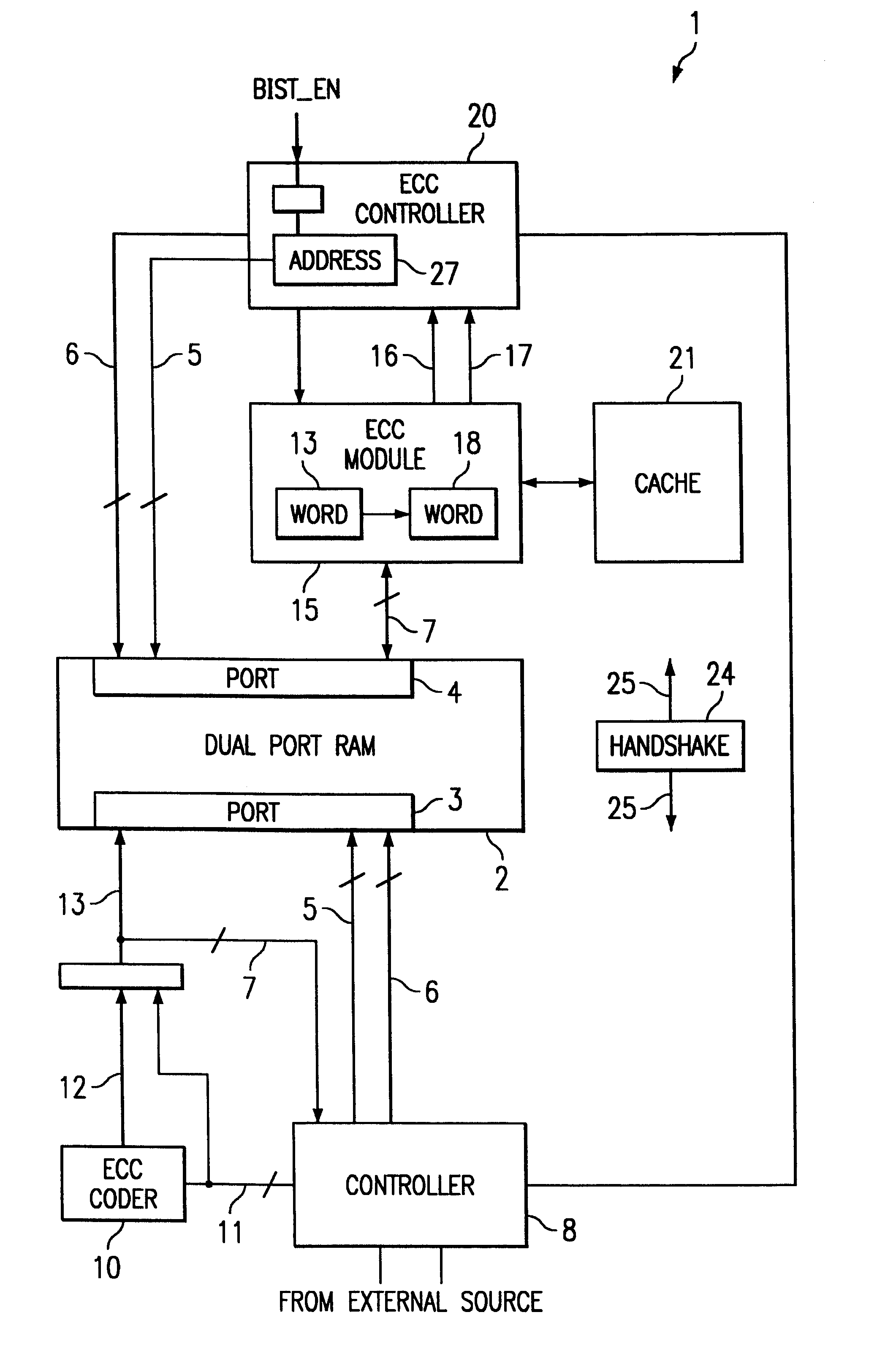

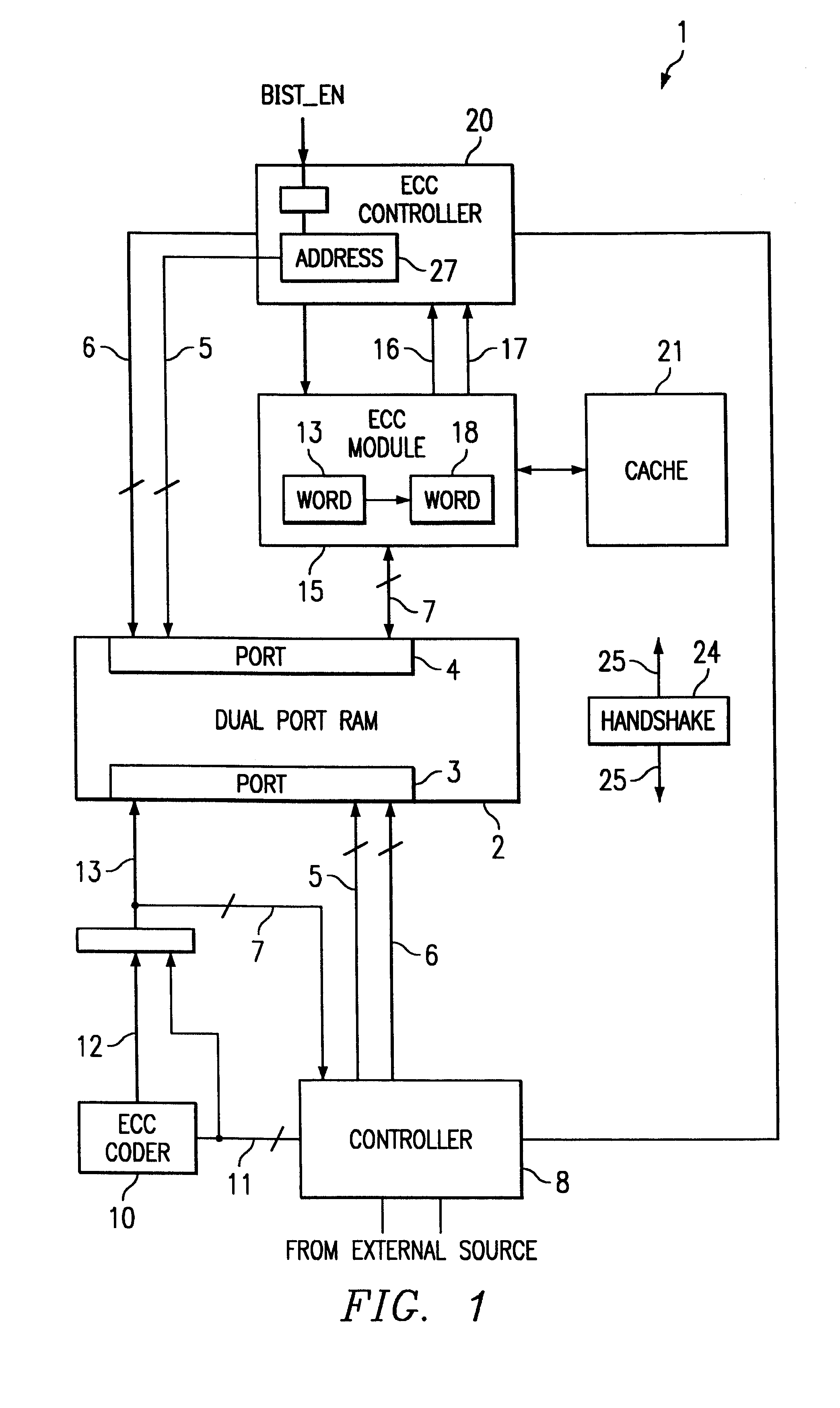

System and method for correcting soft errors in random access memory devices

A circuit and method are disclosed for reducing soft errors in dynamic memory devices using error checking and correcting. In an exemplary embodiment, a memory device includes a dual port memory having a first port for externally-initiated memory access operations and a second port for handling memory access operations associated with error checking and error correction operations. An error module, coupled to the second port of the dual port memory, performs an error checking operation on words read from the dual port memory. An error controller, coupled to the error module, controls the error module to perform error check operations on each word sequentially read from the dual port memory through the second port thereof. The error checking is performed substantially in parallel with externally-initiated memory access operations performed using the first port of the dual port memory. The error module may also generate a corrected word for a word that is detected by the error module as having a correctable error. The error controller may replace in the dual port memory the word having the correctable error with the corrected word.

Owner:STMICROELECTRONICS SRL

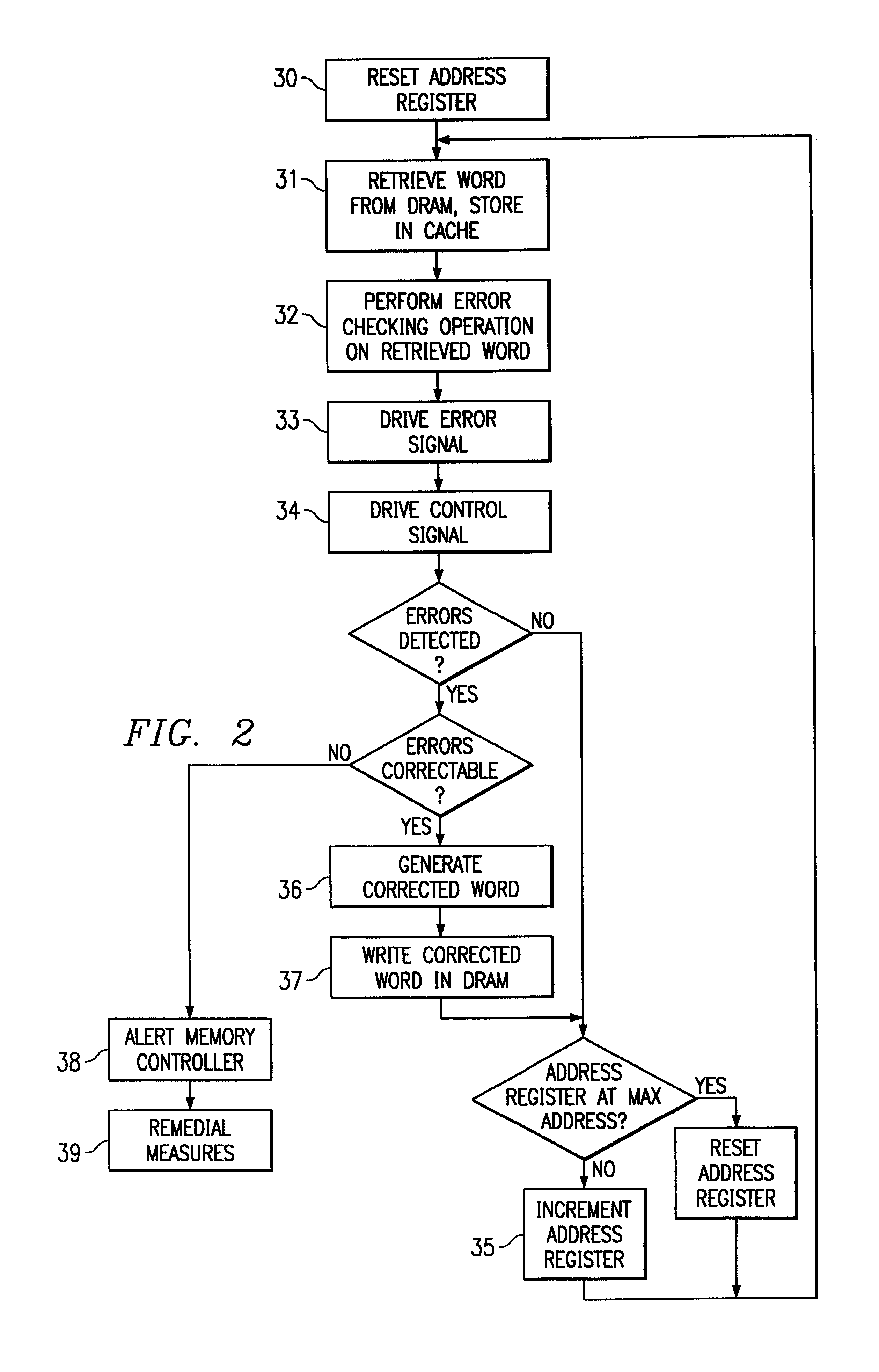

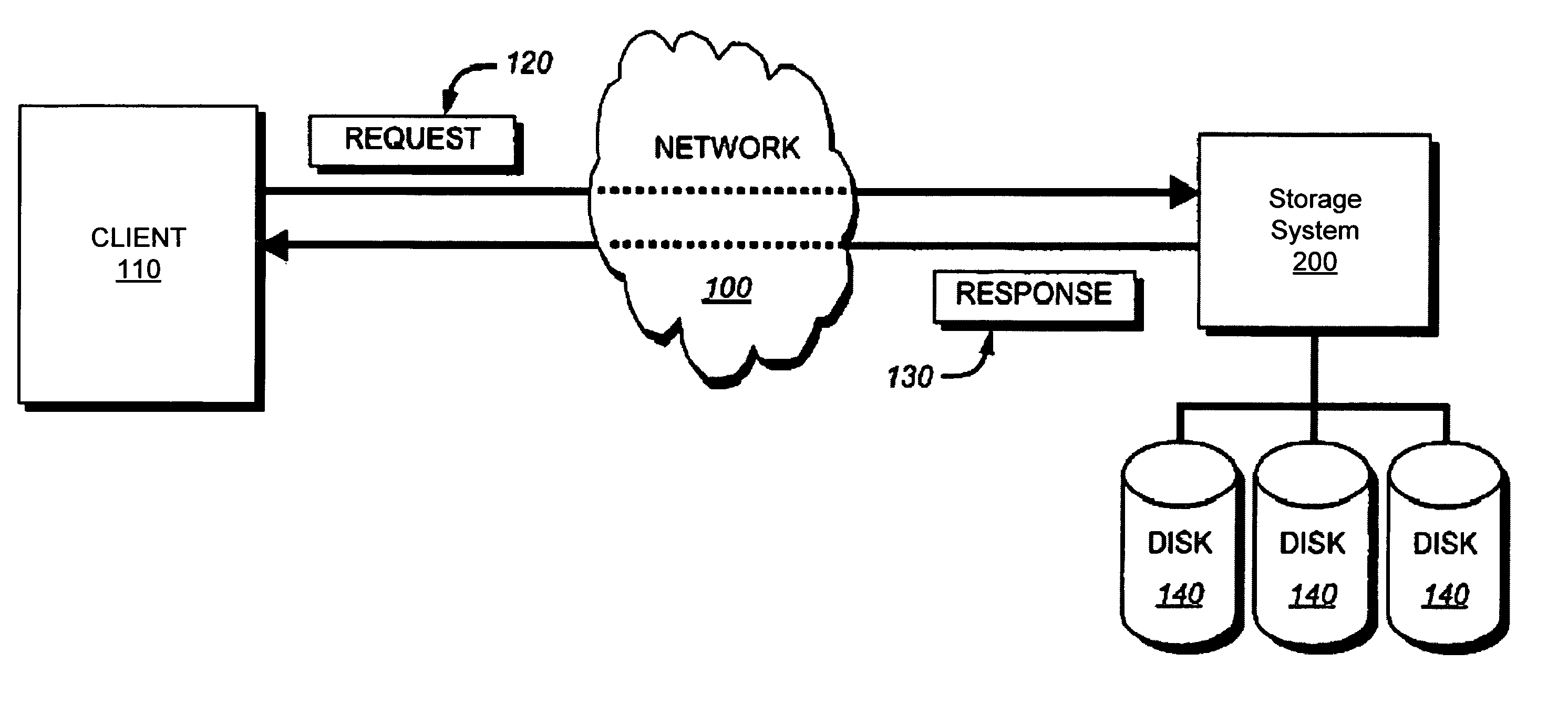

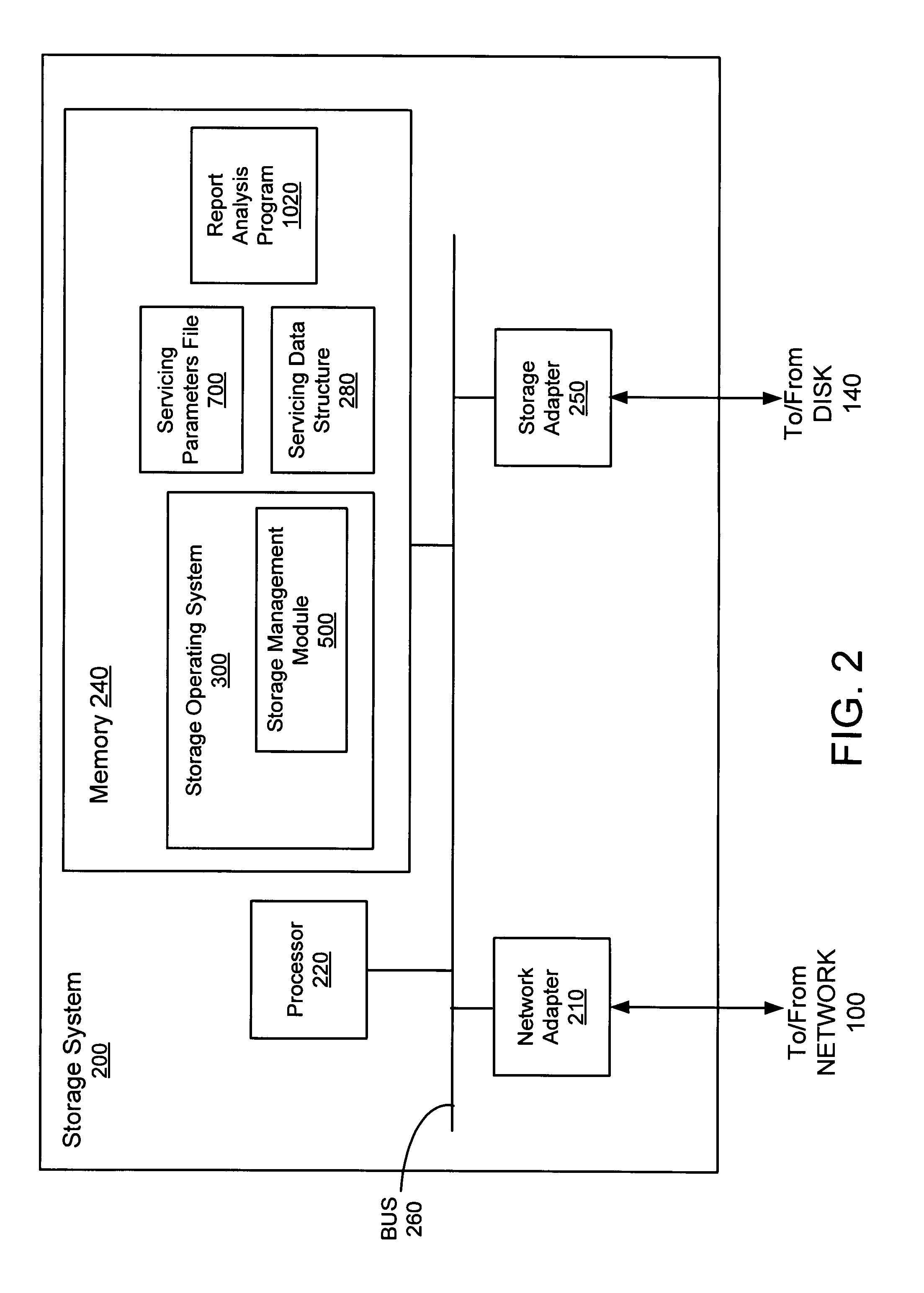

Evaluating and repairing errors during servicing of storage devices

ActiveUS7653840B1Reduce in quantityHigh rateNon-redundant fault processingStatic storagePhysical addressStorage management

A storage management module for evaluating and repairing errors during monitoring or testing of storage devices of a storage system is described herein. When a storage device exhibits errors that reaches (in number) an error threshold, the storage management module determines whether any errors are due to damaged sectors localized in a single physical area of a predetermined size (referred to as a “patch”) of a platter of the storage device using the physical addresses of the errors. Two or more errors may be grouped as a single error if they are located within a predetermined threshold distance from each other on a platter and counted as a single error against the error threshold. A patch containing two or more damaged sectors is referred to as a “damaged” patch. In some embodiments, all sectors of a damaged patch (including undamaged sectors) are reassigned to spare sectors.

Owner:NETWORK APPLIANCE INC