Patents

Literature

32results about How to "Less jitter" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

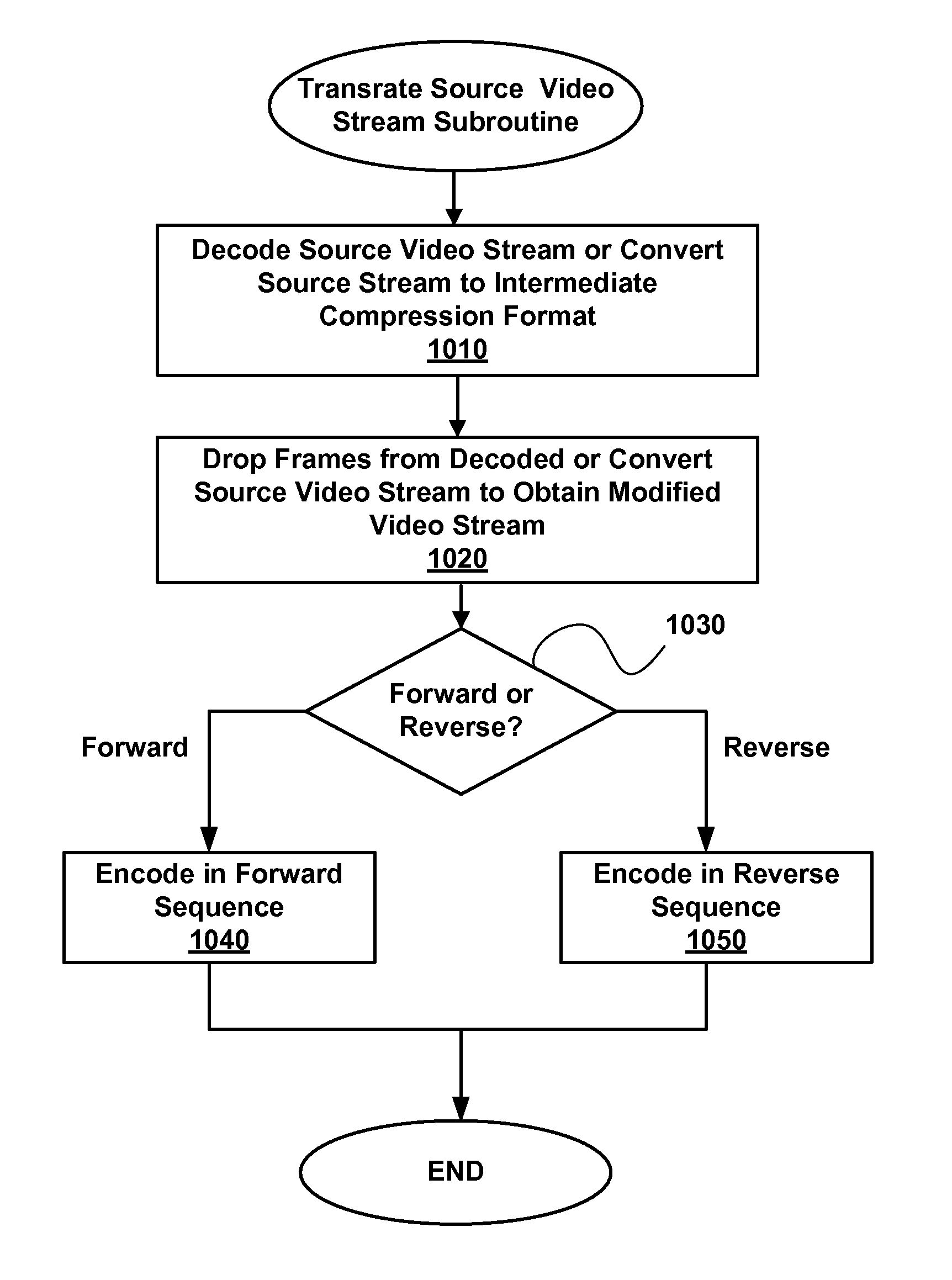

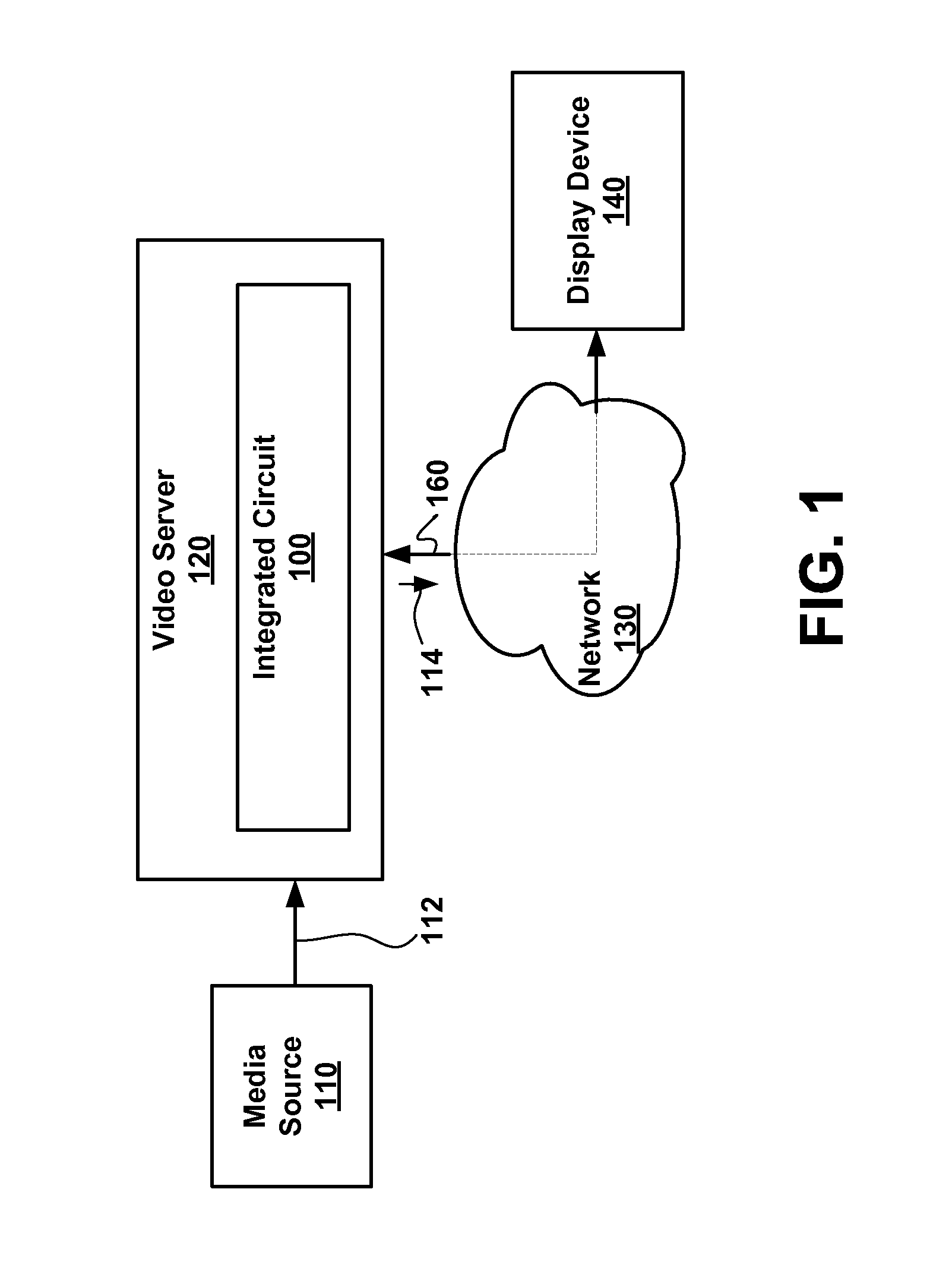

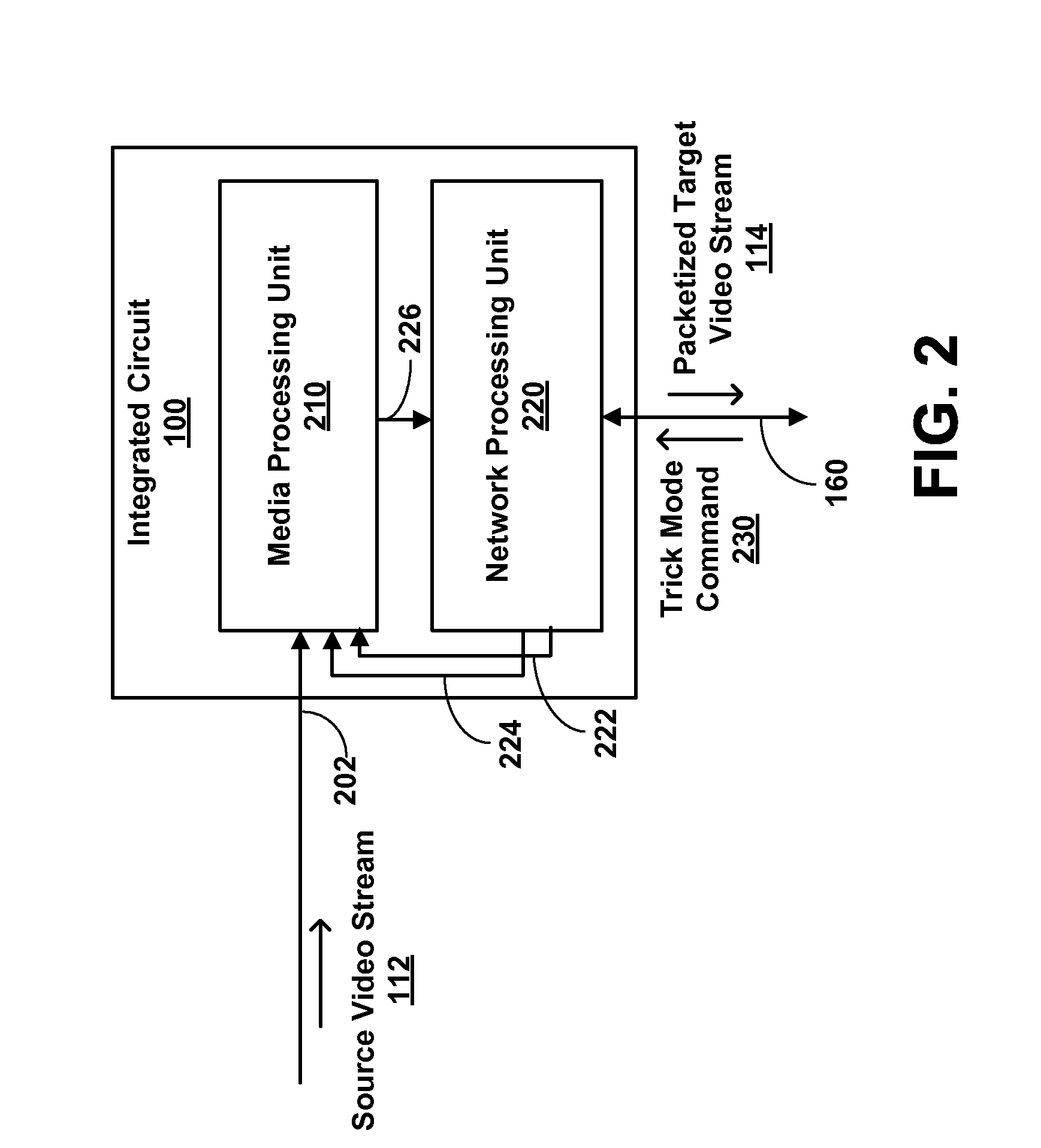

Providing trick mode for video stream transmitted over network

ActiveUS8265168B1Less jitterPlayed back more smoothlyTelevision system detailsColor television with pulse code modulationVideo serverDisplay device

Systems and methods for performing a trick mode of video streams transmitted over a network without increasing the amount of data transmitted over the network. A video server transrates a source video stream to a target video stream by removing pictures from the source video stream. The target video stream has a reduced number of pictures compared to the source video stream. Therefore, when the target video stream is played on a display device, the target video stream has a playback speed faster than the playback speed of the source video stream.

Owner:NXP USA INC

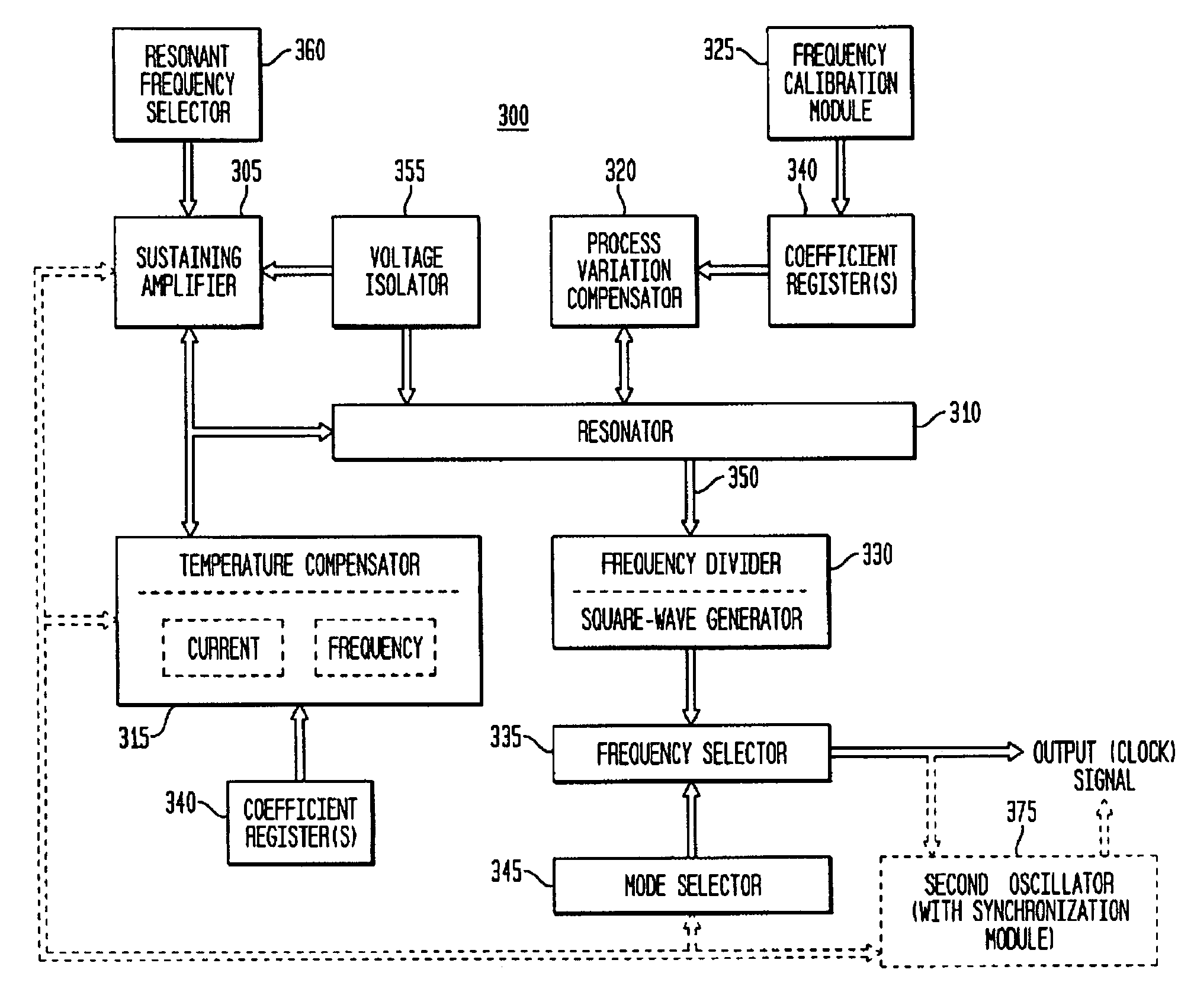

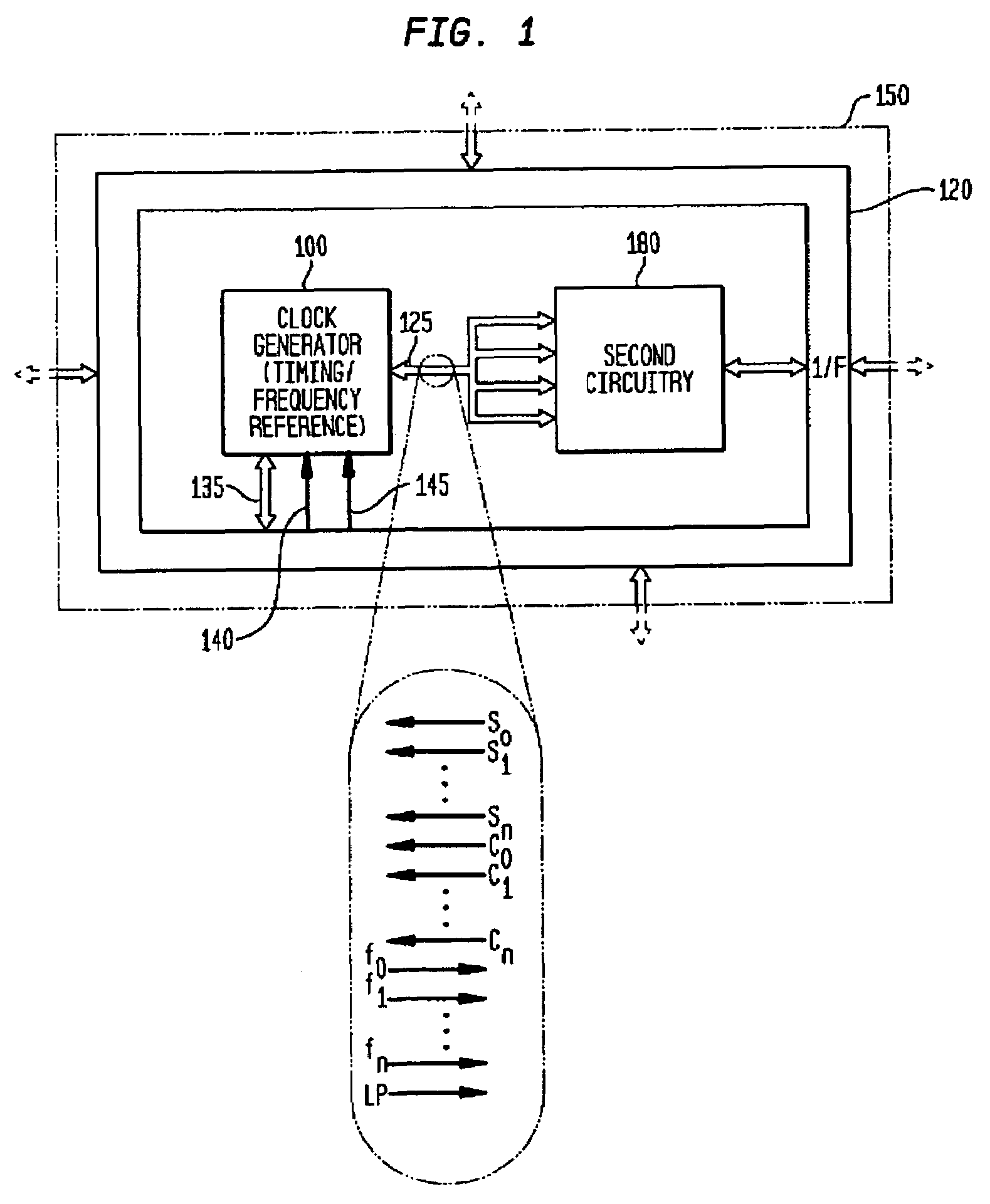

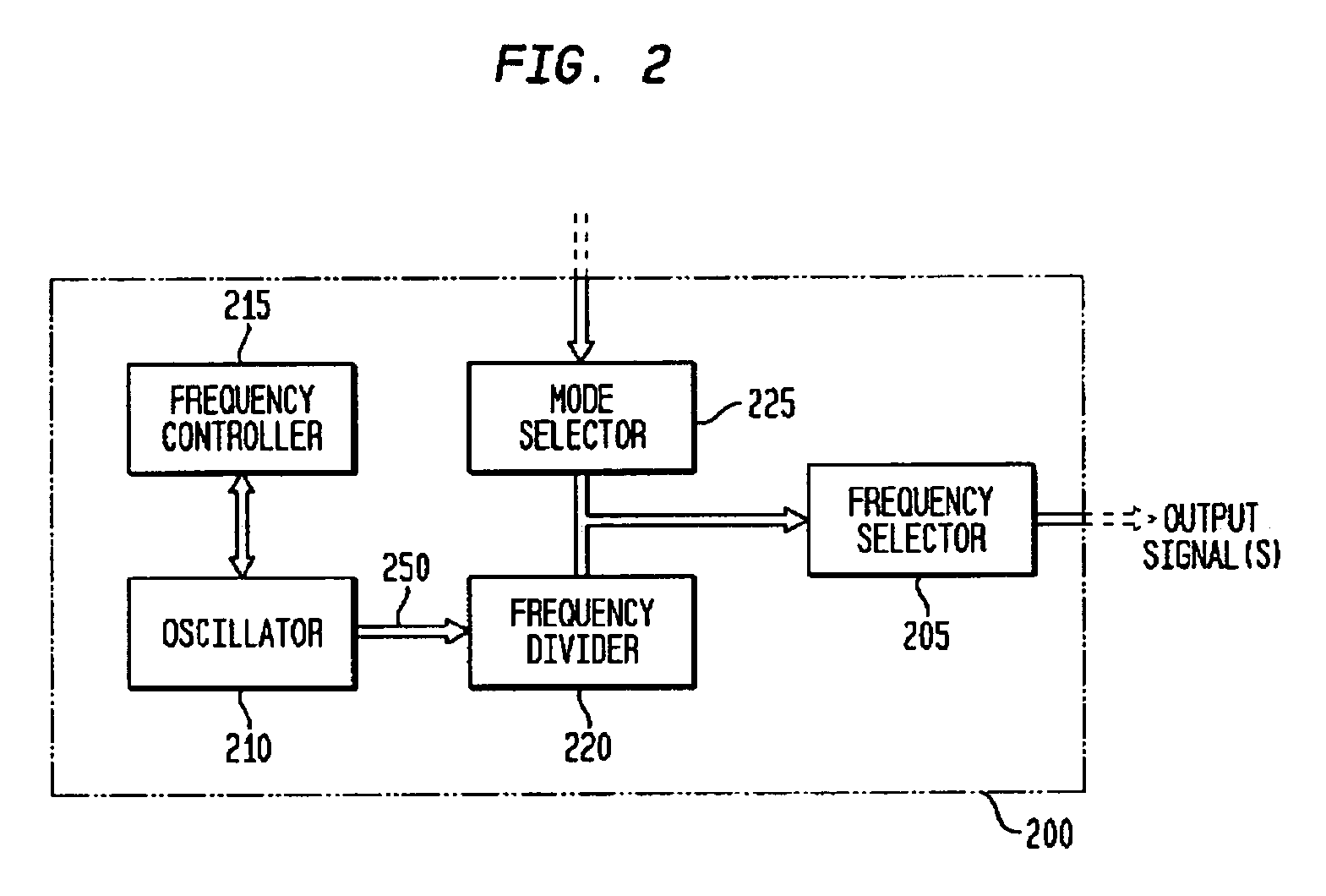

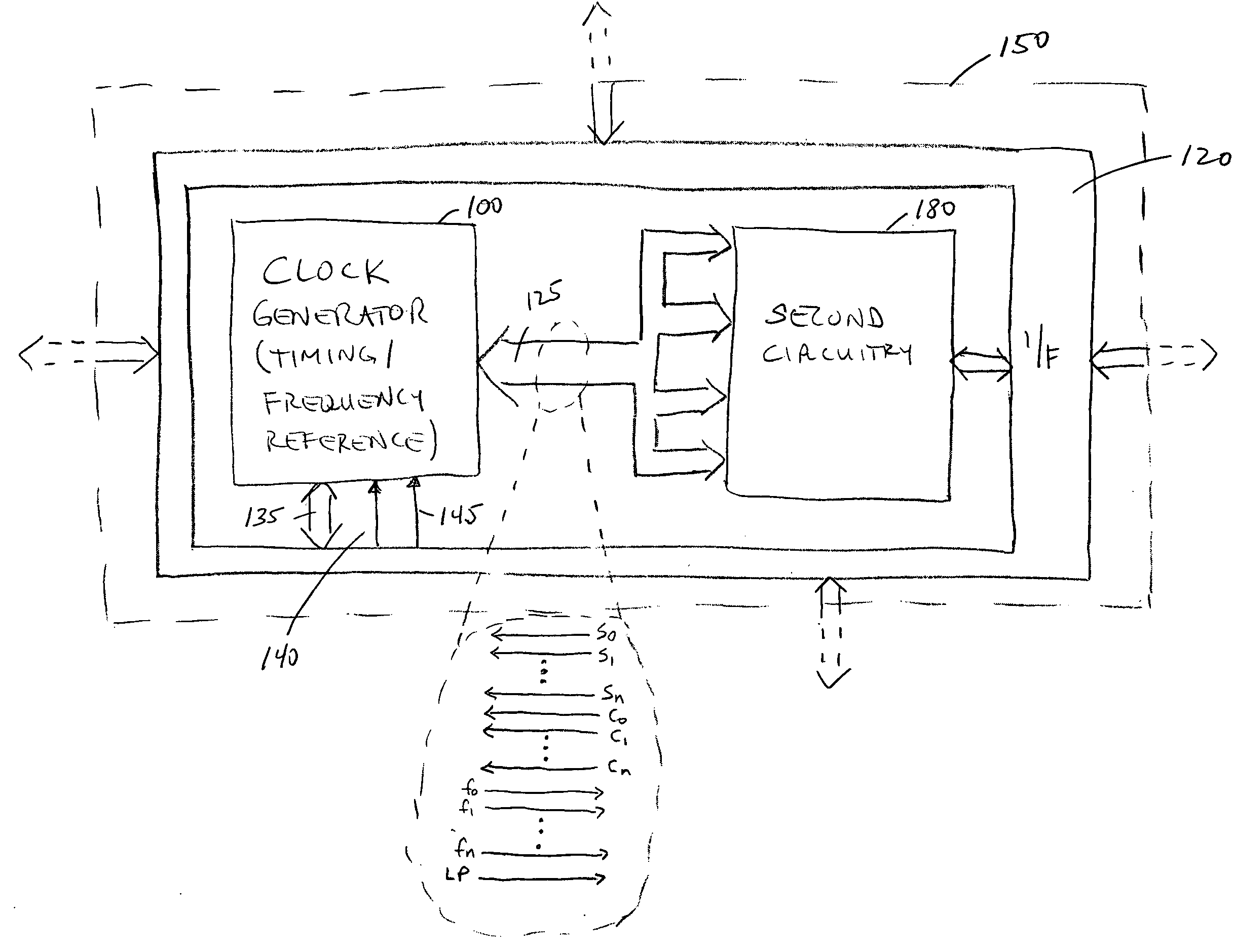

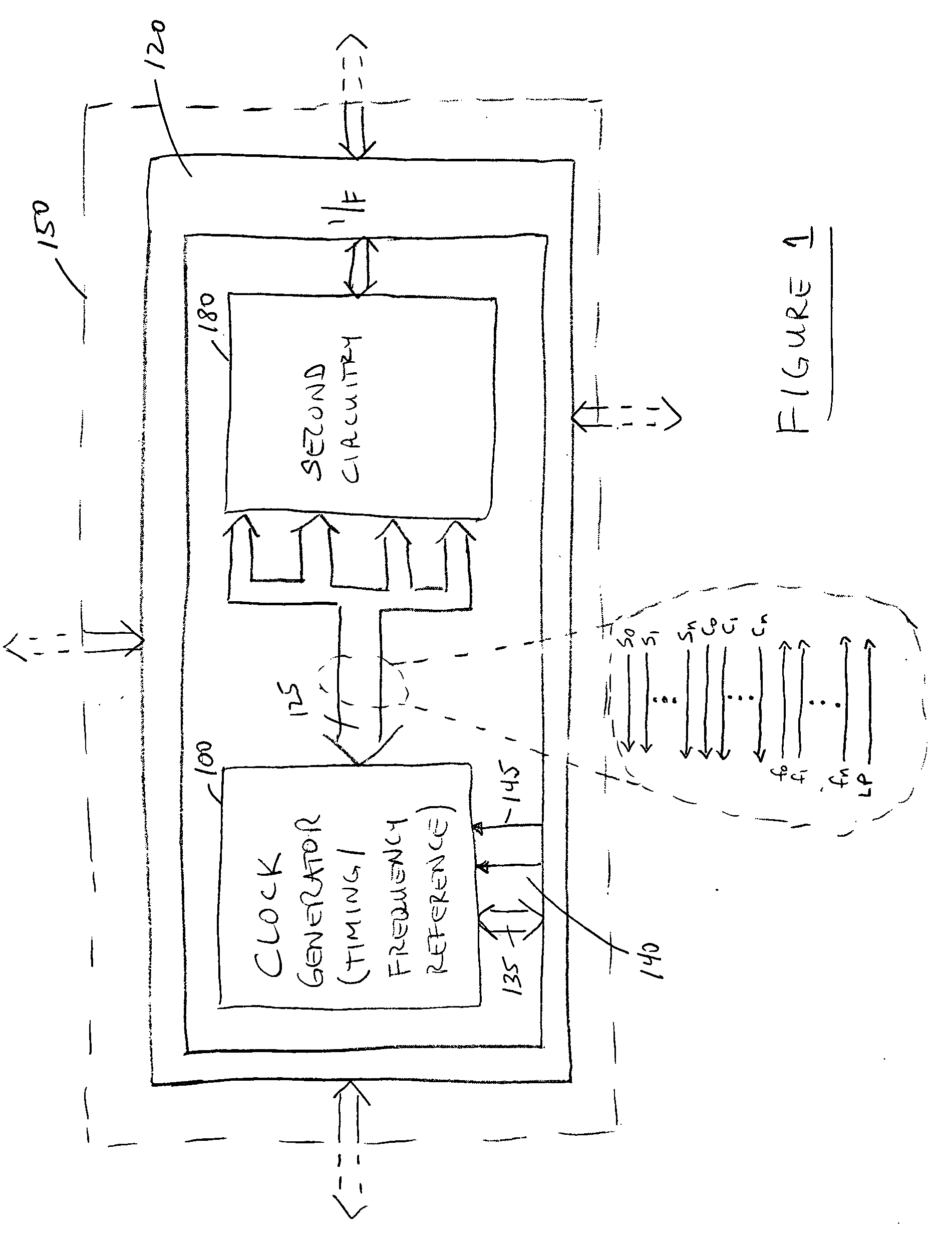

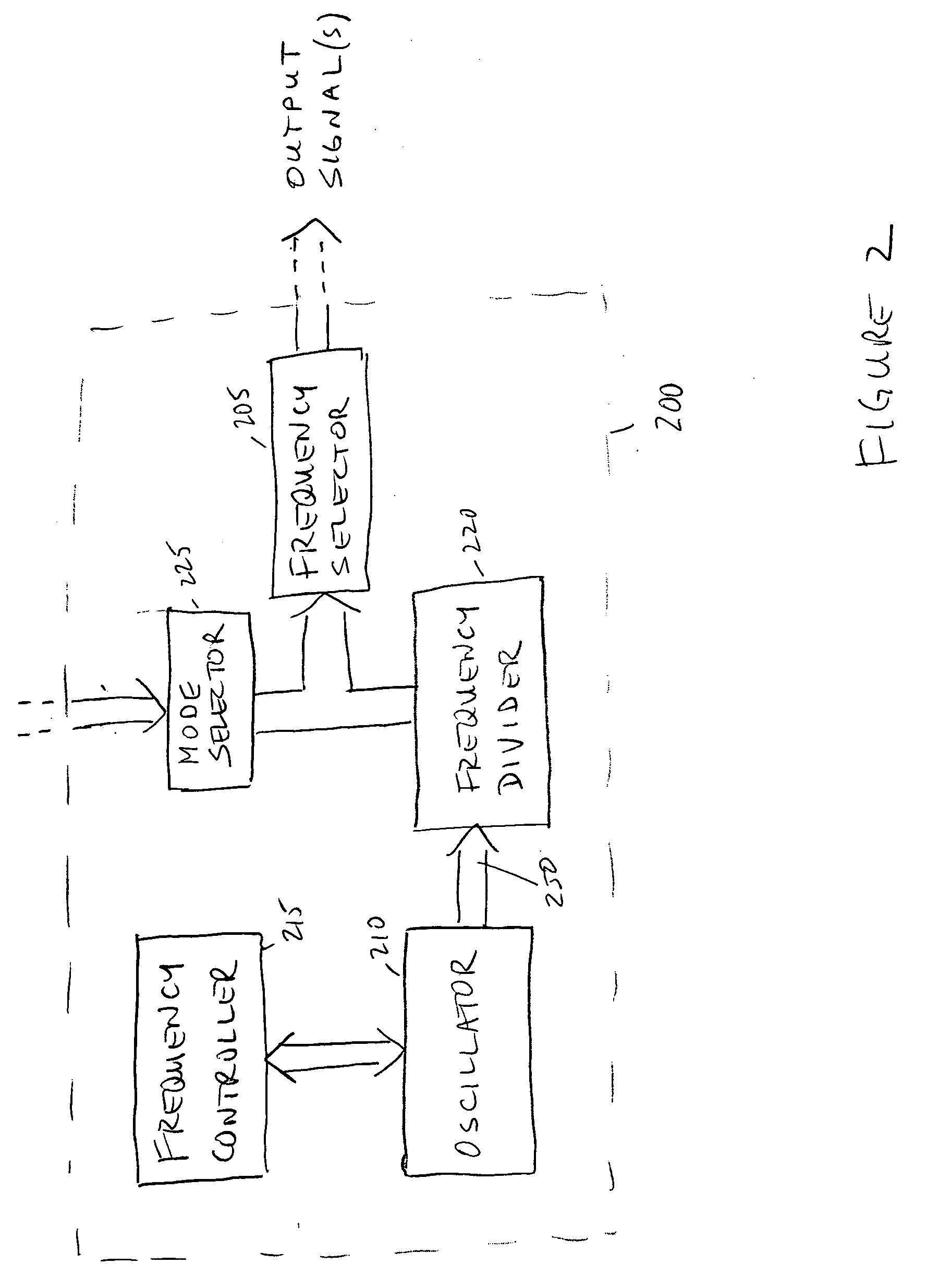

Monolithic clock generator and timing/frequency reference

ActiveUS7227423B2High frequencyLoud noiseResonant circuit tuningPulse automatic controlAudio power amplifierPulsed mode

In various embodiments, the invention provides a clock generator and / or a timing and frequency reference, with multiple operating modes, such power conservation, clock, reference, and pulsed modes. The various apparatus embodiments include a resonator adapted to provide a first signal having a resonant frequency; an amplifier; a temperature compensator adapted to modify the resonant frequency in response to temperature; and a process variation compensator adapted to modify the resonant frequency in response to fabrication process variation. In addition, the various embodiments may also include a frequency divider adapted to divide the first signal having the resonant frequency into a plurality of second signals having a corresponding plurality of frequencies substantially equal to or lower than the resonant frequency; and a frequency selector adapted to provide an output signal from the plurality of second signals. The output signal may be provided in any of various forms, such as differential or single-ended, and substantially square-wave or sinusoidal.

Owner:INTEGRATED DEVICE TECH INC

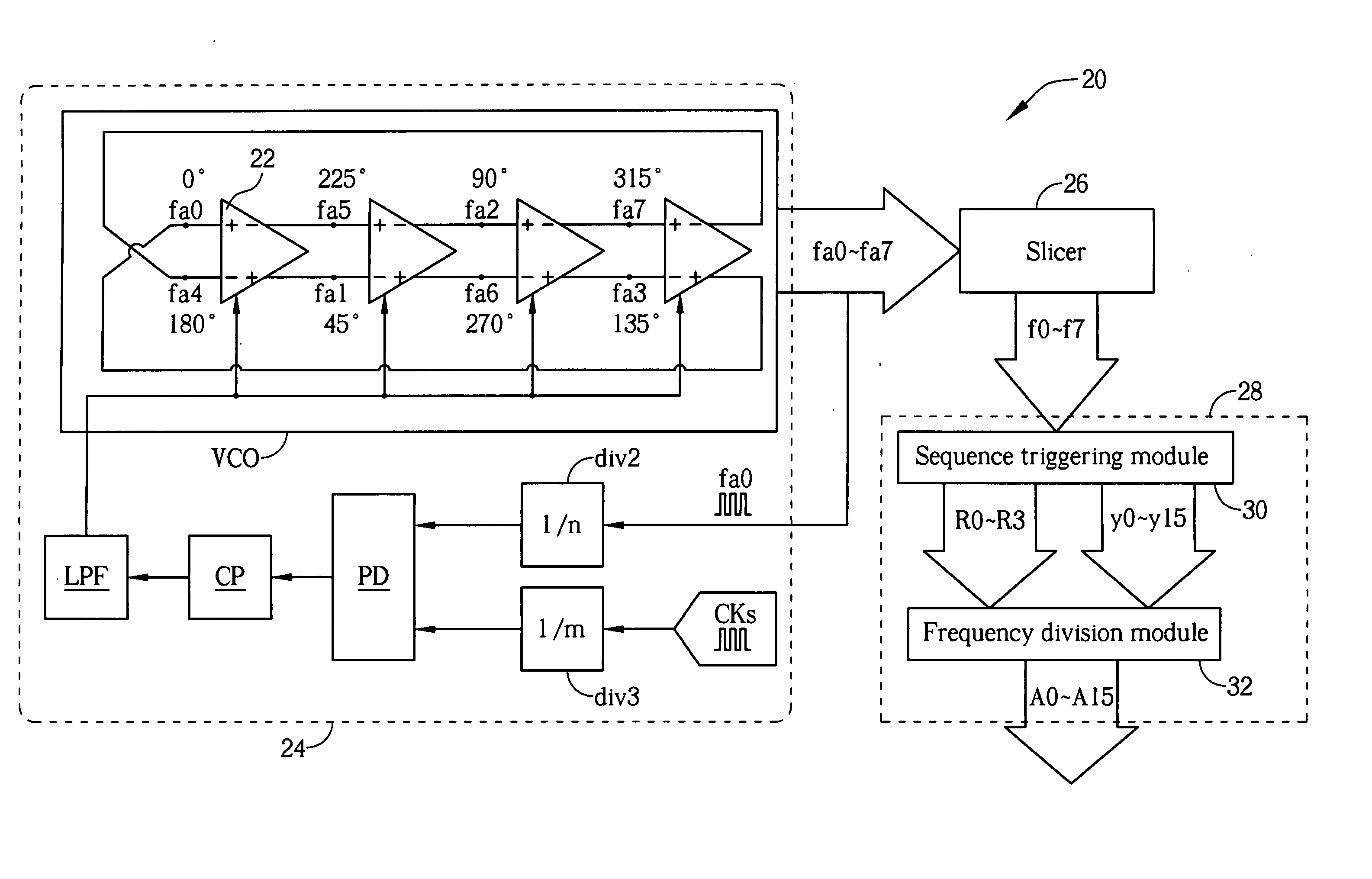

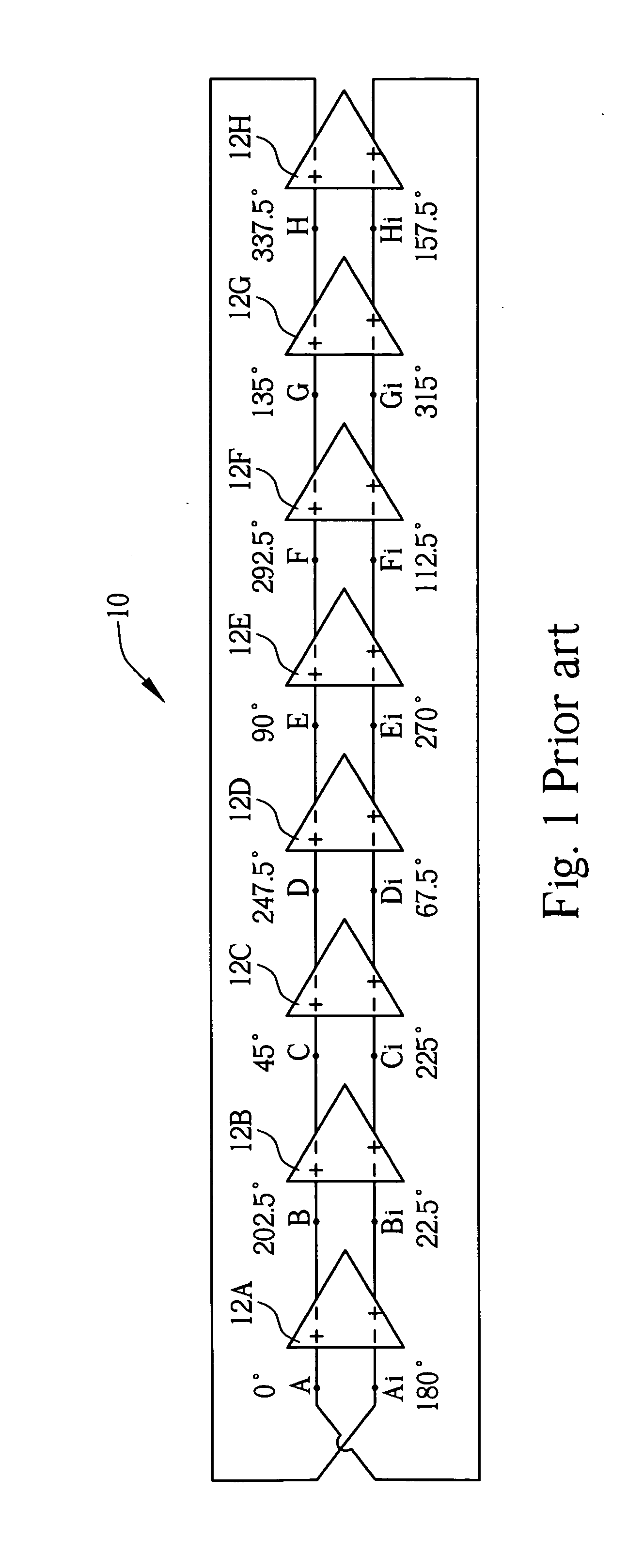

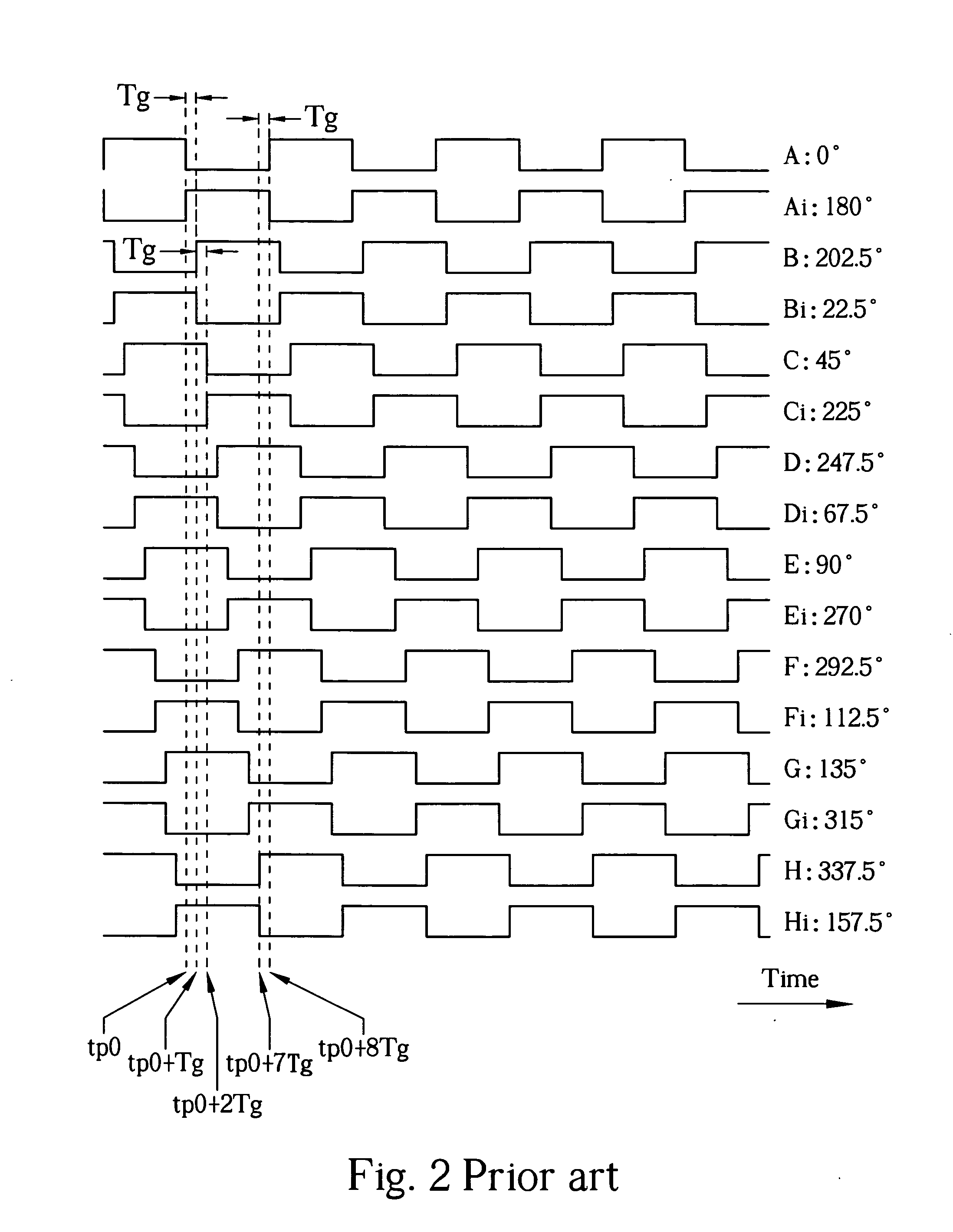

Method for multiple-phase splitting by phase interpolation and circuit the same

ActiveUS20050001665A1Good referenceLess jitterPulse generation by bipolar transistorsPulse automatic controlEngineeringPhase splitting

The invention relates to a method and related circuitry for multiple phase-splitting. The method includes: while generating M output clocks with a same frequency f1 and different phases, generating N reference clocks with a same frequency (M / N)*f1 and different phases (wherein M>N), and triggering (N / M) frequency division using different periods within each reference clock to generate (M / N) output clocks of different phases for each reference clock, such that the M output clocks of different phases are generated from the N reference clocks of different phases.

Owner:VIA TECH INC

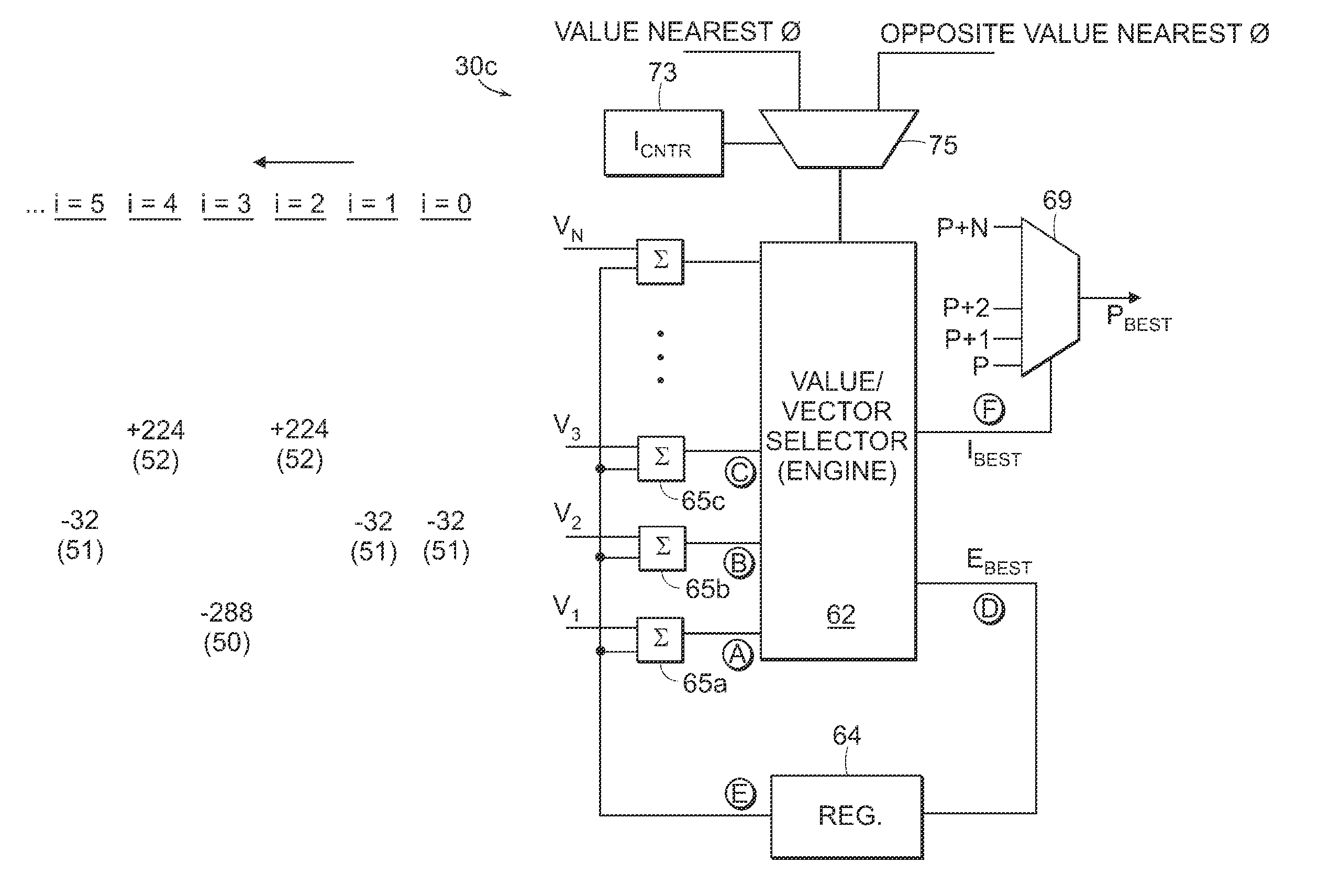

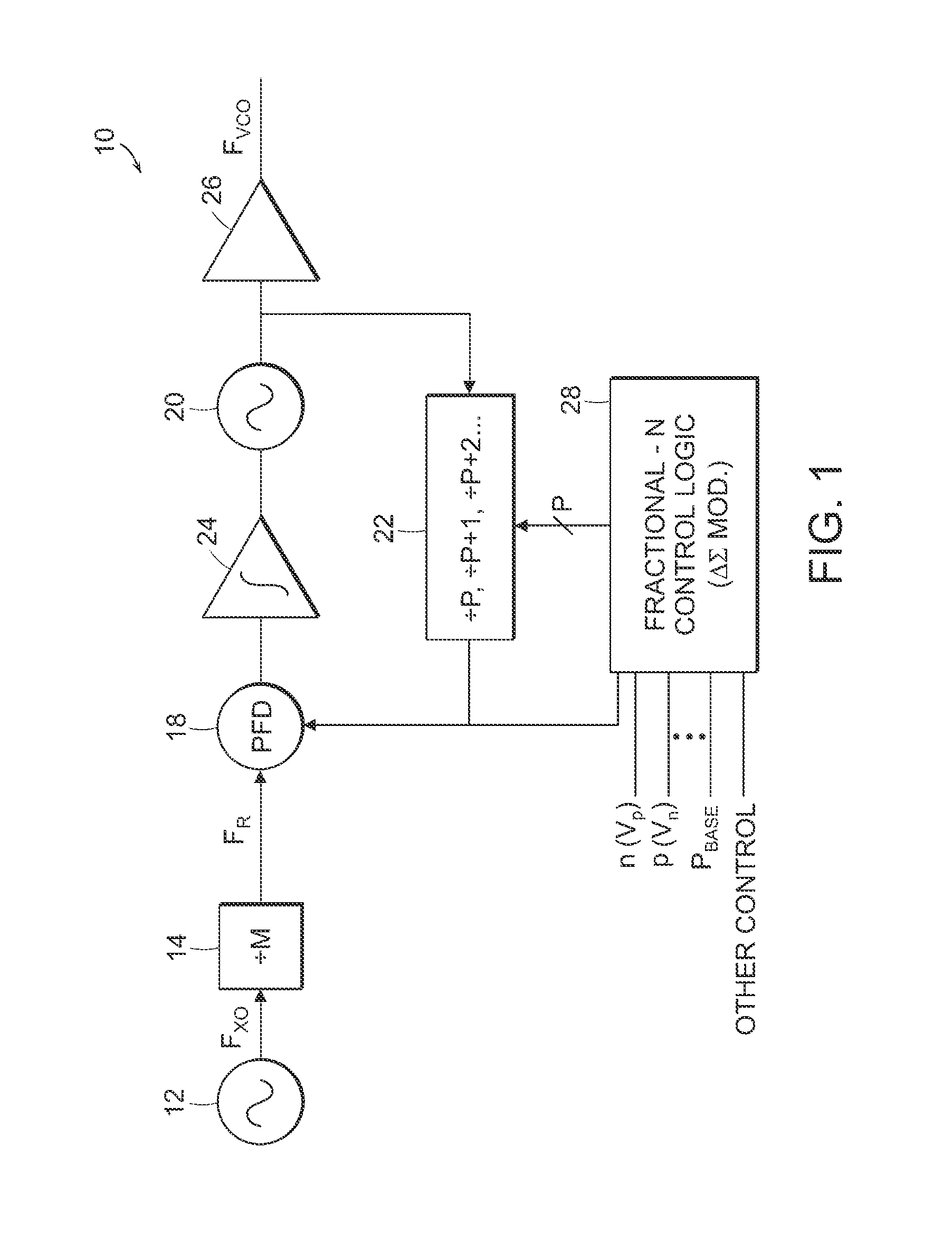

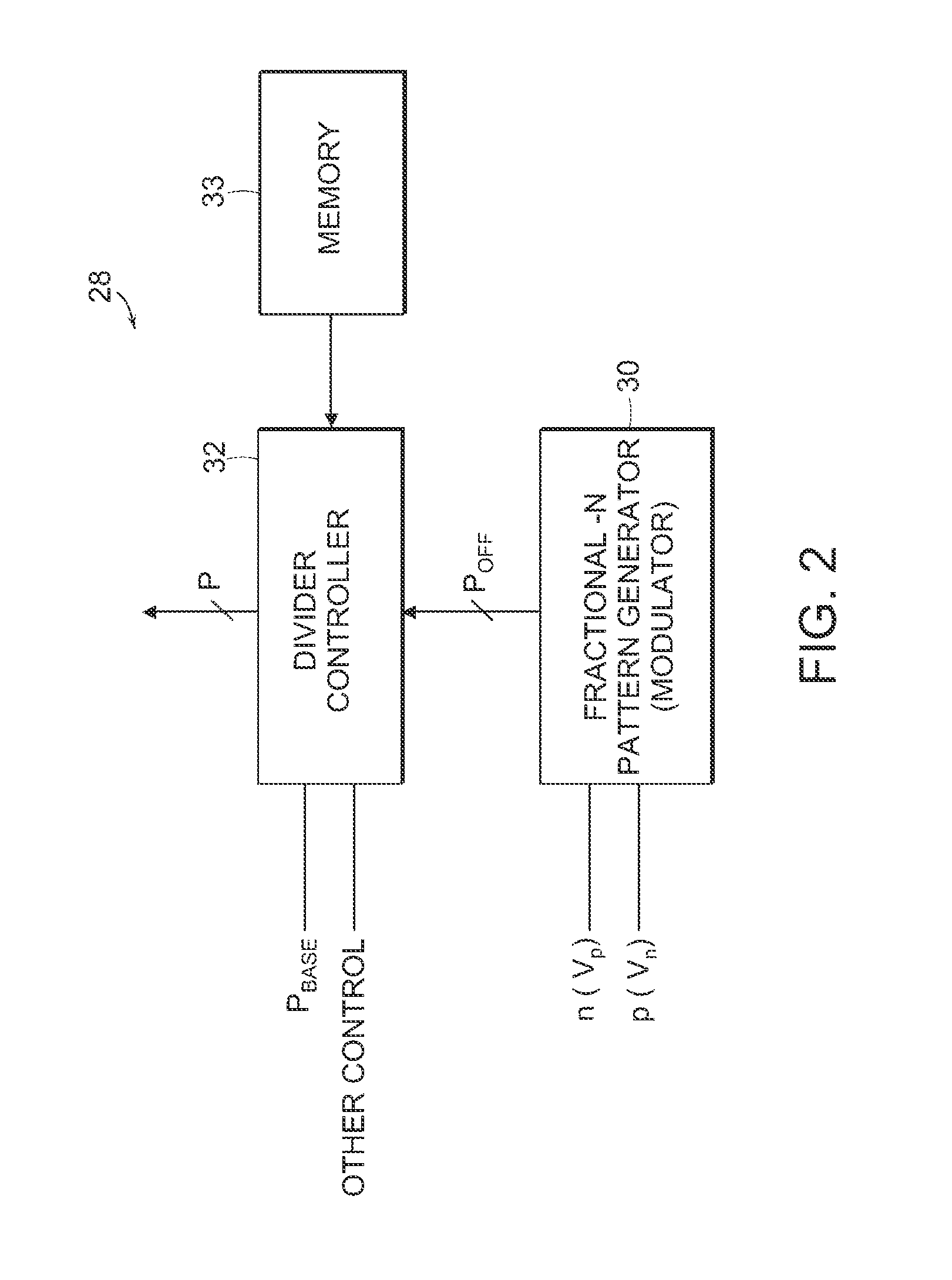

Frequency modulator, circuit, and method that uses multiple vector accumulation to achieve fractional-N frequency synthesis

InactiveUS7405629B2Less jitterJitter is substantially reducedPulse automatic controlAngle modulationEngineeringFrequency modulation

A frequency synthesizer is provided having a fractional-N control circuit and method. The control circuit can operate as having a modulator that selectively applies any fractional ratio to a frequency divider within, for example, a feedback loop of a PLL. The modulator can be a delta-sigma modulator or any sequential state machine that can be implemented as the control circuit, and can select amongst a plurality of vector values. The vector values can be spaced relatively close to each other, and the incoming present vector values can each be added to a value chosen from the immediately preceding set of potential values. The selector circuit chooses from among the present set of vector values depending on whether the sum is nearest a target value. The sum nearest the target value is, therefore, selected as the present vector value, and the process is repeated in time for each vector value having a corresponding P value to form a pattern of P values sent to the divider of the PLL. The incoming frequency can therefore be synthesized based on the modulated P values used by the feedback divider to produce the appropriate fractional-N divide ratio for the synthesized frequency.

Owner:MONTEREY RES LLC

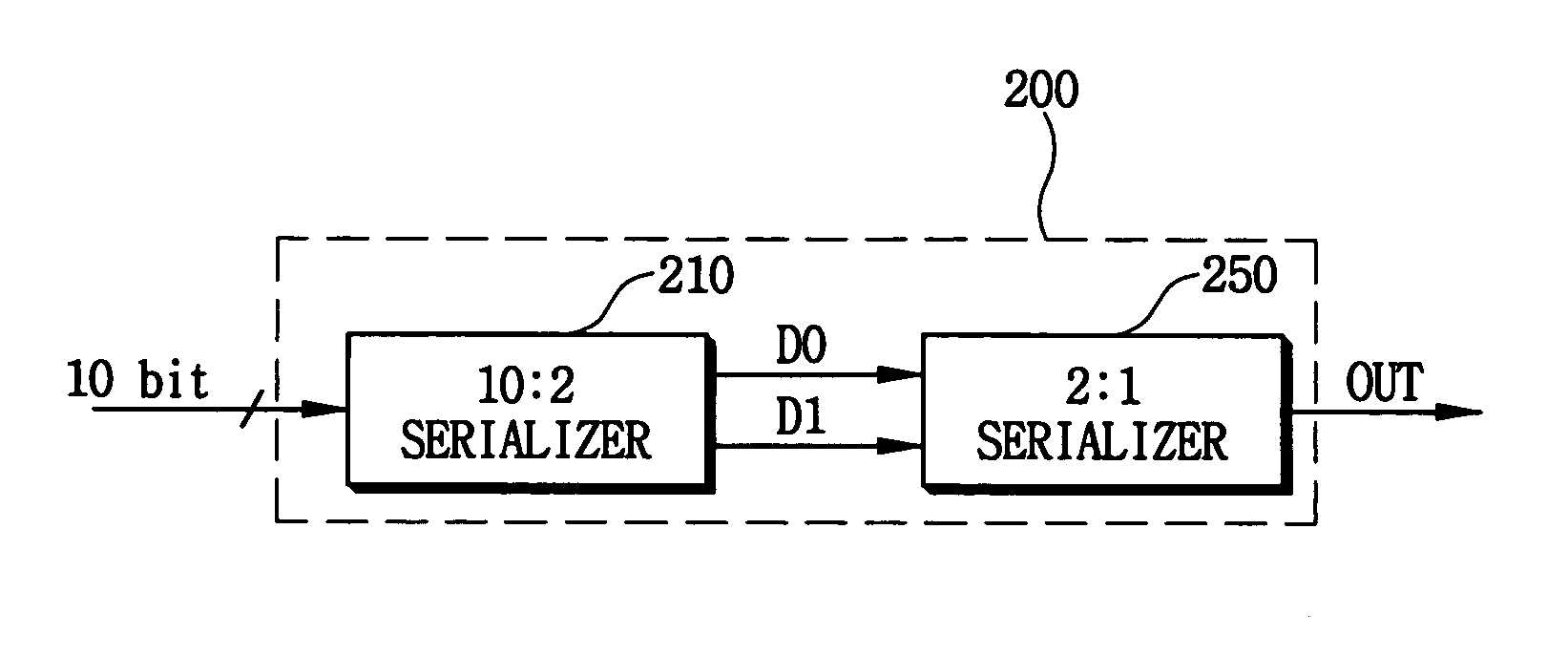

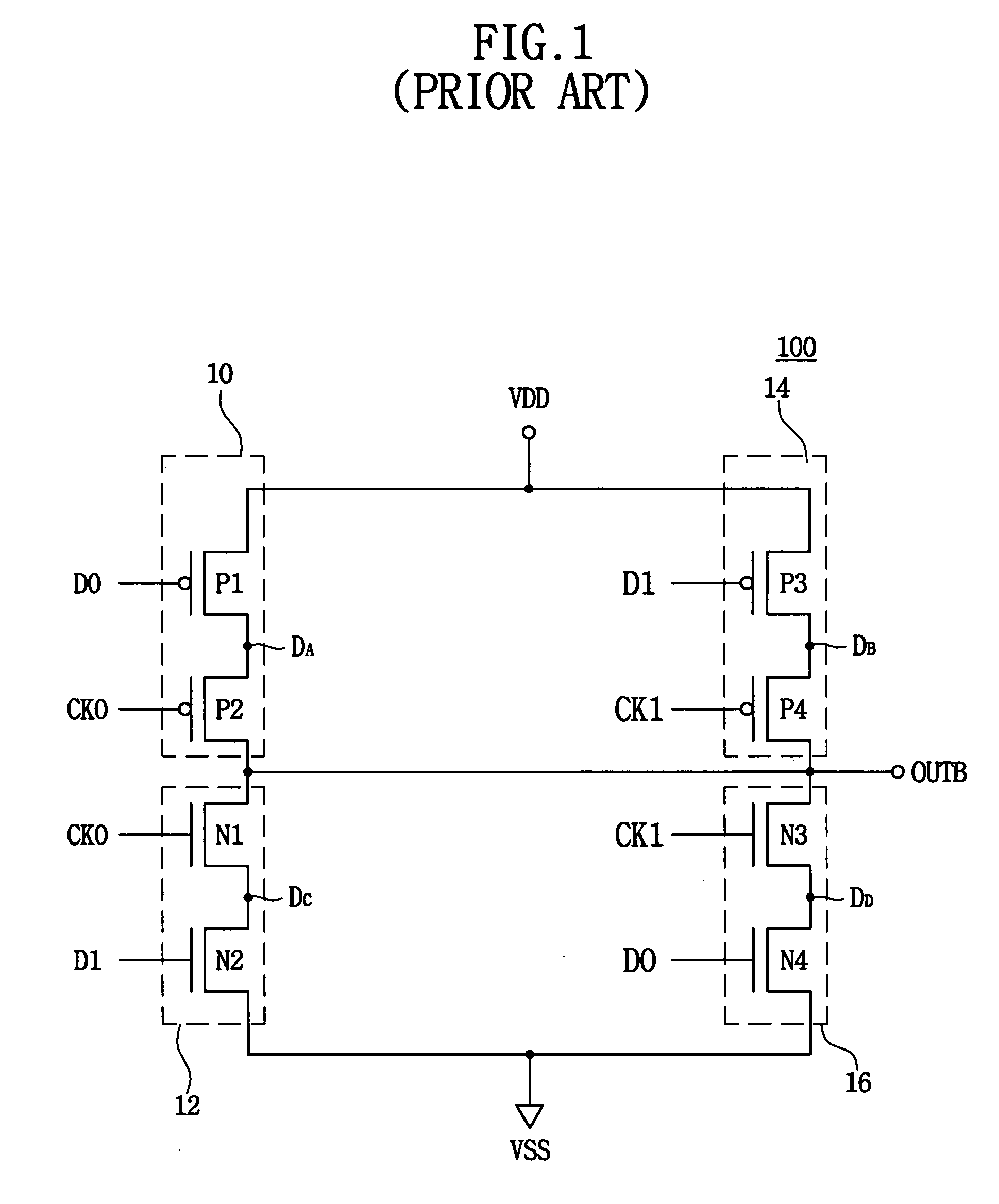

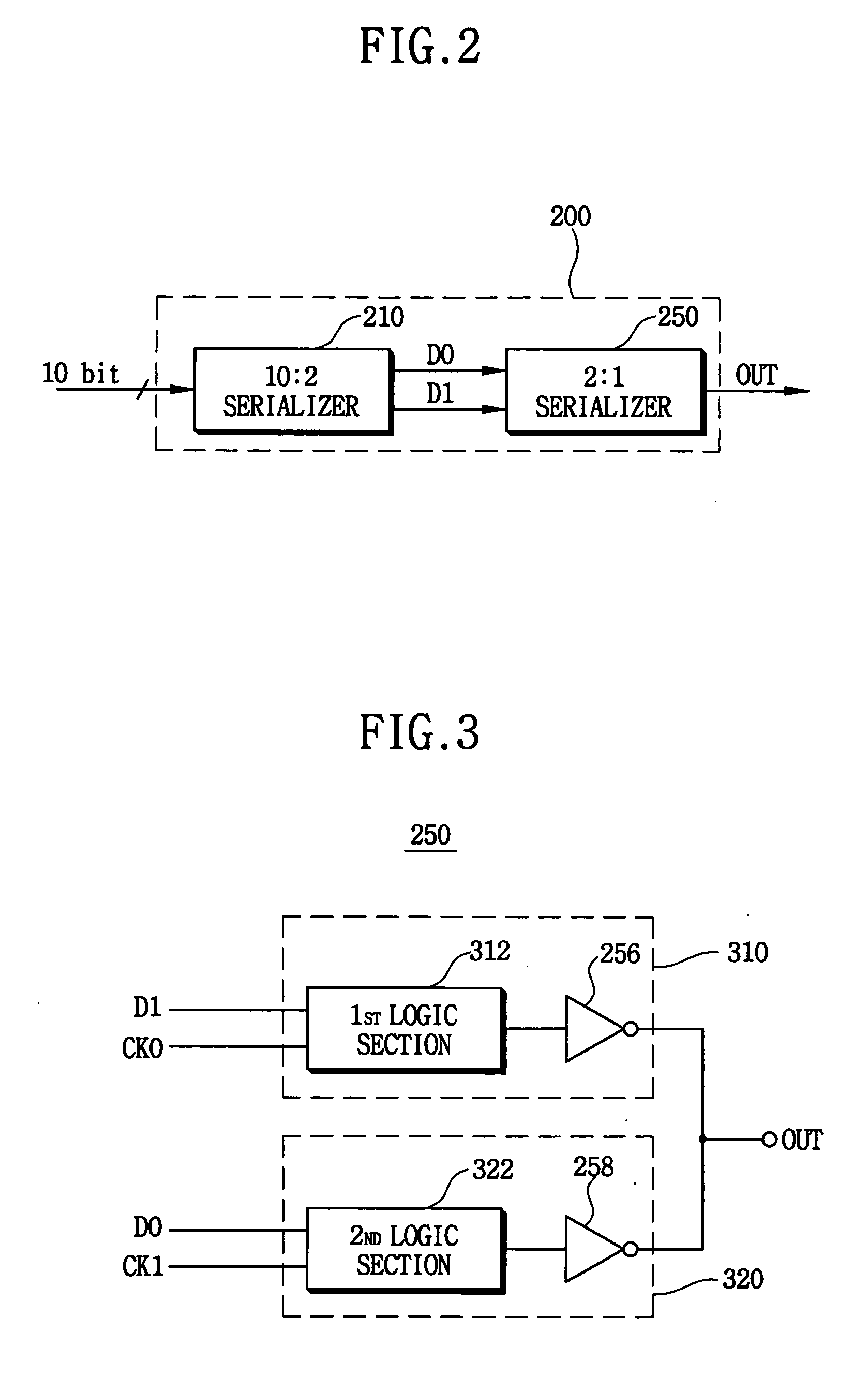

Serializer and method of serializing parallel data into serial data stream

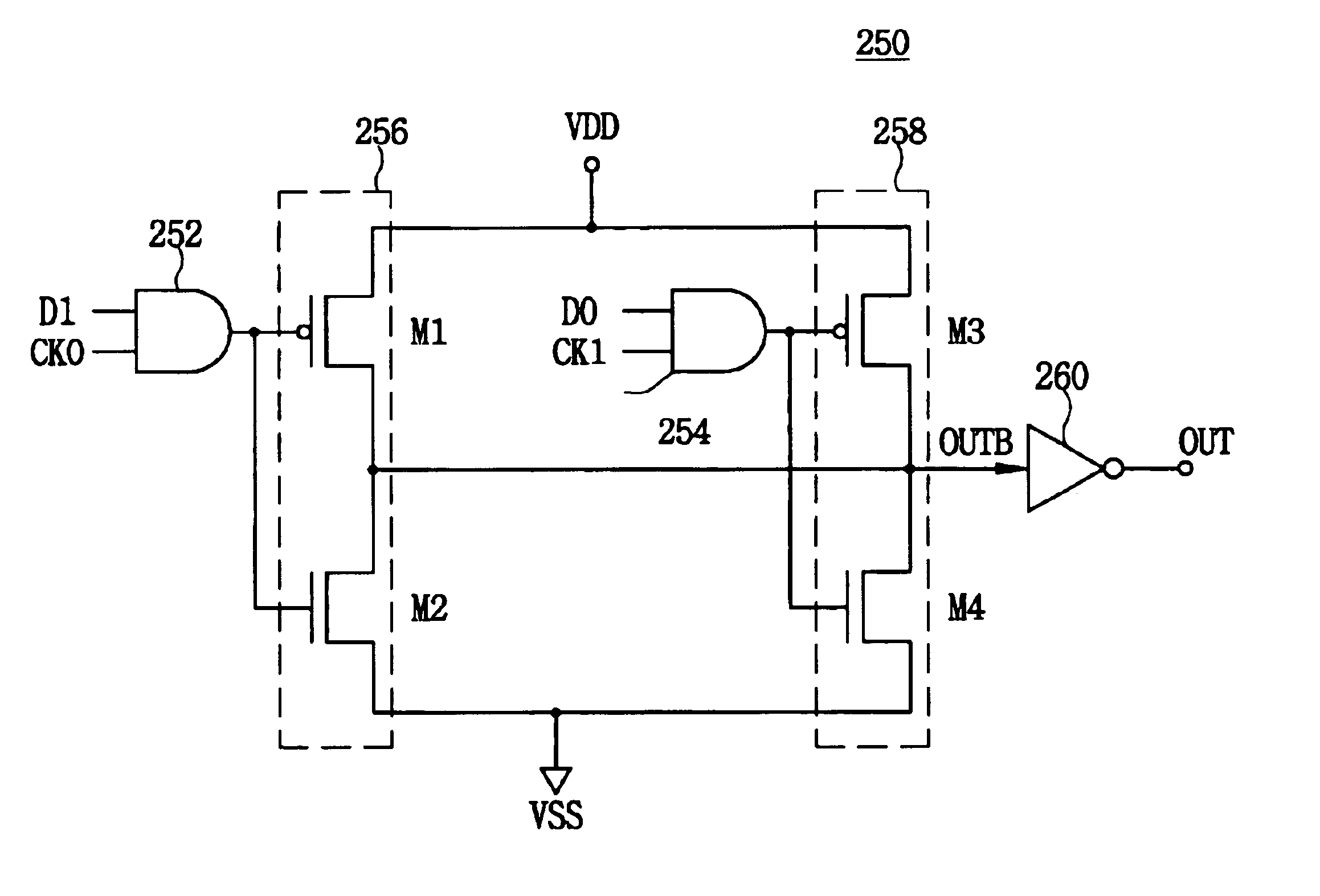

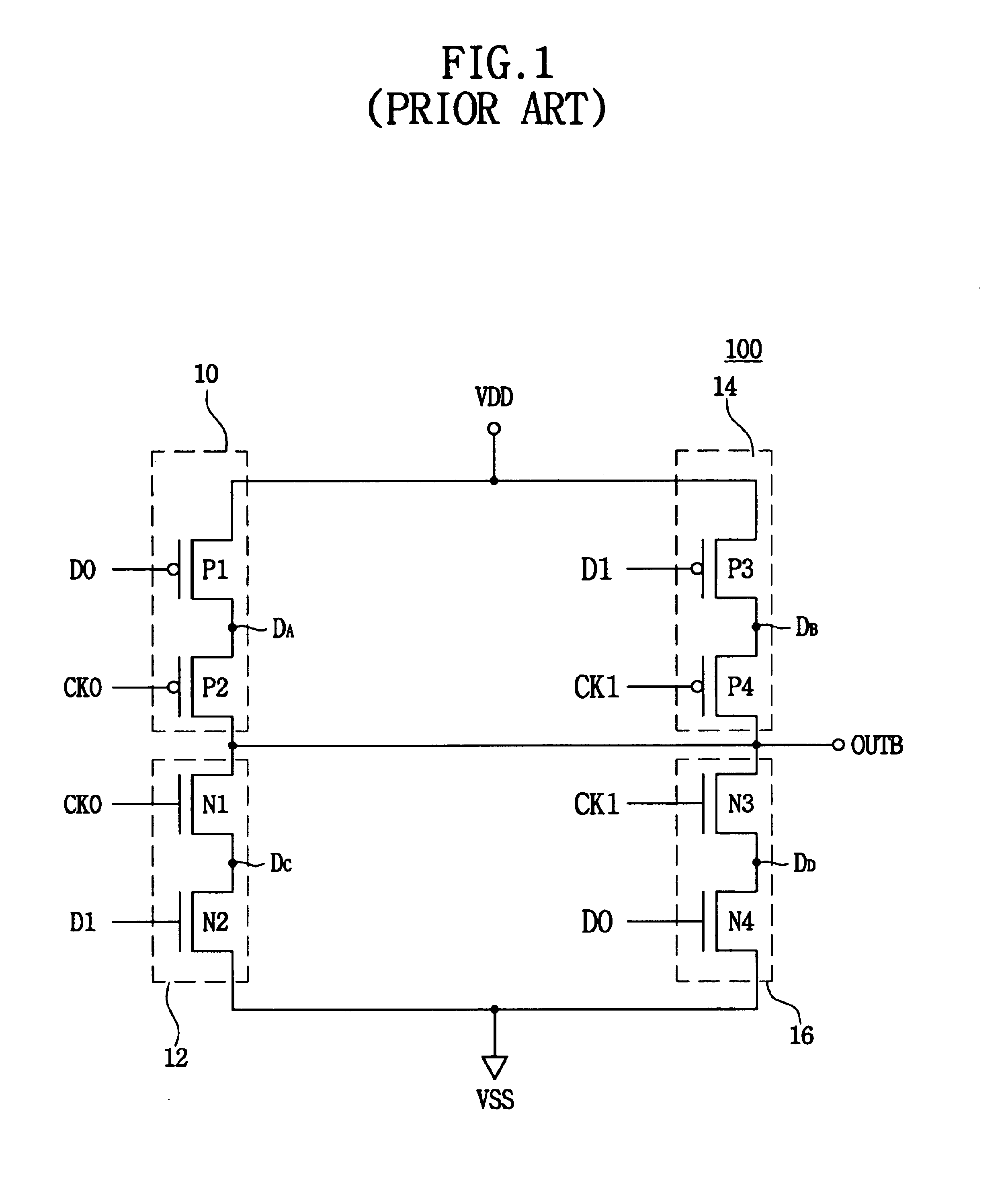

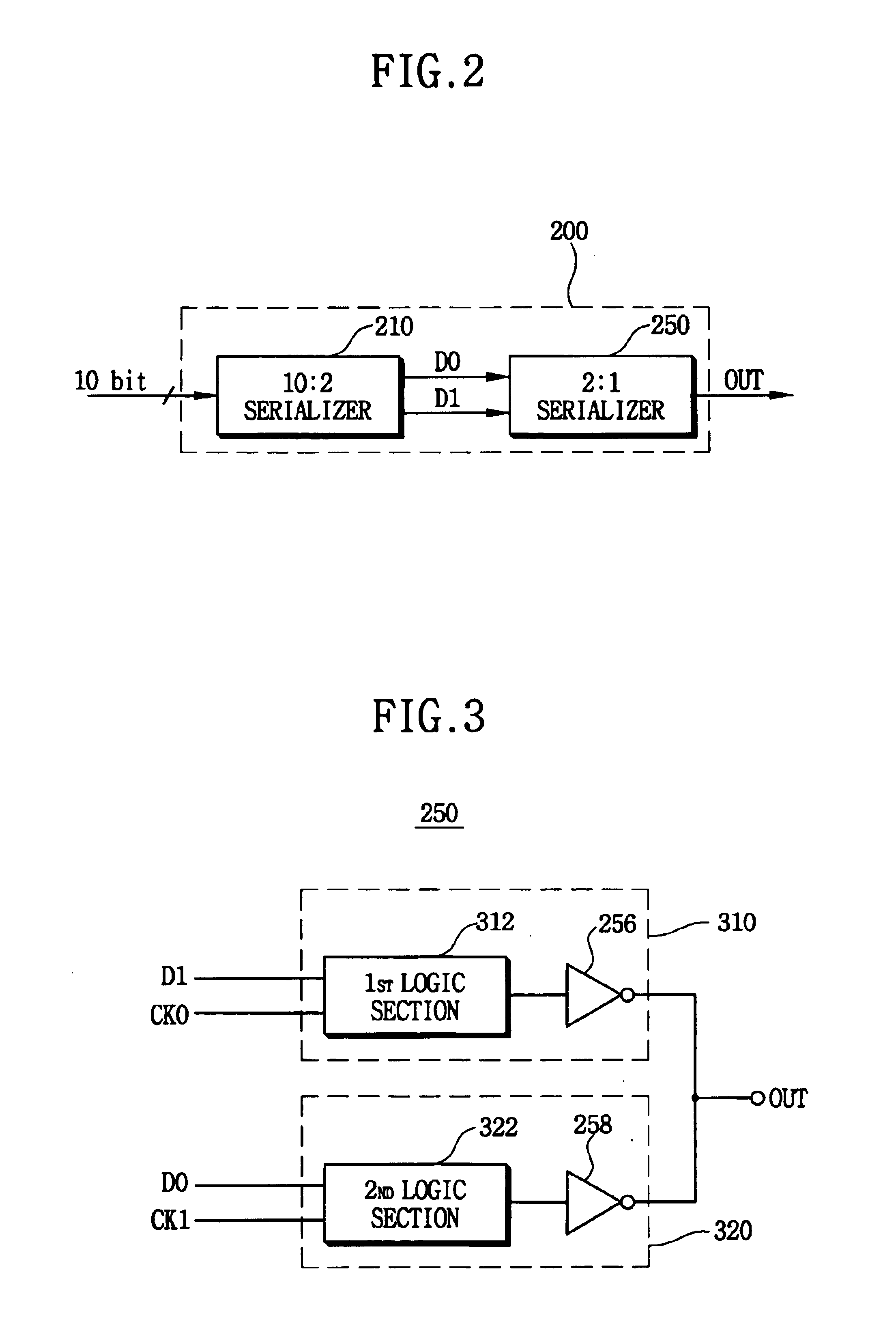

InactiveUS6937173B2Reduce jitterReduce coupling effectParallel/series conversionData streamLogical part

A serializer serializes N data (N>2) in N stages into a serial data stream. Each stage includes a logic section and a first inverter. The logic section receives i-th data (where i is less than or equal to N) of the N parallel data to output the i-th data or inverted i-th data in response to an active status or an inactive status of an j-th clock signal (where j is less than or equal to N) of the N clock signals. The first inverter receives the i-th data or the inverted i-th data from the logic section and inverts the i-th data or the inverted i-th data to output a first output signal. The output signal of the serializer may have reduced jitter even when the serializer operates in a high speed and a low power condition.

Owner:SAMSUNG ELECTRONICS CO LTD

Monolithic clock generator and timing/frequency reference

ActiveUS20050206462A1Less jitterLoud noiseResonant circuit tuningPulse automatic controlAudio power amplifierPulsed mode

In various embodiments, the invention provides a clock generator and / or a timing and frequency reference, with multiple operating modes, such power conservation, clock, reference, and pulsed modes. The various apparatus embodiments include a resonator adapted to provide a first signal having a resonant frequency; an amplifier; a temperature compensator adapted to modify the resonant frequency in response to temperature; and a process variation compensator adapted to modify the resonant frequency in response to fabrication process variation. In addition, the various embodiments may also include a frequency divider adapted to divide the first signal having the resonant frequency into a plurality of second signals having a corresponding plurality of frequencies substantially equal to or lower than the resonant frequency; and a frequency selector adapted to provide an output signal from the plurality of second signals. The output signal may be provided in any of various forms, such as differential or single-ended, and substantially square-wave or sinusoidal.

Owner:INTEGRATED DEVICE TECH INC

Serializer and method of serializing parallel data into serial data stream

InactiveUS20050024243A1Reduce jitterReduce coupling effectParallel/series conversionData streamLogical part

A serializer serializes N data (N>2) in N stages into a serial data stream. Each stage includes a logic section and a first inverter. The logic section receives i-th data (where i is less than or equal to N) of the N parallel data to output the i-th data or inverted i-th data in response to an active status or an inactive status of an j-th clock signal (where j is less than or equal to N) of the N clock signals. The first inverter receives the i-th data or the inverted i-th data from the logic section and inverts the i-th data or the inverted i-th data to output a first output signal. The output signal of the serializer may have reduced jitter even when the serializer operates in a high speed and a low power condition.

Owner:SAMSUNG ELECTRONICS CO LTD

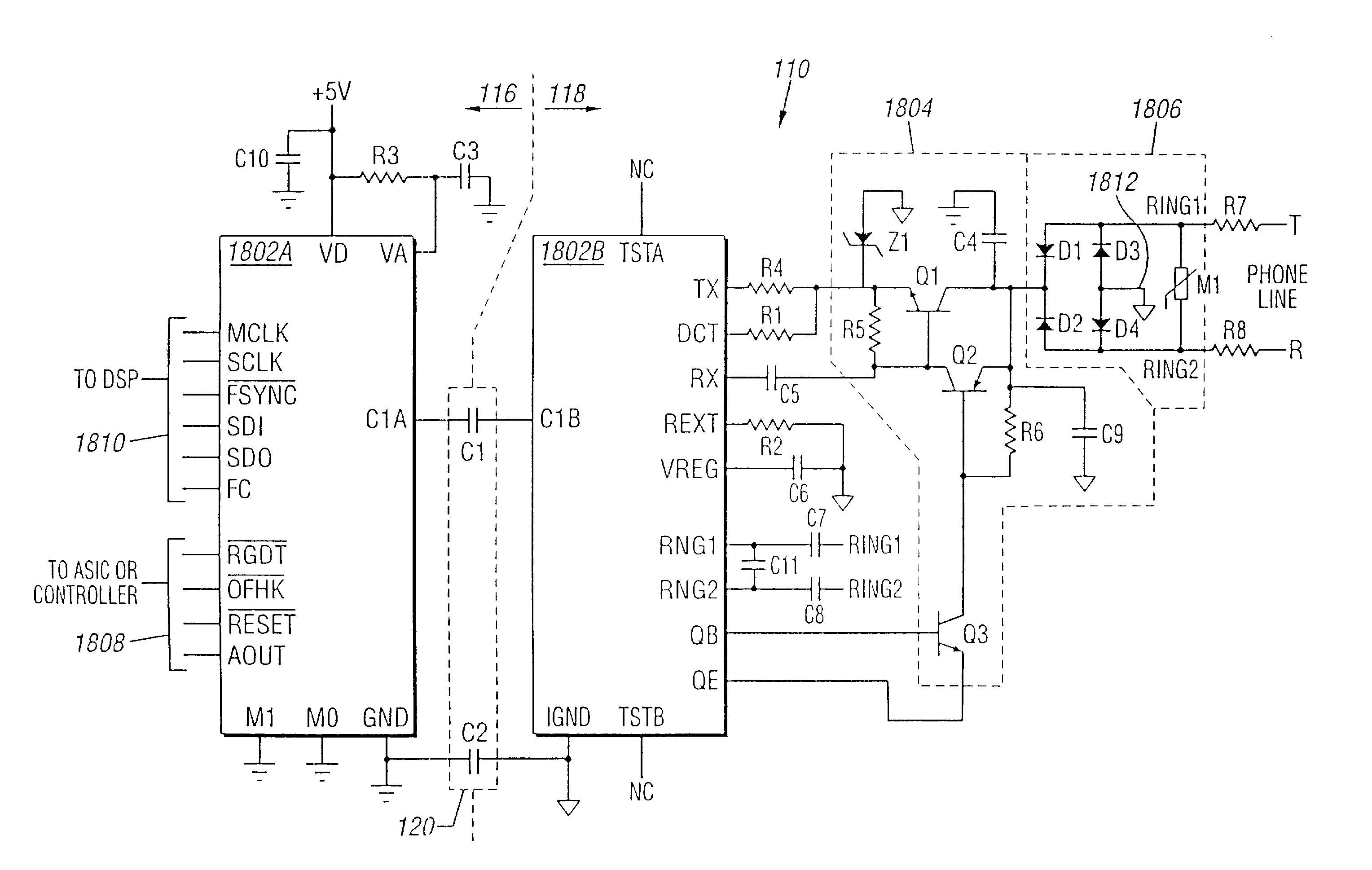

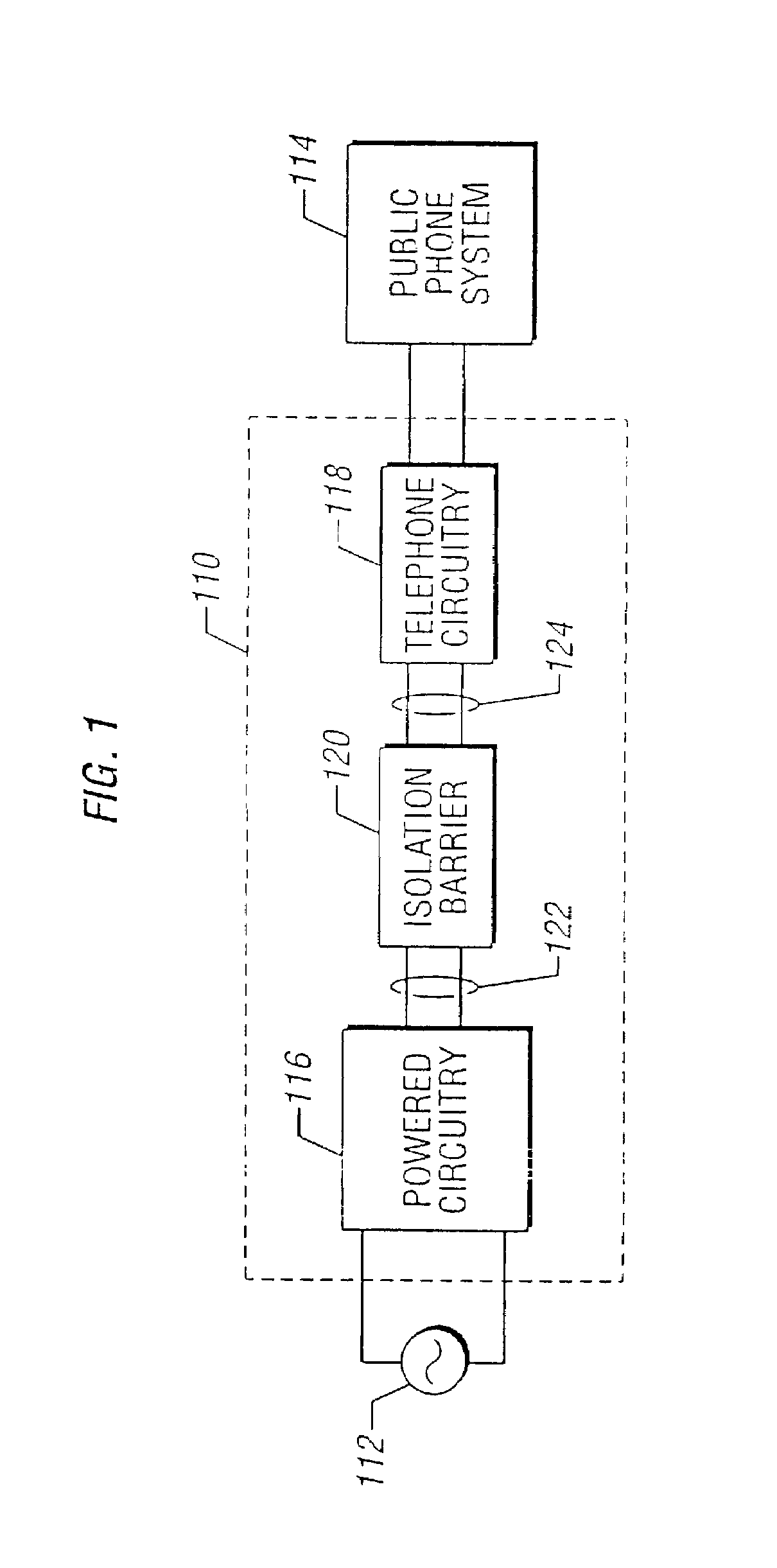

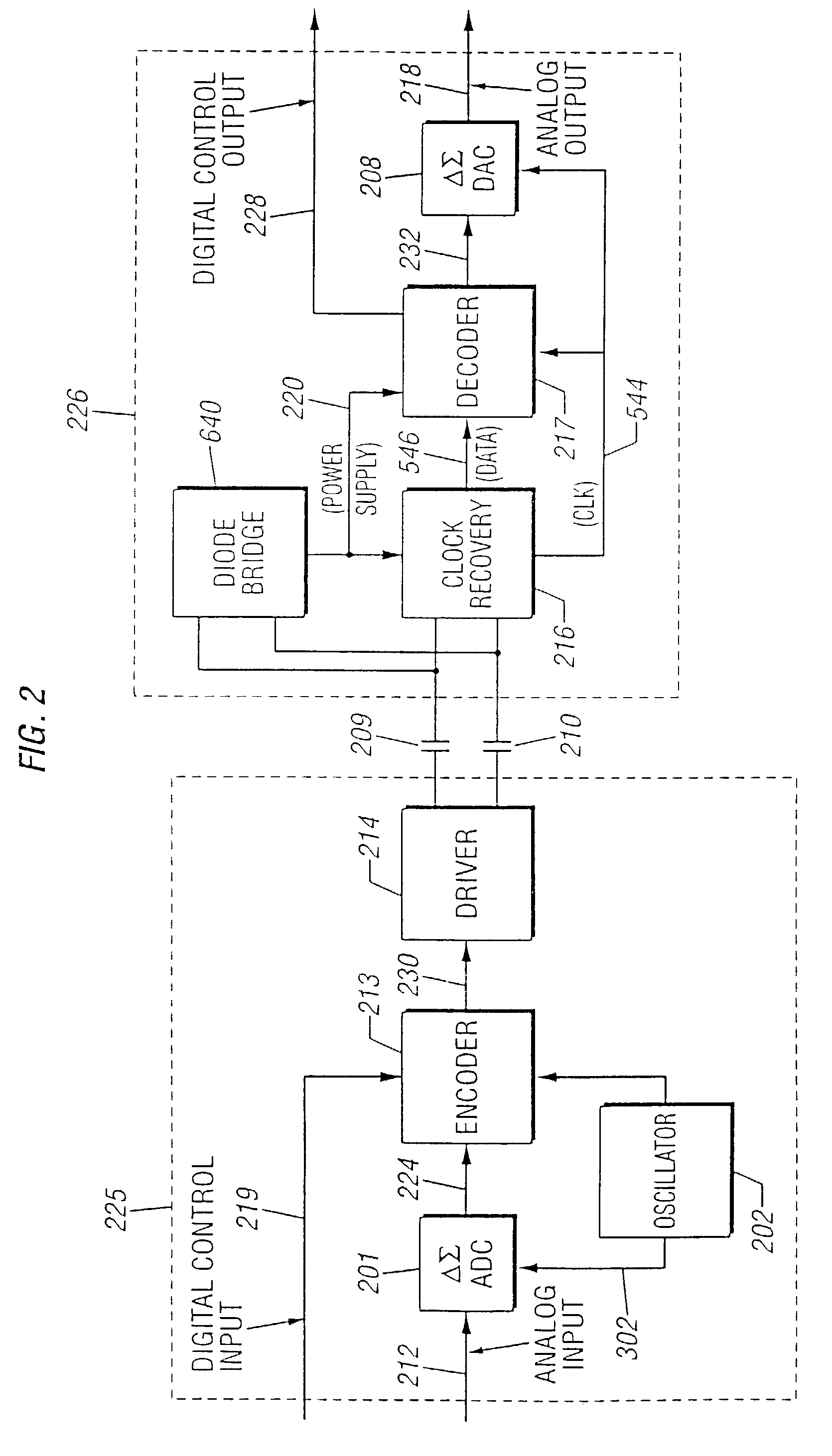

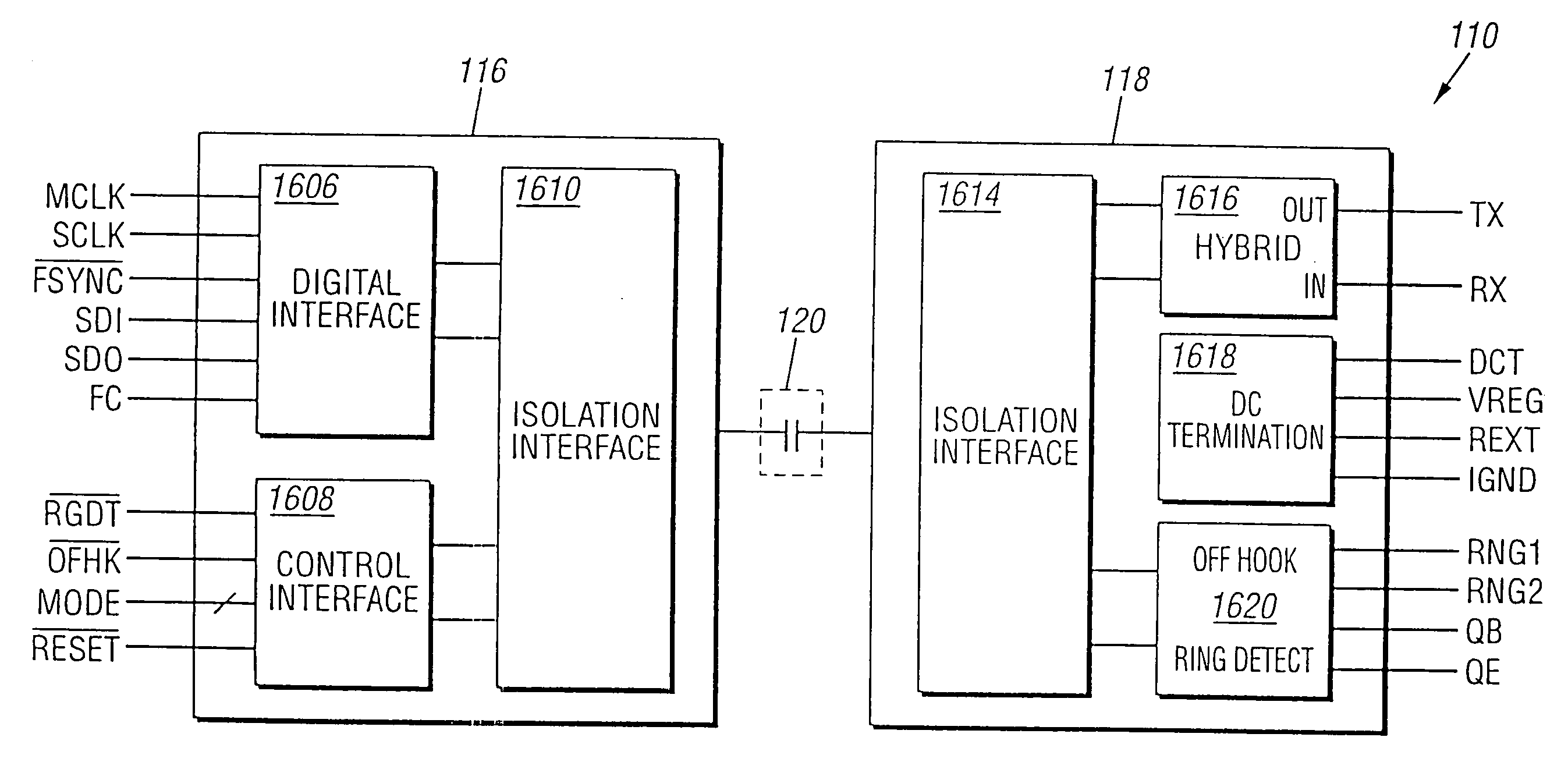

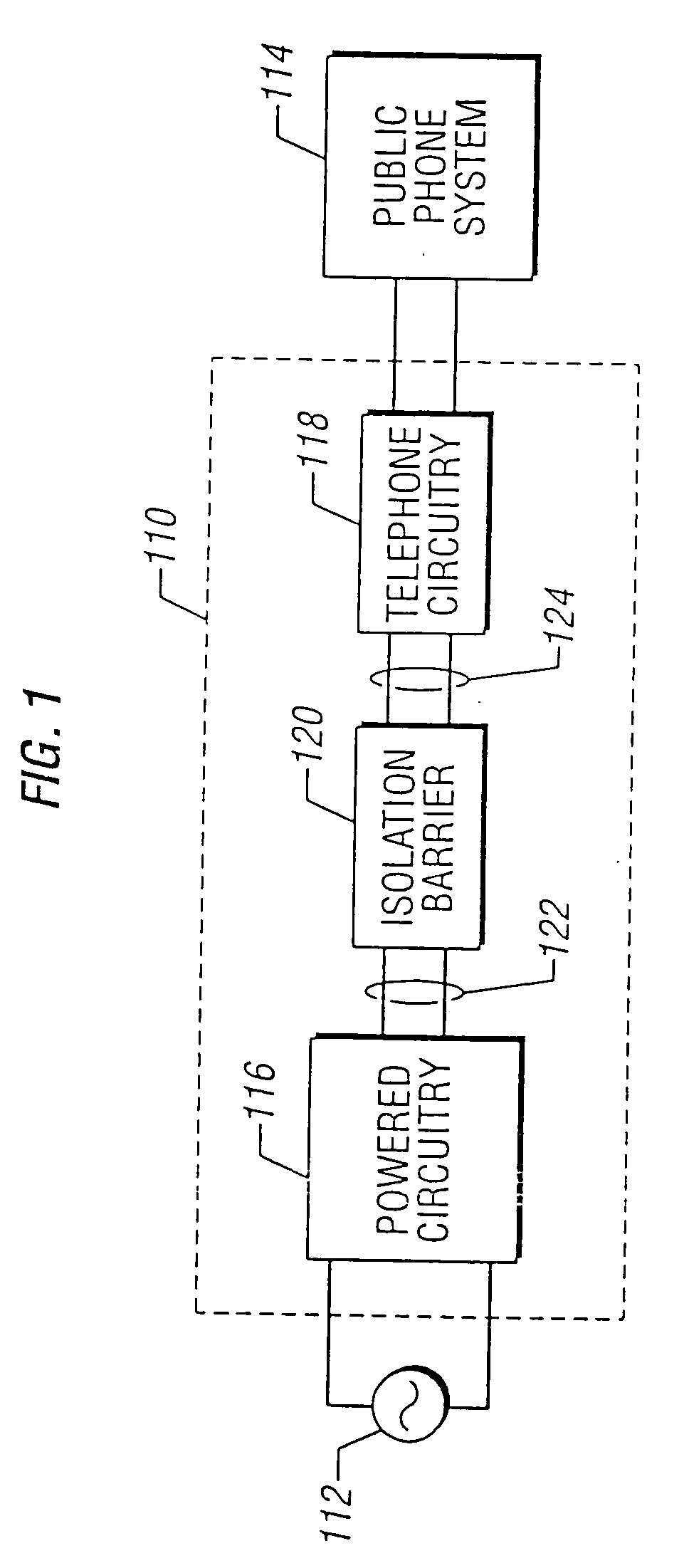

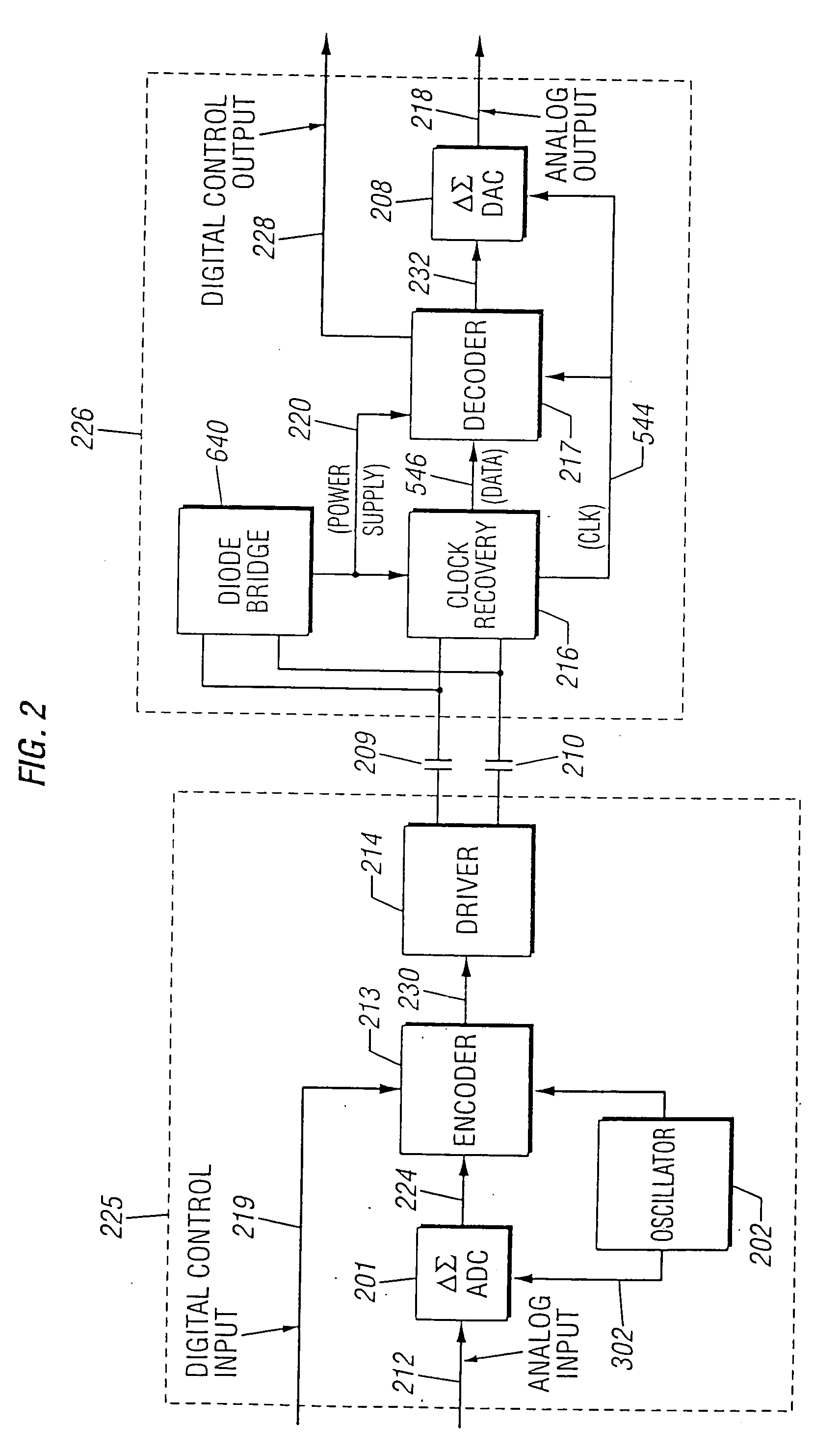

Direct digital access arrangement circuitry and method for connecting to phone lines

InactiveUS7072389B2Accurately reproducedExact reproductionAnalogue/digital conversionElectric signal transmission systemsClock recoveryCapacitance

An isolation system is provided that is suitable for use in telephony, medical instrumentation, industrial process control and other applications. Preferred embodiments of the invention comprise a capacitive isolation barrier across which a digital signal is communicated. The system provides a means of communication across the isolation barrier that is highly immune to amplitude and phase noise interference. Clock recovery circuitry may be employed on one side of the isolation barrier to extract timing information from the digital signal communicated across the barrier, and to filter the effects of phase noise introduced at the barrier. Delta-sigma converters may be disposed on both sides of the isolation barrier to convert signals between analog and digital domains. An isolated power supply may also be provided on the isolated side of the barrier, whereby direct current is generated in response to the digital data received across the isolation barrier. Finally, a bidirectional isolation system is provided whereby bidirectional communication of digital signals is accomplished using a single pair of isolation capacitors. In preferred embodiments, the digital data communicated across the barrier consists of digital delta-sigma data signals multiplexed in time with other digital control, signaling and framing information.

Owner:SILICON LAB INC

Direct digital access arrangement circuitry and method for connecting to phone lines

InactiveUS20060215771A1Exact reproductionLess jitterAnalogue/digital conversionElectric signal transmission systemsDigital dataCapacitance

An isolation system is provided that is suitable for use in telephony, medical instrumentation, industrial process control and other applications. Preferred embodiments of the invention comprise a capacitive isolation barrier across which a digital signal is communicated. The system provides a means of communication across the isolation barrier that is highly immune to amplitude and phase noise interference. Clock recovery circuitry may be employed on one side of the isolation barrier to extract timing information from the digital signal communicated across the barrier, and to filter the effects of phase noise introduced at the barrier. Delta-sigma converters may be disposed on both sides of the isolation barrier to convert signals between analog and digital domains. An isolated power supply may also be provided on the isolated side of the barrier, whereby direct current is generated in response to the digital data received across the isolation barrier. Finally, a bidirectional isolation system is provided whereby bidirectional communication of digital signals is accomplished using a single pair of isolation capacitors. In preferred embodiments, the digital data communicated across the barrier consists of digital delta-sigma data signals multiplexed in time with other digital control, signaling and framing information.

Owner:SILICON LAB INC

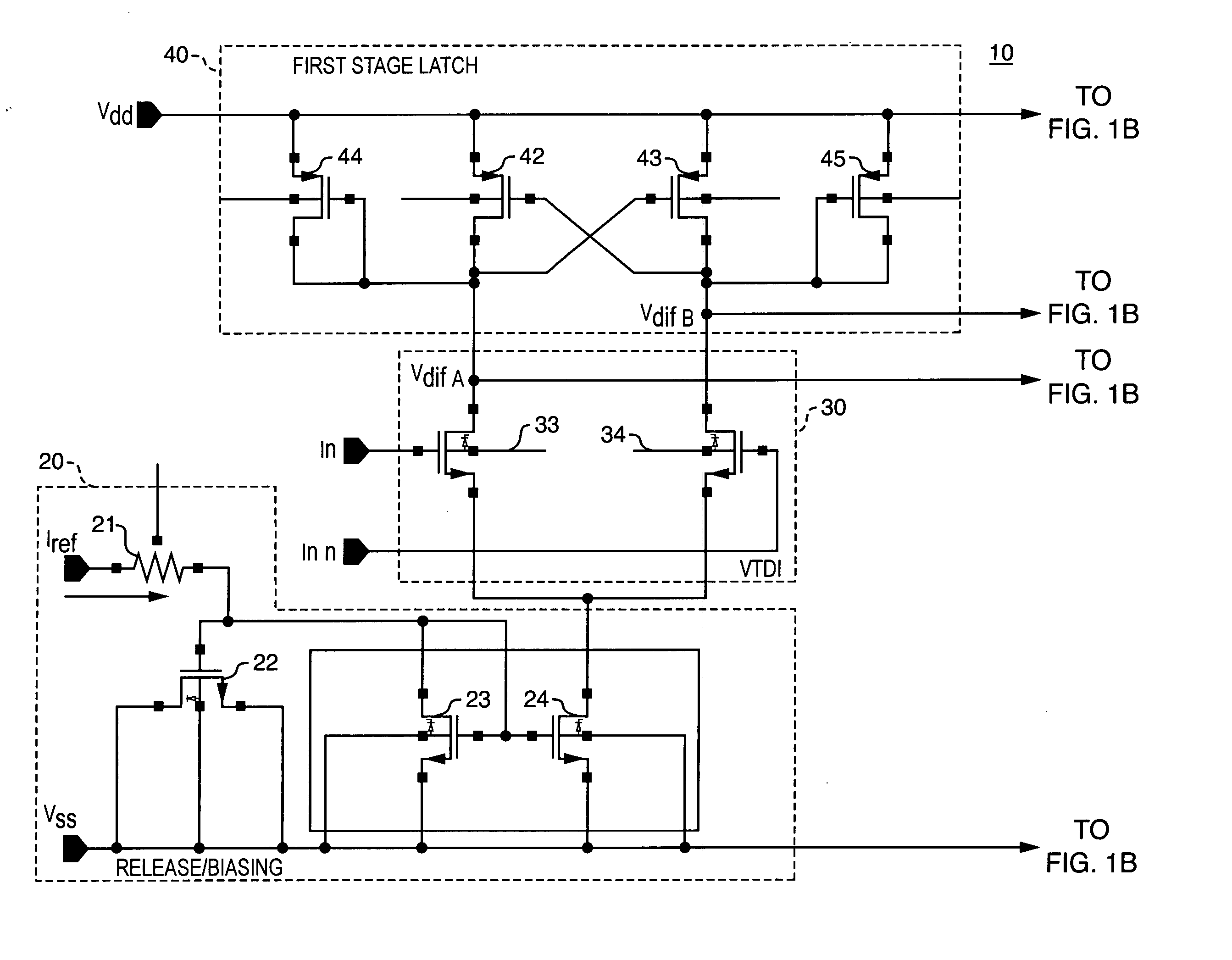

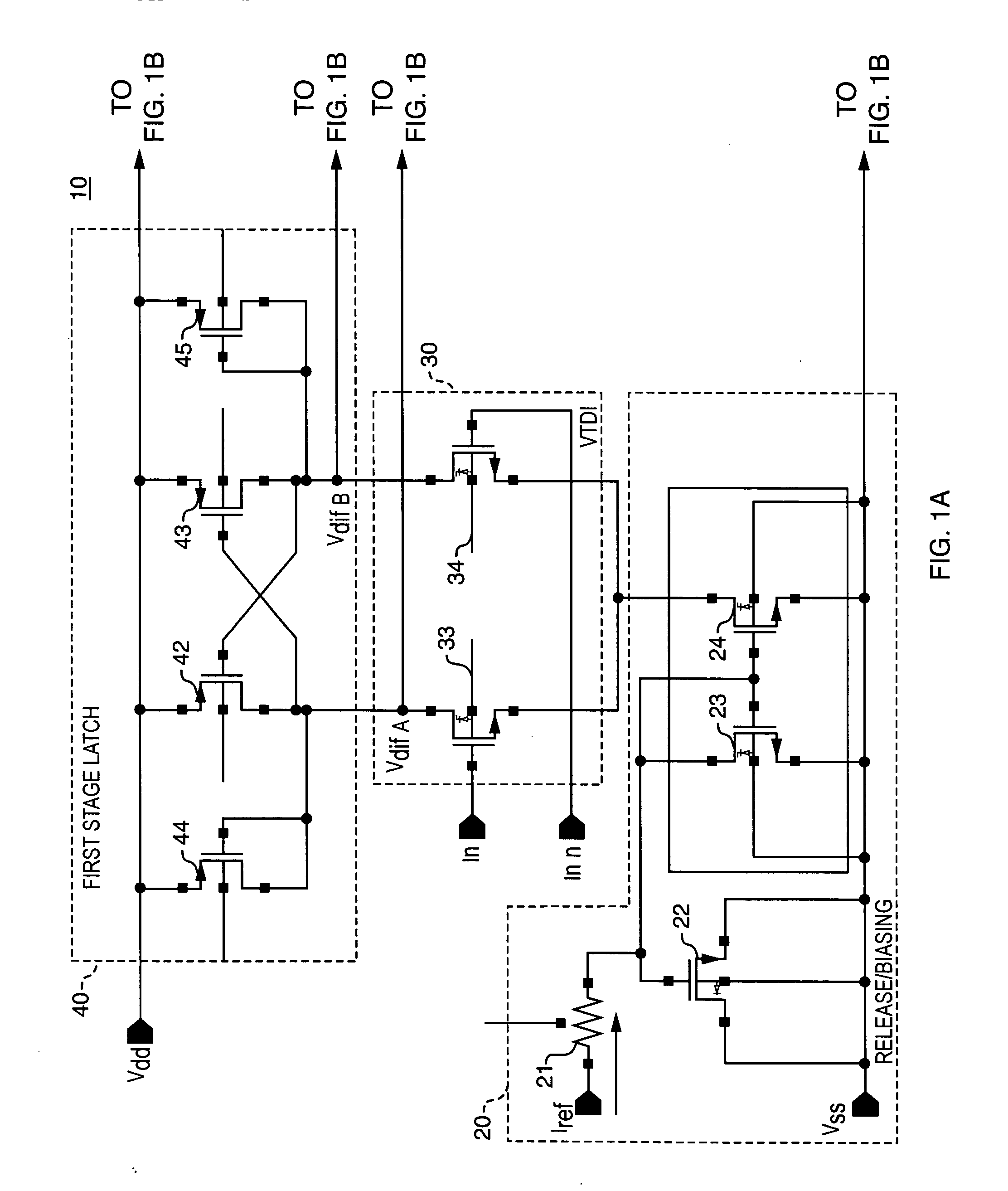

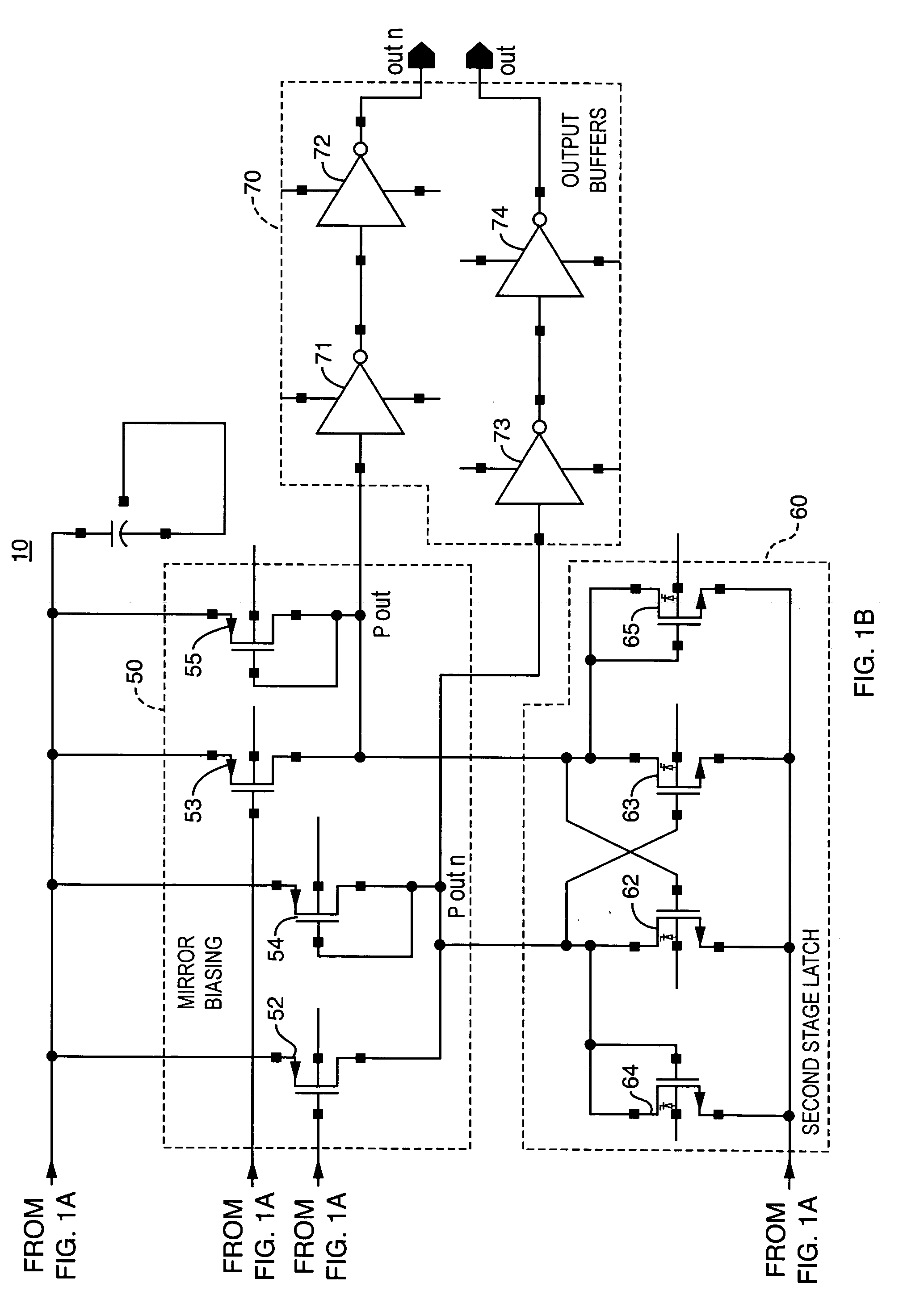

Differential clock input buffer

InactiveUS20060012408A1Improved input hysteresisImprove noise immunityElectric pulse generatorOscillations generatorsLow noiseHysteresis

A compact, differential clock input buffer that converts single-end or differential sine wave or square wave inputs into complementary squarewave digital outputs, with low-jitter, and 50% duty cycle outputs. Low-noise oscillator design concepts are applied to provide at least two stages of regeneration. This minimizes the time the clock buffer spends in the noise-susceptible linear region. A first stage latching circuit consists of a pair of cross coupled transistors (i.e., a differential transistor pair) with resistive loads to provide gain, limiting, hysteresis, and latching functions. These transistors operate in a linear region for only a very small range of input voltage. A second stage latching circuit, which can use a current mirror, is also provided as a pair of cross coupled transistors with resistive loads. The second stage latch provides positive feedback to further limit the linear operating range.

Owner:KENET

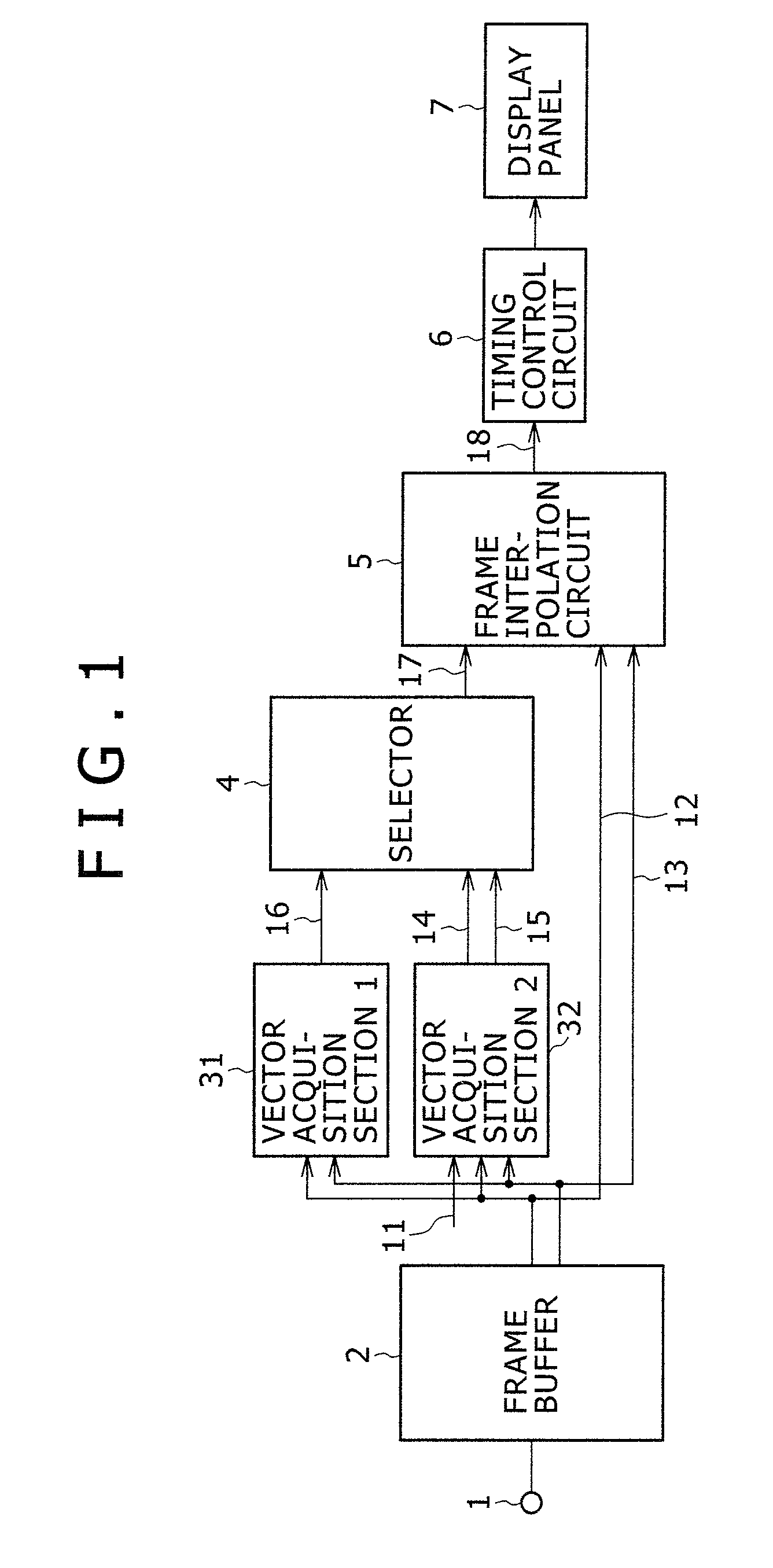

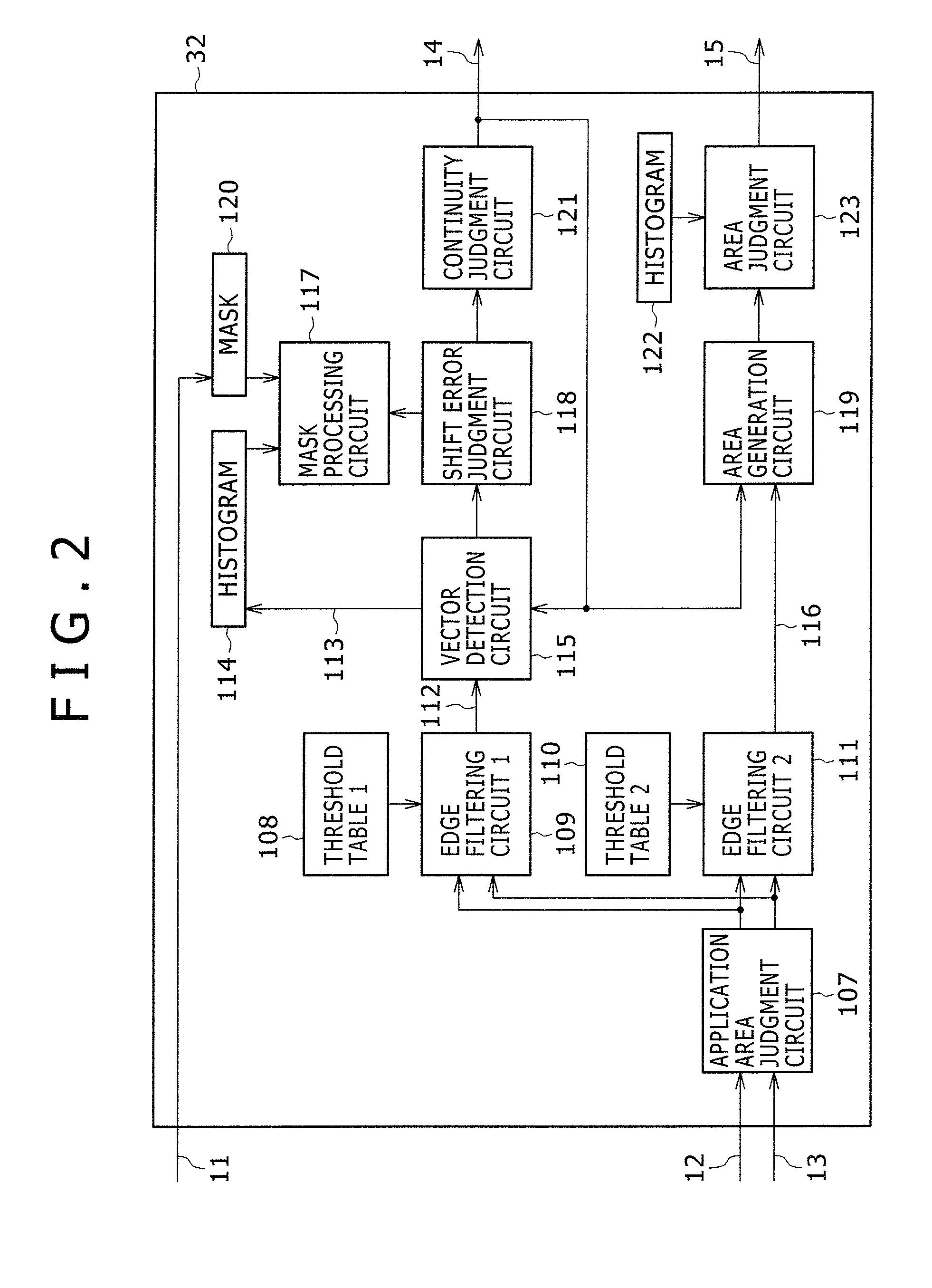

Image processor and image display apparatus comprising the same

ActiveUS8175121B2High quality imagingLess break-upsTelevision system detailsPicture reproducers using cathode ray tubesFrame sequenceMotion vector

An image processor includes a motion vector acquisition section for acquiring and outputting an image motion vector in pixel or a predetermined block unit from plural frames included in an input image signal; and a frame interpolation section for generating an interpolated frame by using the motion vector provided by the motion vector acquisition section and for combining the interpolated frame with a frame of the input image signal, thereby composing a signal of a new frame sequence. The motion vector acquisition section includes a first motion vector acquisition section acquiring a motion vector by matching process and a second motion vector acquisition section acquiring a motion vector based on a relative misalignment of a predetermined edge component between two temporally successive frames in a specific area of an input image signal's frame.

Owner:MAXELL HLDG LTD

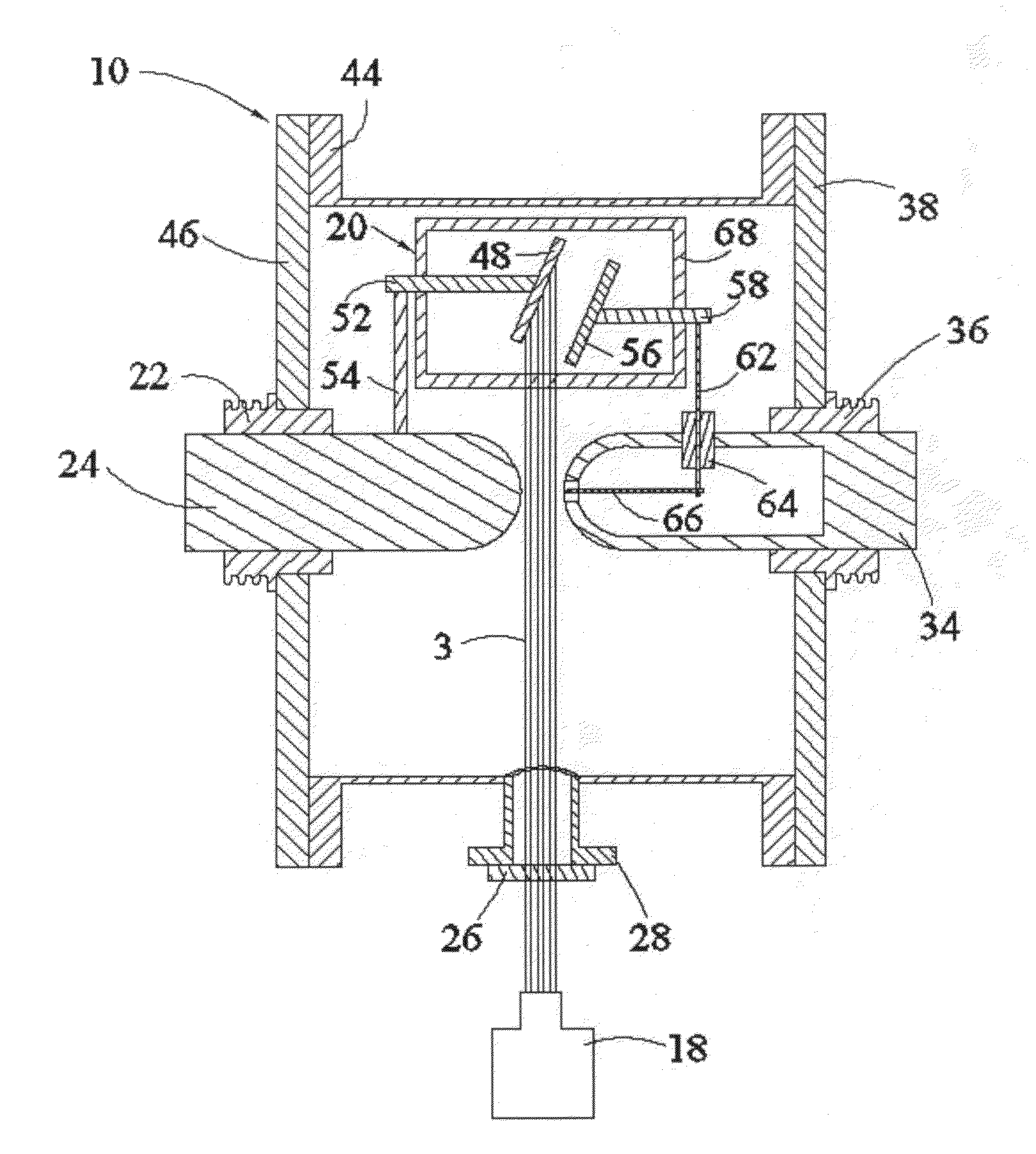

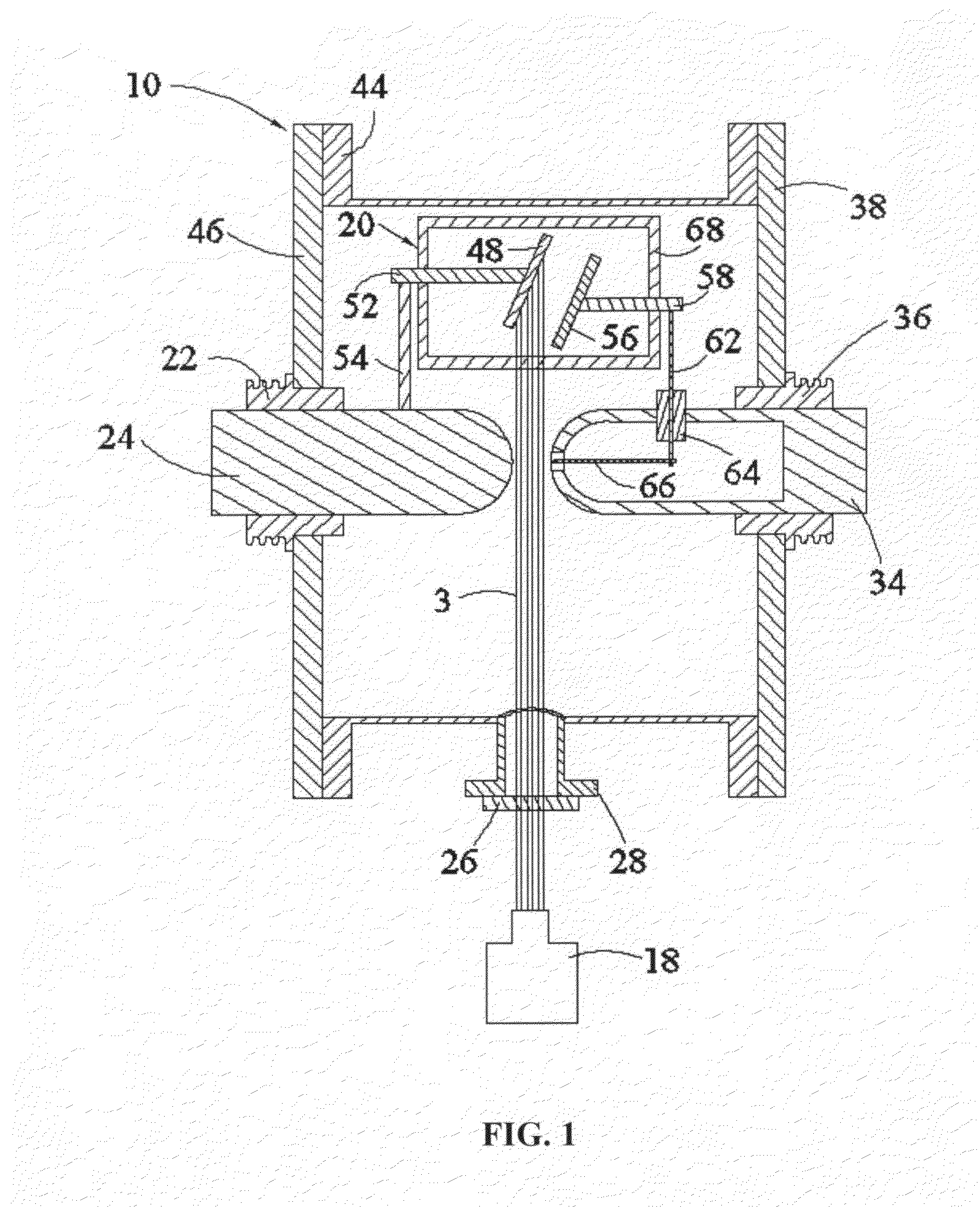

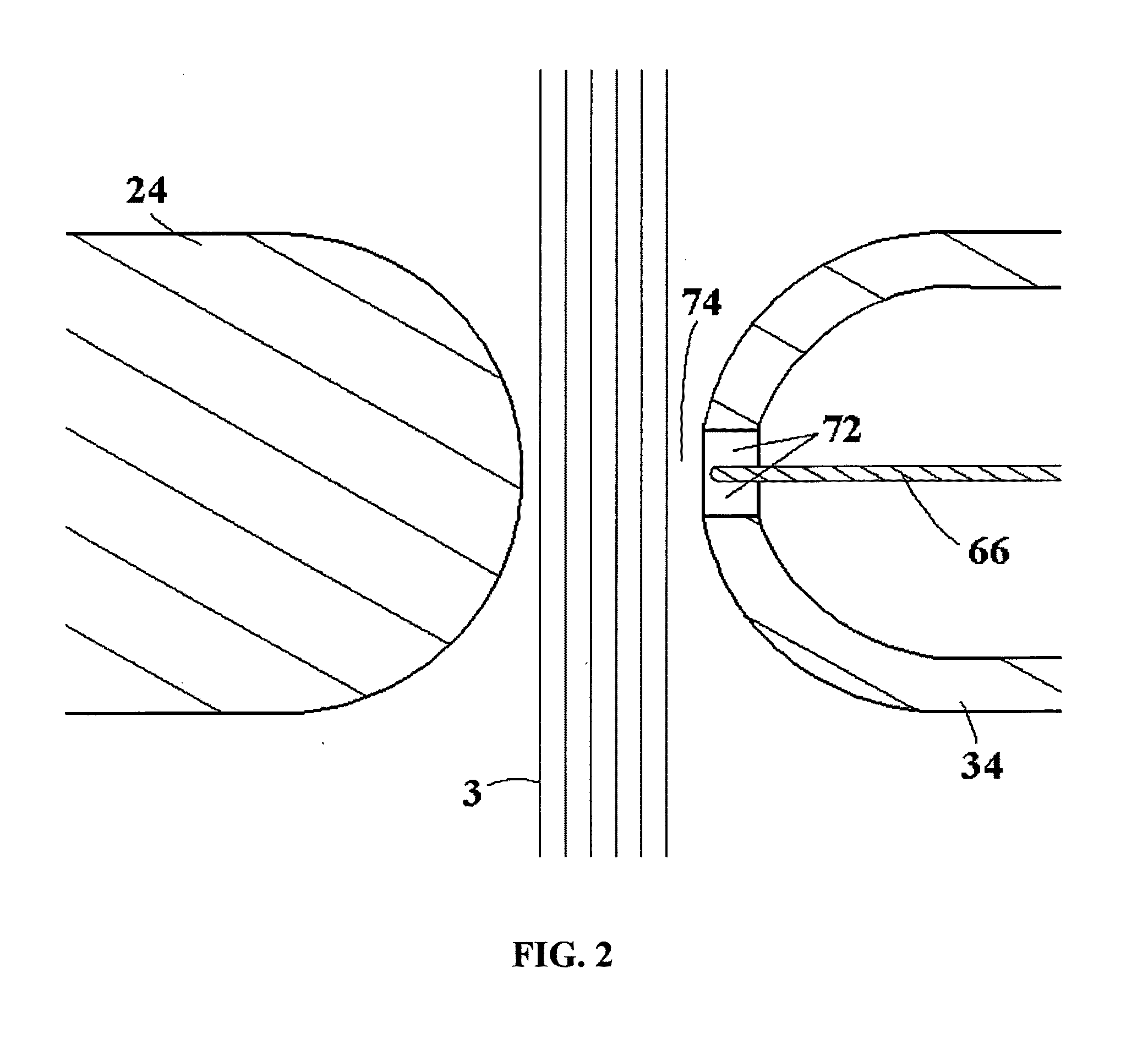

High voltage switch triggered by a laser-photocathode subsystem

InactiveUS20110215717A1Easy to operateLess breakdown delayVacuum tubesSpark gap detailsPhotocathodeLow jitter

A spark gap switch for controlling the output of a high voltage pulse from a high voltage source, for example, a capacitor bank or a pulse forming network, to an external load such as a high gradient electron gun, laser, pulsed power accelerator or wide band radar. The combination of a UV laser and a high vacuum quartz cell, in which a photocathode and an anode are installed, is utilized as triggering devices to switch the spark gap from a non-conducting state to a conducting state with low delay and low jitter.

Owner:DULY RES

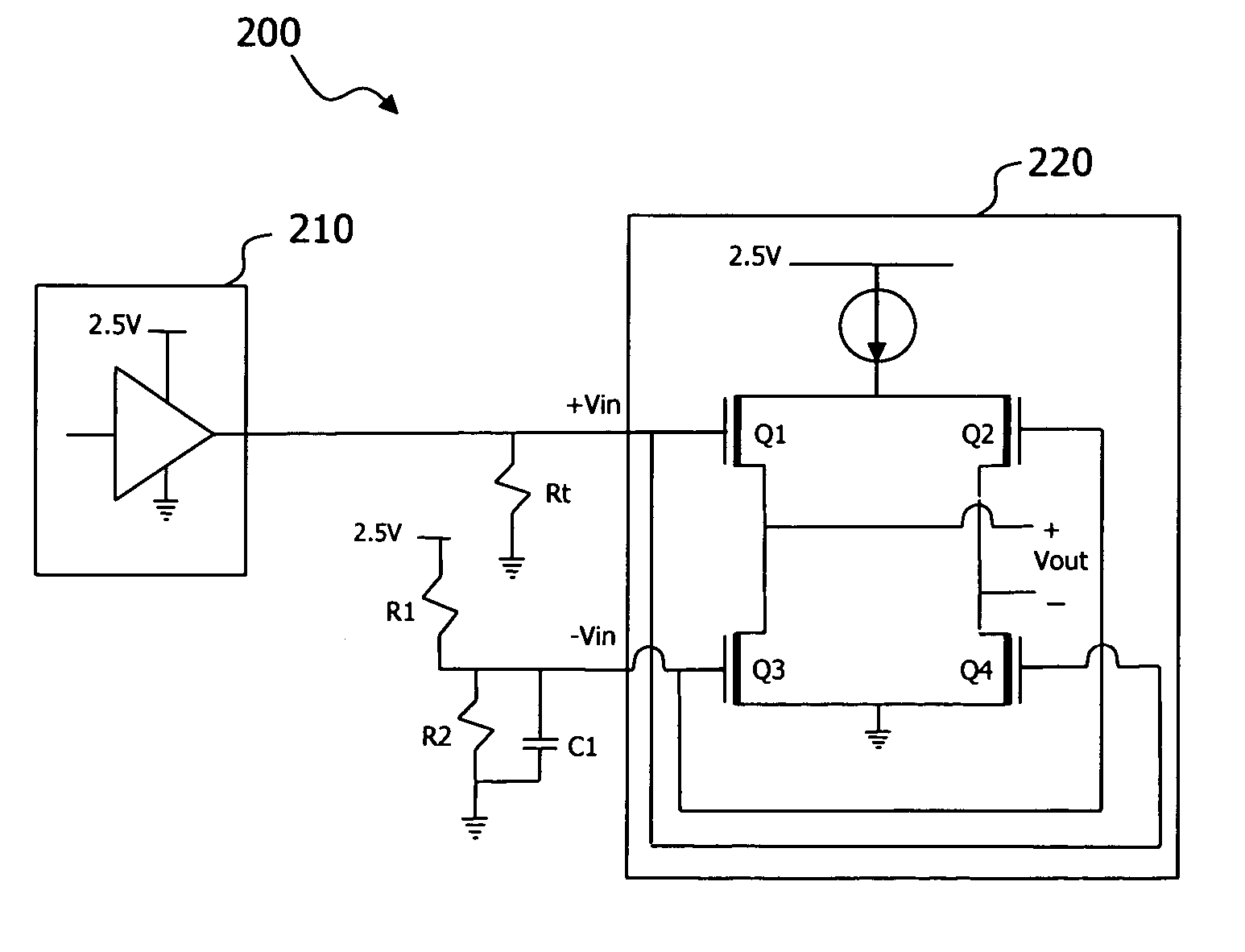

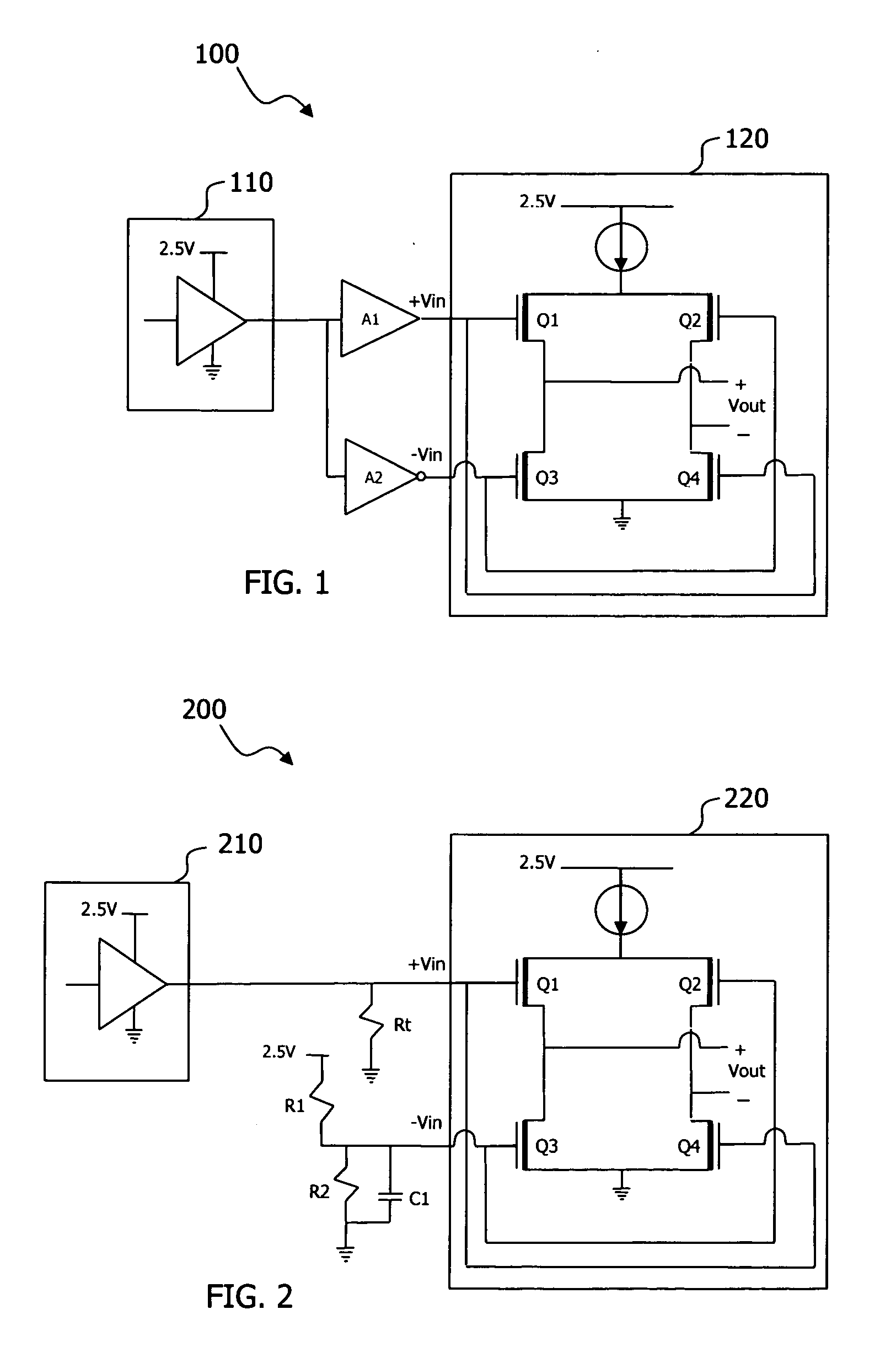

Single-ended CMOS signal interface to differential signal receiver loads

InactiveUS20070139080A1Simple interfaceLow costVoltage/current interference eliminationLogic circuit coupling/interface arrangementsCapacitanceCMOS

The interface of a single-ended CMOS type signal to differential signal loads includes a LVDS load having a +Vin input and a −Vin input, a CMOS circuit having an output signal line, and a resistor Rt connected to the output signal line and ground. A 2.5 volt source line is connected through a resistor R1 to the −Vin input of the LVDS load, the output signal line is connected directly to the +Vin input of the LVDS load, and a resistor R2 and capacitor C1 re connected in parallel between R1 and the −Vin input and ground.

Owner:LSI CORPORATION

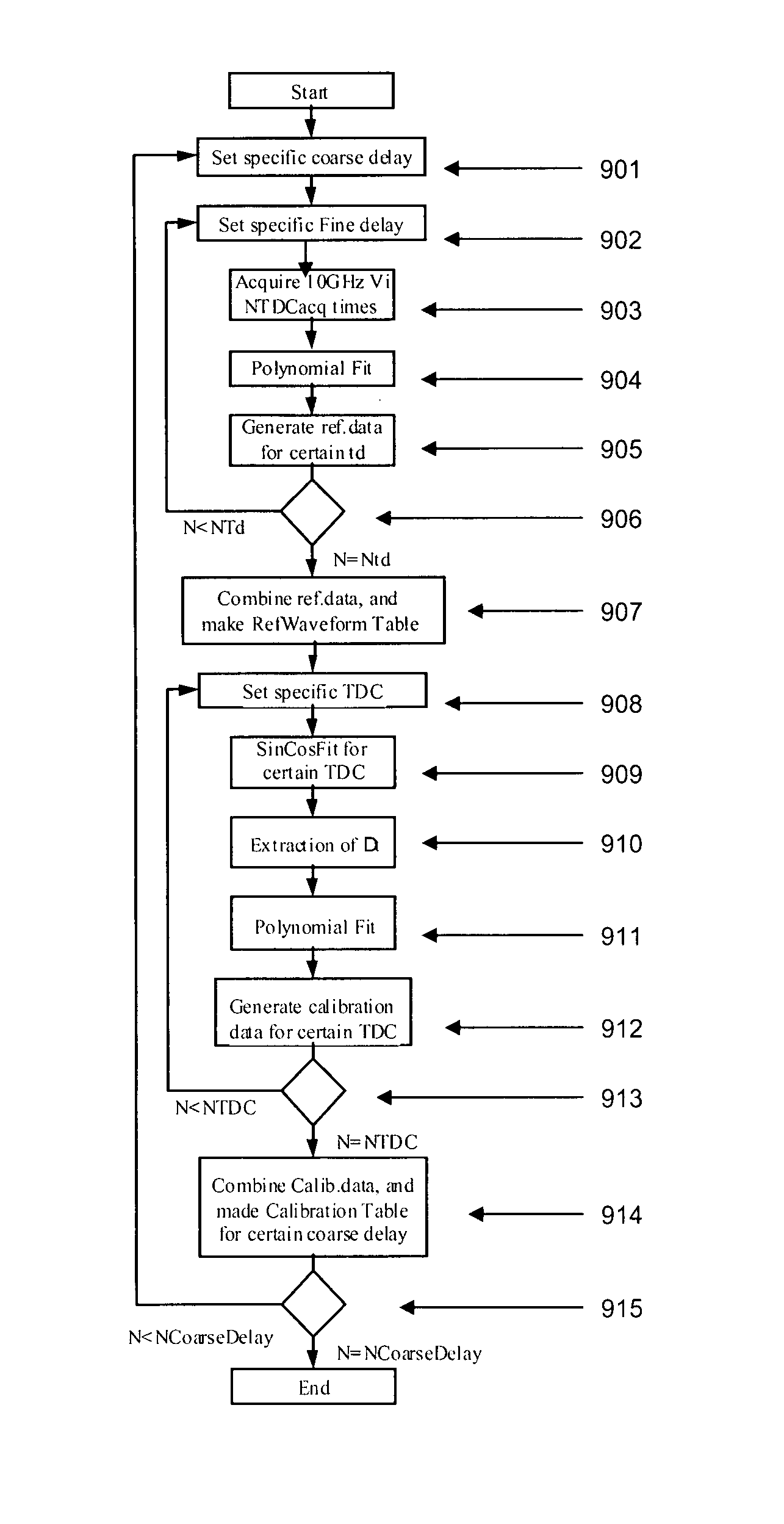

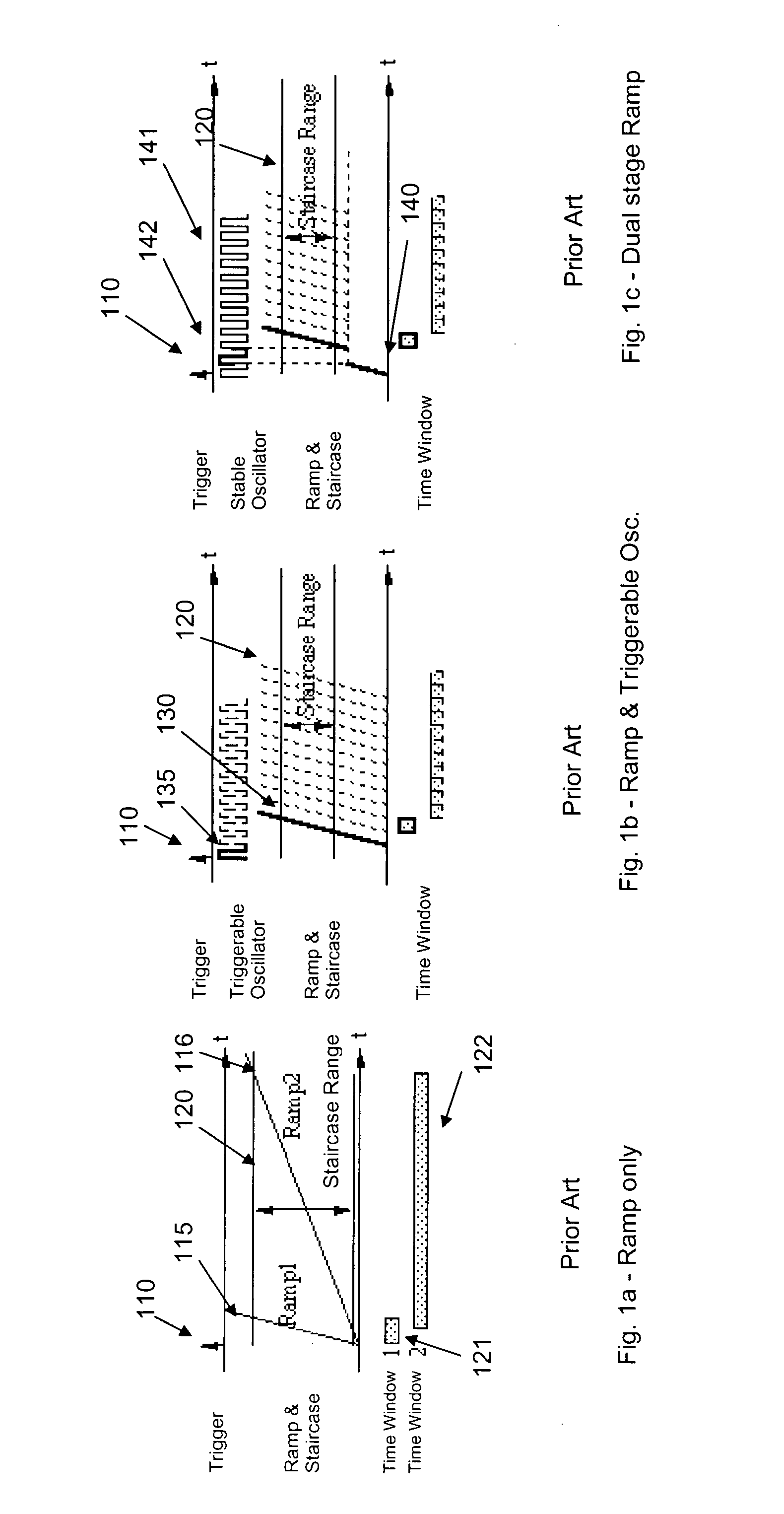

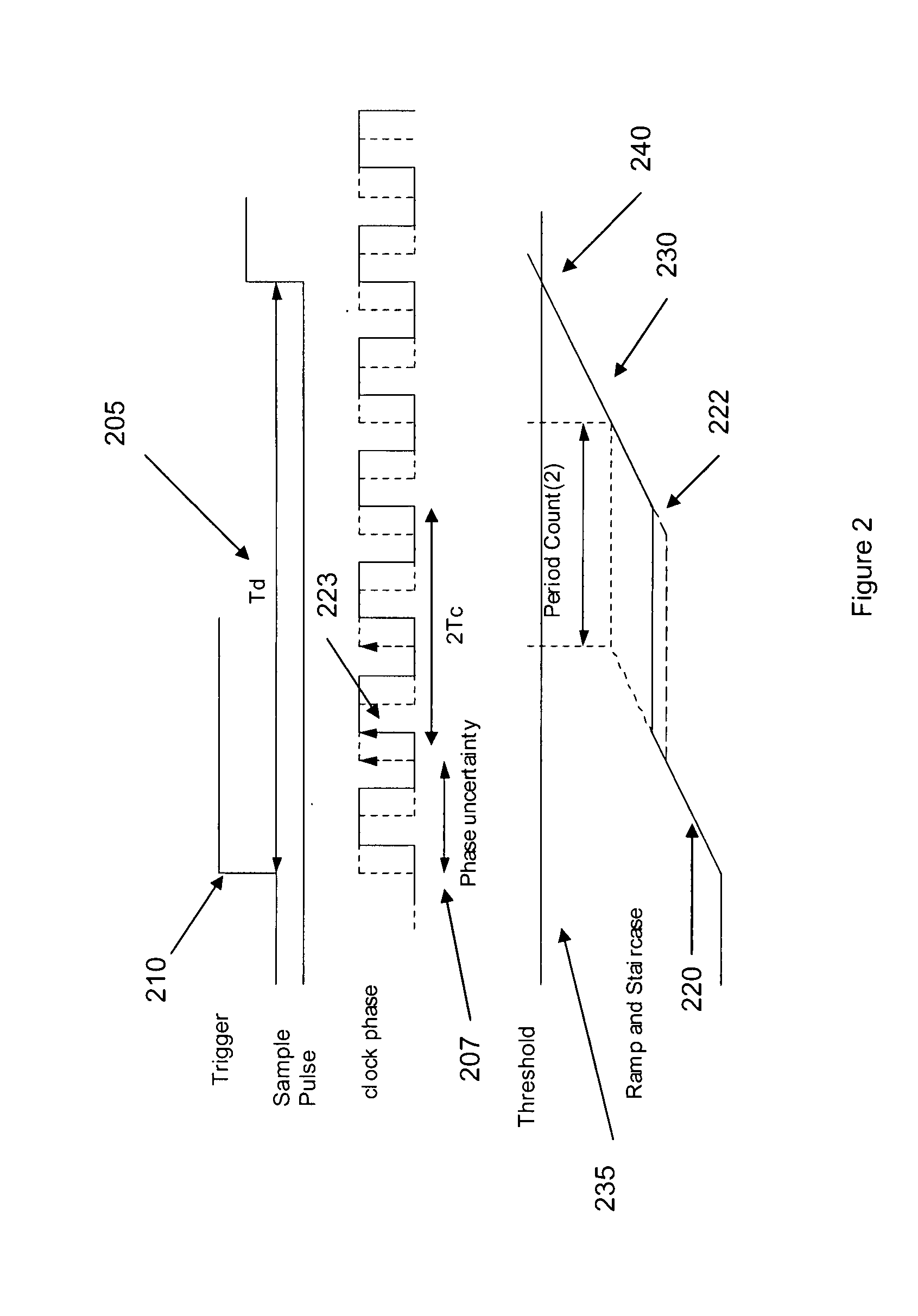

Sequential timebase

ActiveUS7280930B2Long delayLess jitterNoise figure or signal-to-noise ratio measurementPulse automatic controlDigital clockEngineering

A method and apparatus for correcting for deterministic jitter in a sequential sampling timebase. The value of a fine analog delay is held at a substantially constant nominal rate during a duration of a counting of a digital clock. A time difference between a trigger at which a fine analog delay starts measuring time and the occurrence of a digital pulse of a stable clock used to count a coarse delay is measured. An input waveform is sampled at a sample time having a nominal delay time. After sampling, a desired compensation time is provided for the sample of the input waveform in accordance with combinations of three independent variables defining a calibration table. The waveform is reconstructed by shifting a delay time of a sampled value of the input waveform from its nominal delay time in accordance with a value defined by the calibration table.

Owner:TELEDYNE LECROY

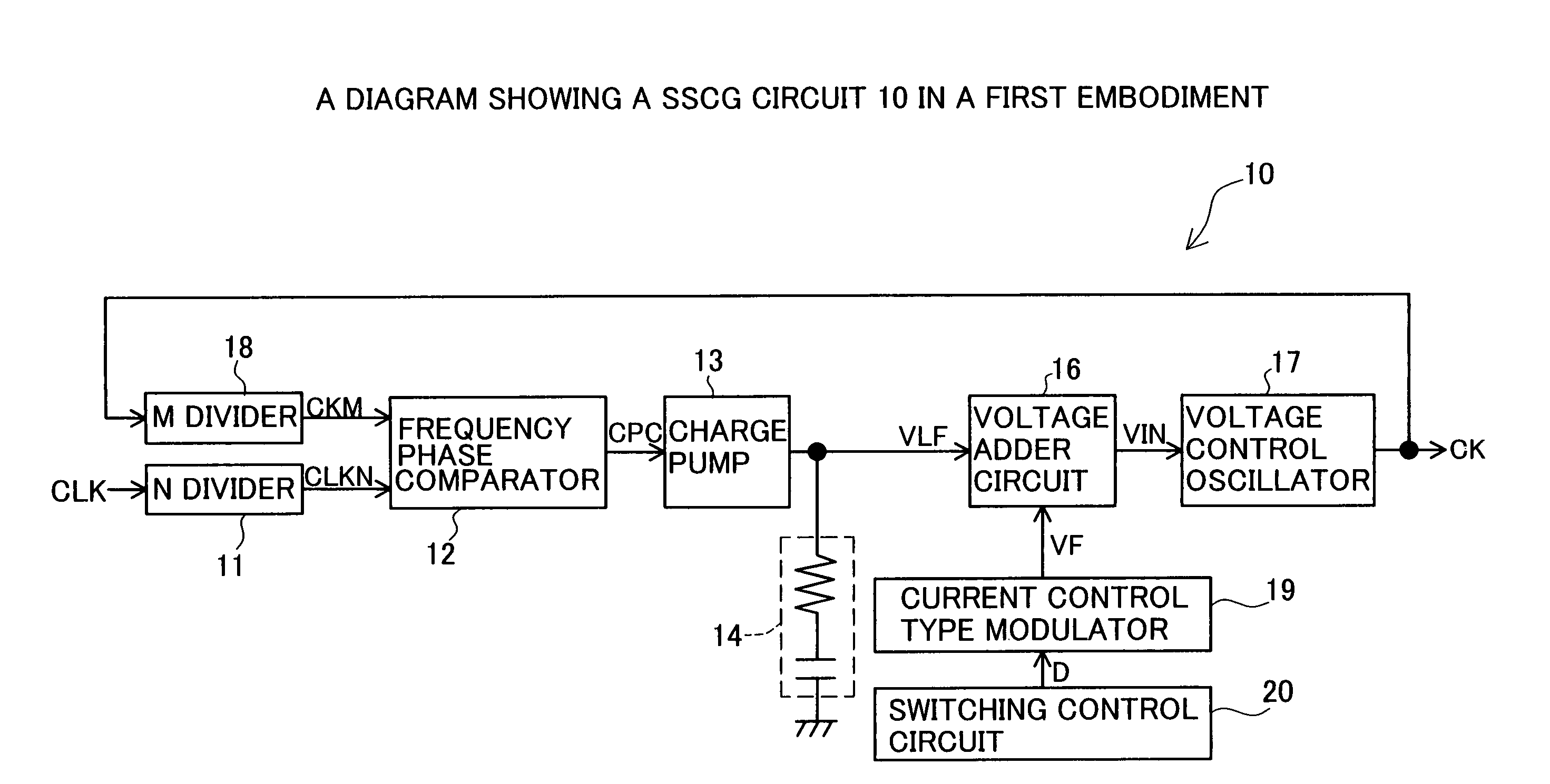

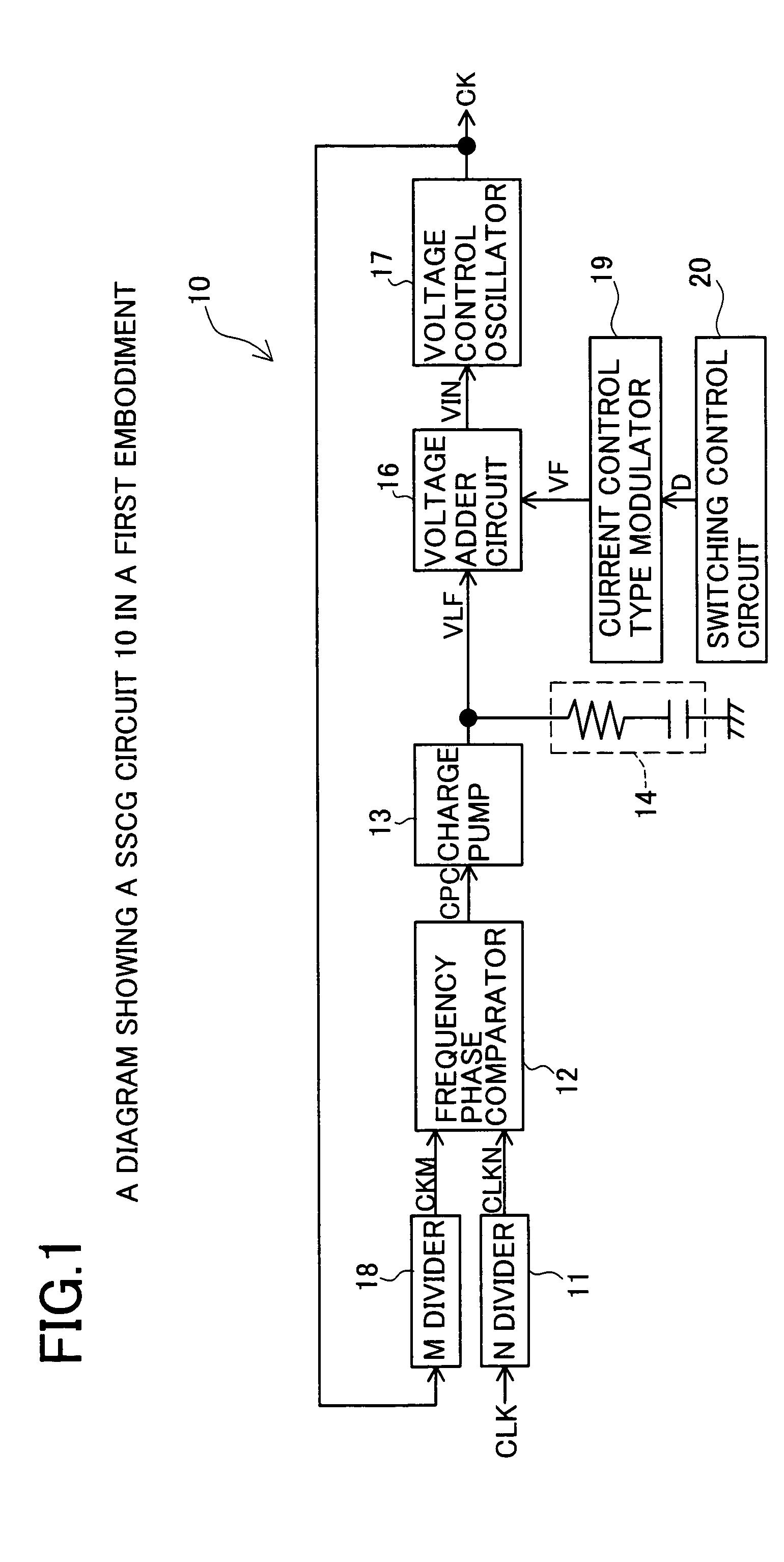

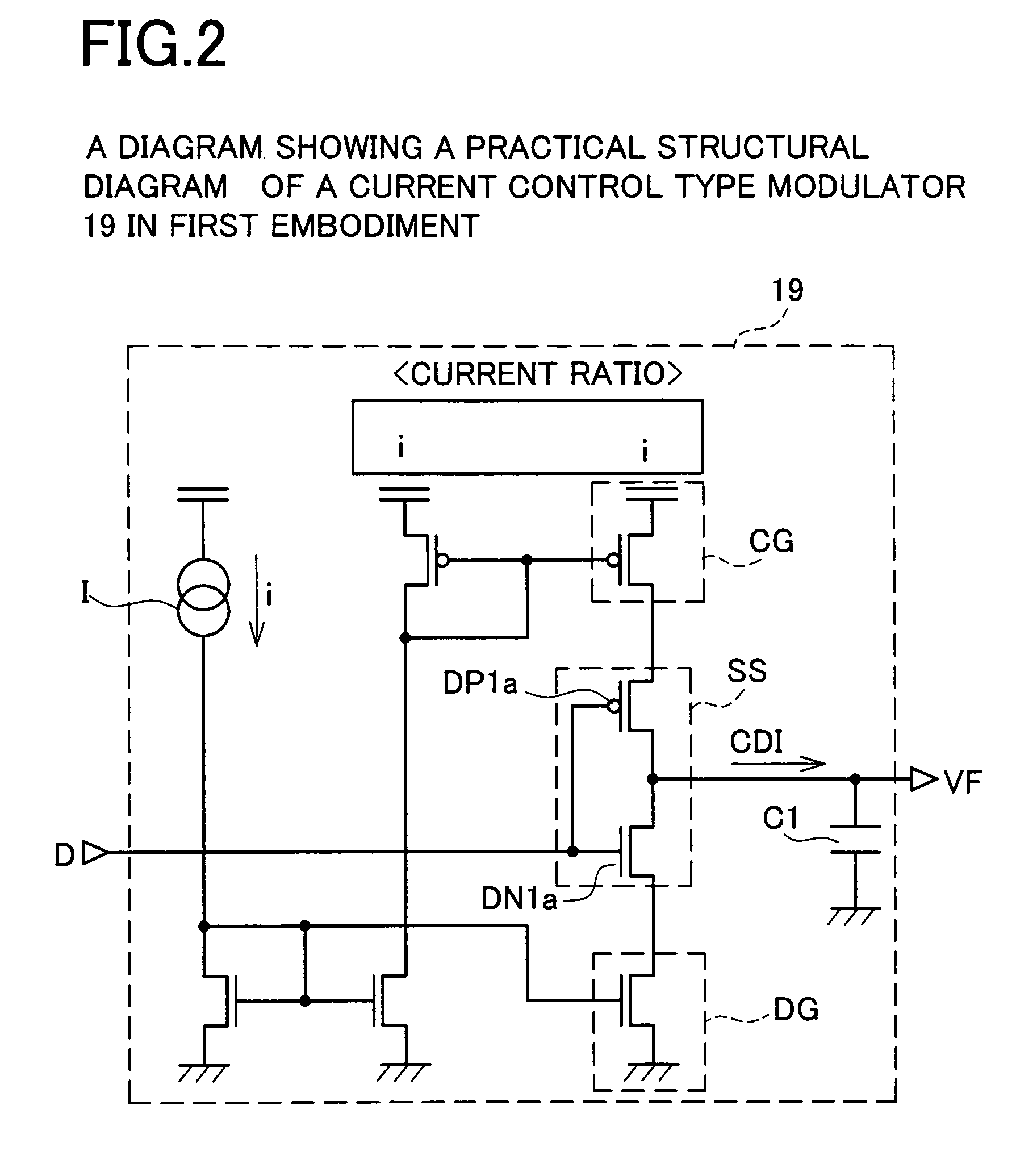

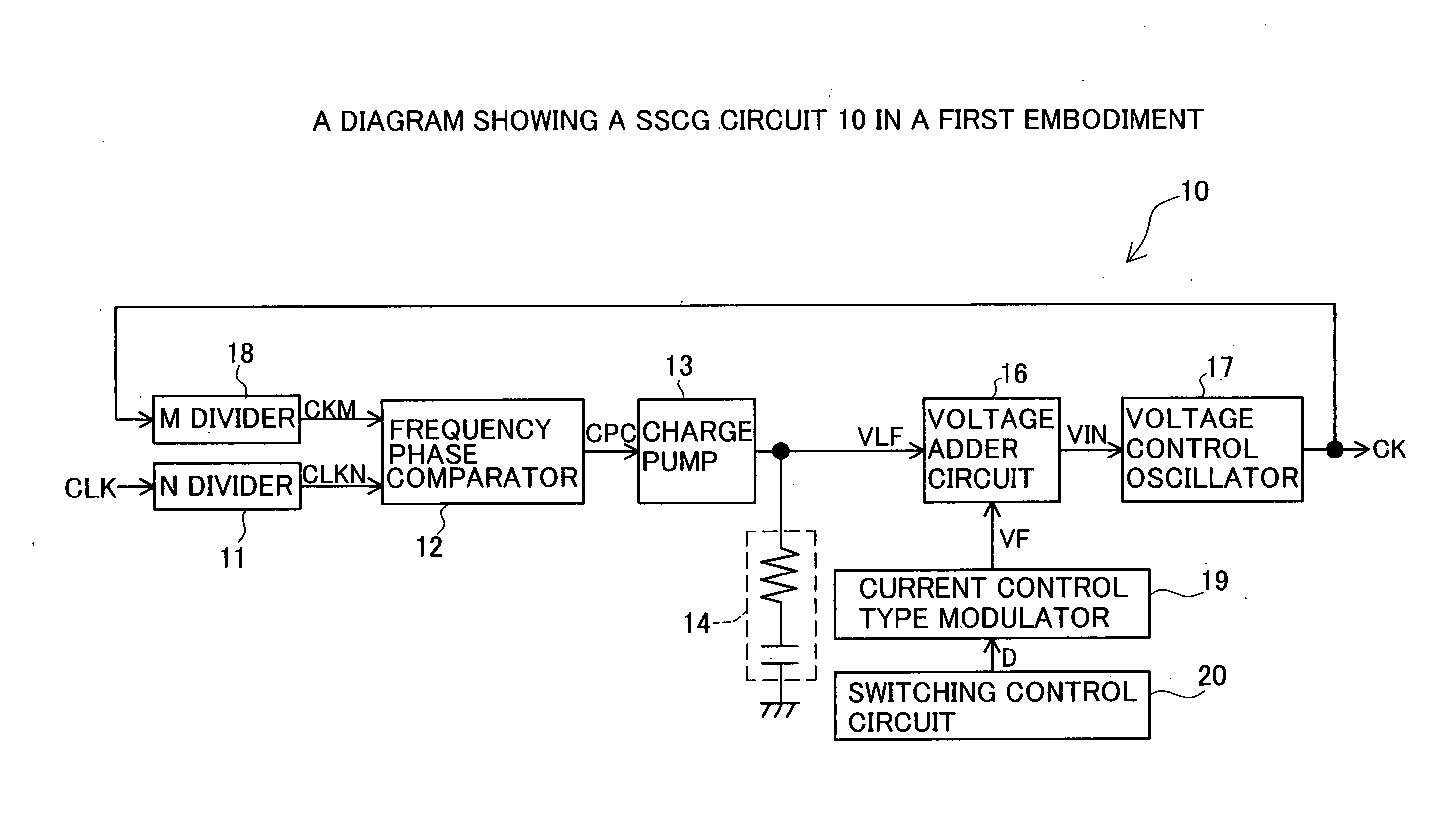

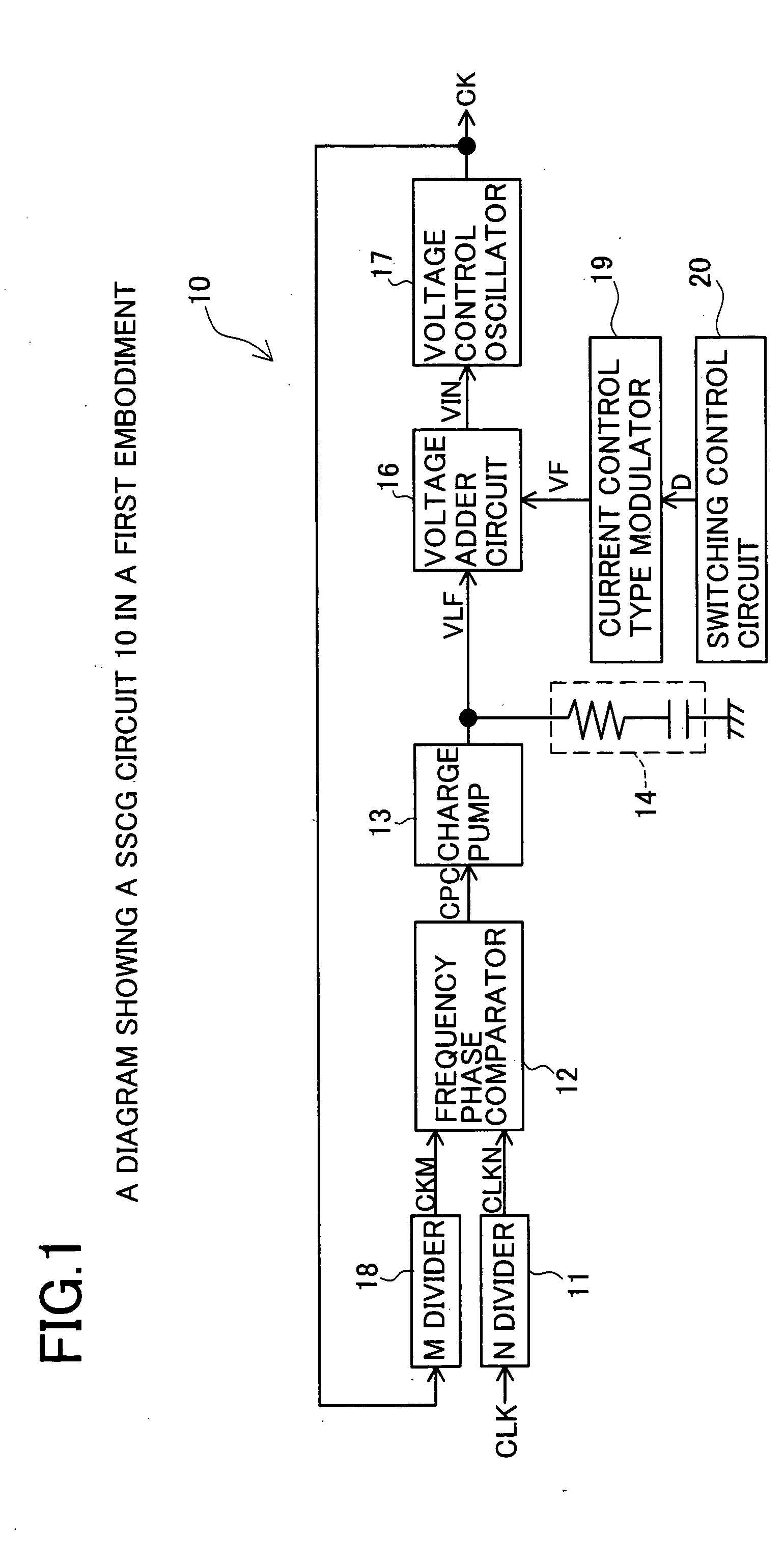

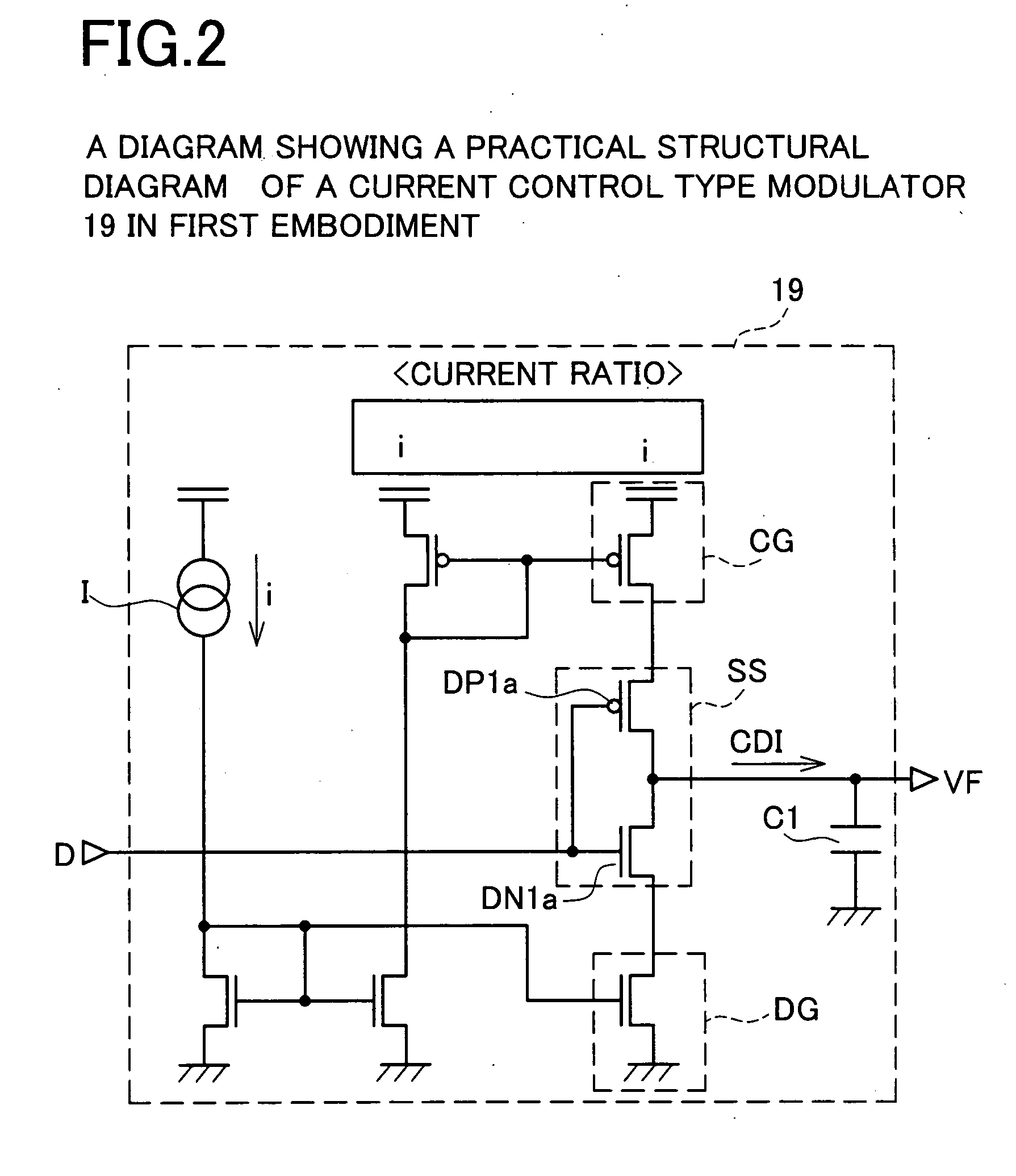

Spread spectrum clock generation circuit and a method of controlling thereof

ActiveUS8503501B2Less jitterSmall-scale circuitPulse automatic controlTransmissionControl circuitSpread spectrum

A spread spectrum clock generation circuit and a controlling method thereof are disclosed, which provide clocks having less jitter and ideal spread spectrum and enable a reduction in circuit scale and in power consumption. To this end, a current control type modulator 19a is equipped with a current source Ia (current 4i). A charger unit CGa and a discharger unit DGa are designed such that currents i, 2i and 4i are allowed to flow, for example, by properly setting the sizes of transistors. Modulation cycles CIa to CIIIa are repeated and an output code is generated from a switching control circuit 20a according to each modulation cycle. A switching unit SSa is controlled according to the output code, thereby charging or discharging a capacitor element C1 with a charge / discharge current CDI corresponding to the output code. Hence, charge amounts and discharge amounts for all the modulation cycles CIa to CIIIa have the same value, i.e., 6i [A·clock].

Owner:CYPRESS SEMICON CORP

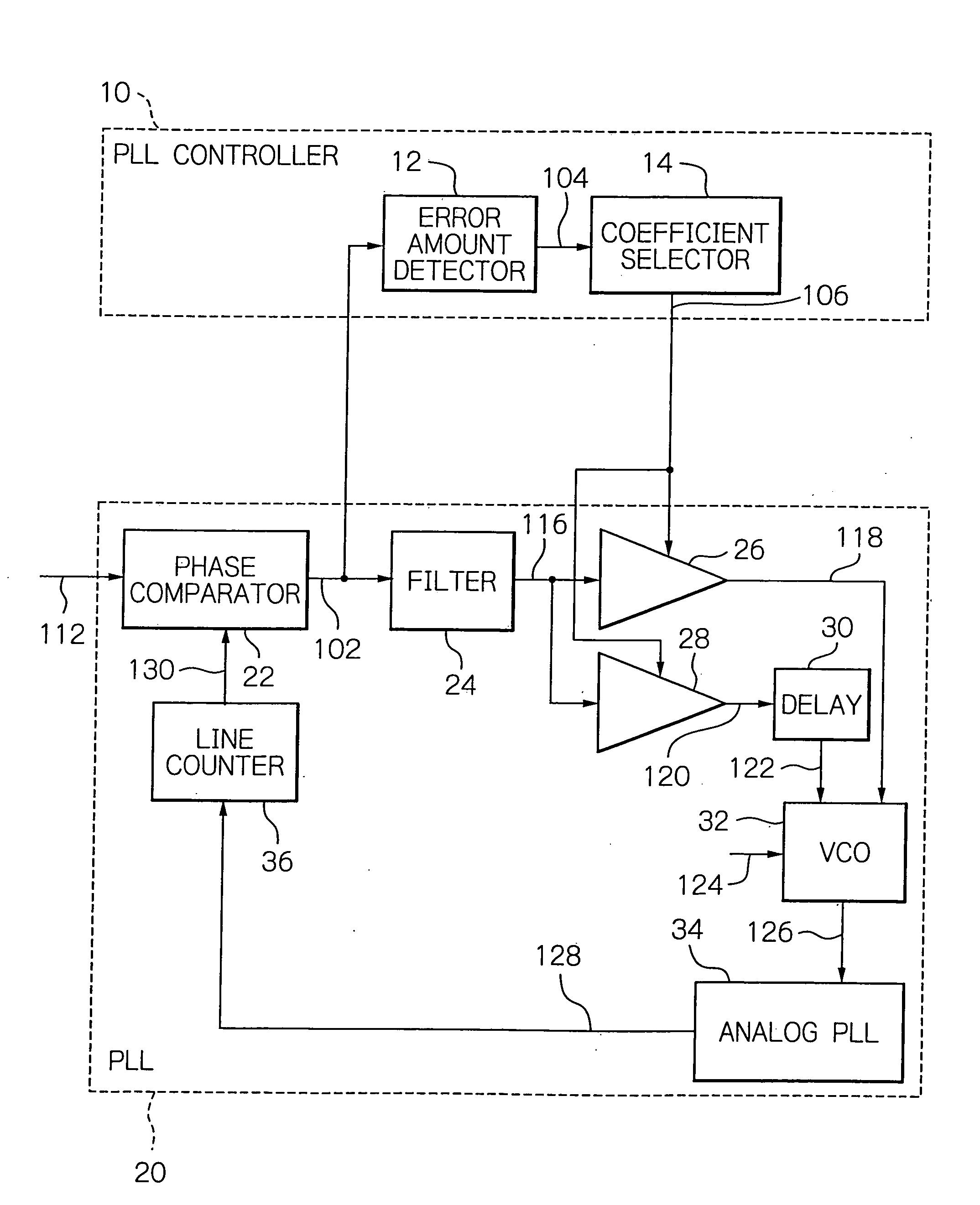

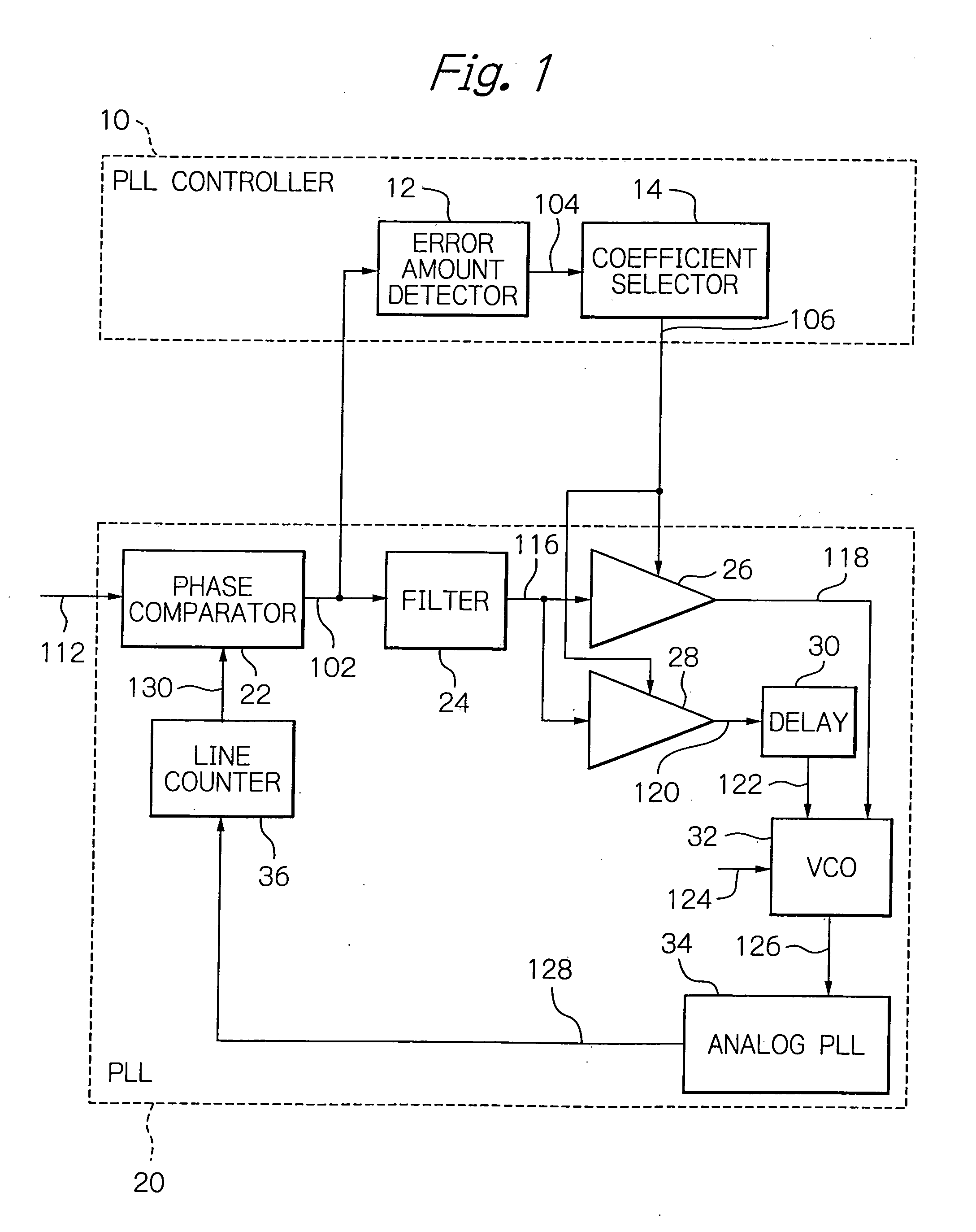

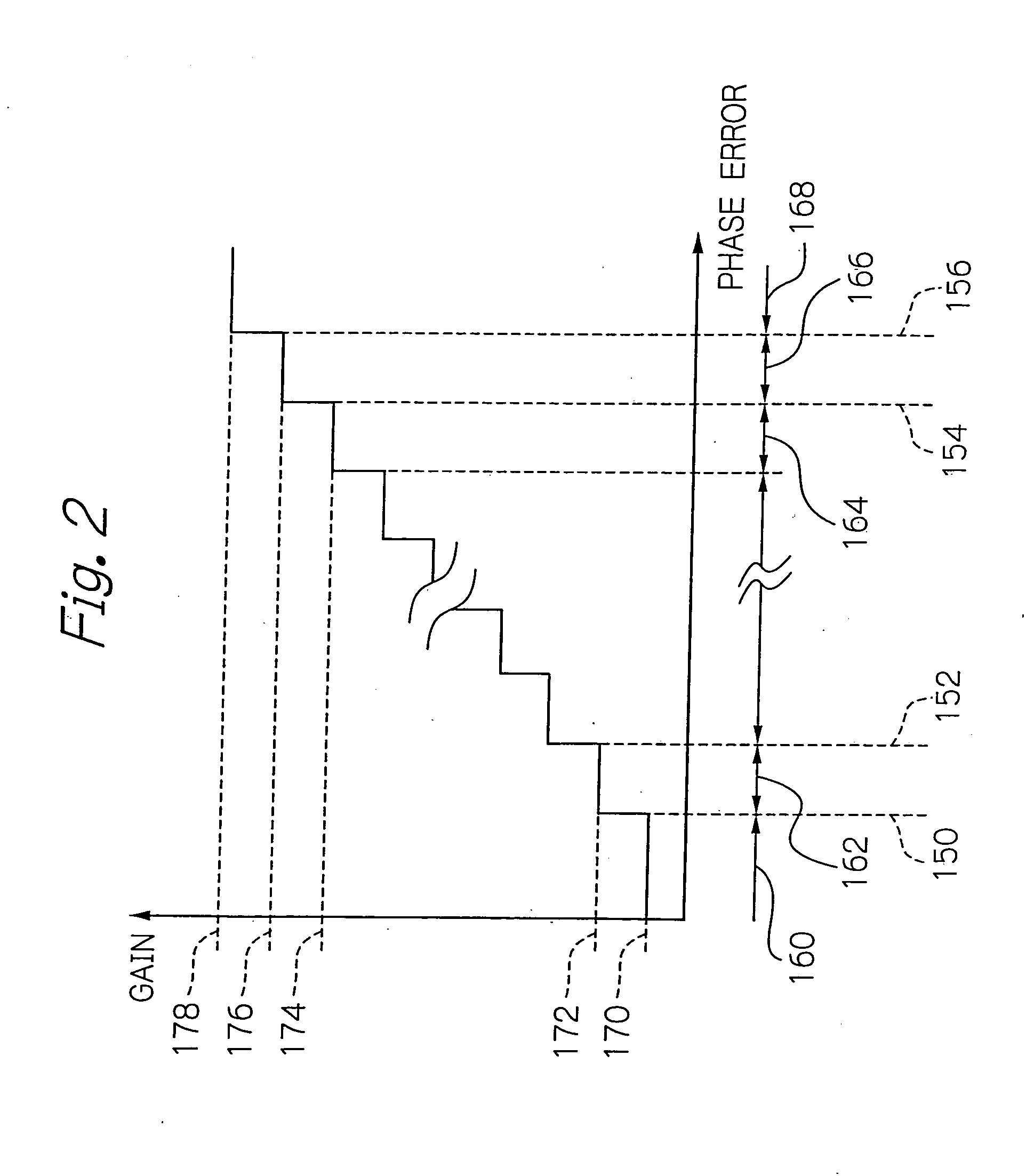

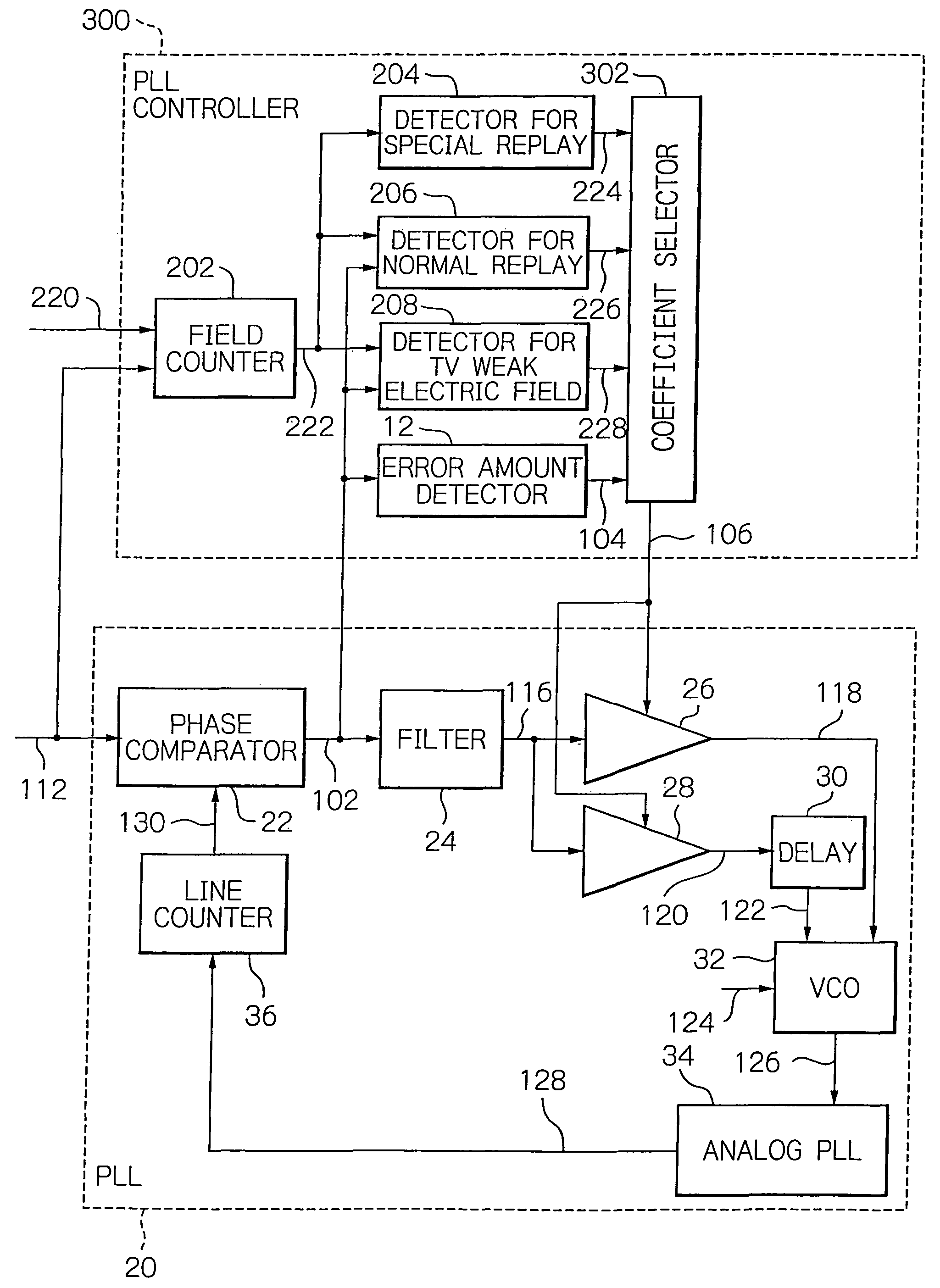

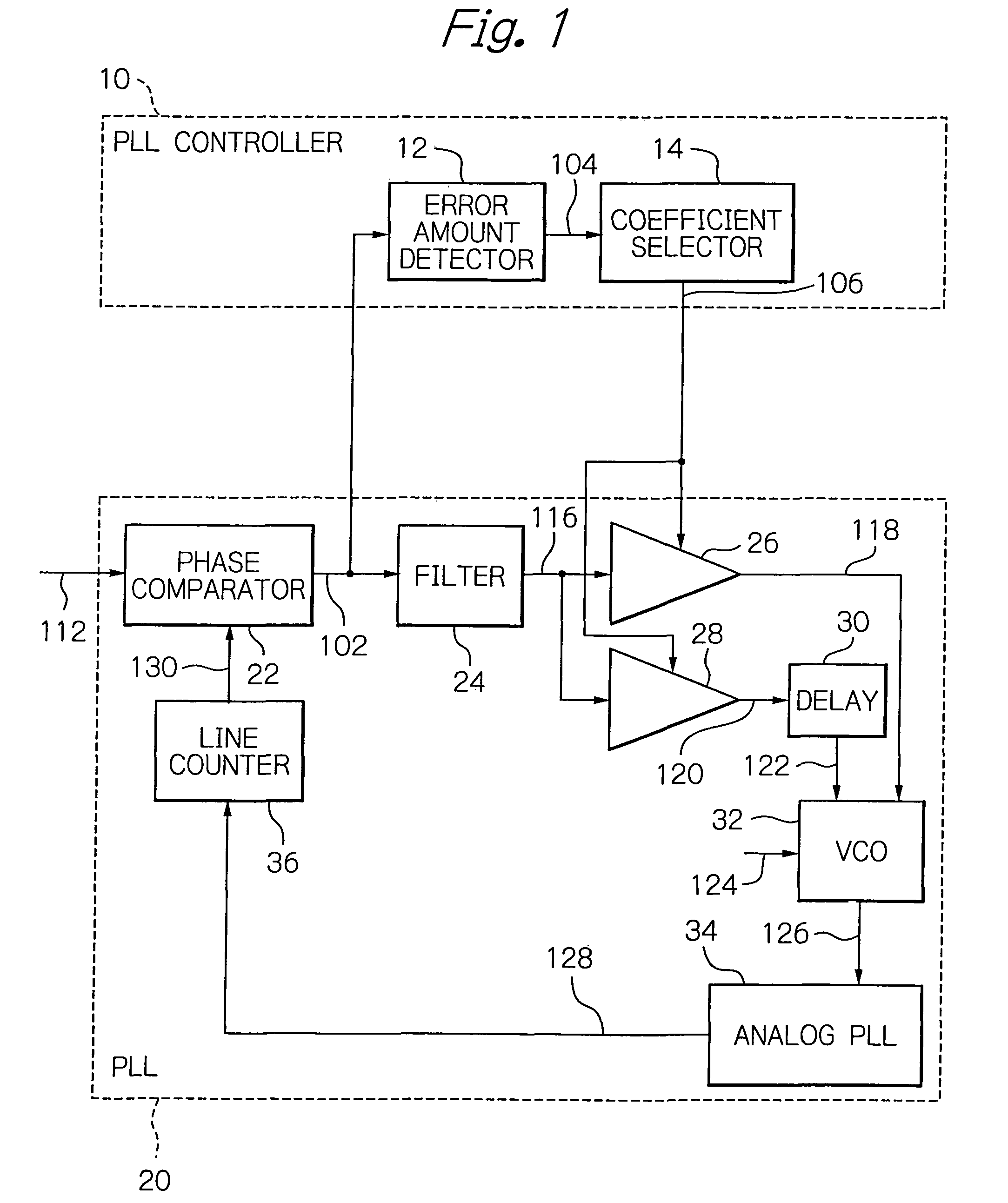

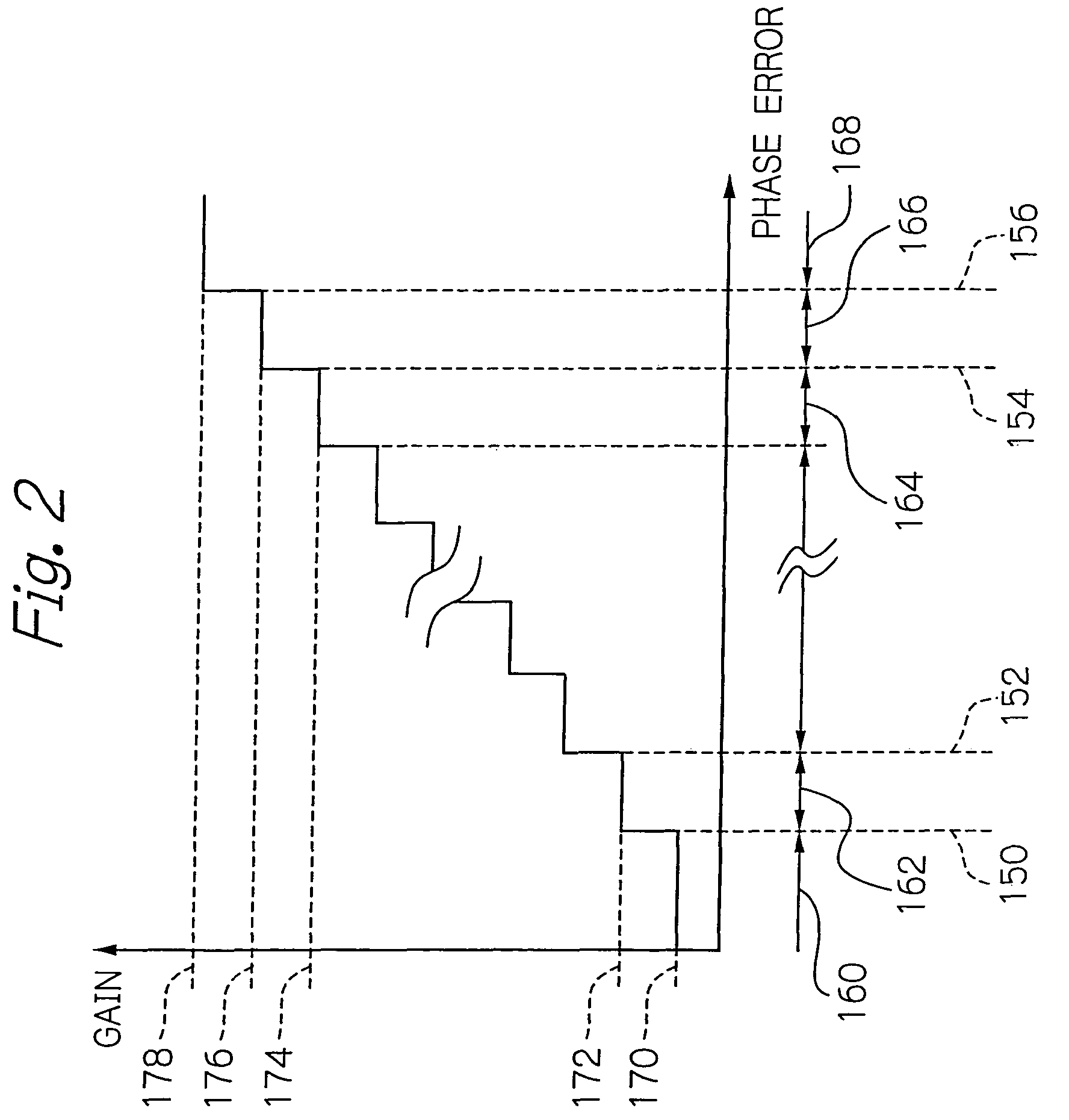

PLL controller applying a multiplier coefficient appropriate for a phase error, and a method therefor

ActiveUS20060274199A1Drawback can be obviatedFaster rateTelevision system detailsPulse automatic controlBinary multiplierControl signal

A PLL controller for controlling the tracking rate of a phase-locked loop (PLL), in particular, controlling coefficients to be input to a device such as a multiplier of the phase-locked loop. A PLL controller receives a phase error between a horizontal sync signal in a video signal and a reference signal. Then an error amount detector measures the phase error using the N thresholds to output a control signal indicating any of N+1 levels. A coefficient selector outputs one of the N+1 gains as a coefficient signal, the one gain corresponding to the level indicated by the control signal, so that the tracking rate of the phase-locked loop is controlled in response to the input video signal, and thus a high-quality video image with less jitter can be provided.

Owner:LAPIS SEMICON CO LTD

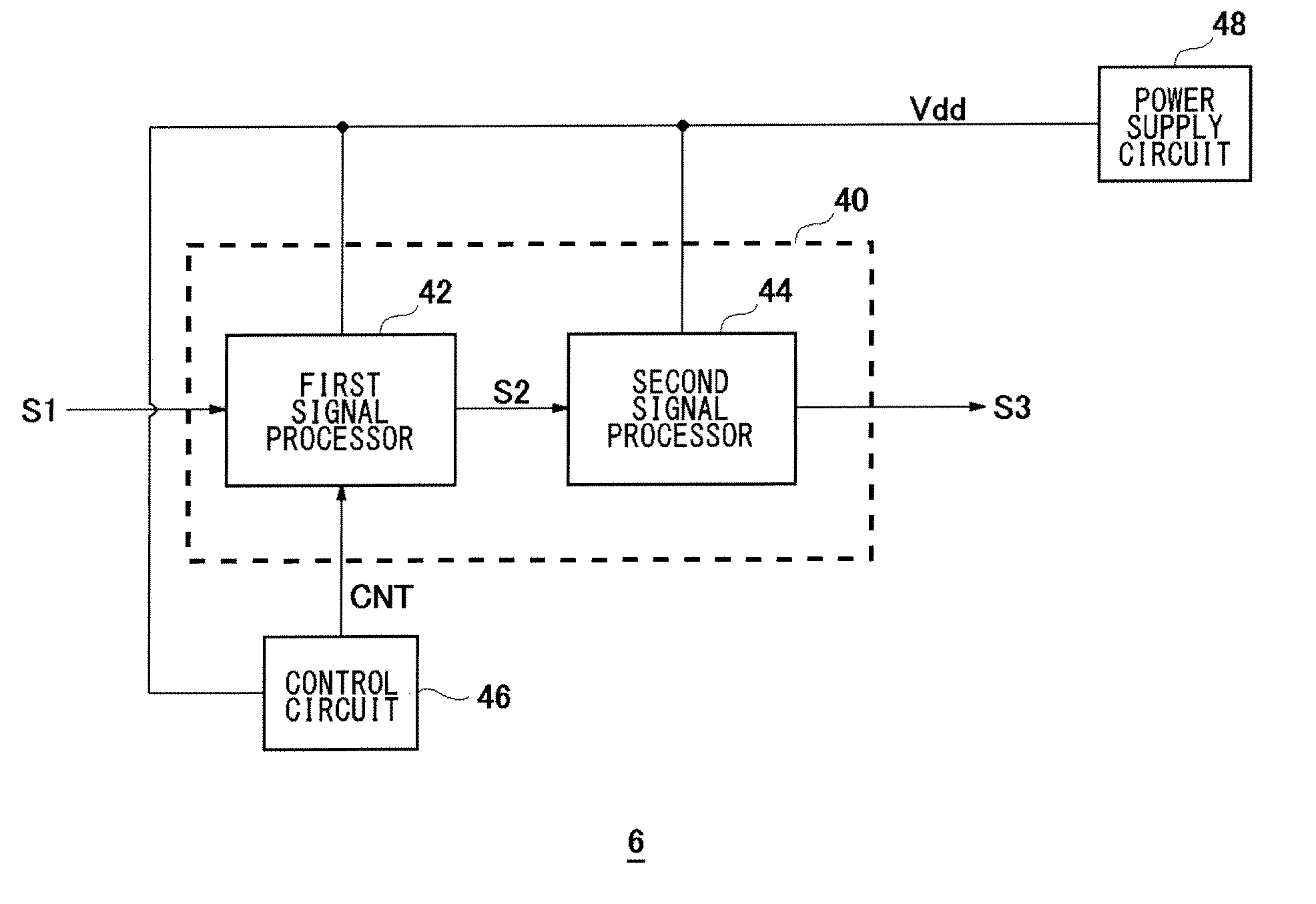

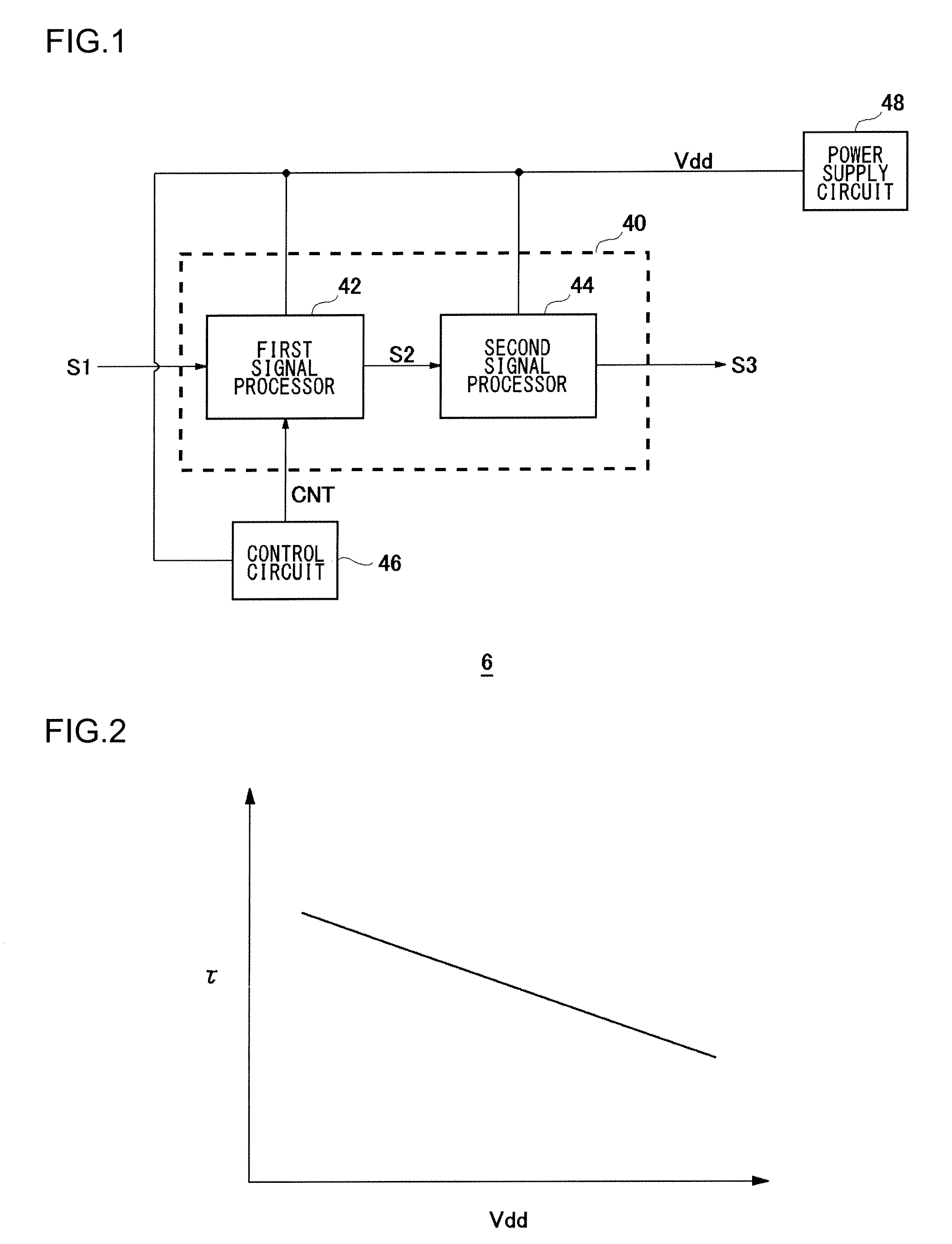

Semiconductor circuit

InactiveUS20100060336A1Enhance accuracyLess jitterPulse automatic controlAmplifier modifications to reduce temperature/voltage variationSignal processingSemiconductor

A first signal processor performs predetermined signal processing on an input signal to provide a change to at least one of the characteristic values thereof. A second signal processor is provided in the subsequent stage of the first signal processor and performs predetermined signal processing on an output signal from the first signal processor to provide a change to a characteristic value thereof. An amount of change provided to the characteristic value of the signal by the second signal processor is dependent on a power supply voltage. An amount of change provided to the characteristic value of the signal by the first signal processor is configured to be adjustable. A control circuit monitors a power supply voltage supplied to the second signal processor and adjusts in accordance with the power supply voltage the amount of change provided to the characteristic value of the signal by the first signal processor.

Owner:ADVANTEST CORP

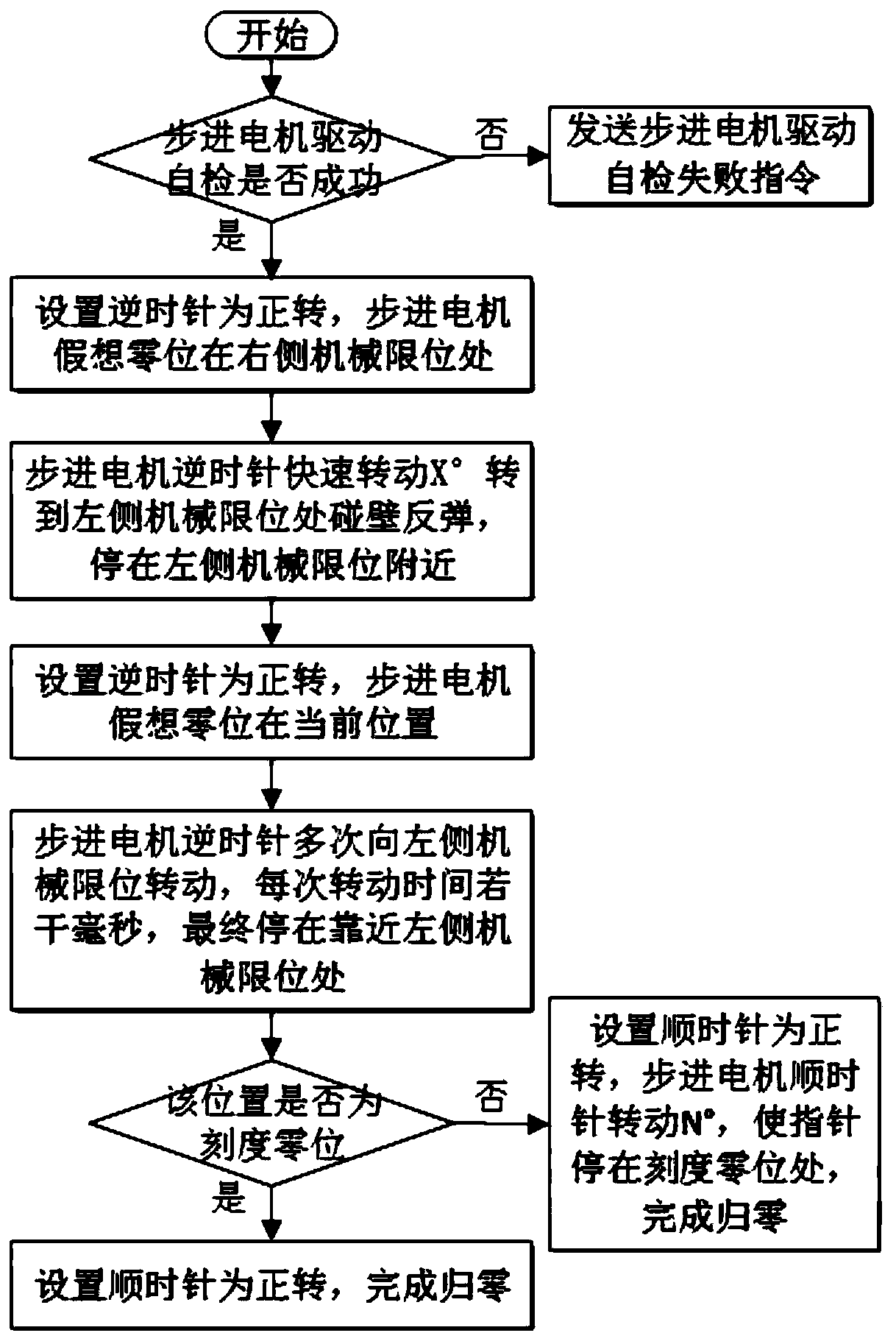

Zeroing algorithm of pointer instrument

The invention relates to a zeroing algorithm of a pointer instrument. The zeroing algorithm concretely includes the zeroing steps that 1, it is assumed that a pointer is located at the position farthest from a zeroing mechanical limit during working of the instrument; 2, a stepping motor rotates rapidly by X degrees in the direction of the zeroing mechanical limit; 3, with a current position beinga hypothetical zero position, the stepping motor rotates clockwise from a farm end mechanical limit to the zeroing mechanical limit; 4, the stepping motor rotates multiples times in the direction ofthe zeroing mechanical limit, and rotation lasts for multiple milliseconds each time; 5, it is set that the stepping motor rotates clockwise from the zeroing mechanical limit to the far end mechanicallimit, and if the current position is set to be a scale zero position, zeroing is completed. Through the zeroing algorithm, whether the pointer of the instrument is located at one initial position oranother, the pointer can return to the same position rapidly and accurately, accordingly, the problem is solved that since the initial positions of the pointer are different, zeroing errors are generated, and it is guaranteed that the instrument can be normally used through one-time power-on zeroing under any condition. Through the algorithm, zeroing speed is high, uniformity is good, and errorsare small.

Owner:BEIJING QINGYUN AVIATION INSTR CO LTD

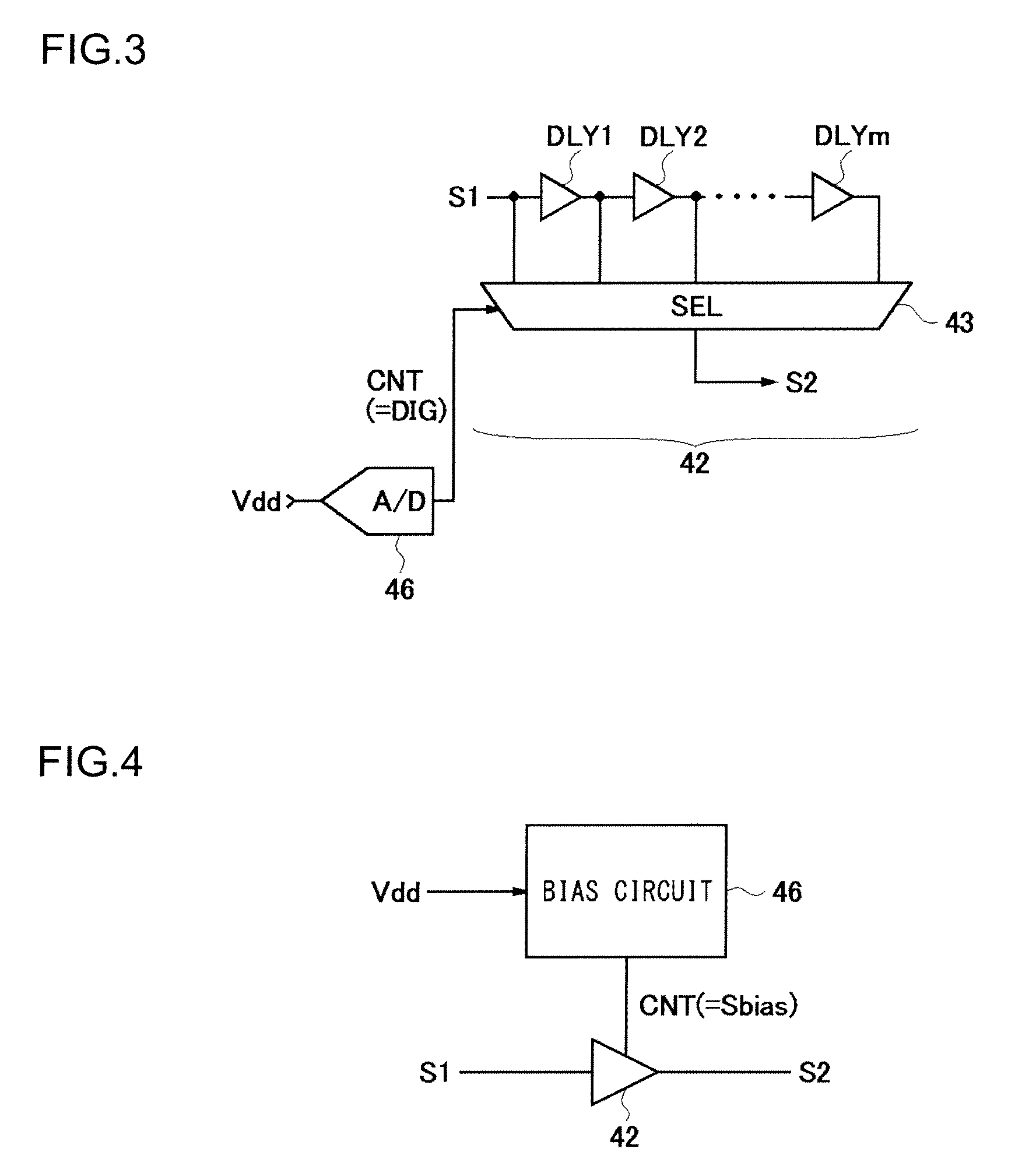

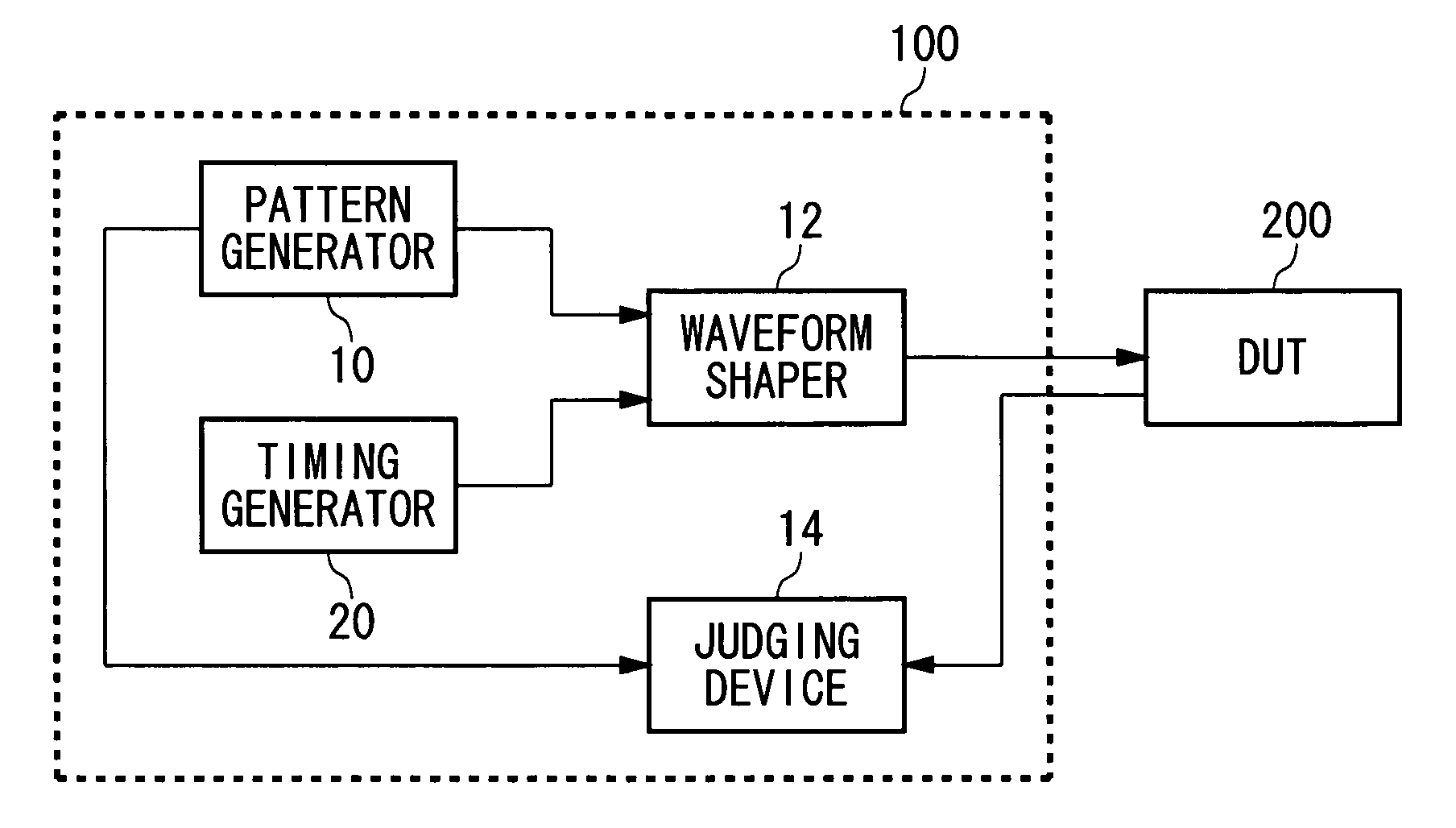

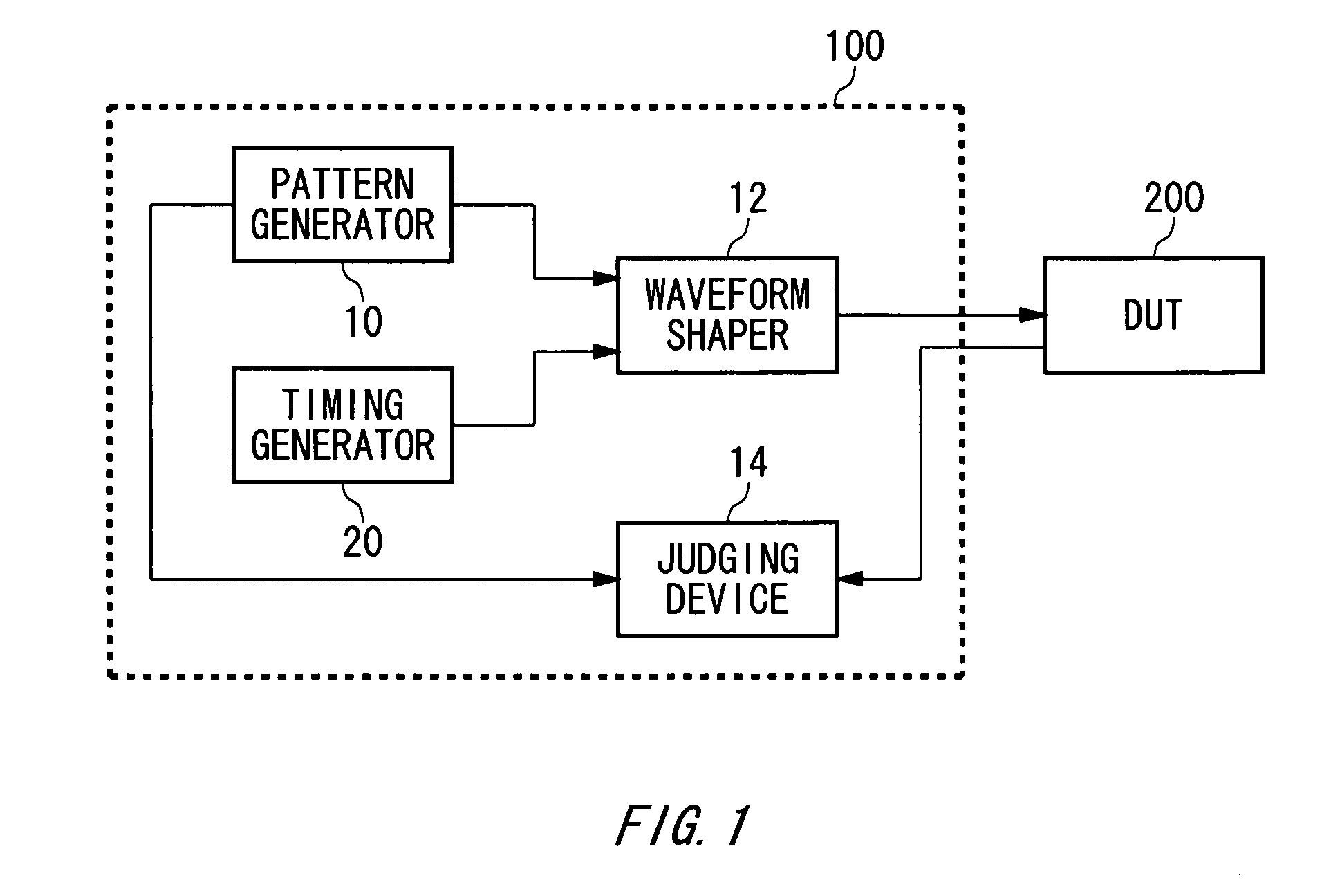

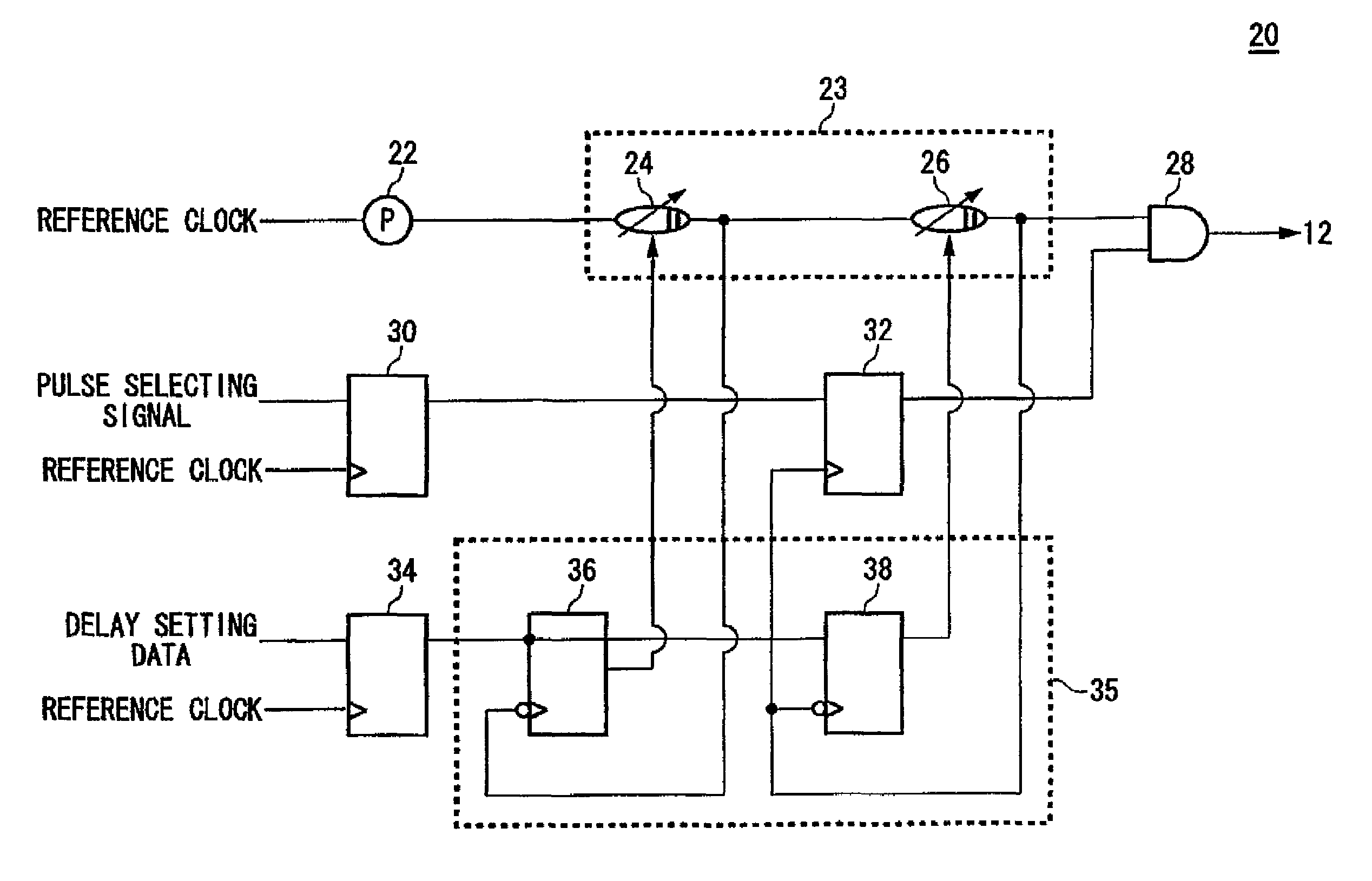

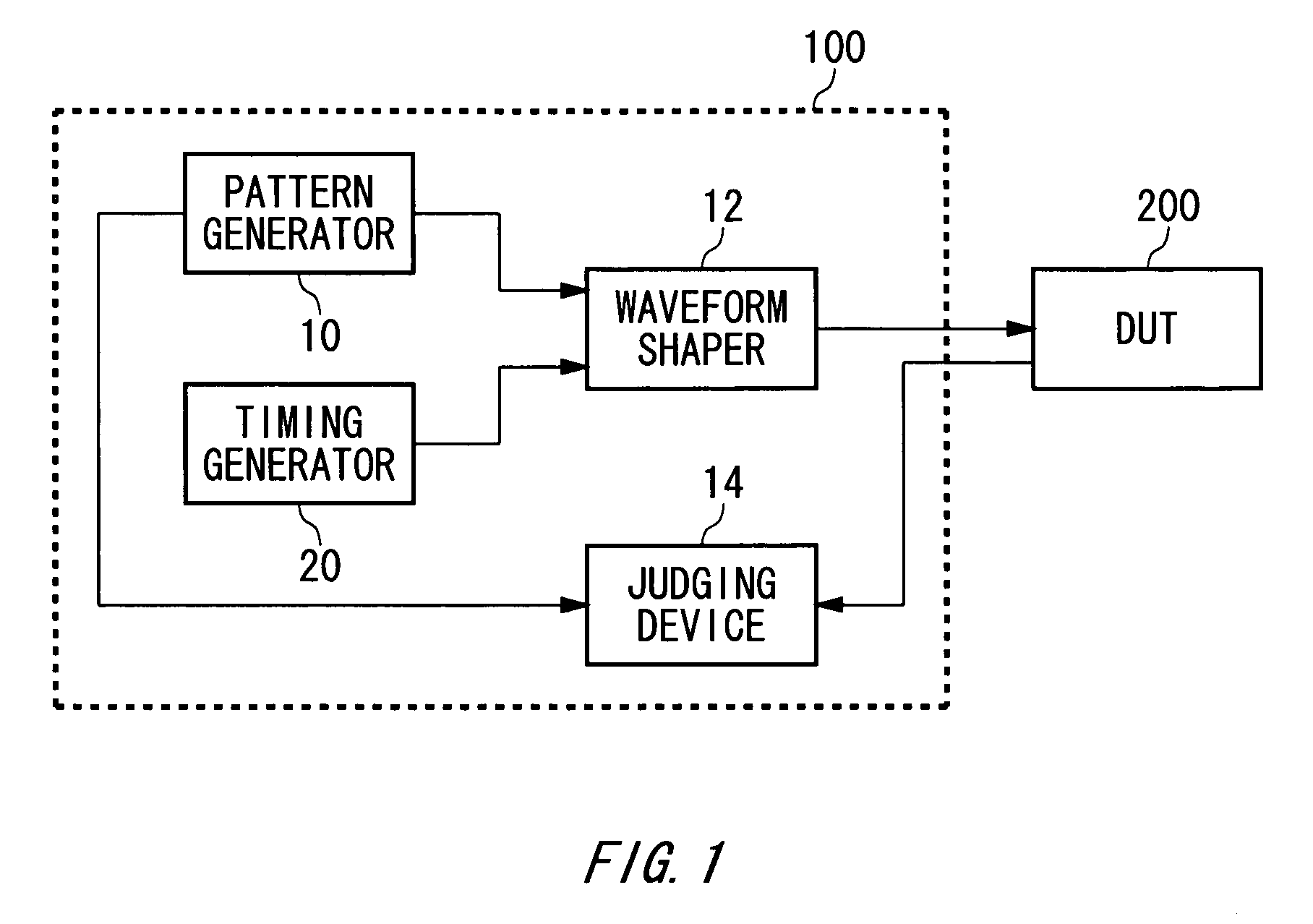

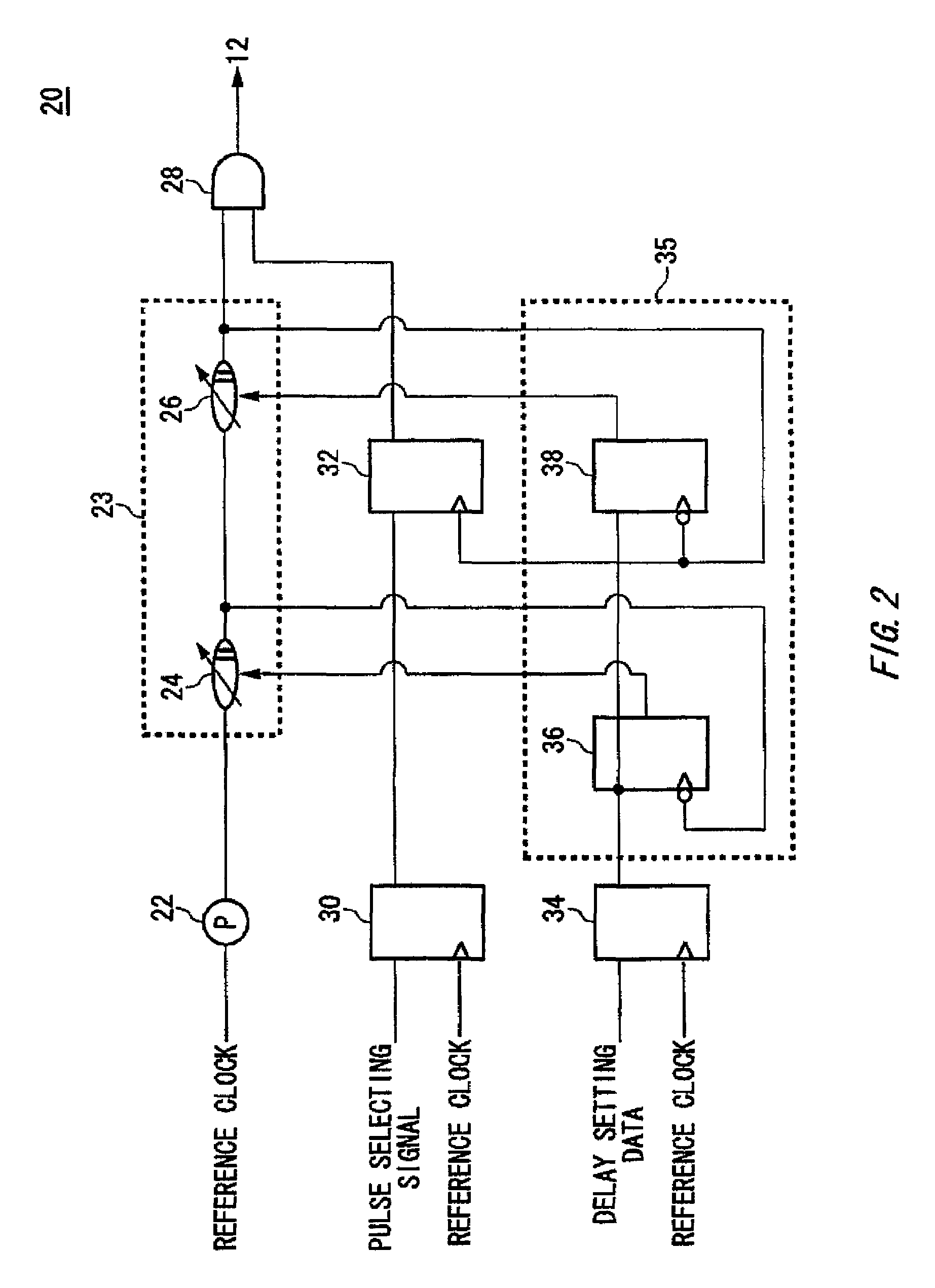

Timing generator and test device

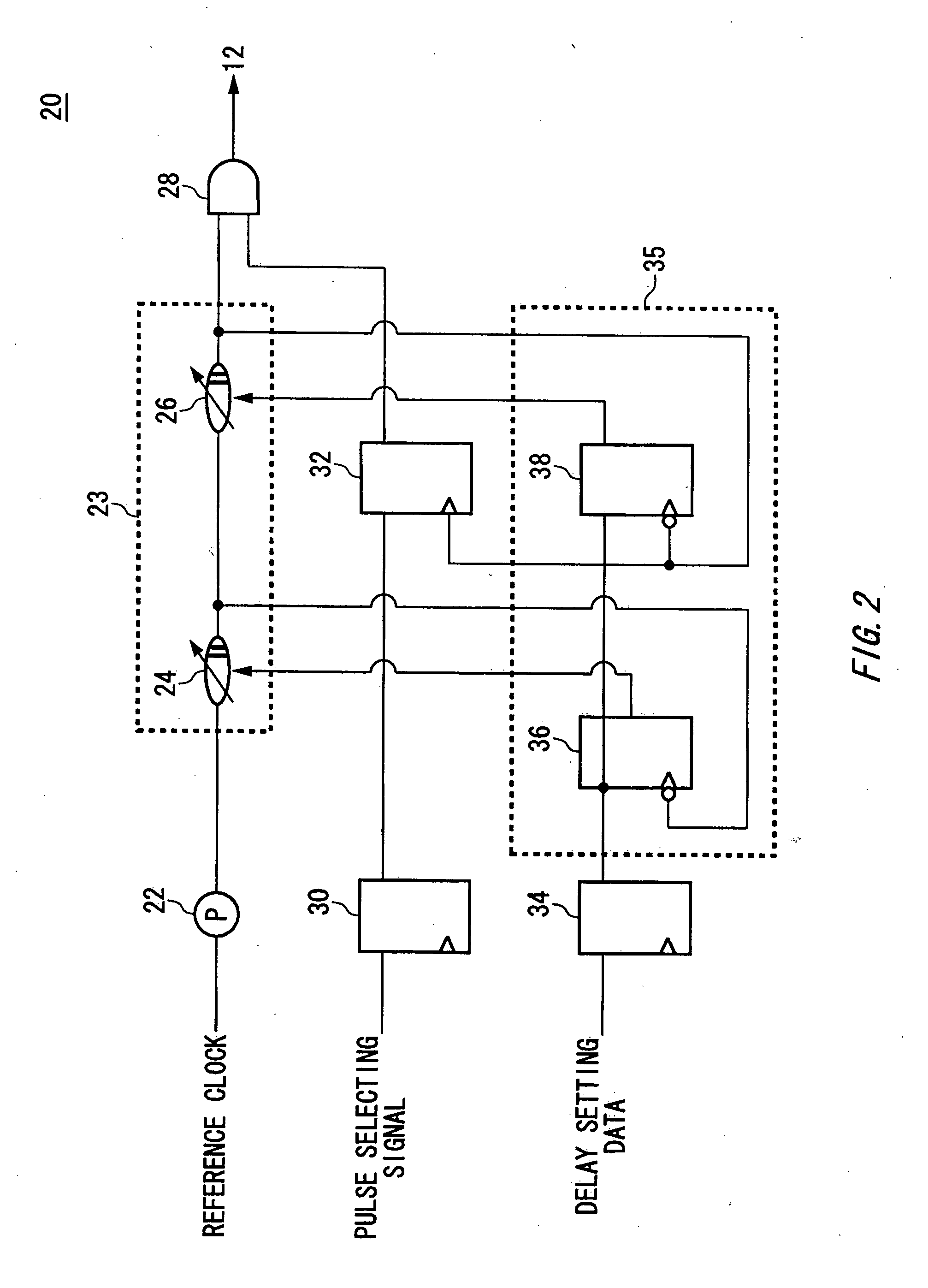

InactiveUS20060087308A1Less jitterMultiple-port networksDigital variable displayTiming generatorTest set

There is provided a timing generator for generating a timing signal based on a given reference clock, having a delaying circuit section for outputting each pulse of the reference clock by delaying by a value of delay given per each of the pulse and a pulse selecting and outputting section for passing and outputting only pulses to be outputted as the timing signal among the pulses outputted out of the delaying circuit section.

Owner:ADVANTEST CORP

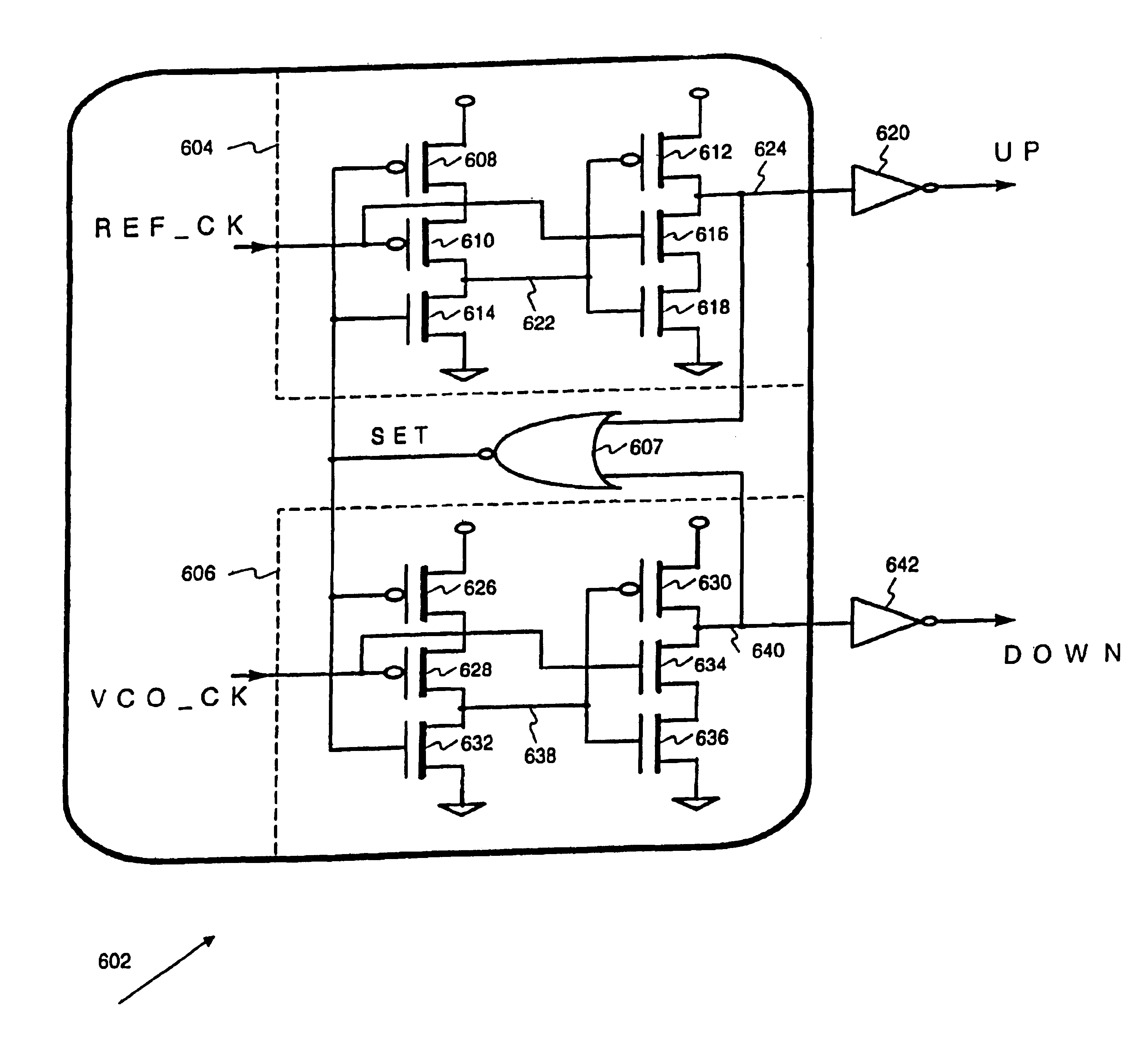

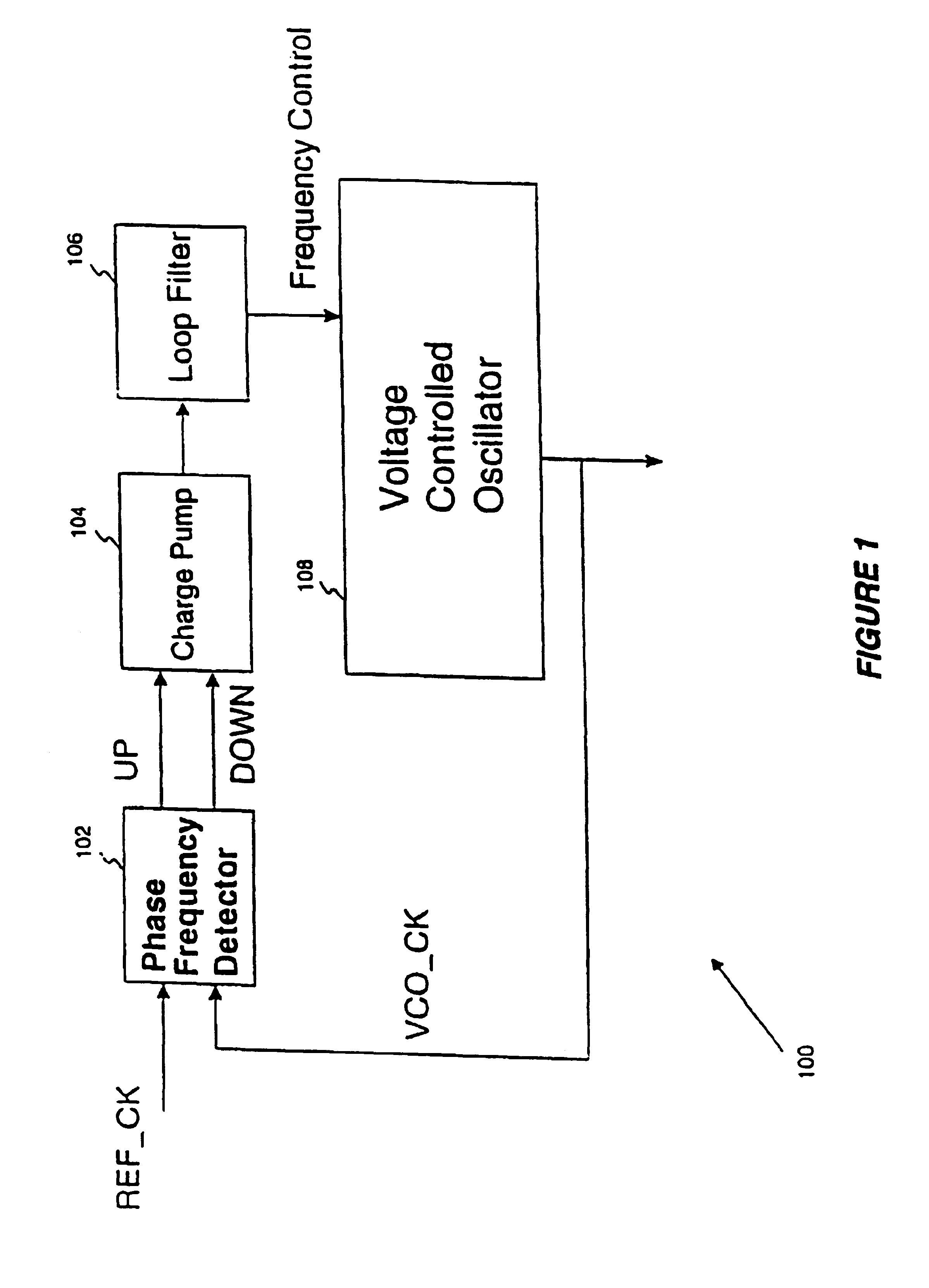

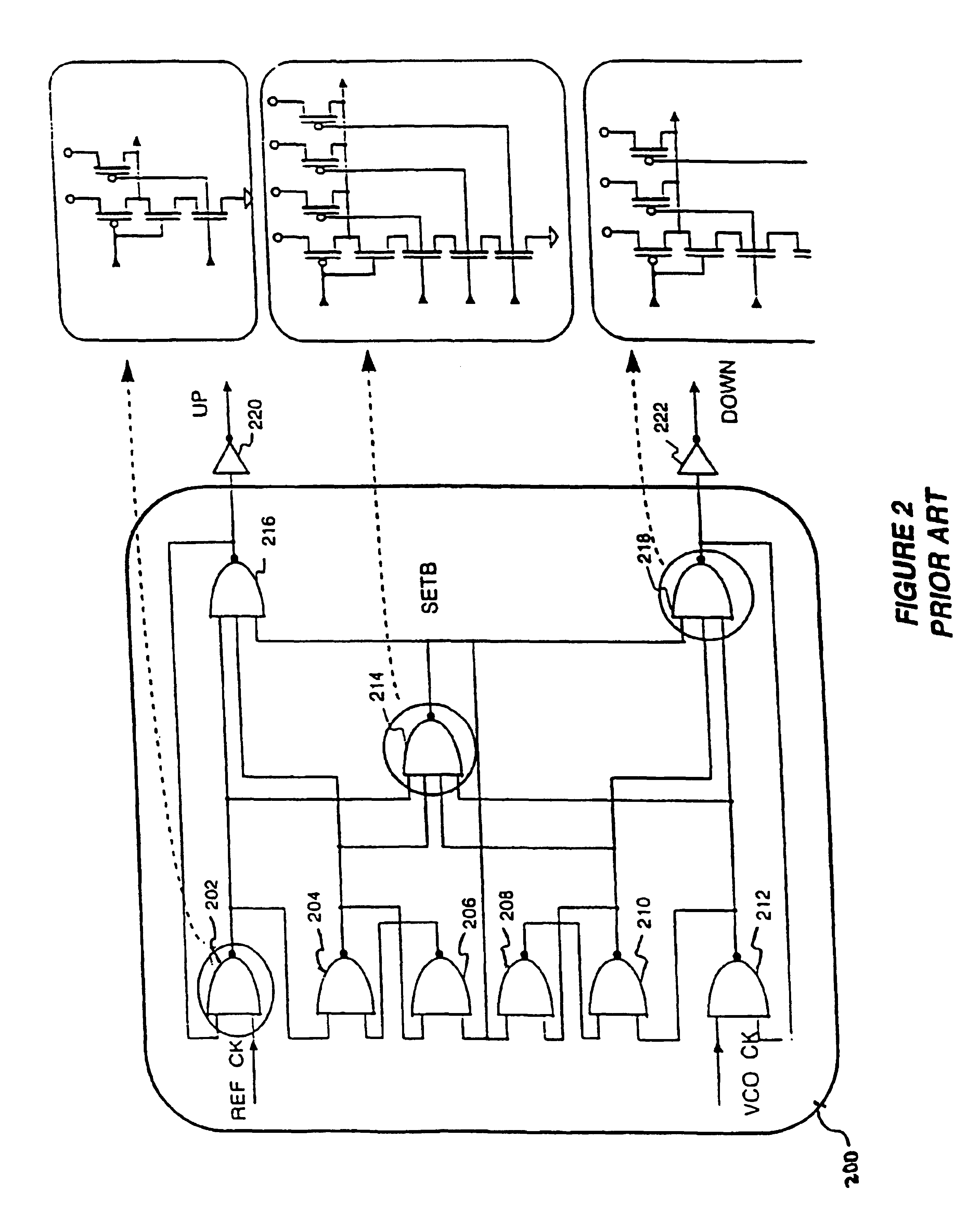

High-speed and high-precision phase locked loop

InactiveUS6930560B2Reduce Propagation DelayImprove accuracyMultiple input and output pulse circuitsPulse automatic controlPhase differencePhase frequency detector

A phase lock loop includes a charge pump, a voltage controlled oscillator (VCO), and a phase frequency detector. The phase frequency detector has a dynamic logic structure. The phase frequency detector generates up and down signals for directing the charge pump to provide a voltage signal to the VCO to vary the frequency of the VCO clock. The difference between the up and down signals is indicative of the phase difference between the reference clock signal and the VCO clock. The phase frequency detector includes up and down signal generators for generating the up and down signals, respectively.

Owner:SUPER INTERCONNECT TECH

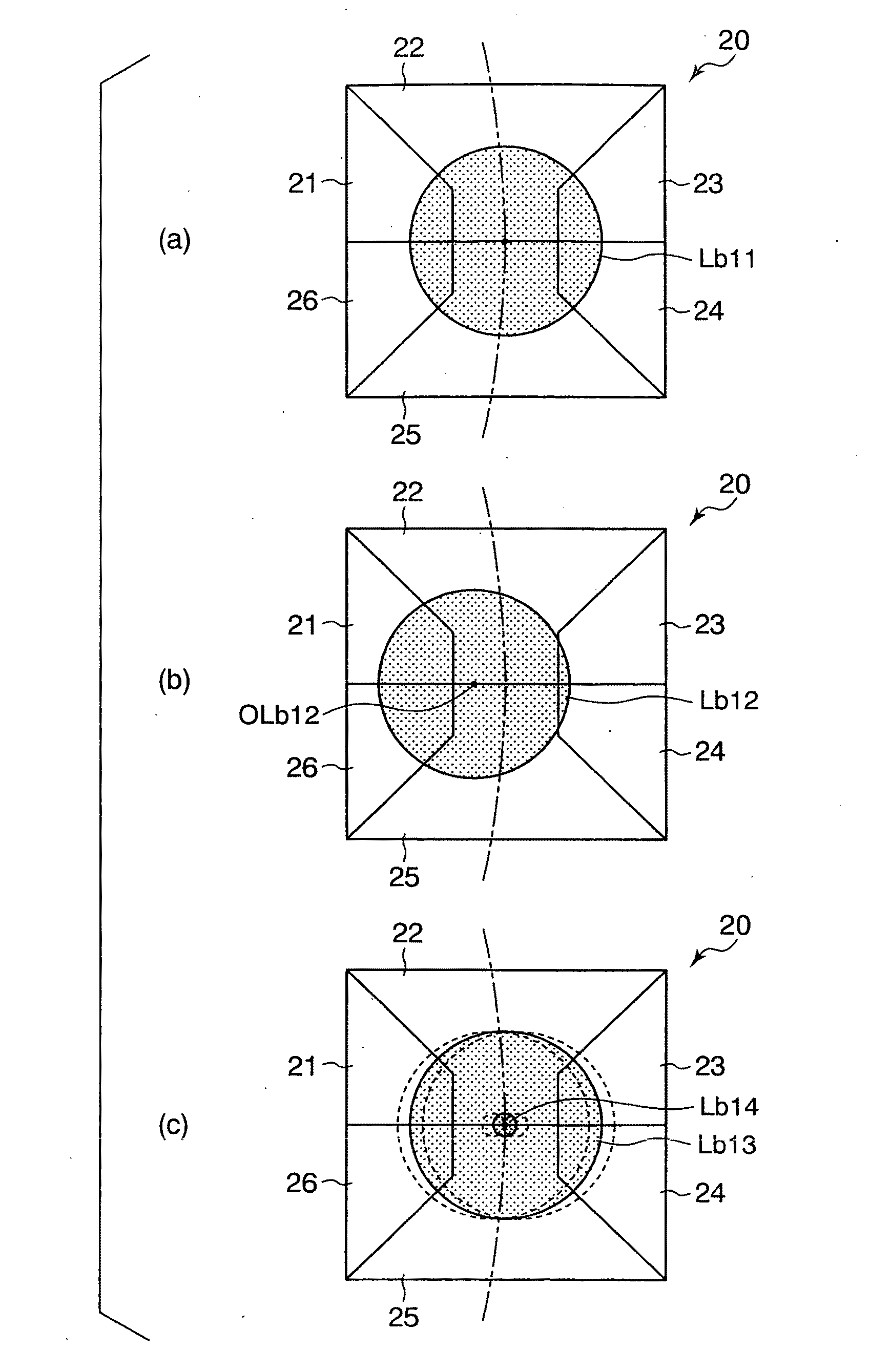

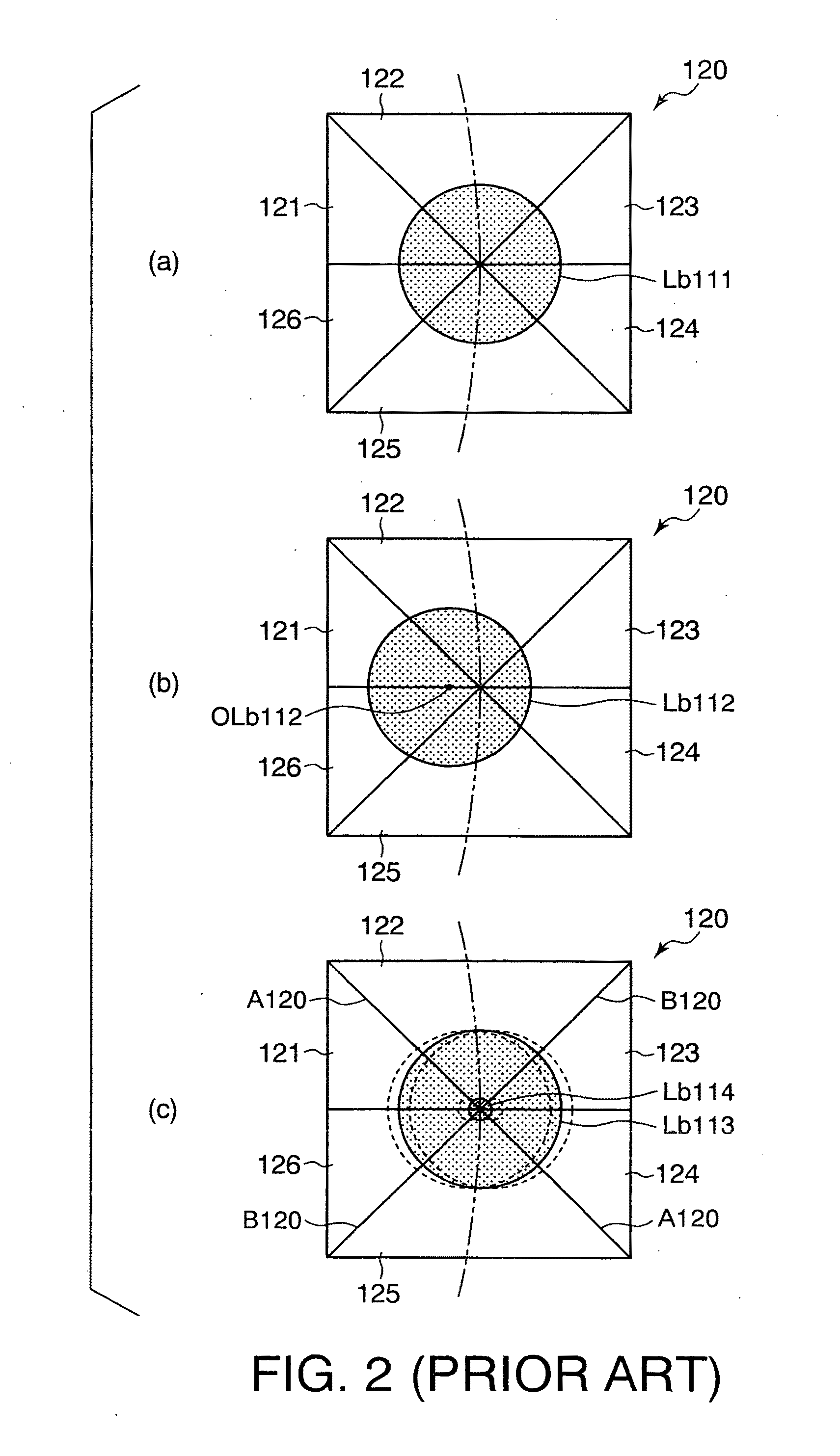

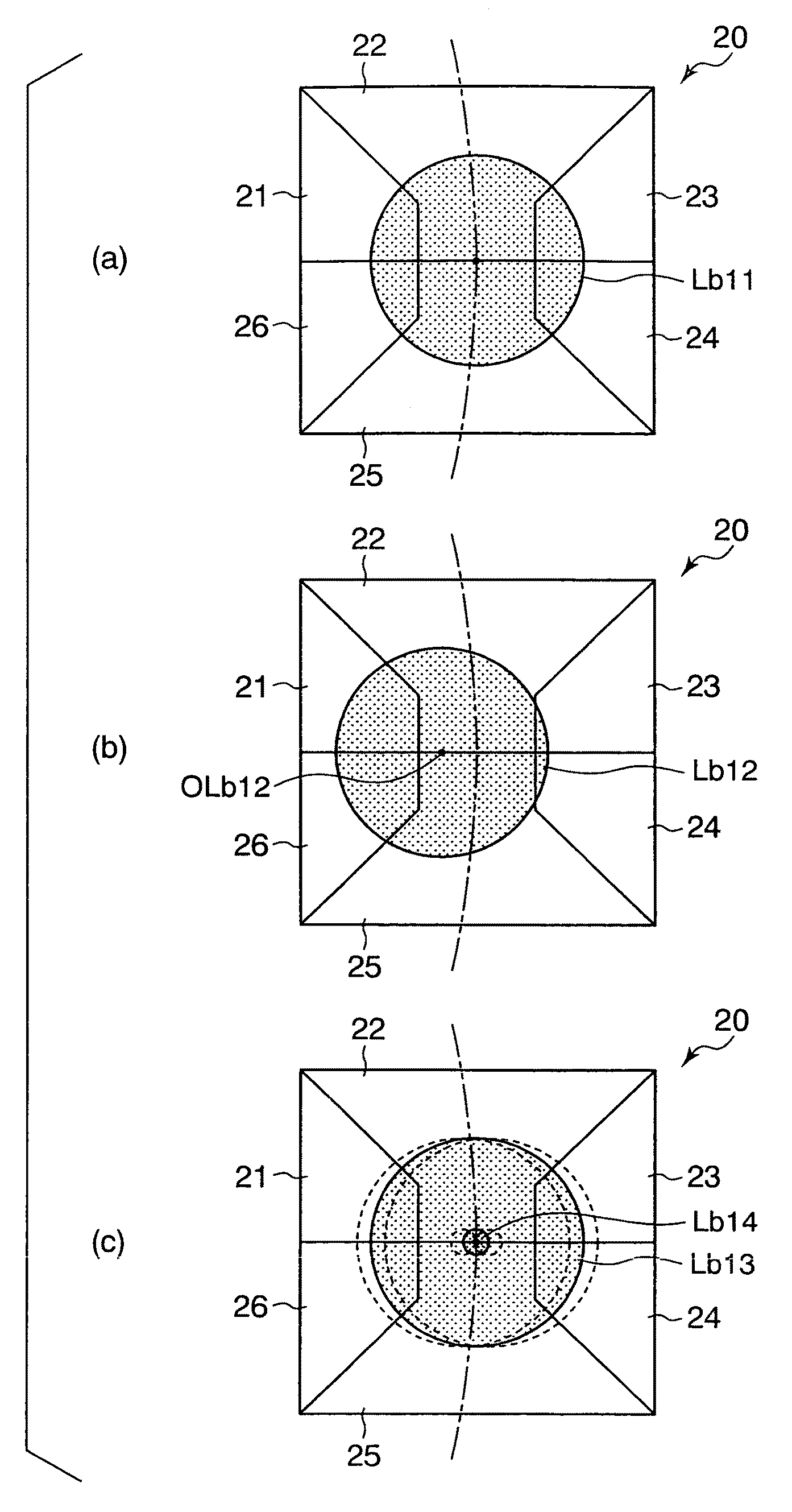

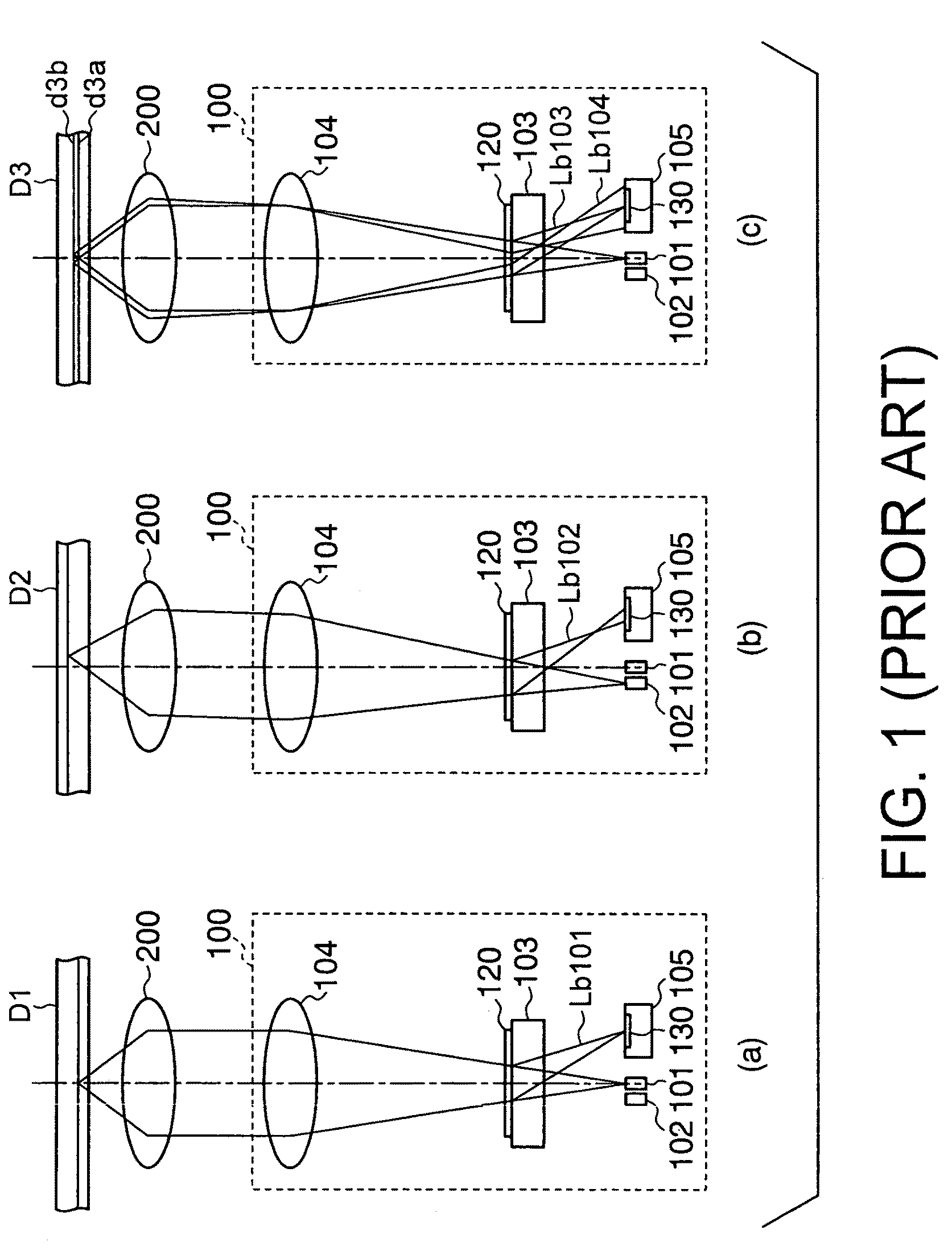

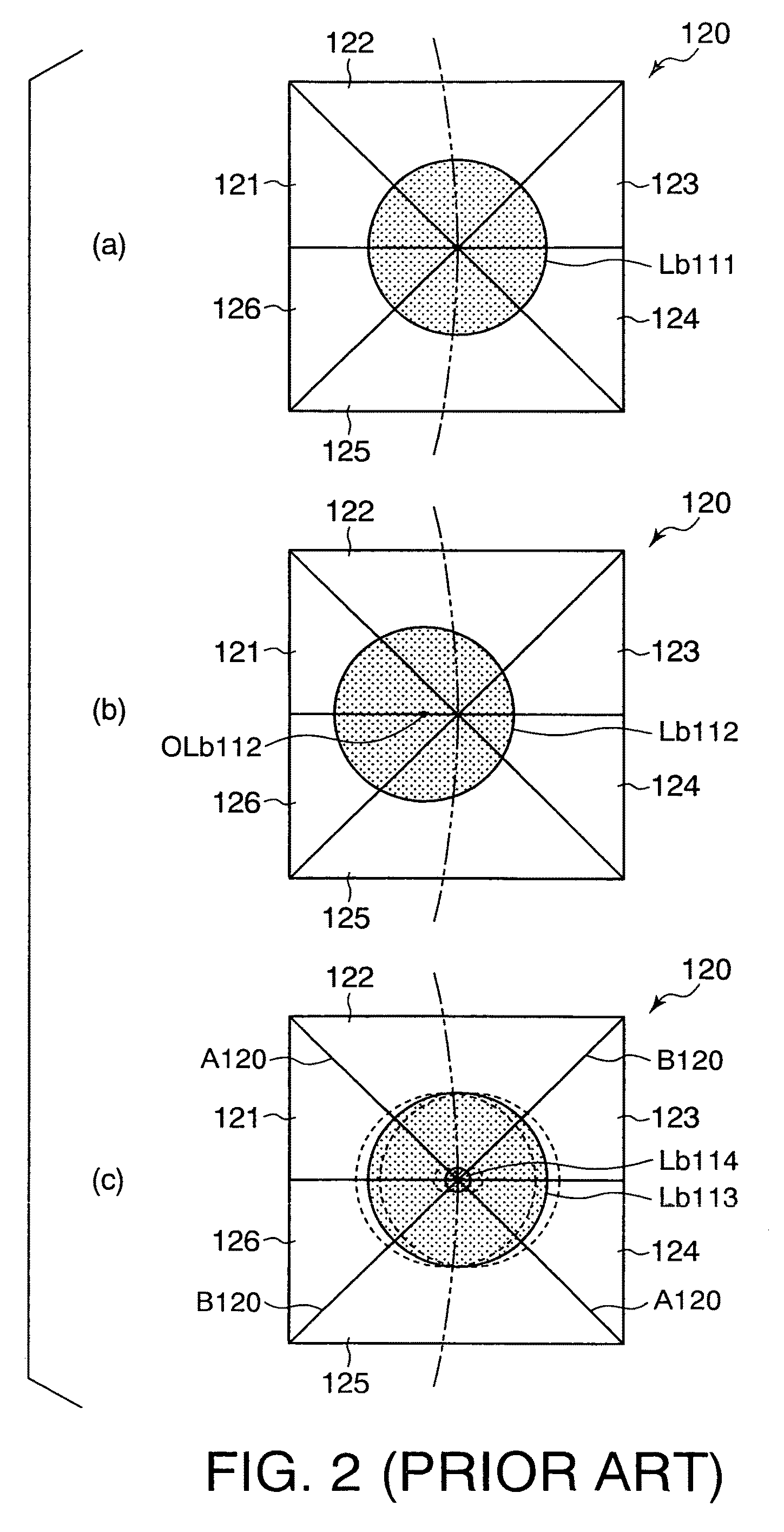

Optical pickup

ActiveUS20100271923A1Constant recording/reproduction performanceHigh sensitivityRecord information storageOptical beam guiding meansOptical pickupAstigmatism

An optical-pickup hologram element has six regions on an x-y plane, divided as follows: the first region with a first line (an x-axis) and a second line that connects points (−xa, 0) and (−xb, yb); the second region with the first and second lines and a third line connecting points (xa, 0) and (xb, yb); the third region with the first and third lines; the fourth region with the first line and a fourth line connecting the point (xa, 0) and a point (xb, −yb); the fifth region with the first and fourth lines and a fifth line connecting the point (−xa, 0) and a point (−xb, −yb); and the sixth region with the first and fifth lines (xa<xb and −xb<−xa). The second and fifth, and the other regions are given astigmatism at different angles to the second line.

Owner:JVC KENWOOD CORP A CORP OF JAPAN

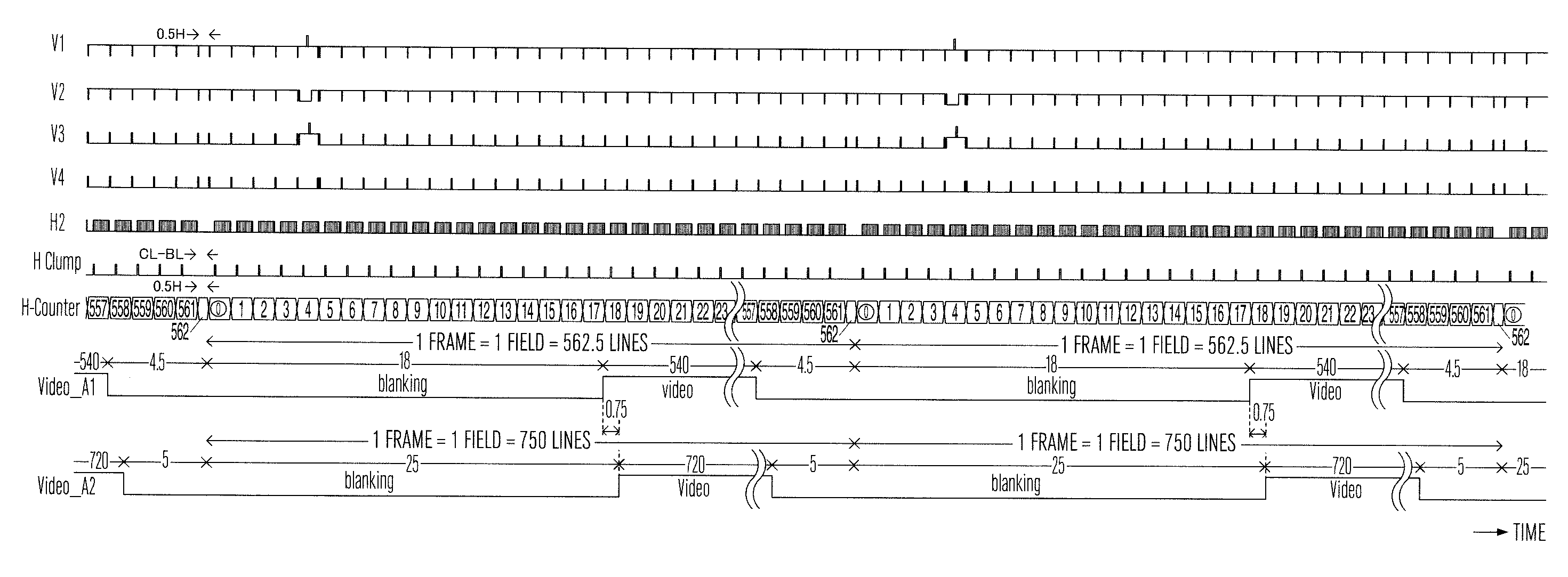

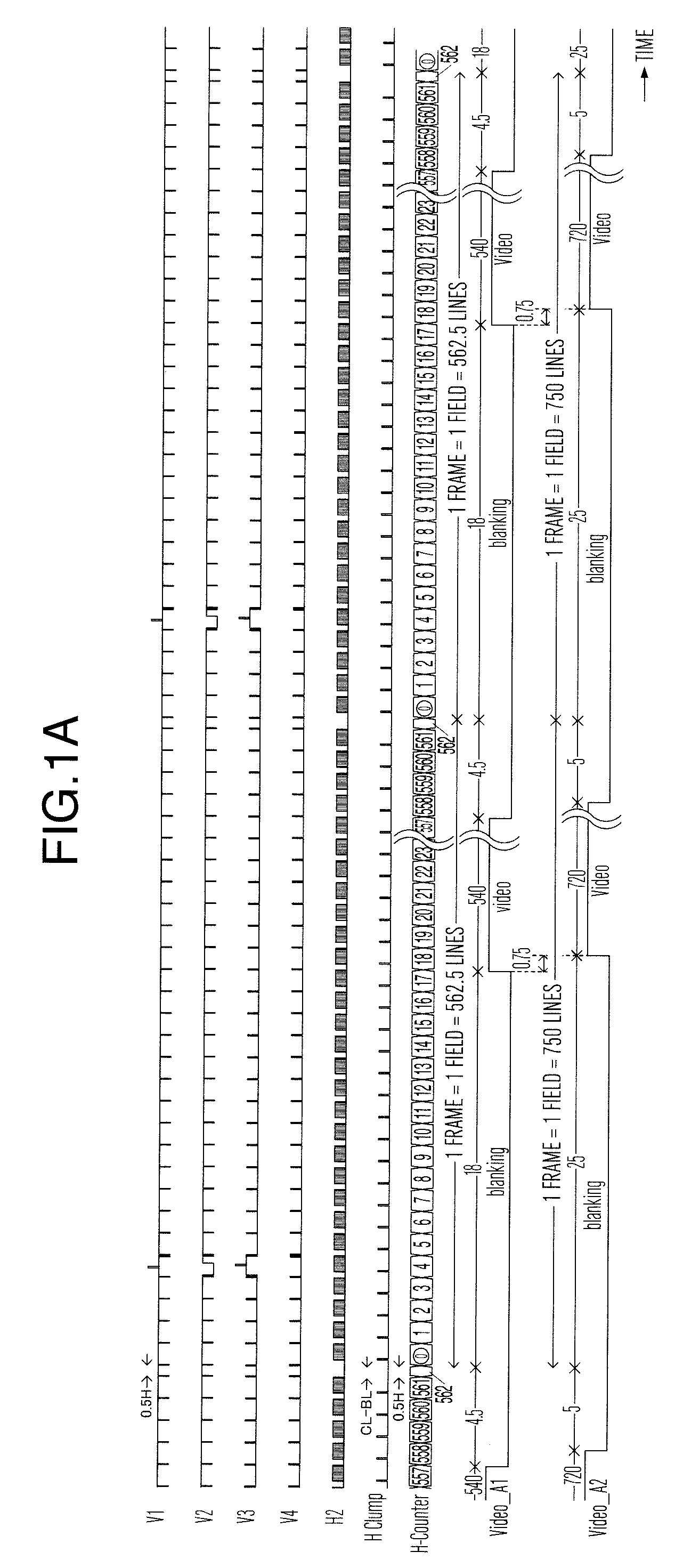

Solid imaging apparatus

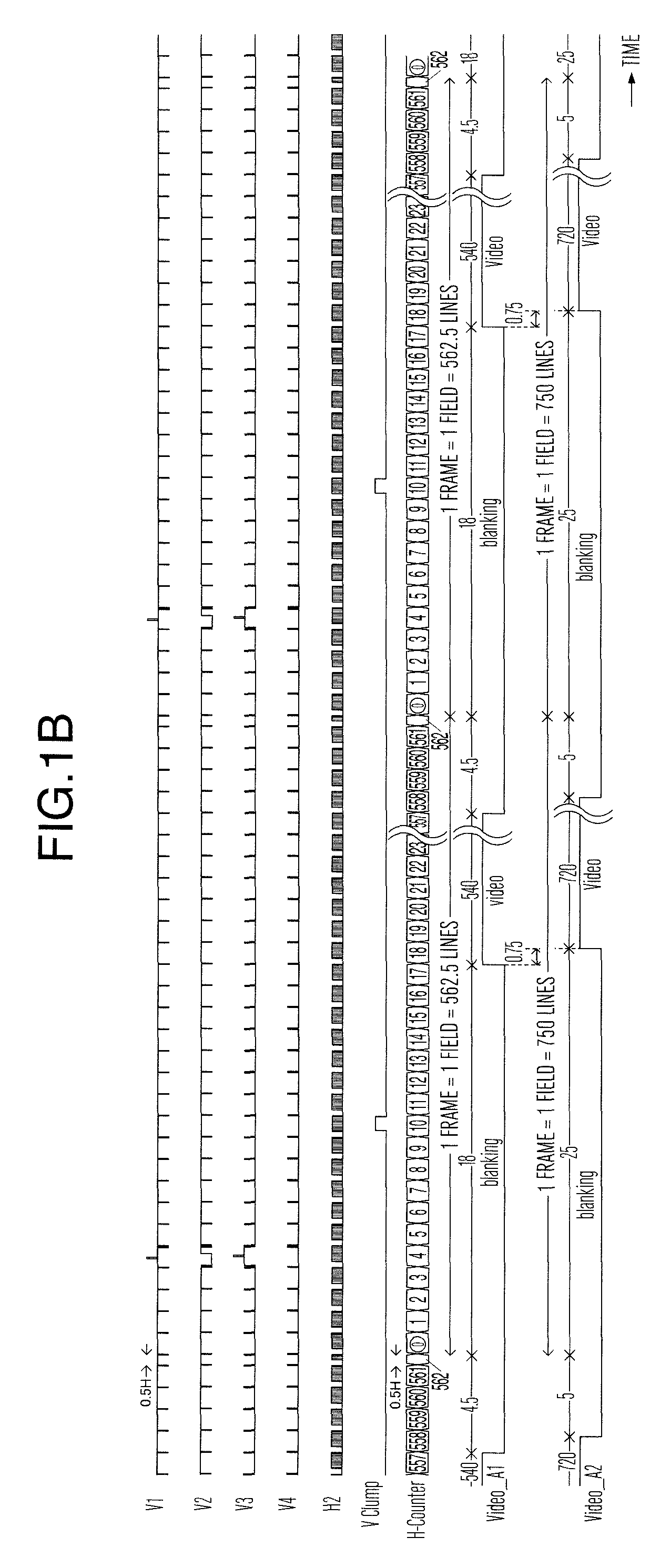

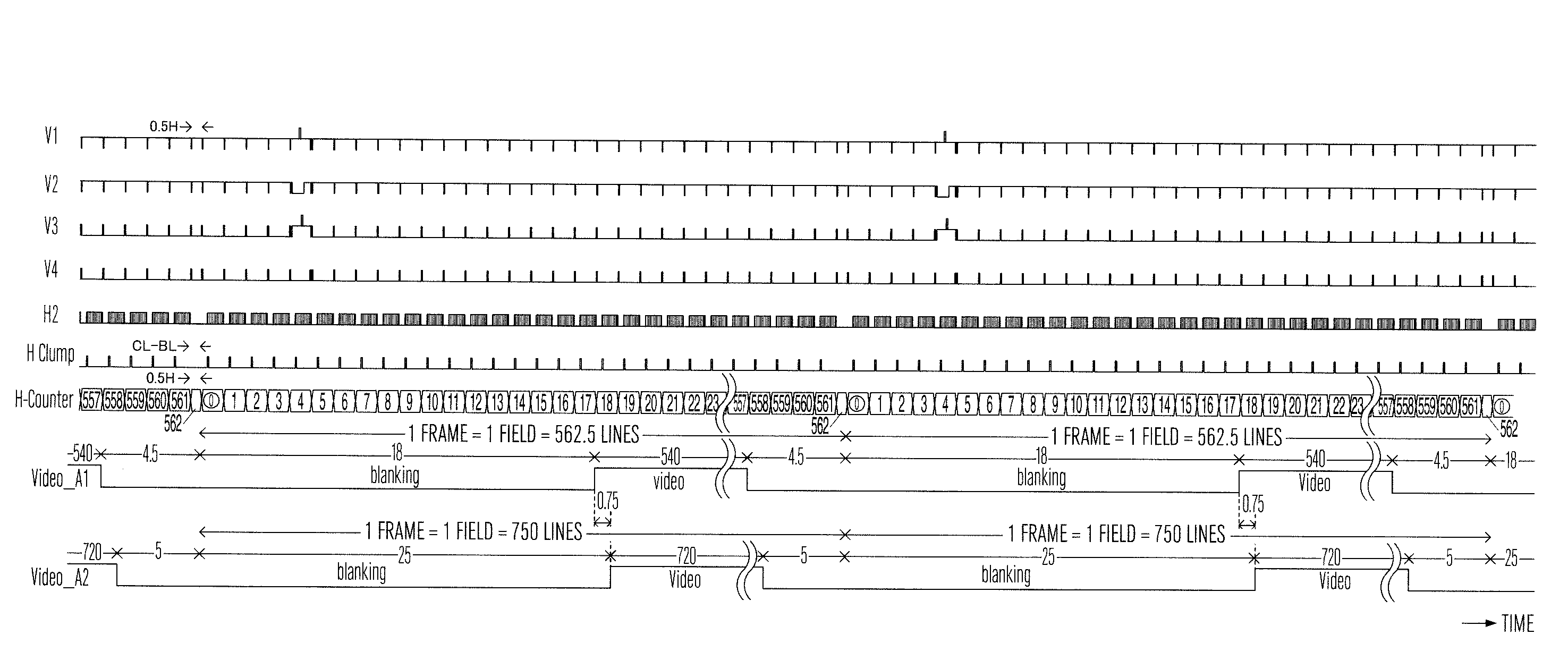

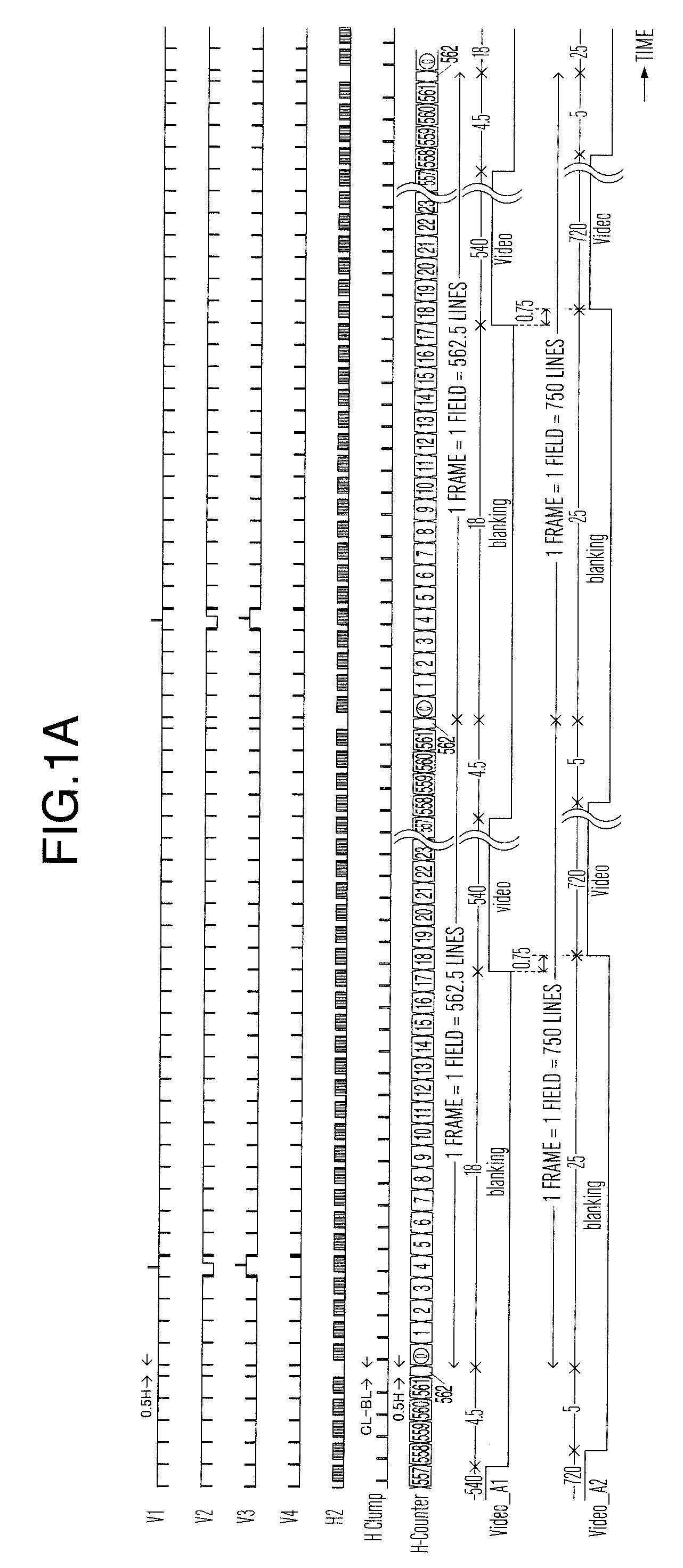

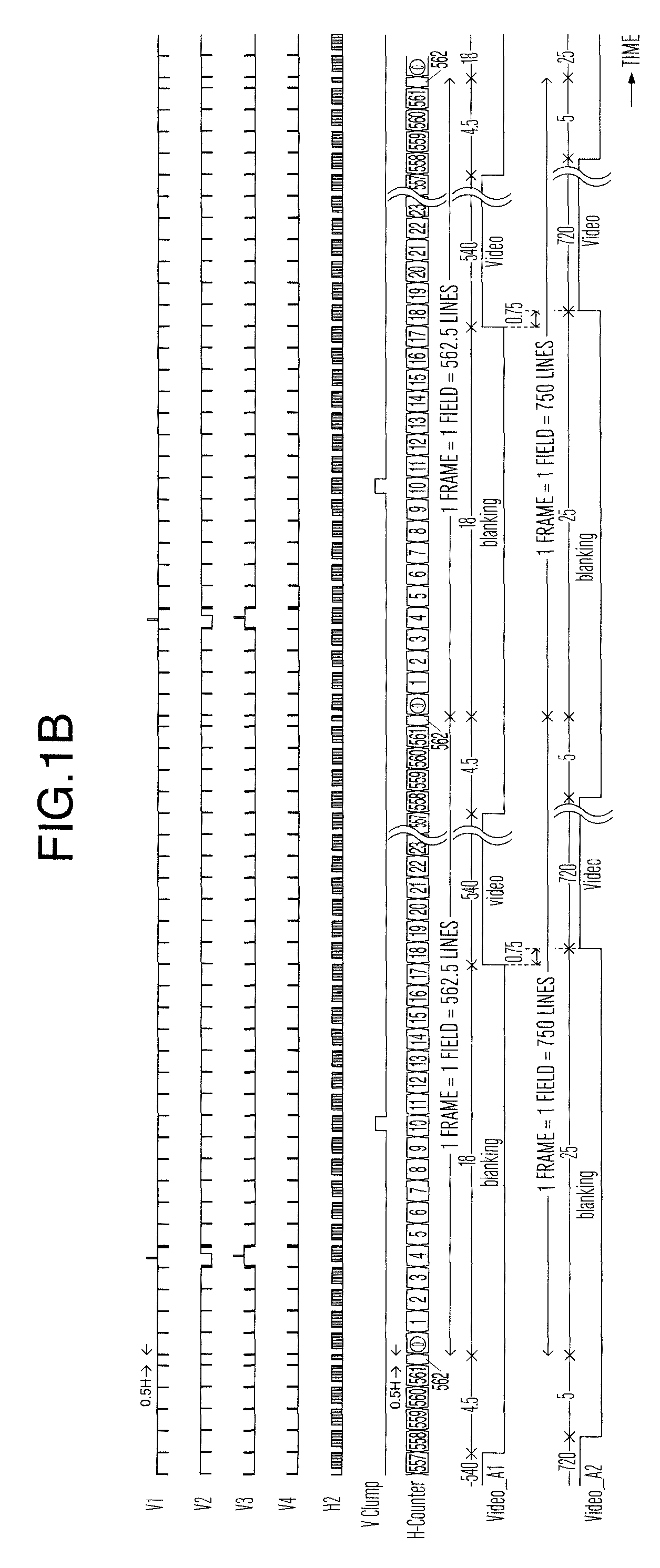

InactiveUS20110261243A1Less jitterTelevision system detailsTelevision system scanning detailsSolid massProgressive scan

In an imaging apparatus which subjects signal electric charges of photodiodes of IT-CCD for interlaced scanning of 1080 effective scanning lines to vertical pixel addition to be read out as image signals, at least one of vertical transfer at the last horizontal period and horizontal transfer at half period in reading of pixels is stopped while fixing pairs of vertical pixels to be subjected to vertical pixel addition to be read out as image signals of progressive scanning of 540 effective scanning lines from the CCD and the read-out image signals of 540 effective scanning lines are subjected to scanning line conversion of 3 to 4 to be converted into image signals of progressive scanning of 720 effective scanning lines, the image signals of progressive scanning of 720 effective scanning lines being outputted.

Owner:KOKUSA ELECTRIC CO LTD

Time Released Caffeine

InactiveUS20160367559A1Increase the length of timeFew or no effectsPill deliveryMicrocapsulesPanicAttention deficits

A pill that increases the availability of caffeine in the bloodstream of a user by delaying release of the drug from the stomach for the treatment of neurological, cognitive, dementia, anxiety, panic, depression, eating, bi-polar, attention deficit disorder, attention deficit hyperactivity disorder, obsessive compulsive disorder, and sleep related disorders. The delay can be enacted by several known means for creating extended release tablets including, polymer based tablets, microencapsulation, and matrix embedding, such that the caffeine is administered to a patient in an effective amount in a time released pill form. This requires fewer administrations of the drug while creating a smoother user experience as the build up and removal of the drug in the body is more gradual.

Owner:BROCKMAN RICHARD

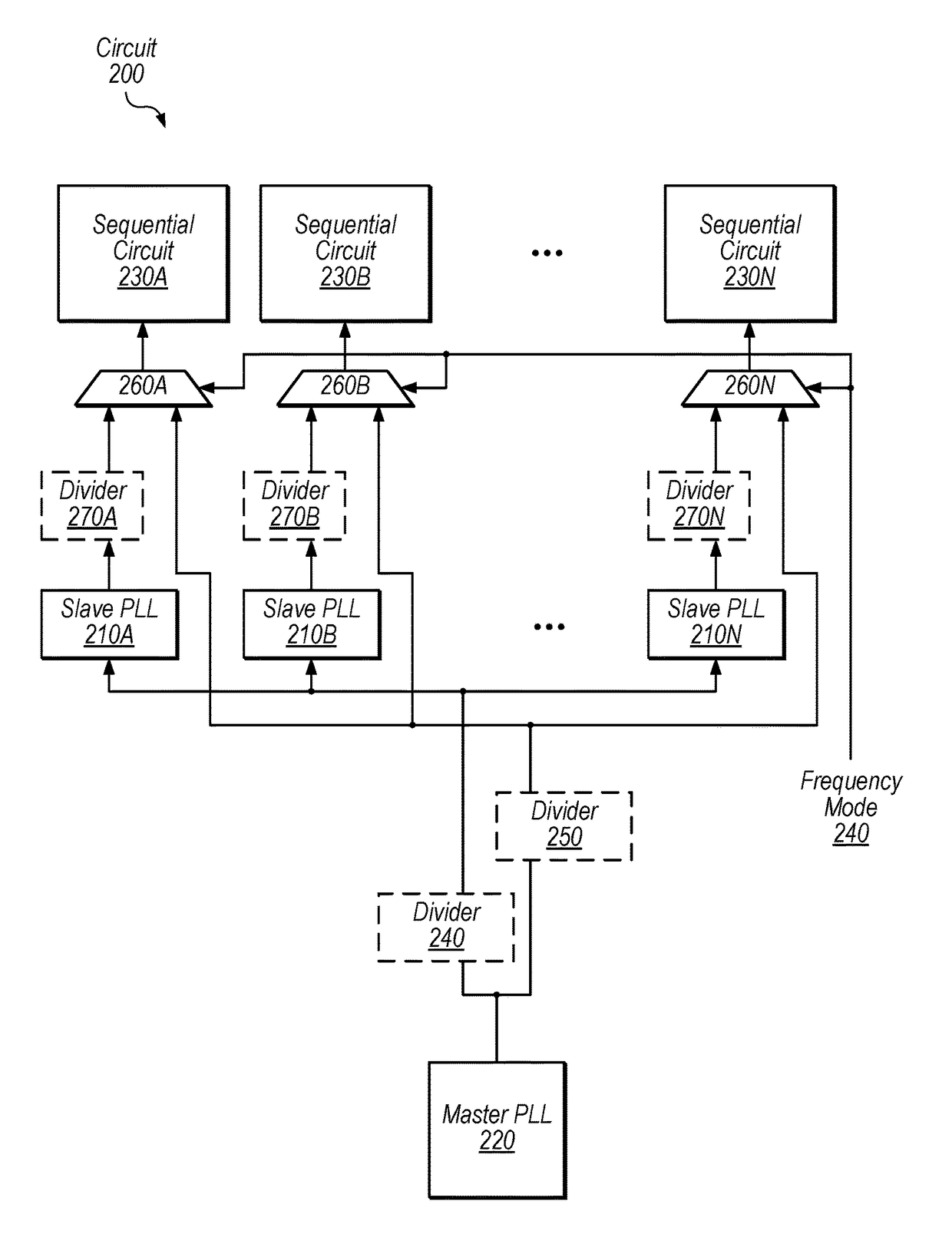

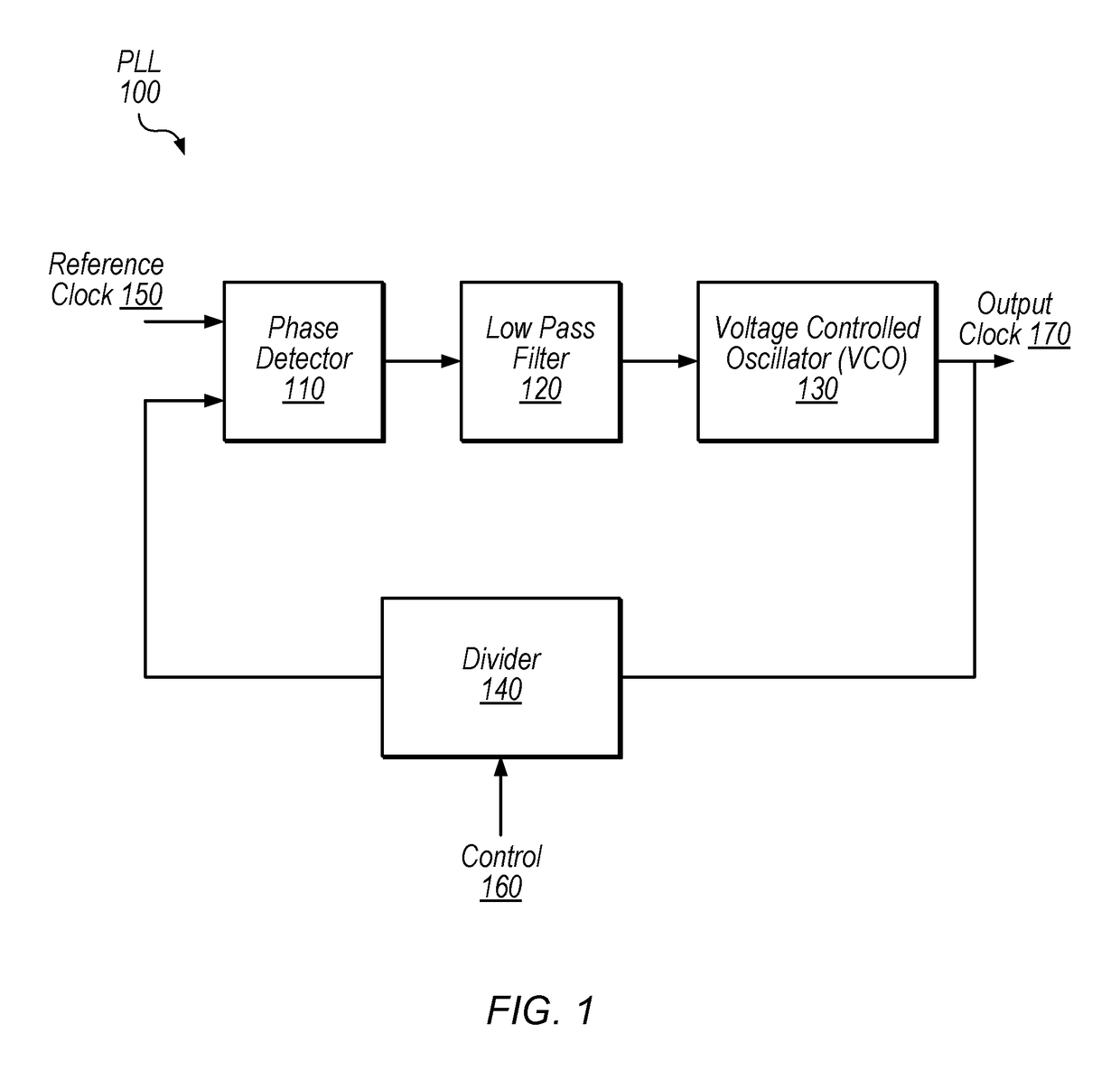

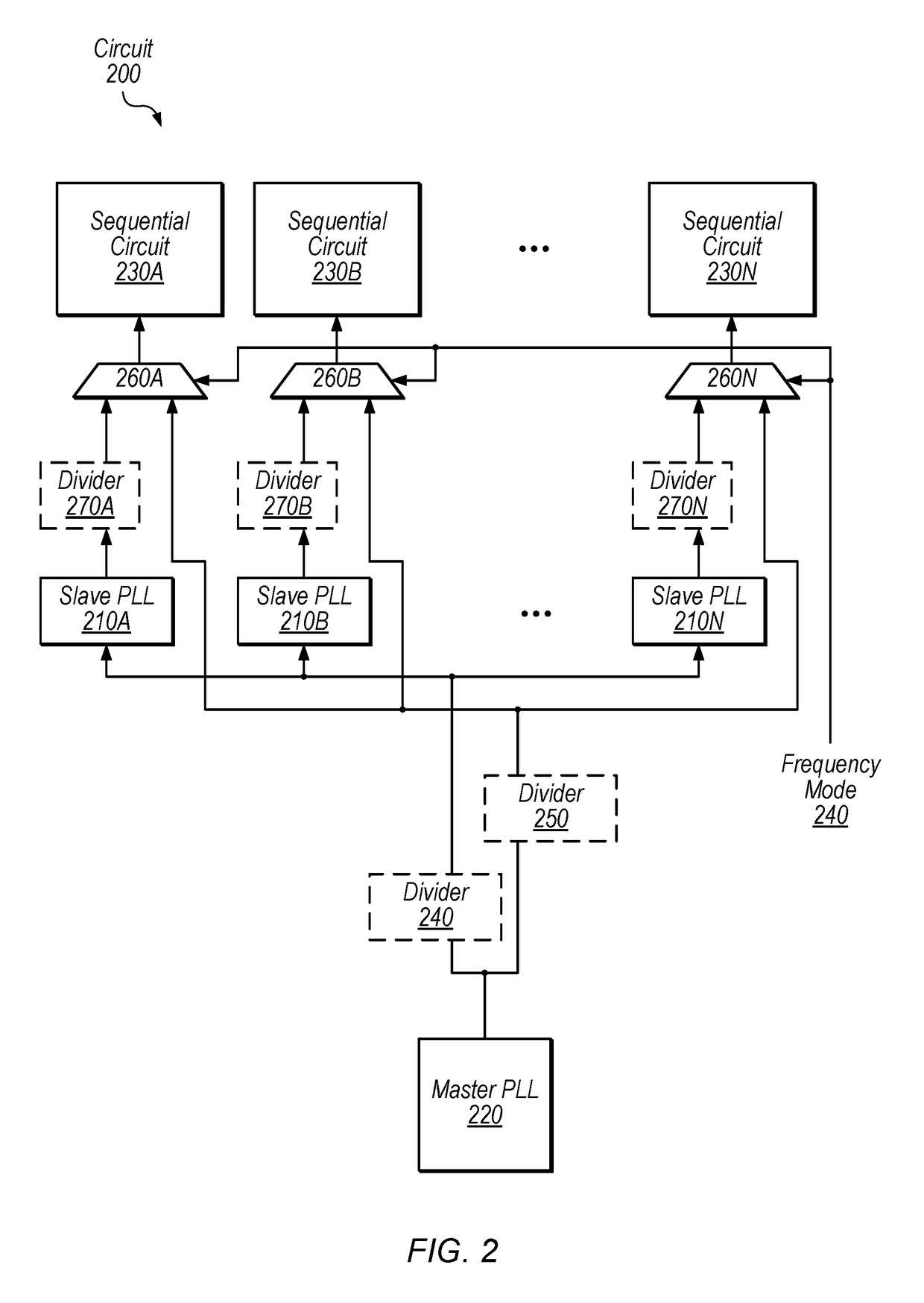

Hierarchical feedback-controlled oscillator techniques

ActiveUS9698797B1Less jitterReduce power consumptionPulse automatic controlPhase-locked loopEngineering

Techniques are disclosed relating to feedback-controlled oscillators (e.g., phase-locked loops) arranged in two or more levels. In some embodiments, in a relatively higher-frequency mode, a first level feedback-controlled oscillator provides reference signals to one or more second level feedback-controlled oscillators that in turn generate output clock signals to clock sequential circuitry. In some embodiments, in a relatively lower-frequency mode, the first level feedback-controlled oscillator bypasses the second level feedback-controlled oscillators and provides output clock signals directly to sequential circuitry (without using any intervening feedback-controlled oscillators).

Owner:ALLLE INC

Timing generator and test device

There is provided a timing generator for generating a timing signal based on a given reference clock, having a delaying circuit section for outputting each pulse of the reference clock by delaying by a value of delay given per each of the pulse and a pulse selecting and outputting section for passing and outputting only pulses to be outputted as the timing signal among the pulses outputted out of the delaying circuit section.

Owner:ADVANTEST CORP

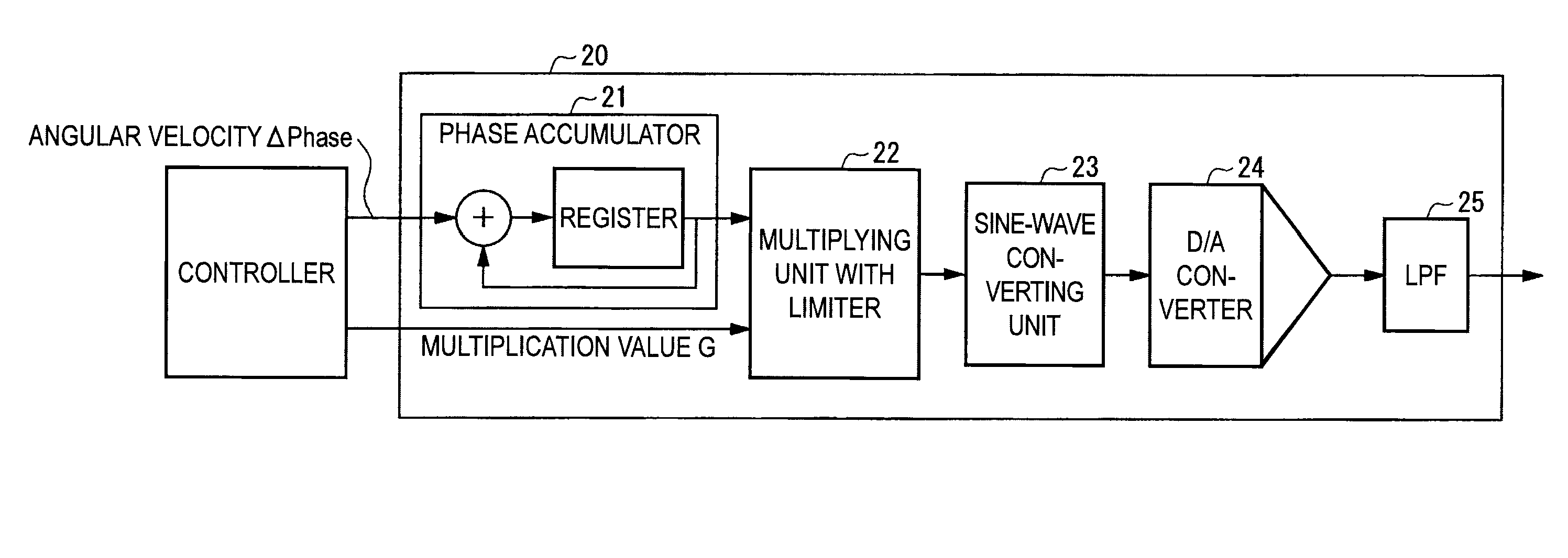

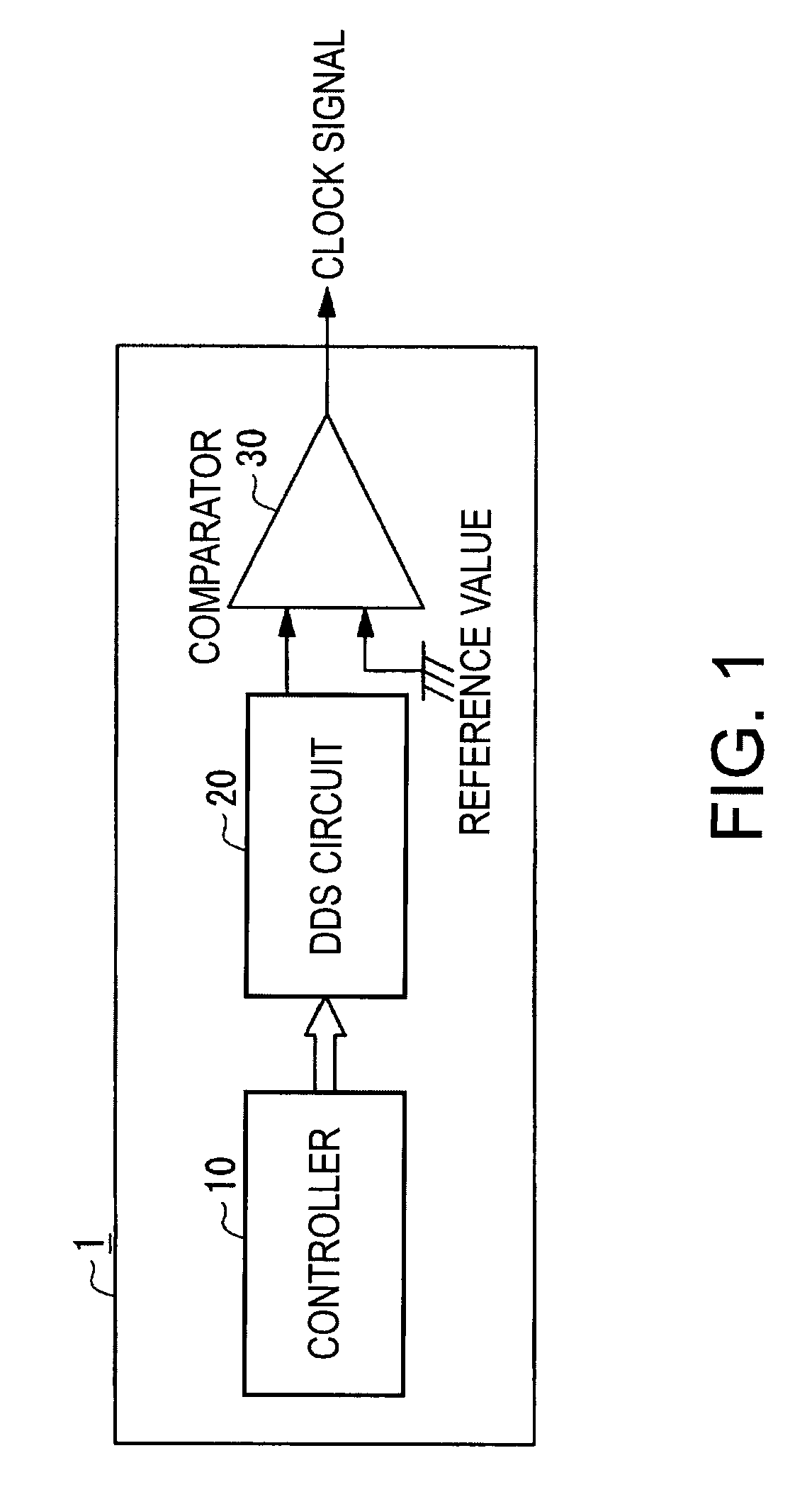

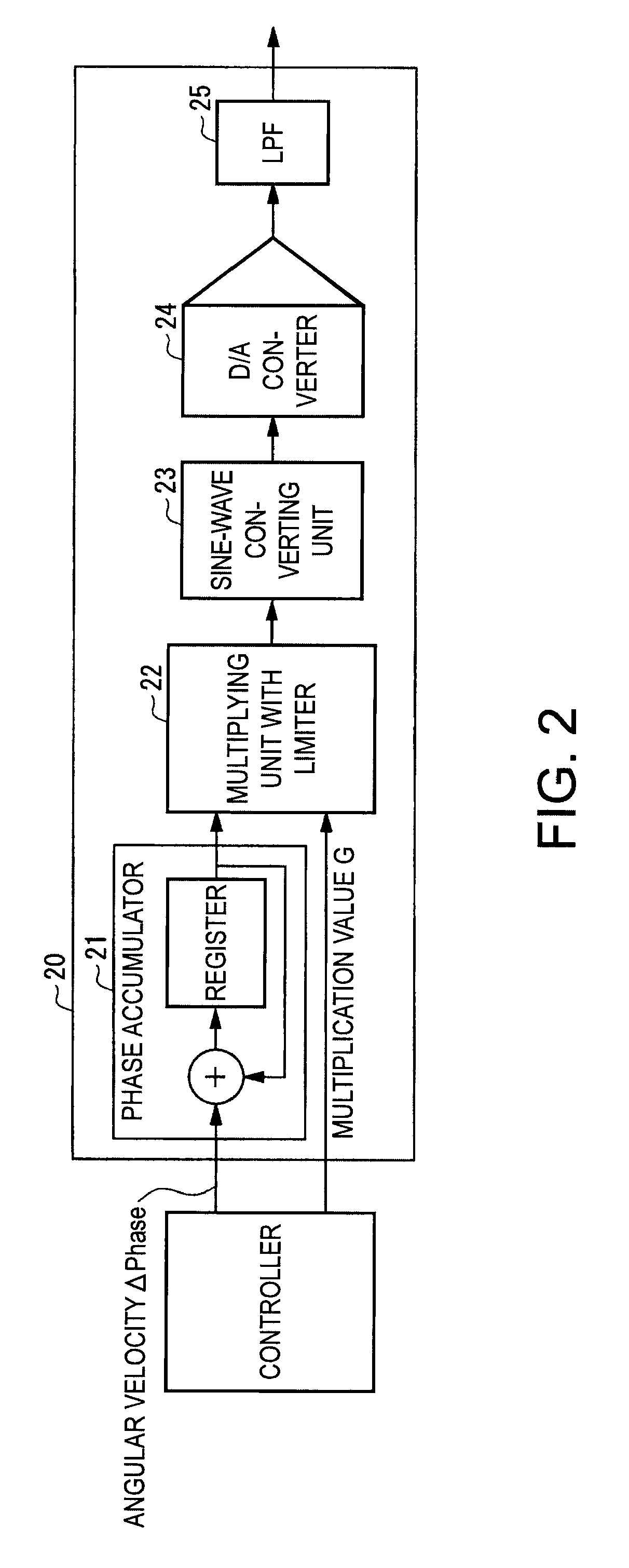

Clock generating device and jitter reducing method in the clock generating device

ActiveUS8339160B2Less jitterTransmission monitoringGenerating/distributing signalsComputer scienceComparator

A clock generating device includes: a DDS circuit that generates a periodic signal; and a comparator that compares an input signal and a reference signal and outputs a binary signal. The clock generating device includes a rate-of-change correcting unit that applies correction for increasing a rate of change at a crossing point with the reference signal to the periodic signal generated by the DDS circuit.

Owner:SEIKO EPSON CORP

PLL controller applying a multiplier coefficient appropriate for a phase error, and a method therefor

ActiveUS7894705B2Less jitterControl changesTelevision system detailsPulse automatic controlControl signalVideo image

A PLL controller for controlling the tracking rate of a phase-locked loop (PLL), in particular, controlling coefficients to be input to a device such as a multiplier of the phase-locked loop. A PLL controller receives a phase error between a horizontal sync signal in a video signal and a reference signal. Then an error amount detector measures the phase error using the N thresholds to output a control signal indicating any of N+1 levels. A coefficient selector outputs one of the N+1 gains as a coefficient signal, the one gain corresponding to the level indicated by the control signal, so that the tracking rate of the phase-locked loop is controlled in response to the input video signal, and thus a high-quality video image with less jitter can be provided.

Owner:LAPIS SEMICON CO LTD

Spread spectrum clock generation circuit and a method of controlling thereof

ActiveUS20060176932A1Less jitterReduction in electromagnetic interference emissionPulse automatic controlTransmissionControl circuitCapacitor

A spread spectrum clock generation circuit and a controlling method thereof are disclosed, which provide clocks having less jitter and ideal spread spectrum and enable a reduction in circuit scale and in power consumption. To this end, a current control type modulator 19a is equipped with a current source Ia (current 4i). A charger unit CGa and a discharger unit DGa are designed such that currents i, 2i and 4i are allowed to flow, for example, by properly setting the sizes of transistors. Modulation cycles CIa to CIIIa are repeated and an output code is generated from a switching control circuit 20a according to each modulation cycle. A switching unit SSa is controlled according to the output code, thereby charging or discharging a capacitor element C1 with a charge / discharge current CDI corresponding to the output code. Hence, charge amounts and discharge amounts for all the modulation cycles CIa to CIIIa have the same value, i.e., 6i [A·clock].

Owner:CYPRESS SEMICON CORP

Video format conversion without a flicker for the solid imaging apparatus

InactiveUS8605186B2Less jitterTelevision system detailsTelevision system scanning detailsInterlaced videoProgressive scan

Owner:KOKUSA ELECTRIC CO LTD

Optical pickup

ActiveUS8072867B2Constant recording/reproduction performanceHigh sensitivityRecord information storageOptical beam guiding meansOptical pickupAstigmatism

An optical-pickup hologram element has six regions on an x-y plane, divided as follows: the first region with a first line (an x-axis) and a second line that connects points (−xa, 0) and (−xb, yb); the second region with the first and second lines and a third line connecting points (xa, 0) and (xb, yb); the third region with the first and third lines; the fourth region with the first line and a fourth line connecting the point (xa, 0) and a point (xb, −yb); the fifth region with the first and fourth lines and a fifth line connecting the point (−xa, 0) and a point (−xb, −yb); and the sixth region with the first and fifth lines (xa<xb and −xb<−xa). The second and fifth, and the other regions are given astigmatism at different angles to the second line.

Owner:JVC KENWOOD CORP