Patents

Literature

46results about How to "Reduce propagation delay" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

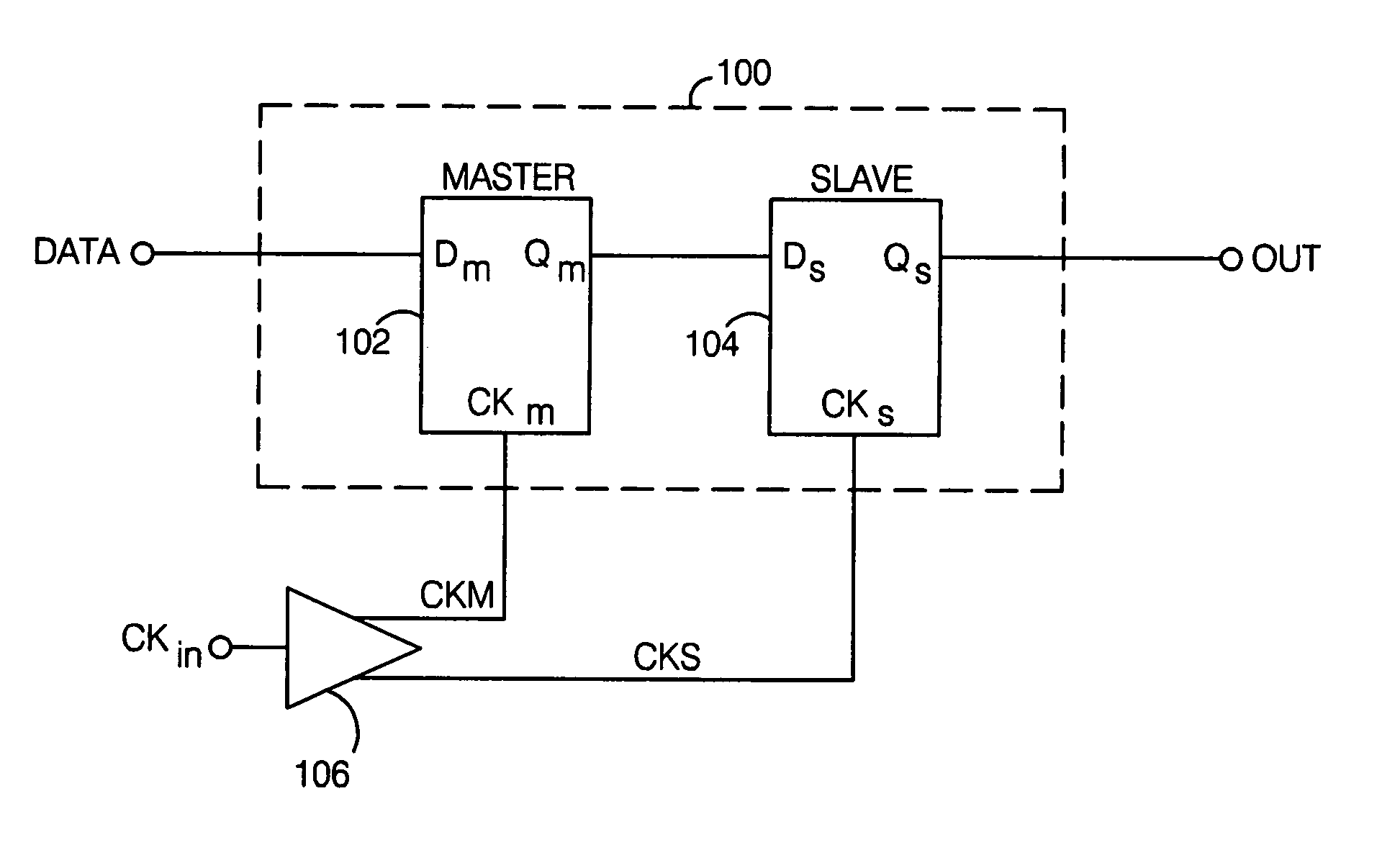

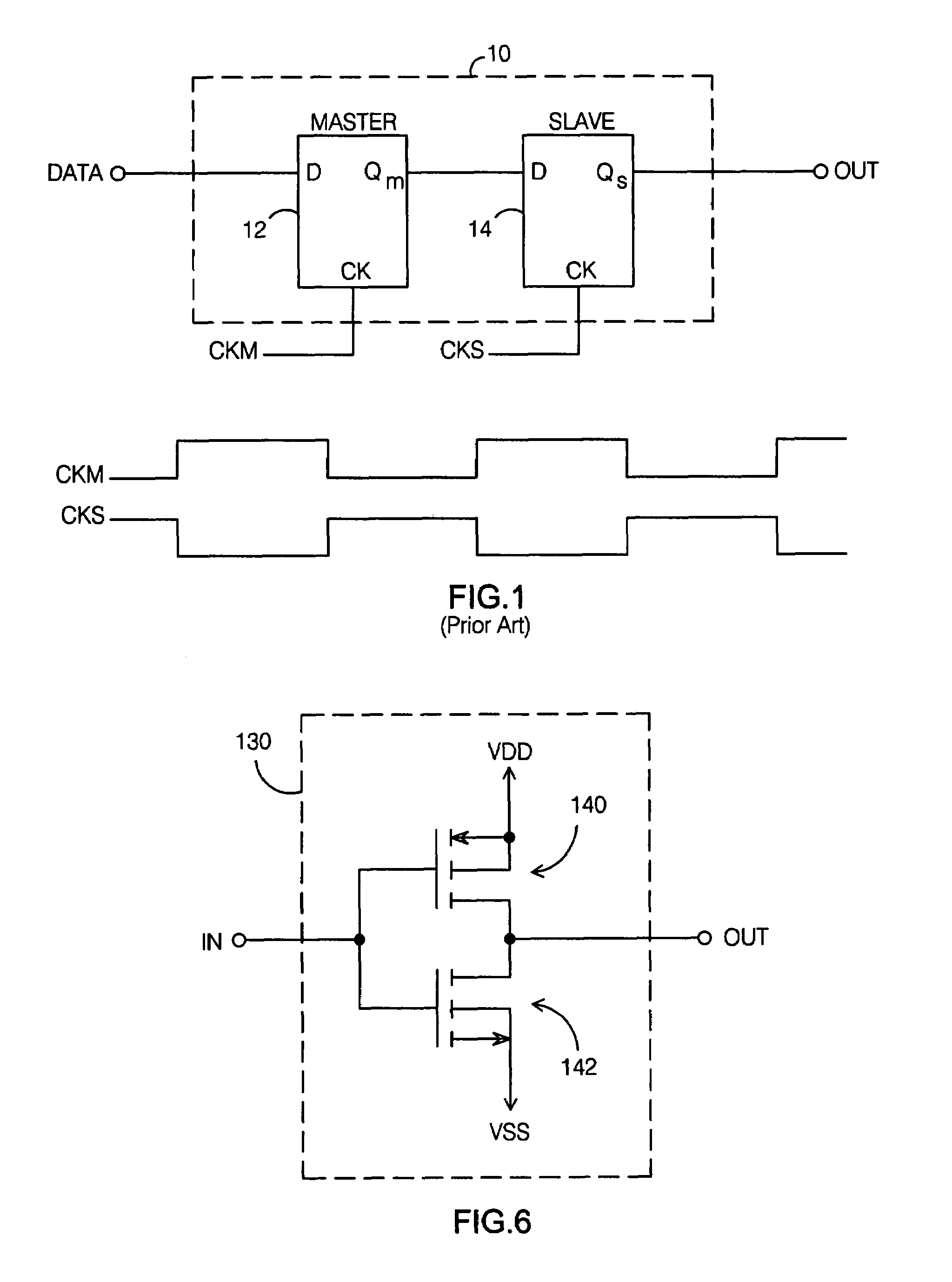

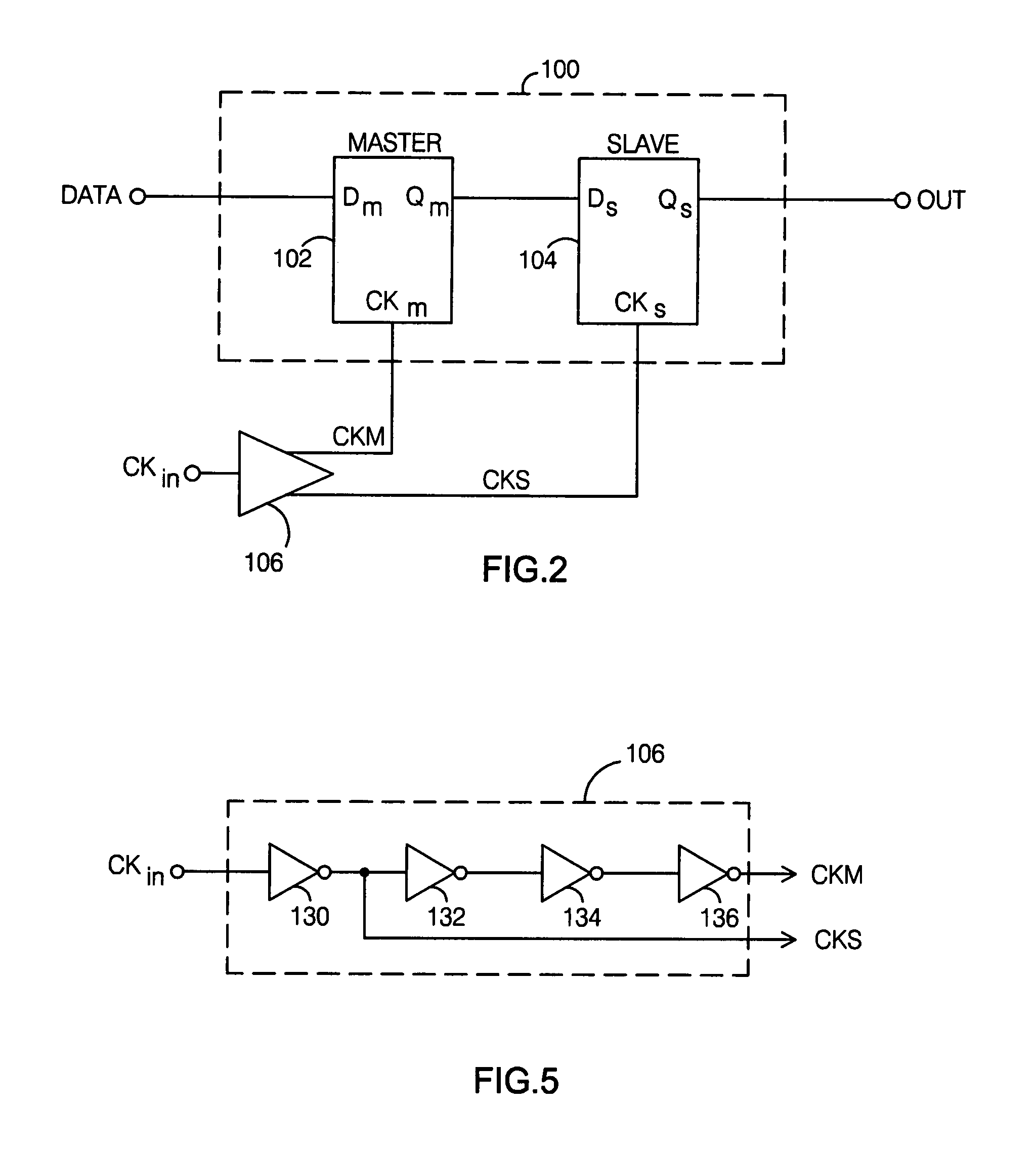

Master-slave flip-flop and clocking scheme

ActiveUS7408393B1Improve performanceReduce propagation delayElectric pulse generatorPulse manipulationData inputClock signal

A master-slave flip-flop comprises master and slave latches, with the data output of the master latch connected to the data input of the slave latch. The latches receive clock signals CKM and CKS at their respective clock inputs; each latch is transparent when its clock signal is in a first state and latches a signal applied to its input when its clock signal is in a second state. A clock buffer receives an input clock CKin and generates nominally complementary clock signals CKM and CKS such that one latch is latched while the other is transparent. The clock buffer is arranged to skew CKS with respect to CKM such that the slave latch is made transparent earlier than it would without the skew, making the minimum delay (tpd) between the toggling of CKin and a resulting change at the slave latch's output less than it would otherwise be.

Owner:MARVELL ASIA PTE LTD

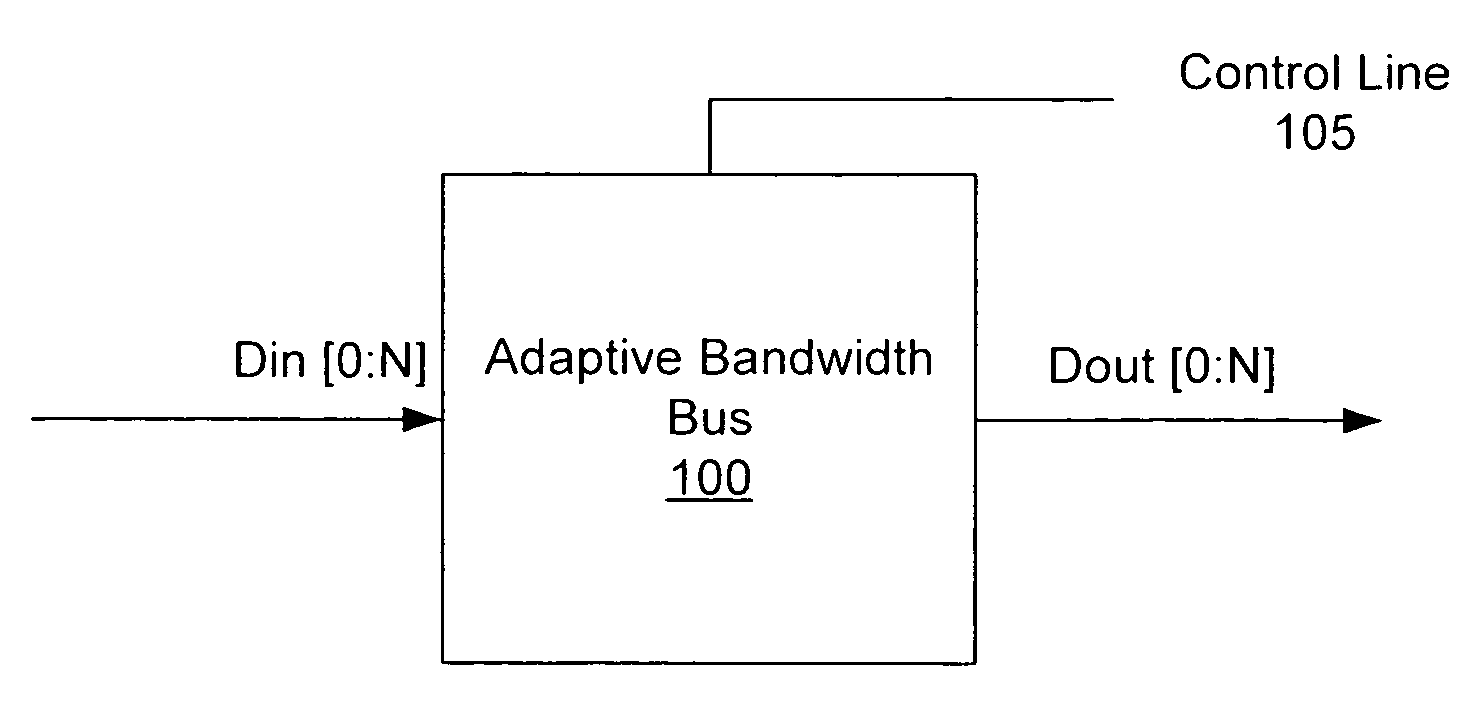

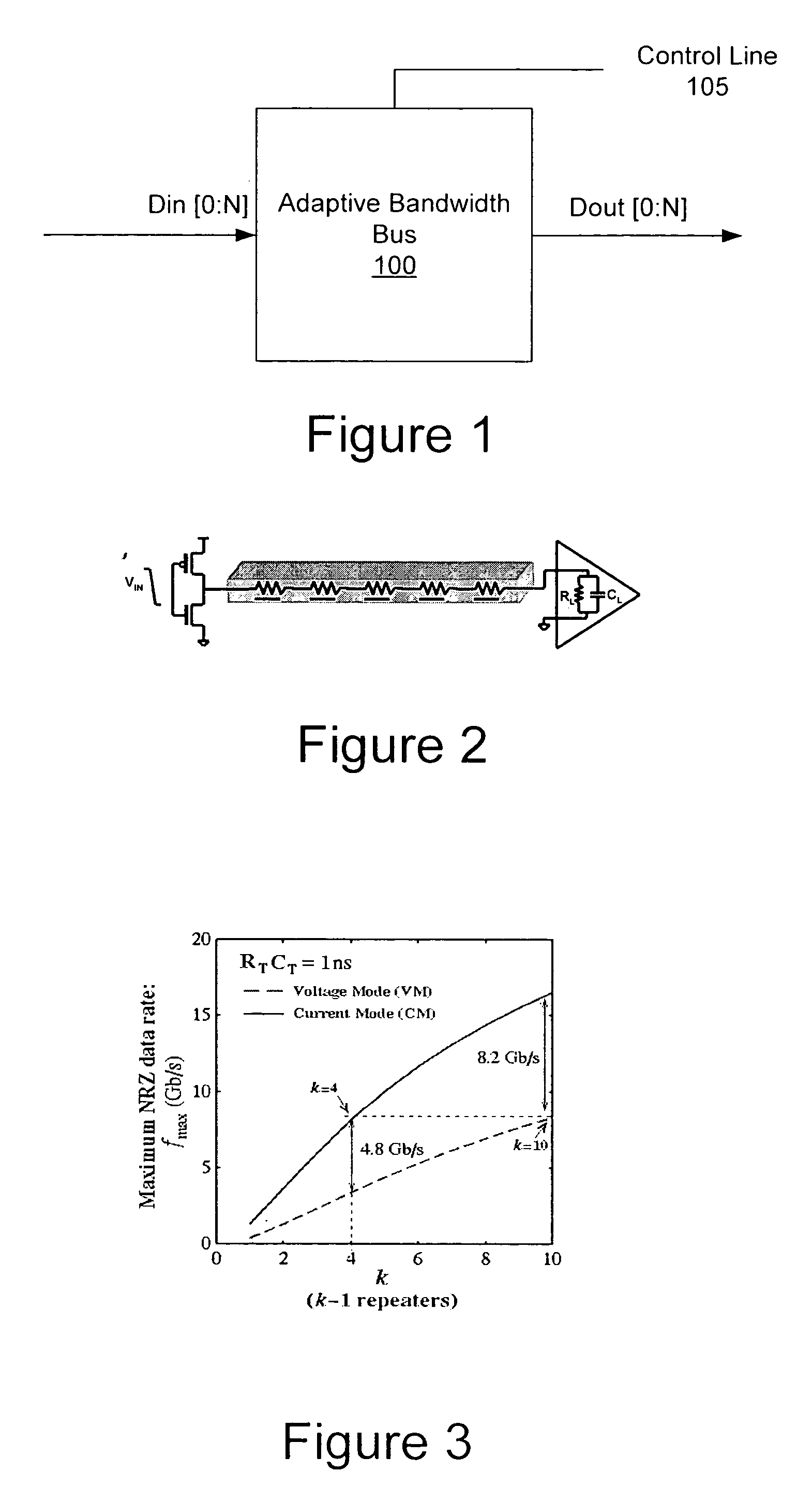

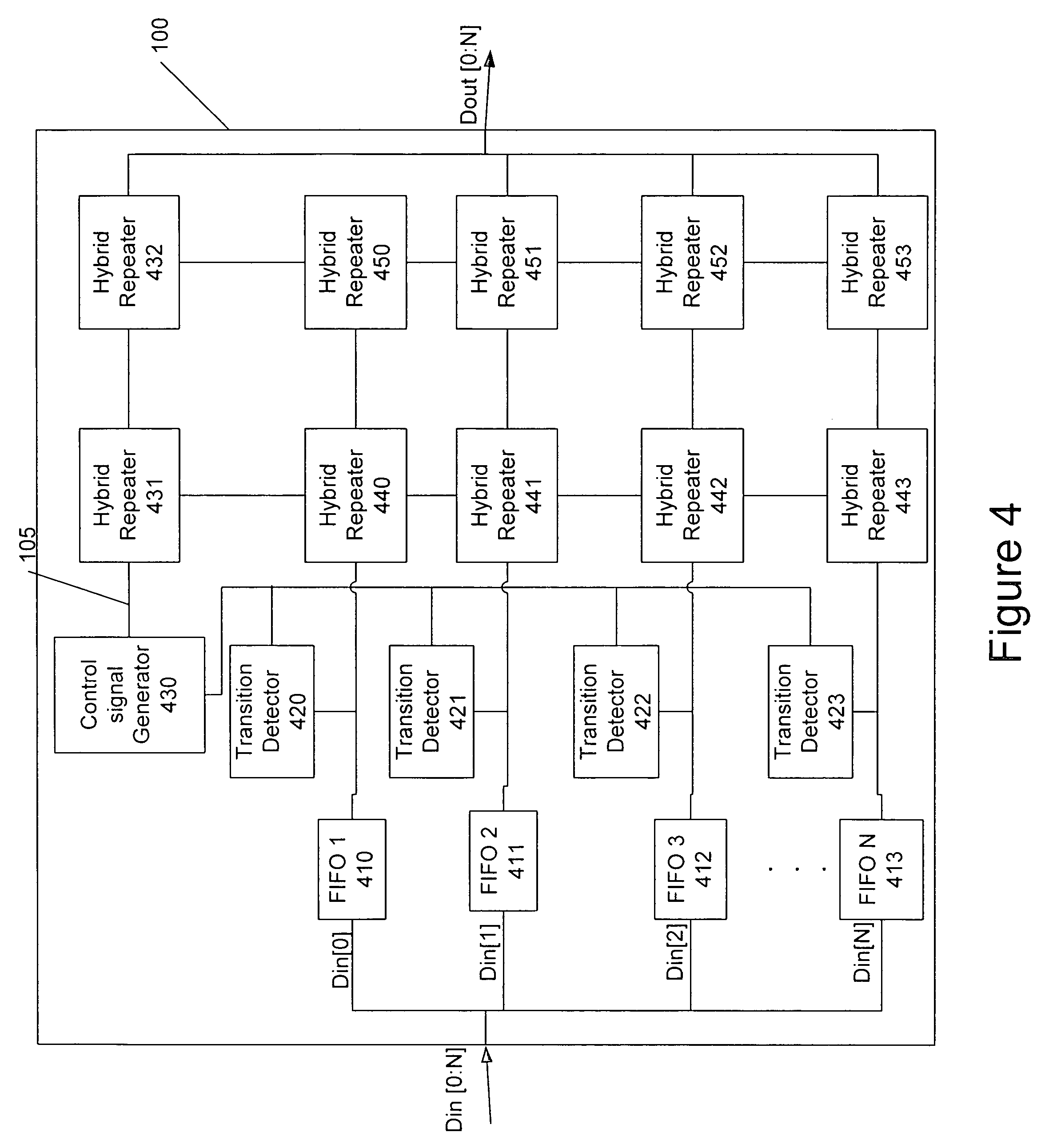

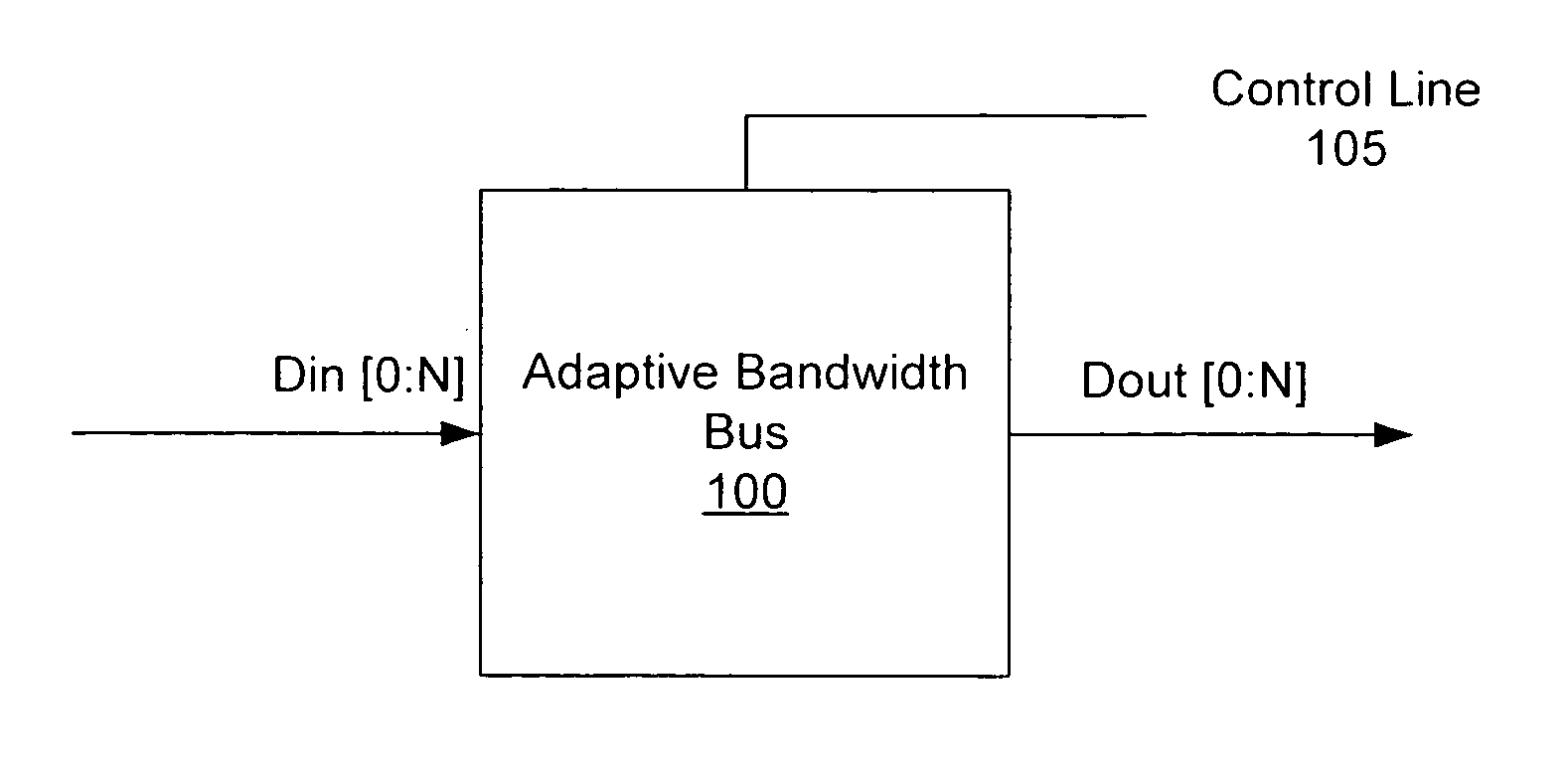

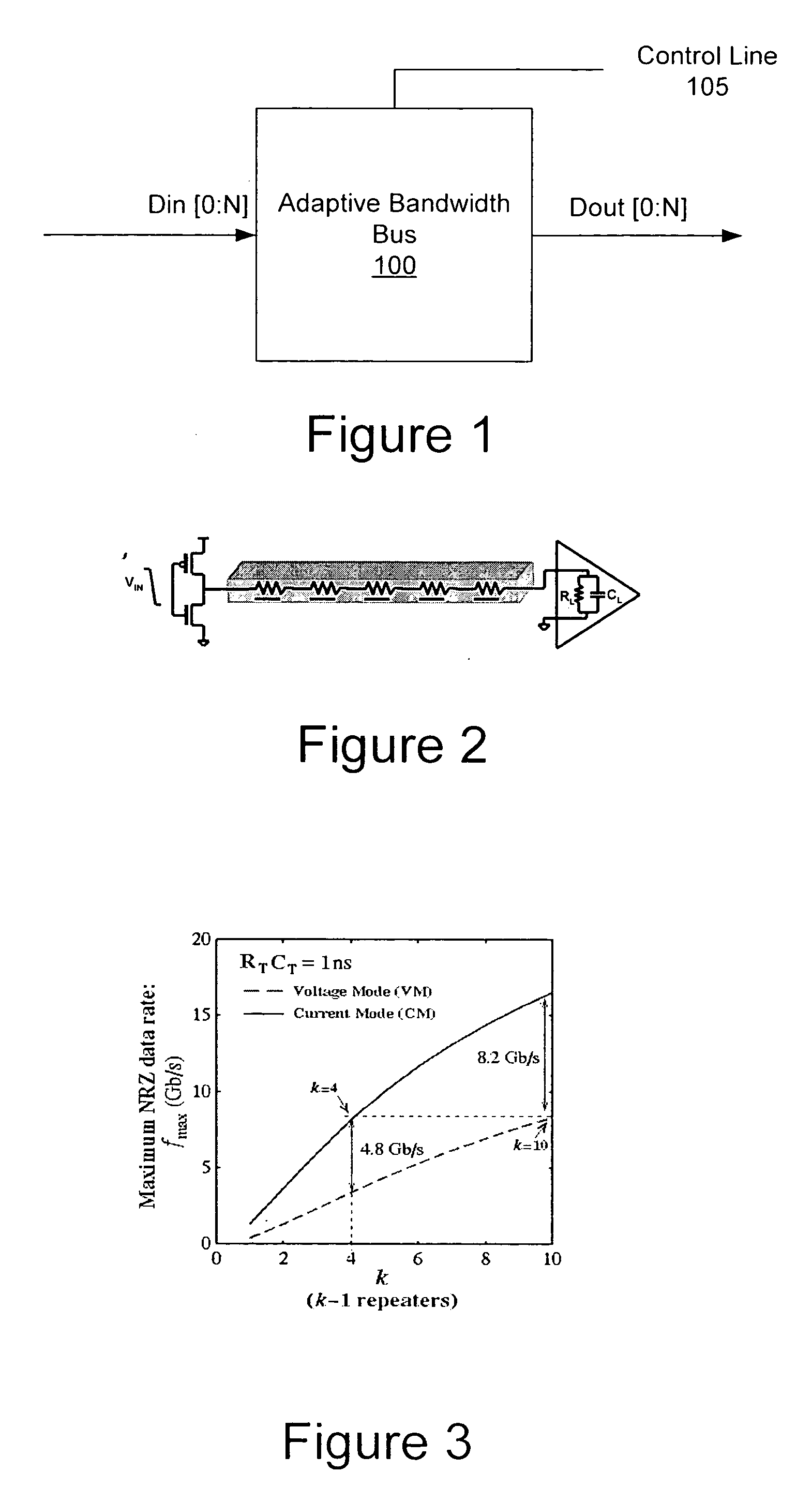

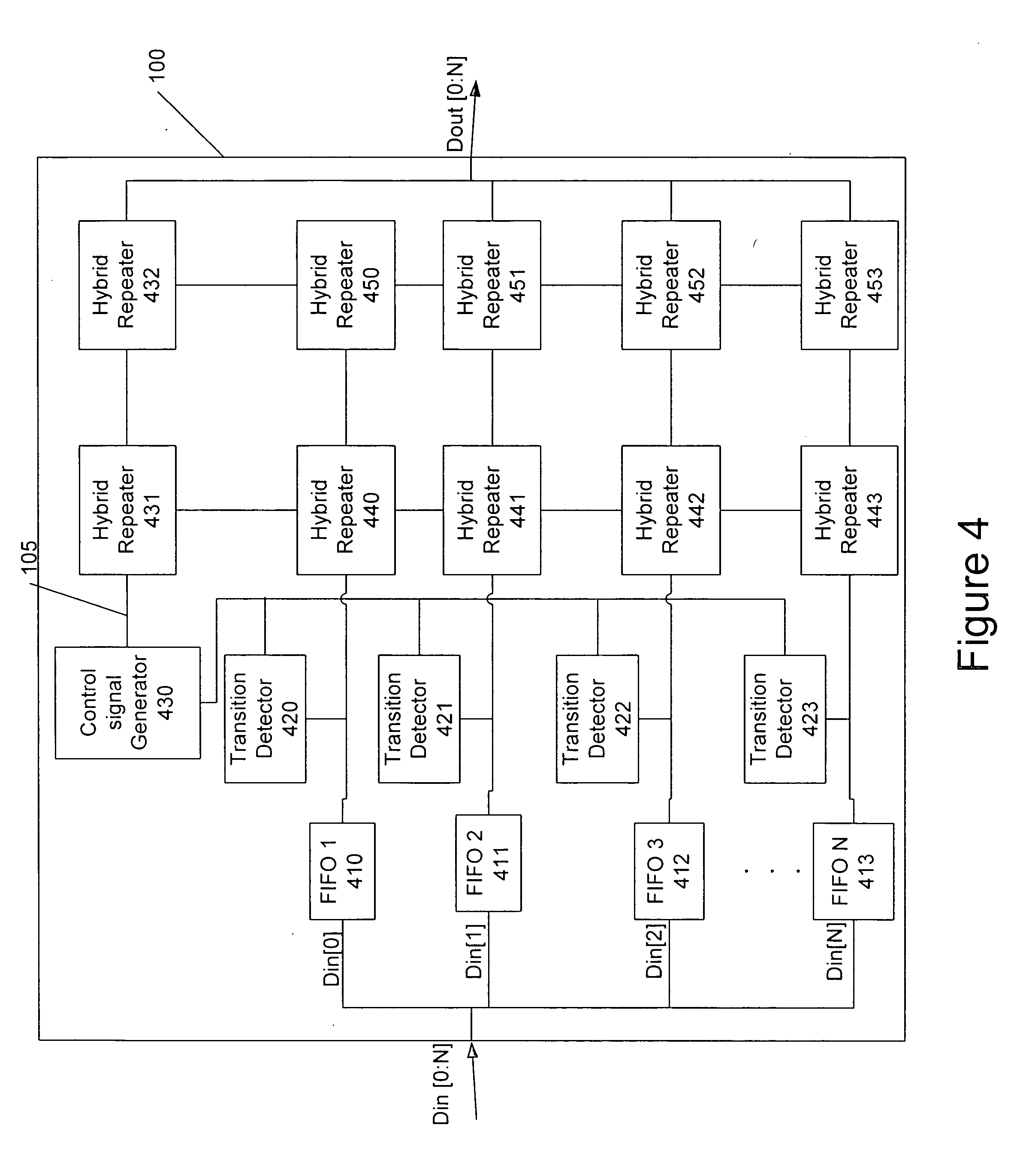

Integrated circuit devices having on-chip adaptive bandwidth buses and related methods

InactiveUS7110420B2Reduce Propagation DelayIncrease signal bandwidthSemiconductor/solid-state device detailsSolid-state devicesControl signalData signal

An adaptive bandwidth bus is provided that switches between a current mode of operation and a voltage mode of operation. Furthermore, related methods include transmitting a data signal in a current mode or a voltage mode and transmitting a control signal to indicate whether the signal should be transmitted in the current mode or the voltage mode.

Owner:NORTH CAROLINA STATE UNIV

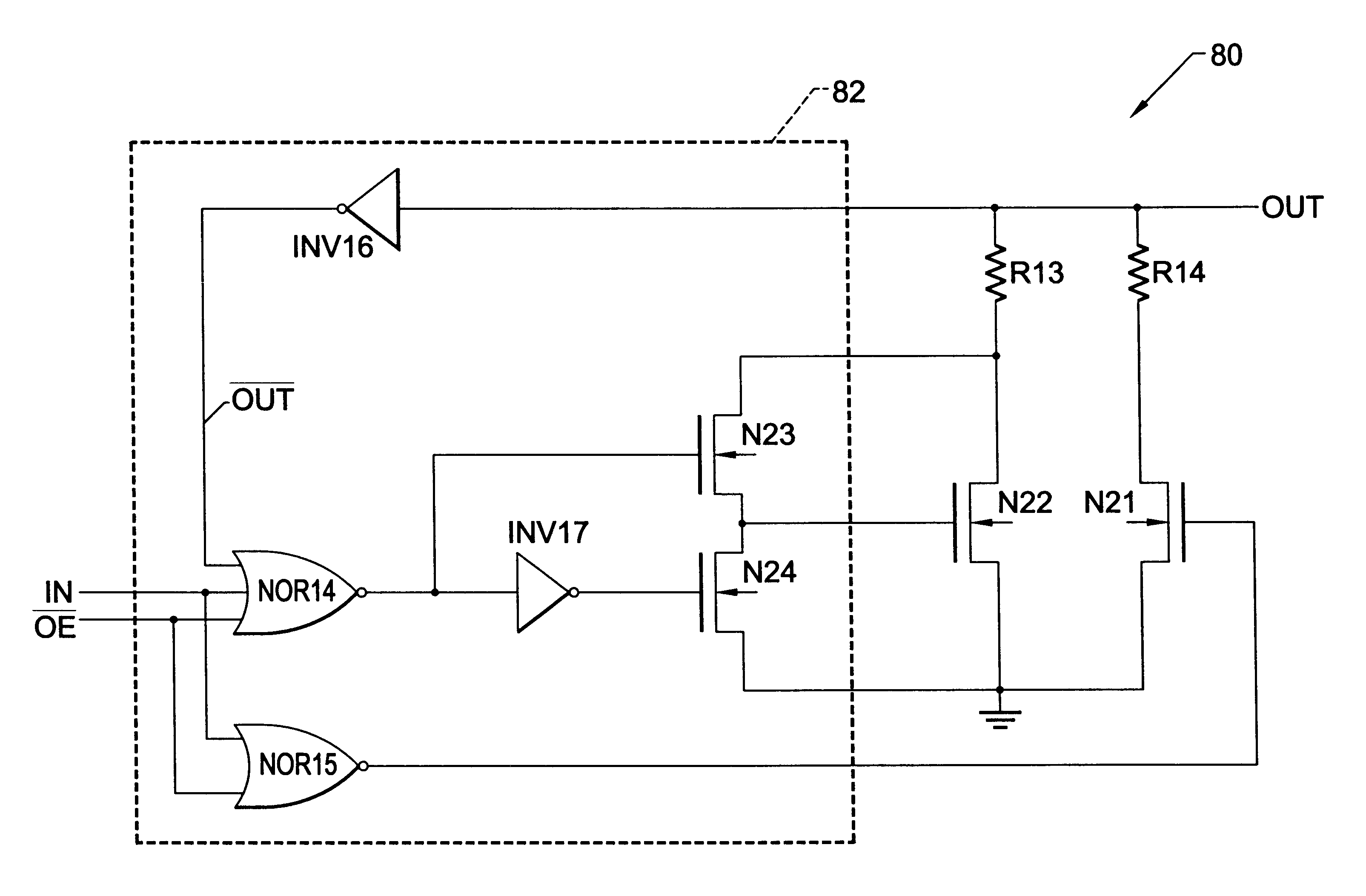

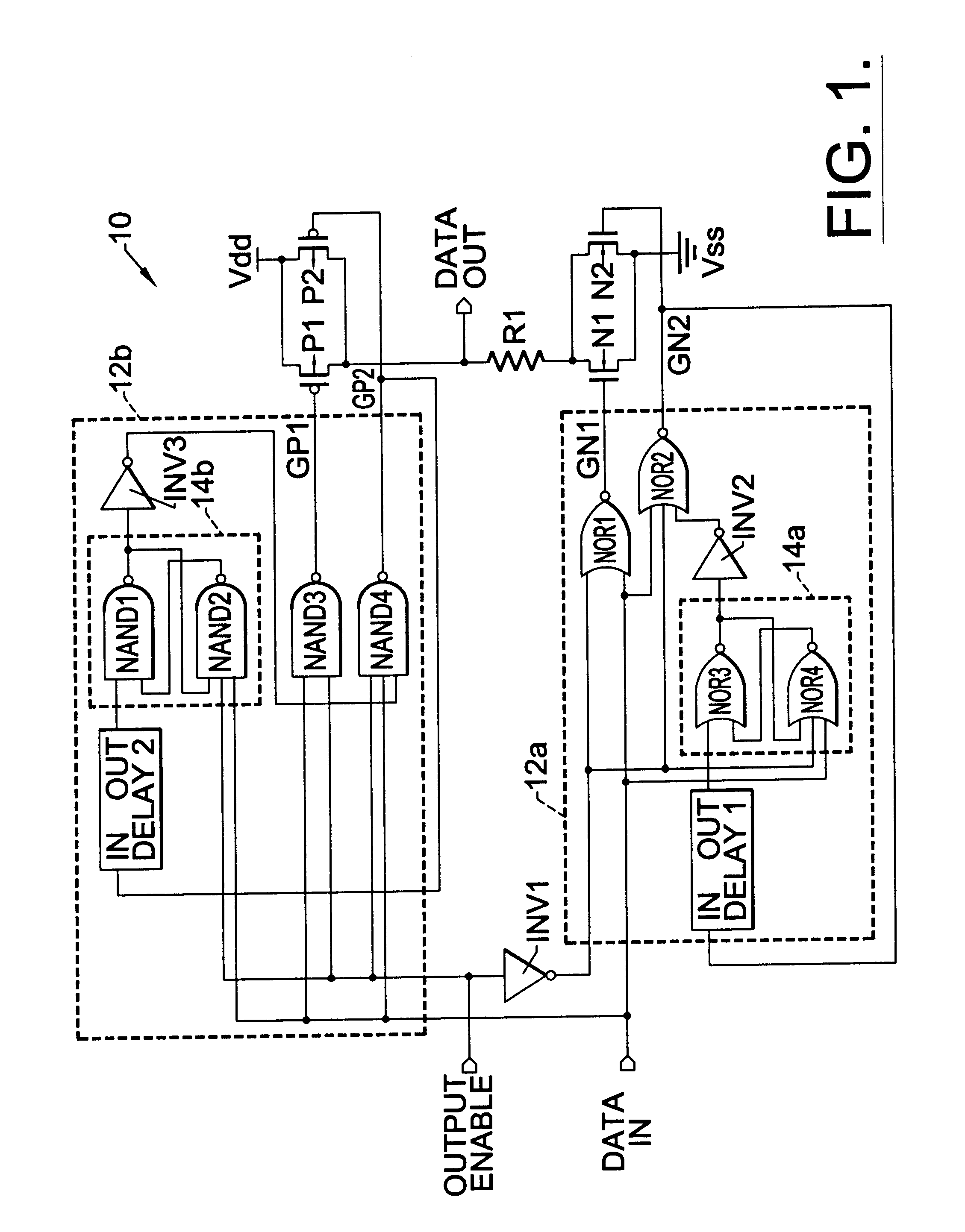

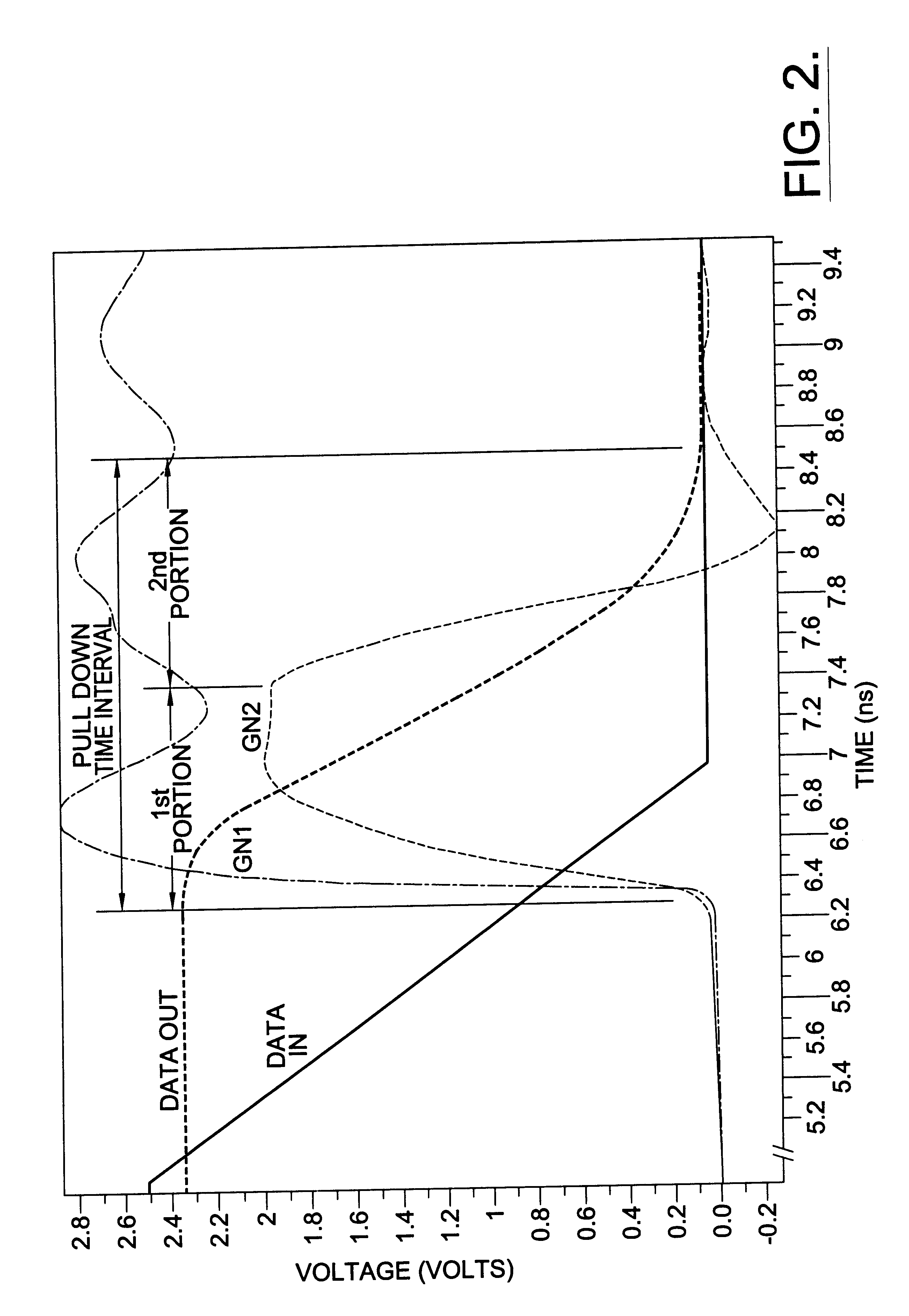

Integrated circuit output buffers having control circuits therein that utilize output signal feedback to control pull-up and pull-down time intervals

InactiveUS6356102B1Reduce Propagation DelayImprove noise characteristicsReliability increasing modificationsElectronic switchingElectricityEngineering

Integrated circuit output buffers include primary and secondary pull-down transistors and an output signal line electrically coupled to a drain of the primary pull-down transistor and a drain of the secondary pull-down transistor. A preferred control circuit is also provided. The control circuit turns on the primary pull-down transistor during first and second consecutive portions of a pull-down time interval and uses a signal fed back from the output signal line to control the timing of when a gate of the secondary pull-down transistor is electrically connected to a drain of the secondary pull-down transistor during the first portion of the pull-down time interval and also control the timing of when the gate electrode of the secondary pull-down transistor is electrically connected to a source of the secondary pull-down transistor during the second portion of the pull-down time interval. A pull-down portion of the control circuit may include a gate pull-up transistor having a drain electrically connected to the drain of the secondary pull-down transistor and a source electrically connected to a gate of the secondary pull-down transistor, and a gate pull-down transistor having a drain electrically connected to the gate of the secondary pull-down transistor and a source electrically connected to a source of the secondary pull-down transistor. These gate pull-up and pull-down transistors can be utilized to selectively turn on the secondary pull-down transistor during a first leading portion of a pull-down time interval and then turn off the secondary pull-down transistor during a second trailing portion of the pull-down time interval.

Owner:INTEGRATED DEVICE TECH INC

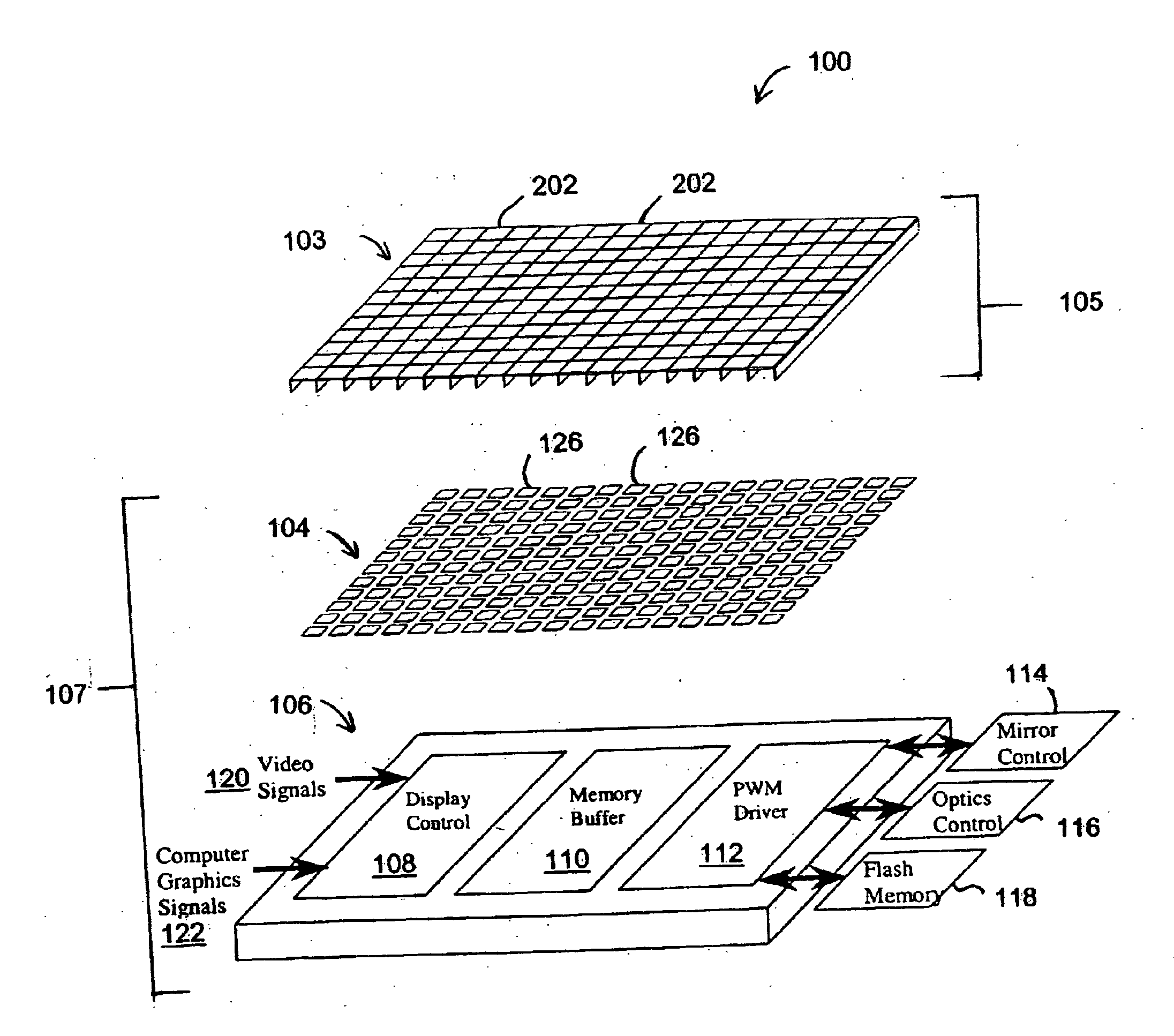

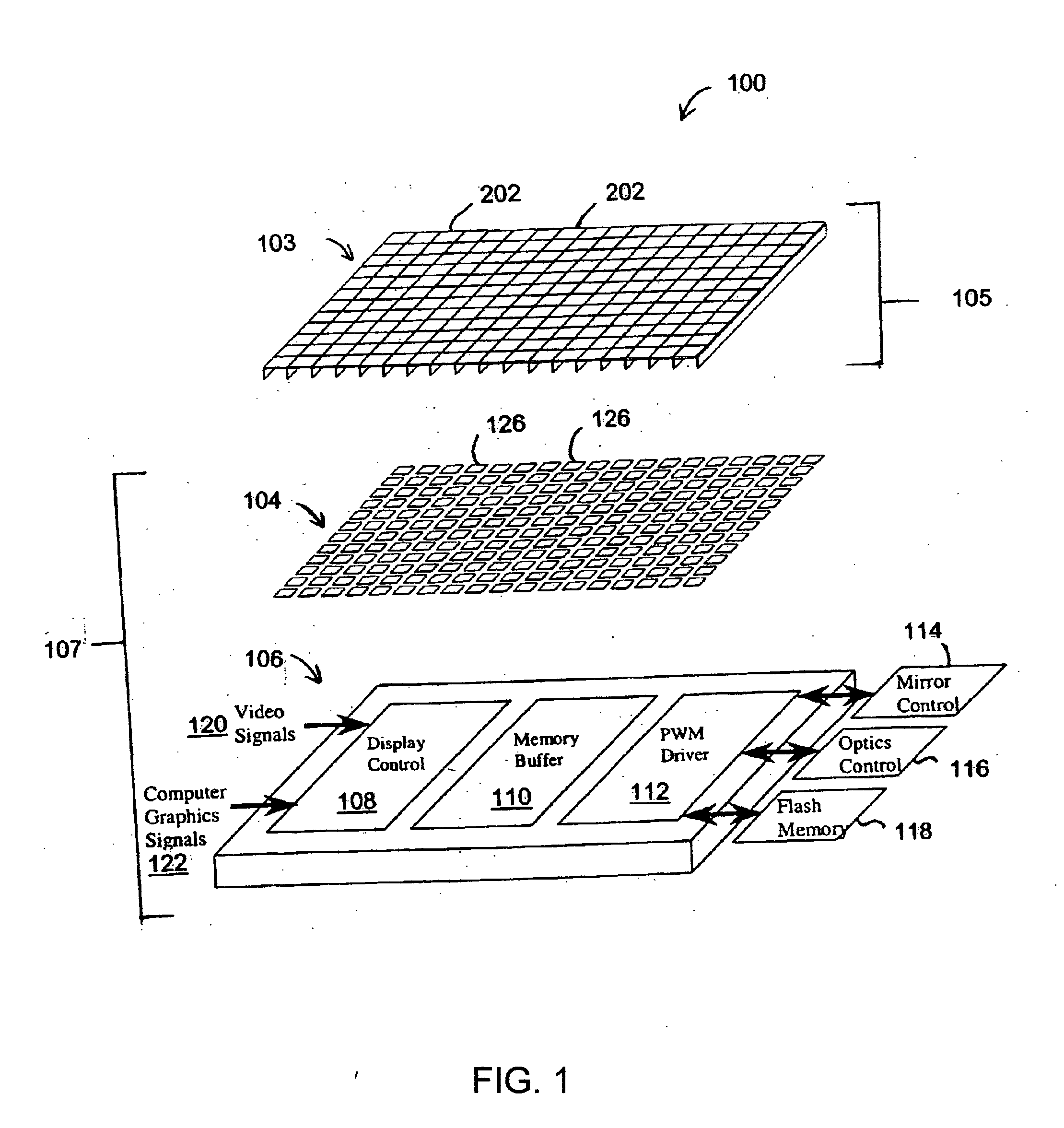

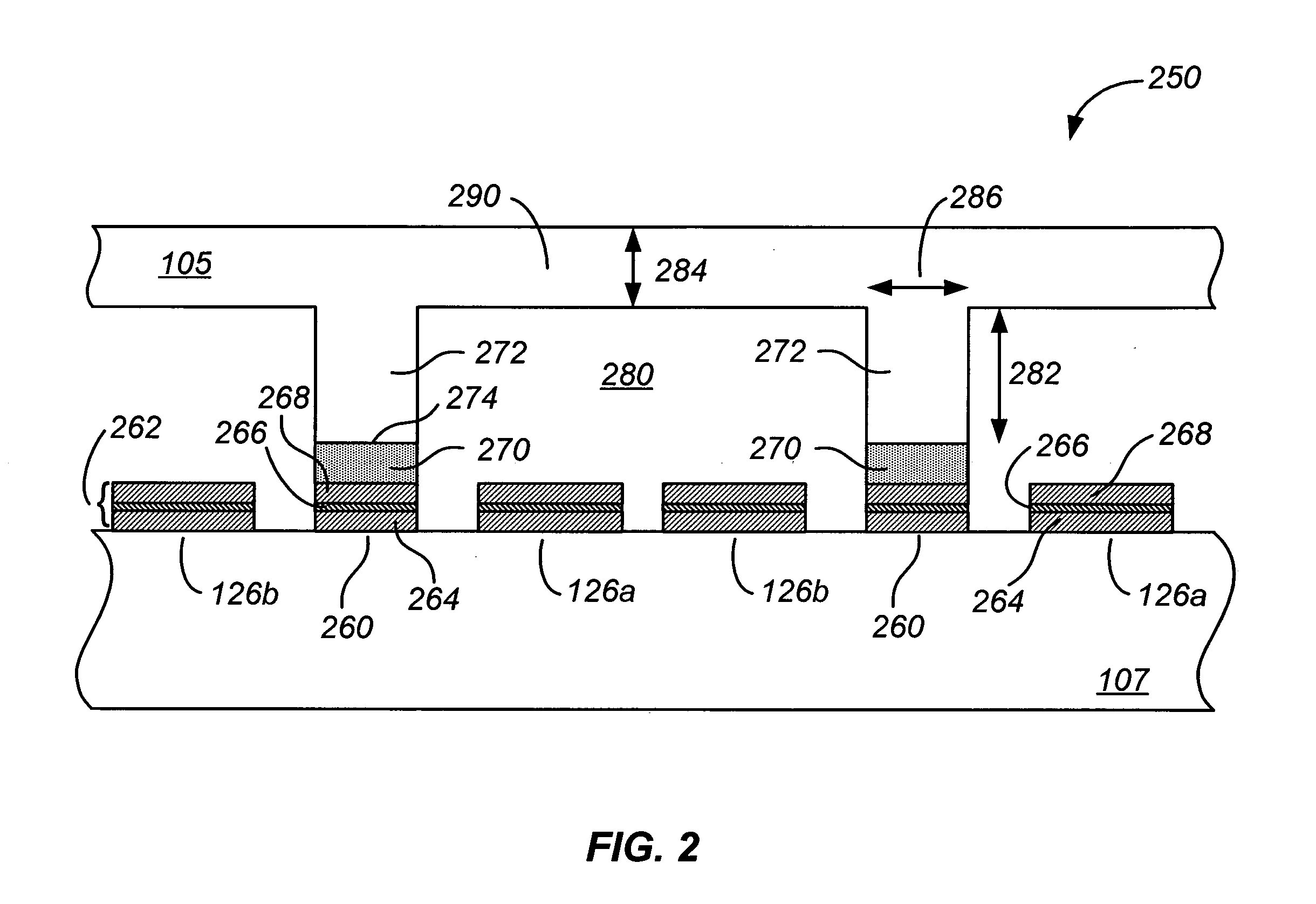

Electrical contact method and structure for deflection devices formed in an array configuration

A method of fabricating an electrical connection for a spatial light modulator includes providing a first substrate including a plurality of bias electrodes and a plurality of dielectric bond pads. The method also includes providing a second substrate of a predetermined thickness, the second substrate including a plurality of recessed regions within the predetermined thickness and arranged in a spatial manner as a second array, each of the recessed regions being bordered by a standoff region, and joining the dielectric bond pads of the first substrate to the standoff region of the second substrate. The method further includes forming mirror structures from a first portion of the second substrate, exposing a portion of the upper surface of the plurality of bias electrodes, and depositing a conductive layer on the mirror structures and the exposed portion of the upper surface of the plurality of bias electrodes.

Owner:MIRADIA INC

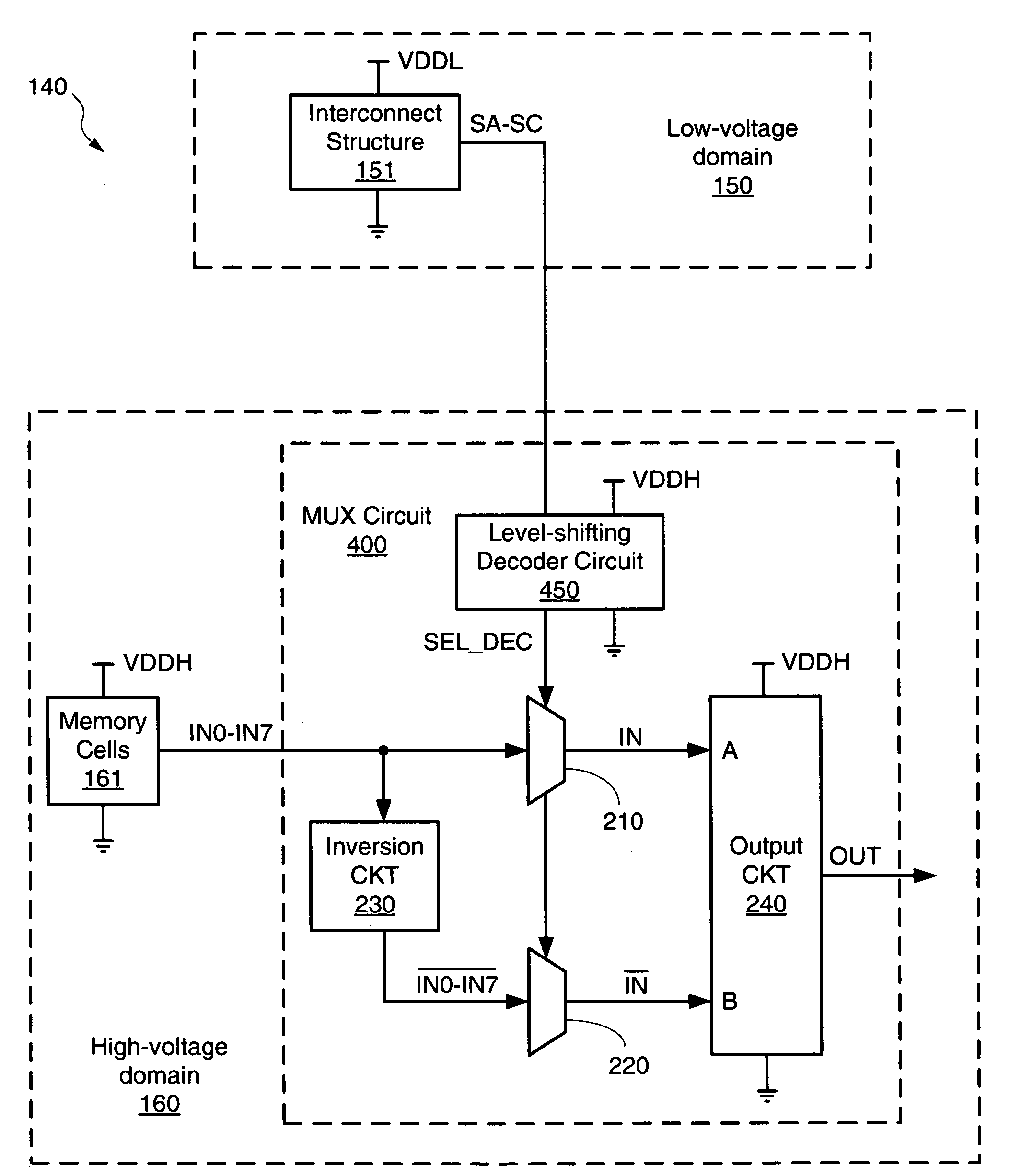

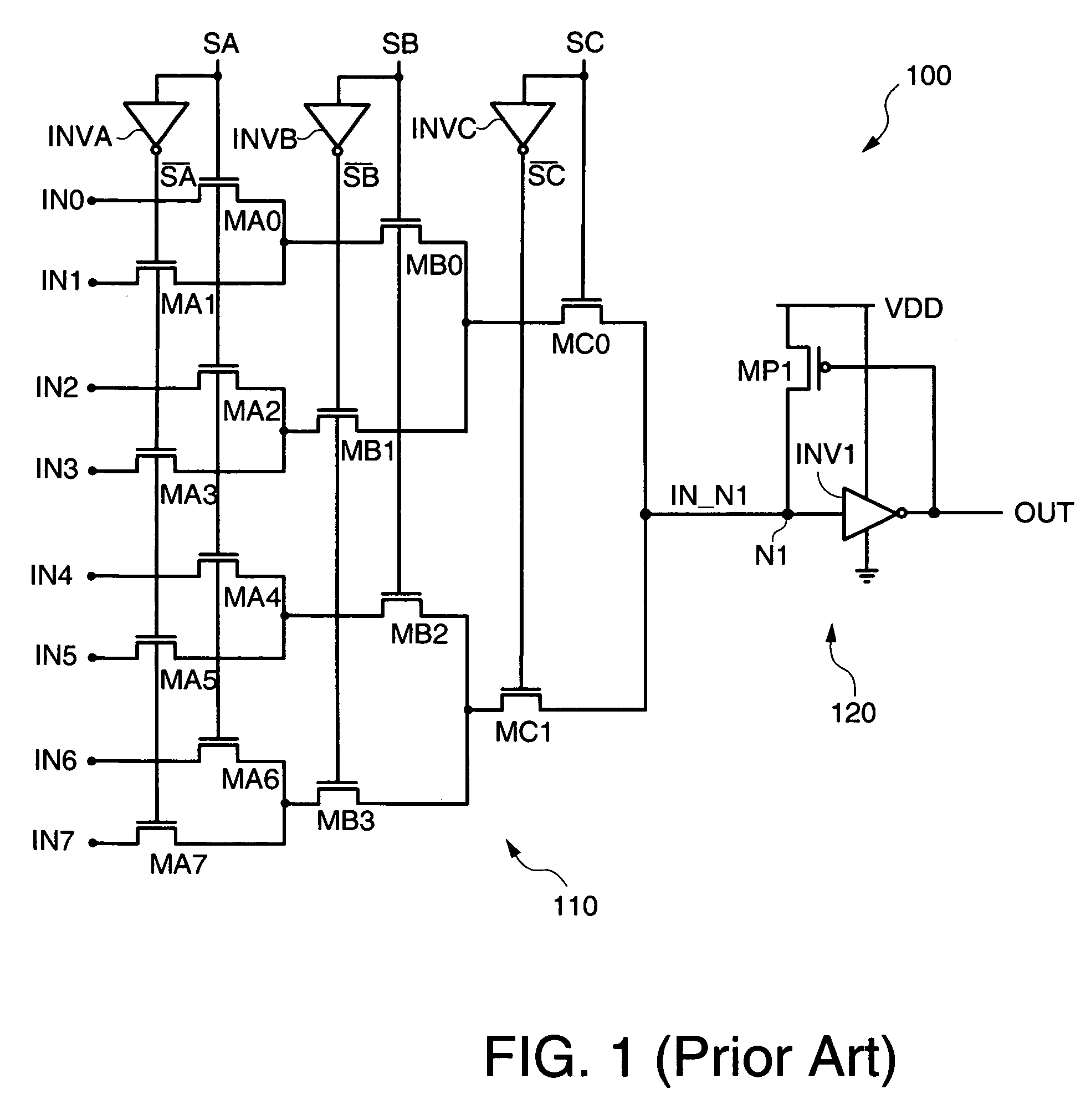

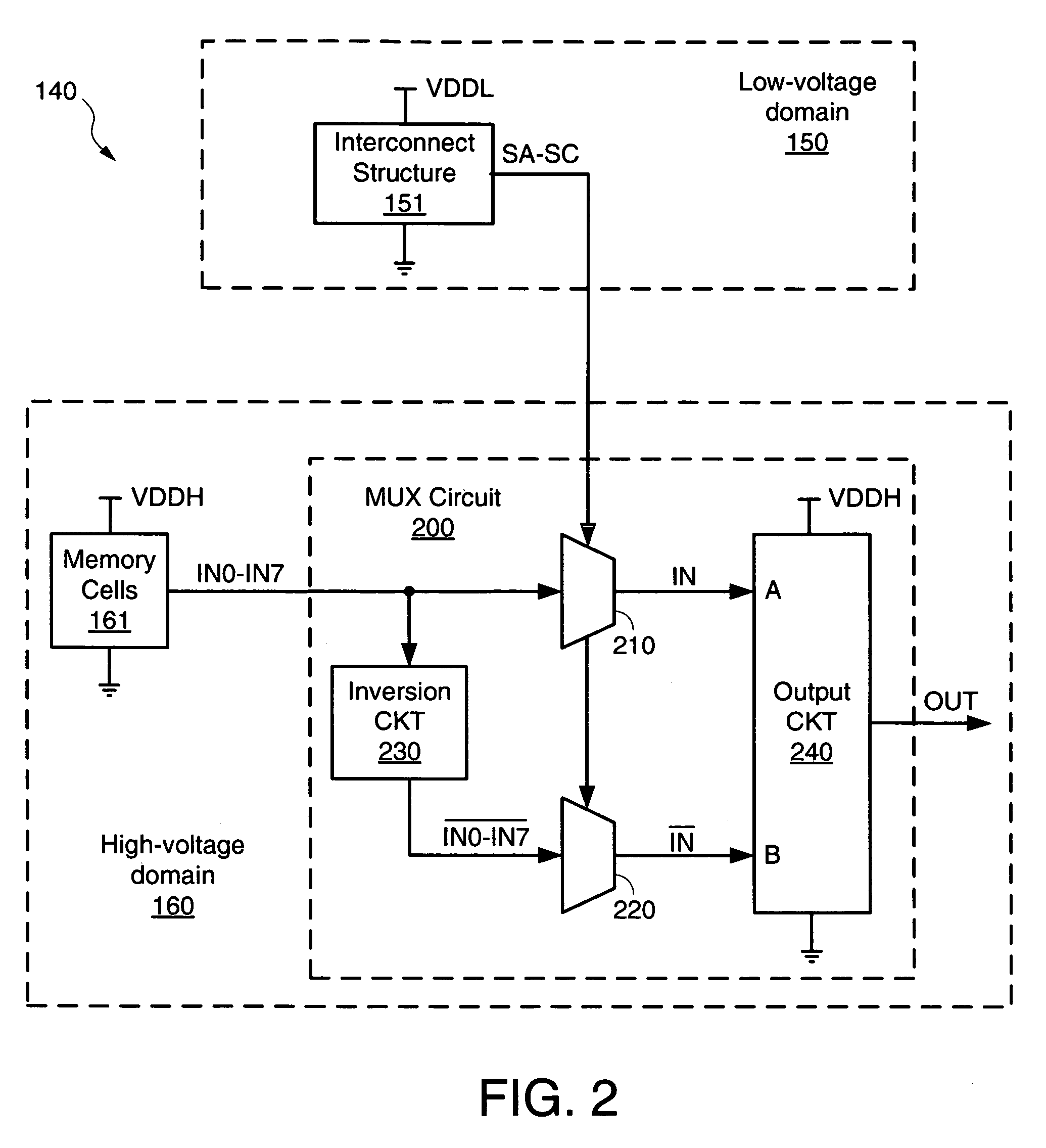

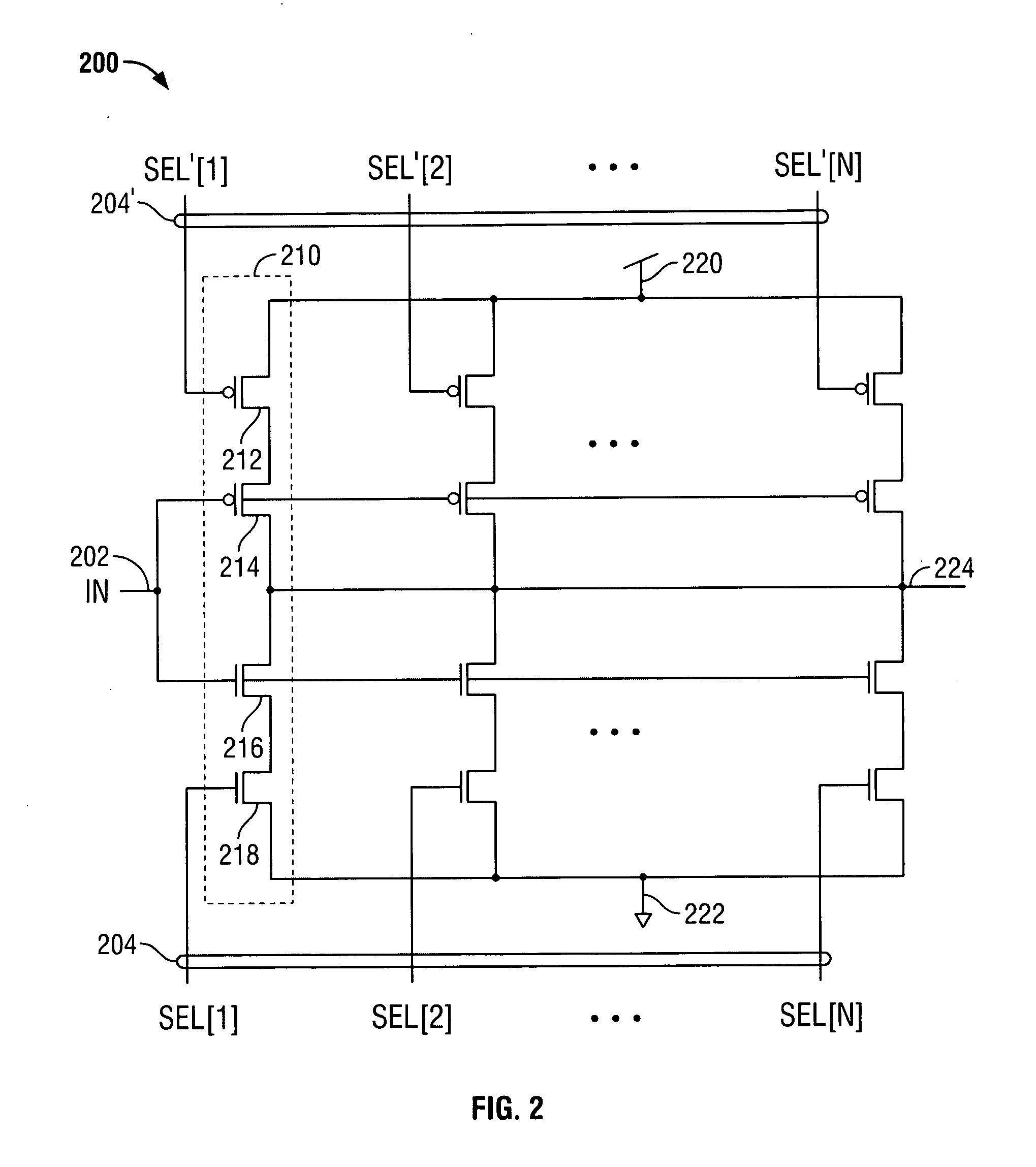

Level-shifting pass gate multiplexer

ActiveUS7368946B1Reduce circuit areaReduce in quantityElectronic switchingLogic circuits using elementary logic circuit componentsMultiplexingLevel shifting

The present invention incorporates level-shifting functions within a multiplexer circuit that may be implemented in IC devices having low and high voltage domains. The multiplexer circuit utilizes pseudo-differential multiplexing architectures and employs level-shifting techniques to convert low-voltage signals received from the low-voltage domain into high-voltage signals more suitable for controlling the propagation of a selected input signal through the pass gates of the multiplexer circuit. For some embodiments, some of the select signals may be decoded to generate a number of decoded select signals that can be used to control the selective routing of signals through the multiplexer.

Owner:XILINX INC

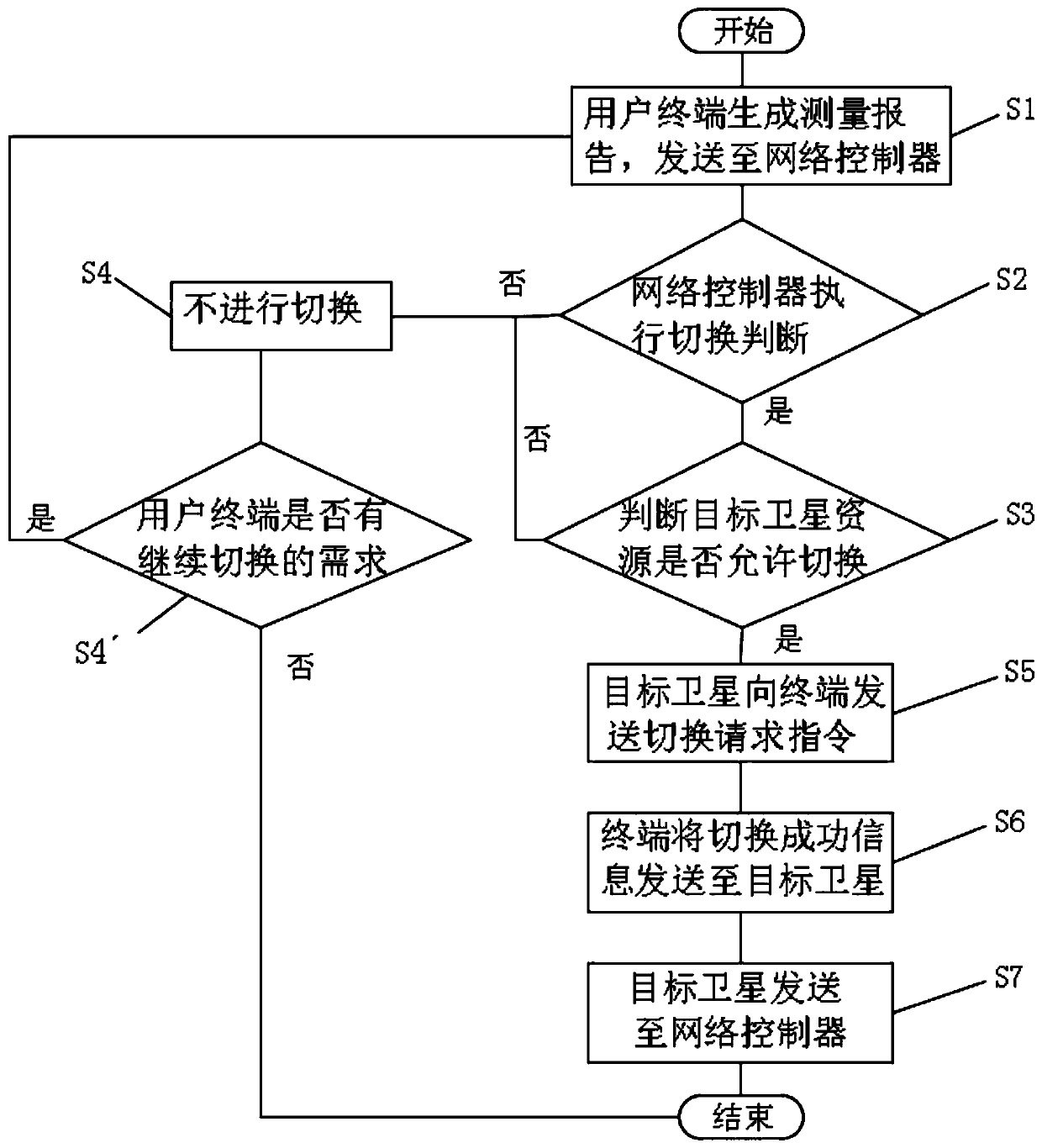

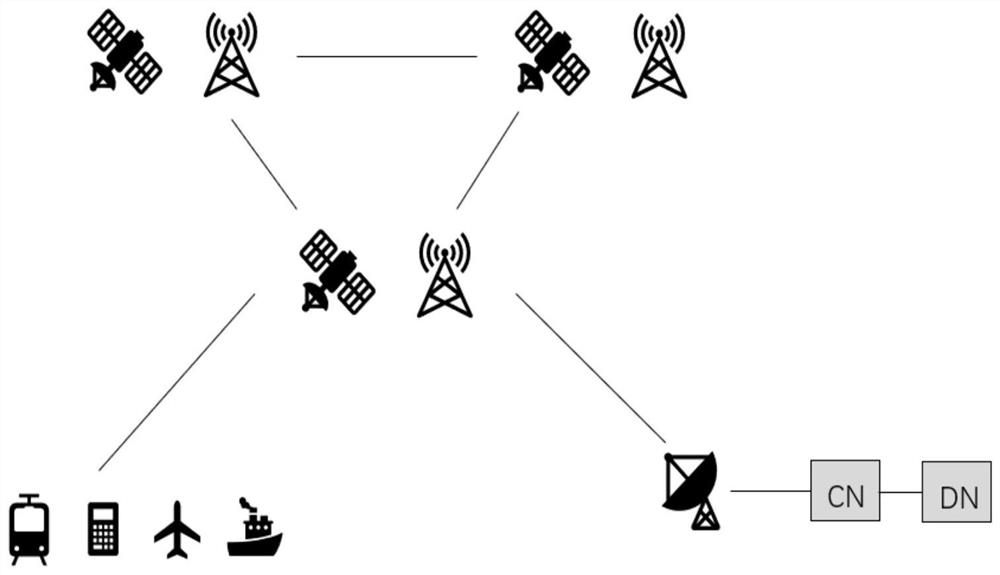

Lossless switching method for inter-satellite data of low-orbit satellites

ActiveCN111211829AGuaranteed reliabilityReduce time overheadRadio transmissionWireless communicationTelecommunicationsSatellite data

The invention discloses a lossless switching method for inter-satellite data of low-orbit satellites, which specifically comprises the following steps that: S1, a user terminal sends a measurement report to a network controller according to the generated measurement report, S2, the network controller executes switching judgment, if switching can be carried out, S3 is executed, and if switching cannot be carried out, S4 is executed, S3, it is judged whether the target satellite resources are allowed to be switched or not, if yes, S5 is executed, and if not, S4 is executed, S4, switching is notcarried out, S4', it is judged whether the user terminal of which the signal stays on the original satellite has a switching continuing demand or not, if so, S1 is executed, and if not, the switchingaction is stopped, S5, the target satellite allocates channel resources to the allowed user terminal, and sends a switching request instruction to the terminal through the service satellite, S6, the terminal receives the switching request and sends switching success information to the target satellite, S7, the network controller immediately releases the temporary storage data and S8, switching iscompleted. The device has the advantages of being simple in structure, smooth in network access and small in loss.

Owner:中国星网网络应用有限公司

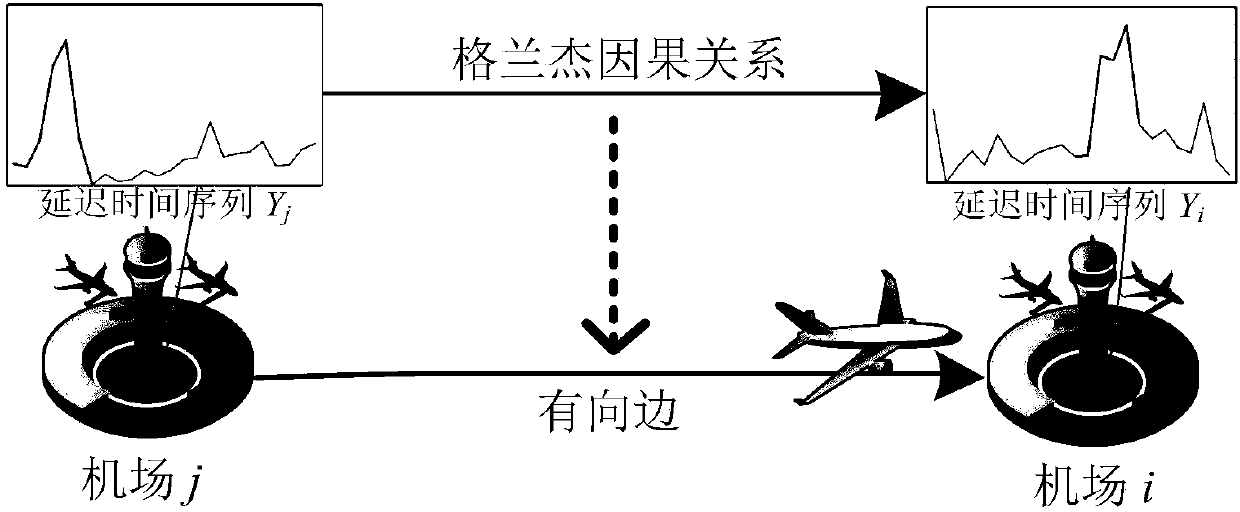

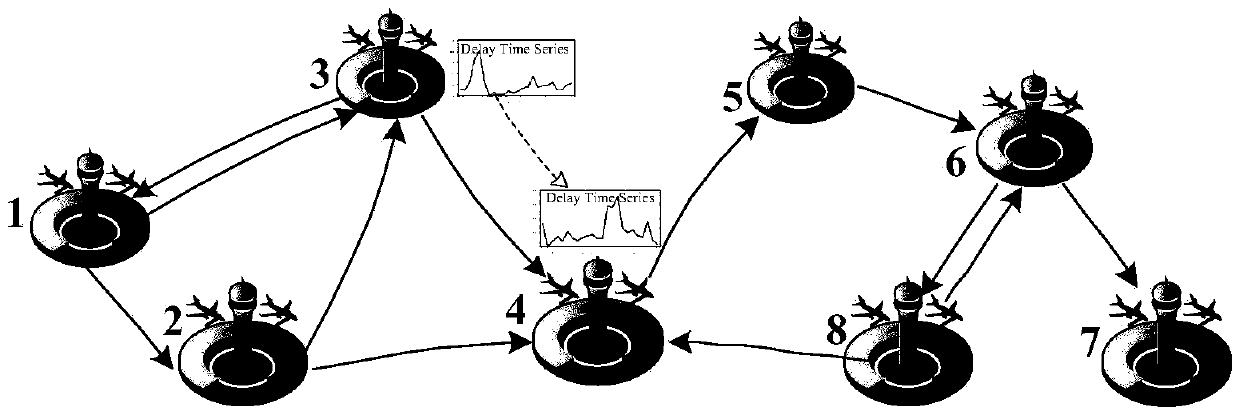

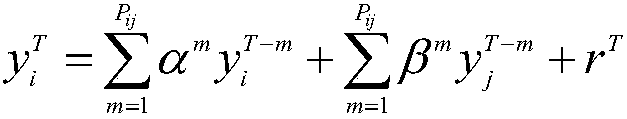

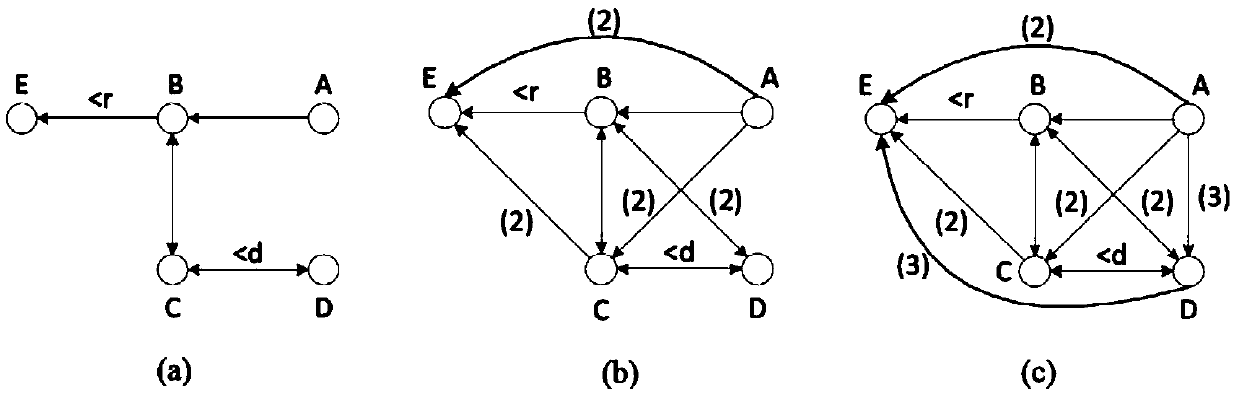

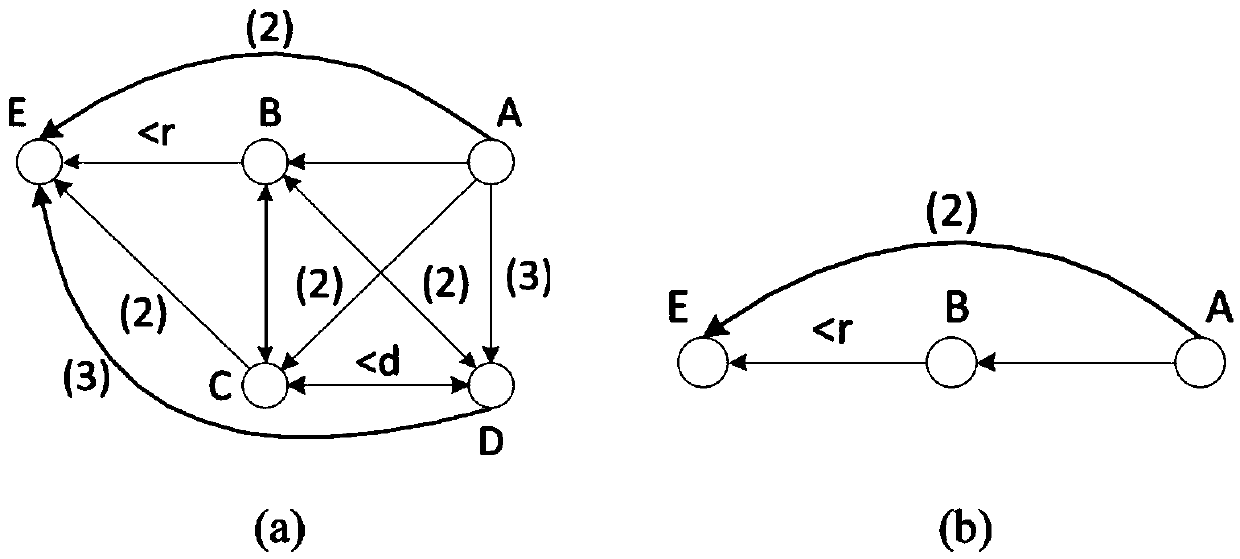

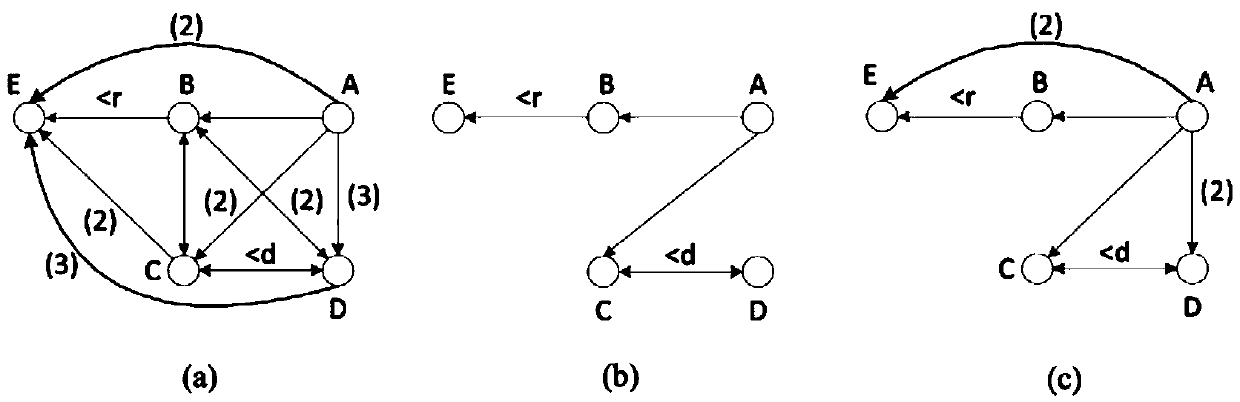

Flight delay causality network building method based on Granger test

ActiveCN108519988AReduce in quantityReduce delay propagationData processing applicationsKnowledge representationDelayed timeCivil aviation

The invention discloses a flight delay causality network building method based on a Granger test, pertaining to the technical field of delay analyses for civil aviation. The method comprises the following steps: firstly, acquiring a delay time sequence of each airport with the set time period according to historical data of flight of airports; then, taking each airport as a node for the network and testing a Granger causality of each pair of airports, when an airport I causes delay of an airport j by the test and establishing a directed edge from a node i to node j; and ultimately, repeating the above processes till selected airports are added to the network and making flight delay analyses by means of the obtained network. Through the established flight delay causality network, the numberof delay dissemination paths is analyzed for some large airports. Therefore, the delay dissemination range is narrowed, thereby effectively resolving a delay problem. The delays disseminated by an overall system are reduced. Therefore, loss caused by many flight delays is lowered.

Owner:BEIHANG UNIV

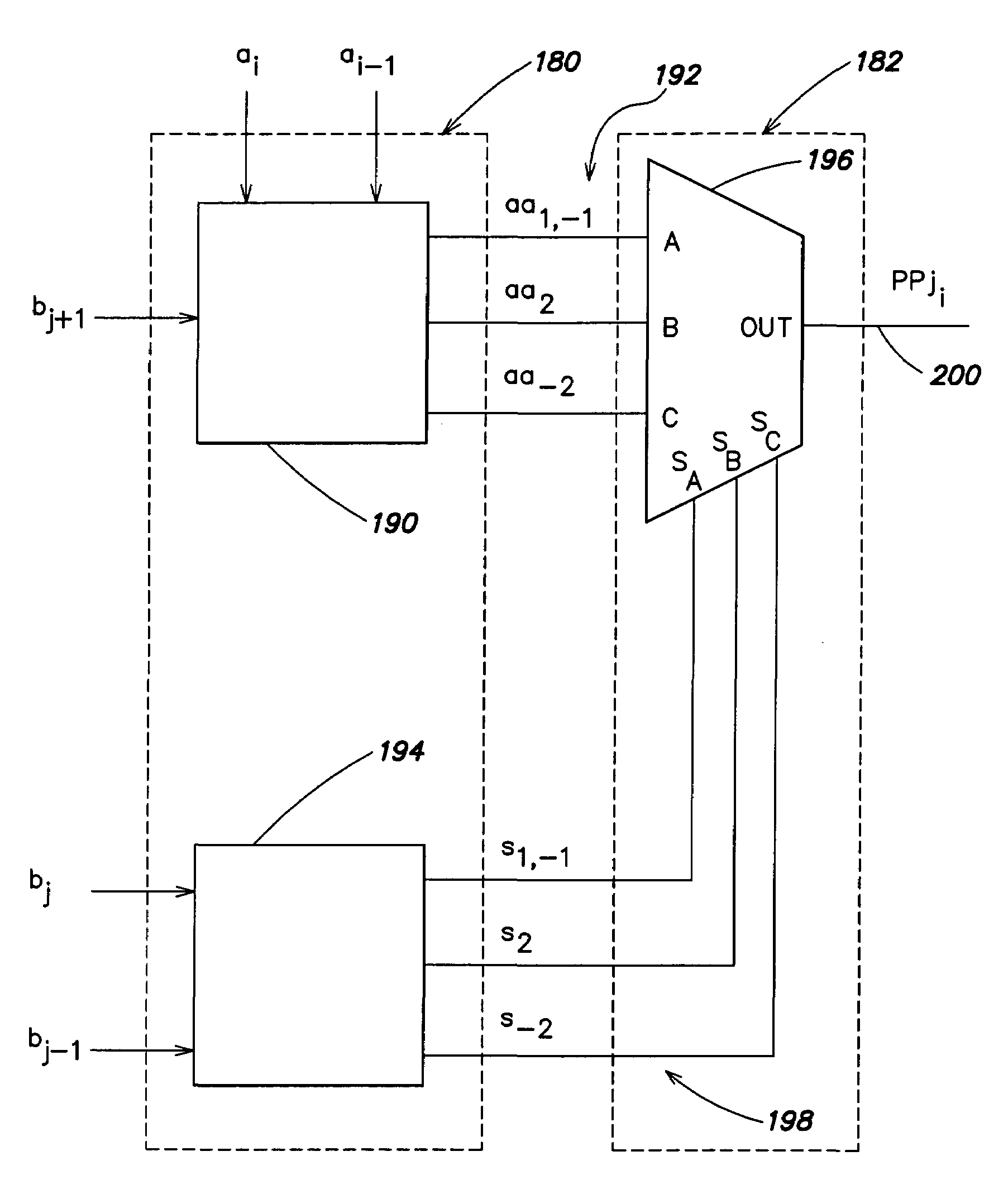

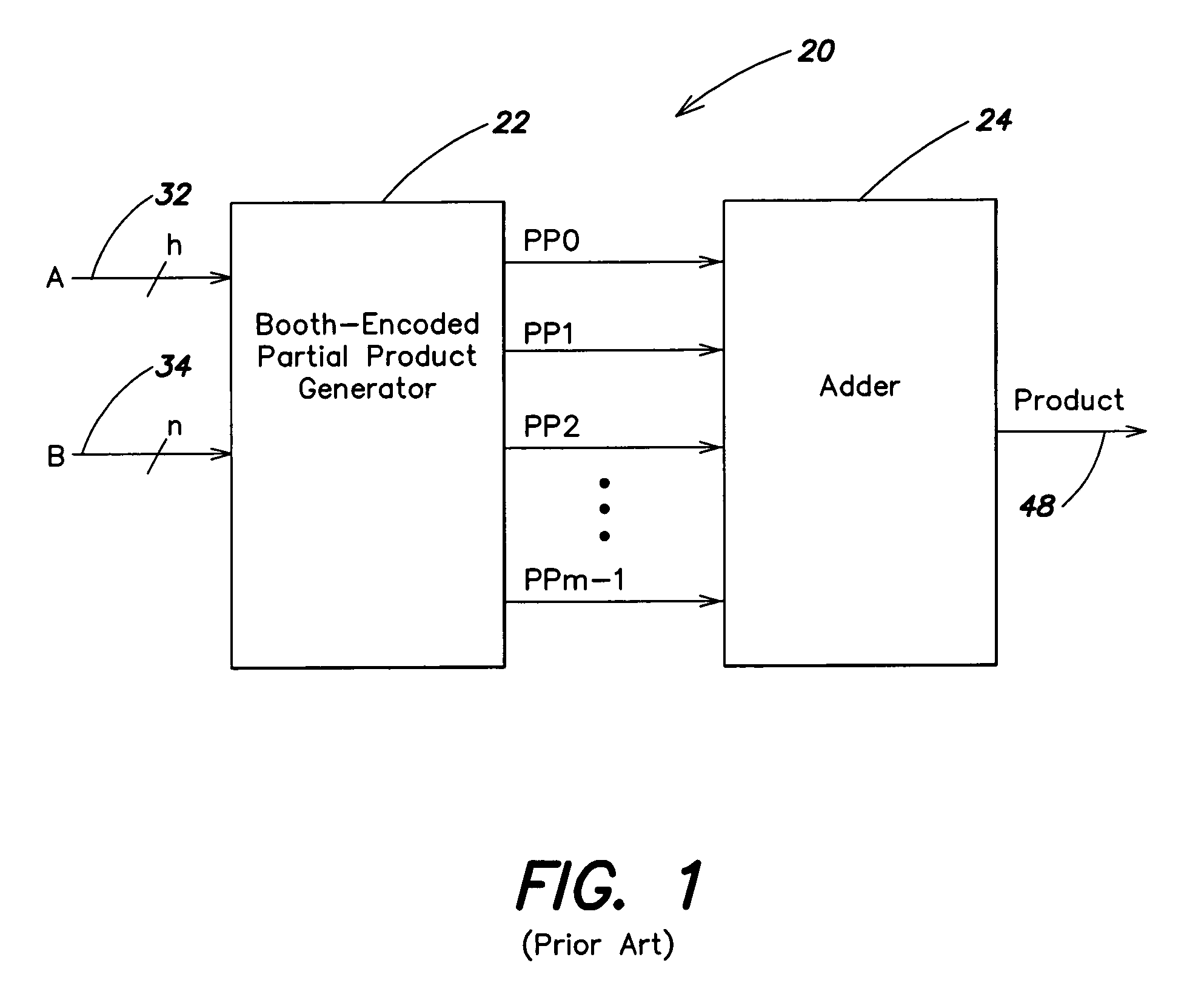

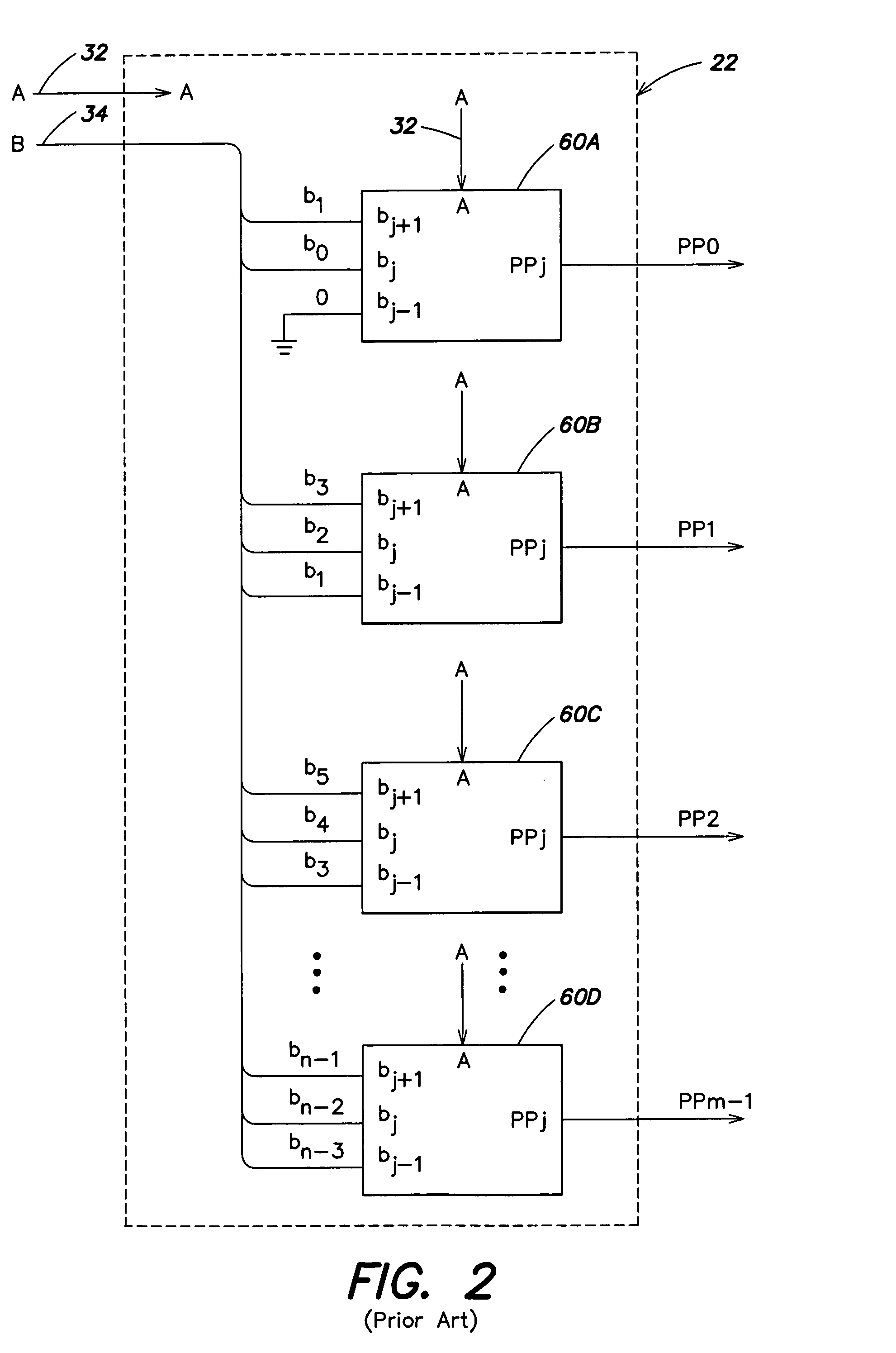

Method and apparatus for use in booth-encoded multiplication

InactiveUS7024445B2Reduce Propagation DelayReduce total powerComputation using non-contact making devicesComputer hardwareLogical operations

A new partial product bit generator is used to generate a partial product bit PPji. In some embodiments, the partial product bit generator generates the partial product bit PPji from intermediate signals that are able to be generated concurrently, for example in two levels of combinatorial logic. The partial product bit PPji is then able to be generated from the intermediate signal, for example in only one level of combinatorial logic. In such embodiments, a long series of combinatorial logic operations is not required.

Owner:ANALOG DEVICES INC

Integrated circuit devices having on-chip adaptive bandwidth buses and related methods

InactiveUS20050005046A1Reduce Propagation DelayIncrease signal bandwidthSemiconductor/solid-state device detailsSolid-state devicesControl signalData signal

An adaptive bandwidth bus is provided that switches between a current mode of operation and a voltage mode of operation. Furthermore, related methods include transmitting a data signal in a current mode or a voltage mode and transmitting a control signal to indicate whether the signal should be transmitted in the current mode or the voltage mode.

Owner:NORTH CAROLINA STATE UNIV

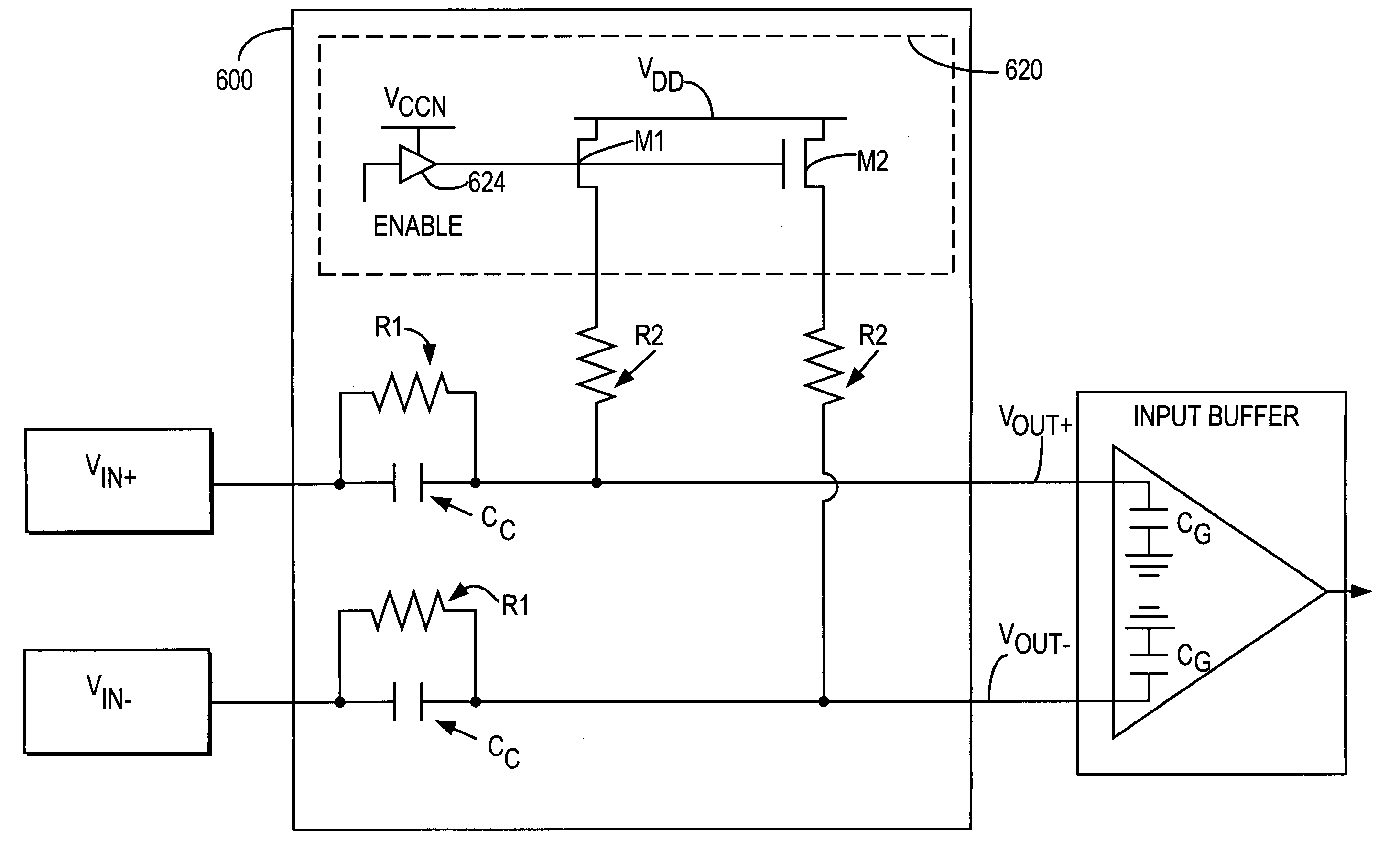

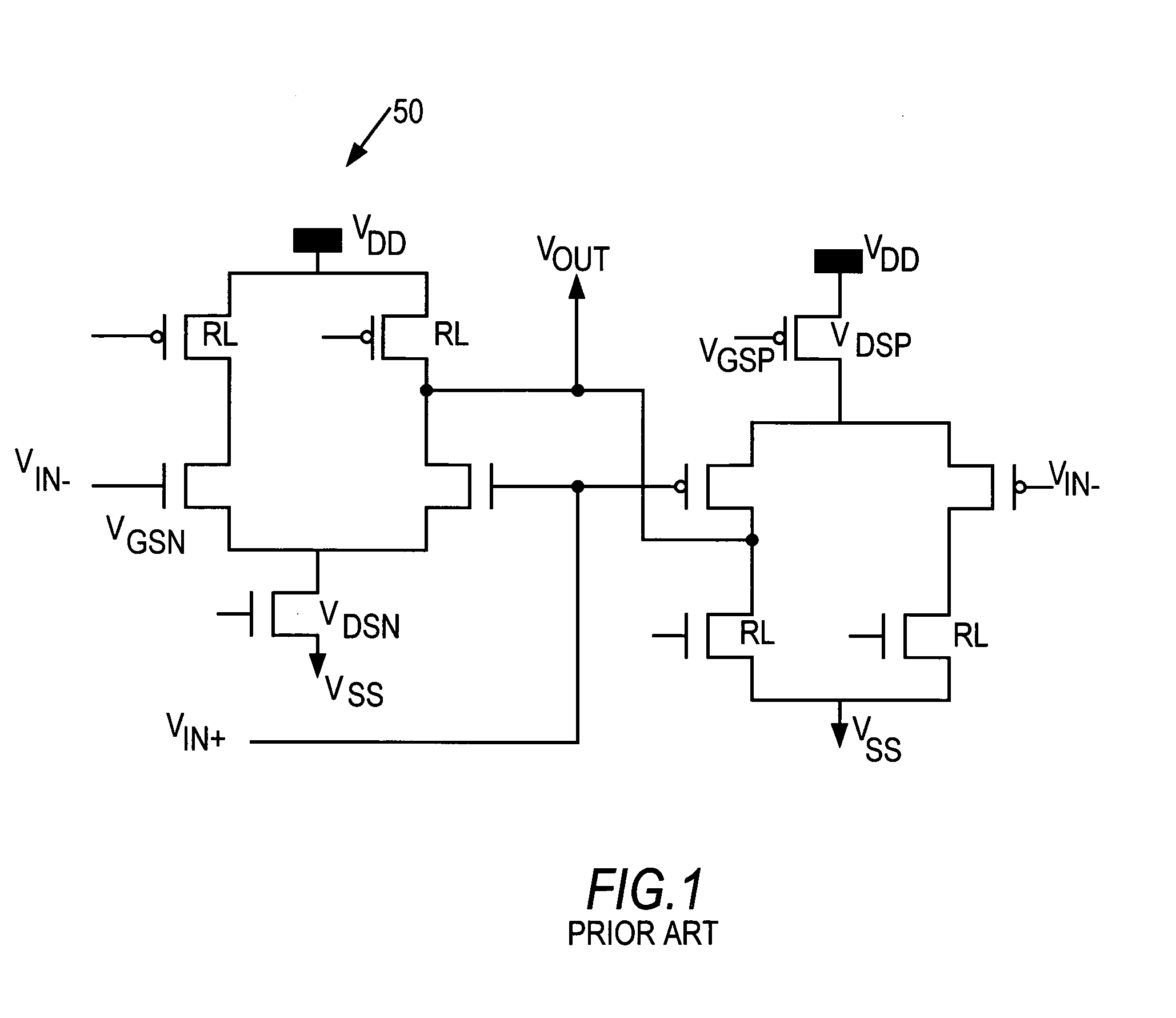

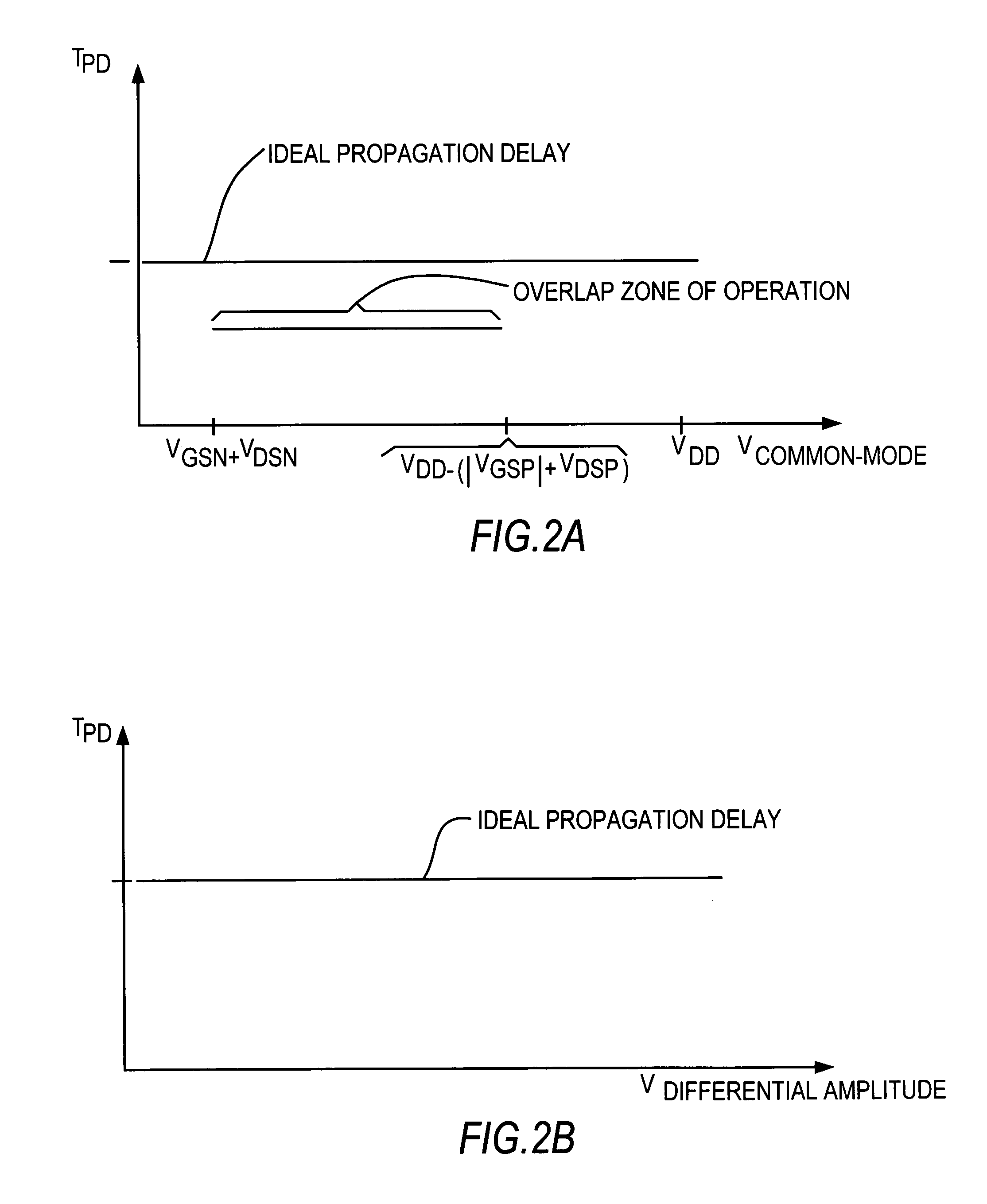

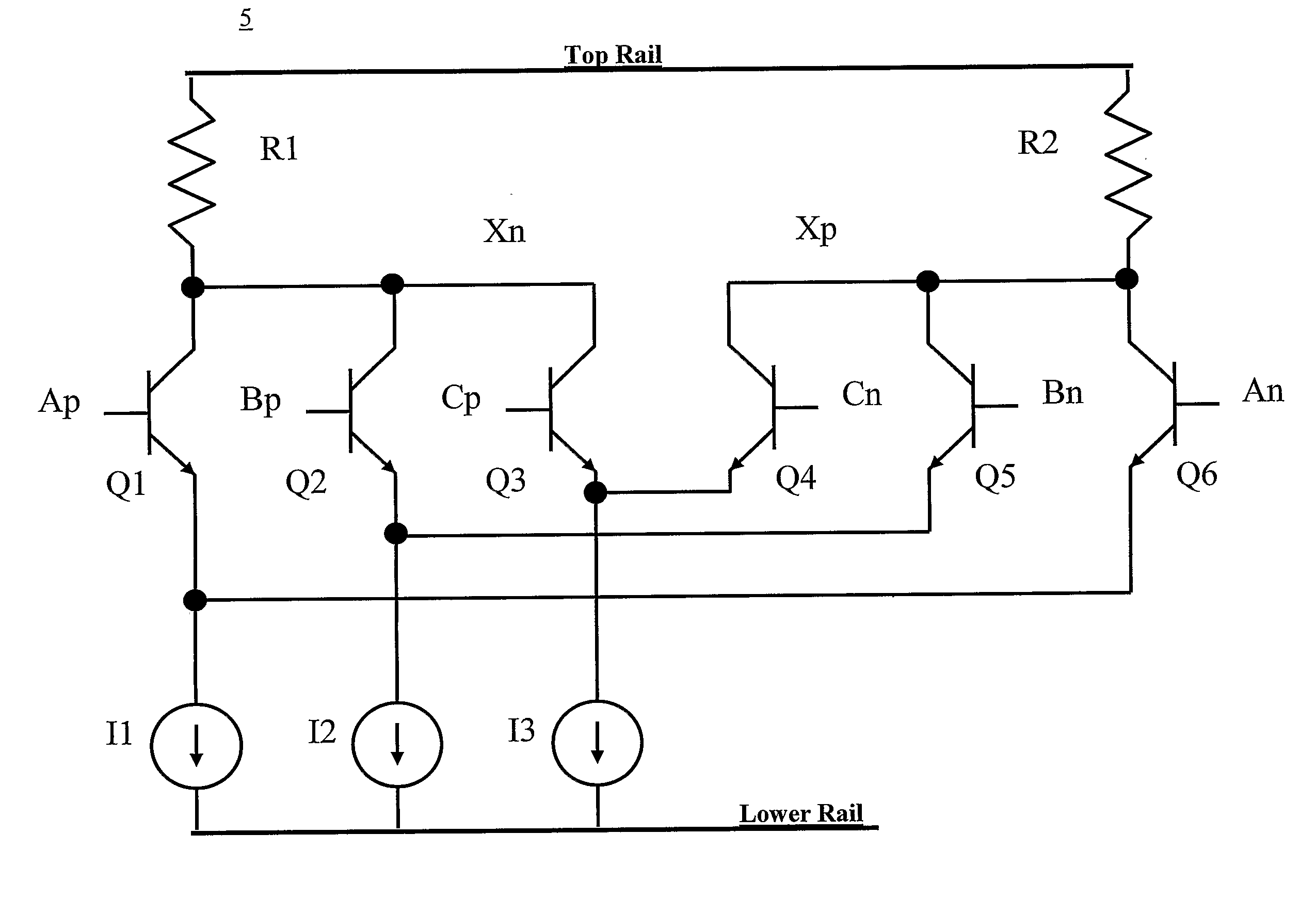

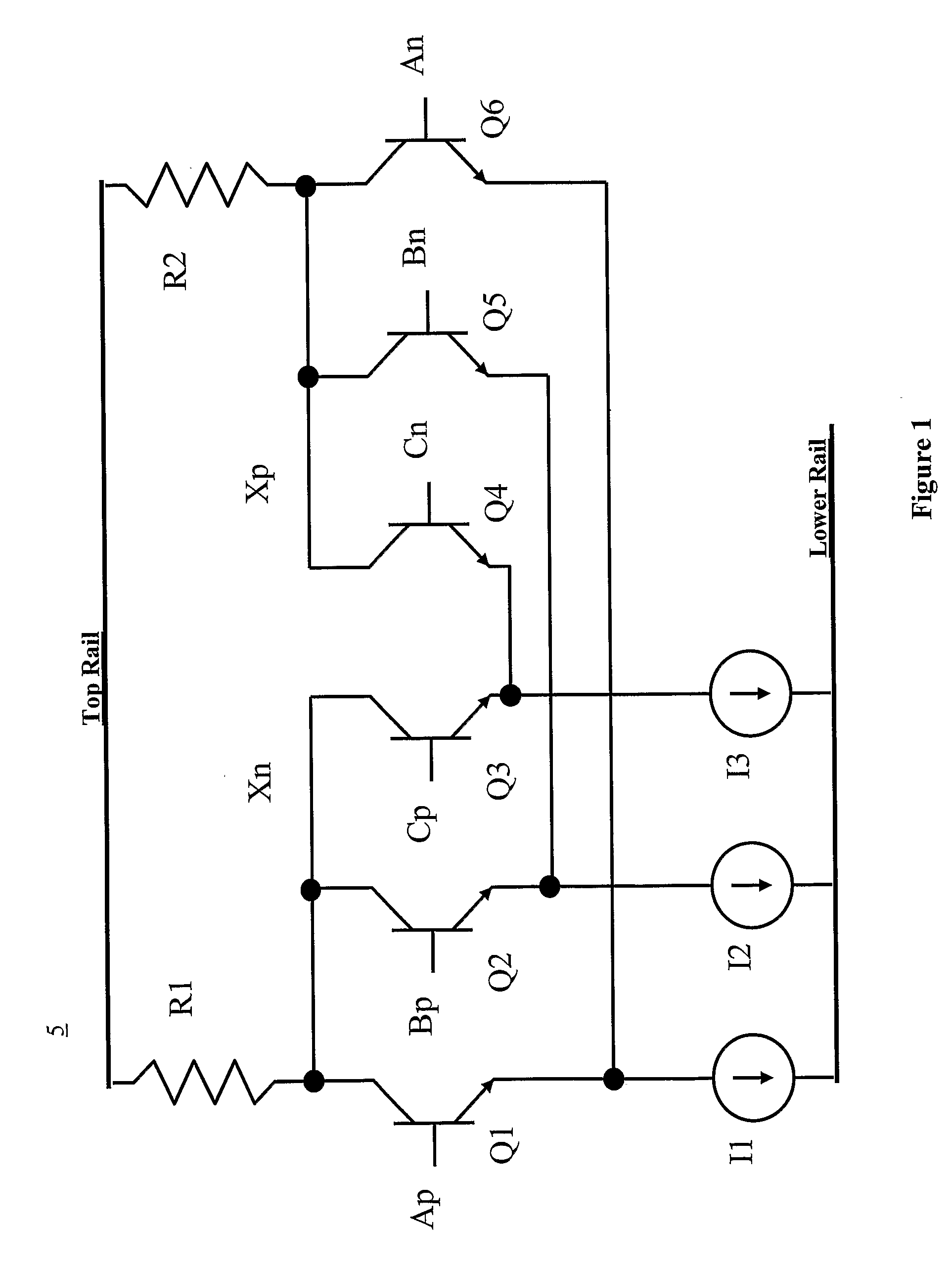

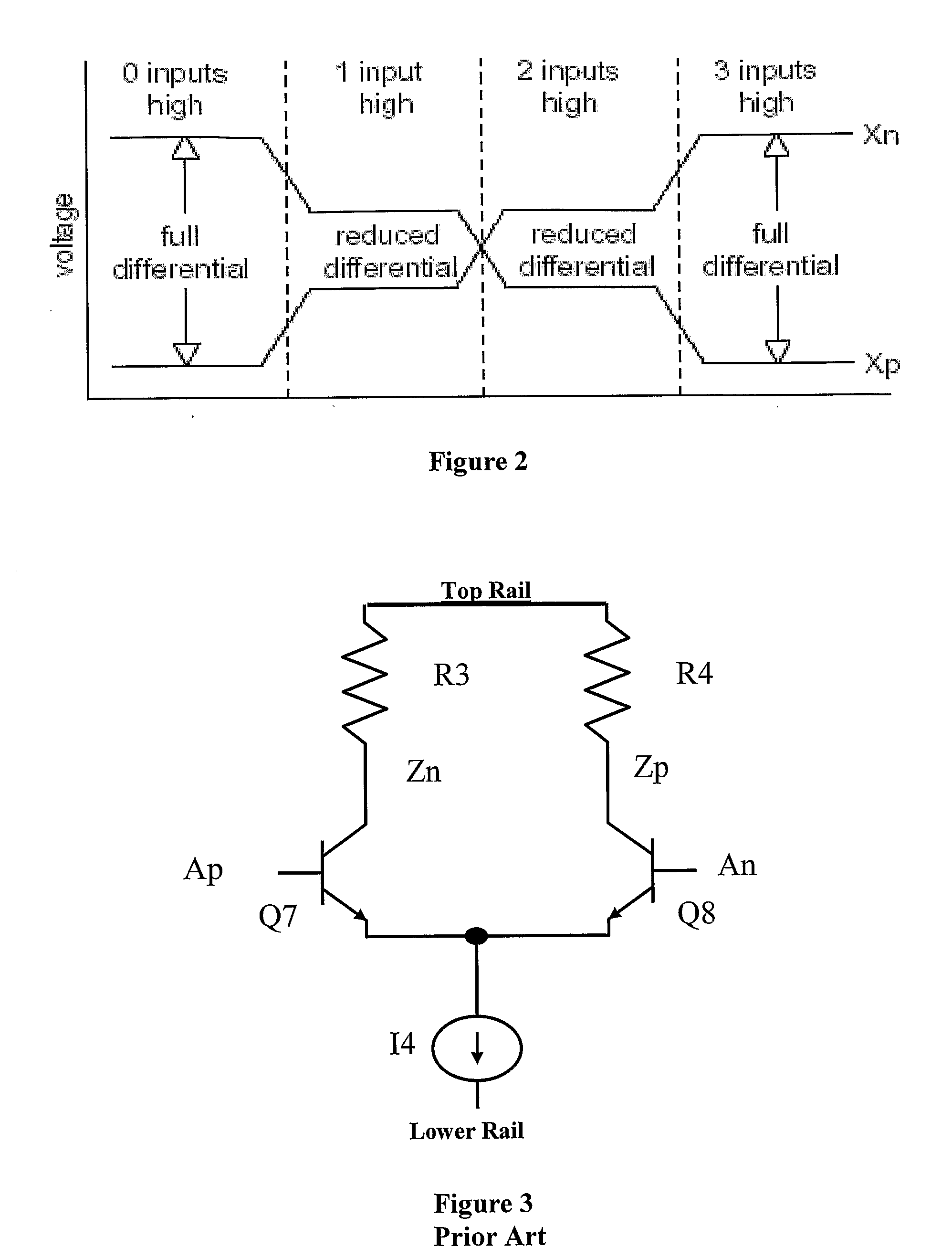

Circuits and techniques for conditioning differential signals

InactiveUS6985021B1Increased propagation delayEasy to operateReliability increasing modificationsPulse automatic controlVoltage amplitudePropagation delay

Circuitry is provided that conditions a differential input signal such that when the signal is received by a multi-standard differential input buffer, the buffer is able to process the conditioned signal without pronounced increases in propagation delay, thereby keeping signal jitter to a minimum. The circuitry further enables input buffers to operate according to desired operating parameters even when the supply voltage powering the input buffer is relatively low. The circuitry operates by shifting the common-mode voltage to a range that puts the input buffer in a favorable common-mode voltage range of operation. The circuitry may be coupled with a programmably controlled amplifier that amplifies the amplitude of the conditioned differential signal prior to being received by the input buffer. Amplifying the signal prevents problems typically associated with data-dependent jitter and intersymbol interference by boosting the voltage amplitude to a level that is readily processed by the input buffer.

Owner:ALTERA CORP

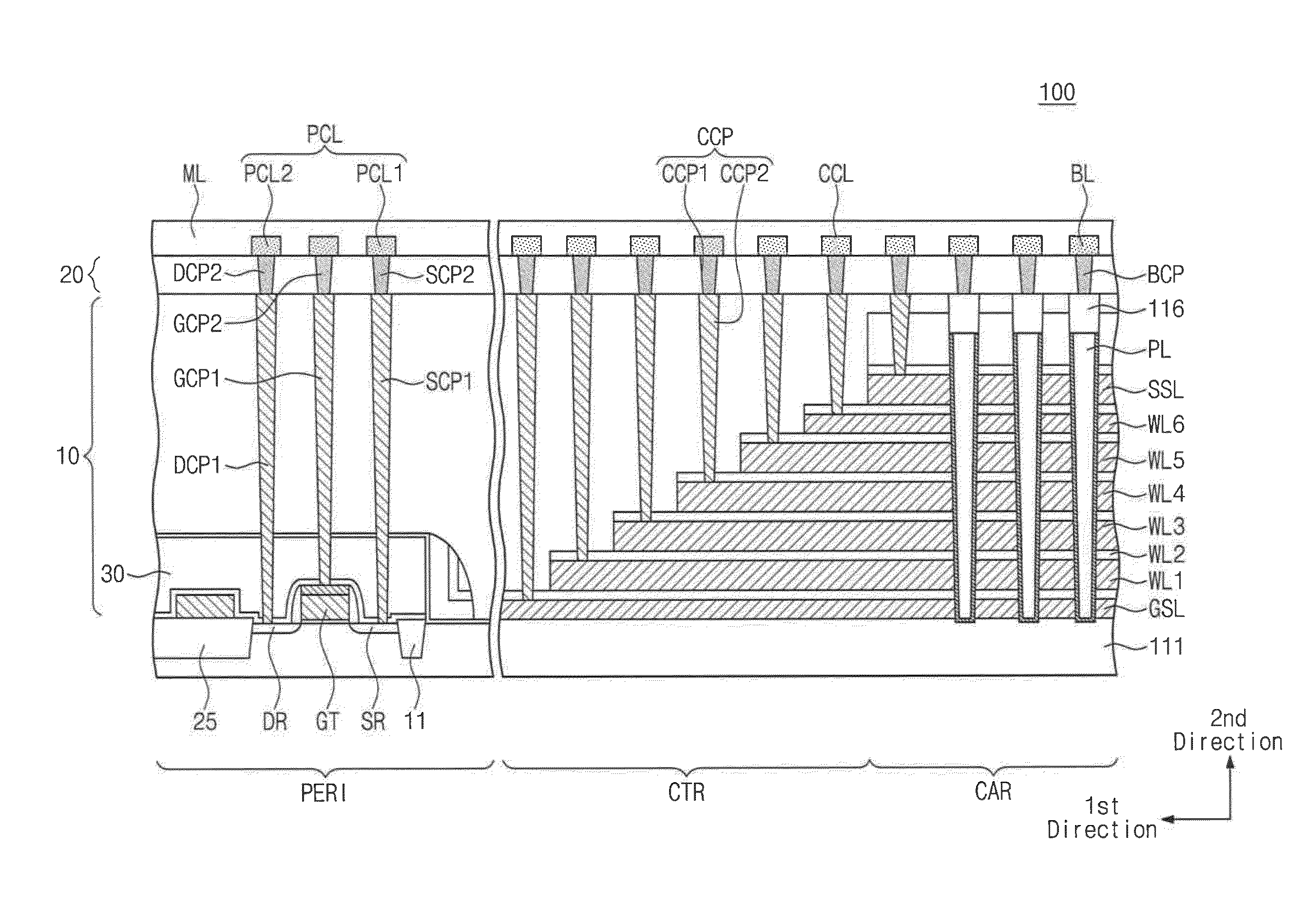

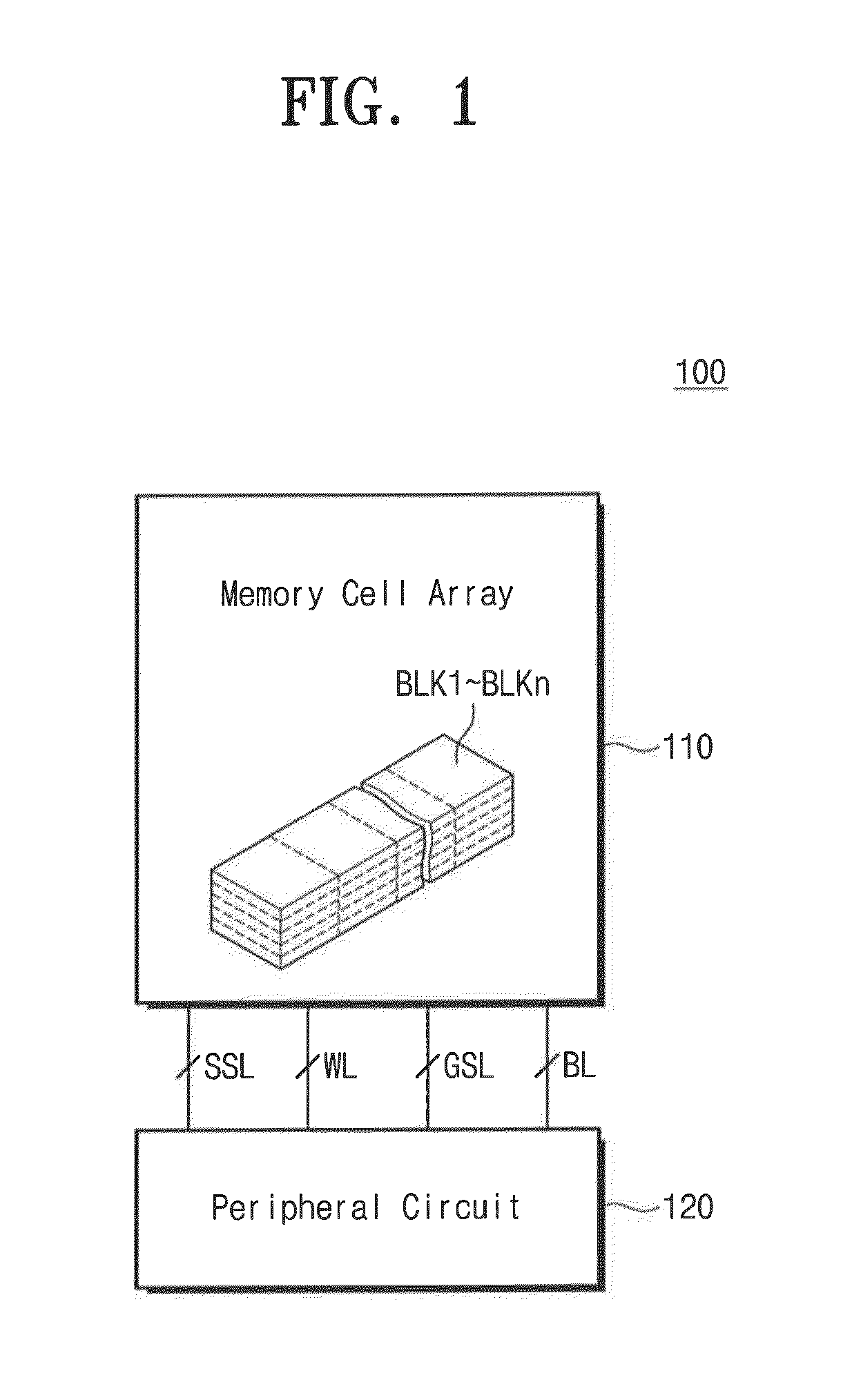

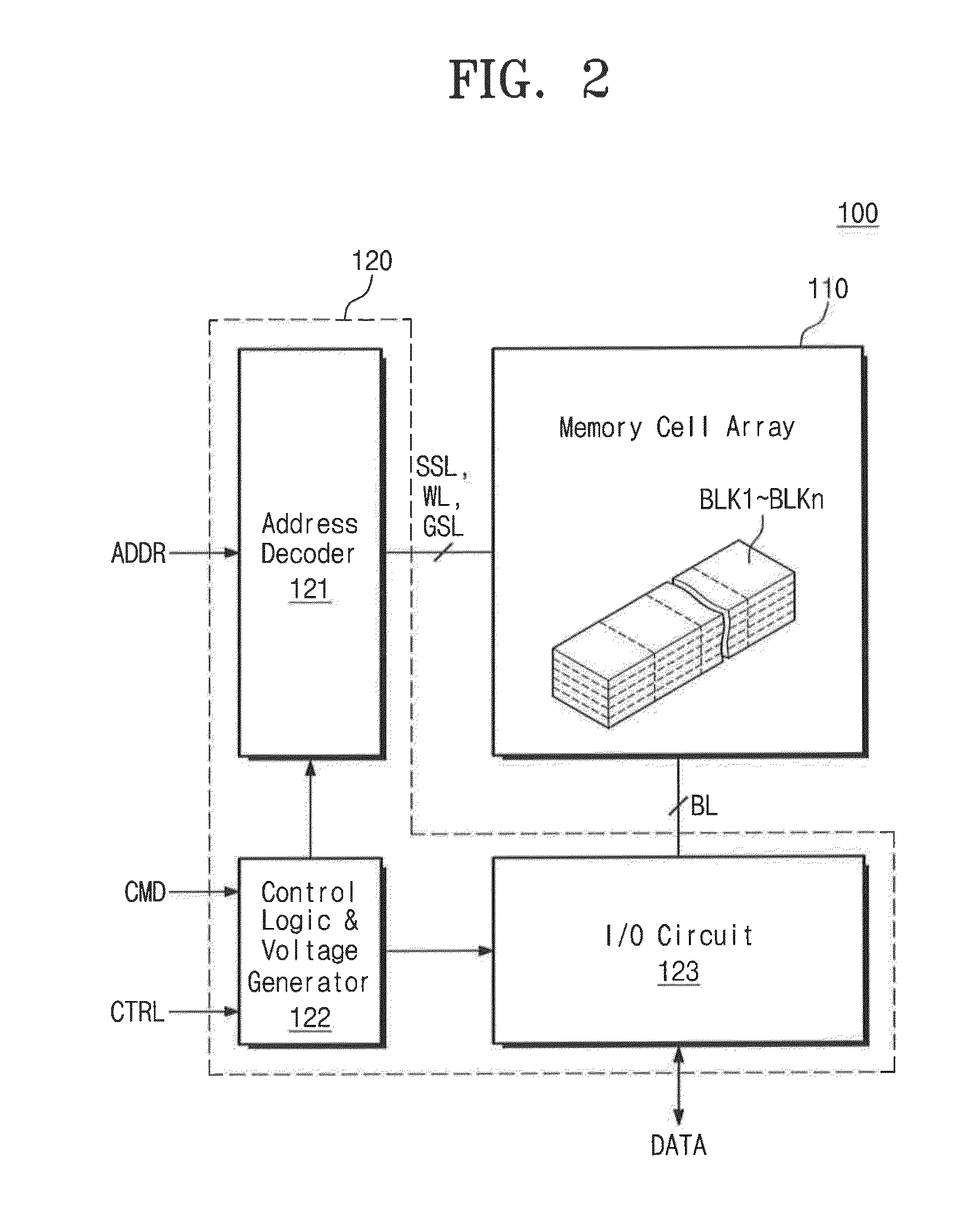

Nonvolatile memory device

ActiveUS20160079259A1Parasitic capacitance and resistanceReduce Propagation DelayTransistorSemiconductor/solid-state device detailsStorage cellNon-volatile memory

A nonvolatile memory device includes a memory cell array and a peripheral circuit. The peripheral circuit is connected to the memory cell array through conductive lines and includes transistors. Each of the transistors is formed on the substrate and includes first and second regions and a gate electrode. In at least one of the transistors, the first region is connected to at least one of the conductive lines through first contact plugs extending in the direction perpendicular to the substrate, and second contact plugs extending in the direction perpendicular to the substrate. A contact area of each of the first contact plugs is different from a contact area of each of the second contact plugs.

Owner:SAMSUNG ELECTRONICS CO LTD

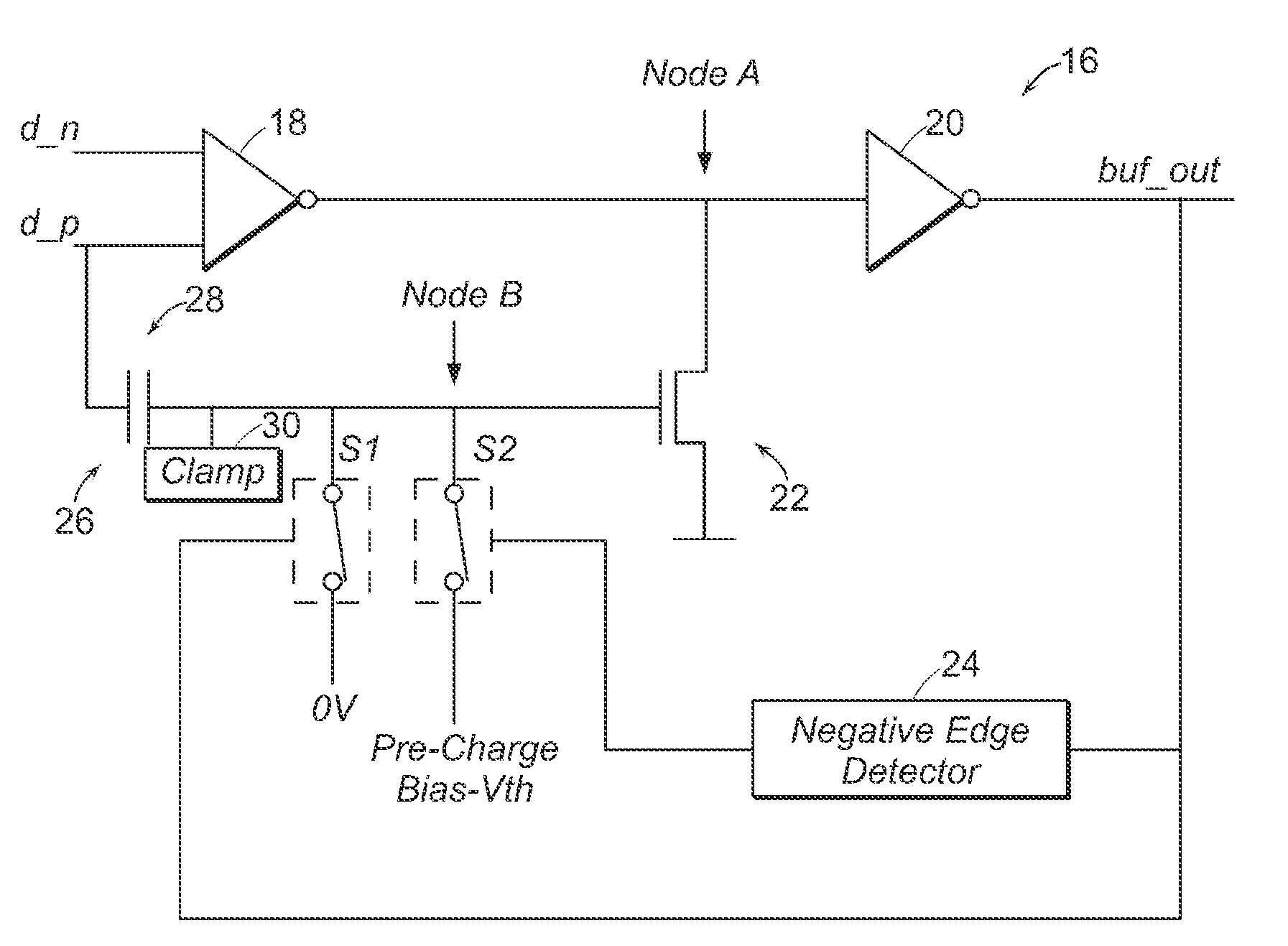

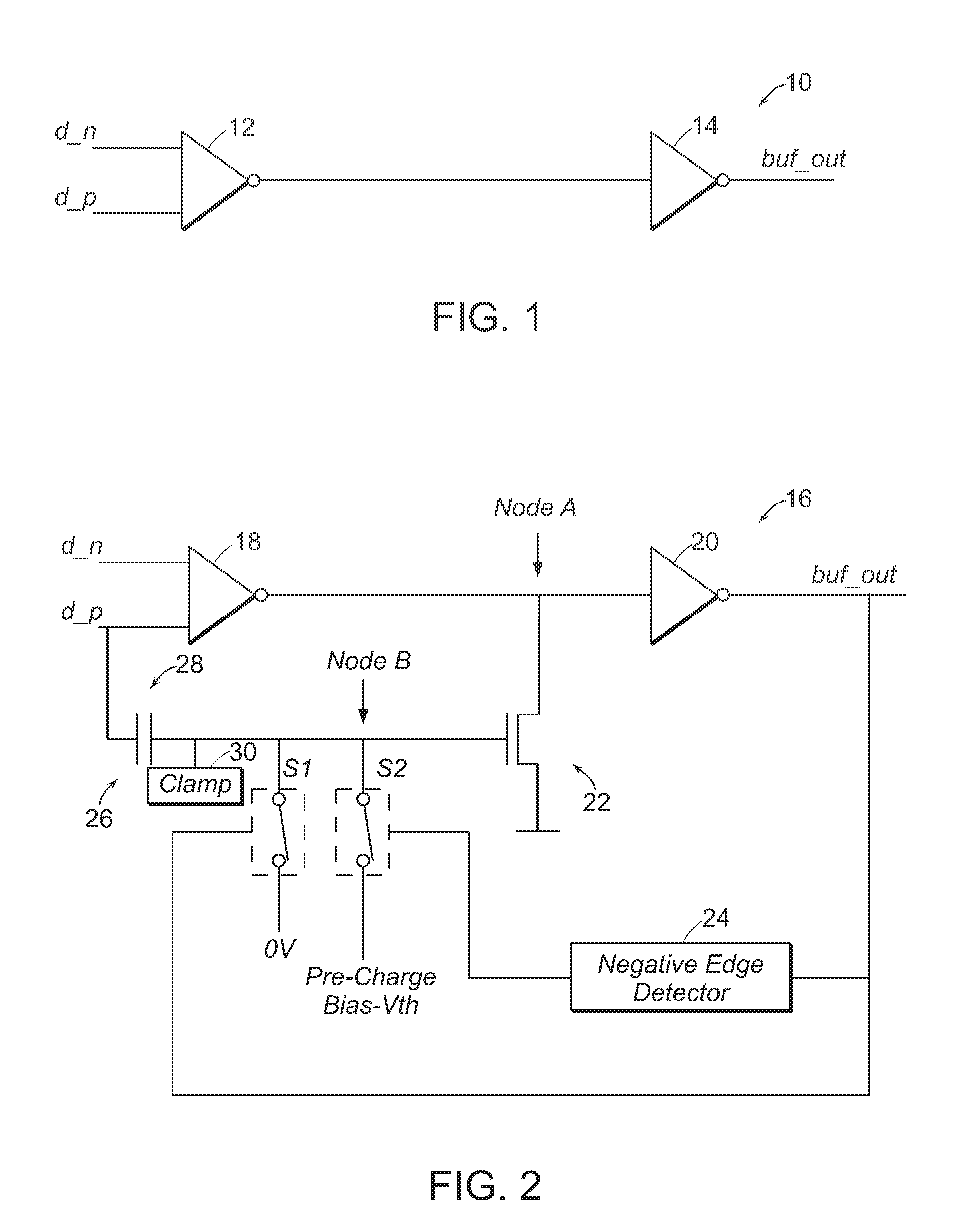

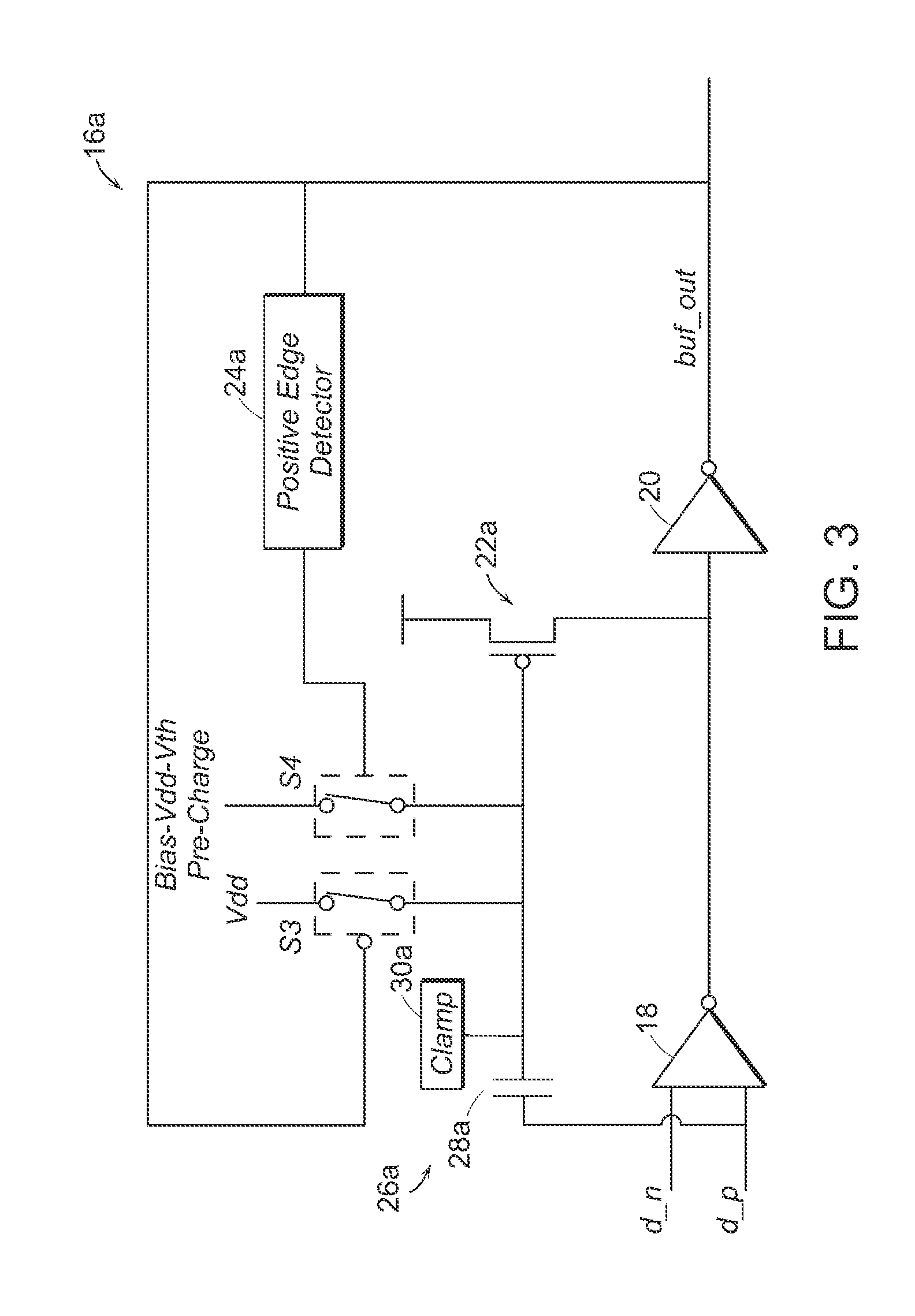

Capacitive feedforward circuit, system, and method to reduce buffer propagation delay

ActiveUS7279925B1Reduce Propagation DelayReduce degradationTransistorReliability increasing modificationsData bufferPropagation delay

A buffer circuit, system, and method are provided. The buffer circuit includes a control circuit coupled to an output of the buffer, or possibly to an output of the first stage of a buffer. A pre-charge circuit is also provided coupled to bias an input of the control circuit to a voltage value approximately near a threshold voltage of the control circuit. The pre-charge bias amount is slightly less than the amount needed to place the control circuit in a high current conduction state. A coupling circuit is thereafter used and adapted to couple an input voltage applied to the buffer circuit to the input of the control circuit. This causes the control circuit to enter the high current conduction state. Depending on the input impedance of the coupling circuit, by pre-charging the coupling circuit input, less time is needed to cause the coupling circuit to enter and thereafter leave a high current conduction state. Therefore, by pre-charging the coupling circuit, output transitions from the buffer circuit can be accelerated and propagation delay reduced. The pre-charge circuit and the control circuit operate on one or more stages of a single or multi-stage buffer, operate on single-ended or differential / complementary input / output, and operate to speed up either the rising, falling, or both edges transitions at the output of the buffer.

Owner:MONTEREY RES LLC

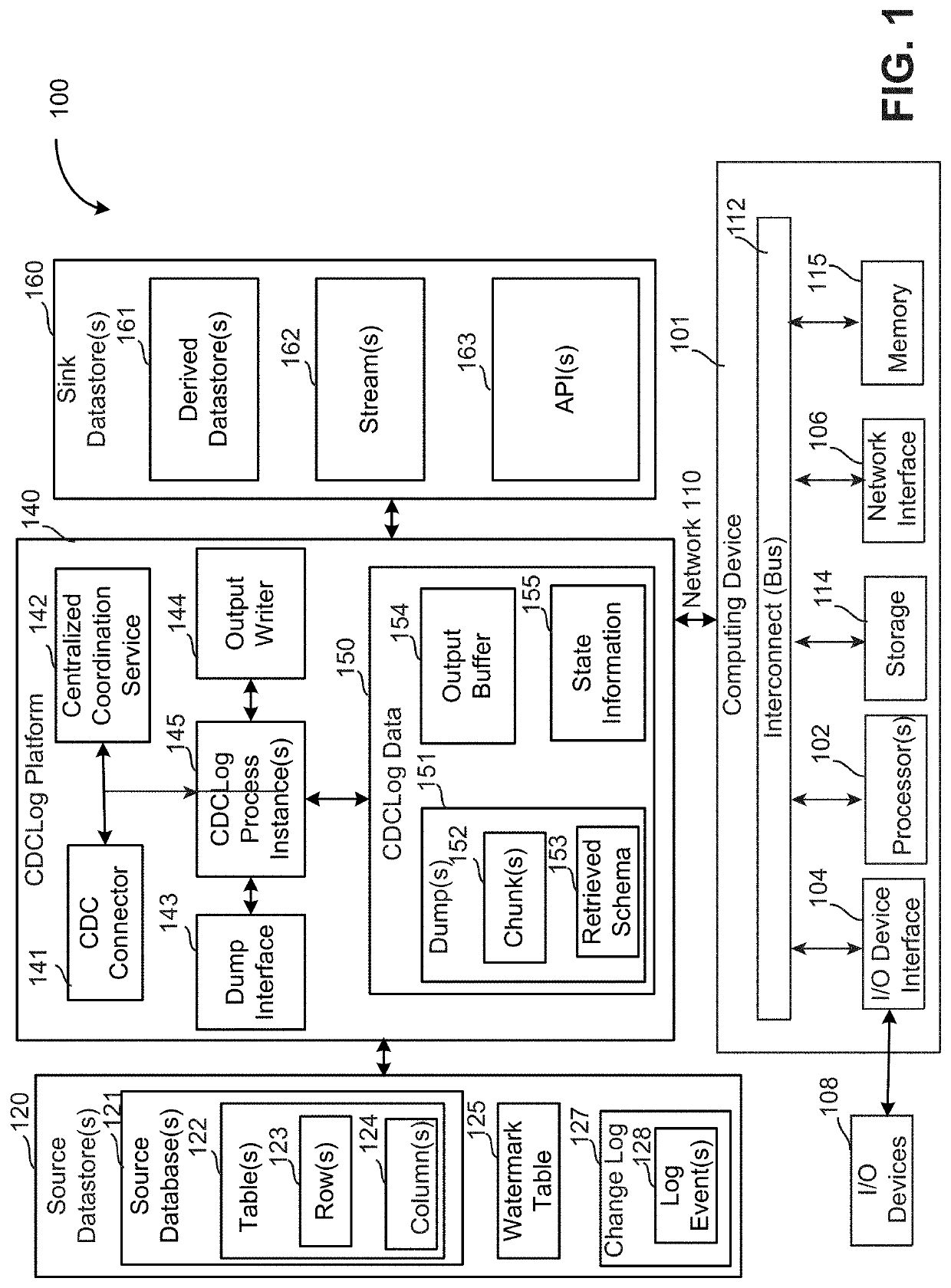

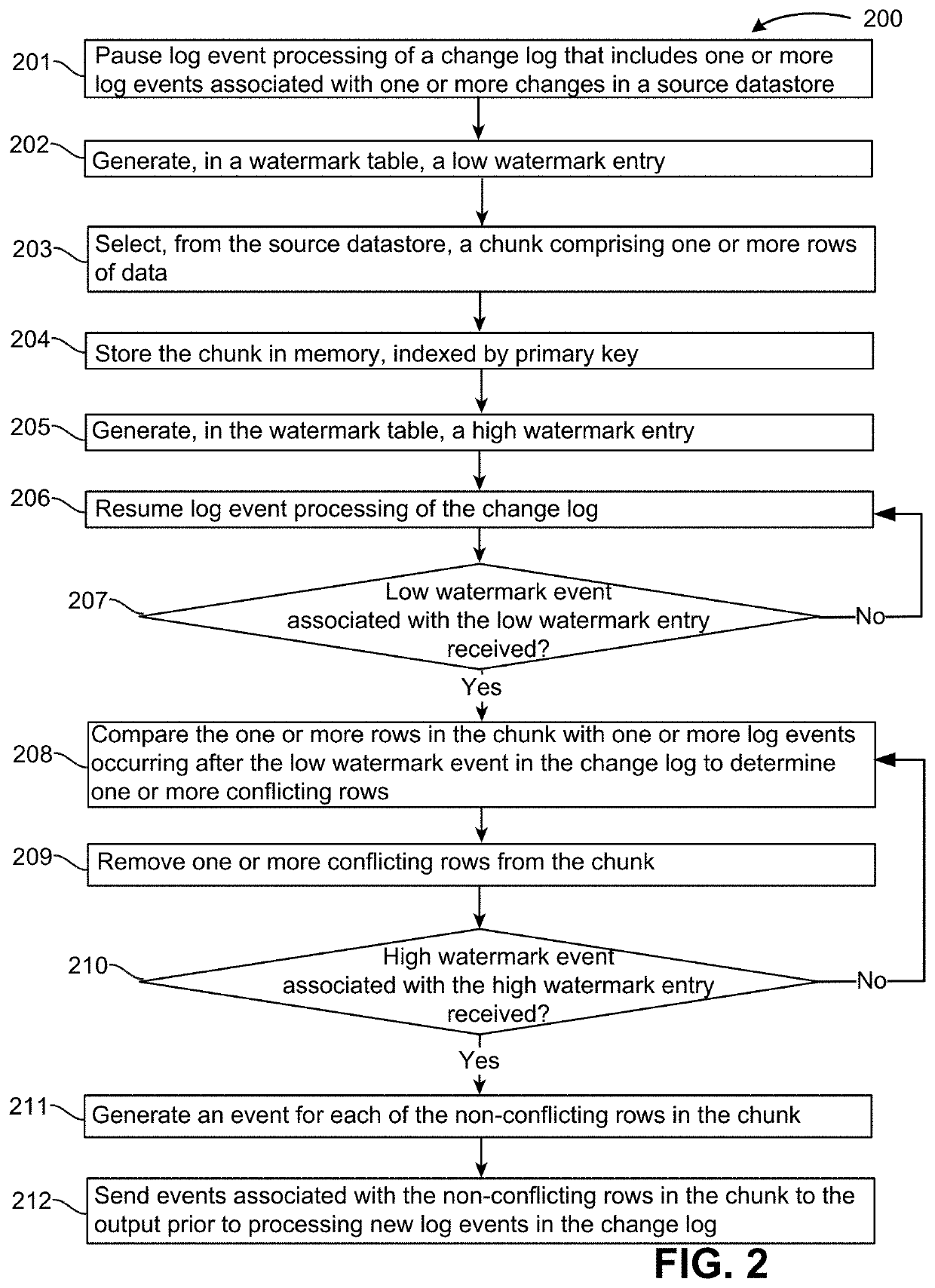

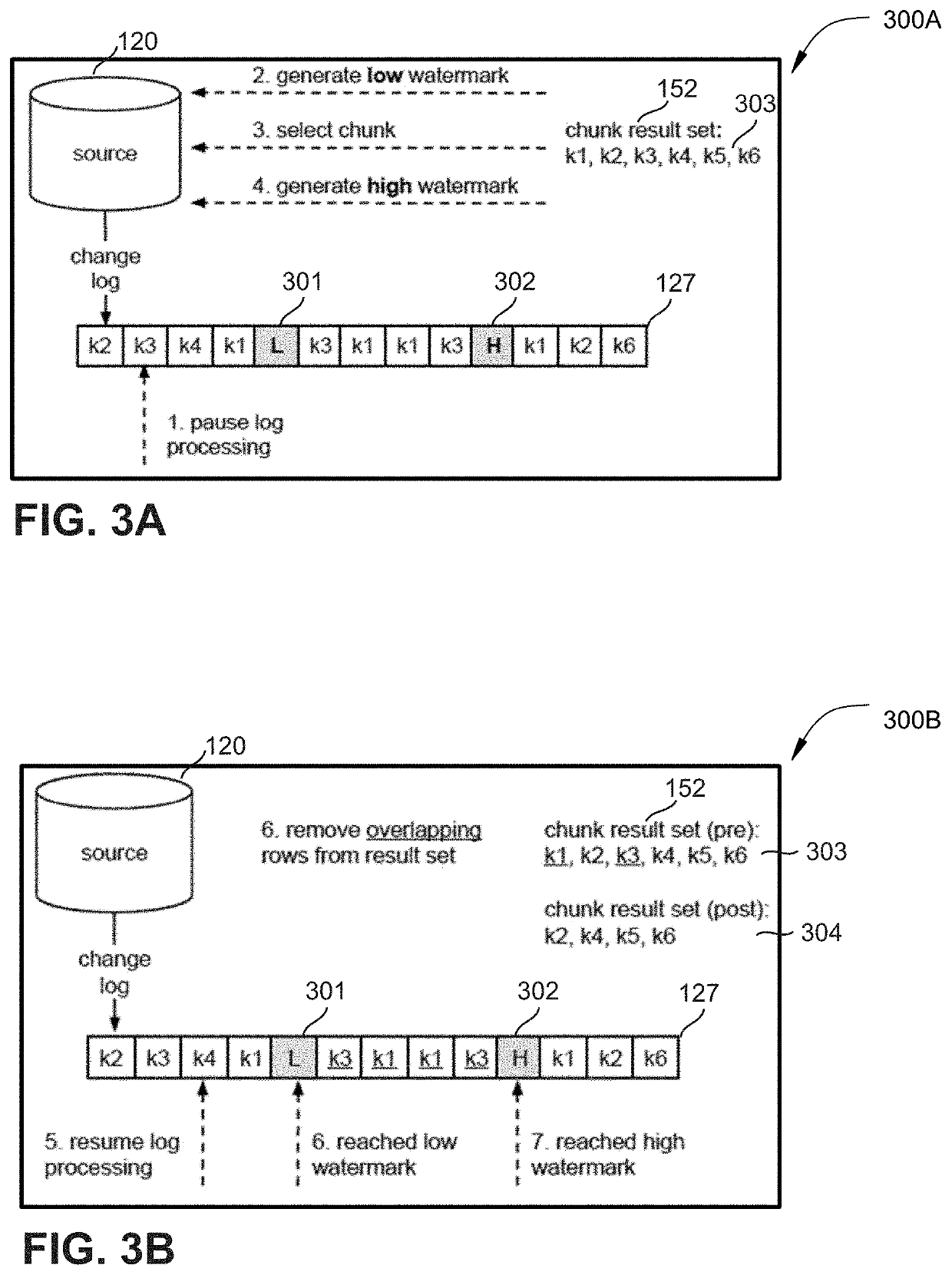

Watermark-based techniques for change-data-capture

ActiveUS20210182267A1Improve usabilityReduce Propagation DelayDatabase updatingDatabase distribution/replicationData miningData store

Various embodiments set forth systems and techniques for concurrent log and dump processing. The techniques include selecting, from a datastore, a chunk comprising one or more rows of data; comparing the one or more rows of data in the chunk with a first set of log events in a change log associated with the datastore, wherein each log event included in the first set of log events occurs after a first log event in the change log and prior to a second log event in the change log; selecting, based on the comparison, one or more non-conflicting rows in the chunk; and transmitting, to an output, one or more log events associated with the one or more non-conflicting rows in the chunk prior to processing a second set of log events in the change log, wherein the second set of log events occur after the second log event.

Owner:NETFLIX

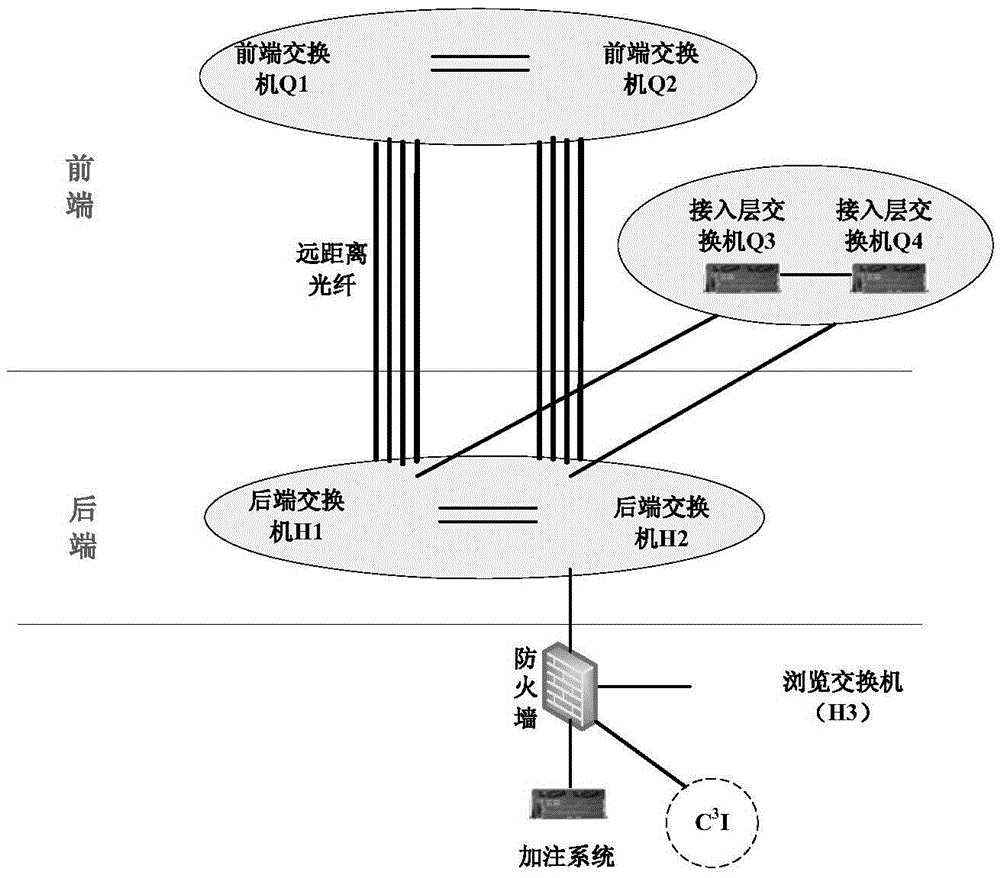

Practical system-level redundant communication network architecture

ActiveCN105610555AReduce occupancySimple topologyError preventionData switching networksIp addressNetwork architecture

The invention discloses practical system-level redundant communication network architecture. Switches of a backbone network of the network architecture adopt a VSS (Virtual Switching System) technology to realize redundancy, two mutually redundant network switches are equivalent to virtual machines and have the same IP (Internet Protocol) address, so that fault switching can be realized in the shorter time; when the virtual switches carry out data communication, IP switching and judgment of the switches are not needed, so that occupation of resources, such as a CPU (Central Processing Unit) and an internal storage, can be effectively reduced; in addition, the network topology is simplified from the logical level through the VSS technology, and the mutually redundant network switches share one gateway address, so that loop-less communication is realized and the reliability of a communication network system can be effectively improved; an optical fiber for connecting a front-end switch and a back-end switch of the backbone network adopts a GEC (Gigabit Ethemet Channel) technology to bind one Ethernet channel, so that the data transmission bandwidth of the communication network can be effectively widened and the information throughput rate can be improved, and thus the propagation delay for front-end communication and back-end communication is reduced.

Owner:BEIJING INST OF ASTRONAUTICAL SYST ENG +1

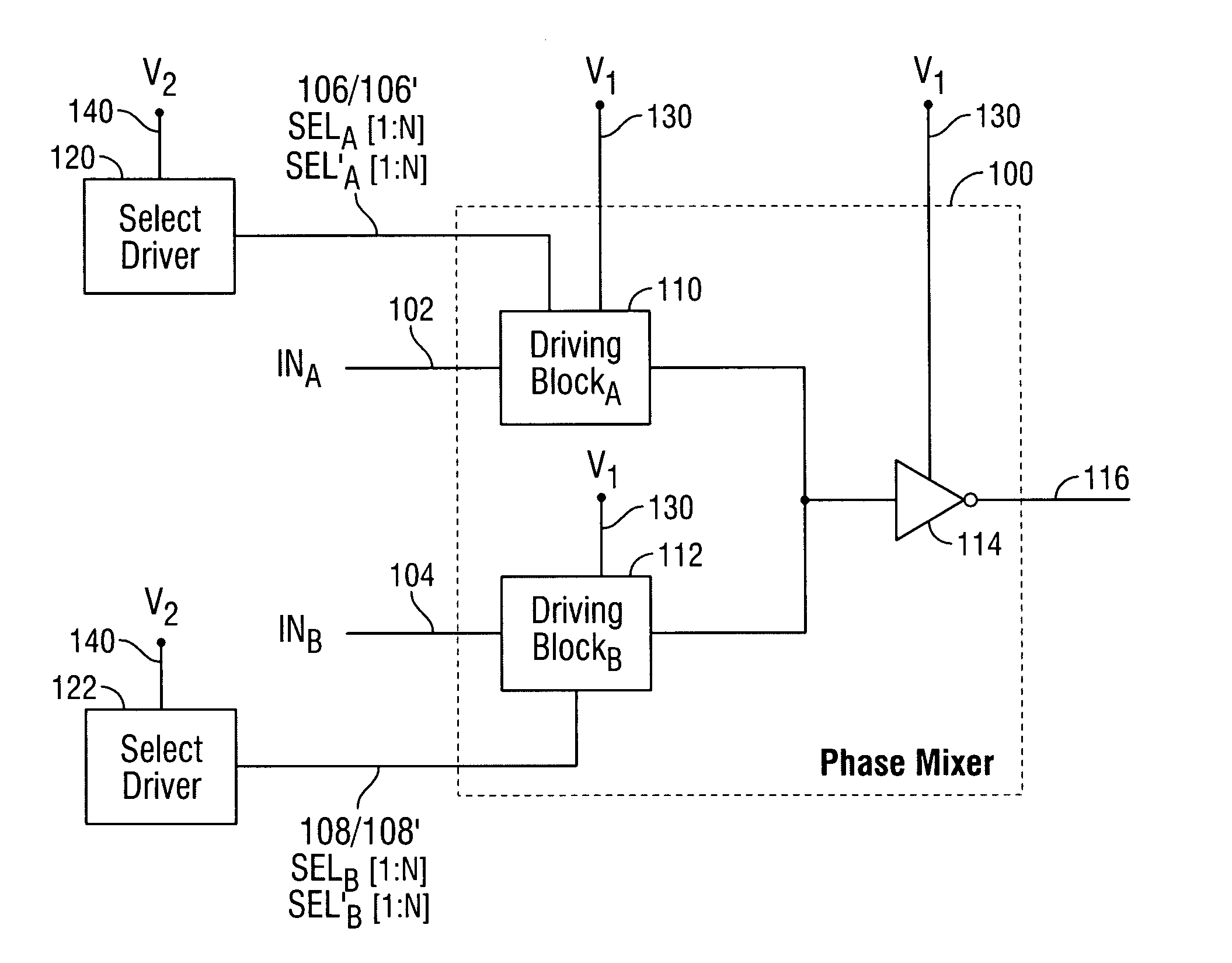

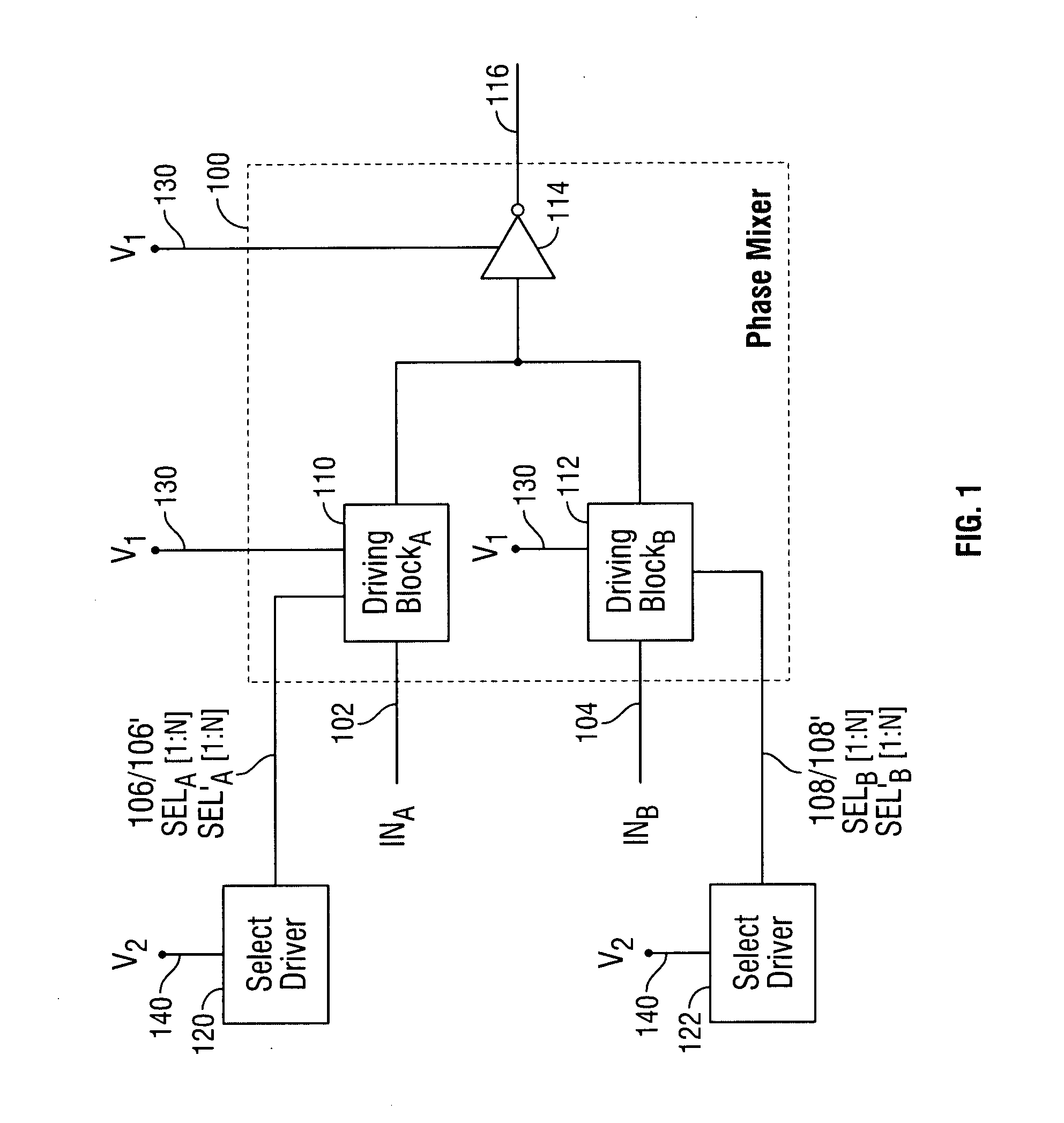

Digital phase mixers with enhanced speed

InactiveUS20050110554A1Reduce Propagation DelayReduce degradationComputations using contact-making devicesInstant pulse delivery arrangementsPropagation delayEngineering

Digital phase mixers with enhanced speed are provided. A phase mixer generates a signal having a phase between the phases of two input signals based on select signals. The propagation delay of the output signal is reduced by using a first voltage source to drive the input signals and the output signal and a second voltage source, having a higher voltage than the first voltage source, to drive the select signals. The higher voltage source reduces the impedance of each transistor driven by the select signals, thus reducing the propagation delay at the output of the phase mixer. For a non-differential digital phase mixer, the propagation delay is reduced in the rising edges of the output signal. For a differential digital phase mixer, the propagation delay is reduced in the rising and falling edges of the output signal.

Owner:ROUND ROCK RES LLC

Expression method for big data association relation in smart city

InactiveCN105512327AReduce Propagation DelayQuick responseRelational databasesSpecial data processing applicationsRelation graphPropagation time

The invention discloses an expression method for the big data association relation in a smart city. According to the method, transmissibility of the data relation is utilized for converting the partial indirect data relation into the direct data relation under the relation transmitting constraint condition, and response speed of data to changes is increased; in a data relation graph, some data relations can be transmitted among multiple data, the first data at the beginning of transmission is called an initial data, and the last data when transmission arrives is called a finishing point data. According to the association relation expression method adopting a data relation network, the basic data relation and the multi-stage data relation are defined, the transmission mechanism of the data relation is utilized for converting the transmission relation into the direct relation, the potential data association is found, propagation time delay for data updating is shortened, the response speed of the data relation graph to the dynamic changes is accelerated, and working efficiency of activating data is improved.

Owner:BEIHANG UNIV

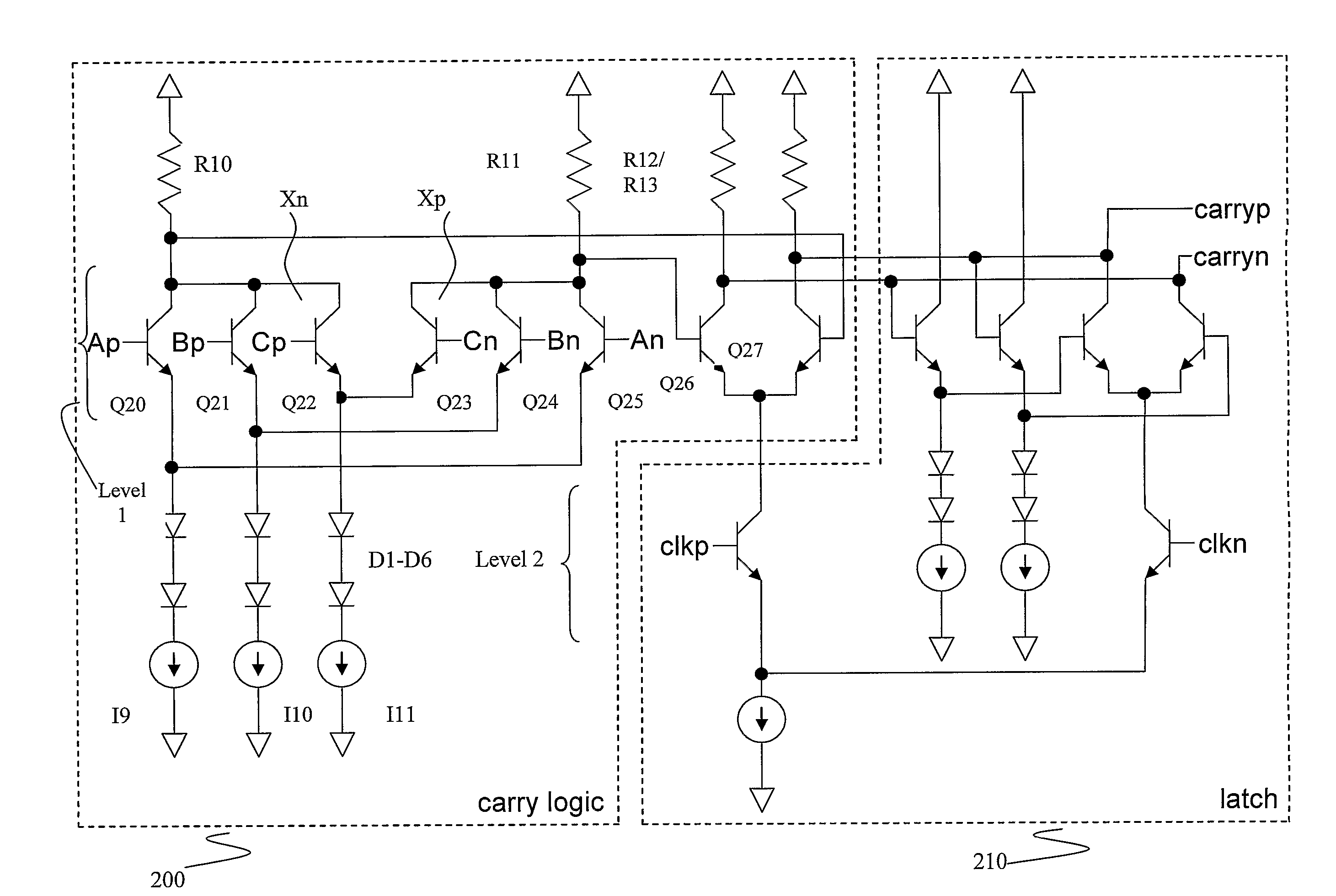

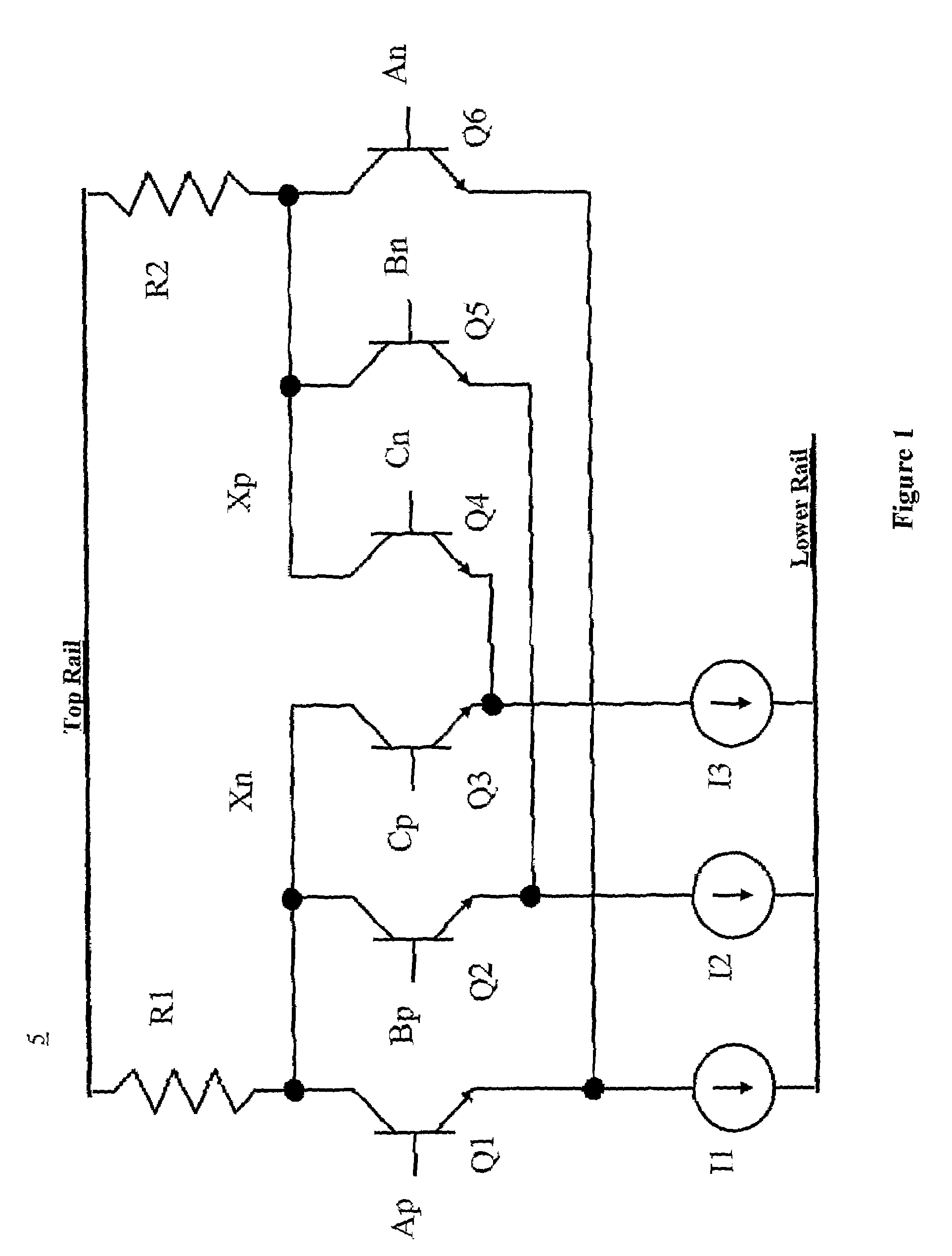

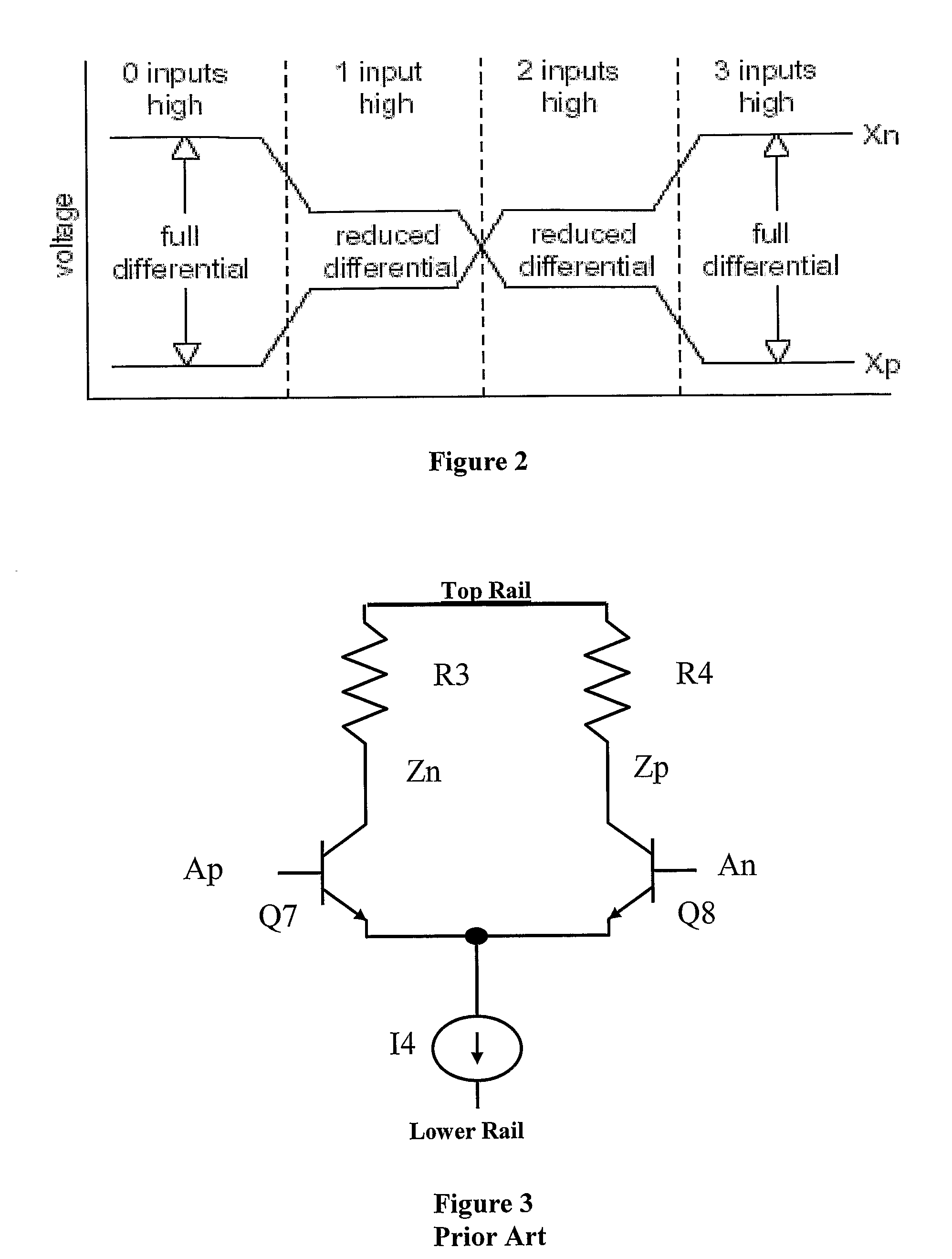

Single-level parallel-gated carry/majority circuits and systems therefrom

InactiveUS7565392B2Increase clock frequencyReduce Propagation DelayExclusive-OR circuitsMajority/minority circuitsEngineeringSingle level

Owner:BAE SYST INFORMATION & ELECTRONICS SYST INTERGRATION INC

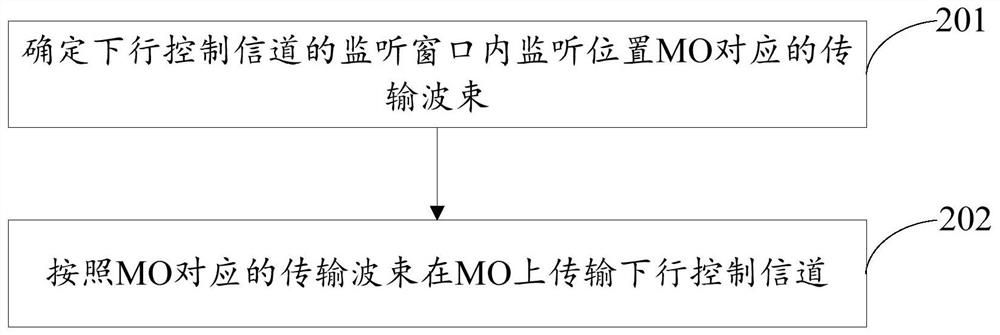

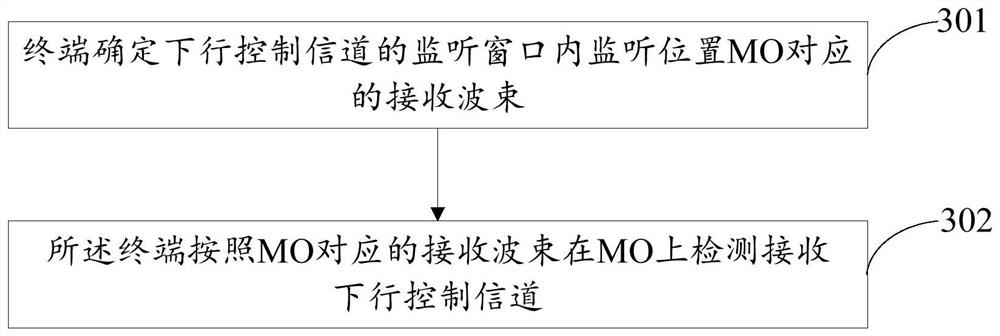

Channel transmission method and communication equipment

ActiveCN112564751AReduce Propagation DelayImprove transmission reliabilityPower managementSpatial transmit diversityPropagation delaySoftware engineering

The embodiment of the invention provides a channel transmission method and communication equipment. The method comprises the following steps: determining a transmission beam corresponding to a monitoring position MO in a monitoring window of a downlink control channel; and transmitting the downlink control channel on the MO according to the transmission beam corresponding to the MO. Thus, when thetransmission beam changes, the propagation delay of the downlink control channel can be reduced, and the transmission reliability of the downlink control channel can be improved.

Owner:DATANG MOBILE COMM EQUIP CO LTD

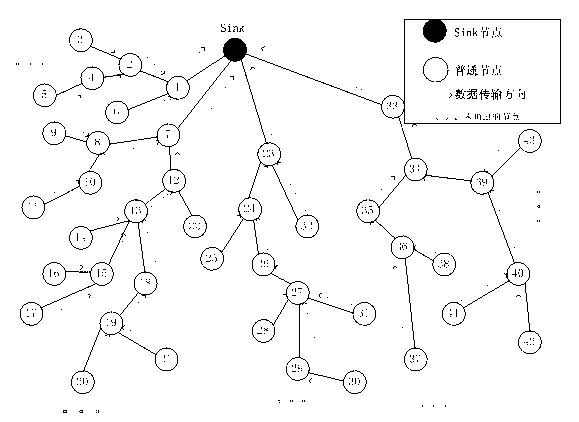

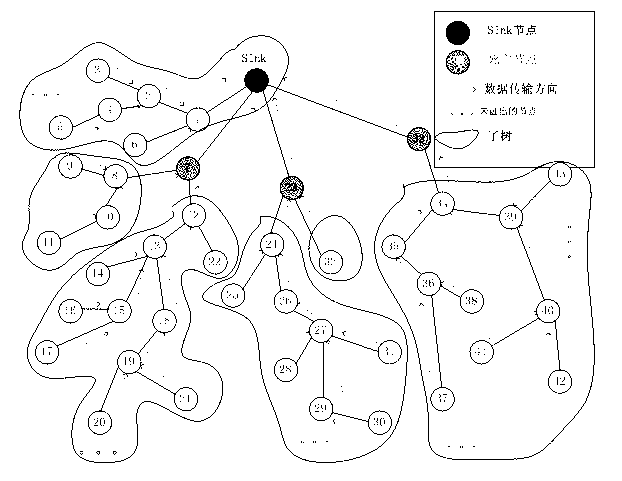

Wireless sensor network data acquisition method based on multiple mobile factors

InactiveCN103269505AExtend the life cycleReduce node energy consumptionNetwork topologiesHigh level techniquesWireless sensor networkingData acquisition

The invention discloses a wireless sensor network data acquisition method based on multiple mobile factors, and aims to save energy consumed by transmission of a large amount of data, effectively use network resources, prolong the service life of a network and balance a relation between multiple hops and cache overflow. The wireless sensor network data acquisition method comprises the following steps of 1, acquiring data by forming a tree-shaped structure by network self-organization; 2, informing node state information to a base station and a direct subsequent node by a low-electric-quantity node; 3, dispatching multiple mobile factors to respective sub-trees to finish corresponding acquisition tasks by the base station, wherein when the whole network is divided into a plurality of sub-trees, the nodes in the sub-trees acquire the data and forward the data to the mobile factors through one hop when the mobile factors dispatched by the base station reach a communication radius range instead of forwarding the data according to an original tree-shaped structure; 4, designing the optimal path of the mobile factors; and 5, cooperatively finishing data acquisition of the whole network by the mobile factors.

Owner:NANJING UNIV OF POSTS & TELECOMM

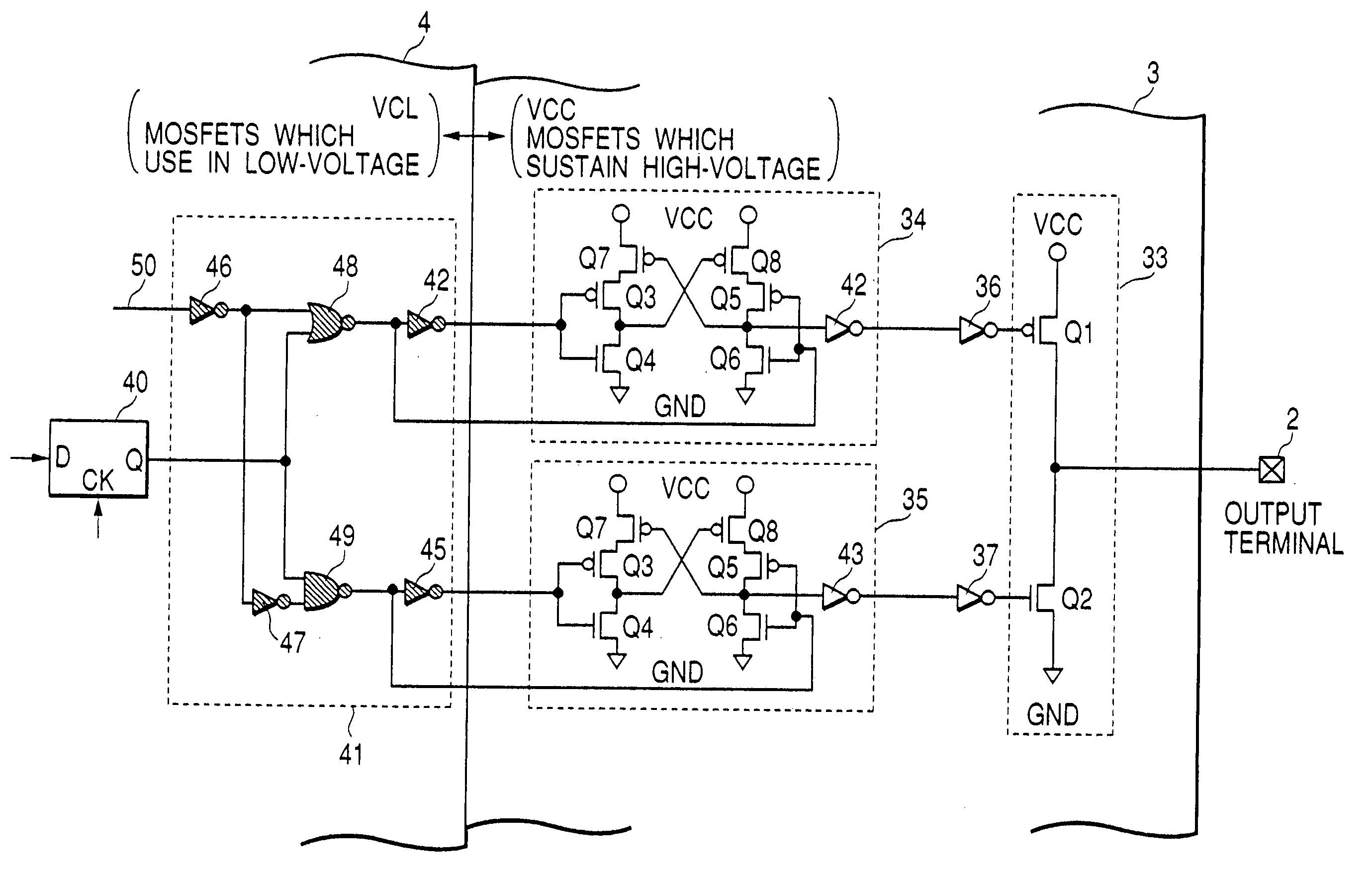

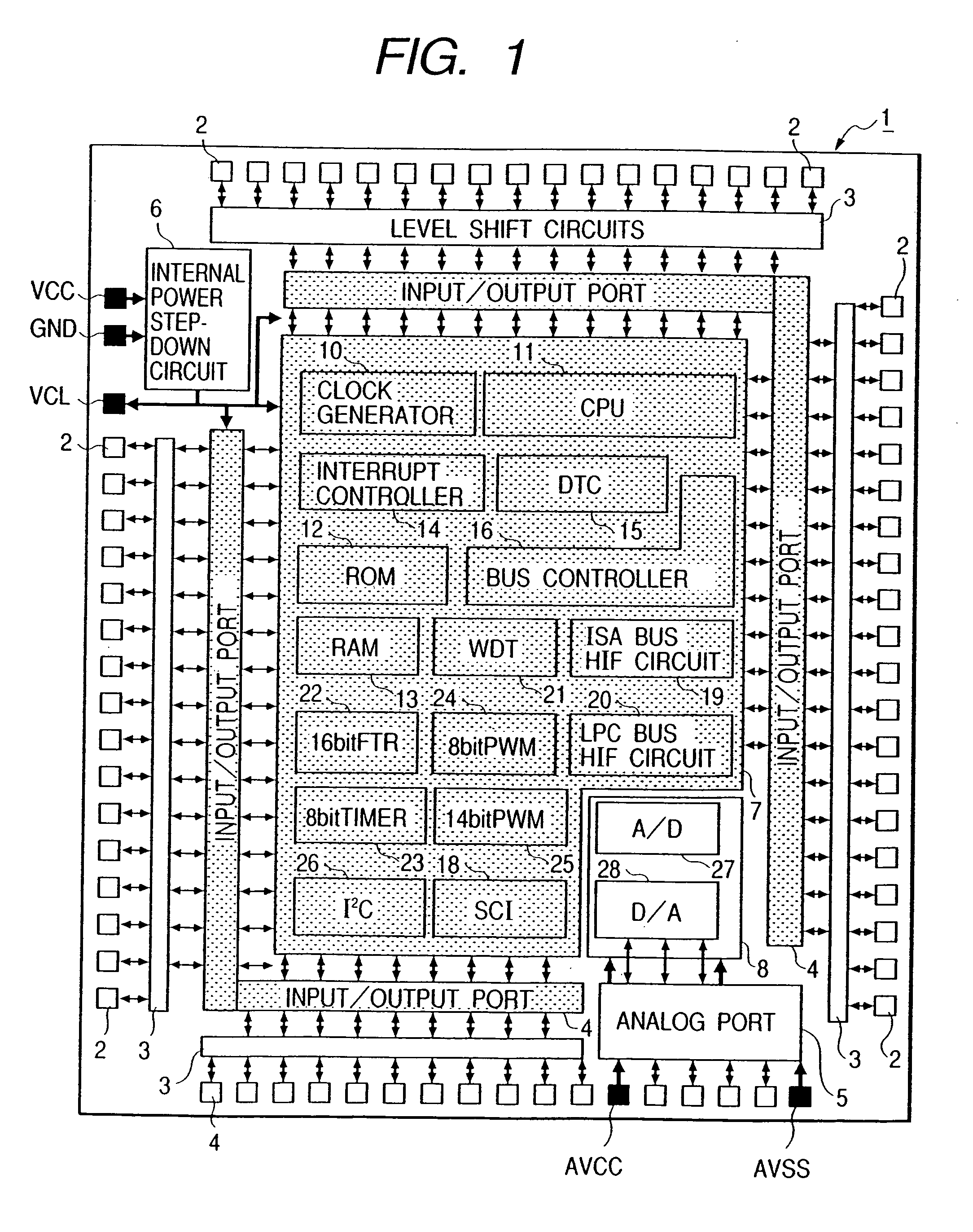

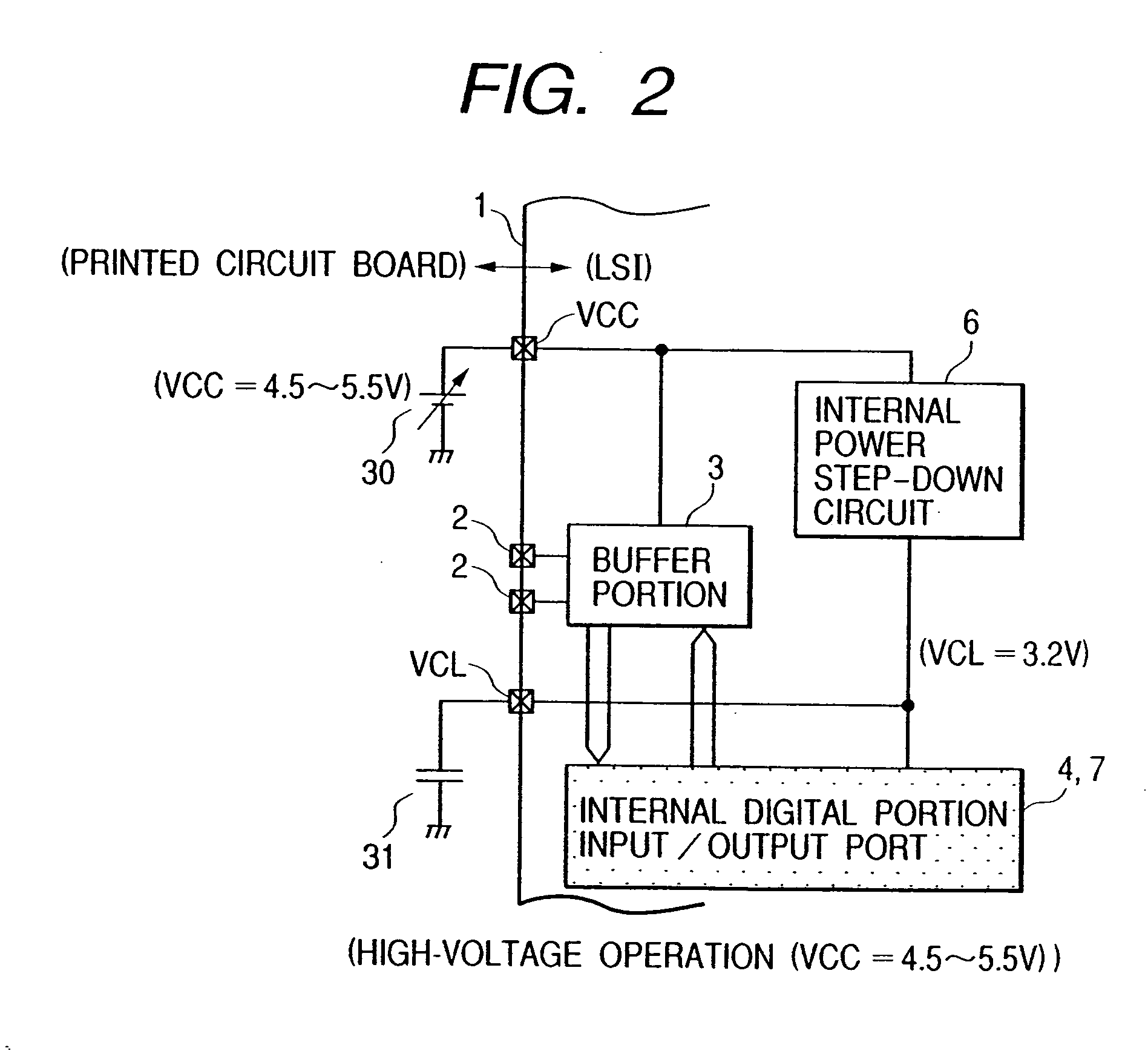

Semiconductor integrated circuit and a burn-in method thereof

InactiveUS20050231262A1Reduce the impactReduce Propagation DelayMultiple input and output pulse circuitsAnalog circuit testingLow voltageHigh pressure

A semiconductor integrated circuit includes a first circuit and a second circuit having a breakdown voltage higher than that of the first circuit. Operation voltages of the first and second circuits can be made equal to or different from each other. The second circuit has a level shift circuit for shifting the level of an output signal of the first circuit in accordance with an operation voltage of the second circuit, an external output buffer having an input that can receive, selectively, an output signal of the level shift circuit or an input signal that bypasses the level shift circuit. When the first and second circuits operate with a low voltage, bypass is selected. In high-voltage operation and burn-in, the level shift circuit is selected.

Owner:RENESAS ELECTRONICS CORP

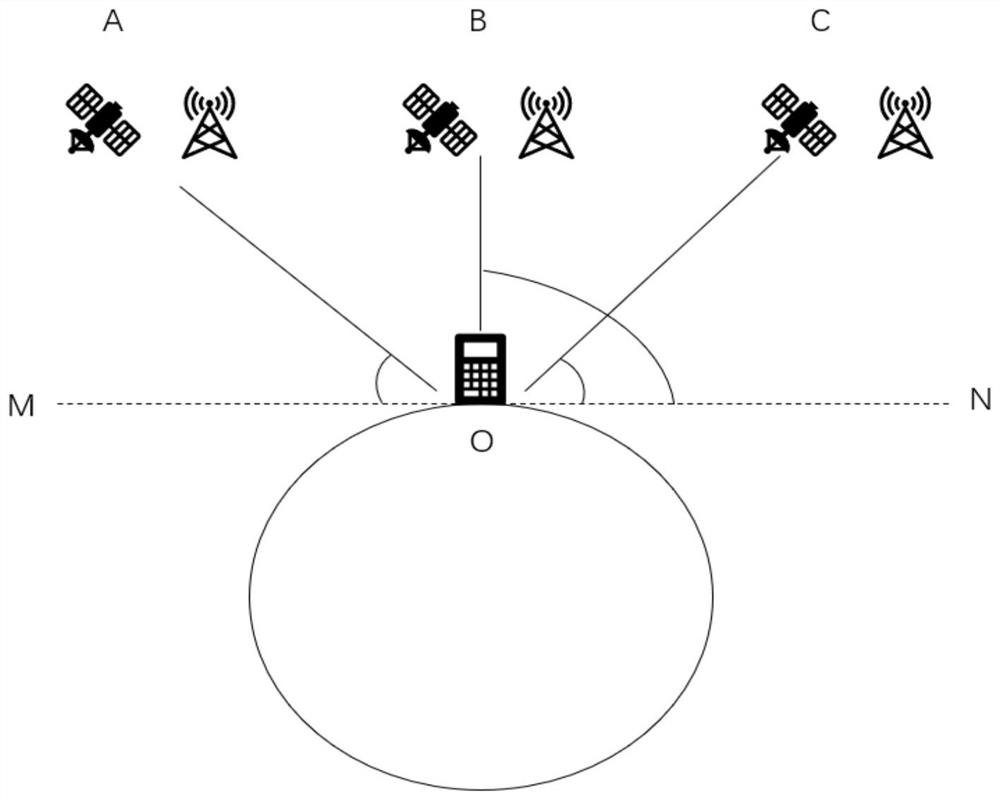

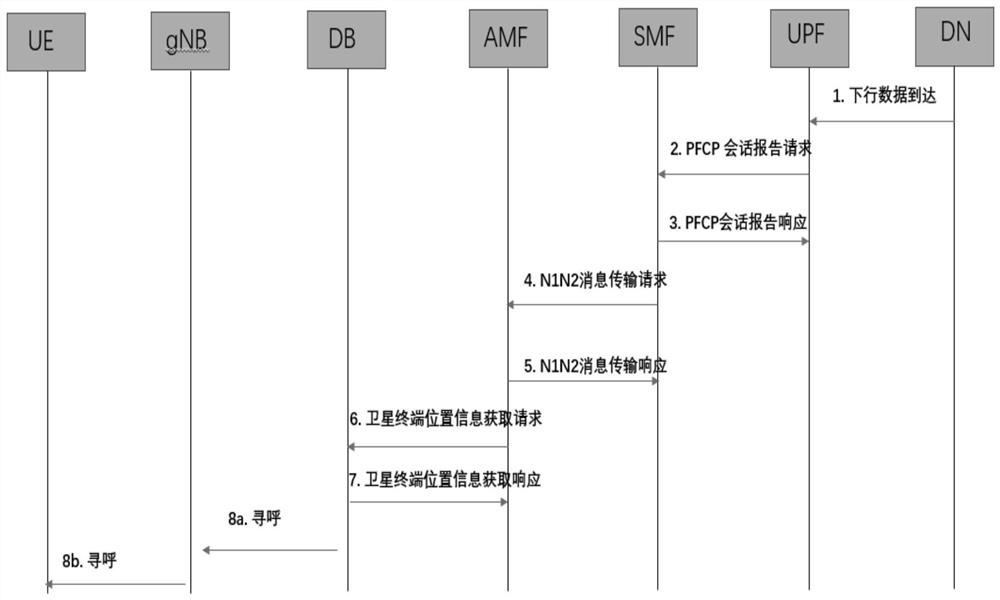

Space-ground integrated fusion network, paging method and core network

ActiveCN113328781AReduce communication overheadSmall queue lengthRadio transmissionHigh level techniquesPropagation delayEngineering

The invention discloses a space-ground integrated fusion network, which comprises a core network and communication satellites. The space-ground integrated fusion network comprises the core network and the plurality of communication satellites, wherein the core network performs routing selection on a set formed by a first communication satellite group and a second communication satellite group, and the plurality of communication satellites determined by the routing selection initiate paging to a satellite terminal, the first communication satellite group and the second communication satellite group respectively comprise at least one communication satellite, an elevation angle of the communication satellite in the first communication satellite group relative to the core network is maximum, and an elevation angle of the communication satellite in the second communication satellite group relative to the satellite terminal is maximum. According to the space-ground integrated fusion network, the reliability of all available communication satellites is considered globally, on one hand, the advantages of acquiring the shortest topological path and the like of a routing selection algorithm can be played, and the properties of channel bandwidth, average communication traffic, communication overhead, queue length, propagation delay and the like of routing can be improved. The space-ground integrated fusion network is widely applied to the technical field of satellite communication.

Owner:IPLOOK NETWORKS CO LTD

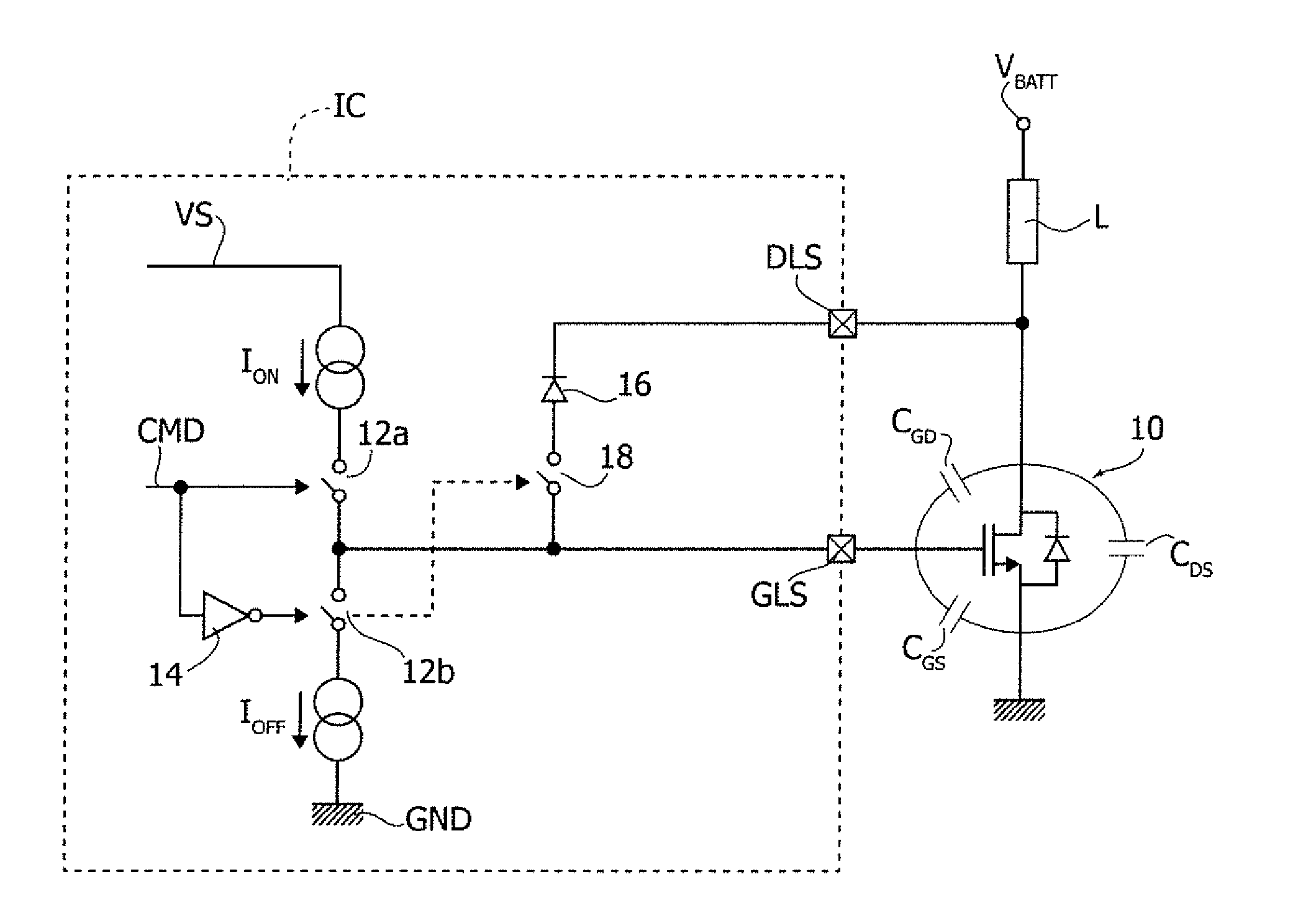

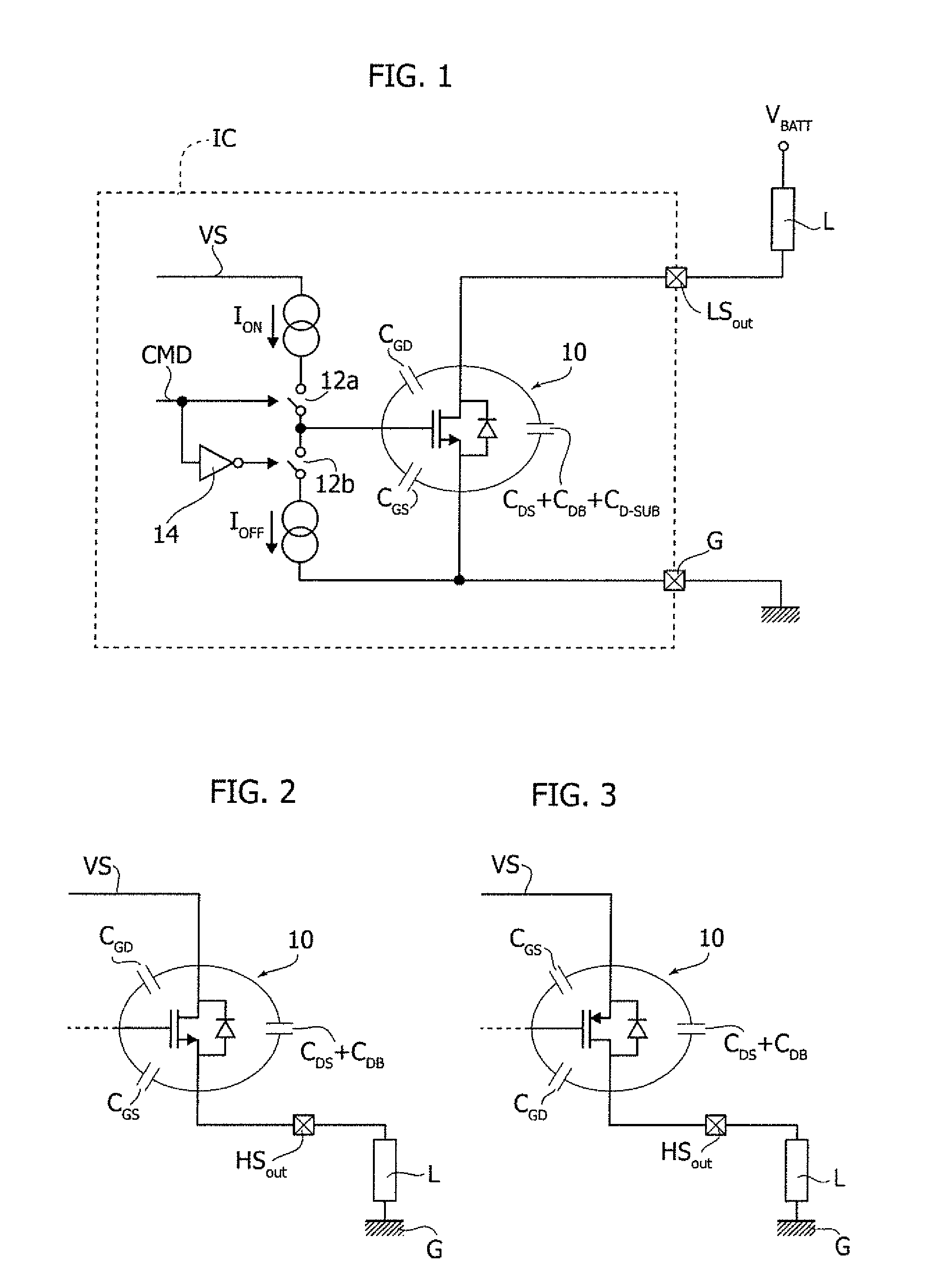

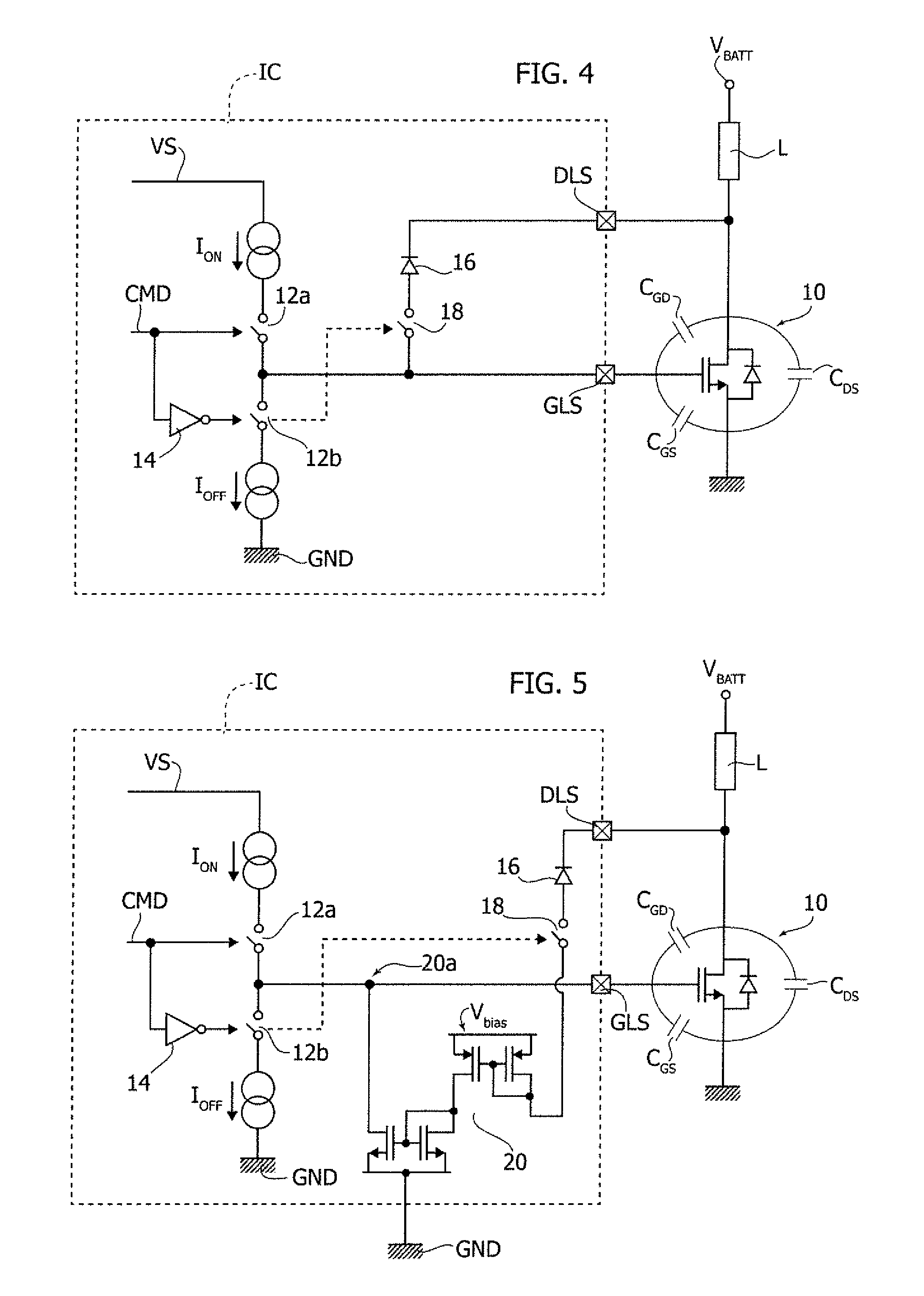

Driver device for transistors, and corresponding integrated circuit

ActiveUS20160094210A1Reduce Propagation DelayEasy to useTransistorElectronic switchingPower flowElectrical current

A driver device is for switching on and off a transistor for supplying a load by driving a control electrode of the transistor. The driver device includes a first terminal connected to the control electrode of the transistor, a second terminal connected between the transistor and the load, and a current-discharge path coupled to the first terminal. The current-discharge path includes a diode and is activated when the transistor is switched off. The diode becomes non-conductive to interrupt the current-discharge path when the voltage on the second terminal reaches a threshold value.

Owner:STMICROELECTRONICS INT NV

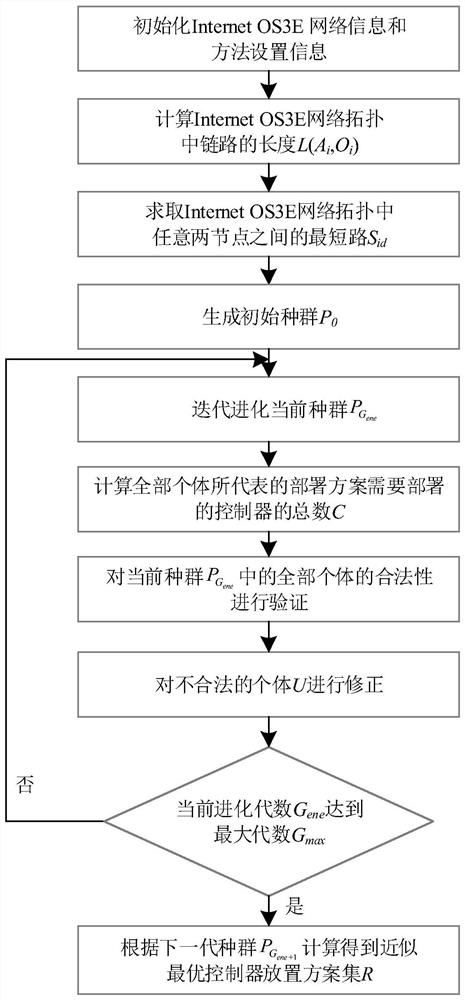

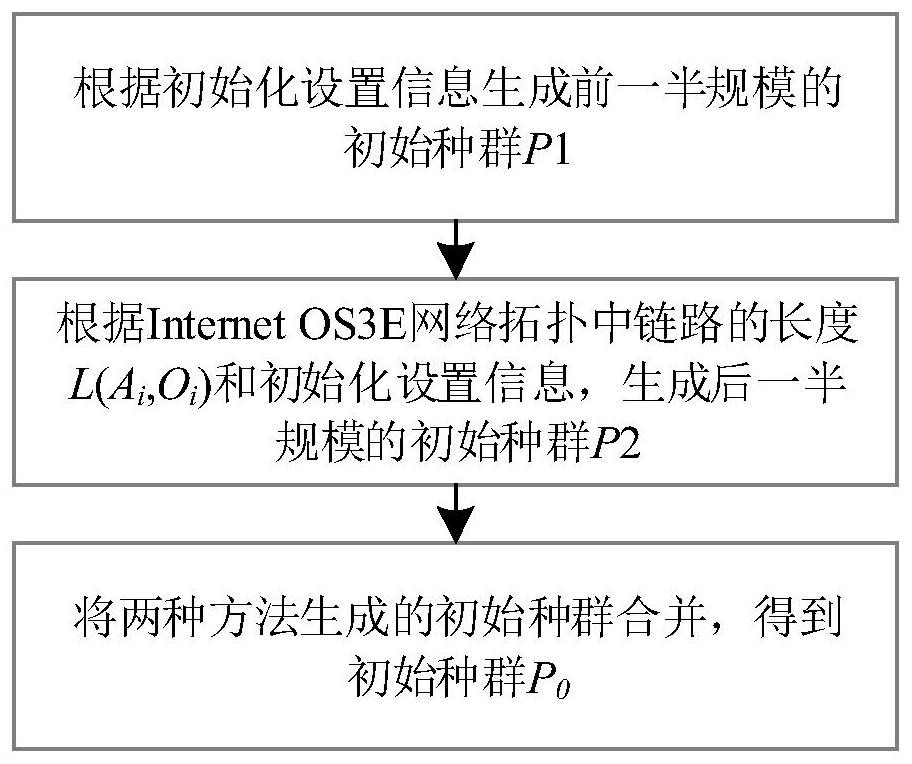

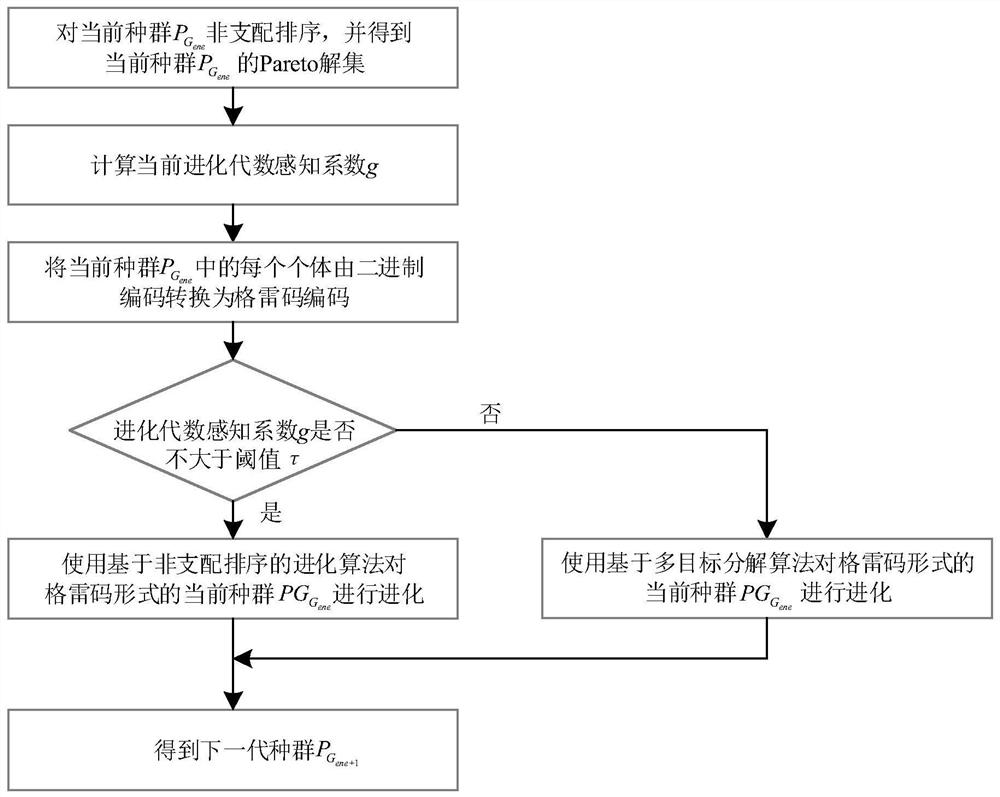

Multi-target controller placement method based on evolution perception in network

ActiveCN113037425AIncrease diversityFast convergenceWavelength-division multiplex systemsPropagation delayTopology information

The invention discloses a multi-target controller placement method based on evolution perception in a network, and mainly solves the problems of overlong propagation delay, high placement cost and large network load difference caused by placement of a controller in a control network in the prior art. According to the implementation scheme, the method comprises the following steps: initializing network topology information and algorithm setting information; preprocessing the initialized information; generating an initialized population, and representing a controller deployment scheme by each individual in the current population; iteratively evolving the current population; checking the legitimacy of the population, and judging all legal individuals and all illegal individuals; correcting illegal individuals to obtain an approximate optimal controller deployment scheme; and placing the controller in the control network according to one scheme in the placement scheme set. According to the method, network resources can be utilized more fully and reasonably, propagation delay and placement cost are reduced, network performance is improved, and the method can be used in a dense wavelength division multiplexing (DWDM) wide-area optical network.

Owner:XIDIAN UNIV

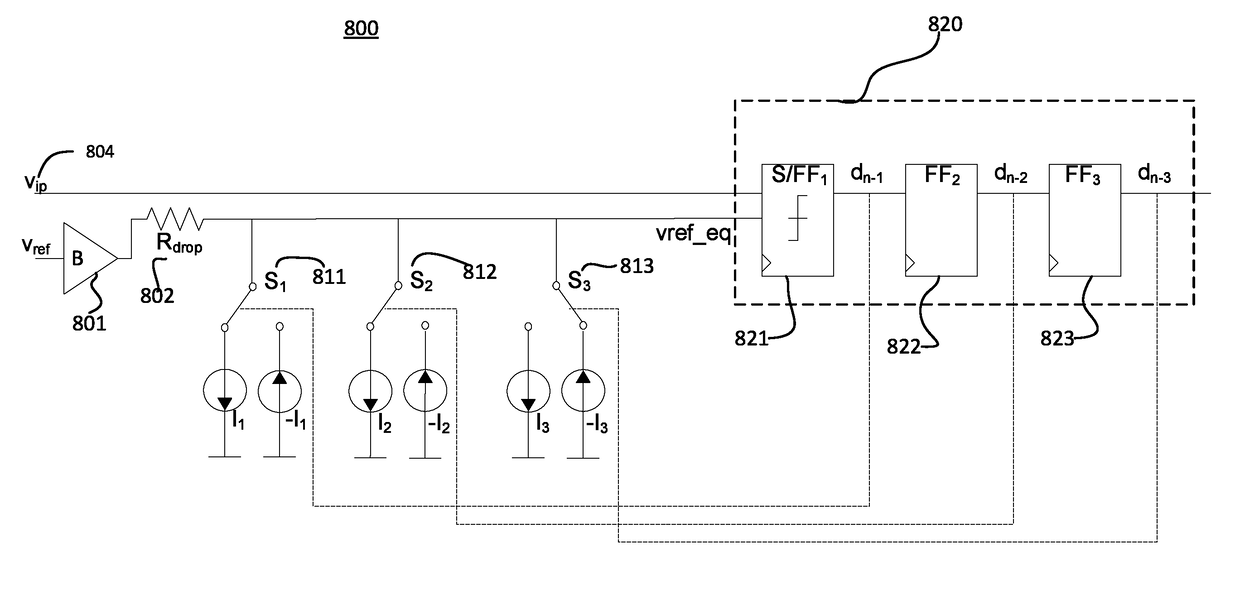

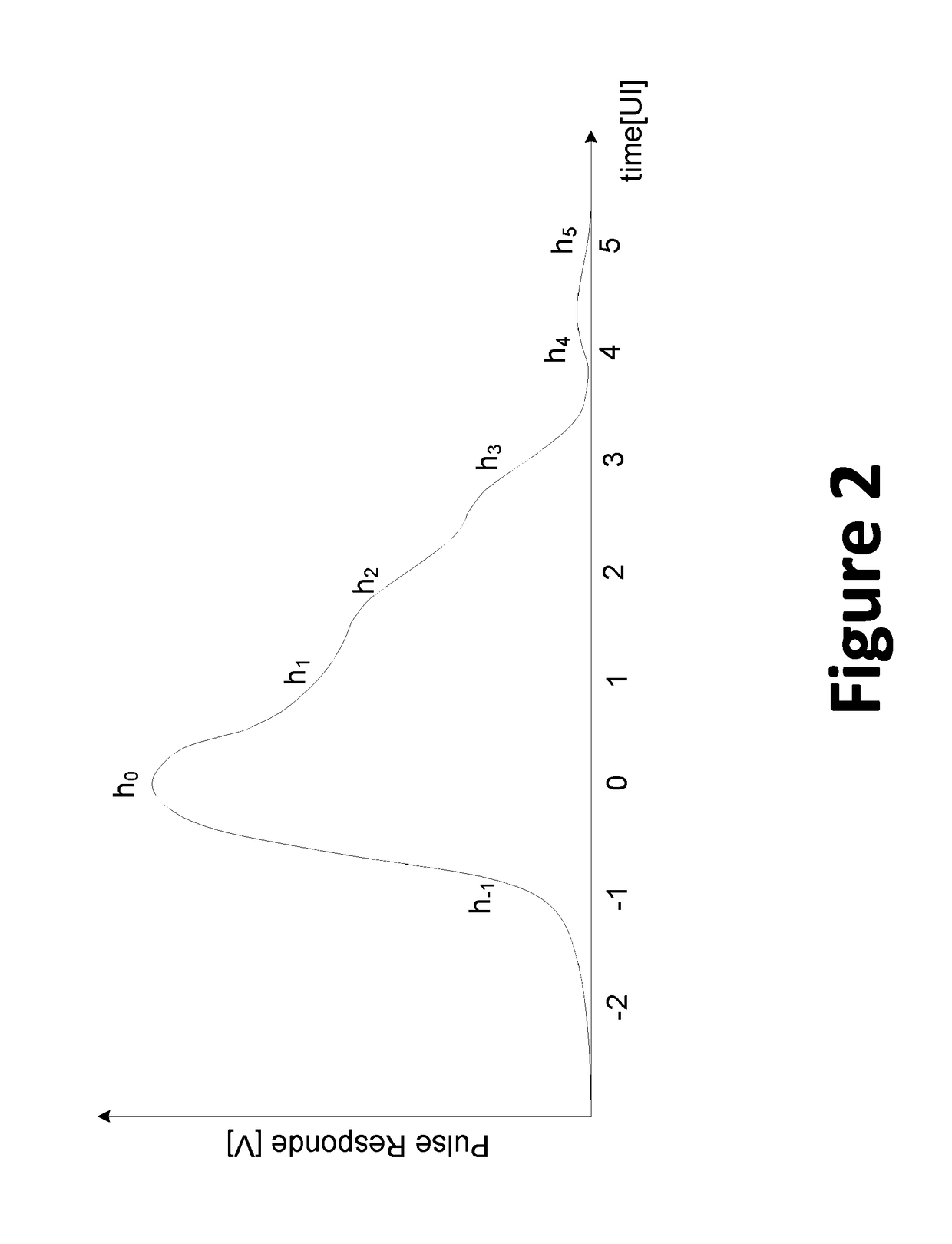

Decision feedback equalizer for single-ended signals to reduce inter-symbol interference

ActiveUS9973355B1Improve linearityHigh bandwidthMultiple-port networksDigital storageElectrical resistance and conductanceShift register

The present invention is directed to communication systems and methods thereof. More specifically, an embodiment of the present invention includes a buffer that is coupled to a reference terminal. A shift register stores decision levels for post-cursor positions. A plurality of switches converts the decision levels to equalization currents during an equalization process. The equalization currents are converted to equalization voltage terms by one or more load resistors. The buffer is provided between the reference terminal and the one or more load resistors. There are other embodiments as well.

Owner:MARVELL ASIA PTE LTD

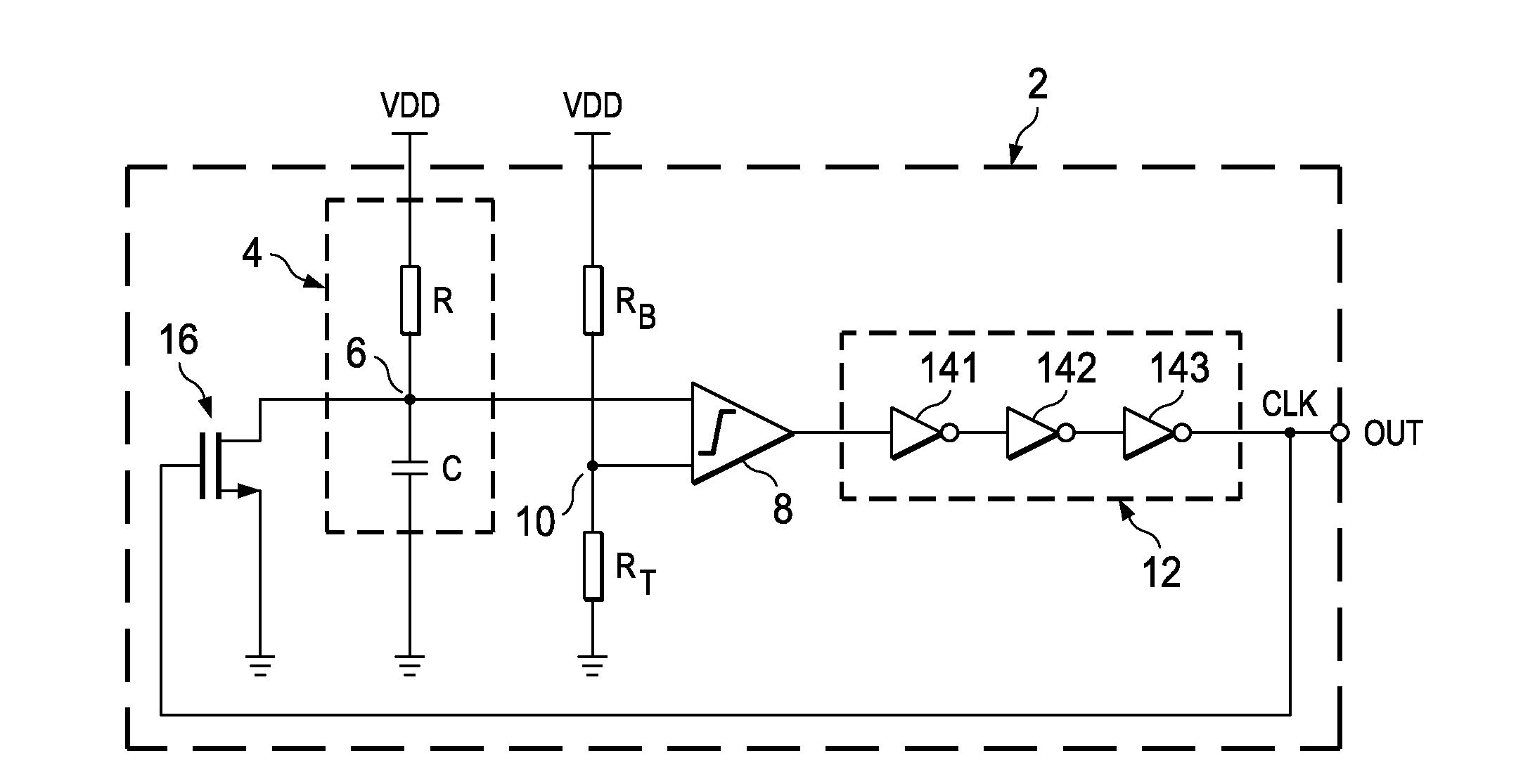

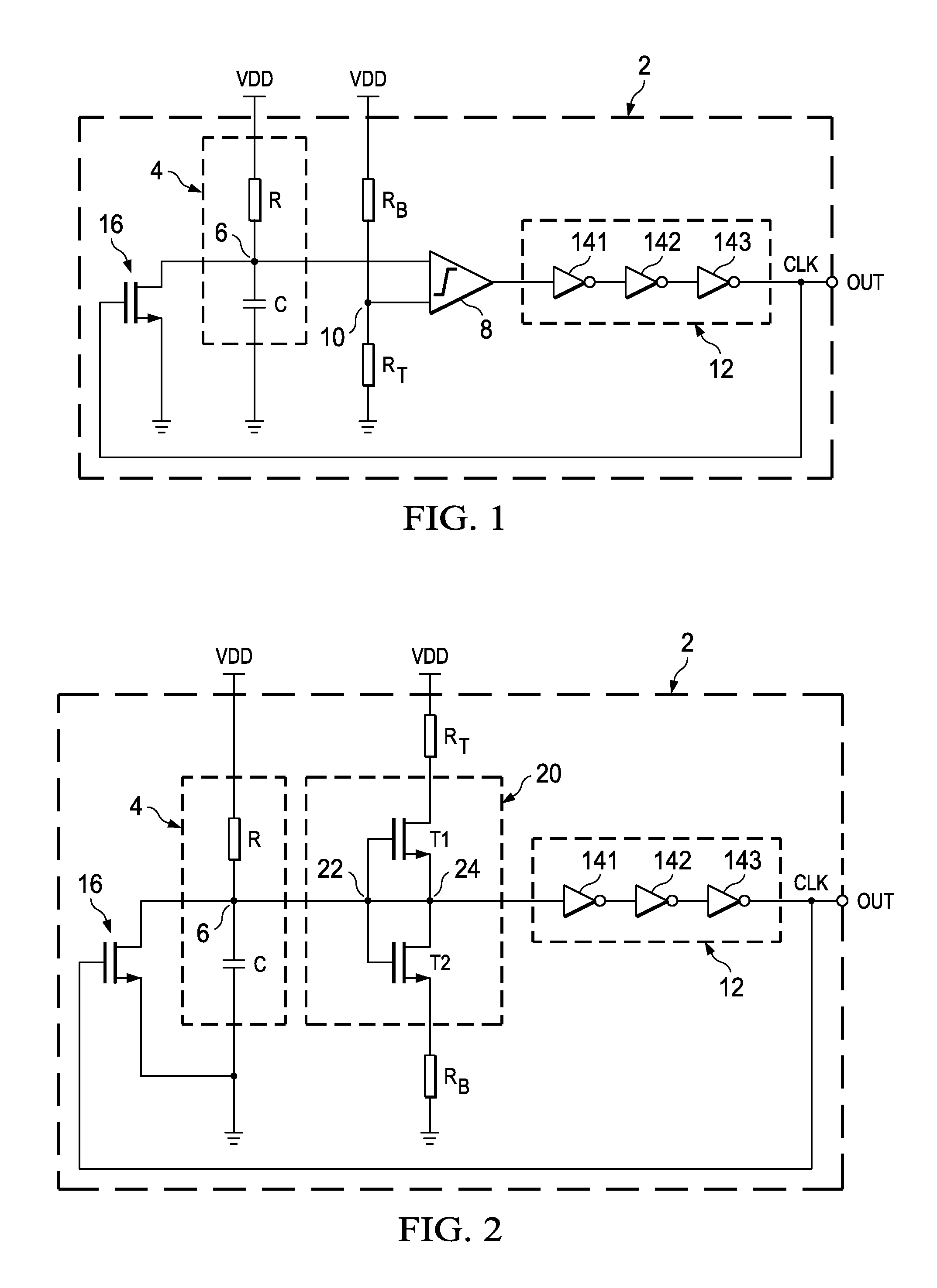

Oscillator comprising an RC-circuit and a push-pull stage and electronic device comprising the oscillator

InactiveUS20130335156A1Reduce Propagation DelayReduce degradationPulse generation by bipolar transistorsPush pullTransistor

Oscillator and electronic device comprising an oscillator, wherein the oscillator has an RC-circuit and a push-pull stage. A tapping point of the RC-circuit is coupled to an input of the push-pull stage and an output of the push-pull stage is fed back to a switching transistor which is coupled to the tapping point of the RC-circuit.

Owner:TEXAS INSTR INC

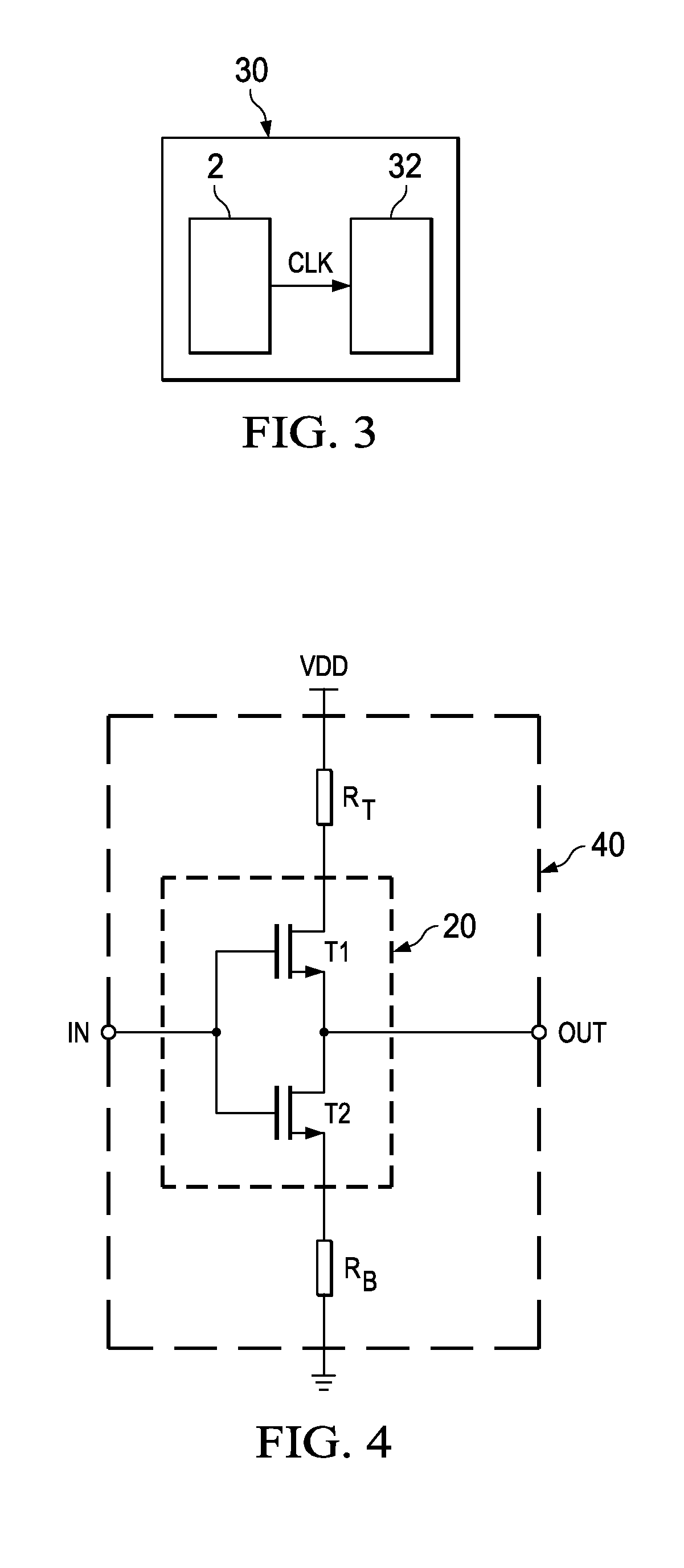

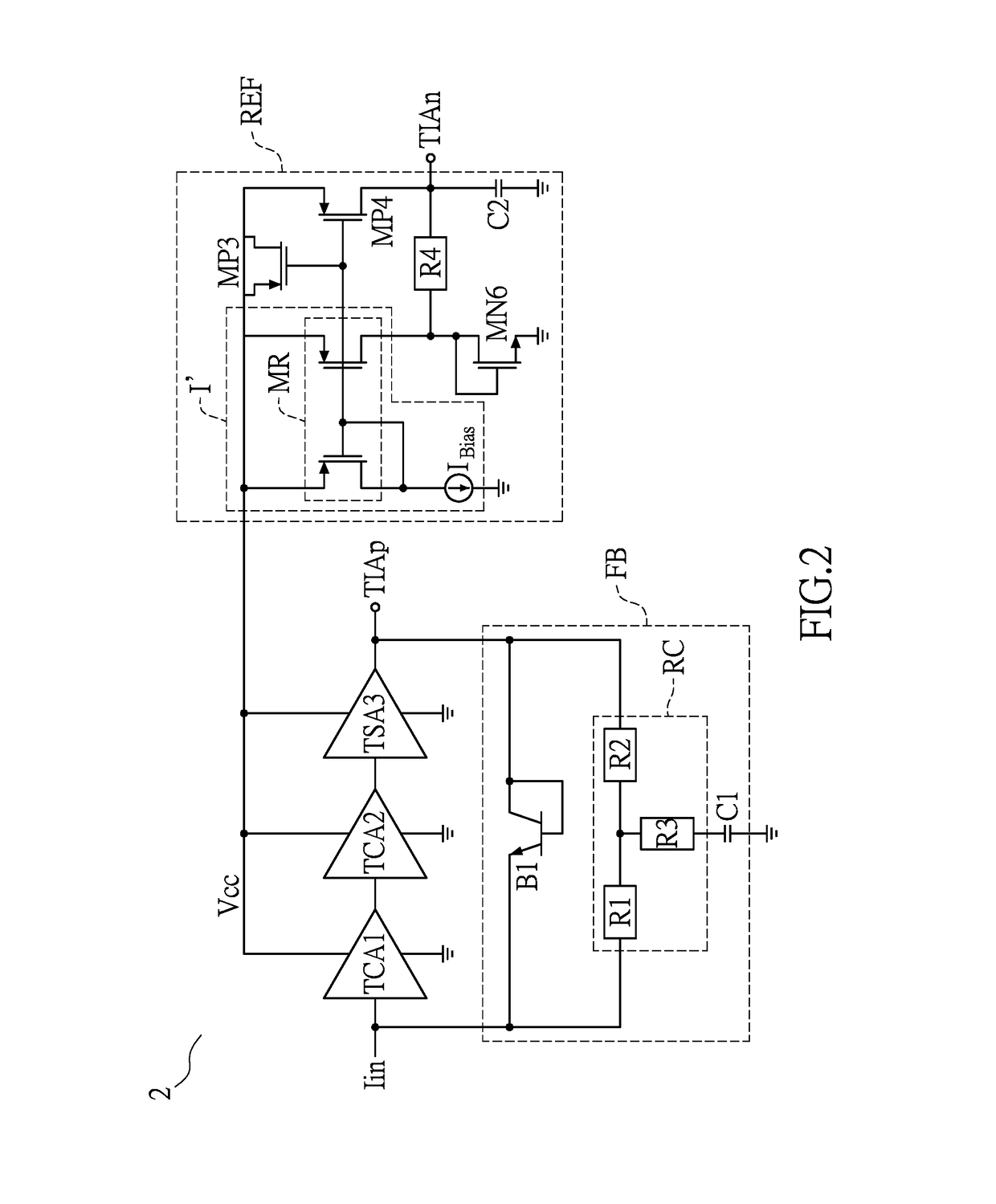

Transimpedance amplifier

ActiveUS9748908B1Reduce Propagation DelayImprove instabilityNegative-feedback-circuit arrangementsAmplifier modifications to reduce temperature/voltage variationAudio power amplifierTransimpedance amplifier

Disclosed is a transimpedance amplifier, comprising a first-stage trans-conductance amplifier TCA, a second-stage TCA, a third-stage amplifier and a feedback circuit. The first-stage TCA is electrically connected to an input current source to receive a first input signal, and outputs a first output signal. The second-stage TCA is electrically connected to the first-stage TCA to receive the first output signal, and outputs a second output signal. The third-stage amplifier is electrically connected to the second-stage TCA to receive the second output signal, and outputs a third output signal. One end of the feedback circuit is electrically connected to the input of the first-stage TCA, and the other end of the feedback circuit is electrically connected to the output of the third-stage amplifier to stabilize the third output signal. The third-stage amplifier is composed of a first output stage and a second output stage.

Owner:LITE ON SINGAPORE PTE LTD

Single-Level Parallel-Gated Carry/majority Circuits and Systems Therefrom

InactiveUS20070208797A1Increase clock frequencyReduce Propagation DelayExclusive-OR circuitsMajority/minority circuitsEngineeringSingle level

A carry / majority circuit, comprising a plurality of differential transistor pairs coupled in parallel and forming a pair of output nodes, with a single parallel gated level. Current is steered through a leg of the transistor pair having a higher input voltage.

Owner:BAE SYST INFORMATION & ELECTRONICS SYST INTERGRATION INC

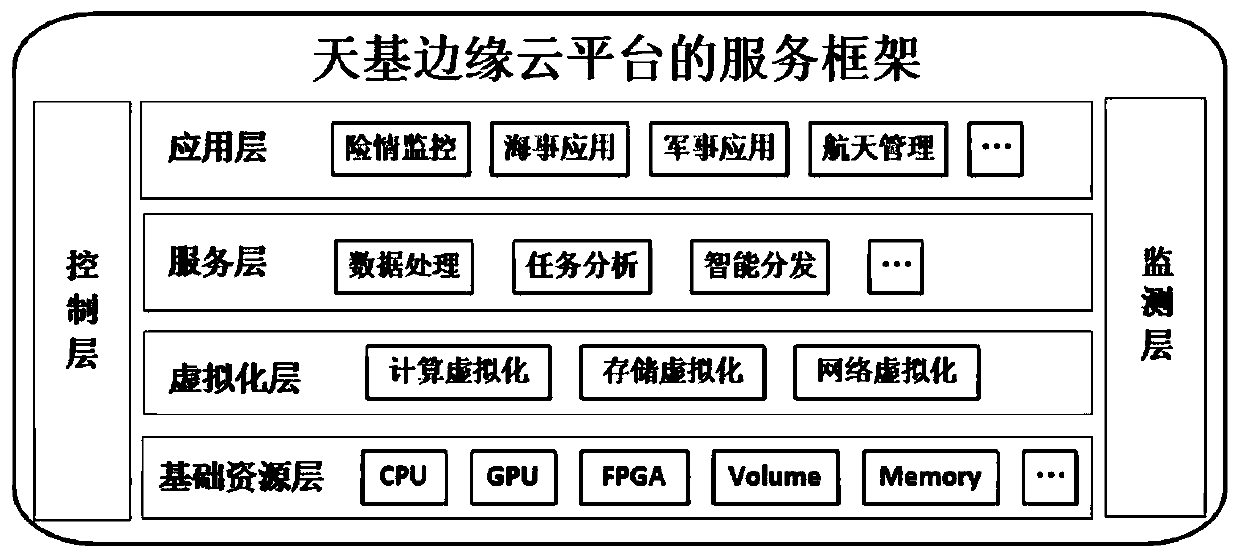

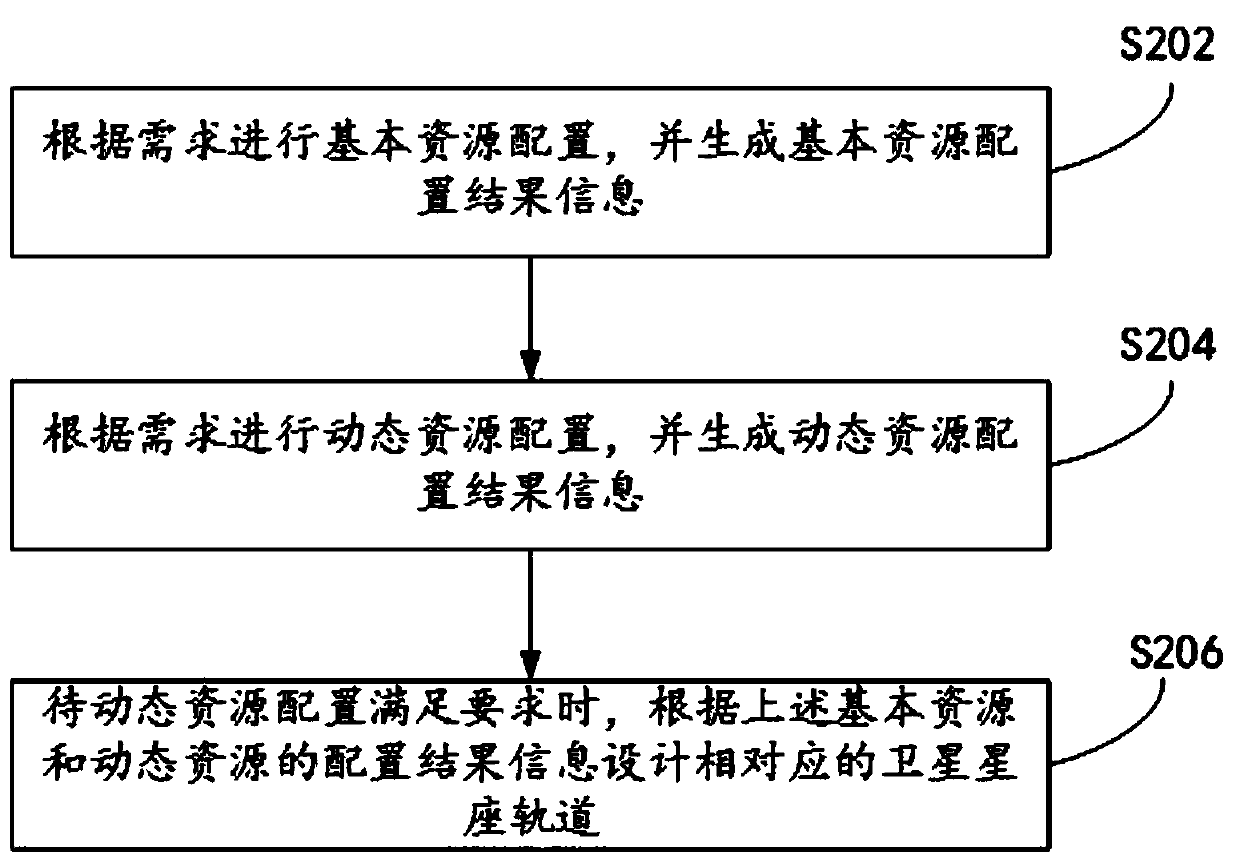

Resource allocation method and system under space-based cloud computing architecture and storage medium

InactiveCN110740183AReduce configuration costsWith on-orbit computing capabilityTransmissionLimited resourcesDynamic resource

The invention provides a resource allocation method and system under a space-based cloud computing architecture and a storage medium. The method comprises: conducting basic resource configuration according to requirements, and generating basic resource configuration result information; performing dynamic resource configuration according to requirements, and generating dynamic resource configuration result information; and when the dynamic resource configuration meets the requirements, designing a corresponding satellite constellation orbit according to the configuration result information of the basic resources and the dynamic resources. By reasonably configuring the computing resources and the storage resources, the requirements of the 5G network can be met, global seamless coverage is achieved. The resource nodes do not interfere with one another, the resource configuration cost is reduced, and the maximization of the resource utilization rate is achieved on the premise of limited resource configuration. Meanwhile, by introducing edge calculation, the satellite has on-orbit calculation capability, propagation time delay is shortened, and the propagation time delay reaches the millisecond level, so that data can be calculated and processed in real time.

Owner:TECH & ENG CENT FOR SPACE UTILIZATION CHINESE ACAD OF SCI

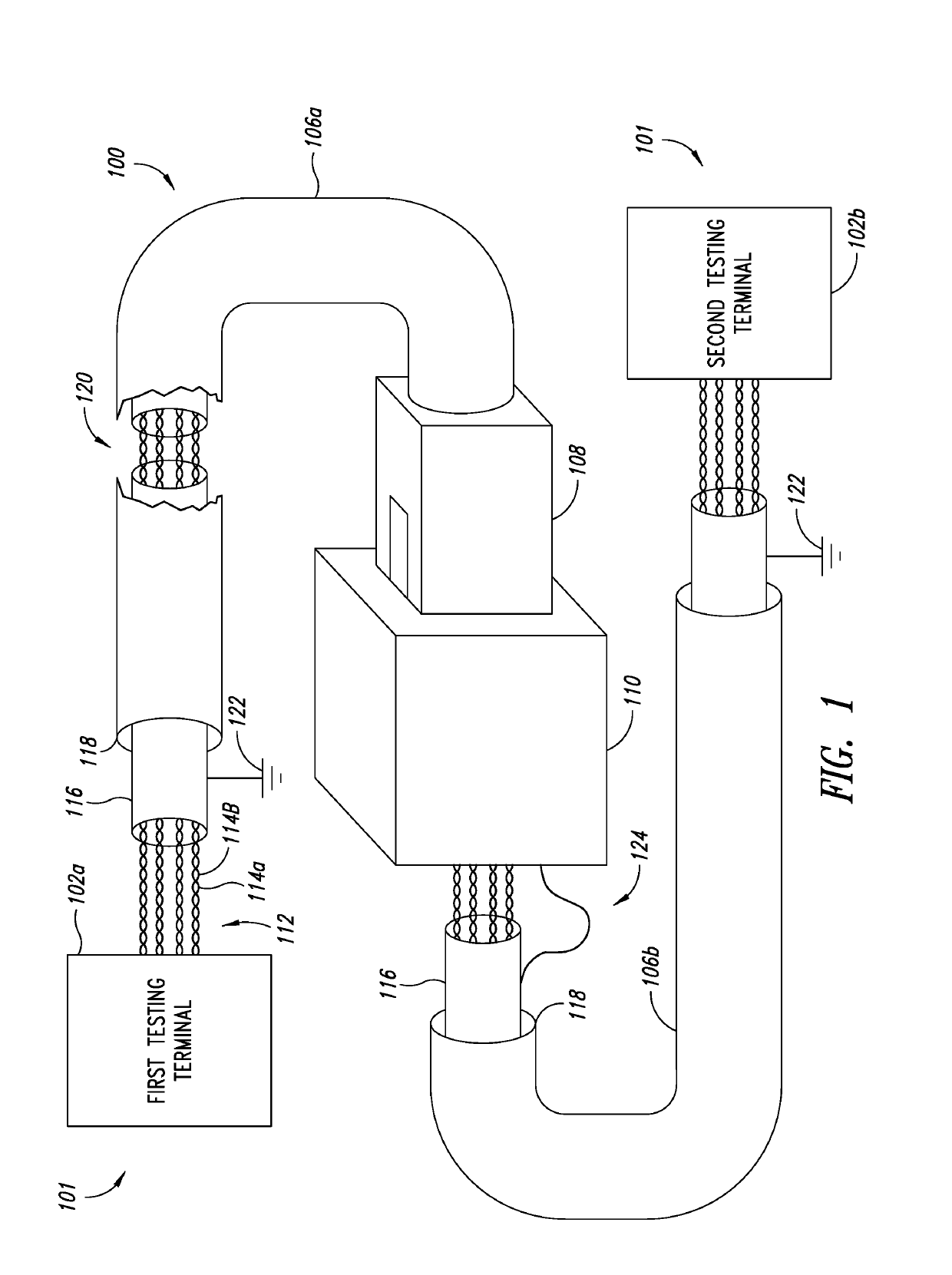

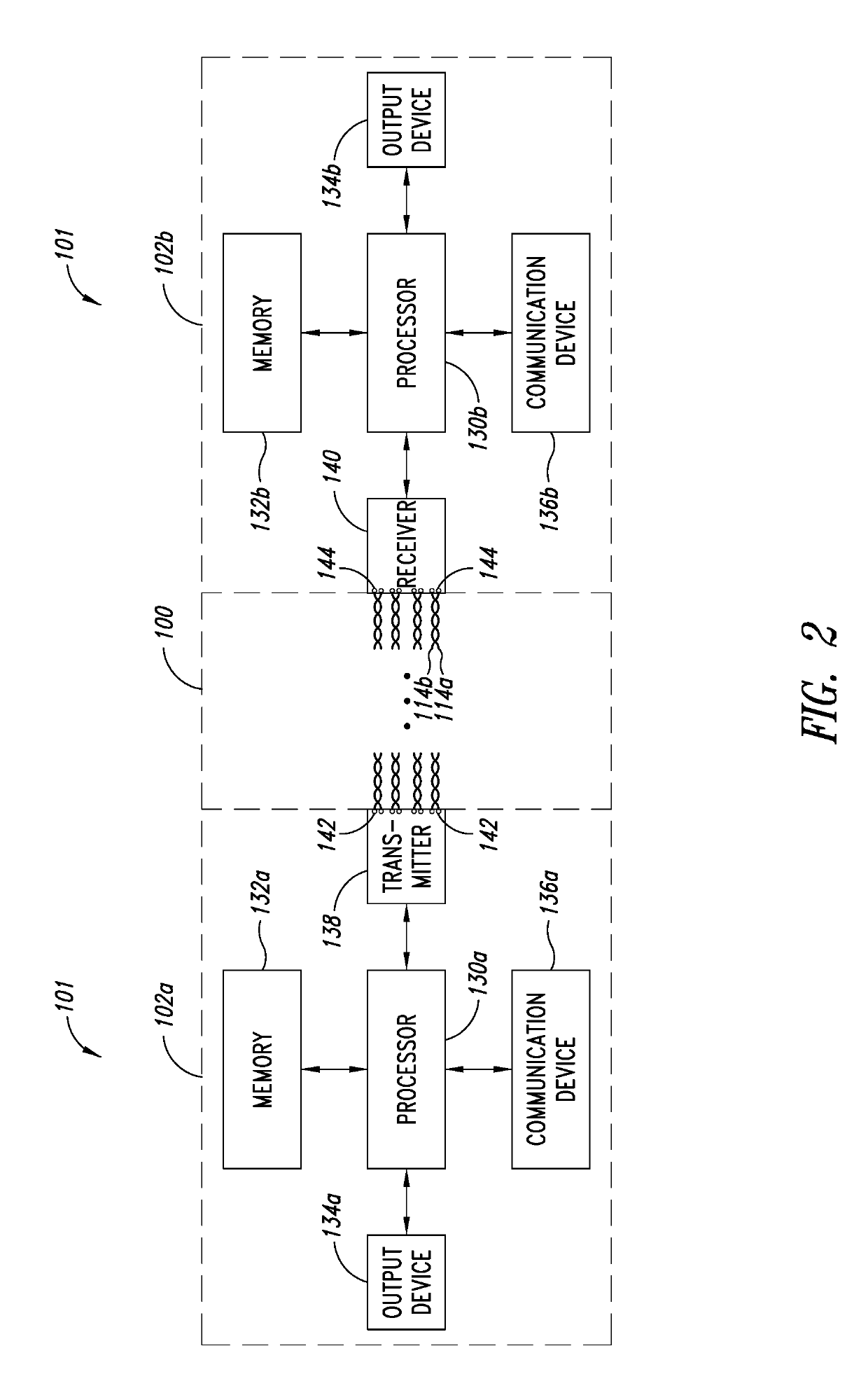

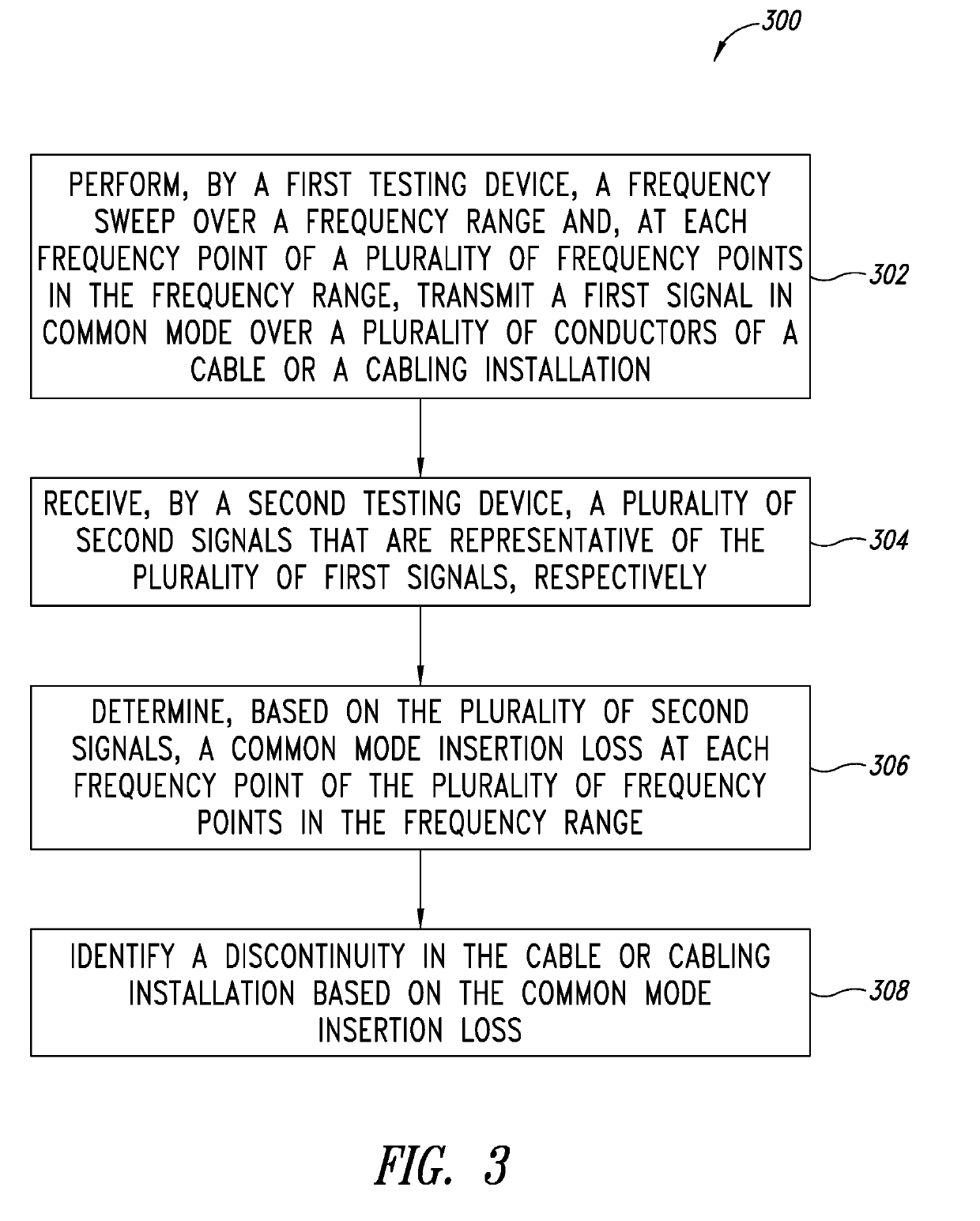

Testing shield continuity of a cable or cabling installation using common mode insertion loss

ActiveUS20190310298A1Increased propagation delayReduce Propagation DelayResistance/reactance/impedenceInsulated cablesElectrical conductorElectric cables

A method and apparatus for testing shield continuity are provided. In the method and apparatus, a transmitter transmits a first signal in common mode over a plurality of conductors of a cable or cabling installation having a shield. The first signal is transmitted in the common mode at a first end of the plurality of conductors. A receiver receives a plurality of second signals representative of the first signal at a second end of the plurality of conductors, respectively, and outputs data representative of the plurality of second signals. A processor receives the data representative of the plurality of second signals, determines a common mode insertion loss for the cable or cabling installation based on the plurality of second signals, determines, based on the common mode insertion loss, whether the shield is continuous or discontinuous and outputs data representative of whether the shield is continuous or discontinuous.

Owner:JOHN FLUKE MFG CO INC

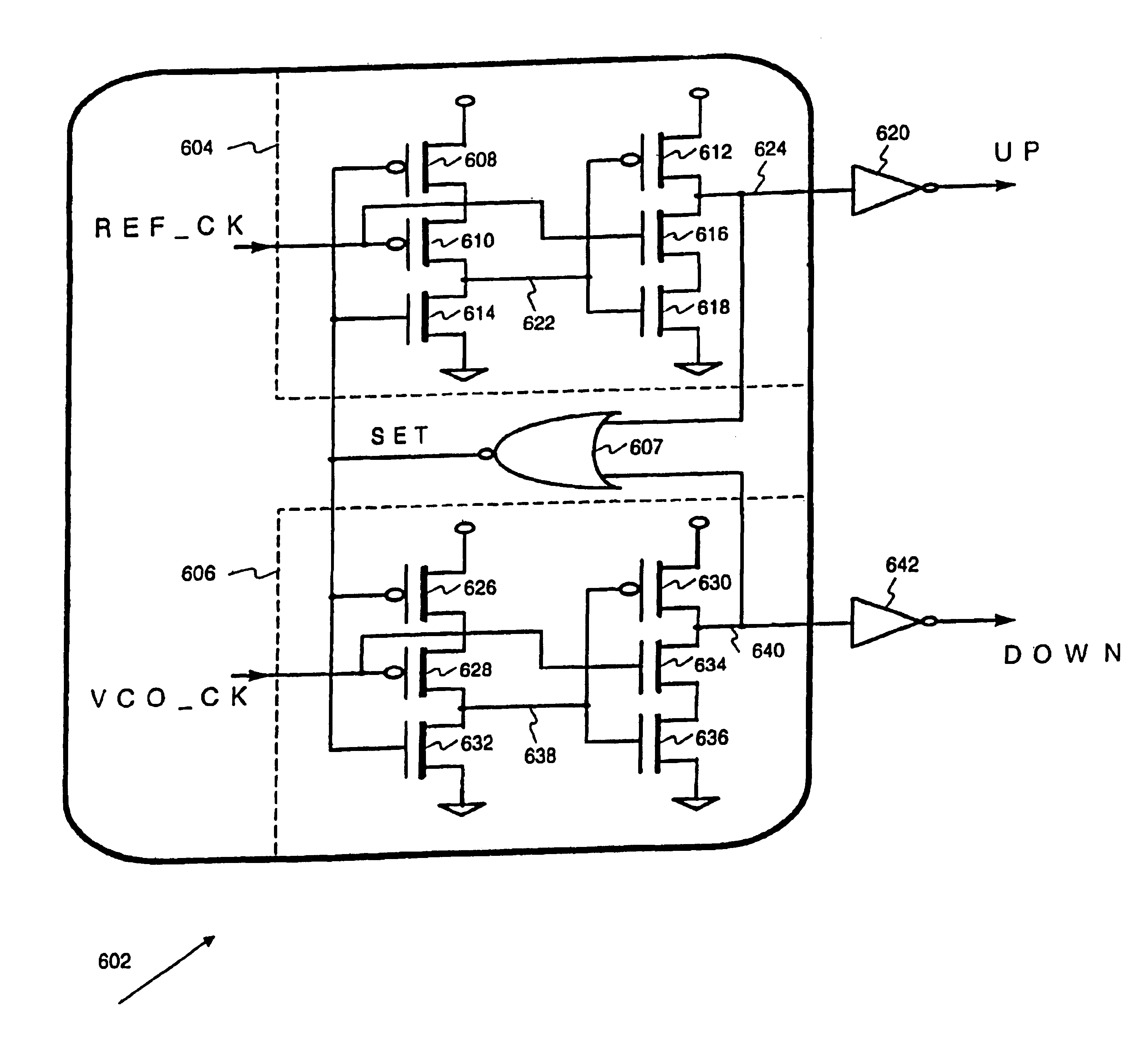

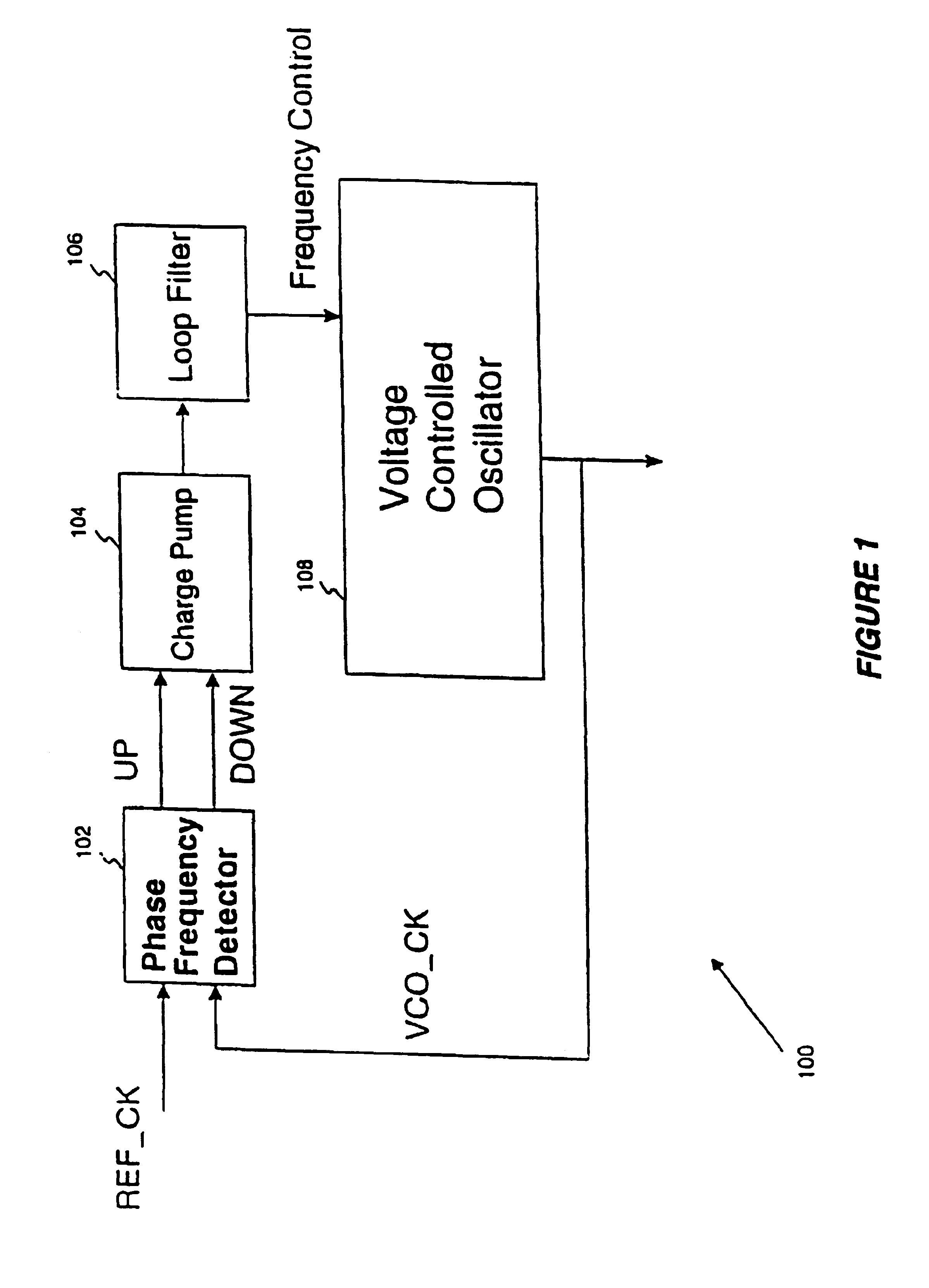

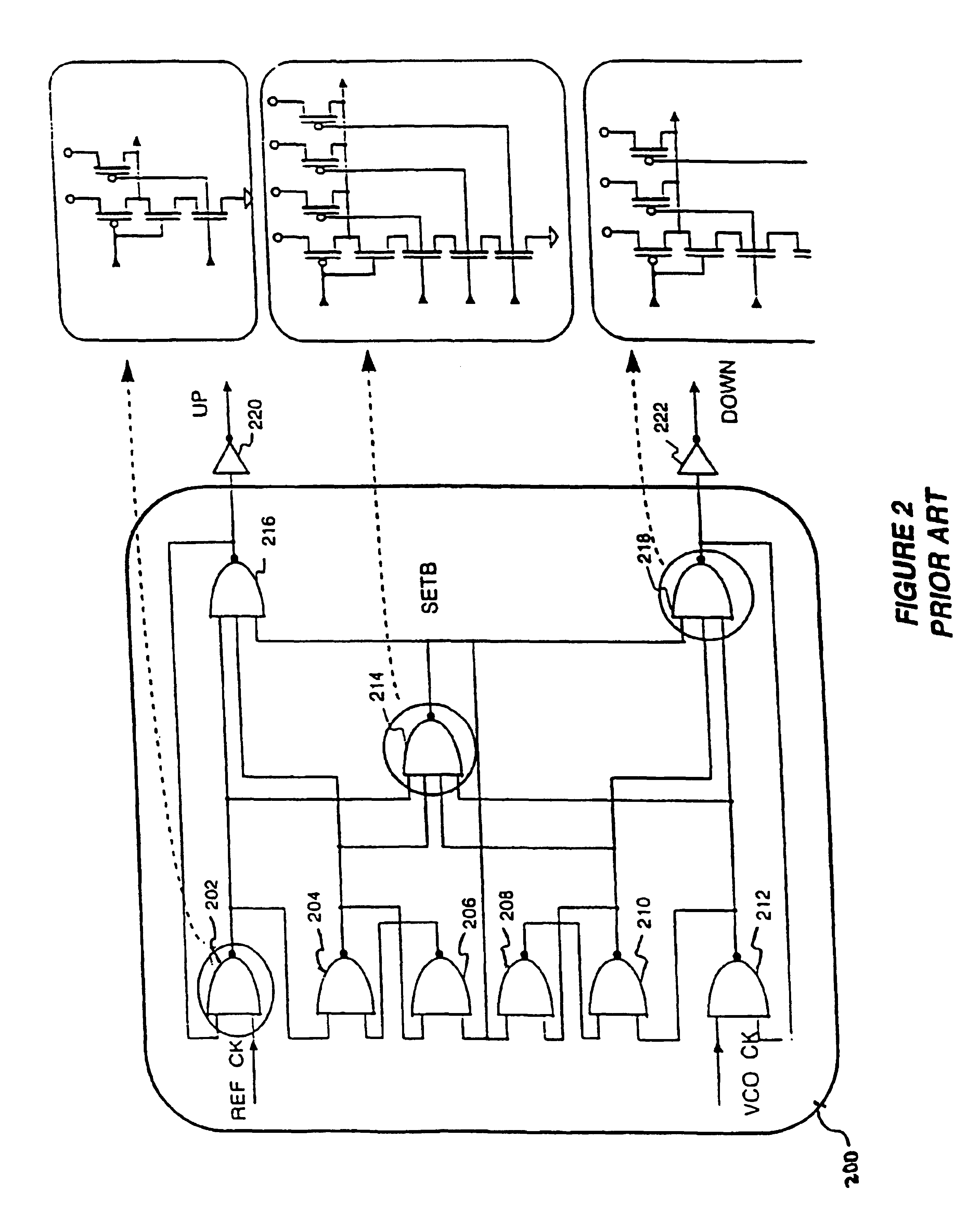

High-speed and high-precision phase locked loop

InactiveUS6930560B2Reduce Propagation DelayImprove accuracyMultiple input and output pulse circuitsPulse automatic controlPhase differencePhase frequency detector

A phase lock loop includes a charge pump, a voltage controlled oscillator (VCO), and a phase frequency detector. The phase frequency detector has a dynamic logic structure. The phase frequency detector generates up and down signals for directing the charge pump to provide a voltage signal to the VCO to vary the frequency of the VCO clock. The difference between the up and down signals is indicative of the phase difference between the reference clock signal and the VCO clock. The phase frequency detector includes up and down signal generators for generating the up and down signals, respectively.

Owner:SUPER INTERCONNECT TECH