Patents

Literature

110results about "Majority/minority circuits" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

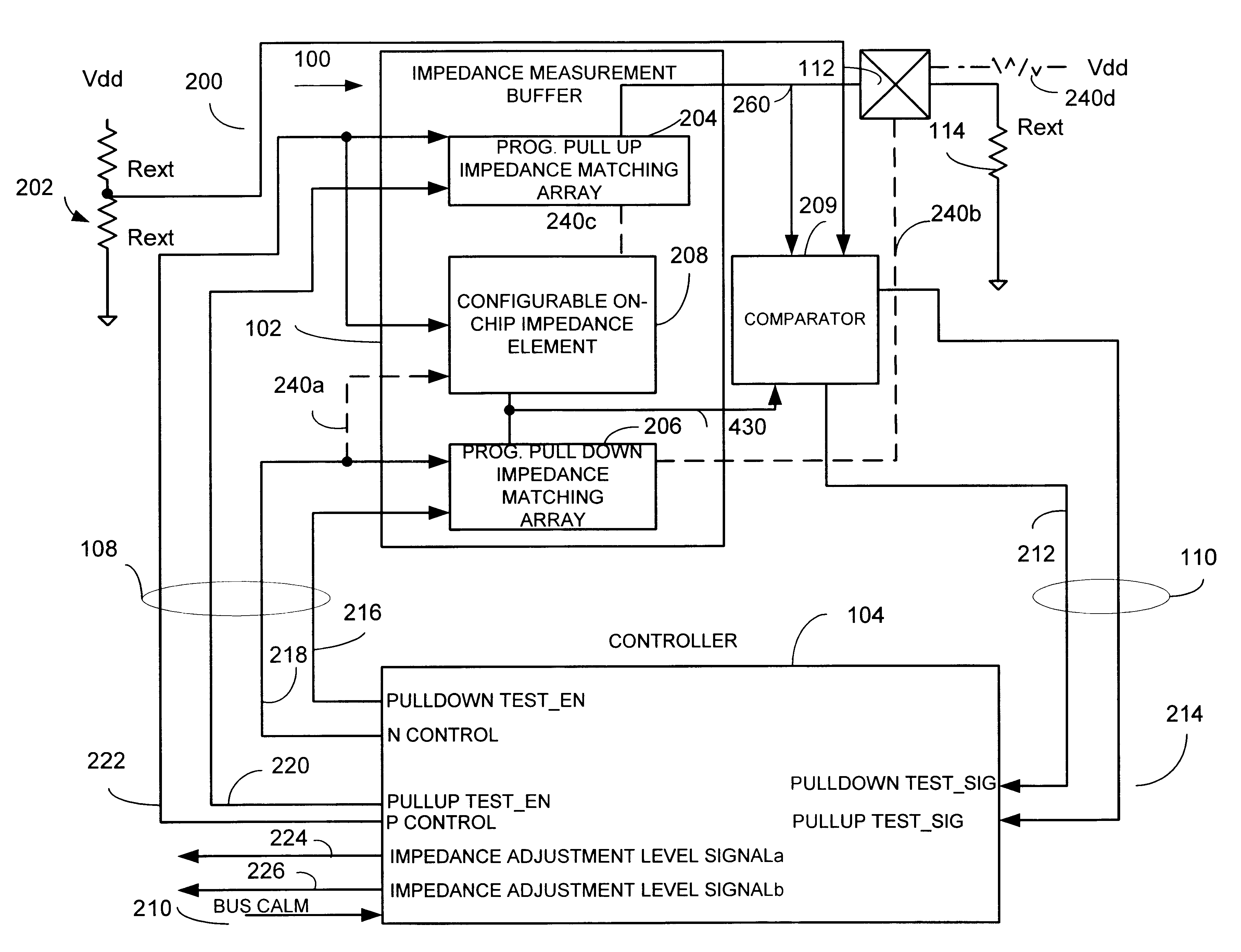

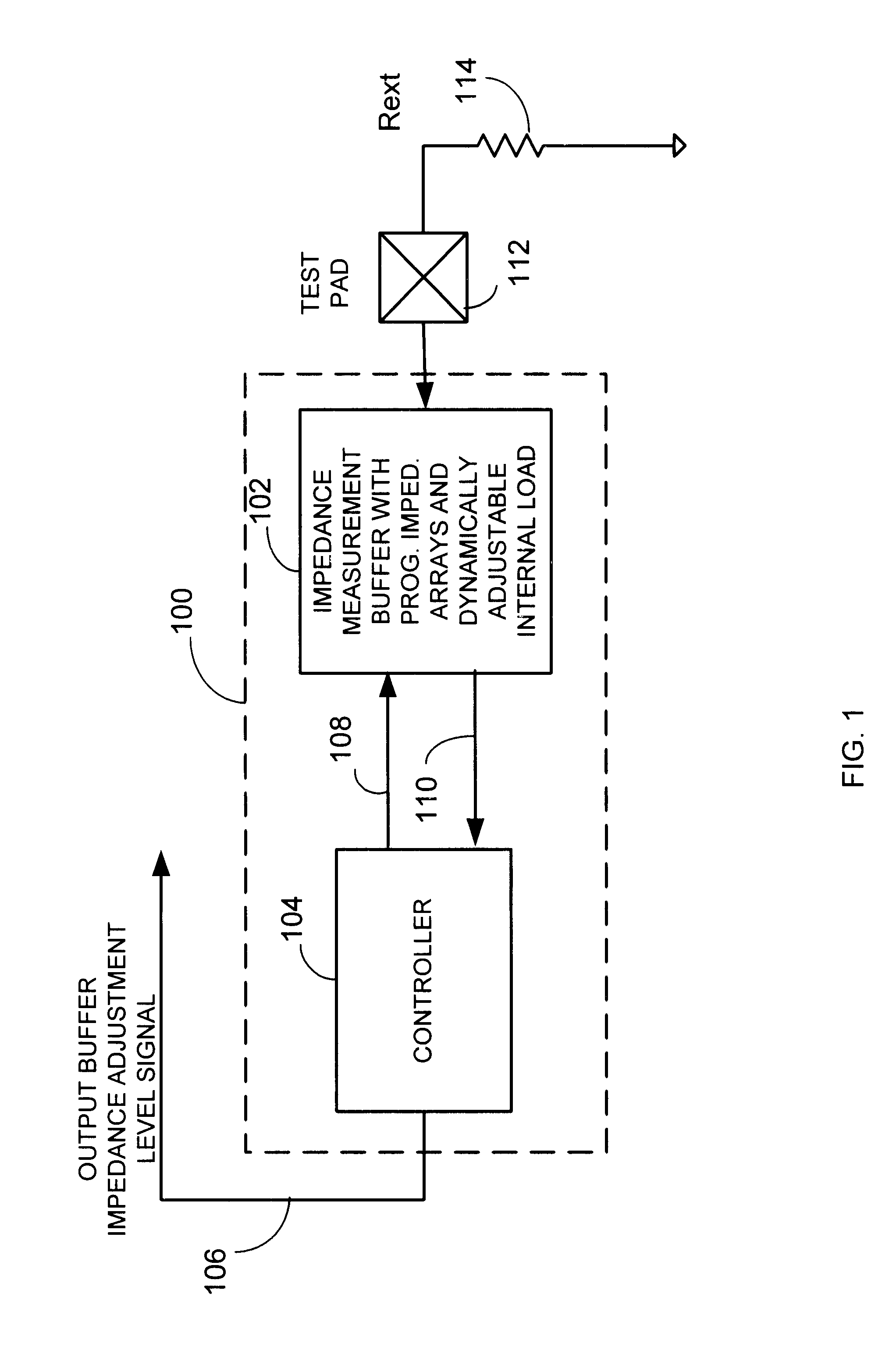

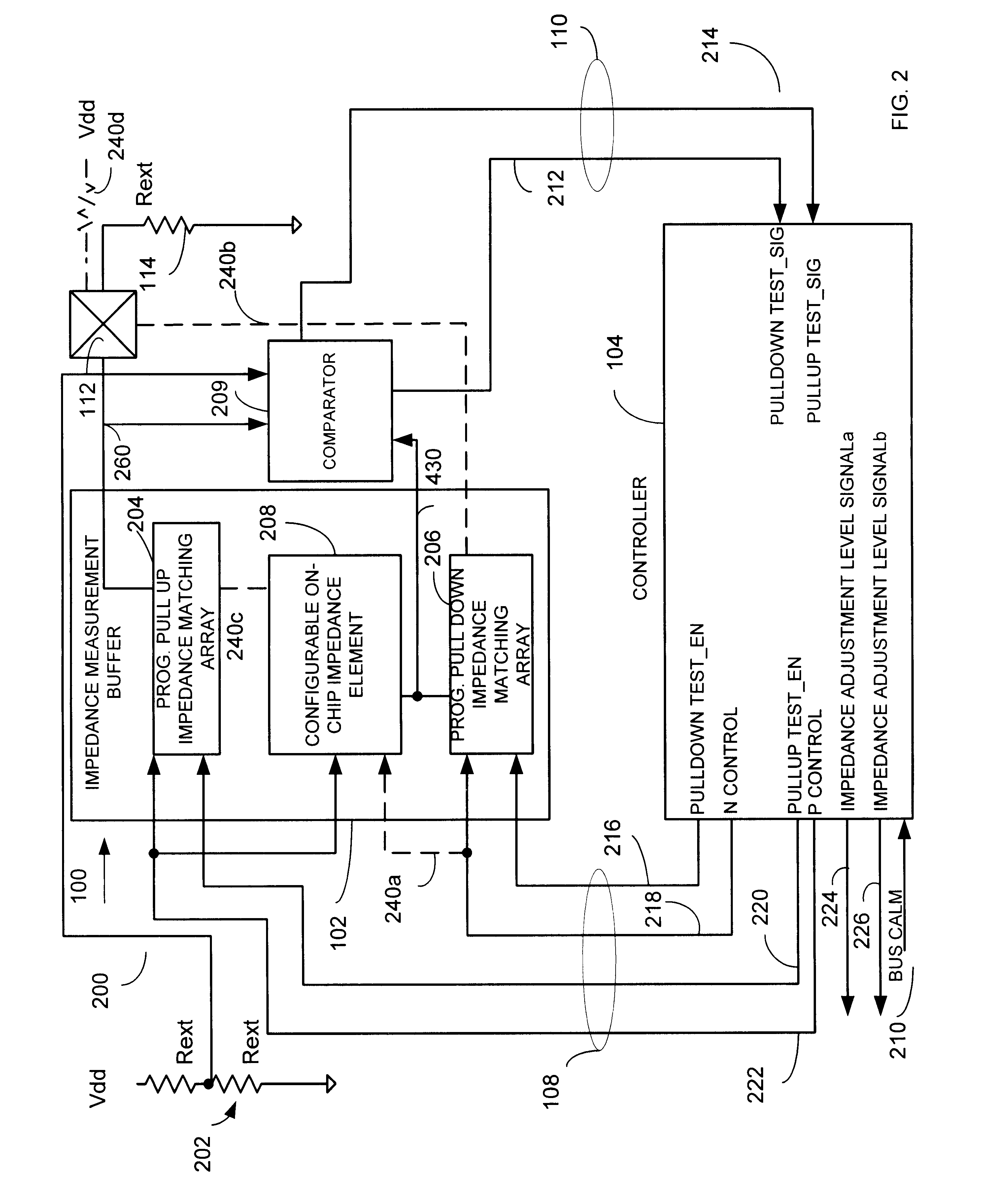

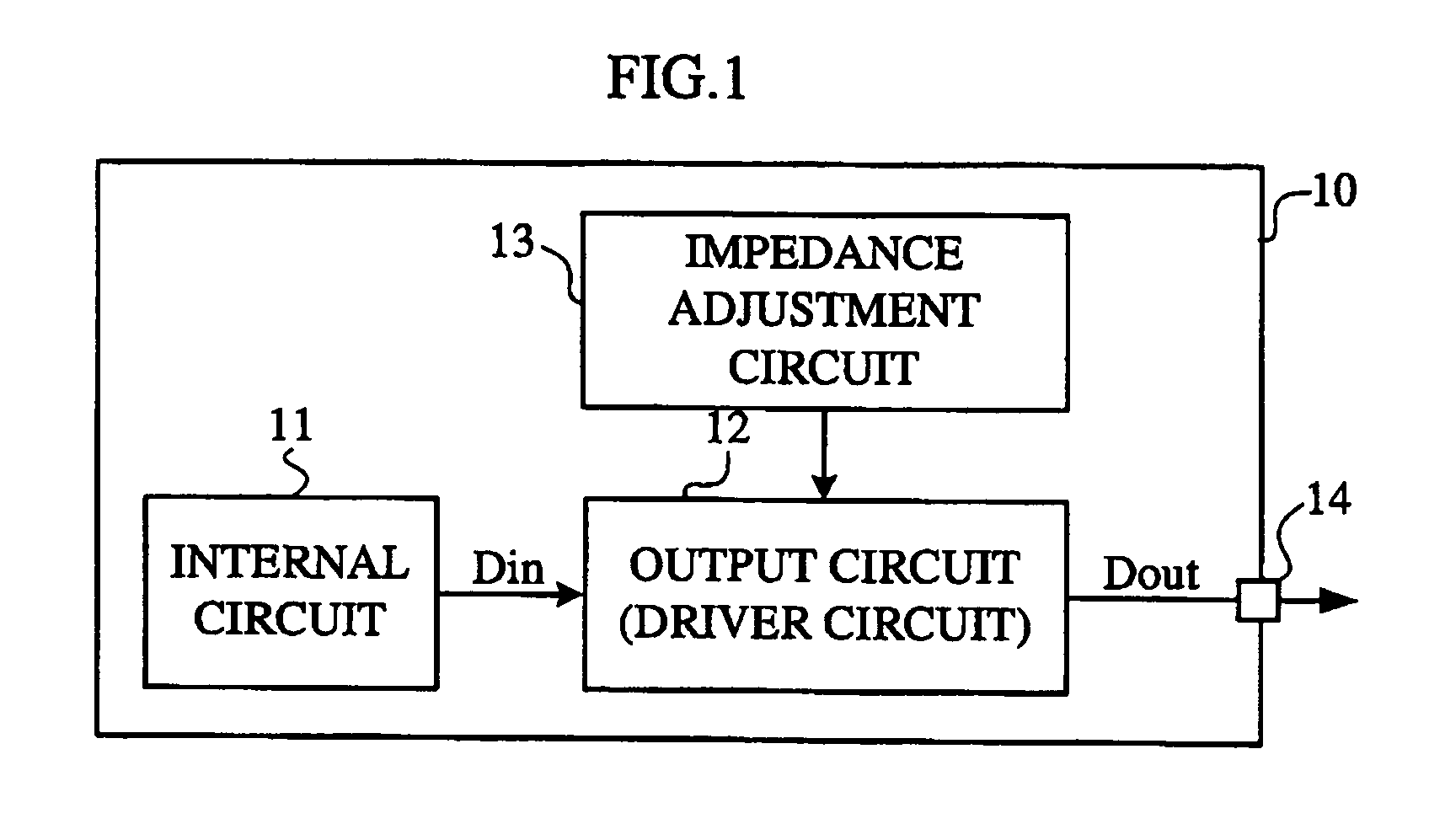

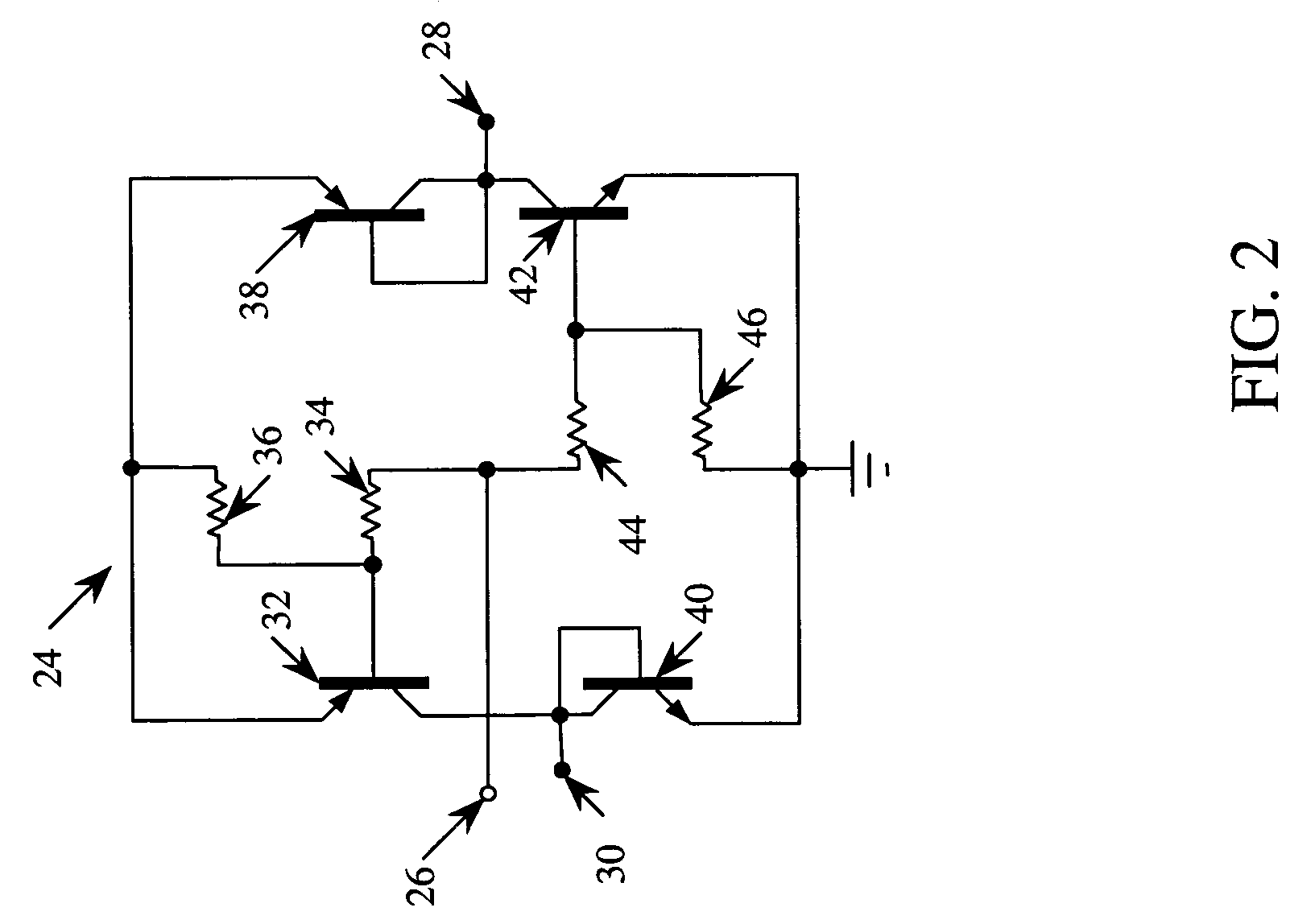

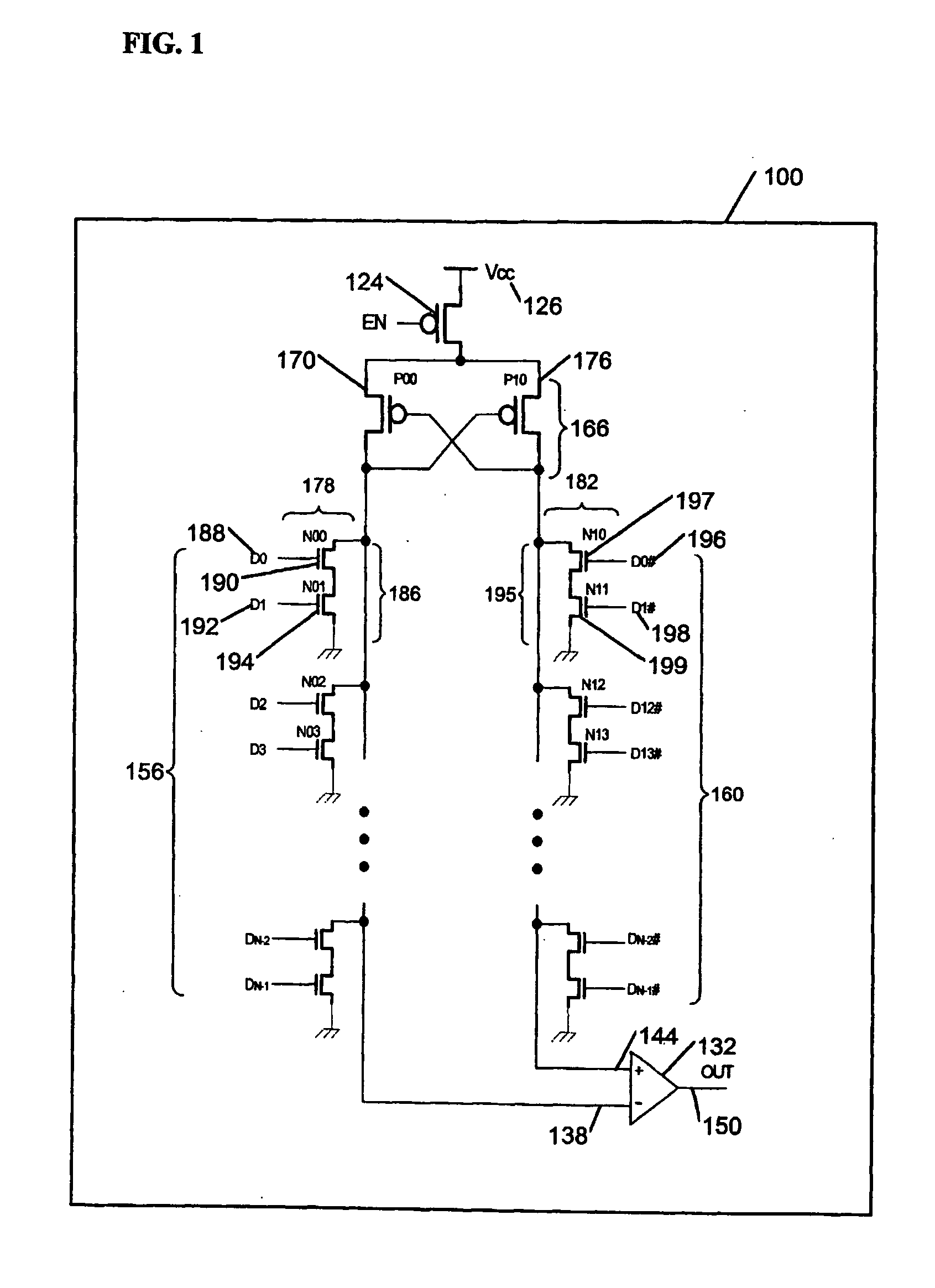

Dynamic impedance compensation circuit and method

InactiveUS6541996B1Input/output impedence modificationReliability increasing modificationsDynamic impedanceEngineering

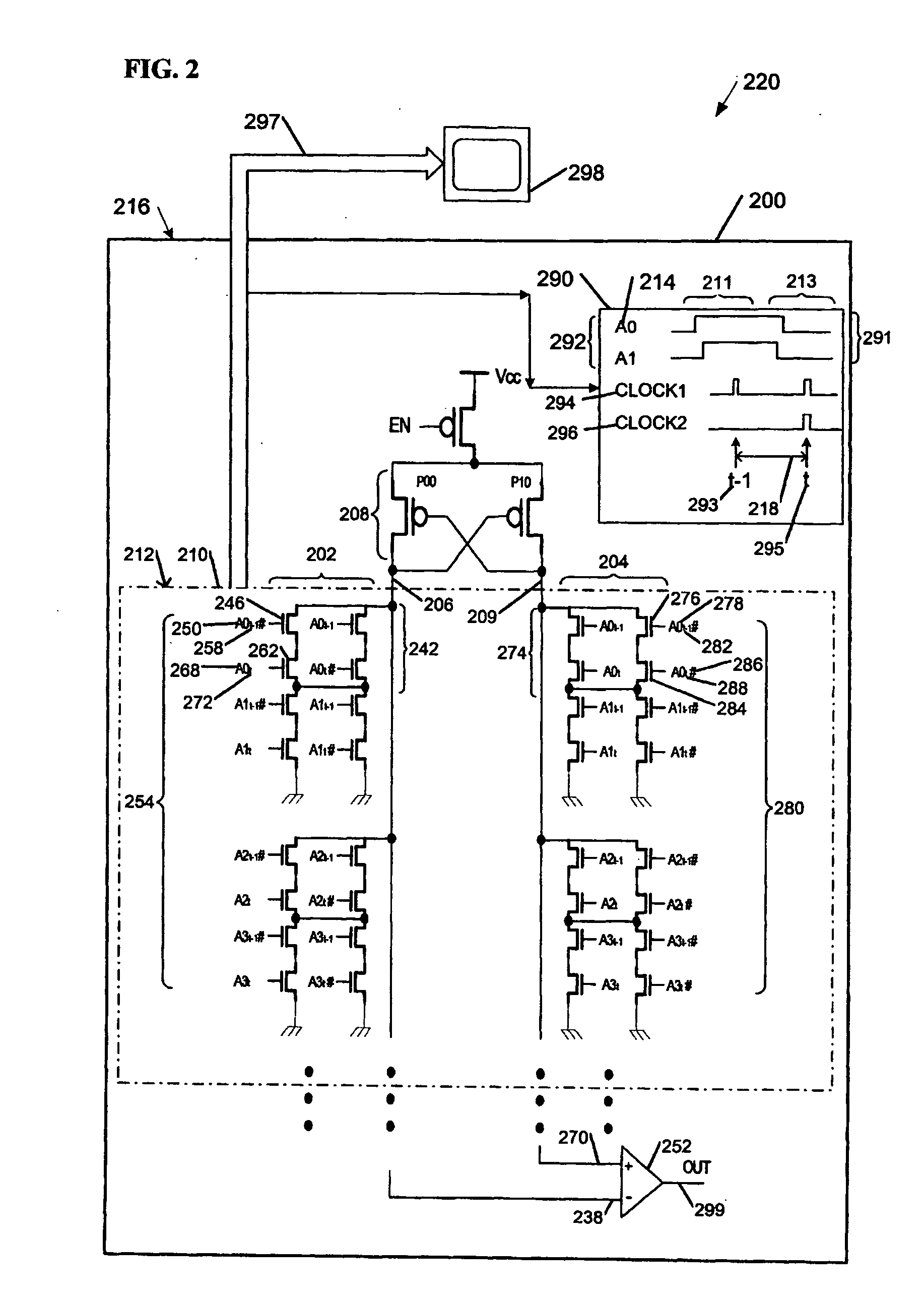

An impedance compensation circuit and method for an input / output buffer provides dynamic impedance compensation by using programmable impedance arrays and a dynamically adjustable on-chip load. Accordingly, among other advantages, only a single off-chip or external calibrated impedance resistor is used and only a single test pad is necessary.

Owner:ATI TECH INC

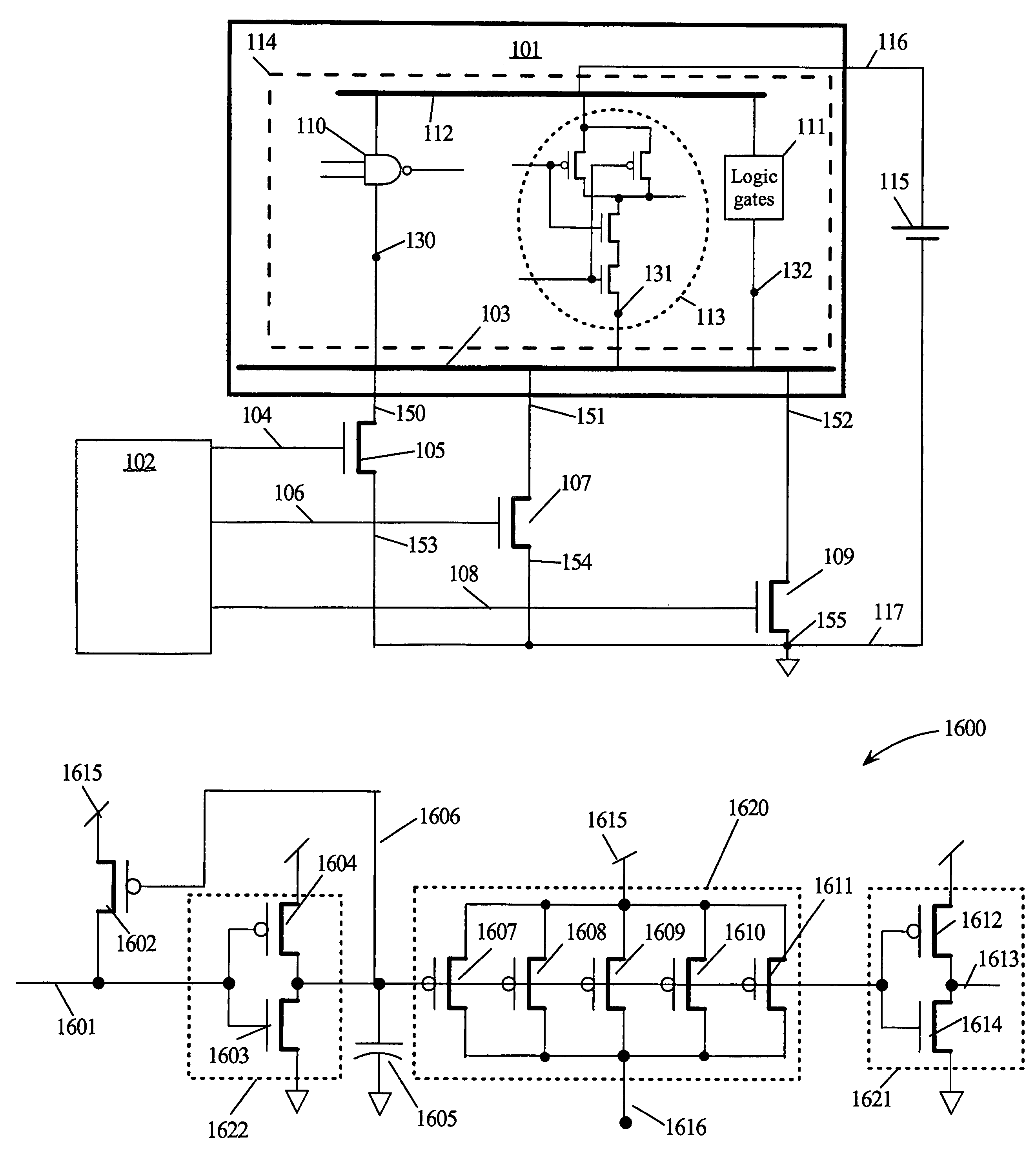

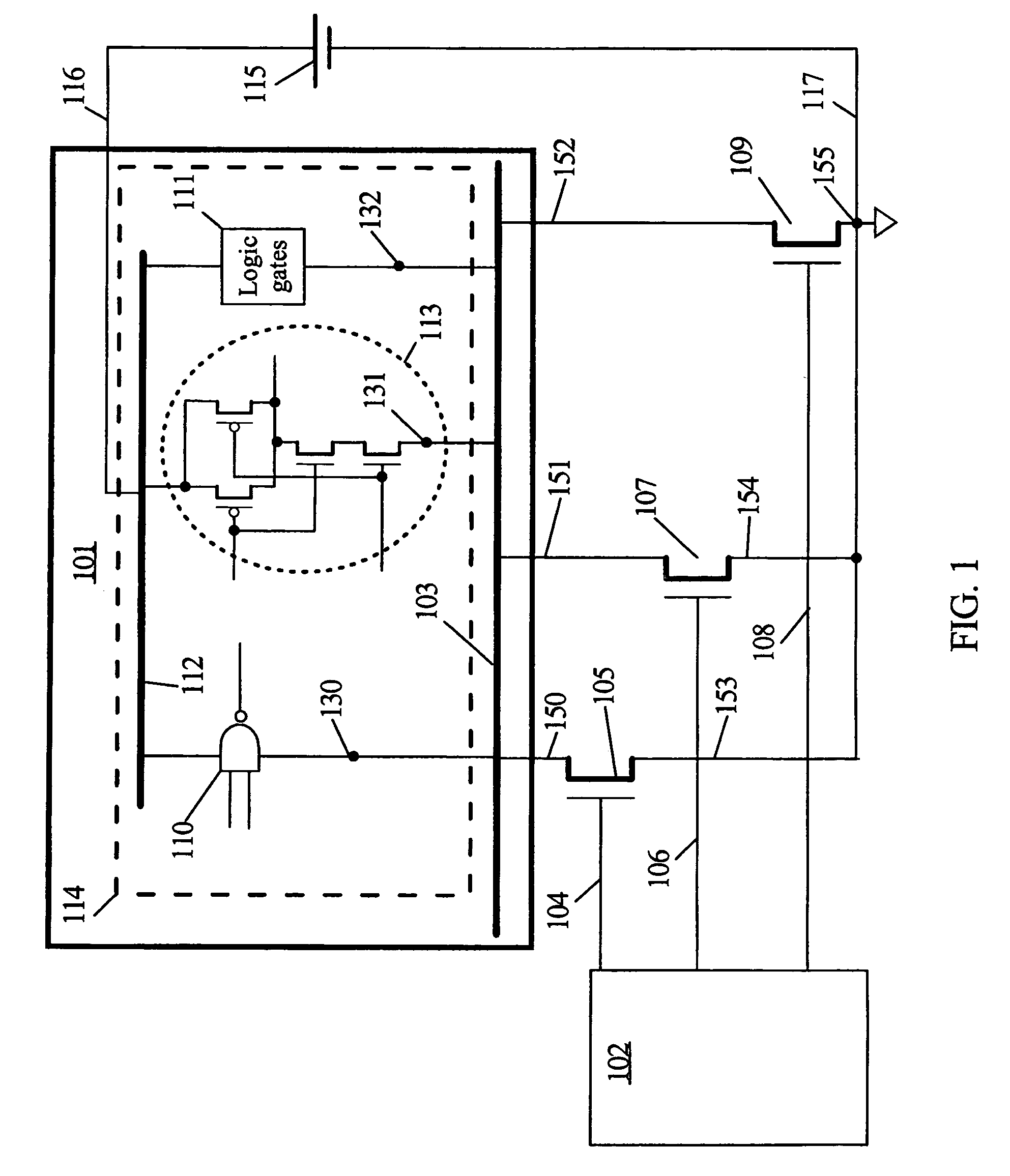

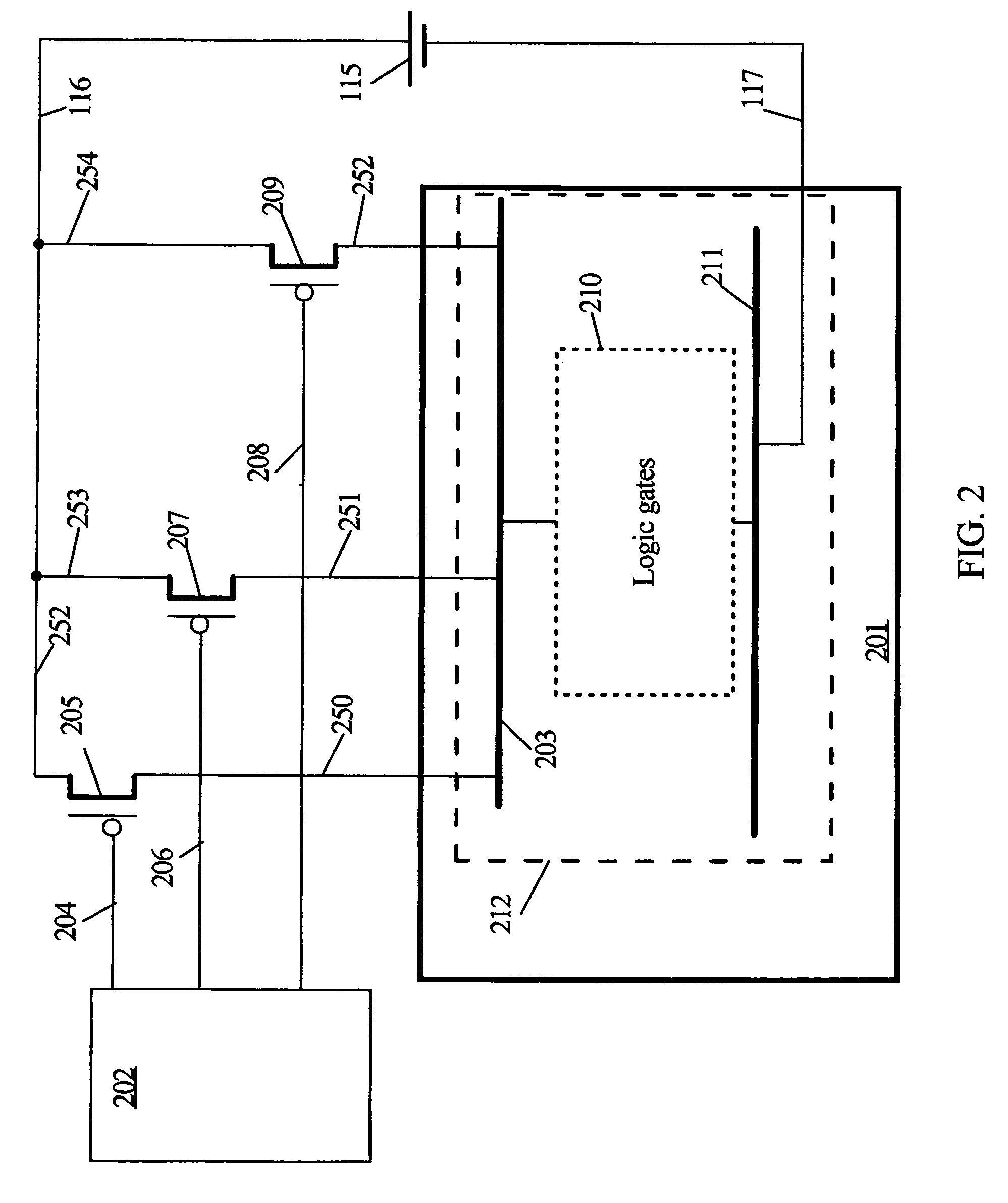

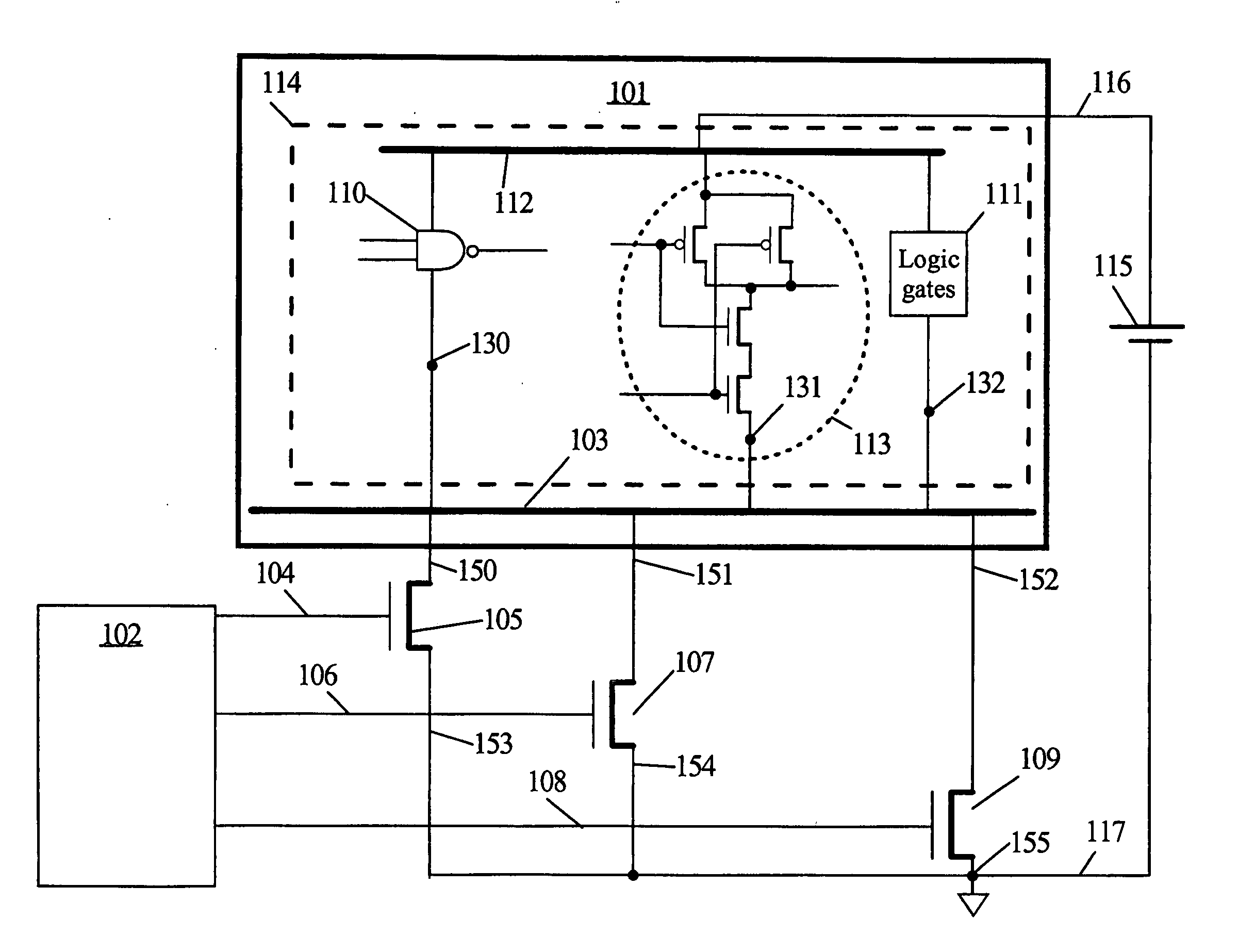

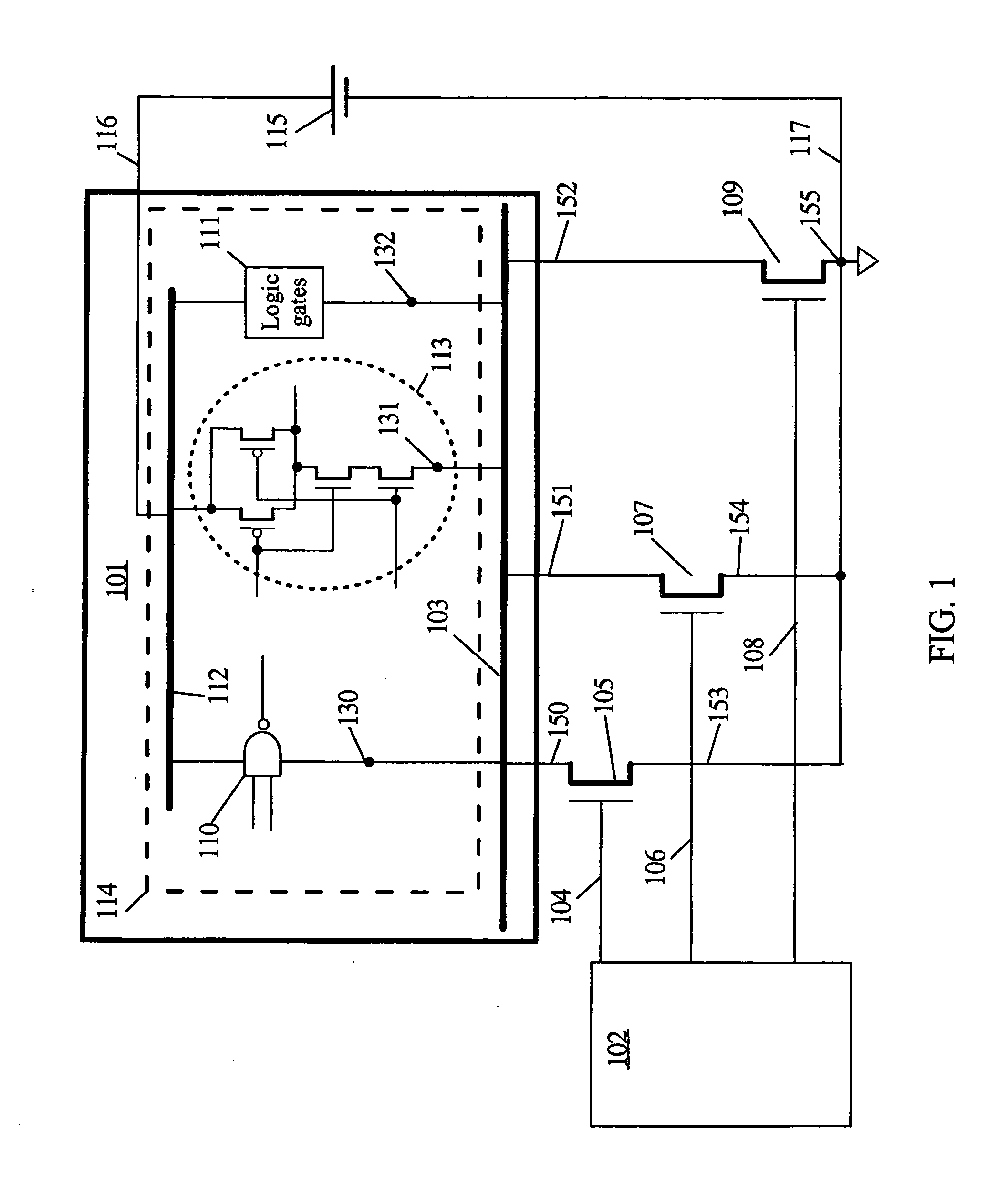

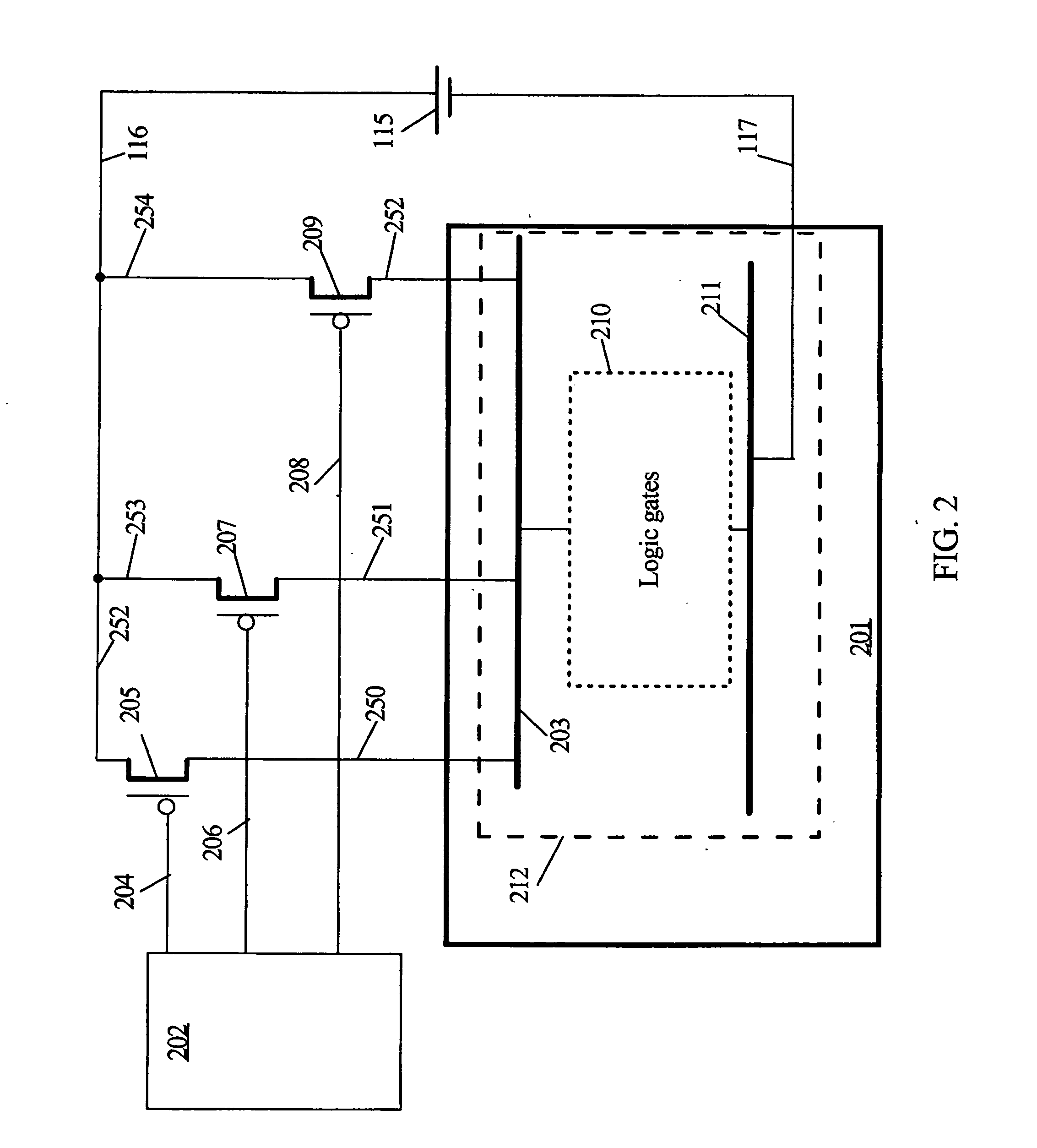

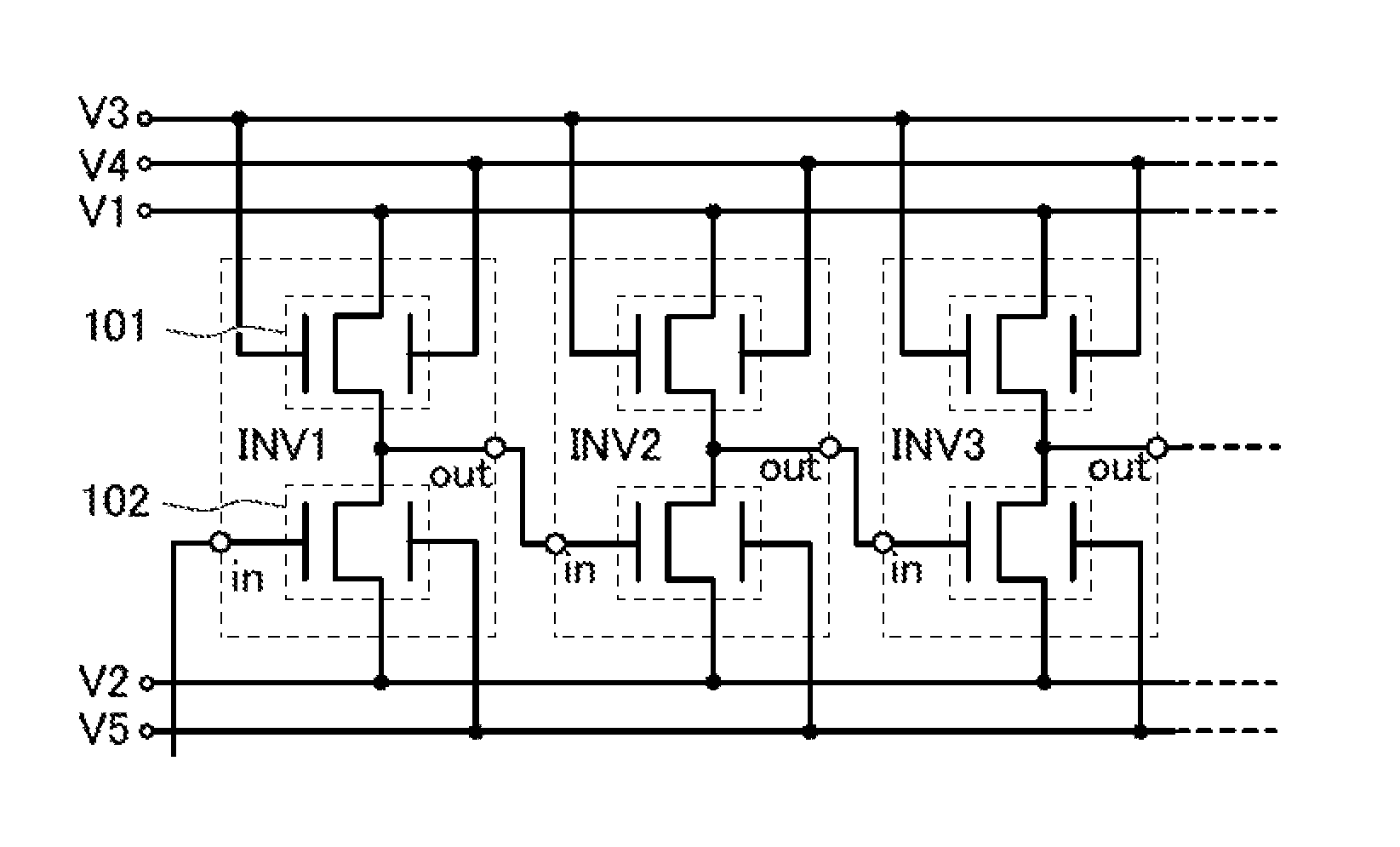

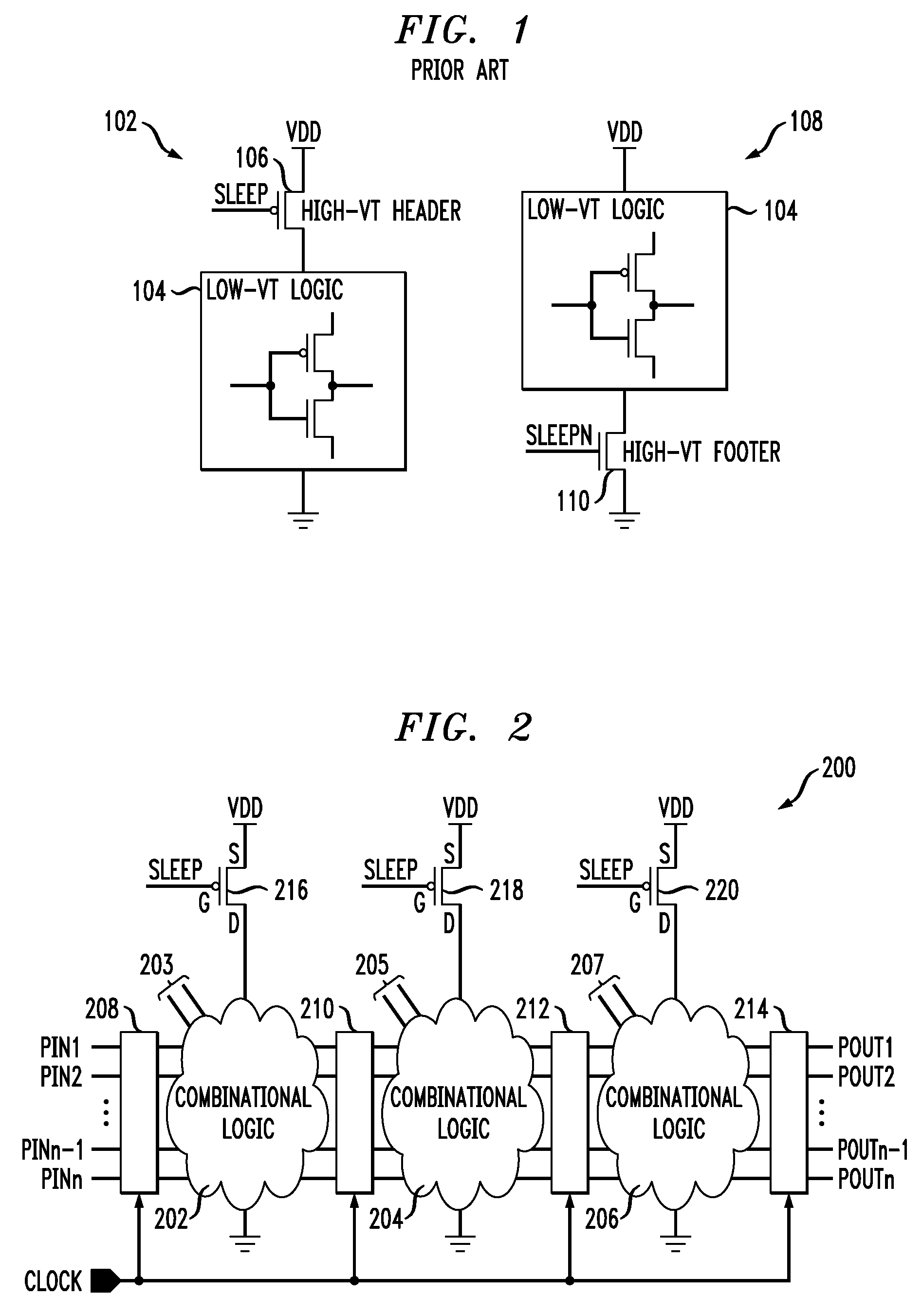

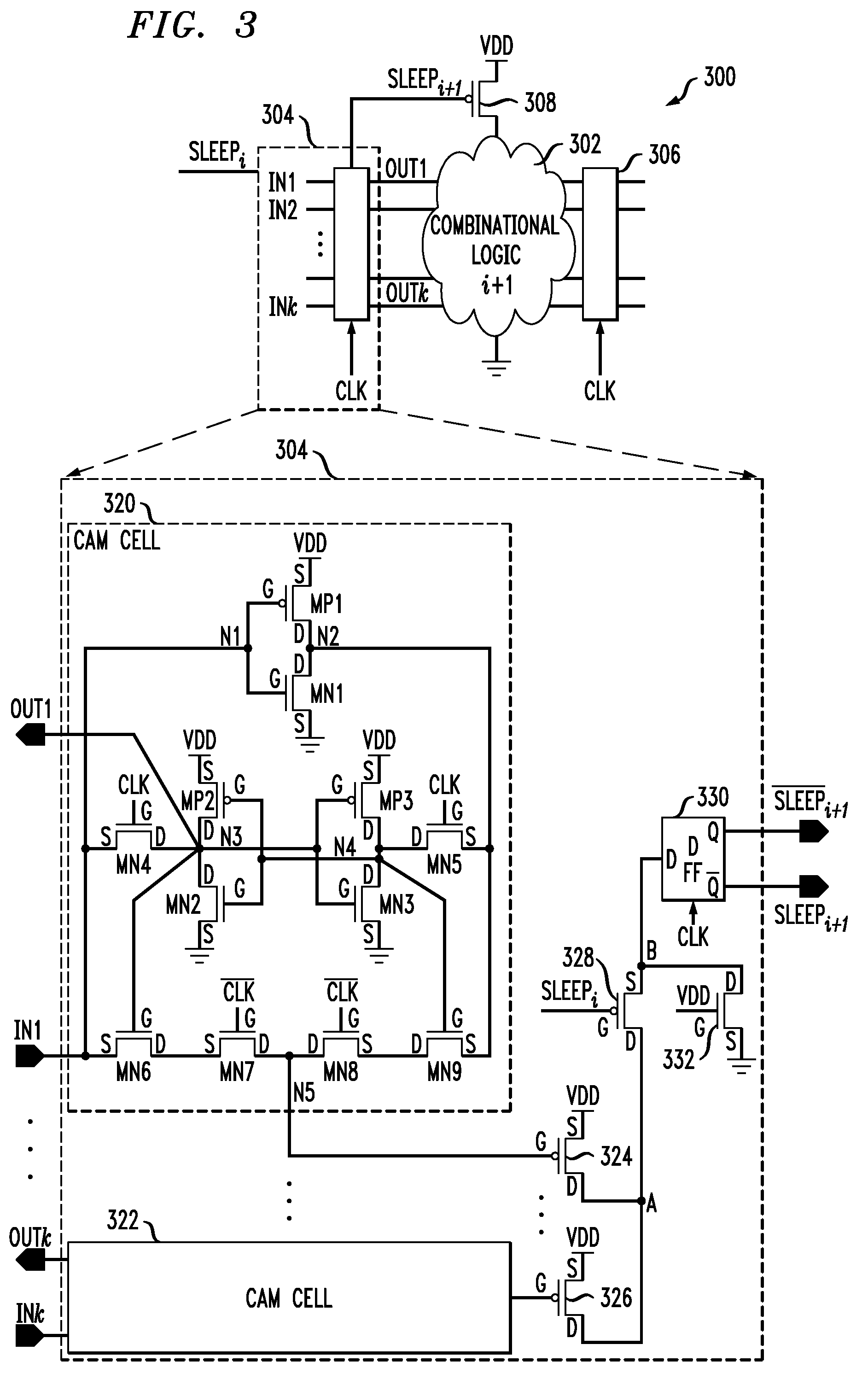

Power-gating cell for virtual power rail control

ActiveUS7276932B2Eliminate delaysReliability increasing modificationsMajority/minority circuitsControl signalPower grid

Virtual power-gated cells (VPC) are configured with control circuitry for buffering control signals and a power-gated block (PGB) comprising two or more NFETs for virtual ground rail nodes and PFETs for virtual positive rail nodes. Each VPC has a control voltage input, a control voltage output, a node coupled to a power supply voltage potential, and a virtual power-gated node that is coupled and decoupled from the power supply potential in response to logic states on the control input. The control signals are buffered by non-power-gated inverters before being applied to the input of a PGB. VPCs may propagate a control signal that is in phase with or inverted from a corresponding control signal at the control input. VPCs may be cascaded to create virtual power rails in chains and power grids. The control signals are latched at the cell boundaries or latched in response to a clock signal.

Owner:IBM CORP

Power-gating cell for virtual power rail control

ActiveUS20060055391A1Eliminate delaysReliability increasing modificationsMajority/minority circuitsControl signalPower grid

Virtual power-gated cells (VPC) are configured with control circuitry for buffering control signals and a power-gated block (PGB) comprising two or more NFETs for virtual ground rail nodes and PFETs for virtual positive rail nodes. Each VPC has a control voltage input, a control voltage output, a node coupled to a power supply voltage potential, and a virtual power-gated node that is coupled and decoupled from the power supply potential in response to logic states on the control input. The control signals are buffered by non-power-gated inverters before being applied to the input of a PGB. VPCs may propagate a control signal that is in phase with or inverted from a corresponding control signal at the control input. VPCs may be cascaded to create virtual power rails in chains and power grids. The control signals are latched at the cell boundaries or latched in response to a clock signal.

Owner:IBM CORP

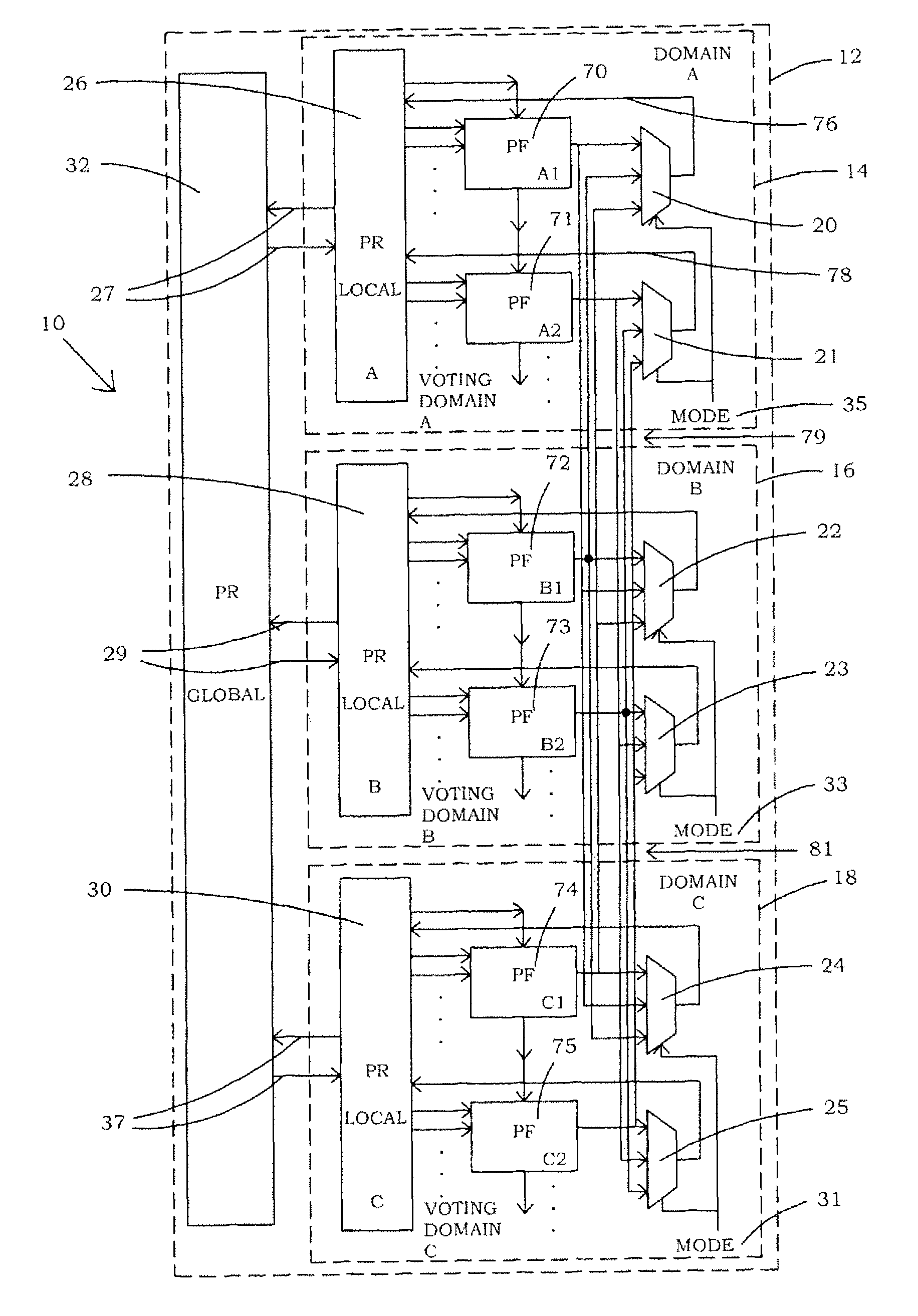

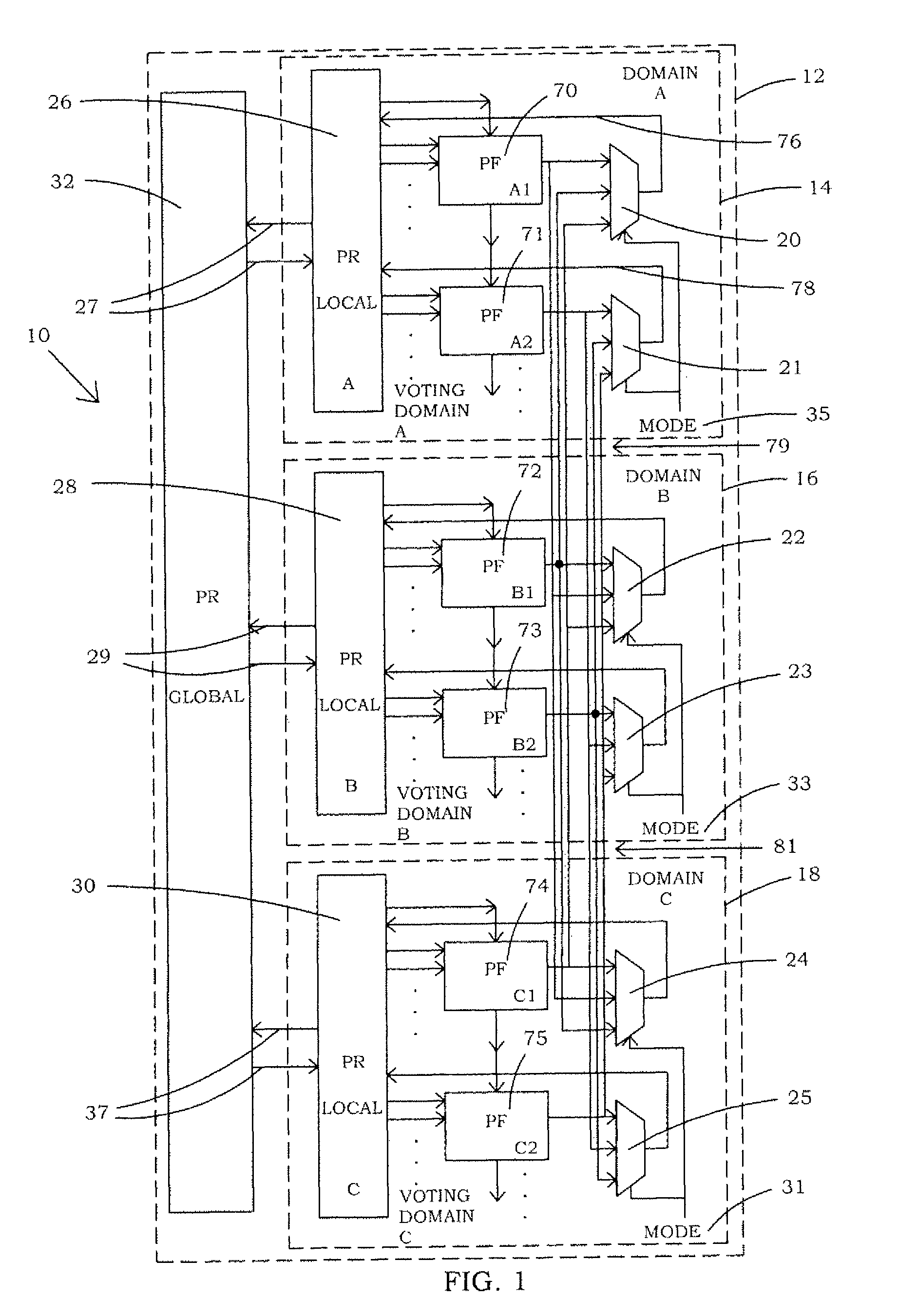

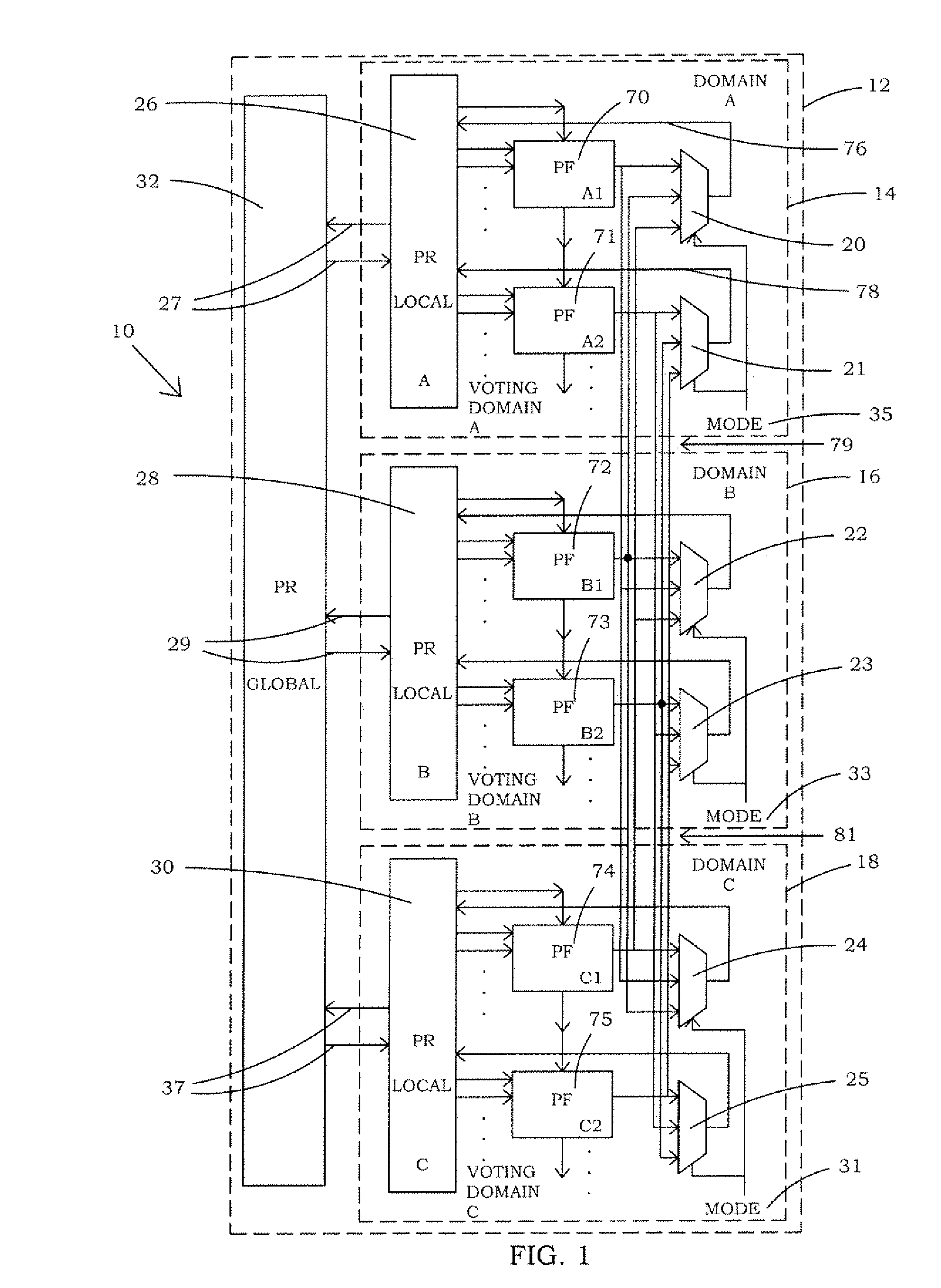

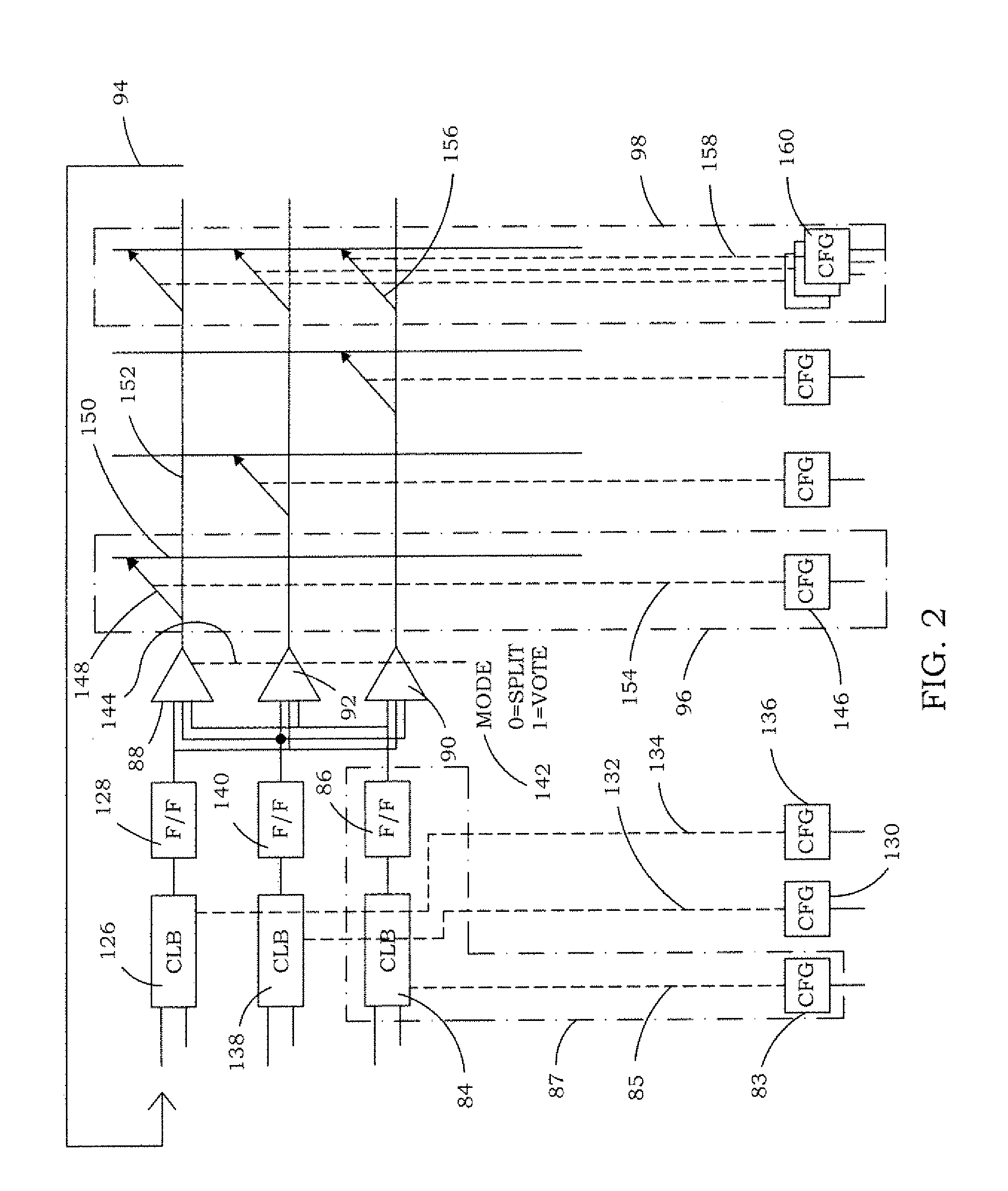

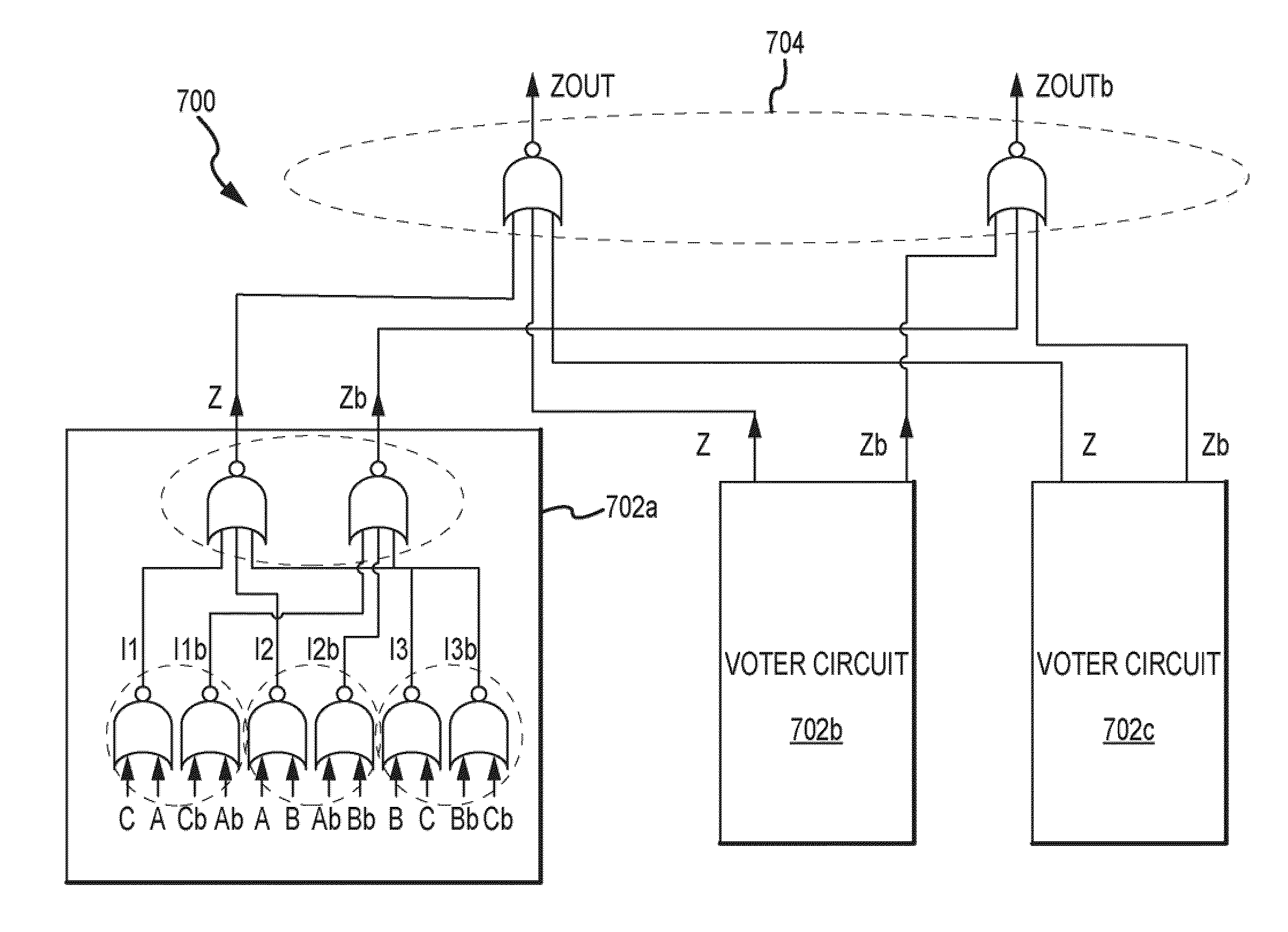

Methods and circuitry for reconfigurable SEU/SET tolerance

InactiveUS7859292B1Large capacityQuicklyMajority/minority circuitsWave amplification devicesComputer scienceMajority voter

Owner:NASA

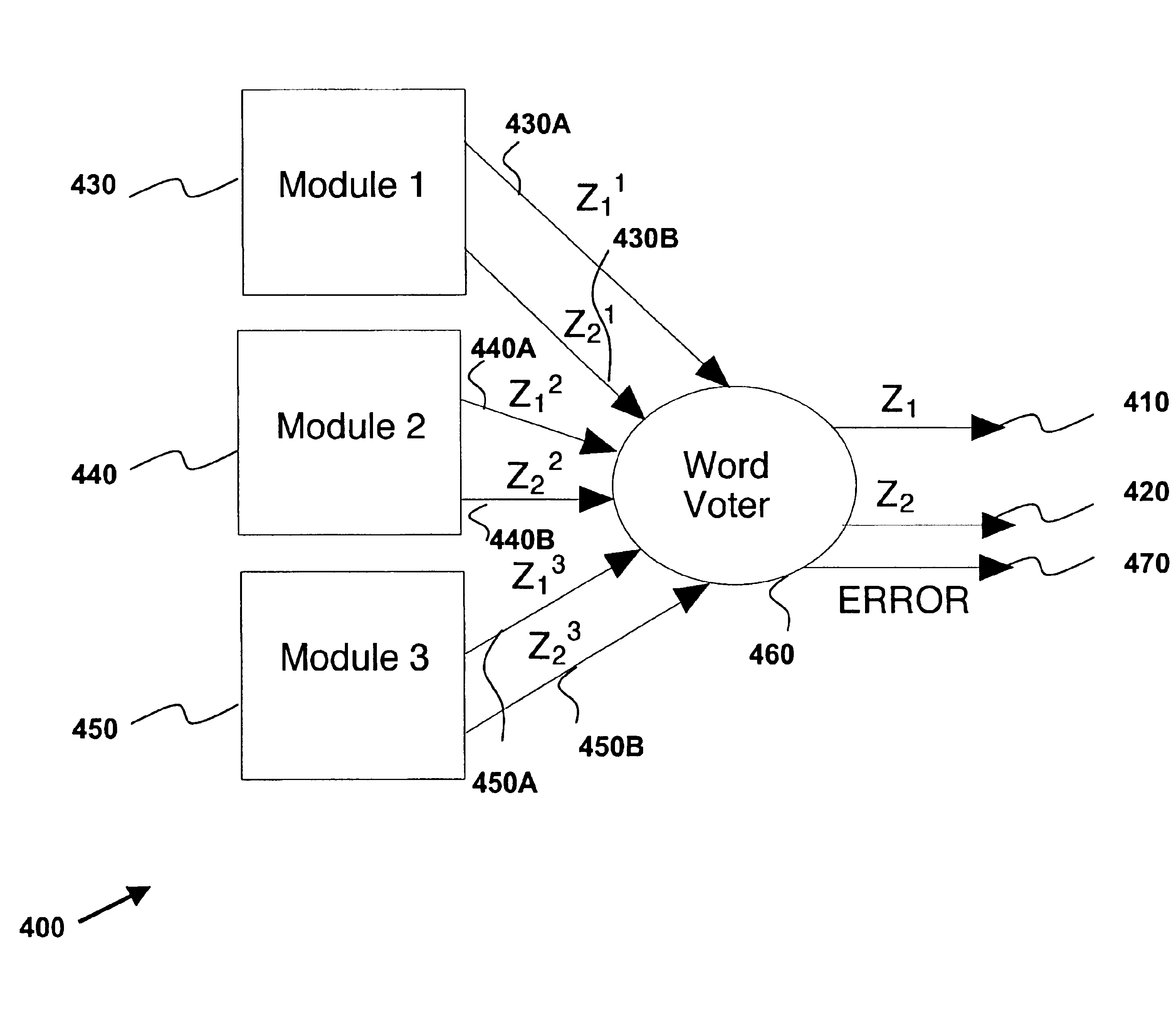

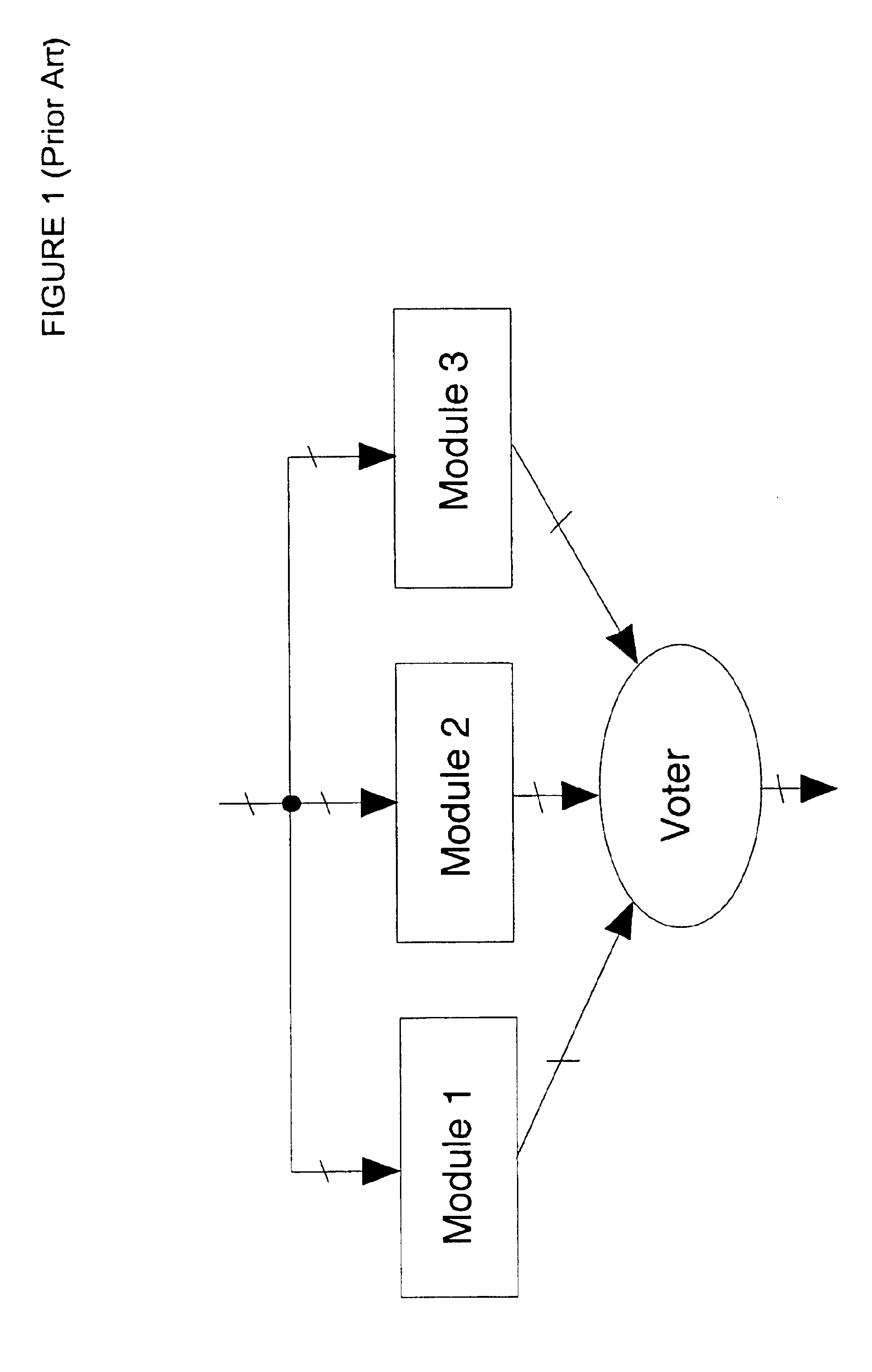

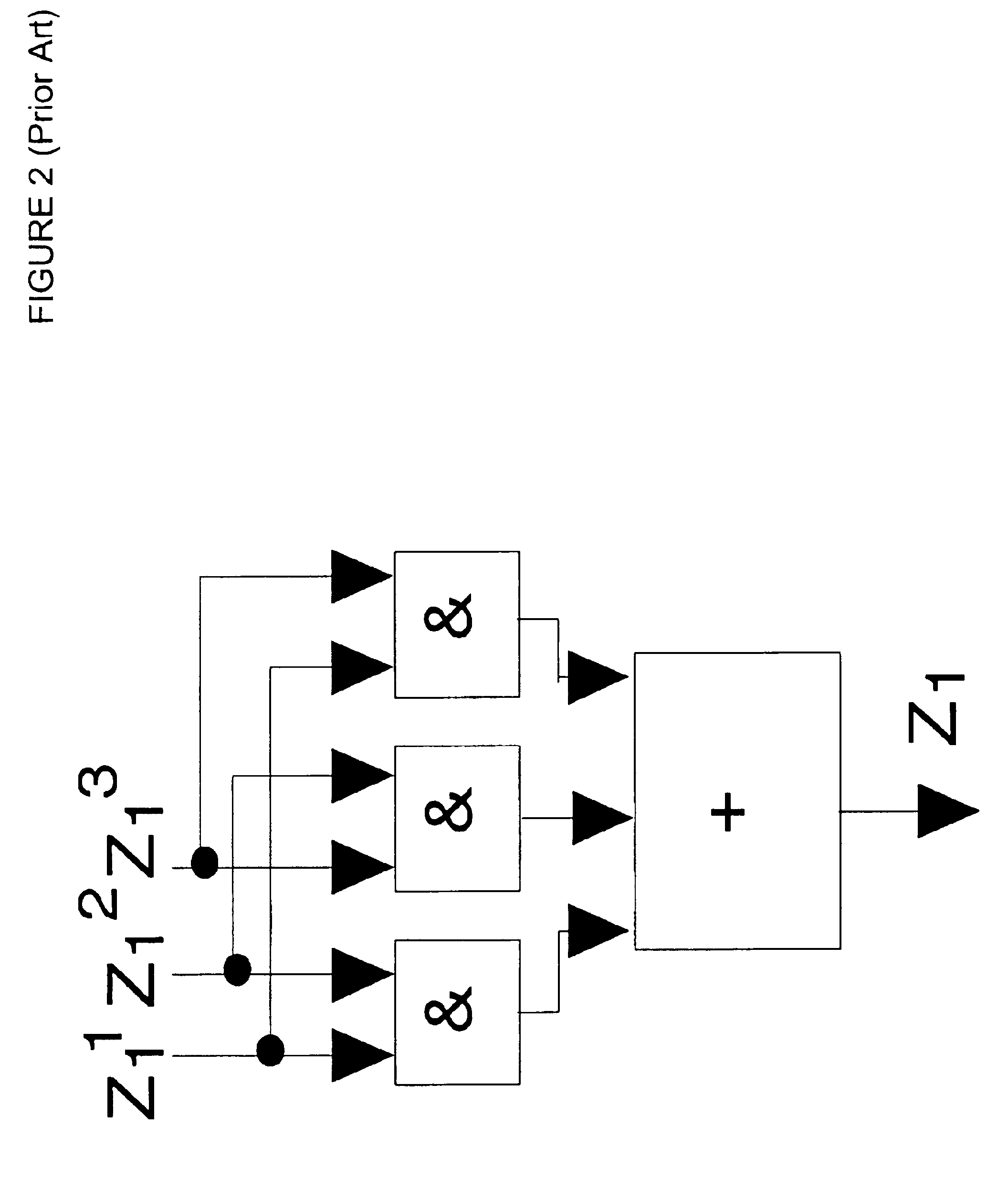

Word voter for redundant systems

InactiveUS6910173B2Efficient designAvoid problemsReliability increasing modificationsMajority/minority circuitsComputer science

The present invention provides a word voter for redundant systems with n modules wherein each of these n modules generates a word output. The word voter receives word outputs from each of the n modules. A voter decision is generated by the word voter utilizing a word basis of the word output of each of the n modules. The voter is based on a majority voting principle. The advantage of the present invention is that the word voter can be used to design redundant systems, such as, but not limited to, TMR systems, that are protected against common mode and multiple output failures. In addition, another advantage of the present invention is that is provides for a technique to efficiently design a TMR simplex system. The present invention provides a word voter for hardware systems.

Owner:THE BOARD OF TRUSTEES OF THE LELAND STANFORD JUNIOR UNIV OFFFICE OF TECH LICENSING

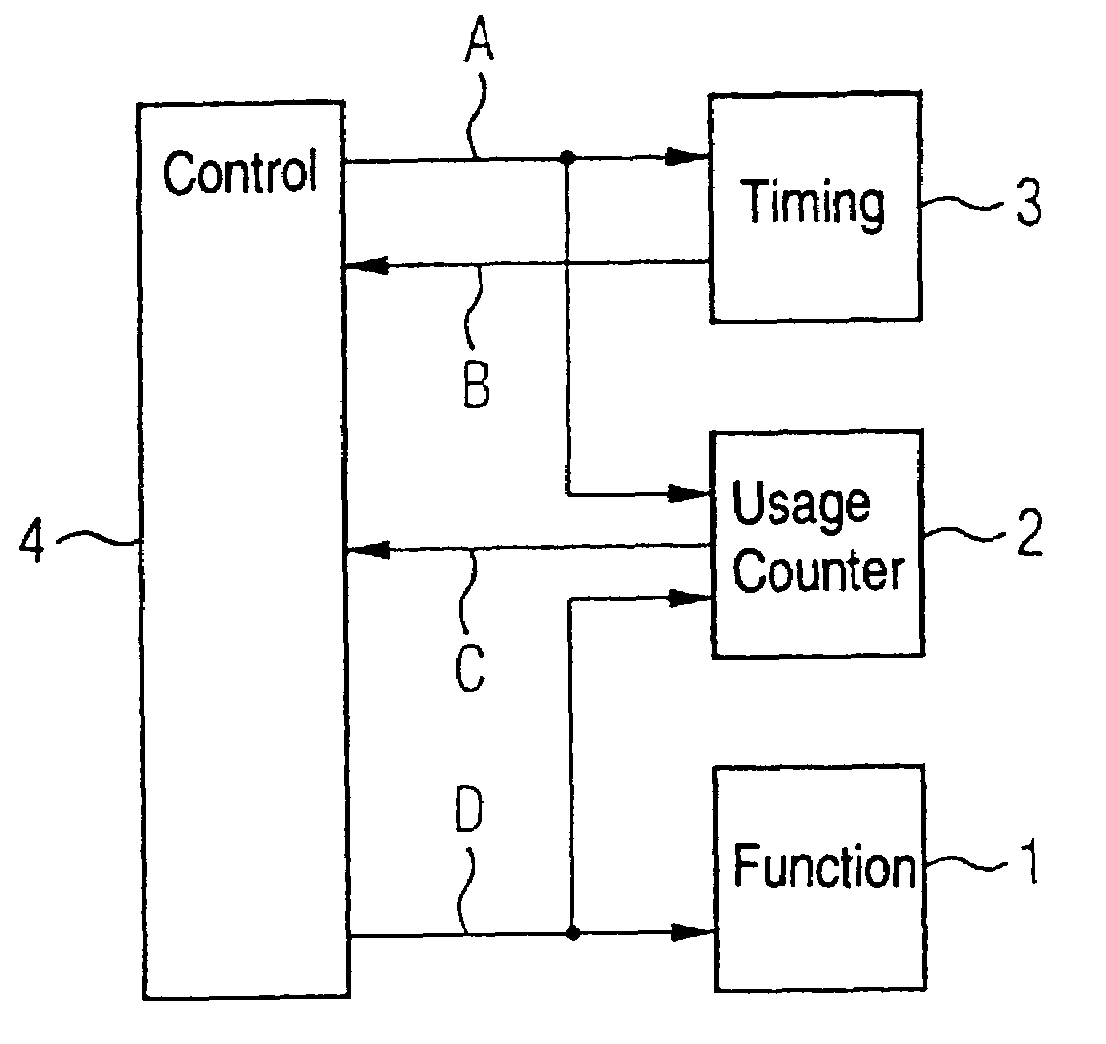

Integrated security circuit

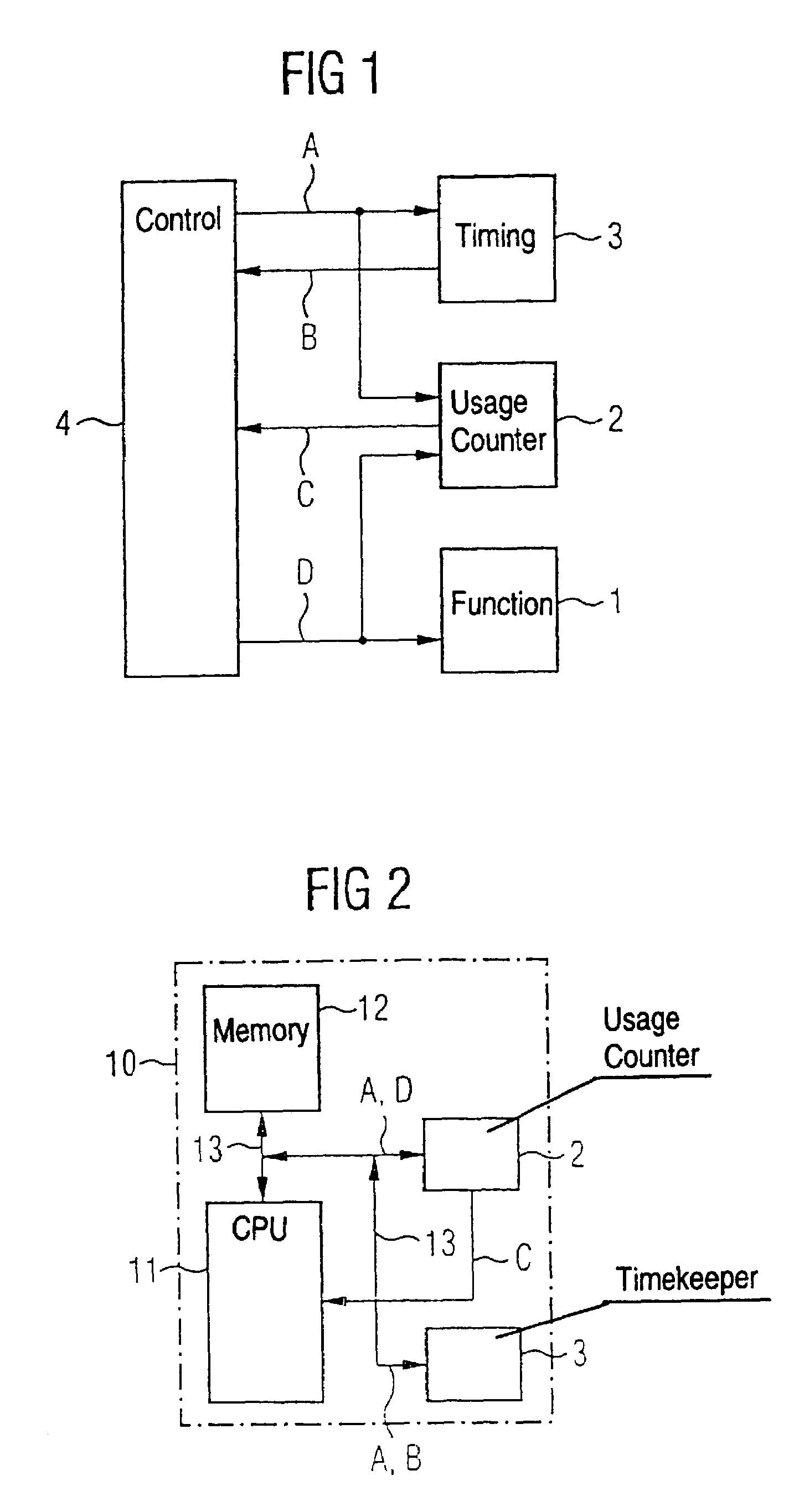

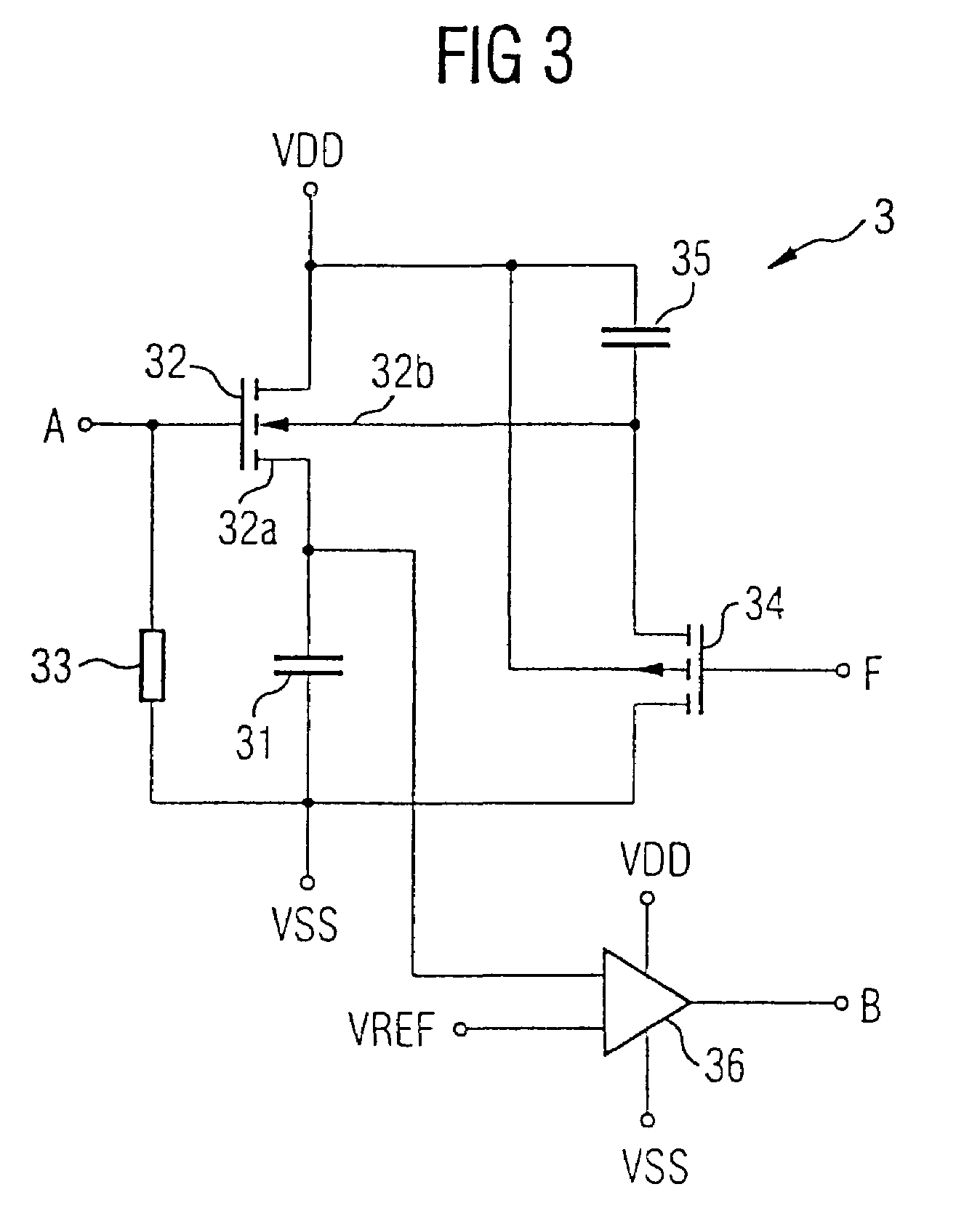

InactiveUS7036018B2Improve security levelImprove stateMajority/minority circuitsBatteries circuit arrangementsMicrocontrollerUnit of time

An integrated security circuit, for example, a microcontroller for smart cards, includes a function unit executing a security function. A control device determines the number of executions of the security function per unit of time. The continued execution of the security function is blocked when a threshold value is exceeded. For such a purpose, an analog timekeeper incorporating a charge storage device is preferably provided that measures the elapsing time even with the supply potential disconnected. A usage counter is updated whenever the security function is called. The security circuit offers increased protection against statistical attacks. The complexity involved in the implementation is justifiably low. The security circuit is compatible with the existing system.

Owner:INFINEON TECH AG

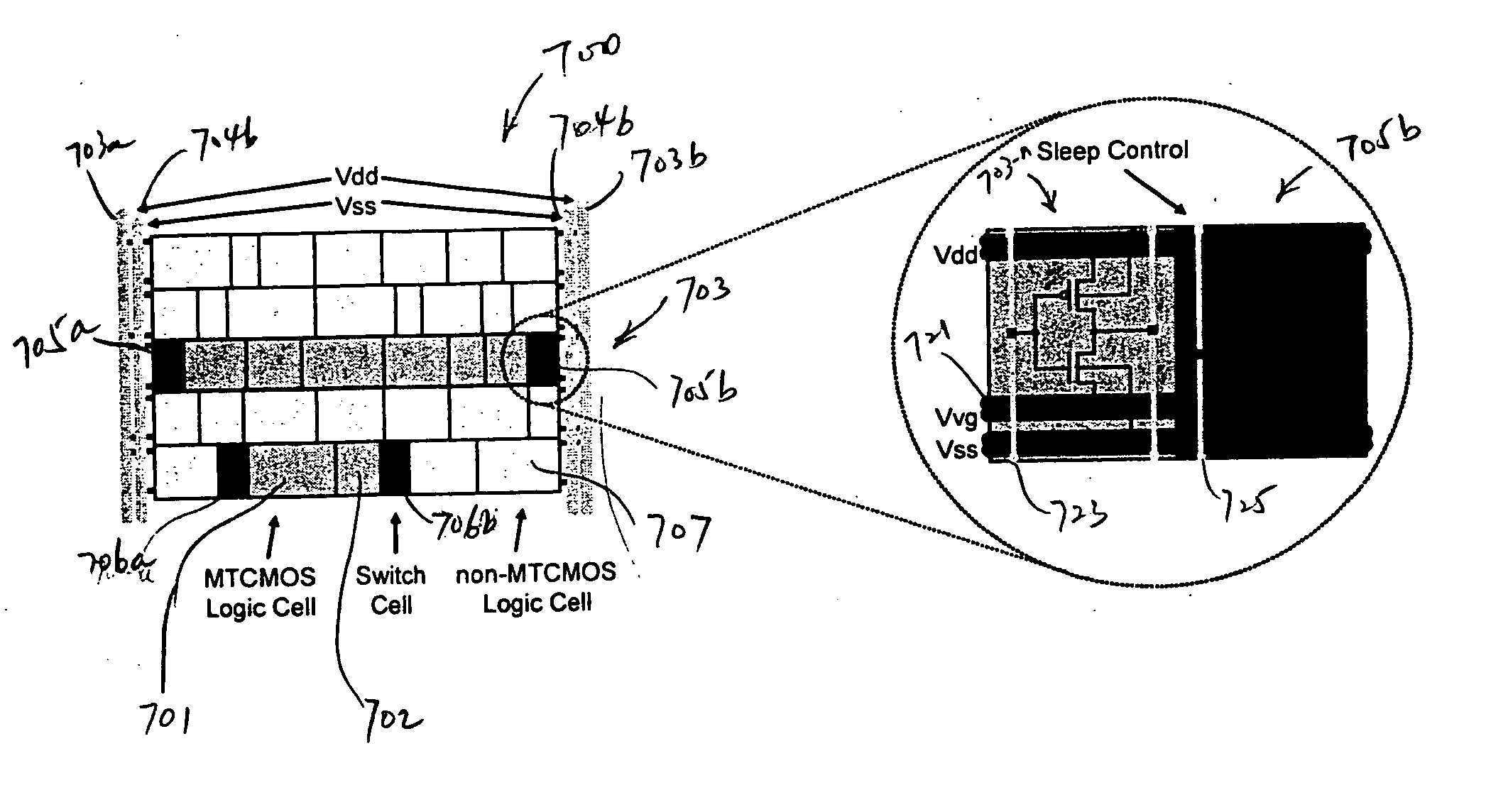

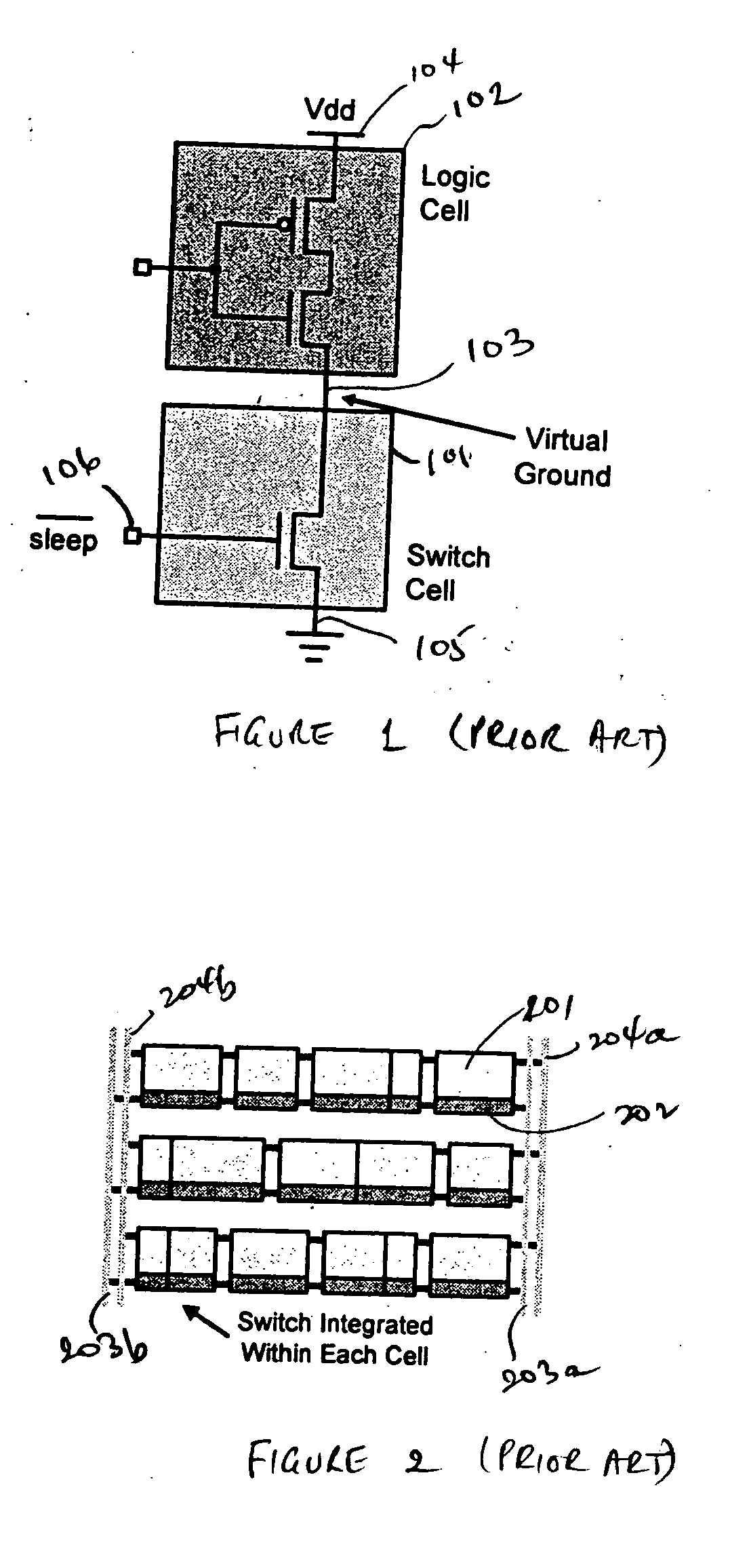

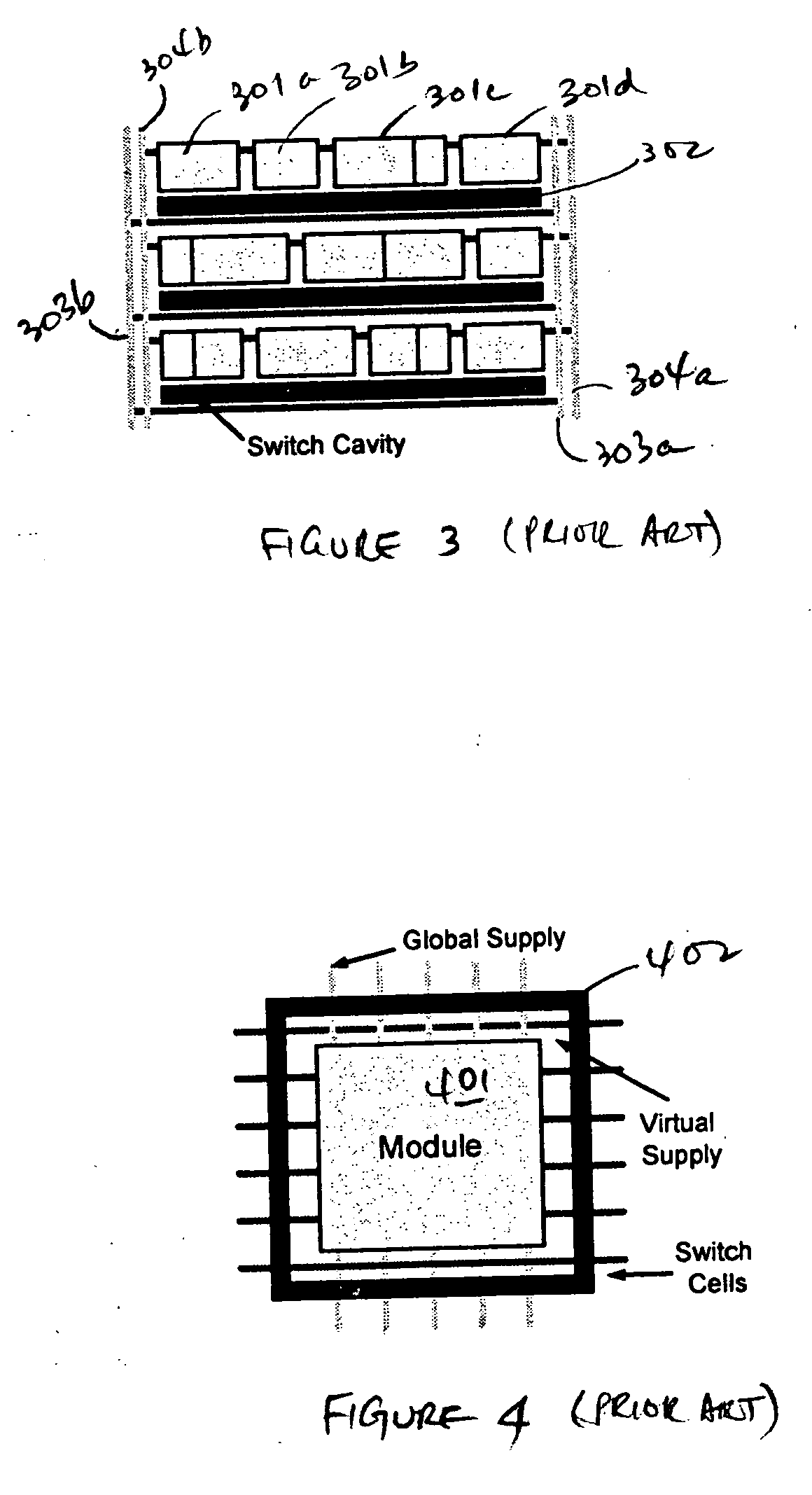

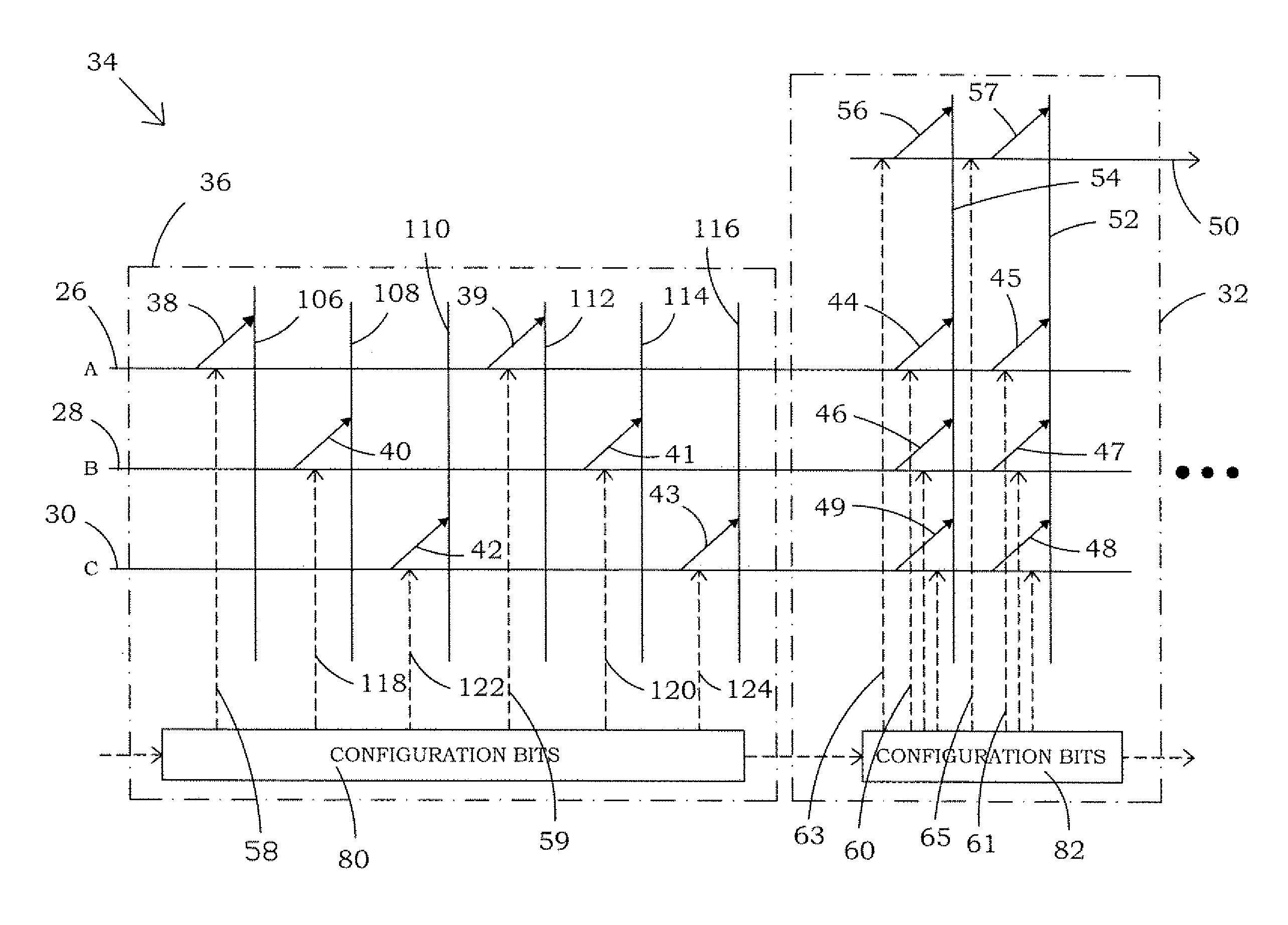

Design method and architecture for power gate switch placement

ActiveUS20060114025A1Improve circuit performanceReduce violationsMajority/minority circuitsPower reduction by control/clock signalLogic cellVoltage reference

A design method places power gates or switch cells using unoccupied locations of logic cell rows. Two types of such switch cells, filler switches and sealer switches, may be provided using the unoccupied locations. In one embodiment, virtual ground voltage references to the logic cells are routed to their associated switch cells. Because conventional standard cell design and placement techniques achieve only a placement density or utilization between 70-80% (i.e., unoccupied space constitutes between 20 to 30% of the available space in each row of logic cells), by placing the power gate cells in the unoccupied space, the method does not increase the silicon real estate requirement even though the power gate cells are introduced into the design. Optimization techniques may be applied to achieve proper sizing and distribution of power gate cells, so as to avoid a performance penalty due to the power gate cells. In one embodiment, fine-grained power gating is achieved by selectively providing non-power-gated logic cells among power-gated logic cells.

Owner:ANSYS

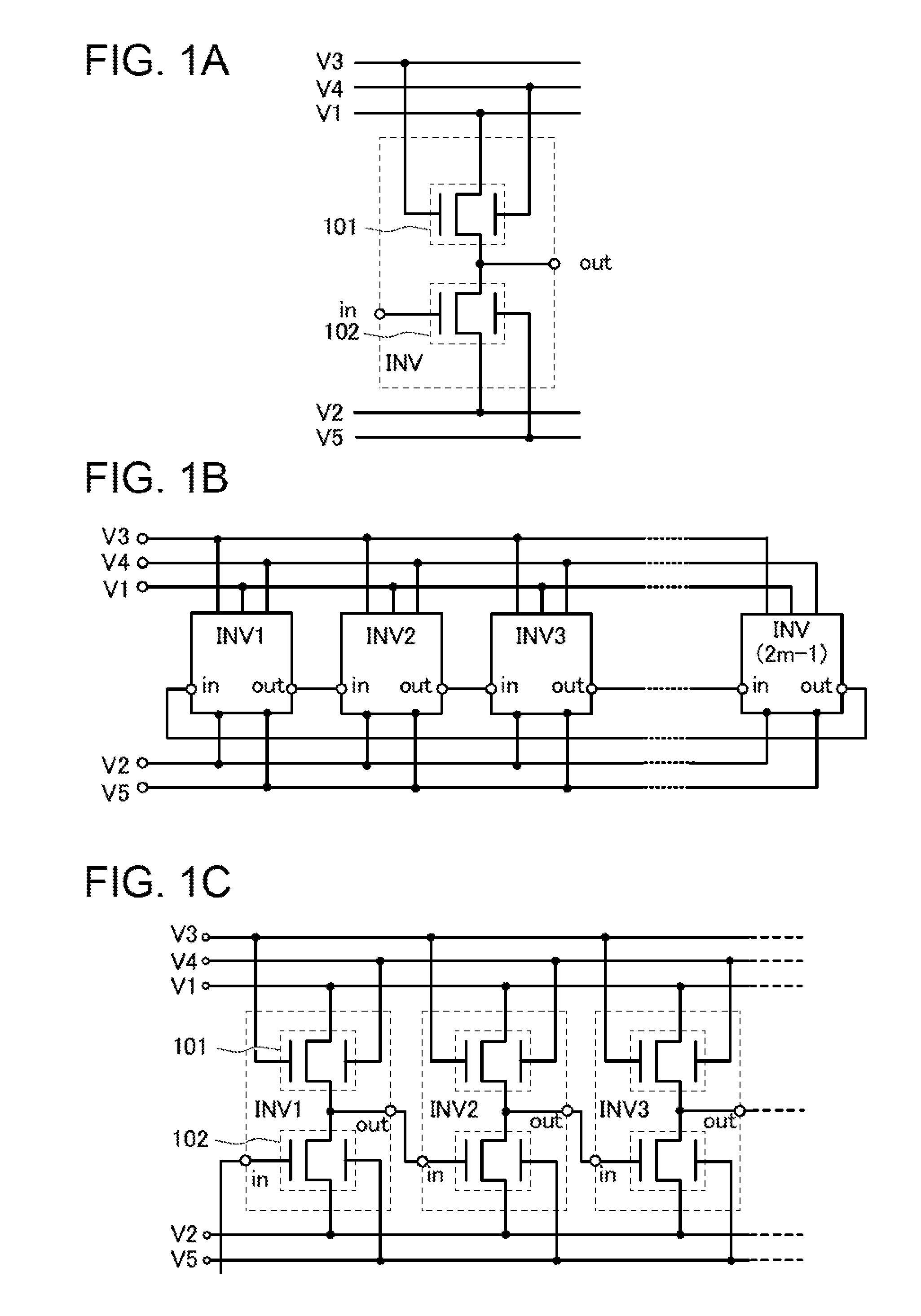

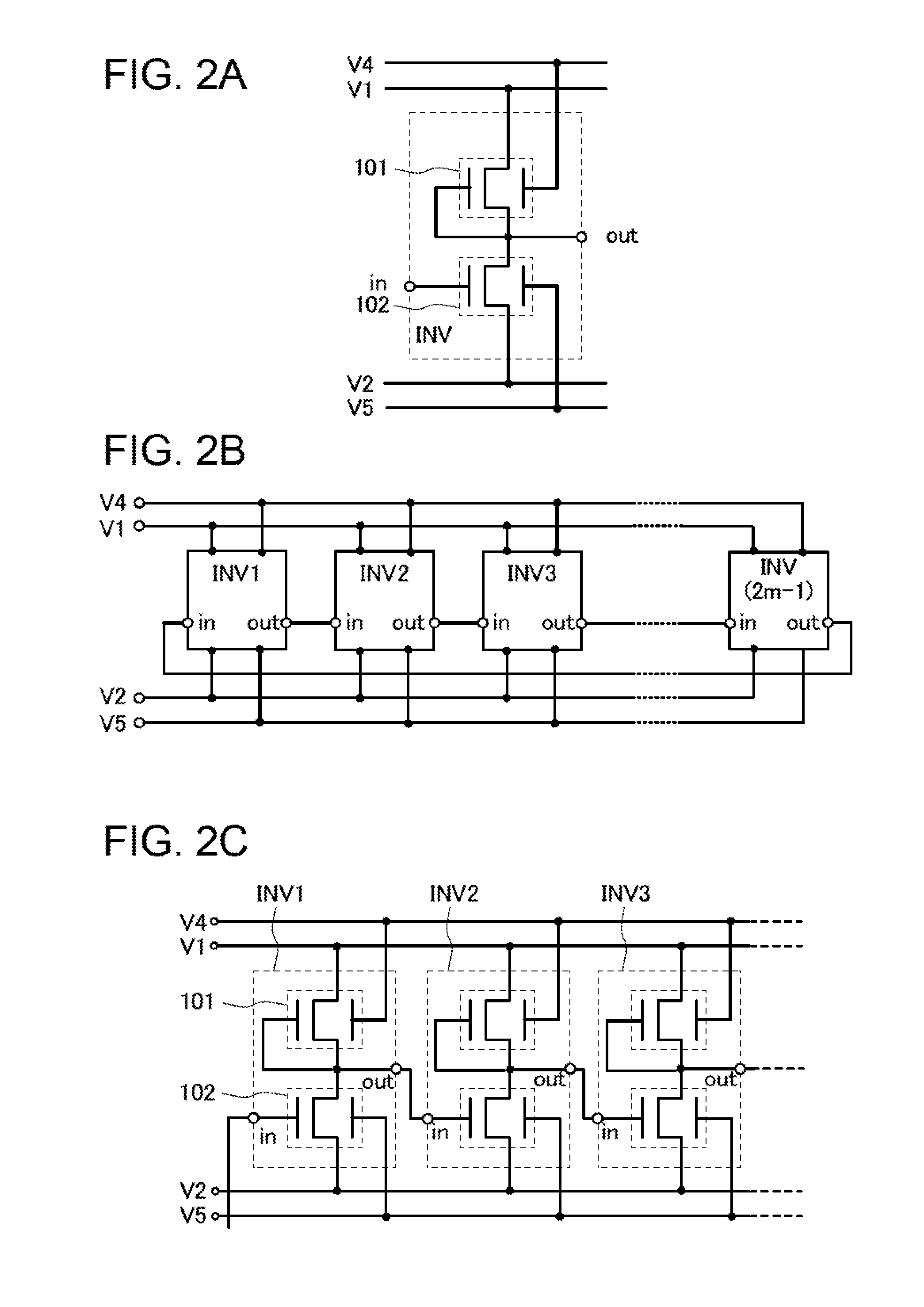

Semiconductor device

ActiveUS8988152B2Increased power consumptionReduce power consumptionPower reduction in field effect transistorsTransistorPower semiconductor deviceEngineering

To provide a semiconductor device including an inverter circuit whose driving frequency is increased by control of the threshold voltage of a transistor or a semiconductor device including an inveter circuit with low power consumption. An inverter circuit includes a first transistor and a second transistor each including a semiconductor film in which a channel is formed, a pair of gate electrodes between which the semiconductor film is placed, and source and drain electrodes in contact with the semiconductor film. Controlling potentials applied to the pair of gate electrodes makes the first transistor have normally-on characteristics and the second transistor have normally-off characteristics. Thus, the driving frequency of the inverter circuit is increased.

Owner:SEMICON ENERGY LAB CO LTD

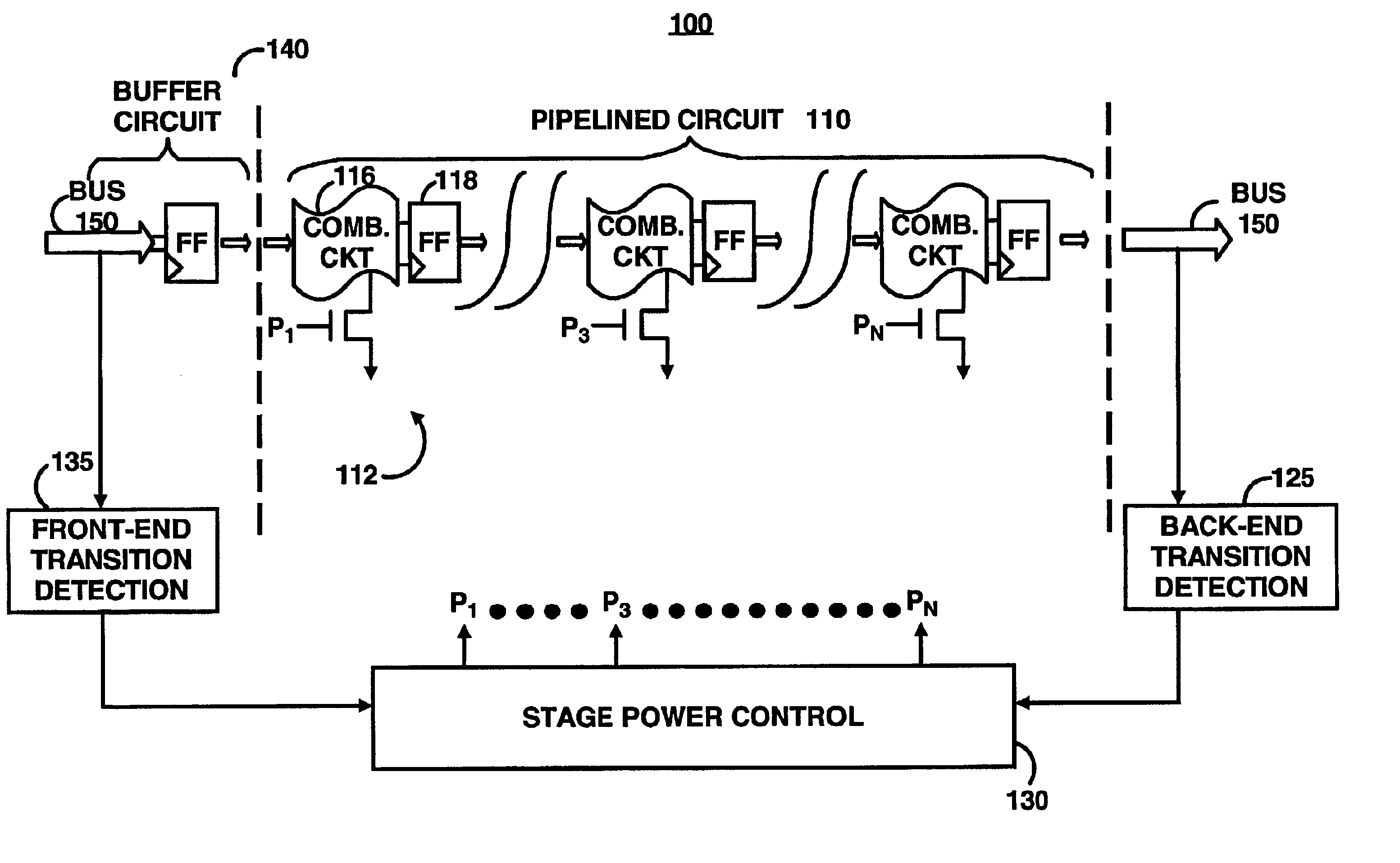

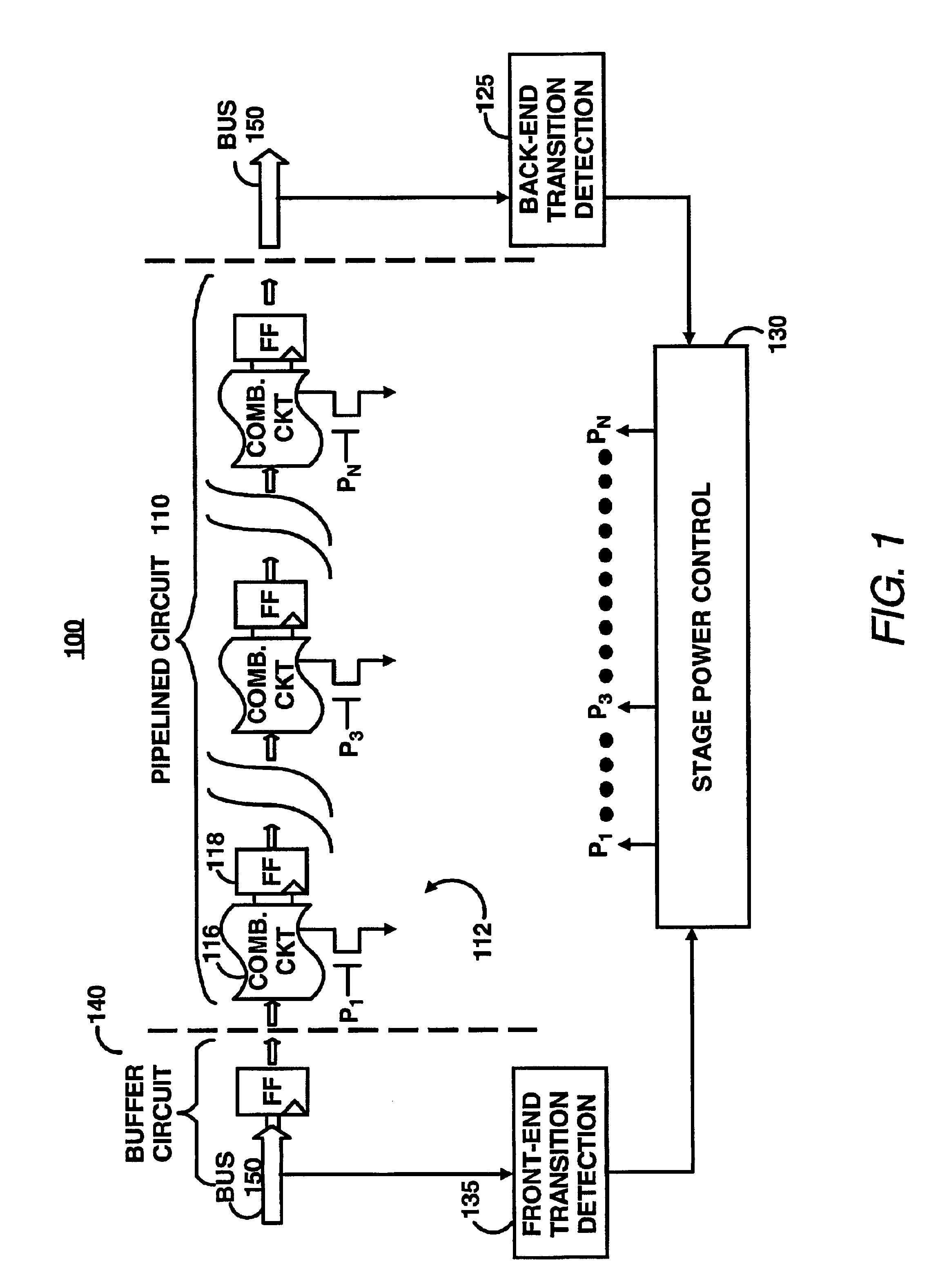

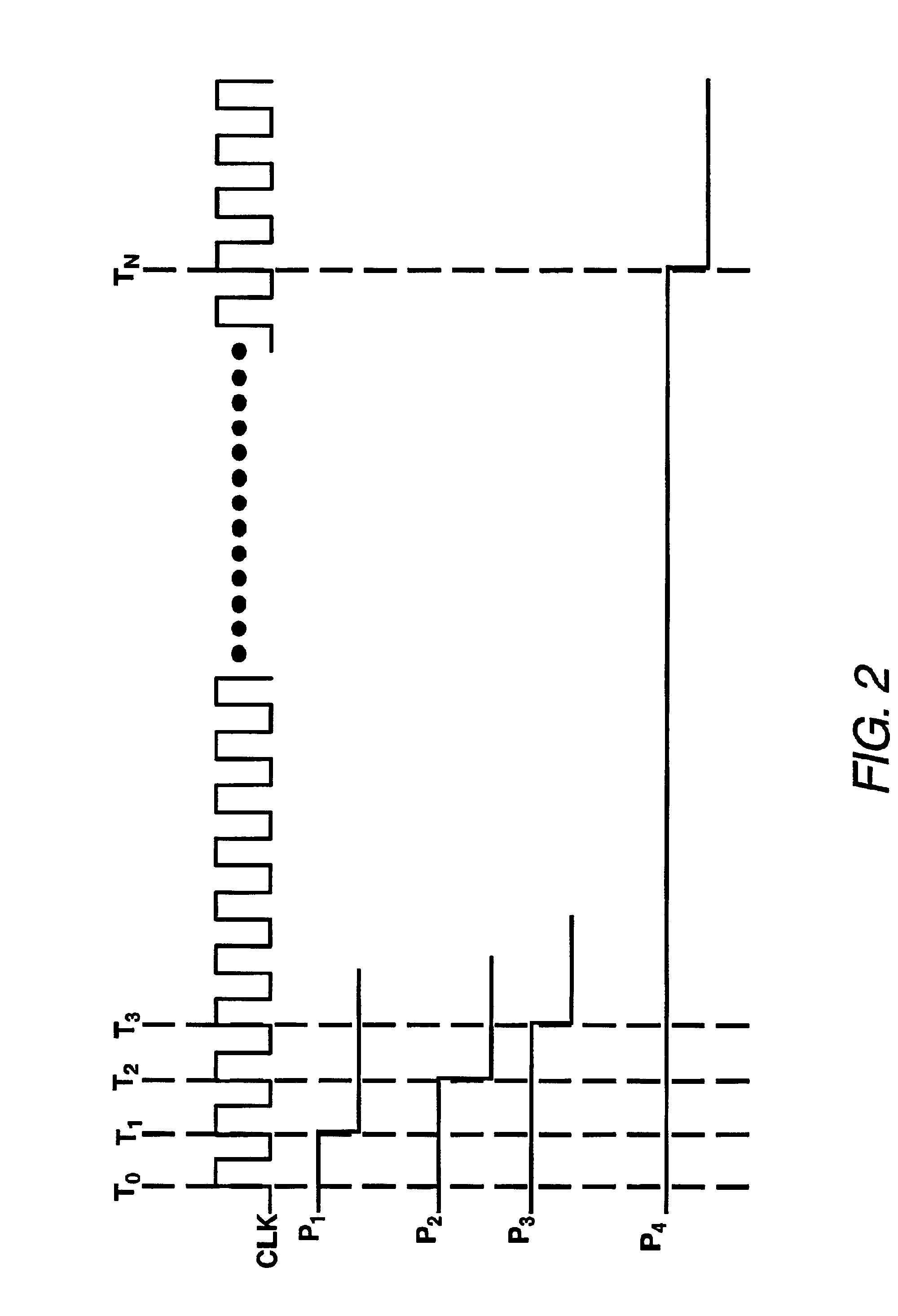

Minimizing power consumption in pipelined circuit by shutting down pipelined circuit in response to predetermined period of time having expired

InactiveUS6907534B2Minimize power consumptionMajority/minority circuitsVolume/mass flow measurementPower consumption

Power consumption in a circuit is minimized. The circuit includes a pipelined circuit having a plurality of stages. A determination is made as to whether a predetermined period of time has expired. The predetermined period of time being associated with a predetermined period of time to detect a transition of an input or an output of the pipelined circuit. If the predetermined period of time is exceeded, a sequential shut-down procedure is performed on each stage in the plurality of stages of the pipelined circuit so that each stage is shut-down.

Owner:HEWLETT-PACKARD ENTERPRISE DEV LP

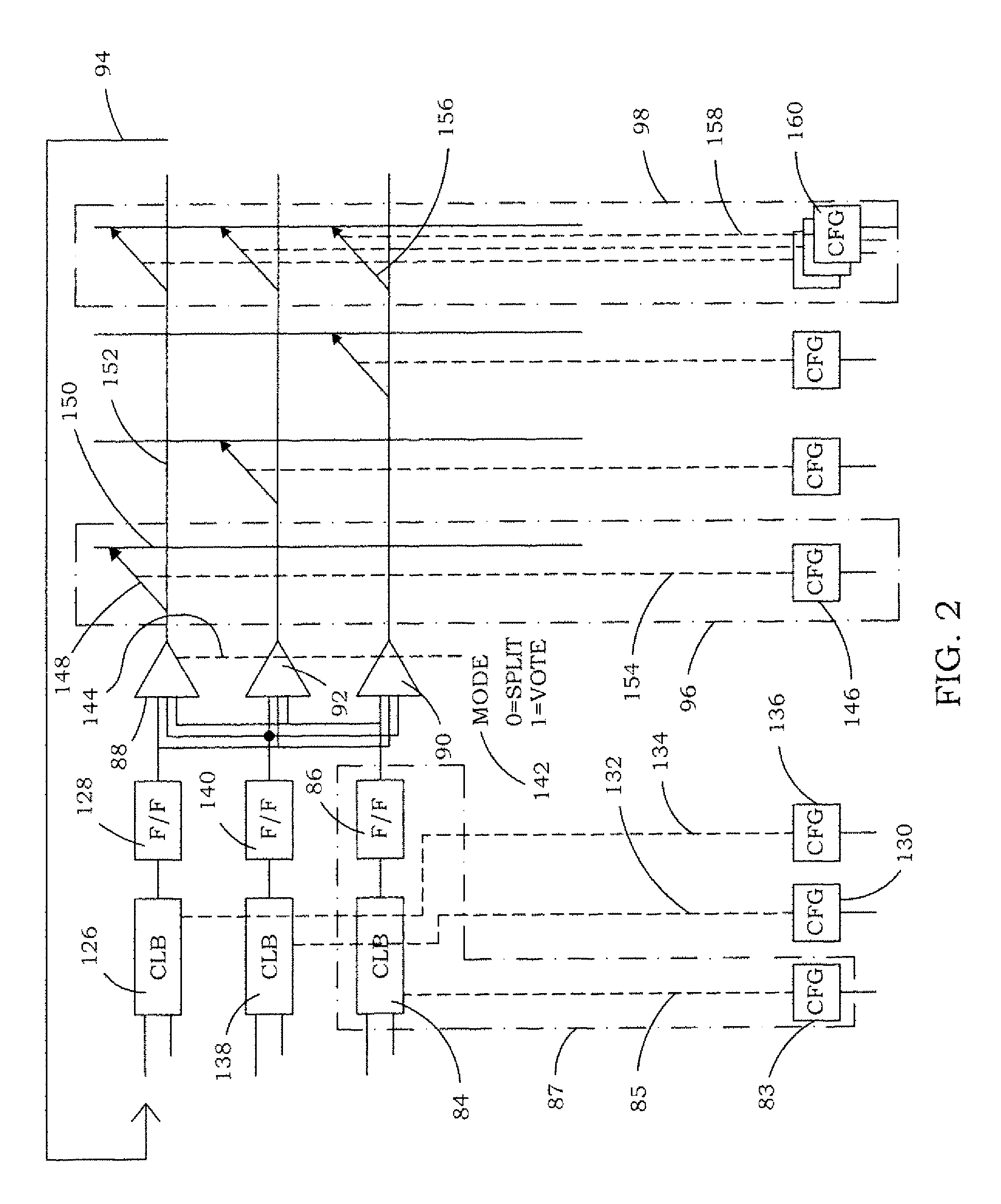

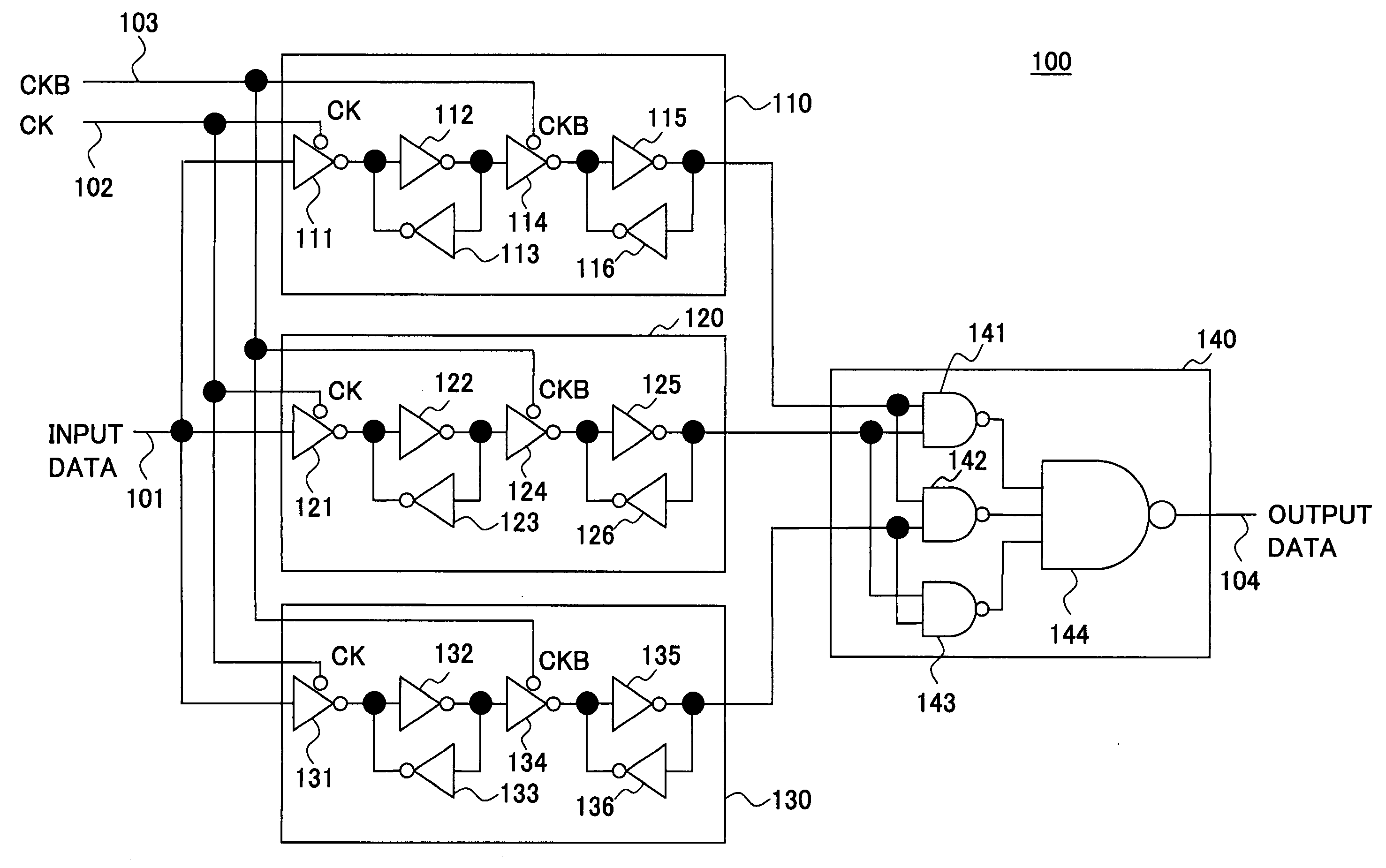

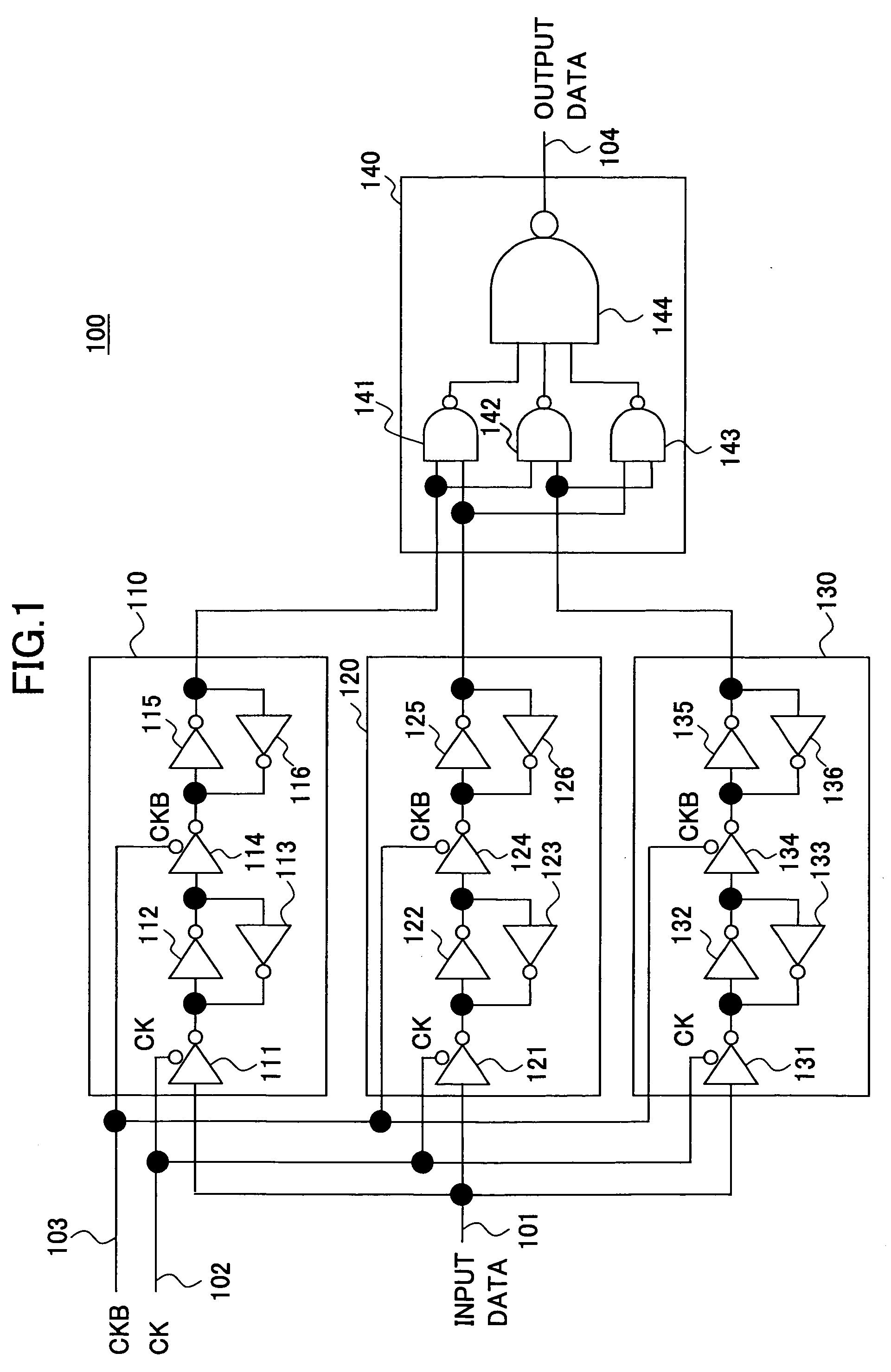

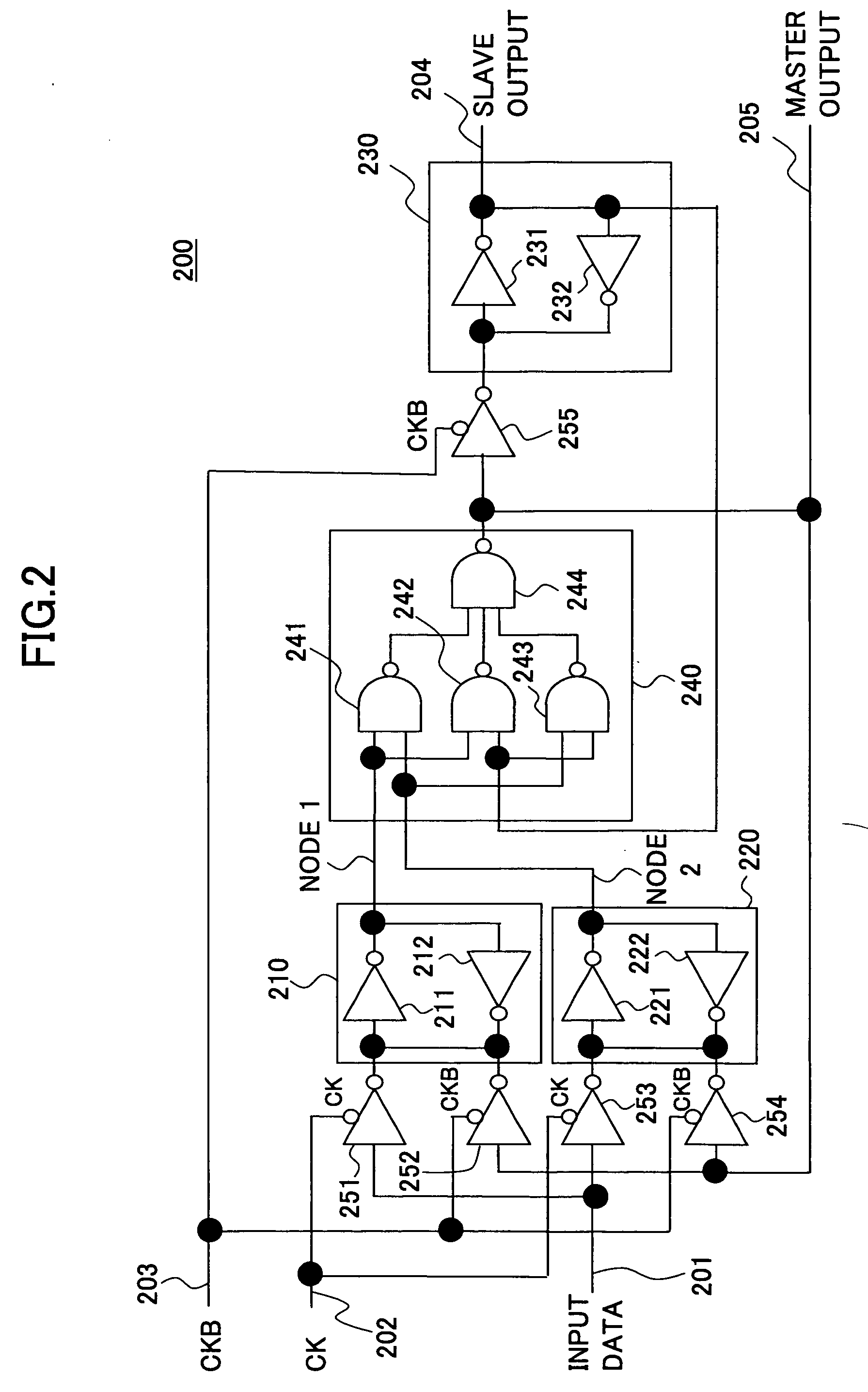

Flip-flop circuit having majority-logic circuit

A flip-flop circuit having a majority-logic circuit is disclosed. The circuit further includes multiple master latches for writing in corresponding input signals, and one slave latch having an input connected to an output of the majority-logic circuit and an output connected to the inputs of the majority-logic circuit. The majority logic-circuit has multiple inputs connected to respective outputs of the master latches. During the period in which the master latches do not write in the corresponding input signals, an output signal of the majority-logic circuit is supplied to respective inputs of the master latches.

Owner:FUJITSU LTD

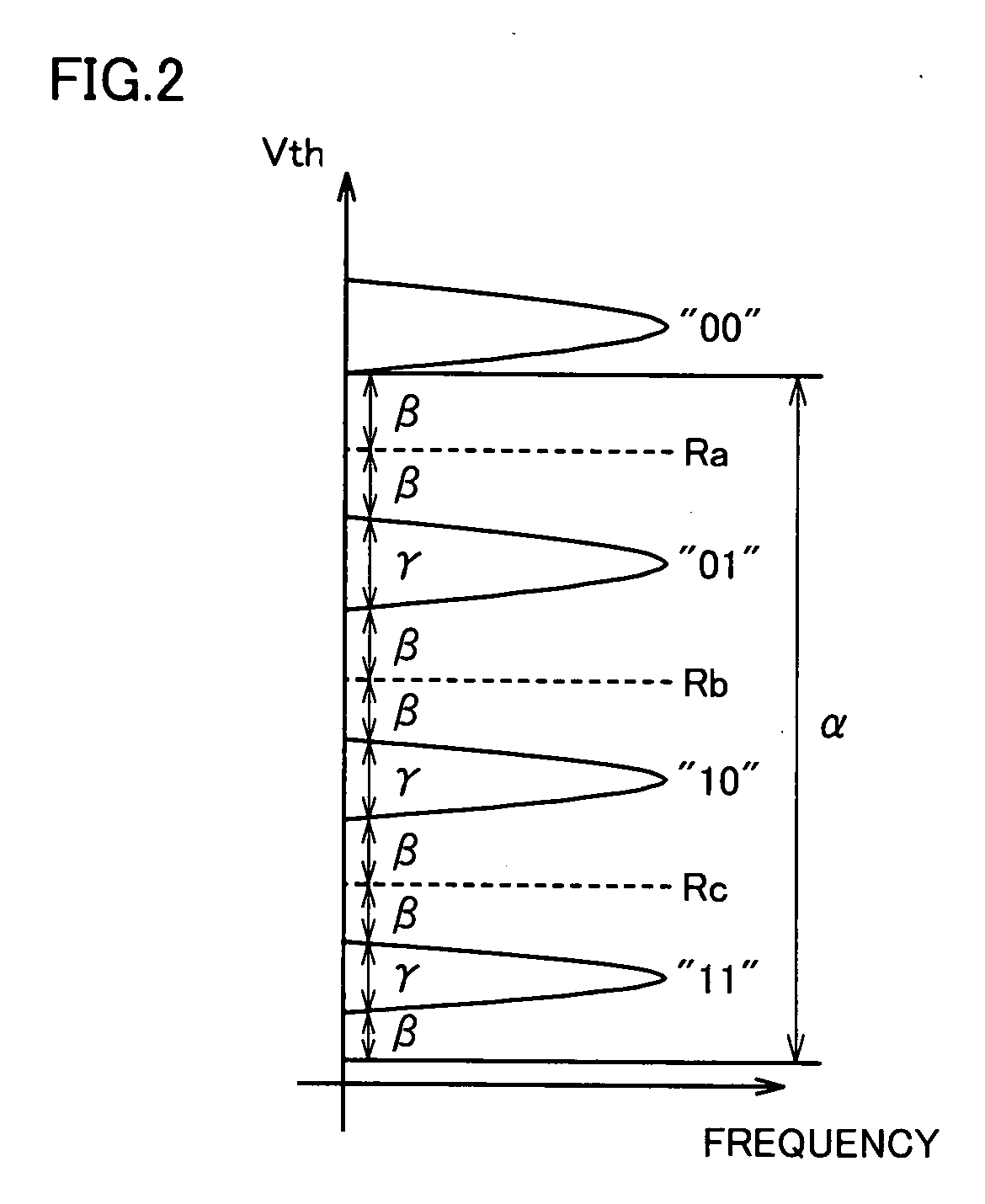

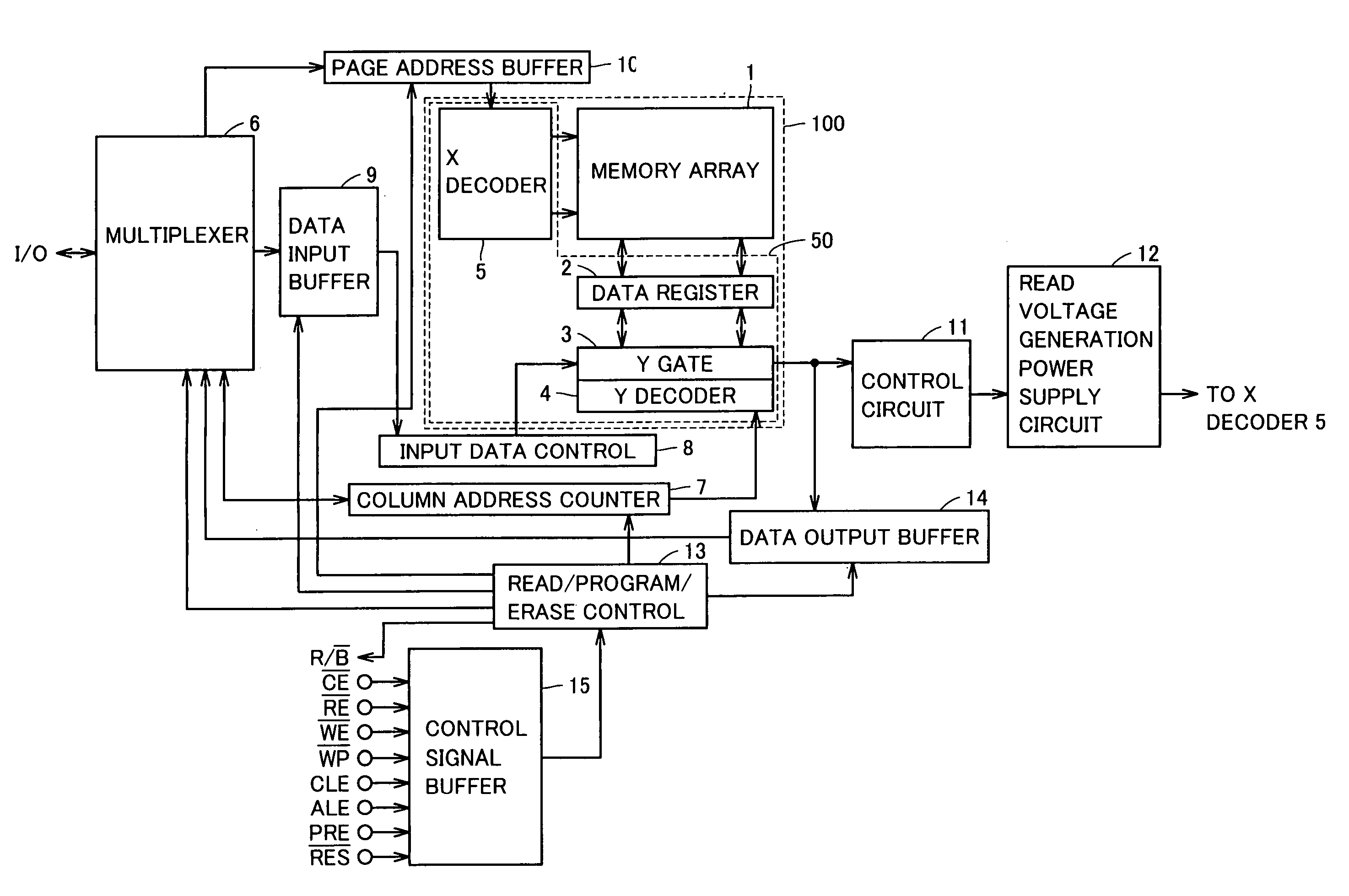

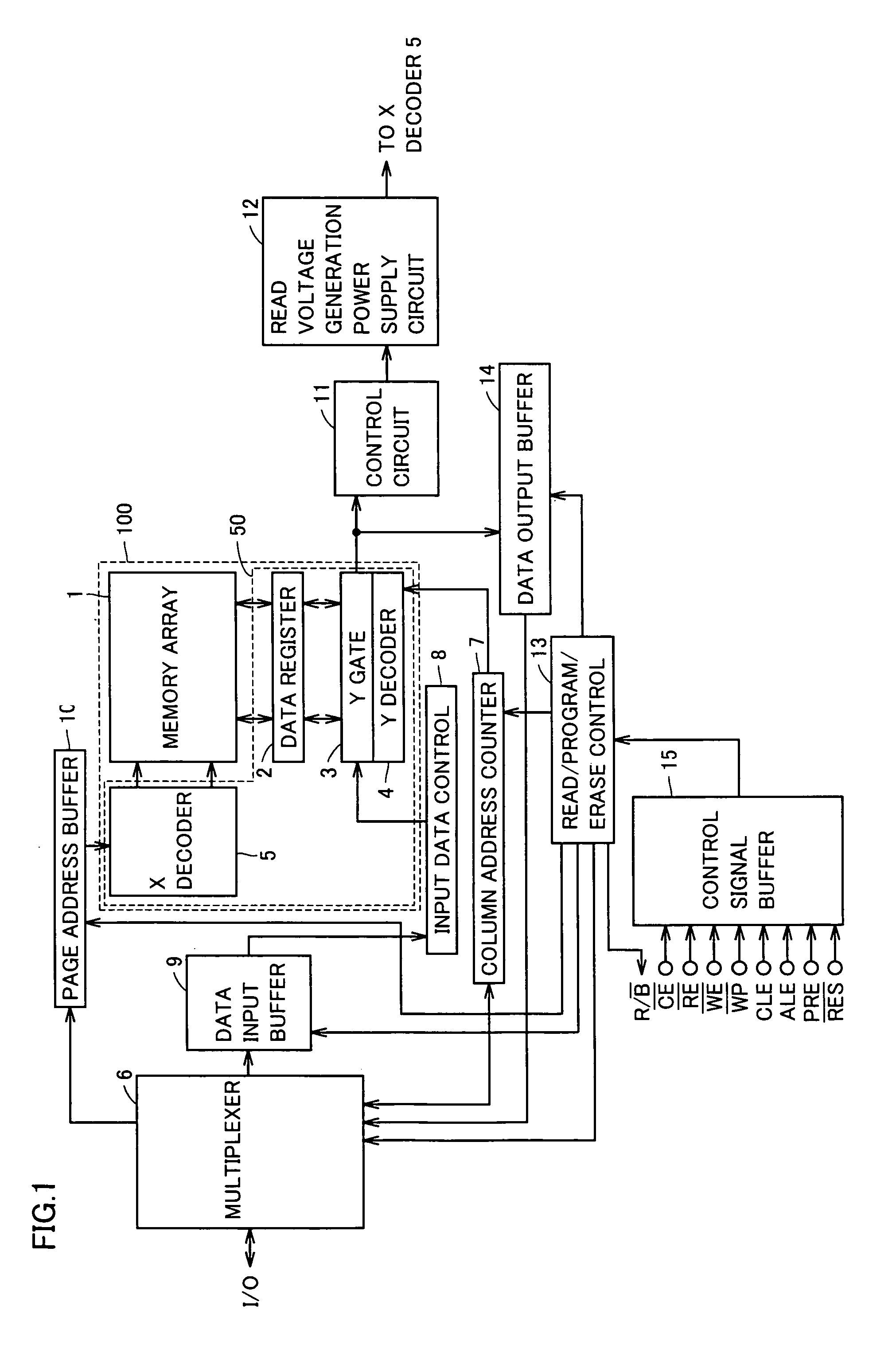

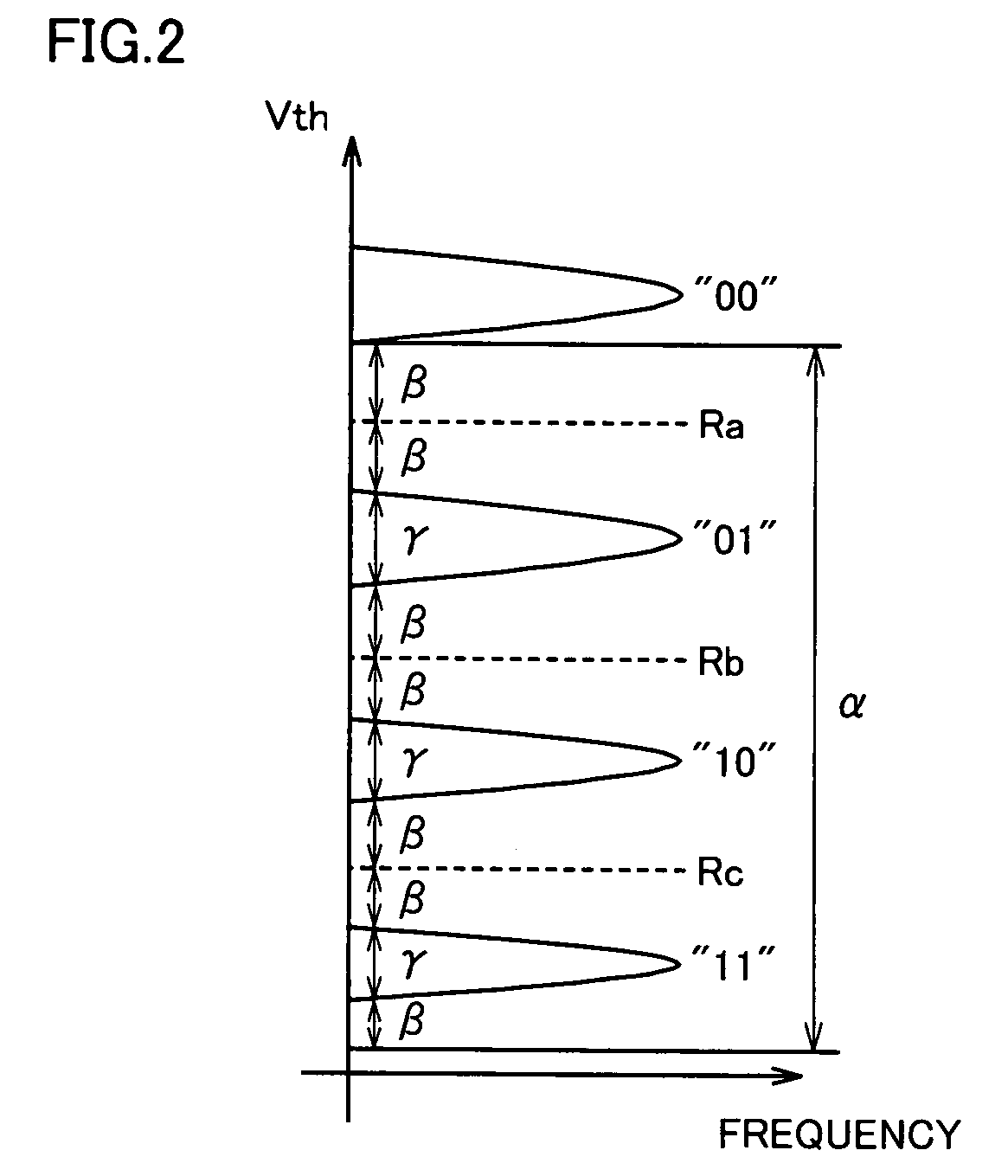

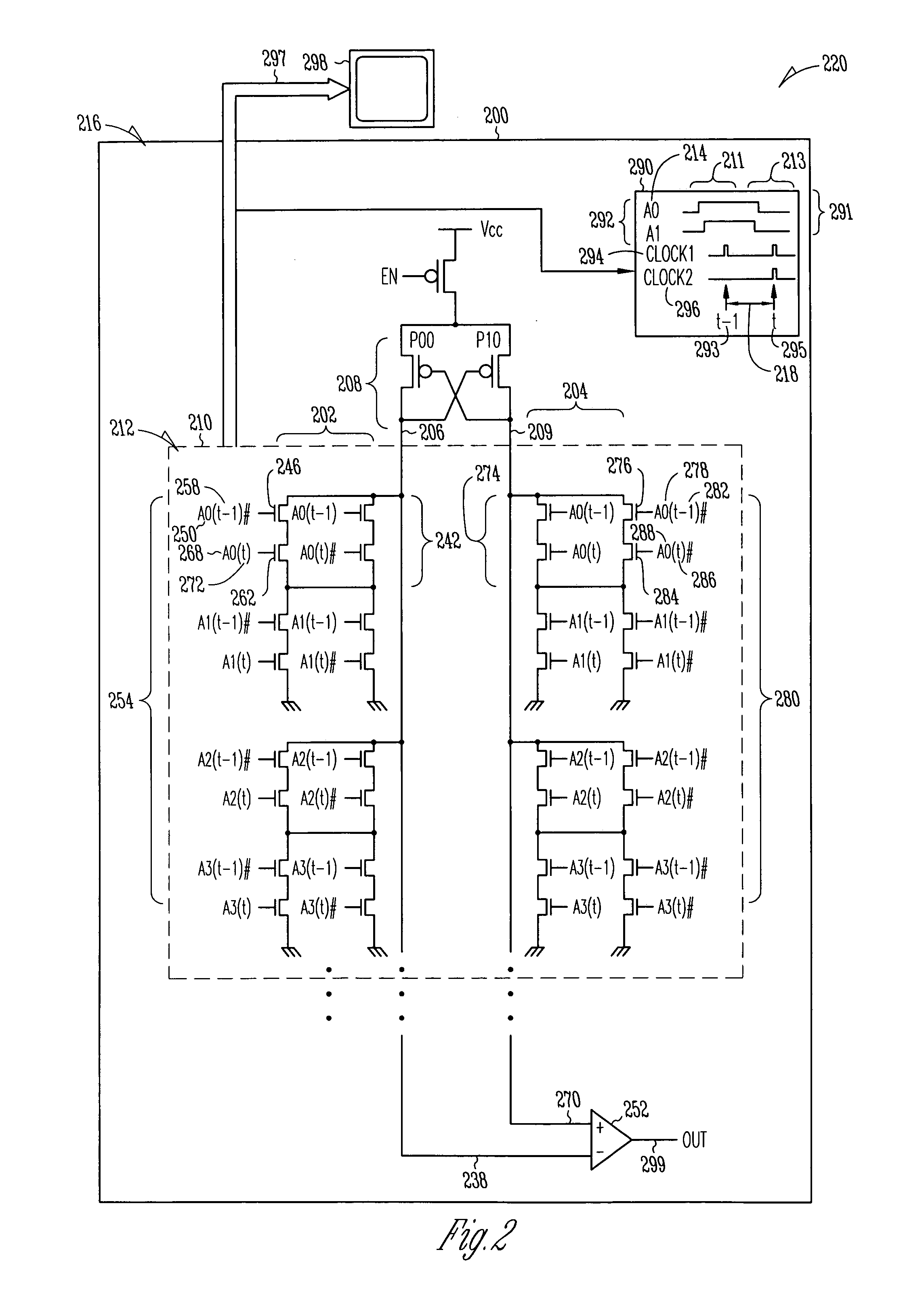

Semiconductor storage device having memory cell for storing data by using difference in threshold voltage

ActiveUS20070002632A1Avoid volatilityRead-only memoriesDuration/width modulated pulse demodulationParallel computingSemiconductor storage devices

A semiconductor storage device which includes a memory array including a plurality of memory cells for storing data by using a difference in a threshold voltage and at least one reference cell for storing data indicative of a state of a corresponding memory cell by using a difference in a threshold voltage, a control circuit for determining a read voltage based on data stored by a reference cell corresponding to a memory cell adjacent to a memory cell to be read, a read unit for executing reading from a memory cell to be read by using a determined read voltage, and a write unit for executing writing, when executing writing to a memory cell to be written to bring the memory cell into a written state, data indicating that the memory cell is in the written state to a reference cell corresponding to the memory cell.

Owner:RENESAS ELECTRONICS CORP

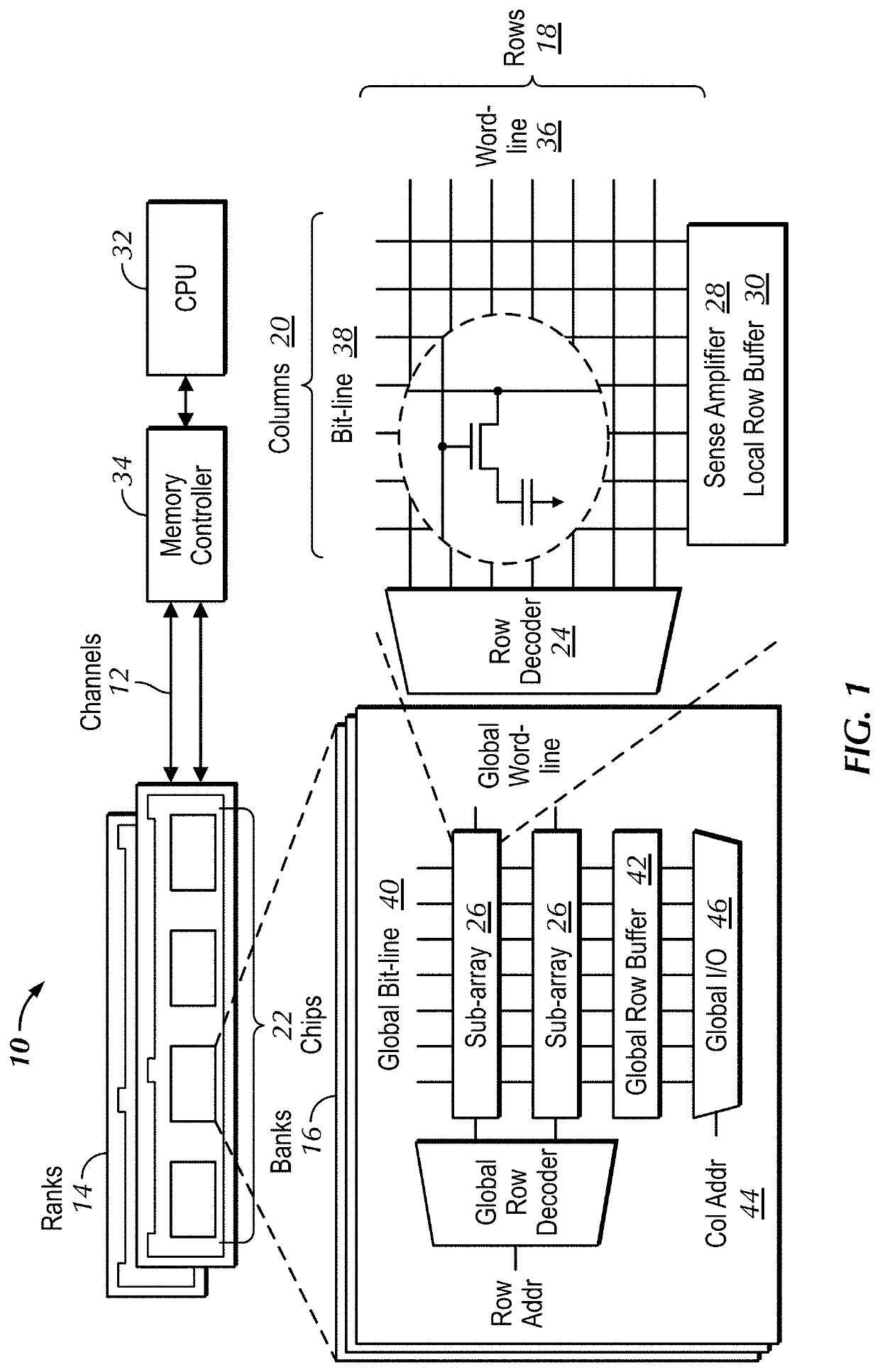

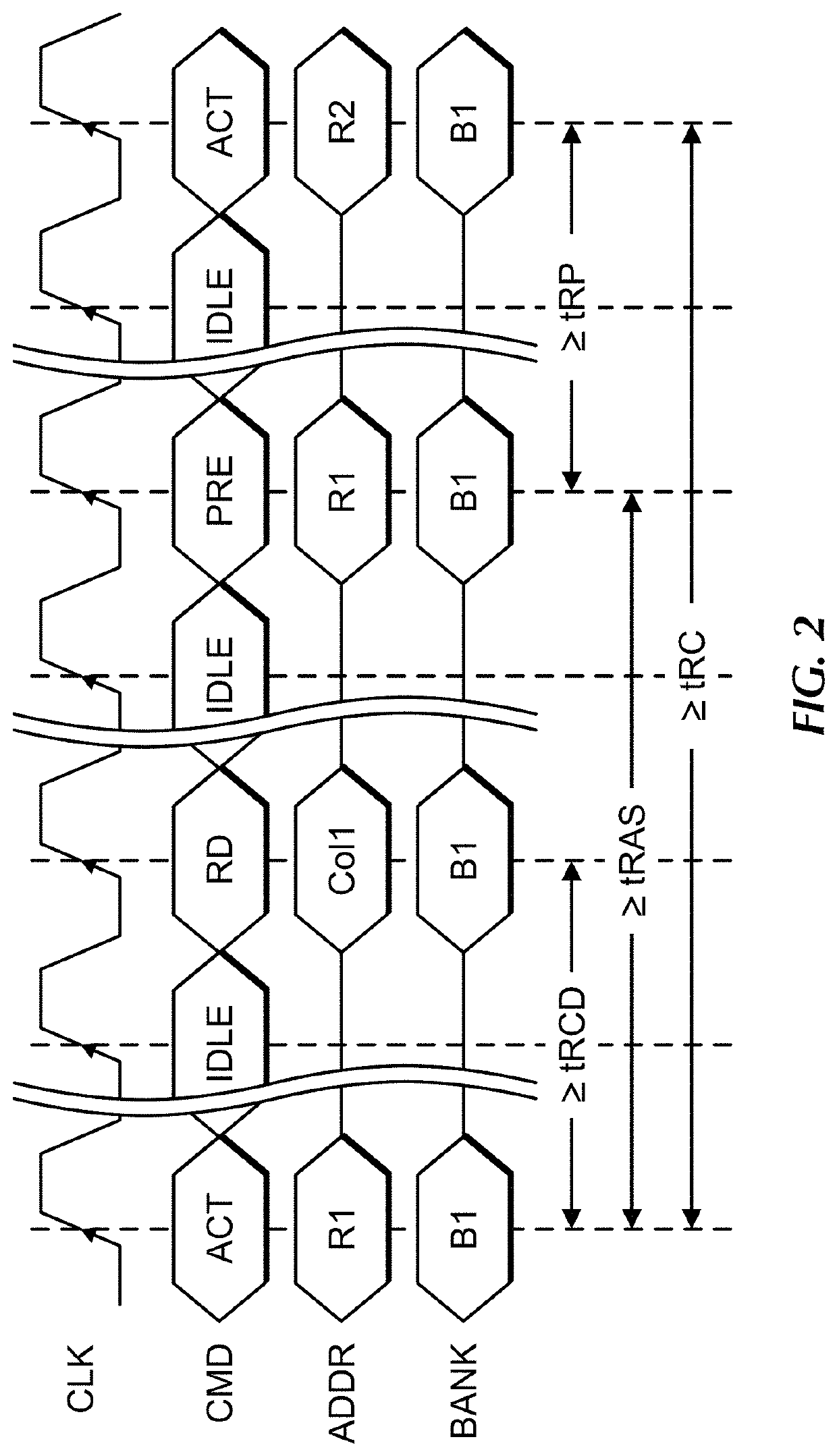

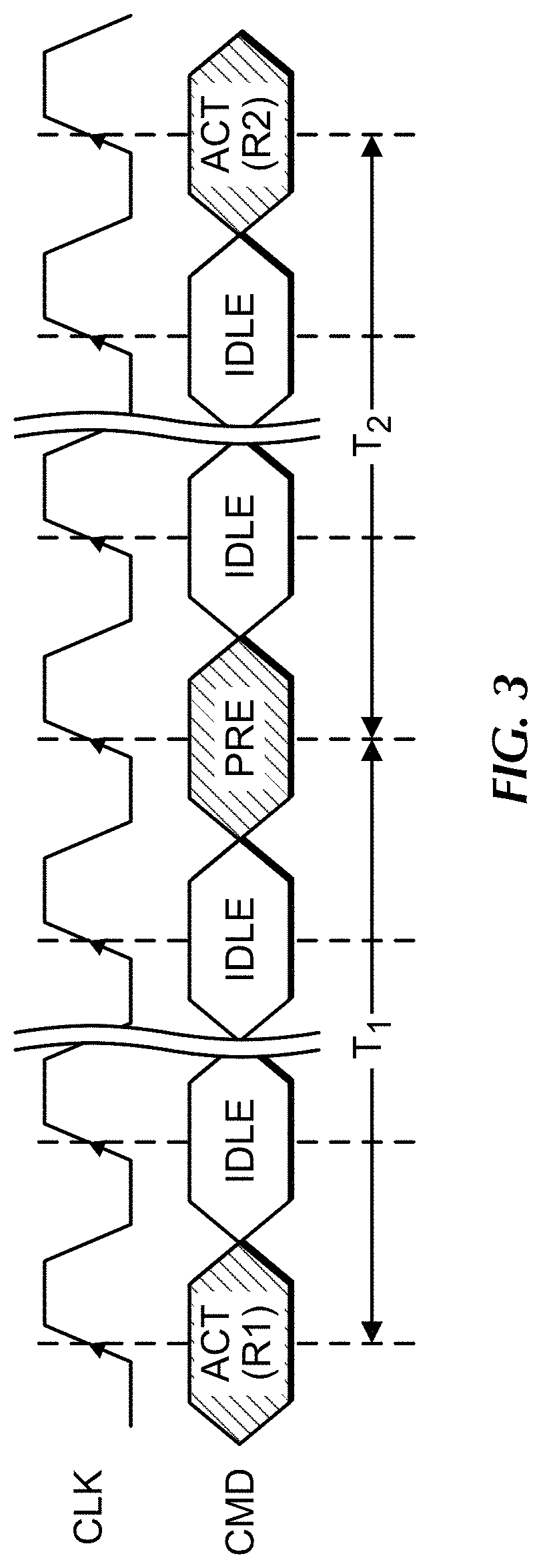

System and method for in-memory compute

According to various embodiments, an in-memory computation system is disclosed. The system includes a dynamic random access memory (DRAM) module. The system further includes a memory controller configured to violate a timing specification for the DRAM module and activate multiple rows of the DRAM module in rapid succession to enable bit-line charge sharing.

Owner:THE TRUSTEES FOR PRINCETON UNIV

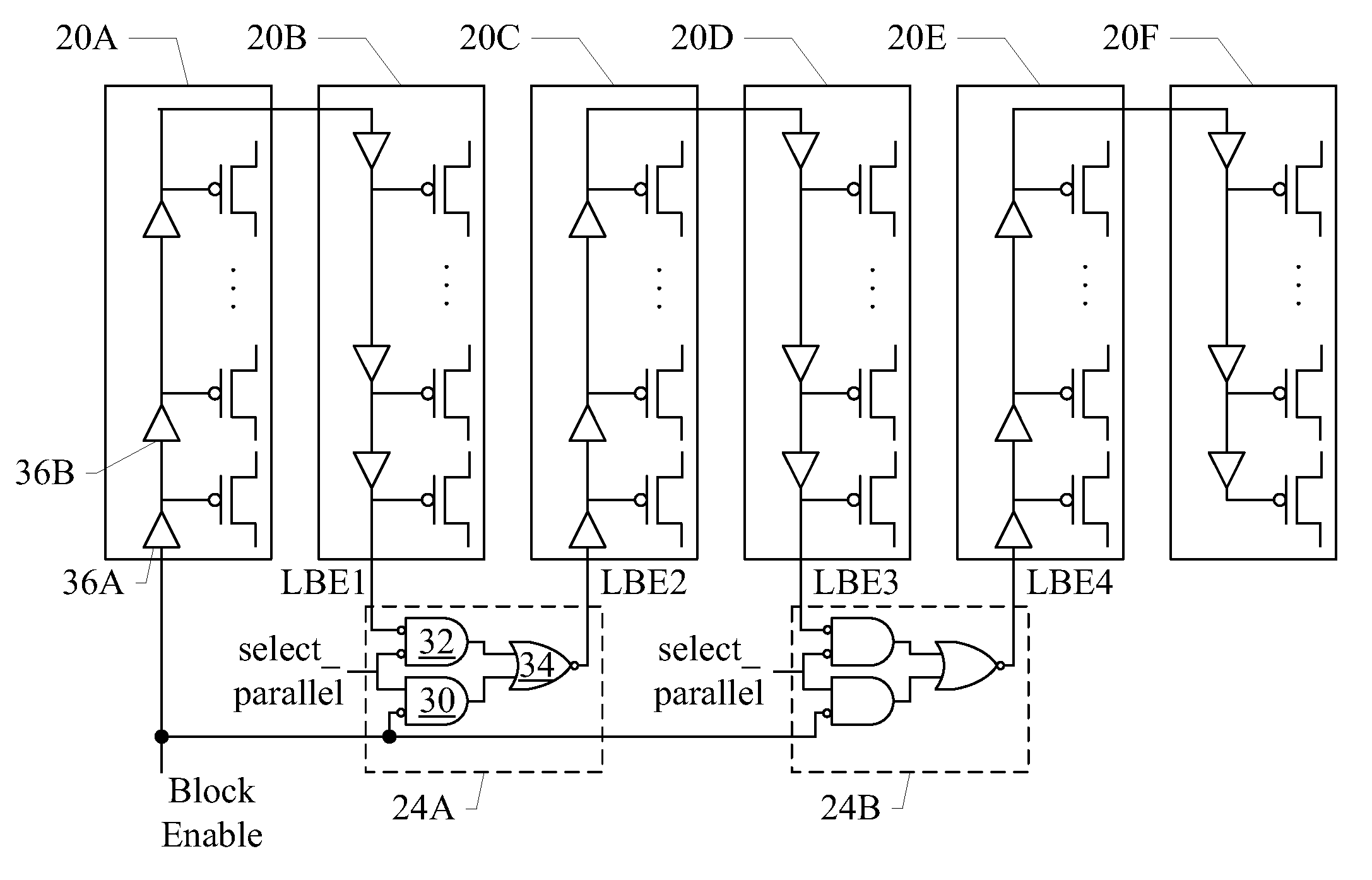

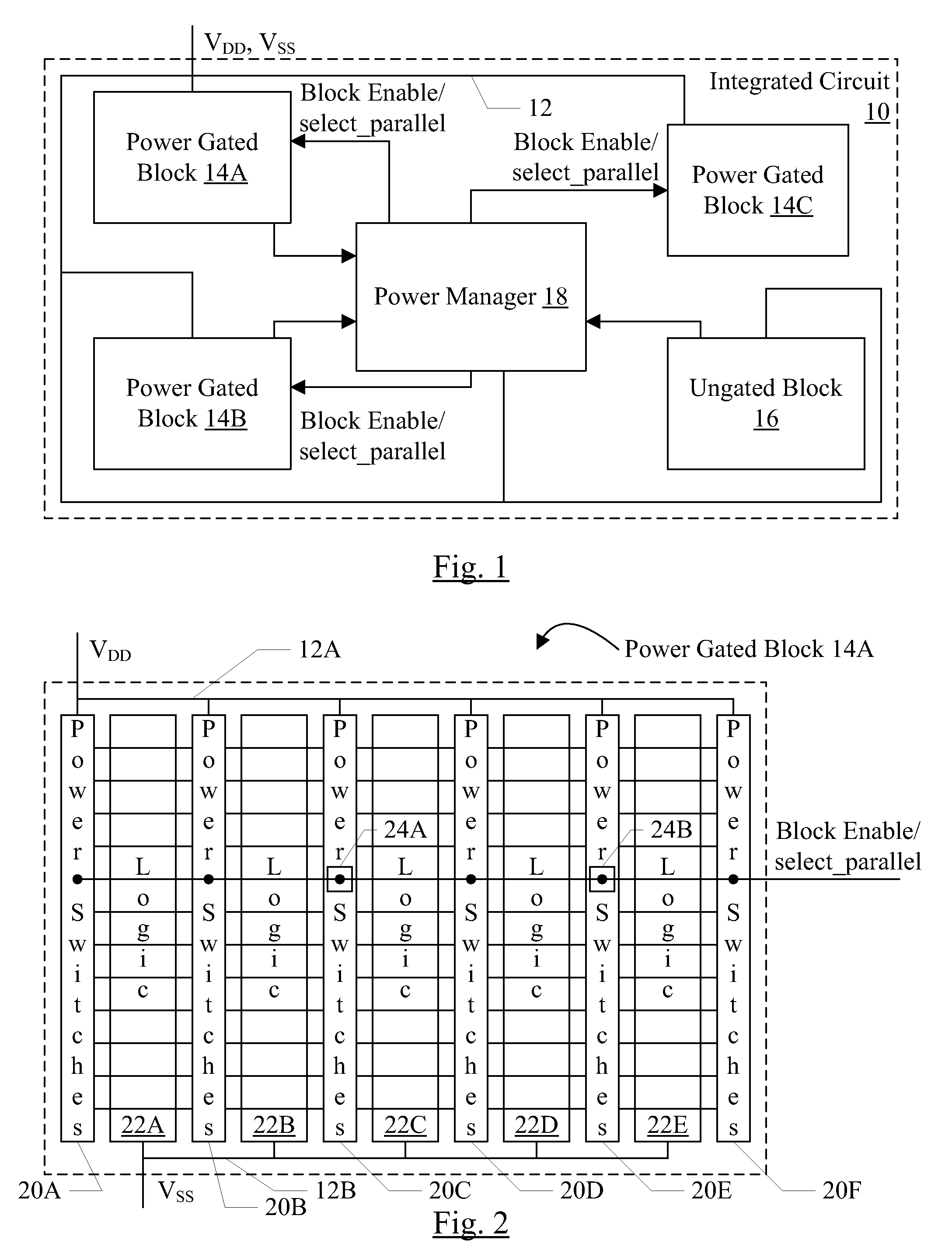

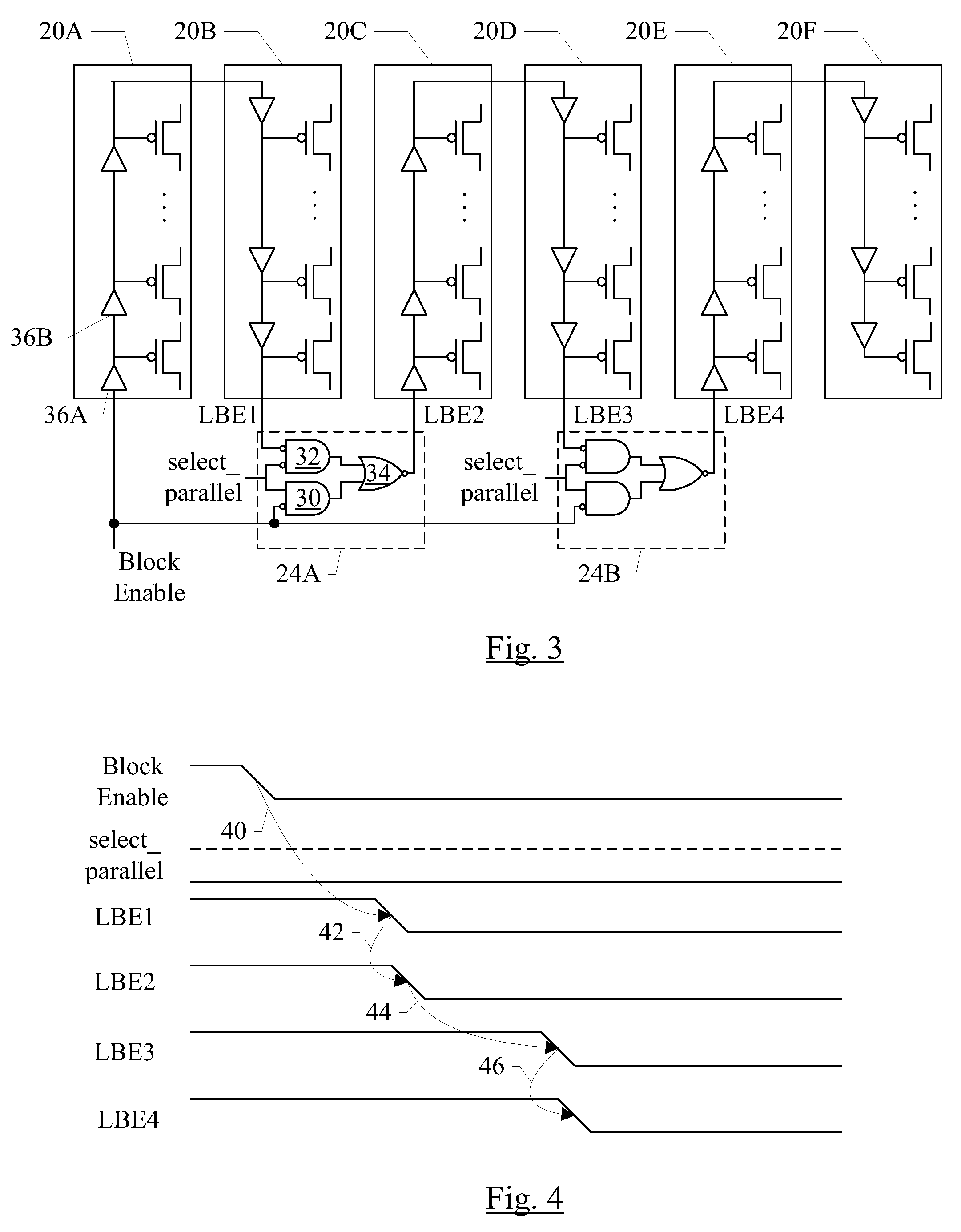

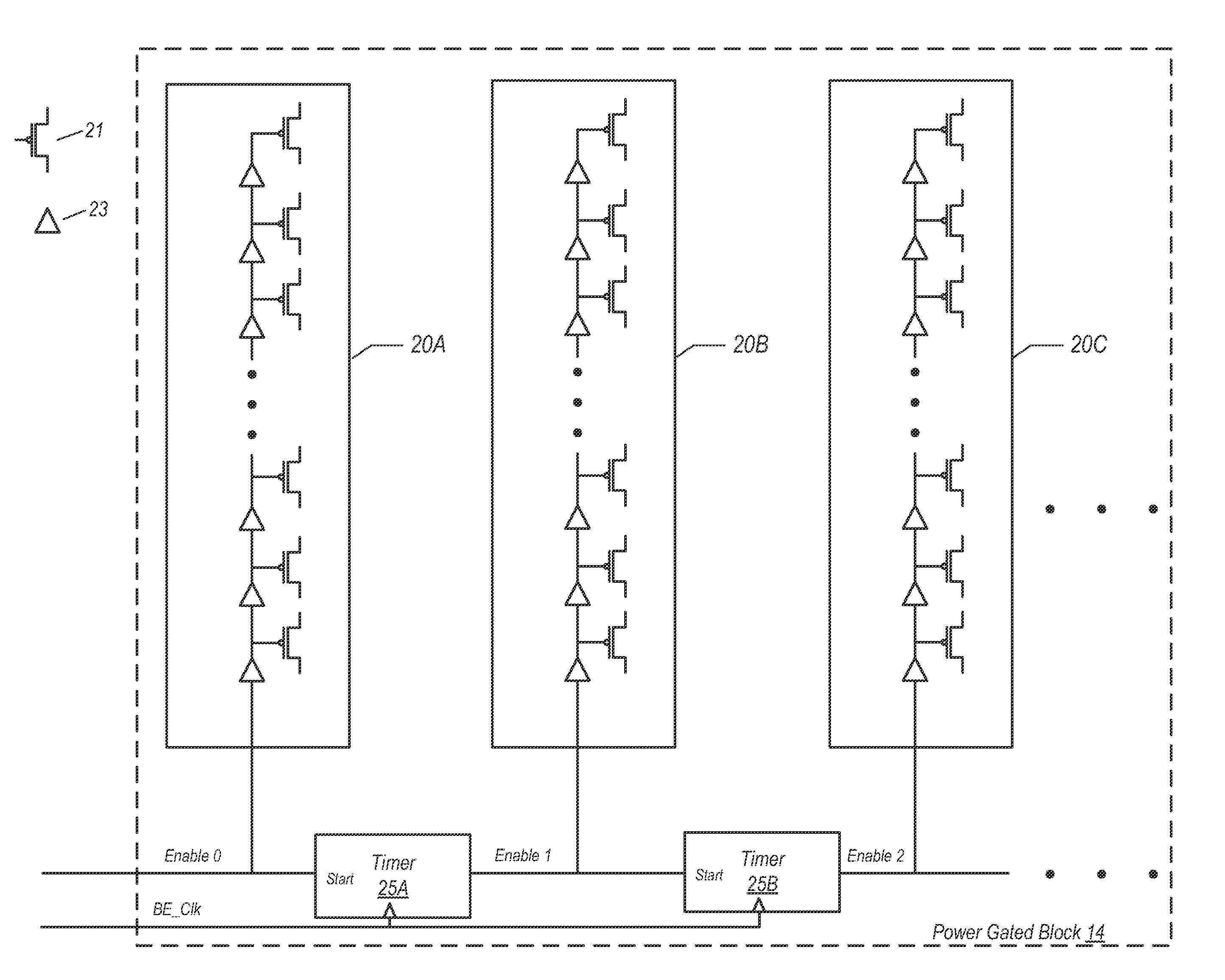

Power switch ramp rate control using programmable connection to switches

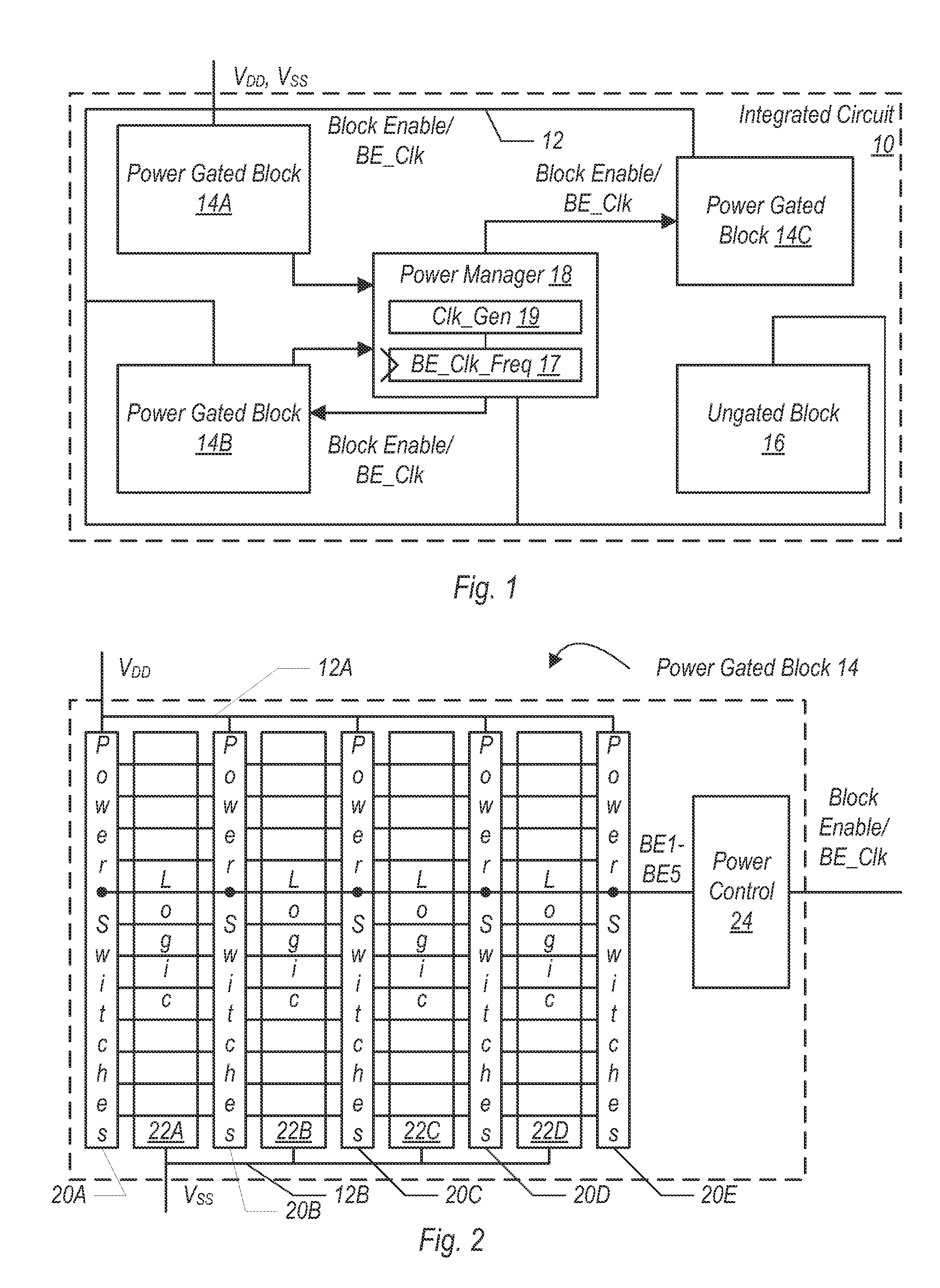

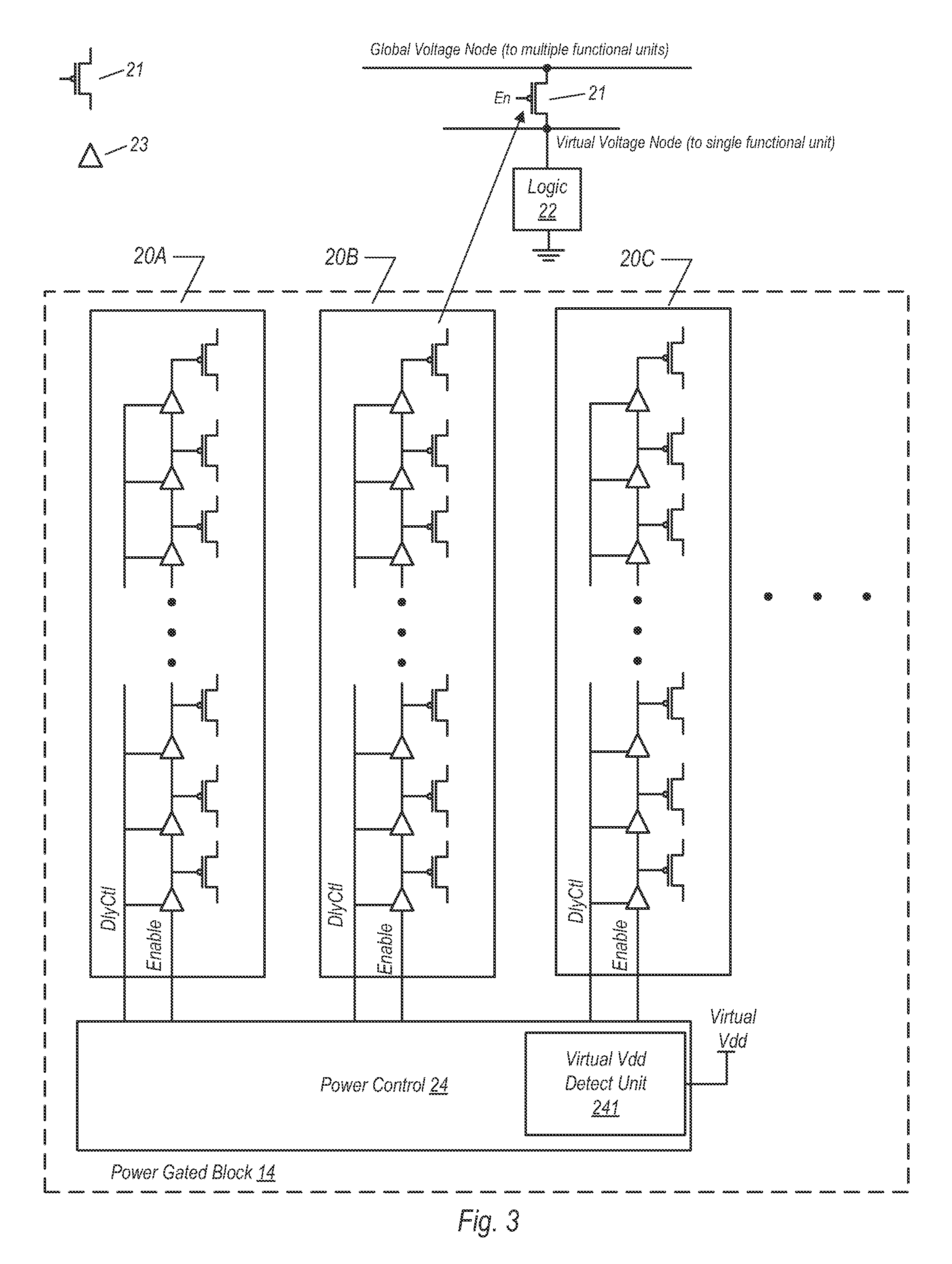

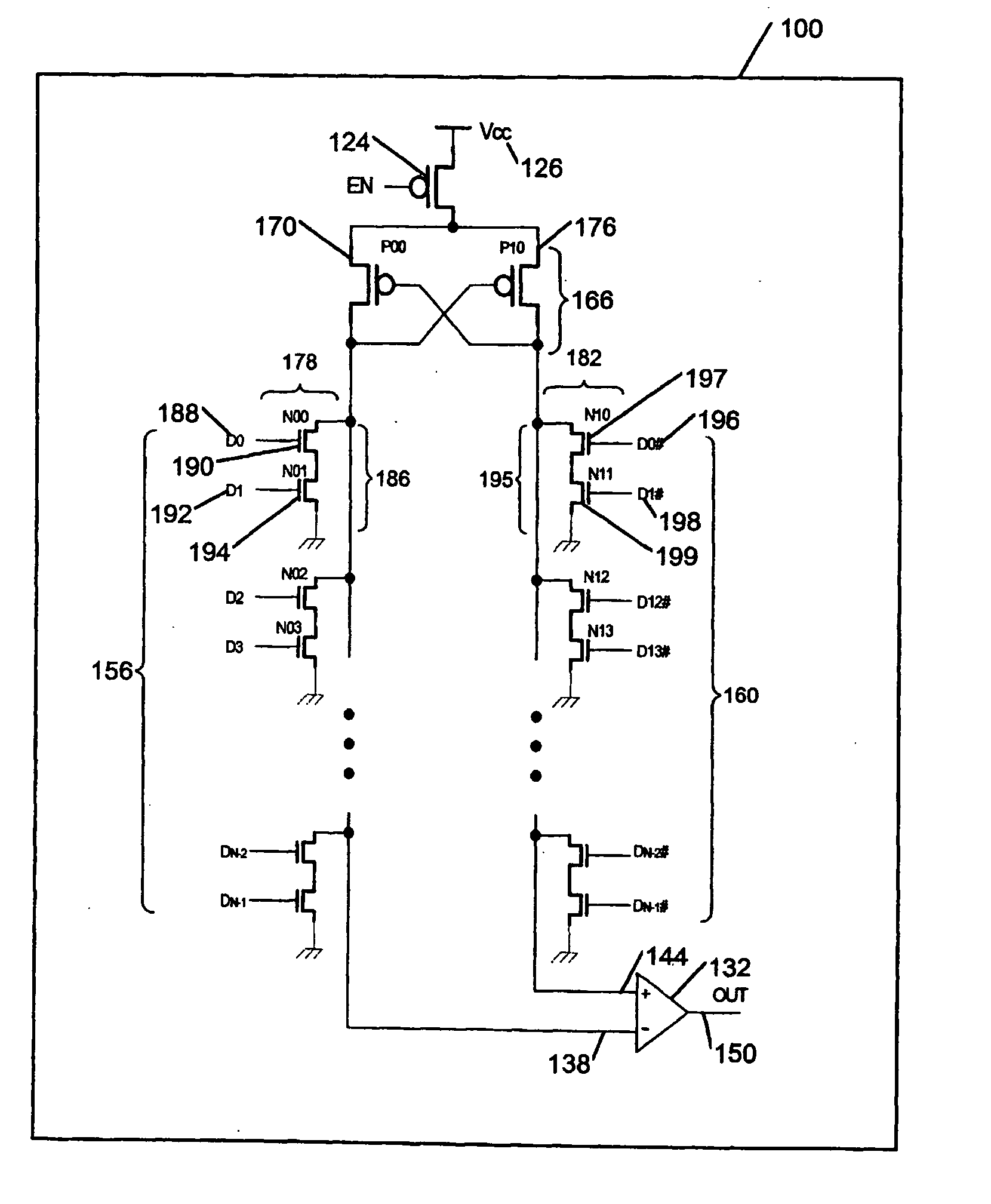

ActiveUS8421499B2Reliability increasing modificationsMajority/minority circuitsEngineeringPower gating

In an embodiment, an integrated circuit includes a power gated block and a power manager circuit. The power manager circuit is configured to provide a block enable signal and at least one select signal to the power gated block. The power manager may generate the select signal responsive to various parameters that affect the speed of the integrated circuit, such as power supply voltage magnitude, operating temperature, and / or process corner. The power gated block may control the rate at which power switches are enabled based on the select signal or signals. For example, the power switches may be enabled in a more parallel or more serial fashion and / or the drive strength of block enable buffering to the power switches may be varied. In another embodiment, the power manager circuit may assert multiple block enables to the power gated block (which are connected to separate sets of power switches), and may control the timing of assertion of the enables to control the rate at which power switches are enabled.

Owner:APPLE INC

Methods and circuitry for reconfigurable seu/set tolerance

InactiveUS20110012638A1Large capacityQuicklyMajority/minority circuitsWave amplification devicesReconfigurable antennaComputer science

Owner:NASA

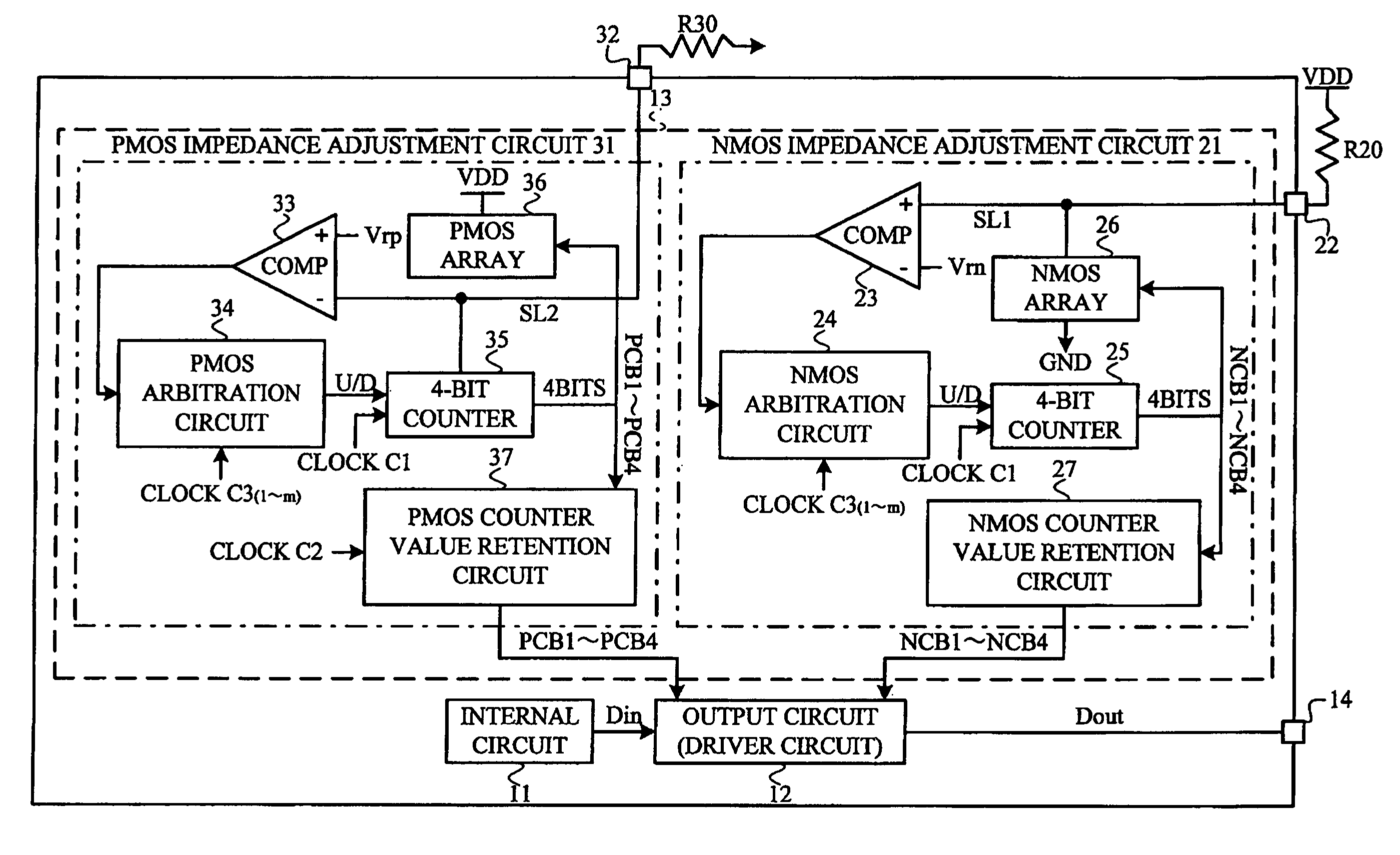

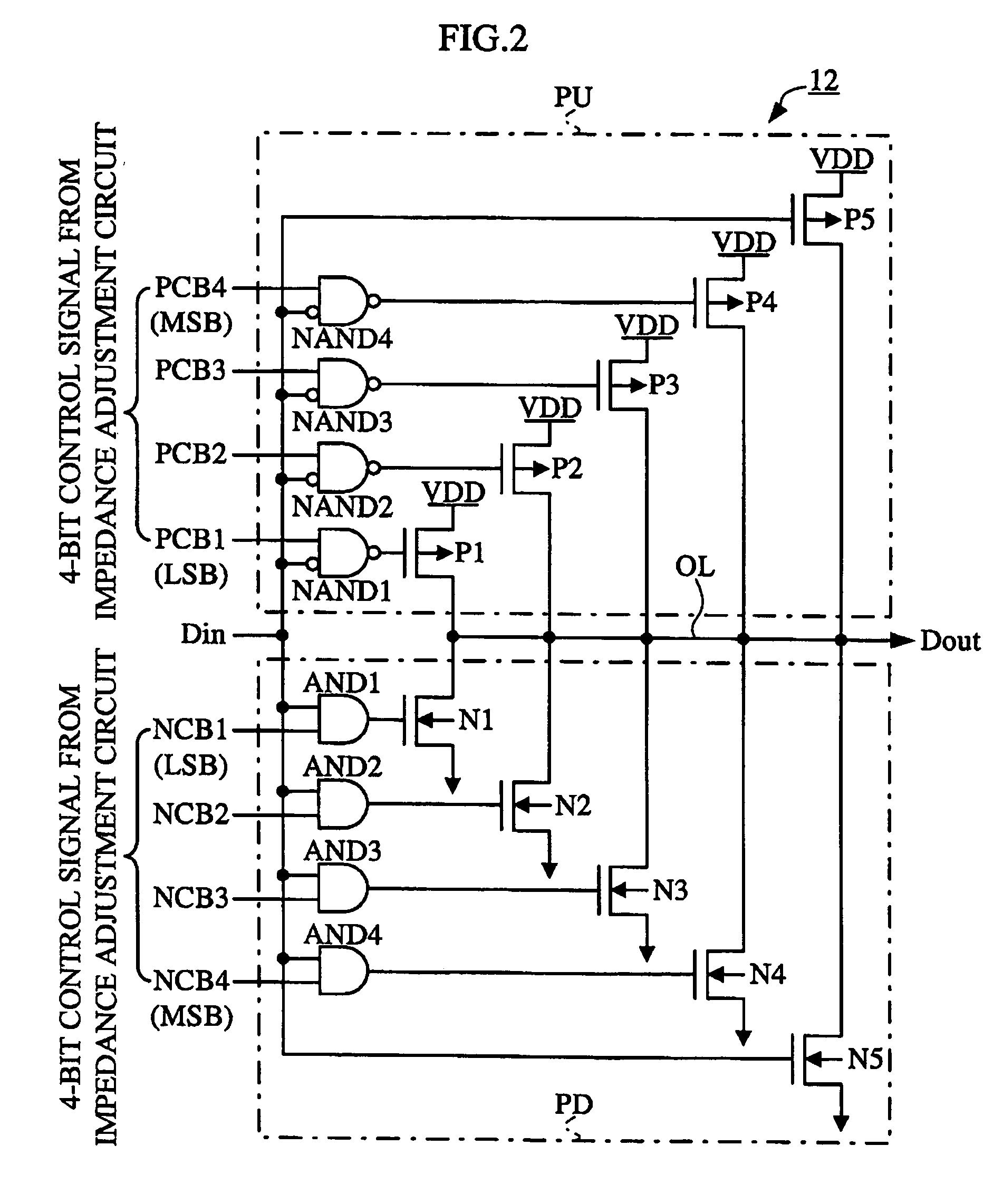

Impedance adjustment circuit, impedance adjustment method, and semiconductor device

InactiveUS7084663B2Avoid errorsExclude influenceInput/output impedence modificationReliability increasing modificationsControl signalEngineering

An impedance adjustment circuit has an external resistor, a comparator which compares the potential of one terminal of the external resistor with a predetermined voltage, a counter whose counted value changes in accordance with an output from the comparator and which outputs a control signal corresponding to the counted value, an NMOS array whose value of resistance changes in accordance with the control signal and which is connected to one terminal of the external resistor and an NMOS arbitration circuit which detects an output from the NMOS comparator a plurality of times and outputs a signal determined by a majority decision logic taken on the detected signals to the counter.

Owner:NEC CORP

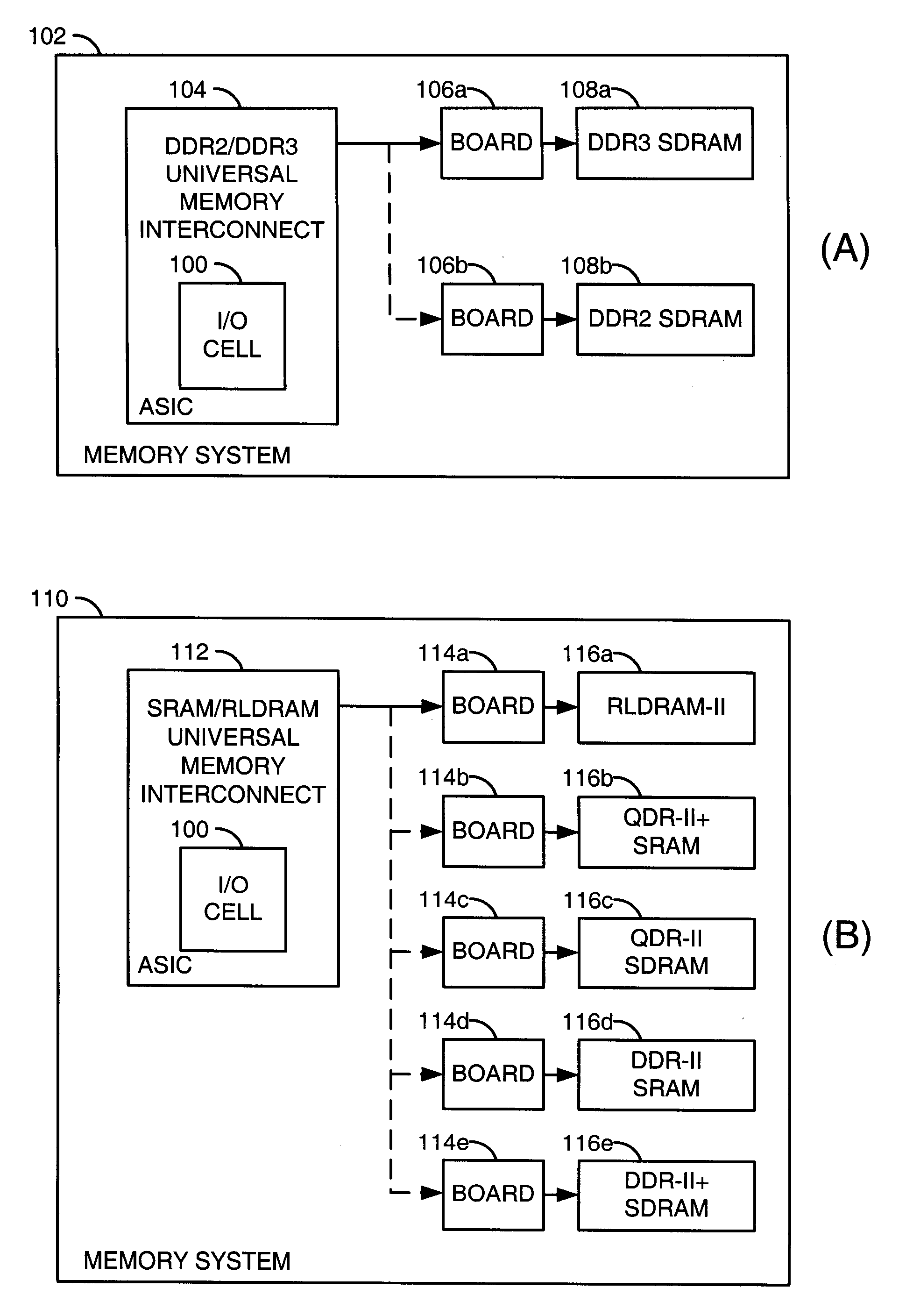

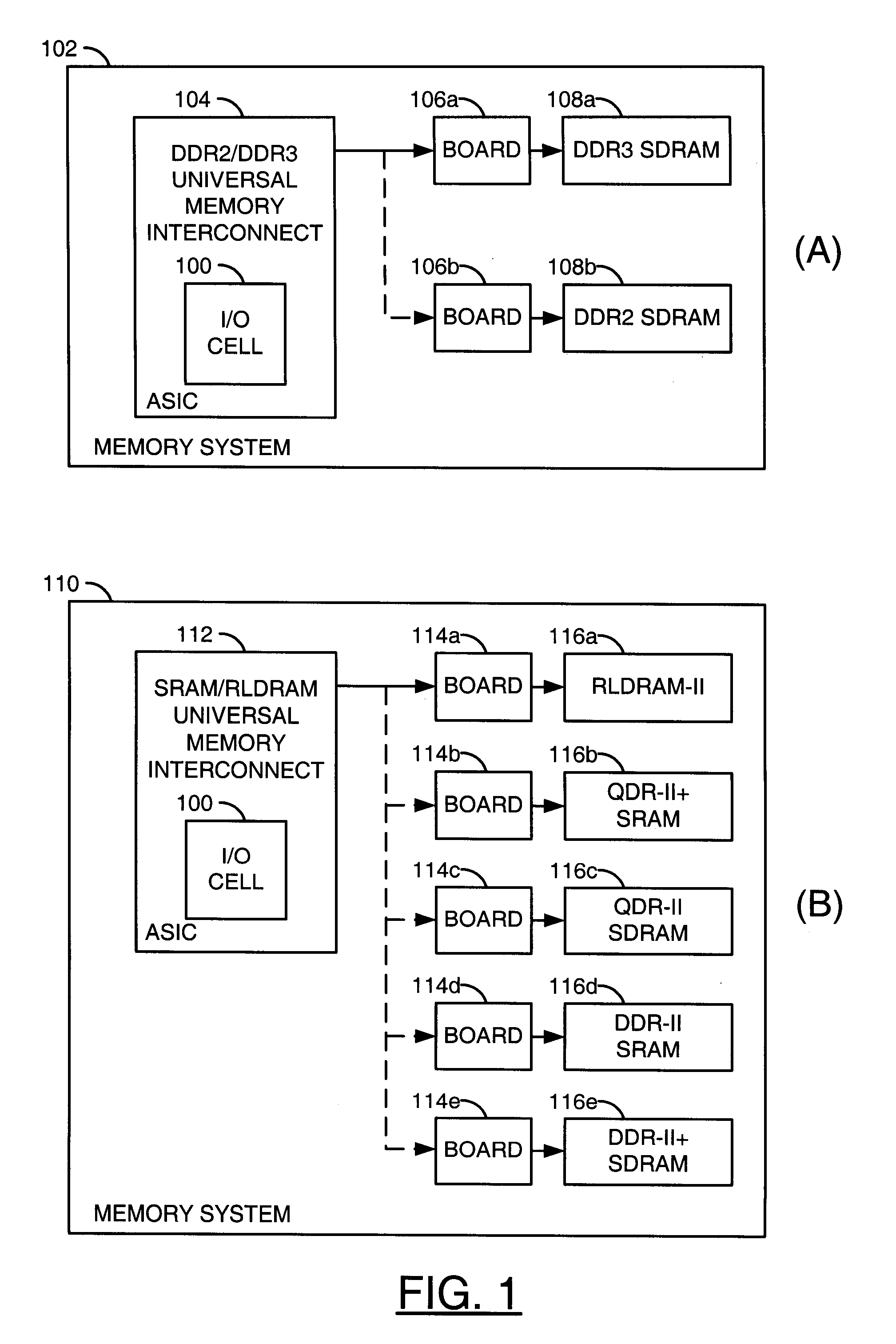

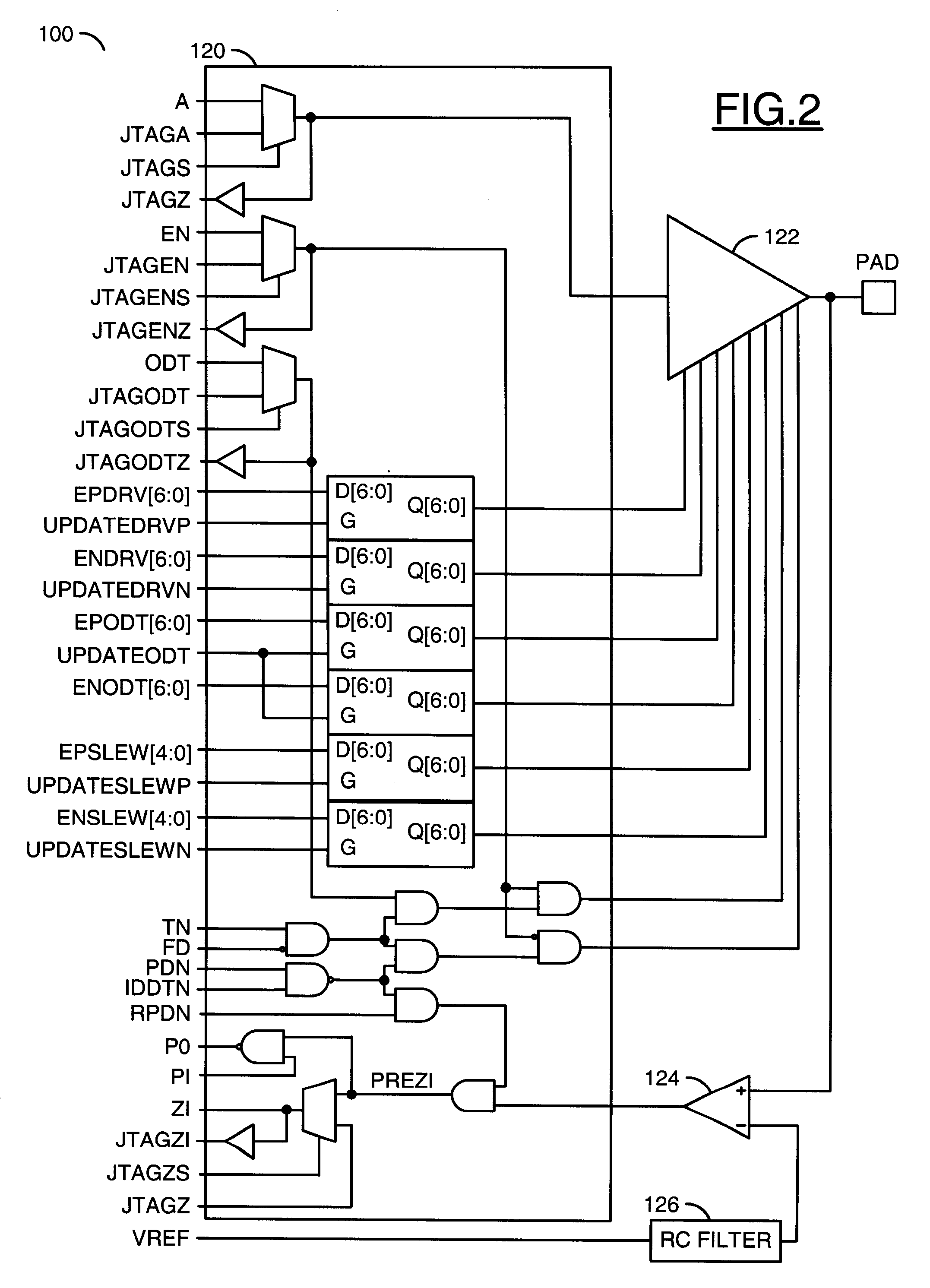

High speed multiple memory interface I/O cell

InactiveUS20090091349A1Reliability increasing modificationsMajority/minority circuitsMemory interfaceOn-die termination

Owner:BROADCOM INT PTE LTD

Fine-grained power management of synchronous and asynchronous datapath circuits

ActiveUS7511535B2Reliability increasing modificationsMajority/minority circuitsDatapath circuitsAsynchronous circuit

Owner:AVAGO TECH INT SALES PTE LTD

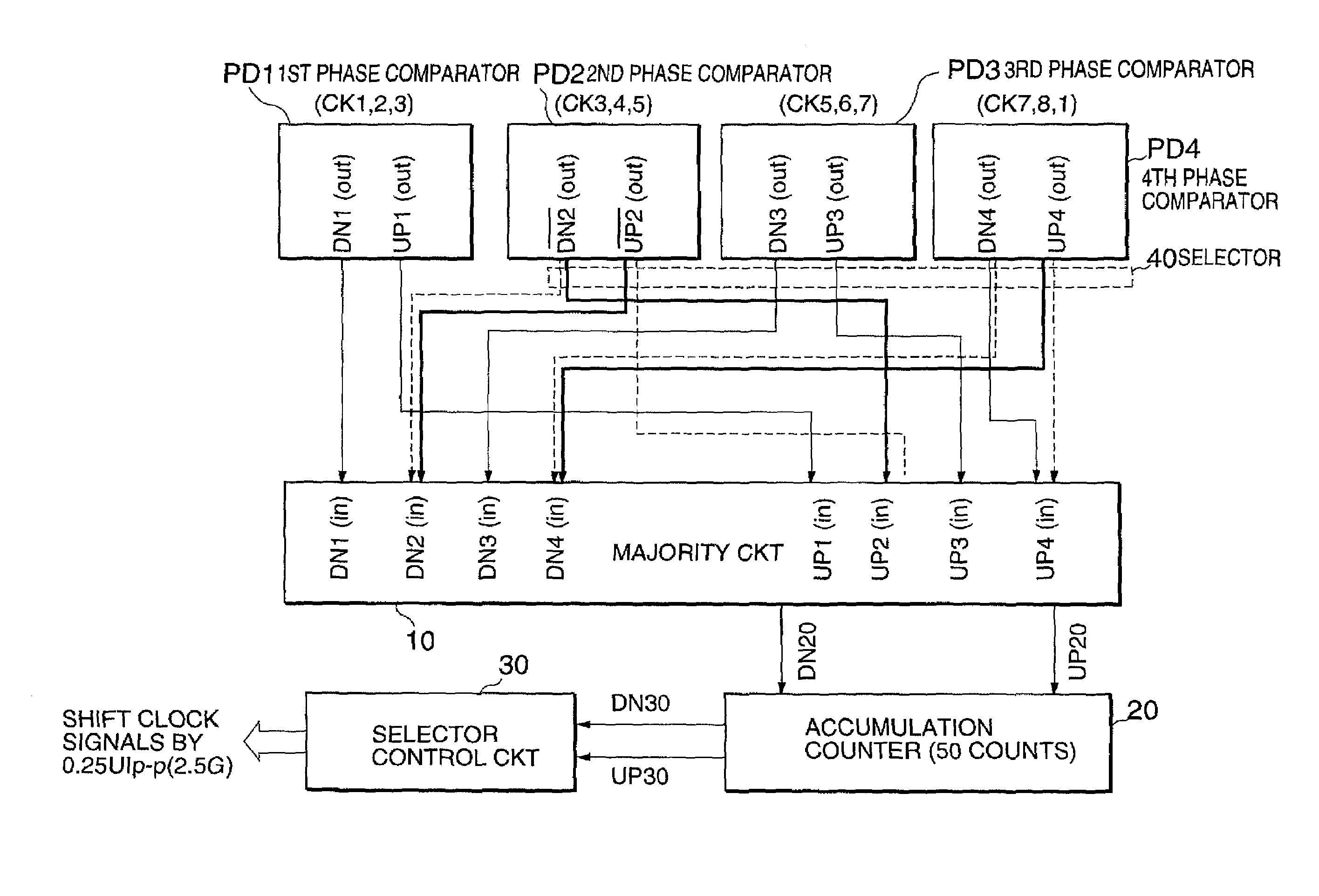

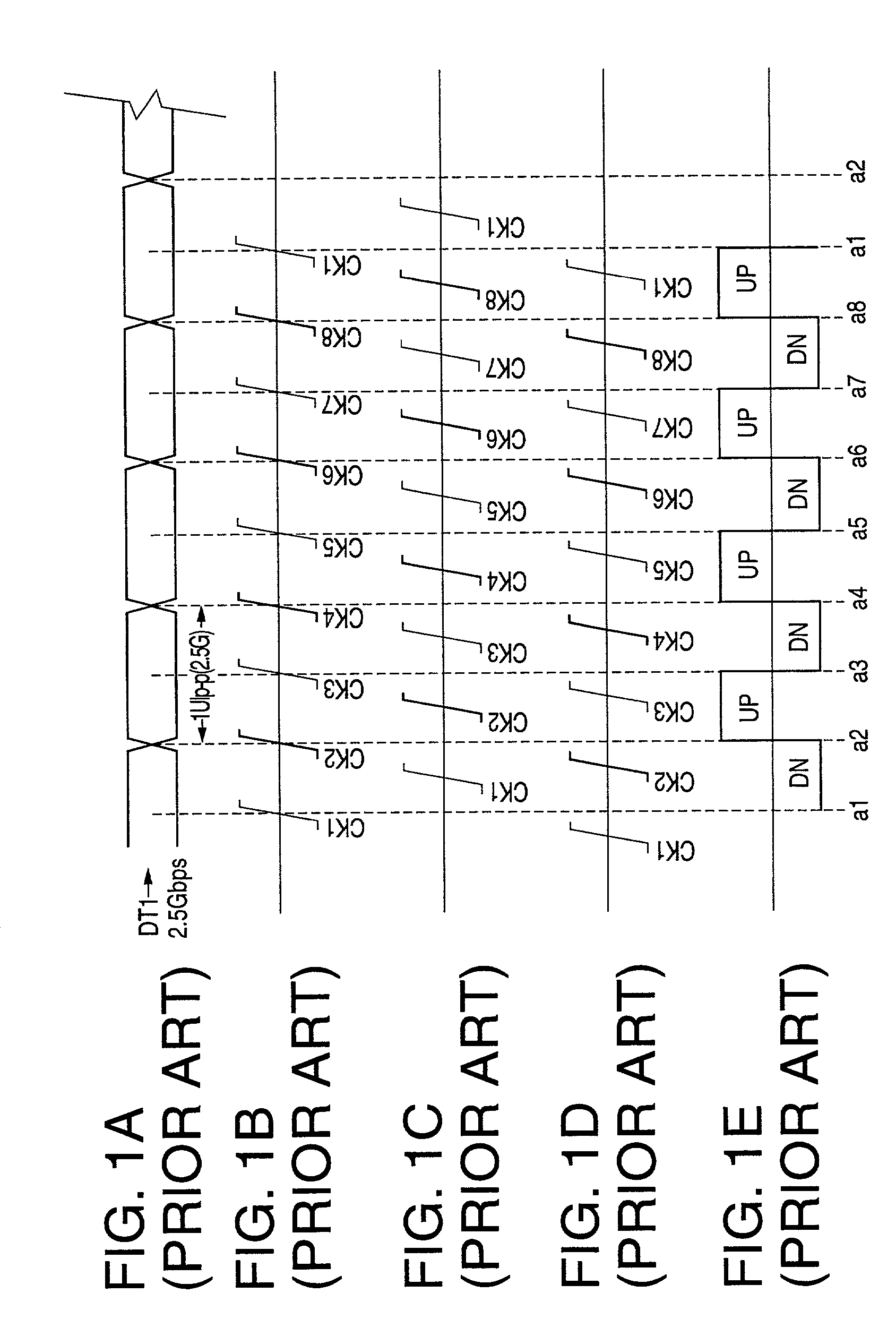

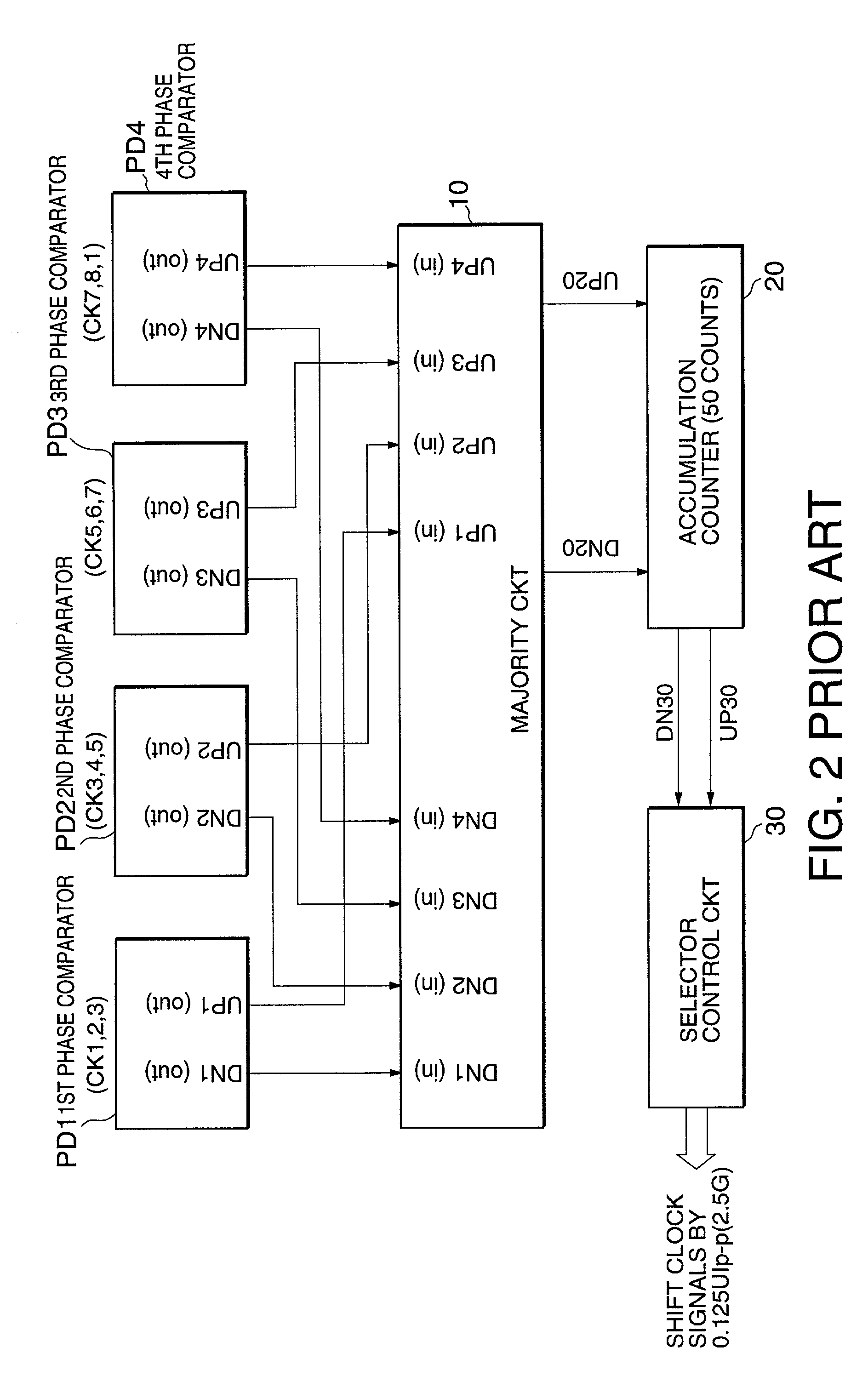

Oversampling clock recovery circuit applicable not only to high rate data but also to low rate data

InactiveUS7167534B2Increase data rateMinimal circuitryMajority/minority circuitsPulse automatic controlHigh rateClock recovery

In an oversampling clock recovery circuit comprising first through fourth phase comparators (PD1 to PD4) and a majority circuit (10), DOWN signal output terminals (DN2(out), DN3(out)) of the second and the third phase comparators are connected to UP signal input terminals (UP3(in), UP4(in)) of the majority circuit and UP signal output terminals (UP3(out), UP4(out)) of the third and the fourth phase comparators are connected to DONW signal input terminals (DN2(in), DN3(in)) of the majority circuit.

Owner:RENESAS ELECTRONICS CORP

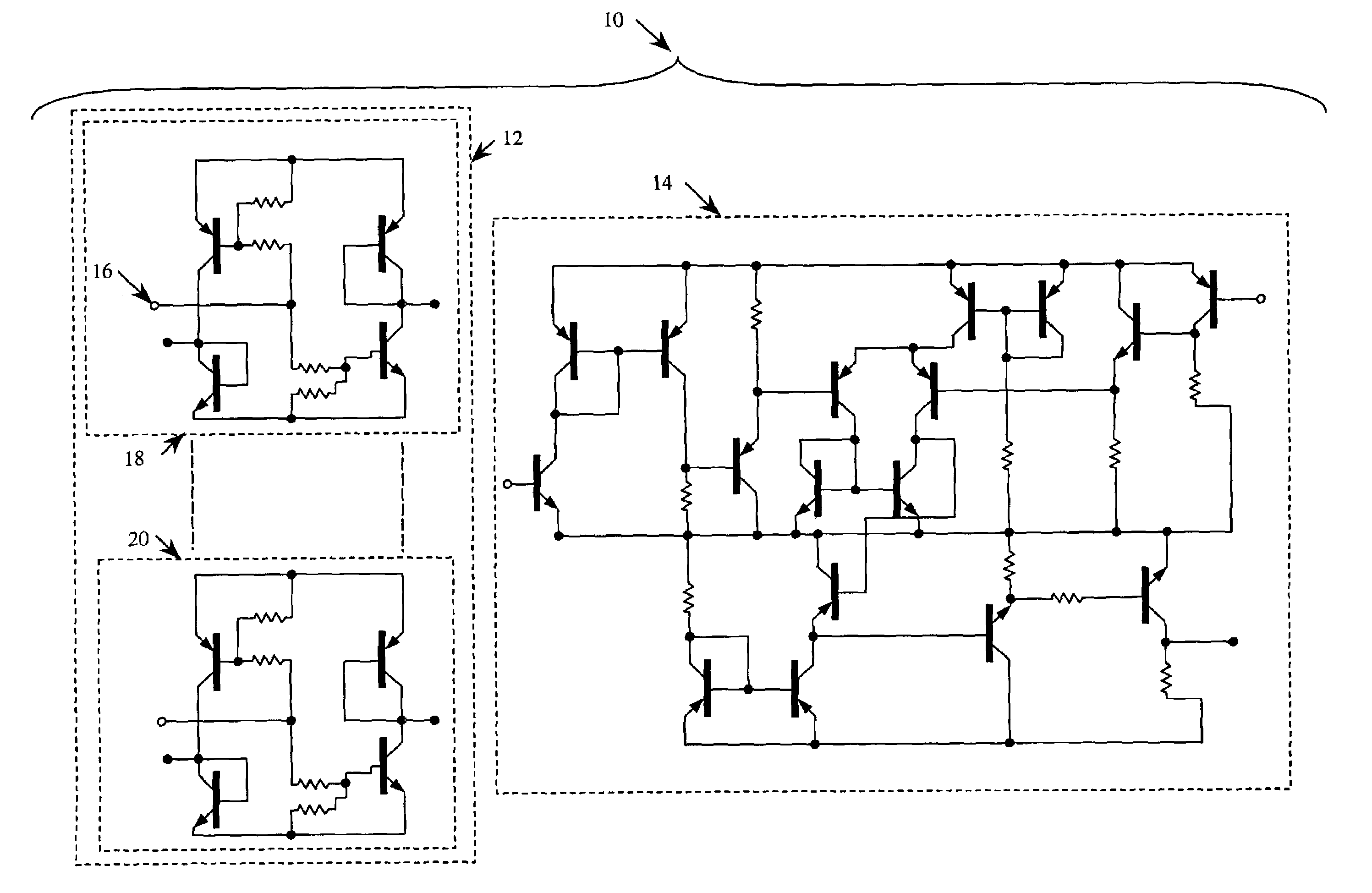

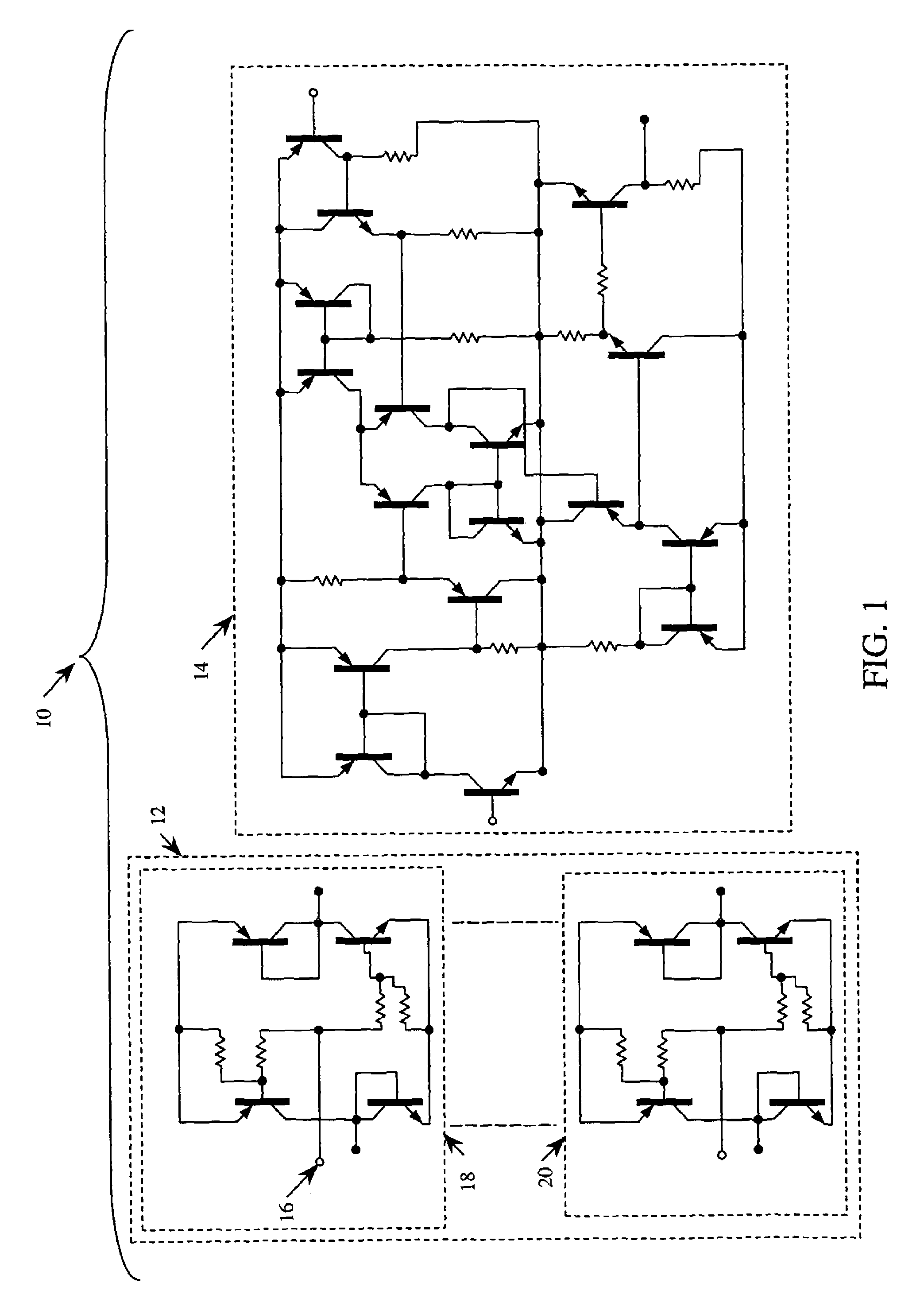

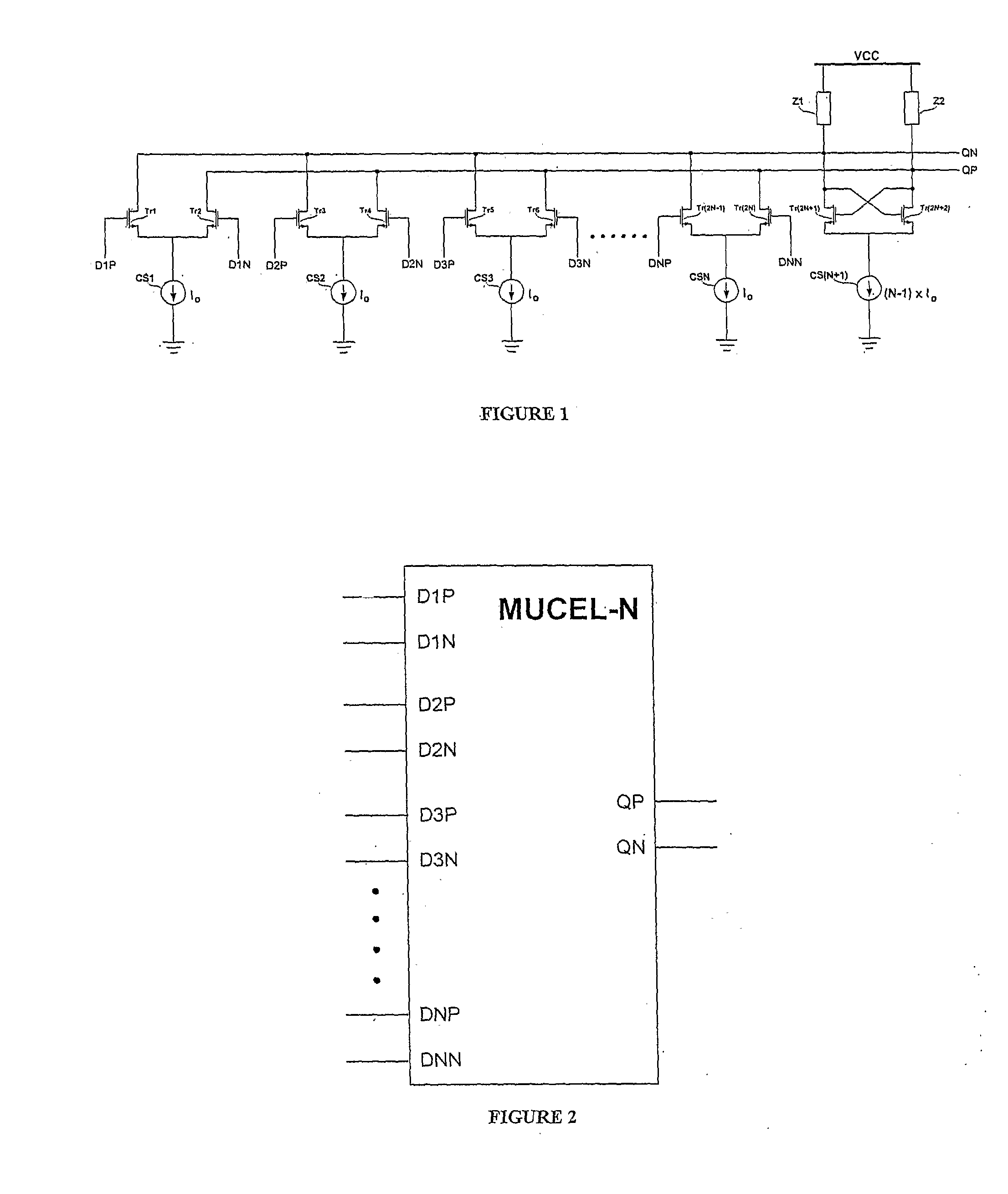

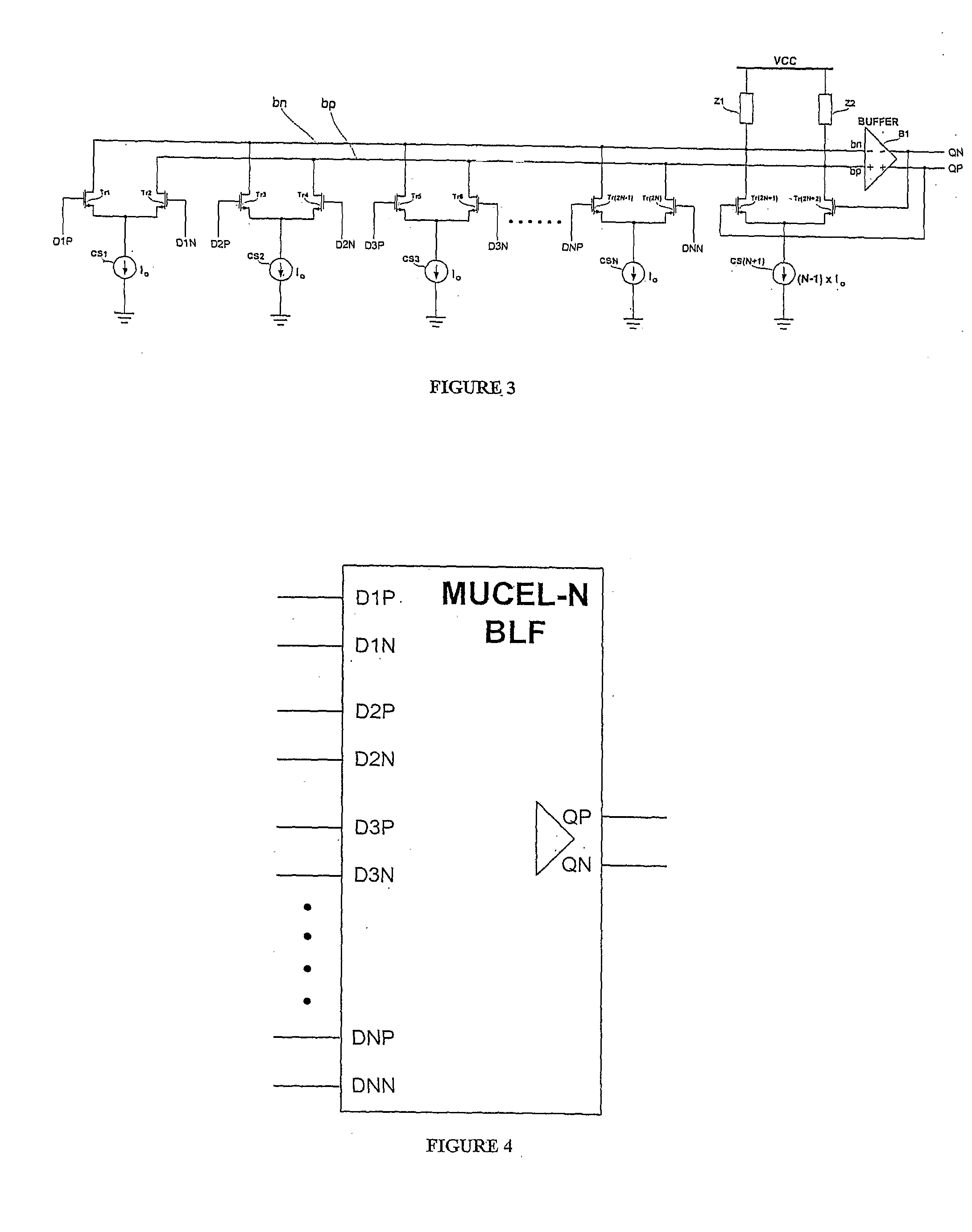

Majority logic circuit

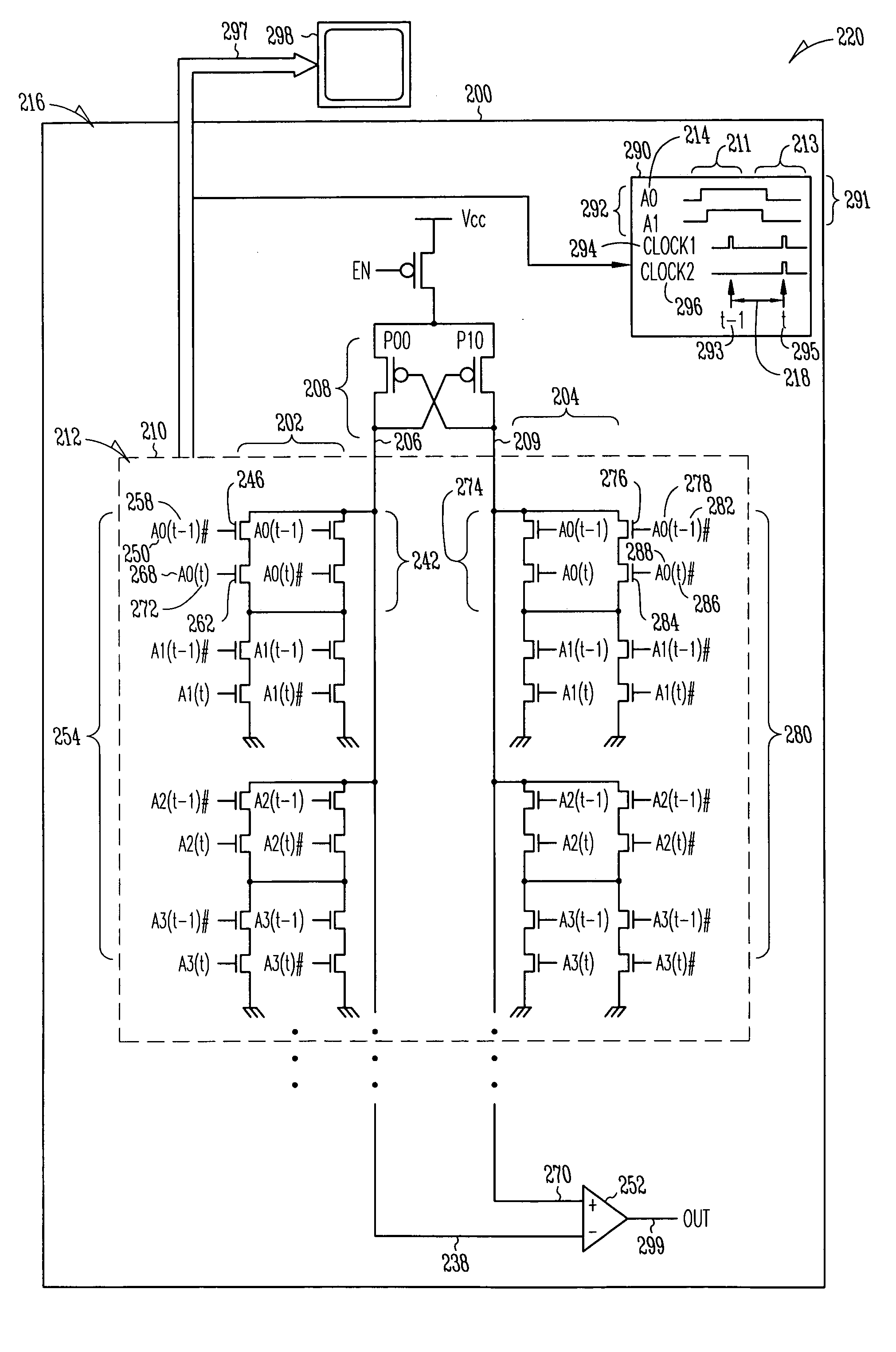

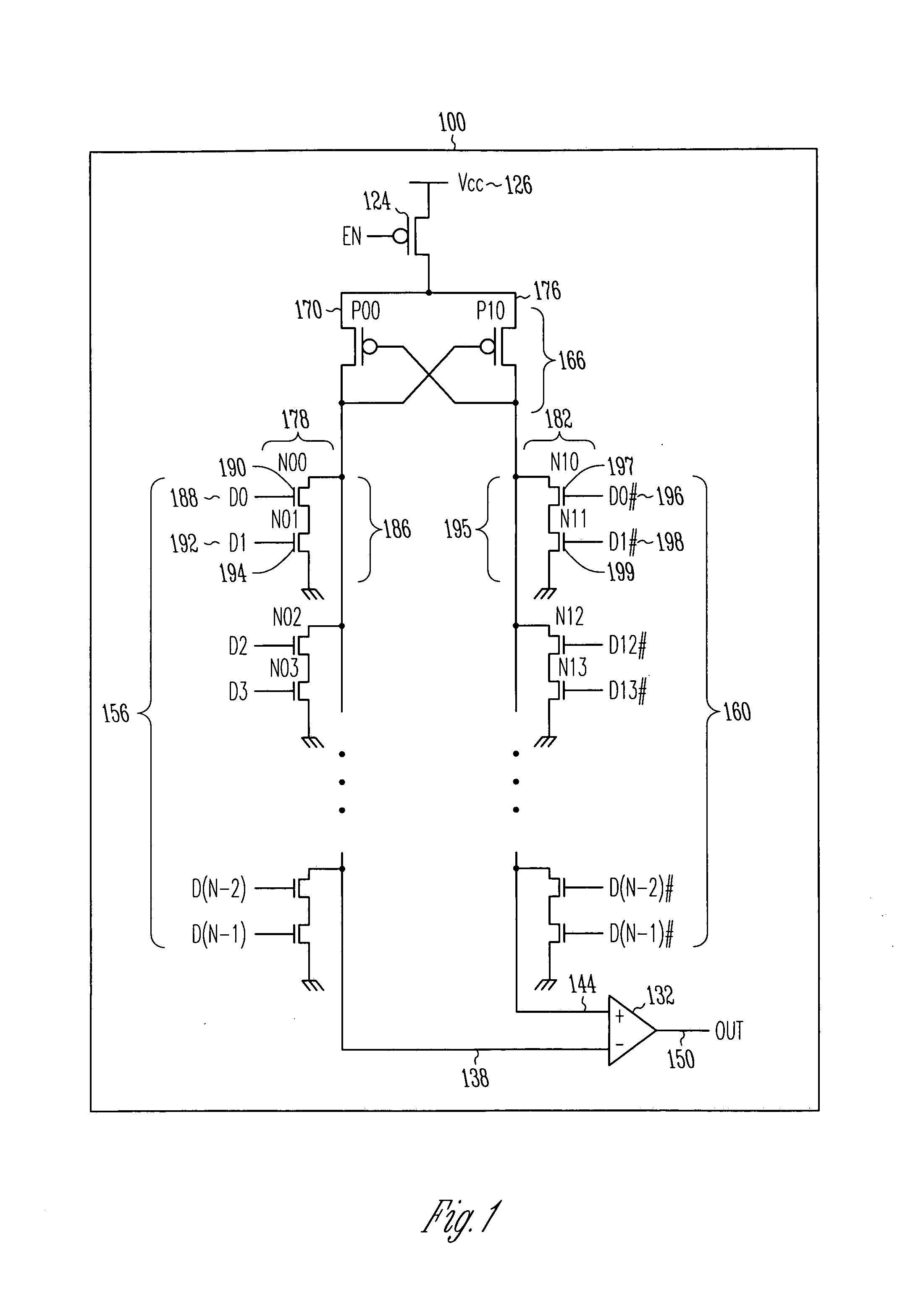

InactiveUS7129742B1Majority/minority circuitsLogic circuits using elementary logic circuit componentsAudio power amplifierEngineering

A novel majority logic circuit is disclosed to determine whether the majority of the inputs are a one, within a constant number of clock cycles, regardless of the number of inputs. The majority logic circuit according to the present invention includes a plurality of current mirror stages and an amplifier stage. For each input, one current mirror stage is used, which outputs either a current source if the input is a one, or a current sink if the input is a zero. The current sources of all the input current mirror stages are connected in parallel to the current source input node of the amplifier stage. The current sinks of all the input current mirror stages are connected in parallel to the current sink input node of the amplifier stage. The amplifier is a differential type, which outputs either a positive voltage or a zero voltage depending upon the majority of the inputs.

Owner:NATIONAL SECURITY AGENCY

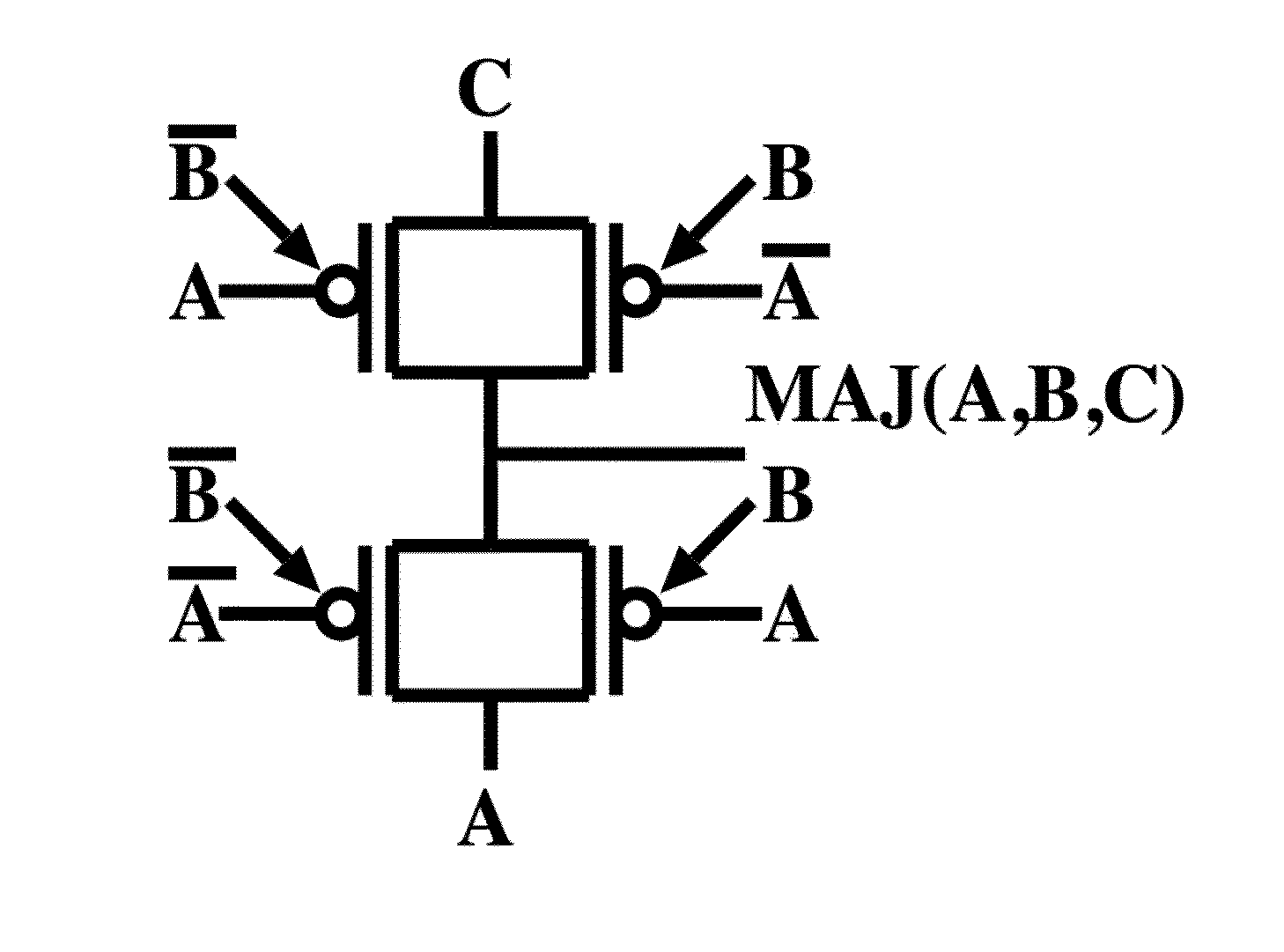

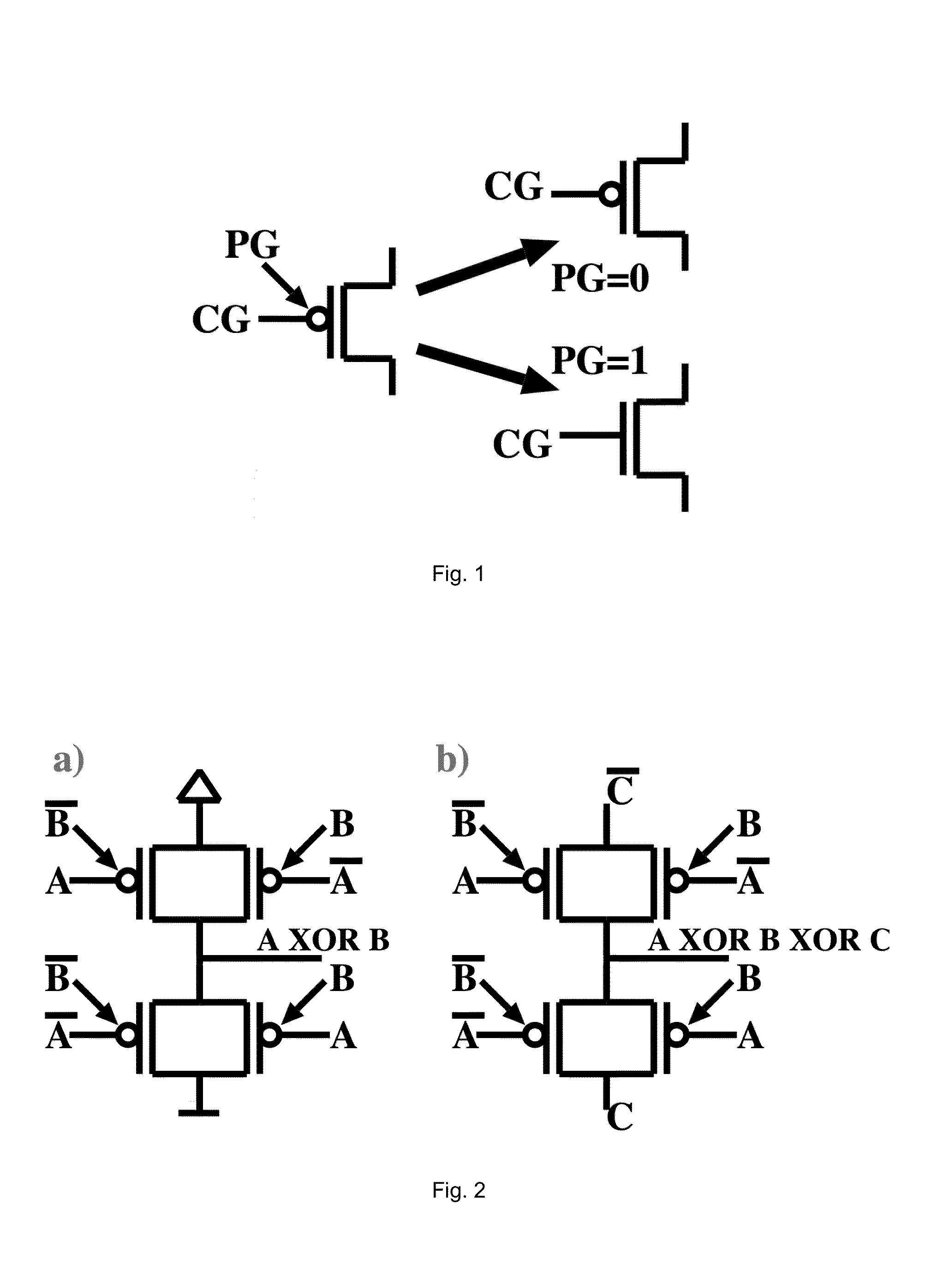

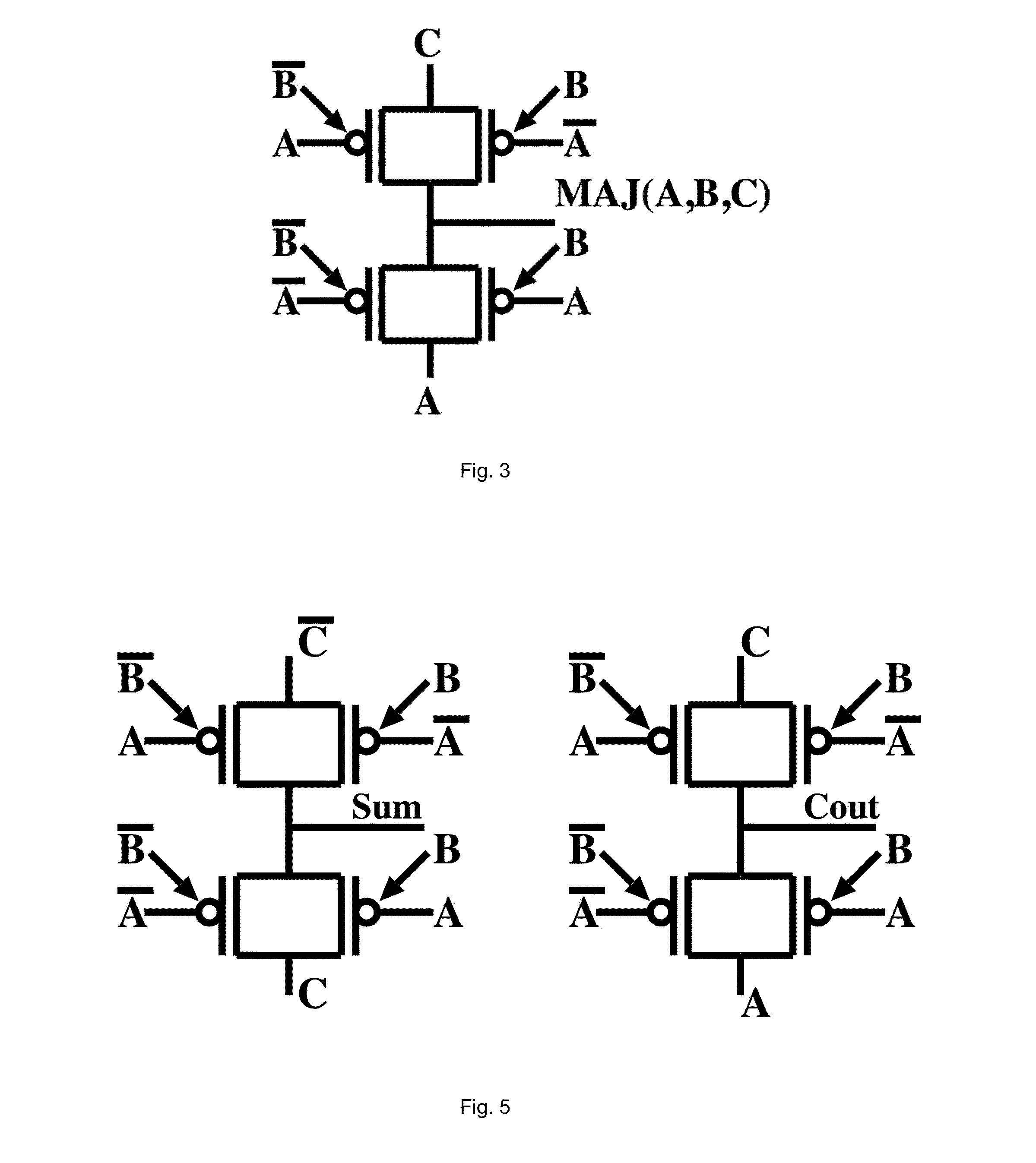

Controllable polarity FET based arithmetic and differential logic

ActiveUS20140043060A1Exclusive-OR circuitsMajority/minority circuitsTransmission gateElectrical polarity

A logic gate with three inputs A, B, and C, and one output implementing a function MAJ(A,B,C)=A*B+B*C+A*C comprising two mutually exclusive transmission gates (TGs) connected in series, based on two parallel double-gate controllable polarity devices, a polarity of each being controlled by input A and a conduction being controlled by input B, or vice-versa, in opposite polarities, and that route either an input A or C from one side of the transmission gates to the output.

Owner:ECOLE POLYTECHNIQUE FEDERALE DE LAUSANNE (EPFL)

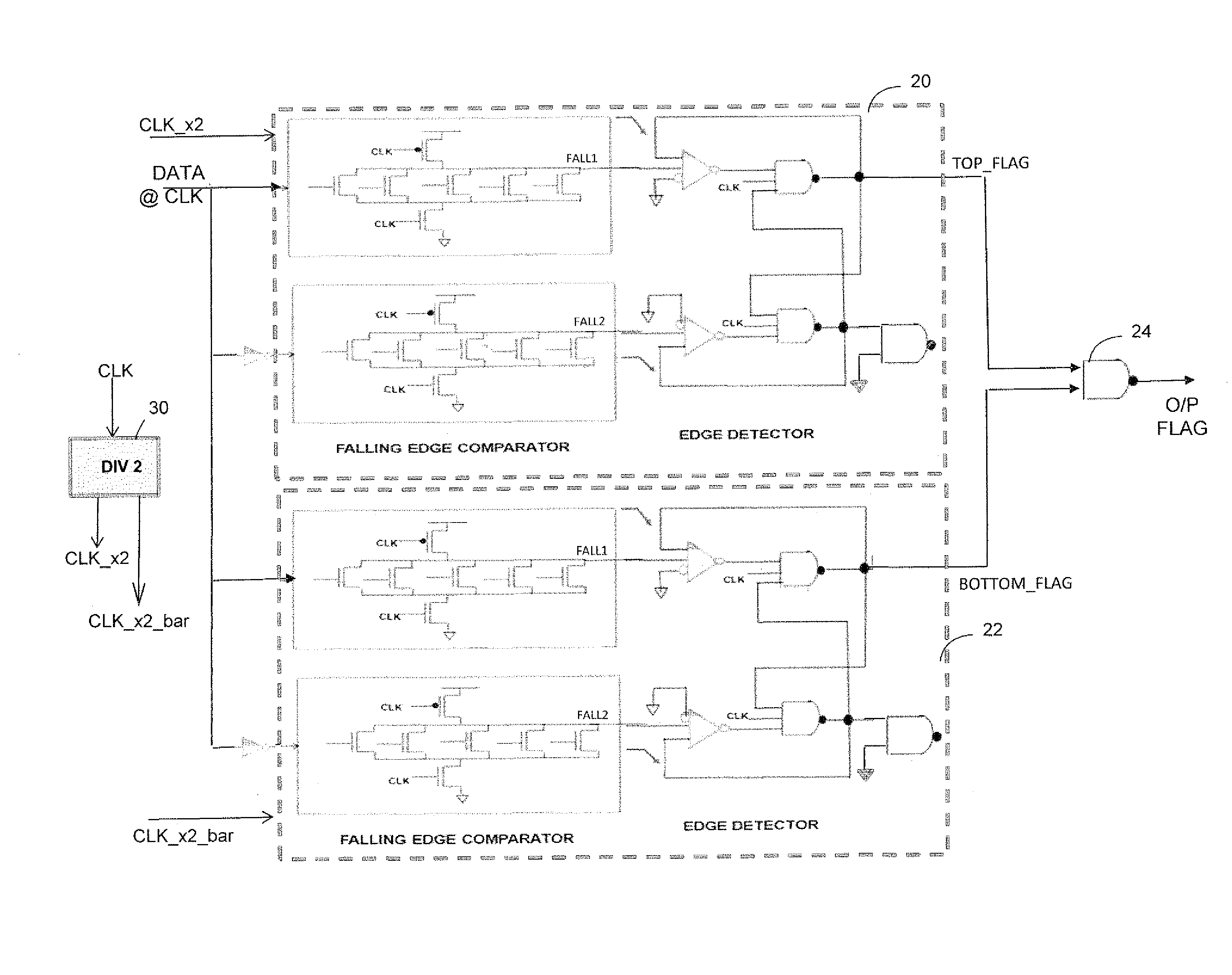

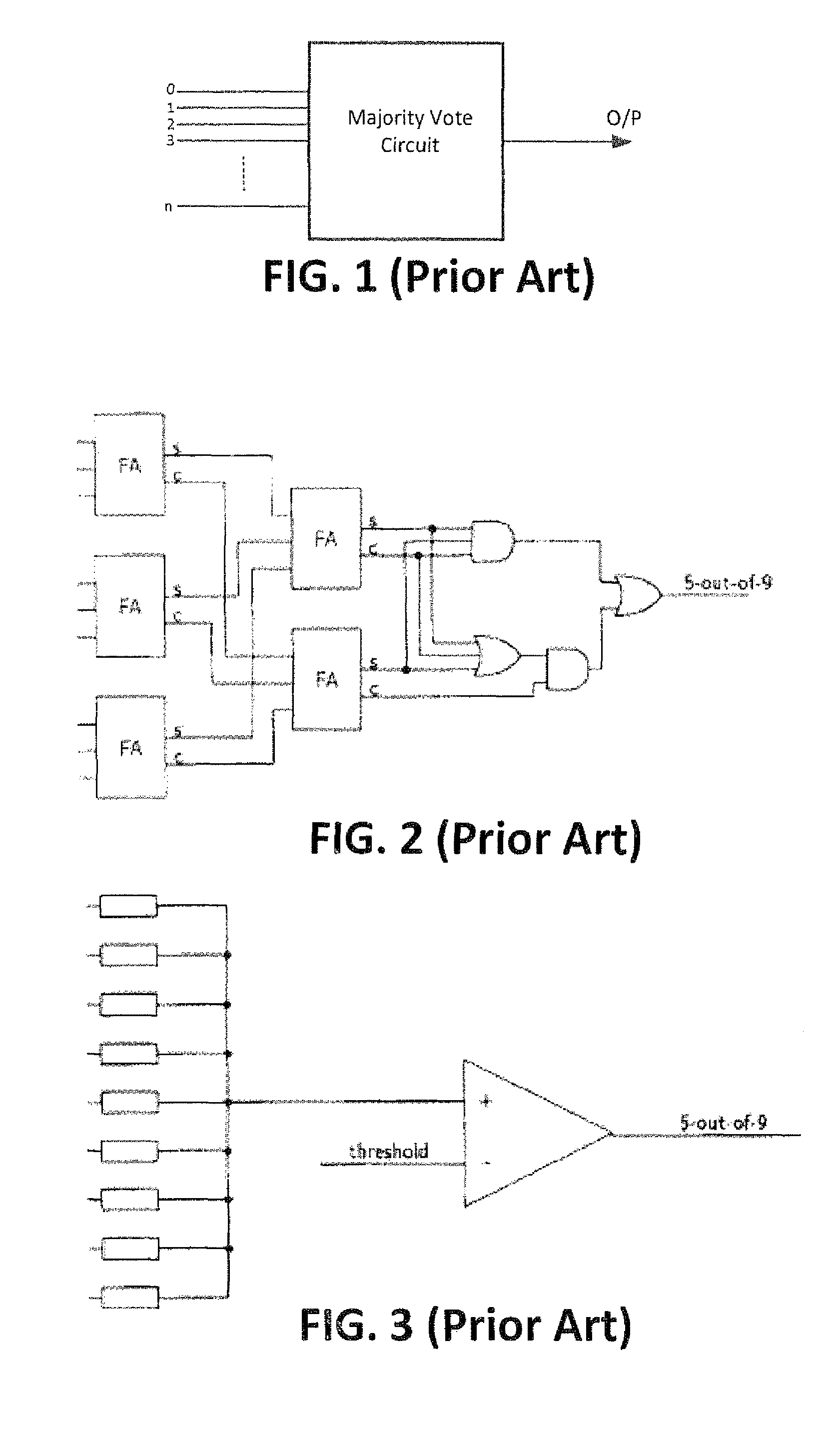

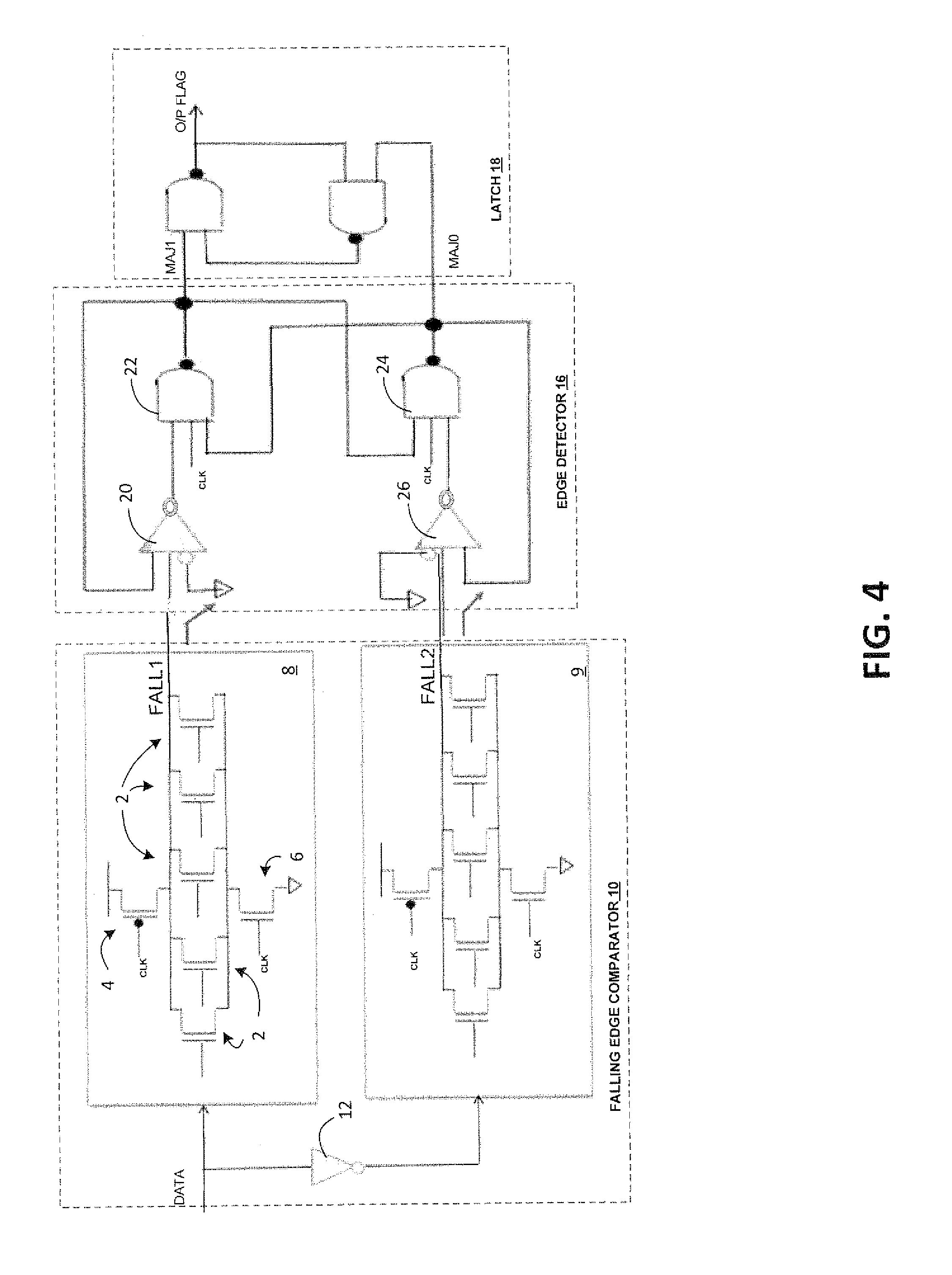

Majority vote circuit

ActiveUS8729923B2Reliability increasing modificationsMajority/minority circuitsPre-chargeAssessment data

Data words from a parallel communication channel are interleaved to two majority vote blocks that operate out of phase, using a divided clock signal that has half the clock frequency of the clock signal associated with the parallel communication channel. As one majority vote block evaluates a data word and outputs a result, the other majority vote block is in pre-charge mode awaiting the next data for evaluation.

Owner:SANDISK TECH LLC

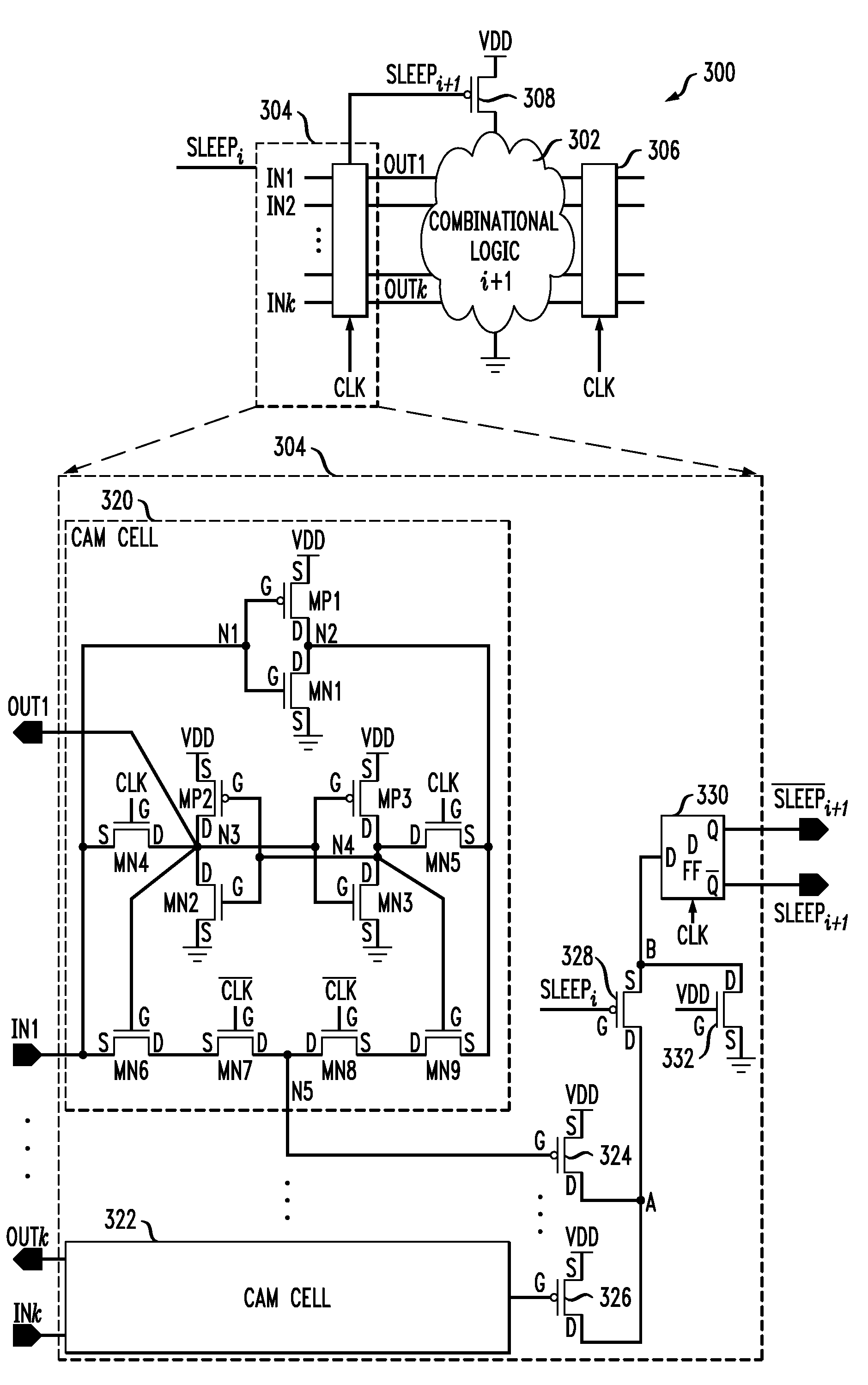

Multi-path power switch scheme for functional block wakeup

ActiveUS8786309B2Control the amount of power supply noiseLimited amount of timeReliability increasing modificationsMajority/minority circuitsElectricityPower switching

A multi-path power switch scheme for functional block wakeup is disclosed. The scheme may be applied to functional blocks of an integrated circuit. When a power on procedure is initiated within a given functional block, a first group of power switches in a functional block may be powered on, while a second group of power switches is inhibited from powering on. After a predetermined time has elapsed, activation of the second group of power switches is initiated. After initiation of a power up procedure for a given functional block, the powering up of a second functional block to be powered on may initially be inhibited. After a predetermined time has elapsed, the powering on of the second functional block may be initiated. Overlap between times when the first and second groups of switches are active may depend on process, voltage, and temperature variations.

Owner:APPLE INC

Majority voter apparatus, systems, and methods

InactiveUS20060061382A1Reliability increasing modificationsMajority/minority circuitsAudio power amplifierArtificial intelligence

Apparatus and systems, as well as methods and articles, may operate to provide a majority voter indication using a sense amplifier coupled to a first plurality of bit inputs and to a second plurality of bit inputs.

Owner:INTEL CORP

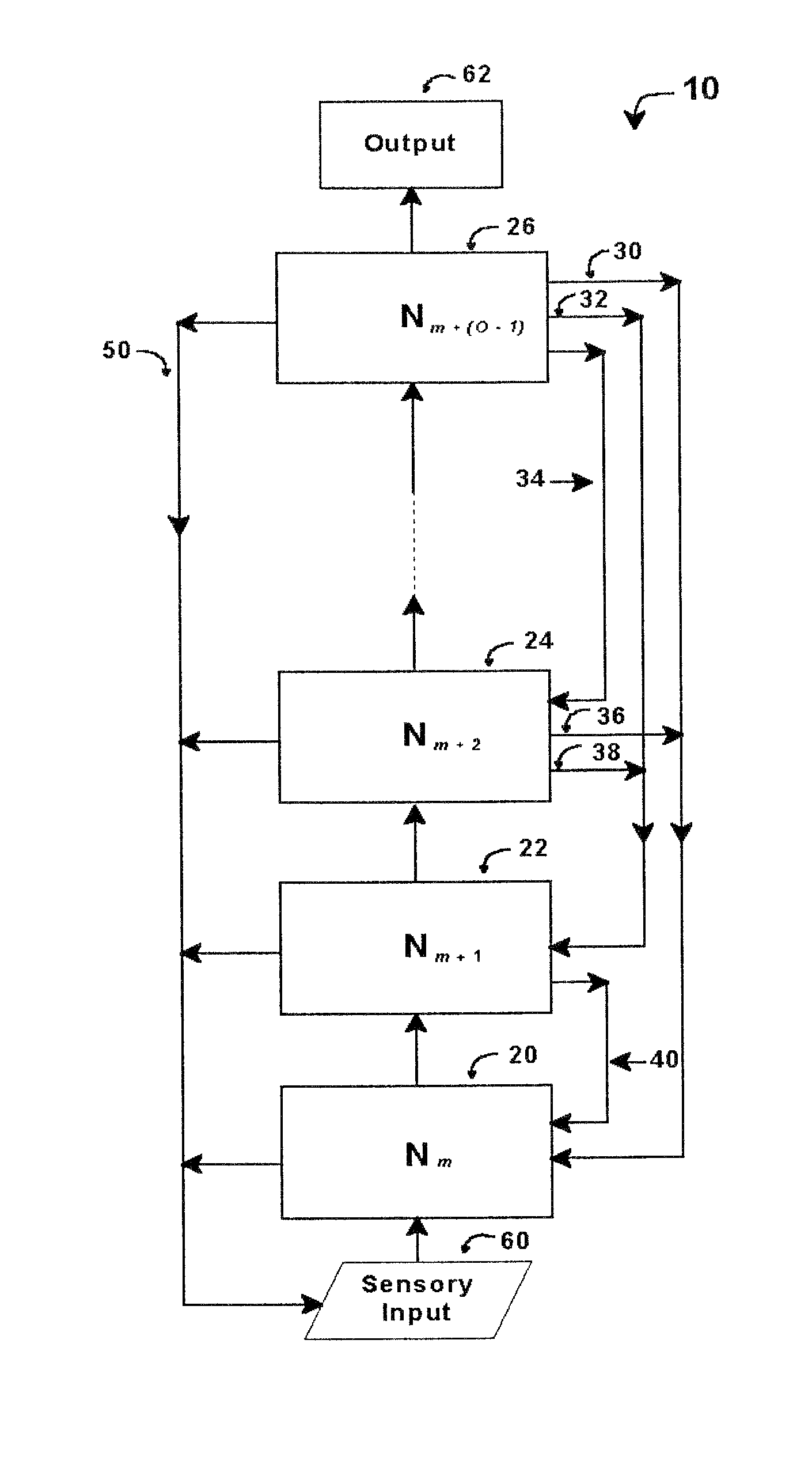

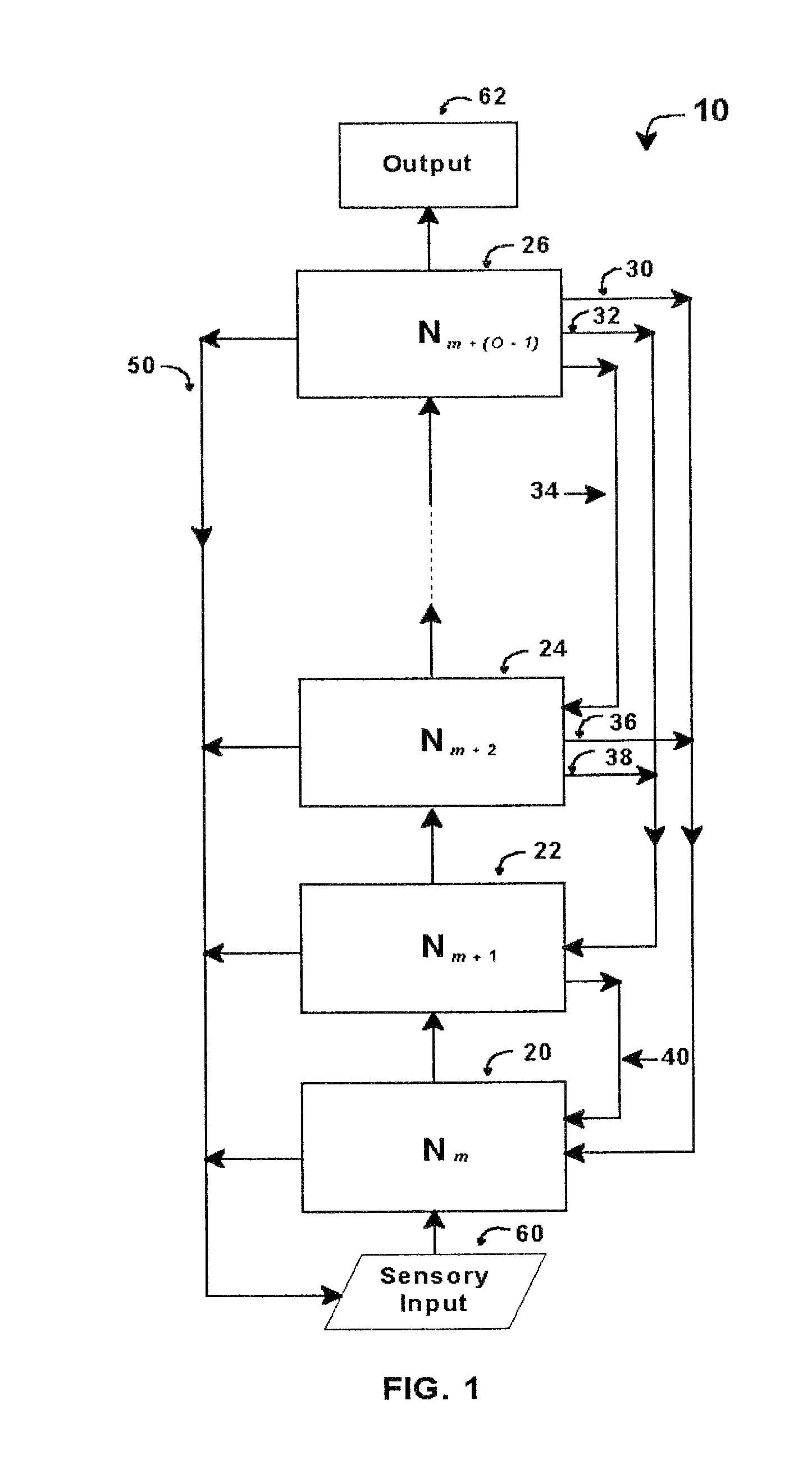

Intelligent control with hierarchical stacked neural networks

InactiveUS8788441B1Increased complexityMajority/minority circuitsGeneral purpose stored program computerExplicit modelInterconnection

An intelligent control system based on an explicit model of cognitive development (Table 1) performs high-level functions. It comprises up to O hierarchically stacked neural networks, Nm, . . . , Nm+(O−1), where m denotes the stage / order tasks performed in the first neural network, Nm, and O denotes the highest stage / order tasks performed in the highest-level neural network. The type of processing actions performed in a network, Nm, corresponds to the complexity for stage / order m. Thus N1 performs tasks at the level corresponding to stage / order 1. N5 processes information at the level corresponding to stage / order 5. Stacked neural networks begin and end at any stage / order, but information must be processed by each stage in ascending order sequence. Stages / orders cannot be skipped. Each neural network in a stack may use different architectures, interconnections, algorithms, and training methods, depending on the stage / order of the neural network and the type of intelligent control system implemented.

Owner:COMMONS MICHAEL LAMPORT +1

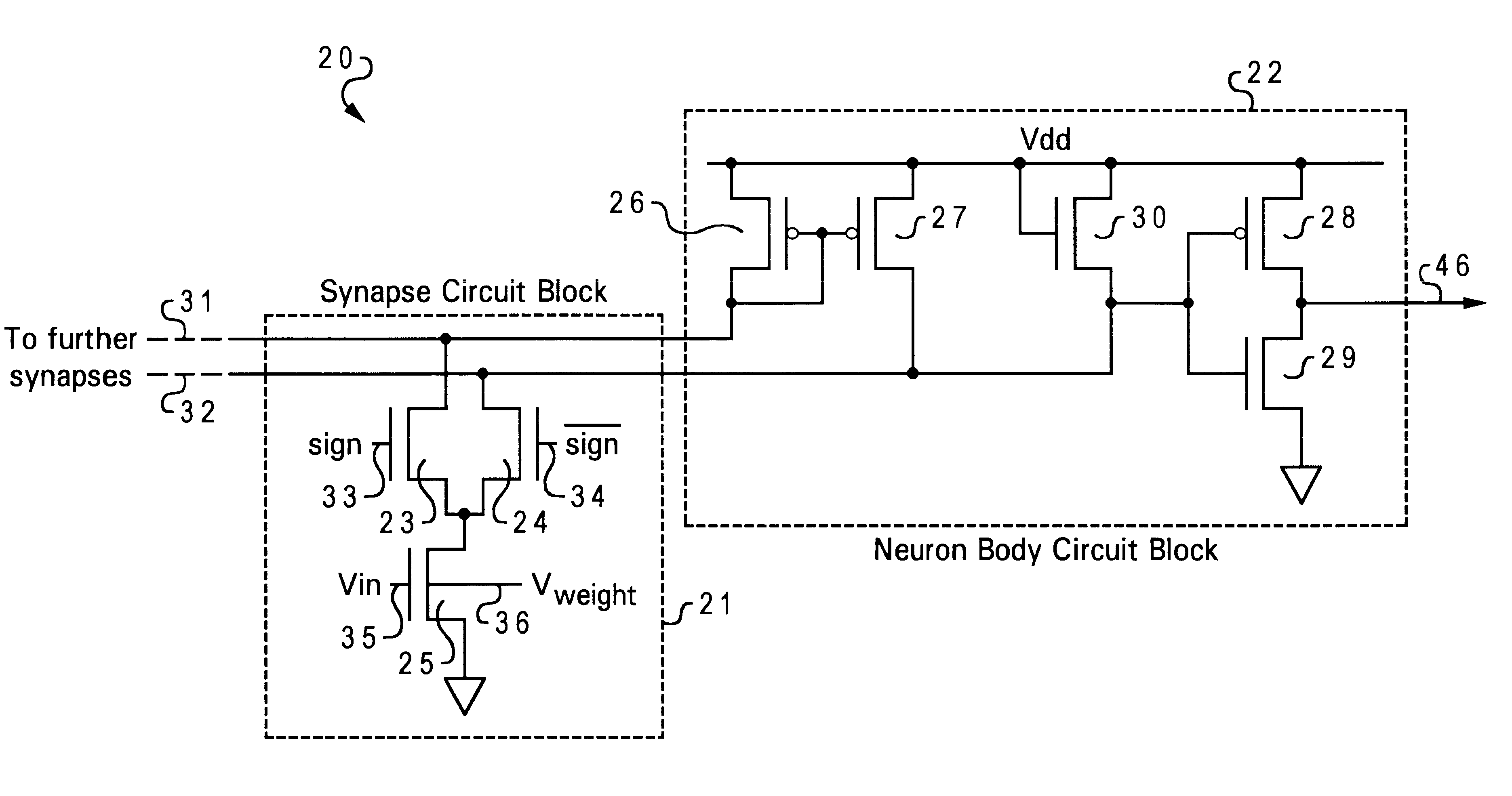

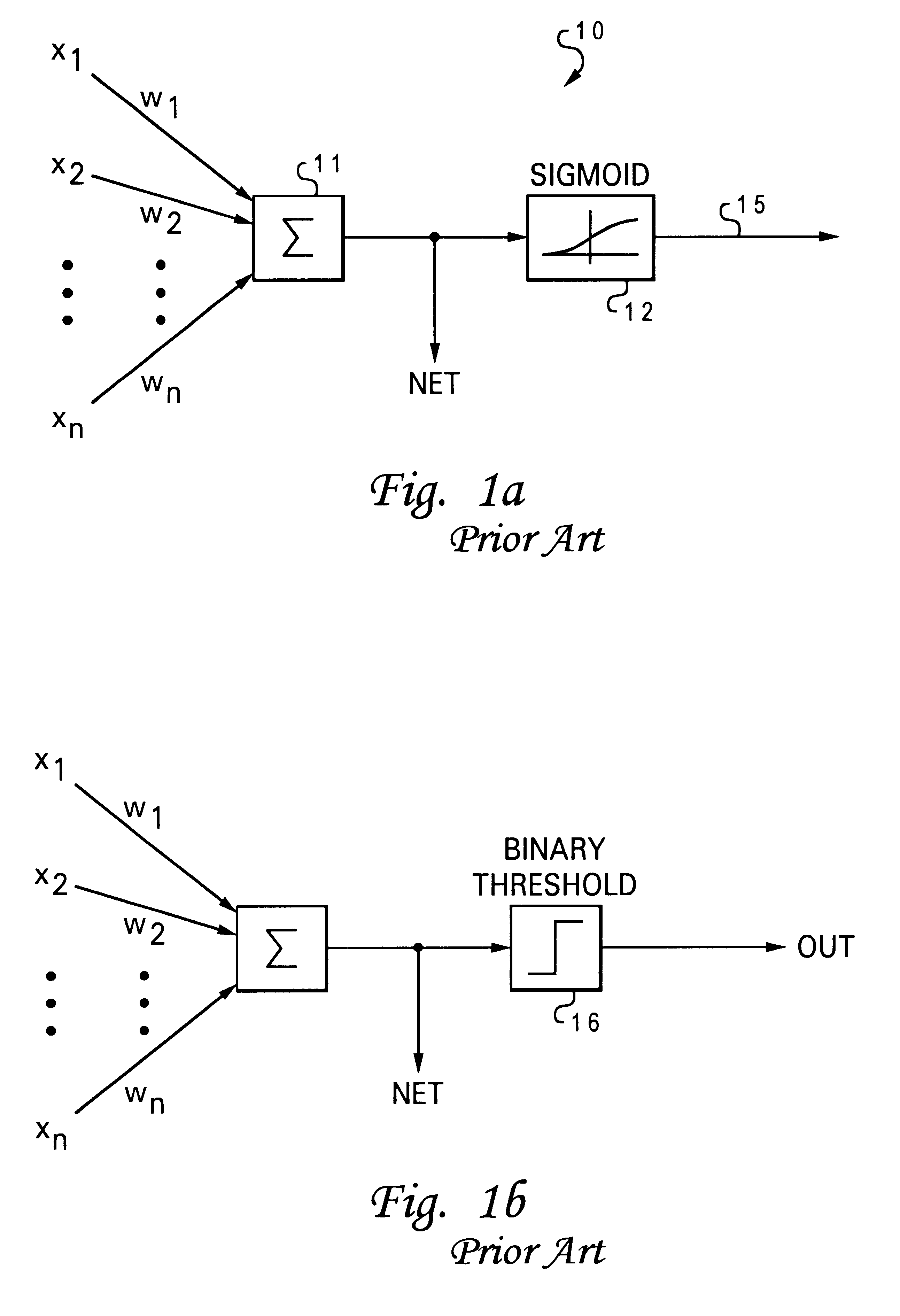

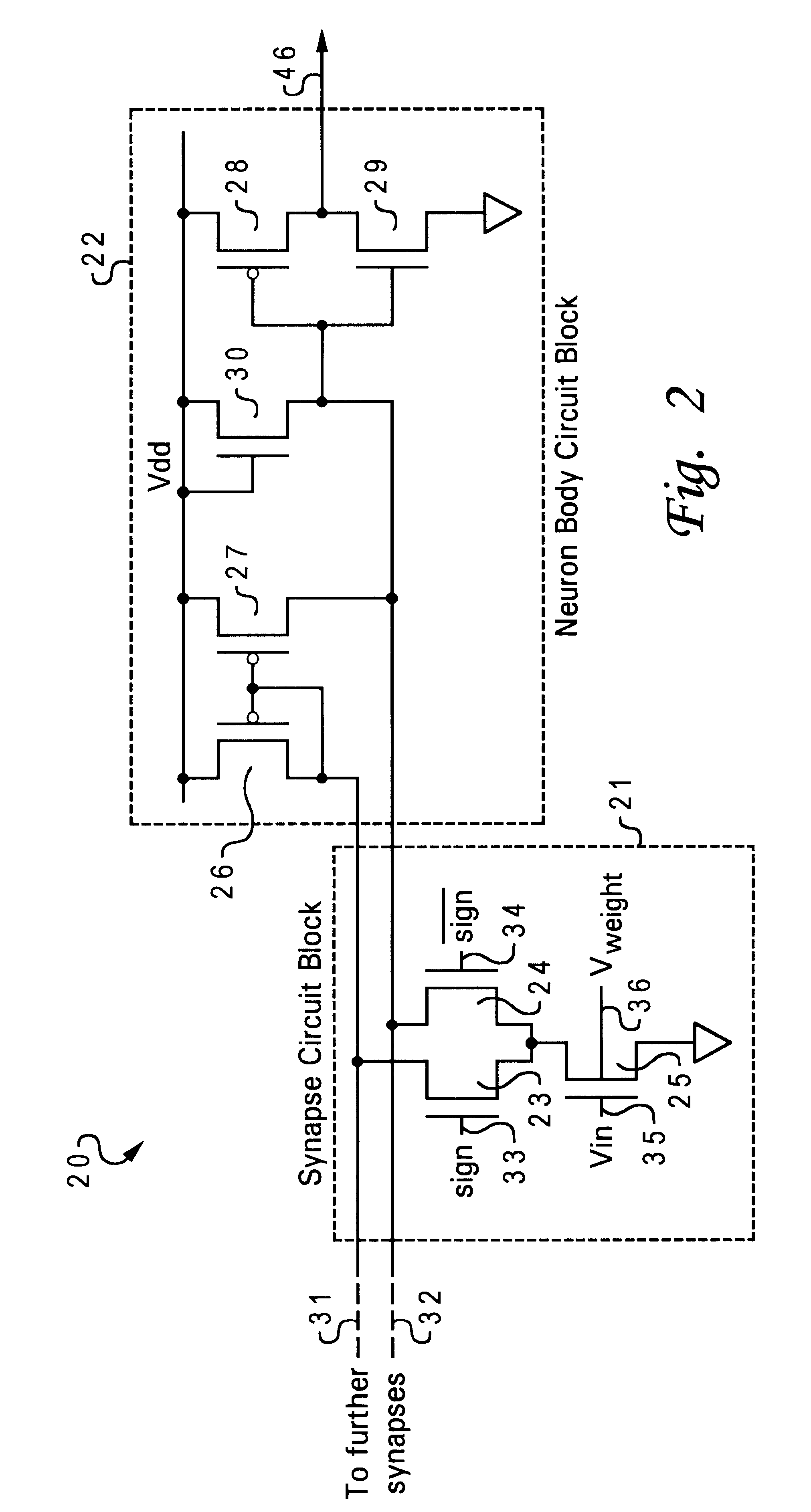

Neuron circuit

InactiveUS6501294B2Reliability increasing modificationsMajority/minority circuitsNeuron circuitSynapse structure

A neuron circuit that can be served as a building block for a neural network implemented in an integrated circuit is disclosed. The neuron circuit includes a synapse circuit block and a neuron body circuit block. The synapse circuit block has three transistors, and the body of one of the three transistors is controlled by a weighted input. The neuron body circuit block includes a current mirror circuit, a summing circuit, and an invertor circuit. The neuron body circuit is coupled to the synapse circuit block to generate an output pulse.

Owner:IBM CORP

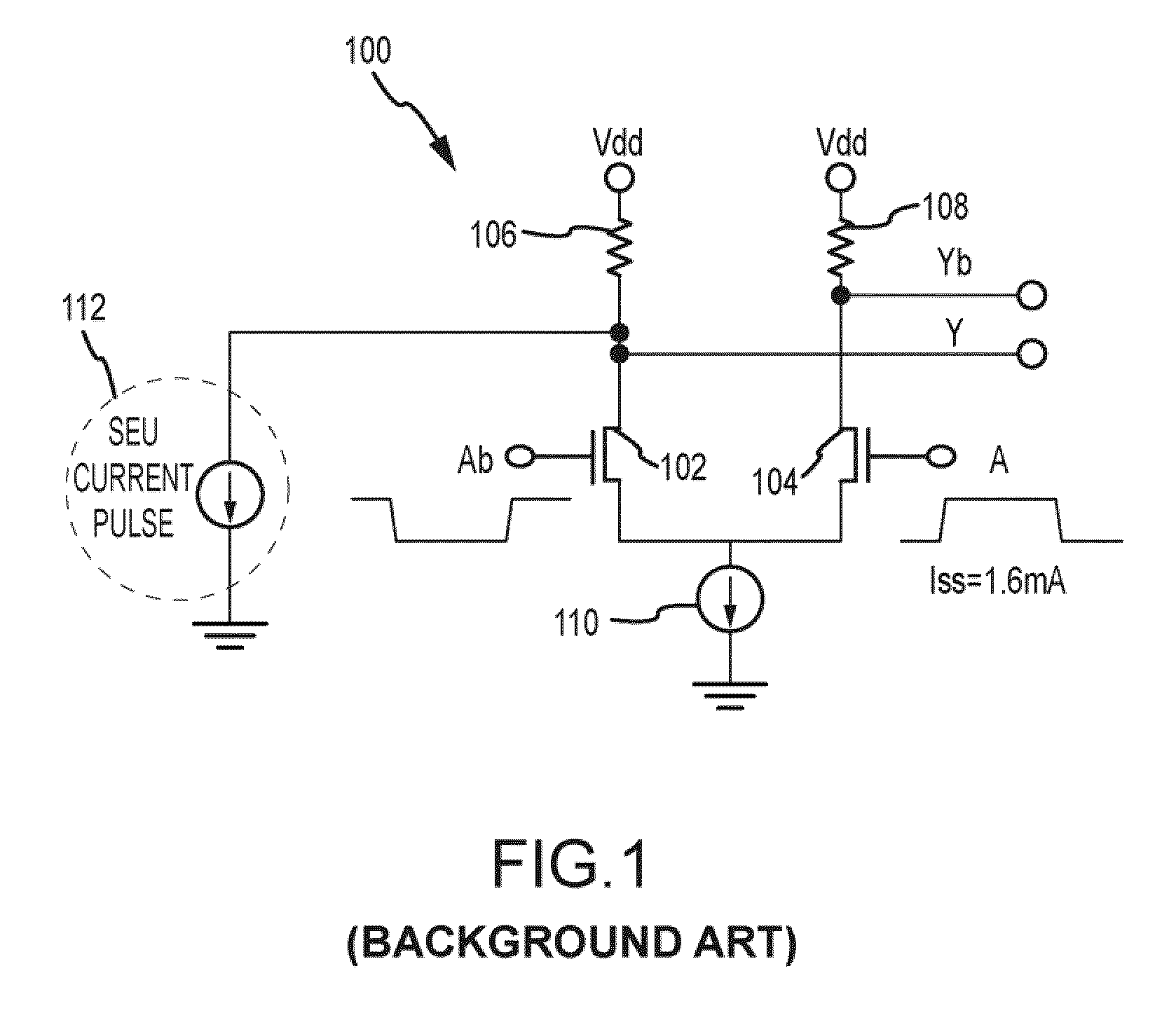

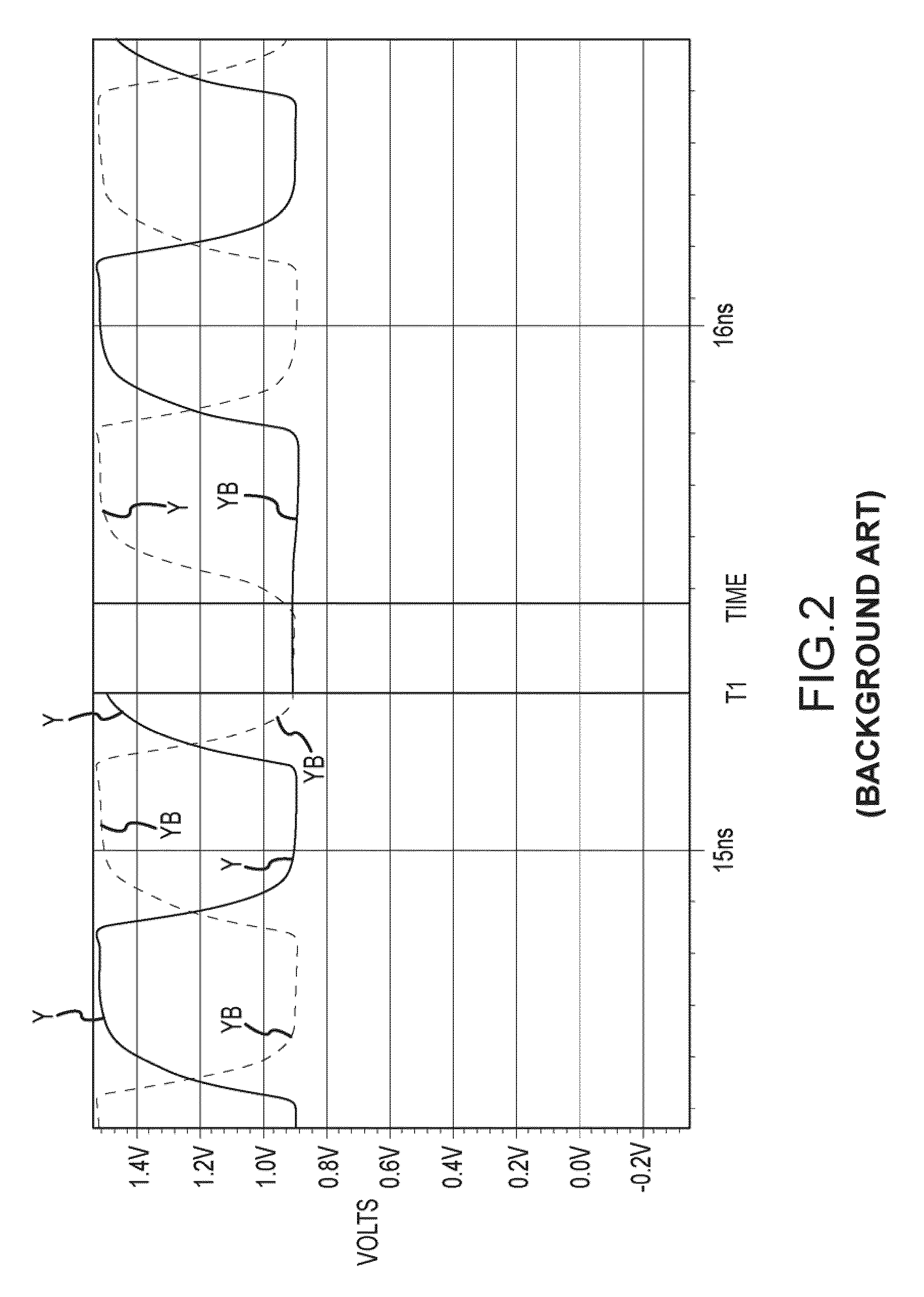

Hardened current mode logic (CML) voter circuit, system and method

ActiveUS20100141296A1Reliability increasing modificationsMajority/minority circuitsNOR gateElectrical and Electronics engineering

A current mode logic voter circuit includes three two-input split NOR gates. Each two-input split NOR gate receives a corresponding pair of input signals and generates a pair of first output signals responsive to the input signals. A three input split NOR gate is coupled to the two-input split NOR gates to receive the first output signals and generates a second pair of output signals responsive to the first output signals from the two-input split NOR gates. The two and three-input split NOR gates can be formed from current mode logic buffer circuits, and in one embodiment in the three-input split NOR gate the buffer circuits are hardened.

Owner:BAE SYST INFORMATION & ELECTRONICS SYST INTERGRATION INC

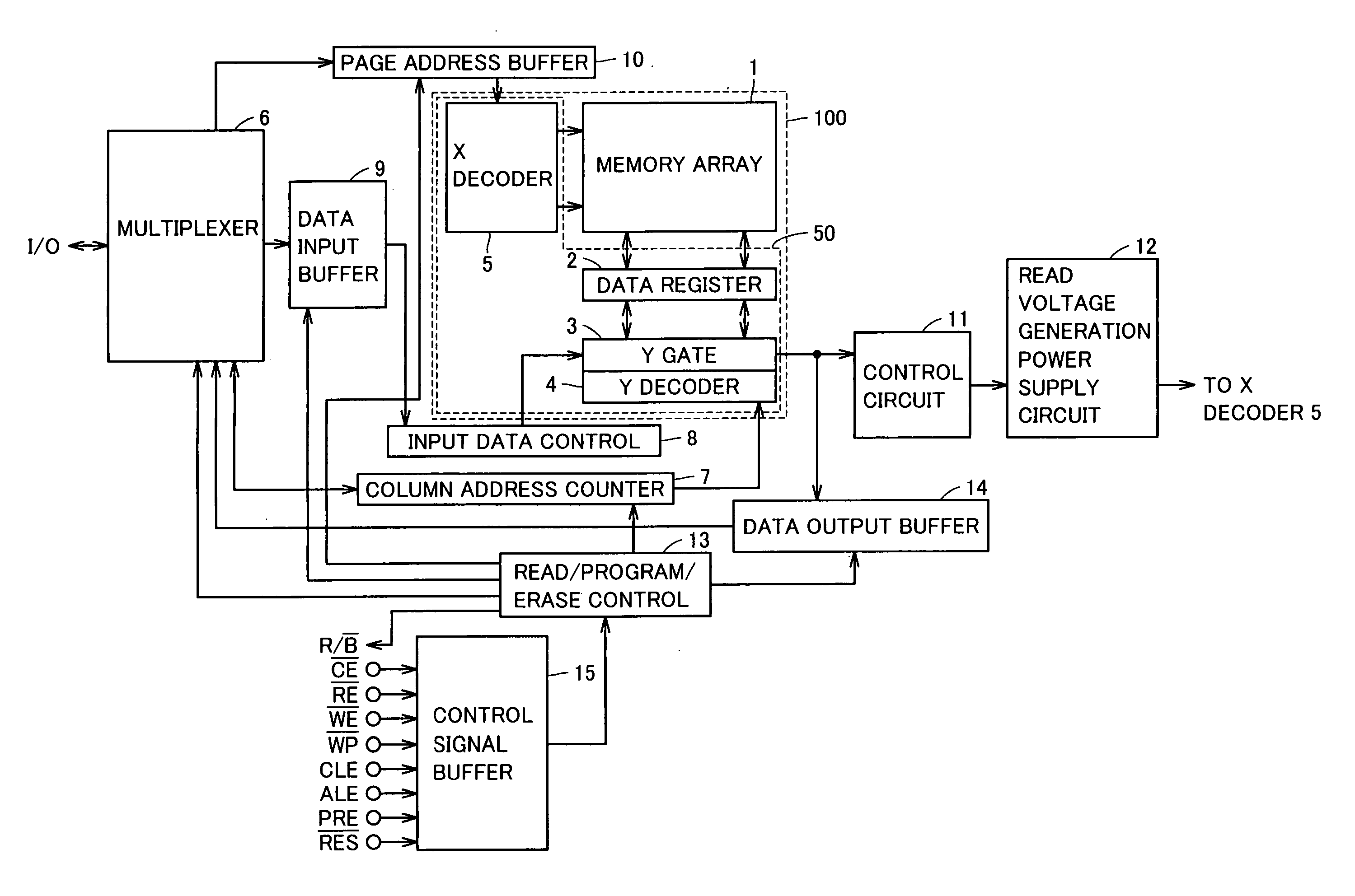

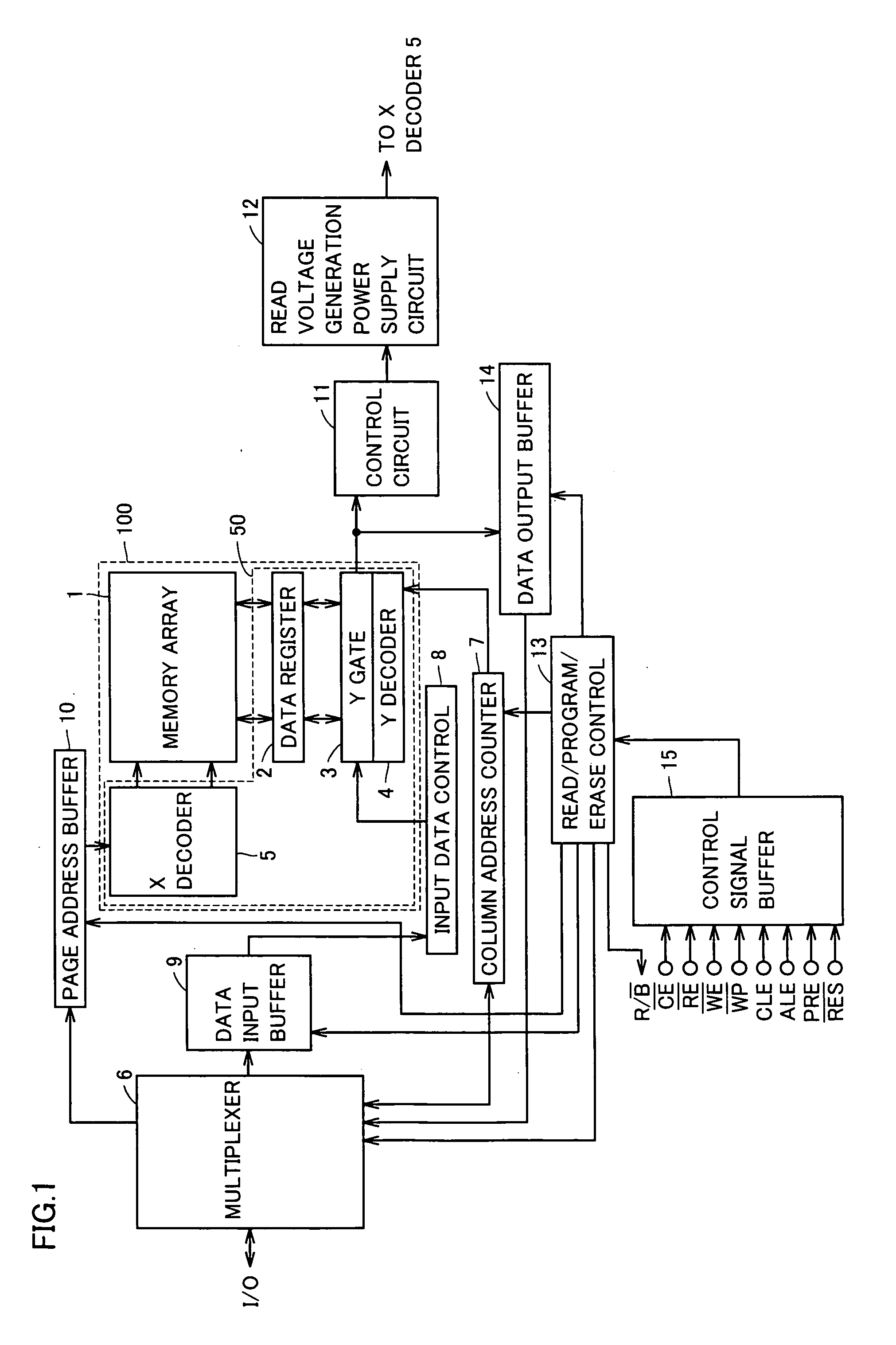

Semiconductor storage device having memory cell for storing data by using difference in threshold voltage

ActiveUS7719900B2Avoid volatilityRead-only memoriesDuration/width modulated pulse demodulationSemiconductor storage devicesParallel computing

A semiconductor storage device which includes a memory array including a plurality of memory cells for storing data by using a difference in a threshold voltage and at least one reference cell for storing data indicative of a state of a corresponding memory cell by using a difference in a threshold voltage, a control circuit for determining a read voltage based on data stored by a reference cell corresponding to a memory cell adjacent to a memory cell to be read, a read unit for executing reading from a memory cell to be read by using a determined read voltage, and a write unit for executing writing, when executing writing to a memory cell to be written to bring the memory cell into a written state, data indicating that the memory cell is in the written state to a reference cell corresponding to the memory cell.

Owner:RENESAS ELECTRONICS CORP

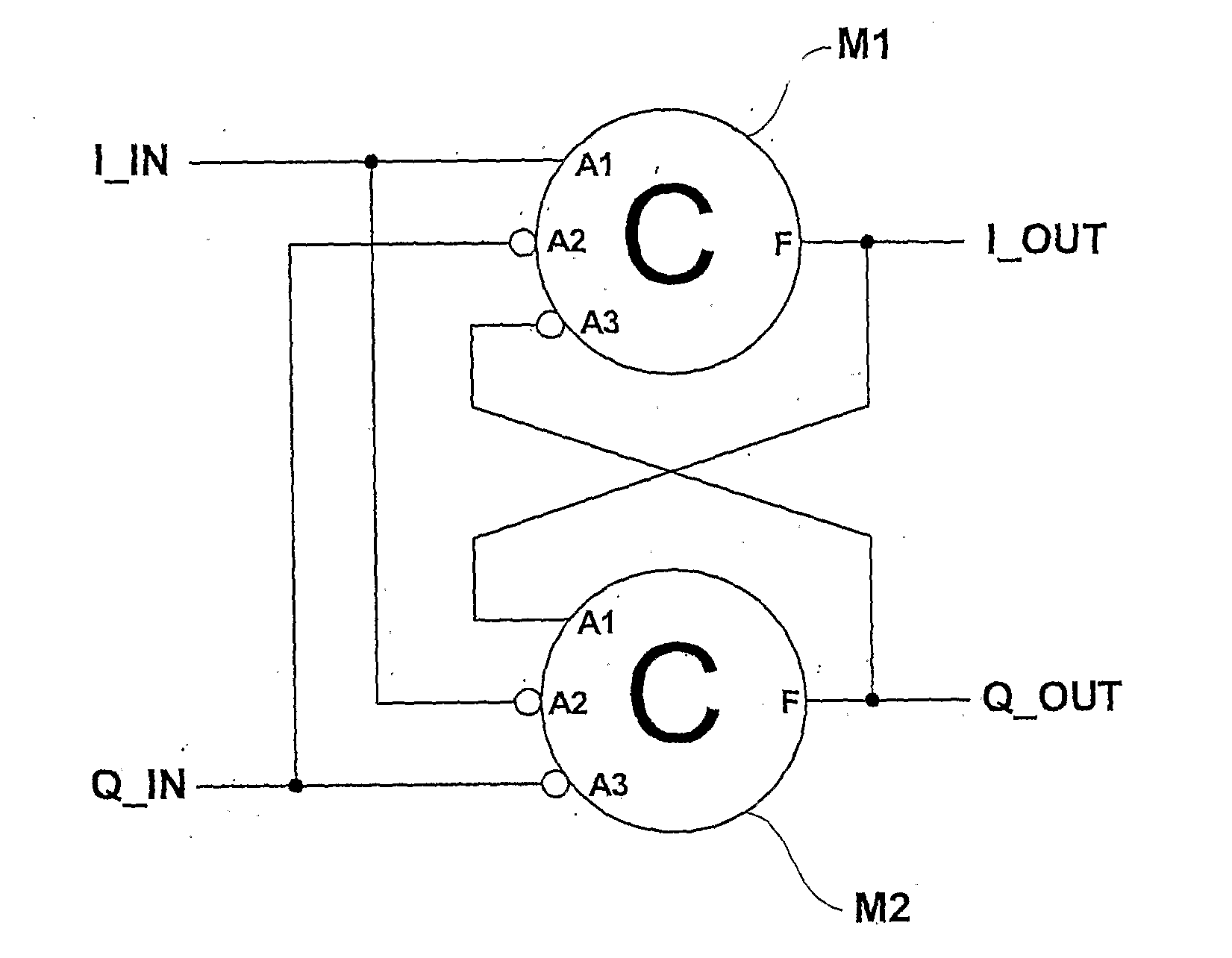

Quadrature Divide-By-Three Frequency Divider and Low Voltage Muller C Element

ActiveUS20080260089A1Cost advantageEnsure effective implementationMajority/minority circuitsPulse counters with static storageLow voltageLocal oscillator

A low voltage, low power, wideband quadrature divide-by-three frequency divider using a wideband low voltage, low power differential Muller C element with multiple inputs operates on quadrature input and quadrature output signals. This frequency divider can be used in frequency synthesisers and as quadrature local oscillator generator.

Owner:TEXAS INSTR INC

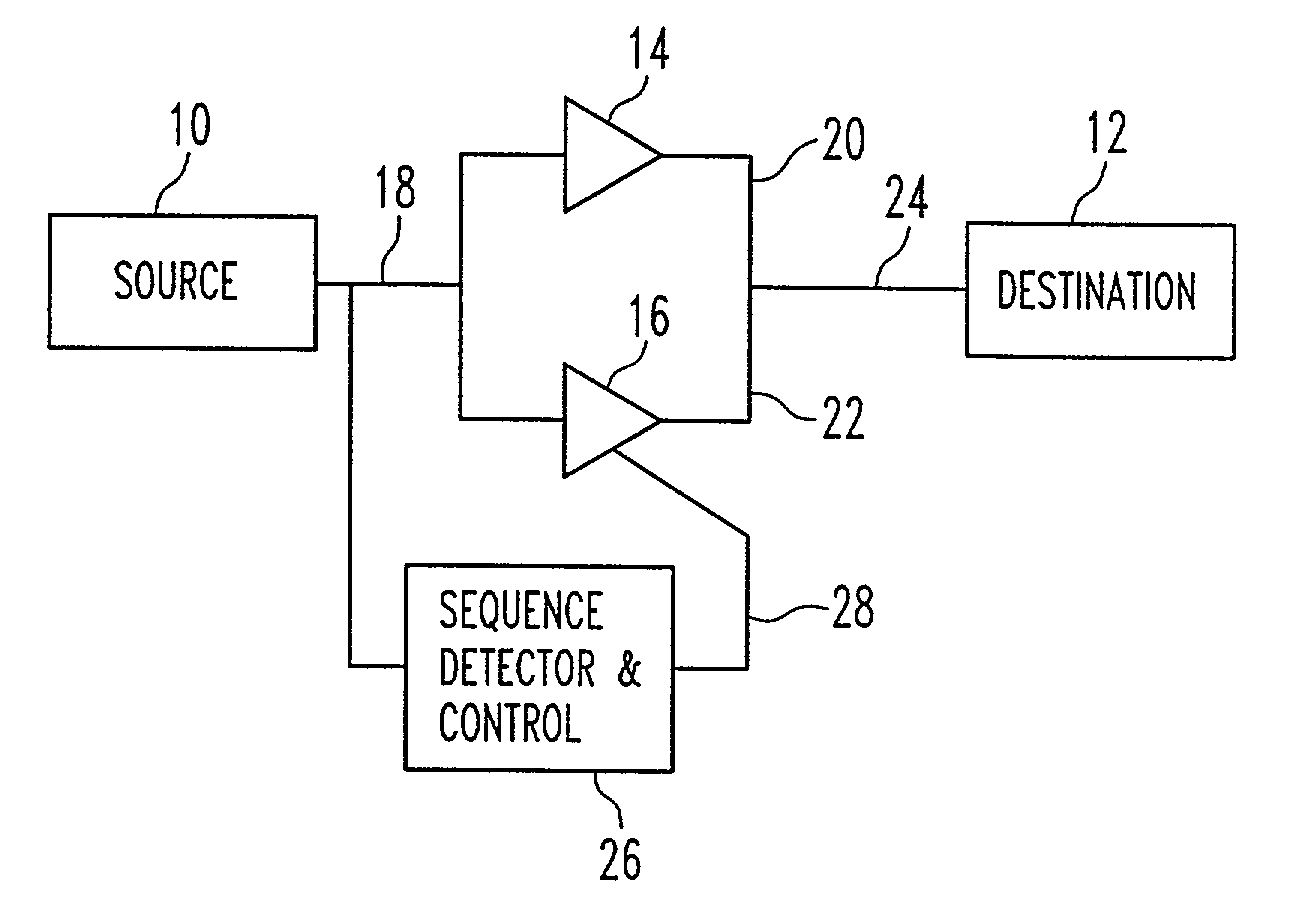

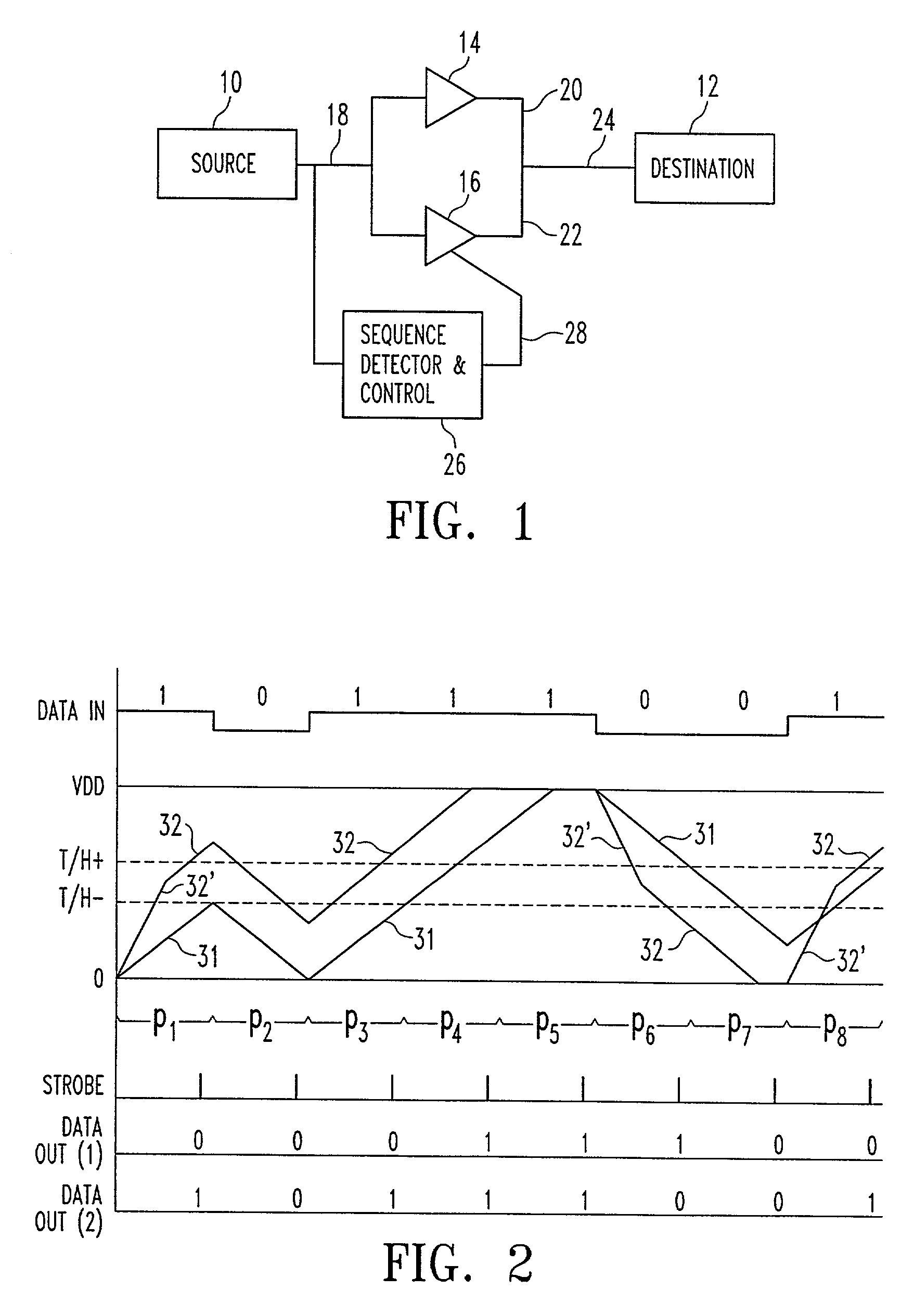

Method and apparatus for selectively providing data pre-emphasis based upon data content history

InactiveUS7051127B2Majority/minority circuitsInput/output processes for data processingControl signalData content

The present invention comprises a method and apparatus for selectively providing pre-emphasis to the output of a first driver during an initial portion of certain data transitions while transmitting data along a data bus from a source to a destination, with the certain data transitions being determined as a function of the content of the history of prior transmitted data cells. In the preferred embodiment, a pre-emphasis driver is connected in parallel to a normal driver and the pre-emphasis driver is activated preferably during the initial portion of a data transition to provide pre-emphasis in response to a control signal being applied to the pre-emphasis driver. The preferred embodiment of the present invention also comprises a sequence detector and control for monitoring the data cells or bits that are inputted to the normal driver to provide a history of the voltage levels of the data bits that are input to the normal driver. Based upon the history, the pre-emphasis driver is selectively operated to increase the slew or magnitude of the slope of a data transition at least during the initial portion of the transition.

Owner:HEWLETT PACKARD DEV CO LP

Majority voter apparatus, systems, and methods

InactiveUS7183795B2Reliability increasing modificationsMajority/minority circuitsAudio power amplifierData mining

Owner:INTEL CORP

Popular searches

Electronic switching Electric pulse generator Oscillations generators Logic circuit coupling/interface arrangements Machines/engines Installations with induction energy storage Fail-safe circuits Radiation hardening Redundant data error correction Computation using denominational number representation