Patents

Literature

31 results about "Majority logic" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

Method and apparatus for channel decoding of tail-biting convolutional codes

InactiveUS6877132B1Error correction/detection using convolutional codesOther decoding techniquesMajority logic decodingMajority logic

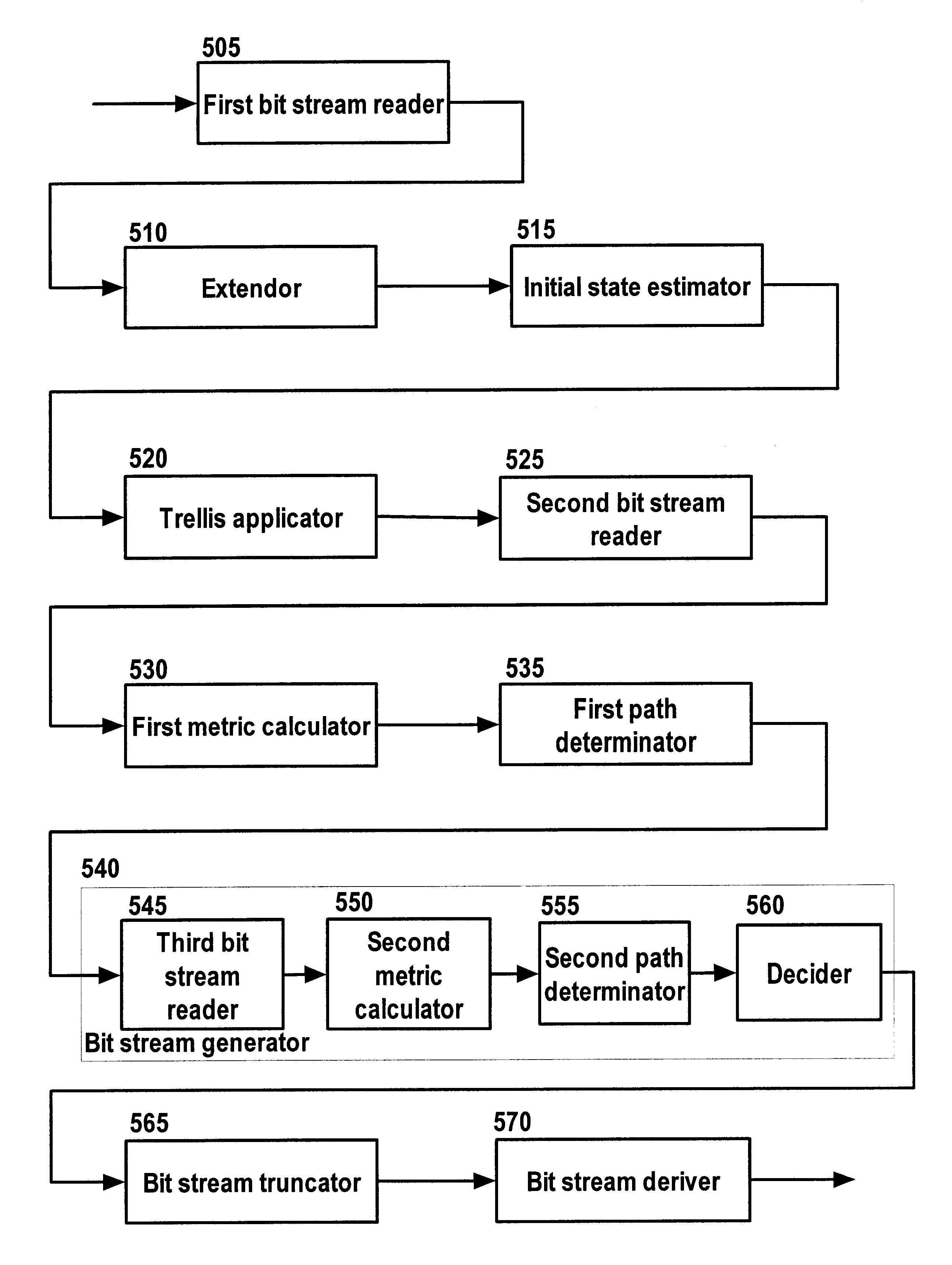

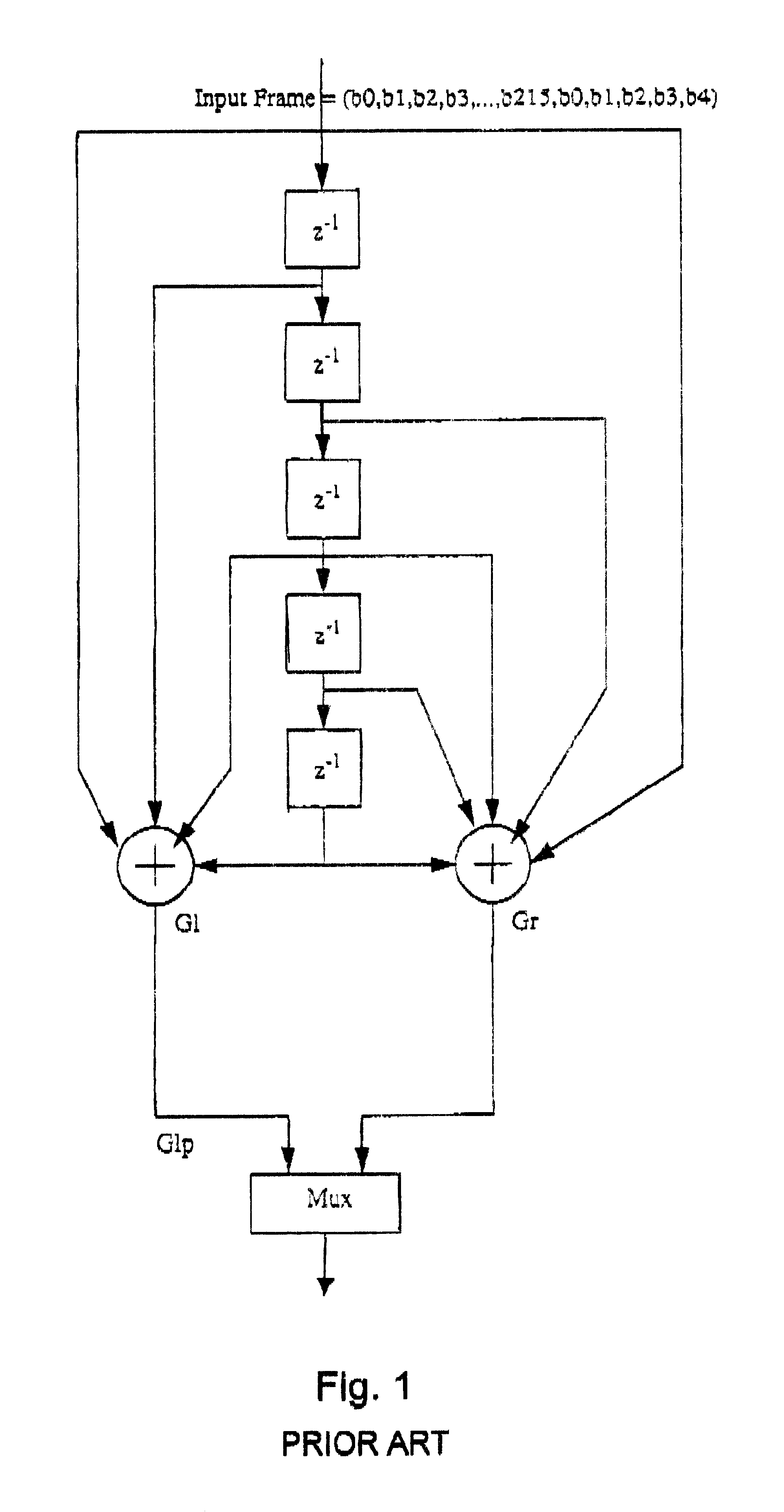

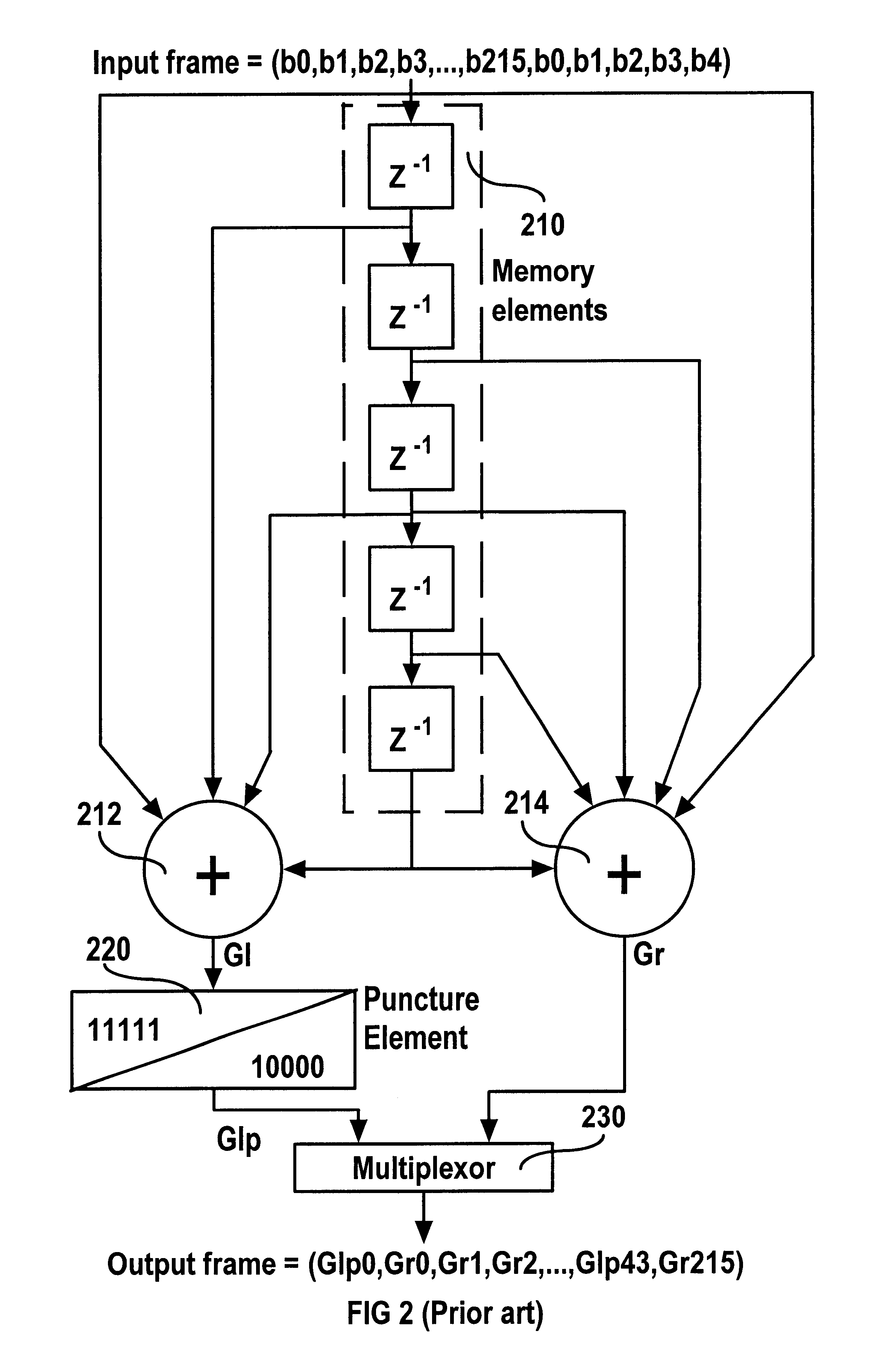

A method for hard-decision channel decoding of tail-biting convolutional codes includes the step of receiving from a channel an input bit stream encoded by a tail-biting convolutional channel encoder. The encoder includes a number of memory elements and a rate. The input bit stream includes a series of symbols; each symbol includes a number of bits; the number of bits is related to the rate of the encoder. The method further includes the step of assuming a probability for each possible initial state of the encoder. The method further includes the step of decoding each symbol of the input bit stream using majority logic, with reference to a trellis structure corresponding to the encoder. The trellis structure represents: a number of states related to the number of memory elements of the encoder; a plurality of transitional branches; and a number of stages related to the number of symbols in the input bit stream.

Owner:APPLE INC

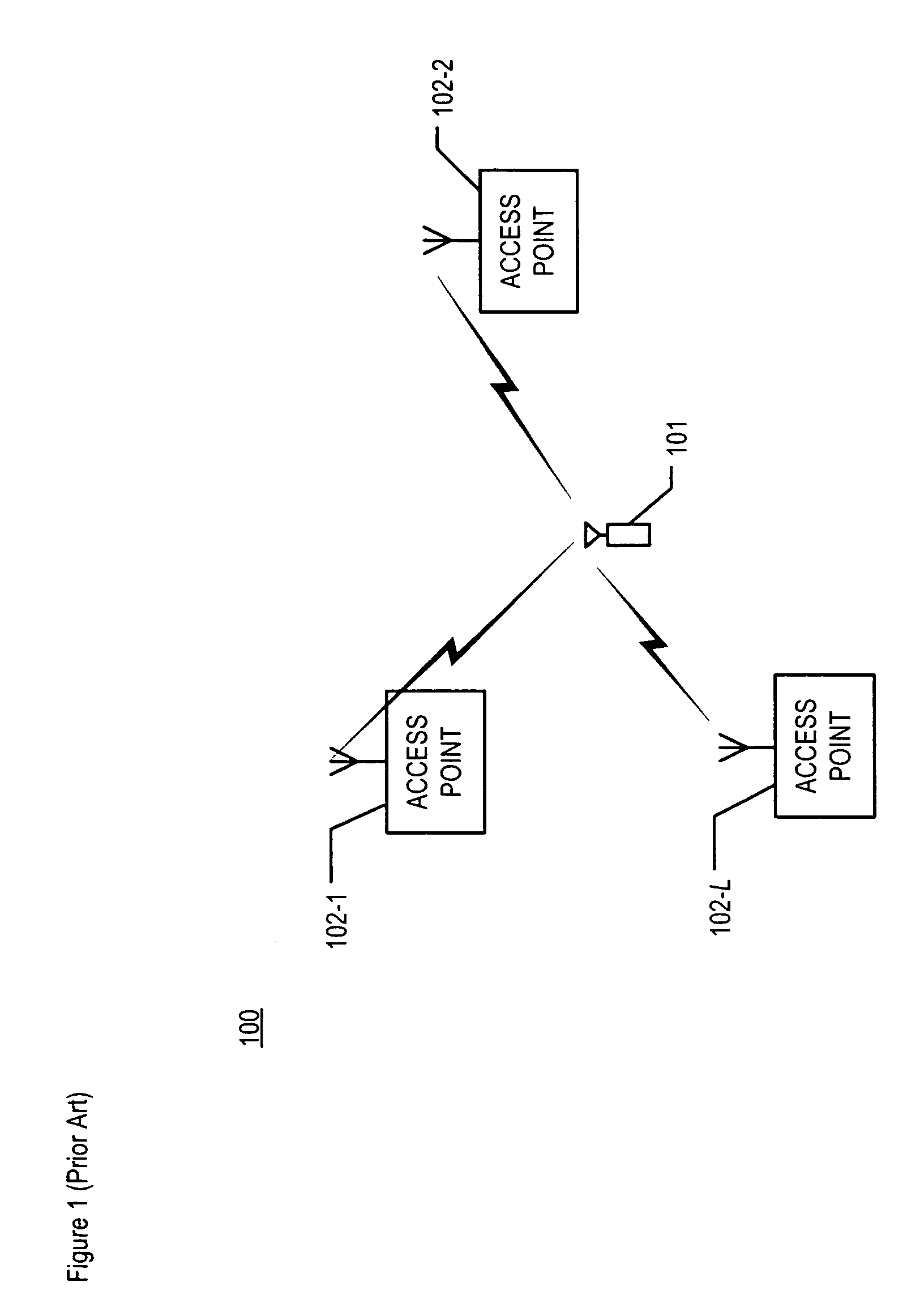

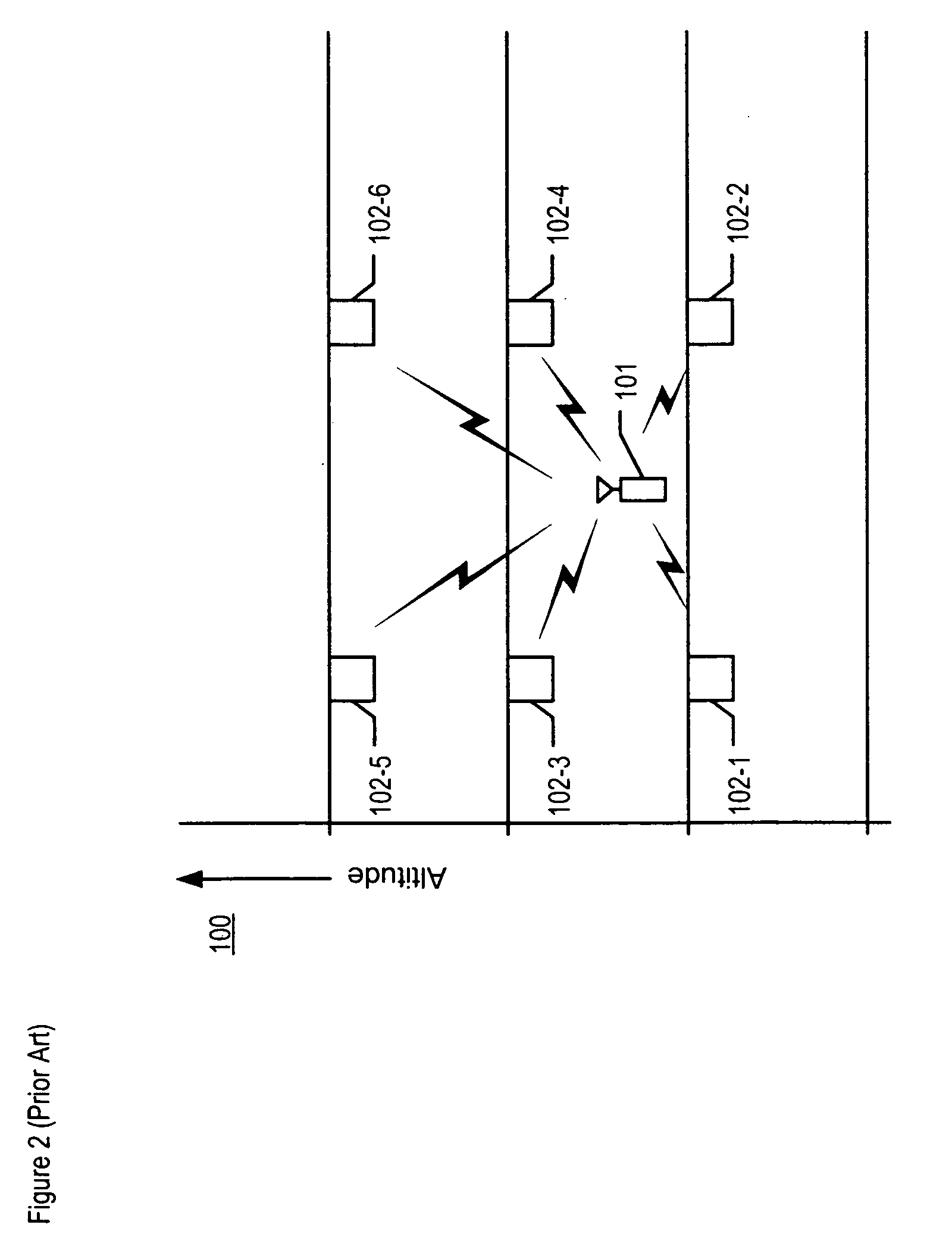

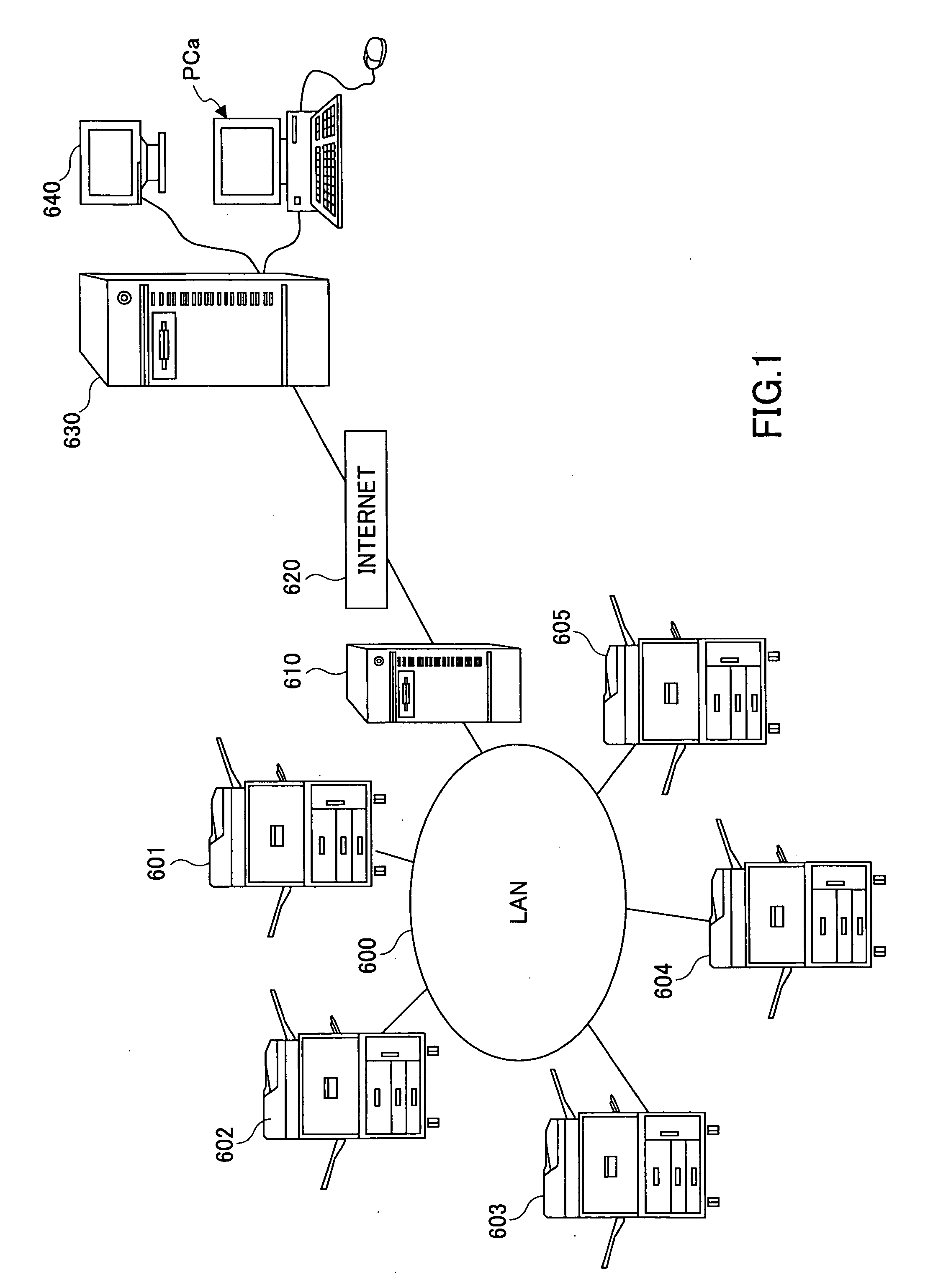

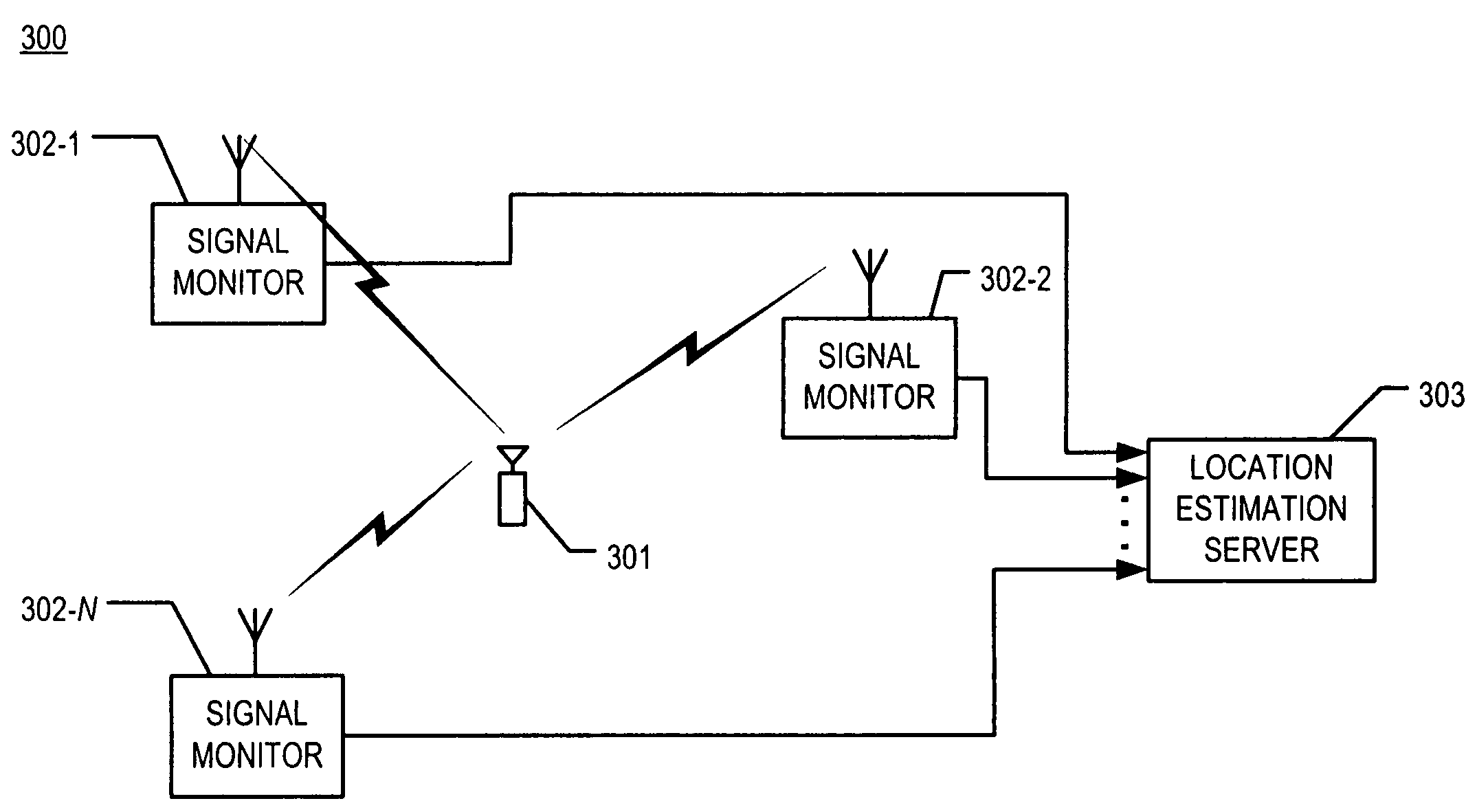

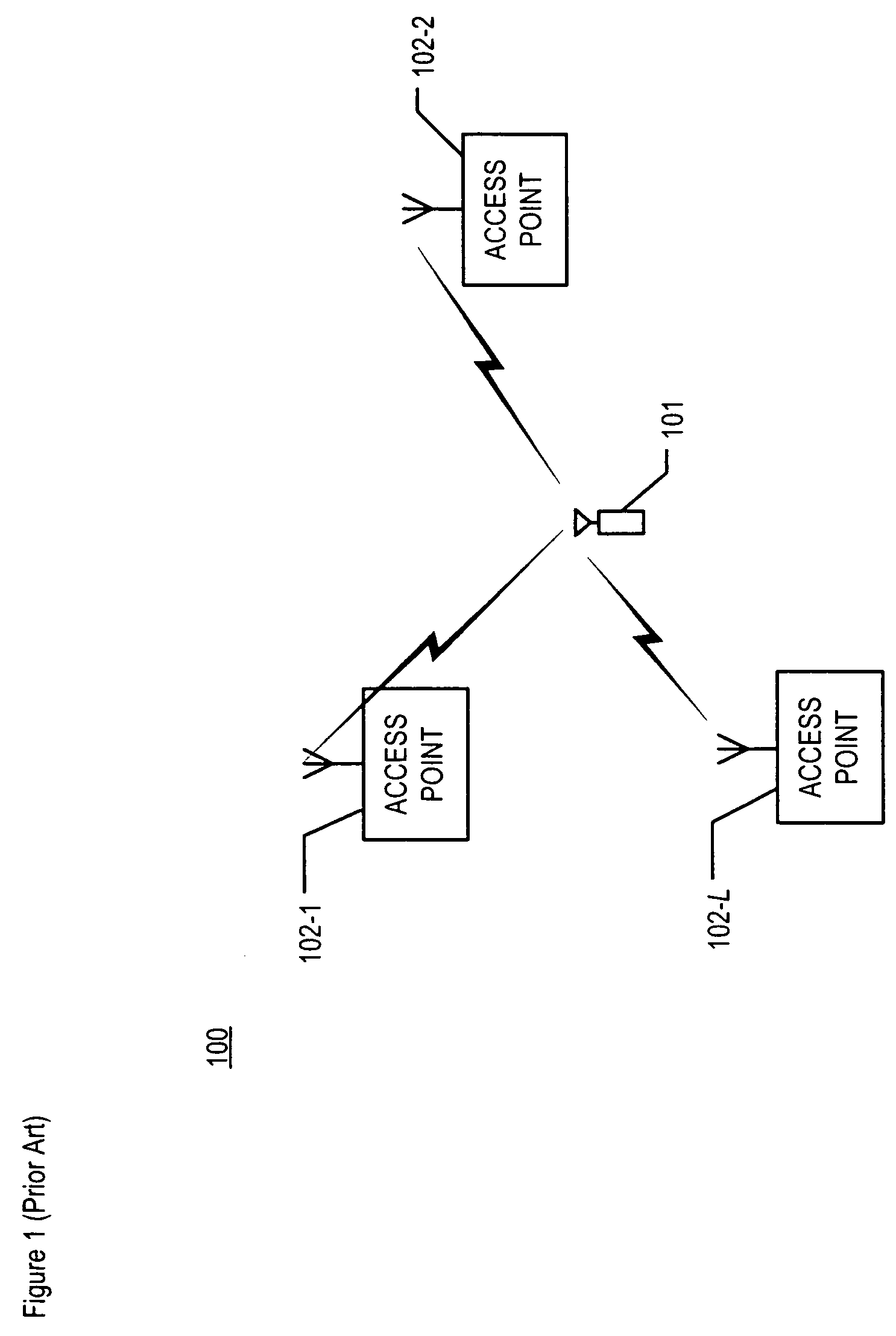

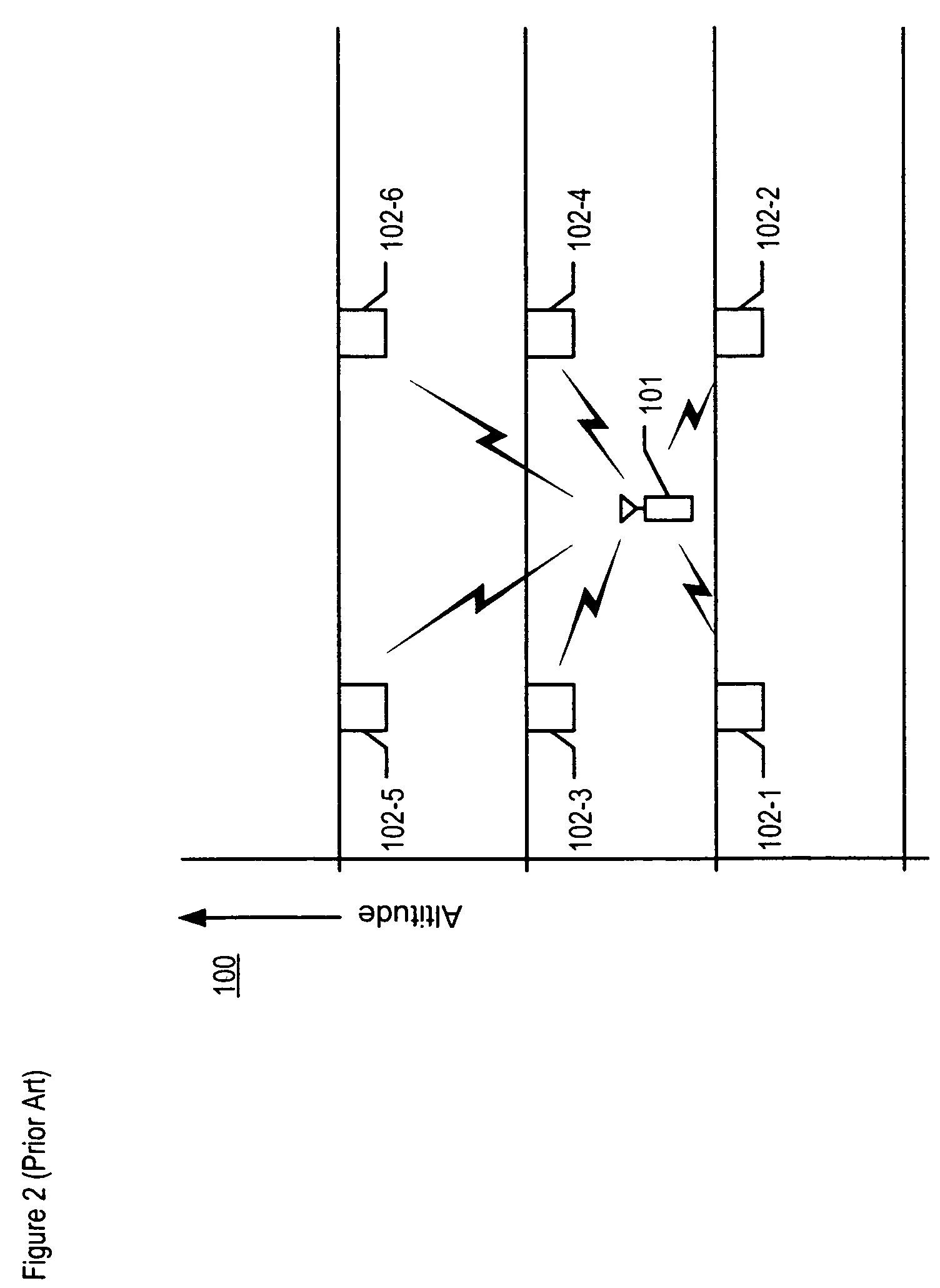

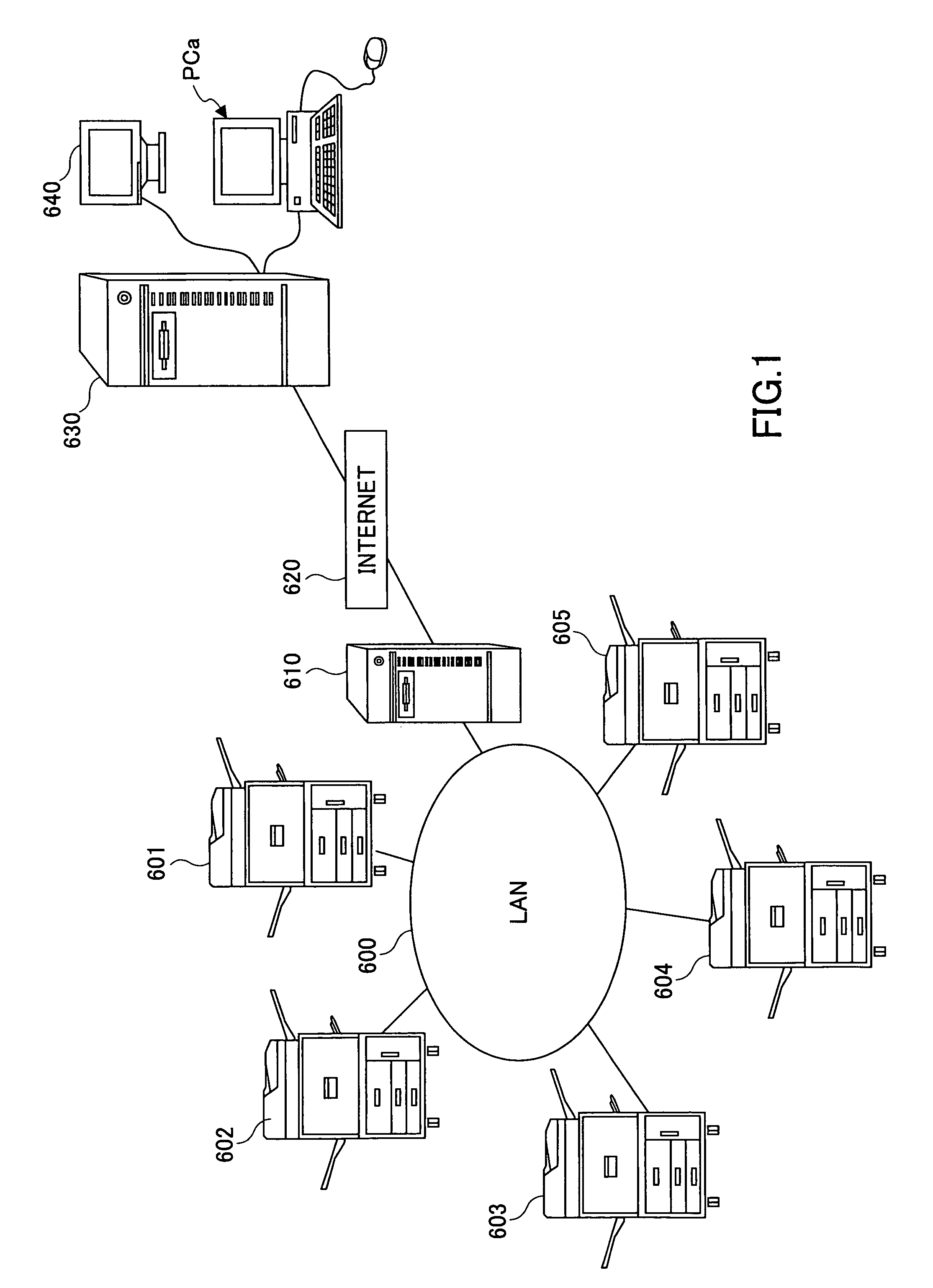

Location estimation of wireless terminals in a multi-story environment

ActiveUS20050176406A1Unauthorised/fraudulent call preventionEavesdropping prevention circuitsTelecommunicationsEngineering

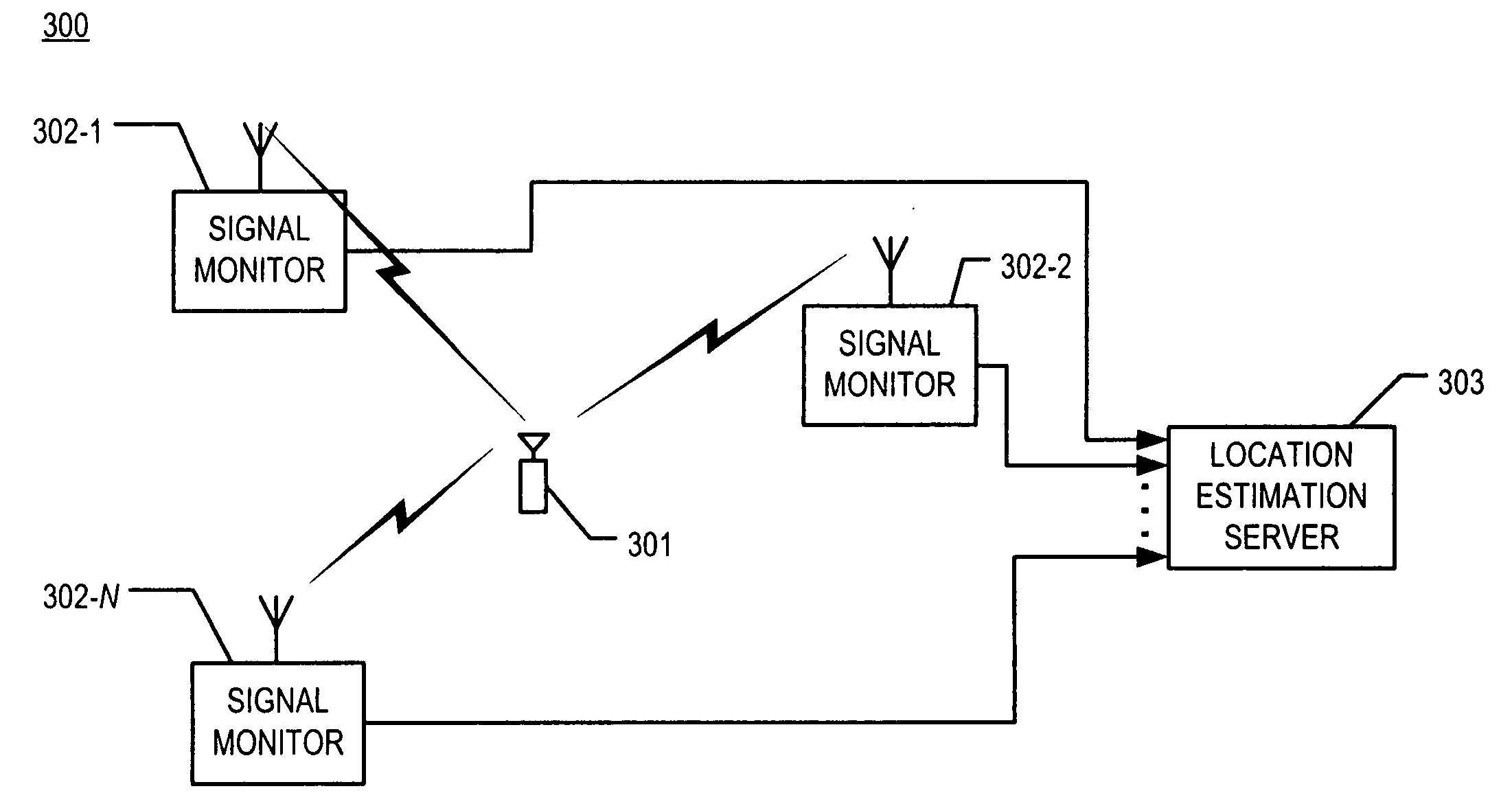

A method and apparatus are disclosed for estimating the location of a wireless terminal across multiple building floors. The illustrative embodiment determines the floor where the wireless terminal is presently located by using a majority logic-based heuristic. A plurality of signal monitors measure signals from the wireless terminal and provide those signal strength measurements to a location estimation server. Alternatively, the wireless terminal measures signals that are transmitted by a plurality of transmitting signal devices and provides those signal strength measurements to a location estimation server. The location estimation server determines the floor of the wireless terminal in accordance with the illustrative embodiment of the present invention.

Owner:AVAYA INC

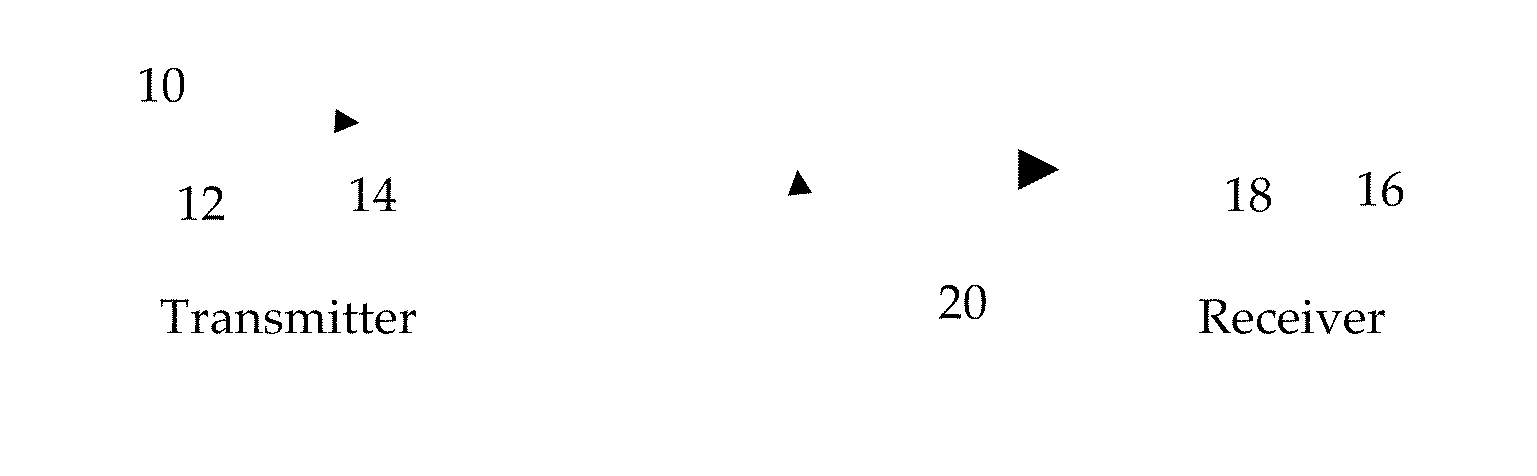

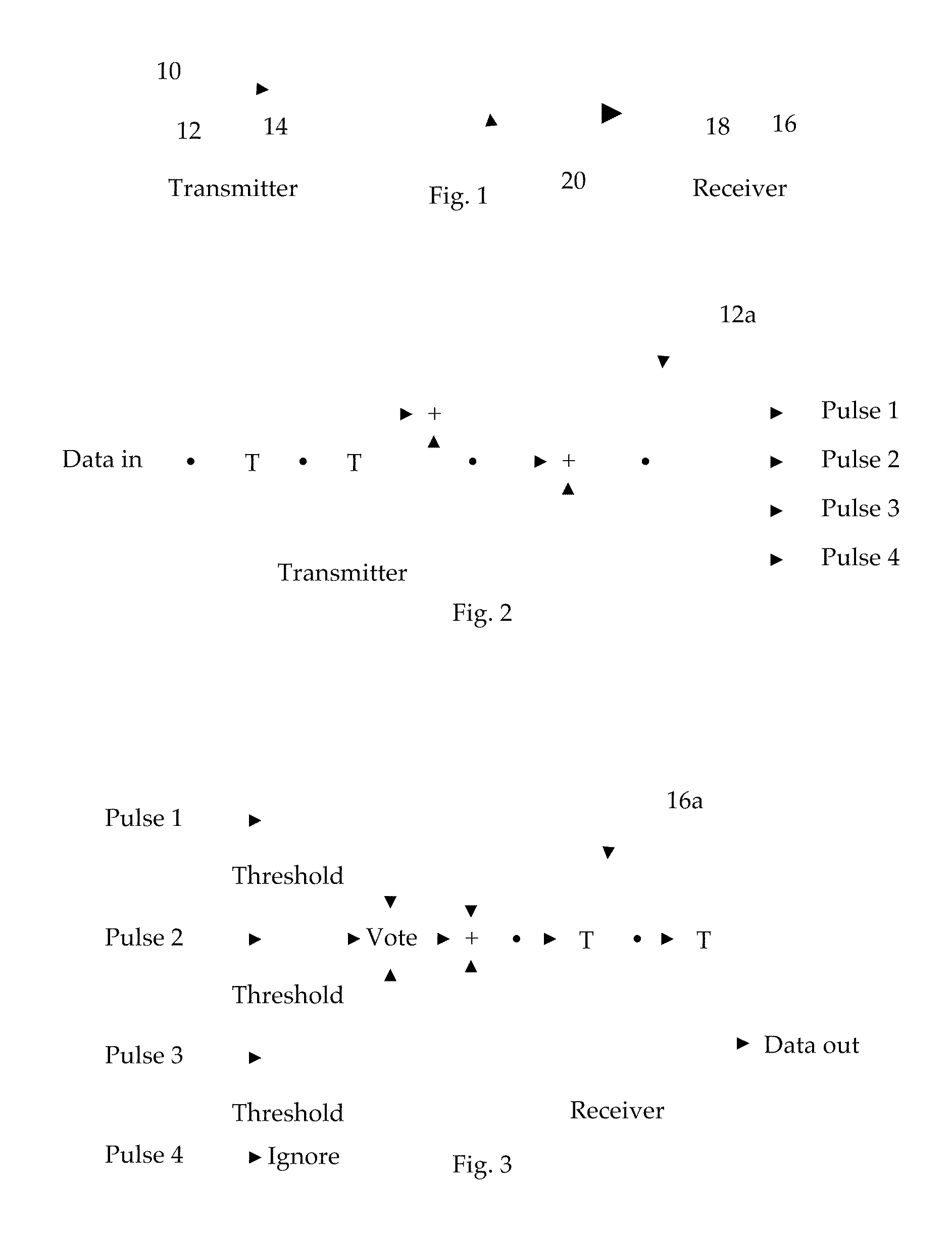

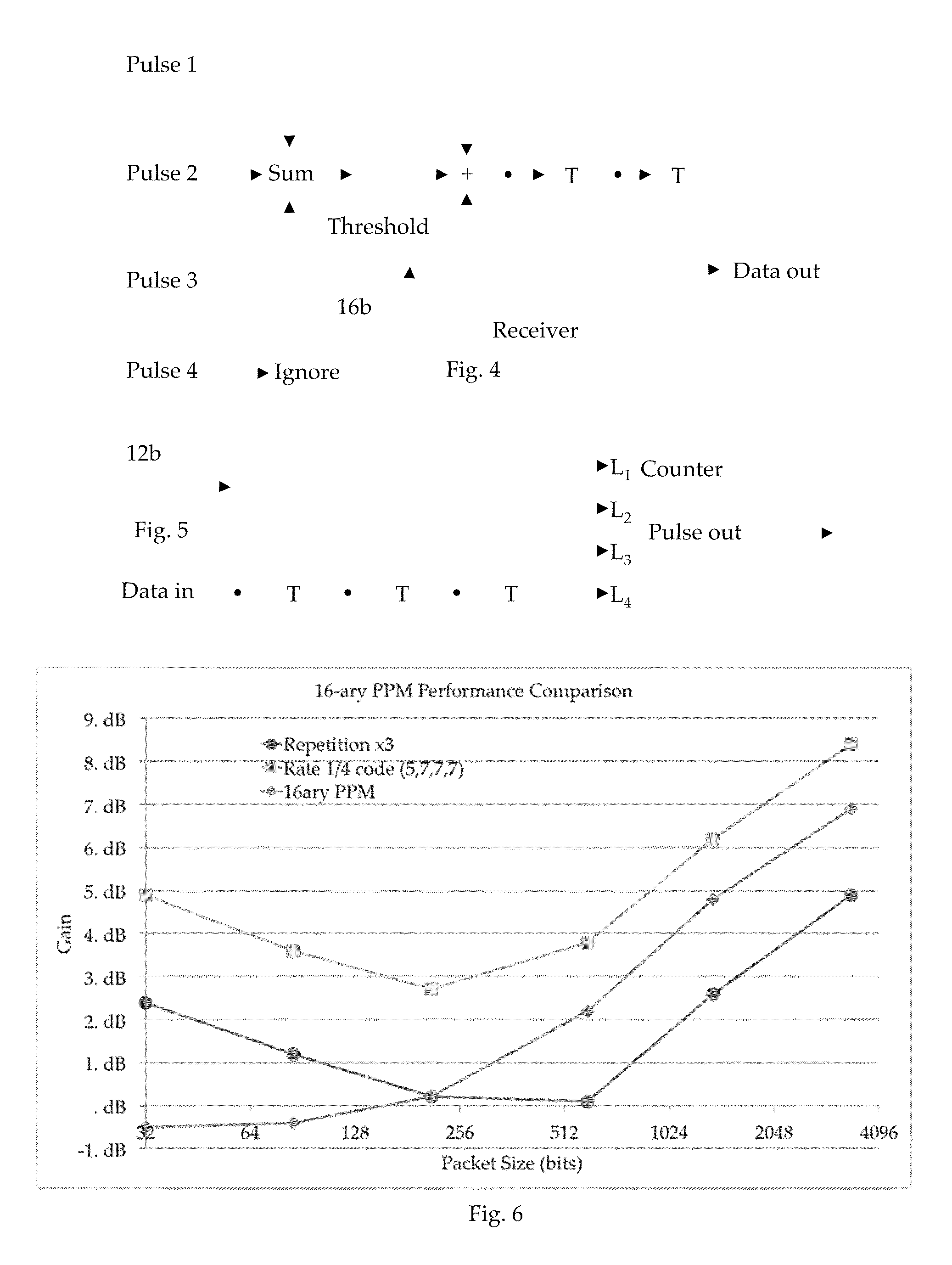

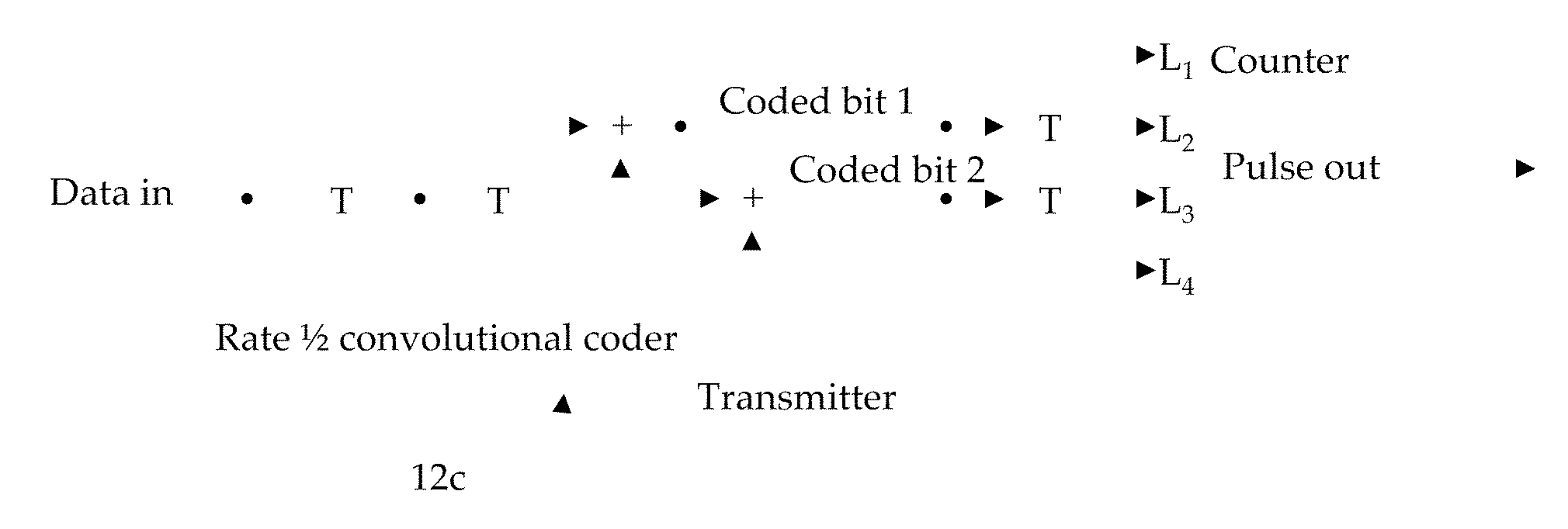

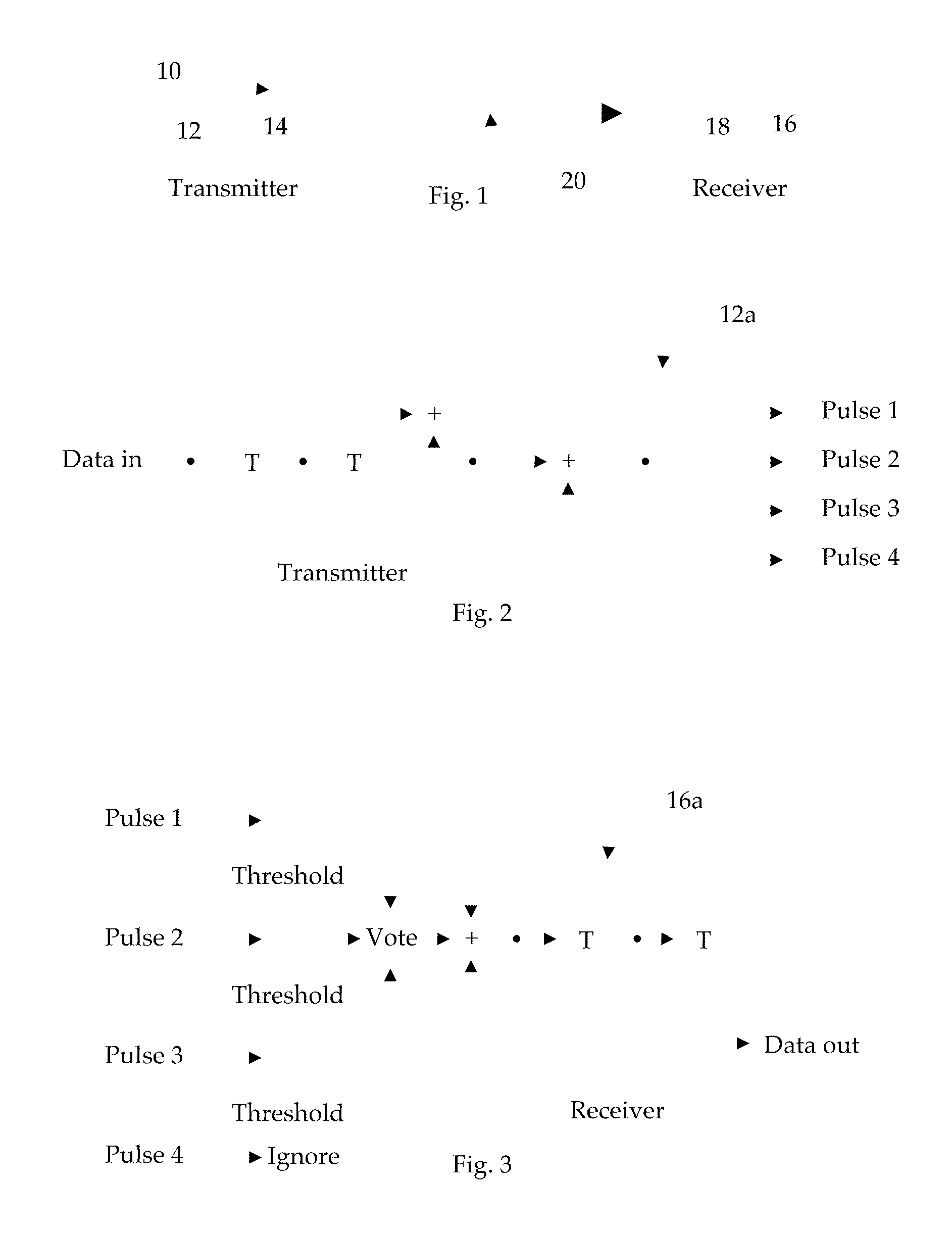

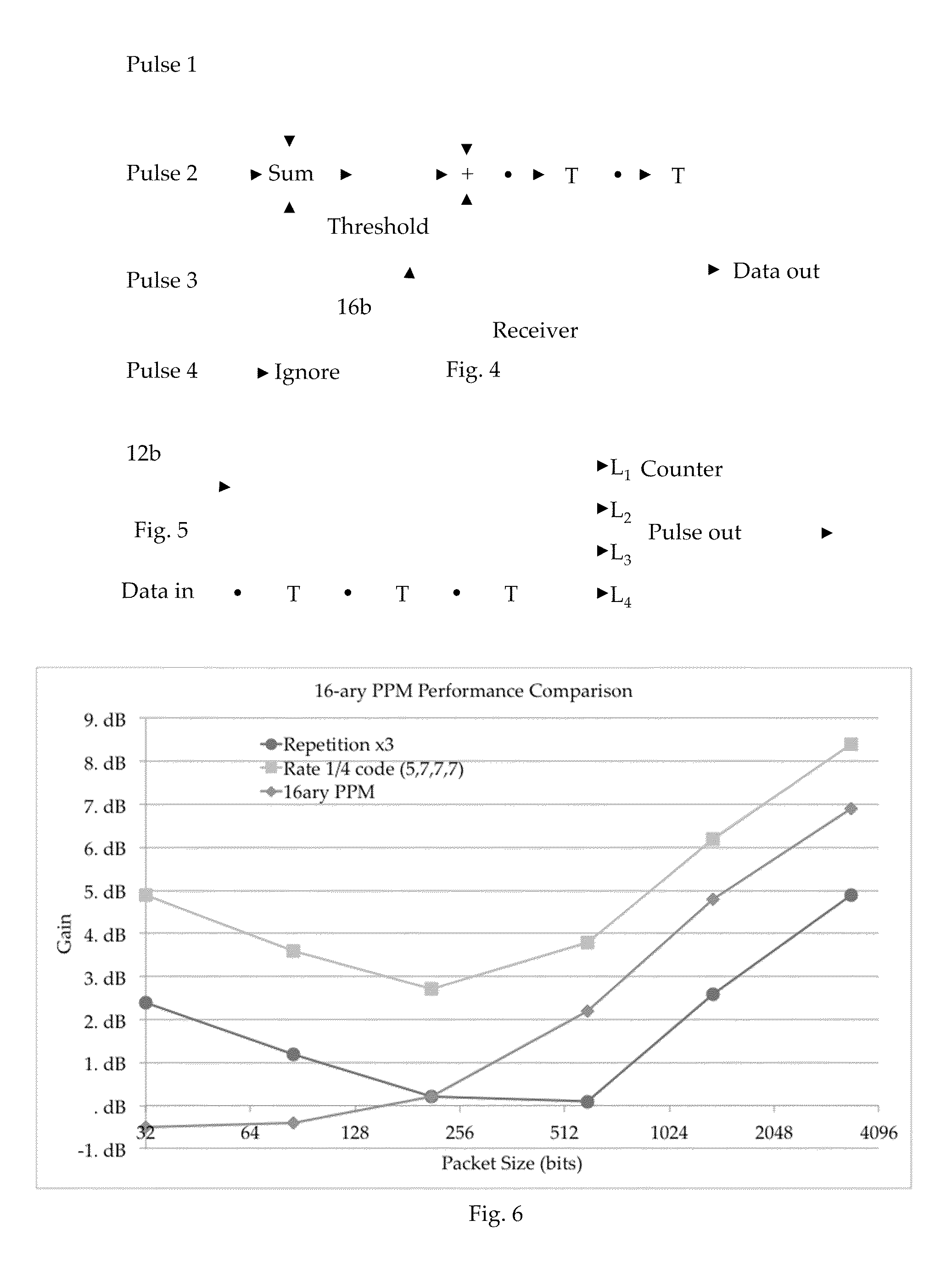

Convolutional code for use in a communication system

ActiveUS8677224B2Error correction/detection using convolutional codesOther decoding techniquesCommunications systemConvolutional code

In a communication system, a transmitter receives an input bit, and in response thereto, generates at least an n-bit codeword, each bit of which is generated by a respective one of n generators of which m are exactly the same, m being greater than n / 2. A receiver comprises: m detectors, each adapted to receive the bit generated by a respective one of the m generators, and provide a respective one of m partial detection signals if a strength of the received bit exceeds a predetermined minimum threshold; and a majority logic element adapted to receive each of the m partial detection signals, and provide an output bit indicative of the input bit only if more than m / 2 of the received m partial detection signals exceeds the minimum threshold.

Owner:DECAWAVE

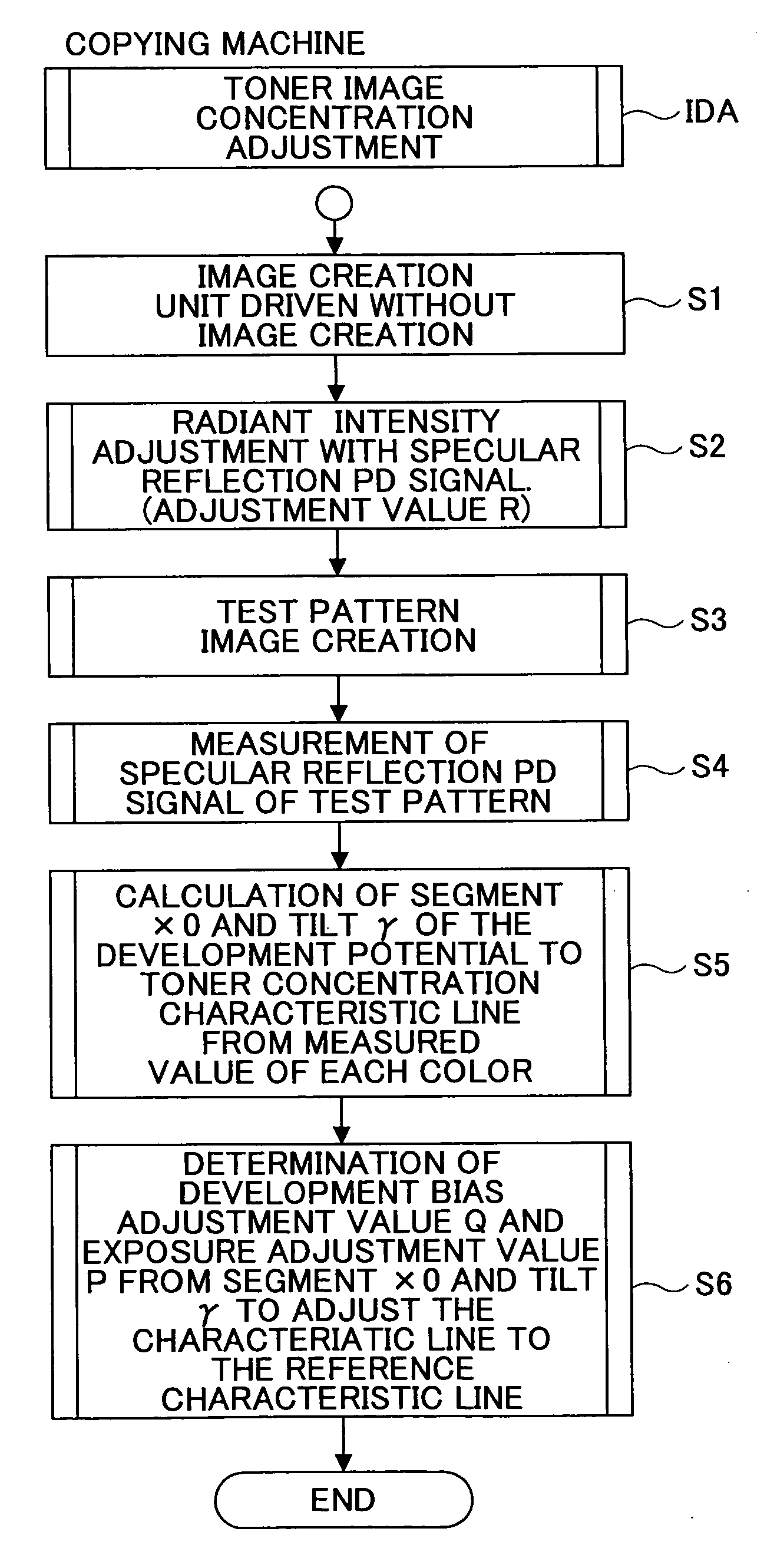

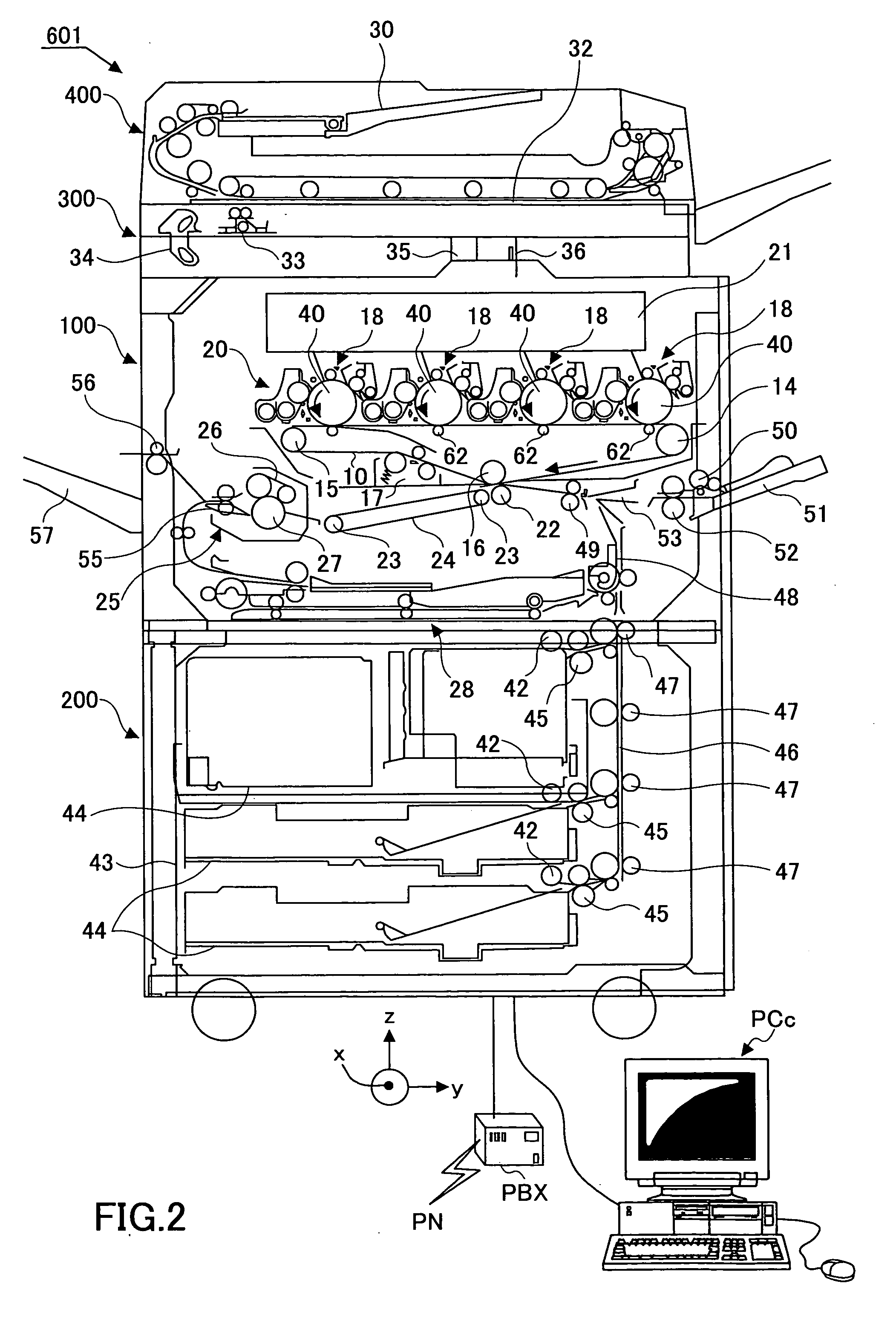

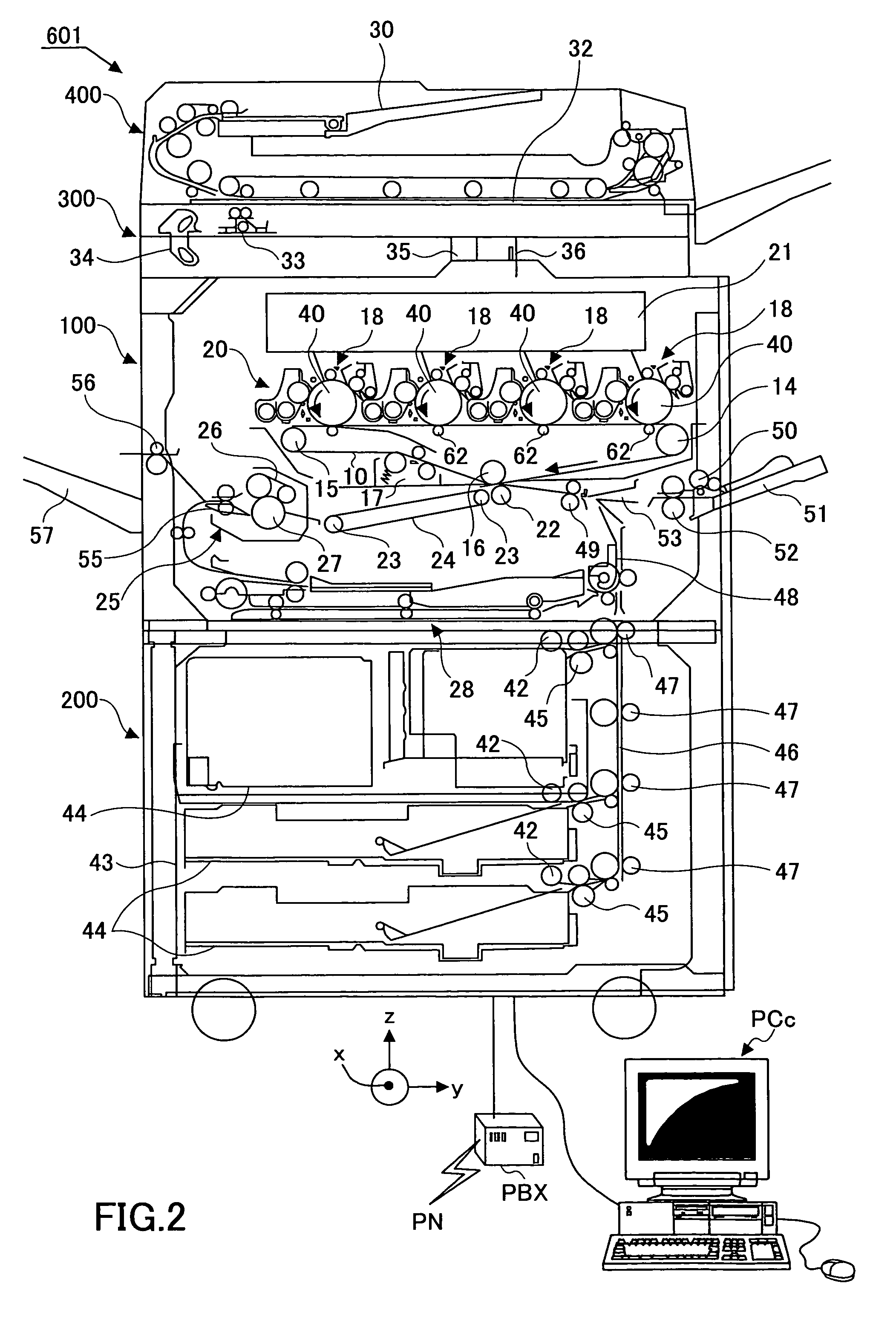

Management device of an image forming apparatus

ActiveUS20090034990A1Improve reliabilitySmall loadElectrographic process apparatusValue setStage determination

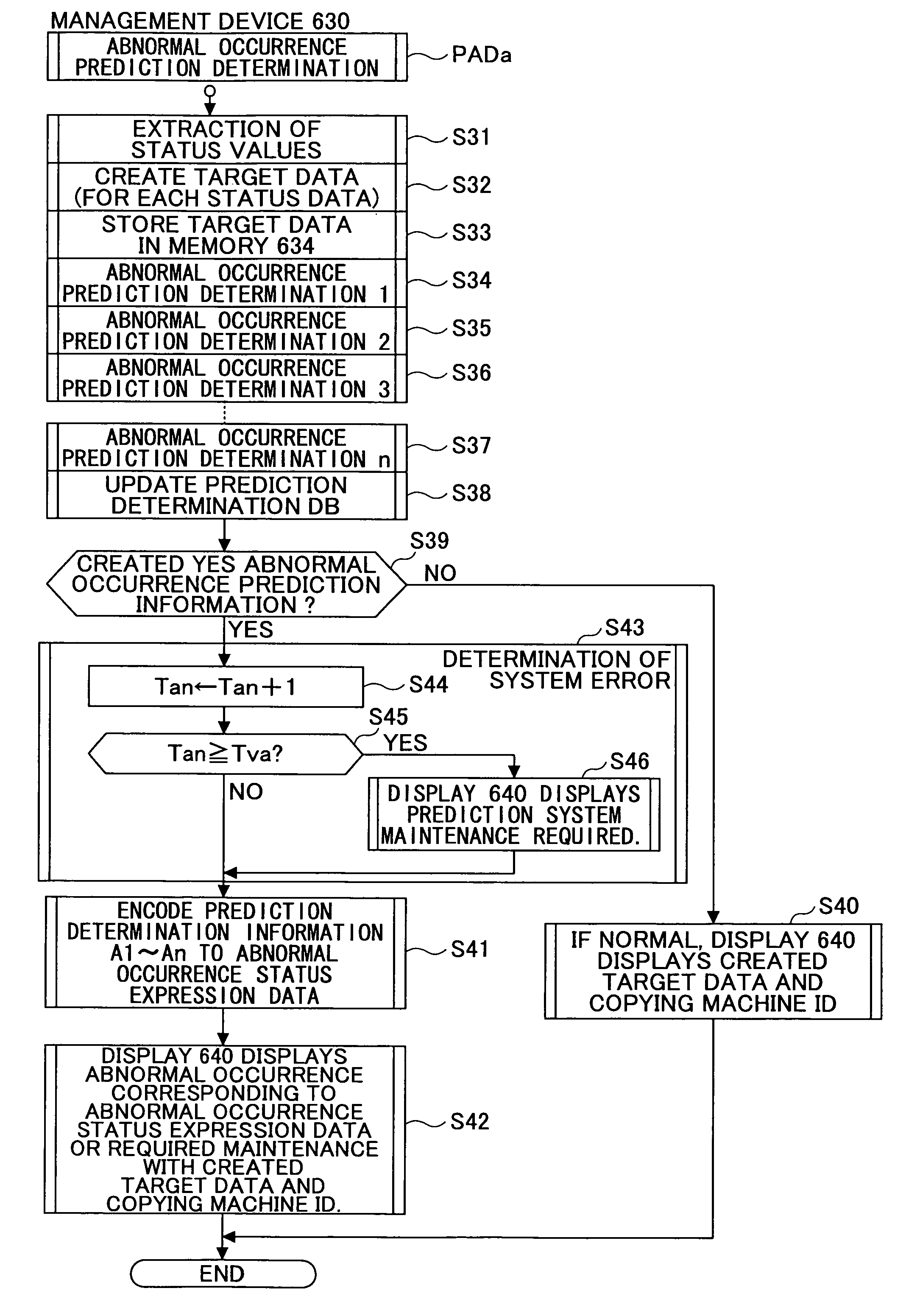

A management device for an image forming apparatus including a status data collection unit where multiple types of status data are received from the image forming apparatus and stored in a status database, a target data creation unit where multiple types of target data are created based upon the multiple types of status data, a first stage determination unit where the multiple types of target data are identified as being above or below reference values set for each type, and a second stage determination unit where a weight value set for each status data type is attached to the determination results of the multiple types of status data of the first stage determination unit and as a whole of the multiple types of status data determined with majority logic for abnormal occurrence prediction.

Owner:RICOH KK

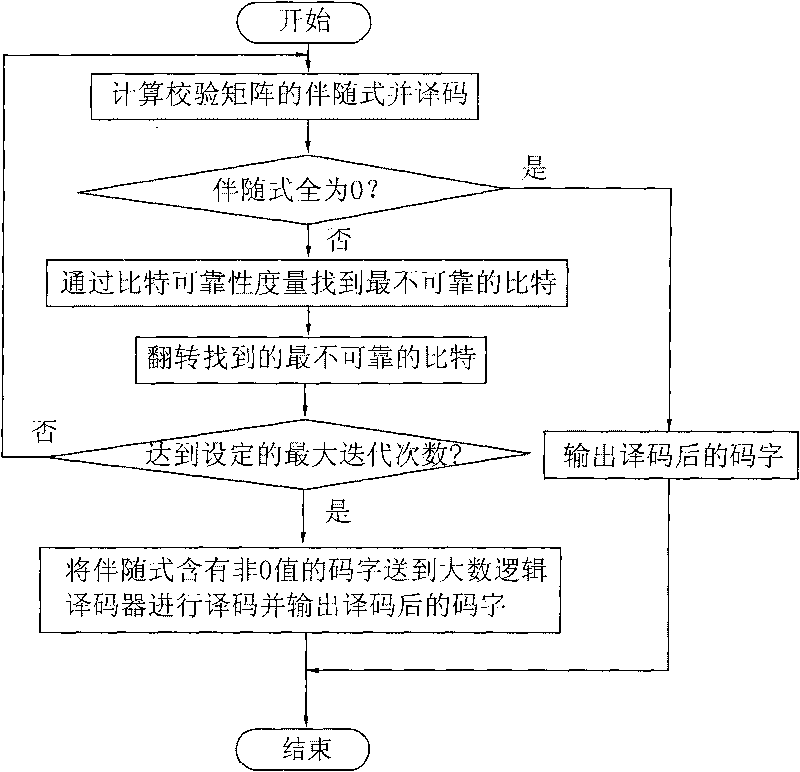

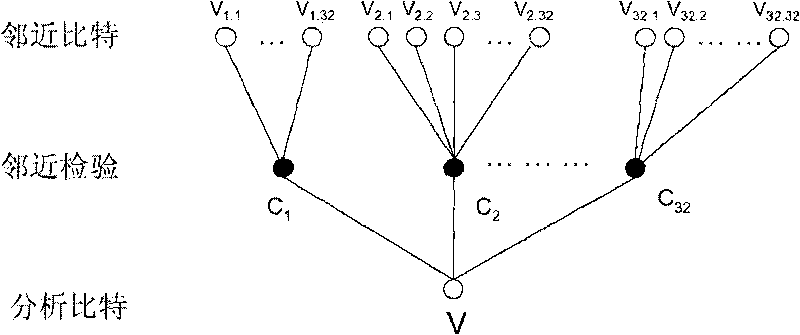

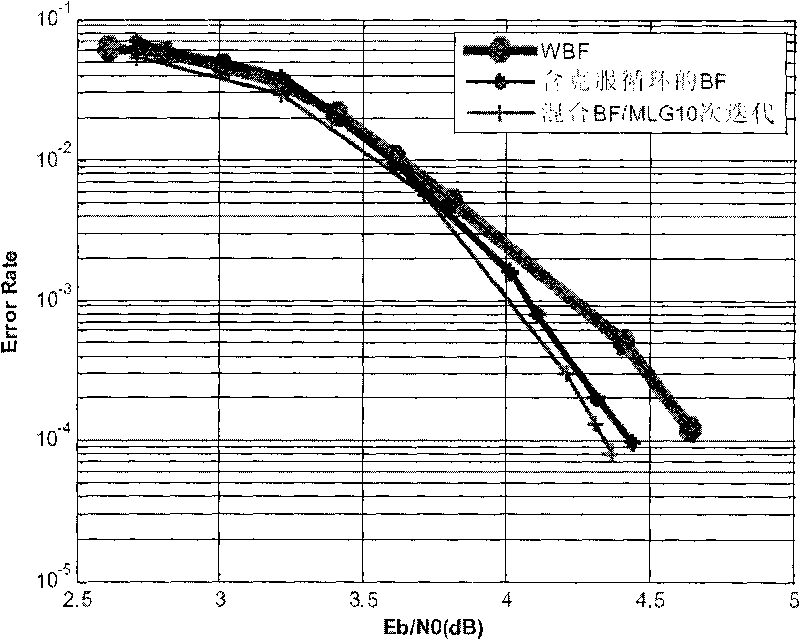

LDPC decoding method combining bit flipping (BF) and majority logic (MLG)

InactiveCN101707485AMany iterations of improvementImproved decoding performance dropsError correction/detection using multiple parity bitsDecoding methodsComputation complexity

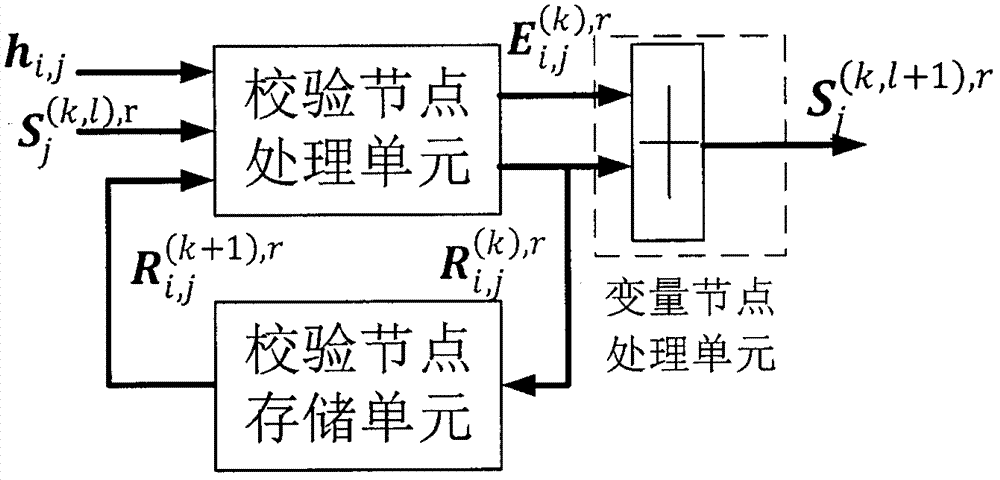

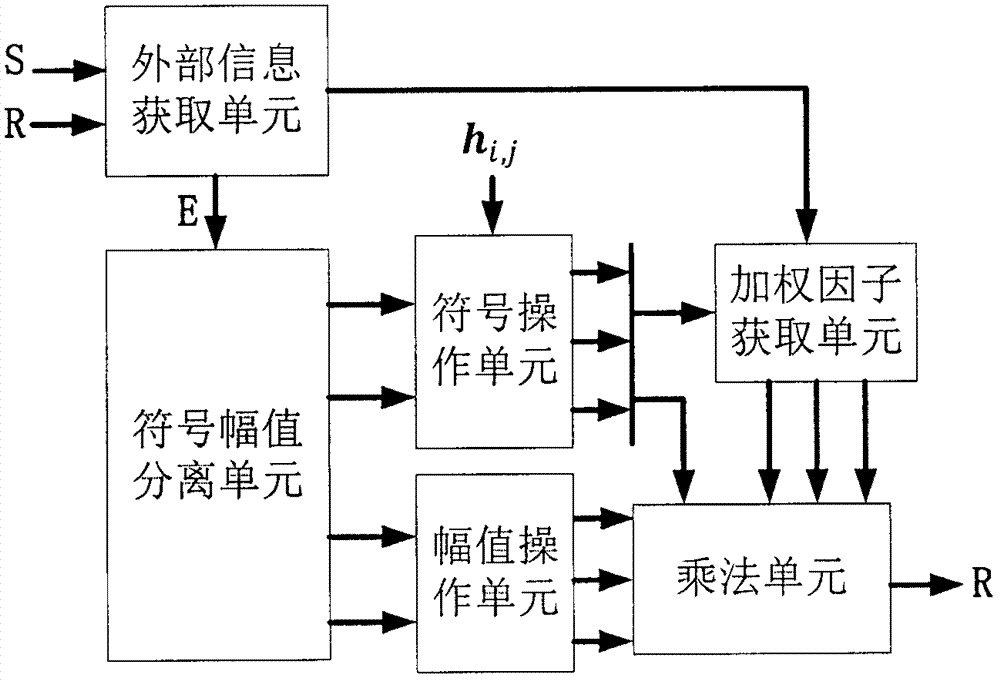

The invention relates to a LDPC decoding method combining bit flipping (BF) and majority logic (MLG), belonging to the technical field of digital information transmission. The LDPC decoding method comprising the following steps of: (1) computing syndromes s of a check matrix of M rows and N columns, wherein s=(s1, s2, to sM), if the syndromes are all 0, and then carrying out step 4; (2) finding the most unreliable bit through a bit reliability measurement; (3) flipping and finding out the most unreliable bit; (4) when a largest iteration is achieved, carrying out step (5), and when all the syndromes are all 0, stopping decoding and outputting corresponding codons to complete decoding treatment, or else, repeating the steps of (1) to (3); and (5) sending the codons containing non 0 value in the syndromes to an MLG decoder for decoding, and finally outputting the codons decoded by the majority logic decoder to complete the decoding treatment. The invention utilizes the decoding method combining BF decoding and MLG without floating point arithmetic in the whole decoding process, reduces computation complexity and time delaying, and has favorable decoding performance.

Owner:TIANJIN BOWEI TECH

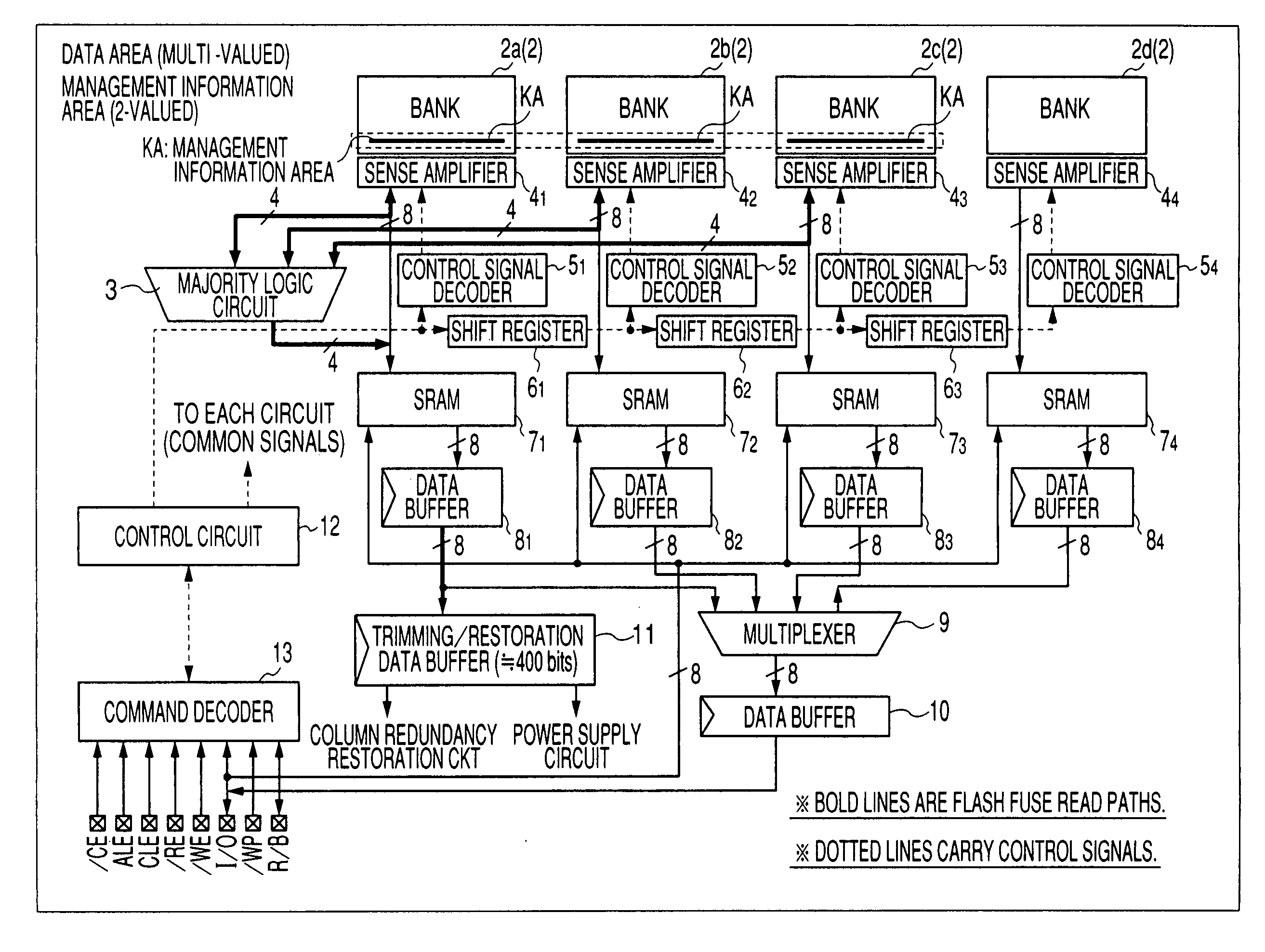

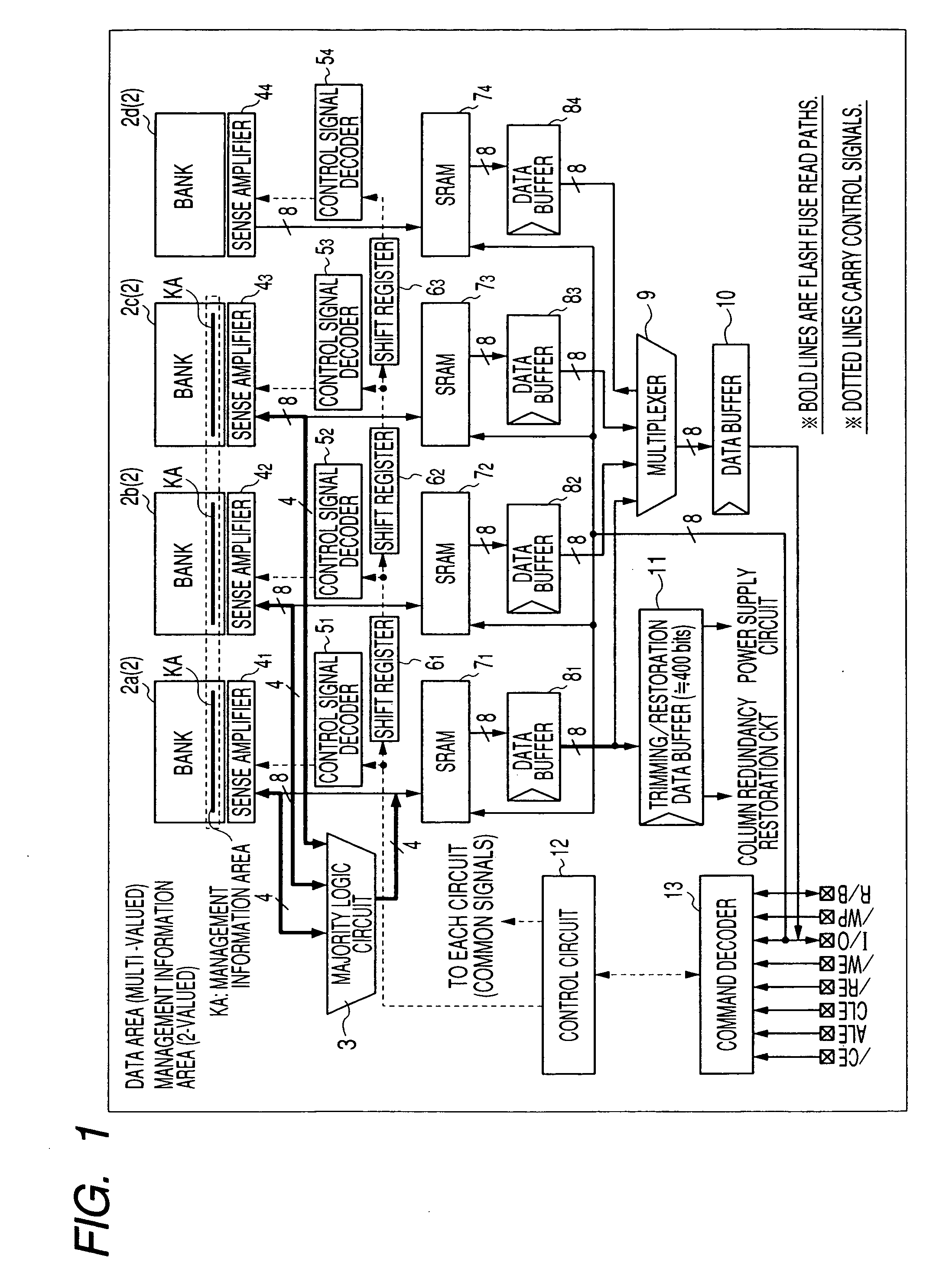

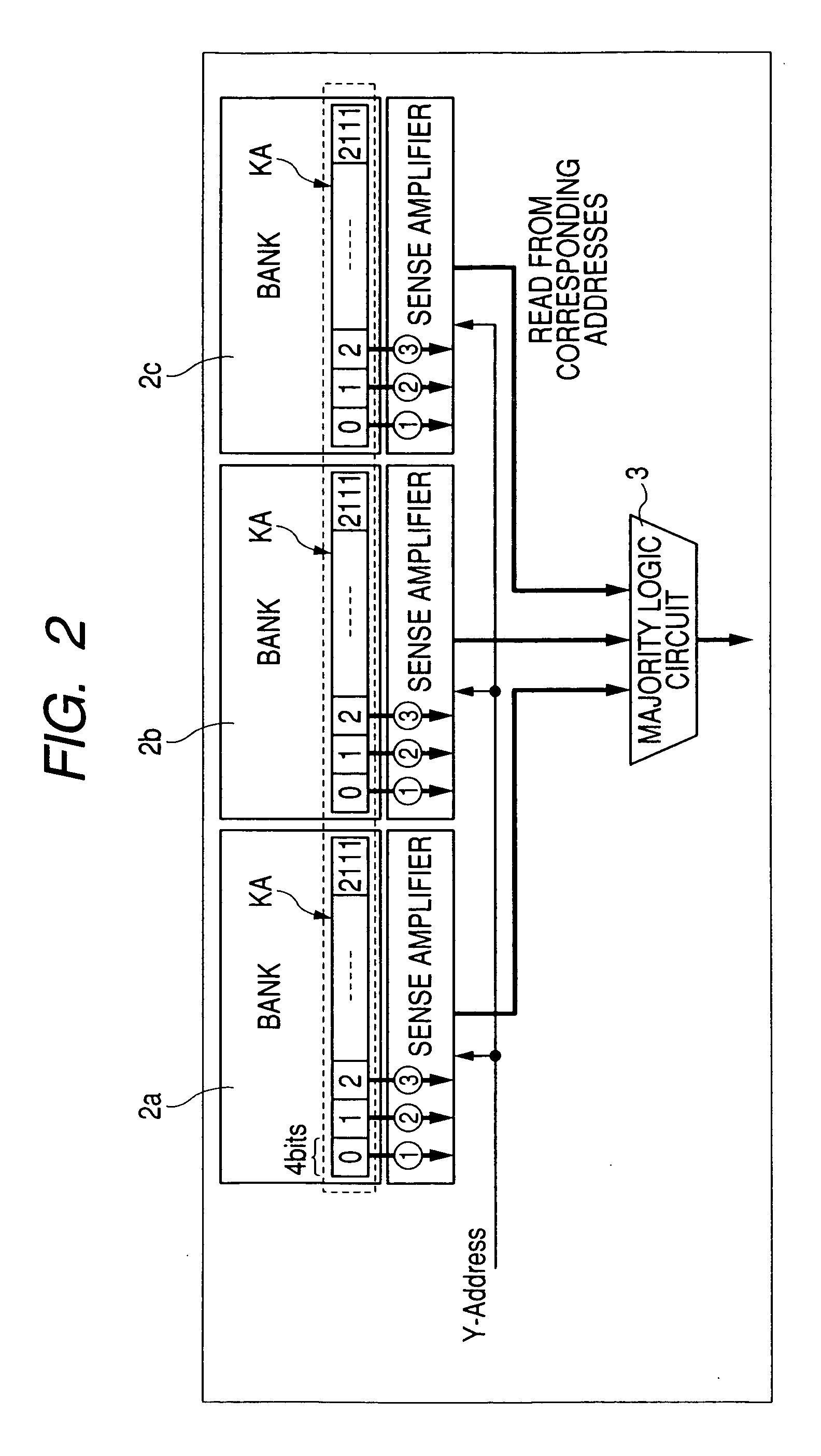

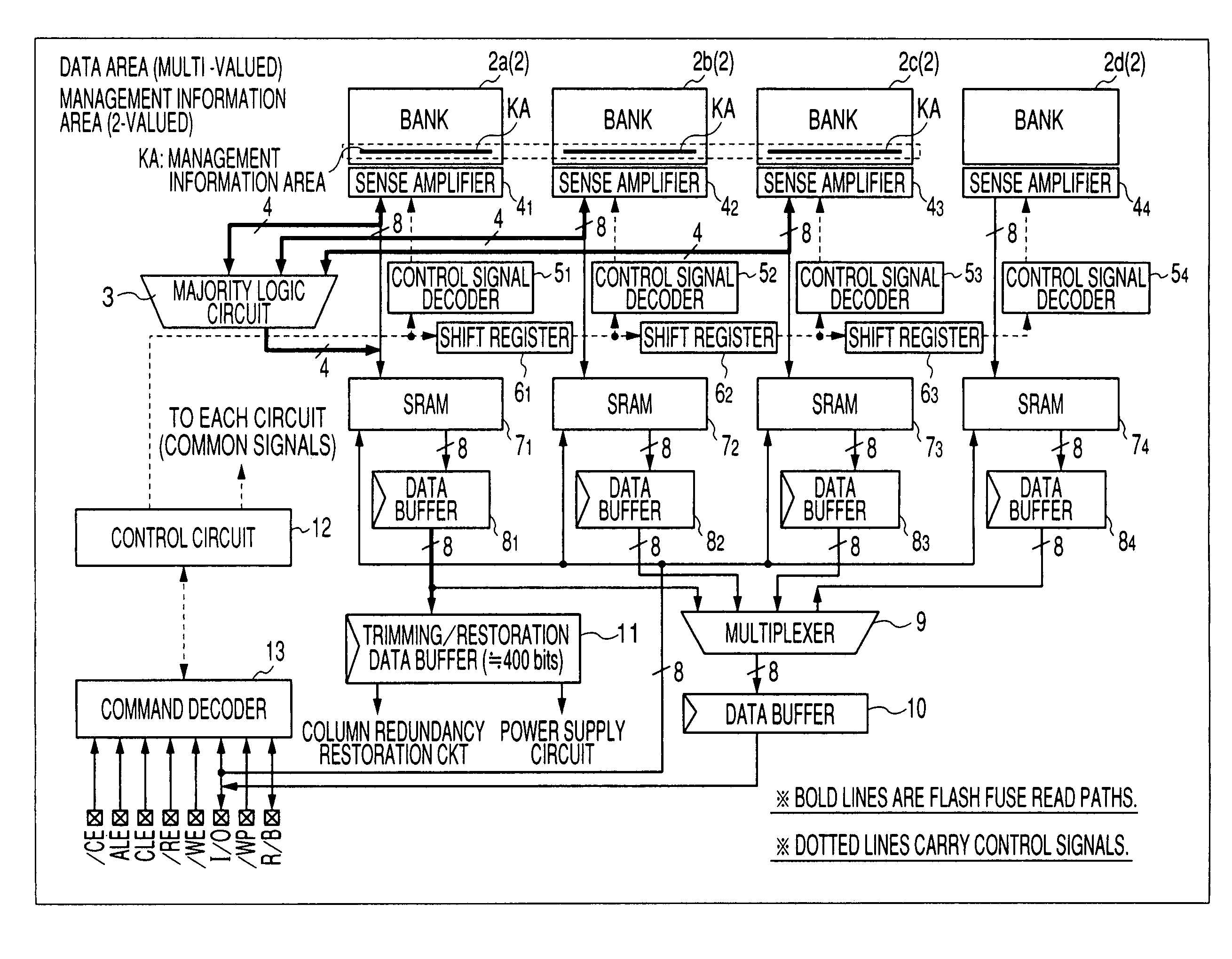

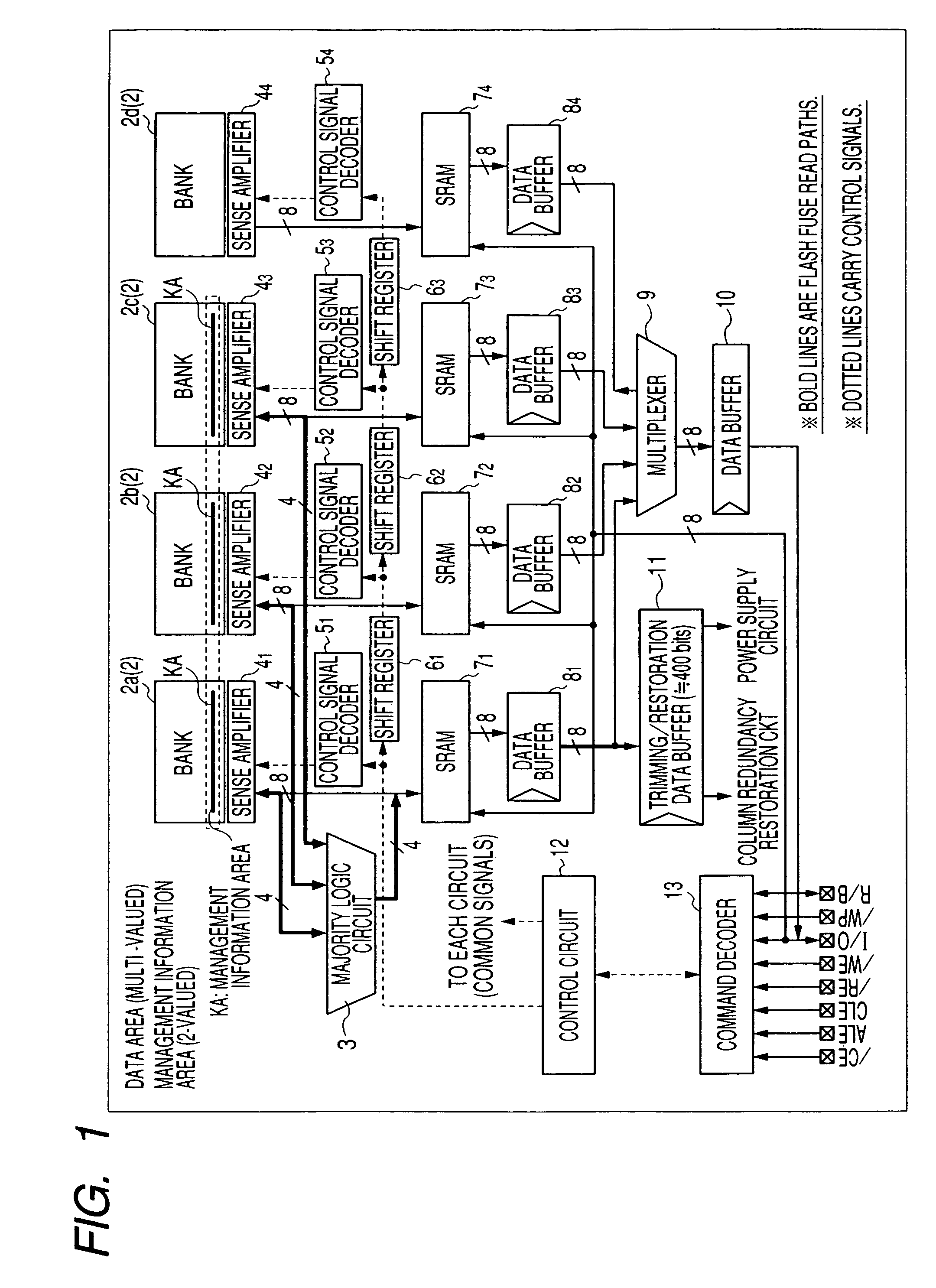

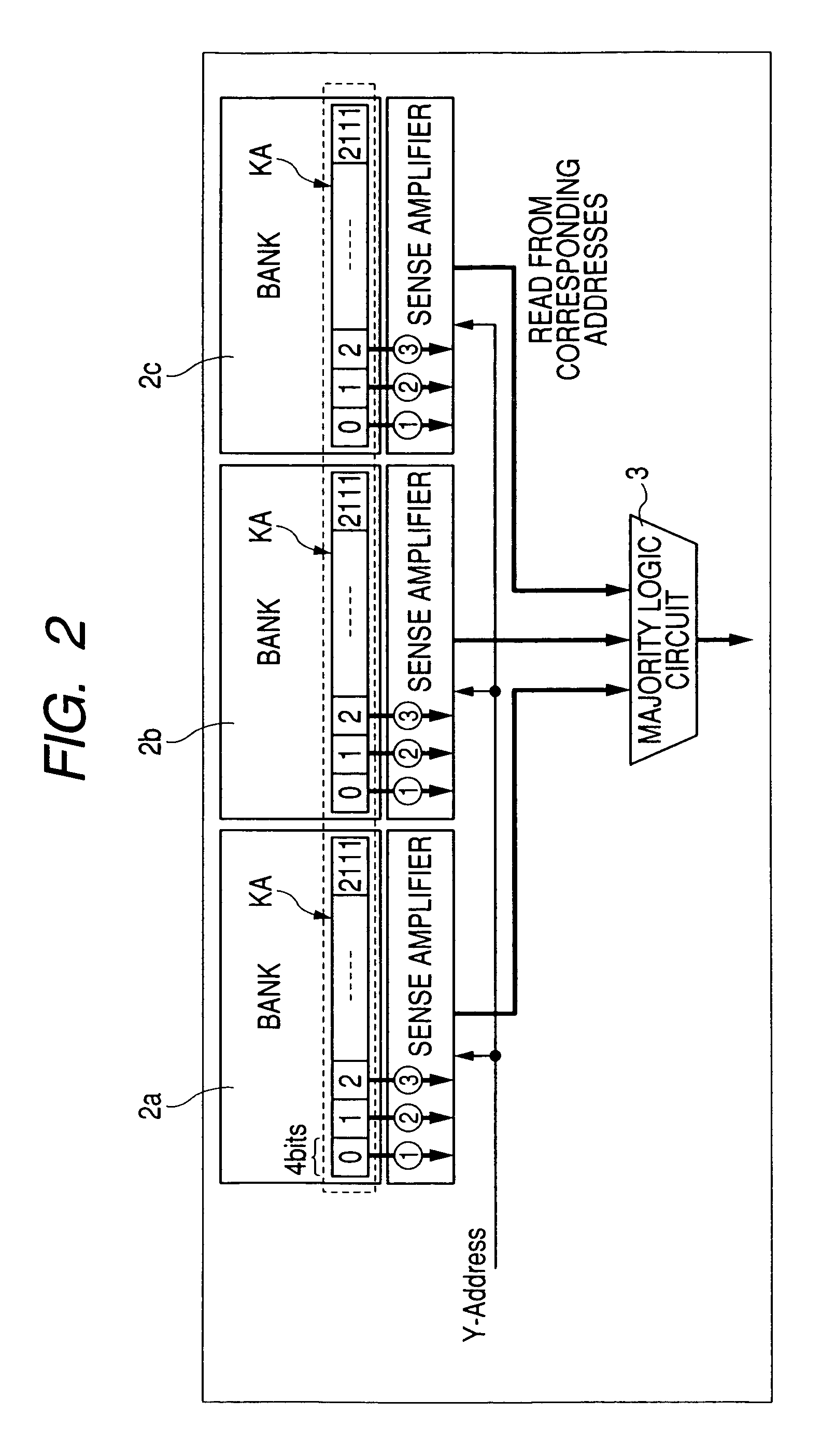

Nonvolatile semiconductor storage device

The disclosed flash memory is provided with a majority logic circuit 3 and shift registers 61 to 63. Three out of the banks 2a to 2c of the memory respectively include management information areas KAs to store binary management information comprising power supply trimming data and bitline restoration data. During initialization of the flash memory, the majority logic circuit 3 performs error correction on management information bits retrieved from the management information areas KAs and outputs that information to a trimming / restoration data buffer 11, thus providing highly reliable management information very quickly. The shift registers 61 to 63 delay a control signal that is output from a control circuit 12 by a certain period of time before outputting the control signal to sense amplifiers 42 to 44. This delay makes it possible to make the operating currents of the banks 2a to 2d start to flow at different times and to suppress a peak current flowing in the flash memory.

Owner:RENESAS ELECTRONICS CORP

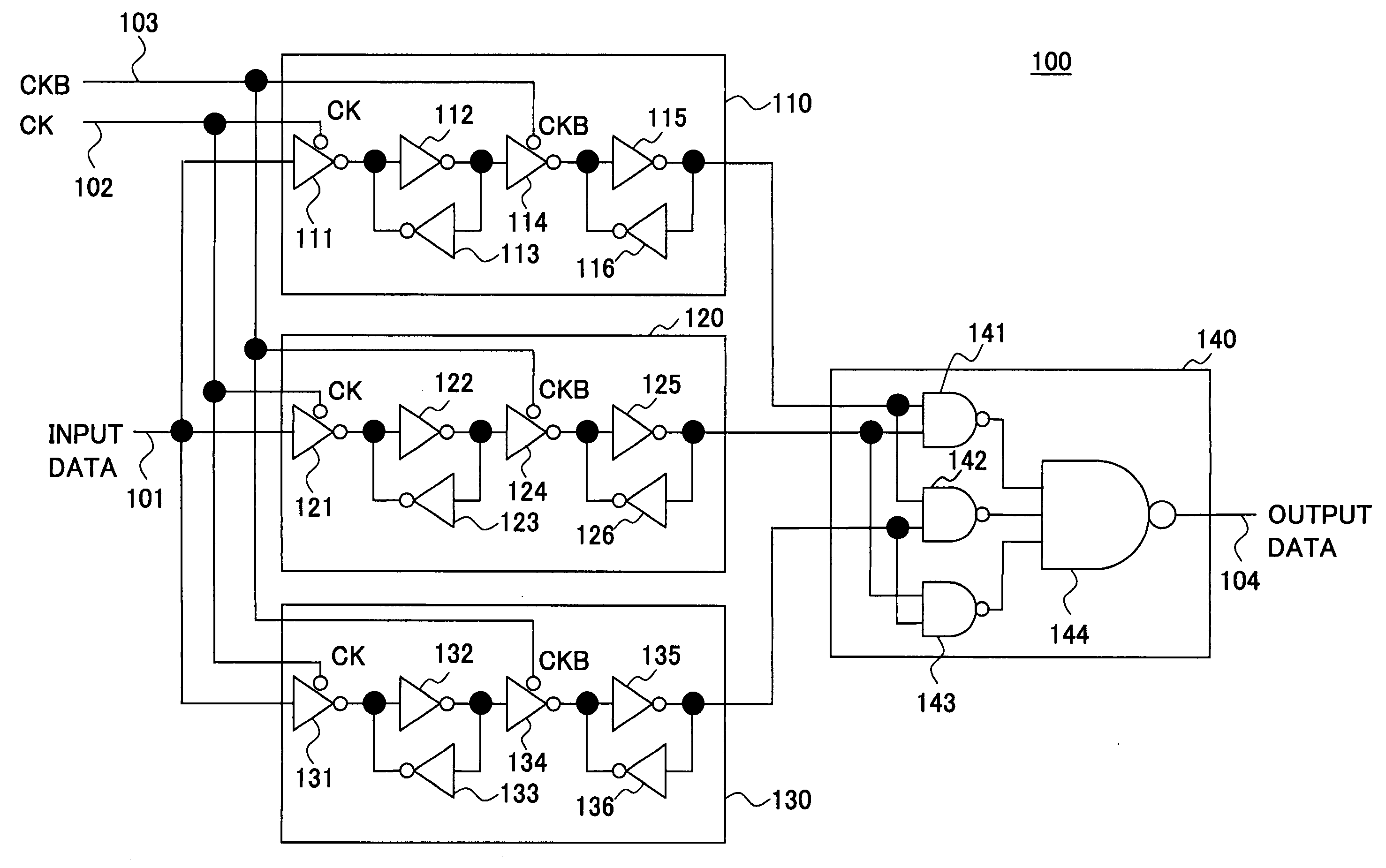

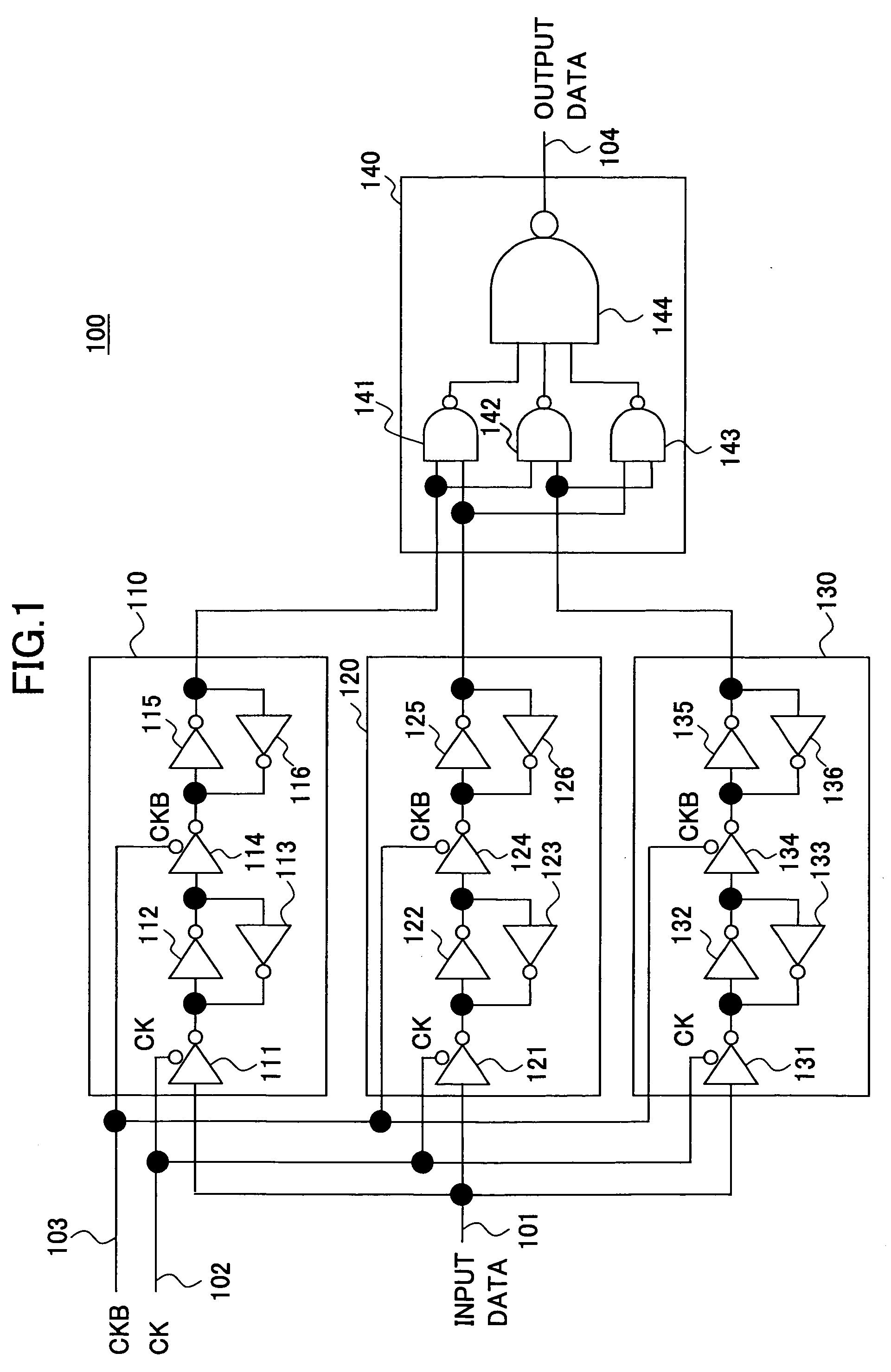

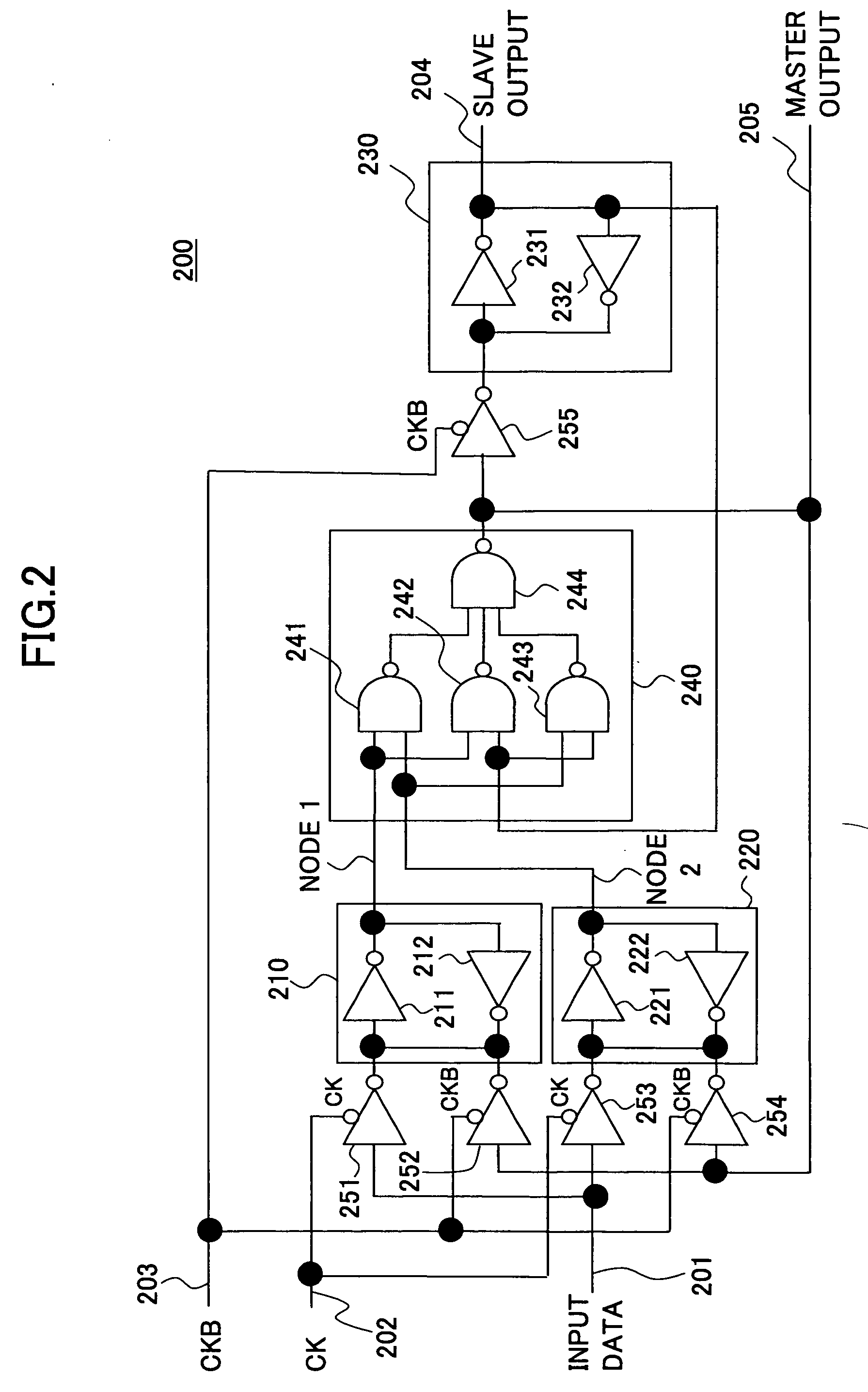

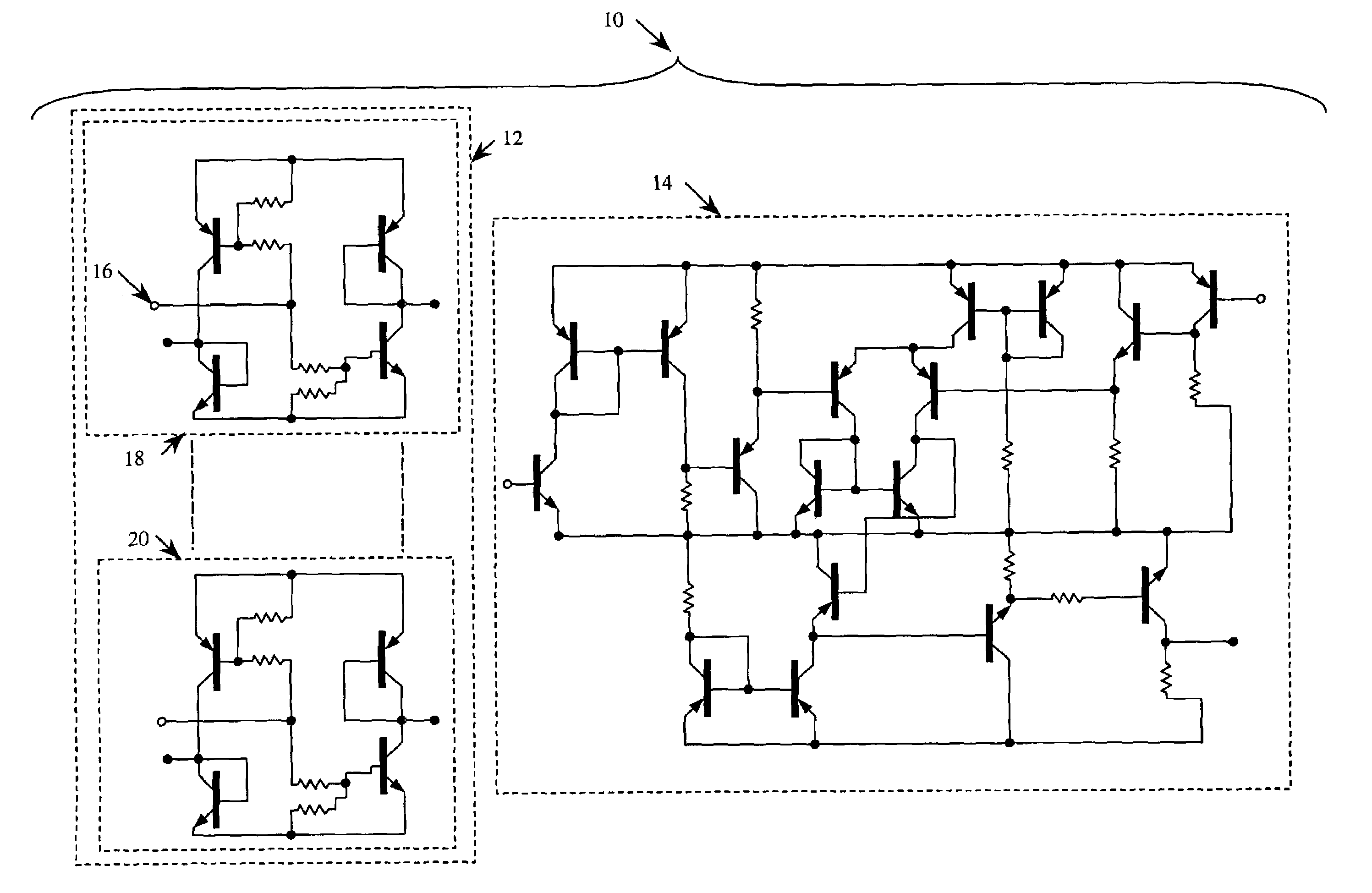

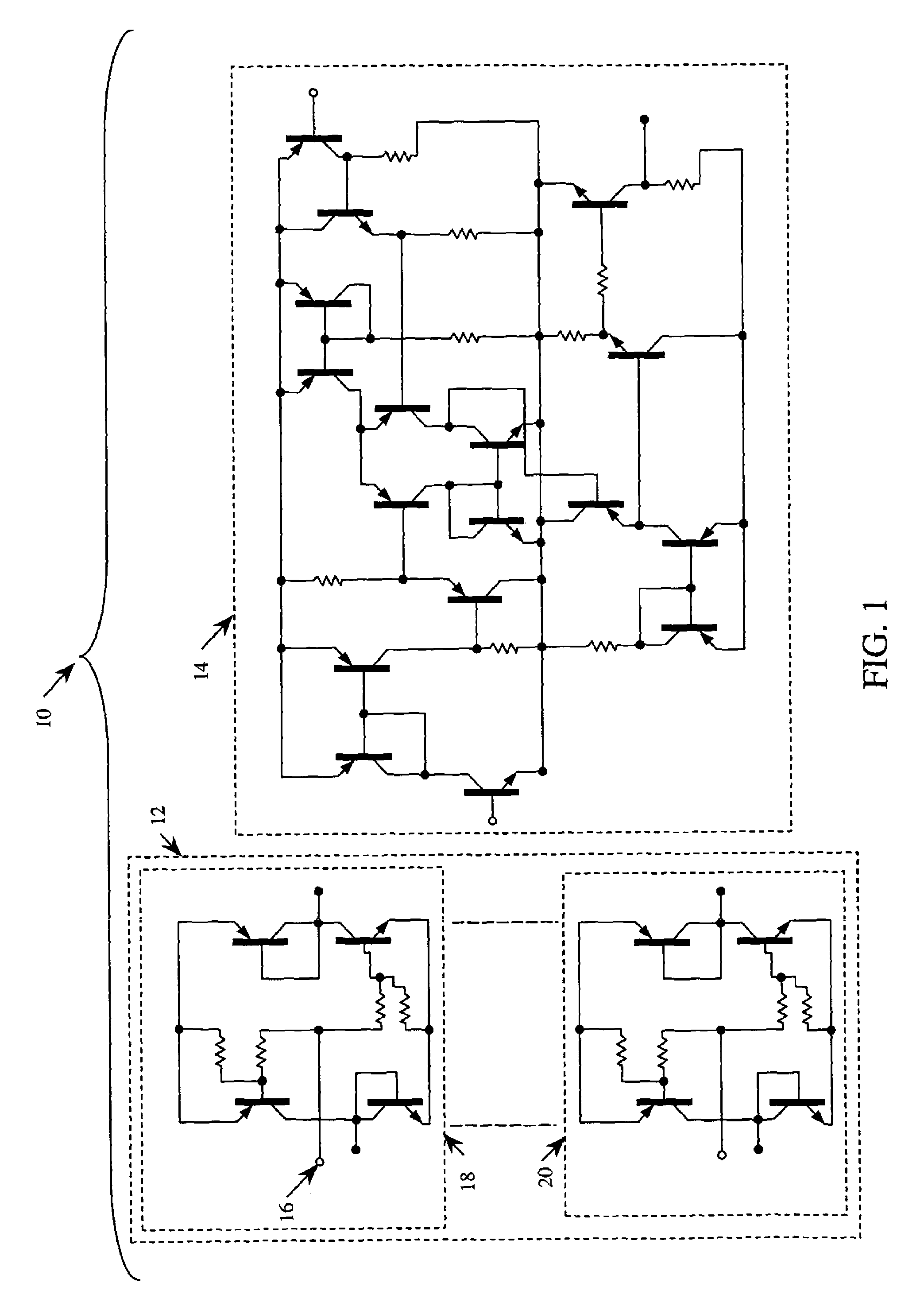

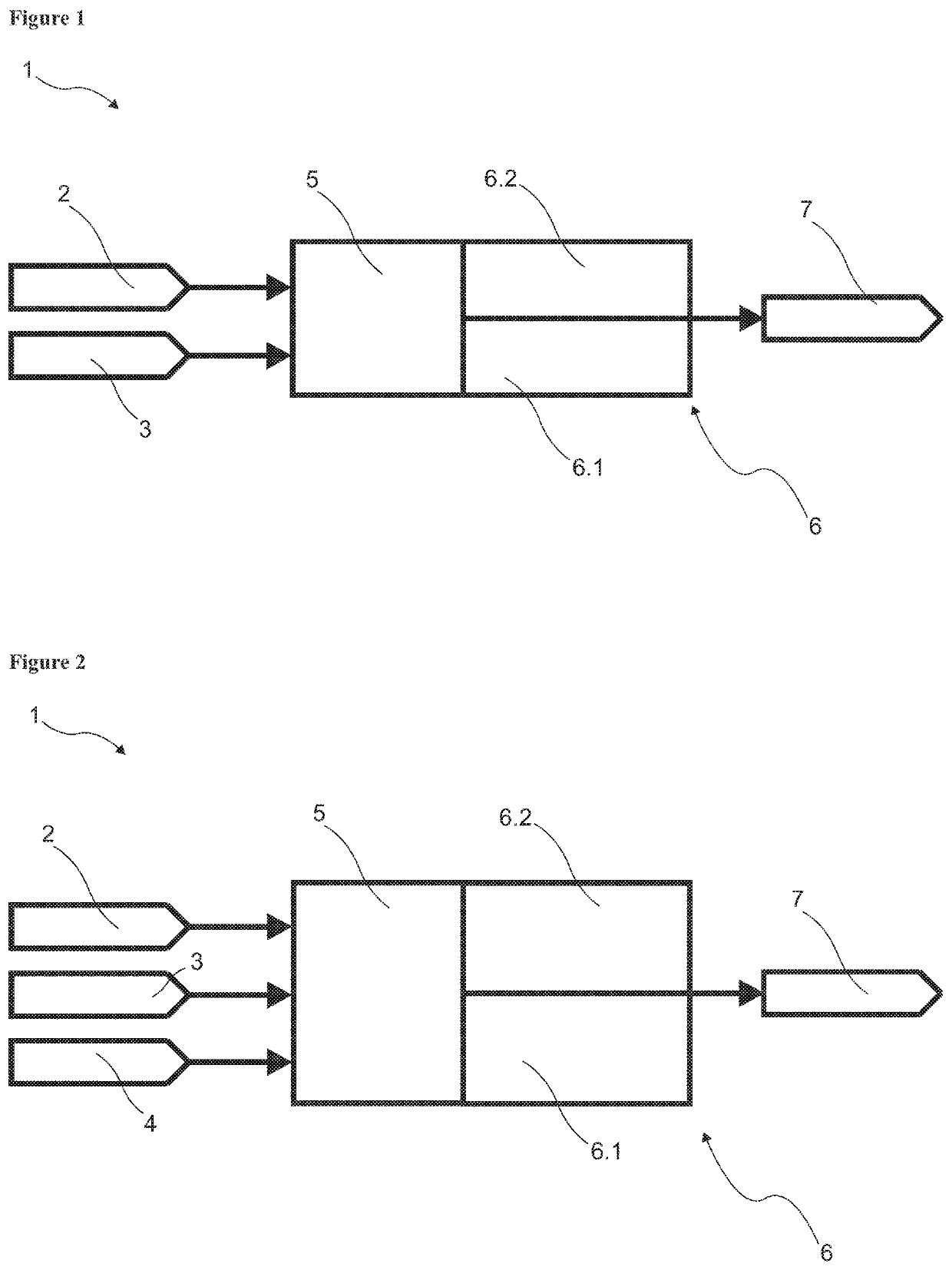

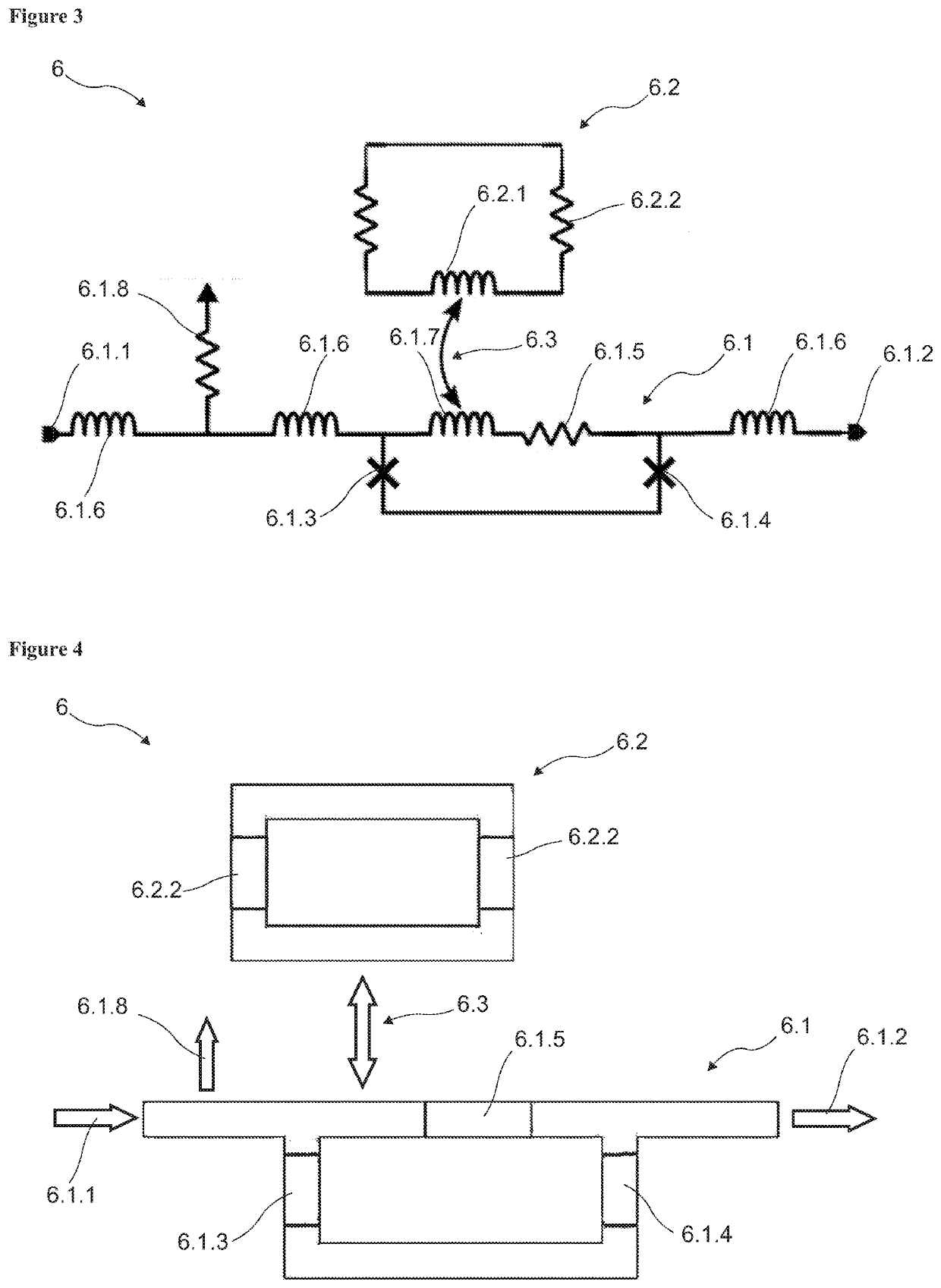

Flip-flop circuit having majority-logic circuit

A flip-flop circuit having a majority-logic circuit is disclosed. The circuit further includes multiple master latches for writing in corresponding input signals, and one slave latch having an input connected to an output of the majority-logic circuit and an output connected to the inputs of the majority-logic circuit. The majority logic-circuit has multiple inputs connected to respective outputs of the master latches. During the period in which the master latches do not write in the corresponding input signals, an output signal of the majority-logic circuit is supplied to respective inputs of the master latches.

Owner:FUJITSU LTD

Location estimation of wireless terminals in a multi-story environment

ActiveUS7272394B2Position fixationData switching by path configurationTelecommunicationsMajority logic

A method and apparatus are disclosed for estimating the location of a wireless terminal across multiple building floors. The illustrative embodiment determines the floor where the wireless terminal is presently located by using a majority logic-based heuristic. A plurality of signal monitors measure signals from the wireless terminal and provide those signal strength measurements to a location estimation server. Alternatively, the wireless terminal measures signals that are transmitted by a plurality of transmitting signal devices and provides those signal strength measurements to a location estimation server. The location estimation server determines the floor of the wireless terminal in accordance with the illustrative embodiment of the present invention.

Owner:AVAYA INC

High-speed decoder based on non-binary LDPC code and decoding method thereof

InactiveCN106936446AImprove data throughputLower latencyError correction/detection using multiple parity bitsCode conversionDecoding methodsClock rate

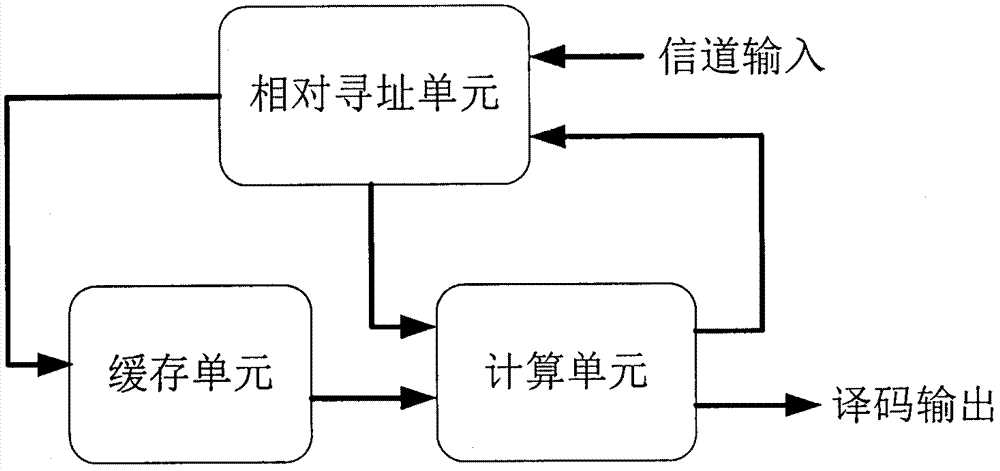

The invention discloses a high-throughput and low-complexity hierarchy decoder suitable for a non-binary LDPC code and a decoding method of the decoder. The decoder comprises a relative addressing unit, a caching unit and a computing unit, wherein the relative addressing unit prestores an input address for each of the computing unit and the caching unit so that a redundant clock period is inexistent between tiers; the depth of the caching unit is 1 so that the delay is maximally lowered; the computing unit comprises 2p-1 basic computing units capable of accomplishing the updating of one tire in a clock unit and optimizing a key path of each module so as to improve the clock frequency. Furthermore, the decoding method disclosed by the invention is a hard decoding method based on majority logic so as to take a compromise on the decoding performance and the complexity; a most reliable message and a secondary reliable message are selected in the method, symbols and confidences thereof are input and output in a bit way, 2p messages are converted into the transmission of P messages, and the storage space is greatly lowered.

Owner:NANJING UNIV

Management device of an image forming apparatus

ActiveUS8064782B2Improve reliabilitySmall loadElectrographic process apparatusStage determinationImage formation

A management device for an image forming apparatus including a status data collection unit where multiple types of status data are received from the image forming apparatus and stored in a status database, a target data creation unit where multiple types of target data are created based upon the multiple types of status data, a first stage determination unit where the multiple types of target data are identified as being above or below reference values set for each type, and a second stage determination unit where a weight value set for each status data type is attached to the determination results of the multiple types of status data of the first stage determination unit and as a whole of the multiple types of status data determined with majority logic for abnormal occurrence prediction.

Owner:RICOH KK

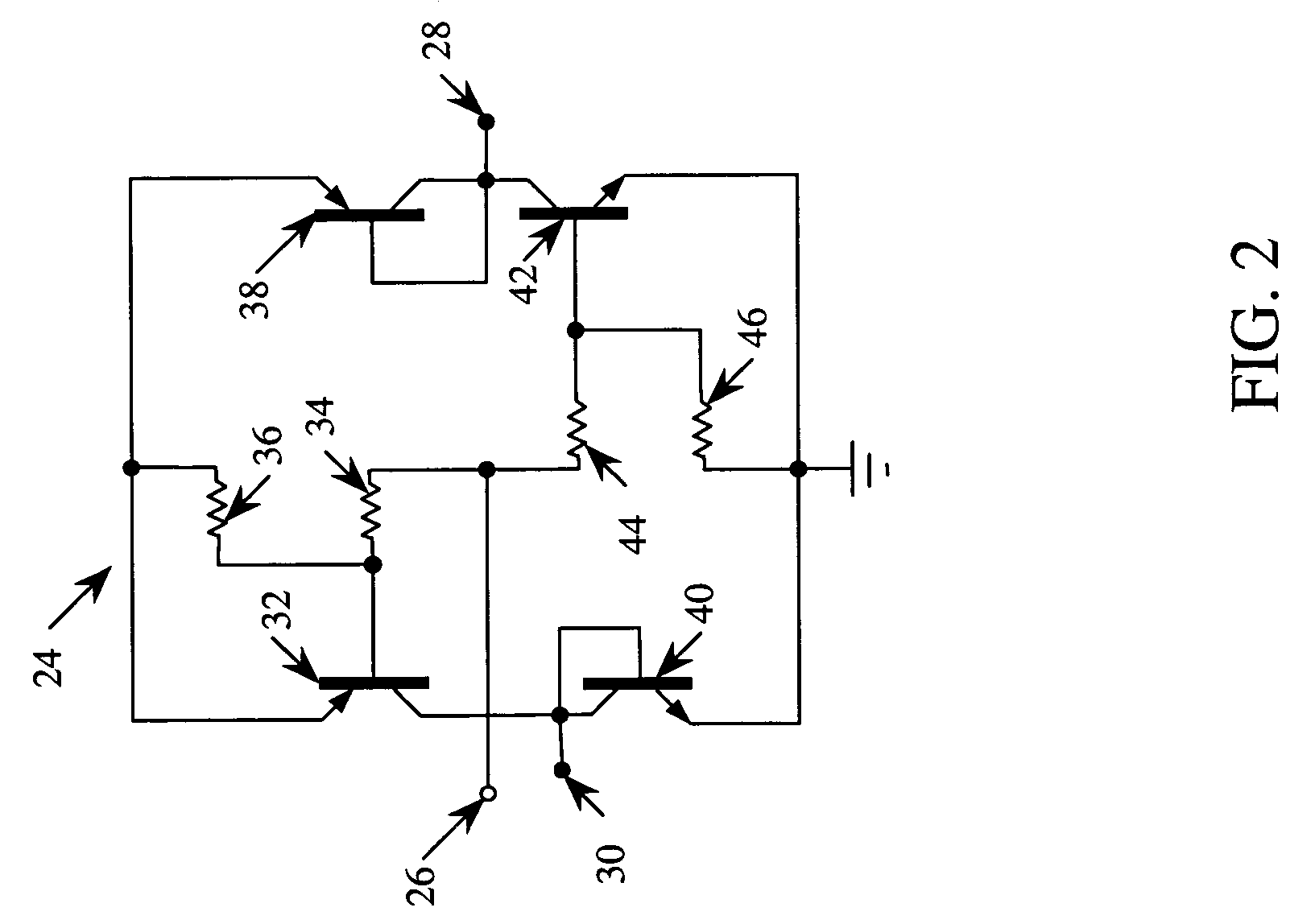

Majority logic circuit

InactiveUS7129742B1Majority/minority circuitsLogic circuits using elementary logic circuit componentsAudio power amplifierEngineering

A novel majority logic circuit is disclosed to determine whether the majority of the inputs are a one, within a constant number of clock cycles, regardless of the number of inputs. The majority logic circuit according to the present invention includes a plurality of current mirror stages and an amplifier stage. For each input, one current mirror stage is used, which outputs either a current source if the input is a one, or a current sink if the input is a zero. The current sources of all the input current mirror stages are connected in parallel to the current source input node of the amplifier stage. The current sinks of all the input current mirror stages are connected in parallel to the current sink input node of the amplifier stage. The amplifier is a differential type, which outputs either a positive voltage or a zero voltage depending upon the majority of the inputs.

Owner:NATIONAL SECURITY AGENCY

Nonvolatile semiconductor storage device

The disclosed flash memory is provided with a majority logic circuit 3 and shift registers 61 to 63. Three out of the banks 2a to 2c of the memory respectively include management information areas KAs to store binary management information comprising power supply trimming data and bitline restoration data. During initialization of the flash memory, the majority logic circuit 3 performs error correction on management information bits retrieved from the management information areas KAs and outputs that information to a trimming / restoration data buffer 11, thus providing highly reliable management information very quickly. The shift registers 61 to 63 delay a control signal that is output from a control circuit 12 by a certain period of time before outputting the control signal to sense amplifiers 42 to 44. This delay makes it possible to make the operating currents of the banks 2a to 2d start to flow at different times and to suppress a peak current flowing in the flash memory.

Owner:RENESAS ELECTRONICS CORP

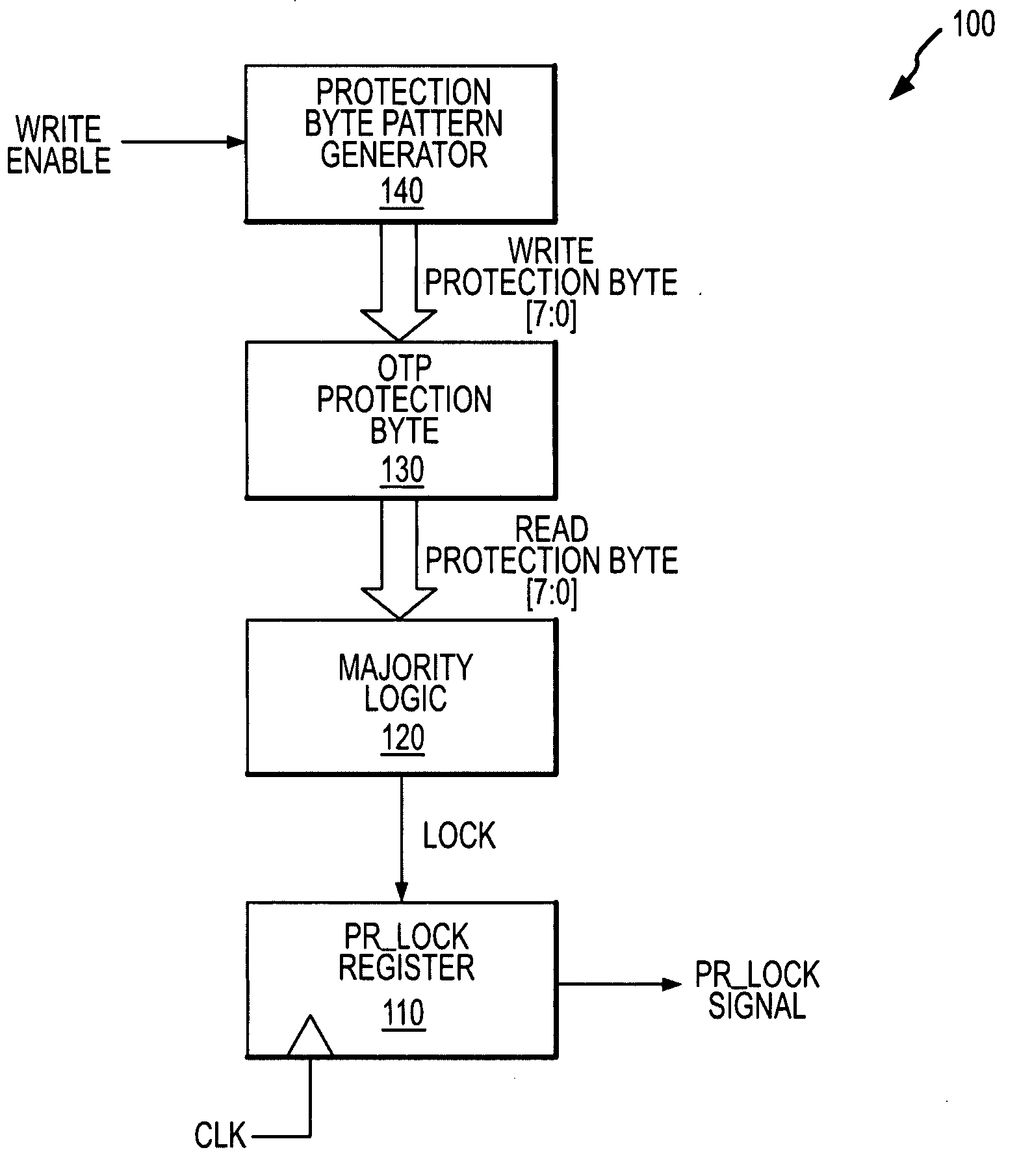

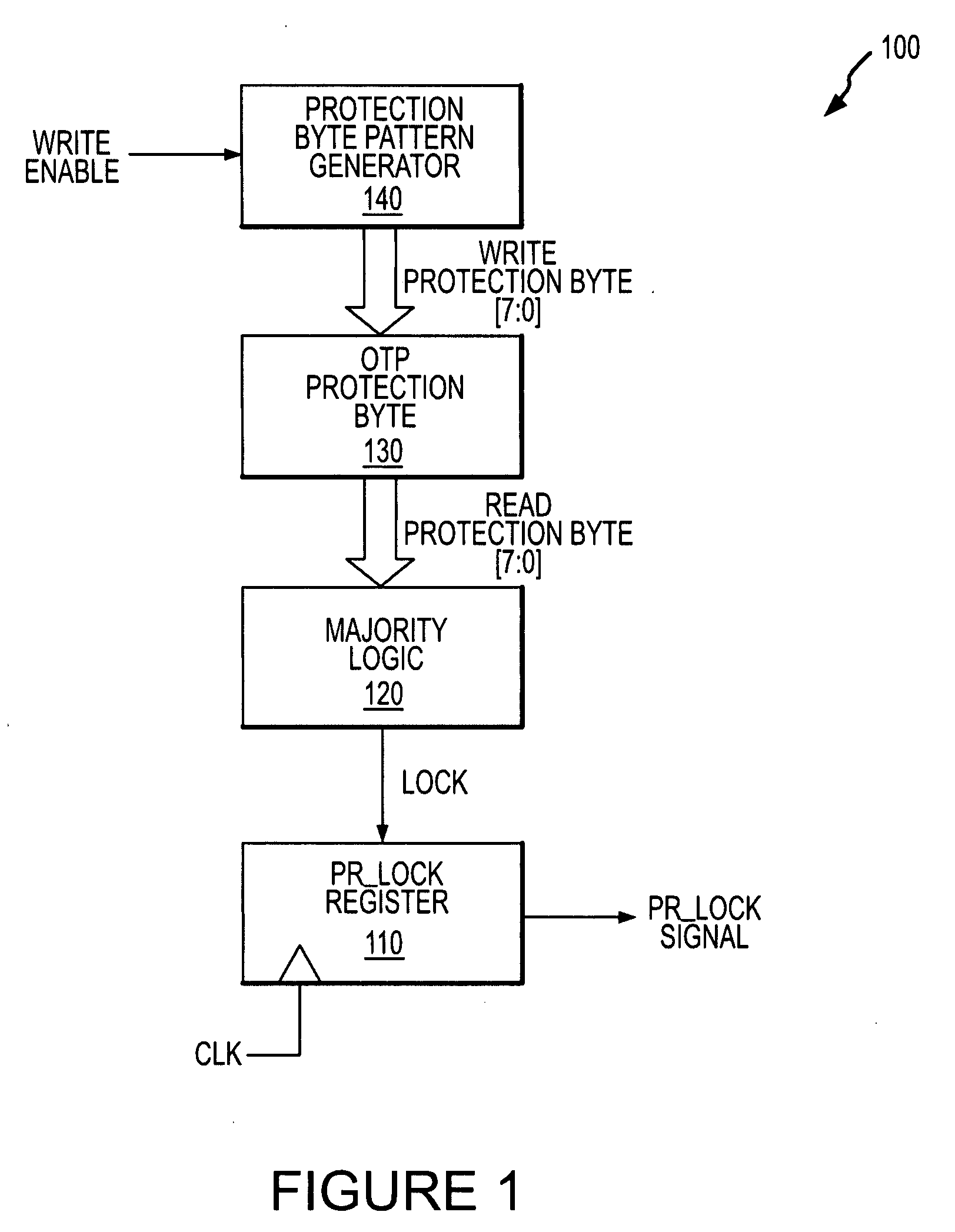

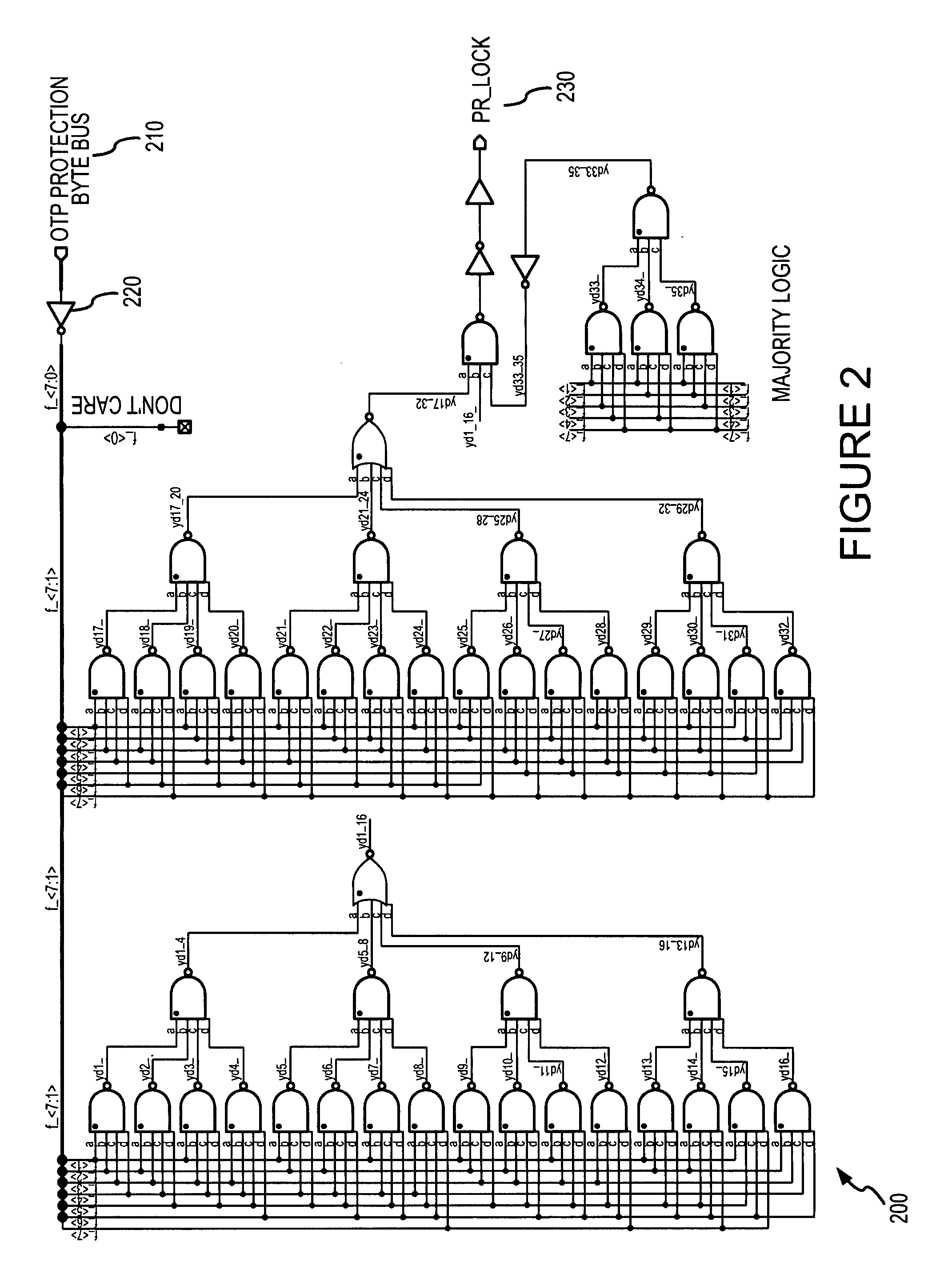

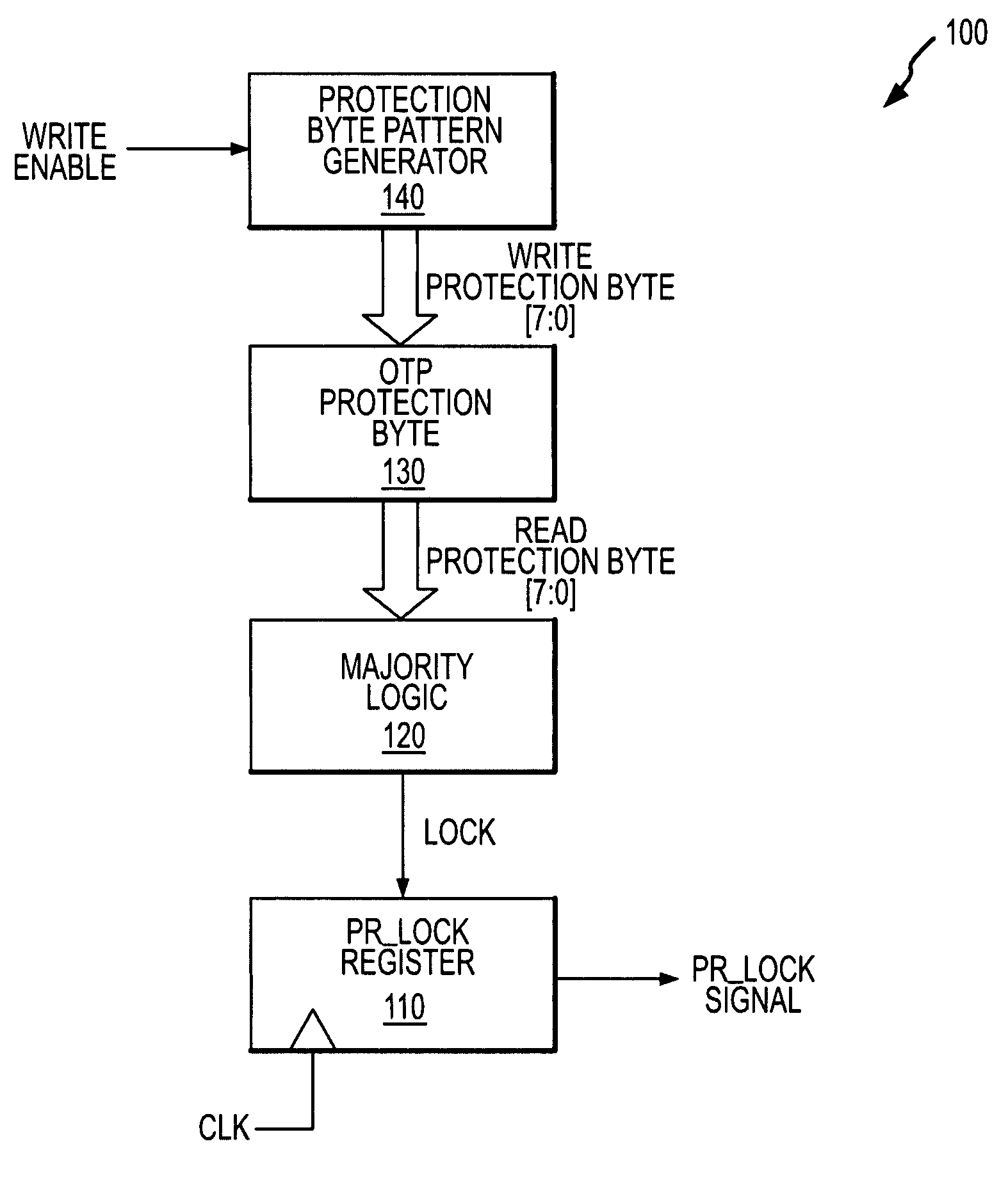

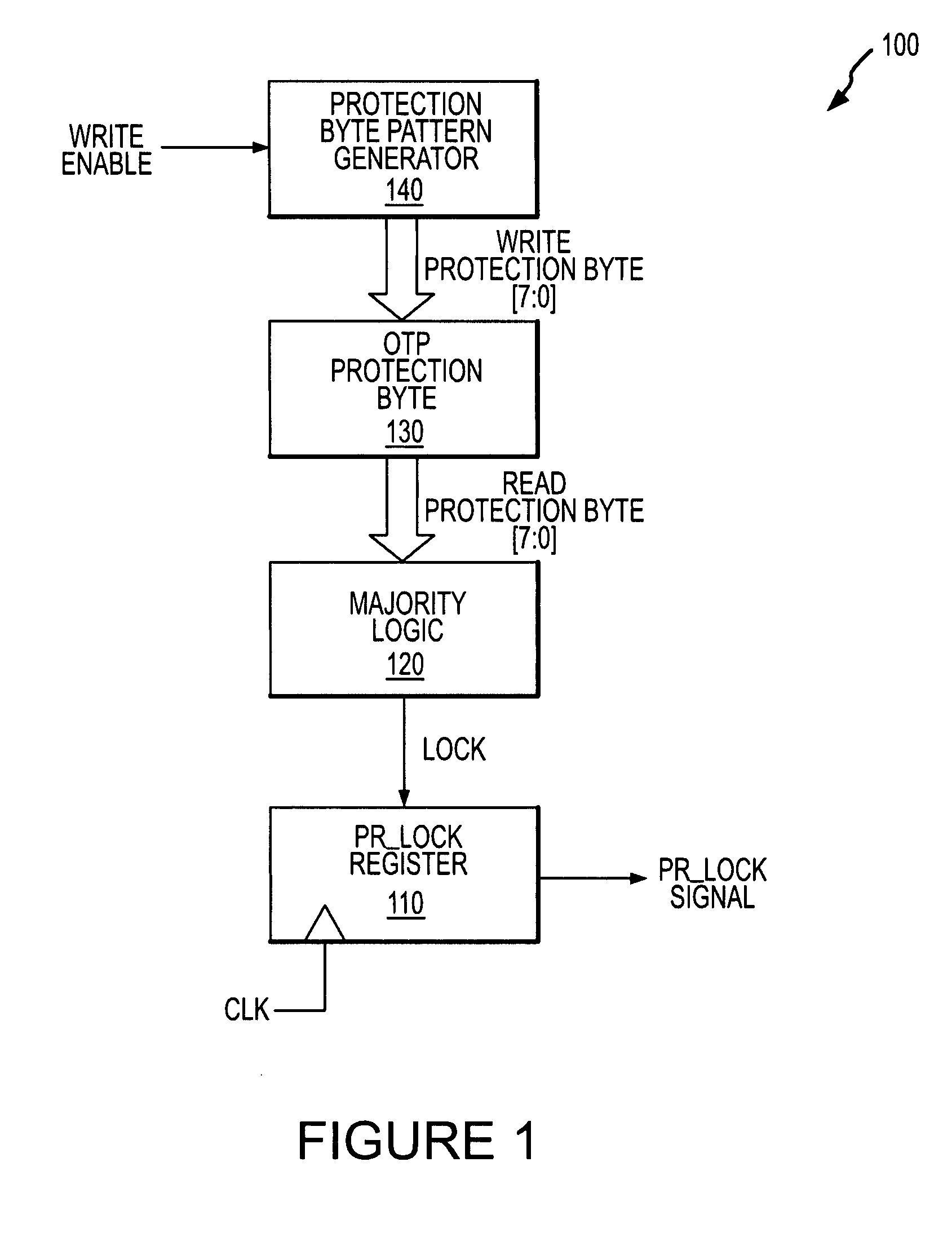

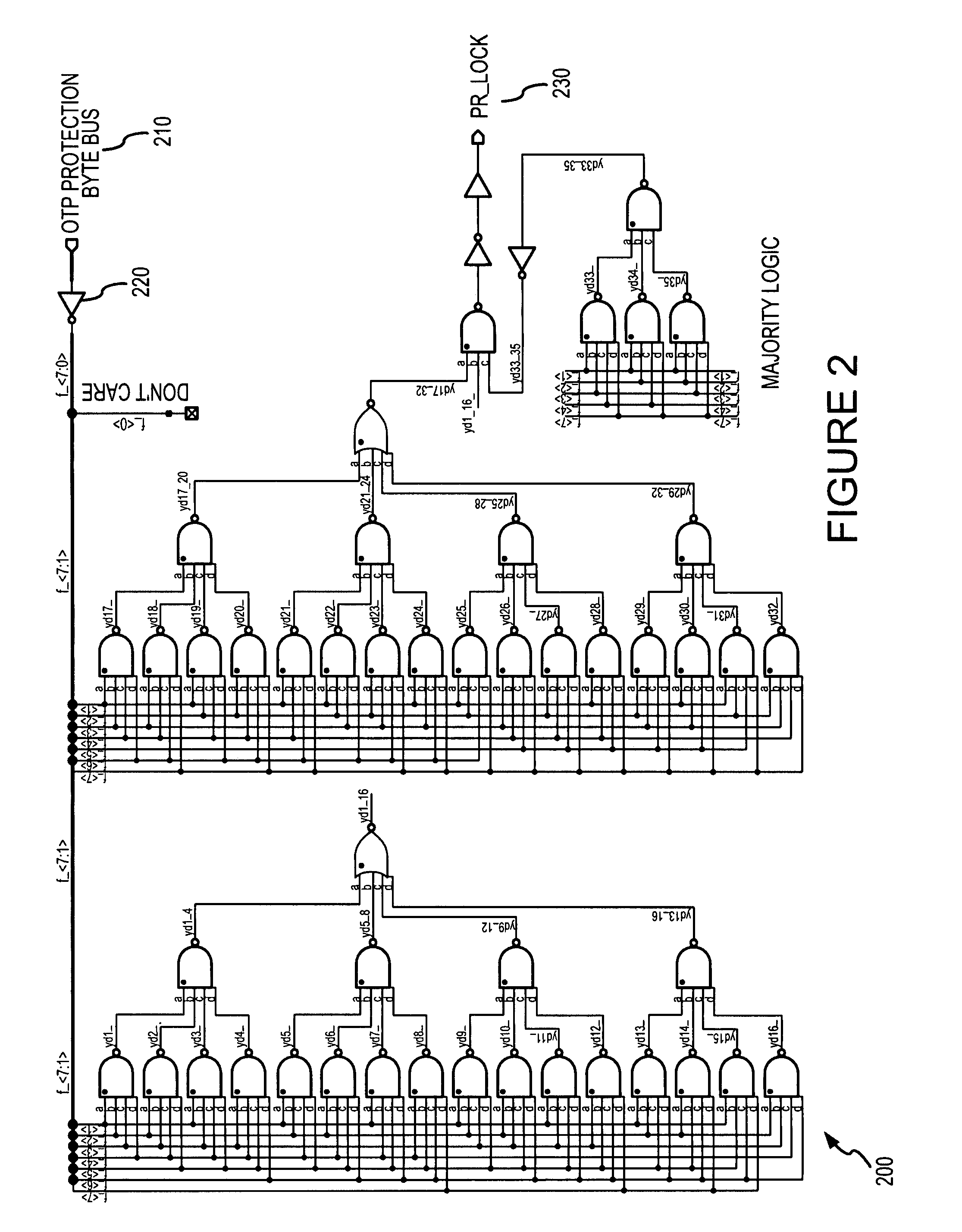

Memory Area Protection System and Methods

In one embodiment, a non-volatile memory device includes a plurality of protection bits denoting that an area of memory in the device must be protected from being erased or programmed. The memory device further includes a majority logic circuit for determining the logic state of the majority of the plurality of protection bits. Another embodiment includes a pattern generator for generating the logic levels to be stored in the plurality of protection bits.

Owner:MICRON TECH INC

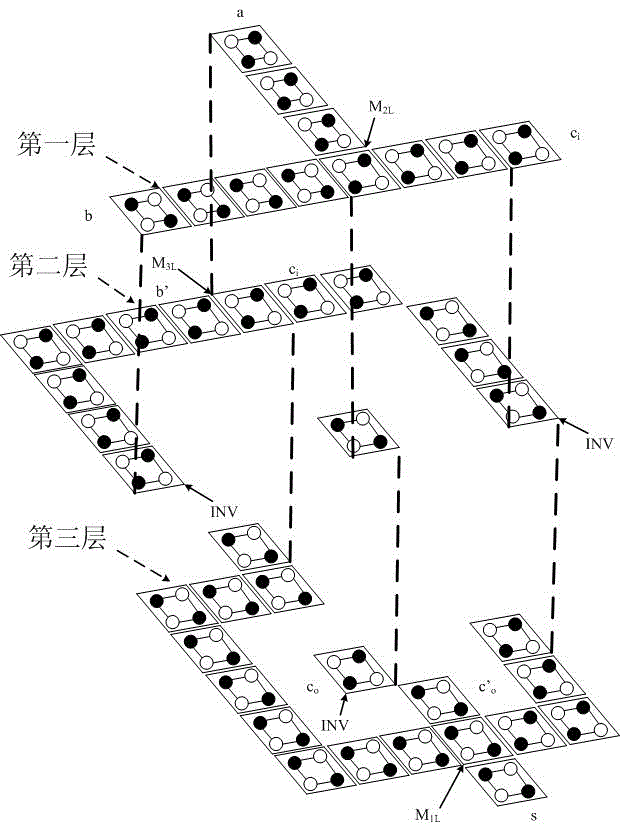

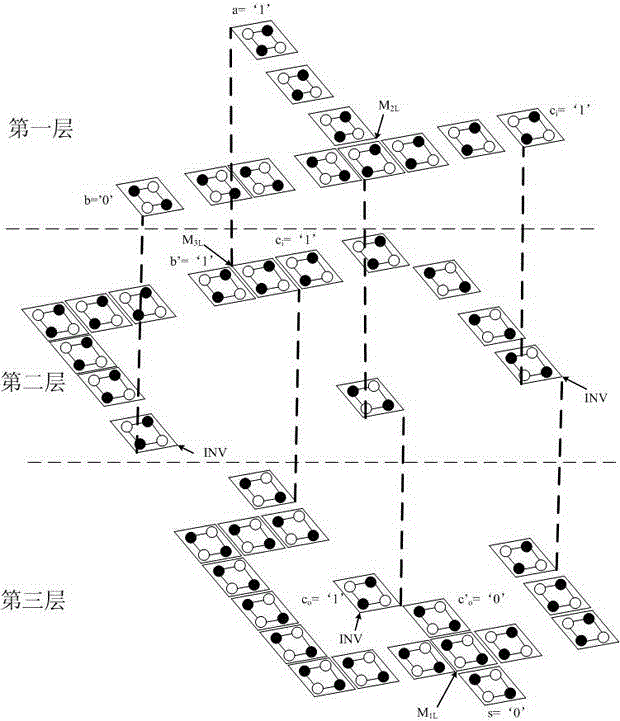

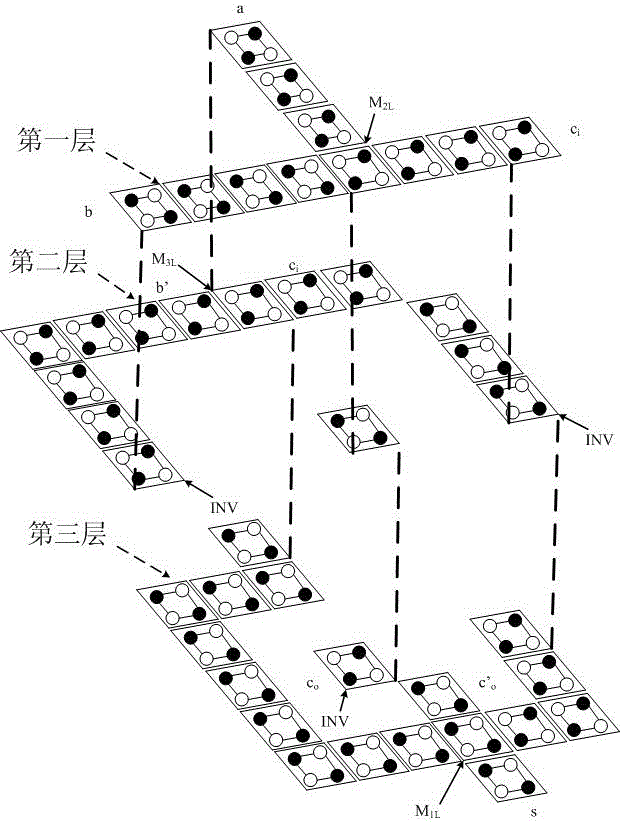

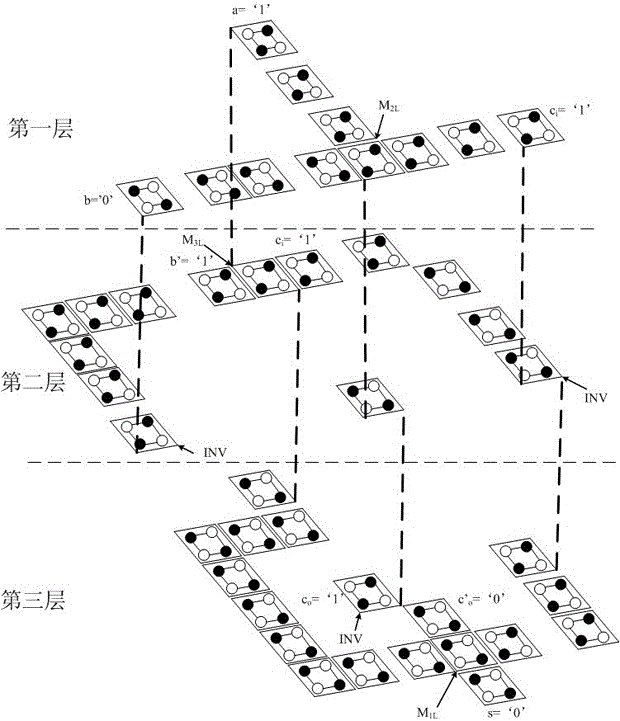

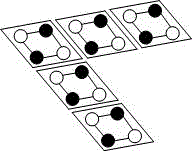

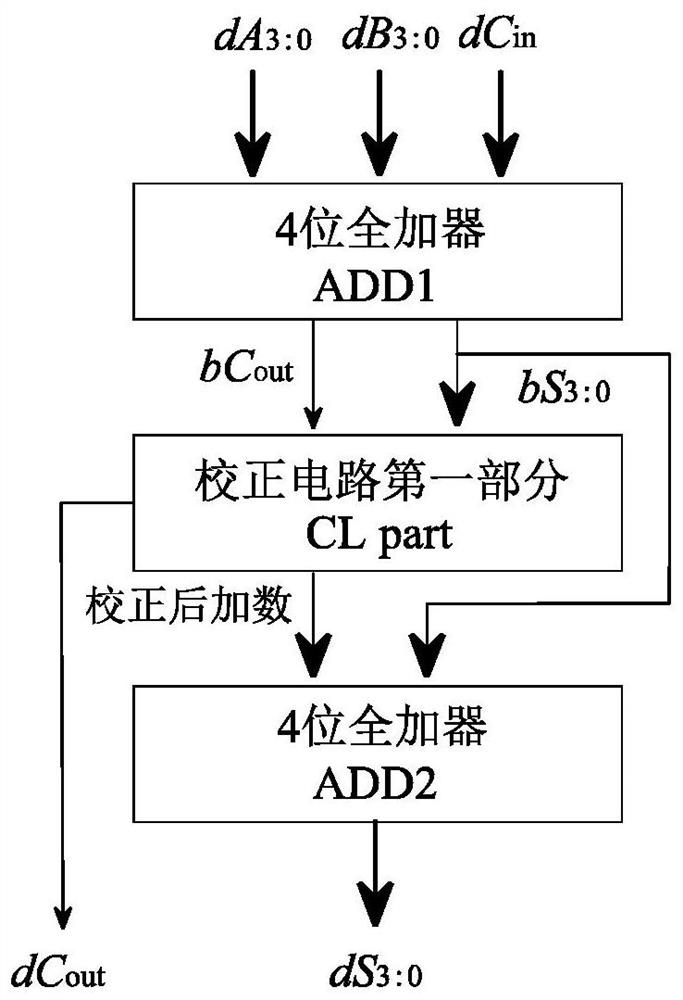

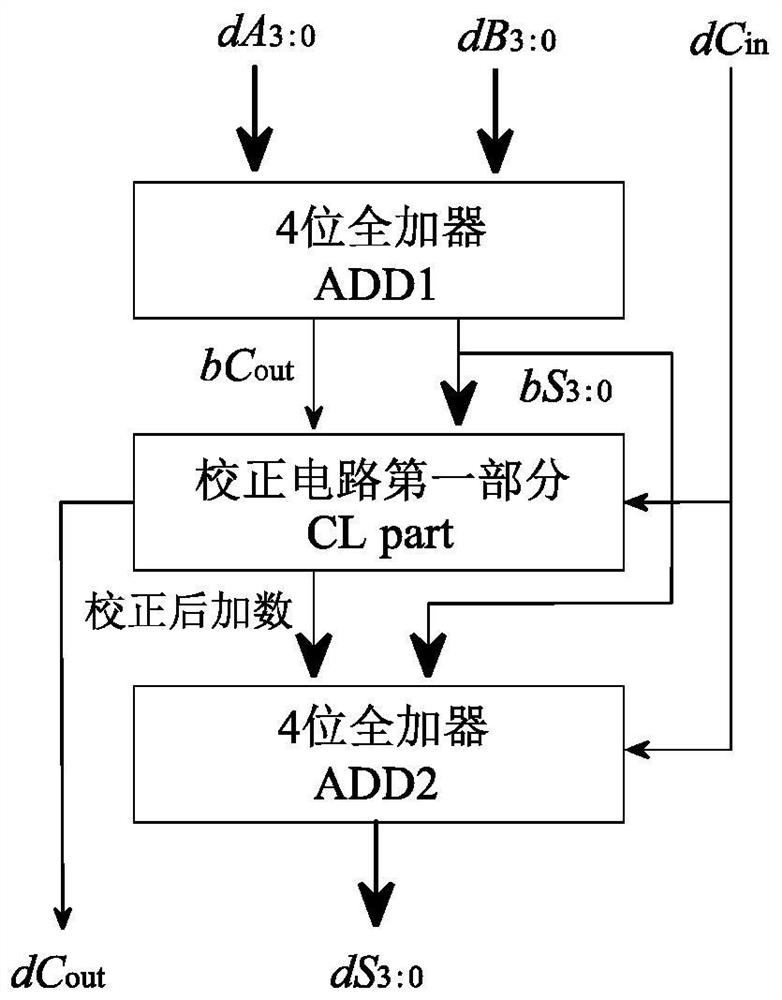

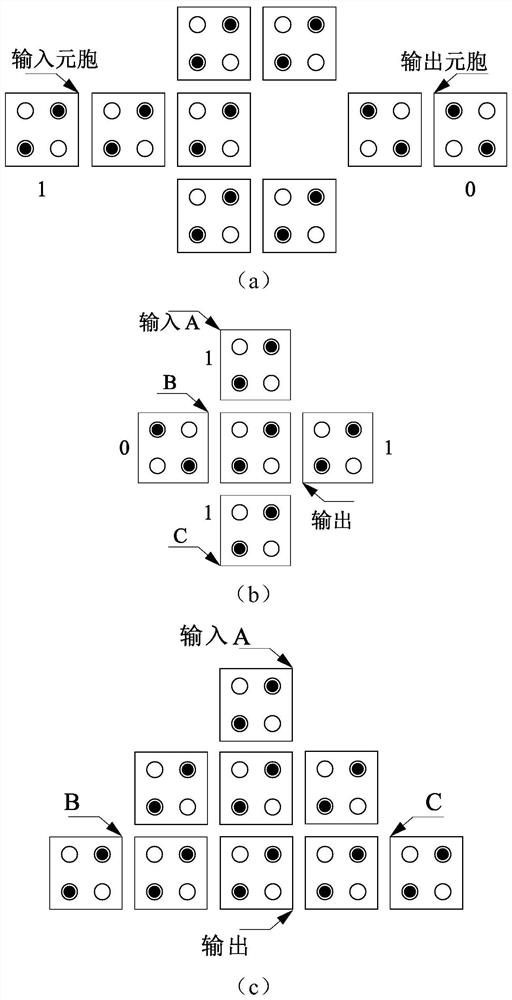

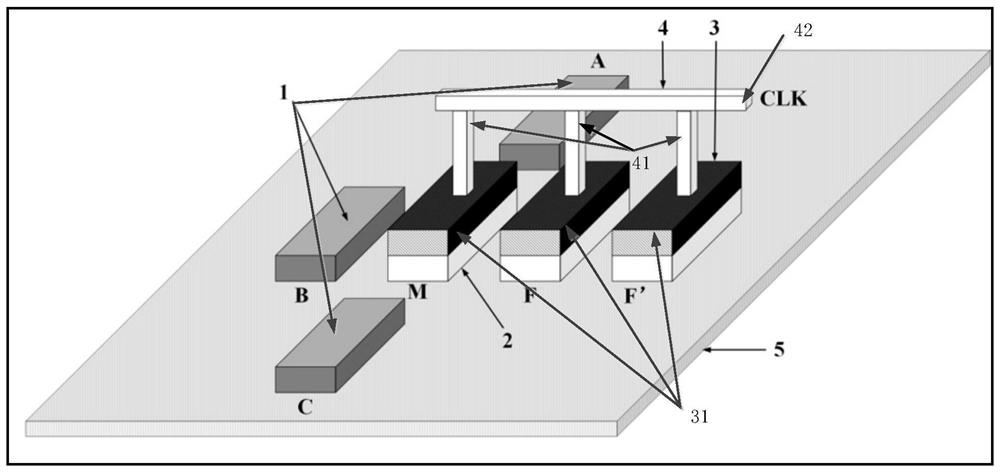

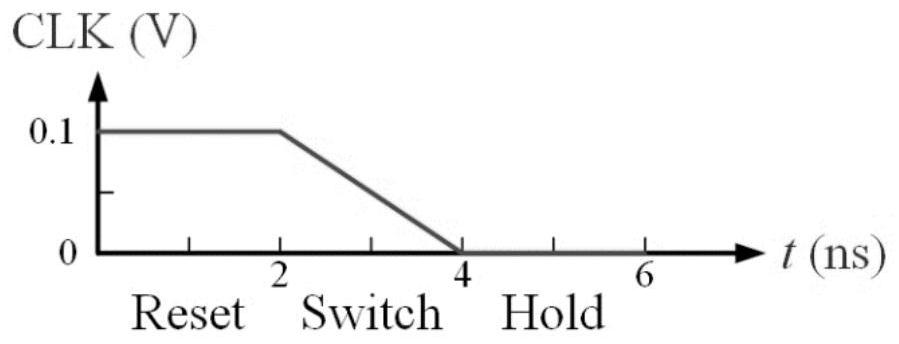

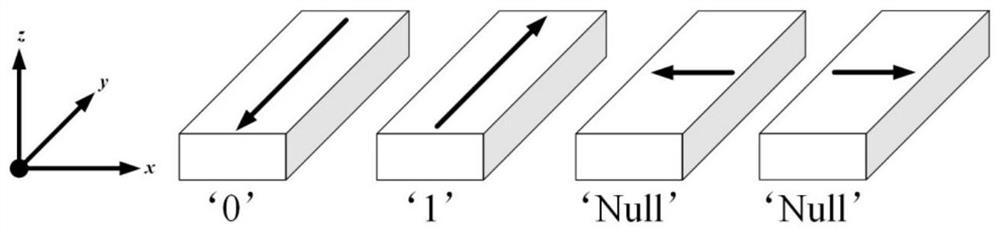

Three-dimensional quantum cellular automata adder

InactiveCN104407835AReduce areaSave hardware resourcesDigital data processing detailsCellular automationMajority logic

The invention discloses a three-dimensional quantum cellular automata adder, which comprises seven quantum cellular automata connecting lines, a two-dimensional majority logic gate, a two-layer three-dimensional majority logic gate, a three-layer three--dimensional majority logic gate, a first three-dimensional phase inverter, a second three-dimensional phase inverter, a third three-dimensional phase inverter, a fourth three-dimensional phase inverter, a first two-dimensional phase inverter and a second two-dimensional phase inverter. Compared with a traditional two-dimensional quantum cellular automata adder, the three-dimensional quantum cellular automata adder provides an extra one-dimensional computation space, so that fewer cells are required, and meanwhile, the space and the power consumption of a circuit are drastically reduced. The three-dimensional quantum cellular automata adder is a novel quantum cellular automata adder which has the advantages of being low in three-dimensional power consumption and small in area.

Owner:NANJING UNIV OF AERONAUTICS & ASTRONAUTICS

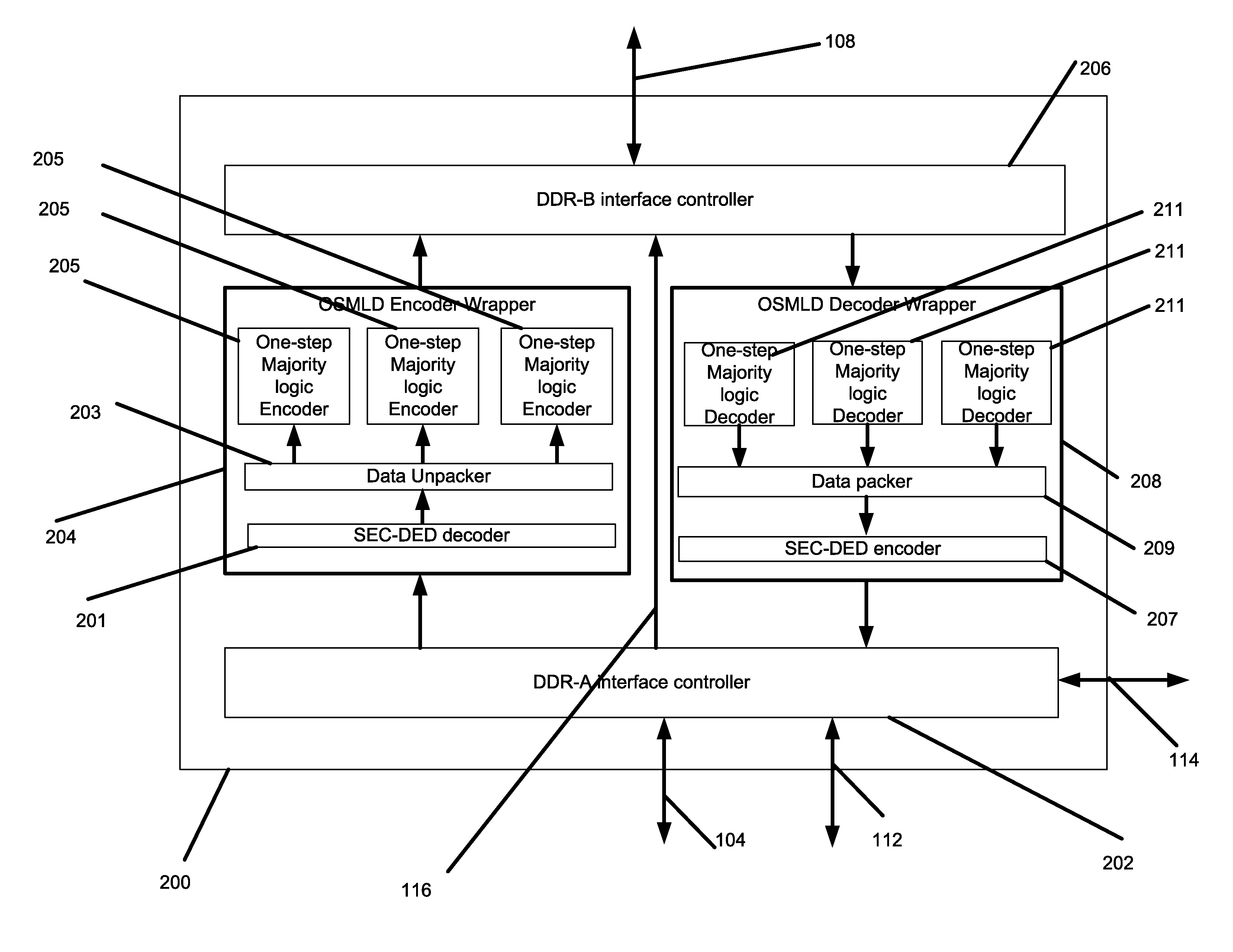

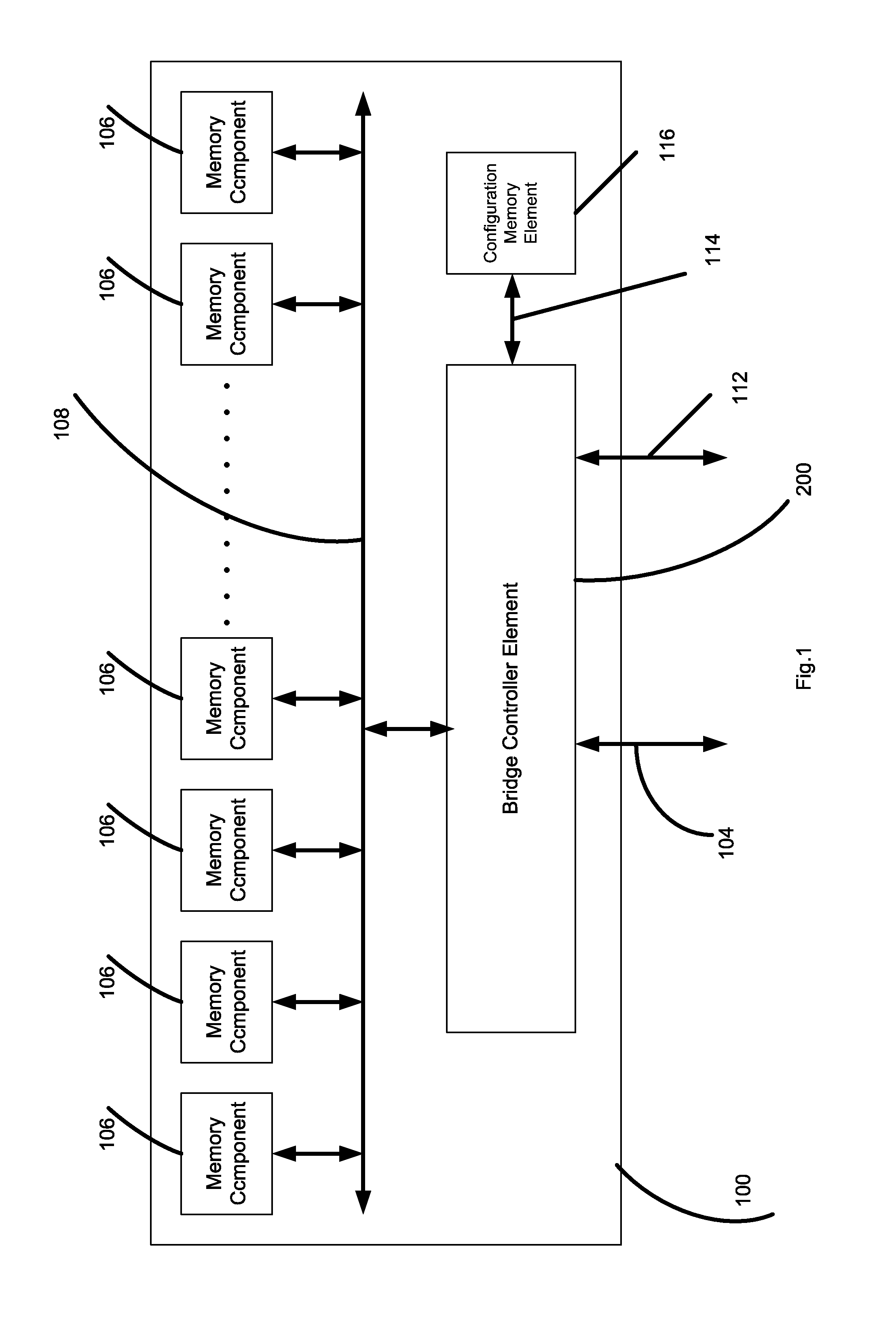

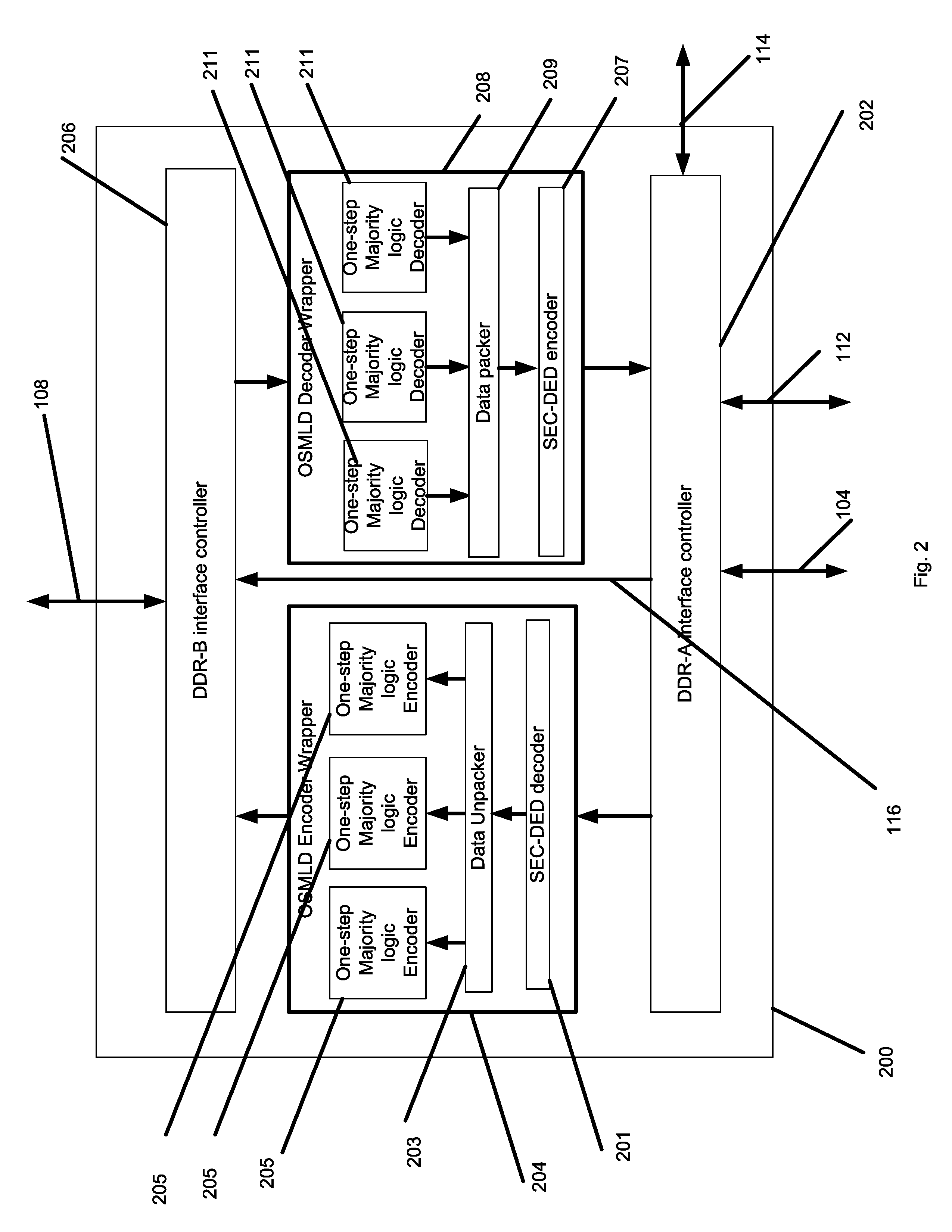

Dual data rate bridge controller with one-step majority logic decodable codes for multiple bit error corrections with low latency

A memory module includes a bridge controller having a first interface and a second interface. The first interface receives commands and data from a host and the second interface is coupled to one or more memory components. The bridge controller performs multiple-bit error detection and correction on data stored in the one or more memory components.

Owner:AVALANCHE TECH

Convolutional code for use in a communication system

ActiveUS20110264988A1Error correction/detection using convolutional codesOther decoding techniquesCommunications systemConvolutional code

In a communication system, a transmitter receives an input bit, and in response thereto, generates at least an n-bit codeword, each bit of which is generated by a respective one of n generators of which m are exactly the same, m being greater than n / 2. A receiver comprises: m detectors, each adapted to receive the bit generated by a respective one of the m generators, and provide a respective one of m partial detection signals if a strength of the received bit exceeds a predetermined minimum threshold; and a majority logic element adapted to receive each of the m partial detection signals, and provide an output bit indicative of the input bit only if more than m / 2 of the received m partial detection signals exceeds the minimum threshold.

Owner:DECAWAVE

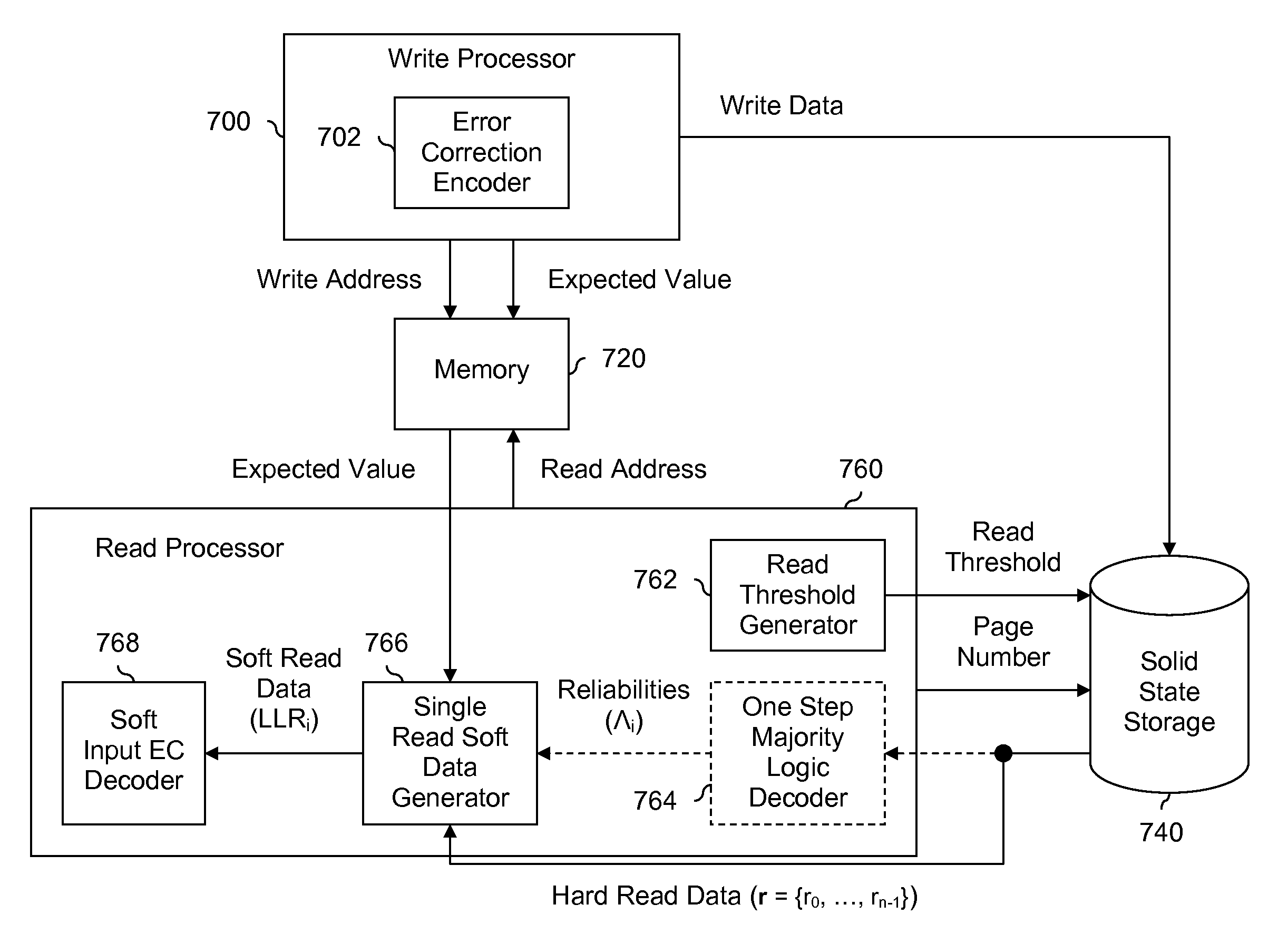

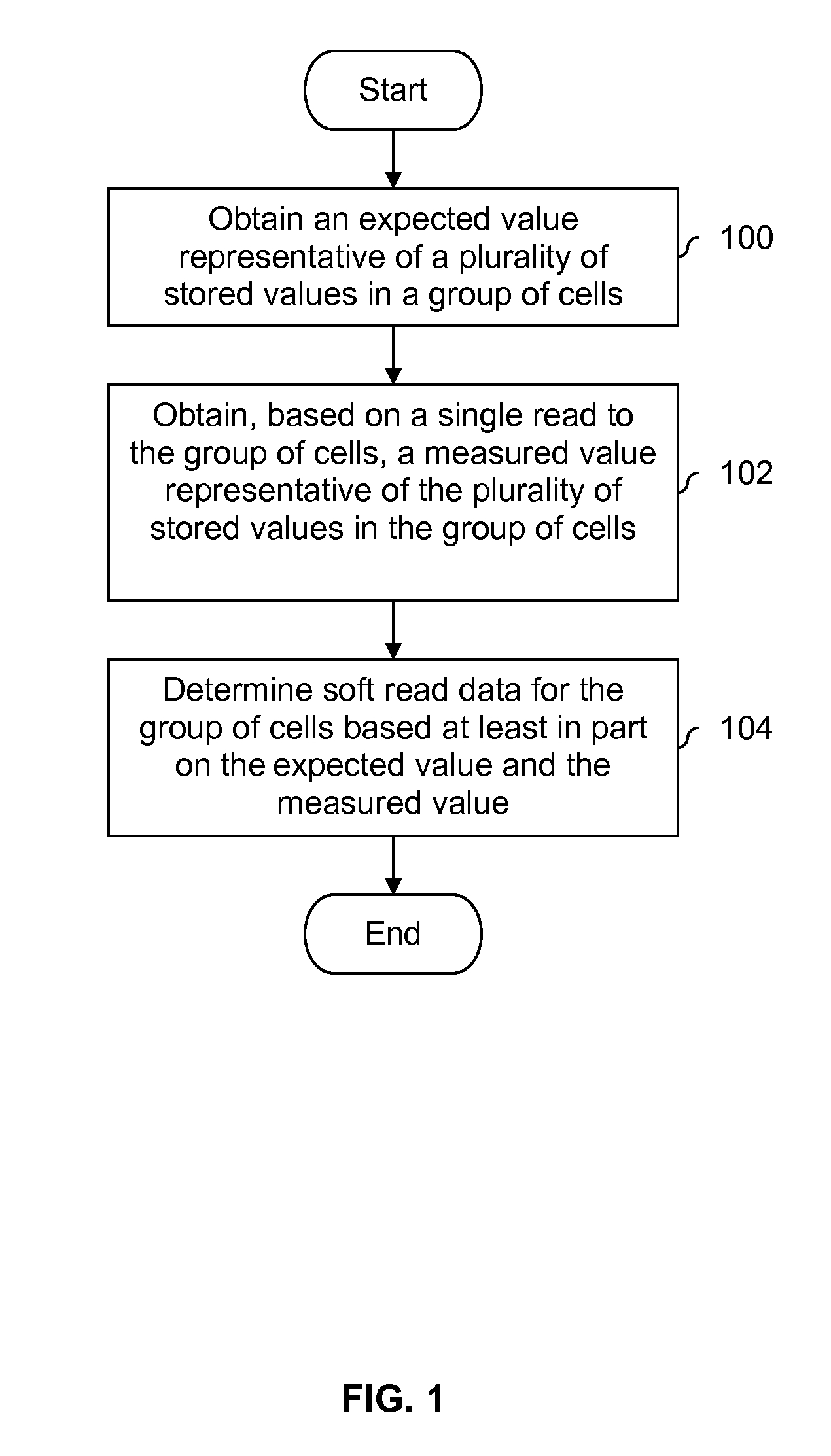

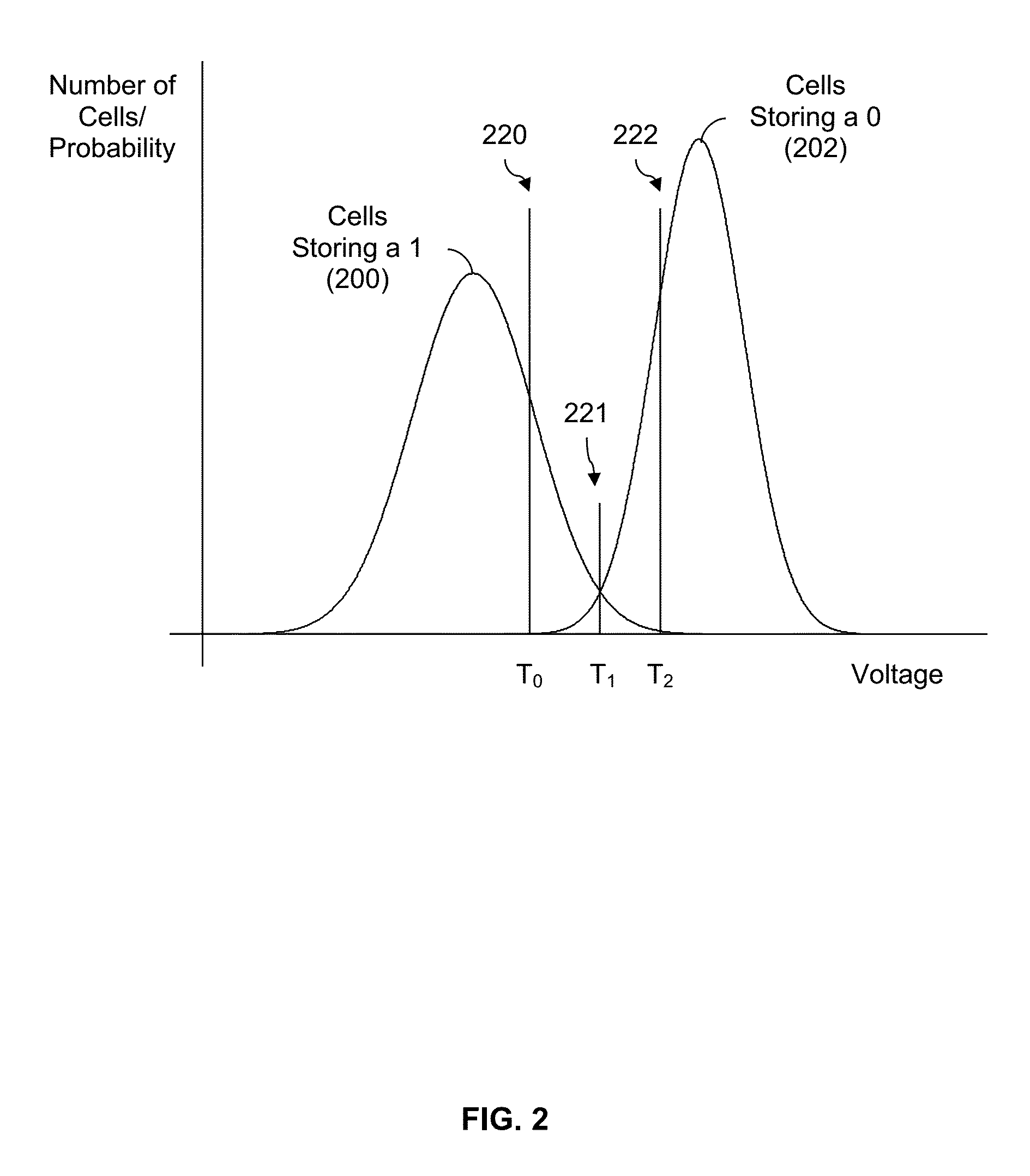

Method and system for generating soft-information after a single read in NAND flash using expected and measured values

ActiveUS9256522B1Memory architecture accessing/allocationMemory adressing/allocation/relocationMajority logic decodingMajority logic

A system and method for determining soft read data for a group of cells in a nonvolatile flash memory are disclosed. An expected value representative of a plurality of stored values in a group of cells is obtained. A measured value representative of the plurality of stored values in the group of cells is obtained, based on a single read to the group of cells. A soft read data for the group of cells is determined based at least in part on the expected value and the measured value. The expected and measured values may include at least one of a number of 0s, a number of 1s, a ratio of 0s to 1s or a ratio of 1s to 0s. A reliability for a bit i may be obtained using a one-step majority logic decoder, and a threshold reliability may be used when determining the soft read data.

Owner:SK HYNIX MEMORY SOLUTIONS

Memory area protection system and methods

ActiveUS9406388B2Read-only memoriesInternal/peripheral component protectionLogic stateMajority logic

In one embodiment, a non-volatile memory device includes a plurality of protection bits denoting that an area of memory in the device must be protected from being erased or programmed. The memory device further includes a majority logic circuit for determining the logic state of the majority of the plurality of protection bits. Another embodiment includes a pattern generator for generating the logic levels to be stored in the plurality of protection bits.

Owner:MICRON TECH INC

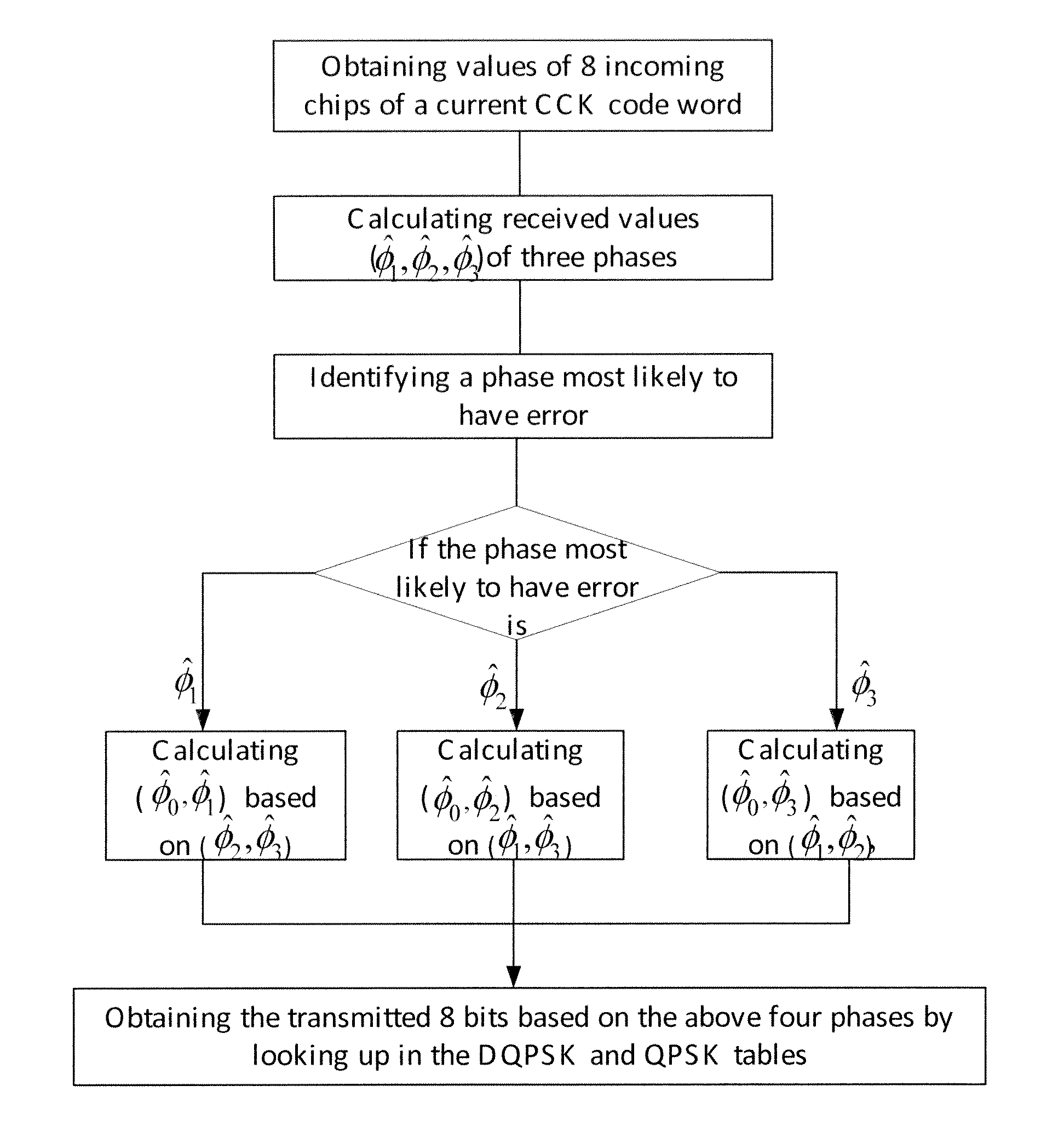

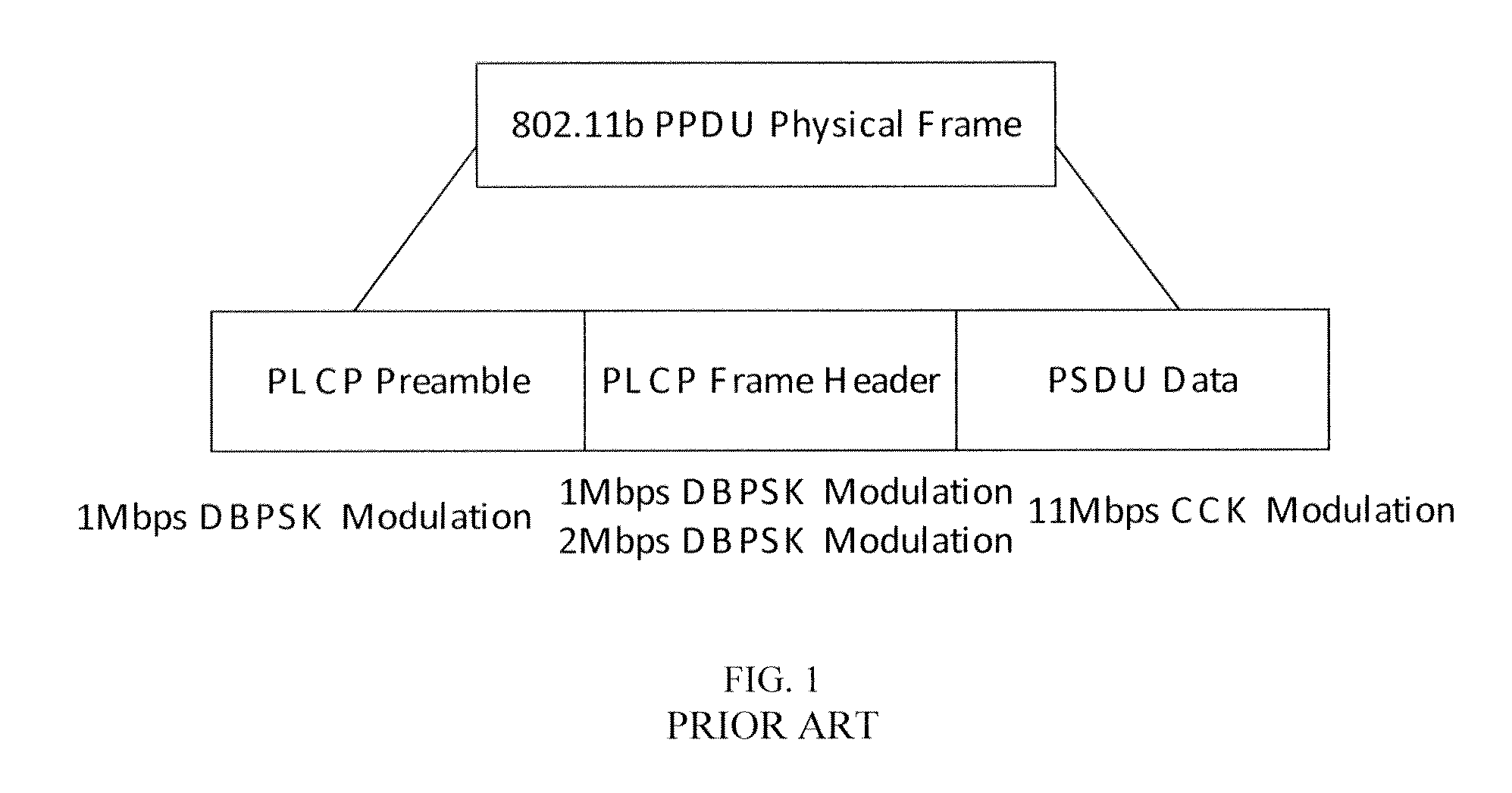

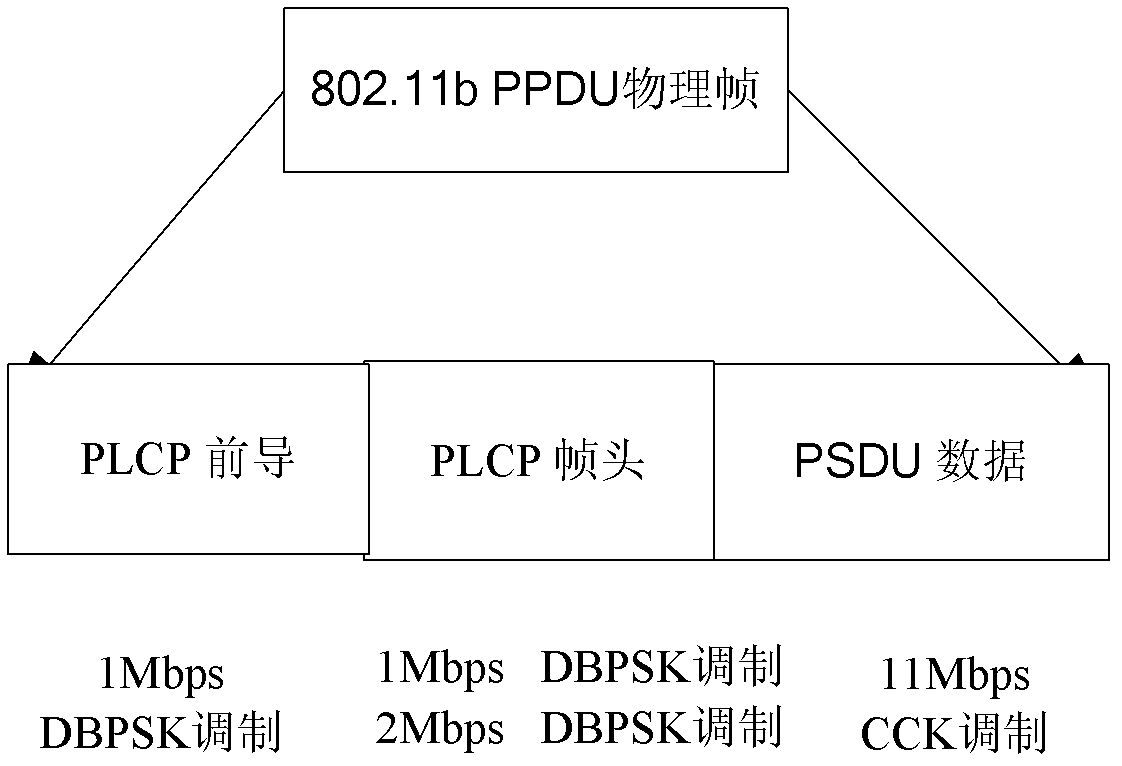

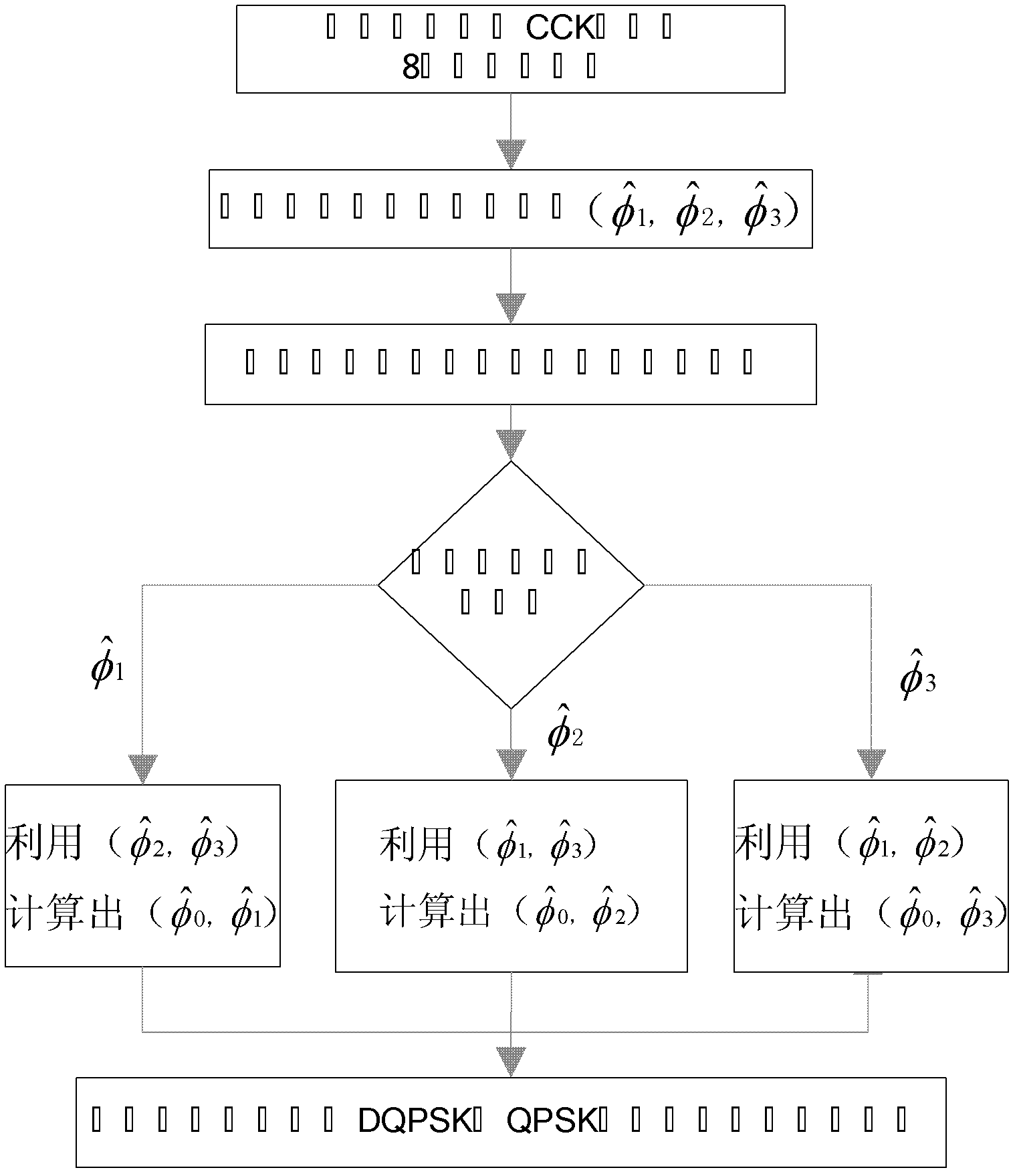

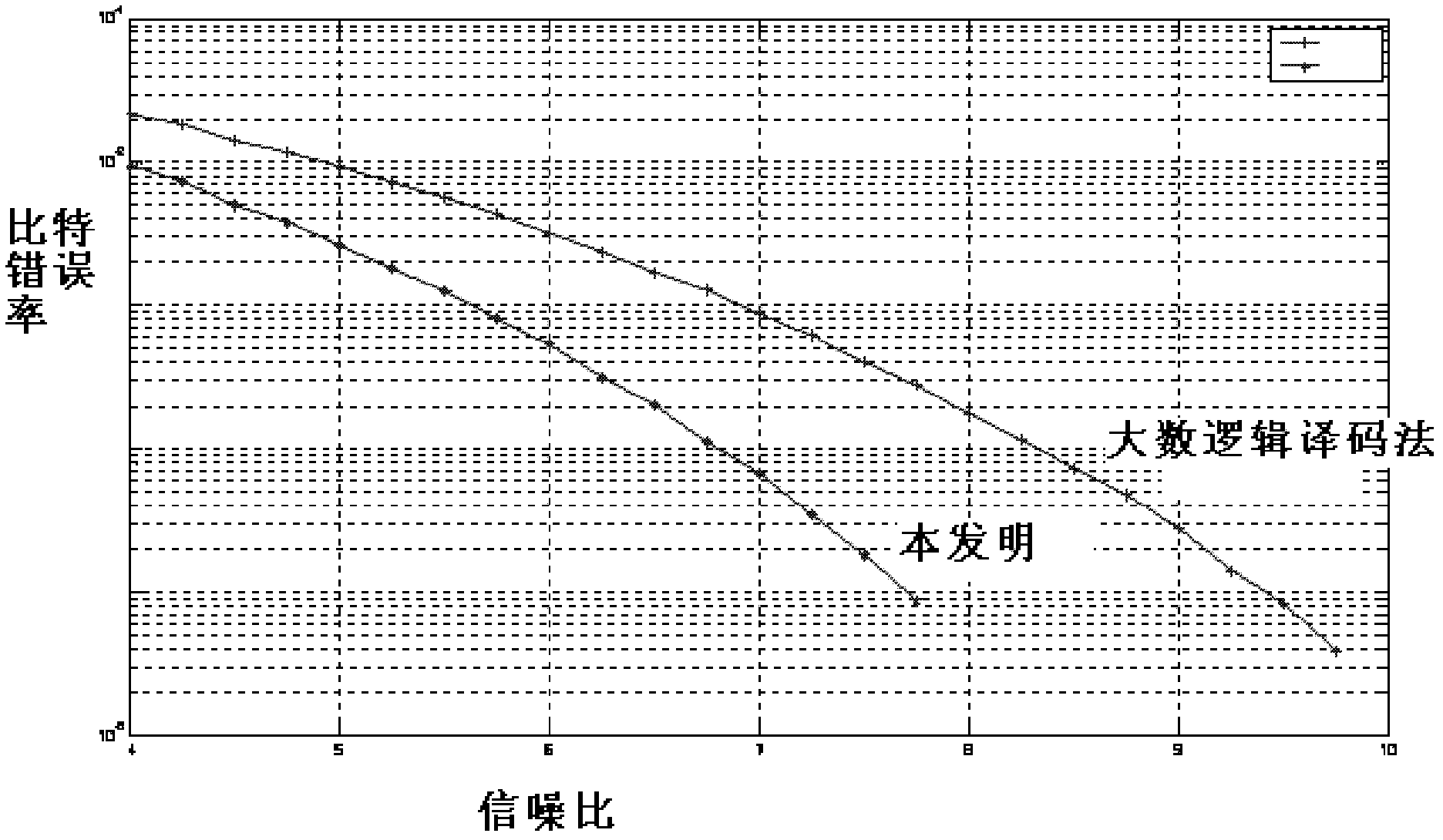

Signal Demodulation Method

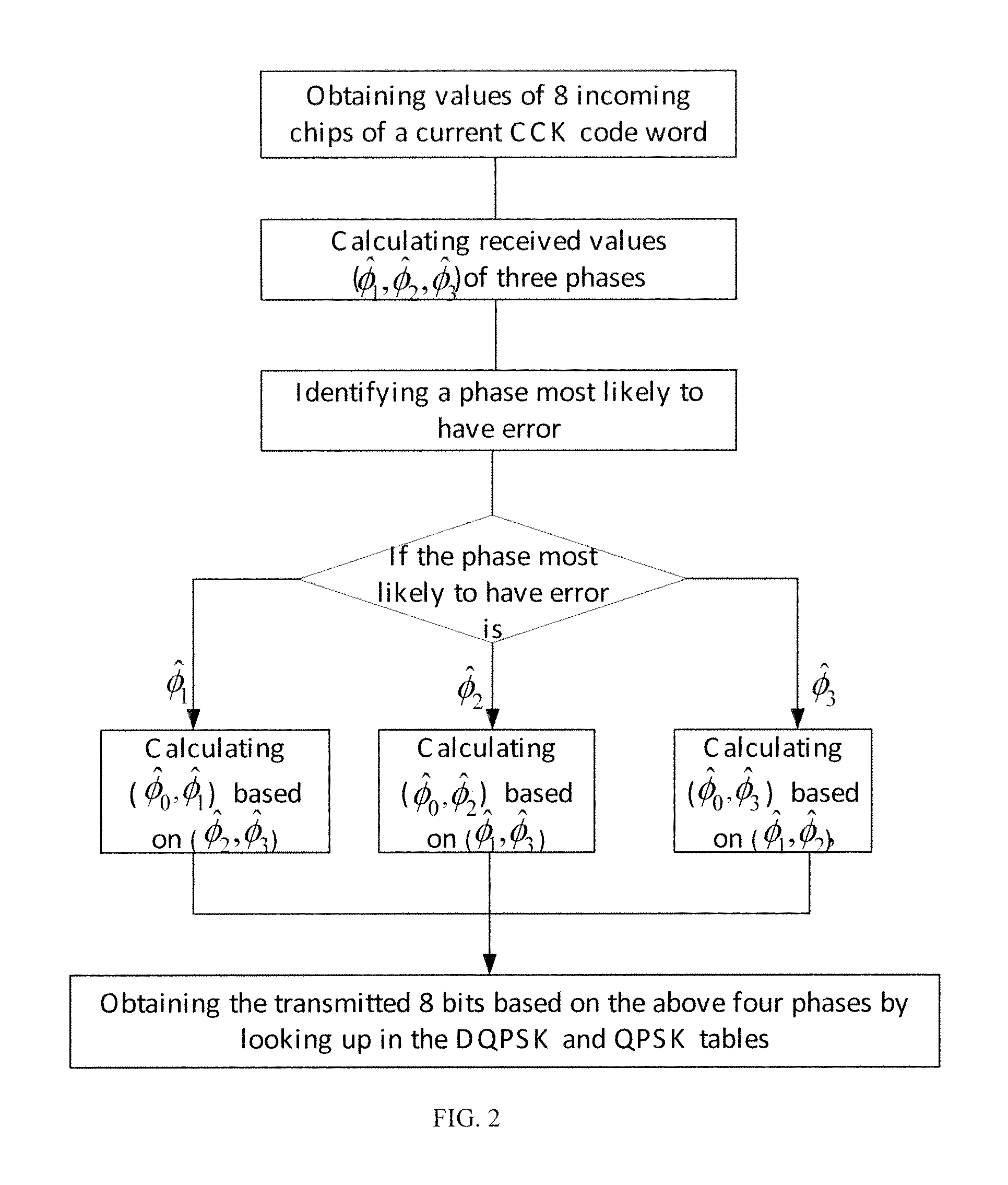

ActiveUS20130058441A1Reduce the impact of noiseImprove demodulation performanceAmplitude-modulated carrier systemsAmplitude demodulationDifferential phaseMajority logic

A signal demodulation method is disclosed, which includes: obtaining a complete transmission code word; calculating estimated values of three non-differential phases of the transmission code based on a majority logic; identifying a most unreliable phase among three non-differential phases and determining the other two reliable phases to obtain their determination values; calculating determination values of the rest two phases based on the two determined phases; and looking up in tables based on determination values of the four phases to obtain incoming bits. The demodulation method of the present invention is capable of sufficiently reducing the effect of noise on signal and effectively improving the signal demodulation performance.

Owner:OMNIVISION TECH (SHANGHAI) CO LTD

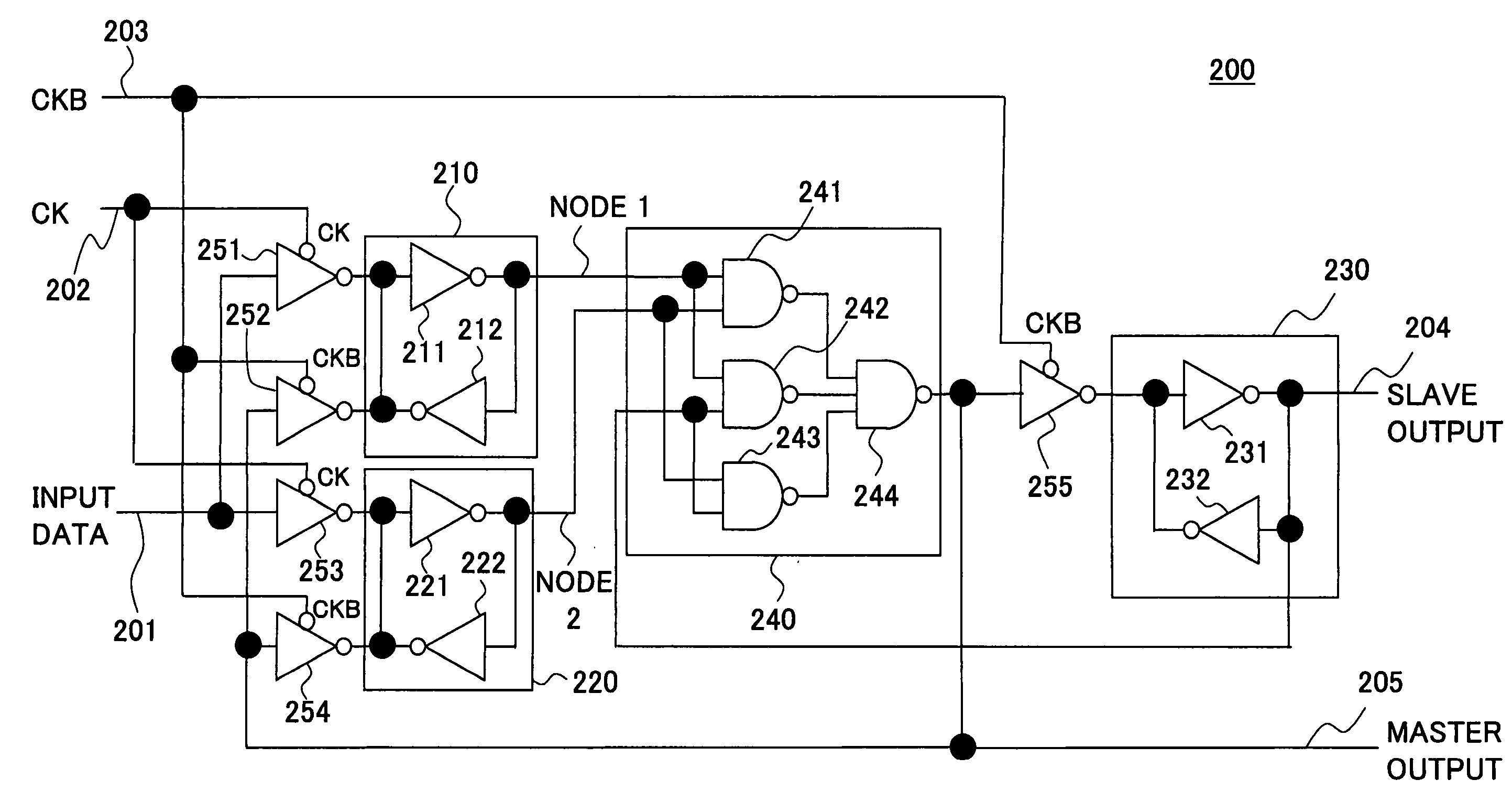

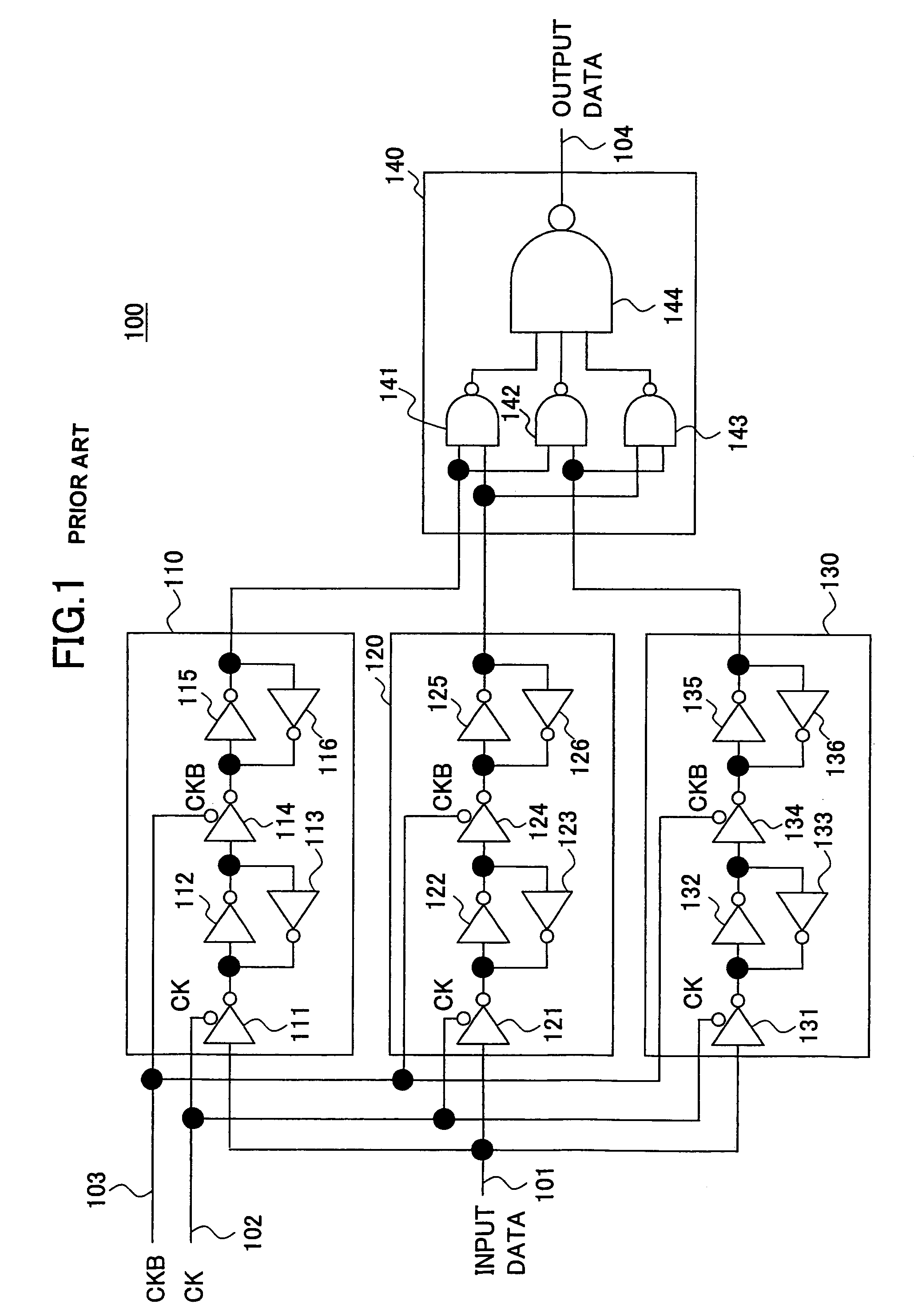

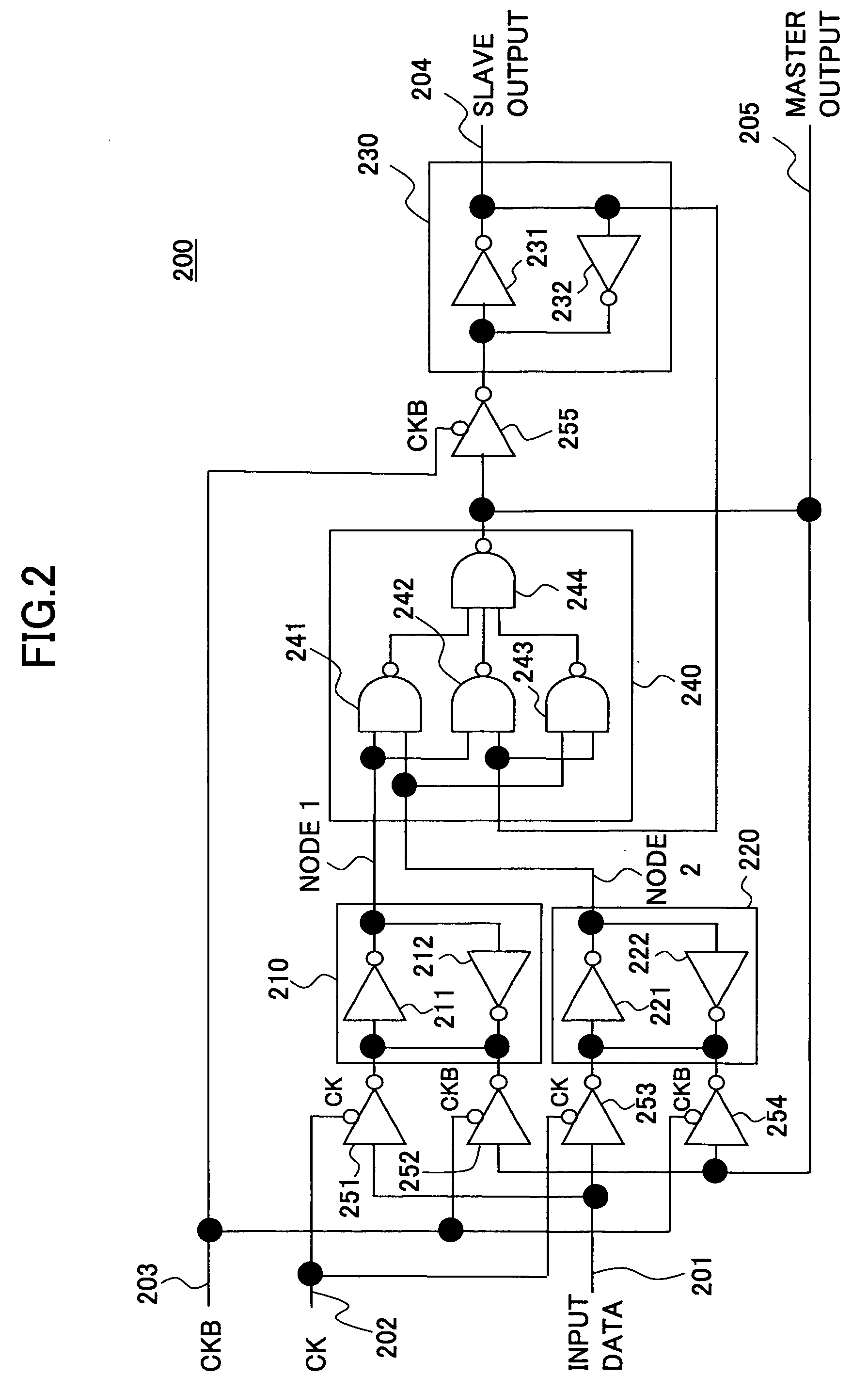

Flip-flop circuit having majority-logic circuit

A flip-flop circuit having a majority-logic circuit is disclosed. The circuit further includes multiple master latches for writing in corresponding input signals, and one slave latch having an input connected to an output of the majority-logic circuit and an output connected to the inputs of the majority-logic circuit. The majority logic-circuit has multiple inputs connected to respective outputs of the master latches. During the period in which the master latches do not write in the corresponding input signals, an output signal of the majority-logic circuit is supplied to respective inputs of the master latches.

Owner:FUJITSU LTD

Signal demodulation method

ActiveCN102333058AImprove demodulation performanceAmplitude-modulated carrier systemsPhase-modulated carrier systemsDifferential phaseMajority logic

Owner:OMNIVISION TECH (SHANGHAI) CO LTD

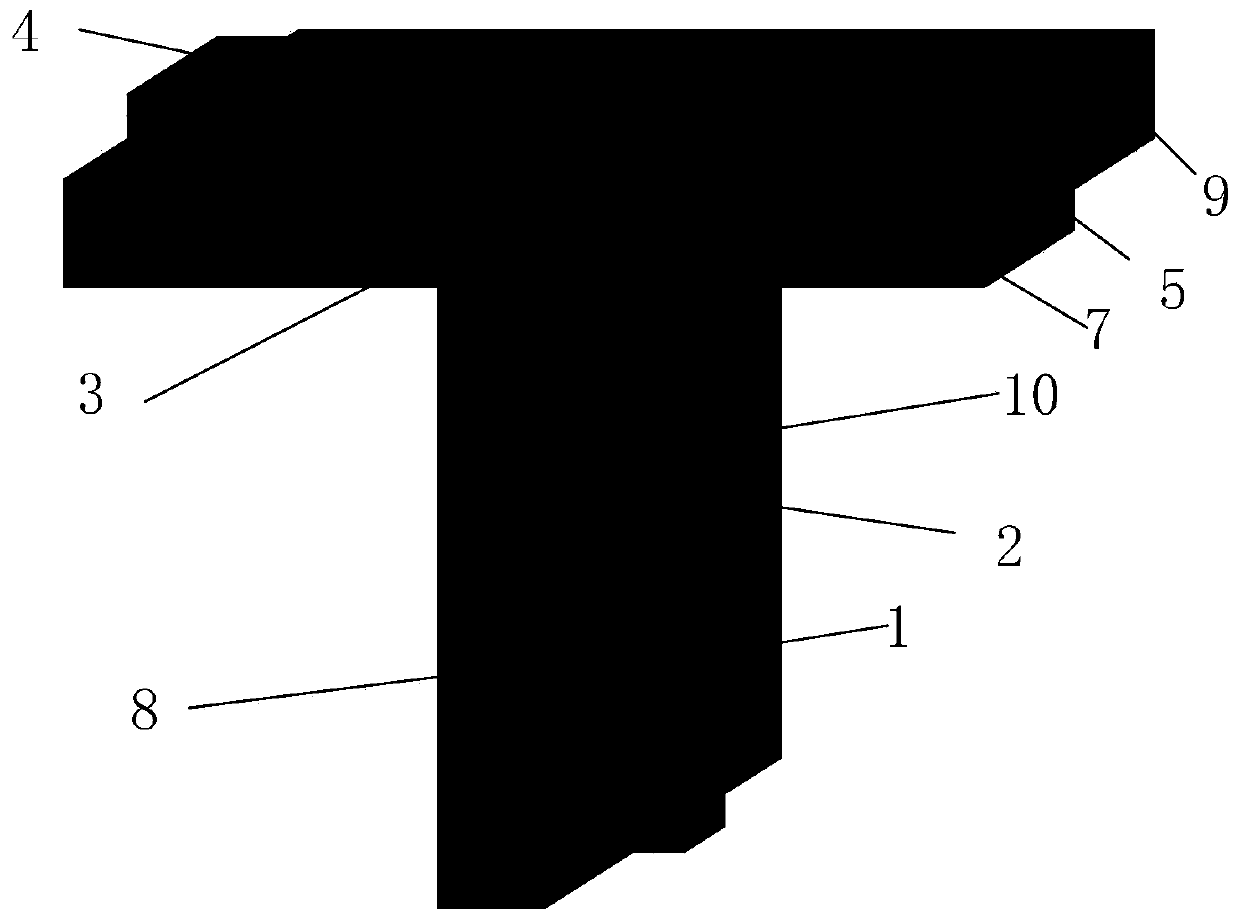

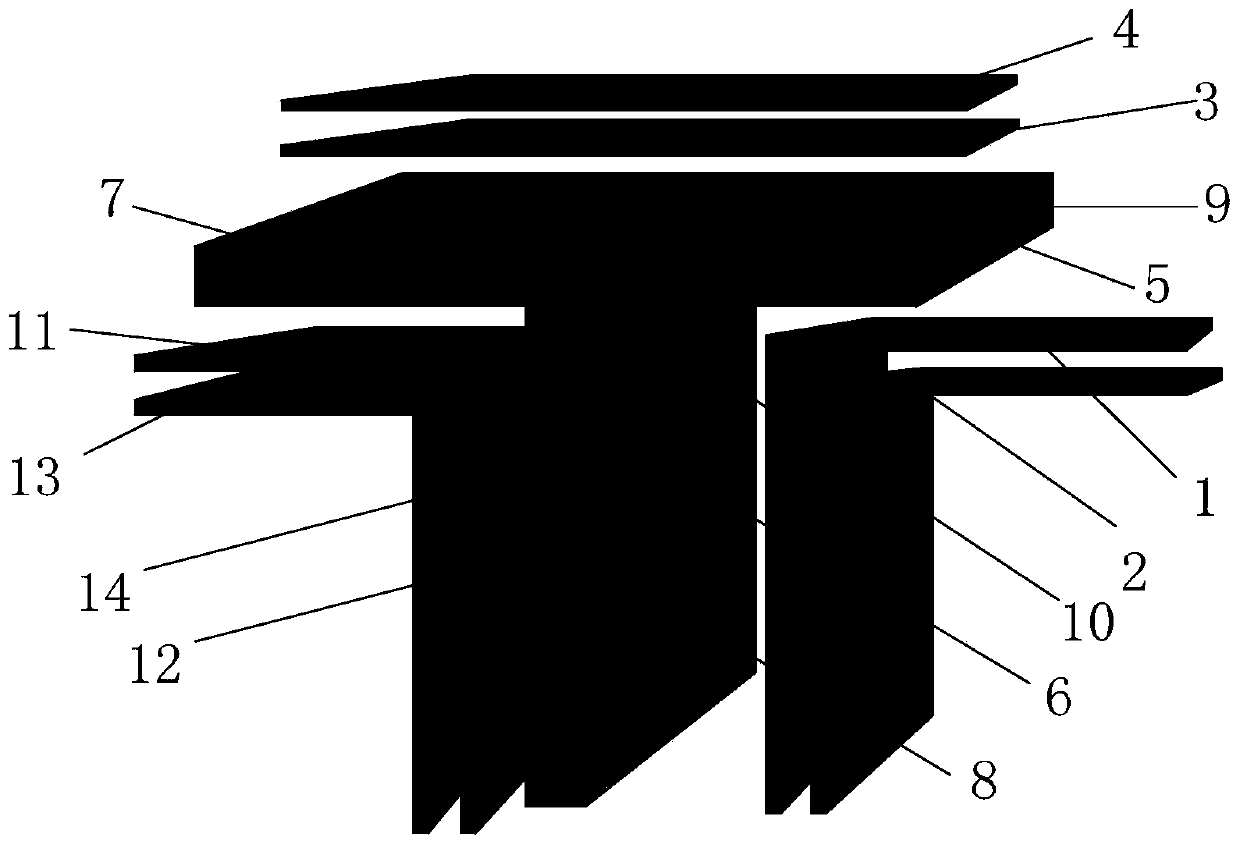

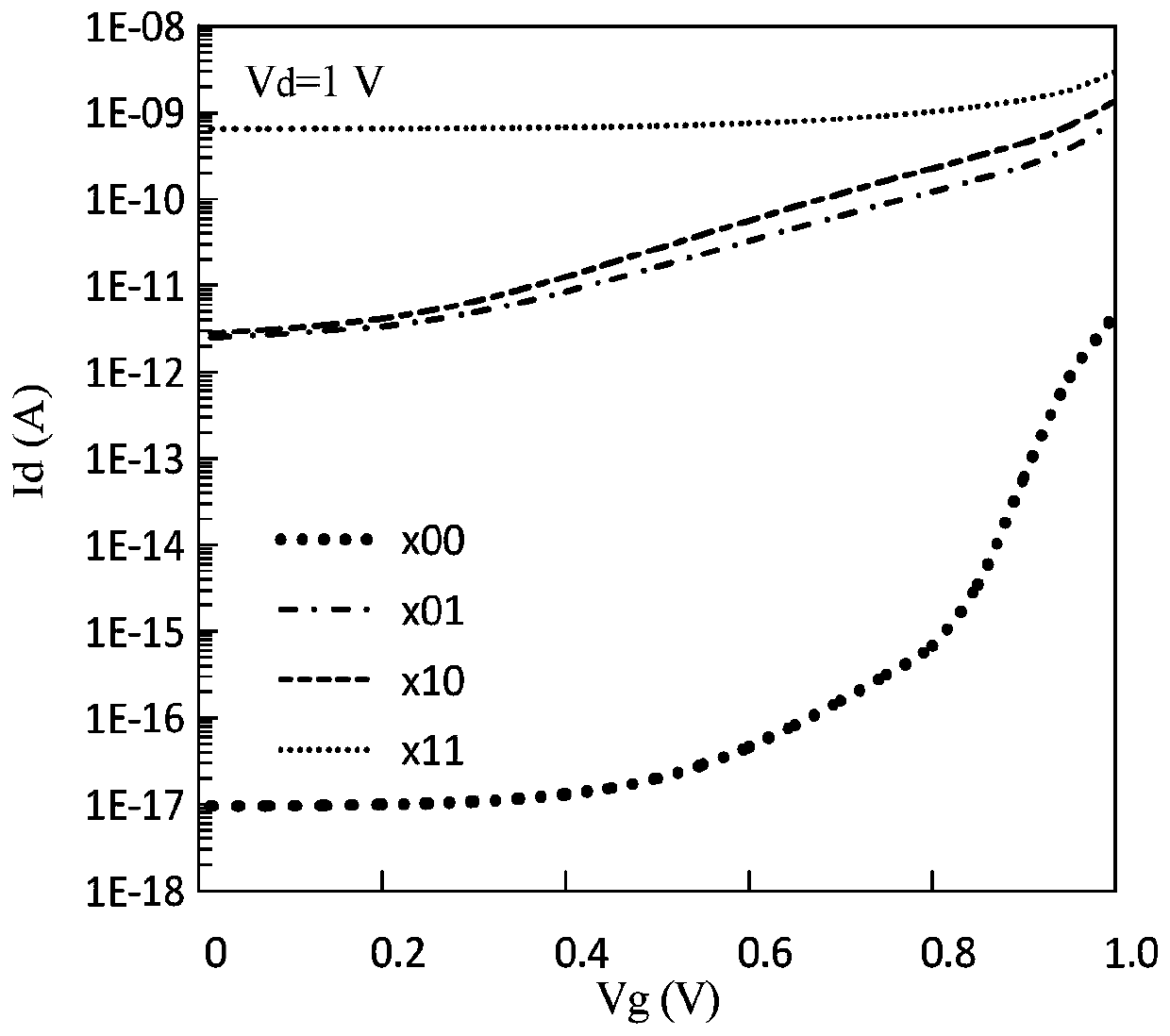

Three-input majority logic device based on TFET

ActiveCN110379851AReduce in quantityTransverse electric field enhancementSemiconductor devicesMajority logicMetal

The invention discloses a three-input majority logic device based on a TFET. The three-input majority logic device comprises a channel region, a source region, a drain region, a first gate oxide layer, a second gate oxide layer, a third gate oxide layer, a first metal gate electrode, a second metal gate electrode and a third metal gate electrode, wherein the channel region is of a T-shaped structure composed of a first rectangular block and a second rectangular block, and the source region is of a T-shaped structure composed of a third rectangular block and a fourth rectangular block. The drain region is of a T-shaped structure composed of a fifth rectangular block and a sixth rectangular block. The structure of the second gate oxide layer and the structure of the first gate oxide layer are bilaterally symmetrical relative to the center line of the second rectangular block in the vertical direction, and the structure of the second metal gate electrode and the structure of the first metal gate electrode are bilaterally symmetrical relative to the center line of the second rectangular block in the vertical direction; the third gate oxide layer is arranged on the upper end surface ofthe first rectangular block, and the third metal gate electrode is arranged on the upper end surface of the third gate oxide layer. The device has the advantages of compact structure, small area and low power consumption.

Owner:NINGBO UNIV

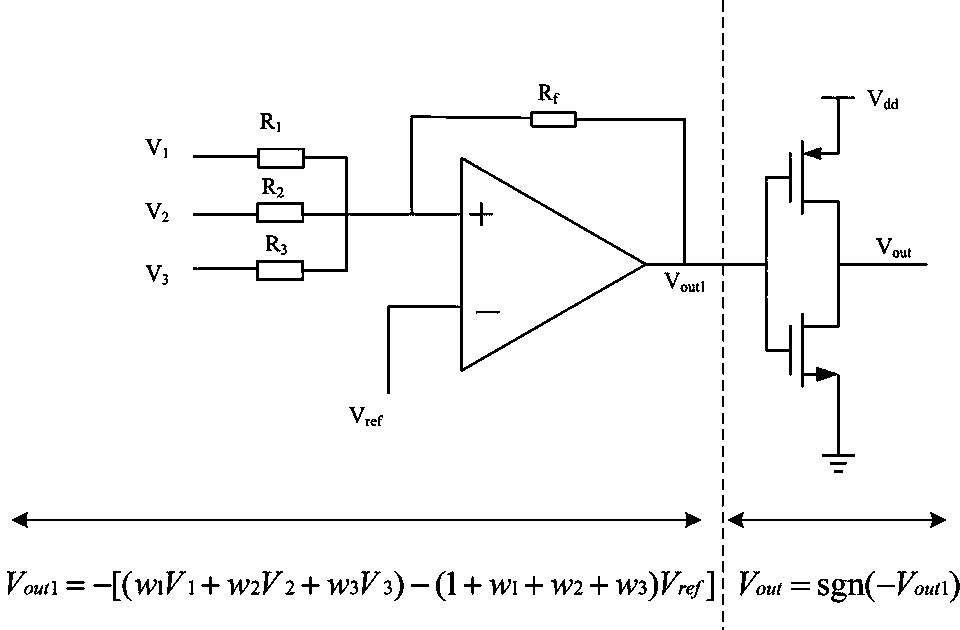

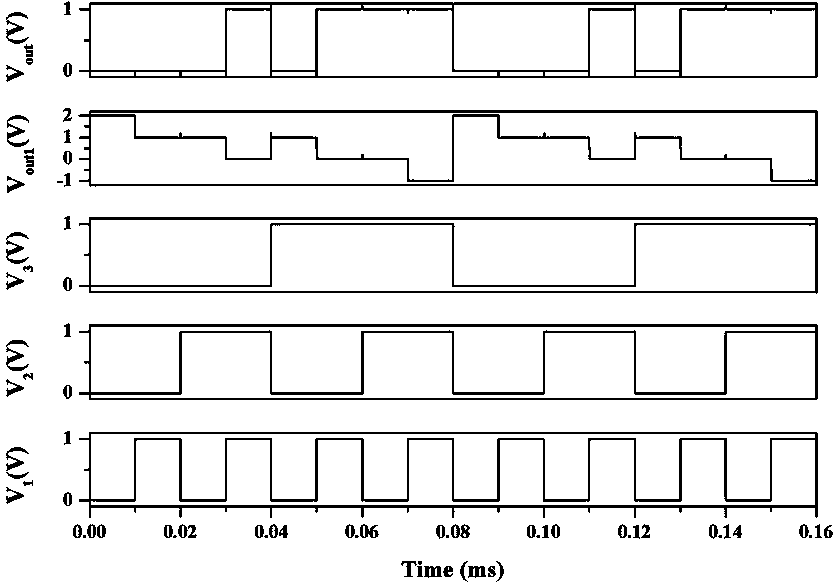

Threshold logic circuit based on CMOS operational amplifier

InactiveCN103560781ASimple structureStrong reconfigurabilityLogic circuits characterised by logic functionAudio power amplifierEngineering

The invention relates to a circuit which is designed on the basis of a CMOS operational amplifier and is capable of achieving threshold logic, in particular to a threshold logic circuit based on the CMOS operational amplifier. The threshold logic circuit is only composed of an input resistor array, the operational amplifier and an inverter. The threshold value of the circuit is determined by reference voltage and input weight, weight of each input end is only relevant to a specific value of feedback resistance and input resistance, so that the reconfigurable performance is good, and different logic functions are achieved. In addition, a design method of the threshold logic circuit for achieving the logic function is introduced with implementation of a majority logic gate serving as an example and the correctness of the function of the circuit is verified through Cadence simulation. The threshold logic circuit based on the CMOS operational amplifier has the advantages of being simple in structure, good in reconfigurable performance and capable of serving as a basic unit to be applied to the fields of a neural network and the like.

Owner:FUZHOU UNIV

3D Quantum Cellular Automata Adder

InactiveCN104407835BReduce areaSave hardware resourcesDigital data processing detailsQuantum cellular automatonCellular automation

Owner:NANJING UNIV OF AERONAUTICS & ASTRONAUTICS

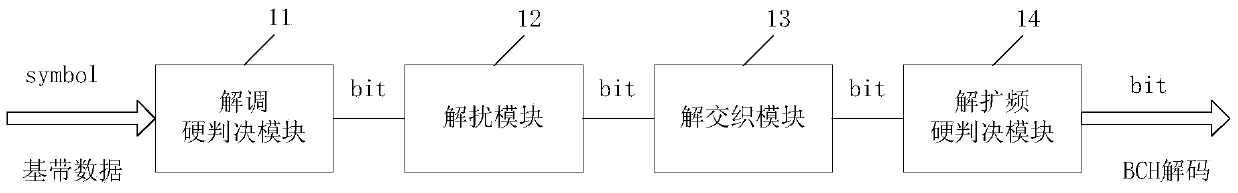

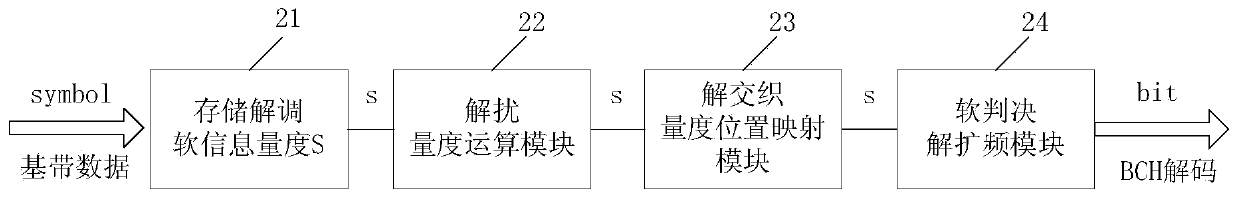

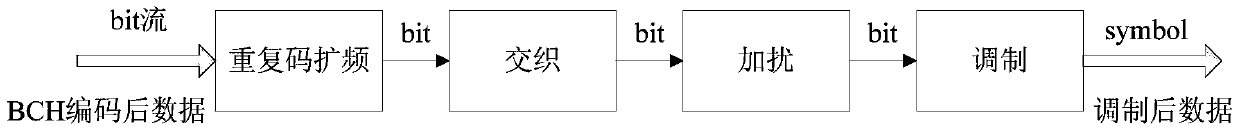

A wireless body area network repetition code despreading system and method

ActiveCN105162492BImplement automatic switch selectionReduce processingError preventionBody area networkSoftware system

The embodiment of the present invention discloses a wireless body area network repetition code despreading system and method. After the obtained baseband signal is sequentially processed by a demodulation hard decision module, a descrambling module and a deinterleaving module, it is judged whether the hard decision receiving sequence satisfies the following requirements: Preset conditions, if yes, perform measurement calculation on the reliability measure obtained by the demodulation hard decision module, and use soft decision algorithm to despread; otherwise, despread the hard decision receiving sequence according to the logic of large numbers , to realize the automatic switching selection of the spread spectrum method. Therefore, compared with the conventional soft despreading system in the prior art, the data processing amount is small and the speed is fast. Compared with the conventional hard despreading system in the prior art Spread spectrum systems are more reliable.

Owner:INST OF MICROELECTRONICS CHINESE ACAD OF SCI

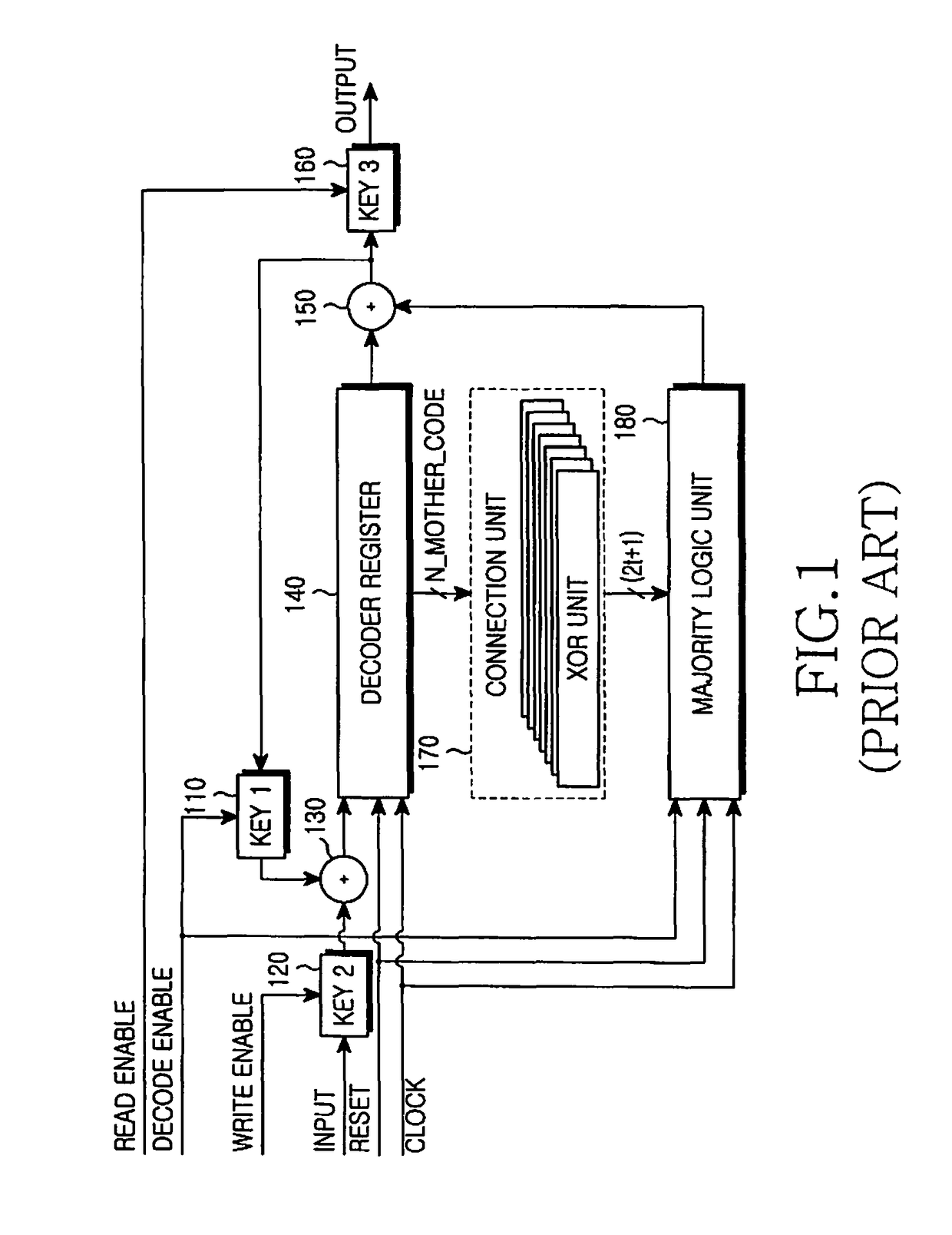

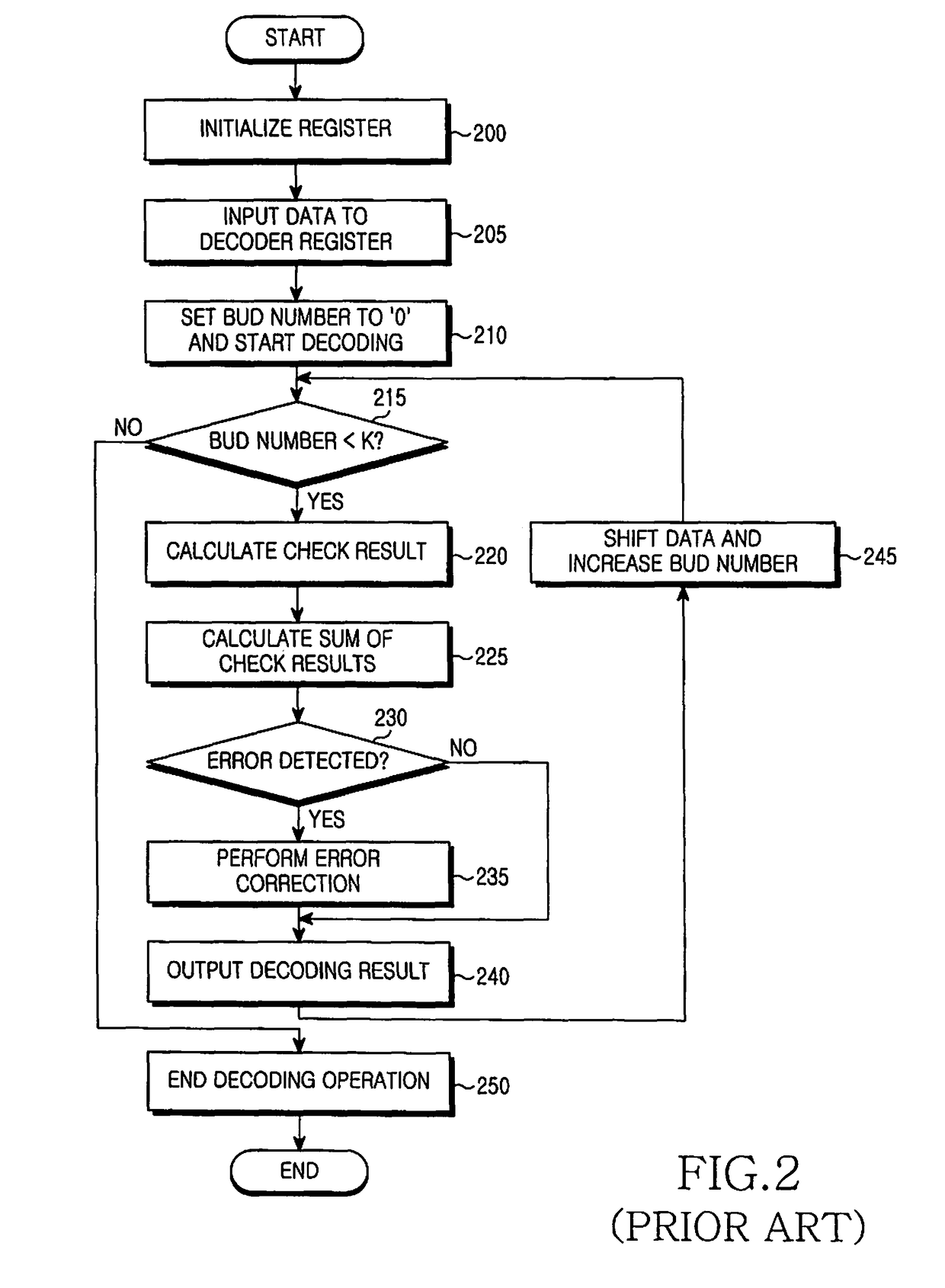

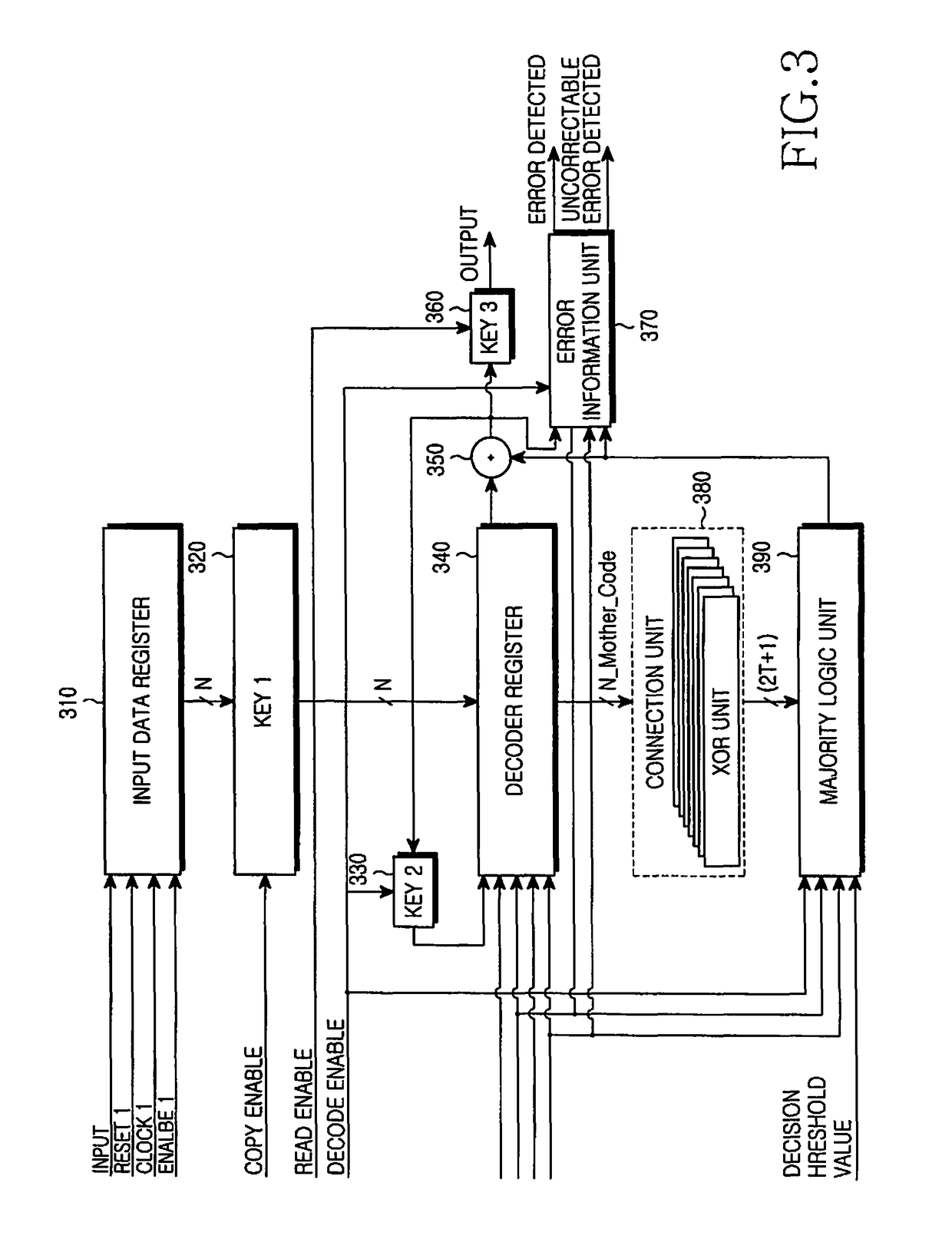

Decoding apparatus and method for a perfect difference-set cyclic code and a difference-set cyclic code

ActiveUS8122318B2Increase ratingsLess powerError preventionTransmission systemsComputer hardwareProcessor register

A decoding apparatus includes a decoder register for receiving data having a codeword including null data bits, and decoding the received data while shifting Bit Under Decoding (BUD) by one bit. A connection unit outputs a check result by applying a predetermined check equation to the data output from the decoder register. A majority logic unit for determines if an error is detected according to the check result output from the connection unit, and outputs the determination result. An error information unit determines if there is an error in the received data and if there is an uncorrectable error in the decoded data.

Owner:SAMSUNG ELECTRONICS CO LTD

A Quantum Cellular Automata Decimal Full Adder

ActiveCN111221497BOptimize the number of logical nodesAdd depthQuantum computersDigital data processing detailsCellular automationSoftware engineering

The invention discloses a decimal full adder of quantum cellular automata. On the premise of not changing the logic function of the circuit, the QCA is optimized by combining the XOR logic operator with stronger expressive ability and the advanced carry structure of the full adder. The number of logic nodes and logic depth required by the decimal full adder, so as to optimize the area and delay of one-bit and multi-bit QCA decimal full adder circuits. Compared with the traditional full adder with the best performance, the quantum cellular automaton decimal full adder proposed by the present invention has excellent performance, and the delay and area are significantly improved, especially in the quantum cellular automaton 8-bit decimal full adder The optimization effect is more obvious, and the delay and area are increased by 27.6% and 53.4% respectively. The invention greatly reduces the circuit cost, and at the same time enriches the circuit research method in circuit design. The invention provides a new research idea for arithmetic circuit design based on majority logic and XOR logic, and has strong practical significance for the development of circuit design.

Owner:NINGBO UNIV

Nanomagnetic logic multiple-selection logic gate circuit based on magnetoelectric effect clock control method

PendingCN113965196AReduce power consumptionHigh speedLogic circuits characterised by logic functionComputer architectureTelecommunications

The invention discloses a nano-magnetic logic multiple-selection logic gate circuit based on a magnetoelectric effect clock control method. The logic gate circuit comprises a first input end, a second input end, a third input end, an intermediate operation circuit, a first output end, a second phase inverter and a second output end, the intermediate operation circuit comprises a plurality of first phase inverters, a first two-input AND gate, a second two-input AND gate, a third two-input AND gate and a three-input OR gate. The intermediate operation circuit is connected with the input end, the output end of the intermediate operation circuit is connected with the three input OR gates, the three input OR gates are connected with the second phase inverter in series, and the output end of the second phase inverter serves as the second output end. The invention designs a clock control scheme based on a magnetoelectric effect on the basis of a majority logic gate circuit. Compared with other known clock control schemes, the clock control scheme can further reduce circuit power consumption and improve circuit speed, and the circuit is simple in structure and easy to prepare. Meanwhile, the clock control scheme is not only suitable for a majority logic gate circuit, but also can be applied to other NML circuits.

Owner:DALIAN NEUSOFT UNIV OF INFORMATION

Logic gate with neuron circuit

PendingUS20220358353A1Consumption of heat be minimizedHeat dissipation be minimizedPhysical realisationLogic circuits using superconductive devicesSimulationNeuron circuit

A logic gate with a neuron circuit which is used in electronic logic circuits, enables the arithmetic inputs to give output signal over the threshold value depending on a set threshold value according to the used AND, OR and MAJORITY logic gates, and enables to realize the logic processes by adjusting the triggering threshold value.

Owner:TOBB EKONOMI VE TEKNOLOJI UNIVERSITESI

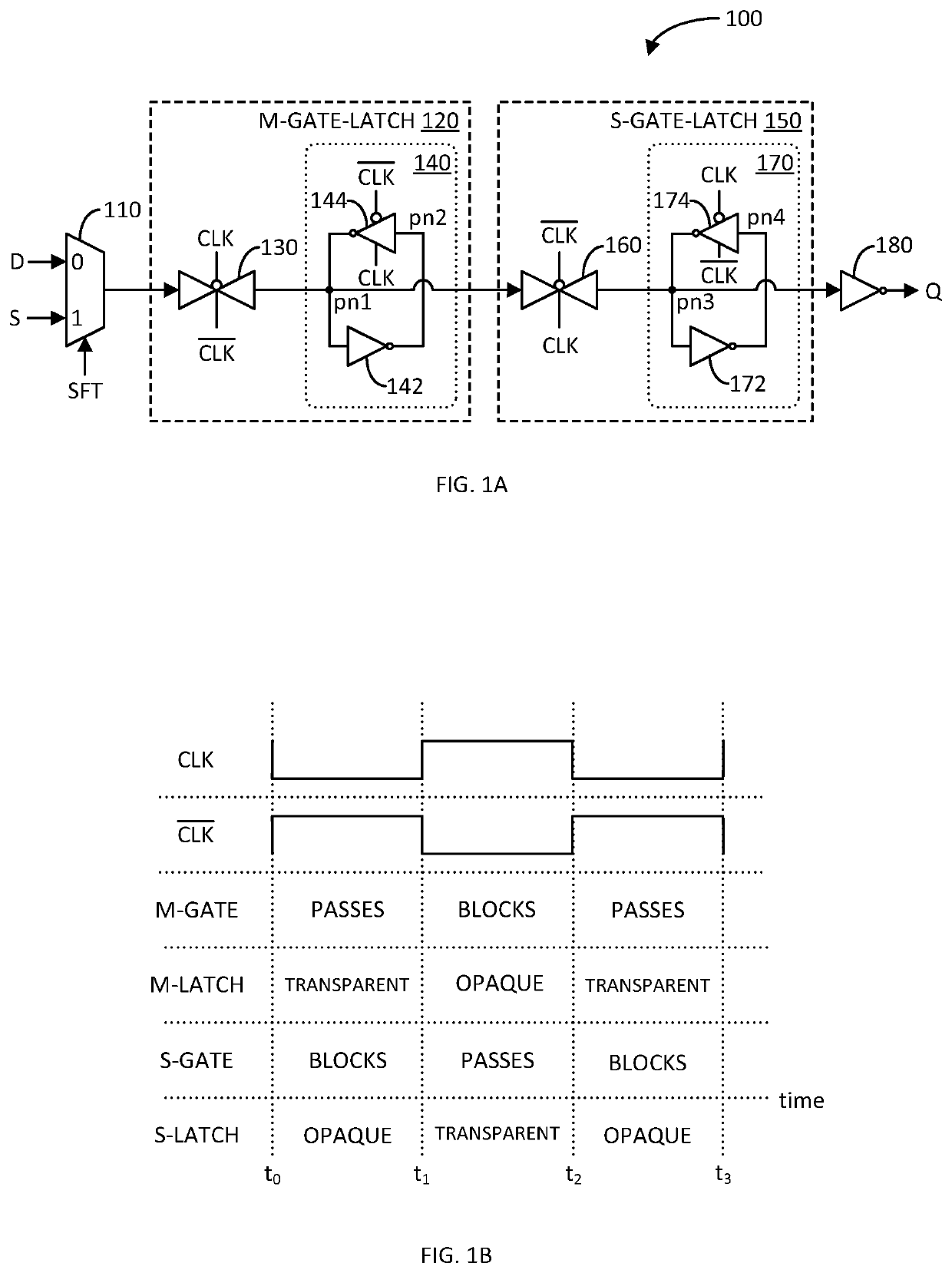

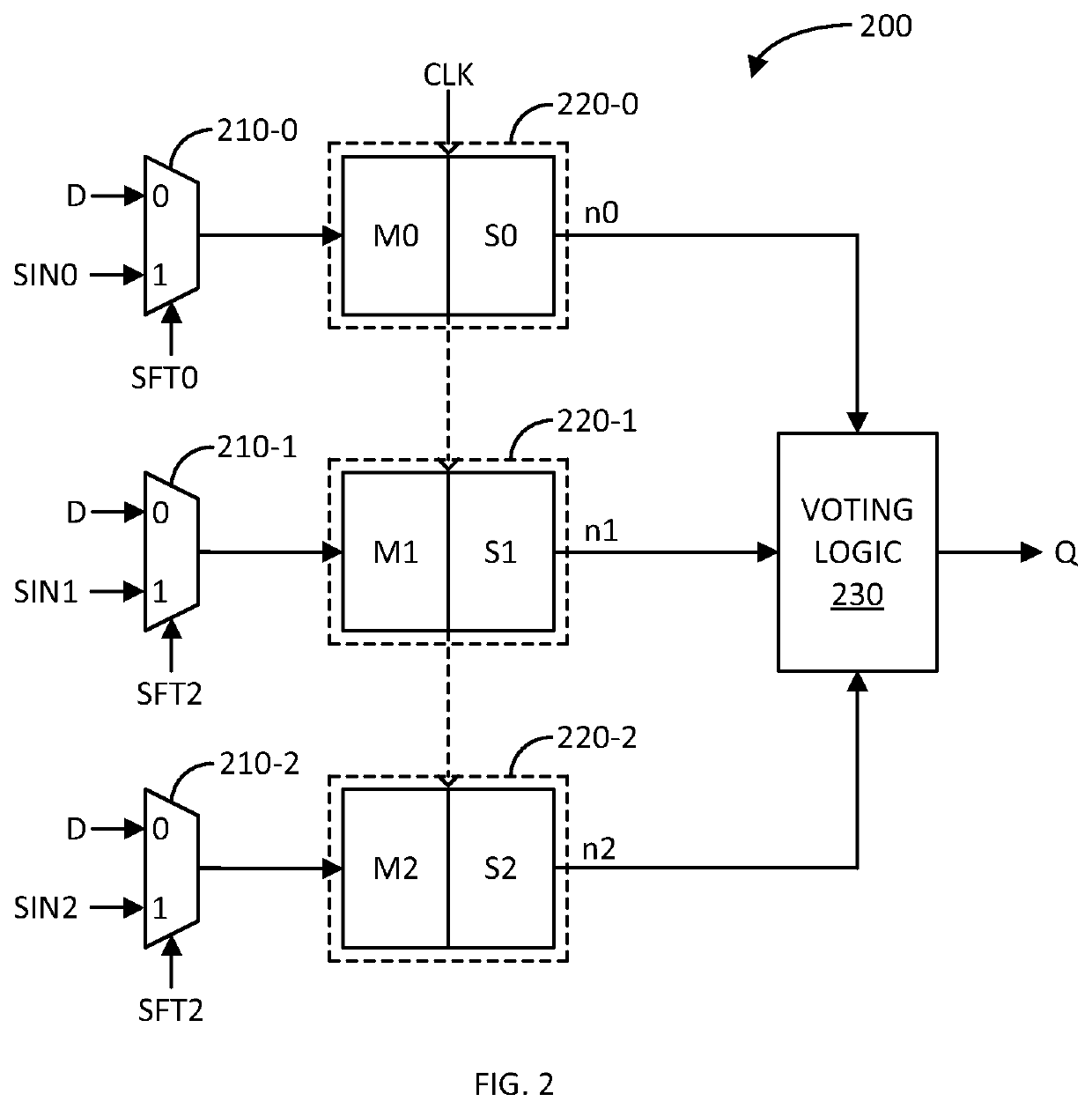

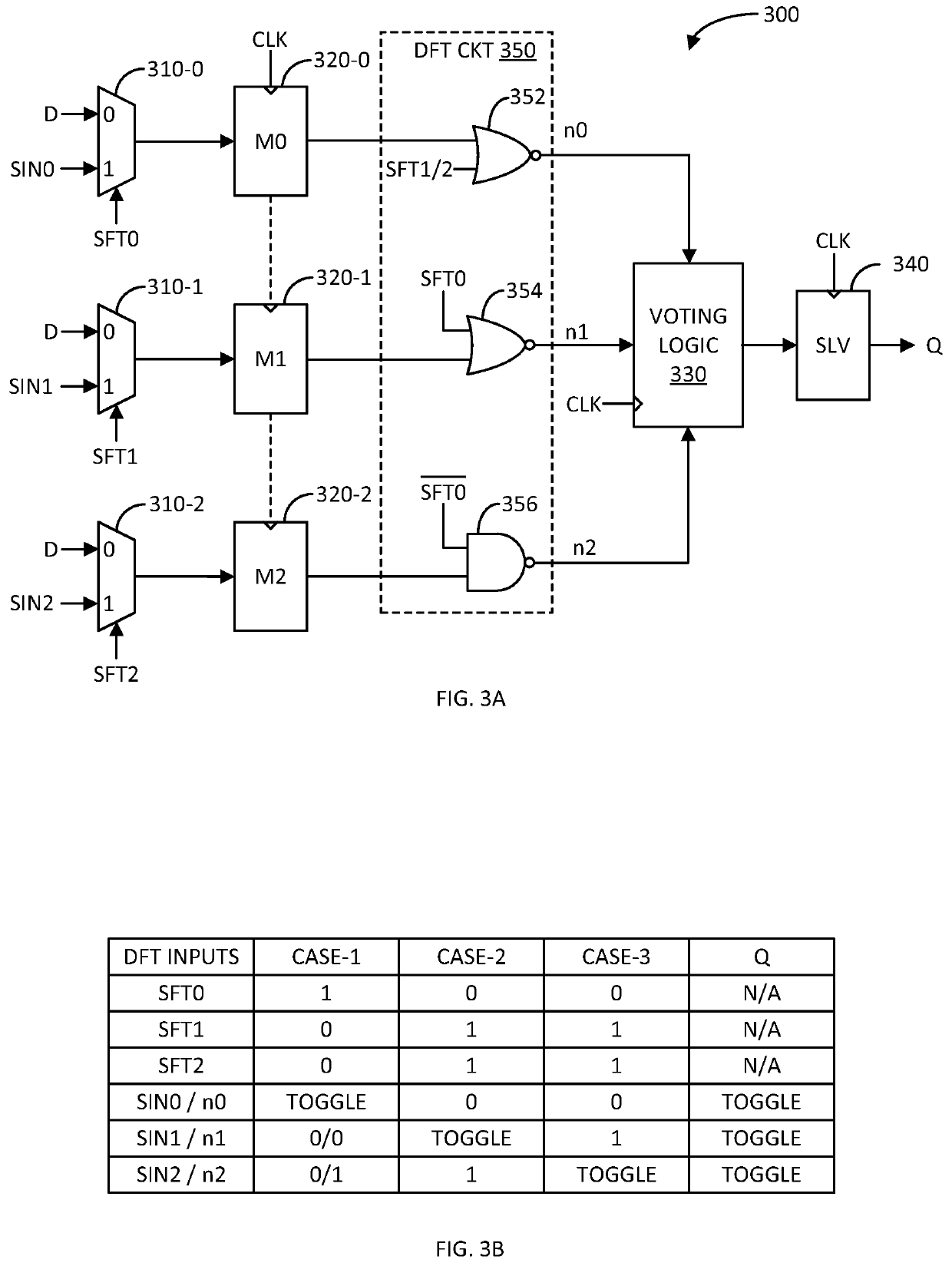

Triple modular redundancy flip-flop with improved power performance area and design for testability

ActiveUS20220109445A1Reliability increasing modificationsMajority/minority circuitsComputer architectureFlip-flop

A triple modular redundancy (TMR) flip-flop includes a set of master-gate-latch circuits including a first set of inputs to receive a first digital signal, and a second set of inputs to receive a clock; and a voting logic circuit including a set of inputs coupled to a set of outputs of the set of master-gate-latch circuits, and an output to generate a second digital signal based on the first digital signal. Another TMR flip-flop includes a set of master-gate-latch circuits to receive a set of digital signals in response to a first edge of a clock, respectively; and latch the set of digital signals in response to a second edge of the clock, respectively; and a voting logic circuit to receive the latched set of digital signals; and generate a second digital signal based on a majority of logic levels of the latched first set of digital signals, respectively.

Owner:QUALCOMM INC