Three-input majority logic device based on TFET

A majority logic, three-input technology, applied in the direction of semiconductor devices, electrical components, circuits, etc., to achieve the effect of saving quantity, reducing circuit area, and small area

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

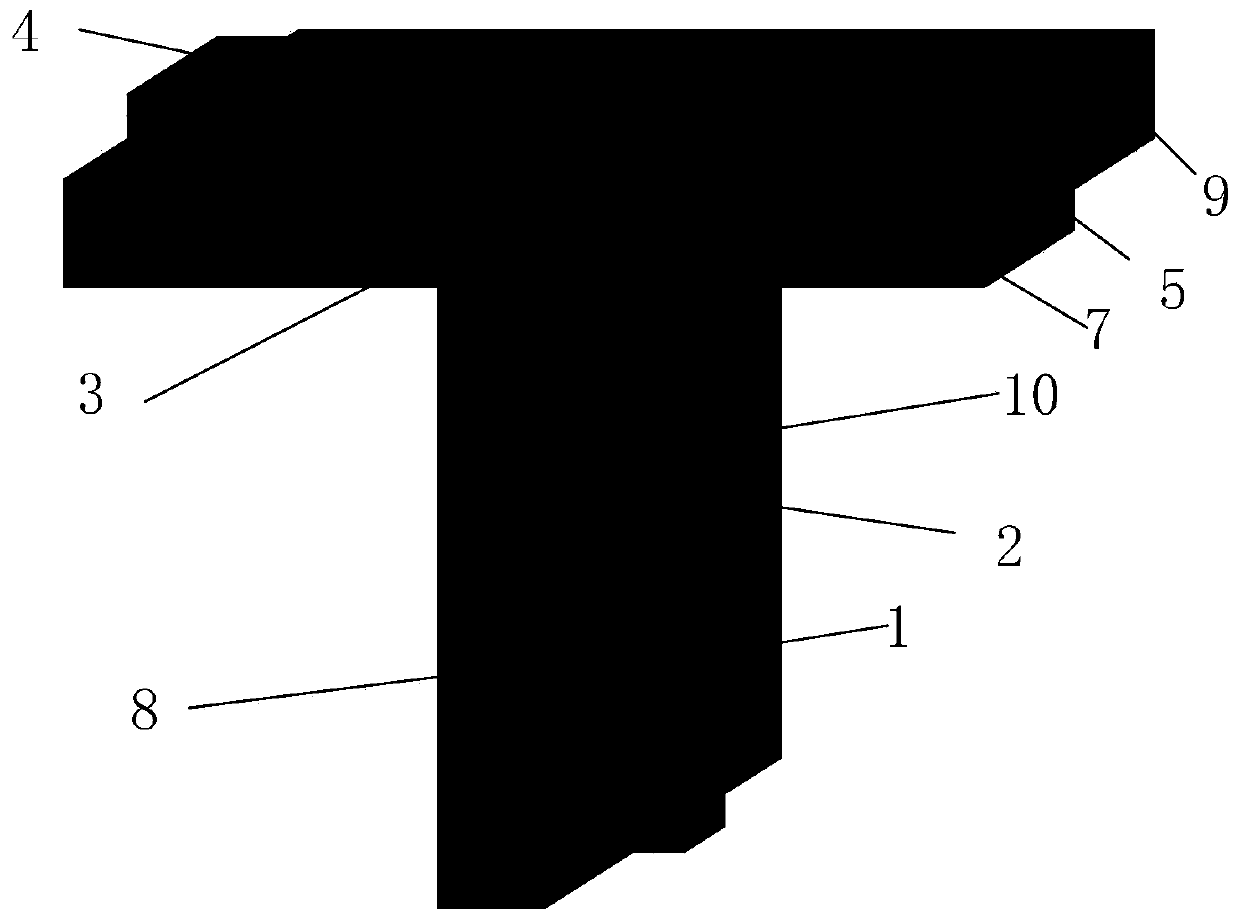

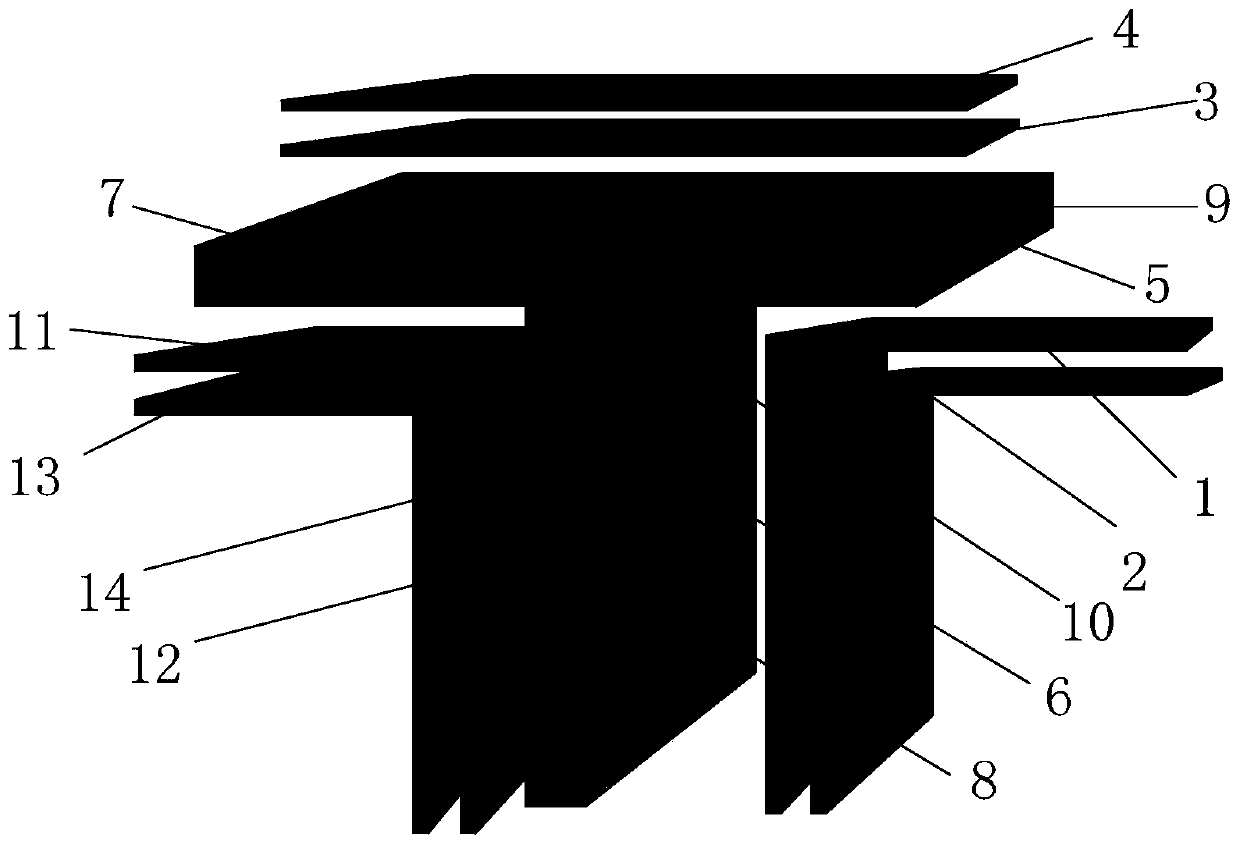

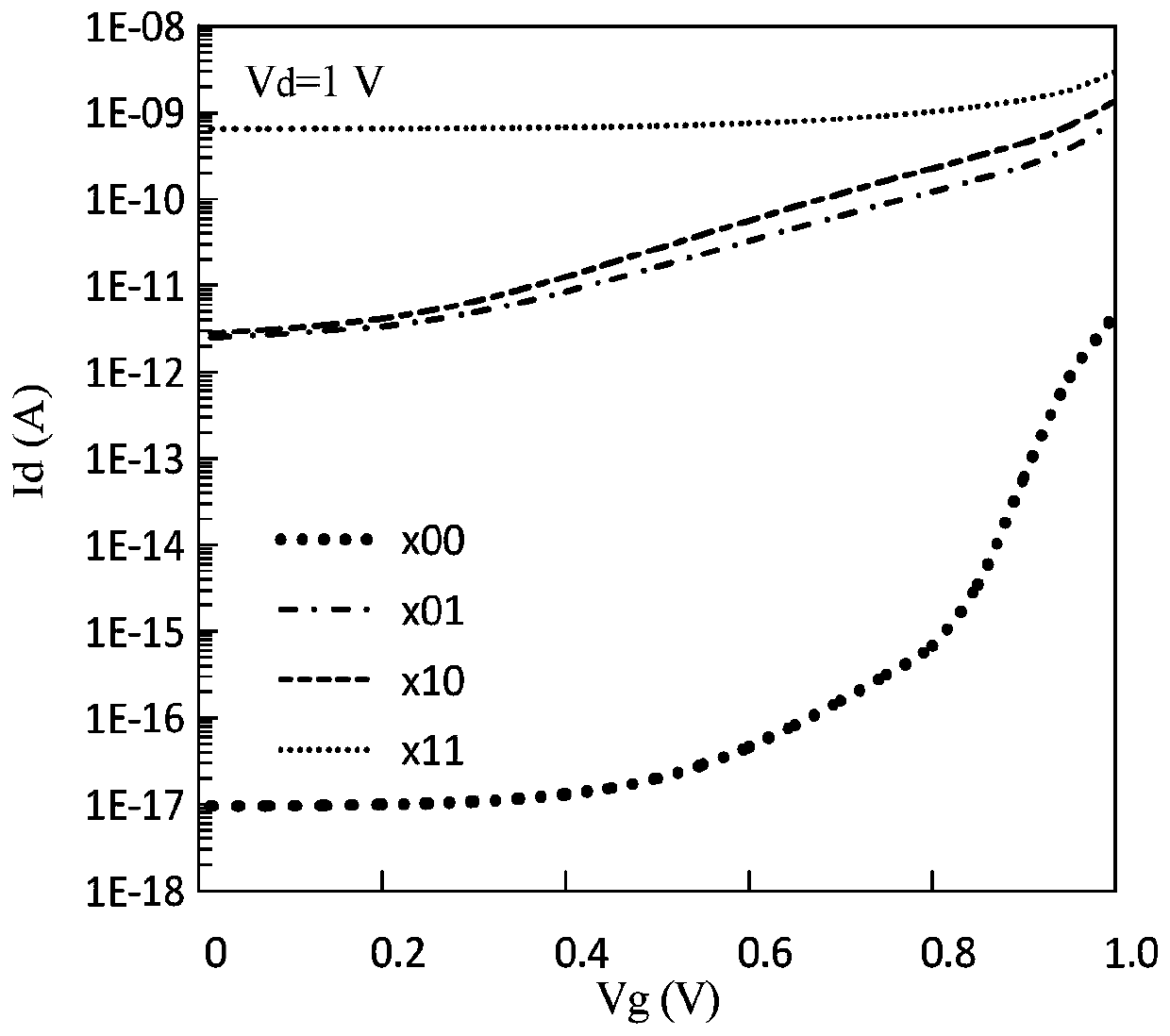

[0018] Embodiment 1: As shown in the figure, a TFET-based three-input majority logic device includes a channel region, a source region, a drain region, a first gate oxide layer, a second gate oxide layer 1, a third gate The oxide layer 2, the first metal gate, the second metal gate 3 and the third metal gate 4; the channel region is a T-shaped structure composed of the first rectangular block 5 and the second rectangular block 6, the first rectangular block 5 is arranged horizontally, the second rectangular block 6 is vertically arranged, the second rectangular block 6 is perpendicular to the first rectangular block 5, the upper end surface of the second rectangular block 6 is connected with the lower end surface of the first rectangular block 5, and the first rectangular block The front end face of the block 5 and the front end face of the second rectangular block 6 are located in the same plane, the rear end face of the first rectangular block 5 and the rear end face of the s...

Embodiment 2

[0021]Embodiment 2: As shown in the figure, a TFET-based three-input majority logic device includes a channel region, a source region, a drain region, a first gate oxide layer, a second gate oxide layer 1, and a third gate The oxide layer 2, the first metal gate, the second metal gate 3 and the third metal gate 4; the channel region is a T-shaped structure composed of the first rectangular block 5 and the second rectangular block 6, the first rectangular block 5 is arranged horizontally, the second rectangular block 6 is vertically arranged, the second rectangular block 6 is perpendicular to the first rectangular block 5, the upper end surface of the second rectangular block 6 is connected with the lower end surface of the first rectangular block 5, and the first rectangular block The front end face of the block 5 and the front end face of the second rectangular block 6 are located in the same plane, the rear end face of the first rectangular block 5 and the rear end face of th...

PUM

| Property | Measurement | Unit |

|---|---|---|

| Doping concentration | aaaaa | aaaaa |

| Work function | aaaaa | aaaaa |

| Length | aaaaa | aaaaa |

Abstract

Description

Claims

Application Information

Login to View More

Login to View More