Patents

Literature

809 results about "Metal gate electrodes" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

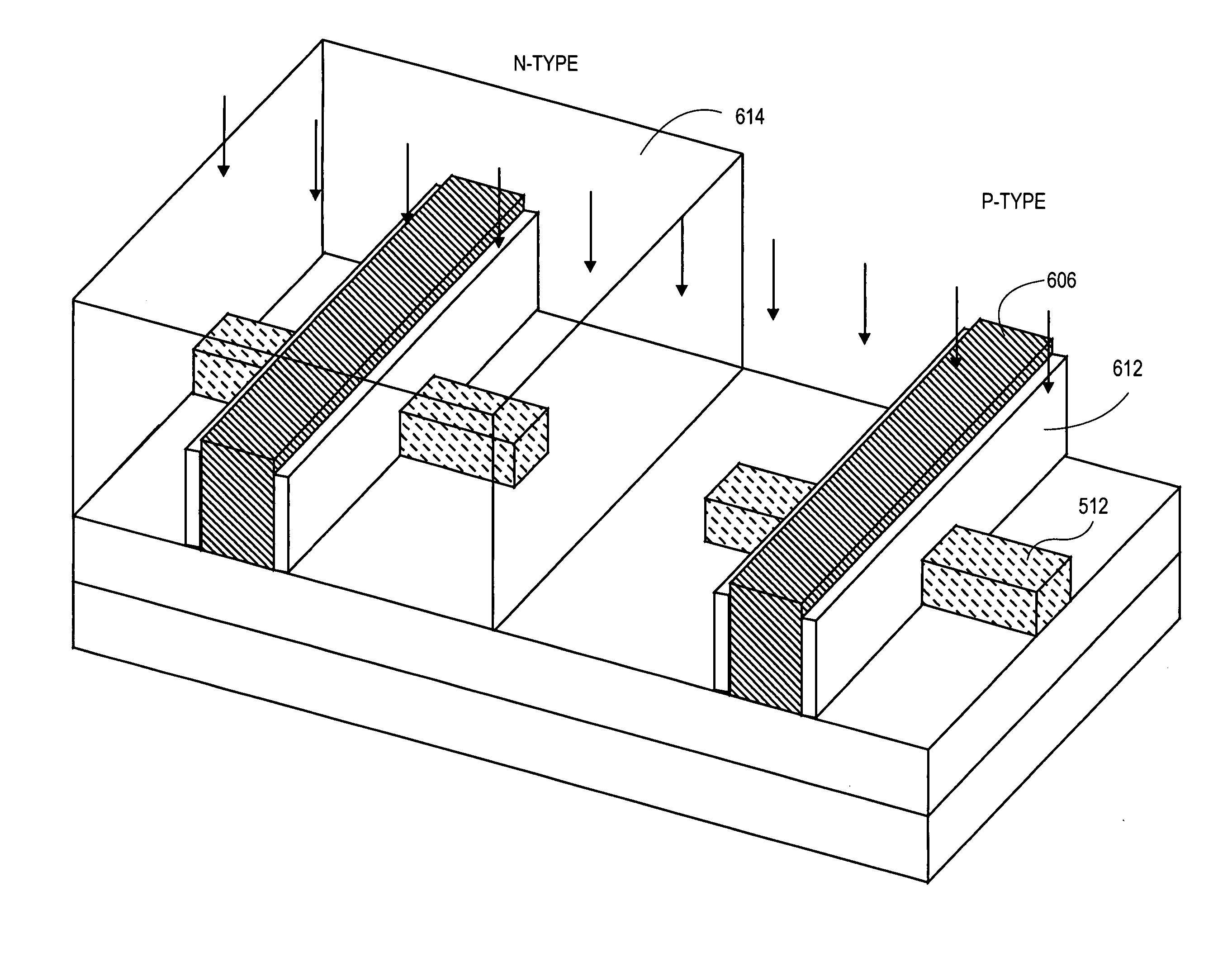

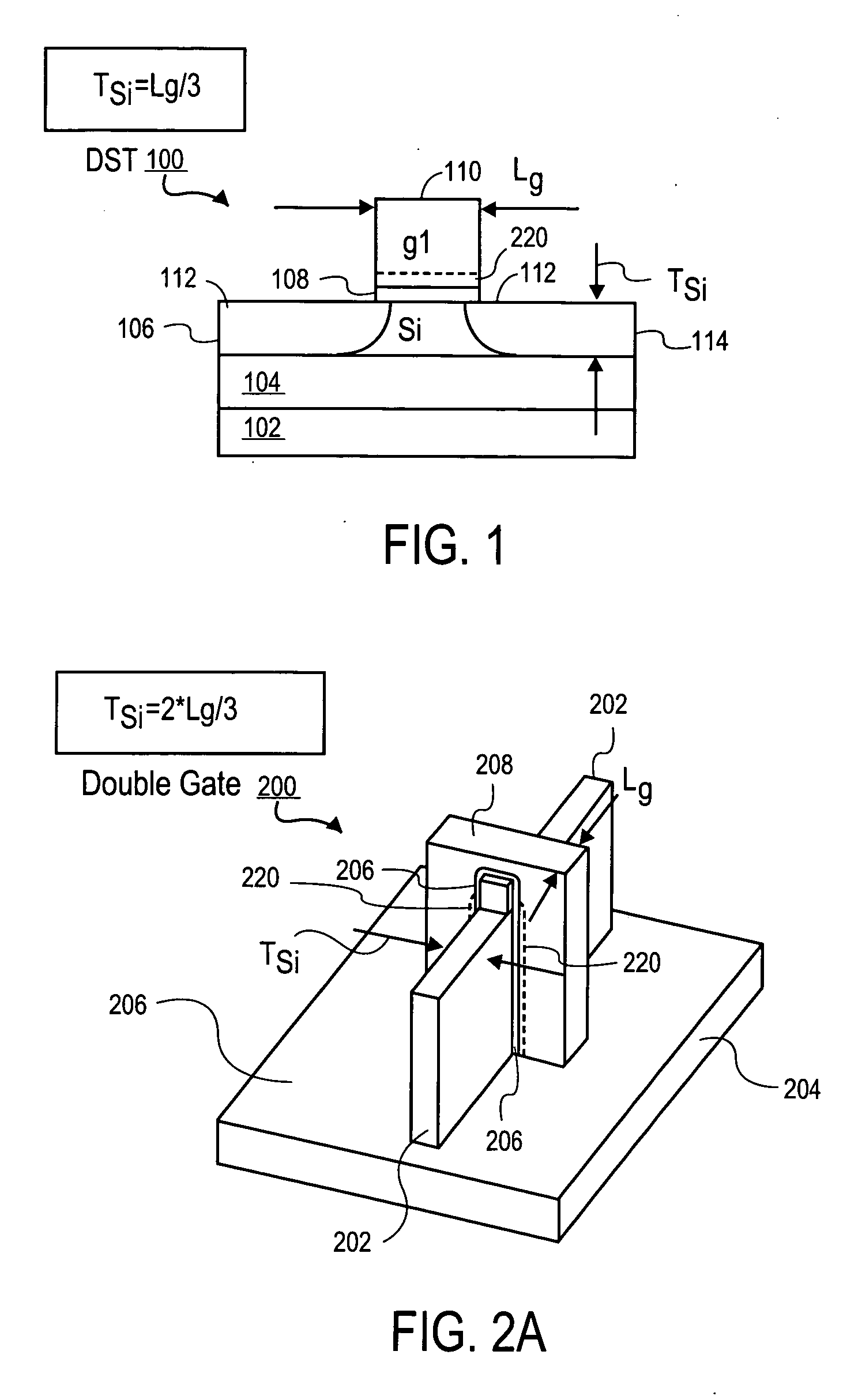

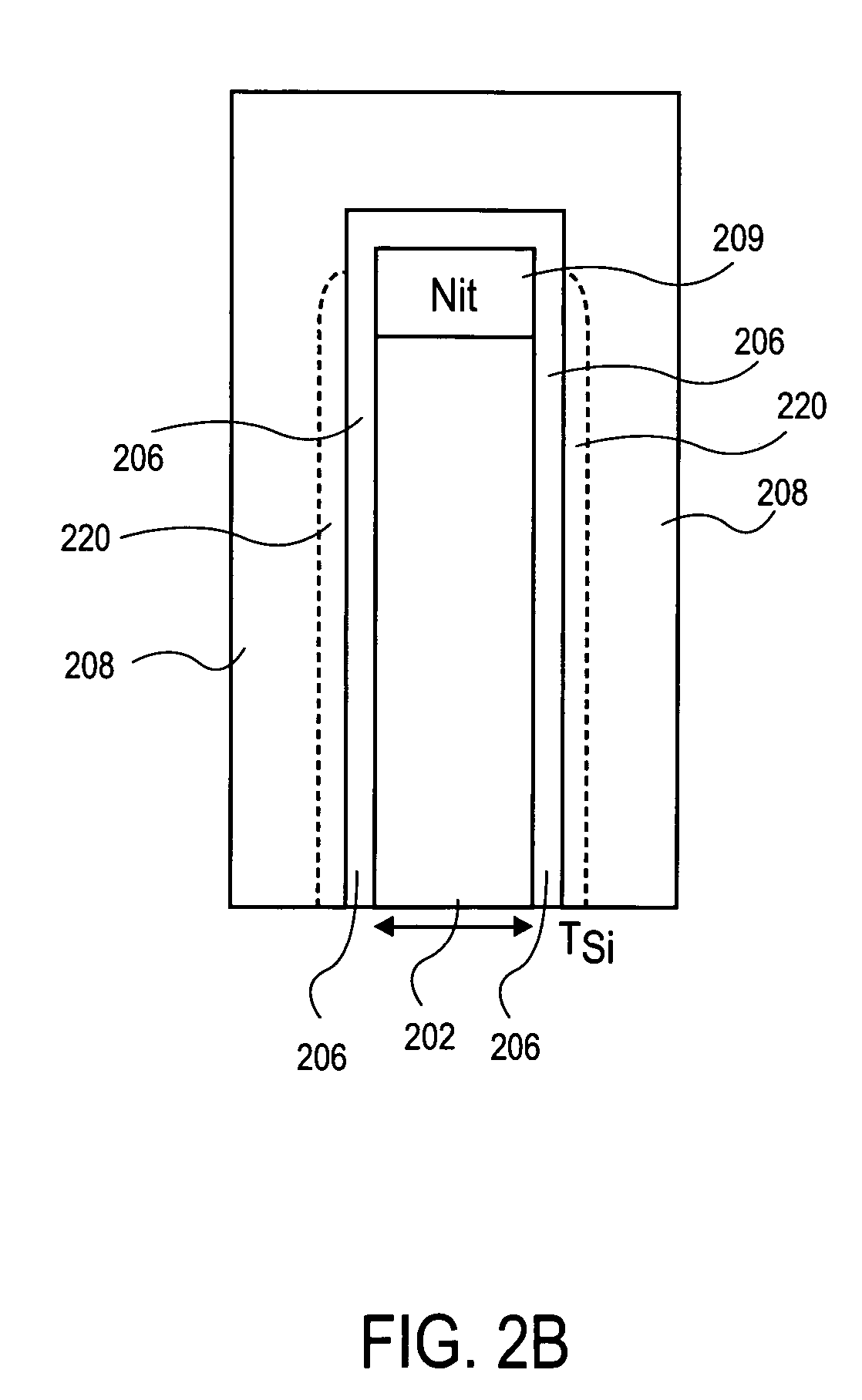

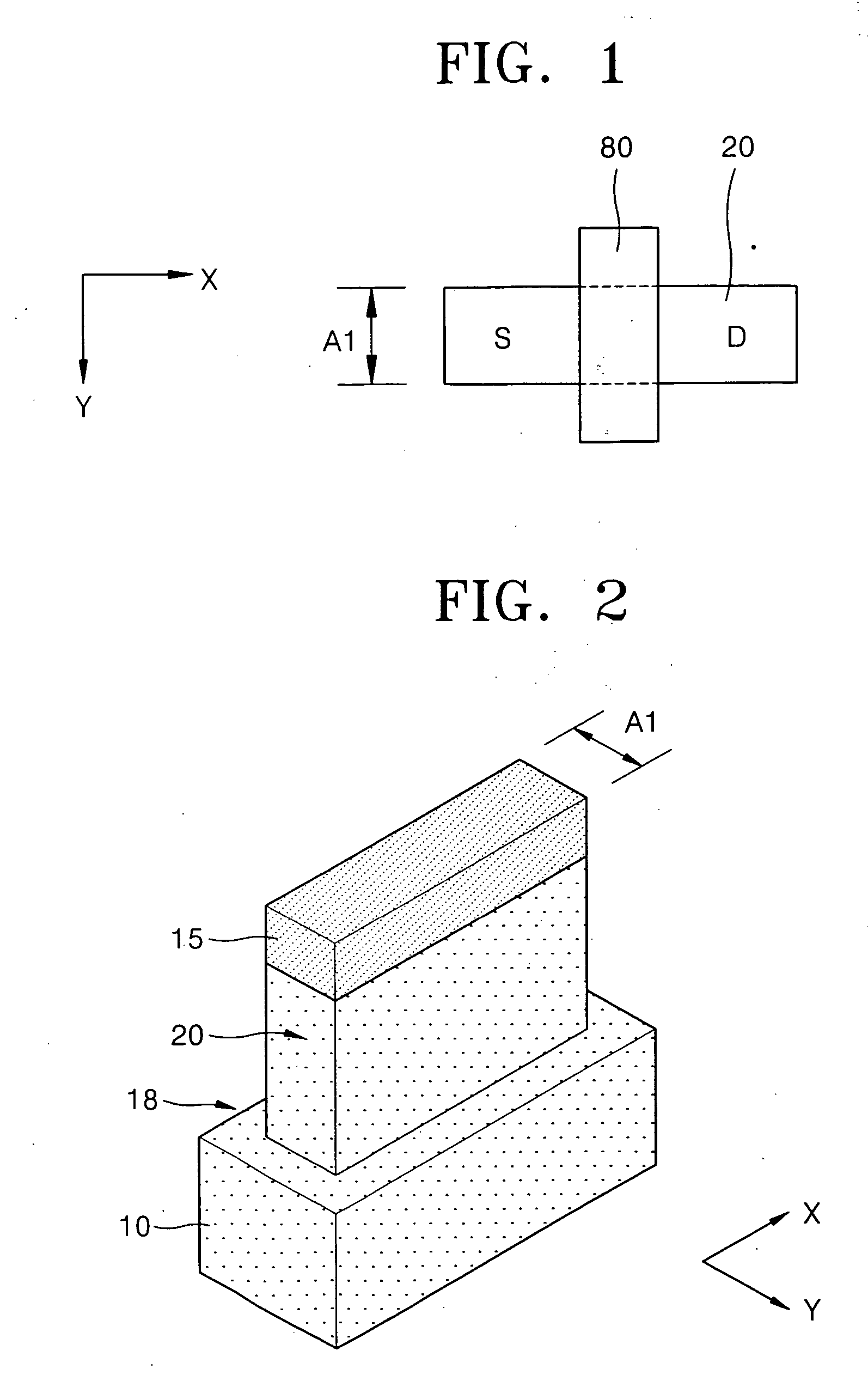

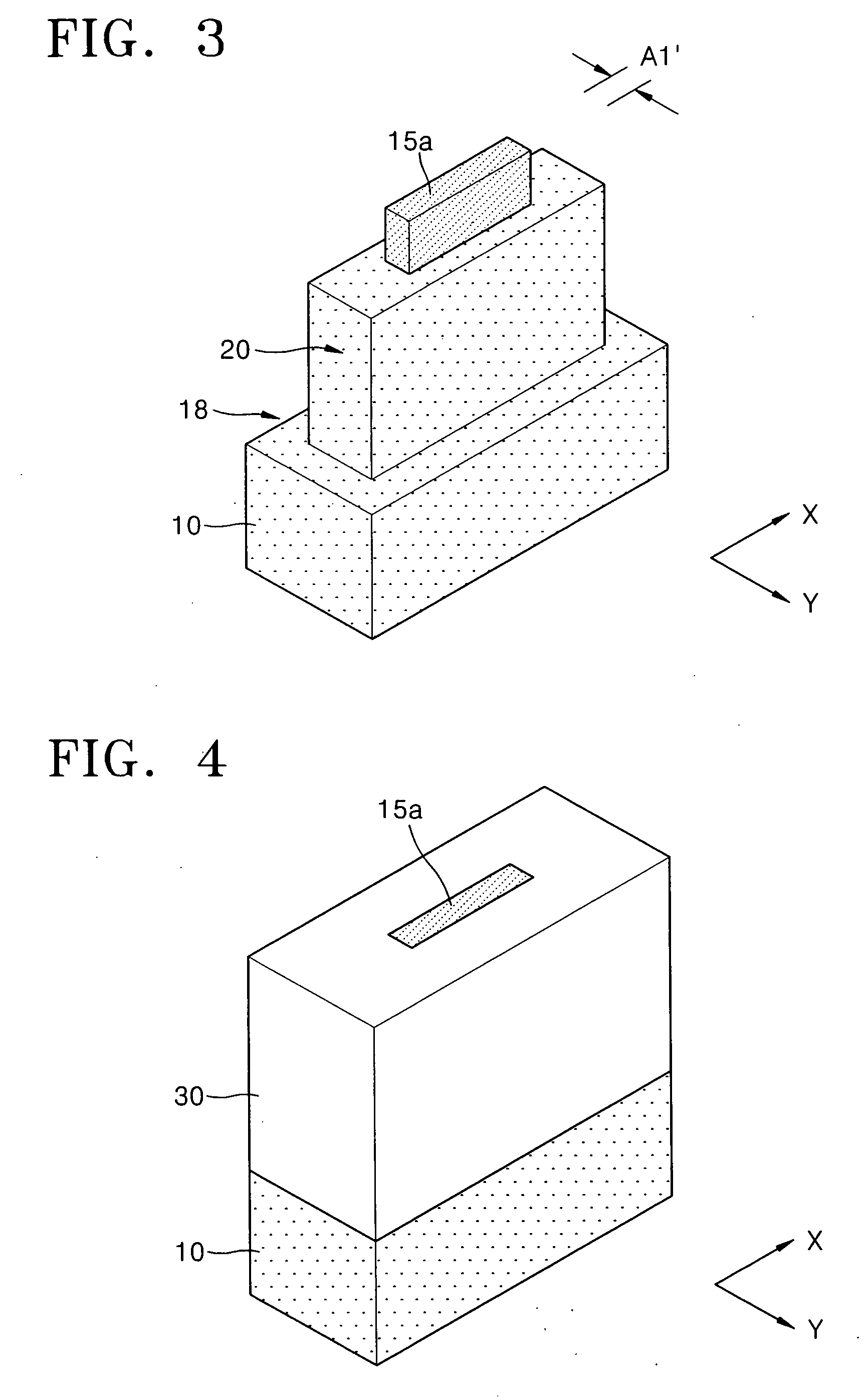

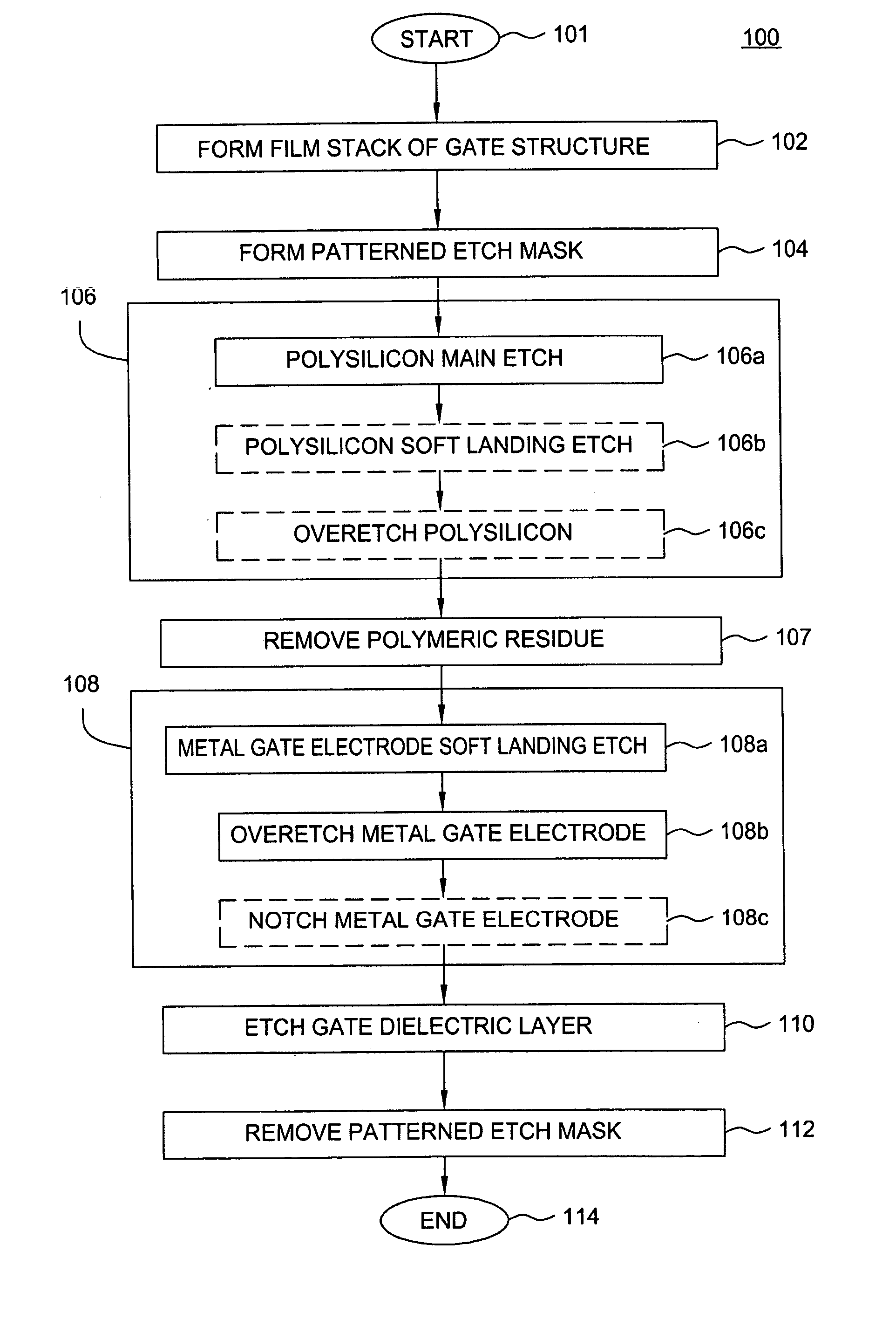

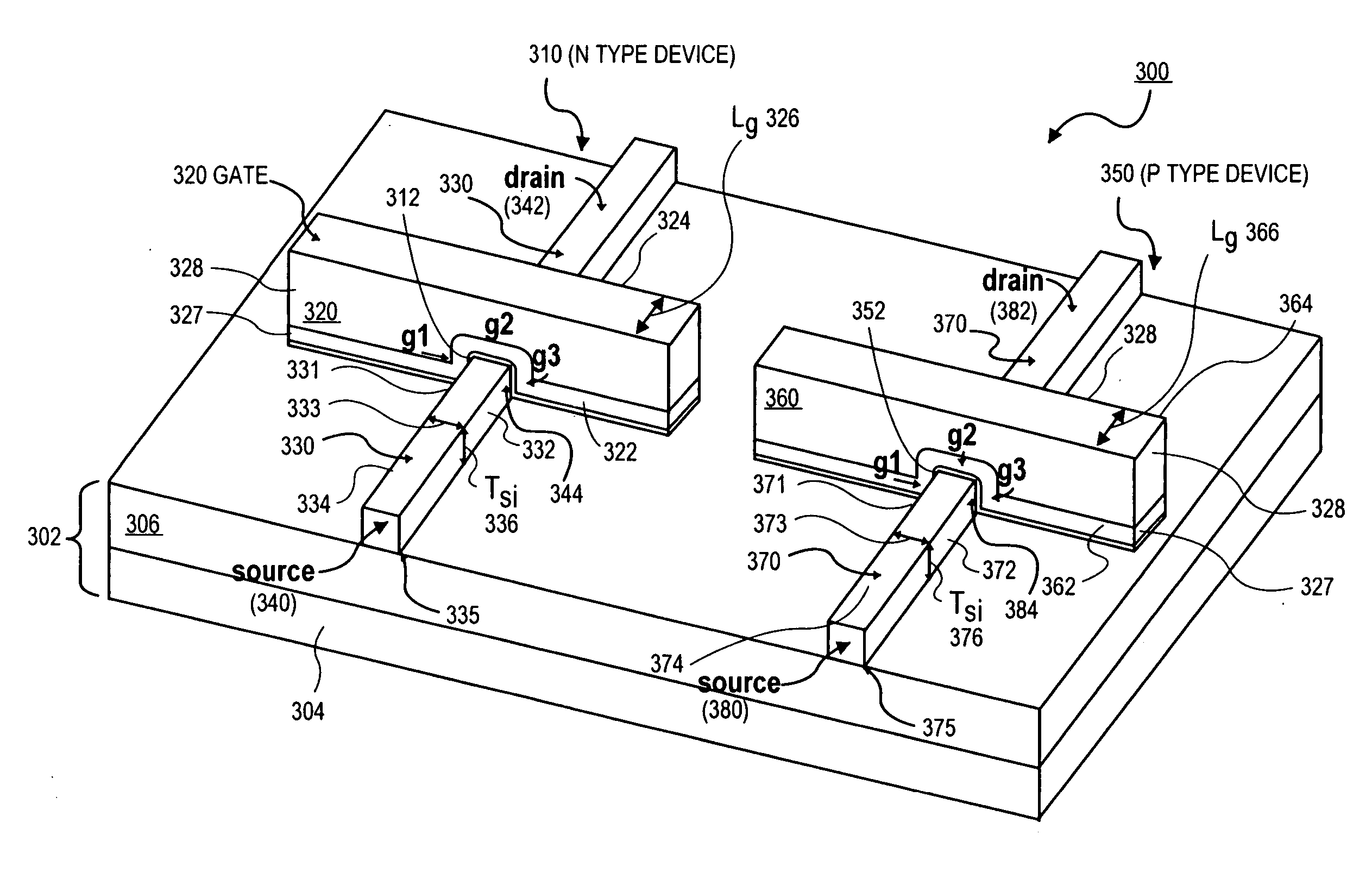

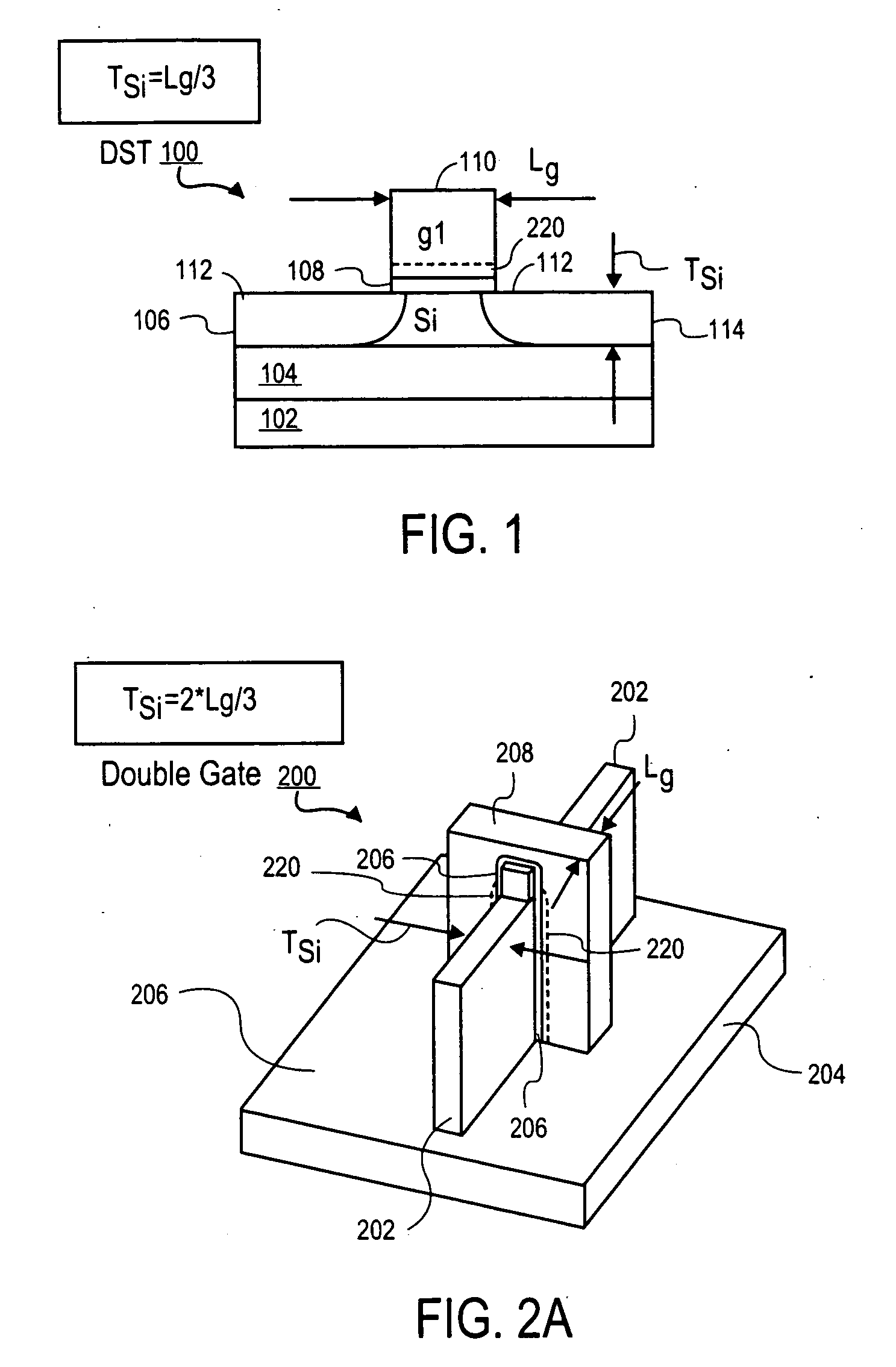

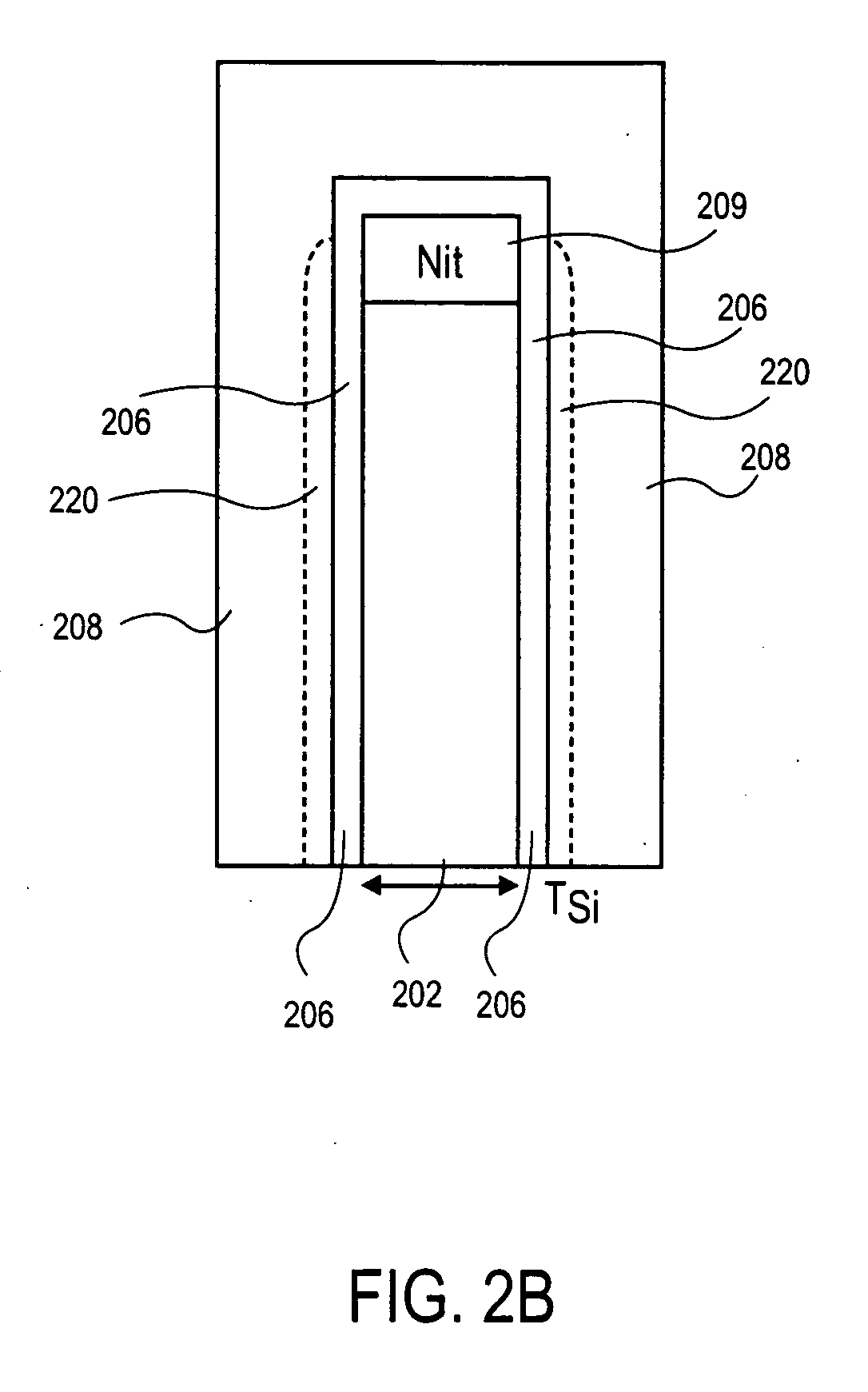

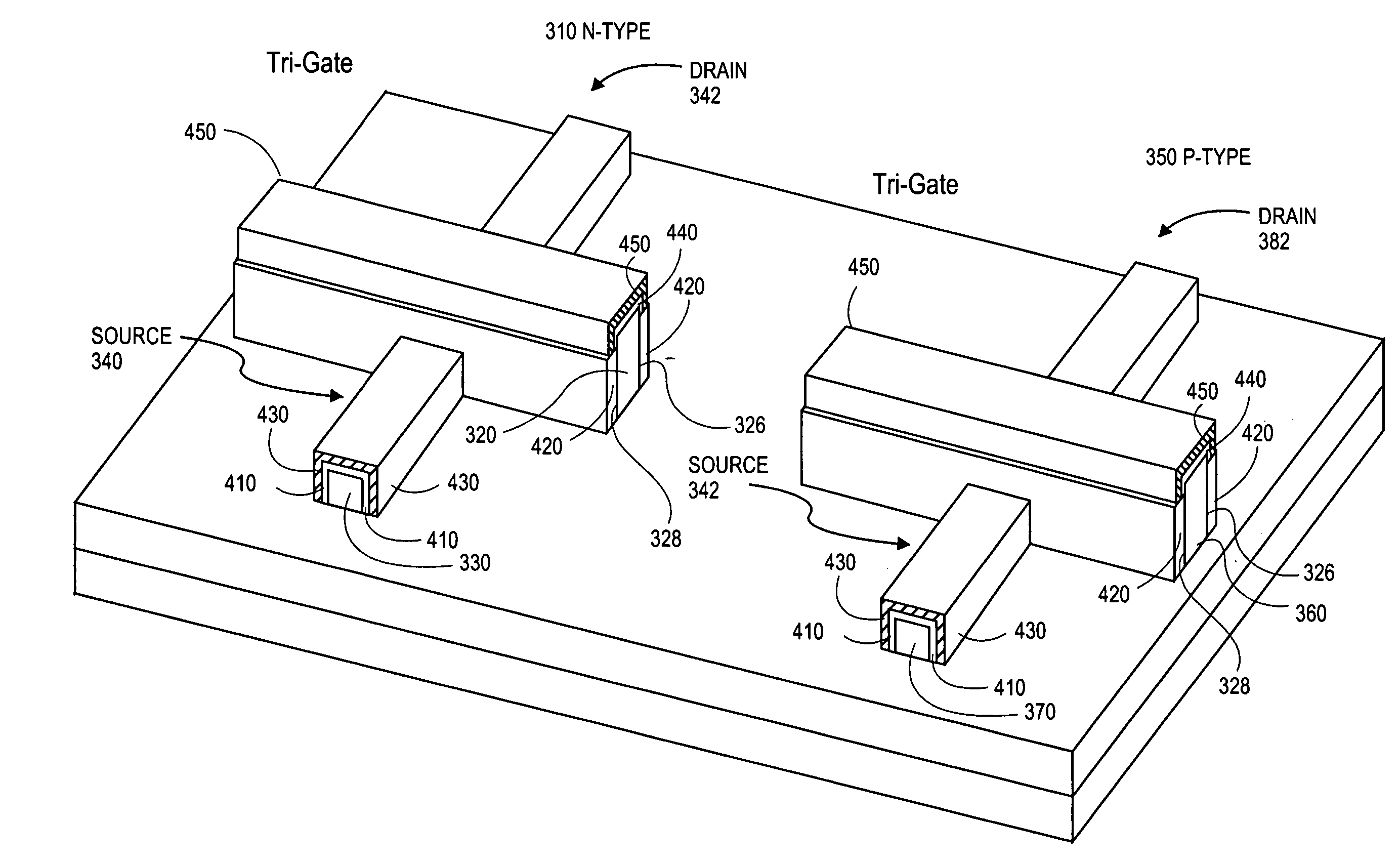

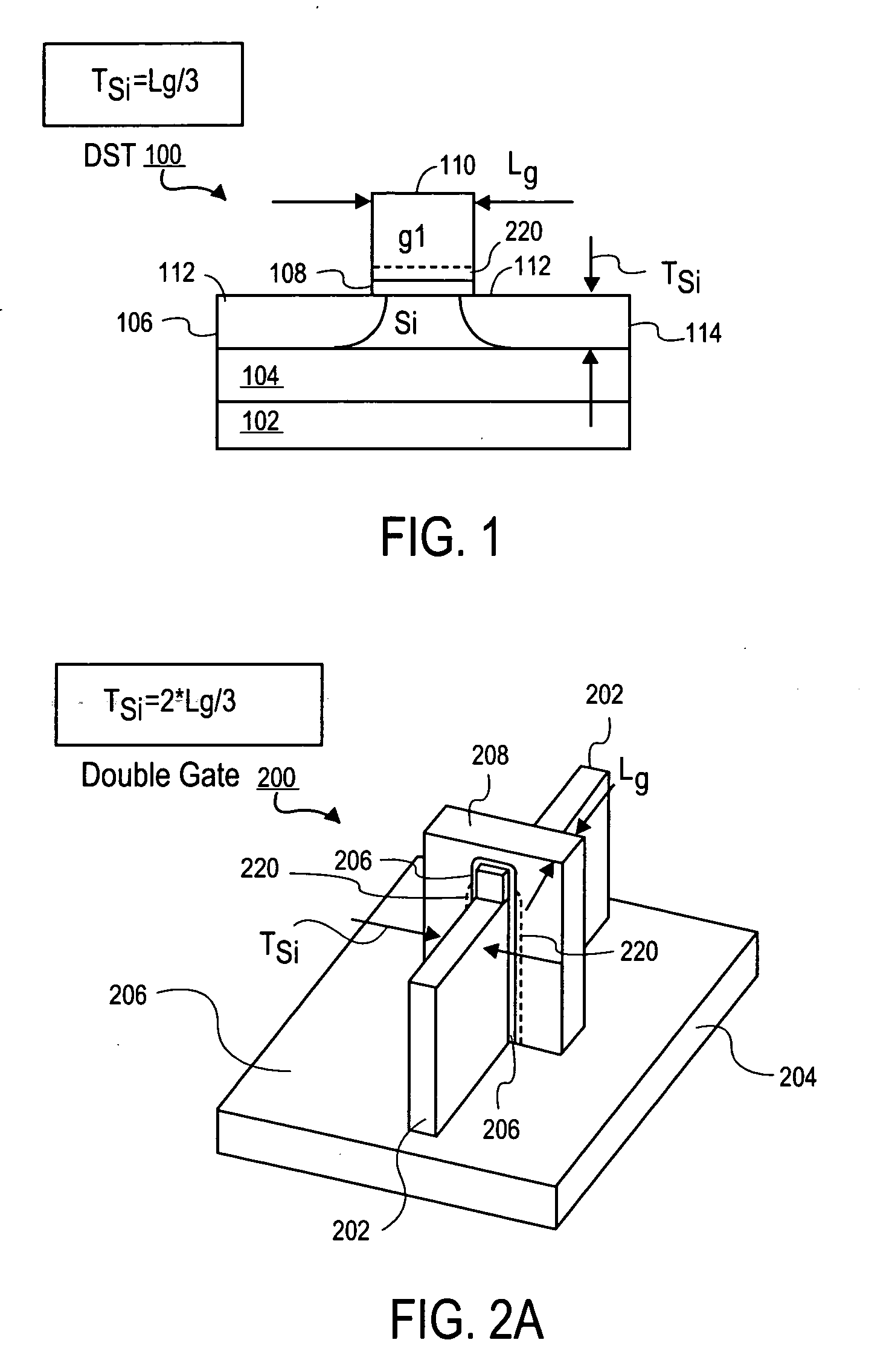

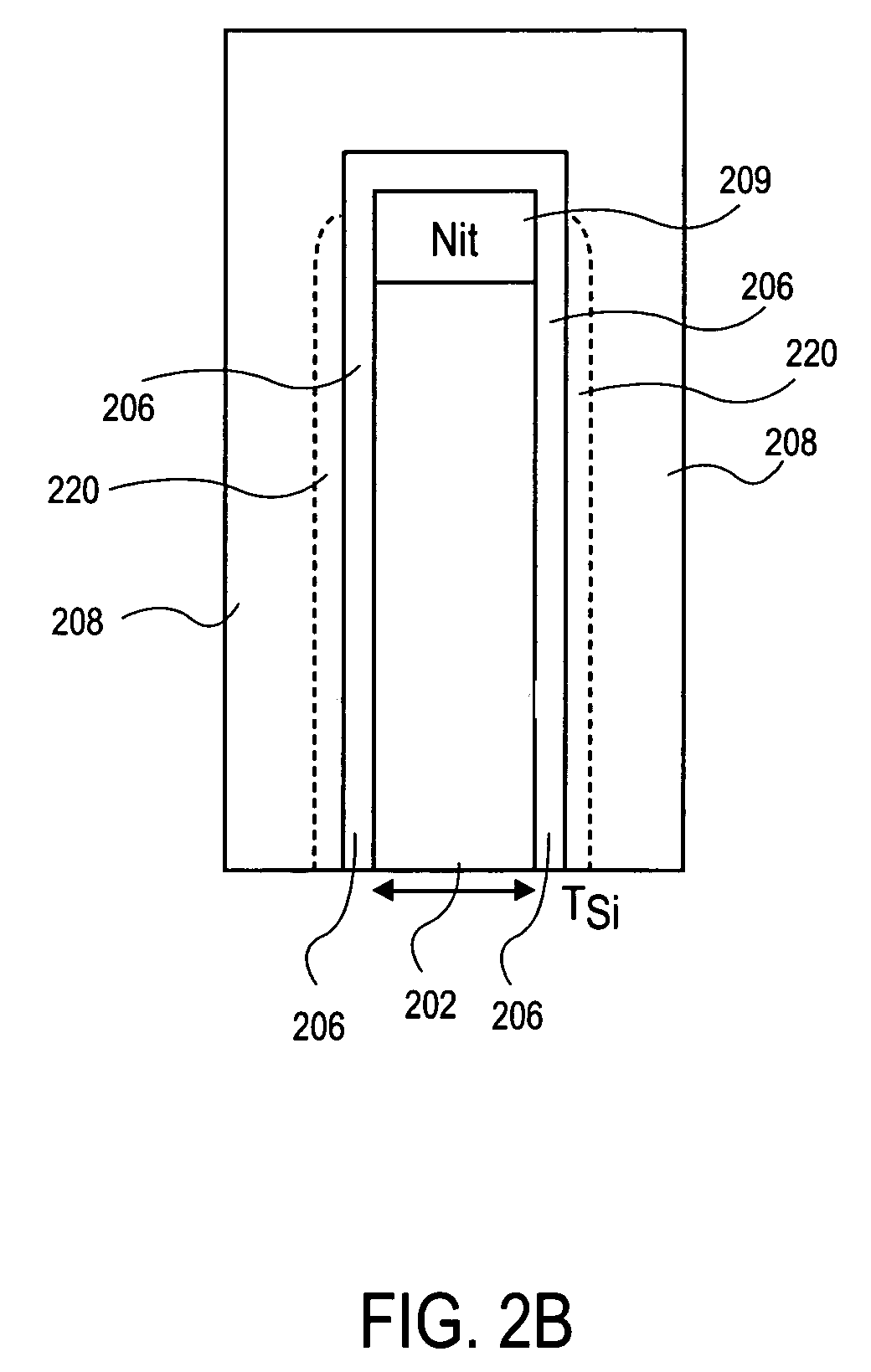

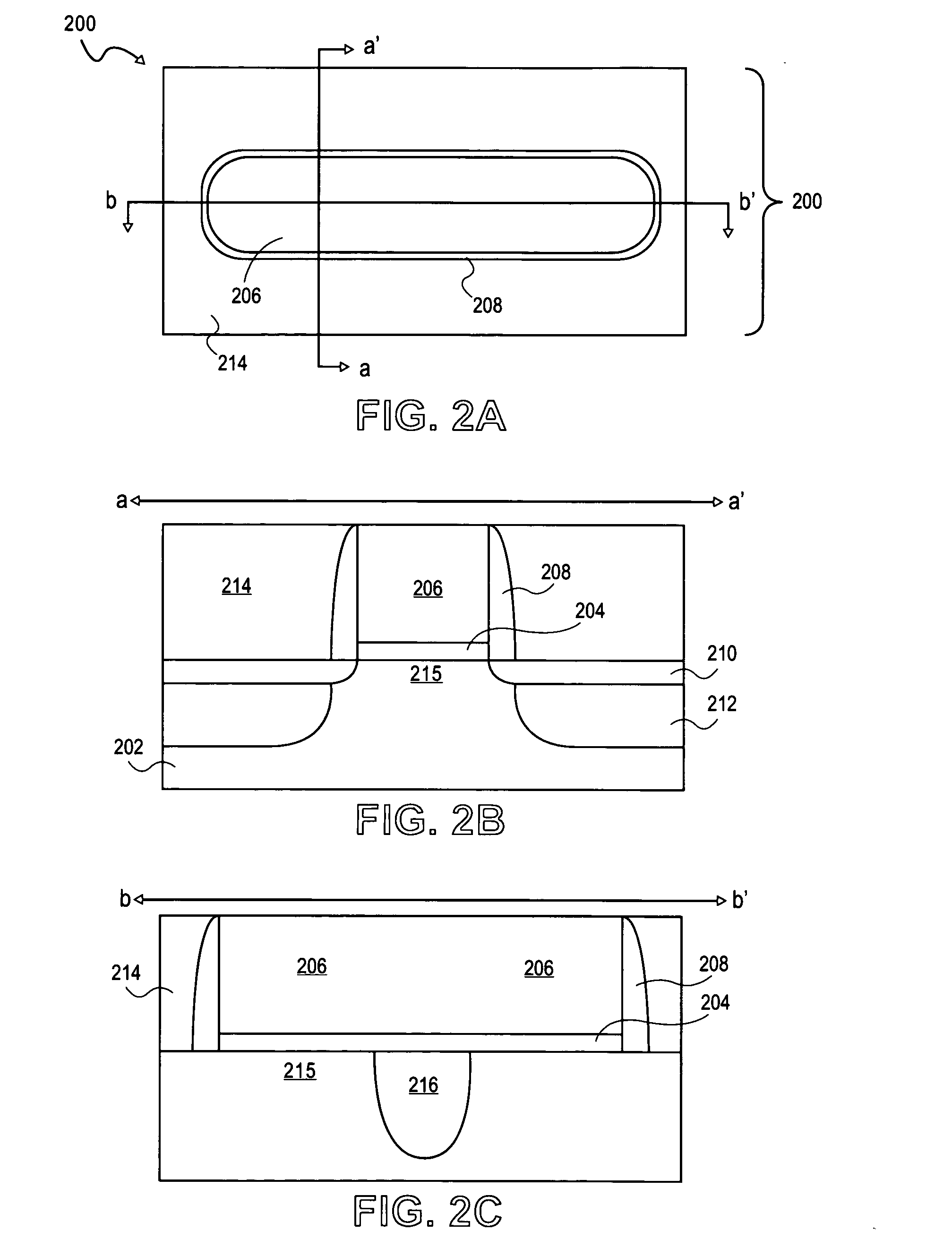

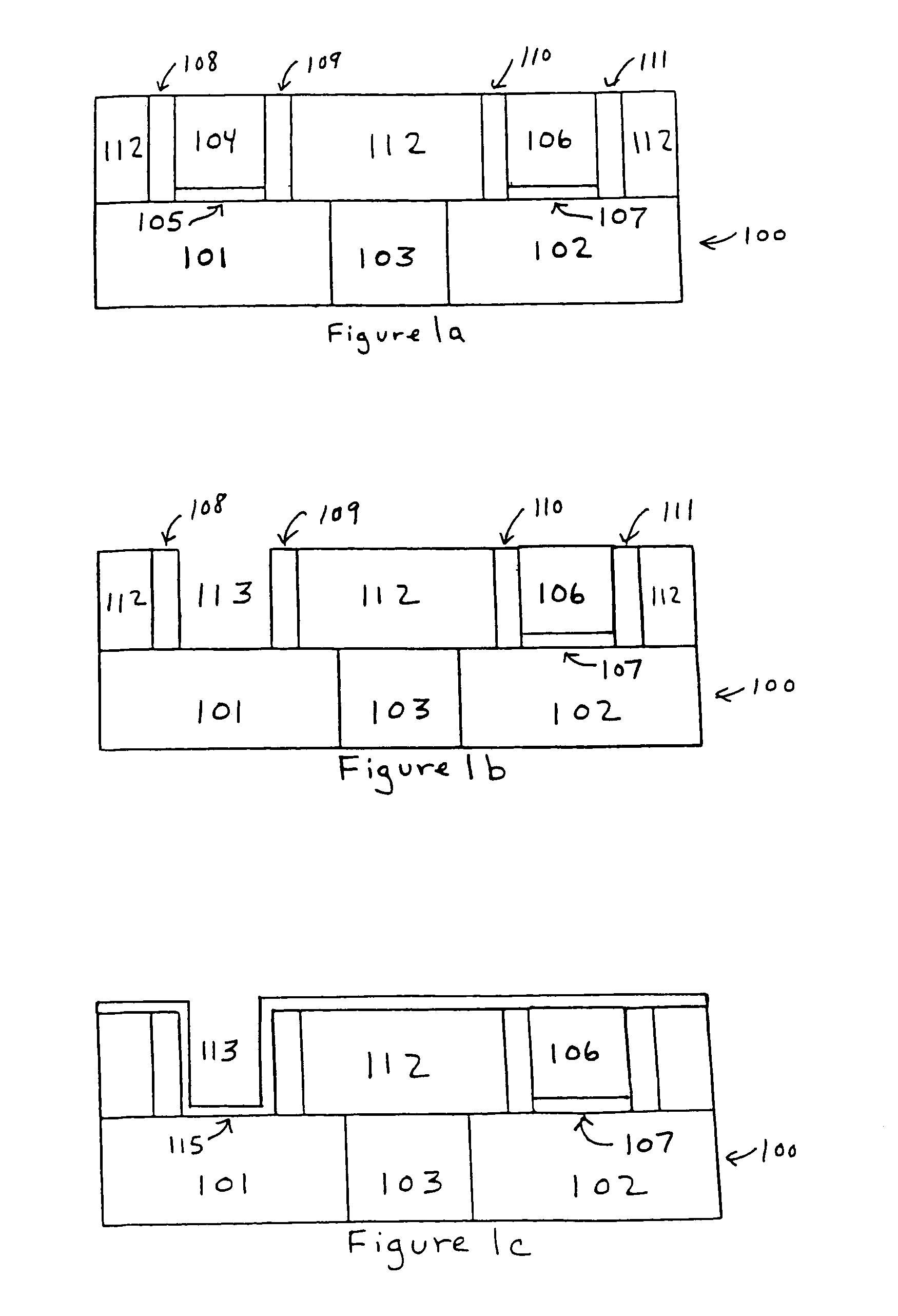

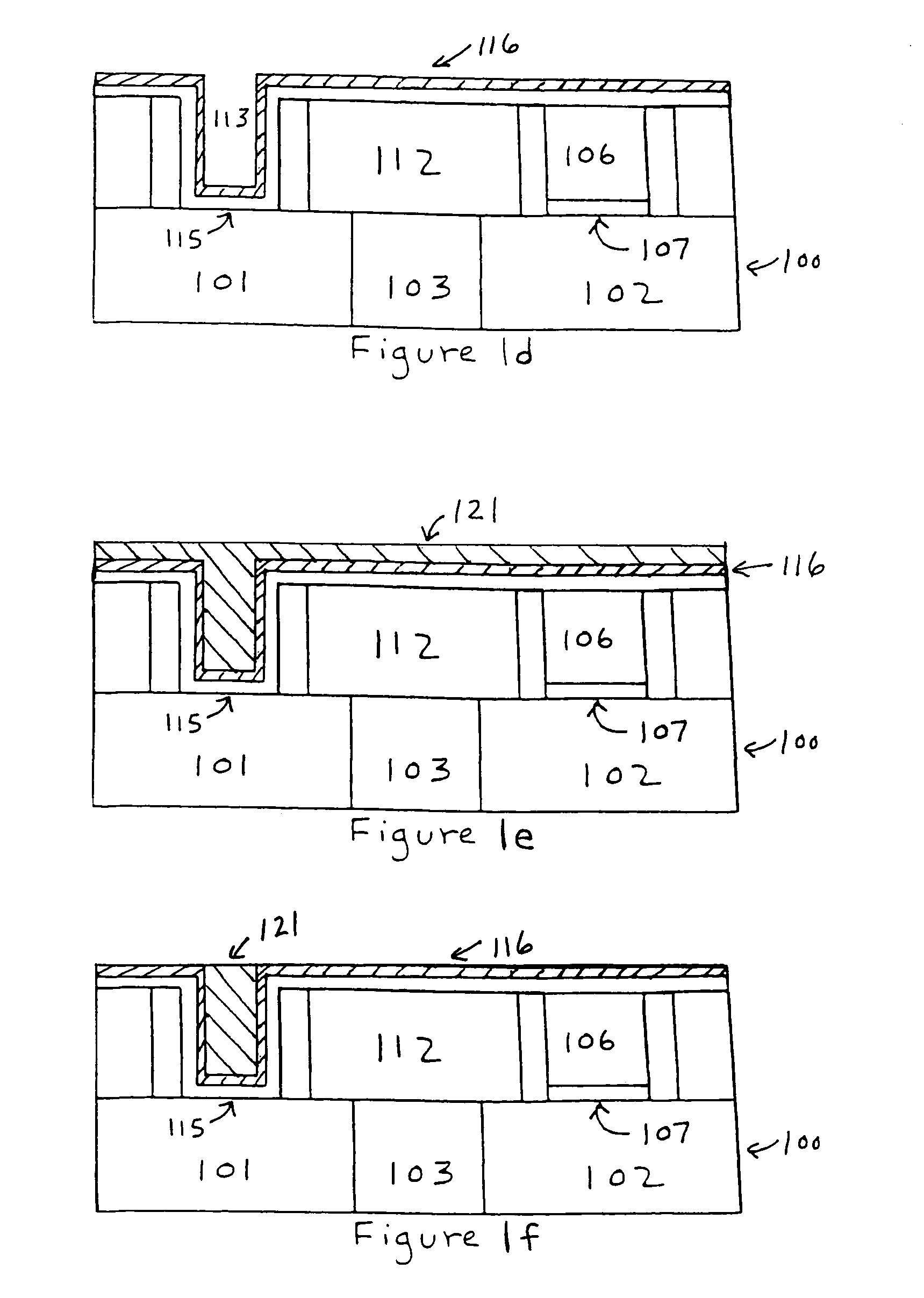

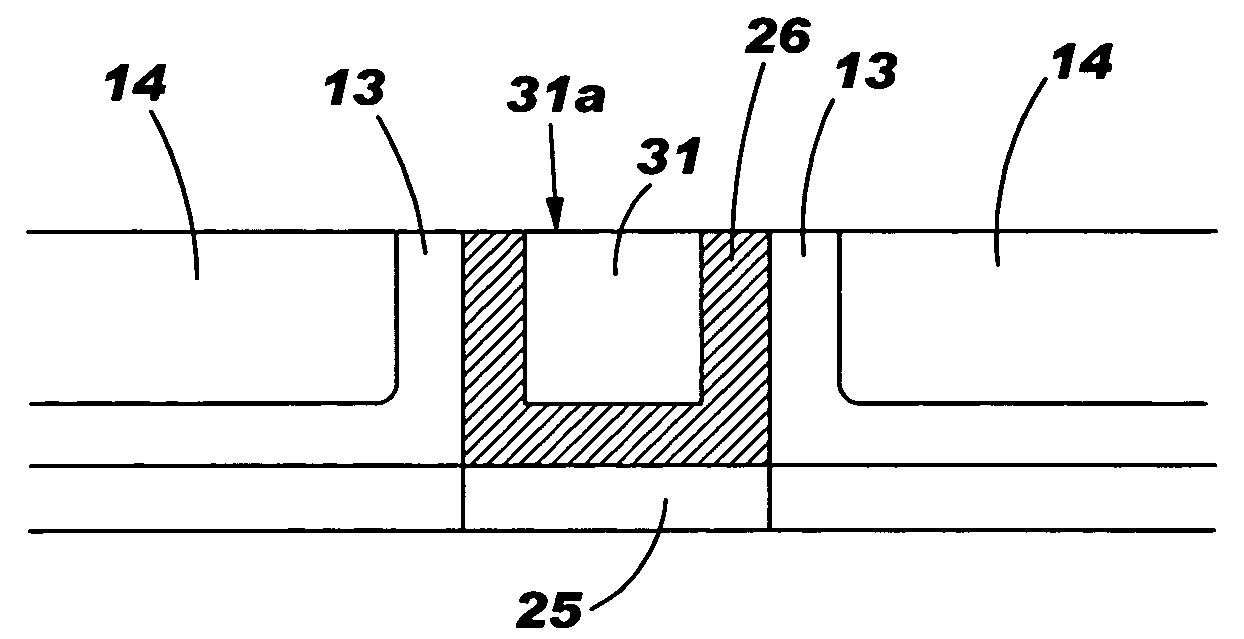

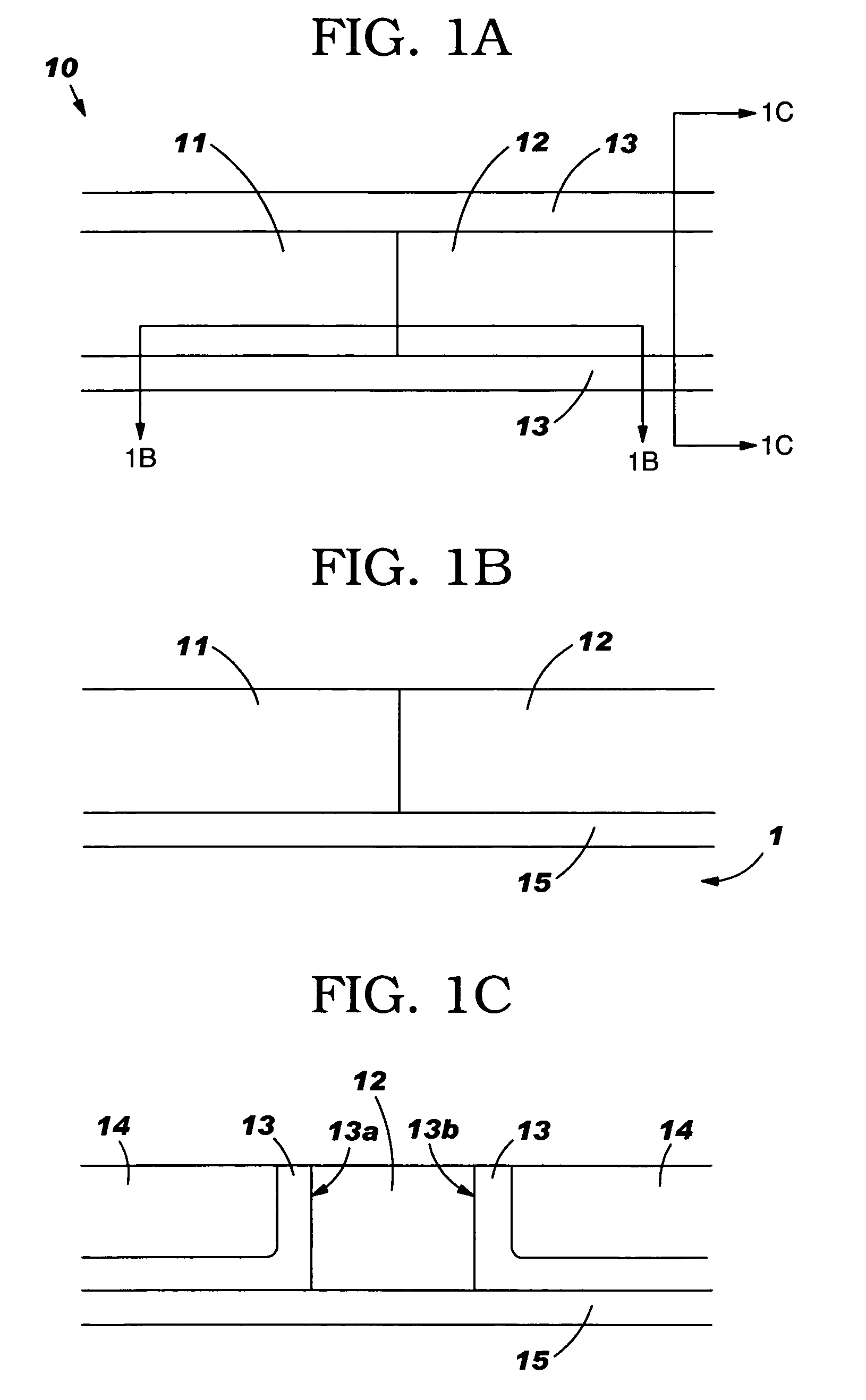

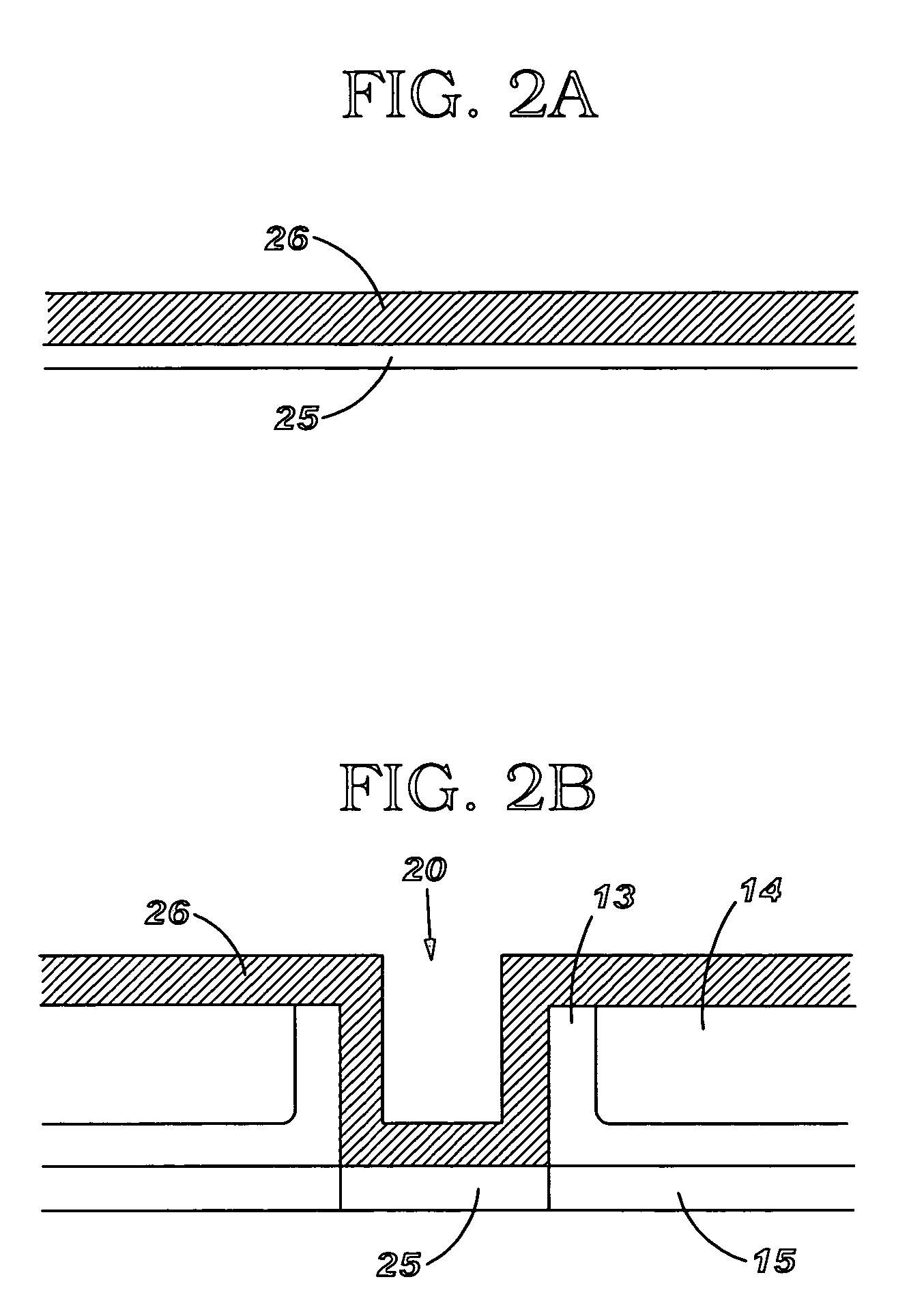

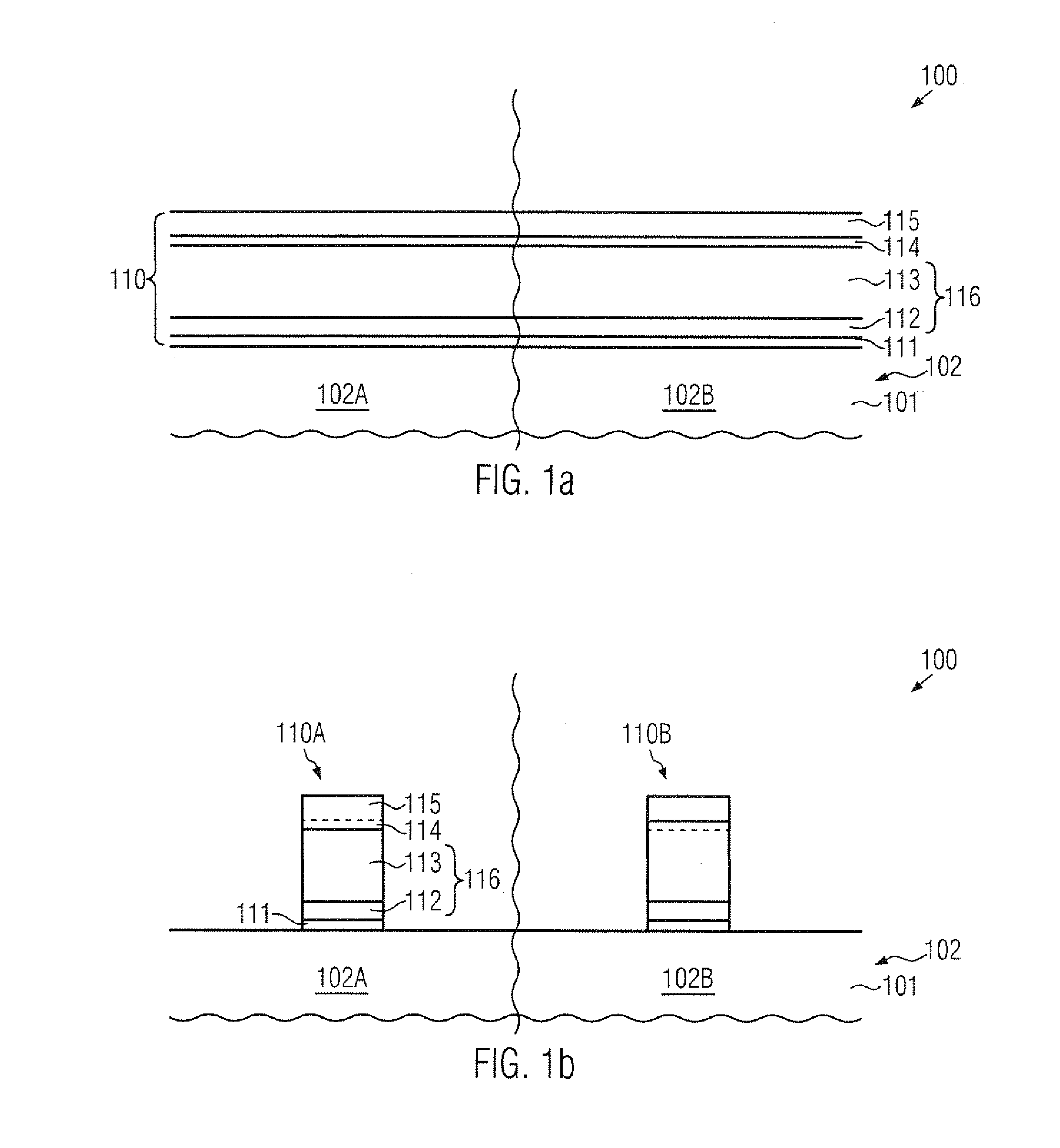

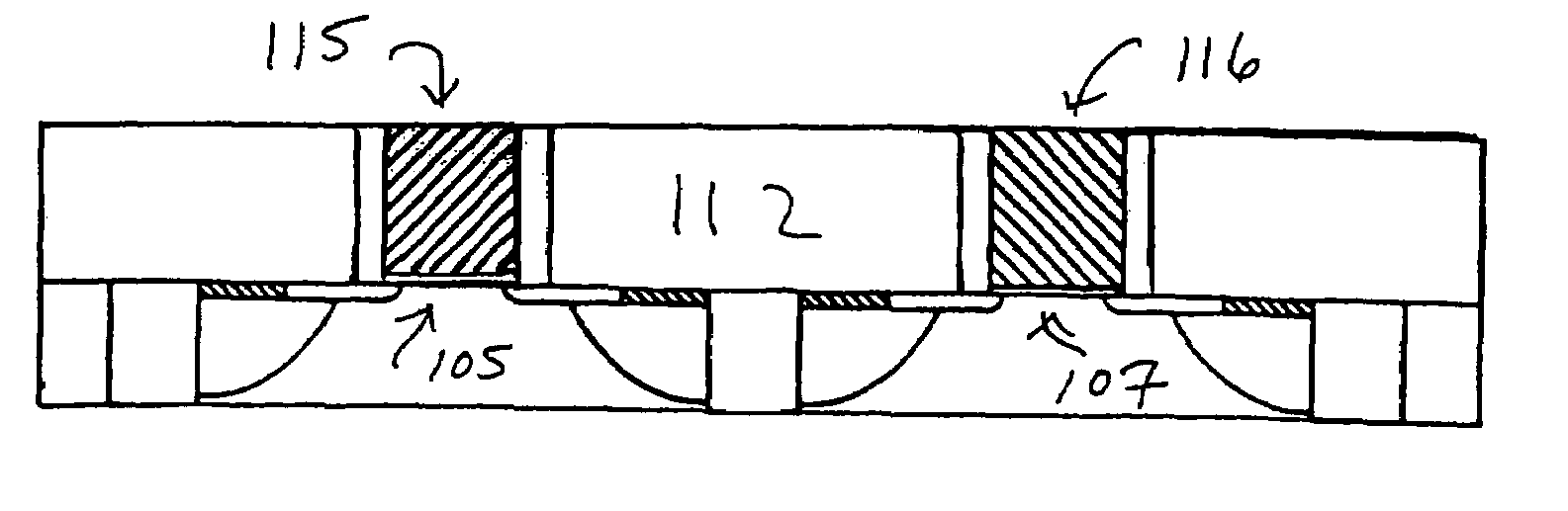

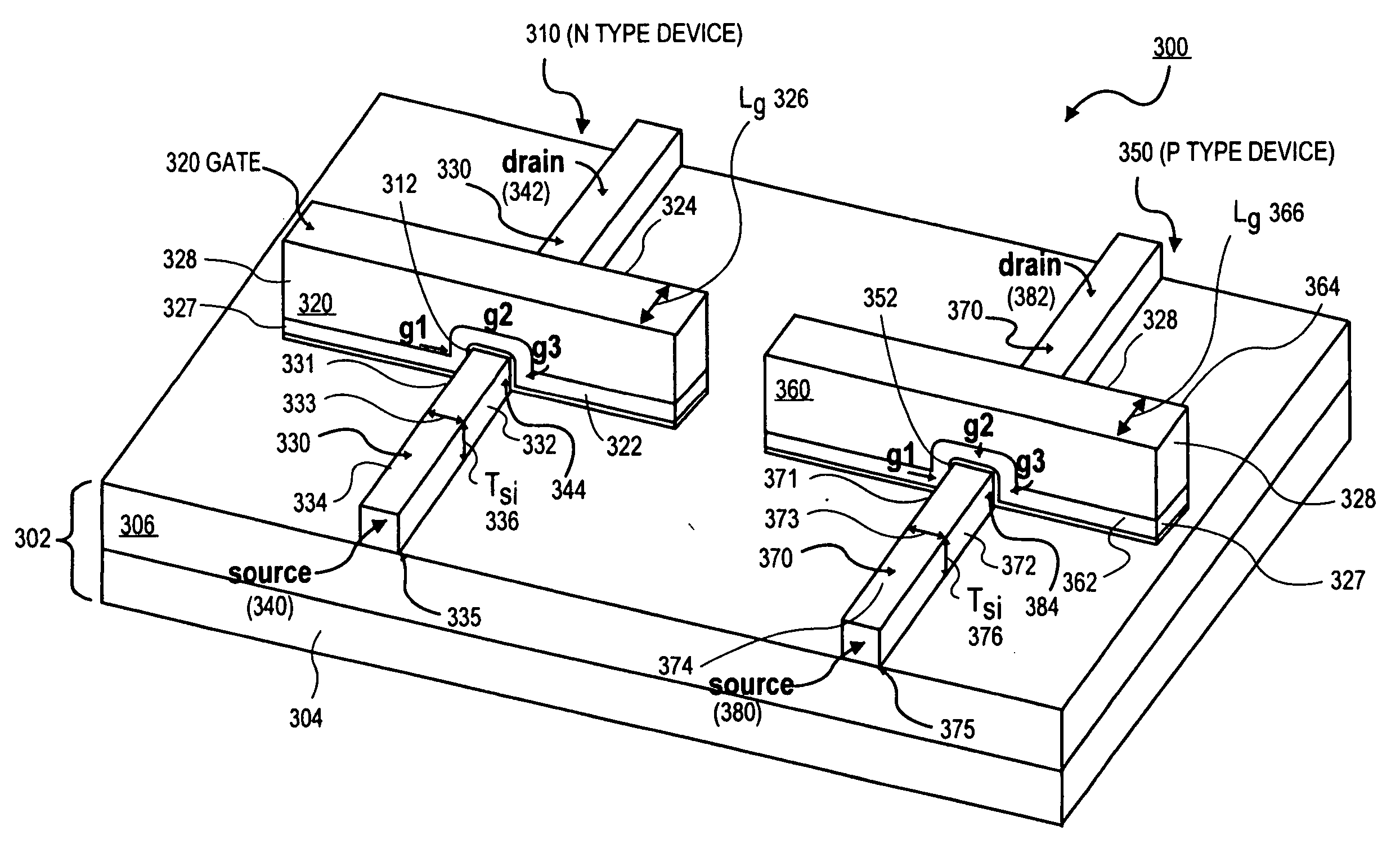

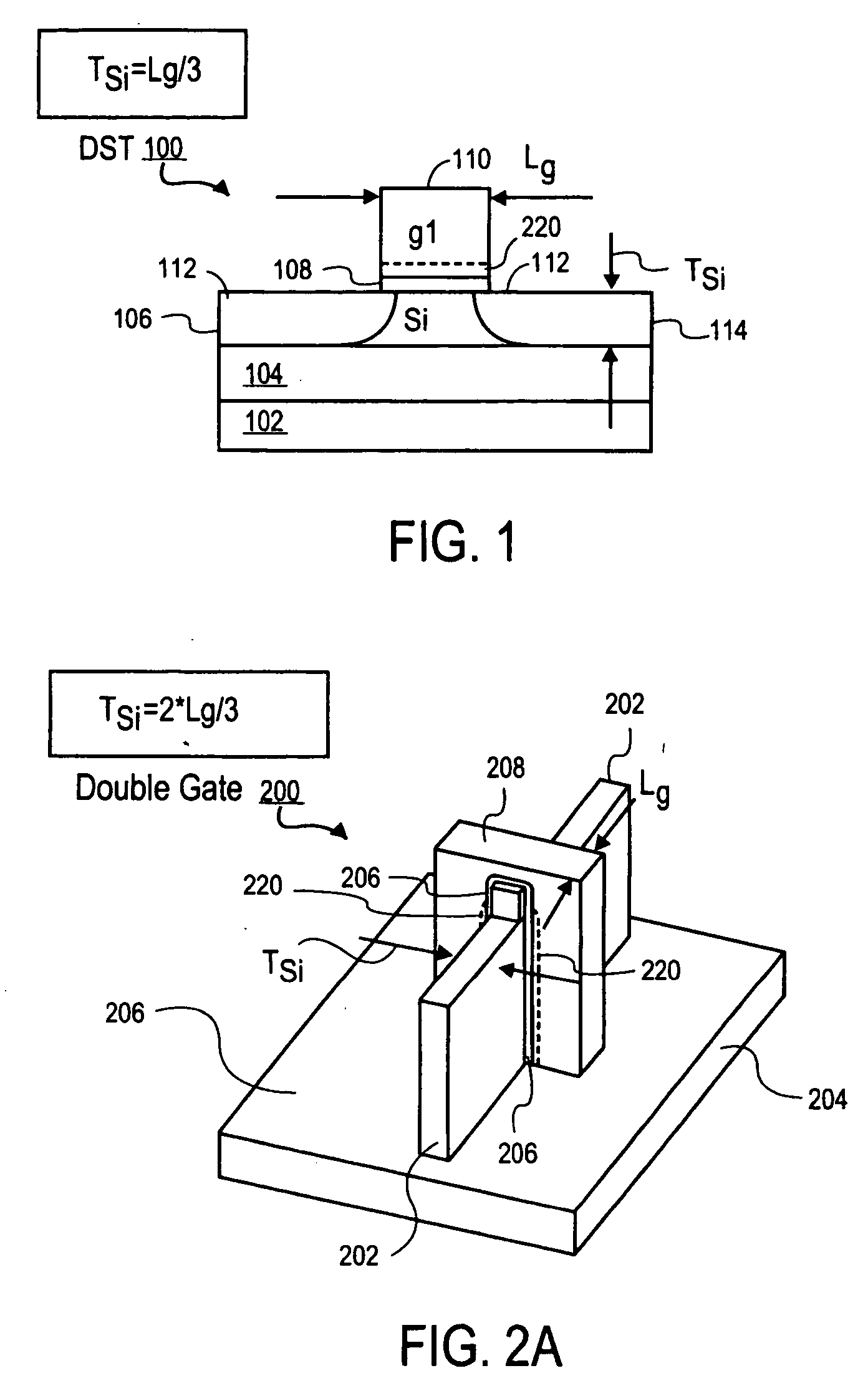

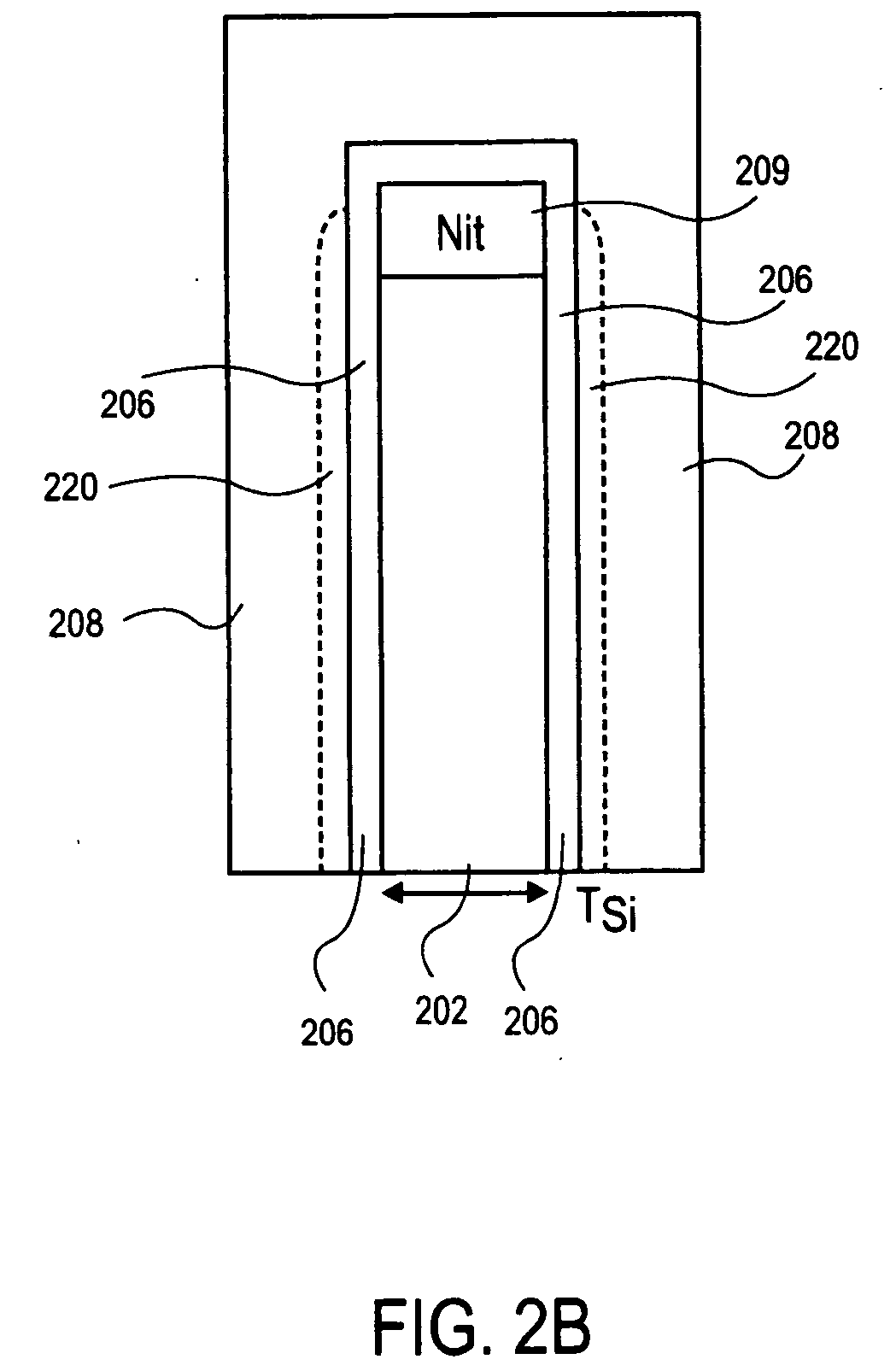

Nonplanar transistors with metal gate electrodes

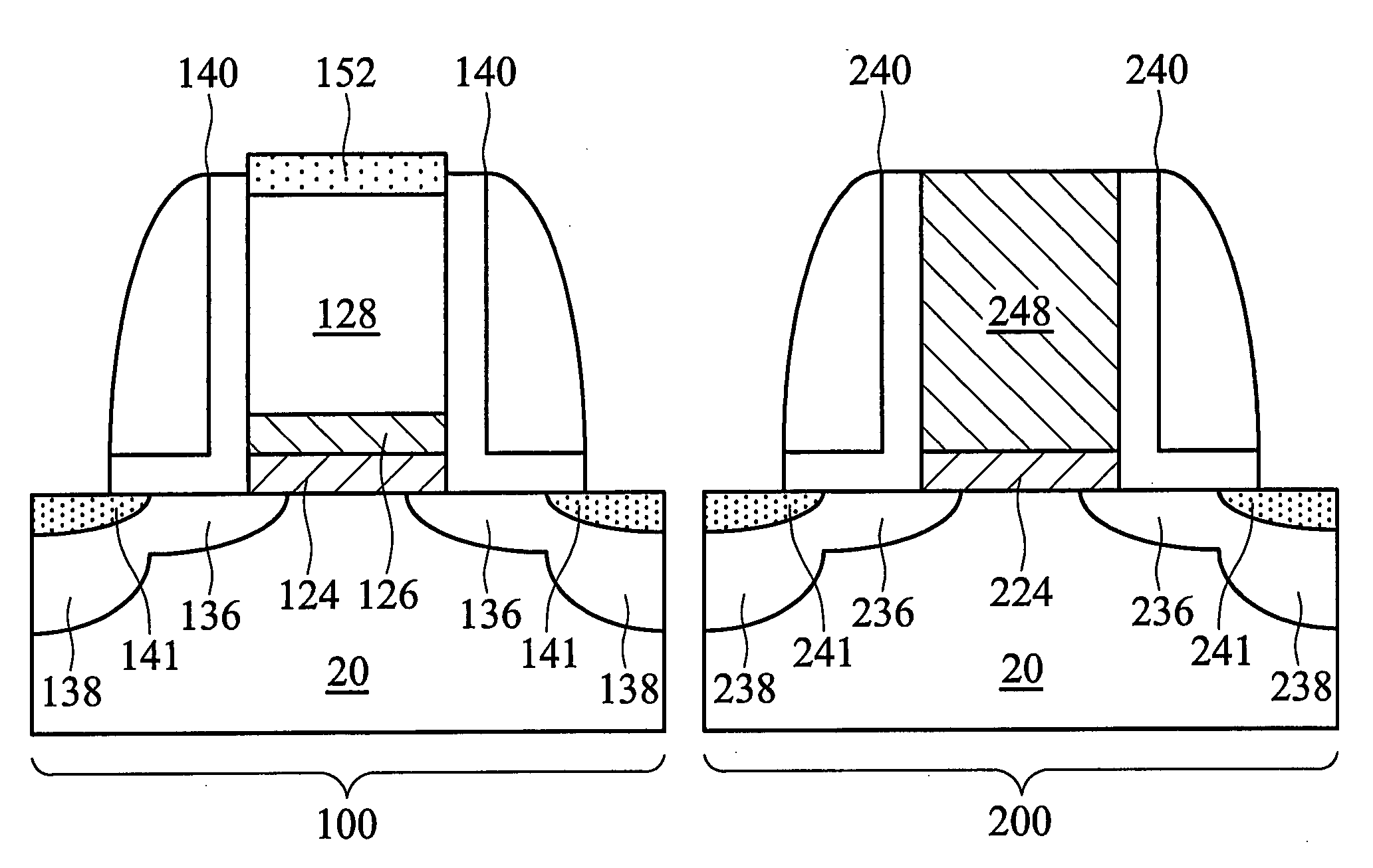

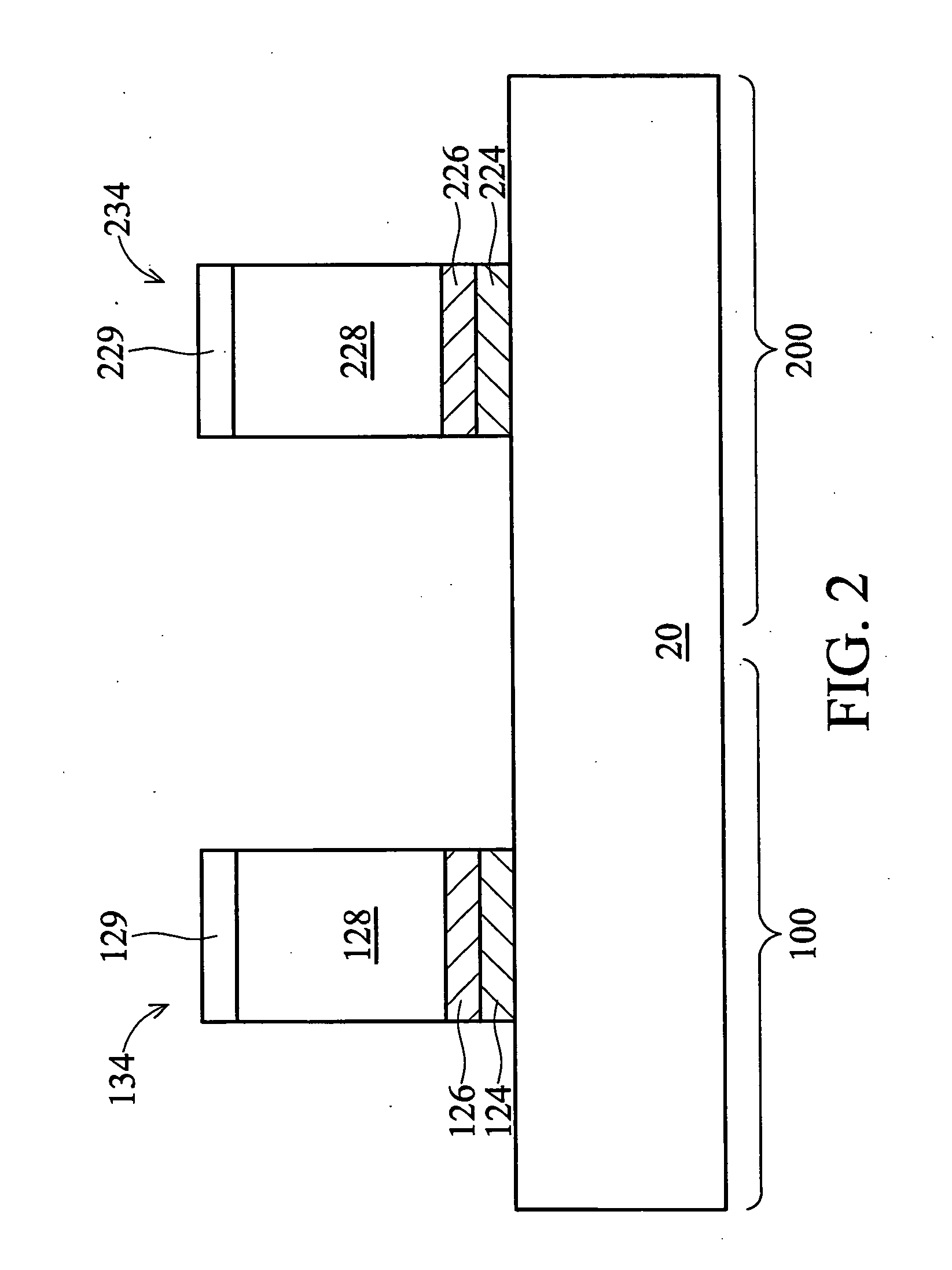

A semiconductor device comprising a semiconductor body having a top surface and a first and second laterally opposite sidewalls as formed on an insulating substrate. A gate dielectric is formed on the top surface of the semiconductor body and on the first and second laterally opposite sidewalls of the semiconductor body. A gate electrode is then formed on the gate dielectric on the top surface of the semiconductor body and adjacent to the gate dielectric on the first and second laterally opposite sidewalls of the semiconductor body. The gate electrode comprises a metal film formed directly adjacent to the gate dielectric layer. A pair of source and drain regions are uniformed in the semiconductor body on opposite sides of the gate electrode.

Owner:TAHOE RES LTD

Semiconductor device including FinFET having metal gate electrode and fabricating method thereof

Provided are a semiconductor device including a FinFET having a metal gate electrode and a fabricating method thereof. The semiconductor device includes: an active area formed in a semiconductor substrate and protruding from a surface of the semiconductor substrate; a fin including first and second protrusions formed of a surface of the active area and parallel with each other based on a central trench formed in the active area and using upper surfaces and sides of the first and second protrusions as a channel area; a gate insulating layer formed on the active area including the fin; a metal gate electrode formed on the gate insulating layer; a gate spacer formed on a sidewall of the metal gate electrode; and a source and a drain formed in the active area beside both sides of the metal gate electrode. Here, the metal gate electrode comprises a barrier layer contacting the gate spacer and the gate insulating layer and a metal layer formed on the barrier layer.

Owner:SAMSUNG ELECTRONICS CO LTD

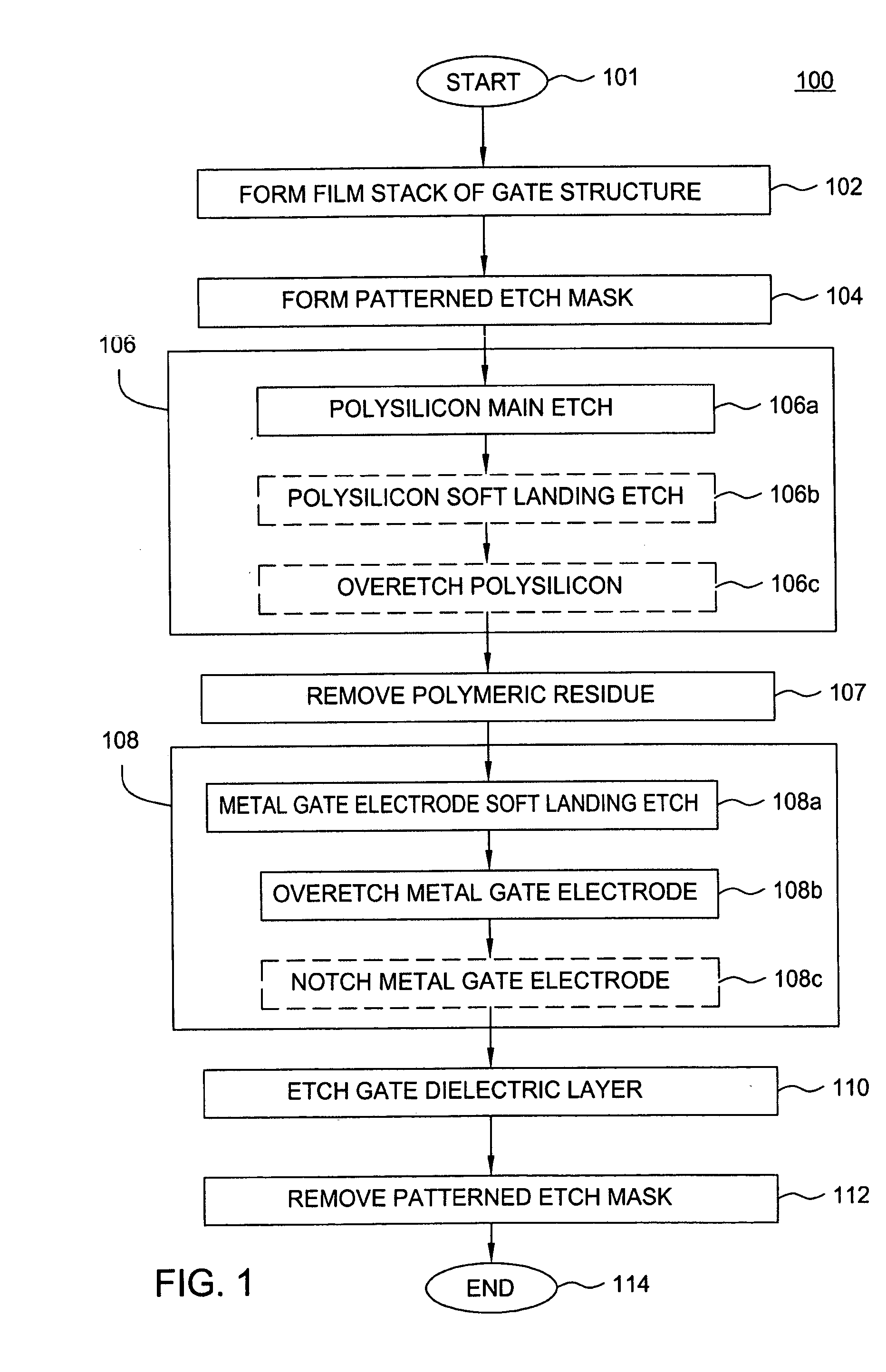

Method of fabricating a gate structure of a field effect transistor having a metal-containing gate electrode

InactiveUS20050009358A1High selectivitySemiconductor/solid-state device detailsSolid-state devicesBromineTitanium nitride

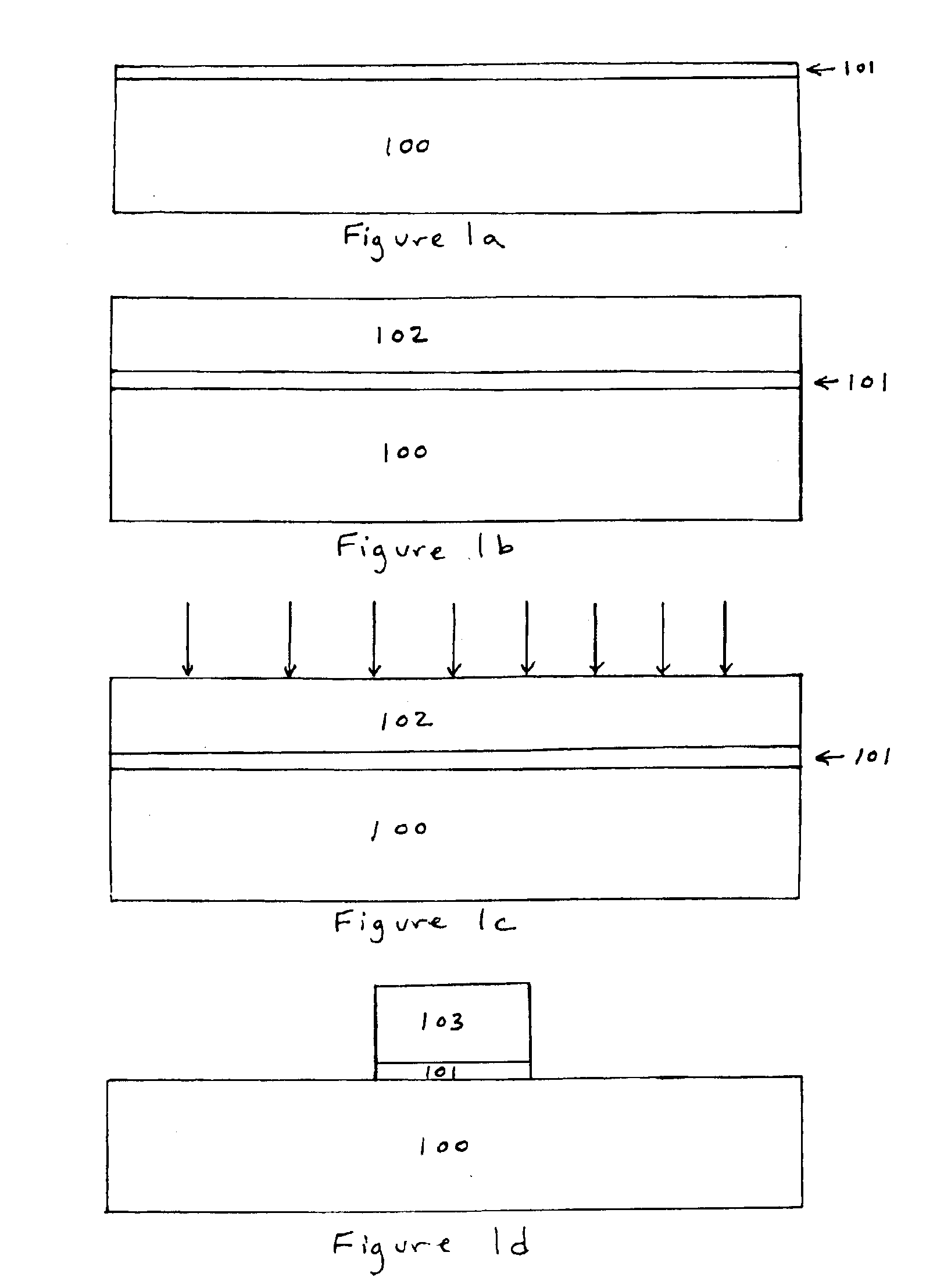

A method of etching metals and / or metal-containing compounds using a plasma comprising a bromine-containing gas. In one embodiment, the method is used during fabrication of a gate structure of a field effect transistor having a titanium nitride gate electrode, an ultra-thin (about 10 to 20 Angstroms) silicon dioxide gate dielectric, and a polysilicon upper contact. In a further embodiment, the gate electrode is selectively notched to a pre-determined width.

Owner:APPLIED MATERIALS INC

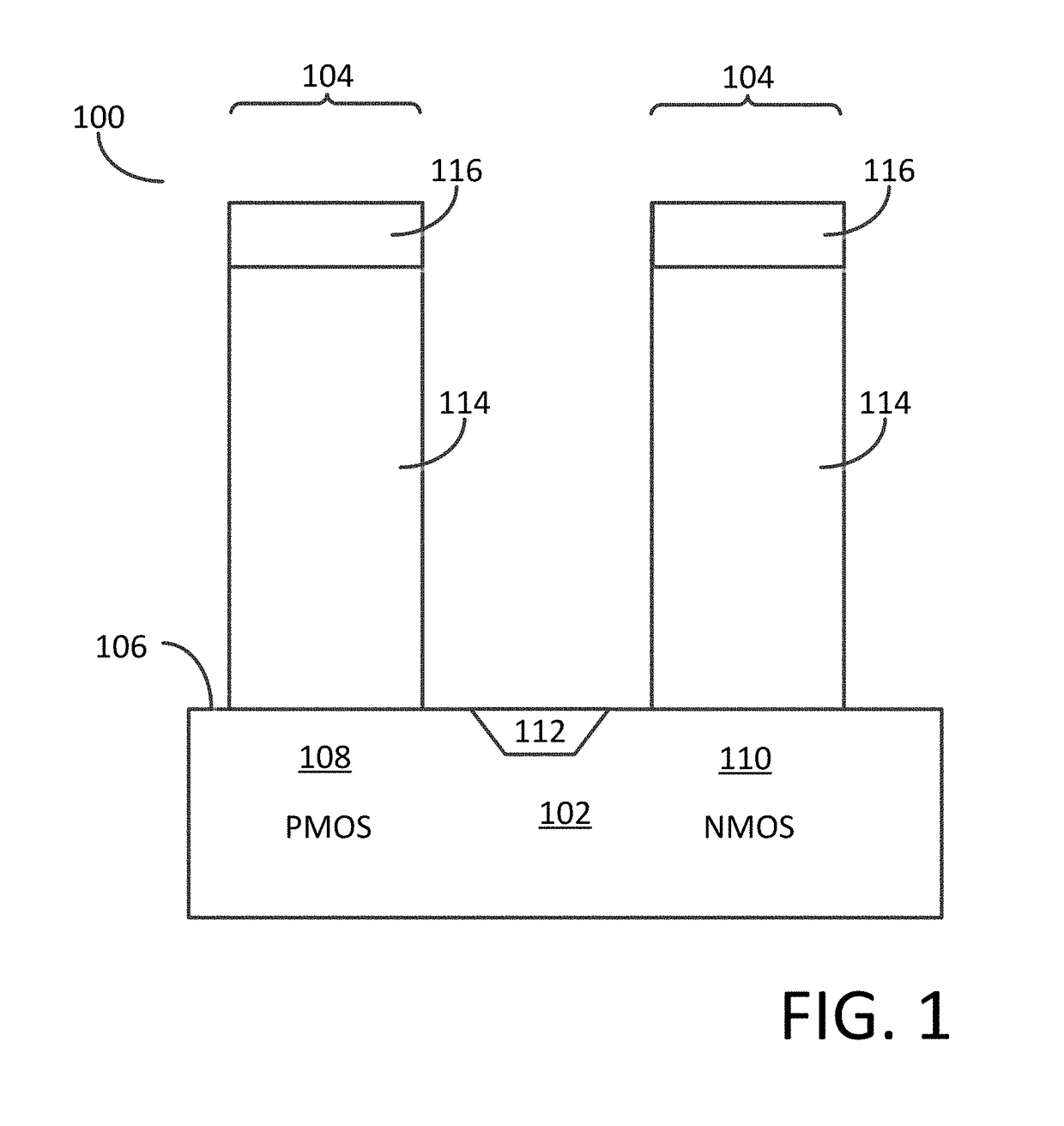

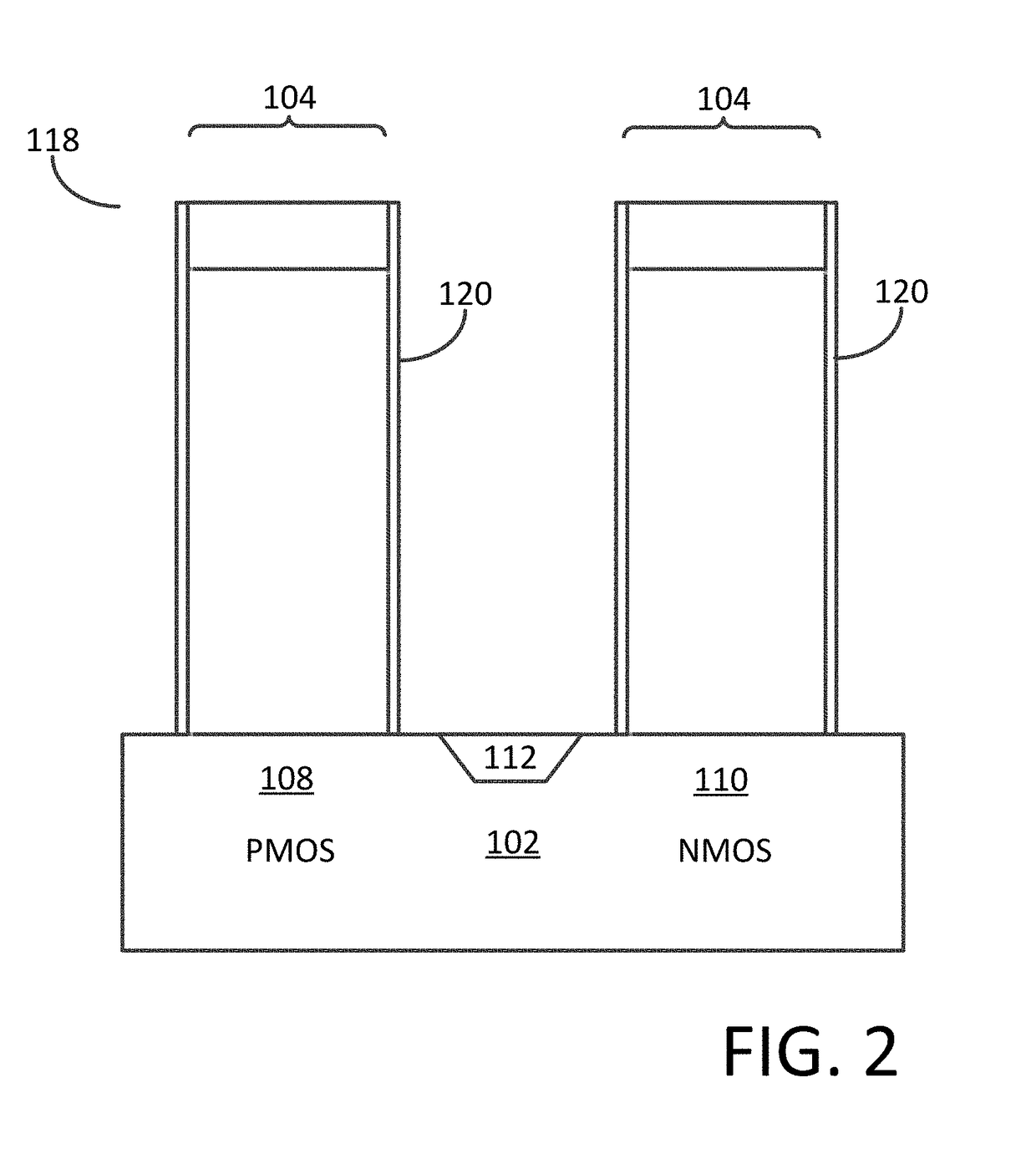

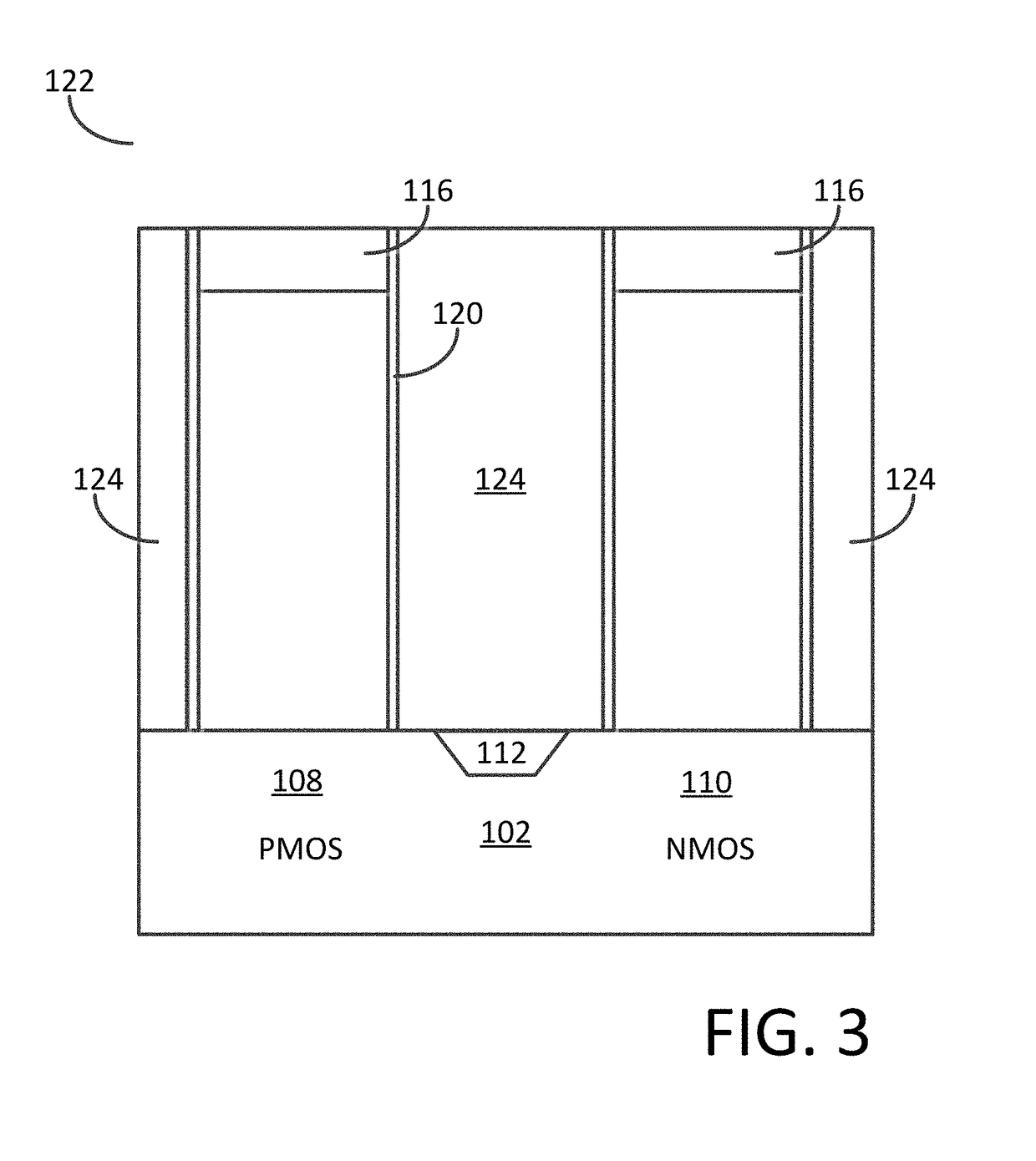

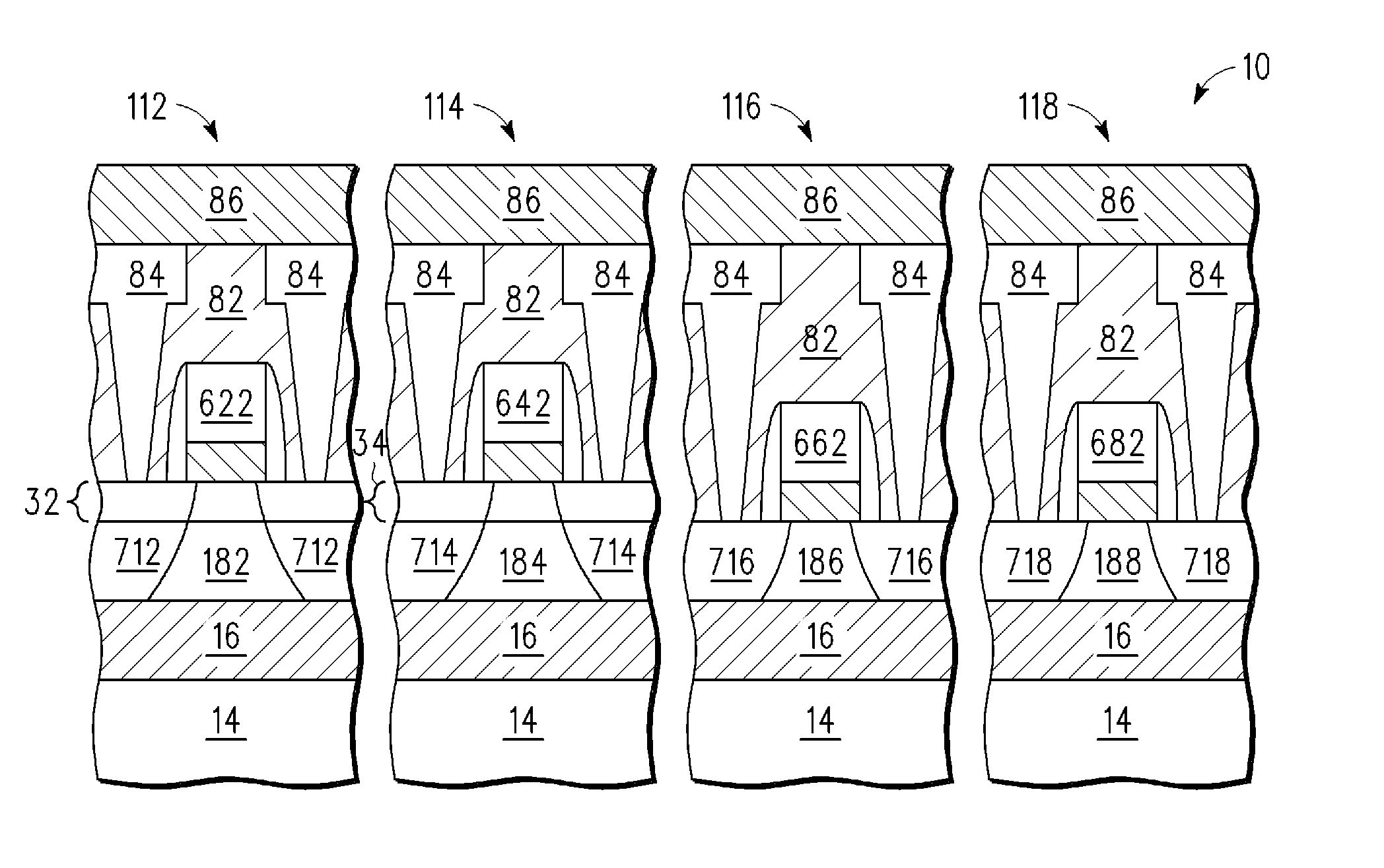

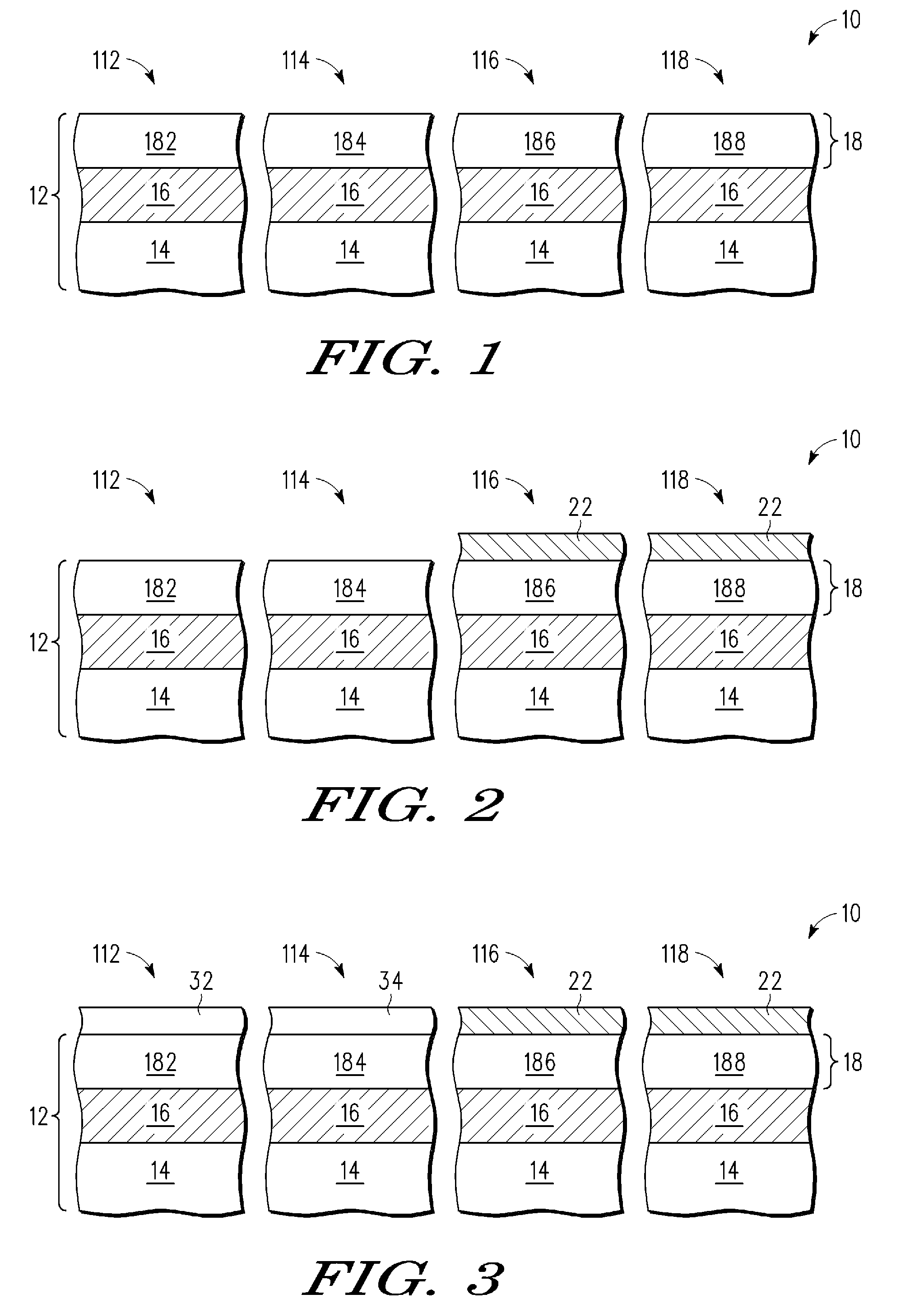

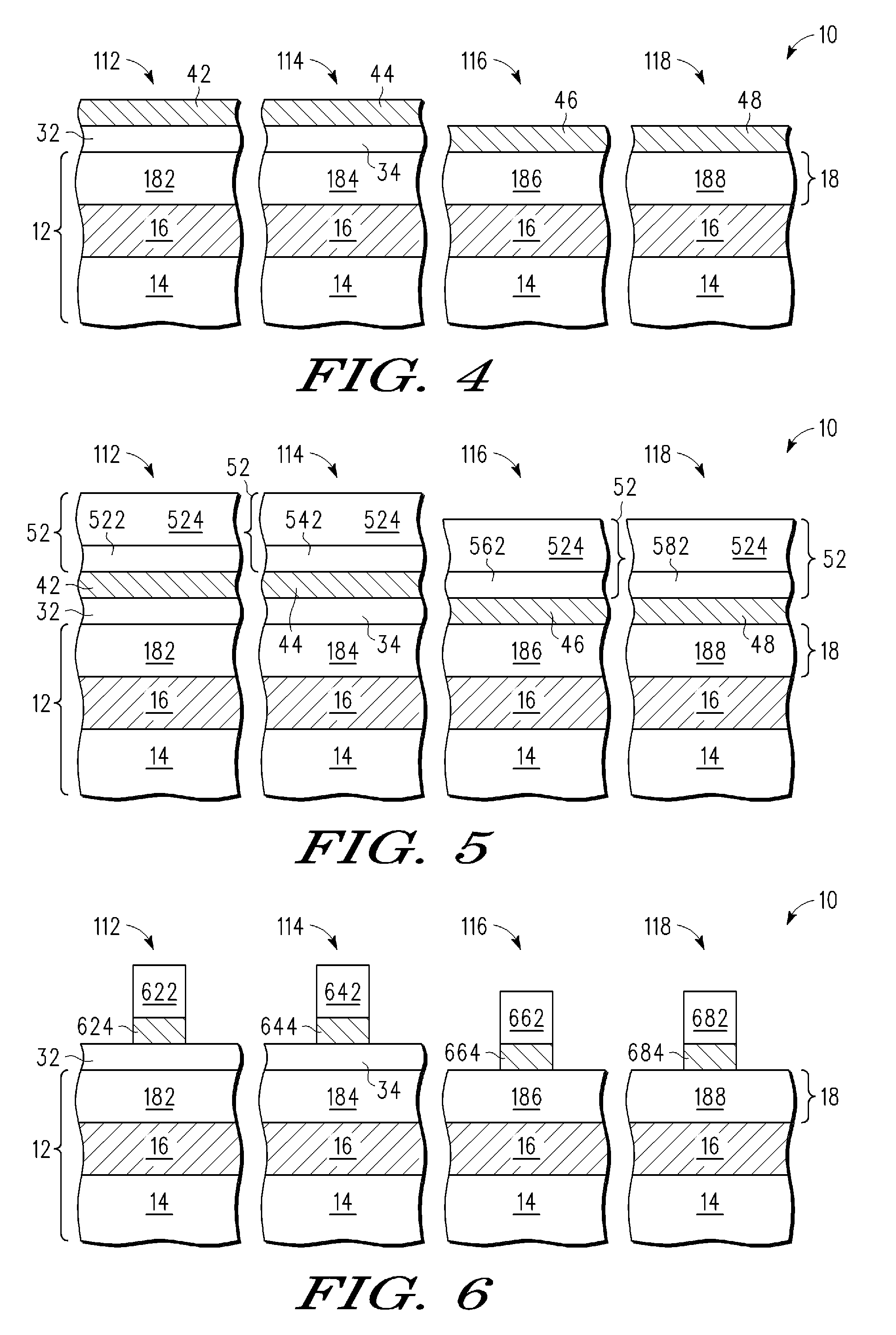

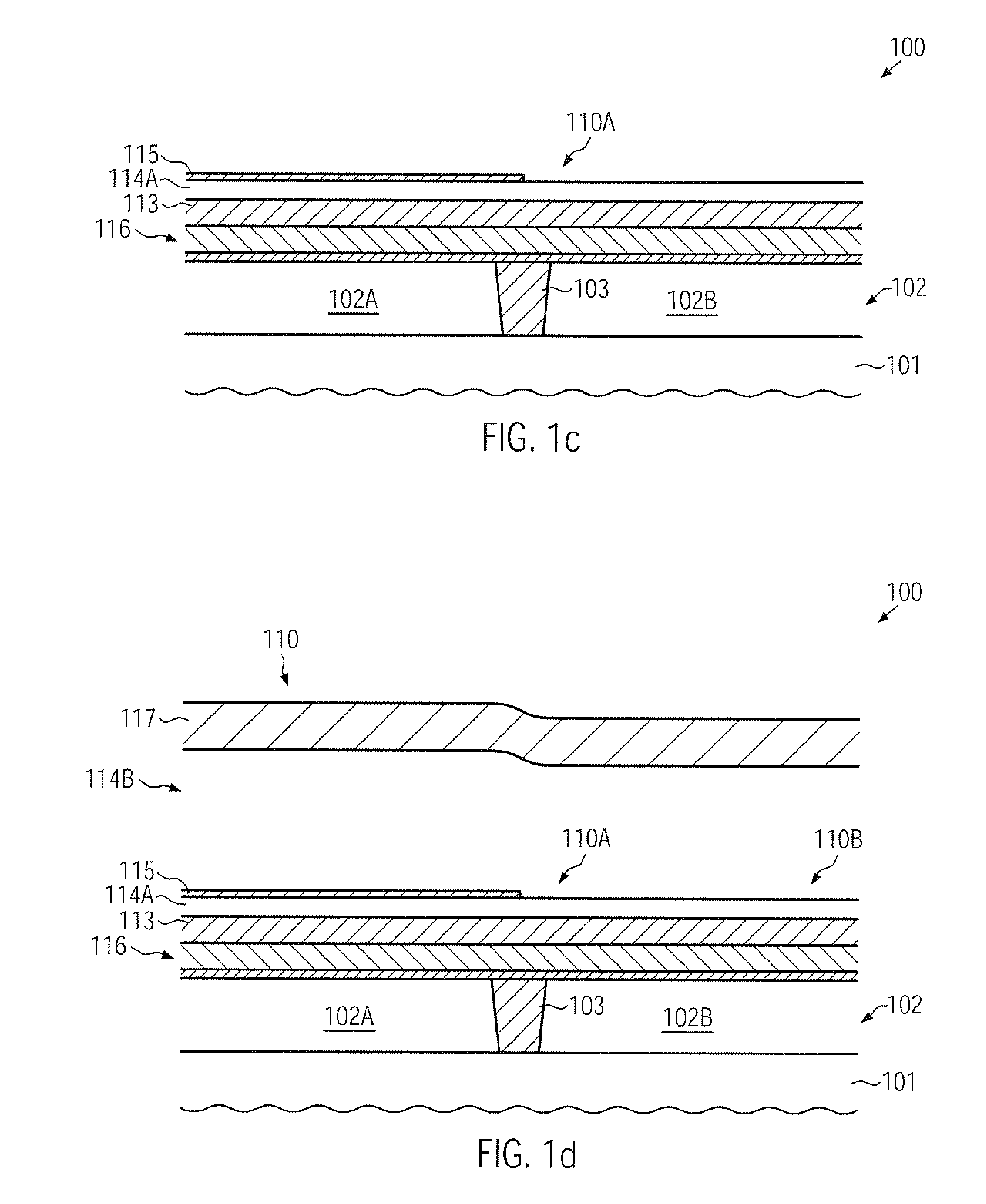

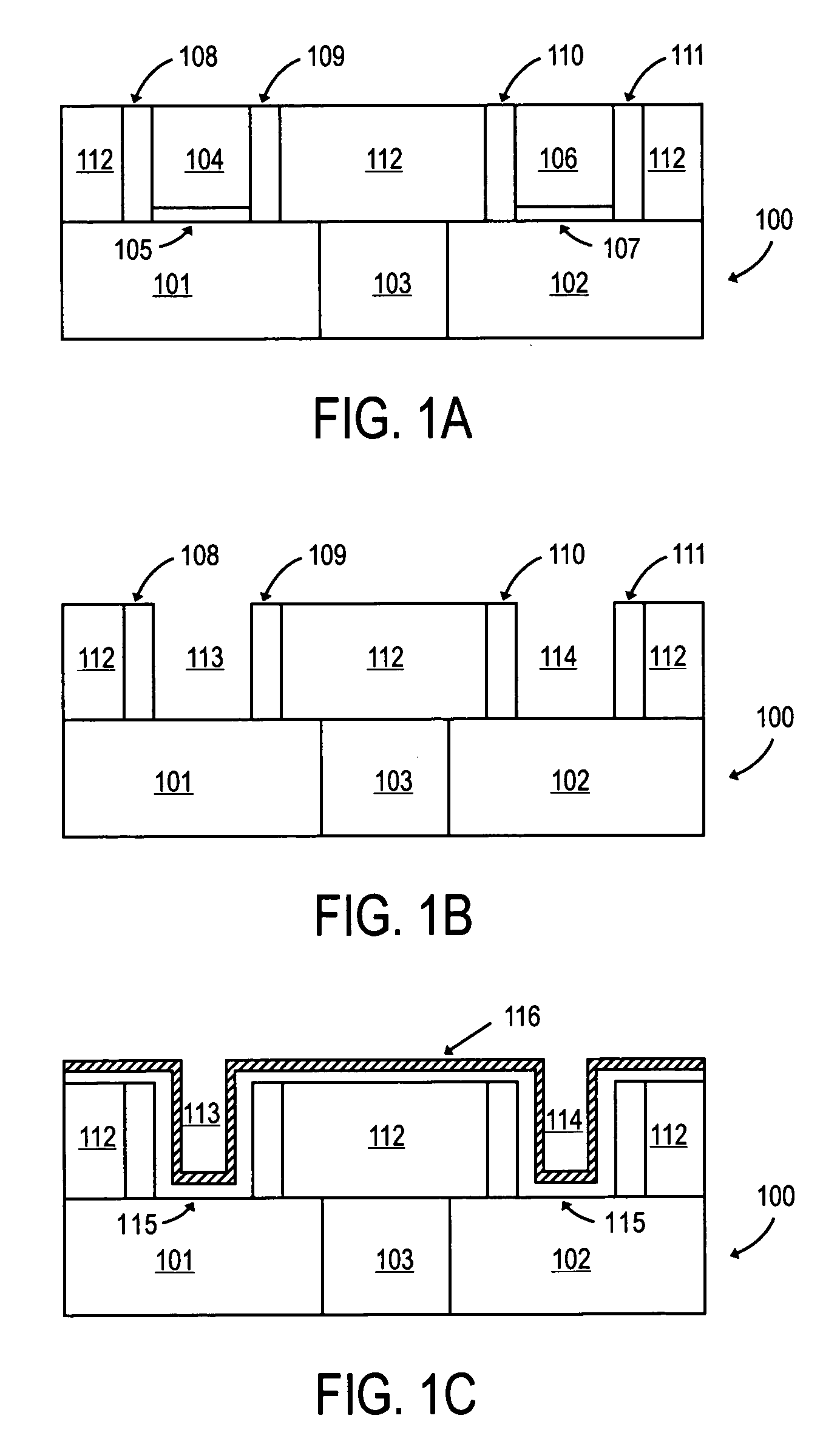

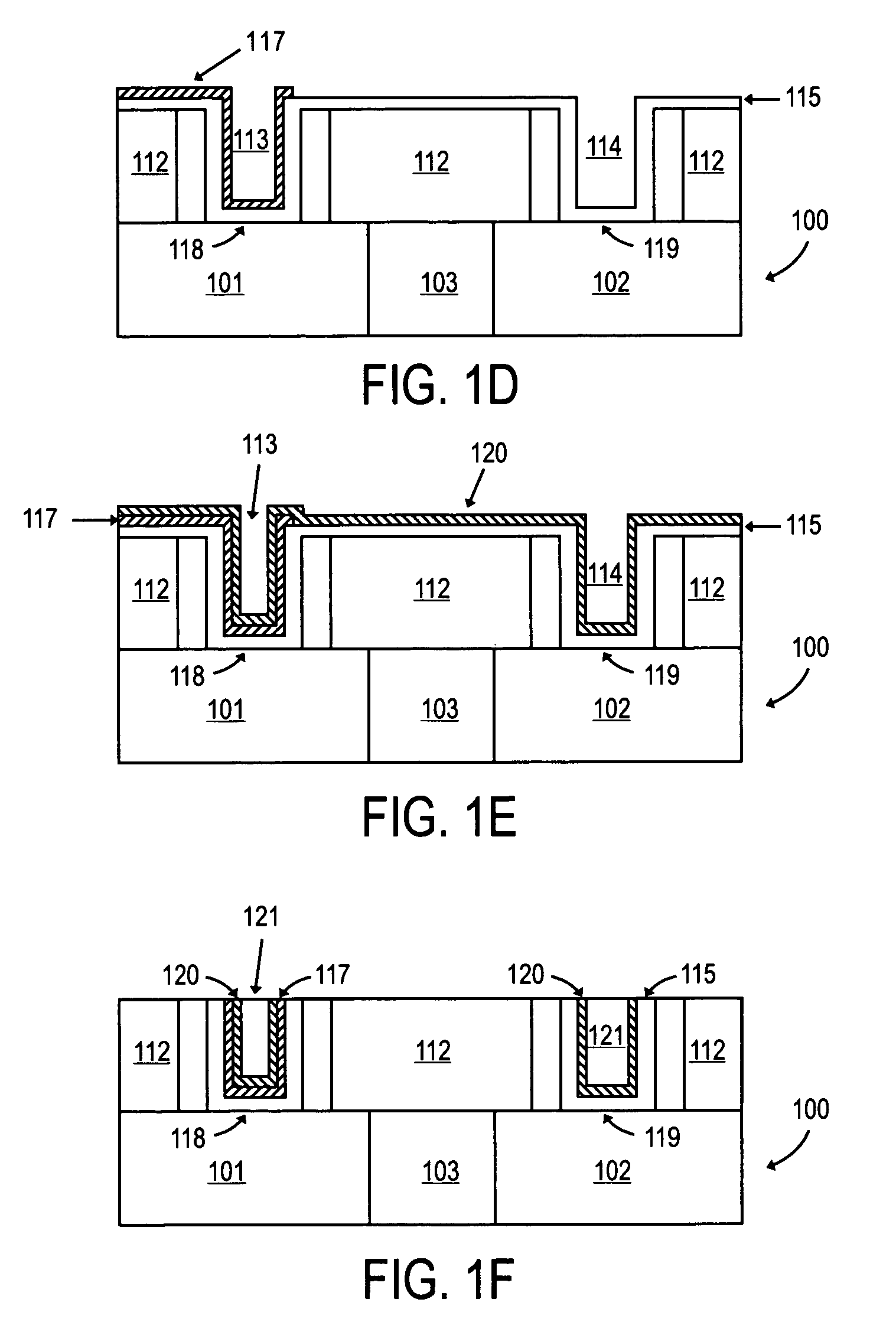

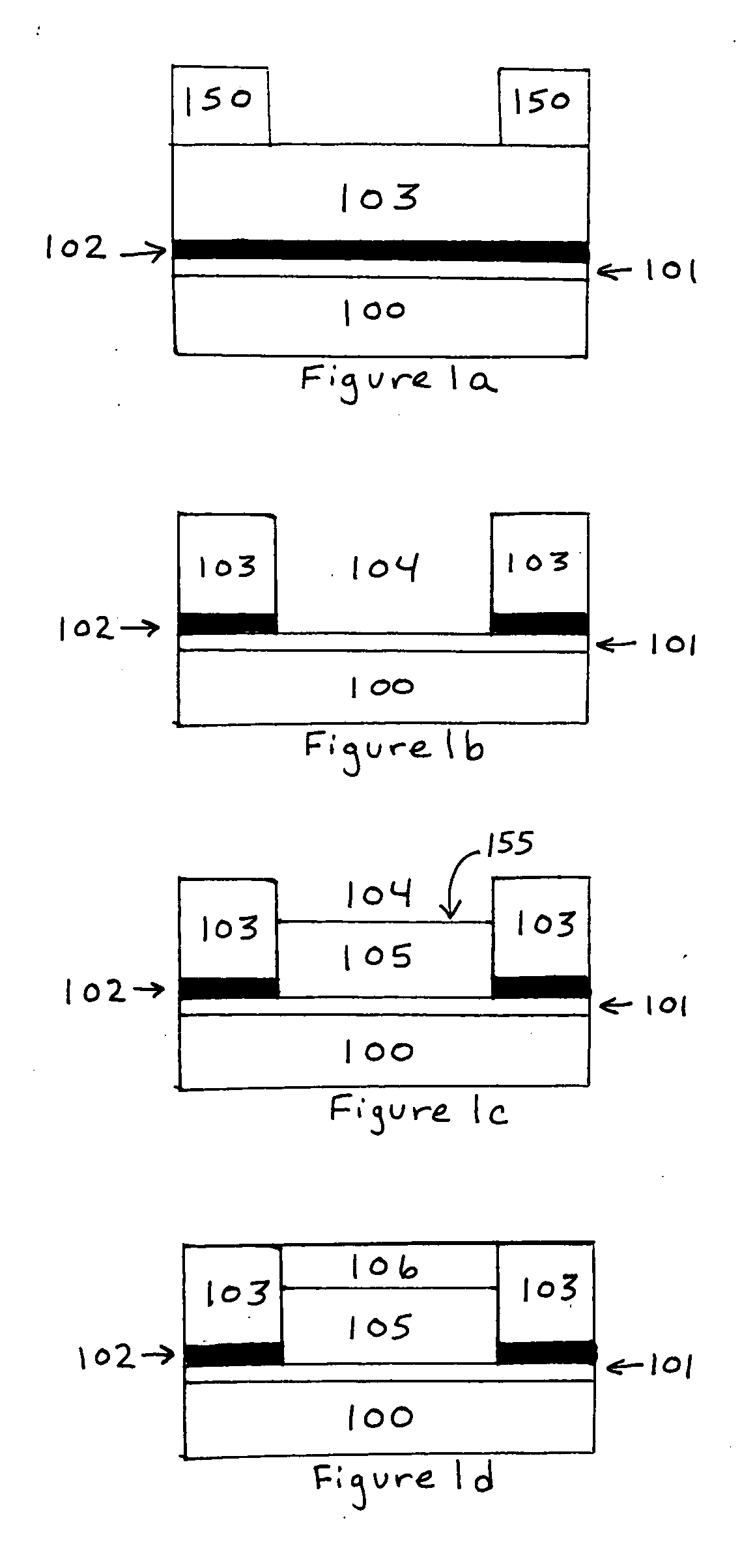

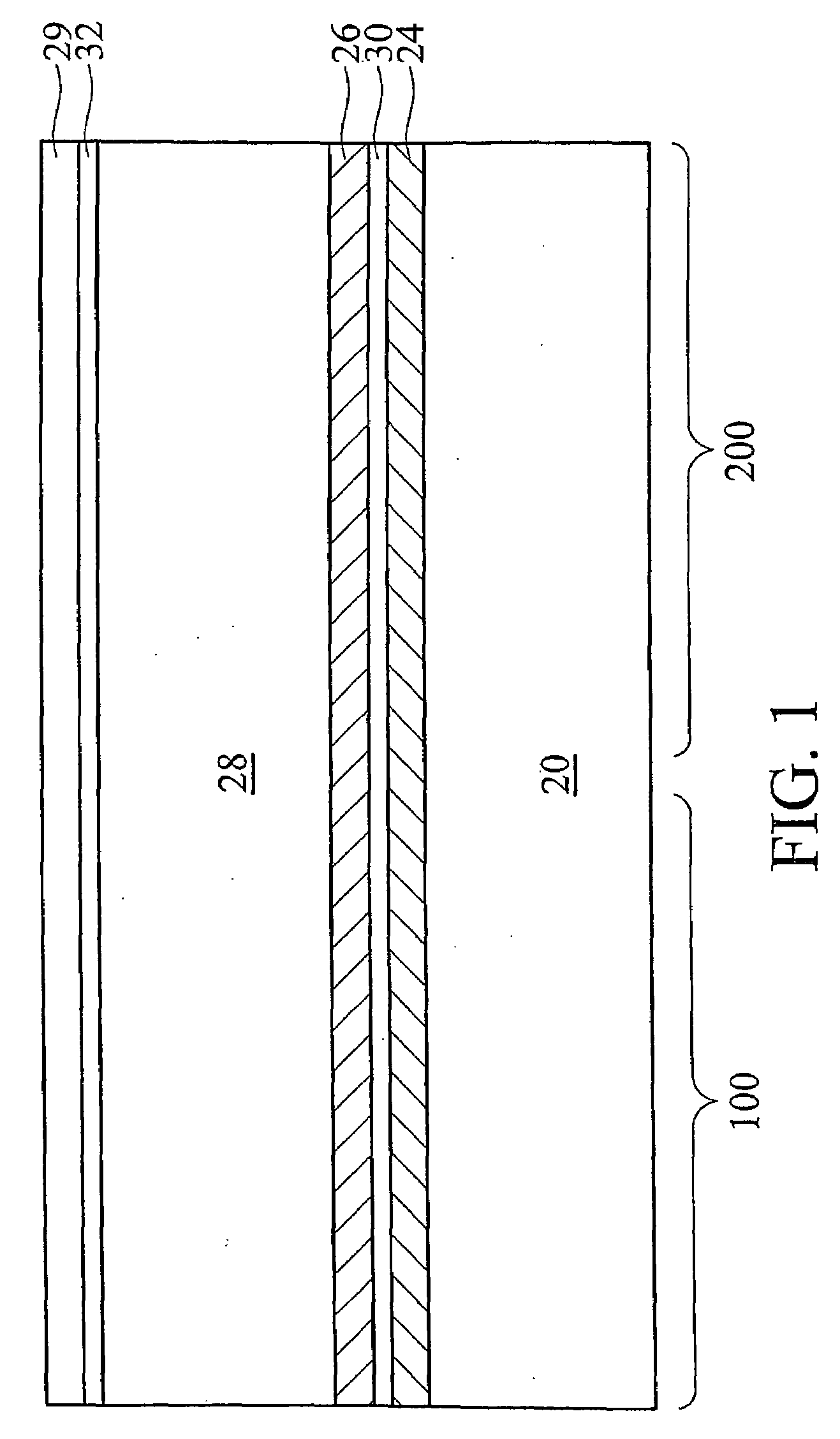

Method for forming a semiconductor device structure and related semiconductor device structures

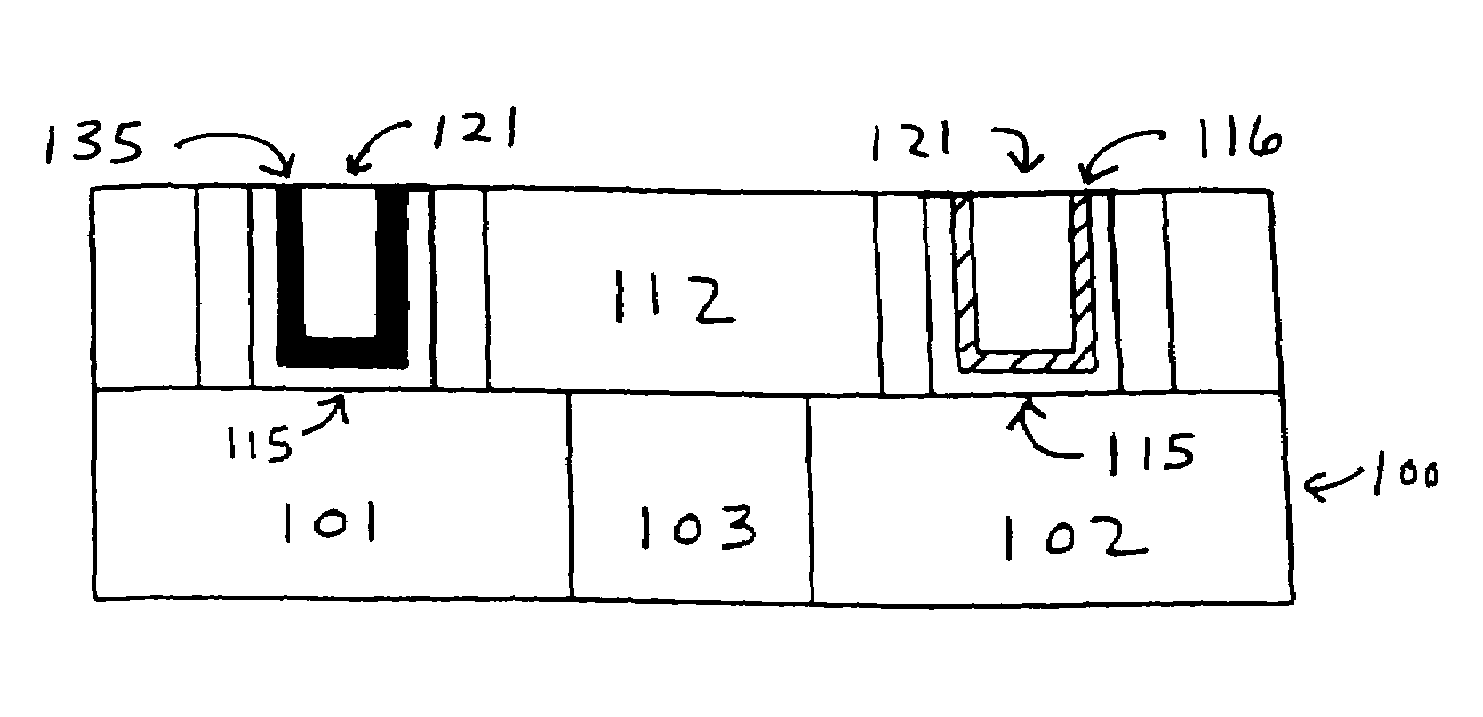

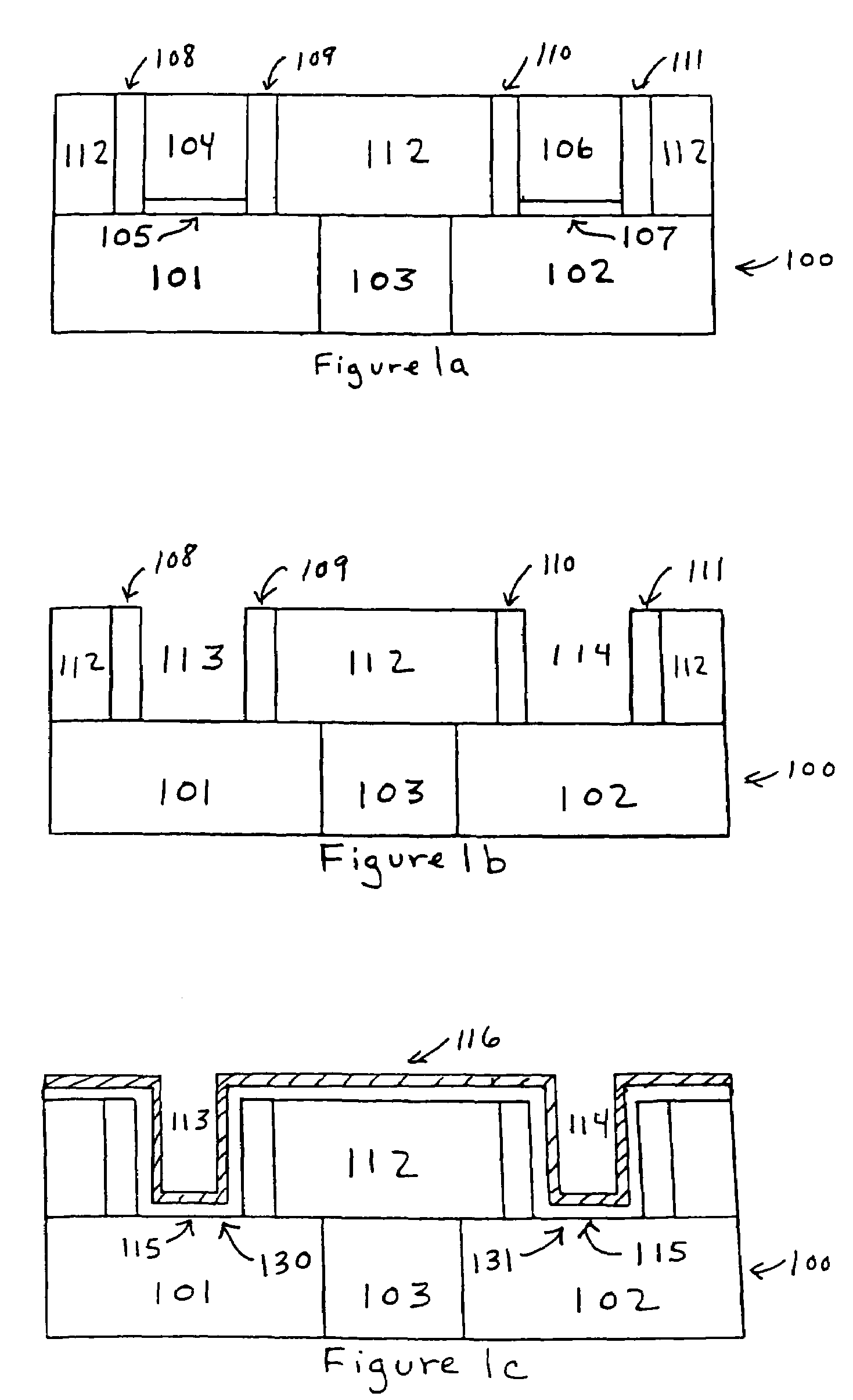

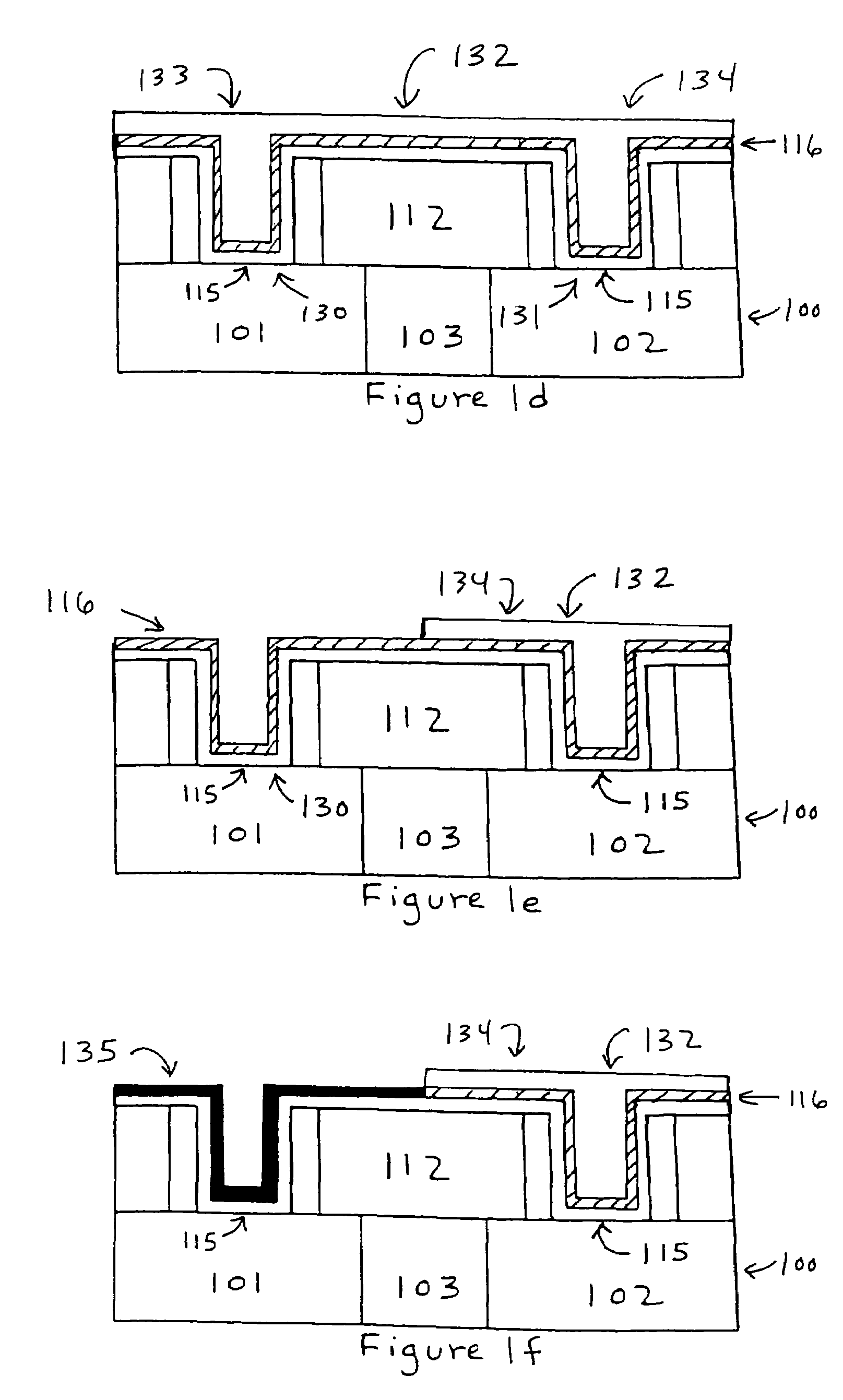

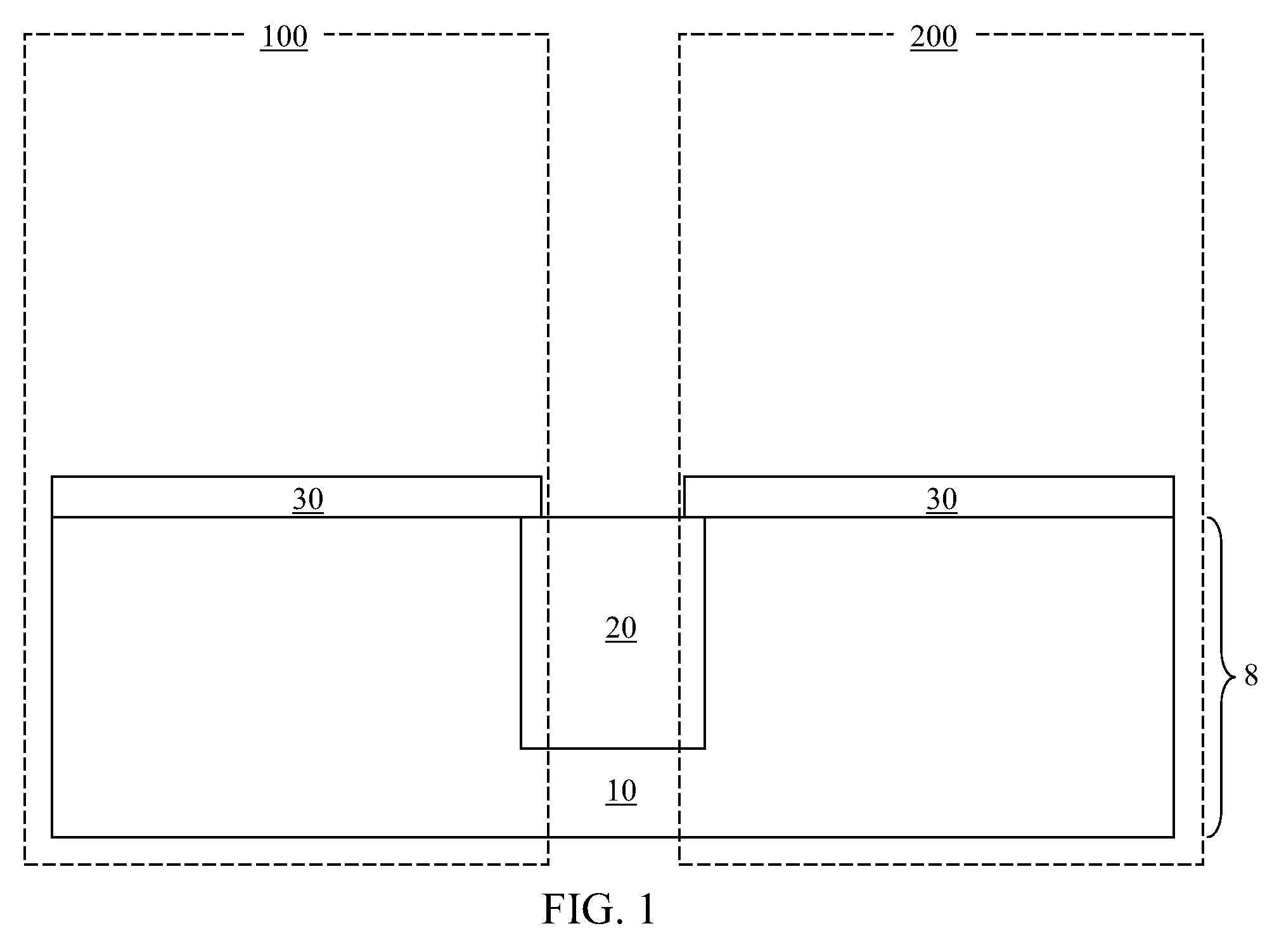

ActiveUS20190088555A1TransistorSemiconductor/solid-state device manufacturingWork functionEngineering

A method for forming a semiconductor device structure is disclosure. The method may include, depositing an NMOS gate dielectric and a PMOS gate dielectric over a semiconductor substrate, depositing a first work function metal over the NMOS gate dielectric and over the PMOS gate dielectric, removing the first work function metal over the PMOS gate dielectric, and depositing a second work function metal over the NMOS gate dielectric and over the PMOS gate dielectric. Semiconductor device structures including desired metal gate electrodes deposited by the methods of the disclosure are also disclosed.

Owner:ASM IP HLDG BV

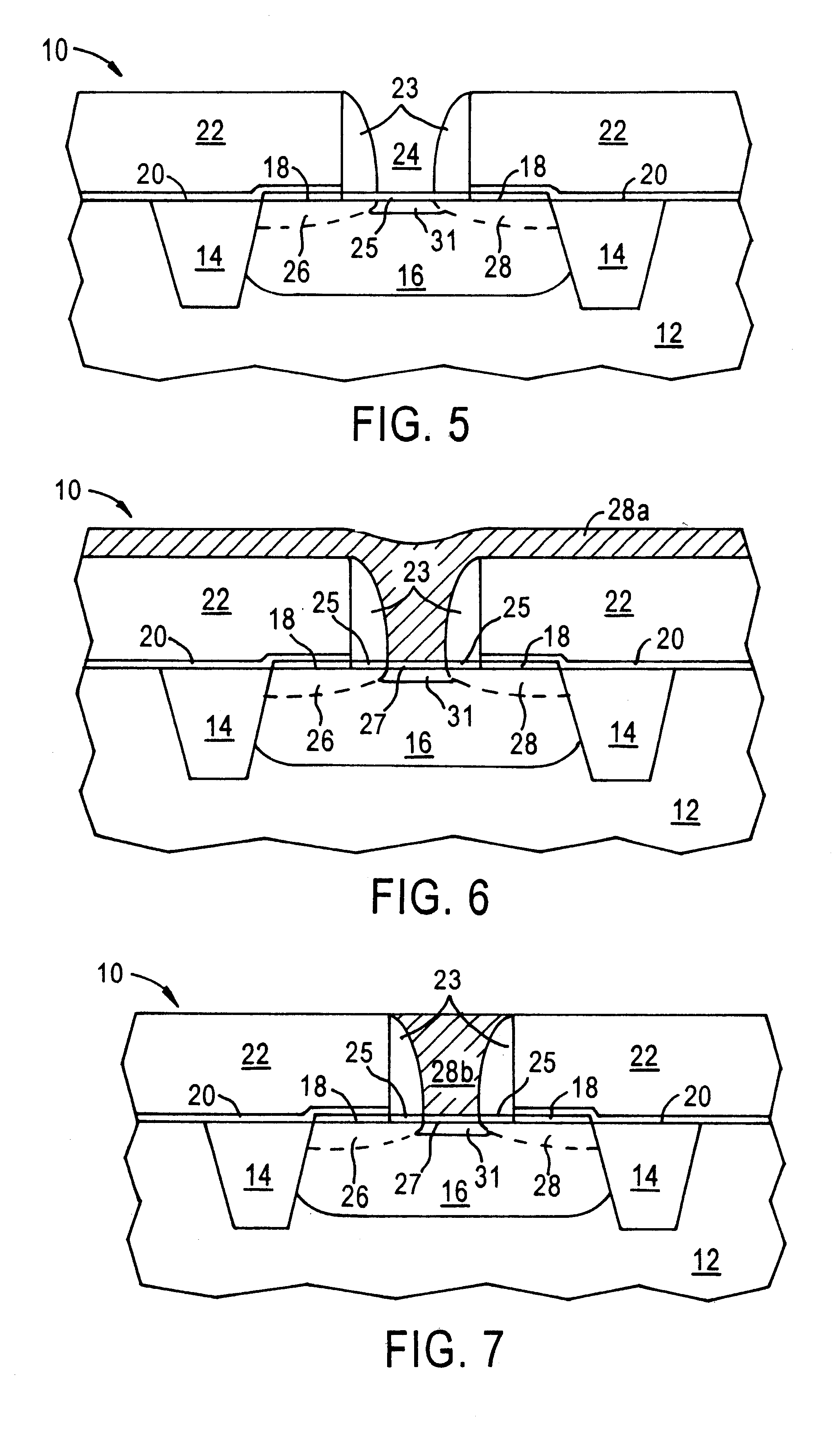

Nonplanar transistors with metal gate electrodes

A semiconductor device comprising a semiconductor body having a top surface and a first and second laterally opposite sidewalls as formed on an insulating substrate is claimed. A gate dielectric is formed on the top surface of the semiconductor body and on the first and second laterally opposite sidewalls of the semiconductor body. A gate electrode is then formed on the gate dielectric on the top surface of the semiconductor body and adjacent to the gate dielectric on the first and second laterally opposite sidewalls of the semiconductor body. The gate electrode comprises a metal film formed directly adjacent to the gate dielectric layer. A pair of source and drain regions are then formed in the semiconductor body on opposite sides of the gate electrode.

Owner:TAHOE RES LTD

Nonplanar transistors with metal gate electrodes

A semiconductor device comprising a semiconductor body having a top surface and a first and second laterally opposite sidewalls as formed on an insulating substrate. A gate dielectric is formed on the top surface of the semiconductor body and on the first and second laterally opposite sidewalls of the semiconductor body. A gate electrode is then formed on the gate dielectric on the top surface of the semiconductor body and adjacent to the gate dielectric on the first and second laterally opposite sidewalls of the semiconductor body. The gate electrode comprises a metal film formed directly adjacent to the gate dielectric layer. A pair of source and drain regions are uniformed in the semiconductor body on opposite sides of the gate electrode.

Owner:TAHOE RES LTD

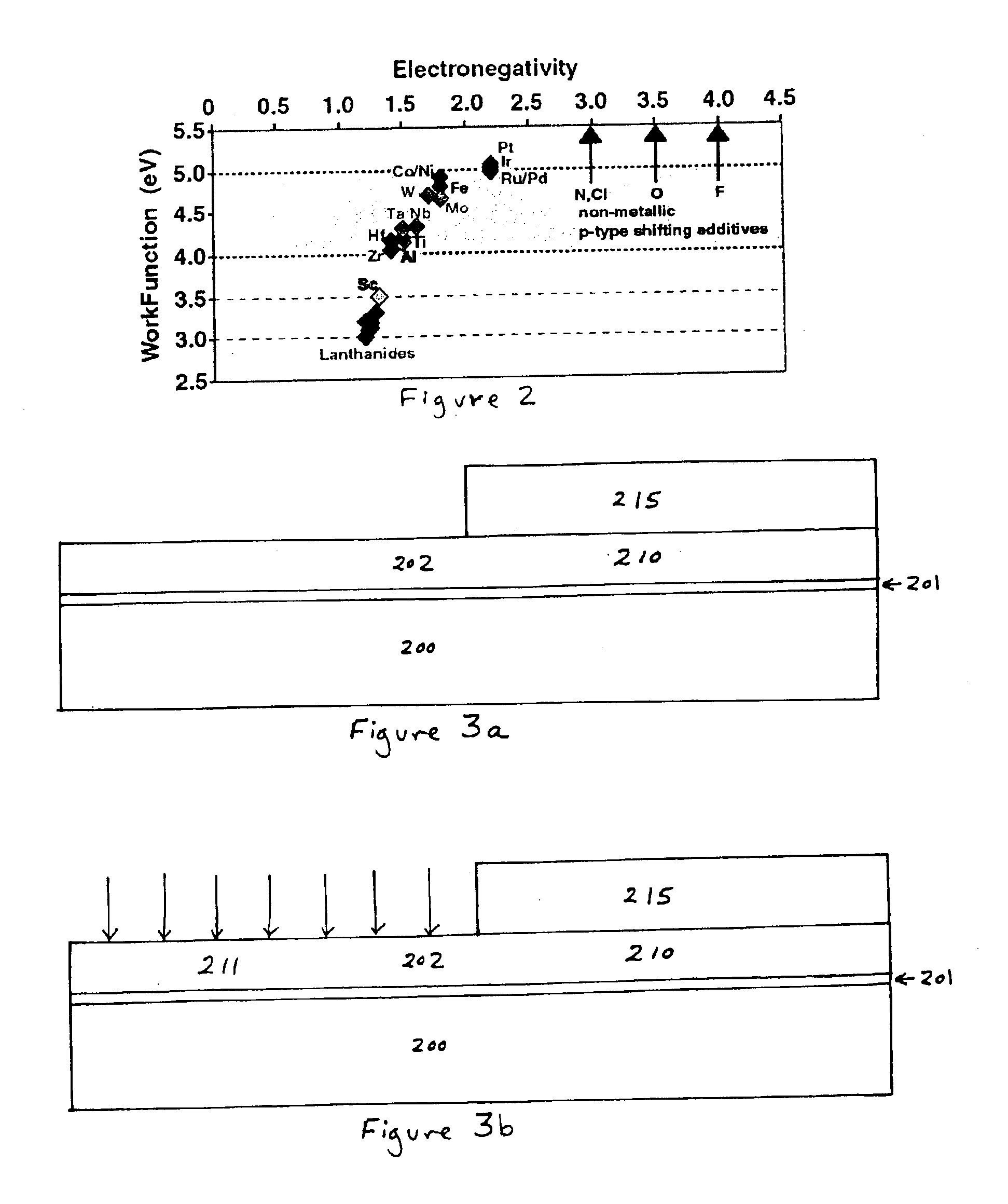

Tunable gate electrode work function material for transistor applications

Described herein are metal gate electrode stacks including a low resistance metal cap in contact with a metal carbonitride diffusion barrier layer, wherein the metal carbonitride diffusion barrier layer is tuned to a particular work function to also serve as a work function metal for a pMOS transistor. In an embodiment, the work function-tuned metal carbonitride diffusion barrier prohibits a low resistance metal cap layer of the gate electrode stack from migrating into the MOS junction. In a further embodiment of the present invention, the work function of the metal carbonitride barrier film is modulated to be p-type with a pre-selected work function by altering a nitrogen concentration in the film.

Owner:TAHOE RES LTD

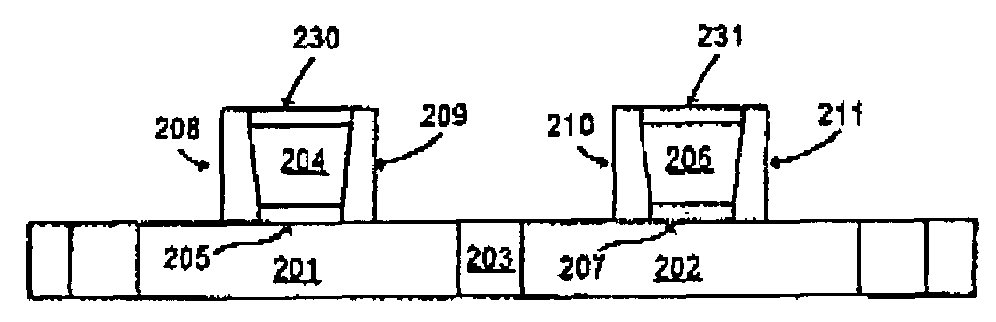

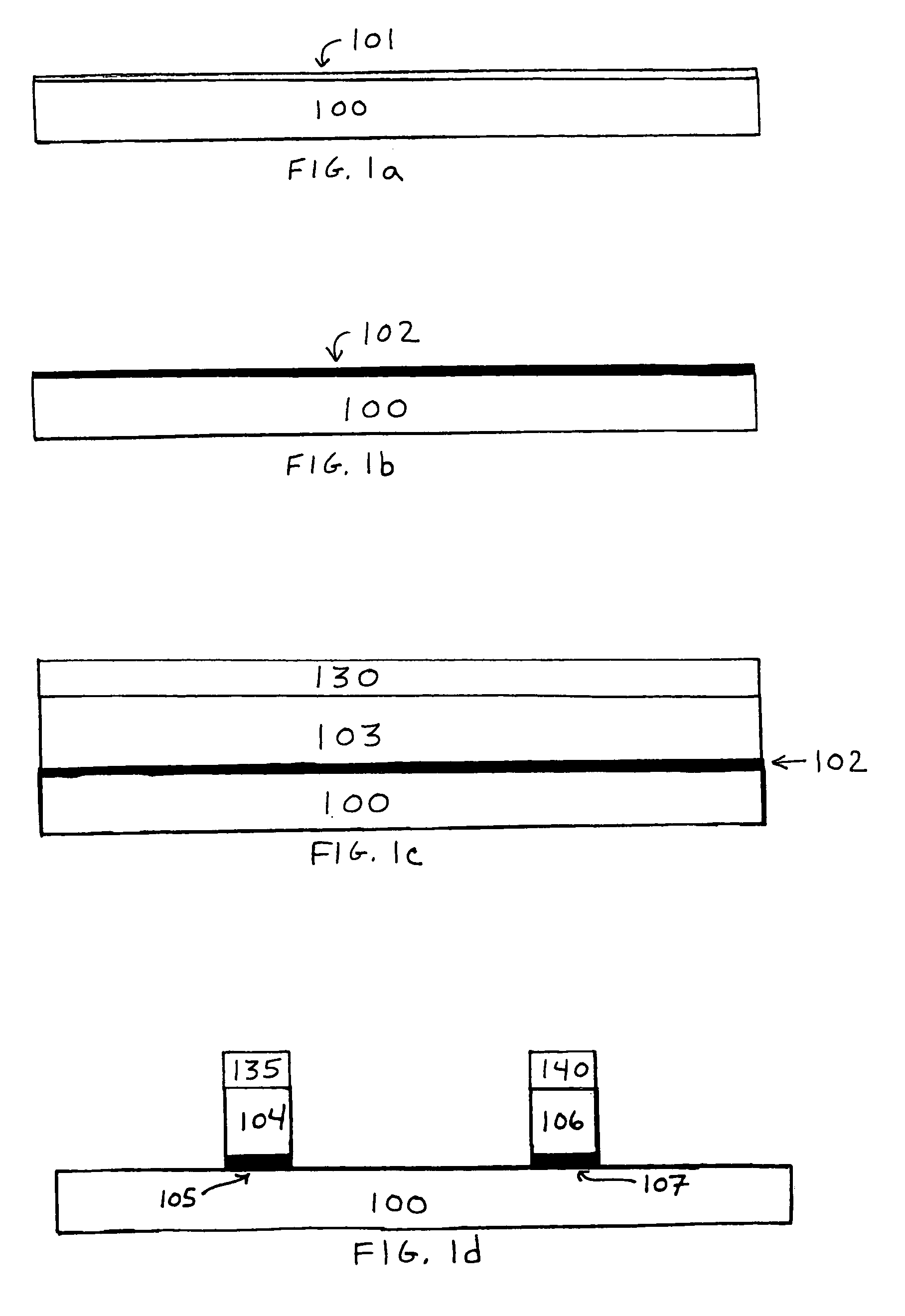

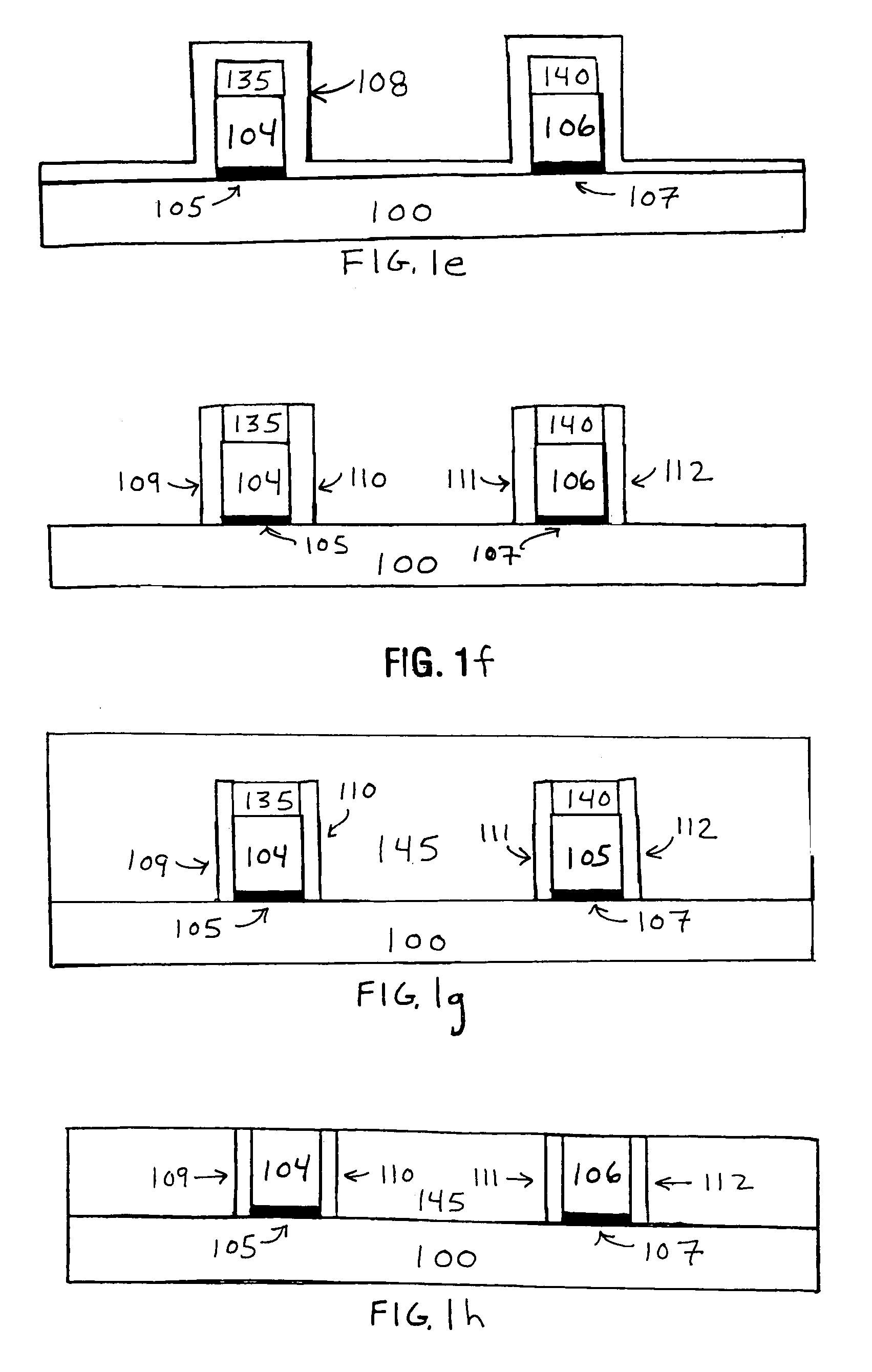

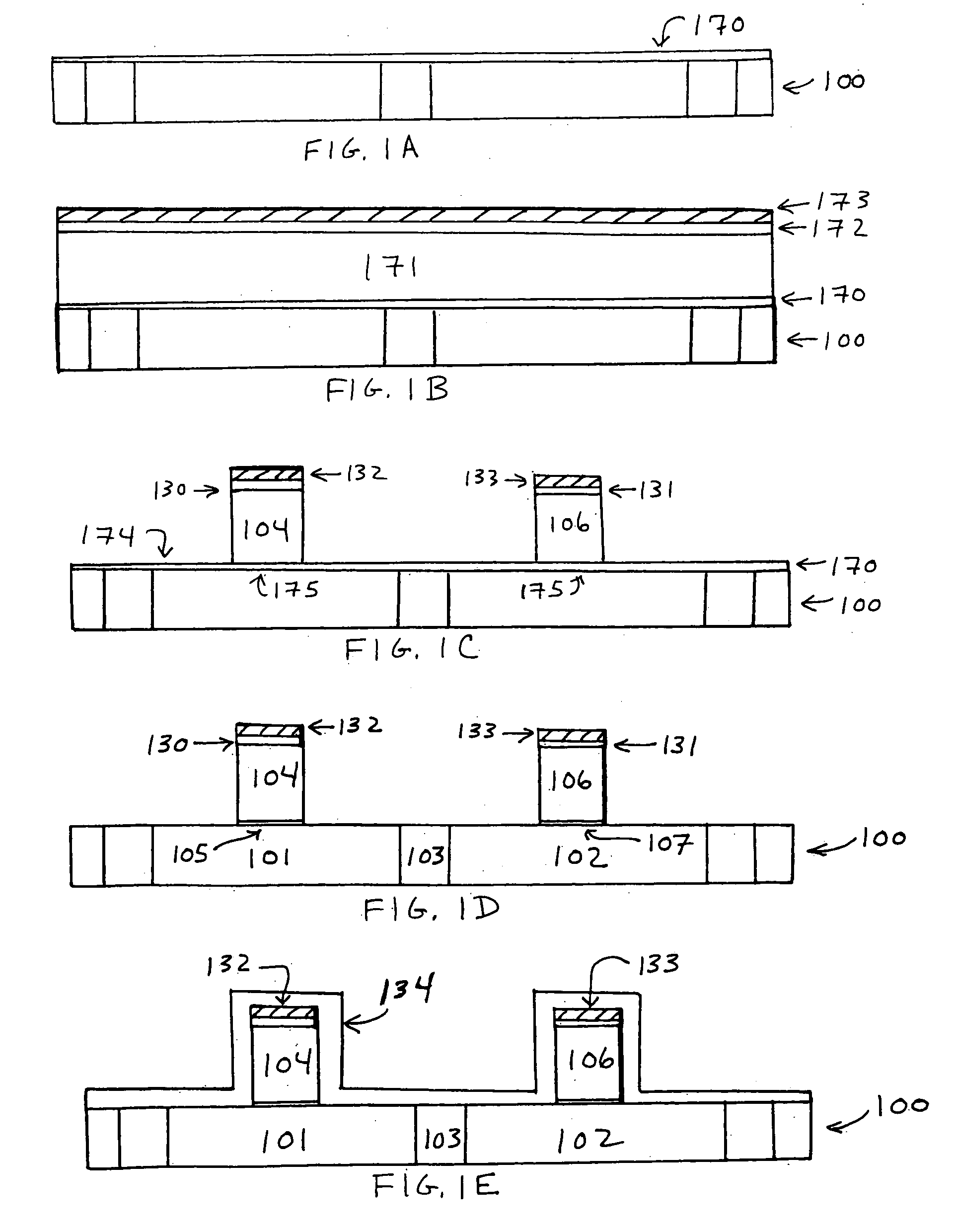

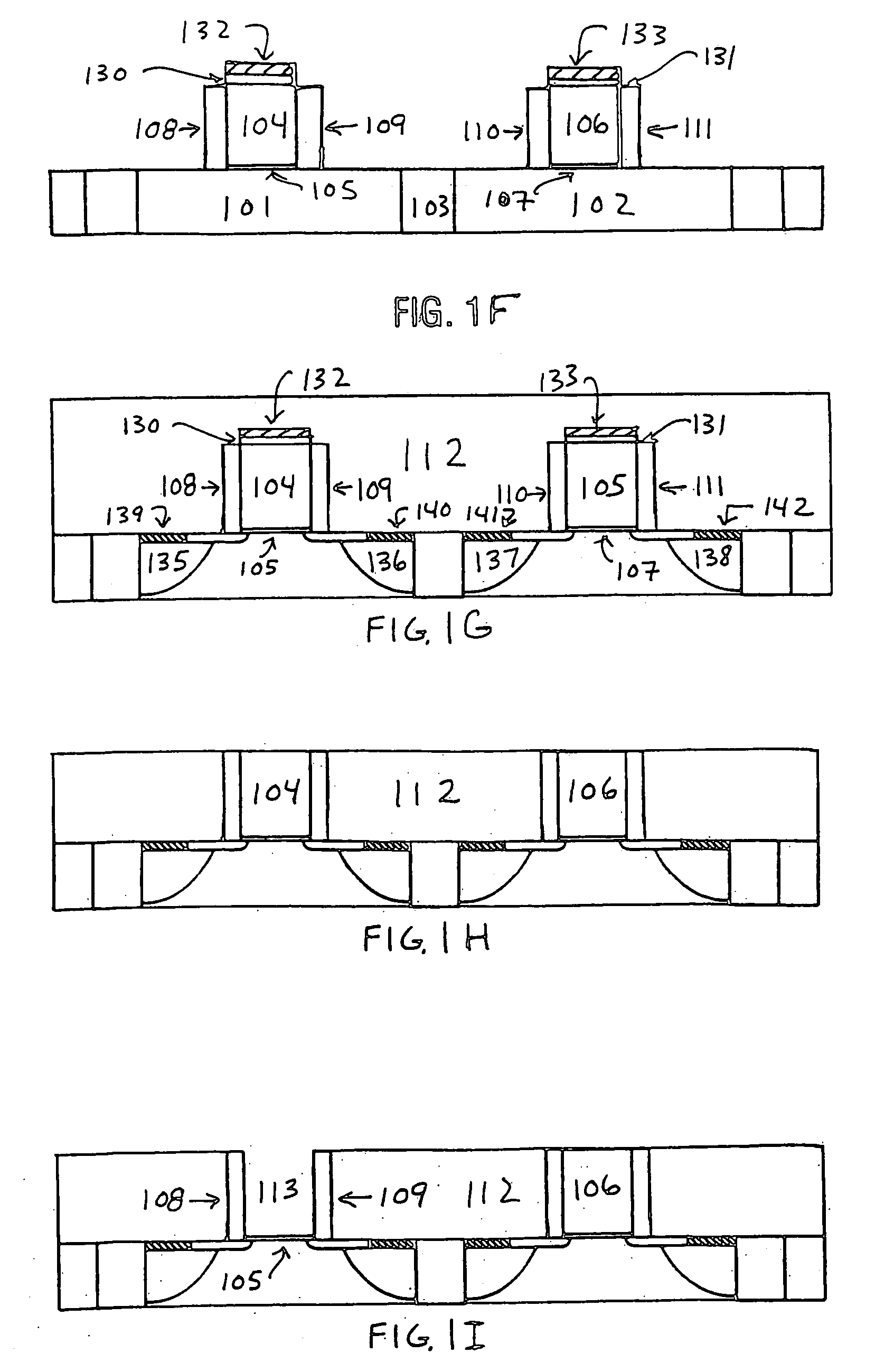

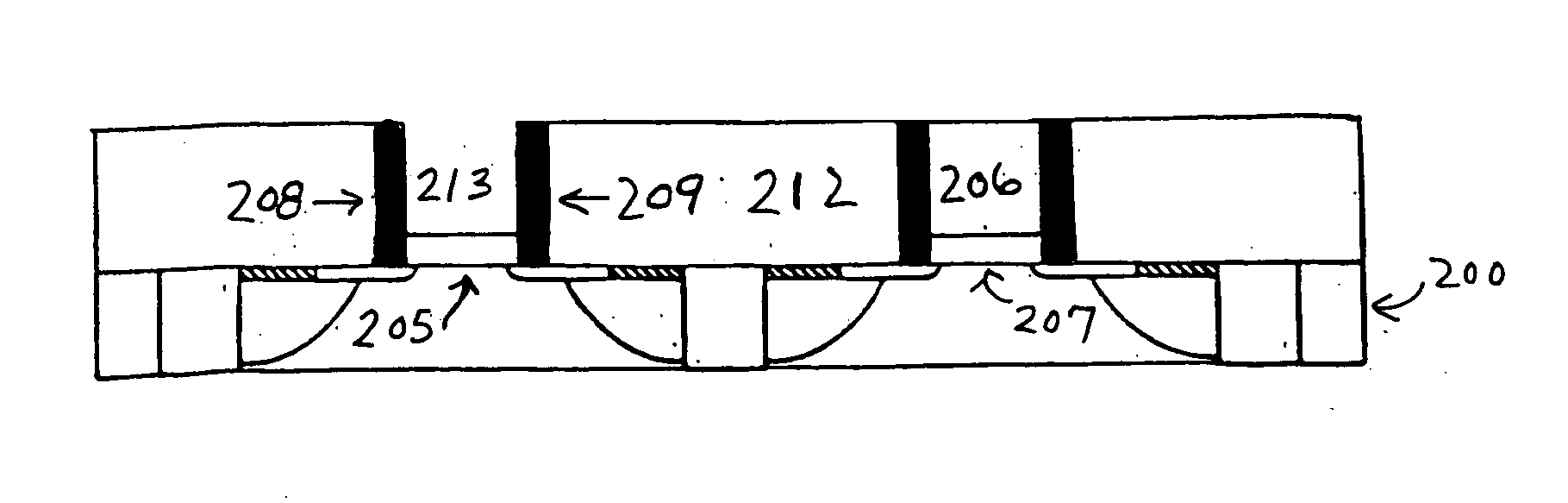

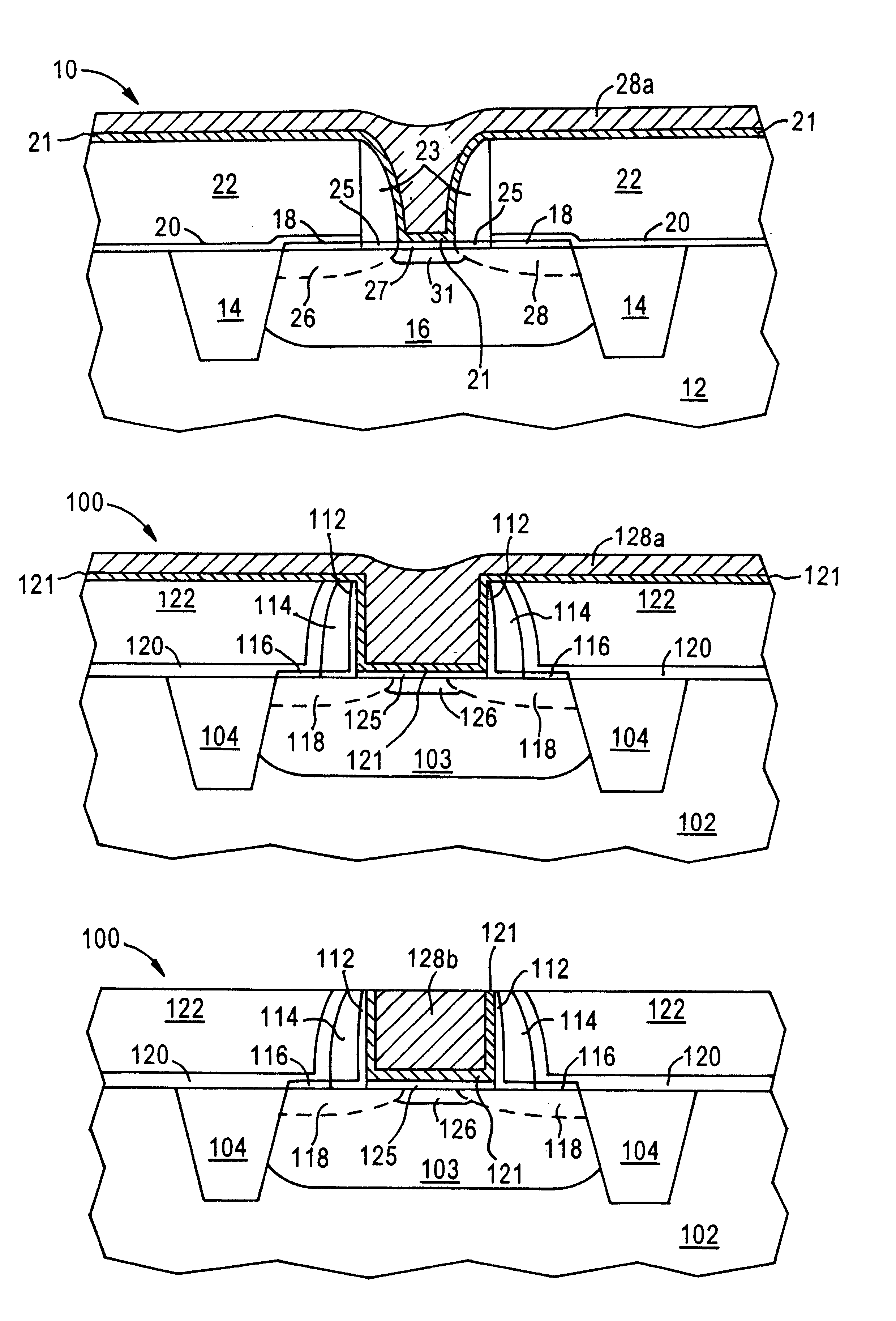

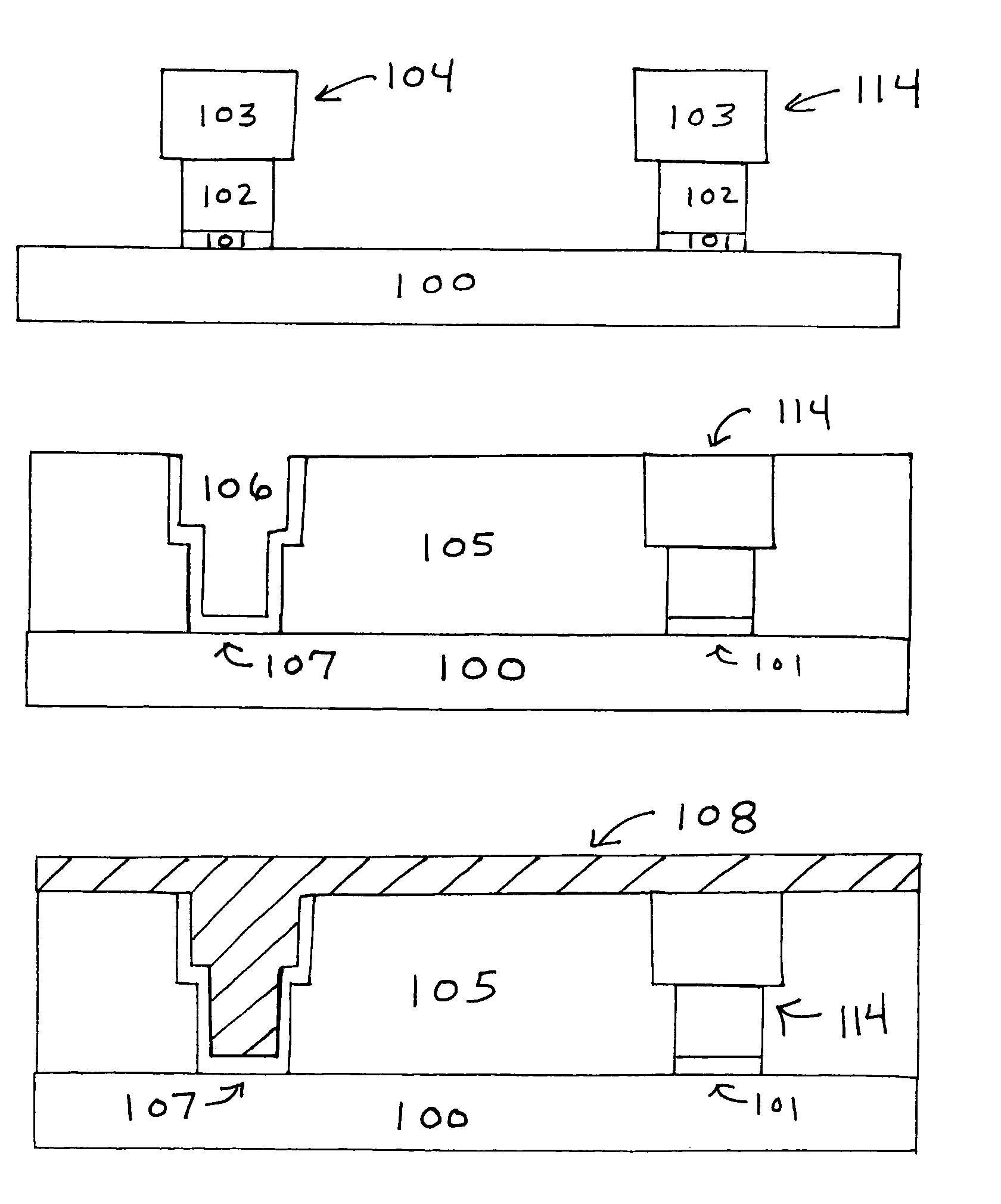

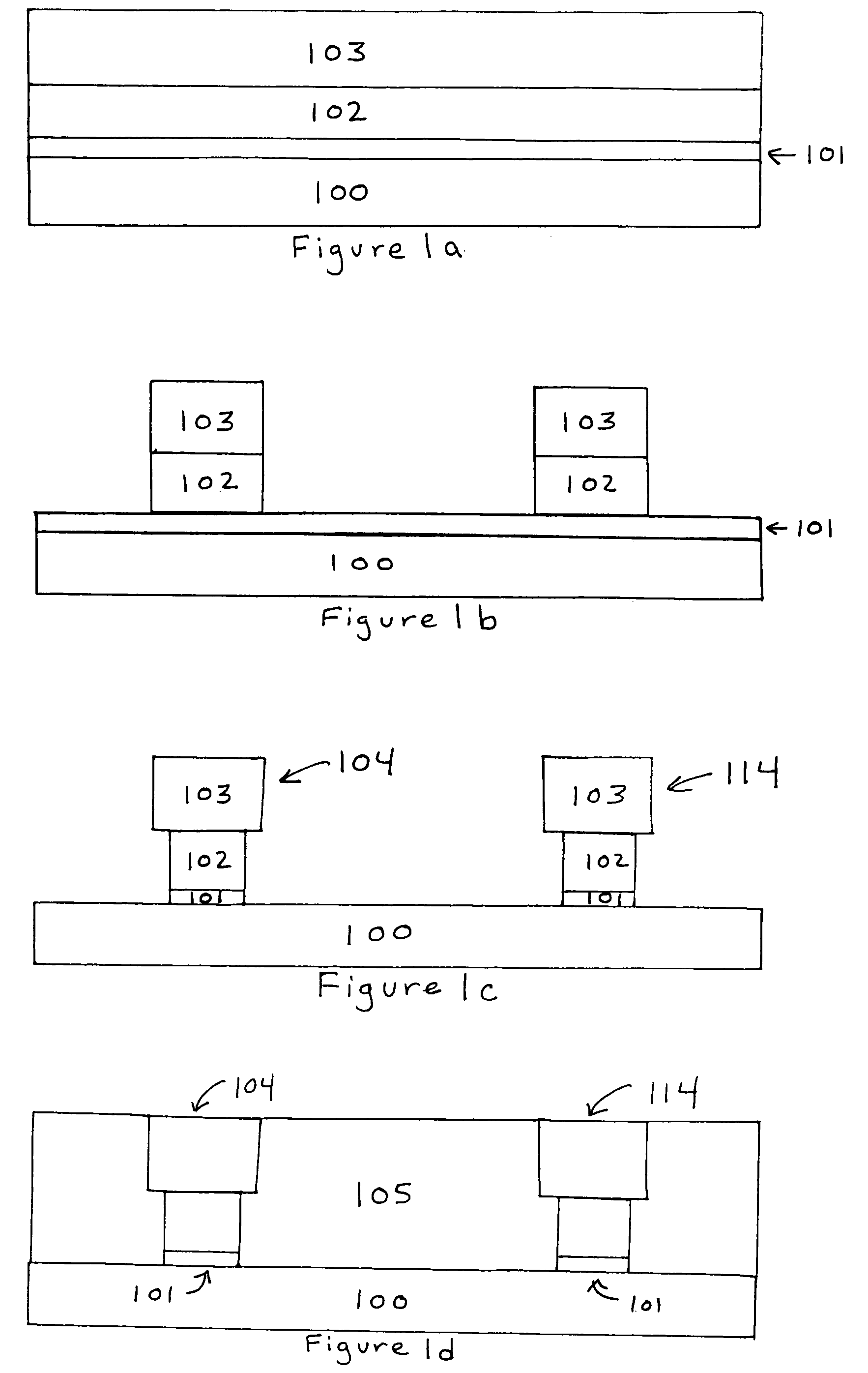

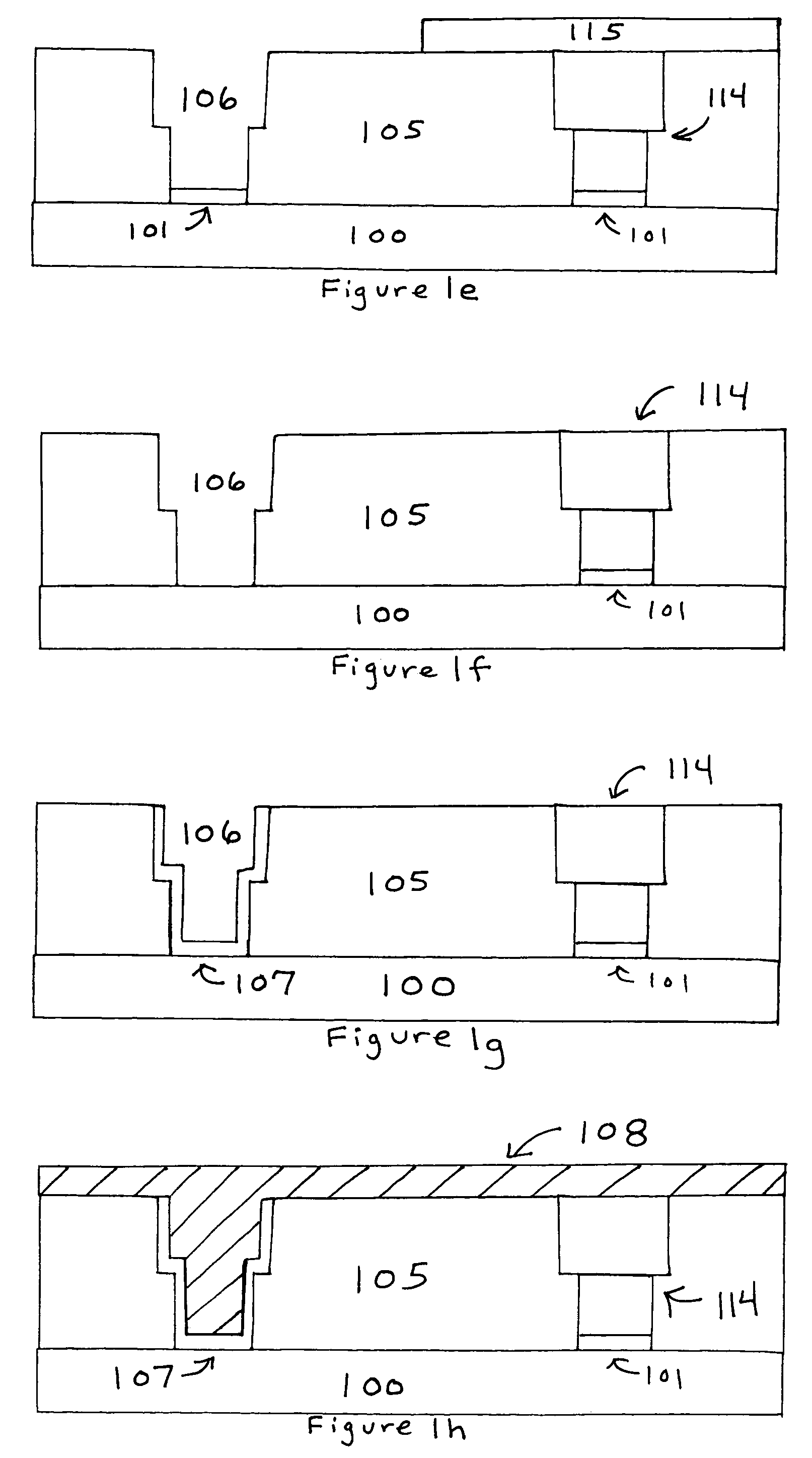

Replacement gate process for making a semiconductor device that includes a metal gate electrode

InactiveUS7208361B2Solid-state devicesSemiconductor/solid-state device manufacturingDielectric layerSemiconductor

A method for making a semiconductor device is described. That method comprises forming a polysilicon layer on a dielectric layer, which is formed on a substrate. The polysilicon layer is etched to generate a patterned polysilicon layer with an upper surface that is wider than its lower surface. The method may be applied, when using a replacement gate process to make transistors that have metal gate electrodes.

Owner:INTEL CORP

Semiconductor device with a high-k gate dielectric and a metal gate electrode

ActiveUS7148548B2Solid-state devicesSemiconductor/solid-state device manufacturingSemiconductorAluminide

A semiconductor device is described that comprises a gate dielectric and a metal gate electrode that comprises an aluminide.

Owner:INTEL CORP

Method for making a semiconductor device having a high-k gate dielectric layer and a metal gate electrode

ActiveUS7157378B2Semiconductor/solid-state device manufacturingSemiconductor devicesDielectric layerSemiconductor

Owner:TAHOE RES LTD

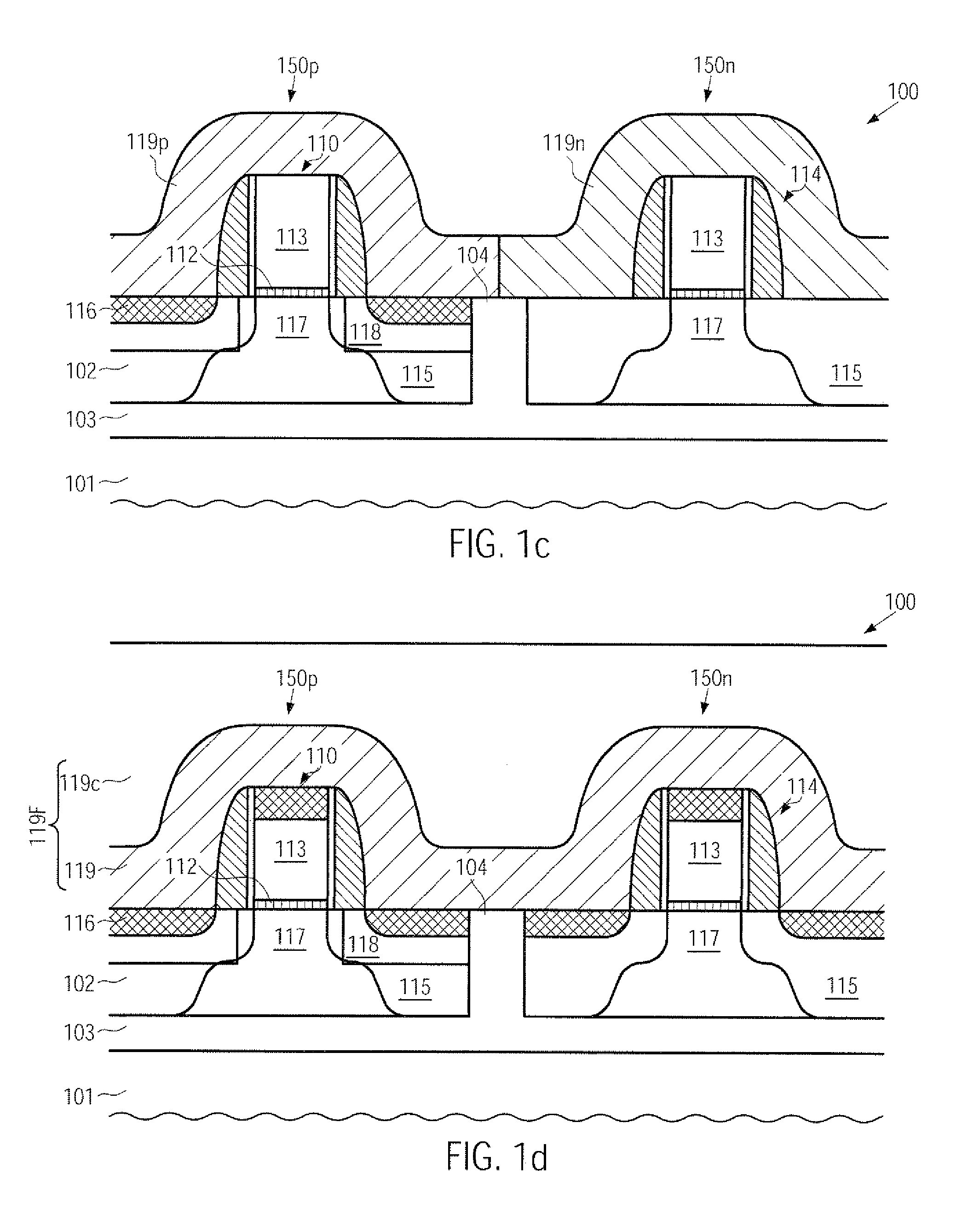

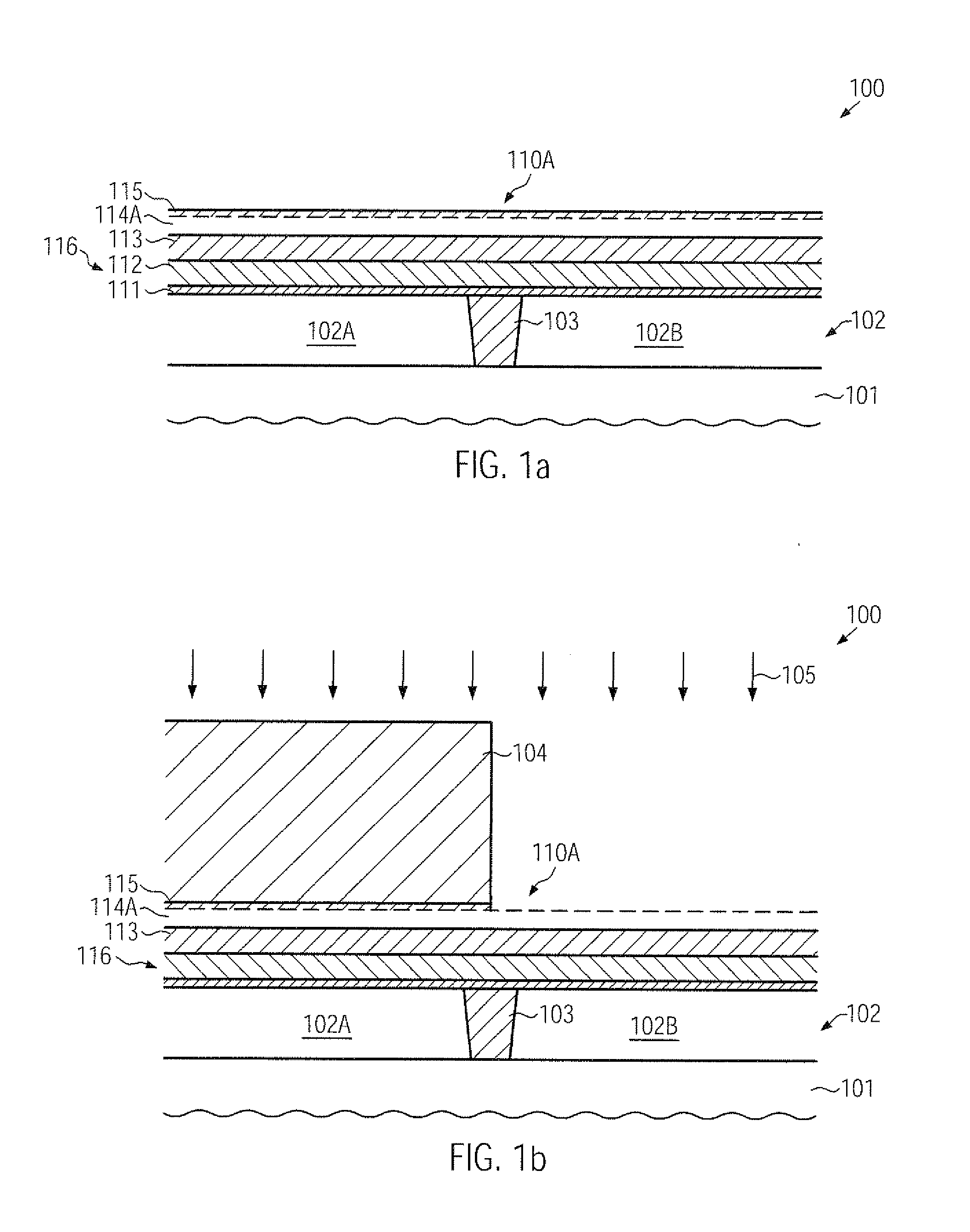

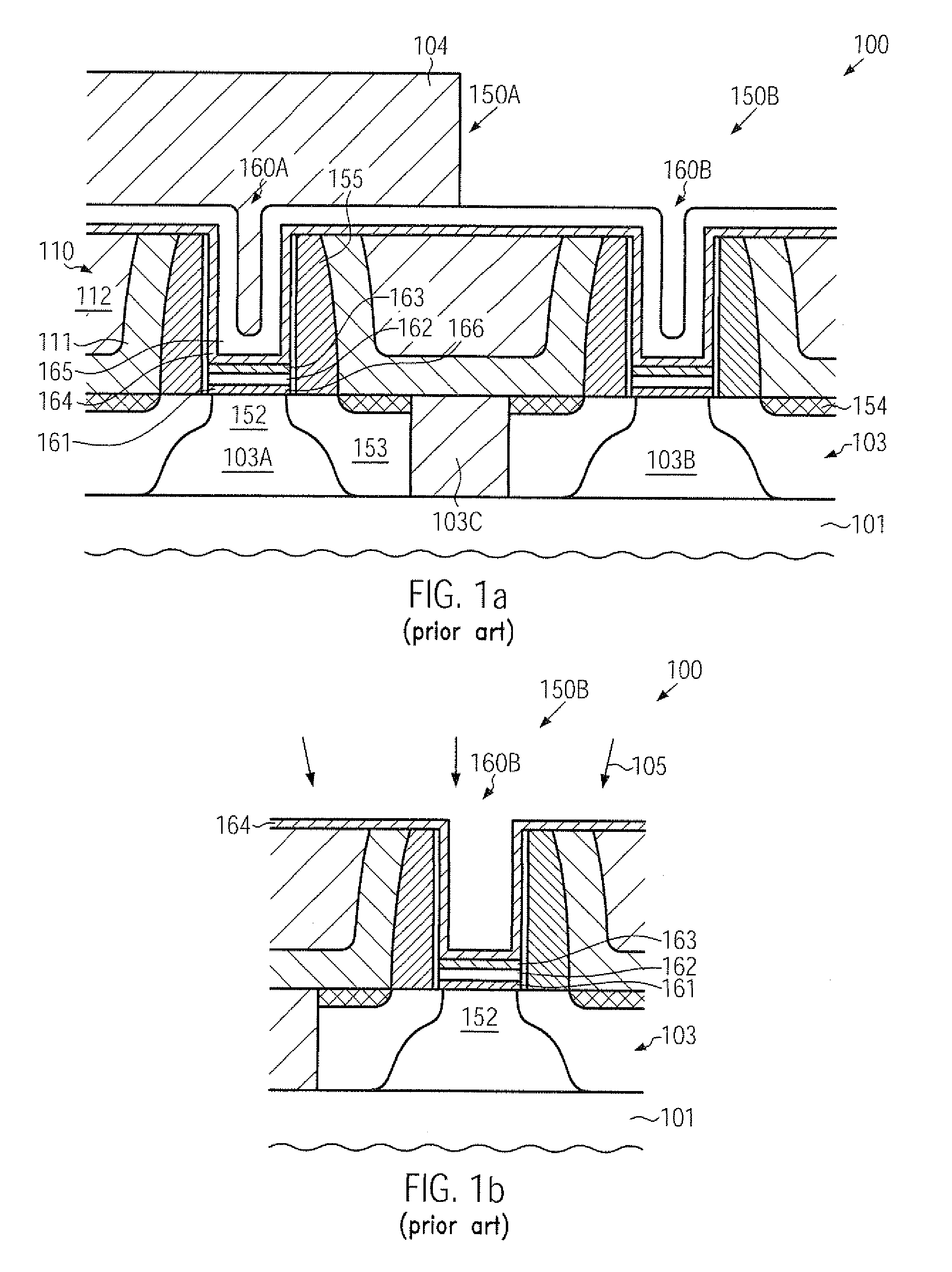

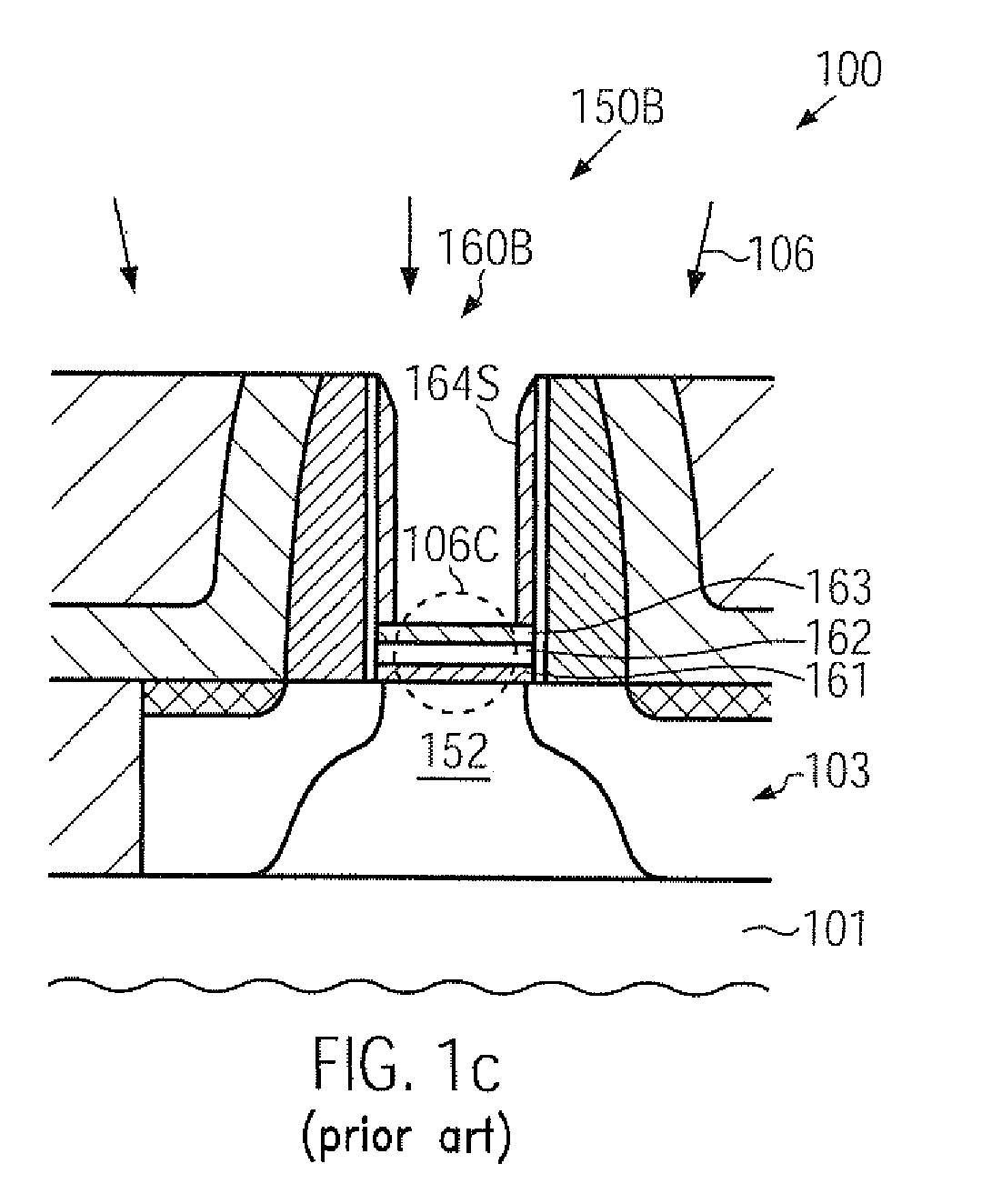

Method of forming high-k gate electrode structures after transistor fabrication

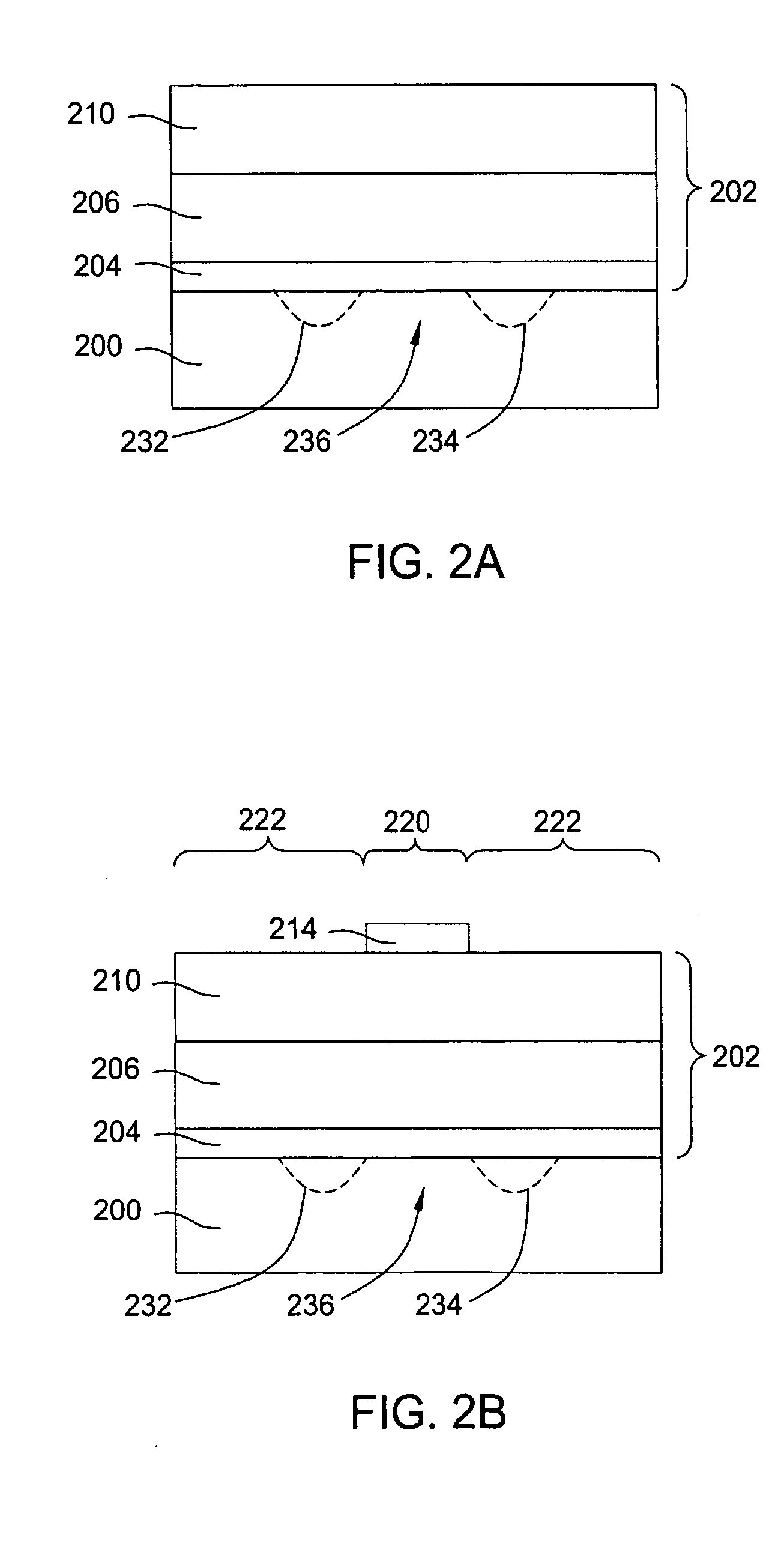

InactiveUS20090087974A1High degreeDeleterious effectSemiconductor/solid-state device manufacturingSemiconductor devicesCMOSDielectric

A sophisticated high-k metal gate electrode structure may be formed after the deposition of a first part of an interlayer dielectric material, thereby providing a high degree of process compatibility with conventional CMOS techniques. Thus, sophisticated strain-inducing mechanisms may be readily implemented in the overall process flow, while nevertheless avoiding any high temperature processes during the formation of the sophisticated high-k dielectric gate stack.

Owner:ADVANCED MICRO DEVICES INC

Process for forming an electronic device including a transistor having a metal gate electrode

An electronic device includes an n-channel transistor and a p-channel transistor. The p-channel transistor has a first gate electrode with a first work function and a first channel region including a semiconductor layer immediately adjacent to a semiconductor substrate. In one embodiment, the first work function is less than the valence band of the semiconductor layer. In another embodiment, the n-channel transistor has a second gate electrode with a second work function different from the first work function and closer to a conduction band than a valence band of a second channel region. A process of forming the electronic device includes forming first and second gate electrodes having first and second work functions, respectively. First and second channel regions having a same minority carrier type are associated with the first and second gate electrodes, respectively.

Owner:NORTH STAR INNOVATIONS

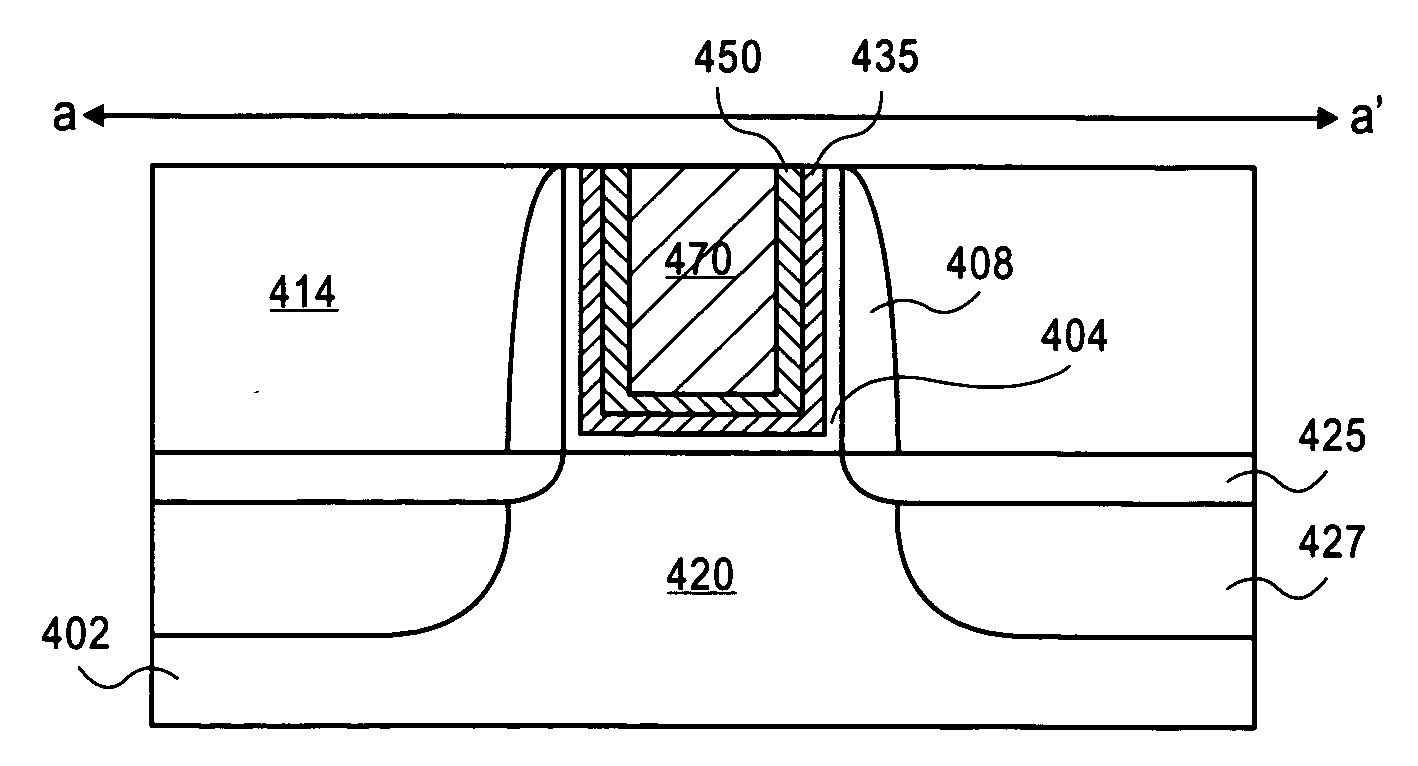

FET gate structure with metal gate electrode and silicide contact

A method is provided for fabricating a single-metal or dual metal replacement gate structure for a semiconductor device; the structure includes a silicide contact to the gate region. A dummy gate structure and sacrificial gate dielectric are removed to expose a portion of the substrate; a gate dielectric is formed thereon. A metal layer is formed overlying the gate dielectric and the dielectric material. This metal layer may conveniently be a blanket metal layer covering a device wafer. A silicon layer is then formed overlying the metal layer; this layer may also be a blanket wafer. A planarization or etchback process is then performed, so that the top surface of the dielectric material is exposed while other portions of the metal layer and the silicon layer remain in the gate region and have surfaces coplanar with the top surface of the dielectric material. A silicide contact is then formed which is in contact with the metal layer in the gate region.

Owner:GLOBALFOUNDRIES U S INC

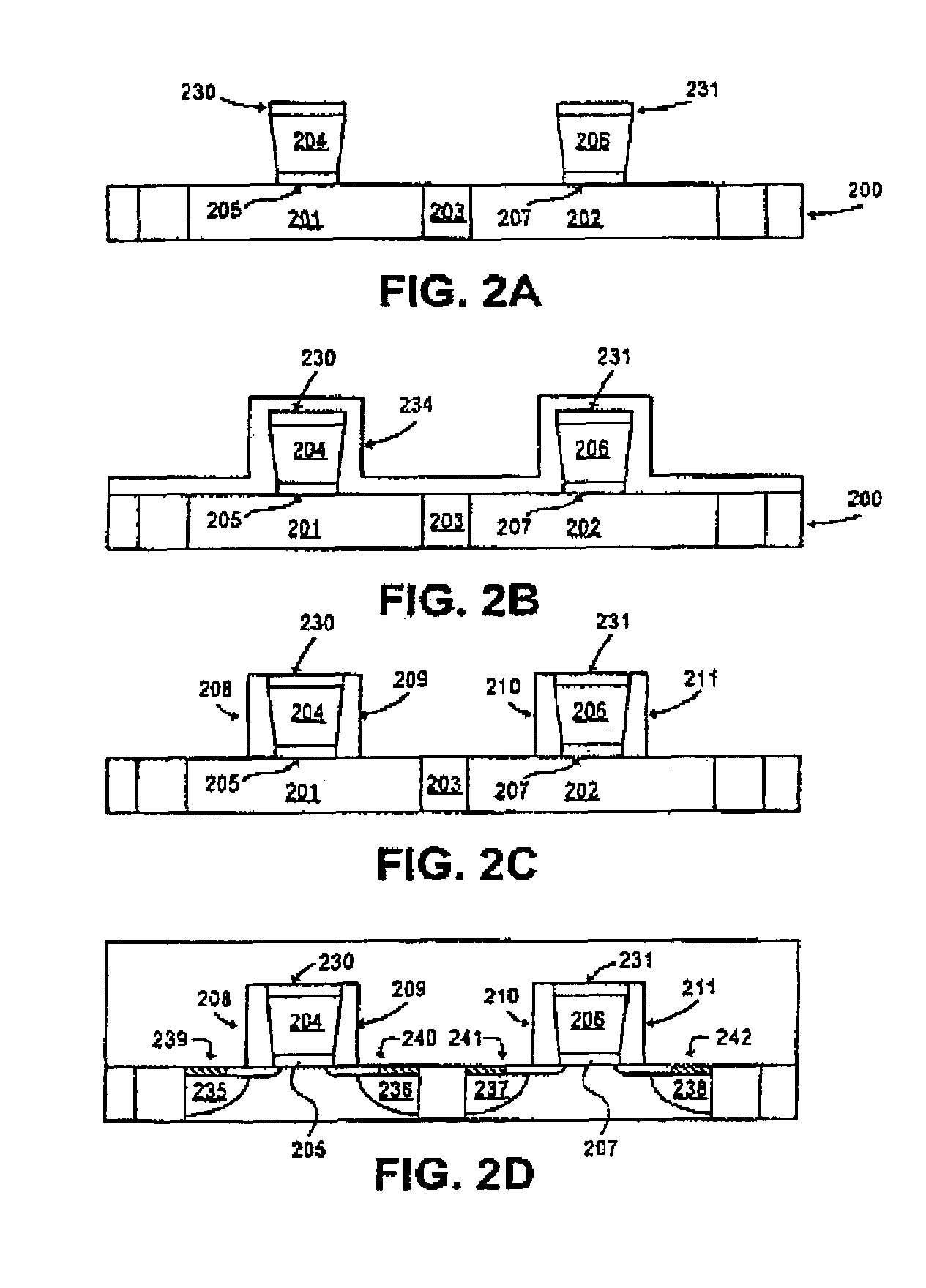

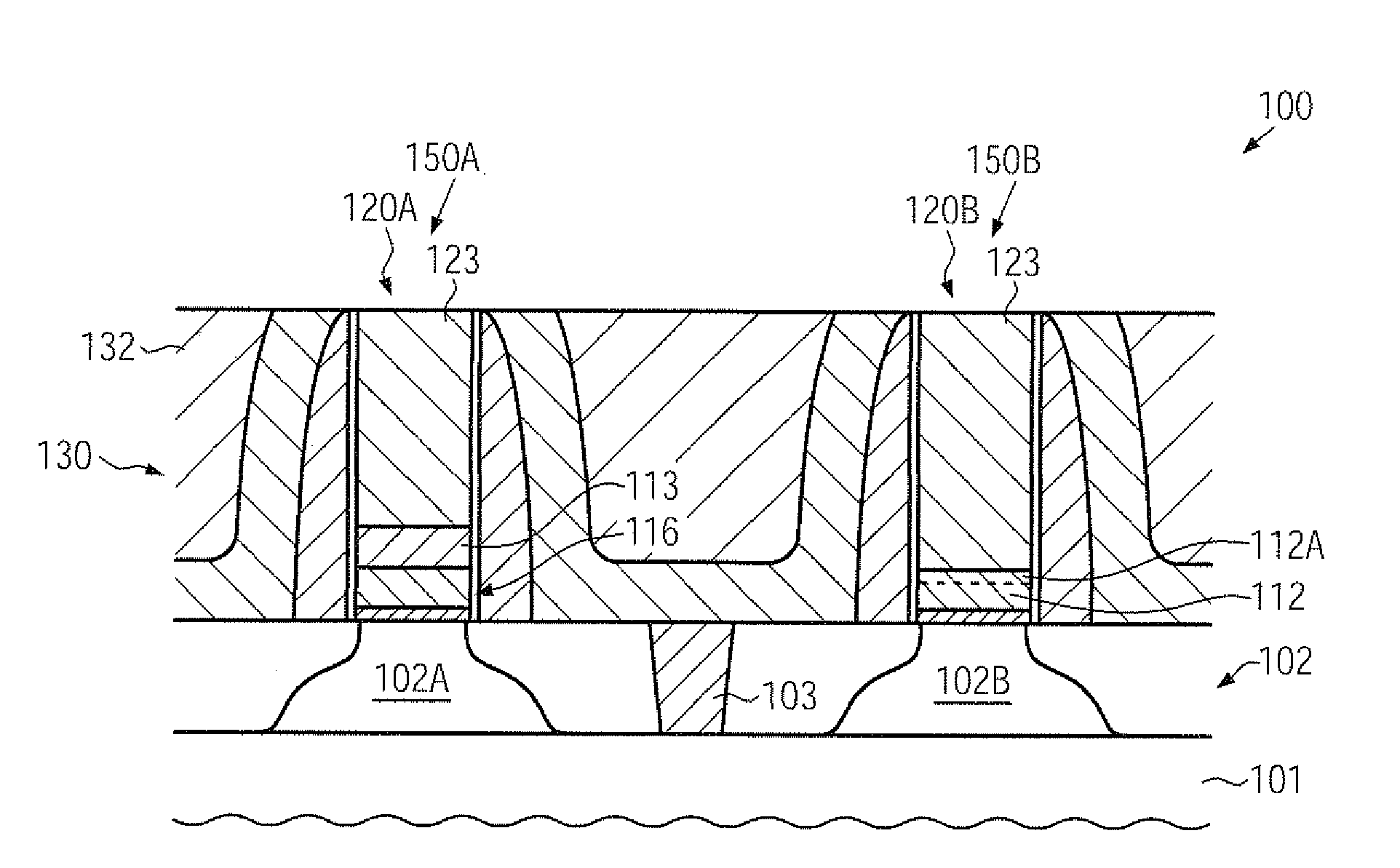

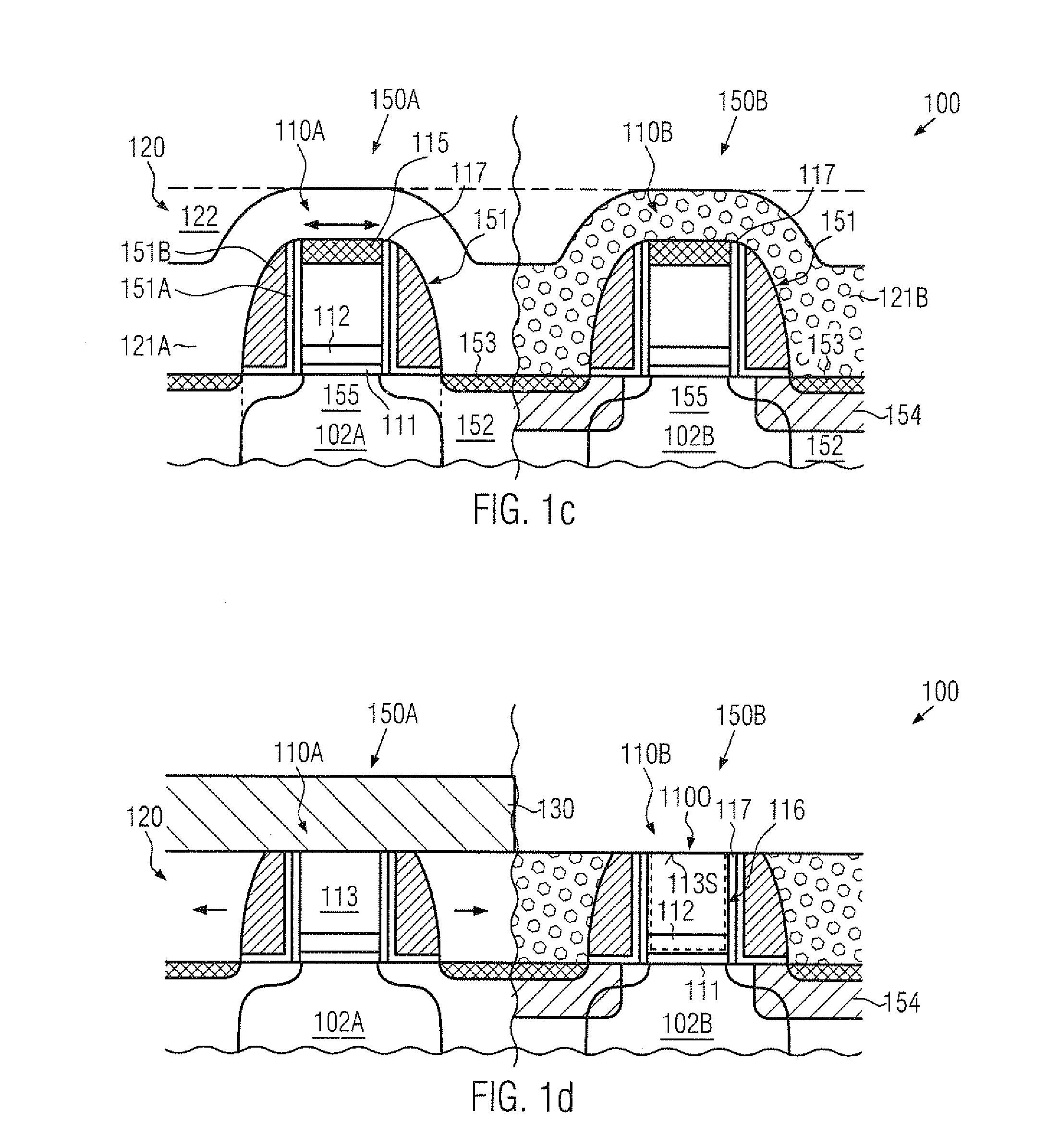

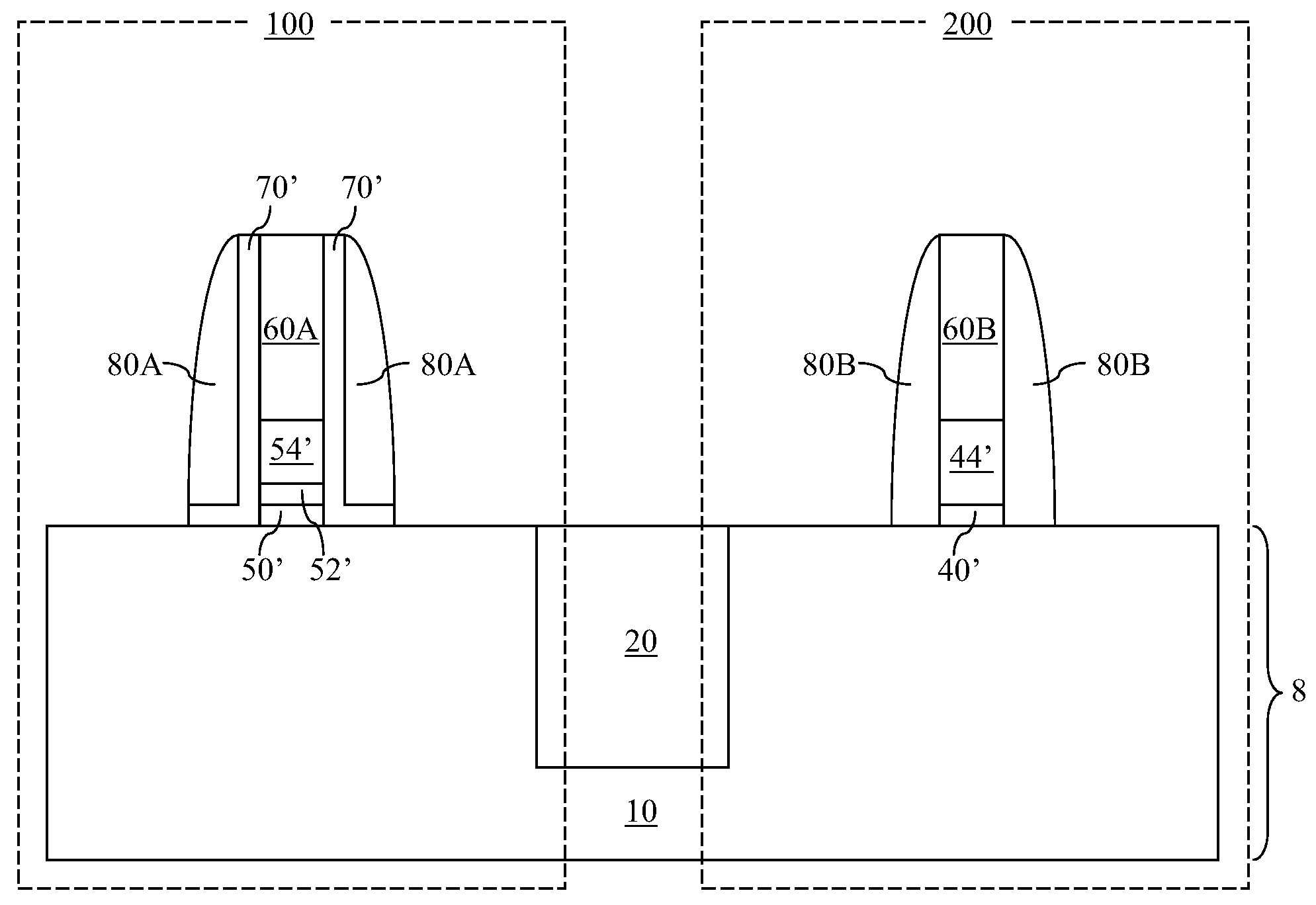

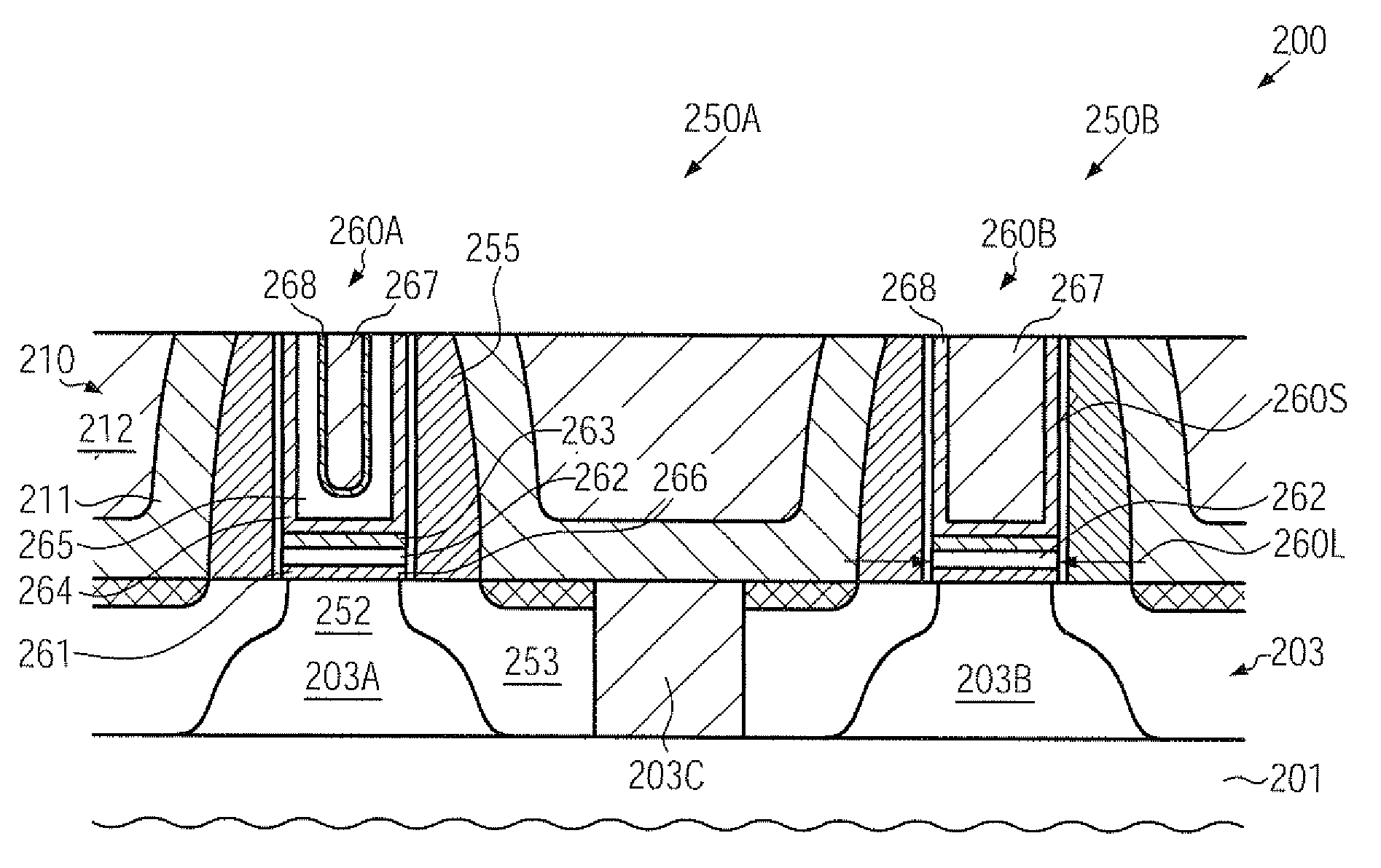

Threshold adjustment of transistors including high-k metal gate electrode structures comprising an intermediate etch stop layer

ActiveUS20100244141A1Reduce probabilitySimple process conditionsTransistorSemiconductor/solid-state device manufacturingPattern sequenceWork function

During the formation of sophisticated gate electrode structures, a replacement gate approach may be applied in which plasma assisted etch processes may be avoided. To this end, one of the gate electrode structures may receive an intermediate etch stop liner, which may allow the replacement of the placeholder material and the adjustment of the work function in a later manufacturing stage. The intermediate etch stop liner may not negatively affect the gate patterning sequence.

Owner:GLOBALFOUNDRIES US INC

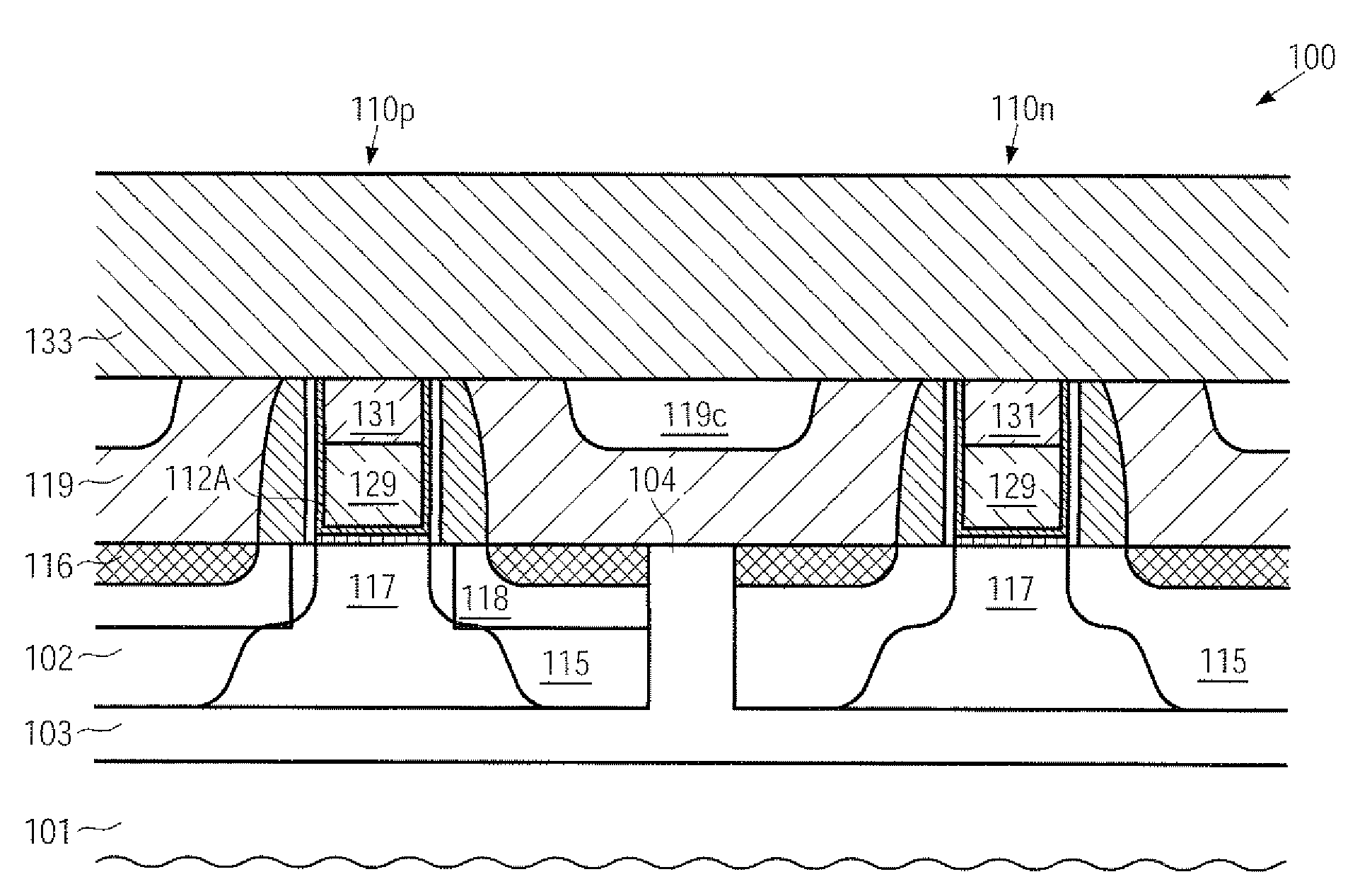

High-k metal gate electrode structures formed at different process stages of a semiconductor device

ActiveUS20110156154A1Improve device performanceEffective regulationTransistorSemiconductor/solid-state device manufacturingWork functionGate stack

Sophisticated high-k metal gate electrode structures are provided on the basis of a hybrid process strategy in which the work function of certain gate electrode structures is adjusted in an early manufacturing stage, while, in other gate electrode structures, the initial gate stack is used as a dummy material and is replaced in a very advanced manufacturing stage. In this manner, superior overall process robustness in combination with enhanced device performance may be achieved.

Owner:GLOBALFOUNDRIES US INC

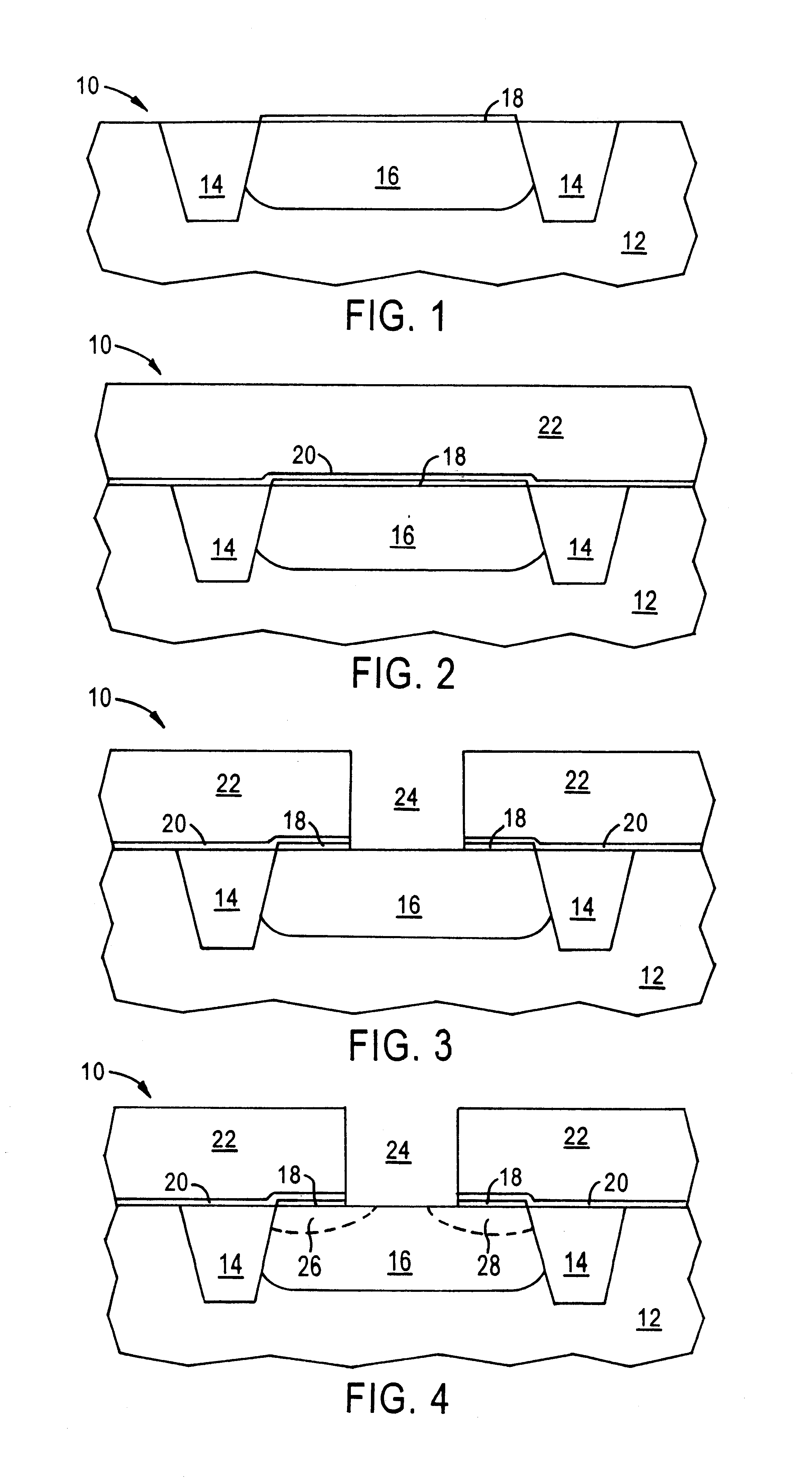

Method for making a semiconductor device with a high-k gate dielectric and a metal gate electrode

ActiveUS7381608B2Semiconductor/solid-state device manufacturingSemiconductor devicesNitrogenSilicon dioxide

Owner:DAEDALUS PRIME LLC

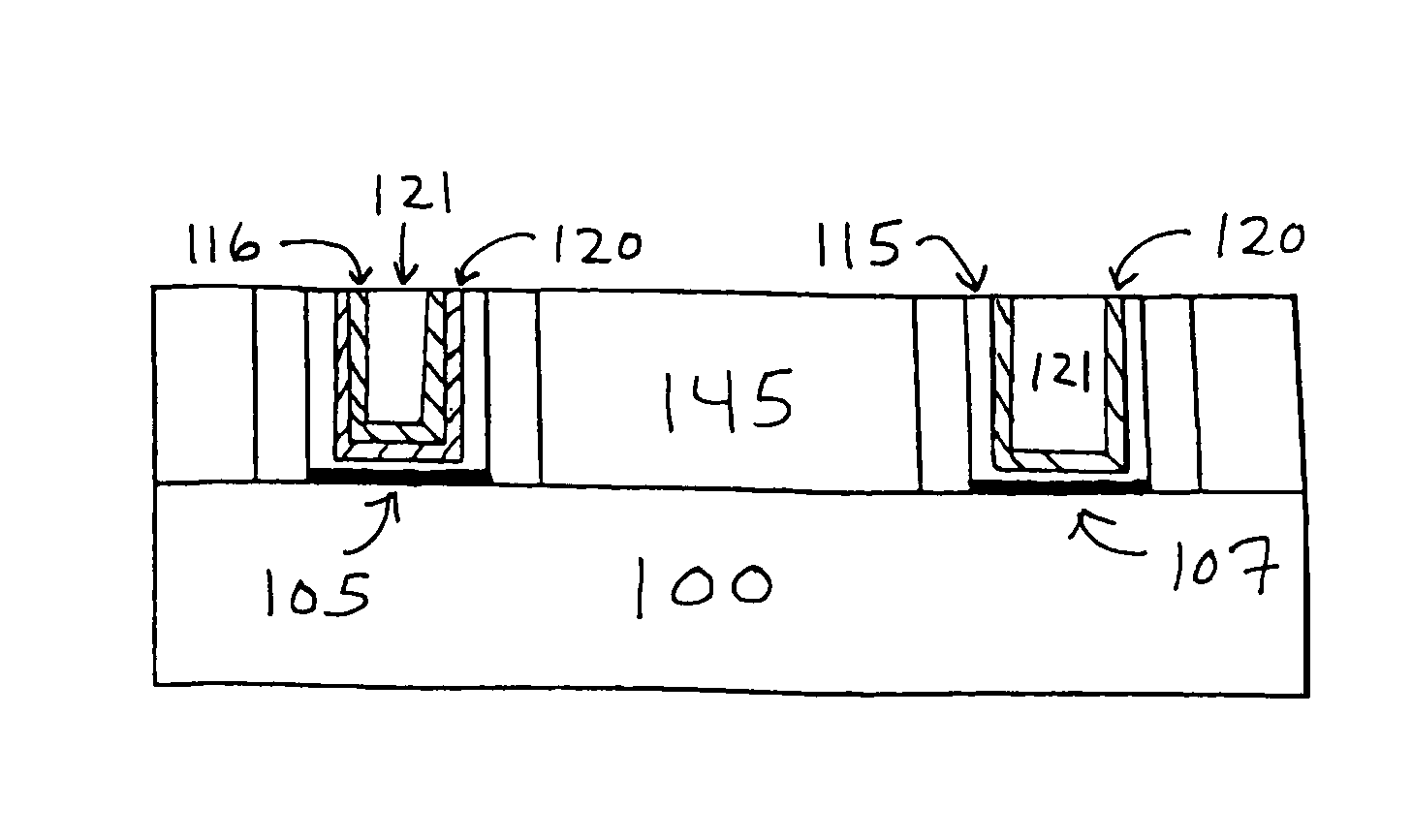

Method for making a semiconductor device having a high-k gate dielectric layer and a metal gate electrode

ActiveUS7153784B2TransistorSemiconductor/solid-state device manufacturingDielectric layerSemiconductor

A method for making a semiconductor device is described. That method comprises forming a first dielectric layer on a substrate, then forming a trench within the first dielectric layer. After forming a second dielectric layer on the substrate, a first metal layer is formed within the trench on a first part of the second dielectric layer. A second metal layer is then formed on the first metal layer and on a second part of the second dielectric layer.

Owner:INTEL CORP

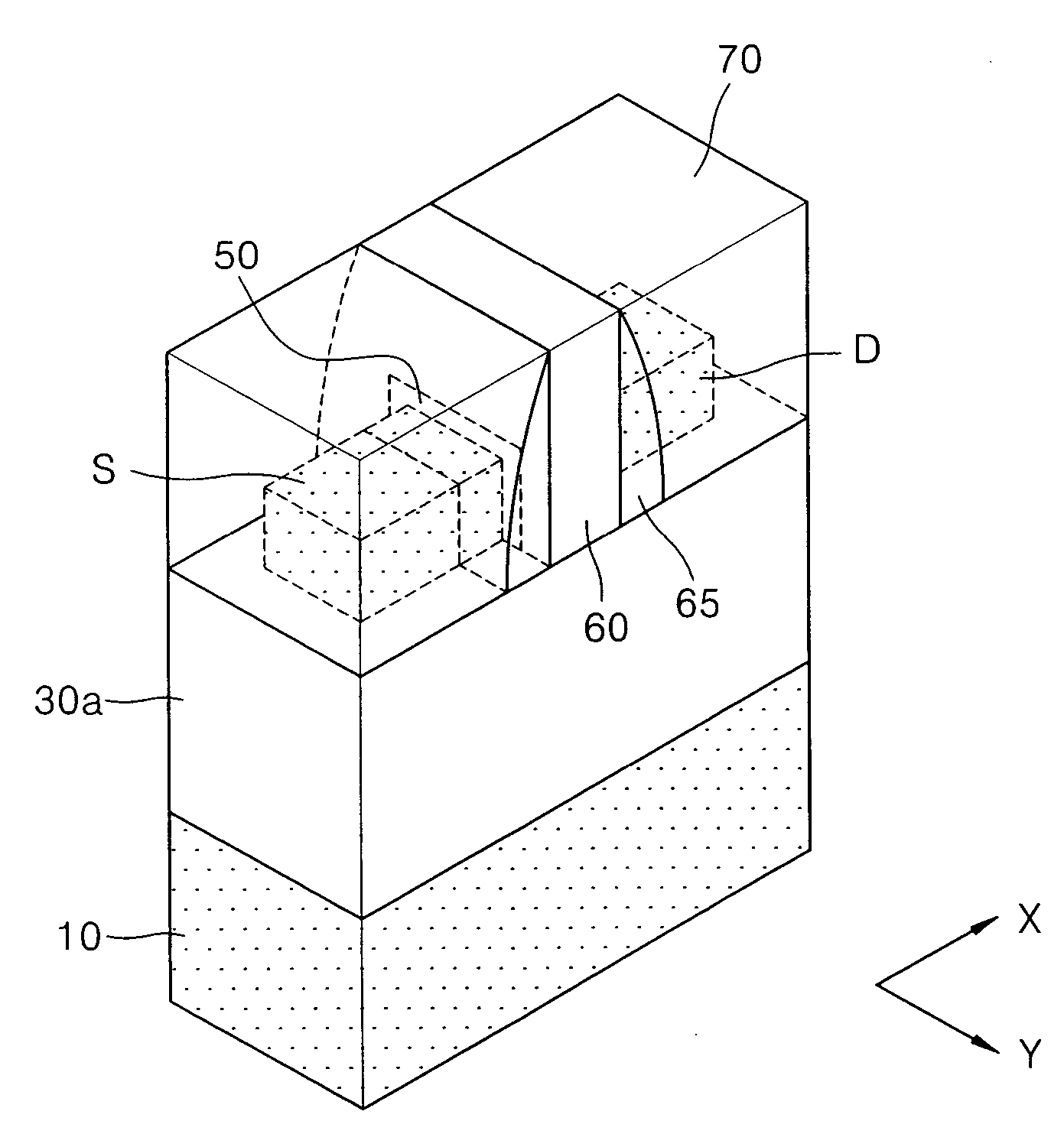

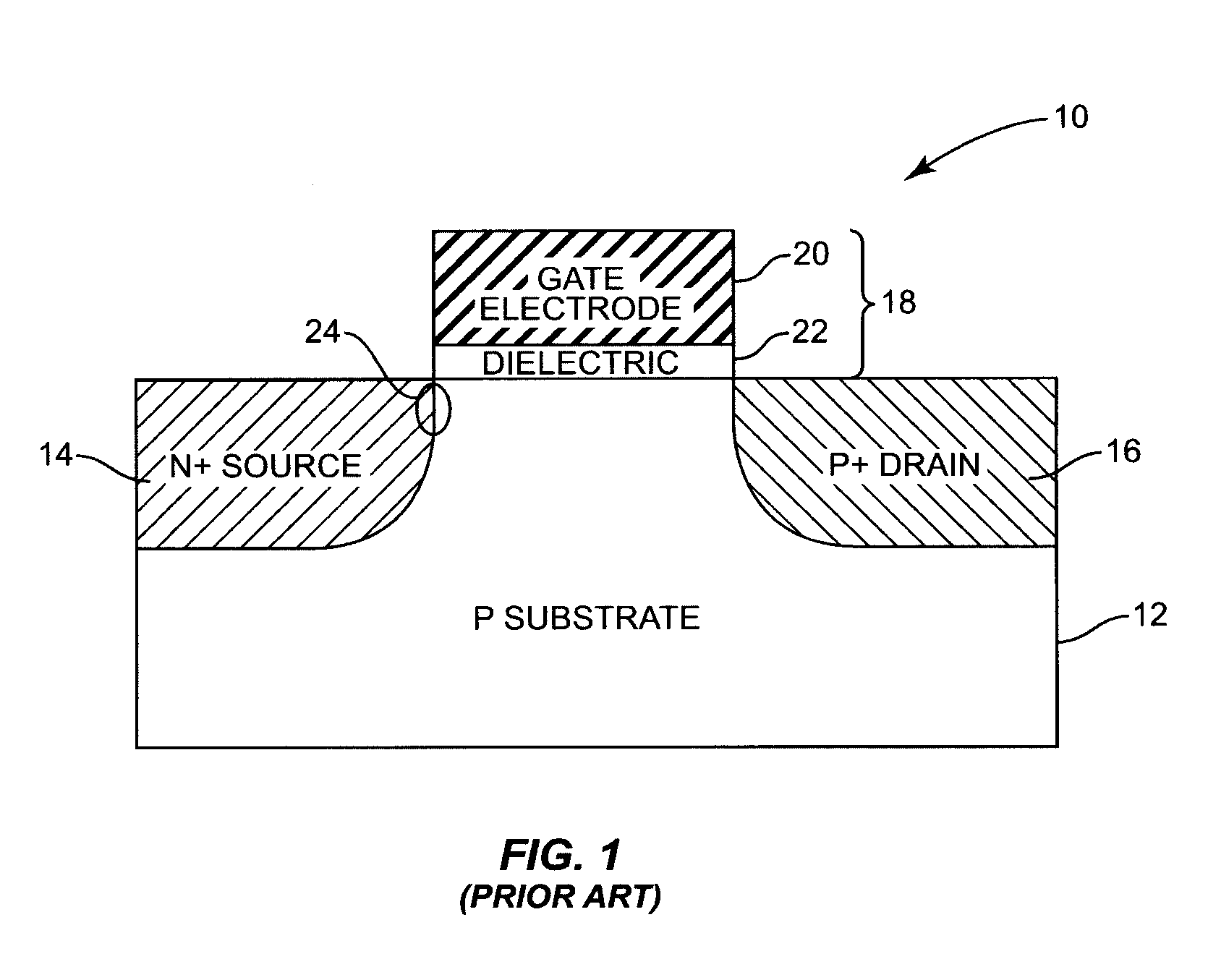

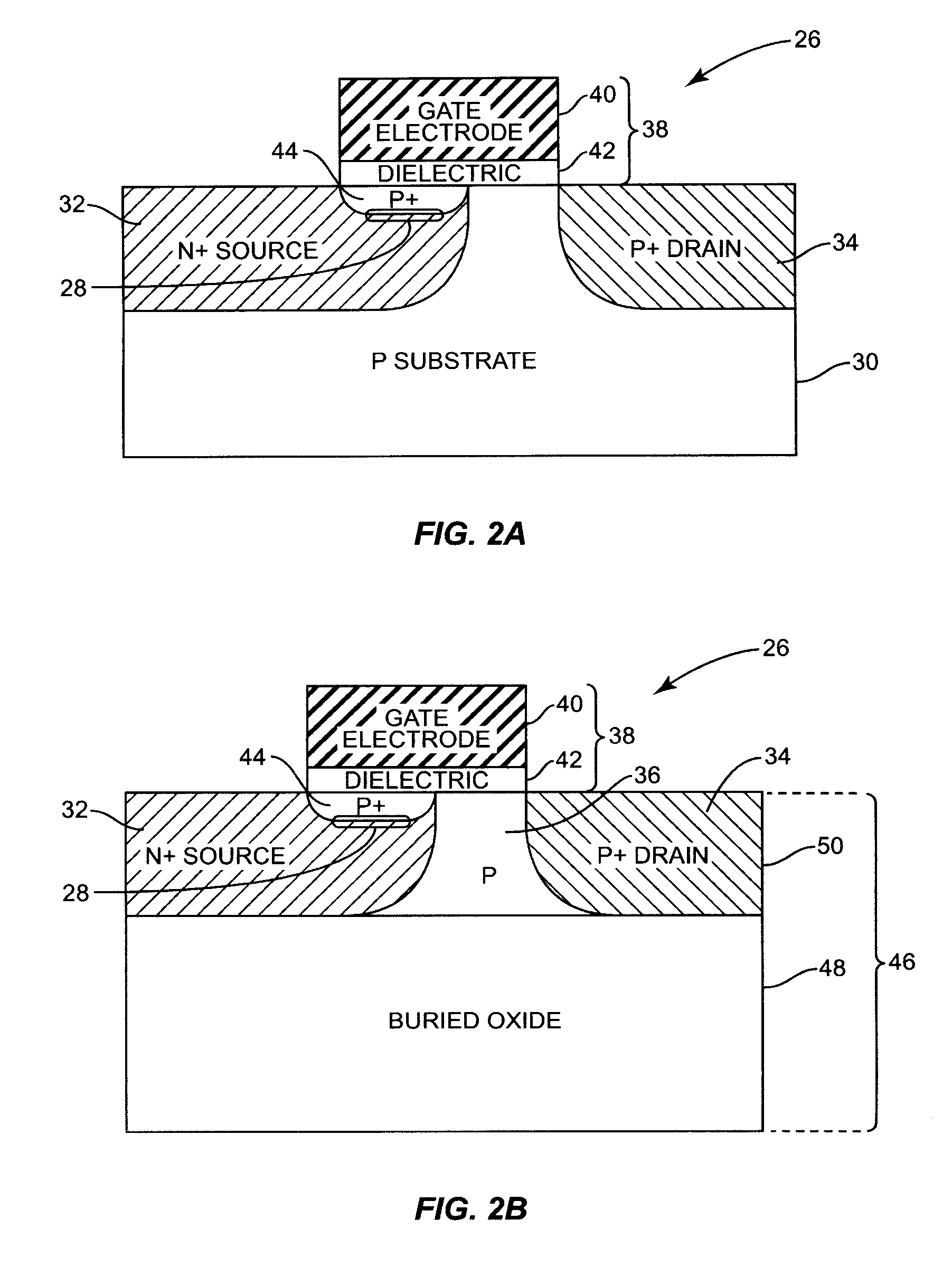

Tunneling transistor suitable for low voltage operation

InactiveUS8384122B1Increase the on-currentOn-current of the tunneling transistor is substantially improvedNanotechnologySuperconductor devicesLow voltageEngineering

Several embodiments of a tunneling transistor are disclosed. In one embodiment, a tunneling transistor includes a semiconductor substrate, a source region formed in the semiconductor substrate, a drain region formed in the semiconductor substrate, a gate stack including a metallic gate electrode and a gate dielectric, and a tunneling junction that is substantially parallel to an interface between the metallic gate electrode and the gate dielectric. As a result of the tunneling junction that is substantially parallel with the interface between the metallic gate electrode and the gate dielectric, an on-current of the tunneling transistor is substantially improved as compared to that of a conventional tunneling transistor. In another embodiment, a tunneling transistor includes a heterostructure that reduces a turn-on voltage of the tunneling transistor.

Owner:RGT UNIV OF CALIFORNIA

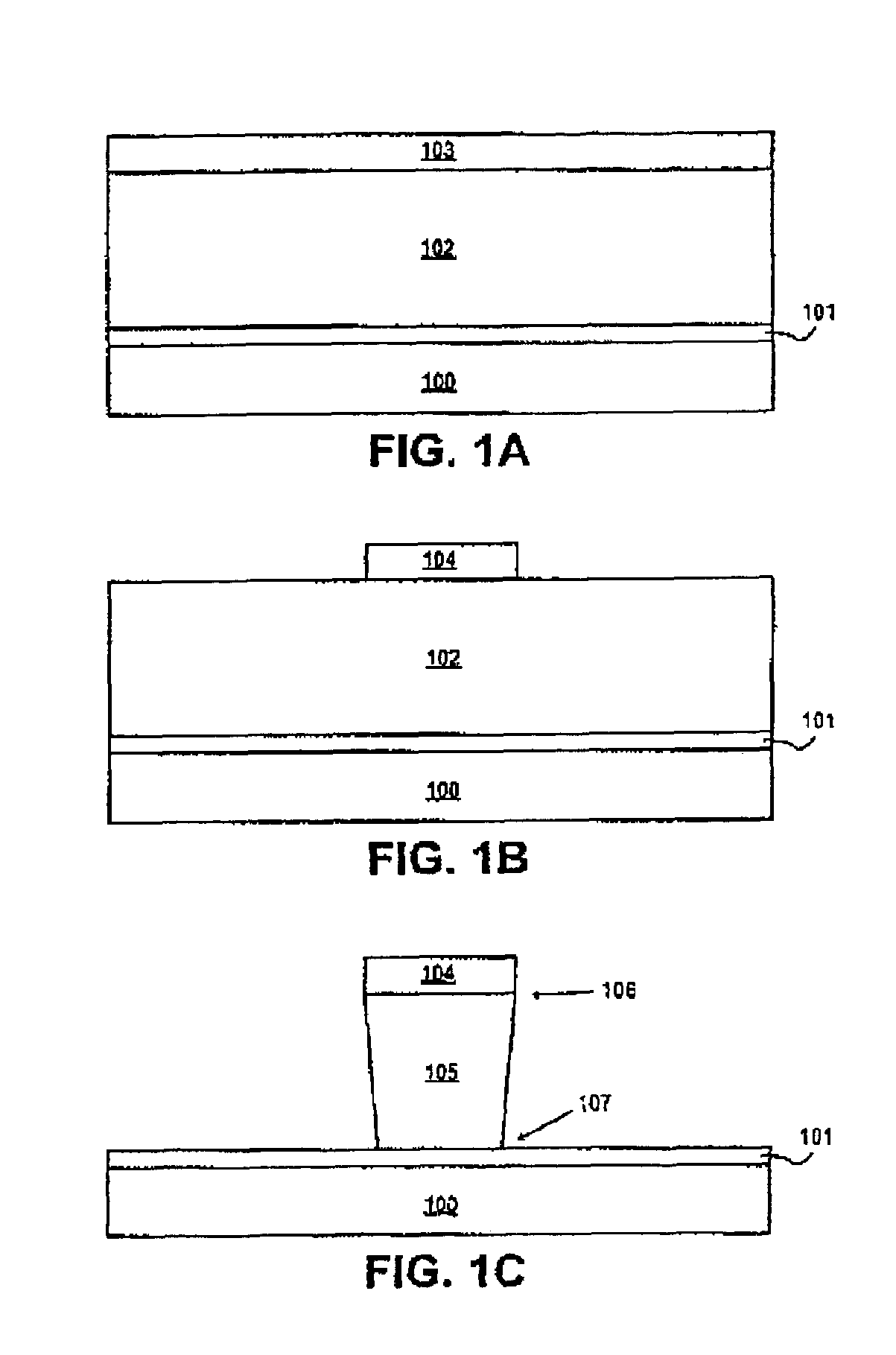

Method for making a semiconductor device with a metal gate electrode that is formed on an annealed high-k gate dielectric layer

InactiveUS7220635B2Semiconductor/solid-state device manufacturingSemiconductor devicesSemiconductorMetal

A method for making a semiconductor device is described. That method comprises forming a high-k gate dielectric layer on a substrate, and forming a sacrificial layer on the high-k gate dielectric layer. After etching the sacrificial layer, first and second spacers are formed on opposite sides of the sacrificial layer. After removing the sacrificial layer to generate a trench that is positioned between the first and second spacers, a metal layer is formed on the high-k gate dielectric layer.

Owner:INTEL CORP

Method for making a semiconductor device with a high-k gate dielectric and a metal gate electrode

ActiveUS20060121678A1Semiconductor/solid-state device manufacturingSemiconductor devicesDevice materialNitrogen

A method for making a semiconductor device is described. That method comprises adding nitrogen to a silicon dioxide layer to form a nitrided silicon dioxide layer on a substrate. After forming a sacrificial layer on the nitrided silicon dioxide layer, the sacrificial layer is removed to generate a trench. A high-k gate dielectric layer is formed on the nitrided silicon dioxide layer within the trench, and a metal gate electrode is formed on the high-k gate dielectric layer.

Owner:DAEDALUS PRIME LLC

Replacement gate process for making a semiconductor device that includes a metal gate electrode

InactiveUS20050272191A1Semiconductor/solid-state device manufacturingSemiconductor devicesDevice materialSemiconductor

A method for making a semiconductor device is described. That method comprises forming a sacrificial layer on a substrate, and forming a trench within the sacrificial layer. After forming a dummy gate electrode within the trench, a hard mask is formed on the dummy gate electrode and within the trench.

Owner:INTEL CORP

Doping of thin amorphous silicon work function control layers of MOS gate electrodes

InactiveUS6518113B1Semiconductor/solid-state device manufacturingSemiconductor devicesCMOSControl layer

Work function control layers are provided in in-laid, metal gate electrode, Si-based MOS transistors and CMOS devices by a process which avoids deleterious dopant implantation processing resulting in damage to the thin gate insulator layer and undesirable doping of the underlying channel region. According to the invention, an amorphous Si layer is formed over the thin gate insulator layer by a low energy deposition process which does not adversely affect the gate insulator layer and subsequently doped by means of another low energy process, e.g., low sheath voltage plasma doping, which does not damage the gate insulator layer or dope the underlying channel region of the Si-based substrate. Subsequent thermal processing during device manufacture results in activation of the dopant species and conversion of the a-Si layer to a doped polycrystalline Si layer of substantially increased electrical conductivity.

Owner:ADVANCED MICRO DEVICES INC

Method for making a semiconductor device having a high-k gate dielectric layer and a metal gate electrode

A method for making a semiconductor device is described. That method comprises forming a first dielectric layer on a substrate, a trench within the first dielectric layer, and a second dielectric layer on the substrate. The second dielectric layer has a first part that is formed in the trench and a second part. After a first metal layer with a first workfunction is formed on the first and second parts of the second dielectric layer, part of the first metal layer is converted into a second metal layer with a second workfunction.

Owner:TAHOE RES LTD

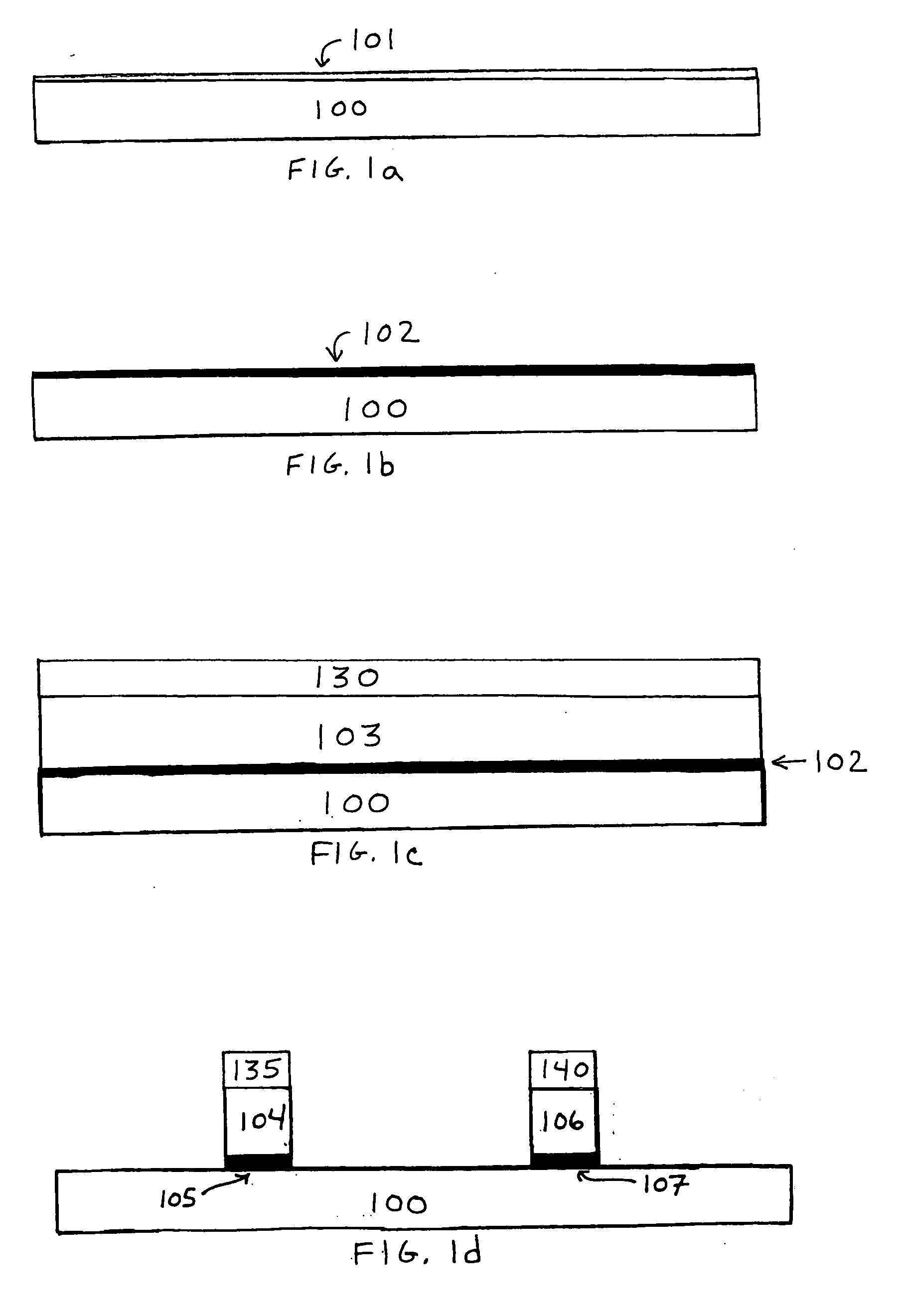

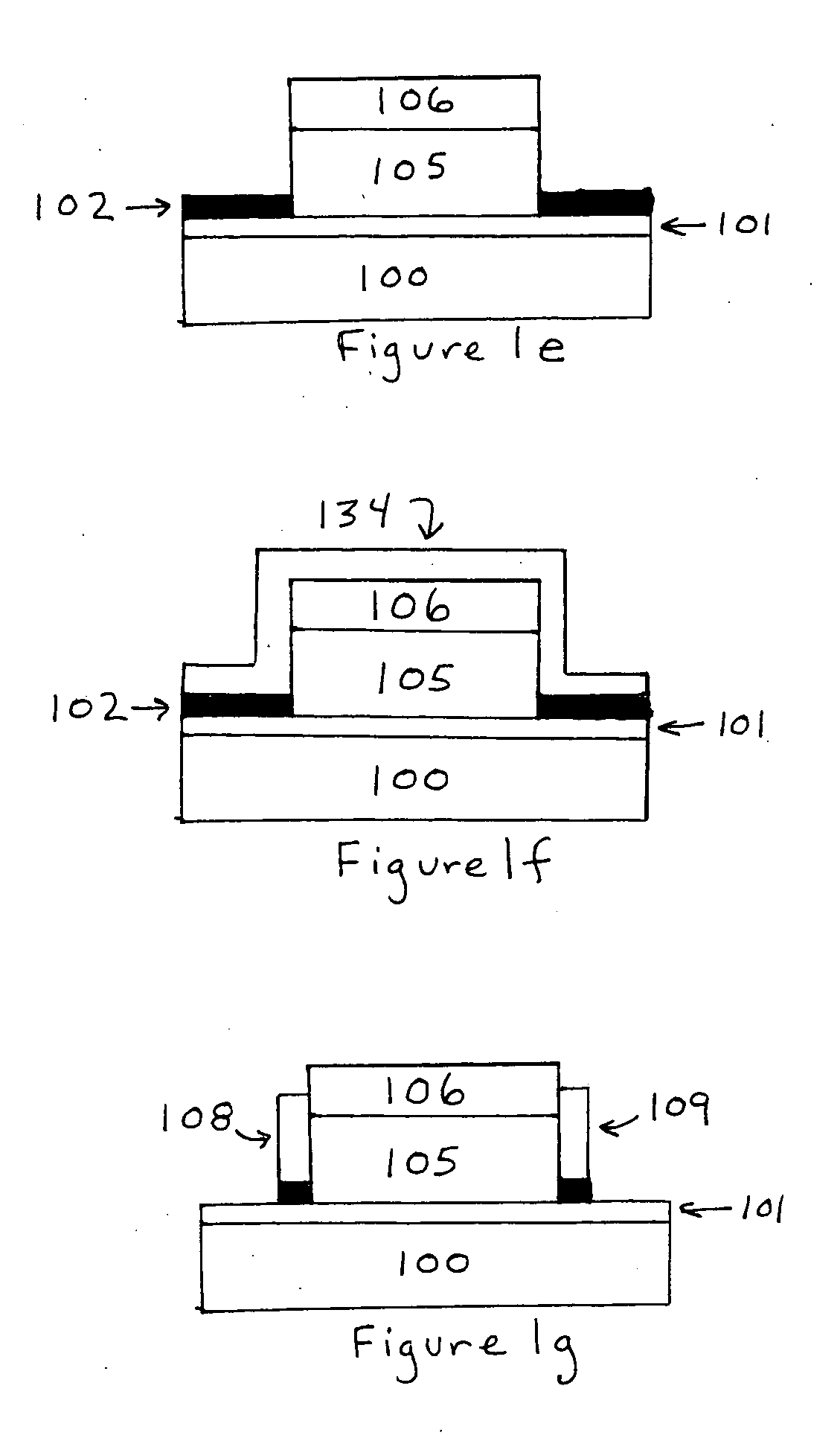

Nonplanar transistors with metal gate electrodes

InactiveUS20060138552A1Solid-state devicesSemiconductor/solid-state device manufacturingDevice materialSemiconductor

A semiconductor device comprising a semiconductor body having a top surface and a first and second laterally opposite sidewalls as formed on an insulating substrate is claimed. A gate dielectric is formed on the top surface of the semiconductor body and on the first and second laterally opposite sidewalls of the semiconductor body. A gate electrode is then formed on the gate dielectric on the top surface of the semiconductor body and adjacent to the gate dielectric on the first and second laterally opposite sidewalls of the semiconductor body. The gate electrode comprises a metal film formed directly adjacent to the gate dielectric layer. A pair of source and drain regions are then formed in the semiconductor body on opposite sides of the gate electrode.

Owner:TAHOE RES LTD

Method for making a semiconductor device having a metal gate electrode

InactiveUS6890807B2Semiconductor/solid-state device manufacturingSemiconductor devicesDielectric layerImpurity

A method for making a semiconductor device is described. That method comprises forming a dielectric layer on a substrate, and forming an impurity containing metal layer on the dielectric layer. A metal gate electrode is then formed from the impurity containing metal layer. Also described is a semiconductor device that comprises a metal gate electrode that is formed on a dielectric layer, which is formed on a substrate. The metal gate electrode includes a sufficient amount of an impurity to shift the workfunction of the metal gate electrode by at least about 0.1 eV.

Owner:TAHOE RES LTD

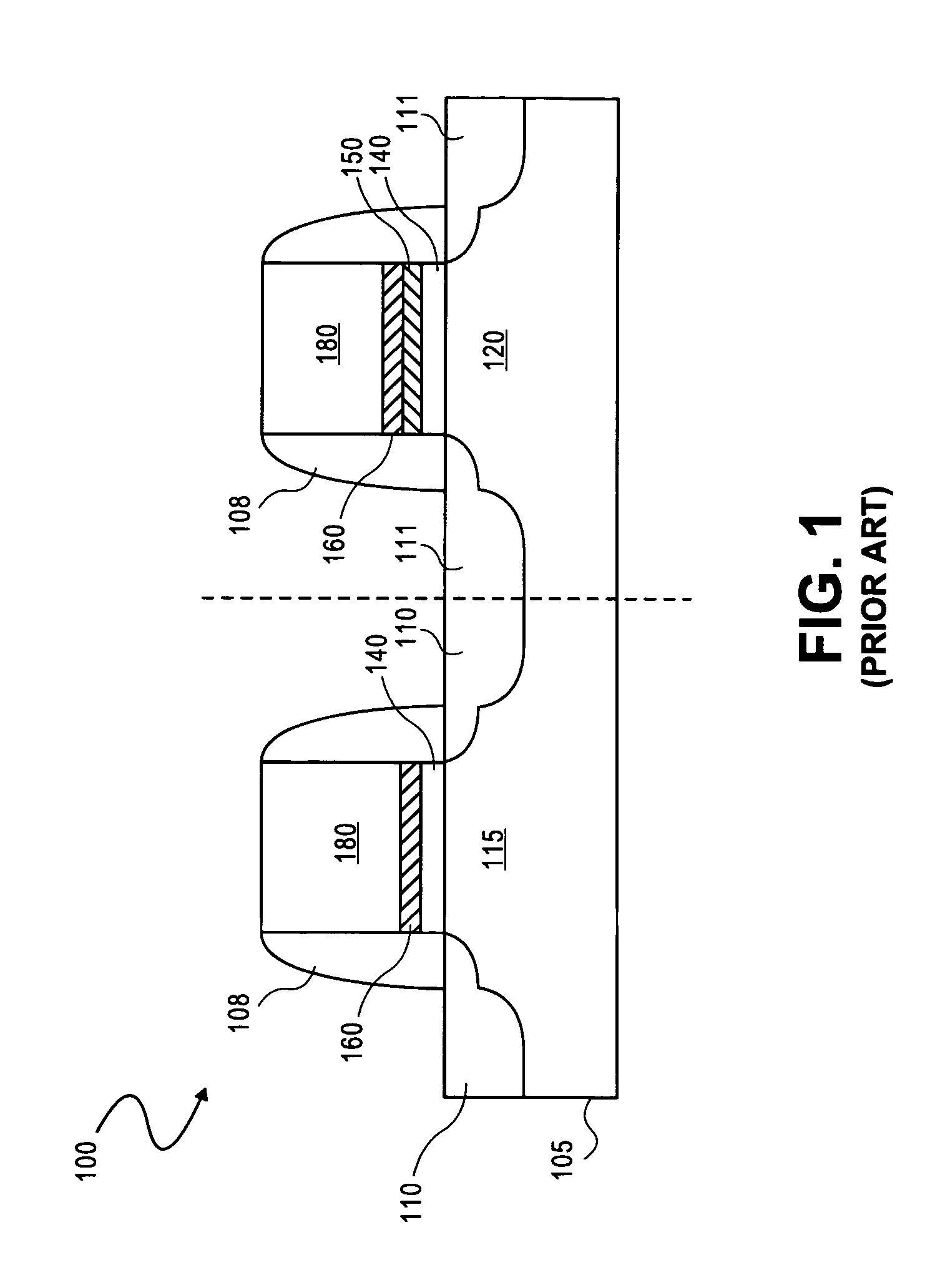

Metal gate stack and semiconductor gate stack for CMOS devices

A semiconductor gate stack comprising a silicon oxide based gate dielectric and a doped semiconductor material is formed on a semiconductor substrate. A high-k material metal gate electrode comprising a high-k gate dielectric and a metal gate portion is also formed on the semiconductor substrate. Oxygen-impermeable dielectric spacers are formed on the sidewalls of the semiconductor gate stack and the high-k material metal gate stack. The oxygen-impermeable dielectric spacer on the semiconductor gate stack is removed, while the oxygen impermeable dielectric spacer on the high-k material metal gate electrode is preserved. A low-k dielectric spacer is formed on the semiconductor gate stack, which provides a low parasitic capacitance for the device employing the semiconductor gate stack.

Owner:TAIWAN SEMICON MFG CO LTD

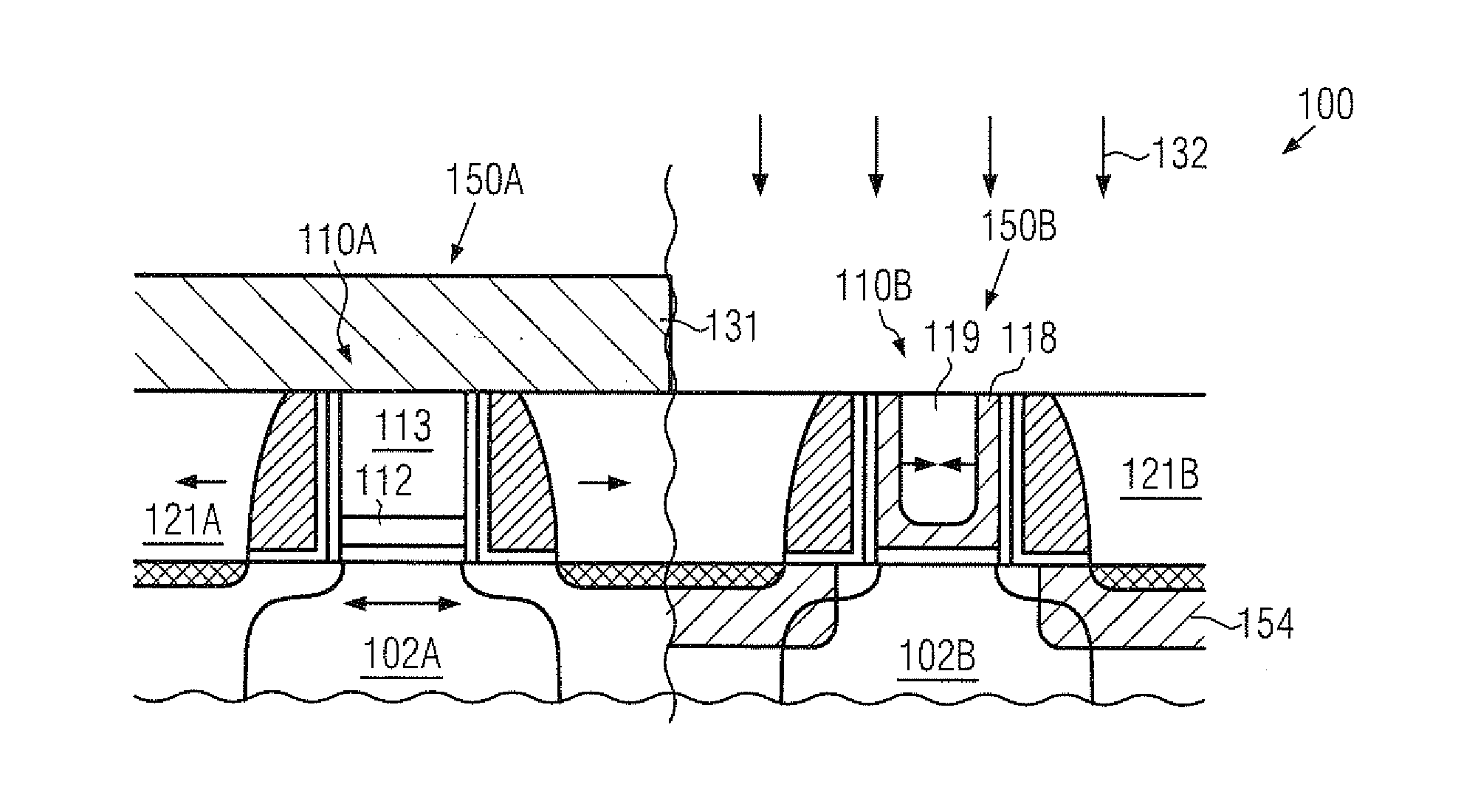

Work function adjustment in high-k metal gate electrode structures by selectively removing a barrier layer

ActiveUS20100301427A1Degree of improvementImprove uniformityTransistorSolid-state devicesTantalum nitrideWork function

In a replacement gate approach in sophisticated semiconductor devices, a tantalum nitride etch stop material may be efficiently removed on the basis of a wet chemical etch recipe using ammonium hydroxide. Consequently, a further work function adjusting material may be formed with superior uniformity, while the efficiency of the subsequent adjusting of the work function may also be increased. Thus, superior uniformity, i.e., less pronounced transistor variability, may be accomplished on the basis of a replacement gate approach in which the work function of the gate electrodes of P-channel transistors and N-channel transistors is adjusted after completing the basic transistor configuration.

Owner:GLOBALFOUNDRIES US INC

Method for making a semiconductor device that includes a metal gate electrode

InactiveUS7176090B2Semiconductor/solid-state device manufacturingSemiconductor devicesDielectric layerSemiconductor

A method for making a semiconductor device is described. That method comprises forming on a substrate a dielectric layer and a sacrificial structure that comprises a first layer and a second layer, such that the second layer is formed on the first layer and is wider than the first layer. After the sacrificial structure is removed to generate a trench, a metal gate electrode is formed within the trench.

Owner:INTEL CORP

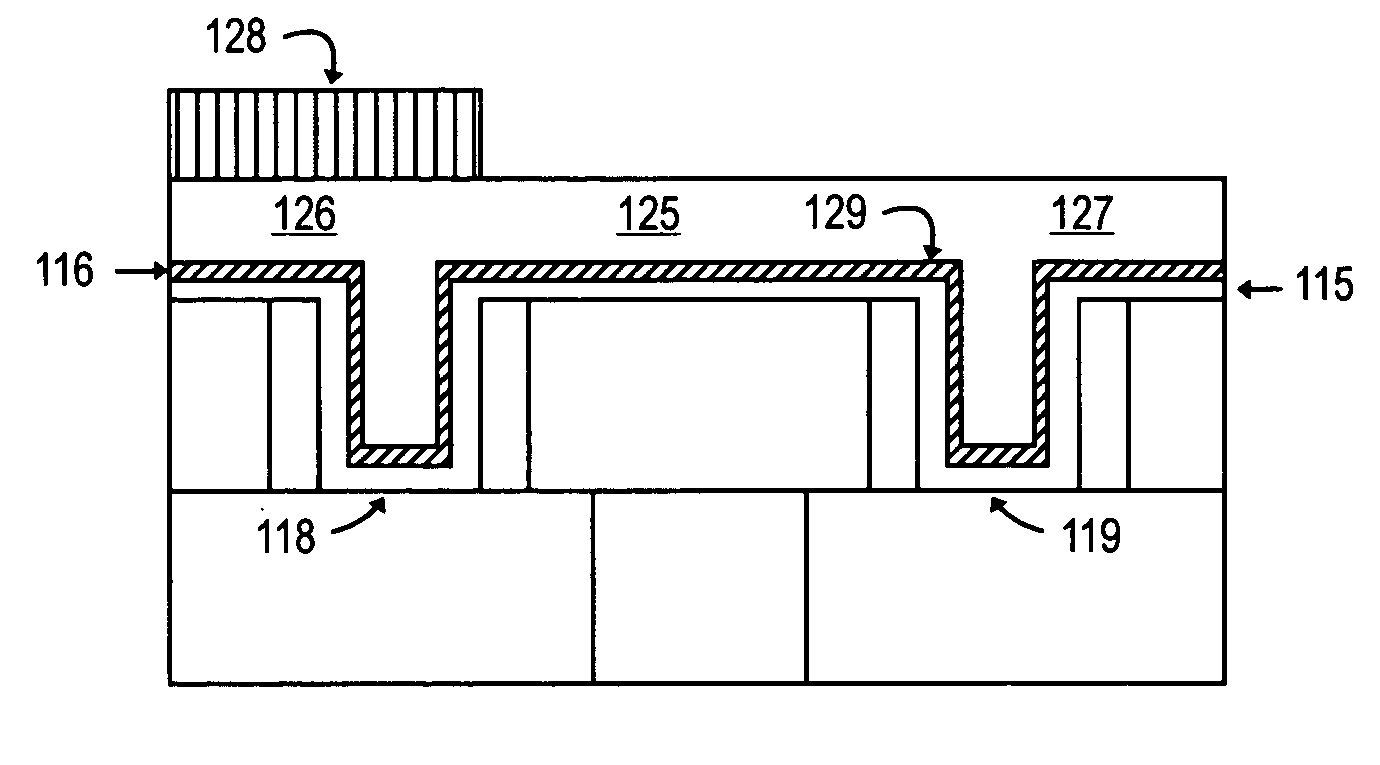

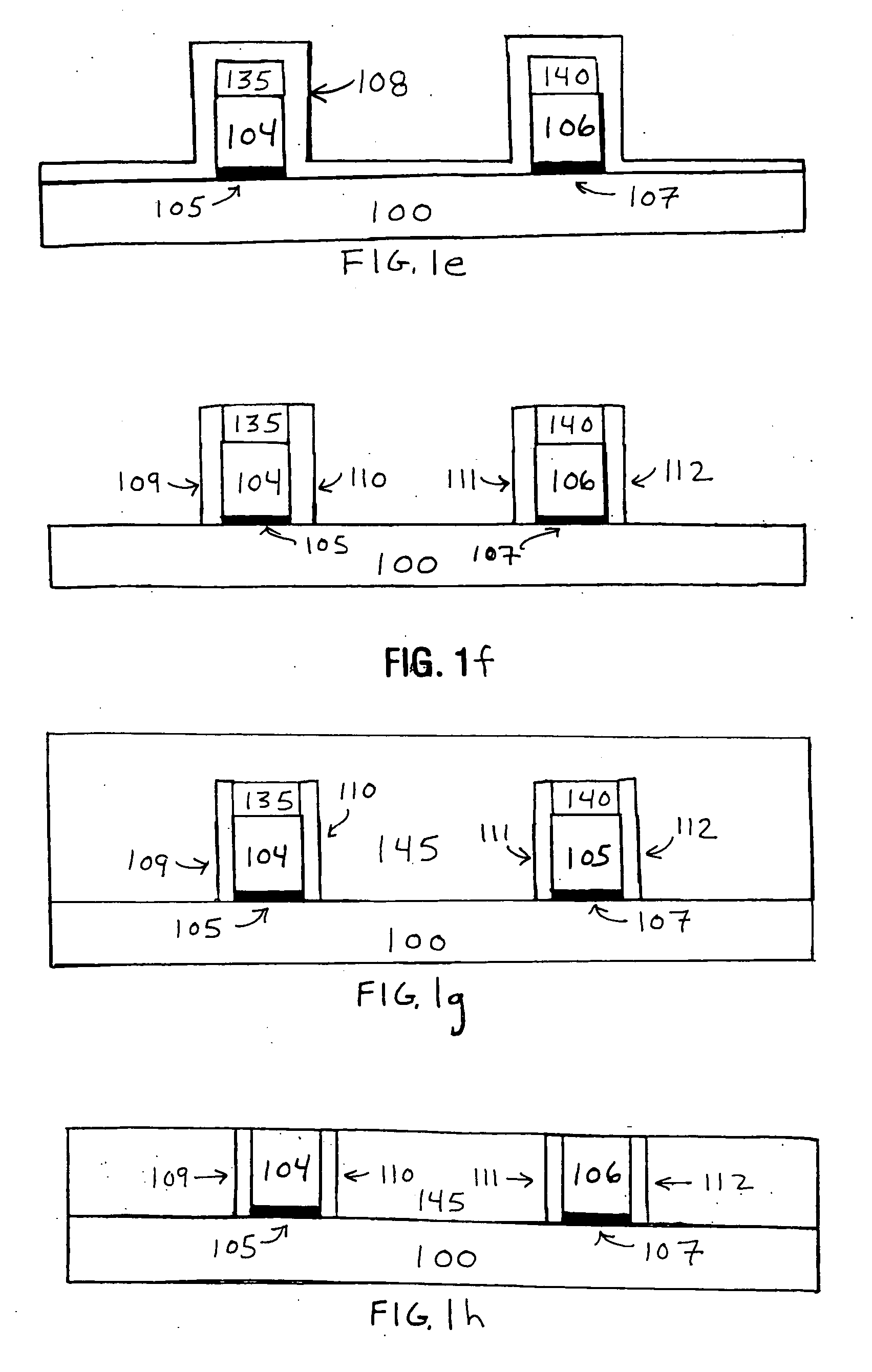

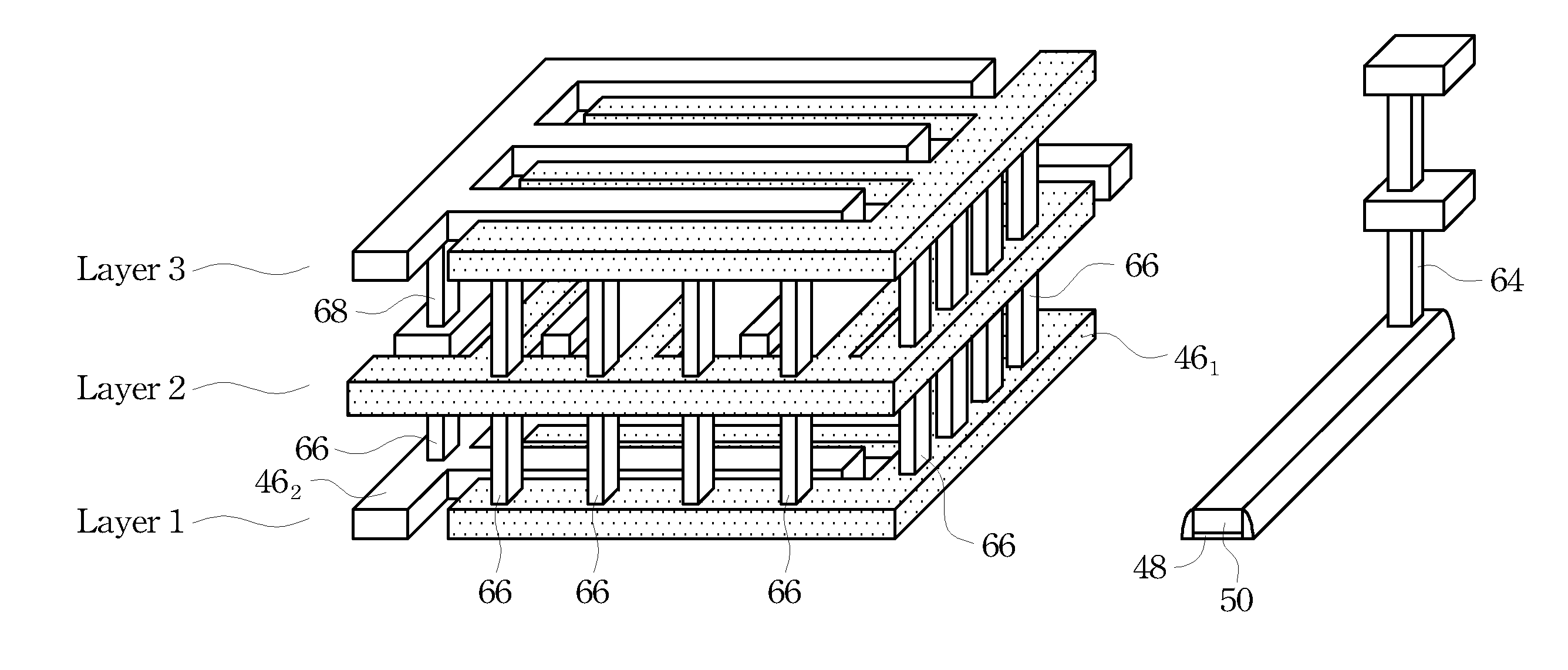

Capacitors Integrated with Metal Gate Formation

ActiveUS20090090951A1Increase capacitanceImprove electrical performanceTransistorSemiconductor/solid-state device detailsCapacitanceSemiconductor structure

A semiconductor structure including a capacitor having increased capacitance and improved electrical performance is provided. The semiconductor structure includes a substrate; and a capacitor over the substrate. The capacitor includes a first layer including a first capacitor electrode and a second capacitor electrode, wherein the first capacitor electrode is formed of a metal-containing material and is free from polysilicon. The semiconductor structure further includes a MOS device including a gate dielectric over the substrate; and a metal-containing gate electrode on the gate dielectric, wherein the metal-containing gate electrode is formed of a same material, and has a same thickness, as the first capacitor electrode.

Owner:TAIWAN SEMICON MFG CO LTD

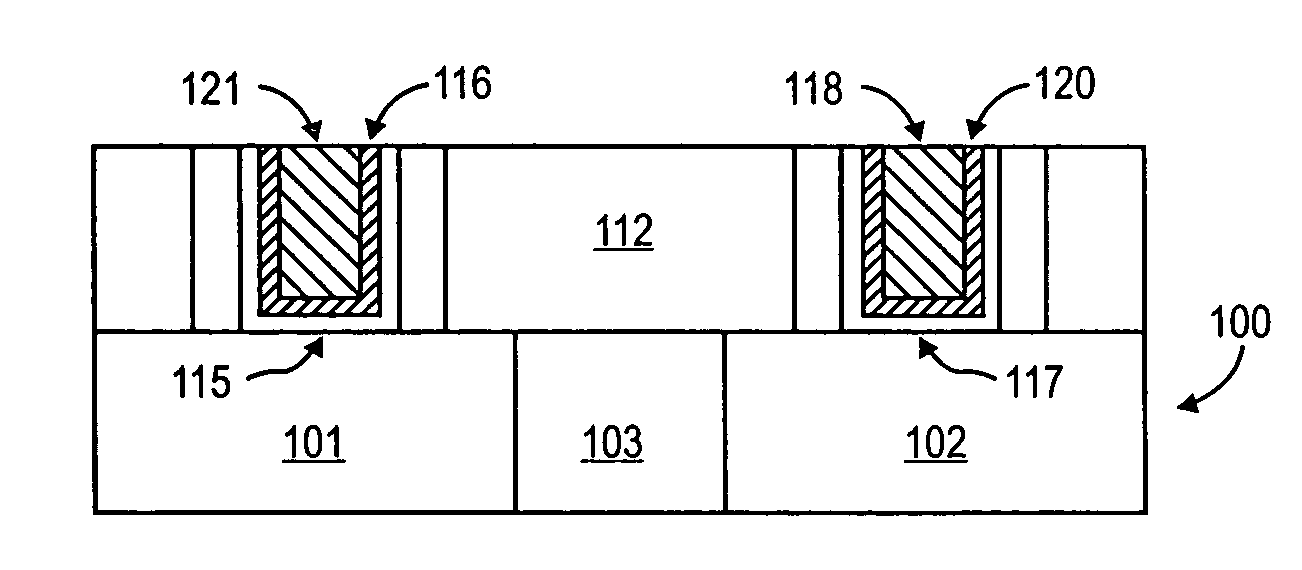

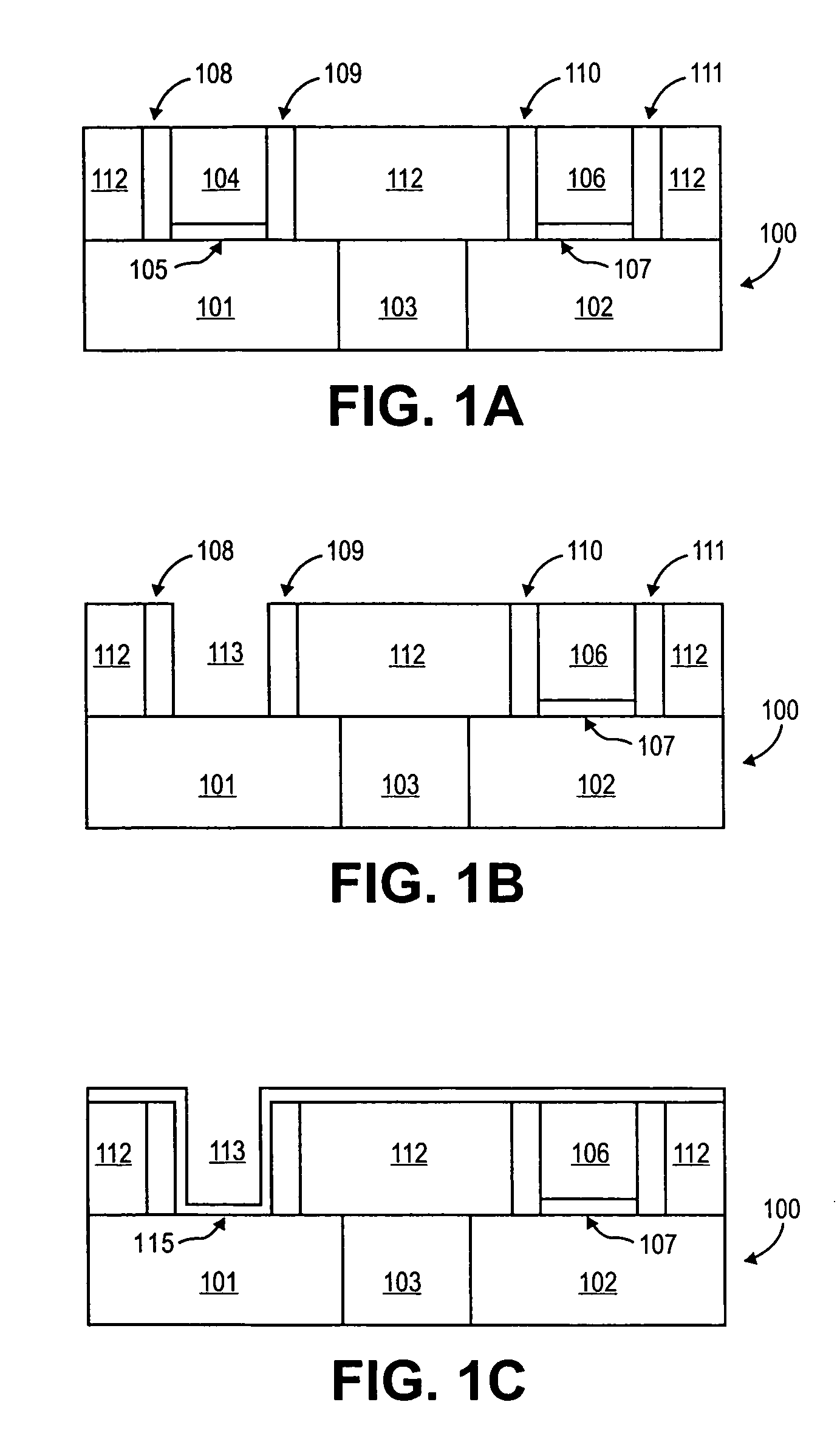

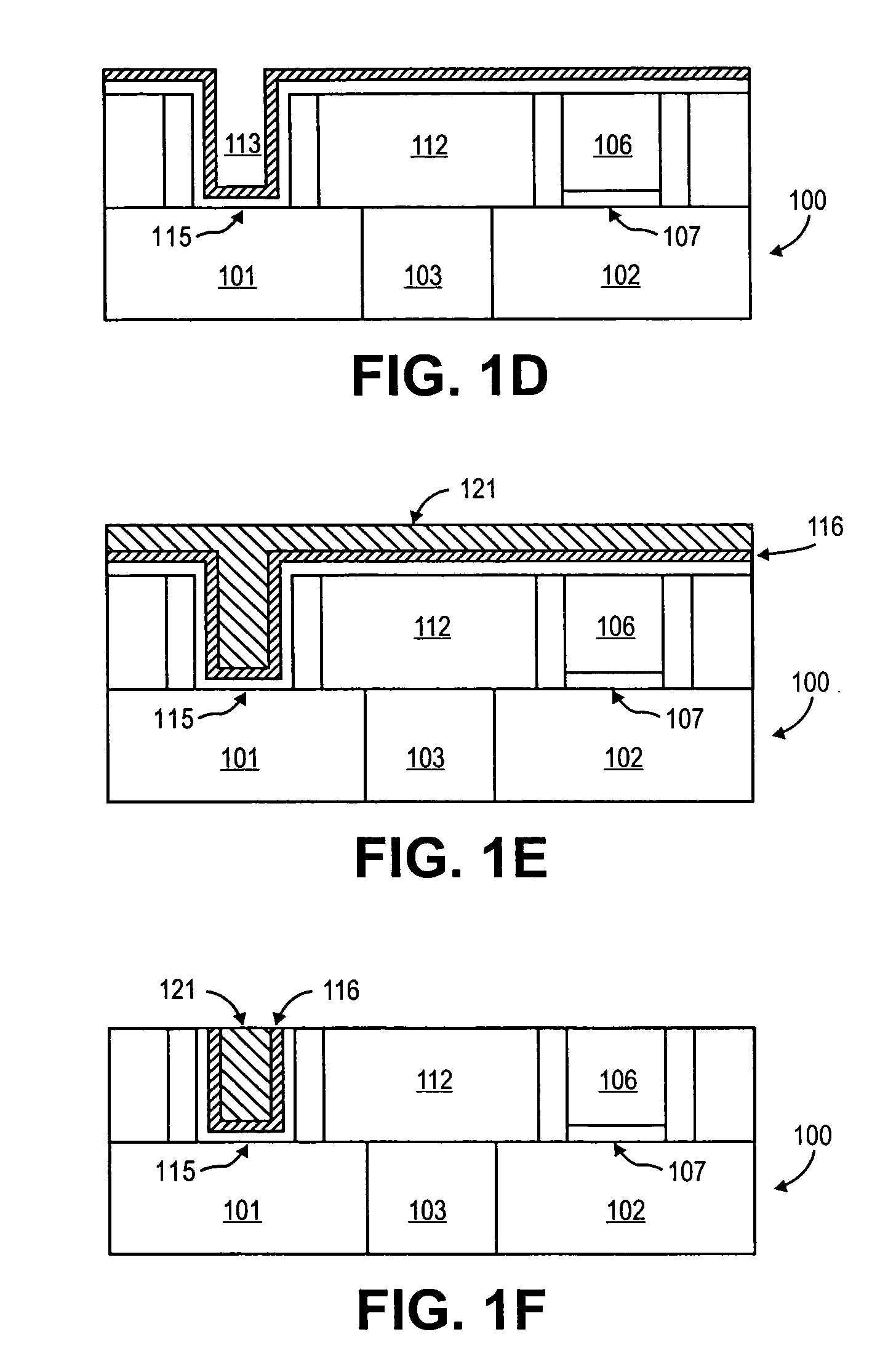

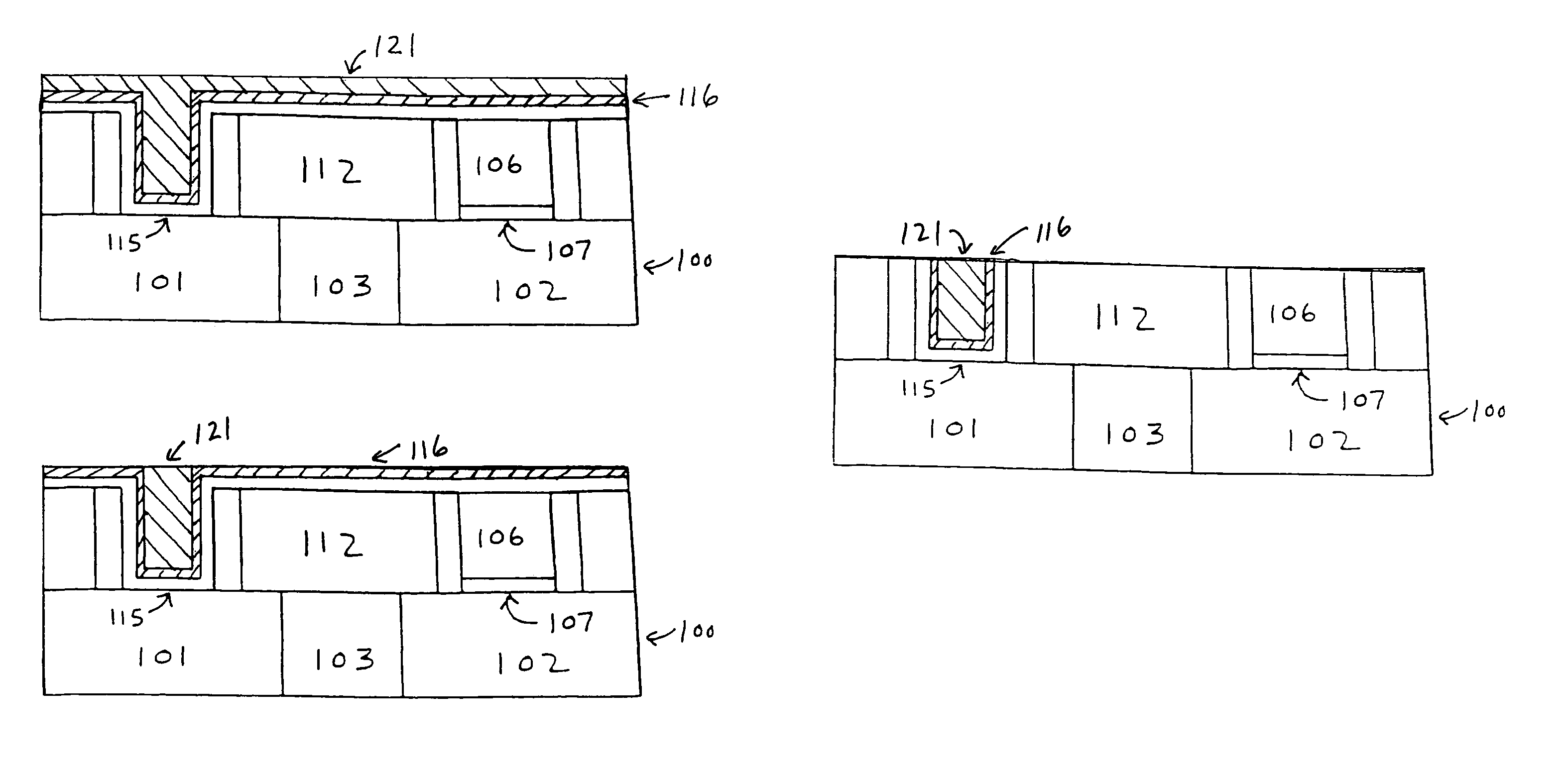

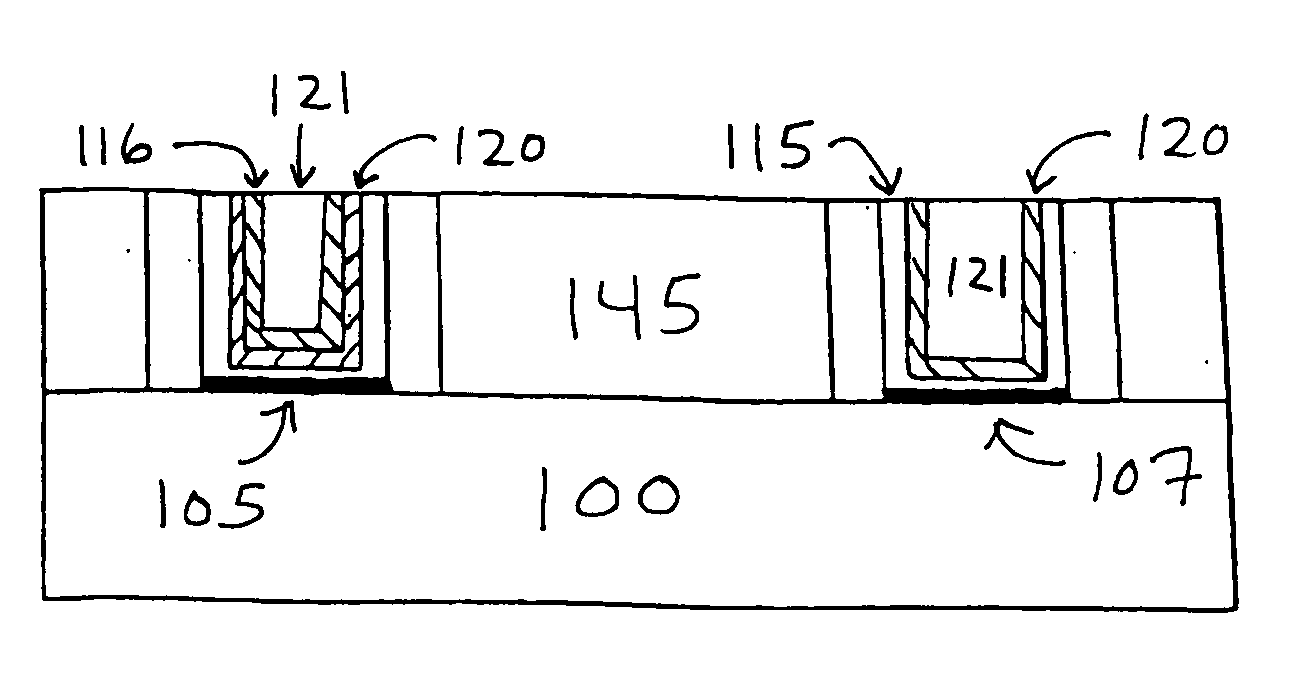

Hybrid process for forming metal gates

InactiveUS20080173947A1Prevents work function shiftReduce manufacturing costTransistorSemiconductor/solid-state device manufacturingSemiconductor structureSilicon

A semiconductor structure and methods for forming the same are provided. The semiconductor structure includes a first MOS device of a first conductivity type and a second MOS device of a second conductivity type opposite the first conductivity type. The first MOS device includes a first gate dielectric on a semiconductor substrate; a first metal-containing gate electrode layer over the first gate dielectric; and a silicide layer over the first metal-containing gate electrode layer. The second MOS device includes a second gate dielectric on the semiconductor substrate; a second metal-containing gate electrode layer over the second gate dielectric; and a contact etch stop layer having a portion over the second metal-containing gate electrode layer, wherein a region between the portion of the contact etch stop layer and the second metal-containing gate electrode layer is substantially free from silicon.

Owner:TAIWAN SEMICON MFG CO LTD