Patents

Literature

70results about How to "High switching current ratio" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

Junctionless lengthways tunneling field effect transistor

ActiveCN103280464ASmall sizeReduce processing difficultyTransistorSemiconductor materialsSwitched current

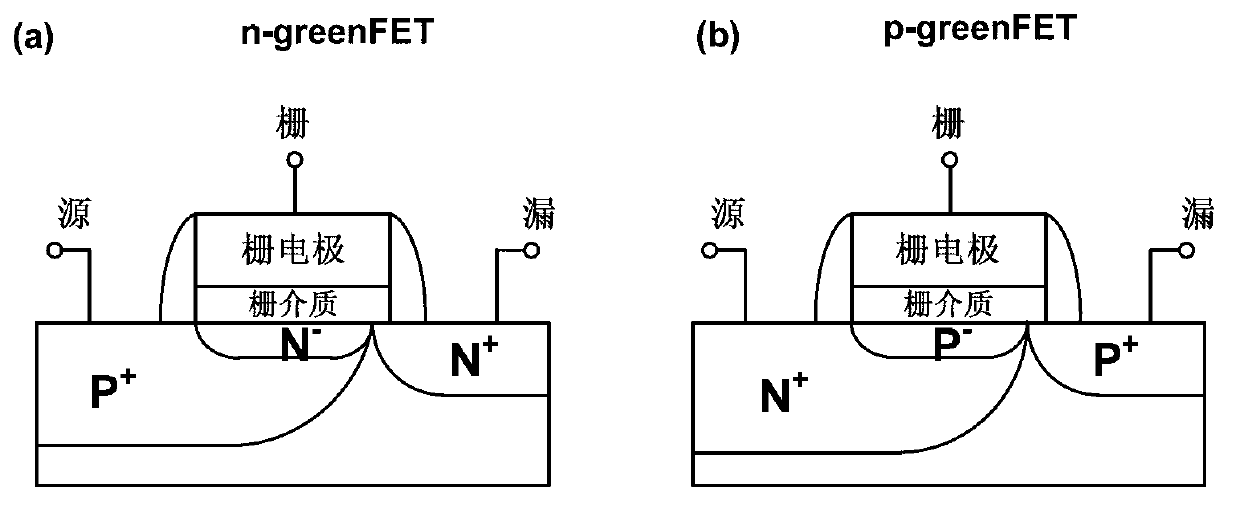

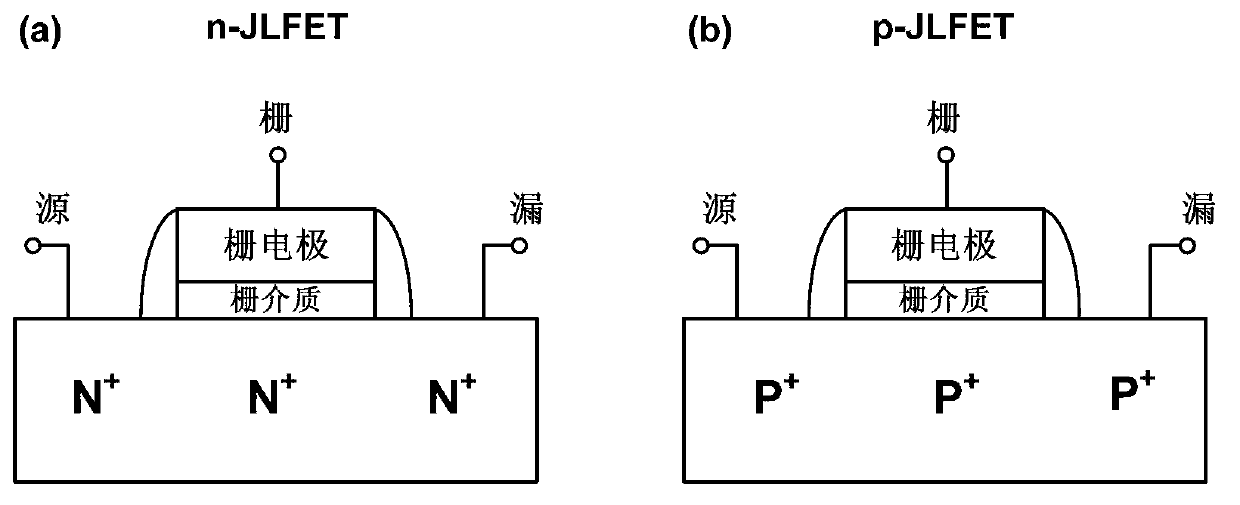

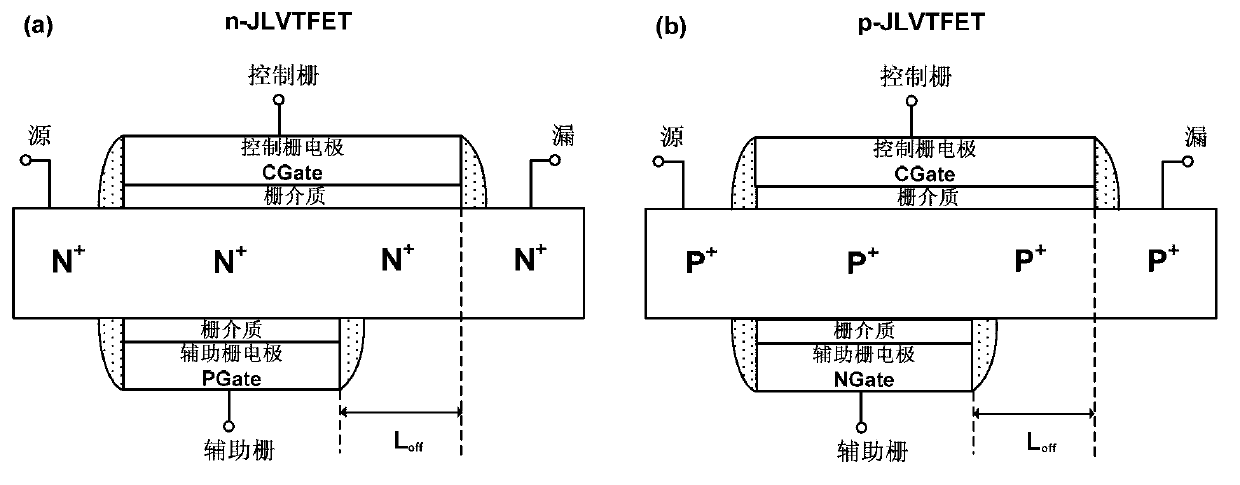

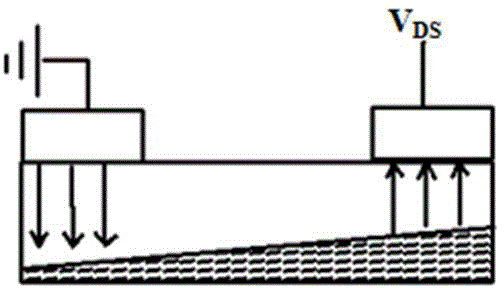

The invention provides a junctionless lengthways tunneling field effect transistor, comprising a source region, a drain region, a channel region, a control grid and an auxiliary grid, wherein the source region, the drain region and the channel region are formed into a whole and adopt the same doped semiconducting material; the doping concentration from the source region to a channel and the drain region is the same; the control grid and the auxiliary grid are respectively located on the two sides of the channel; at least a part of the control grid and a part of the auxiliary grid are opposite to each other; the control grid is used for controlling the breakover and closing of a device; and the auxiliary grid is used for making a semiconducting region under the auxiliary grid generate transoid. The junctionless lengthways tunneling field effect transistor has only one doping type, no PN junction is needed to be made, the process difficulty is reduced, the size reduction of the device is facilitated, a short channel effect is restrained, the switching current ratio is increased, off-state current leakage is further reduced through the distance region between the control grid and the auxiliary grid, the characteristics such as a subthreshold slope can be improved, the tunneling length is effectively reduced through controlling the thickness of a semiconductor film, and the tunneling current is increased.

Owner:TSINGHUA UNIV

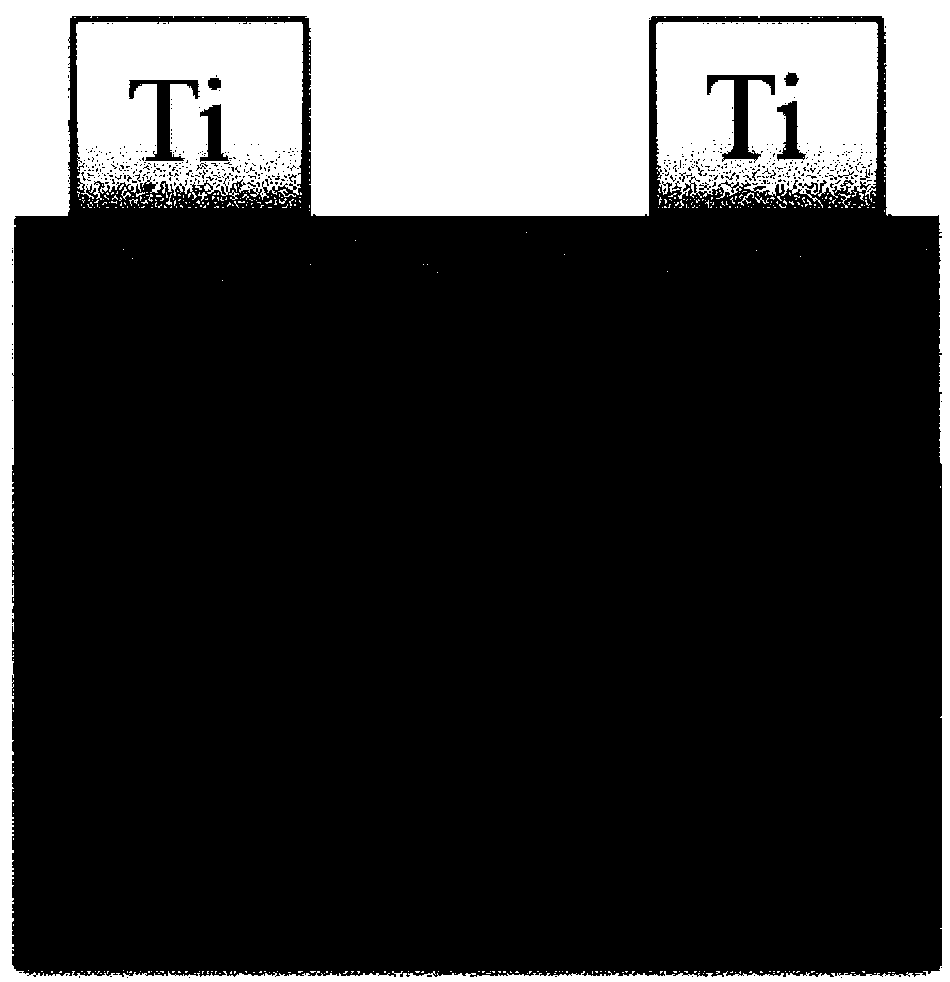

Germanium-based NMOS (N-metal-oxide-semiconductor) device and preparation method thereof

ActiveCN102222687AHigh switching current ratioSmall subthreshold slopeSemiconductor/solid-state device manufacturingSemiconductor devicesHafniumOxygen

The invention provides a germanium-based NMOS (N-metal-oxide-semiconductor) device and a preparation method thereof, belonging to the technical field of ultra large scale integration (ULSI) circuit manufacturing. Two layers of insulation medium material are inserted among metal source and drain electrodes and a substrate of the germanium based-NMOS device, and the bottom layer is S medium material with high pinning coefficient, such as hafnium oxide, silicon nitride or hafnium silica, and the upper layer of medium material is delta EC medium material with low conduction band offset, such as titanium dioxide, gallium oxide or strontium titanium oxygen. According to the invention, the fermi energy level pinning effect can be weakened, the electronic potential barrier is reduced, and furtherthe performances of a germanium-based schottky NMOS device are improved; and compared with the traditional method in which a single layer of insulation medium material such as AL2O3 is adopted, the preparation method can be used for effectively reducing the schottky potential barrier and maintaining lower source and drain resistance, therefore, the performances of the device are improved to a large extent.

Owner:SEMICON MFG INT (BEIJING) CORP +1

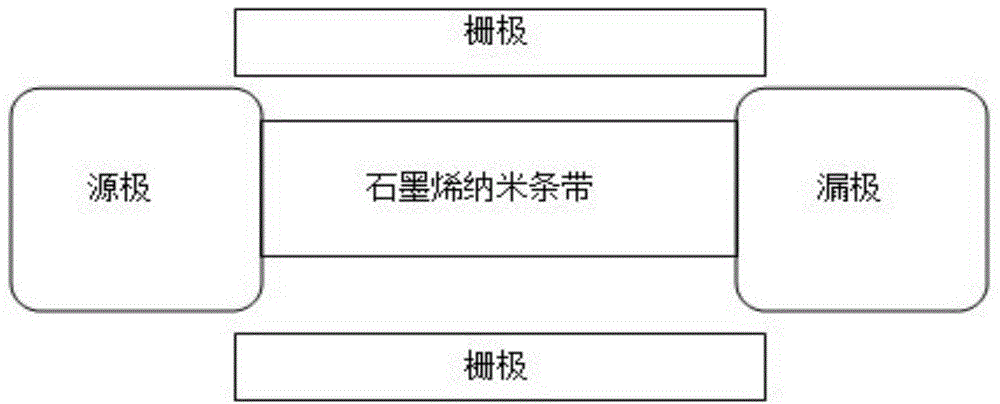

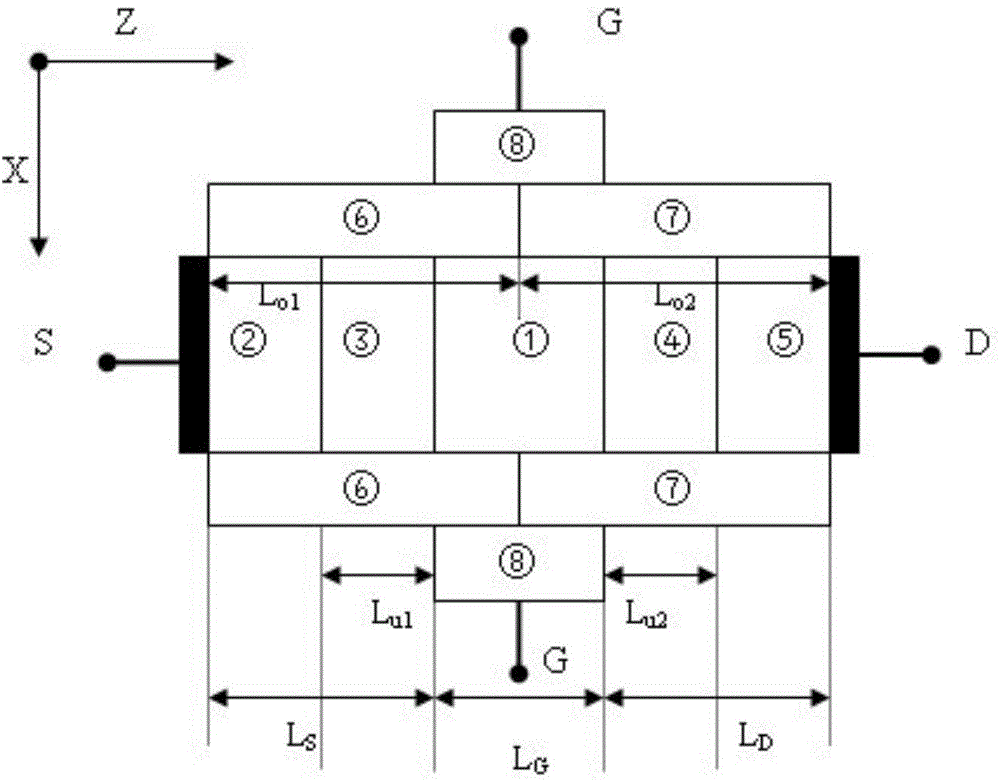

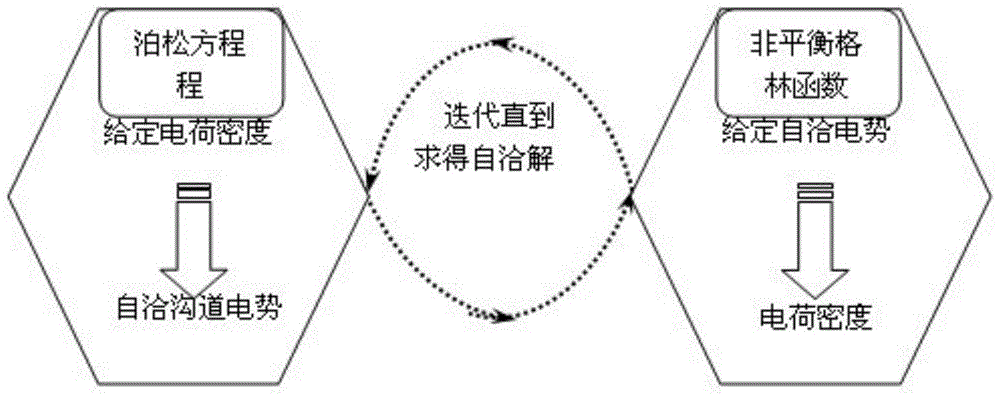

Graphene nanoribbon field-effect tube (GNRFET) with asymmetric HALO-lightly-doped drain (HALO-LDD) structure

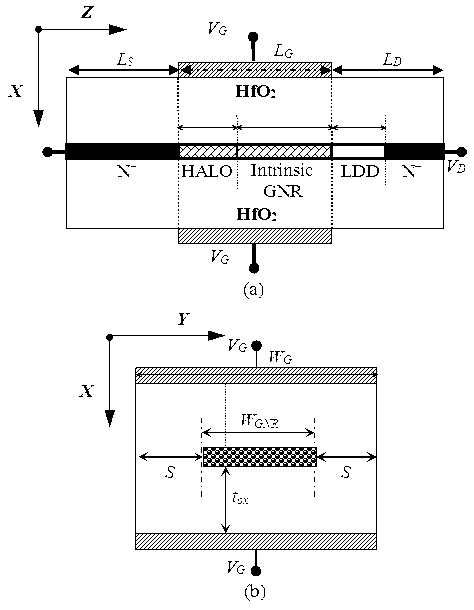

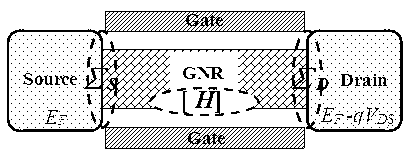

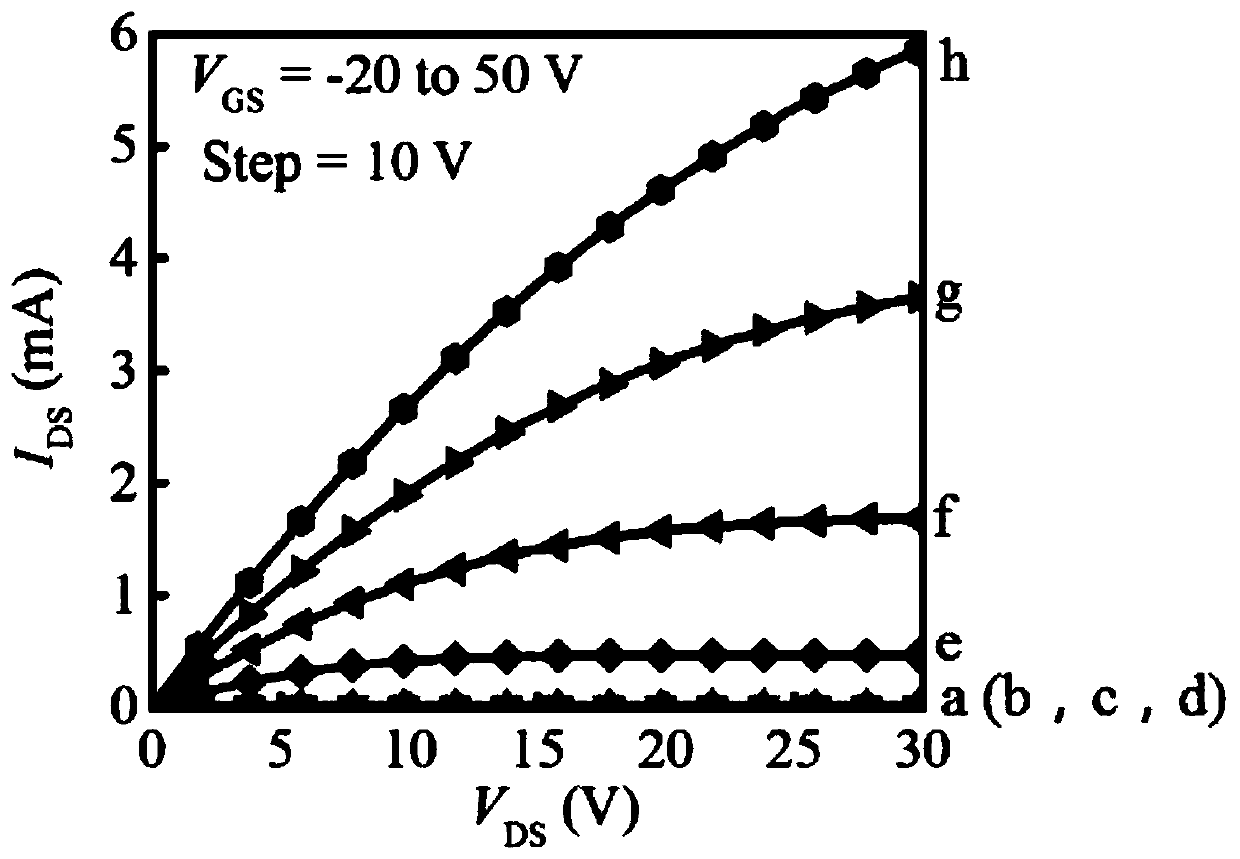

InactiveCN103077968AReduce off-state currentGood gating abilitySemiconductor devicesPower flowSwitched current

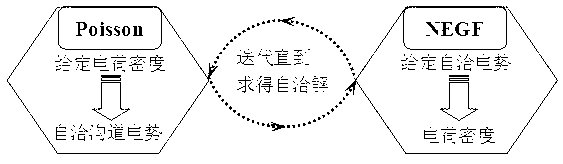

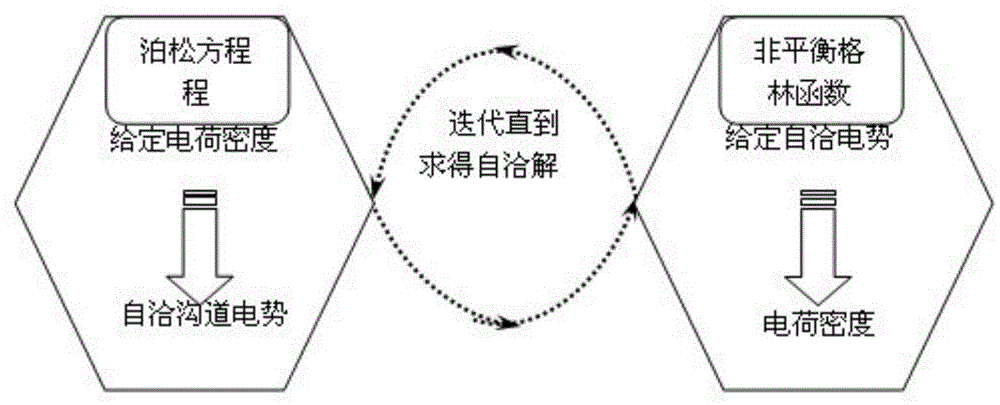

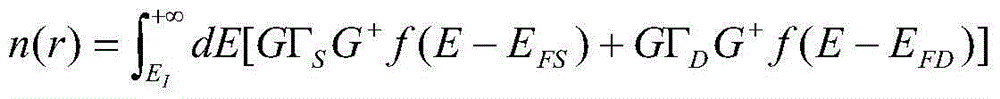

The invention discloses a graphene nanoribbon field-effect tube (GNRFET) with an asymmetric HALO-lightly-doped drain (HALO-LDD) structure. A transport model which is suitable for a non-uniformly-doped GNRFET is constructed on the basis of a quantum mechanics non-balance Green function theoretical frame under an open boundary condition through self-consistent solution of 3D-Poisson and Schr.dinger equations, and the influence of an asymmetric HALO-LDD doping strategy on the electrical properties of the GNRFET is analyzed and calculated by using the model. As proved by comparison and analysis of the electric properties such as the output properties, transfer properties, switch current ratios, sub-threshold amplitudes and threshold voltage drifts of GNRFETs for which other doping strategies are adopted, the GNRFET with the doping structure has a higher switch current ratio, lower drain current, a smaller sub-threshold amplitude and a smaller threshold voltage drift, i.e., the GNRFET for which the asymmetric HALO-LDD doping strategy is adopted has a better grid control capability, and a short-groove effect and a hot carrier effect can be effectively restrained.

Owner:NANJING UNIV OF POSTS & TELECOMM

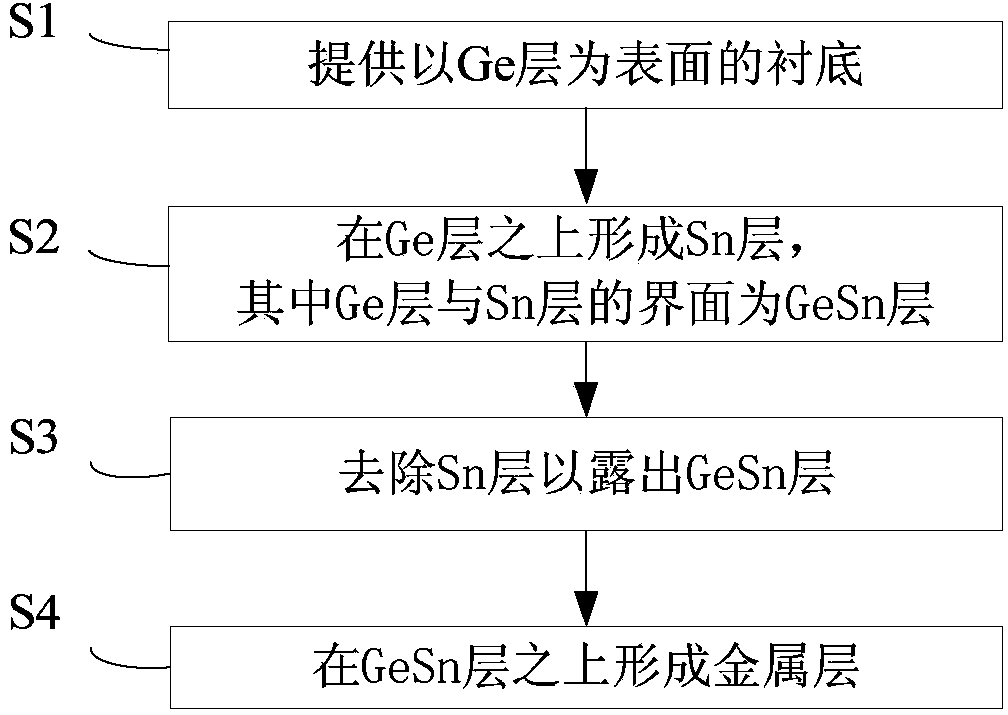

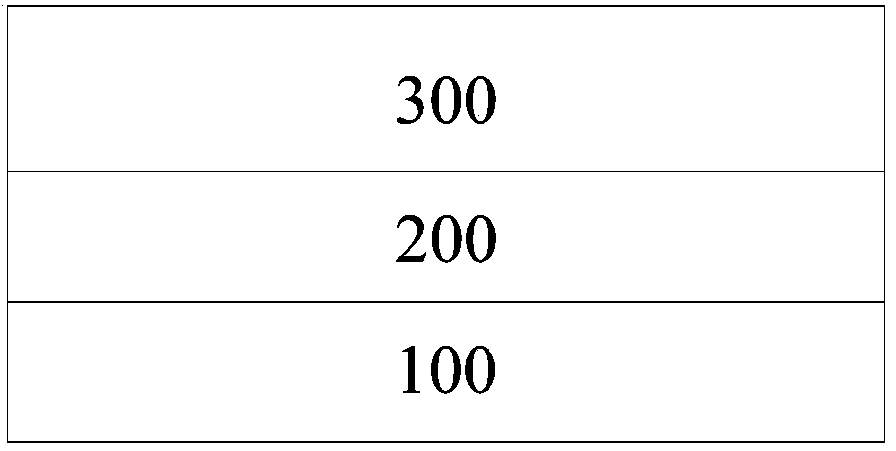

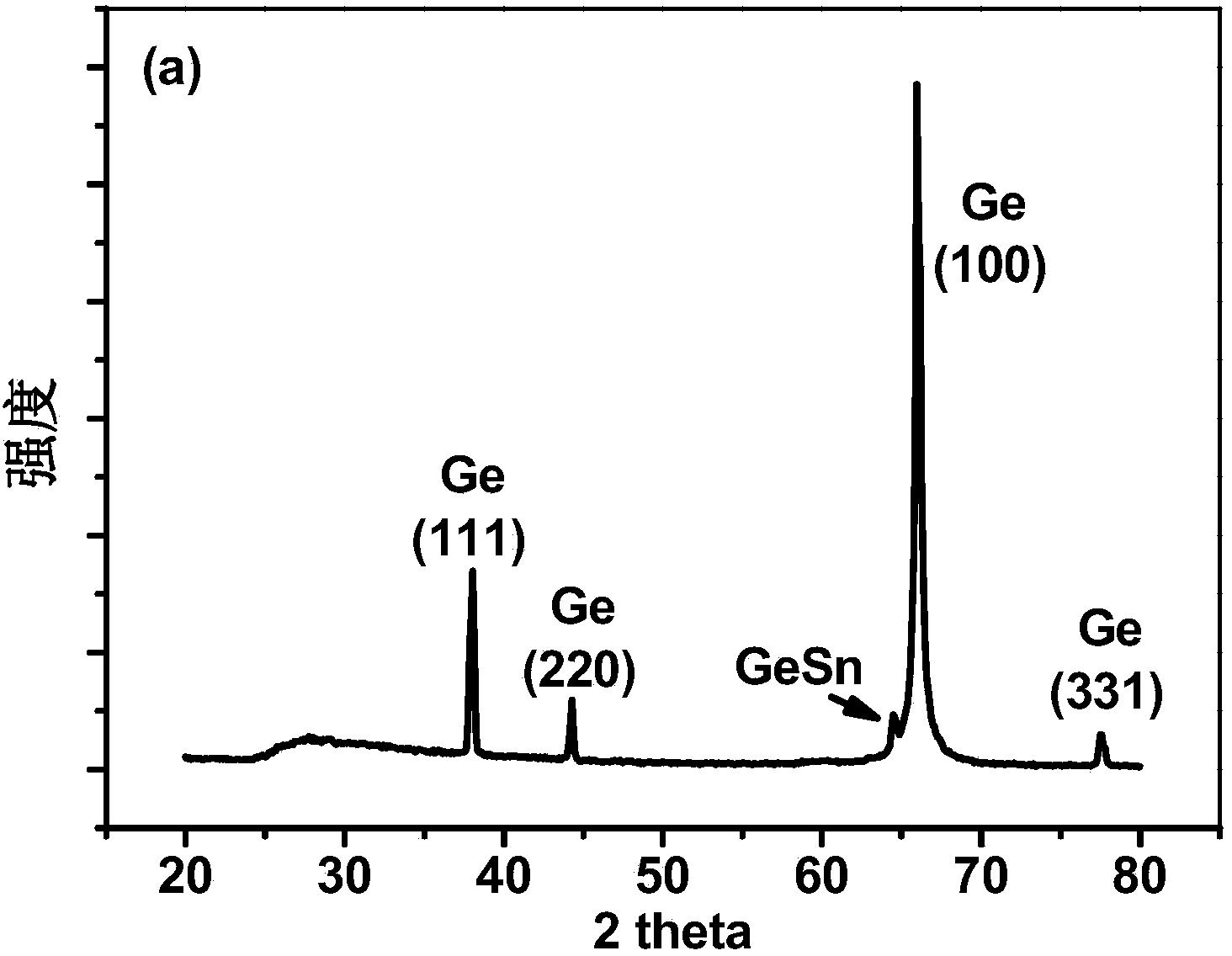

Metal source-drain structure and forming method thereof

ActiveCN103594518AHigh switching current ratioRaise the electron barrier heightSemiconductor/solid-state device manufacturingSemiconductor devicesOptoelectronicsMetal

The invention provides a metal source-drain structure and a forming method thereof. The method includes the following steps of providing a substrate with a Ge layer as the surface, forming an Sn layer on the Ge layer, removing the Sn layer so as to expose a GeSn layer which is the interface between the Ge layer and the Sn layer and forming a metal layer on the GeSn layer. The metal source-drain structure and the forming method thereof can improve the on-off ratio of a component and the electronic barrier height of a Schottky component and have the advantages of being simple, easy to achieve and low in cost.

Owner:TSINGHUA UNIV

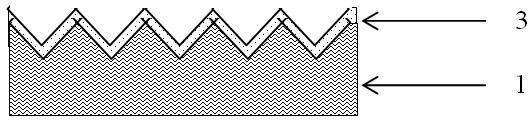

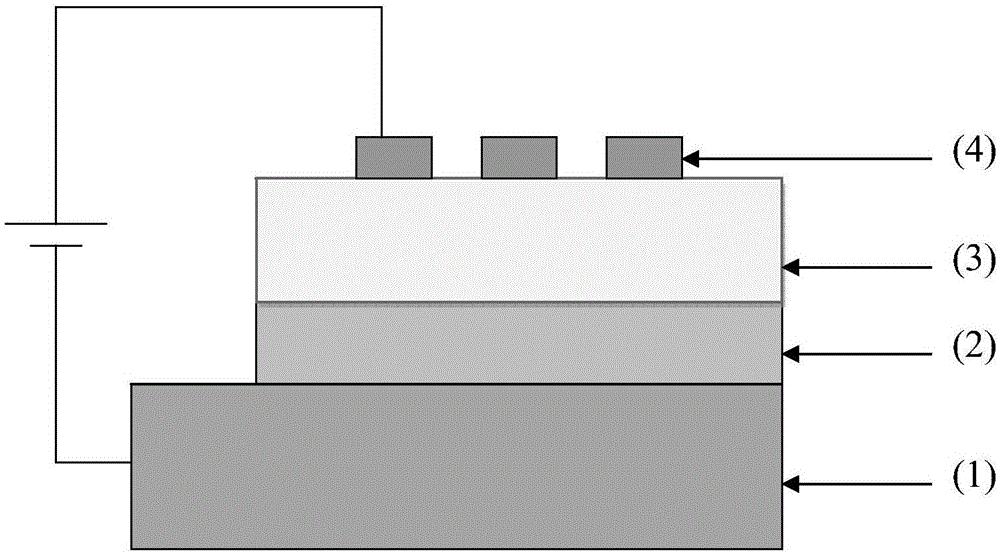

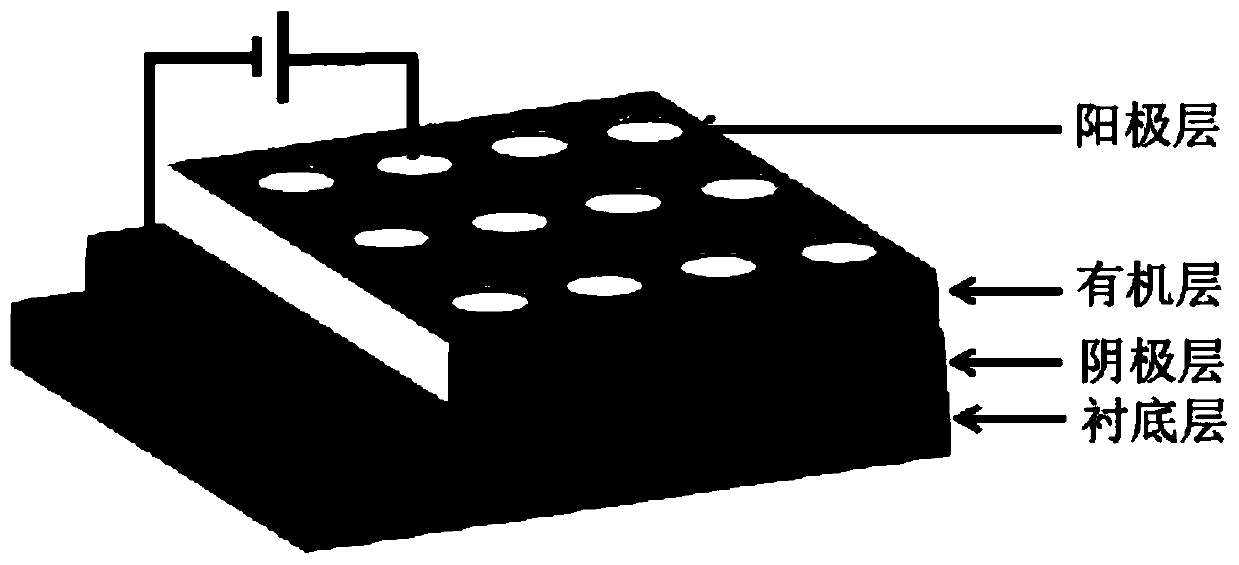

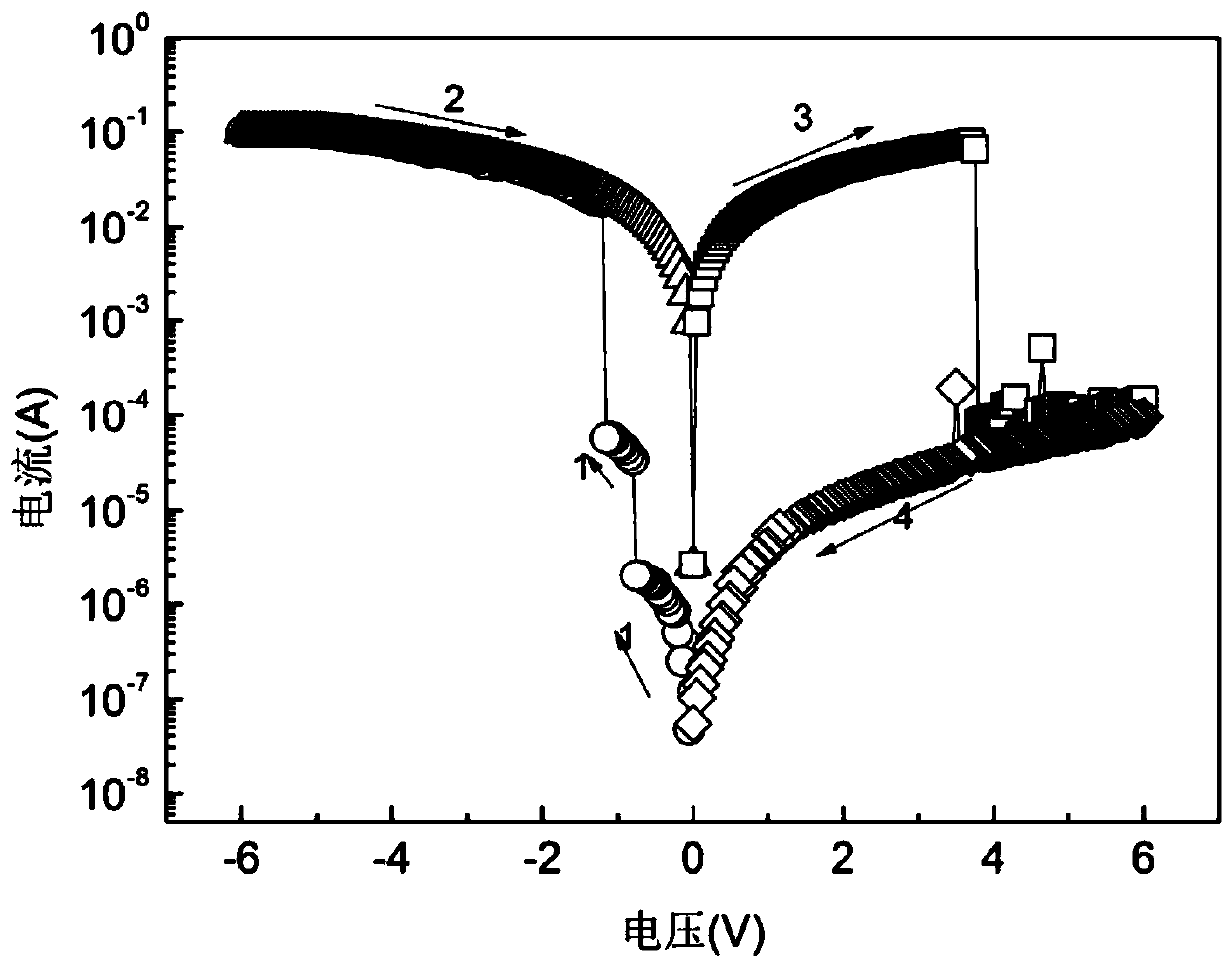

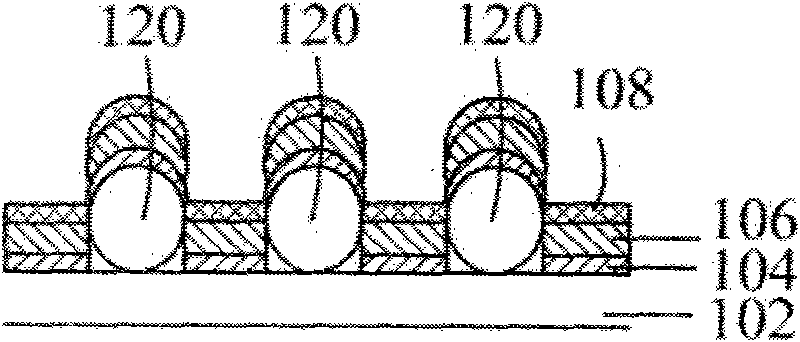

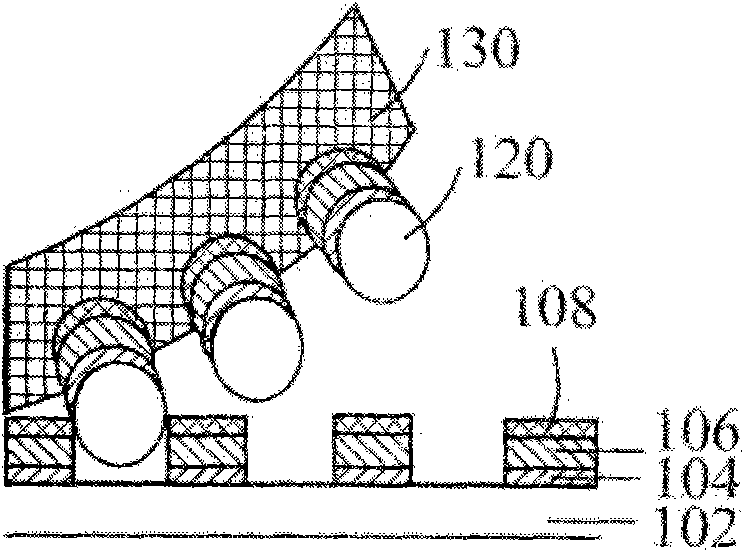

Organic resistive random access memory (RRAM) with peak shaped bottom electrode and manufacture method thereof

InactiveCN102157692AHigh repeatabilityGood repeatabilitySolid-state devicesSemiconductor/solid-state device manufacturingMicroelectronicsElectrically conductive

The invention belongs to the technical field of microelectronics, specifically relates to an organic resistive random access memory (RRAM) with peak shaped bottom electrode and flat top electrode and a manufacture method thereof. The method related by the invention comprises steps of: first manufacturing a substrate with peak figures; and depositing a bottom electrode, spin coating an organic medium layer and depositing a top electrode in turn; finally forming an organic RRAM device with a peak shaped bottom electrode. The RRAM with the peak shaped bottom electrode can form a certain electric field distribution on the medium layer, and the electric field at the peak part is maximum, so conductive filaments are formed preferentially at the peak part, thereby improving the repeatability and current switch rate of the RRAM well. The method of invention is suitable for the organic RRAM device based on filament conduction principle.

Owner:FUDAN UNIV

Bilinear doping drainage heterogeneous material gate oxide layer graphene tunneling field-effect transistor

InactiveCN104091829AGood gating abilityImprove gate control abilitySemiconductor devicesDelayed timeLow leakage

The invention discloses a bilinear doping drainage heterogeneous material gate oxide layer graphene tunneling field-effect transistor (DL-HTFETs). The field-effect transistor undergoes P / N type heavy doping at a source region and a drain region, linear doping is carried out on regions, close to a channel, of the source end and the drain end, an oxidation layer close to a source electrode is formed by low-K oxide (SiO2), the oxidation layer close to a drain layer is formed by high-K oxide (HfO2), a conveying model of the novel bilinear doping drainage heterogeneous material gate oxide layer graphene tunneling field-effect transistor is built by means of a quantum mechanics model, and electrical properties of a high-K tunneling field-effect transistor (HK-TFETs), a common gate oxide tunneling field-effect transistor (LK-TFETs), a heterogeneous oxide tunneling field-effect transistor (HTFETs), a common filed-effect transistor and the DL-HTFETs are compared and analyzed by means of the model. As is shown by a research result, the DL-HTFETs have the advantages of low leakage currents, a high current switch ratio, low power consumption and short delay time and the like.

Owner:NANJING UNIV OF POSTS & TELECOMM

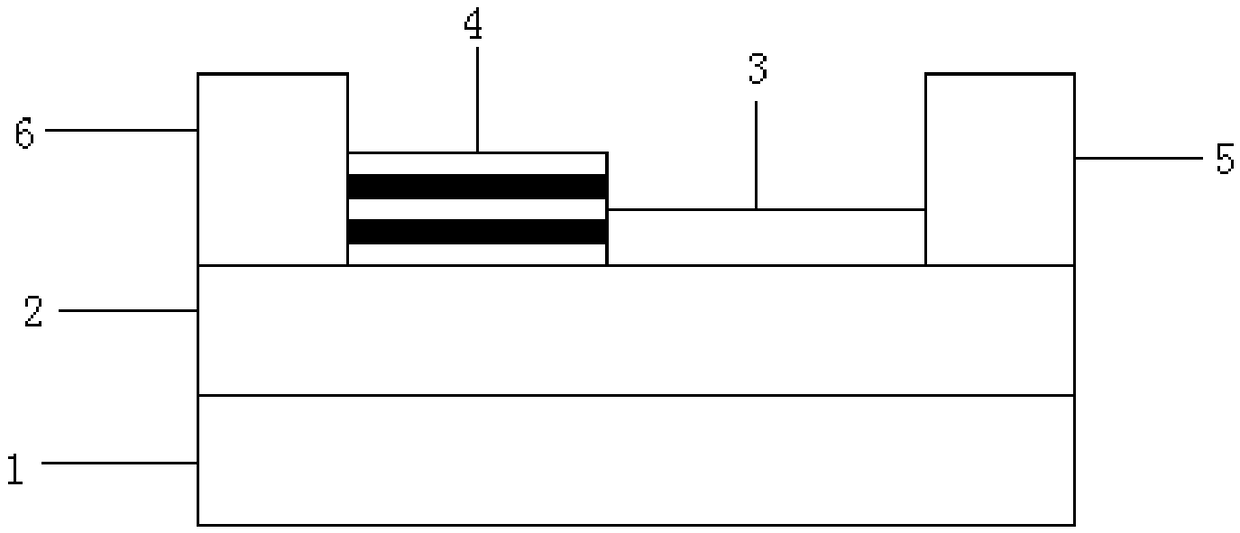

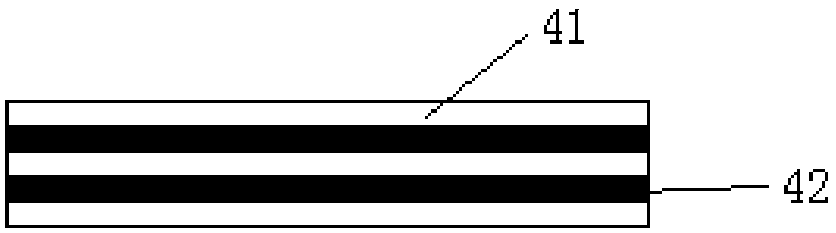

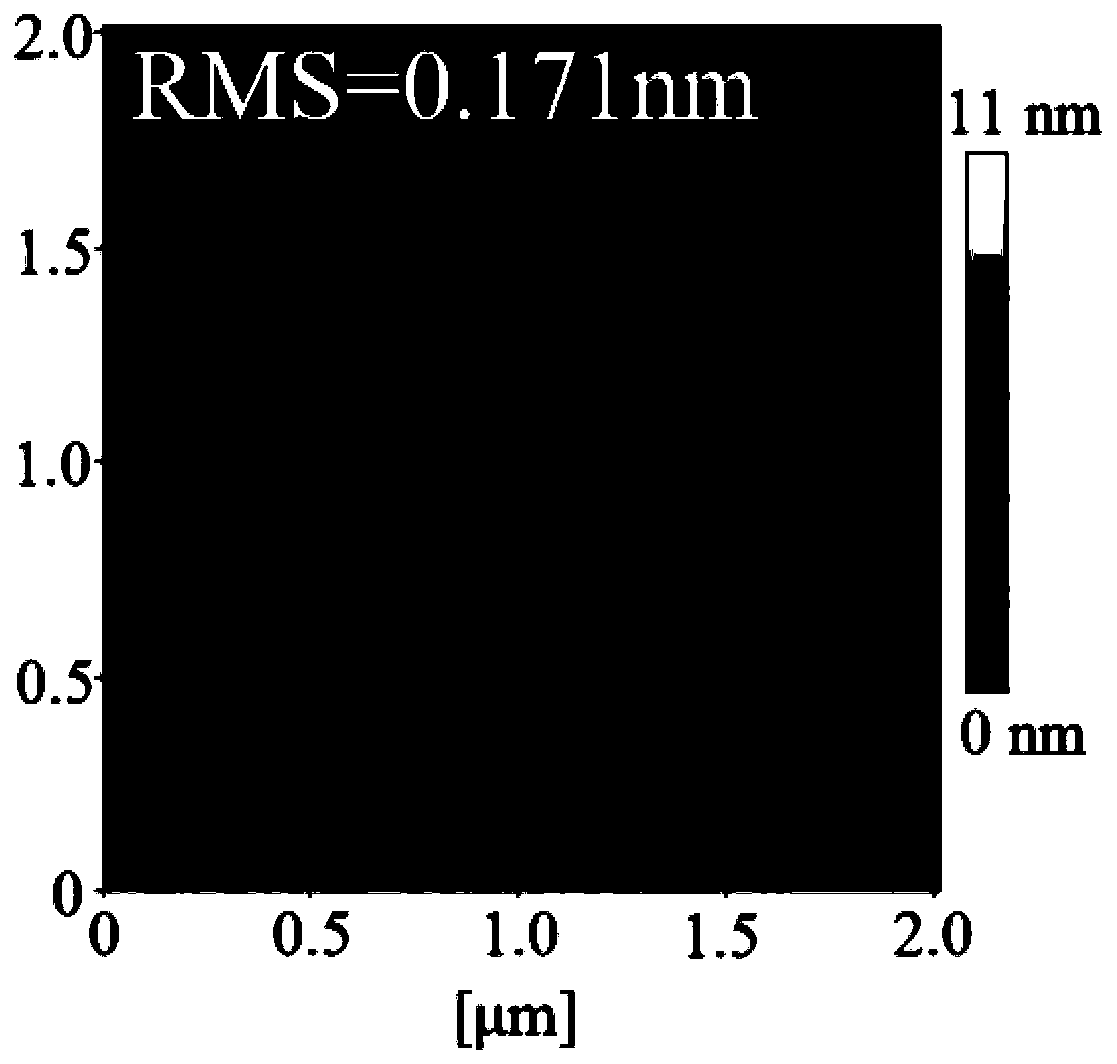

Efficient two-dimensional superlattice heterojunction photovoltaic device and preparation thereof

ActiveCN108899423AImprove light absorption efficiencyHigh switching current ratioSolid-state devicesSemiconductor/solid-state device manufacturingHeterojunctionState of art

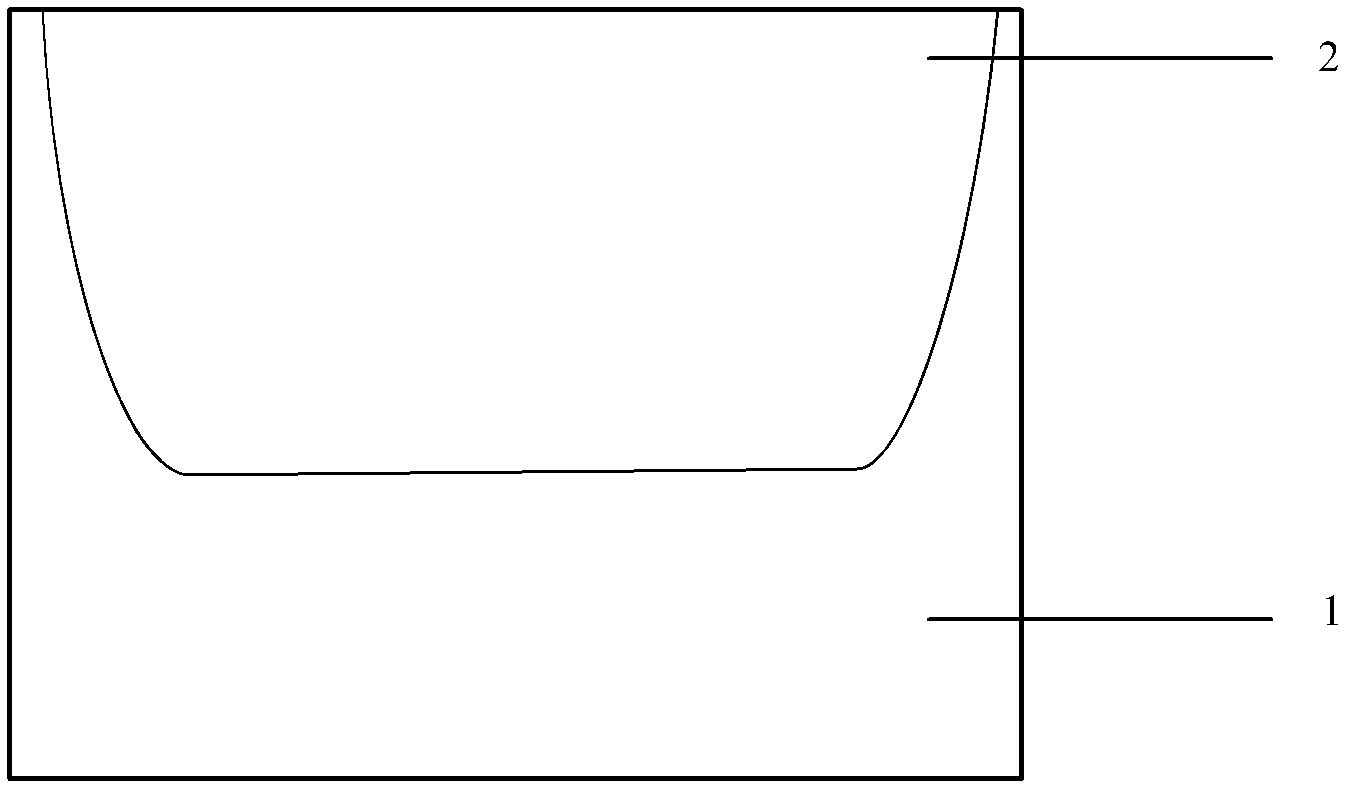

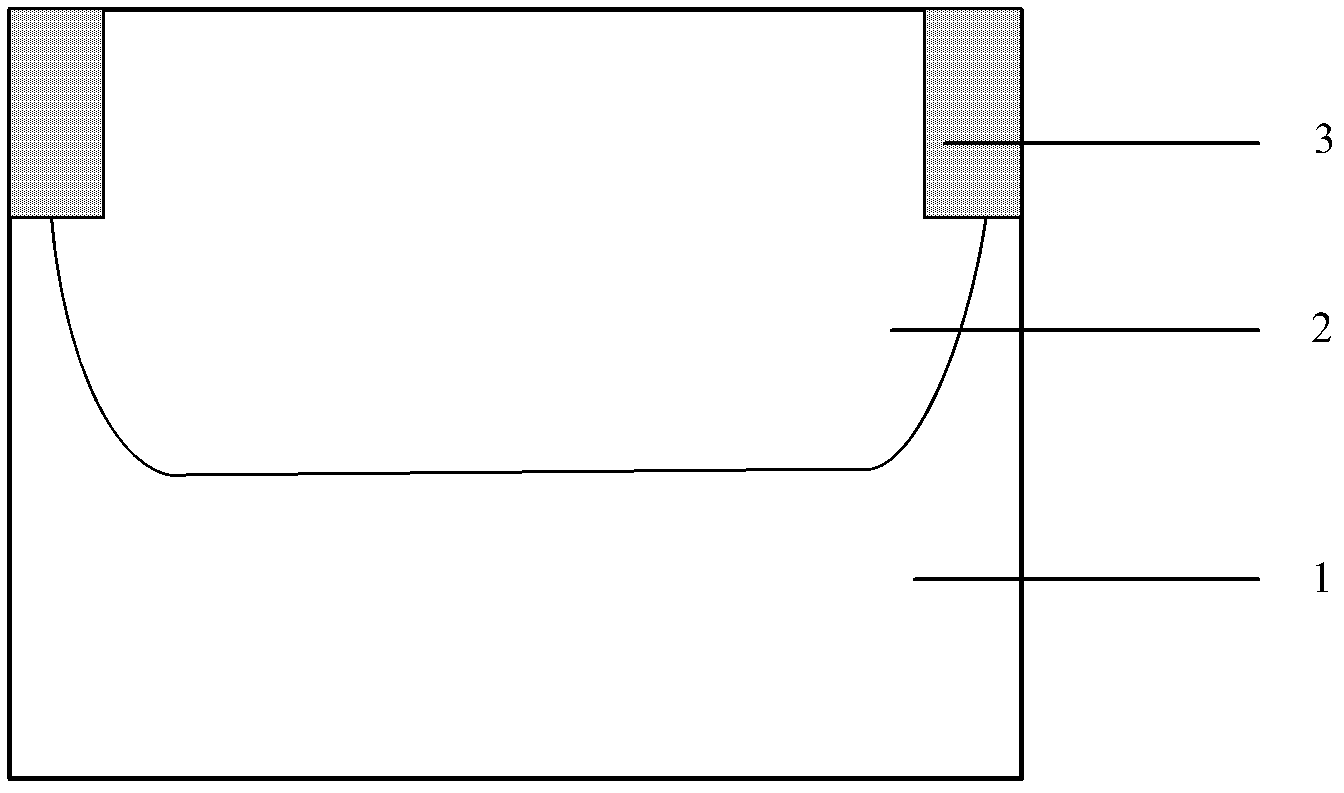

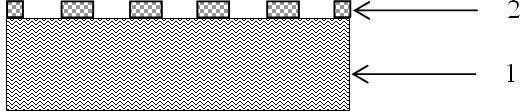

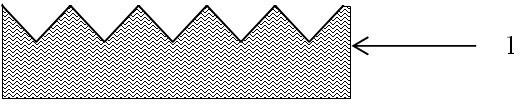

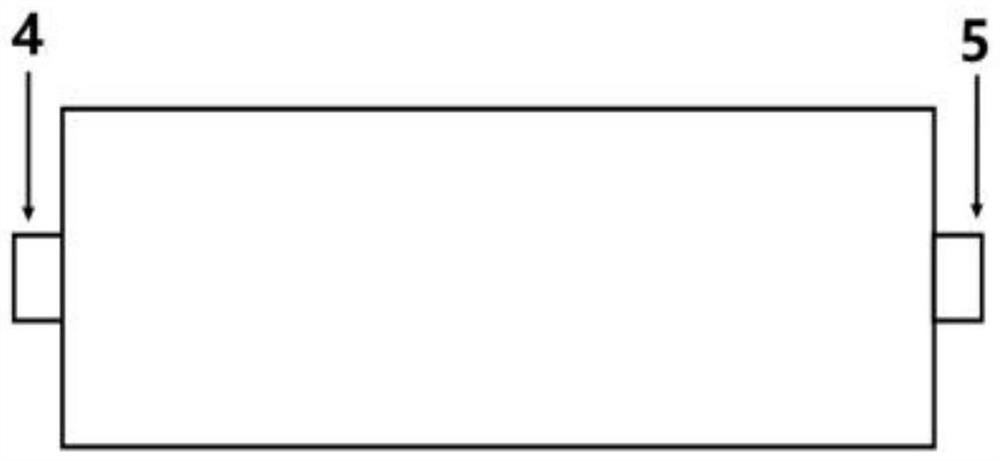

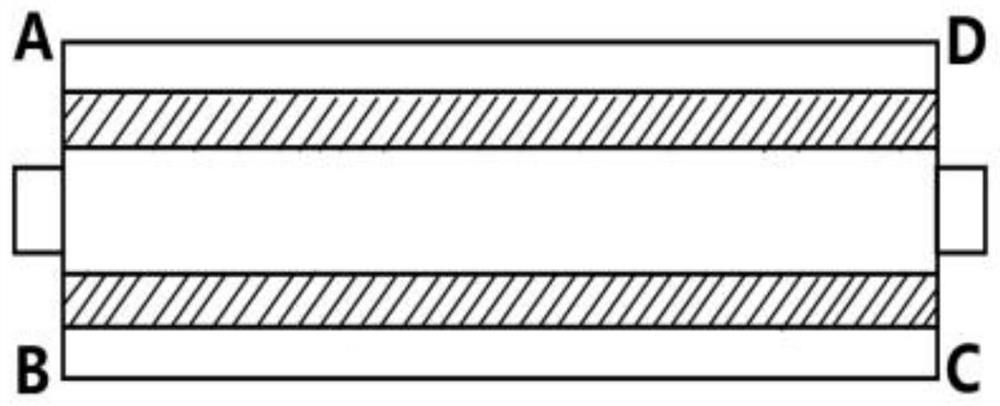

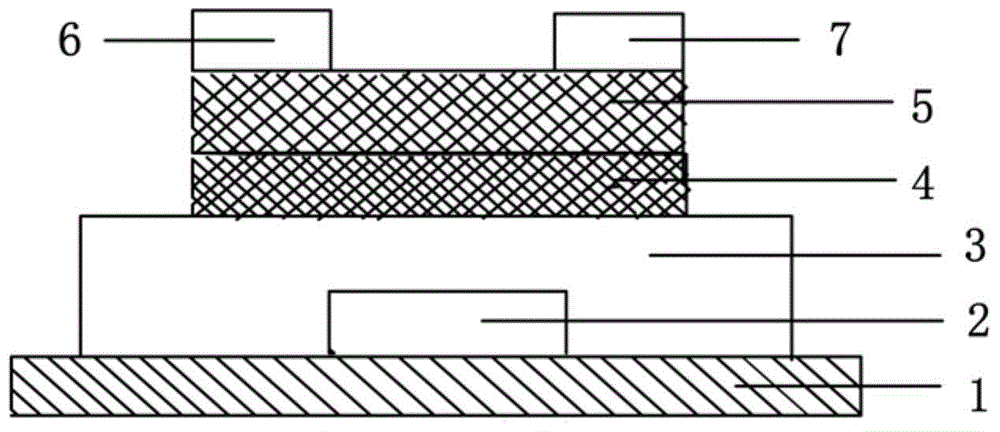

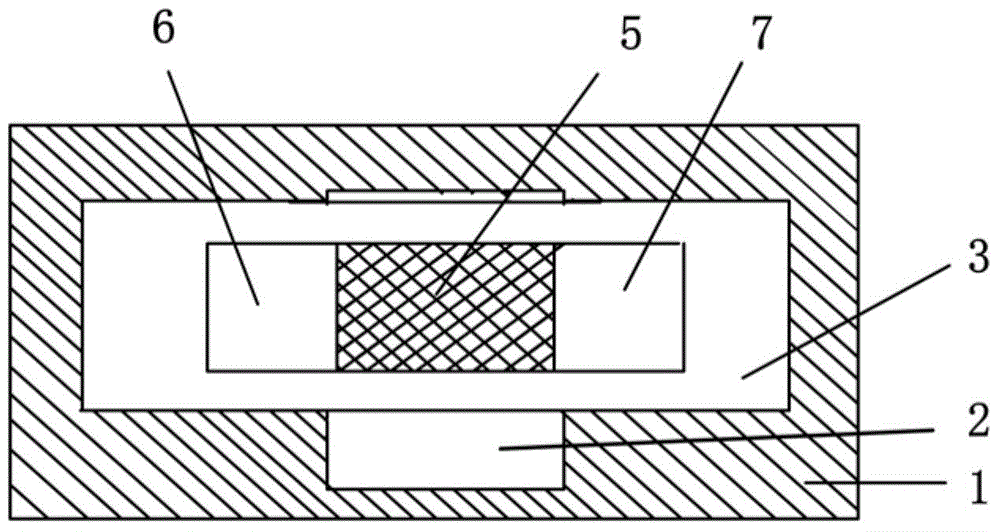

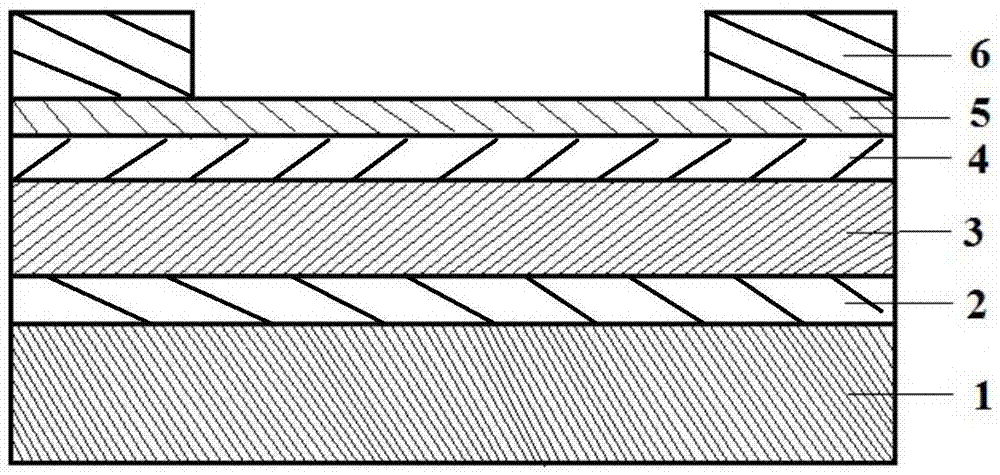

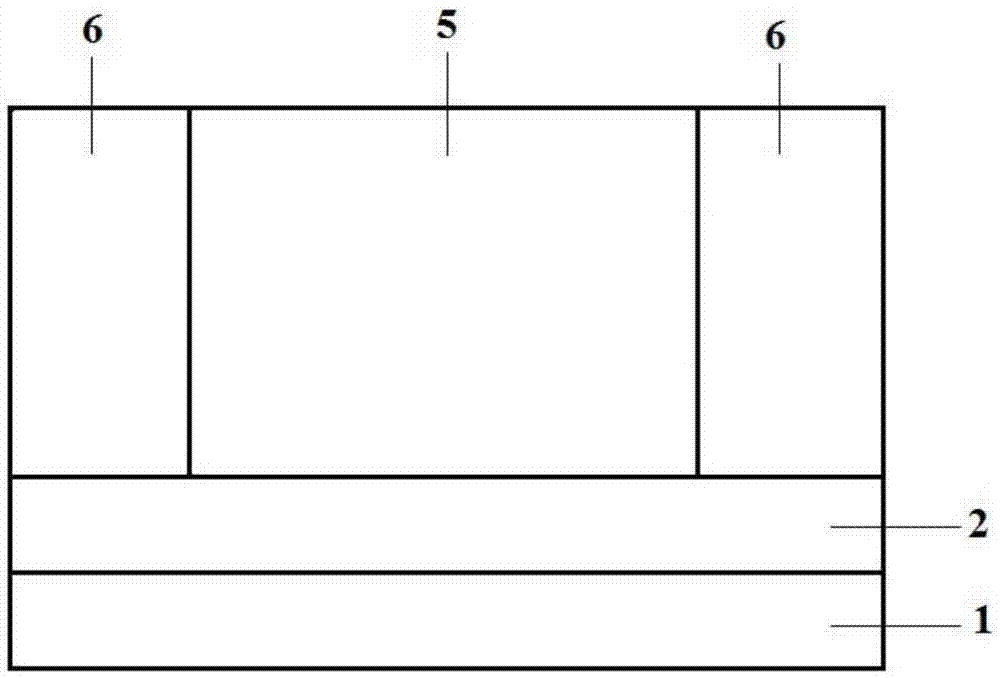

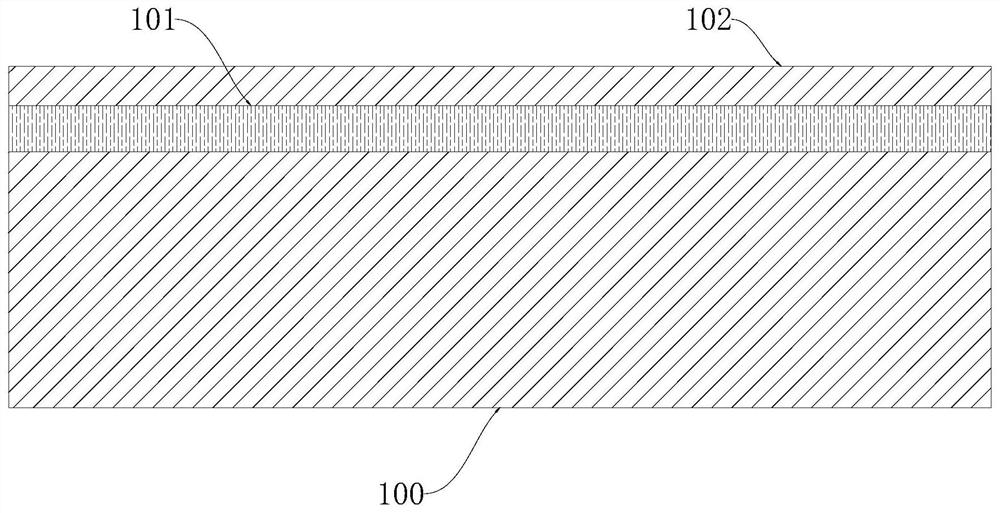

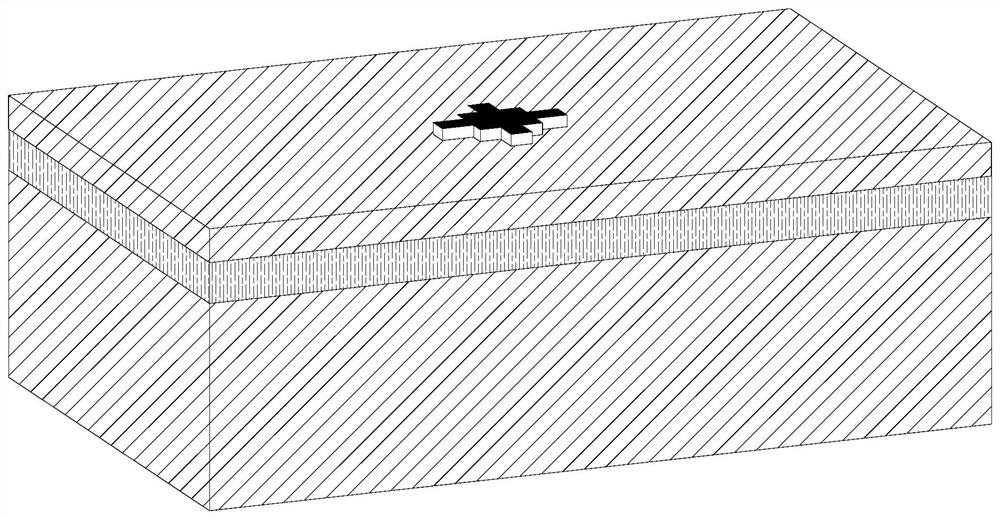

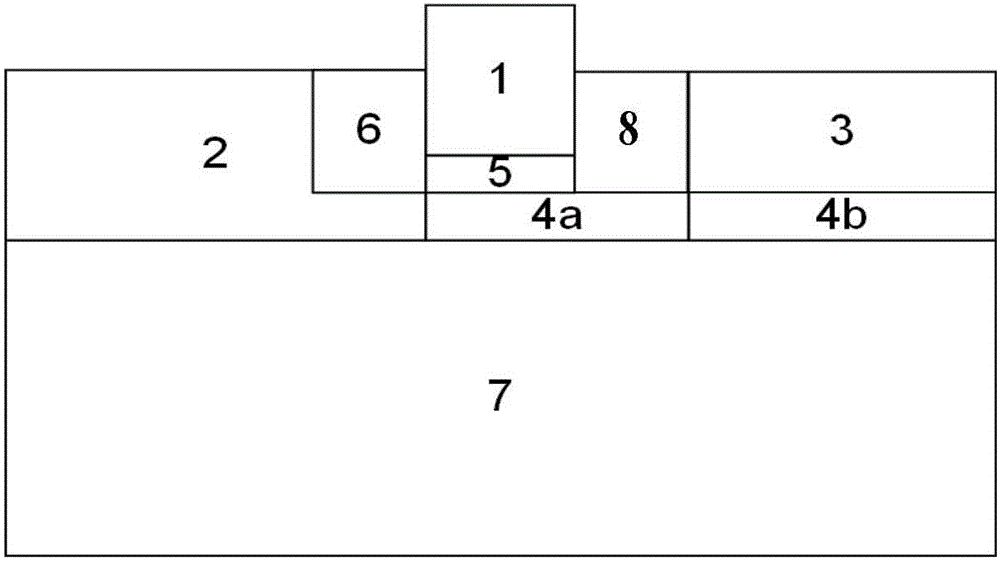

The invention relates to an efficient two-dimensional superlattice heterojunction photovoltaic device and preparation thereof. The preparation method of the efficient two-dimensional superlattice heterojunction photovoltaic device includes the steps: a) immersing a device structure composed of a substrate (1), a silicon dioxide layer (2) and multiple layers of two-dimensional materials into an electrolyte solution containing organic molecules; b) preparing a three-electrode system on the multiple layers of two-dimensional materials and applying a negative voltage to insert organic molecules with positive charges into part of the region of the multiple layers of two-dimensional materials to form a two-dimensional superlattice structure (4), and then obtaining a two-dimensional superlatticeheterostructure; and c) finally, growing metal electrodes at both ends of the two-dimensional superlattice heterostructure, thus completing the preparation process. Compared with the prior art, the present invention discloses stable superlattice materials in which two-dimensional materials and organic molecular layers alternate with each other. The superlattice materials and the two-dimensional multilayer material constitute a heterojunction photovoltaic device, and the result is equivalent to parallel connection of a plurality of two-dimensional material heterojunctions, and the light absorption efficiency is high, and the mobility and the stability are high.

Owner:SHANGHAI UNIVERSITY OF ELECTRIC POWER

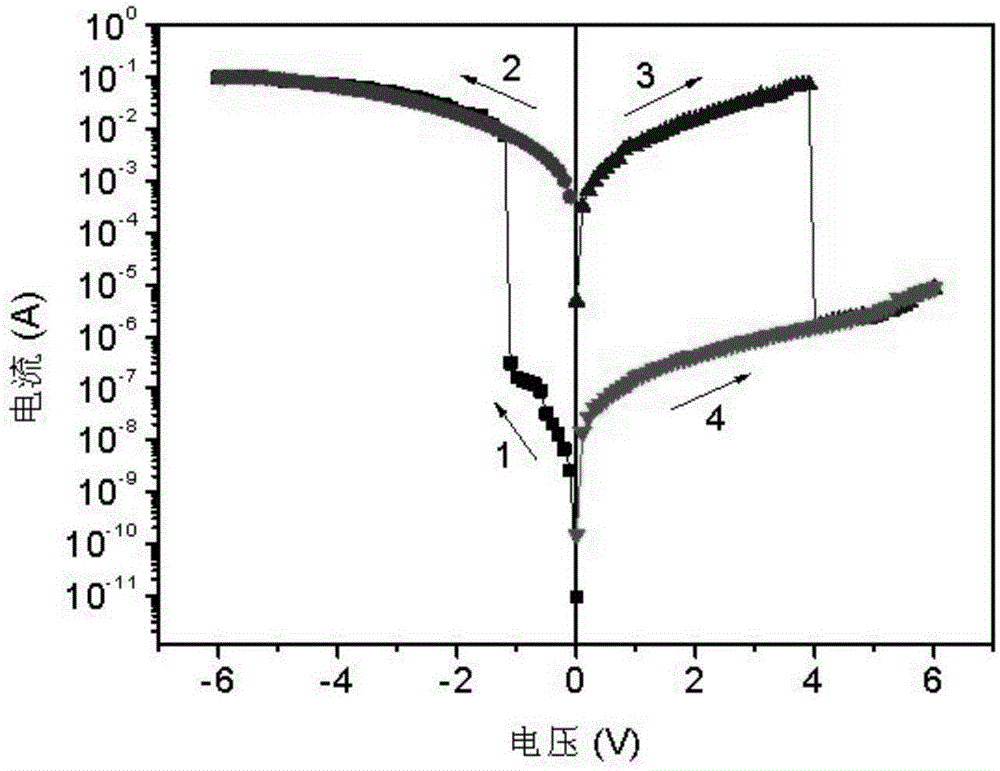

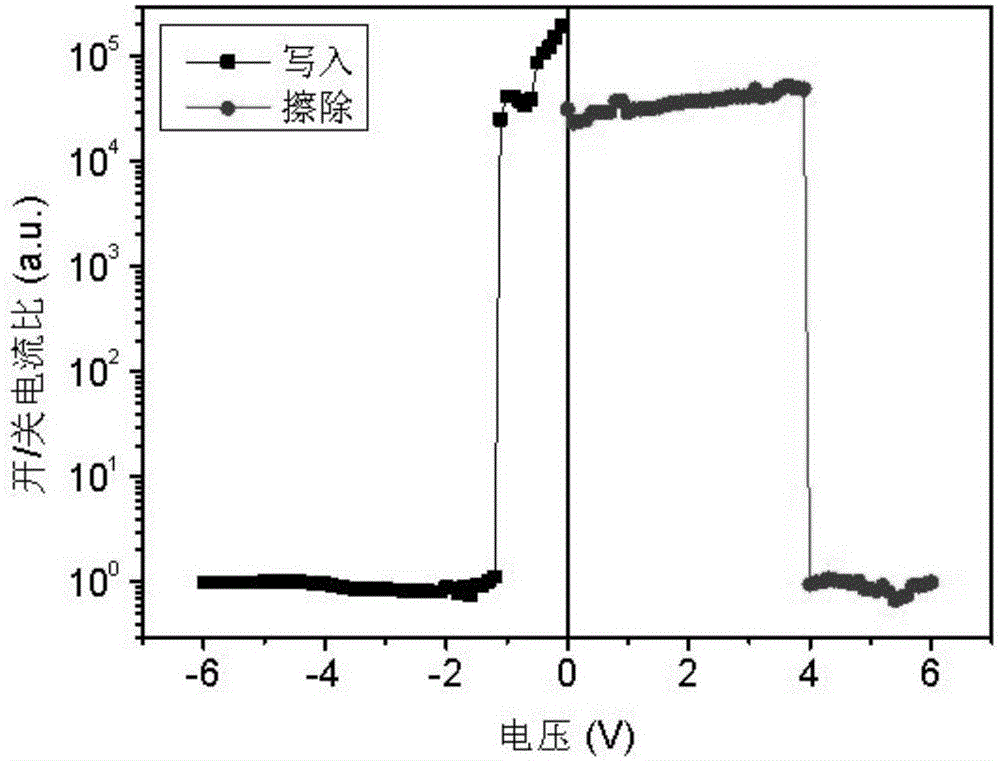

Flash type electrical storage material and preparation method of electrical storage device

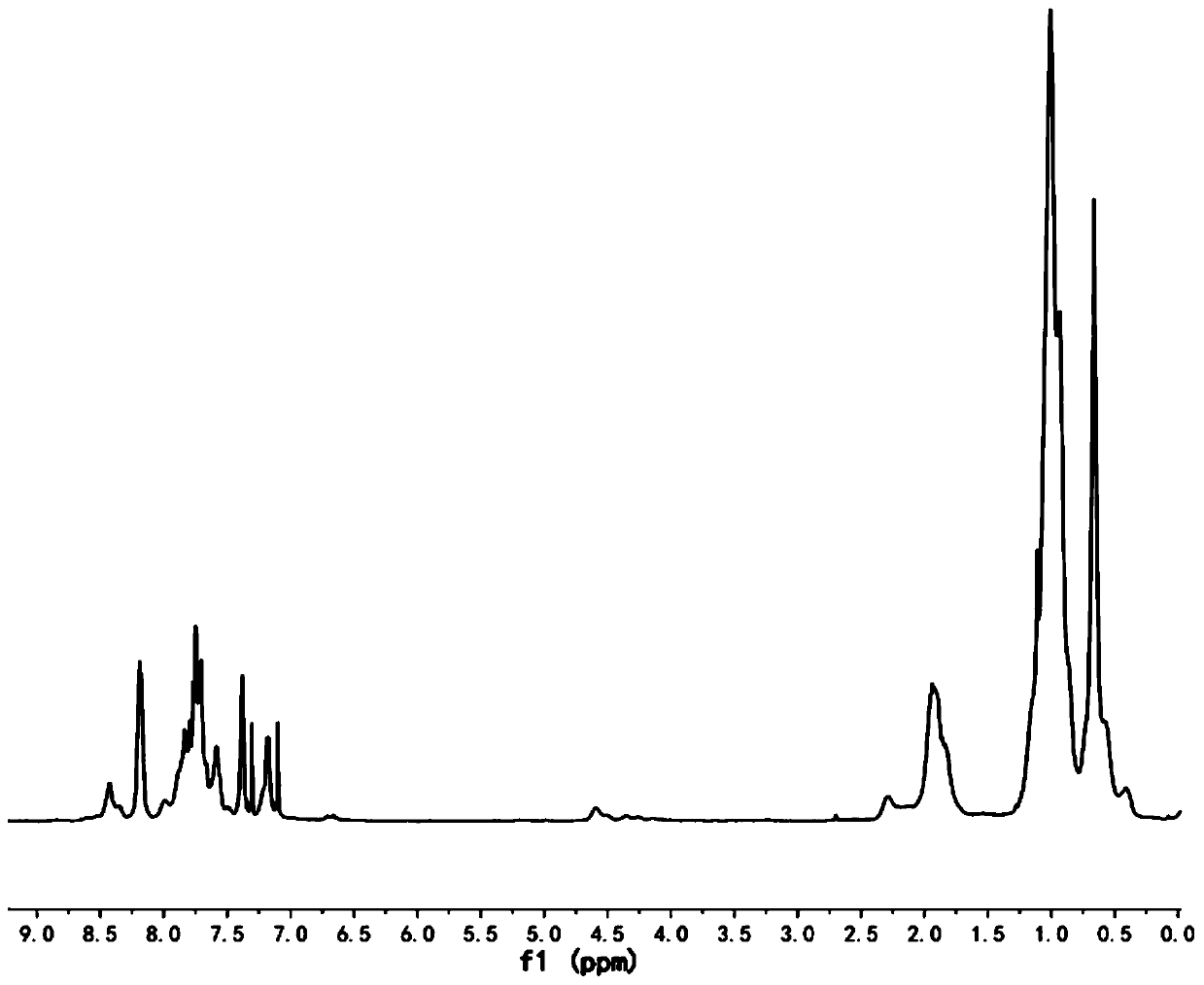

InactiveCN105098078AImprove solubilityReduce error rateSolid-state devicesSemiconductor/solid-state device manufacturingSolventChemistry

The invention belongs to the field of electrical storage device materials and technologies, and particularly relates to a Flash type electrical storage material and a preparation method of an electrical storage device. The preparation process of the Flash type electrical storage device comprises the steps of preparing a fluorene-triphenylamine conjugated polymer or a mixture of the fluorene-triphenylamine conjugated polymer and a fullerene derivative PCBM into a chlorobenzene solution with the concentration being 5-15mg / mL, then spin-coating the chlorobenzene solution on a piece of clean ITO glass, carrying out vacuum drying, and removing the solvent; and finally plating a top electrode Al on the polymer by using a vacuum evaporation method. An organic electrical storage device prepared by using the method provided by the invention has the characteristics of simple technological operation and low cost. In addition, the electrical storage material in the invention has an electron donor group (triphenylamine) and an electron acceptor (PCBM), so that the prepared storage device has the characteristics of low operating voltage and high switching current ratio, and has good application prospects in the field of information storage.

Owner:HEILONGJIANG UNIV

Full-surrounded gate synapse transistor, preparation method and circuit connection method

ActiveCN111739944AReduce leakage currentImprove controlTransistorSolid-state devicesHemt circuitsComputational physics

The invention relates to a full-surrounded gate synapse transistor, a preparation method and a circuit connection method. The full-surrounded gate synapse transistor comprises an active layer, an insulating layer, a gate electrode, a source electrode and a drain electrode. The active layer is a cylinder; the insulating layer and the gate electrode are sequentially wrapped on the outer side of theactive layer; one end of the active layer is provided with a source electrode, and the other end of the active layer is provided with a drain electrode; both the source electrode and the drain electrode are cylinders; the bottom surface diameters of the source electrode and the drain electrode are smaller than the bottom surface diameter of the active layer; and the active layer, the source electrode and the drain electrode are coaxially arranged. According to the invention, the gate voltage can control the channel current from all directions, and the control capability of the gate electrode is improved, so that the power consumption of the device is reduced.

Owner:SHANGHAI UNIV

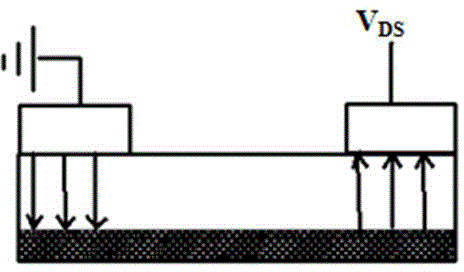

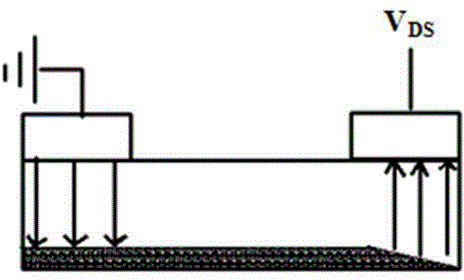

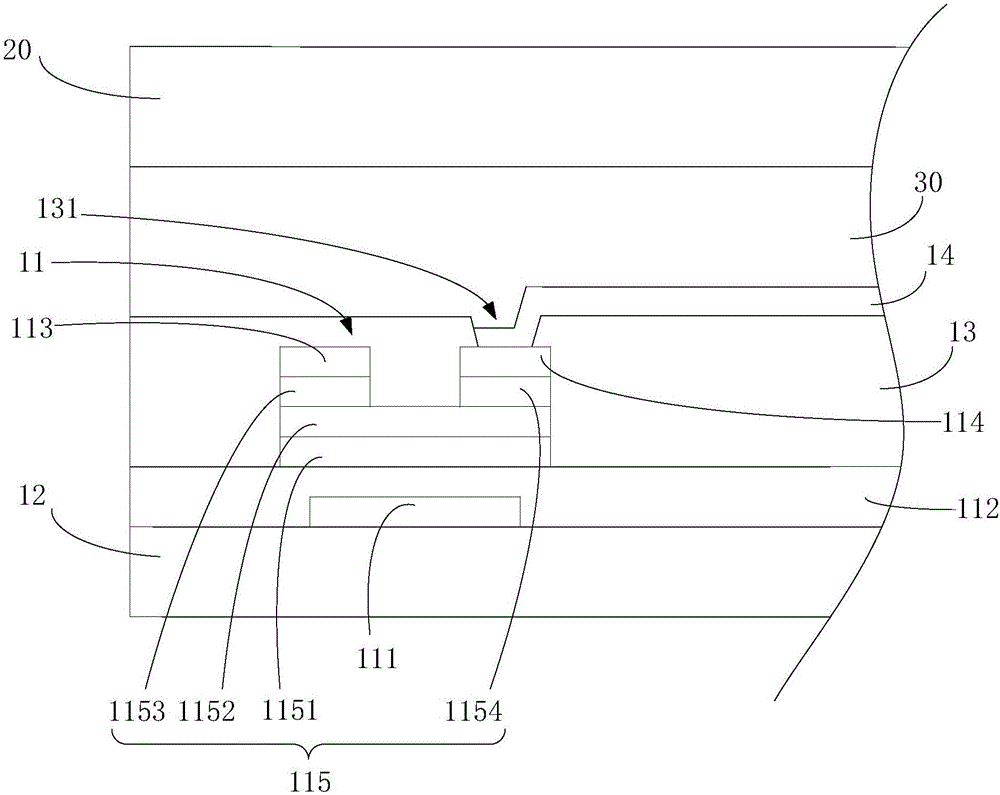

Double-active layer structured zinc oxide-based thin film transistor and preparation method thereof

The invention discloses a double-active layer structured zinc oxide-based thin film transistor. The double-active layer structure zinc oxide-based thin film transistor includes a substrate, a gate, a gate insulating dielectric layer, a first zinc oxide-based semiconductor active layer, a second zinc oxide-based semiconductor active layer, a source electrode and a drain electrode; the gate is formed on the substrate; the gate insulating dielectric layer covers the gate and the substrate; the active layers are formed on the gate insulating dielectric layer; the source electrode and the drain electrode are arranged on the second zinc oxide-based semiconductor active layer; the doping element of the first zinc oxide-based semiconductor active layer is one or two kinds of elements selected from Ga, Al, Hf, In and Sn; the second zinc oxide-based semiconductor active layer is a silicon-doped zinc oxide thin film; and the resistance value of the second zinc oxide-based semiconductor active layer is higher than that of the first zinc oxide-based semiconductor active layer. With the above technical scheme of the invention adopted, the zinc oxide-based thin film transistor has the advantages of effectively-decreased off-state current, improved on-off current ratio, improved light transmission performance in a visible light range, and improved stability.

Owner:SOUTH CHINA UNIV OF TECH

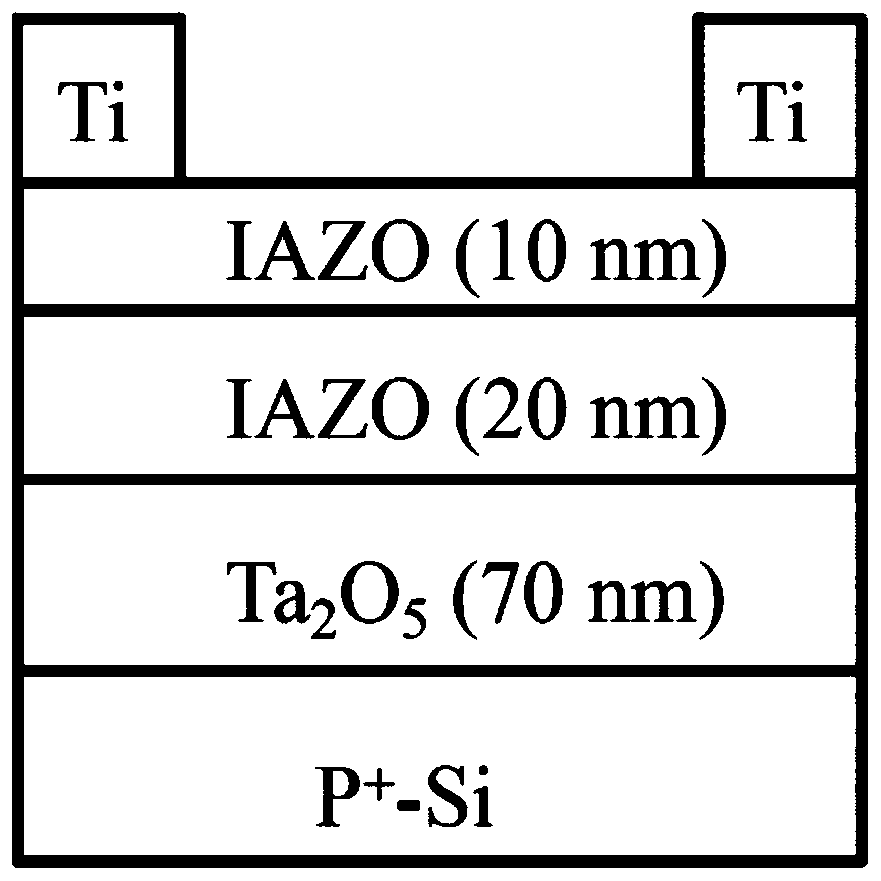

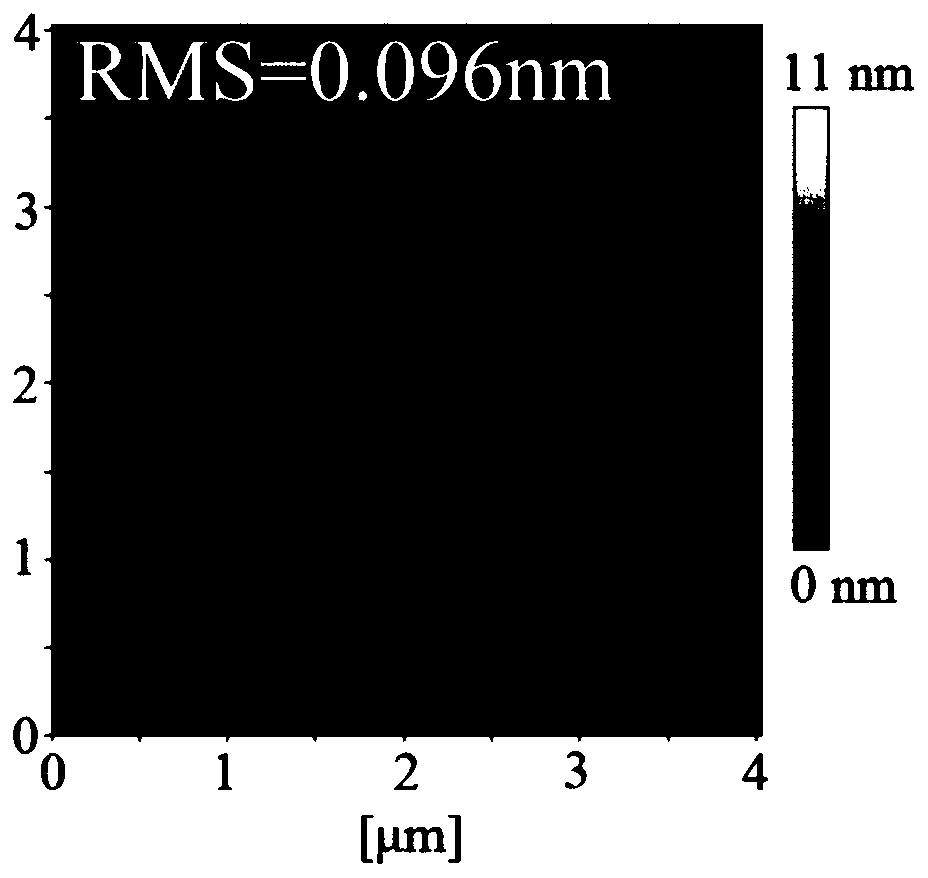

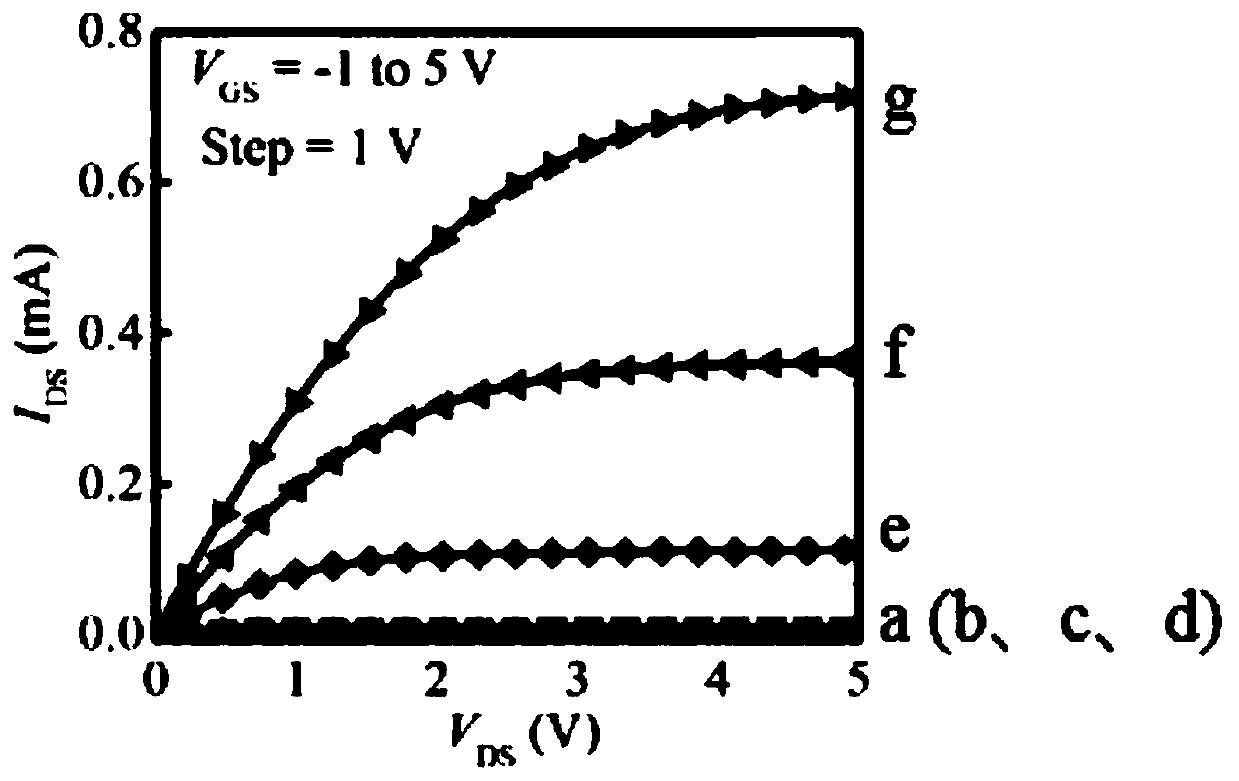

Indium aluminum zinc oxide thin film transistor based on gate dielectric layer with high dielectric constant and full room temperature preparation method thereof

InactiveCN110299415AQuality improvementImprove performanceTransistorSemiconductor/solid-state device manufacturingGate dielectricIndium

The invention relates to an indium aluminum zinc oxide thin film transistor based on a gate dielectric layer with high dielectric constant and a full room temperature preparation method thereof. The indium aluminum zinc oxide thin film transistor includes a P<+>-Si substrate, a Ta2O5 gate dielectric layer, double active layers, a source electrode and a drain electrode which are arranged in turn from bottom to top. The preparation method includes the following steps: (1) growing a Ta2O5 gate dielectric layer on a P<+>-Si substrate; (2) growing a first layer of IAZO film on the Ta2O5 gate dielectric layer; (3) growing a second layer of IAZO film on the first layer of IAZO film; and (4) growing a source electrode and a drain electrode on the second layer of IAZO film. An IAZO TFT with excellent performance is prepared in a room temperature environment by exploring and optimizing the sputtering preparation conditions of the Ta2O5 gate dielectric layer. The prepared IAZO TFT shows extremelyhigh electrical performance, and has a broad application prospect in flexible display and integrated circuits in the future.

Owner:SHANDONG UNIV

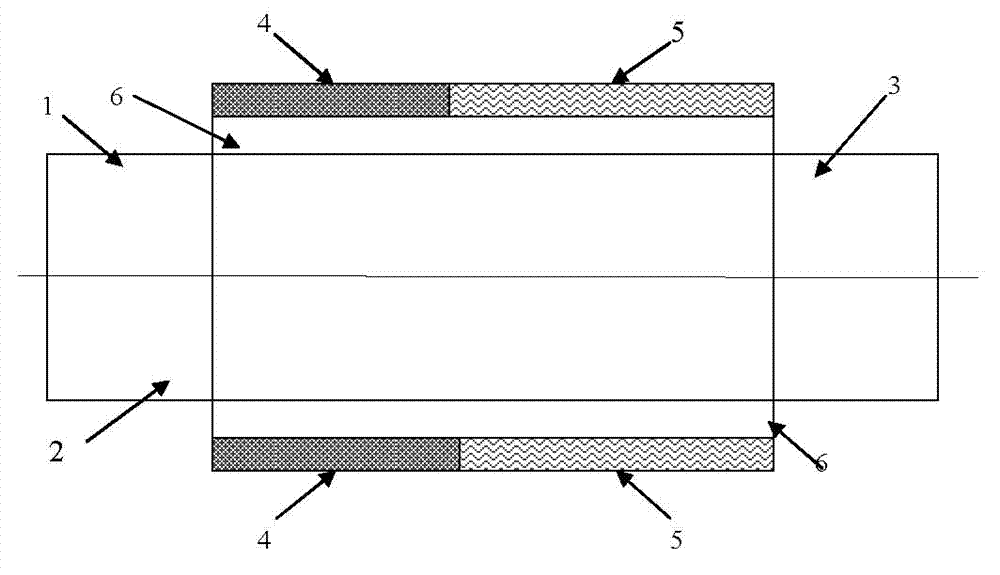

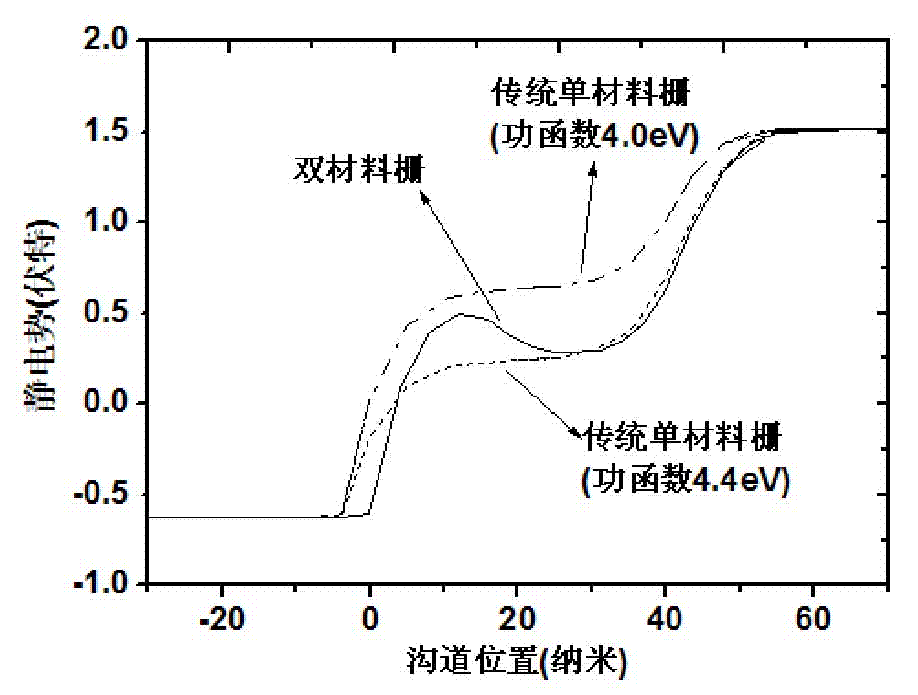

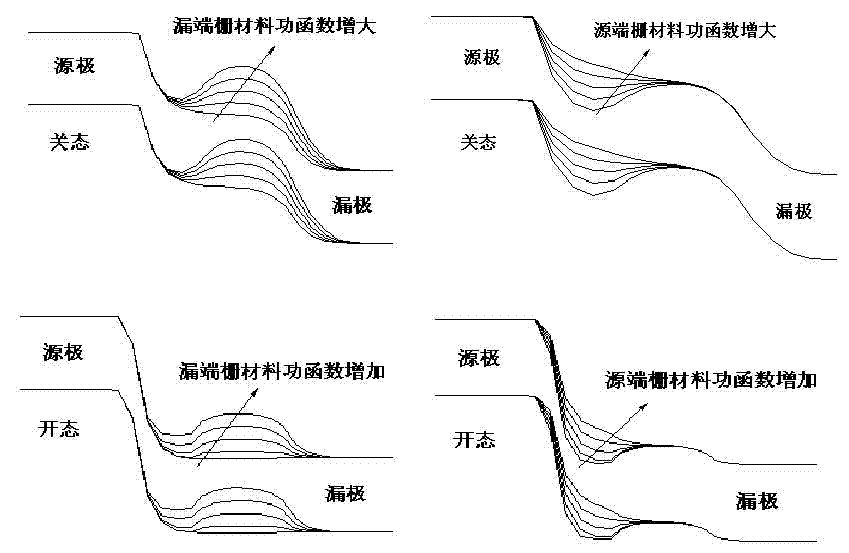

Bi-material railing nanowire tunneling field effect device and manufacturing method thereof

ActiveCN102956709AReduces off-state leakage currentHigh switching current ratioSemiconductor/solid-state device manufacturingSemiconductor devicesOxide semiconductorPhysics

The invention relates to a bi-material railing nanowire tunneling field effect device and a manufacturing method thereof. According to the bi-material railing nanowire tunneling field effect device, a channel is arranged at the center, and a source region and a drain region are respectively arranged at two ends, and an oxide and a gate electrode are covered at the periphery of the channel in sequence. The manufacturing method comprises the steps: SF6 etching a silicon column on a silicon wafer by using a round silicon nitride hard mask; conducting high-temperature oxidation, corroding and reducing the size of the silicon column to be a set diameter value of 6nm-30nm with HF aqueous solution, and conducting high-temperature oxidation to form a silicon column coated by an oxidation layer with set thickness; completing the preparation of a bi-material railing structure by adopting deposition and photoetching technology; and injecting boron and phosphorus of 1*10<20>cm<-2> / 10keV and 5*10<18>cm<-2> / 10keV at 120-150 DEG C respectively, and annealing at 900 DEG C / 10s-1100 DEG C / 10s to prepare the source region and the drain region; completing preparation of a metal electrode by CMOS (Complementary Metal-Oxide-Semiconductor) process; and manufacturing the bi-material railing nanowire tunneling field effect device.

Owner:PEKING UNIV SHENZHEN GRADUATE SCHOOL

Linear doped spin field-effect tube (Spin-FET)

InactiveCN103094327AReduce off-state currentRaise the threshold voltageSemiconductor devicesSwitched currentSchrödinger equation

The invention discloses a spin field-effect tube (Spin-FET) with a linear light dope structure. A transport model which is suitable for the linear doped Spin-FET is constructed based on the quantum mechanics nonequilibrium green function theoretical framework and through the self-consistent solving Poisson and the Schrodinger equation, and the influence of a linear doping strategy and a common doping strategy on the electrical properties of the Spin-FET is calculated by using the model. Compared with the electrical properties of other doping strategies such as output characteristics, transfer characteristics, switch current ratio and magnetism current rate, the linear doped Spin-FET has larger switch current ratio, higher magnetism current rate, and smaller sub-threshold swing and threshold voltage drift. Not only can show that linear doping has better grid control capability, but also short-channel effect and hot carrier effect can be effectively restrained.

Owner:NANJING UNIV OF POSTS & TELECOMM

Double-active layer Cu2O/SnOp channel thin film transistor and preparation method thereof

InactiveCN105449000AImprove mobilityOptimize the valence band structureTransistorSemiconductor/solid-state device manufacturingSwitched currentOxygen vacancy

The invention belongs to the technical field of semiconductors, and discloses a double-active layer Cu2O / SnOp channel thin film transistor and a preparation method thereof. The thin film transistor comprises a substrate, a grid electrode, a grid insulating medium layer, a first semiconductor active layer, a second semiconductor active layer, a source electrode and a drain electrode from bottom to top, wherein the first semiconductor active layer is a p-type SnO semiconductor active layer and the second semiconductor active layer is a Cu2O semiconductor active layer. According to the p-type SnO semiconductor active layer, oxygen vacancy is imported to properly optimize the valence band structure, so that the hole migration rate is improved; and through depositing a layer of Cu2O membrane on the SnO active layer, the surface leakage current is decreased, the switch current ratio is improved, the influences on the SnO layer from the external oxygen and water are decreased and the device stability is improved.

Owner:SOUTH CHINA UNIV OF TECH

Polymeric / carbon nano-tube composite flash memory material with side chain containing carbazole, synthetic method and use

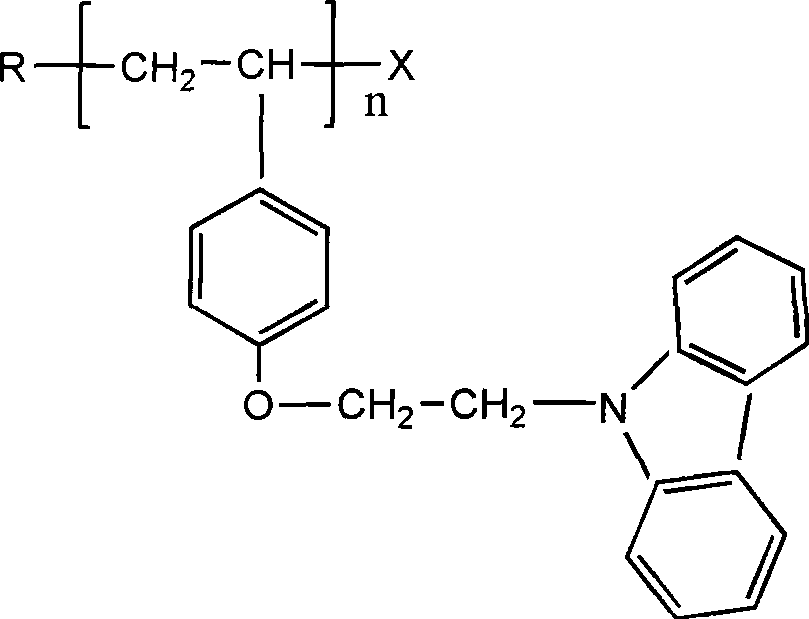

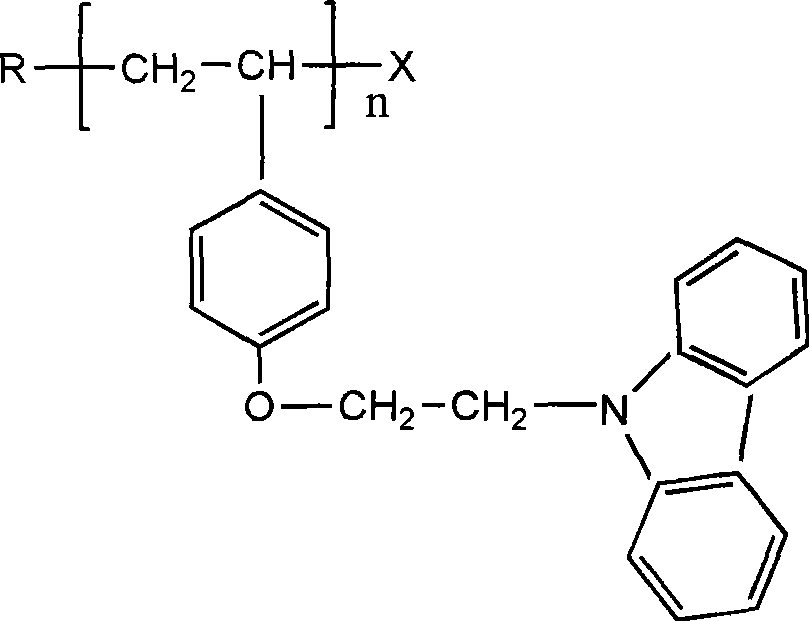

InactiveCN101412794AImprove distributionImprove microcompatibilityRead-only memoriesChemical structureCarbazole

The invention relates to a macromolecular / carbon nanotube composite flash memory material, a synthesis method thereof and application of the macromolecular / carbon nano tube composite flash memory material. The macromolecular / carbon nanotube composite flash memory material the side chains of which contain carbazole is characterized in that the macromolecular / carbon nanotube composite flash memory material has a chemical structure of a general formula on the right, wherein R is a carbon nanotube, X is Cl or Br, and n is between 20 and 200. The composite flash memory material has lower cut-in voltage and higher switched current ratio.

Owner:WUHAN INSTITUTE OF TECHNOLOGY

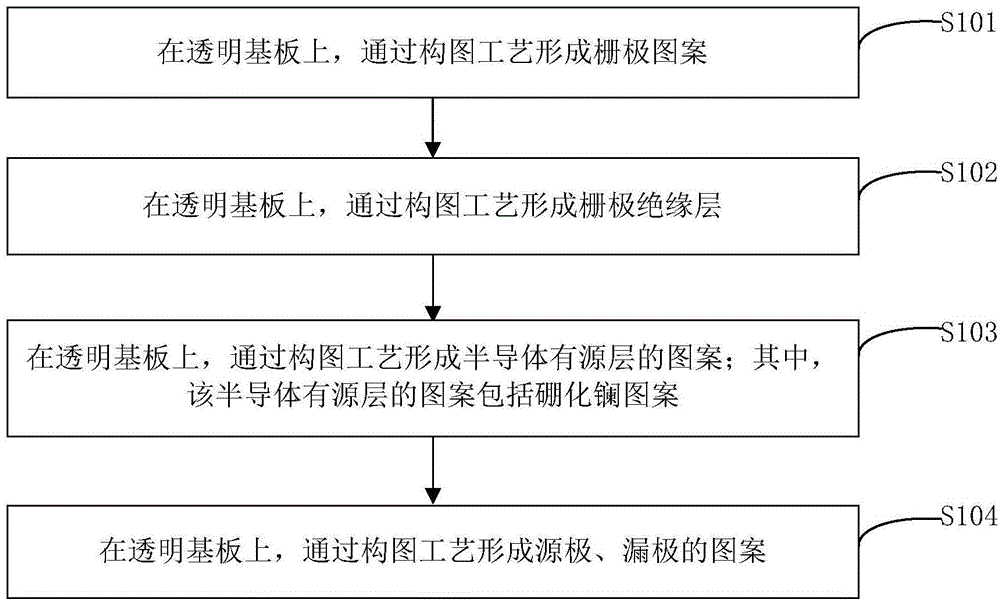

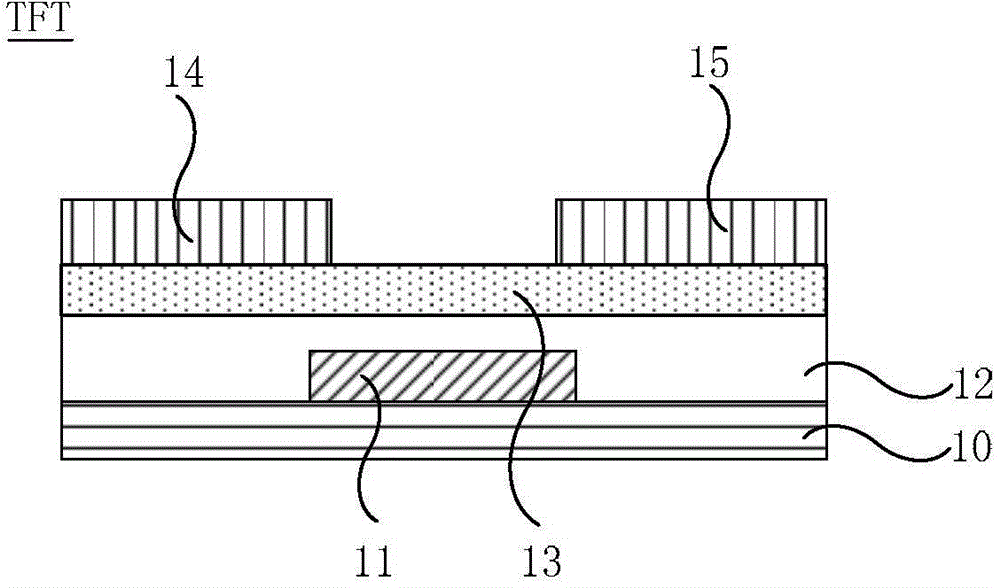

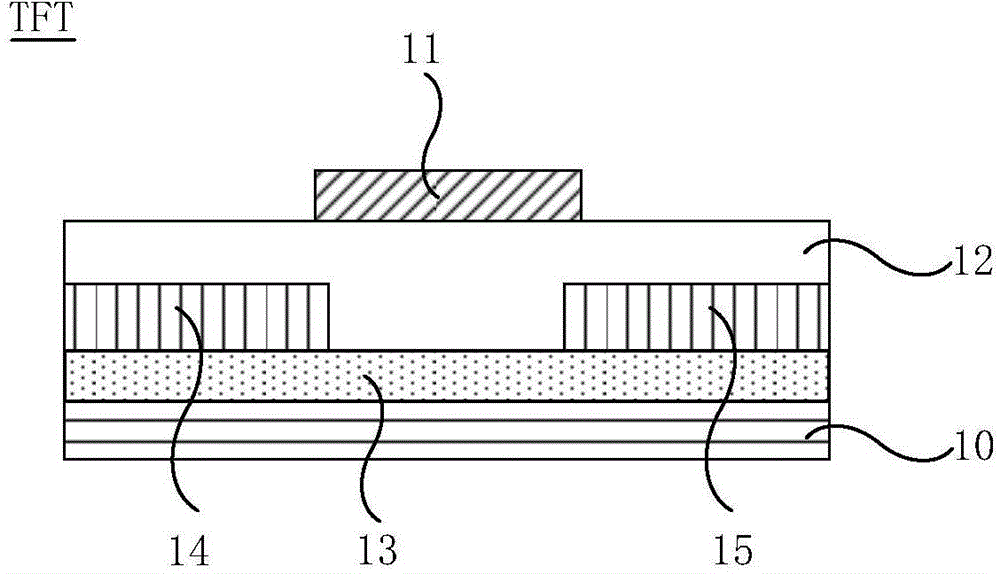

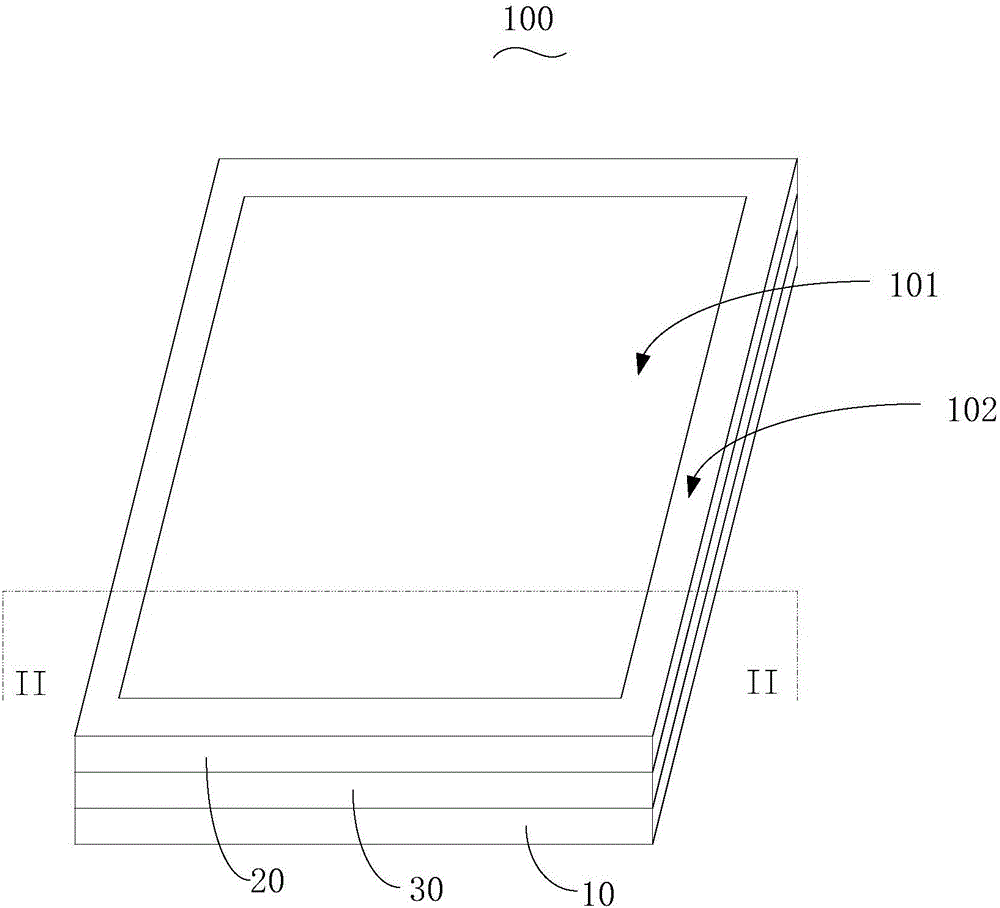

Film transistor, array substrate and preparation method thereof, display device

ActiveCN104934482AHigh switching current ratioImprove mobilityTransistorSolid-state devicesIndiumDisplay device

The invention embodiment provides a film transistor, an array substrate and a preparation method thereof, and a display device, and relates to the display technical field; indium element in an active layer of a semiconductor can be reduced in usage, thus solving the rising making cost problems caused by rareness of the indium element; the film transistor preparation method comprises the following steps: using composition technology to form a semiconductor active layer pattern on a transparent substrate, wherein the semiconductor active layer pattern comprises a lanthanum boride pattern.

Owner:BOE TECH GRP CO LTD +1

Terpolymer and preparation method of electric storage device thereof

ActiveCN111349217AGood opticsExcellent electrochemical propertiesSolid-state devicesSemiconductor/solid-state device manufacturingSwitched currentOrganic chemistry

The invention provides a terpolymer and an electric storage device prepared by using the terpolymer as an organic layer. The prepared electric storage device is low in turn-on voltage, high in switchcurrent ratio, rapid in response, capable of performing repeated cyclic reading and writing, and excellent in performance. The terpolymer is simple in synthesis method and stable in electric storage device preparation process, has ternary electric storage performance, can realize industrial production, and has a good application prospect in the field of information storage.

Owner:HEILONGJIANG UNIV

Method for preparing indium-aluminum-zinc oxide thin film transistor in low temperature environment

ActiveCN110310894AImprove performanceHigh saturation mobilityTransistorSemiconductor/solid-state device manufacturingIndiumOxide thin-film transistor

The invention relates to a method for preparing an indium-aluminum-zinc oxide thin film transistor in a low temperature environment. The multi-element amorphous metal oxide thin film transistor sequentially comprises a substrate, an IAZO active layer, a source electrode and a drain electrode from bottom to top, wherein the source electrode and the drain electrode are grown on the IAZO active layer. The preparation method is carried out at a temperature ranging between 20 DEG C and 70 DEG C and includes the steps of (1) growing an IAZO film on a substrate to prepare an IAZO active layer; (2) placing the generated device in UV-ozone, wherein the processing time is 5 minutes; and (3) growing a source electrode and a drain electrode on the surface of the IAZO active layer so as to obtain the indium-aluminum-zinc oxide thin film transistor. The high-performance IAZO TFT is prepared in the low temperature environment through exploring the optimizing the treatment carried out by UV-ozone on the IAZO active layer.

Owner:SHANDONG UNIV

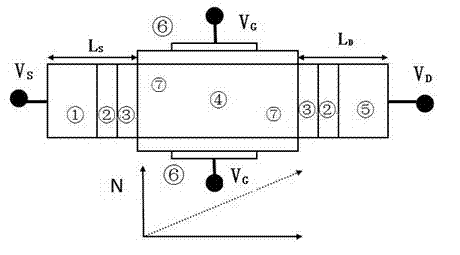

Tunneling field effect device for channel potential barrier height control

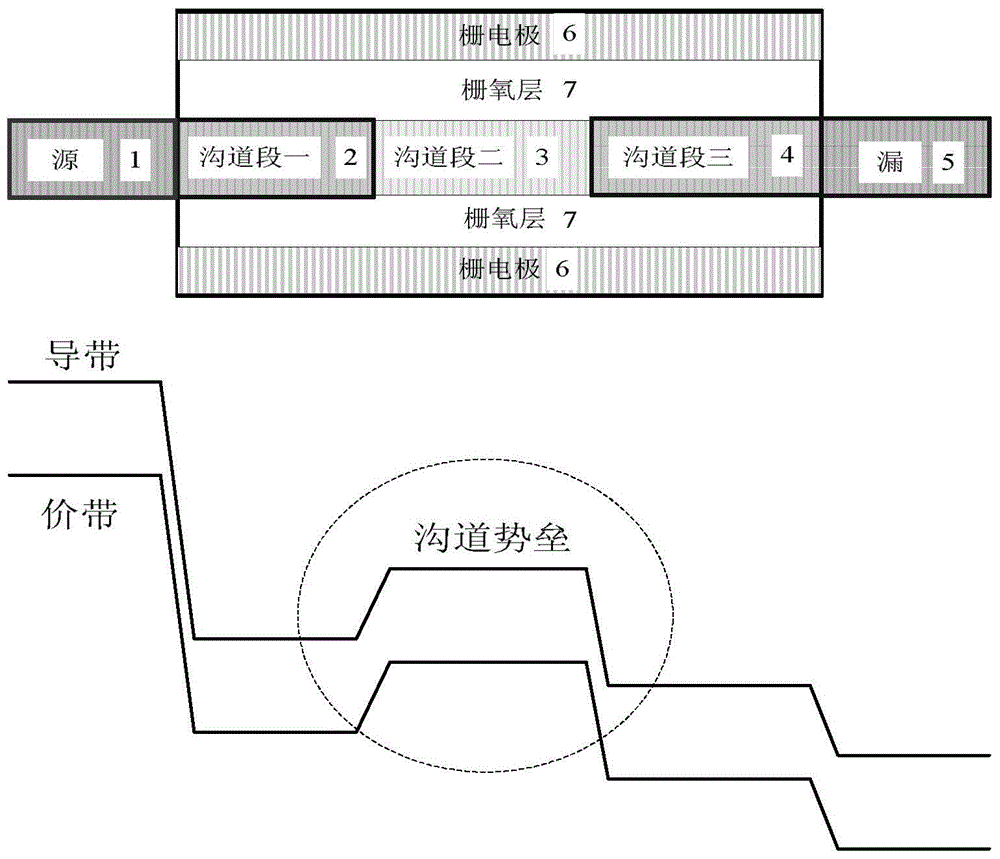

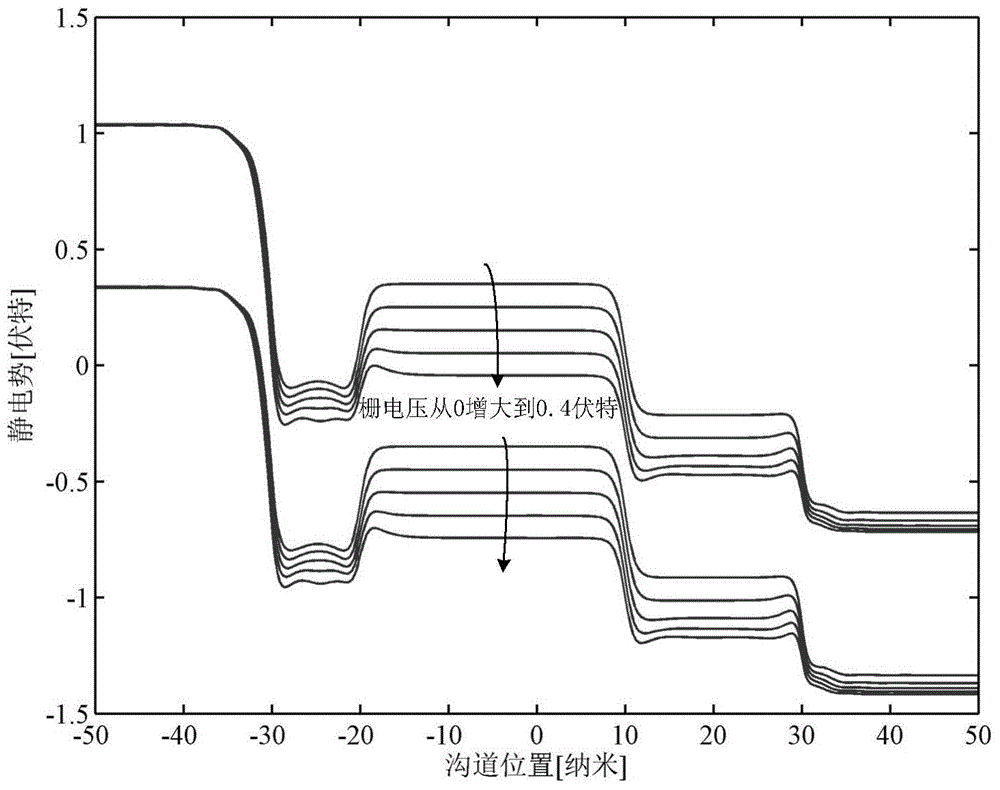

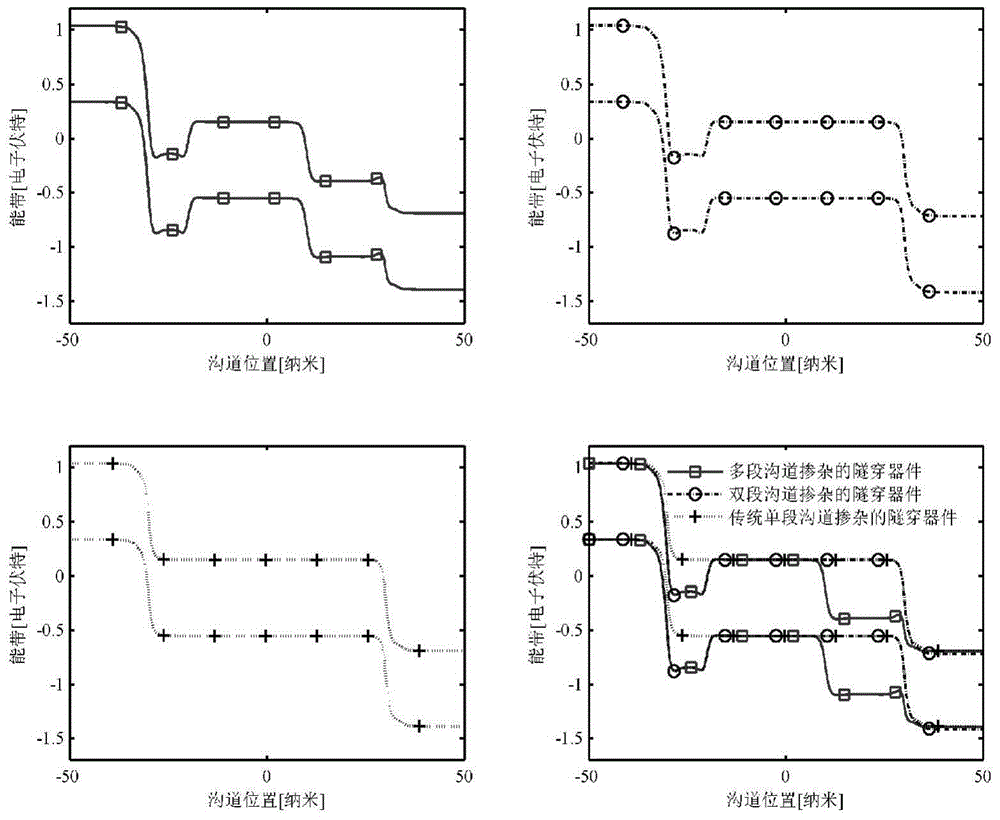

InactiveCN104882484AMaterial adjustableAdjustable thicknessSemiconductor devicesSub thresholdGate oxide

The invention belongs to the field of semiconductor integrated circuits, and specifically relates to a tunneling field effect device for channel potential barrier height control. The center of the device is provided with a channel, two ends of the channel are provided with a source terminal and a drain terminal of different conductive types, a tunneling junction is formed between the source terminal and the channel, the channel is formed by the adoption of three or more than three potential barrier areas, the energy band of the potential barrier area at the middle section is higher than the energy bands of the channel close to the drain terminal and the source terminal, the device also comprises a gate oxide layer fully covering the channel, and the gate oxide layer is fully covered by a gate electrode. The portion of the channel of the device employs materials of different doping concentrations or types, and three sections or more sections of the potential barrier structures are formed in the channel. According to the simulation research result of the tunneling device structure for channel potential barrier height control, the off-state leakage current of the device can be effectively reduced, the sub-threshold slope is reduced, the short-channel effect and the DIBL effect are suppressed, the transconductance characteristic is good, and comprehensive optimization of the performance of the device is realized.

Owner:WUHAN UNIV

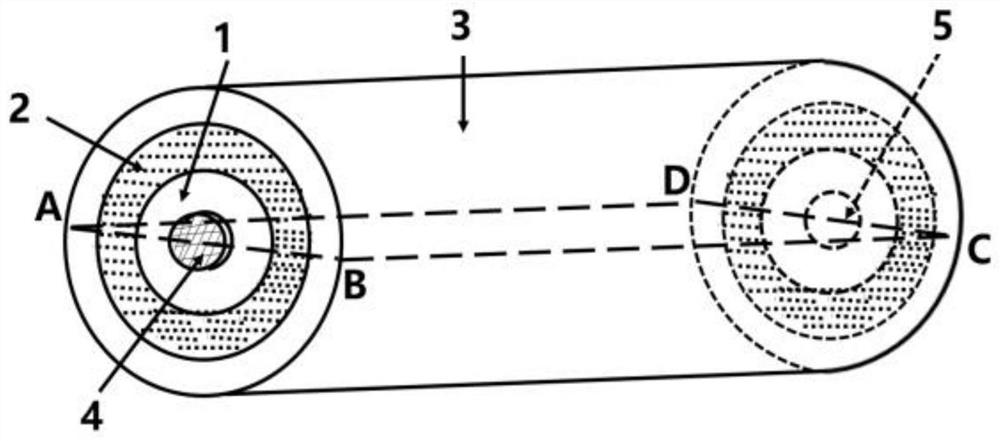

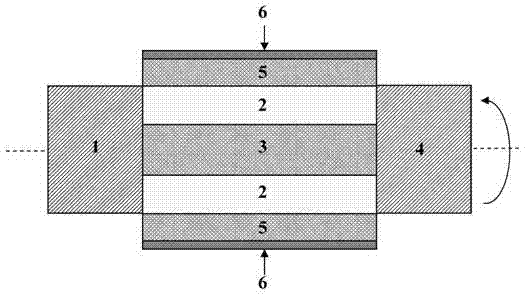

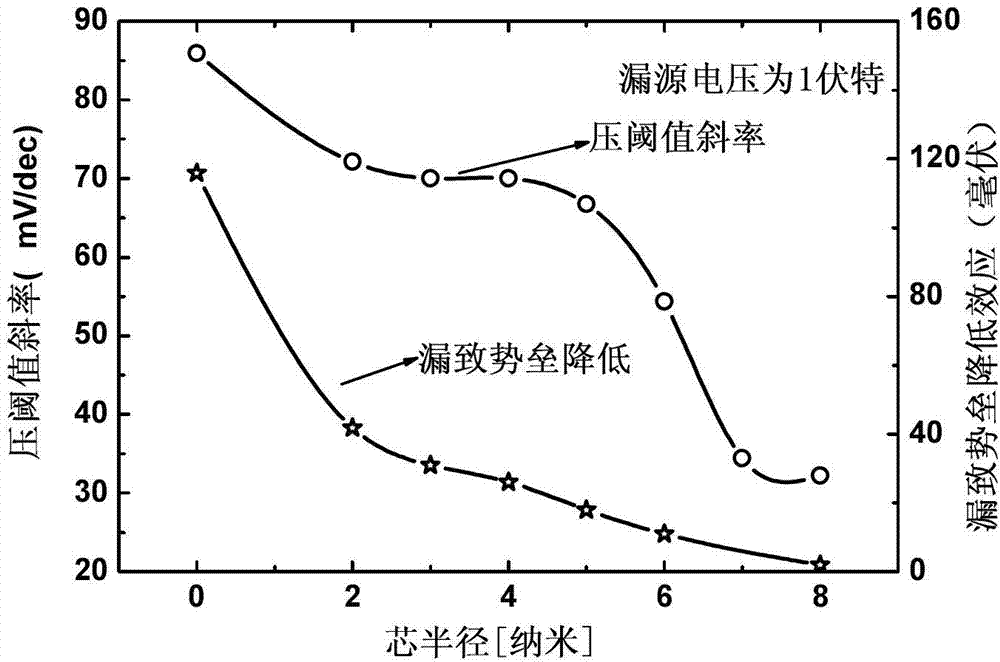

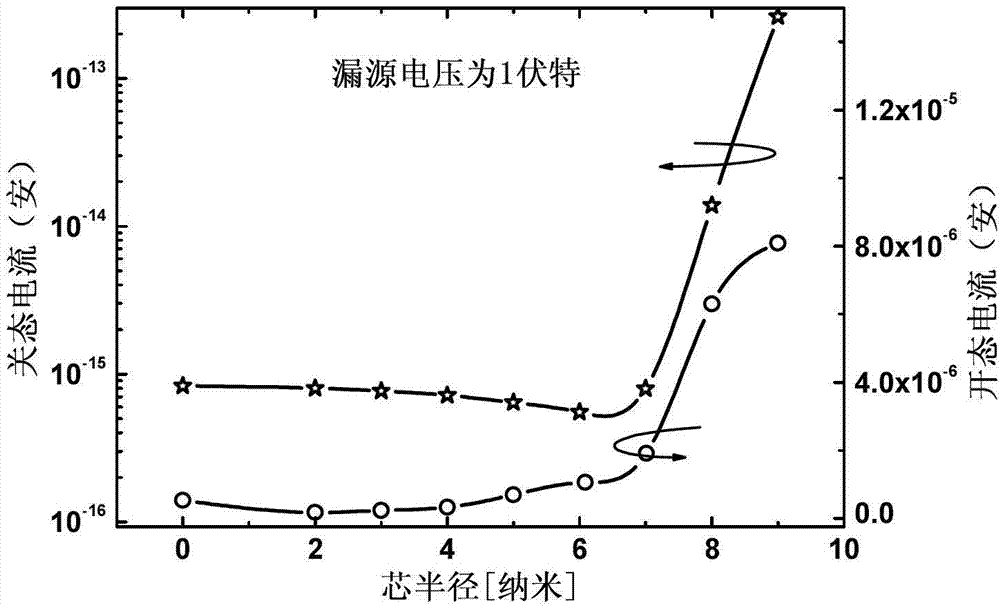

Core shell structure nanowire tunneling field effect device

InactiveCN102969365AReduce off-state currentHigh Switching Current RatioTransistorNanoinformaticsLow leakageShort-channel effect

The invention relates to a core shell structure nanowire tunneling field effect device which comprises a gate electrode (6), a source region (1), a drain region (4), a central region and a gate dielectric layer (5), wherein the central region is in a coaxially symmetrical core shell structure; the core in the core shell structure is made of an insulator material; the shell in the core shell structure is made of a semiconductor material; the gate dielectric layer is completely sleeved into the central region and is used for electrically isolating the central region and the gate electrode; the gate electrode is completely sleeved into the dielectric layer; the grate electrode (6), the gate dielectric layer (5) and the central region are equal in length; and the source region and the drain region are respectively arranged at two sides of the central region. A field effect transistor has low leakage current, high grid-control capability and low subthreshold slope, and the drain induced barrier lowing and the short-channel effect are effectively suppressed, so that various nonideal effects of a ring gate nanowire tunneling field effect device in the size reducing process are reduced, and the comprehensive performance of the device is improved.

Owner:PEKING UNIV SHENZHEN GRADUATE SCHOOL

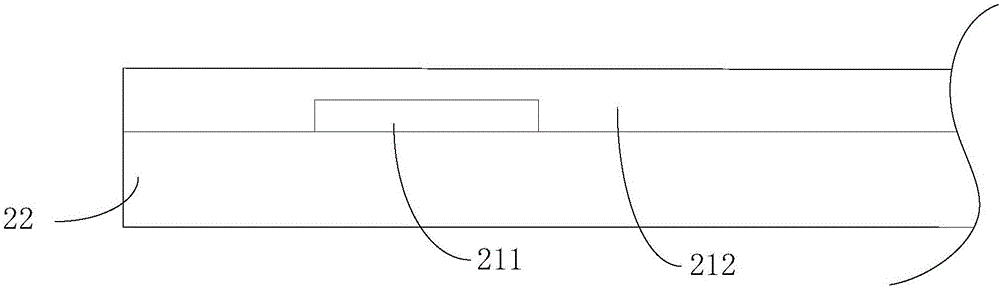

Vertical thin film transistor (TFT) and manufacturing method thereof as well as display device and manufacturing method thereof

ActiveCN102082178BImprove stress resistanceImprove the degree of conductionTransistorStatic indicating devicesDisplay deviceEngineering

Owner:吴江汾湖科技创业服务有限公司

Drain current-improved thin film transistor

The invention provides a drain current-improved thin film transistor. The drain current-improved thin film transistor includes a substrate, a gate insulating layer, an active layer, a source, a drain and a gate. The drain current-improved thin film transistor is characterized in that the active layer is doped, and a doping layer is gradient, or doping concentration is gradient; the gradient of the doping layer is increased from the source to the drain; and the gradient of the doping concentration is increased from the source to the drain. A material with a certain gradient is doped in the active layer, and therefore, when voltage of the source and the drain is boosted, a large number of carriers are adjacent to the drain, and thus, so the drain current at a saturated region will be increased, and a higher switching current ratio can be realized, and the switching speed of the component will become higher.

Owner:FUZHOU UNIVERSITY

Thin film transistor array substrate, manufacturing method thereof and display panel

ActiveCN106409840AHigh switching current ratioHigh electron mobilitySolid-state devicesSemiconductor/solid-state device manufacturingElectricityPower flow

The invention provides a thin film transistor array substrate, a manufacturing method thereof and a display panel. The thin film transistor array substrate comprises thin film transistors, wherein each thin film transistor is internally provided with an active layer composed of a carbon nanotube semiconductor layer and a non-doped amorphous silicon layer, and the non-doped amorphous silicon layer is arranged between the corresponding carbon nanotube semiconductor layer and a source as well as a drain. Therefore, when the thin film transistor is turned on, electricity is mainly conducted by means of the carbon nanotube semiconductor layer in the active layer, and the carbon nanotube semiconductor layer has high electron mobility and forms a high ON-state current; and when the thin film transistor is turned off, a leakage current is mainly released by means of the non-doped amorphous silicon layer in the active layer, and the leakage current is small, thus the thin film transistor has a high switching current ratio.

Owner:BOE TECH GRP CO LTD +1

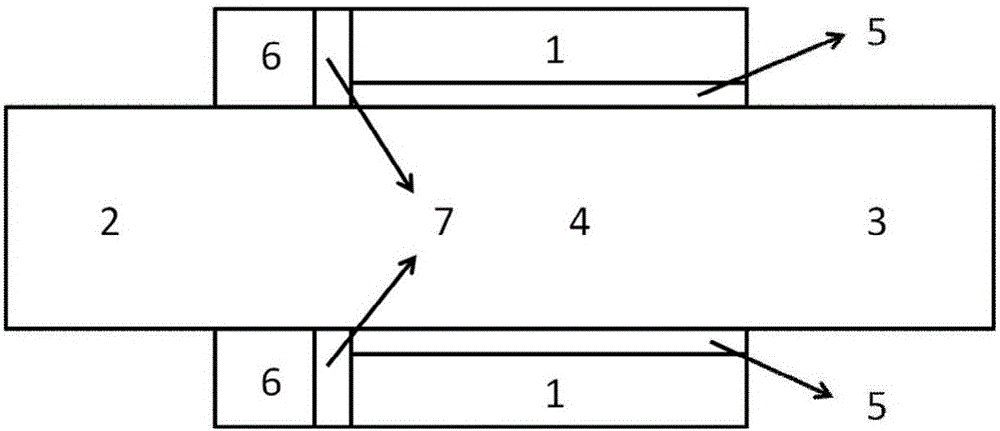

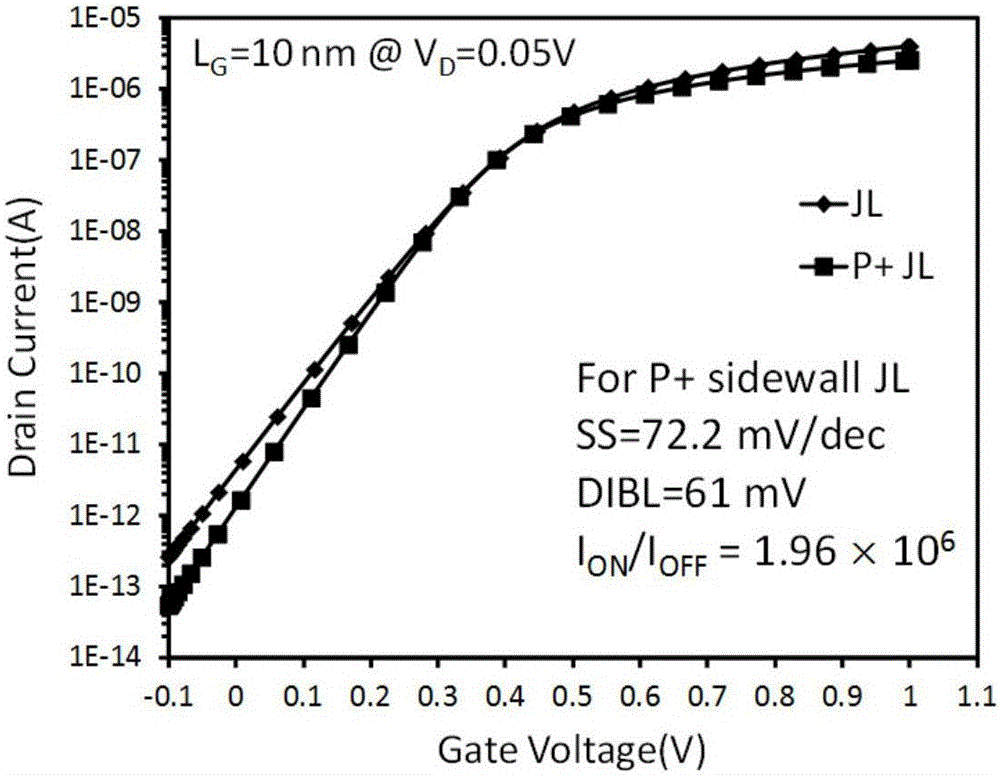

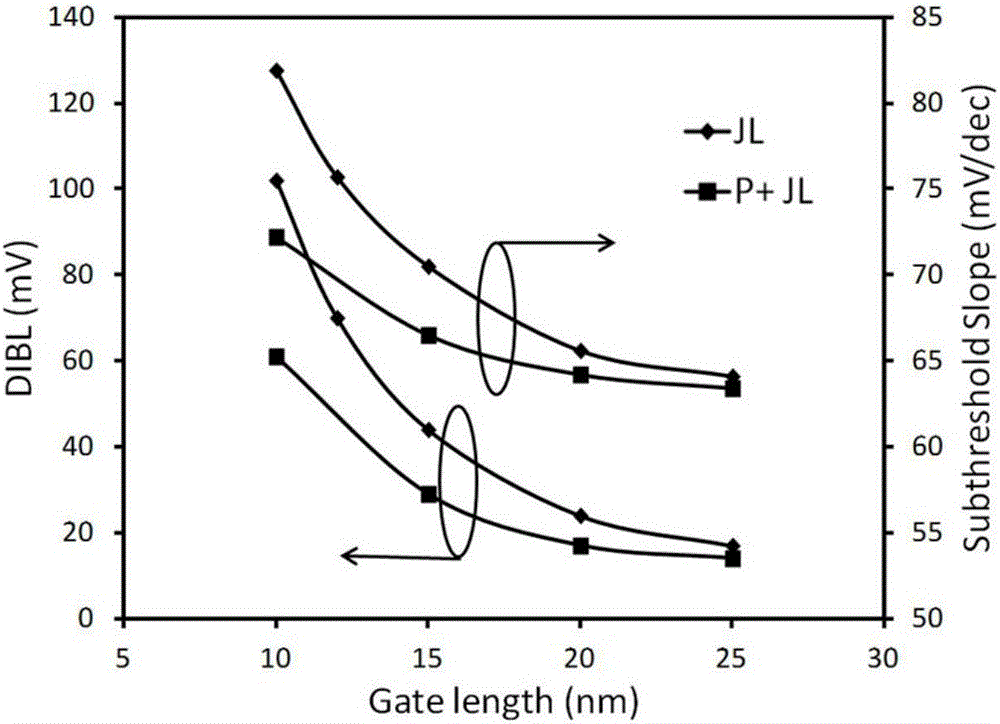

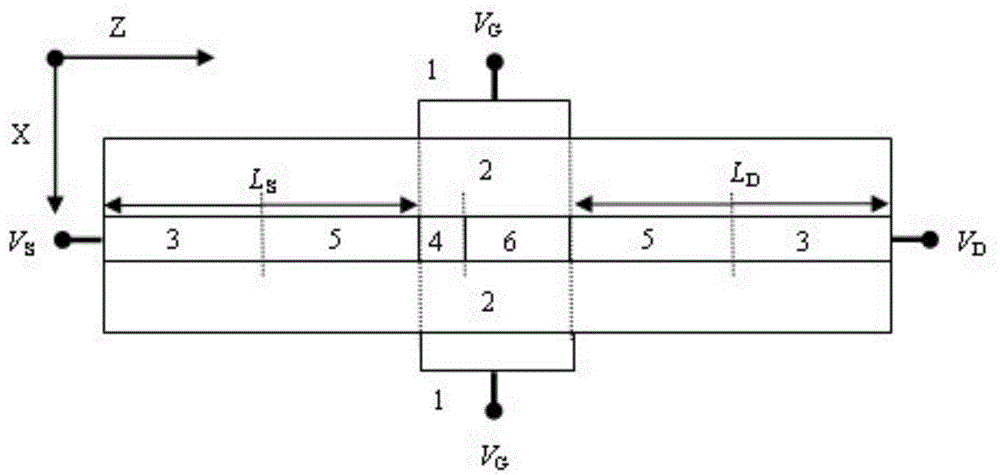

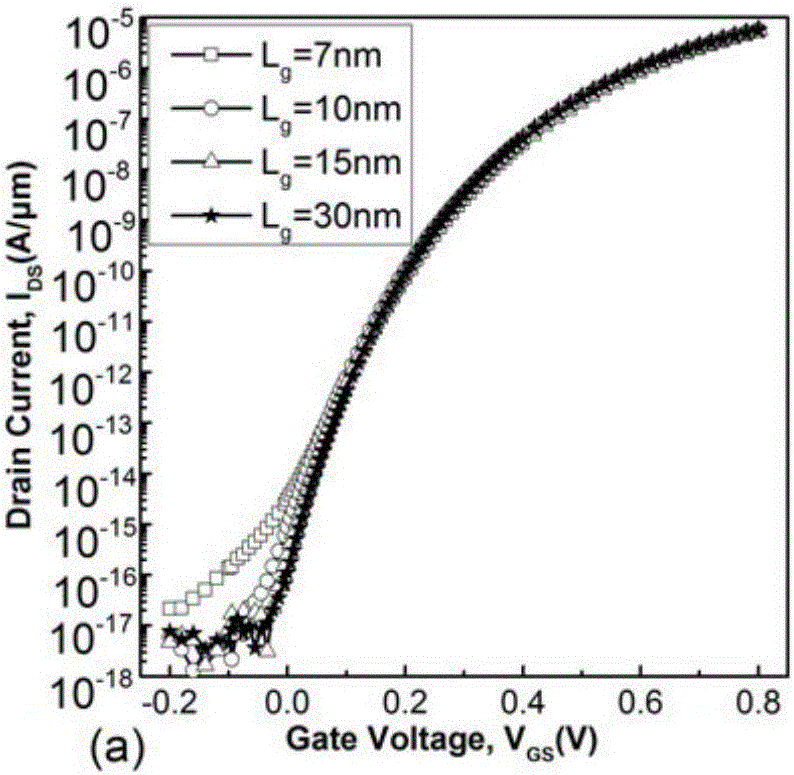

Novel P<+> sidewall non-junction field effect transistor

ActiveCN105810741ALower off currentShutdown current does not decreaseSemiconductor devicesGate dielectricSub threshold

The invention discloses a P<+> sidewall non-junction device. The P<+> sidewall non-junction device consists of dual gates, a source region, a drain region, a channel region, gate dielectric layers, P<+> sidewalls and isolation layers. For a conventional non-junction device, when the length of a gate is reduced to 10nm, a leakage current is greatly increased, so that the inhibition of the magnitude of the leakage current becomes an important task of a small-sized device. For the conventional non-junction device, a turn-off current of the device in a turn-off state cannot be effectively controlled only by the control capability of the gate. According to the P<+> sidewall non-junction device, PN junction depletion can be formed for assisting in depletion of the device, and when the device is turned on, the gate controls a P<+> region for weakening the PN junction depletion, so that a turn-on current is not influenced. Compared with the conventional non-junction device, the novel P<+> sidewall tri-gate nanowire non-junction device has great advantages, and the advantages are especially remarkable when the gate is very short. The novel device mainly can improve the characteristics of a sub-threshold slope, a turn-on and turn-off current ratio and the like of the conventional non-junction device.

Owner:HANGZHOU DIANZI UNIV

Carbon nanotube field effect transistor (CNTFET) with peak-symmetric linearity doped structure

InactiveCN104103692AReduce off-state currentHigh switching current ratioNanoinformaticsSemiconductor devicesSwitched currentDelayed time

The invention discloses a carbon nanotube field effect transistor (CNTFET) with a peak-symmetric linearity doped structure. A transportation model applicable to the CNTFET with the peak-symmetric linearity doped structure is constructed, and by means of the model, the influence of a HALO-Linear doping strategy on electrical properties of the CNTFET is analyzed and calculated. Through contrastive analysis of electrical properties of CNTFETs using other doping strategies, the CNTFET with the peak-symmetric linearity doped structure has a higher switched current ratio, lower leakage current, a smaller subthreshold amplitude, higher cut-off frequency and shorter delay time, that is, the CNTFET using the HALO-Linear doping strategy has better grid-control capacity and better switching characteristics and is capable of effectively inhibiting a short-channel effect and a hot carrier effect.

Owner:NANJING UNIV OF POSTS & TELECOMM

Semiconductor device and manufacturing method thereof, integrated circuit and electronic equipment

ActiveCN112652664AReduced subthreshold swingReduce leakage currentSemiconductor/solid-state device manufacturingSemiconductor devicesNanowireDevice material

The invention provides a semiconductor device and a manufacturing method thereof, an integrated circuit and electronic equipment. The semiconductor device may include, but is not limited to, a semiconductor substrate, a nanowire channel, a metal gate, a first epitaxial portion, a metal interposer, a second epitaxial portion, a gate, a source, a drain, etc. The nanowire channel is formed on the semiconductor substrate, and the metal gate is arranged around the nanowire channel in a surrounding manner. The first epitaxial portion is formed on the nanowire channel, the metal interposer is arranged around the first epitaxial portion in a surrounding mode, and the second epitaxial portion is arranged around the metal interposer in a surrounding mode. The gate is connected with the metal gate, the source is connected with the second epitaxial portion, and the drain is connected with the semiconductor substrate. The integrated circuit comprises the semiconductor device, and the electronic equipment comprises the semiconductor device or the integrated circuit. The invention can provide the semiconductor transistor with low sub-threshold swing and high switching current ratio, and the semiconductor transistor provided by the invention has the advantages of high on-state current, low leakage current, high integration level and the like.

Owner:INST OF MICROELECTRONICS CHINESE ACAD OF SCI

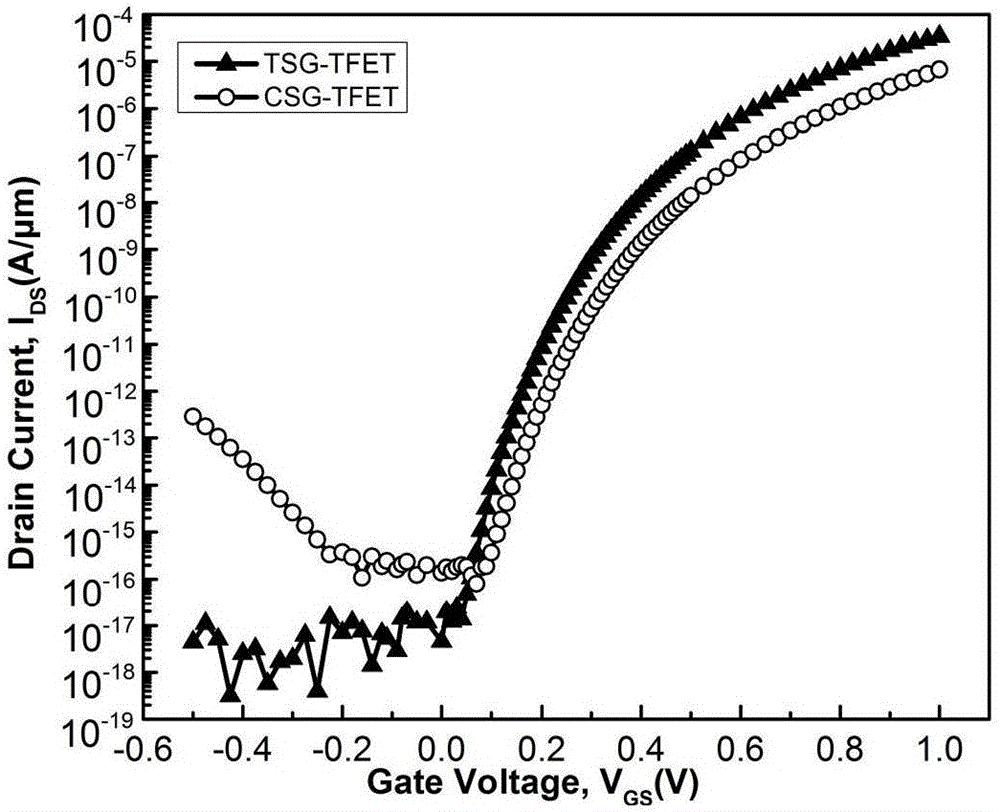

Ultrathin channel groove tunneling field effect transistor

The invention discloses an ultrathin channel groove tunneling field effect transistor which is composed of a grid electrode, a source region, a drain region, a first channel region, a second channel region, a grid dielectric layer, a first isolating layer, a second isolating layer and buried oxide layer, wherein the grid electrode and the grid dielectric layer arranged on the position of the channel regions, and the isolation layers are arranged at the two sides of the grid electrode. The new structure has an ultrathin channel so that coupling of the grid electrode and the channel can be enhanced, and thus control capability of the grid electrode can be enhanced and tunneling current of a device can be increased. Another characteristic of the structure is that the intrinsic region (low-doped region) of the channel extends to the drain region. In a word, compared with conventional tunneling transistors, the device of the structure is obviously improved in the aspects of the electrical characteristics of subthreshold swing and switching current ratio and stability.

Owner:HANGZHOU DIANZI UNIV

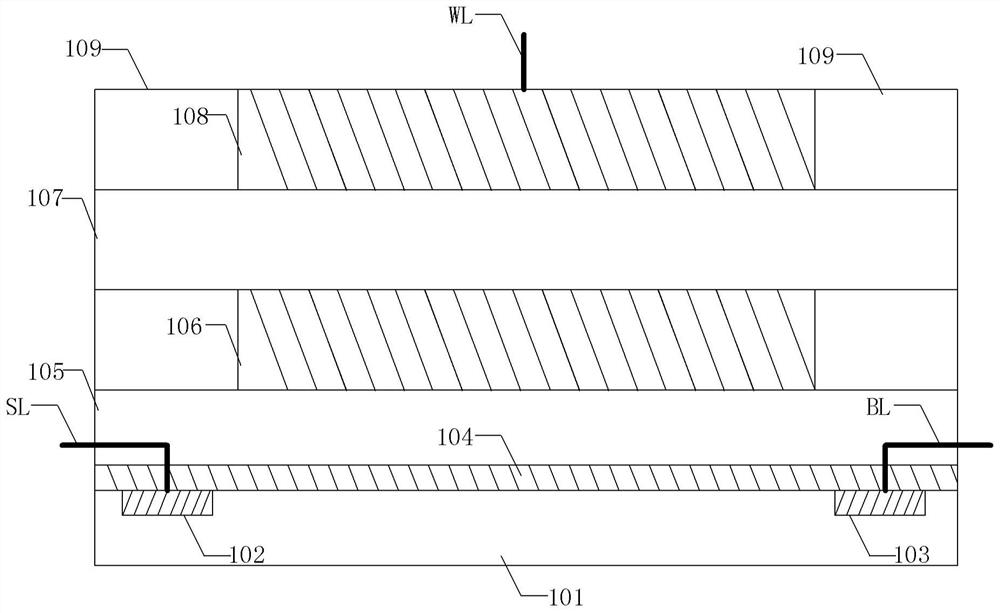

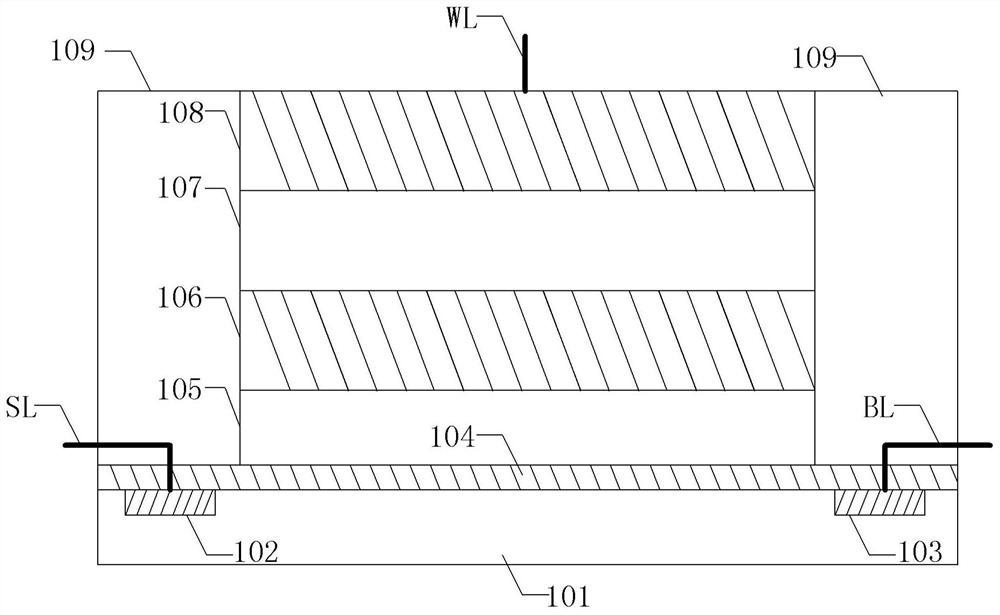

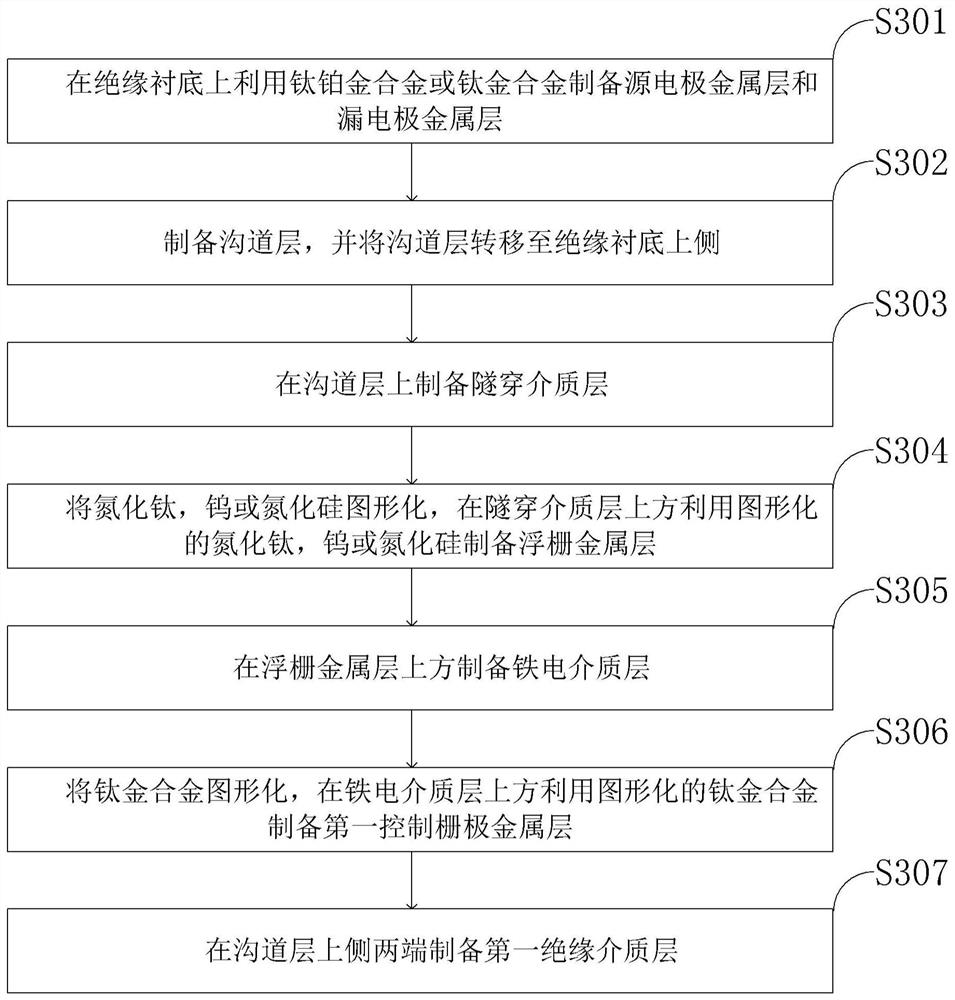

Ferroelectric floating gate memory unit string and preparation method

ActiveCN112490248AImprove performanceMaximize bindingSolid-state devicesSemiconductor devicesDielectric layerCondensed matter physics

The invention discloses a ferroelectric floating gate memory unit string and a preparation method thereof, and the ferroelectric floating gate memory unit string is characterized in that a channel layer is arranged on the upper side of an insulating substrate, a tunneling dielectric layer is arranged on the channel layer, and a composite unit is arranged on the upper side of the tunneling dielectric layer; the composite unit comprises a floating gate metal layer, a ferroelectric dielectric layer and a first control gate metal layer which are sequentially arranged from bottom to top, and at least two ends of the floating gate metal layer and the first control gate metal layer are covered with first insulating dielectric layers; and a source electrode metal layer and a drain electrode metallayer are embedded at two ends of the upper side of the insulating substrate. According to the ferroelectric floating gate memory unit string provided by the invention, electronic behaviors are controlled through the floating gate metal layer, the constraint effect of a ferroelectric polarization electric field generated by the ferroelectric dielectric layer on charges can be maximized, the storage time is effectively prolonged, the response time is reduced, and the overall performance of the ferroelectric floating gate memory unit string is improved.

Owner:INST OF MICROELECTRONICS CHINESE ACAD OF SCI

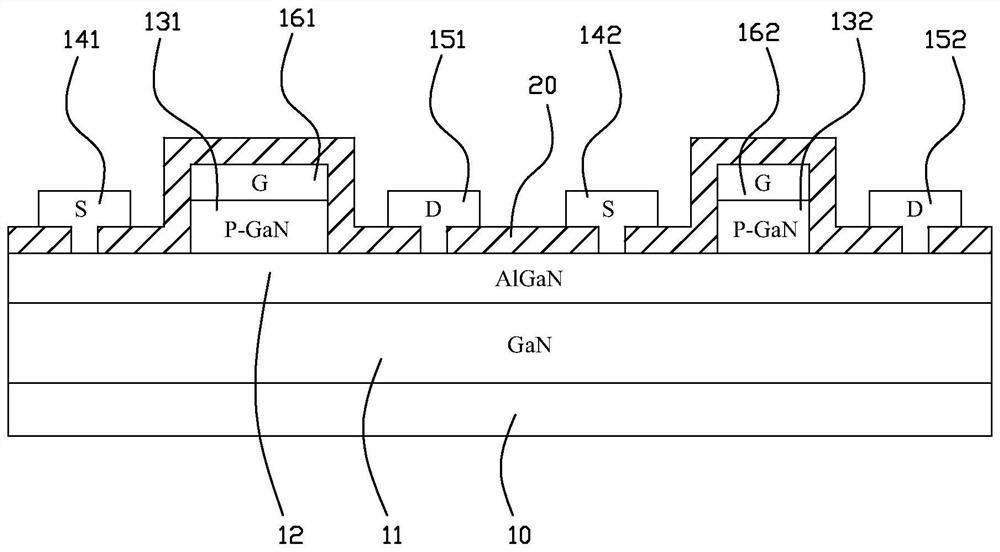

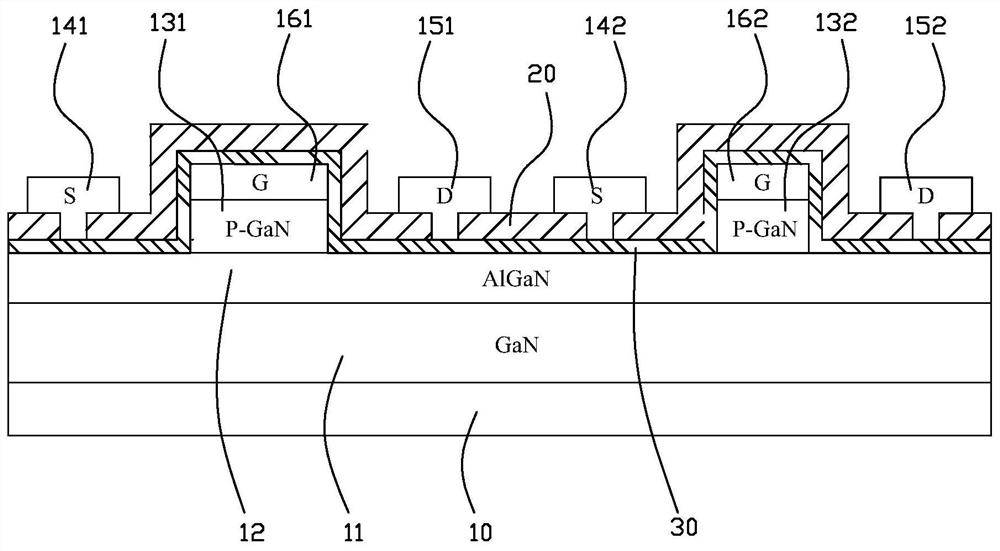

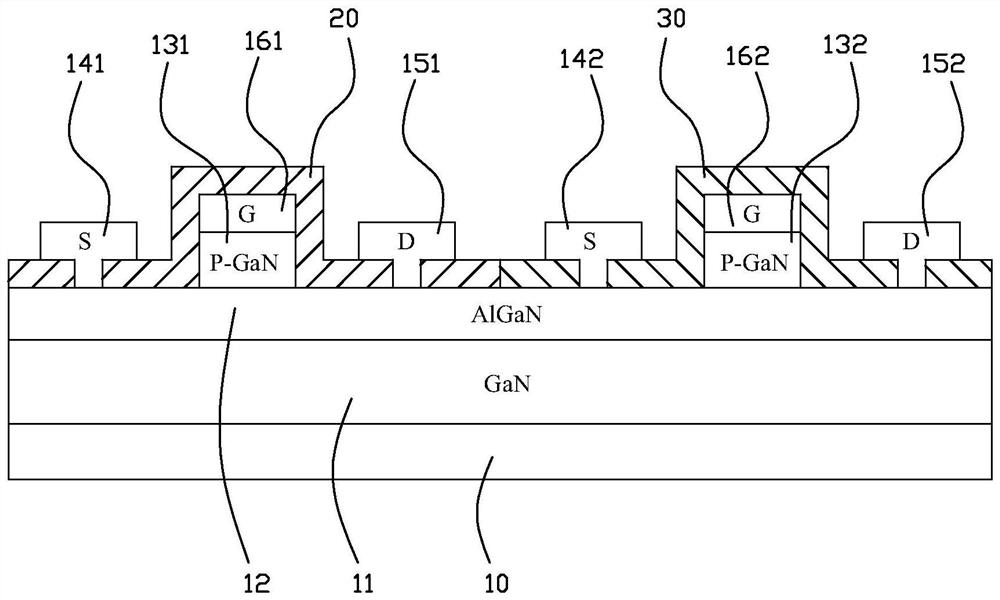

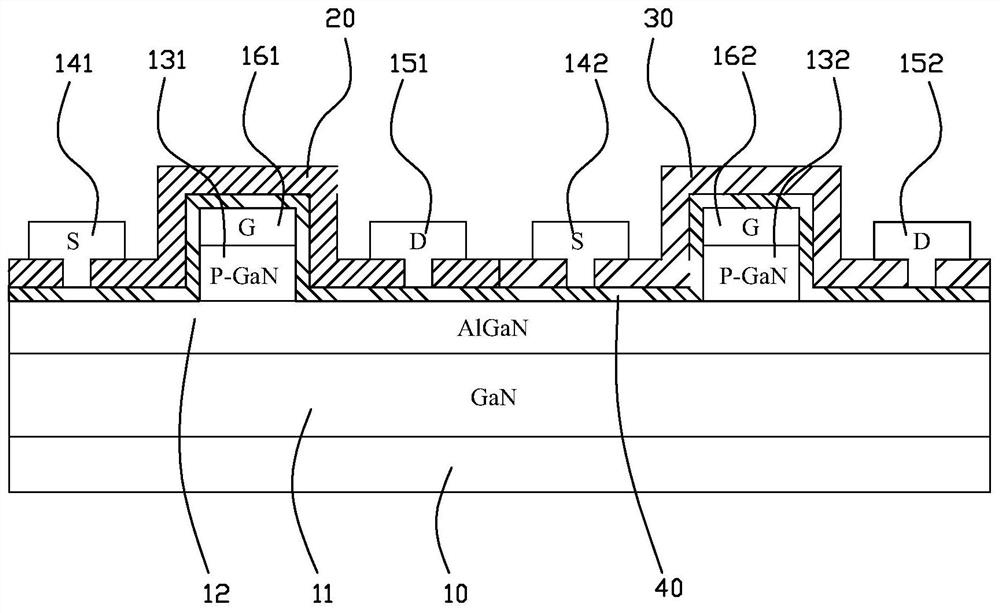

Integrated chip of enhanced and depletion type HEMT device and preparation method

ActiveCN112614834AReduce gate leakageHigh switching current ratioEfficient power electronics conversionSolid-state devicesHeterojunctionDevice material

The invention relates to an integrated chip of an enhanced and depletion type HEMT (High Electron Mobility Transistor) device and a preparation method. The correlation between the influence of the stress of a dielectric layer on the threshold voltage of the device and the gate line width of the device is used to regulate and control the stress of a barrier layer below a P-type nitride gate layer and change the polarization electric field intensity of the barrier layer. Finally, monolithic integration of P-type nitride gate enhanced and depletion type HEMT devices is realized. When the depletion type semiconductor device is prepared, the P type nitride layer below the gate metal does not need to be etched, etching damage does not exist on the contact interface of the gate metal and the semiconductor, gate electric leakage of the device can be effectively reduced, the switching current ratio of the device is increased, and power consumption is reduced. Compared with a conventional P-type nitride gate enhanced HEMT, the enhanced semiconductor device prepared by the invention has the advantages that the polarization electric field intensity of the barrier layer below the P-type nitride gate layer is weakened, the polarization charge surface density of a heterojunction interface is reduced, and the threshold voltage of the enhanced semiconductor device is further improved.

Enhanced and depletion type HEMT integrated device and preparation method

ActiveCN112614835AReduce gate leakageHigh switching current ratioEfficient power electronics conversionSolid-state devicesHeterojunctionDevice material

The invention relates to an enhanced and depletion type HEMT (high electron mobility transistor) integrated device and a preparation method. Media with different stresses are deposited on a P-type nitride gate layer, the stress of a barrier layer below the P-type nitride gate layer is regulated and controlled, the polarization electric field intensity of the barrier layer is changed, and finally, monolithic integration of P-type nitride gate enhanced and depletion type HEMT devices is realized. When the depletion type semiconductor device is prepared, the P type nitride layer below the gate metal does not need to be etched, etching damage does not exist on the contact interface of the gate metal and the semiconductor, gate electric leakage of the device can be effectively reduced, the switching current ratio of the device is increased, and power consumption is reduced. Compared with a conventional P-type nitride gate enhanced HEMT, the enhanced semiconductor device prepared by the invention has the advantages that the polarization electric field intensity of the barrier layer below the P-type nitride gate layer is weakened, the polarization charge surface density of a heterojunction interface is reduced, and the threshold voltage of the enhanced semiconductor device is further improved.

Owner:HUNAN SANAN SEMICON CO LTD