Patents

Literature

60results about How to "Reduced Threshold Voltage Drift" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

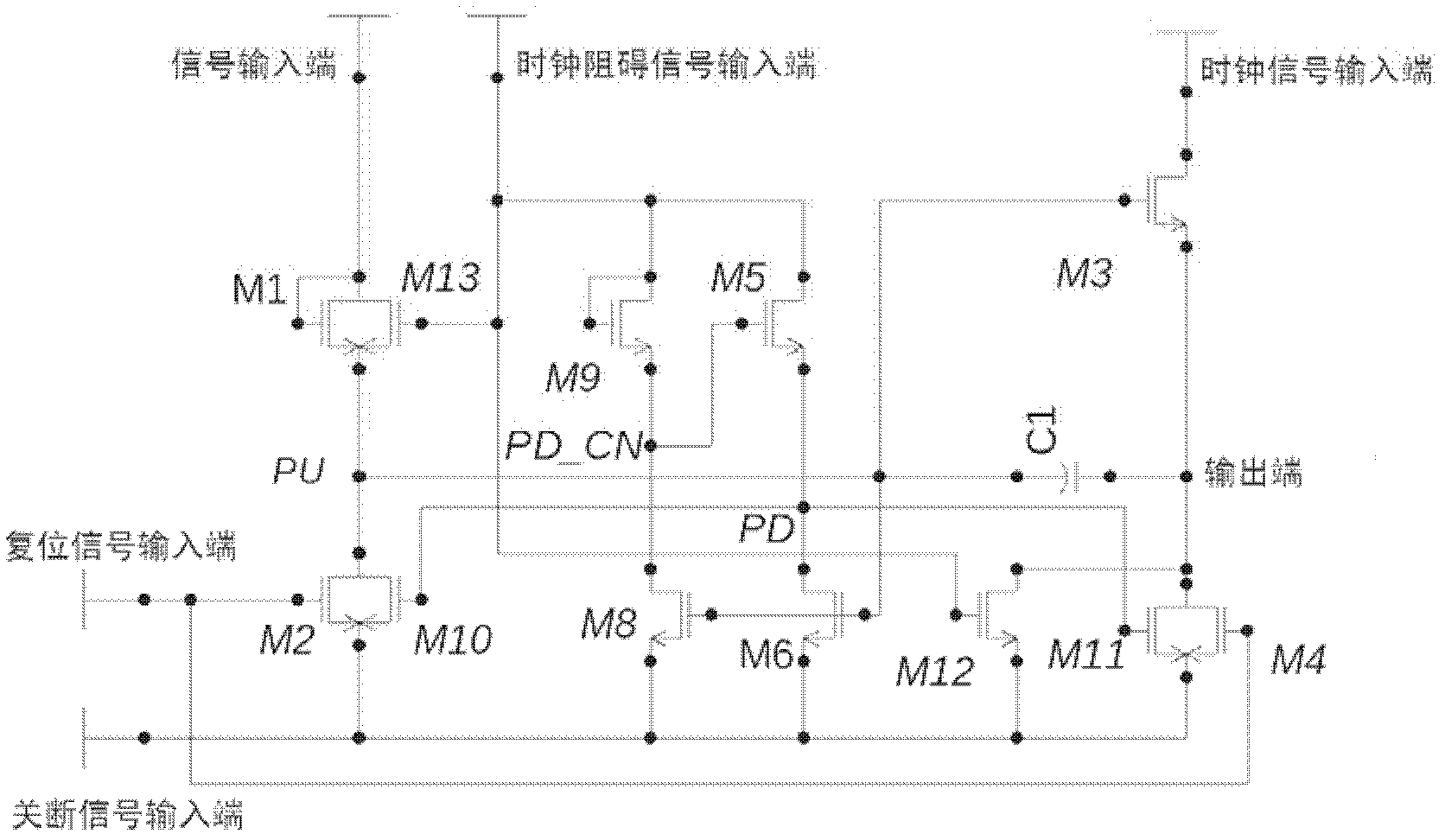

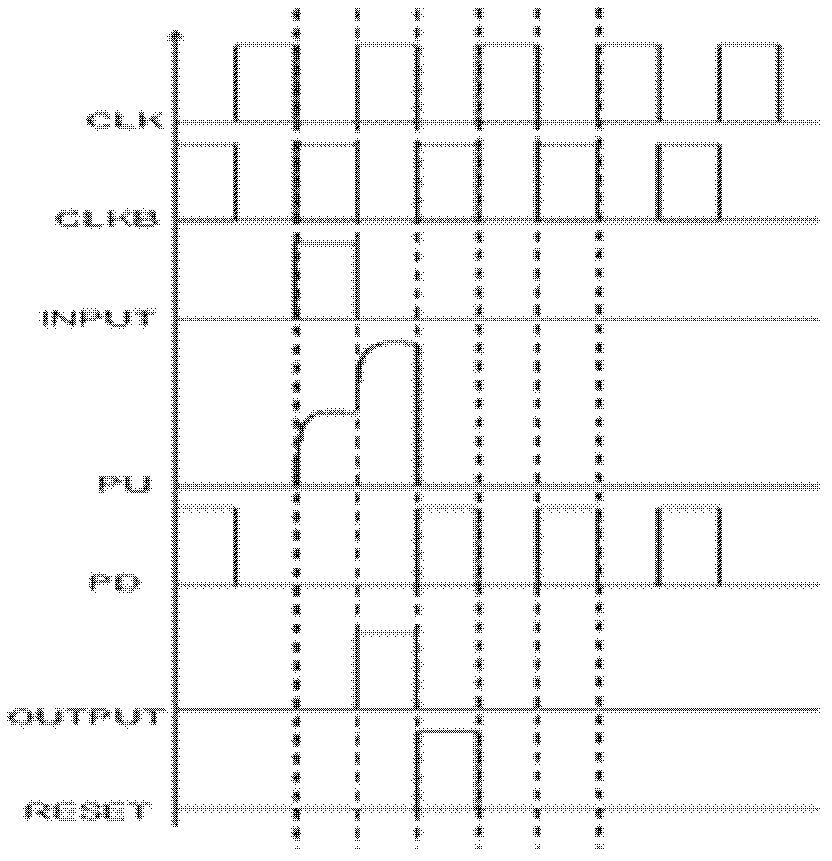

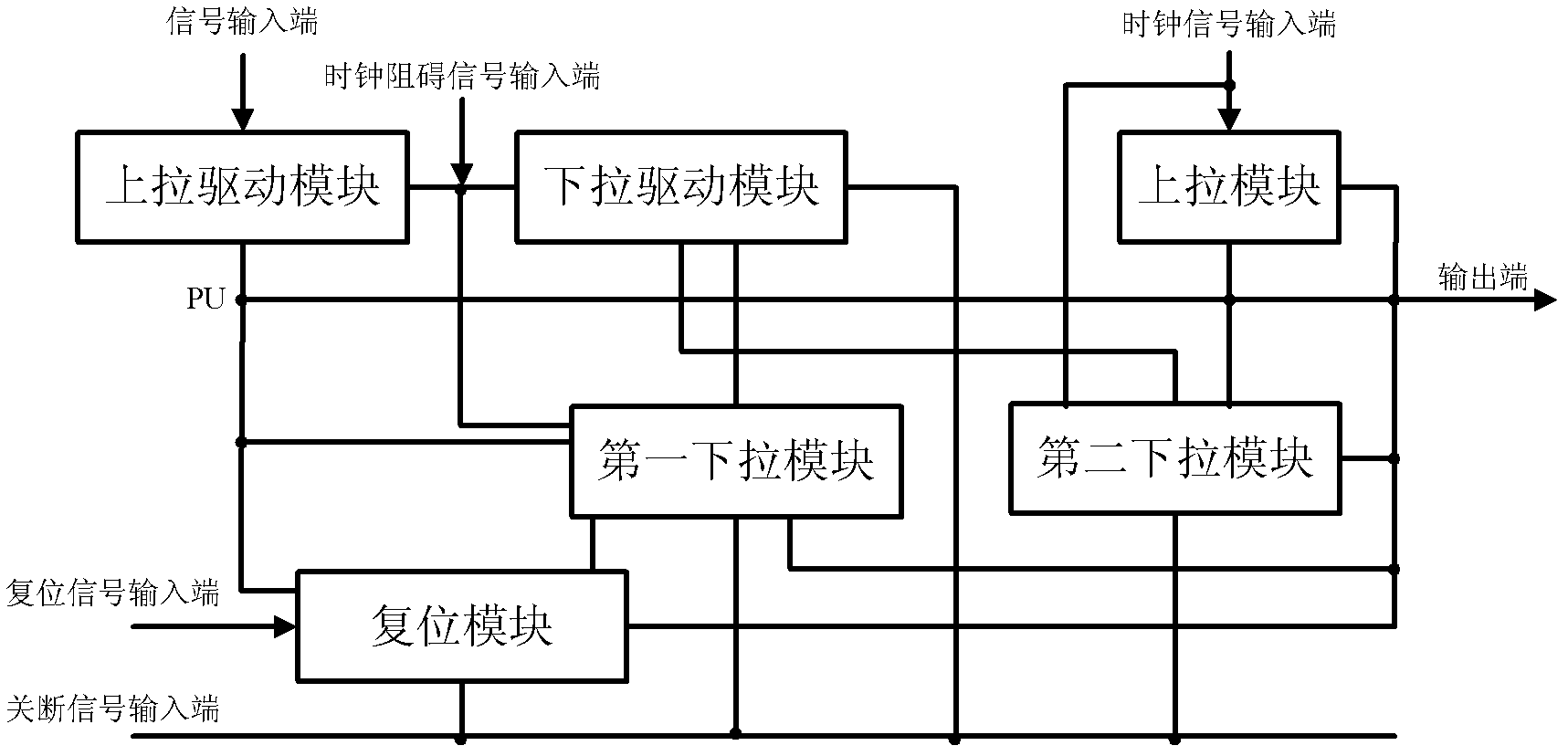

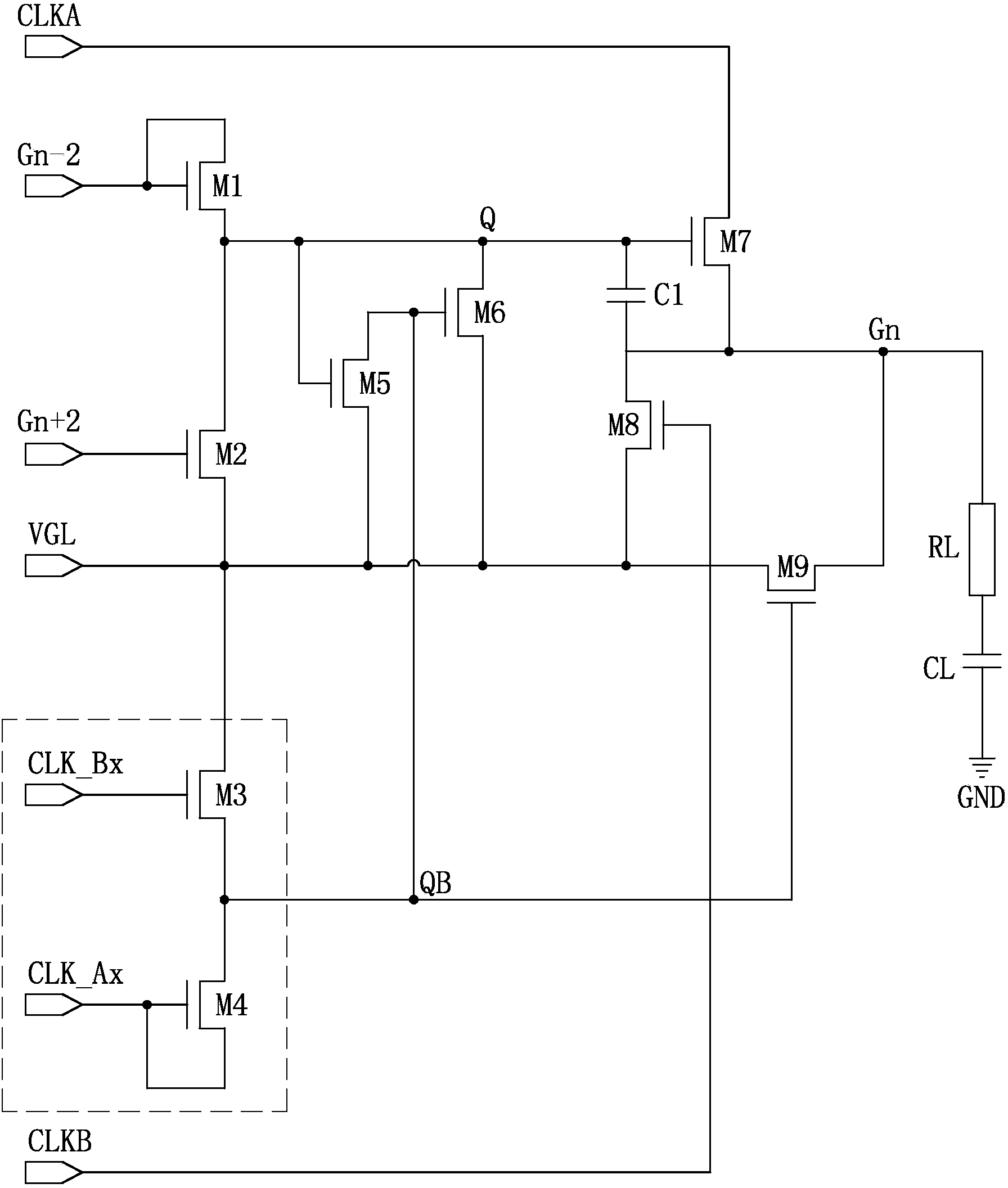

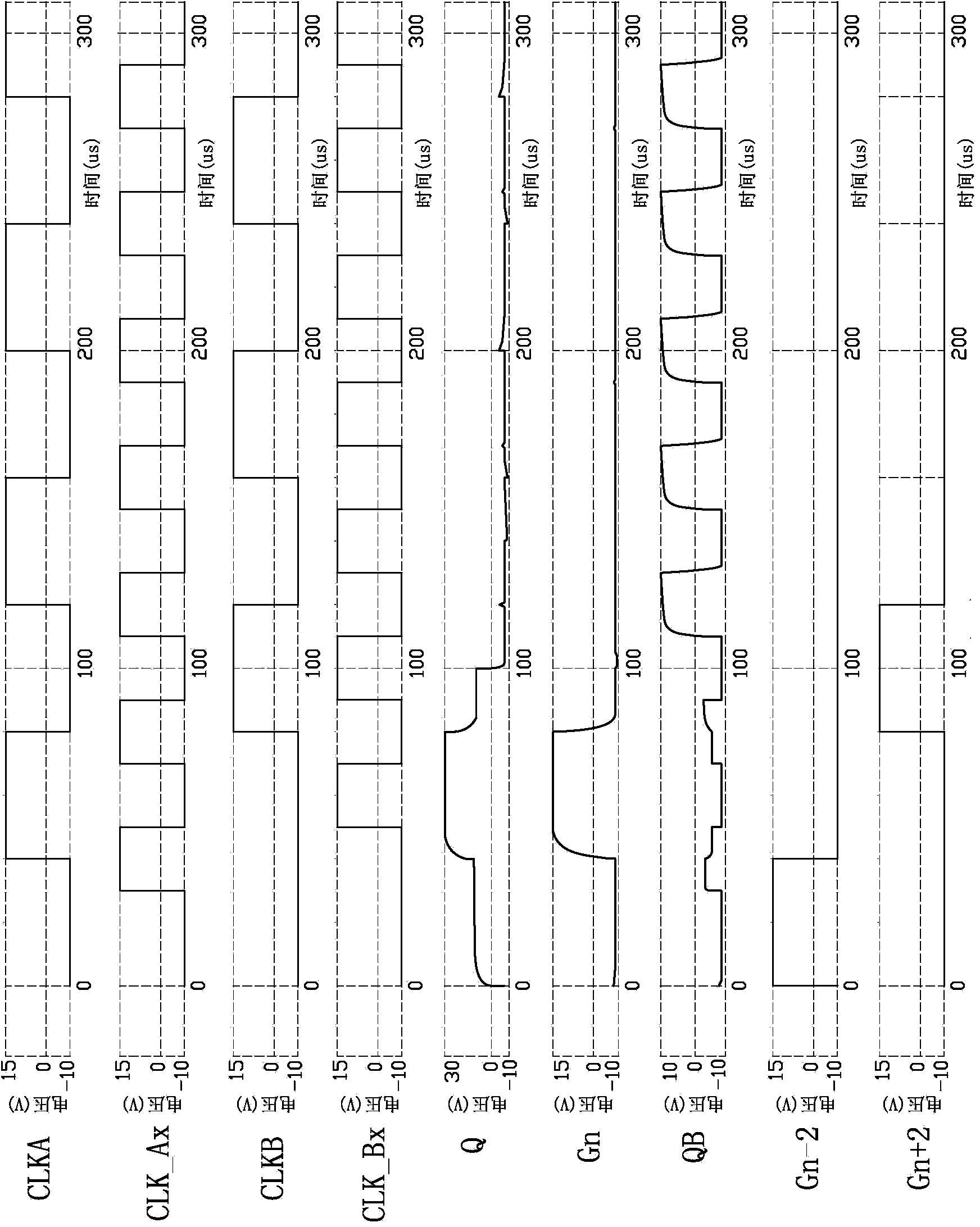

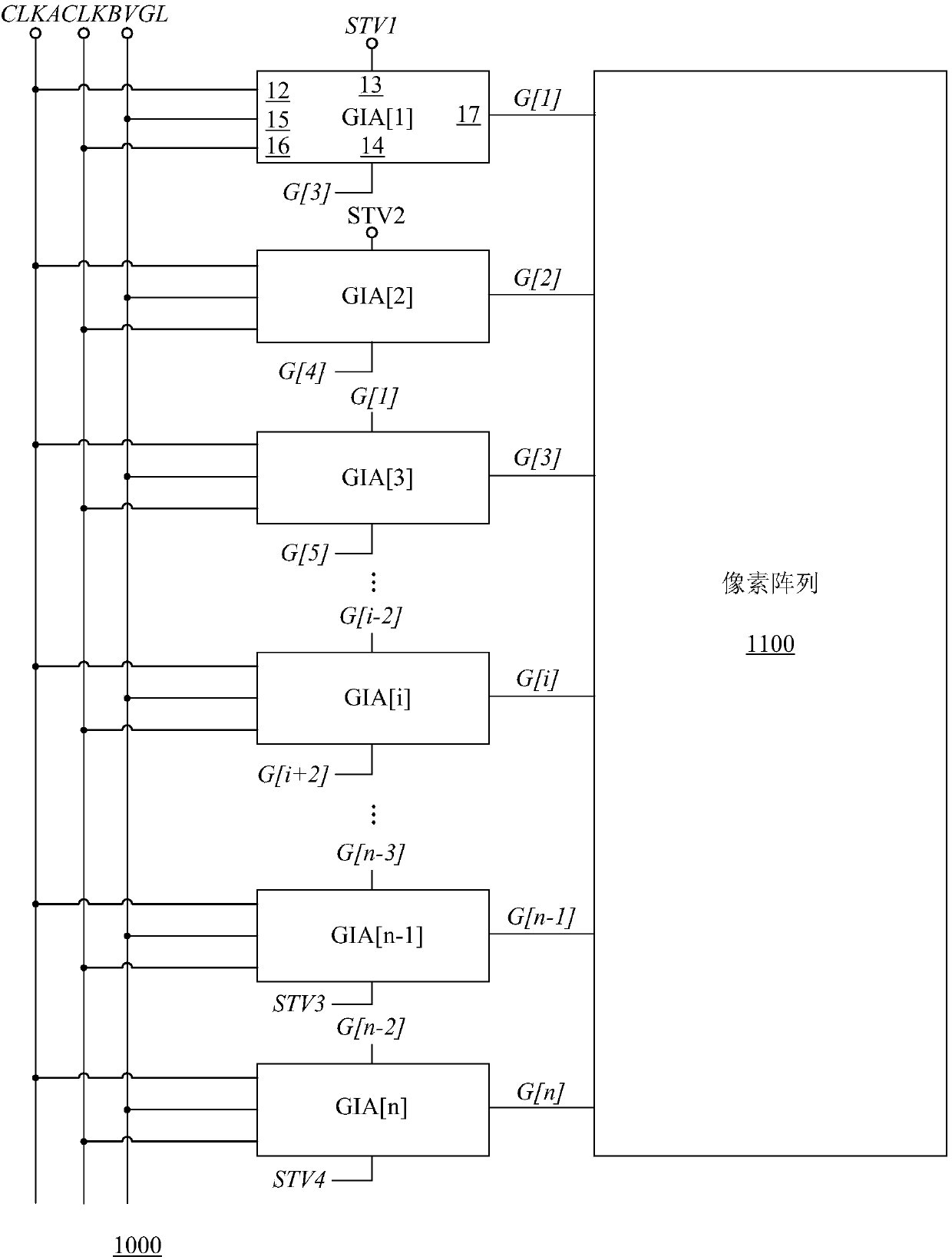

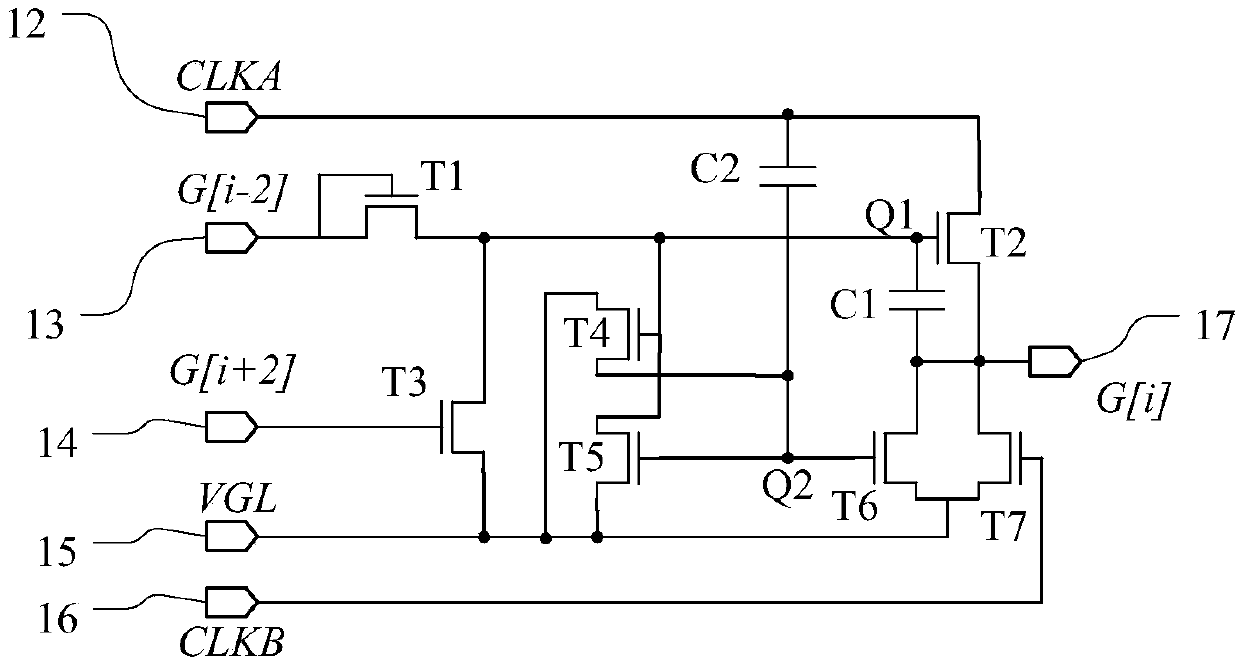

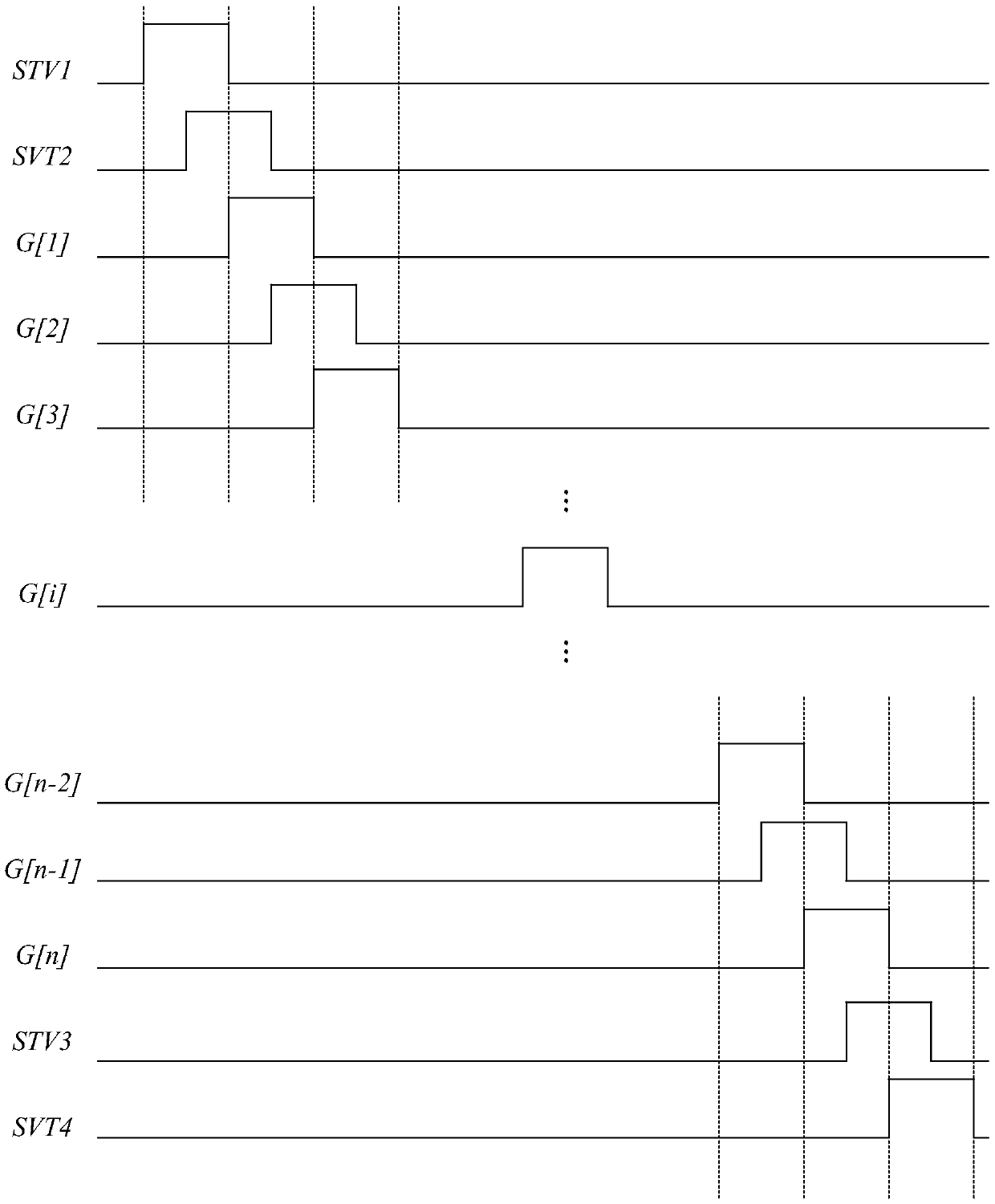

Shift register electrode, grid electrode driver, array substrate and display device

InactiveCN102654986AReduced Threshold Voltage DriftReduce noiseStatic indicating devicesDigital storageLiquid-crystal displayEngineering

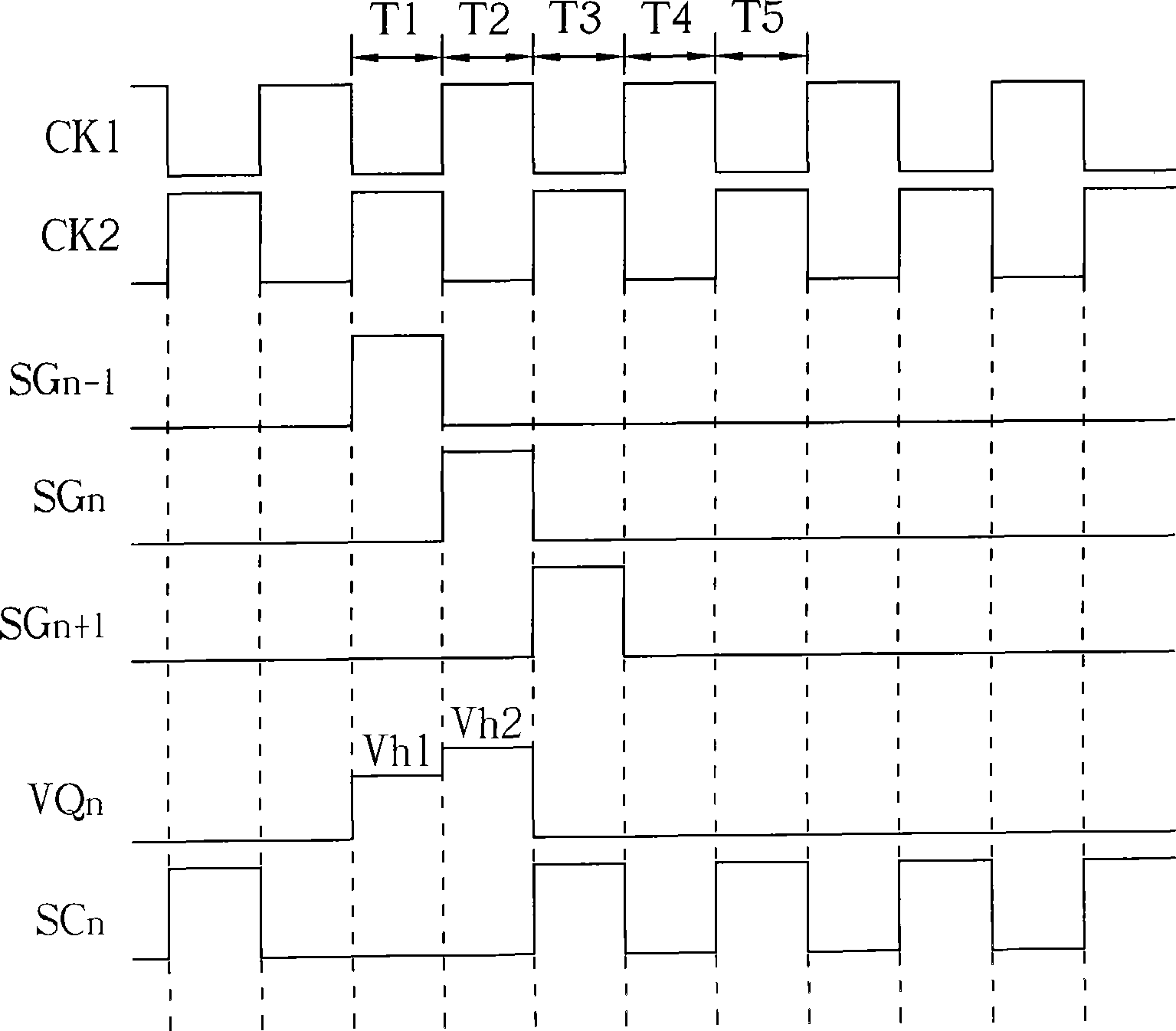

The invention discloses a shift register electrode, a grid electrode driver, an array substrate and a display device, relating to the technical field of liquid crystal display. The electrode comprises a pull-up module, a first pull-down module, a second pull-down module, a pull-up drive module, a pull-down drive module and a reset module, wherein the first pull-down module is used for outputting shut-off signals to an output terminal according to signals input from a clock block signal input terminal and signals input from a reset signal input terminal; the second pull-down module is used for outputting shut-off signals to the output terminal according to signals input from a clock signal input terminal; and the phases of signals input from a signal input terminal are the same with those of the signals input from the clock signal input terminal, and the phases of the signals input from the clock signal input terminal are the same with those of the signals input from the clock block signal input terminal. The shift register electrode can be used for effectively avoiding the defect of threshold voltage drift caused by bias stress on a grid electrode, and can reduce noises generated during outputting voltages.

Owner:BOE TECH GRP CO LTD +1

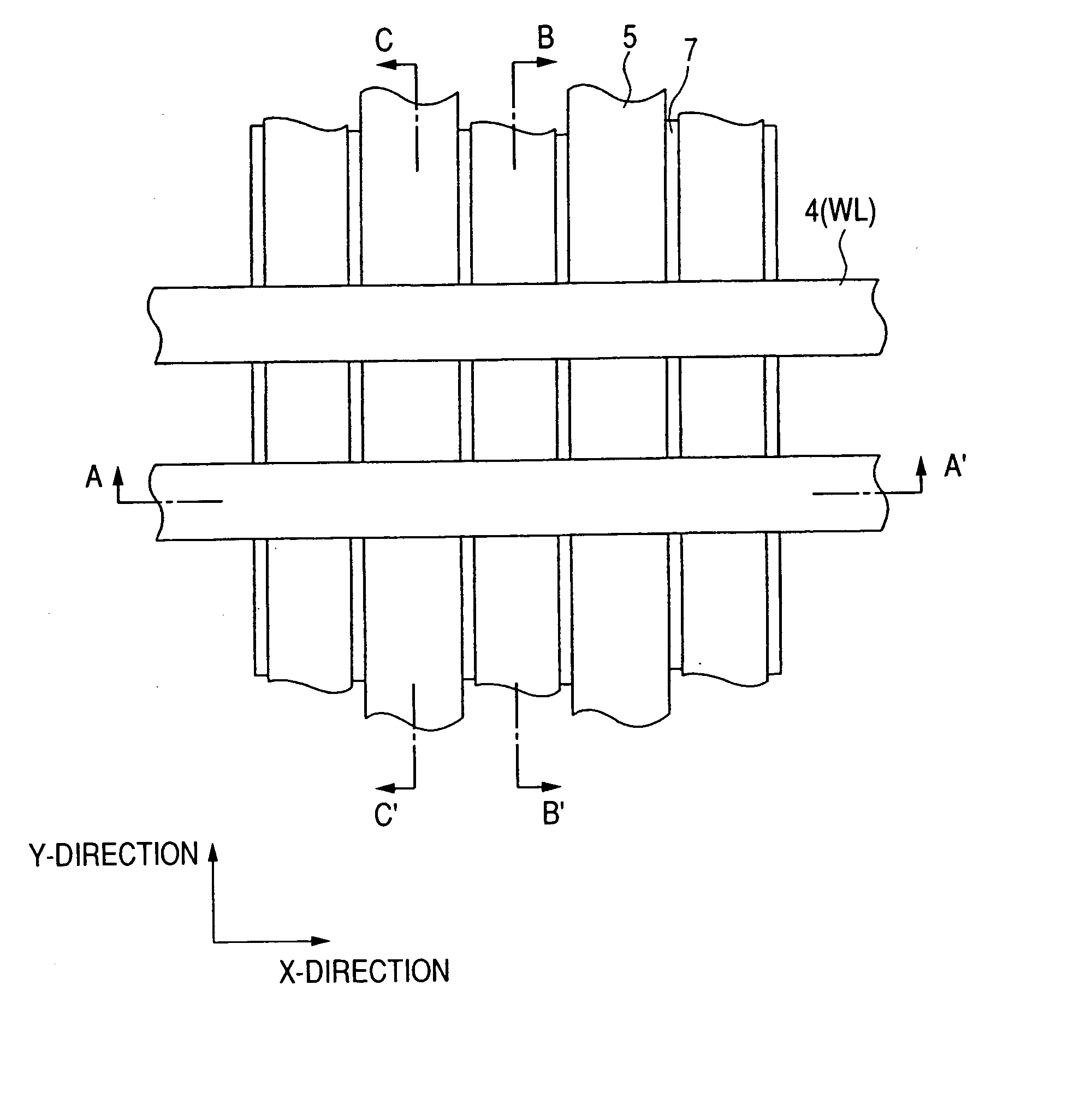

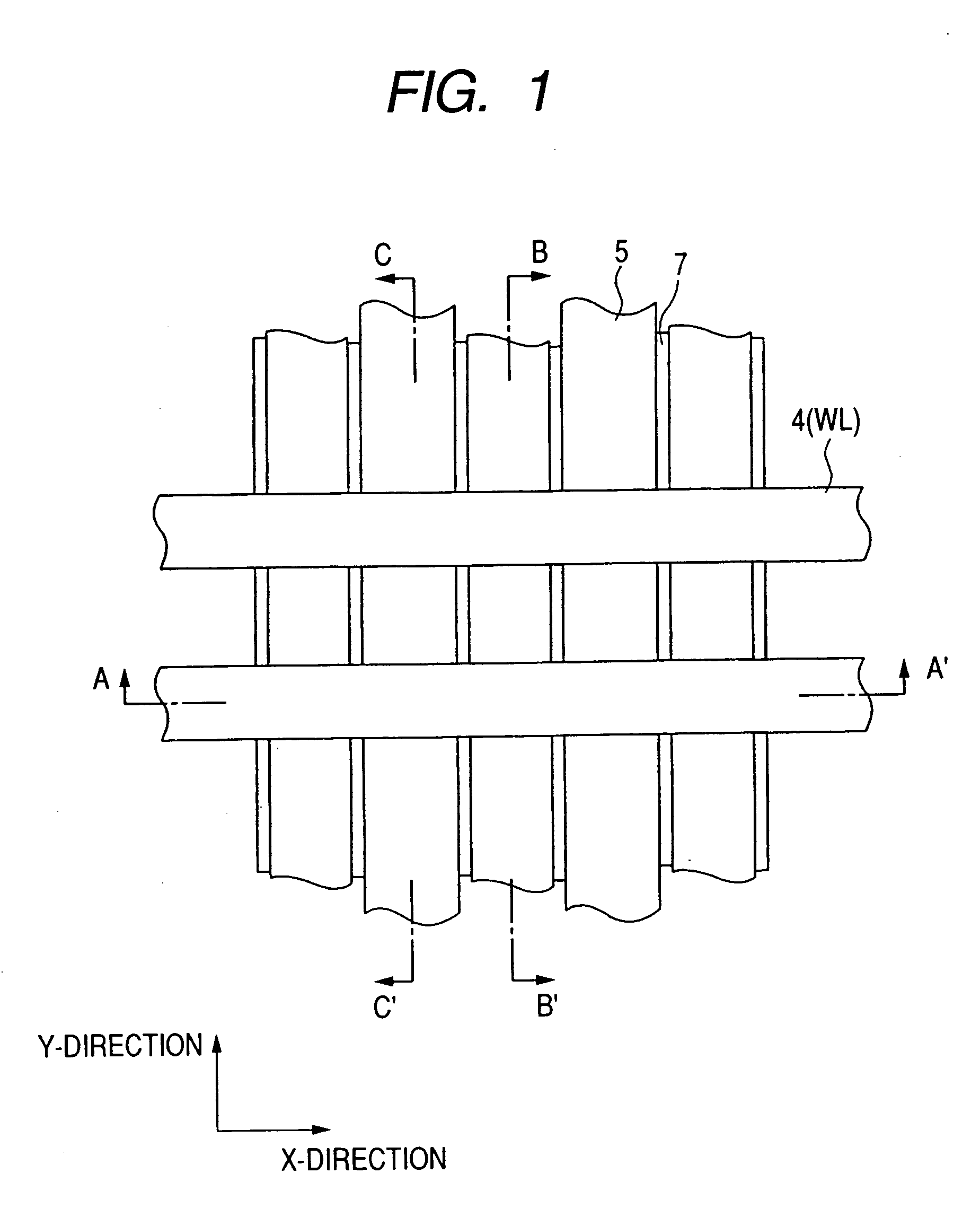

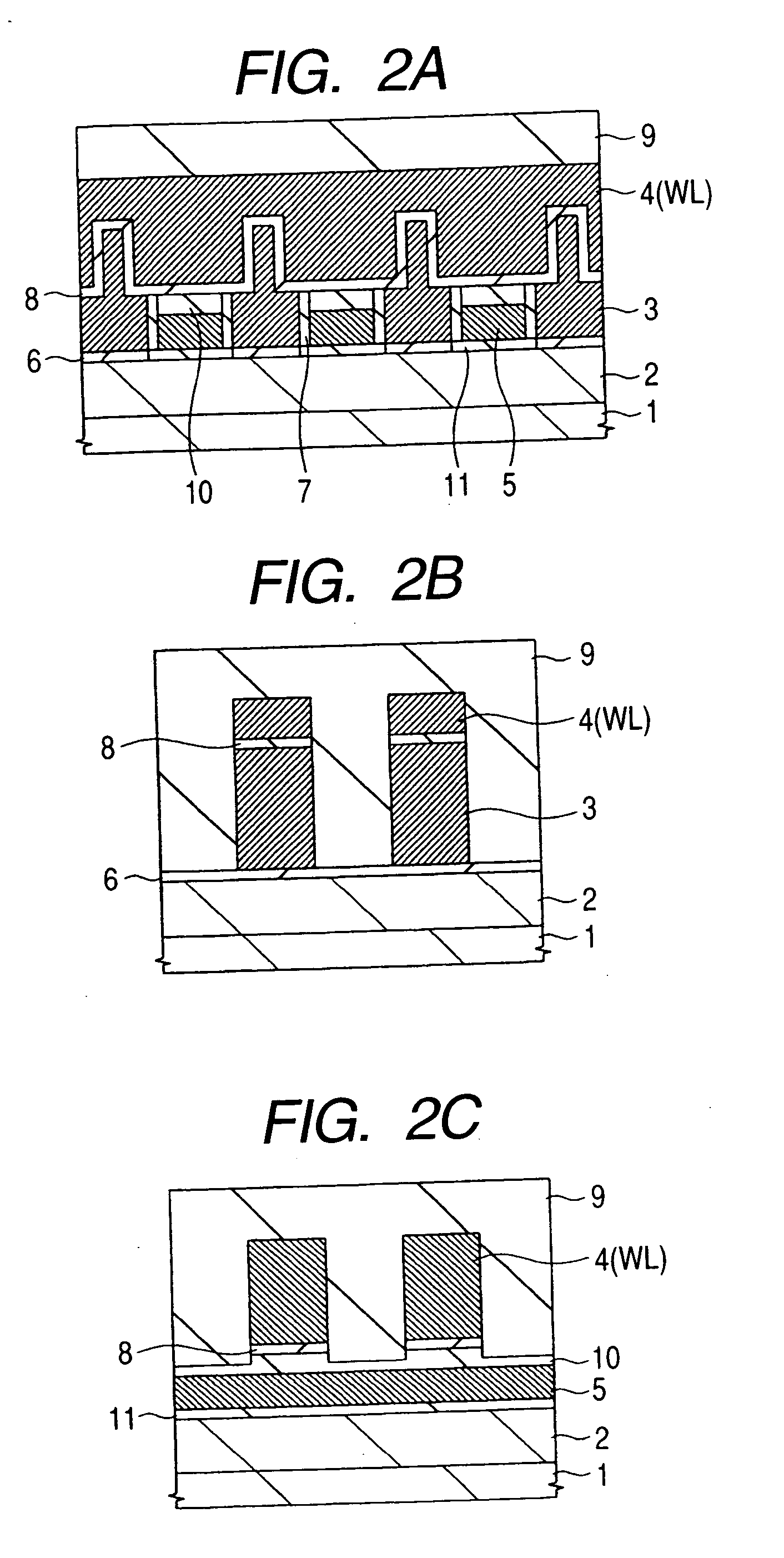

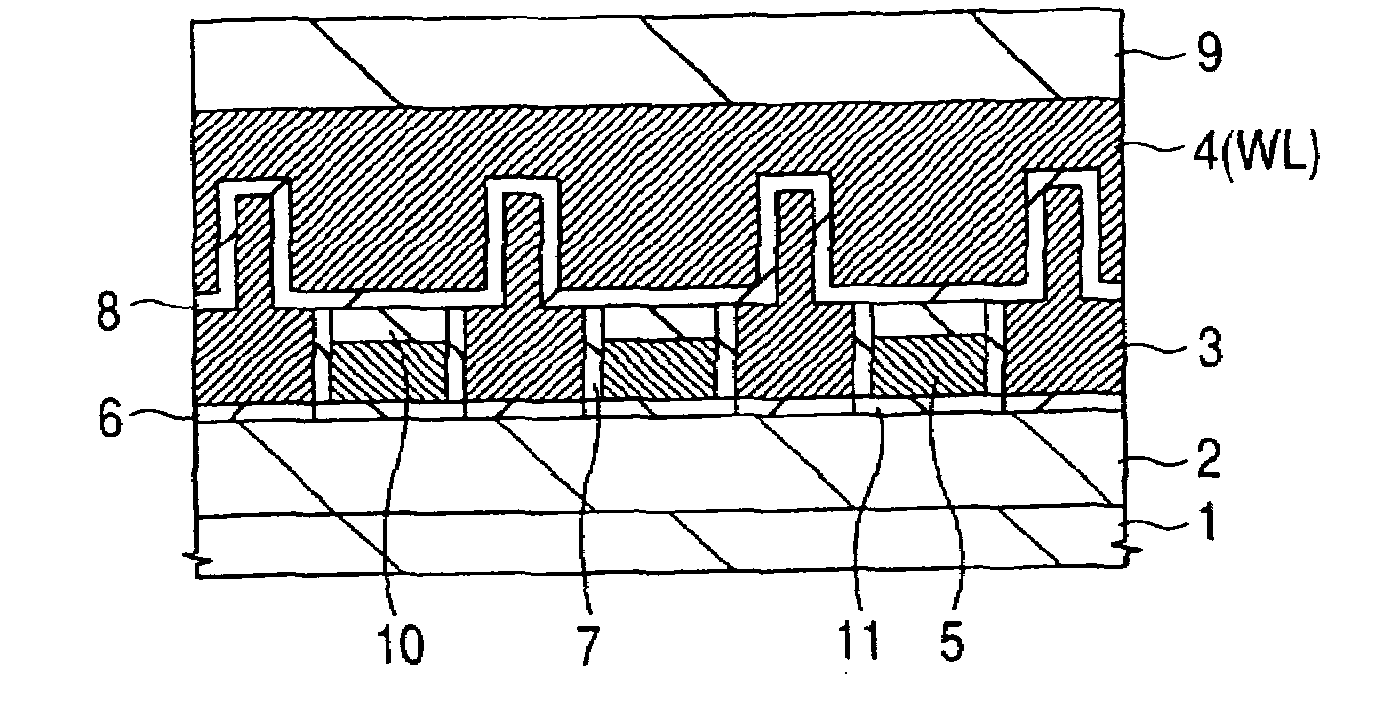

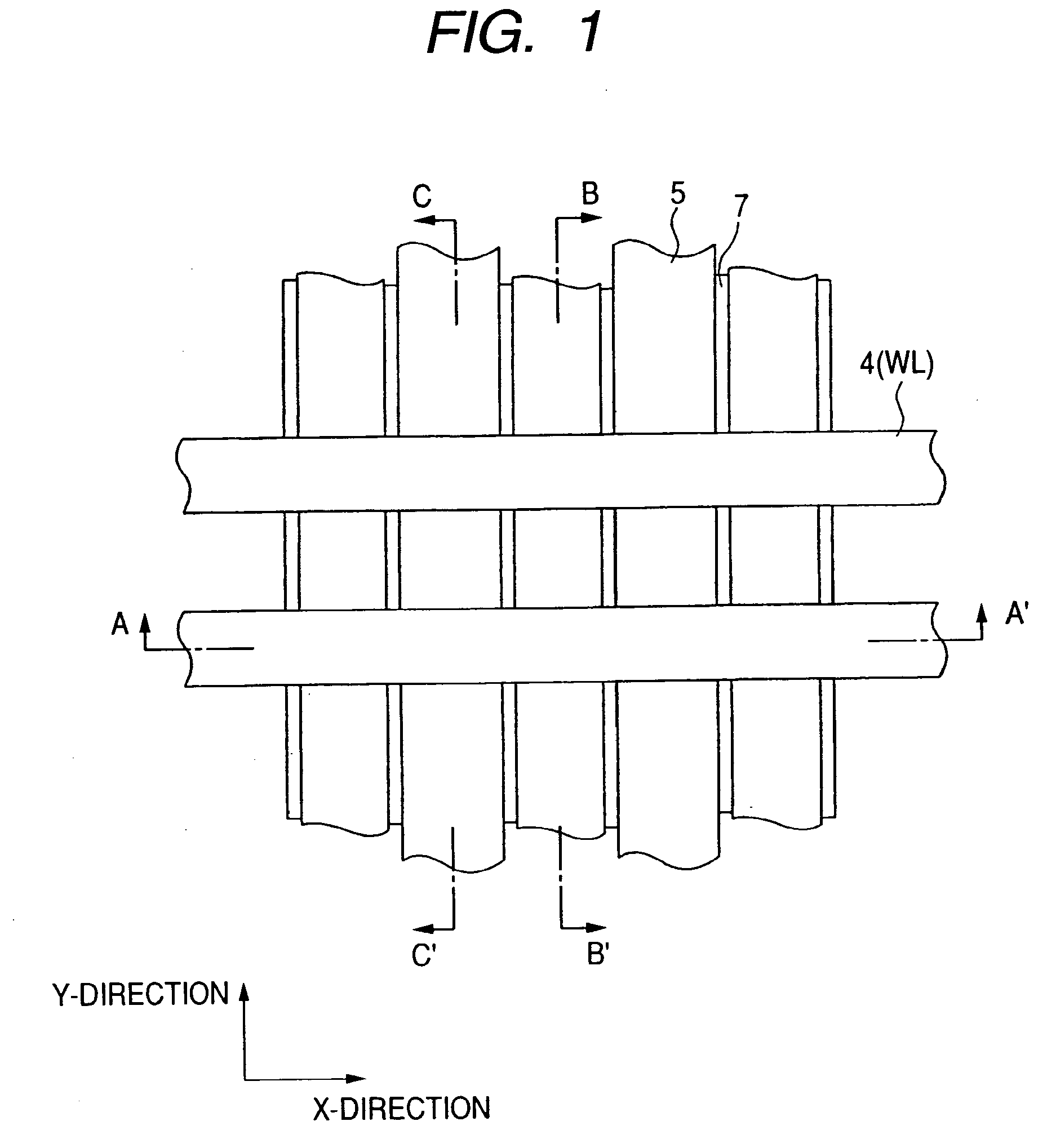

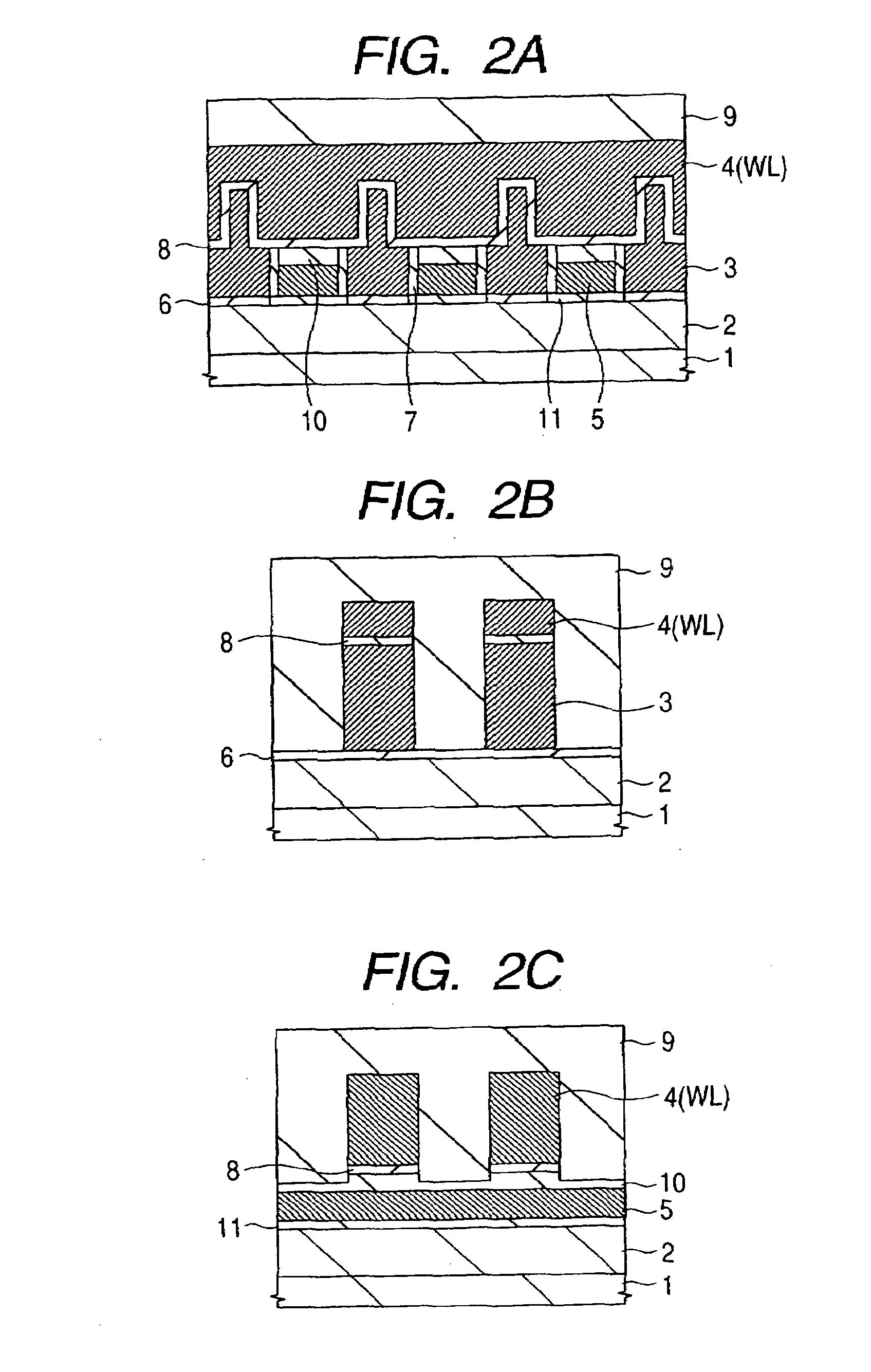

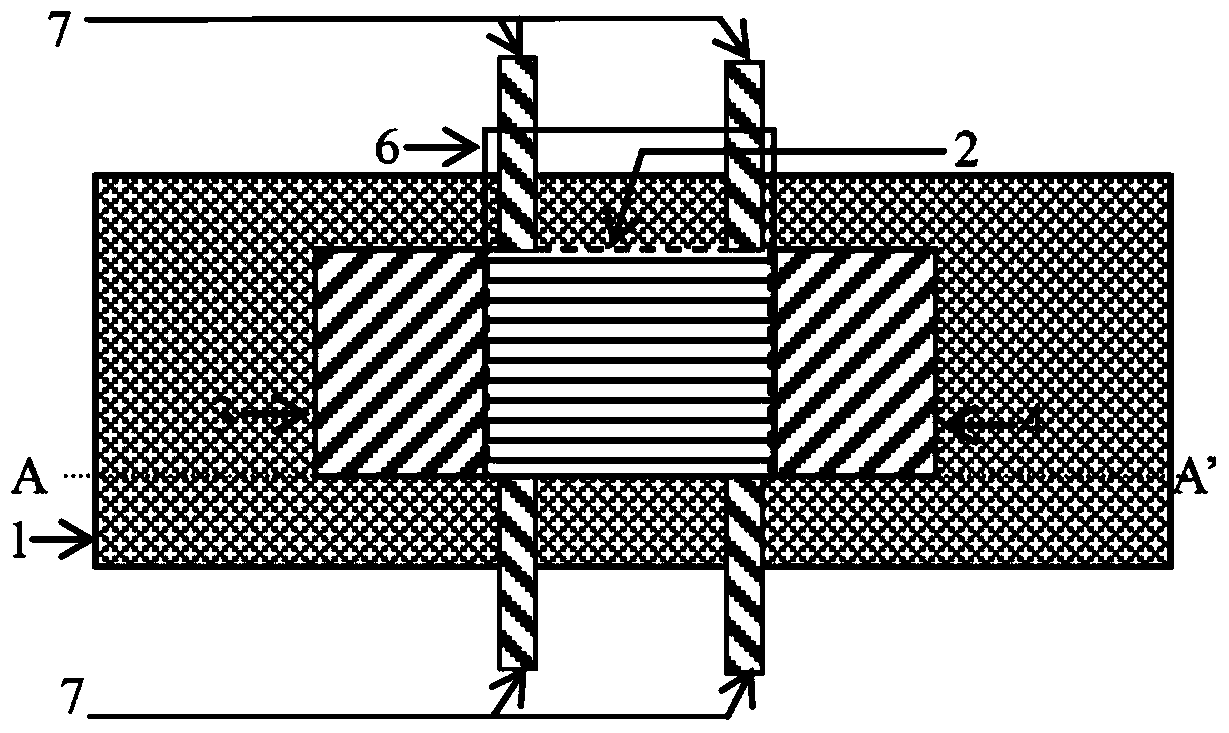

Nonvolatile semiconductor memory device and manufacturing method thereof

InactiveUS20050212034A1Reduce controlReduced Threshold Voltage DriftTransistorSolid-state devicesCapacitanceMiniaturization

A technology realizing decreases of capacitance between the adjoining floating gates and of the threshold voltage shift caused by interference between the adjoining memory cells in a nonvolatile semiconductor memory device with the advances of miniaturization in the period following the 90 nm generation. By having the floating gate 3 of a memory cell with an inverse T-shape and the dimension of a part of the floating gate through the control gate 4 and the second insulator film 8 being smaller than the bottom part of the floating gate, the effects of a threshold voltage shift is reduced maintaining the adequate area of the gap between the floating gate 3 and the control gate 4, decreasing the opposing area of the gap of the floating gates 3 underneath the adjoining word lines WL, maintaining the capacity coupling ratio between the floating gate 3 and the control gate, and reducing the opposing area of the gap of the adjoining floating gates 3.

Owner:RENESAS TECH CORP

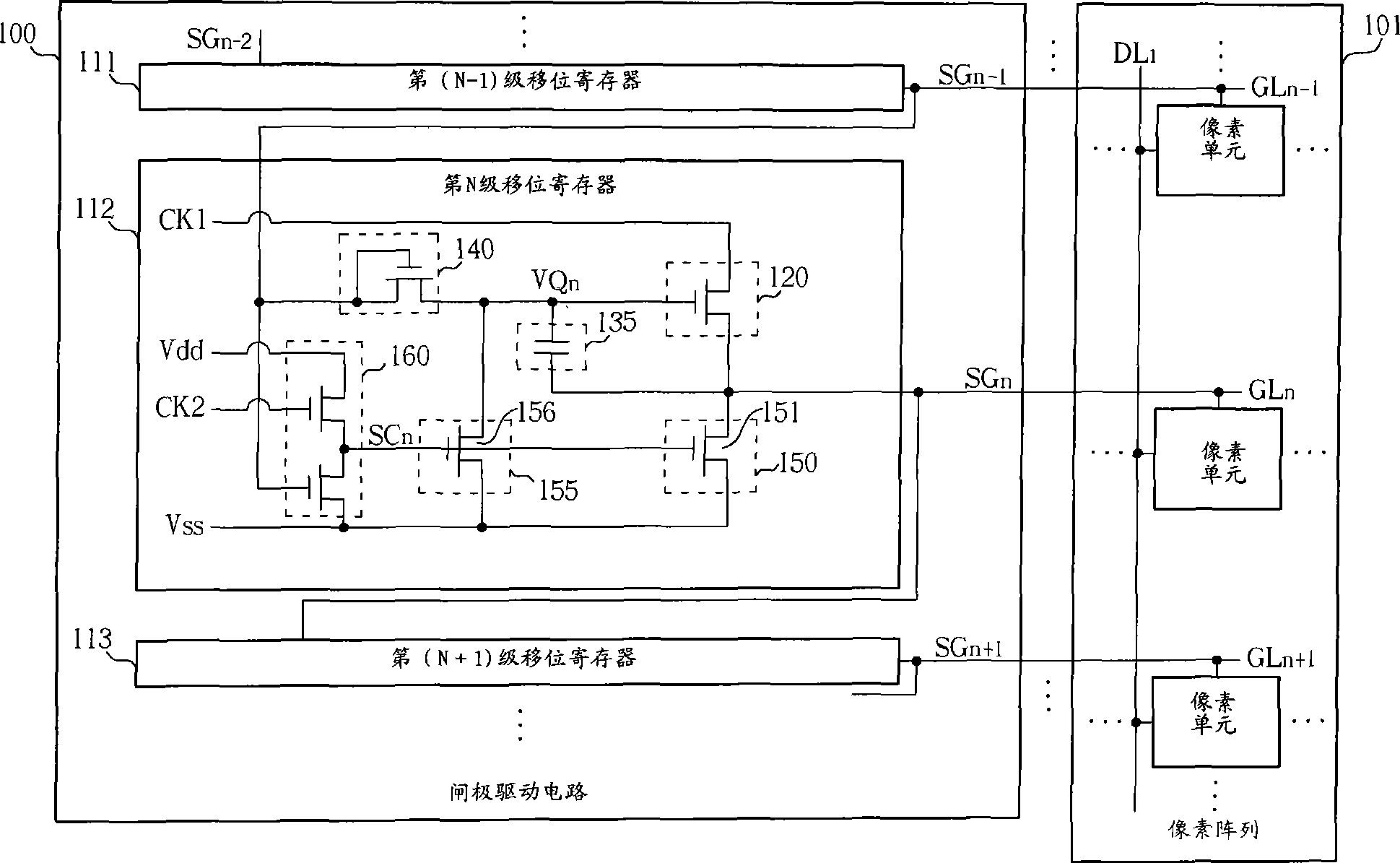

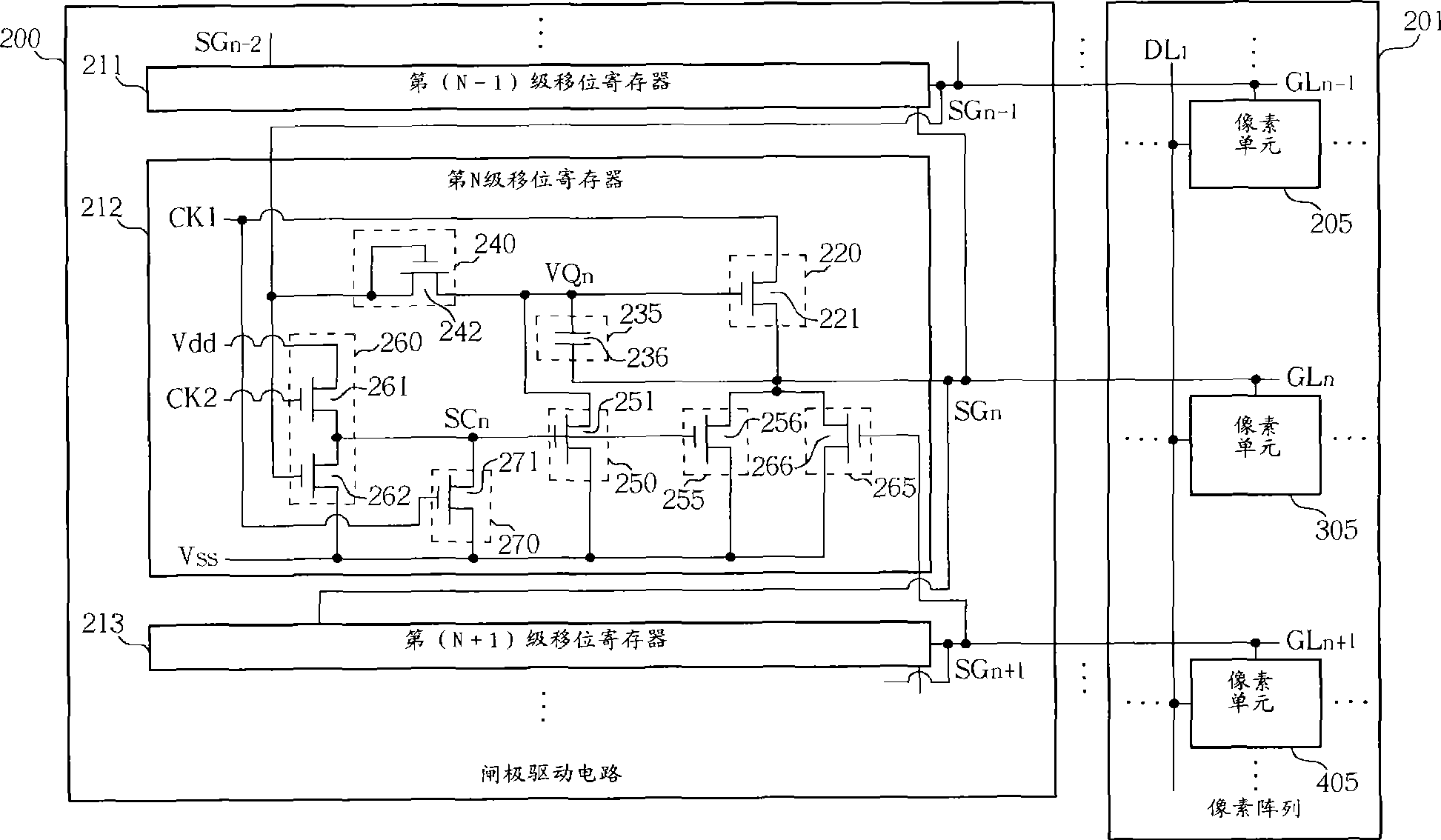

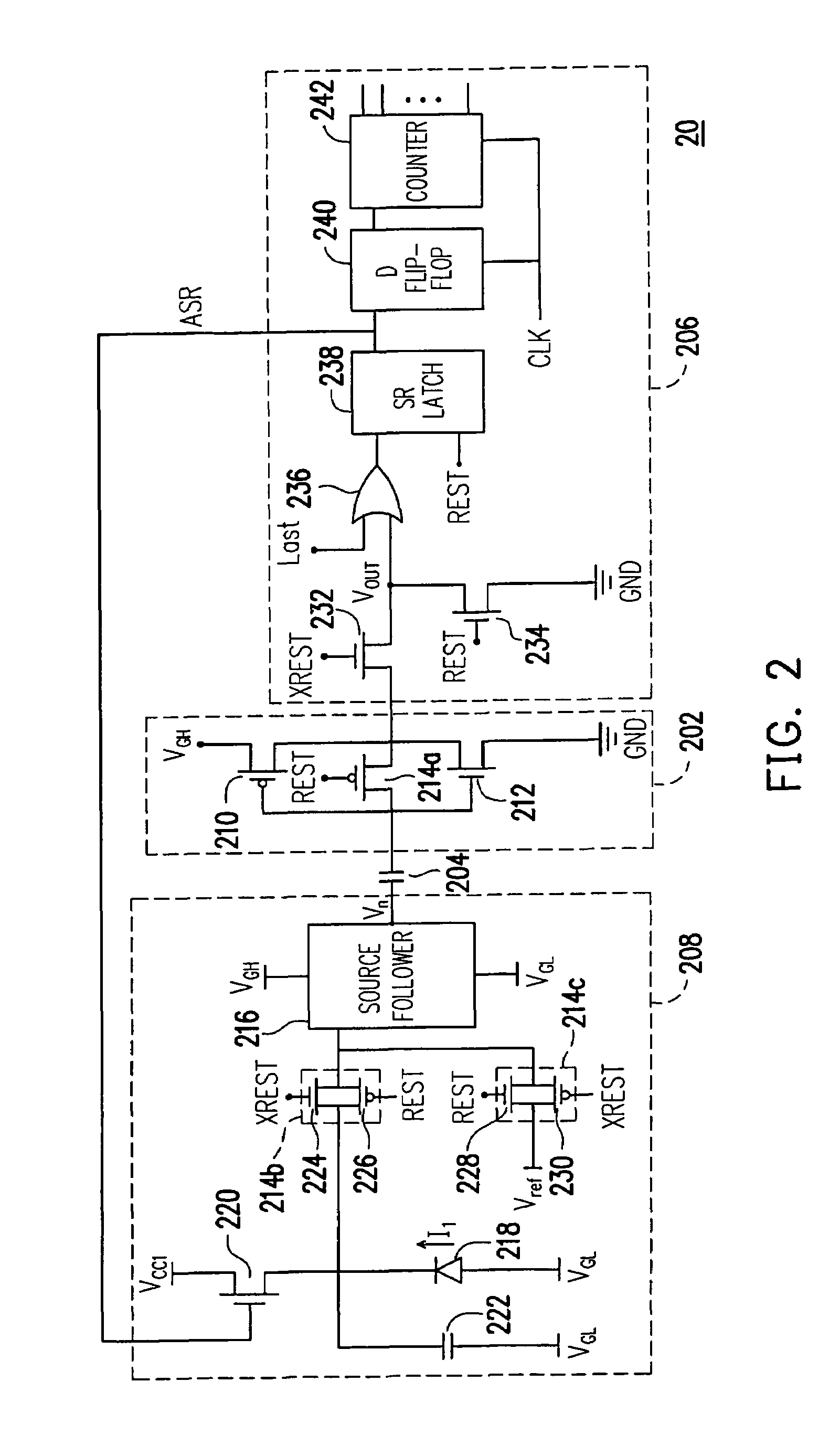

Gate drive for inhibiting drift of a critical voltage

InactiveCN101533623AImprove reliabilityExtended service lifeStatic indicating devicesDriver circuitShift register

The invention is appropriate for the field of gate drive technology, which provides a gate drive for inhibiting drift of a critical voltage, so as to provide a multi-gate signal to a multi-gate line, where the gate drive includes multi-level shift register, where each level shift register includes a pull-up unit, an energy storage unit, a buffer unit, a discharge unit, a pull-down unit, a control unit and a signal switch unit, where the pull-up unit pulls a gate signal up according to a drive control voltage and a first frequency; the buffer unit is used for receiving a input signal; the energy storage unit executes a charging procedure according to an input signal so as to supply a drive control voltage; the discharge unit pulls the drive control voltage down according to a control signal; the pull-down unit pulls a gate signal down according to the control signal; the control unit generates the control signal according to the input signal and a second frequency with opposite phase relative to the first frequency; and the signal switch unit switches the control signal according to the first frequency.

Owner:SHENZHEN HUAYING DISPLAY TECH CO LTD +1

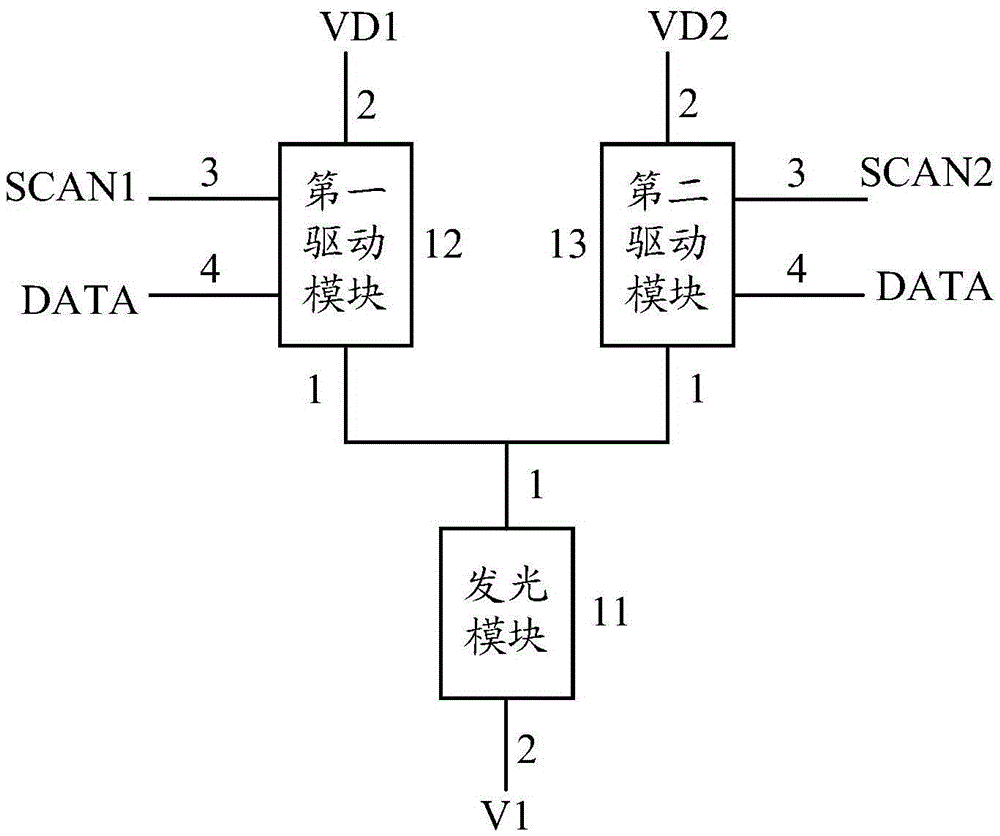

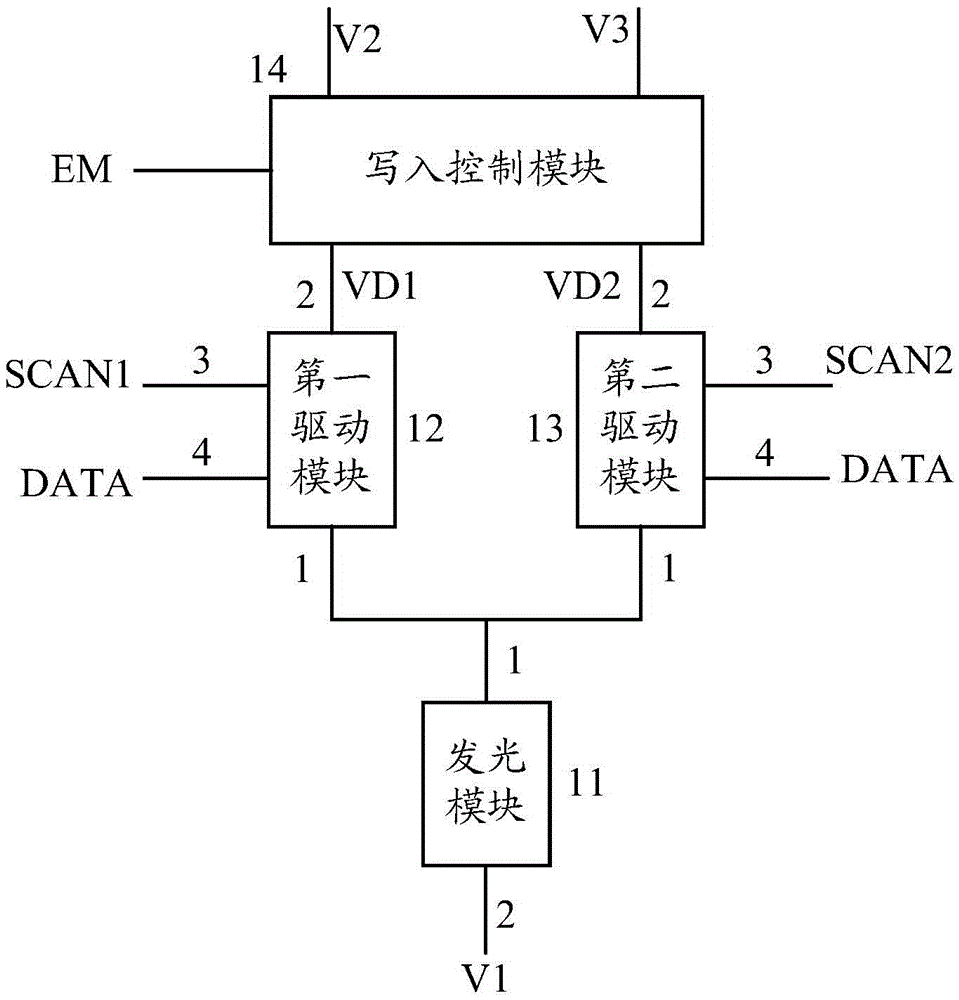

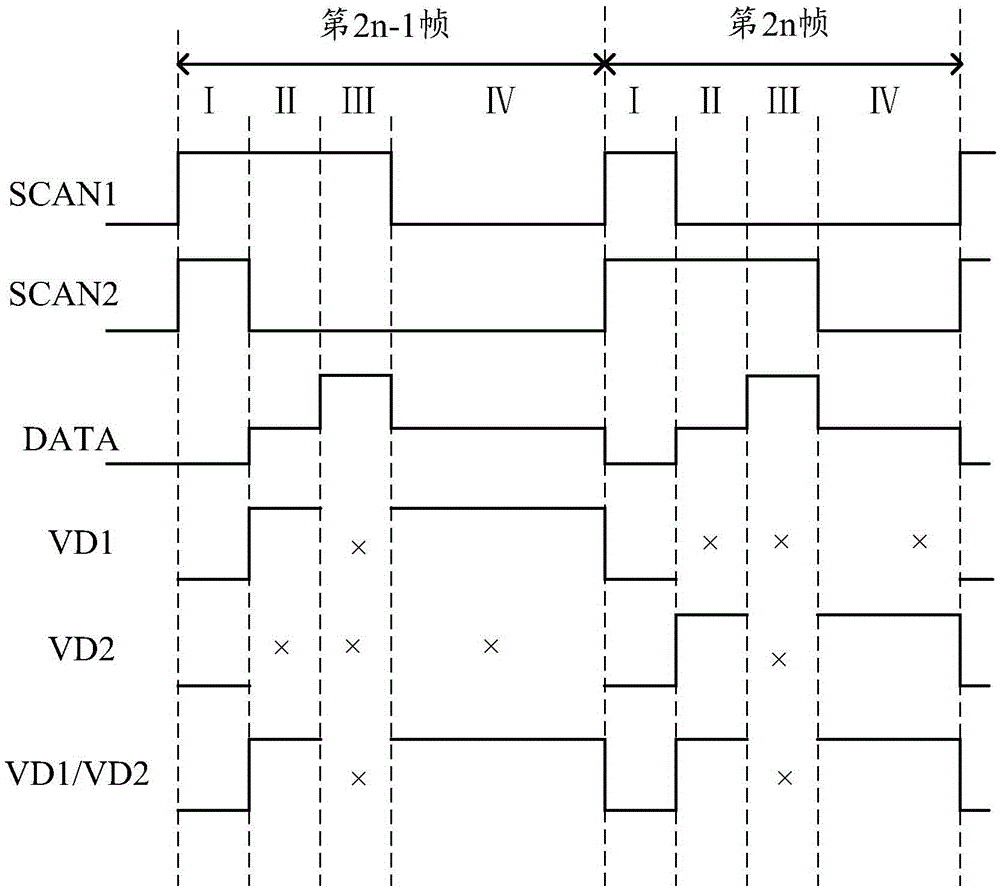

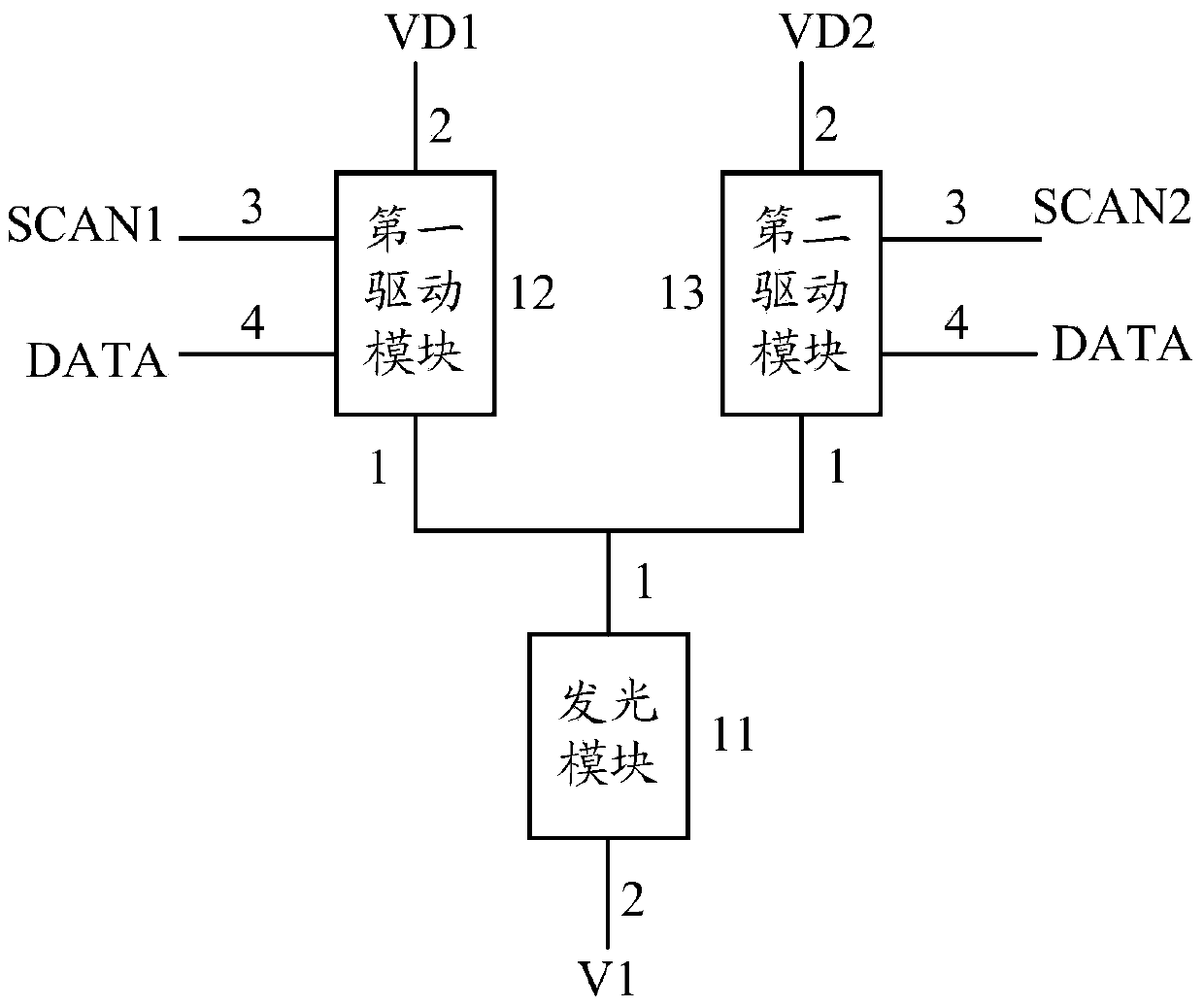

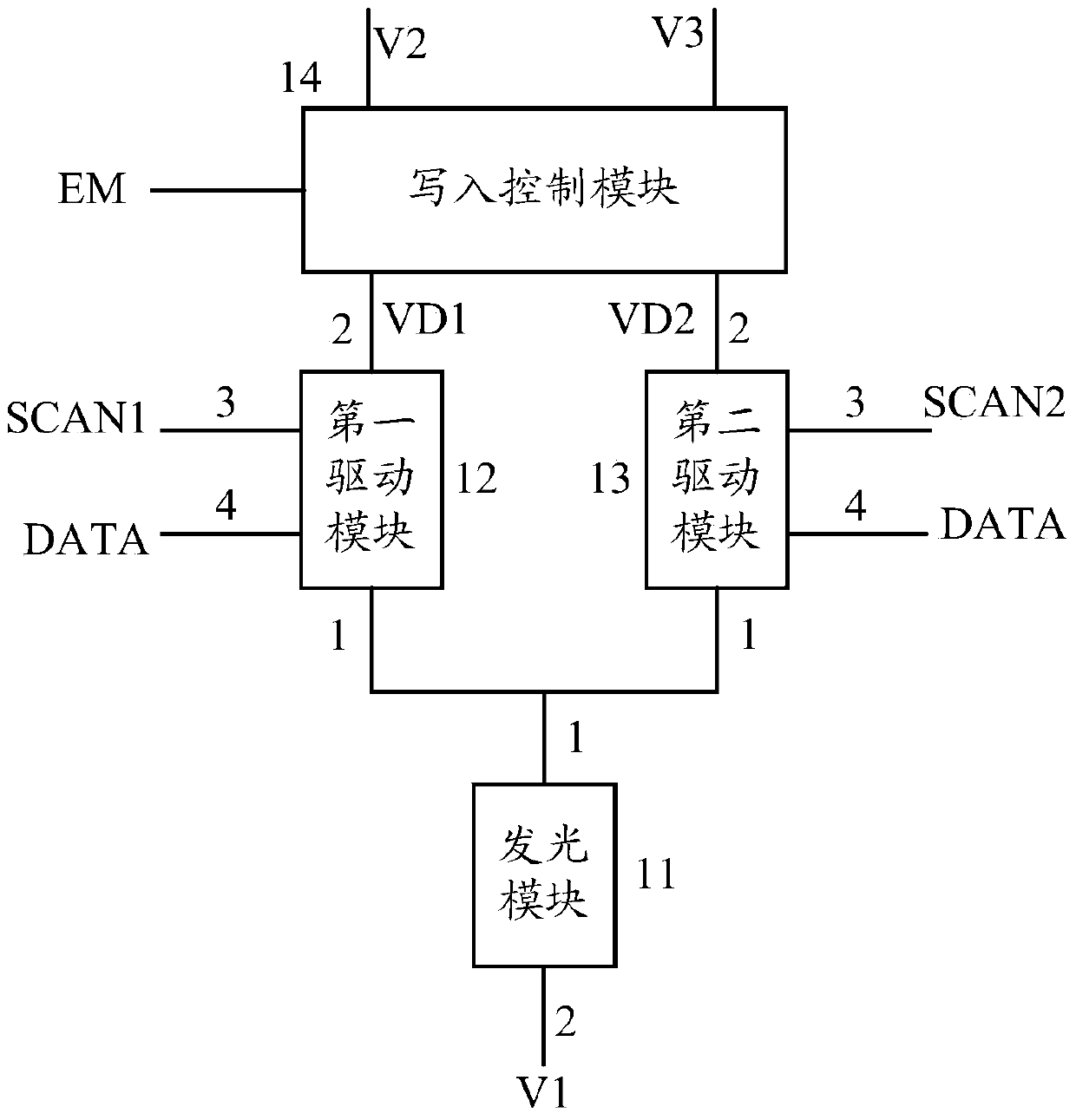

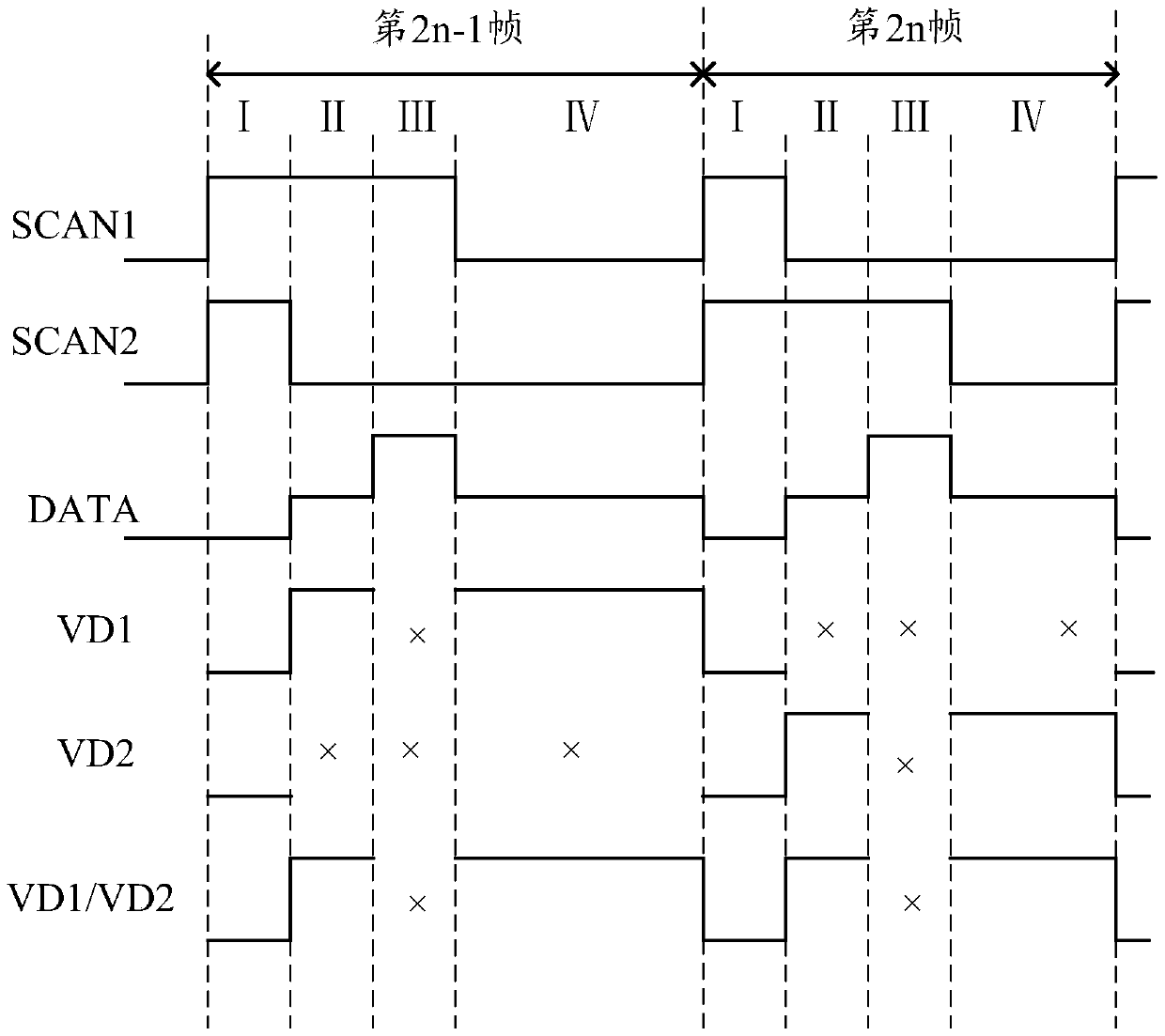

Pixel circuit and driving method thereof, display panel

ActiveCN105609047AReduced Threshold Voltage DriftExtended service lifeStatic indicating devicesEngineeringRecovery stage

The invention discloses a pixel circuit and a driving method thereof, a display panel including the pixel circuit. The pixel circuit is composed of a light emitting module, a first driving module and a second driving module. The first driving module drives the light emitting module to emit light at a first period under the control of a first scanning signal from a first scanning control terminal; and the second driving module drives the light emitting module to emit light at a second period under the control of a second scanning signal from a second scanning control terminal, wherein the first period and the second period are not overlapped. Because the two driving modules drive the light emitting module alternately to emit light, one driving module enters a recovery stage when the other driving module drives the light emitting module to emit light, so that threshold voltage drifting of driving transistors of all driving modules can be reduced; and service lives of f driving transistors of all driving modules can be prolonged.

Owner:BOE TECH GRP CO LTD

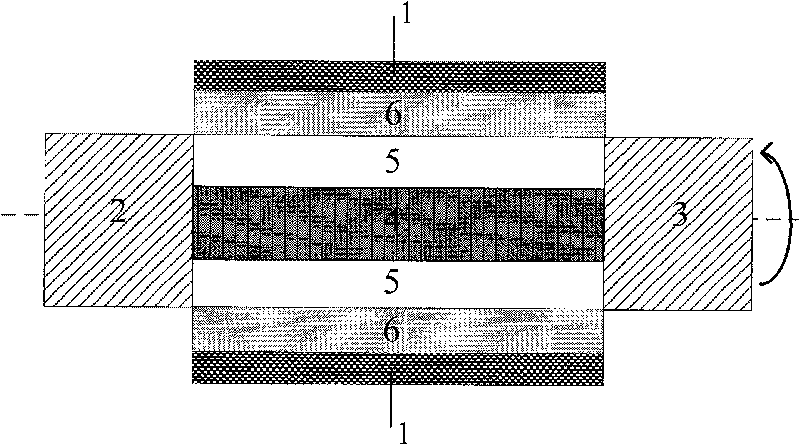

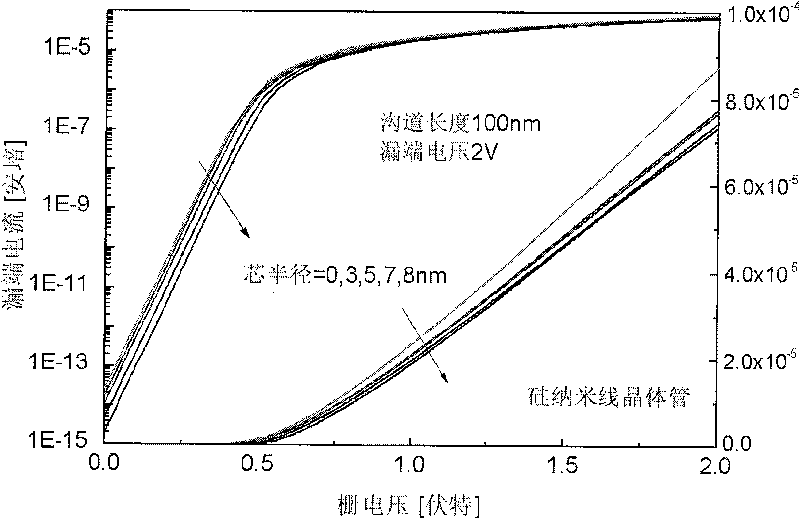

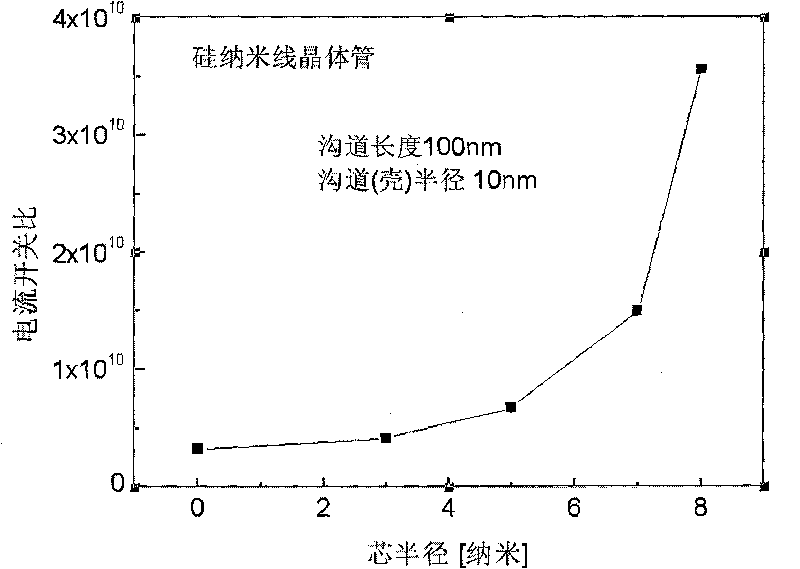

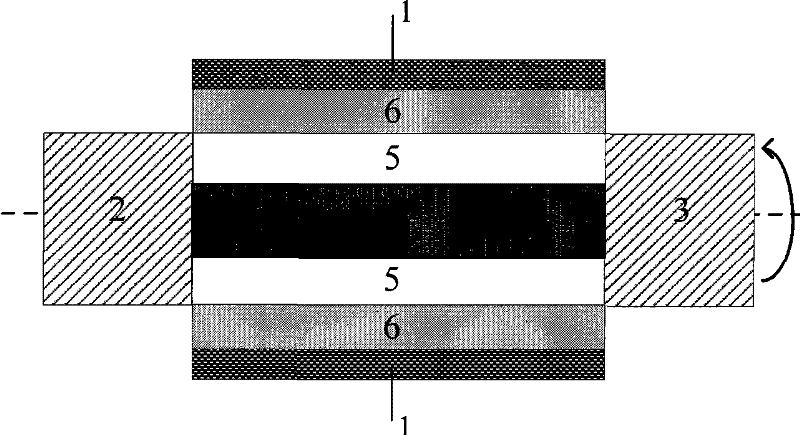

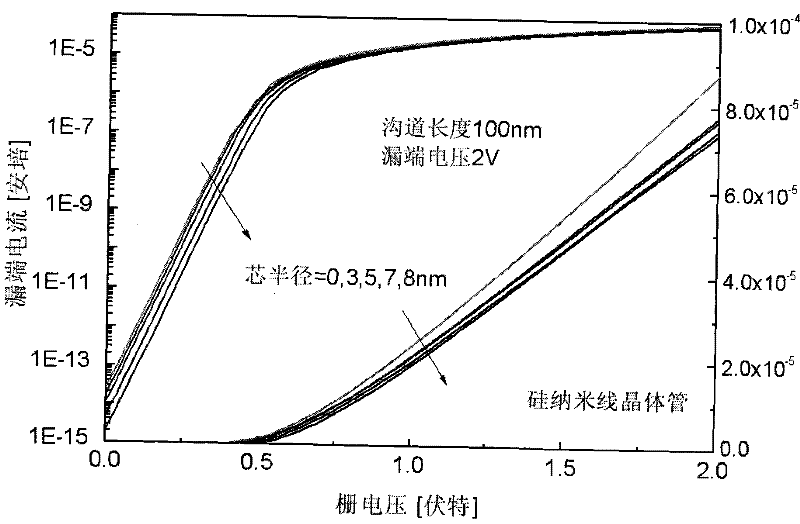

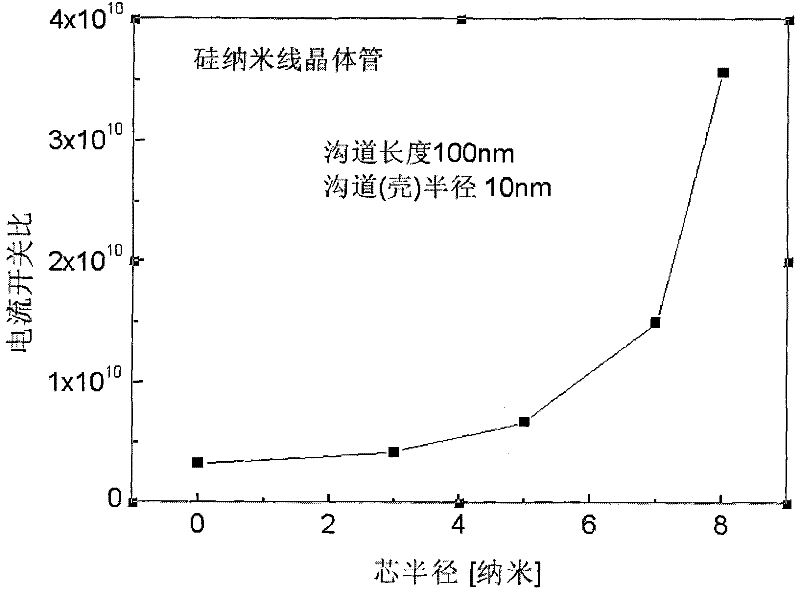

Nano-wire field effect transistor

ActiveCN101740619AReduce off-state currentReduce static power consumptionSemiconductor devicesGate dielectricNanowire

The invention discloses a nano-wire field effect transistor comprising a gate electrode, a source region, a drain region, a central region and a gate dielectric layer. The central region is in the core-shell structures which are coaxial; the gate dielectric layer fully surrounds the central region; the gate electrode fully surrounds the gate dielectric layer; the source region and the drain region are respectively arranged on two sides of the central region; the core structure of the central region is made from insulating material, and the shell structure of the central region is made from semiconductor material; the doping type and the doping concentration of the semiconductor material of the shell structure of the central region are adjustable; the lengths of both the core structure and the shell structure and the radii of both the core structure and the shell structure are adjustable; and the materials of the gate dielectric layer, the gate electrode, the source region and the drain region are adjustable. Due to the adoption of the insulating core structure, the off-current of the traditional nano-wire transistor can be reduced effectively, and the current on-off ratio of the devices can be increased. The threshold voltage shifting and the drain induced barrier lowering of the nano-wire field effect transistor are less affected by the short channel effect, and the size reducing performance of the nano-wire field effect transistor is more excellent.

Owner:SEMICONDUCTOR MANUFACTURING INTERNATIONAL (BEIJING) CORP +1

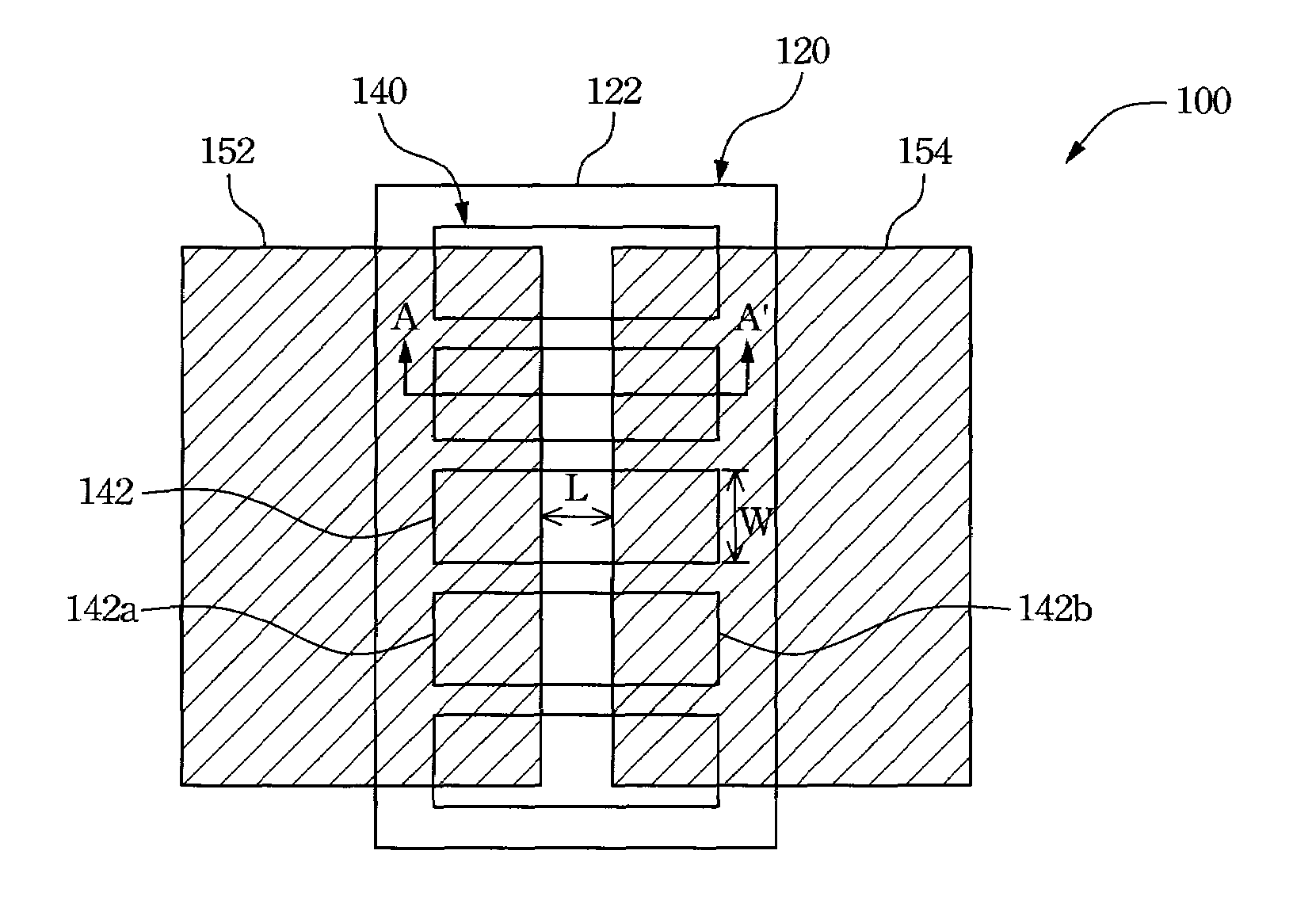

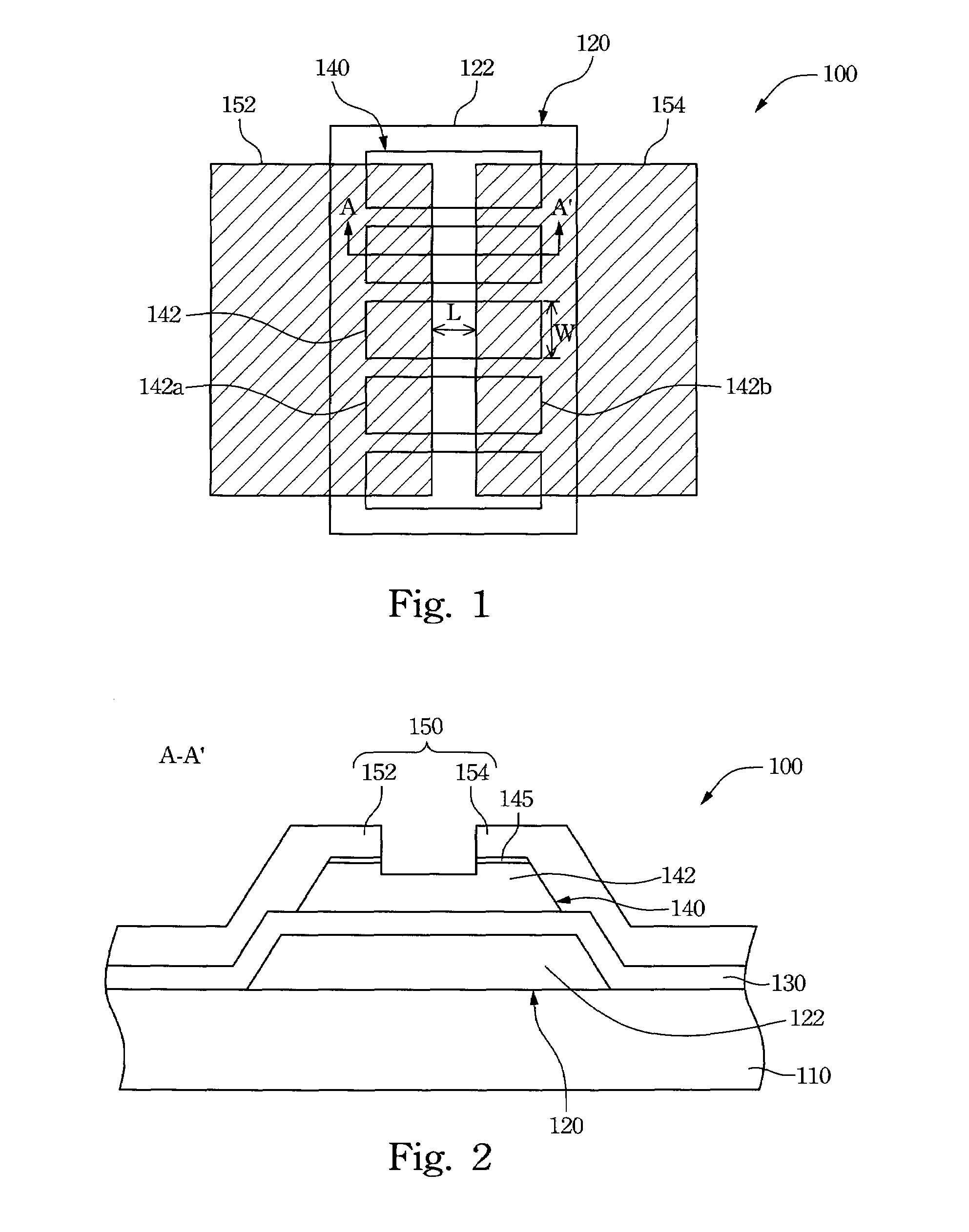

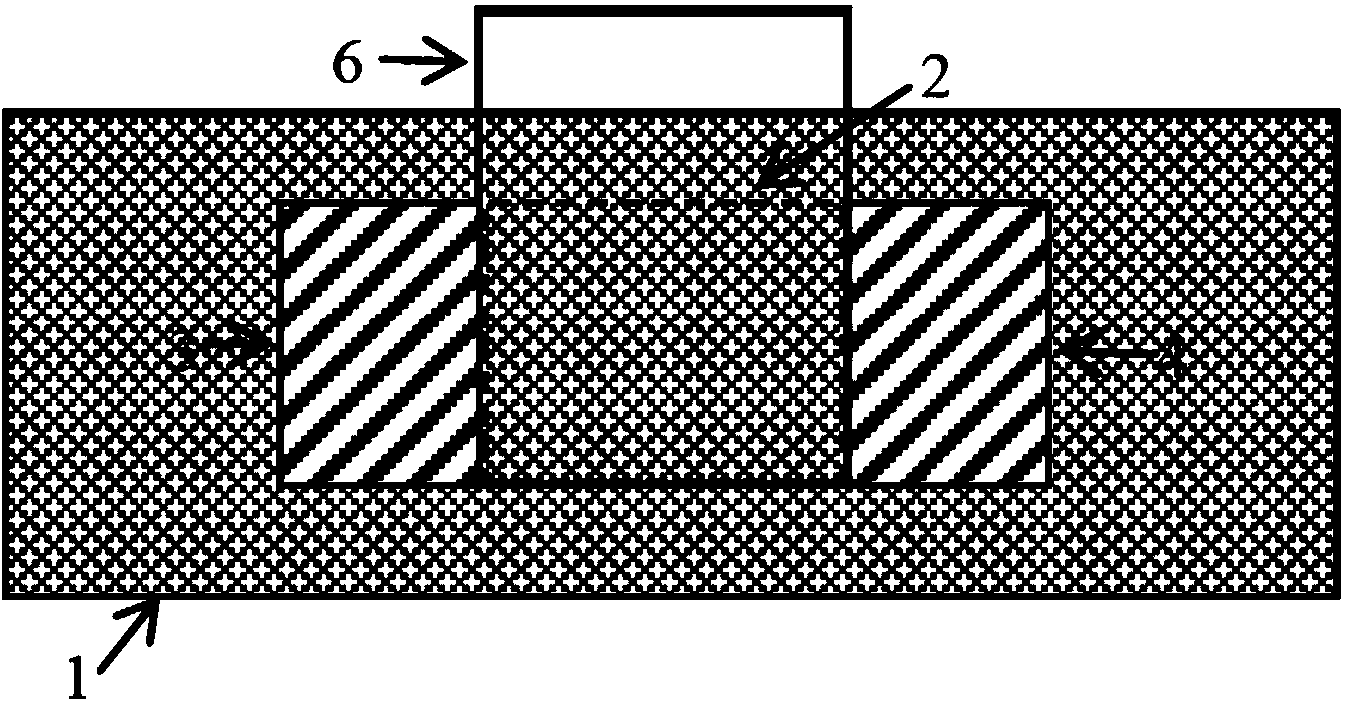

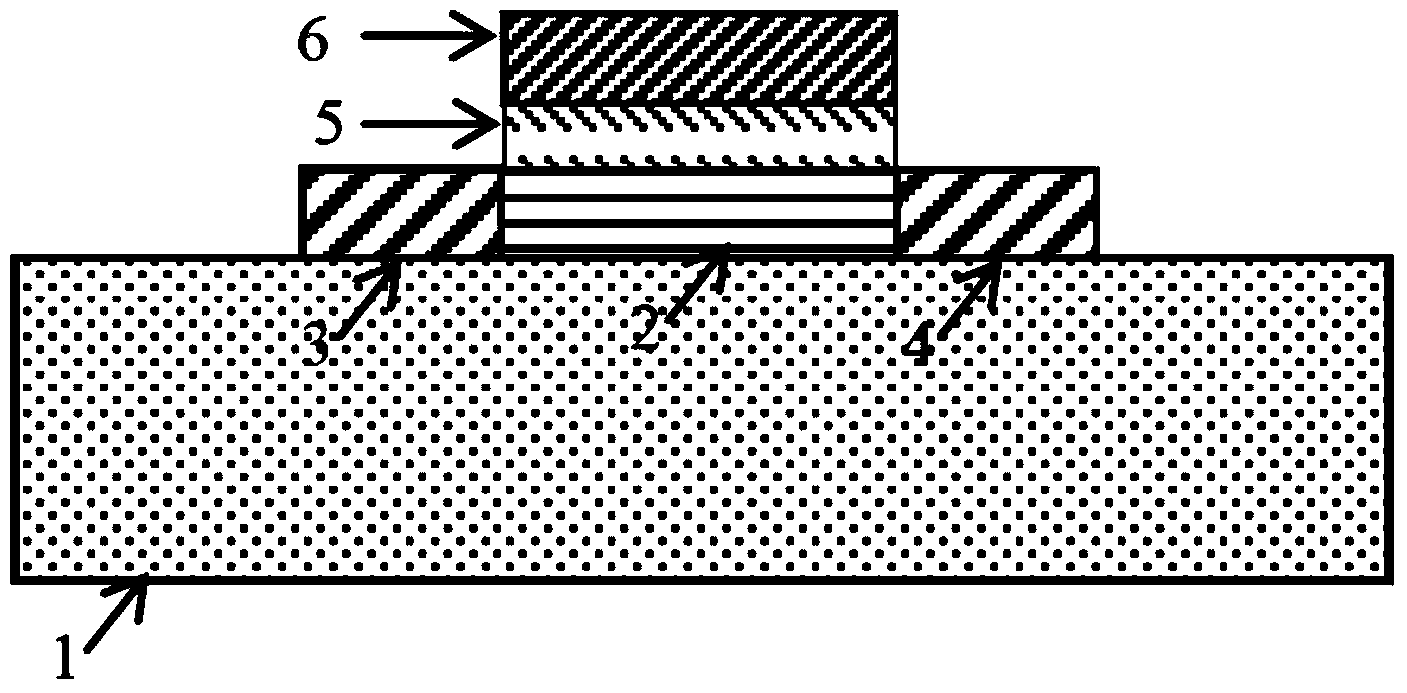

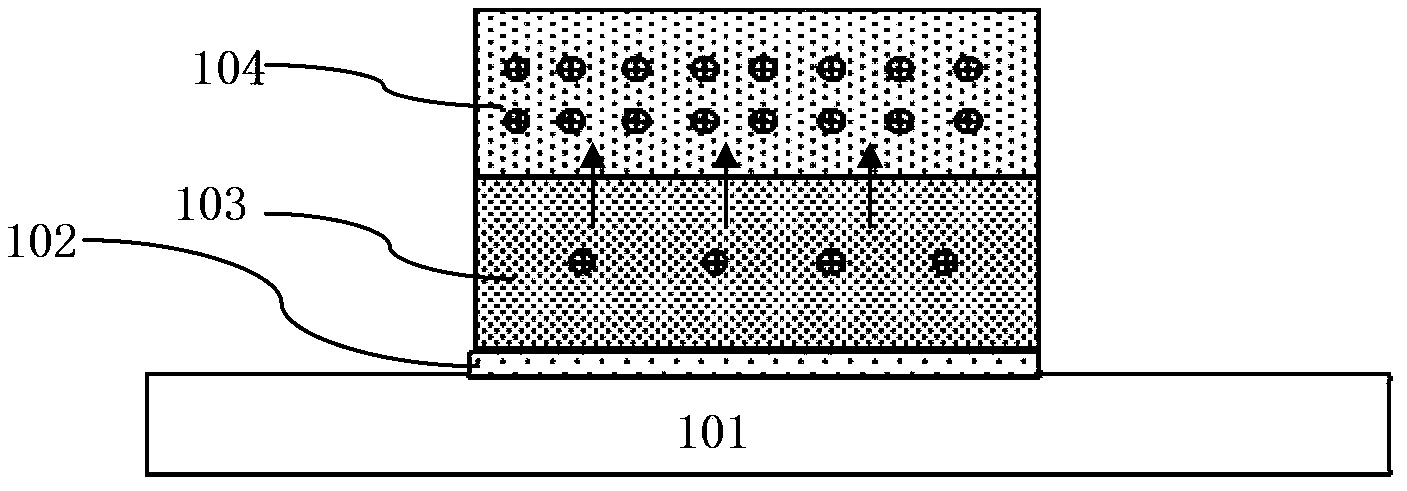

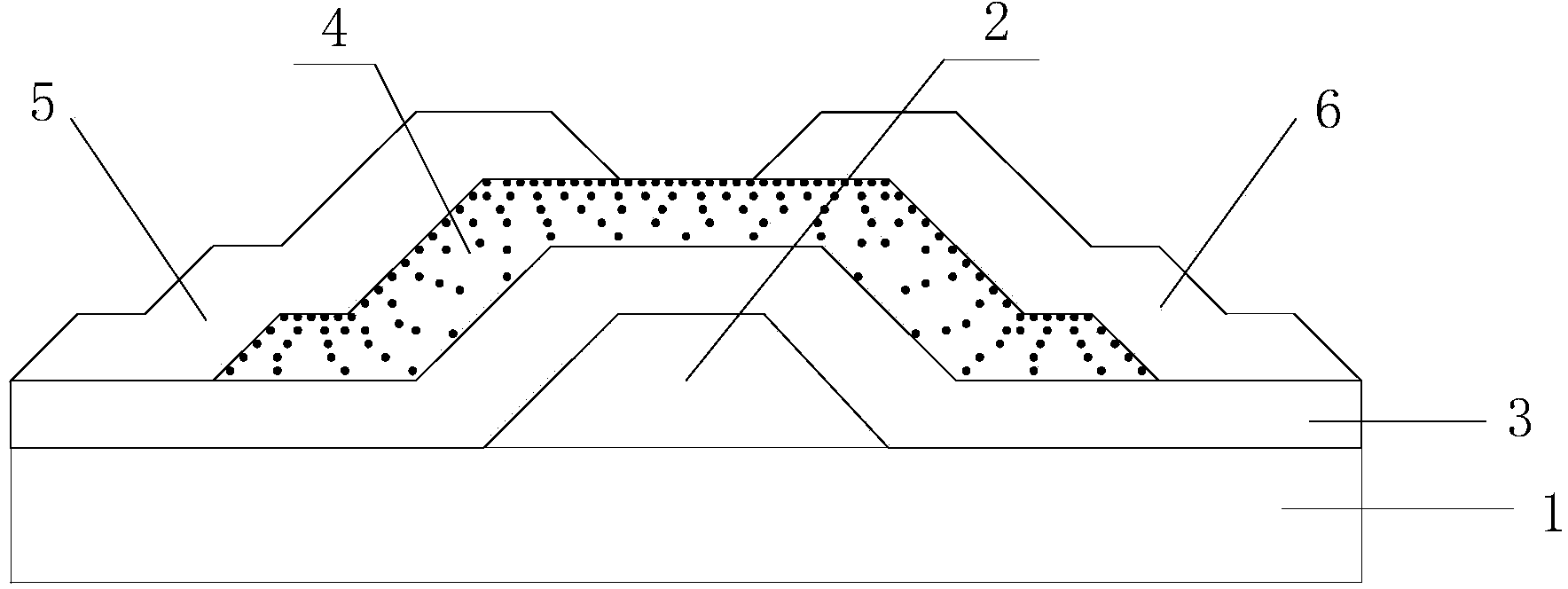

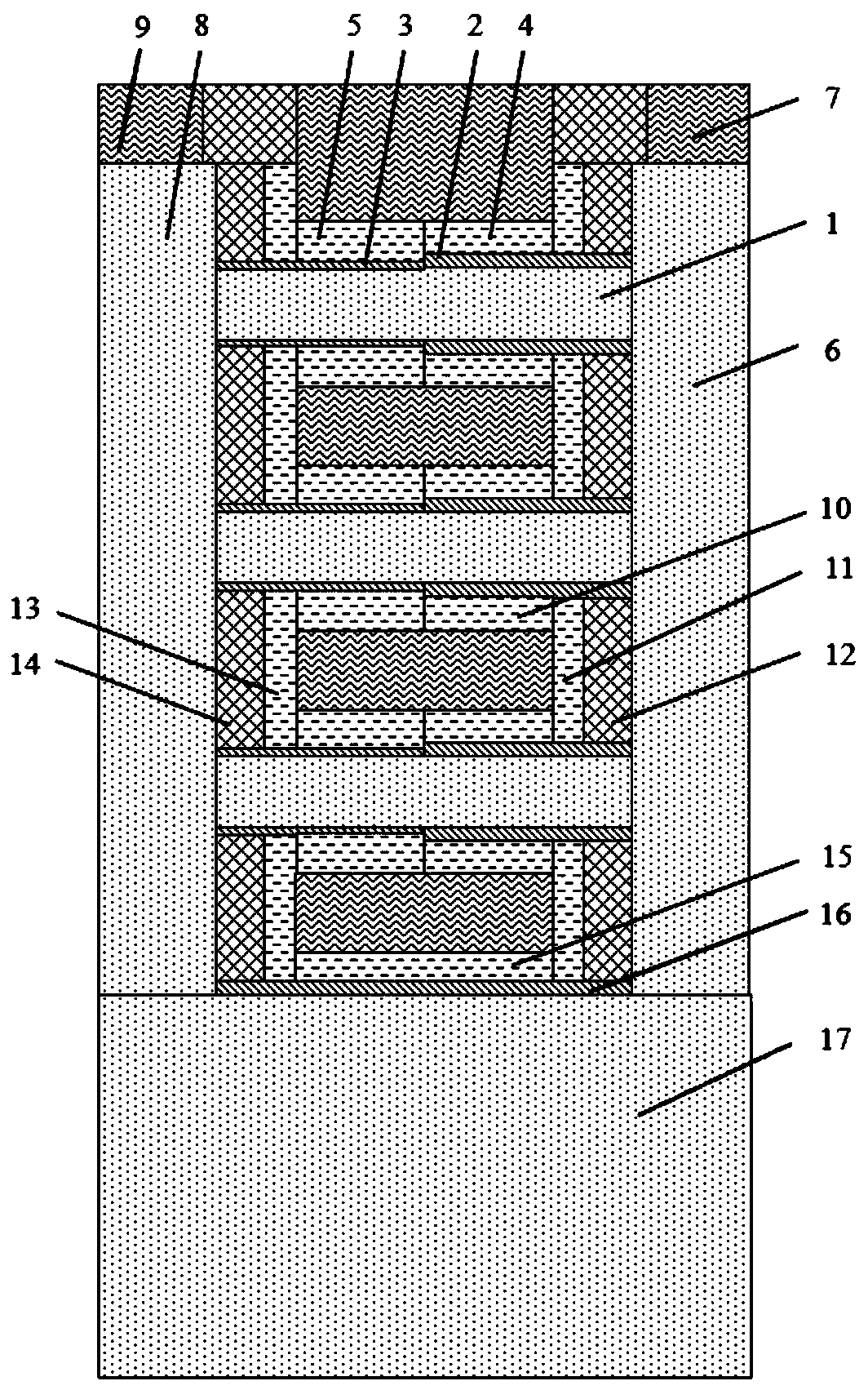

Multi-channel thin film transistor structure

ActiveUS7531837B2Reduced Threshold Voltage DriftEasy to useTransistorSolid-state devicesSemiconductorTransistor

A multi-channel thin film transistor structure including a first conducting layer, an insulating layer, a semiconductor layer and a second conducting layer is provided. The first conducting layer formed on a substrate includes a gate electrode. The insulating layer covers the first conducting layer. The semiconductor layer formed on the insulating layer includes a plurality of semiconductor islands located above the gate electrode. The second conducting layer formed on the insulating layer and on the semiconductor layer includes a source electrode and a drain electrode. Each one of the semiconductor islands is coupled electrically with the source electrode at one end and coupled electrically with the drain electrode at the other end.

Owner:E INK HLDG INC

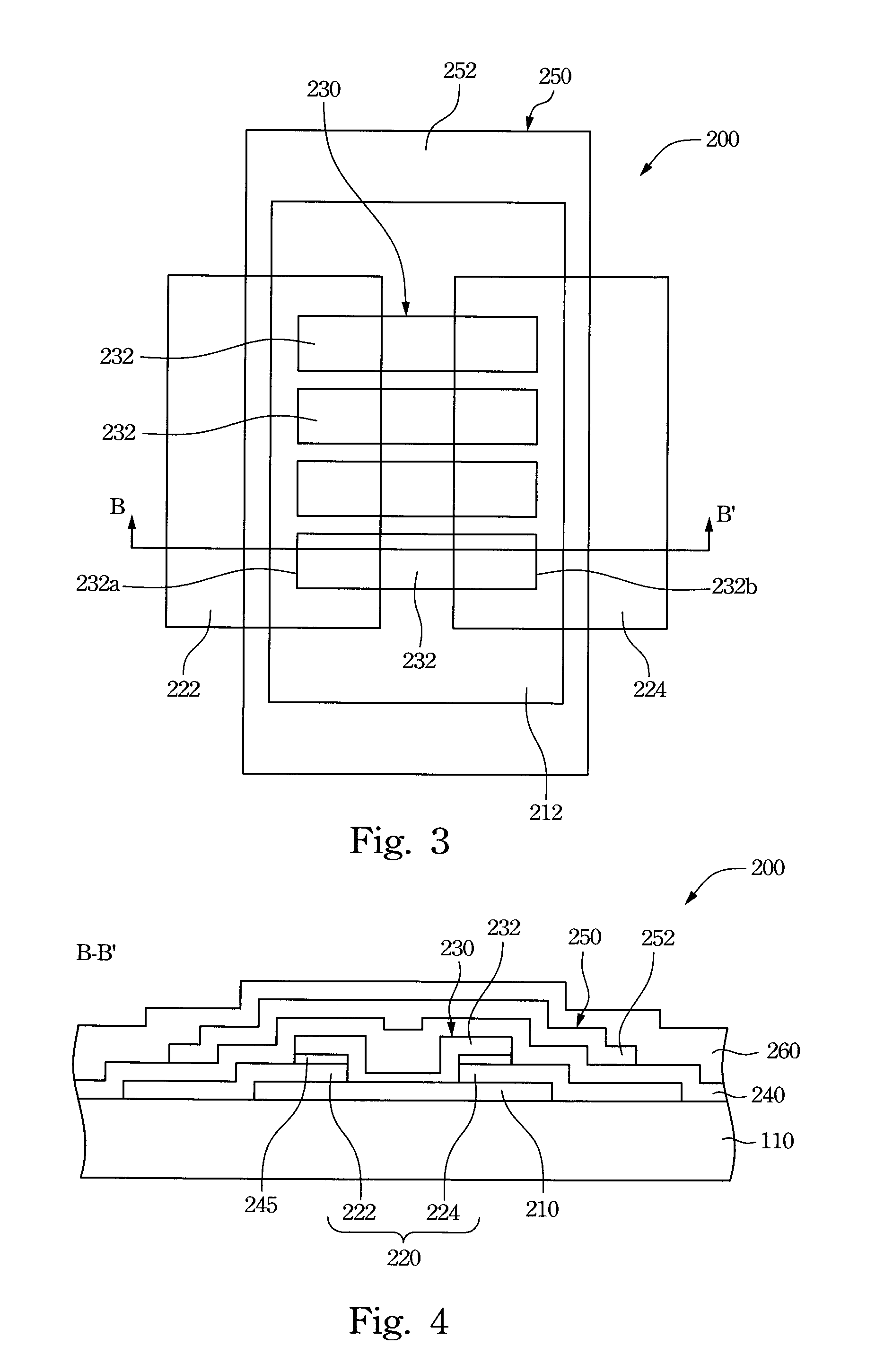

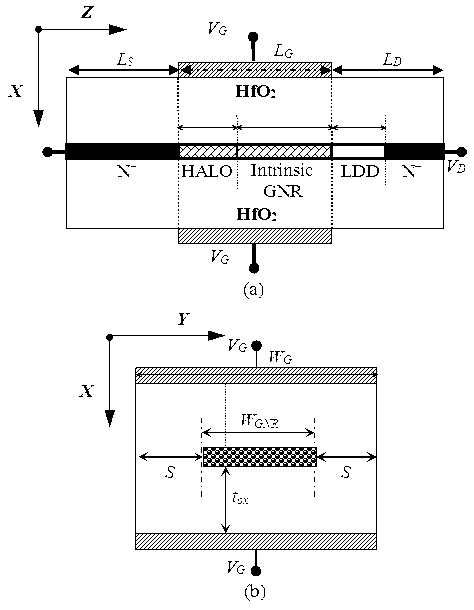

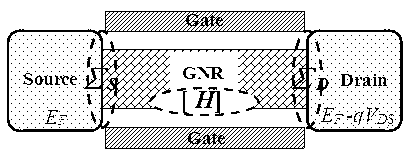

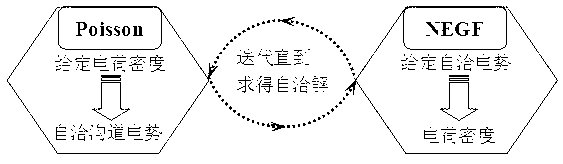

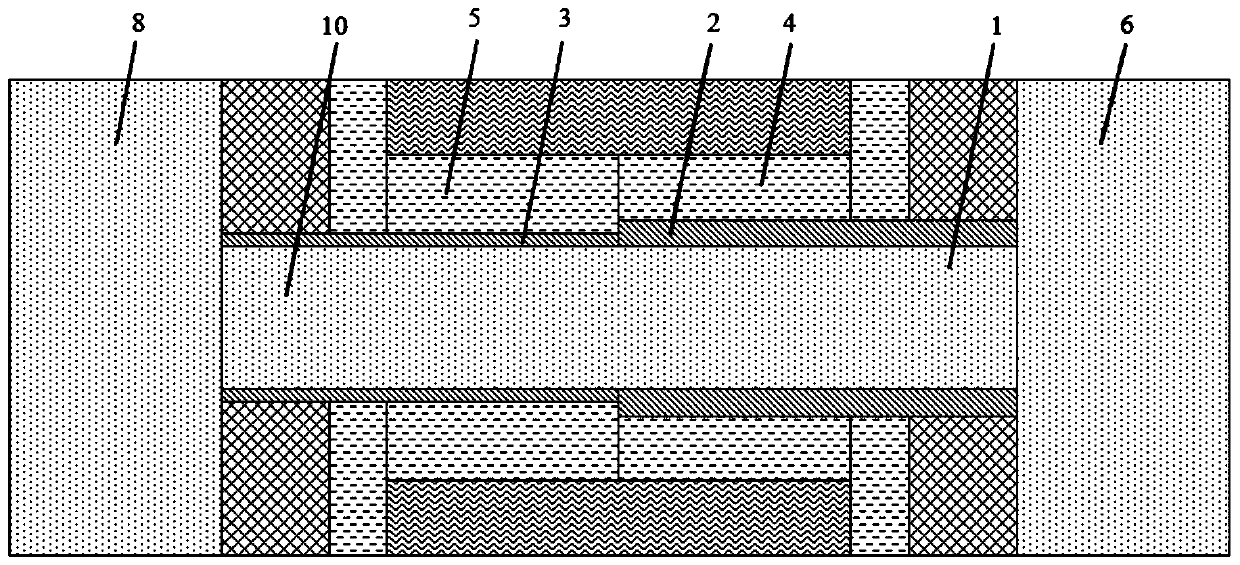

Graphene nanoribbon field-effect tube (GNRFET) with asymmetric HALO-lightly-doped drain (HALO-LDD) structure

InactiveCN103077968AReduce off-state currentGood gating abilitySemiconductor devicesPower flowSwitched current

The invention discloses a graphene nanoribbon field-effect tube (GNRFET) with an asymmetric HALO-lightly-doped drain (HALO-LDD) structure. A transport model which is suitable for a non-uniformly-doped GNRFET is constructed on the basis of a quantum mechanics non-balance Green function theoretical frame under an open boundary condition through self-consistent solution of 3D-Poisson and Schr.dinger equations, and the influence of an asymmetric HALO-LDD doping strategy on the electrical properties of the GNRFET is analyzed and calculated by using the model. As proved by comparison and analysis of the electric properties such as the output properties, transfer properties, switch current ratios, sub-threshold amplitudes and threshold voltage drifts of GNRFETs for which other doping strategies are adopted, the GNRFET with the doping structure has a higher switch current ratio, lower drain current, a smaller sub-threshold amplitude and a smaller threshold voltage drift, i.e., the GNRFET for which the asymmetric HALO-LDD doping strategy is adopted has a better grid control capability, and a short-groove effect and a hot carrier effect can be effectively restrained.

Owner:NANJING UNIV OF POSTS & TELECOMM

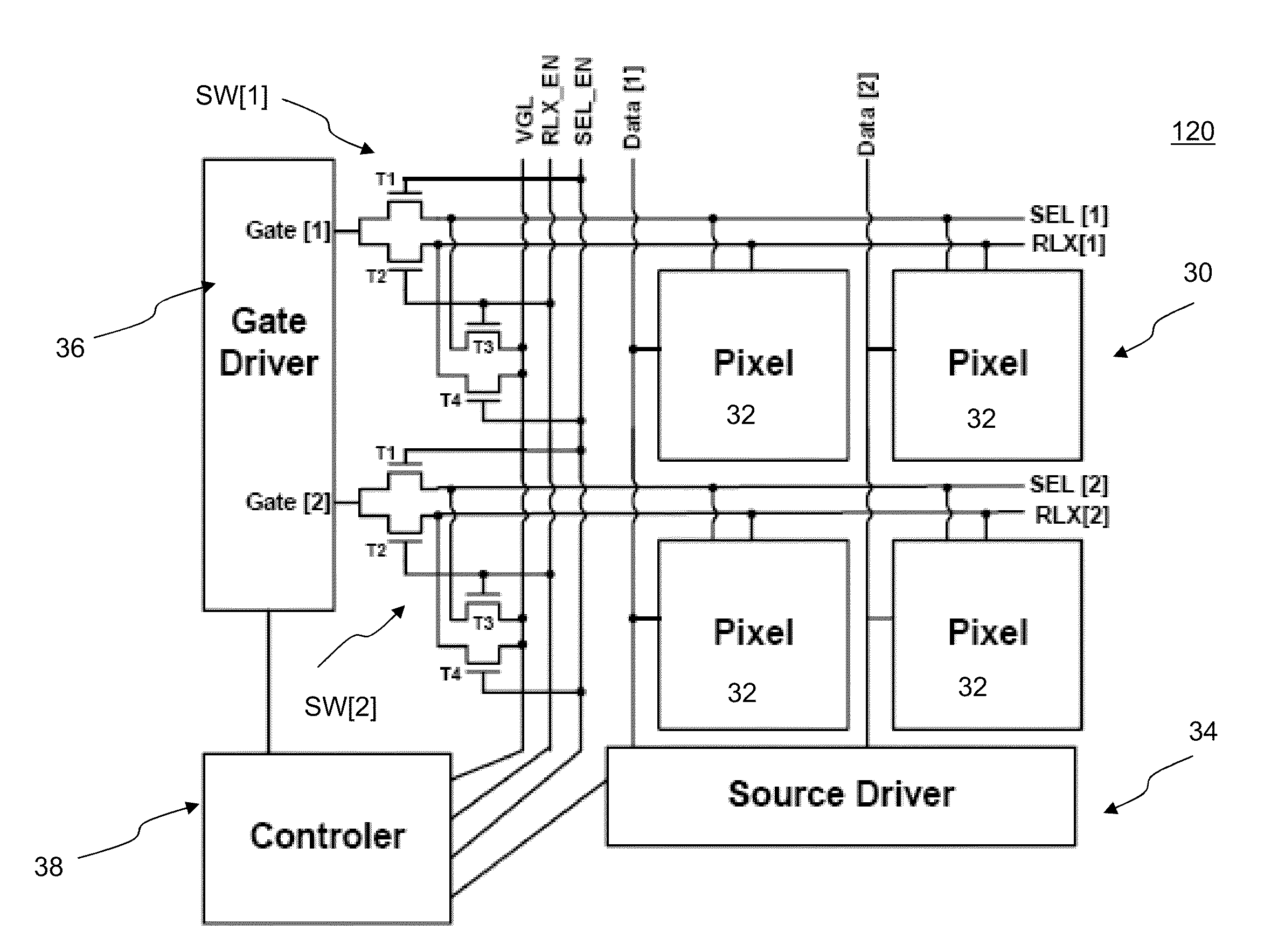

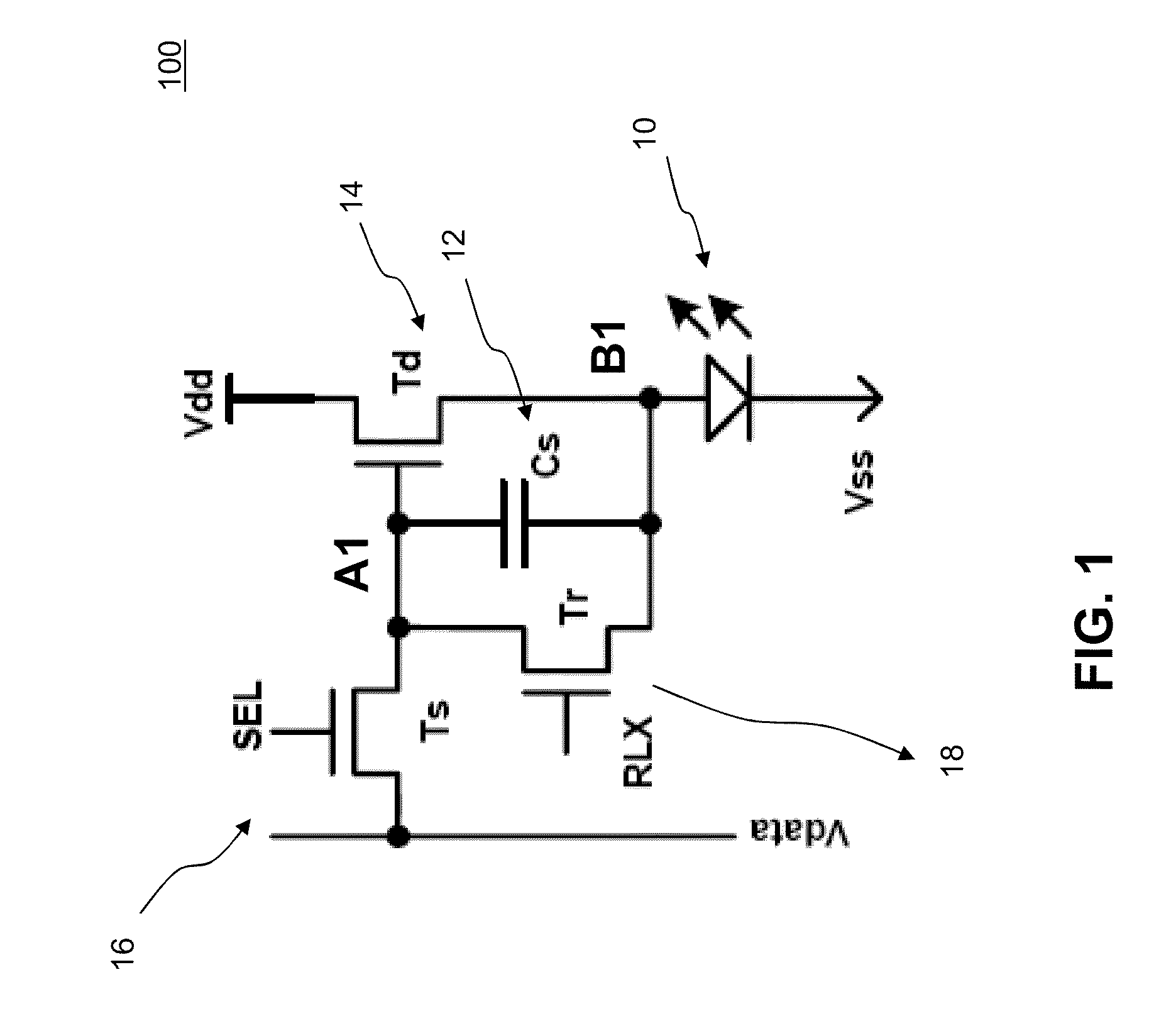

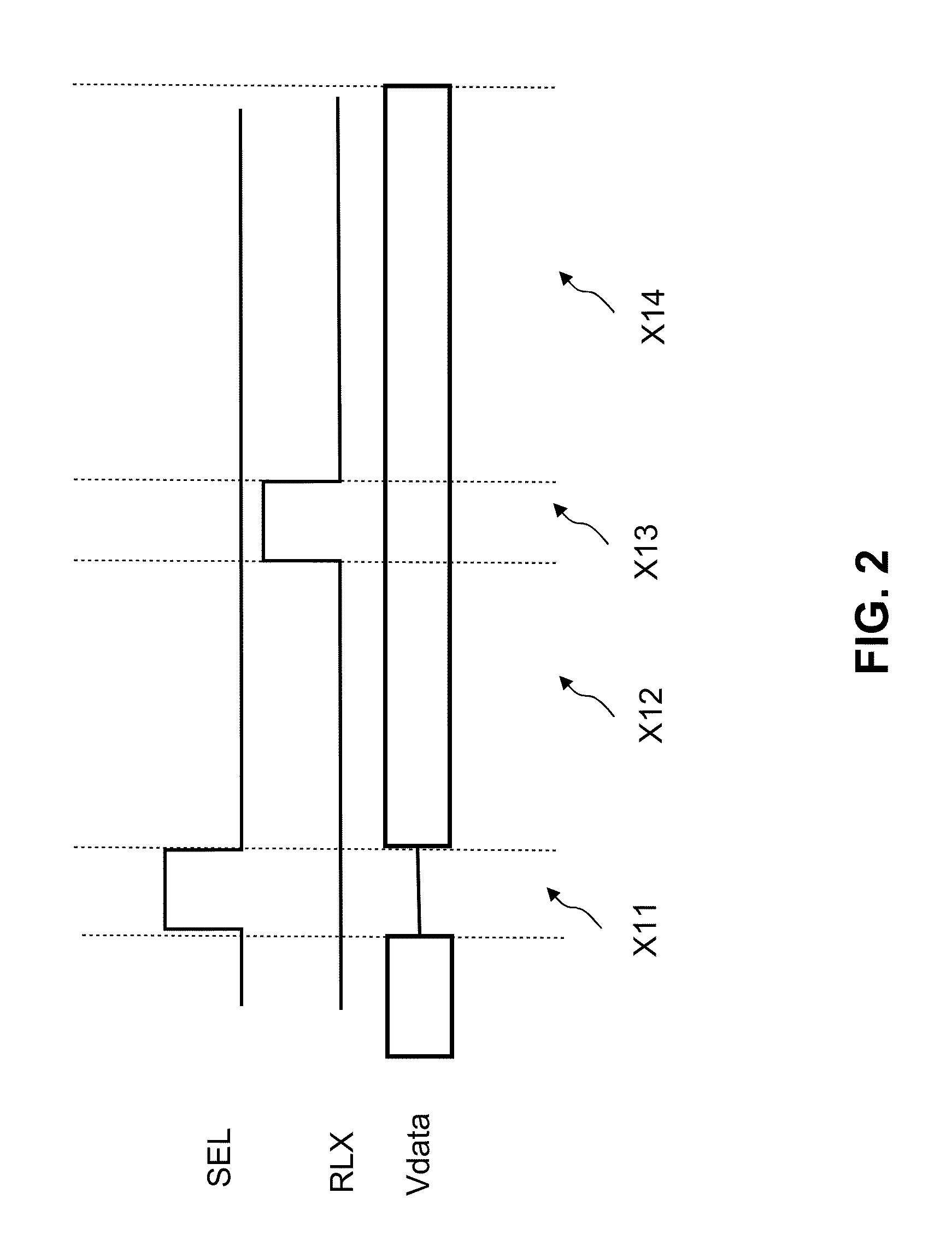

Pixel circuit, display system and driving method thereof

ActiveUS8299984B2Reduced Threshold Voltage DriftRelieve pressureElectrical apparatusElectroluminescent light sourcesDisplay deviceLight emitting device

A display system and method for the same is provided. A display includes a plurality of pixels, each having a light emitting device and a driving transistor for driving the light emitting device, the driving transistor and the light emitting device being coupled in series between a first power supply and a second power supply. The method includes: at a first frame, programming a pixel with a first programming voltage different from a programming voltage for a valid image, and charging at least one of the first power supply and the second power supply so that at least one of the driving transistor and the light emitting device is under a negative bias. The pixel circuit includes: a light emitting device; a driving transistor for driving the light emitting device, the driving transistor having a gate terminal, a first terminal coupled to the light emitting device, and a second terminal; a storage capacitor; a first switch transistor coupled to a data line for providing a programming data and the gate terminal of the driving transistor; and a second switch transistor for reducing a threshold voltage shift of the driving transistor, the storage capacitor and the second switch transistor being coupled in parallel to the gate terminal of the driving transistor and the first terminal of the driving transistor. The method includes: at a first cycle, implementing an image display operation having programming the pixel circuit for a valid image and driving the light emitting device; and at a second cycle, implementing a relaxation operation for reducing a stress on the pixel circuit, including: selecting a relaxation switch transistor coupled to the storage capacitor in parallel.

Owner:IGNIS INNOVATION

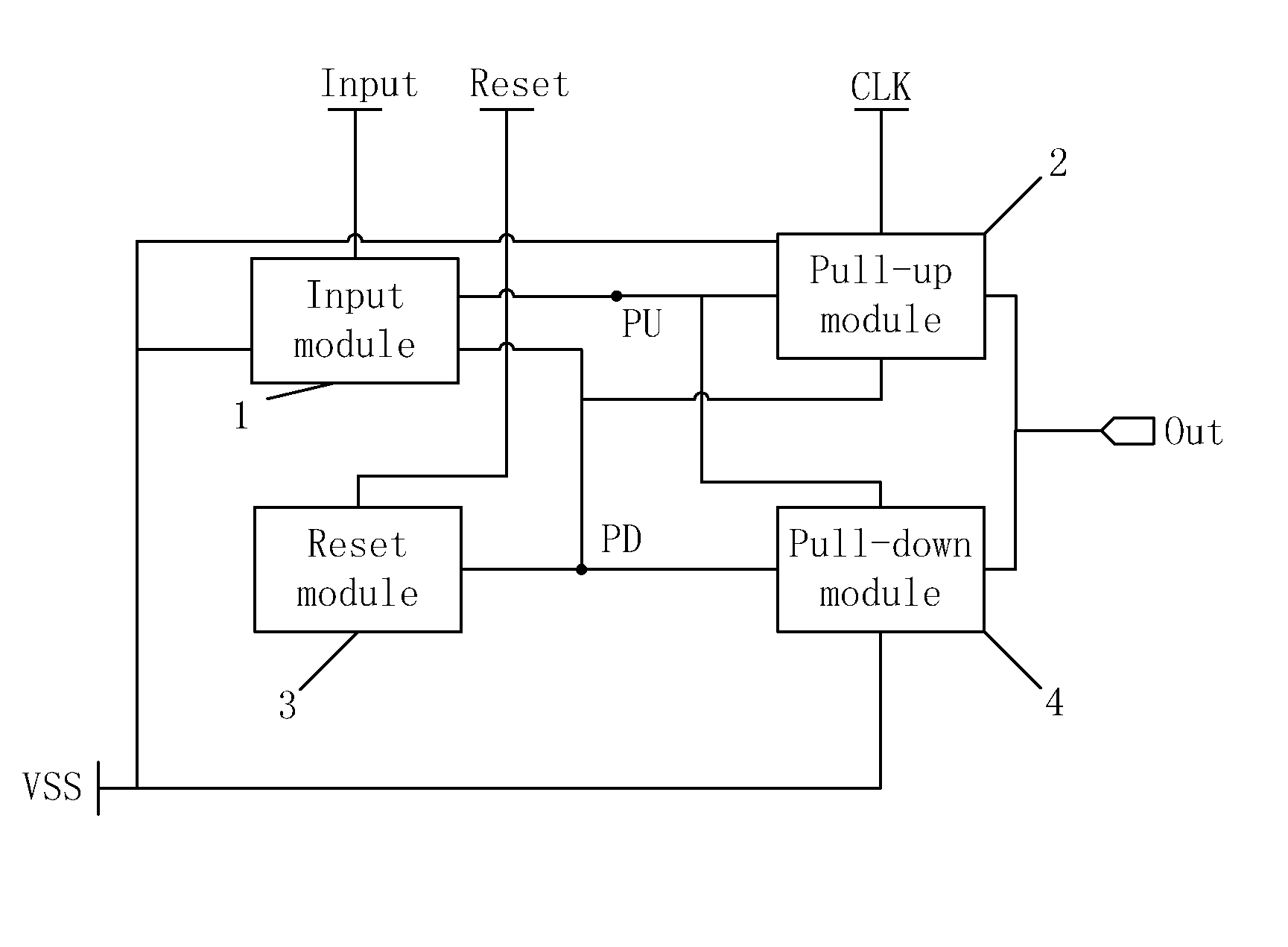

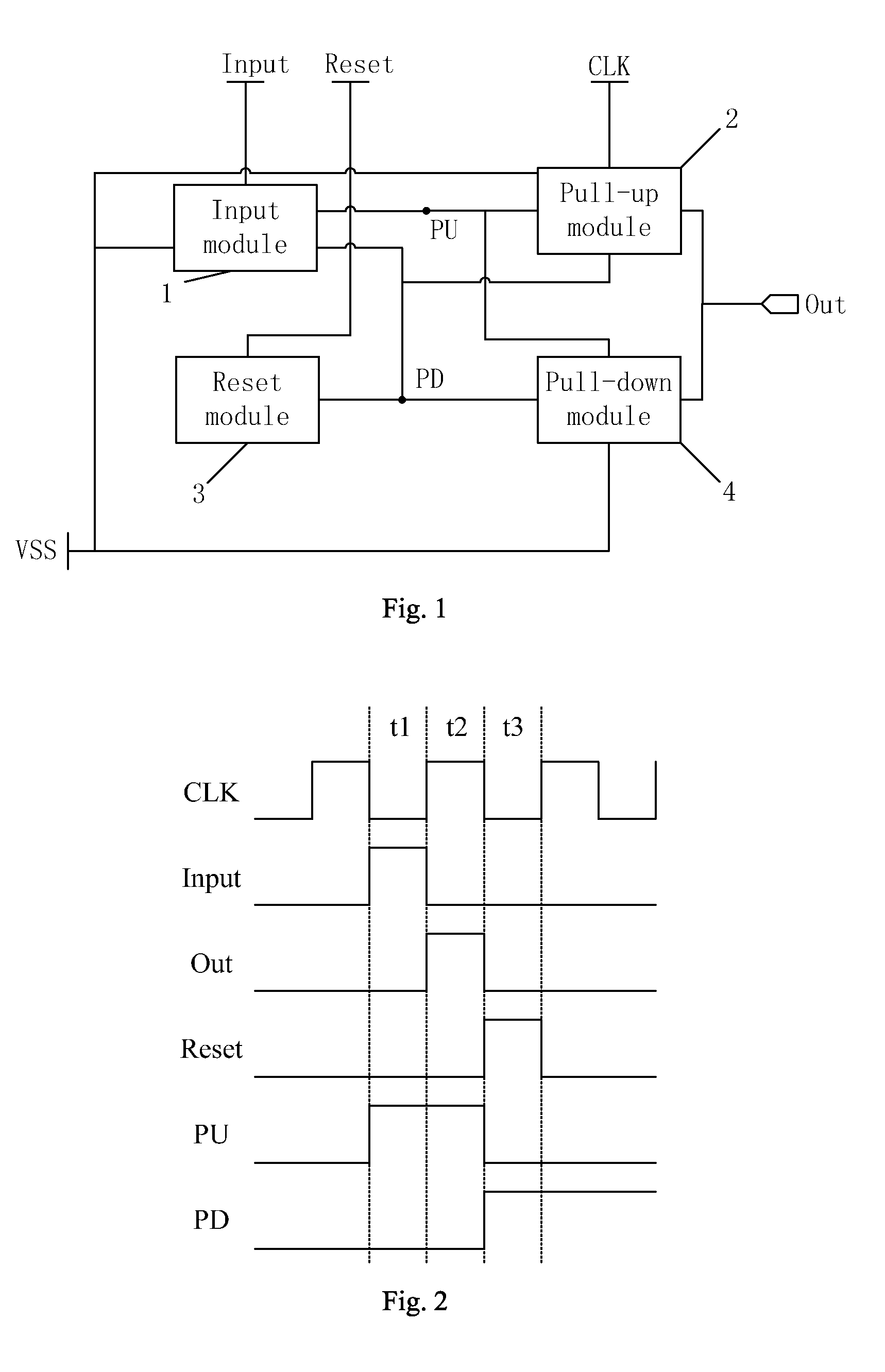

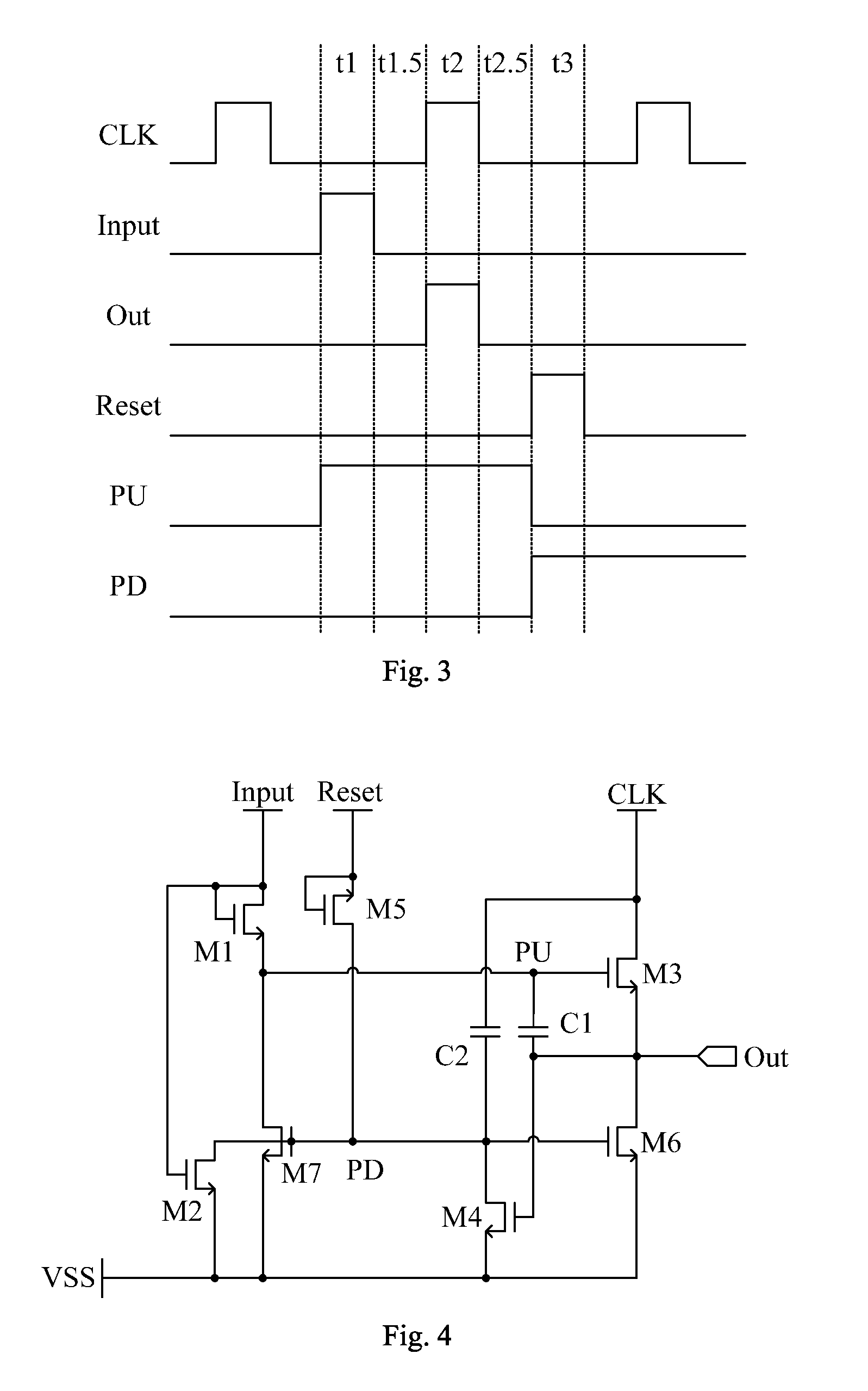

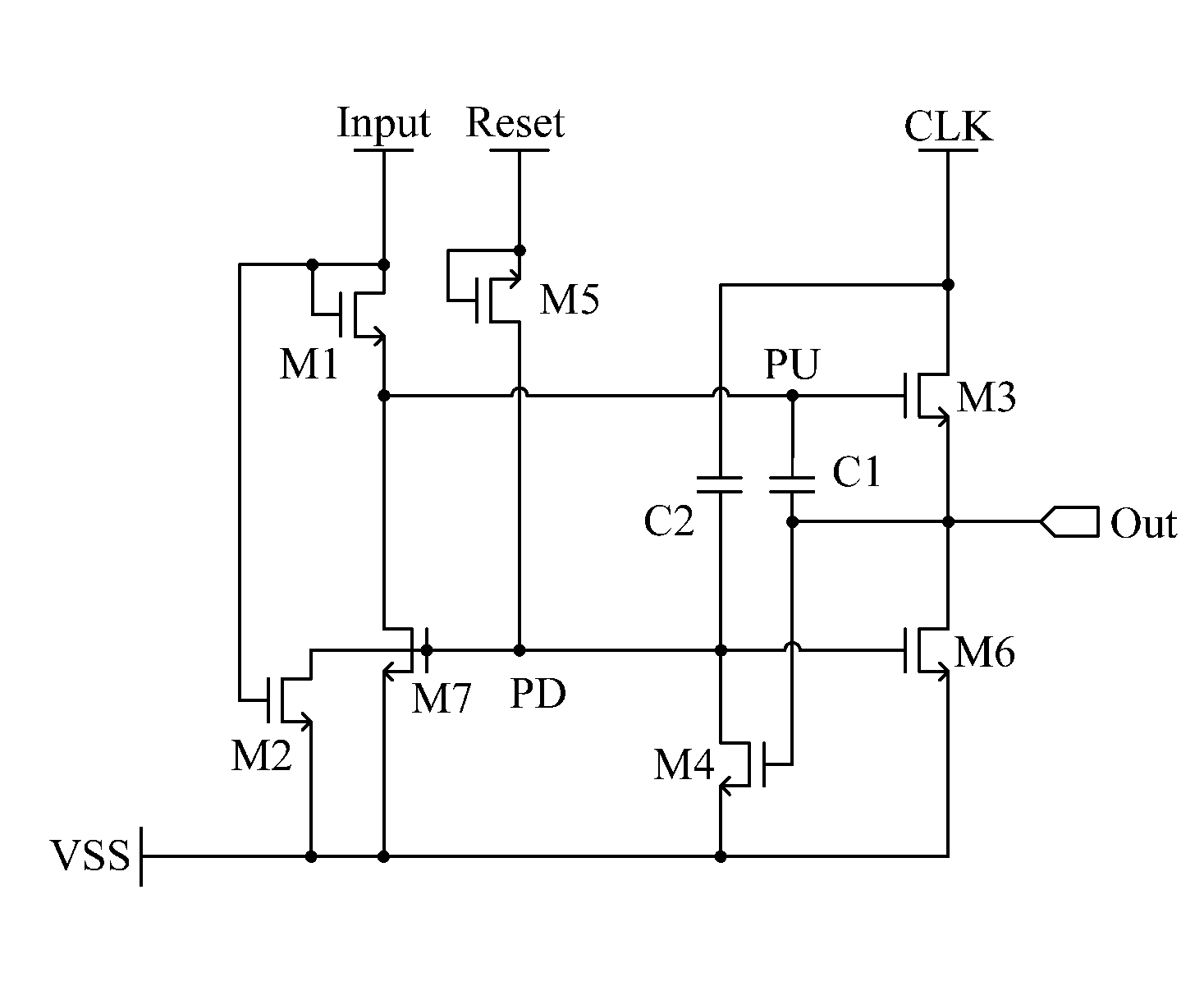

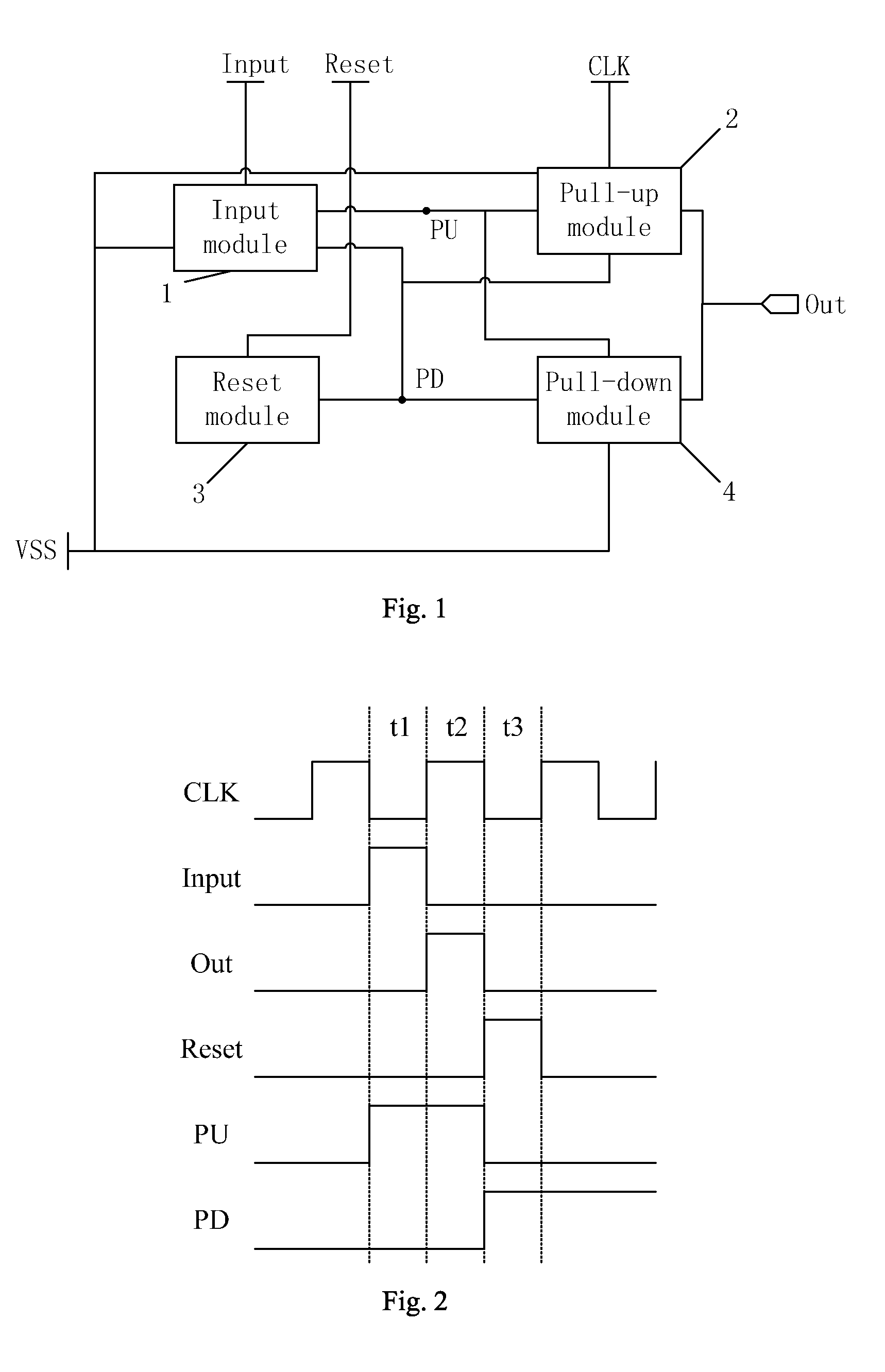

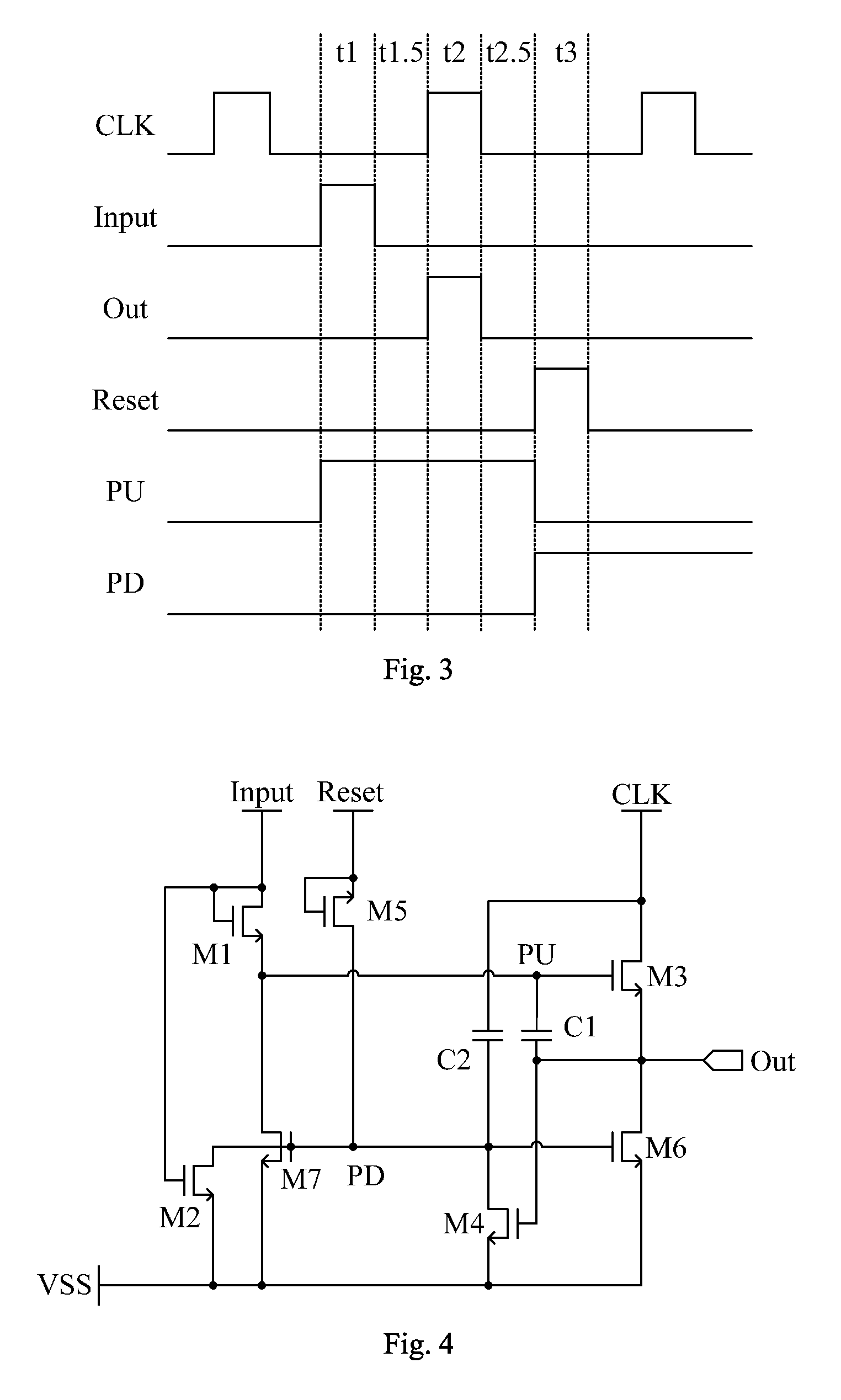

Shift register unit, gate driving circuit, and display device

ActiveUS20150302936A1Improve stabilityReduce wiring spaceStatic indicating devicesDigital storageShift registerProcessor register

The present invention provides a shift register unit, a gate driving circuit and a display device. The shift register unit comprises: an input module for, in response to turn-on level input via the shift register input terminal, providing turn-on level to the first node and providing turn-off level to the second node; a pull-up module for, in response to turn-on level of the first node, providing a clock signal to the shift register output terminal, and also used for, in response to turn-on level output by the shift register output terminal, providing turn-off level to the second node; a reset module for, in response to turn-on level input via the reset signal input terminal, providing the turn-on level to the second node; and a pull-down module for, in response to turn-on level of the second node, providing turn-off level to the shift register output terminal and the first node.

Owner:BOE TECH GRP CO LTD +1

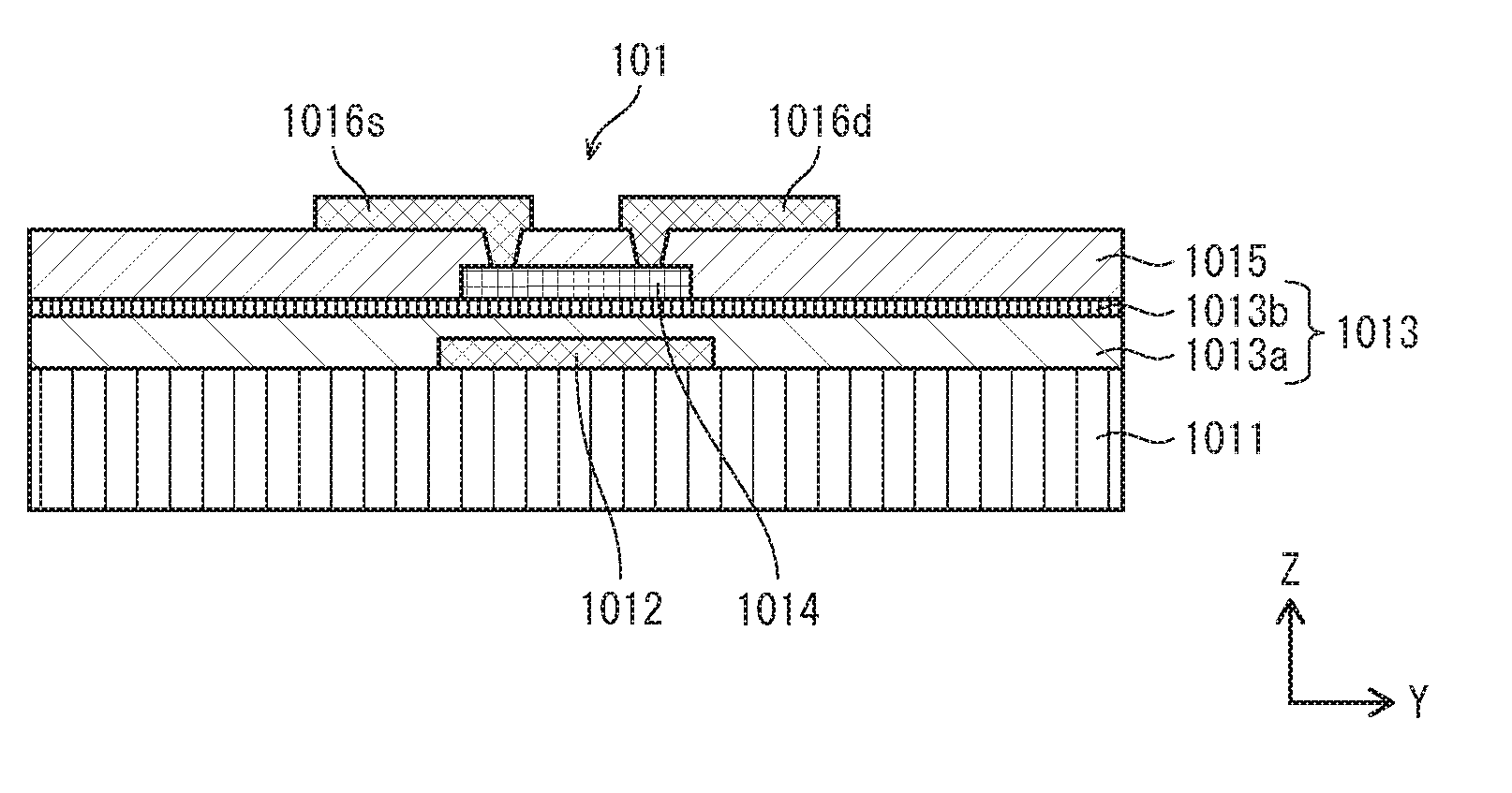

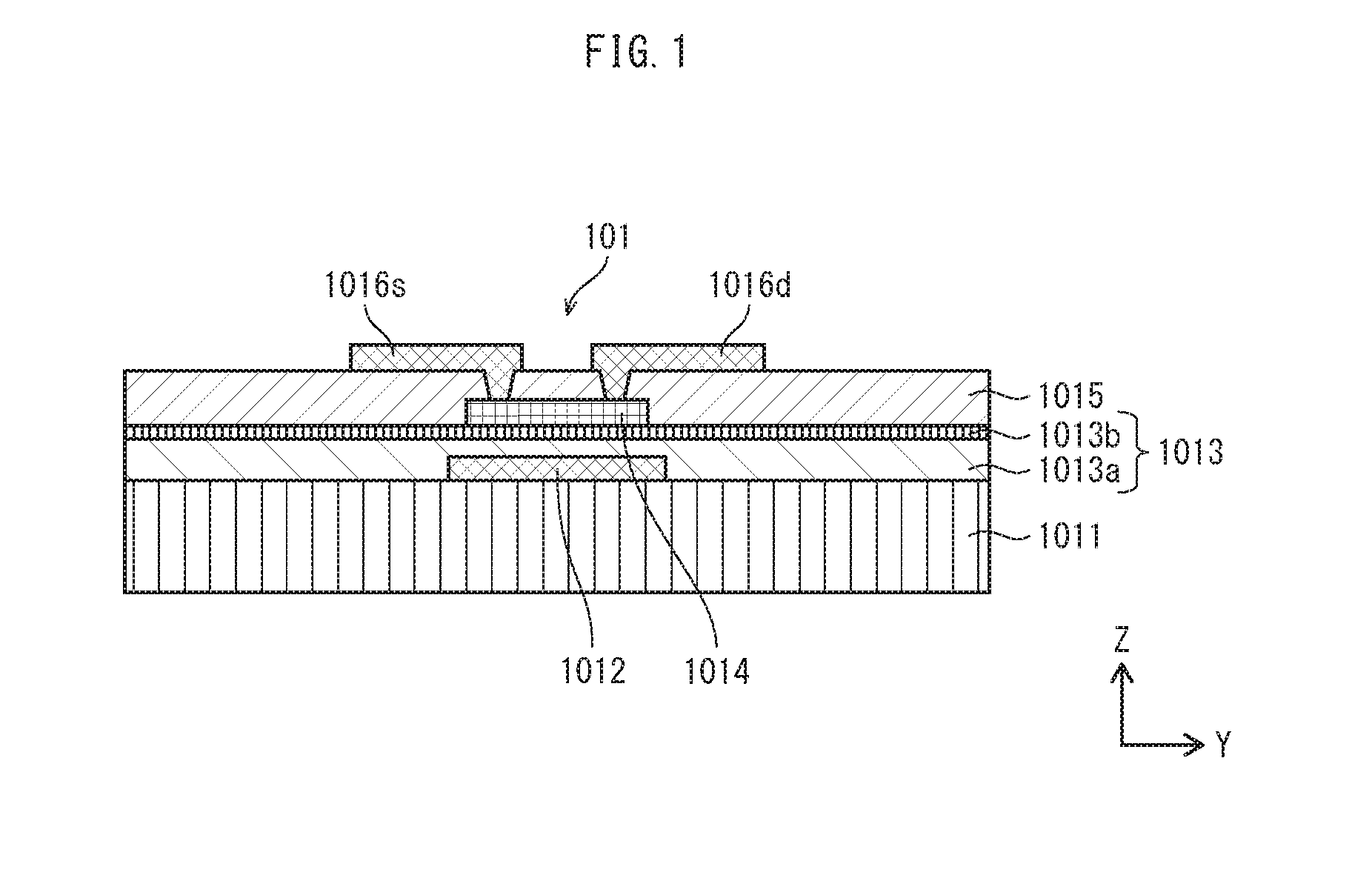

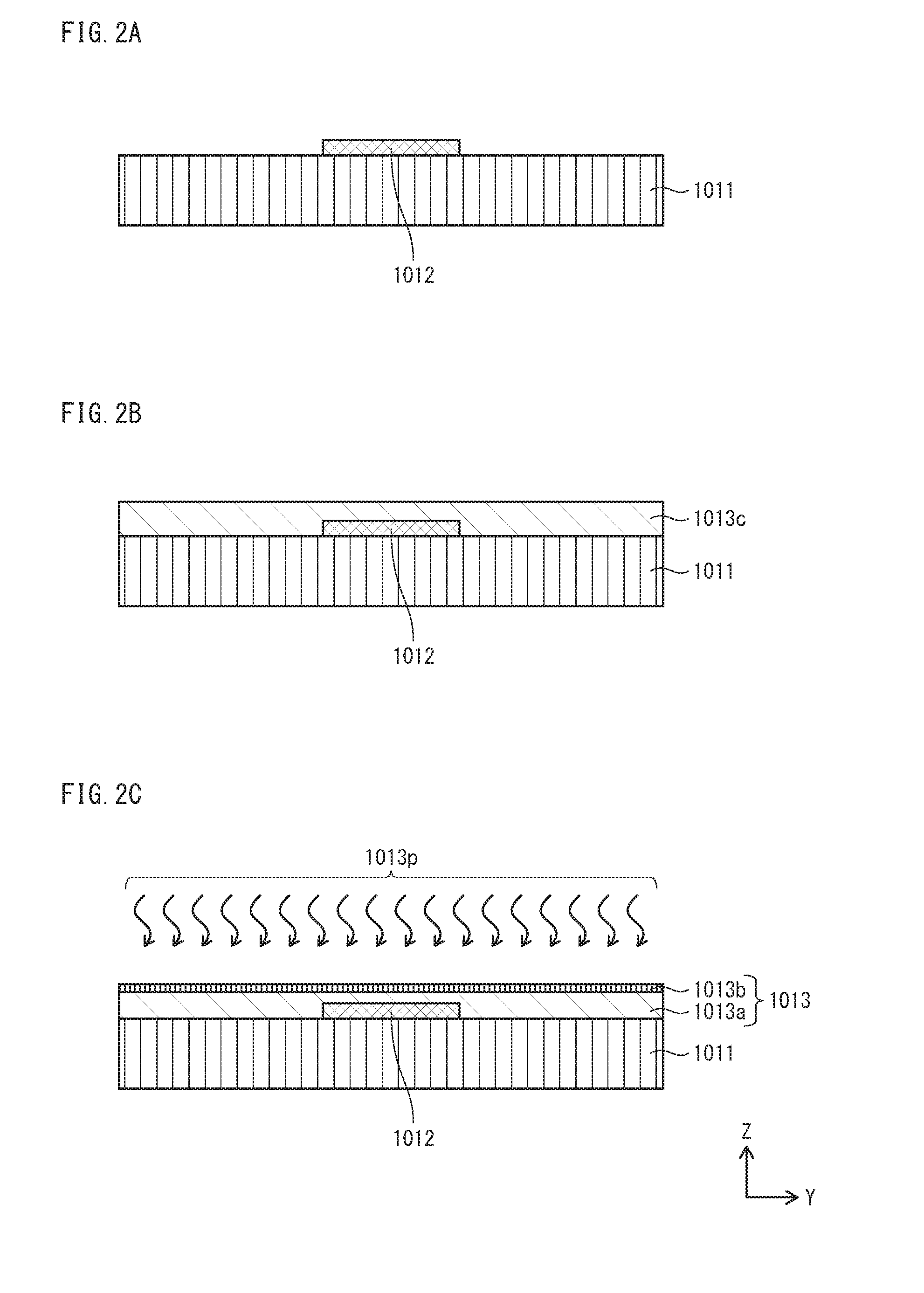

Thin film transistor element, production method for same, and display device

A thin-film transistor includes: a gate electrode; a source electrode; a drain electrode; a channel layer that is in contact with the source electrode and the drain electrode, and includes oxide semiconductor; and a gate insulating layer that is disposed between the gate electrode and the channel layer, and is in contact with the gate electrode and the channel layer, wherein a region of the gate insulating layer that is in contact with the channel layer is a silicon compound film, and the silicon compound film contains silicon, nitrogen, and oxygen, and is formed by performing plasma processing for introducing, into a film containing silicon and one of nitrogen and oxygen, the other of nitrogen and oxygen.

Owner:JOLED INC

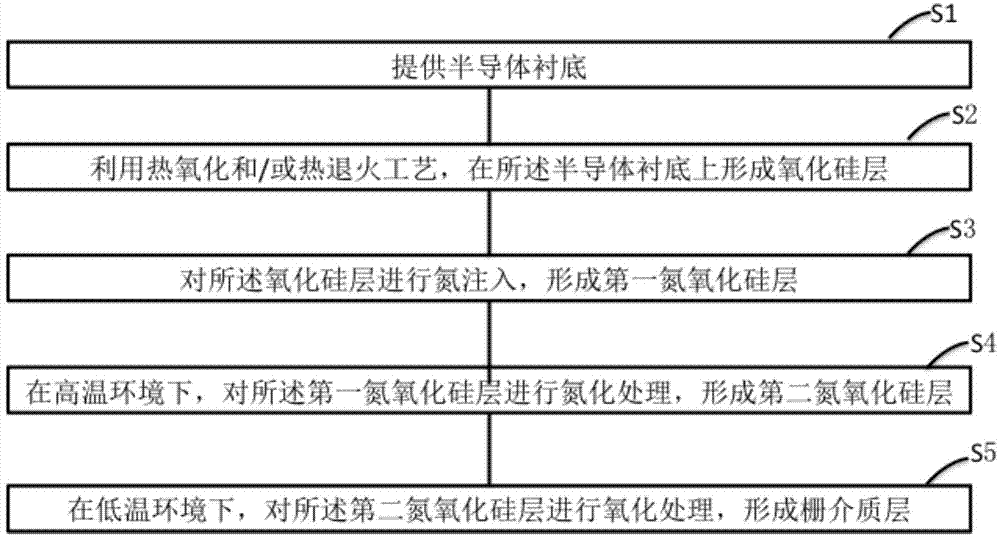

Manufacturing method of gate dielectric layer

InactiveCN103903986ARepair damageSi-N bond is stableSemiconductor/solid-state device manufacturingSemiconductor devicesGate dielectricNitrogen

The invention provides a manufacturing method of a gate dielectric layer. The manufacturing method comprises the steps that a semiconductor substrate is provided; a silicon oxide layer is formed on the semiconductor substrate by using a thermal oxidation technology and / or a thermal annealing technology; nitride injection is conducted on the silicon oxide layer to form a first silicon oxynitride layer; under high-temperature environment, nitriding processing is conducted on the first silicon oxynitride layer to form a second silicon oxynitride layer; under low-temperature environment, oxidizing processing is conducted on the second silicon oxynitride layer to form the gate dielectric layer. The gate dielectric layer formed through the method has a higher dielectric constant, and meanwhile can effectively prevent impurities from dispersing in the gate dielectric layer.

Owner:SHANGHAI HUALI MICROELECTRONICS CORP

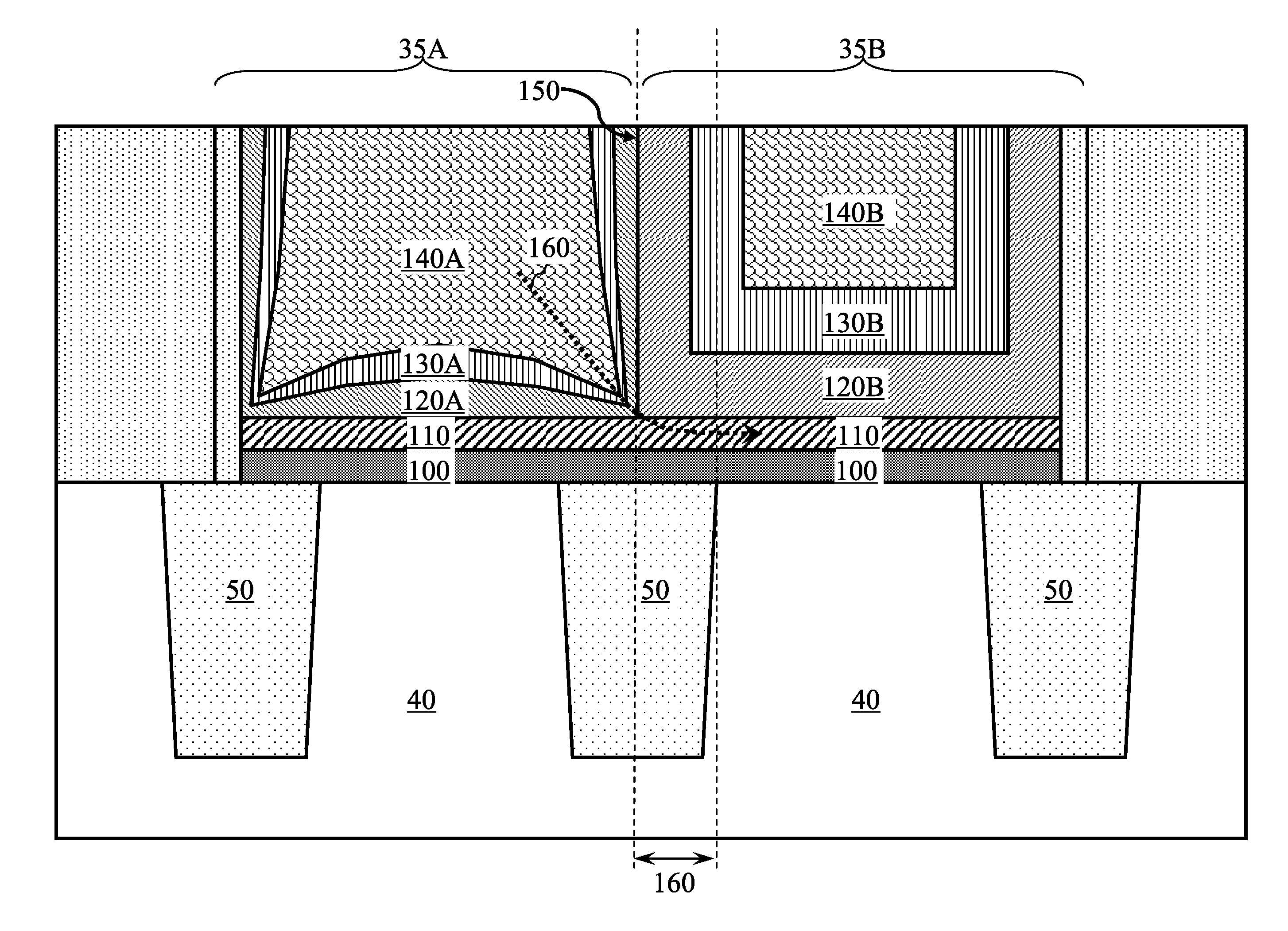

Nonvolatile semiconductor memory device and manufacturing method thereof

InactiveUS20080261365A1Reduce capacitanceReduced Threshold Voltage DriftTransistorSolid-state devicesCapacitanceMiniaturization

A technology realizing decreases of capacitance between the adjoining floating gates and of the threshold voltage shift caused by interference between the adjoining memory cells in a nonvolatile semiconductor memory device with the advances of miniaturization in the period following the 90 nm generation. By having the floating gate 3 of a memory cell with an inverse T-shape and the dimension of a part of the floating gate through the control gate 4 and the second insulator film 8 being smaller than the bottom part of the floating gate, the effects of a threshold voltage shift is reduced maintaining the adequate area of the gap between the floating gate 3 and the control gate 4, decreasing the opposing area of the gap of the floating gates 3 underneath the adjoining word lines WL, maintaining the capacity coupling ratio between the floating gate 3 and the control gate, and reducing the opposing area of the gap of the adjoining floating gates 3.

Owner:SASAGO YOSHITAKA +1

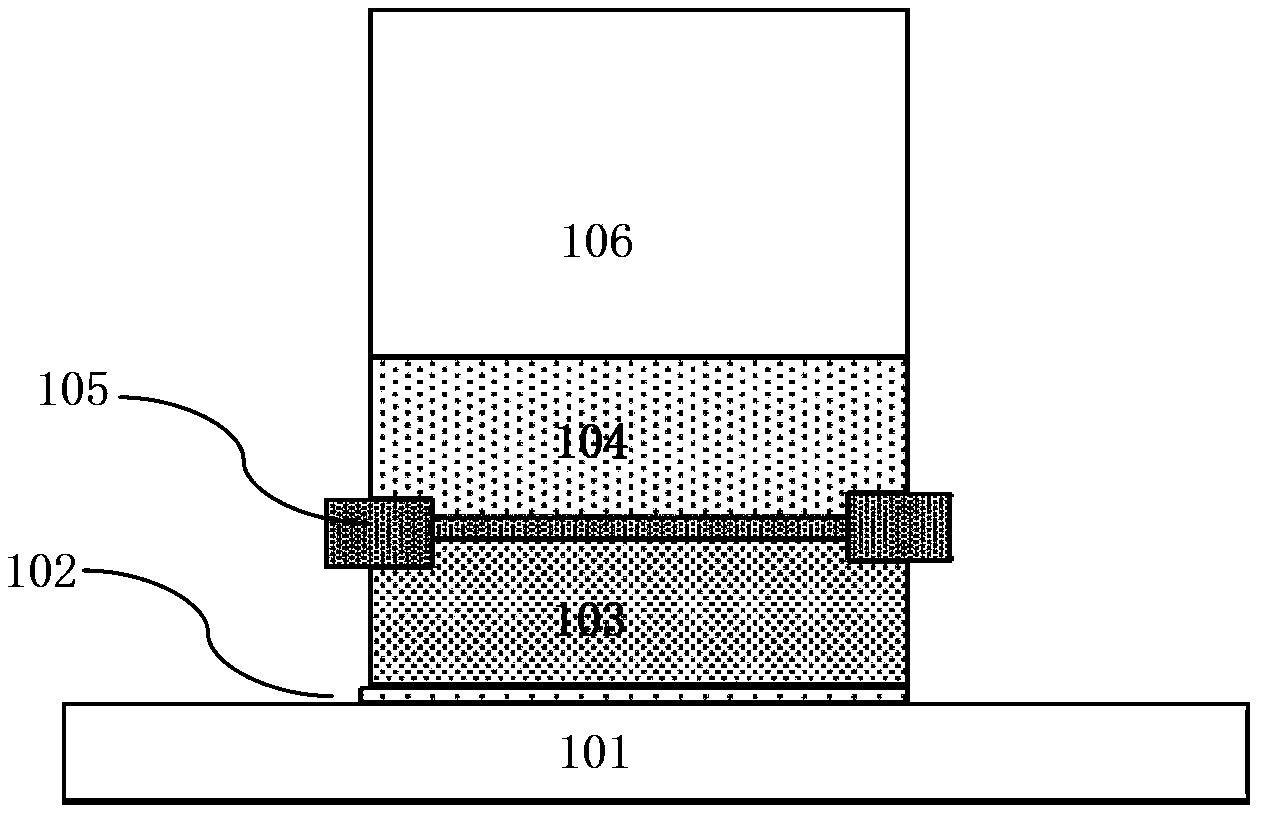

Thin film transistor

ActiveCN103730514AReduce processing difficultyNo effect on normal workTransistorCircuit reliabilityCharge carrier

The invention discloses a thin film transistor. The thin film transistor comprises a substrate, a semiconductor channel region, a gate insulating layer, a source region, a leakage region, a source electrode, a leakage electrode and a gate electrode. The thin film transistor further comprises a current carrier injection structure. The thin film transistor can remarkably reduce device degradation and threshold voltage drift, the device and circuit reliability of the thin film transistor is improved, the complexity of the threshold voltage compensating circuit design is simplified. In addition, the thin film transistor is low in process difficulty and does not influence normal work of devices.

Owner:SUZHOU UNIV

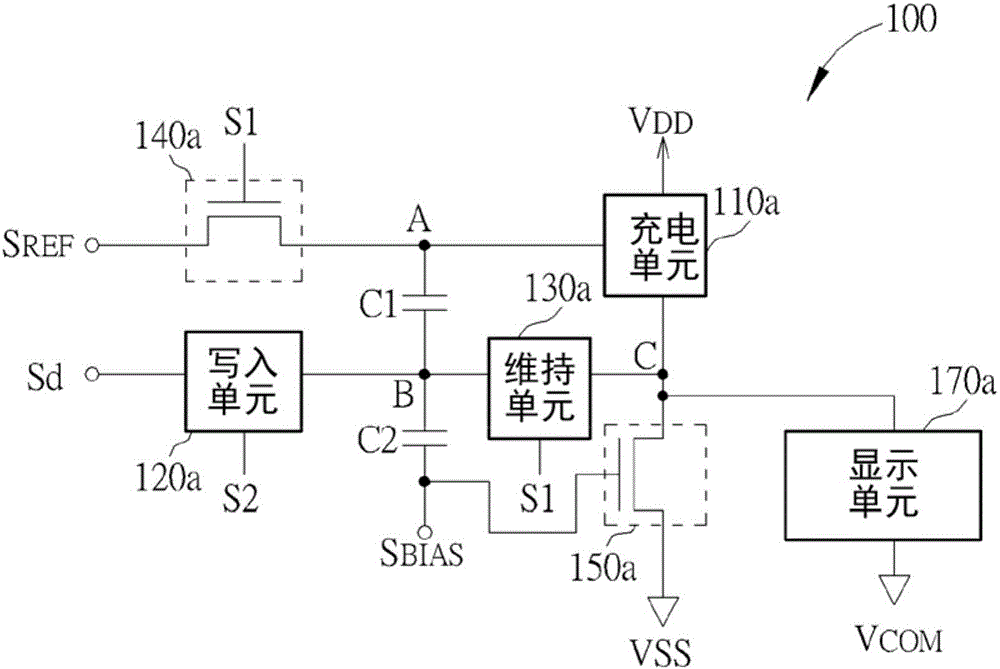

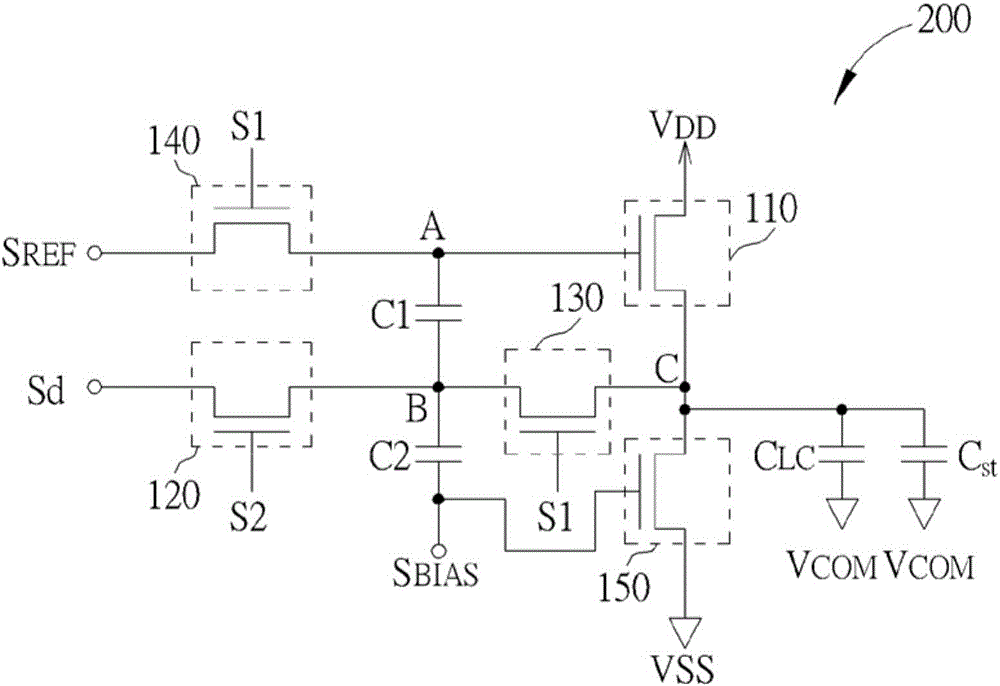

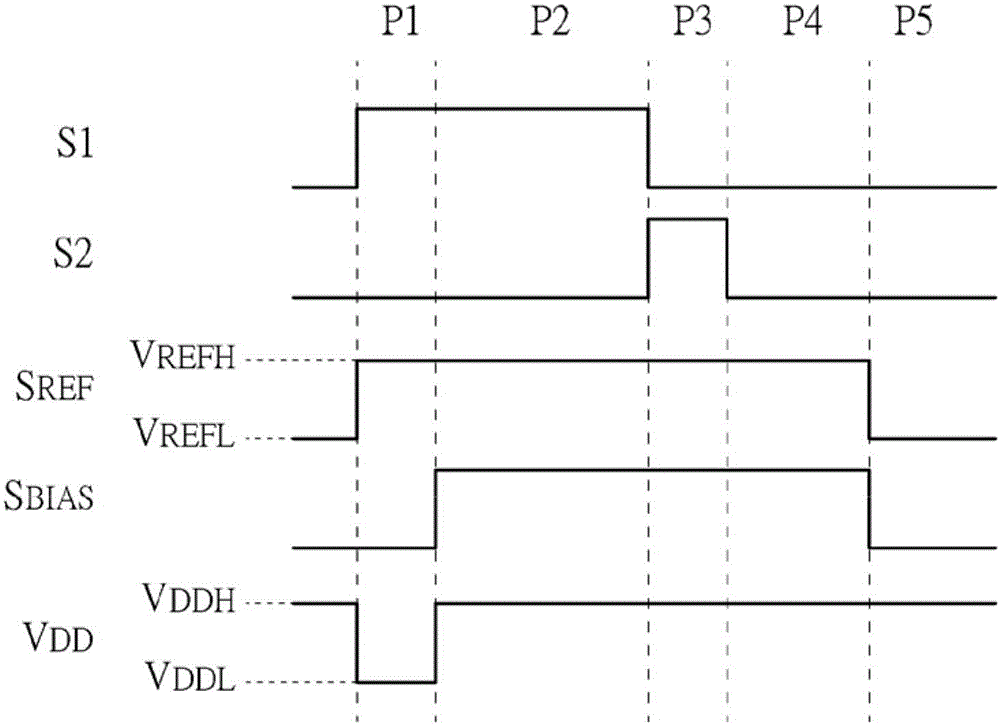

Display control circuit and its operation method

ActiveCN106782359AReduced Threshold Voltage DriftStable brightnessStatic indicating devicesCapacitanceData signal

The present invention discloses a display control circuit including a charging unit, a writing unit, a display unit, a sustaining unit, a first control unit, a second control unit, a first capacitor and a second capacitor, and a method of operating the same. The write unit is used to receive the data signal. The display unit is electrically coupled to the charging unit and the common voltage terminal for displaying the image. The sustaining unit is electrically coupled to the writing unit, the display unit and the second capacitor. The first capacitor is electrically coupled to the first control unit and the writing unit. The second control unit is electrically coupled to the charging unit and the reference level.

Owner:AU OPTRONICS CORP

Grid driving circuit and display device using same

ActiveCN104050943AReduced Threshold Voltage DriftReduce noiseStatic indicating devicesDisplay deviceEngineering

The invention provides a grid driving circuit. The grid driving circuit comprises multiple levels of grid driving units, and each level of grid driving unit comprises a first switching element, a second switching element...a ninth switching element. All the levels of grid driving units receive external signals including a first clock signal, a second clock signal, a first steady signal, a second steady signal, first grid driving signals output by the grid driving units higher than the grid driving units for receiving the external signals by two levels and second grid driving signals output by the grid driving units lower than the grid driving units for receiving the external signals by two levels. According to the grid driving circuit, the sixth switching elements and the ninth switching elements are controlled by the first steady signal and the second steady signal to work intermittently, noise, generated by clock hopping, of an output level is reduced, meanwhile, influences on the stability of the grid driving signals from the sixth switching elements and the ninth switching elements are reduced, therefore, the stable grid driving signals can be output, the reliability is high and design is simple.

Owner:KUSN INFOVISION OPTOELECTRONICS

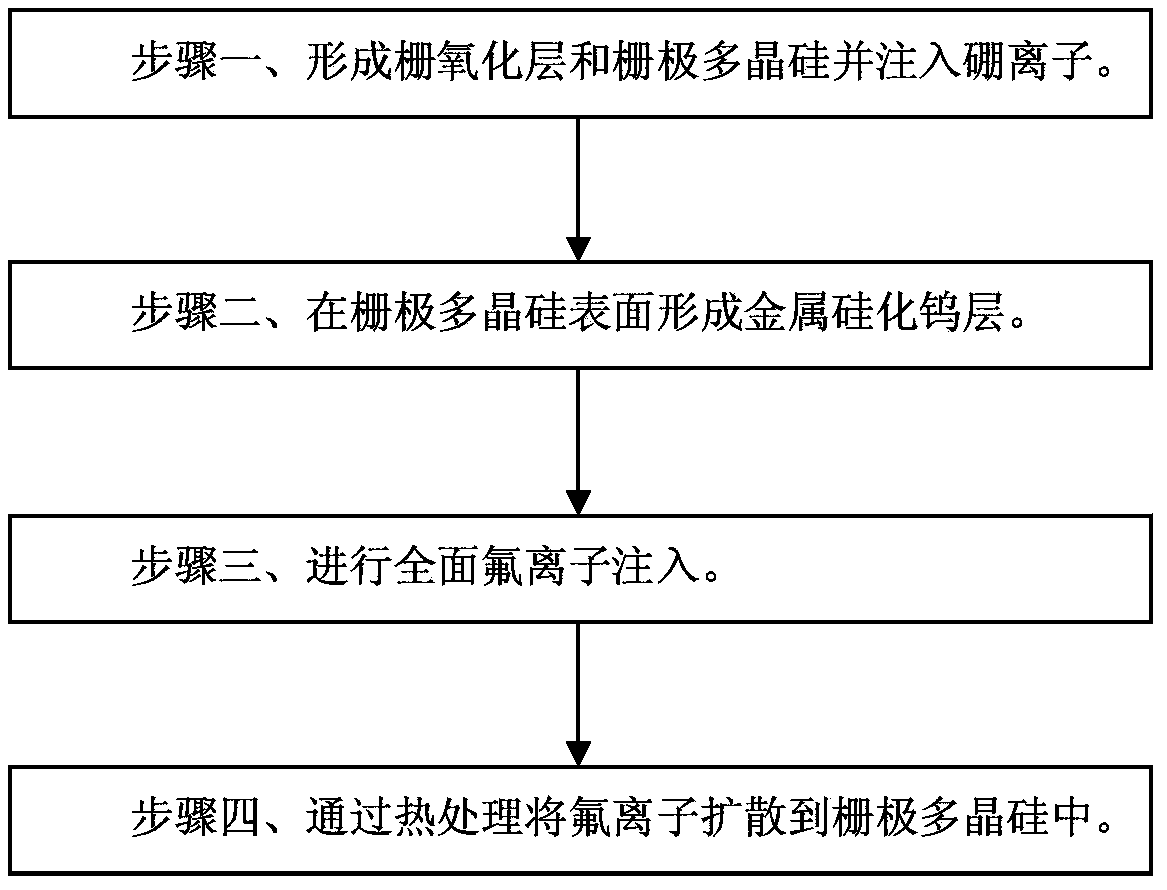

Method for improving negative bias temperature stability of grid of PMOS device

ActiveCN104347370AReduced Threshold Voltage DriftImproved Negative Bias Temperature StabilitySemiconductor/solid-state device manufacturingSemiconductor devicesHydrogenSilicon oxide

The invention discloses a method for improving the negative bias temperature stability of the grid of a PMOS device. The method comprises the following steps: forming a grid oxide layer and grid polysilicon, and injecting boron ions; forming a metal tungsten silicide layer on the surface of the grid polysilicon; performing comprehensive fluorinion injection; and diffusing fluorinions into the grid polysilicon through thermal treatment. According to the invention, the stress at the interface of silicon and silicon oxide of the grid can be decreased, the interface state generated due to the existence of hydrogen bonds is reduced, the stability of the interface of the silicon and the silicon oxide can be enhanced, the threshold voltage drift of the PMOS device can be effectively reduced, and the negative bias temperature stability of the grid of the PMOS device is improved.

Owner:SHANGHAI HUAHONG GRACE SEMICON MFG CORP

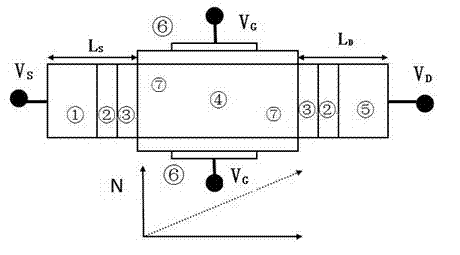

Linear doped spin field-effect tube (Spin-FET)

InactiveCN103094327AReduce off-state currentRaise the threshold voltageSemiconductor devicesSwitched currentSchrödinger equation

The invention discloses a spin field-effect tube (Spin-FET) with a linear light dope structure. A transport model which is suitable for the linear doped Spin-FET is constructed based on the quantum mechanics nonequilibrium green function theoretical framework and through the self-consistent solving Poisson and the Schrodinger equation, and the influence of a linear doping strategy and a common doping strategy on the electrical properties of the Spin-FET is calculated by using the model. Compared with the electrical properties of other doping strategies such as output characteristics, transfer characteristics, switch current ratio and magnetism current rate, the linear doped Spin-FET has larger switch current ratio, higher magnetism current rate, and smaller sub-threshold swing and threshold voltage drift. Not only can show that linear doping has better grid control capability, but also short-channel effect and hot carrier effect can be effectively restrained.

Owner:NANJING UNIV OF POSTS & TELECOMM

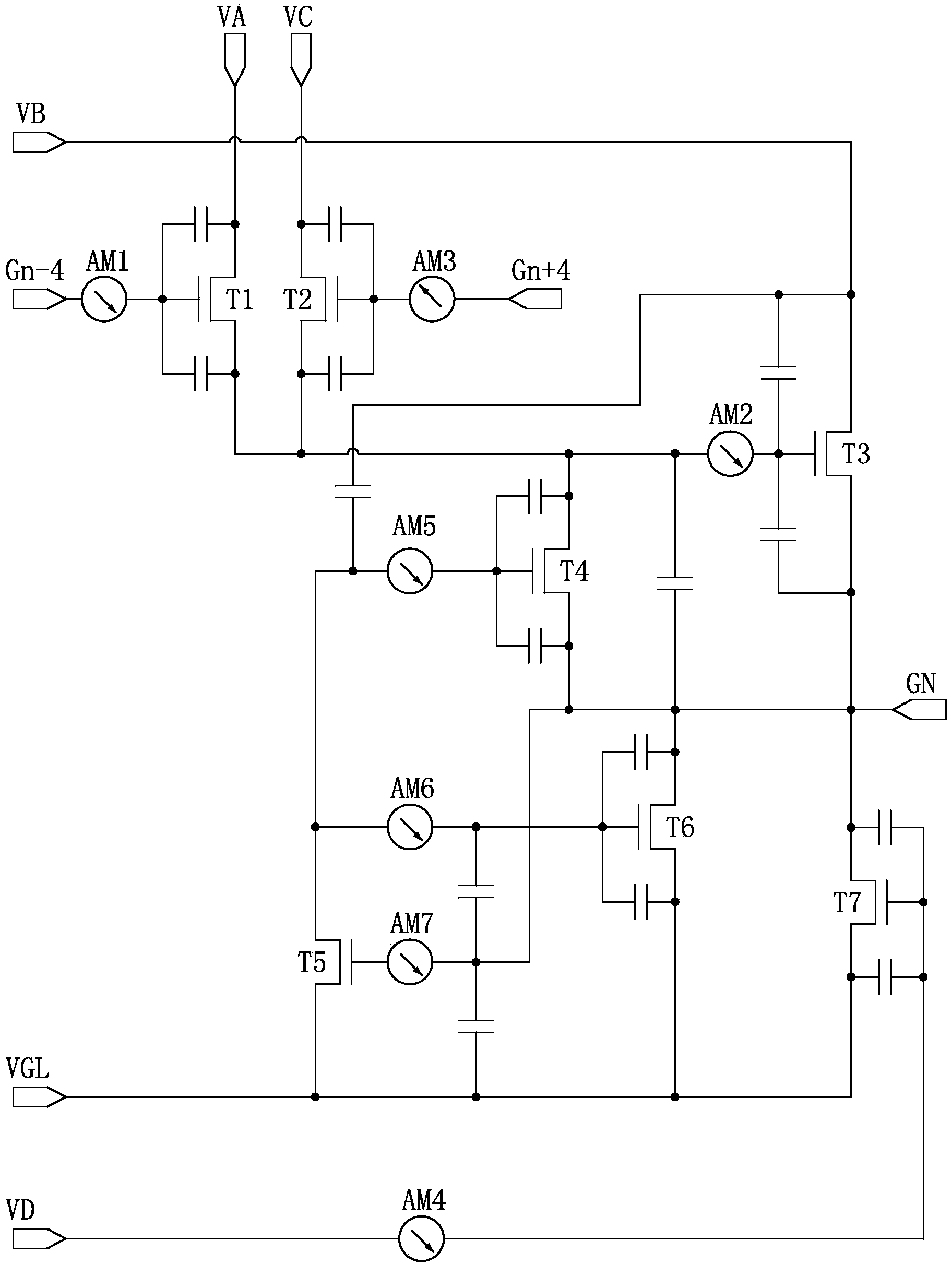

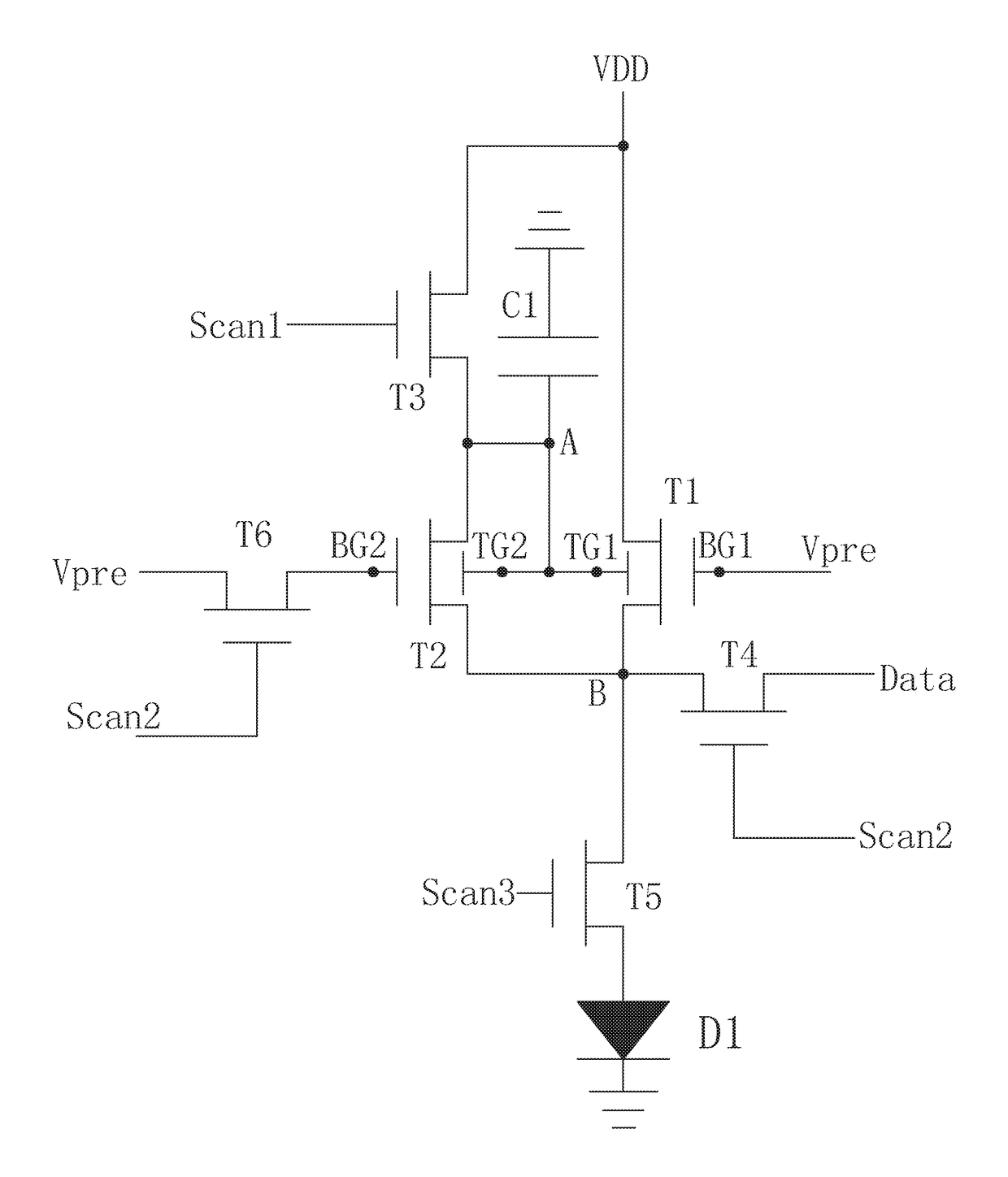

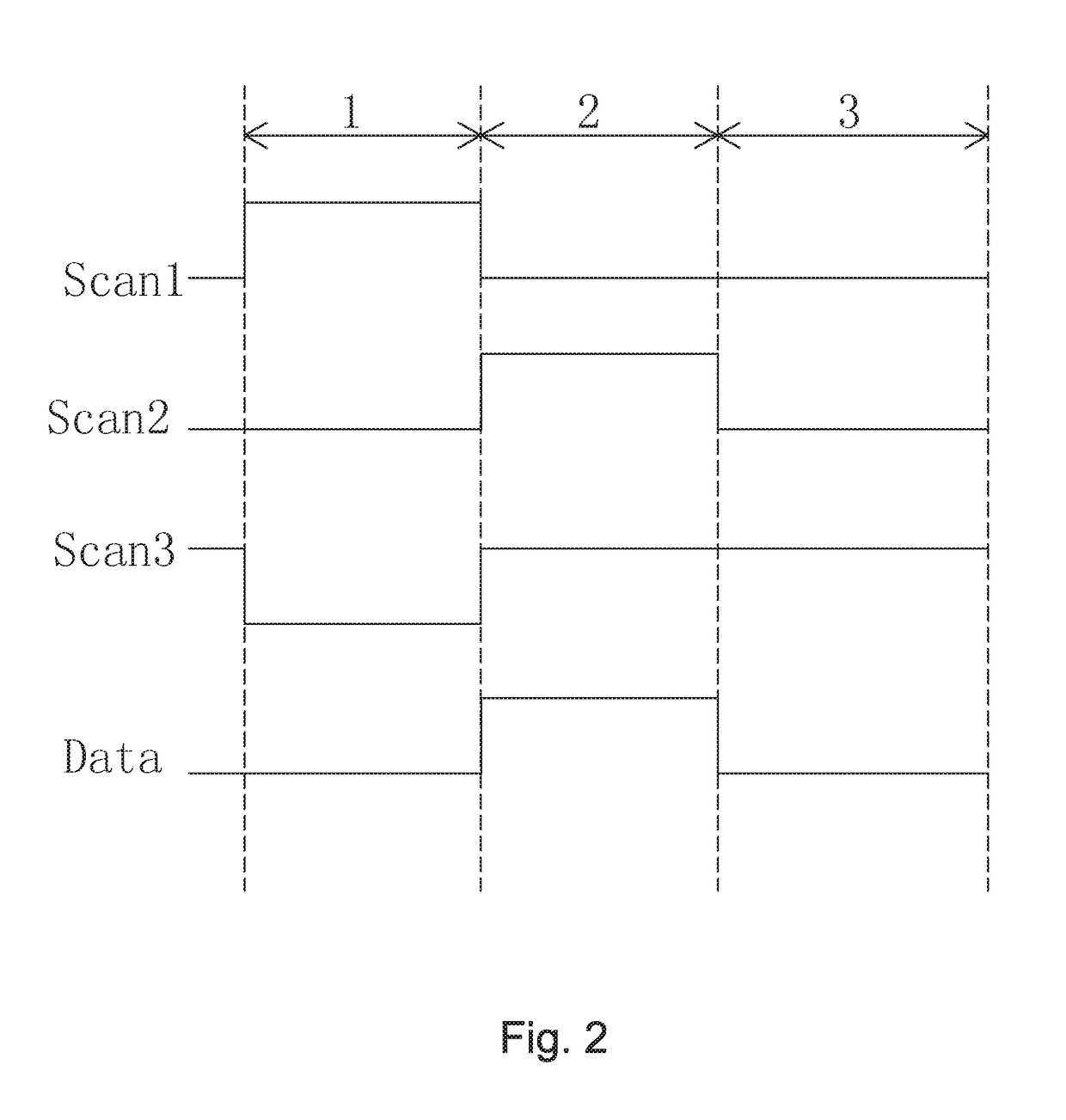

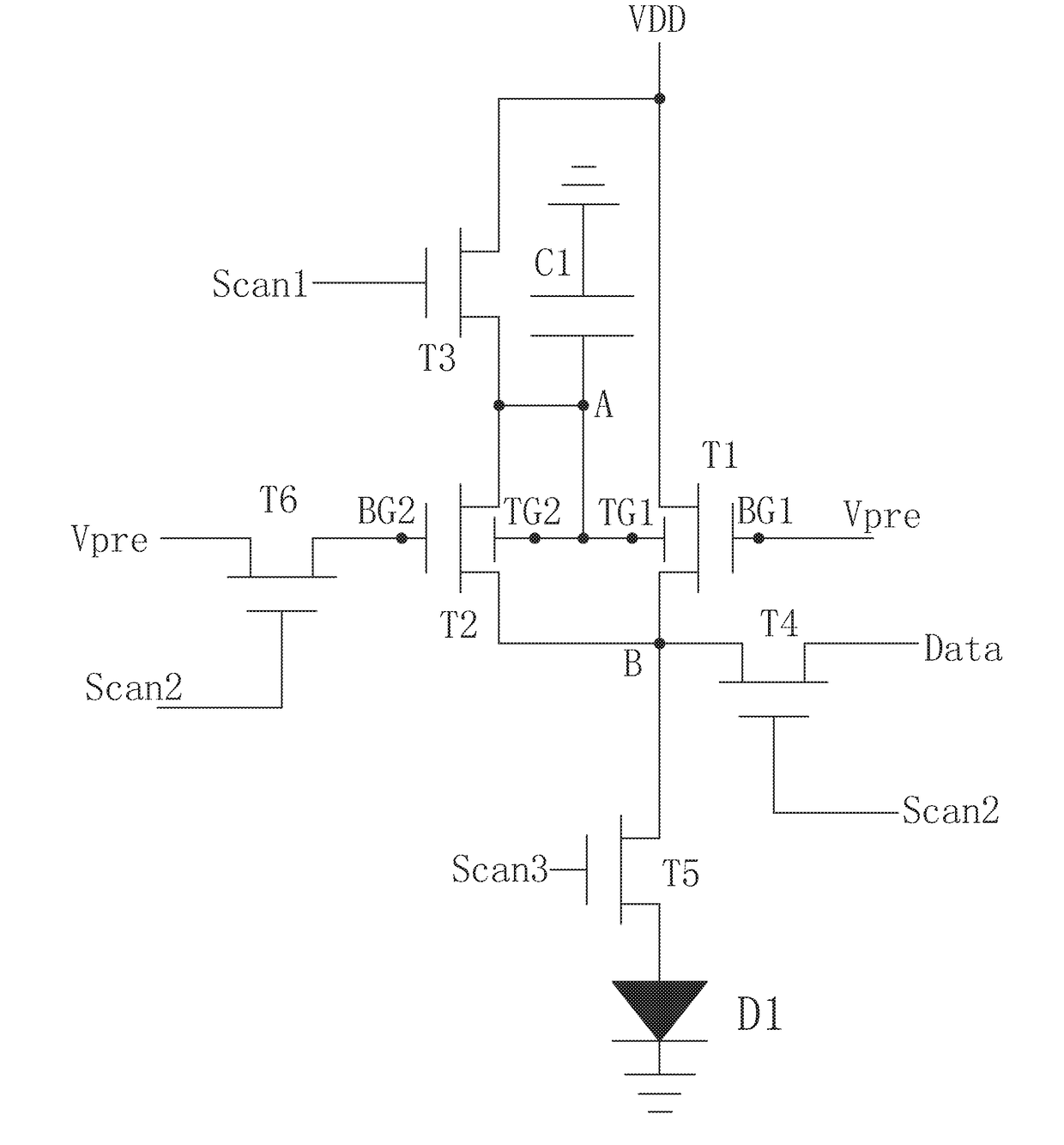

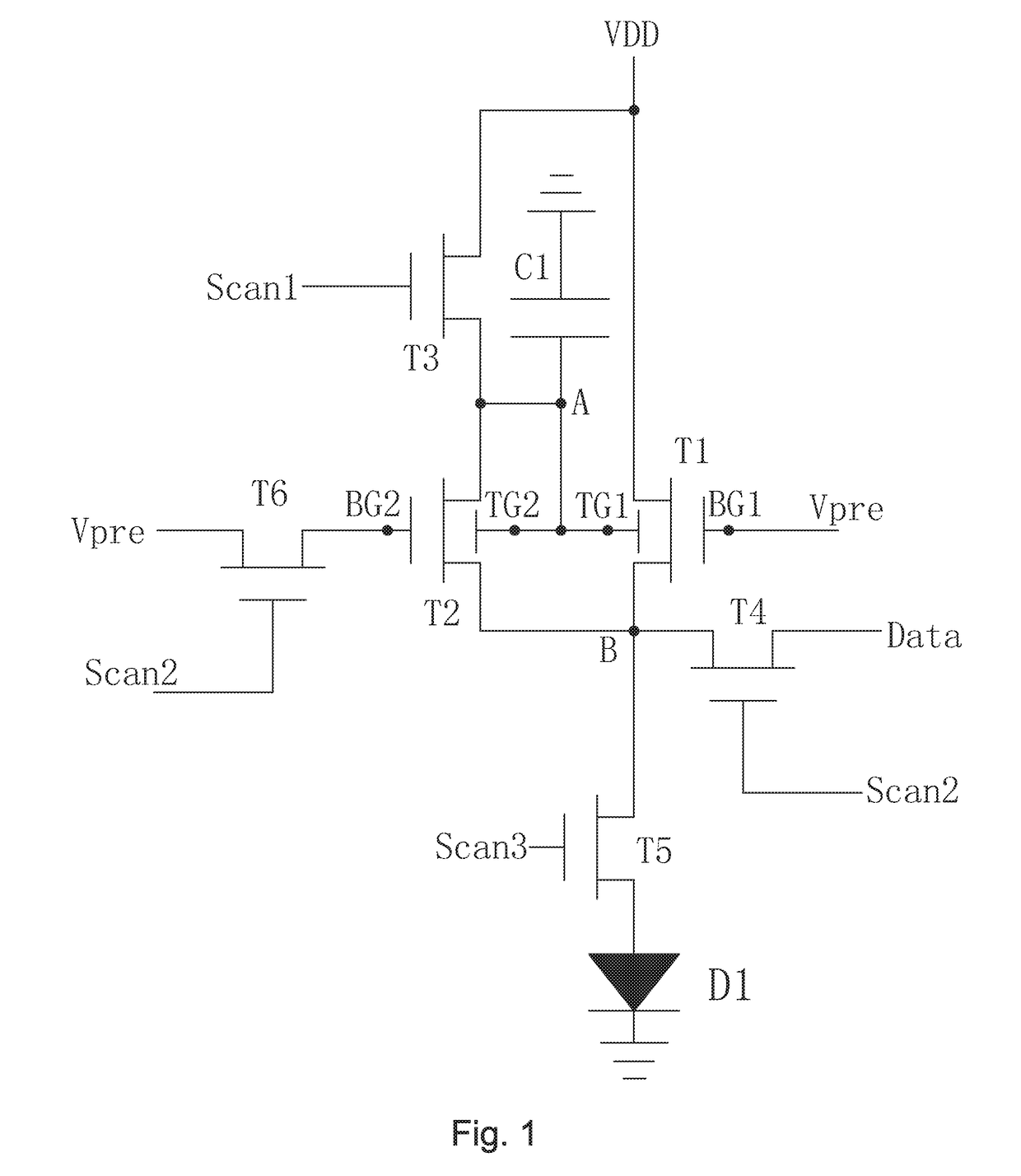

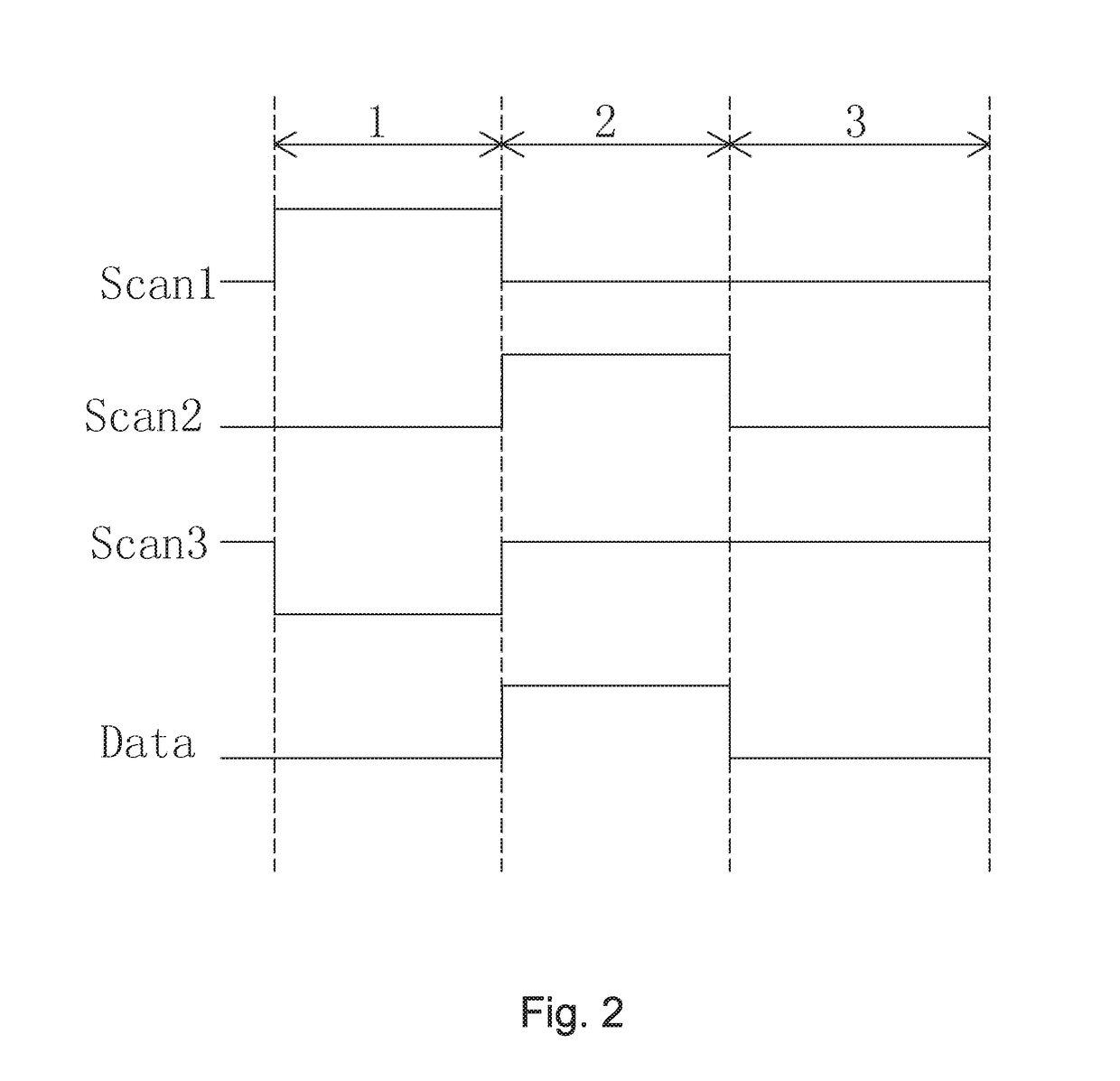

AMOLED pixel driver circuit and pixel driving method

ActiveUS10056037B1Uniform luminanceImprove display resultStatic indicating devicesSolid-state devicesDouble gateEngineering

The invention provides an AMOLED pixel driver circuit and pixel driving method. The AMOLED pixel driver circuit has a 6T1C structure, comprising a first thin film transistor (TFT) (T1), a second TFT (T2) forming mirror relation with the first TFT (T1), a third TFT (T3), a fourth TFT (T4), a fifth TFT (T5), a sixth TFT (T6), a capacitor (c1), and an organic light-emitting diode (OLED) (D1), and receiving a first scan signal (Scan1), a second scan signal (Scan2), a third scan signal (Scan3), a data signal (Data), and a predefined voltage (Vpre). The circuit can effectively compensate the threshold voltage of the driving TFT to solve the problem of unstable current flowing through the OLED caused by the threshold voltage drift. Moreover, the use of double-gate TFT as driving TFT allows designating the threshold voltage of the driving TFT through inputting predefined voltage.

Owner:TCL CHINA STAR OPTOELECTRONICS TECH CO LTD

Zinc-oxide-base amorphous oxide semiconductor thin film transistor and manufacturing method thereof

InactiveCN103840011AEasy to adaptReduce defectsTransistorSemiconductor/solid-state device manufacturingMechanical stabilityActive layer

The invention discloses a zinc-oxide-base amorphous oxide semiconductor thin film transistor and a manufacturing method of the zinc-oxide-base amorphous oxide semiconductor thin film transistor. The zinc-oxide-base amorphous oxide semiconductor thin film transistor comprises a substrate, a grid electrode, a grid insulating layer, an active layer, a source electrode and a drain electrode, wherein the grid electrode is formed on the substrate, the grid electrode and the substrate are covered with the grid insulating layer, the active layer is formed on the grid insulating layer and corresponds to the grid electrode, and the two ends of the active layer are covered with the source electrode and the drain electrode respectively; a zinc-oxide-base amorphous oxide semiconductor doped with X and Y serves as the active layer, when the distance between the active layer and the grid insulating layer gradually increases, the content of the X gradually decreases, and the content of the Y gradually increases; the X is one of Cd, In, Sn, Sb, Ti, Pb and As, and the Y is one of Ga, Al, Hf, Ge, Ca and Cu. According to the zinc-oxide-base amorphous oxide semiconductor thin film transistor and the manufacturing method of the zinc-oxide-base amorphous oxide semiconductor thin film transistor, the mobility ratio of a device can be effectively improved, the magnitude of the working current of the device can be effectively improved, the frequency of the phenomenon of threshold voltage drift of the device is reduced, influence of the technology, illumination and gas in the outside world on the device is reduced, and mechanical stability of the device is improved.

Owner:HUAZHONG UNIV OF SCI & TECH

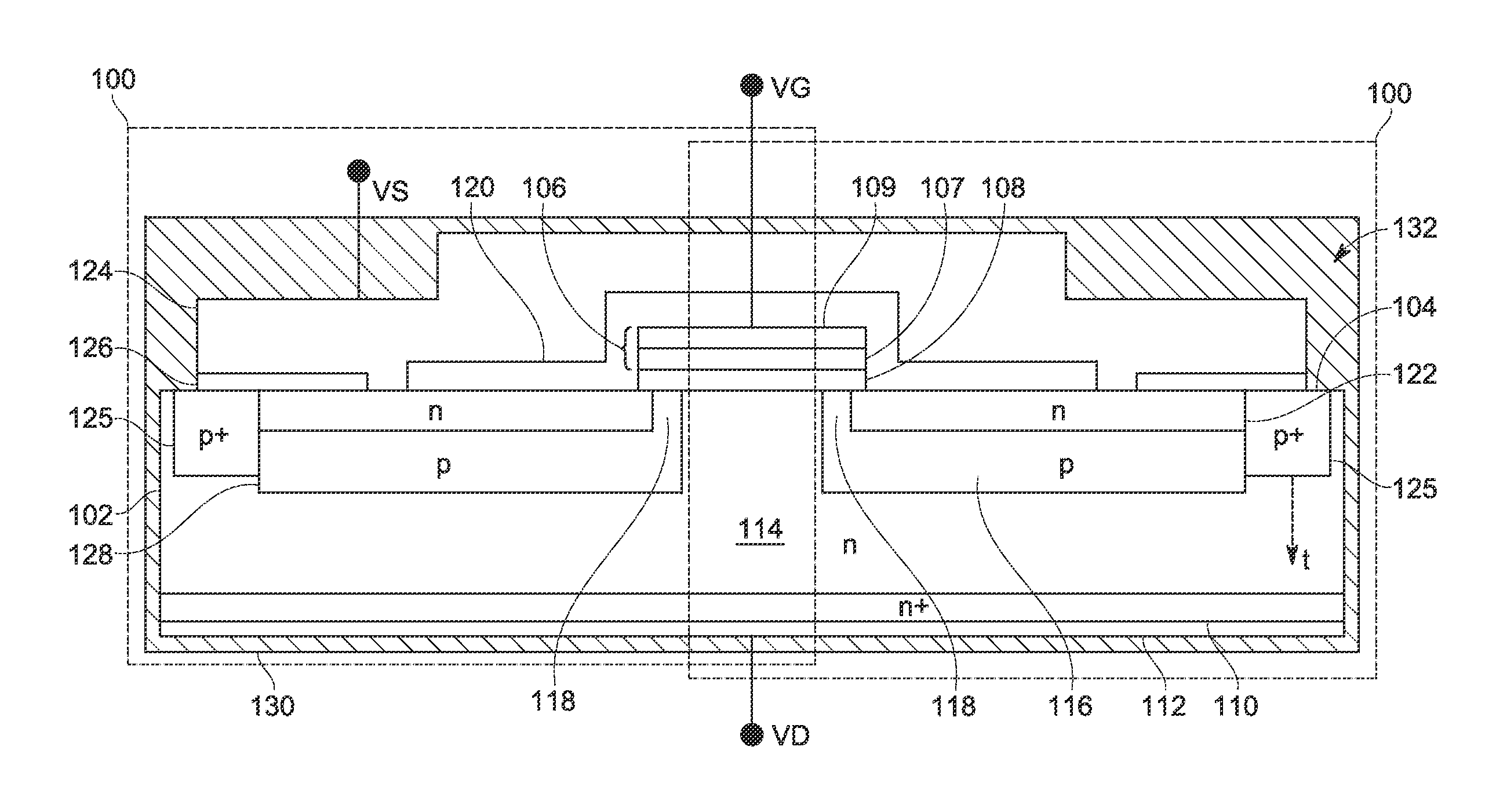

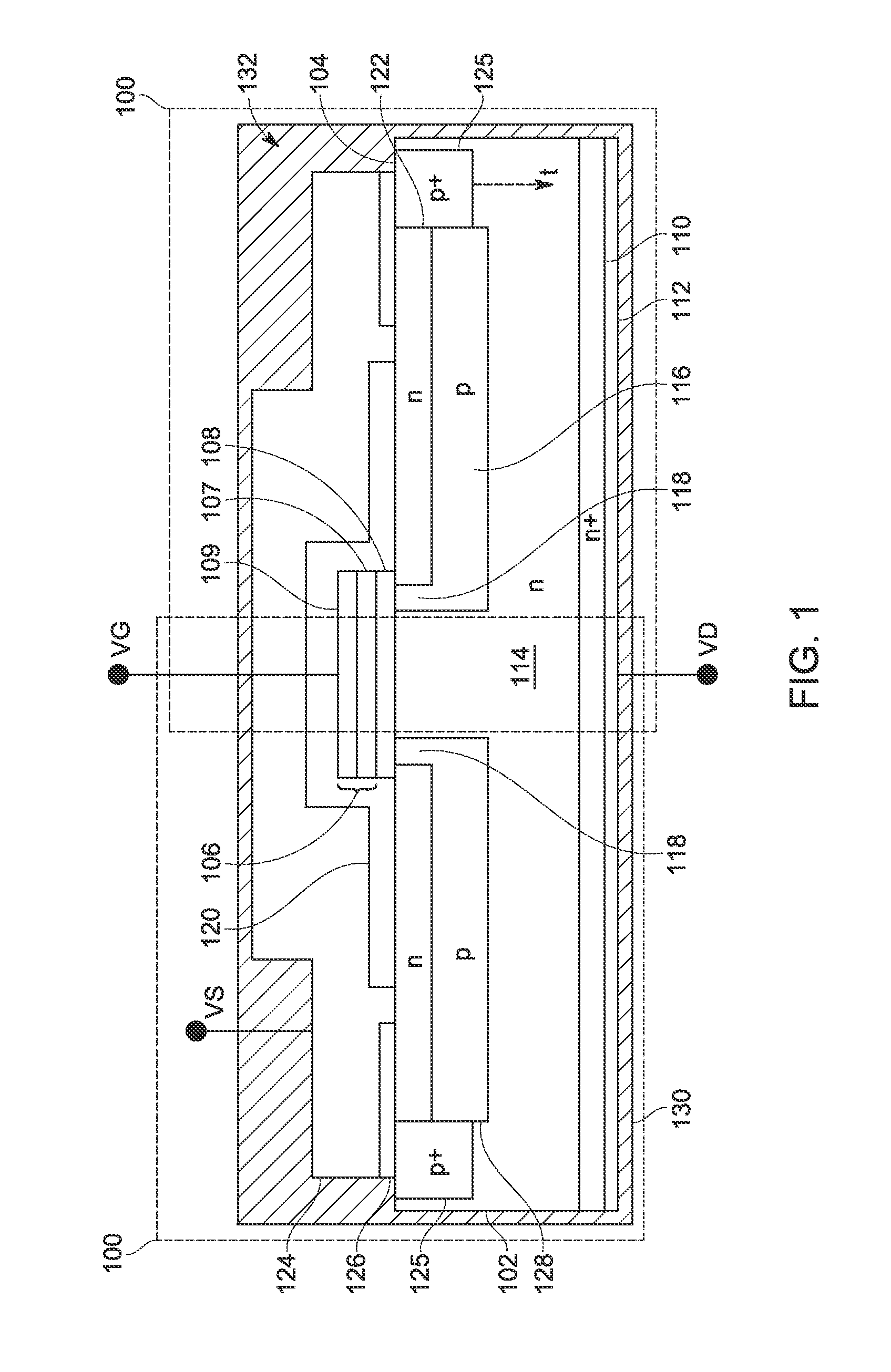

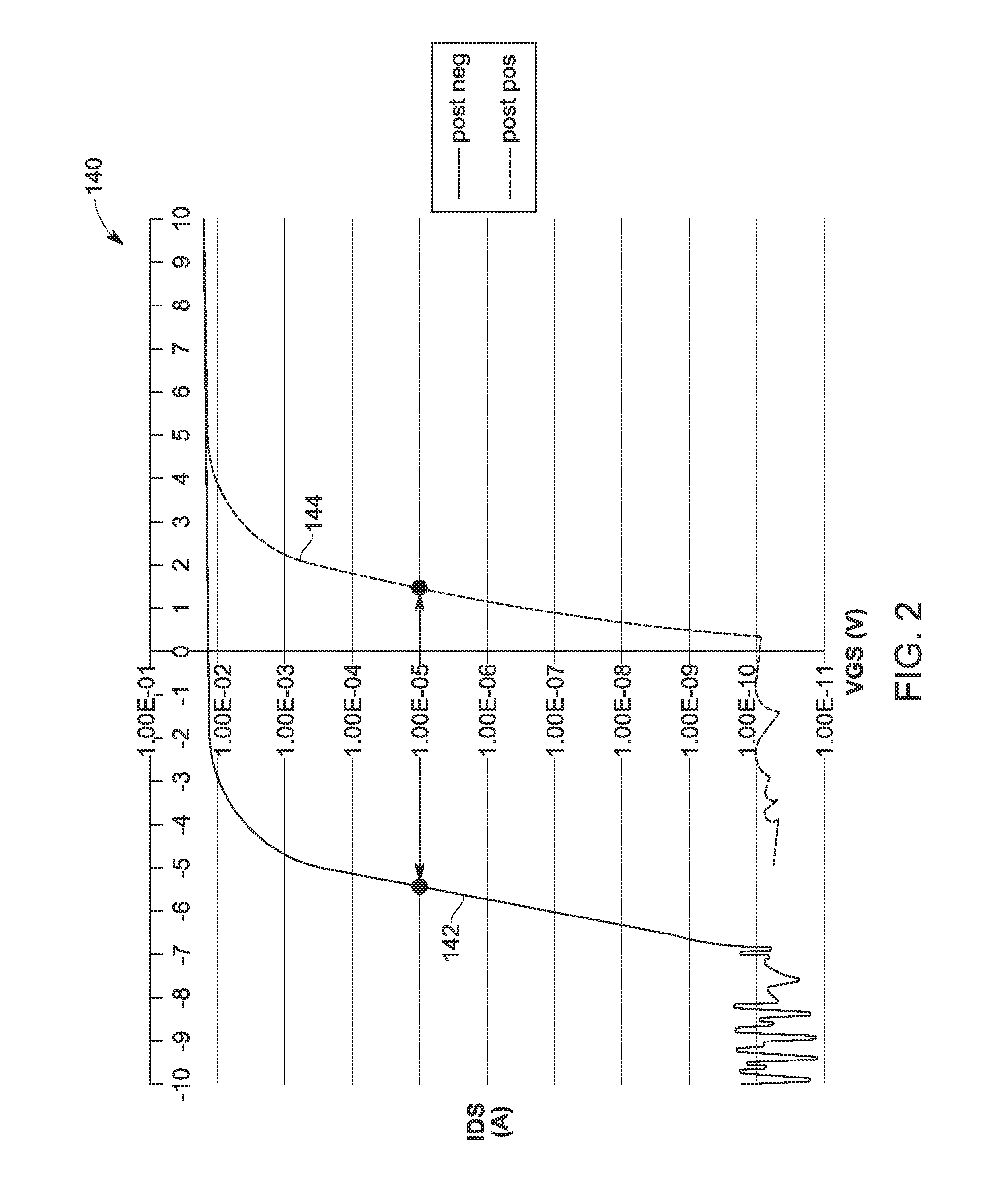

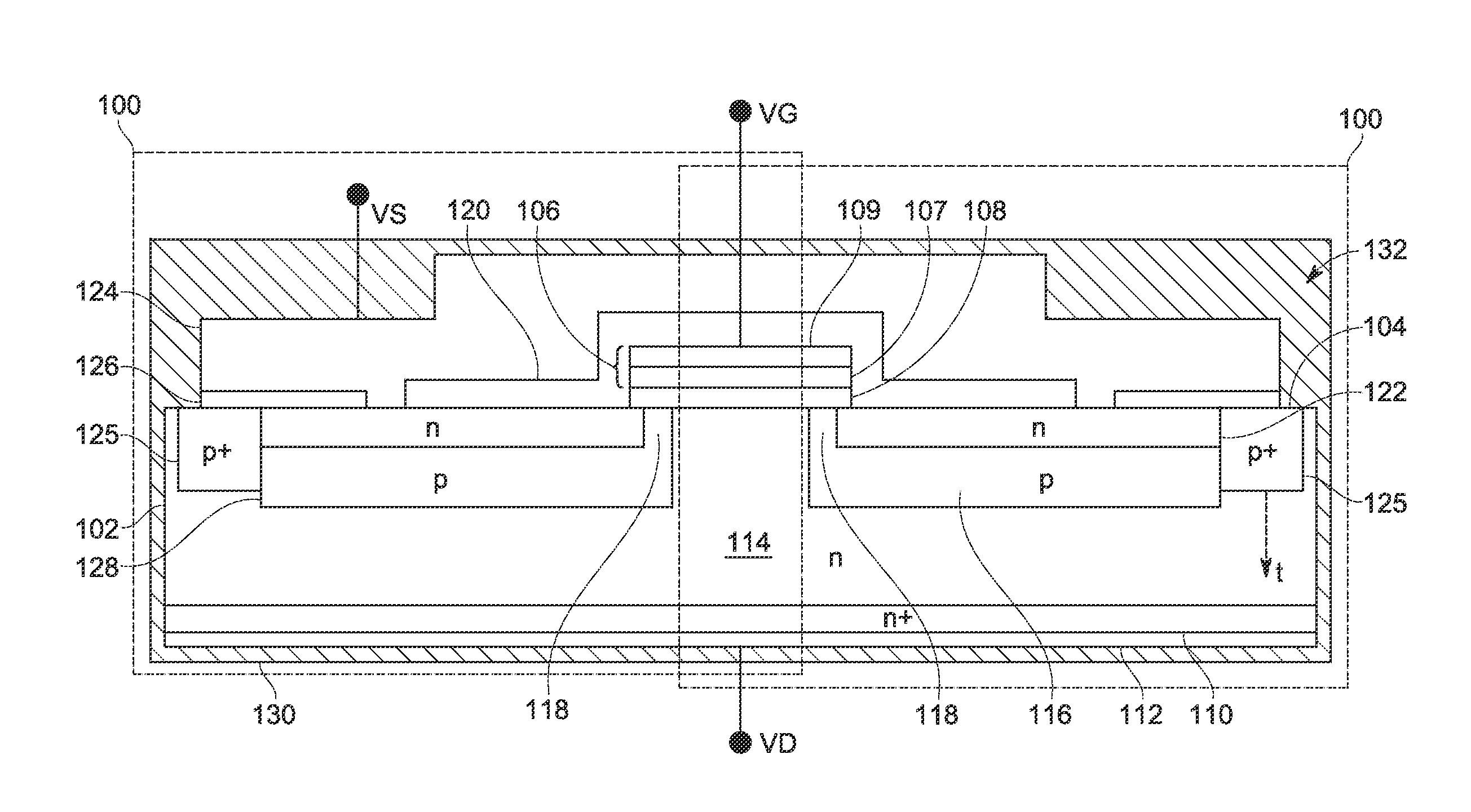

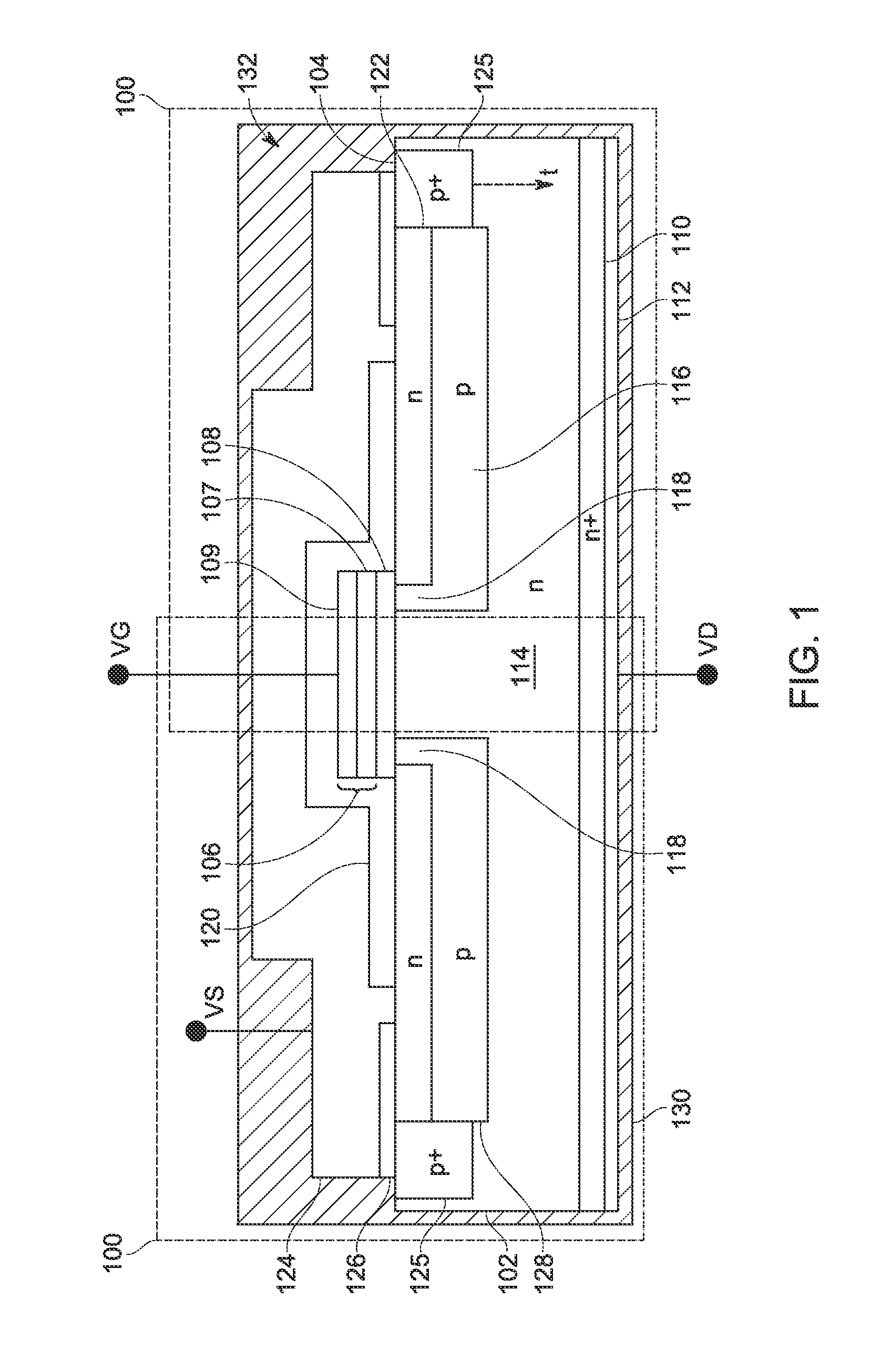

Semiconductor device and method for reduced bias temperature instability (BTI) in silicon carbide devices

ActiveUS20140027782A1Reduce pressureReduced Threshold Voltage DriftSemiconductor/solid-state device detailsSolid-state devicesInstabilityEngineering

A system includes a silicon carbide (SiC) semiconductor device and a hermetically sealed packaging enclosing the SiC semiconductor device. The hermetically sealed packaging is configured to maintain a particular atmosphere near the SiC semiconductor device. Further, the particular atmosphere limits a shift in a threshold voltage of the SiC semiconductor device to less than 1 V during operation.

Owner:GENERAL ELECTRIC CO

Compensation circuit and display device

ActiveCN107767827AReduced Threshold Voltage DriftThreshold Voltage Drift RecoveryStatic indicating devicesDisplay deviceVoltage reference

The invention discloses a compensation circuit and a display device. The compensation circuit comprises a first switching tube receiving a first reference voltage, a second switching tube receiving asecond reference voltage, a pre-charging unit, a charging unit and a pull-down unit. A second access terminal of the first switching tube is connected with a second access terminal of the second switching tube to provide an output signal; the first switching tube and the second switching tube are in conduction alternately with frame switching; and phases of the first reference voltage and the second reference voltage are opposite. The pre-charging unit enables one of the first switching tube and the second switching tube to be in conduction according to a pre-stage gate drive signal; the charging unit maintains the conduction or turning-off state of the first switching tube or the second switching tube according to a local-stage gate drive signal; and the pull-down unit controls the firstswitching tube and the second switching tube according to a post-stage gate drive signal. Because transistors in the compensation circuit work alternately, the threshold voltage drifts of the transistors can be reduced and recovery of the threshold voltage drifts of the transistors is realized.

Owner:KUSN INFOVISION OPTOELECTRONICS

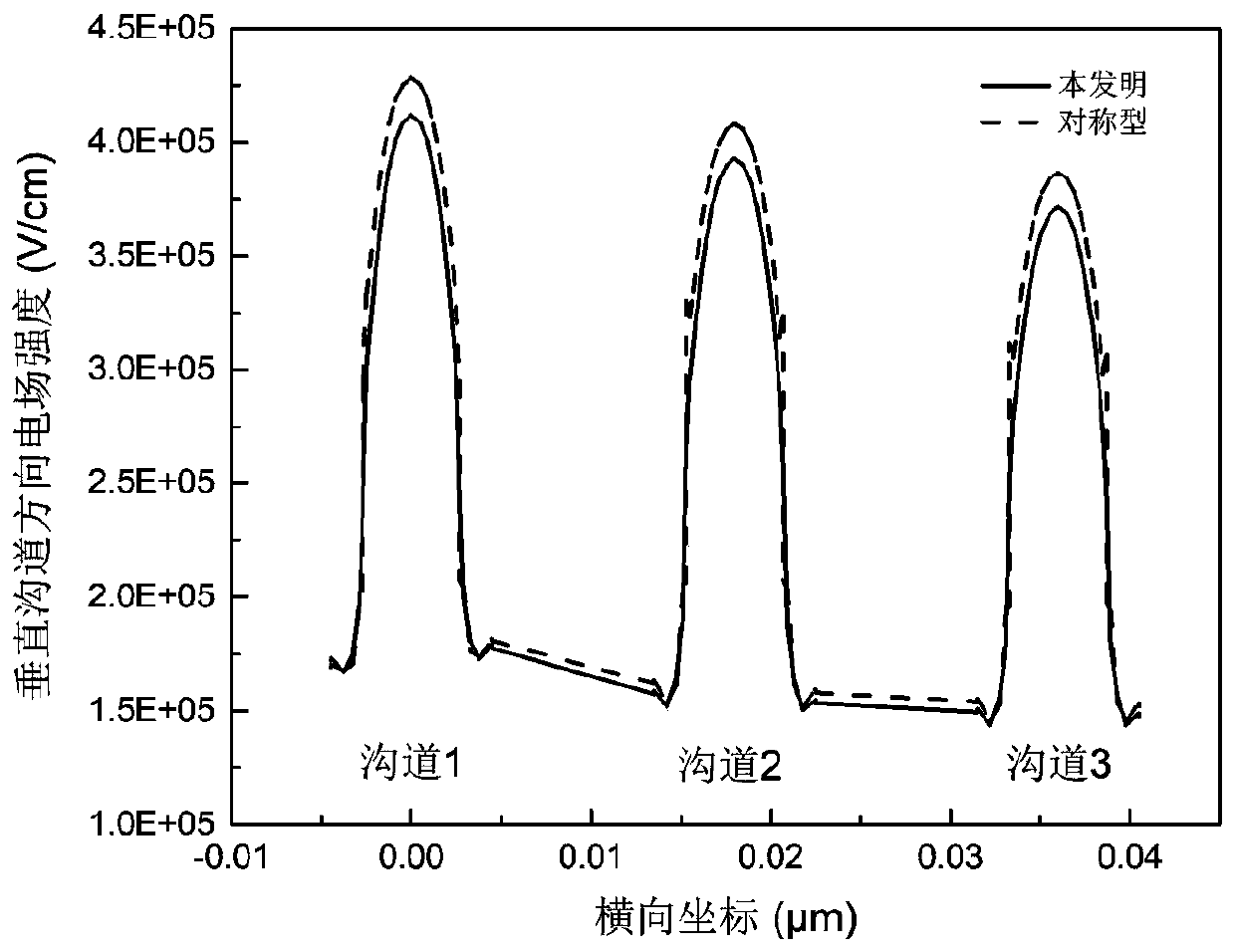

Nano-sheet ring gate field effect transistor with asymmetric gate oxygen structure

ActiveCN110690290AReduced Threshold Voltage DriftInhibition of DIBL effectNanoinformaticsSemiconductor devicesEngineeringField effect

The invention discloses a nano-sheet ring gate field effect transistor with an asymmetric gate oxygen structure. The nano-sheet ring gate field effect transistor comprises a vertically stacked nano-sheet channel, a double-layer gate oxide wrapping outside the channel, a source and a drain arranged at the two ends of the channel, a double-layer side wall and a substrate arranged at the bottom. Thenano-sheet ring gate field effect transistor is characterized in that the gate oxide is formed by stacking a low dielectric constant material and a high dielectric constant material and is divided into two parts near the drain and the source with half of the channel length as the boundary. The total physical thickness of gate oxygen in the two parts is the same, and the low dielectric constant gate oxide is thinner and the high dielectric constant gate oxide is thicker in the double-layer gate oxides near the drain so as to form the nano-sheet ring gate field effect transistor with the asymmetric gate oxygen structure. Compared with the prior symmetrical type technology, the drain end electric field is lower and the hot carrier effect of the device can be effectively inhibited; it has moreideal on-state and off-state current and higher current switching ratio;and the leakage potential is more stable, the leakage-induced barrier reduction effect is suppressed and the short channel characteristics are improved.

Owner:EAST CHINA NORMAL UNIV +1

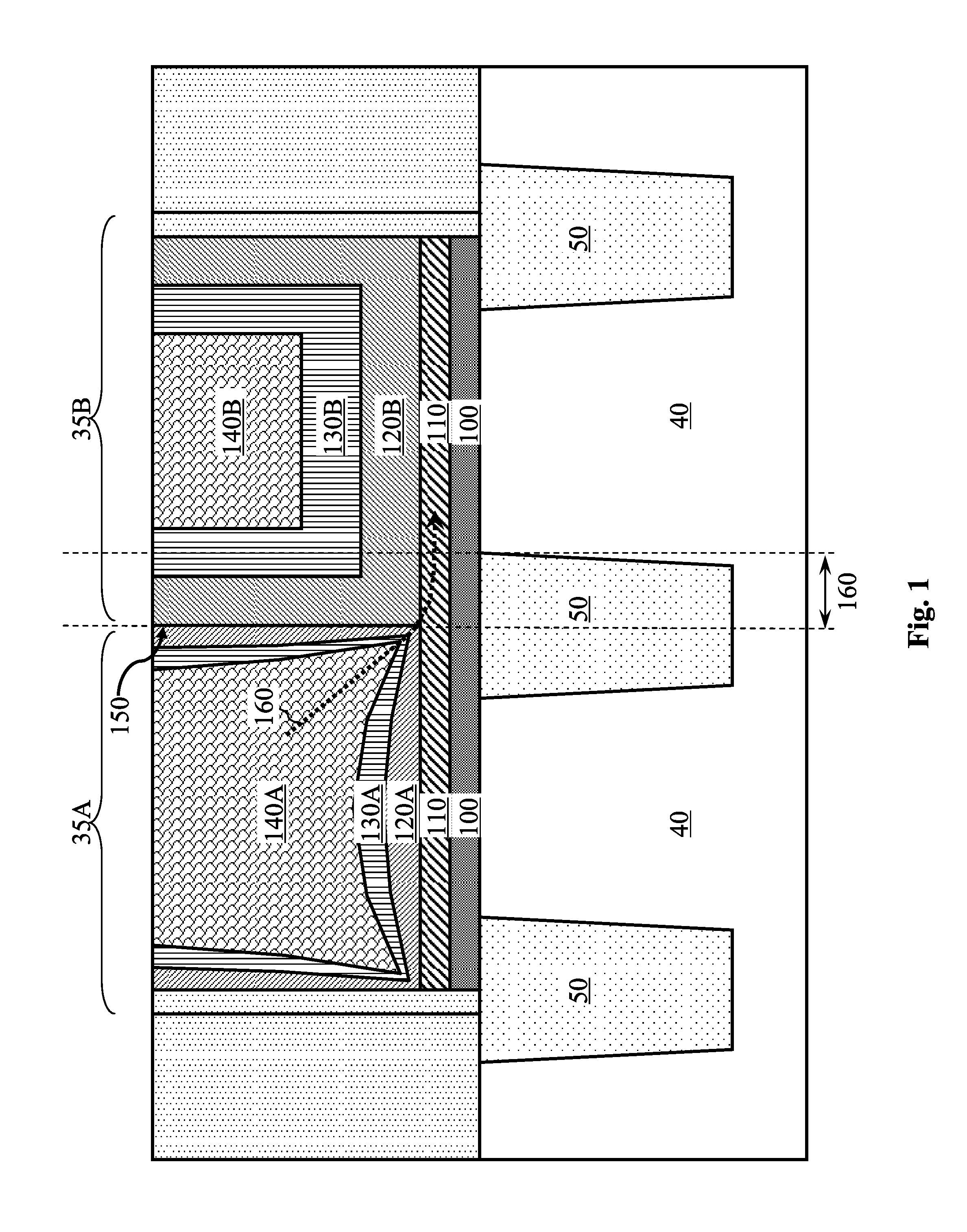

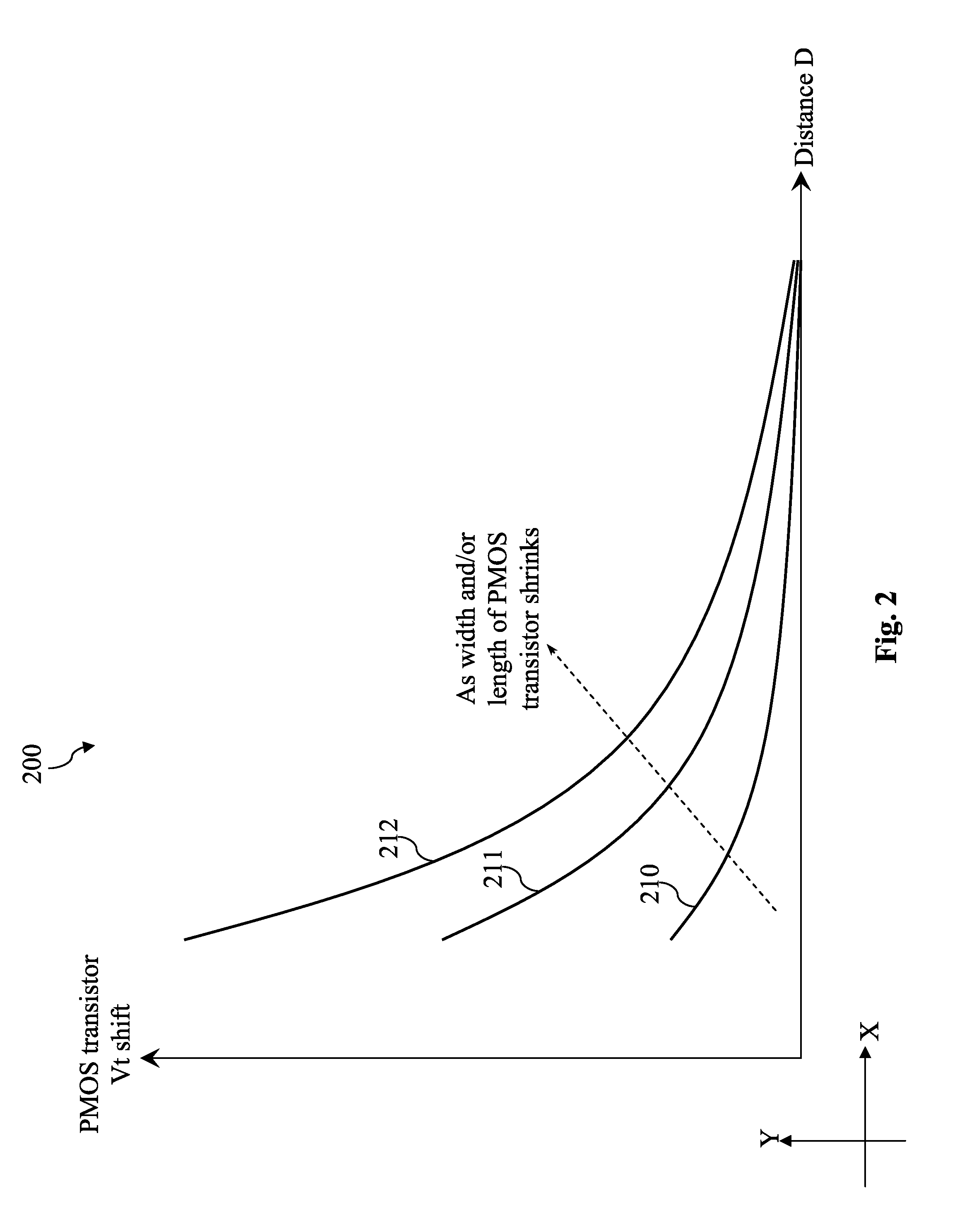

N/P Boundary Effect Reduction for Metal Gate Transistors

ActiveUS20140203374A1Significantly different lengthReduce boundary effectsTransistorSolid-state devicesBoundary effectsDevice material

Owner:TAIWAN SEMICON MFG CO LTD

Semiconductor device and method for reduced bias temperature instability (BTI) in silicon carbide devices

ActiveUS9576868B2Reduce pressureReduced Threshold Voltage DriftSemiconductor/solid-state device detailsSolid-state devicesDevice materialEngineering

A system includes a silicon carbide (SiC) semiconductor device and a hermetically sealed packaging enclosing the SiC semiconductor device. The hermetically sealed packaging is configured to maintain a particular atmosphere near the SiC semiconductor device. Further, the particular atmosphere limits a shift in a threshold voltage of the SiC semiconductor device to less than 1 V during operation.

Owner:GENERAL ELECTRIC CO

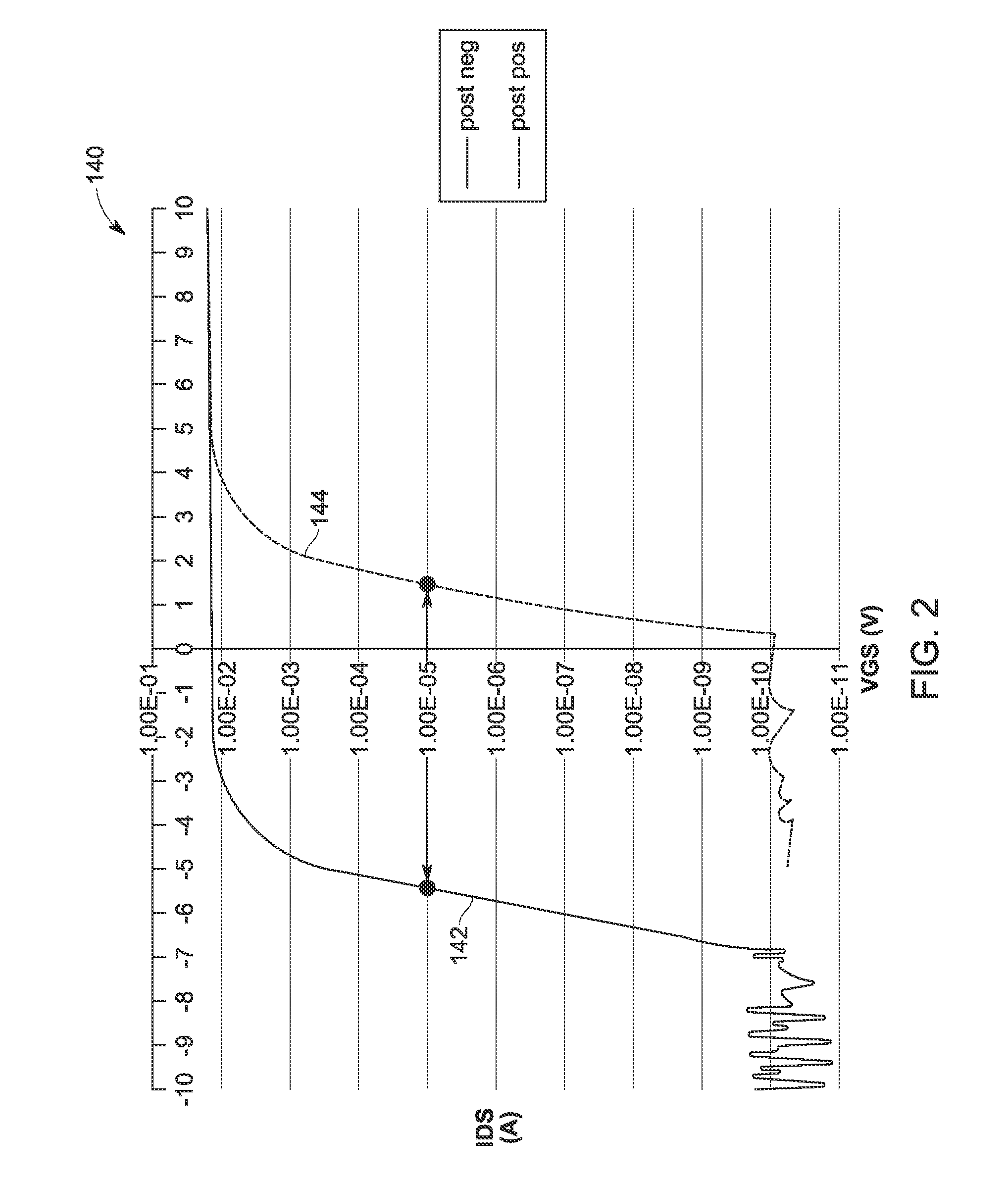

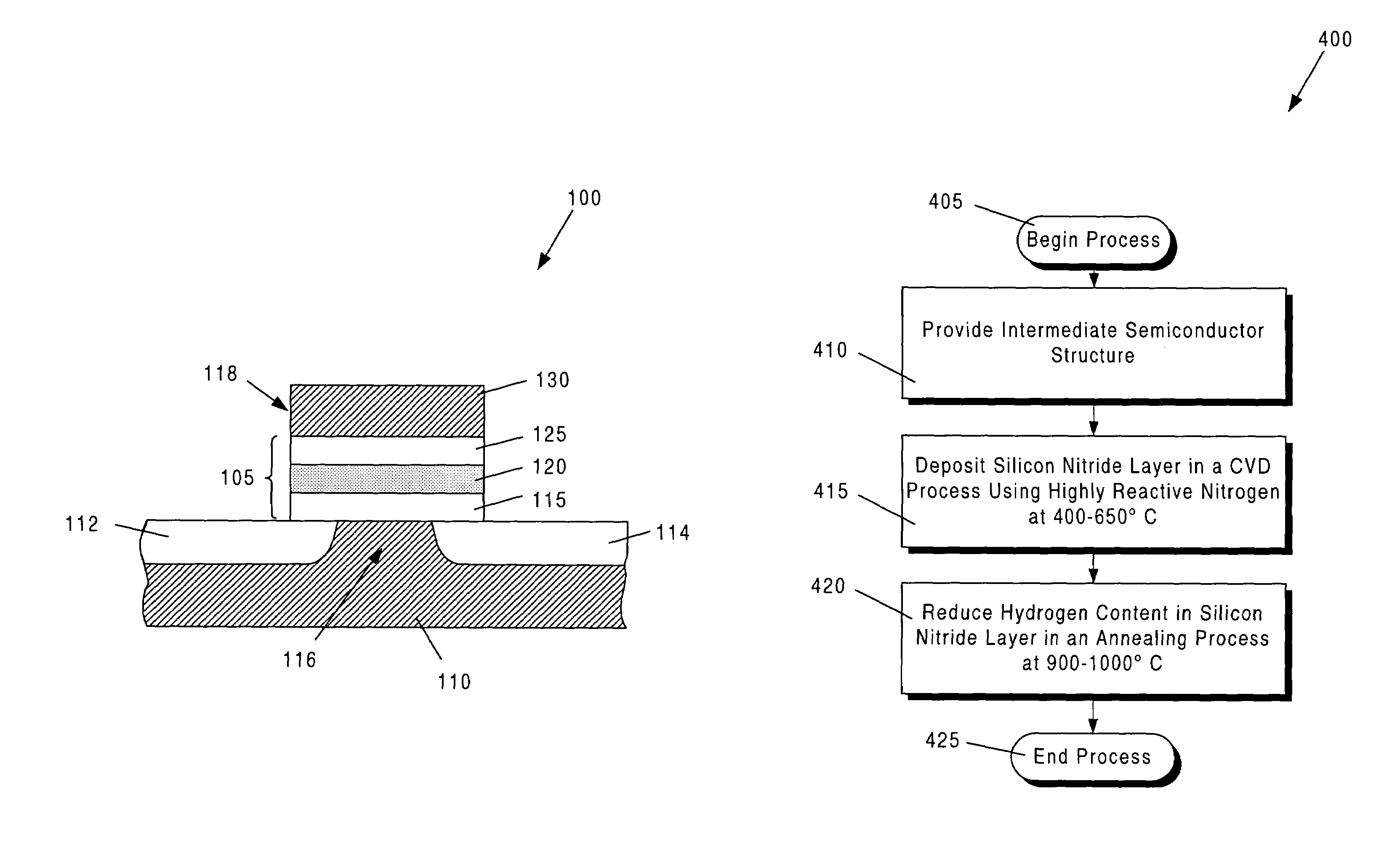

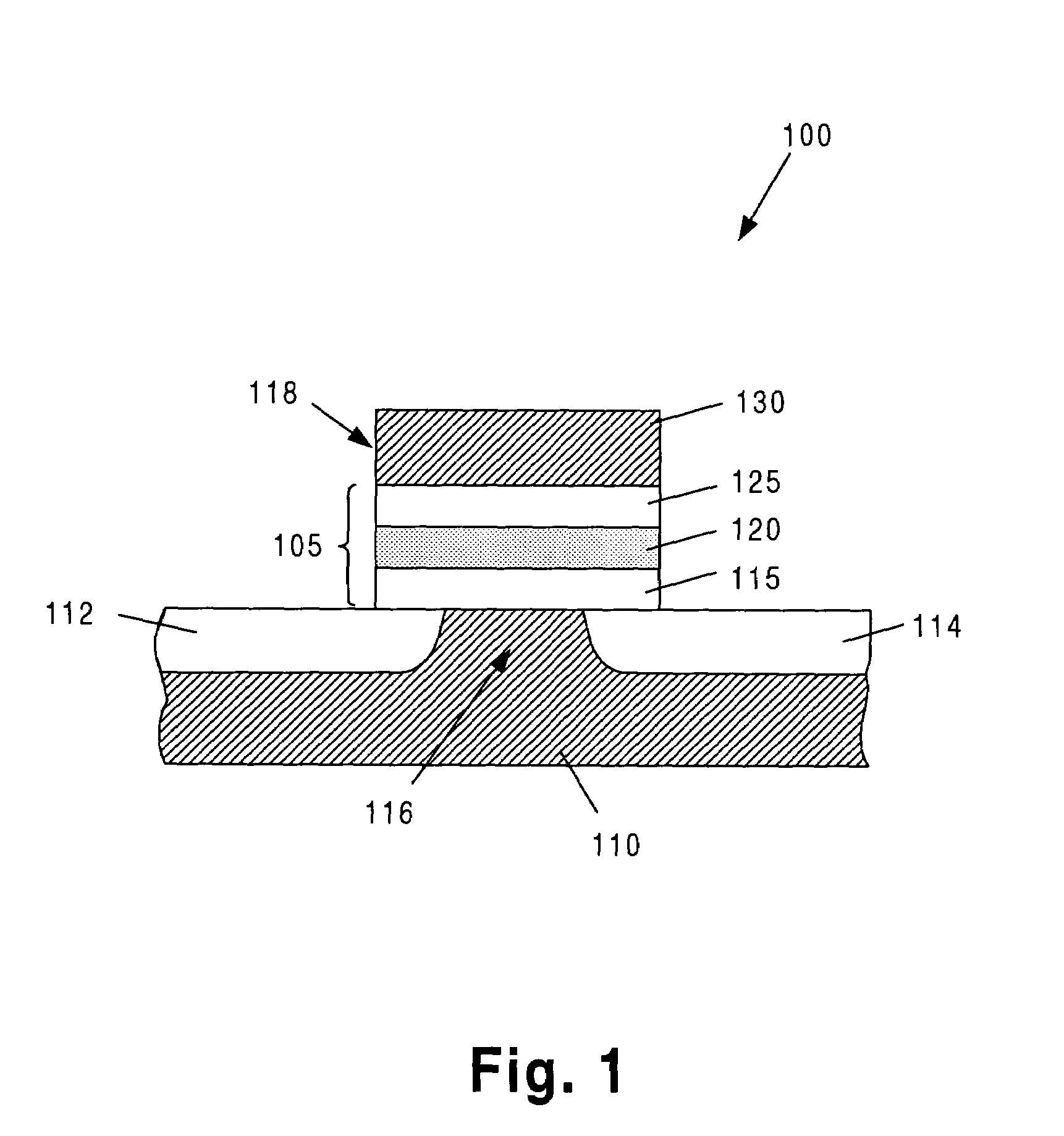

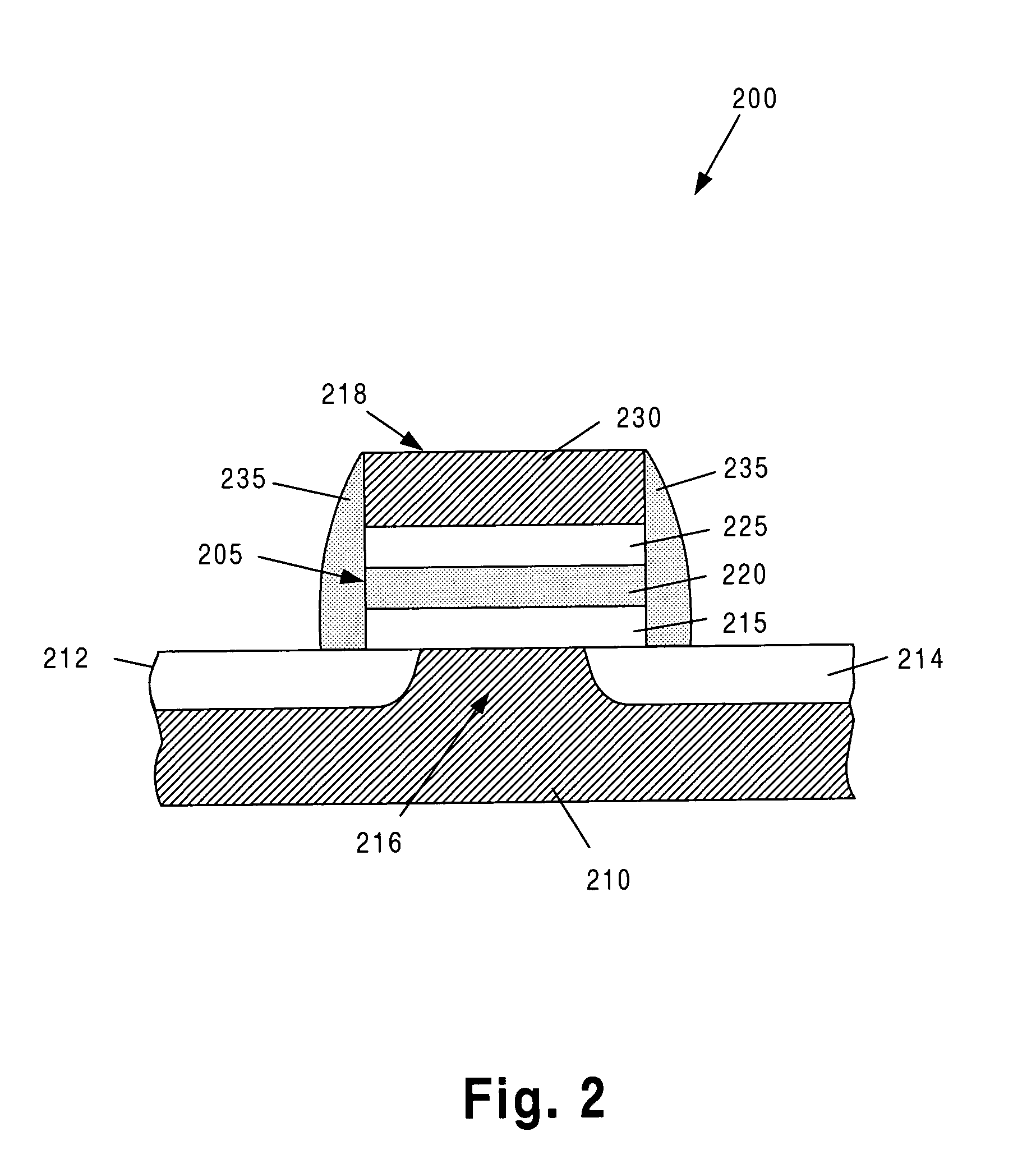

Memory cell structure having nitride layer with reduced charge loss and method for fabricating same

InactiveUS6992370B1Reduce charging lossReduced Threshold Voltage DriftTransistorSemiconductor/solid-state device detailsHydrogen contentSilicon oxide

According to one embodiment, a memory cell structure comprises a semiconductor substrate, a first silicon oxide layer situated over the semiconductor substrate, a charge storing layer situated over the first silicon oxide layer, a second silicon oxide layer situated over the charge storing layer, and a gate layer situated over the second silicon oxide layer. In the exemplary embodiment, the charge storing layer comprises silicon nitride having reduced hydrogen content, e.g., in the range of about 0 to 0.5 atomic percent. As a result, the reduced hydrogen content reduces the charge loss in the charge storing layer. The reduced charge loss in the charge storing layer has the benefit of reducing threshold voltage shifts, programming data loss, and programming capability loss in the memory device, thereby improving memory device performance.

Owner:MONTEREY RES LLC

Nano-wire field effect transistor

ActiveCN101740619BReduce off-state currentReduce static power consumptionSemiconductor devicesSemiconductor materialsGate dielectric

The invention discloses a nano-wire field effect transistor comprising a gate electrode, a source region, a drain region, a central region and a gate dielectric layer. The central region is in the core-shell structures which are coaxial; the gate dielectric layer fully surrounds the central region; the gate electrode fully surrounds the gate dielectric layer; the source region and the drain region are respectively arranged on two sides of the central region; the core structure of the central region is made from insulating material, and the shell structure of the central region is made from semiconductor material; the doping type and the doping concentration of the semiconductor material of the shell structure of the central region are adjustable; the lengths of both the core structure andthe shell structure and the radii of both the core structure and the shell structure are adjustable; and the materials of the gate dielectric layer, the gate electrode, the source region and the drain region are adjustable. Due to the adoption of the insulating core structure, the off-current of the traditional nano-wire transistor can be reduced effectively, and the current on-off ratio of the devices can be increased. The threshold voltage shifting and the drain induced barrier lowering of the nano-wire field effect transistor are less affected by the short channel effect, and the size reducing performance of the nano-wire field effect transistor is more excellent.

Owner:SEMICON MFG INT (BEIJING) CORP +1

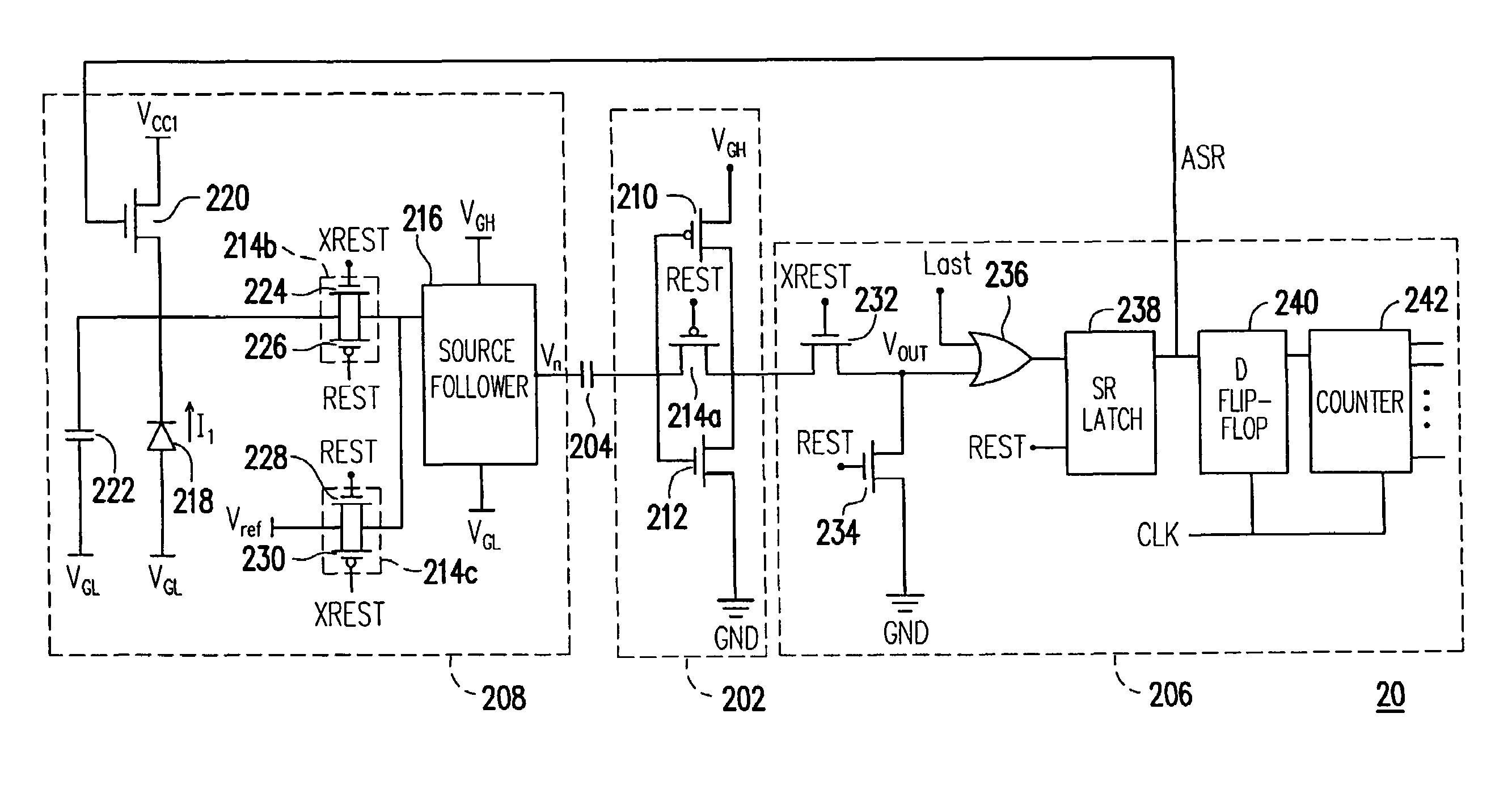

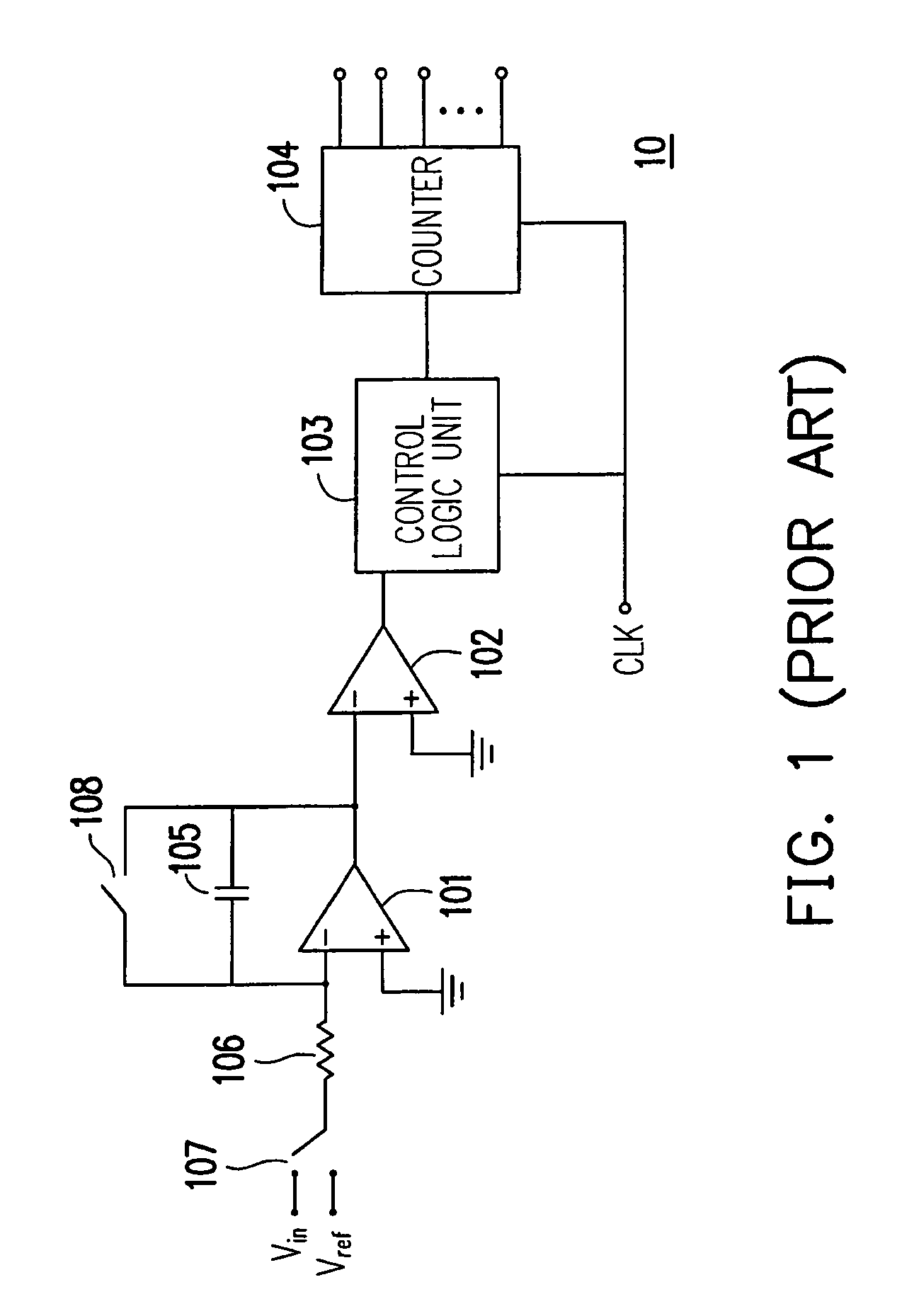

Optical-to-electrical converter and analog-to-digital converter thereof

ActiveUS7659844B2Reduced Threshold Voltage DriftReduce power consumptionElectric signal transmission systemsAnalogue-digital convertersControl signalPhotoelectric conversion

An analog-to-digital converter (ADC) for converting an optical signal into an electrical signal is disclosed. The ADC includes a detection module, a first P-type metal oxide semiconductor (PMOS) transistor, a first N-type metal oxide semiconductor (NMOS) transistor, a first switch unit, and an output module. The first PMOS transistor and the first NMOS transistor form an inverter. The first switch unit is disposed between the input terminal and the output terminal of the inverter and is turned on / off according to a first control signal. The output module is coupled to the output terminal of the inverter for counting the time that an input voltage is greater than a reference voltage and generating a digital signal.

Owner:AU OPTRONICS CORP

Amoled pixel driver circuit and pixel driving method

ActiveUS20180240402A1Effective compensationReduced Threshold Voltage DriftStatic indicating devicesSolid-state devicesDriver circuitData signal

The invention provides an AMOLED pixel driver circuit and pixel driving method. The AMOLED pixel driver circuit has a 6T1C structure, comprising a first thin film transistor (TFT) (T1), a second TFT (T2) forming mirror relation with the first TFT (T1), a third TFT (T3), a fourth TFT (T4), a fifth TFT (T5), a sixth TFT (T6), a capacitor (c1), and an organic light-emitting diode (OLED) (D1), and receiving a first scan signal (Scan1), a second scan signal (Scan2), a third scan signal (Scan3), a data signal (Data), and a predefined voltage (Vpre). The circuit can effectively compensate the threshold voltage of the driving TFT to solve the problem of unstable current flowing through the OLED caused by the threshold voltage drift. Moreover, the use of double-gate TFT as driving TFT allows designating the threshold voltage of the driving TFT through inputting predefined voltage.

Owner:TCL CHINA STAR OPTOELECTRONICS TECH CO LTD

Shift register unit, gate driving circuit, and display device

ActiveUS9530521B2Reduced Threshold Voltage DriftImprove stabilityStatic indicating devicesDigital storageShift registerProcessor register

The present invention provides a shift register unit, a gate driving circuit and a display device. The shift register unit comprises: an input module for, in response to turn-on level input via the shift register input terminal, providing turn-on level to the first node and providing turn-off level to the second node; a pull-up module for, in response to turn-on level of the first node, providing a clock signal to the shift register output terminal, and also used for, in response to turn-on level output by the shift register output terminal, providing turn-off level to the second node; a reset module for, in response to turn-on level input via the reset signal input terminal, providing the turn-on level to the second node; and a pull-down module for, in response to turn-on level of the second node, providing turn-off level to the shift register output terminal and the first node.

Owner:BOE TECH GRP CO LTD +1

Pixel circuit, driving method thereof, and display panel

ActiveCN105609047BExtended service lifeReduced Threshold Voltage DriftStatic indicating devicesRecovery stageLight emitting device

Disclosed are a pixel circuit, a driving method thereof, and a display panel including the pixel circuit. The pixel circuit includes: a light emitting module, a first driving module and a second driving module, the first driving module drives the light emitting module during a first period under the control of the first scanning signal of the first scanning control terminal emit light, and the second driving module drives the light emitting module to emit light during a second period under the control of the second scan signal of the second scan control terminal, and the first period and the second period do not overlap with each other . By using two driving modules to alternately drive the light-emitting device to emit light, the other driving module enters the recovery phase when one driving module drives the light-emitting device to emit light, so that the threshold voltage drift of the driving transistor in each driving module can be reduced, and at the same time, each driving module can be extended. The service life of the drive transistor of the module.

Owner:BOE TECH GRP CO LTD