Method for improving negative bias temperature stability of grid of PMOS device

A technology of negative bias temperature and stability, which is applied in semiconductor devices, semiconductor/solid-state device manufacturing, electrical components, etc. shift and other issues, to solve the problem of negative bias temperature instability, improve the stability of negative bias temperature, and reduce the effect of threshold voltage drift

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

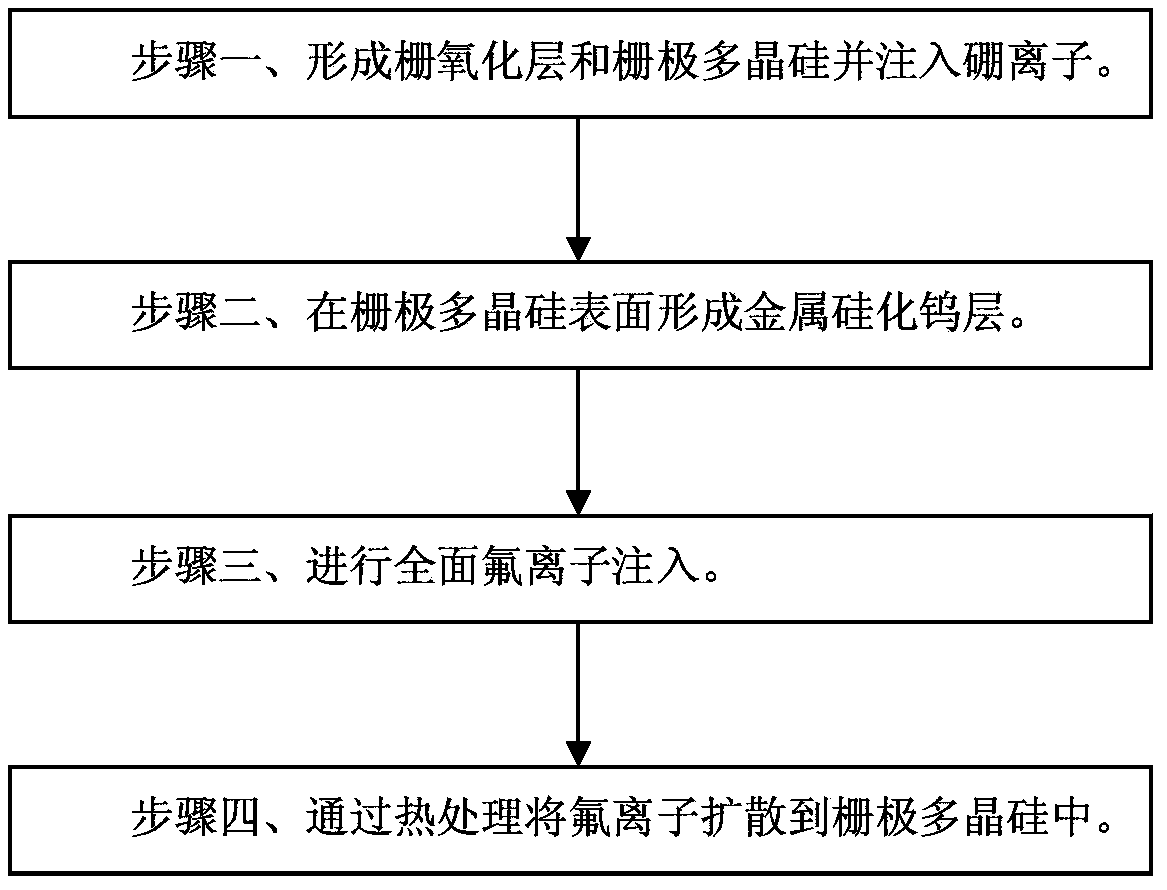

[0024] Such as image 3 Shown is the flow chart of the method of the embodiment of the present invention; the step of forming the gate of the PMOS device in the method for improving the negative bias temperature stability of the gate of the PMOS device in the embodiment of the present invention includes:

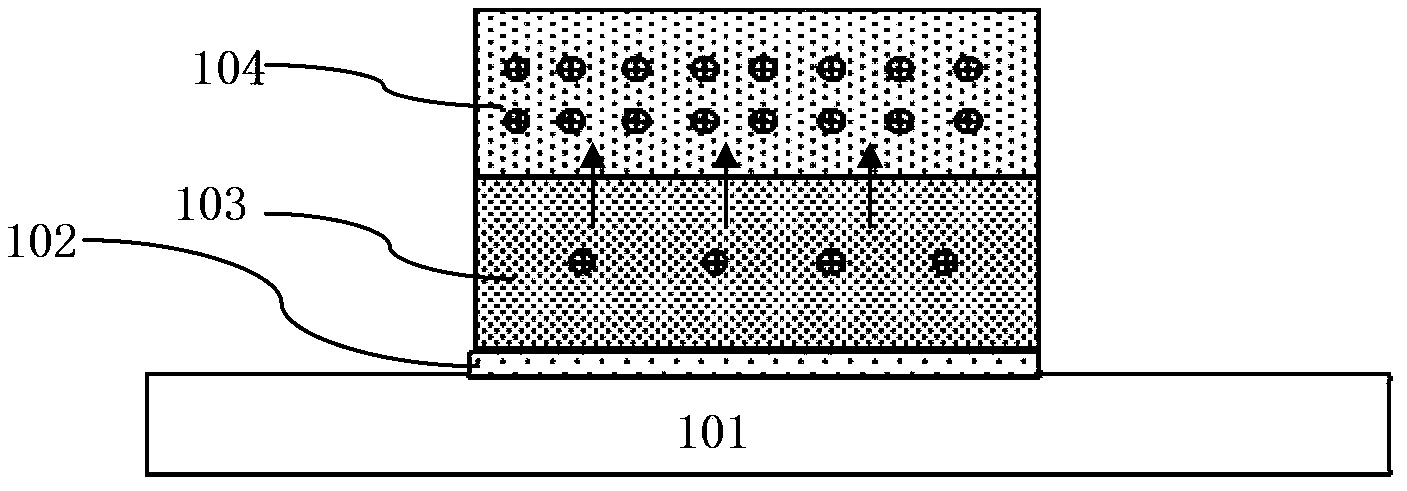

[0025] Step 1, such as Figure 4A As shown, a gate oxide layer 2 and a gate polysilicon 3 are sequentially formed on a silicon substrate 1, and boron ions are implanted into the gate polysilicon 3 in the PMOS device formation region. 1E15cm -2 ~1E16cm -2 , making the gate polysilicon 3 in the region where the PMOS device is formed have a P-type doped structure.

[0026] Step two, such as Figure 4A As shown, after boron ion implantation, a metal tungsten silicide layer 4 is formed on the surface of the gate polysilicon 3 .

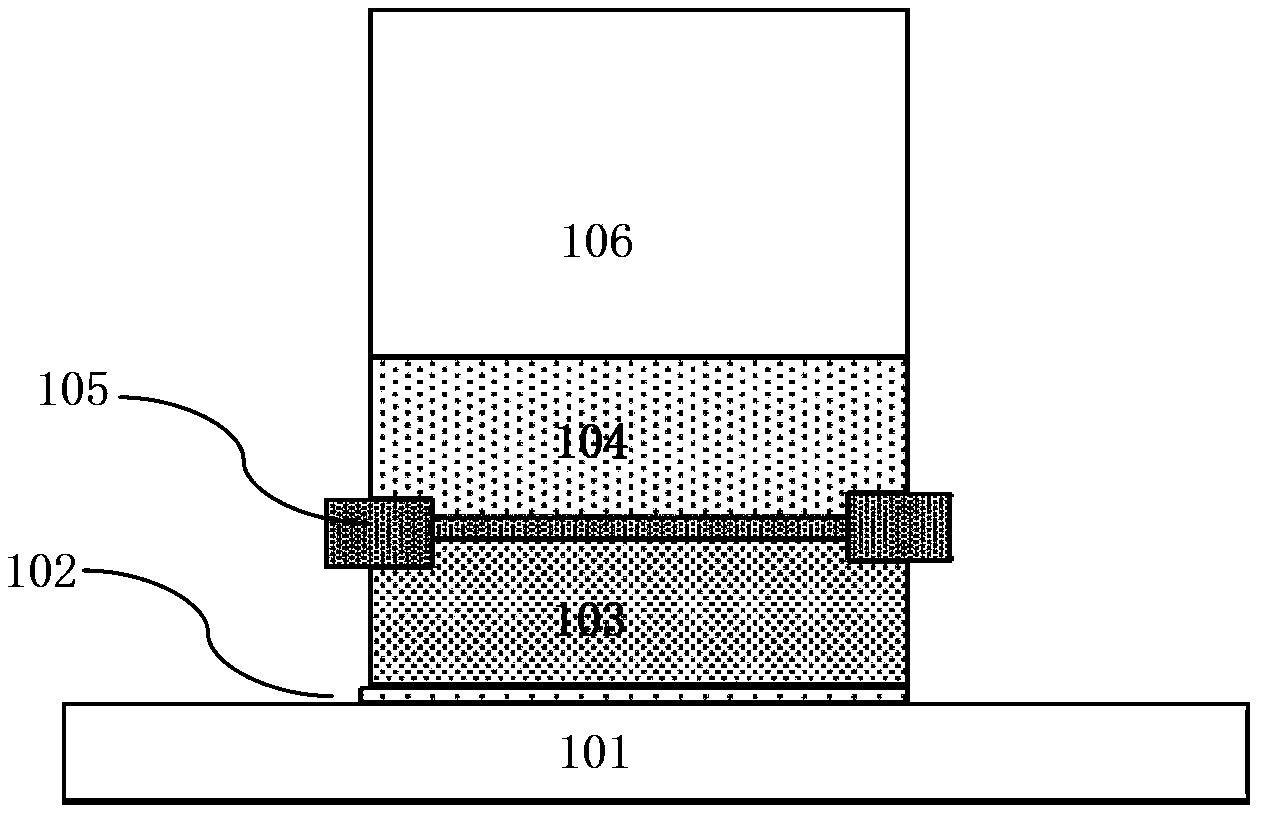

[0027] Step three, such as Figure 4B As shown, fluorine ion implantation is performed to implant fluorine ions into the metal tungsten silicide l...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More