Thin film transistor

A thin film transistor and semiconductor technology, applied in transistors, semiconductor devices, electrical components, etc., can solve the problems of increasing pixel circuit area, large parasitic resistance, increasing the complexity of driving circuits, etc., to reduce threshold voltage drift, reduce device degradation, The effect of improving reliability

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

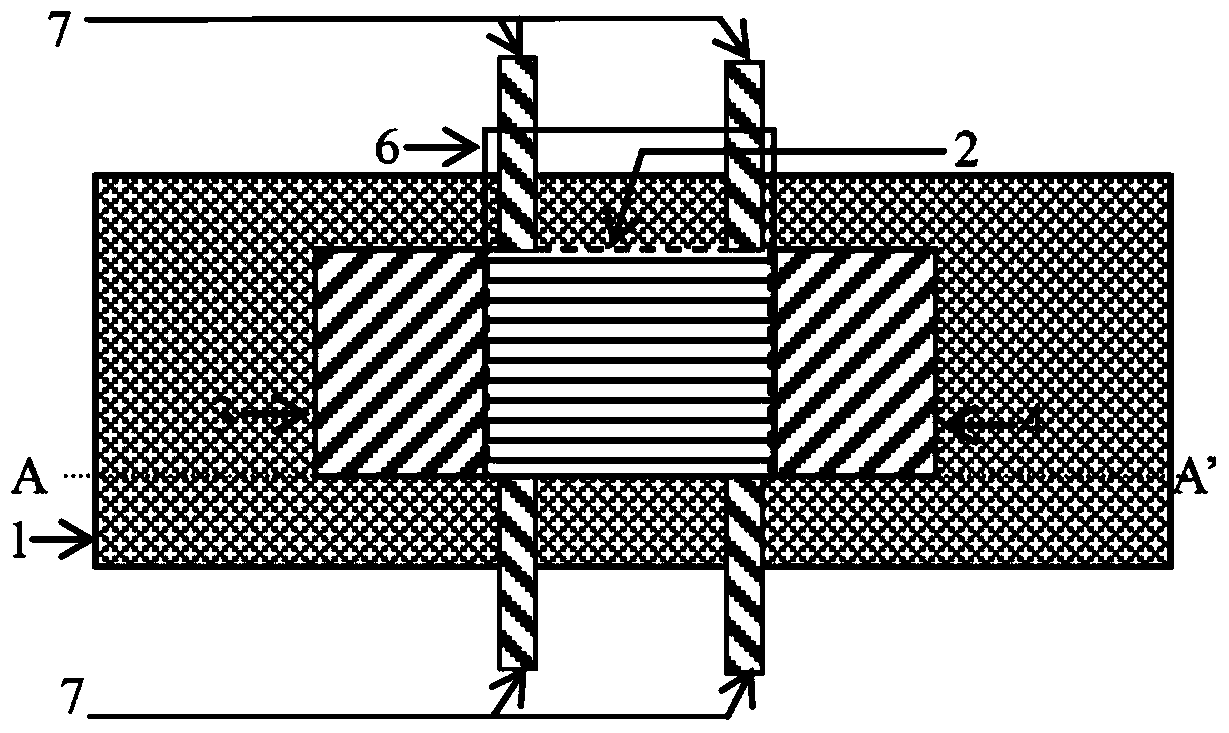

[0043] ginseng Figure 4a , 4b As shown, the thin film transistor device structure in this embodiment is a top-gate self-aligned structure, including: an insulating substrate 100, a source-drain region 101, a semiconductor channel region 102, a gate insulating layer 103, a gate 104, and a passivation layer 105 , the source and drain electrodes 106 and the carrier injection region 107 .

[0044] The carrier injection region 107 is in the same layer as the semiconductor channel region 102, and is located on both sides of the semiconductor channel region 102 and is in close contact with the semiconductor channel region 102. The carrier injection region 107 is used to provide the semiconductor channel region 102 with a carrier. Ryuko.

Embodiment 2

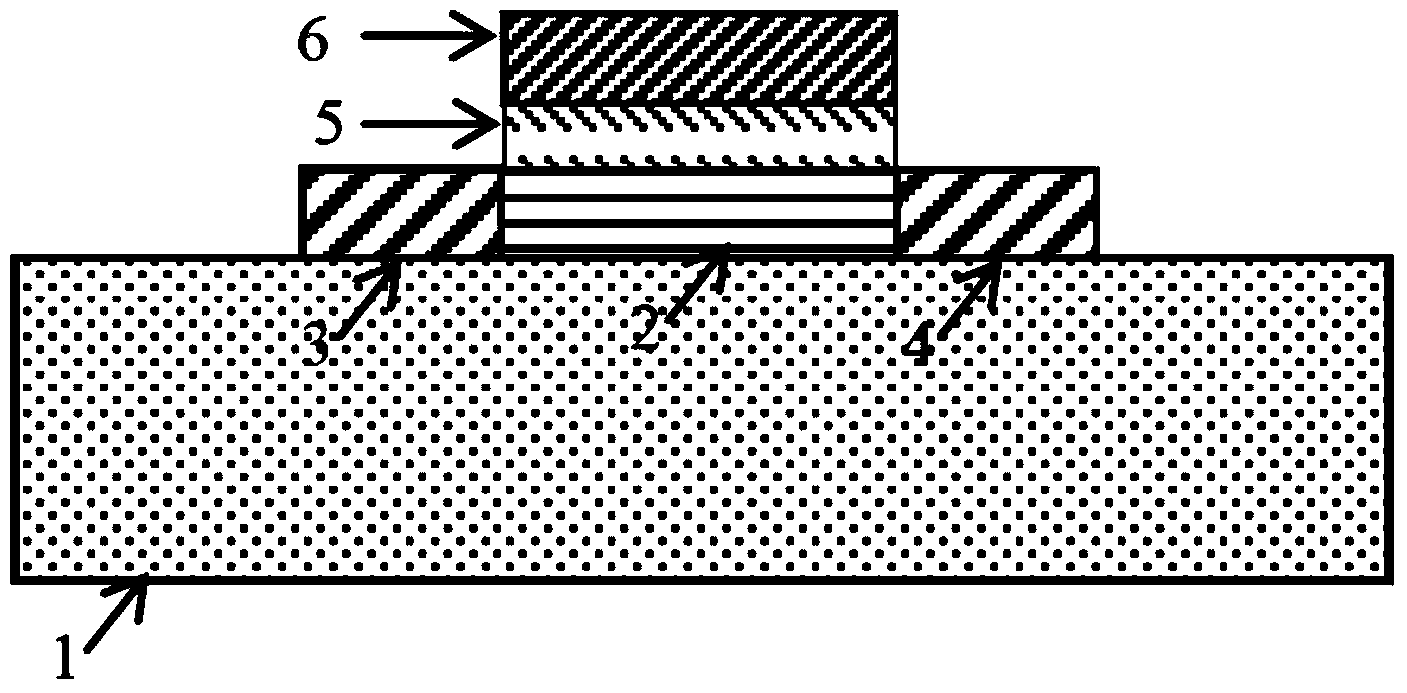

[0046] ginseng Figure 5a , 5b As shown, the TFT device structure in this embodiment is a top-gate self-aligned structure, including: an insulating substrate 200, a source-drain region 201, a semiconductor channel region 202, a gate insulating layer 203, a gate 204, and a passivation layer 205 , source and drain electrodes 206 and carrier injection layer 207 .

[0047] The carrier injection layer 207 is located below the semiconductor channel region 202 and is in close contact with the semiconductor channel region 202 , and can provide carriers to the semiconductor channel region 202 .

Embodiment 3

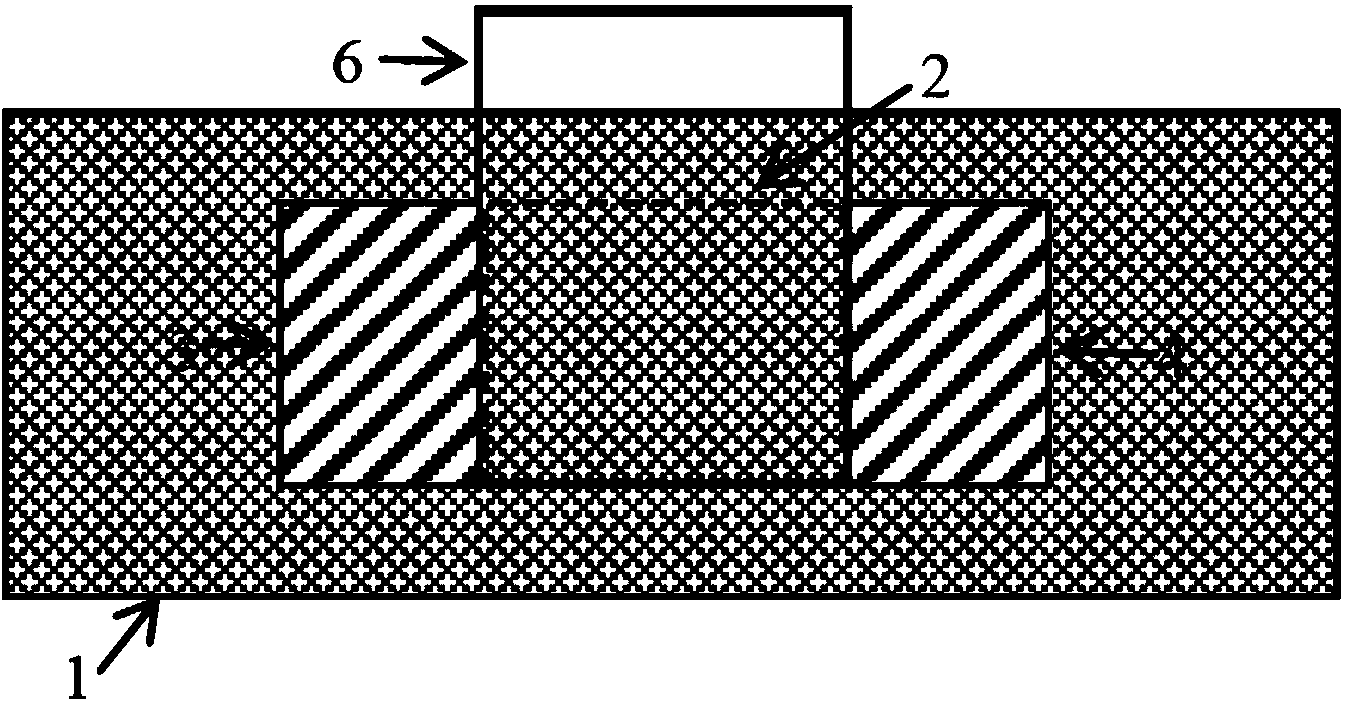

[0049] ginseng Figure 6a , 6b As shown, the TFT device structure in this embodiment is a bottom-gate structure, including: an insulating substrate 300 , a gate 301 , a gate insulating layer 302 , a semiconductor channel region 303 , source and drain electrodes 304 and a carrier injection layer 305 .

[0050] The carrier injection layer 305 is above the semiconductor channel region 303 and in close contact with the semiconductor channel region 303 . Carriers can be provided by the carrier injection layer 305 , and provide carriers to the channel through the region where the carrier injection layer 305 is in contact with the semiconductor channel region 303 .

[0051] In this embodiment, it can be as Figure 6a As shown, the carrier injection layer 305 is designed in segments, and the middle position of the semiconductor channel region 303 is not provided with a carrier injection layer. Of course, in other implementation modes, such as Figure 6c As shown, the carrier inject...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More