Pixel circuit and driving method thereof, display panel

A pixel circuit and non-driving technology, applied in static indicators, instruments, etc., can solve problems such as failure of threshold voltage compensation function, increased threshold voltage drift of driving transistors, and poor display effect of organic light-emitting diode display devices, etc., to achieve extended Effects of service life, increased service life, and reduced threshold voltage drift

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0033] In order to make the objects, technical solutions, and advantages of the embodiments of the present invention more apparent, exemplary embodiments of the present invention will be described in detail below with reference to the accompanying drawings. Apparently, the described exemplary embodiments are only some embodiments of the present invention, rather than all embodiments of the present invention, and all other embodiments obtained by those skilled in the art without paying creative efforts should fall into the present invention. within the scope of protection of the invention.

[0034] Here, it is to be noted that, in the drawings, the same reference numerals are assigned to components having substantially the same or similar structures and functions, and repeated descriptions about them will be omitted.

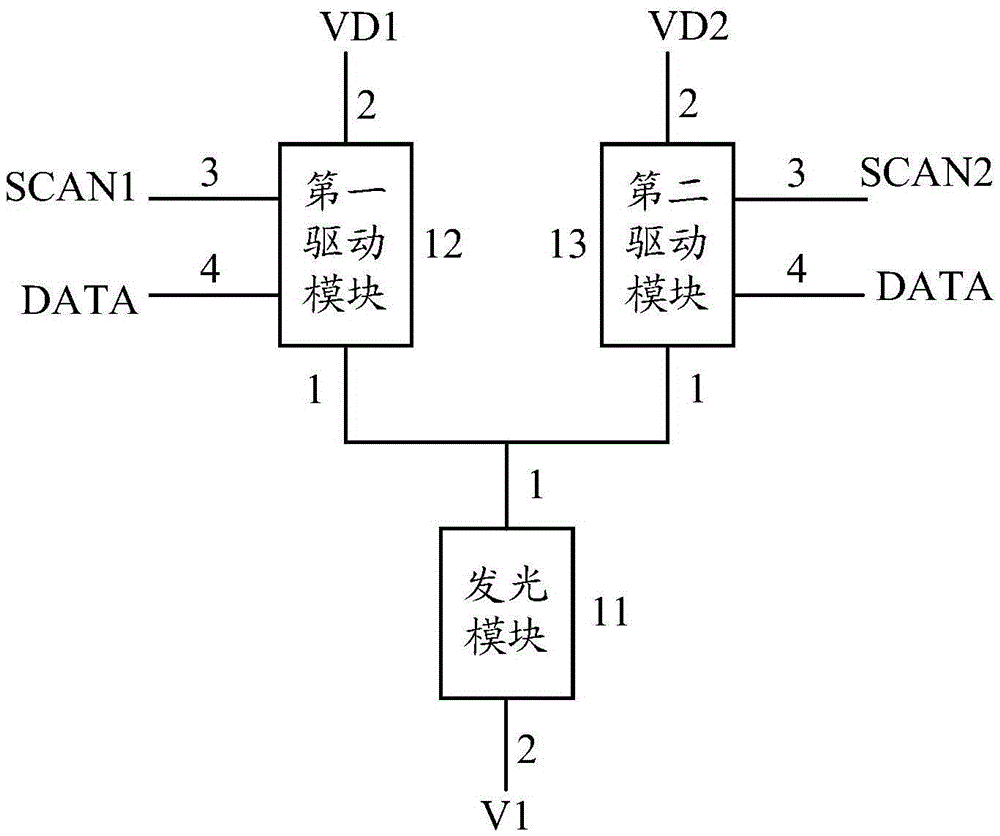

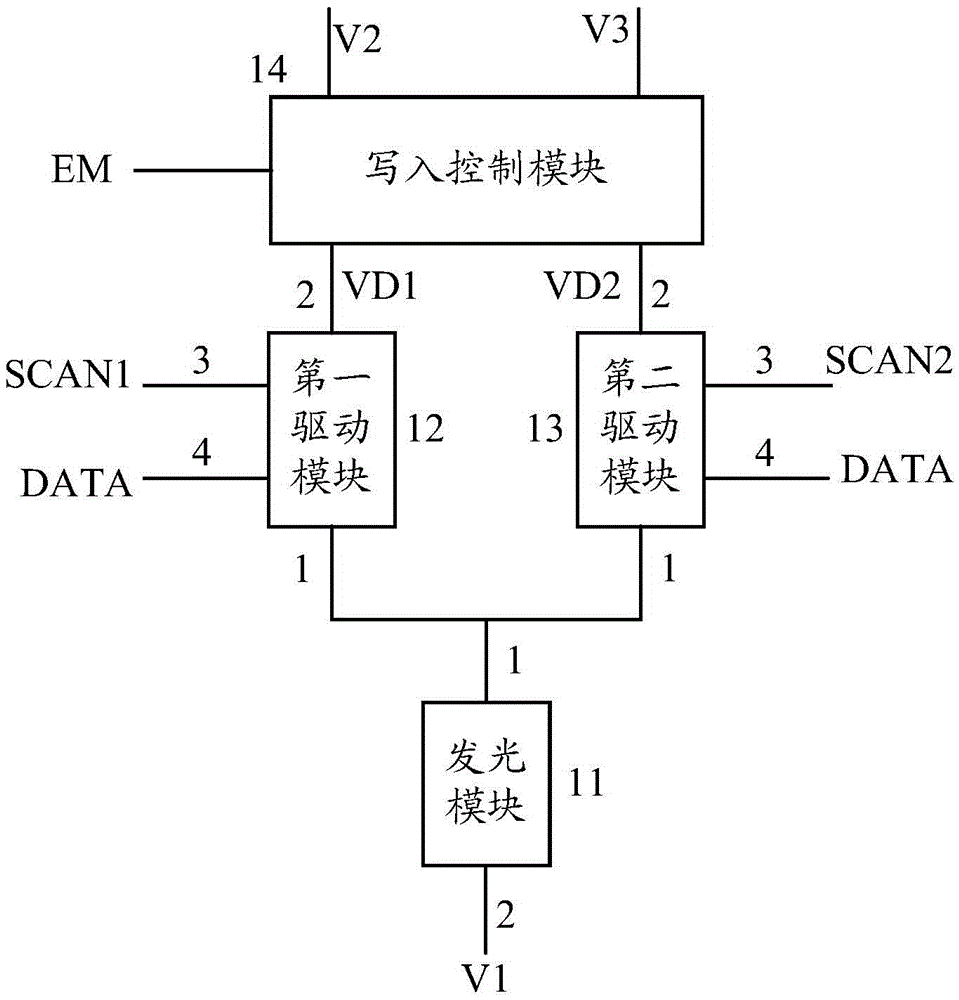

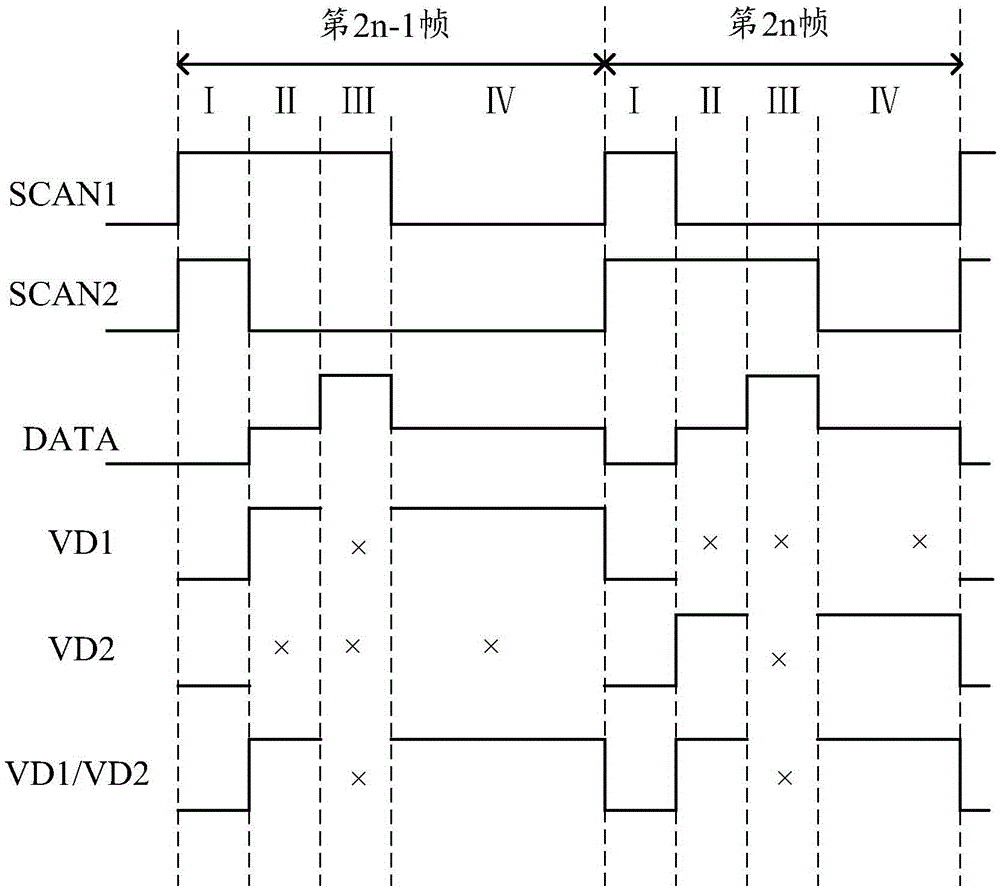

[0035] figure 1 is a schematic block diagram of a pixel circuit according to an embodiment of the present invention. Such as figure 1 As shown, the pixel circ...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More