Patents

Literature

56results about How to "Increase the current switch ratio" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

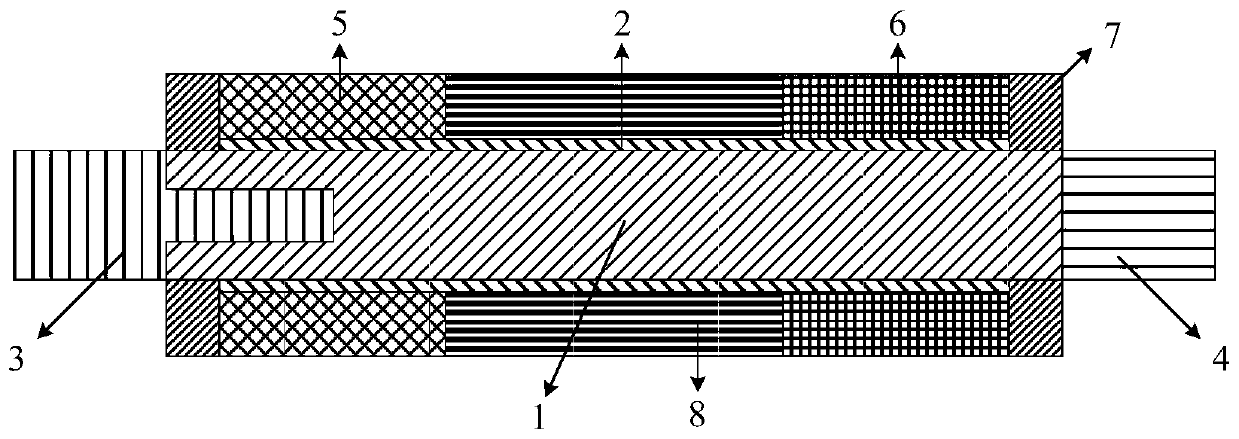

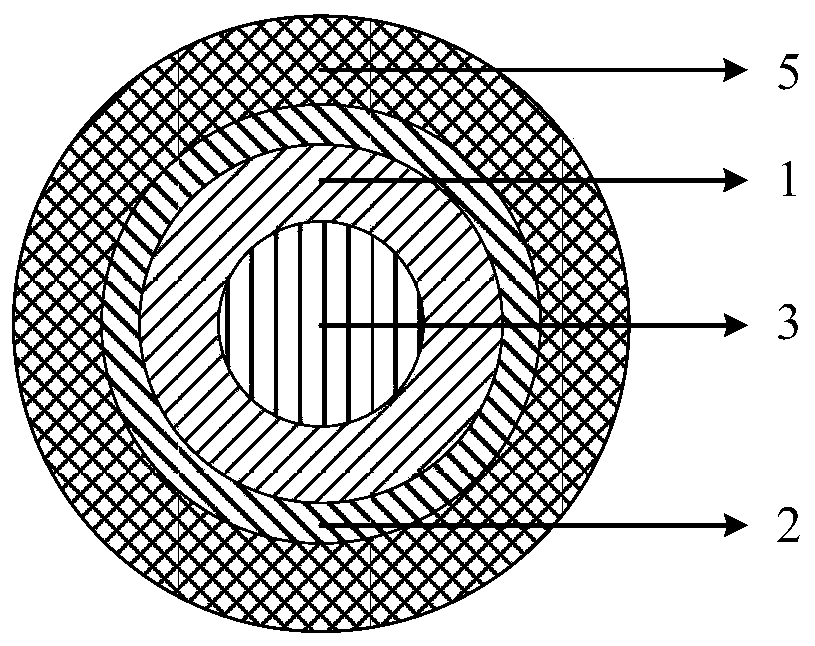

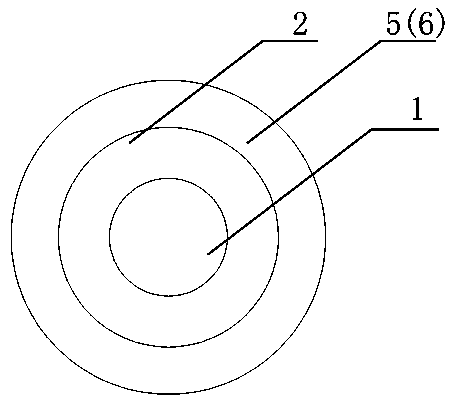

Nano-wire field effect transistor

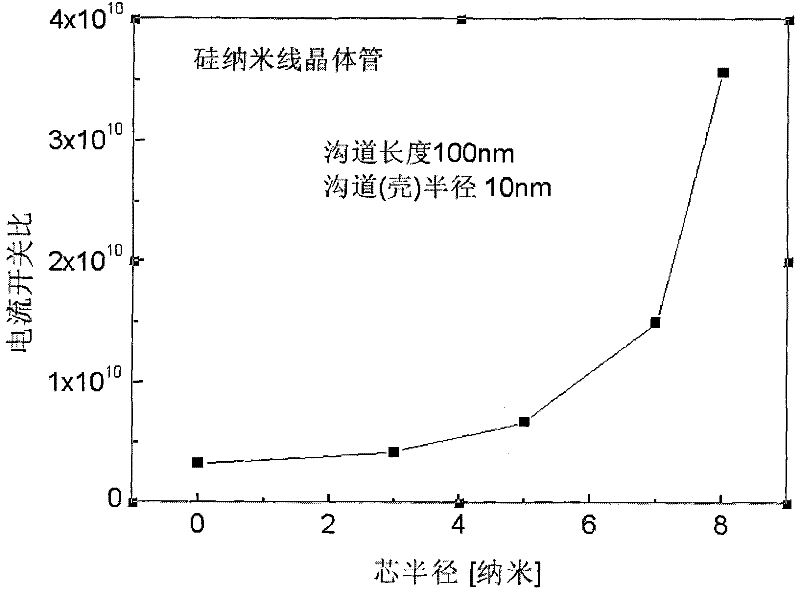

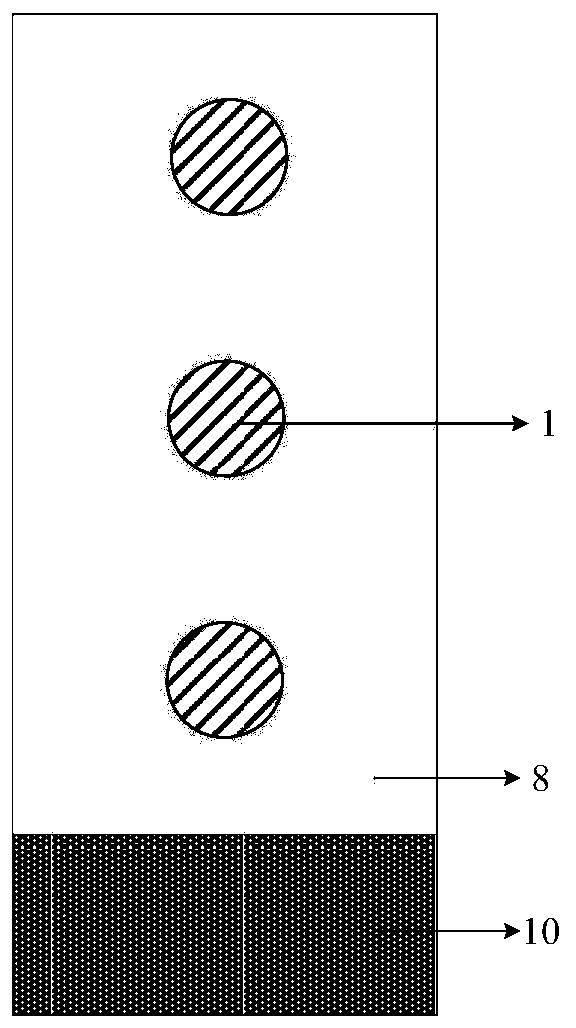

ActiveCN101740619AReduce off-state currentReduce static power consumptionSemiconductor devicesGate dielectricNanowire

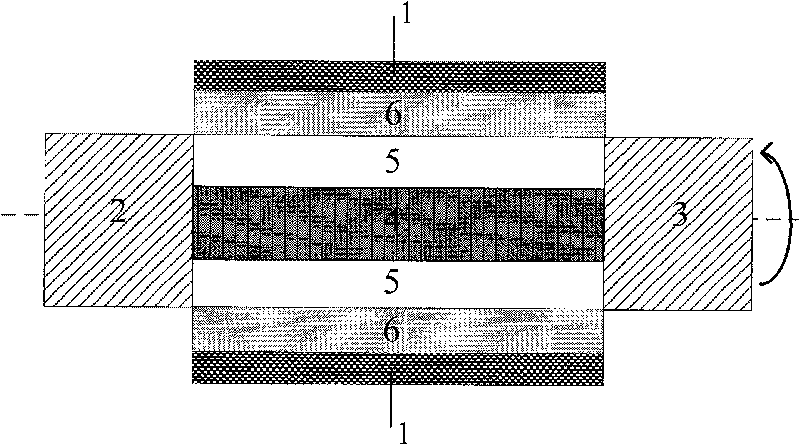

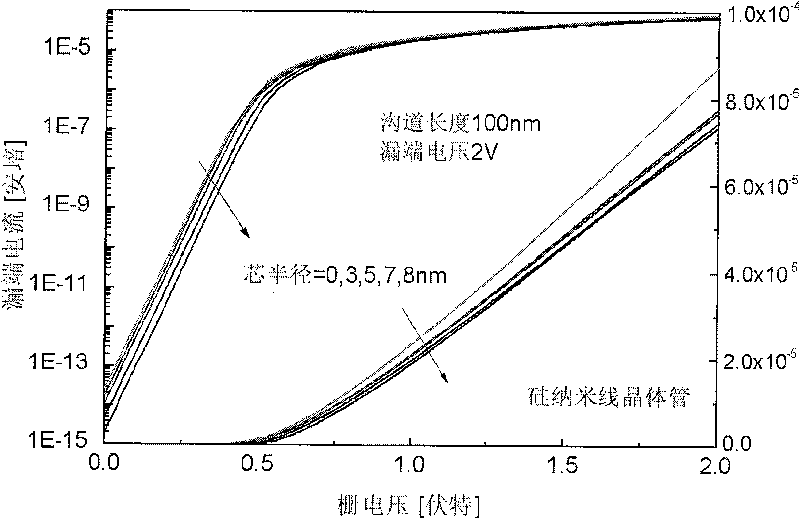

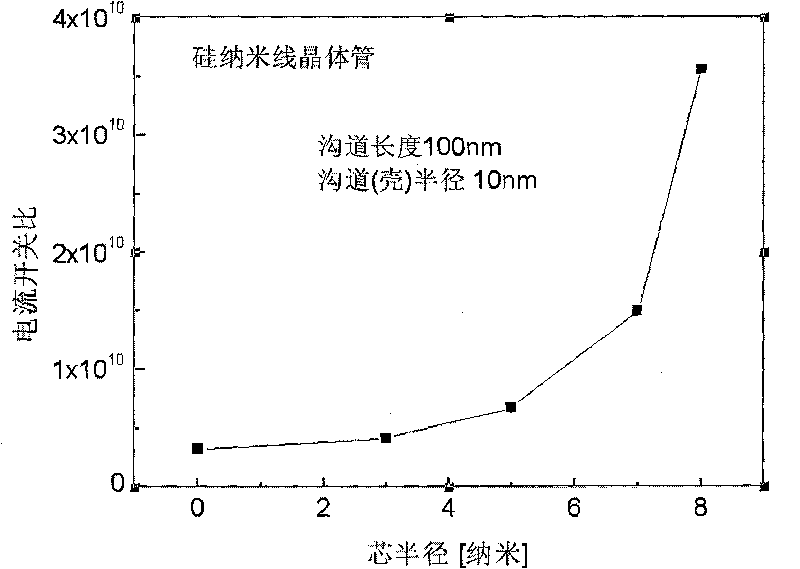

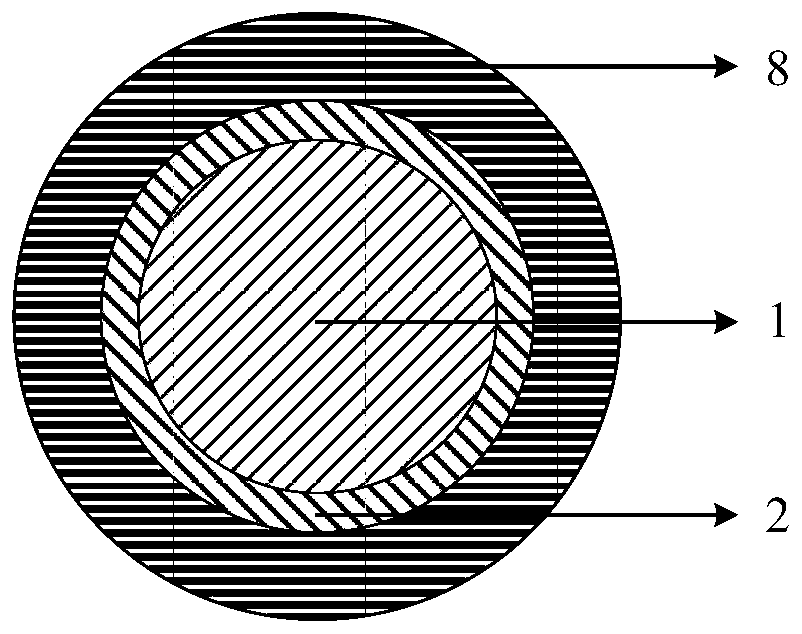

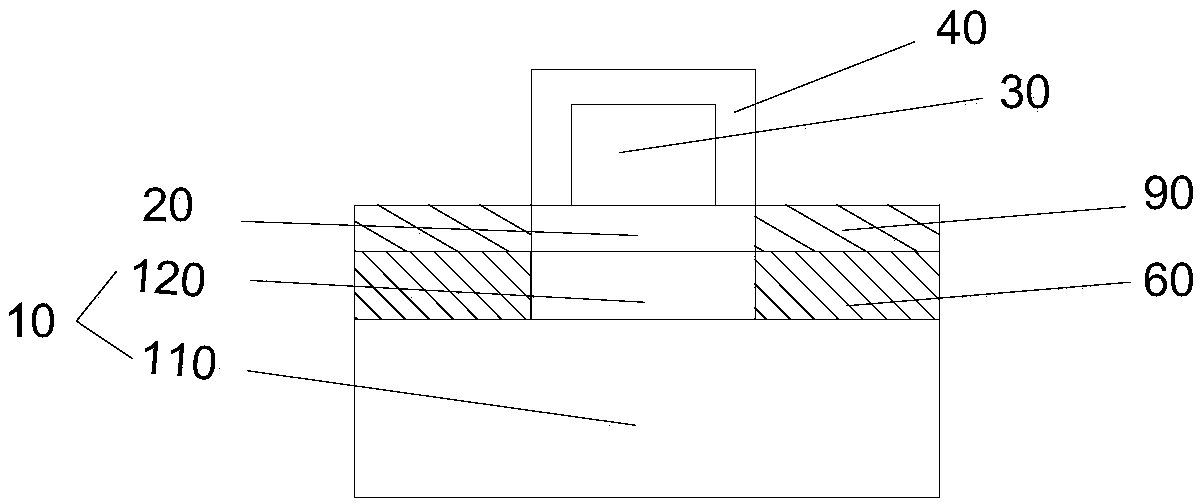

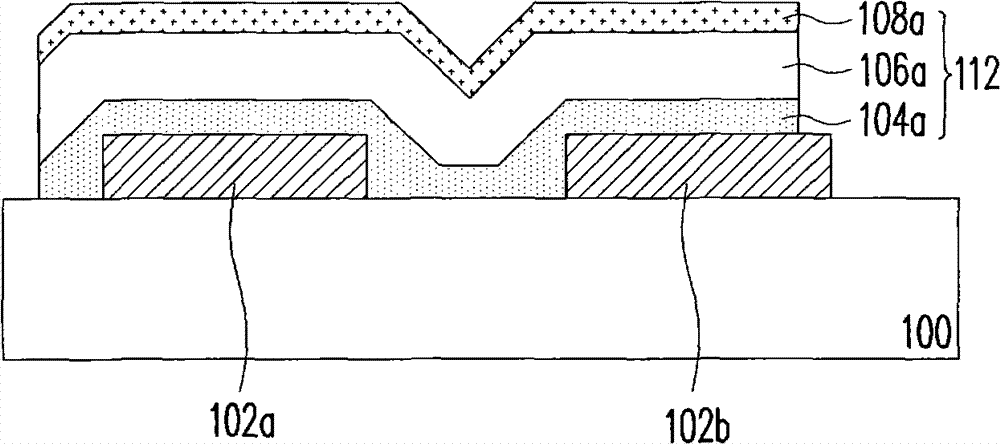

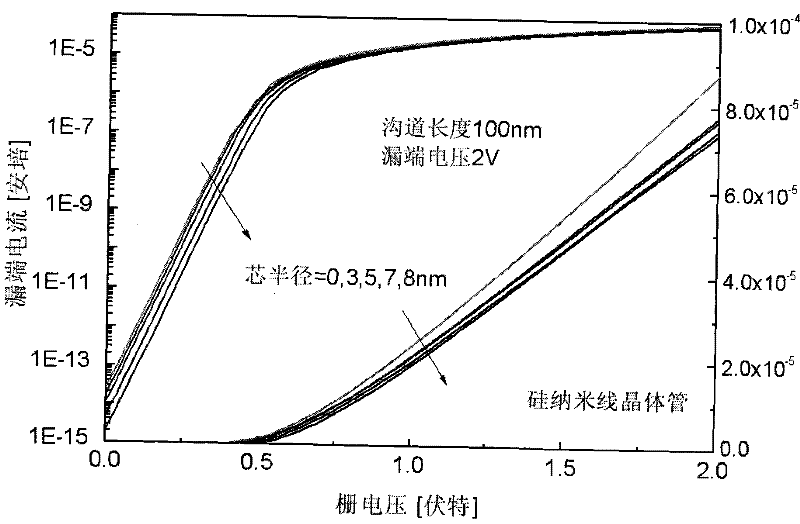

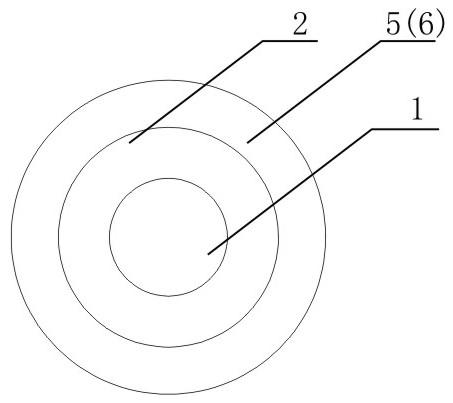

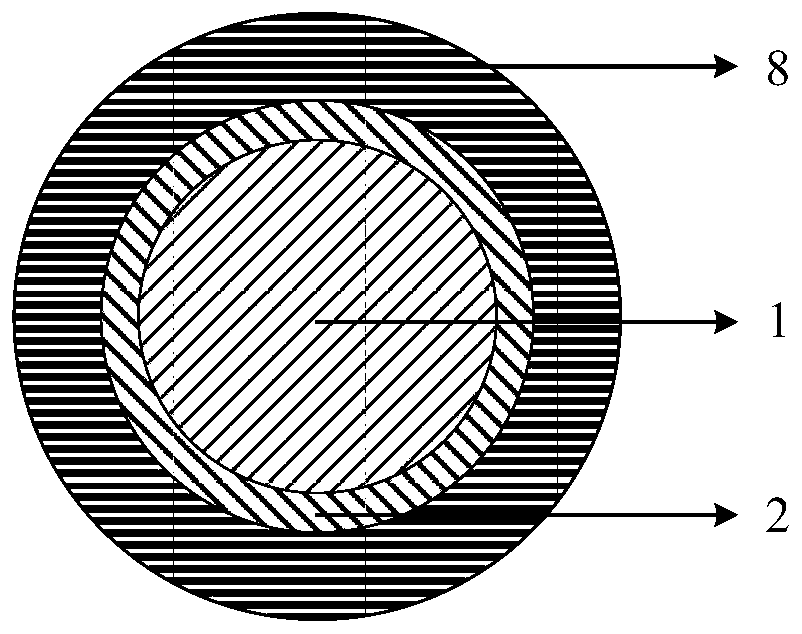

The invention discloses a nano-wire field effect transistor comprising a gate electrode, a source region, a drain region, a central region and a gate dielectric layer. The central region is in the core-shell structures which are coaxial; the gate dielectric layer fully surrounds the central region; the gate electrode fully surrounds the gate dielectric layer; the source region and the drain region are respectively arranged on two sides of the central region; the core structure of the central region is made from insulating material, and the shell structure of the central region is made from semiconductor material; the doping type and the doping concentration of the semiconductor material of the shell structure of the central region are adjustable; the lengths of both the core structure and the shell structure and the radii of both the core structure and the shell structure are adjustable; and the materials of the gate dielectric layer, the gate electrode, the source region and the drain region are adjustable. Due to the adoption of the insulating core structure, the off-current of the traditional nano-wire transistor can be reduced effectively, and the current on-off ratio of the devices can be increased. The threshold voltage shifting and the drain induced barrier lowering of the nano-wire field effect transistor are less affected by the short channel effect, and the size reducing performance of the nano-wire field effect transistor is more excellent.

Owner:SEMICONDUCTOR MANUFACTURING INTERNATIONAL (BEIJING) CORP +1

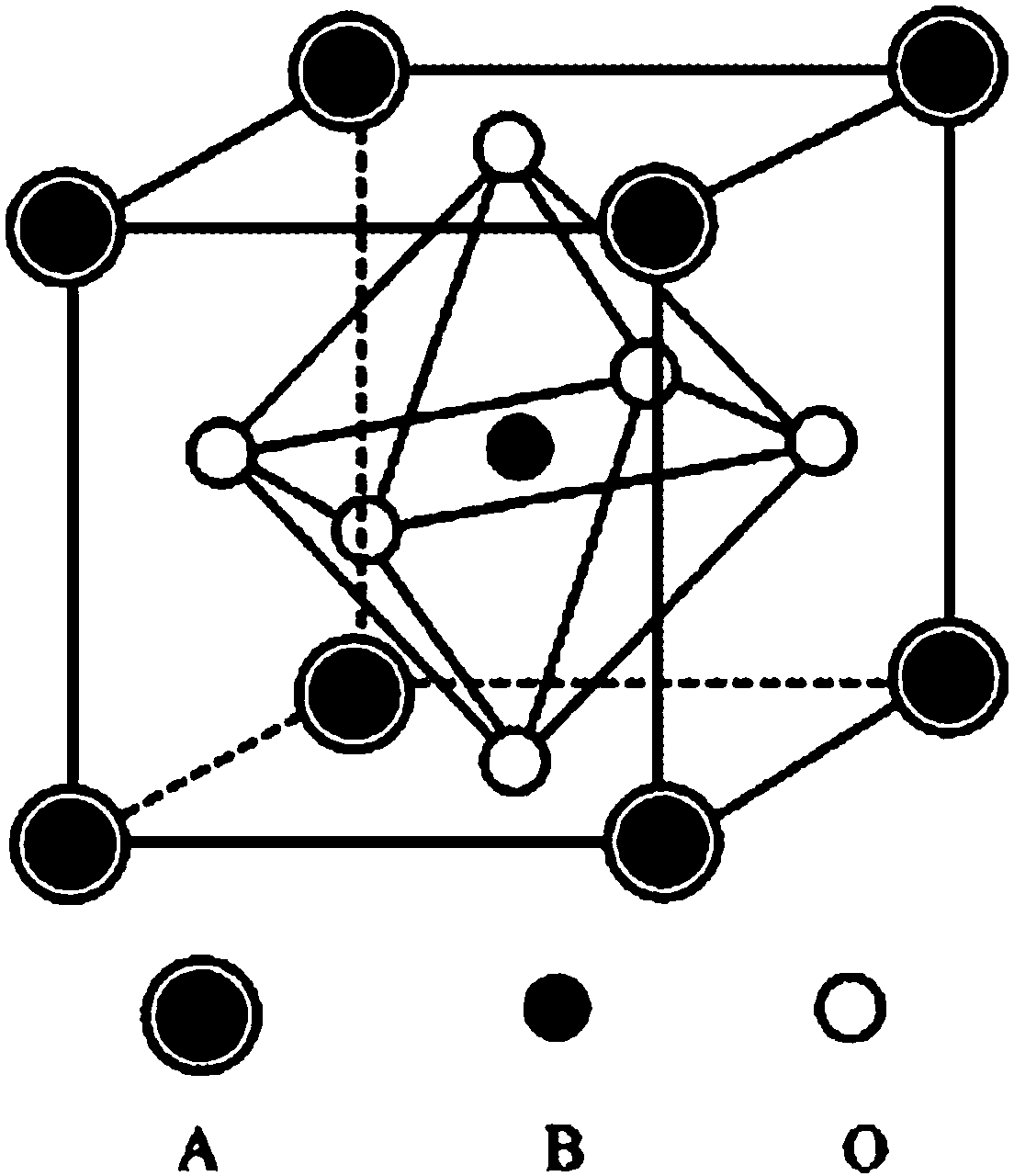

Inorganic metal oxide semiconductor film of perovskite structure and metallic oxide thin film transistor

ActiveCN104218096AStrong acid resistanceSimple preparation processTransistorRare-earth elementOxide thin-film transistor

The invention provides an inorganic metal oxide semiconductor film of a perovskite structure and a metallic oxide thin film transistor. The inorganic metal oxide semiconductor film of the perovskite structure is used as an active layer. The inorganic metal oxide semiconductor film of the perovskite structure is expressed as the chemical expression: MxA1-xBo3, wherein 0.01<=x<=0.5, A is at least one chemical element of Ca, Sr and Ba, B is a chemical element of Ti and Sn, and M is at least one chemical element of Sc, Y, rare earth elements, Al and In. The inorganic metal oxide semiconductor film of the perovskite structure is composed of crystal particles of the perovskite structure, and sizes of the crystal particles vary from 2mm to 900mm. The thickness of the inorganic metal oxide semiconductor film of the perovskite structure varies from 10nm to 500nm. When the inorganic metal oxide semiconductor film of the perovskite structure is used as the active layer, electronic mobility is high, and the metallic oxide thin film transistor prepared by using the inorganic metal oxide semiconductor film of the perovskite structure is good in light stability, low in sub-threshold swing amplitude, simple in preparation technology and low in cost.

Owner:SOUTH CHINA UNIV OF TECH

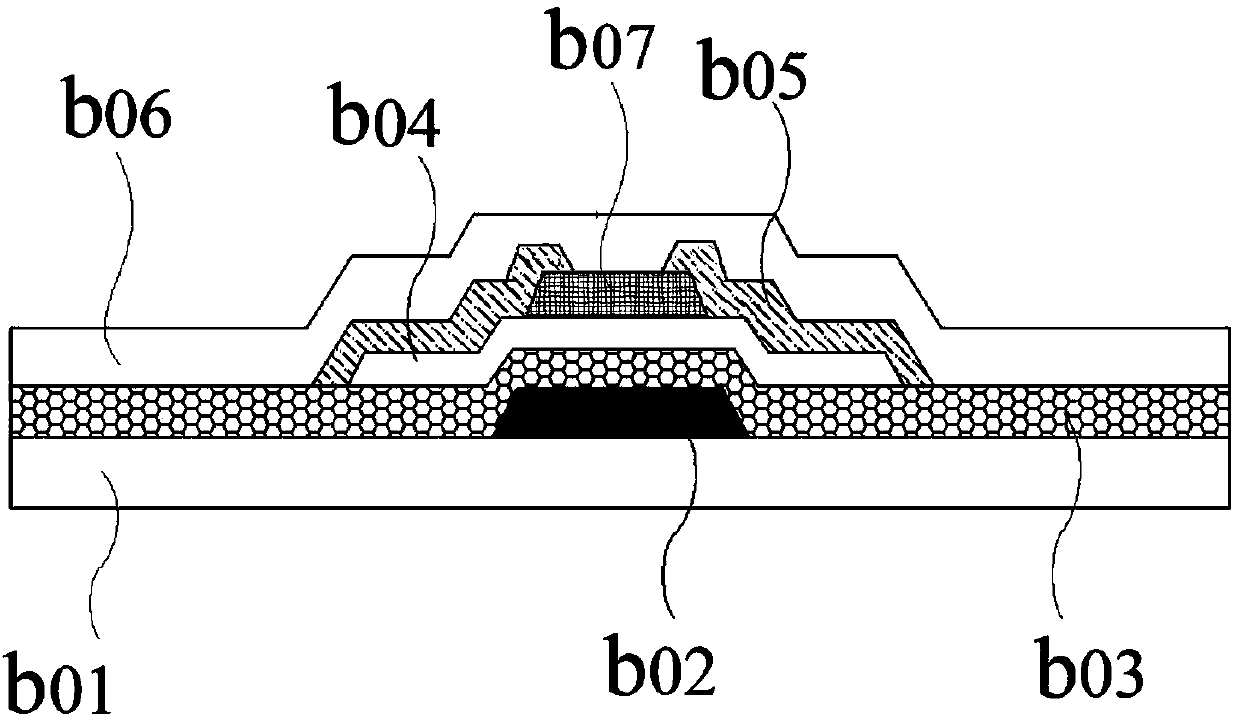

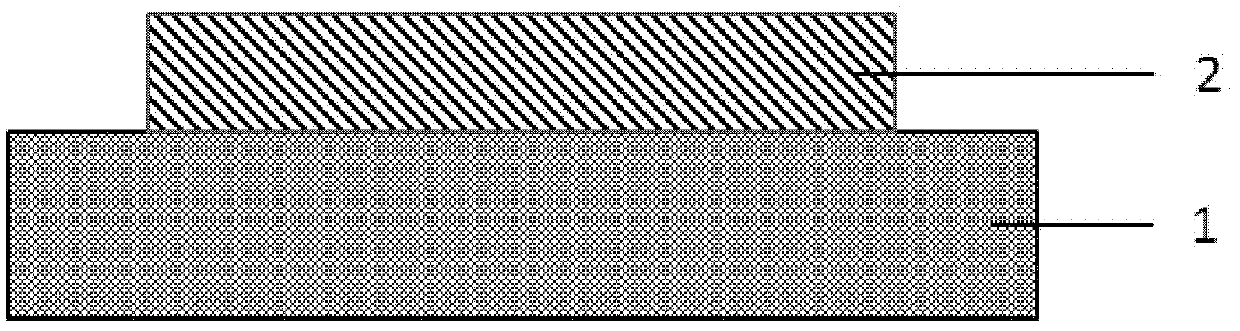

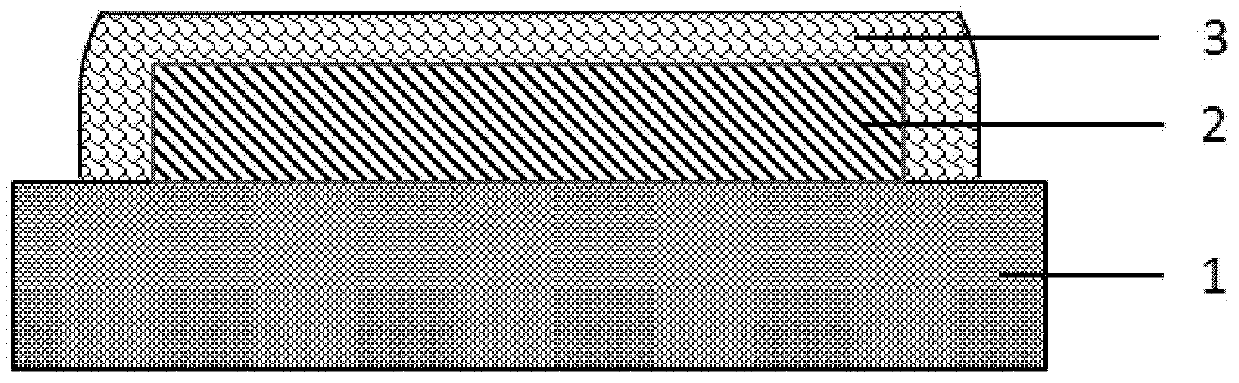

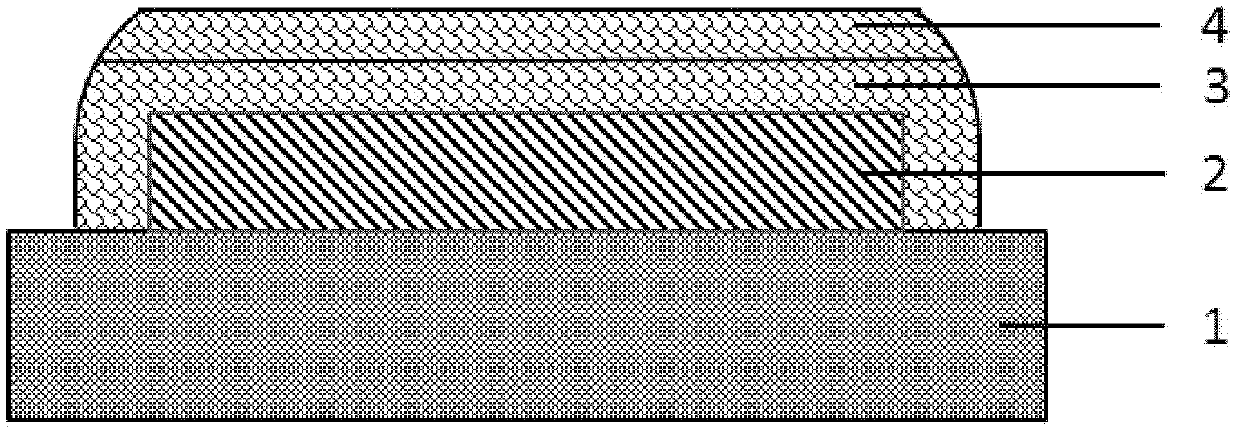

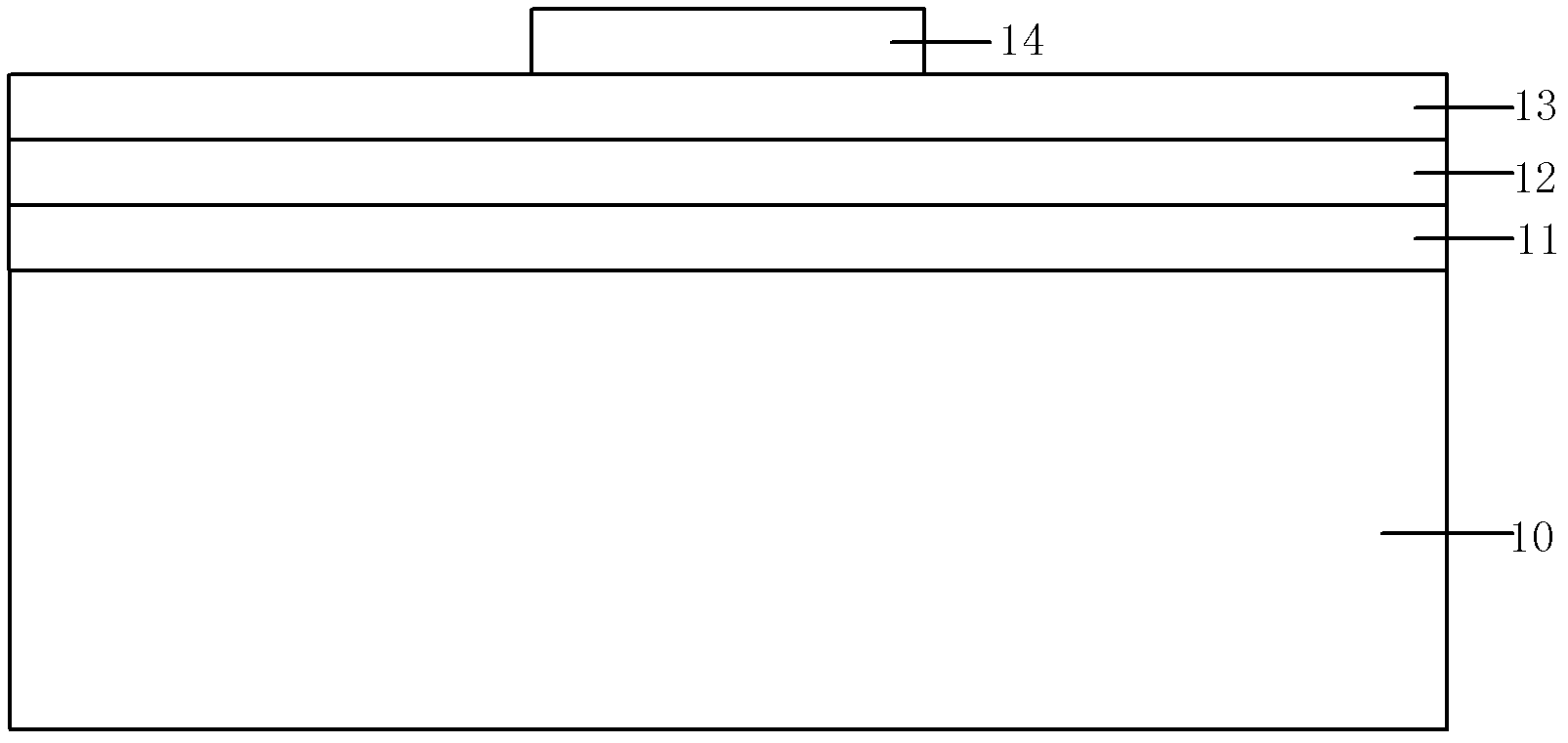

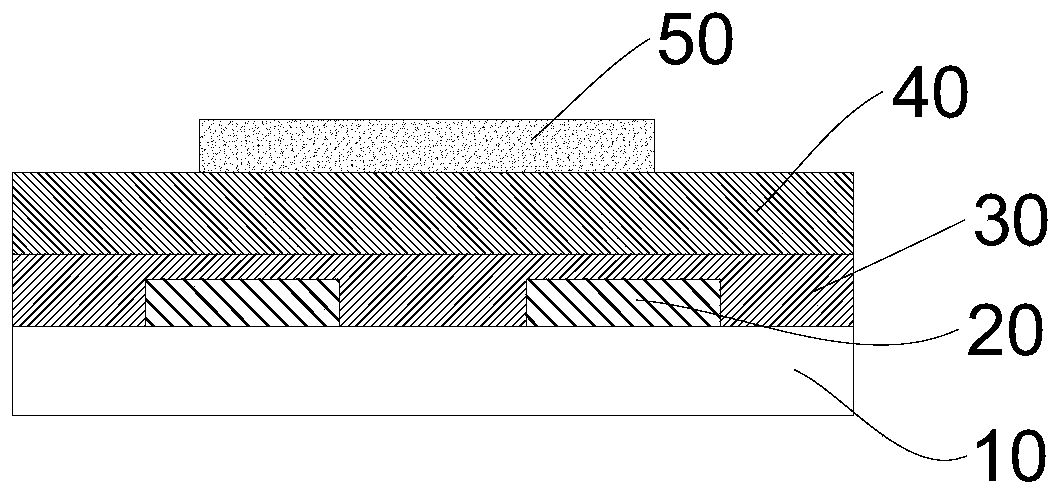

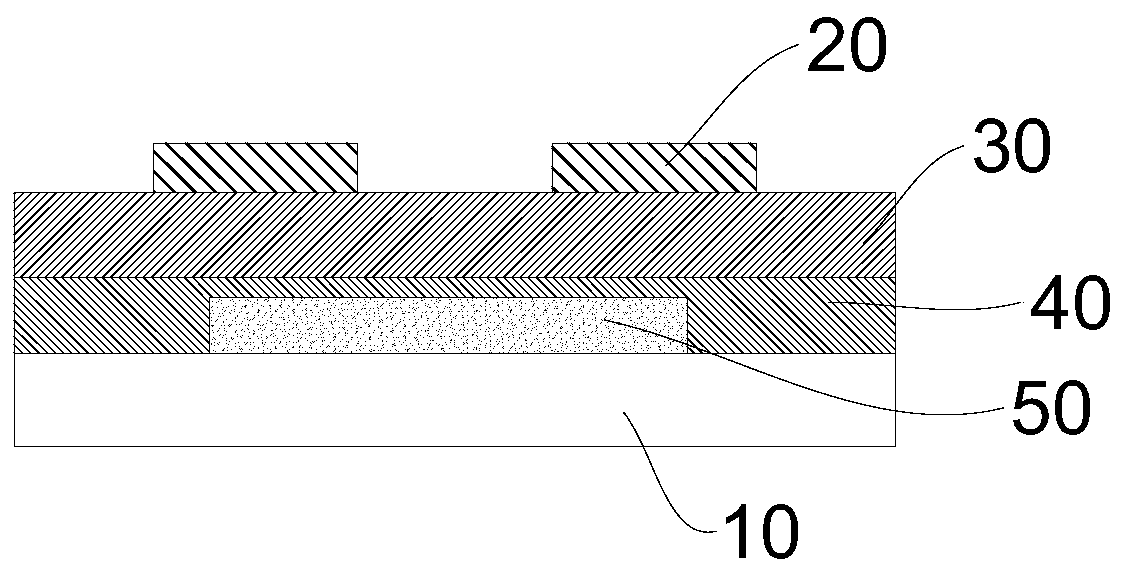

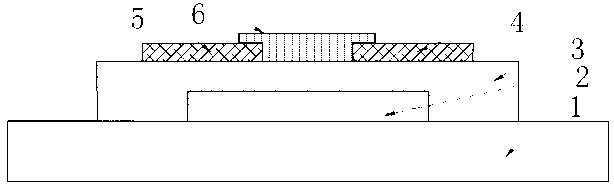

Metal oxide thin film transistor with top gate structure and manufacturing method thereof

InactiveCN102683423AImproved interface contactImprove interface contact resistanceTransistorComposite filmOxide thin-film transistor

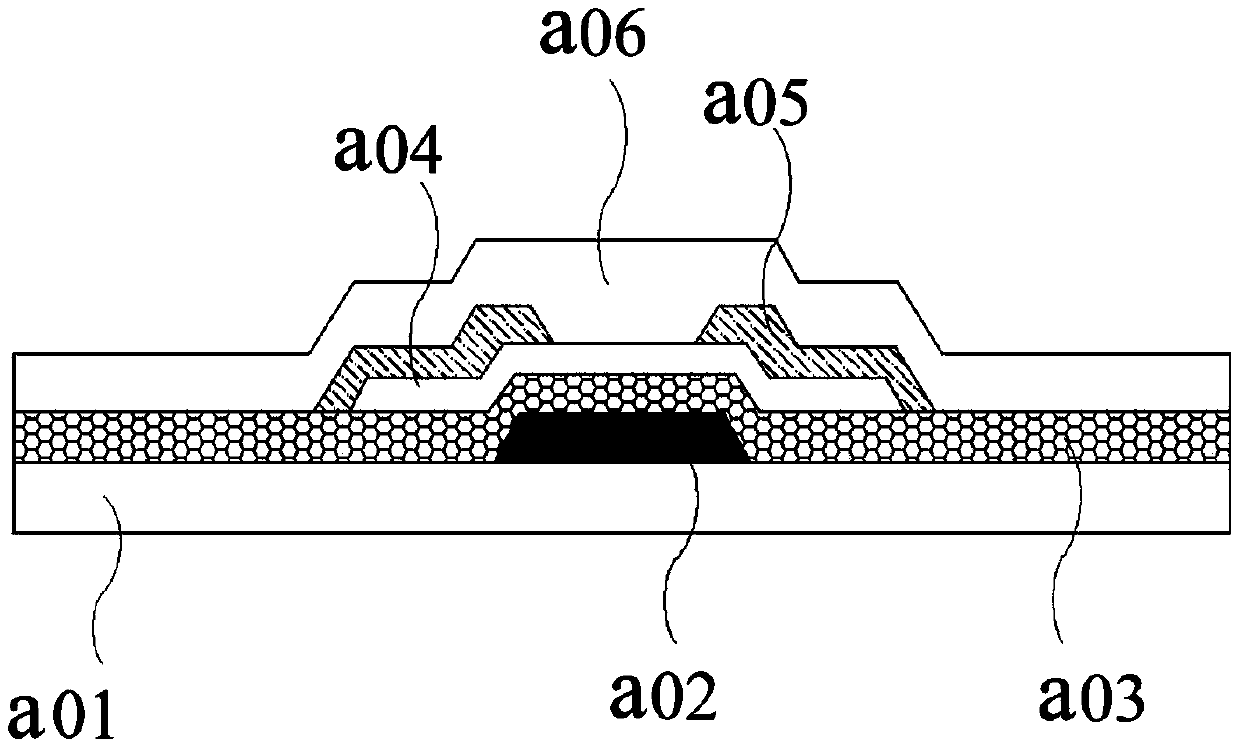

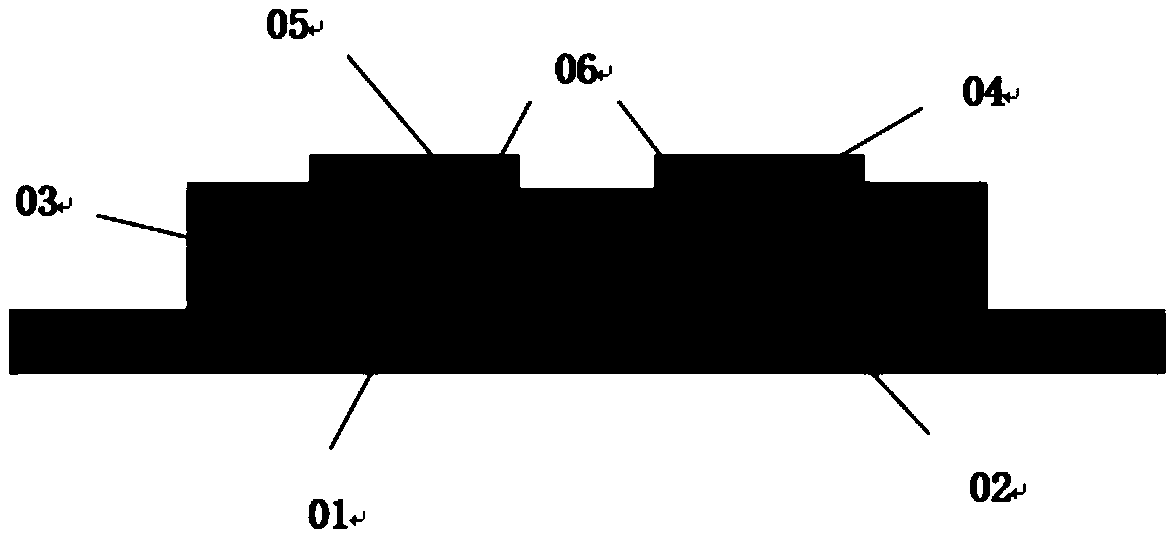

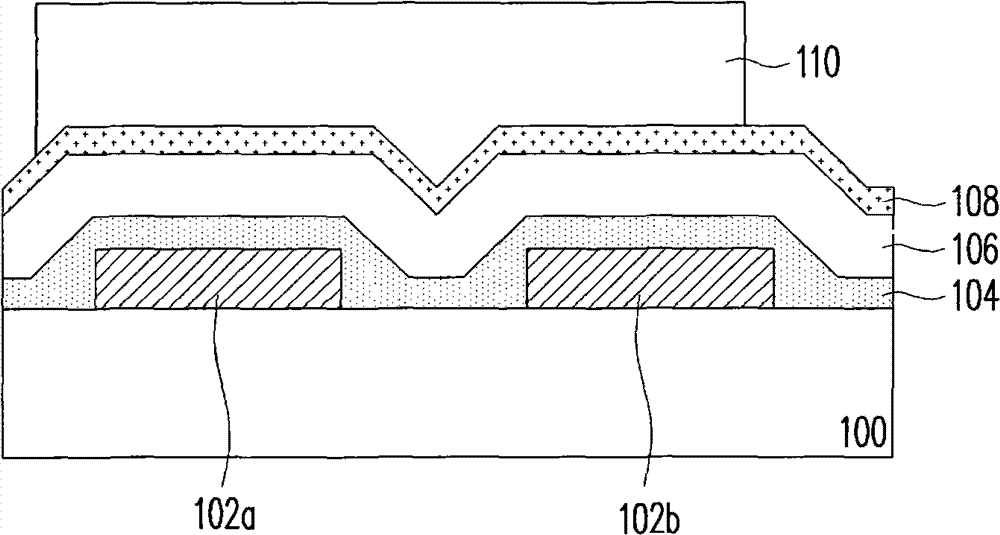

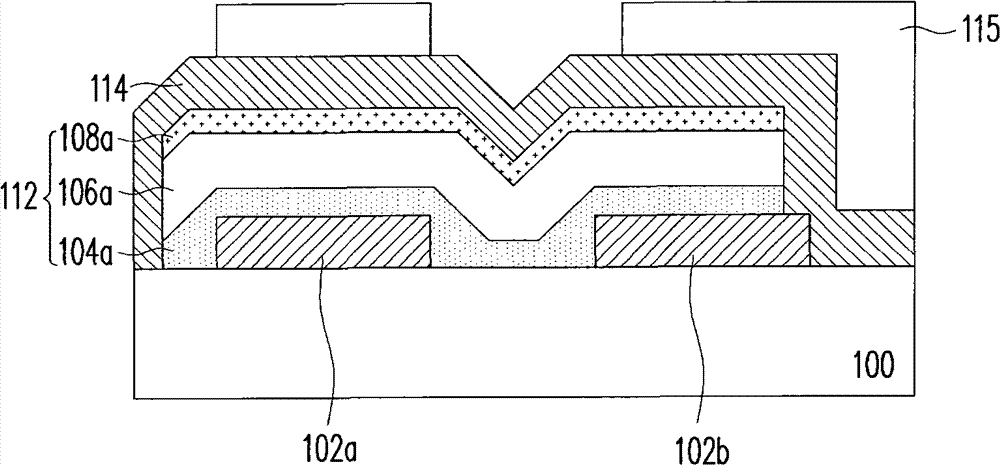

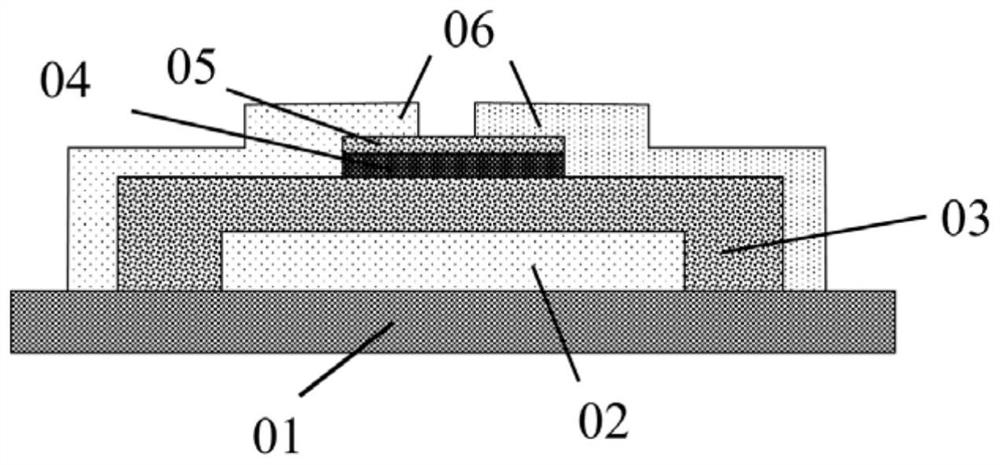

The invention discloses a metal oxide thin film transistor with a top gate structure and a manufacturing method thereof. The thin film transistor comprises a substrate, an active layer, an insulating layer, a gate, a source and a drain, wherein the active layer is arranged on the substrate; the source is arranged at one end of the upper side of the active layer; the drain is arranged at the other end of the upper side of the active layer; the insulating layer is arranged in the middle of the upper side of the active layer; the gate is arranged on the insulating layer; a metallization layer is arranged between the active layer and the source; a metallization layer is also arranged between the active layer and the drain; and the active layer has a composite film structure and sequentially comprises an oxygen-poor metal oxide film layer and an oxygen-enriched metal oxide film layer from bottom to top. The active layer is made into the composite film layer through the same material and different processes, and the contact resistance in a source / drain electrode contact region is reduced through a metallization method; and the insulating layer is manufactured by employing an optimized sputtering process, and the plasma is prevented from damaging a channel active layer. Through the annealing treatment, the high-performance metal oxide thin film transistor with the top gate structure is obtained.

Owner:东莞彩显有机发光科技有限公司 +2

Ultra-low-power organic resistance changing memory device and manufacturing method thereof

ActiveCN102610755AEasy to prepareEasy to scale upSolid-state devicesSemiconductor/solid-state device manufacturingAsic technologyUltra low power

The invention discloses an ultra-low-power organic resistance changing memory device and a manufacturing method of the ultra-low-power organic resistance changing memory device, belonging to the technical field of organic electronics and CMOS-mixed integrated circuit. The device is manufactured on a substrate, a device unit is an MIM capacity structure, a bottom layer of the MIM structure is an inert electrode such as metal or non-metal conductive thin-film, a top layer of the MIM structure is an active electrode such as metal Al, a middle function layer of the MIM sturcture is a poly-p-xylylene polymer film growing after multi-deposition. According to the invention, the device adopts the poly-p-xylylene polymer film growing after multi-deposition as the function layer, programming current of a memory is less than 0.5 muA, and erase current of the memory is reduced to about 10 nA or lower, therefore, the ultra-low-power operations of the organic resistance changing memory are implemented.

Owner:SEMICON MFG INT (SHANGHAI) CORP +1

Preparation method of germanium-based Schottky N-type field effect transistor

ActiveCN102136428ADoes not significantly increase parasitic resistanceIncrease the current switch ratioSemiconductor/solid-state device manufacturingSemiconductor devicesField-effect transistorSchottky transistor

The invention provides a preparation method of a germanium-based Schottky N-type field effect transistor, belonging to the technical field of technical manufacturing of ultra large scale integrations (ULSI). In the preparation method, a high-k medium thin layer is formed among a germanium substrate, a metal source and a metal drain. On one hand, the thin layer can prevent an electron wave function in metal from introducing an MIGS (Metal Induction Gap Strip) interface state into a semiconductor forbidden band and can passivate a dangling bond of a germanium interface; and on the other hand, an insulating medium layer is very thin and electrons can freely pass through the insulating medium layer basically, so that the parasitic resistances of the source and the drain cannot be increased remarkably. By adopting the method, the Fermi level pinning effect can be wakened, the Fermi level is close to the conduction band position of germanium, and the electronic barrier is lowered, therefore, the electric current on-off ratio of the germanium-based Schottky transistor is increased, and the performance of an NMOS (Negative Channel Metal Oxide Semiconductor) device is improved.

Owner:SEMICONDUCTOR MANUFACTURING INTERNATIONAL (BEIJING) CORP +1

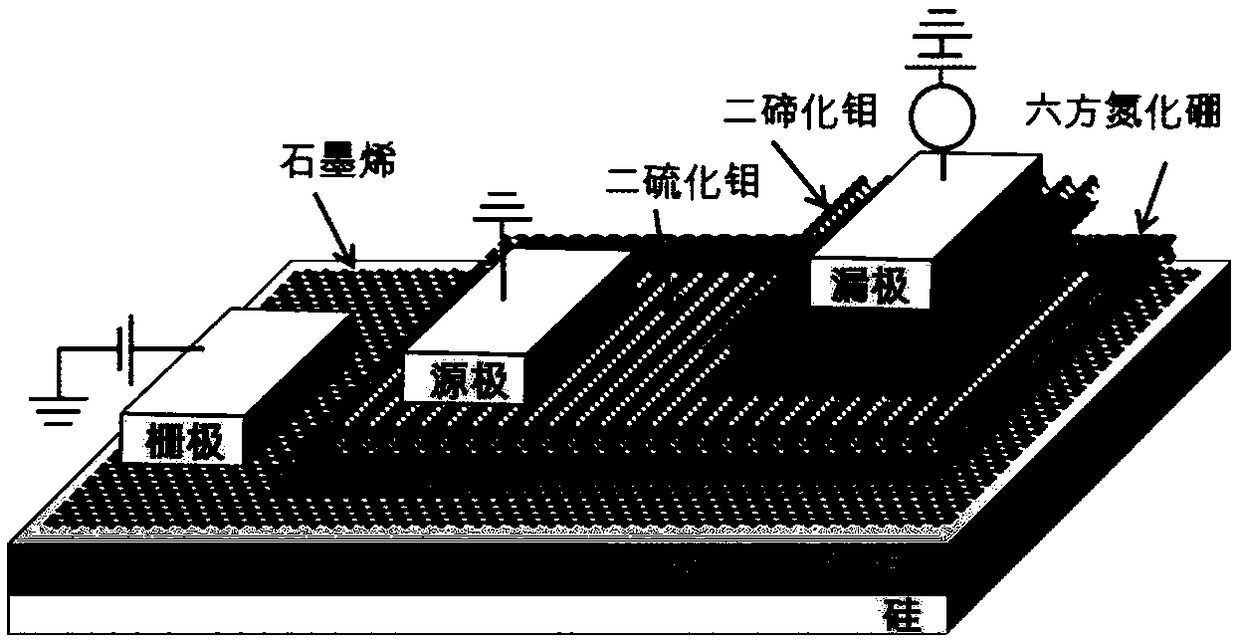

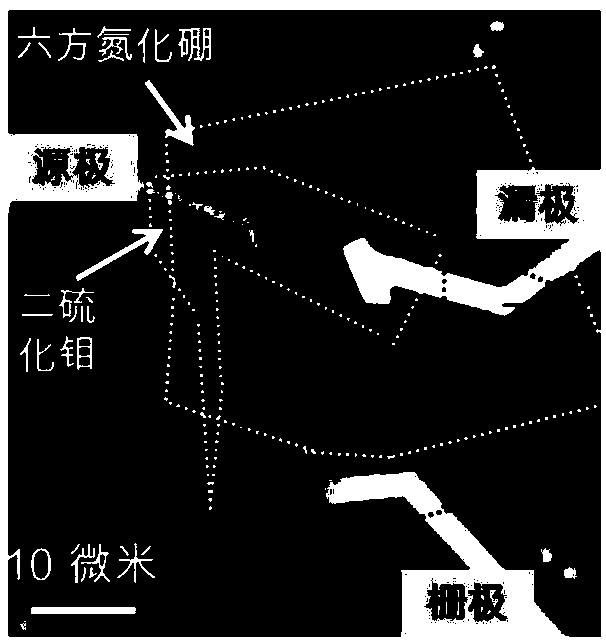

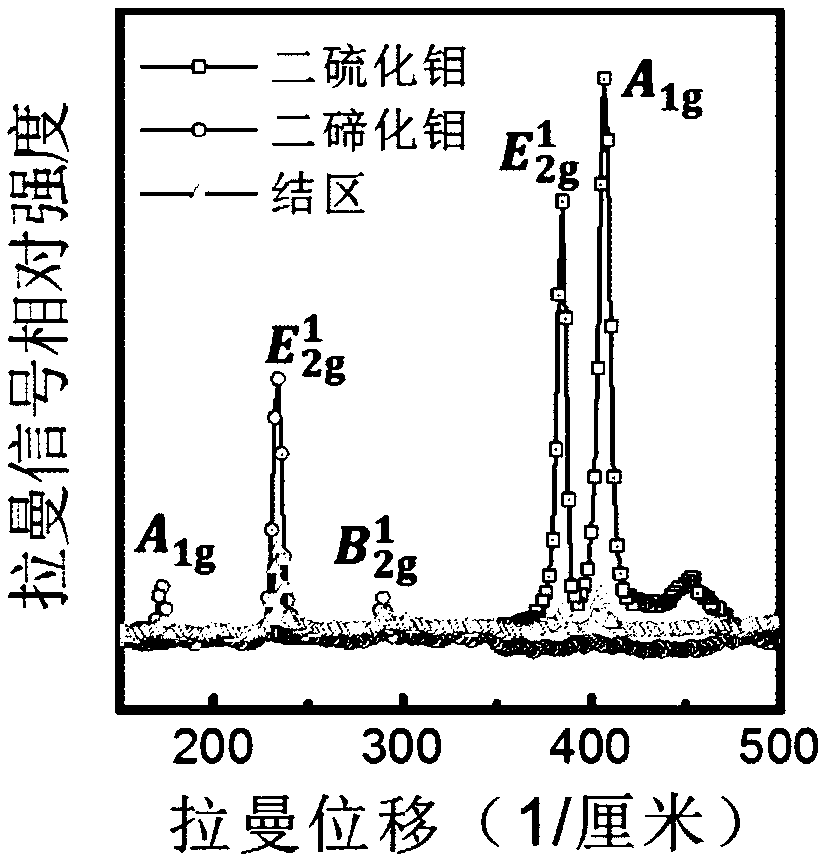

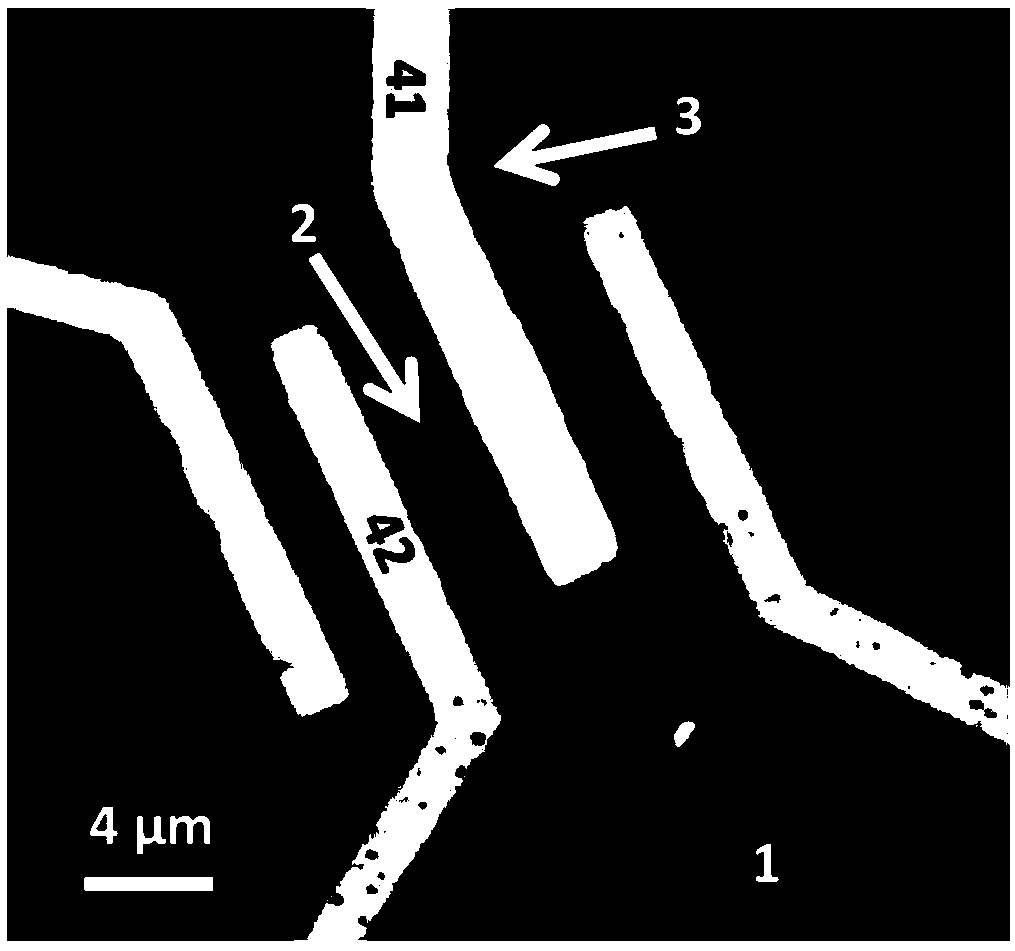

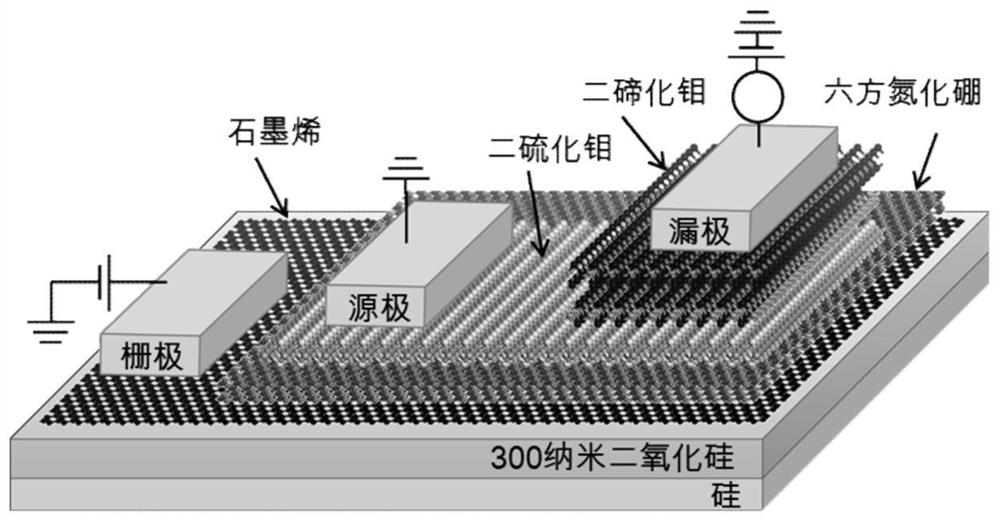

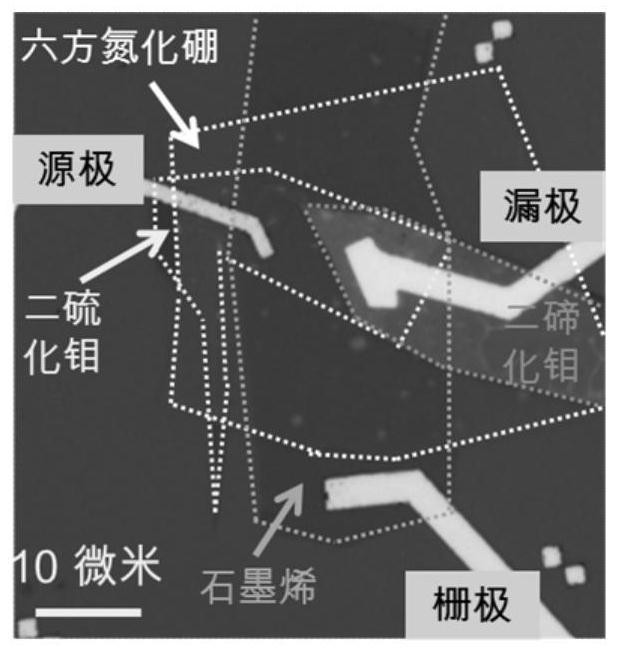

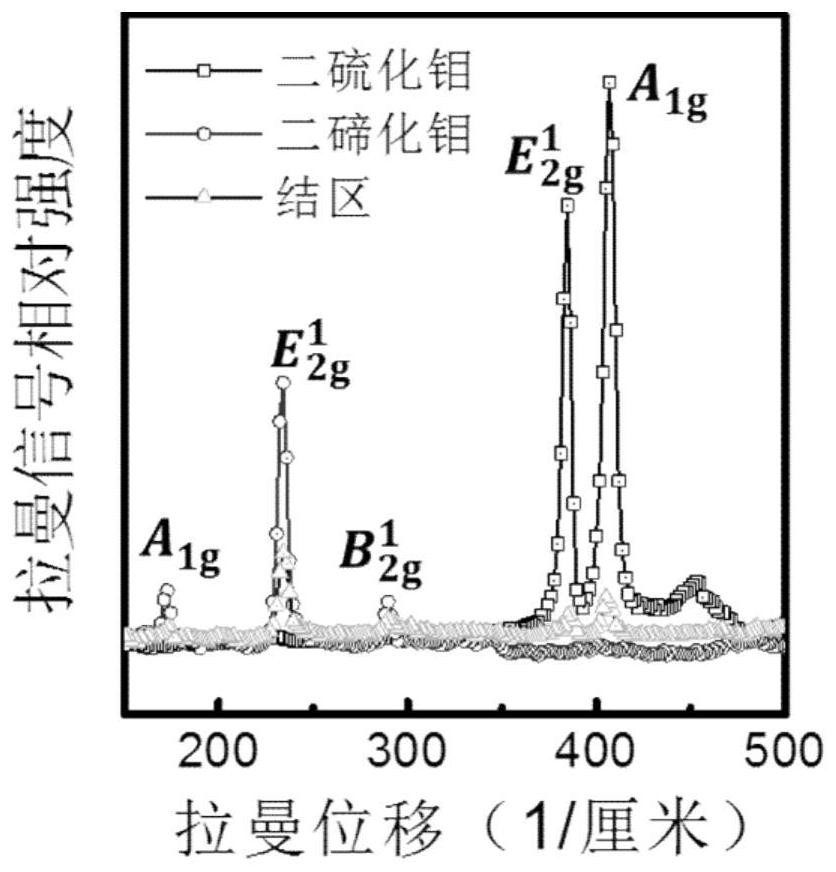

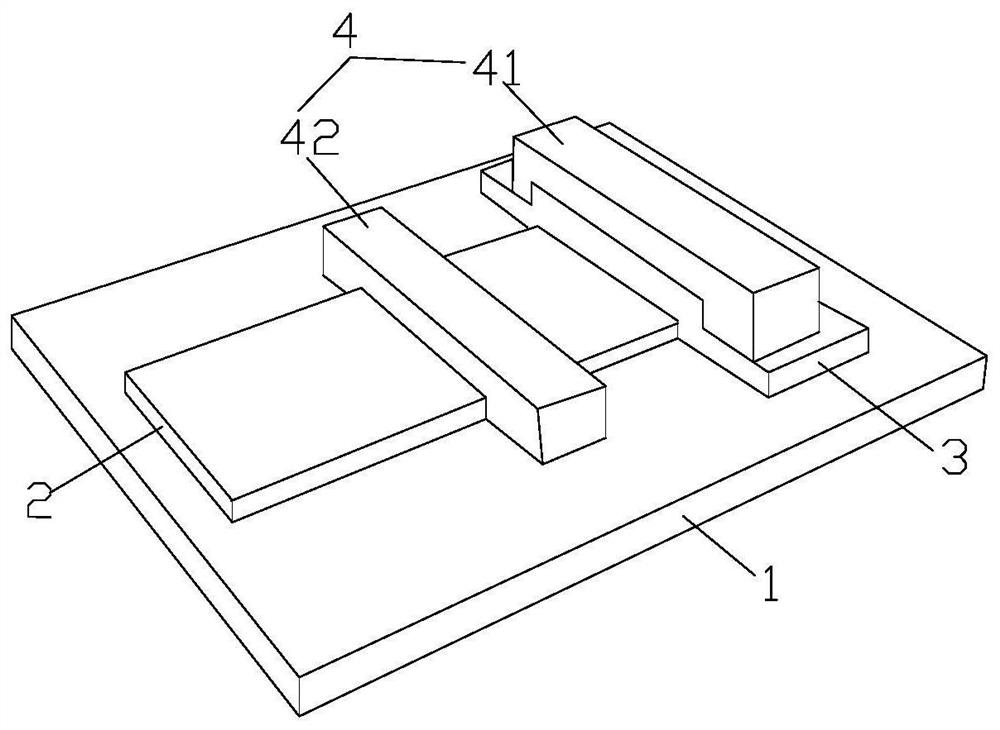

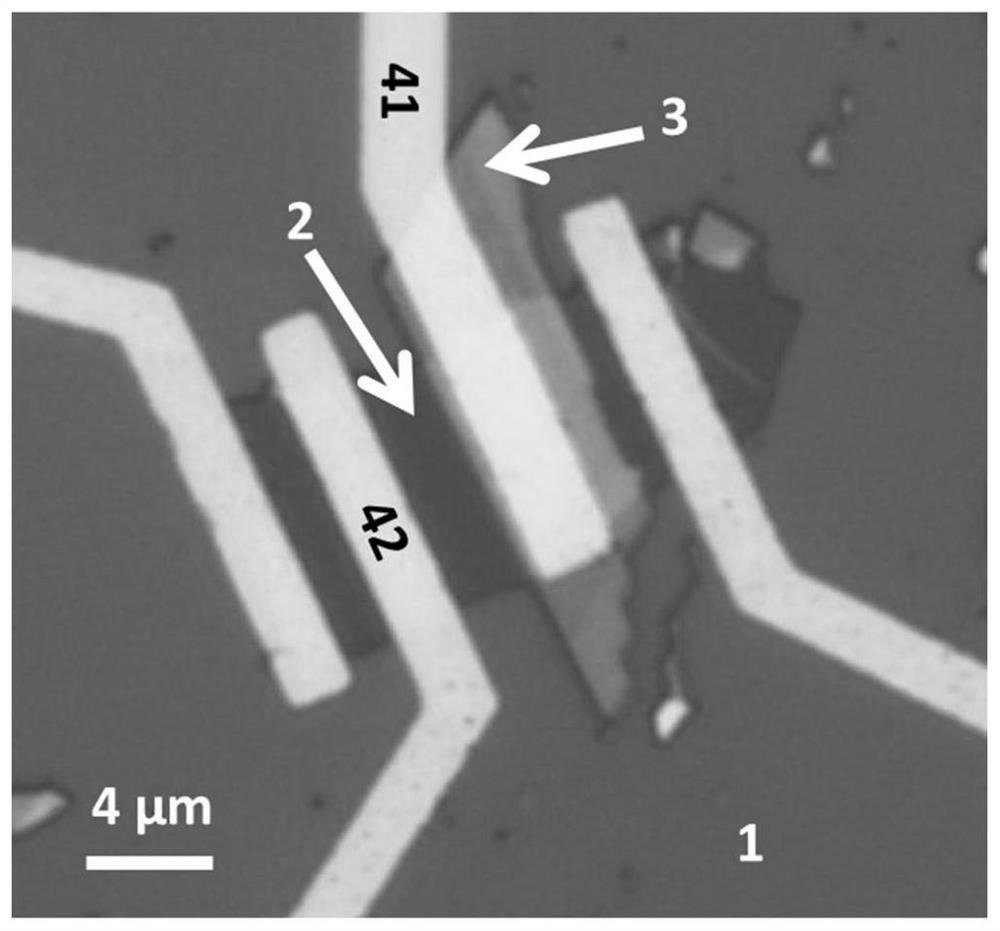

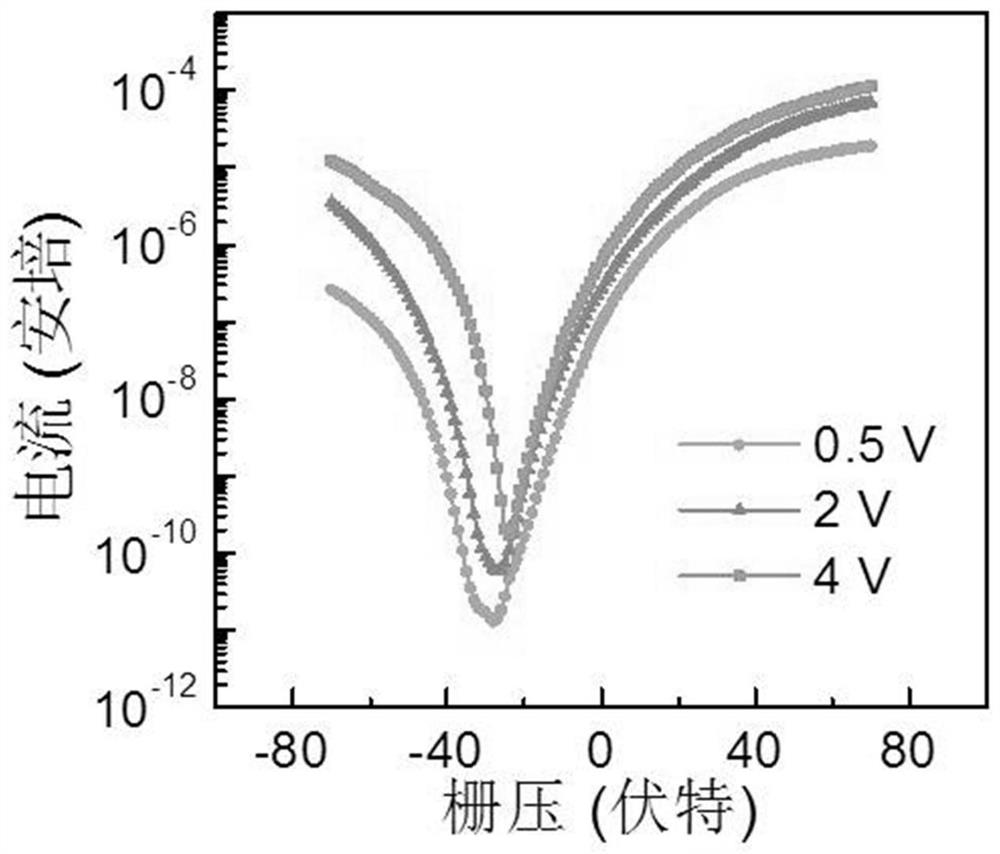

Asymmetric van der Waals heterojunction device, preparation method and use thereof

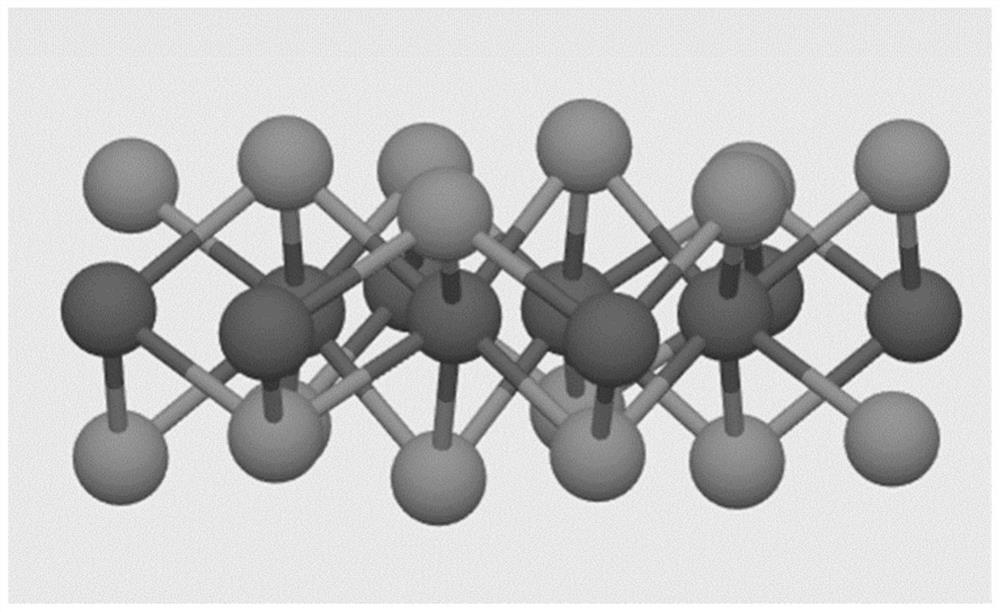

ActiveCN109004016AIncrease the current switch ratioImprove responsivenessSolid-state devicesSemiconductor devicesHeterojunctionMolybdenum telluride

The invention provides an asymmetric van der Waals heterojunction device, comprising graphene nanosheets, hexagonal boron nitride nanosheets, molybdenum disulfide nanosheets and molybdenum telluride nanosheets sequentially arranged from bottom to top; The graphene nano sheet and the hexagonal boron nitride nano sheet, the molybdenum disulfide nano sheet and the molybdenum telluride nano sheet havean overlapping region; A surface area of that molybdenum disulfide nanosheet is lar than that of the molybdenum telluride nanosheet, and parts of the molybdenum disulfide nanosheet do not overlap with the molybdenum telluride nanosheet. The invention also provides the preparation and application of the asymmetric van der Waals heterojunction device. The asymmetric van der Waals heterojunction device of the invention can realize the organic unity of ultra high performance and multiple functions. When operating as a transistor, the device exhibits ultra-high current switching ratio, ultra-smallsubthreshold swing and obvious negative transconductance behavior. When operating as a rectifier, the device exhibits an ultra-high current rectification ratio. When operating as memory, the device exhibits an ultra-high erase / write current ratio and current rectification ratio.

Owner:THE NAT CENT FOR NANOSCI & TECH NCNST OF CHINA

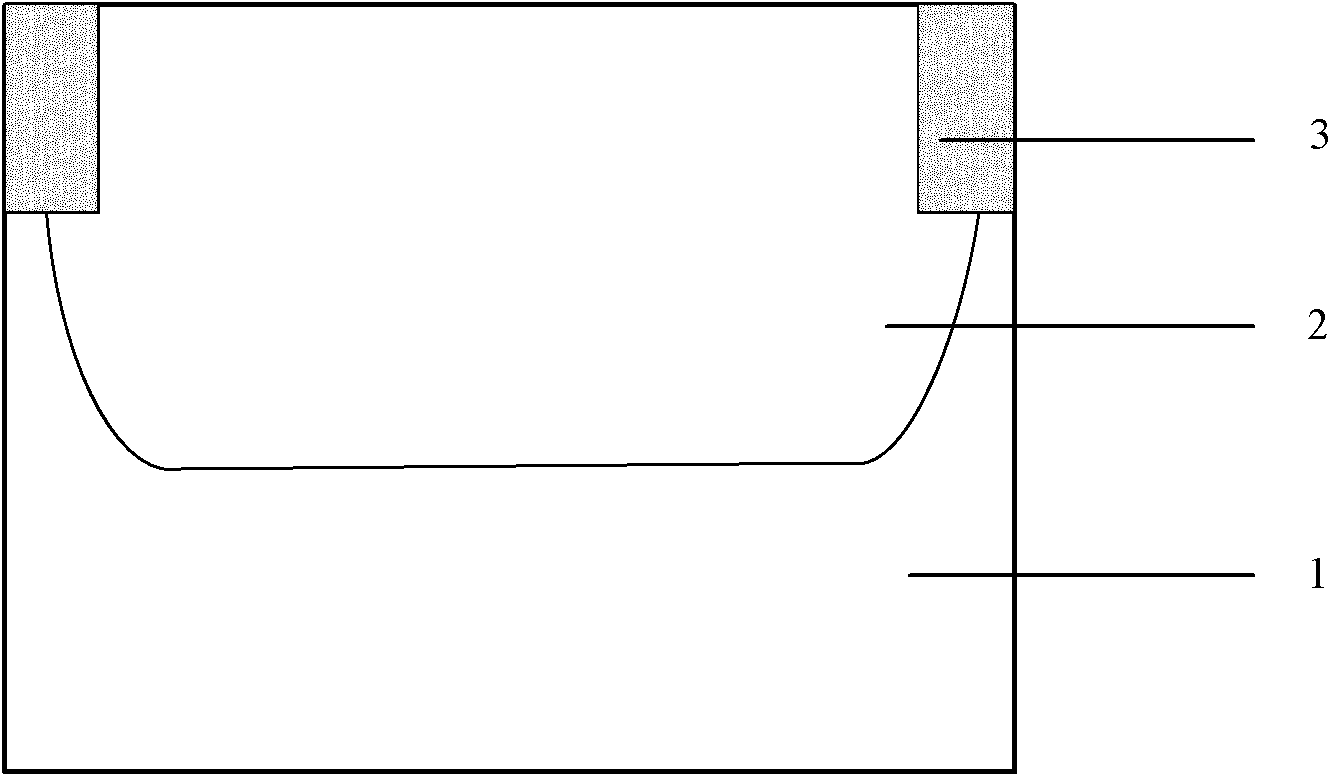

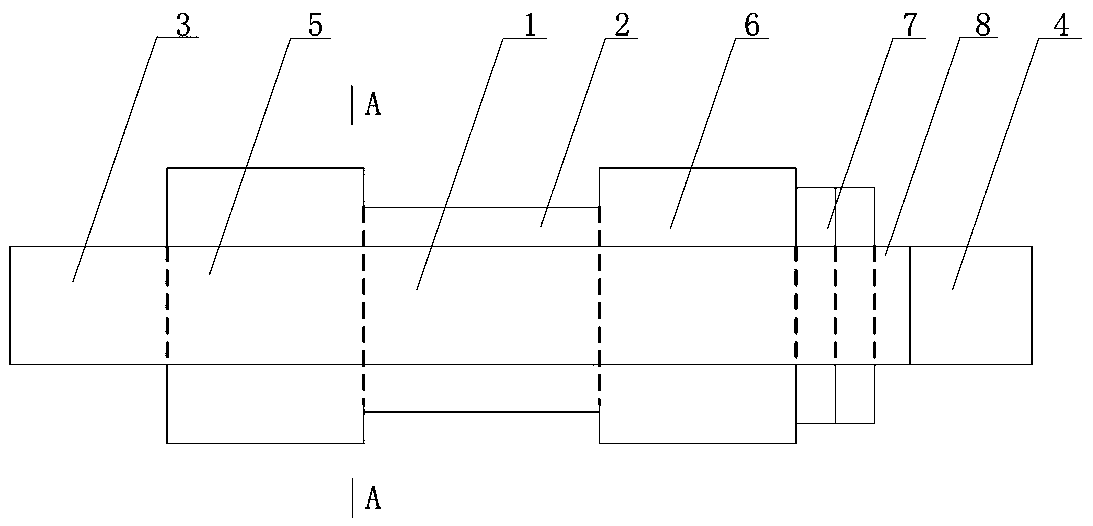

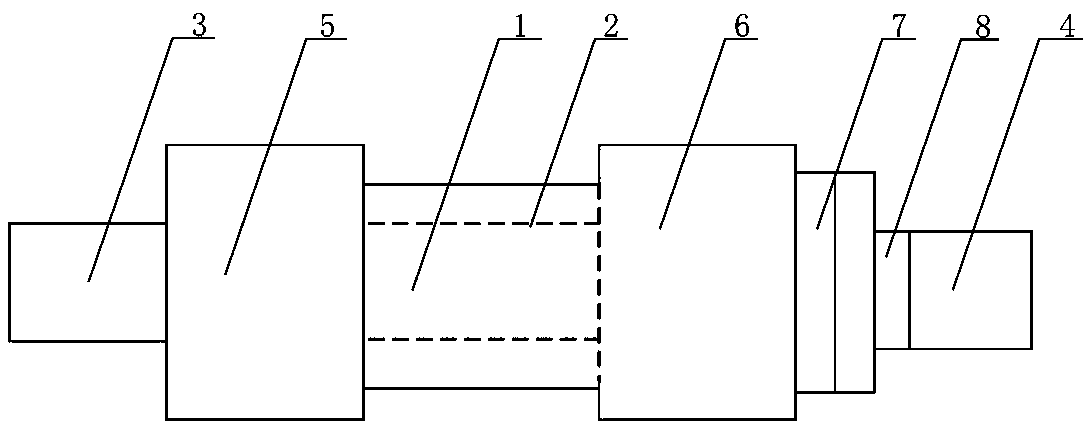

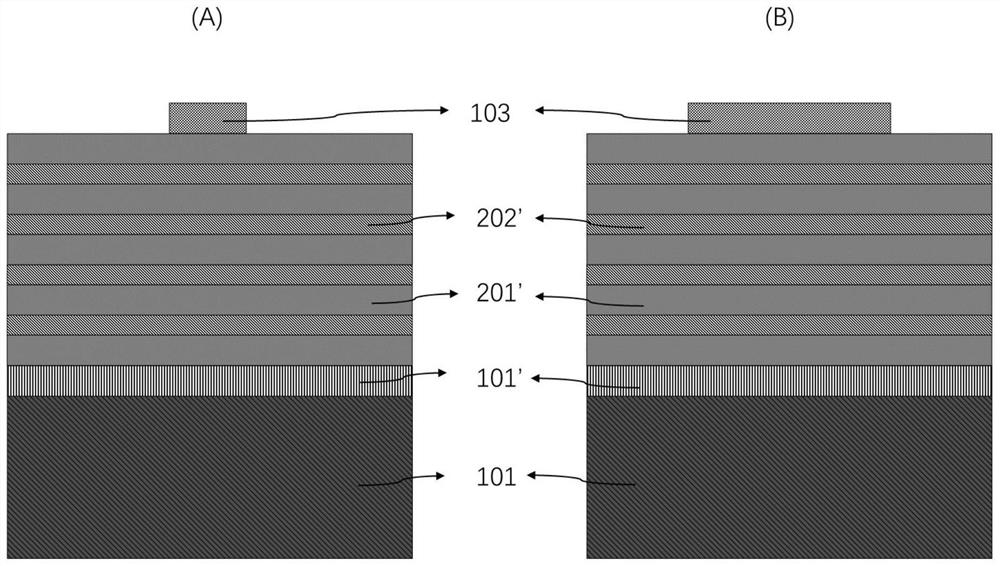

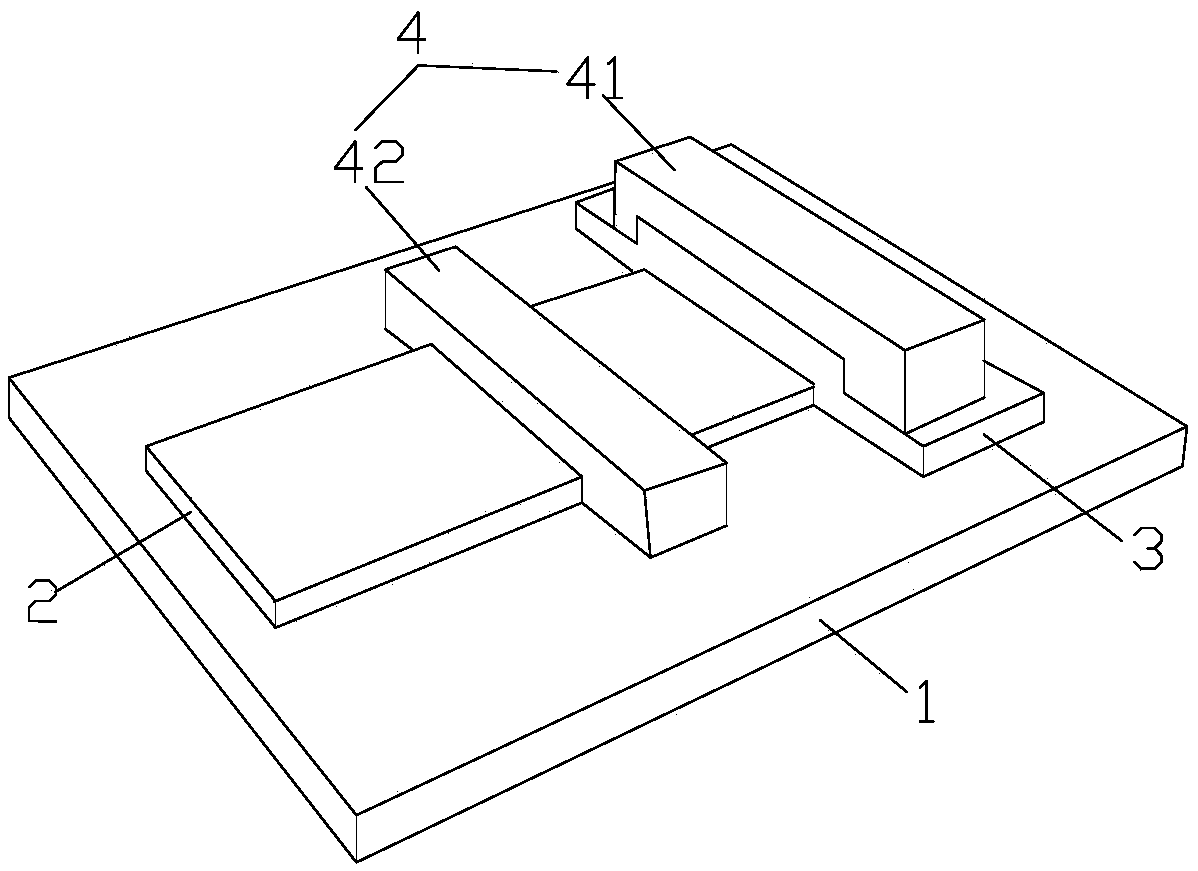

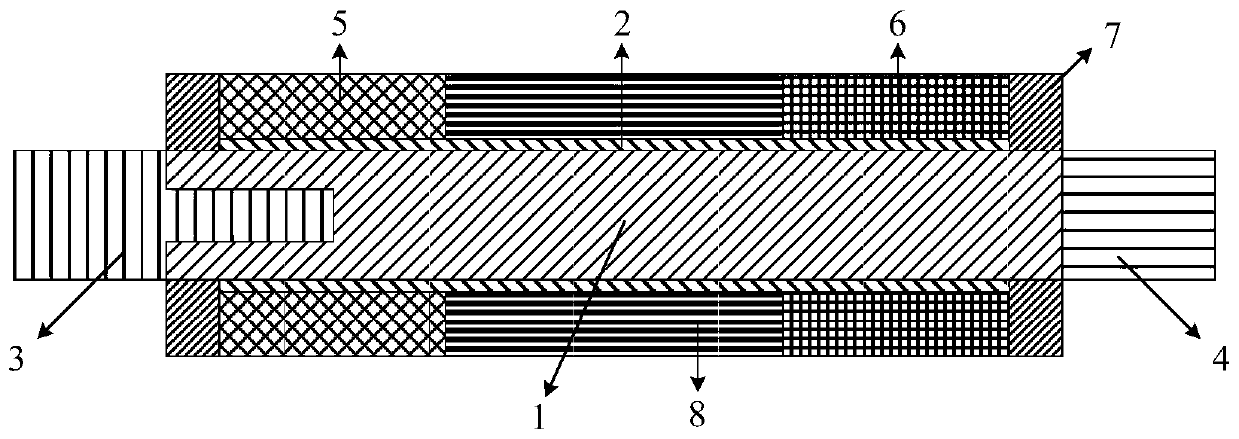

Asymmetric reconfigurable field effect transistor

ActiveCN110164958AReduced switching delay timeIncrease clock frequencySolid-state devicesSemiconductor/solid-state device manufacturingNanowireField-effect transistor

The invention discloses an asymmetric reconfigurable field effect transistor. The transistor includes a trench; a drain electrode arranged at one end of the trench; a source electrode which is arranged at the other end of the trench and extends into the trench; gate oxide which is arranged at the outer side of the channel; a control grid electrode and a polar grid electrode which are respectivelyarranged at the source electrode end and the drain electrode end and outside the grid electrode oxide; side walls which are respectively arranged outside the two ends of the trench and used for electrically isolating the control grid electrode, the polar grid electrode, the source electrode and the drain electrode; and the grid isolation part which is arranged outside the grid electrode oxide andused for isolating the control grid electrode from the polar grid electrode. The contact area between the source end extending into the trench and a nanowire trench is larger, the tunneling area of carriers is increased, and the starting current is increased. In a switching-off state, a drain electrode structure and a common RFET drain electrode structure have the same non-overlapping area, and aleakage current is basically kept unchanged, so that the current switch ratio is improved, and the operation delay time of a logic gate current is shortened under the condition that the static power consumption is not changed.

Owner:EAST CHINA NORMAL UNIV +1

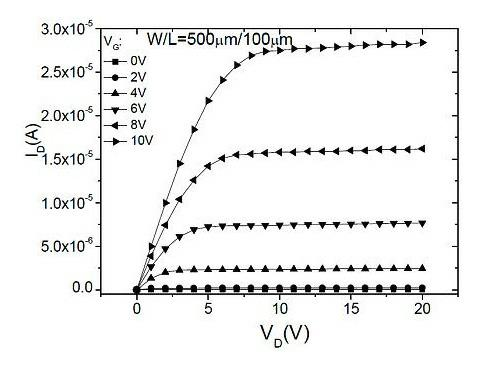

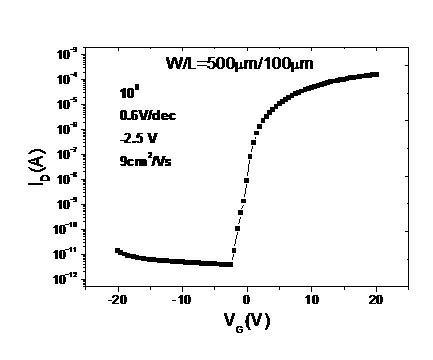

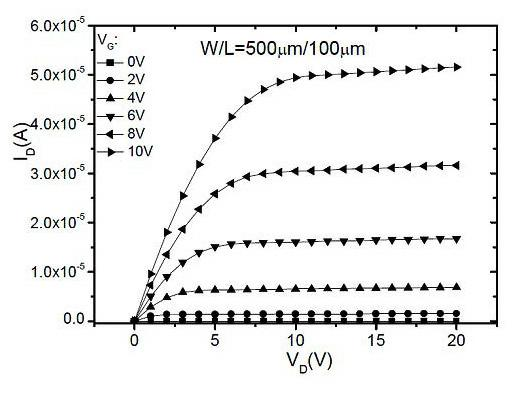

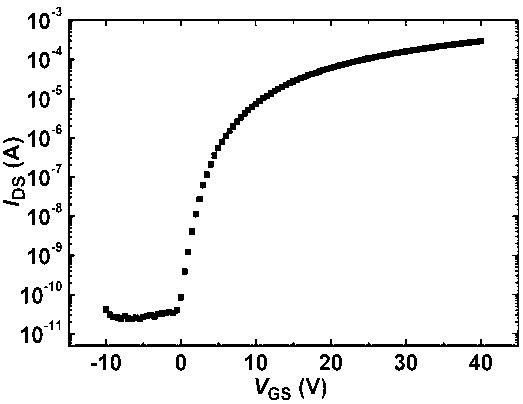

Praseodymium indium zinc oxide thin film transistor and preparation method thereof

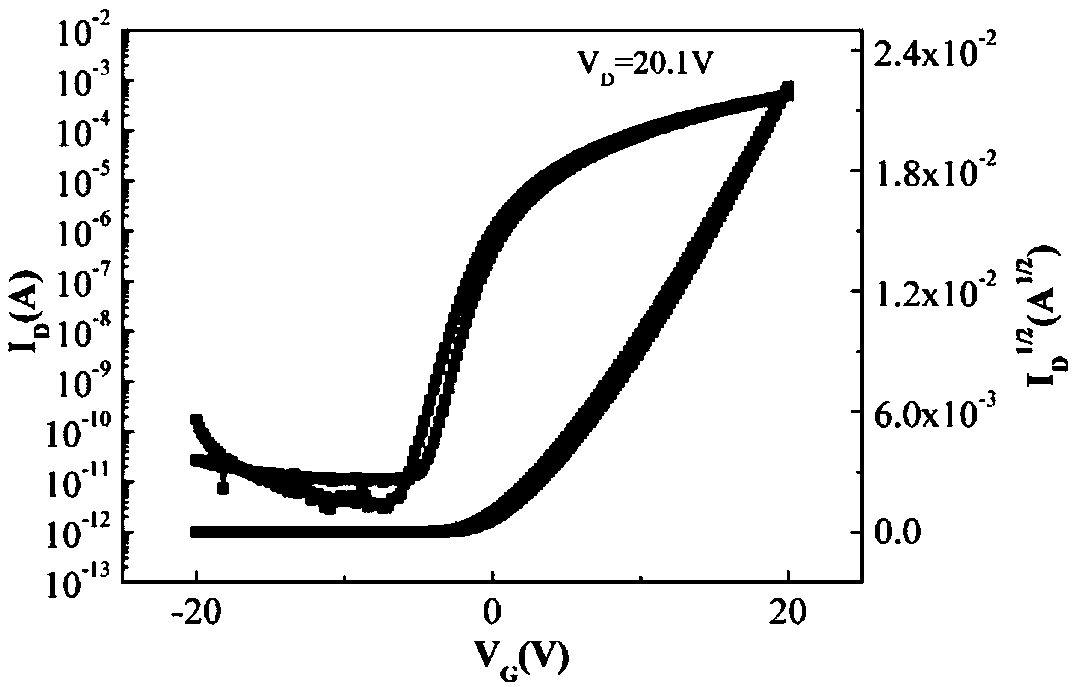

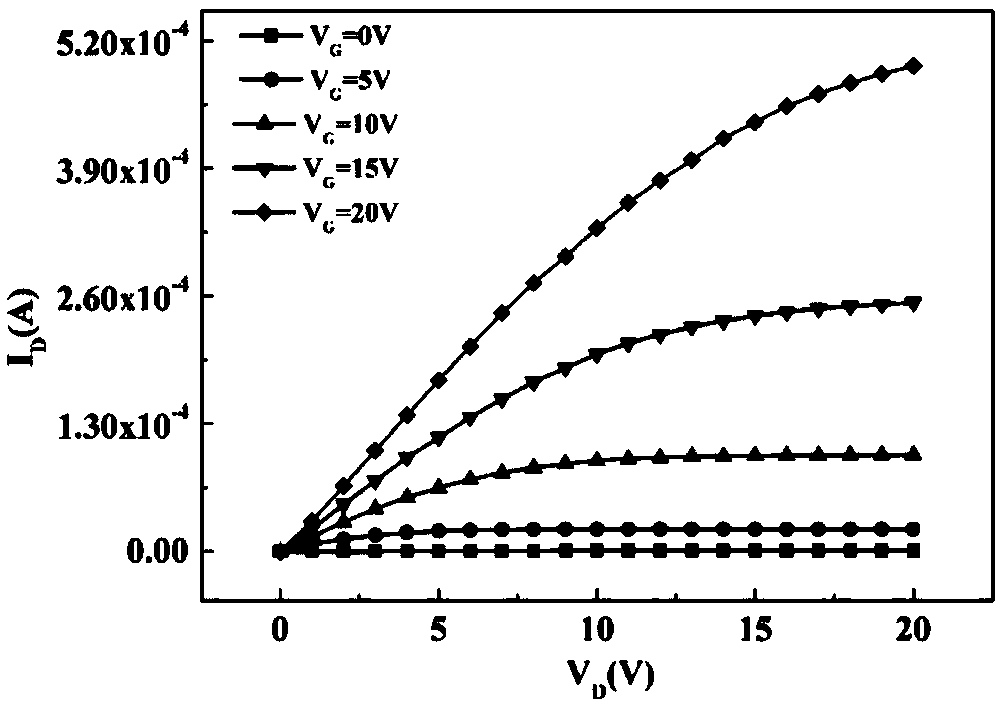

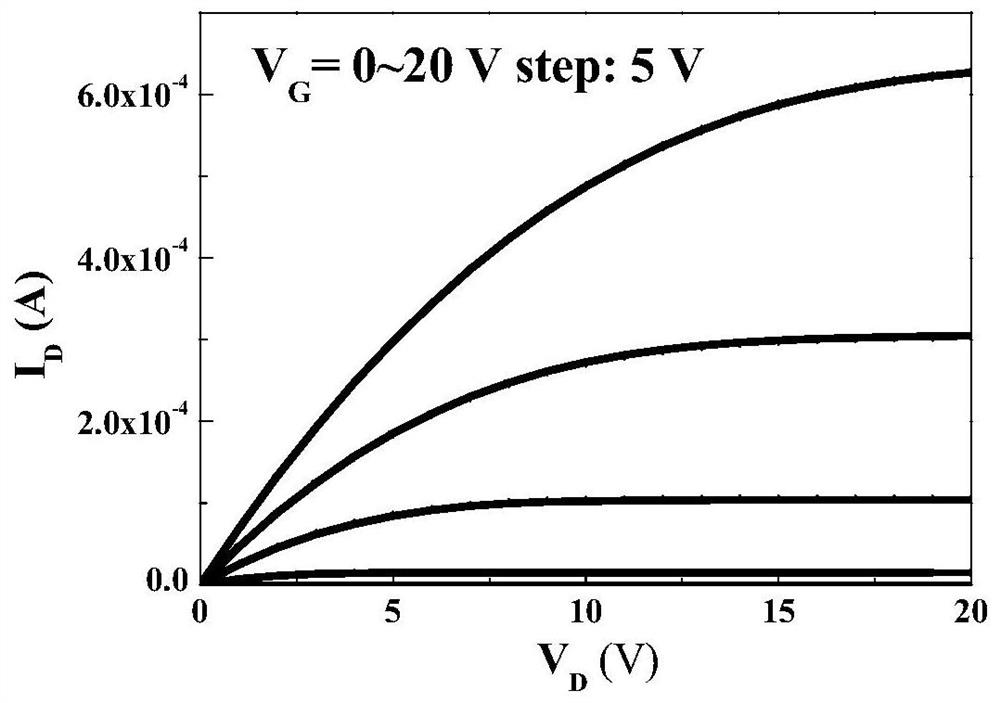

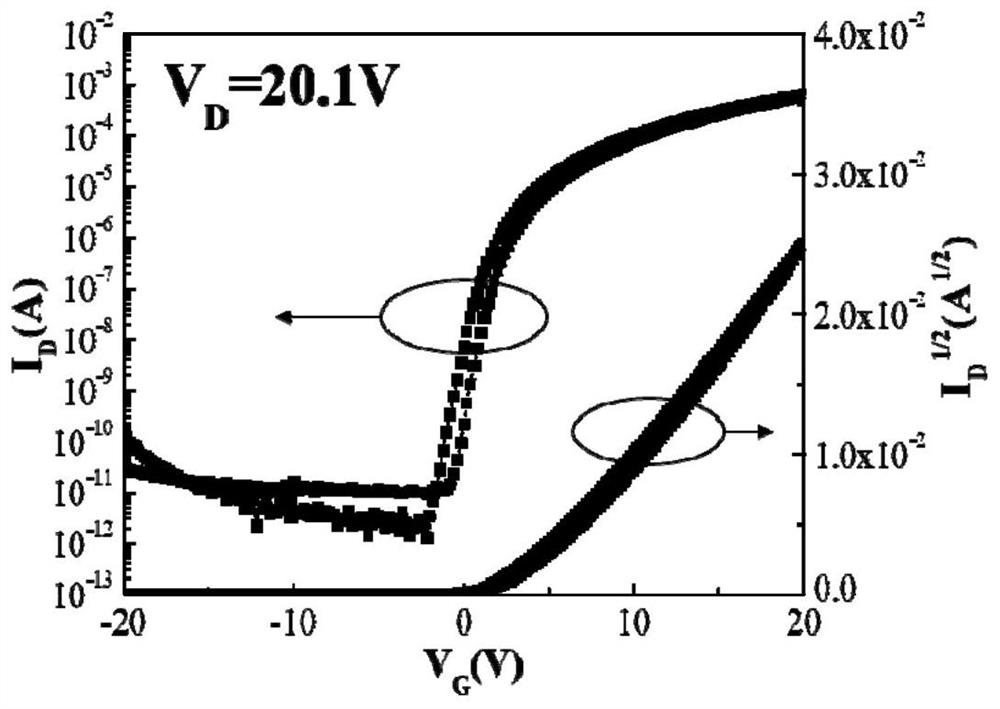

ActiveCN108735821AImprove mobilityIncrease the current switch ratioTransistorSemiconductor/solid-state device manufacturingSputteringOxide thin-film transistor

The invention belongs to the technical field of display devices, and discloses a praseodymium indium zinc oxide thin film transistor and a preparation method thereof. The thin film transistor is composed of a substrate, a metal gate, a gate insulating layer, a Pr-IZO semiconductor active layer, an oxide insulator passivation layer and metal source drain electrodes. Pr element doping is introducedinto the IZO semiconductor, and a Pr-IZO active layer thin film is deposited by a room temperature sputtering process; and by combination of an ultra-thin Al<2>O<3> passivation layer, carrier transportation under an electric field is controlled, so that the high-mobility and high-current-switching-ratio oxide thin film transistor can be realized at room temperature.

Owner:SOUTH CHINA UNIV OF TECH

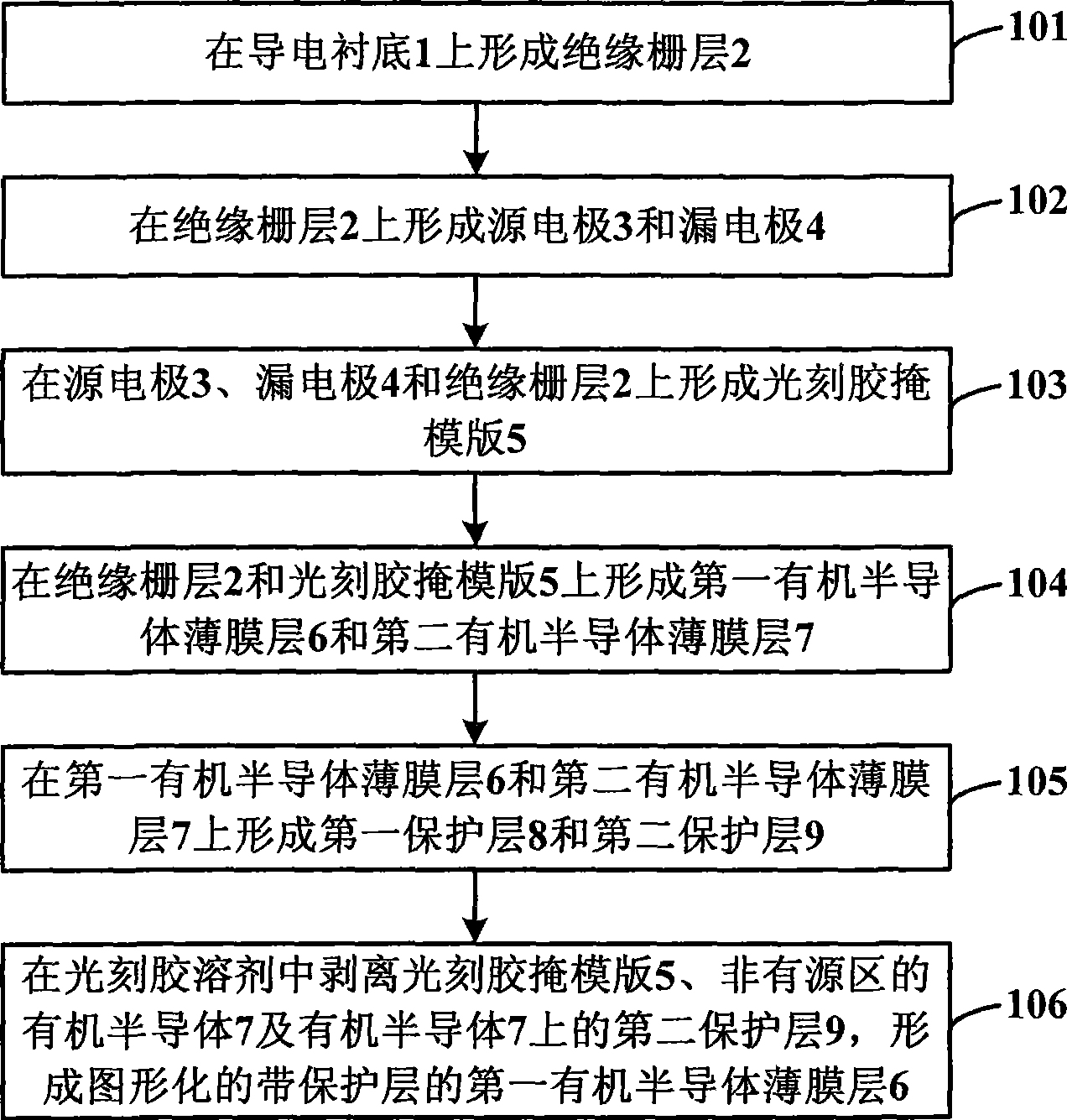

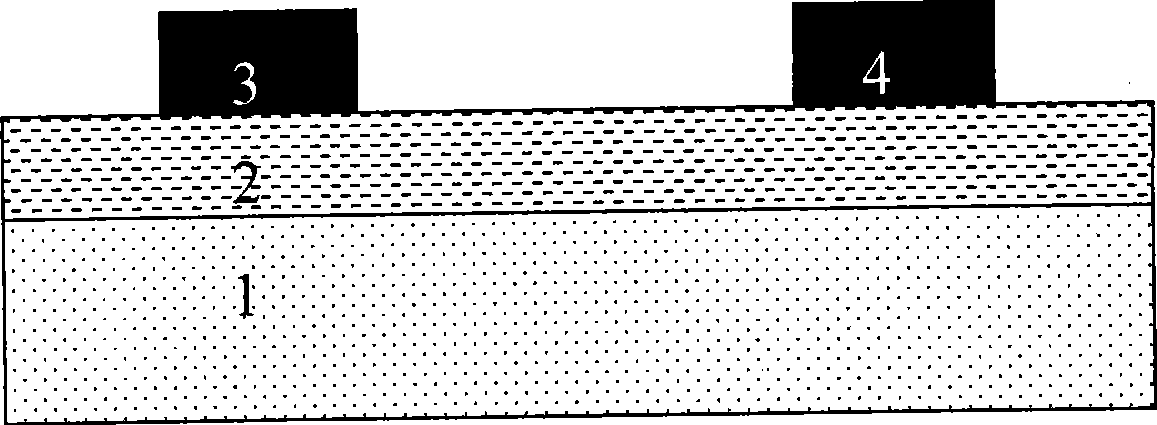

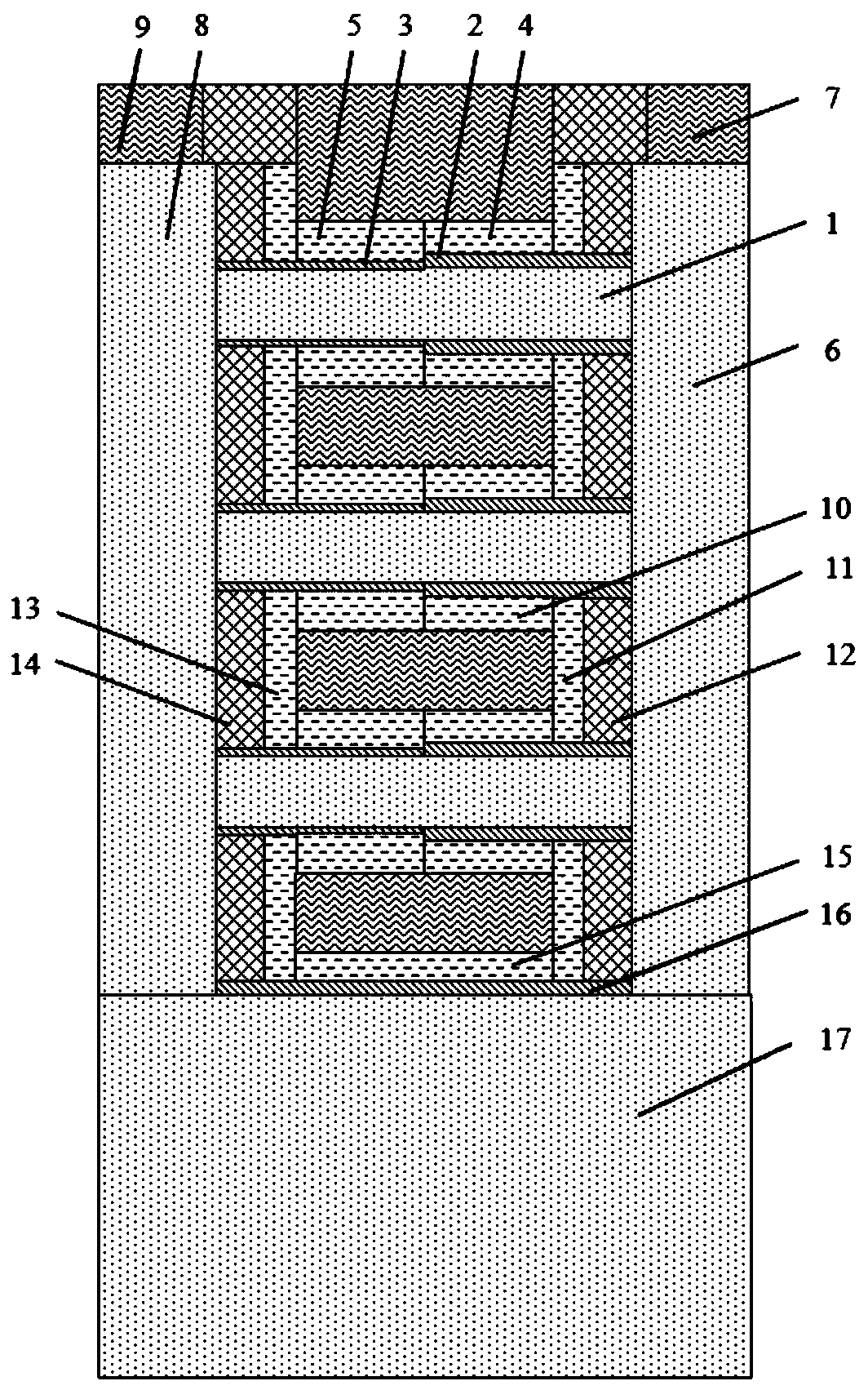

Production method for organic thin-film transistor with graphic active layer

ActiveCN101420015AWon't breakSimple processSolid-state devicesSemiconductor/solid-state device manufacturingResistRoom temperature

The invention relates to the technical field of organic semiconductor devices and micro processing and discloses a method for preparing an active patternized organic thin-film transistor. The method adopts a photoresist as a mask after the preparation of a metal source-drain electrode. Firstly an organic semiconductor thin film layer is prepared with a vacuum vaporization method. Then a room temperature PECVD method is adopted to prepare a protective layer on the organic semiconductor thin film layer. The total thickness of the organic semiconductor thin film layer and the protective layer is smaller than the thickness of the metal source-drain electrode to ensure that a resist remover does not contact the organic semiconductor thin film layer so as to cause damage to the performance of the organic semiconductor thin film layer when the photoresist mask is removed. The invention can be completely compatible with the traditional IC process. The prepared active patternized organic thin-film transistor has the properties of small off-state current and high ratio of current switching.

Owner:SEMICON MFG INT (SHANGHAI) CORP +1

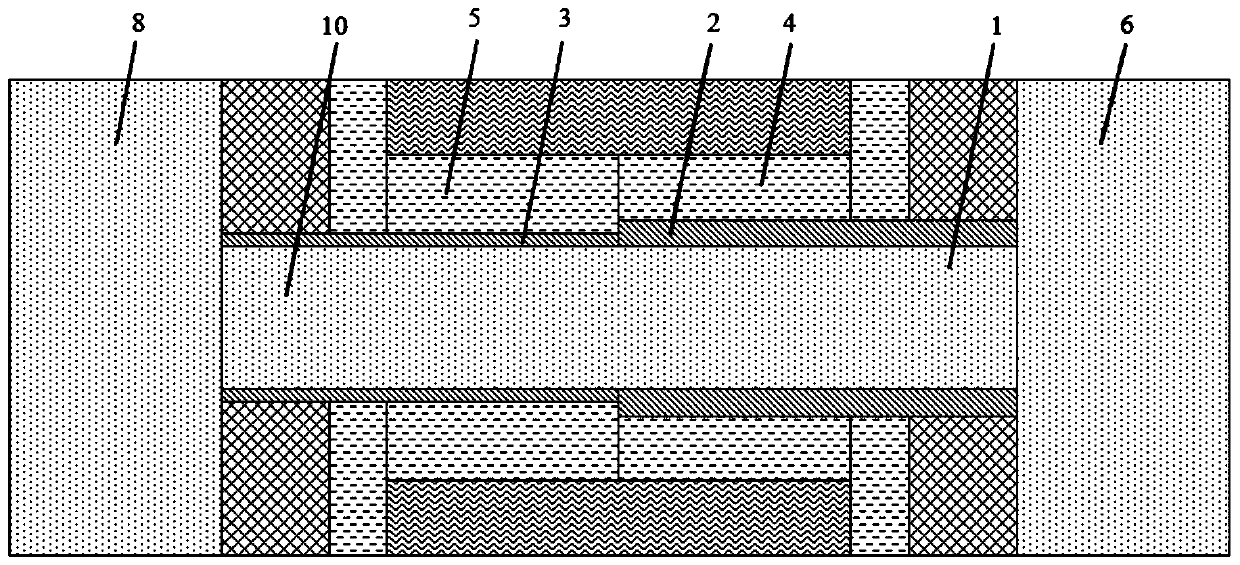

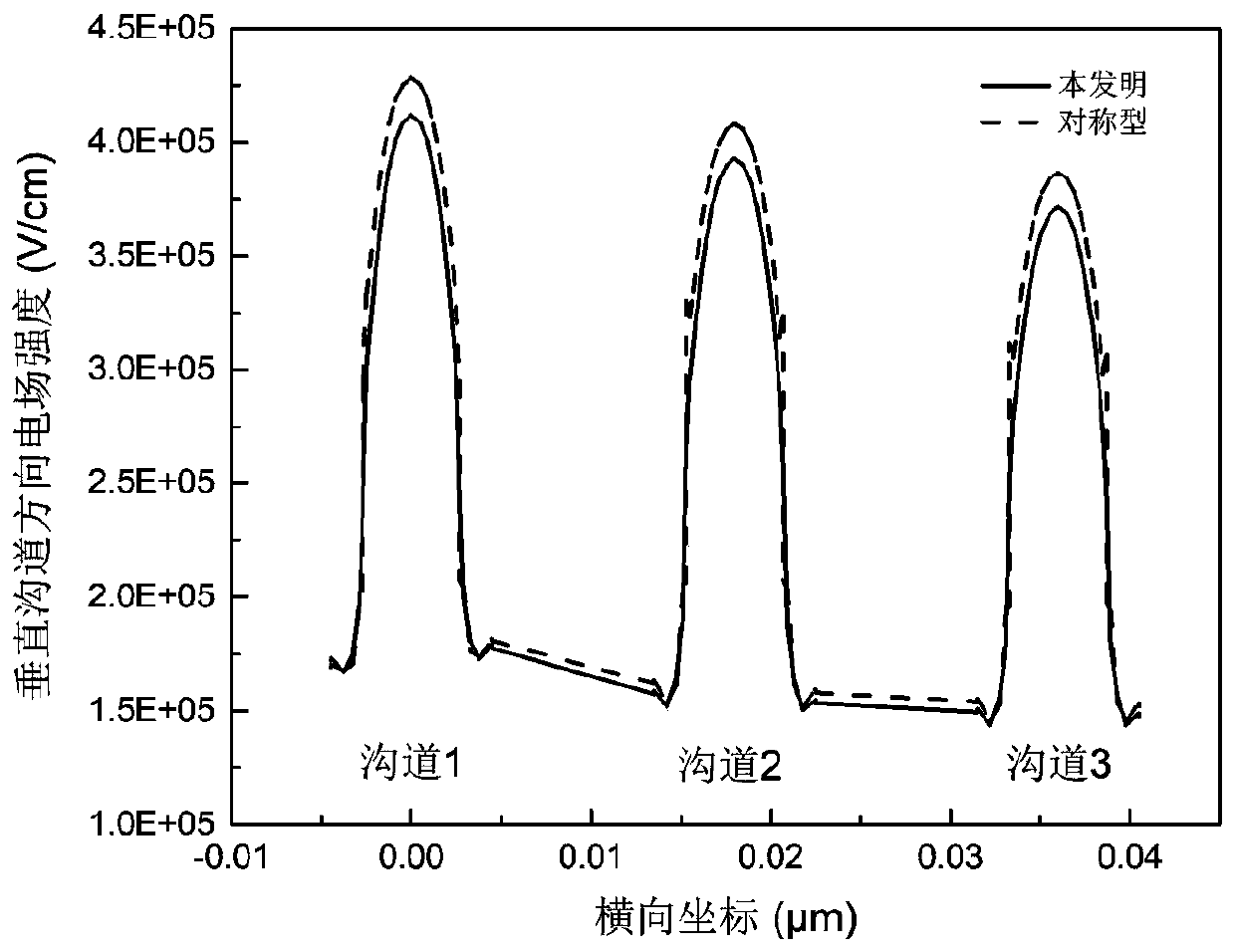

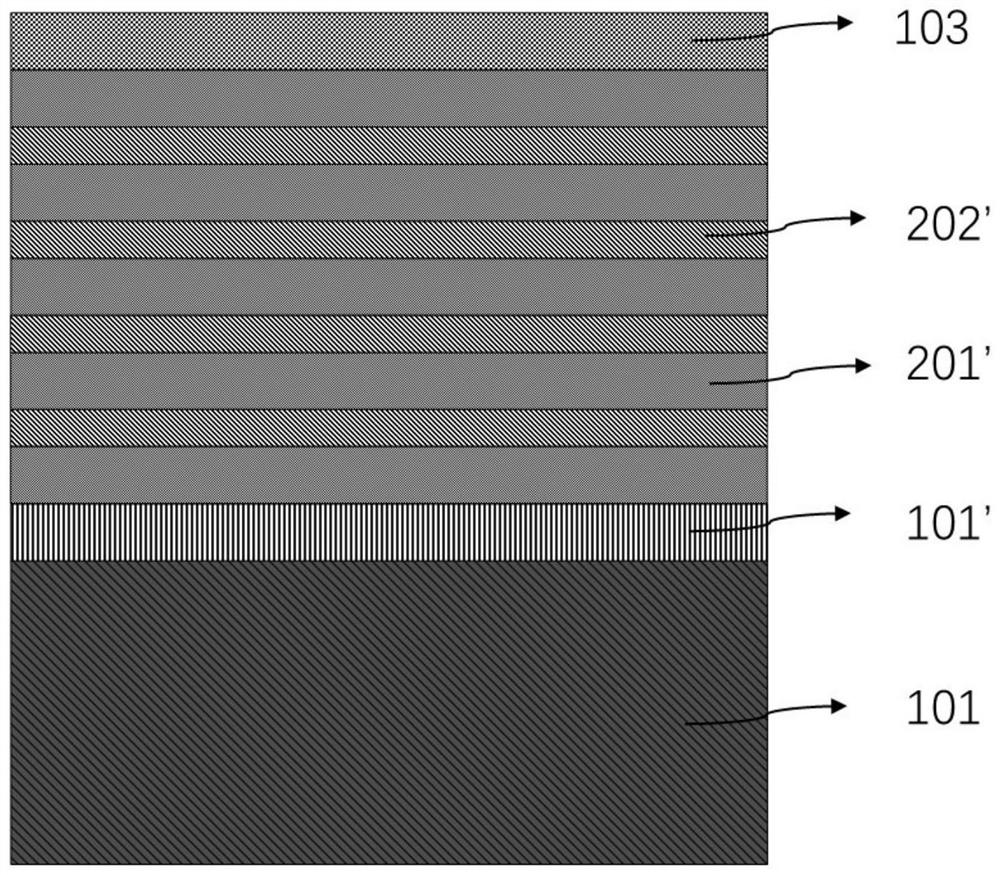

Nano-sheet ring gate field effect transistor with asymmetric gate oxygen structure

ActiveCN110690290AReduced Threshold Voltage DriftInhibition of DIBL effectNanoinformaticsSemiconductor devicesEngineeringField effect

The invention discloses a nano-sheet ring gate field effect transistor with an asymmetric gate oxygen structure. The nano-sheet ring gate field effect transistor comprises a vertically stacked nano-sheet channel, a double-layer gate oxide wrapping outside the channel, a source and a drain arranged at the two ends of the channel, a double-layer side wall and a substrate arranged at the bottom. Thenano-sheet ring gate field effect transistor is characterized in that the gate oxide is formed by stacking a low dielectric constant material and a high dielectric constant material and is divided into two parts near the drain and the source with half of the channel length as the boundary. The total physical thickness of gate oxygen in the two parts is the same, and the low dielectric constant gate oxide is thinner and the high dielectric constant gate oxide is thicker in the double-layer gate oxides near the drain so as to form the nano-sheet ring gate field effect transistor with the asymmetric gate oxygen structure. Compared with the prior symmetrical type technology, the drain end electric field is lower and the hot carrier effect of the device can be effectively inhibited; it has moreideal on-state and off-state current and higher current switching ratio;and the leakage potential is more stable, the leakage-induced barrier reduction effect is suppressed and the short channel characteristics are improved.

Owner:EAST CHINA NORMAL UNIV +1

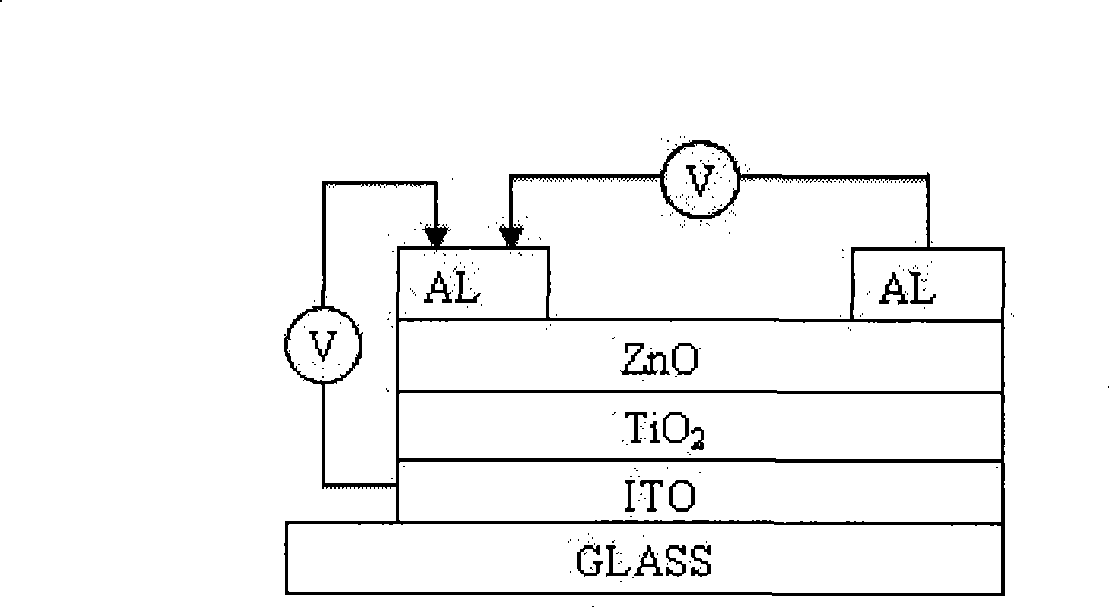

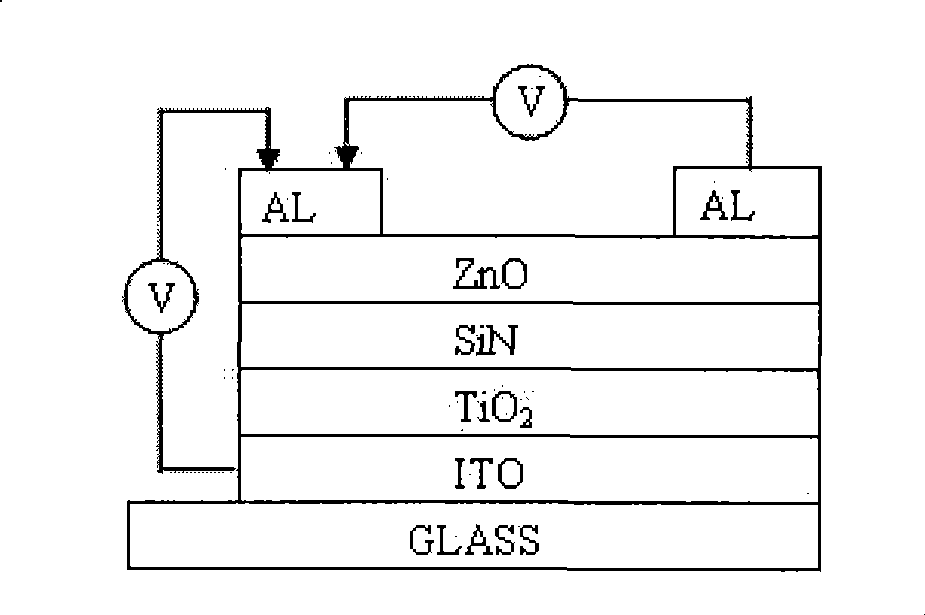

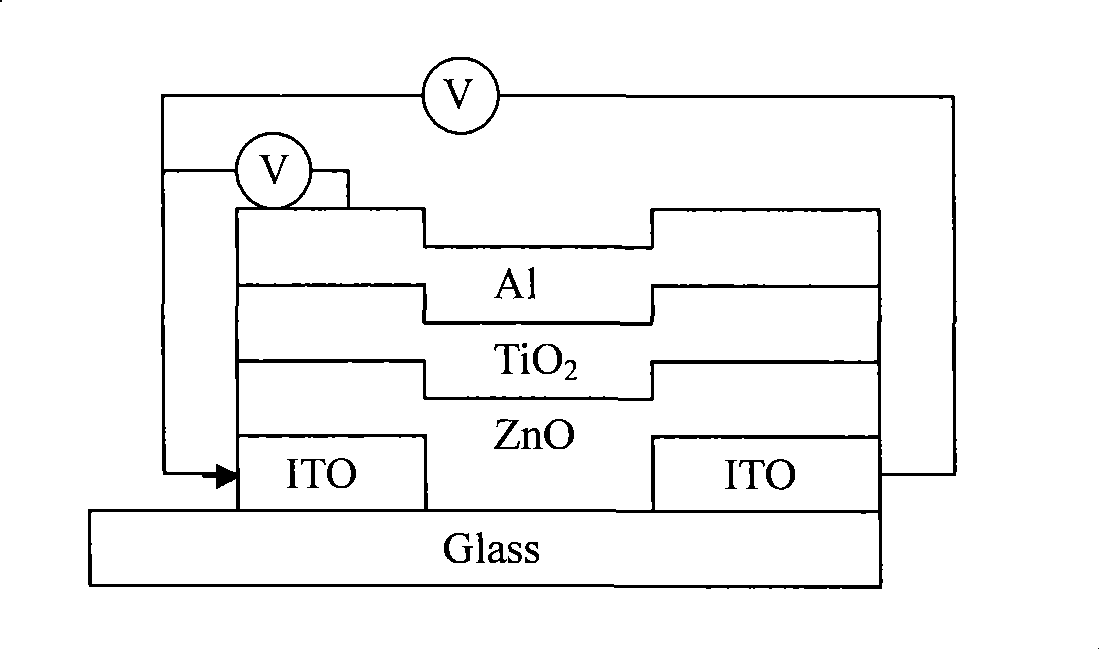

Method for preparing inorganic thin-film transistor by complete solution treatment process

InactiveCN101388342AHigh dielectric constantSimple processSemiconductor/solid-state device manufacturingLow voltagePlastic materials

The invention relates to a process for preparing an inorganic film triode TFT by the all solution processing method, which adopts the all solution processing method to prepare the insulating layer TiO2 and the active layer ZnO of the triode, and specifically comprises the following steps: firstly preparing TiO2 and ZnO into solution with 0.05ml-0.1ml concentration through adopting the hydrothermal method and the sol-gel process, and coating the ZnO and TiO2 obtained in the first step on a substrate electrode through the spin-coating method, Czochralski method or the titration covering method to form a ZnO and TiO2 film which can form the micro-crystallization through the high-temperature annealing or the laser annealing technology. The invention can prepare the TiO2 film and the ZnO film with temperature lower than 500 DEG C, has relatively simple technology, is beneficial for reducing device cost and accelerating preparation speed, and is beneficial for the industrialization, can prepare on cheap materials such as glass and the like, and is compatible with elastic and plastic materials technology. TFT components with high dielectric constant insulating layer and super-high charge mobility active layer can be obtained, which have milliamp level heavy current density and current switch ratio as high as hundreds of thousand, and can drive low-voltage OLED.

Owner:SHANGHAI UNIV

A reconfigurable field effect transistor with asymmetric structure

ActiveCN109037339AIdeal off-state currentIncrease the current switch ratioSemiconductor/solid-state device manufacturingSemiconductor devicesSubthreshold swingElectrical polarity

The invention discloses a reconfigurable field effect transistor with an asymmetric structure, comprises a source electrode and a drain electrode arranged on both ends of the channel, and a field effect transistor composed of a control gate electrode and a polar gate electrode respectively arranged on one side of the source electrode and the drain electrode. The polar gate electrode is provided with an underoverlapped region of a deposition side wall on the side close to the drain electrode to form a reconfigurable field effect transistor with an asymmetric structure. Compared with the prior art, the device of the invention has ideal on-state, off-state current, larger current switching ratio, steep subthreshold swing and the like. The current switching ratio is improved significantly whenthe device is of an n-FET structure compared with a p-FET structure, and the off-state current is almost the same compared with a symmetric reconfigurable transistor, so the leakage current is controlled effectively.

Owner:EAST CHINA NORMAL UNIV +1

Schottky barrier transistor and preparation method thereof

ActiveCN109671780AIncrease the on-state currentReduce off-state currentFinal product manufactureSemiconductor/solid-state device manufacturingPower flowSchottky barrier

The present invention provides a Schottky barrier transistor and a preparation method thereof. The Schottky barrier transistor includes a substrate and a gate structure on the substrate. The Schottkybarrier transistor further includes: a channel region located at the surface of the substrate corresponding to the gate structure, wherein the channel region comprises a first metal silicide layer; and a source-drain region comprising a second metal silicide layer and a third metal silicide layer located at two sides of the channel region, wherein the second metal silicide layer is located in thesubstrate, the third metal silicide layer is located at the surface of the substrate corresponding to the second metal silicide layer, and the work function of the second metal silicide layer is smaller than the work function of the third metal silicide layer. The Schottky barrier transistor has a high mobility channel to improve the device on-state current and reduce the off-state current of thetransistor so as to improve the current switching ratio of the device.

Owner:INST OF MICROELECTRONICS CHINESE ACAD OF SCI

Ambipolar inverter device structure and manufacturing method thereof

InactiveCN103165596AImprove performanceIncrease the current switch ratioSolid-state devicesSemiconductor/solid-state device manufacturingEngineeringElectron blocking layer

An ambipolar inverter device suitable for use in an integrated circuit. An electron blocking layer and a hole blocking layer are respectively disposed at two sides of the ambipolar semiconductor layer, so that the operation of the inverter may be executed in a single device. In addition, the manufacturing method of the disclosure is simple, adopting only one patterning step, so as to effectively improve the performance of the ambipolar device.

Owner:IND TECH RES INST

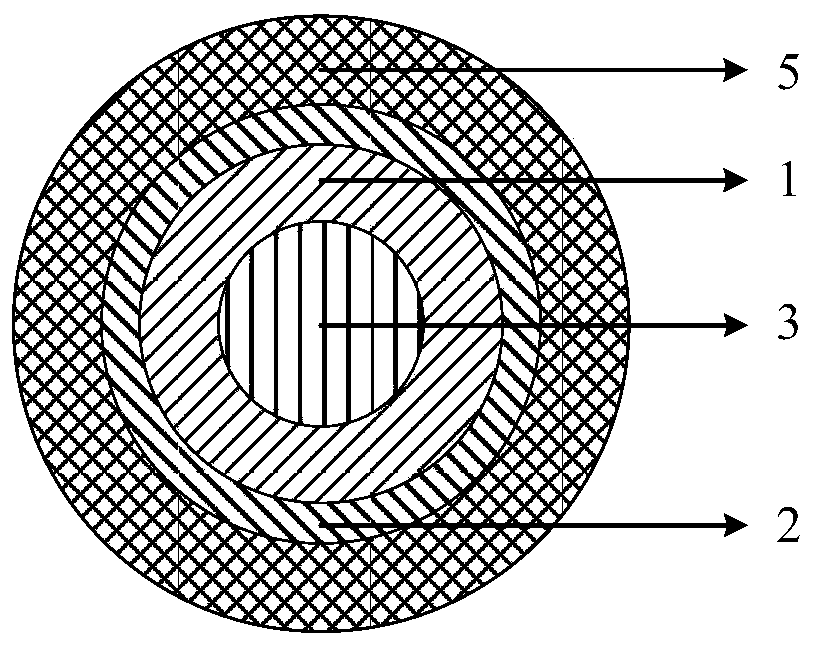

Nano-wire field effect transistor

ActiveCN101740619BReduce off-state currentReduce static power consumptionSemiconductor devicesSemiconductor materialsGate dielectric

The invention discloses a nano-wire field effect transistor comprising a gate electrode, a source region, a drain region, a central region and a gate dielectric layer. The central region is in the core-shell structures which are coaxial; the gate dielectric layer fully surrounds the central region; the gate electrode fully surrounds the gate dielectric layer; the source region and the drain region are respectively arranged on two sides of the central region; the core structure of the central region is made from insulating material, and the shell structure of the central region is made from semiconductor material; the doping type and the doping concentration of the semiconductor material of the shell structure of the central region are adjustable; the lengths of both the core structure andthe shell structure and the radii of both the core structure and the shell structure are adjustable; and the materials of the gate dielectric layer, the gate electrode, the source region and the drain region are adjustable. Due to the adoption of the insulating core structure, the off-current of the traditional nano-wire transistor can be reduced effectively, and the current on-off ratio of the devices can be increased. The threshold voltage shifting and the drain induced barrier lowering of the nano-wire field effect transistor are less affected by the short channel effect, and the size reducing performance of the nano-wire field effect transistor is more excellent.

Owner:SEMICON MFG INT (BEIJING) CORP +1

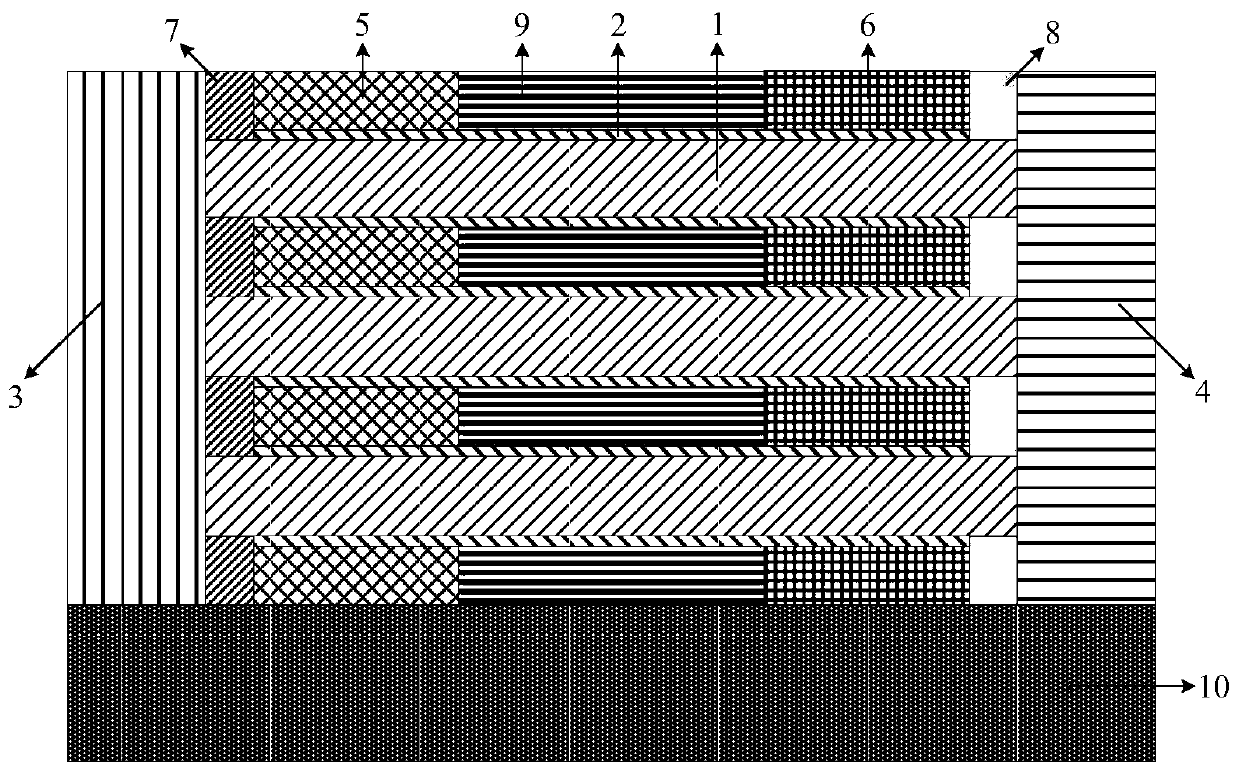

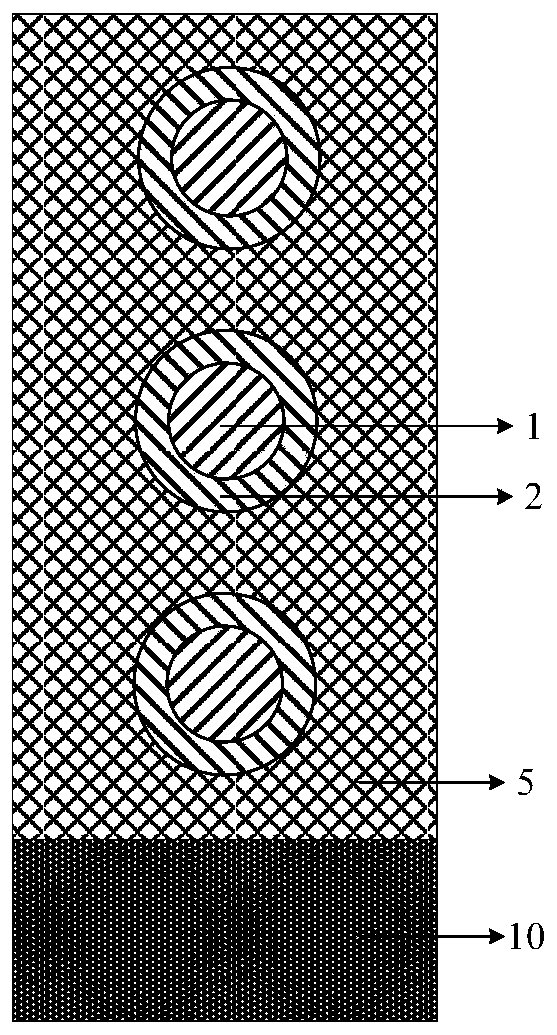

Reconfigurable field effect transistor with structure of asymmetric sidewalls and vertically stacked channels

InactiveCN110416315AImprove the coupling effectReduce off-state currentTransistorEngineeringPower flow

The invention discloses a reconfigurable field effect transistor with a structure of asymmetric sidewalls and vertically stacked channels. The transistor comprises multiple vertically stacked channels, gate oxides wrapping the outer side of the channels, source and drain electrodes which are arranged on the two ends of the channels, a source sidewall arranged at the right side of the source electrode, a source sidewall arranged at the left side of the drain electrode, a control gate arranged at the right side of the source sidewall, a polar gate arranged at the left side of the drain sidewall,a gate isolation arranged between the control gate and the polar gate and a substrate arranged at the bottom. The transistor is characterized in that the source sidewall and the drain sidewall use different materials, and the length of the source sidewall is less than or equal to the length of the drain sidewall; and the channels are stacked at least twice along the direction perpendicular to thesubstrate. The higher current density can be obtained on the same area so that the effect of reducing the delay of the combinational logic and improving the current driving ability can be achieved.

Owner:EAST CHINA NORMAL UNIVERSITY +1

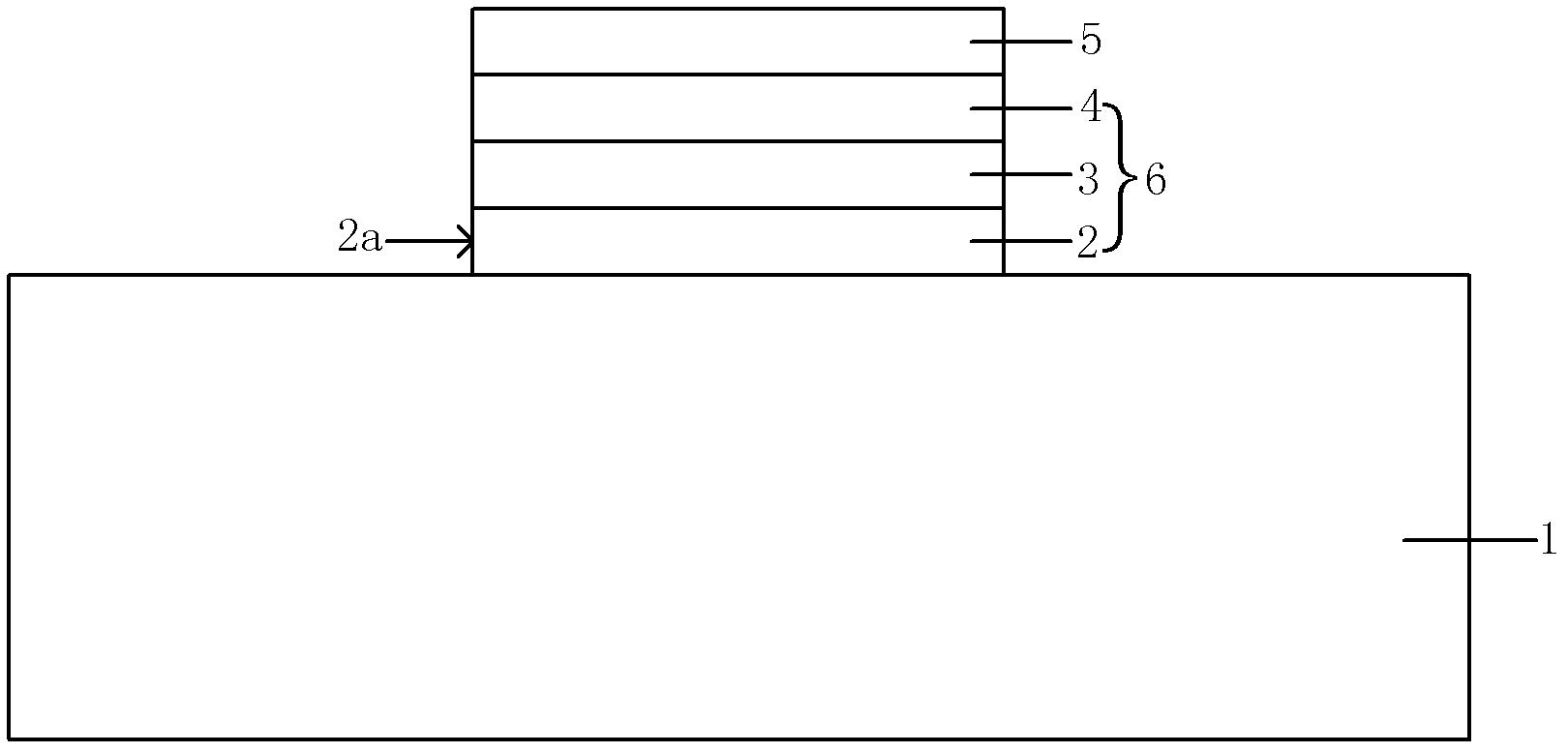

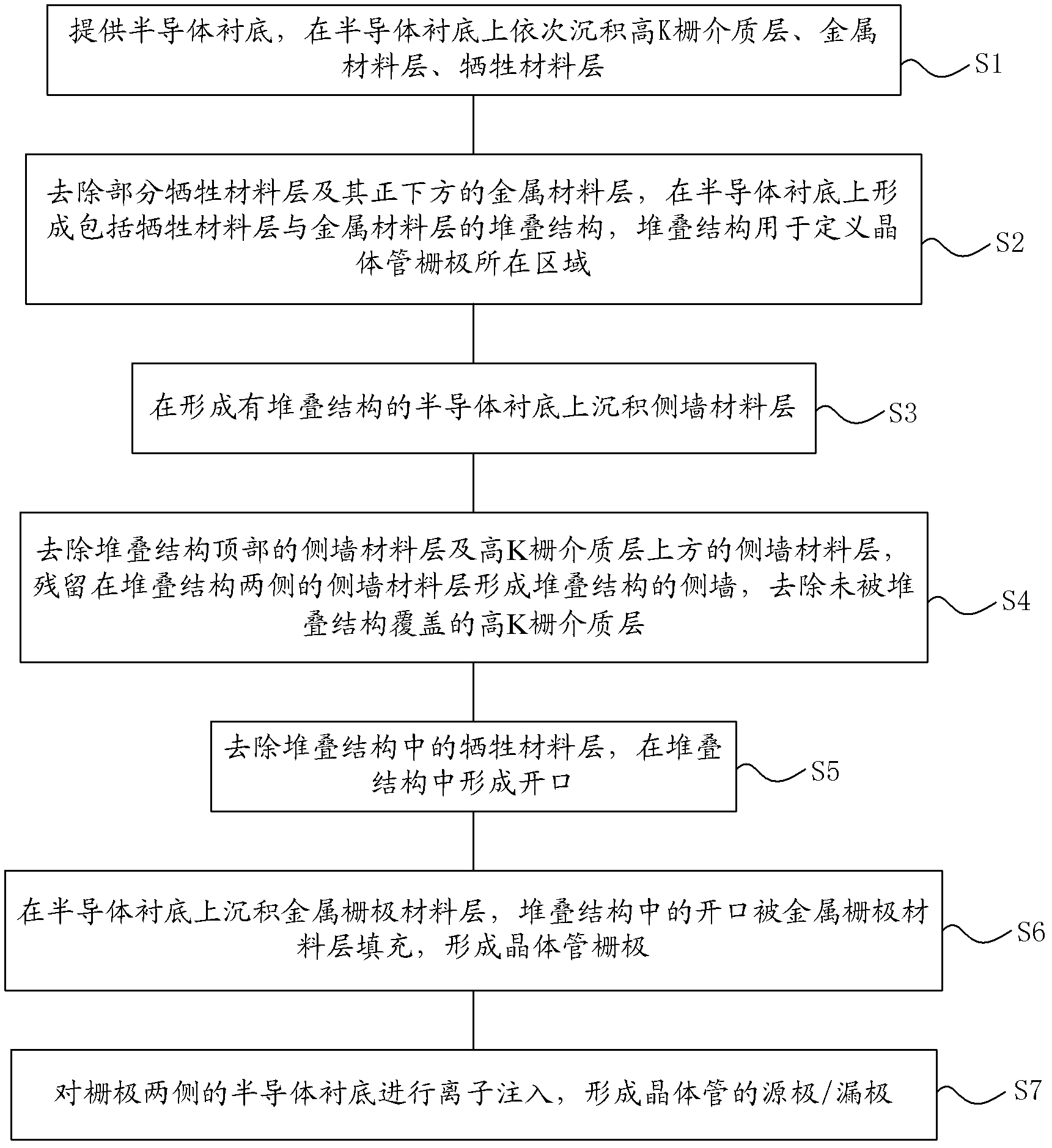

Transistor and production method thereof

ActiveCN103177966ALess current leakageIncrease the current switch ratioSemiconductor/solid-state device manufacturingSemiconductor devicesDrain currentMetallic materials

The invention provides a transistor and a production method thereof. The production method includes the following steps: a semiconductor substrate is provided; a high K gate medium layer, a metal material layer and a sacrificial material layer are sequentially deposited on the semiconductor substrate; partial sacrificial material layer and partial metal material layer located right under the sacrificial material layer are removed, and a stacked structure comprising the sacrificial material layer and the metal material layer and used for defining the area where a transistor fate is located is formed on the semiconductor substrate; a side wall material layer is deposited on the semiconductor substrate provided with the stacked structure; and the stacked structure and the side wall material layer located above the high K gate medium layer are removed, the side wall material layer remained on two sides of the stacked structure forms side walls of the stacked structure, and the high K gate medium layer not covered by the stacked structure is removed. The high K gate medium layer in the formed transistor cannot cause current leakage so that current switching ratio, Gate Induced Drain Leakage (GIDL) performance and the like of the transistor are improved, and the transistor gate can generate little current leakage.

Owner:SEMICON MFG INT (SHANGHAI) CORP

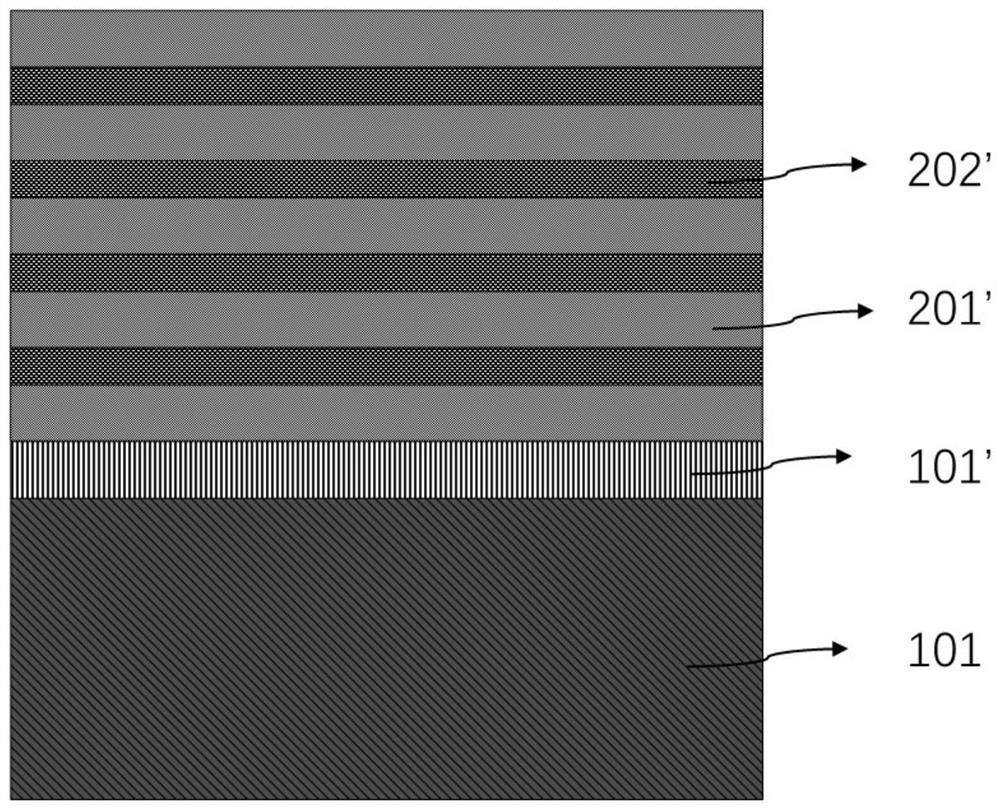

Oxide semiconductor device and production method thereof

PendingCN113471295AImprove subthreshold characteristicsSuppression of short channel effectsTransistorNanoinformaticsPhysicsOxide semiconductor

The invention relates to an oxide semiconductor device which includes an insulating substrate; a source electrode and a drain electrode are oppositely arranged on the insulating substrate; a nanosheet stack part is included and is arranged on the substrate to form a plurality of conducting channels; the nanosheet stack part comprises a plurality of metal oxide semiconductor nanosheets which are vertically stacked to form the nanosheet stack part, and the two ends of the metal oxide semiconductor nanosheets are embedded into the source electrode and the drain electrode respectively; and a surrounding type grid electrode is included and surrounds the periphery of the plurality of metal oxide semiconductor nanosheets in the nanometer stack part. The design of the novel structure gate-all-around OS-TFT (GAA OS-TFT) can significantly improve the sub-threshold characteristic, the current switch ratio and the short channel effect of the device; the working current of the device can be obviously improved by utilizing the design of combining the multiple layers of nanosheets and the supporting structure; the preparation process of the device is compatible with a mainstream CMOS process and is simple; and through the structure design of the surrounding type grid device, the channel carrier mobility can be remarkably improved, the electrical performance of the device is increased, and the reliability and the stability of the device can also be improved.

Owner:INST OF MICROELECTRONICS CHINESE ACAD OF SCI

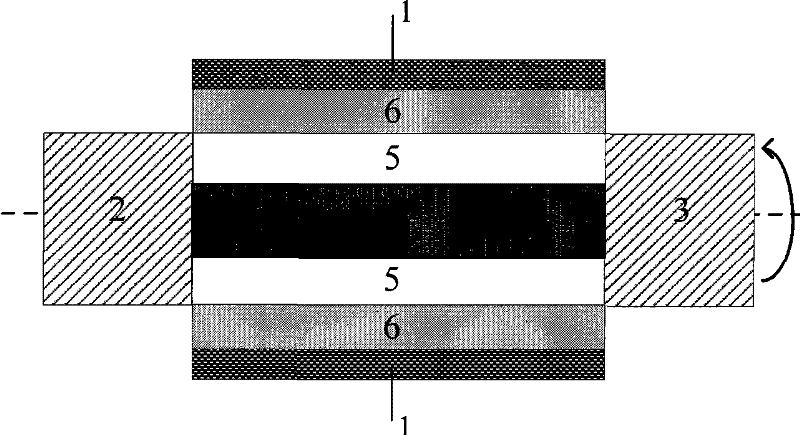

Van der Waals heterojunction device, preparation method thereof and application thereof

ActiveCN109390388AIncrease the current switch ratioHigh current rectification ratioSemiconductor/solid-state device manufacturingSemiconductor devicesHeterojunctionMolybdenum telluride

The invention provides a van der Waals heterojunction device which comprises a substrate, a molybdenum telluride nanosheet, a molybdenum disulfide nanosheet and a metal electrode arranged in order from the bottom to top, and the cross-sectional area of the molybdenum telluride nanosheet is larger than that of the molybdenum disulfide nanosheet. According to the van der Waals heterojunction device,the dynamic adjustment of conductive polarity can be achieved. Under different bias voltage conditions, a field effect transistor based on the van der Waals heterojunction device can realize double polarities and an N-type conductivity polarity, and an ultra-high current switching ratio (10<7>) and current rectification ratio (10<6>) and excellent photovoltaic performance are exhibited, and the device can be applied to a novel two-dimensional electronic and optoelectronic device.

Owner:THE NAT CENT FOR NANOSCI & TECH NCNST OF CHINA

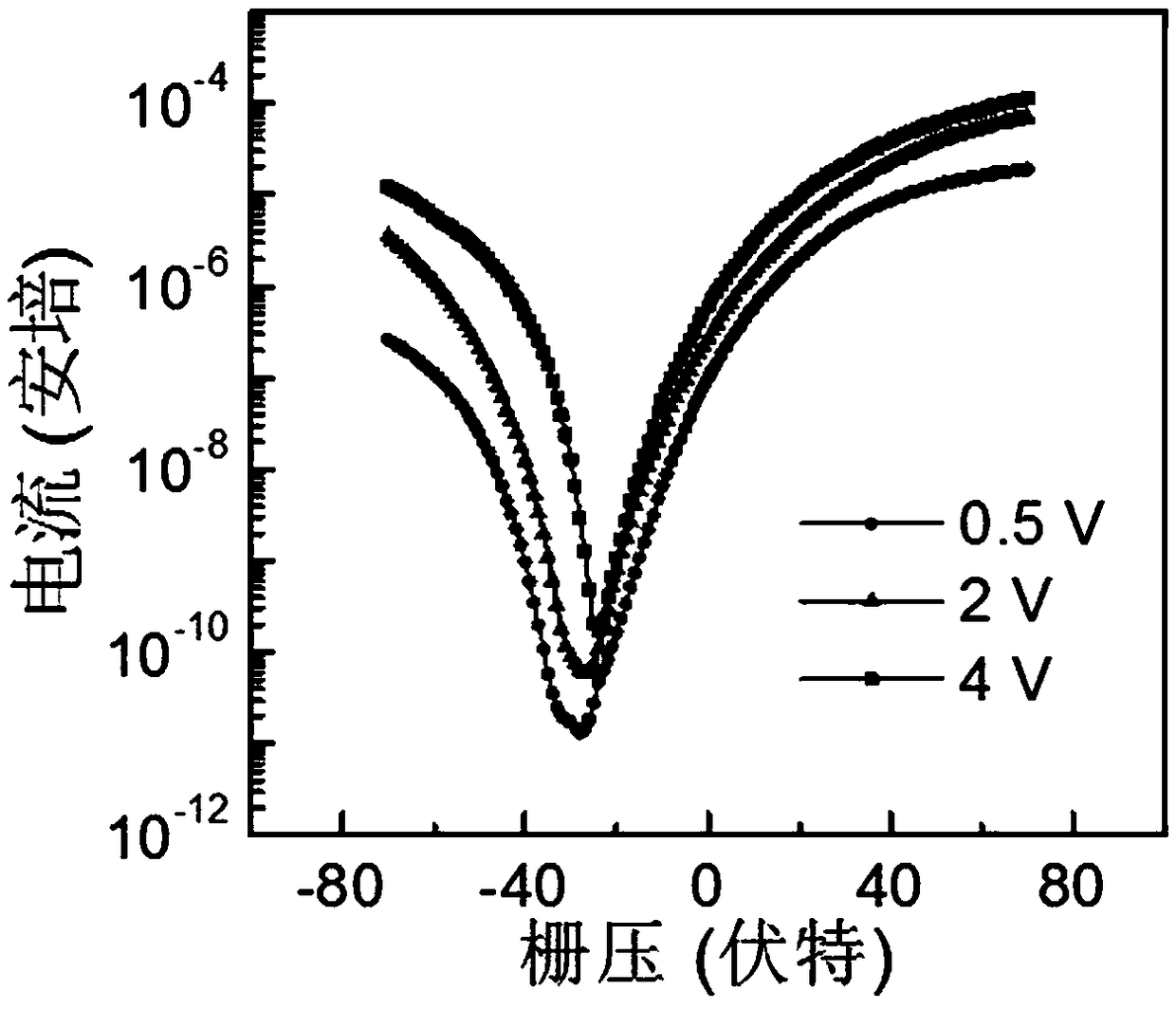

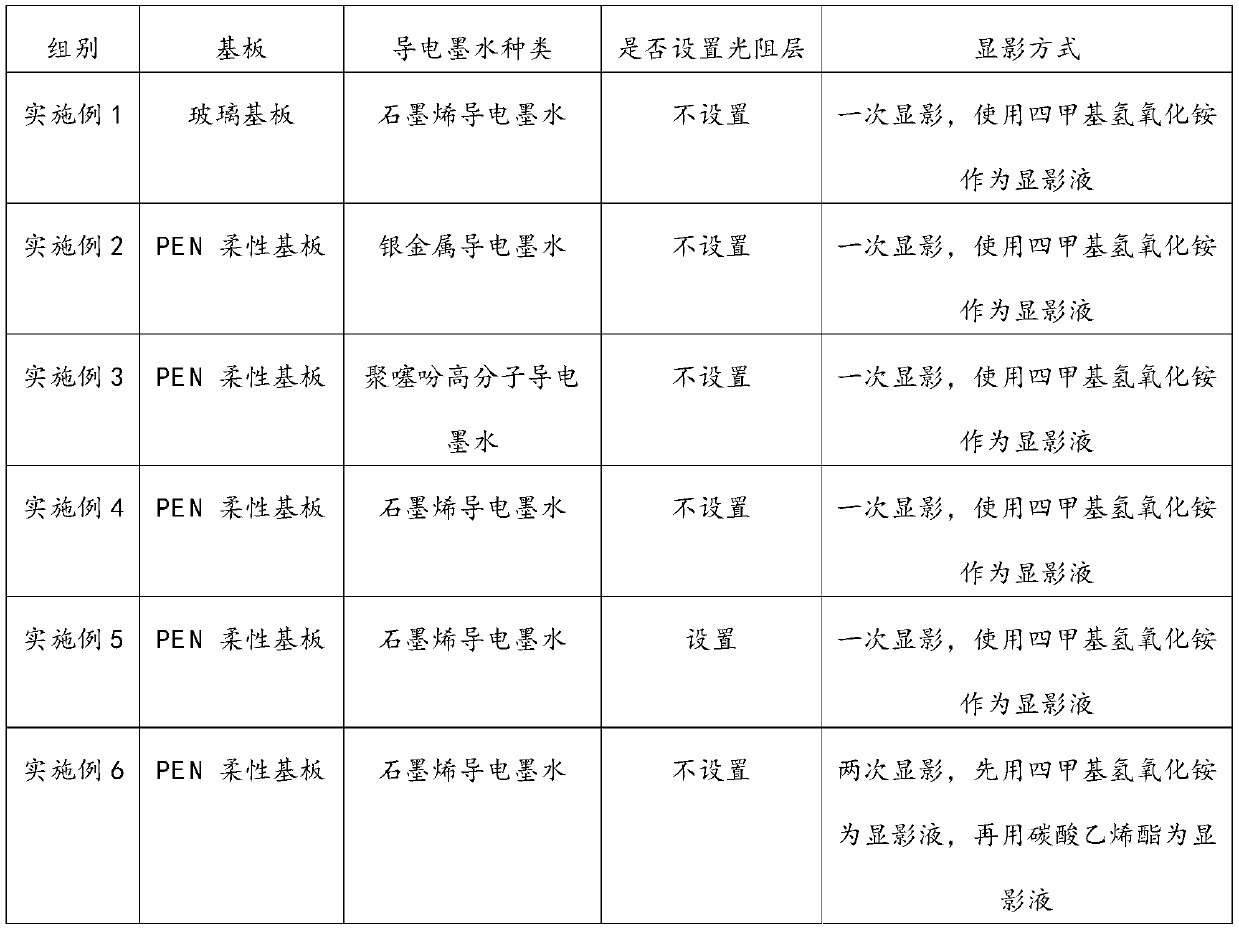

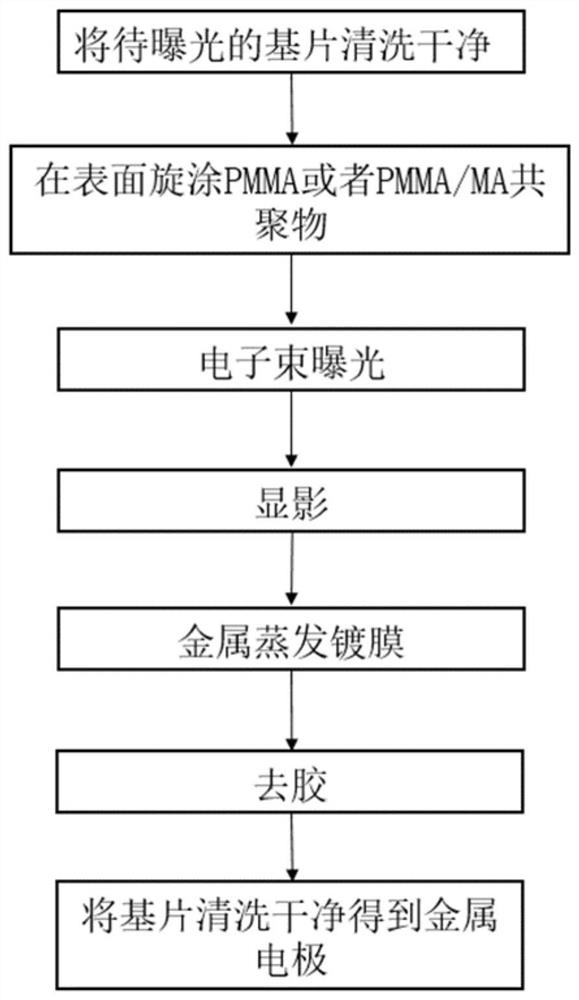

Organic thin film transistor and preparation method thereof

InactiveCN109698277APerformance impactHigh carrier mobilitySolid-state devicesSemiconductor/solid-state device manufacturingOrganic semiconductorPhotoresist

The invention provides an organic thin film transistor and a preparation method thereof, which belong to the technical fields of organic electronics and photo-electronics. The organic thin film transistor includes a substrate, a source-drain layer containing a source and a drain, an organic semiconductor layer, a gate insulating layer and a gate layer. One surface of the substrate is the source-drain layer. The surface of the source-drain layer away from the substrate is the organic semiconductor layer. The surface of the organic semiconductor layer away from the source-drain layer is the gateinsulating layer. The surface of the gate insulating layer away from the organic semiconductor layer is the gate layer. The source-drain layer is made of conductive ink. The preparation method of theorganic thin film transistor includes the following steps: coating one surface of a substrate with conductive ink; curing the conductive ink to form a first electrode layer; and exposing, developingand heat-treating the first electrode layer to obtain a source-drain layer. The organic thin film transistor prepared by the method needs neither a flat layer nor a photoresist layer, and can be patterned directly.

Owner:NINGBO GRAPHENE INNOVATION CENT CO LTD

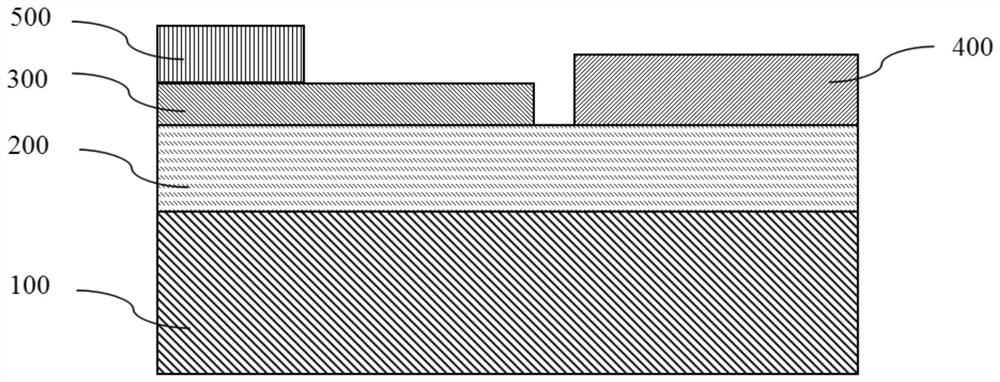

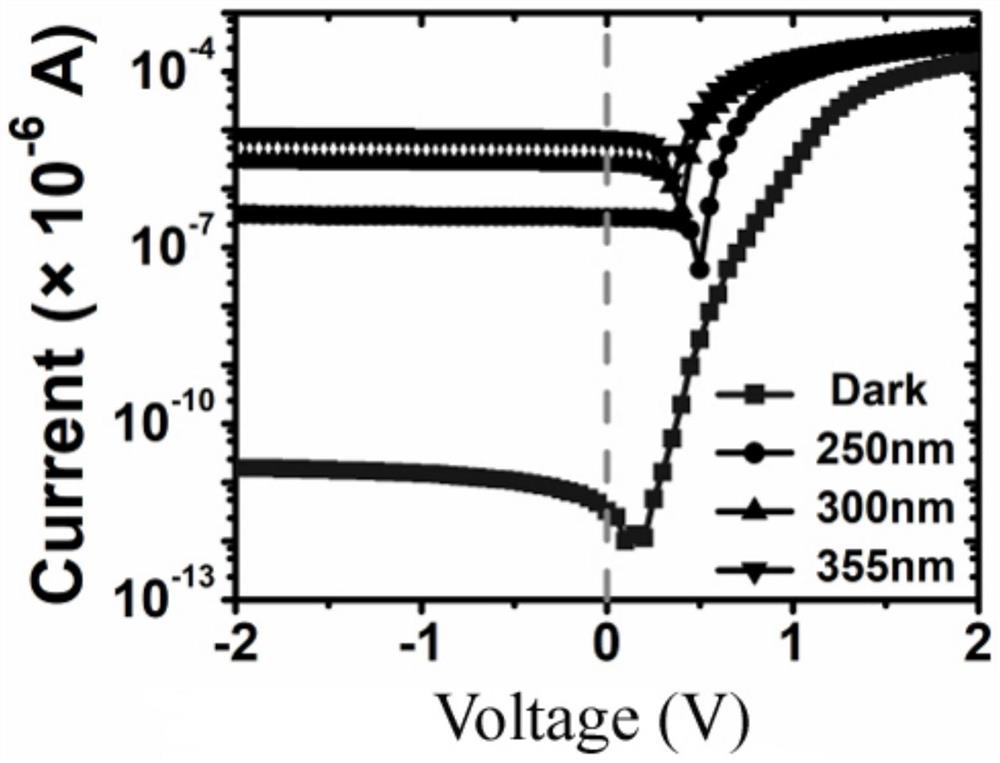

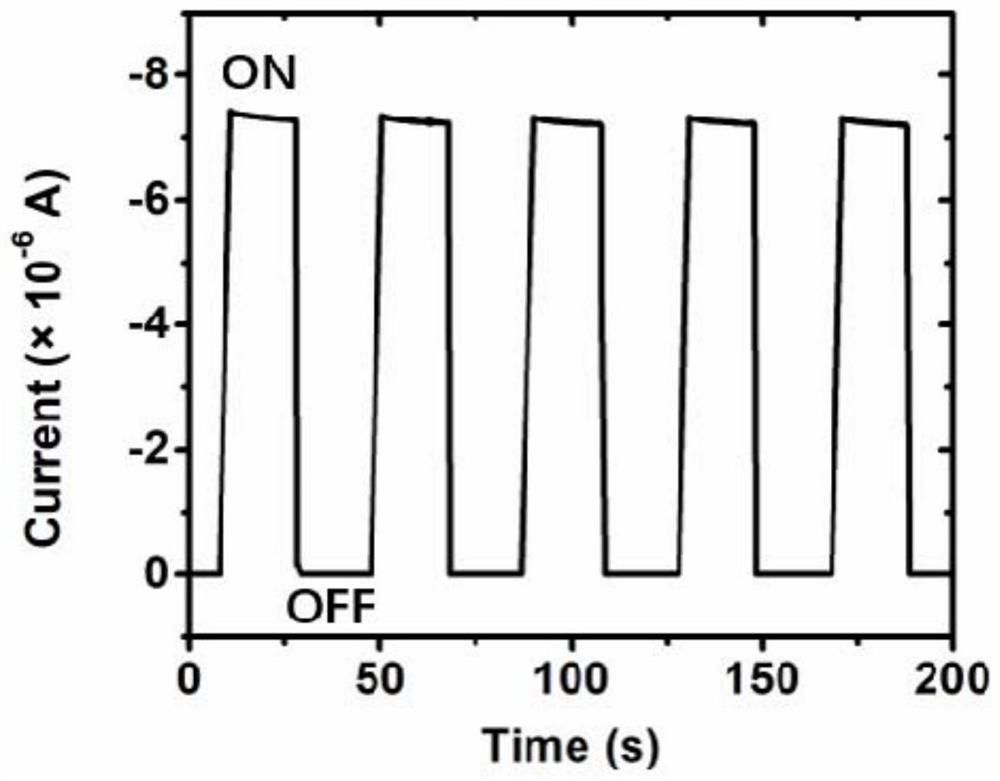

Ultraviolet photodiode and preparation method thereof

ActiveCN112164732AEfficient separationImprove photoelectric performanceSemiconductor devicesResponsivityOhmic contact

The invention belongs to the technical field of semiconductors, and discloses an ultraviolet photodiode and a preparation method thereof. The ultraviolet photodiode comprises the following structures:a substrate; a GaN layer which is arranged on the upper surface of the substrate; a Ti3C2 Schottky contact layer and a ohmic contact layer which are oppositely arranged on the two sides of the uppersurface of the GaN layer; and a metal contact layer which is arranged on the upper surface of the Ti3C2 Schottky contact layer. The ultraviolet photodiode has the advantages of excellent ultraviolet detection performance, high responsivity, high specific detection rate, high response speed and high current switch ratio; and the preparation method does not need a complex metal deposition or sputtering process, does not damage the surface of the semiconductor, and is simple in process.

Owner:WUYI UNIV

Electric heating fabric with pressure sensitive characteristic, preparation method of electric heating fabric, electric blanket and sitting and bedding

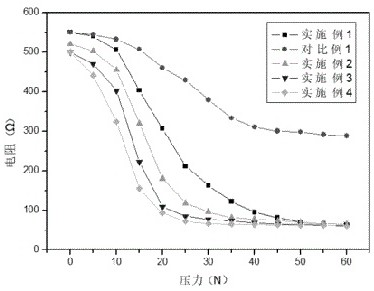

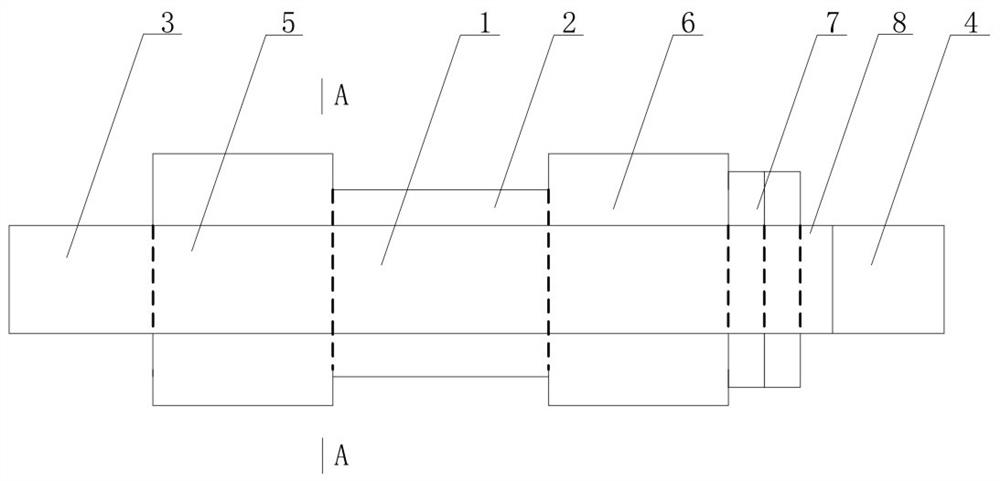

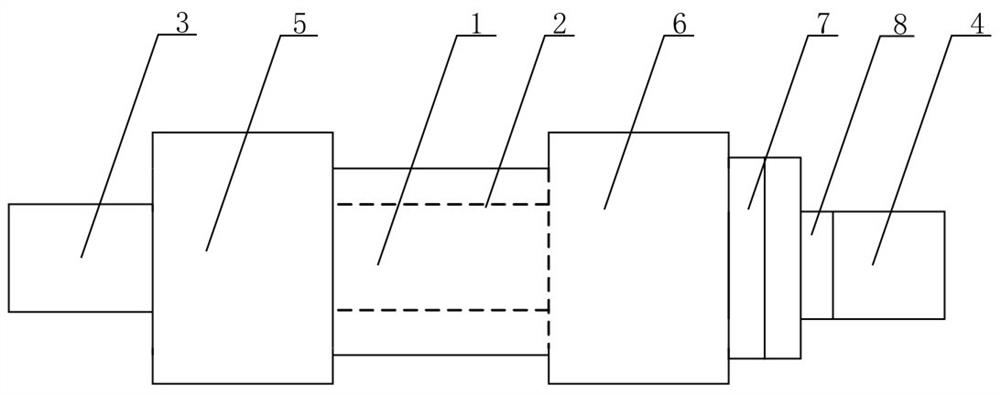

PendingCN114536876AReduce fill rateGood pressure sensitivitySynthetic resin layered productsOhmic-resistance heating detailsPolymer scienceProtection layer

The invention discloses an electric heating fabric with a pressure sensitive characteristic, a preparation method of the electric heating fabric, and an electric blanket and a bedding made of the fabric with the pressure sensitive characteristic. The electric heating fabric with the pressure sensitive characteristic comprises a fabric layer and an electric heating film, the electrothermal film is provided with a lower protection layer, a heating layer, an upper protection layer, an electrode attached to the heating layer and a lead-out wire. The heating layer is prepared from the following components: 95 to 98 weight percent of polyurethane resin, 2 to 5 weight percent of graphene and 0.01 to 0.5 weight percent of black phosphorus / metal oxide nano composite material. The polyurethane film is filled with the graphene filler which is slightly lower than the conductive percolation threshold range of the polyurethane film, and a small amount of black phosphorus / metal oxide nano composite material is added to enhance the pressure sensitive characteristic of the film. After the electric heating film of the electric heating fabric is connected with a power supply, when no external pressure exists, the resistance of the heating layer is large, and the heating layer does not emit heat; when the outside endows the electrothermal film with certain pressure, the electrothermal film begins to heat, and after the external force disappears, the heating layer restores to the original shape and stops heating.

Owner:武汉中科先进材料科技有限公司

A Reconfigurable Field-Effect Transistor with Asymmetric Structure

ActiveCN109037339BIdeal off-state currentIncrease the current switch ratioSemiconductor/solid-state device manufacturingSemiconductor devicesSubthreshold swingElectrical polarity

The invention discloses a reconfigurable field effect transistor with an asymmetric structure, comprises a source electrode and a drain electrode arranged on both ends of the channel, and a field effect transistor composed of a control gate electrode and a polar gate electrode respectively arranged on one side of the source electrode and the drain electrode. The polar gate electrode is provided with an underoverlapped region of a deposition side wall on the side close to the drain electrode to form a reconfigurable field effect transistor with an asymmetric structure. Compared with the prior art, the device of the invention has ideal on-state, off-state current, larger current switching ratio, steep subthreshold swing and the like. The current switching ratio is improved significantly whenthe device is of an n-FET structure compared with a p-FET structure, and the off-state current is almost the same compared with a symmetric reconfigurable transistor, so the leakage current is controlled effectively.

Owner:EAST CHINA NORMAL UNIV +1

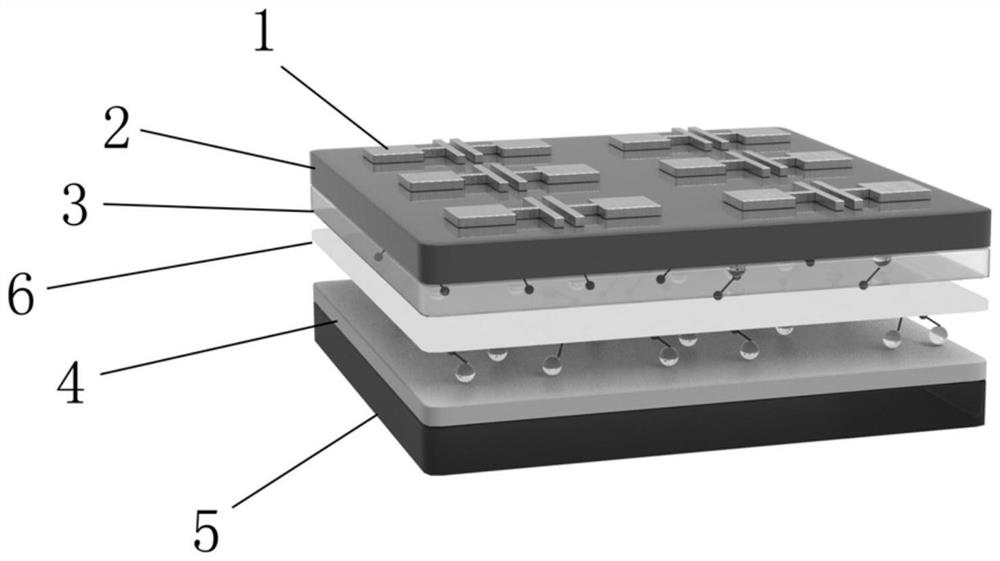

Organic field effect transistor memory based on polyvinyl alcohol and preparation method thereof

PendingCN114512606AQuality improvementGood lookingSolid-state devicesSemiconductor/solid-state device manufacturingOrganic field-effect transistorPolyvinyl alcohol

The invention discloses a polyvinyl alcohol-based organic field effect transistor memory and a preparation method thereof. The memory structurally comprises a source electrode, a drain electrode, an organic semiconductor layer, a charge storage layer, a gate insulating layer and a gate electrode serving as a substrate from top to bottom in sequence, wherein a hydrophobic film layer is also arranged between the charge storage layer and the gate insulating layer; the hydrophobic film layer is prepared by spin-coating a hydrophobic film solution on the gate insulating layer, and the hydrophobic film solution is formed by dispersing polytetrafluoroethylene in water; and the charge storage layer is prepared by spin-coating a polyvinyl alcohol solution on the hydrophobic film layer. According to the method, the polytetrafluoroethylene film is introduced between the silicon wafer and the polyvinyl alcohol film in a spin-coating mode, the hydrogen bond acting force between PVA and the silicon wafer is isolated, formation of surface dipoles is hindered, and the spin-coated polytetrafluoroethylene serves as a hydrophobic film, so that the quality of the upper PVA film is greatly improved, and the morphology of the PVA film is improved.

Owner:NANJING UNIV OF POSTS & TELECOMM

Rhenium disulfide-based field effect transistor and manufacturing method thereof

PendingCN113437144AControl the size of the drain-source currentImprove performanceSemiconductor/solid-state device manufacturingSemiconductor devicesPhysicsShort-channel effect

The invention relates to a rhenium disulfide-based field effect transistor and a manufacturing method thereof, the rhenium disulfide-based field effect transistor comprises a substrate, the substrate comprises a silicon substrate and an oxide layer growing on the silicon substrate, a rhenium disulfide channel is etched on the oxide layer, the field effect transistor further comprises a drain-source electrode growing in the source-drain contact region, a gate oxide layer covering the rhenium disulfide channel and a metal lead located at the bottom of the silicon substrate, a gate electrode grows on the gate oxide layer, and the drain-source electrode comprises a Cr electrode and an Au electrode which are sequentially located on the oxide layer. The field effect transistor has a high switching current ratio, the short channel effect caused by device size reduction is effectively reduced, and meanwhile, the structure of the top gate and the back gate is also beneficial to regulation and control of source and drain currents.

Owner:LANZHOU UNIVERSITY

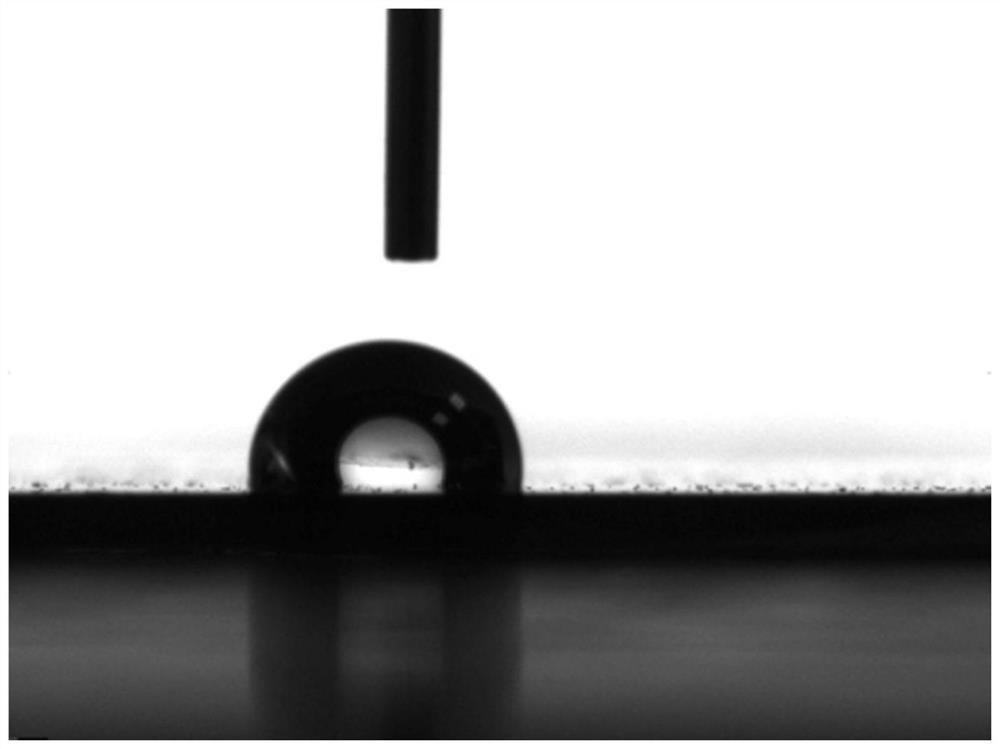

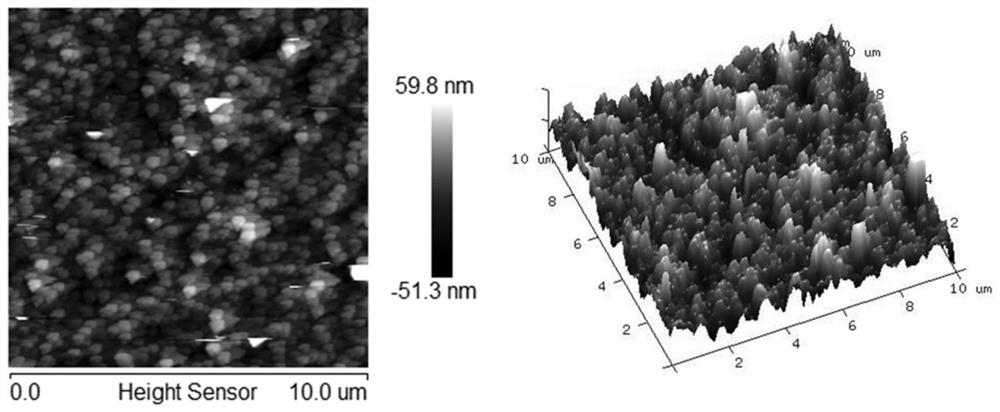

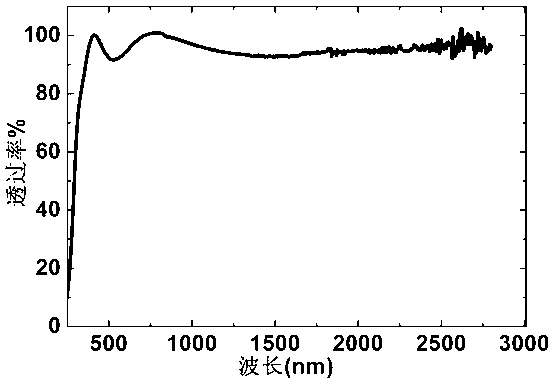

Amorphous oxide thin film for thin film transistor channel layer and manufacturing method thereof

InactiveCN103219393AImprove mobilityElectrical properties are similarTransistorVacuum evaporation coatingMetallurgySurface roughness

The invention discloses an amorphous oxide thin film for a thin film transistor channel layer and a manufacturing method of the amorphous oxide thin film for the thin film transistor channel layer. The chemical formula is that SixZnSnO2x+3, 0.06<=x<=0.14. The surface roughness RMS is less than 2nm and the carrier concentration is 1014-1017cm<-3>. A pulsed laser deposition method is adopted for preparation and the target material is obtained by mixing and sintering of SiO2 powder, ZnO powder and SnO2 powder with purity more than 99.9%. The atomic ratio of the SiO2 powder, the ZnO powder and the SnO2 powder is Si: Zn: Sn=0.06-0.14:1:1. The growth temperature of the thin film is 25 DEG C-400 DEG C. The amorphous oxide thin film for the thin film transistor channel layer has the advantages of being high in grade of transparency in a visible region, low in roughness of the surface, high in mobility ratio, low in preparing temperature, ample in raw material reserve volume and low in cost.

Owner:ZHEJIANG UNIV

An Asymmetric Reconfigurable Field Effect Transistor

ActiveCN110164958BIncrease the longitudinal electric fieldIncrease turn-on currentSolid-state devicesSemiconductor/solid-state device manufacturingNanowireElectrical polarity

The invention discloses an asymmetrical reconfigurable field effect transistor. The transistor comprises a channel, a drain arranged at one end of the channel, a source extended to the inside of the channel at the other end of the channel, and a drain arranged at one end of the channel. The gate oxide on the outside, the control gate and the polarity gate respectively arranged on the source and drain terminals and outside the gate oxide, respectively arranged outside the two ends of the channel, are used for the control gate, the polarity gate The side wall electrically isolating the source and the drain, and the gate isolation arranged outside the gate oxide for isolating the control gate and the polarity gate. In the present invention, the contact area between the source end extending into the channel and the nanowire channel is larger, thereby increasing the tunneling area of carriers and increasing the turn-on current. When it is turned off, the drain structure is the same as the non-overlapping area of the general RFET drain structure, and the leakage current remains basically unchanged, so the current switching ratio is improved, and the logic gate current is shortened while keeping the static power consumption unchanged. operation delay time.

Owner:EAST CHINA NORMAL UNIV +1

A kind of neodymium indium zinc oxide thin film transistor and its preparation method

ActiveCN108336135BImprove performanceImprove mobilityTransistorSemiconductor/solid-state device manufacturingDisplay deviceEngineering

The invention belongs to the technical field of display devices, and discloses a neodymium indium zinc oxide thin film transistor and a preparation method thereof. The thin film transistor is composed of a substrate, a metal gate, a gate insulating layer, an Nd-IZO semiconductor active layer, an oxide insulator passivation layer and metal source and drain electrodes. In the present invention, a certain proportion of Nd element doping is introduced into the IZO semiconductor target, and the Nd-IZO active layer film with high carrier concentration is deposited by a room temperature sputtering process, combined with ultra-thin Al 2 o 3 The passivation layer controls the carrier transport under the electric field, which can optimize the electrical properties of the device to obtain high-performance thin film transistors.

Owner:SOUTH CHINA UNIV OF TECH

Asymmetric van der Waals heterojunction device, its preparation method and use

ActiveCN109004016BIncrease the current switch ratioImprove responsivenessSolid-state devicesSemiconductor devicesHeterojunctionMolybdenum telluride

Owner:THE NAT CENT FOR NANOSCI & TECH NCNST OF CHINA

A van der Waals heterojunction device and its preparation method and application

ActiveCN109390388BIncrease the current switch ratioHigh current rectification ratioSemiconductor/solid-state device manufacturingSemiconductor devicesHeterojunctionMolybdenum telluride

The invention provides a van der Waals heterojunction device, comprising a base, a molybdenum ditelluride nanosheet, a molybdenum disulfide nanosheet and a metal electrode sequentially arranged from bottom to top, and the cross-sectional area of the molybdenum ditelluride nanosheet is larger than The cross-sectional area of the molybdenum disulfide nanosheets. The van der Waals heterojunction device of the invention can realize the dynamic adjustment of the conduction polarity. Under different bias conditions, field-effect transistors based on this van der Waals heterojunction device can achieve bipolar and N-type conduction polarity, respectively, and exhibit an ultrahigh current switching ratio (~10 7 ), current rectification ratio (~10 6 ) and excellent photovoltaic performance, which can be applied in new two-dimensional electronic and optoelectronic devices.

Owner:THE NAT CENT FOR NANOSCI & TECH NCNST OF CHINA