Patents

Literature

52results about How to "Increase turn-on current" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

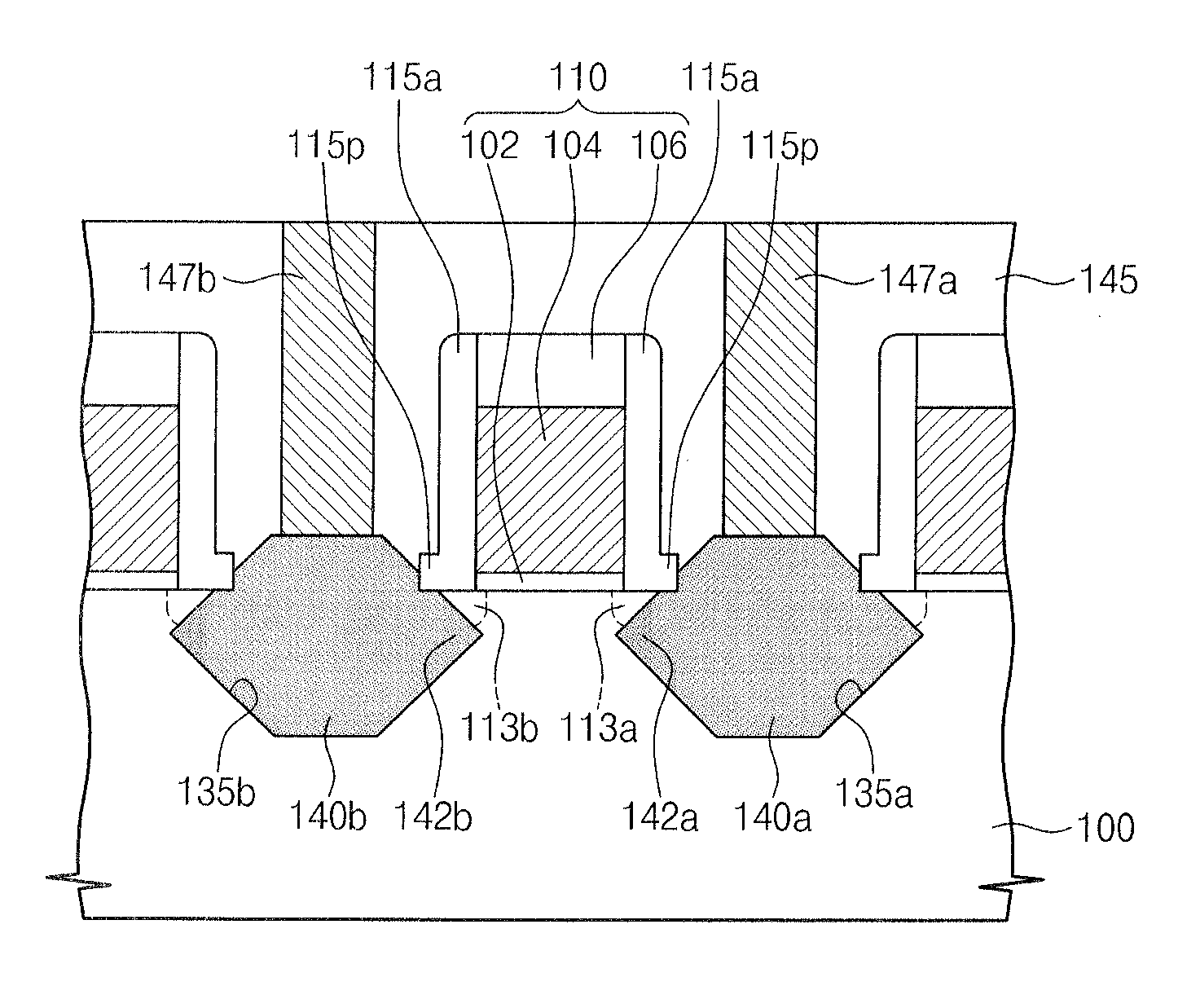

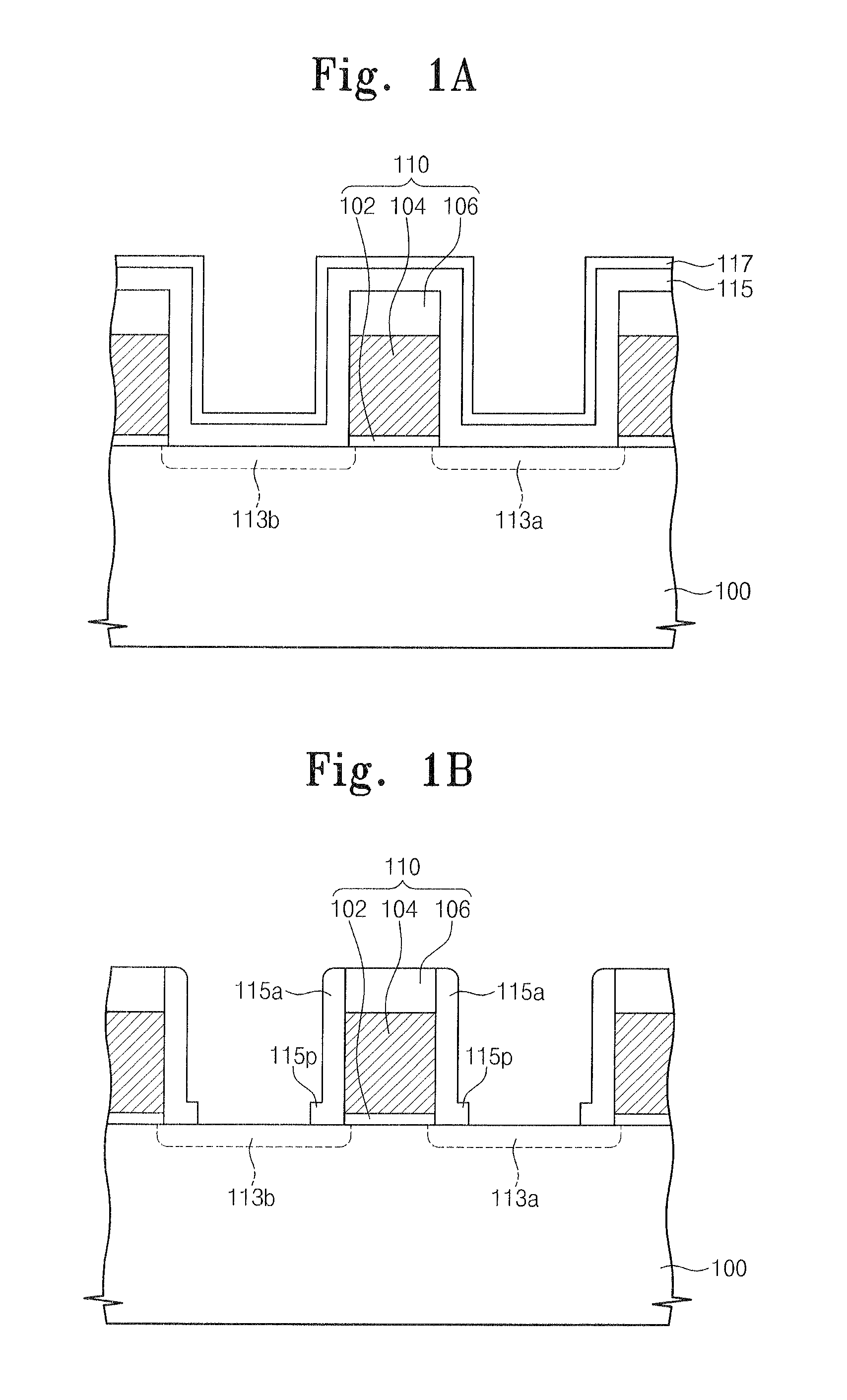

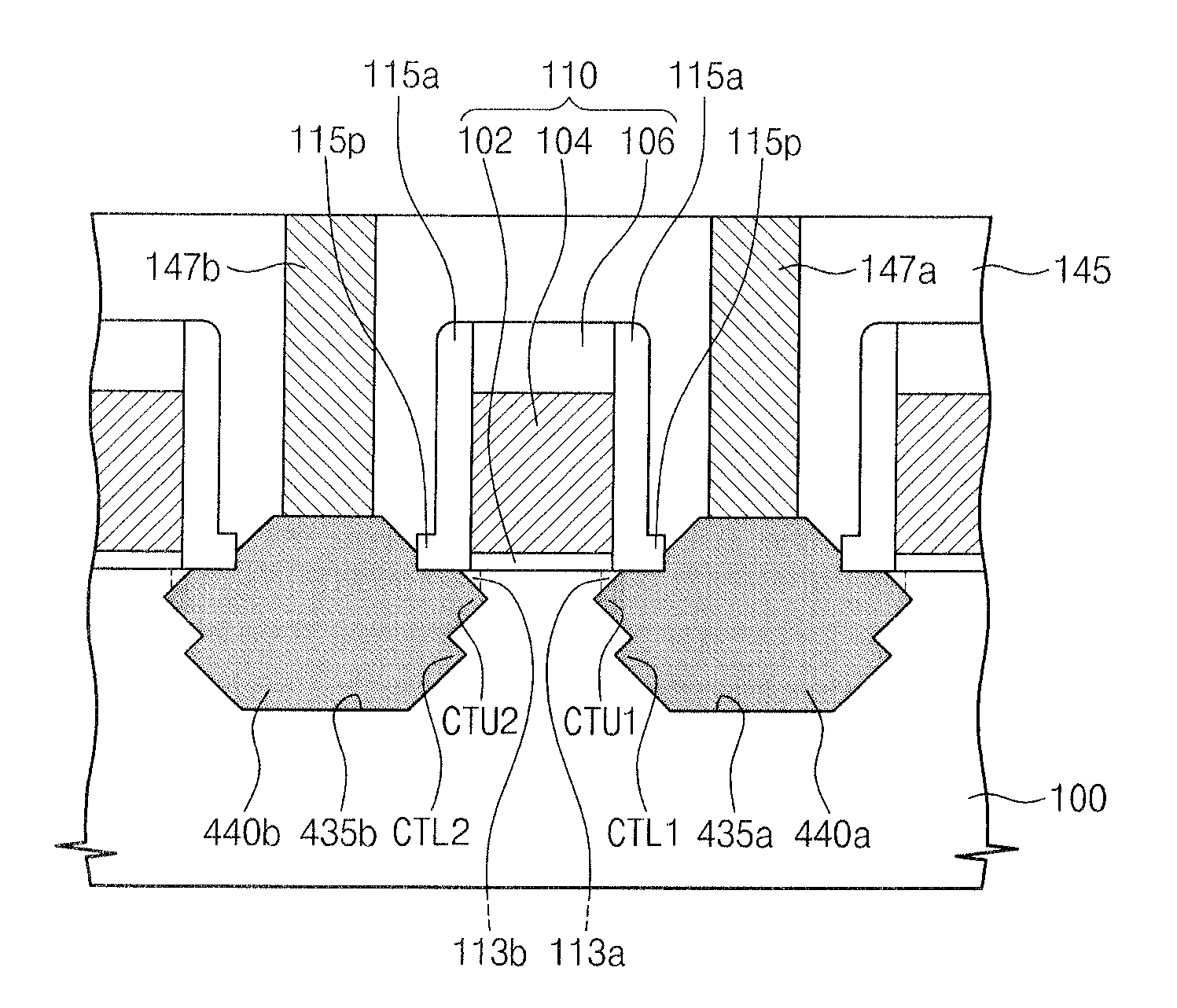

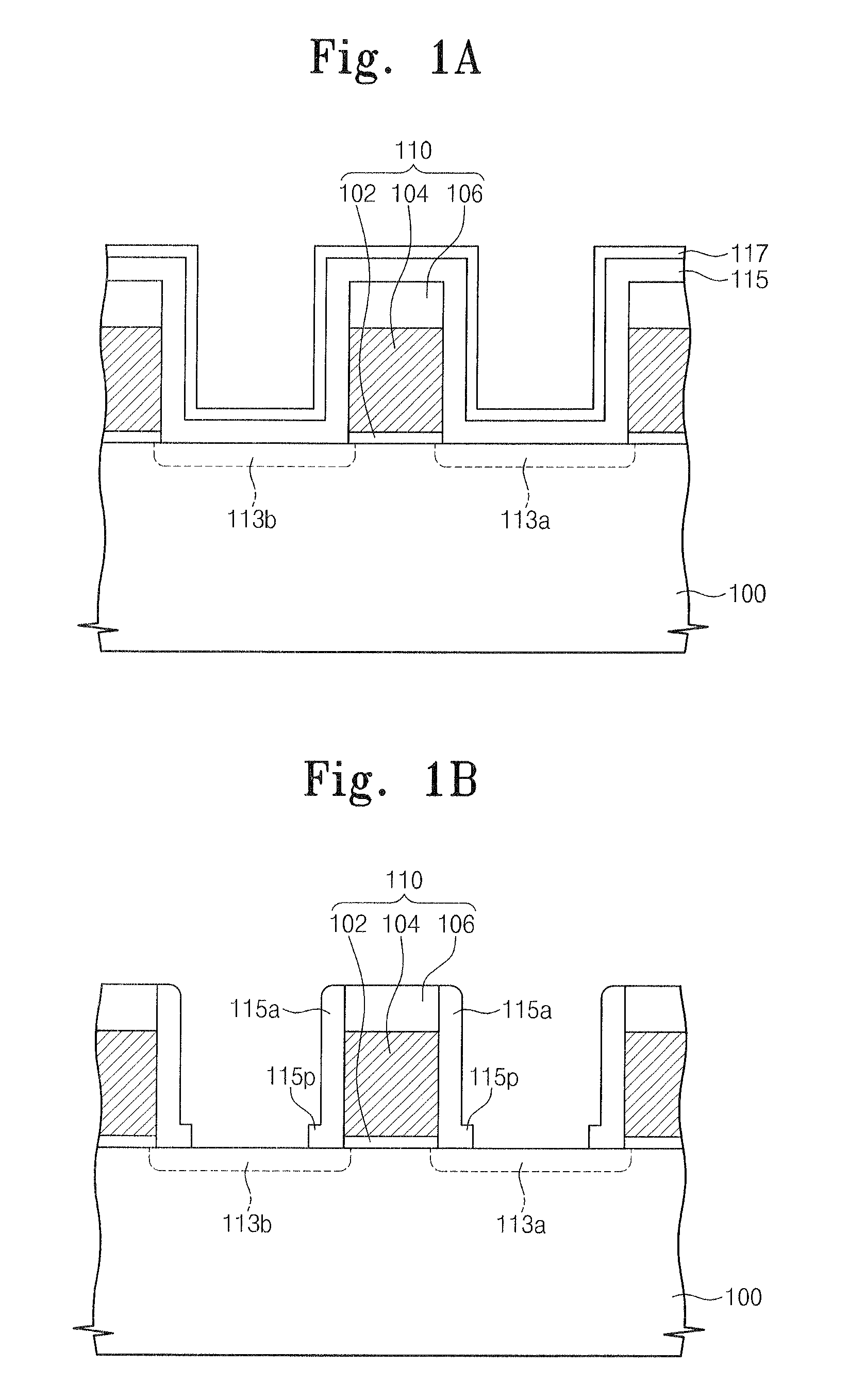

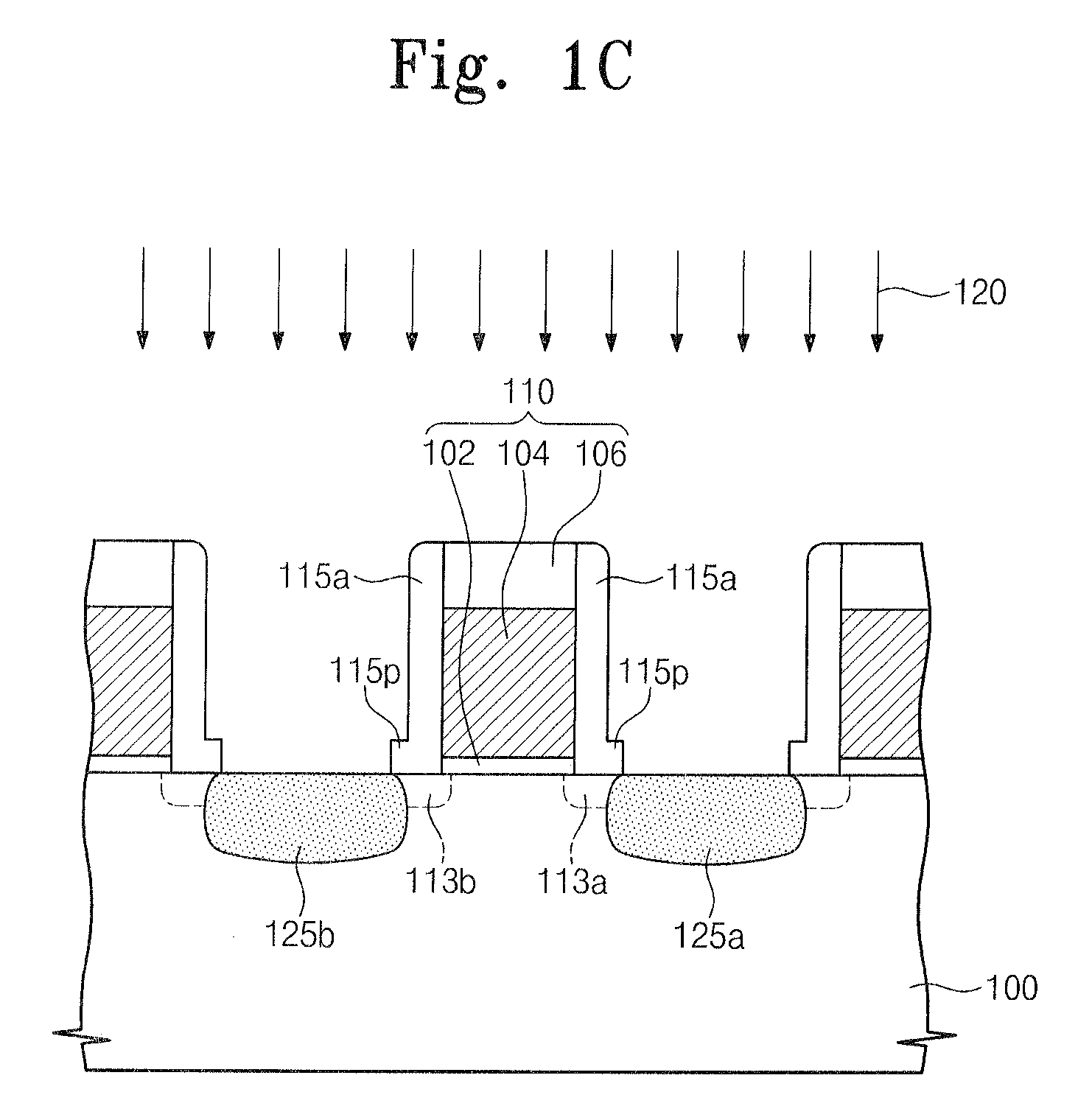

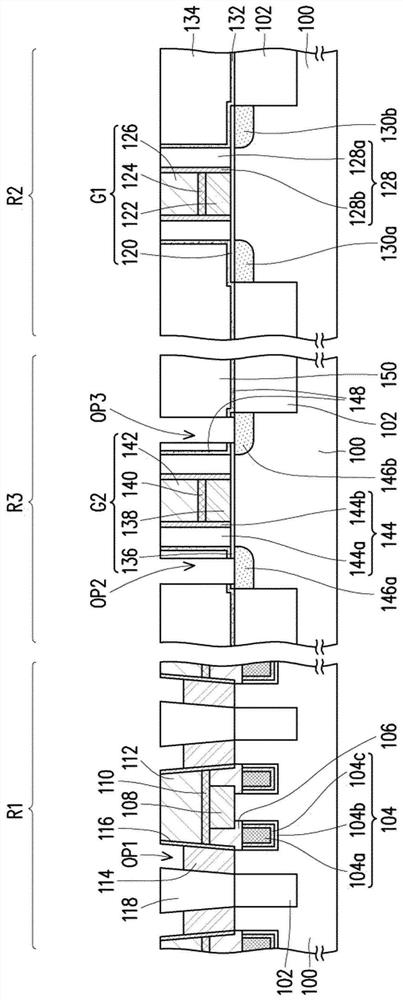

Semiconductor devices and methods of manufacturing the same

ActiveUS20130045589A1Improve methodImprove reliabilityTransistorSemiconductor/solid-state device manufacturingDevice materialSemiconductor

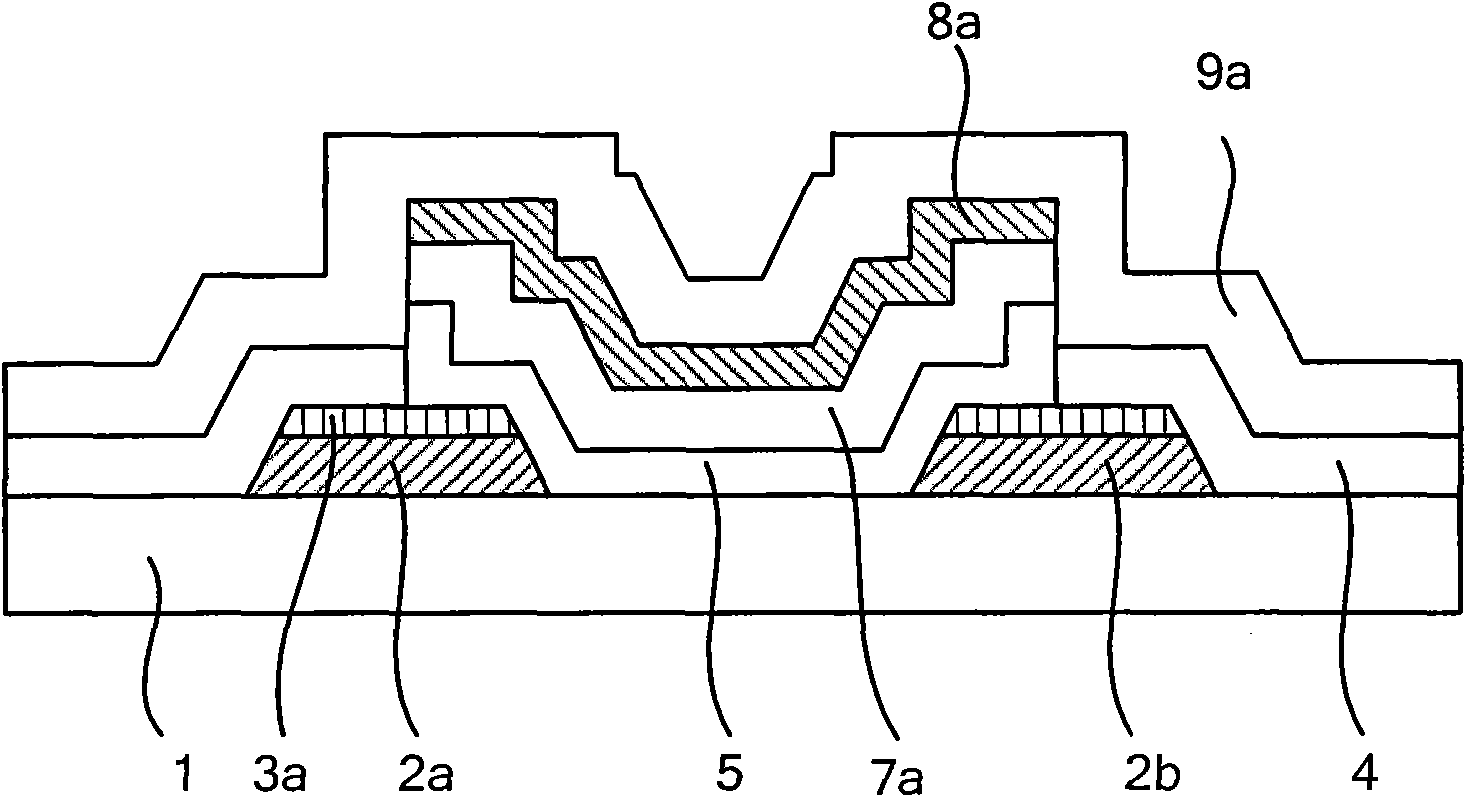

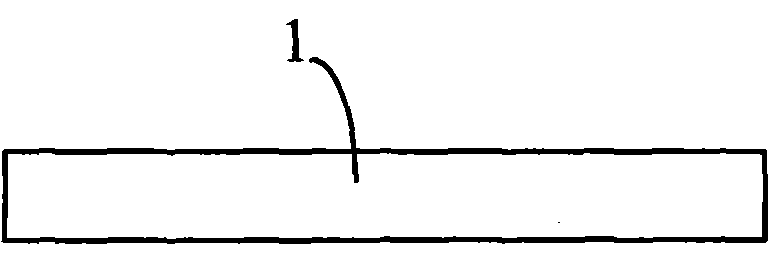

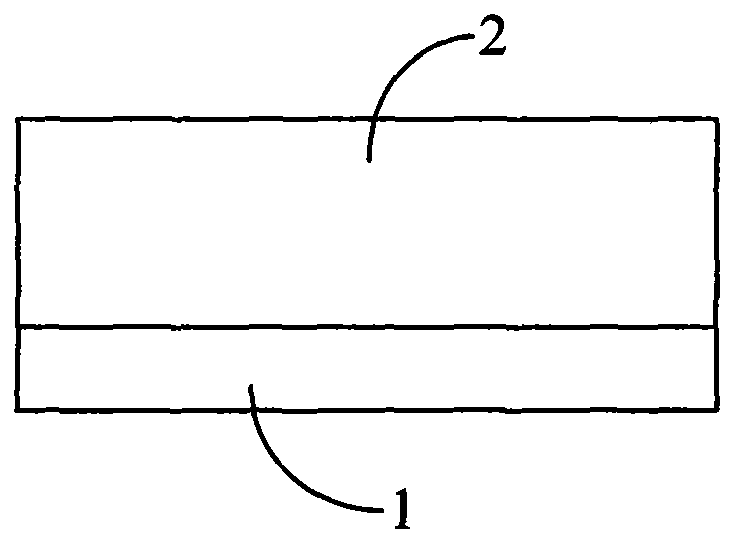

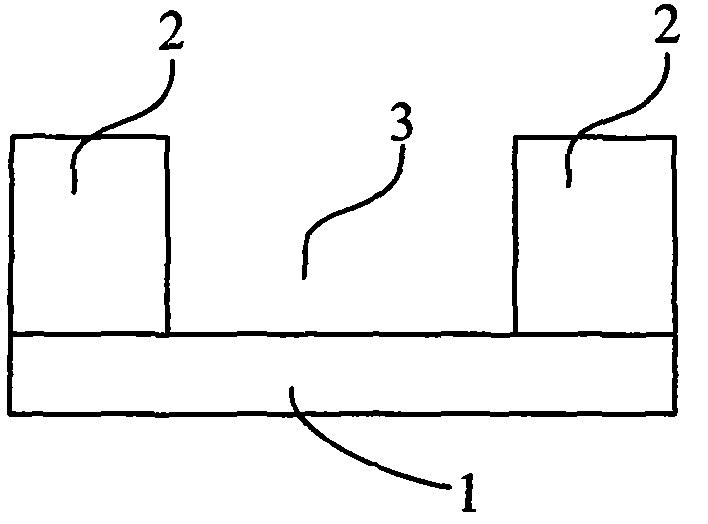

A method of manufacturing a transistor of a semiconductor device, the method including forming a gate pattern on a semiconductor substrate, forming a spacer on a sidewall of the gate pattern, wet etching the semiconductor substrate to form a first recess in the semiconductor substrate, wherein the first recess is adjacent to the spacer, and wet etching the first recess to form a second recess in the semiconductor substrate.

Owner:SAMSUNG ELECTRONICS CO LTD

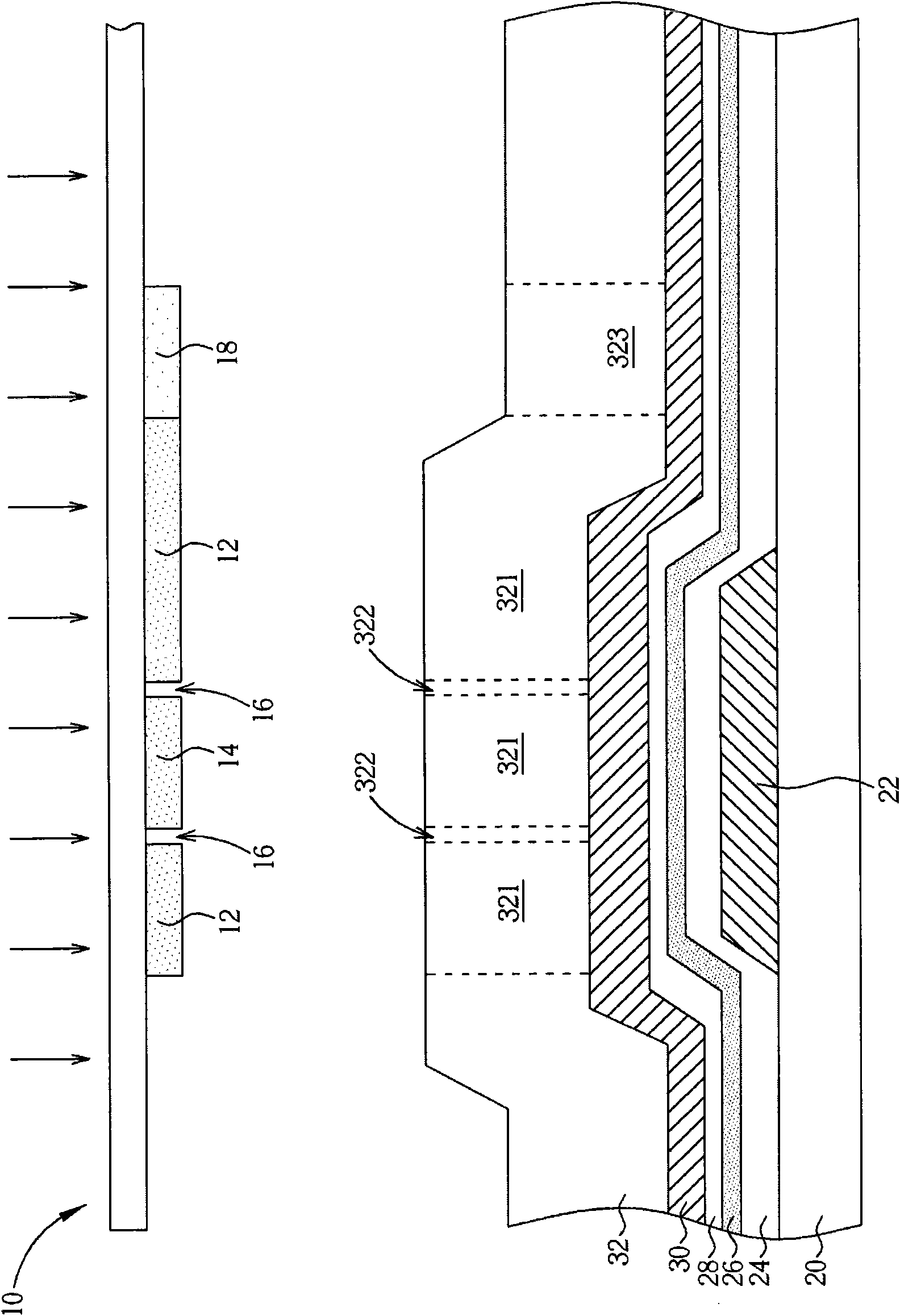

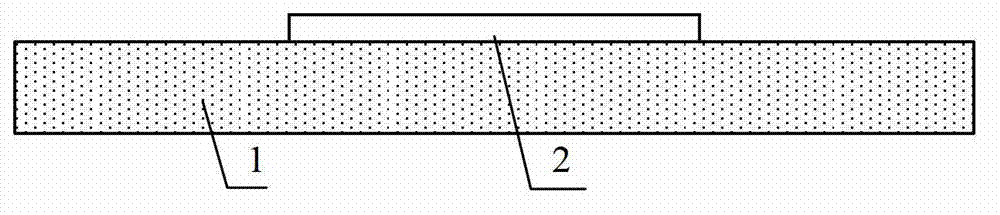

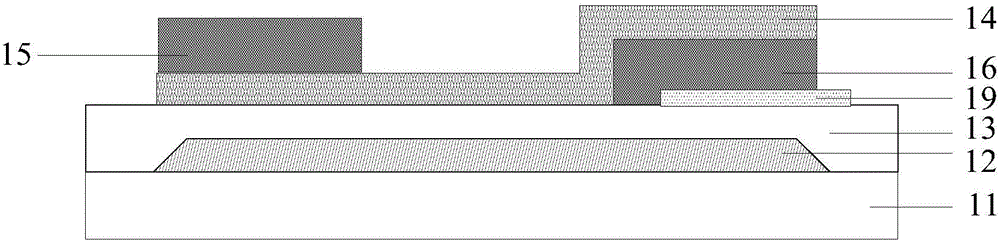

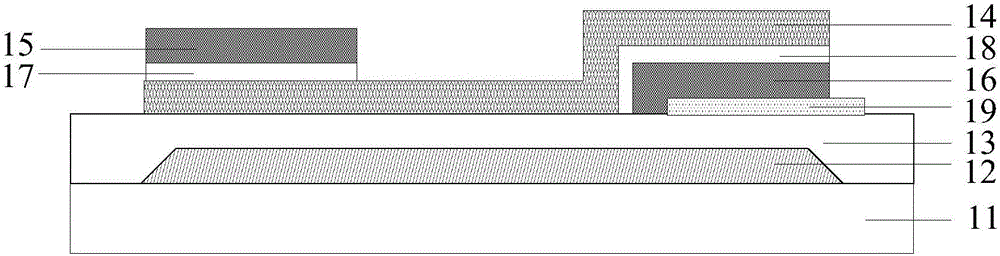

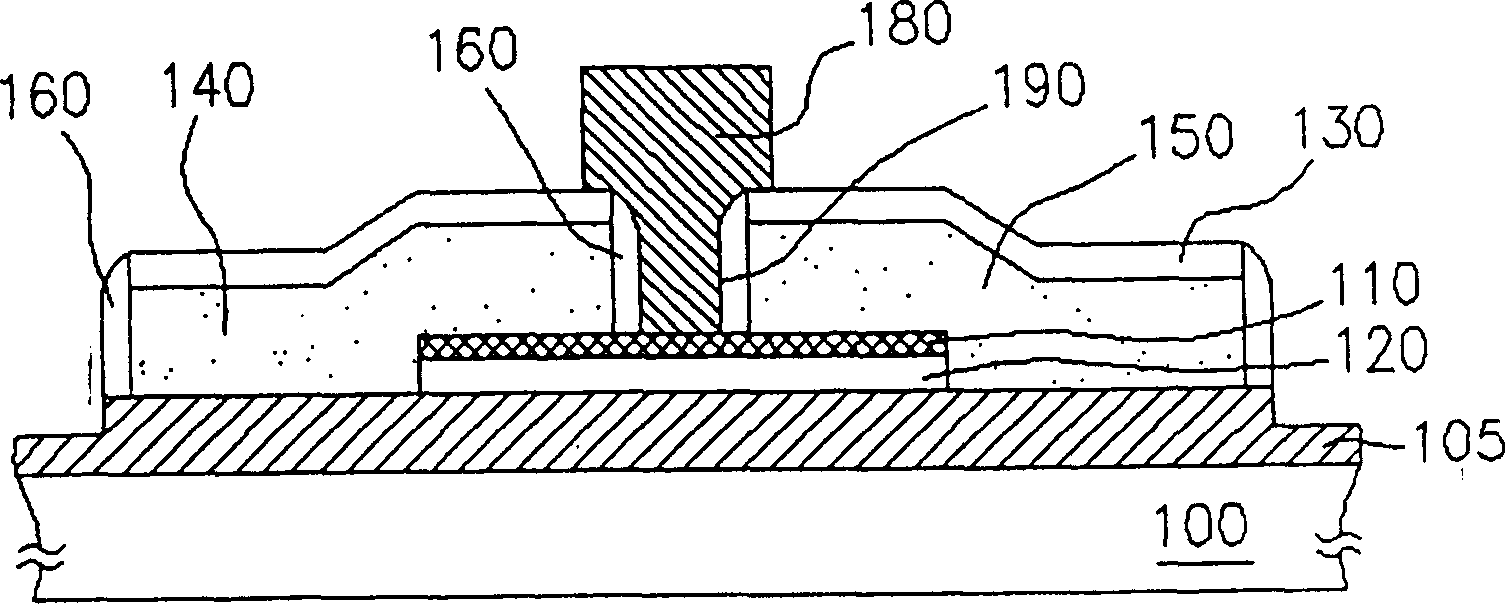

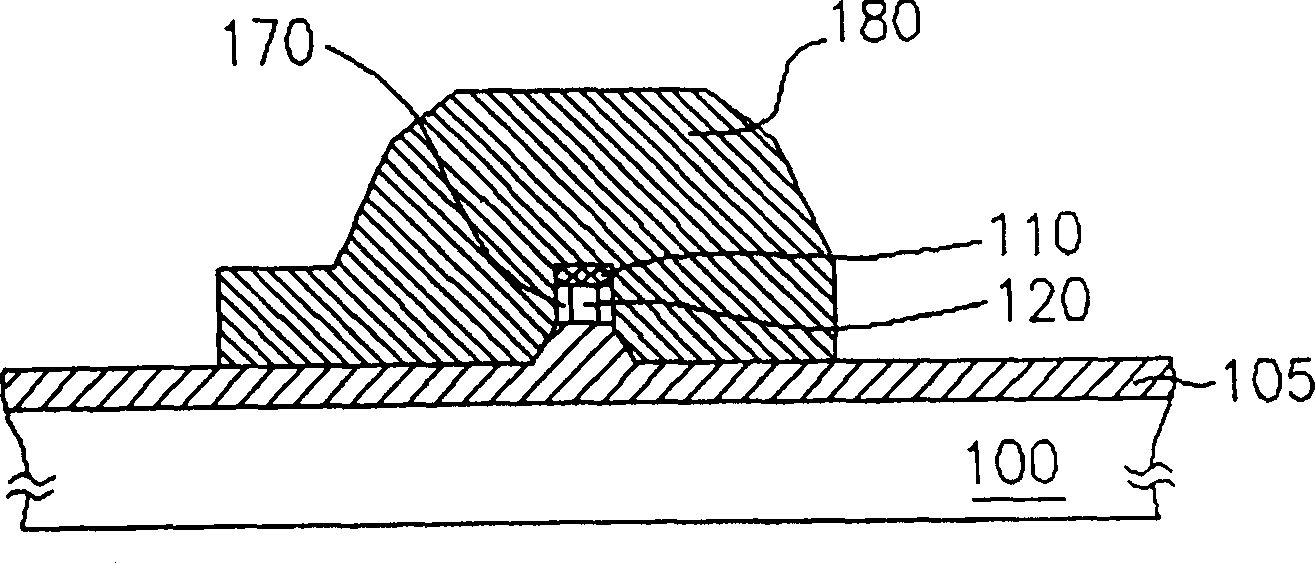

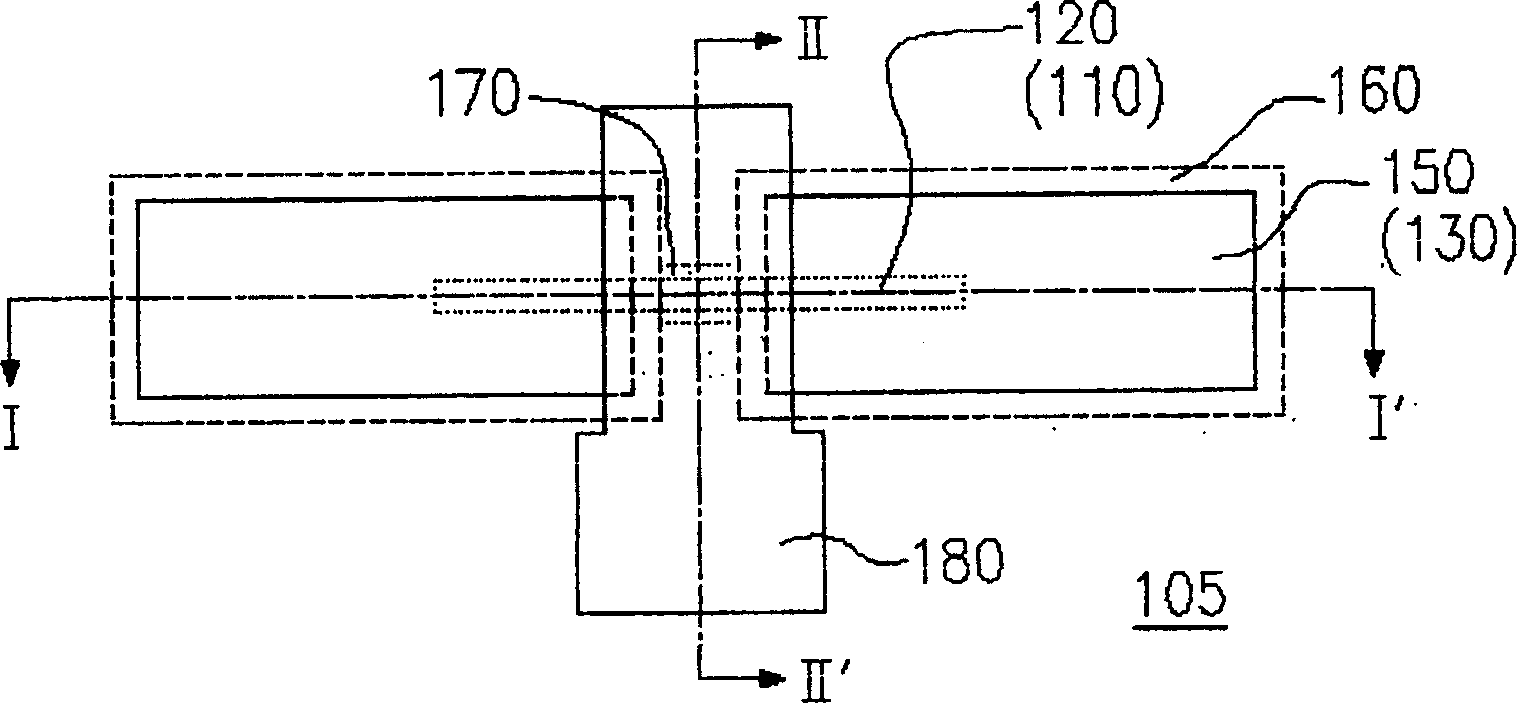

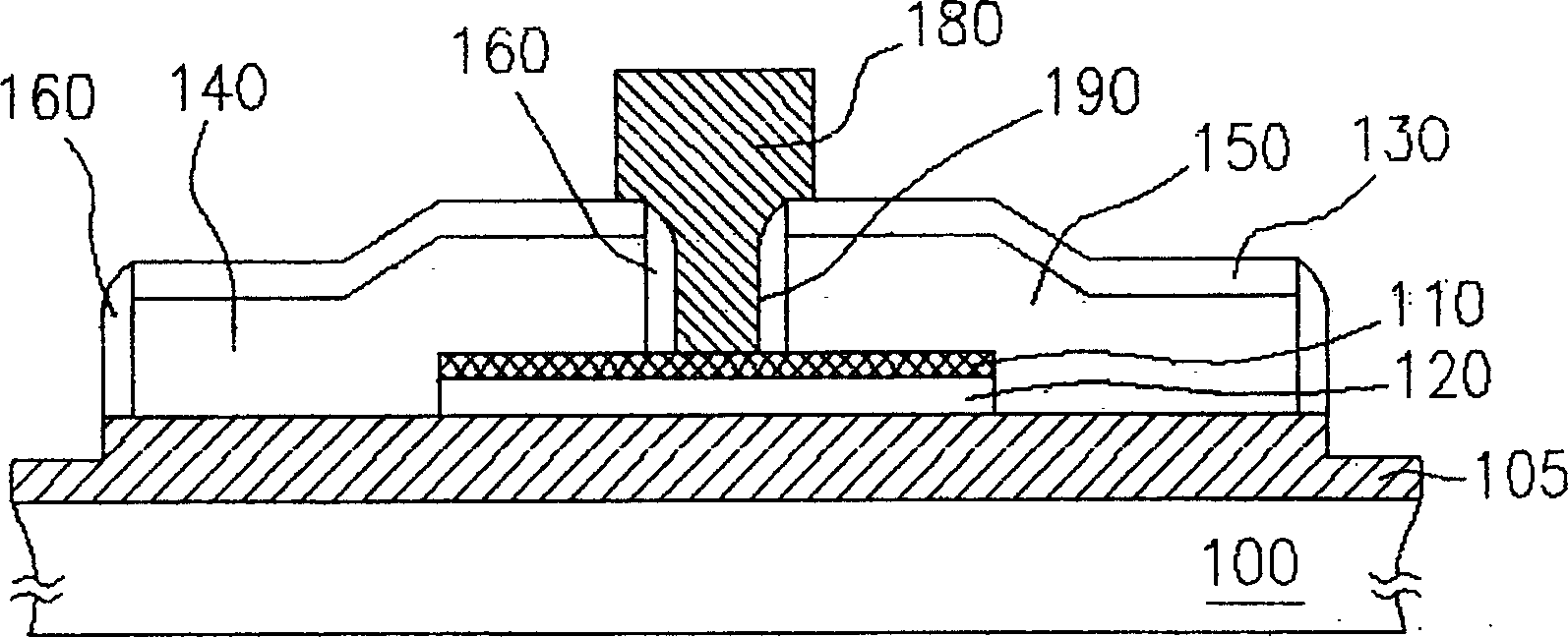

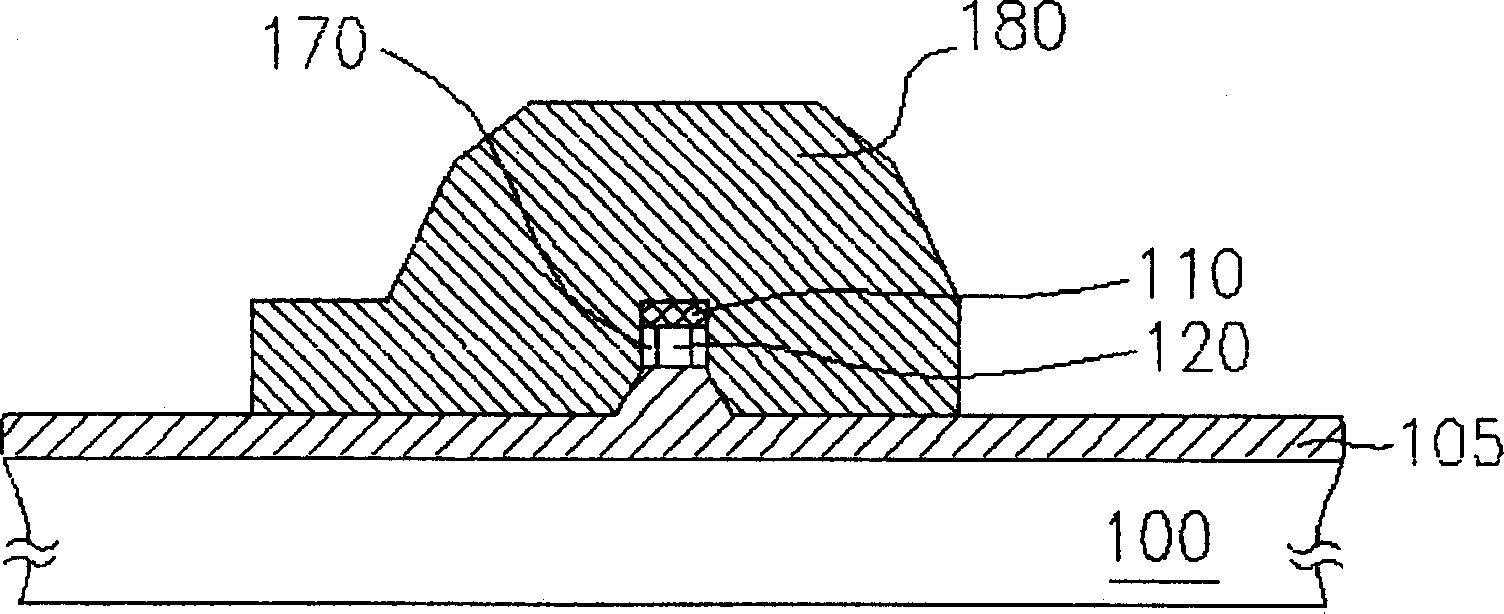

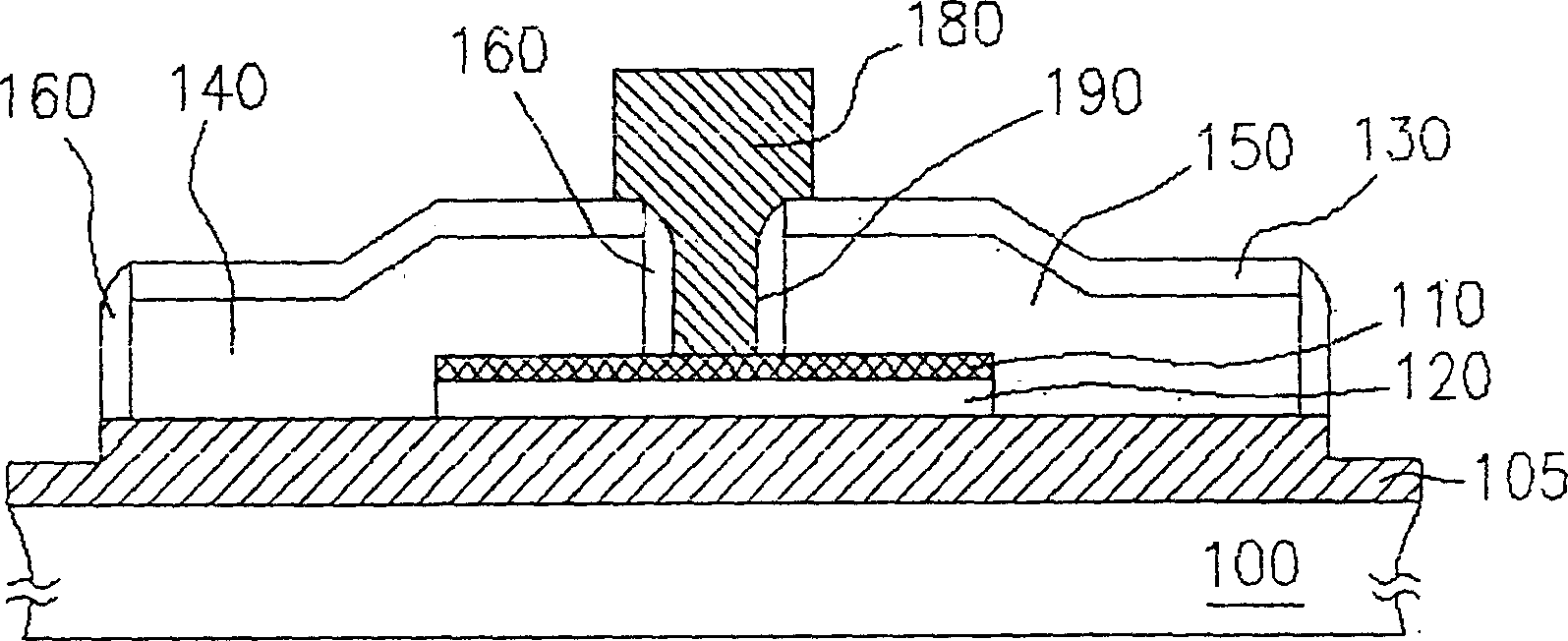

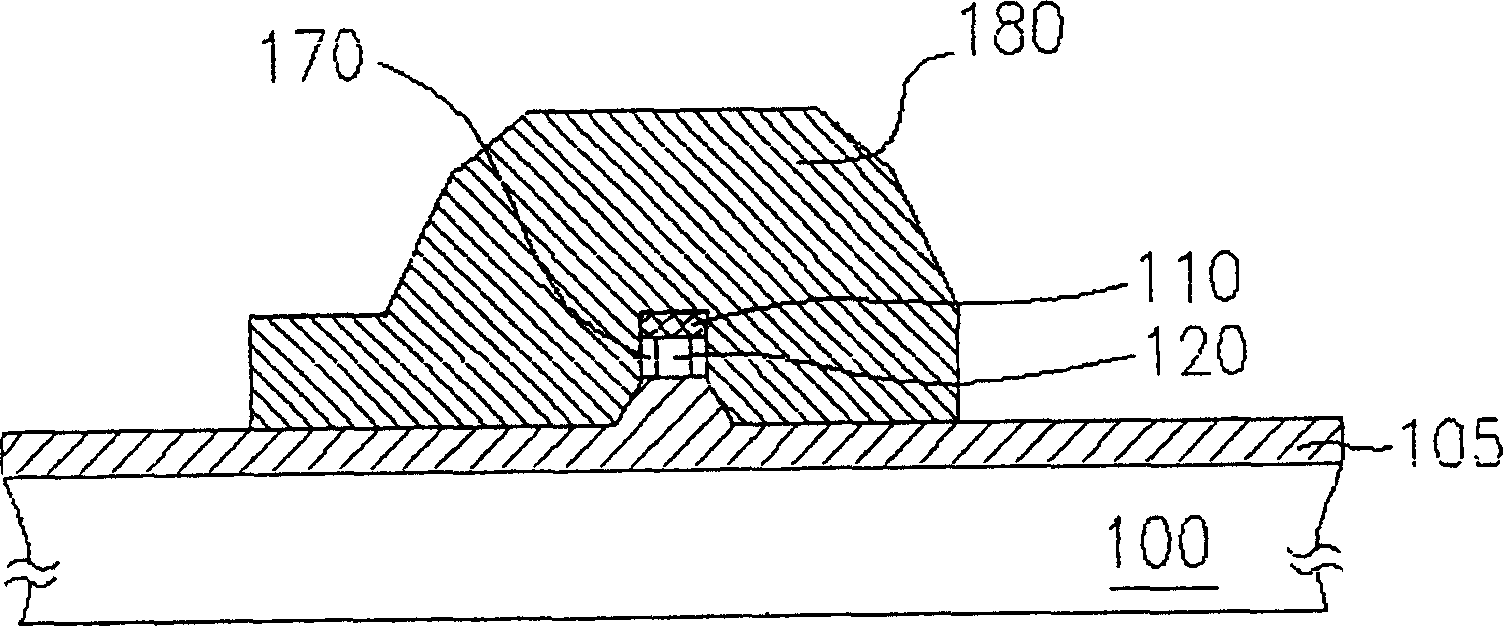

Photomask, thin film transistor element and manufacturing method of thin film transistor element

ActiveCN101598894AReduce channel lengthIncrease turn-on currentTransistorSemiconductor/solid-state device manufacturingTranslightSemiconductor

The invention provides a photomask, a thin film transistor element and a manufacturing method of the thin film transistor element. The photomask comprises a first shading pattern, a second shading pattern, a translucent single slit and a semi-translucent pattern, wherein the translucent single slit is positioned between the first shading pattern and the second shading pattern; the width of the translucent single slit is between 1.5 and 2.5 microns; and the semi-translucent pattern is connected with the first shading pattern and the second shading pattern. The photomask adopts a design of the translucent single slit and the semi-translucent pattern, wherein the translucent single slit can reduce the channel length making the thin film transistor element; and the semi-translucent pattern can define an extension part of a semiconductor layer. Therefore, the thin film transistor element has a higher starting current.

Owner:AU OPTRONICS CORP

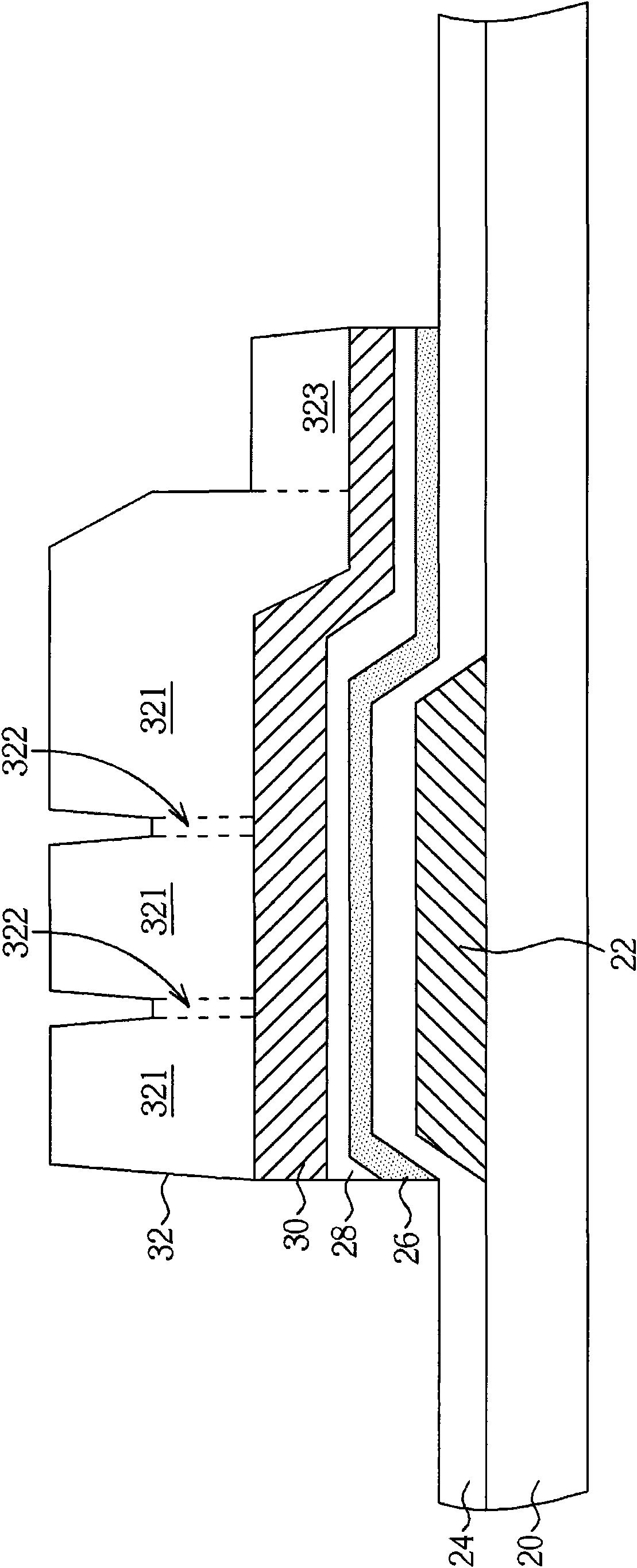

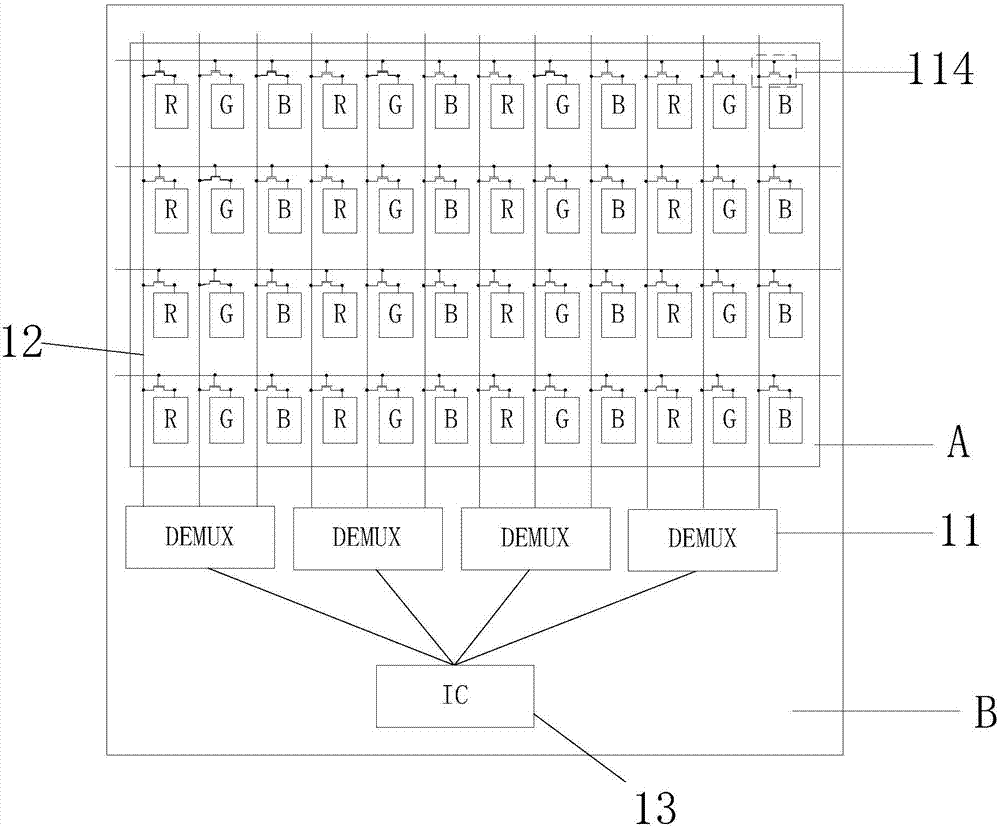

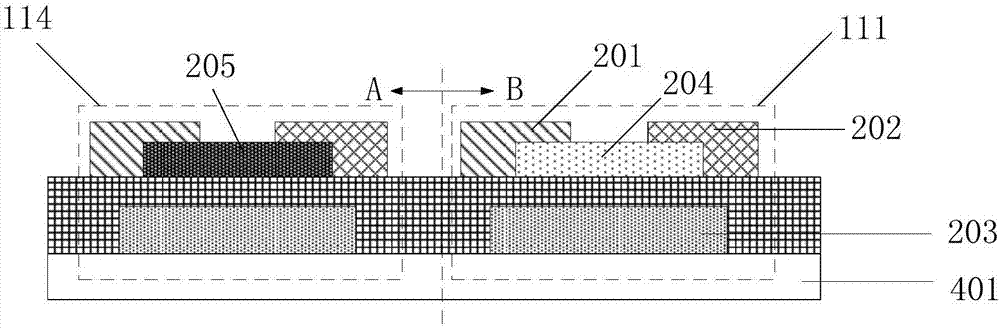

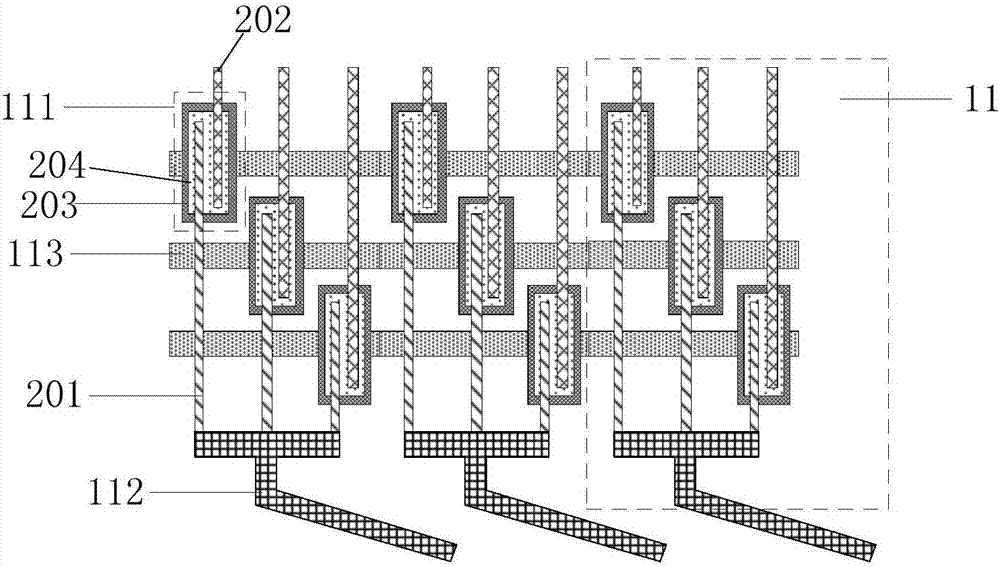

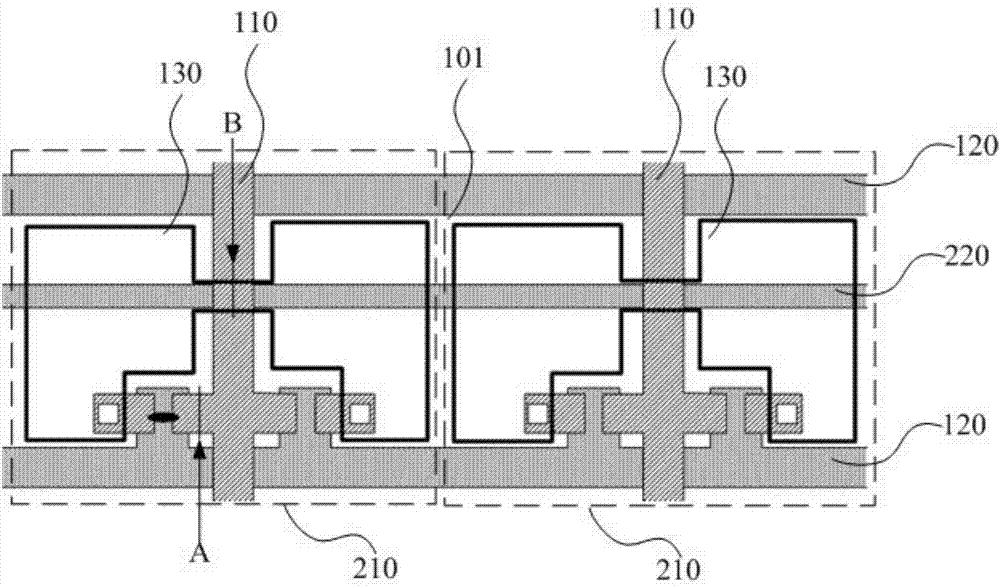

Array substrate, manufacturing method of array substrate, display panel and display device

ActiveCN107887420AIncrease turn-on currentImprove mobilitySolid-state devicesSemiconductor devicesControl signalMultiplexer

The invention discloses an array substrate, a manufacturing method of the array substrate, a display panel and a display device. The array substrate comprises multiple first thin film transistors which are arranged in a display area, wherein each first thin film transistor comprises a first active layer and the material of the first active layer includes amorphous silicon; and at least one multiplexer which is arranged in a non-display area. The multiplexer comprises multiple second thin film transistor, one input end and multiples control signal lines. The first electrode of each second thinfilm transistor is electrically connected with the input end, the second electrode of each second thin film transistor is electrically connected with different data lines in the display area, and thecontrol end of each second thin film transistor is electrically connected with different control signal lines. Each second thin film transistor comprises a second active layer, and the material of thesecond active layer includes polysilicon. The material of the second active layer includes polysilicon so that the number of leads connected with the data lines can be reduced on the basis of meetingthe signal transmission speed of the data lines and the frame can be reduced.

Owner:SHANGHAI AVIC OPTOELECTRONICS

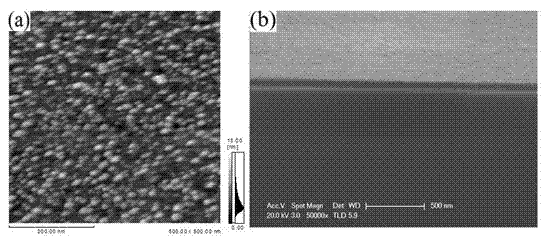

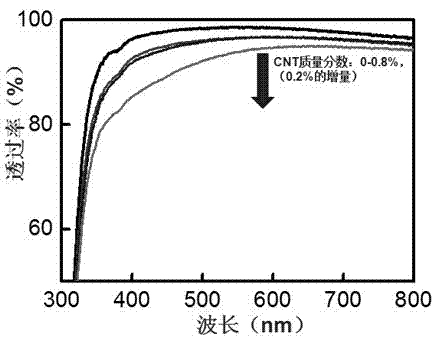

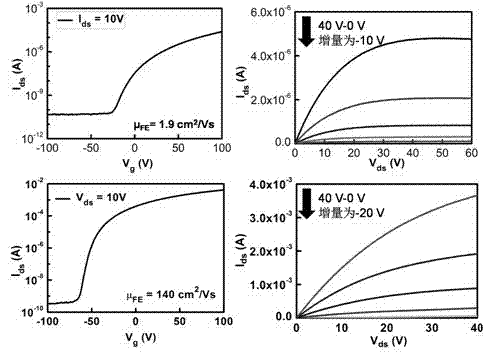

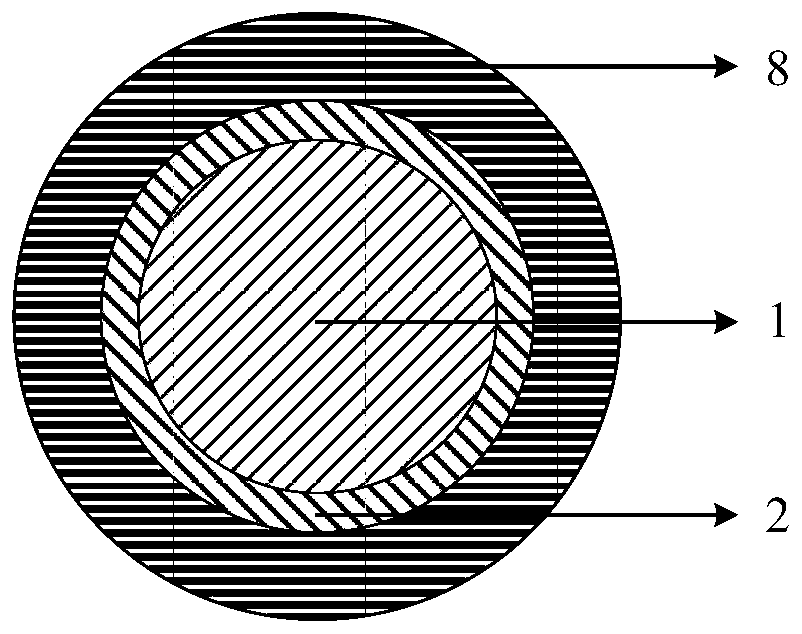

Amorphous indium zinc oxide/carbon nanotube composite film transistor and preparation method thereof

InactiveCN102394242AIncrease turn-on currentImprove mobilityTransistorSemiconductor/solid-state device manufacturingCarbon nanotubeIndium

The invention provides an amorphous indium zinc oxide / carbon nanotube composite film transistor. A flexible indium zinc oxide / carbon nanotube composite film is taken as a semiconductor channel layer. In the composite film, a mass ratio of the carbon nanotube to the indium zinc oxide is between 0.027% and 2.74%. The carbon nanotube is added into an indium salt-zinc salt composite colloid solution so as to prepare a carbon nanotube / indium salt-zinc salt composite colloid solution. A spin coating technology is used to prepare the indium zinc oxide / carbon nanotube composite film with high performance. And then through subsequent thermal annealing, photoetching, etching, photoetching, evaporation and stripping of an electrode, an indium zinc oxide / carbon nanotube composite film field effect transistor with high mobility can be prepared. Through optimizing some technologies, the indium zinc oxide / carbon nanotube with the high field effect and the mobility can be successfully prepared and the indium zinc oxide / carbon nanotube possesses a high mechanical property. Experimental costs are low. A requirement to an experiment condition is low. Repeatability of an experiment result is high. Large-scale batch production can be realized.

Owner:WUHAN UNIV

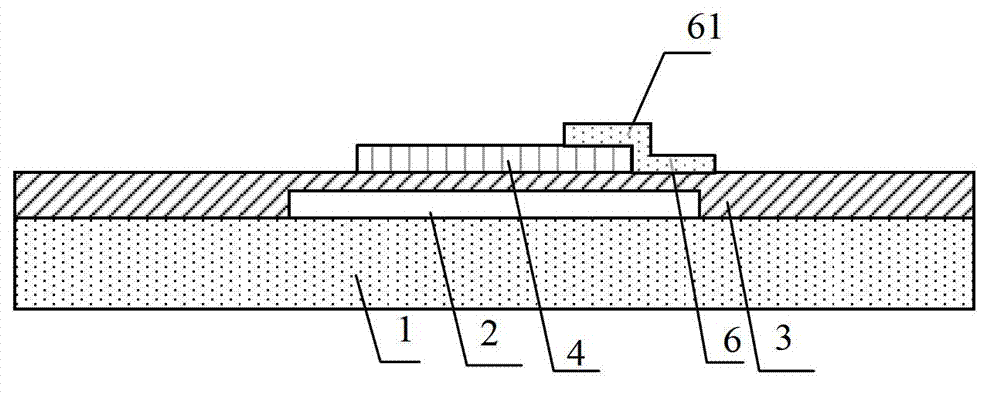

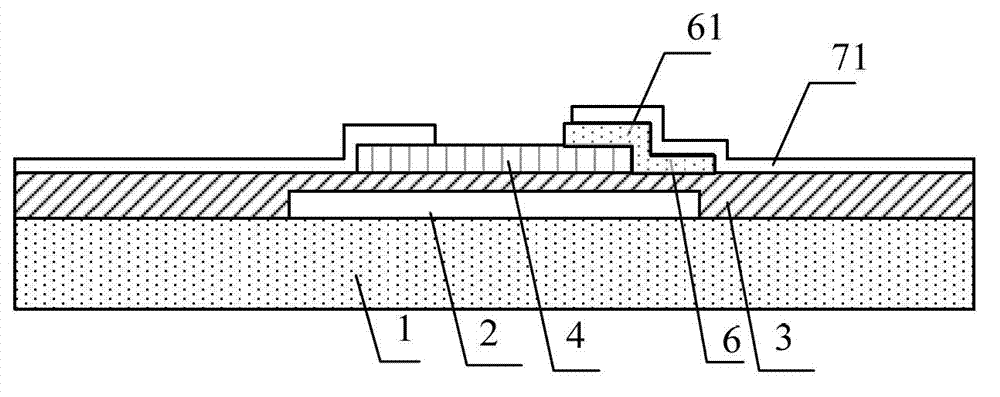

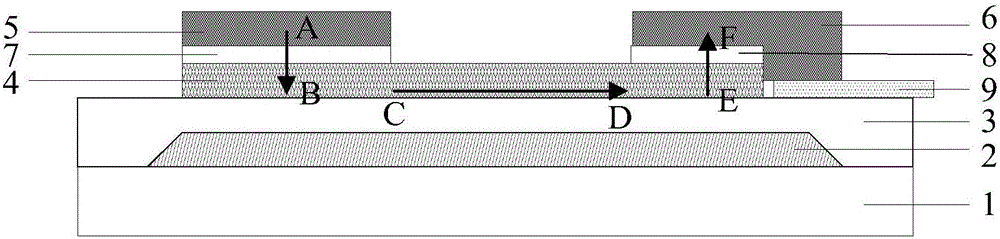

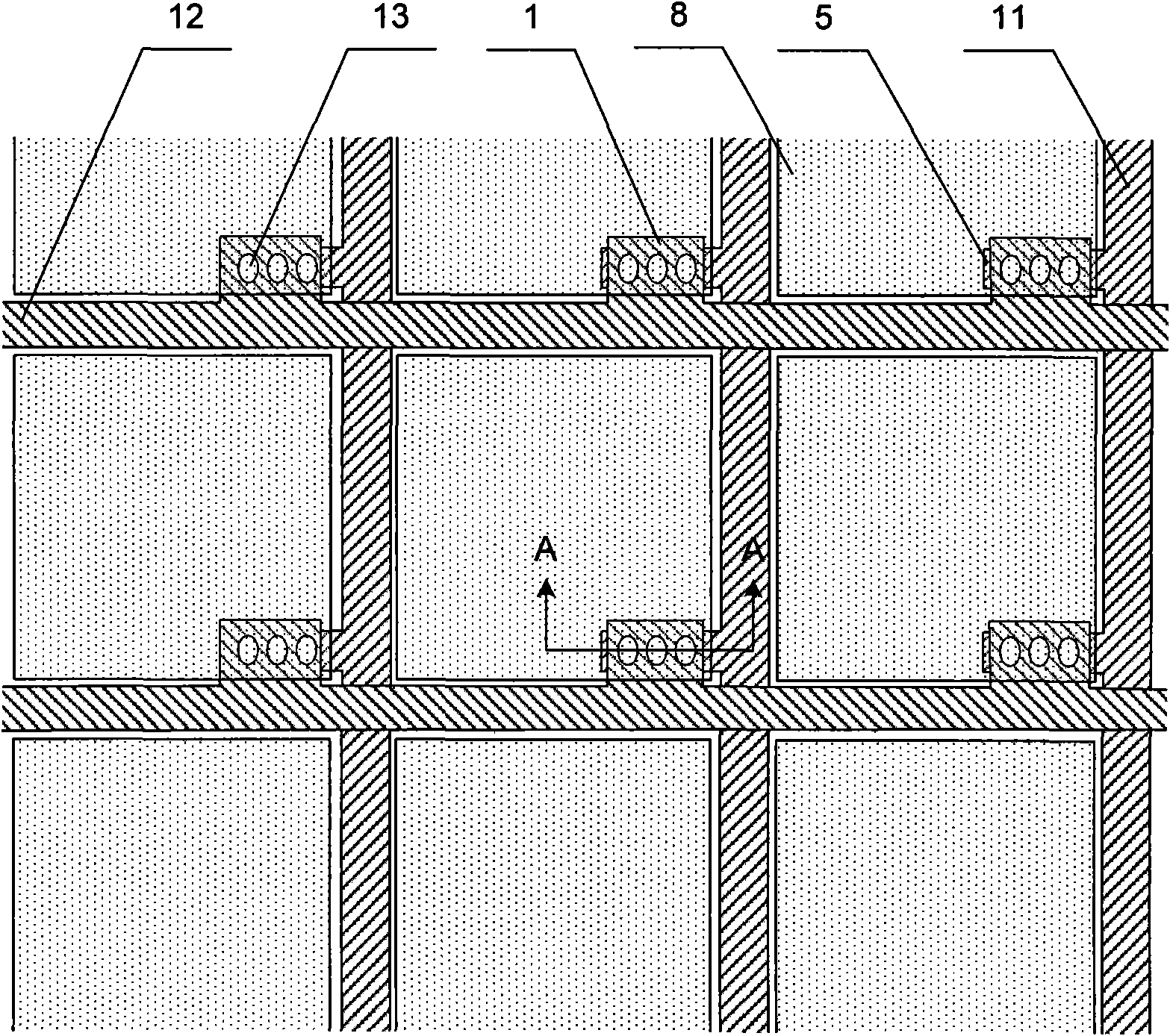

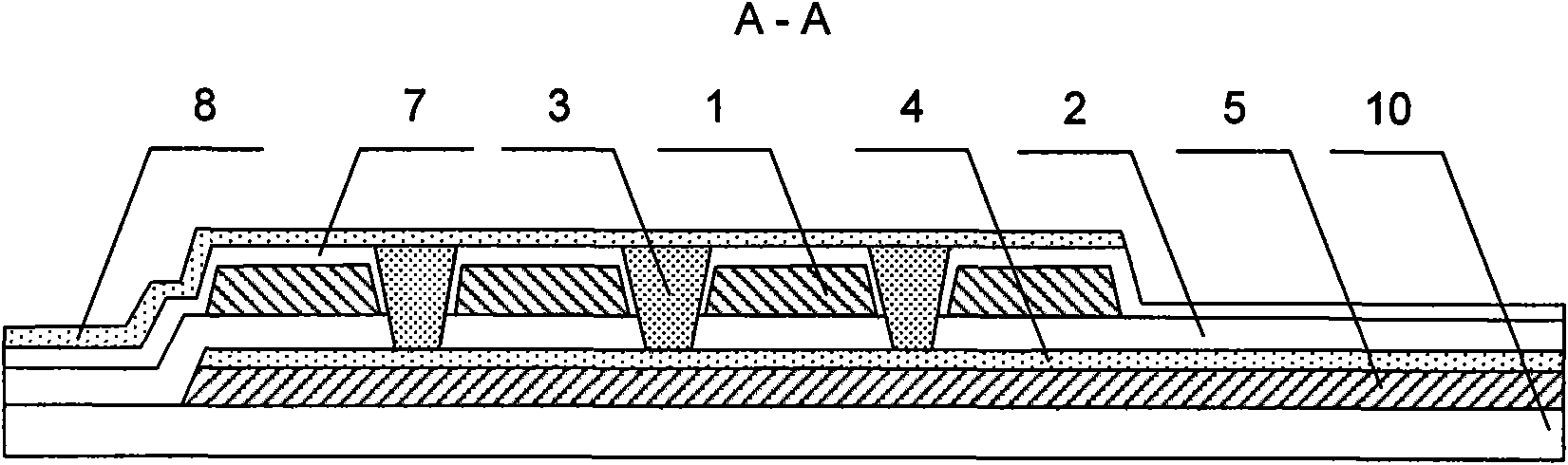

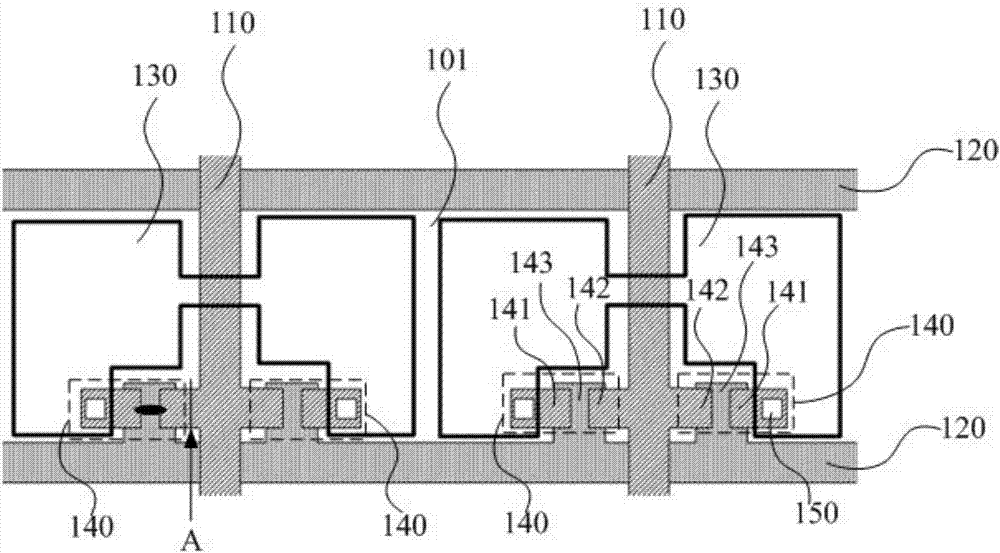

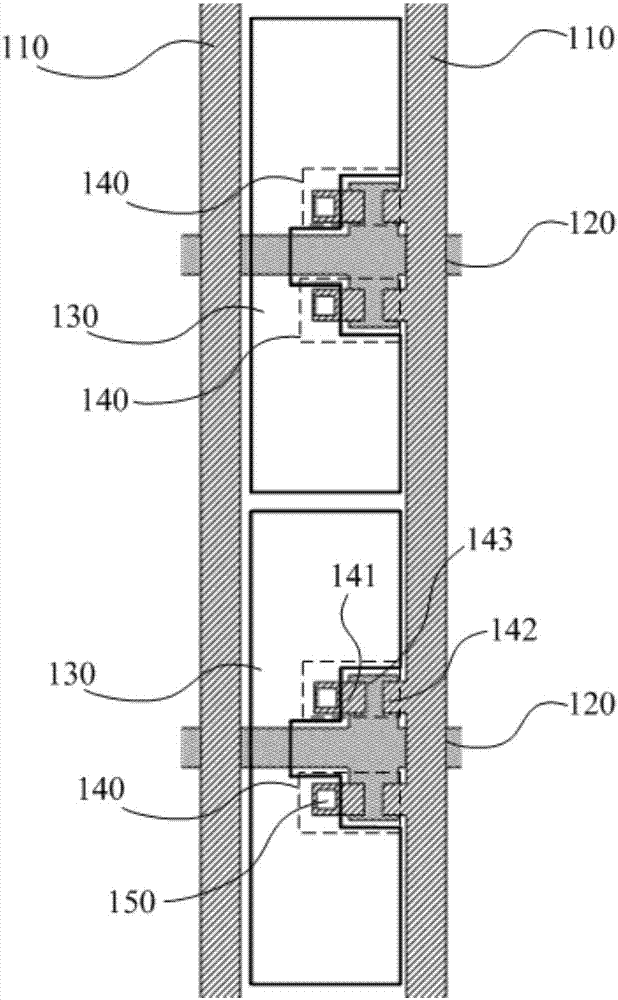

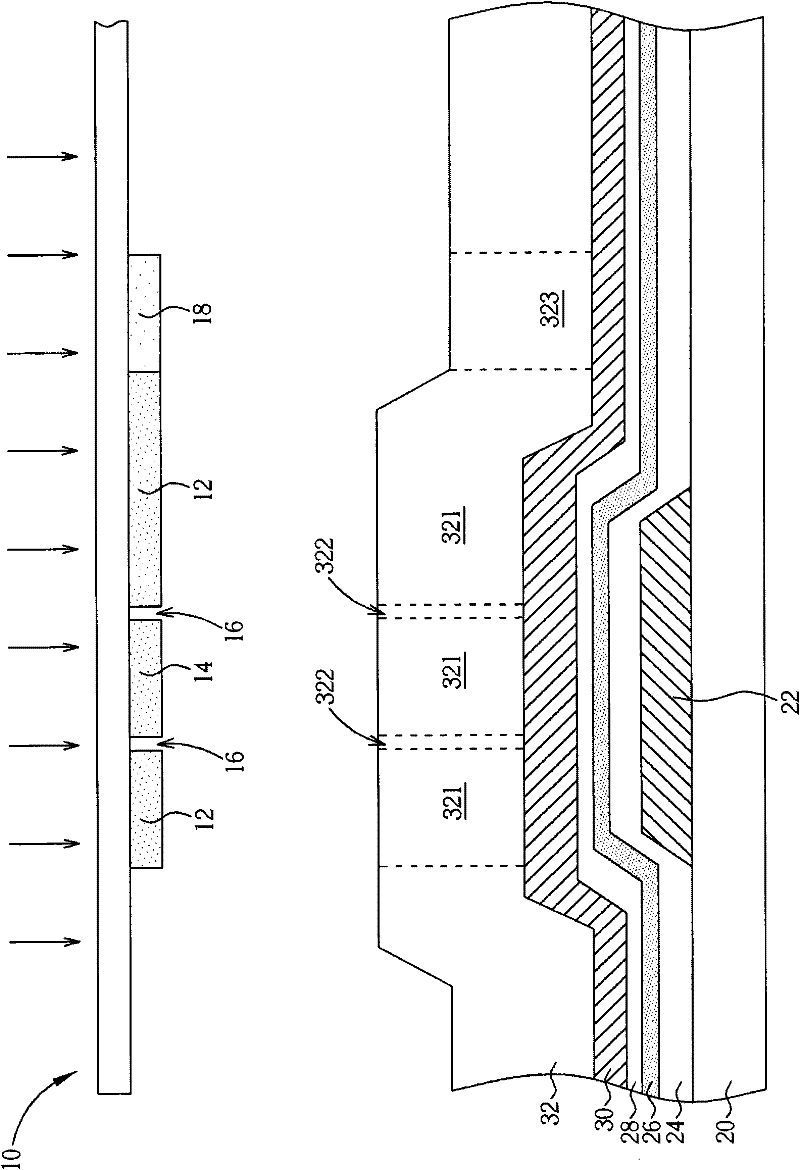

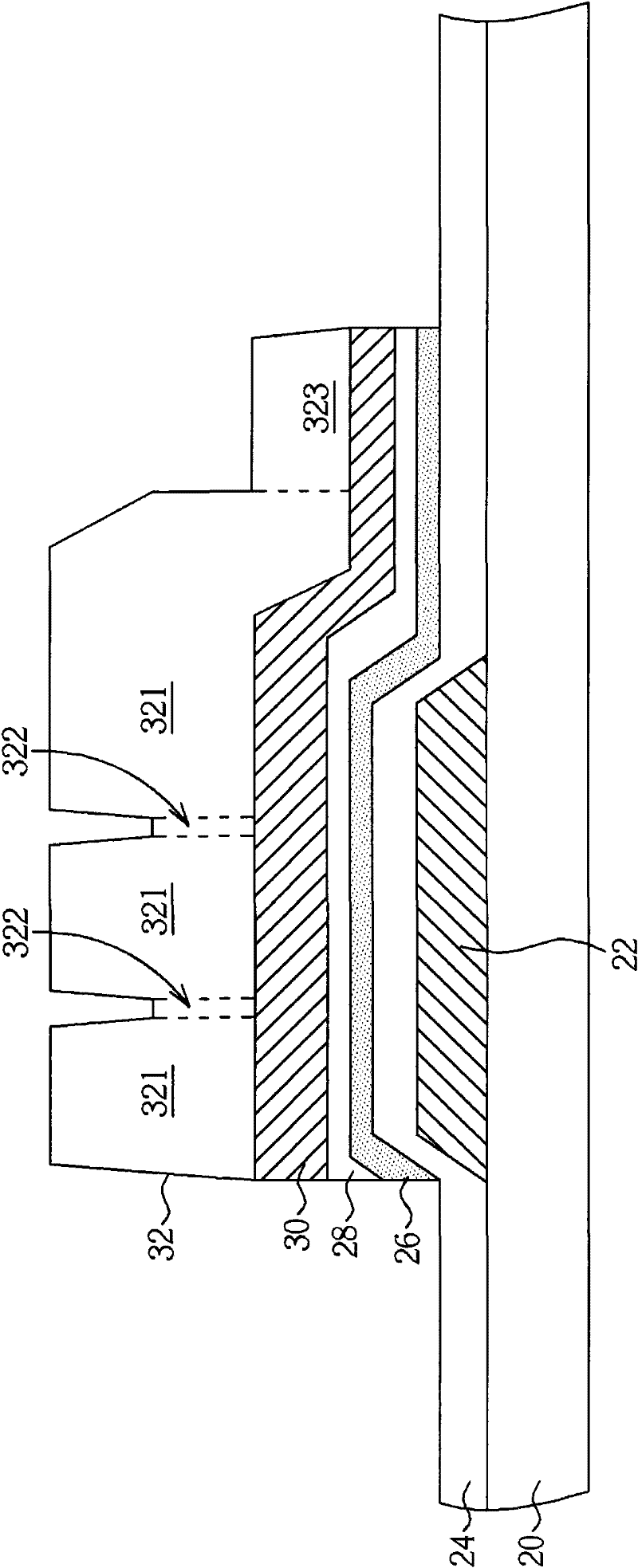

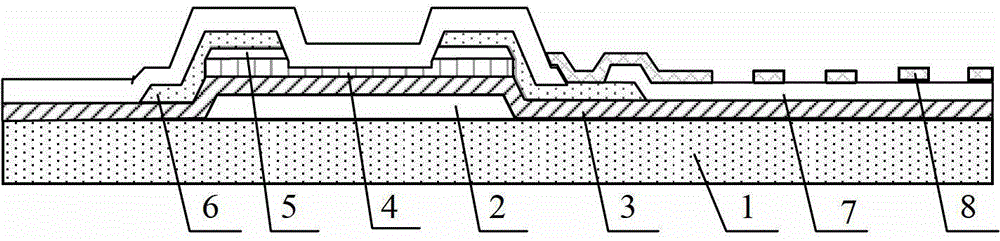

Array substrate, manufacture method of array substrate, liquid crystal display panel and display device

InactiveCN103048840AReduce channel lengthIncrease turn-on currentSemiconductor/solid-state device manufacturingNon-linear opticsIonLiquid-crystal display

The invention provides an array substrate, a manufacture method of the array substrate, a liquid crystal display panel and a display device, and belongs to the field of liquid crystal display. A source electrode and a drain electrode of the array substrate are located at different layers. In the manufacture method of the array substrate, the source electrode and the drain electrode located at different layers are respectively formed through twice picture composition processes. By adopting the array substrate, the manufacture method of the array substrate, the liquid crystal display panel and the display device, the channel length between the source electrode and the drain electrode can be reduced as far as possible, and further starting current Ion of thin film transistors (TFTs) is greatly improved.

Owner:BOE TECH GRP CO LTD

Thin film transistor, display substrate and liquid crystal display device

InactiveCN106024906AIncrease turn-on currentUniform distribution of electrons and holesTransistorSolid-state devicesLiquid-crystal displayEngineering

The present application provides a thin film transistor, a display substrate and a liquid crystal display device, so as to increase the turn-on current of the thin film transistor and reduce the turn-off current of the thin film transistor. The thin film transistor provided by the present application includes: a gate electrode, a gate insulating layer, and an active layer arranged on the substrate in sequence, and also includes: a source electrode arranged on the active layer, and an electrode arranged on the The drain between the gate insulating layer and the active layer.

Owner:BOE TECH GRP CO LTD +1

TFT-LCD array substrate and manufacturing method thereof

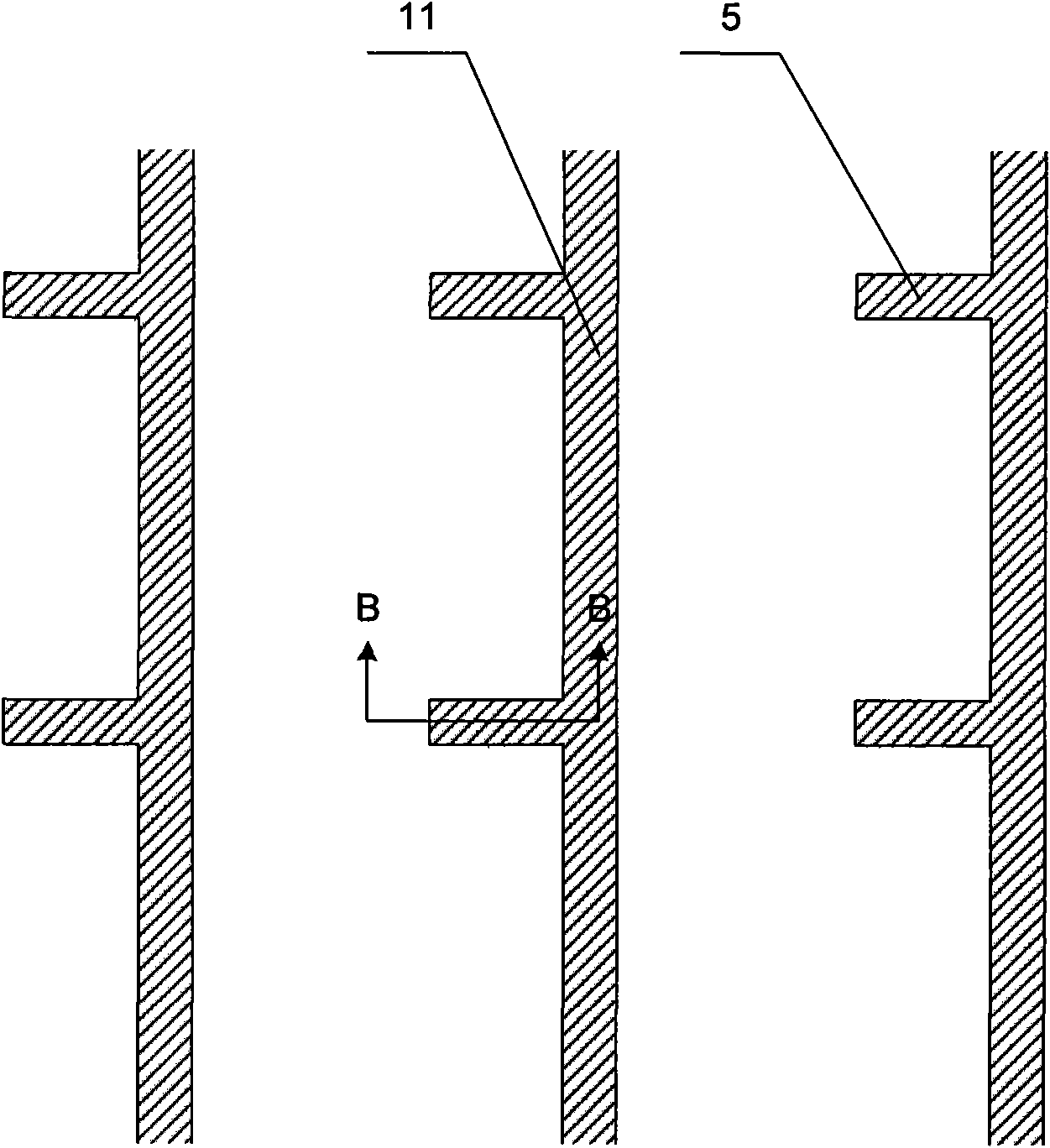

InactiveCN101620350AReduce electrical influenceExcellent electrical propertiesTransistorSolid-state devicesSpatial structureEngineering

The invention relates to a TFT-LCD array substrate and a manufacturing method thereof. The array substrate comprises a grid wire, a data wire, a pixel electrode and a thin film transistor. The array substrate is characterized in that the thin film transistor comprises a grid electrode connected with the grid wire and a source electrode connected with the data wire; at least one through hole is formed on the grid electrode or a through groove is formed on at least one side of the grid electrode; and a semiconductor layer which is connected with the pixel electrode and the source electrode respectively is filled in the through hole or the through groove. The array substrate changes a 'planar type' TFT structure which is universally adopted in the prior art, changes the planar structure into a spatial structure, and has the characteristics of simple and compact structure, good parameter property, simple manufacturing process and the like. The array substrate realizes the effect of increasing the starting current and has certain improvement on other electrical parameters, and the spatial structure of the array substrate reduces the planar size and increases the spatial utilization rate so as to increase the opening ratio.

Owner:BOE TECH GRP CO LTD +1

Semiconductor devices and methods of manufacturing the same

ActiveUS8883651B2Improve methodImprove reliabilityTransistorSemiconductor/solid-state device manufacturingDevice materialEngineering

Owner:SAMSUNG ELECTRONICS CO LTD

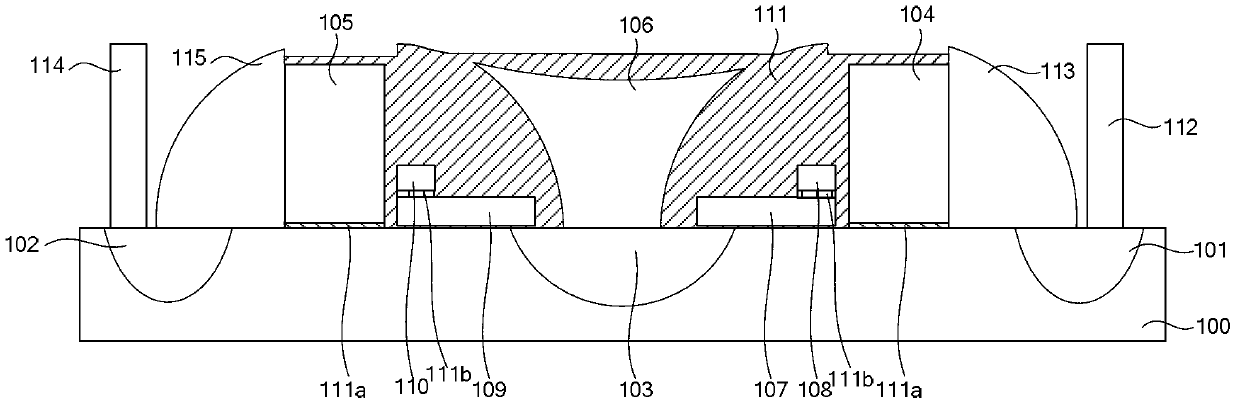

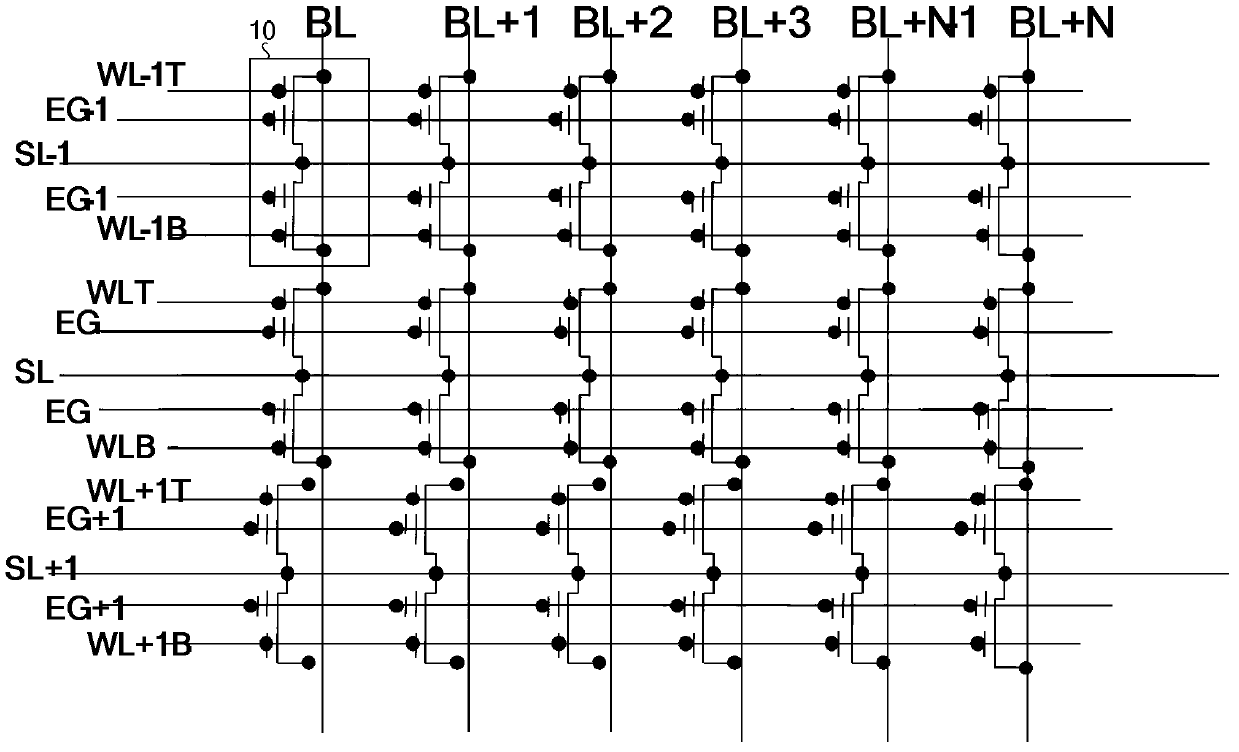

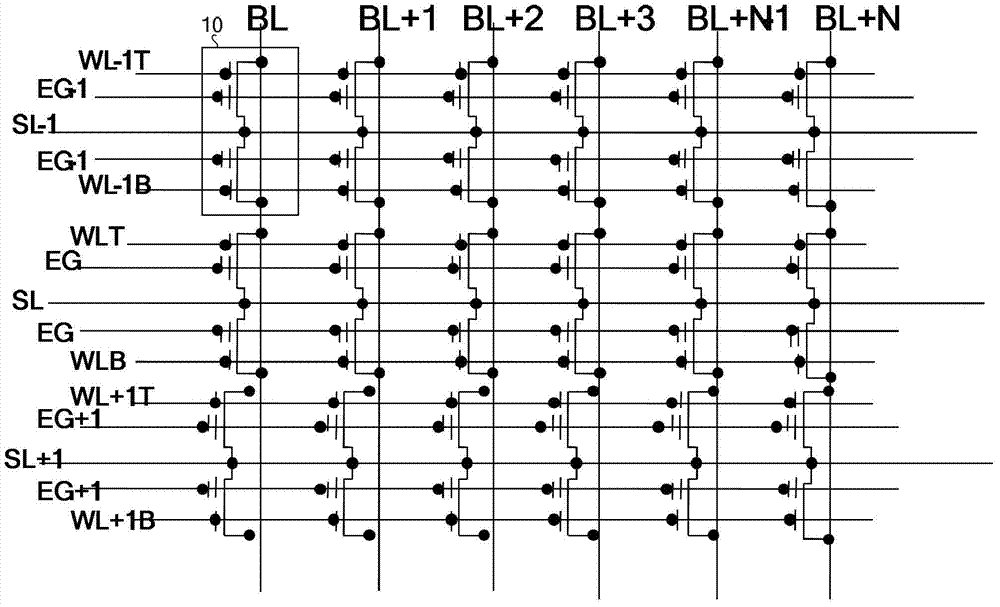

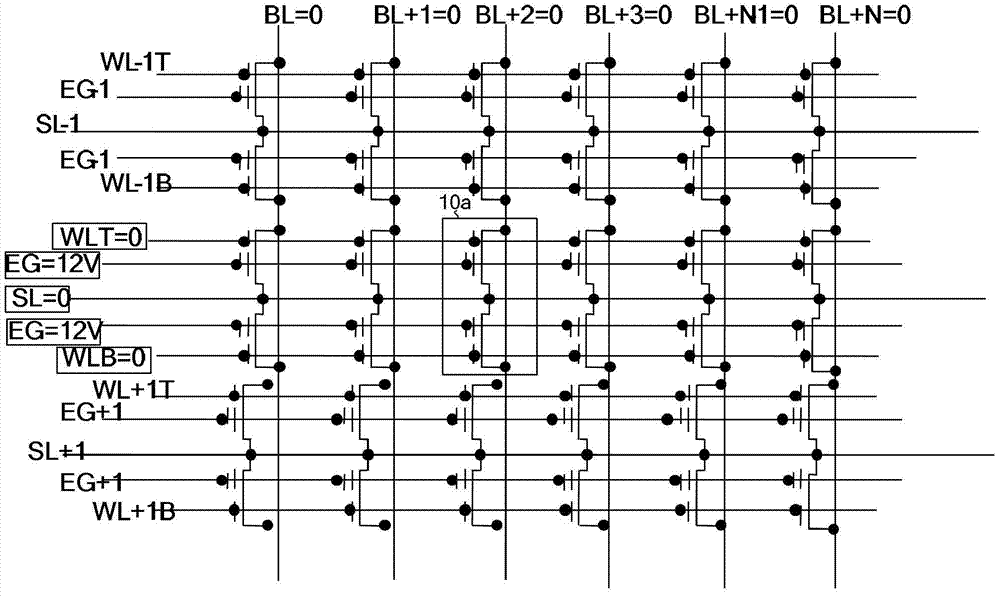

Semiconductor memory

ActiveCN102983139AIncrease turn-on currentReduce leakage currentTransistorSolid-state devicesBit planeVoltage

The invention provides a semiconductor memory. The semiconductor memory is not provided with a control grid, wherein as a first erasure grid and a second erasure grid are respectively arranged on a first floating grid and a second floating grid, the semiconductor memory can directly conduct the erasure operation through the first erasure grid and the second erasure grid in the erasure stage, a higher erasure pressure does not need to be applied to a first bit line or a second bit line, therefore, the thickness of a word line oxidizing medium layer between the bit line and a semiconductor substrate can be reduced, the firing current is improved, the leak current can also be reduced at the same time, a lower closing current is kept, meanwhile, the reading current of the bit line is reduced during reading, so that the power consumption of the semiconductor memory is saved.

Owner:SHANGHAI HUAHONG GRACE SEMICON MFG CORP

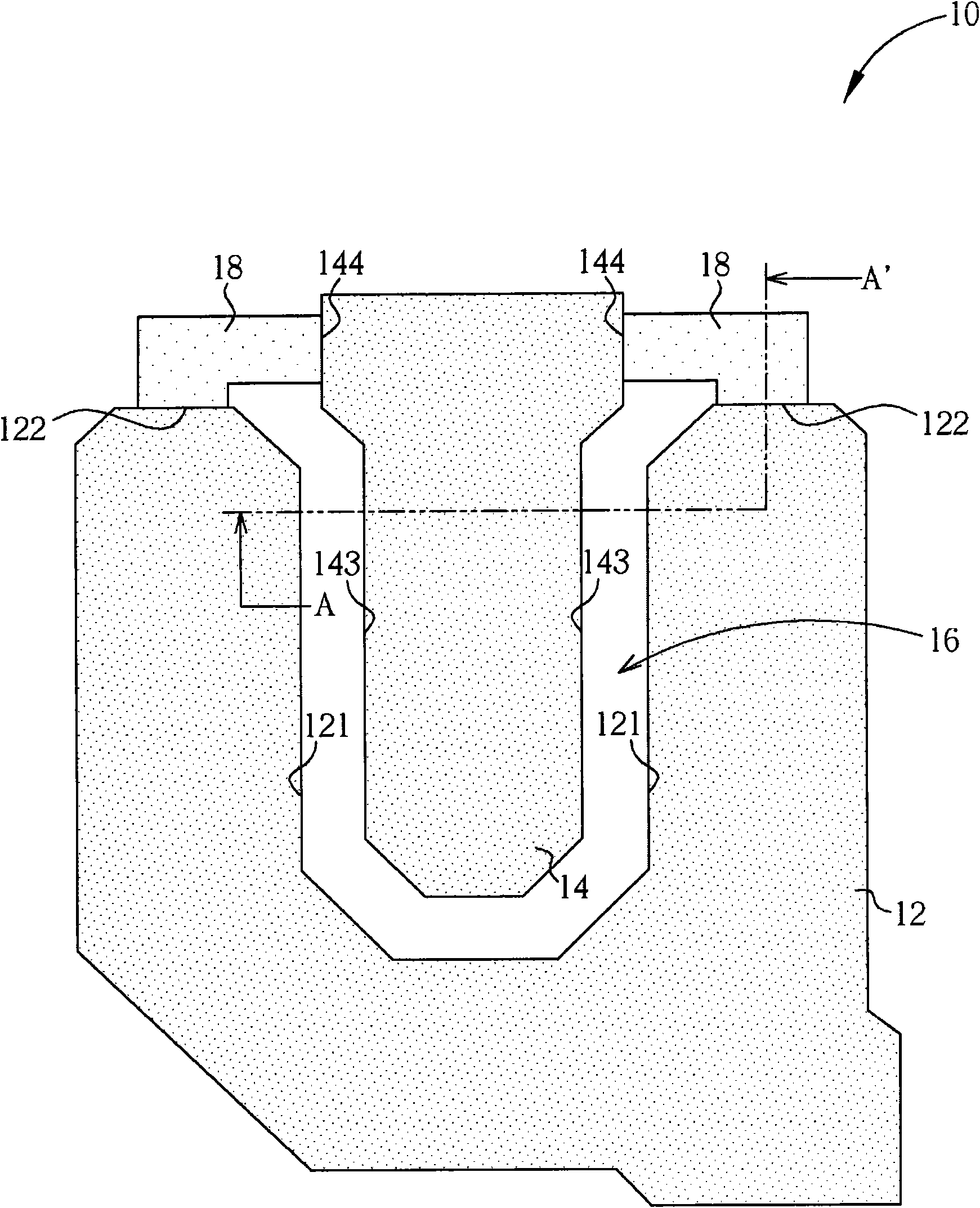

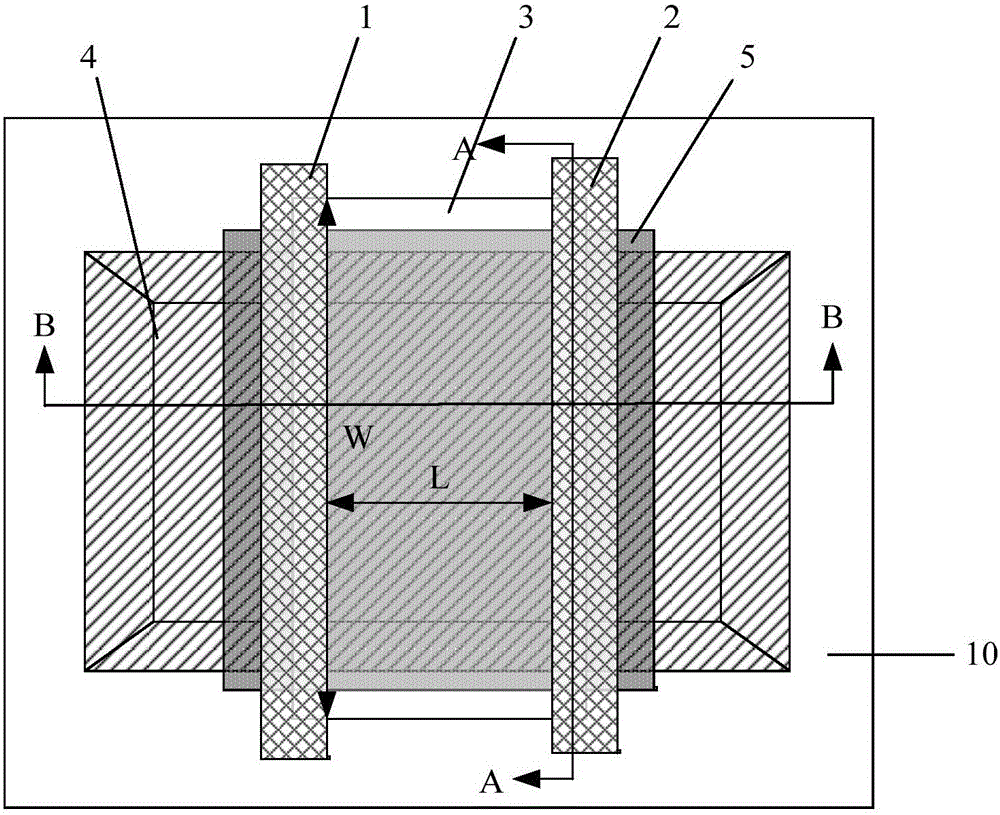

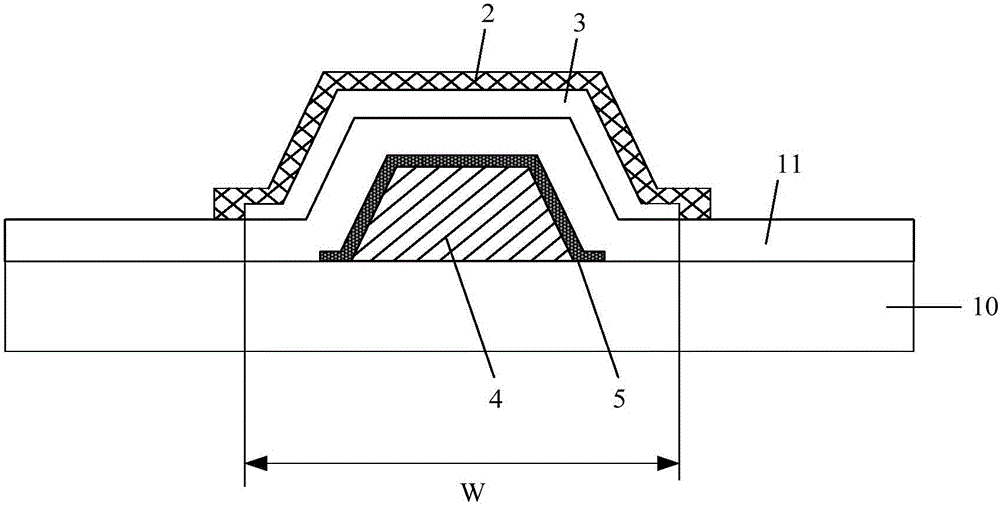

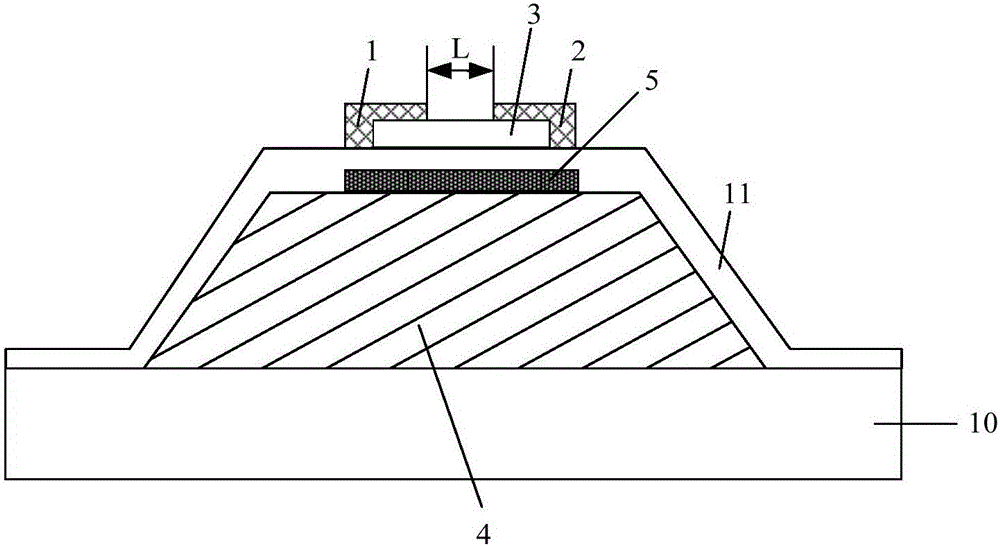

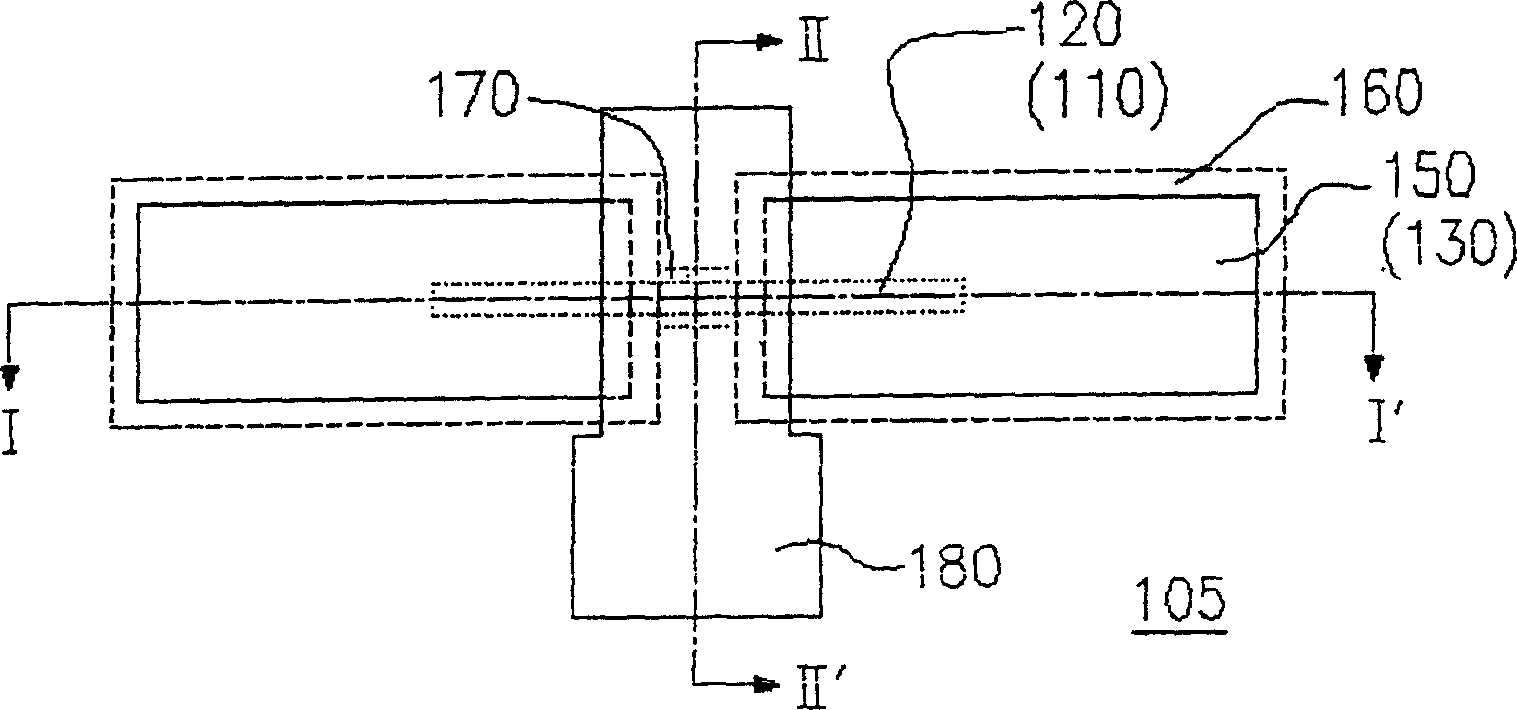

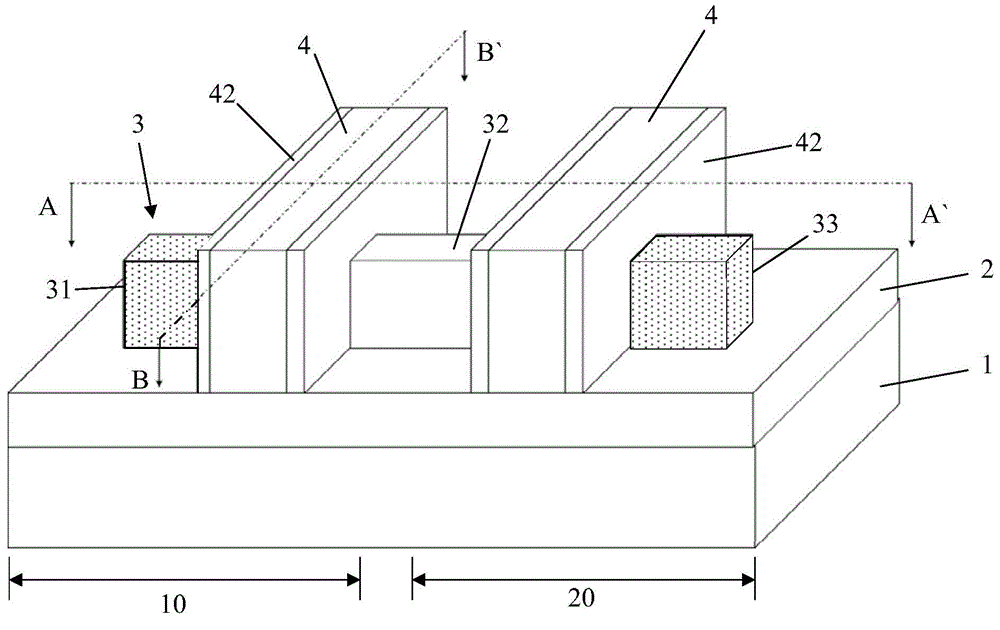

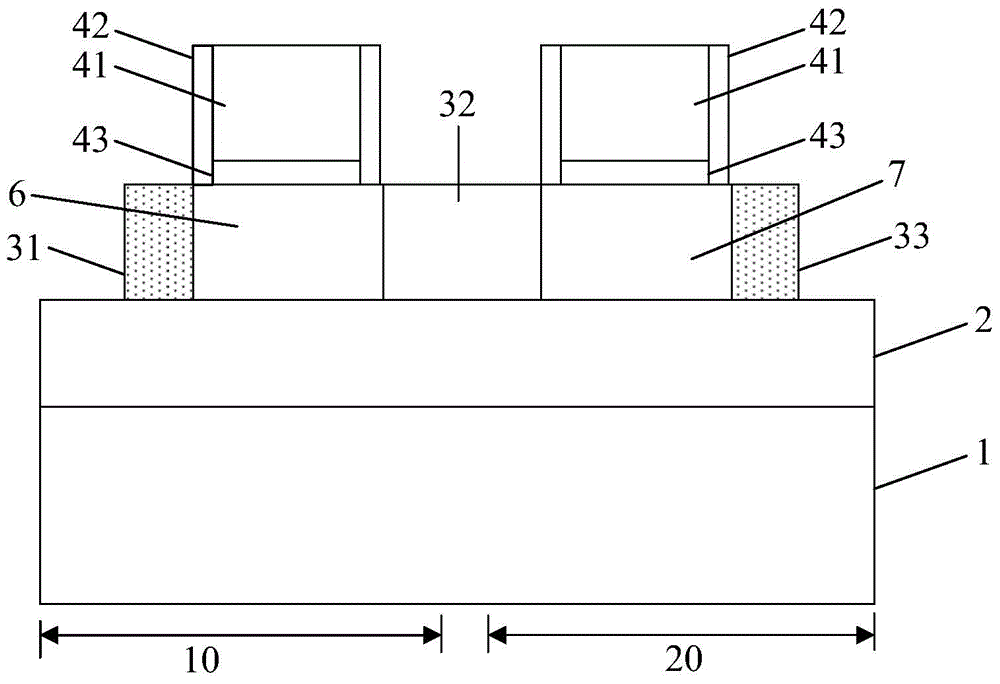

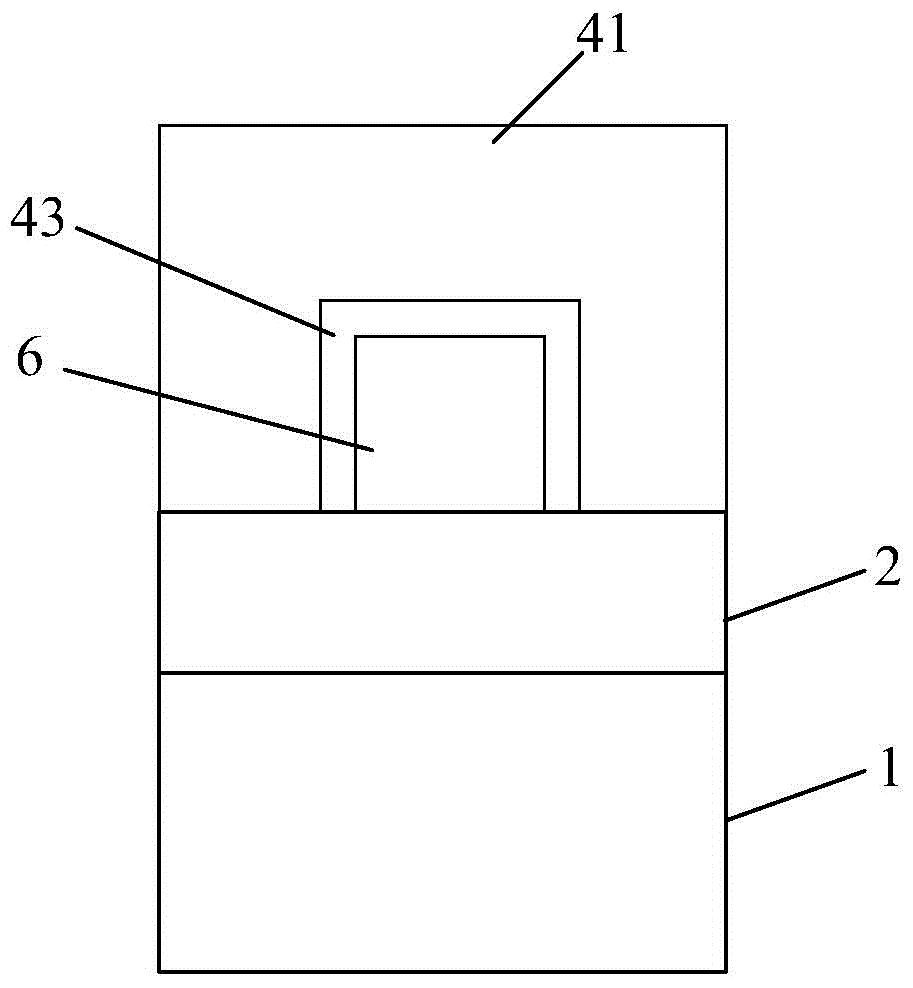

Asymmetric reconfigurable field effect transistor

ActiveCN110164958AReduced switching delay timeIncrease clock frequencySolid-state devicesSemiconductor/solid-state device manufacturingNanowireField-effect transistor

The invention discloses an asymmetric reconfigurable field effect transistor. The transistor includes a trench; a drain electrode arranged at one end of the trench; a source electrode which is arranged at the other end of the trench and extends into the trench; gate oxide which is arranged at the outer side of the channel; a control grid electrode and a polar grid electrode which are respectivelyarranged at the source electrode end and the drain electrode end and outside the grid electrode oxide; side walls which are respectively arranged outside the two ends of the trench and used for electrically isolating the control grid electrode, the polar grid electrode, the source electrode and the drain electrode; and the grid isolation part which is arranged outside the grid electrode oxide andused for isolating the control grid electrode from the polar grid electrode. The contact area between the source end extending into the trench and a nanowire trench is larger, the tunneling area of carriers is increased, and the starting current is increased. In a switching-off state, a drain electrode structure and a common RFET drain electrode structure have the same non-overlapping area, and aleakage current is basically kept unchanged, so that the current switch ratio is improved, and the operation delay time of a logic gate current is shortened under the condition that the static power consumption is not changed.

Owner:EAST CHINA NORMAL UNIV +1

Thin film transistor, array substrate and display device

ActiveCN105097895AImprove performanceSmall sizeTransistorSolid-state devicesLiquid-crystal displayImage resolution

The invention relates to the technical field of liquid crystal display, and discloses a thin film transistor, an array substrate and a display device. The thin film transistor is arranged on a substrate base plate; in the direction vertical to the surface of the substrate base plate, the broadside outline of a channel of the thin film transistor comprises a curved section which changes up and down in a curved line, so that the width-to-length ratio of the channel can be increased under the condition that the projection area of the thin film transistor on the substrate base plate is fixed; the firing current of the thin film transistor is increased; and the performance of the thin film transistor is improved. Meanwhile, the performance of the thin film transistor can be ensured; the size of the thin film transistor is reduced; the resolution ratio of the display device is increased; and the display quality is ensured.

Owner:BOE TECH GRP CO LTD

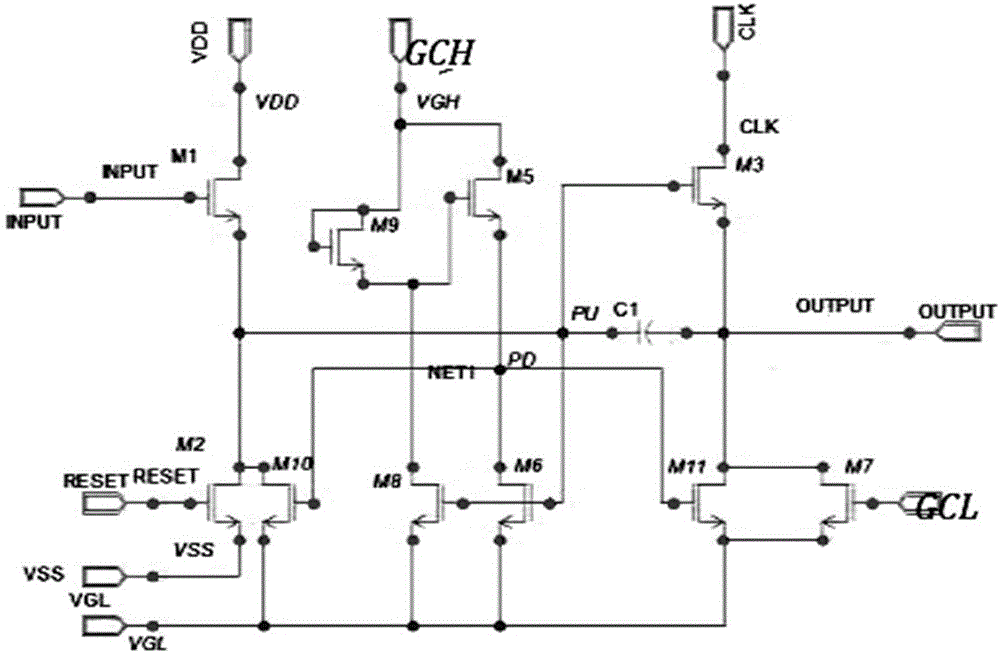

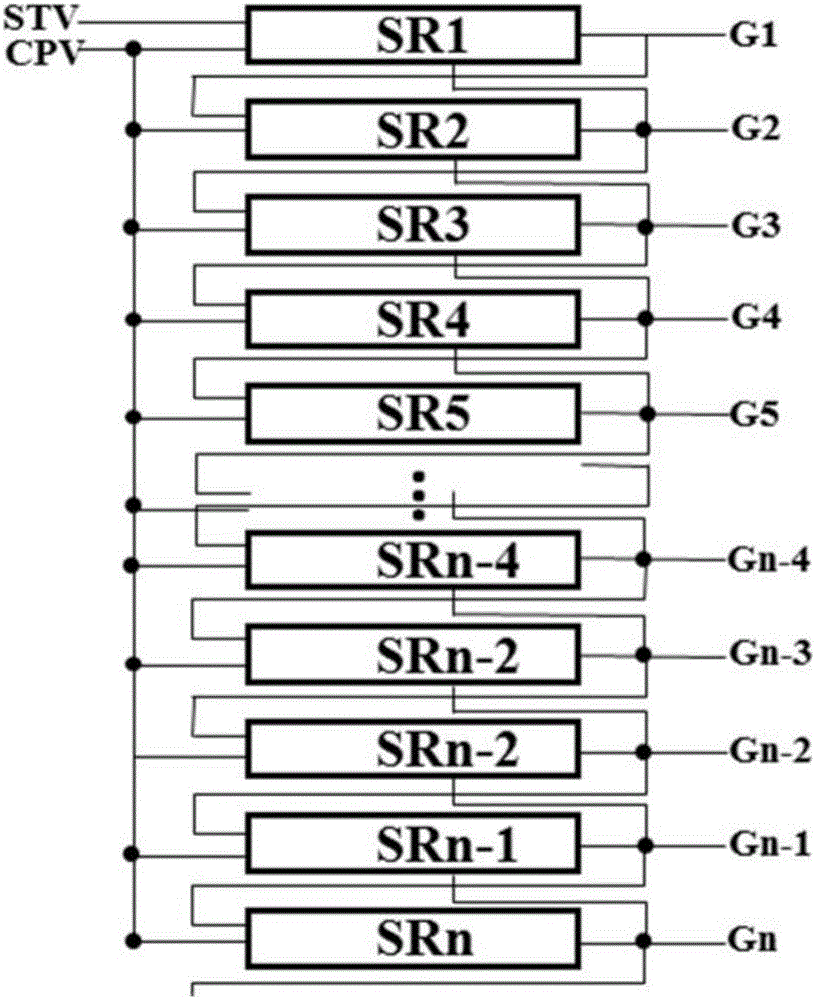

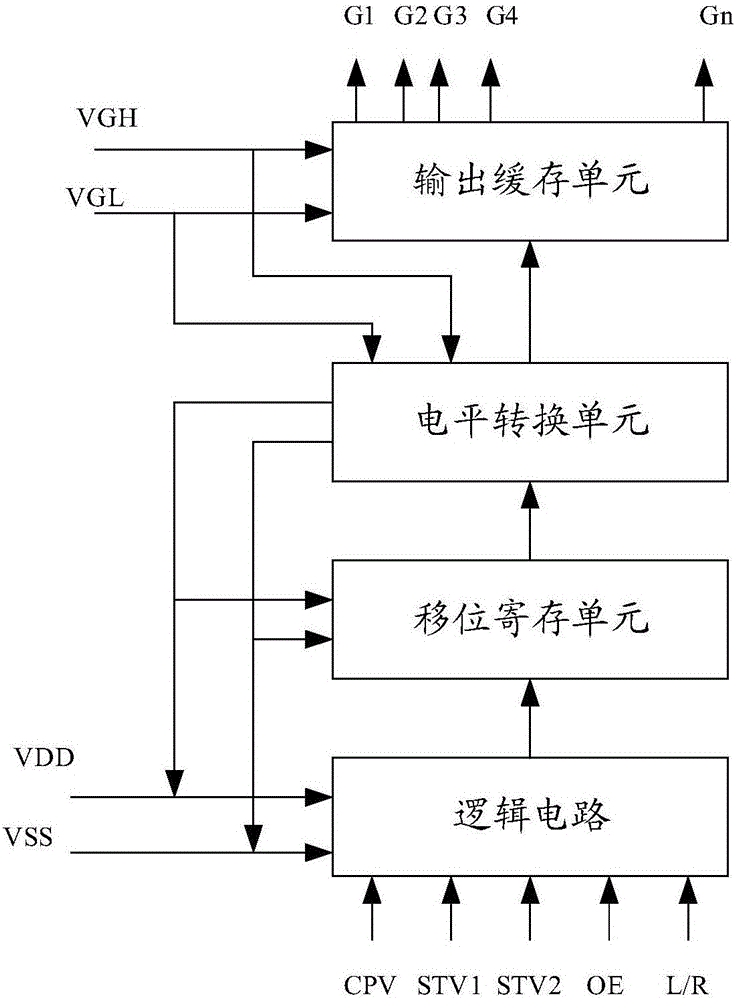

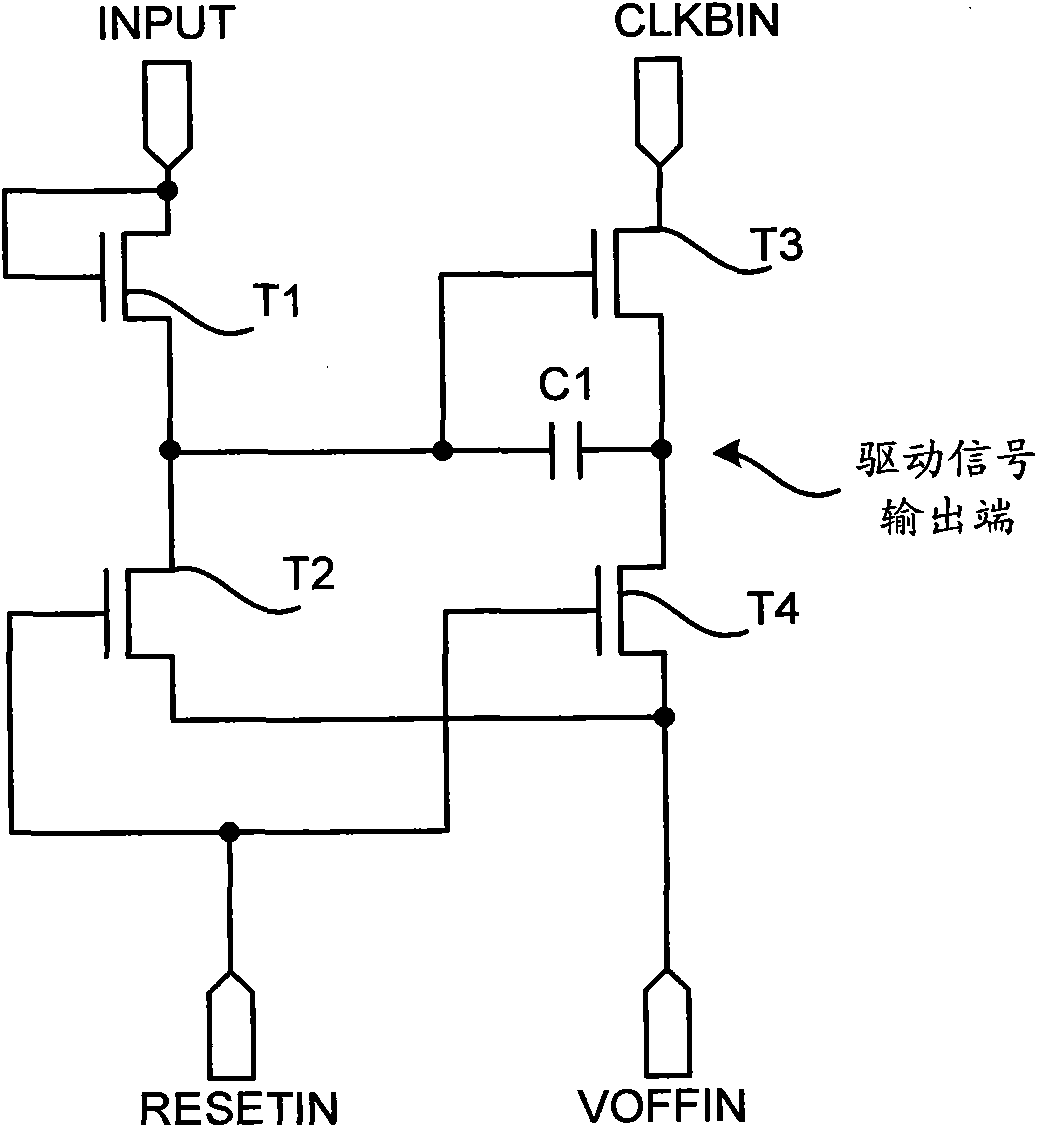

Display driving device and method, shifting register and display device

InactiveCN106710567AAvoid bad alignment problemsIncrease turn-on currentStatic indicating devicesDigital storageTime scheduleHigh pressure

The invention discloses a display driving device and method, a shifting register and a display device. The display driving device comprises a time schedule controller and the shifting register, wherein the shifting register comprises a logical control unit and a power switching unit which are connected with each other; the power switching unit is configured with more than one group of high-voltage driving clock signals; the logical control unit is used for controlling the power switching unit to select and output one group of the more than one group of high-voltage driving clock signals according to a sub-pixel line position displayed by a current driver and / or current temperature information provided by the time schedule controller to serve as the high-voltage driving clock signal of the shifting register. By adopting the display driving device and method, the shifting register and the display device in the embodiment of the invention, proper high-voltage driving clock signals can be selected specific to different conditions, and the problem of defective grating line caused by insufficient charging is solved.

Owner:BOE TECH GRP CO LTD +1

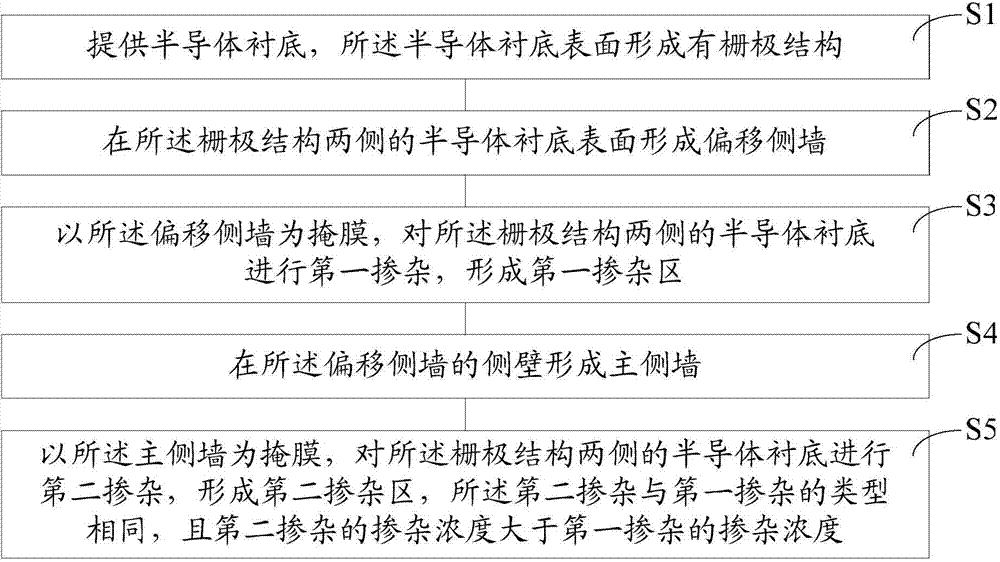

Semiconductor device and forming method thereof

ActiveCN104752205AReduce leakage currentIncrease channel lengthSemiconductor/solid-state device manufacturingSemiconductor devicesElectrical performanceSemiconductor

A semiconductor device and a forming method thereof are provided. The forming method of the semiconductor device comprises the following steps: providing a semiconductor substrate; performing first doping on the semiconductor substrate to form a first doped region; forming a patterned mask layer on the surface of the semiconductor substrate, wherein the patterned mask layer has an opening which exposes the surface of the semiconductor substrate; etching part of the semiconductor substrate in the thickness direction with the patterned mask layer as a mask to form a groove in the semiconductor substrate; and performing second doping on the semiconductor substrate to form a second doped region, wherein the first doping and the second doping are of the same doping type, the doping concentration of the second doping is greater than the doping concentration of the first doping, and the second doped region and the first doped region are connected. By adopting the method of the invention, the opening current of the semiconductor device is increased, the leakage current is reduced, and the electrical performance of the semiconductor device is improved.

Owner:SEMICON MFG INT (SHANGHAI) CORP

Array substrate and liquid crystal display device

InactiveCN107272293AAdjust the intensityControl deflectionStatic indicating devicesNon-linear opticsLiquid-crystal displayTransistor

The invention discloses an array substrate and a liquid crystal display device. The array substrate comprises multiple parallel data cables and multiple scanning lines which perpendicularly insect with the data cables, and the data cables and the scanning lines are insulated at the junction; the array substrate further comprises pixel electrodes, and each pixel electrode is driven by n thin film transistors which share the same data cable and the same scanning line, wherein n is a positive integer larger than or equal to 2. The liquid crystal display device comprises the array substrate. According to the array substrate and the liquid crystal display device, compared with the prior art, the technical problem that pixel electrodes of an existing array substrate are low in charging efficiency is solved.

Owner:BOE TECH GRP CO LTD +1

Method for manufacturing metal oxide semiconductor field effect transistor and device thereof

ActiveCN101593703AReduce channel lengthIncrease turn-on currentSemiconductor/solid-state device manufacturingSemiconductor devicesElectrical conductorDevice form

The invention discloses a method for manufacturing a metal oxide semiconductor field effect transistor and a device thereof. The manufacturing method comprises the following steps: providing a semiconductor substrate; forming an insulating layer on the surface of the semiconductor substrate; forming a groove on the insulating layer; forming light dope drain regions in the semiconductor substrate below the lateral wall of the groove respectively; forming grid flank walls on the lateral wall of the groove respectively; forming grid dielectric layers on the groove surfaces between the grid flank walls; forming grids in an accommodating space encircled by the grid flank walls and the grid dielectric layers; removing the insulating layer; and forming a source region and a drain region respectively in the semiconductor substrates on two sides of the grid flank walls. The manufacturing method breaks through the limitation of the minimum grid length which can be achieved by a photoetching device, and reduces the length of a channel formed between the source region and the drain region; and the device formed according to the method is helpful for enhancing the firing current and reducing the electric leakage caused by short-channel effect.

Owner:SHANGHAI HUAHONG GRACE SEMICON MFG CORP

Photomask, thin film transistor element and manufacturing method of thin film transistor element

ActiveCN101598894BReduce channel lengthIncrease turn-on currentTransistorSemiconductor/solid-state device manufacturingTranslightSemiconductor

The invention provides a photomask, a thin film transistor element and a manufacturing method of the thin film transistor element. The photomask comprises a first shading pattern, a second shading pattern, a translucent single slit and a semi-translucent pattern, wherein the translucent single slit is positioned between the first shading pattern and the second shading pattern; the width of the translucent single slit is between 1.5 and 2.5 microns; and the semi-translucent pattern is connected with the first shading pattern and the second shading pattern. The photomask adopts a design of the translucent single slit and the semi-translucent pattern, wherein the translucent single slit can reduce the channel length making the thin film transistor element; and the semi-translucent pattern can define an extension part of a semiconductor layer. Therefore, the thin film transistor element has a higher starting current.

Owner:AU OPTRONICS CORP

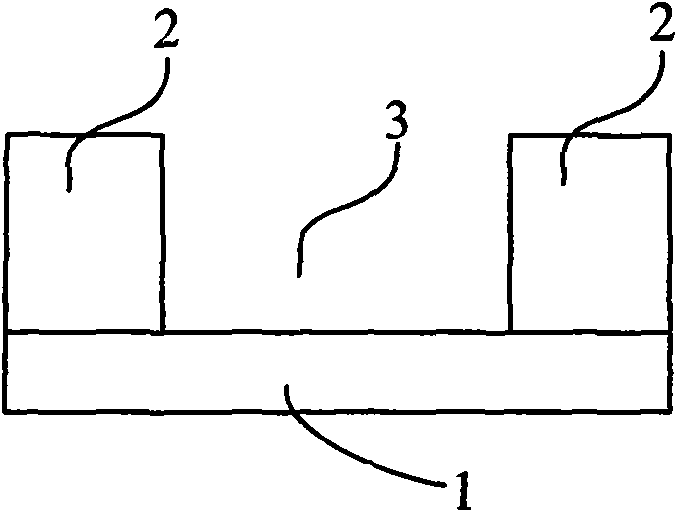

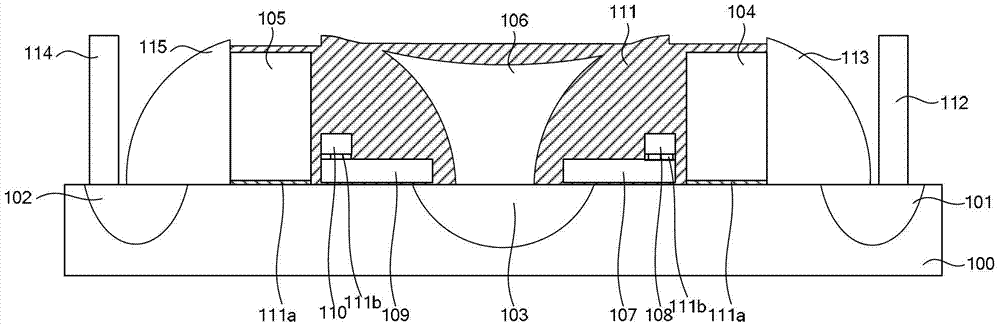

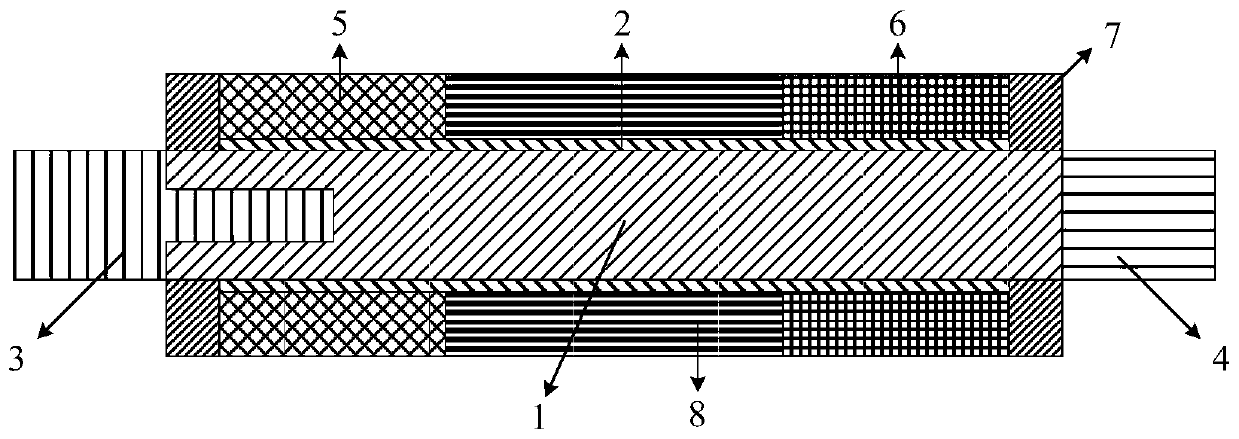

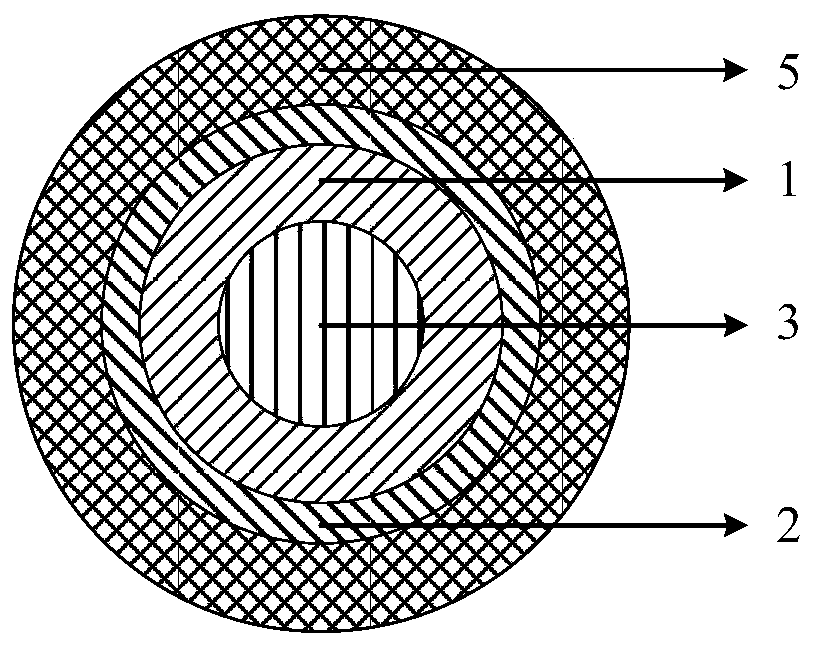

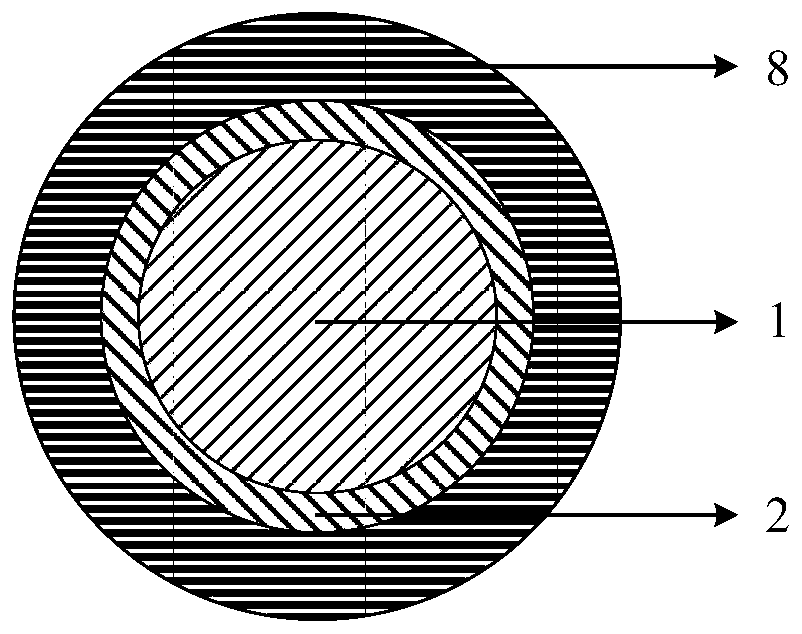

MOSFET and its manufacture

InactiveCN1453880APerformance is not affectedAvoiding problems with FinFET devicesSemiconductor/solid-state device manufacturingSemiconductor devicesMOSFETEngineering

The MOSFET features the channel inside the semiconductor substrate, the information channel area constituted with one doped semiconductor layer across the channel, the grid in and over the channel and around the information channel area with grid dielectric layer in between. The grid is separated from the side wall and bottom with one gapping wall and one insulating layer. The manufacture of the MOSFET includes following steps: forming channel filled with insulating layer on the substrate, eliminating the upper layer of the insulating layer, forming gapping wall on the side wall of channel,filling the channel with sacrificial layer; forming and defining one doped semiconductor layer on the substrate to form device area across the sacrificial layer; eliminating the sacrificial and forming grid dielectric layer on the surface of the device; forming conducting layer on the substrate filled into the channel and defining the conducting layer to form the grid; and forming source and drain on two sides of the grid.

Owner:WINBOND ELECTRONICS CORP

Array substrate, manufacture method of array substrate, liquid crystal display panel and display device

InactiveCN103048840BReduce distanceReduce channel lengthSemiconductor/solid-state device manufacturingNon-linear opticsLiquid-crystal displayDisplay device

The present invention relates to an array substrate and a manufacture method of the same, a liquid crystal display panel, and a display device, which are relative to a liquid crystal display field. Further, source electrodes and drain electrodes of the array substrate are arranged on different layers. In the manufacture method of the array substrate, the source electrodes and the drain electrodes are formed on different layers by two patterning processes. According to the technical scheme of the present invention, a length of a channel between the source electrodes and the drain electrodes can be decreased as much as possible, thereby increasing a start current Ion of a TFT.

Owner:BOE TECH GRP CO LTD

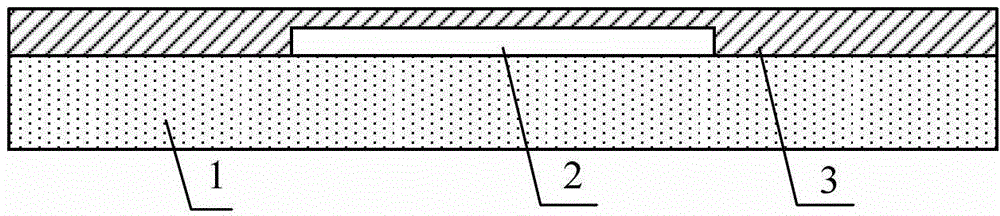

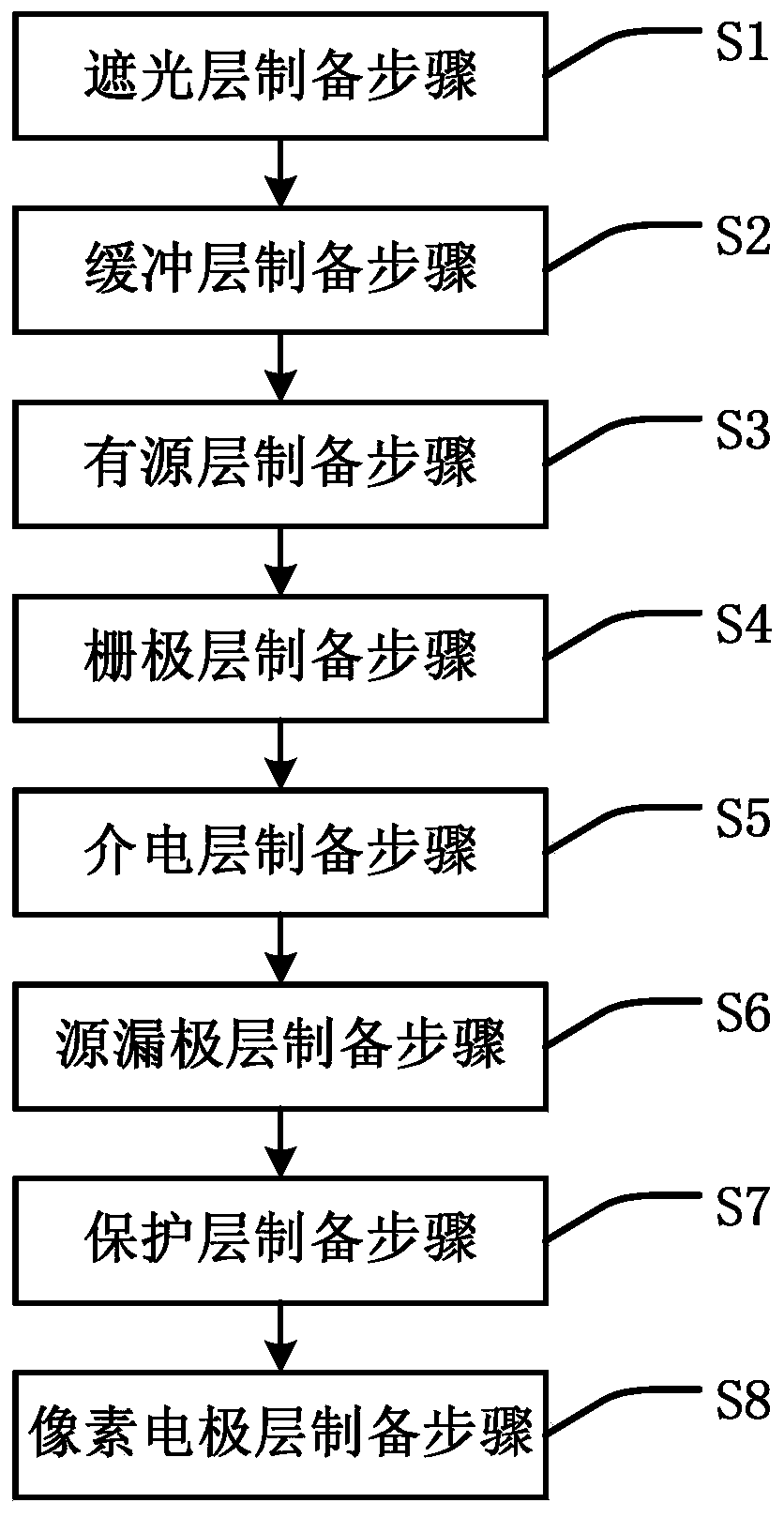

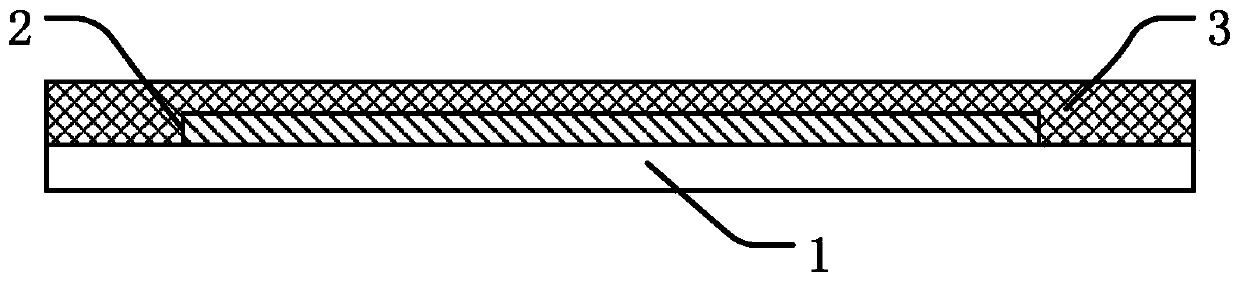

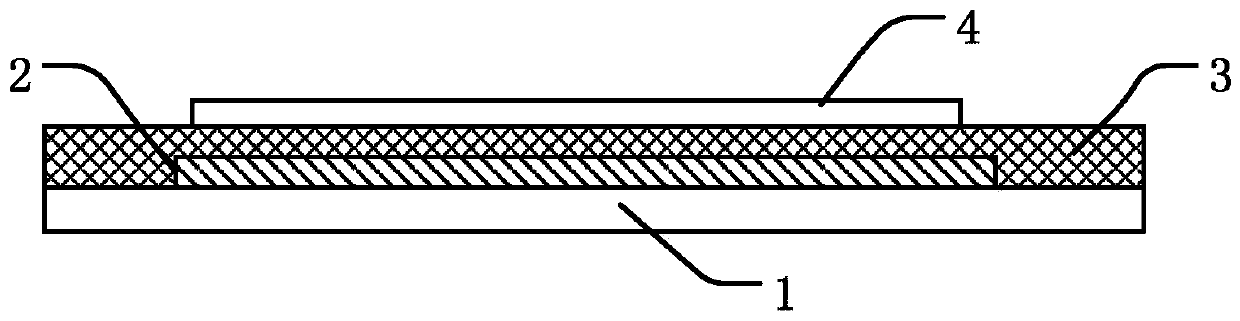

Thin film transistor device and preparation method thereof

InactiveCN110190132AIncrease turn-on currentExcellent electrical propertiesTransistorSemiconductor/solid-state device manufacturingPower flowDisplay device

The invention provides a thin film transistor device and a preparation method thereof. The thin film transistor device comprises a substrate, an active layer, a gate insulating layer, a conductive layer and a gate layer. The preparation method of the thin film transistor includes a shading layer preparation step, a buffer layer preparation step, an active layer preparation step and a gate layer preparation step. The technical effects of the invention lie in that the conductive layer exists at all positions on the upper surface of the gate insulating layer, the corresponding active layer belowthe whole gate insulating layer is enabled to be controlled, the turn-on current of the thin film transistor device is increased, the electrical characteristics of the thin film transistor device areenhanced, and the display effect of the display device is improved.

Owner:SHENZHEN CHINA STAR OPTOELECTRONICS SEMICON DISPLAY TECH CO LTD

MOSFET and its manufacture

InactiveCN1507073APerformance is not affectedAvoiding problems with FinFET componentsSemiconductor/solid-state device manufacturingSemiconductor devicesMOSFETElectrical conductor

The present invention is MOSFET and its manufacture. The MOSFET features the semiconductor substrate with one channel, the passage area being one thin doped semiconductor layer across the channel, and the gate located inside and over the channel and around the passage area with gate dielectric layer in between. The manufacture process includes the steps of: providing one semiconductor substrate and forming one channel on the substrate; filling the channel with sacrificed layer, forming one doped semiconductor layer, defining one element area across the sacrificed layer and exposing partial sacrificed layer; removing the sacrificed layer to expose the lower element area surface over the channel and forming one gate dielectric layer on the surface of element area and the channel; forming one conducting layer on the gate dielectric layer, filling the channel and defining the conducting layer to form gate in and over the channel; and forming source and drain beside the gate.

Owner:WINBOND ELECTRONICS CORP

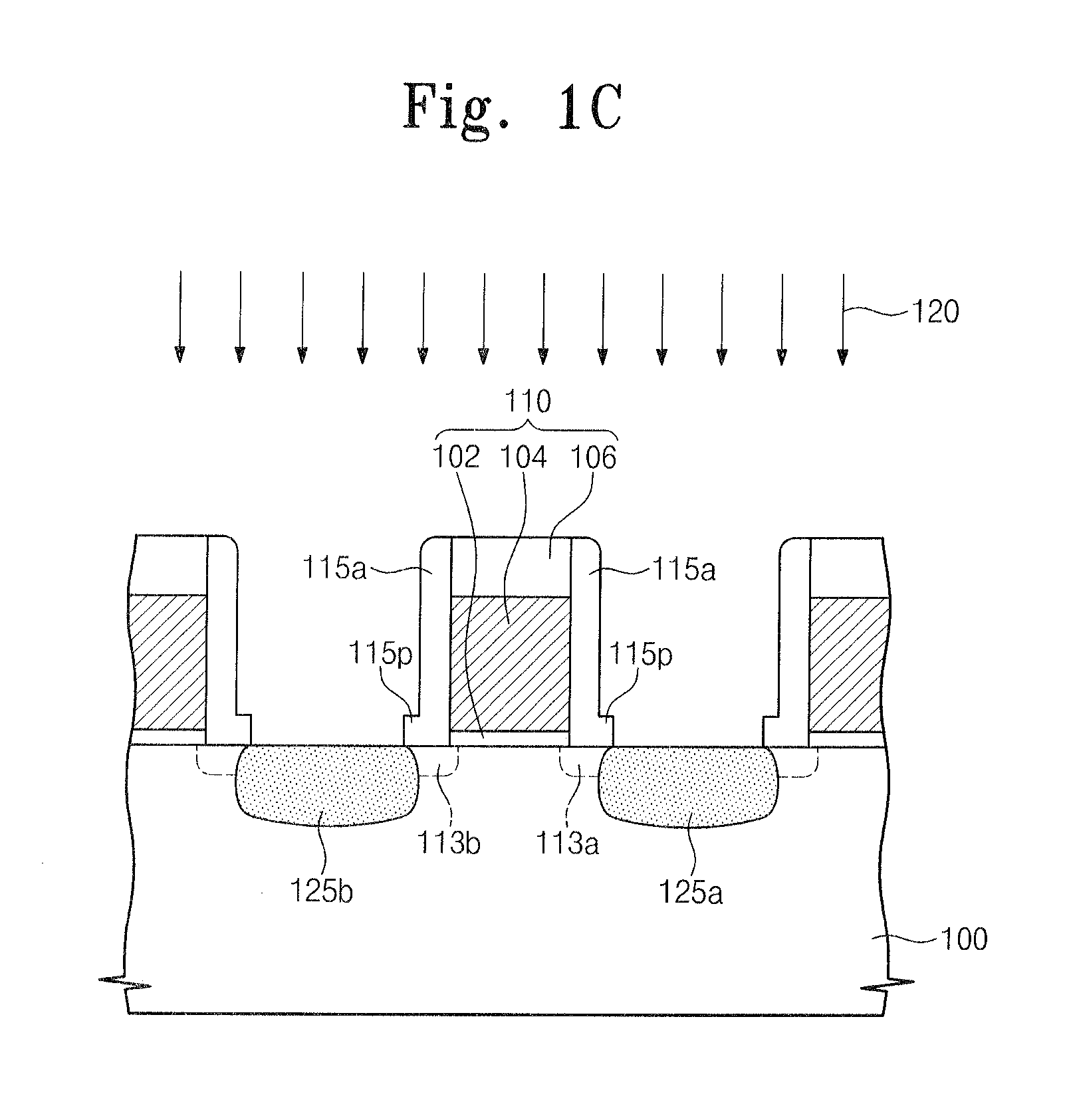

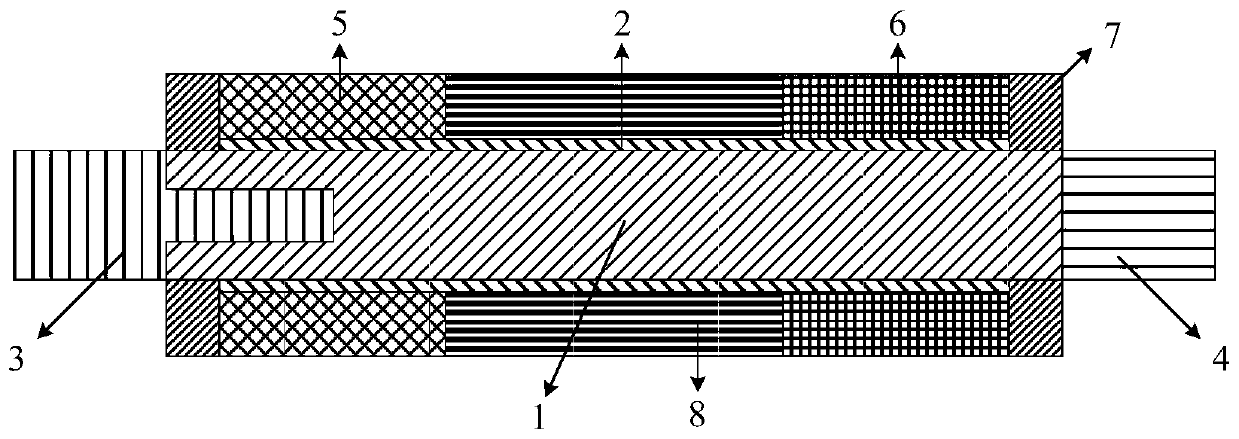

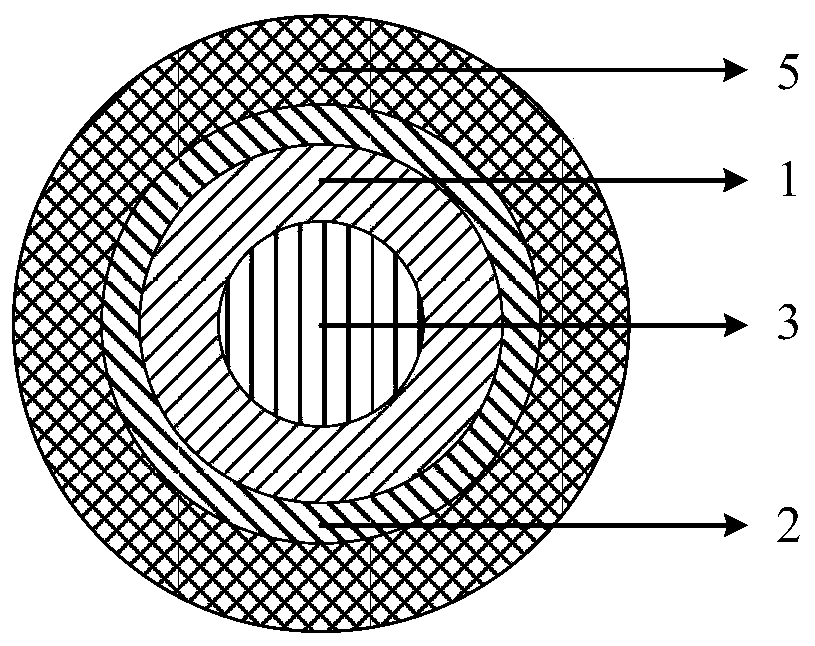

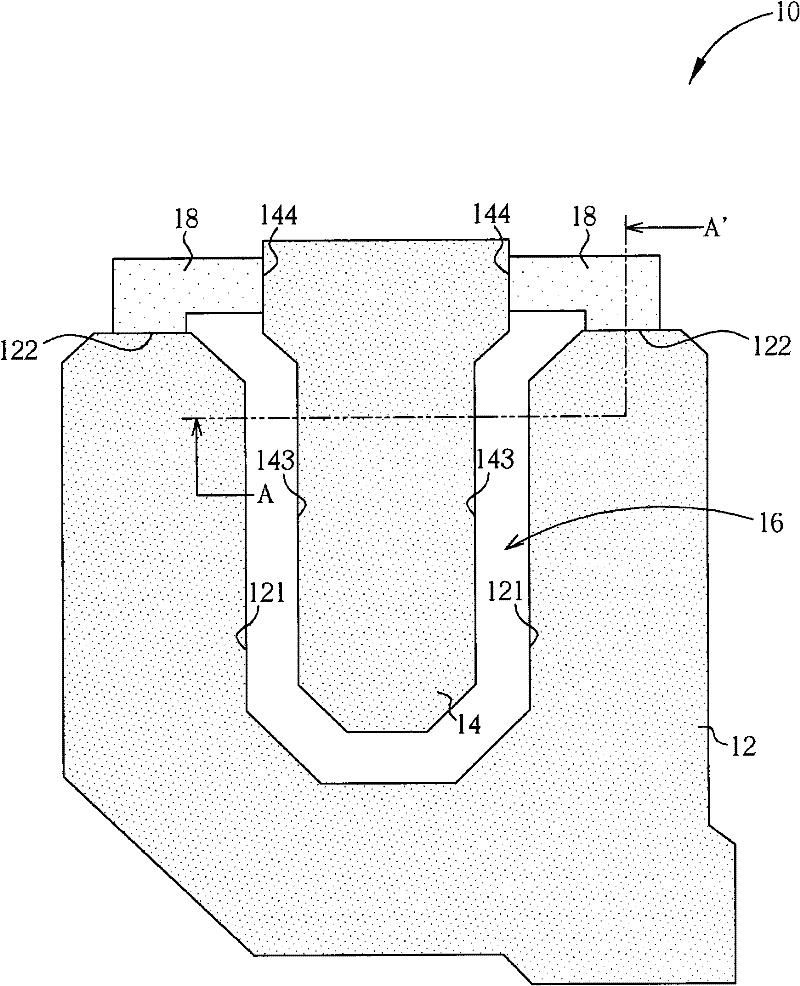

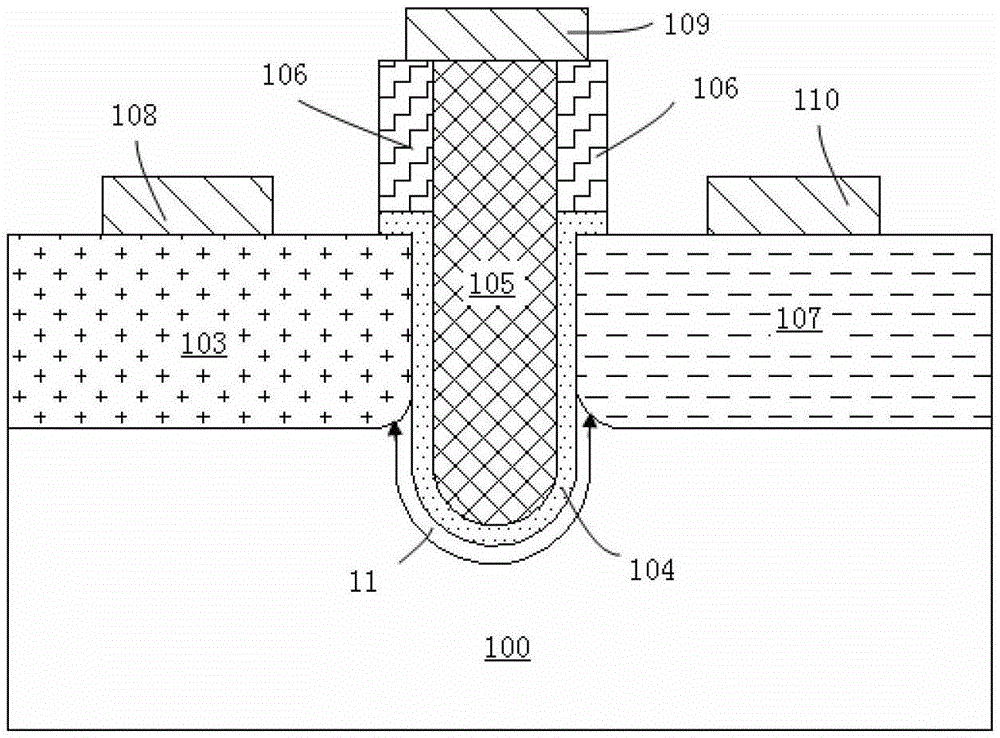

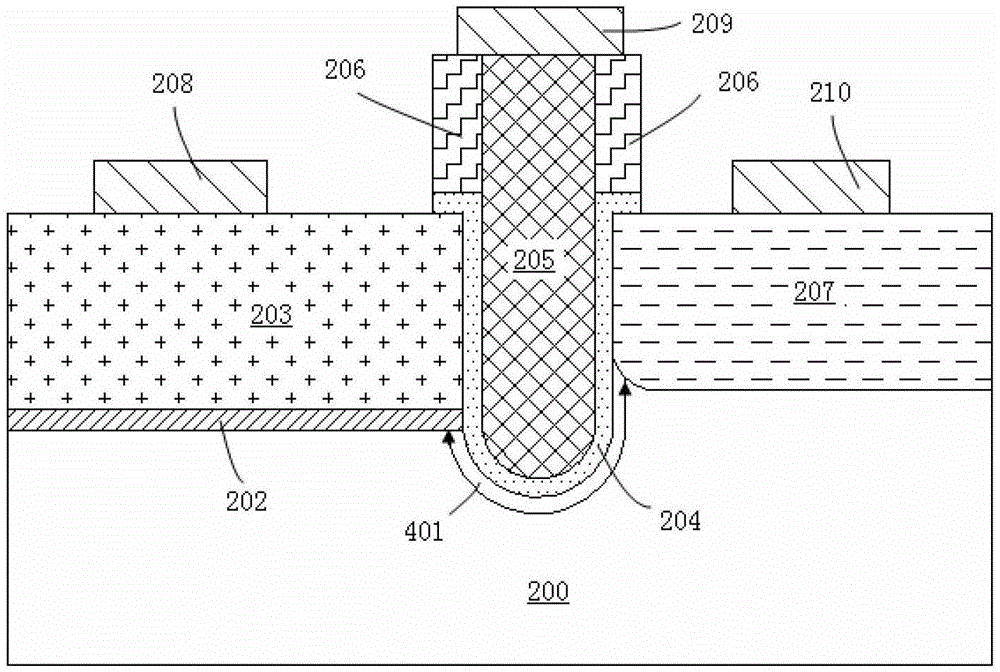

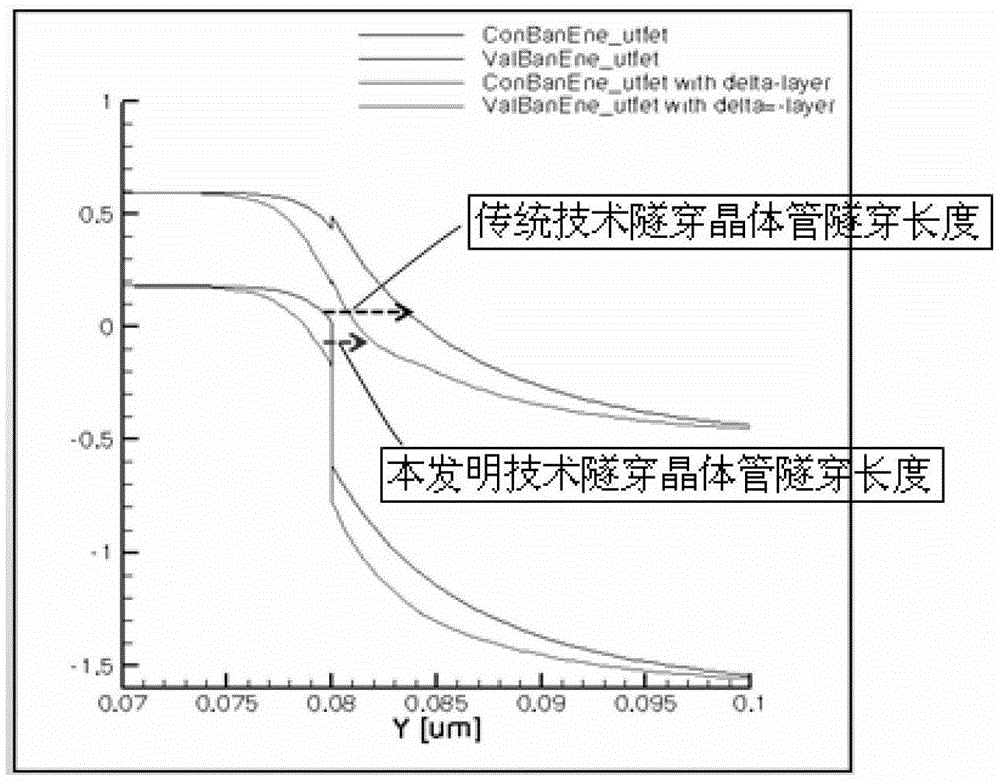

A U-type channel tunneling transistor with stacked structure and its preparation method

InactiveCN103151383BNarrow band gapIncreased band bendingSemiconductor/solid-state device manufacturingSemiconductor devicesBand bendingSubthreshold swing

Owner:FUDAN UNIV

semiconductor memory

ActiveCN102983139BReduce power consumptionReduce thicknessTransistorSolid-state devicesBit planeMedia layer

The present invention provides a semiconductor memory. The semiconductor memory of the present invention is not provided with a control gate, and by disposing a first erase gate and a second erase gate on the first floating gate and the second floating gate respectively, then In the erasing phase, the semiconductor memory can directly perform erasing operations through the first and second erasing gates, and there is no need to apply a higher erasing voltage to the first bit line and the second bit line. , therefore the thickness of the word line oxide dielectric layer between the word line and the semiconductor substrate can be reduced. Reducing the thickness of the word line oxide dielectric layer not only increases the turn-on current, but also reduces the leakage current and maintains a small turn-off current. When reading, the read voltage of the word line is reduced, thereby saving the power consumption of the semiconductor memory.

Owner:SHANGHAI HUAHONG GRACE SEMICON MFG CORP

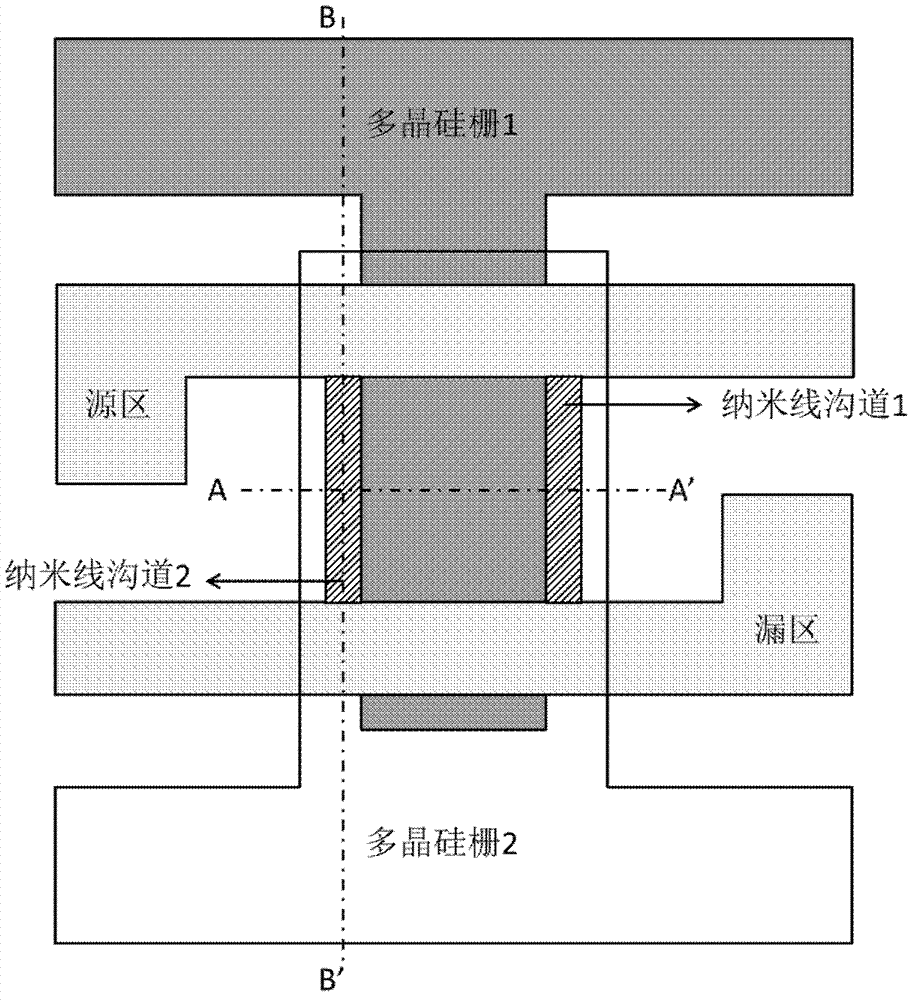

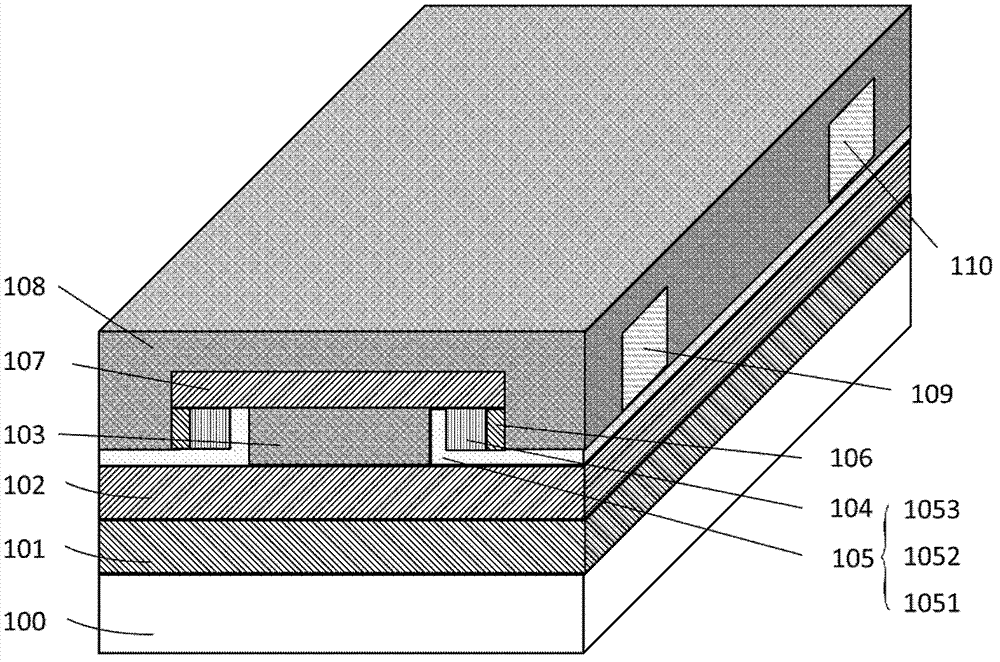

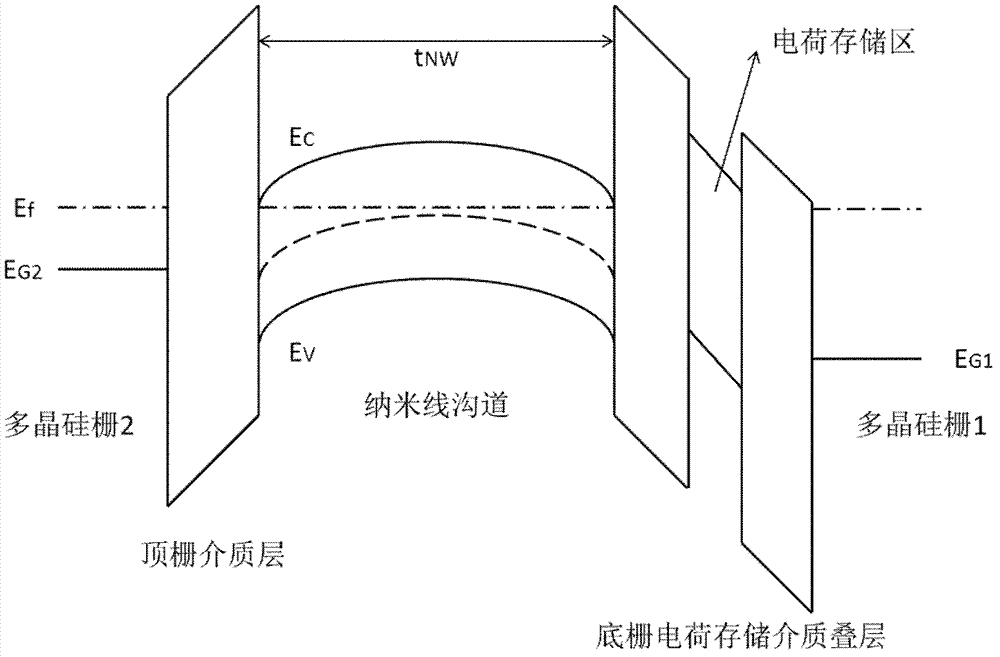

Double-grid electric charge capturing memory and manufacture method thereof

ActiveCN103247669BImprove programming and erasing speedReduce thicknessSolid-state devicesSemiconductor/solid-state device manufacturingNanowireField-effect transistor

The invention relates to a double-grid electric charge capturing memory based on a polycrystalline silicon nanowire field effect transistor and a manufacture method thereof. The double-grid electric charge capturing memory is provided with two polycrystalline silicon grid electrodes, and comprises a semiconductor substrate, a first dielectric buffer layer formed on the semiconductor substrate, a second dielectric buffer layer formed on the first dielectric buffer layer, a polycrystalline silicon bottom grid formed on the second dielectric buffer layer, two nanowire channels symmetrically distributed on the two sides of the polycrystalline silicon bottom grid, two electric charge capturing memory dielectric layers formed between the polycrystalline silicon bottom grid and the nanowire channels respectively, two top grid dielectric layers formed on the outer side of the two nanowire channels, a hard masking layer formed on the polycrystalline silicon bottom grid, the electric charge capturing memory dielectric layers, the nanowire channels and the top grid dielectric layers, a polycrystalline silicon top grid formed on the hard masking layer and the electric charge capturing memory dielectric layers and a source region and a drain region, spanning the two nanowire channels.

Owner:INST OF MICROELECTRONICS CHINESE ACAD OF SCI

An Asymmetric Reconfigurable Field Effect Transistor

ActiveCN110164958BIncrease the longitudinal electric fieldIncrease turn-on currentSolid-state devicesSemiconductor/solid-state device manufacturingNanowireElectrical polarity

The invention discloses an asymmetrical reconfigurable field effect transistor. The transistor comprises a channel, a drain arranged at one end of the channel, a source extended to the inside of the channel at the other end of the channel, and a drain arranged at one end of the channel. The gate oxide on the outside, the control gate and the polarity gate respectively arranged on the source and drain terminals and outside the gate oxide, respectively arranged outside the two ends of the channel, are used for the control gate, the polarity gate The side wall electrically isolating the source and the drain, and the gate isolation arranged outside the gate oxide for isolating the control gate and the polarity gate. In the present invention, the contact area between the source end extending into the channel and the nanowire channel is larger, thereby increasing the tunneling area of carriers and increasing the turn-on current. When it is turned off, the drain structure is the same as the non-overlapping area of the general RFET drain structure, and the leakage current remains basically unchanged, so the current switching ratio is improved, and the logic gate current is shortened while keeping the static power consumption unchanged. operation delay time.

Owner:EAST CHINA NORMAL UNIV +1

MOSFET and its manufacture

InactiveCN1282254CReduce leakage currentEliminate leakage currentSemiconductor/solid-state device manufacturingSemiconductor devicesMOSFETElectrical conductor

A metal oxide semiconductor field effect transistor and its manufacturing method, the metal oxide semiconductor field effect transistor is characterized by a trench in the semiconductor substrate, and the channel region is a doped semiconductor across the trench thin layer, and the gate is located in the trench and above the trench, and surrounds the channel region through the gate dielectric layer. The steps of another manufacturing method are as follows: first, a semiconductor substrate is provided, and then a trench is formed on it. Then fill up the trench with a sacrificial layer, form a doped semiconductor layer, and define it to form an element region. The element region crosses the sacrificial layer and exposes a part of the sacrificial layer. Then the sacrificial layer is removed to expose the lower surface of the element region above the trench, and then a gate dielectric layer is formed on the surface of the element region and the trench. Next, a conductor layer is formed on the gate dielectric layer and filled into the trench, and then the conductor layer is defined to form a gate located in and above the trench. Then, a source and a drain are formed on both sides of the gate.

Owner:WINBOND ELECTRONICS CORP

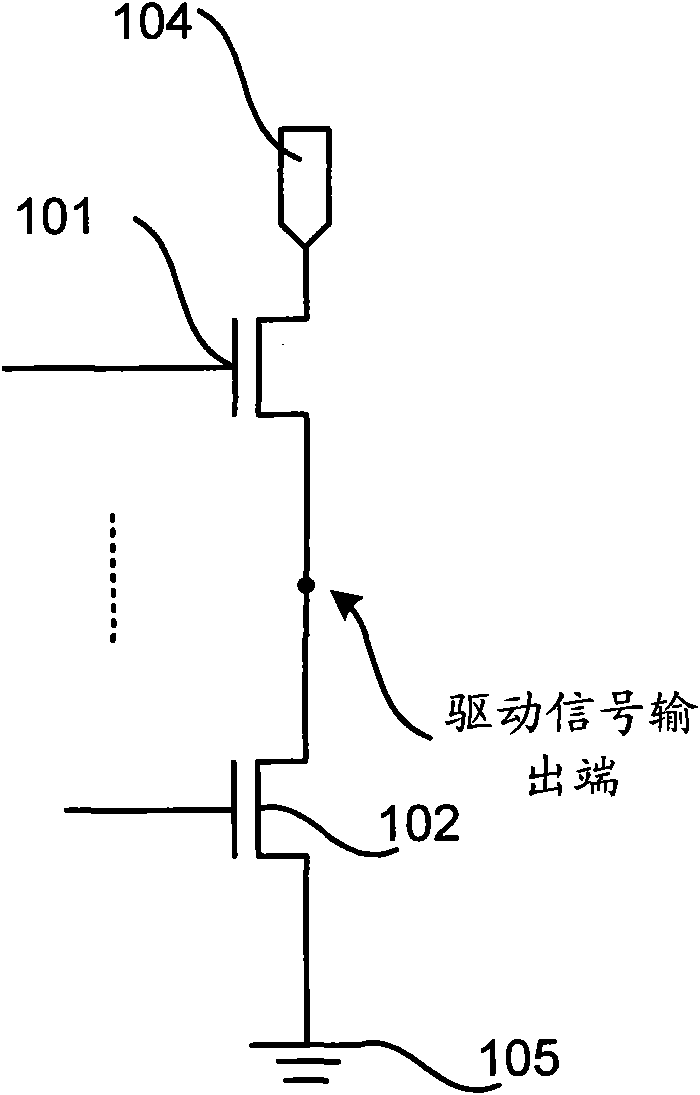

tft-lcd, driving device and manufacturing method thereof

InactiveCN102466937BIncrease turn-on currentReduce aspect ratioStatic indicating devicesSolid-state devicesBottom gateThin-film-transistor liquid-crystal display

Owner:BEIJING BOE OPTOELECTRONCIS TECH CO LTD

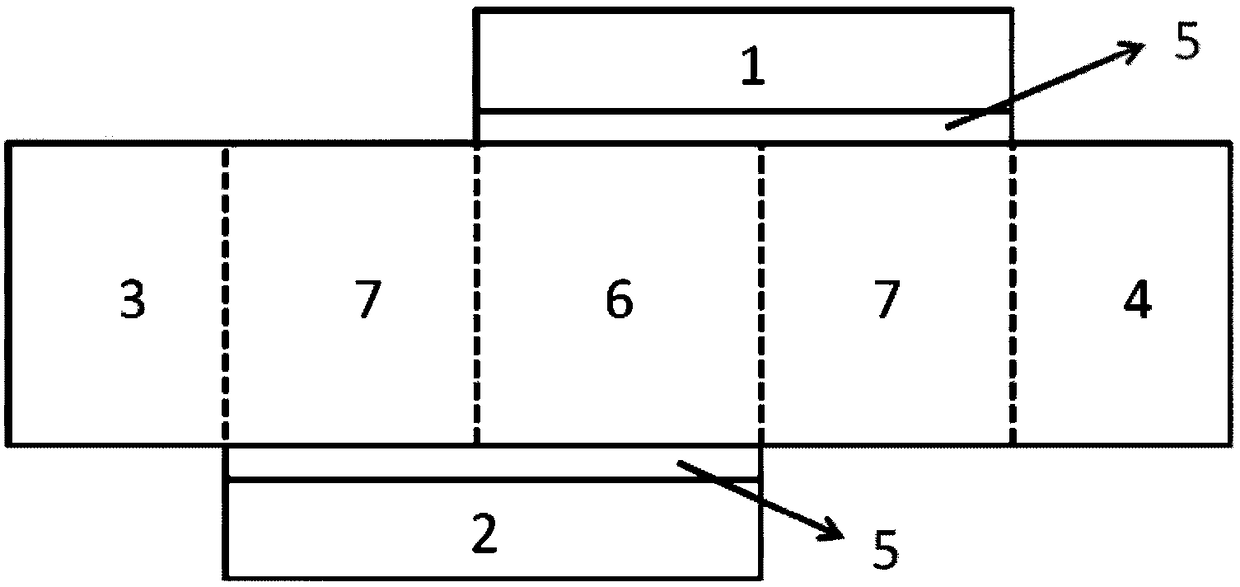

No-junction field effect transistor and manufacturing method therefor

InactiveCN105448718ALower resistanceReduce contact resistanceSemiconductor/solid-state device manufacturingSemiconductor devicesElectrical resistance and conductancePower flow

The invention discloses a no-junction field effect transistor and a manufacturing method therefor, and the method comprises the steps: providing a substrate; carrying out the doping so as to form a first doping region and a second doping region and to enable the doping types of the first and second doping regions to be different; forming a first grid structure and a second grid structure; removing a part of substrate, so as to form a first opening and a second opening; forming metal layers in the first and second openings; and carrying out the annealing of the metal layers and the substrate, so as to form source-drain regions. The invention also provides a no-junction field effect transistor, and the field effect transistor comprises the substrate; the first doping region and the second doping region; the first grid structure and the second grid structure; and the first and second openings, wherein the interiors of the first and second openings are provided with material layers containing metal, and the material layers serve as the source-drain regions. The beneficial effects of the invention lie in that the contact resistance between the source-drain regions and a conductive plug is smaller; the starting current is increased; the performance of the no-junction field effect transistor is improved; the technological difficulty is simplified; and the degree of interface scattering which may happen in the doping regions is reduced to some degree.

Owner:SEMICON MFG INT (SHANGHAI) CORP

Method for manufacturing metal oxide semiconductor field effect transistor and device thereof

ActiveCN101593703BReduce channel lengthIncrease turn-on currentSemiconductor/solid-state device manufacturingSemiconductor devicesElectrical conductorDevice form

The invention discloses a method for manufacturing a metal oxide semiconductor field effect transistor and a device thereof. The manufacturing method comprises the following steps: providing a semiconductor substrate; forming an insulating layer on the surface of the semiconductor substrate; forming a groove on the insulating layer; forming light dope drain regions in the semiconductor substrate below the lateral wall of the groove respectively; forming grid flank walls on the lateral wall of the groove respectively; forming grid dielectric layers on the groove surfaces between the grid flank walls; forming grids in an accommodating space encircled by the grid flank walls and the grid dielectric layers; removing the insulating layer; and forming a source region and a drain region respectively in the semiconductor substrates on two sides of the grid flank walls. The manufacturing method breaks through the limitation of the minimum grid length which can be achieved by a photoetching device, and reduces the length of a channel formed between the source region and the drain region; and the device formed according to the method is helpful for enhancing the firing current and reducing the electric leakage caused by short-channel effect.

Owner:SHANGHAI HUAHONG GRACE SEMICON MFG CORP

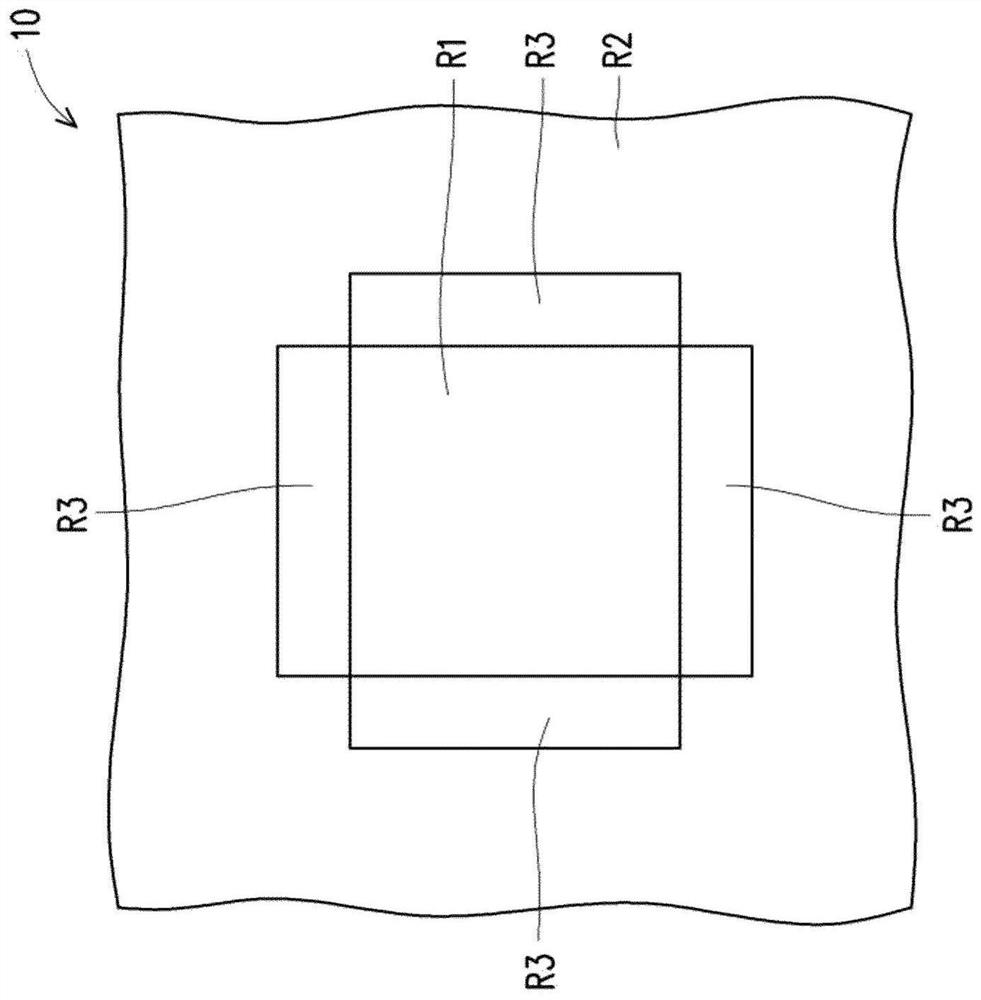

Memory structure and manufacturing method thereof

PendingCN113394219AImprove electrical performanceAvoid damageTransistorSemiconductor/solid-state device manufacturingMemory cellMetal silicide

The invention discloses a memory structure and a manufacturing method thereof. The memory structure includes a substrate, an isolation structure, a memory cell, a first transistor, a first contact window structure and a second contact window structure. The first transistor comprises a first gate structure, a first doped region, a second doped region, a first metal silicide layer and a second metal silicide layer. The first contact window structure is located on the first metal silicide layer. The second contact window structure is located on the second metal silicide layer. The first metal silicide layer is not in contact with the isolation structure. The second metal silicide layer is not in contact with the isolation structure. The top view area of the first metal silicide layer is larger than that of the first contact window structure. The top view area of the second metal silicide layer is larger than the top view area of the second contact window structure.

Owner:POWERCHIP SEMICON MFG CORP

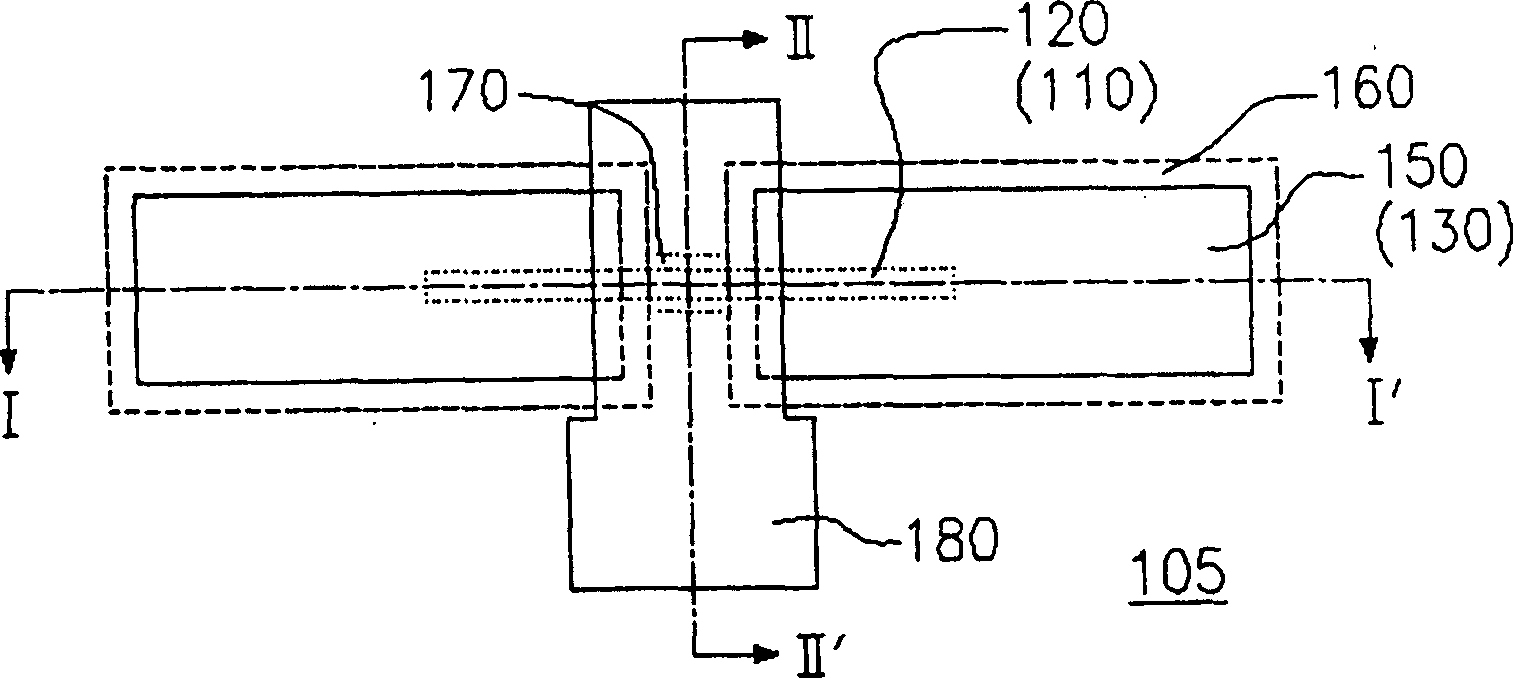

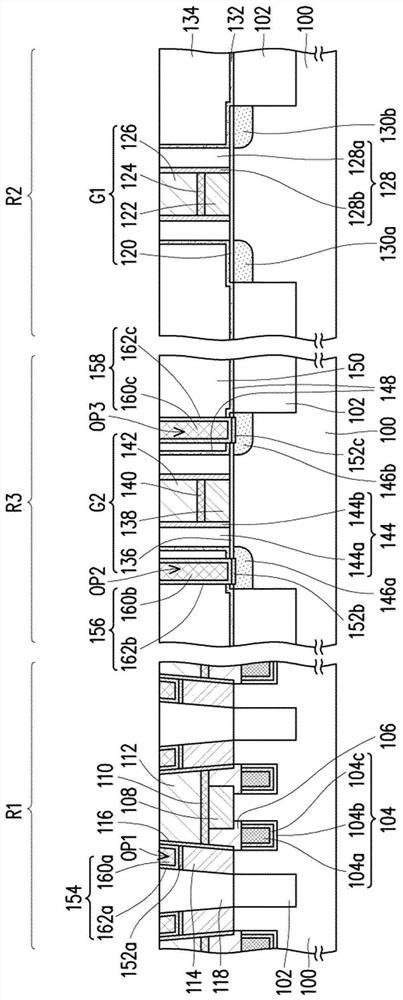

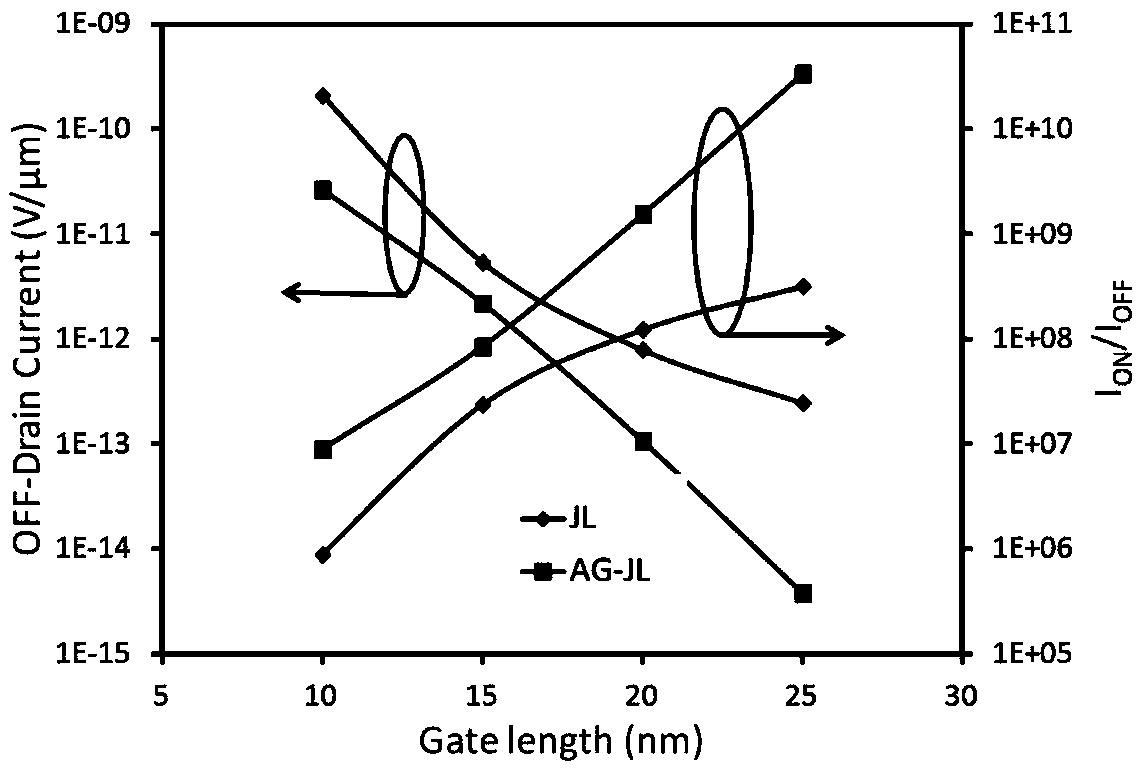

An Asymmetric Dual-Gate Junctionless Field-Effect Transistor

ActiveCN105826391BOff current goodIncrease turn-on currentSemiconductor devicesGate dielectricBottom gate

The invention discloses a novel asymmetric double-gate junctionless field effect transistor comprising a top gate, a bottom gate, a source region, a drain region, gate dielectric layers, a channel overlap region, and channel non-overlap regions. The top gate and the bottom gate are respectively disposed in an upper position and in a lower position of a channel, and are of an asymmetric structure. There is an overlap region between the top gate and the bottom gate, namely, the channel overlap region. The channel overlap region is between the channel non-overlap regions. The source region and the drain region are respectively disposed at the two sides of the channel non-overlap regions. The gate dielectric layers are respectively arranged between the top gate and the channel and between the bottom gate and the channel. Because of the asymmetric gate structure, smaller channel length is achieved when the device is opened, and larger channel length is achieved when the device is closed. The structure can ensure that the novel device has higher closing current and greater gate control capability at the closing moment and has higher opening current at the opening moment.

Owner:HANGZHOU DIANZI UNIV